Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

213 results about "Gallium arsenate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Gallium arsenide (GaAs) is a compound of the elements gallium and arsenic. It is a III-V direct bandgap semiconductor with a Zinc blende crystal structure.

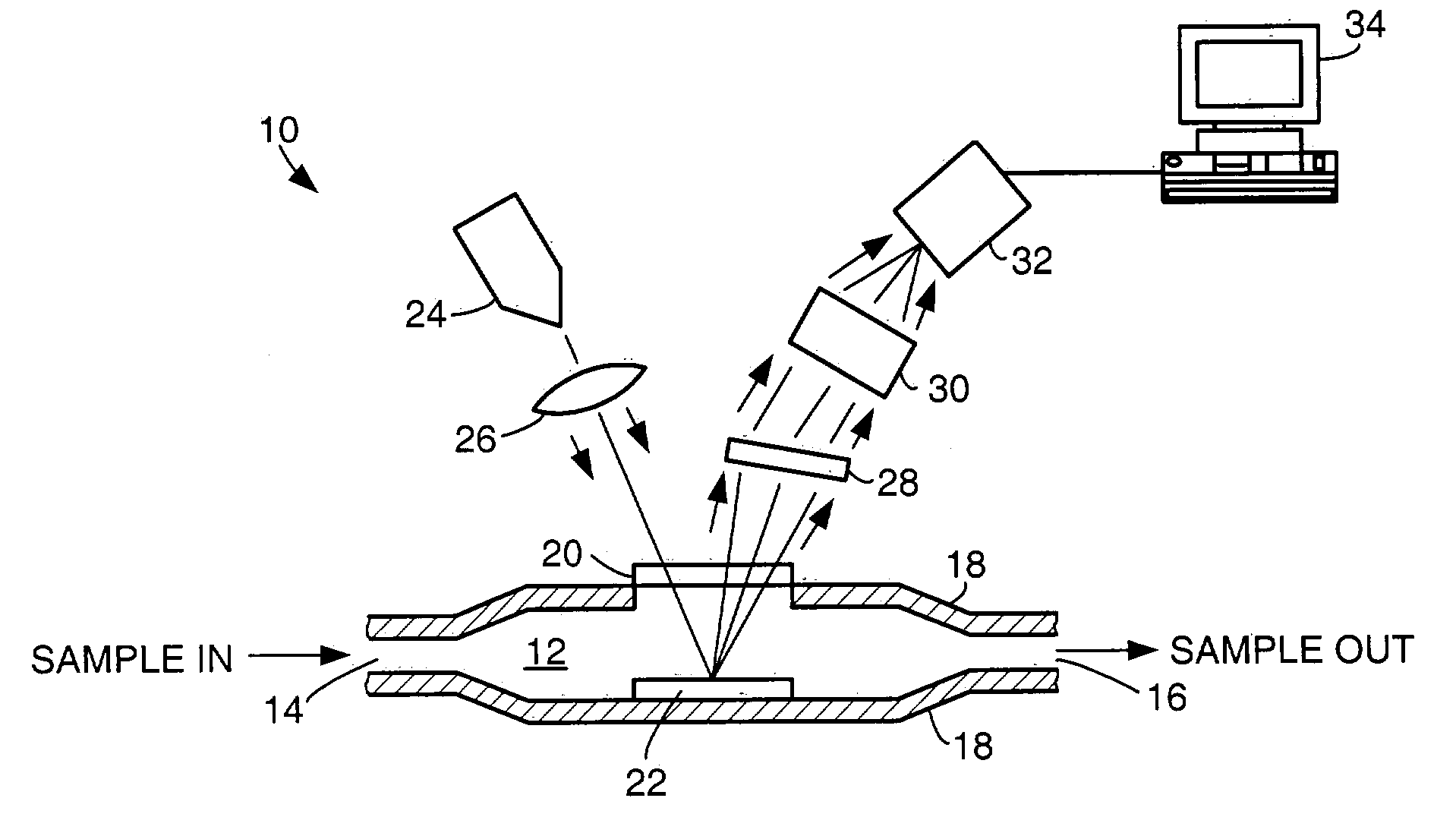

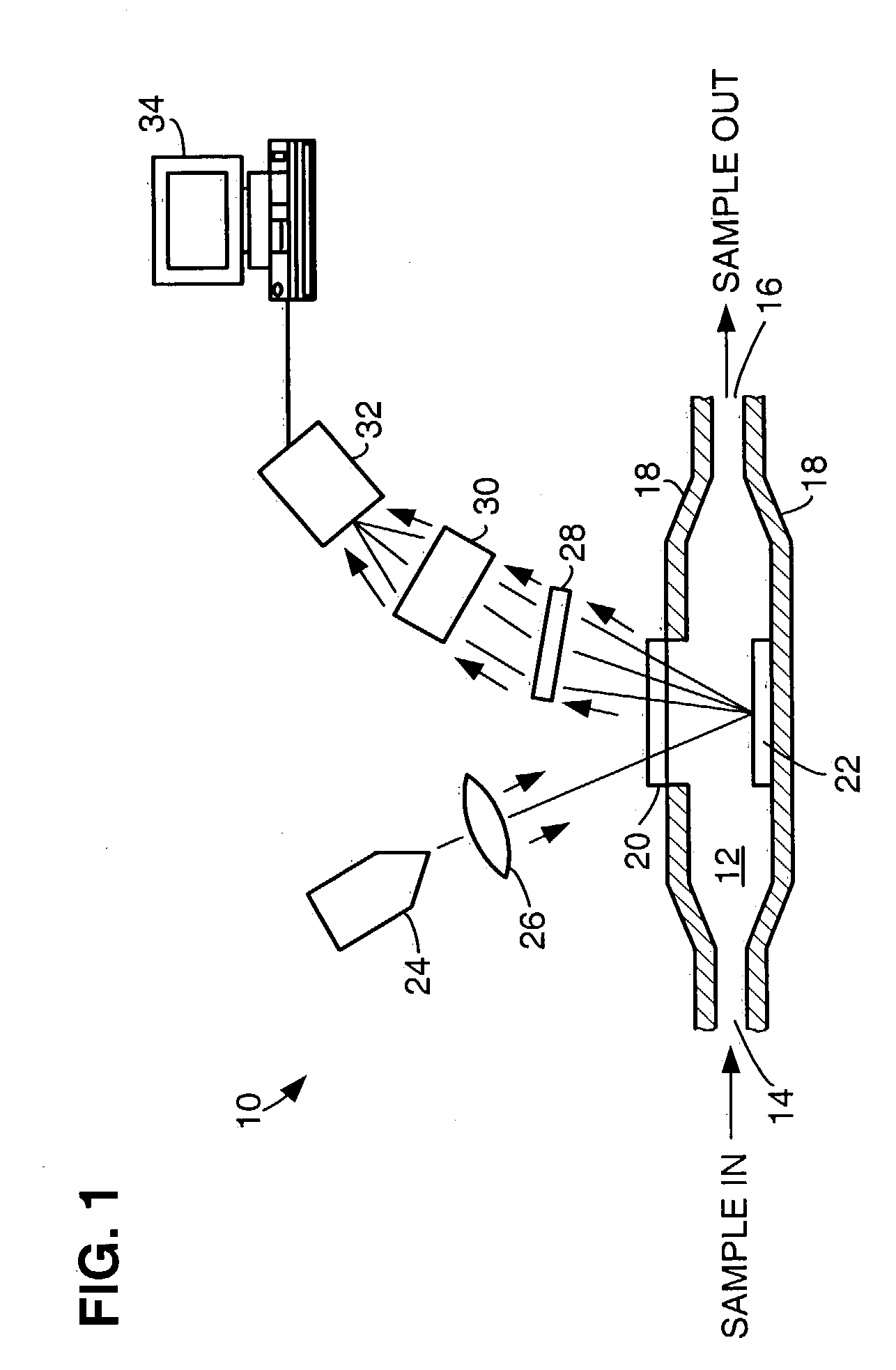

Method, structure, and apparatus for Raman spectroscopy

Disclosed herein are a Raman spectroscopy structure comprising a porous material substrate, and a method of performing Raman spectroscopy of a sample disposed adjacent to the structure comprising the porous material substrate. Generally, the substrate includes one or more layers of a porous material such as porous silicon, porous polysilicon, porous ceramics, porous silica, porous alumina, porous silicon-germanium, porous germanium, porous gallium arsenide, porous gallium phosphide, porous zinc oxide, and porous silicon carbide. It has been discovered that such a substrate material, when excited with near-infrared light, does not exhibit undesired background fluorescence characteristic of other known Raman spectroscopy substrates.

Owner:INTEL CORP

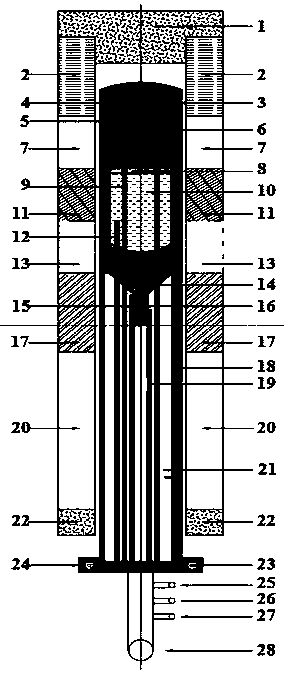

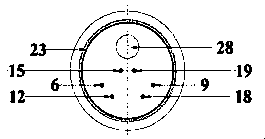

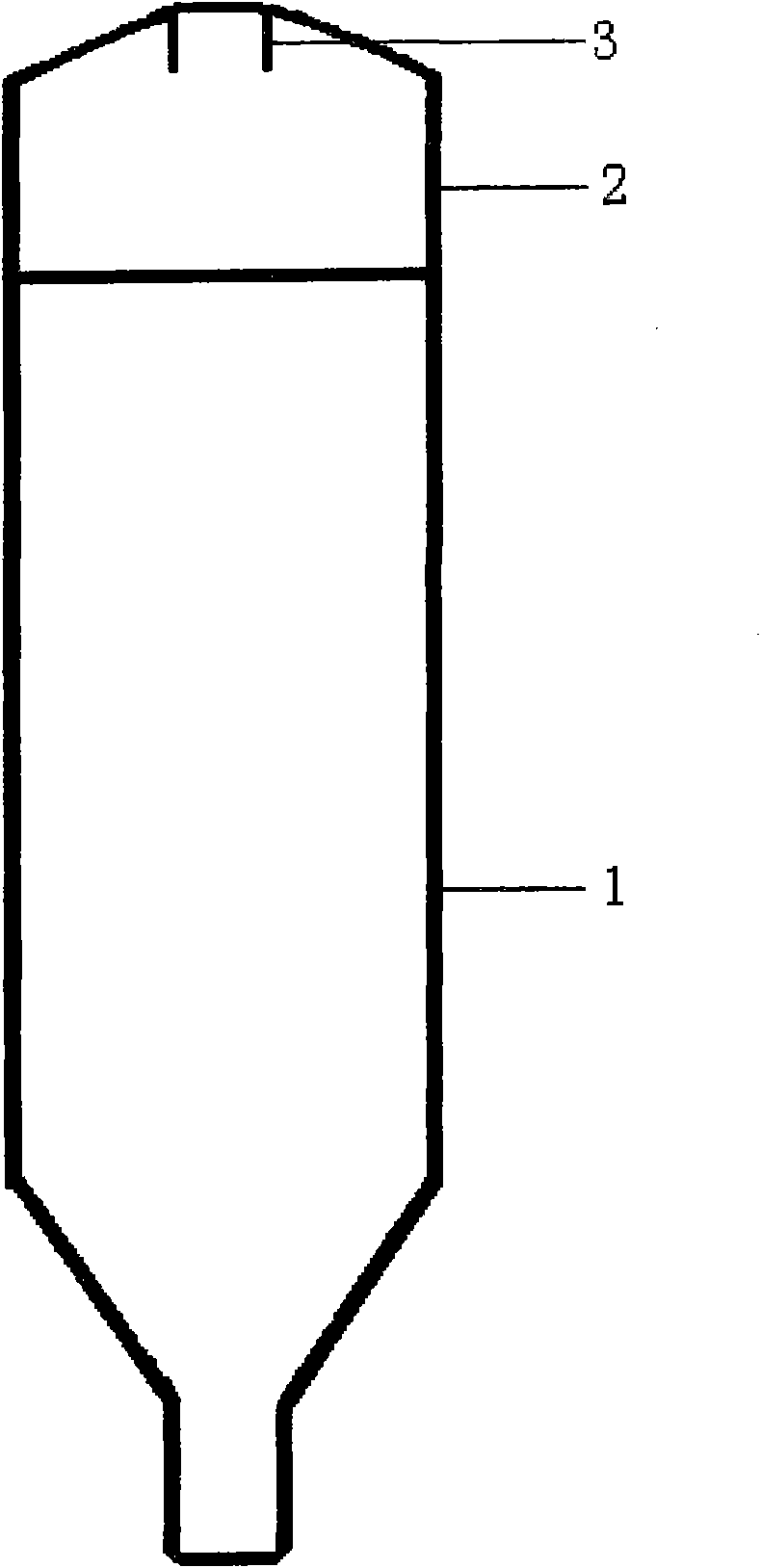

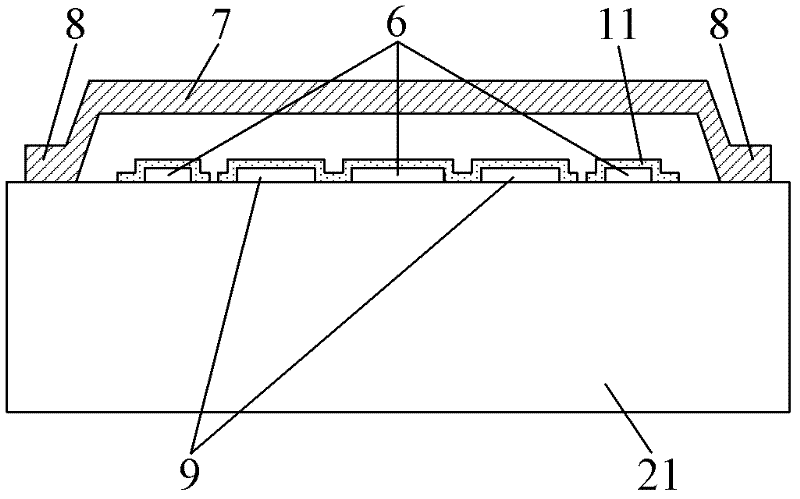

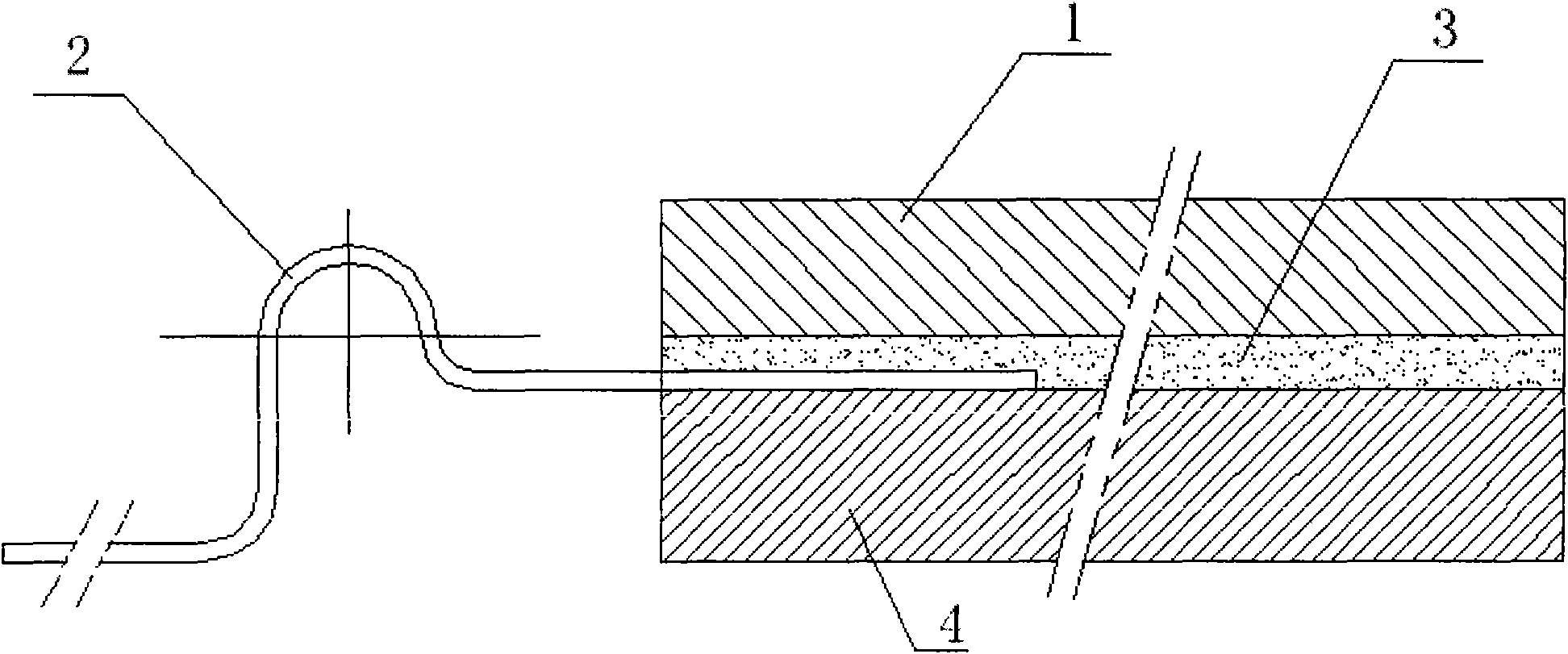

VGF/VB gallium arsenide single-crystal furnace structure and growing method

InactiveCN109252220AIncreased crystallization latent heat releaseIncrease crystallization ratePolycrystalline material growthFrom frozen solutionsSingle crystalMaximum size

The invention discloses a VGF / VB gallium arsenide single-crystal furnace structure and a growing method. According to the VGF / VB gallium arsenide single-crystal furnace structure, a resistance heatingfurnace which is relatively lowest in production cost and is provided with multiple temperature zones is adopted; a support structure adopts graphite; the support strength is improved; the loading amount is favorably increased; release of latent heat of growth crystallization is facilitated; the crystal yield of crystal growth is favorably improved; a sealing structure with a reusable quartz tubeand a stainless steel flange is adopted; a 1-atm air charging and discharging automatic valve is additionally arranged on an air channel pipeline, so that the balance of inner air pressure and outerair pressure of the quartz tube can be effectively guaranteed, and the influence of deformation of the quartz tube on reuse is avoided. A VGF method and a VB method are used for growing crystals; whenthe crystals are grown by the VB method, the sunken degree of a concave solid-liquid interface of the VGF growth method can be improved, so that the crystal yield is favorably improved. The single-crystal furnace and the growth method are used for growing the gallium arsenide single crystals with maximum size of 8 inches; meanwhile, the quartz tube can be reused, so that the production cost can be reduced; a CO atmosphere doping manner also can be used for controlling the resistivity and the axial resistivity uniformity of semi-insulating gallium arsenide.

Owner:CHINA ELECTRONICS TECH GRP NO 46 RES INST

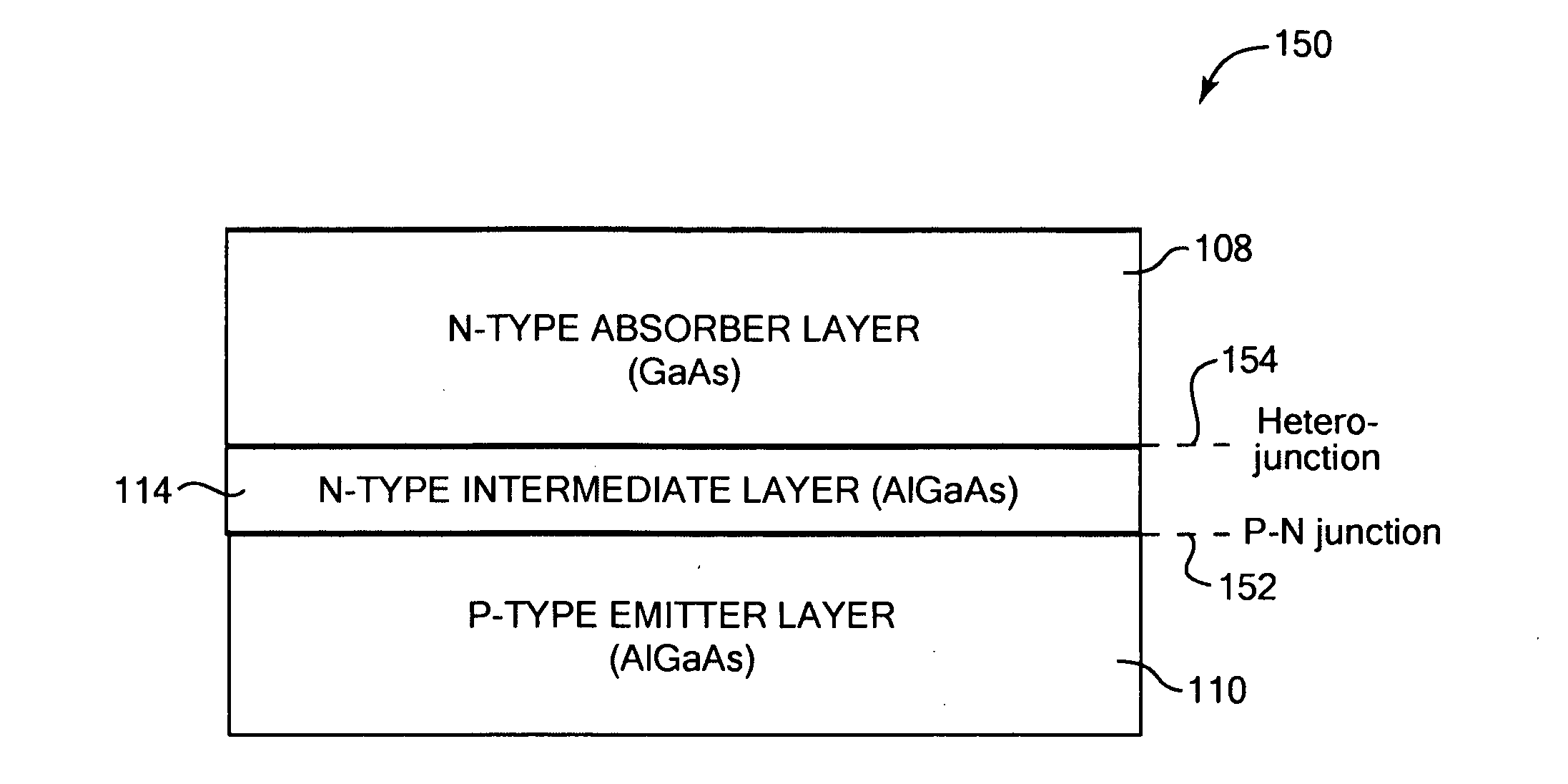

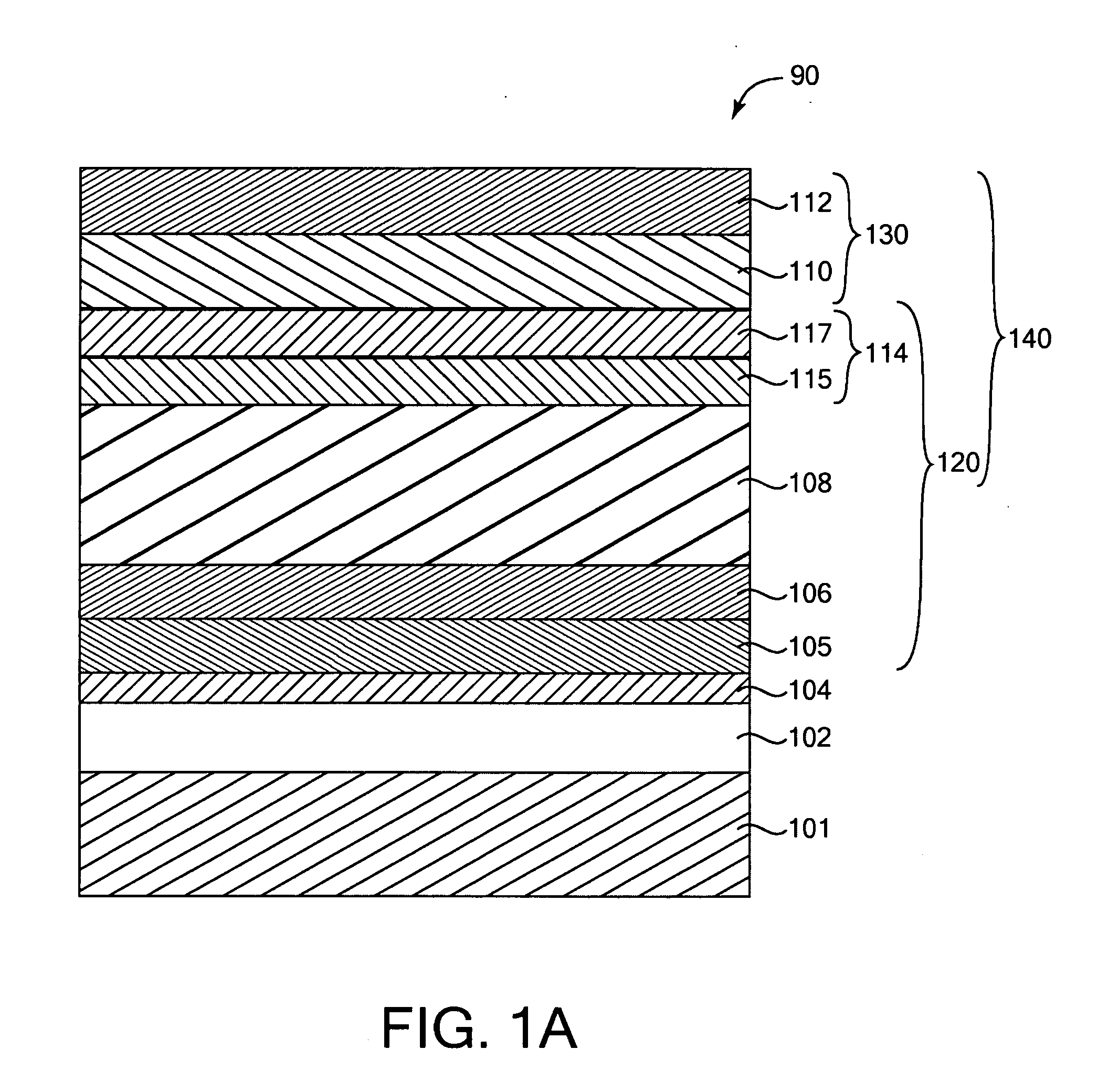

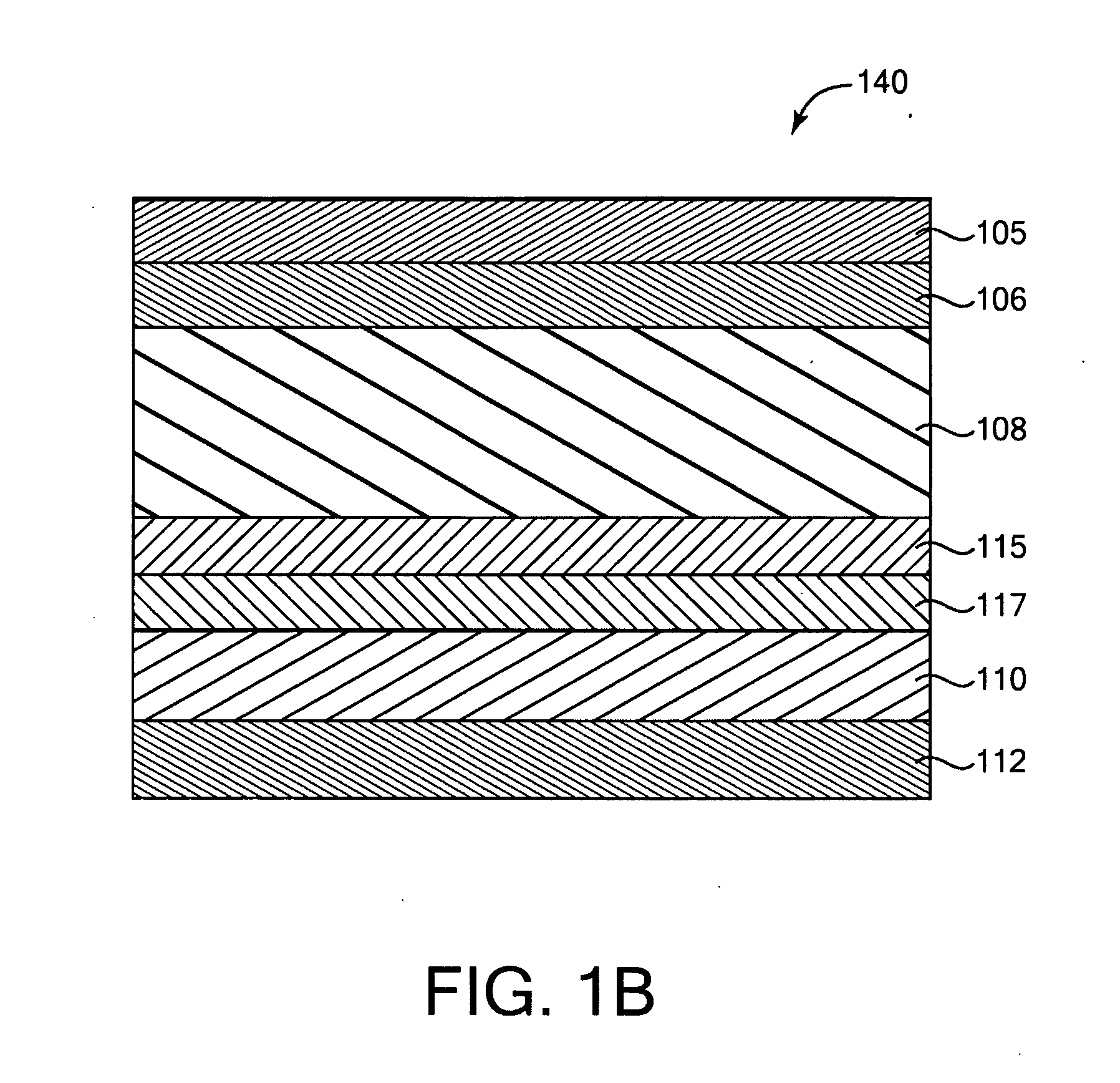

Optoelectronic devices including heterojunction

InactiveUS20120104460A1Increase the bandgapImprove efficiencySemiconductor/solid-state device manufacturingPhotovoltaic energy generationHeterojunctionDevice material

Embodiments of the invention generally relate to optoelectronic semiconductor devices such as photovoltaic devices including solar cells. In one aspect, an optoelectronic semiconductor device includes an absorber layer made of gallium arsenide (GaAs) and having only one type of doping. An emitter layer is located closer than the absorber layer to a back side of the device, the emitter layer made of a different material than the absorber layer and having a higher bandgap than the absorber layer. A heterojunction formed between the emitter layer and the absorber layer, and a p-n junction is formed between the emitter layer and the absorber layer and at least partially within the different material at a location offset from the heterojunction. The p-n junction causes a voltage to be generated in the device in response to the device being exposed to light at a front side of the device.

Owner:ALTA DEVICES INC

LED gallium arsenide substrate dewaxing cleaning agent

InactiveCN101974377AImprove solubilityAvoid the disadvantage of low flash pointSurface-active non-soap compounds and soap mixture detergentsAlkaneHalohydrocarbon

Owner:JIANGSU TIANHENG NANO SCI & TECH

Silica tube for growing semi-insulated gallium arsenide and method for doping carbon in gallium arsenide

InactiveCN101603208AGood electrical uniformityC concentration is easy to controlPolycrystalline material growthDiffusion/dopingCrucibleGraphite

The invention relates to a method for doping carbon in the gallium arsenide by using a silica tube for growing semi-insulated gallium arsenide. The method comprises the following steps: step 1: polycrystally synthesizing 7N Ga and 7N As to form a GaAs polycrystal; step 2: putting the synthesized GaAs polycrystal, seed crystal and B2O3 in a PBN crucible; step 3: putting the PBN crucible in a quartz body of the silica tube; step 4: fixing pure graphite in a silica groove on a silica cap of the silica tube; step 5: covering the quartz body and the silica cap, vacuumizing and welding the quartz body and the silica cap of the silica tube on oxyhydrogen flame; step 6: putting the welded silica tube in a VGF single crystal furnace for atmosphere doping and single crystal growth; and step 7: soaking the PBN crucible in methanol after the single crystal growth to obtain a GaAs single crystal and finish the preparation of the GaAs single crystal.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

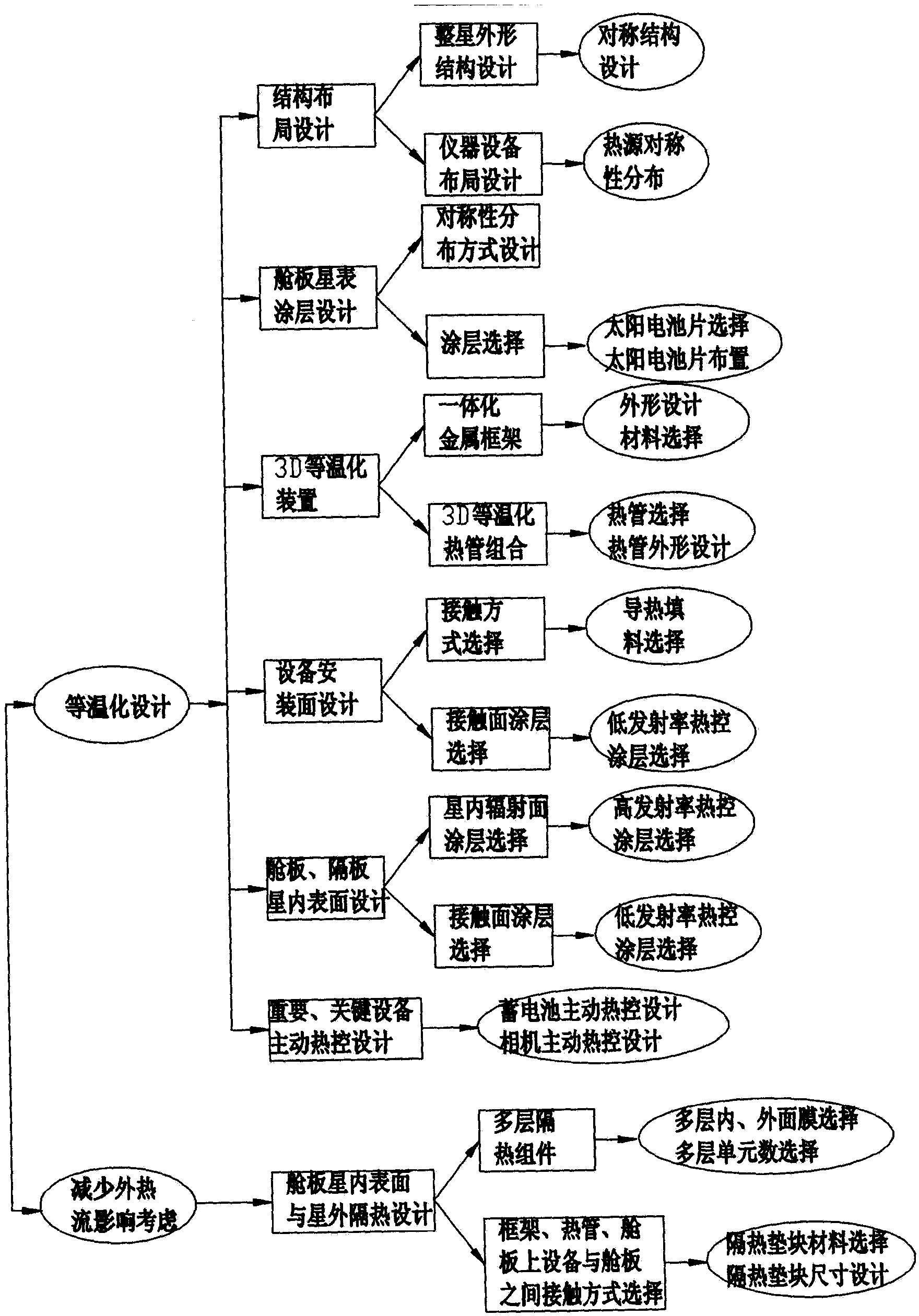

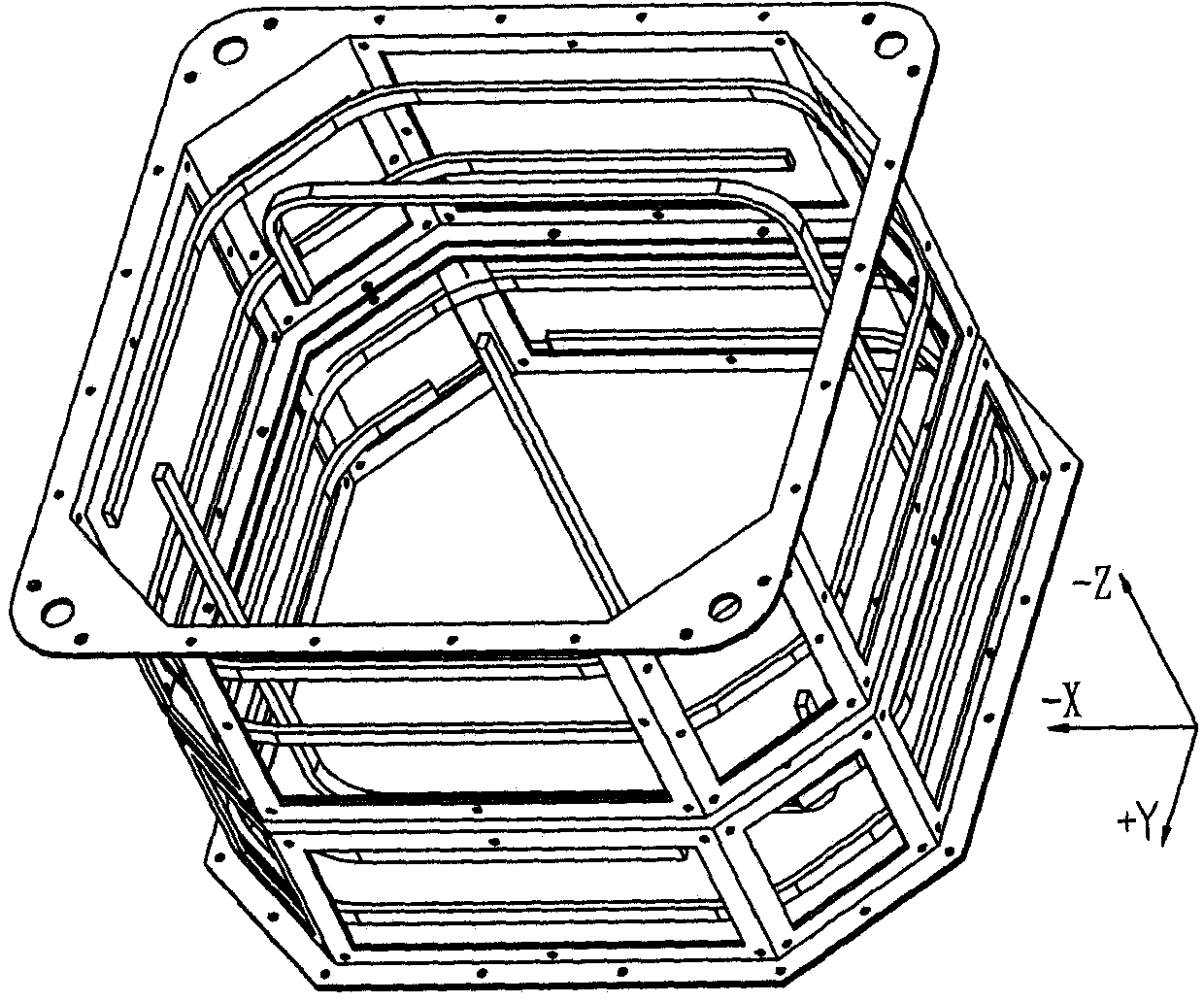

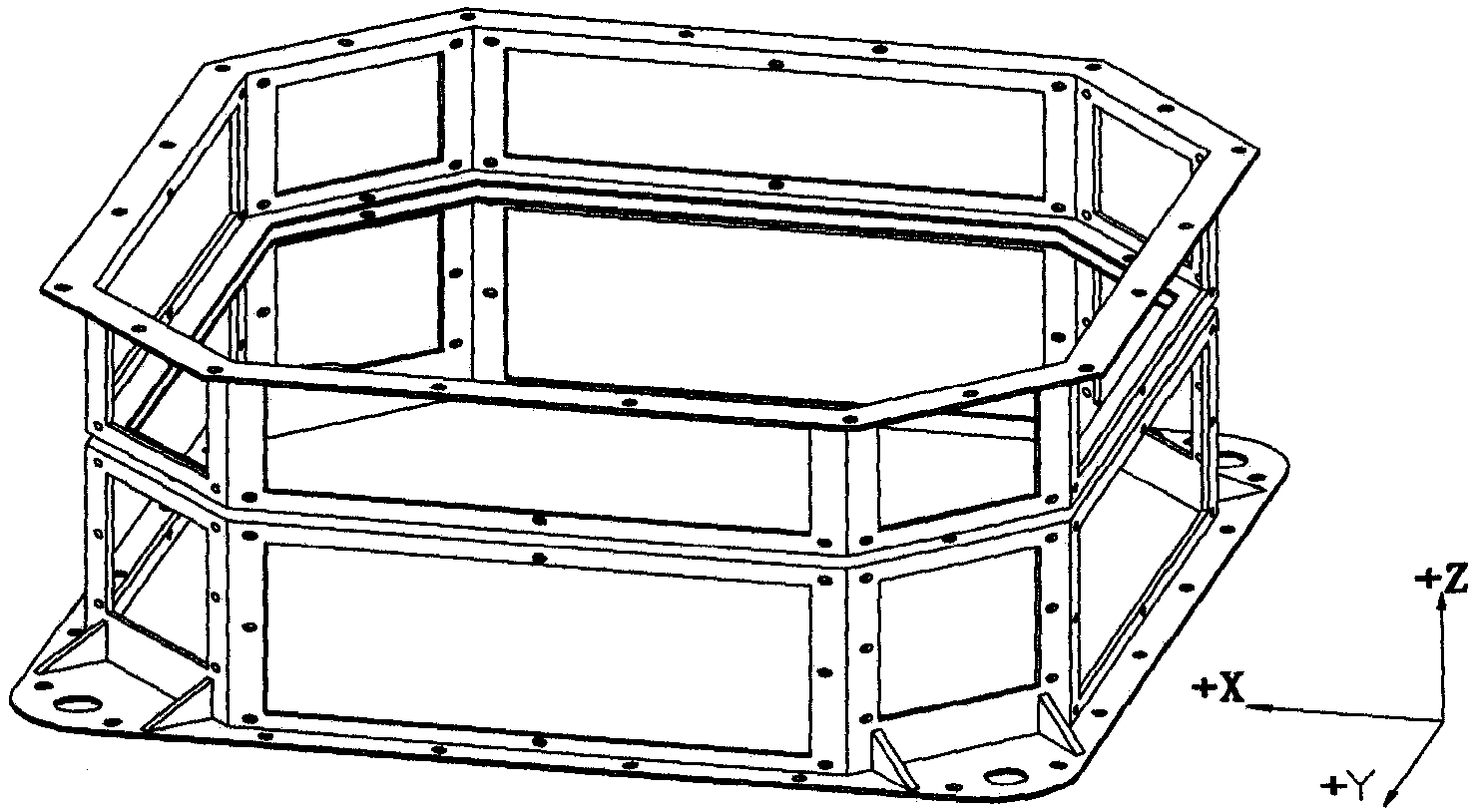

Thermal Control Method for Attitudeless Satellite

ActiveCN105659752BSolve the problem of guaranteeing temperature levelsEnhanced radiation heat transferCosmonautic environmental control arrangementSystems designGallium arsenate

The thermal control method of the non-attitude satellite, paste or spray the high-emissivity thermal control coating on the equipment in the star, fill the thermal conductive filler between the equipment installed on the partition and the installation surface, and spray the high-emissivity thermal control coating on the inner surface of the rest of the structure star Floor. The inner surface of the cabin board is covered with multi-layer heat insulation components to reduce the impact of drastic changes in heat flow outside the outer orbit of the star. Except for the installation surface of the instrument and equipment, the structural star module is pasted with third-order gallium arsenide solar cells. From the perspective of top-level system design, the present invention is based on the whole star isothermal design idea, fully utilizes the whole star structure heat storage, and utilizes solar cells as energy supply equipment and temperature control means at the same time, and adopts three-dimensional direction 3D isothermal heat pipe combination and integration The 3D isothermal device composed of a metal frame solves the problem of ensuring the temperature level of the entire satellite when there is no attitude control.

Owner:BEIJING INST OF SPACECRAFT SYST ENG

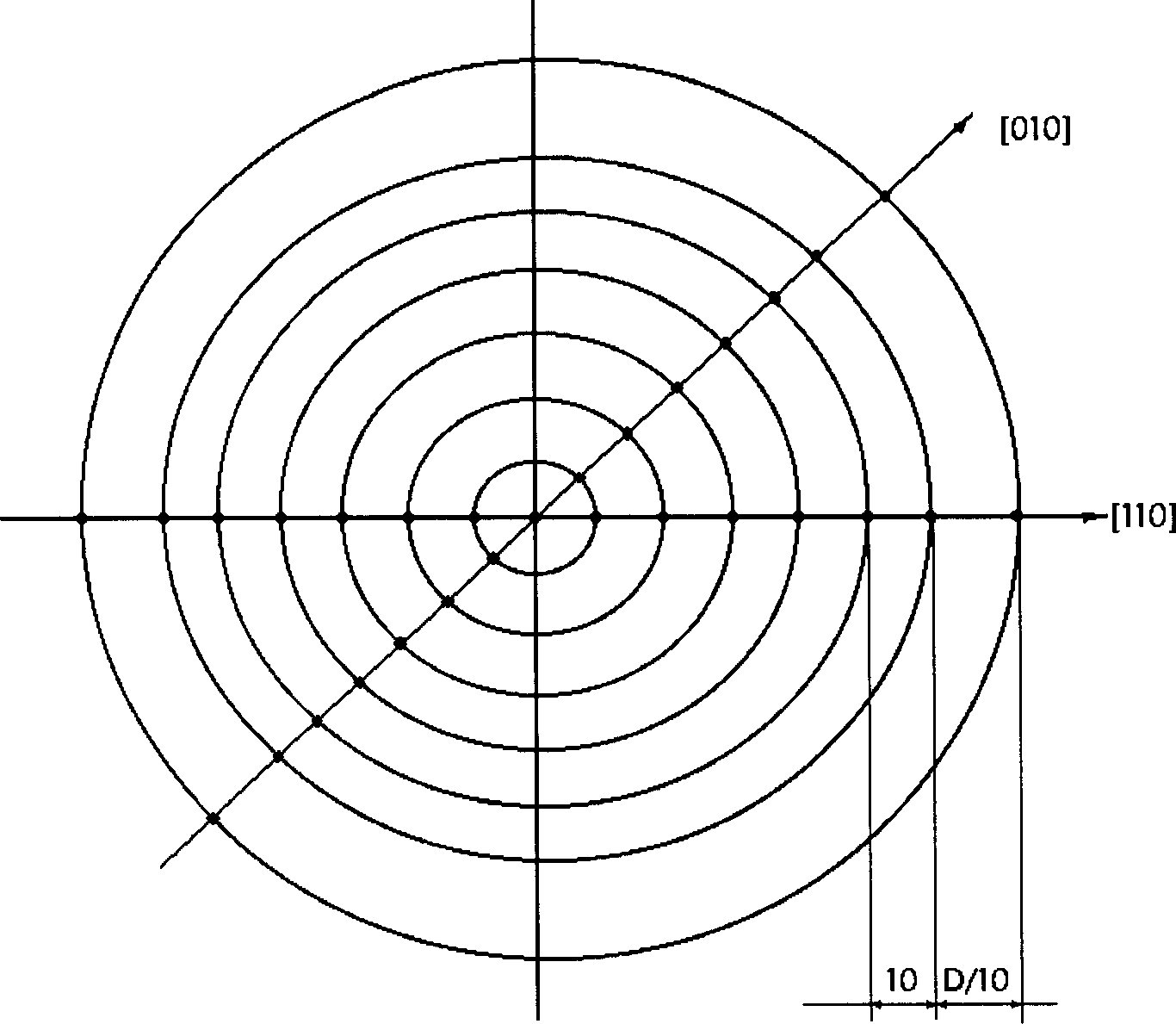

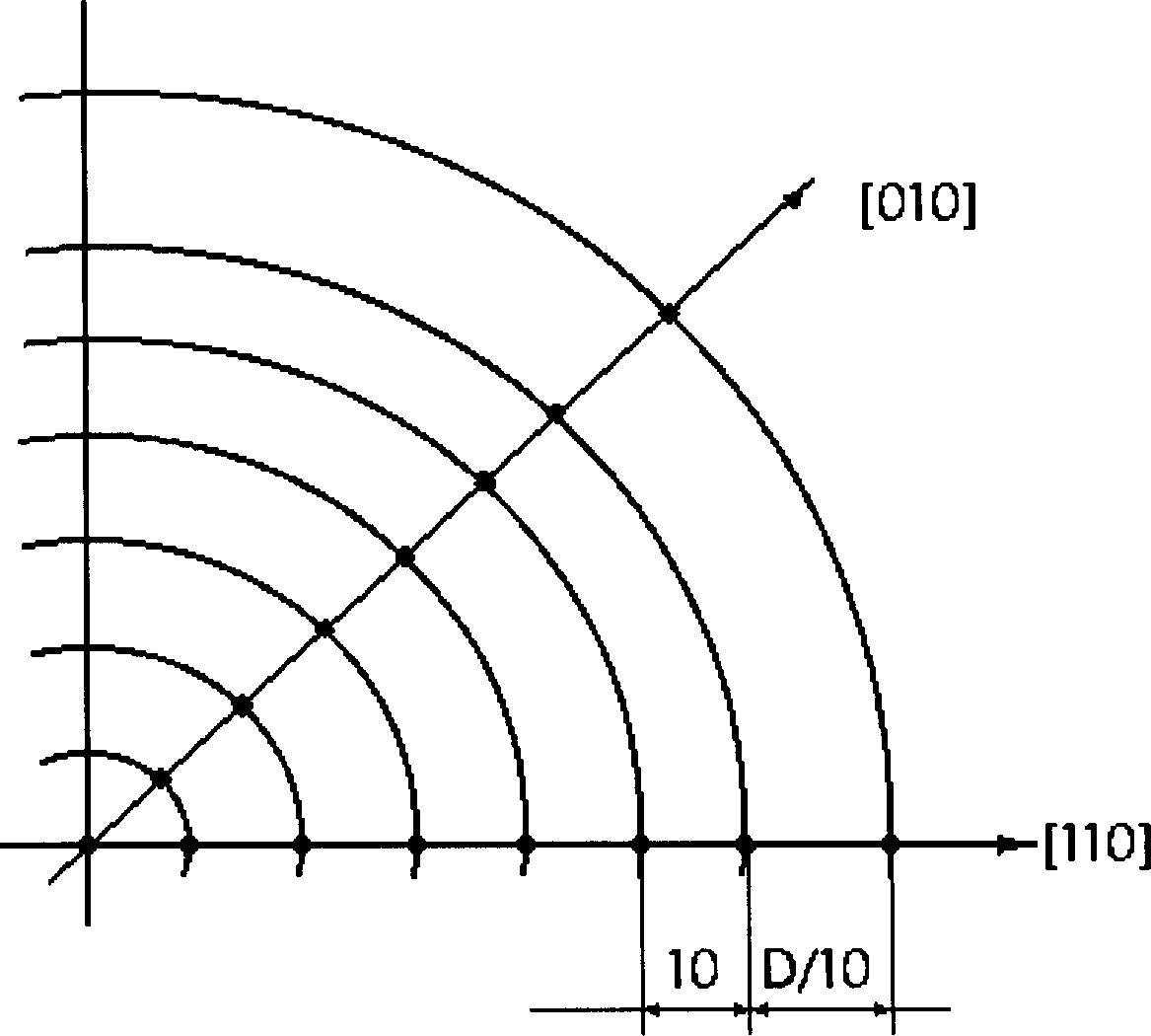

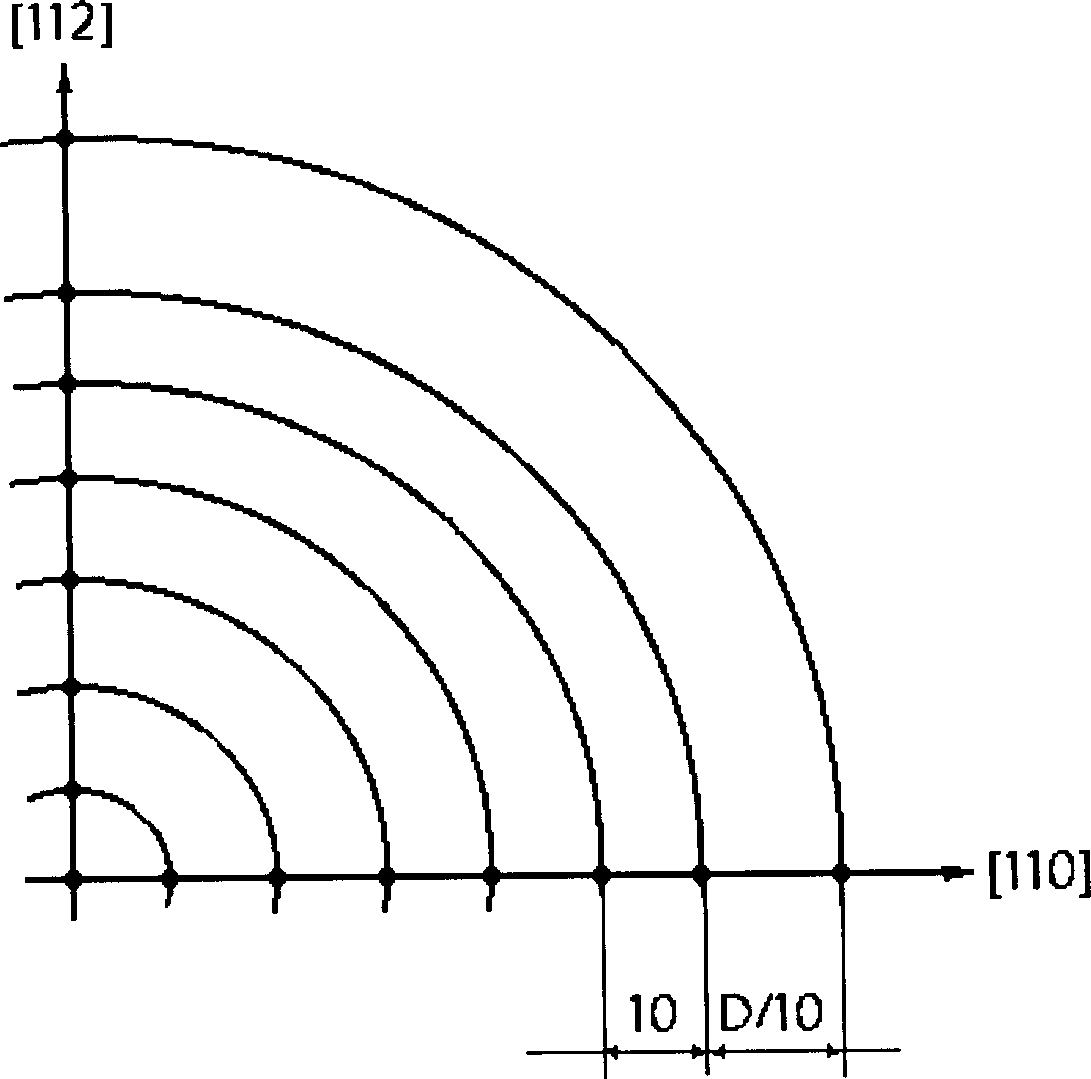

Method for detecting defect of single crystal structure of gallium arsenide in large size

InactiveCN1796968AAccurate detectionThe detection method is simplePreparing sample for investigationOptically investigating flaws/contaminationVisual field lossGallium arsenate

The invention is a defect detecting method for a large-size GaAs monocrystalline structure, comprising: grinding and polishing, i.e. mechanically or chemically polishing, where the formula of the adopted polishing solution is that the ratio of sulphuric acid to oxydol to water is 3 : 1 : 1; dislocation corroding, i.e. placing potassium hydroxide in a silver pot and heating to melt potassium hydroxide into a clear state and immediately placing the clear-state potassium hydroxide in a wafer sample for corroding, then taking out the sample and cooling, and then washing with water and blow-dry; selecting measuring direction, measuring point position and number of measuring points, observing visual field area, where the first measuring point is D / 10mm apart from the wafer edge and the others are selected at 10 mm intervals, each of which is a measuring visual field; calculating for the selected measuring points. The invention enlarges the range of dislocation density detection, convenient and simple to operate and saving time.

Owner:CHINA ELECTRONICS TECH GRP NO 46 RES INST

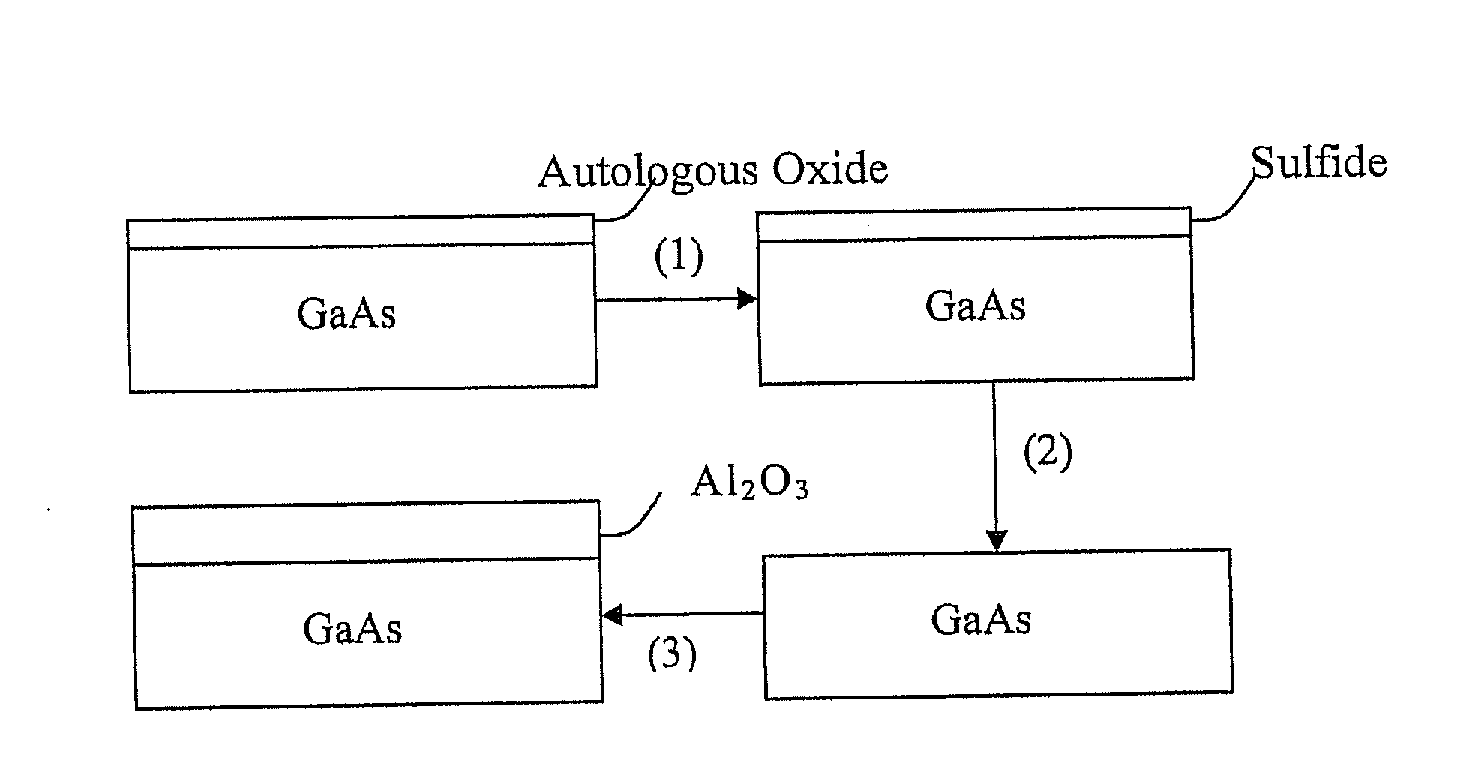

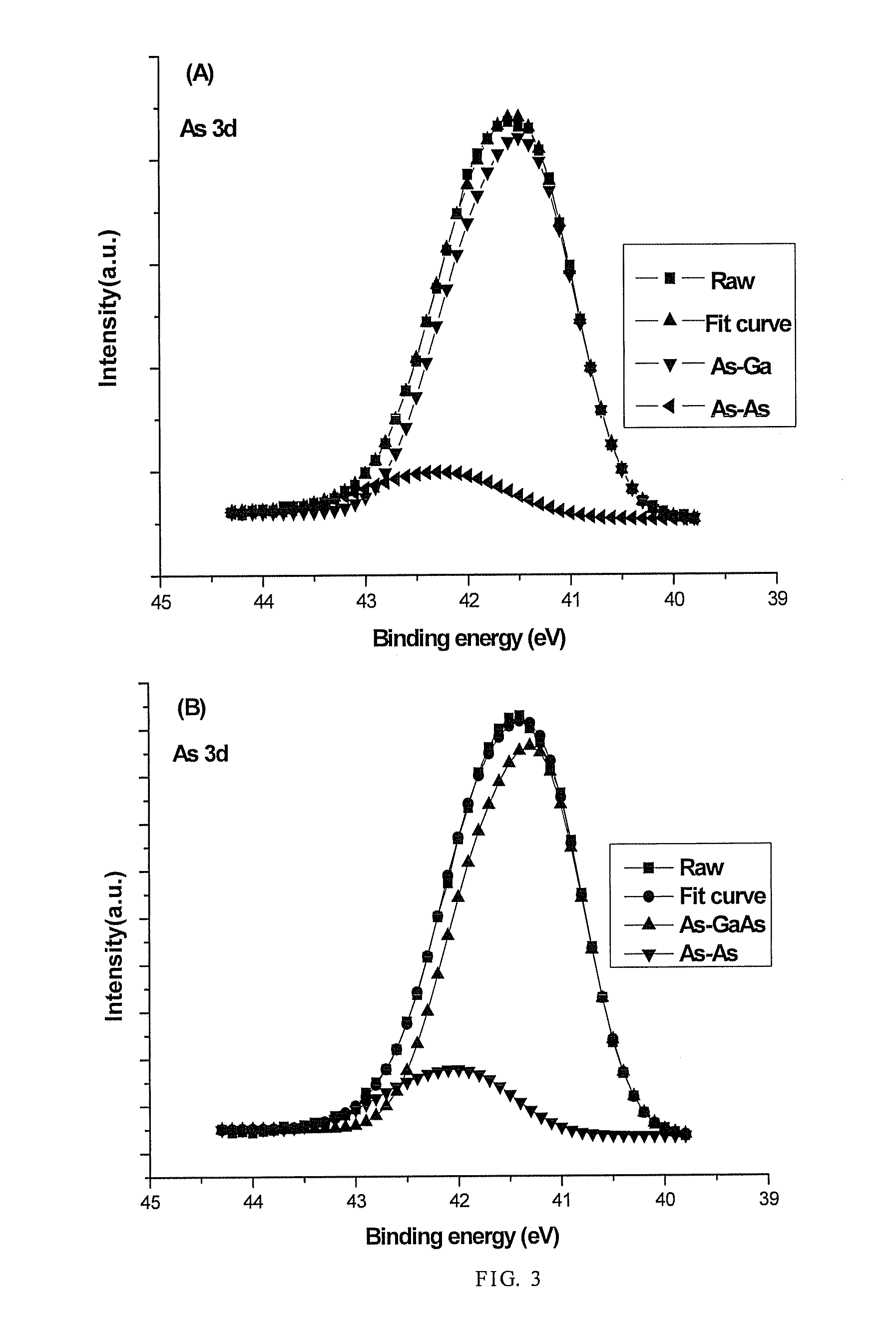

Method for cleaning & passivating gallium arsenide surface autologous oxide and depositing al2o3 dielectric

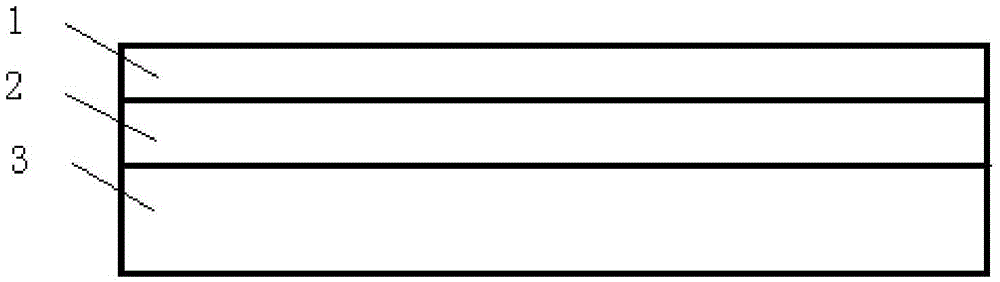

InactiveUS20130078819A1Quality improvementPreventing the GaAs from oxidatingPolycrystalline material growthPretreated surfacesDielectricGate dielectric

The present invention belongs to the technical field of semiconductor materials and specifically relates to a method for cleaning & passivizing gallium arsenide (GaAs) surface autologous oxide and depositing an Al2O3 dielectric. This method includes: use a new-type of sulfur passivant to react with the autologous oxide on the GaAs surface to clean it and generate a passive sulfide film to separate the GaAs from the outside environment, thus preventing the GaAs from oxidizing again; further cleaning the residuals such as autologous oxides and sulfides on the GaAs surface through the pretreatment reaction of the reaction source trimethyl aluminum (TMA) of the Al2O3 ALD with the GaAs surface, and then deposit high-quality Al2O3 dielectric through ALD as the gate dielectric which fully separates the GaAs from the outside environment. The present invention features a simple process and good effects, and can provide preconditions for manufacturing the GaAs devices.

Owner:FUDAN UNIV

Method for preparing Nano cerium oxdie, and application in chemical mechanical polishing chip of gallium arsenide

InactiveCN1760132ASmall granularityEvenly distributedAqueous dispersionsRare earth metal compoundsCerium nitrateWafering

A process for preparing cerium oxide nanoparticles includes such steps as proportionally dissolving cerium nitrate and hexamethylenetetraamine (HMT) respectively in alcohol and distilled water, mixing, stirring, sealing, heating at 70-90 deg.C for 1-2 hr, cooling, ageing for 1-2 hr, filter, washing deposit, and drying at 60-80 deg.C for 6-10 hr. The obtained CeO2 nanoparticles can be used to prepare the polishing liquid for polishing the semiconductor wafer of gallium arsenide.

Owner:JIANGSU POLYTECHNIC UNIVERSITY

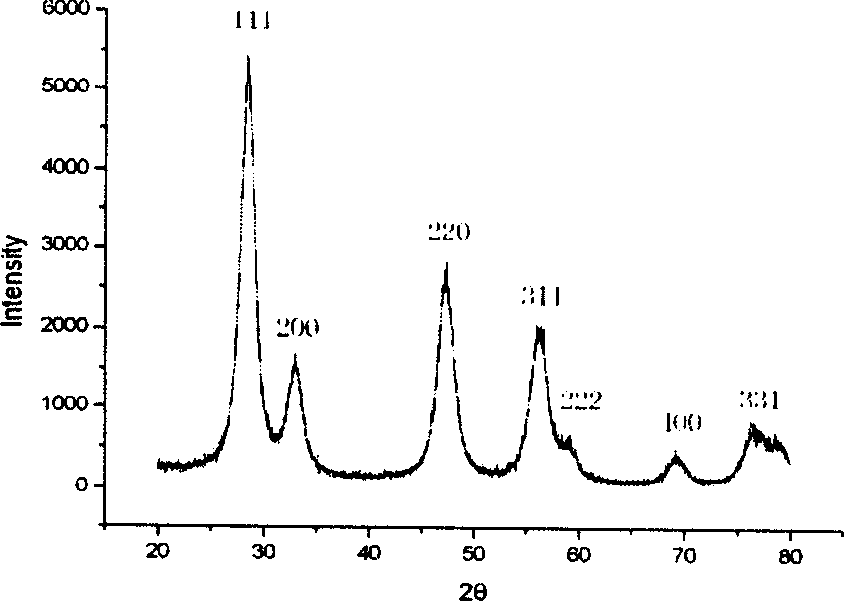

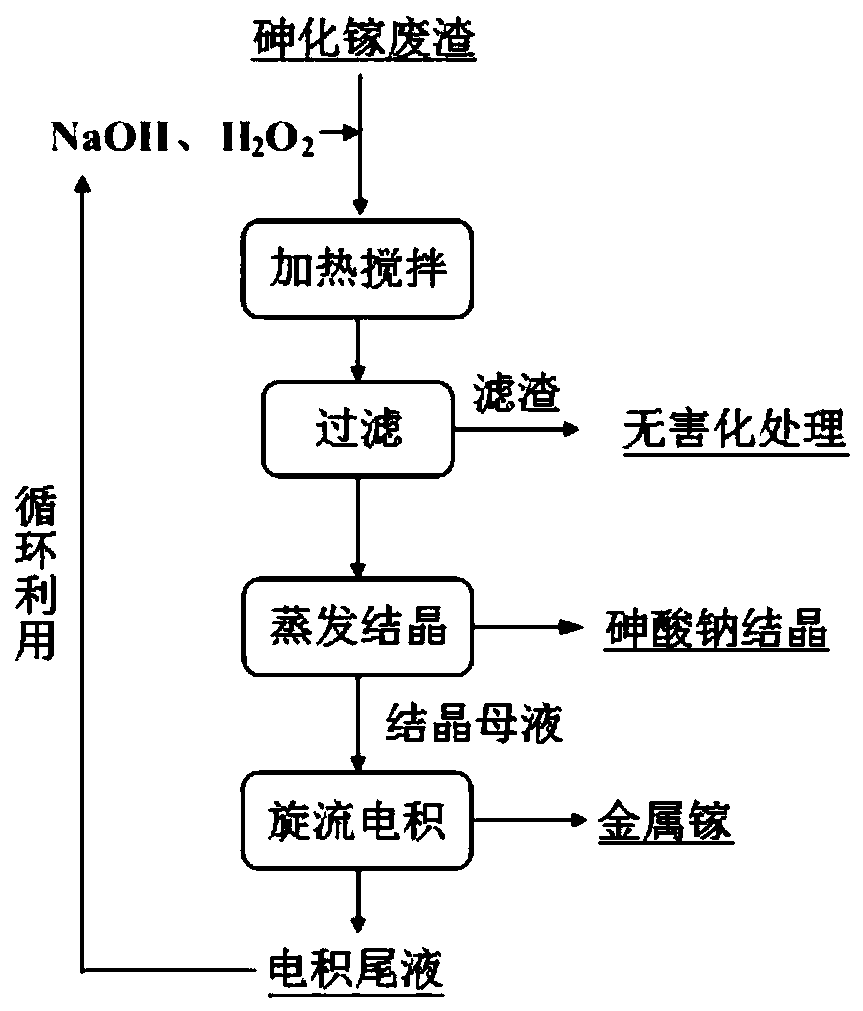

Method for recycling and preparing sodium arsenate and gallium metal from gallium arsenide waste residue

ActiveCN110938742AEasy to separateHigh purityPhotography auxillary processesArsenites/arsenatesGallium arsenateGallium

The invention relates to a method for recycling and preparing sodium arsenate and gallium metal from gallium arsenide waste residue. The method comprises the following steps of leaching the gallium arsenide waste residue in an alkaline-oxidized solution system after the gallium arsenide waste residue is dried, crushed and screened, wherein the conditions of the NaOH concentration, the oxidant concentration, the time, the temperature and the like during leaching are controlled so that arsenic and gallium are simultaneously quickly dissolved in a leaching solution to the great extent; performingevaporative crystallization to make the sodium arsenate crystallize preferentially to realize quick effective separation of the arsenic and the gallium; performing recrystallization to improve the purity of the sodium arsenate; and performing cyclone electrowinning to obtain high-purity gallium metal. The raw material gallium arsenide waste residue is from solid waste landfill and is sampled without cost; according to the method provided by the invention, the sodium arsenate and gallium metal are recycled and prepared from the waste residue; the purity of the prepared sodium arsenate is at least 95 percent; the purity of the prepared gallium metal is at least 3N; the prepared sodium arsenate and gallium metal have great utilization value; the recycled and purified sodium arsenate can serve as a chemical raw material; and the method disclosed by the invention effectively solves the problems of environment pollution and resource waste and meets the requirements of sustainable development society.

Owner:YANGZHOU NINGDA NOBLE METAL CO LTD

Growing method of gallium arsenide monocrystalline

ActiveCN106319630ASolving the problem of not wetting with quartz cruciblesSolve the problem of low crystal growth ratePolycrystalline material growthFrom frozen solutionsGallium arsenateSeed crystal

The invention provides a growing method of gallium arsenide monocrystalline. The method comprises the following components: (1) a quartz crucible is cleaned; (2) the quartz crucible is placed in a quartz tube which contains gallium of high purity, vacuum-pumping and inflation operation are repeatedly carried out for the quartz tube, and finally inert gas or nitrogen is filled; (3) the quartz tube is heated till the temperature in the quartz tube reaches to 1240 DEG C or above and insulation is carried out, and the quartz tube is cooled to room temperature; (4) the quartz crucible is taken out from the quartz tube and is immersed in acid, deionized water is used for washing, absolute ethyl alcohol is used for carrying out dehydration treatment, and the quartz crucible is placed in a drying box for standby; (5) seed crystal, polycrystalline materials, and the balance being arsenic are placed in the quartz crucible in order according to charging requirements, the quartz crucible is placed in a quartz ampoule, and vacuum-pumping, baking and soldering and sealing treatment are carried out; (6) a traditional VGF method is used for accomplishing the growth of gallium arsenide monocrystalline. PBN crucibles are not used, a liquid sealing agent B2O3 is not used, and GaAs monocrystalline is not polluted by extra introduction of B element from the source.

Owner:广东先导微电子科技有限公司

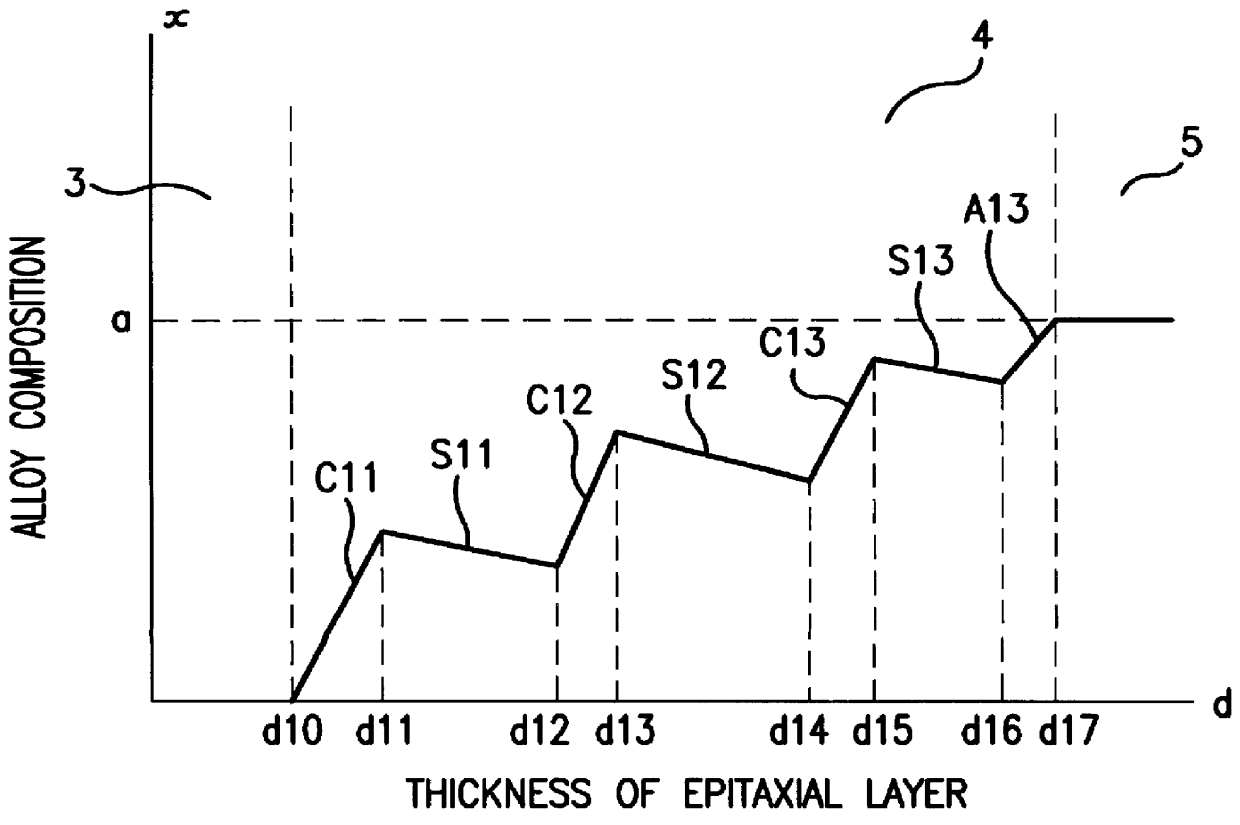

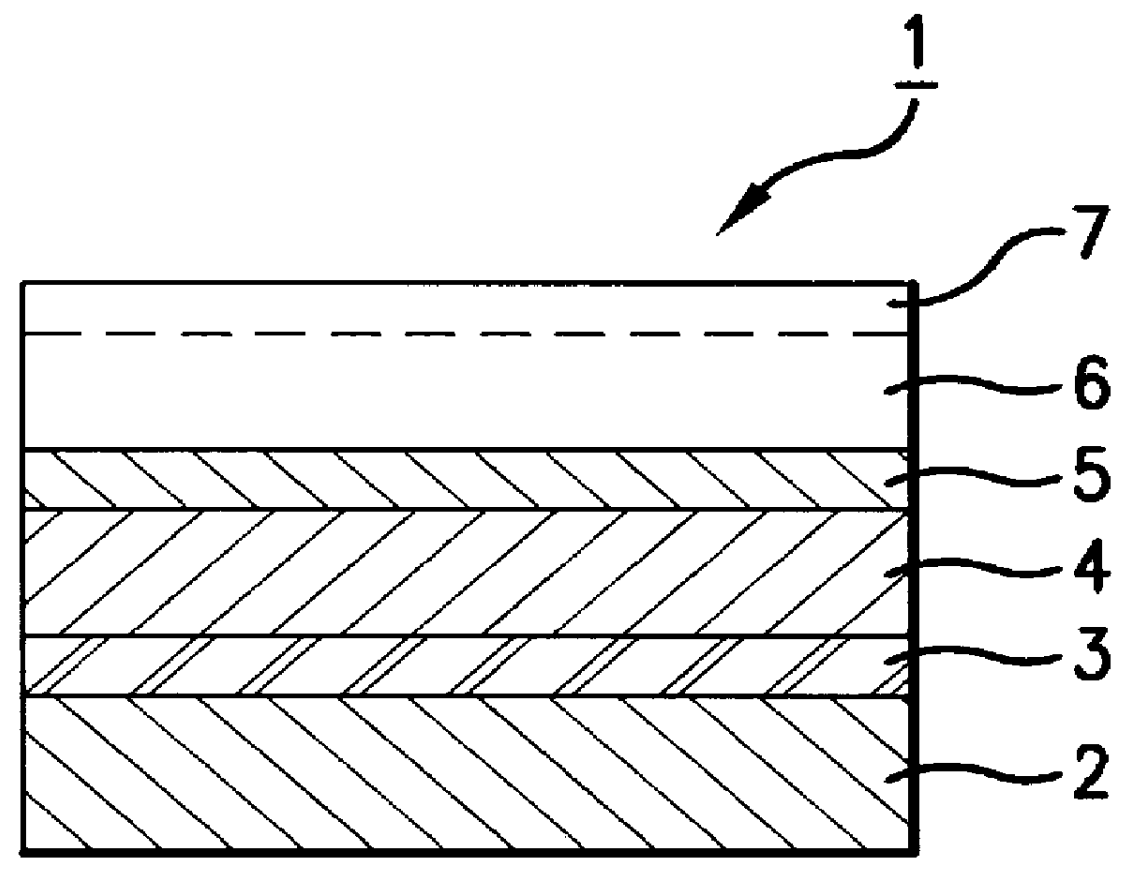

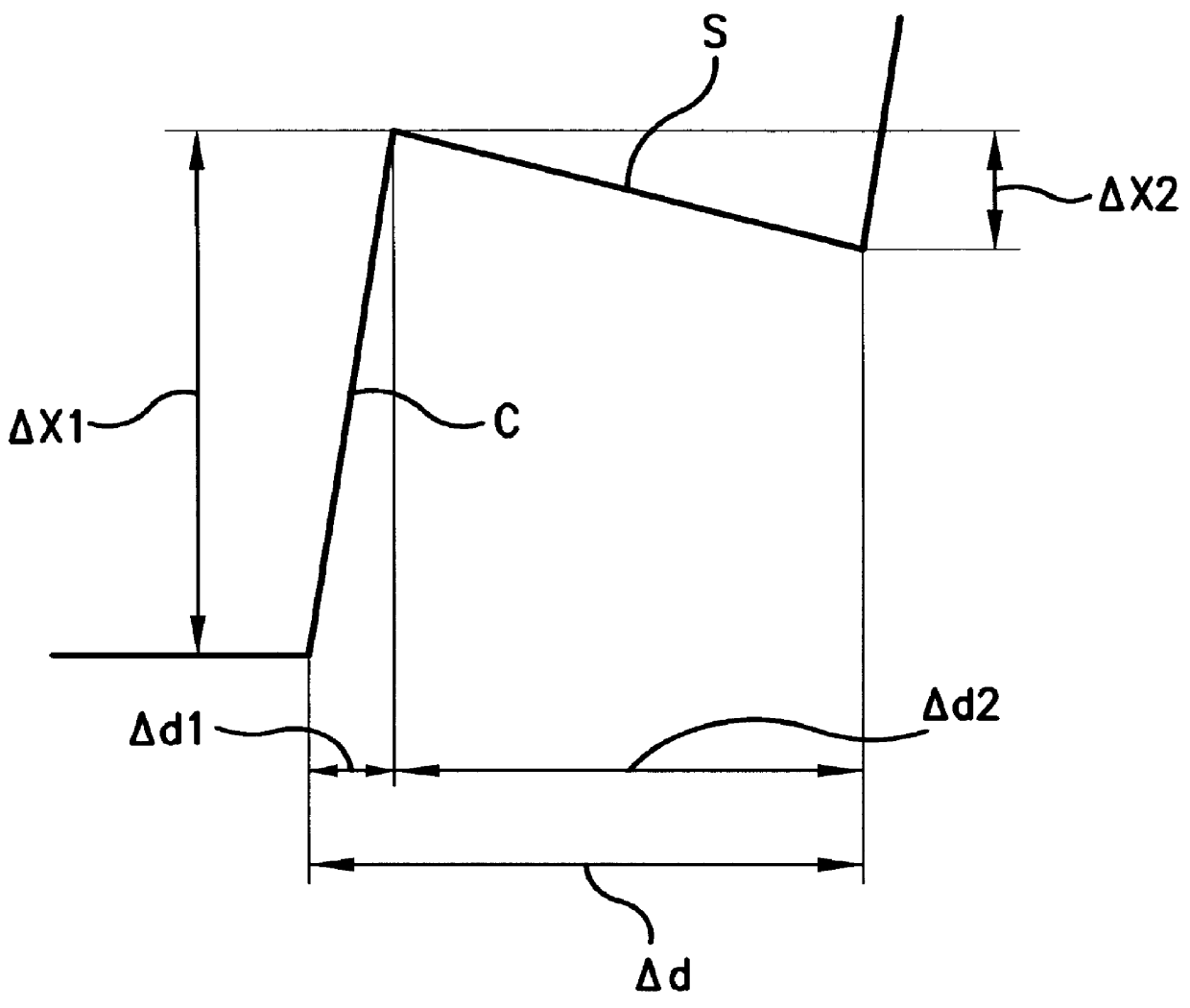

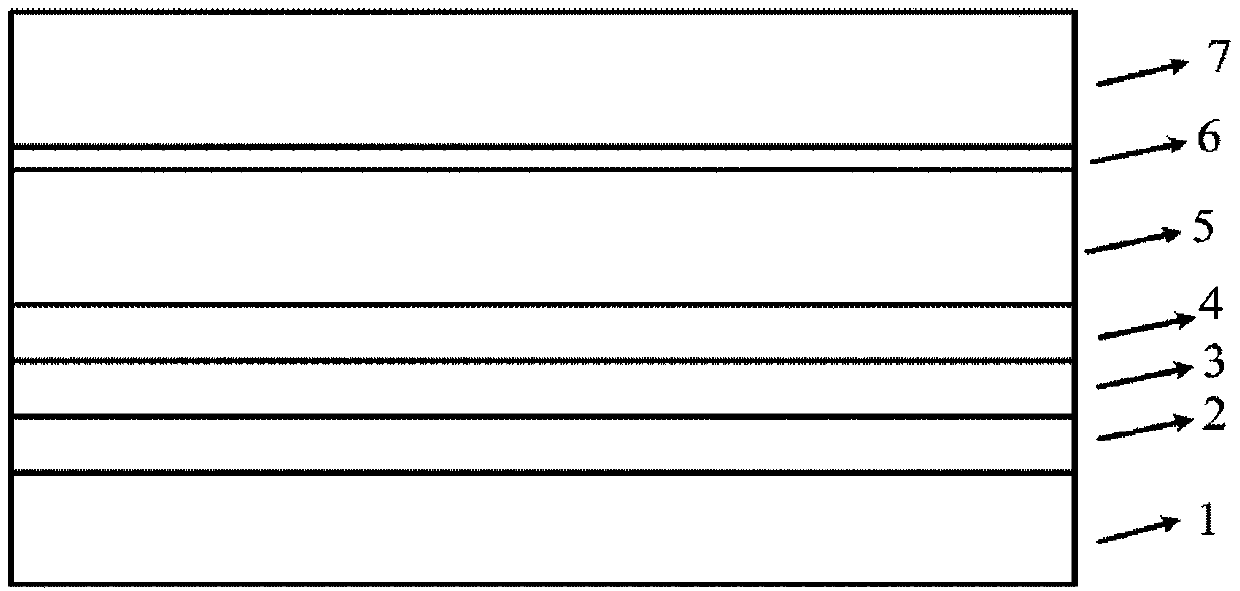

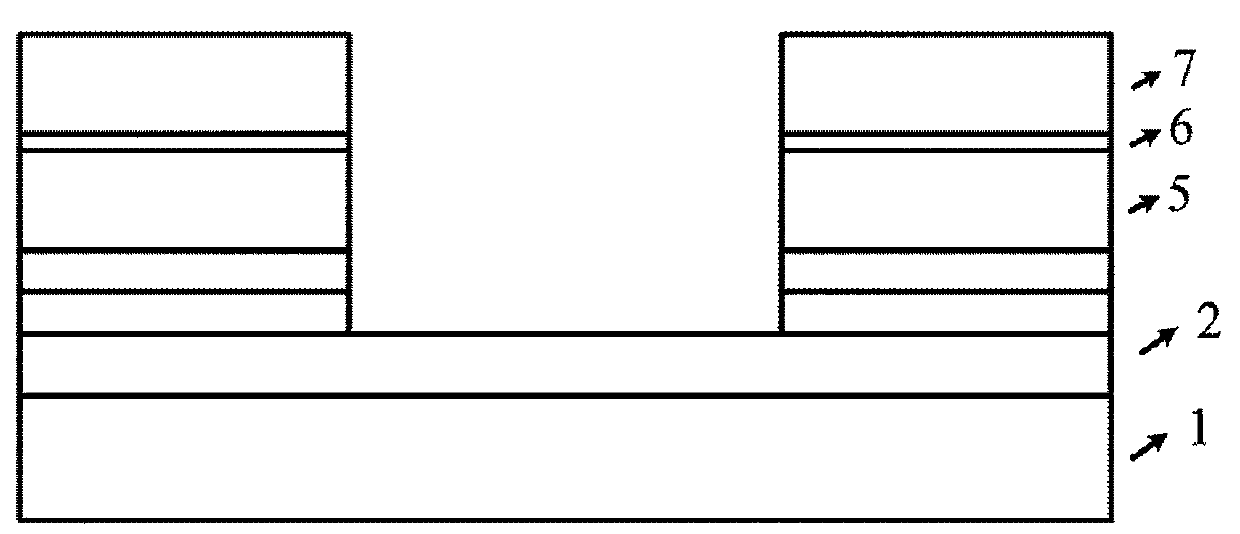

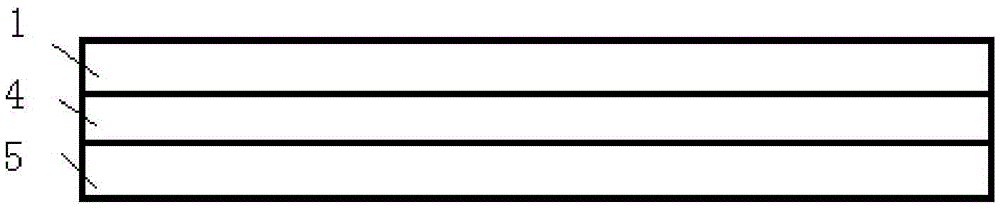

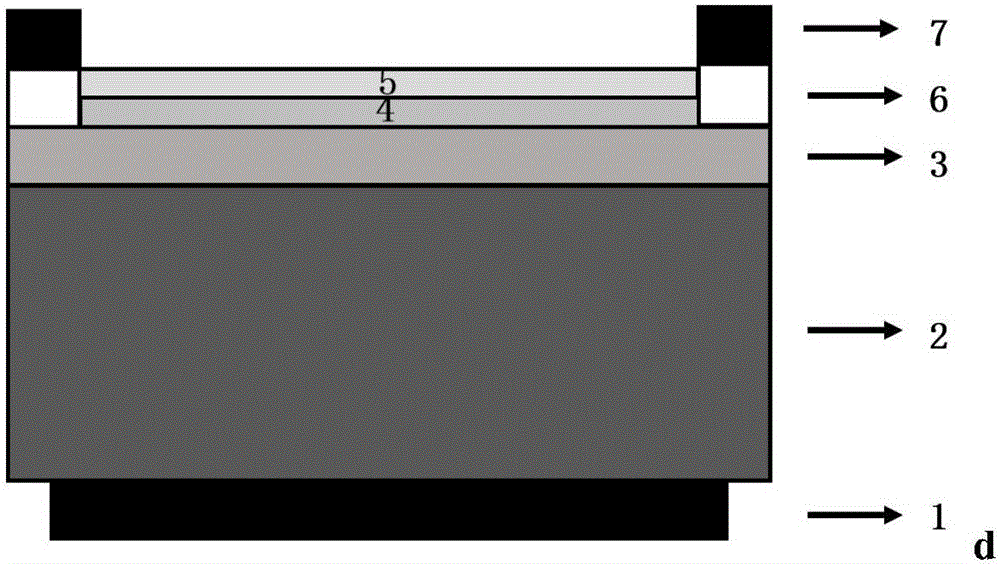

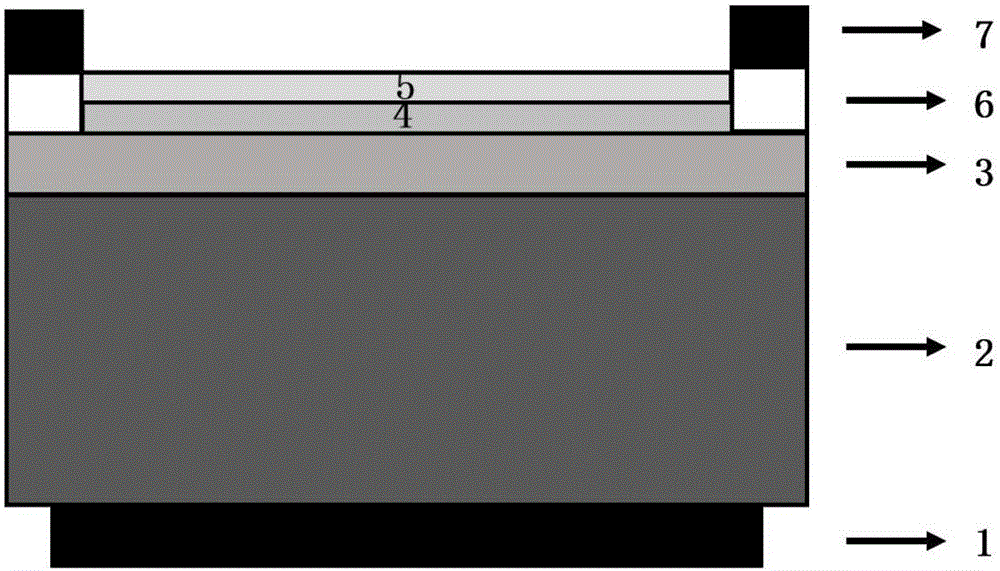

Compound semiconductor epitaxial wafer

InactiveUS6057592AHigh ratePrevent dislocationSemiconductor/solid-state device manufacturingSemiconductor devicesCrystallographyWafering

PCT No. PCT / JP97 / 00050 Sec. 371 Date Oct. 21, 1998 Sec. 102(e) Date Oct. 21, 1998 PCT Filed Jan. 13, 1997 PCT Pub. No. WO97 / 25747 PCT Pub. Date Jul. 17, 1997At the time of forming an alloy composition gradient layer 4 of gallium arsenide phosphide GaAsxP1-x having an arsenic alloy composition x changed in such a range as not to exceed a predetermined alloy composition a with an increase of a layer thickness d between a GaP layer 3 and a composition constant layer 5 of gallium arsenide phosphide GaAsaP1-a having the predetermined alloy composition a to be grown above the GaP layer; the alloy composition x is abruptly ascended as in composition ascending zones C11 to C13 with the ascended thickness d of an epitaxial layer and then descended as in crystal stabilizing zones S11 to S13 in such a range as not to cancel the previous ascent amount. One or more combinations of such ascent and descent in the alloy composition are repeated to form as distributed in the alloy composition gradient layer 4, and then the alloy composition x is ascended to the predetermined alloy composition a. Thereby there is obtained a compound semiconductor epitaxial wafer which can effectively eliminate stresses caused by lattice mismatching, can be made thinner with an excellent productivity, and can have a high luminance due to employment of a reflective layer.

Owner:SHIN-ETSU HANDOTAI CO LTD

Direct bonding method for indium phosphide and gallium arsenide materials

InactiveCN100356507CPositive effects are obviousDifferent corrosion recipesLaser detailsSemiconductor/solid-state device manufacturingAlcoholSurface cleaning

The invention relates to direct bonding method of InP and GaAs including thee technical processes of surface cleaning, laminating and high-temp annealing. The characteristic is that surface of InP and GaAs is processed two times by deoxidizing before bonding, then it is direct soaked in reducibility nitrogen solution without drying by high-purity nitrogen, after being soaked, it is direct put into anti-oxide alcohol solution. Laminate is processed in the alcohol solution, burnishing surface of InP is downward to be put on burnishing surface of GaAs straight, InP and GaAs are coincided together that side and side are aligned, bonding temp. is from 500 to 700 deg.C, annealed after being bonded, keeping time is from 30 to 40 minutes, both bonding and annealing are proceeded by nitrogen protection. Optical and electrical performance of whole material structure can not be reduced since the bonded IP and GaAs interface.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

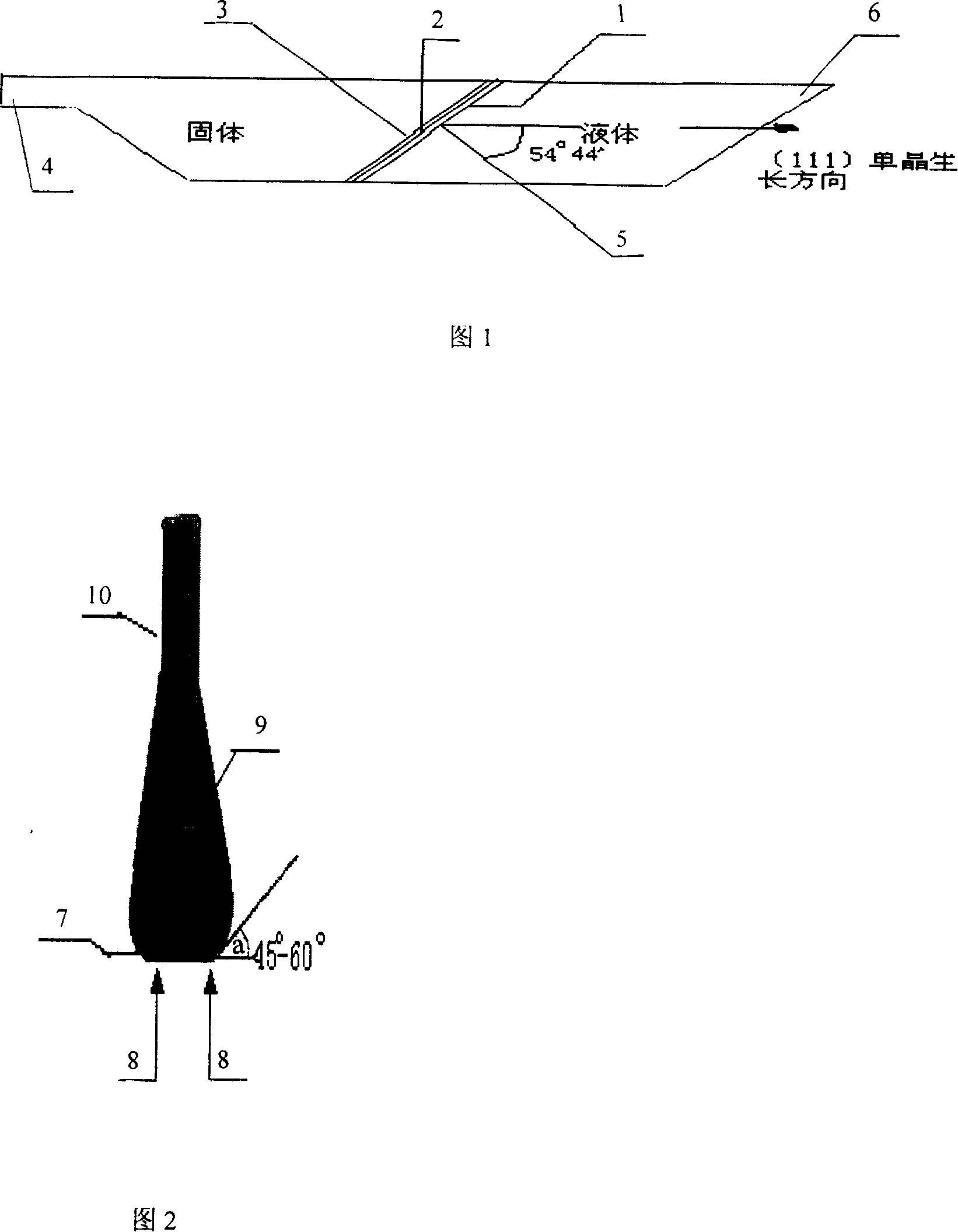

Technique for cutting horizontal gallium arsenide single-crystal wafer with inside diameter slicer

InactiveCN101130265ALess bendingControl deformationSemiconductor/solid-state device manufacturingStone-like material working toolsWaferingHigh volume manufacturing

The invention relates to a process that inside diameter slicing machine is used to cut level gallium arsenide single-crystal wafer, which comprises following procedures. (1) edge cutting treatment is carried out for level gallium arsenide single-crystal ingot with the length of 50-500mm. (2) the single-crystal ingot is bonded with the surface of graphite strip and the surface of graphite support. (3) bonded single-crystal ingot is fixed on the ingot-pushing device of inside diameter slicing machine. (4) cutting blade is installed; switch is on and the machine runs. (5) working table is lift and a piece of wafer is cut to confirm crystal orientation; after confirmation calibrating thickness of single-wafer cutting is set; said cutting orientations are parts of (100) to the nearest [100] and [011]; the angle between the crystal orientation and the growth orientation of gallium arsenide single crystal is 54degree 44'. (6) cutting speed is set to cut wafers in multiple piece automatically and continuously. (7) after the whole single-crystal ingot is cut cutting blade is washed and machine is off. Level gallium arsenide single-crystal wafer with the diameter of Phi50. 8mm-Phi76mm and the thickness of 280um-470um can be cut in the process and average production yield can be more than 95%. Production stability and repeatability are good and mass production can be realized.

Owner:GENERAL RESEARCH INSTITUTE FOR NONFERROUS METALS BEIJNG +1

Gallium arsenide monocrystal growing method

InactiveCN102677175AEvenly heatedReduce thermal stressPolycrystalline material growthFrom frozen solutionsGallium arsenateCrucible

The invention discloses a gallium arsenide monocrystal growing method. The gallium arsenide monocrystal growing method comprises the following steps: putting a gallium arsenide polycrystal raw material into PNB (phosphorus nitrogen boron) crucibles in which seed crystals are put in advance; putting the PNB crucibles on a descending table in a growing furnace, wherein 1-5 PNB crucibles are put on the descending table; adjusting the furnace temperature of the growing furnace to 1200-1300 DEG C so as to rotate the descending table while descending the descending table after the tops of the seed crystals are melted; after crystal growing, moving the PNB crucibles to a constant-temperature area in the growing furnace to perform in-situ annealing on GaAs (gallium arsenide) crystals, wherein in the annealing process, the temperature in the growing furnace is controlled at 950-1100 DEG C, and the annealing time is 8-12 h; and cooling the GaAs crystals to room temperature at a speed rate of 20-70 DEG C per hour, thus obtaining GaAs monocrystals. By the gallium arsenide monocrystal growing method, the grown crystals are small in thermal stress, good in uniformity and relatively low in dislocation density.

Owner:SHANGHAI INST OF TECH

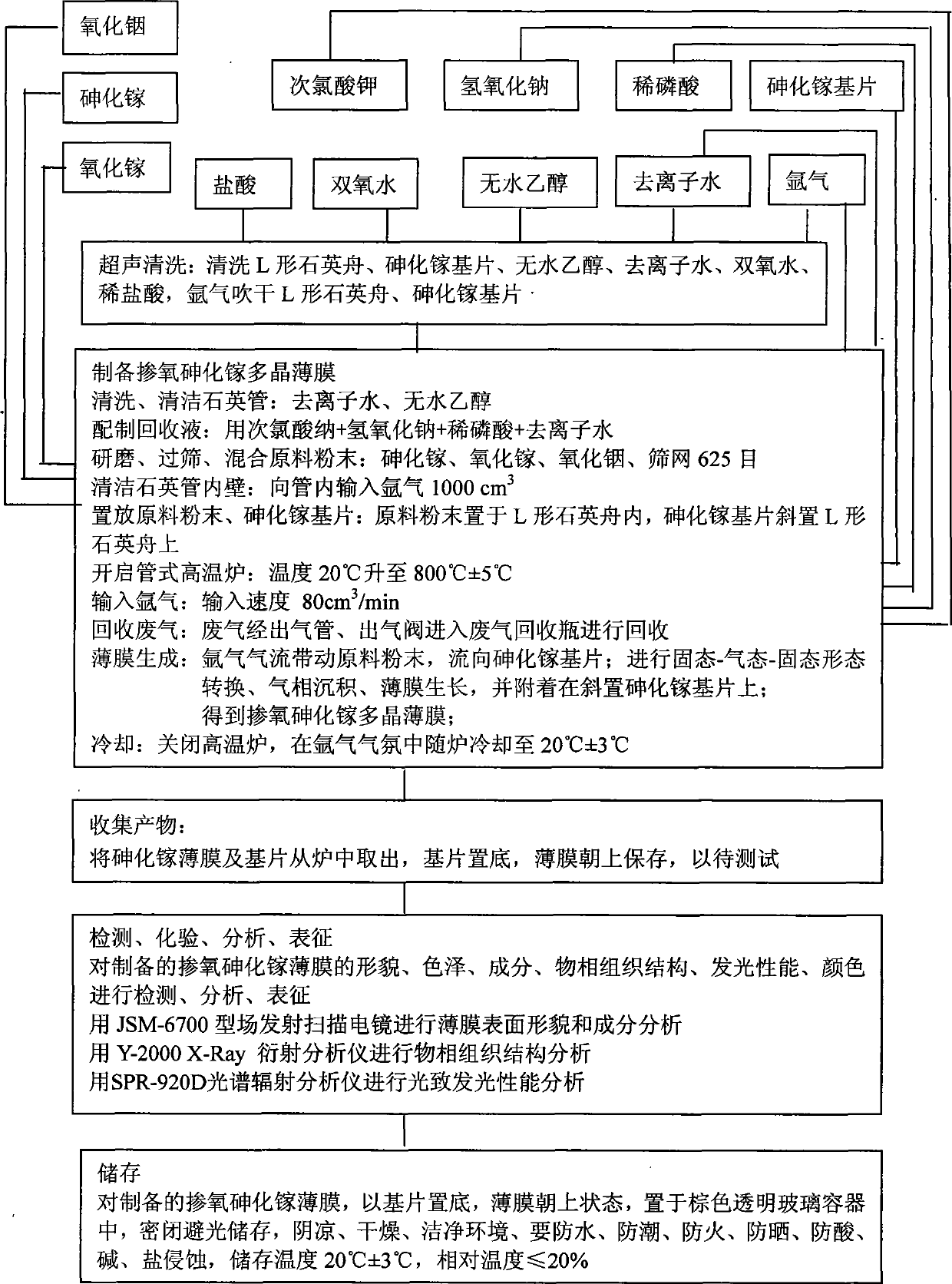

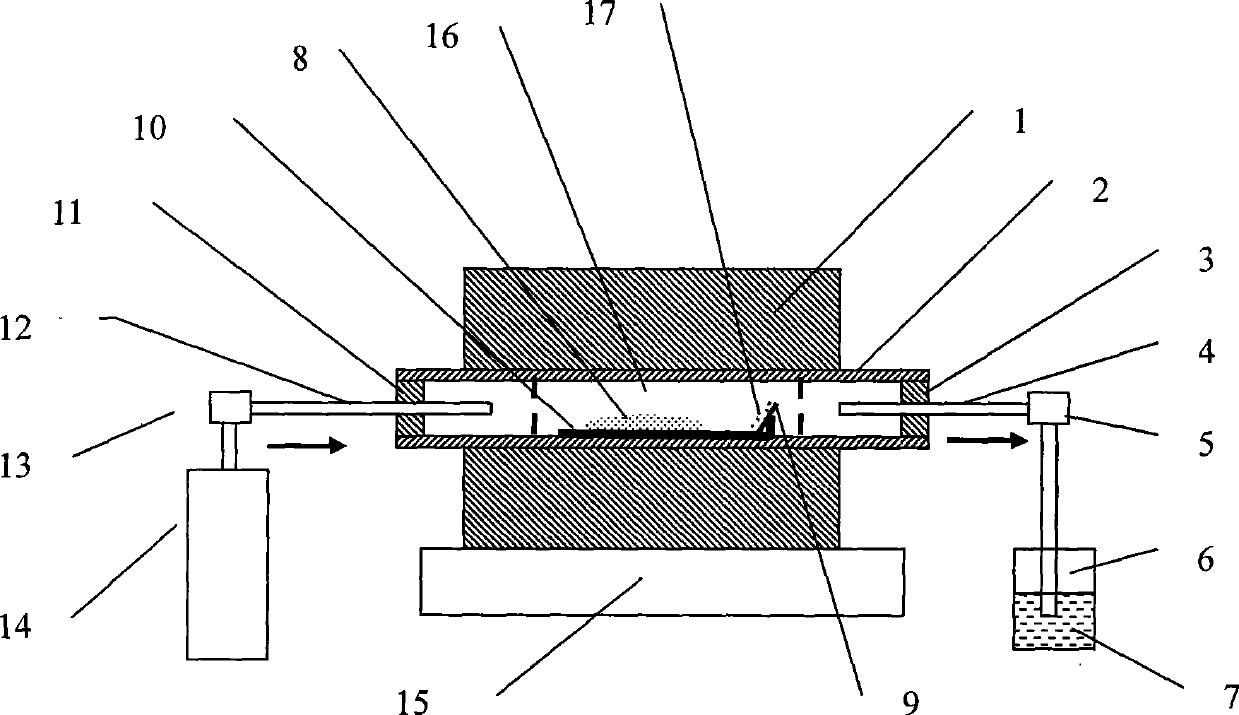

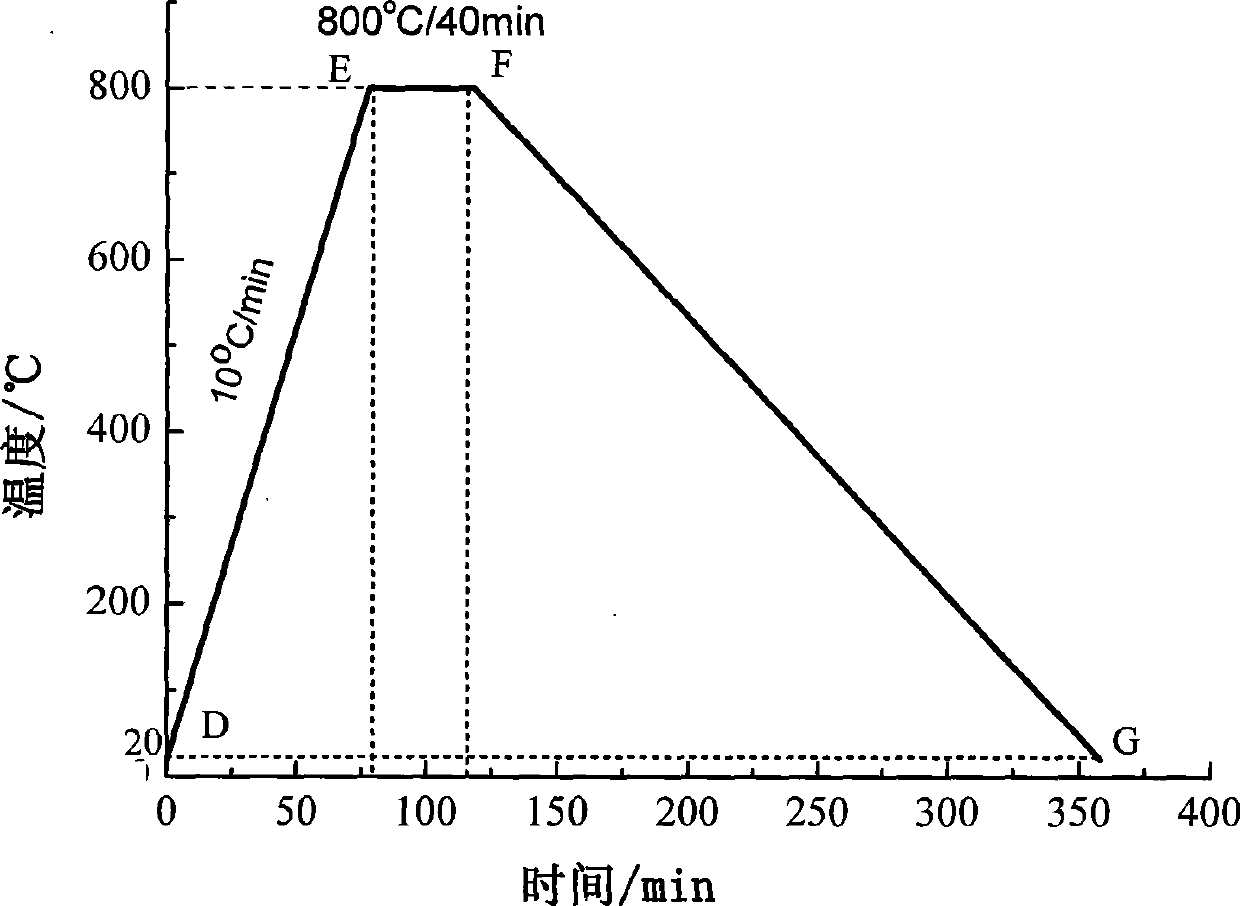

Preparation of glowing oxygen doped gallium arsenide polycrystalline film

ActiveCN101372760AFast formingHigh purityPolycrystalline material growthSemiconductor/solid-state device manufacturingIndiumGallium arsenate

The invention relates to a preparation method for an oxygen doped gallium arsenide polycrystal film which can give out red lights. In the method, gallium arsenide, gallium oxide and indium oxide are used as materials; a gallium arsenide substrate is used as the growing carrier of the film; hydrochloric acid, absolute ethyl alcohol, oxyful and de-ionized water are used as the washing agents; argon is used as a supporting gas and a protective gas; sodium hypochlorite, sodium hydroxide, phosphoric acid and de-ionized water are used as waste gas recycling agents; the preparation is carried out in a tubular high temperature furnace; an L-shaped quartz boat is arranged in a high temperature section in a quartz tube; the powder of the materials is arranged at the left part of the L-shaped quartz boat; the gallium arsenide substrate is obliquely arranged at the right part; under the temperature of 800 minus or plus 5 DEG C and the atmosphere of argon, state conversion, vapor deposition and film growing are carried out on the powder of the materials to grow into the black oxygen doped gallium arsenide polycrystal film which is in a wave shape formed by connecting gluing particles and gives out red lights; poisonous gases are recycled in the preparation, thus not polluting the environment; the preparation method has the advantages of short technique flow, fast film shaping and high product purity which can achieve 99 percent.

Owner:SHANXI FEIHONG MICRO NANO PHOTOELECTRONICS SCI & TECH

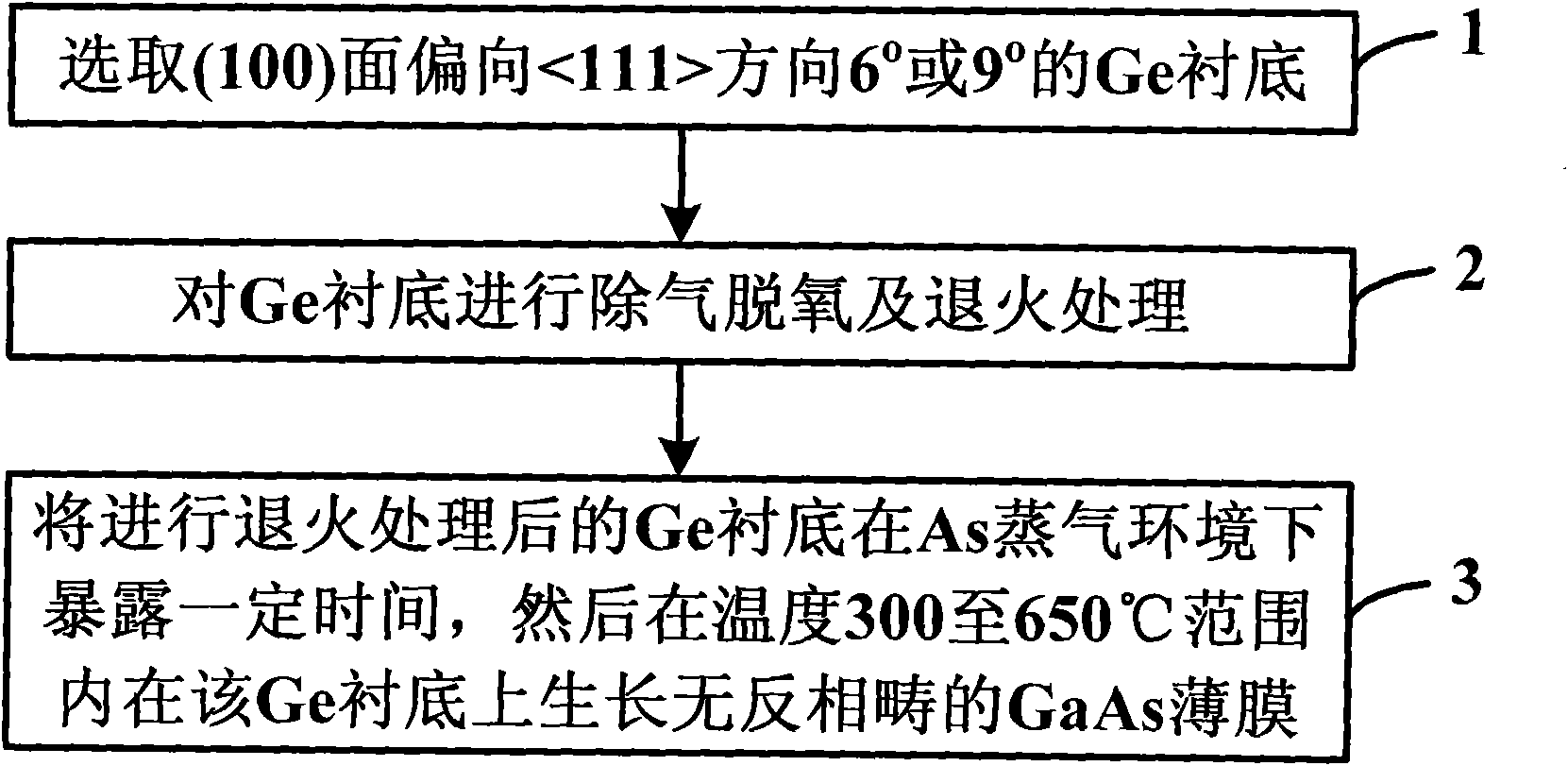

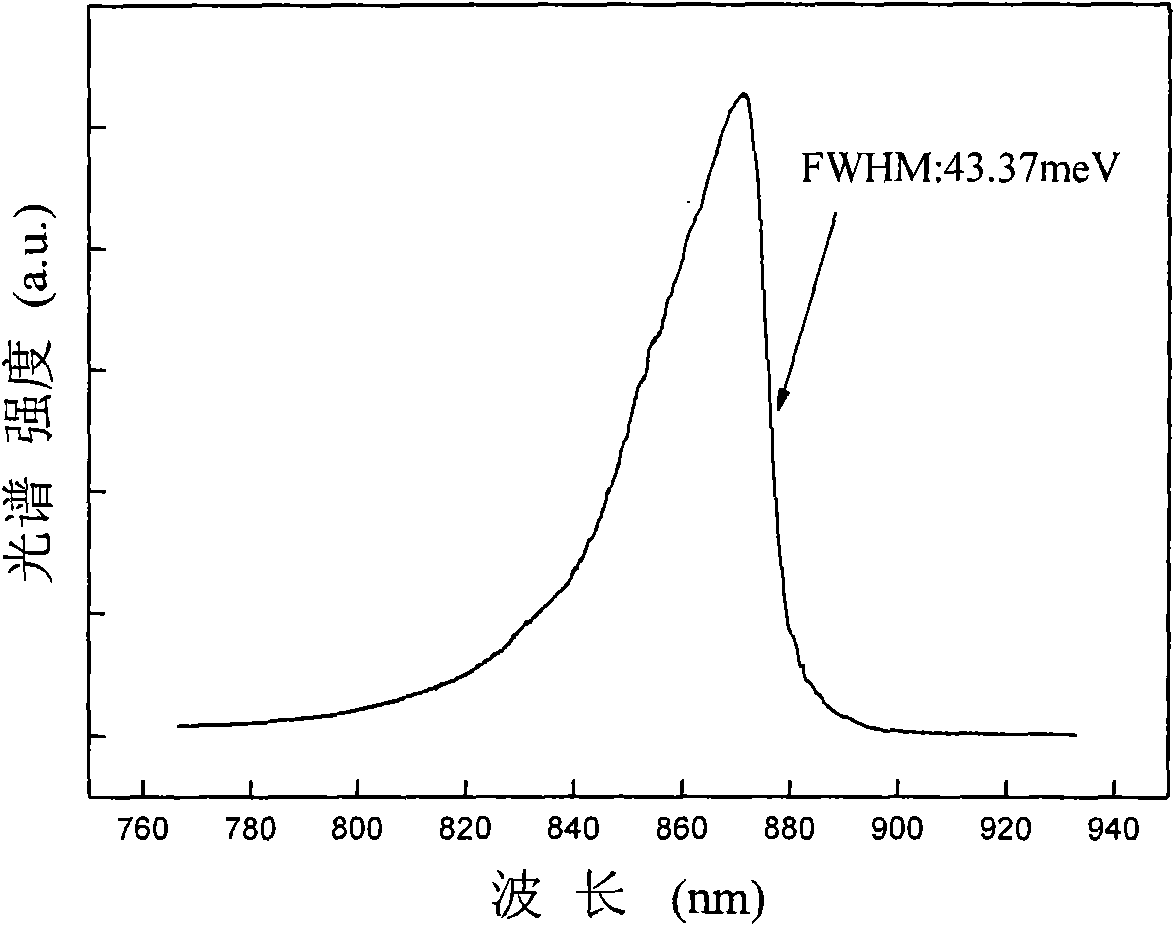

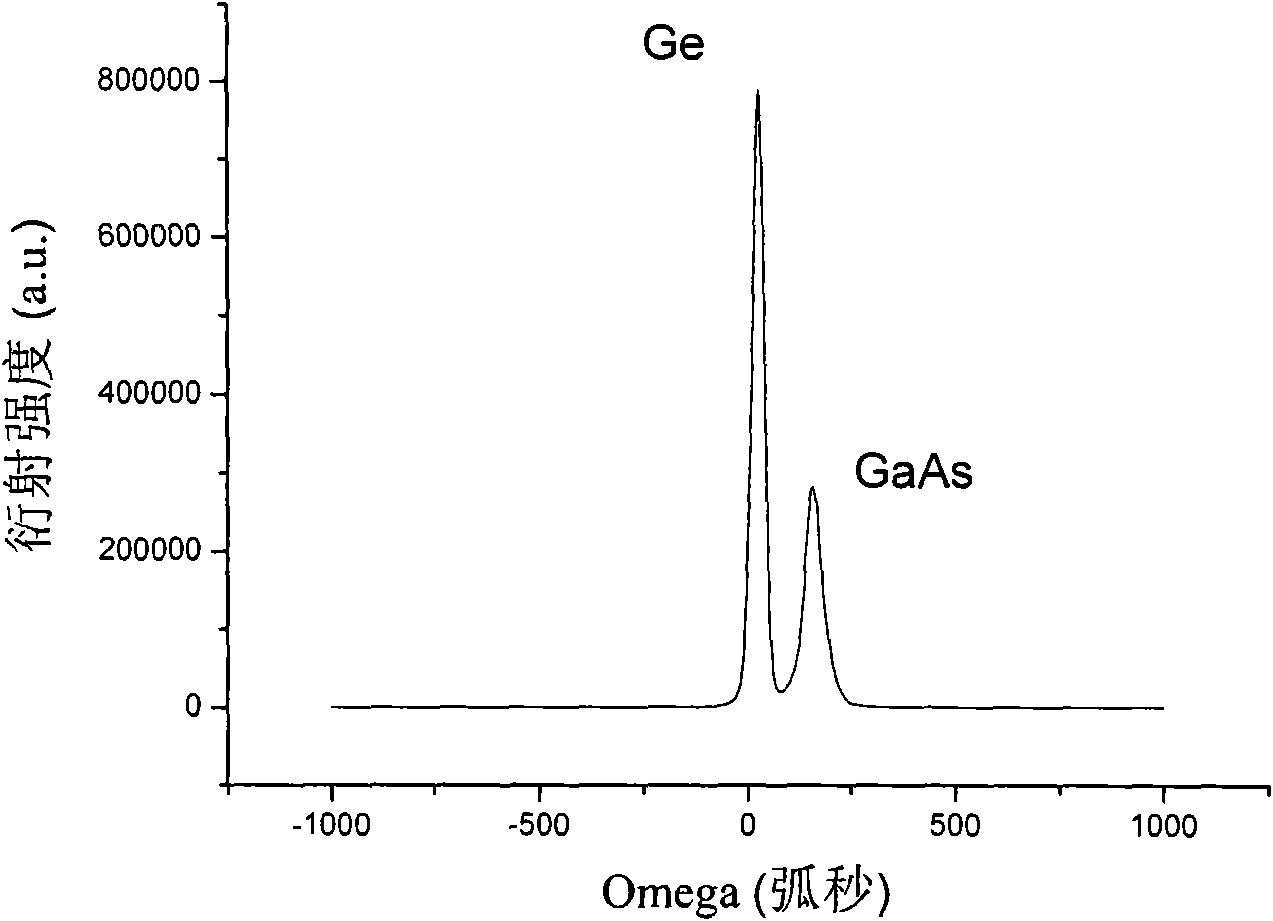

Molecular beam epitaxial method for growing non-antiphase domain gallium arsenide film on germanium substrate

InactiveCN101624725AImprove crystal qualityPolycrystalline material growthSemiconductor/solid-state device manufacturingGallium arsenateSurface roughness

The method discloses a molecular beam epitaxial method for growing a non-antiphase domain gallium arsenide film on a germanium substrate. The method comprises the followings steps of : step one, selecting the Ge substrate of which the (100) plane deviates 6 to 9 degrees from the <111> direction; step two, performing the degassing deoxidation and the annealing treatment of the Ge substrate; and step three, exposing the Ge substrate undergoing the annealing treatment under an environment of As vapor for a period of time, and growing the non-antiphase domain GaAs film on the Ge substrate at a temperature of between 300 and 650 DEG C. Tests show that the surface roughness of the GaAs film grown by the method is only 0.718nm, namely the generation of the antiphase domain is successfully inhibited, and the crystal mass of the film is better than the best result in the present world.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

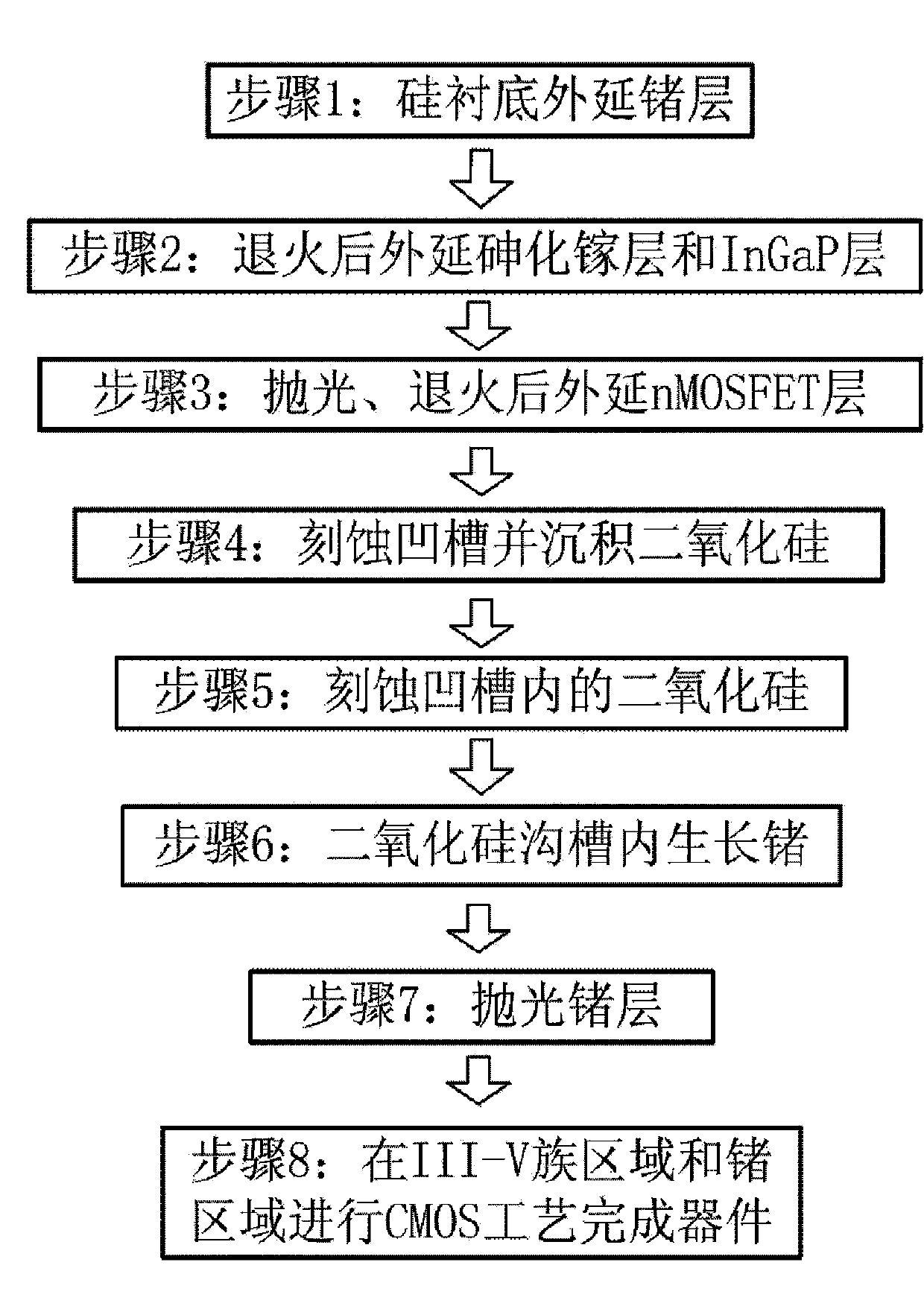

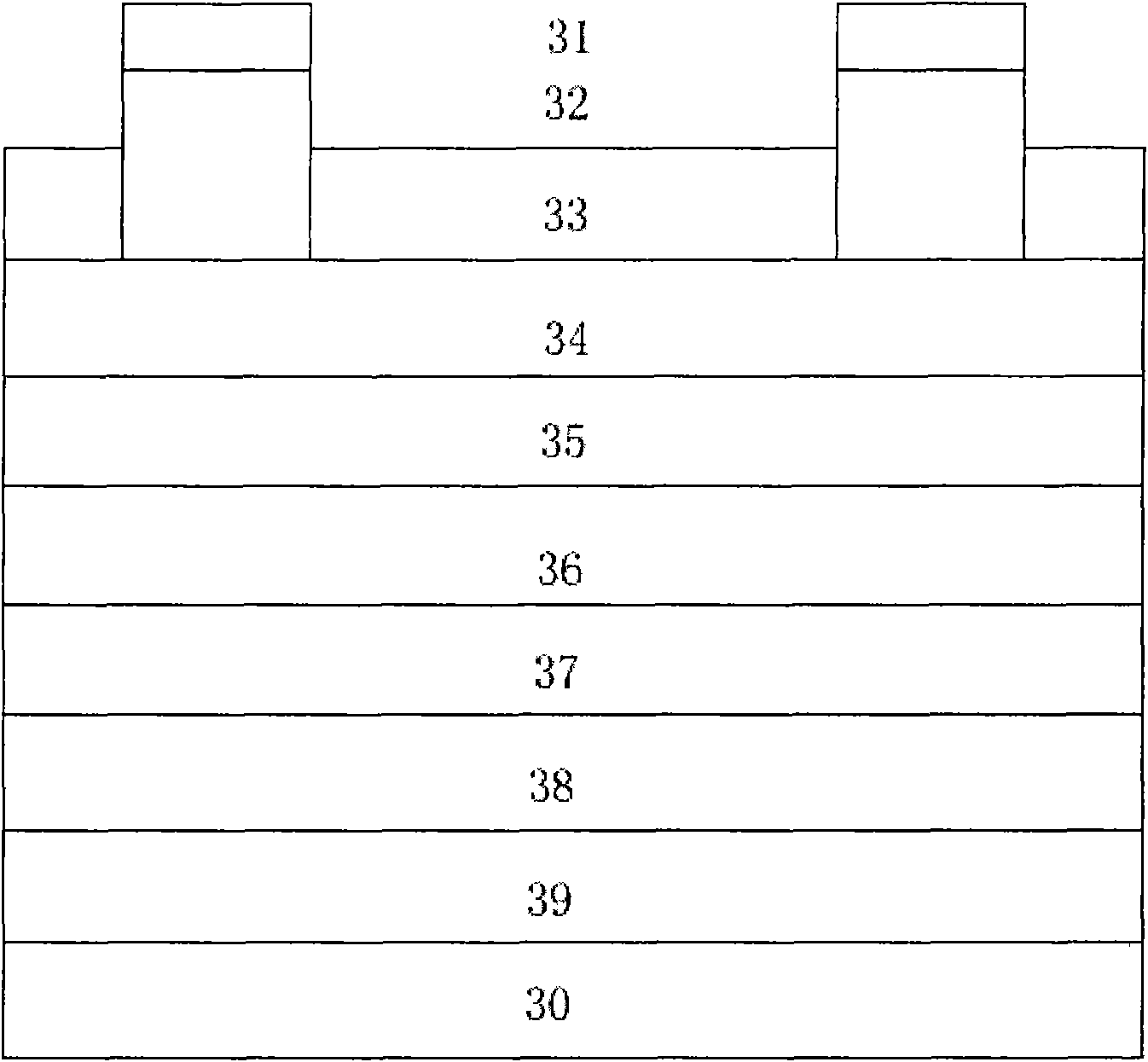

Method for preparing silicon-based high-mobility CMOS (complementary metal-oxide-semiconductor) provided with III-V/Ge channel

ActiveCN103390591AImprove lattice qualitySolid-state devicesSemiconductor/solid-state device manufacturingUltra-high vacuumGallium arsenate

The invention discloses a method for preparing a silicon-based high-mobility CMOS provided with an III-V / Ge channel. The method comprises steps as follows: a germanium layer is grown on a silicon substrate; a low-temperature nucleation gallium arsenide layer, a high-temperature gallium arsenide layer, an on-growth semi-insulating InGaP (gallium indium phosphide) layer and a gallium arsenide cover coating are sequentially grown on the germanium layer after the first annealing, so that a sample is formed; the gallium arsenide cover coating of the sample is subjected to a gallium arsenide polishing process, and a nMOSFET (metal oxide semiconductor field effect transistor) structure is grown after the sample is subjected to secondary annealing; an area is selected on the surface of the nMOSFET structure for ICP (inductively coupled plasma) etching, downward etching from the nMOSFET structure to the germanium layer is performed to form a groove, and silicon dioxide layers are grown in the groove and on the surface of the nMOSFET structure in a PECVD (plasma enhanced chemical vapor deposition) manner; the area selected for etching is subjected to ICP etching again from the silicon dioxide layers to the germanium layer, and a groove is formed; the sample is cleaned, and a germanium nucleating layer and a germanium top layer are grown in the groove with an ultra-high vacuum chemical vapor deposition method; the germanium top layer is polished, and a part of silicon dioxide layers on the nMOSFET structure are removed; and the CMOS process of source, drain and grid electrodes is performed on the nMOSFET structure and the germanium top layer, so that the preparation of the device is finished.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

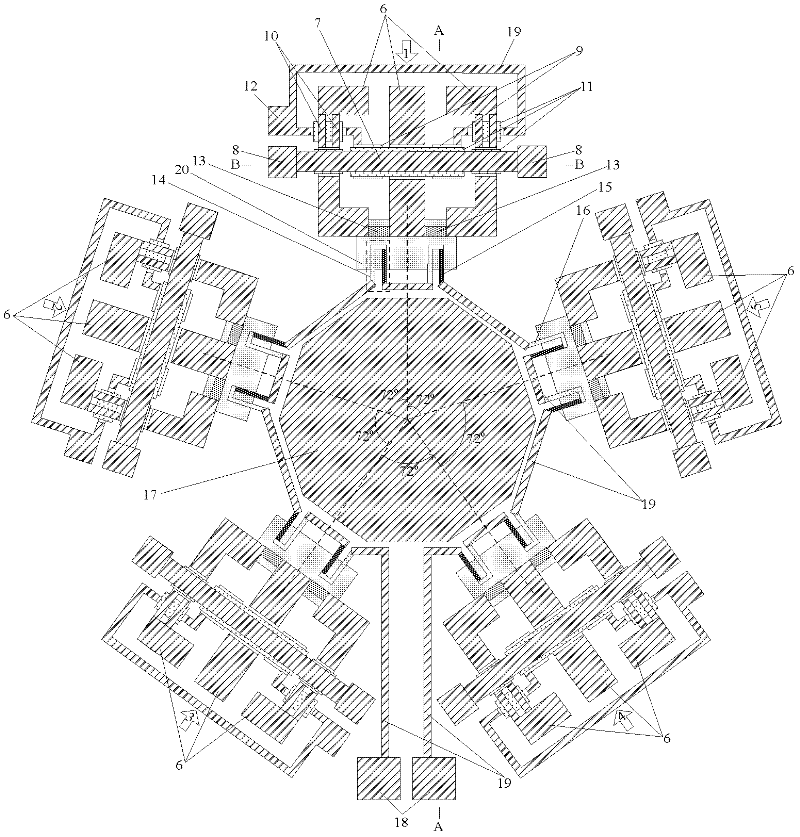

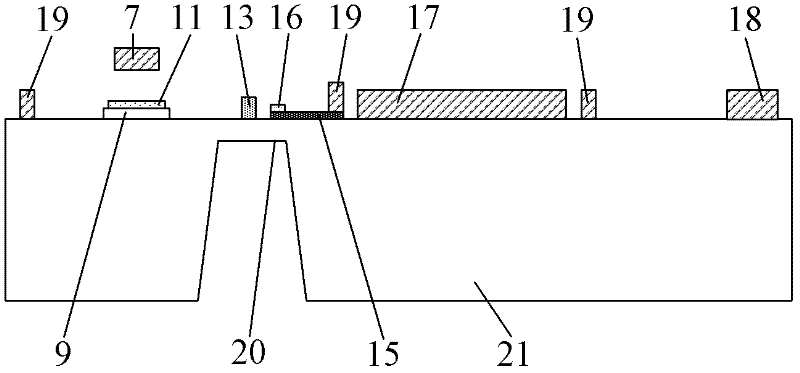

Five-port capacitance type microwave power sensor based on micro mechanical clamped beam

InactiveCN102411086AReduce lossHigh sensitivityDecorative surface effectsSolid-state devicesCapacitancePower sensor

The invention provides a five-port capacitance type microwave power sensor based on a micro mechanical clamped beam, which not only has the advantages of the traditional thermoelectric type power sensor of low loss, high sensitivity and good linearity, but also realizes the measurement of the microwave power of five ports. Meanwhile, some ports into which the microwave power is input can be detected and the proportion of a watt level of the microwave power can be detected; and the five-port capacitance type microwave power sensor has the advantages of high integrated level and compatibility with a gallium arsenide monolithic microwave integrated circuit. In the structure, five CPW (Coplanar Waveguide) input ends for transmitting microwave signals are arranged on a gallium arsenide substrate, the input ends are symmetrically placed and form a 72-degree angle between every two input ends; each CPW output end is connected with two terminal matched resistors and a thermoelectric couple isarranged near each terminal resistor; the five pairs of thermoelectric couples are symmetrically placed and are connected in series to form a thermoelectric pile and the angle between every two of the five pairs of thermoelectric couples is also 72 degrees; an MEMS (Micro Electro Mechanical System) clamped beam is stretched across each CPW and two anchor areas of the clamped beam are located outside a CPW earth wire; and a sensing electrode is placed between a CPW signal wire and the CPW earth wire.

Owner:SOUTHEAST UNIV

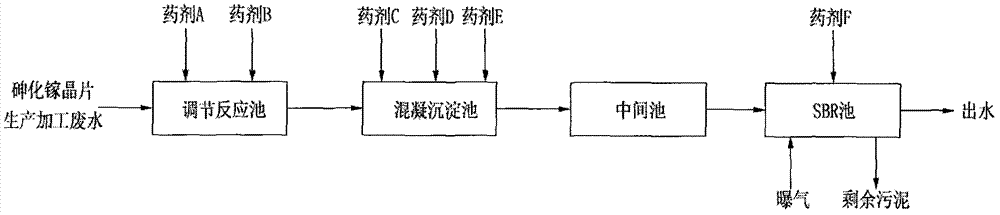

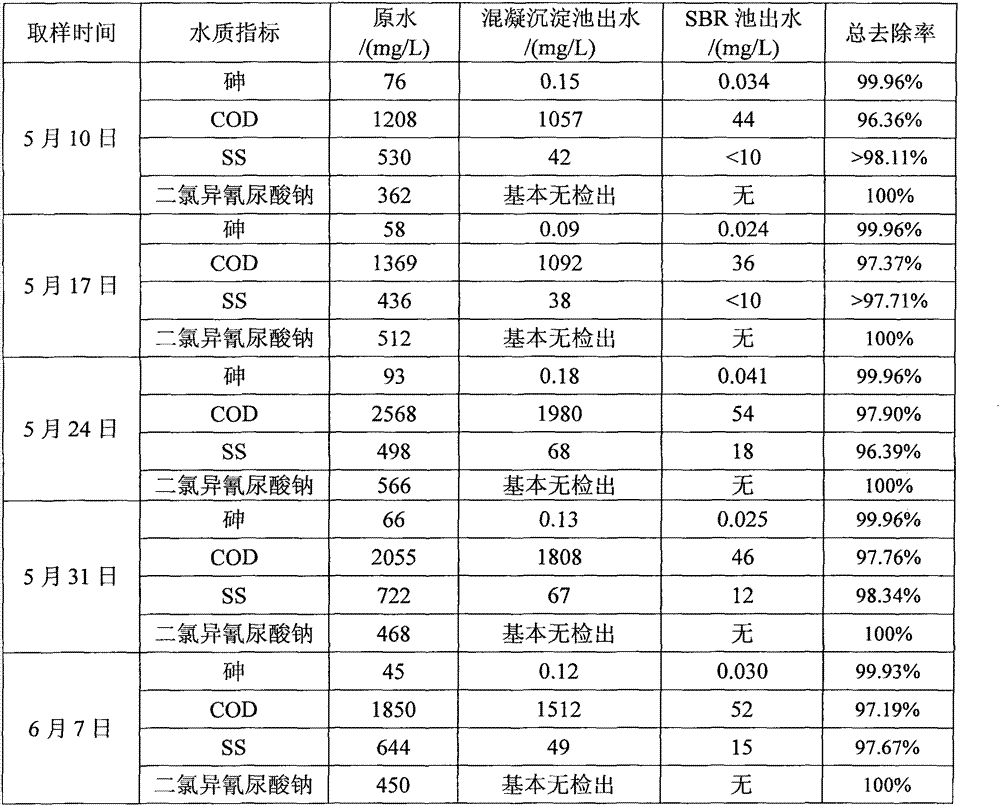

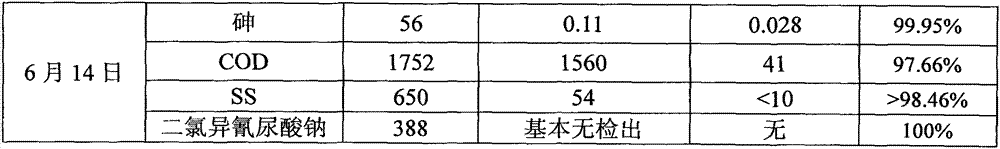

Treatment method for removing arsenic and COD in wastewater in gallium arsenide wafer production treatment simultaneously

InactiveCN102765859AImprove processing efficiencyImprove running stabilityMultistage water/sewage treatmentActivated sludgeChemical oxygen demand

Owner:BEIJING MUNICIPAL RES INST OF ENVIRONMENT PROTECTION

Germanium-silicon-based gallium arsenide material and preparation method thereof, and application of germanium-silicon-based gallium arsenide material

ActiveCN110364428AQuality improvementSuppression of antiphase domainsSemiconductor/solid-state device manufacturingLattice mismatchSingle crystal

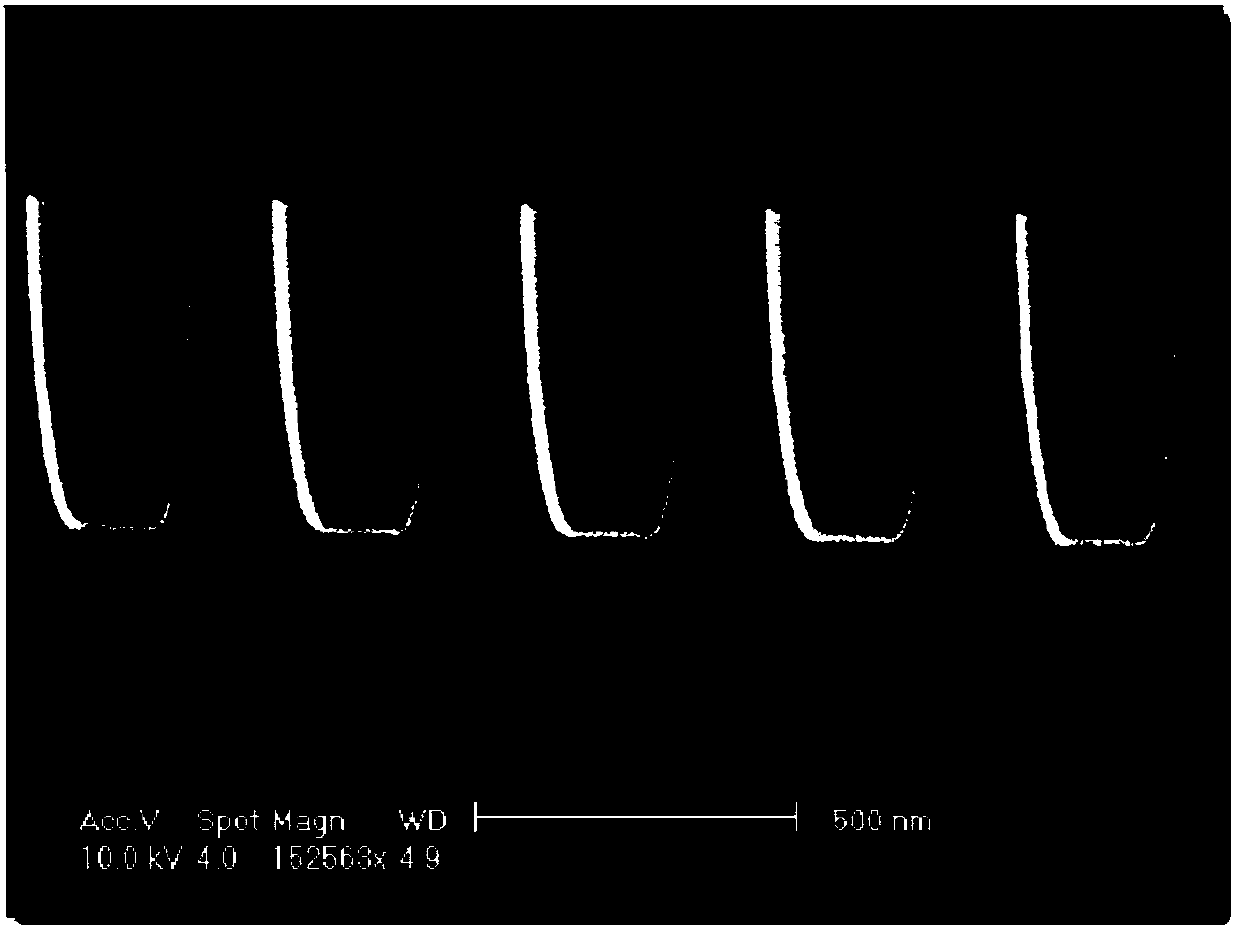

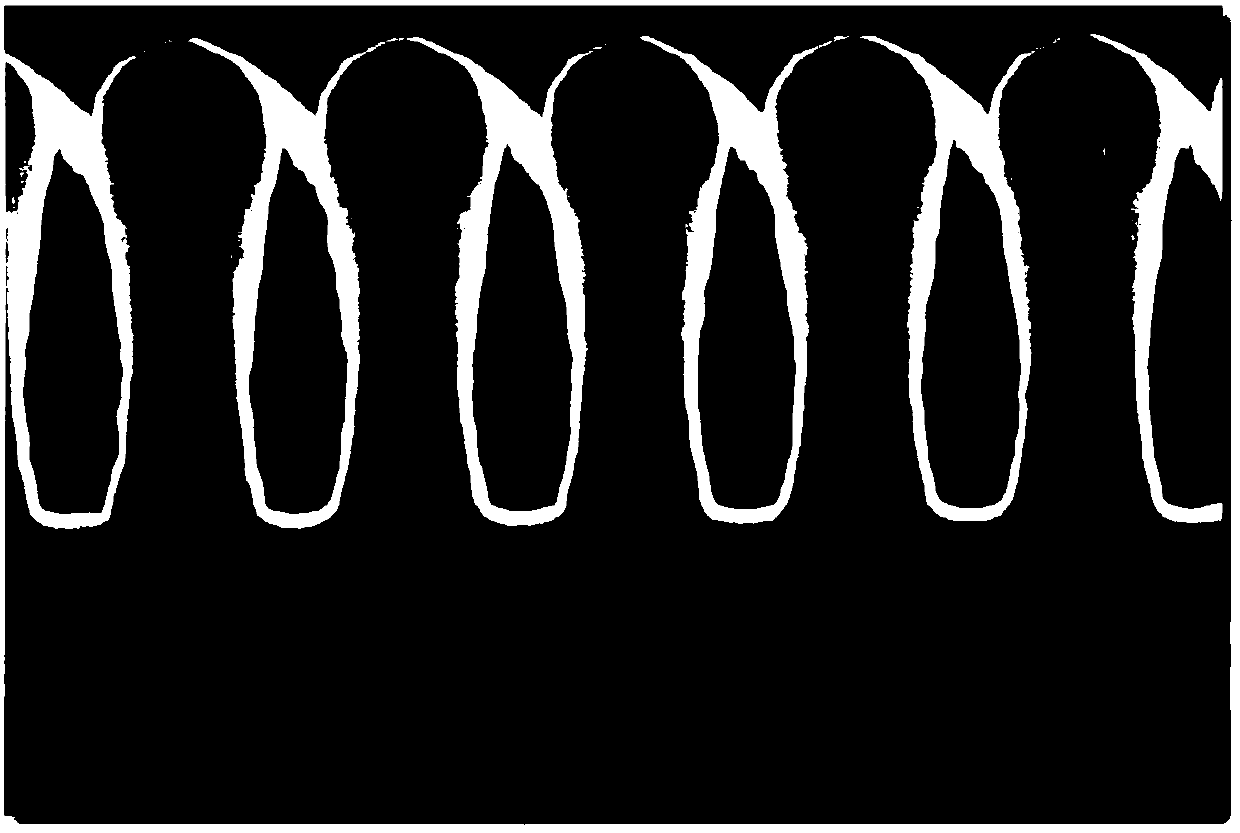

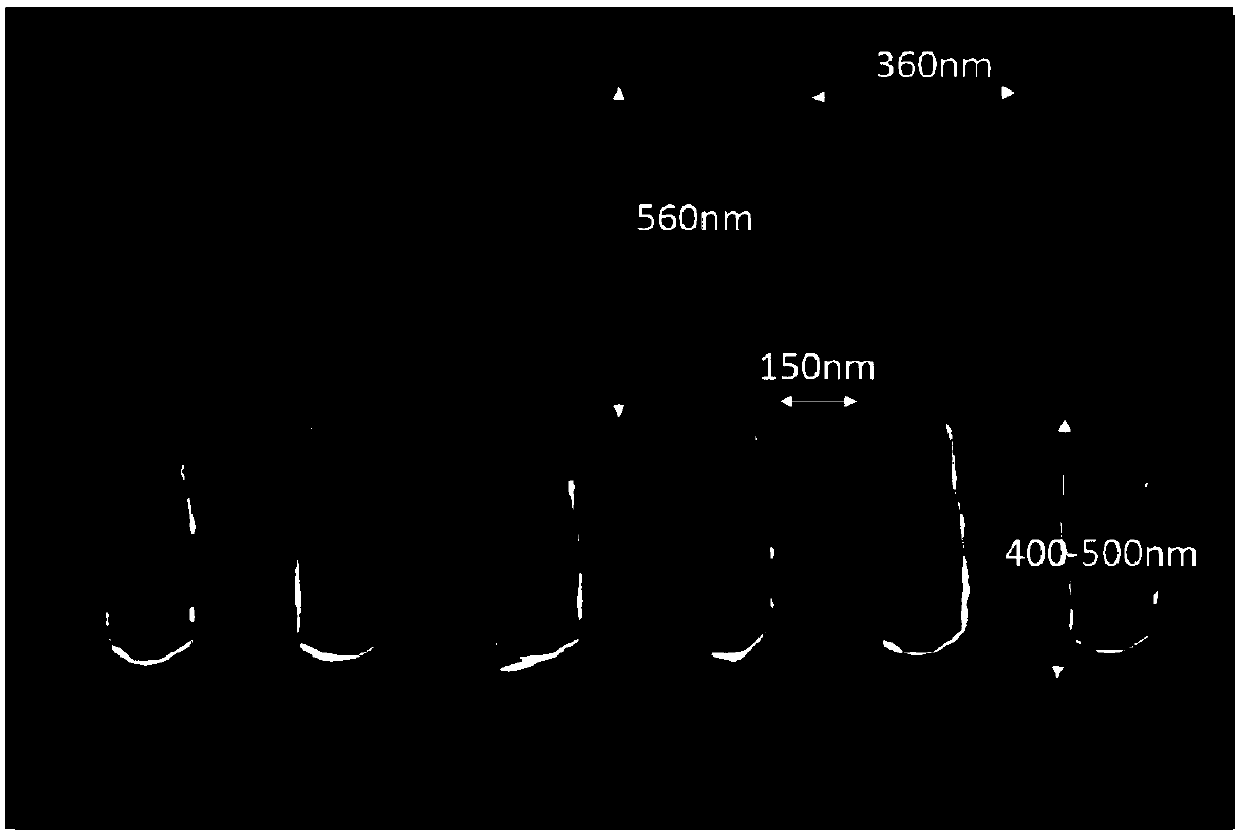

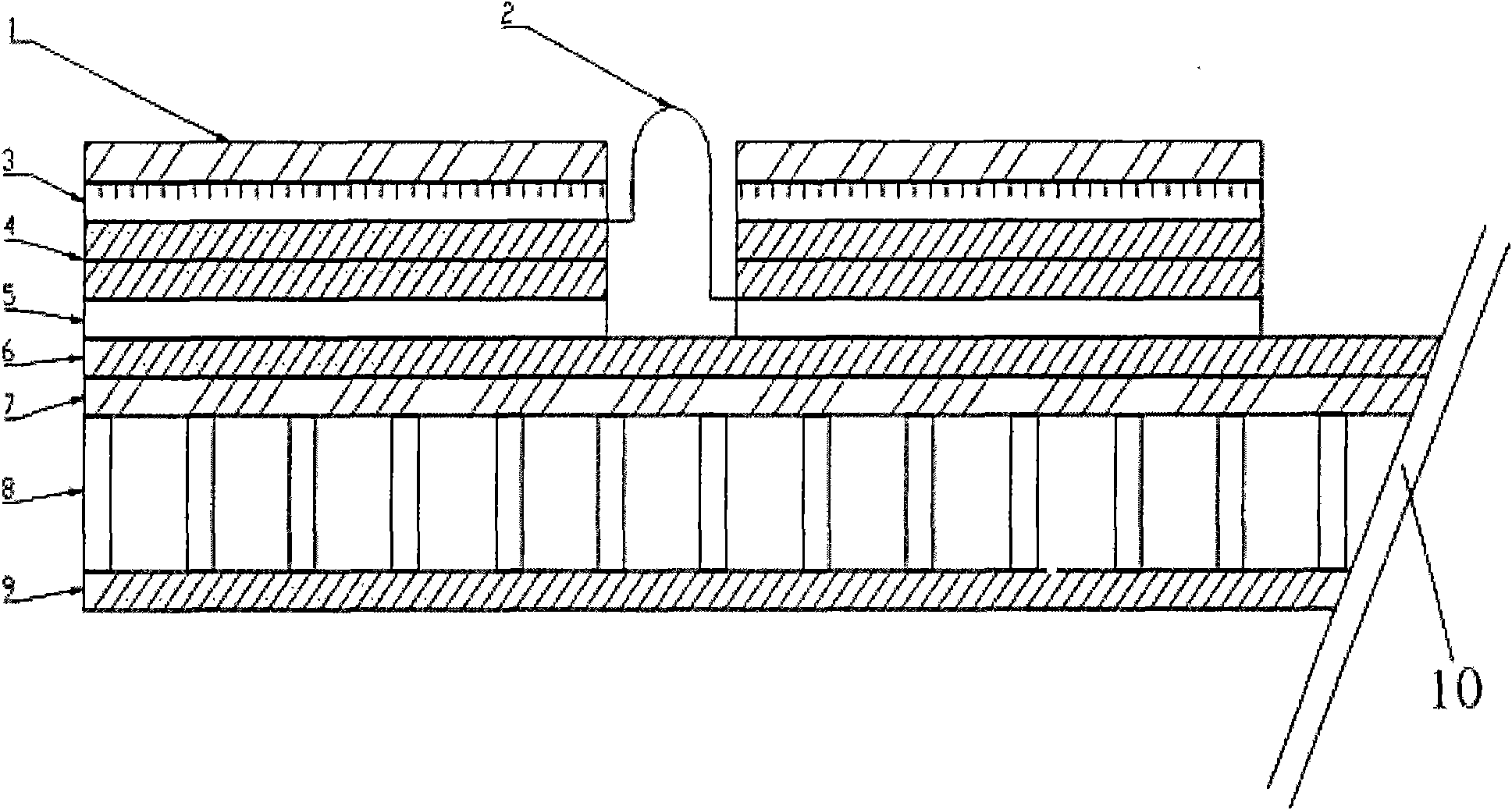

The invention provides a germanium-silicon-based gallium arsenide material and a preparation method thereof, and application of a germanium-silicon-based gallium arsenide material. The germanium-silicon-based gallium arsenide material comprises a silicon substrate having a surface with a periodic groove structure, a germanium middle layer attached to the surface of the silicon substrate, and a gallium arsenide layer attached to the surface of the germanium middle layer. The stress is eliminated generated by lattice mismatch of silicon and gallium arsenide by utilizing the inhibiting effect ofthe germanium (113) crystal face on the gallium arsenide antiphase domain and the characteristic of lattice matching of germanium and gallium arsenide, thereby achieving the epitaxial growth of high-quality single-crystal and ultrathin gallium arsenide on the silicon (100) substrate on an III-V family molecular beam epitaxial device.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

Space GaAs/Ge single-junction gallium arsenide solar cell array

InactiveCN102054884AImprove photoelectric conversion efficiencyHigh mechanical strengthFinal product manufacturePhotovoltaic energy generationLight energyGallium arsenate

The invention belongs to the field of new energy sources and space power supply-solar photovoltaic application and particularly discloses a GaAs / Ge single-junction gallium arsenide solar cell array which works under a space solar synchronous orbit. Through the photovoltaic characteristic of an efficient GaAs / Ge solar cell, light energy can be converted into electric energy during a light period, so that stable and efficient electric energy can be provided for a load; the solar cell array consists of a left wing, a right wing, six solar panels and 12,988 GaAs / Ge single-junction gallium arsenide solar cell plates; and constitution units mainly comprise a substrate, a laminated GaAs / Ge solar cell, a connecting piece, a power transmission circuit and the like. The GaAs / Ge single-junction gallium arsenide solar cell array has the characteristics of high efficiency, low temperature coefficient, high radiation resistance and high reliability, can adapt to radiation and charging environments of a low earth orbit (LEO) particle radiation region and a high-energy low-density plasma region and is fully suitable for working conditions of high temperature alternative frequency of the solar synchronous orbit.

Owner:SHANGHAI INST OF SPACE POWER SOURCES

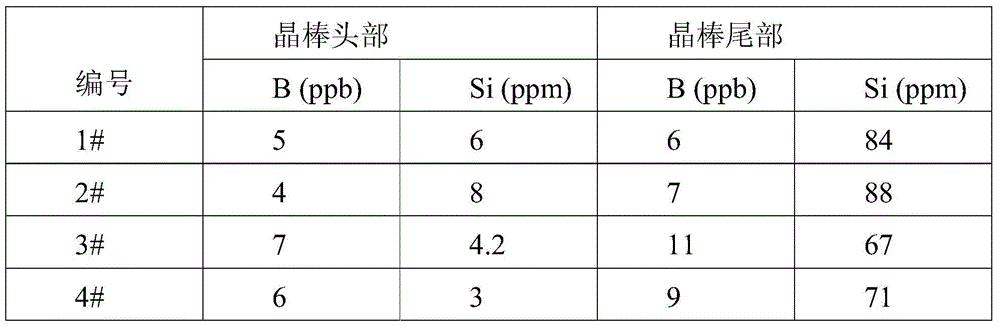

Gallium arsenide-doped single crystal growth process

ActiveCN111893571AControl oxygen contentReduce oxygen contentPolycrystalline material growthFrom frozen solutionsOxygen contaminationSemiconductor materials

The invention relates to the technical field of semiconductor material preparation, and in particular, relates to a gallium arsenide-doped single crystal growth process; oxygen released in the environment and in the high-temperature process of arsenic, gallium and a quartz tube is absorbed by adding materials with high oxygen reaction activity in two links of polycrystalline synthesis and single crystal growth, and oxygen pairs are preventd from entering polycrystals and single crystals, so the influence of oxygen pollution on the material performance is greatly reduced. Si doping is carried out in the polycrystalline synthesis process, silicon enters gallium arsenide and performs effective occupying, boron oxide does not exist, and polycrystalline synthesis does not cause B to pollute polycrystalline. C, Al or Ti is placed in a quartz tube to absorb oxygen in the quartz tube in the single crystal growth process, the oxygen content in the single crystal is controlled, and polycrystalline doped impurities are not added any more. During single crystal growth, boron oxide is added to improve the single crystal rate and realize selective adsorption of impurities. The desired crystal properties are achieved.

Owner:SHANXI CHINA CRYSTAL TECH CO LTD

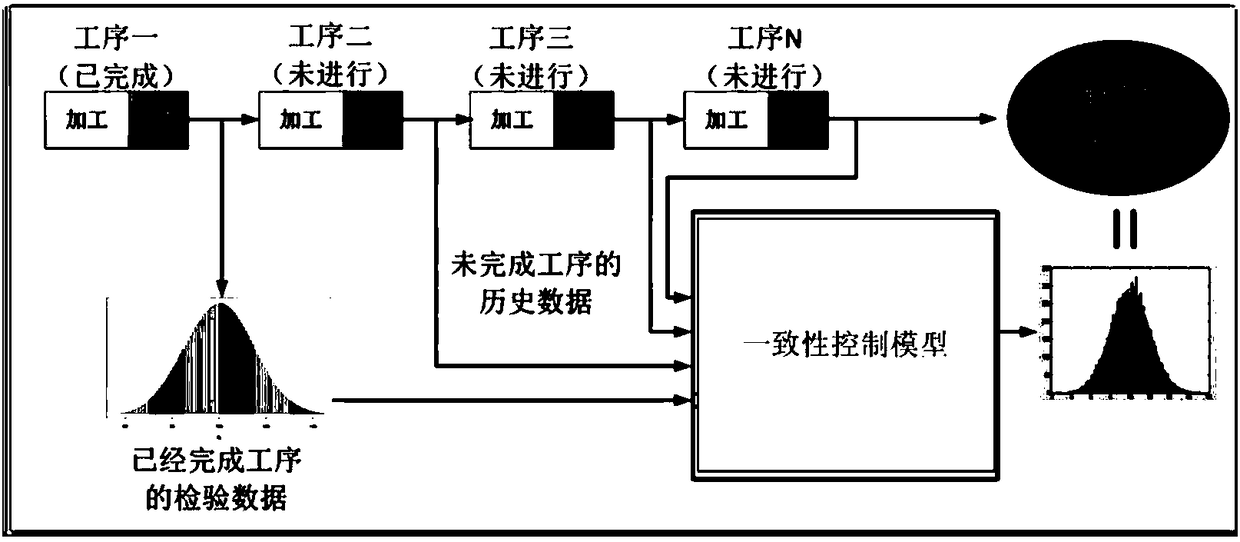

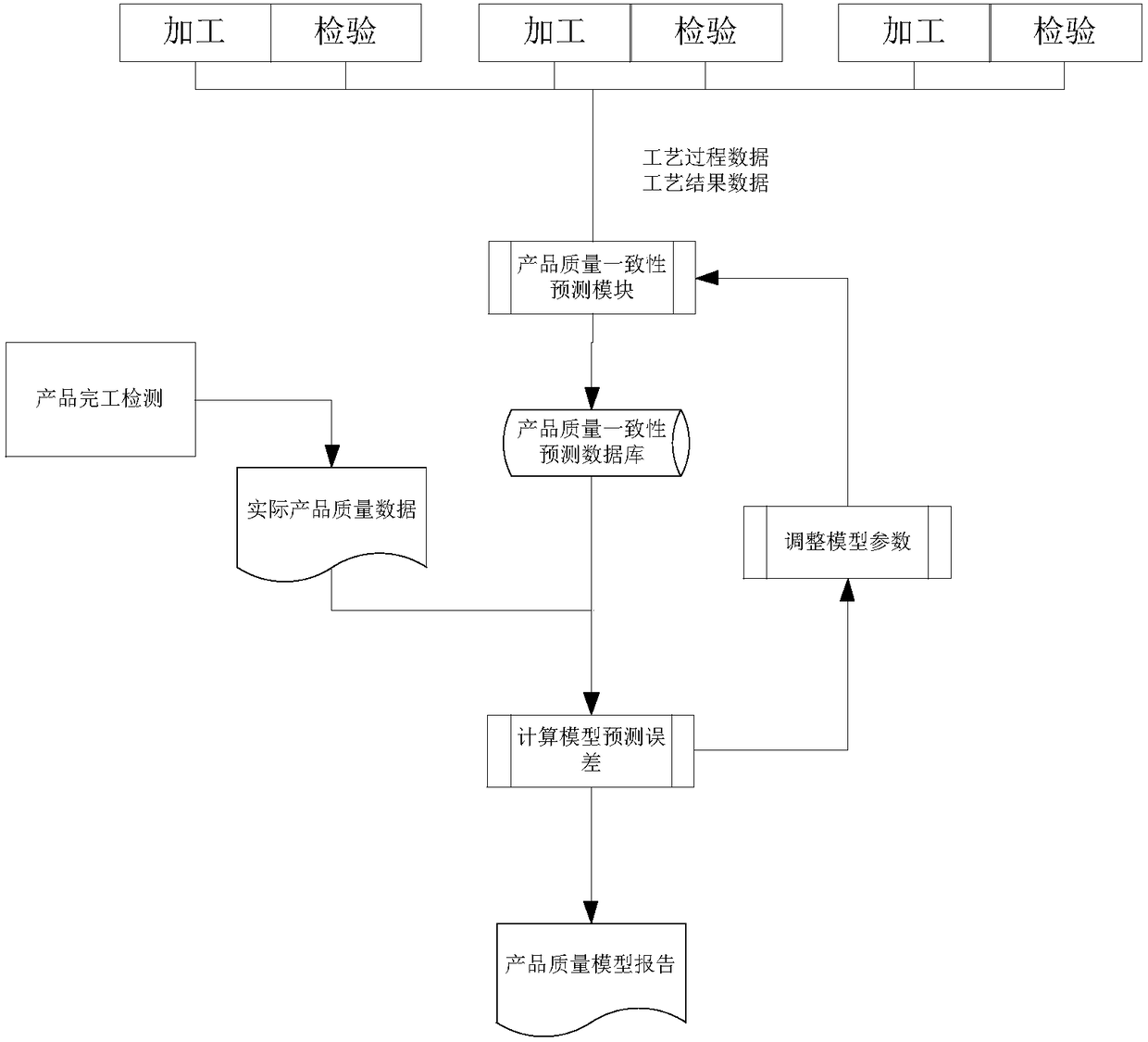

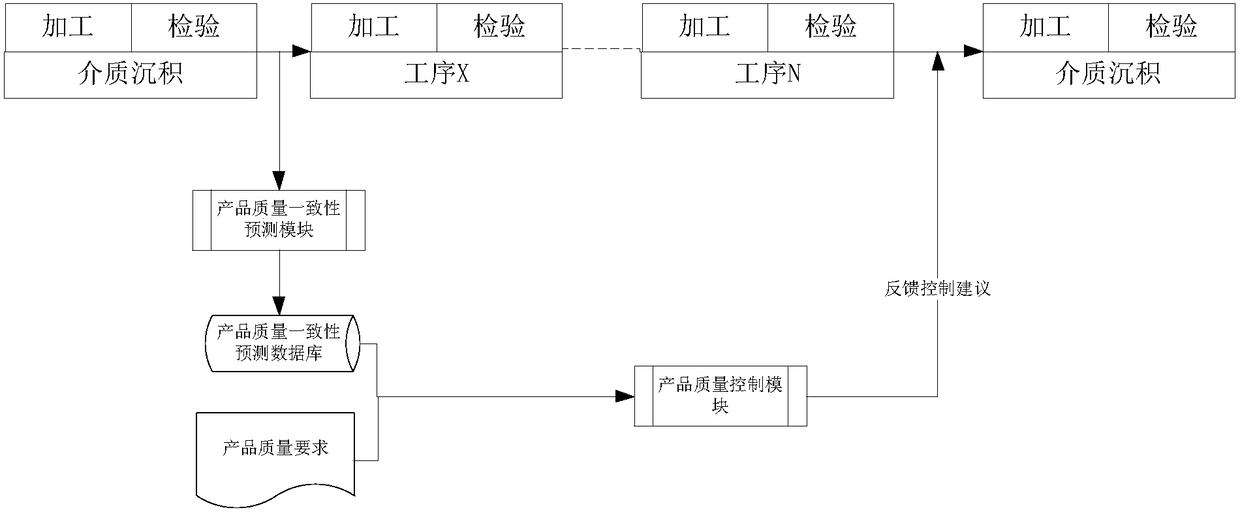

Method and system for controlling quality consistency of gallium arsenide product

InactiveCN108415393AStrong automationStrong semi-automation abilityTotal factory controlProgramme total factory controlModel sampleMathematical model

A method for controlling quality consistency of a gallium arsenide product comprises the following steps of 1, arranging historical process data for forming an original model sample database; 2, performing mathematical modeling on the process data in a production process by means of an artificial neural network; and 3, performing product quality forecasting, namely performing final product qualityforecasting by means of a mathematical model through the process data of the step, and after product finishing, comparing actual data of the product with forecast result data, thereby generating a product quality model report.

Owner:CHEUNG KONG UNION BEIJING TECH CO LTD +2

Method for transferring gallium arsenide epitaxial layer to flexible metal substrate

ActiveCN105470115AImprove thermal conductivityImprove conductivitySemiconductor/solid-state device manufacturingMetal foilGallium arsenate

The invention discloses a method for transferring a gallium arsenide epitaxial layer to a flexible metal substrate. A metal foil is used as a transfer support substrate, so that the weight of a device is effectively reduced, the gravimetric specific power is increased, and a flexible function is achieved. A metal bonding method is used, a stable and high-conductivity connection mode is provided, and a bonding metal layer is prepared in a vacuum evaporation mode, so that the thickness control is easy to realize and the uniformity is good. A graphite flake is adopted as a buffer gasket, so that the bonding quality can be effectively improved, cavities are reduced, and the finished product rate is increased. According to the method, the gallium arsenide epitaxial layer is transferred to the flexible metal substrate with a metal bonding process. The method has the technical characteristics of portability and flexibility. The application range of III-V family epitaxial products can be expanded.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 18 RES INST

Preparation method of silicon-aluminum alloy

The invention relates to a preparation method of a silicon-aluminum alloy, which comprises steps as follows: a casting or powder metallurgy process is utilized to prepare a silicon-aluminum material of which the mass percent of silicon is 25-90% and the silicon phase dimension is 0.1-20 mm; the prepared silicon-aluminum material can be further welded onto an aluminum sheet, copper sheet, silicon sheet, silicon carbide sheet, germanium sheet, gallium arsenide sheet, gallium nitride sheet or aluminum nitride sheet; and the independent silicon-aluminum block material or silicon-aluminum layer welded on the aluminum sheet, copper sheet, silicon sheet, silicon carbide sheet, germanium sheet, gallium arsenide sheet, gallium nitride sheet or aluminum nitride sheet is subjected to stirring friction to obtain the compact silicon-aluminum composite material of which the mass percent of silicon is 25-90% and the silicon phase dimension is 0.5-50 mu m. The silicon-aluminum material can independently form a block or be compounded on the surface of the aluminum sheet, copper sheet, silicon sheet, silicon carbide sheet, germanium sheet, gallium arsenide sheet, gallium nitride sheet or aluminum nitride sheet.

Owner:XI AN JIAOTONG UNIV

Graphene/gallium arsenide solar cell preparation method

ActiveCN106409988AFacilitates lateral transportReduced compound centerFinal product manufacturePhotovoltaic energy generationConductive materialsSolar cell

The invention provides a graphene / gallium arsenide solar cell preparation method. The graphene / gallium arsenide solar cell preparation method comprises the following steps of: 1) preparing a window layer on the surface of a gallium arsenide epitaxial wafer and then preparing a heavily-doped gallium arsenide cap layer on the surface of the window layer; 2) preparing a positive electrode on the surface of the heavily-doped gallium arsenide cap layer, and preparing a negative electrode on the surface of the gallium arsenide epitaxial wafer away from the window layer; 3) etching the heavily-doped gallium arsenide cap layer between positive electrode grid lines by the chemical etching method so as to expose the window layer; 4) preparing a graphene layer on the surface of the exposed window layer; 5) preparing an anti-reflection layer on the surface of the graphene layer to obtain a graphene / gallium arsenide solar cell. In the invention, graphene is applied to the gallium arsenide solar cell as a transparent conductive material, so the conversion efficiency of the gallium arsenide solar cells is further improved and is much higher than that of graphene / gallium arsenide Schottky junction solar cells. In addition, the cost for solar cell preparation is low and the process is simple, which is conducive to industrialization application.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

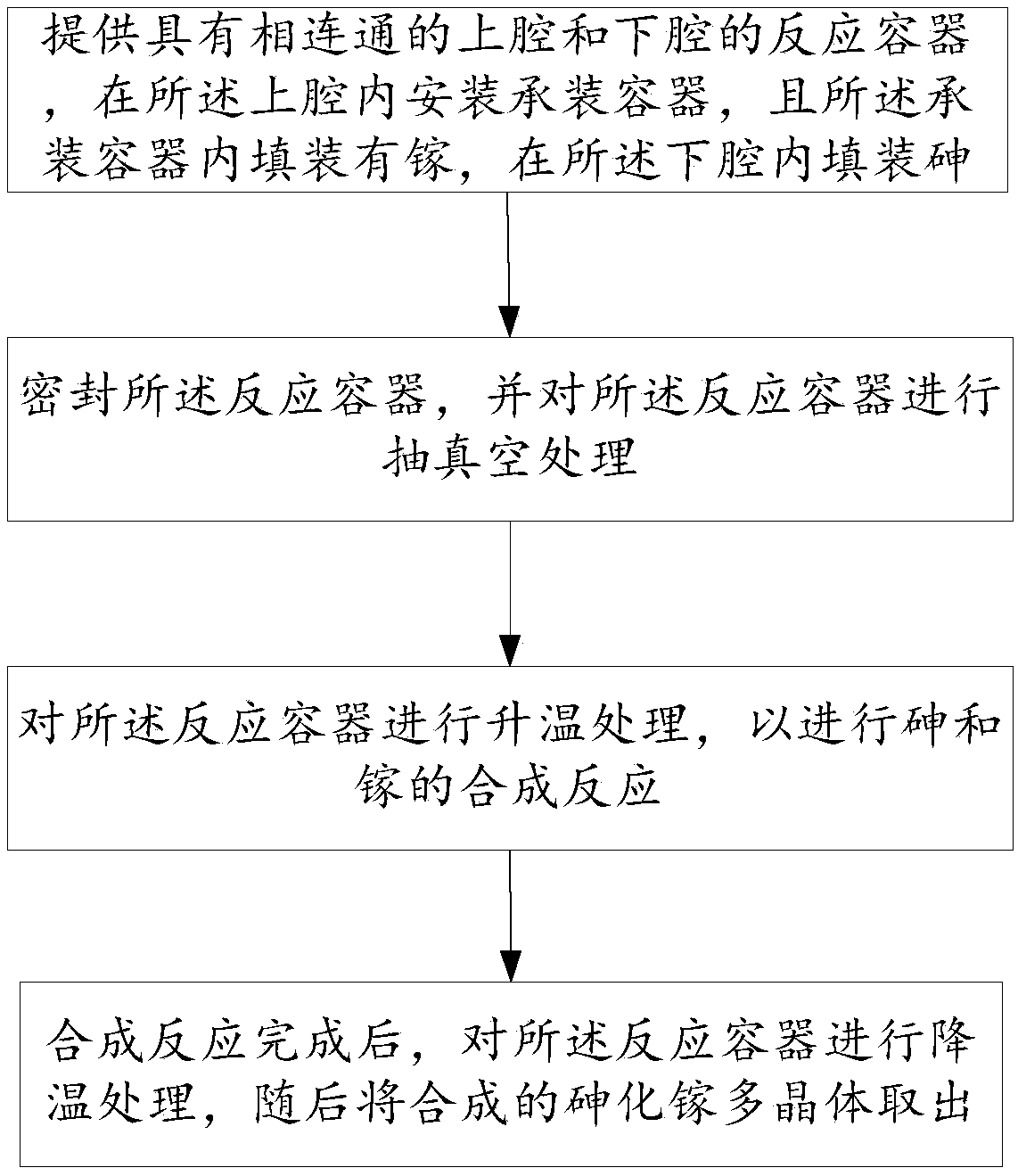

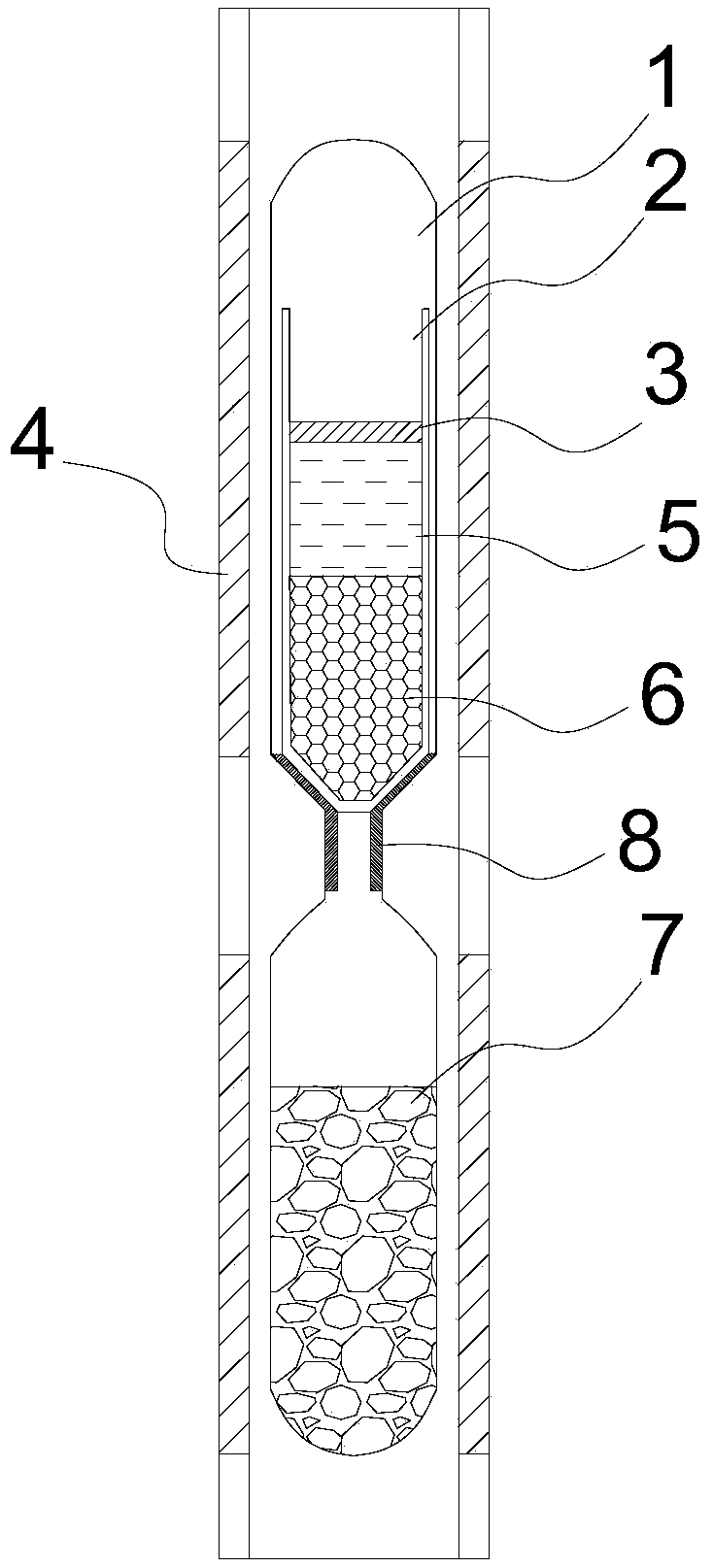

Gallium arsenide polycrystal synthesis method

InactiveCN108866630AGallium-freeReduce manufacturing costPolycrystalline material growthSingle crystal growth detailsBridgman methodSynthesis methods

The invention provides a gallium arsenide polycrystal synthesis method. The gallium arsenide polycrystal synthesis method comprises the following steps: providing a reaction container with an upper cavity and a lower cavity, which are communicated; filling arsenic into the lower cavity, mounting a bearing container into the upper cavity and filling gallium into the bearing container; then sealingand vacuumizing the reaction container; then carrying out temperature rising treatment on the reaction container so as to carry out synthesis reaction on the arsenic and the gallium; finally, carryingout cooling treatment on the reaction container, and taking out a synthesized gallium arsenide polycrystal. According to the gallium arsenide polycrystal synthesis method, polycrystal synthesis is carried out by adopting a vertical Bridgman method and the production capacity is high; a polycrystal material is molded in the bearing container, so that a single crystal can be completely matched withthe bearing container when being charged, so that the feeding amount of each heat is reduced and the single crystal production cost is reduced; the reaction container is vertically arranged and is provided with the upper cavity and the lower cavity; temperature gradient distribution of a heat field of the reaction container is uniform and the synthesized polycrystal material is dense and has no holes and no rich gallium; the synthesis ratio is greatly improved when being compared with the previous synthesis ratio.

Owner:HANERGY NEW MATERIAL TECH CO LTD

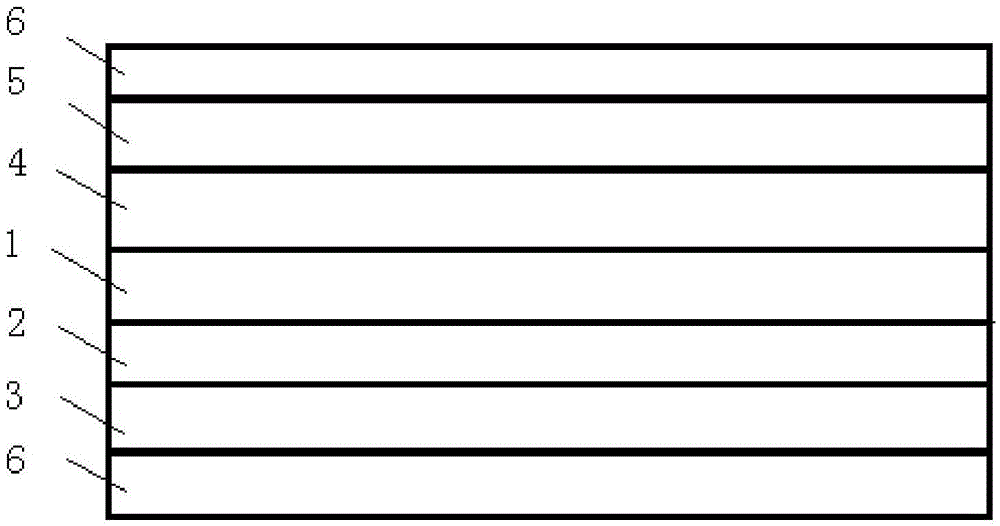

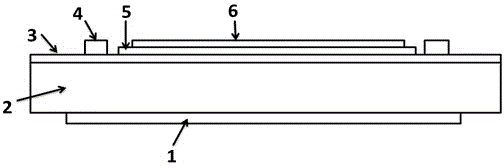

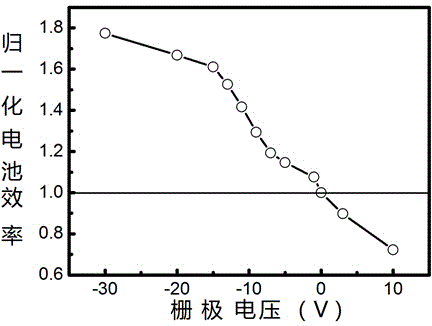

Electric field controlled graphene/gallium arsenide solar cell and preparation method thereof

ActiveCN104576787AImprove conversion efficiencySimple processFinal product manufacturePhotovoltaic energy generationGallium arsenateGraphite

The invention relates to an electric field controlled graphene / gallium arsenide solar cell and a preparation method thereof. The electric field controlled graphene / gallium arsenide solar cell is provided with a back electrode, a gallium arsenide layer, a graphene layer, an insulating medium layer and a grid electrode from bottom to top sequentially; the electric field controlled graphene / gallium arsenide solar cell is further provided with front electrodes, and the front electrodes are arranged on the graphene layer. The preparation method of the electric field controlled graphene / gallium arsenide solar cell comprises steps as follows: the back electrode is manufactured on one side of a gallium arsenide piece; graphene is transferred to the other side of the gallium arsenide piece after the gallium arsenide piece is cleaned; the front electrodes are manufactured on the graphene; the insulating medium layer is manufactured on the graphene; finally, the grid electrode is manufactured on the insulating medium layer, and the solar cell is obtained. According to the electric field controlled graphene / gallium arsenide solar cell, the graphene doping state can be controlled through an external electric field, and the photoelectric converting efficiency of the graphene / gallium arsenide solar cell can be further improved.

Owner:ZHEJIANG UNIV

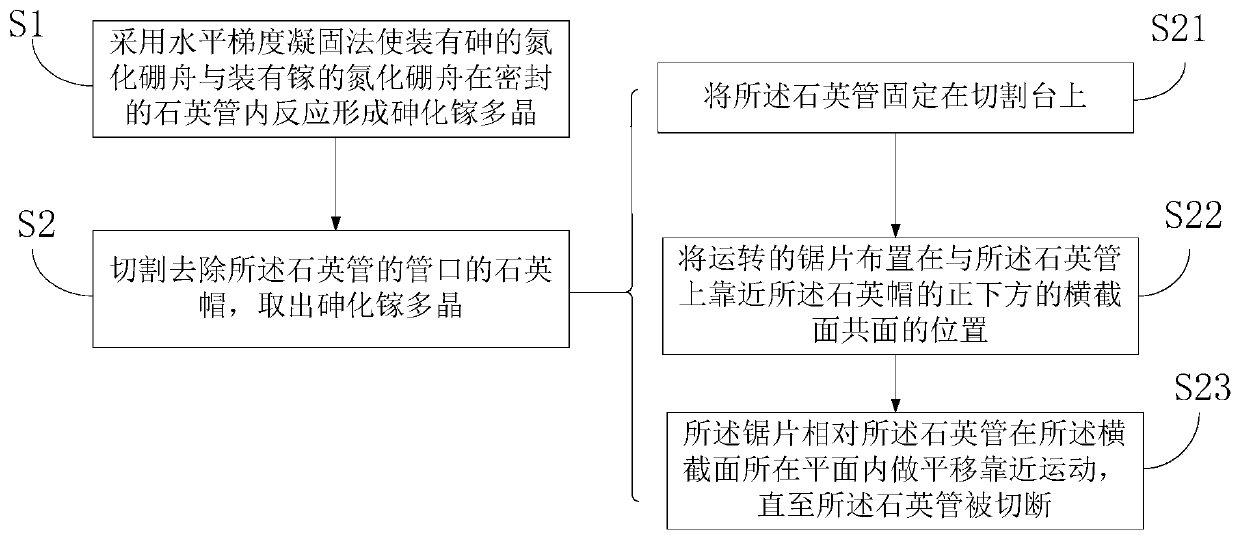

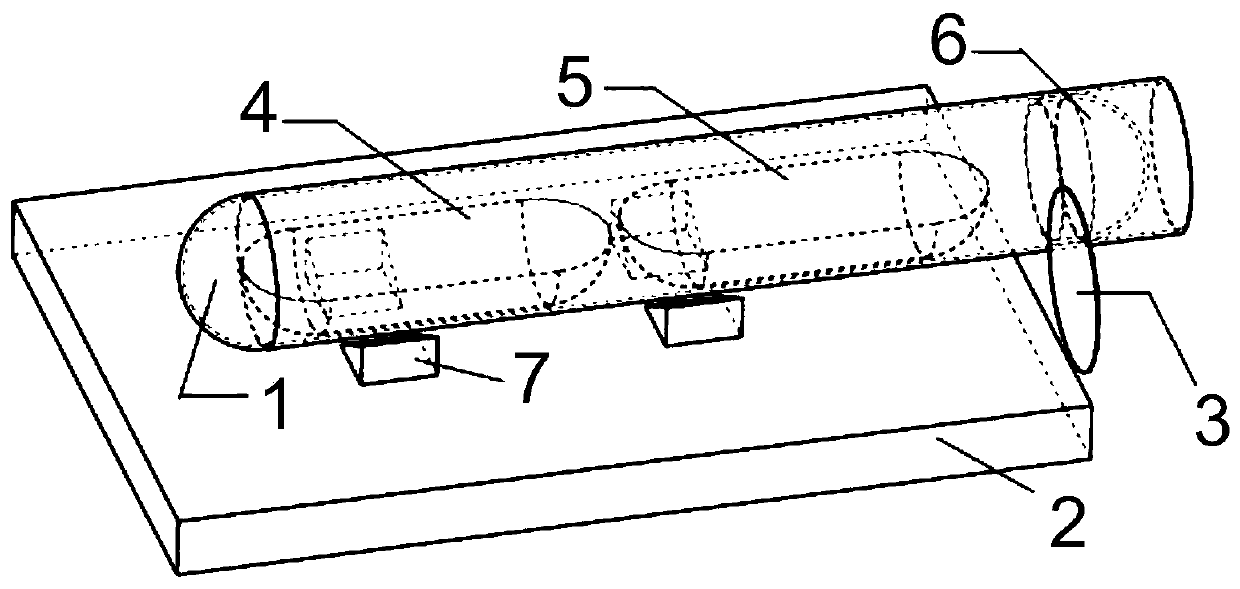

Method and device for manufacturing gallium arsenide polycrystals

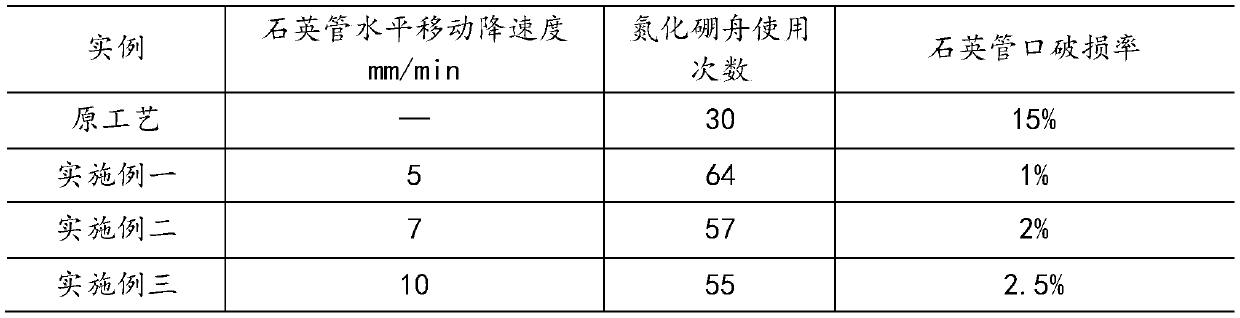

InactiveCN110144623ASolve the high breakage rateExtended service lifePolycrystalline material growthSingle crystal growth detailsBoron nitrideBreakage rate

The invention discloses a method and a device for manufacturing gallium arsenide polycrystals. The method comprises the following steps: reacting an arsenic-loaded nitride boat with a gallium-loaded boron nitride boat in a sealed quartz tube through a horizontal gradient solidification process to form the gallium arsenide polycrystals; and cutting off a quartz cap at the tube mouth of the quartz tube, and taking out the gallium arsenide polycrystals, wherein the cutting process is carried out by the following steps: fixing the quartz tube on a cutting table; arranging a running saw blade at aposition coplanar with the cross section, right below the quartz cap, of the quartz tube; and moving the saw blade to the quartz tube in the plane of the cross section until the quartz tube is cut out. The manufacturing method can effectively avoid the problem of breakage of two ends of every boron nitrides boat, caused by the frequent collision of the boron nitride boats with the gallium arsenidepolycrystals, so the service life of the boron nitride boats is effectively improved, and the tube mouth breakage rate of the quartz tube is effectively reduced.

Owner:FIRST SEMICON MATERIALS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com