Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

105results about How to "Reduce surface electric field" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

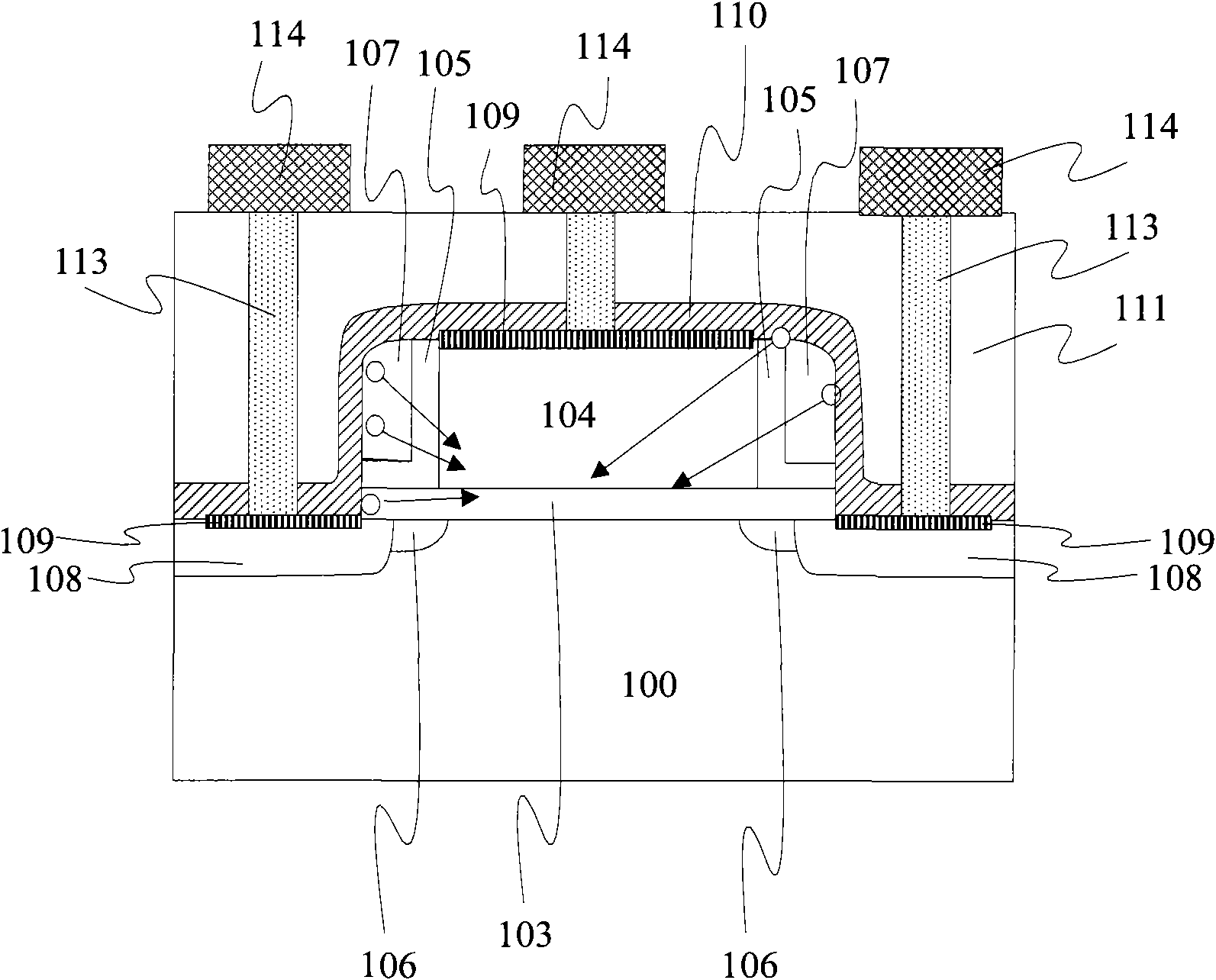

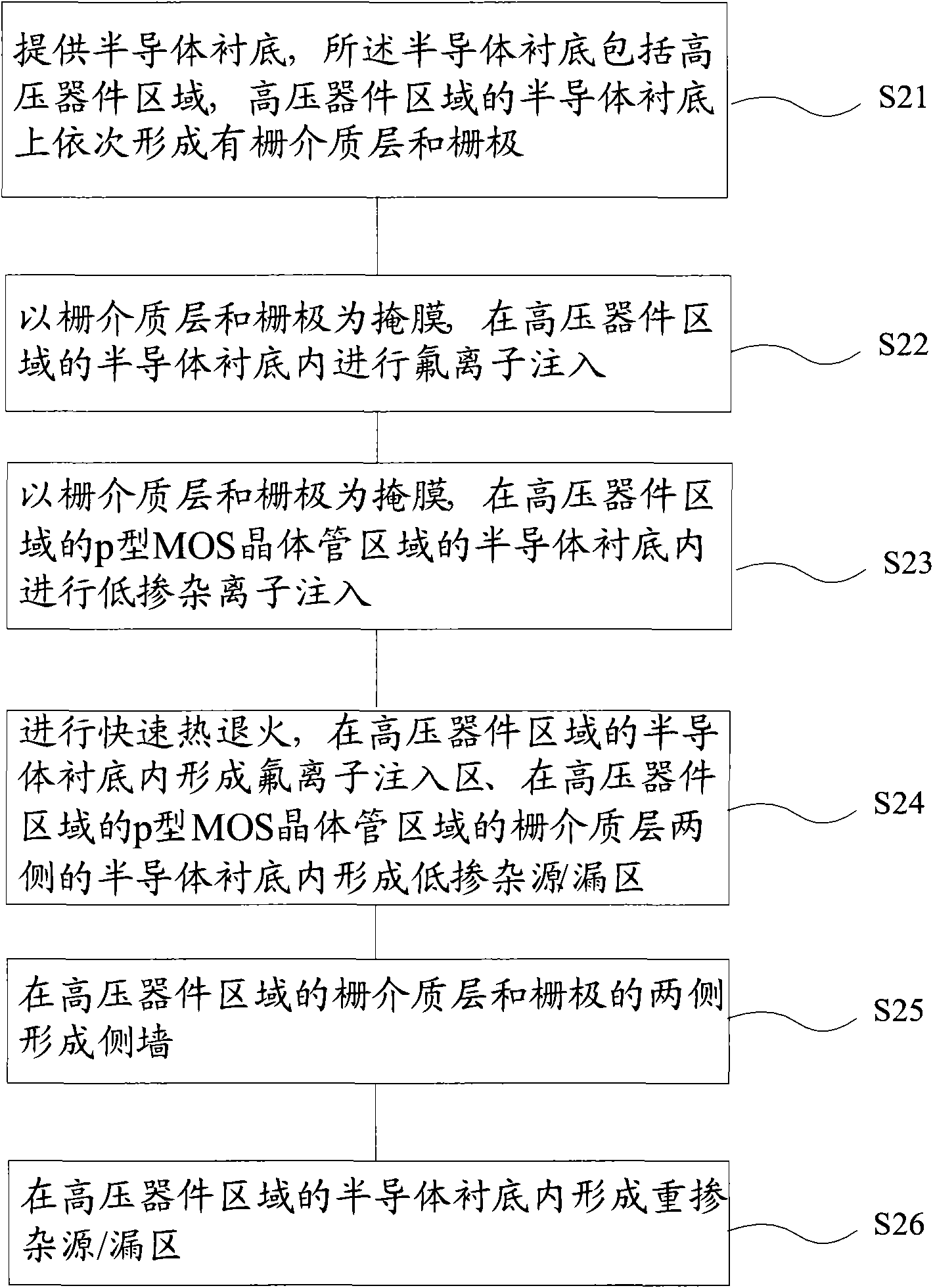

Semiconductor device, p-type MOS transistor and manufacturing method thereof

ActiveCN101572250AAvoid formingReduce dislocation defectsSolid-state devicesSemiconductor/solid-state device manufacturingHigh pressureMedia layer

The invention relates to a semiconductor device, a p-type MOS transistor and a manufacturing method thereof. The method for manufacturing the semiconductor device comprises the following steps: providing a semiconductor substrate; taking a grid medium layer and a grid electrode as masks, and implanting fluorine ions into a semiconductor substrate in a high-voltage device region; taking the grid medium layer and the grid electrode as the masks, and implanting low doped ions into a semiconductor substrate in the p-type MOS transistor region of the high-voltage device region; performing quick thermal annealing; forming side walls on both sides of the grid medium layer and the grid electrode in the high-voltage device region; and forming a heavy doping source / drain region in the semiconductor substrate of the high-voltage device region. The invention also provides the semiconductor device, the p-type MOS transistor and the manufacturing method thereof. The invention is favorable for restricting the influence of the NBTI effect on the MOS transistor by forming a fluorine ion implantation region on a low doping source / drain region in the p-type MOS transistor region of the high-voltage device region, and simultaneously can reduce the hot carrier injection effect.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

P-i-n-(-n)-type GaN single-photon avalanche detector

ActiveCN106409967AHigh Avalanche GainIncrease freedomSemiconductor devicesMinority carrier injectionHole injection layer

The present invention provides a p-i-n-(-n)-type GaN single-photon avalanche detector. The detector comprises a p-GaN upper contact layer, an i-GaN avalanche multiplication layer, an n<->-GaN hole-injection layer and an n-AlGaN lower contact layer arranged from up to down, wherein the n<->-GaN hole-injection layer is light doping. The p-i-n-(-n)-type GaN single-photon avalanche detector replaces an n-GaN layer with a traditional pin-type structure with the n<->GaN / n-AlGaN heterojunction, takes the n<->-GaN as an absorption injection layer, and takes the n-AlGaN as the lower contact layer so as to facilitate the improvement of the crystalline quality of epitaxial materials of an active region and improve the external quantum efficiency and the cavity minority carrier injection efficiency; and moreover, the parameters, such as doping concentration, thickness and the like, of the n<->-GaN layer are flexible and adjustable, and a very high avalanche gain can be obtained under the low work bias through compromise optimization.

Owner:THE 44TH INST OF CHINA ELECTRONICS TECH GROUP CORP

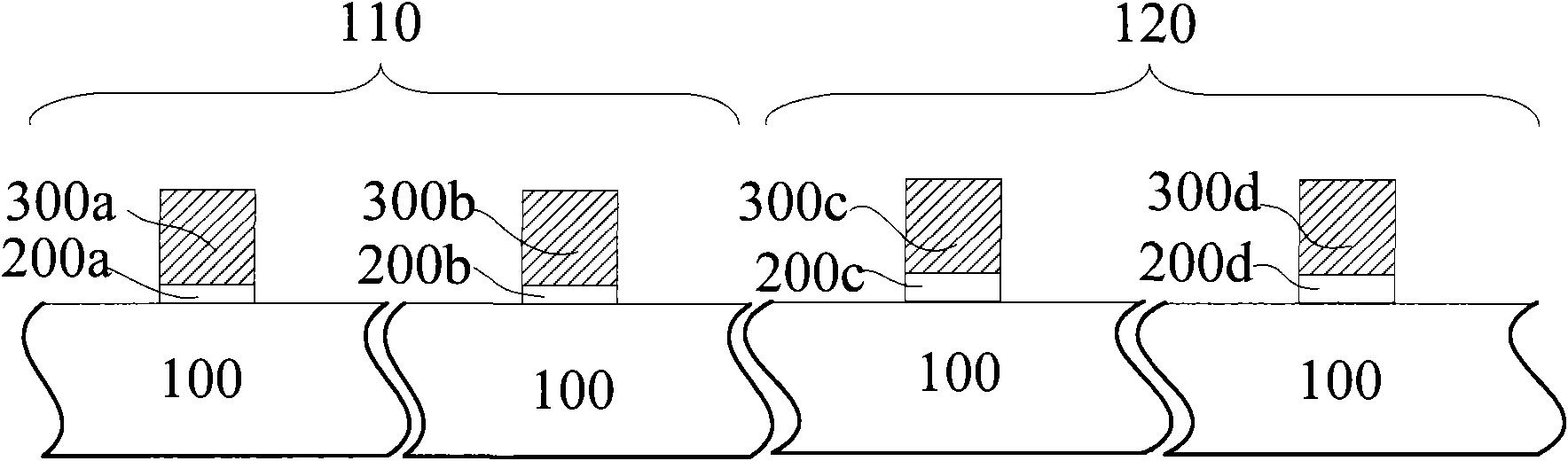

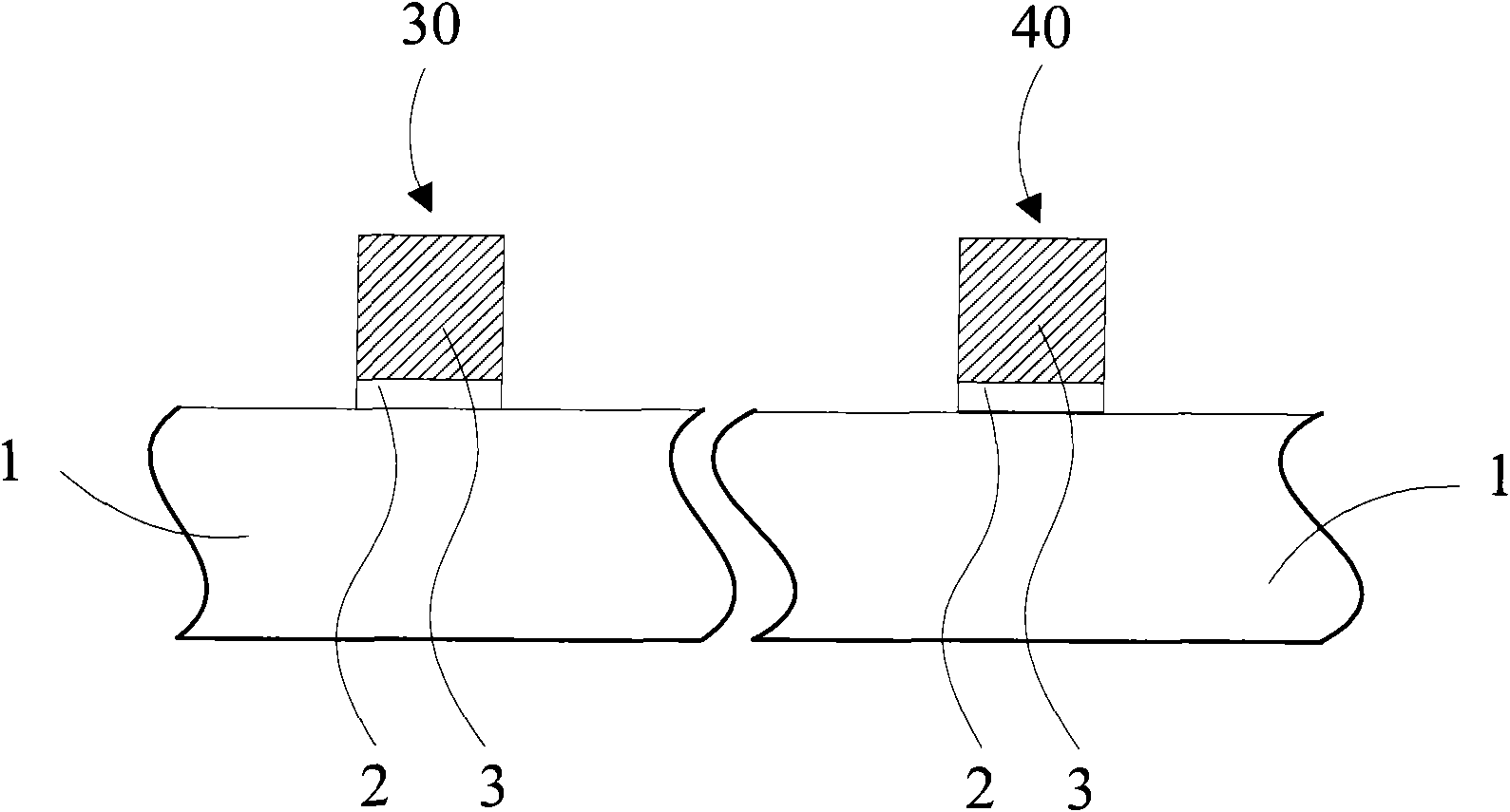

Semiconductor device, n-type MOS transistor and manufacturing method thereof

ActiveCN101572251AInhibition formationInhibition of agglomerationTransistorSemiconductor/solid-state device manufacturingHot carrier effectInput/output

The invention relates to a semiconductor device, an n-type MOS transistor and a manufacturing method thereof. The semiconductor device comprises a semiconductor substrate, a grid medium layer, a grid electrode, side walls, a light doping source / drain region, a heavy doping source / drain region, and a fluorine ion implantation region, wherein the gird medium layer, the grid electrode and the side wall are positioned inside an input / output device region of the semiconductor substrate; the low doping source / drain region and the heavy doping source / drain region are positioned inside semiconductor substrates in an n-type MOS transistor region and a p-type MOS transistor region of the input / output device region; and the fluorine ion implantation region is positioned inside a semiconductor substrate in the n-type MOS transistor region of the input / output device region. Correspondingly, the invention also provides a method for manufacturing the semiconductor device, the n-type MOS transistor and the method for manufacturing the n-type MOS transistor. The fluorine ion implantation region is formed in the low doping source / drain region of the n-type MOS transistor region, and fluorine ions in the fluorine ion implantation region and silicon in the semiconductor substrate form fluorine-silicon groups so as to prevent the formation of charge traps, prevent the aggregation of charges in the low doping source / drain region under the condition of additional voltage, and forming hot carrier effect.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

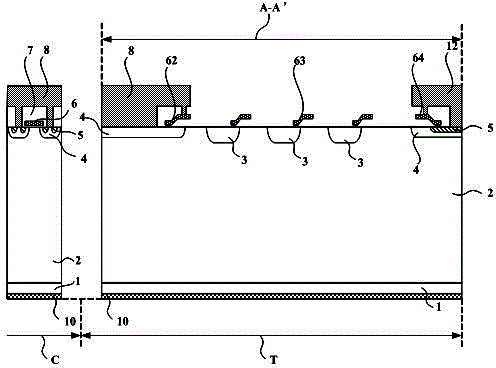

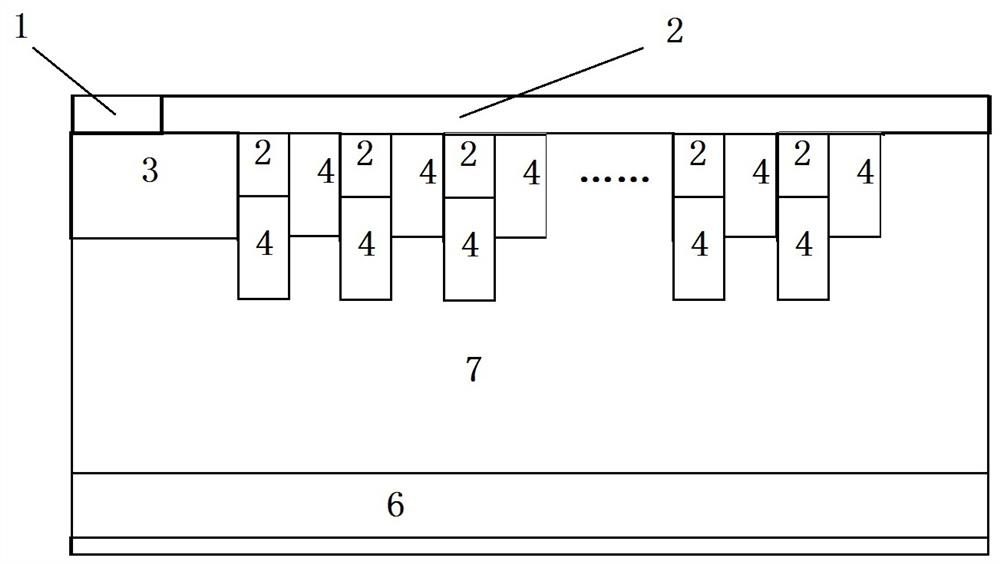

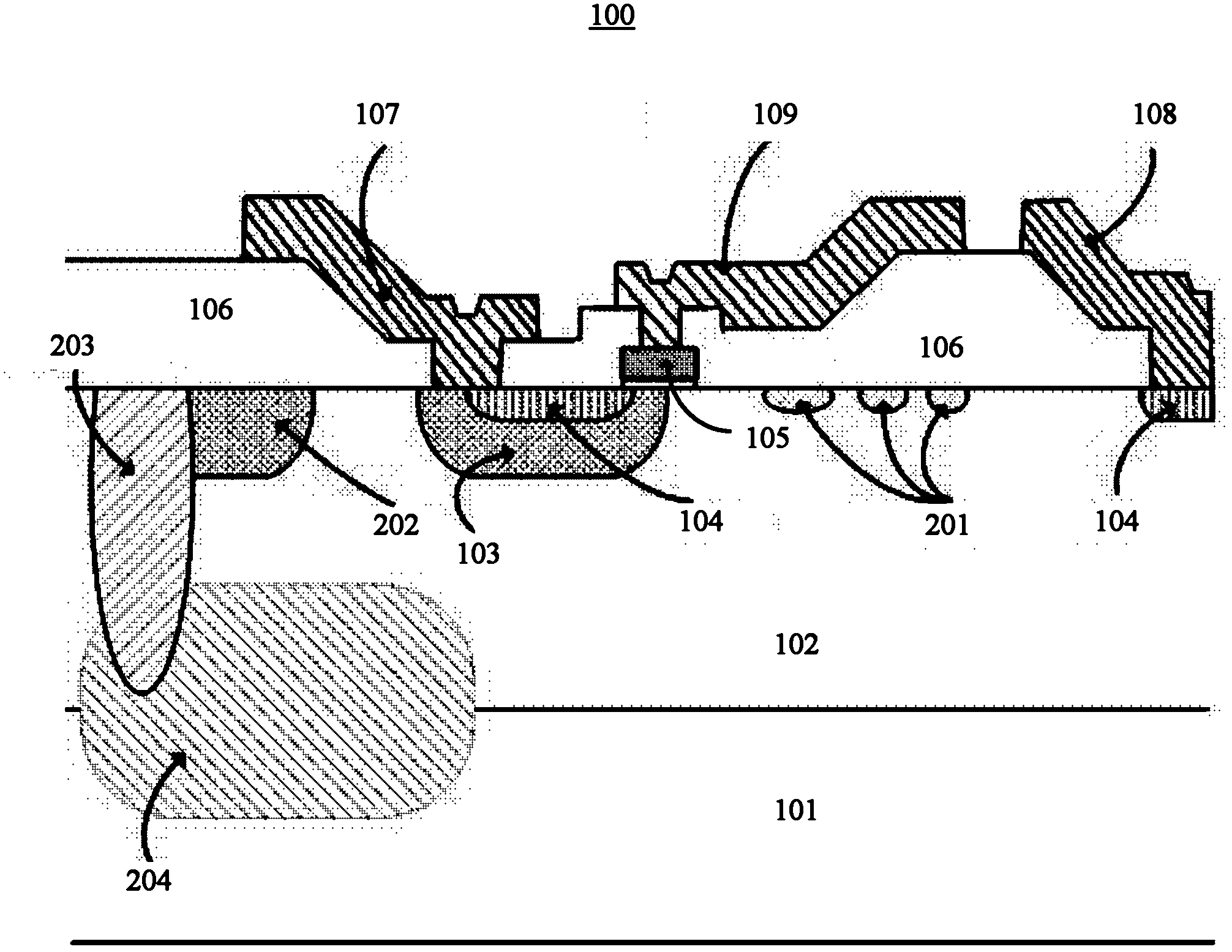

Semiconductor device with super junction structure

InactiveCN103779399AManufacturing process will not increaseImprove reliabilitySemiconductor devicesGate oxideDielectric layer

The invention provides a semiconductor device with a super junction structure. The semiconductor device comprises an N-type doped semiconductor substrate and an N-type doped epitaxial layer, wherein the N-type doped semiconductor substrate and the N-type doped epitaxial layer are sequentially arranged from bottom to top, and a first P-type filling well region, a second P-type filling well region and a third P-type filling well region are arranged inside the N-type doped epitaxial layer. A first P-type doping region is arranged on the upper side of the first P-type filling well region and provided with an N-type doping region, and a second P-type doping region is arranged on the upper side of the second P-type filling well region. A terminal pressure-withstanding structure T is arranged on the periphery of a primitive cell source electrode region C, wherein the terminal pressure-withstanding structure T comprises the second P-type filling well region, the second P-type doping region, the third P-type filling well region and the corresponding part of the N-type doped epitaxial layer, and the primitive cell source electrode region C comprises the first P-type filling well region, the first P-type doping region, the N-type doping region and the corresponding part of the N-type doped epitaxial layer. The parts, corresponding to polycrystalline silicon arranged in a part of dielectric layer above a gate oxide layer, of the terminal pressure-withstanding structure T and the primitive cell source electrode region C form a gate electrode structure and a polycrystalline silicon field plate structure respectively.

Owner:XIAN SEMIPOWER ELECTRONICS TECH

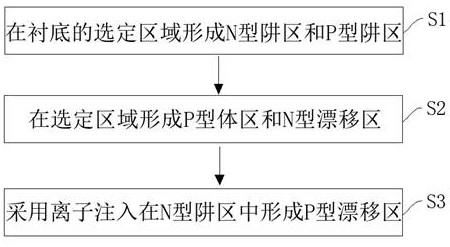

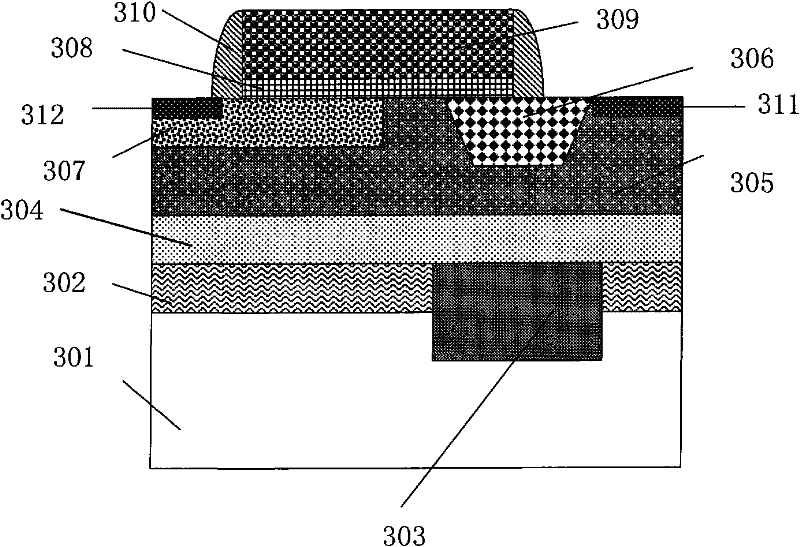

Lateral double-diffused metal oxide semiconductor field effect transistor and manufacturing method thereof

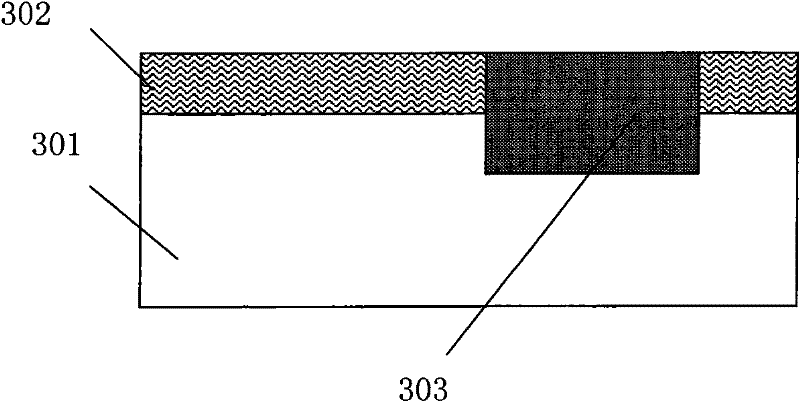

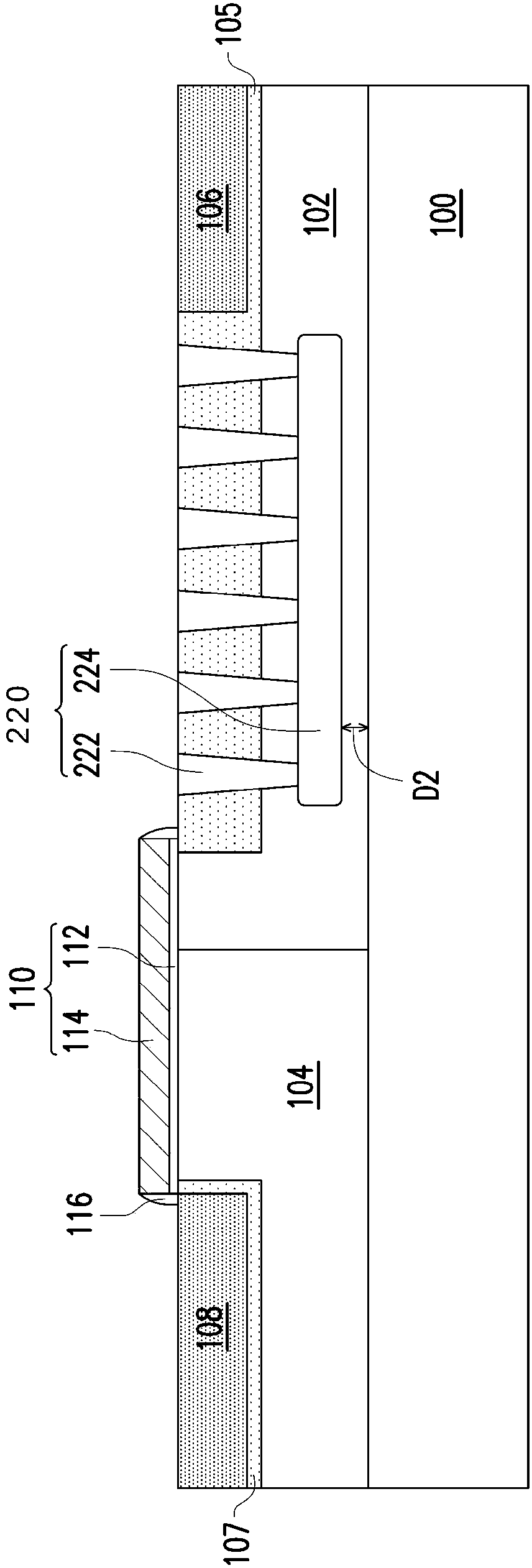

InactiveCN113964188AReduce surface electric fieldLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryField-effect transistor

The invention relates to the technical field of semiconductors, and provides a lateral double-diffused metal oxide semiconductor field effect transistor and a manufacturing method thereof. The lateral double-diffused metal oxide semiconductor field effect transistor comprises a substrate, a gate region, a source region, a drain region, a P-type body region, and an N-type well region, a P-type well region and an N-type drift region which are positioned on the substrate, and further comprises a P-type drift region formed by ion implantation, wherein the P-type drift region is located in the N-type well region, and a preset distance exists between the P-type drift region and the P-type body region. According to the invention, the P-type drift region is added in the N-type well region, the contact surface of the P-type drift region and the N-type well region forms a PN junction, and the P-type drift region and the N-type drift region form a dual RESURF structure, so that the surface electric field of the device is reduced, higher breakdown voltage can be borne, and lower on-resistance can be maintained.

Owner:BEIJING CHIP IDENTIFICATION TECH CO LTD +2

Longitudinal high-voltage semiconductor device

InactiveCN104900702AIncreased transverse compressive lengthReduce areaSemiconductor devicesHigh concentrationDopant

The invention discloses a longitudinal high-voltage semiconductor device, comprising an N-type doped semiconductor substrate, an N-type doped epitaxial layer, a P-type doped well region, a P-type dopant region, a high-concentration N-type doped region, a first polycrystalline silicon field plate, a second polycrystalline silicon field plate, a third polycrystalline silicon field plate, a fourth polycrystalline silicon field plate, a drain metal electrode and a stop ring electrode. The device can realize bidirectional exhaust during voltage tolerance, reduces the size of a chip, and lowers the production cost.

Owner:西安西奈电子科技有限公司

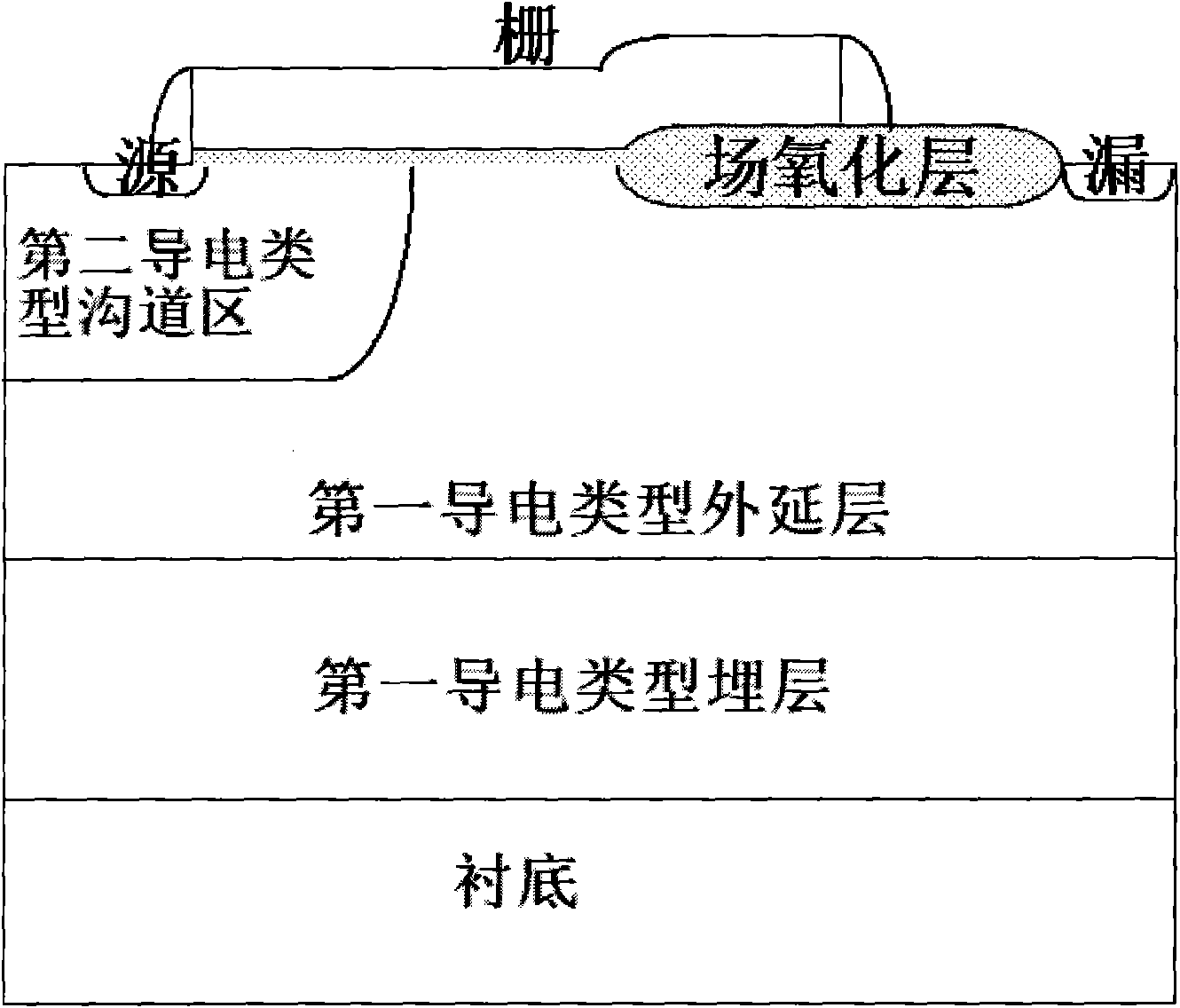

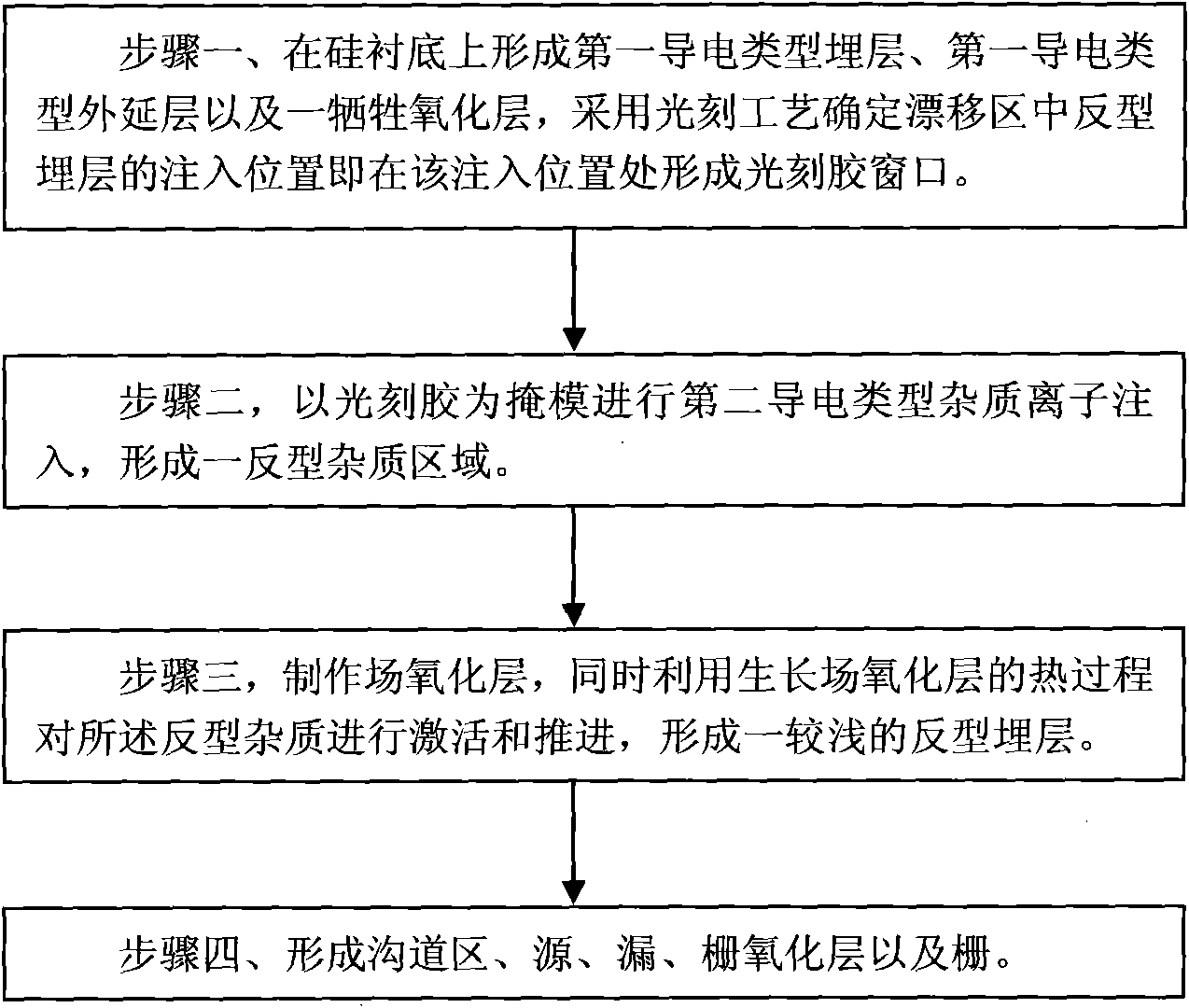

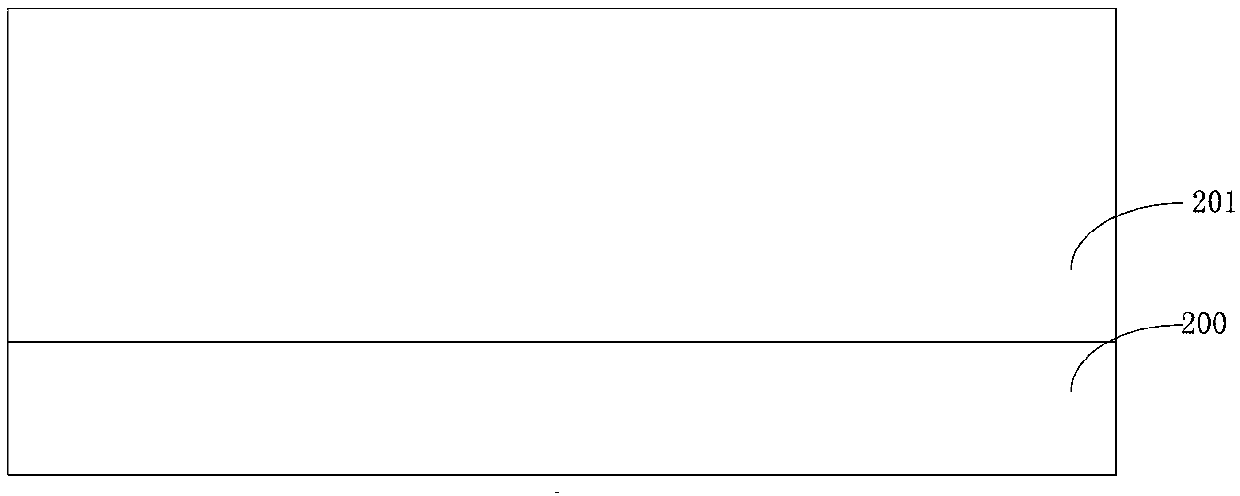

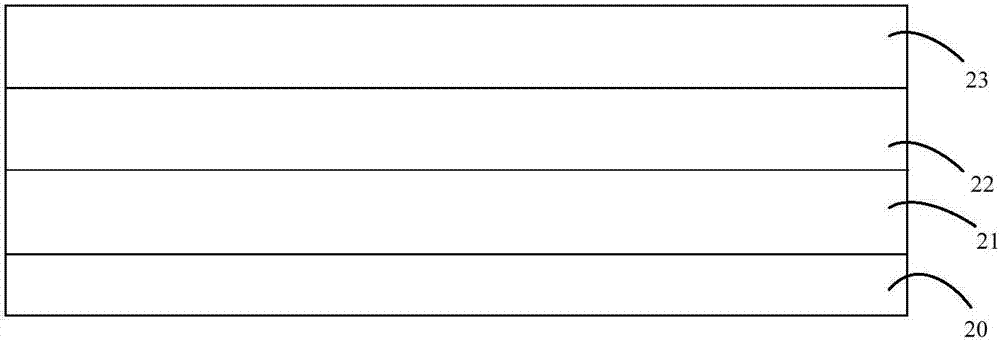

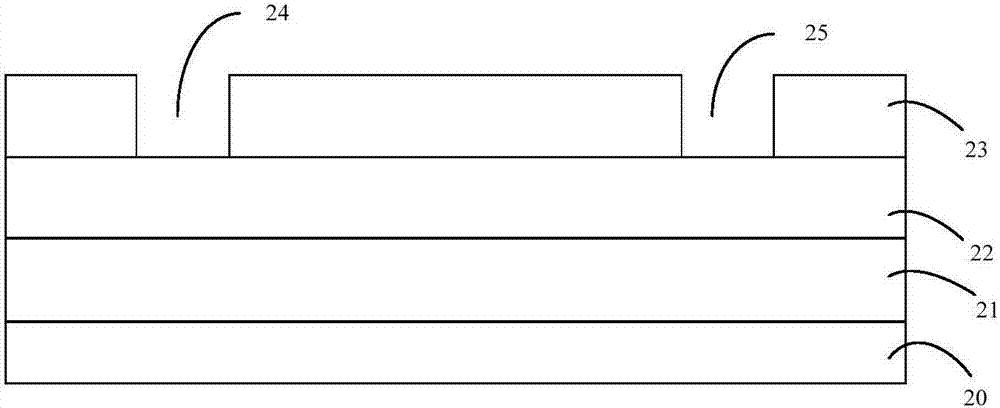

Transverse high-voltage MOS device and manufacturing method thereof

ActiveCN102054866AImprove reliabilityReduce surface electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotoresist

The invention discloses a transverse high-voltage metal oxide semiconductor (MOS) device, which is formed by burying an inversion buried layer into a drifting region of the device. The invention also discloses a method for manufacturing the transverse high-voltage MOS device, which comprises the following steps of: forming a first conduction type buried layer, a first conduction type epitaxial layer and a sacrifice oxide layer on a silicon substrate, and determining an implantation position of the inversion buried layer in the drifting region by adopting a photoetching process; performing second conduction type foreign ion implantation by taking photoresist as a mask to form an inversion impurity region; manufacturing a field oxide layer, and activating and boosting inversion impurities simultaneously in the thermal process of growing the field oxide layer to form the shallow inversion buried layer in the drifting region; and forming a channel region, a source oxide layer, a drain oxide layer, a gate oxide layer and a gate. Electric-field distribution in the drifting region can be changed, a surface electric field of a device can be reduced and withstand voltage performance and reliability can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

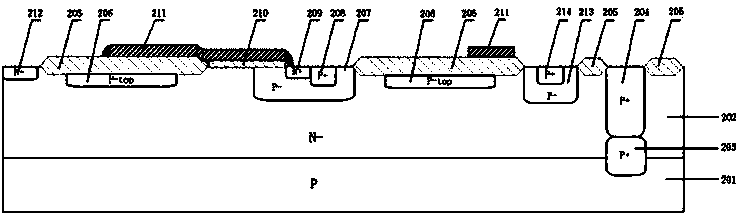

High-sided transverse double diffused field effect transistor

ActiveCN104037231AIncreased avalanche breakdown voltageReduce surface electric fieldSemiconductor devicesDiffuse fieldBody area

The invention discloses a high-sided transverse double diffused field effect transistor. The high-sided transverse double diffused field effect transistor comprises a P type substrate, an N- epitaxial layer, a P+ buried layer, a P+ P-N junction isolation, field oxygen, a P- top layer, P- body areas, a P- body area contact P+, an N+ source electrode, a gate oxygen layer, a polycrystalline silicon gate electrode and an N+ drain electrode, wherein the N- epitaxial layer is arranged above the P type substrate; the P+ buried layer and the P+ P-N junction isolation are arranged at one side of the N- epitaxial layer and are used to isolate different types of devices; furthermore, another P- body area is arranged between the P- body area and the P+ P-N junction isolation; the body area contact P+ is arranged in the P- body area; the P- top layer is arranged between the P- body area and the another P- body area. According to the high-sided transverse double diffused field effect transistor disclosed by the invention, an avalanche breakdown voltage between the source electrode and the substrate is greatly increased, that is, an isolation performance is greatly improved, so that application in the field which requires relatively high working voltage is satisfied.

Owner:ZHEJIANG UNIV

Method for manufacturing high reliability glass passivated miniature surface-mounted diode

InactiveCN107393821AReduce surface electric fieldGood reversing performanceSemiconductor/solid-state device manufacturingSemiconductor devicesThermal expansionBoron trioxide

The invention provides a method for manufacturing high reliability glass passivated miniature surface-mounted diode. The method comprises diode core preparation, electrode welding and processing and package. A forward sand blasting cutting mode is used by chip separation to form a positive oblique angle, the surface electric field of a device is greatly reduced, and the stability of a chip surface is improved. In a chip corrosion process, acid corrosion is used to remove a chip mesa damage layer, a corrosion process is used to remove heavy metal ions adhered to the chip surface, a process of neutralizing alkali metal ions in a thermal passivation mode and growing a silicon dioxide passivation protection layer at the chip surface is used, the chip surface is cleaned to the maximum, the influence of interface charge is reduced, thus the device has good reverse performance, and the reliability of the product is improved. Passivation glass powder with the main components of zinc oxide, diboron trioxide and silicon dioxide is subjected to high temperature molding to realize the passivation and packaging effect of a chip mesa, the thermal expansion coefficients of an electrode and chip are same with that of a glass passivation layer, the ability of resistance to temperature shock of the product is improved, a special solder is used to sinter the electrode and an axial product, and a surface-mounted package structure is realized.

Owner:CHINA ZHENHUA GRP YONGGUANG ELECTRONICS CO LTD STATE OWNED NO 873 FACTORY

ESD (electrostatic discharge) high-voltage DMOS (diffused metal oxide semiconductor) device and manufacturing method thereof

ActiveCN102130163ALower breakdown voltageLower the trigger voltageSemiconductor/solid-state device detailsSolid-state devicesImpurity ionsIon implantation

The invention discloses an ESD (electrostatic discharge) high-voltage DMOS (diffused metal oxide semiconductor) device which comprises an ESD ion injection region, wherein the ESD ion injection region is formed in part of a drift region under a field oxide layer, impurity ions are injected into a buried layer and enter into the drift region by annealing, propelling and diffusing, and the ESD ion injection region has impurity distribution with gradually reduced concentration between the buried layer and the bottom of the field oxide layer. The invention further discloses a manufacturing methodof the ESD high-voltage DMOS device. By adopting the device and the manufacturing method, the trigger voltage of the device can be effectively reduced, the resistance of the drift region and the on-resistance of the device can be reduced, the strength of a surface electric field of the drift region can be reduced, and a gate oxide can be protected.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Silicon carbide MOSFET device and preparation method thereof

PendingCN109755322AImprove freewheeling abilityReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETPower flow

The invention discloses a silicon carbide MOSFET device and a preparation method thereof. The silicon carbide MOSFET device comprises, form bottom to top, a leakage electrode, a N+substrate and N-epitaxial layer. The N-epitaxial layer is provided with first P-well areas, a first metal, second well areas and a second metal. The first P-well areas are provided with P+areas and N+areas; first ohmic contact is formed by the first metal, the upper surfaces of the P+areas and part of the upper surfaces of the N+areas; the second P-well areas are arranged between every two adjacent first P-well areas, the second P-well areas and the first P-well areas arranged on two side of the second P-well areas are all provided with first gaps, and grooves are encircled by the second P-well areas; and the second metal covers the surface of the groove to form second ohmic contact and the upper surface of the first gap to form Schottky contact. According to the silicon carbide MOSFET device, the flow-continuing ability is improved, and meanwhile the problem that the leakage current of the Schottky contact area in a high-pressure blockage mode is too large is solved.

Owner:厦门芯光润泽科技有限公司

NLDMOS device and manufacturing method thereof

ActiveCN104064596ALower on-resistanceAchieve regulationTransistorSemiconductor/solid-state device manufacturingIon implantationBreakdown voltage

The invention discloses an NLDMOS device. A drift region is composed of a first N-type ion injection region which is formed in an N-type epitaxial layer, a first P-type ion injection region which is arranged on the bottom part of the first N-type ion injection region, and an N-type epitaxial layer. The first N-type ion injection region can greatly increase conduction current and reduce conduction resistance; and longitudinal exhausting can be performed on the first N-type ion injection region from the bottom part by the first P-type ion injection region so that electric field distribution in the drift region can be changed, a device surface electric field can be reduced, voltage-withstanding performance of the device can be enhanced and reduction of breakdown voltage of the device can be avoided when conduction current increases. The invention also discloses a manufacturing method for the NLDMOS device. The NLDMOS device is great in compatibility with an existing BCD technology platform, stable in technology and relatively low in cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

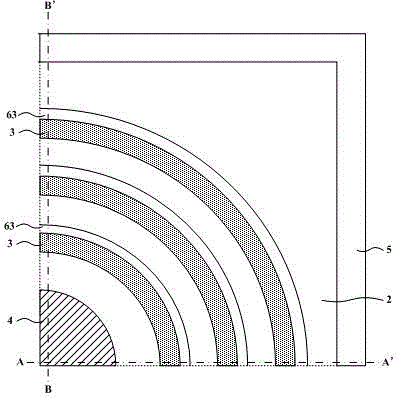

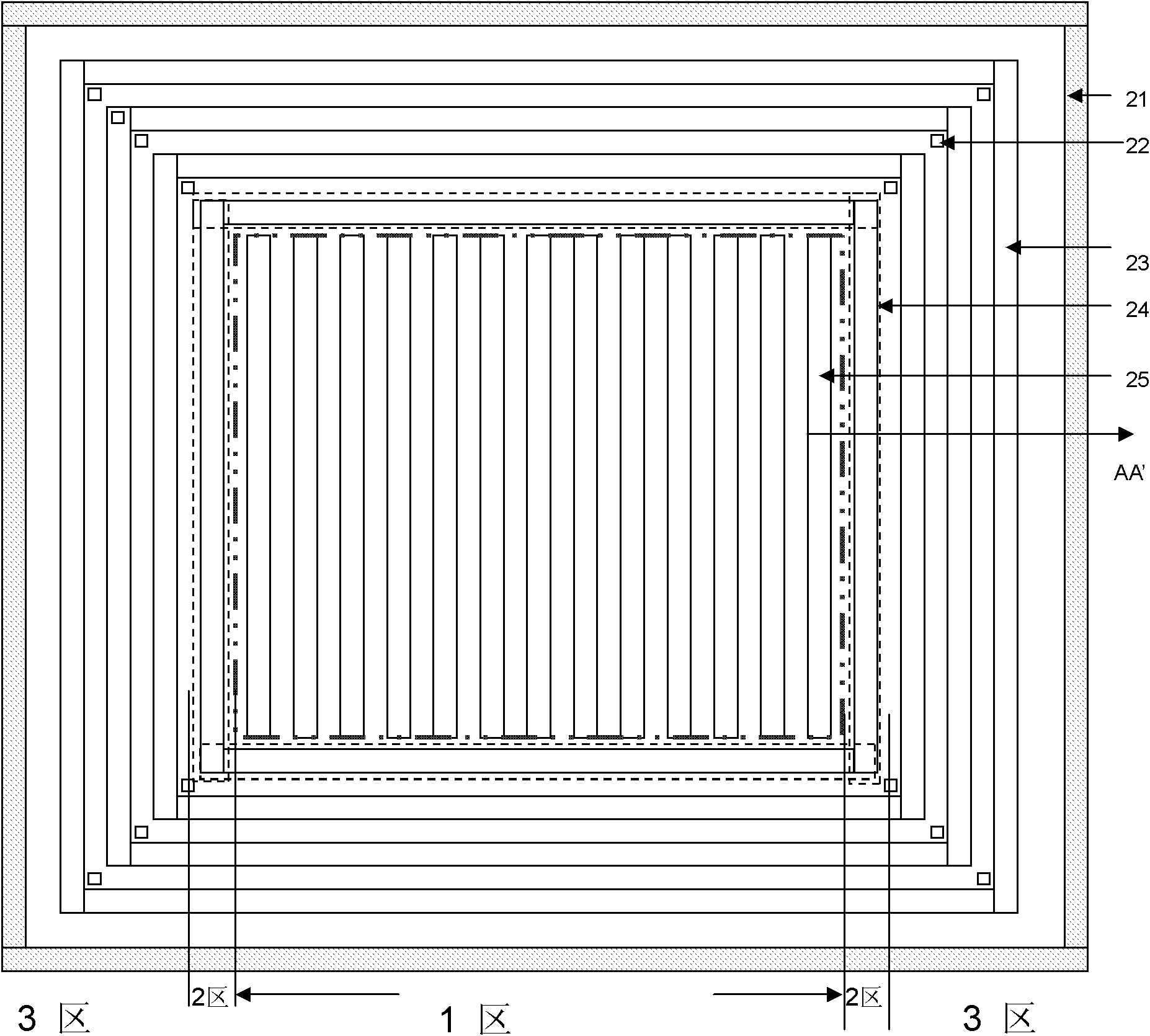

Terminal structure of metal oxide semiconductor field effect transistor and manufacturing method of terminal structure of metal oxide semiconductor field effect transistor

ActiveCN104465773AImprove breakdown voltageImprove the effective use of areaSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETField-effect transistor

The invention relates to a terminal structure of a metal oxide semiconductor field effect transistor (MOSFET). The terminal structure comprises an N-type cut-off ring and further comprises a first P-type low-doped region and a second P-type low-doped region, wherein the first P-type low-doped region and the second P-type low-doped region are formed between the cut-off ring and an active region through ion implantation, the implantation dose ranges from 1.5*10<11> / cm<2> to 2*10<13> / cm<2>, implantation energy ranges from 20 kilo electron volts to 80 kilo electron volts, the first P-type low-doped region is closer to the active region than the second P-type low-doped region, and the length of the first P-type low-doped region is smaller than that of the second P-type low-doped region. The invention further relates to a manufacturing method of the terminal structure of the MOSFET. The two P-type low-doped regions are adopted for reducing a surface electric field and increasing the breakdown voltage of the MOSFET, the terminal structure replaces a traditional terminal structure with a plurality of voltage dividing rings, the terminal size is greatly reduced, the effective use area of a chip is increased, and parameters of the chip are more excellent under the same area.

Owner:深圳深爱半导体股份有限公司

Super junction device terminal protection structure and manufacturing method thereof

ActiveCN102738207AImprove withstand voltage characteristicsIncreased current handling capabilitySolid-state devicesSemiconductor/solid-state device manufacturingHigh concentrationEngineering

The invention discloses a terminal protection structure of a super junction device. The composite structure of polysilicon field plates and metal field plates is employed, and a group of polysilicon field plates and metal field plates simultaneously cover the step structure of a terminal dielectric film, thus an electric field on the device surface is eased. According to the invention, a P-type ring with a high concentration is kept under a field plate, thus the current processing capability of the application of the device in an inductive circuit is improved. In the terminal protection structure provided by the invention, the depth of a P-type column and a N-type column is lower than the depth of a P-type area and a N-type area in a current flowing area to ensure that the device is turned off when the device is applied in the inductive circuit and that the position where an avalanche breakdown occurs in the terminal protection structure is close to the position of the obverse of a silicon chip when a current overshoot occurs, and to improve the capacity of anti-overshoot current of the device. The invention further discloses the super junction device terminal protection structure and a manufacturing method thereof. According to the invention, the breakdown characteristic, the current processing capability and the reliability of the device is improved without process cost increasement.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

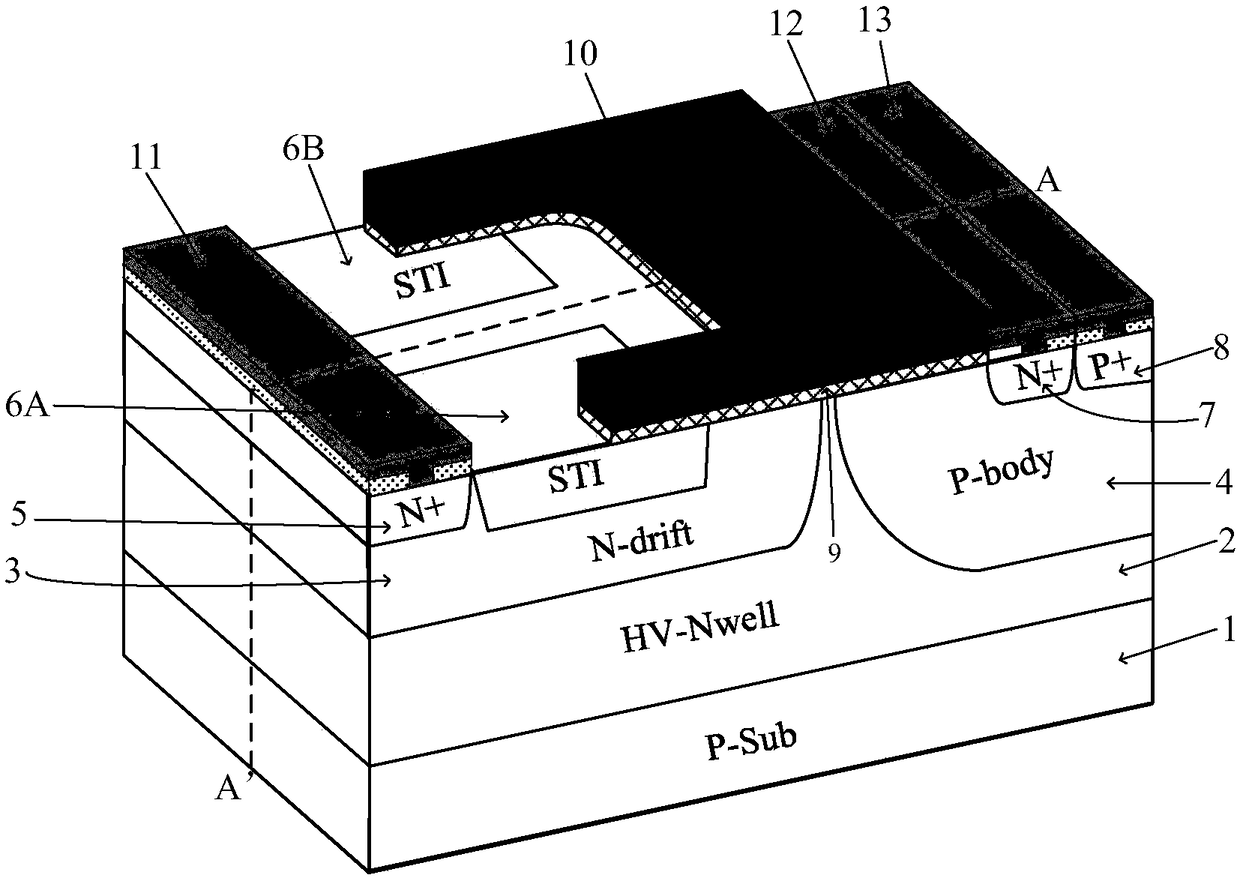

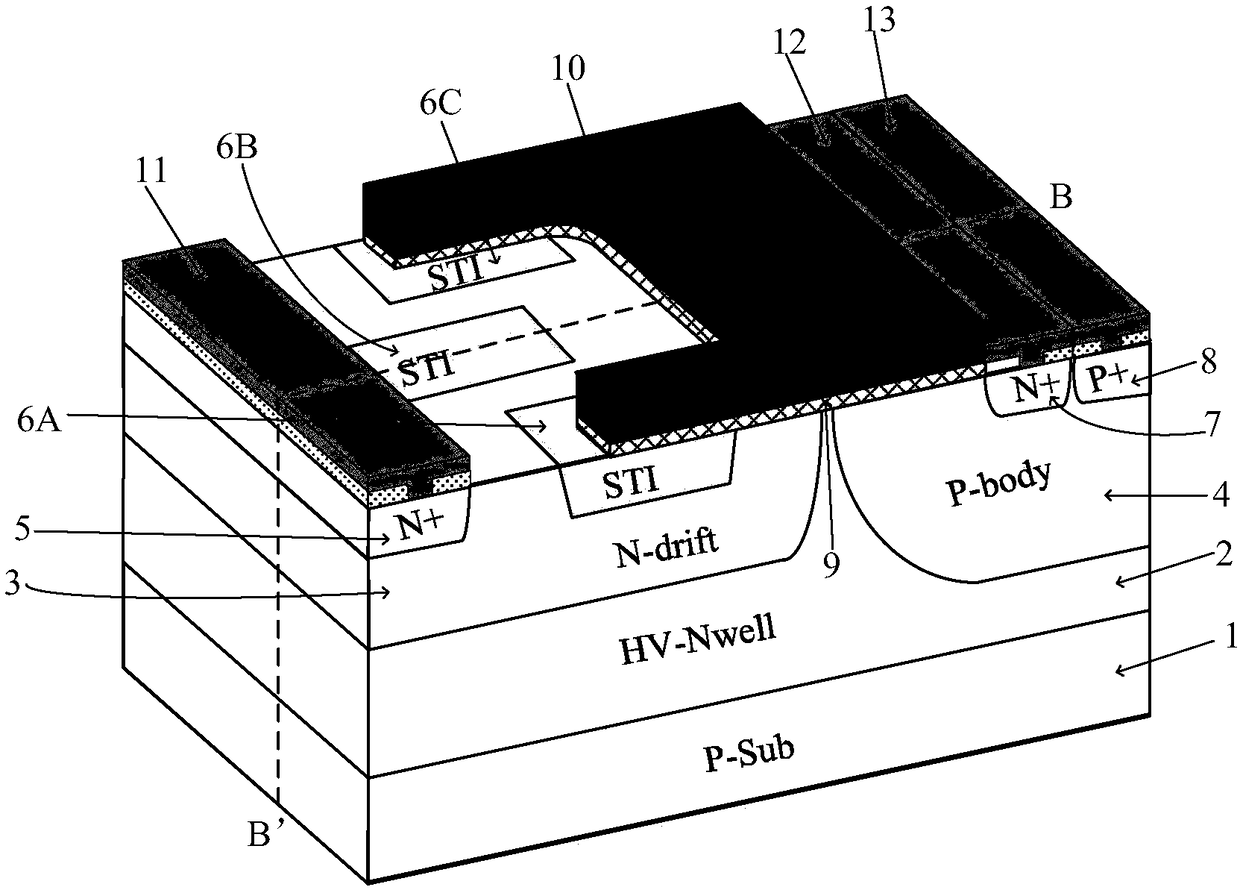

Shallow-groove isolation structure transverse semiconductor device arranged in staggered and interdigital way

ActiveCN108807541AShorten the lengthThe breakdown voltage does not changeSemiconductor/solid-state device manufacturingSemiconductor devicesGate oxideHigh pressure

A shallow-groove isolation structure transverse semiconductor device arranged in a staggered and interdigital way comprises a P-type substrate, wherein a high-voltage N-type region is arranged on theP-type substrate, an N-type drift region and a P-type body region are arranged on the high-voltage N-type region, an N-type drain region and three shallow-groove isolation regions are arranged in theN-type drift region, an N-type source region and a P-type region are arranged in the P-type body region, a U-shaped gate oxide layer is further arranged on the high-voltage N-type region, a U-shaped opening of the gate oxide layer faces a drain end, two ends of the gate oxide layer respectively extend to a part above the P-type body region and a part above the shallow-groove isolation regions, a poly-silicon gate field plate is arranged on the gate oxide layer, drain metal contact, source metal contact and body region metal contact are respectively arranged on upper surfaces of the N-type drain region, the N-type source region and the P-type region, and the shallow-groove isolation structure transverse semiconductor device is characterized in that the shallow-groove isolation regions are arranged in the drift region in the staggered and interdigital way. By the structure, relatively low conduction resistance can be obtained on the basis that the breakdown voltage is not changed.

Owner:SOUTHEAST UNIV

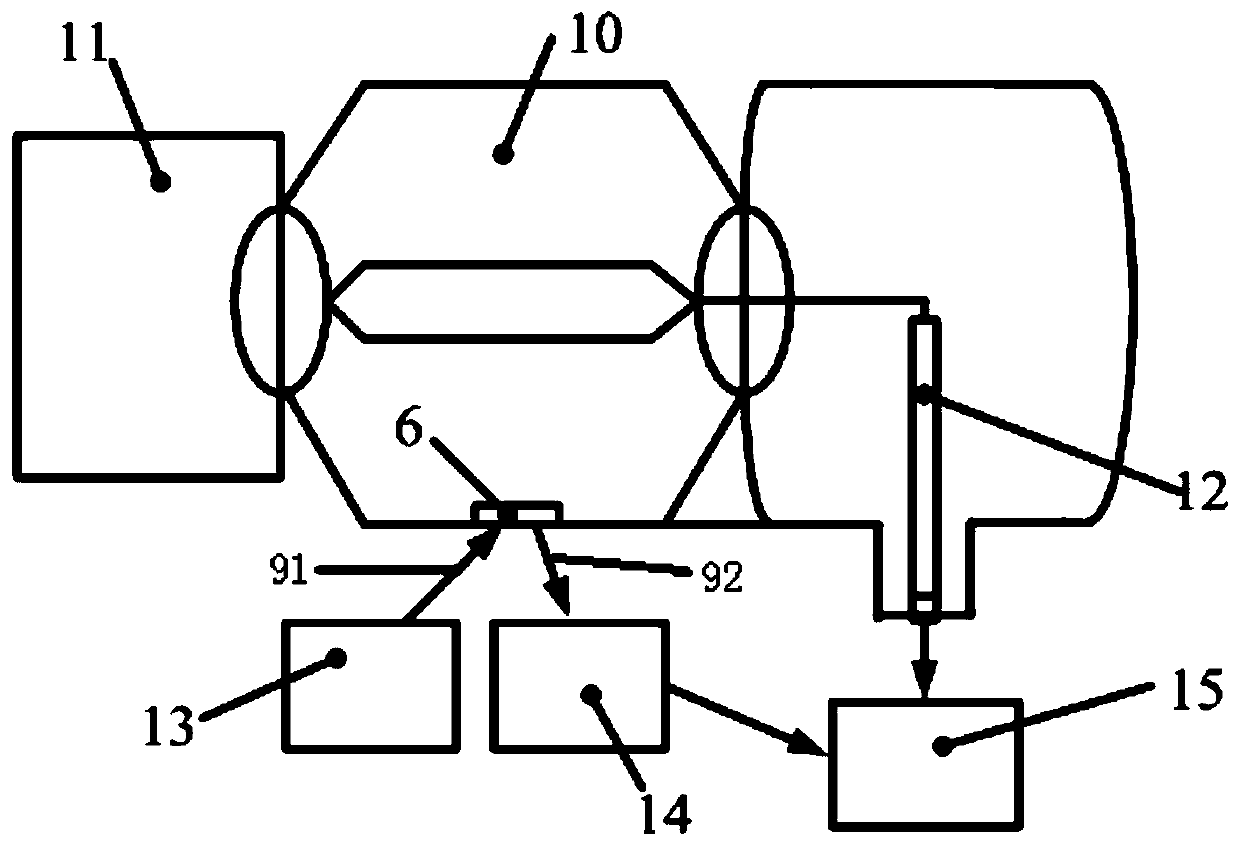

Mounting assembly for all-optical overvoltage sensor for overvoltage measurement

ActiveCN105388354AAvoid measuringReduce surface electric fieldCurrent/voltage measurementOvervoltageMeasurement device

The invention relates to a mounting assembly for an all-optical overvoltage sensor, and belongs to the technical field of voltage measurement. The mounting assembly comprises a sensor fixing housing, a transmission conductor expansion sleeve, a PVC hose, a polarization maintaining optical fiber patch cord disposed in the hose in a sleeving manner, an optical fiber insulator provided internally with a polarization maintaining optical fiber, and a connecting fitting. The transmission conductor expansion sleeve sleeves a transmission conductor fixedly. A sensor is mounted in the sensor fixing housing. The sensor fixing housing sleeves the transmission conductor expansion sleeve fixedly. Two ends of the PVC hose are respectively connected with the sensor fixing housing and the optical fiber insulator. Two ends of the polarization maintaining optical fiber patch cord in the PVC hose are respectively connected with a tail fiber of the sensor and the polarization maintaining optical fiber disposed in the optical fiber insulator. According to the invention, the mounting assembly can be used for fixing the sensor onto a transmission line for long term monitoring, non-electrical connection between a sensor measurement device and a power system is achieved, the safety of measurement is improved, and meanwhile, the impact of a non-measurement phase on the measurement is greatly reduced.

Owner:STATE GRID SICHUAN ELECTRIC POWER CORP ELECTRIC POWER RES INST +1

JTE and buried FLR composite terminal structure power device and preparation method thereof

ActiveCN111755497ASimple structure and processImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSurface charges

The invention discloses a power device JTE and buried FLR composite terminal structure and a preparation method thereof. The novel terminal structure is mainly formed by combining three structures: anupper layer of a junction terminal region of an N-type (or P-type) epitaxial voltage-withstanding layer is a P-type layer (when the epitaxy is P-type, the P-type layer is N-type) which is doped opposite to the epitaxial layer, a plurality of discrete groove rings are arranged in the upper P-type layer, and SiO2 or other High-K media are filled in grooves; a P-type ring buried field limiting ringstructure which is doped opposite to the epitaxial layer is further arranged under each groove, the upper portions of the P-type rings are connected with the P-type layer on the upper layer, and therefore the composite structure voltage-withstanding terminal with the JTE structure on the upper layer and the FLR on the lower layer is formed. The composite terminal is simple in structure and process, is not sensitive to JTE concentration or process deviation of FLR ring width and spacing and surface charges, and can greatly improve the voltage endurance capability of the device terminal and reduce the chip area of the required voltage endurance terminal.

Owner:BEIJING CENTURY GOLDRAY SEMICON CO LTD

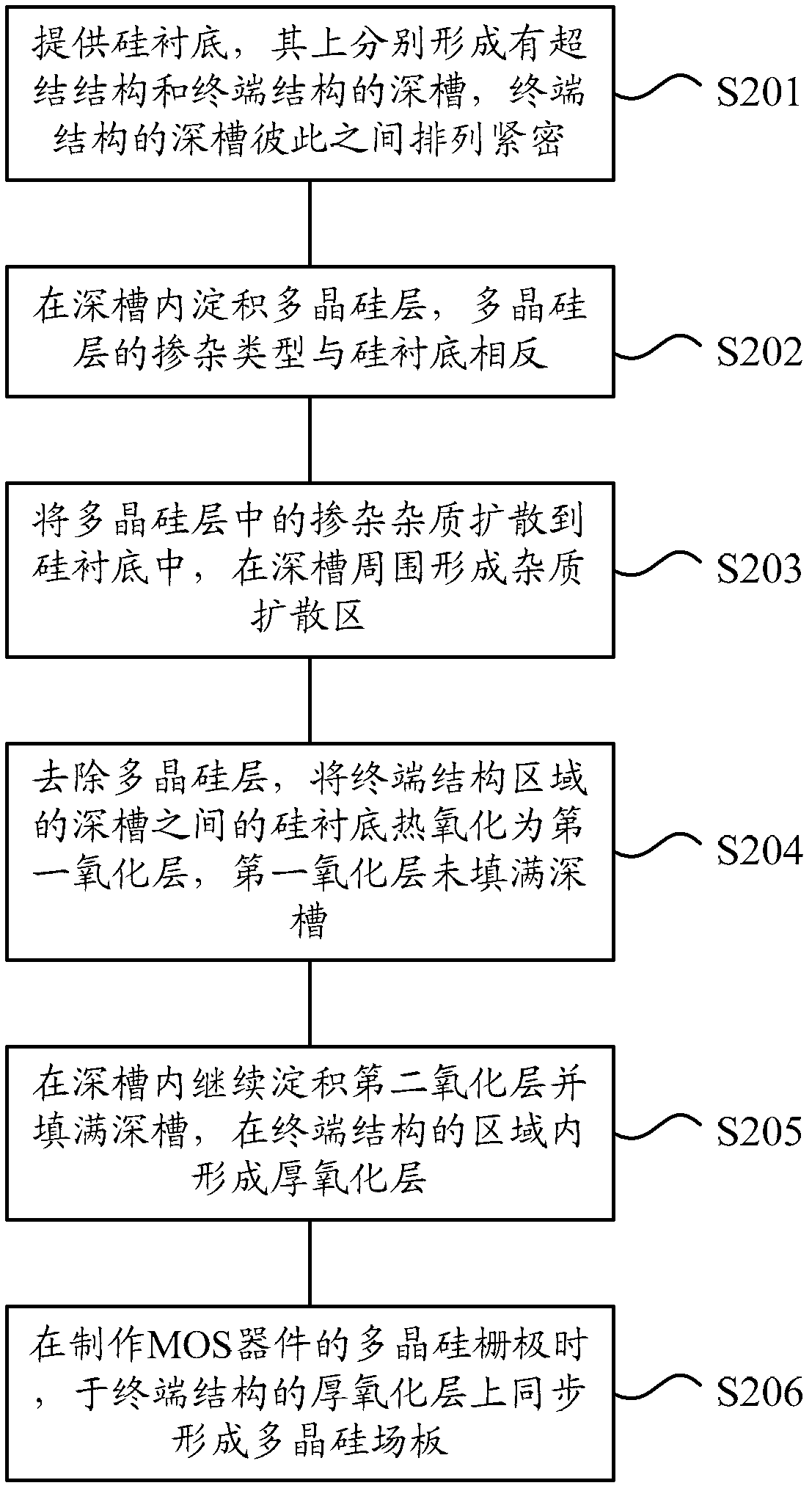

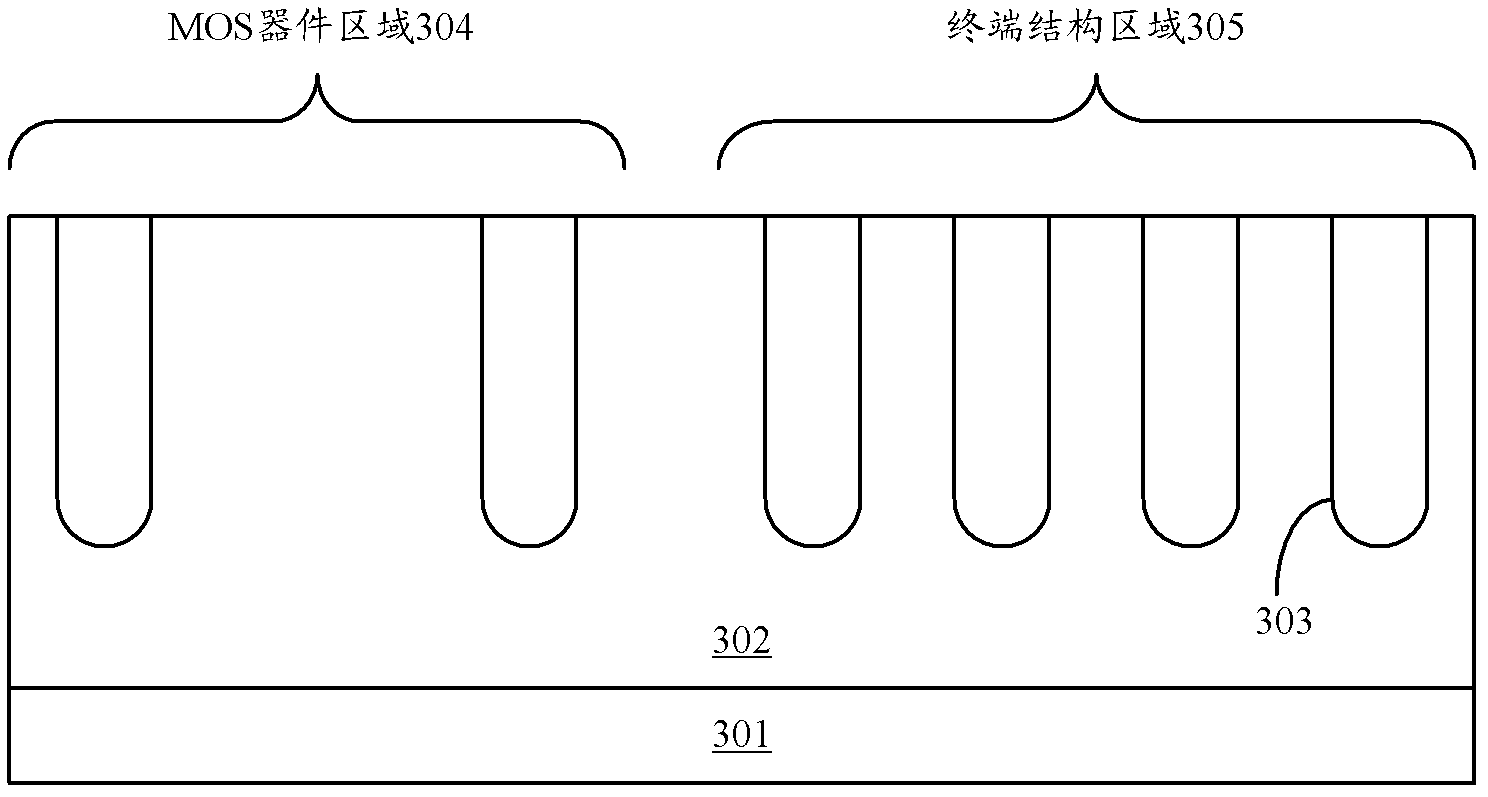

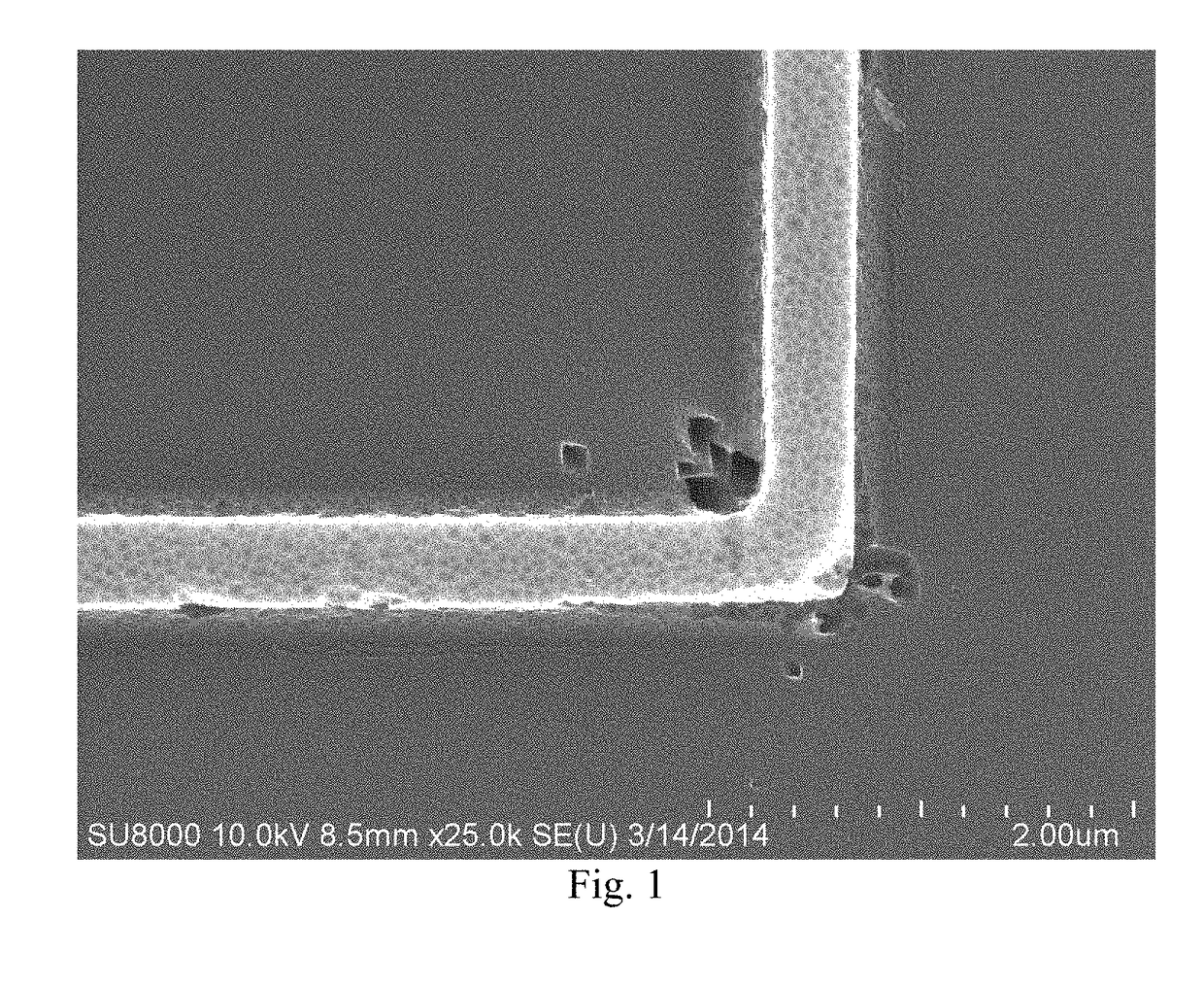

Method for manufacturing terminal structure of deep-groove super-junction metal oxide semiconductor (MOS) device

InactiveCN102214581AReduce surface electric fieldGood partial pressure effectSemiconductor/solid-state device manufacturingSemiconductor devicesImpurity diffusionMetal

The invention provides a method for manufacturing a terminal structure of a deep-groove super-junction metal oxide semiconductor (MOS) device, which comprises the following steps of: providing a silicon substrate, wherein deep grooves with a super-junction structure and a terminal structure are formed on the silicon substrate respectively, and the deep grooves with the terminal structure are formed closely; depositing polycrystalline silicon layers in the deep grooves, wherein the doping type of the polycrystalline silicon layers is opposite to that of the silicon substrate; diffusing doped impurities in the polycrystalline silicon layers to the silicon substrate, and forming impurity diffusion areas at the peripheries of the deep grooves; performing thermal oxidation on the silicon substrate between the polycrystalline silicon layers and the deep grooves in a terminal structure area to form oxide layers for completely filling the deep grooves, and forming a thick oxide layer in the terminal structure area; and synchronously forming a polycrystalline silicon field plate on the thick oxide layer in the terminal structure area when a polycrystalline silicon grid of the MOS device is manufactured. The field plate is formed by the polycrystalline silicon grid in the terminal structure area and is combined with the thick oxide layer, and the voltage division effect of the thick oxide layer is effectively utilized, so that the surface field of the device is reduced; and by combining the effects of a deep groove reduced surface field (RESURF) and the field plate, the pressure division effect is obvious, and the area of a terminal is reduced to a great extent.

Owner:ADVANCED SEMICON MFG CO LTD

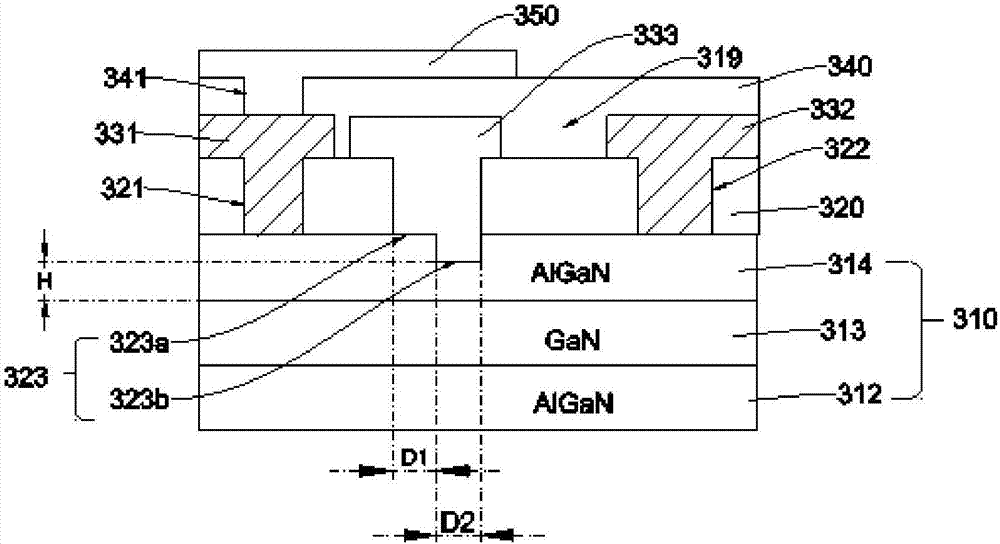

GaN semiconductor device and fabrication method thereof

ActiveCN107316892AReduce contact resistanceImprove breakdown characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerSemiconductor materials

The invention relates to the technical field of a semiconductor material, and provides a GaN semiconductor device. The GaN semiconductor device comprises a GaN epitaxial layer, a hafnium oxide dielectric layer, a source, a drain, a grid, an insulation layer and a field plate metal layer, wherein the hafnium oxide dielectric layer is arranged on the GaN epitaxial layer, the source, the drain and the grid are arranged on the dielectric layer, penetrate through the dielectric layer and are connected with the GaN epitaxial layer, the insulation layer is arranged on the source, the drain, the grid and the dielectric layer, and the field plate metal layer is arranged on the insulation layer. By the GaN semiconductor device, an aluminum nitride Ga layer is difficult to break down, the problems of electric leakage and breakdown occurring in the GaN semiconductor device are further prevented, the GaN semiconductor device is effectively protected, and the reliability of the GaN semiconductor device is improved.

Owner:SHENZHEN JING XIANG TECH CO LTD

Full-range calibration device and method of high voltage nanosecond pulse voltage divider calibration factors

ActiveCN110031789AReduce equivalent inductanceLight weightElectrical measurementsPhysicsElectric field

The invention provides a full-range calibration device and method of high voltage nanosecond pulse voltage divider calibration factors to reduce the measurement deviation of nanosecond pulse voltage in a pulse power technology. According to the full-range calibration device and method, the characteristic that the calibration coefficient of a nanosecond pulse electric field measuring probe can be calibrated by devices such as a GTEM cell or a TEM cell in a large amplitude range is utilized, by correlating the nanosecond pulse voltage and the nanosecond pulse electric field, the present situation of a nanosecond pulse voltage non-standard measurement system under a high-voltage level is skillfully avoided, the calibration of the calibration coefficient of the nanosecond pulse divider under hundreds of kilovolts voltage level is achieved, and the traceability problem of hundreds of kilovolts voltage measurement in the pulse power technology is solved.

Owner:NORTHWEST INST OF NUCLEAR TECH

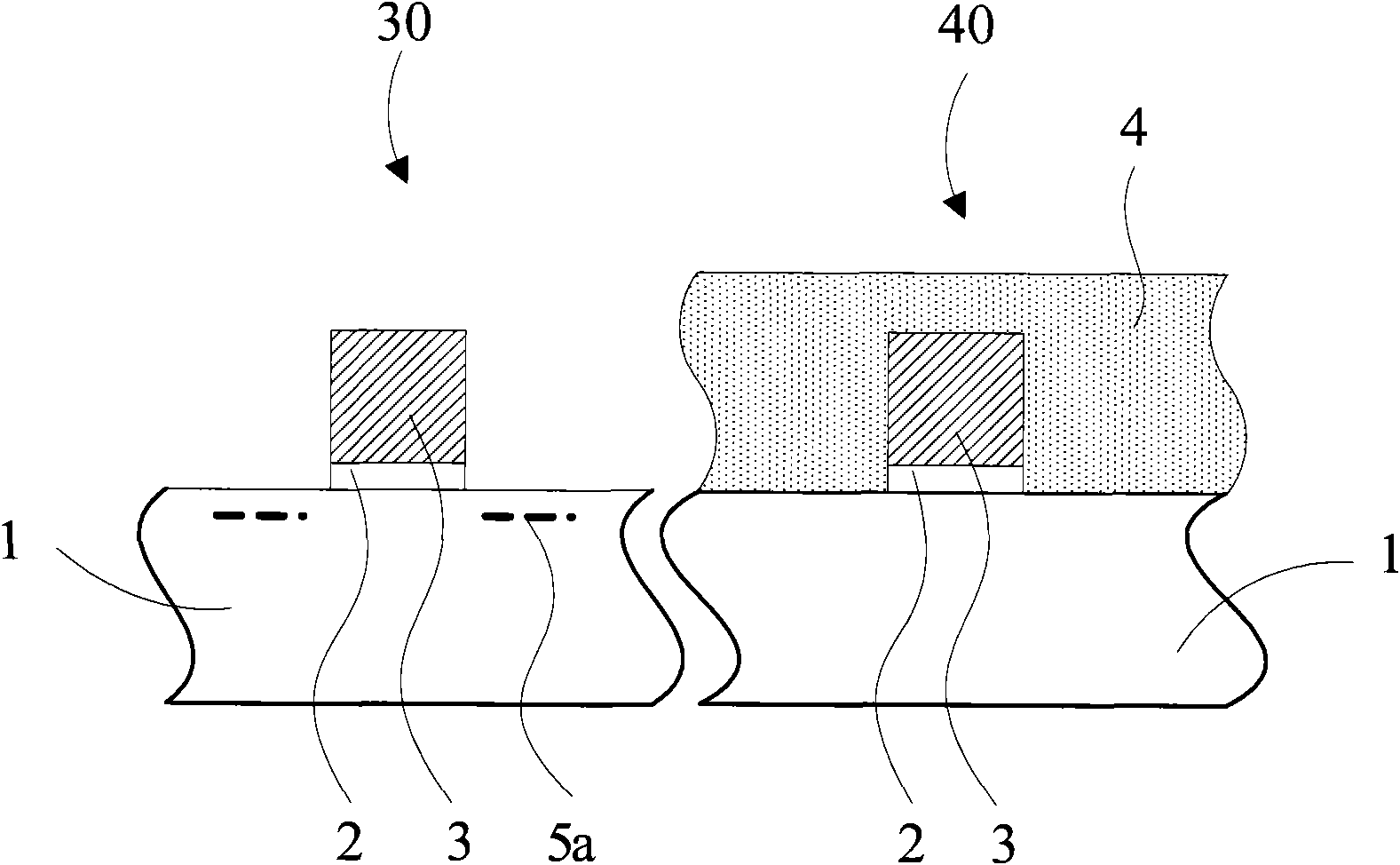

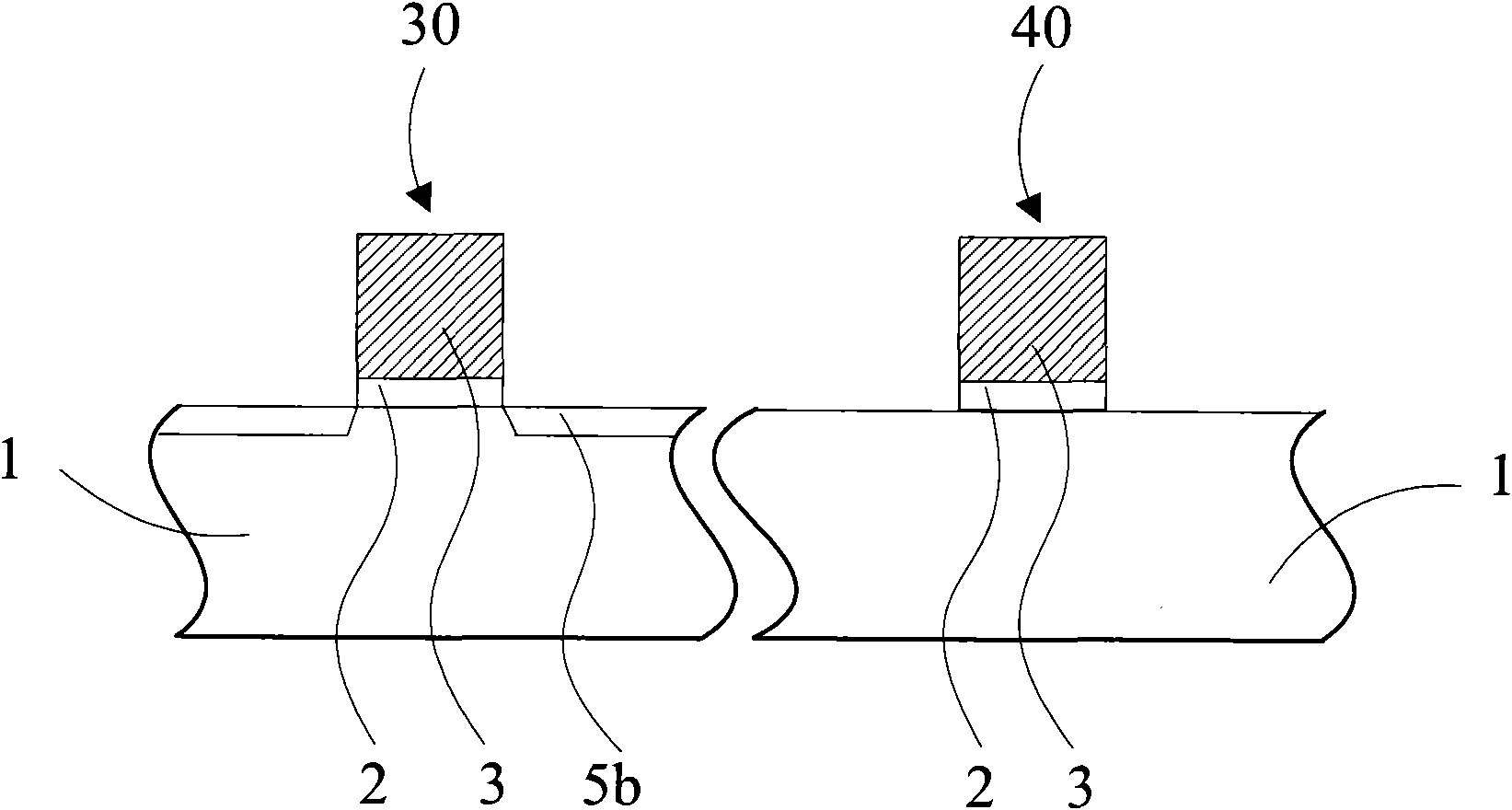

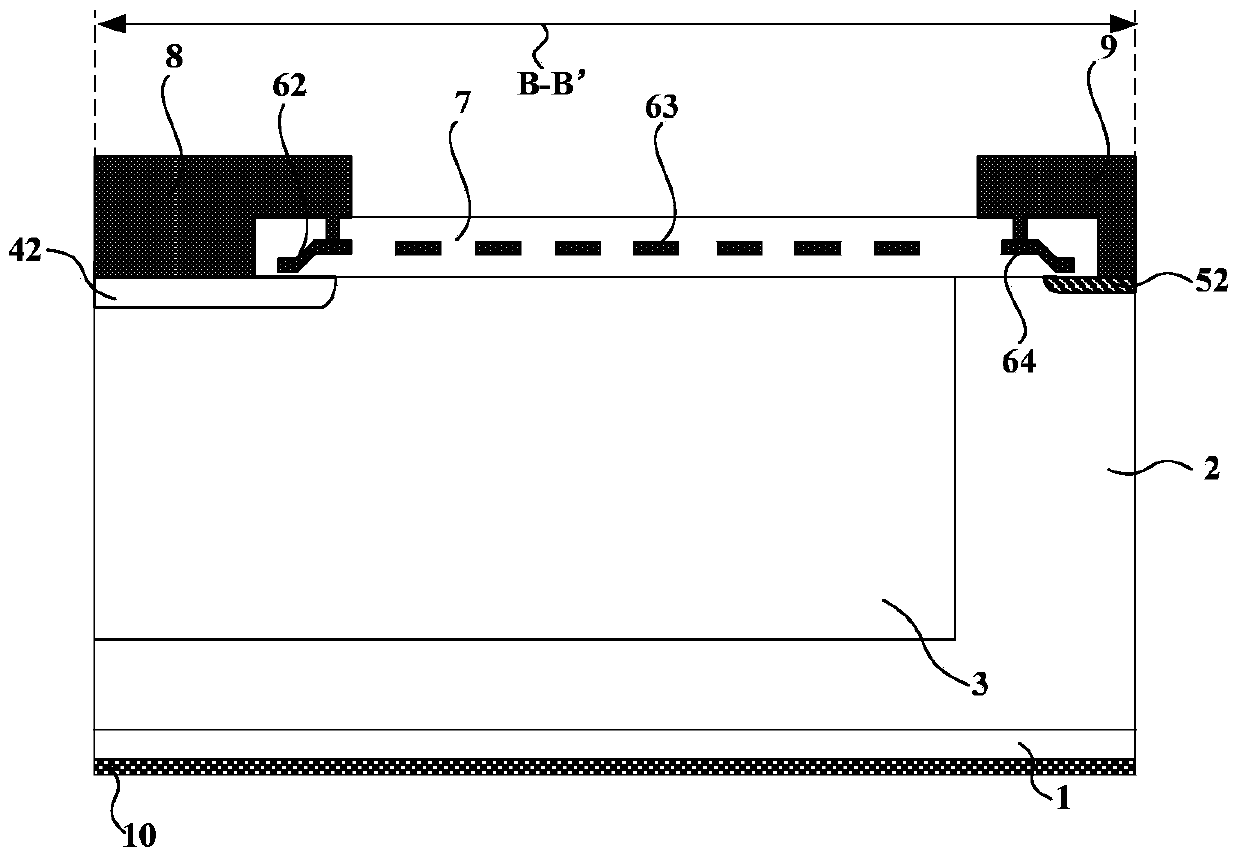

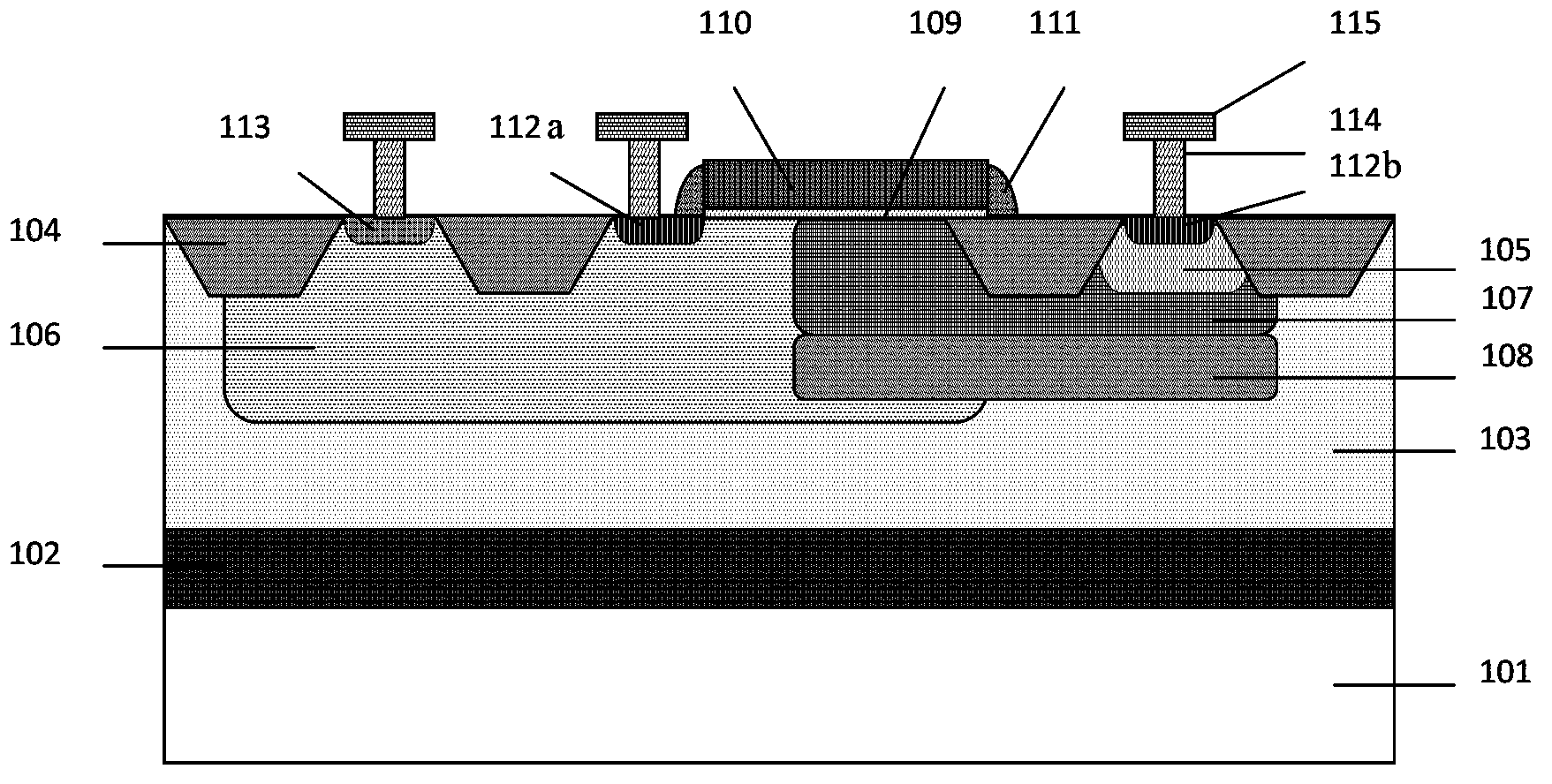

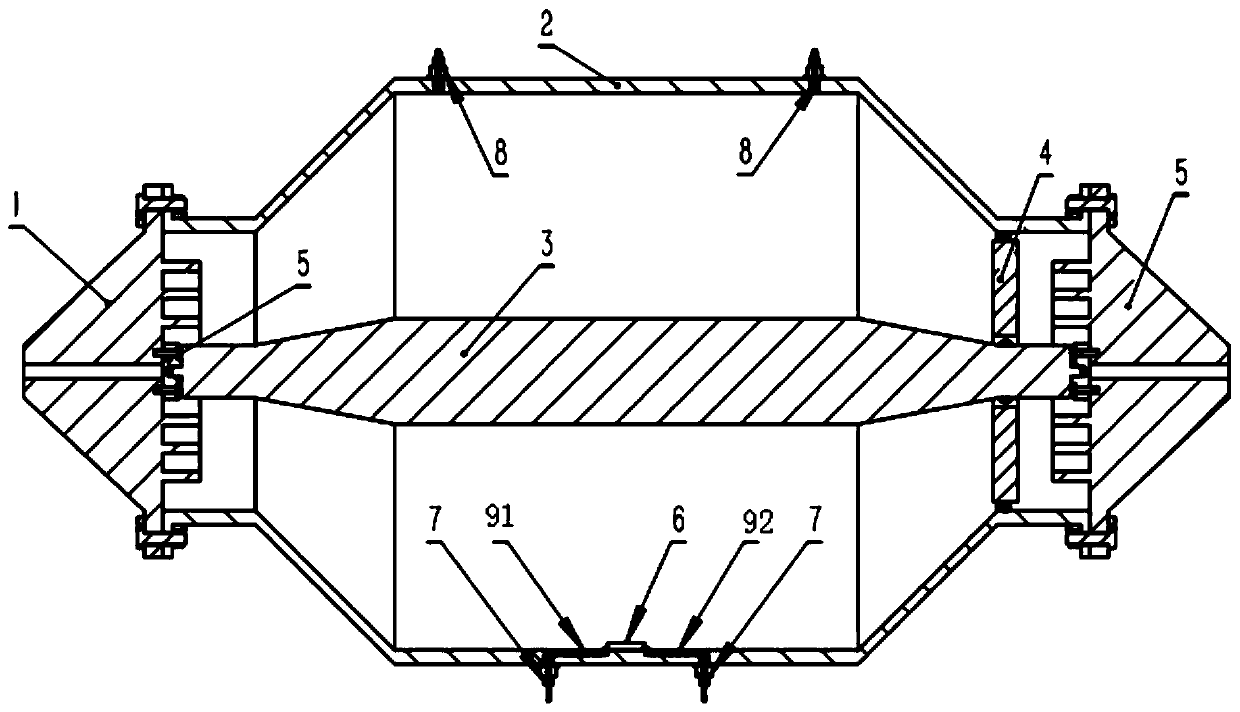

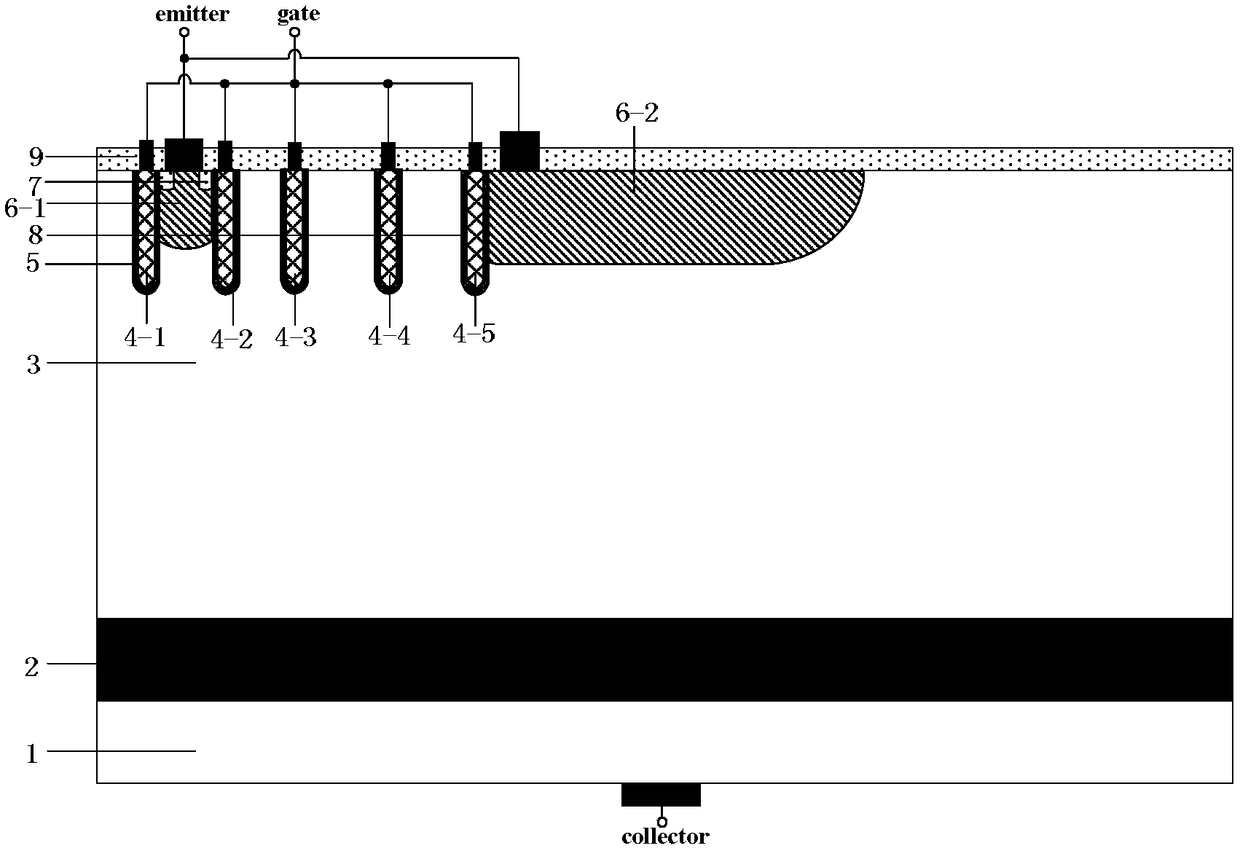

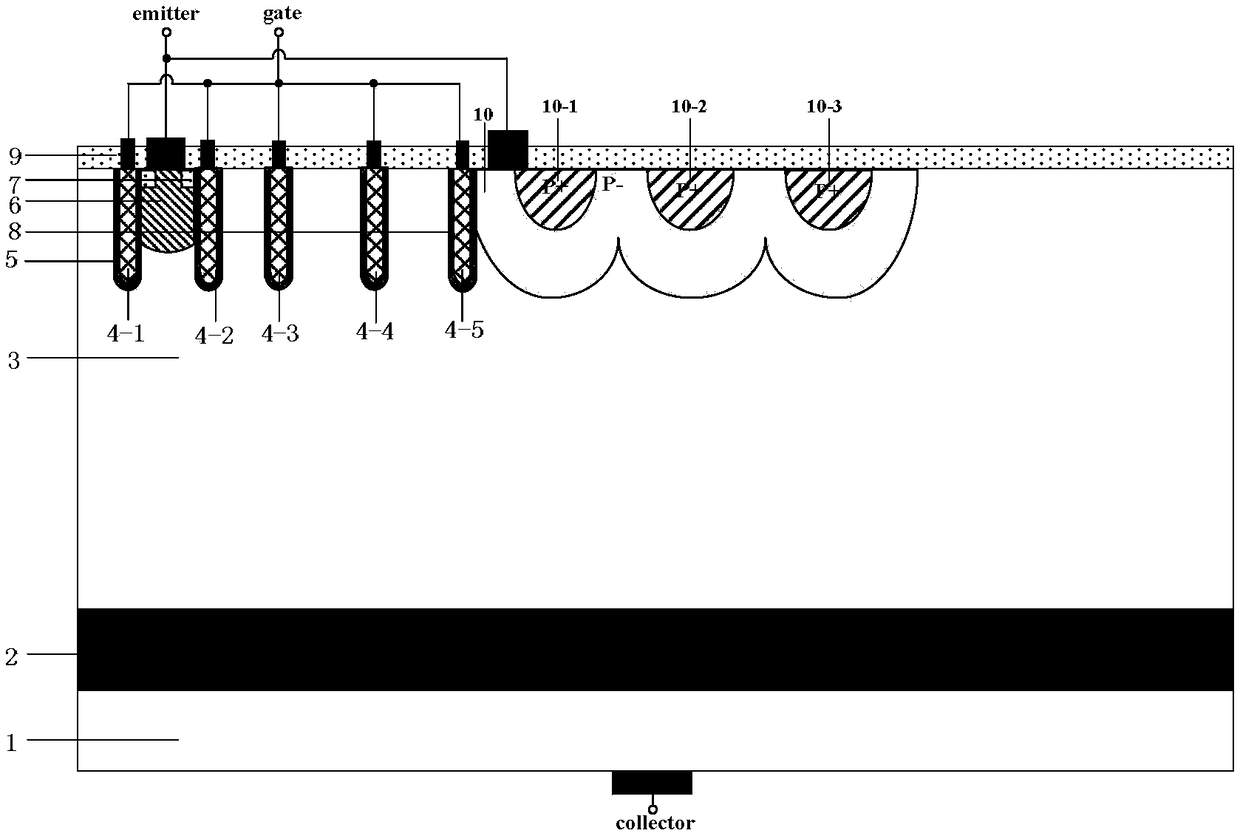

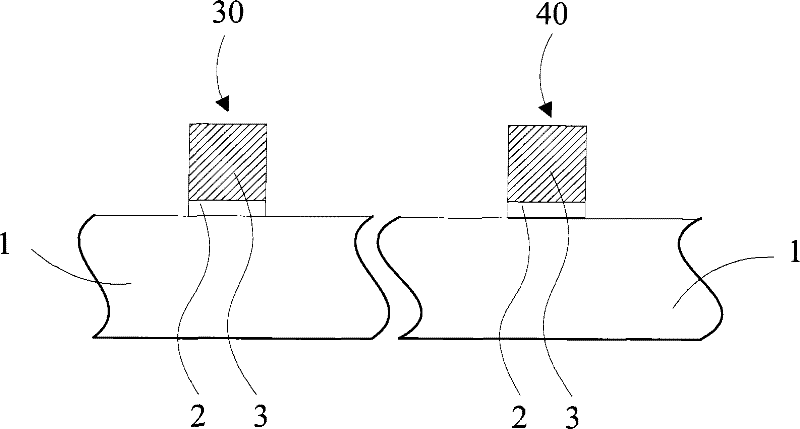

Power semiconductor device with wave type field limiting ring structure and preparation method of device

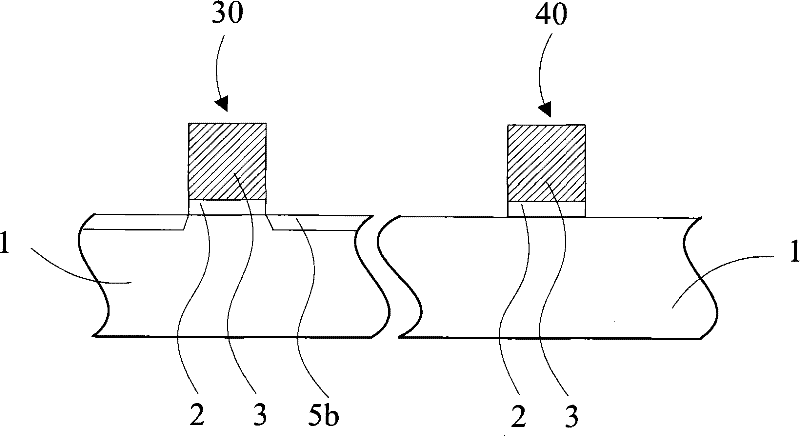

InactiveCN108511512AReduce surface electric fieldSuppression of dynamic avalanchesSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionPhysics

The invention relates to a power semiconductor device with a wave type field limiting ring structure. The device comprises a P-type substrate (1). An N-type buffer layer (2) is arranged on the P-typesubstrate (1). An N-type epitaxial layer (3) is arranged on the N-type buffer layer (2). The N-type epitaxial layer (3) is divided into a cell region, a transition region, and a termination region. Gate trenches (4-1) and (4-2) are formed in the cell region. Gate trenches (4-3), (4-4) and (4-5) are formed in the transition region. A P-type body region (6) is arranged between the gate trenches (4-1) and (4-2). A heavily doped N-type emitter (7) is arranged in the P-type body region (6). The device is characterized in that a wave-type overlapped ion diffusion region (10) is arranged in the terminal region; and ion implantation regions (10-1), (10-2) and (10-3) are arranged in the wave-type ion diffusion region (10). The device structure of the present invention is capable of suppressing electric field spikes generated when the device is turned off, thereby suppressing dynamic avalanche.

Owner:SOUTHEAST UNIV +1

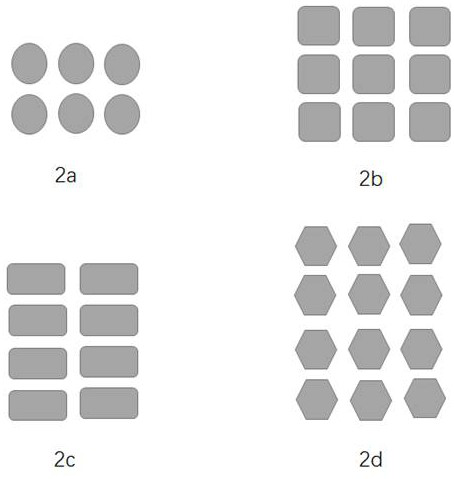

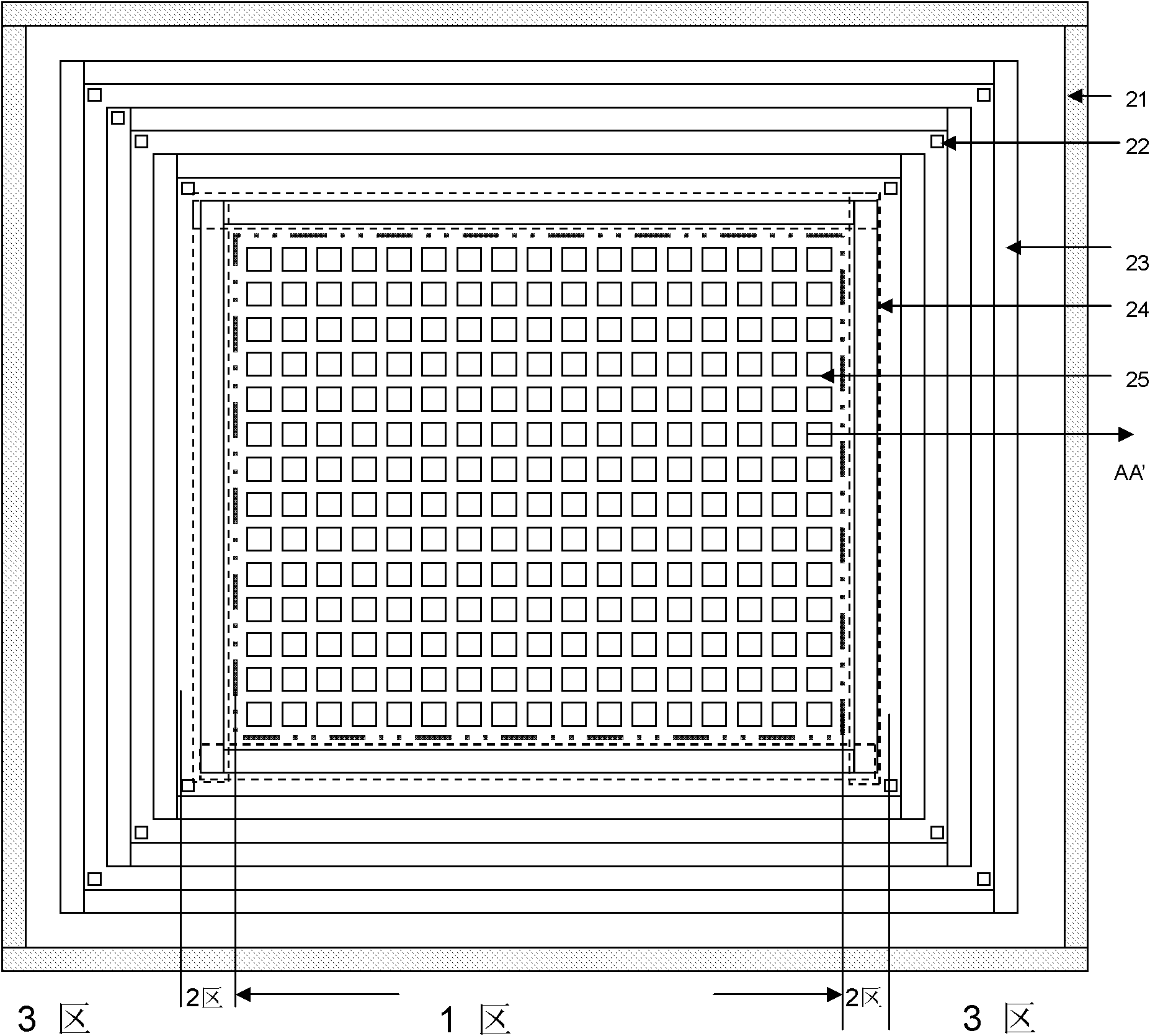

High-voltage semiconductor component

ActiveCN109560119AImprove breakdown voltageCrash Voltage ReducedSolid-state devicesSemiconductor devicesHigh pressureCondensed matter physics

The invention discloses a high-voltage semiconductor component comprising a substrate, a first well region having a second conductivity type, a second well region having a first conductivity type, a first doped region, a second doped region, a gate structure and multiple isolation structures. The first well region is located on the substrate. The second well region is located on the substrate nextto the first well region. The first doped region is located in the first well region. The second doped region is located in the second well region. The gate structure is loated on the substrate between the first doped region and the second doped region. The isolation structures are located in the first well region. The isolation structures are staggered in an array. Each isolation structure includes a dielectric pillar and a top doped region below the dielectric pillar. The bottom surface of the first well region is lower than the bottom surface of each isolation structure.

Owner:NUVOTON

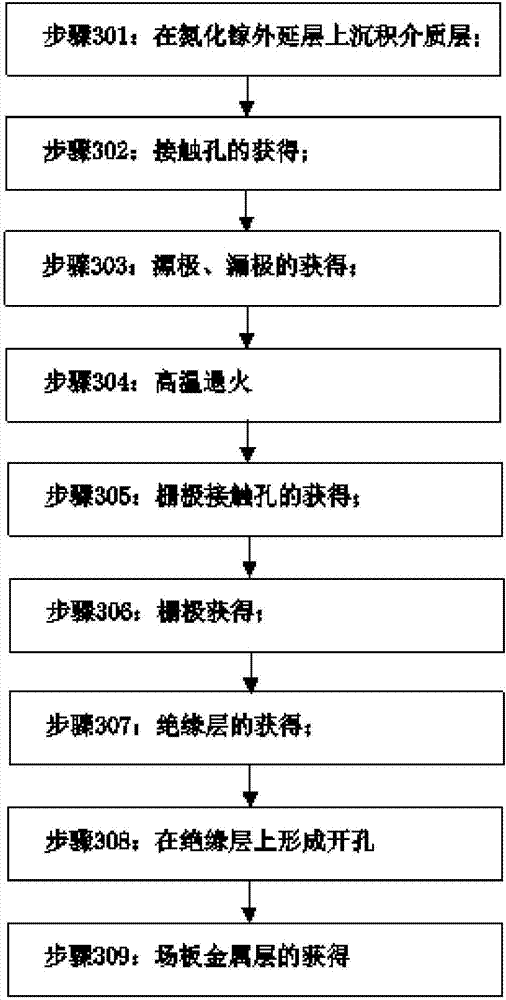

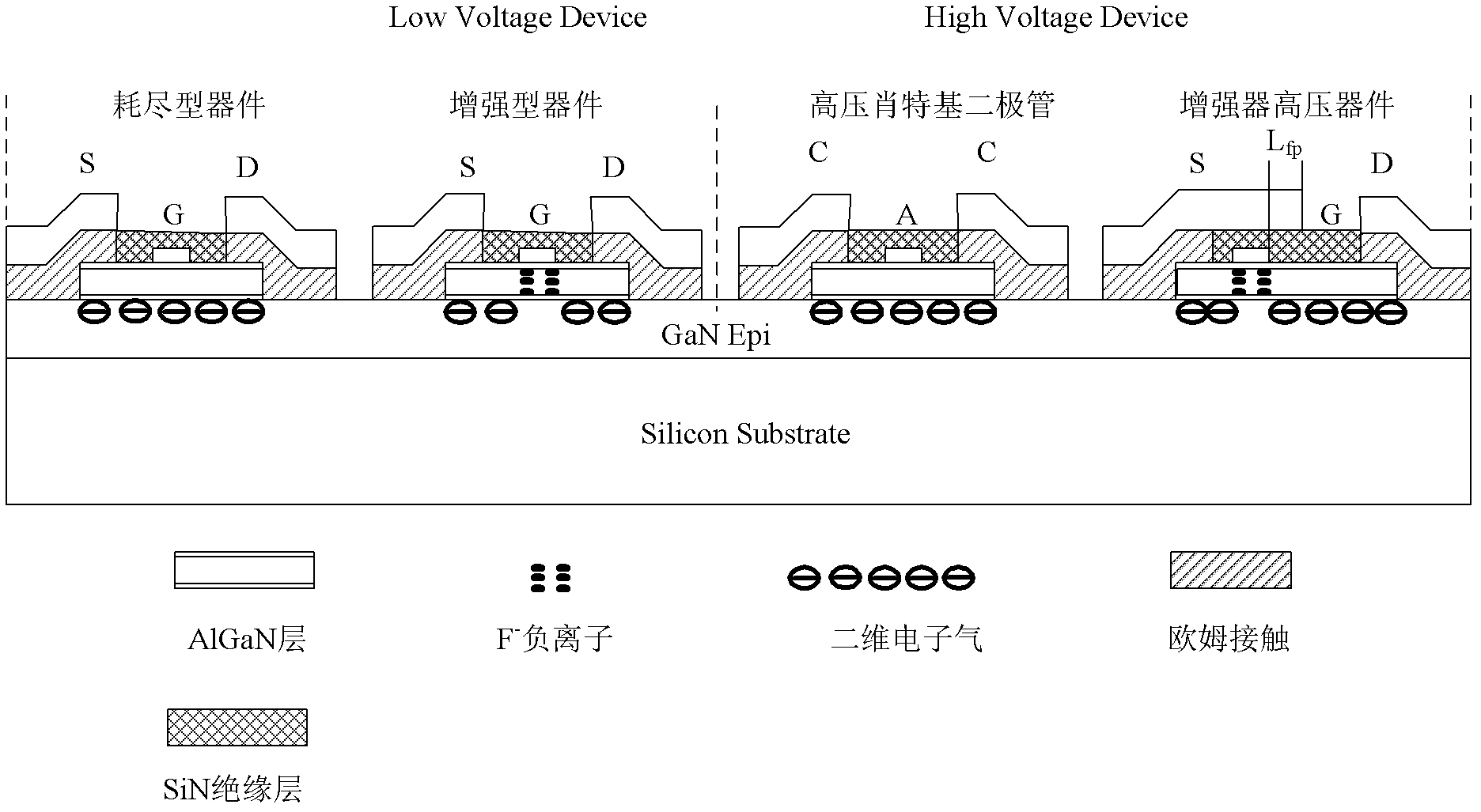

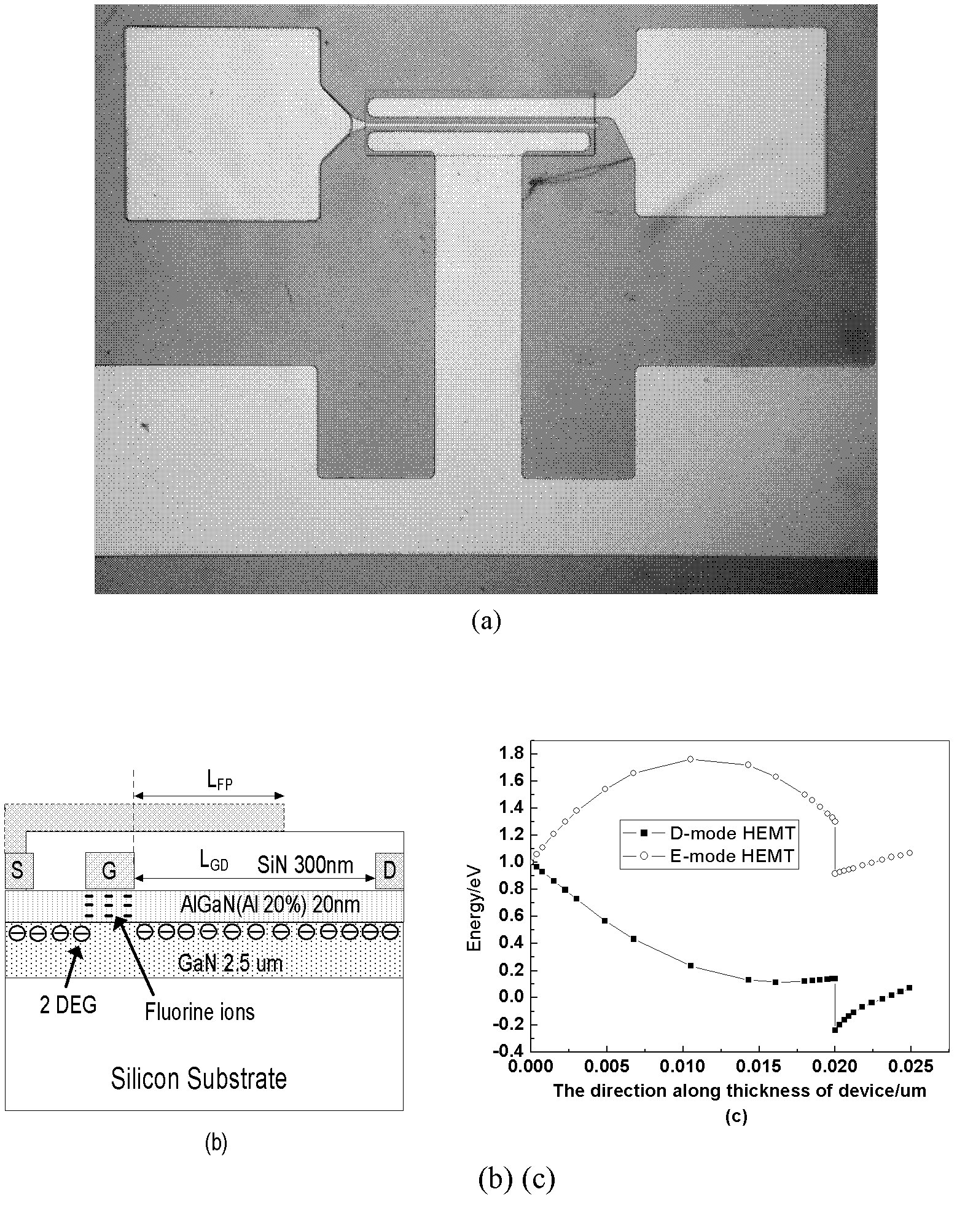

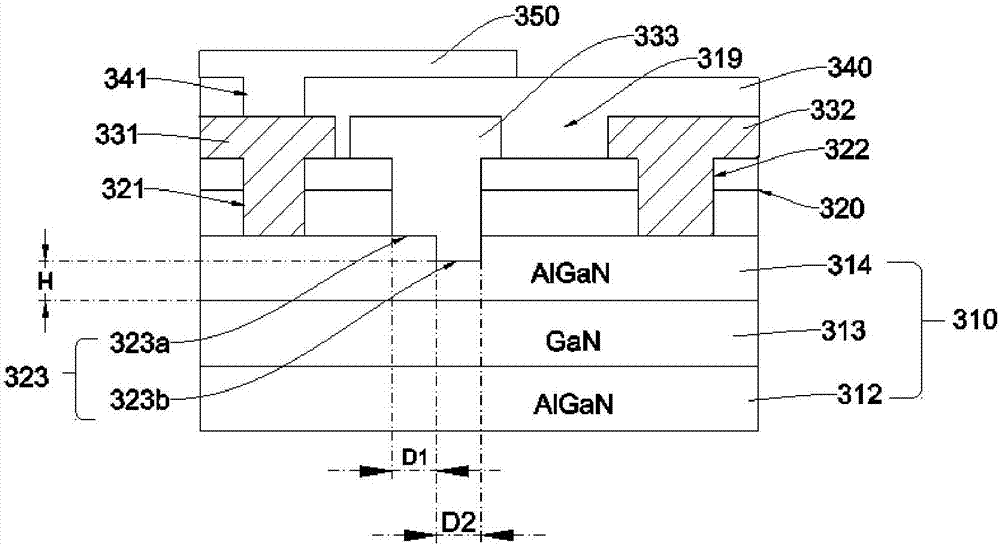

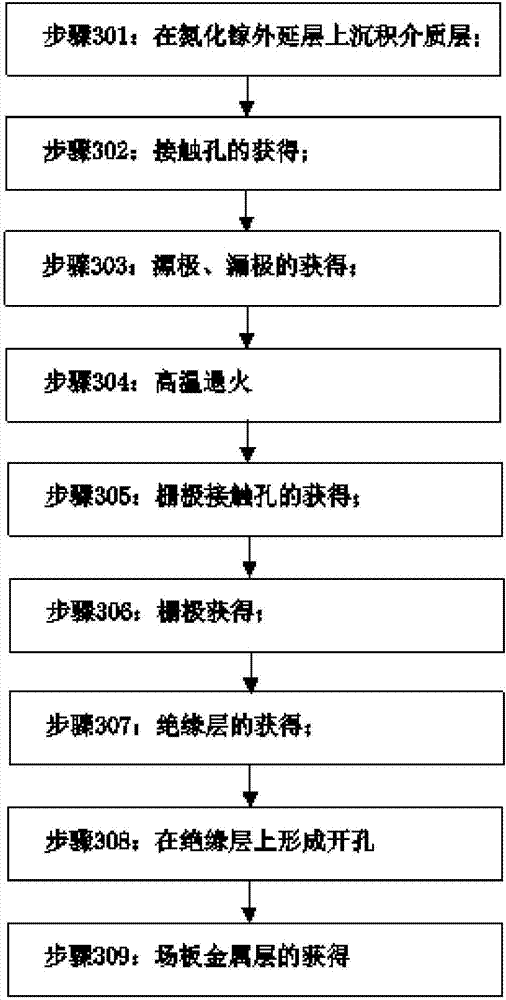

Process for manufacturing gallium nitride-base GaN power integrated circuit

InactiveCN102543871ASimple integration process stepsThe process steps are simpleSemiconductor/solid-state device manufacturingCapacitanceHeterojunction

The invention discloses a process for manufacturing a gallium nitride-base GaN power integrated circuit. According to the process, current channels in a high-voltage area and a low-voltage area are cut off by the anisotropic etching of an inductively coupled plasma (ICP) etching technology to realize electric isolation in the areas. An F-ionic layer with negative charges is formed in an AlGaN potential barrier area under a metal gate Ni / Au by utilizing a reactive ion etching (RIE) autoregistration plasma etching technology, and high-density two-dimensional electron gas in a heterogenous junction is exhausted, so that an exhausted channel is converted into an enhanced channel, and the normally-closed characteristic of an AlGaN / GaN high electron mobility transistors (HEMTs) device is formed. By means of a reduced surface field (Resurf) voltage withstanding structure and a surface source field plate of an epitaxial layer GaN / silicon substrate, the electric-field distribution of a drifting area of a high-voltage device is optimized, an offset area of the device is designed, and the influence of Miller capacitance Cgd on the frequency response of the device is shielded to acquire normally-closed gallium nitride-base AlGaN / GaN (HEMTs) high-voltage device which is applied to a high-speed switch.

Owner:WUXI JINGKAI TECH

Semiconductor device, n-type MOS transistor and manufacturing method thereof

ActiveCN101572251BInhibition formationInhibition of agglomerationTransistorSemiconductor/solid-state device manufacturingMedia layerIon implantation

The invention relates to a semiconductor device, an n-type MOS transistor and a manufacturing method thereof. The semiconductor device comprises a semiconductor substrate, a grid medium layer, a grid electrode, side walls, a light doping source / drain region, a heavy doping source / drain region, and a fluorine ion implantation region, wherein the gird medium layer, the grid electrode and the side wall are positioned inside an input / output device region of the semiconductor substrate; the low doping source / drain region and the heavy doping source / drain region are positioned inside semiconductor substrates in an n-type MOS transistor region and a p-type MOS transistor region of the input / output device region; and the fluorine ion implantation region is positioned inside a semiconductor substrate in the n-type MOS transistor region of the input / output device region. Correspondingly, the invention also provides a method for manufacturing the semiconductor device, the n-type MOS transistor and the method for manufacturing the n-type MOS transistor. The fluorine ion implantation region is formed in the low doping source / drain region of the n-type MOS transistor region, and fluorine ions inthe fluorine ion implantation region and silicon in the semiconductor substrate form fluorine-silicon groups so as to prevent the formation of charge traps, prevent the aggregation of charges in thelow doping source / drain region under the condition of additional voltage, and forming hot carrier effect.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

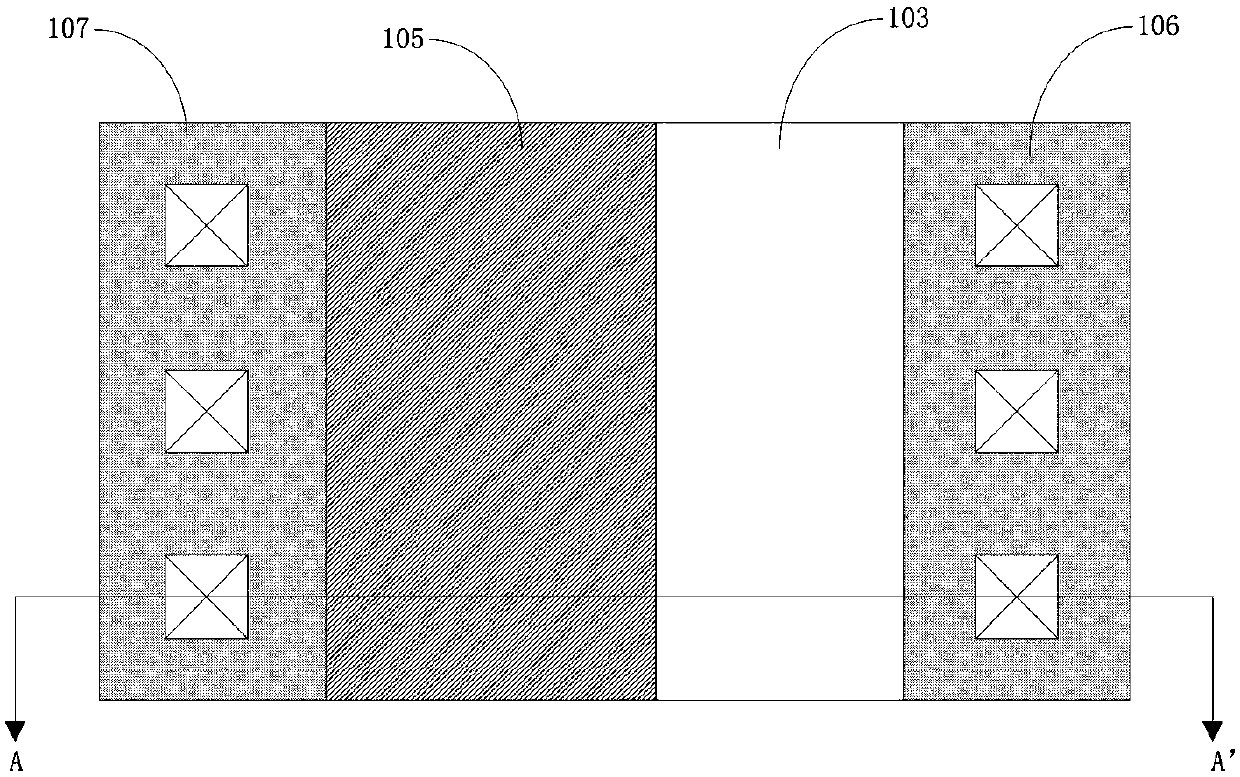

Gallium nitride semiconductor device and preparation method therefor

ActiveCN107275385AReduce contact resistanceImprove breakdown characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesGalliumGallium nitride

The invention relates to the technical field of semiconductor devices, and provides a gallium nitride semiconductor device. The semiconductor device comprises a gallium nitride epitaxial layer; a silicon nitride and plasma enhanced ethyl orthosilicate composite dielectric layer which is disposed on the gallium nitride epitaxial layer; a source electrode, a drain electrode and a grid electrode, which are all disposed on the composite dielectric layer and respectively pass through the composite dielectric layer to be connected with the gallium nitride epitaxial layer; insulating layers which are disposed on the source electrode, the drain electrode, the grid electrode and the composite dielectric layer, and field plate metal layers which is disposed on the insulating layers. According to the invention, the semiconductor device is not liable to break down an aluminium nitride gallium layer, thereby avoiding the electric leakage and breakdown of the gallium nitride semiconductor device, effectively protecting the gallium nitride semiconductor device, and improving the reliability of the gallium nitride semiconductor device.

Owner:SHENZHEN JING XIANG TECH CO LTD +1

Semiconductor structure and forming method thereof

ActiveCN108054202AReduce surface electric fieldImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureBody region

The invention provides a semiconductor structure and a forming method thereof. The forming method comprises the steps that a semiconductor substrate is provided, and a body region is formed in the semiconductor substrate; a drift region is formed in the body region, and the doping type of the drift region is opposite to that of the body region; a channel region is formed in the body region, the part of the channel region extends in the direction where the drift region is located to form at least one channel extension region, the channel extension regions and the drift region are distributed inan interdigital shape, and the doping type of the channel region is identical to that of the body region; an isolation region is formed in the drift region, and the end portions of the channel extension regions are located below the isolation region; a grid structure is formed on the surface of the semiconductor substrate; a source region is formed in the channel region at one side of the grid structure, and a drain region is formed in the drift region and located at the side, away from the channel region, of the isolation region.

Owner:JOULWATT TECH INC LTD

Production method for enhanced GaN transistor

InactiveCN107230619AReduce surface electric fieldImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricGallium nitride

The embodiment of the invention provides a production method for an enhanced GaN transistor. The method comprises the steps of growing a phosphorus-doped GaN dielectric layer, an AlGaN dielectric layer and an Si3N4 dielectric layer on the surface of a silicon substrate in sequence; etching the Si3N4 dielectric layer; depositing metal layers on the upper surfaces of the exposed AlGaN dielectric layer and the residual Si3N4 dielectric layer; carrying out dry etching downward along a predetermined area of the surface of the exposed Si3N4 dielectric layer; and depositing an SiO2 dielectric layer in a gate contact hole as gate dielectric. According to the embodiment of the invention, the phosphorus-doped GaN dielectric layer is grown on the surface of the silicon substrate and a surface electric field of the enhanced GaN transistor is reduced, so the voltage resistance is improved; and moreover, phosphorus is doped in a gate of the enhanced GaN transistor and the composition of electrons and holes exists, so the on resistance is reduced, and a technology demand that the on resistance of the GaN transistor is relatively low and the voltage resistance is relatively high is realized.

Owner:PEKING UNIV +2

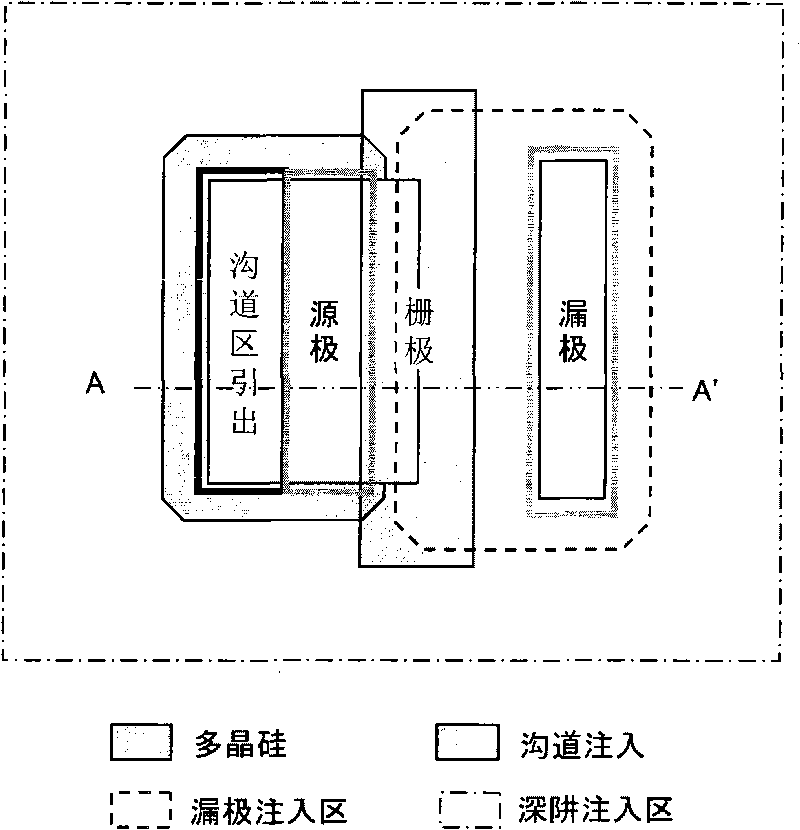

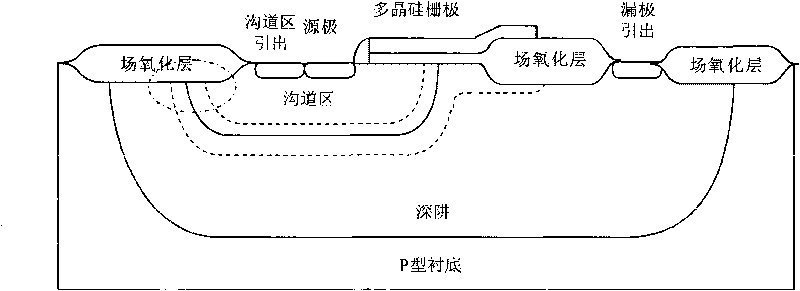

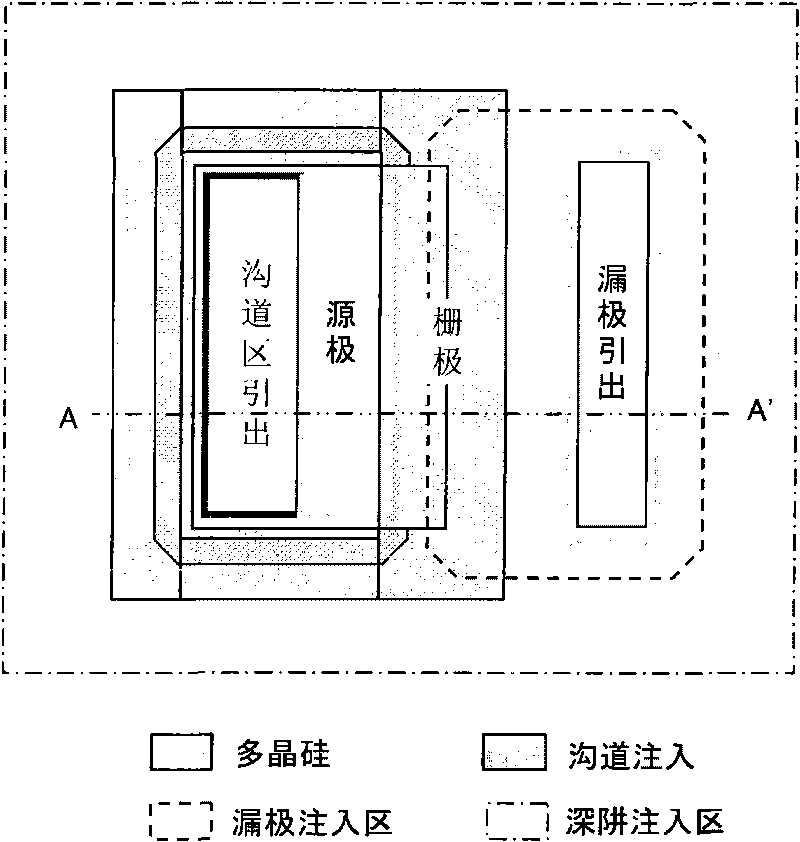

Laterally diffused metal oxide semiconductor (LDMOS) structure for protecting channel district by utilizing polysilicon field polar plate

InactiveCN101740614AImprove breakdown voltageIncrease the maximum voltageSemiconductor devicesLDMOSEngineering

The invention discloses an laterally diffused metal oxide semiconductor (LDMOS) structure for protecting a channel district by utilizing a polysilicon field polar plate, comprising a deep trap, a source electrode, a drain electrode, a grid electrode and the channel district, wherein the source electrode, the drain electrode, the grid electrode and the channel district are in the deep trap; the source electrode and the channel district are positioned at one side of the grid electrode; the drain electrode is positioned at the other side of the grid electrode; the doping types of the source electrode, the deep trap and the drain electrode are the same; the doping types of the source electrode, the deep trap and the channel district are opposite; and the polysilicon field polar plate is arranged above the edge of the channel district and the deep trap, or the polysilicon field polar plate is arranged above the edge of a PN junction of the channel district and the drain electrode. The LDMOS structure can reduce surface electric field between an LDMOS underway and the drain electrode so as to enhance the breakdown voltage of the LDMOS.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

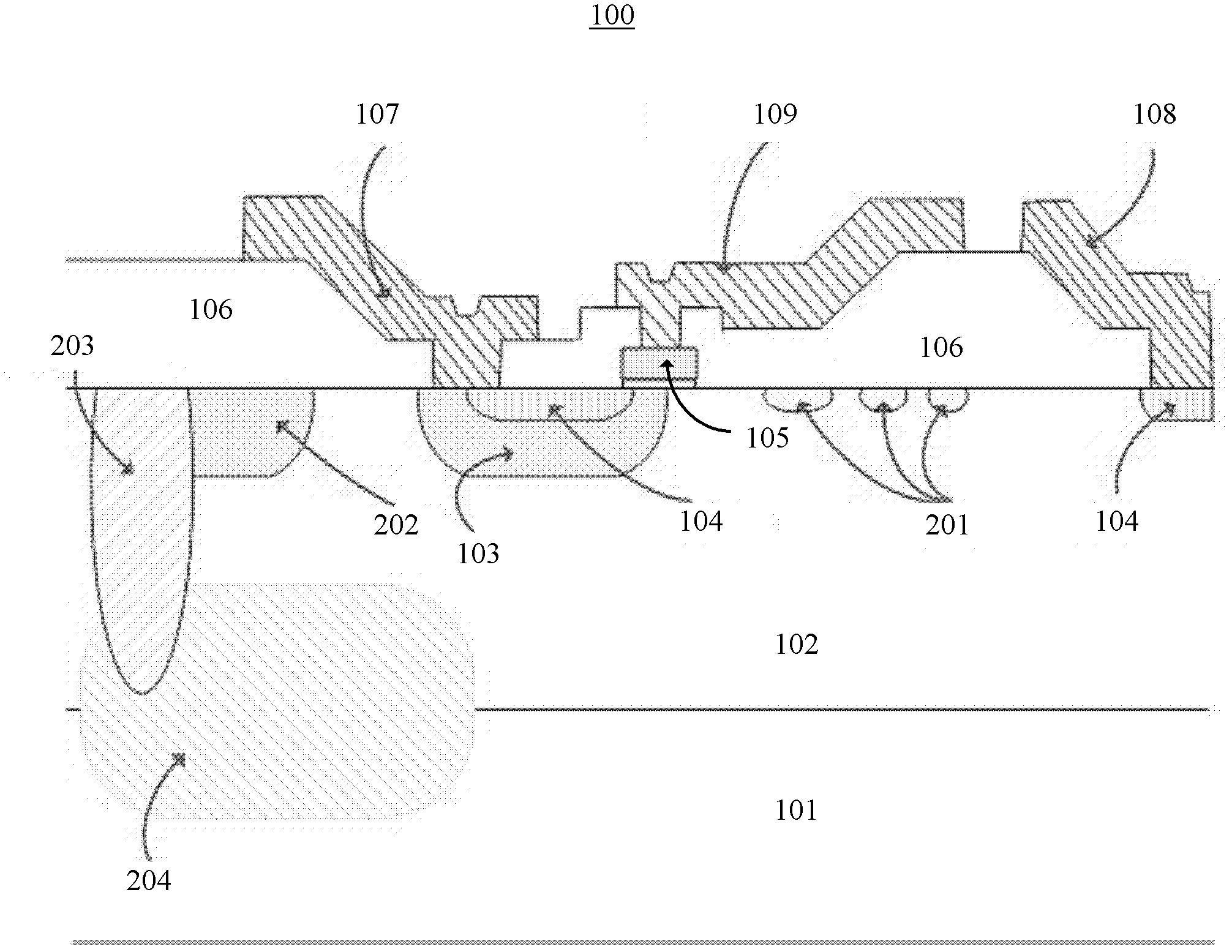

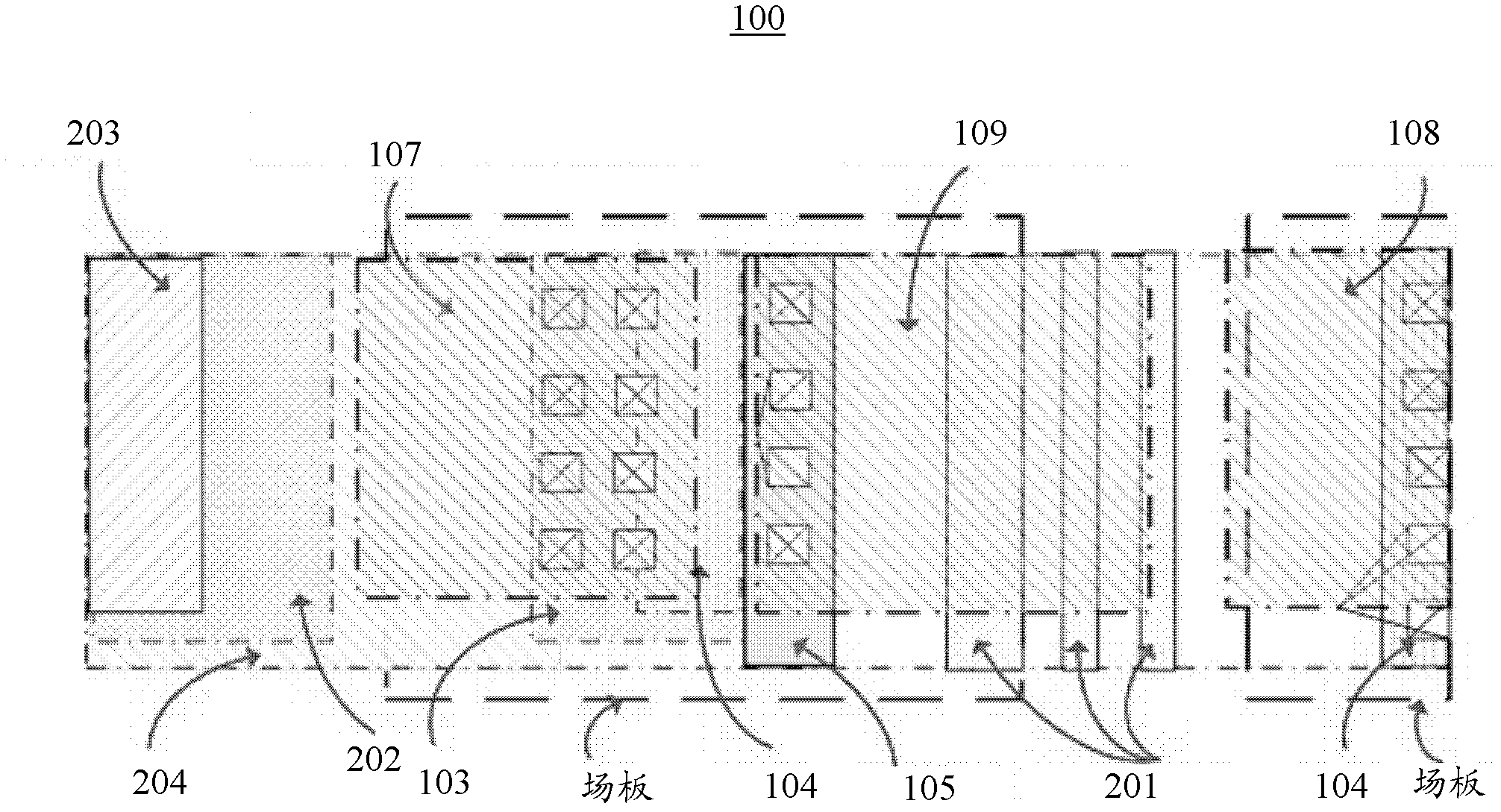

LDMOS structure in ultrahigh voltage BCD technology

InactiveCN102496627AIncrease the switching frequencyLow Gate Parasitic ResistanceSemiconductor devicesSource fieldEngineering

The invention provides an LDMOS structure in an ultrahigh voltage BCD technology. The LDMOS structure is in an N-epitaxial layer on a P-substrate. Moreover, the LDMOS structure comprises: a first high voltage P type body region, which is at the N- epitaxial layer surface; two high voltage N+ injection regions, which are respectively at the first high voltage P type body region and a drain electrode position; a gate oxide and polysilicon gate, which is at the upper surface of the N-epitaxial layer and is connected with the first high voltage P type body region; an interlayer dielectric layer, which is covered on the upper surface of the N-epitaxial layer as well as is opened with windows at a source electrode position and the drain electrode position of the LDMOS structure and the polysilicon gate position; a source electrode field plate is arranged on the interlayer dielectric layer as well as is short-circuited with the first high voltage P type body region through the source electrode window; a drain source field plate, which is arranged on the interlayer dielectric layer as well as is connected with the drain electrode through the drain electrode window; and a gate field plate, which is arranged on the interlayer dielectric layer as well as is connected with the polysilicon gate through the gate window. According to the invention, the filed plates that can reduce surface electric fields and improve an overpressure resistant performance are provided; and moreover, parasitic resistance of the polysilicon gate can be substantially reduced; and gate switching frequency can be enhanced.

Owner:ADVANCED SEMICON MFG CO LTD

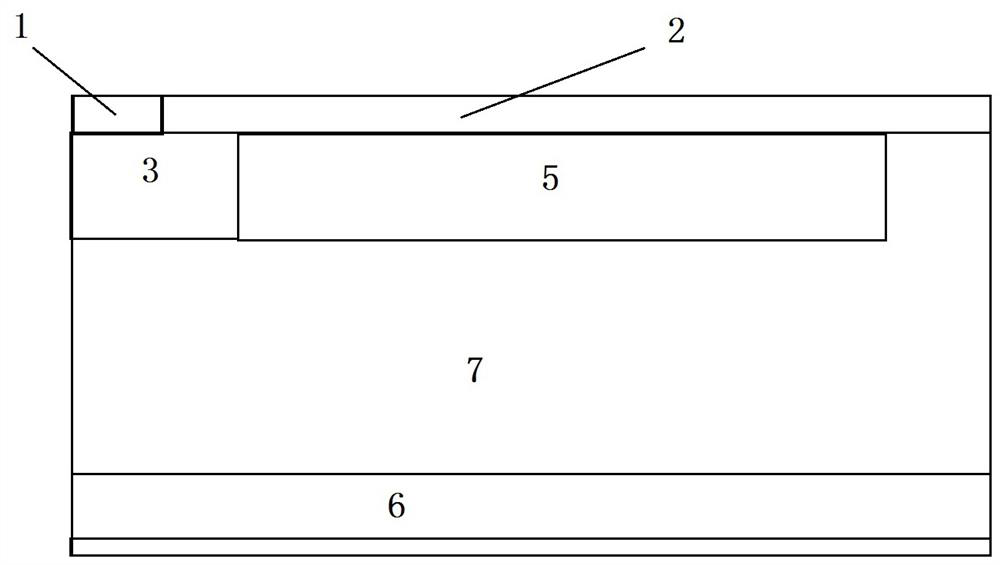

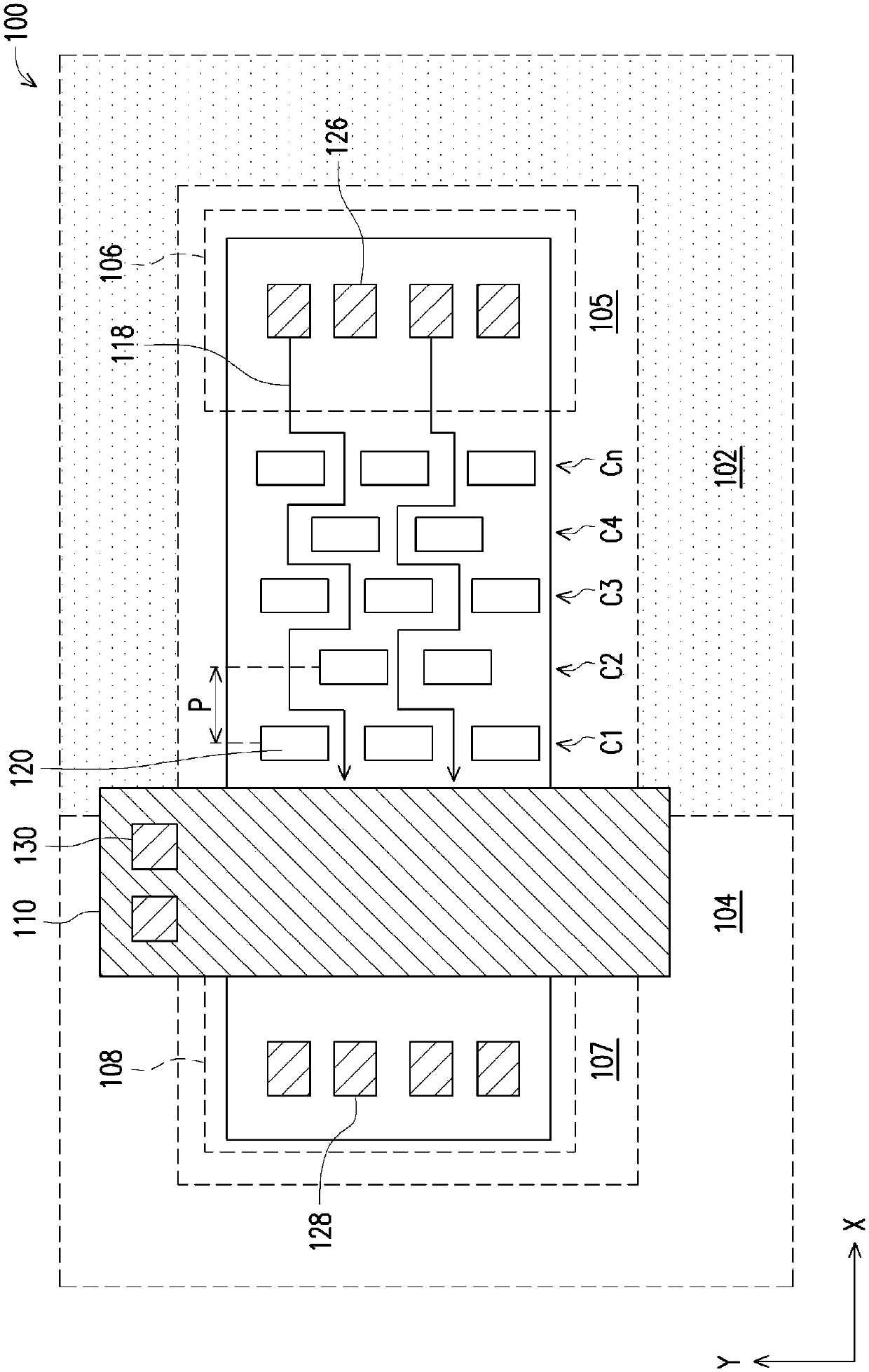

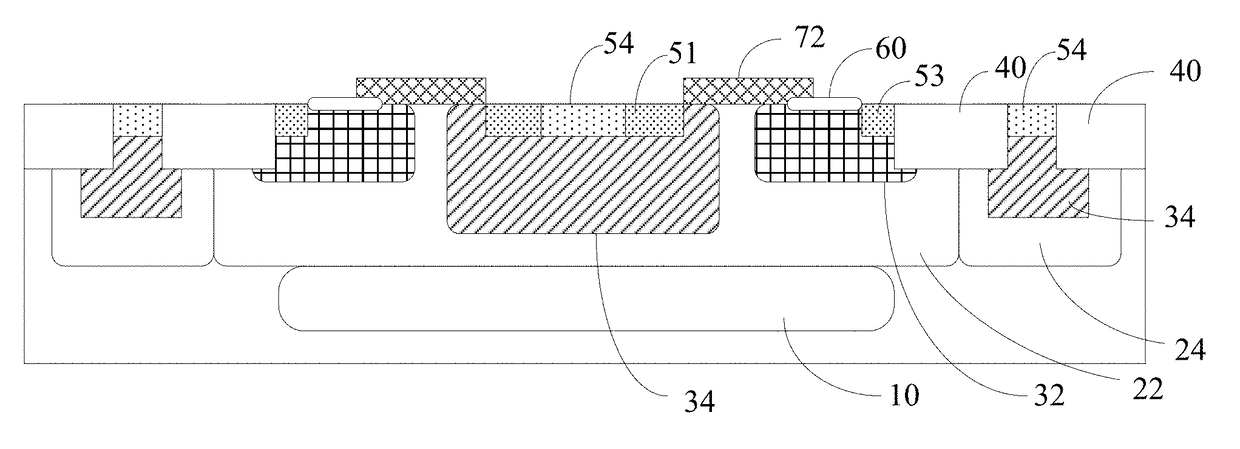

Method for manufacturing laterally insulated-gate bipolar transistor

ActiveUS20170358657A1Less stressReduce surface electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPolysilicon gate

The present invention relates to a method for manufacturing a laterally insulated-gate bipolar transistor, comprising: providing a wafer having an N-type buried layer (10), an STI (40), and a first N well (22) / a first P well (24) which are formed successively from above a substrate; depositing and forming a high-temperature oxide film on the first N well (22) of the wafer; performing thermal drive-in on the wafer and performing photoetching and etching on the high-temperature oxide film to form a mini oxide layer (60); performing photoetching and ion implantation so as to form a second N well (32) inside the first N well (22) and second P wells (34) inside the first N well (22) and the first P well (24); then successively forming a gate oxide layer and a polysilicon gate (72), wherein one end of the gate oxide layer and the polysilicon gate (72) extends onto the second P well (34) inside the first N well (22), and the other end extends onto the mini oxide layer (60) on the second N well (32); and photoetching and injecting N-type ions between the mini oxide layer (60) and the STI (40) adjacent to the mini oxide layer (60) to form a drain electrode, and at the same time forming a source electrode (51) inside the second P well (34).

Owner:CSMC TECH FAB2 CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com