Method for manufacturing terminal structure of deep-groove super-junction metal oxide semiconductor (MOS) device

A technology of MOS device and terminal structure, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as very high process consistency requirements and complex structure design, achieve obvious voltage division effect and reduce surface electric field. , the effect of saving terminal area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The present invention will be further described below in conjunction with specific embodiments and accompanying drawings, but the protection scope of the present invention should not be limited thereby.

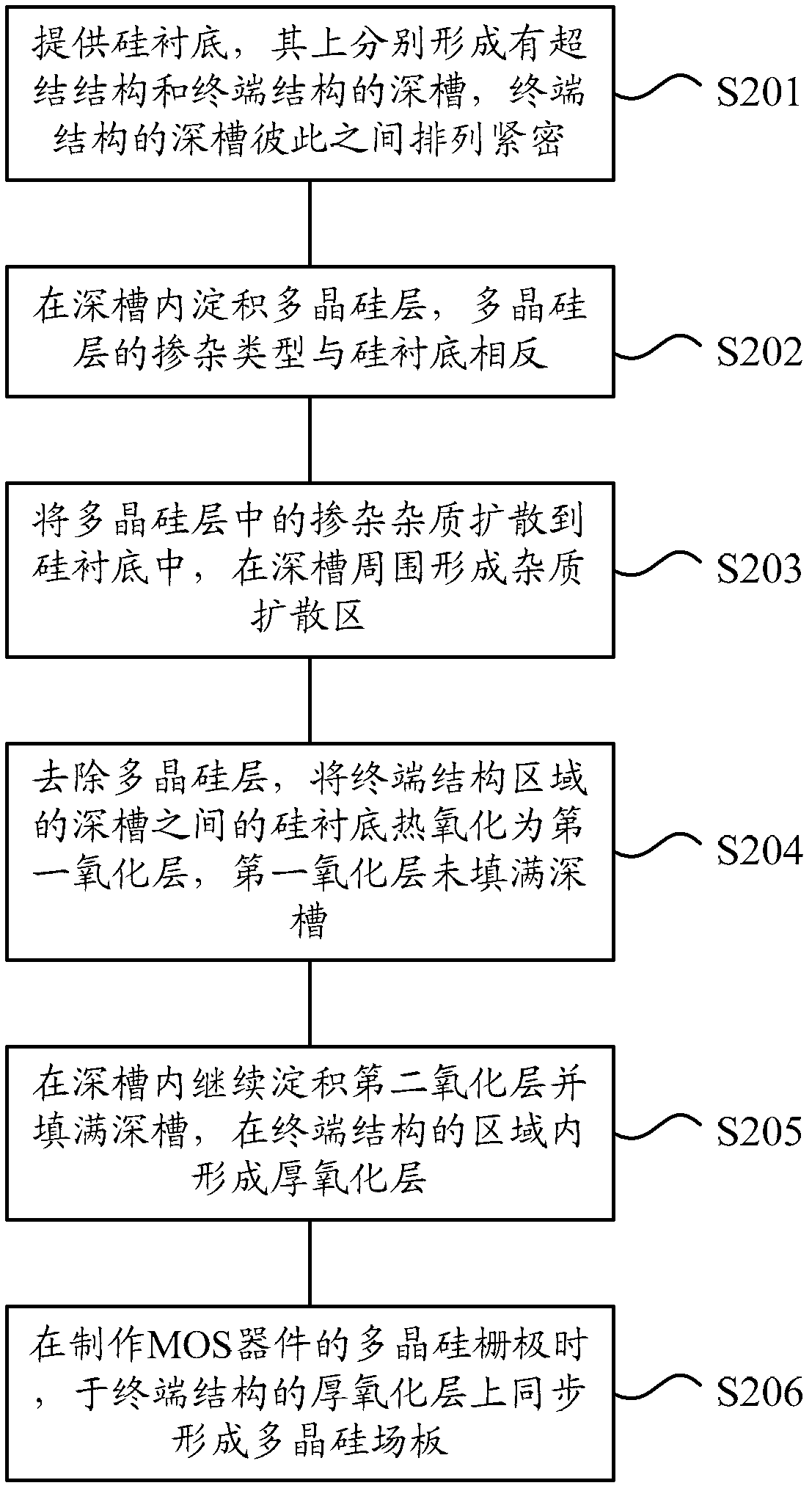

[0040] figure 1 It is a schematic flow chart of a manufacturing method for a terminal structure of a deep-trench super-junction MOS device according to an embodiment of the present invention. As shown in the figure, the manufacturing method of the terminal structure may include:

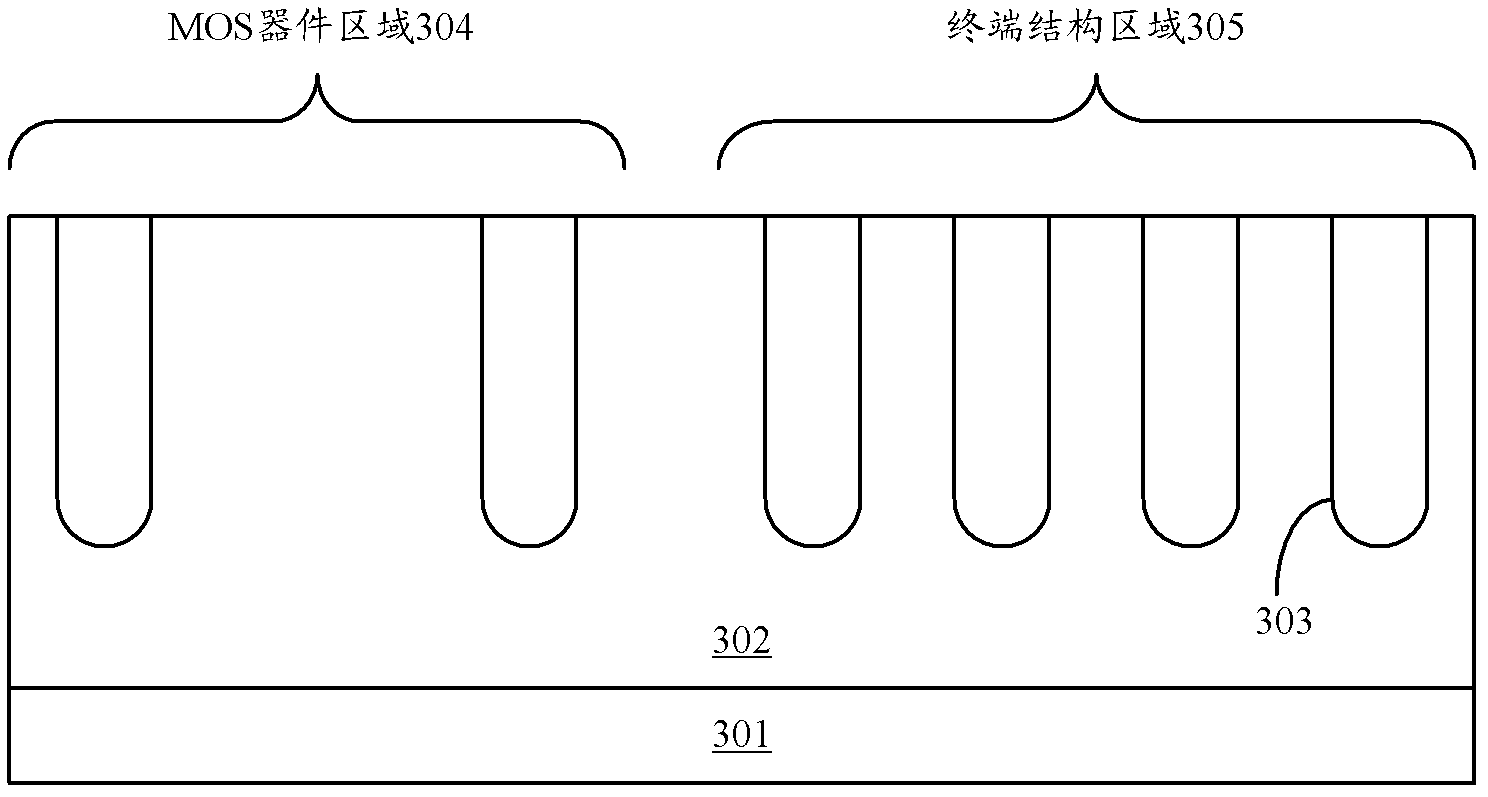

[0041] Step S101 is performed to provide a silicon substrate on which deep grooves of a super junction structure and a terminal structure are respectively formed, and the deep grooves of the terminal structure are closely arranged with each other;

[0042] Execute step S102, depositing a polysilicon layer in the deep groove, the doping type of the polysilicon layer is opposite to that of the silicon substrate;

[0043] Executing step S103, diffusing dopant impurities in the polysilicon laye...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com