Semiconductor device, p-type MOS transistor and manufacturing method thereof

A technology of MOS transistors and manufacturing methods, applied in the field of p-type MOS transistors and their manufacturing, and semiconductor devices, can solve the problems of NBTI effect enhancement, avalanche collision, and influence on the characteristics and reliability of semiconductor devices, and achieve the effect of reducing the impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

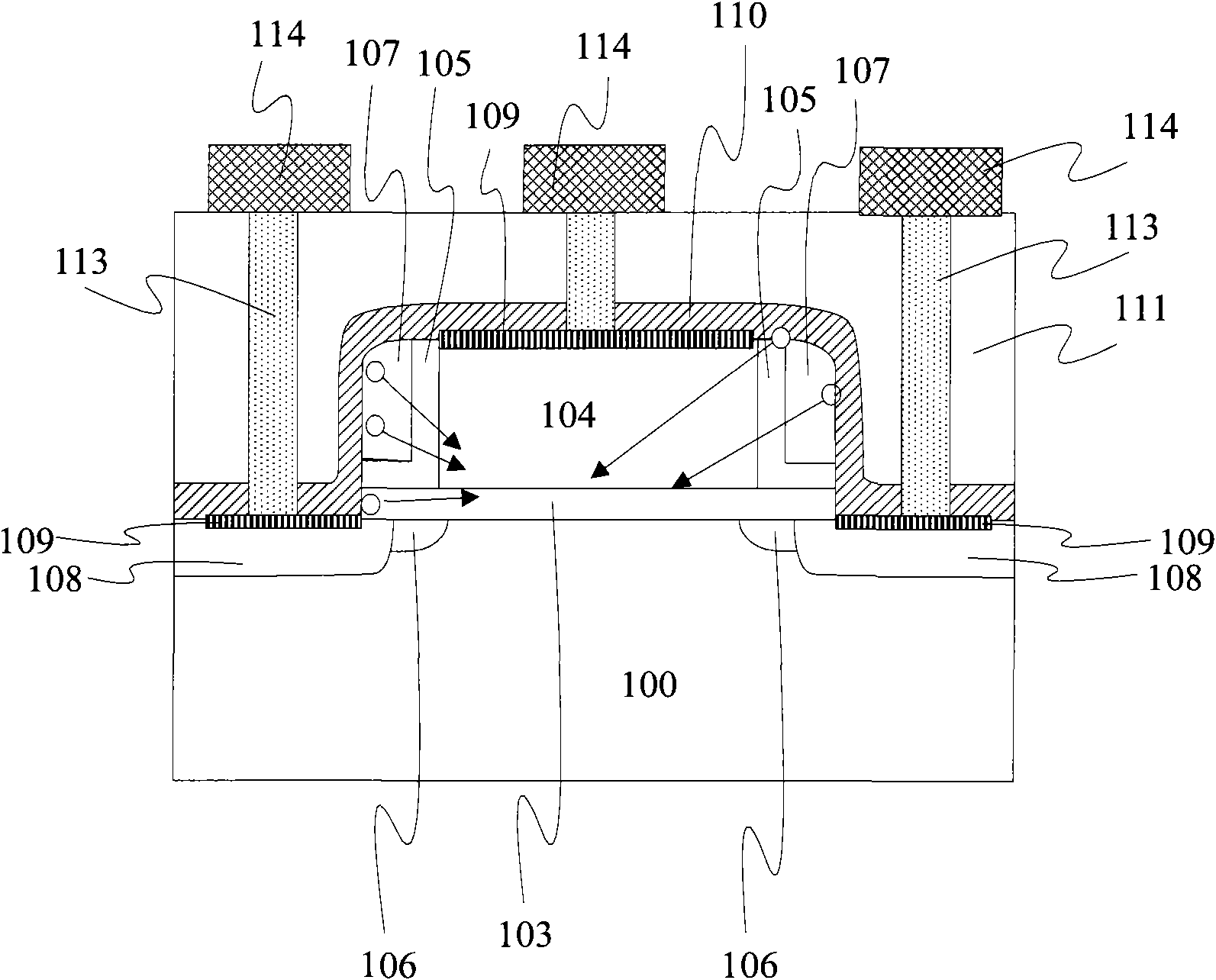

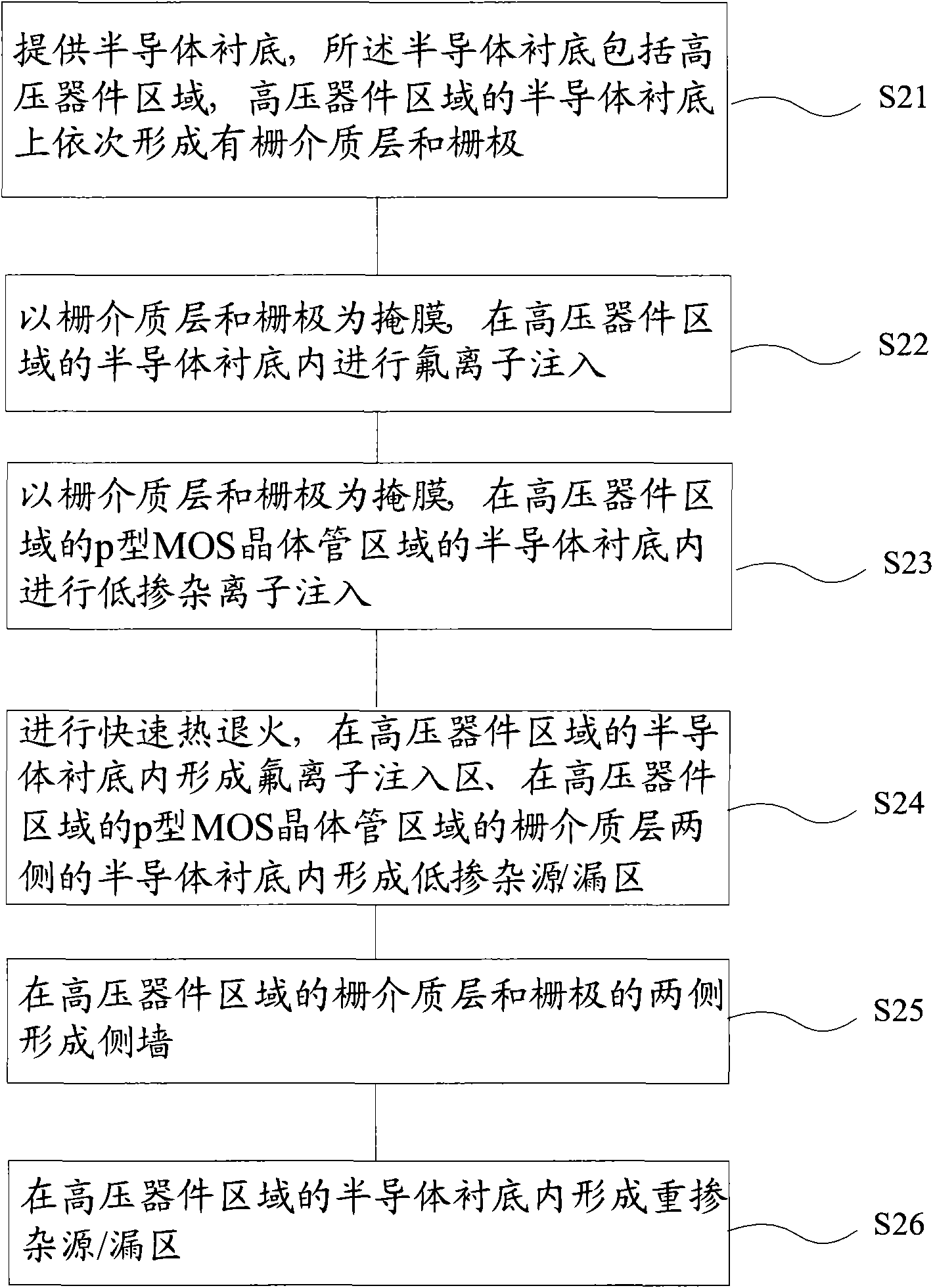

[0034] In the present invention, a fluorine ion implantation area is formed on the surface of the semiconductor substrate on the low-doped source / drain area of the p-type MOS transistor area of the high voltage device area, and the fluorine ion in the fluorine ion implantation area and the silicon in the semiconductor substrate form fluorine silicon Since the silicon-fluorine bond is stronger than the silicon-hydrogen bond, it prevents the formation of Si dangling bonds at high temperatures, thereby reducing the impact of the NBTI effect on the MOS transistor.

[0035] In the present invention, a fluorine ion implantation area is formed on the surface of the semiconductor substrate on the low-doped source / drain area of the p-type MOS transistor area of the high voltage device area, and the fluorine ion in the fluorine ion implantation area and the silicon in the semiconductor substrate form fluorine silicon The group is beneficial to reduce the trap charge and dislocation ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com