Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

260 results about "Hot electrons" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

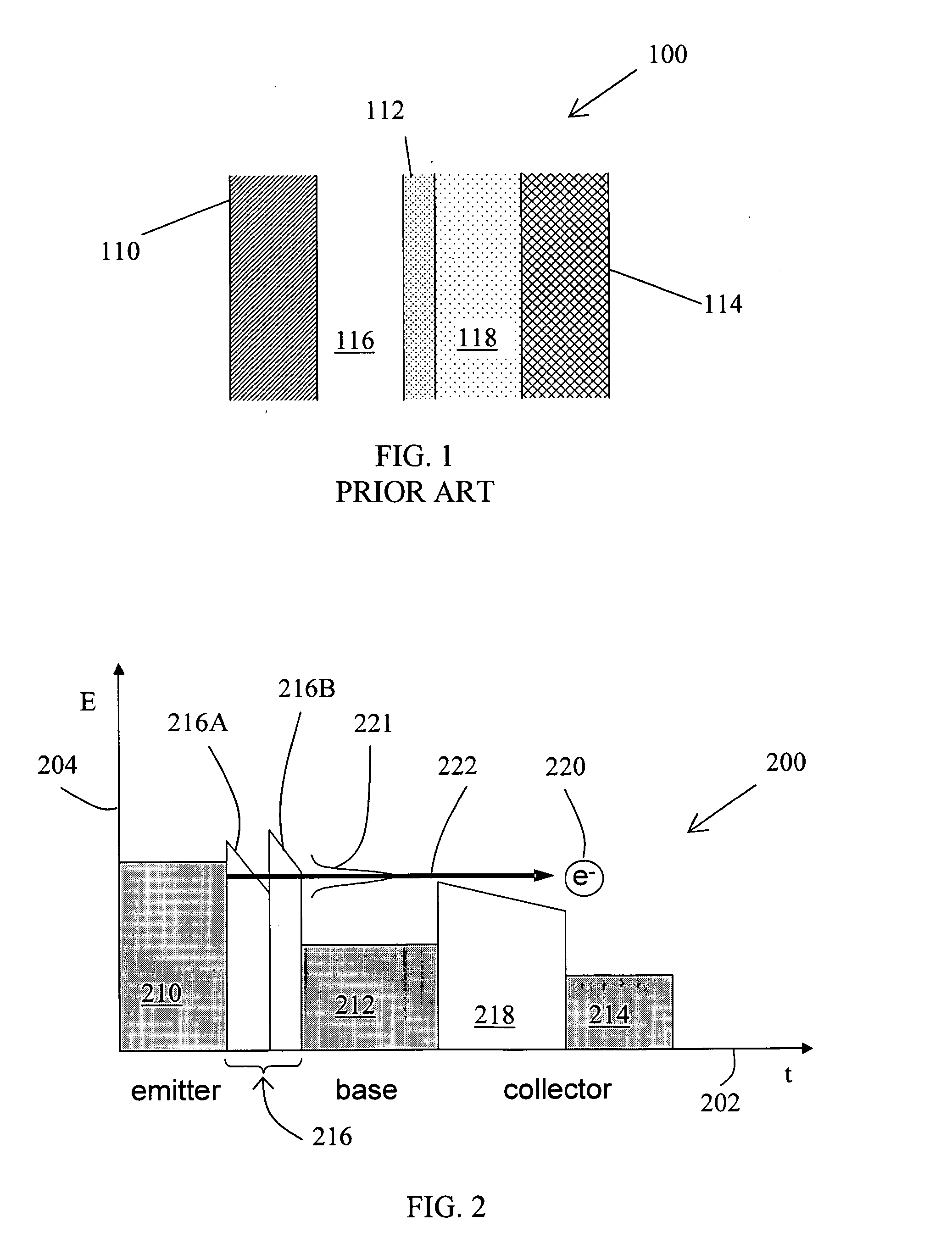

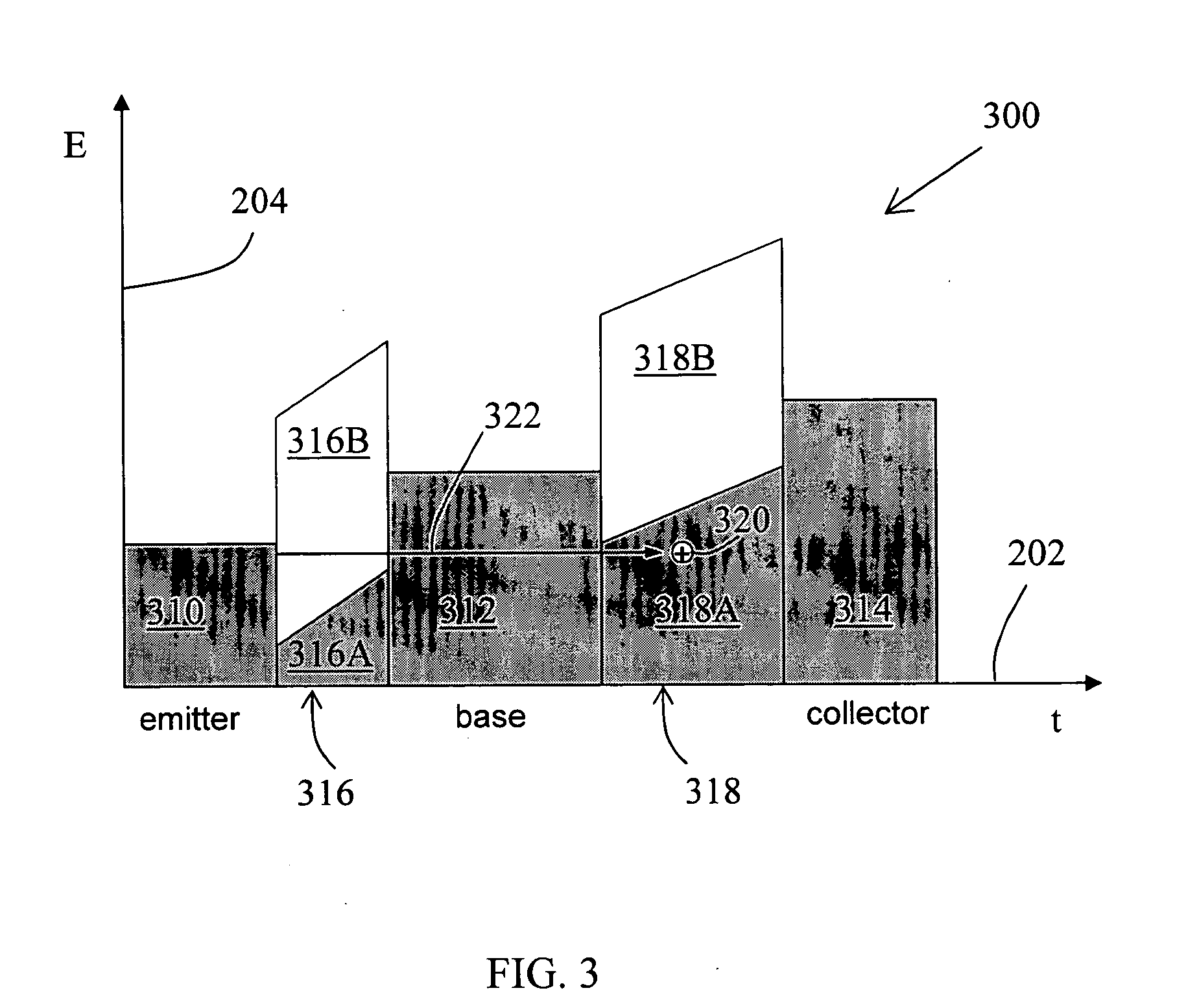

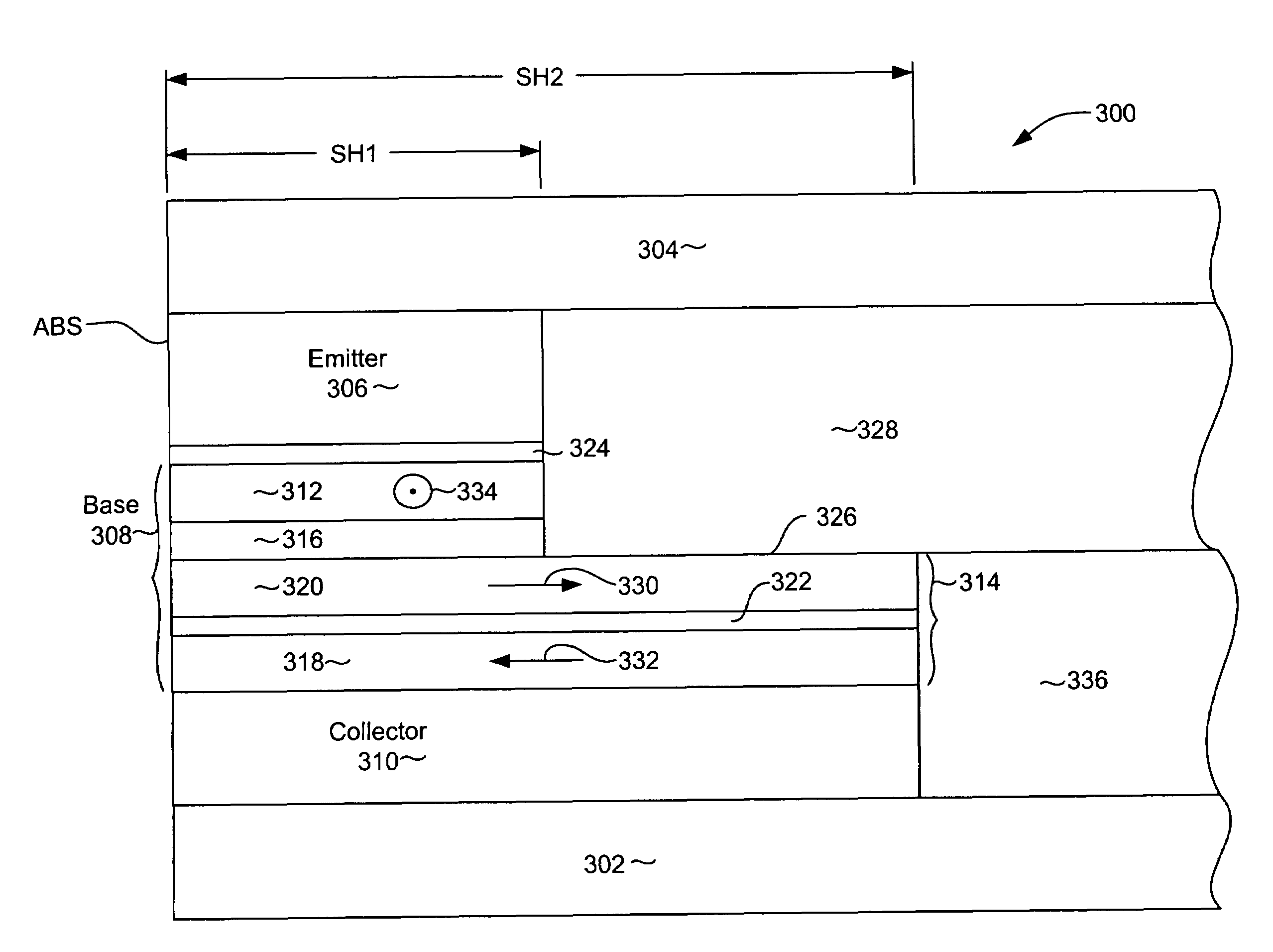

Thin-film transistors based on tunneling structures and applications

A hot electron transistor includes an emitter electrode, a base electrode, a collector electrode, and a first tunneling structure disposed and serving as a transport of electrons between the emitter and base electrodes. The first tunneling structure includes at least a first amorphous insulating layer and a different, second insulating layer such that the transport of electrons includes transport by means of tunneling. The transistor further includes a second tunneling structure disposed between the base and collector electrodes. The second tunneling structure serves as a transport of at least a portion of the previously mentioned electrons between the base and collector electrodes by means of ballistic transport such that the portion of the electrons is collected at the collector electrode. An associated method for reducing electron reflection at interfaces in a thin-film transistor is also disclosed.

Owner:UNIV OF COLORADO THE REGENTS OF

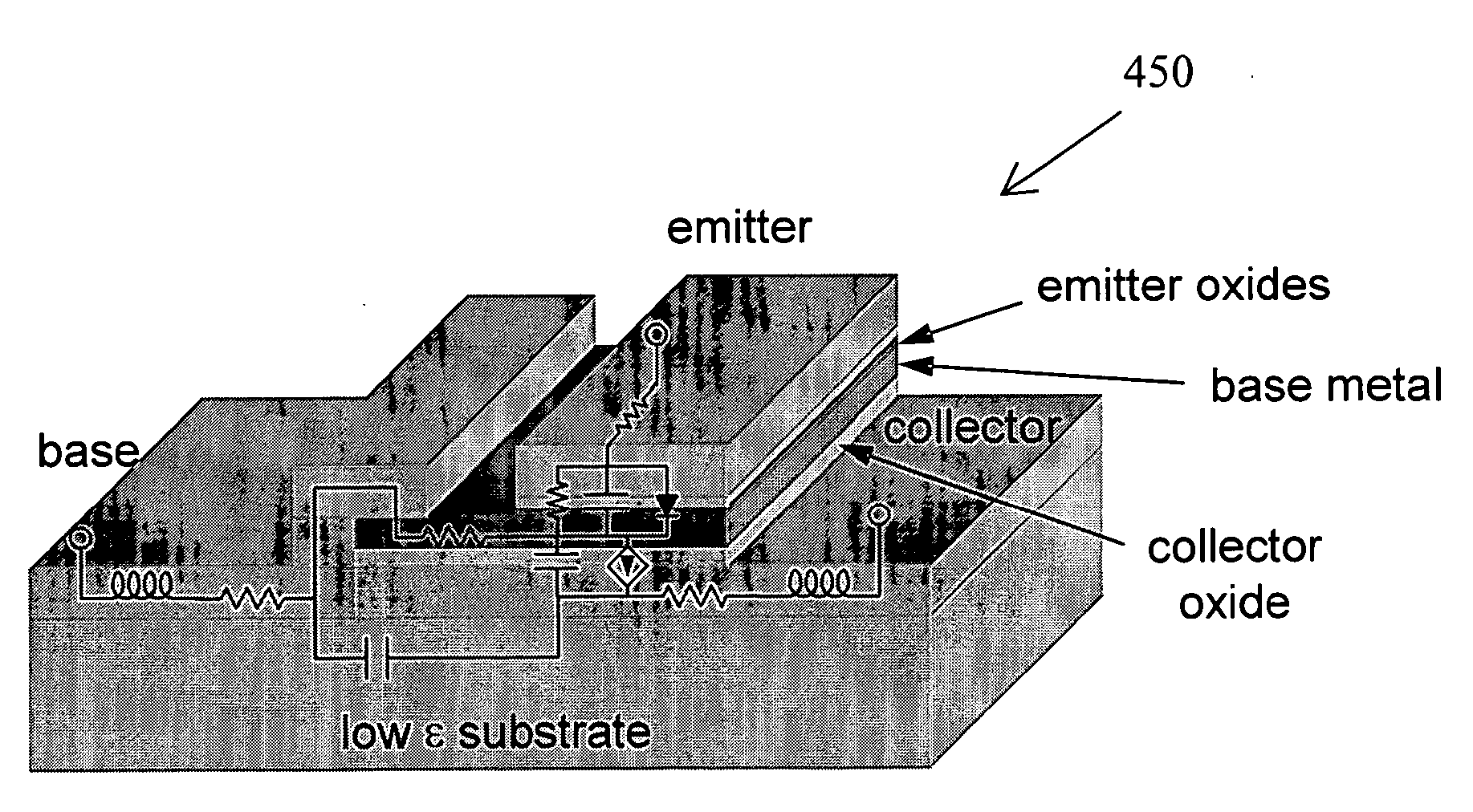

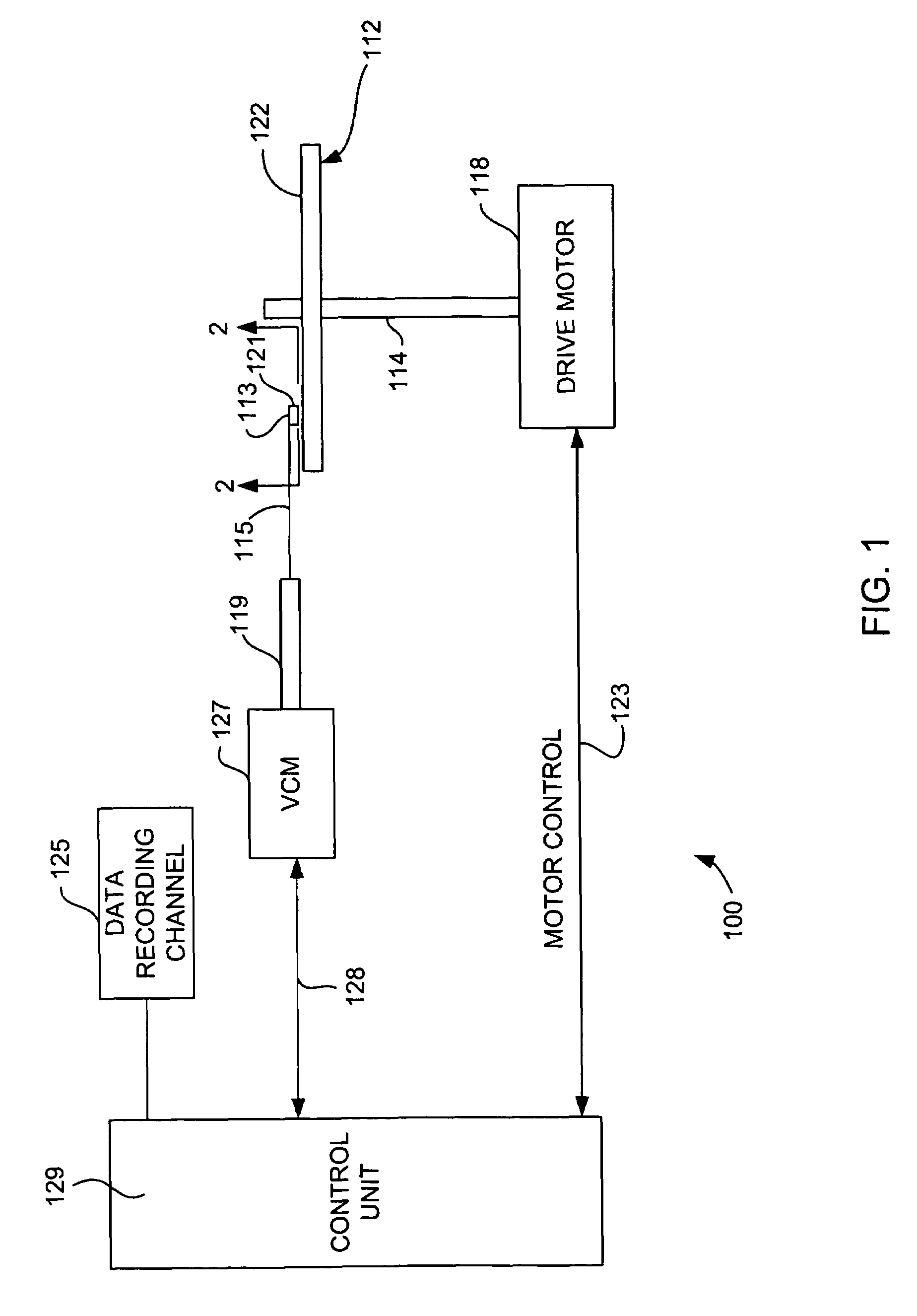

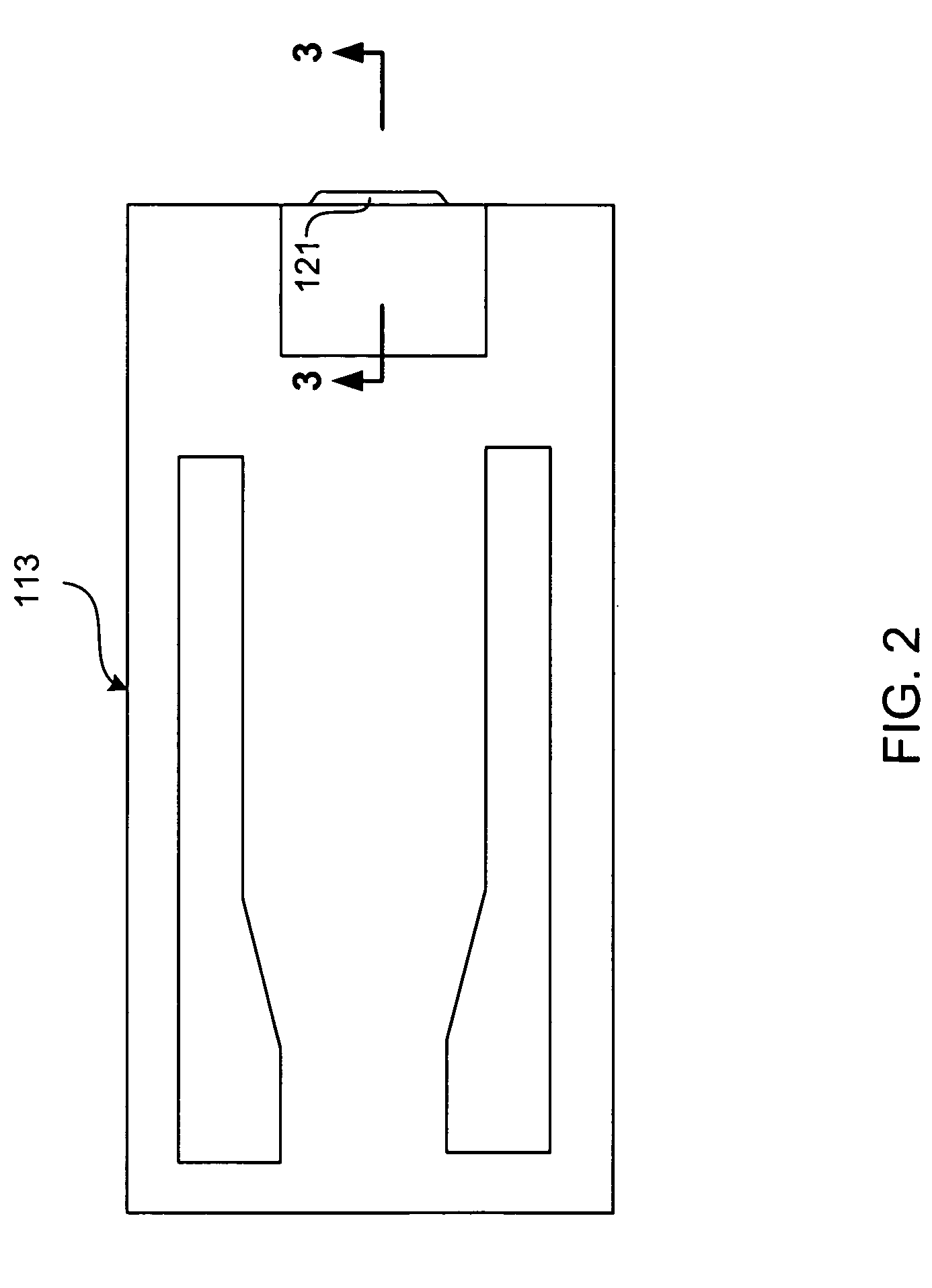

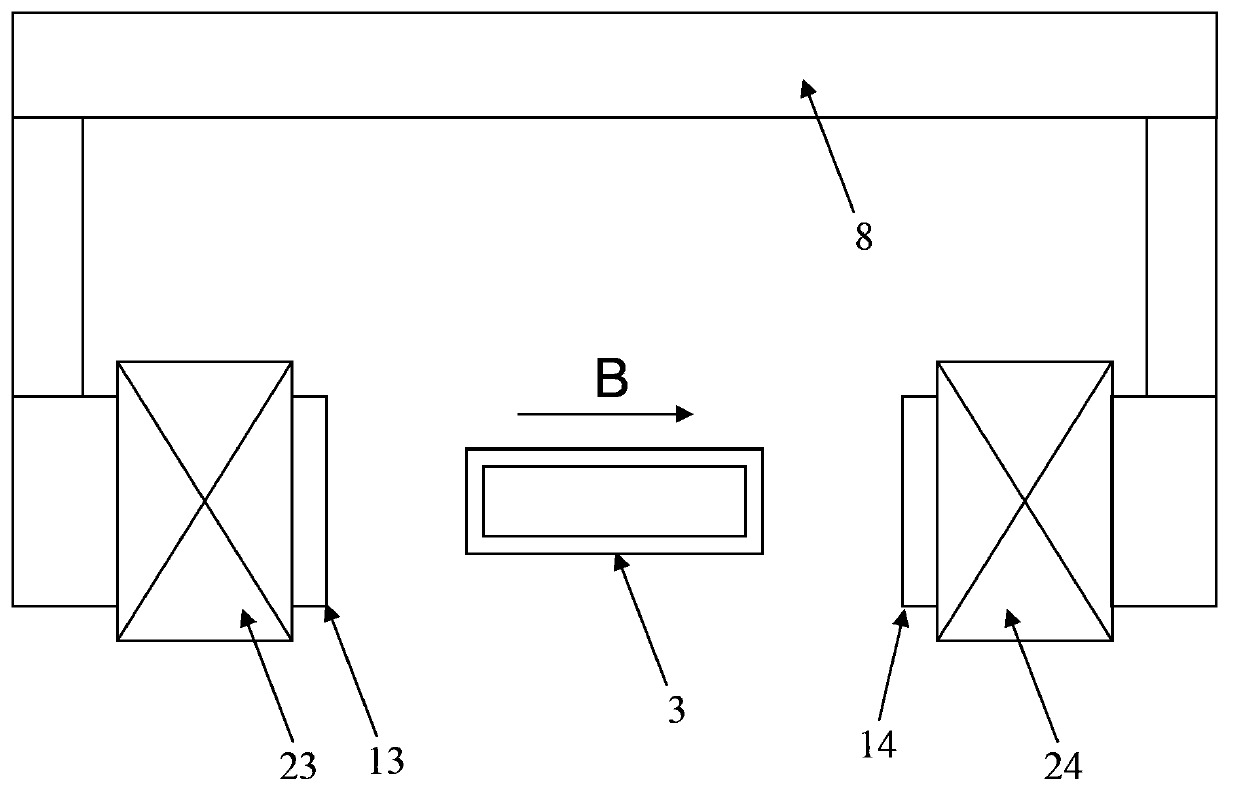

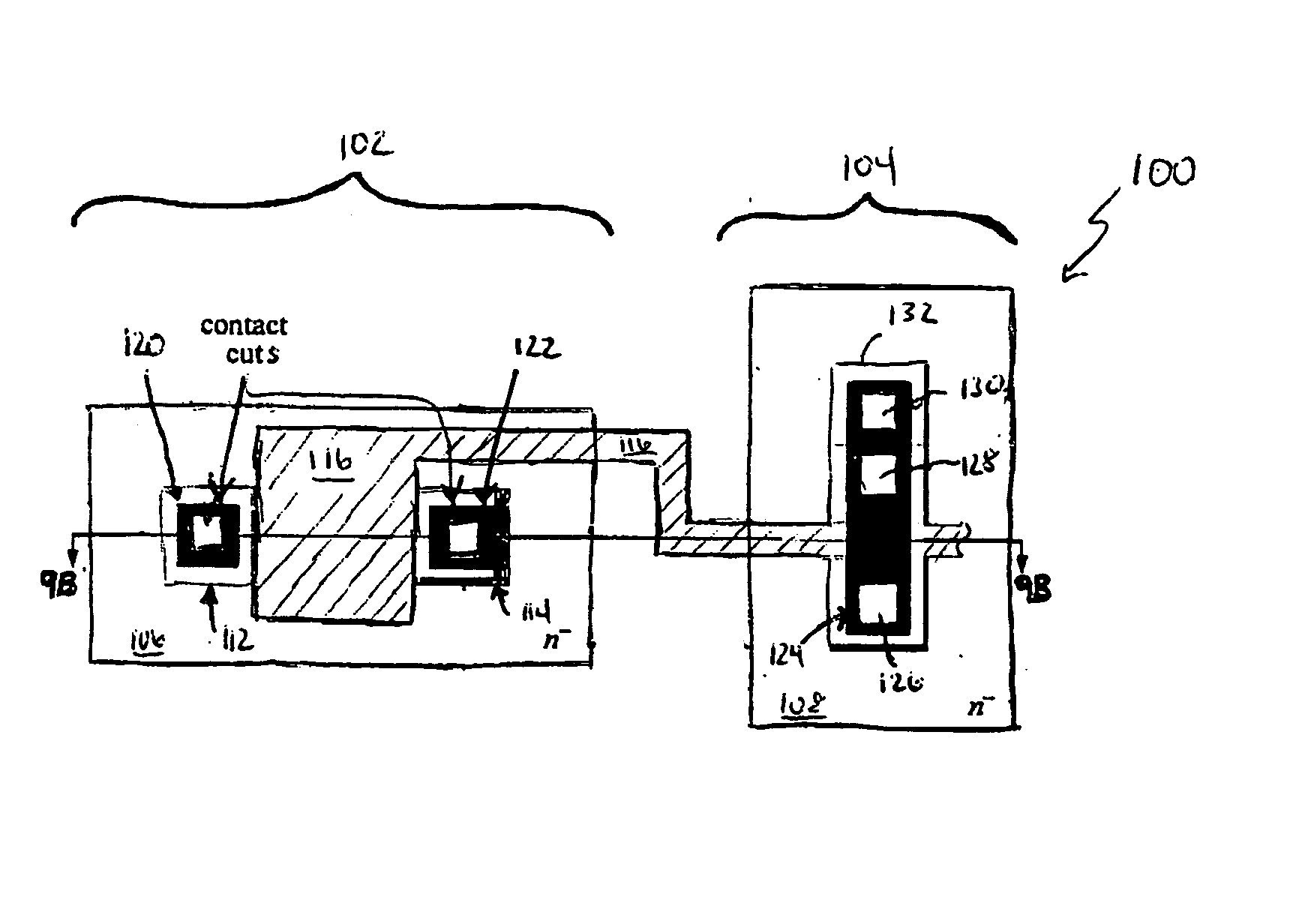

Magnetic tunnel transistor with high magnetocurrent and stronger pinning

InactiveUS7372674B2Improve performanceReduce in quantityNanoinformaticsMagnetic field measurement using galvano-magnetic devicesMagnetic currentPerformance enhancement

A magnetic tunnel transistor (MTT) having a pinned layer that is extended in a stripe height direction and is exchange coupled with an antiferromagnetic (AFM) layer in the extended portion outside of the active area of the sensor. Exchange coupling only the extended portion of the pinned layer with the AFM results in strong, robust pinning of the pinned layer while eliminating the AFM layer from the active portion of the sensor. The presence of an AFM layer within the active area of the sensor would result in an extreme loss of hot electrons resulting in a prohibitively large loss of performance. Therefore, eliminating the AFM layer from the active area provides a very large performance enhancement while maintaining robust pinning.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

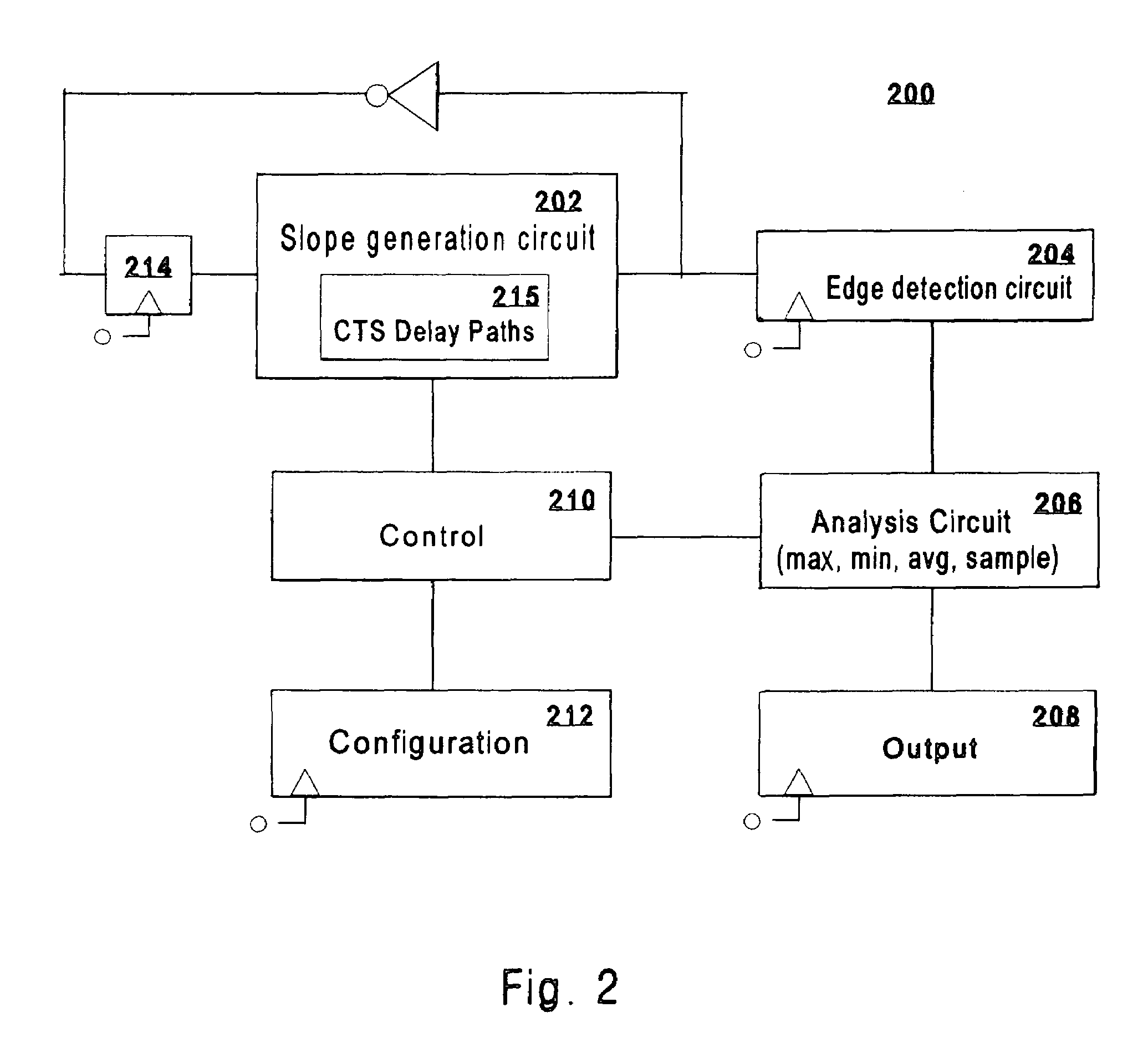

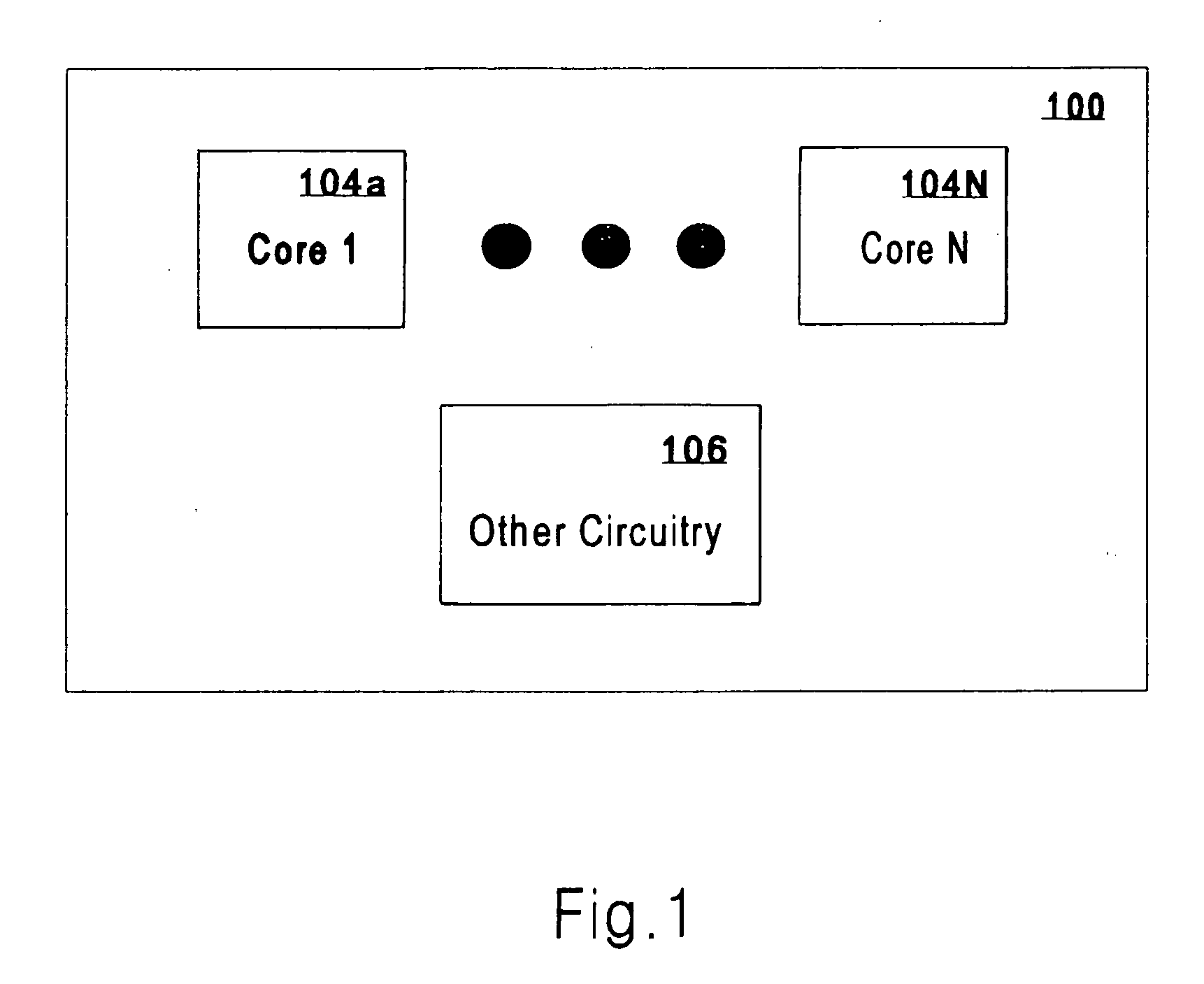

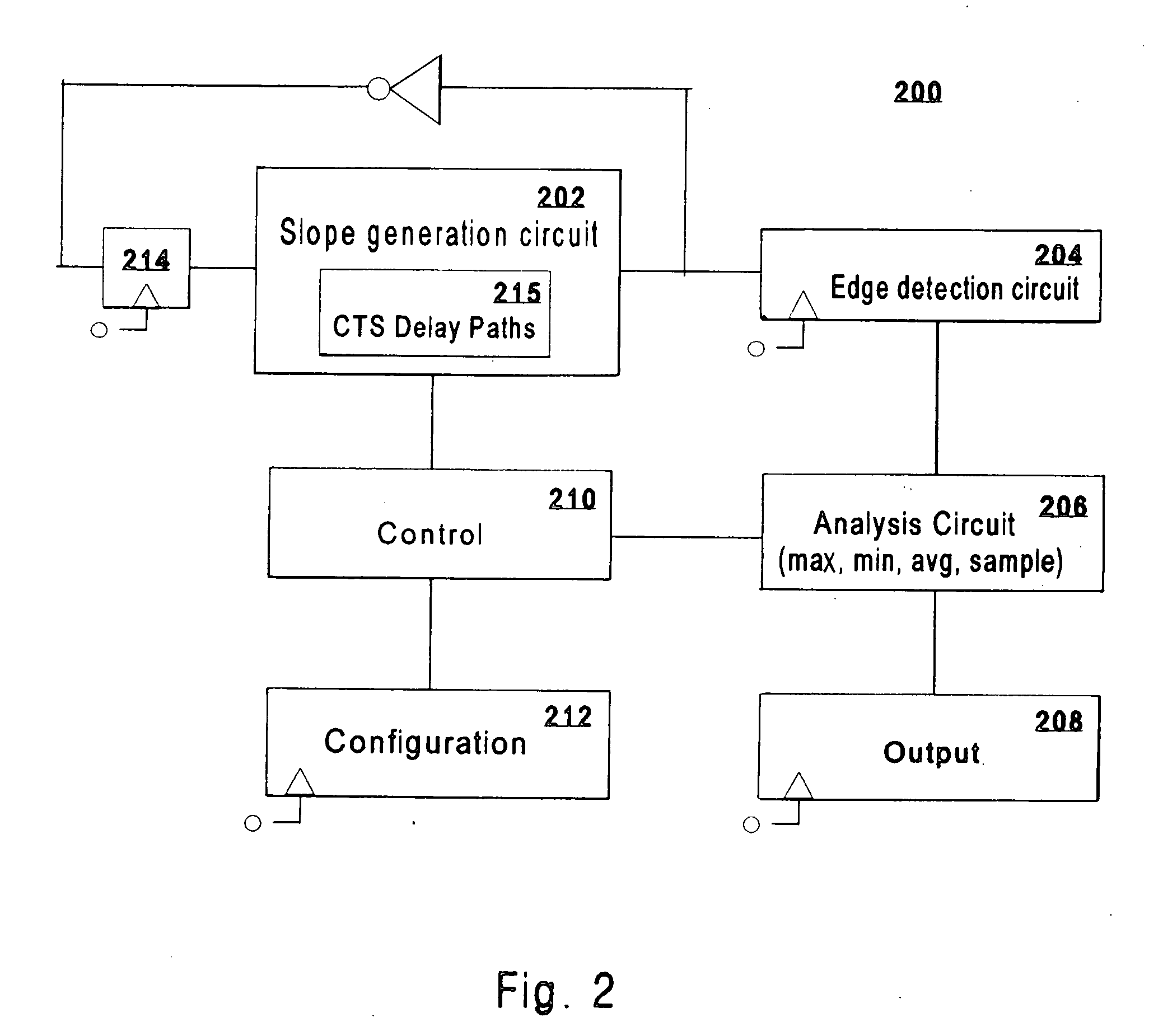

Circuit for dynamic circuit timing synthesis and monitoring of critical paths and environmental conditions of an integrated circuit

InactiveUS7576569B2Multiple input and output pulse circuitsPulse characteristics measurementsEngineeringCritical path method

A circuit for dynamically monitoring the operation of an integrated circuit under differing temperature, frequency, and voltage (including localized noise and droop), and for detecting early life wear-out mechanisms (e.g., NBTI, hot electrons).

Owner:INT BUSINESS MASCH CORP

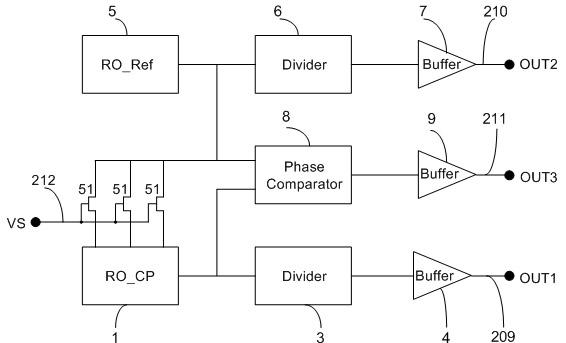

Multifunctional test circuit of integrated circuit stress degradation and test method thereof

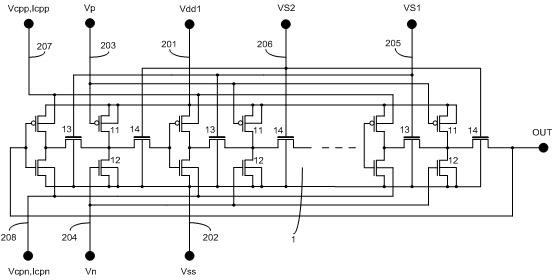

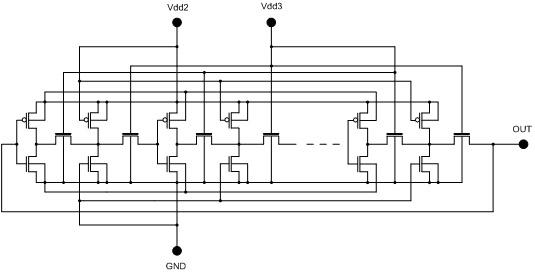

The invention belongs to a integrated circuit reliability test technology field and especially relates to a multifunctional test circuit of integrated circuit stress degradation and a test method thereof. A core part of the test circuit takes an annular oscillator as a basis. Several auxiliary transistors, switch transistors and control terminals are added. By using the circuit and the method of the invention, a negative bias temperature instability, a positive bias temperature instability, hot hole injection or hot electron injection stress can be applied to pMOSFETs or nMOSFETs in a ring vibration inverter respectively; a ring oscillator is in a normal oscillation and stress oscillation state; the pMOSFETs or nMOSFETs of the inverter in the ring oscillator is in a measuring state of a charge pump. The degradation of the MOSFETs in the ring vibration inverter can be shown through changes of a ring oscillator oscillation frequency after the stress and can be shown through the changes of a CP current (Icpp or Icpn) of the pMOSFETs or nMOSFETs in the ring oscillator.

Owner:FUDAN UNIV

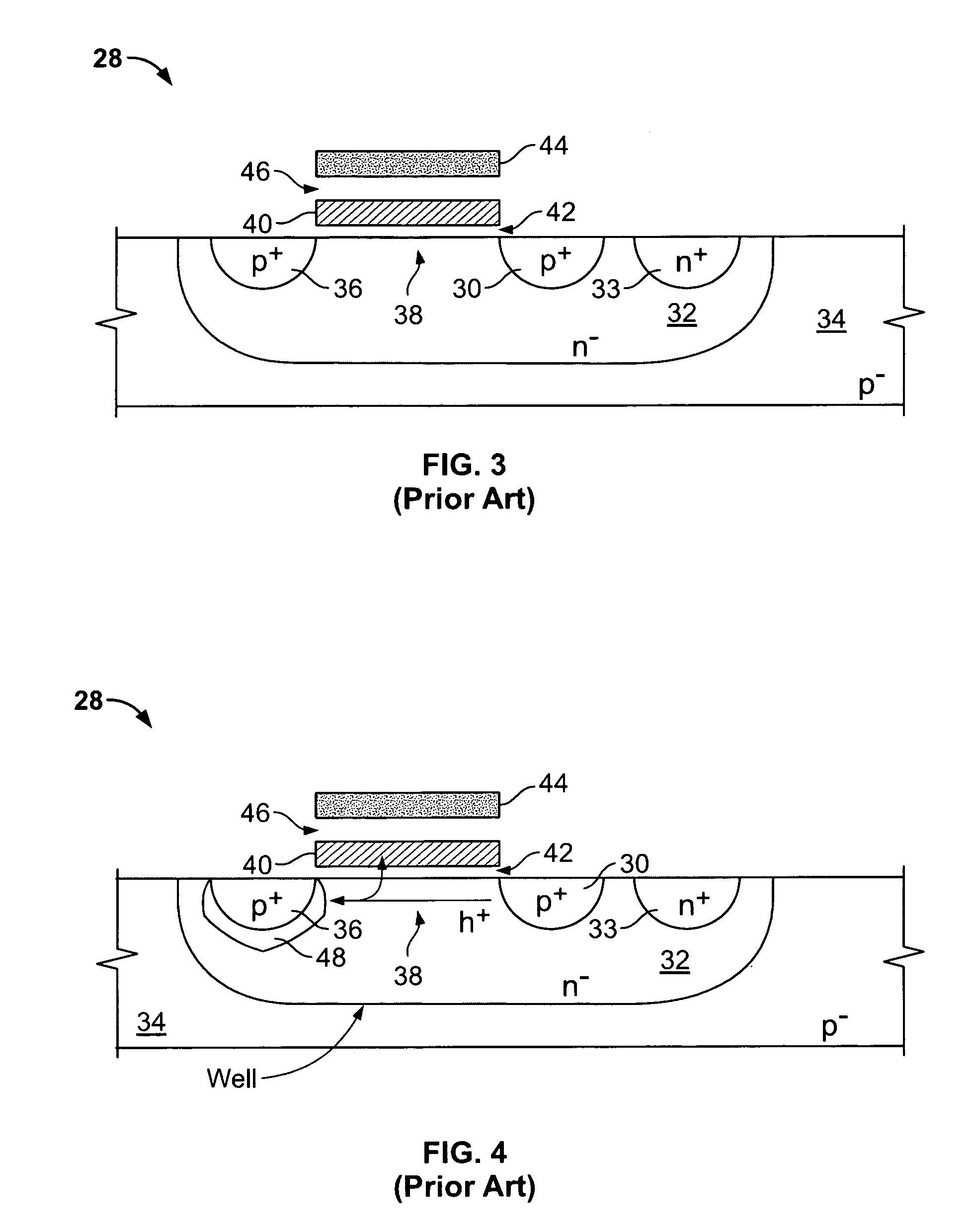

Method and apparatus for programming single-poly pFET-based nonvolatile memory cells

Methods and apparatuses for programming a single-poly pFET-based nonvolatile memory cell bias the cell so that band-to-band tunneling (BTBT) is induced and electrons generated by the BTBT are injected onto a floating gate of the cell. Following a predetermined event, the single-poly pFET is biased to induce impact-ionized hot-electron injection (IHEI). The predetermined event may be, for example, the expiration of a predetermined time period or a determination that a channel has been formed by the BTBT injection process that is sufficiently conducting to support IHEI. Employing BTBT permits a previously overerased or stuck bit to be “unstuck” or “removed” and thus be made usable (i.e., able to be programmed) again.

Owner:SYNOPSYS INC

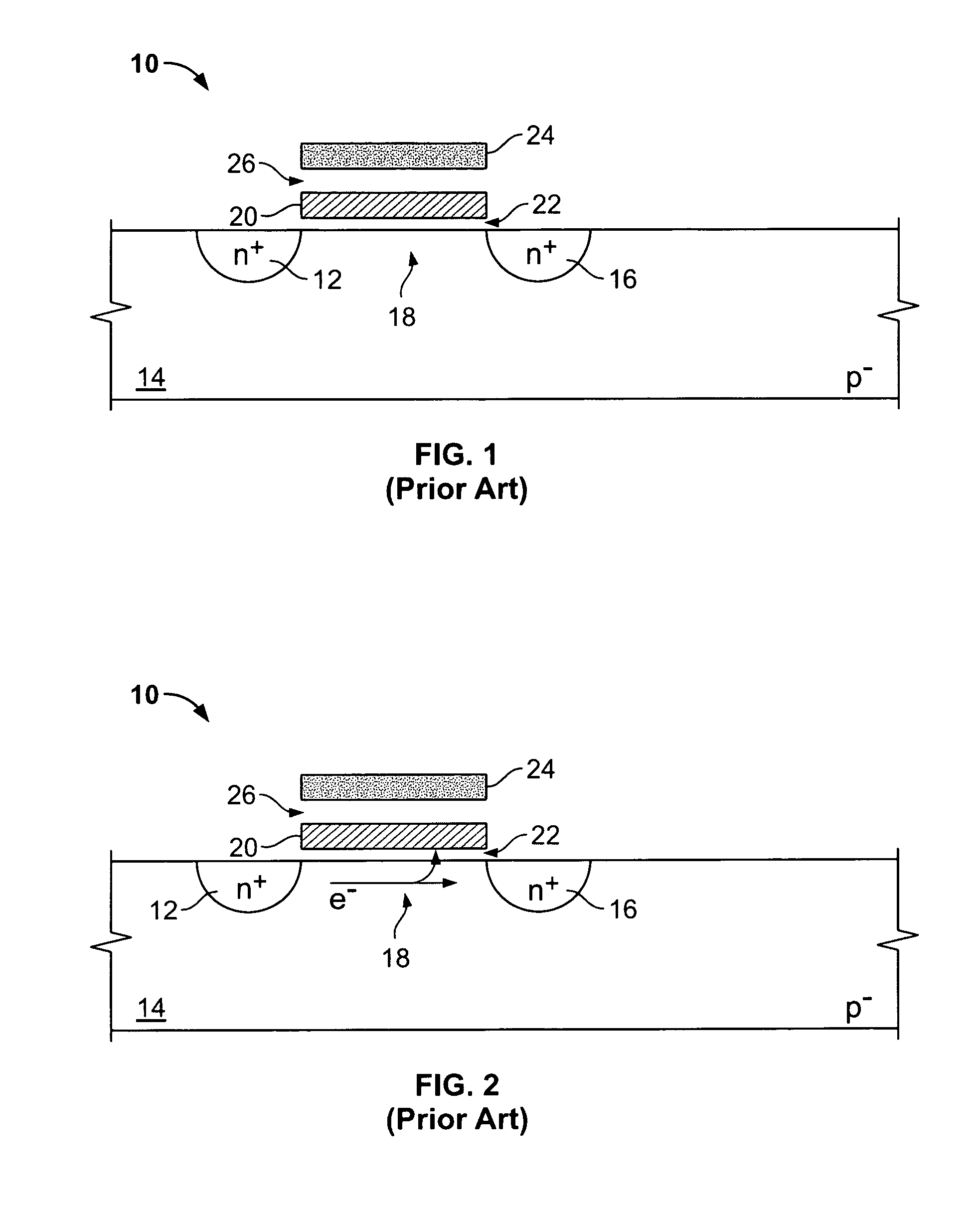

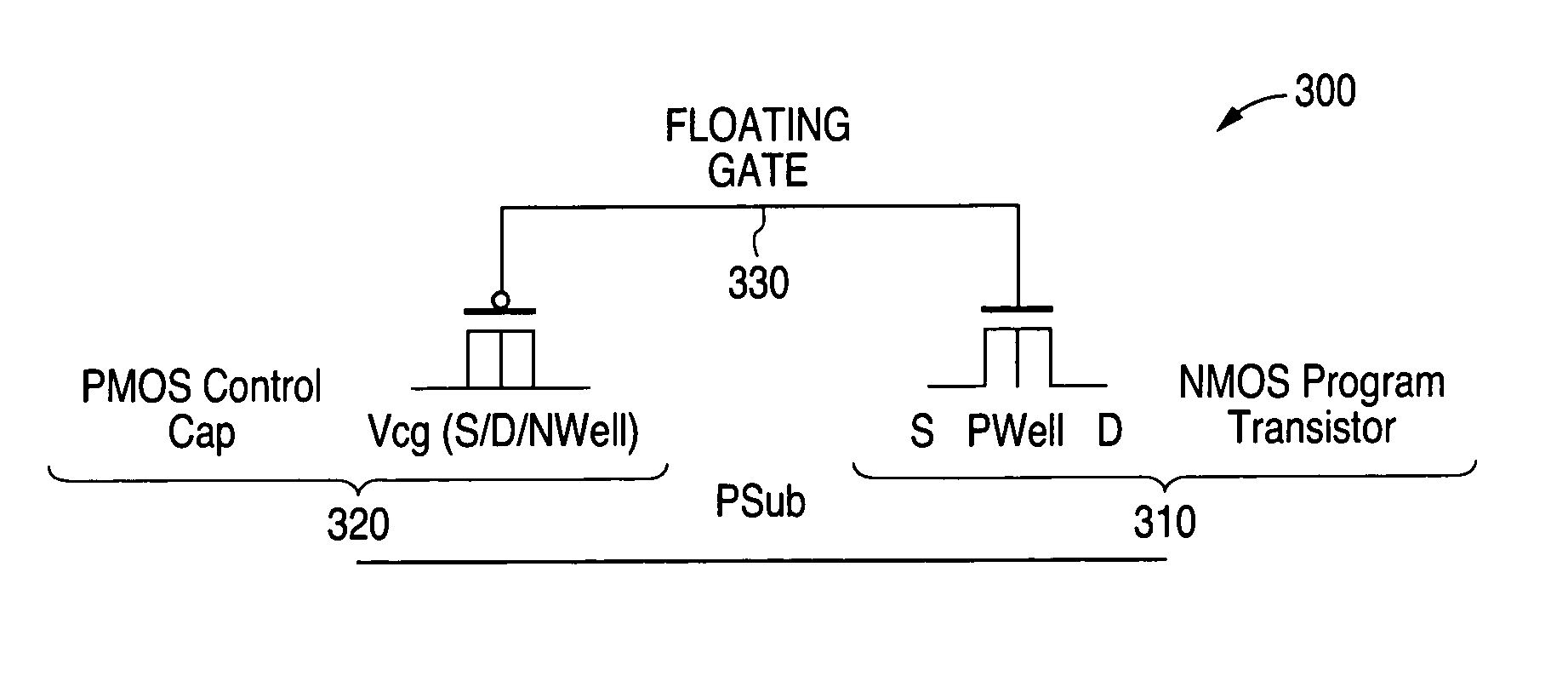

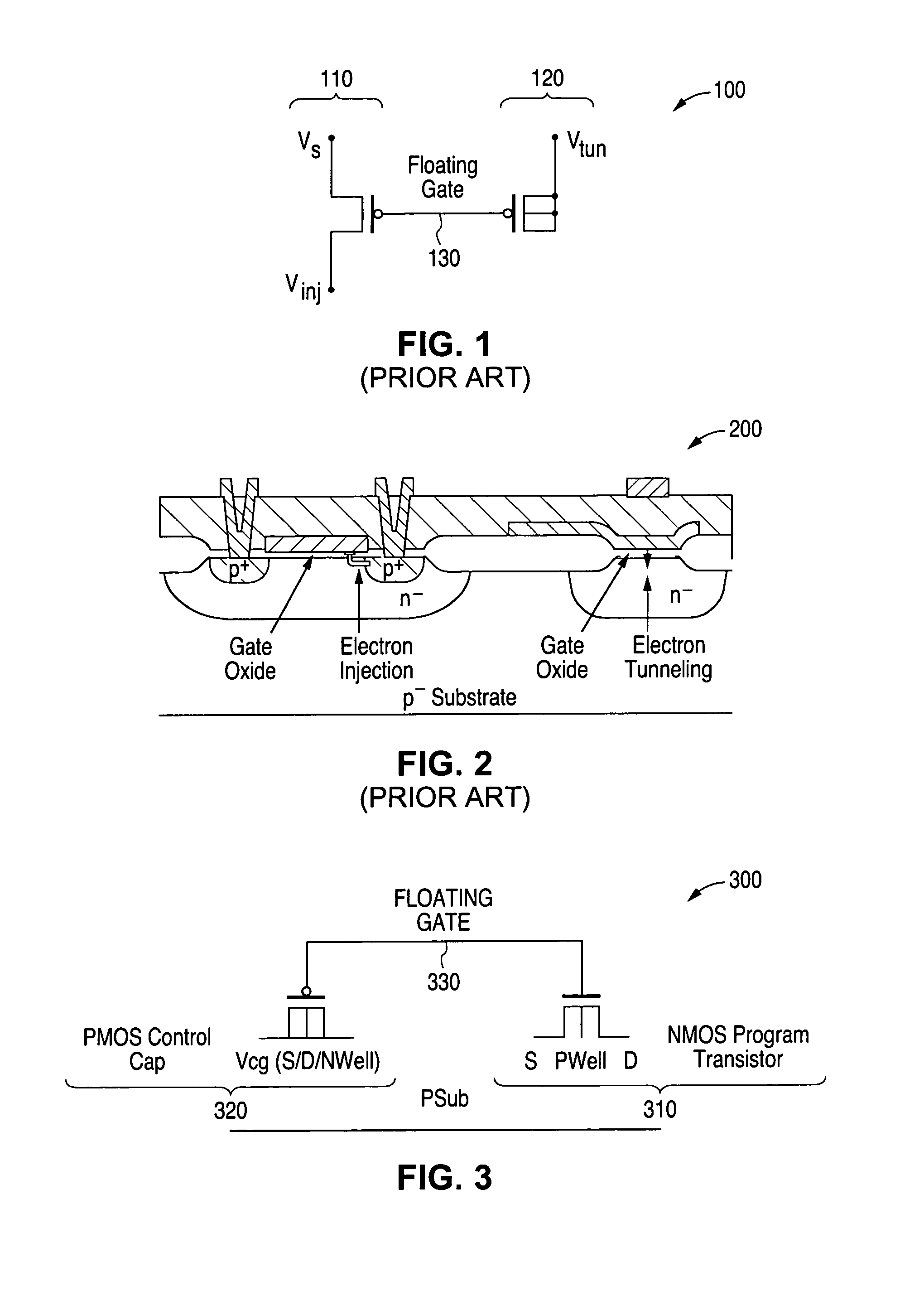

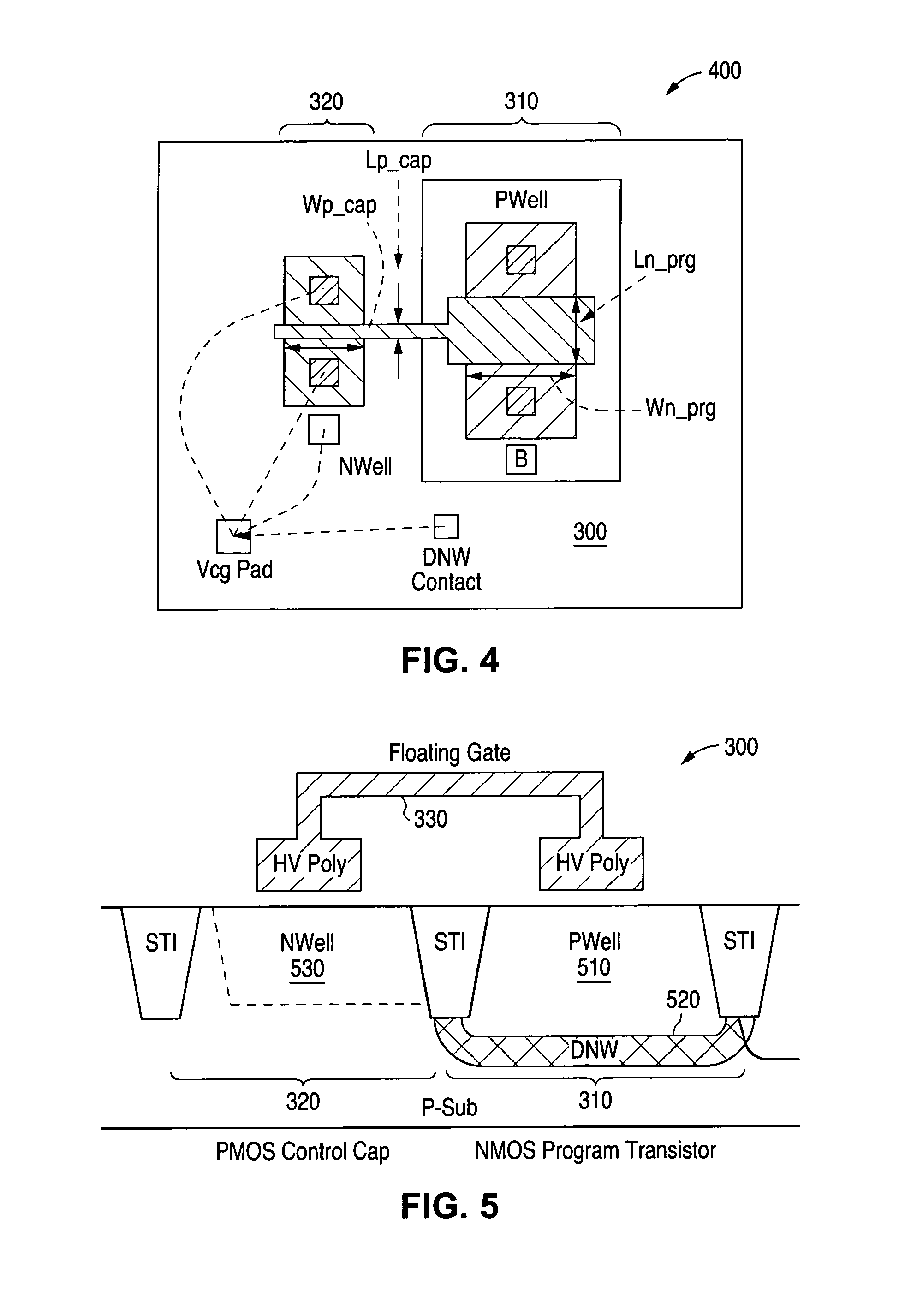

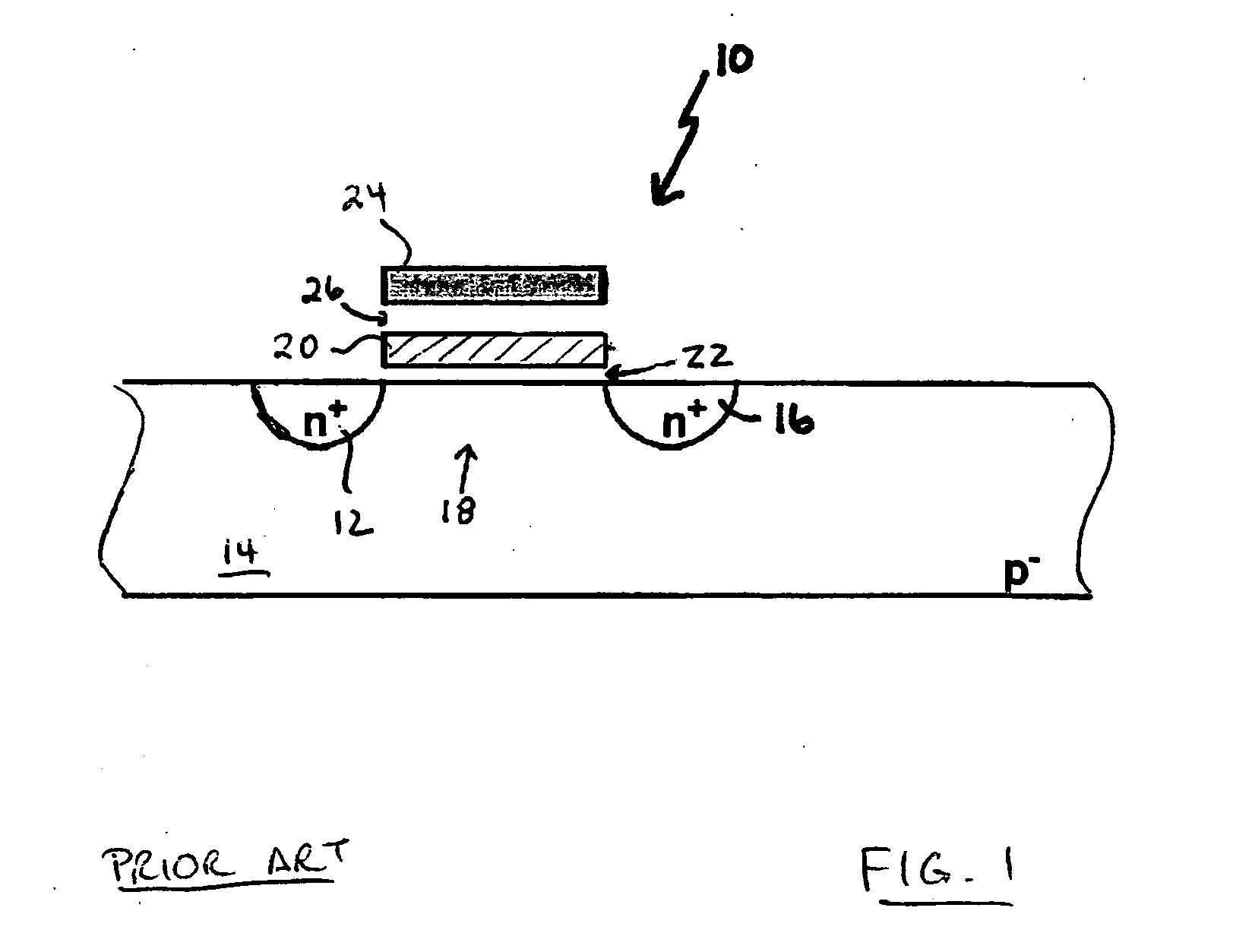

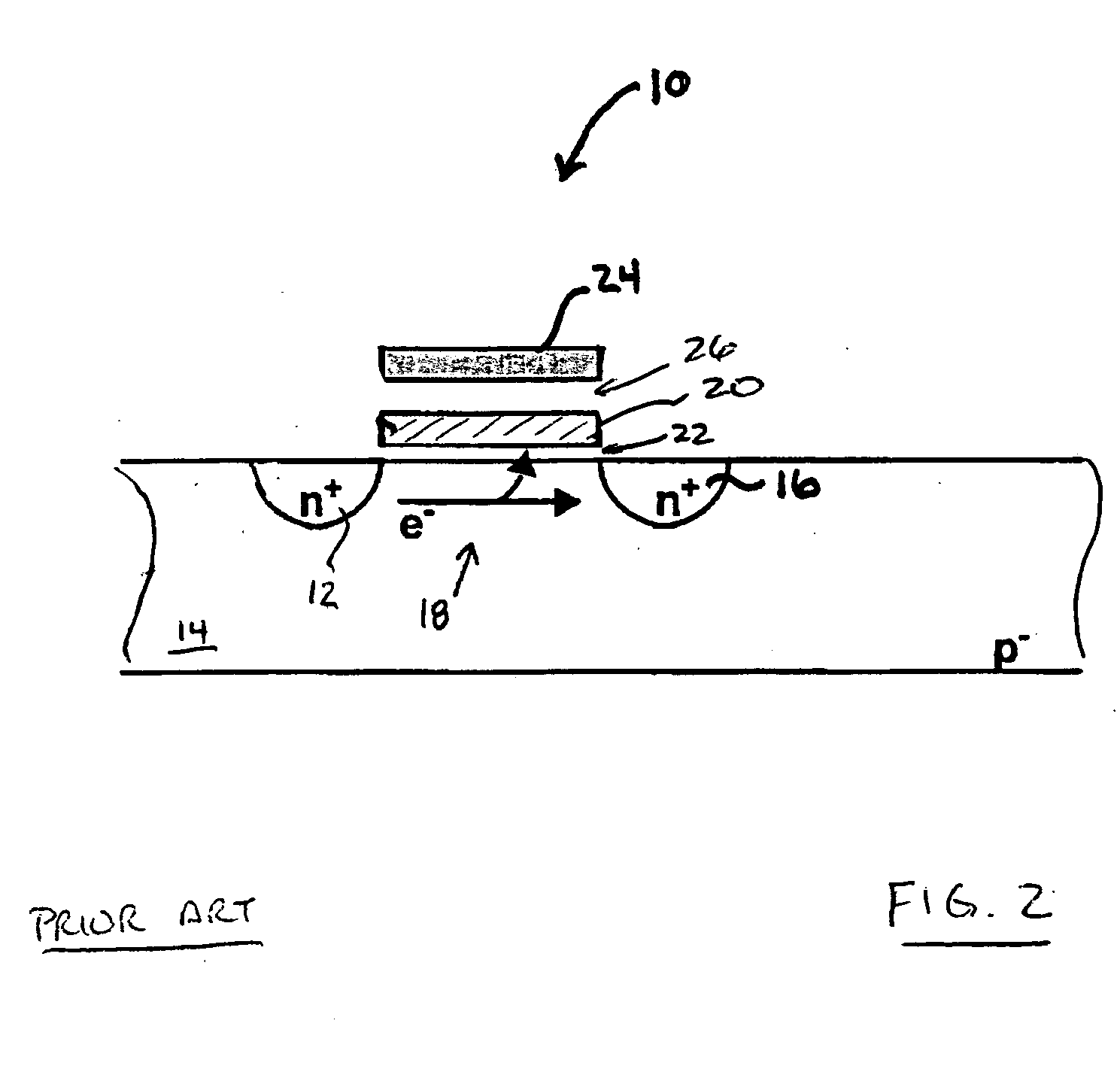

System and method for providing a CMOS compatible single poly EEPROM with an NMOS program transistor

A system and method is disclosed for providing a CMOS compatible single poly electrically erasable programmable read only memory (EEPROM) with memory cells that comprise an NMOS program transistor. In a first embodiment the memory cells of the EEPROM comprise a PMOS control capacitor. In a second embodiment the memory cells of the EEPROM comprise an NMOS control capacitor. A well bias voltage is applied to the NMOS program transistor instead of a gate bias voltage. The well bias voltage enables the injection of (1) channel hot electrons, (2) second hot electrons initiated by the channel hot electrons, and (3) drain impact ionization hot electrons into a floating gate of the NMOS program transistor.

Owner:NAT SEMICON CORP

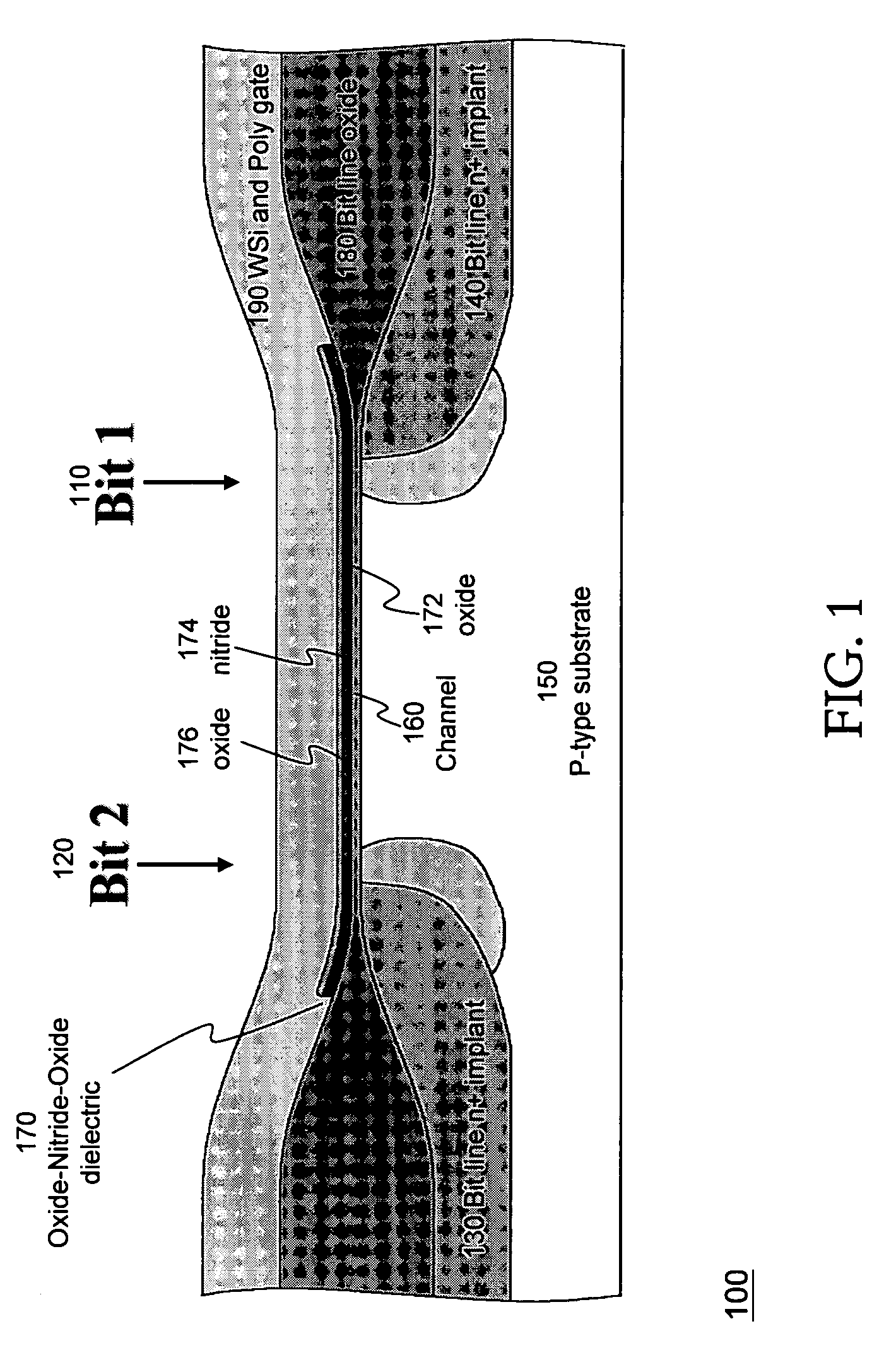

Hole annealing methods of non-volatile memory cells

ActiveUS7301818B2Reduce the amount requiredMinimize holeRead-only memoriesDigital storageNitrideThreshold voltage

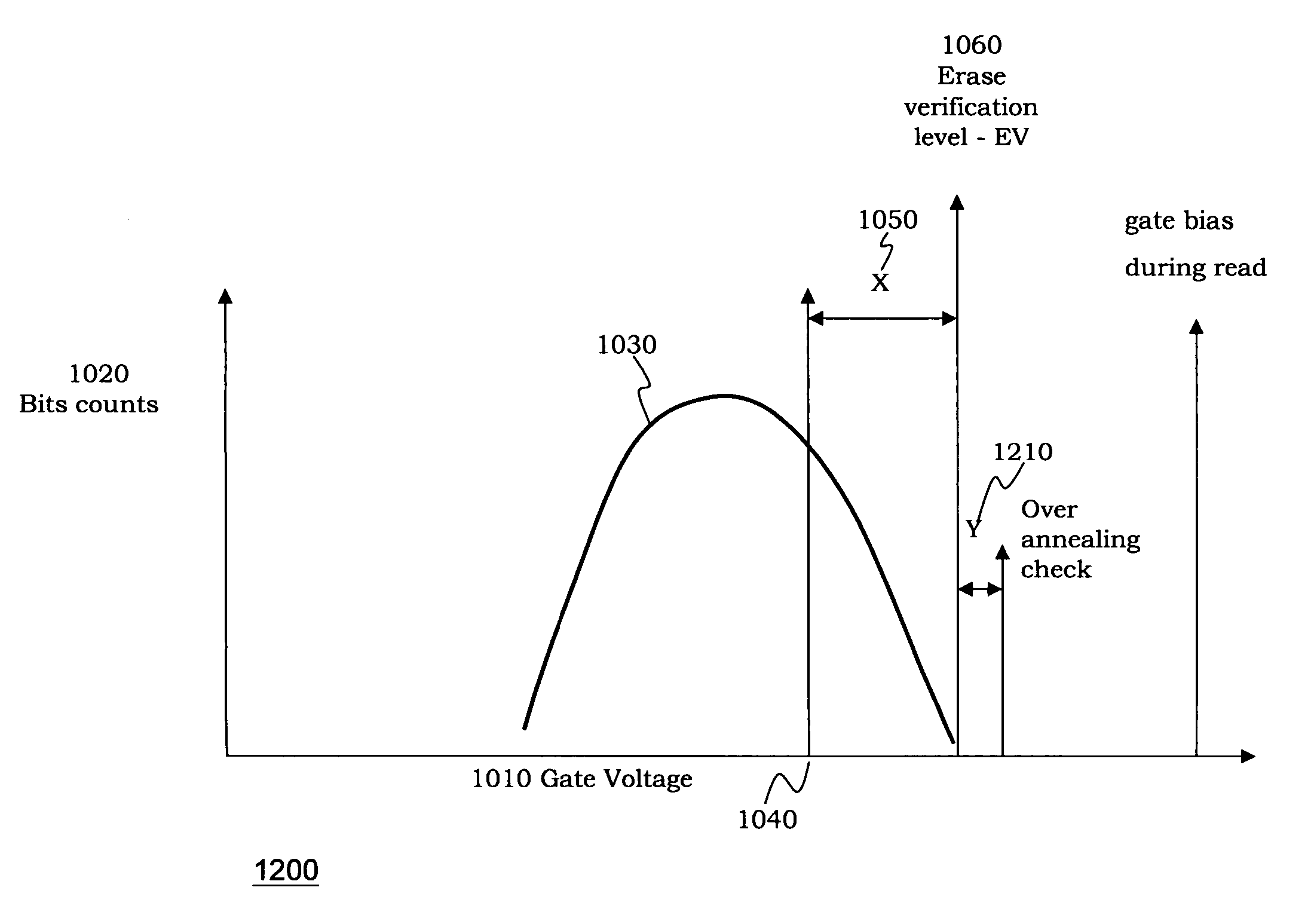

Hole annealing methods are described after erasure of nitride storage memory cells for compensating trapped holes to minimize the holes from detrapping in order to reduce the amount of threshold voltage from drifting significantly higher. A soft hot electron program is used to selected nitride storage memory cells that have been detected to have a threshold voltage that is higher than a presetting threshold voltage (EV) minus a wordline delta X. The effect of the soft electron program neutralizes the excess holes introduced by erasure of nitride storage memory cells that decreases the amount of threshold voltage from drifting higher. In one embodiment, a hole annealing method describes a soft hot electron programming to nitride storage memory cells in a block of nitride memory array that have been determined to have a threshold voltage higher than the presetting threshold voltage minus the wordline delta X.

Owner:MACRONIX INT CO LTD

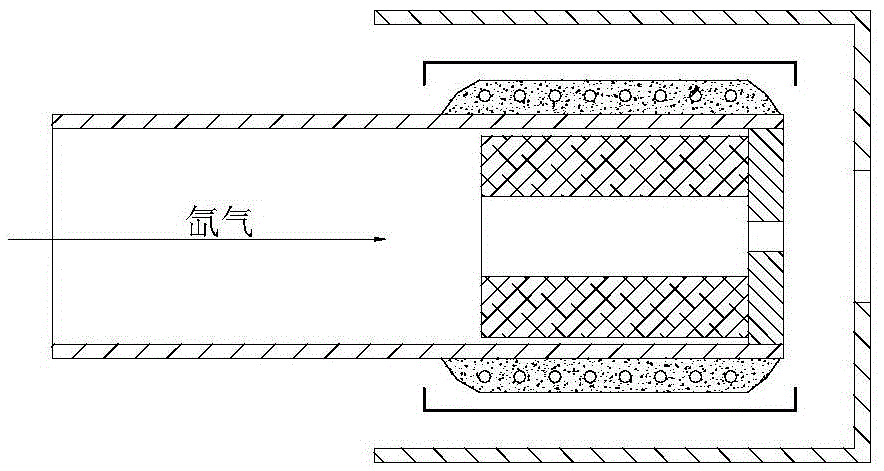

Plume neutralizer of space electric thruster

ActiveCN105626410AAvoid harmful effectsGuaranteed dockingMachines/enginesUsing plasmaGas-discharge lampPower flow

The invention discloses a plume neutralizer of a space electric thruster. The neutralizer comprises an ignition electrode, a top hole plate, a heater, a heat shielding cylinder, an emitting body and a support pipe; the emitting body is mounted in the support pipe; the top hole plate shields out of the emitting body, and is fixedly connected with the support pipe; the heater is mounted out of the support pipe opposite to the emitting body; a heating area covers the whole emitting body; the heater is wrapped with an insulation ceramic layer; the heat shielding cylinder covers the heater, and forms gaps with the heater and the insulation ceramic layer; the ignition electrode is mounted at the downstream of the top hole plate, and forms a gap with a small hole of the top hole plate; and a center hole of the ignition electrode is coaxial with the small hole of the top hole plate. The neutralizer generates a lot of electrons through a hot electron ionized gas discharge mode; continuously emitted electrons are high in density; after the gas discharge is stabilized, the self-heating can be performed to maintain discharge, so that the system power consumption is saved; the equivalent potential is low; the effective acceleration voltage of the thruster is higher; and the specific impulse of the thruster is high.

Owner:SHANGHAI INST OF SPACE PROPULSION

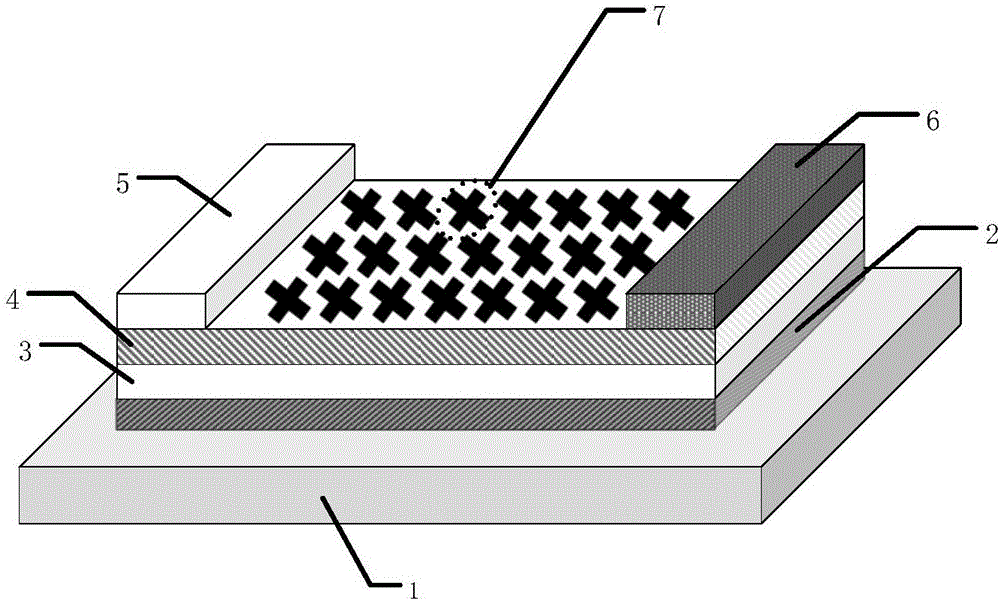

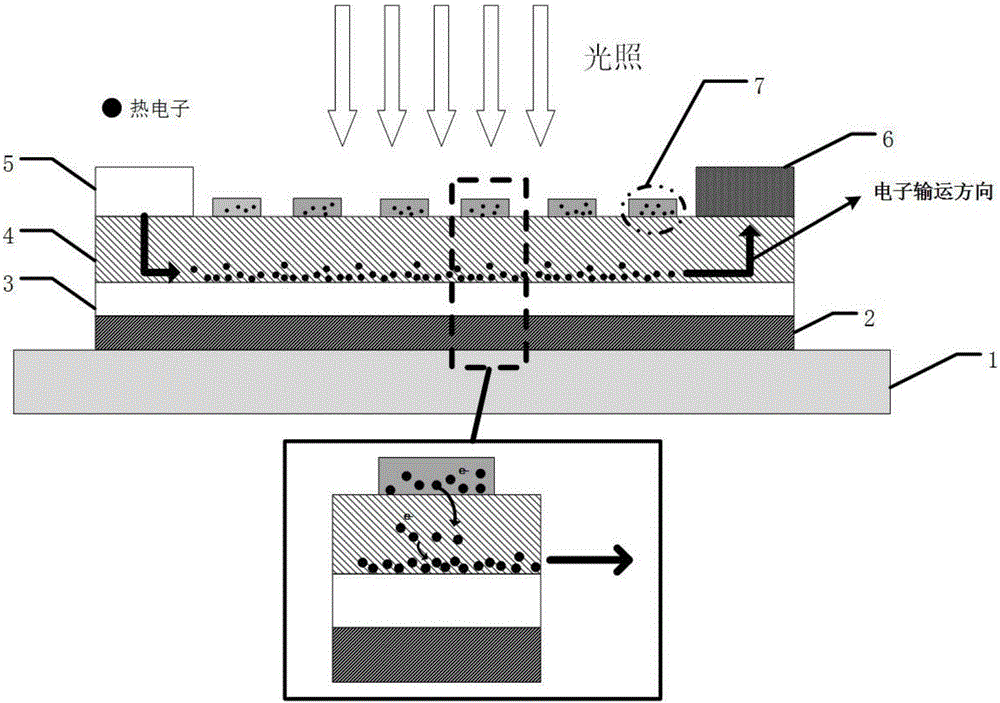

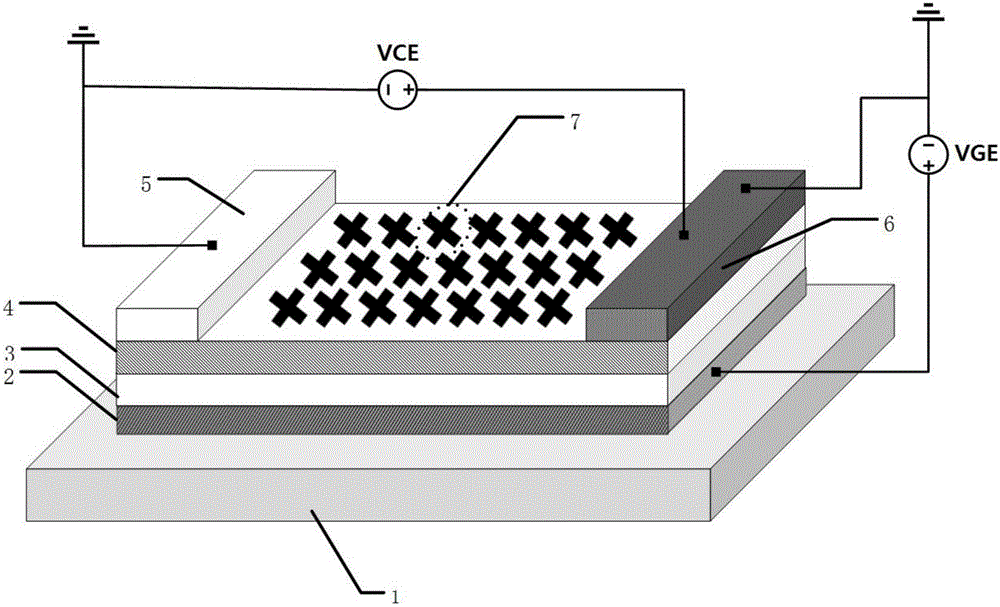

Polarization sensitive photoelectric detector

InactiveCN106257692AImplement detectionMiniaturizationFinal product manufacturePhotometry using electric radiation detectorsPolarizerPhotocurrent

The invention discloses a polarization sensitive photoelectric detector based on the metal plasmon structure hot electron effect. The polarization sensitive photoelectric detector comprises an insulating substrate, a metal back gate electrode, an insulating isolation layer, a channel active layer, a drain electrode, a source electrode and a plasmon structure of which plasmon resonance is sensitive to polarized light. The material forbidden bandwidth of the channel active layer is greater than photon energy of incident light. The plasmon structure is a metal nanostructure. Detection of light polarization information is realized by using the characteristic of strong dependence for the incident light polarization state generated by the hot electrons of the plasmon structure. The polarization sensitive photoelectric detector has the following advantages that 1, detection of the light polarization information can be realized by using the plasmon structure without additional arrangement of optical elements (polarizer / polarization analyzer) so that miniaturization and integration of the device are facilitated; and 2, photocurrent can be amplified by applying bias voltage through the metal back gate electrode, and the metal back gate electrode structure and the metal nanometer plasmon structure are enabled to form a super surface structure to enhance light absorption so that the degree of photoelectric response can be enhanced.

Owner:SOUTHEAST UNIV

Circuit for Dynamic Circuit Timing Synthesis and Monitoring of Critical Paths and Environmental Conditions of an Integrated Circuit

InactiveUS20080104561A1Multiple input and output pulse circuitsPulse characteristics measurementsEngineeringCritical path method

A circuit for dynamically monitoring the operation of an integrated circuit under differing temperature, frequency, and voltage (including localized noise and droop), and for detecting early life wear-out mechanisms (e.g., NBTI, hot electrons).

Owner:IBM CORP

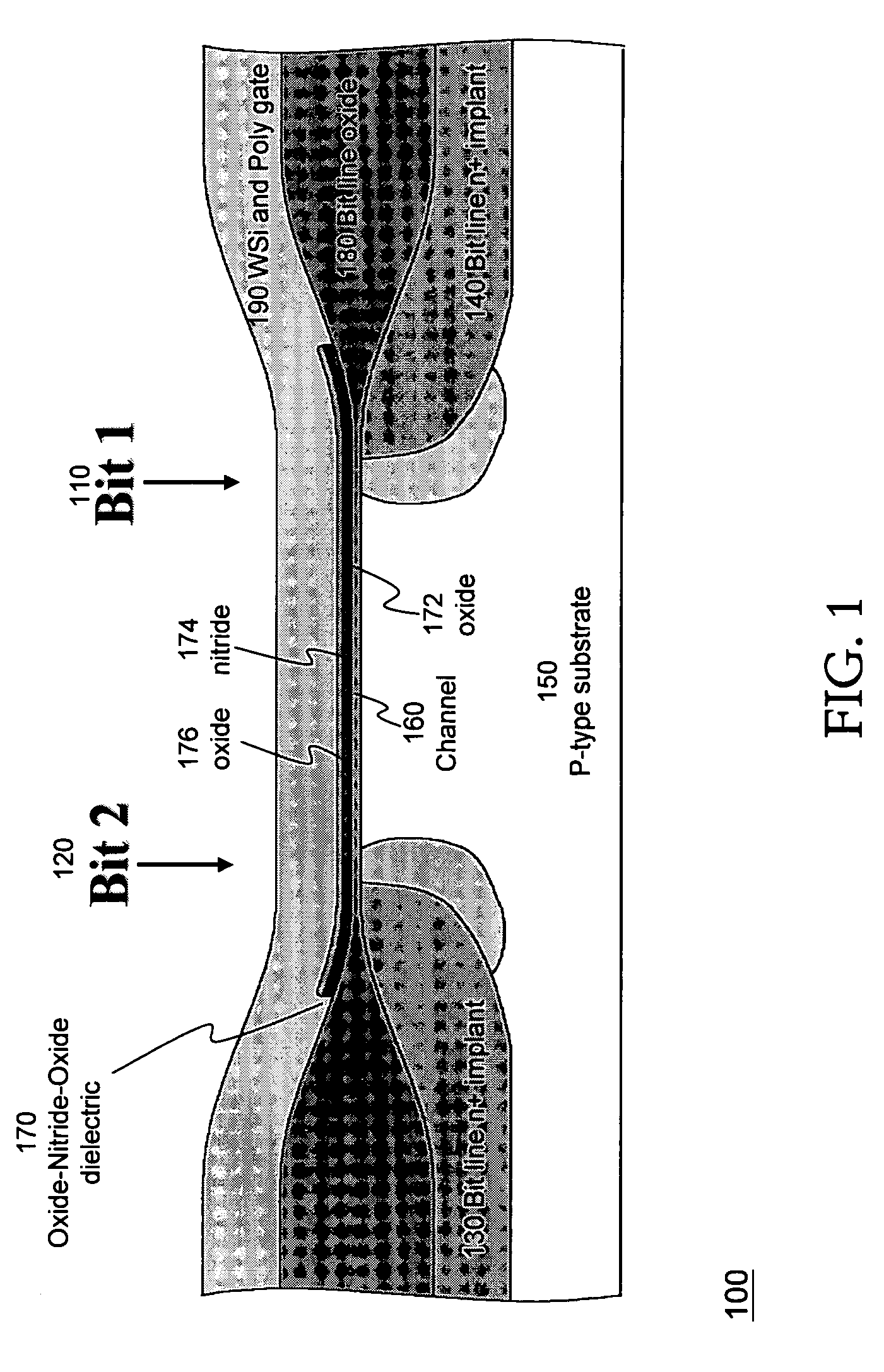

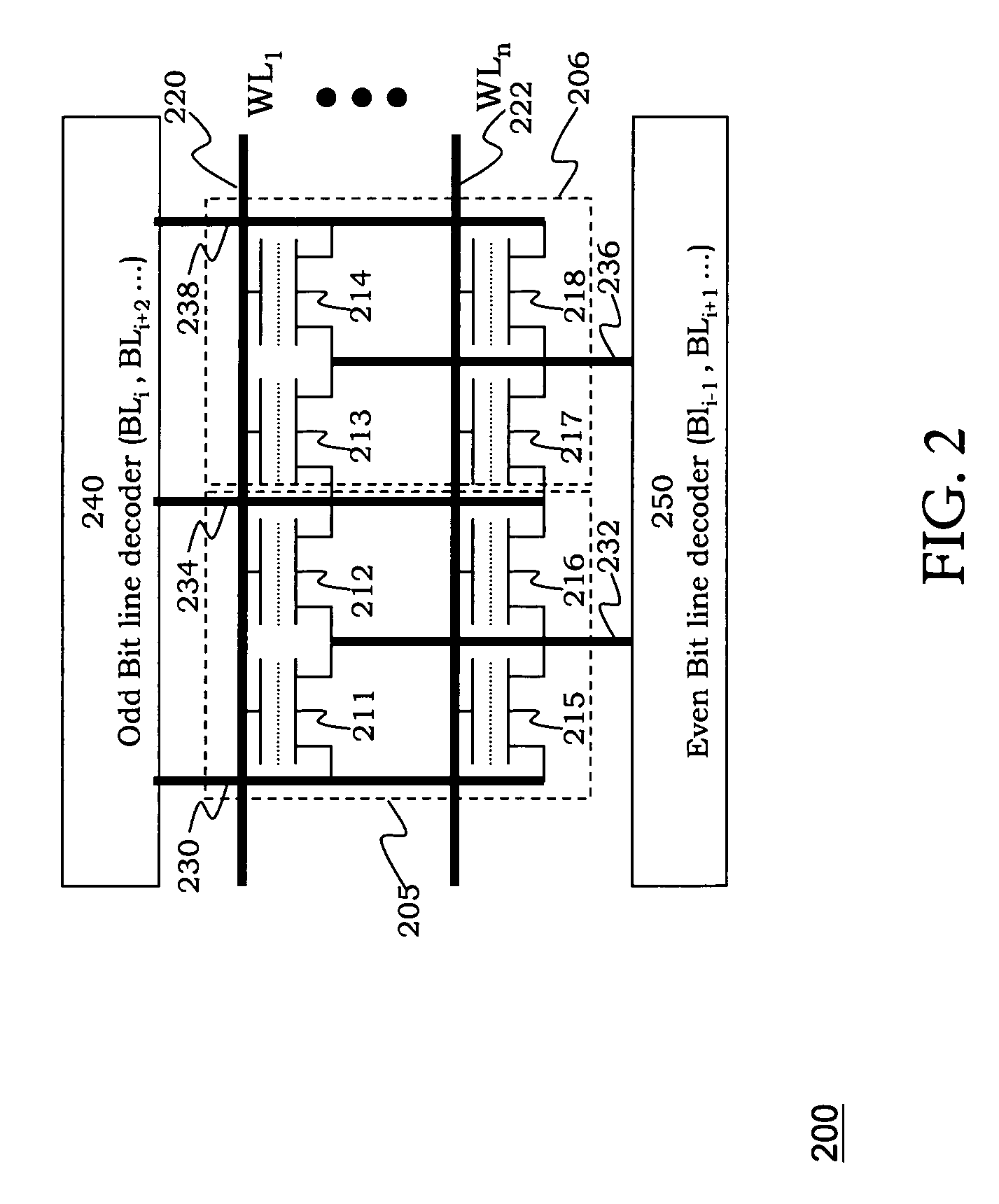

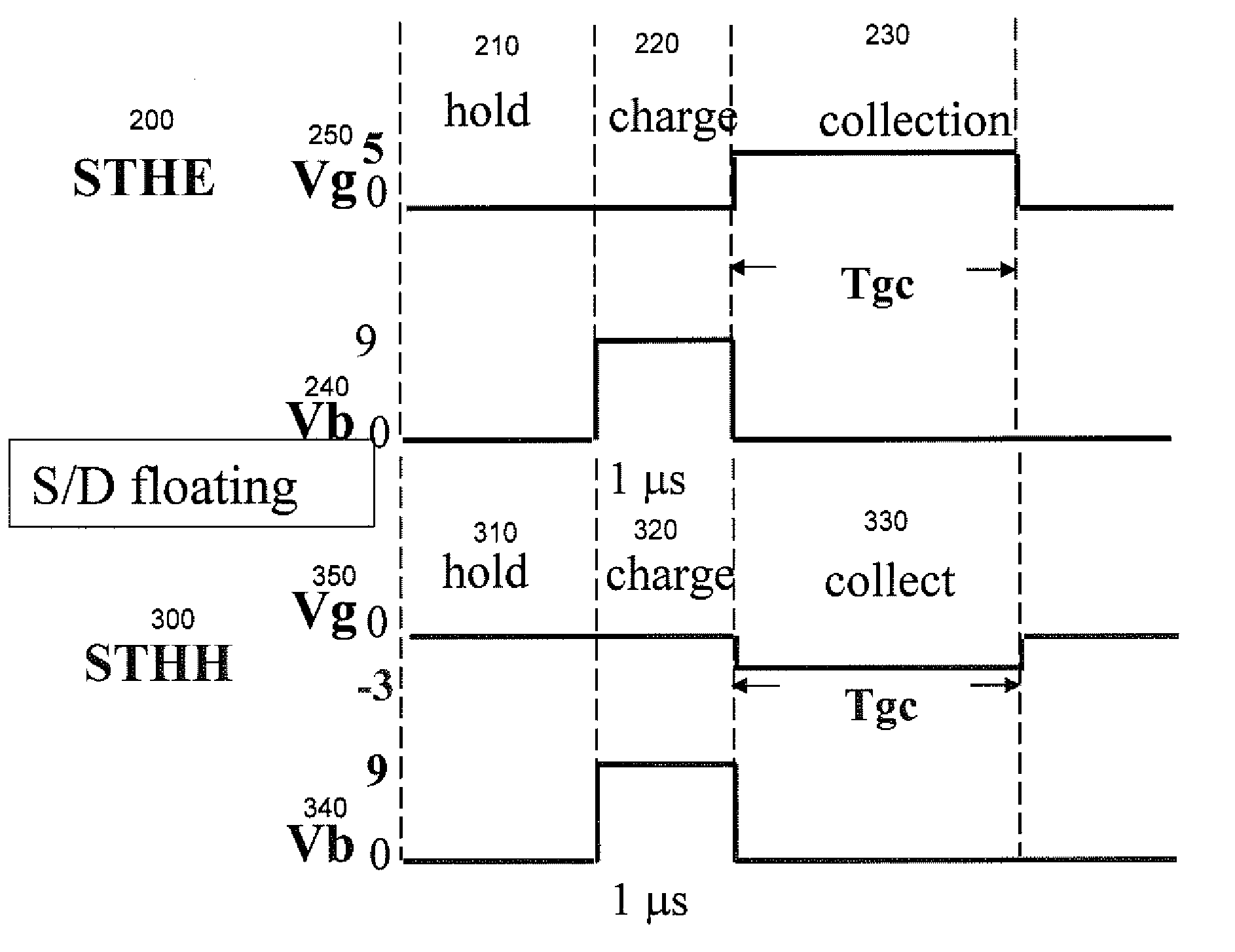

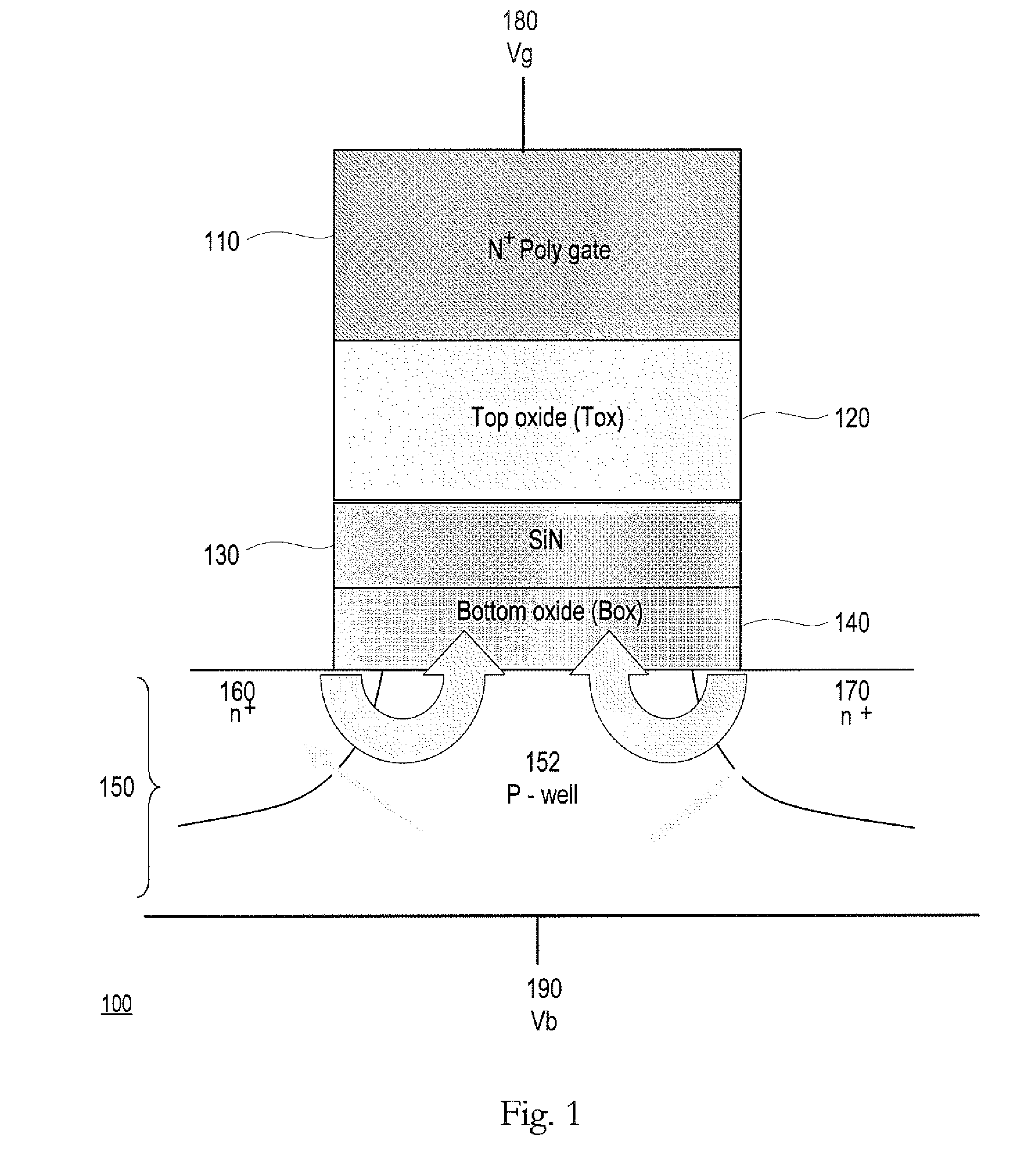

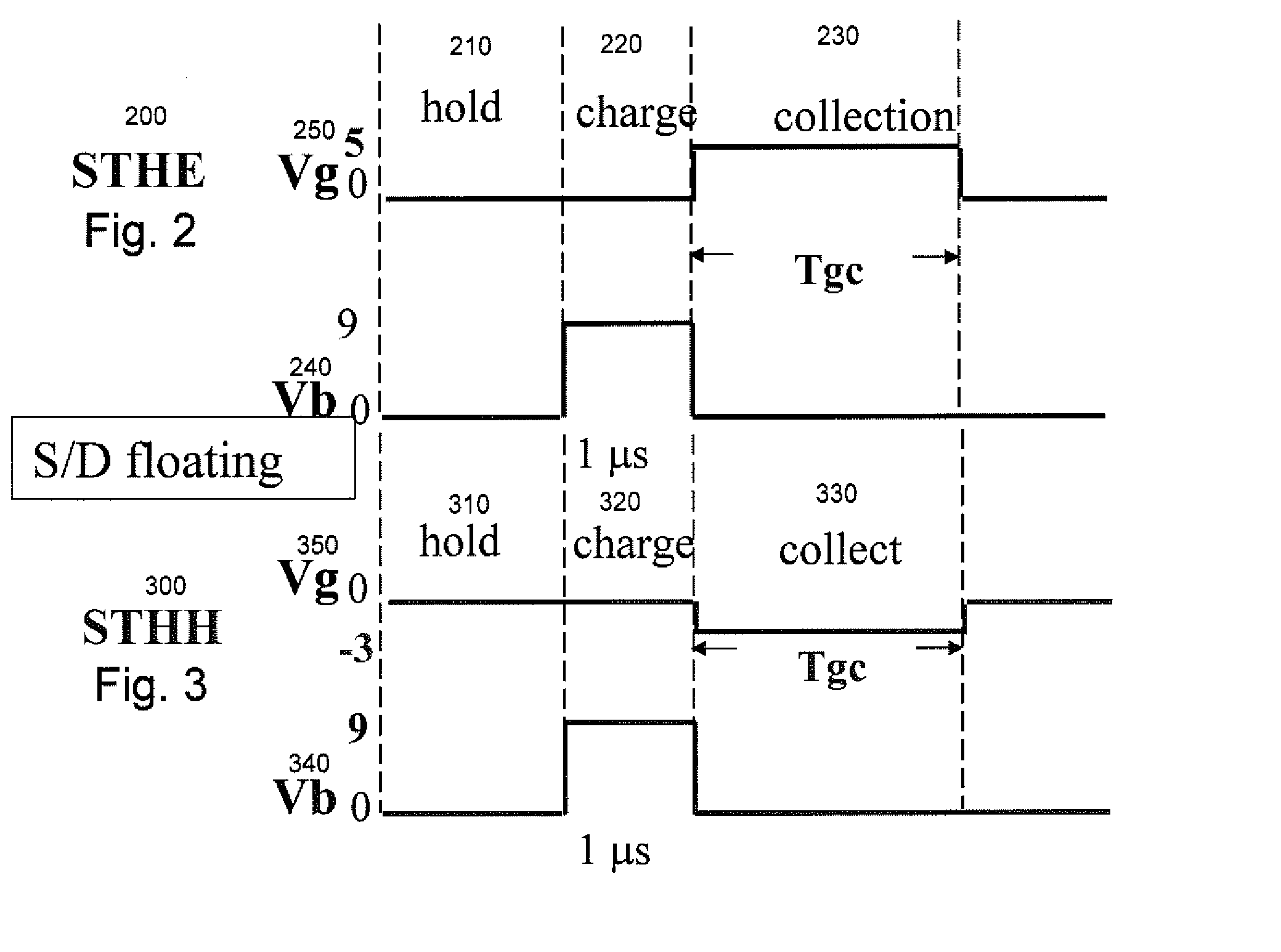

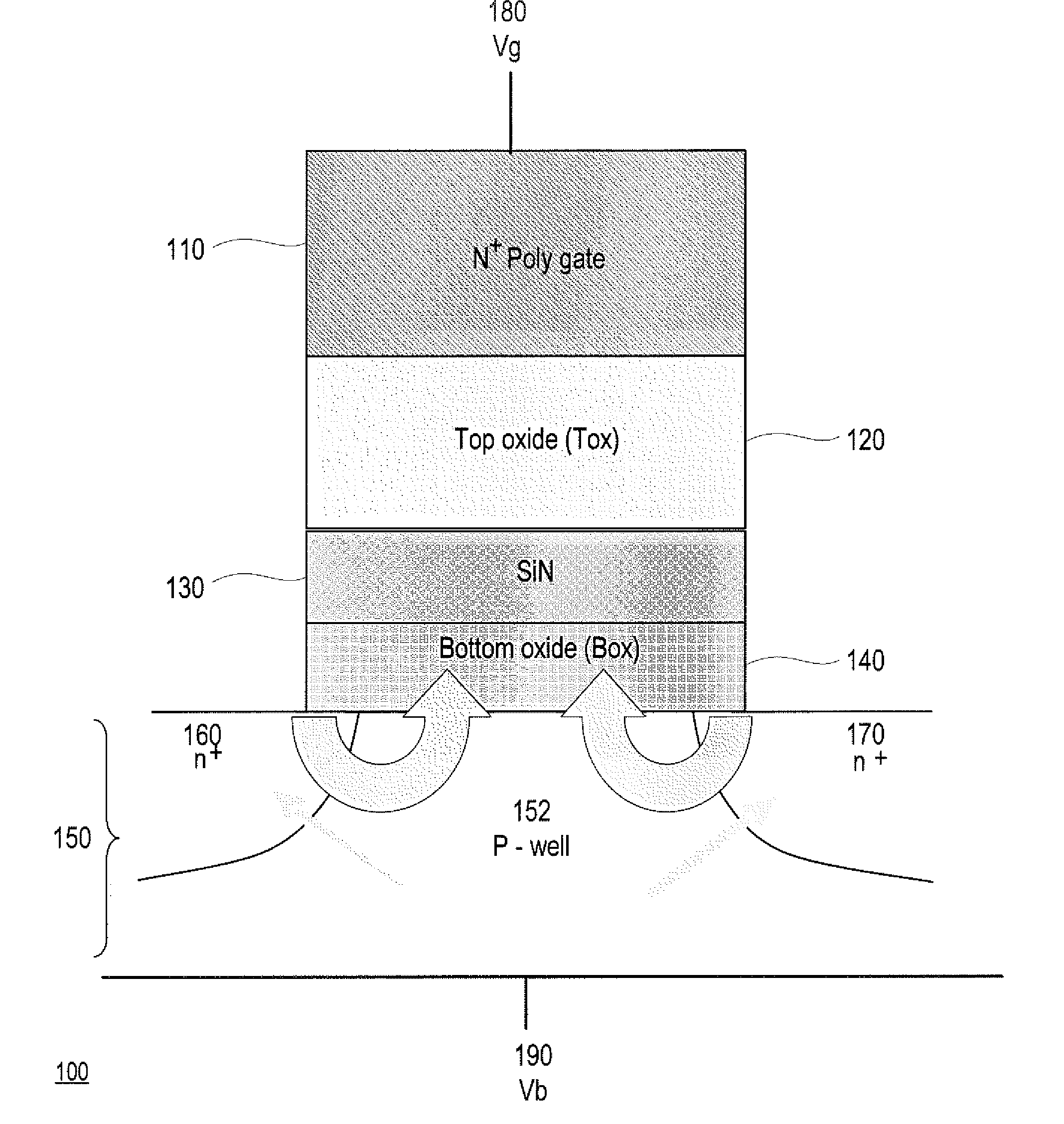

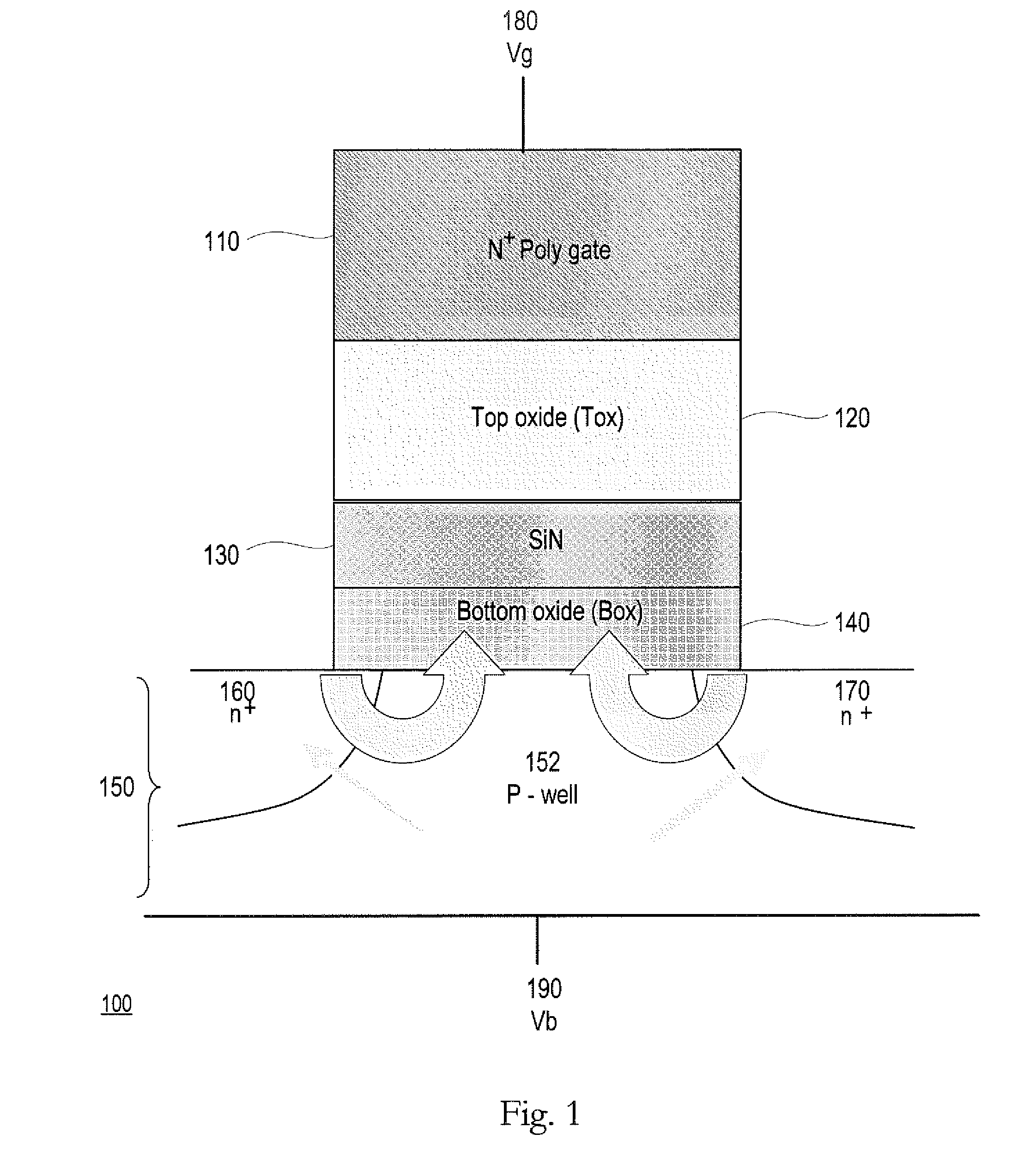

Program and erase methods with substrate transient hot carrier injections in a non-volatile memory

InactiveUS7590005B2Reduce bias voltageShort operating timeRead-only memoriesDigital storageTrappingEngineering

The present invention describes a uniform program method and a uniform erase method of a charge trapping memory by employing a substrate transient hot electron technique for programming, and a substrate transient hot hole technique for erasing, which emulate an FN tunneling method for NAND memory operation. The methods of the present invention are applicable to a wide variety of charge trapping memories including n-channel or p-channel SONOS types of memories and floating gate (FG) type memories. The programming of the charge trapping memory is conducted using a substrate transient hot electron injection in which a body bias voltage Vb has a short pulse width and a gate bias voltage Vg has a pulse width that is sufficient to move electrons from a channel region to a charge trapping structure.

Owner:MACRONIX INT CO LTD

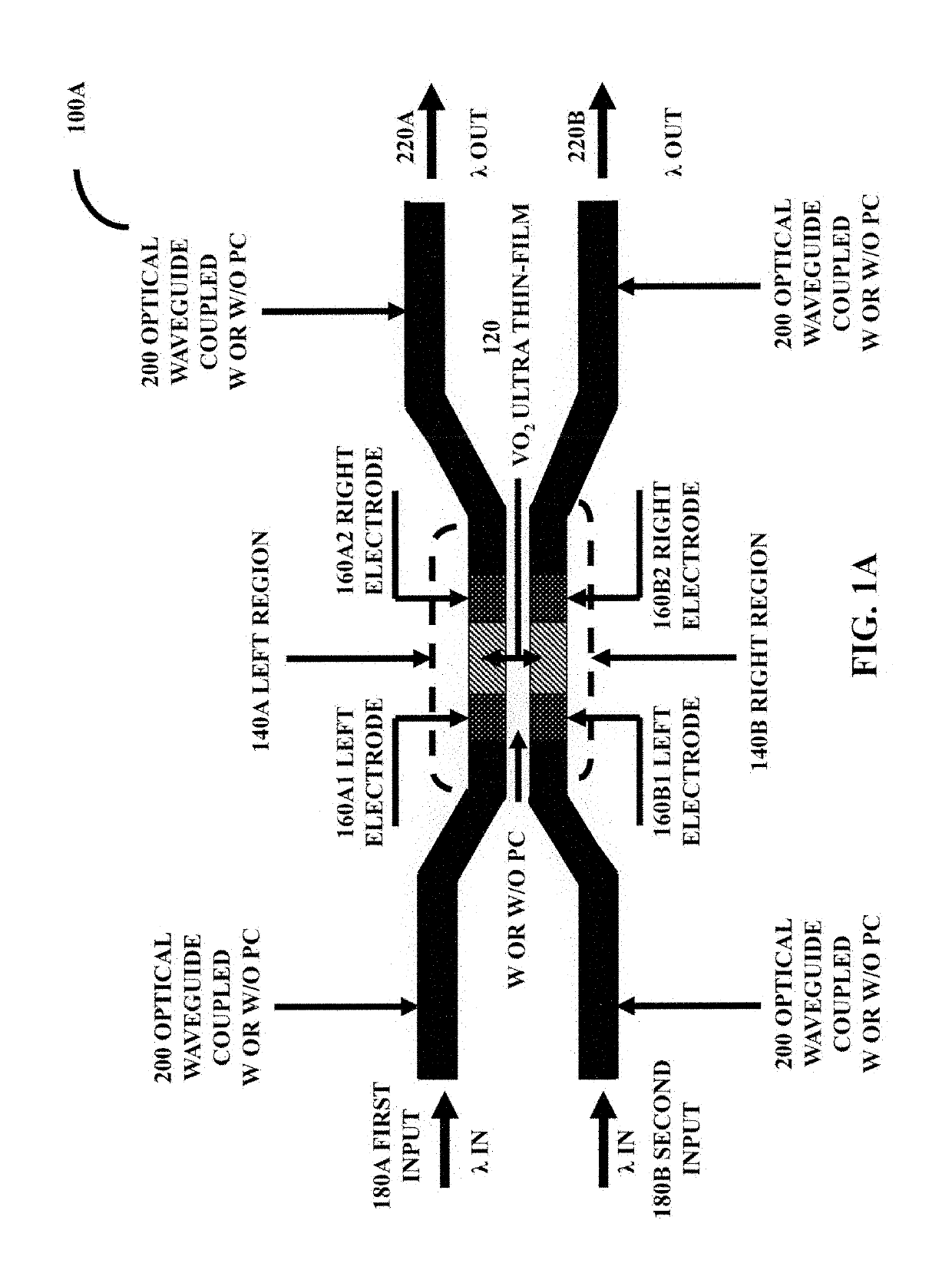

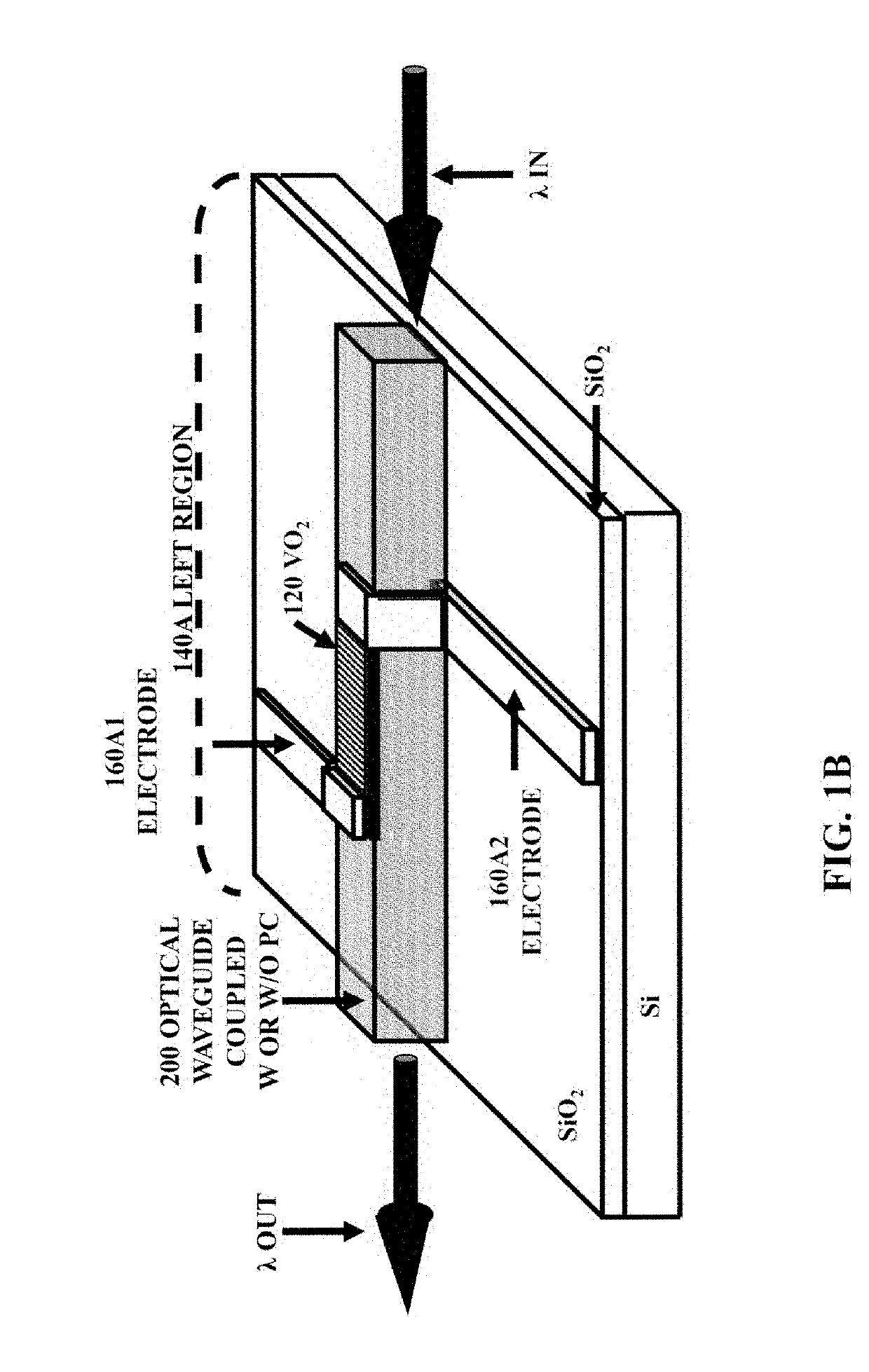

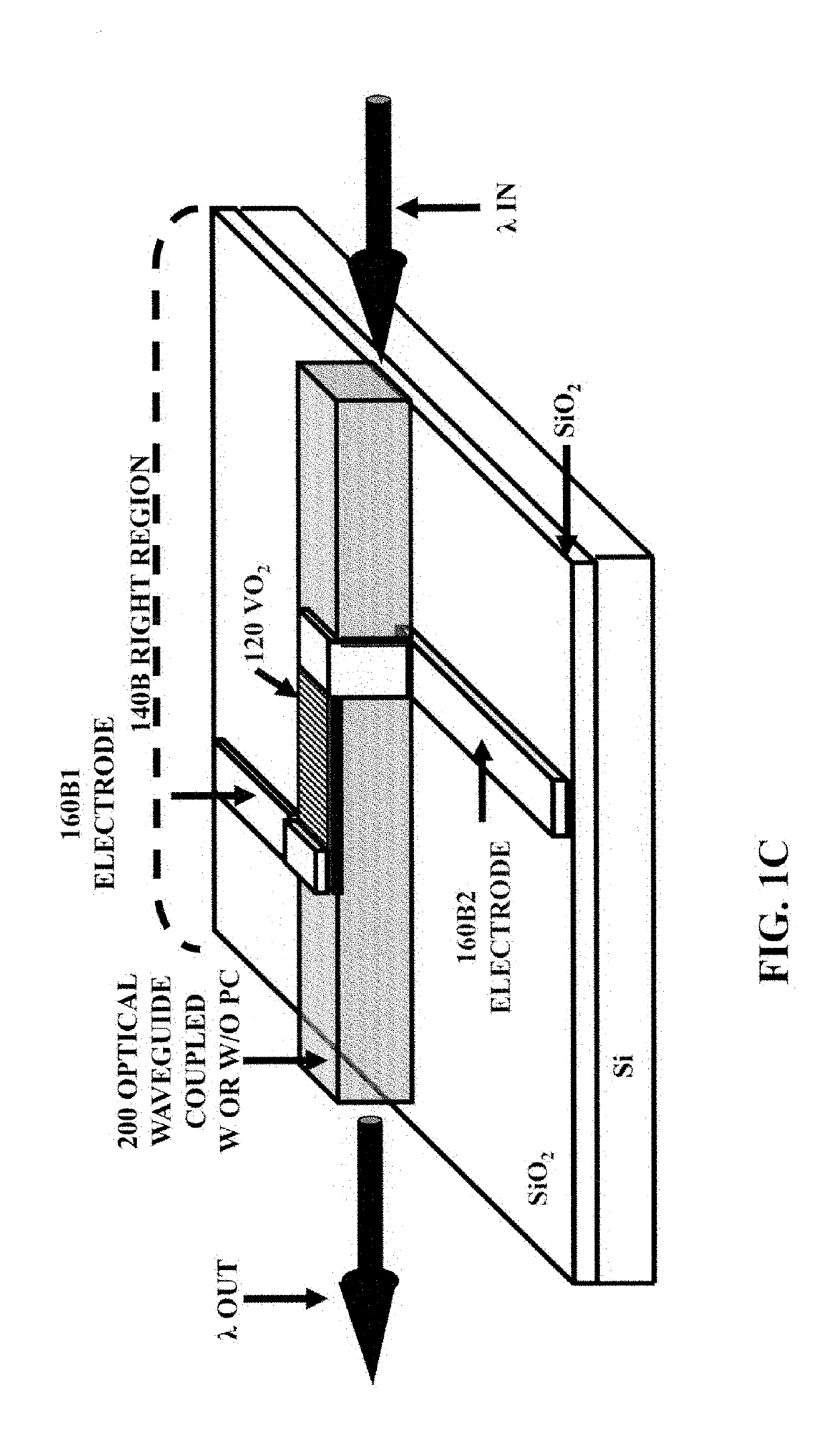

Fast optical switch and its applications in optical communication

InactiveUS20190253776A1Reduce noiseIncrease power consumptionMultiplex system selection arrangementsLight demodulationVoltage pulseMott insulator

A fast optical (with or without a photonic crystal) switch is fabricated / constructed, utilizing a phase transition material / Mott insulator, activated by either an electrical pulse (a voltage pulse or a current pulse) and / or a light pulse and / or pulses in terahertz (THz) frequency of a suitable field strength and / or hot electrons. The applications of such a fast optical switch for an on-demand optical add-drop subsystem, integrating with (a) a light slowing / light stopping component (based on metamaterials and / or nanoplasmonic structures) and (b) with or without a wavelength converter are also described.

Owner:CELERIS SYST INC

Program and Erase Methods with Substrate Transient Hot Carrier Injections in a Non-Volatile Memory

InactiveUS20070236994A1Reduce bias voltageShort operating timeRead-only memoriesDigital storageTrappingEngineering

The present invention describes a uniform program method and a uniform erase method of a charge trapping memory by employing a substrate transient hot electron technique for programming, and a substrate transient hot hole technique for erasing, which emulate an FN tunneling method for NAND memory operation. The methods of the present invention are applicable to a wide variety of charge trapping memories including n-channel or p-channel SONOS types of memories and floating gate (FG) type memories. the programming of the charge trapping memory is conducted using a substrate transient hot electron injection in which a body bias voltage Vb has a short pulse width and a gate bias voltage Vg has a pulse width that is sufficient to move electrons from a channel region to a charge trapping structure.

Owner:MACRONIX INT CO LTD

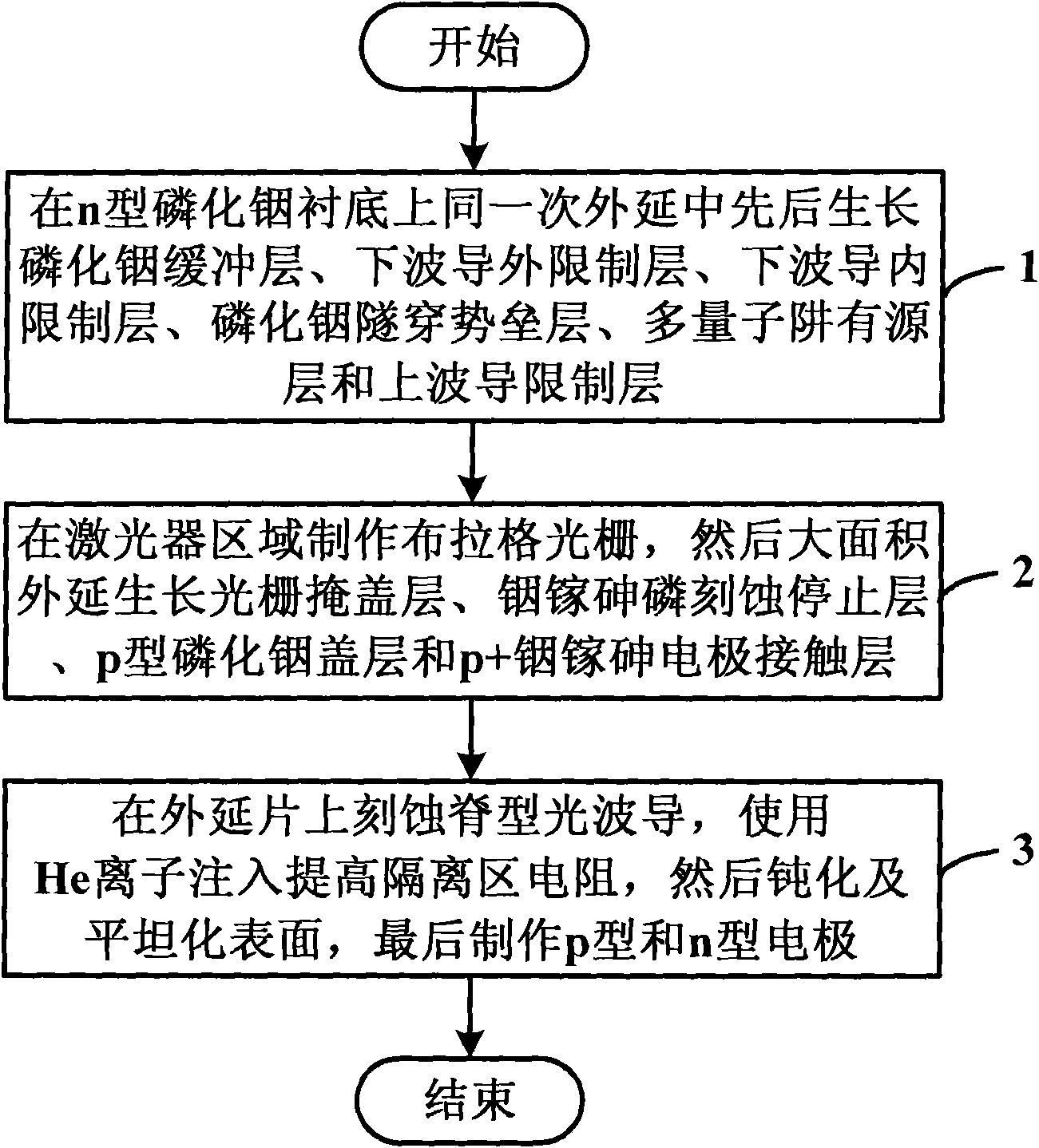

Making method of electrical absorption modulation tunneling injection type distributed feedback semiconductor laser

InactiveCN102055133AEliminate performance impactRaise the characteristic temperatureLaser detailsLaser output parameters controlGratingElectrode Contact

The invention discloses a making method of an electrical absorption modulation tunneling injection type distributed feedback semiconductor laser, which comprises the following steps of: 1, growing an n-type indium phosphide buffer layer, a lower waveguide external limit layer, a lower waveguide internal limit layer, an indium phosphide tunneling barrier layer, a multiple quantum well active layer and an upper waveguide limit layer on an n-type indium phosphide substrate during the same epitaxy; 2, making a Bragg grating in a laser region, then epitaxially growing a p-type indium phosphide grating covering layer, an InGaAsP etching stopping layer, a p-type indium phosphide covering layer and a p+ InGaAs electrode contact layer largely; and 3, etching a ridge type optical waveguide on an epitaxial wafer, injecting with He ions to improve the resistance of an isolation region, and then passivating and flatting the surface and finally making a p-type and an n-type electrodes. The invention has the advantages of simple process and high reliability, eliminates the influence of hot electrons on the property of the laser, improves the characteristic temperature of the laser, and can realize a certain independent optimization on the laser and a modulator.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

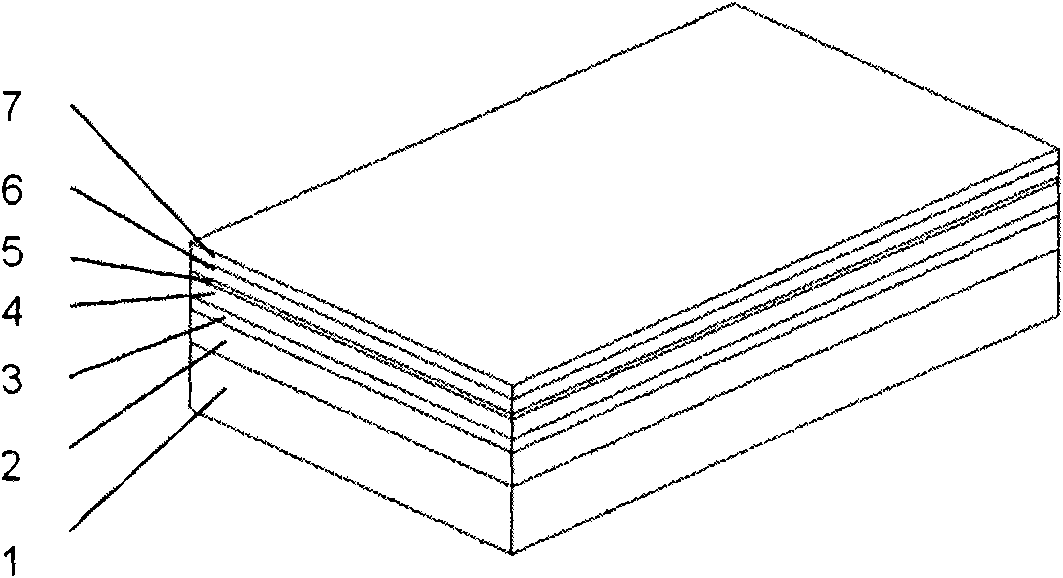

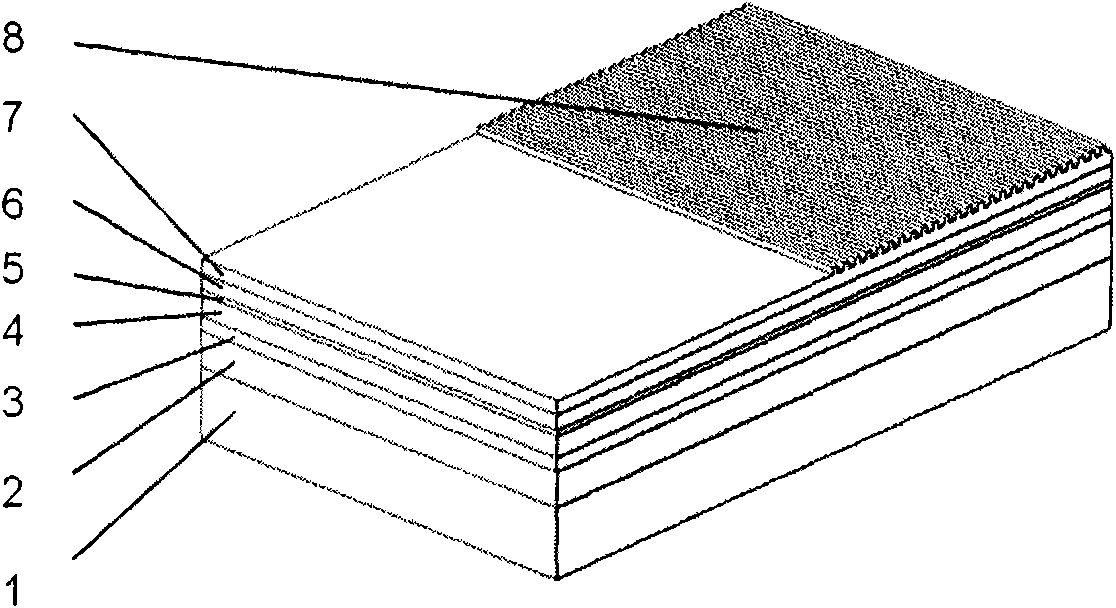

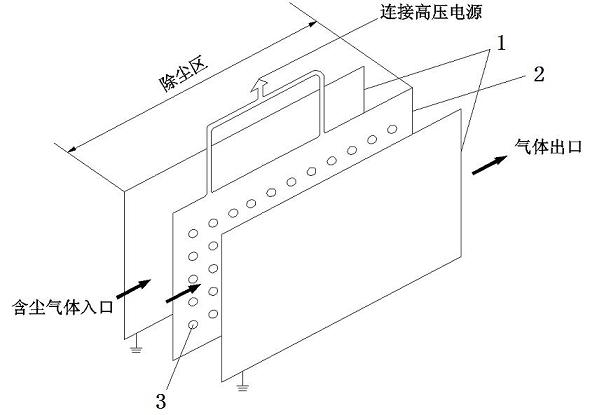

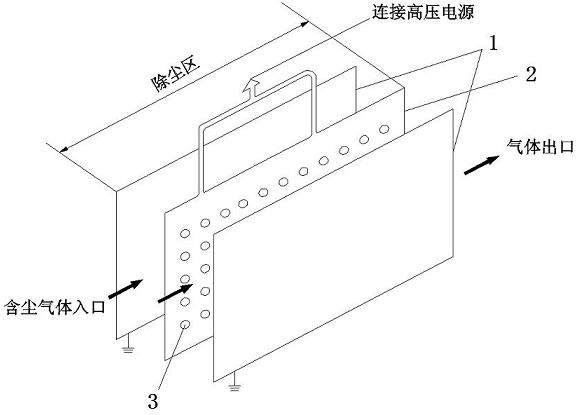

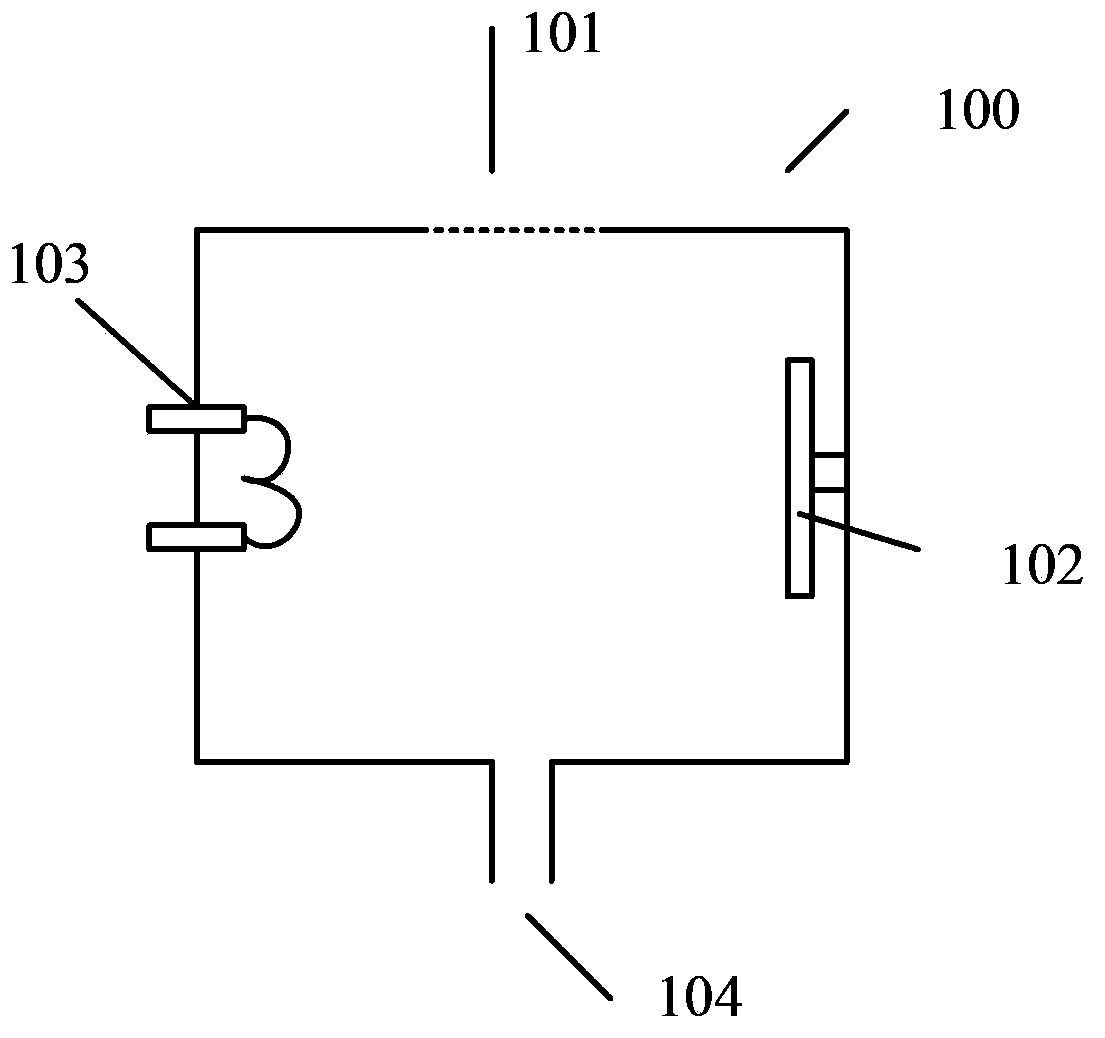

Single-zone plate type high-temperature electrostatic dust collector

InactiveCN102078841AHigh densityEfficient use ofExternal electric electrostatic seperatorElectrode constructionsHigh pressureSingle zone

The invention discloses a single-zone plate type high-temperature electrostatic dust collector and belongs to the technical field of environmental-protection dust collecting equipment. The equipment mainly comprises positive plates, a negative plate, emitter electrodes, a high-temperature power supply, wherein two stainless steel plates are grounded and parallelly arranged to serve as positive plates; a stainless steel plate which has the same shape and size as the positive plates is connected with the negative pole of a high-temperature power supply to serve as the negative plate; the negative plate is suspended in the middle of the two positive plates and parallel to the positive plates; and all disc-like emitter electrodes are embedded on the two sides of the negative plate. In the invention, a single-zone plate type structure is adopted, so the structure of the equipment is compact and the electrical field is uniform, and the stability and reliability of the high temperature operation of the equipment are improved; and the emitter electrode is made of cerium oxide-doped barium-tungsten hot electron emitting material, which contributes to improving dust collection efficiency and prolonging the service life of the equipment.

Owner:苏州南师大智慧创意产业有限公司

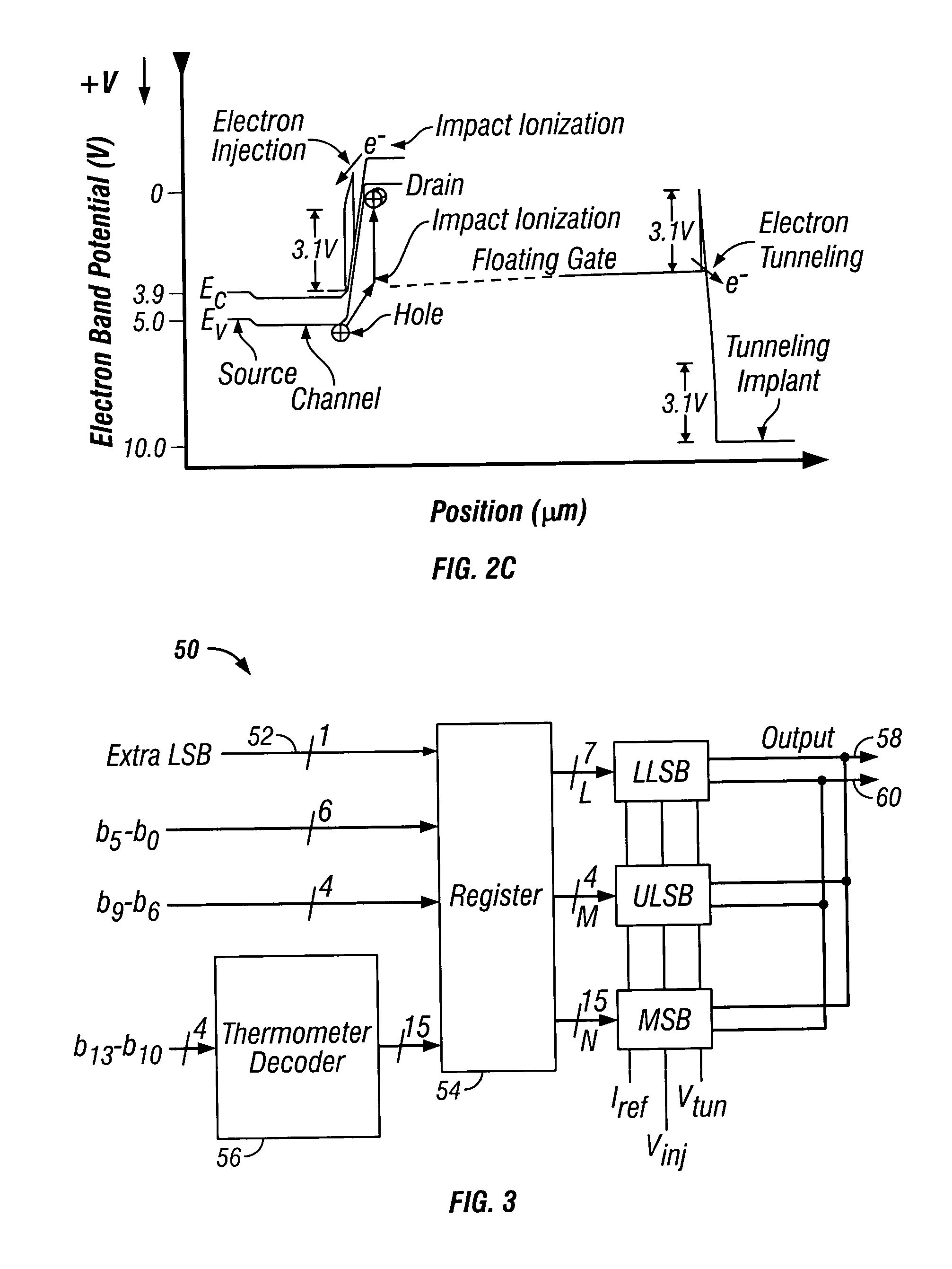

Apparatus for trimming high-resolution digital-to-analog converter

A method and apparatus for trimming a high-resolution digital-to-analog converter (DAC) utilizes floating-gate synapse transistors to trim the current sources in the DAC by providing a trimmable current source. Fowler-Nordheim electron tunneling and hot electron injection are the mechanisms used to vary the amount of charge on the floating gate. Since floating gate devices store charge essentially indefinitely, no continuous trimming mechanism is required, although one could be implemented if desired. By trimming the current sources with high accuracy, a DAC can be built with a much higher resolution and with smaller size than that provided by intrinsic device matching.

Owner:SYNOPSYS INC

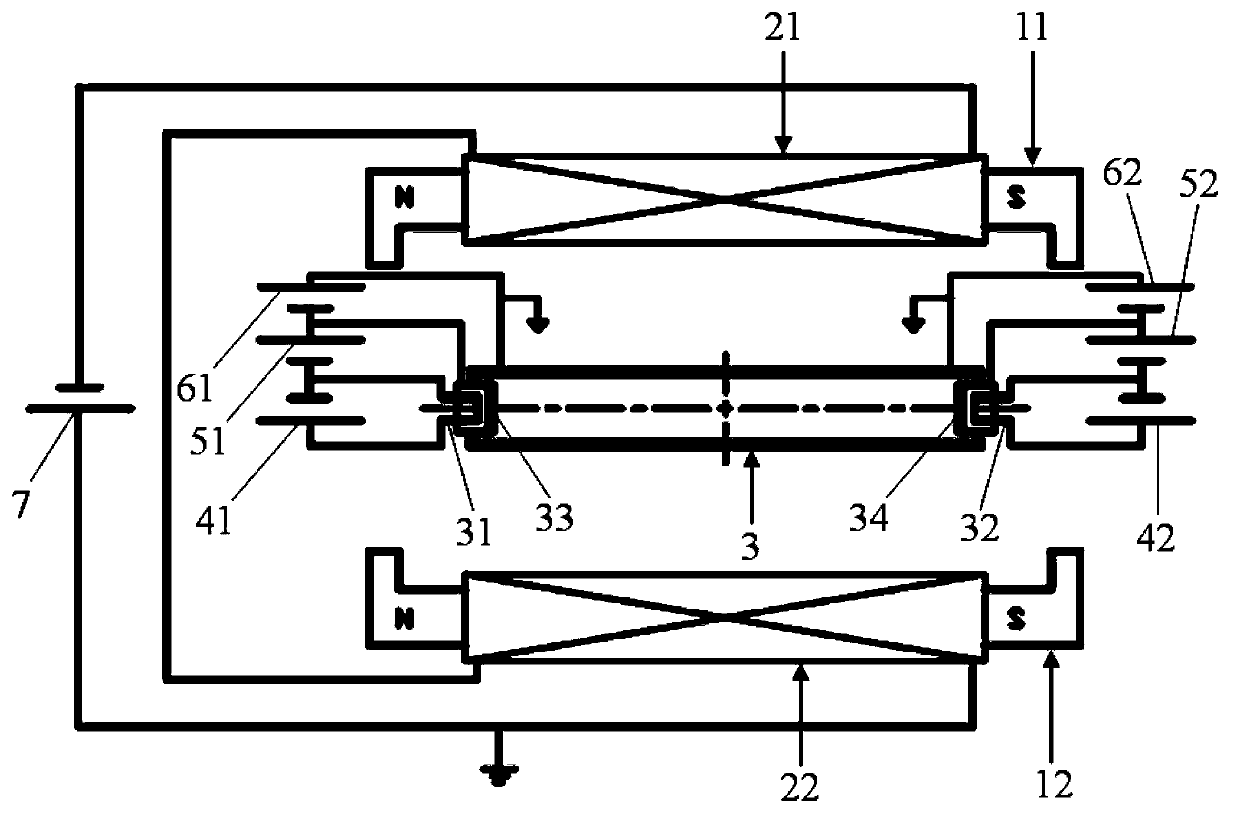

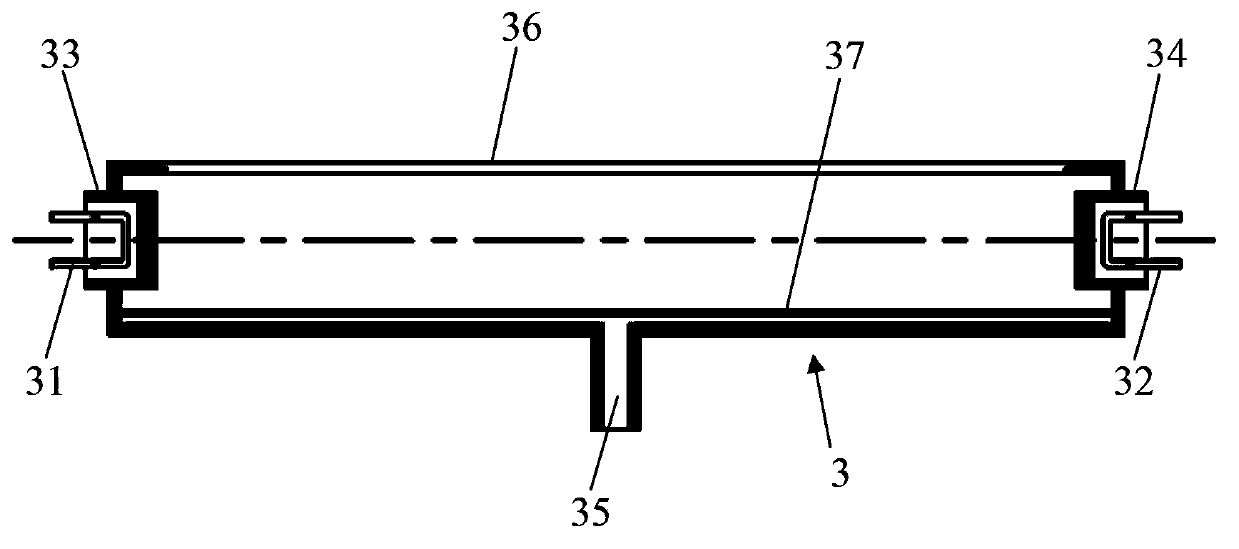

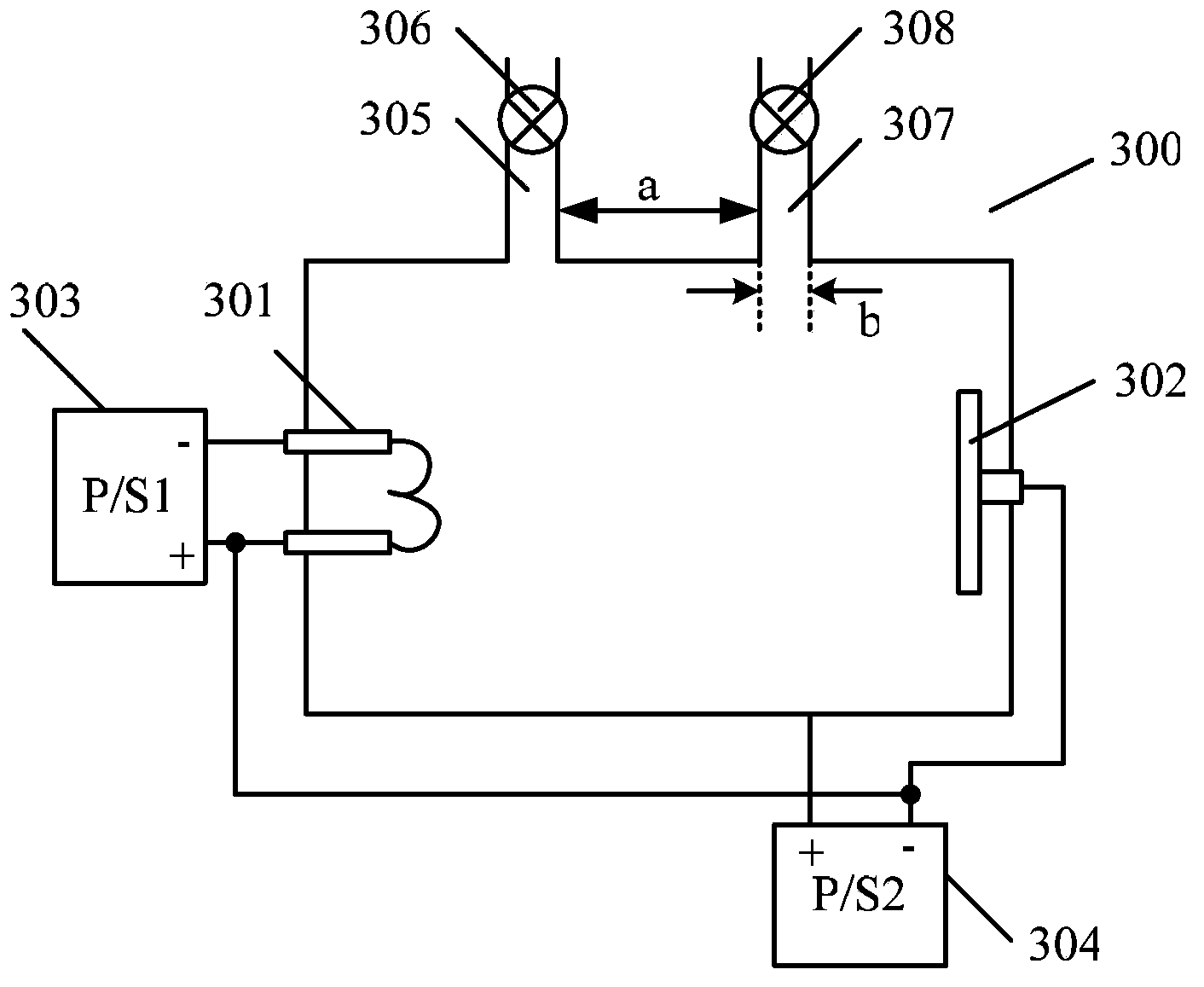

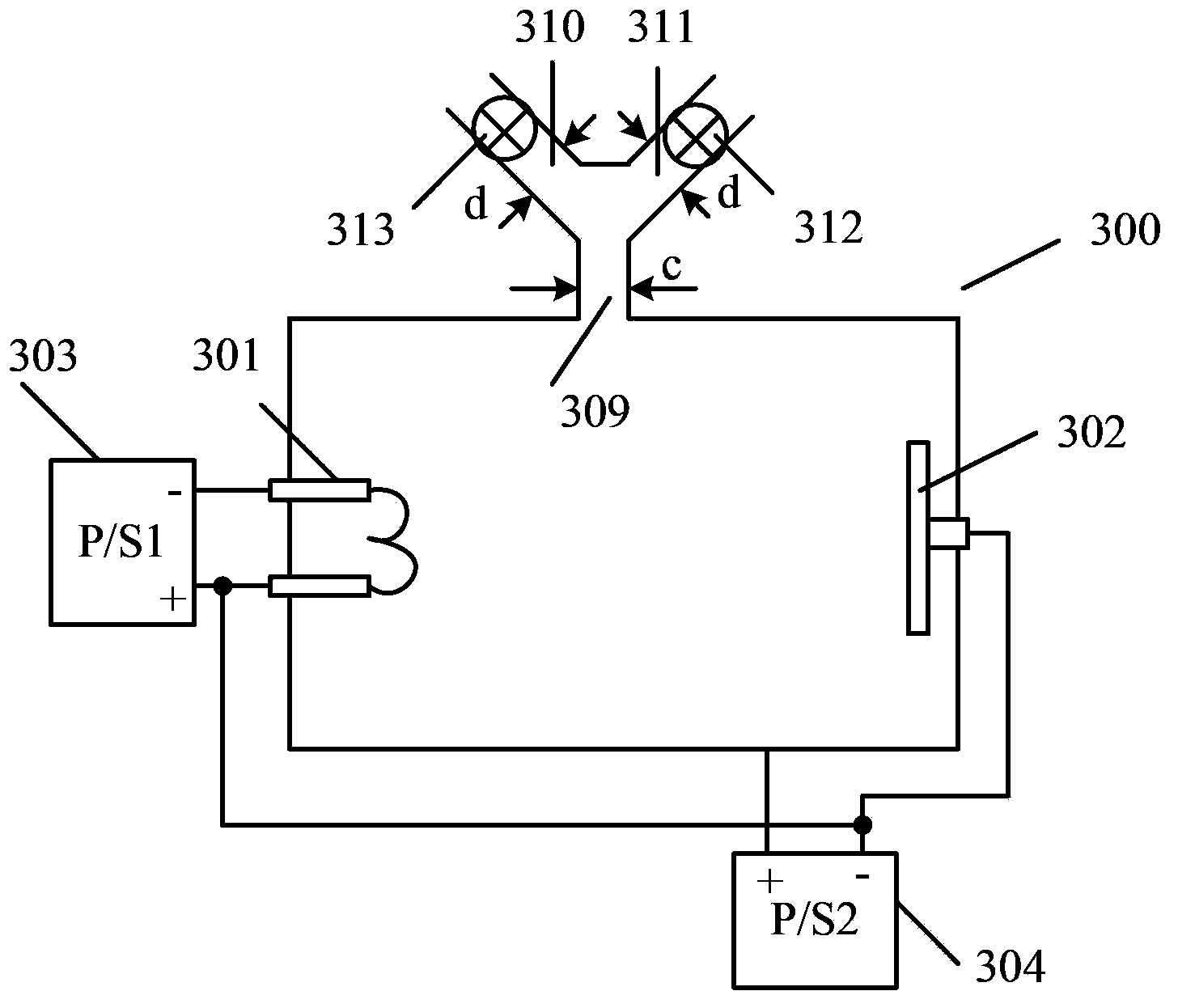

Wide-beam ion source device used for ion implanter

InactiveCN103871809AIncrease widthStrong beam intensityElectric discharge tubesIon beamParticle physics

The invention discloses a wide-beam ion source device used for an ion implanter. The device comprises a source magnetic field iron core, a source magnetic field coil, an arc chamber and an extraction electrode, one end of the arc chamber is provided with a first filament and a first cathode, the other end of the arc chamber is provided with a second filament and a second cathode, the first filament and the second filament are connected with filament power supplies respectively, a first bias power supply is connected between the first filament and the first cathode, a second bias power supply is connected between the second filament and the second cathode, a first arc voltage power supply is connected between the first cathode and the arc chamber, and a second arc voltage power supply is connected between the second cathode and the arc chamber. Since the arc chamber adopts an indirect-heating type double-cathode structure with double filaments and double cathodes, so that a gas medium and hot electrons emitted by the cathodes fully collide, and a relatively wide ion beam and relatively high beam intensity can be generated, thereby facilitating increase of the width of the ion beam, and directly obtaining a parallel wide-band beam that covers the width of a target implantation silicon wafer.

Owner:BEIJING ZHONGKEXIN ELECTRONICS EQUIP

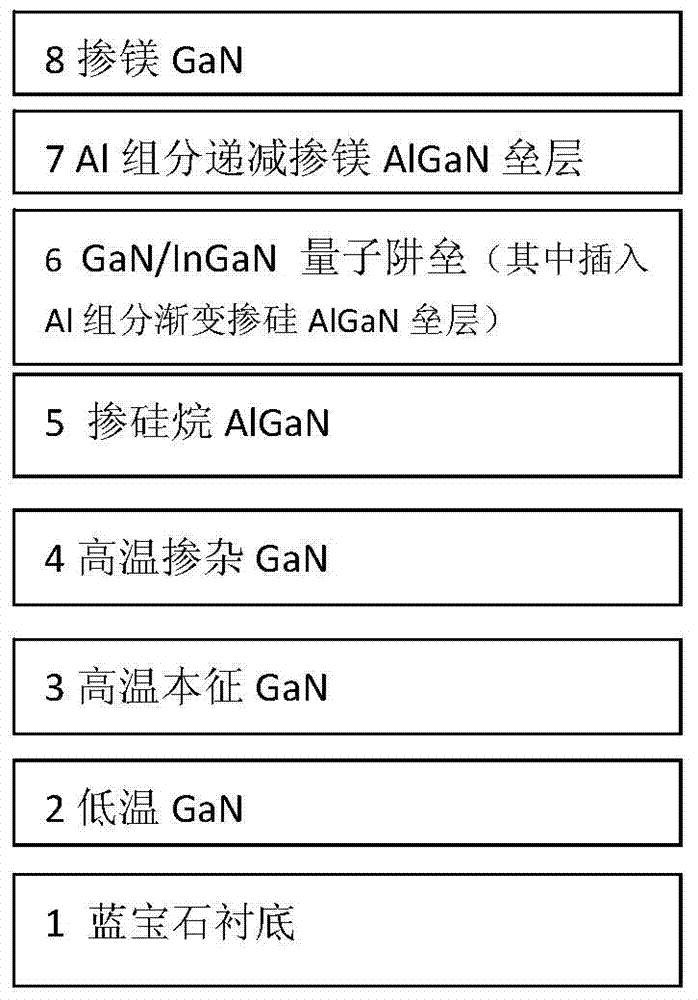

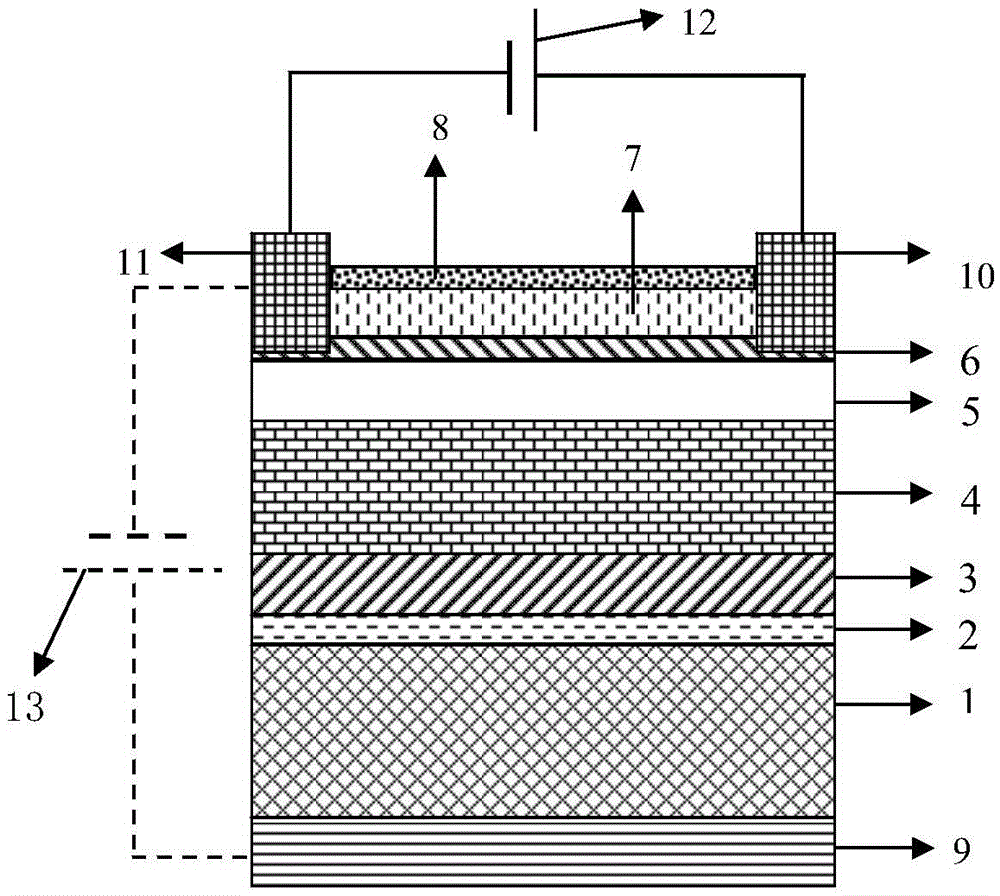

Epitaxial growth method for improving luminous efficiency of LED

InactiveCN103887392AReduce the injected kinetic energyReduce spillover effectsSemiconductor devicesPotential wellElectron hole

The invention provides an epitaxial growth method for improving luminous efficiency of an LED. According to the method, a layer of doped n-type AlGaN barrier layer is added in a growth GaN / InGaN quantum well barrier periodic structure, an Al component gradient structure is adopted, electrons in an n area can be blocked partially, the injection kinetic energy of the electrons can be reduced, hot electrons can be captured by a potential well easily and can easily generate recombination luminescence with electron holes in a later quantum well area, and the electron overflow effect is reduced. The Al component gradient structure is adopted by a later p-type AlGaN barrier layer, growth quality of materials can be improved, and compared with a former single component structure, the gradient structure can facilitate the injection effect of the electron holes and play the function of secondary blocking.

Owner:西安利科光电科技有限公司

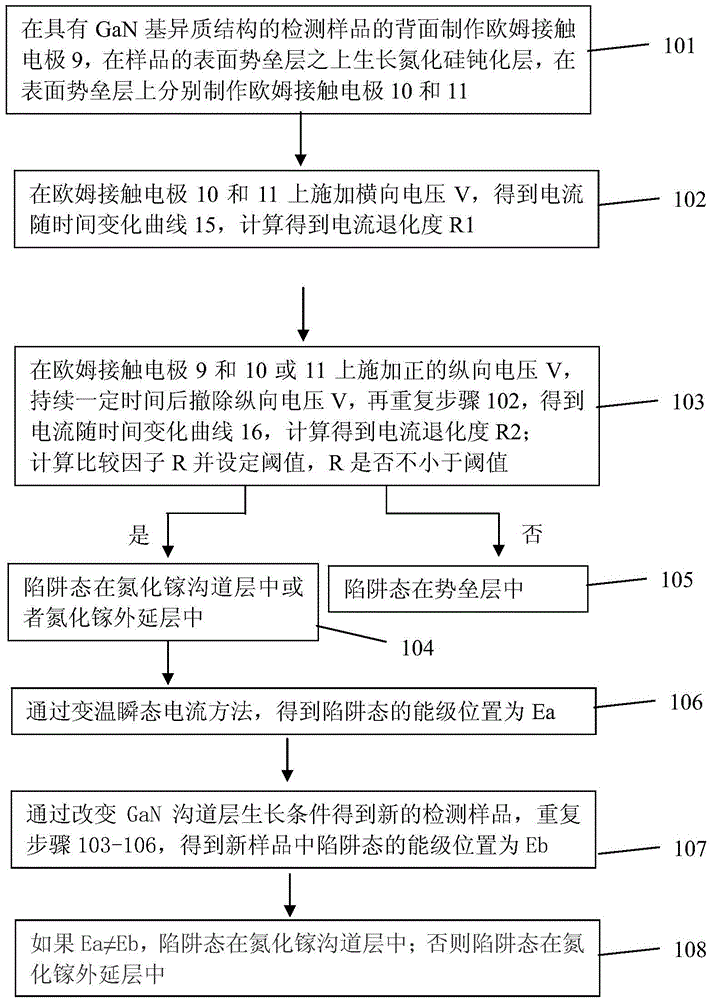

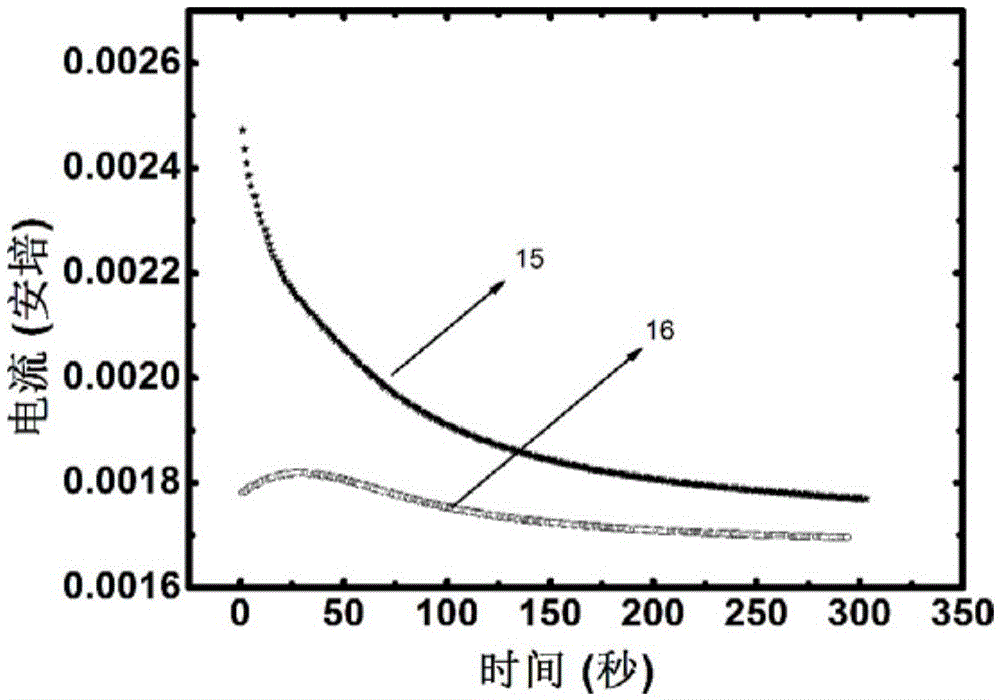

Detection method and structure for detecting trap states in GaN base heterostructure

ActiveCN105466970AReduce the difficulty of test analysisImprove accuracyMaterial analysis by electric/magnetic meansSemiconductor characterisationOhmic contactGallium nitride

The invention discloses a detection method and structure for detecting trap states in gallium nitride base heterostructure. The detection method comprises the steps that the detection structure of trap states in the GaN base heterostructure is prepared; the trap states in the GaN base heterostructure is detected, conduction characteristics of a substrate and the sample surface are used for forming three-terminal ohmic contact on the sample surface and the substrate back, capture and ejection processes of hot electrons are studied by applying transverse and longitudinal electrical stress respectively; accordingly, whether the trap position in the sample is located on the GaN channel layer, or the GaN epitaxial layer, or the epitaxial layer is finally determined by changing the sample structure, and localization state information of the traps can be obtained. The method is simple, quick and effective, the trap states in the GaN base heterostructure can be determined, and the detection method and structure are good for further improvement of device reliability.

Owner:北京中博芯半导体科技有限公司

Application of UB2 film to black cavity

ActiveCN107068205AReduce the difficulty of demoulding processReduce outputNuclear energy generationVacuum evaporation coatingX-rayProtection layer

The invention provides an application of a UB2 film to a black cavity, belongs to the technical field of laser fusion engineering and specifically relates to the application of the UB2 film having black cavity scattering reduction and protection functions. The invention is to solve the problems that an existing uranium black cavity is complex in structure, an Au / B scattering reduction layer is poor in chemical stability and component proportion and distribution are difficult to regulate and control. The UB2 film is applied to the black cavity as a scattering reduction / protection layer instead of a black cavity Au / B scattering reduction layer and an Au protection layer. The advantages are that through application of the UB2 film to the black cavity, precise control of film components can be realized, black cavity mold release process difficulty is reduced, and laser plasma stimulated Brillouin scattering is suppressed effectively; and meanwhile, the UB2 film also has the functions of reducing M-band hot electron yield, improving laser-X ray conversion efficiency and protecting a uranium black cavity conversion layer. The UB2 film integrates functions of scattering reduction and protection, and effectively simplifies ignition black cavity and other high-performance and high-conversion-rate black cavity structures and preparation processes thereof.

Owner:LASER FUSION RES CENT CHINA ACAD OF ENG PHYSICS

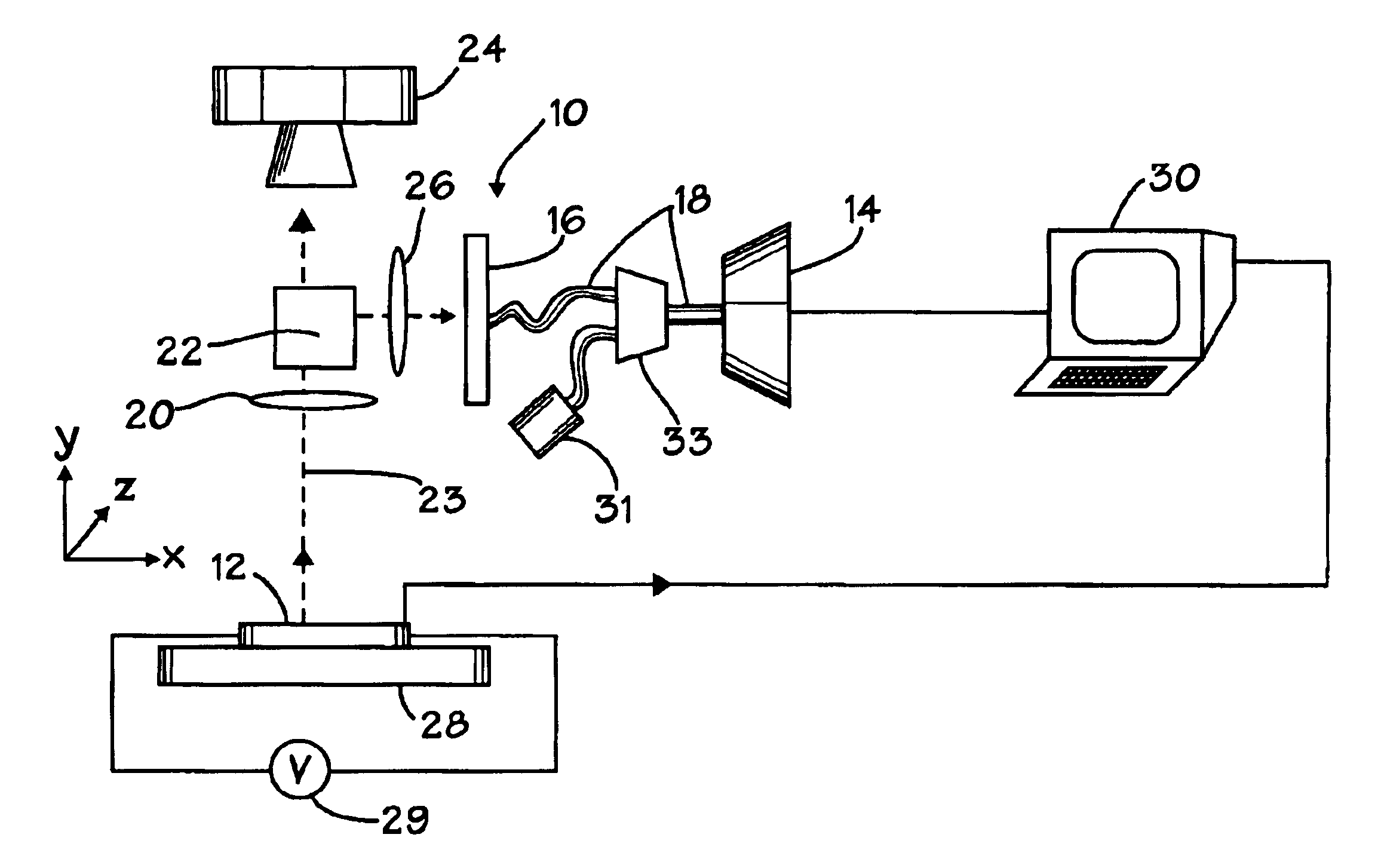

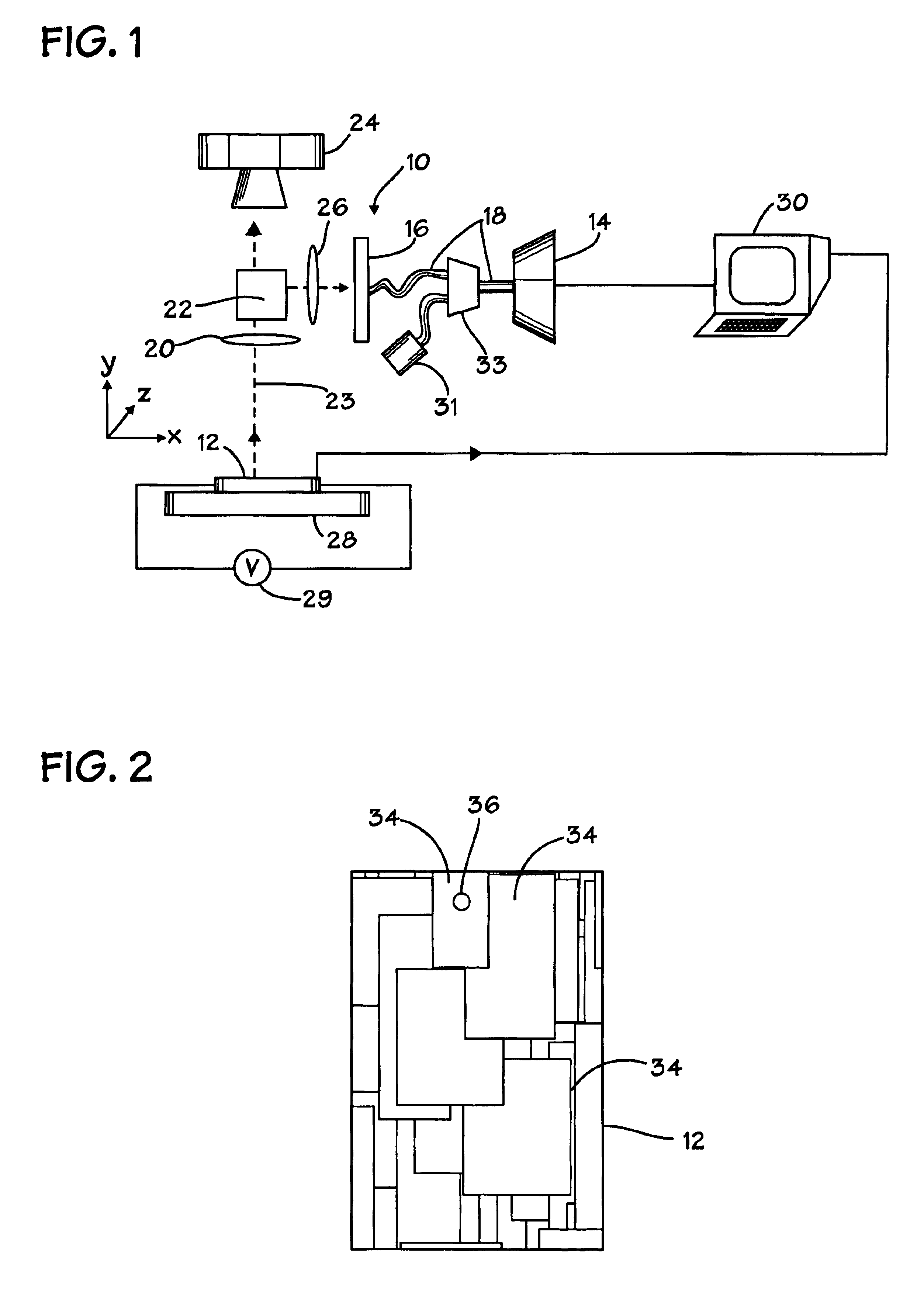

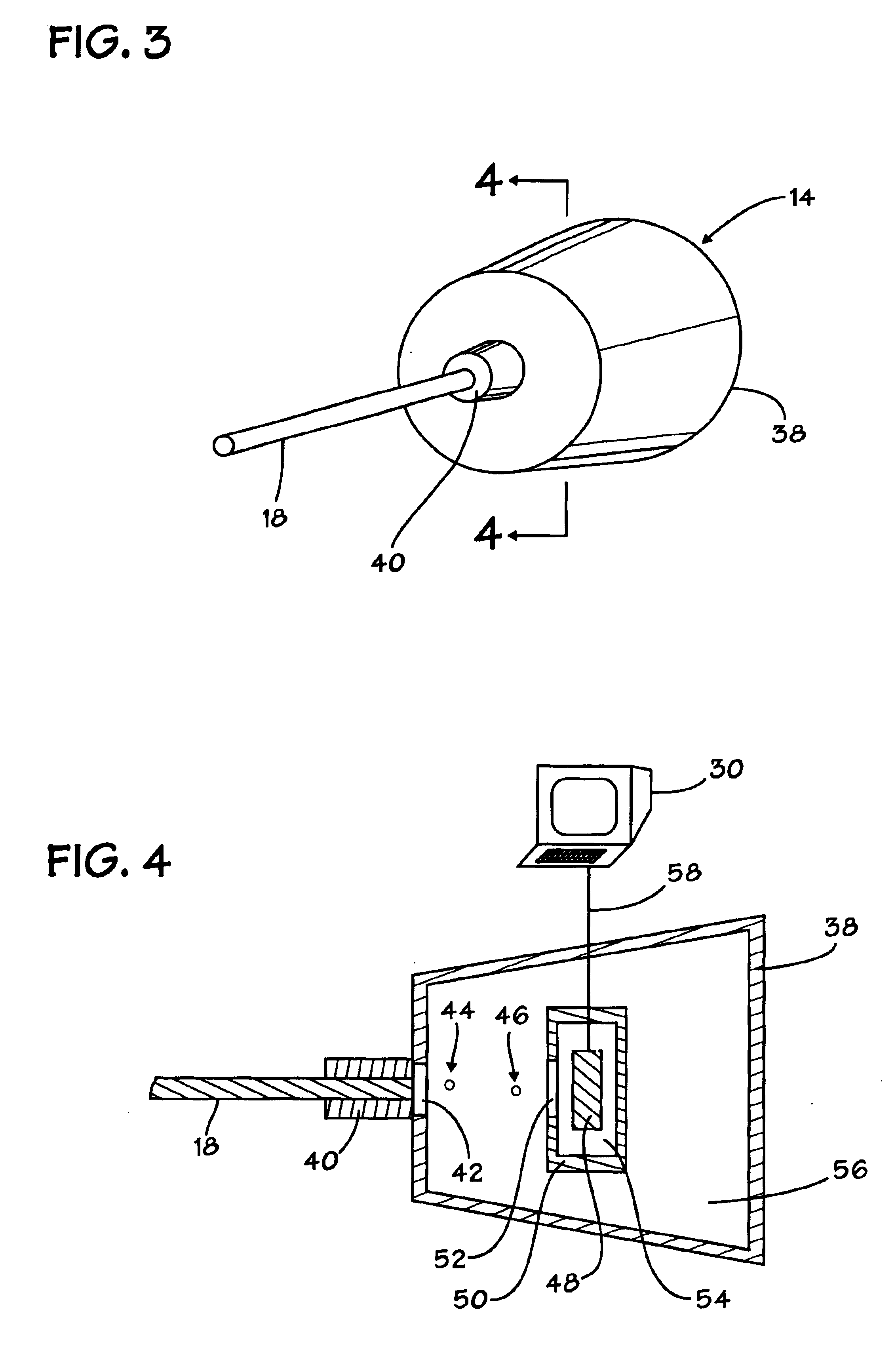

Photon detection enhancement of superconducting hot-electron photodetectors

InactiveUS6828809B1Investigating moving sheetsIndividual semiconductor device testingQuantum efficiencyPhoton emission

Various methods of hot-electron imaging a workpiece are provided. In one aspect, a method of examining a workpiece is provided that includes directing a first photon at a photodetector at a first known time and stimulating a circuit device of the workpiece at a second known time to produce a condition in the circuit device conducive to photon emission. At least one photon emitted by the circuit device in response to the stimulation is detected. The first photon increases the quantum efficiency of the photodetector in detecting the at least one photon. The detection of the at least one photon relative to the first known time and the second known time is time correlated to temporally distinguish the first photon and the at least one photon and to temporally correlate the stimulation of the circuit device to the detection of the at least one photon.

Owner:ADVANCED MICRO DEVICES INC

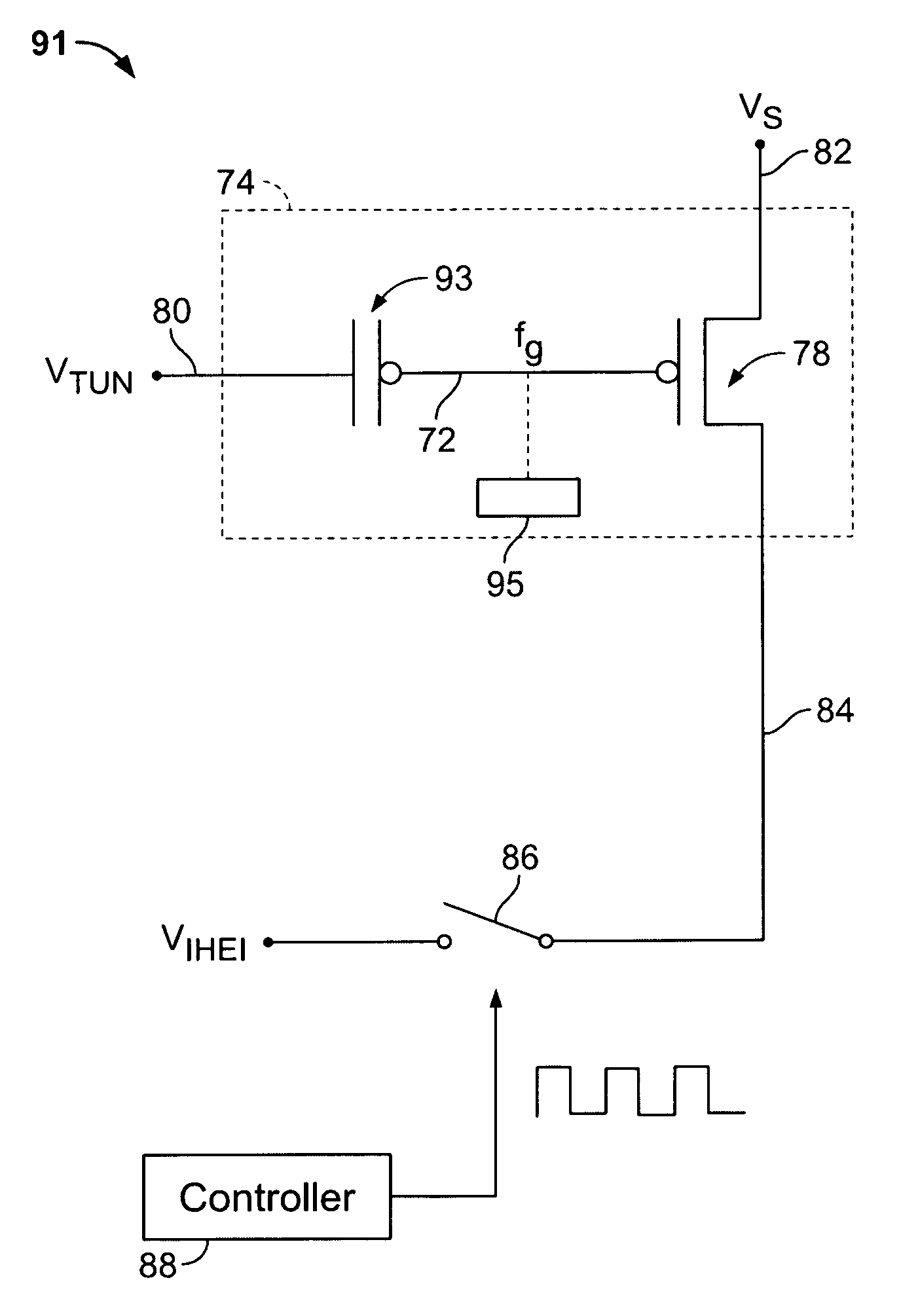

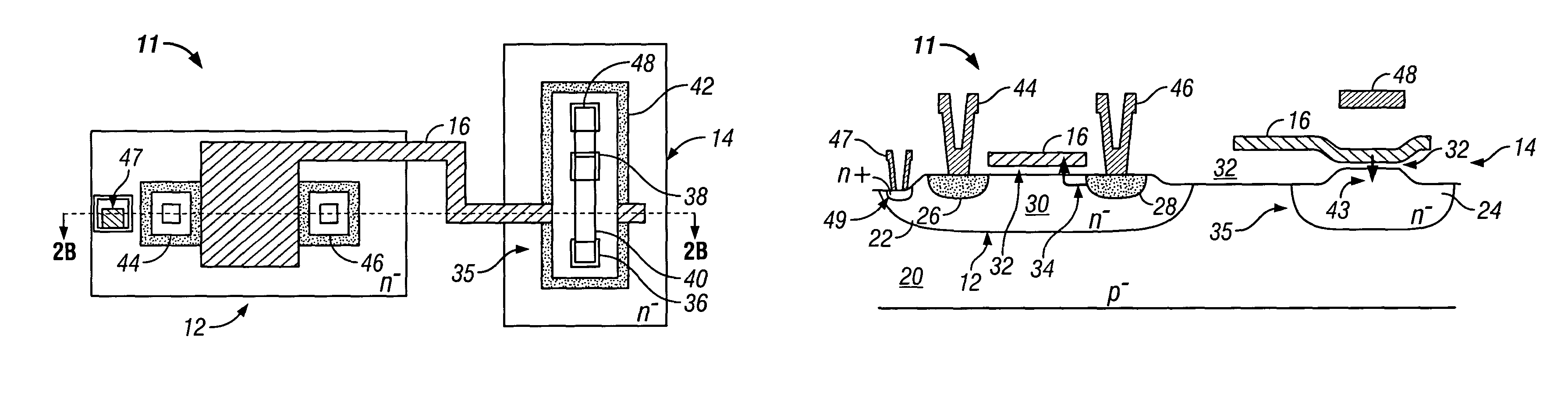

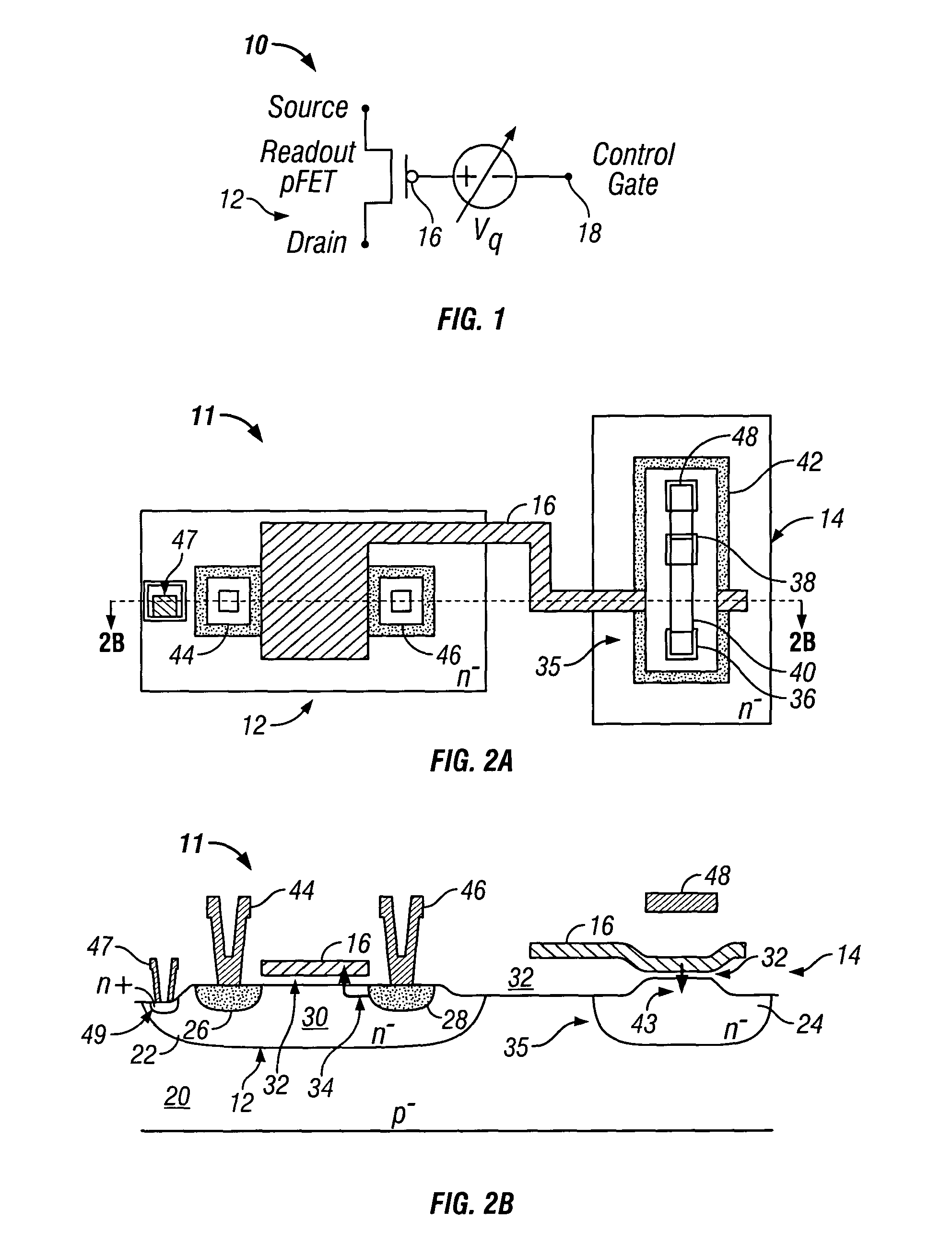

Method and apparatus for programming single-poly pFET-based nonvolatile memory cells

Methods and apparatuses for programming a single-poly pFET-based nonvolatile memory cell bias the cell so that band-to-band tunneling (BTBT) is induced and electrons generated by the BTBT are injected onto a floating gate of the cell. Following a predetermined event, the single-poly pFET is biased to induce impact-ionized hot-electron injection (IHEI). The predetermined event may be, for example, the expiration of a predetermined time period or a determination that a channel has been formed by the BTBT injection process that is sufficiently conducting to support IHEI. Employing BTBT permits a previously overerased or stuck bit to be “unstuck” or “removed” and thus be made usable (i.e., able to be programmed) again.

Owner:SYNOPSYS INC

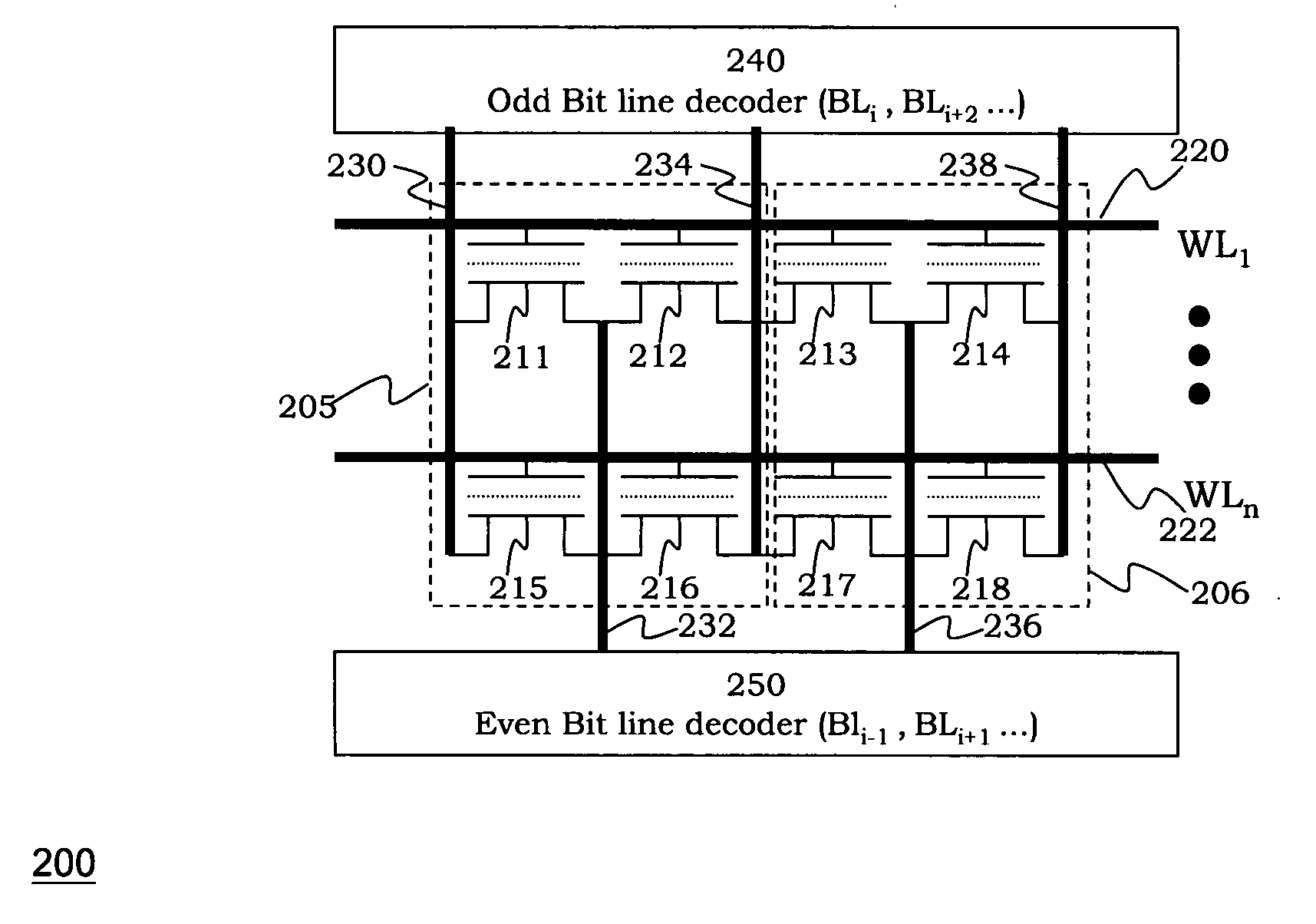

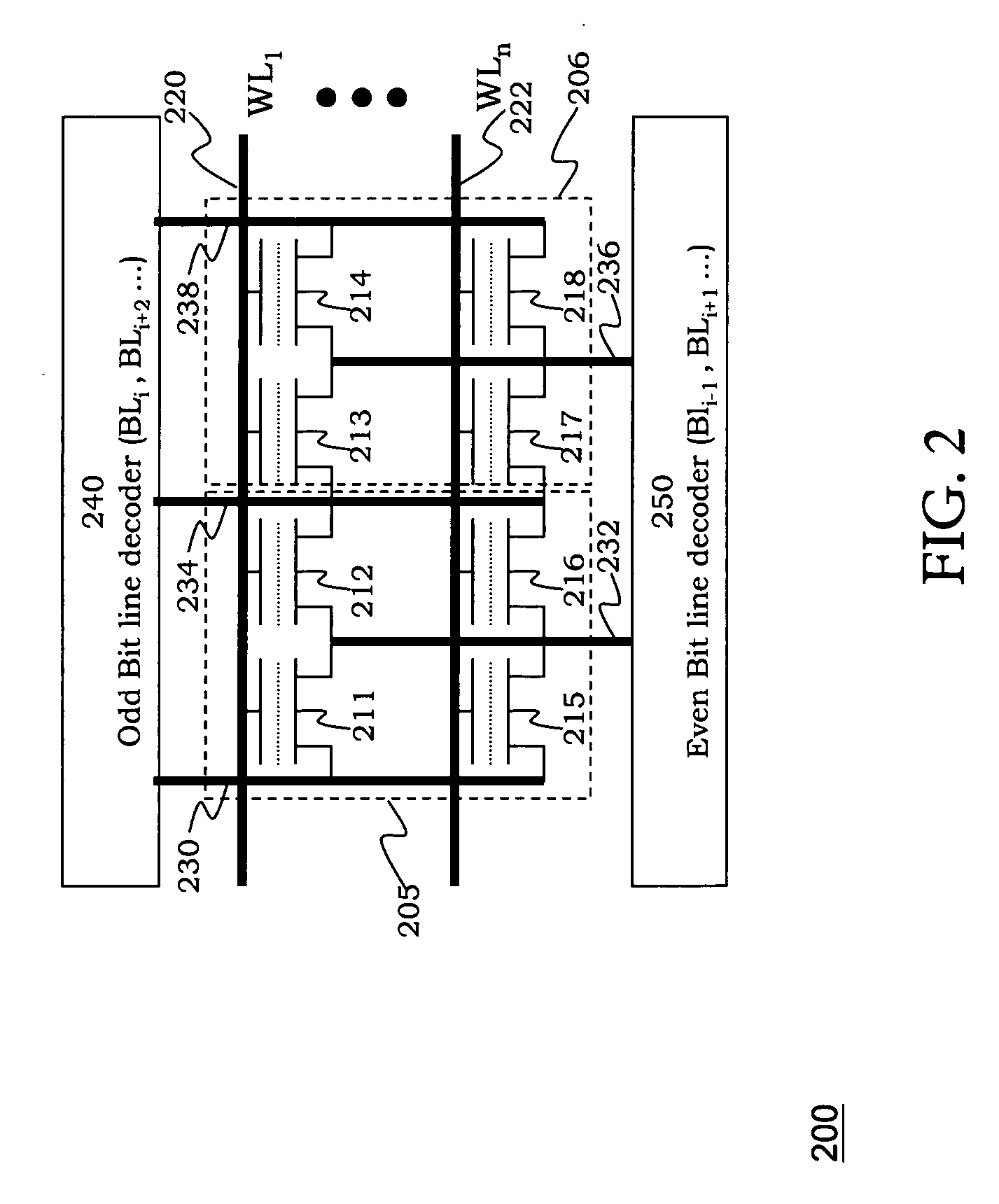

High voltage generation and control in source-side injection programming of non-volatile memory

Non-volatile memory is programmed using source side hot electron injection. To generate a high voltage bit line for programming, the bit line corresponding to a selected memory cell is charged to a first level using a first low voltage. A second low voltage is applied to unselected bit lines adjacent to the selected bit line after charging. Because of capacitive coupling between the adjacent bit lines and the selected bit line, the selected bit line is boosted above the first voltage level by application of the second low voltage to the unselected bit lines. The column control circuitry for such a memory array does not directly apply the high voltage and thus, can be designed to withstand lower operating voltages, permitting low operating voltage circuitry to be used.

Owner:SANDISK TECH LLC

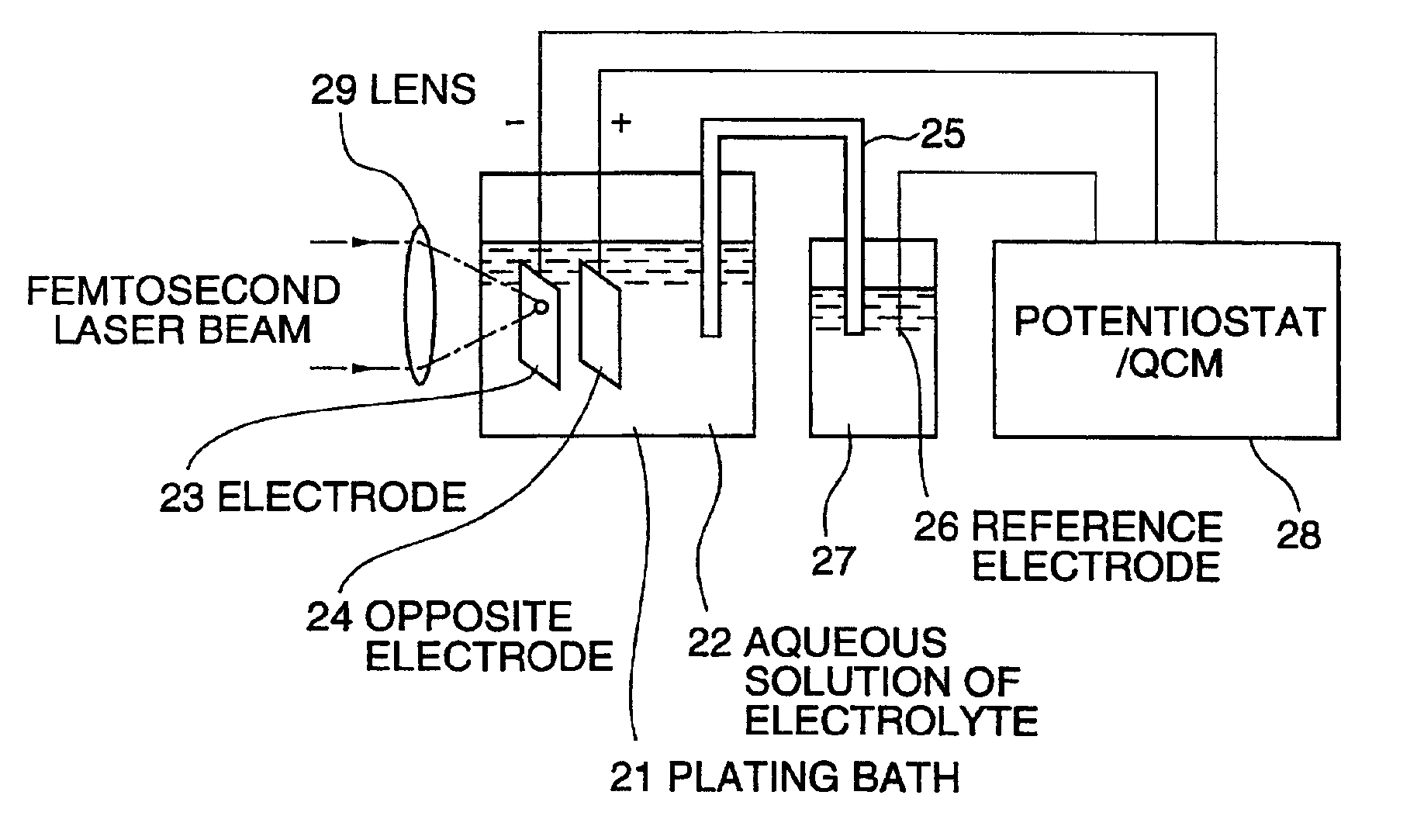

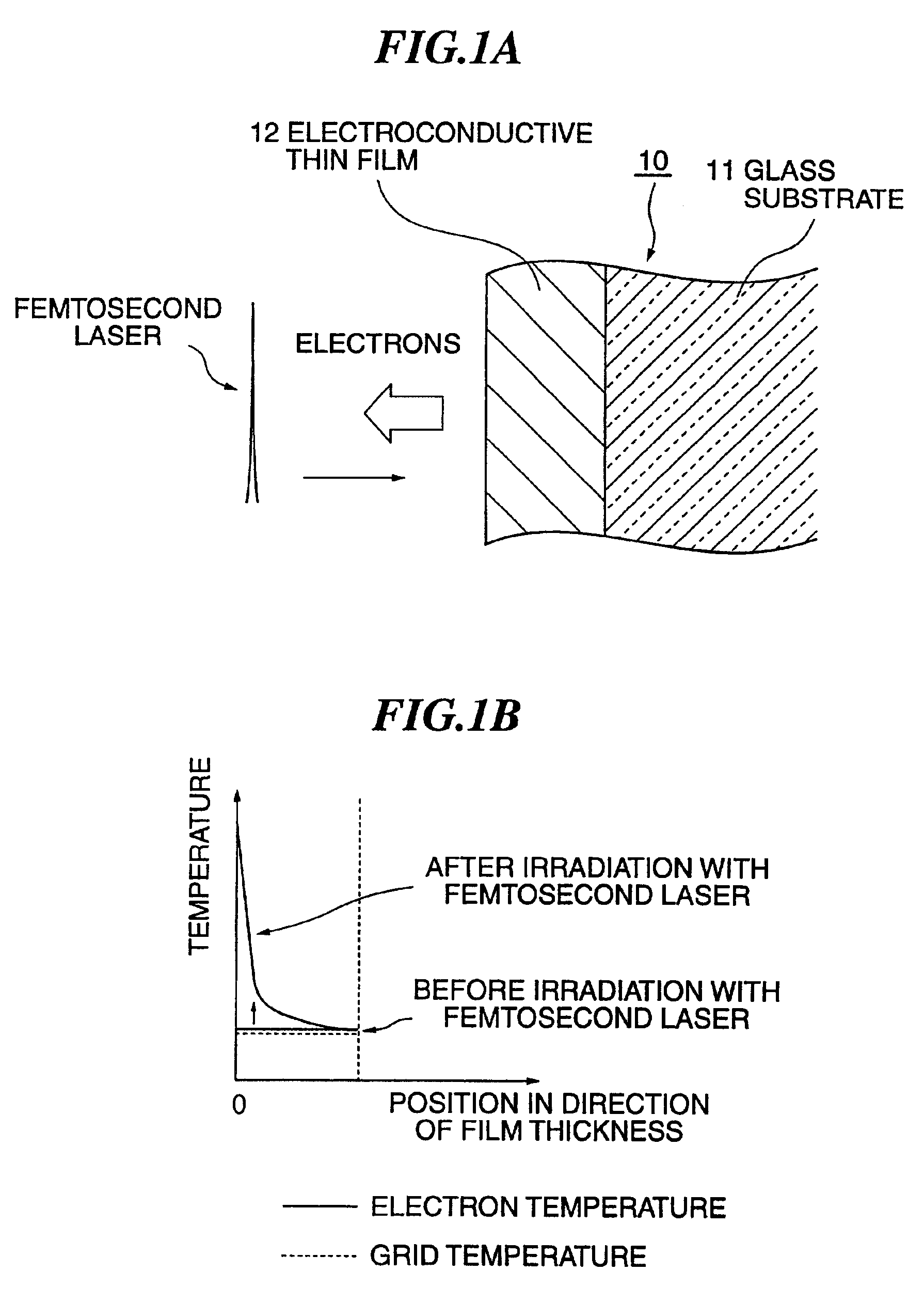

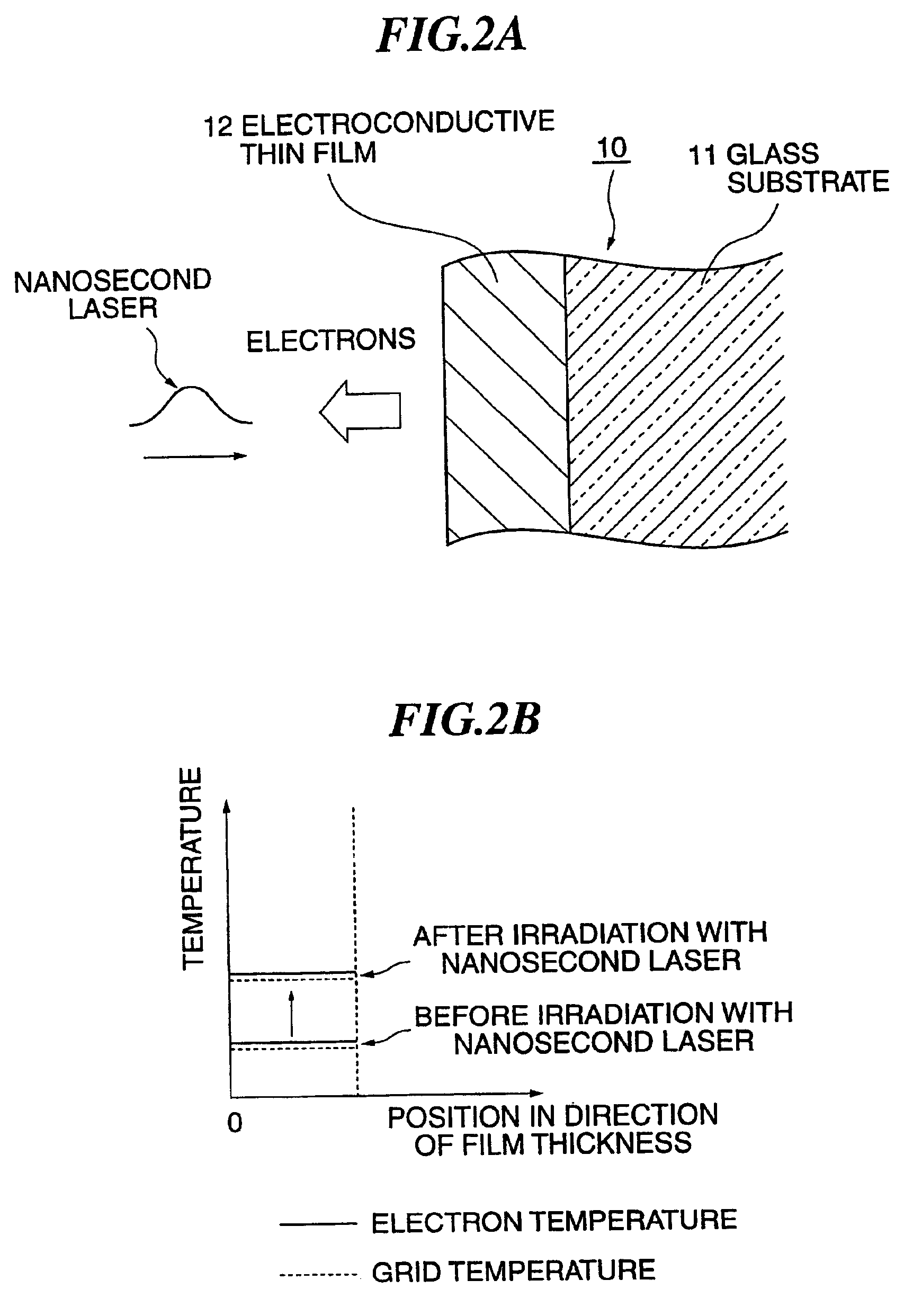

Method for electrodeposited film formation, method for electrode formation, and apparatus for electrodeposited film formation

A method permitting less energy consumption and efficient formation of high quality electrodes is provided. An electrode is formed as an electrodeposited film by irradiating the surface of an object to be treated, the surface at least permitting generation of charged particles when irradiated with a laser beam, with a fentosecond laser beam and metal-plating the surface of a substrate using hot electrons generated by this laser irradiation.

Owner:FUJIFILM BUSINESS INNOVATION CORP

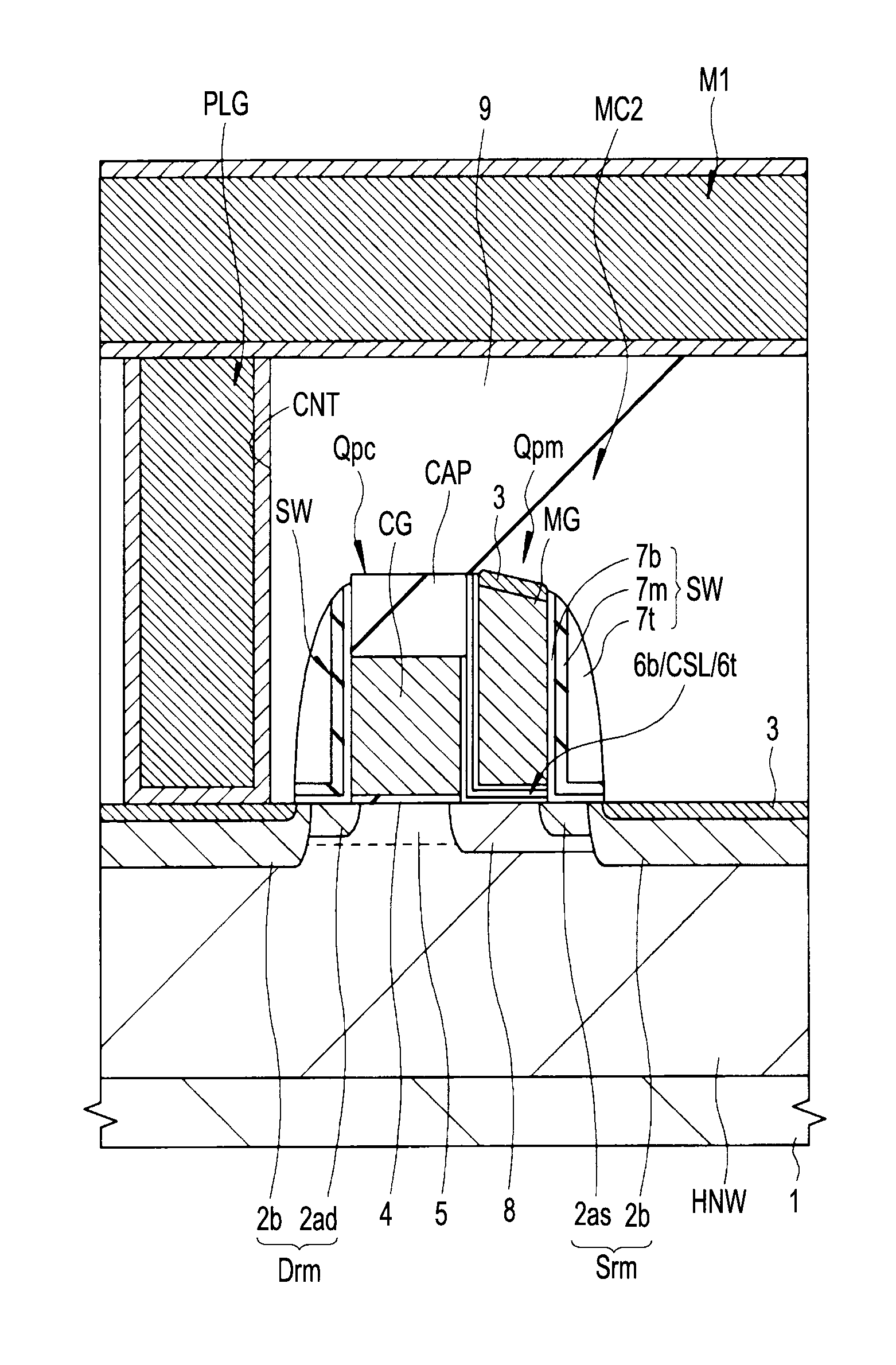

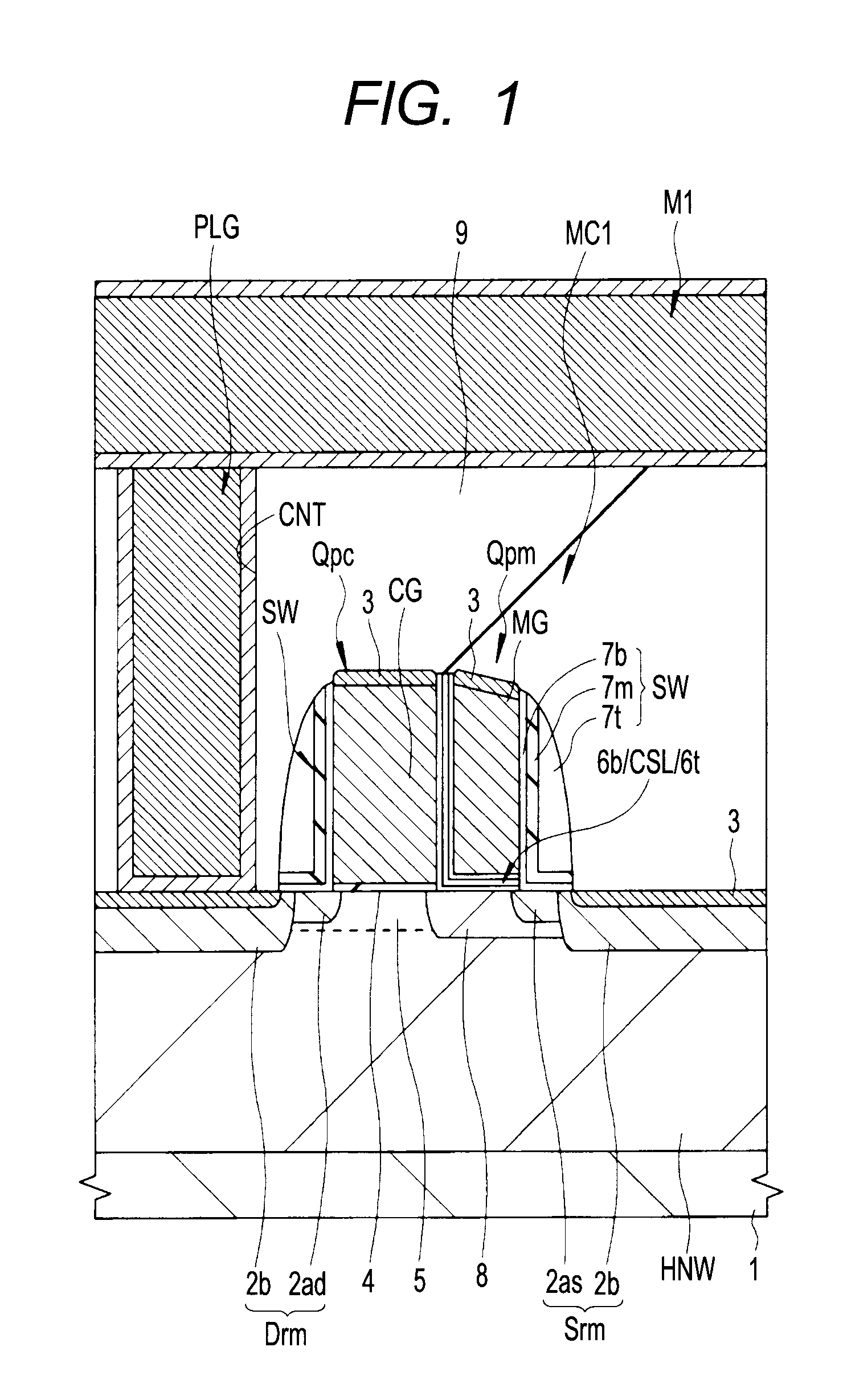

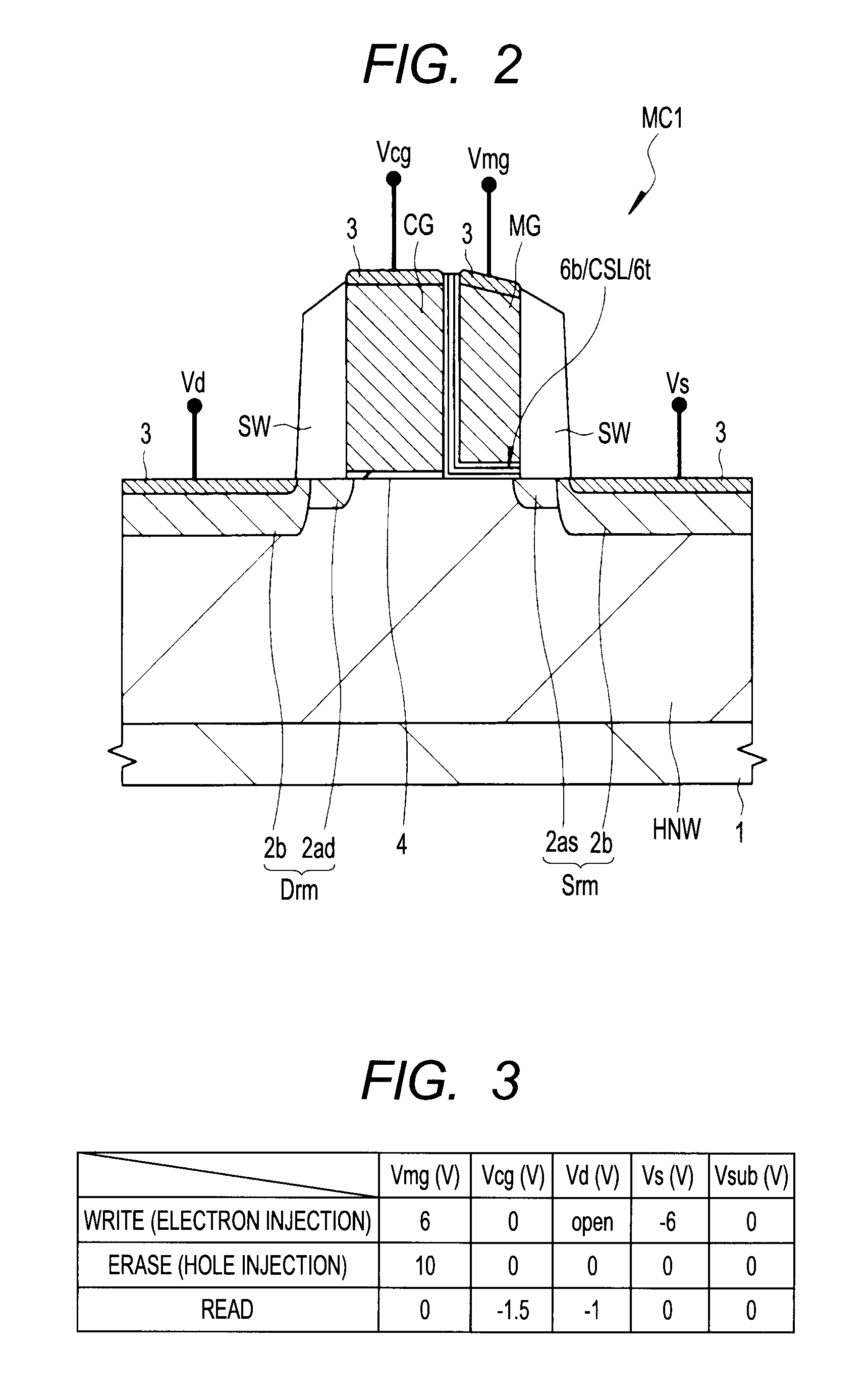

Semiconductor device having a nonvolatile memory cell with a cap insulating film formed over a selection gate electrode

InactiveUS8344444B2Improve reliabilitySuppressing reduction of drive forceTransistorSolid-state devicesSemiconductorHot electrons

Owner:RENESAS ELECTRONICS CORP

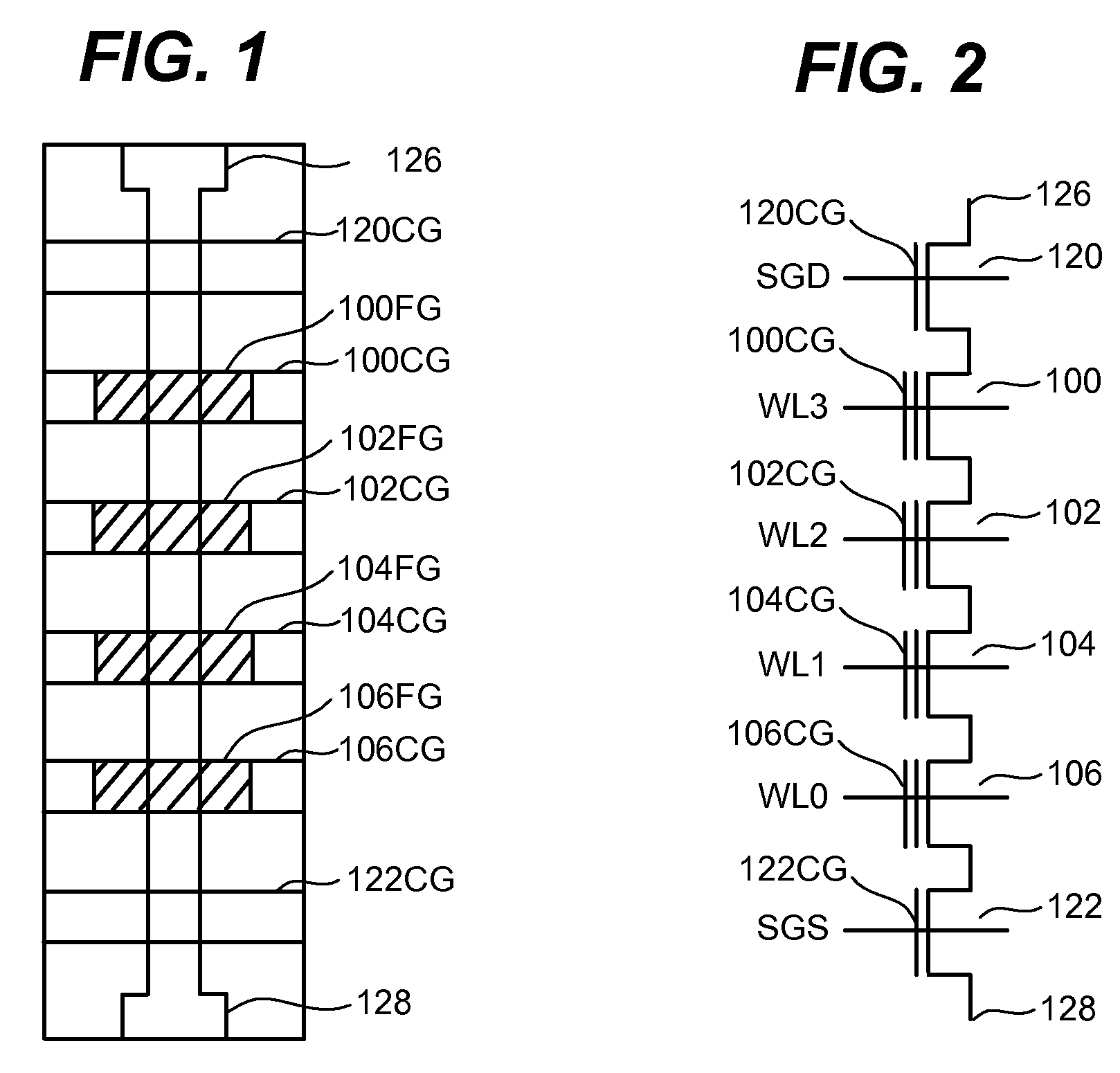

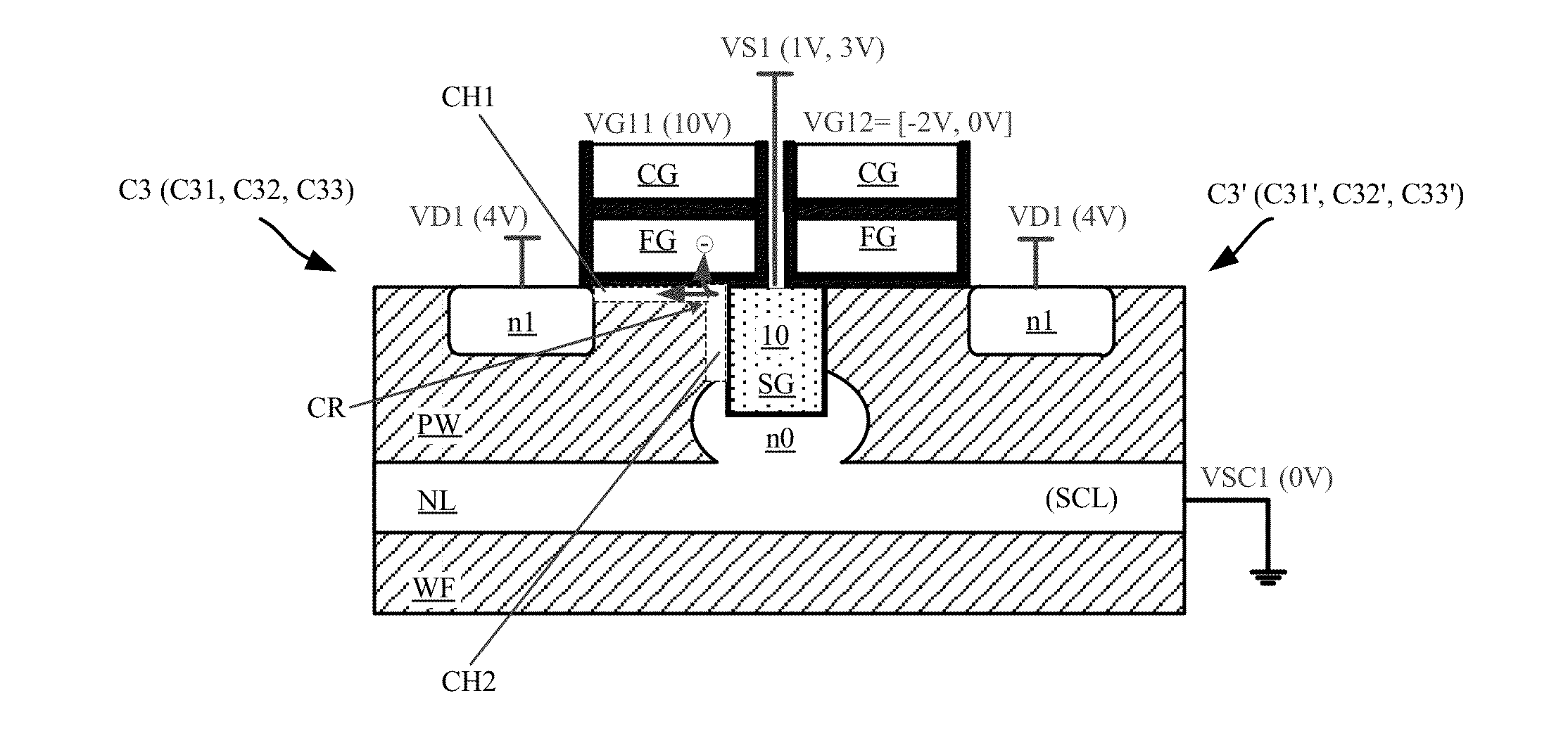

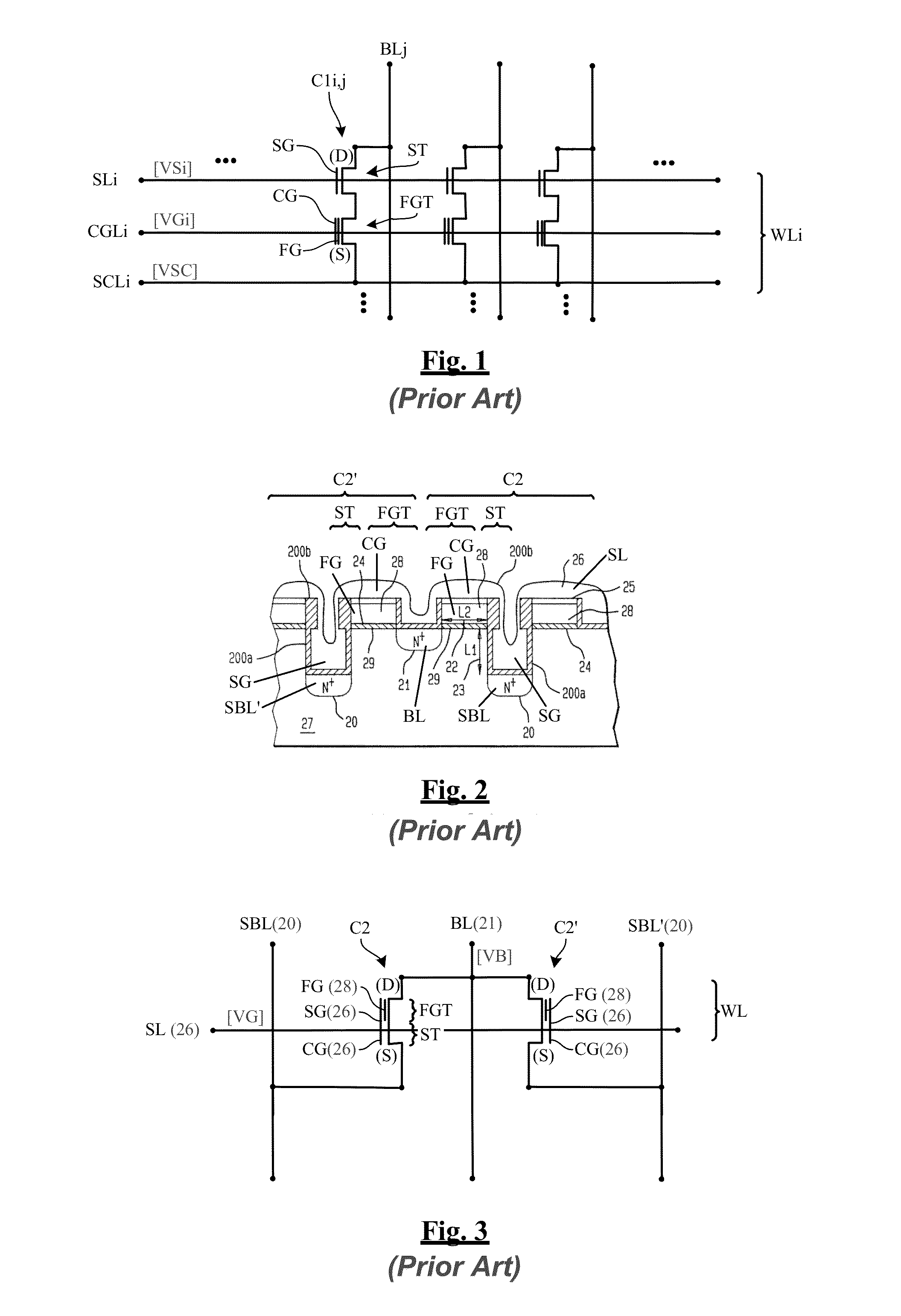

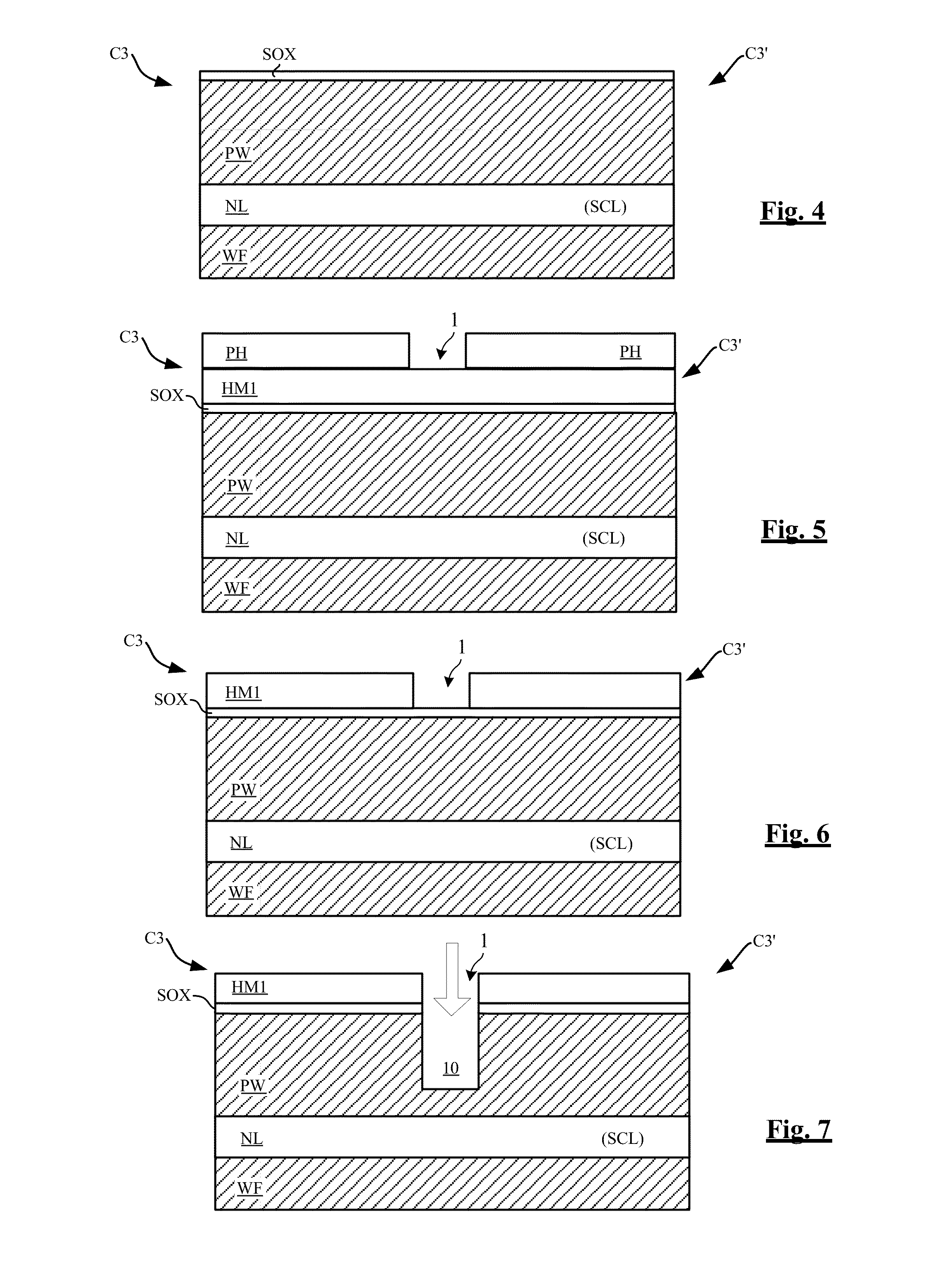

Memory cell comprising non-self-aligned horizontal and vertical control gates

The present disclosure relates to a memory cell comprising a vertical selection gate extending in a trench made in a substrate, a floating gate extending above the substrate, and a horizontal control gate extending above the floating gate, wherein the floating gate also extends above a portion of the vertical selection gate over a non-zero overlap distance. Application mainly to the production of a split gate memory cell programmable by hot-electron injection.

Owner:STMICROELECTRONICS (ROUSSET) SAS

Hole annealing methods of non-volatile memory cells

ActiveUS20070058440A1Minimize holeReducing threshold amountRead-only memoriesDigital storageNitrideThreshold voltage

Hole annealing methods are described after erasure of nitride storage memory cells for compensating trapped holes to minimize the holes from detrapping in order to reduce the amount of threshold voltage from drifting significantly higher. A soft hot electron program is used to selected nitride storage memory cells that have been detected to have a threshold voltage that is higher than a presetting threshold voltage (EV) minus a wordline delta X. The effect of the soft electron program neutralizes the excess holes introduced by erasure of nitride storage memory cells that decreases the amount of threshold voltage from drifting higher. In one embodiment, a hole annealing method describes a soft hot electron programming to nitride storage memory cells in a block of nitride memory array that have been determined to have a threshold voltage higher than the presetting threshold voltage minus the wordline delta X.

Owner:MACRONIX INT CO LTD

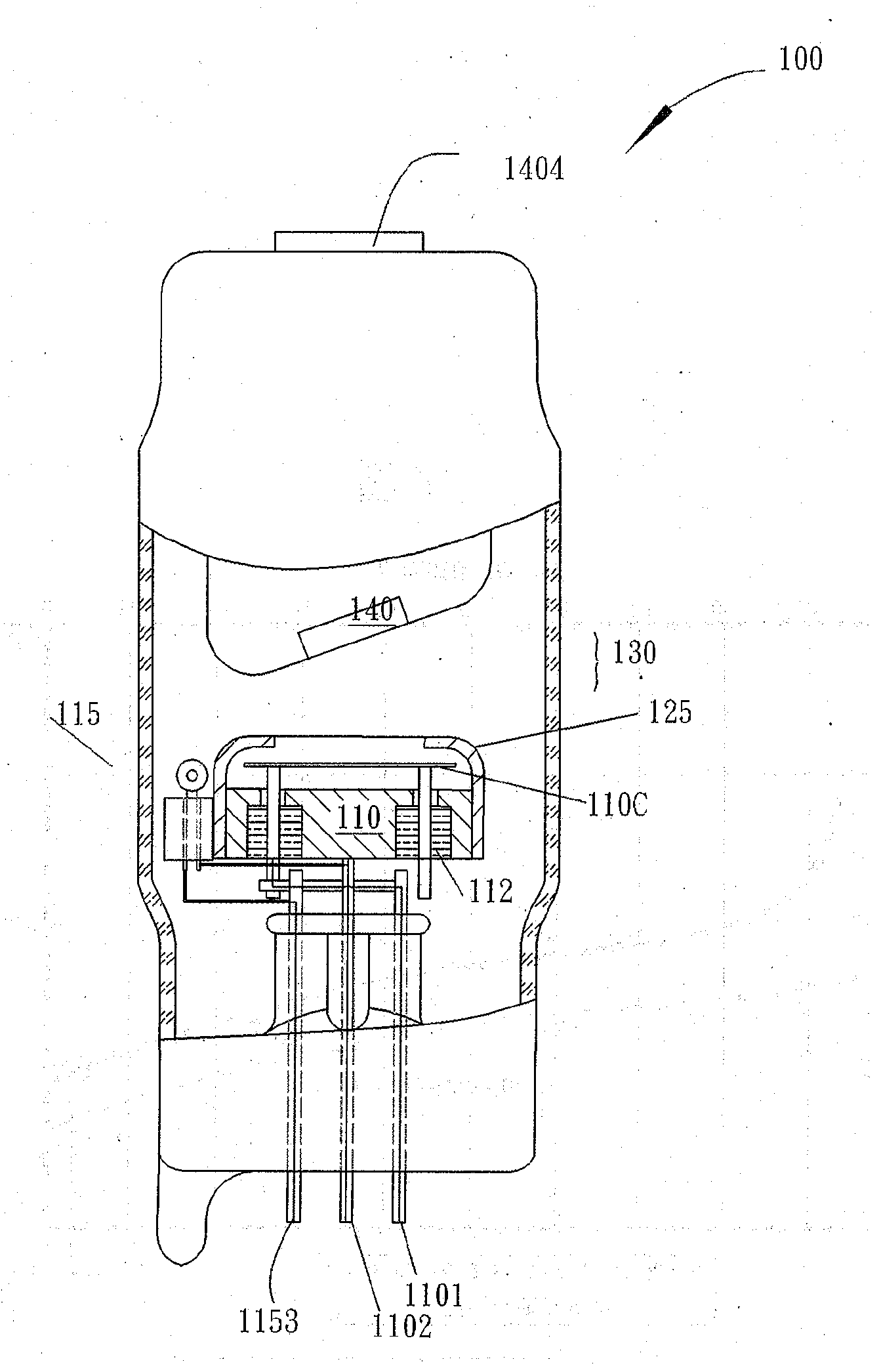

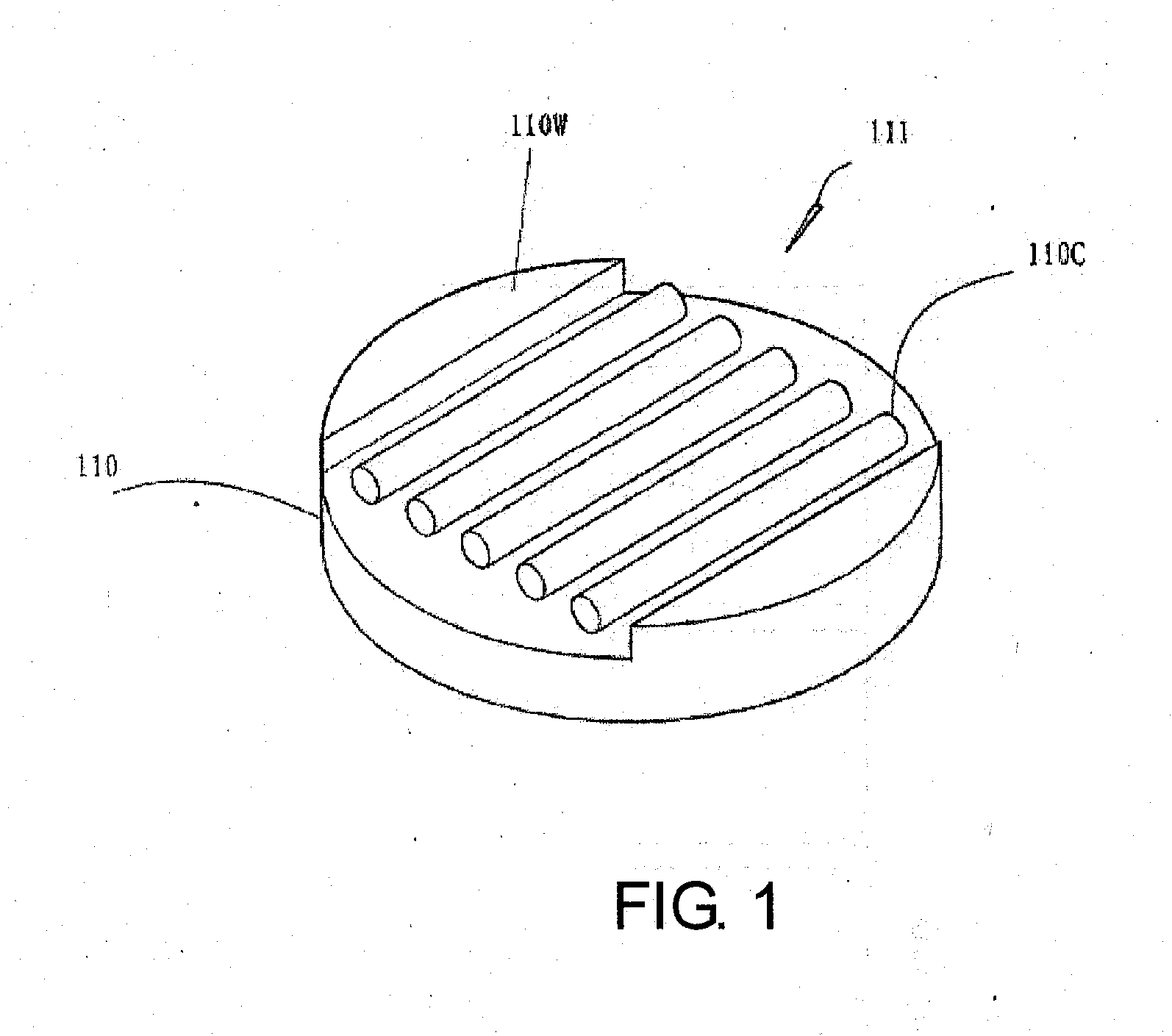

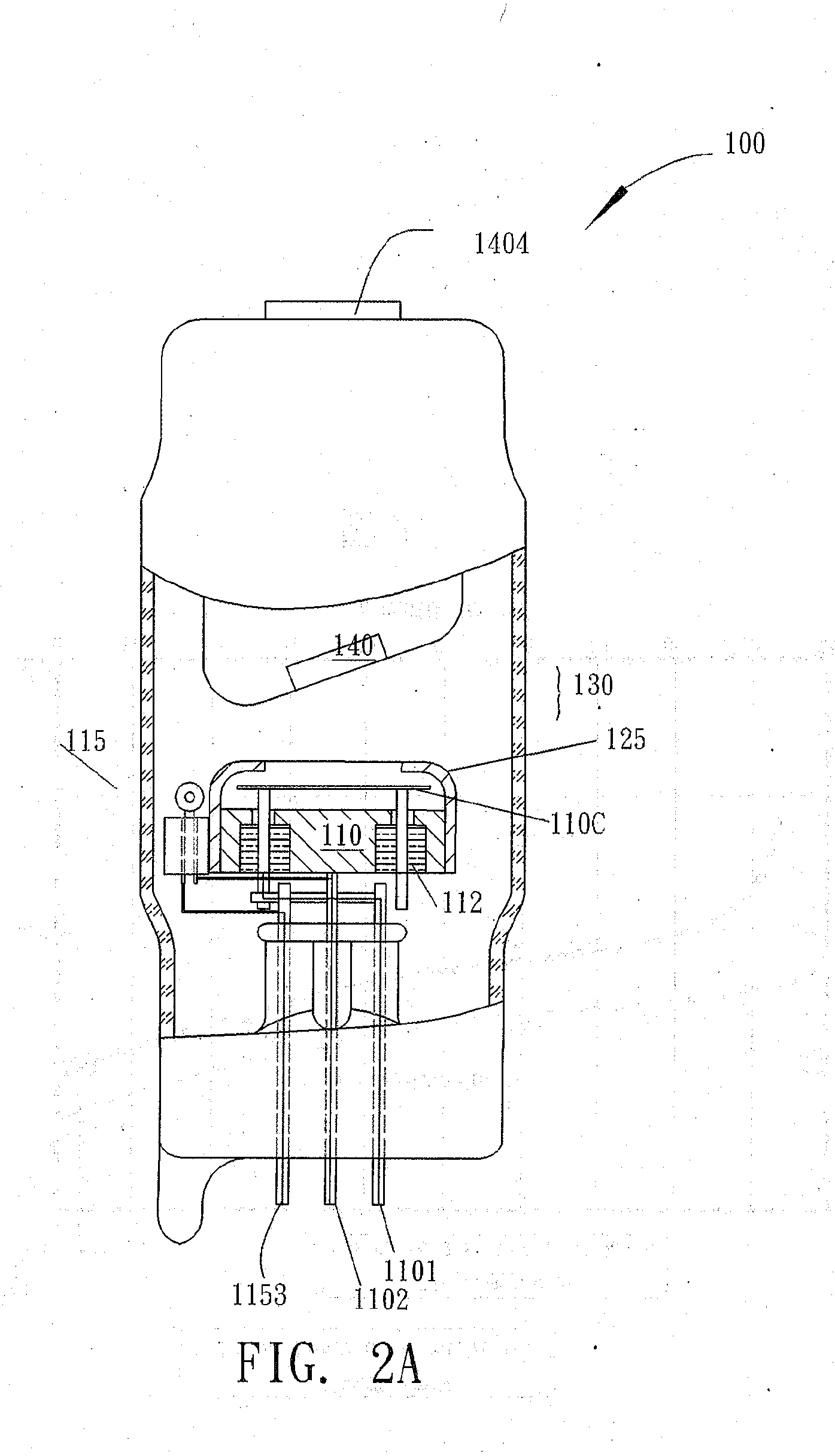

Encapsulated structure for x-ray generator with cold cathode and method of vacuuming the same

ActiveUS20160148777A1Well in qualityCost reductionX-ray tube electrodesTube/lamp vessel degassingSingle useGlass ball

An encapsulated structure of an X ray generator with a cold cathode and method of vacuuming the same are disclosed. The X ray generator has a glass ball-tube having a base, a tungsten filament, a cold cathode, a focus cap, and an anode target inside, associated with a first electrode pin, a second electrode pin, a single-used pin, and anode pin extended out. The tungsten filament located at the periphery of the base has a first wire end connected with the second electrode pin and a second wire end connected with the single-used pin. While vacuuming the glass ball-tube before melting an end to seal, a voltage is exerting on the single use pin to heat the tungsten, and a high voltage is exerting on the anode target to accelerate the hot electrons emitting from the filament to bombard the inside wall of the glass ball-tube and the anode target so as to shorten the vacuuming time and increase the vacuum level.

Owner:ENERGY RESOURCES INT

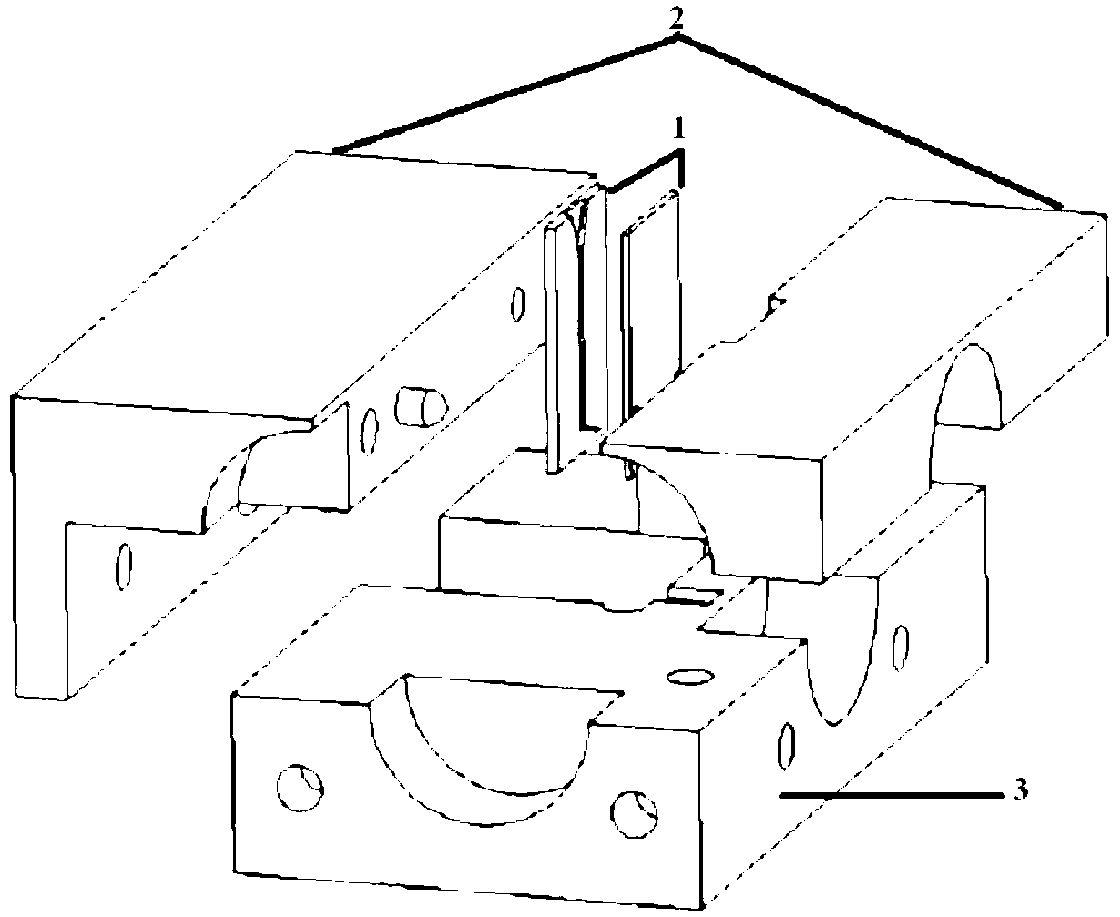

Ion source of injection device and ion injection method

ActiveCN103887132AExtended service lifeImprove stabilityIon beam tubesInjection deviceIon implantation

The invention provides an ion source of an injection device and an ion injection method. The ion source comprises an arc-starting chamber which is used for accommodating plasma, a lamp filament which is arranged on the side wall of the arc-starting chamber and is used for producing heat so as to enable the ion source gas input to the arc-starting chamber to be ionized as the plasma; a reflector electrode which is arranged on the side wall, opposite to the lamp filament, of the arc-starting chamber and is used for reflecting hot electron generated by the lamp filament; a slit which is arranged on the top of the arc-starting chamber and serves as the outlet of the plasma; a source gas inlet which is arranged on the side wall, between the reflector electrode and the lamp filament, of the arc-starting chamber, and is used for inputting the ion source gas; and a clean gas inlet which is arranged in the side wall, at the same side of the source gas inlet, of the arc-starting chamber and is used for inputting inertia clean gas. The service life of the ion source is prolonged.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Terahertz front-end integrated receiving device based on bulk silicon MEMS (micro-electromechanical system) technical antenna

InactiveCN103219587AReduce processing costsHighly integratedDecorative surface effectsAntenna supports/mountingsIntermediate frequencySuperconductivity

The invention relates to a terahertz front-end integrated receiving device based on a bulk silicon MEMS (micro-electromechanical system) technical antenna, and the device is suitable for terahertz low-frequency stage and belongs to the technical field of terahertz. The device mainly comprises an antenna, a mixer chip, a base and a back panel, wherein the antenna comprises an H-face horn antenna based on a bulk silicon MEMS and a plane gradually changing type plantar slot antenna (ALTSA in short); the mixer chip is a superheterodyne detector and comprises a room temperature schottky diode mixer, a superconductivity tunnel junction mixer, and a hot electron bolometric resistance mixer; the external part of the base remains the position which is in physical match with the chip and an intermediate frequency terminal and the like; and the back panel also remains the space which is in physical match with the chip and the intermediate frequency terminal. According to the device, the antenna is processed through the bulk silicon MEMS technology; the processing precision of the terahertz device can be satisfied; and the device is convenient to manufacture and produce in mass, and is easy to assemble. Through the integral assembling method of the antenna, the mixer and a bias circuit, the success ratio of micro-packaging the components is improved, the integration level of the integral receiving device is improved; and the device has the advantages of small size, light weight and low cost.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com