Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

325 results about "Synapse" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

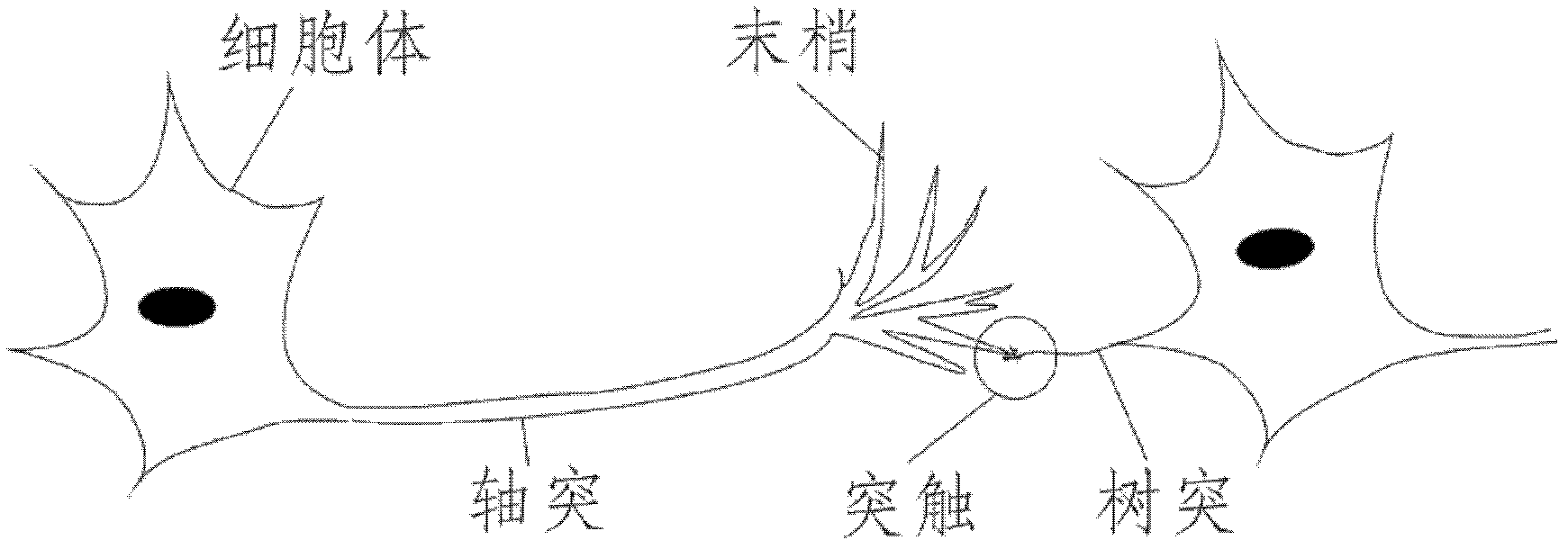

In the nervous system, a synapse is a structure that permits a neuron (or nerve cell) to pass an electrical or chemical signal to another neuron or to the target effector cell. Santiago Ramón y Cajal proposed that neurons are not continuous throughout the body, yet still communicate with each other,(like cabbages) an idea known as the neuron doctrine. The word "synapse" – from the Greek synapsis (συνάψις), meaning "conjunction", in turn from συνάπτεὶν (συν ("together") and ἅπτειν ("to fasten")) – was introduced in 1897 by the English neurophysiologist Charles Sherrington in Michael Foster's Textbook of Physiology. Sherrington struggled to find a good term that emphasized a union between two separate elements, and the actual term "synapse" was suggested by the English classical scholar Arthur Woollgar Verrall, a friend of Foster. Some authors generalize the concept of the synapse to include the communication from a neuron to any other cell type, such as to a motor cell, although such non-neuronal contacts may be referred to as junctions (a historically older term).

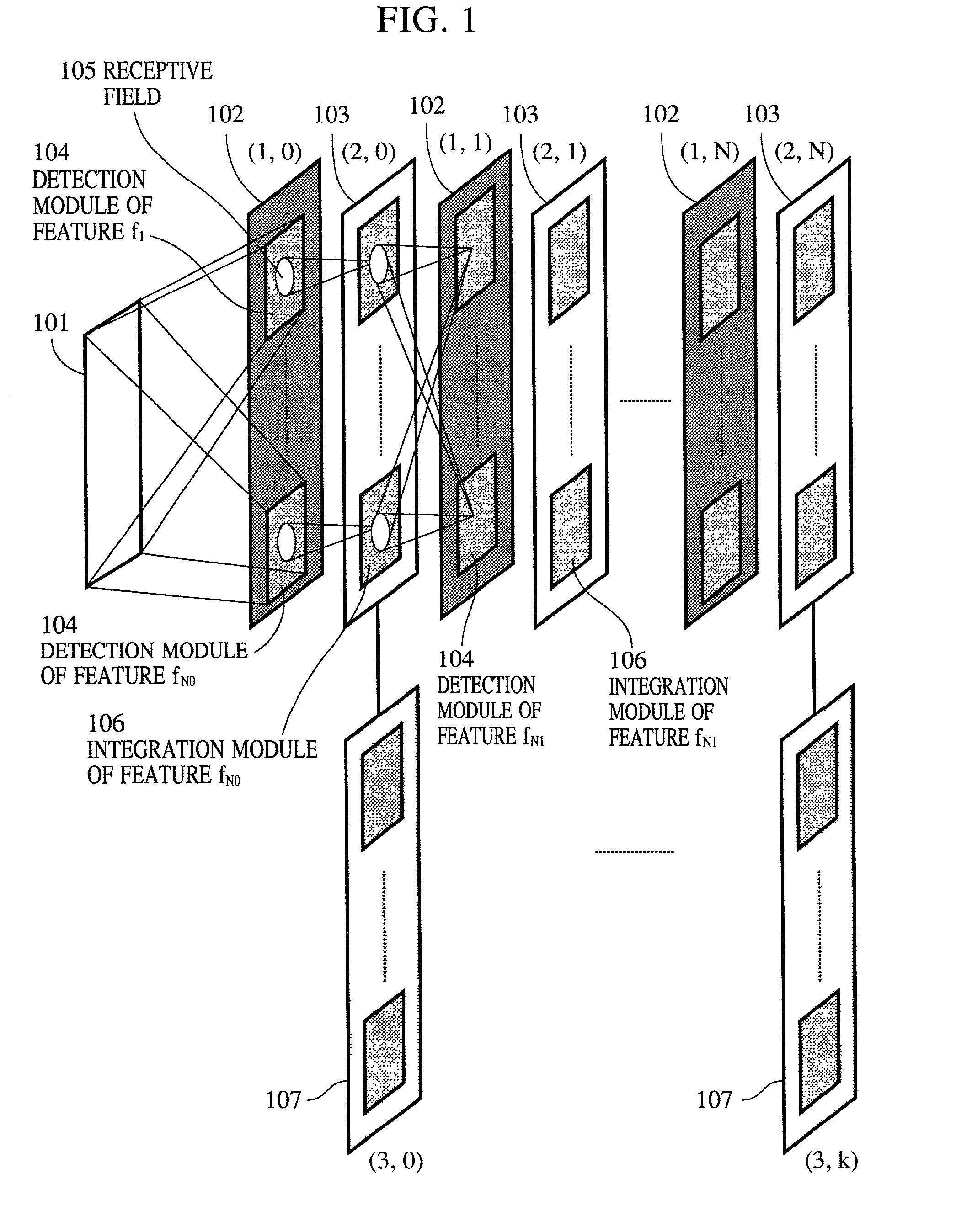

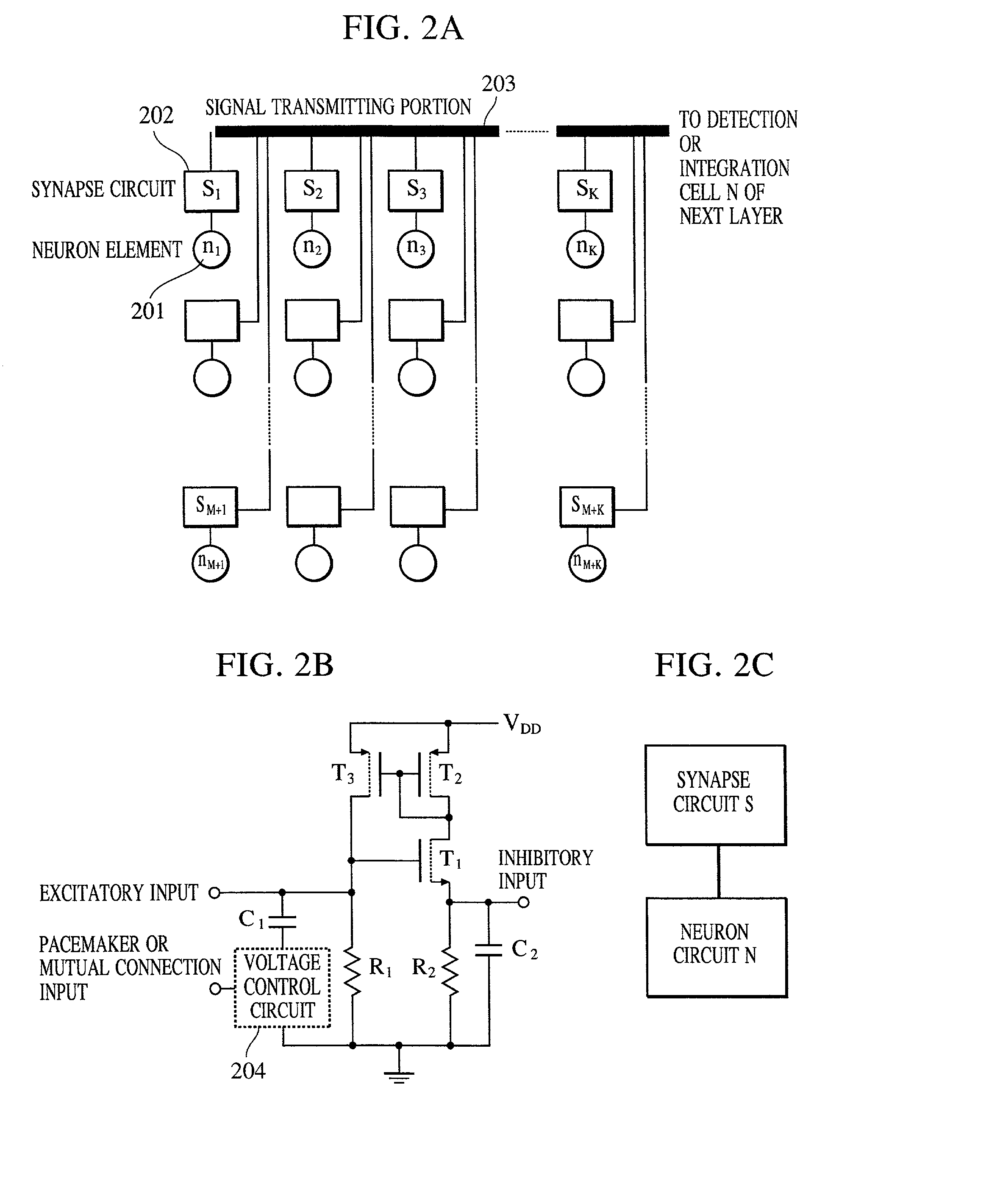

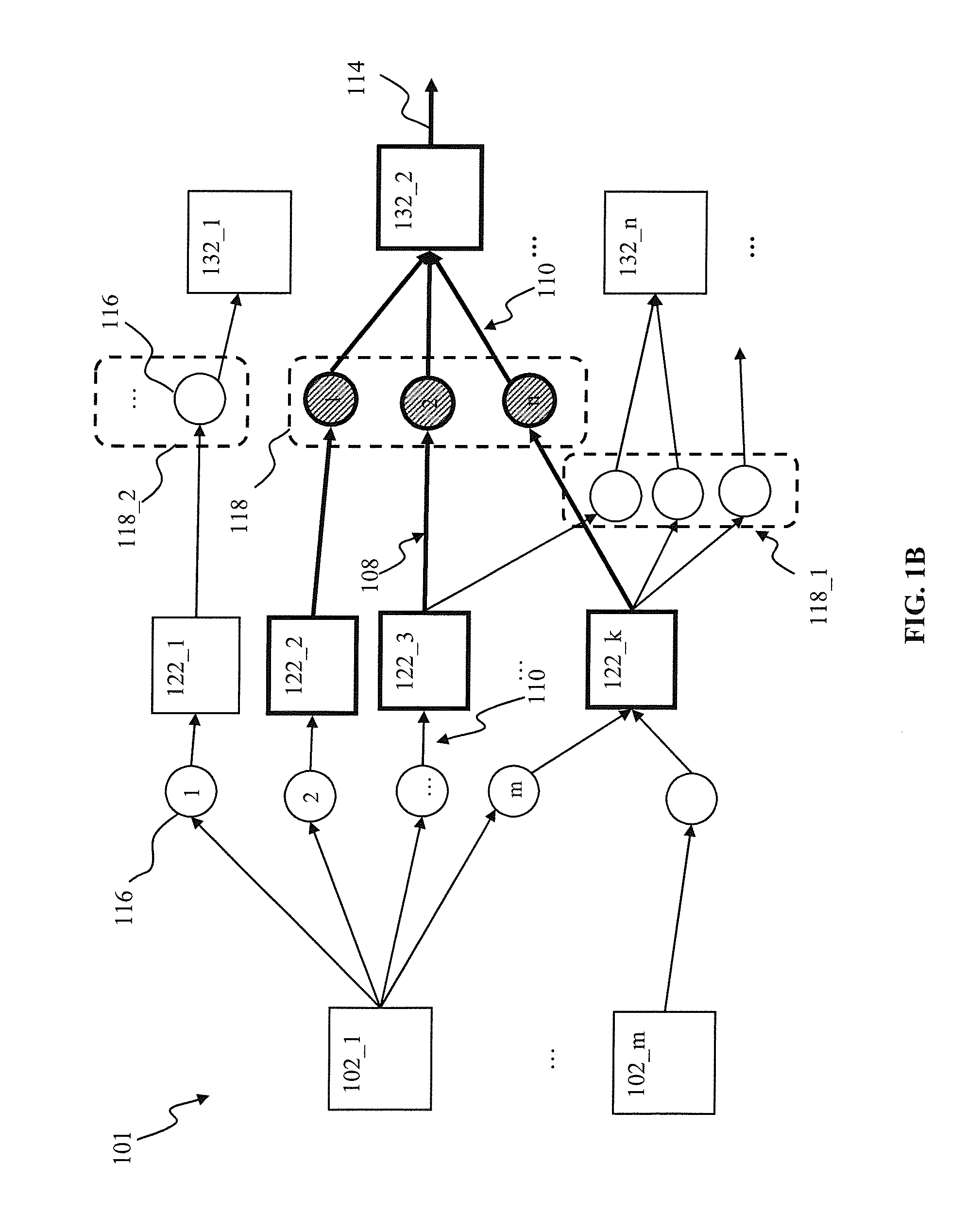

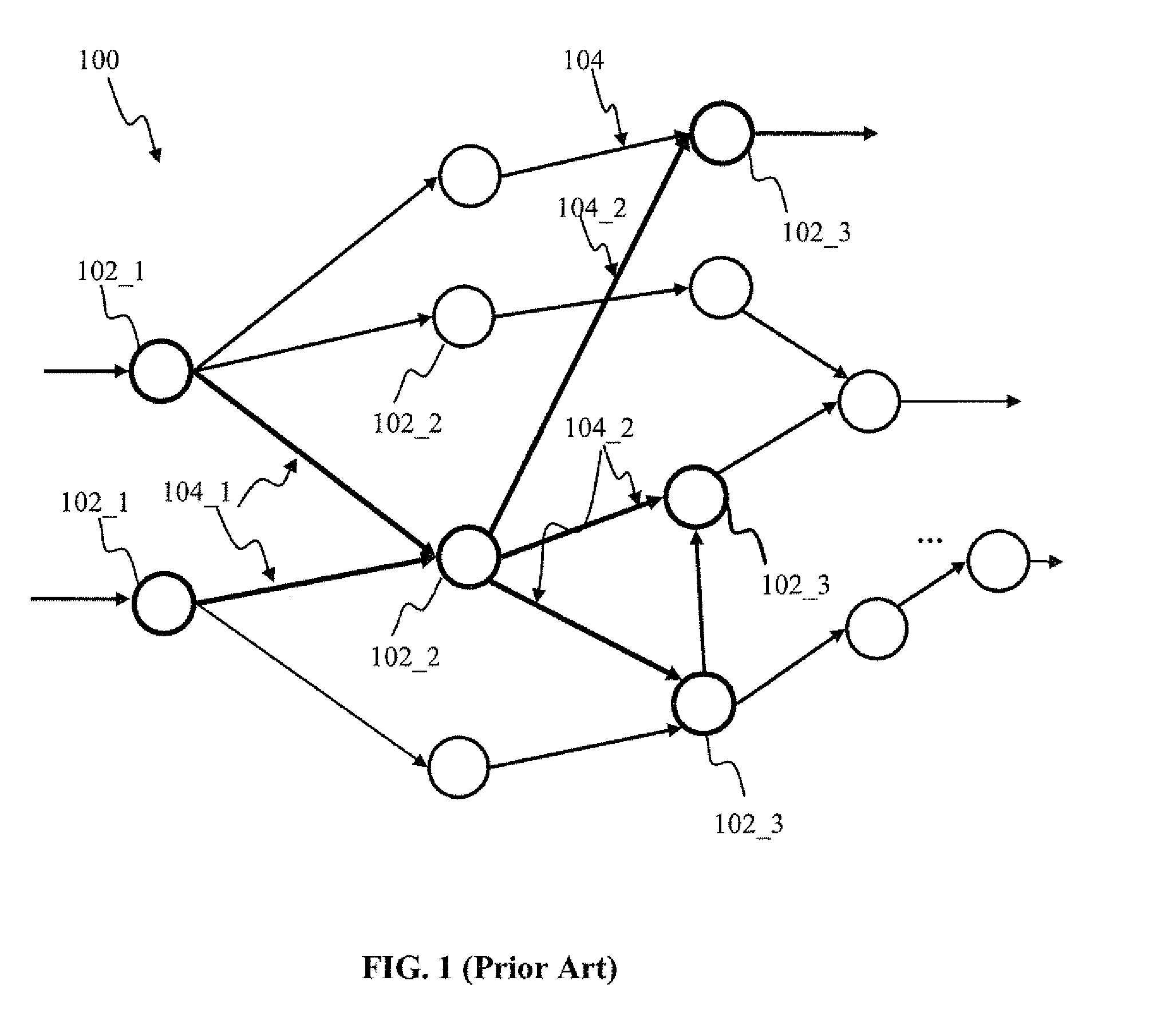

Apparatus and method for detecting or recognizing pattern by employing a plurality of feature detecting elements

InactiveUS20020038294A1Easy constructionReduce in quantityDigital computer detailsCharacter and pattern recognitionSynapsePattern detection

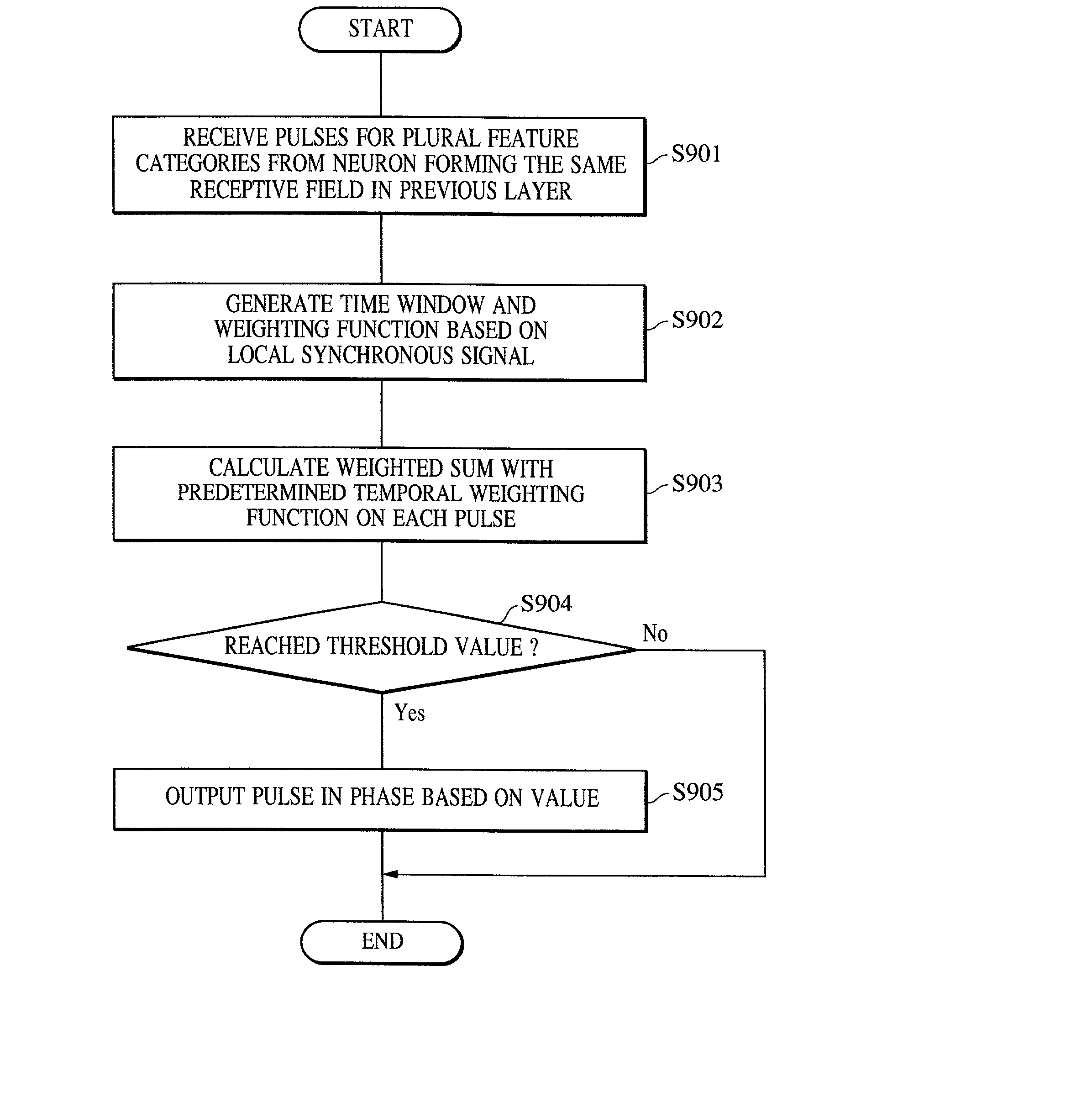

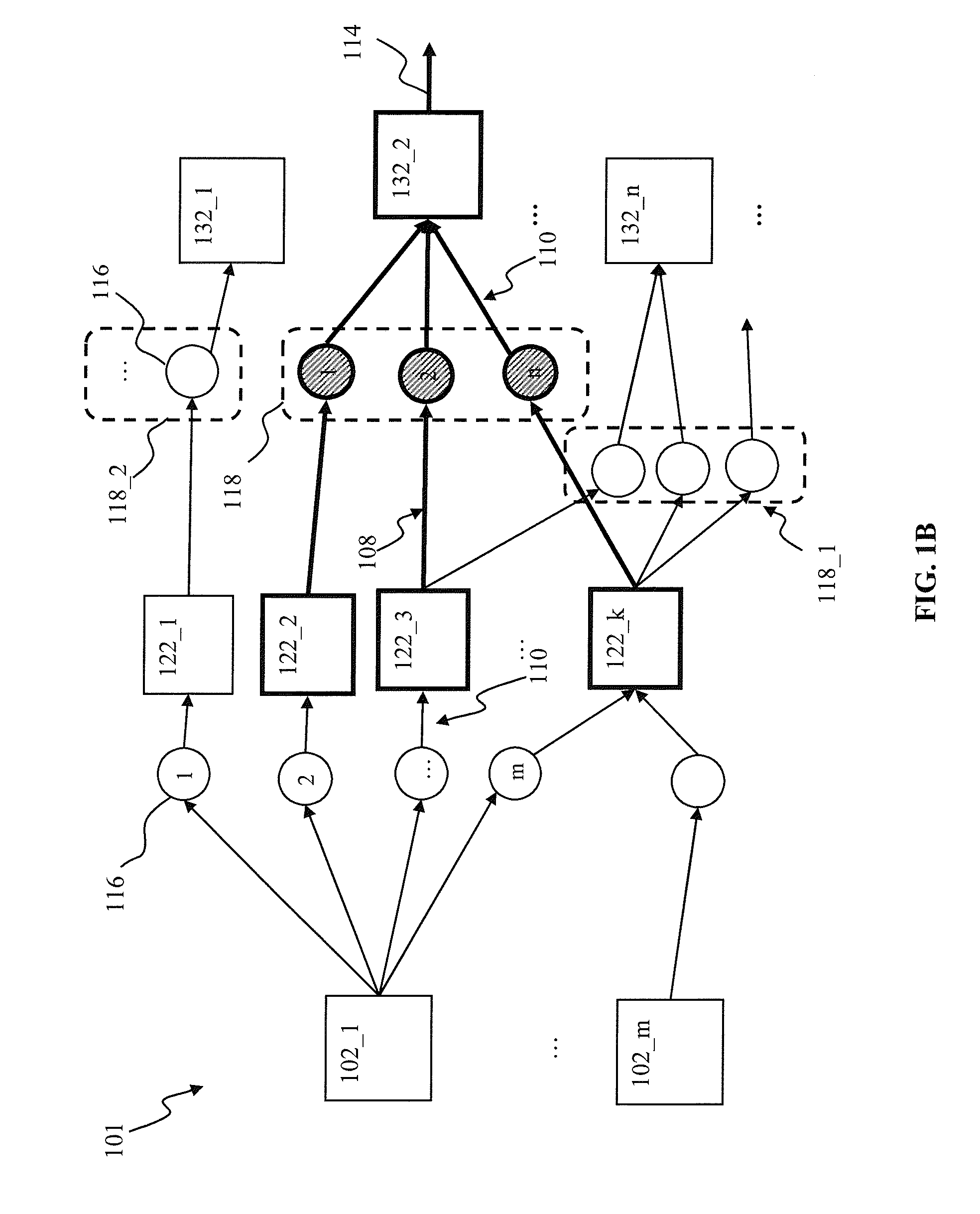

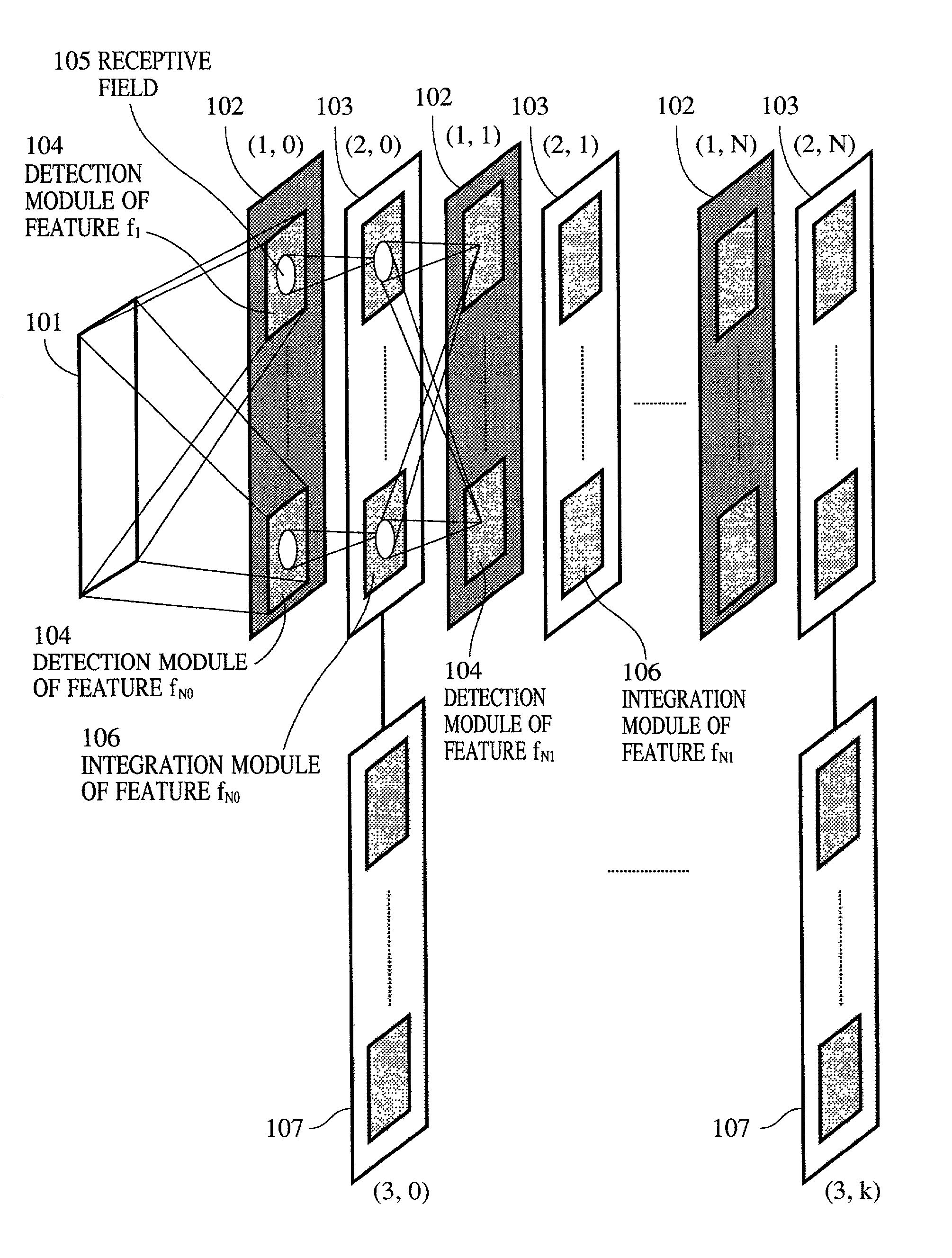

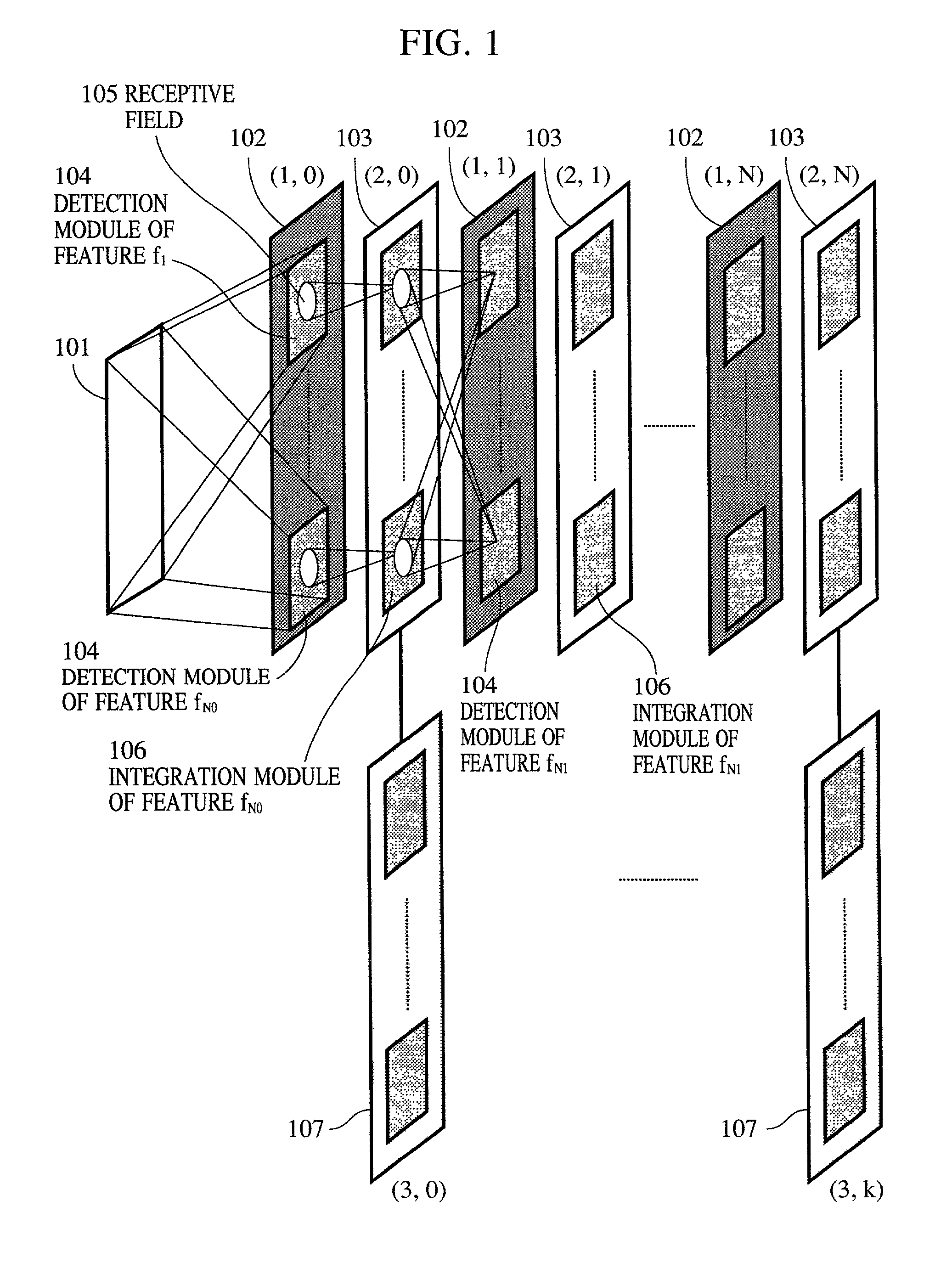

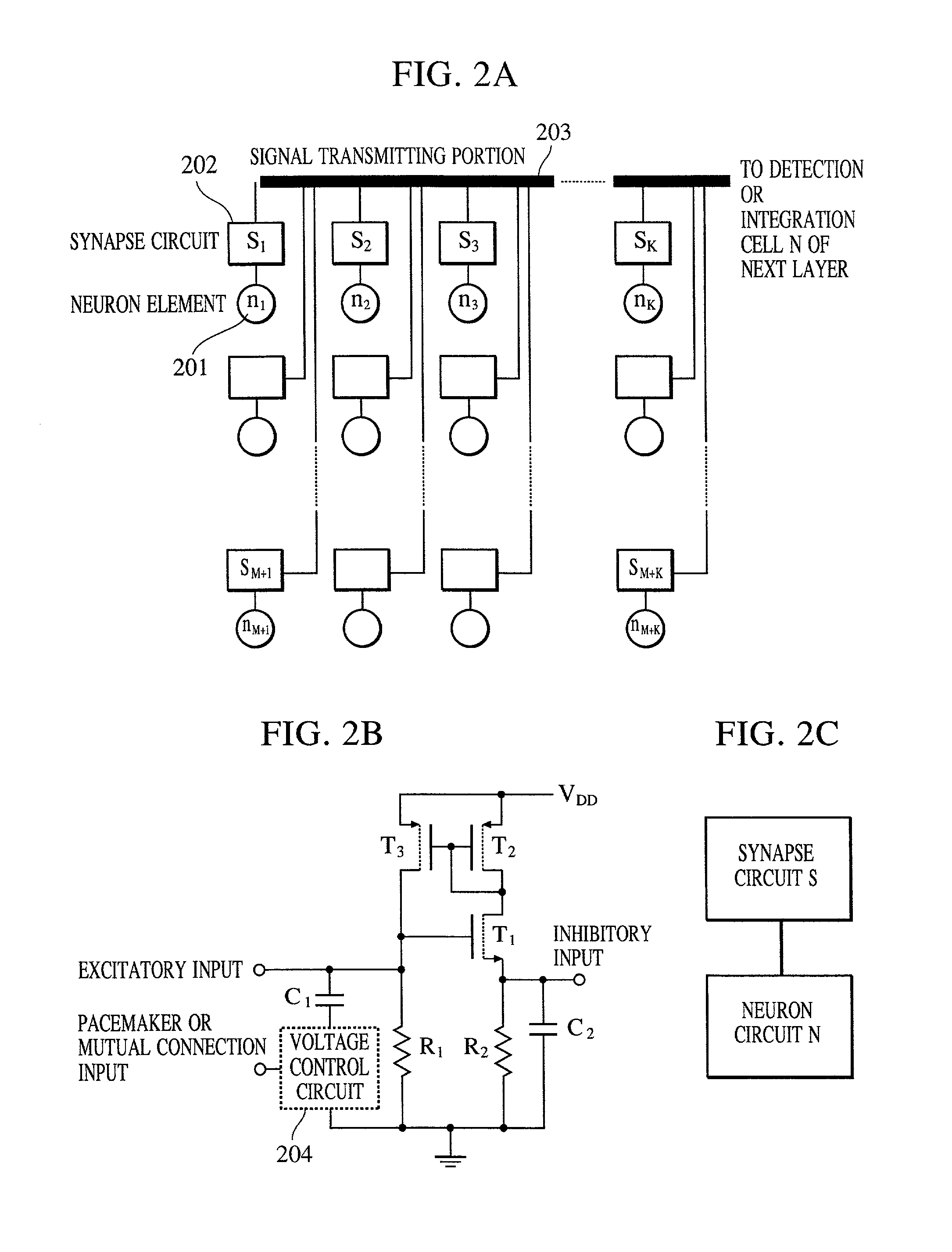

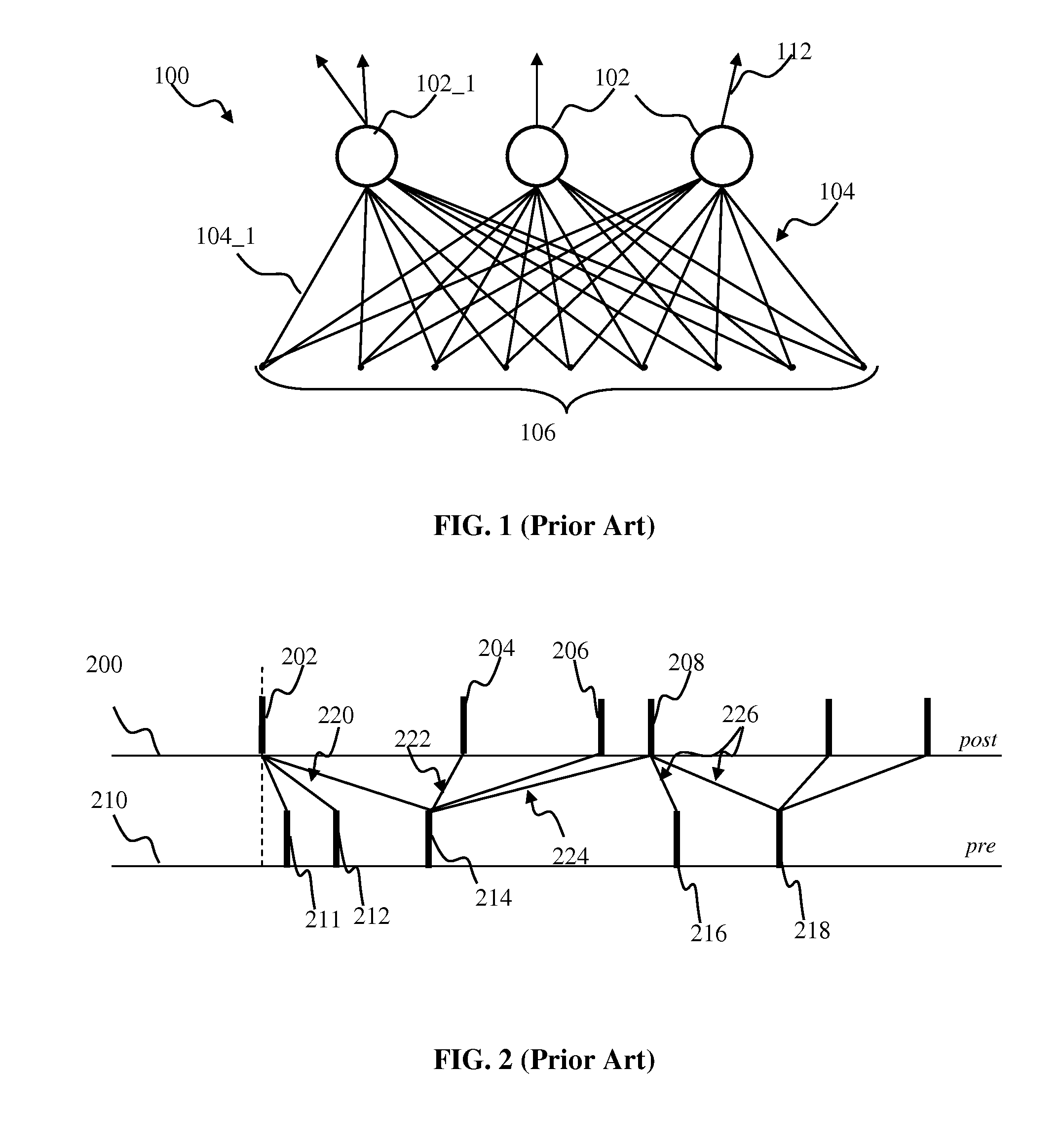

A pattern detecting apparatus has a plurality of hierarchized neuron elements to detect a predetermined pattern included in input patterns. Pulse signals output from the plurality of neuron elements are given specific delays by synapse circuits associated with the individual elements. This makes it possible to transmit the pulse signals to the neuron elements of the succeeding layer through a common bus line so that they can be identified on a time base. The neuron elements of the succeeding layer output the pulse signals at output levels based on a arrival time pattern of the plurality of pulse signals received from the plurality of neuron elements of the preceding layer within a predetermined time window. Thus, the reliability of pattern detection can be improved, and the number of wires interconnecting the elements can be reduced by the use of the common bus line, leading to a small scale of circuit and reduced power consumption.

Owner:CANON KK

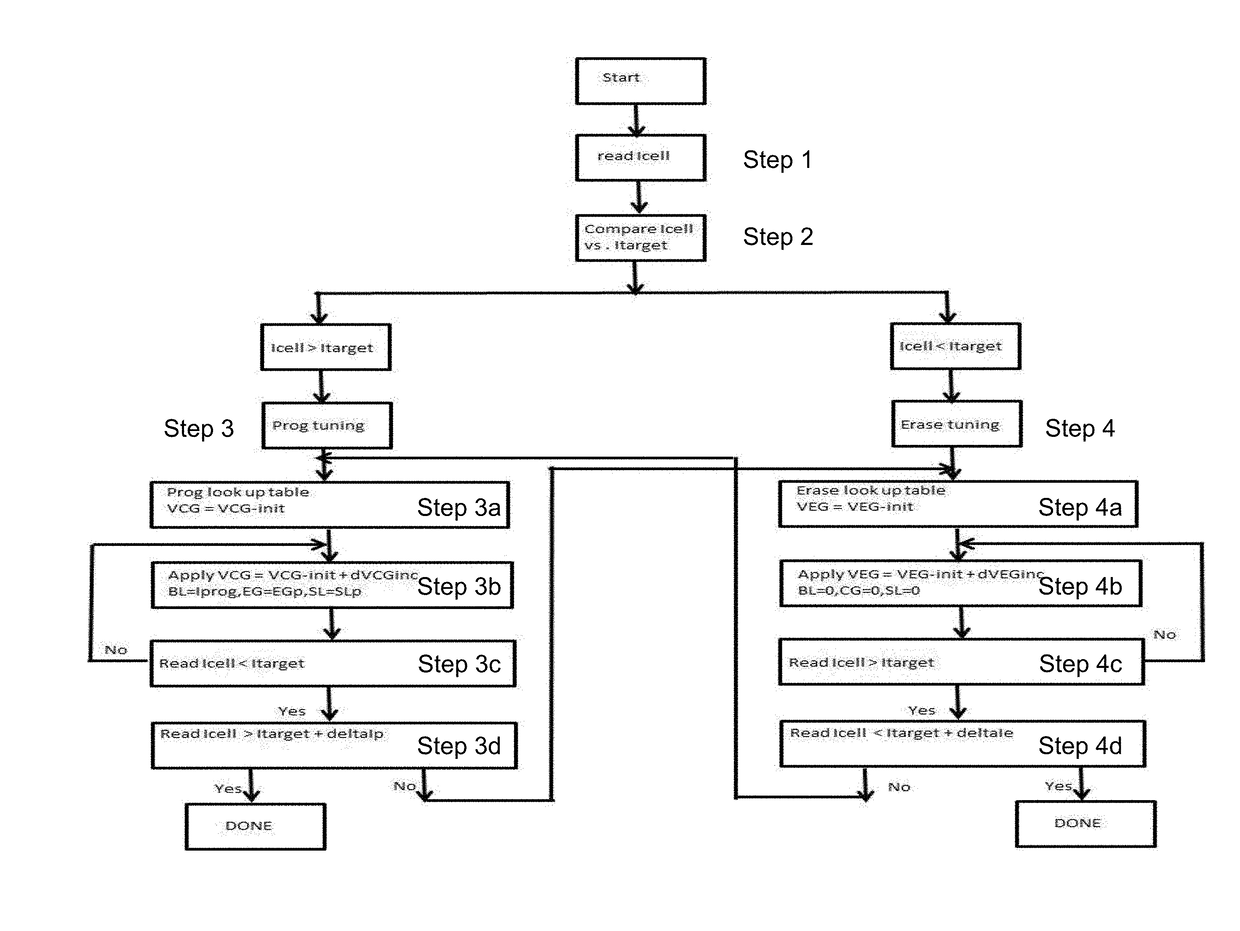

Deep Learning Neural Network Classifier Using Non-volatile Memory Array

ActiveUS20170337466A1Input/output to record carriersRead-only memoriesSynapseNeural network classifier

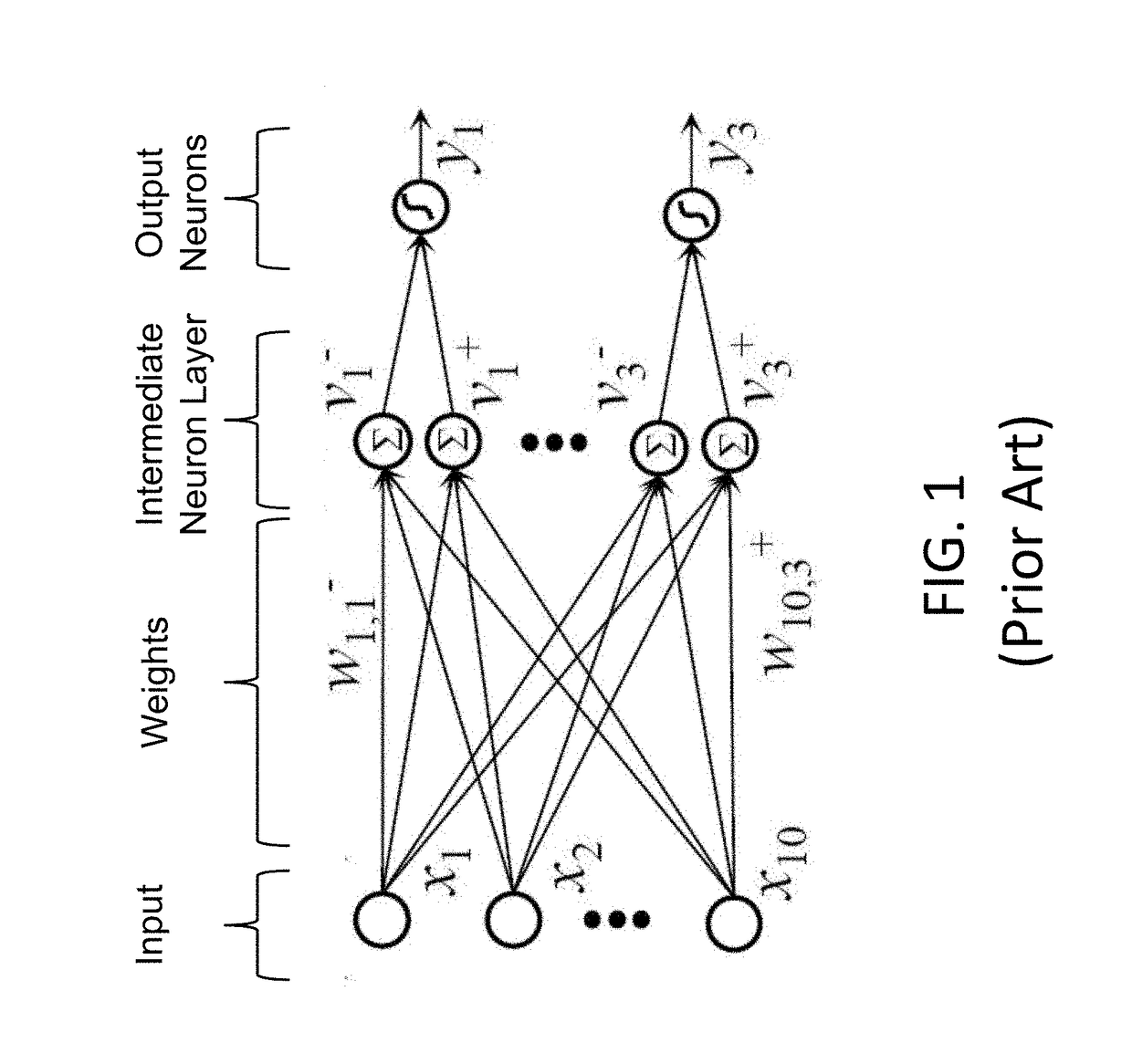

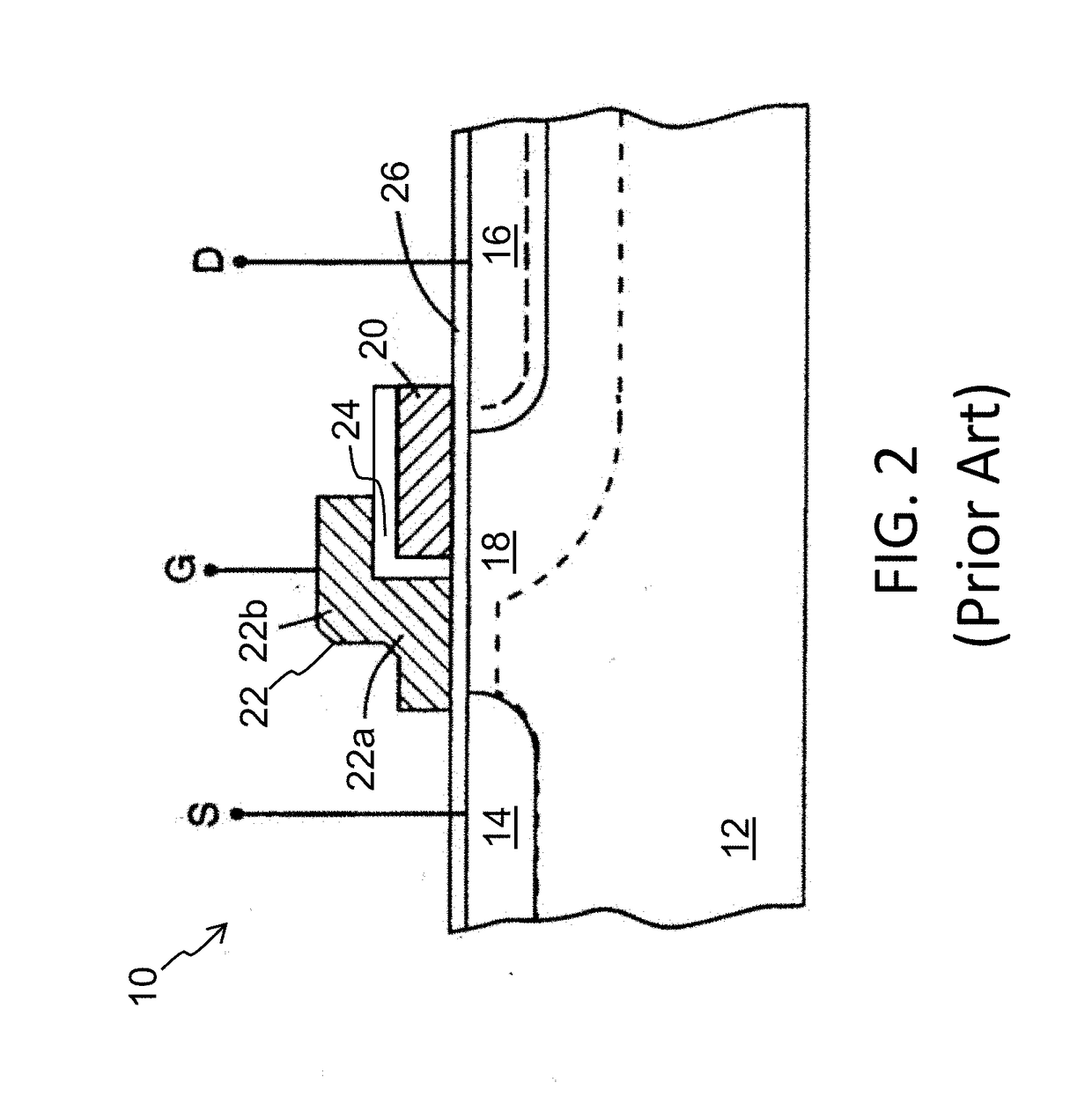

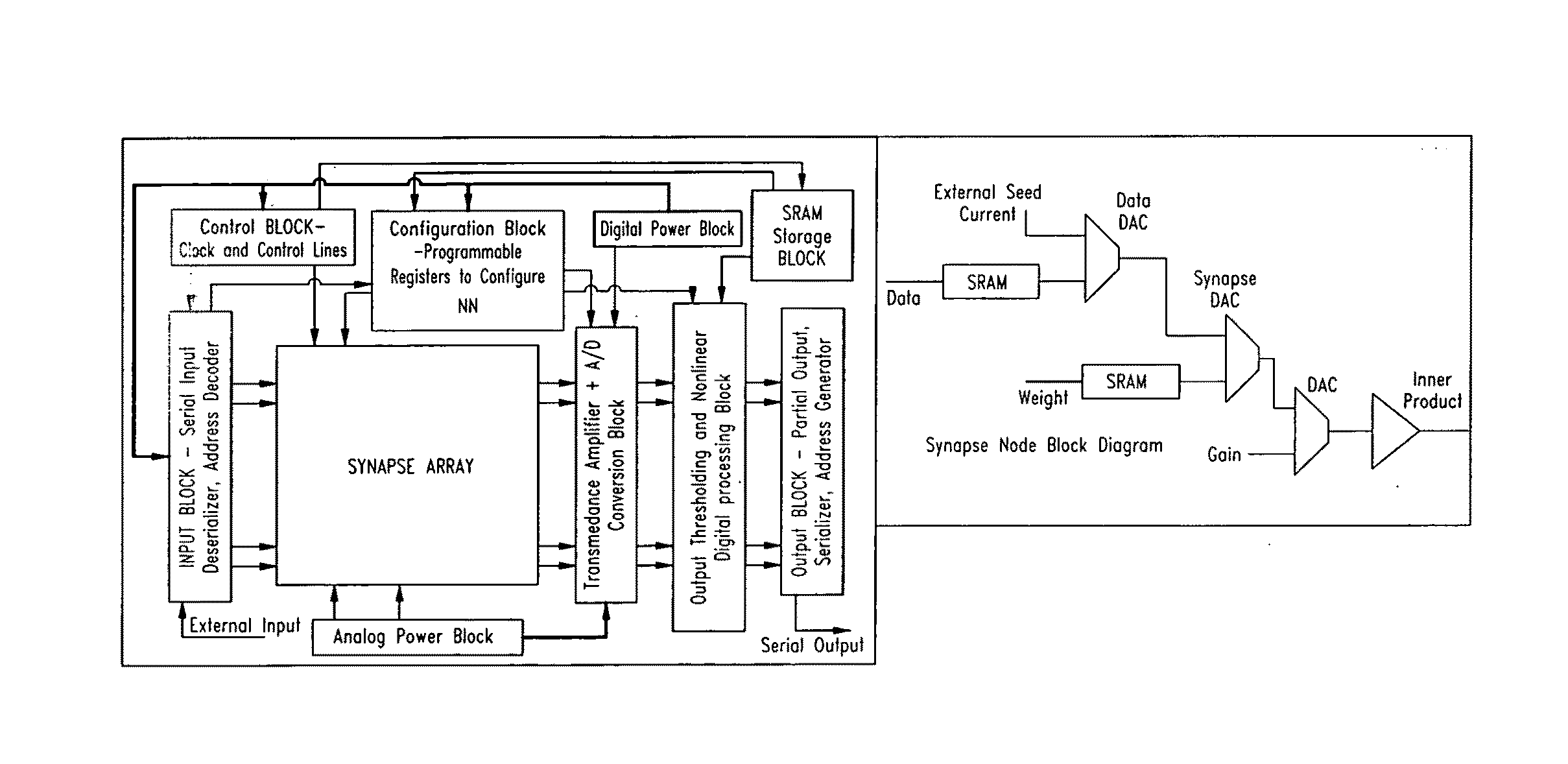

An artificial neural network device that utilizes one or more non-volatile memory arrays as the synapses. The synapses are configured to receive inputs and to generate therefrom outputs. Neurons are configured to receive the outputs. The synapses include a plurality of memory cells, wherein each of the memory cells includes spaced apart source and drain regions formed in a semiconductor substrate with a channel region extending there between, a floating gate disposed over and insulated from a first portion of the channel region and a non-floating gate disposed over and insulated from a second portion of the channel region. Each of the plurality of memory cells is configured to store a weight value corresponding to a number of electrons on the floating gate. The plurality of memory cells are configured to multiply the inputs by the stored weight values to generate the outputs.

Owner:RGT UNIV OF CALIFORNIA +1

Apparatus and methods for synaptic update in a pulse-coded network

InactiveUS20130073491A1Reducing memory bus overheadReduce overheadDigital computer detailsDigital dataSynapseSpiking neural network

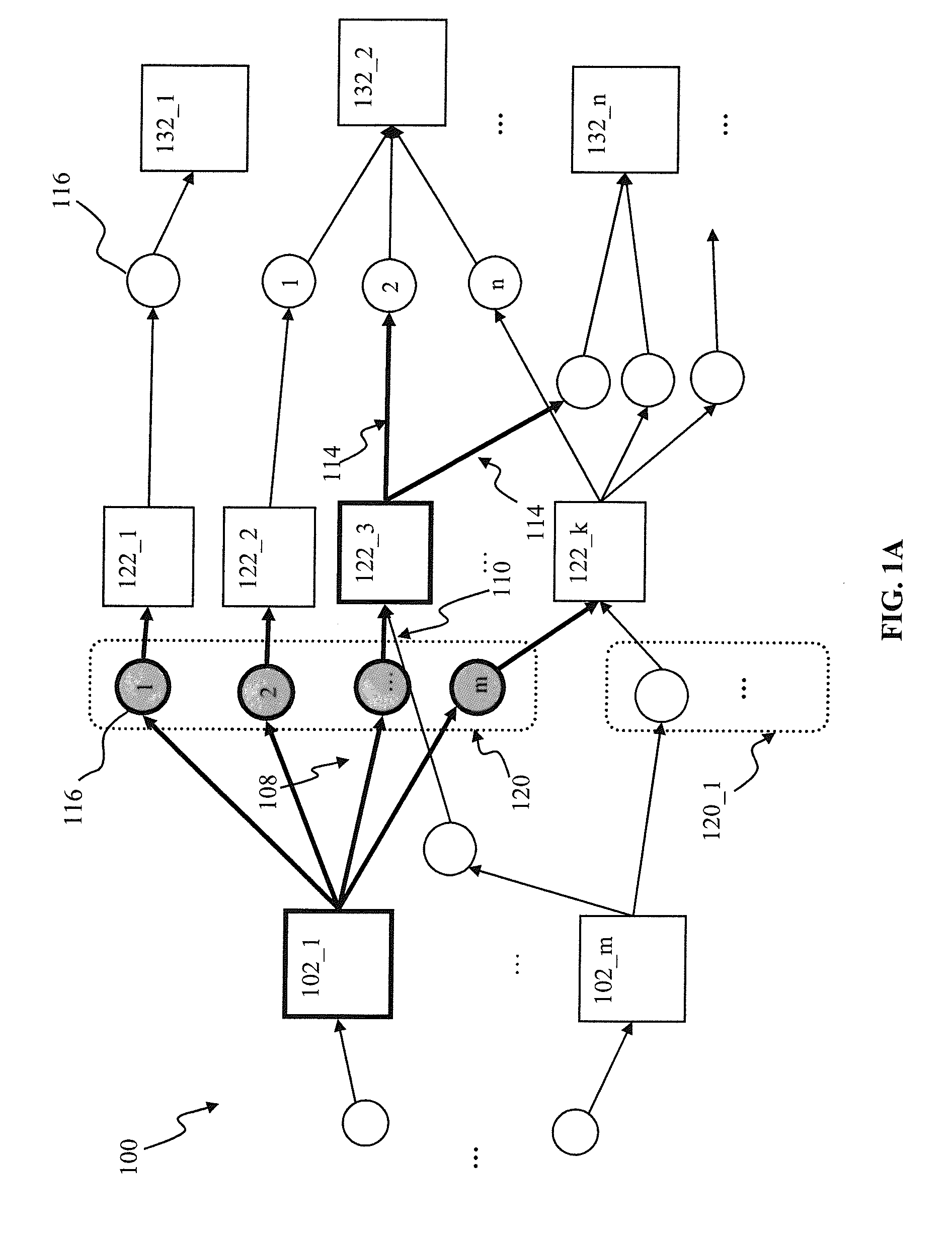

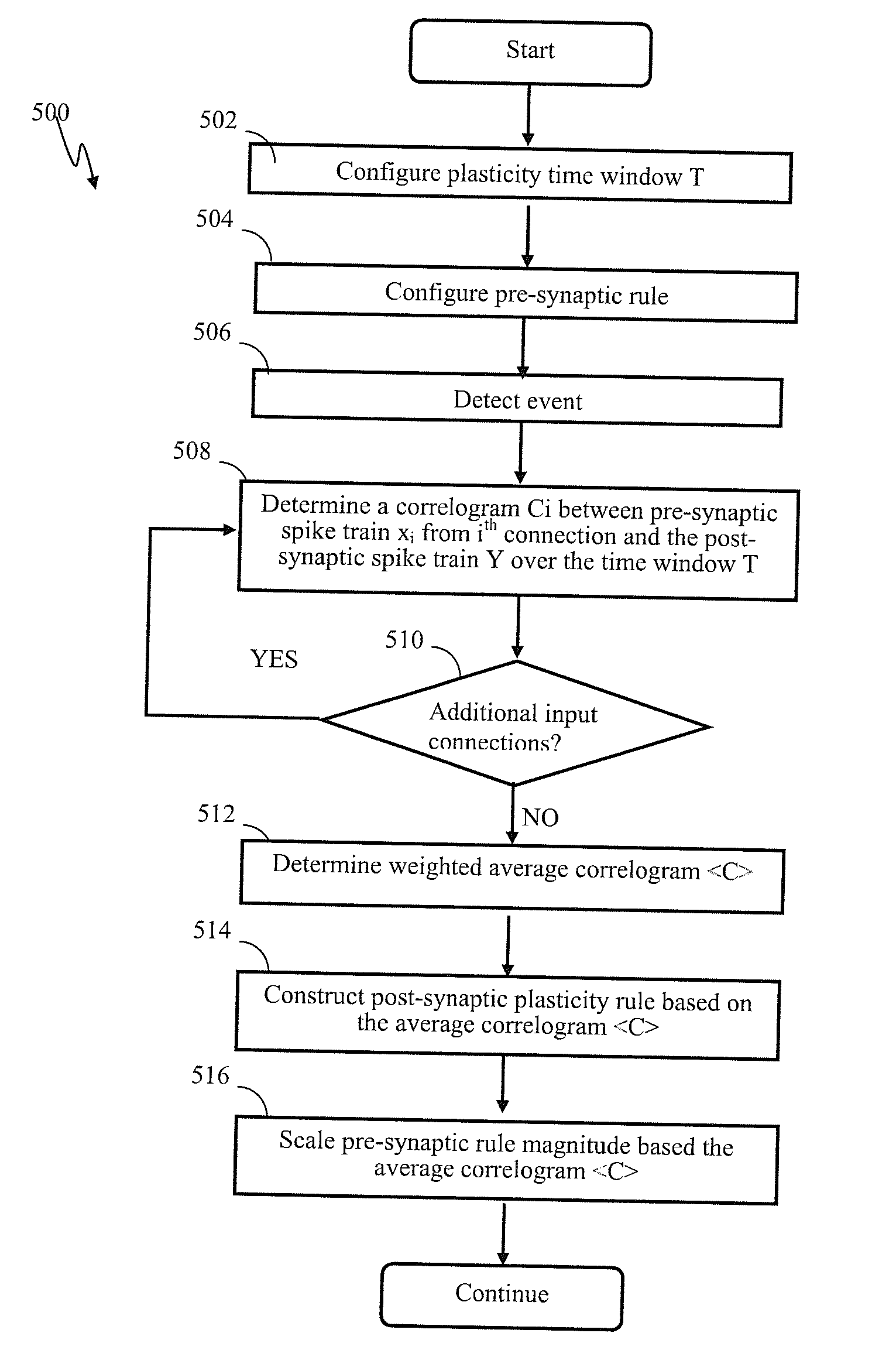

Apparatus and methods for efficient synaptic update in a network such as a spiking neural network. In one embodiment, the post-synaptic updates, in response to generation of a post-synaptic pulse by a post-synaptic unit, are delayed until a subsequent pre-synaptic pulse is received by the unit. Pre-synaptic updates are performed first following by the post-synaptic update, thus ensuring synaptic connection status is up-to-date. The delay update mechanism is used in conjunction with system “flush” events in order to ensure accurate network operation, and prevent loss of information under a variety of pre-synaptic and post-synaptic unit firing rates. A large network partition mechanism is used in one variant with network processing apparatus in order to enable processing of network signals in a limited functionality embedded hardware environment.

Owner:QUALCOMM INC

Apparatus and method for detecting or recognizing pattern by employing a plurality of feature detecting elements

InactiveUS7054850B2High-precision detectionImprove process capabilityDigital computer detailsCharacter and pattern recognitionSynapsePattern detection

Owner:CANON KK

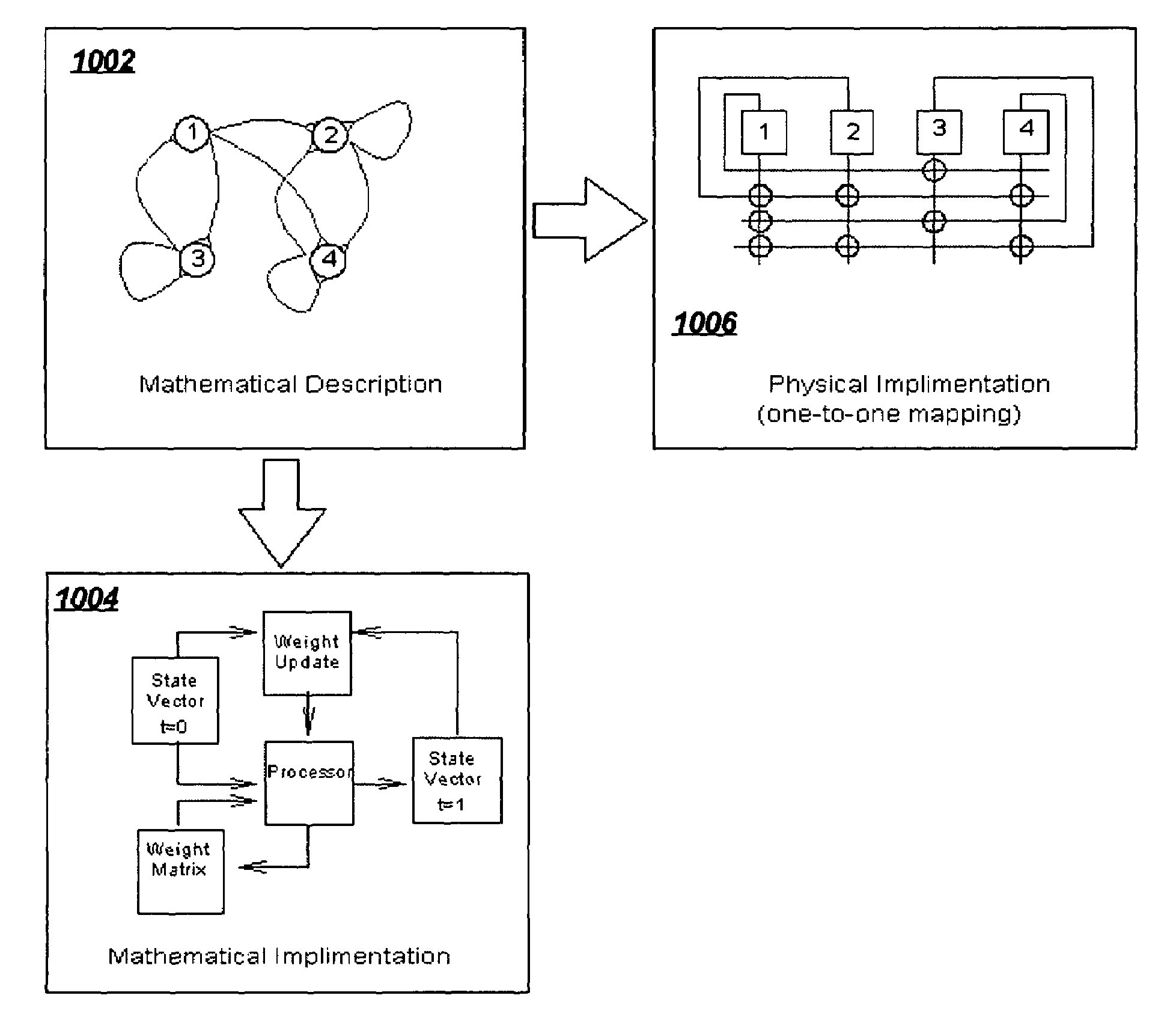

Training of a physical neural network

Owner:KNOWM TECH

Apparatus and methods for efficient updates in spiking neuron network

Efficient updates of connections in artificial neuron networks may be implemented. A framework may be used to describe the connections using a linear synaptic dynamic process, characterized by stable equilibrium. The state of neurons and synapses within the network may be updated, based on inputs and outputs to / from neurons. In some implementations, the updates may be implemented at regular time intervals. In one or more implementations, the updates may be implemented on-demand, based on the network activity (e.g., neuron output and / or input) so as to further reduce computational load associated with the synaptic updates. The connection updates may be decomposed into multiple event-dependent connection change components that may be used to describe connection plasticity change due to neuron input. Using event-dependent connection change components, connection updates may be executed on per neuron basis, as opposed to per-connection basis.

Owner:QUALCOMM INC

Apparatus and method for partial evaluation of synaptic updates based on system events

Apparatus and methods for partial evaluation of synaptic updates in neural networks. In one embodiment, a pre-synaptic unit is connected to a several post synaptic units via communication channels. Information related to a plurality of post-synaptic pulses generated by the post-synaptic units is stored by the network in response to a system event. Synaptic channel updates are performed by the network using the time intervals between a pre-synaptic pulse, which is being generated prior to the system event, and at least a portion of the plurality of the post synaptic pulses. The system event enables removal of the information related to the portion of the post-synaptic pulses from the storage device. A shared memory block within the storage device is used to store data related to post-synaptic pulses generated by different post-synaptic nodes. This configuration enables memory use optimization of post-synaptic units with different firing rates.

Owner:QUALCOMM INC

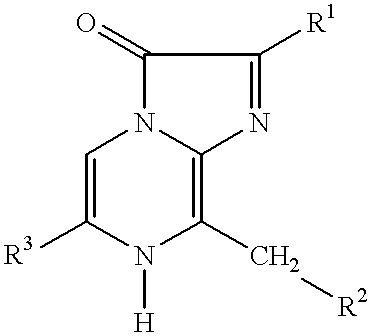

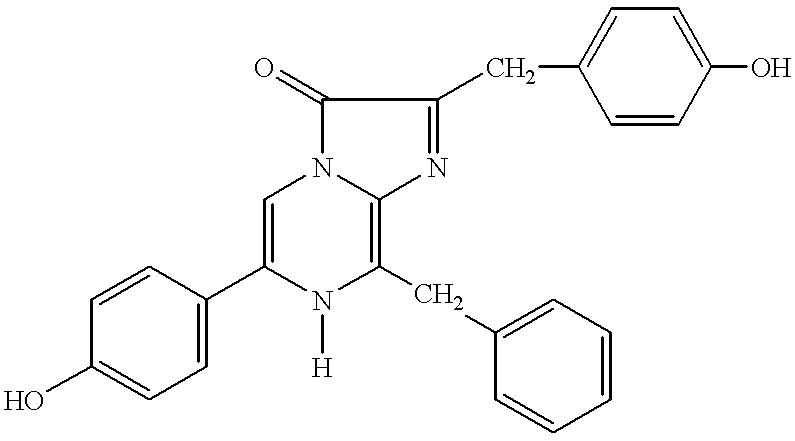

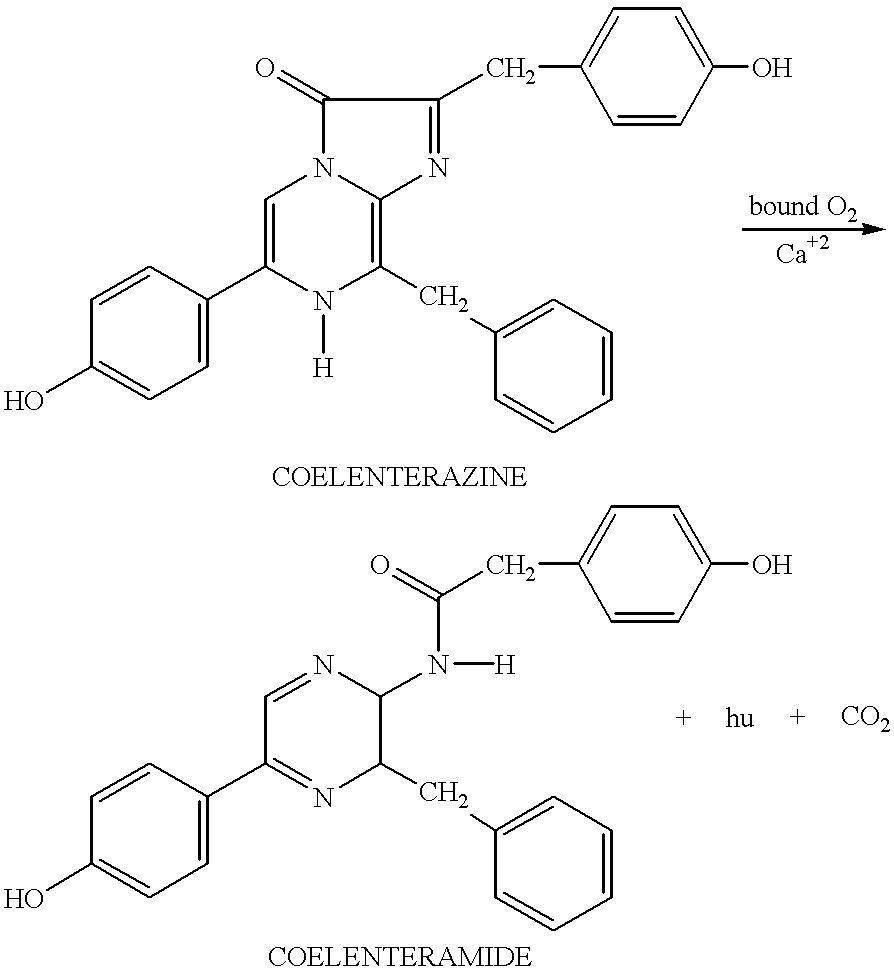

Apparatus and method for detecting and identifying infectious agents

Solid phase methods for the identification of an analyte in a biological medium, such as a body fluid, using bioluminescence are provided. A chip designed for performing the method and detecting the bioluminescence is also provided. Methods employing biomineralization for depositing silicon on a matrix support are also provided. A synthetic synapse is also provided.

Owner:PROLUME

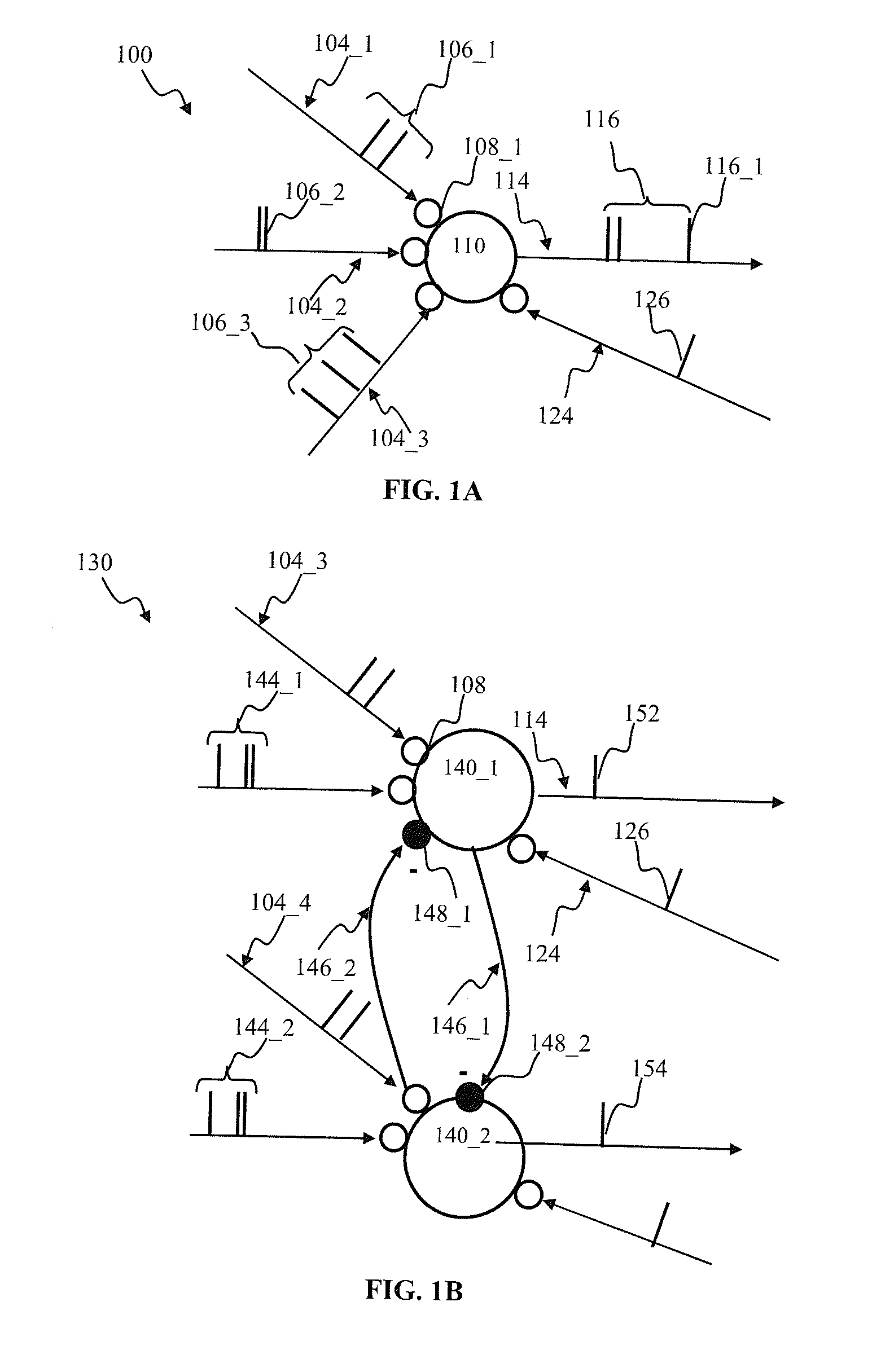

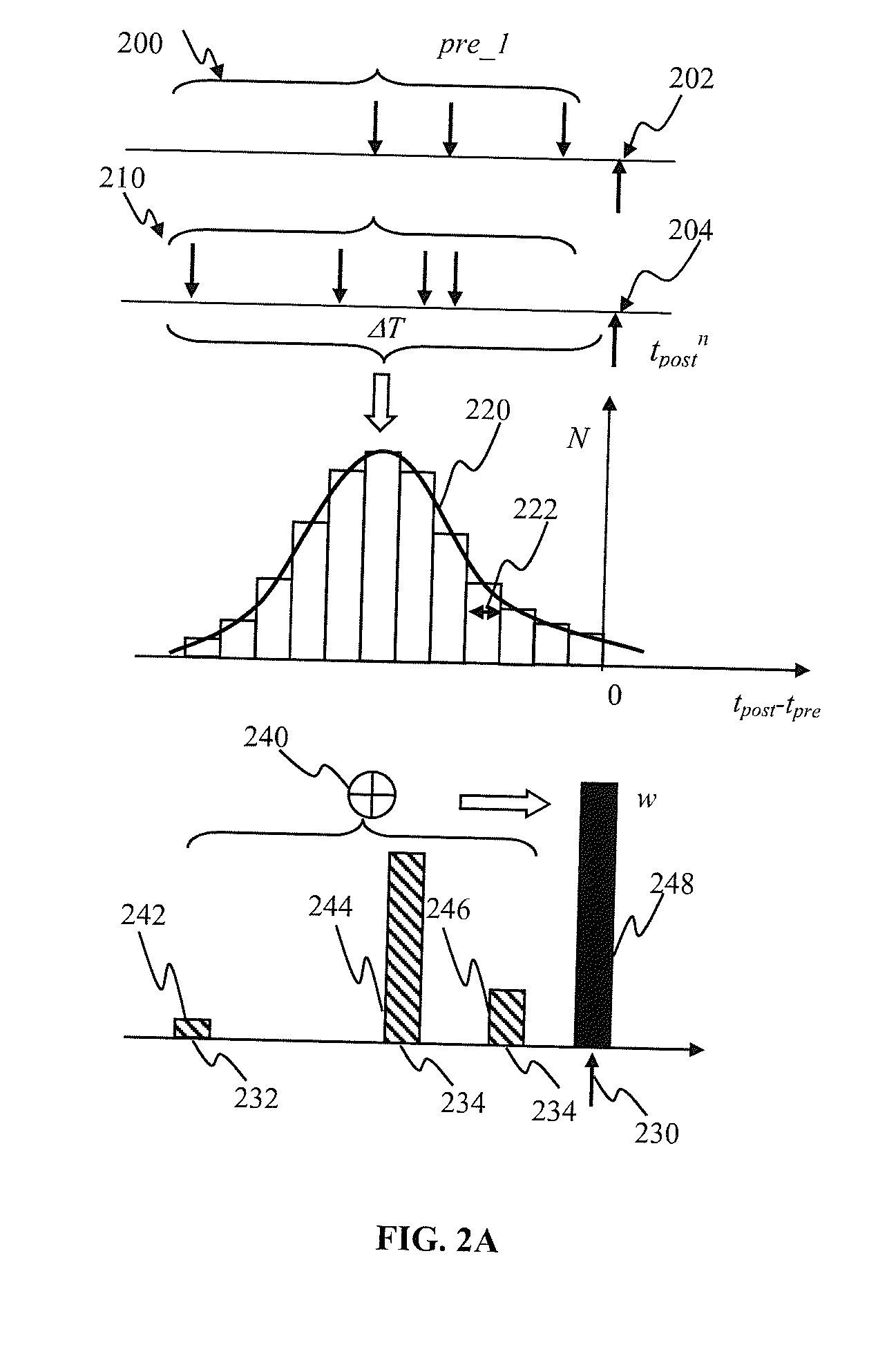

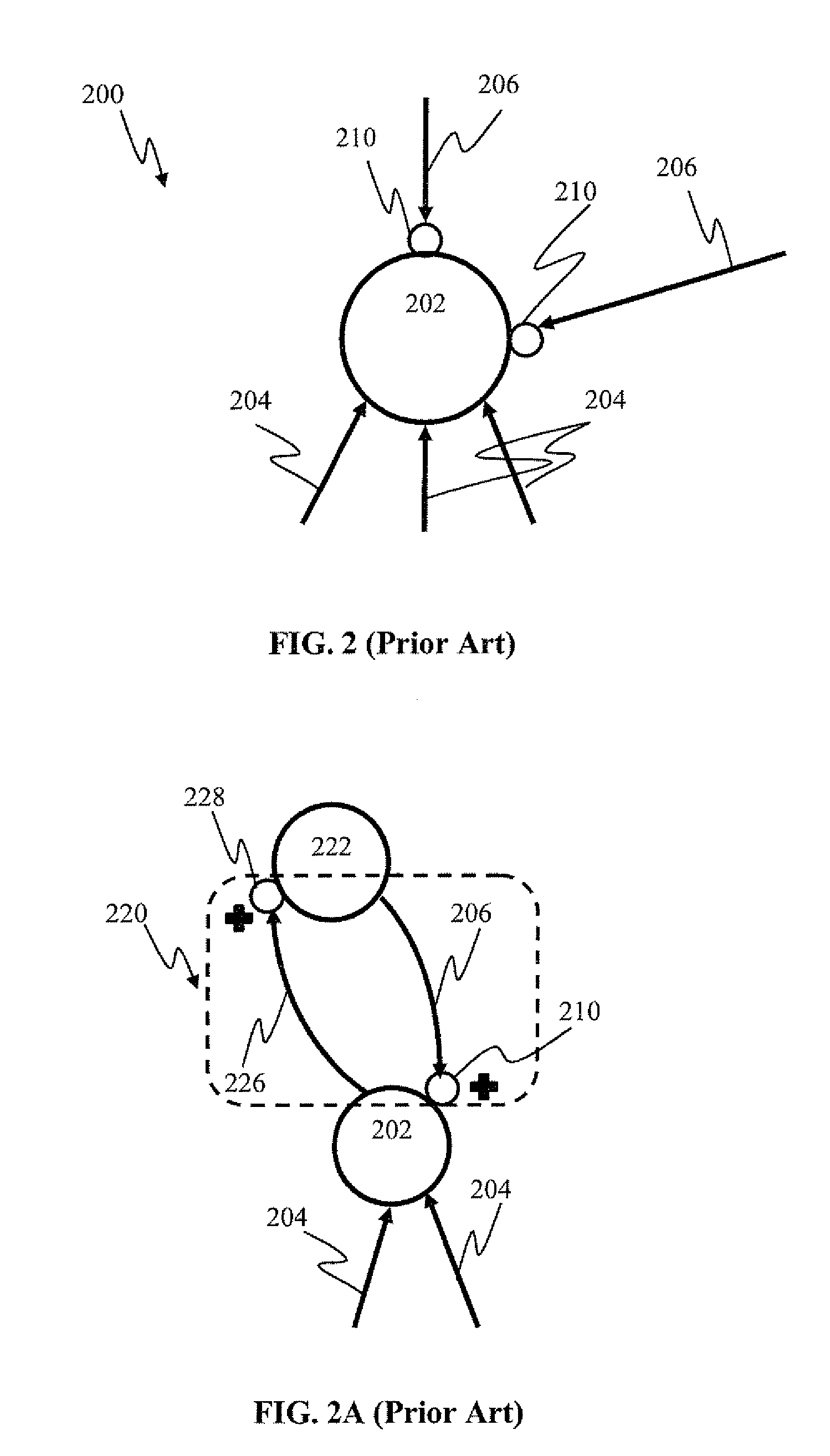

Modulated plasticity apparatus and methods for spiking neuron network

Apparatus and methods for modulated plasticity in a spiking neuron network. A plasticity mechanism may be configured for example based on a similarity measure between post-synaptic activities of two or more neurons that may be receiving the same feed-forward input. The similarity measure may comprise a dynamically determined cross-correlogram between the output spike trains of two neurons. An a priori configured similarity measure may be used during network operation in order to update efficacy of inhibitory connections between neighboring neurons. Correlated output activity may cause one neuron to inhibit output generation by another neuron thereby hindering responses by multiple neurons to the same input stimuli. The inhibition may be based on an increased efficacy of inhibitory lateral connection. The inhibition may comprise modulation of the pre synaptic portion the plasticity rule based on efficacies of feed-forward connection and inhibitory connections and a statistical parameter associated with the post-synaptic rule.

Owner:BRAIN CORP

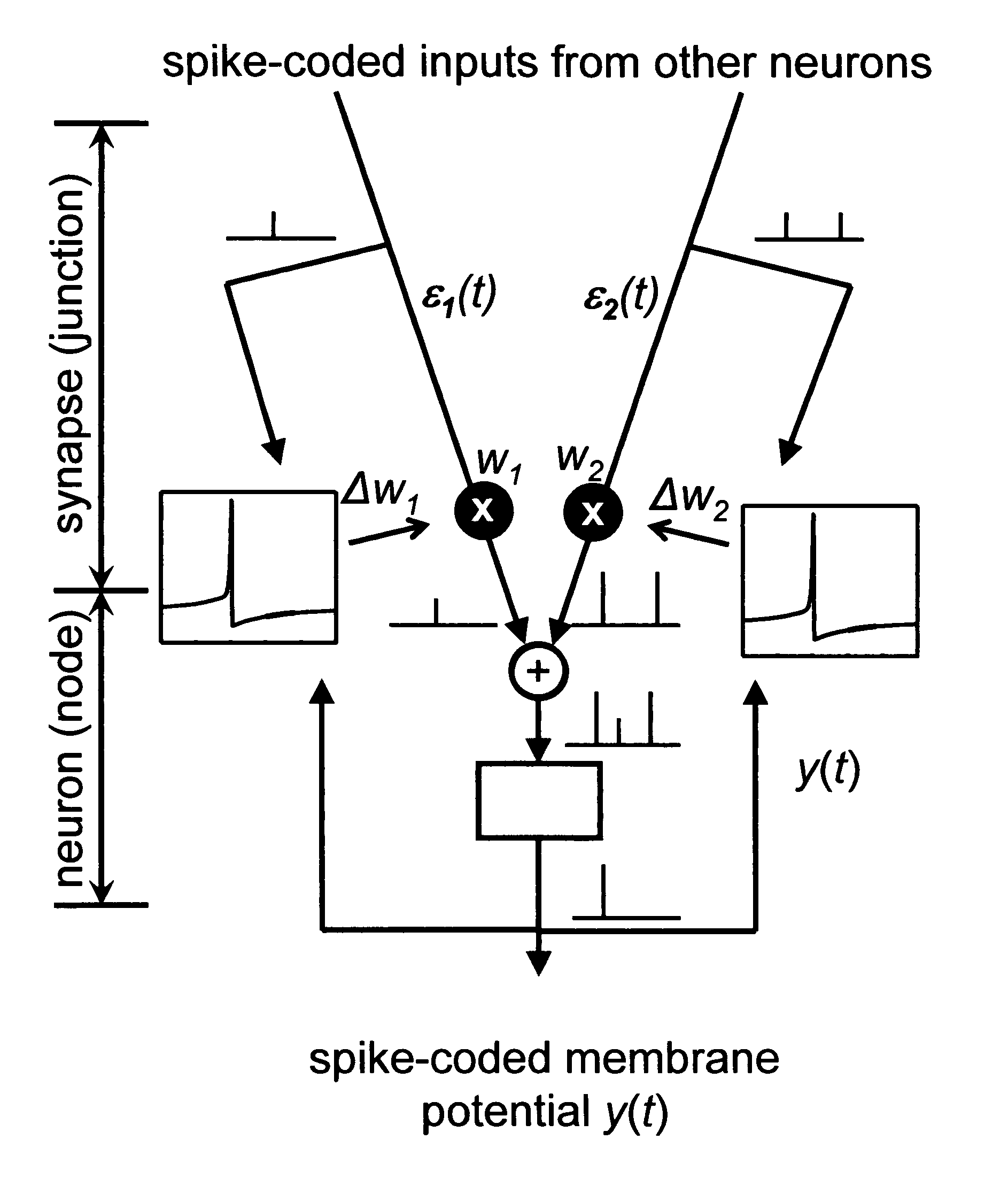

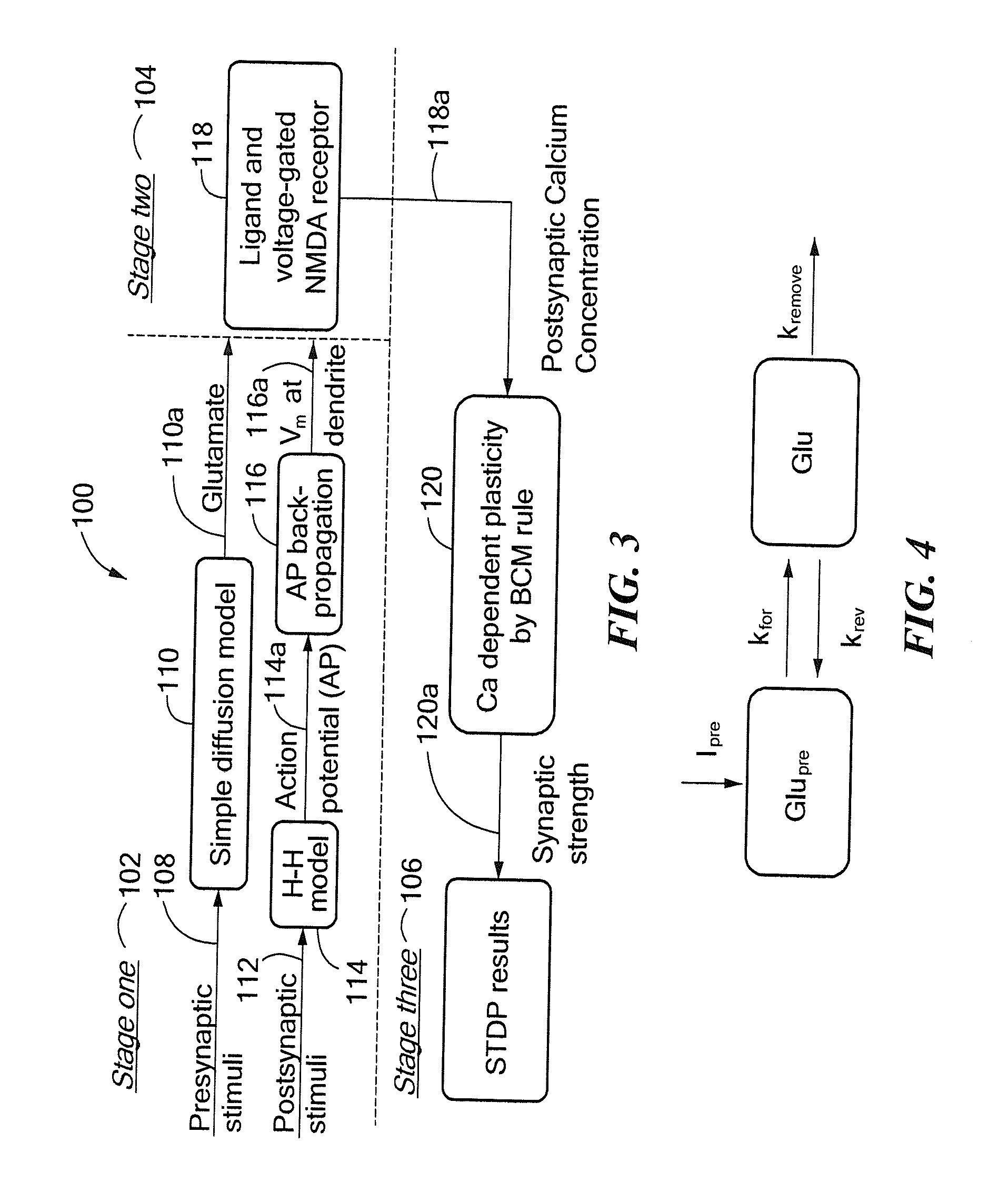

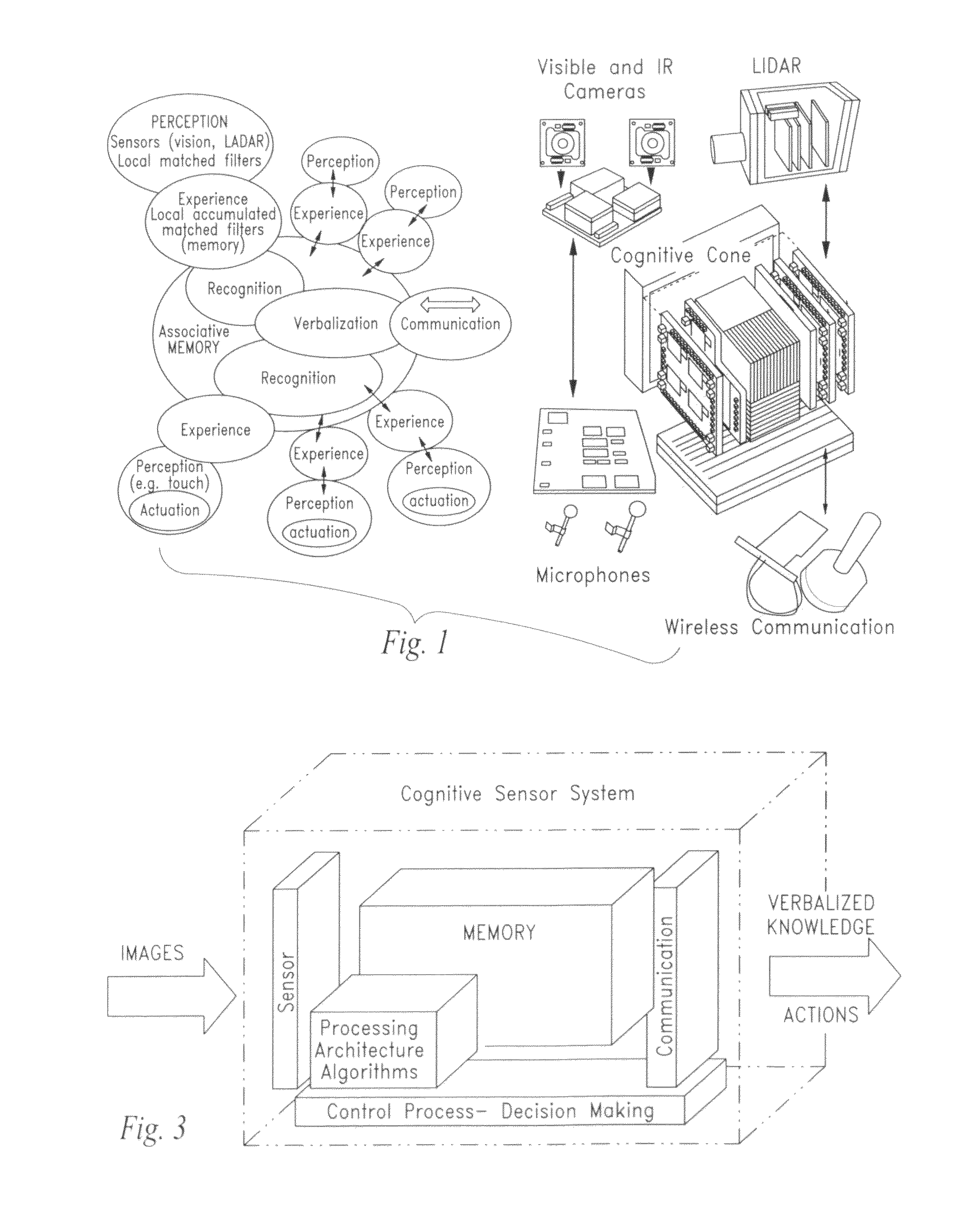

Applications of an algorithm that mimics cortical processing

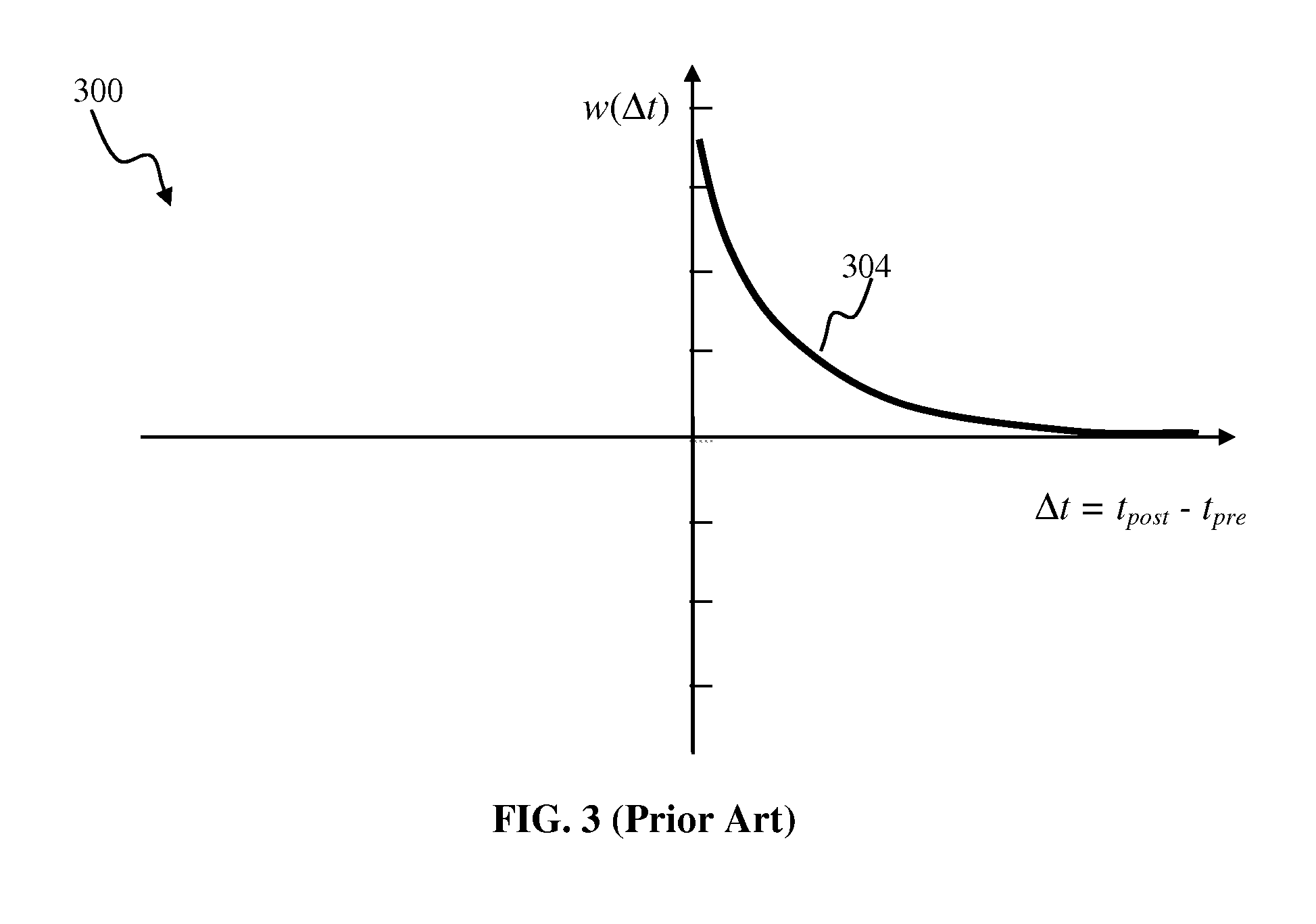

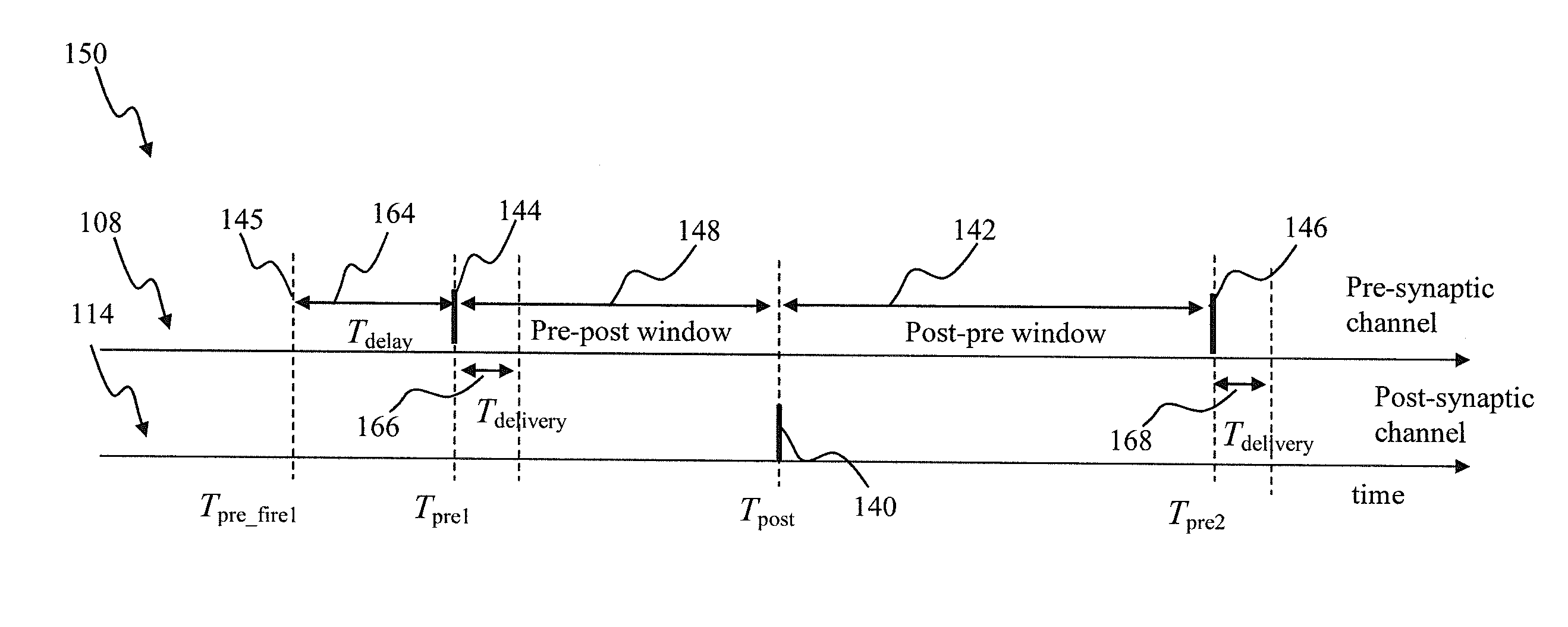

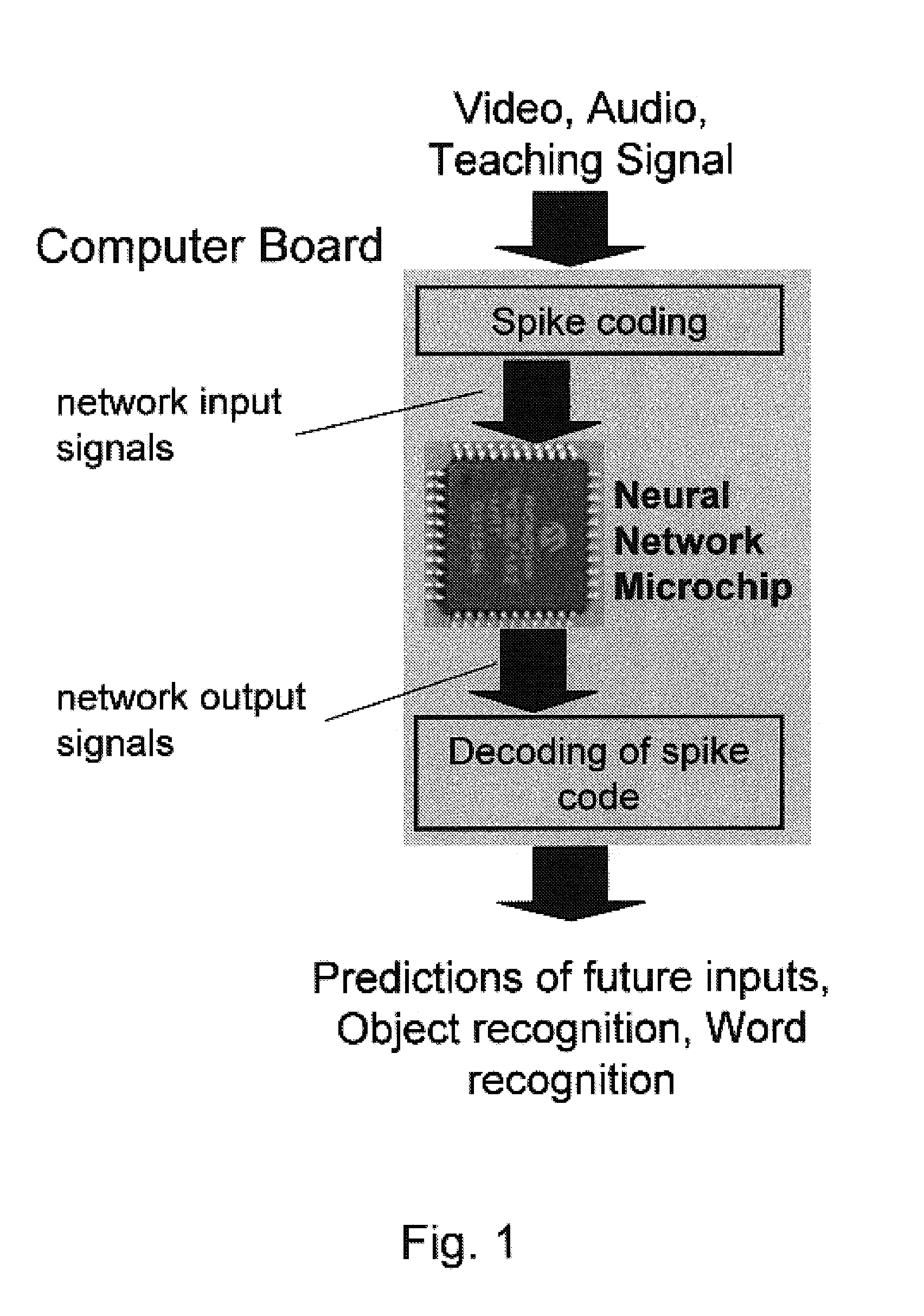

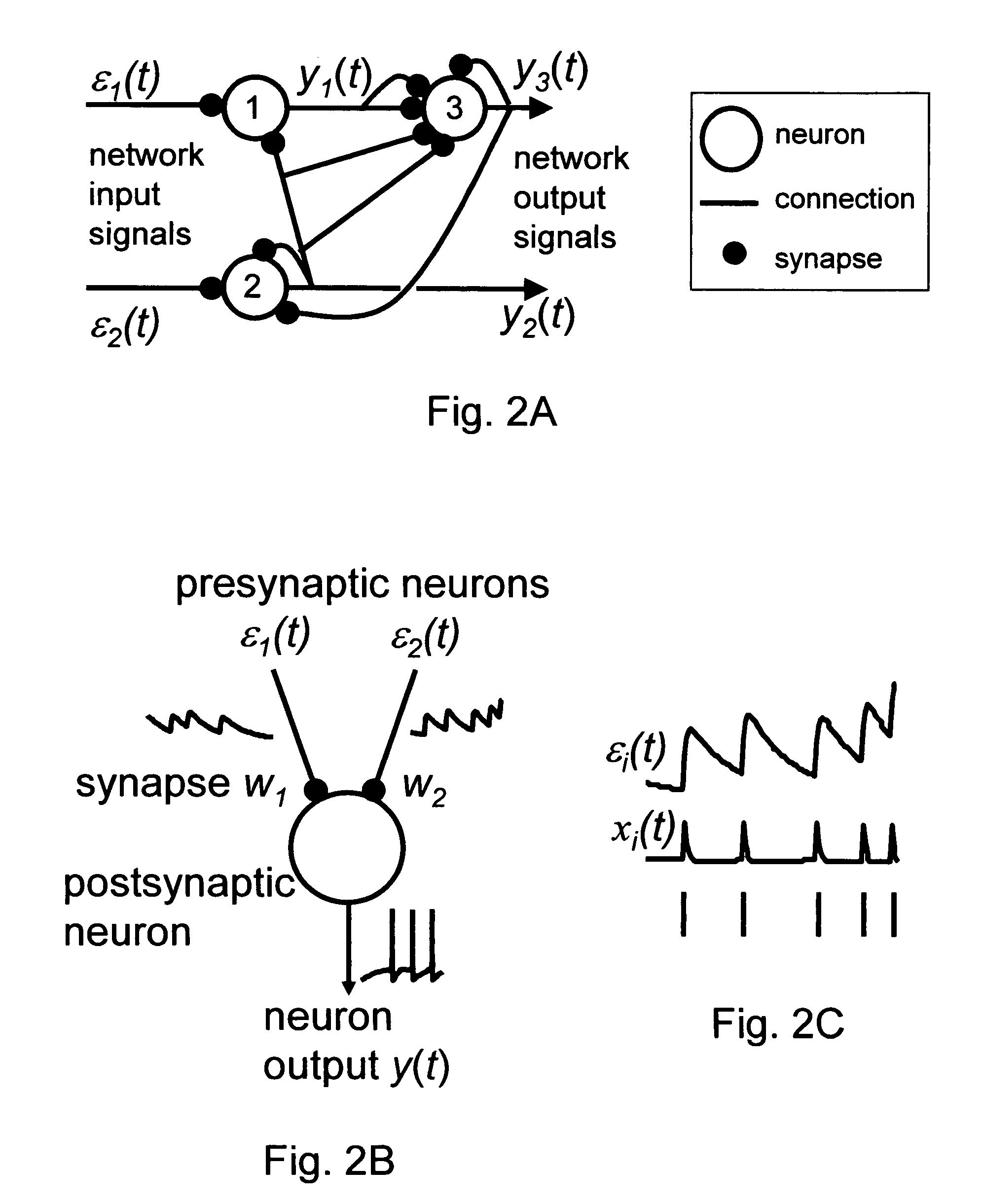

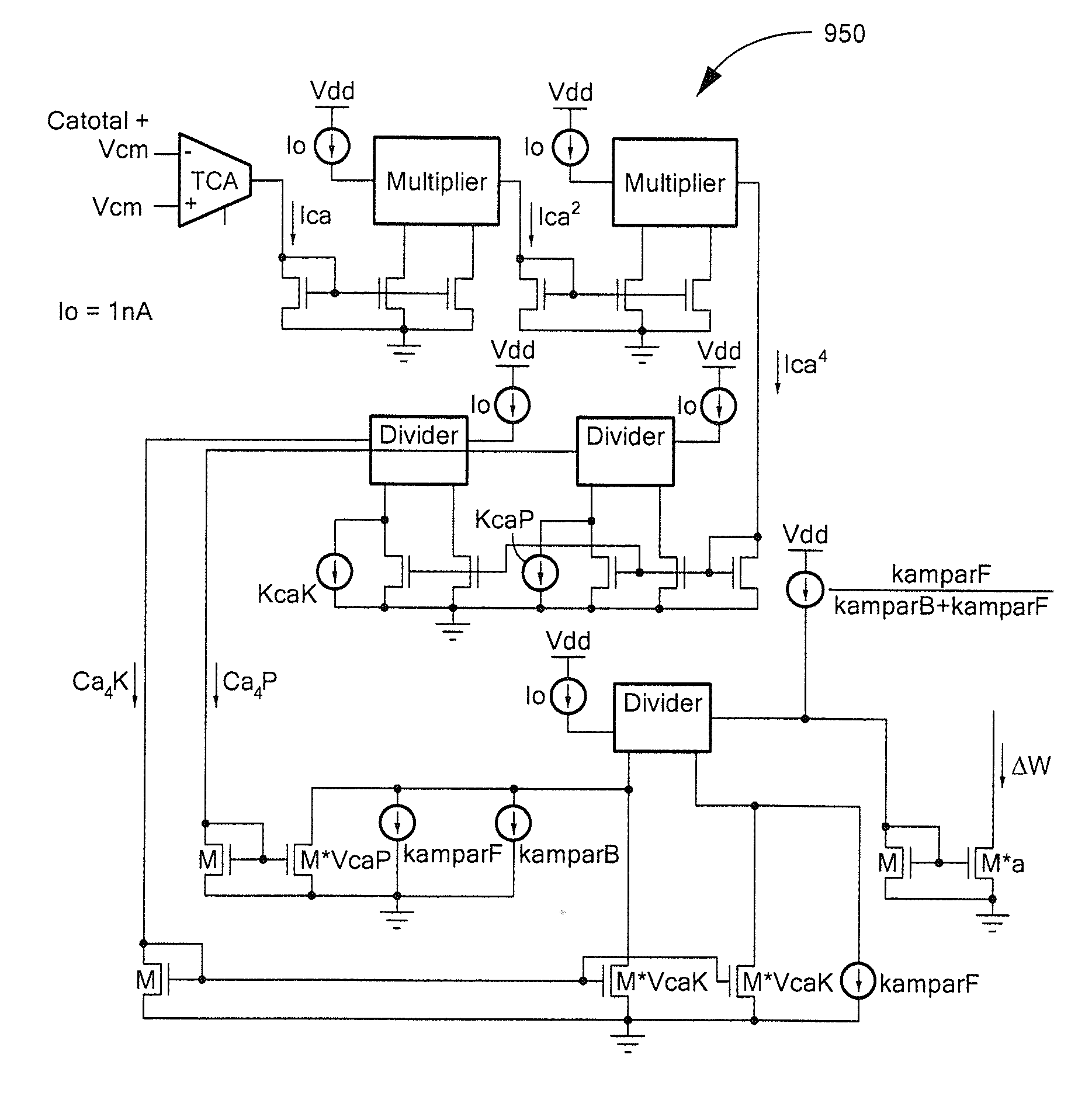

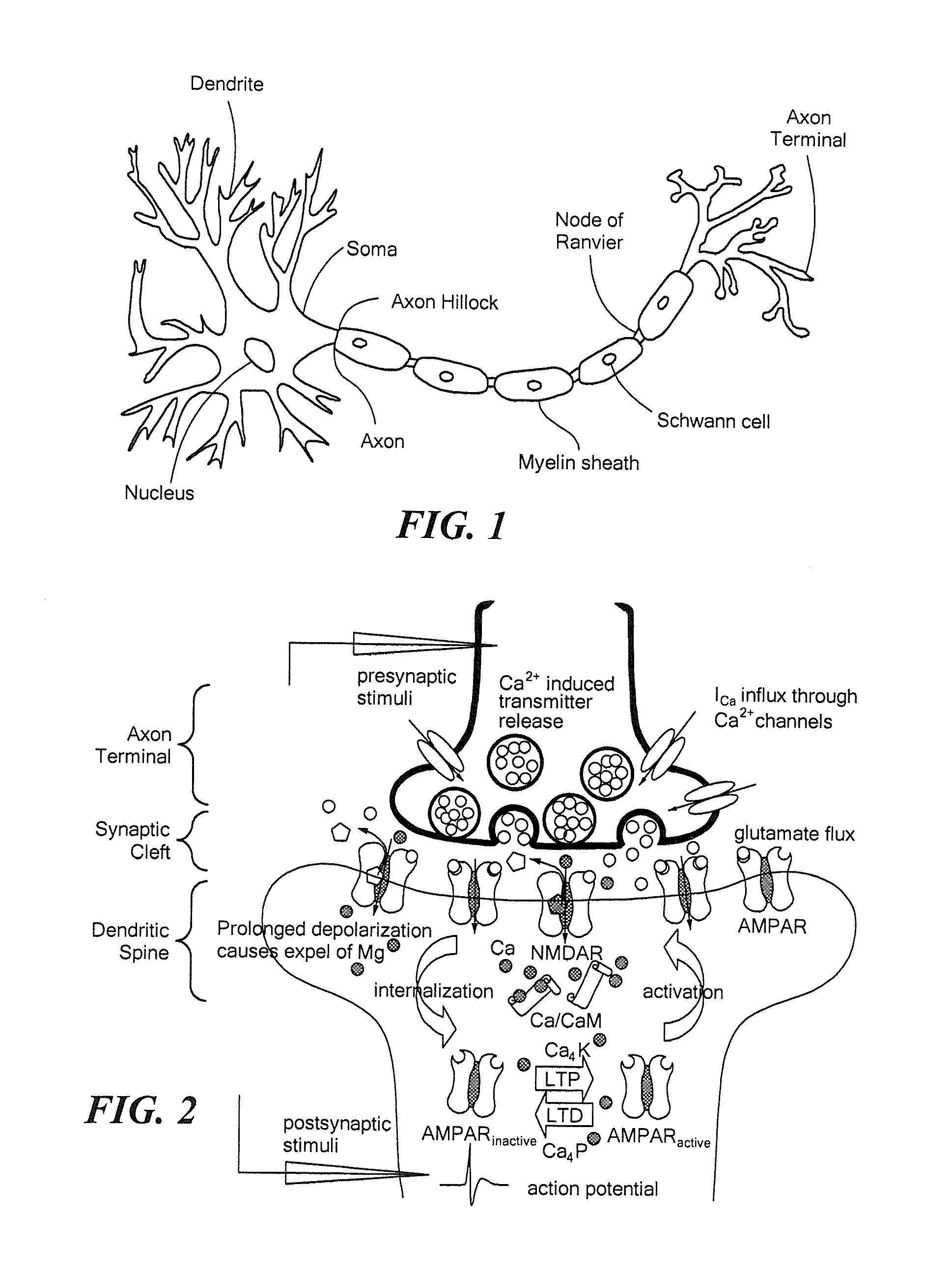

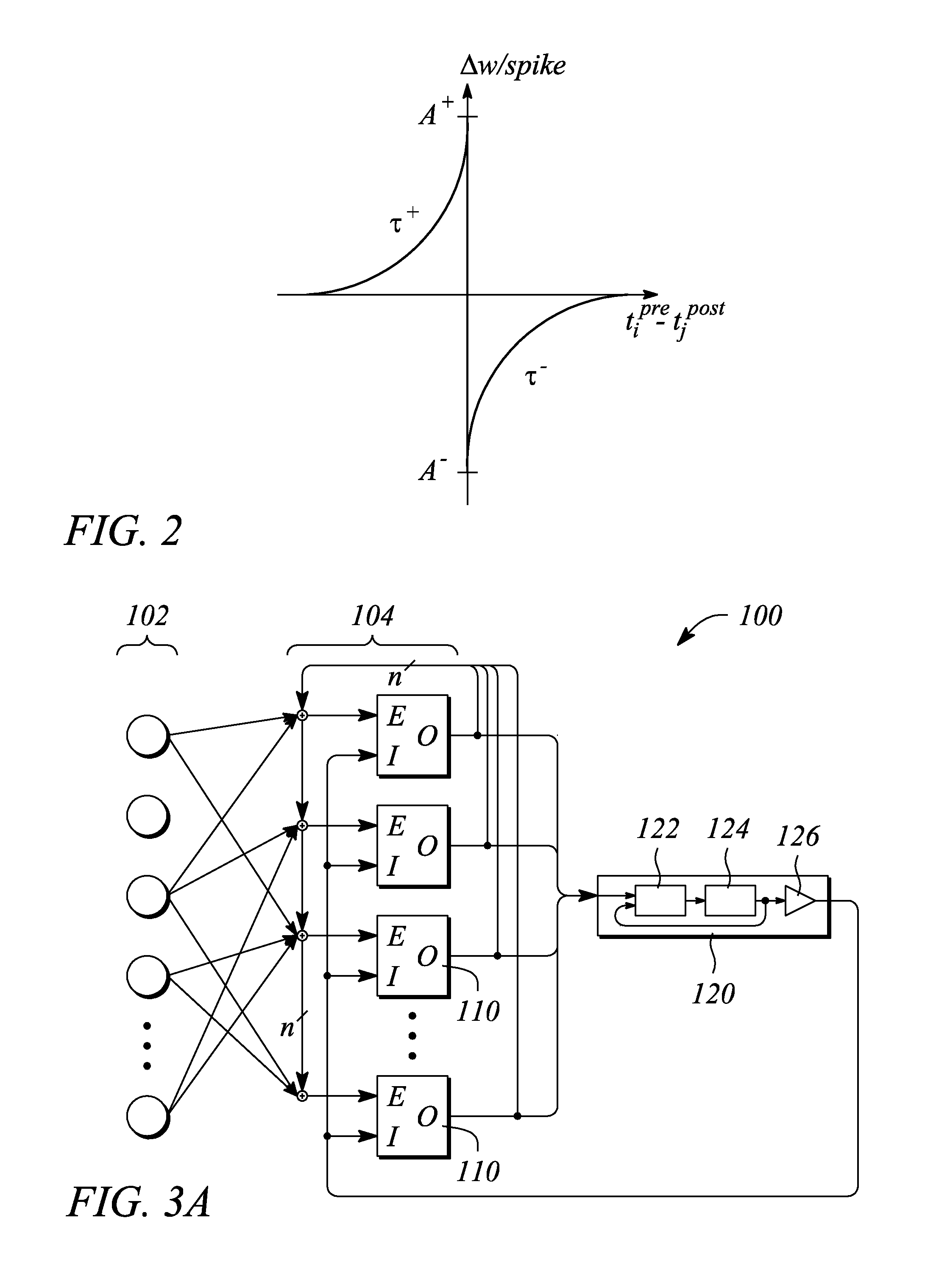

An information processing system having neuron-like signal processors that are interconnected by synapse-like processing junctions that simulates and extends capabilities of biological neural networks. The information processing systems uses integrate-and-fire neurons and Temporally Asymmetric Hebbian learning (spike timing-dependent learning) to adapt the synaptic strengths. The synaptic strengths of each neuron are guaranteed to become optimal during the course of learning either for estimating the parameters of a dynamic system (system identification) or for computing the first principal component. This neural network is well-suited for hardware implementations, since the learning rule for the synaptic strengths only requires computing either spike-time differences or correlations. Such hardware implementation may be used for predicting and recognizing audiovisual information or for improving cortical processing by a prosthetic device.

Owner:SURI ROLAND ERWIN

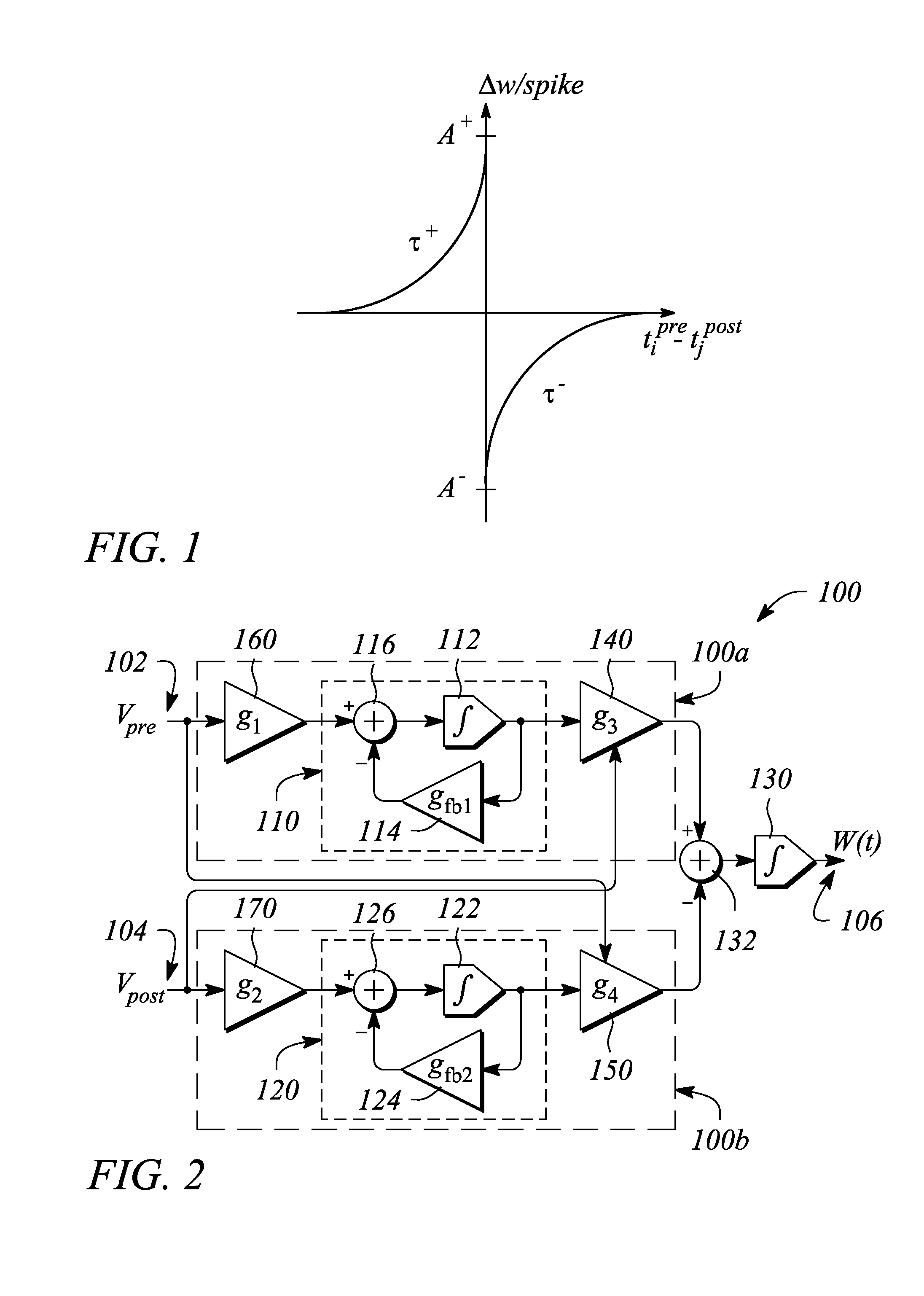

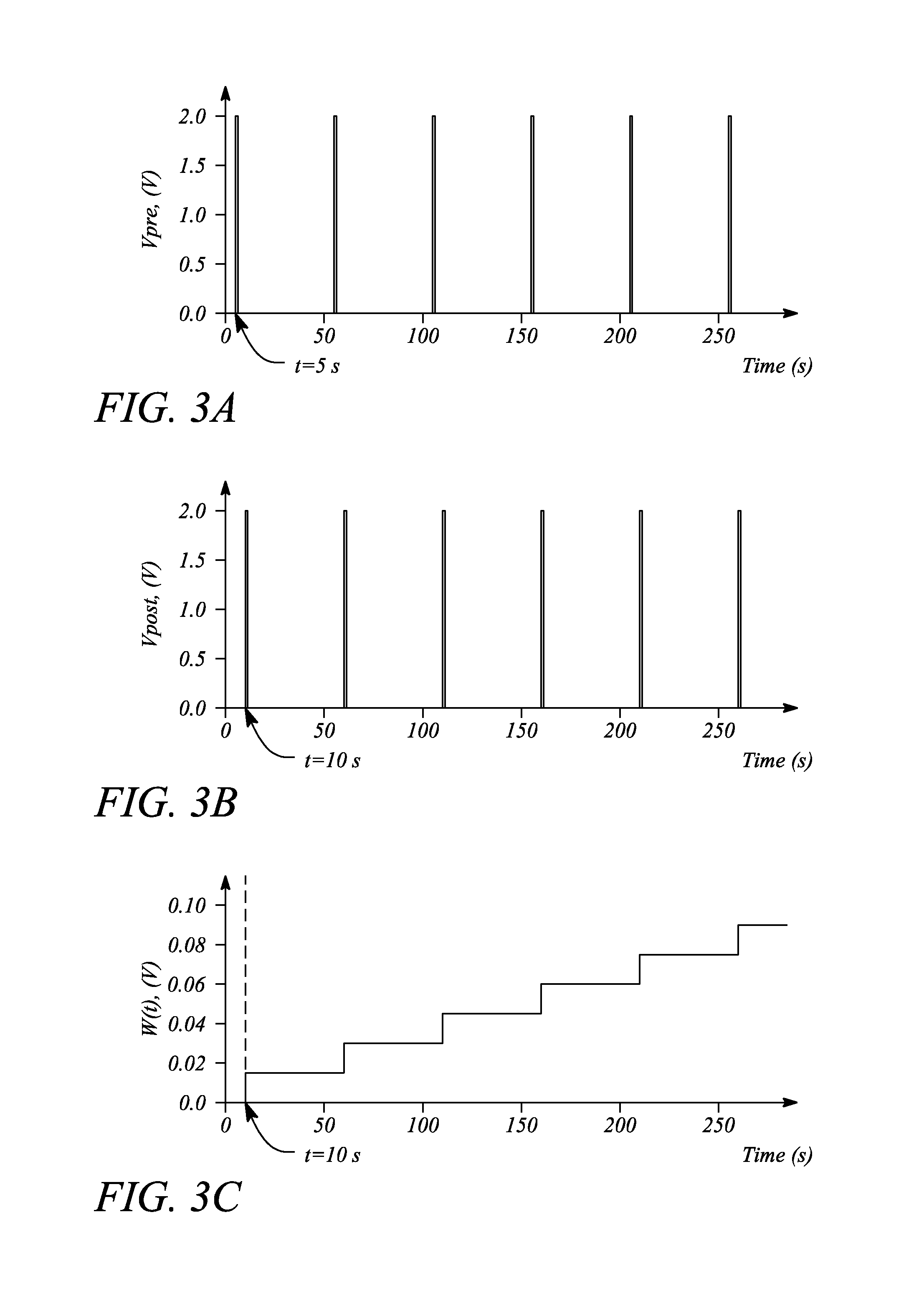

Circuits and Methods Representative of Spike Timing Dependent Plasticity of Neurons

InactiveUS20110137843A1Digital computer detailsNeural architecturesSynapseSpike-timing-dependent plasticity

A neuromorphic circuit performs functions representative of spiking timing dependent plasticity of a synapse.

Owner:UNIVERSITY OF NEW HAMPSHIRE +1

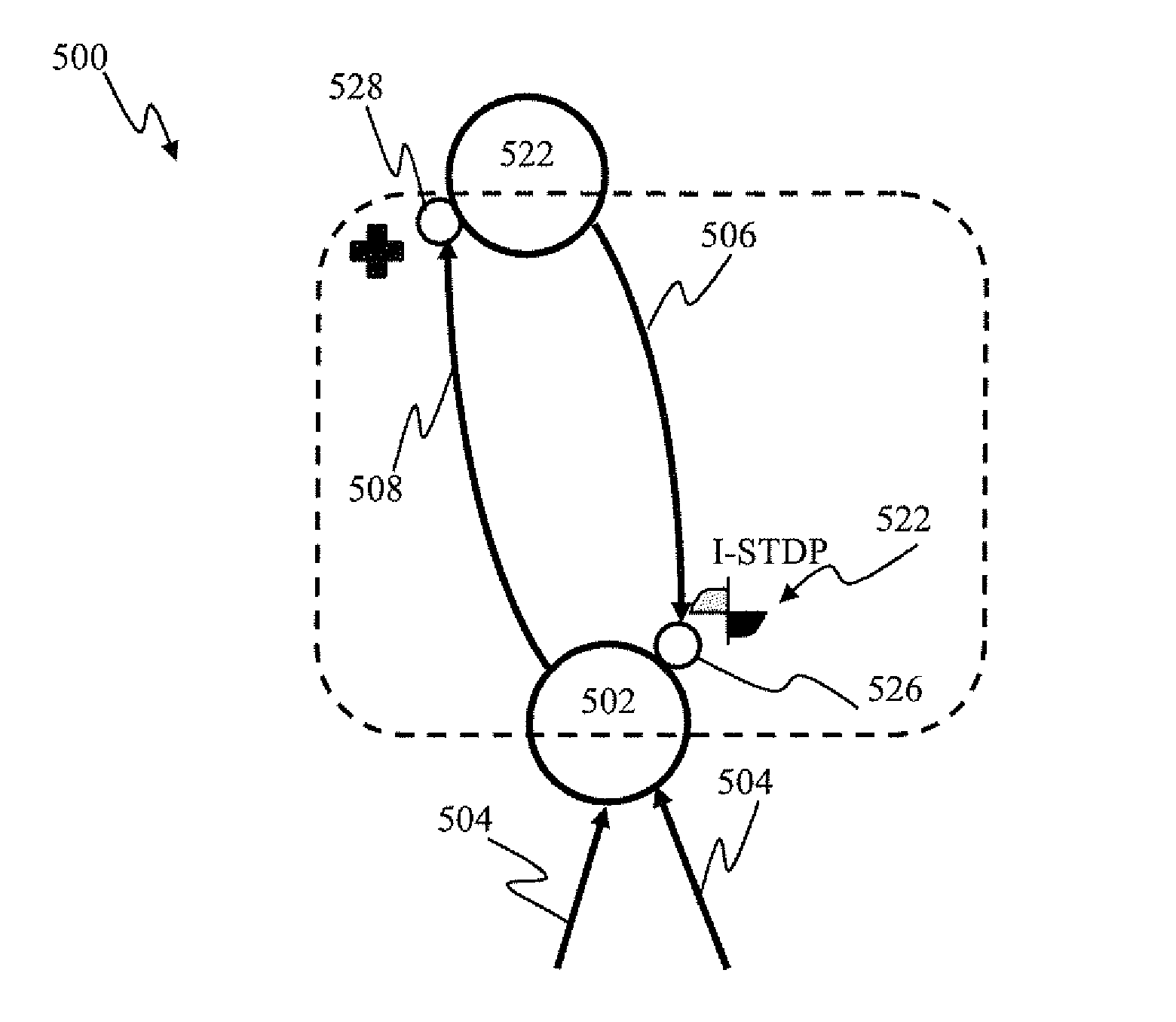

Spiking neural network object recognition apparatus and methods

InactiveUS20130297539A1Reduce probabilityDigital computer detailsDigital dataSynapseSpiking neural network

Apparatus and methods for feedback in a spiking neural network. In one approach, spiking neurons receive sensory stimulus and context signal that correspond to the same context. When the stimulus provides sufficient excitation, neurons generate response. Context connections are adjusted according to inverse spike-timing dependent plasticity. When the context signal precedes the post synaptic spike, context synaptic connections are depressed. Conversely, whenever the context signal follows the post synaptic spike, the connections are potentiated. The inverse STDP connection adjustment ensures precise control of feedback-induced firing, eliminates runaway positive feedback loops, enables self-stabilizing network operation. In another aspect of the invention, the connection adjustment methodology facilitates robust context switching when processing visual information. When a context (such an object) becomes intermittently absent, prior context connection potentiation enables firing for a period of time. If the object remains absent, the connection becomes depressed thereby preventing further firing.

Owner:BRAIN CORP

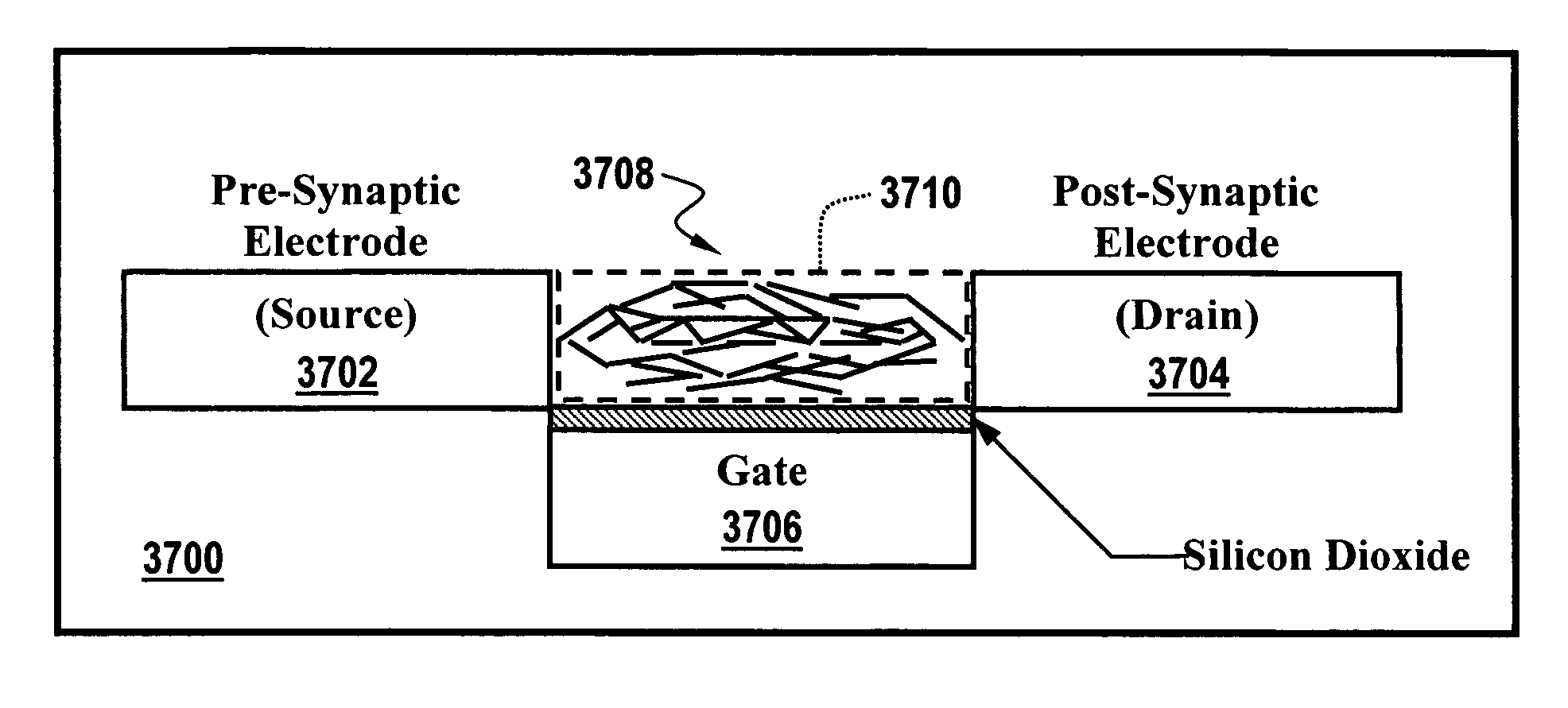

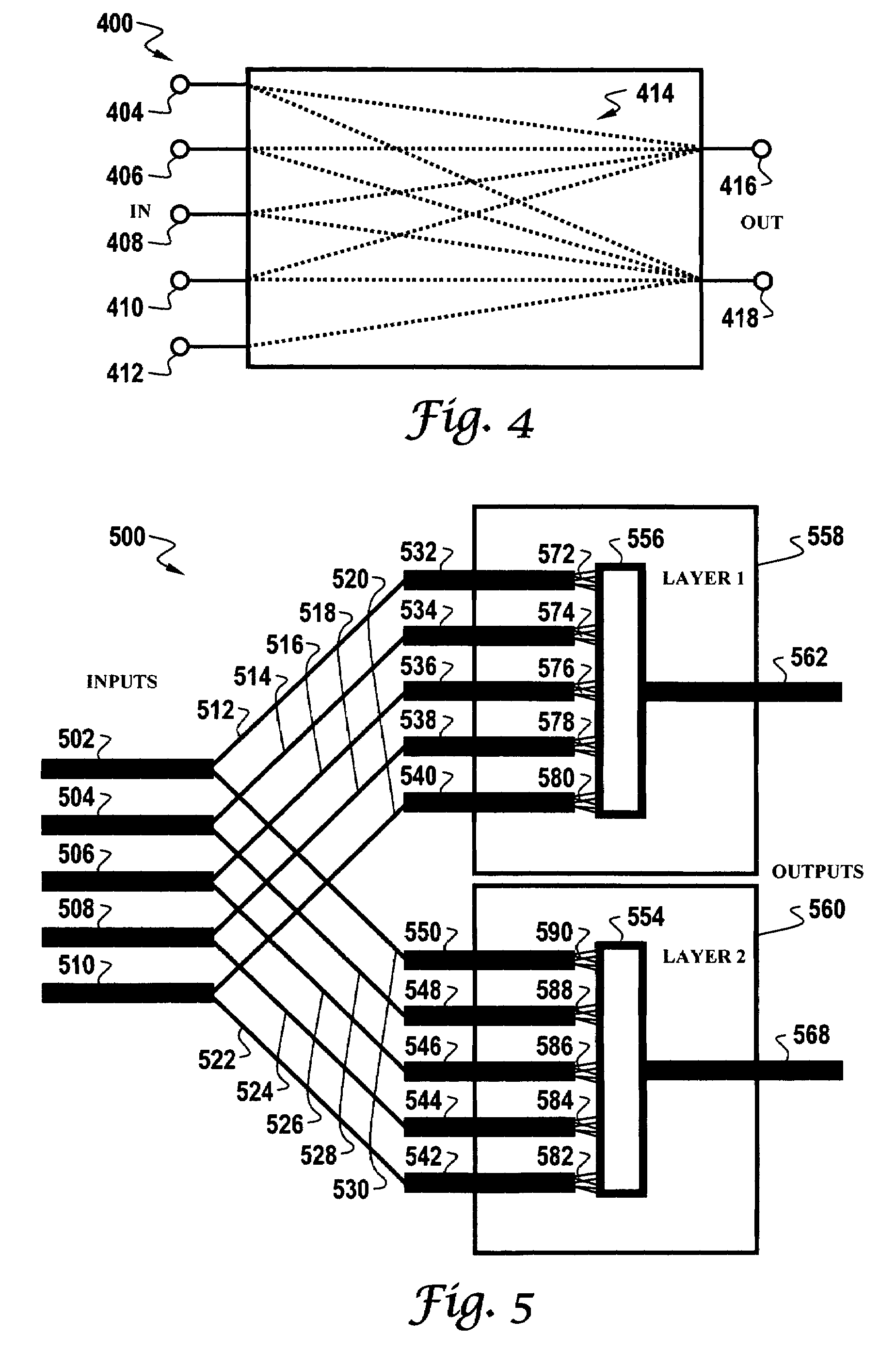

Application of hebbian and anti-hebbian learning to nanotechnology-based physical neural networks

Methods and systems are disclosed herein in which a physical neural network can be configured utilizing nanotechnology. Such a physical neural network can comprise a plurality of molecular conductors (e.g., nanoconductors) which form neural connections between pre-synaptic and post-synaptic components of the physical neural network. Additionally, a learning mechanism can be applied for implementing Hebbian learning via the physical neural network. Such a learning mechanism can utilize a voltage gradient or voltage gradient dependencies to implement Hebbian and / or anti-Hebbian plasticity within the physical neural network. The learning mechanism can also utilize pre-synaptic and post-synaptic frequencies to provide Hebbian and / or anti-Hebbian learning within the physical neural network.

Owner:KNOWM TECH

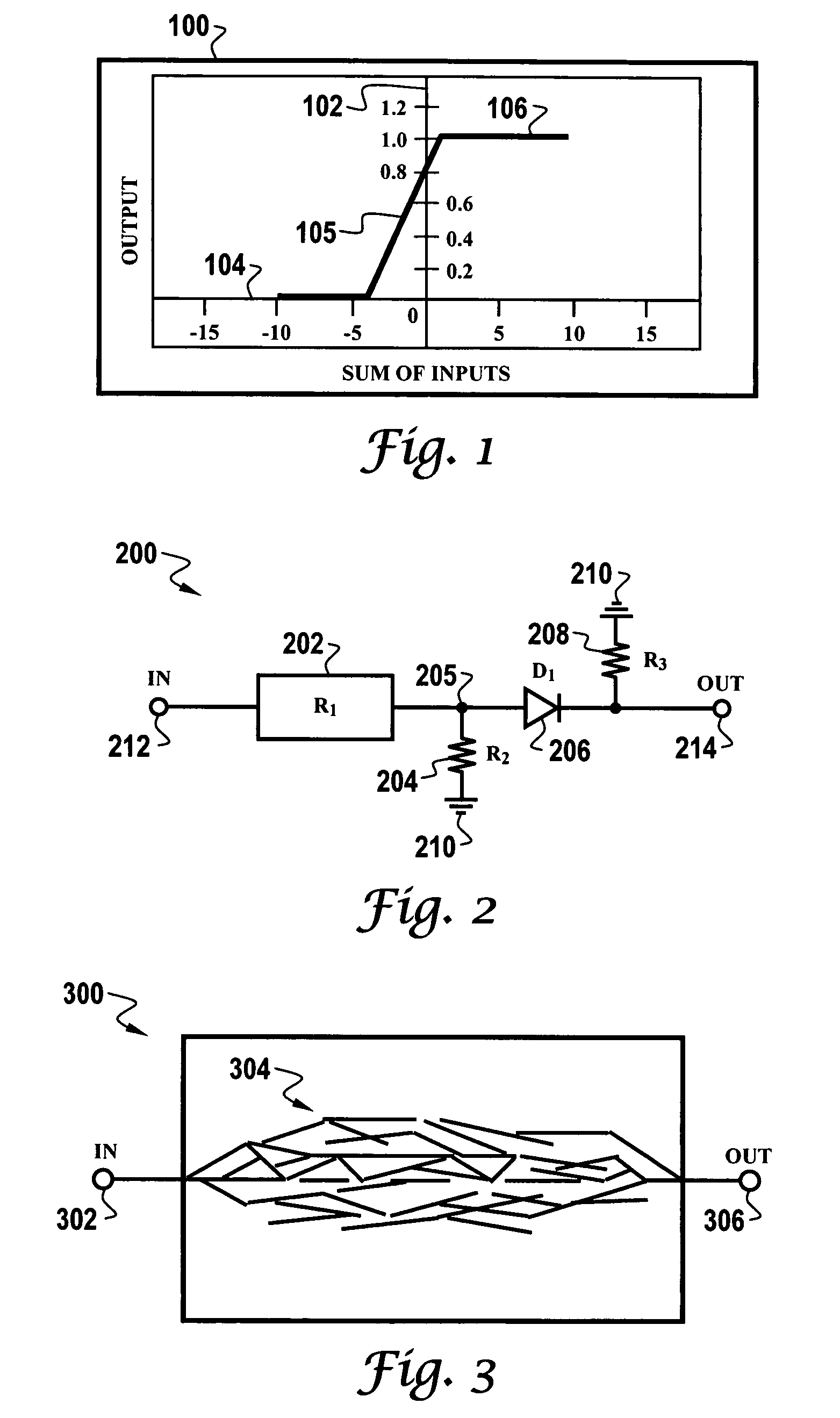

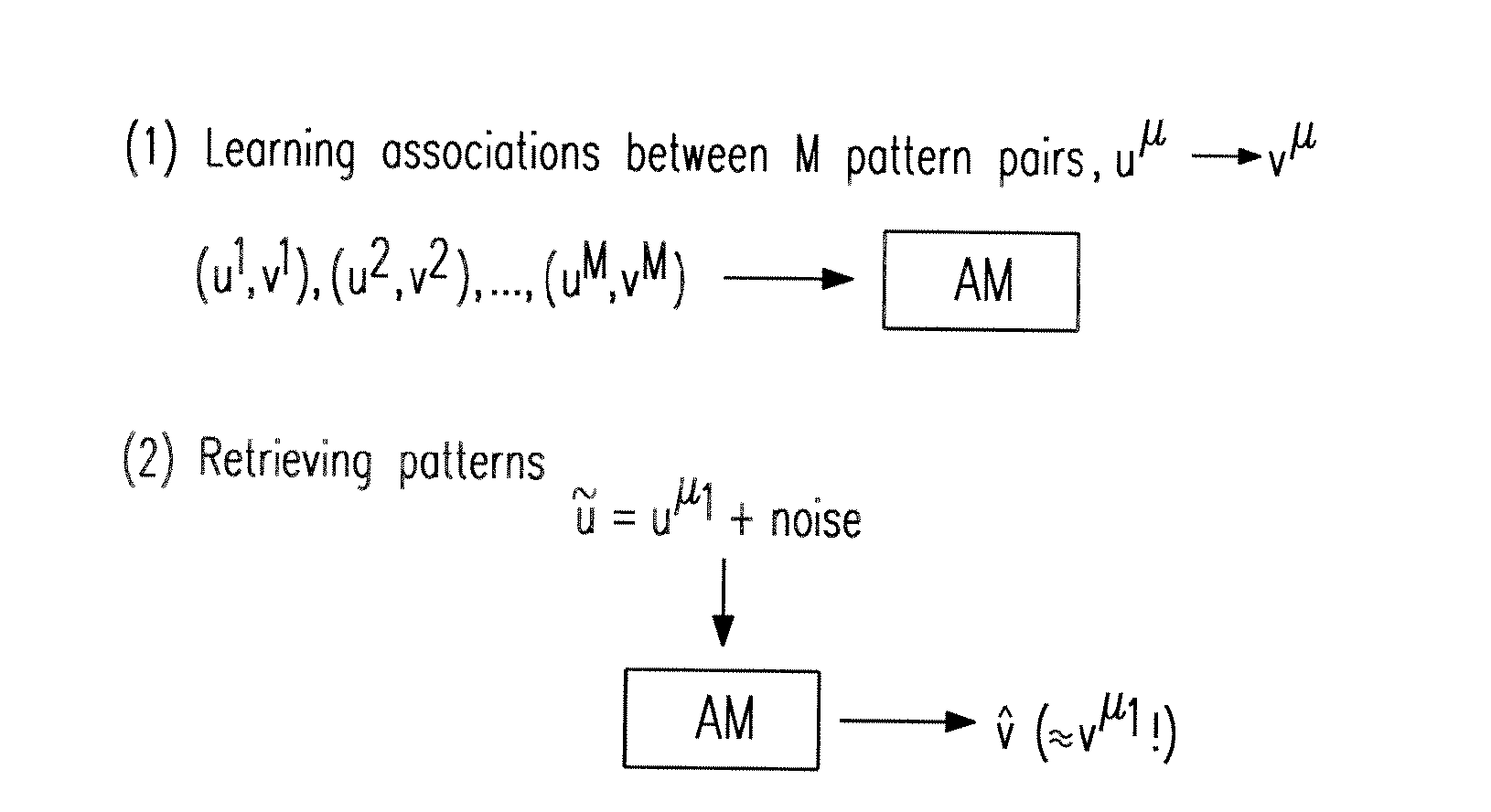

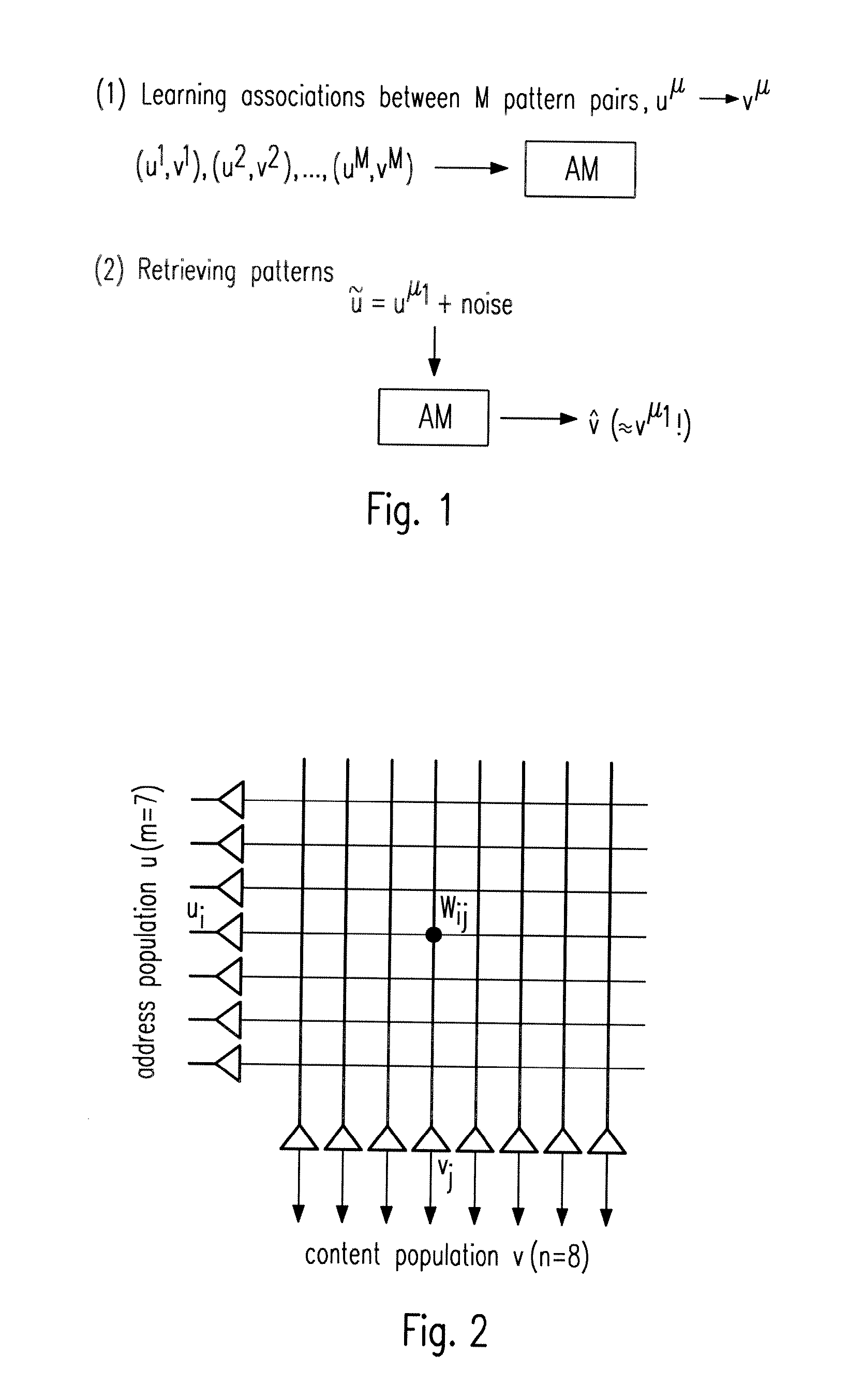

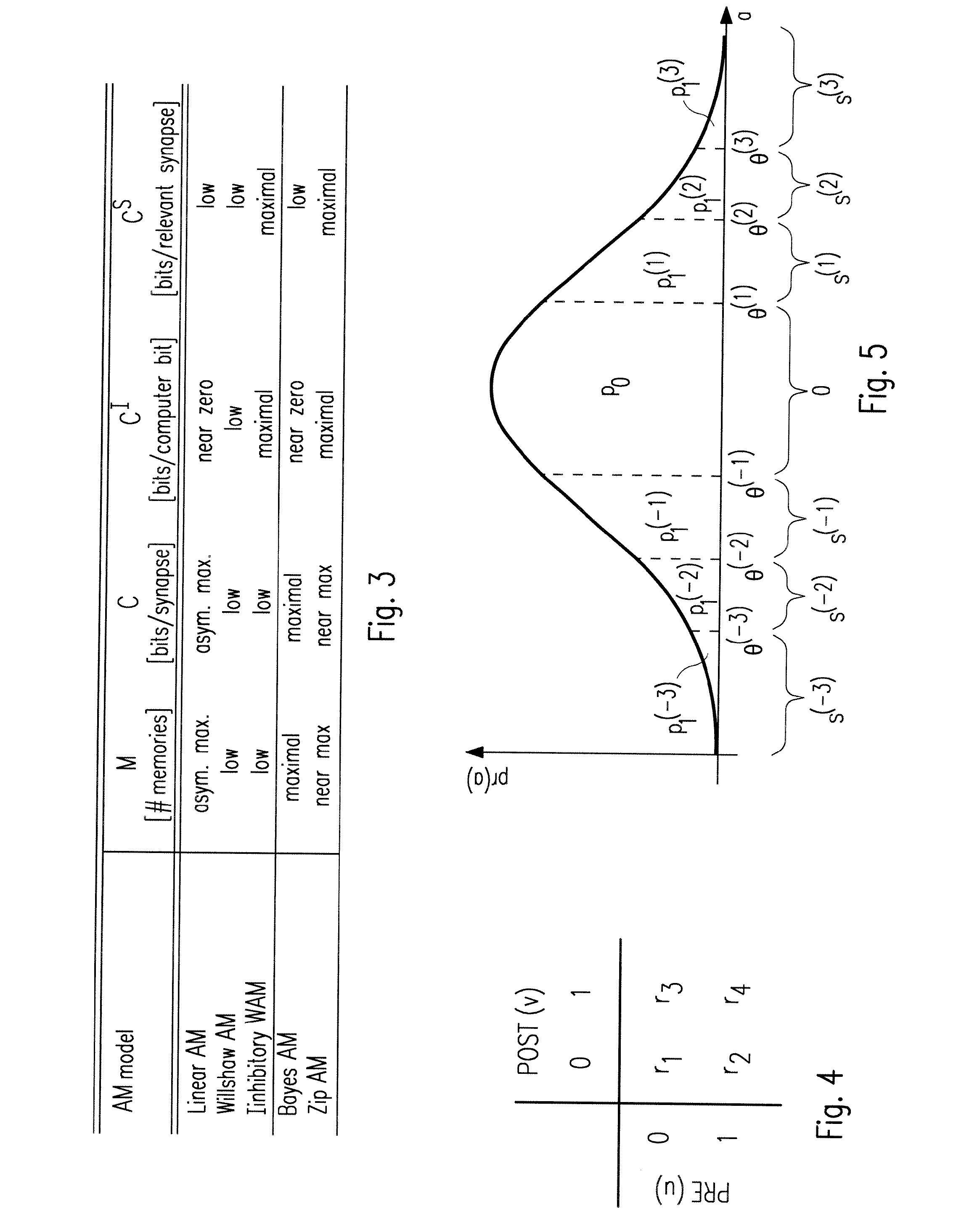

Implementing a neural associative memory based on non-linear learning of discrete synapses

InactiveUS20100312735A1Minimizing output noiseOptimize networkDigital computer detailsDigital dataSynapseMemory address

This invention is in the field of machine learning and neural associative memory. In particular the invention discloses a neural associative memory structure for storing and maintaining associations between memory address patterns and memory content patterns using a neural network, as well as methods for retrieving such associations. A method for a non-linear synaptic learning of discrete synapses is disclosed, and its application on neural networks is laid out.

Owner:HONDA RES INST EUROPE

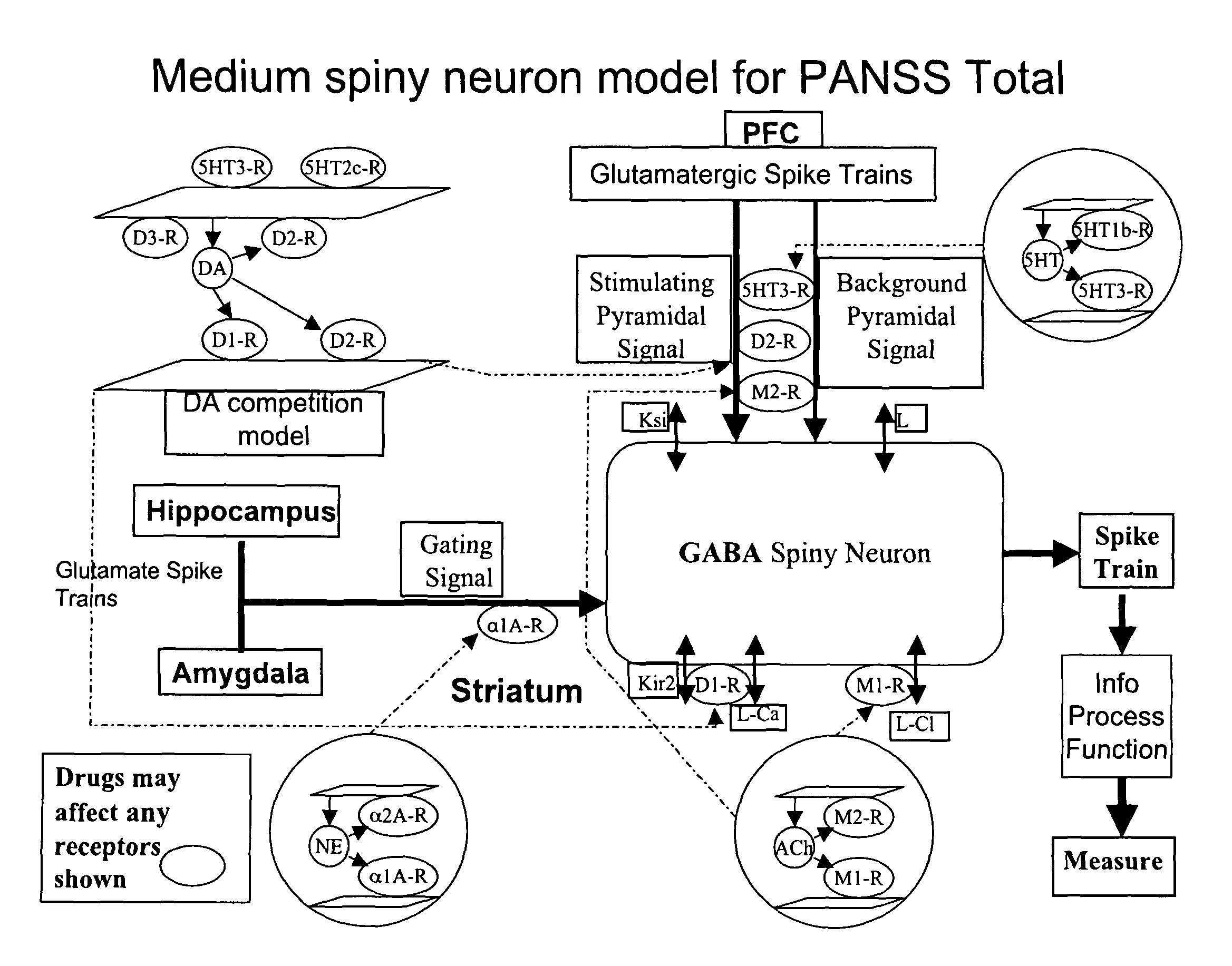

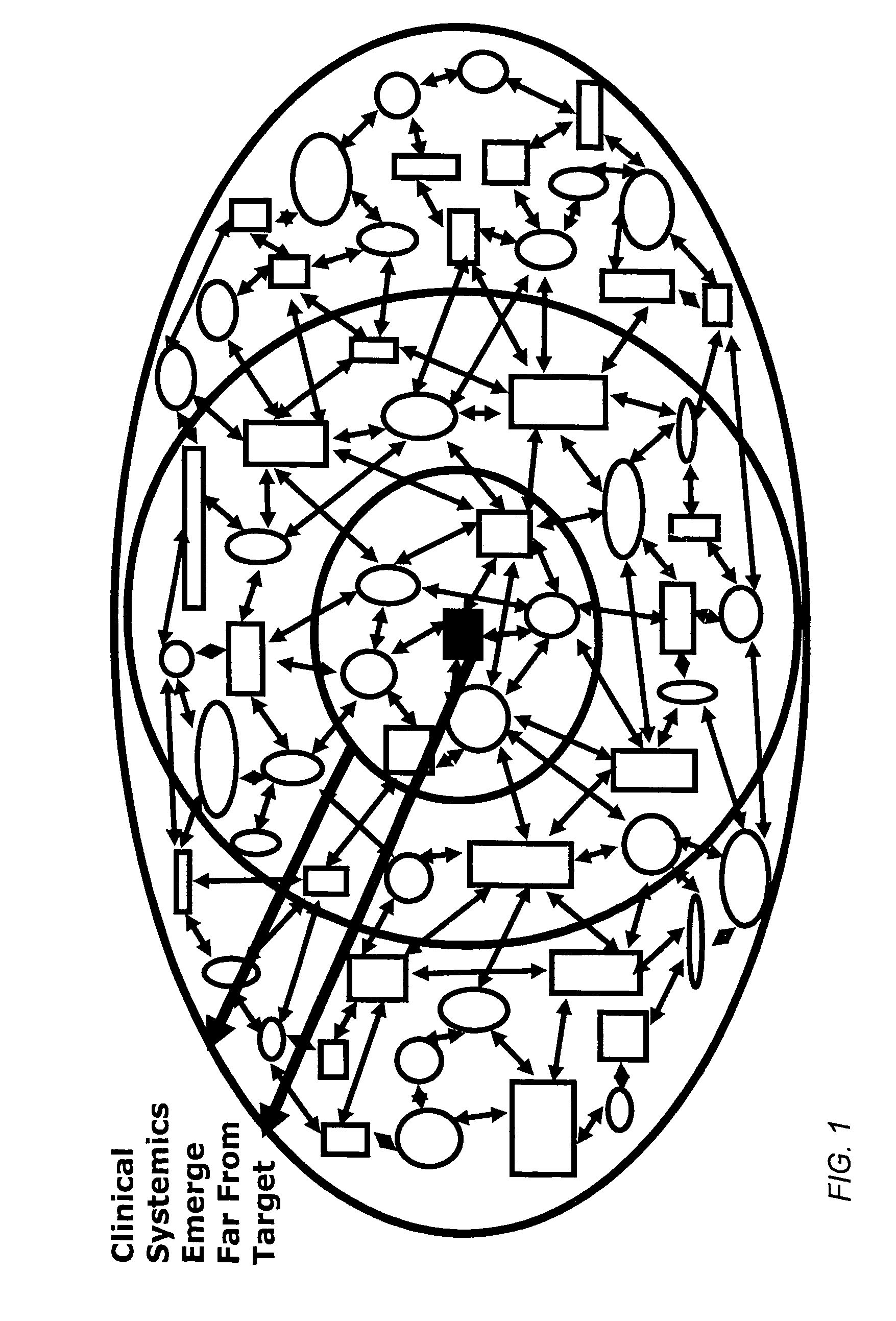

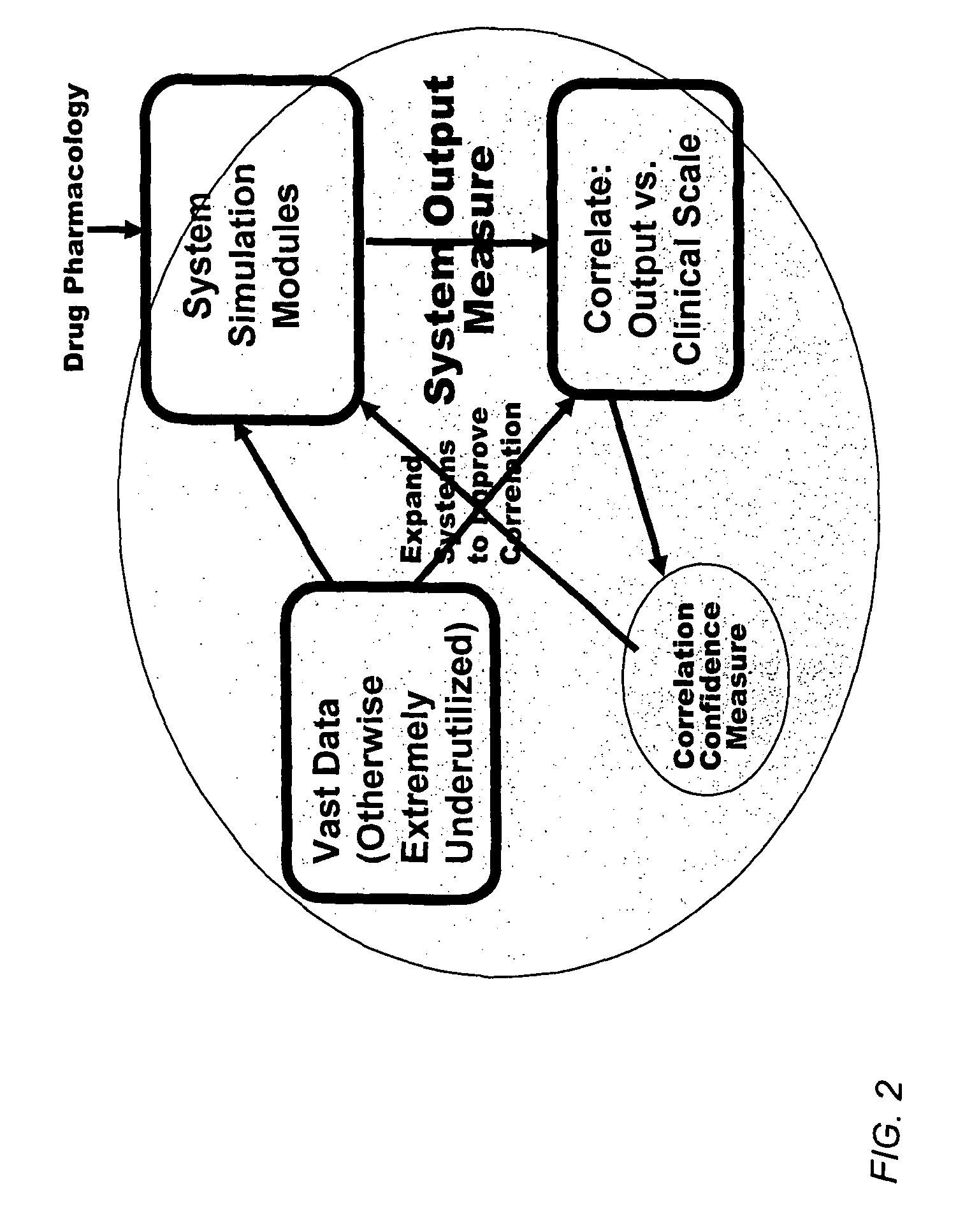

Method and apparatus for computer modeling of the interaction between and among cortical and subcortical areas in the human brain for the purpose of predicting the effect of drugs in psychiatric and cognitive diseases

ActiveUS8150629B2Easy to set upImprove clinical outcomesMedical simulationAnalogue computers for chemical processesSubstance abuserAmygdala

Computer modeling of interactions between and among cortico and subcortical areas of the human brain, for example in a normal and a pathological state resembling schizophrenia which pathological state has inputs representing the effects of a drug(s), for the purpose of using the outputs to predict the effect of drugs in psychiatric and cognitive diseases on one or more clinical scales. Diseases that can be modeled include psychiatric disorders, such as schizophrenia, bipolar disorder, major depression, ADHD, autism, obsessive-compulsive disorder, substance abuse and cognitive deficits therein and neurological disorders such as Alzheimer's disease, Mild Cognitive impairment, Parkinson's disease, stroke, vascular dementia, Huntington's disease, epilepsy and Down syndrome. The computer model preferably uses the biological state of interactions between and among cortico and subcortical areas of the human brain, to define the biological processes related to the biological state of the generic synapse model, the striatum, Locus Coeruleus, Dorsal raphe, hippocampus, amygdala and cortex, as well as certain mathematical relationships related to interactions among biological variables associated with the biological processes.

Owner:CERTARA USA INC

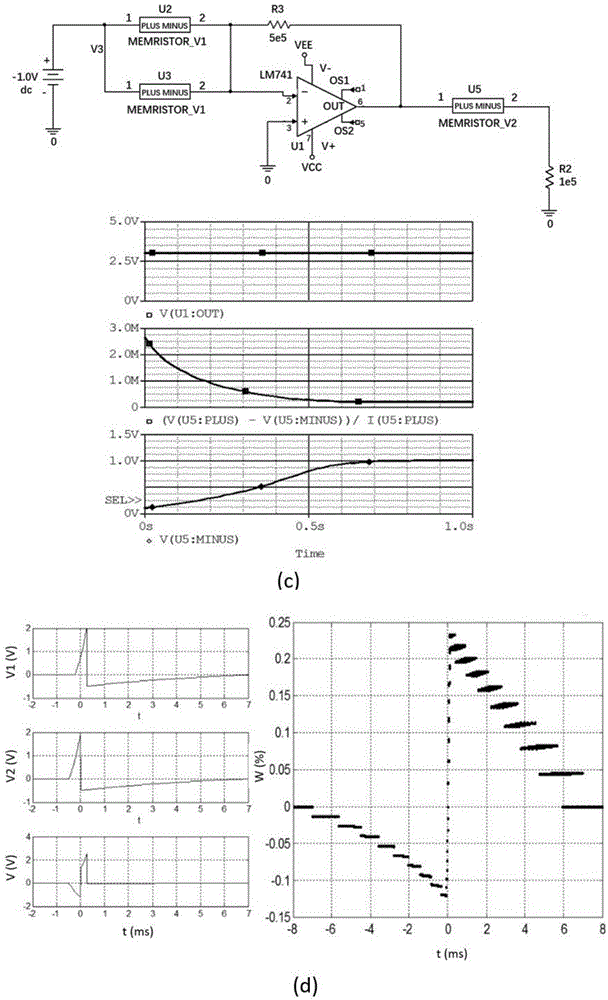

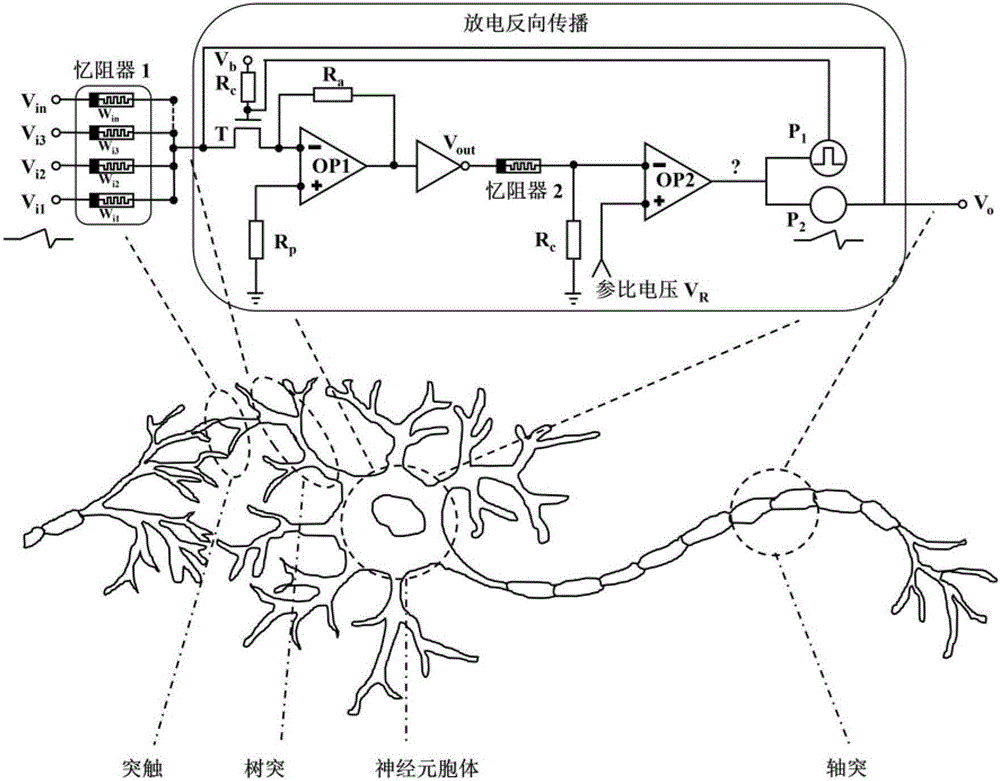

Memristor-based neuron circuit

ActiveCN106845634ARealize integrated discharge functionImplement time encodingPhysical realisationInformation processingSynapse

The invention discloses a memristor-based neuron circuit. According to the neuron circuit, partially volatile bipolar resistive transition devices are selected and used as memristors of a synapse array, and a volatile resistive transition device is selected and used as a memristor for expressing membrane potential of neurons, so that the neuron circuit is formed; and synapse basis units are arranged. The neuron circuit can realize an integral discharge function in biological neurons and express local graded potentials; and synapses have partial volatility, can express spike-timing-dependent plasticity, and have great similarity with biological neurons and synapses in the aspects of information storage, transmission and processing. According to the neuron circuit, the basic units can be provided for hardware to simulate a cerebral neural network structure; the technical problems of neuron discharge time delay, difficulty in realizing high-density integration and the like in the prior art are solved; and the neuron circuit can be used for constructing a brain-like information processing system, can quickly process a large amount of information in parallel, and has a greatly high application value in realizing a cerebral neurologic calculation network.

Owner:HUAZHONG UNIV OF SCI & TECH

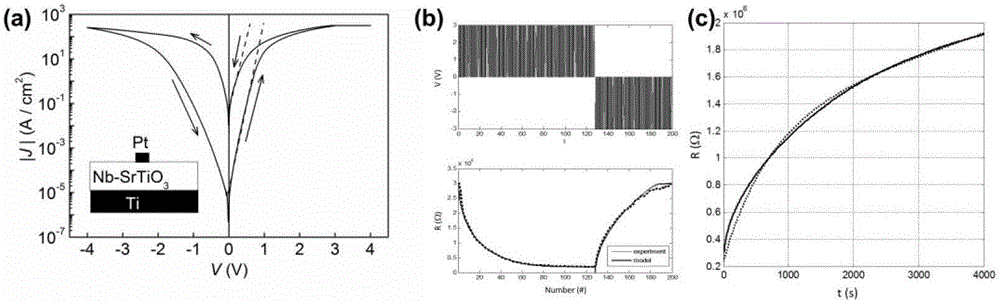

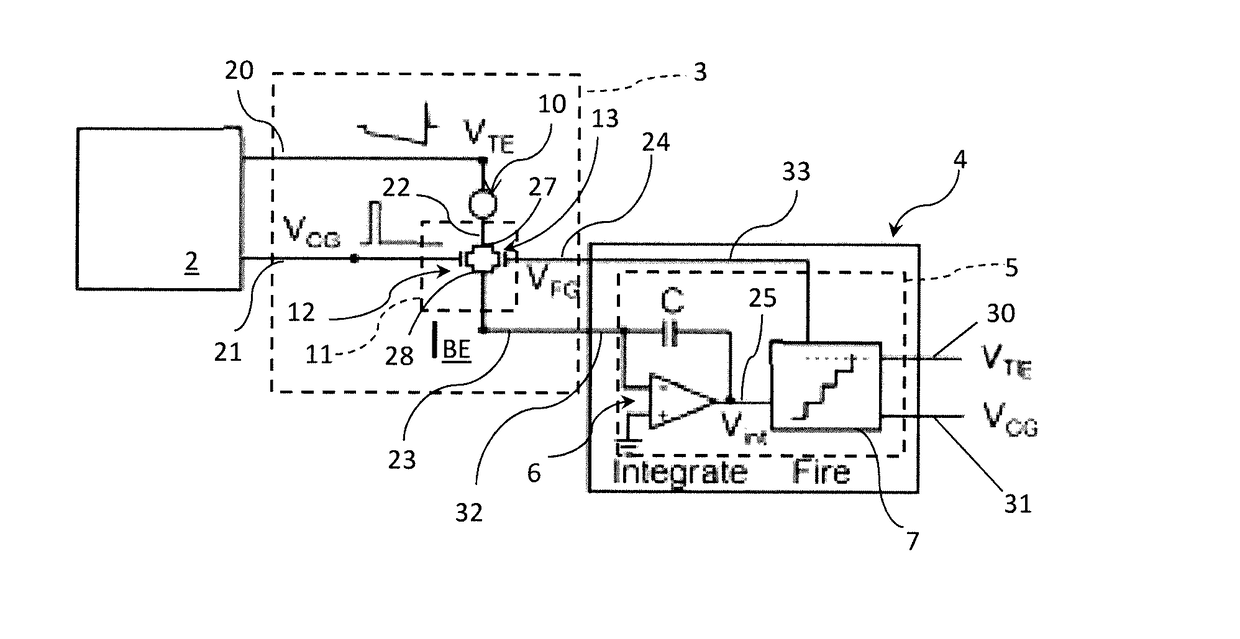

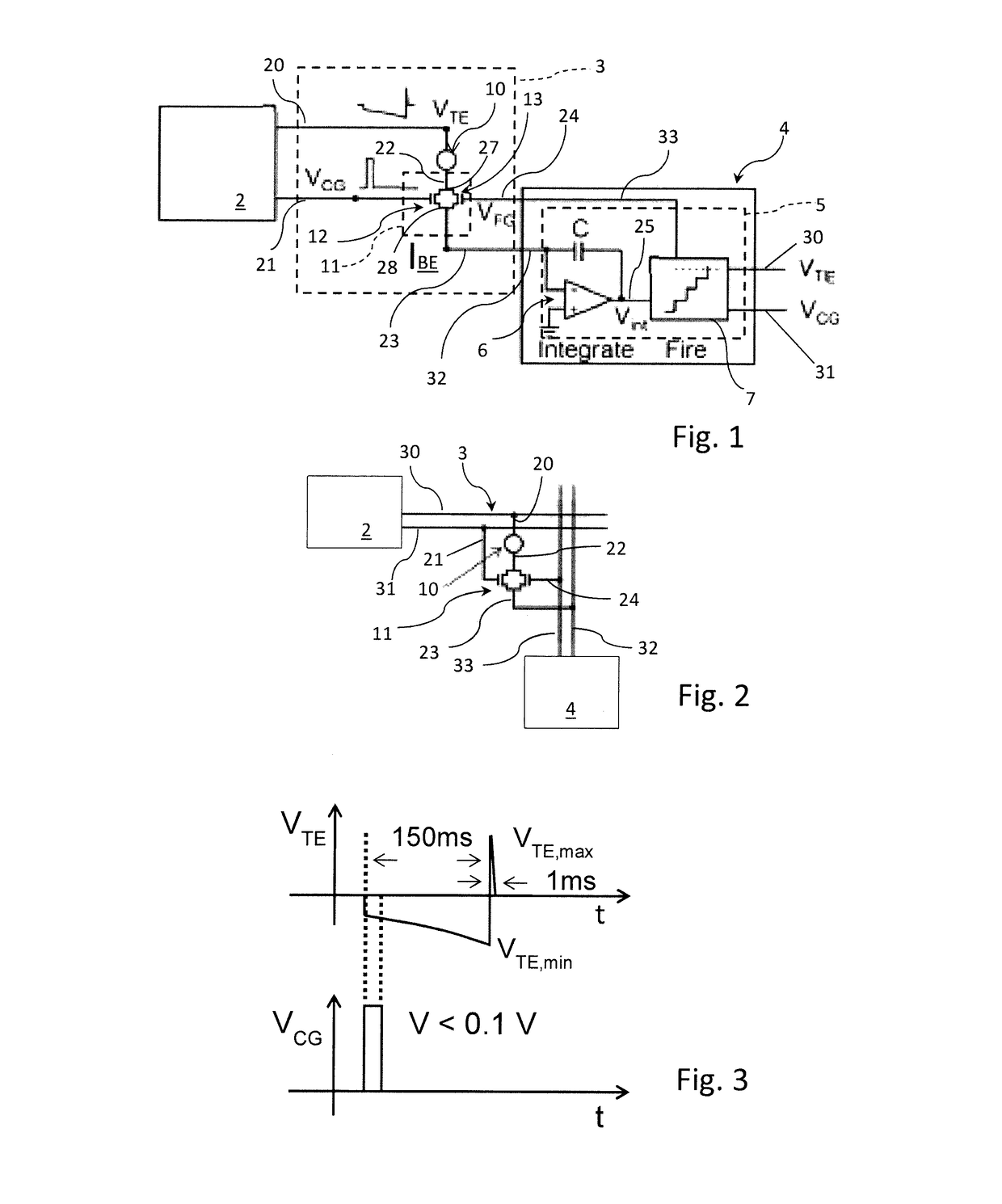

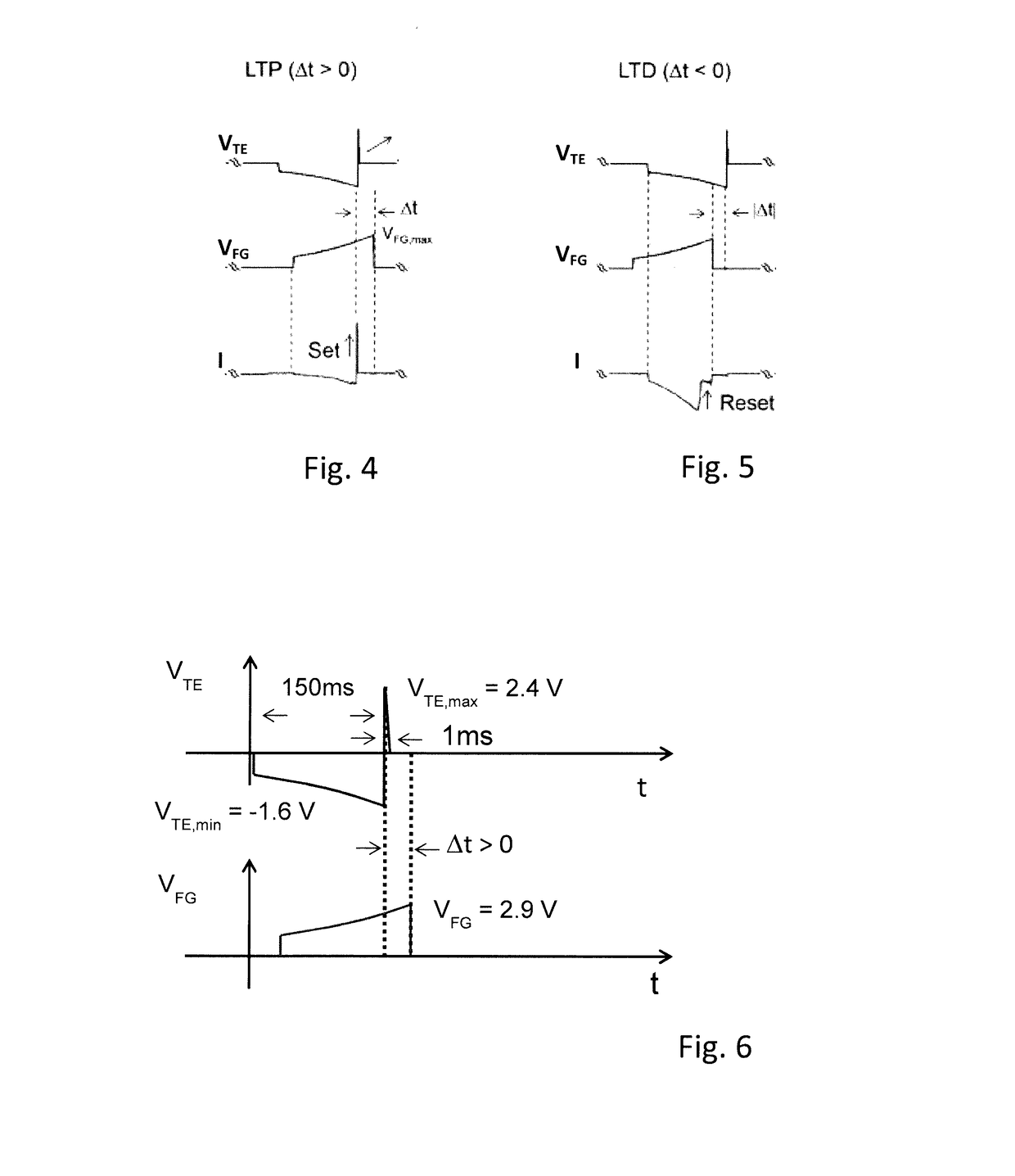

Electronic Neuromorphic System, Synaptic Circuit With Resistive Switching Memory And Method Of Performing Spike-Timing Dependent Plasticity

ActiveUS20170083810A1Neural architecturesPhysical realisationSynapseSpike-timing-dependent plasticity

A synaptic circuit performing spike-timing dependent plasticity STDP interposed between a pre-synaptic neuron and a post-synapse neuron includes a memristor having a variable resistance value configured to receive a first signal from the pre-synaptic neuron. The circuit has an intermediate unit connected in series with the memristor for receiving a second signal from the pre-synaptic neuron and provides an output signal to the post-synaptic neuron. The intermediate unit receives a retroaction signal generated from the post-synaptic neuron and the memristor modifies the resistance value based on a delay between two at least partially overlapped input pulses, a spike event of the first signal and a pulse of the retroaction signal, in order to induct a potentiated state STP or a depressed state STD at the memristor. An electronic neuromorphic system having synaptic circuits and a method of performing spike timing dependent plasticity STDP by a synaptic circuit are also provided.

Owner:POLITECNICO DI MILANO

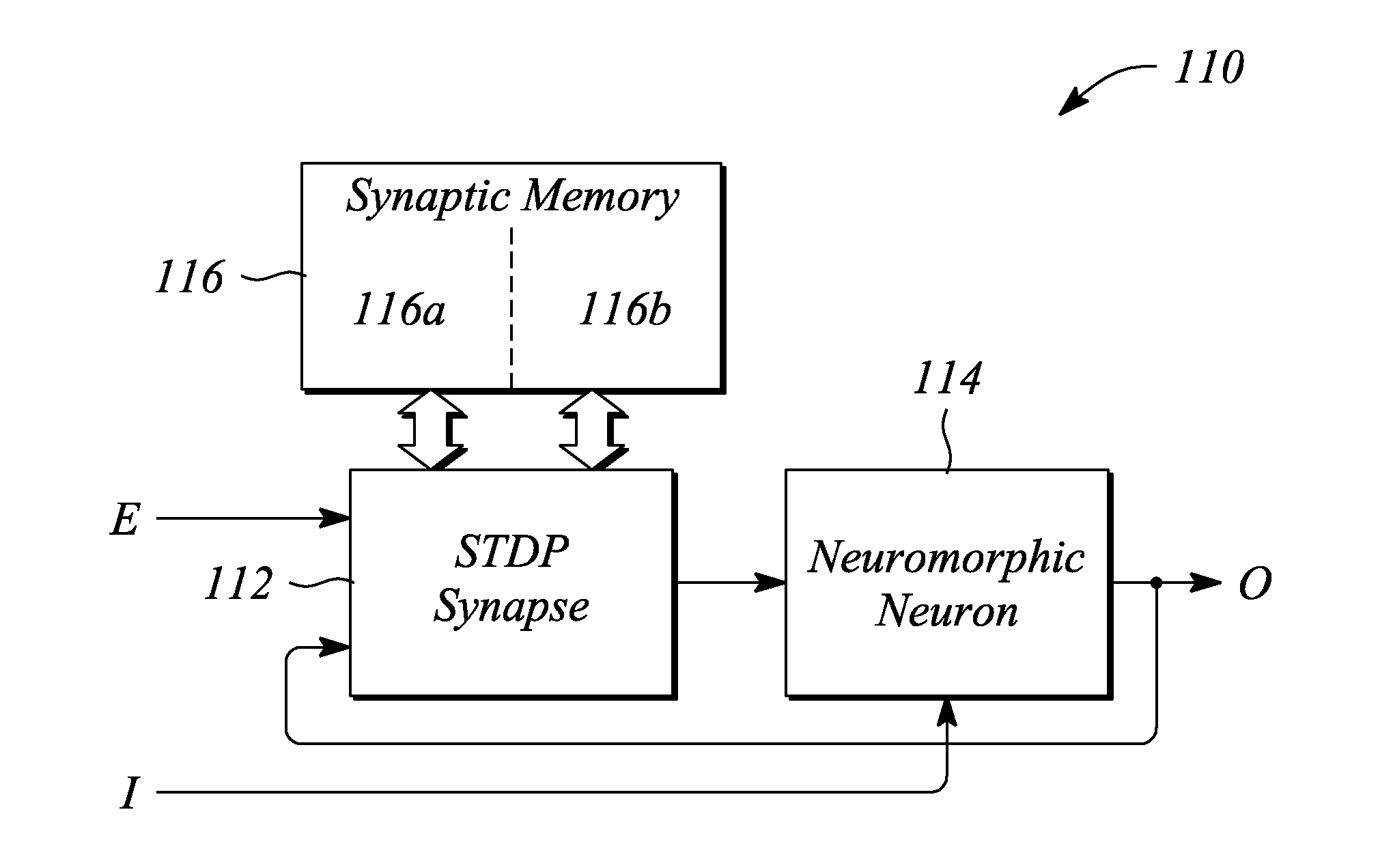

Cortical neuromorphic network, system and method

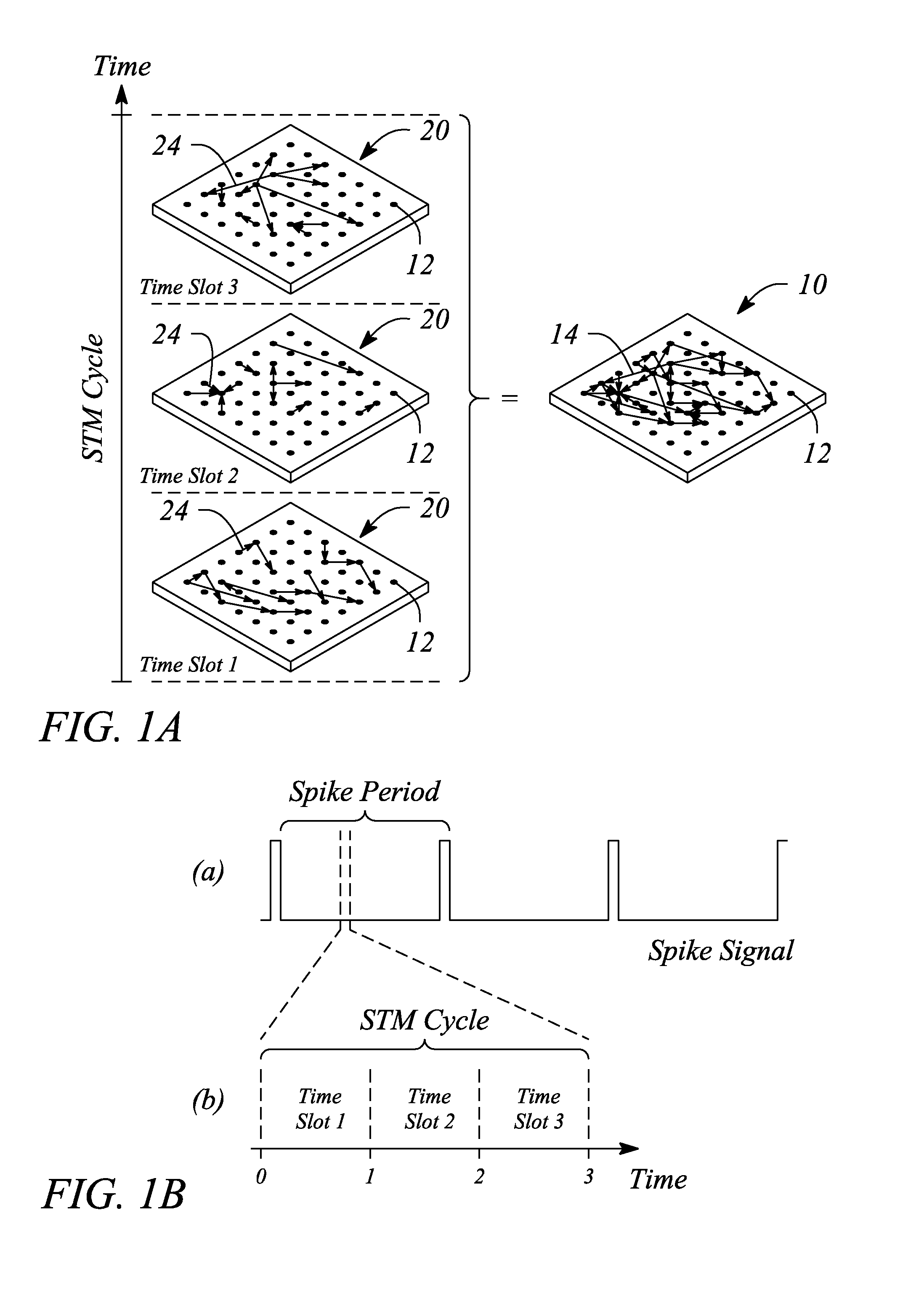

A cortical neuromorphic network, system and method employ a plurality of neuromorphic nodes arranged in a network layer. The cortical neuromorphic network includes a neuromorphic node of the network layer in which the neuromorphic node includes a spike timing dependent plasticity (STDP) synapse and a neuromorphic neuron. The neuromorphic node is configured to receive a feedforward spike signal from selected ones of a plurality of input neurons of an input layer and to provide an output spike signal as a recurrent spike signal to the neuromorphic nodes of the network layer. A combination of the recurrent and feedforward spike signals is an excitatory spike signal of the neuromorphic node. The cortical neuromorphic system includes the neuromorphic nodes configured to operate according to a cycle and time slots of synaptic time multiplexing. The method includes receiving and weighting the excitatory spike signal using the STDP synapse and producing the output spike signal.

Owner:HRL LAB

Apparatus comprising artificial neuronal assembly

Owner:PFG IP +1

Targeted delivery of botulinum toxin to the sphenopalatine ganglion

ActiveUS20080279895A1Effective prophylactic treatmentReducing and preventing symptomNervous disorderBacteriaSynapseVascular disease

Owner:ALLERGAN INC

Targeted delivery of botulinum toxin for the treatment and prevention of trigeminal autonomic cephalgias, migraine and vascular conditions

ActiveUS7655244B2Effective treatmentReducing and preventing symptomBacterial antigen ingredientsNervous disorderSynapseVascular disease

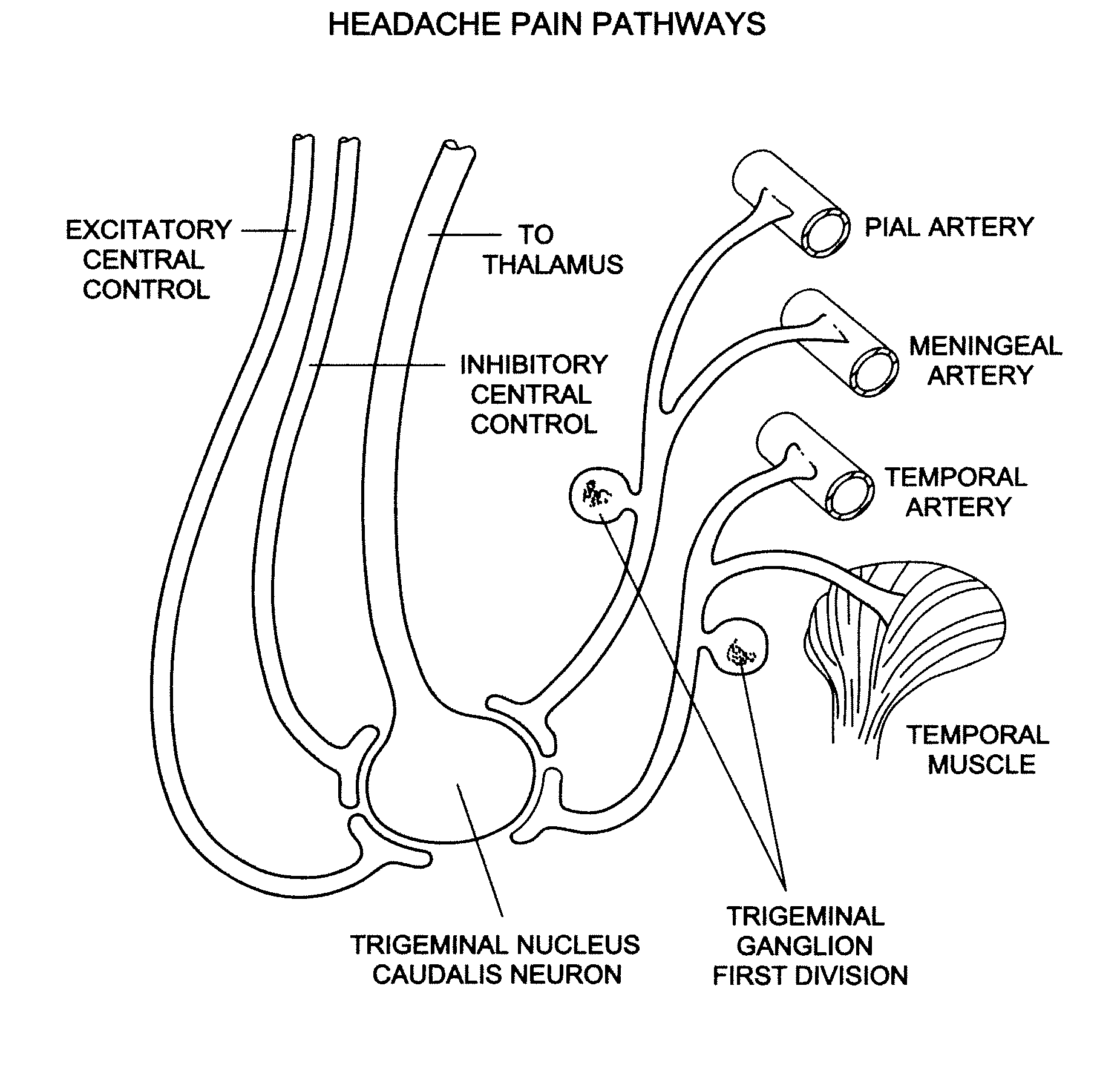

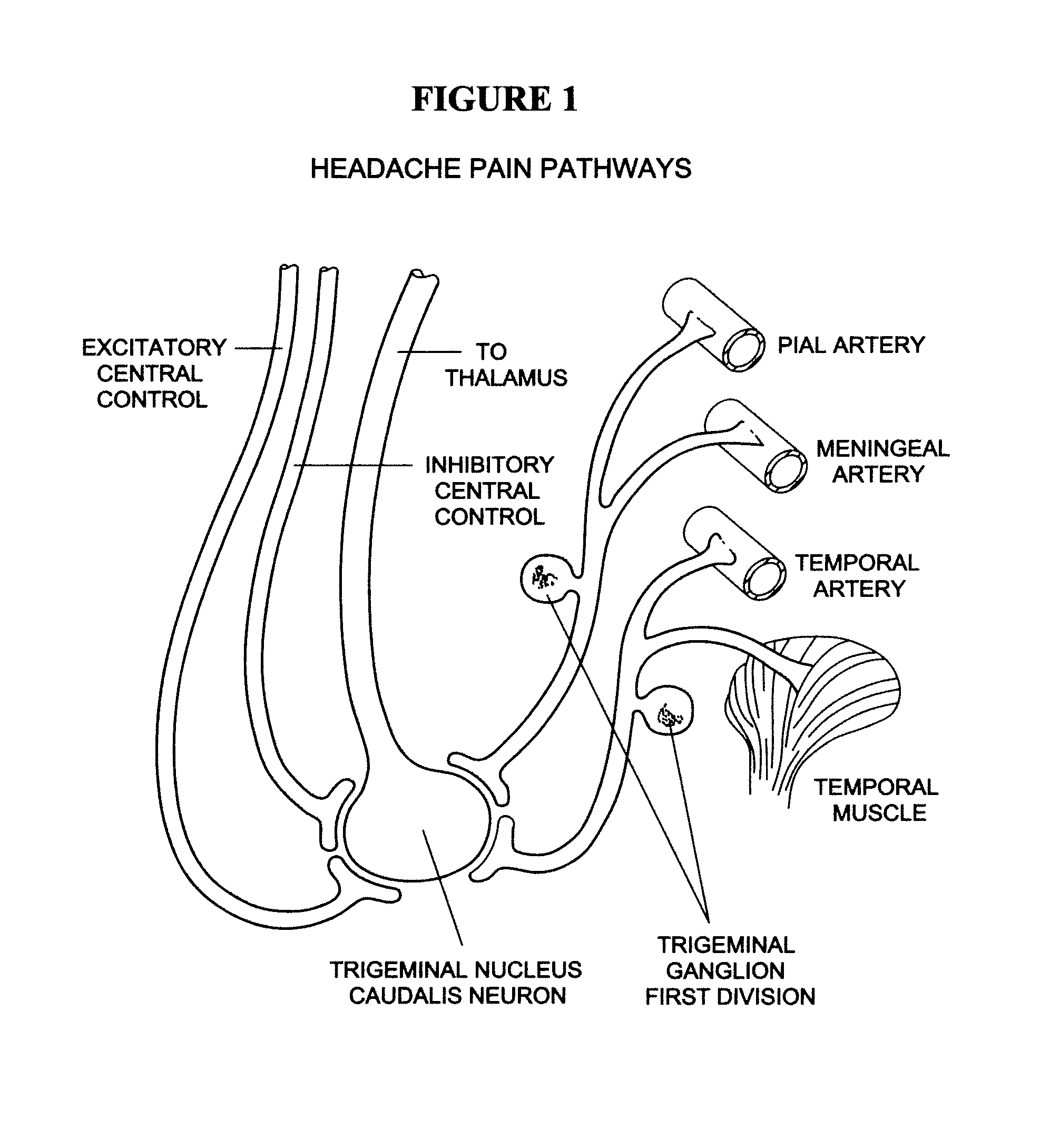

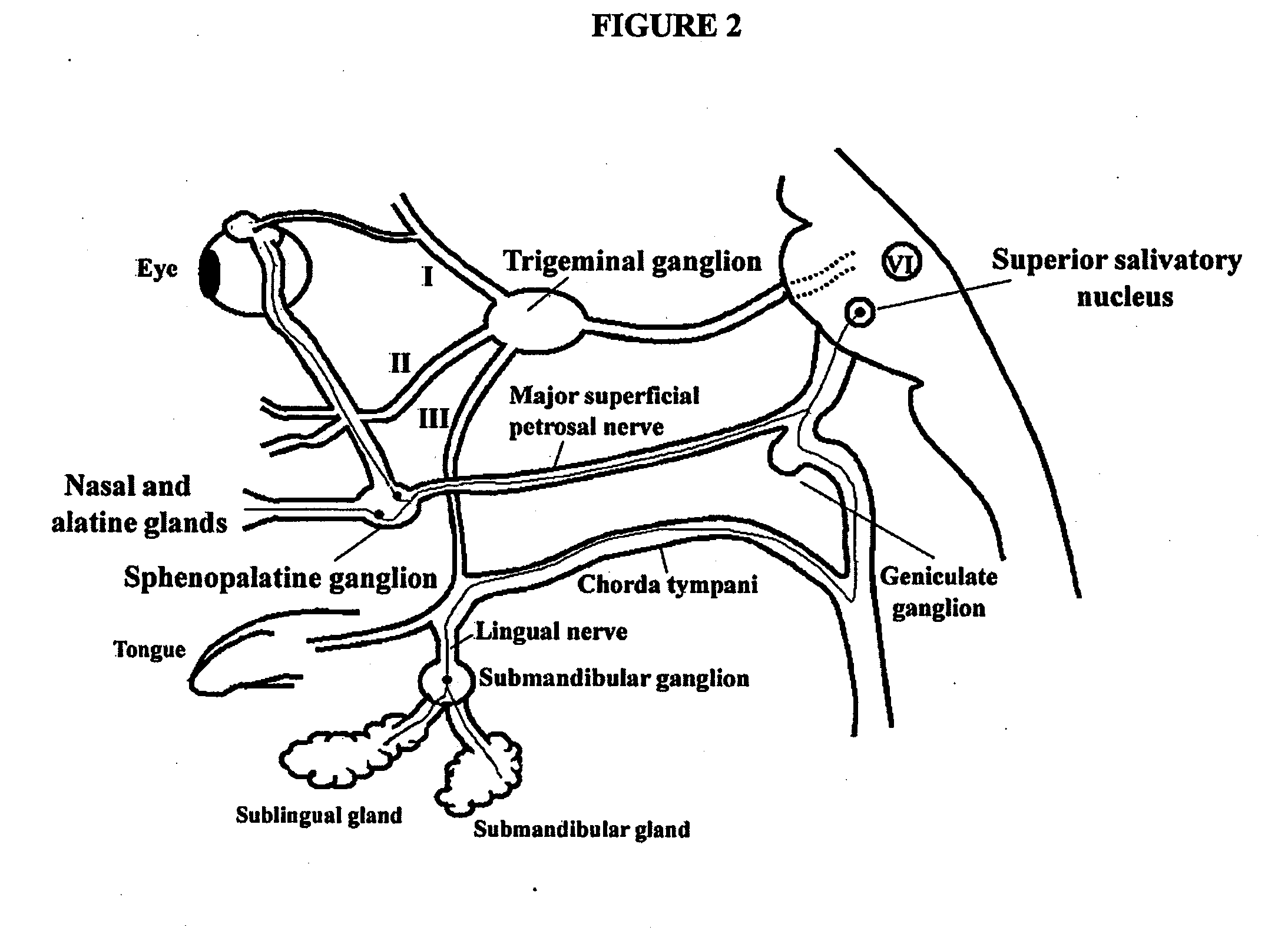

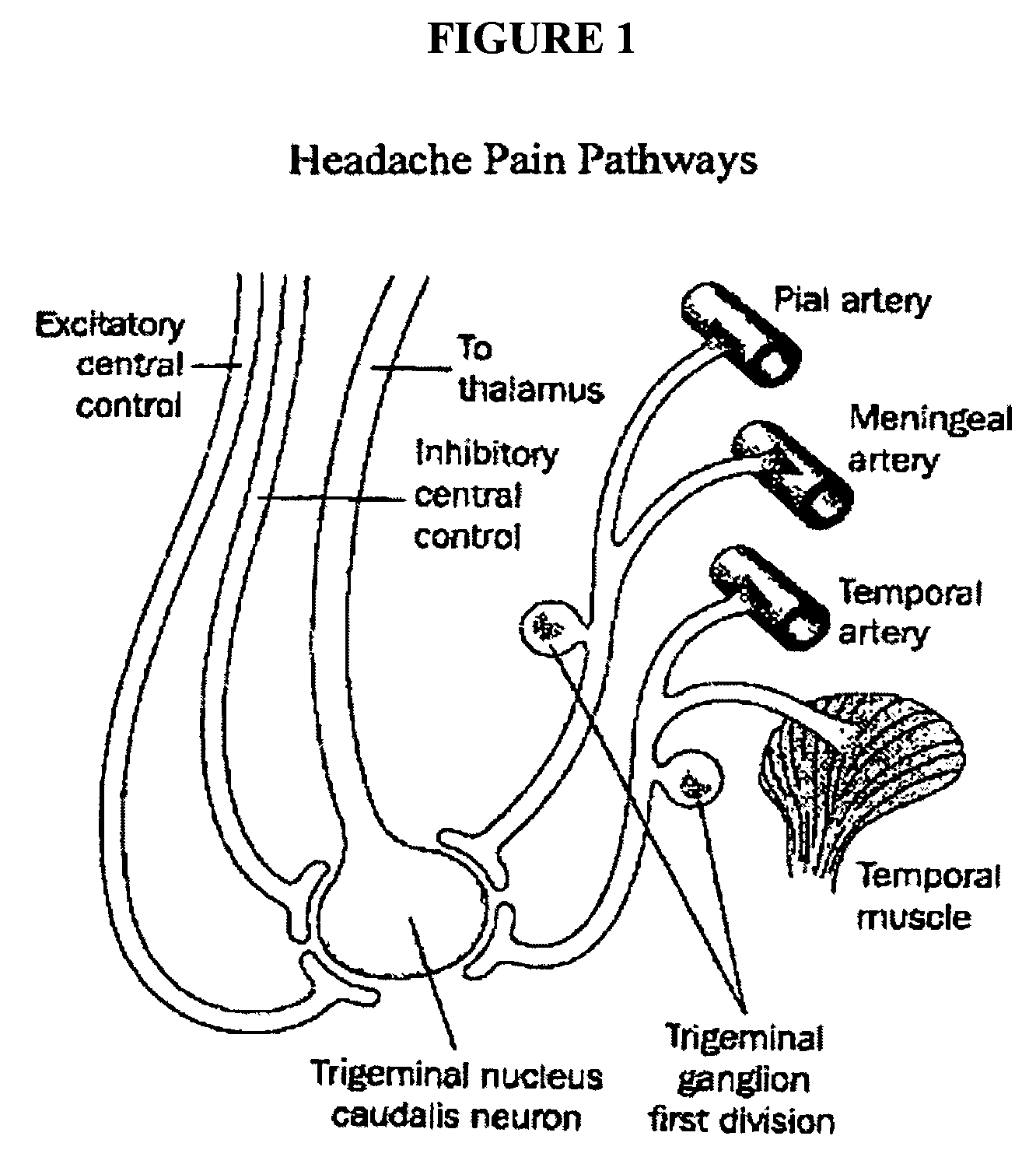

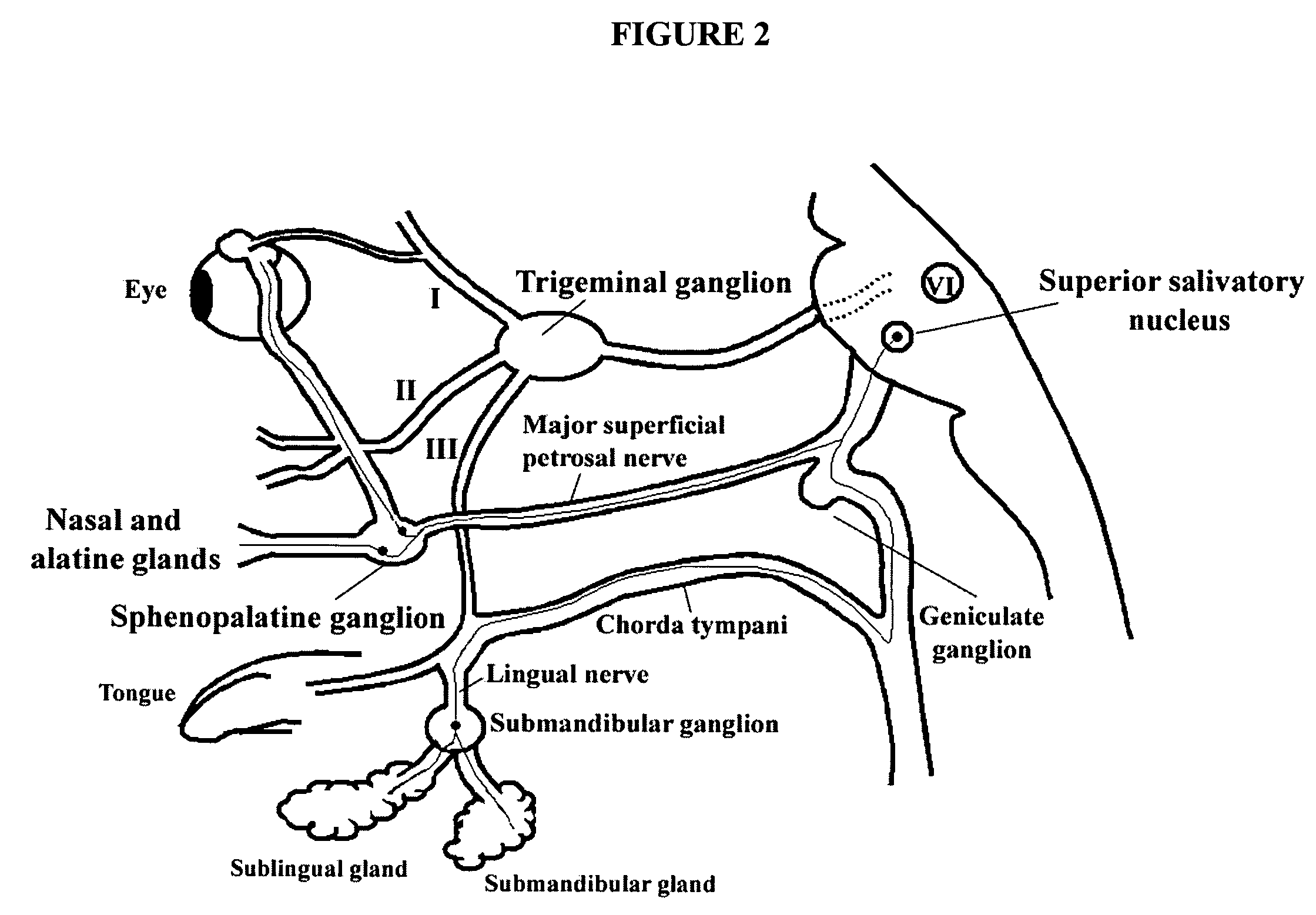

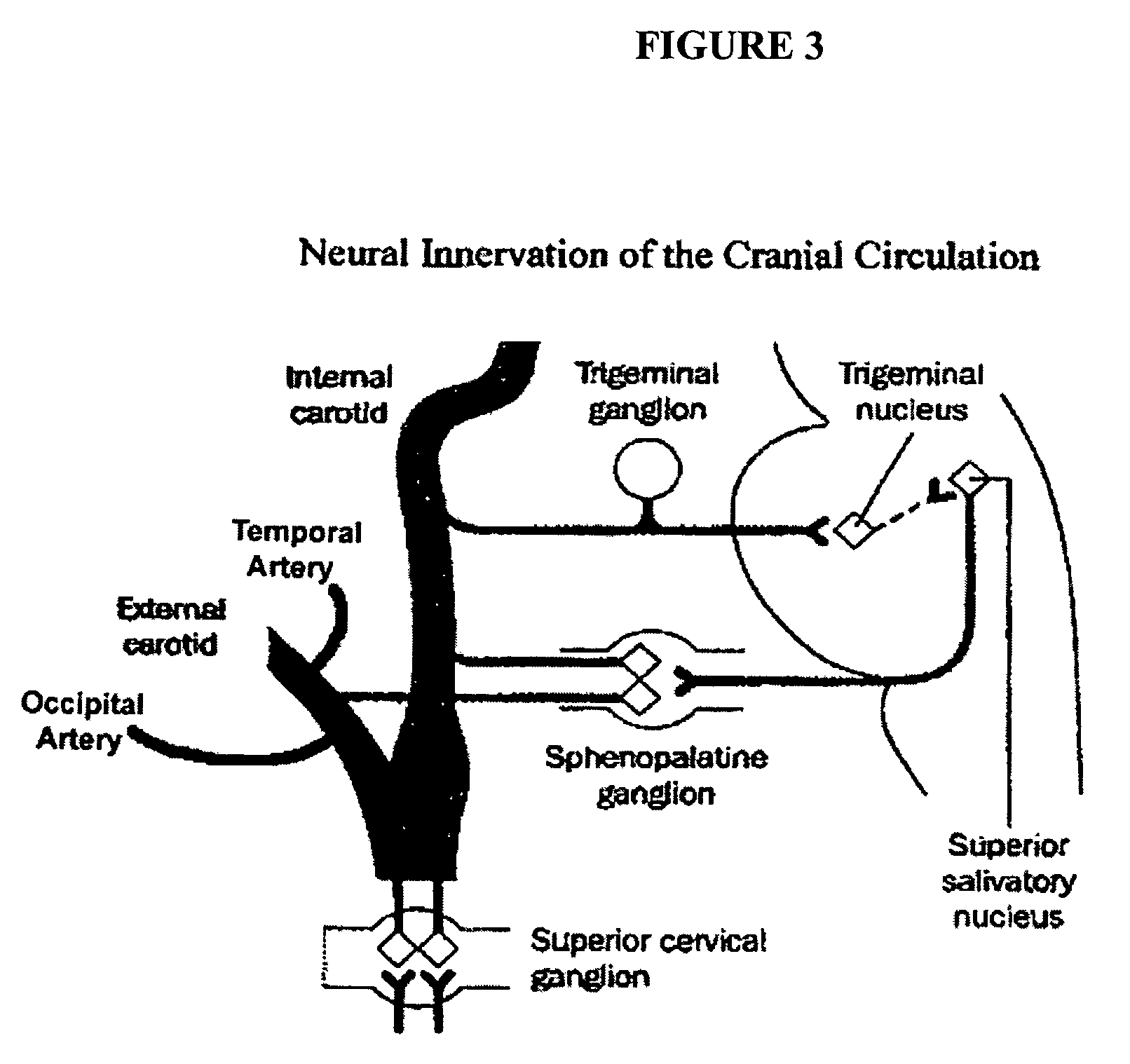

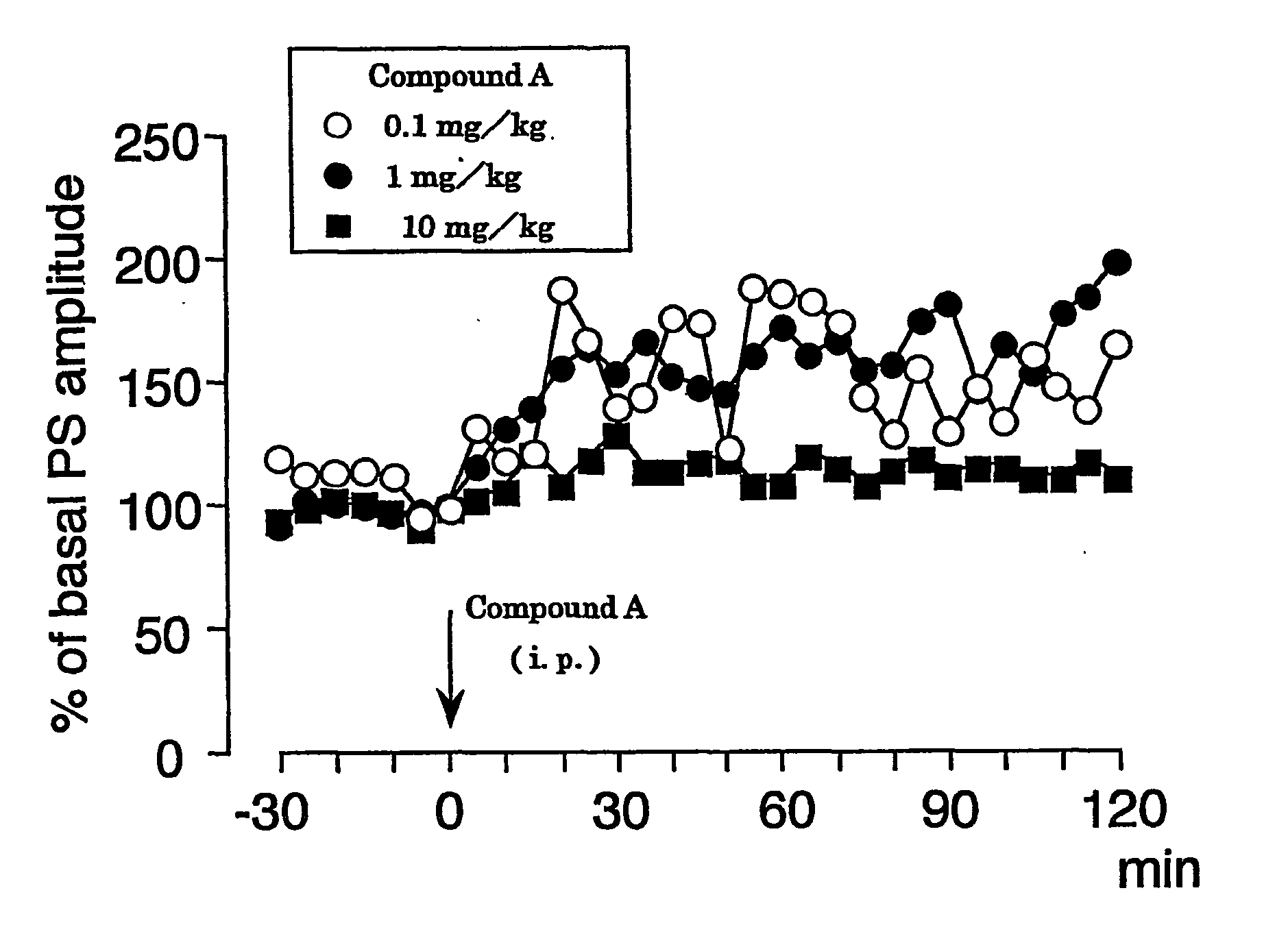

Botulinum toxin, among other presynaptic neurotoxins is used for the treatment and prevention of migraine and other headaches associated with vascular disorders. Presynaptic neurotoxins are delivered focally, targeting the nerve endings of the trigeminal nerve, the occipital nerve and the intranasal terminals of the parasympathetic fibers originating in the Sphenopalatine ganglion. The administration preferably targets the extracranial nerve endings of the trigeminal nerve in the temporal area, the extracranial occipital nerve endings in the occipital area, and the intranasal terminals of the trigeminal nerve and parasympathetic fibers originating in the Sphenopalatine ganglion. The delivery is carried out by way of injection or topically.

Owner:ALLERGAN INC

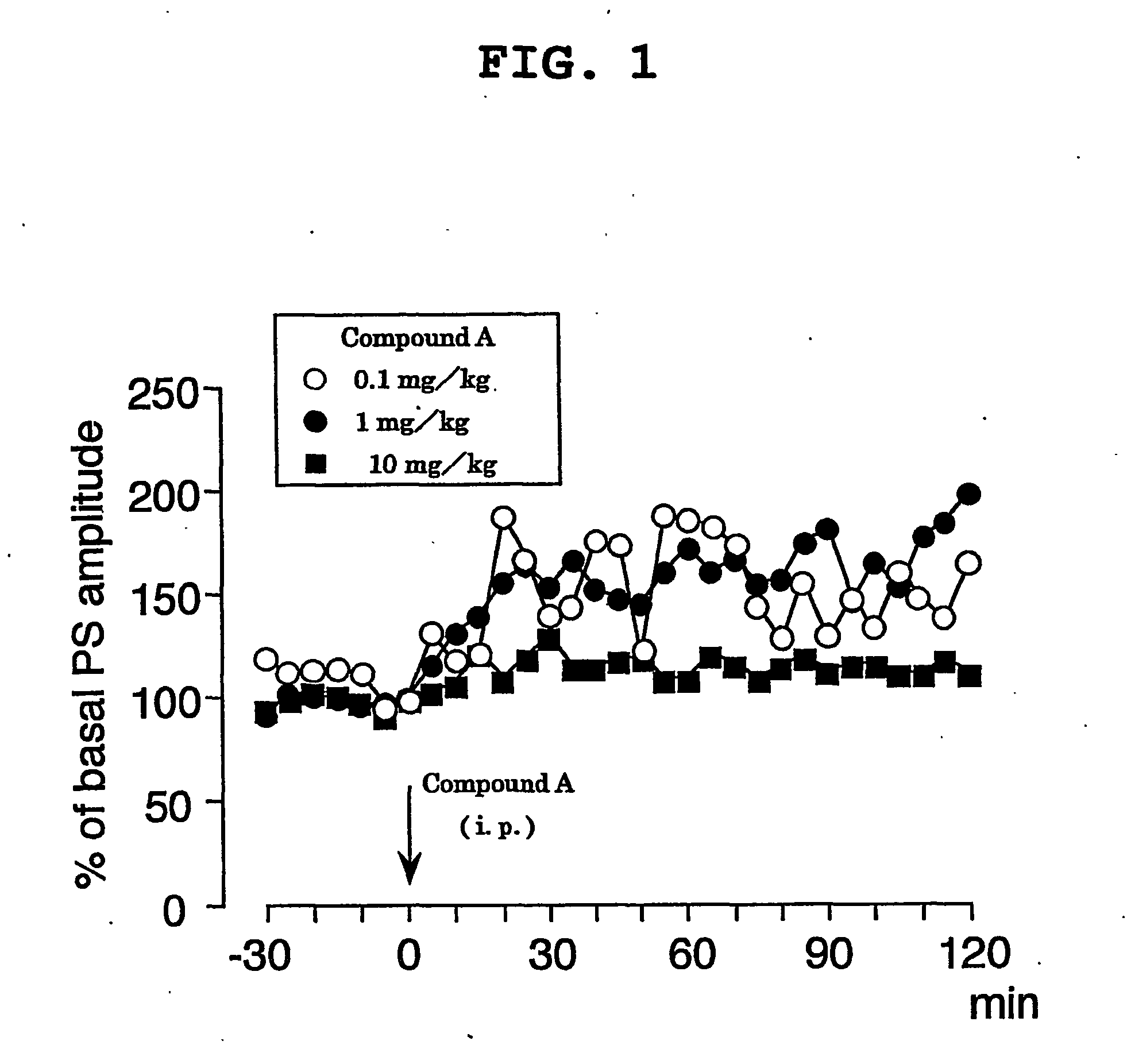

Carboxylic acid compound cyclopropane ring

InactiveUS20050075393A1Lower metabolismSmooth transmissionBiocideNervous disorderSynapseMemory disorder

A carboxylic acid compound having cyclopropane ring(s) of the formula (I): wherein R is alkyl or alkenyl optionally having one or more 1,2-cyclopropylene in a carbon chain and / or optionally having cyclopropyl at the end of a chain, X is a single bond or alkylene, wherein the total number of carbon less the number of cyclopropane ring is 10-25, and a pharmaceutically acceptable salt thereof are provided. The compound (I) shows an LTP-like potentiation of synaptic transmission, allows slow metabolism in the living body, shows a stable LTP-like potentiation of synaptic transmission, and is useful as an agent for LTP-like potentiation of synaptic transmission, a cognition-enhancing drug or an agent for the prophylaxis and treatment of dementia, a learning and memory disorder and a neurotransmitter release disorder.

Owner:NISHIZAKI BIOINFORMATION RES INST +1

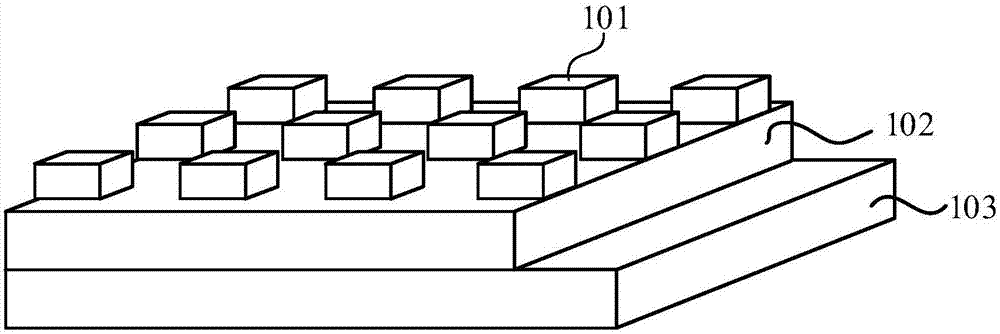

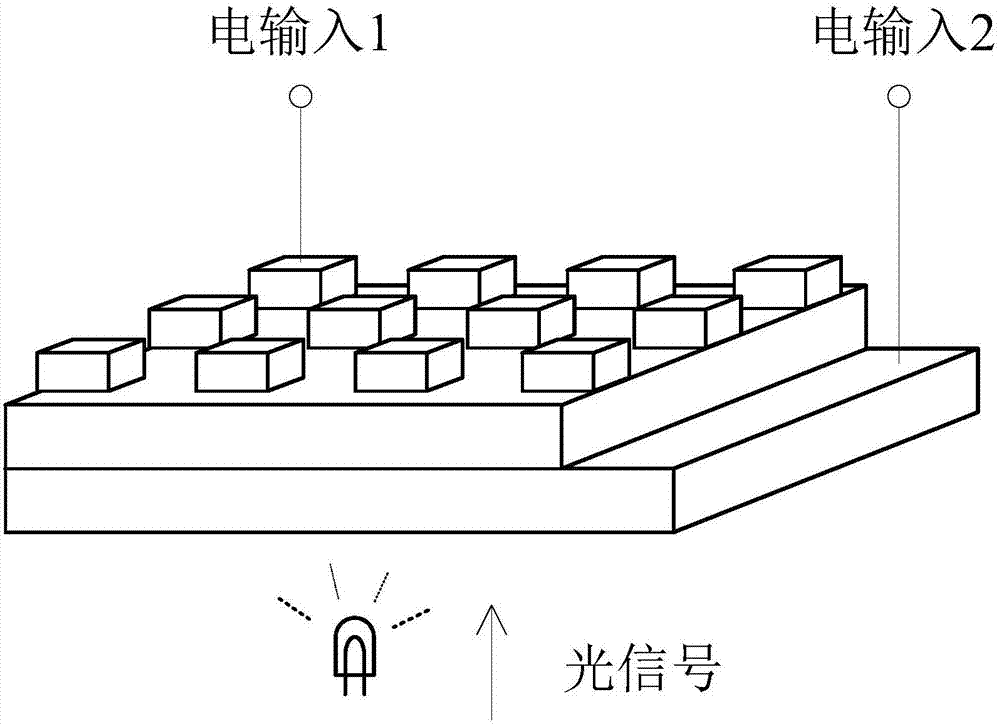

Artificial synaptic device based on photoelectric coupling memristor and modulation method of artificial synapse device

The invention discloses an artificial synaptic device based on a photoelectric coupling memristor and a modulation method of the artificial synaptic device. The artificial synaptic device comprises an upper electrode, a lower electrode and a functional material layer, wherein the functional material layer is arranged between the upper electrode and the lower electrode, the upper electrode, the functional material layer and the lower electrode jointly form a sandwich structure, the functional material layer is made of a material having a photoelectric effect, the lower electrode is a transparent conductive electrode, an electrical signal is input through the upper electrode and the lower electrode, and an optical signal is input through the transparent conductive electrode. In the artificial synaptic device provided by the invention, light is introduced as a control signal of the other end except the electrical signal, two control ends of the artificial synapse device are expanded to three ends, the artificial synaptic device can generate resistance change under an external optical excitation signal by the additionally-arranged end, the artificial synaptic device can be configured to be in a plurality of resistance states correspondingly by selection and control of intensity, frequency and optical pulse time of the optical excitation signal, and various synaptic plasticity functions are correspondingly achieved.

Owner:HUAZHONG UNIV OF SCI & TECH

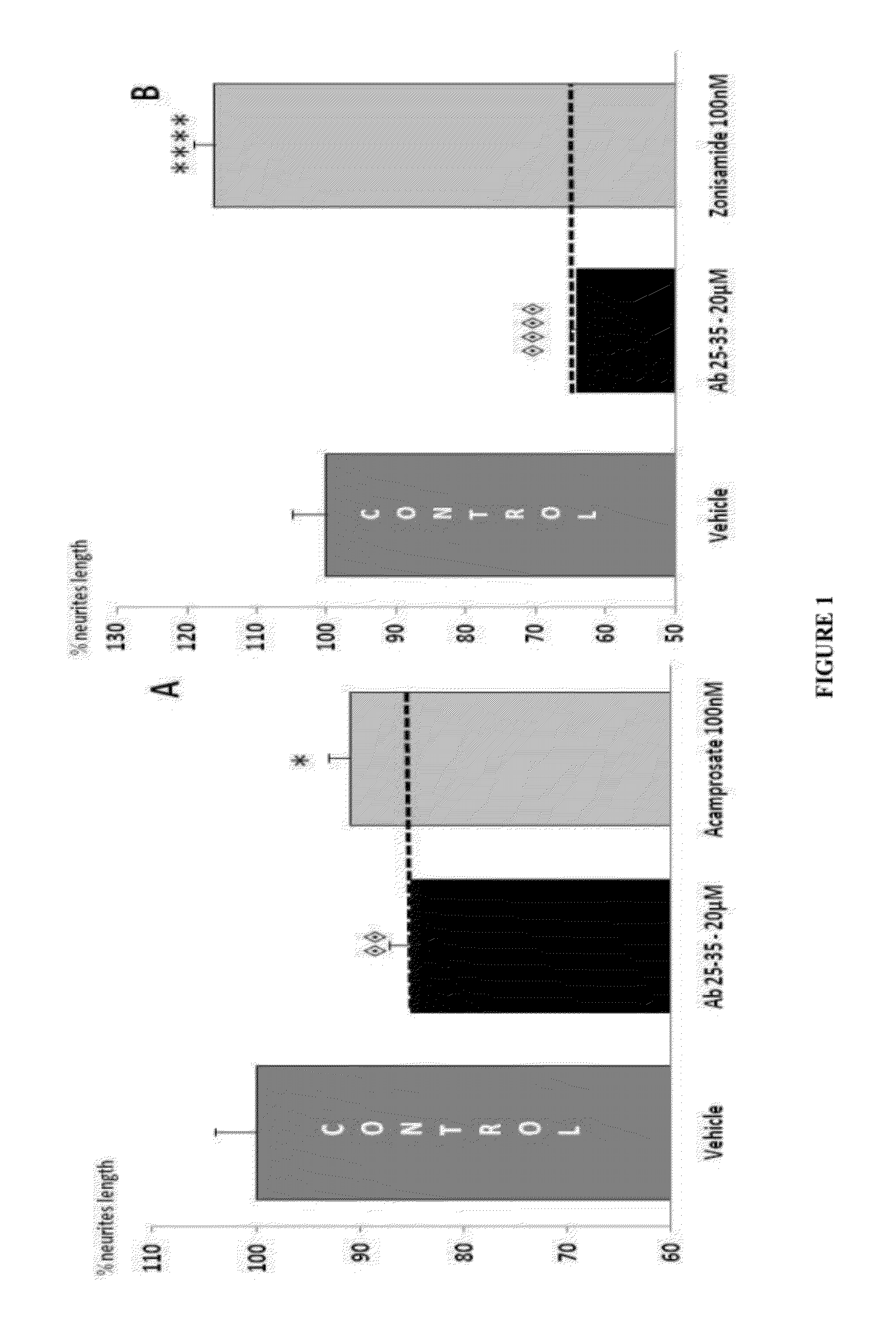

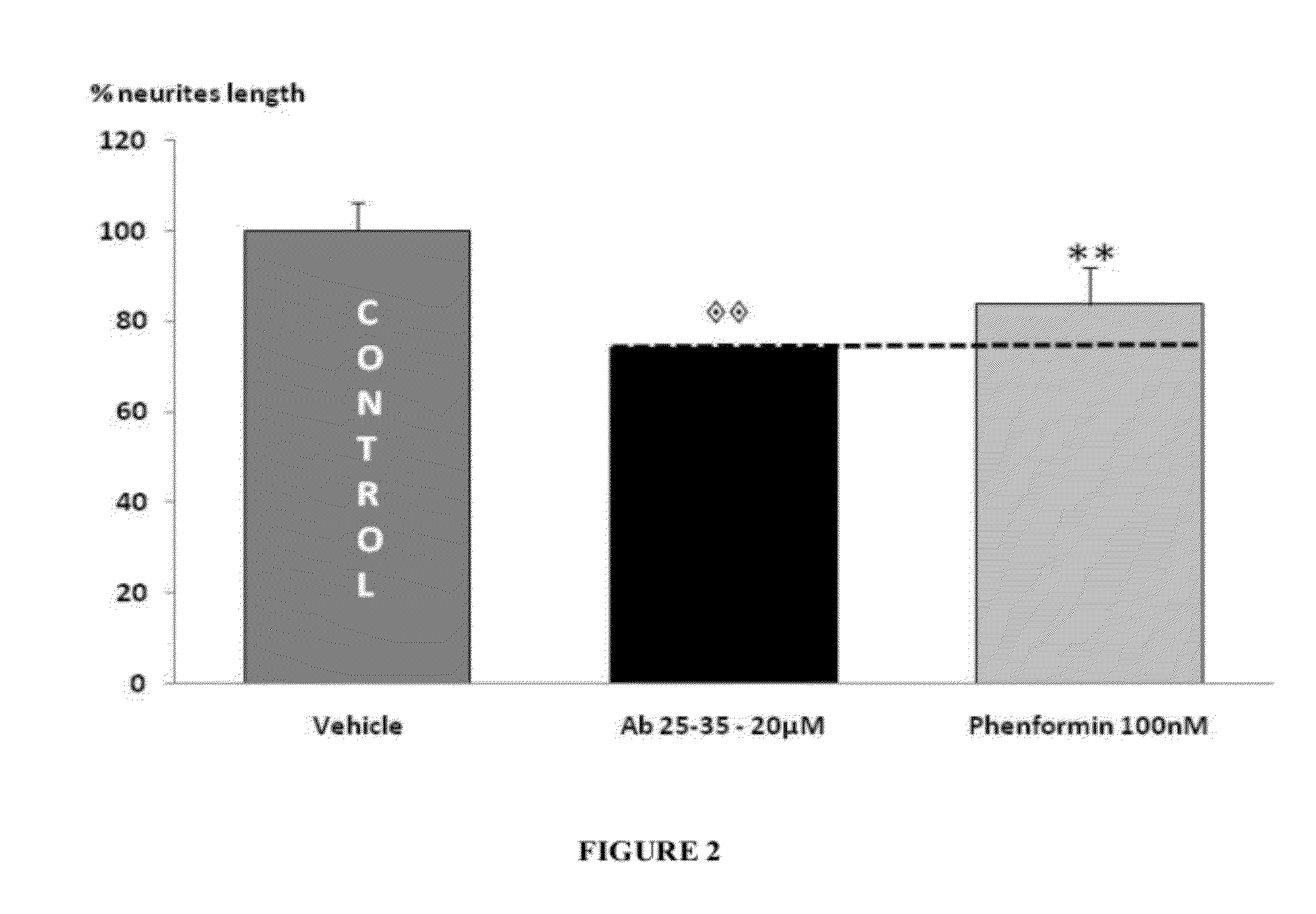

Therapeutic approaches for treating alzheimer's disease

InactiveUS20120270836A1Significant comprehensive benefitsLow dosBiocideNervous disorderSynapseAngiogenesis growth factor

The present invention relates to compositions and methods for the treatment of Alzheimer's disease and related disorders. More specifically, the present invention relates to novel combinatorial therapies of Alzheimer's disease and related disorders. In particular, the invention concerns compounds which, alone or in combination(s), can effectively modulate synapse function and / or angiogenesis and / or cell stress response. The invention also relates to methods of producing a drug or a drug combination for treating Alzheimer's disease and to methods of treating Alzheimer's disease or a related disorder.

Owner:PHARNEXT

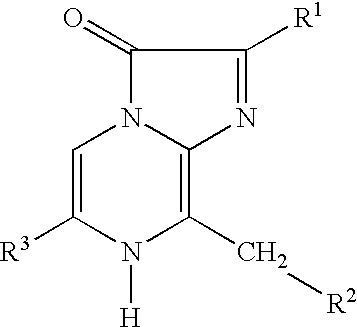

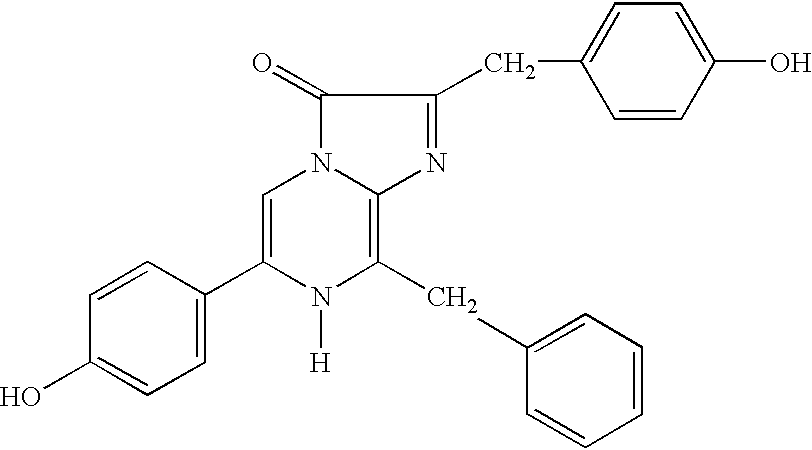

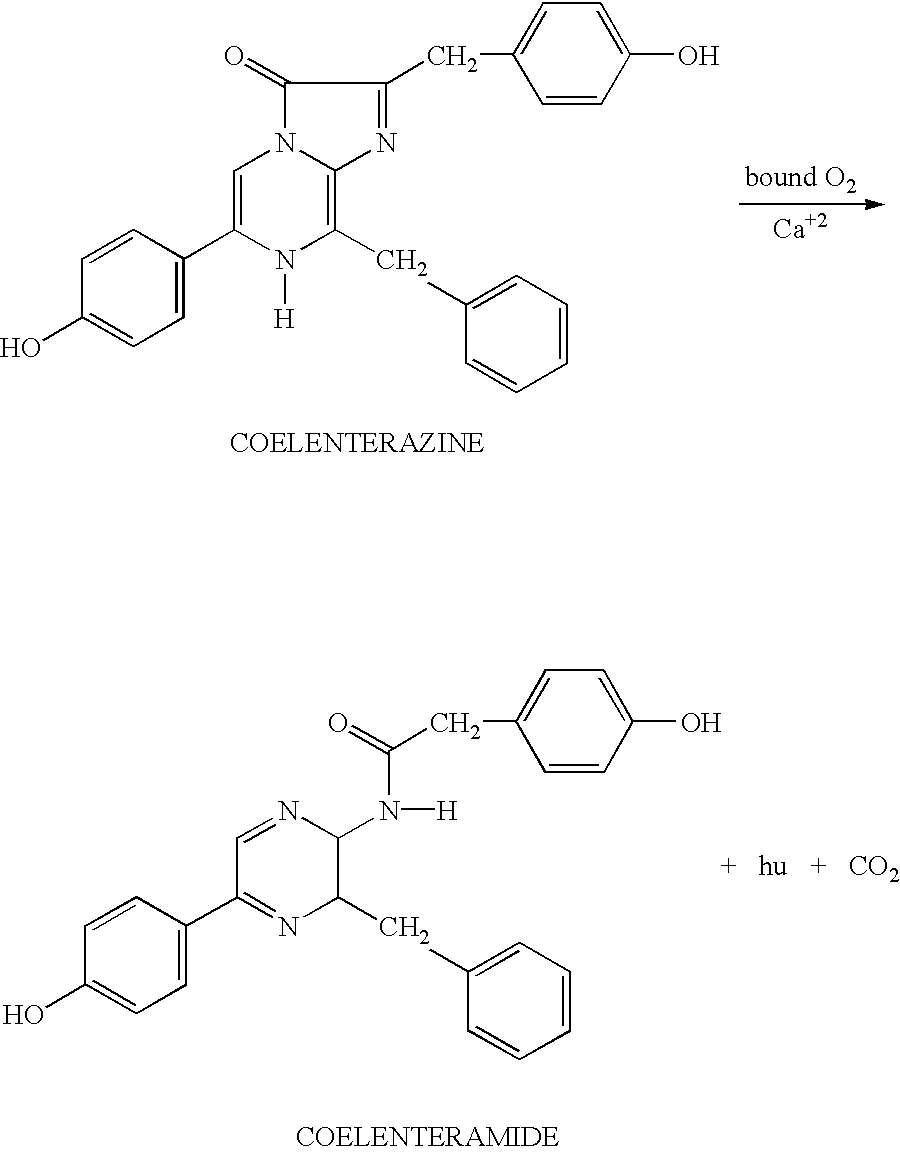

Apparatus and method for detecting and identifying infectious agents

Solid phase methods for the identification of an analyte in a biological medium, such as a body fluid, using bioluminescence are provided. A chip designed for performing the method and detecting the bioluminescence is also provided. Methods employing biomineralization for depositing silicon on a matrix support are also provided. A synthetic synapse is also provided.

Owner:PROLUME

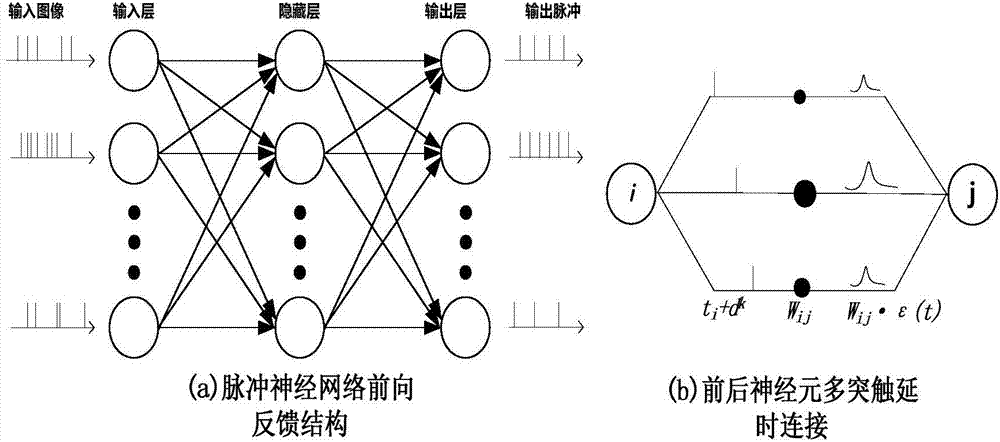

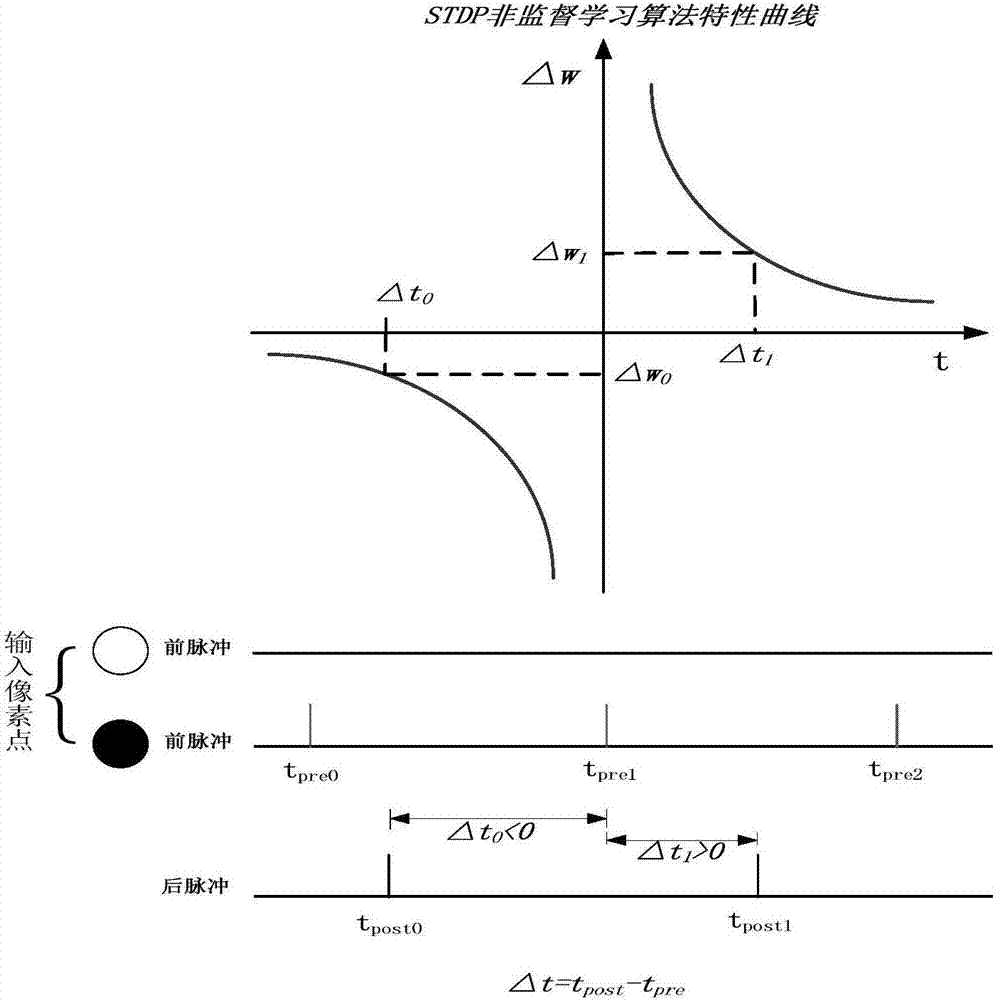

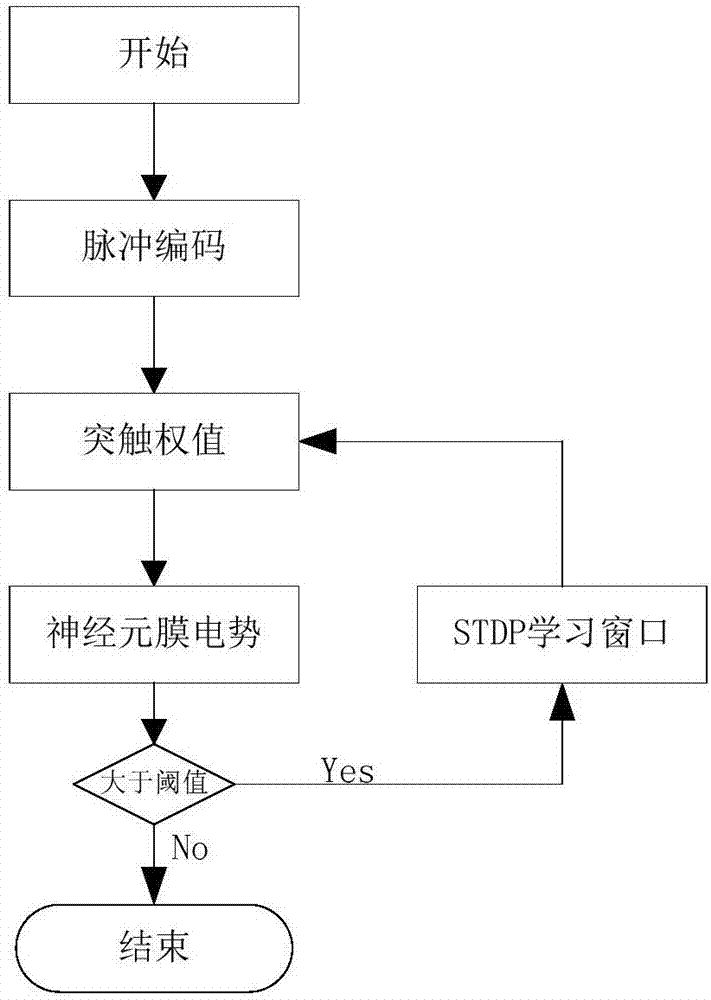

Hardware friendly pulse neural network model based on STDP non-supervised learning algorithm

ActiveCN107092959AImprove simplicityImprove stabilityNeural architecturesPhysical realisationSynapseNerve network

The invention discloses a hardware friendly pulse neural network model based on an STDP non-supervised learning algorithm. The pulse neural network model is a polysynaptic time-delay forward feedback neural network model, each-layer neural elements are in interconnection with neural elements of other layers through multiple synapses, and internal neural elements of each layer are mutually independent. The model is advantaged in that model design of the pulse neural network is carried out completely based on a digital hardware circuit platform, the STDP non-supervised learning algorithm is innovatively applied to learning training of the pulse neural network model, special functions can be realized, the hardware platform pulse neural network model has relatively high stability, a relatively fast speed is realized on the condition that occupied hardware resources are relatively a few, moreover, a network structure has a parallel connection characteristic, expansibility is substantially improved, and a new concept is provided for realizing a super-scale pulse neural network.

Owner:WUHAN UNIV

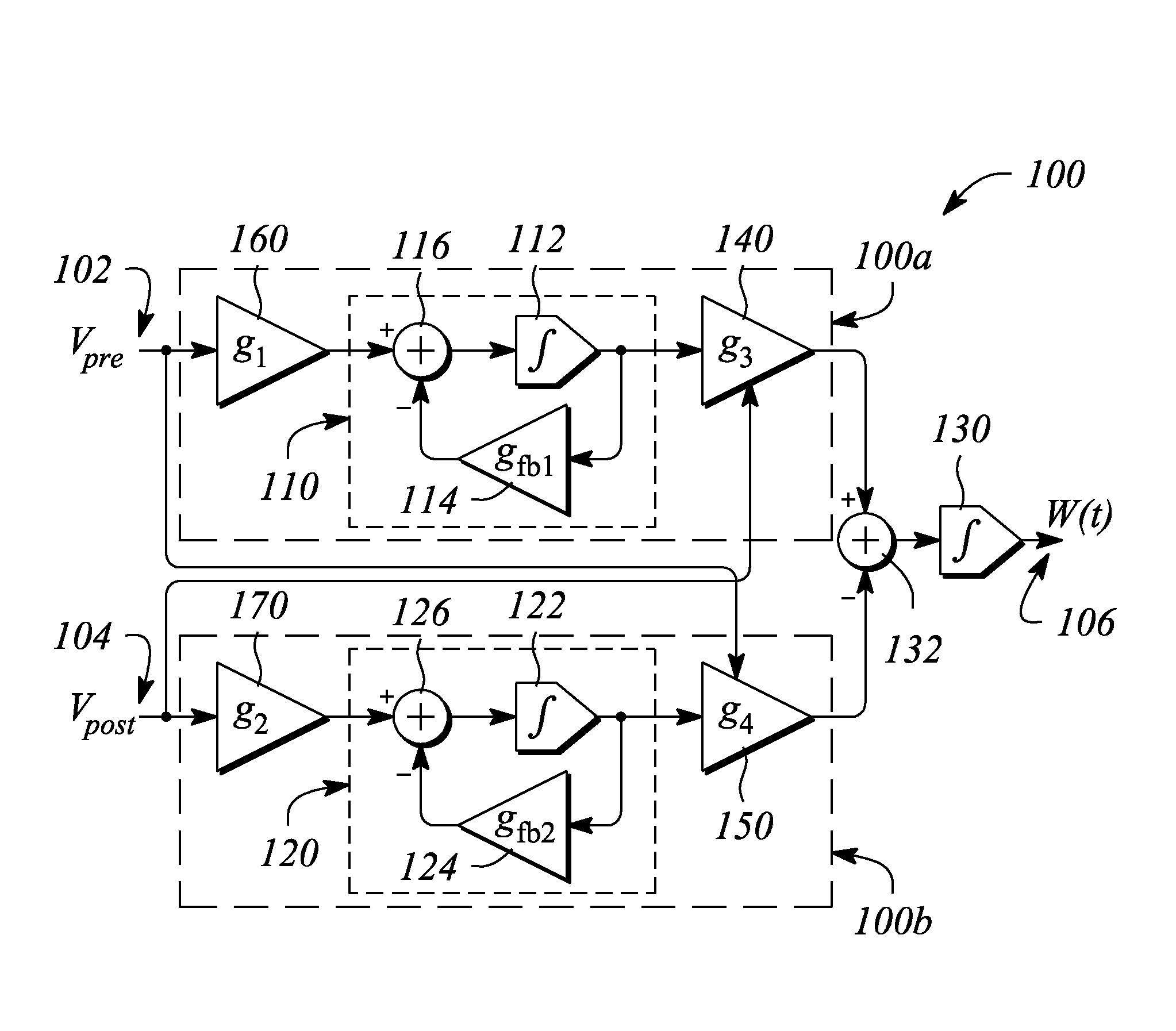

Spike timing dependent plasticity apparatus, system and method

A spike timing dependent plasticity (STDP) apparatus, neuromorphic synapse system and a method provide STDP processing of spike signals. The STDP apparatus includes a first leaky integrator to receive a first spike signal and a second leaky integrator to receive a second spike signal. An output of the first leaky integrator is gated according to the second spike signal to produce a first gated integrated signal and an output of the second leaky integrator is gated according to the first spike signal to produce a second gated integrated signal. The STDP apparatus further includes an output integrator to integrate a difference of the first and second gated integrated signals to produce a weighted signal. The system includes a synapse core and the STDP apparatus. The method includes integrating the spike signals, gating the integrated signals and integrating a difference of the gated integrated signals.

Owner:HRL LAB

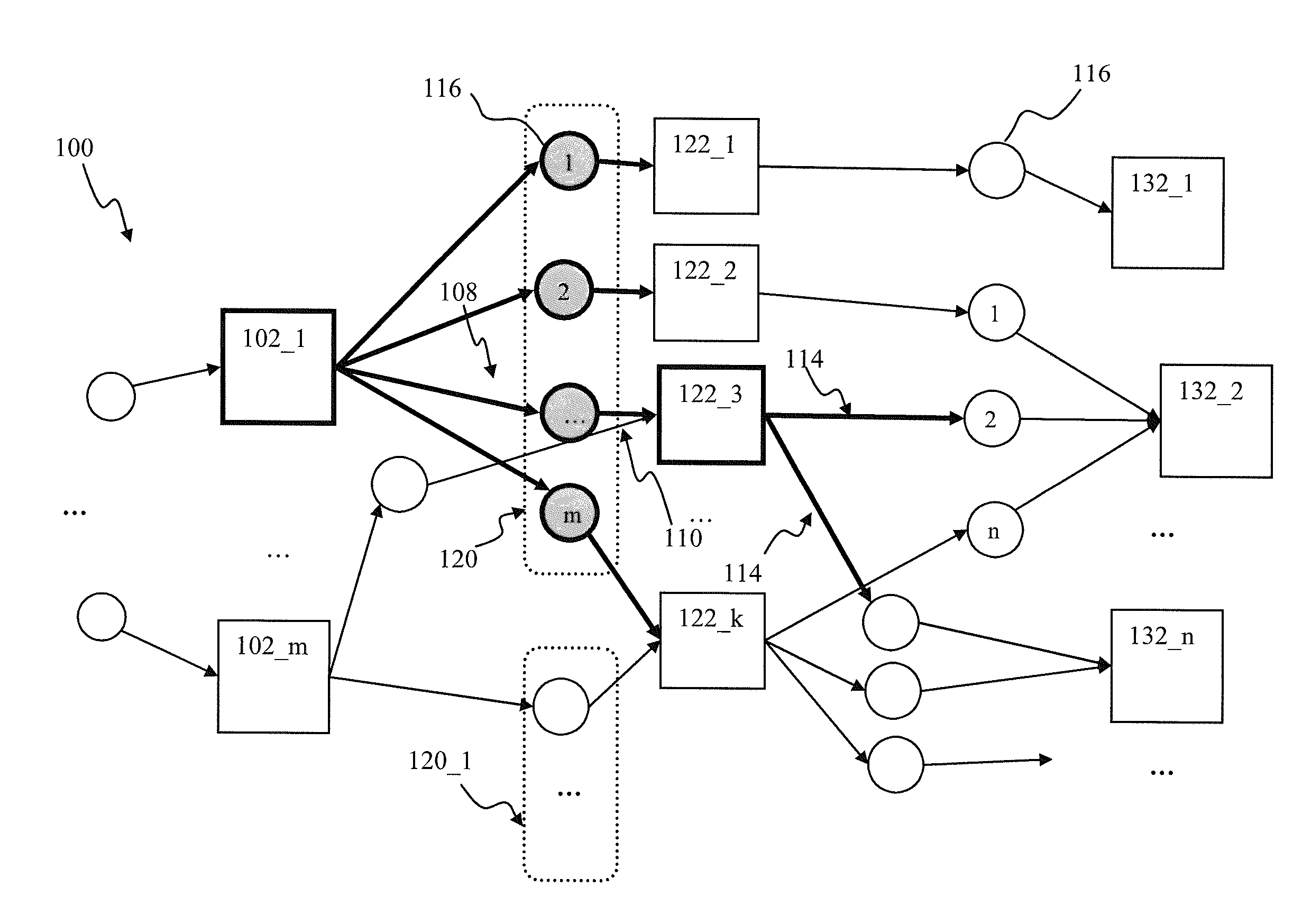

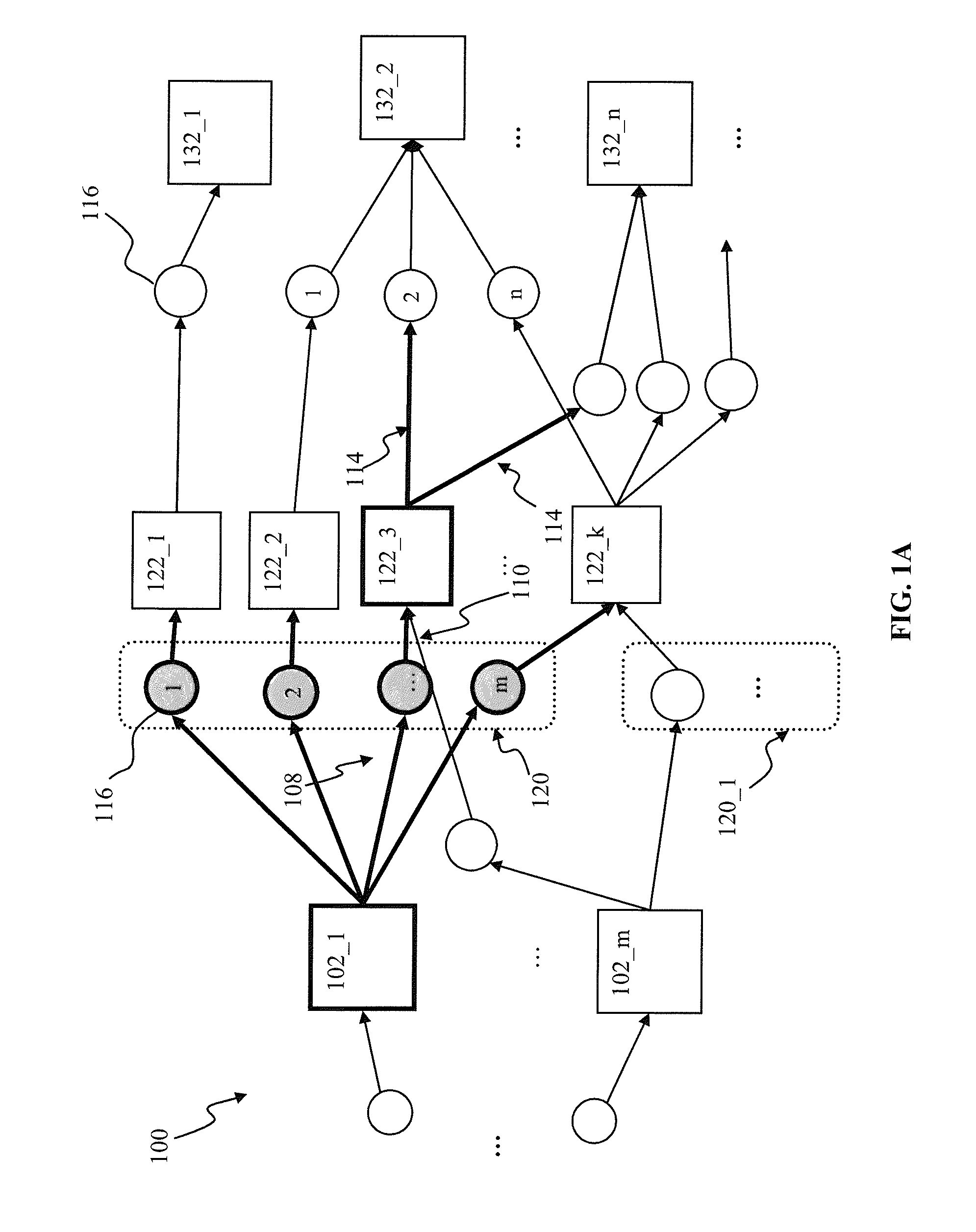

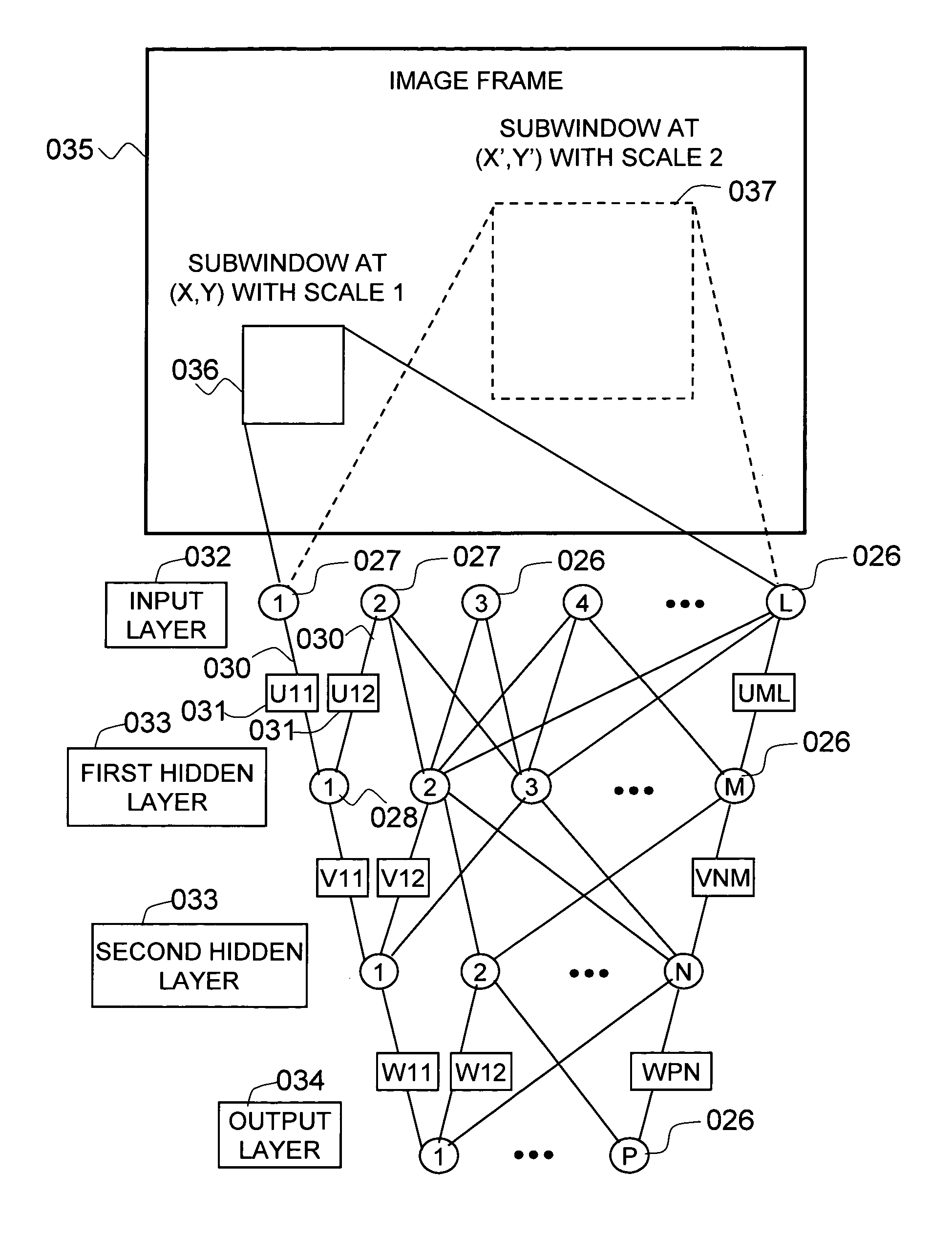

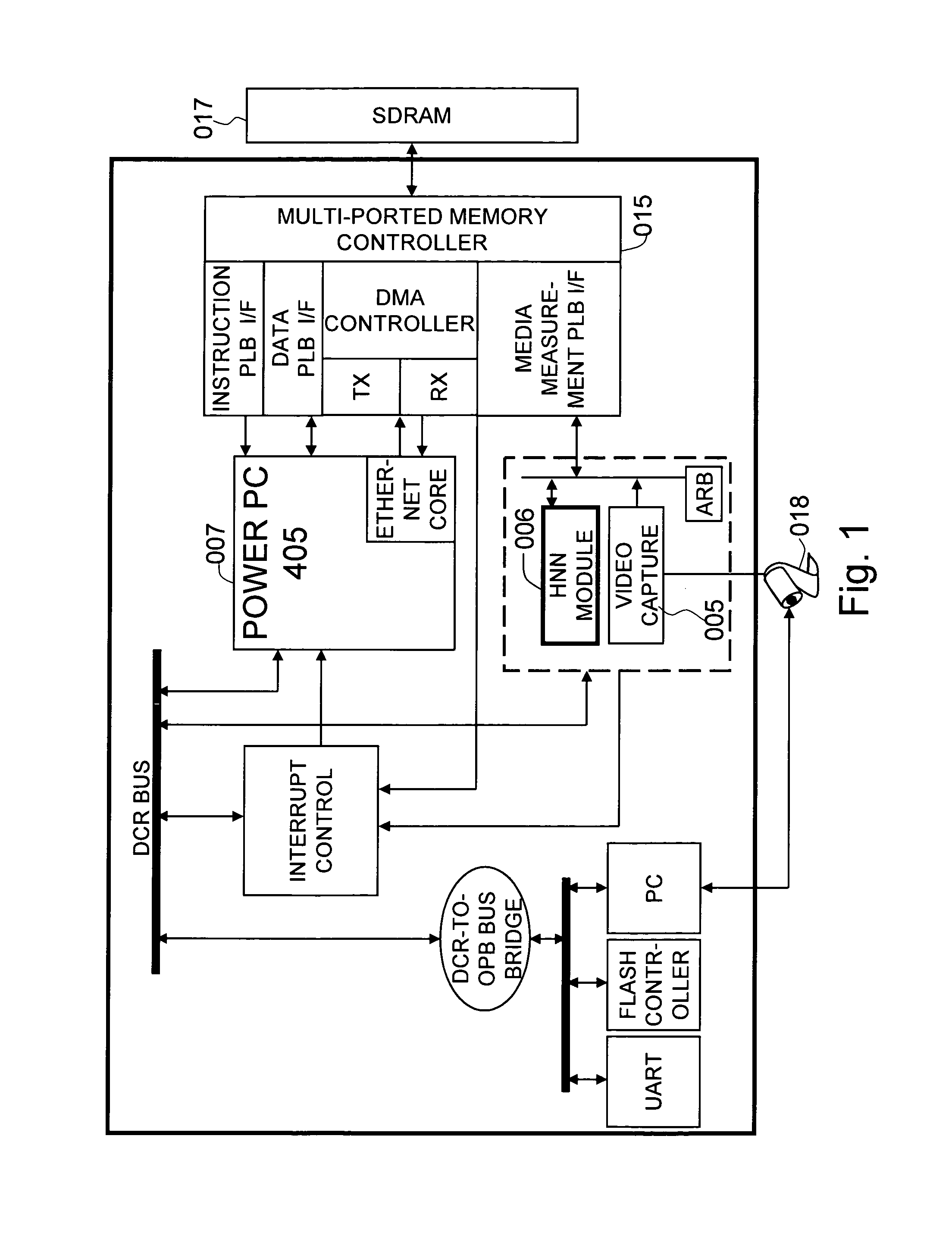

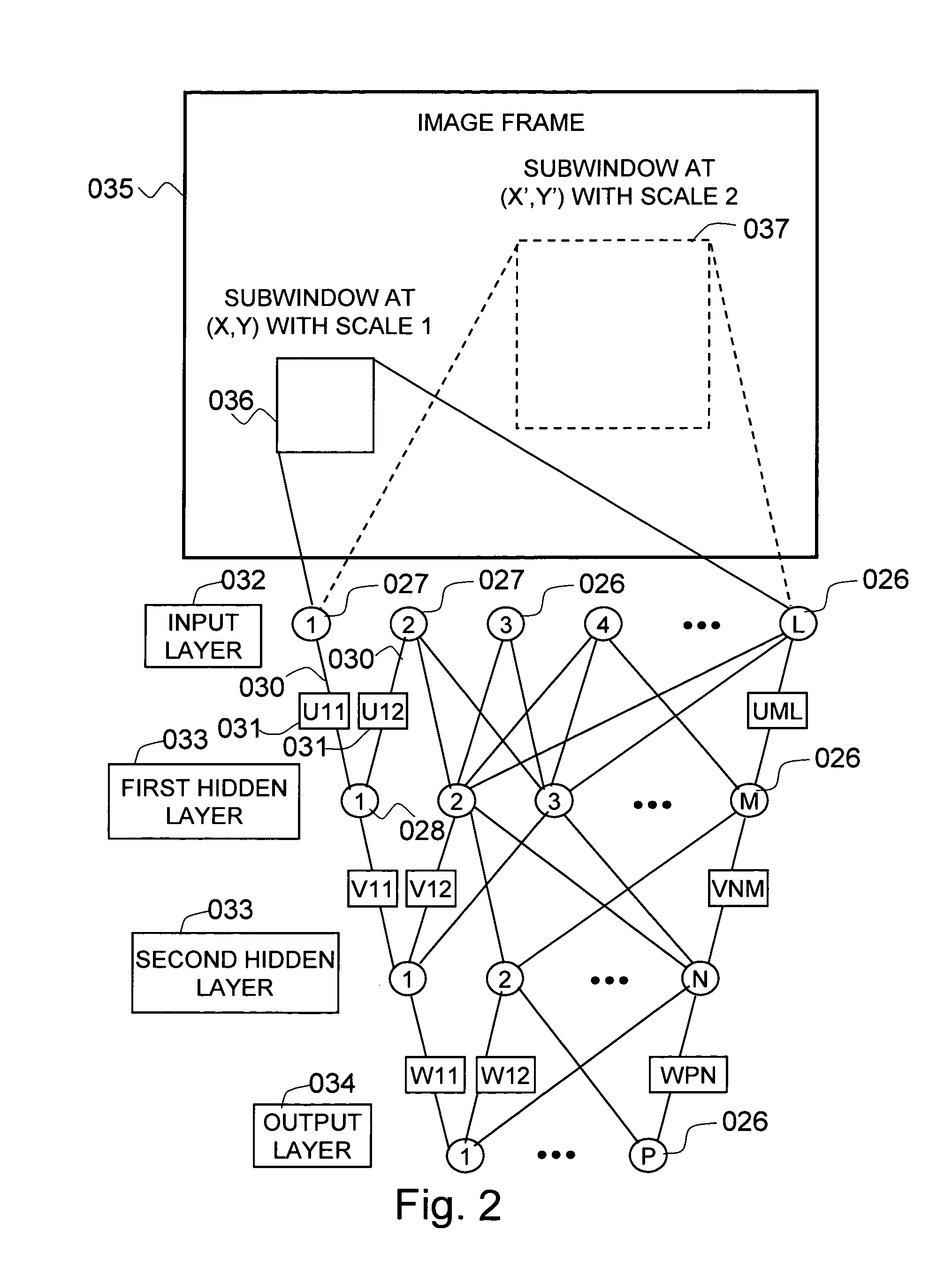

Apparatus and method for hardware implementation of object recognition from an image stream using artificial neural network

ActiveUS8081816B1Function evaluation is facilitatedReduce processing requirementsDigital computer detailsCharacter and pattern recognitionMultiple componentSynapse

The present invention is an apparatus and method for object recognition from at least an image stream from at least an image frame utilizing at least an artificial neural network. The present invention further comprises means for generating multiple components of an image pyramid simultaneously from a single image stream, means for providing the active pixel and interlayer neuron data to at least a subwindow processor, means for multiplying and accumulating the product of a pixel data or interlayer data and a synapse weight, and means for performing the activation of an accumulation. The present invention allows the artificial neural networks to be reconfigurable, thus embracing a broad range of object recognition applications in a flexible way. The subwindow processor in the present invention also further comprises means for performing neuron computations for at least a neuron. An exemplary embodiment of the present invention is used for object recognition, including face detection and gender recognition, in hardware. The apparatus comprises a digital circuitry system or IC that embodies the components of the present invention.

Owner:MOTOROLA SOLUTIONS INC

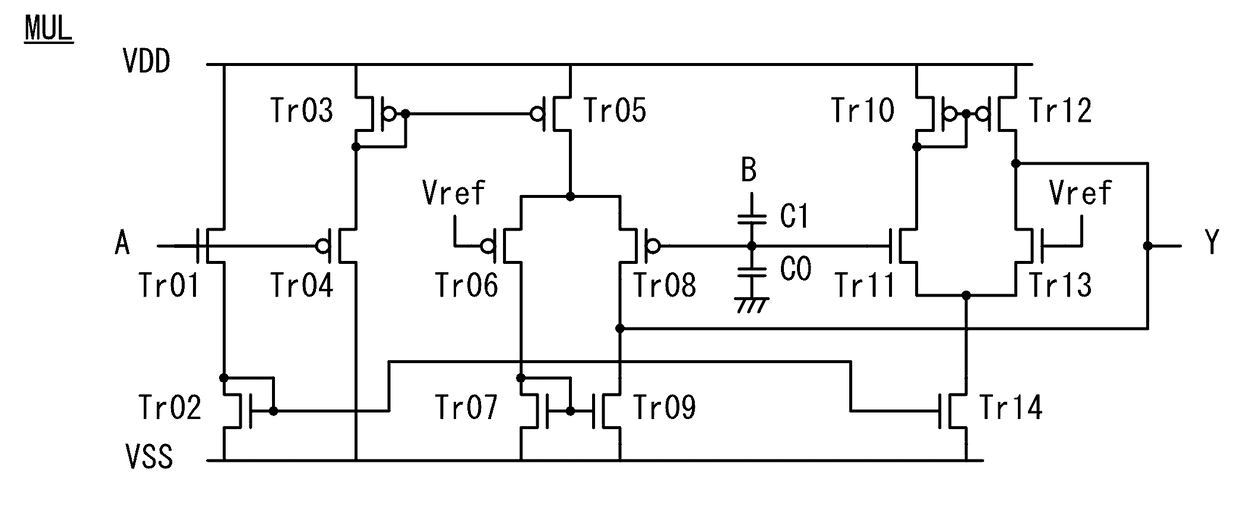

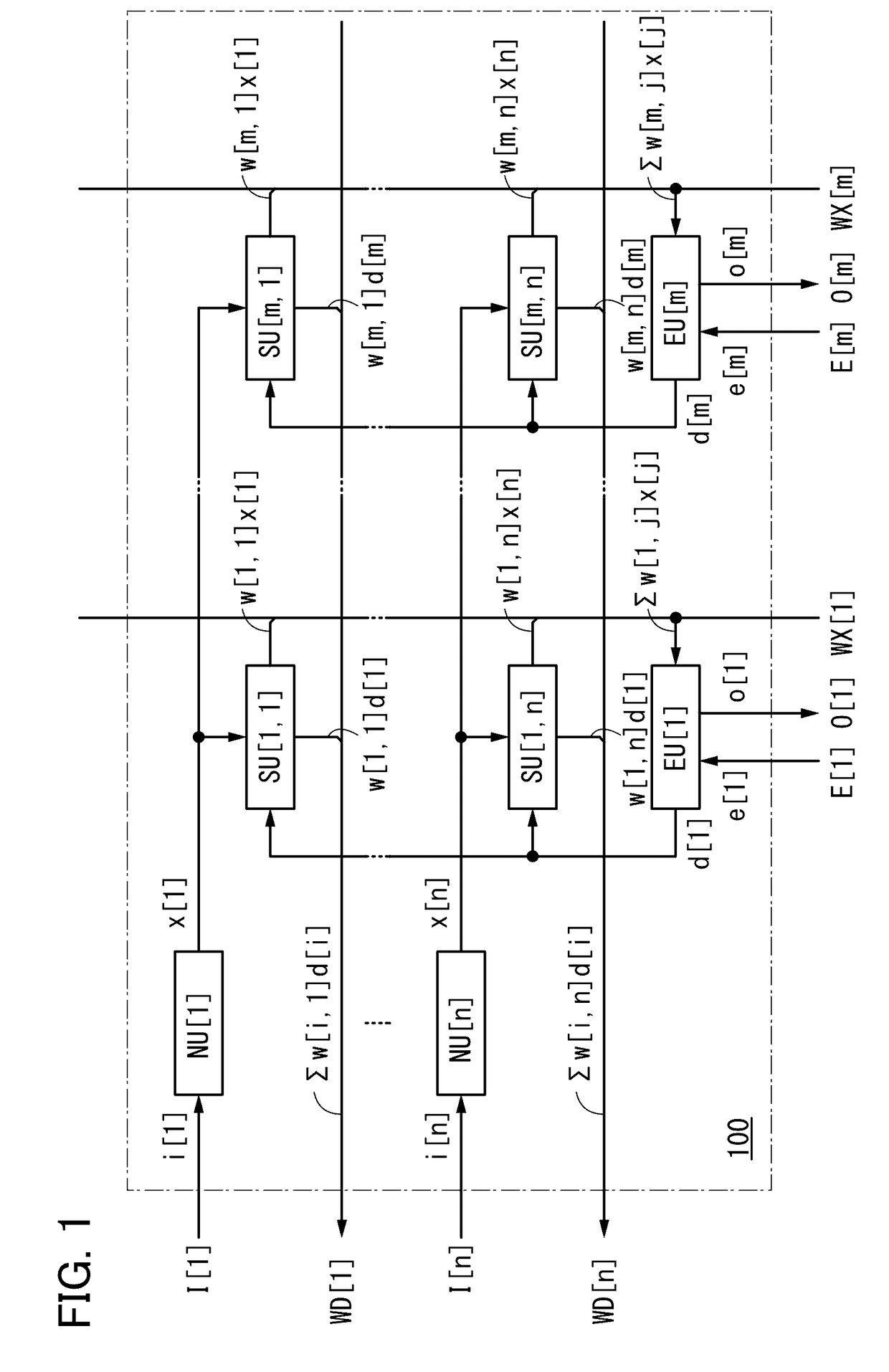

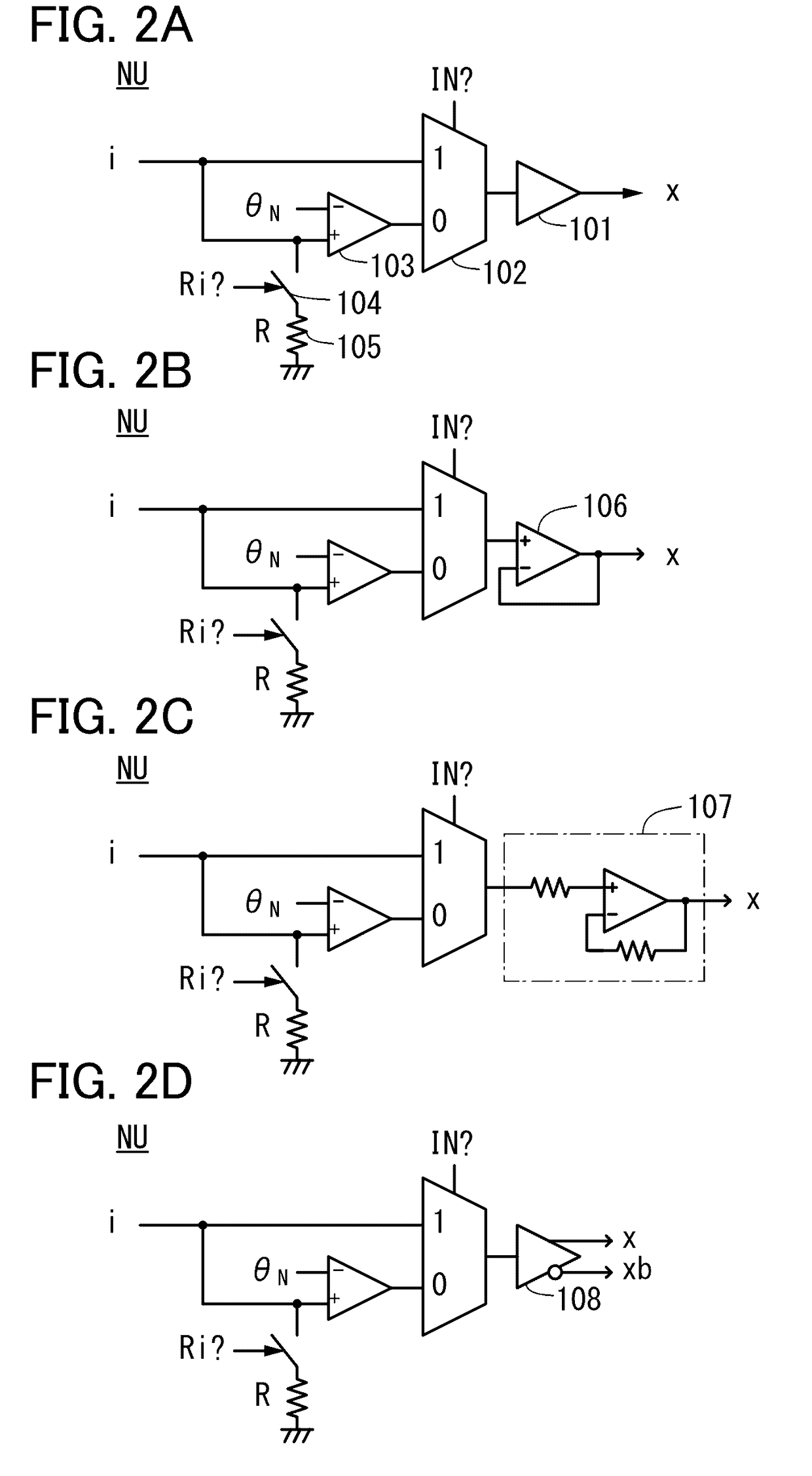

Semiconductor device and electronic device

ActiveUS20170116512A1Novel configurationReduce chip areaElectric analogue storesDigital storageSynapseNeuron circuit

A neuron circuit can switch between two functions: as an input neuron circuit, and as a hidden neuron circuit. An error circuit can switch between two functions: as a hidden error circuit, and as an output neuron circuit. A switching circuit is configured to be capable of changing the connections between the neuron circuit, a synapse circuit, and the error circuit. The synapse circuit includes an analog memory that stores data that corresponds to the connection strength between the input neuron circuit and the hidden neuron circuit or between the hidden neuron circuit and the output neuron circuit, a writing circuit that changes the data in the analog memory, and a weighting circuit that weights an input signal in reaction to the data of the analog memory and outputs the weighted output signal. The analog memory includes a transistor comprising an oxide semiconductor with extremely low off-state current.

Owner:SEMICON ENERGY LAB CO LTD

Weight adjustment circuit for variable-resistance synapses

InactiveCN102610274AImplement STDP weight adjustment functionSimple structureDigital storageSynapseNerve network

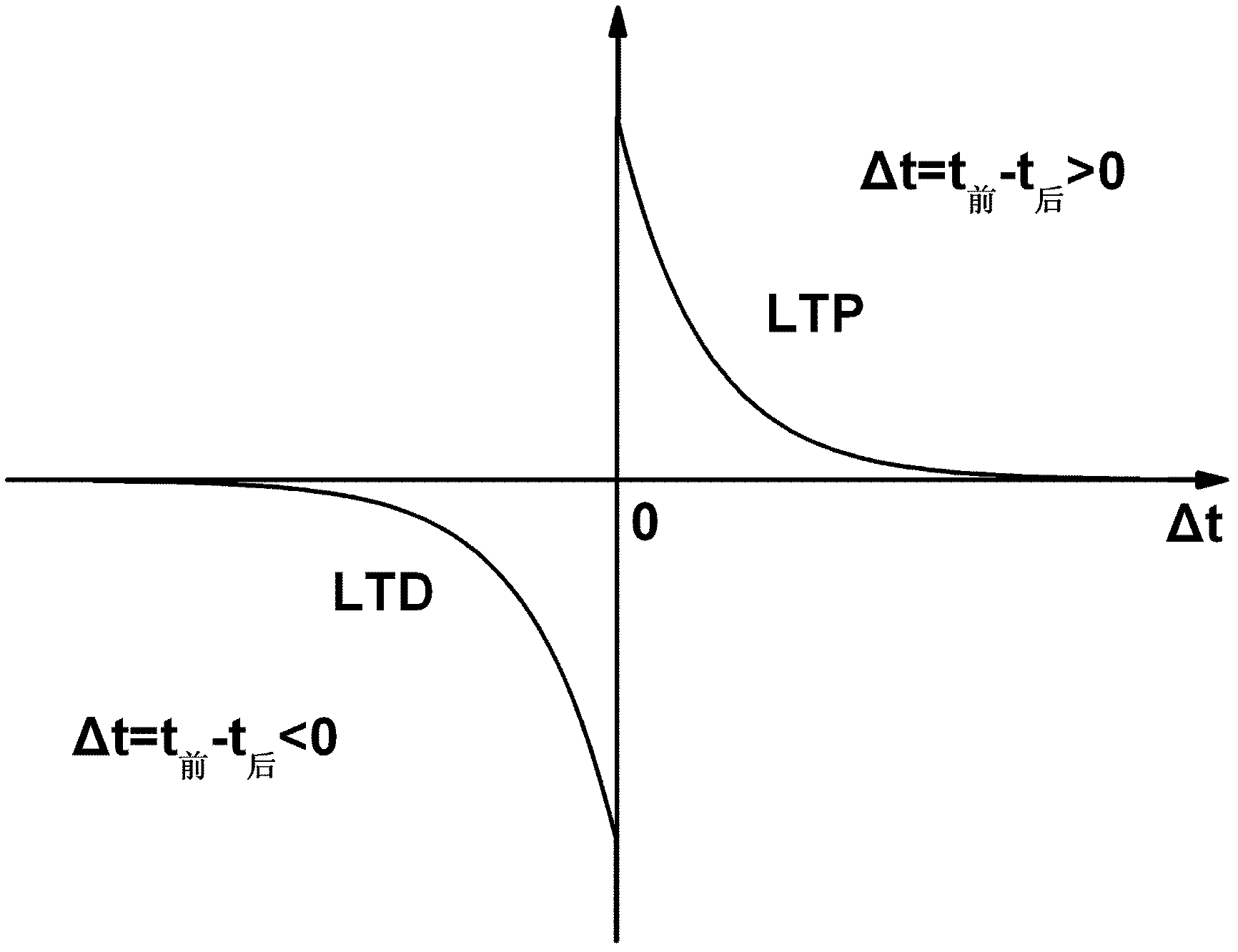

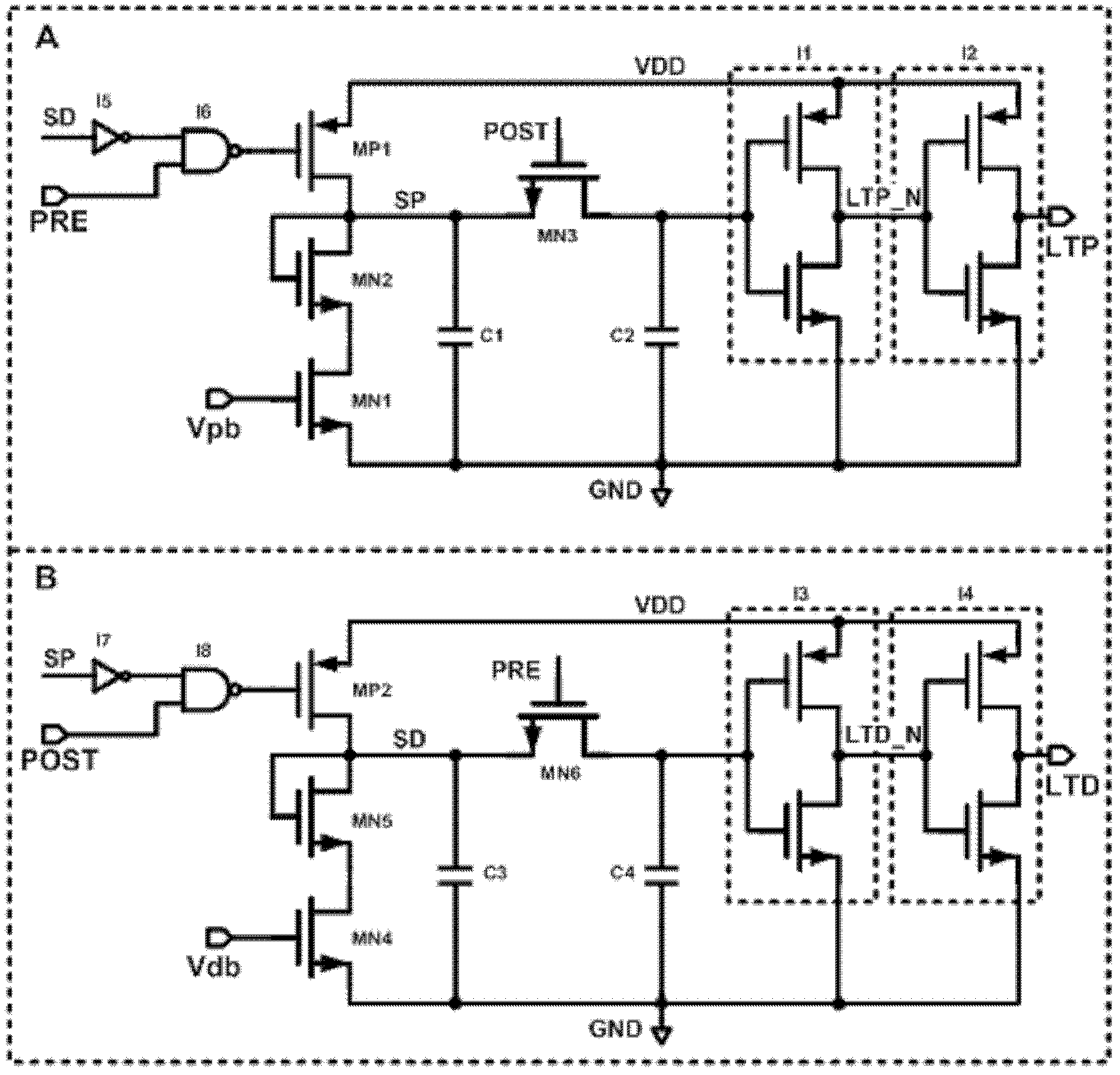

The invention discloses a weight adjustment circuit for variable-resistance synapses, which relates to the fields of integrated circuits and neural networks, and is used for carrying out weight adjustment on variable-resistance synapses. The circuit is composed of a weight enhancement adjustment subcircuit A (LTP (long term potentiation) adjustment) and a weight inhibition adjustment subcircuit B (LTD (long term depression) adjustment), wherein the two subcircuits respectively contain a charging pole, a discharging pole, a charge storage pole and an output pole. The core of the circuit is implemented by using an analog circuit mode, therefore, the number of transistors required by the circuit is greatly reduced; and meanwhile, through the setting of the bias voltage on a discharge tube in the discharge pole, the size of a weight adjustment time window can be adjusted conveniently. The circuit disclosed by the invention follows an STDP (spike timing dependent plasticity) learning rule, and LTP and LTD pulse outputs are generated according to the activities of nerve units at the two ends of the variable-resistance synapses so as to carry out corresponding weight adjustment on the variable-resistance synapses. The circuit disclosed by the invention is simple in structure, convenient in parameter adjustment, and suitable for applications, such as weight adjustment on electronic synapses of a large-scale neural network, and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com