Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

146 results about "Synaptic device" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

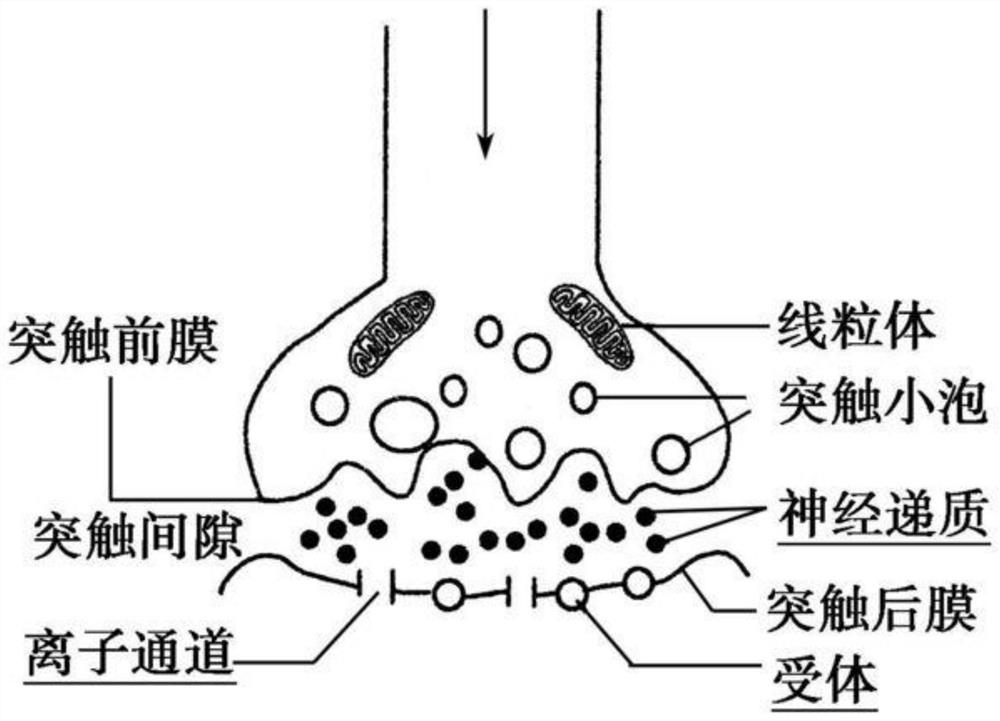

The artificial synaptic device developed by the research team is an electrical synaptic device that simulates the function of synapses in the brain as the resistance of the tantalum oxide layer gradually increases or decreases depending on the strength of the electric signals.

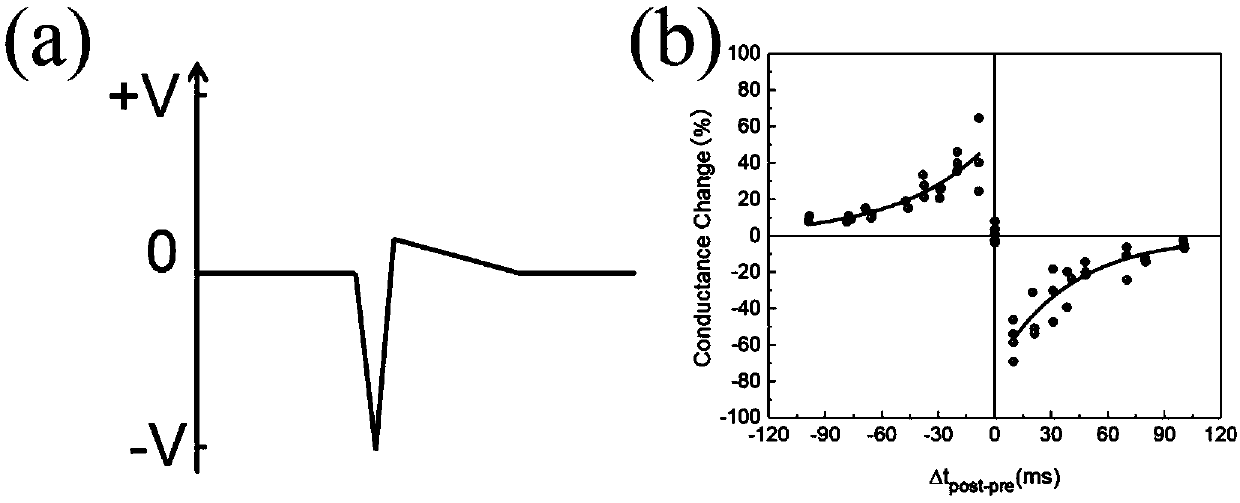

Producing spike-timing dependent plasticity in a neuromorphic network utilizing phase change synaptic devices

ActiveUS20120084241A1Digital computer detailsDigital storageSynaptic deviceSpike-timing-dependent plasticity

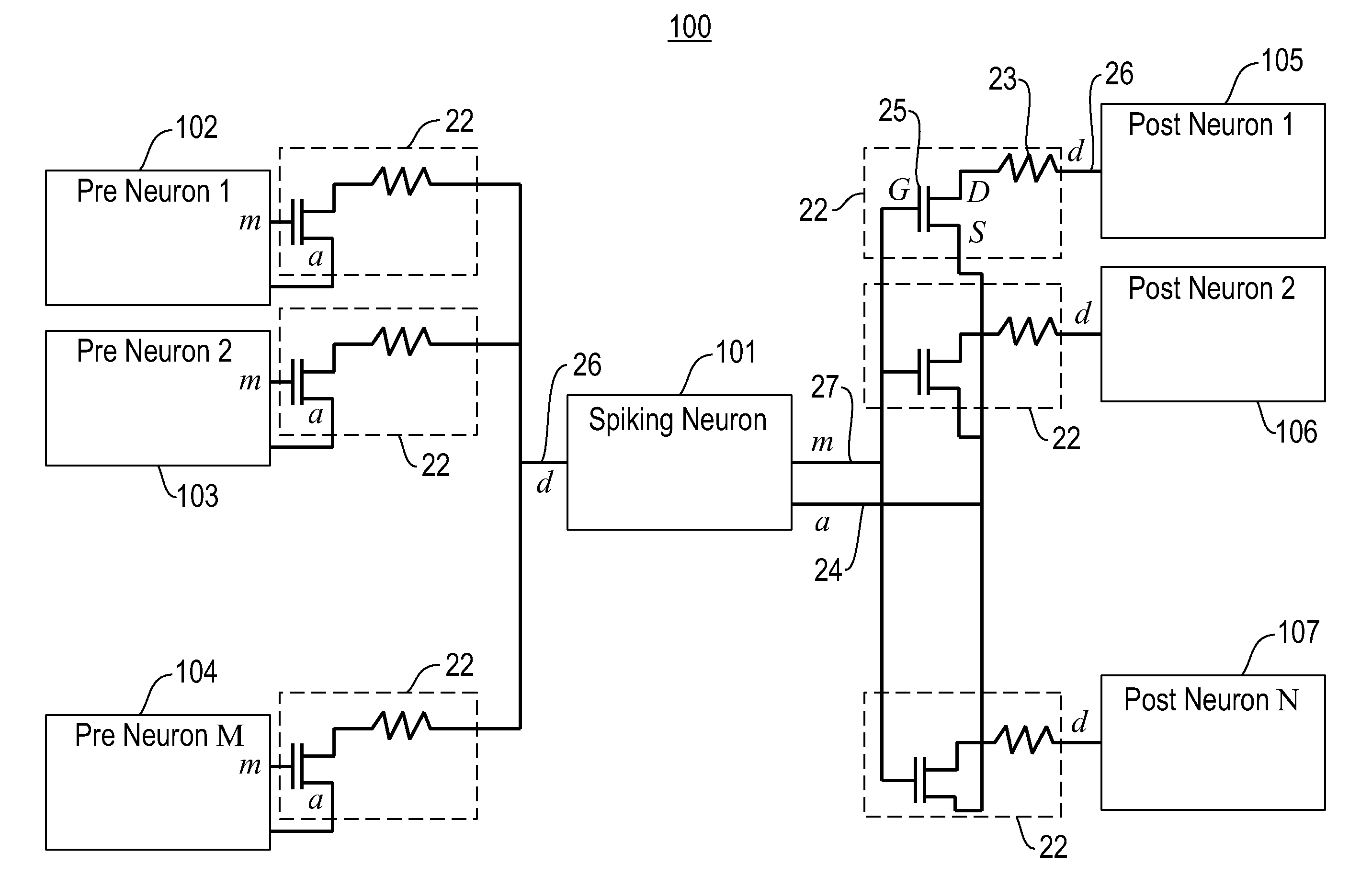

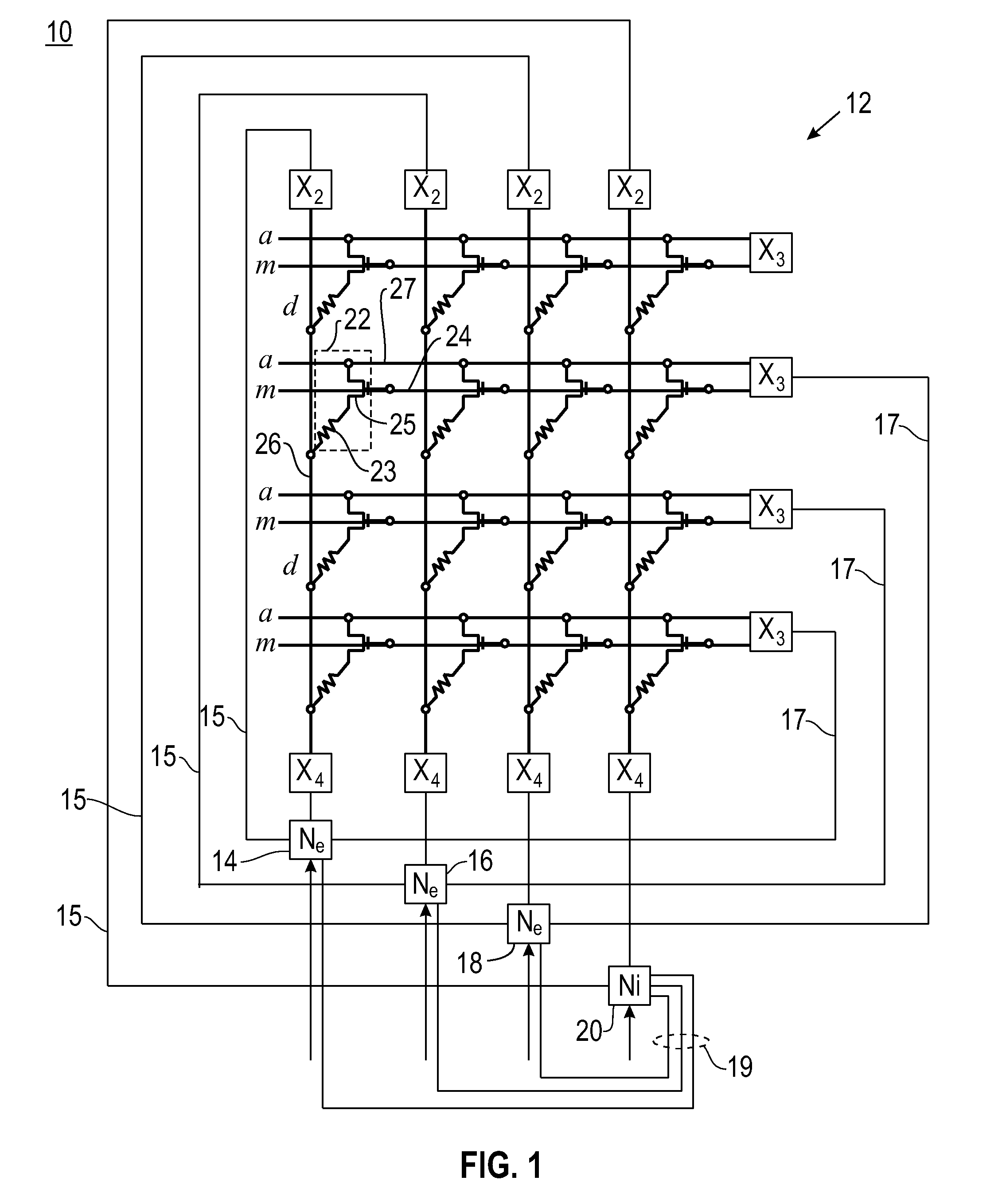

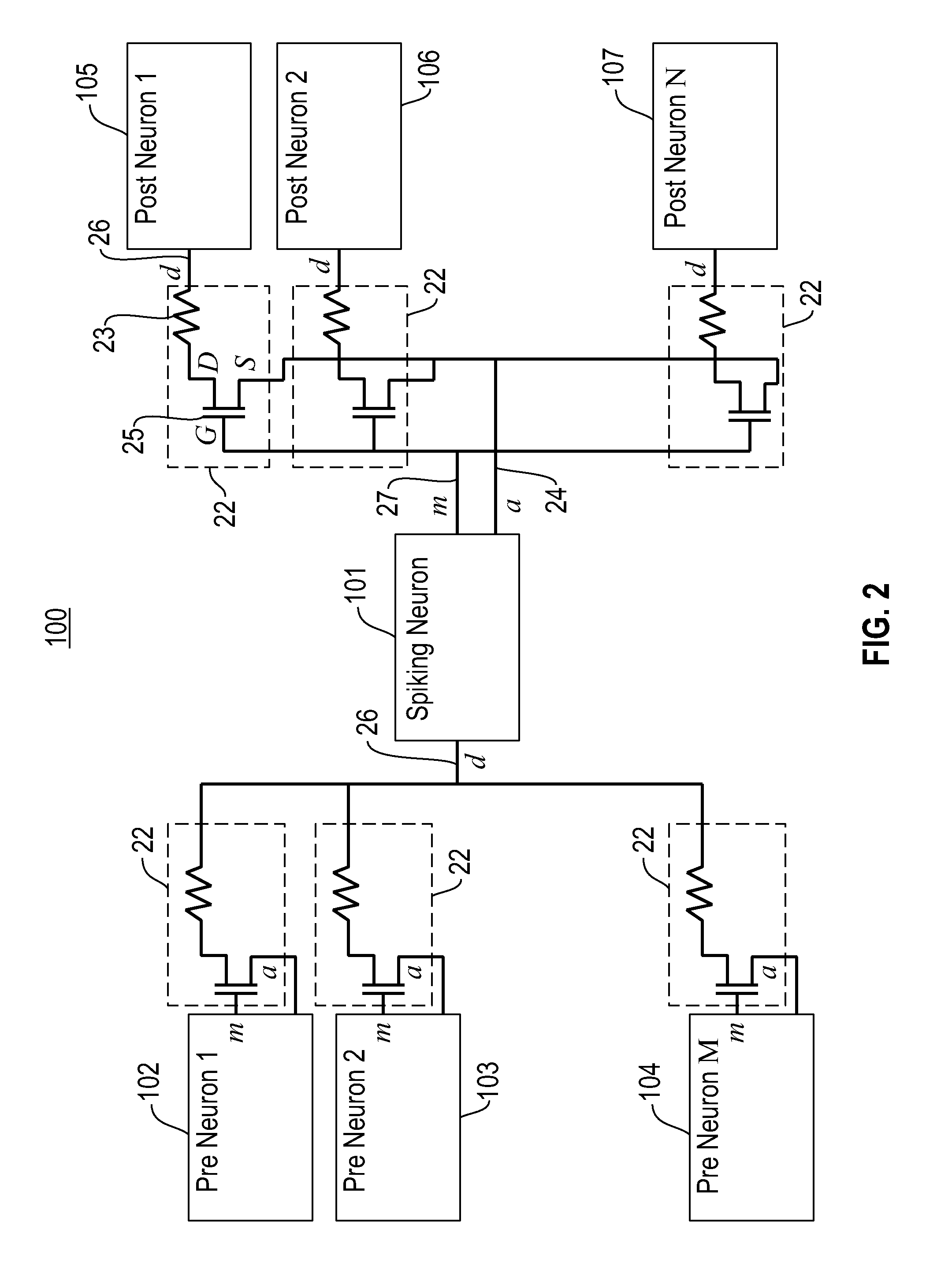

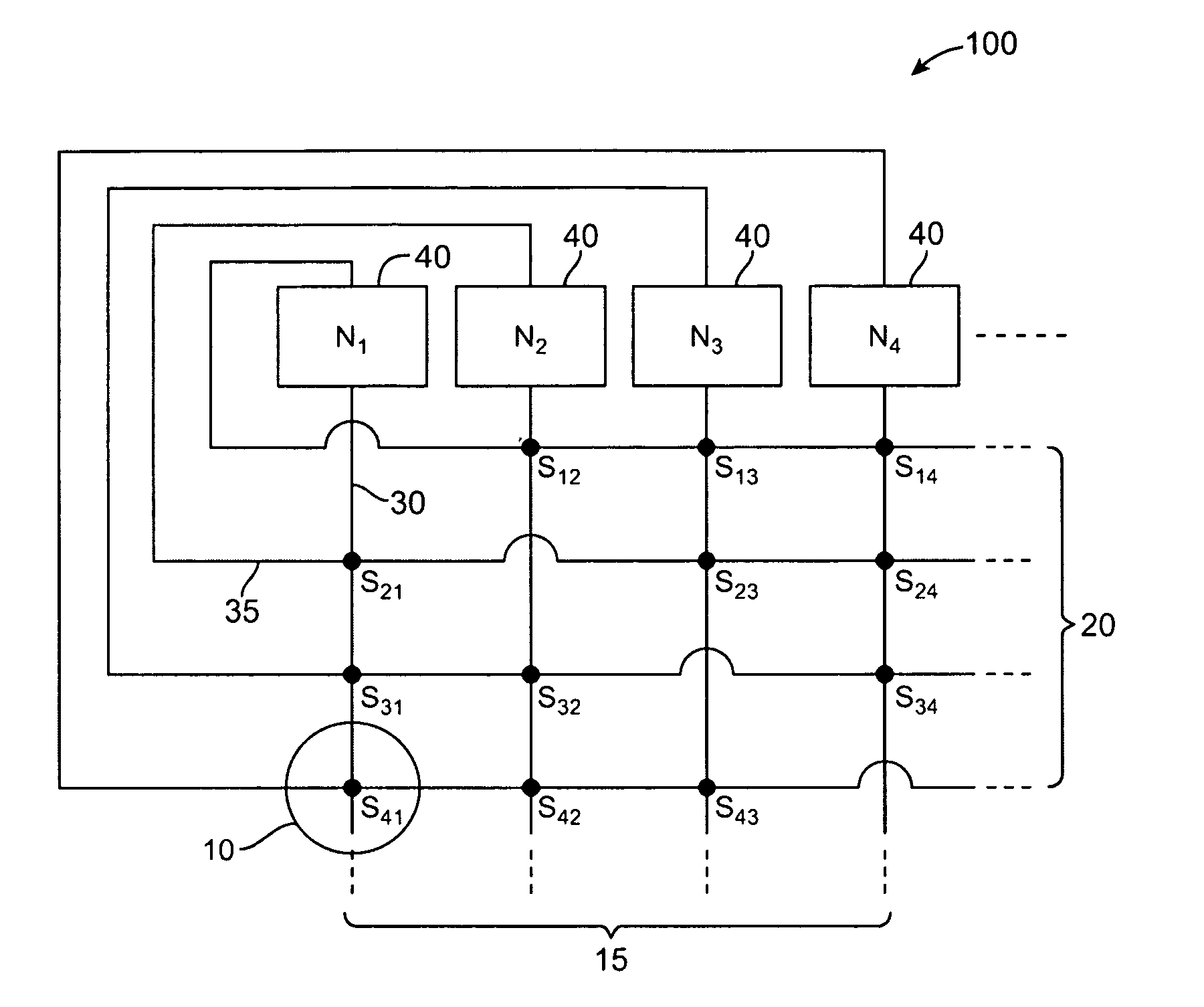

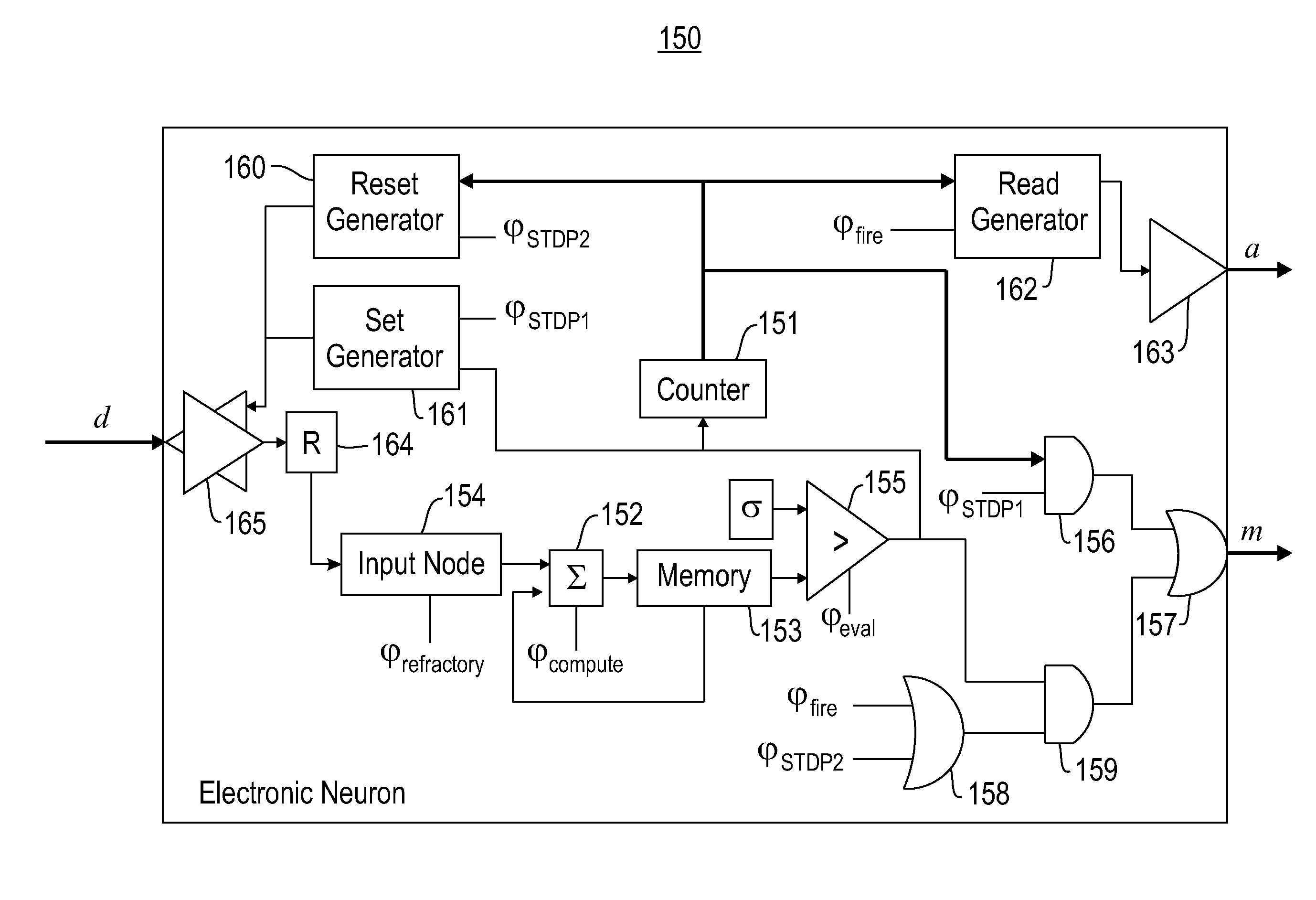

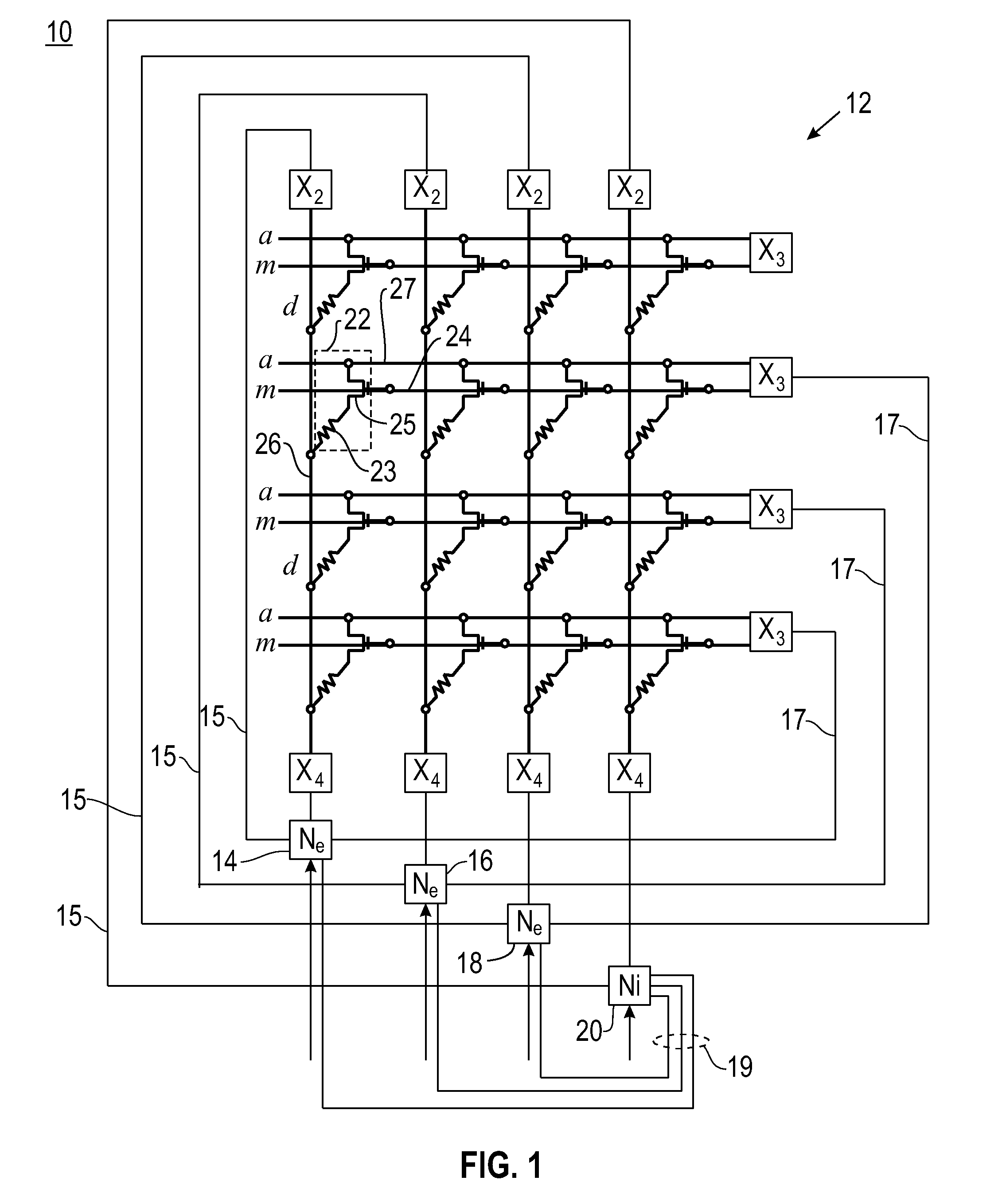

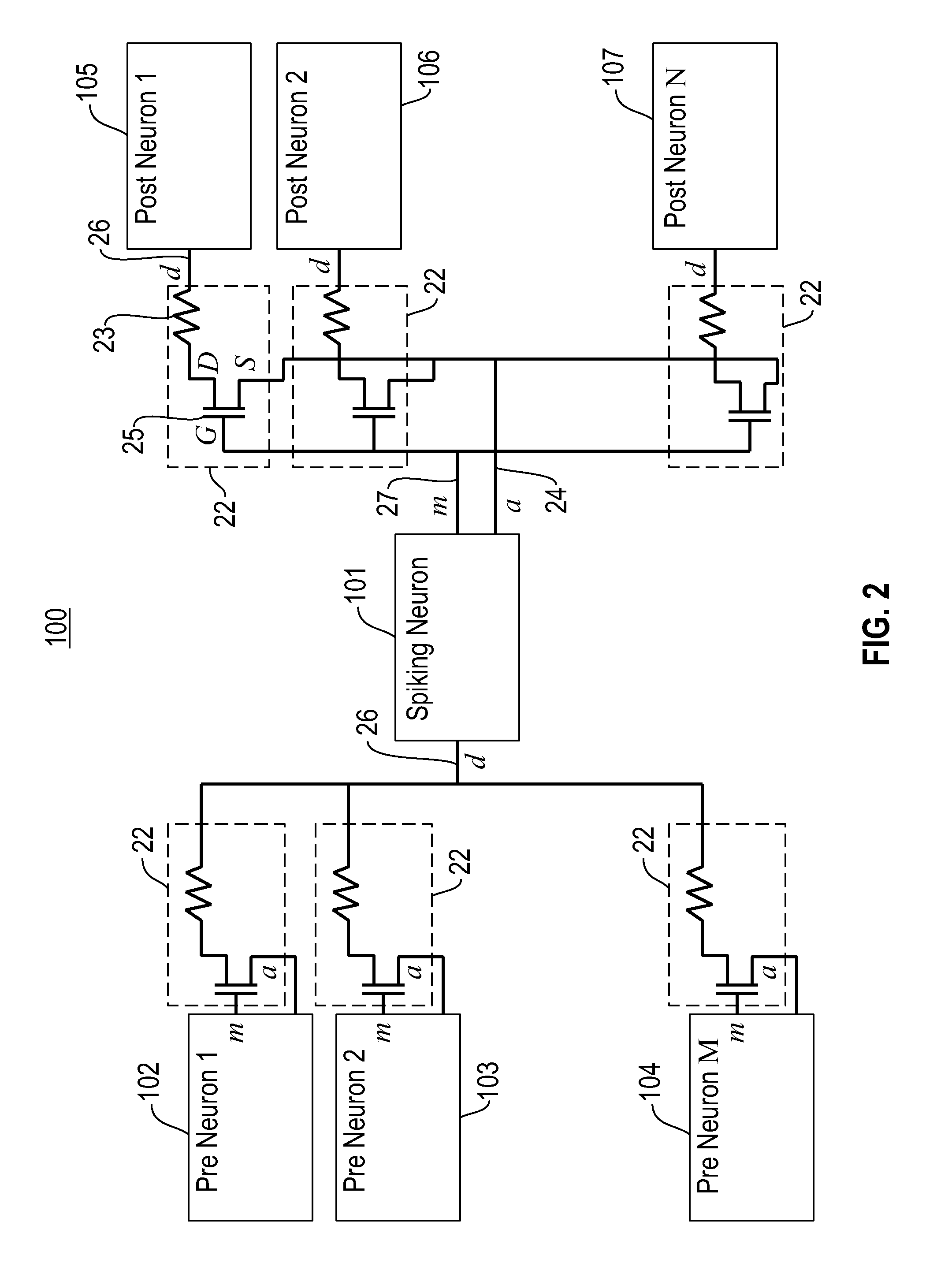

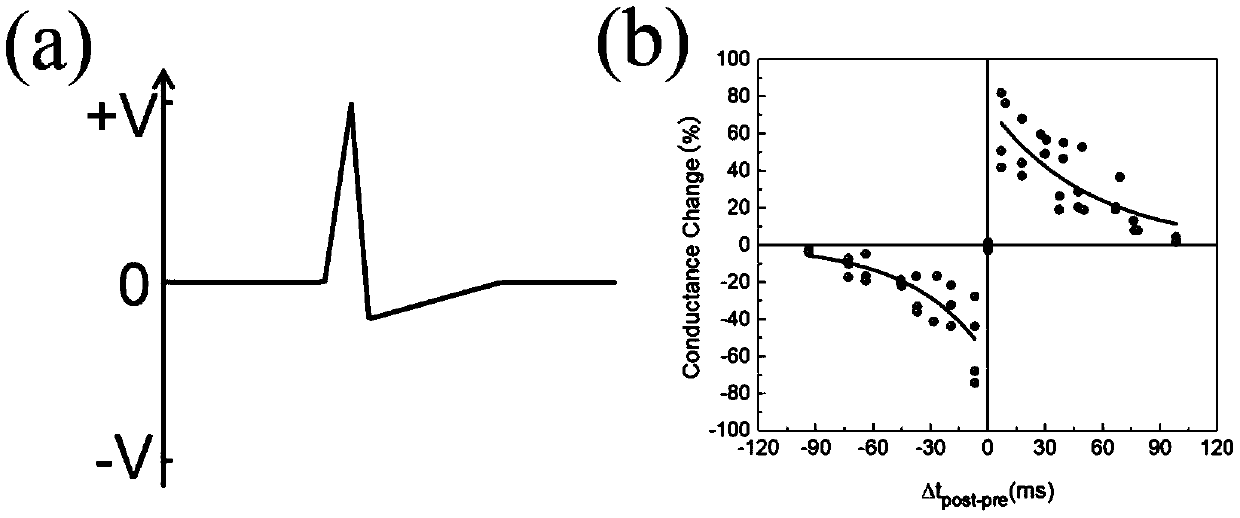

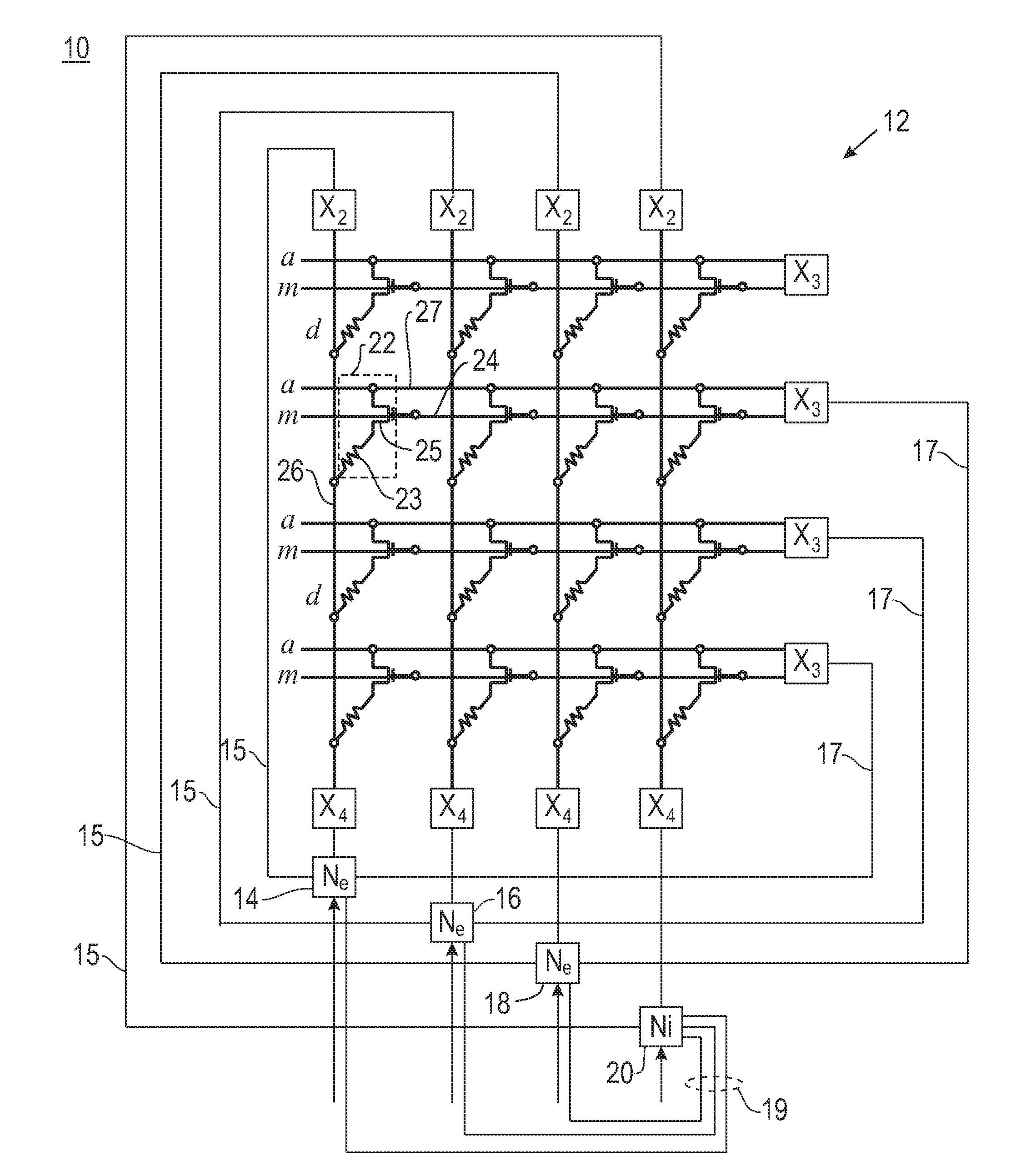

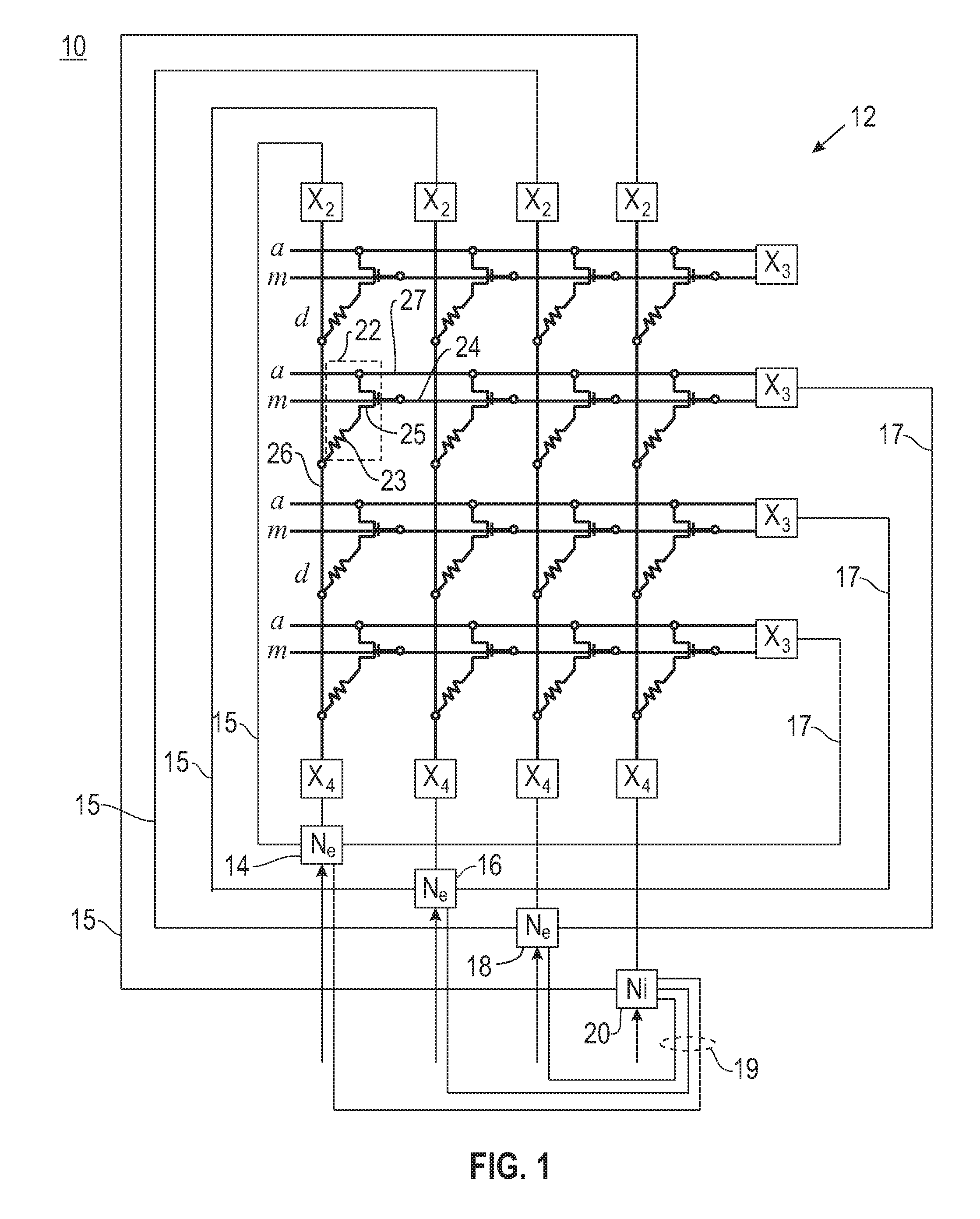

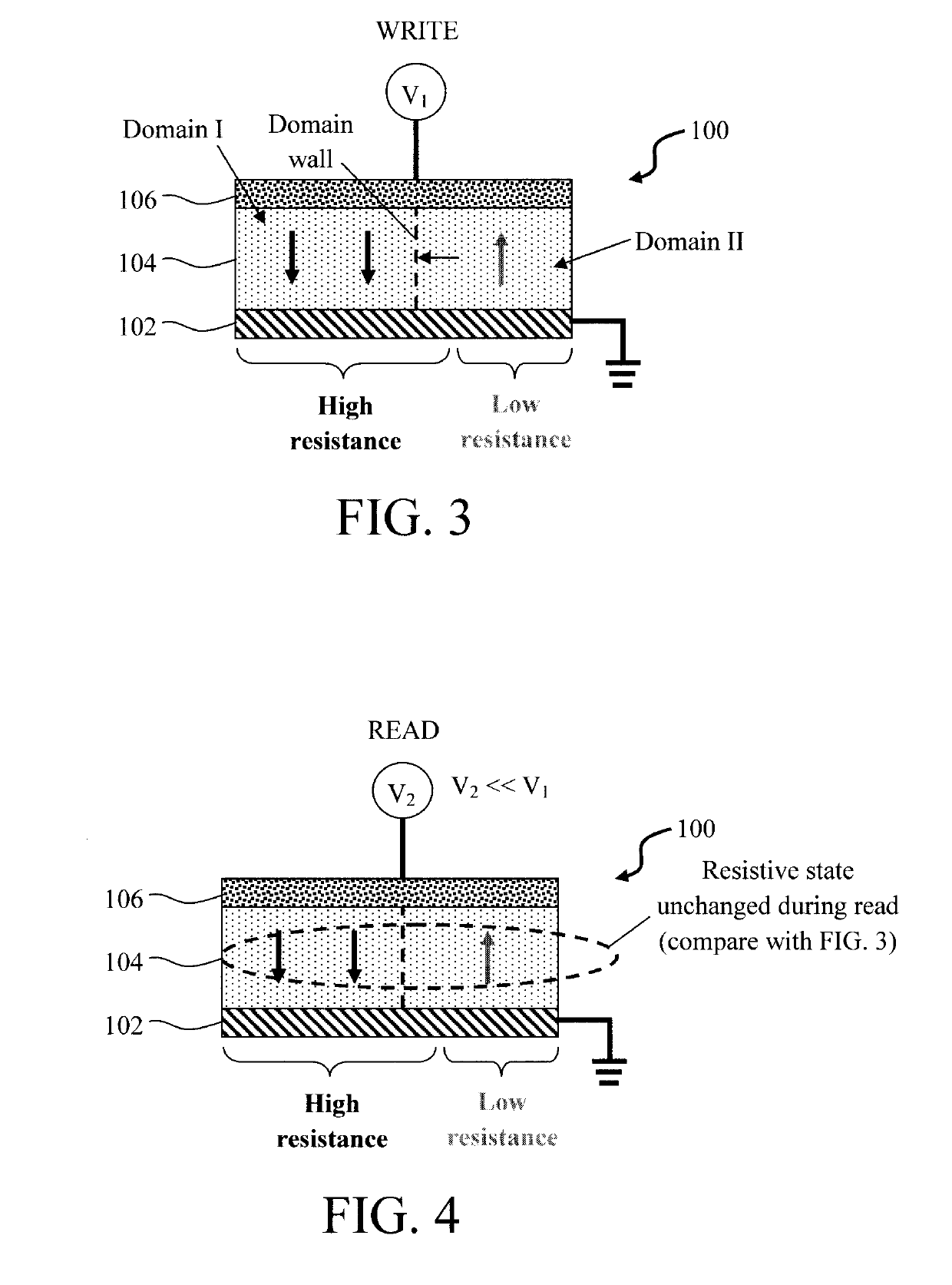

Embodiments of the invention relate to a neuromorphic network for producing spike-timing dependent plasticity. The neuromorphic network includes a plurality of electronic neurons and an interconnect circuit coupled for interconnecting the plurality of electronic neurons. The interconnect circuit includes plural synaptic devices for interconnecting the electronic neurons via axon paths, dendrite paths and membrane paths. Each synaptic device includes a variable state resistor and a transistor device with a gate terminal, a source terminal and a drain terminal, wherein the drain terminal is connected in series with a first terminal of the variable state resistor. The source terminal of the transistor device is connected to an axon path, the gate terminal of the transistor device is connected to a membrane path and a second terminal of the variable state resistor is connected to a dendrite path, such that each synaptic device is coupled between a first axon path and a first dendrite path, and between a first membrane path and said first dendrite path.

Owner:IBM CORP

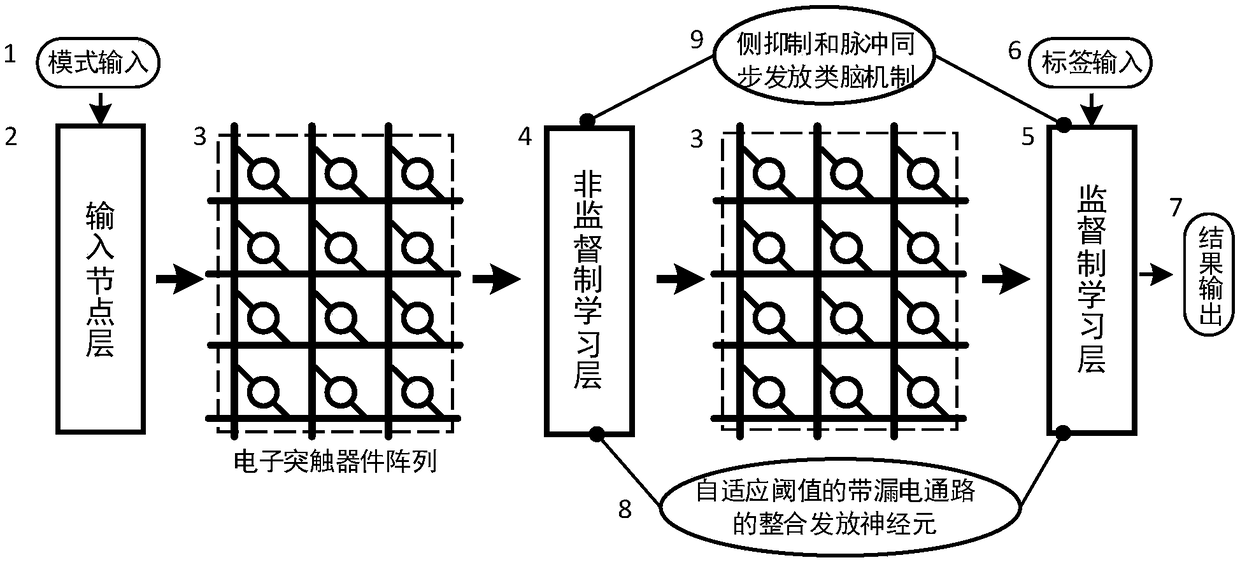

A hardware impulse neural network system

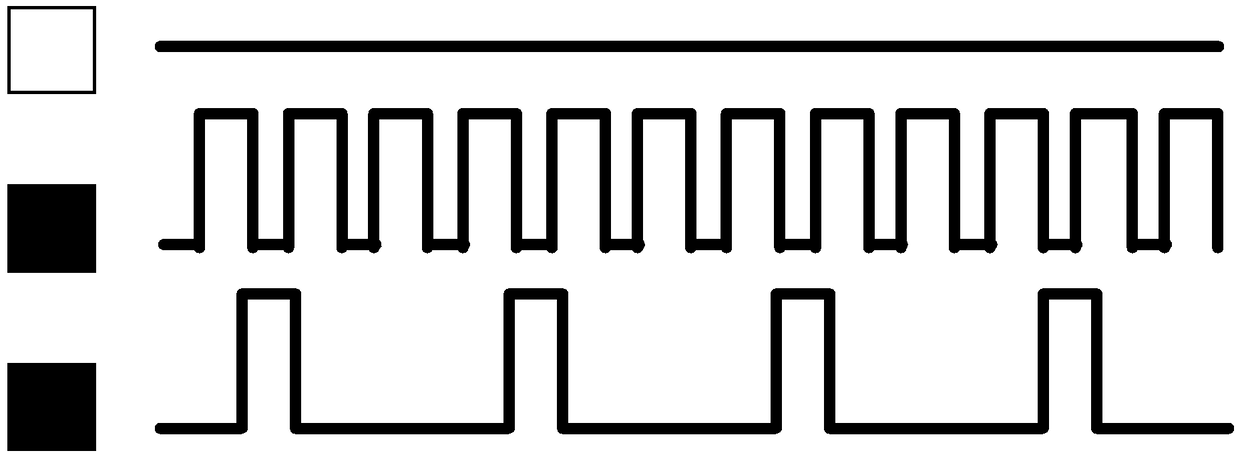

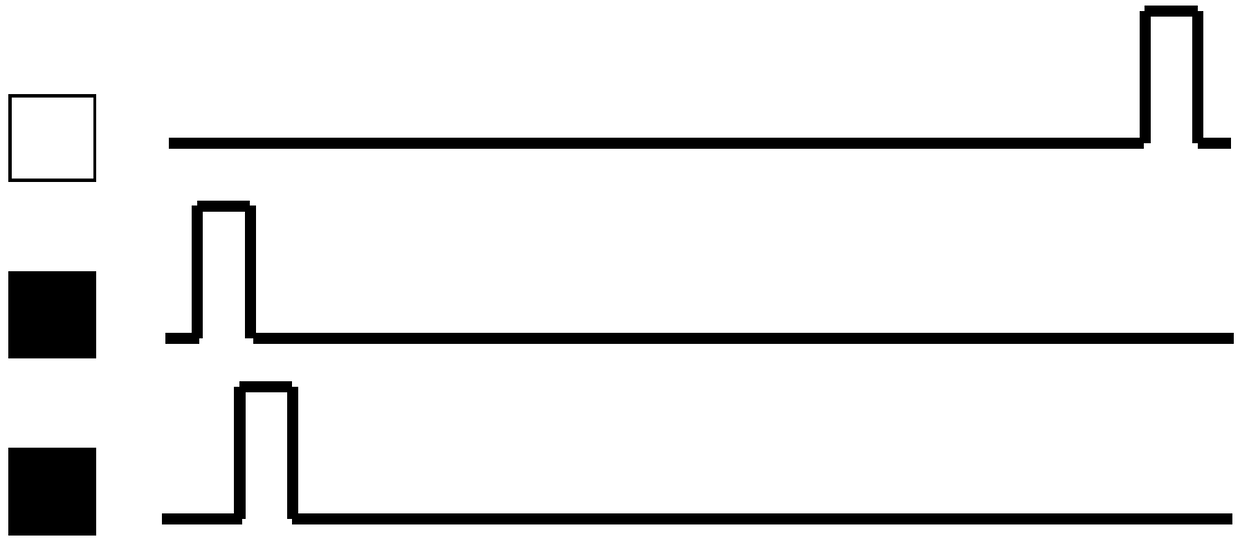

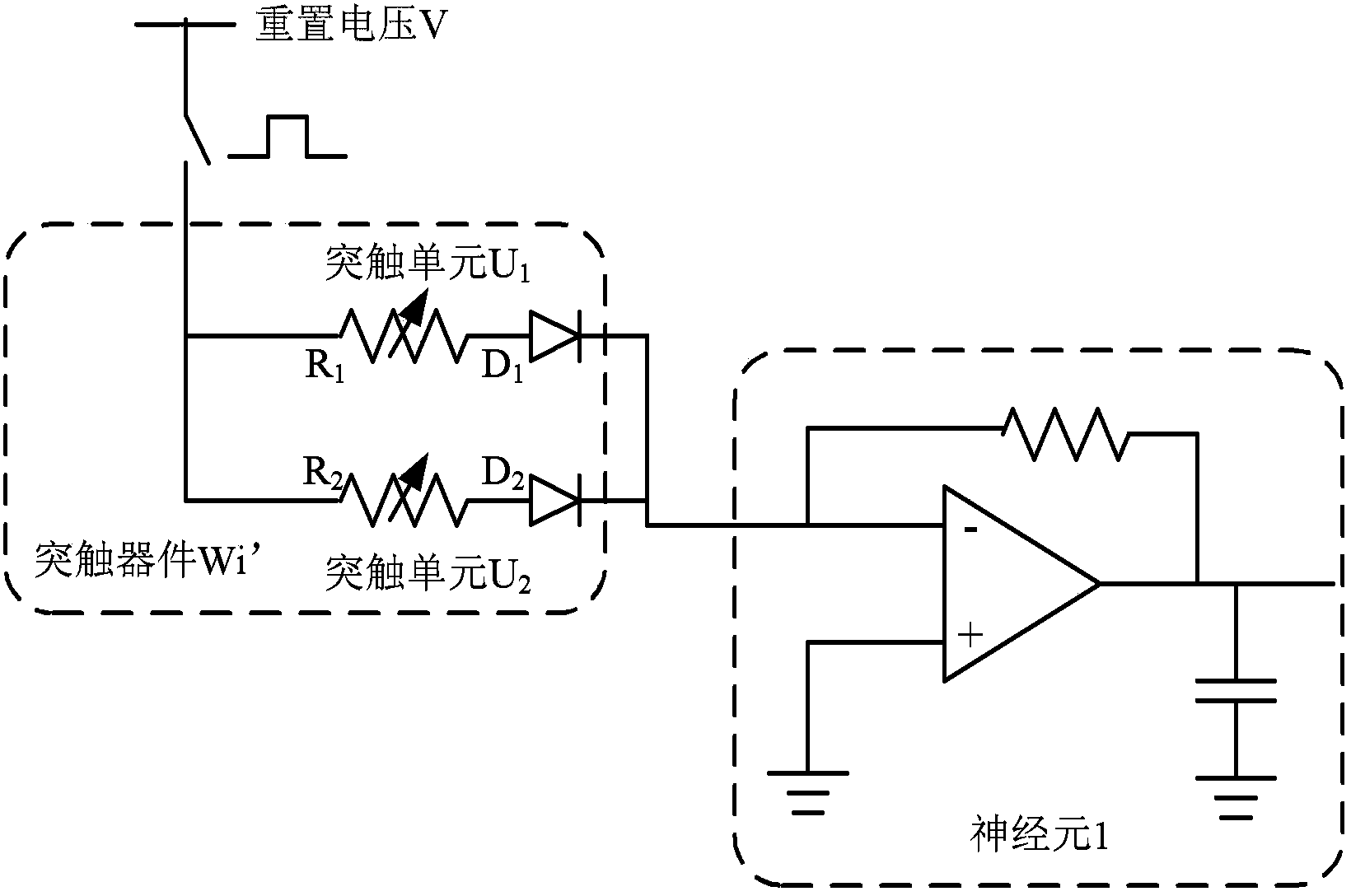

ActiveCN108985447AEasy to identifyImprove robustnessPhysical realisationNeural network systemSynaptic weight

The invention discloses a hardware impulse neural network system, comprising: an input node layer and an unsupervised learning layer are connected through a synaptic connection unit in a neuron full connection mode; the unsupervised learning layer and the supervised learning layer are connected through another synaptic connection unit in a neuron full connection mode; the input node layer and theunsupervised learning layer are connected through a synaptic connection unit in a synaptic connection mode. The input node layer realizes the information input under different coding modes, the non-supervisory learning layer adopts the non-supervisory learning mode, and the supervisory learning layer adopts the supervisory learning mode. A synaptic connection unit is realized by an electronic synaptic device, so that that synaptic connection unit has a pulse time dependent plasticity STDP. The synaptic array unit receives as presynaptic pulses the stimulation signals from the neurons in the front layer and the postsynaptic pulses the action potential pulses excited by the neurons in the back layer. The time difference between the presynaptic pulses and the postsynaptic pulses determines the synaptic weight adjustment amount of the synaptic connection unit. The neural network system provided by the invention has a wide application value.

Owner:HUAZHONG UNIV OF SCI & TECH

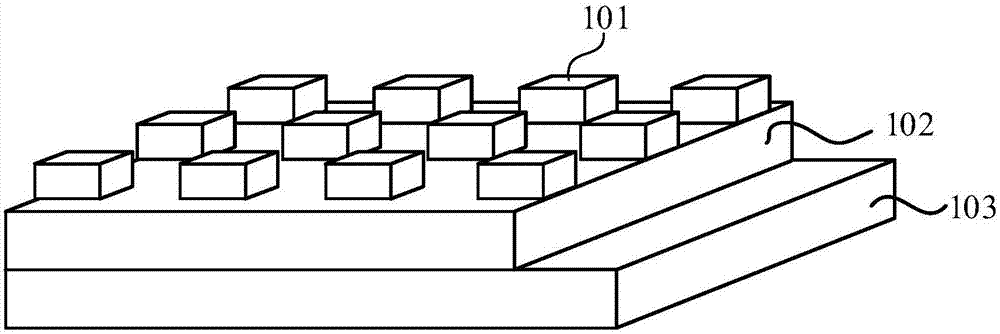

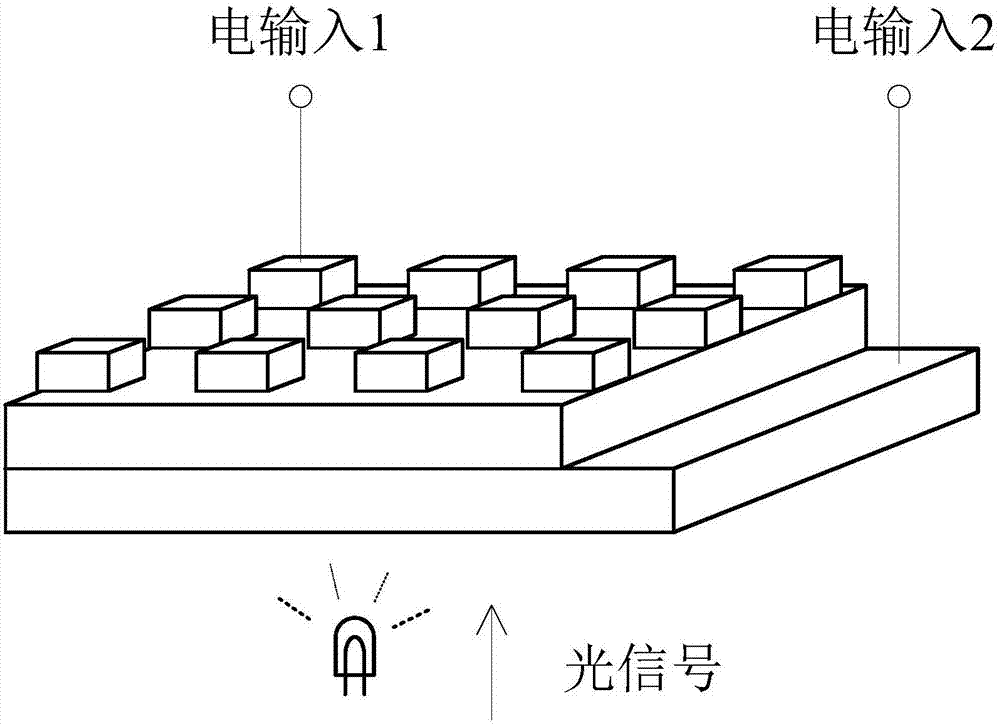

Artificial synaptic device based on photoelectric coupling memristor and modulation method of artificial synapse device

The invention discloses an artificial synaptic device based on a photoelectric coupling memristor and a modulation method of the artificial synaptic device. The artificial synaptic device comprises an upper electrode, a lower electrode and a functional material layer, wherein the functional material layer is arranged between the upper electrode and the lower electrode, the upper electrode, the functional material layer and the lower electrode jointly form a sandwich structure, the functional material layer is made of a material having a photoelectric effect, the lower electrode is a transparent conductive electrode, an electrical signal is input through the upper electrode and the lower electrode, and an optical signal is input through the transparent conductive electrode. In the artificial synaptic device provided by the invention, light is introduced as a control signal of the other end except the electrical signal, two control ends of the artificial synapse device are expanded to three ends, the artificial synaptic device can generate resistance change under an external optical excitation signal by the additionally-arranged end, the artificial synaptic device can be configured to be in a plurality of resistance states correspondingly by selection and control of intensity, frequency and optical pulse time of the optical excitation signal, and various synaptic plasticity functions are correspondingly achieved.

Owner:HUAZHONG UNIV OF SCI & TECH

Electronic synapse

An electronic synapse device is provided. One embodiment of the invention includes a metastable switching synaptic device. Changing conductance of the metastable switching synaptic device occurs by receiving opposite signed first and second voltage pulses at the metastable switching synaptic device where magnitude of the first voltage pulse and the second voltage pulse each are below a switching voltage magnitude threshold. A magnitude difference between the first voltage pulse and the second voltage pulse exceeds the switching voltage magnitude threshold by an amount, wherein the amount is a function of a relative timing between the first voltage pulse and the second voltage pulse.

Owner:IBM CORP

Producing spike-timing dependent plasticity in a neuromorphic network utilizing phase change synaptic devices

ActiveUS9269042B2Digital computer detailsDigital storageSynaptic deviceSpike-timing-dependent plasticity

Owner:INT BUSINESS MASCH CORP

Synaptic device for artificial neural network and artificial neural network

The invention provides a synaptic device for an artificial neural network. The artificial neural network comprises multiple neurons which are connected through a synaptic device array, the synaptic device array comprises multiple synaptic devices, and two or three or more synaptic devices are connected in parallel. The invention further provides the artificial neural network including the synaptic devices.

Owner:PEKING UNIV

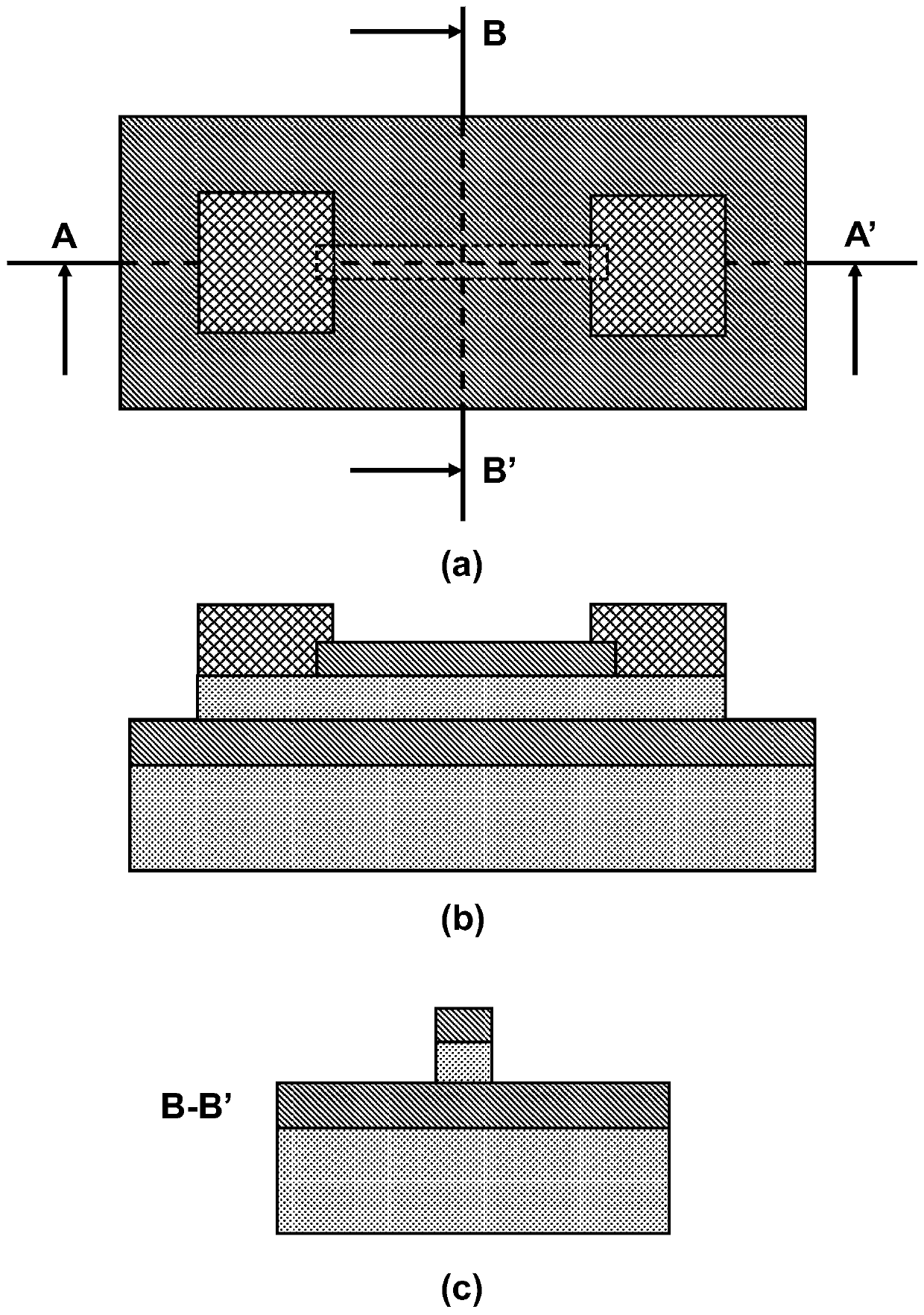

Synaptic transistor, synaptic device, manufacturing method of synaptic transistor and synaptic device, and operation array

ActiveCN110246891AMiniaturizationEasy to integrateSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsMiniaturization

The invention provides a synaptic transistor, a synaptic device, a manufacturing method of the synaptic transistor and the synaptic device, and an operation array. The material of a channel layer of the device or the transistor is a semiconductor material with ferroelectric characteristics. By use of ferroelectric characteristics of a semiconductor material, a voltage is applied to the channel layer through a grid electrode or a source electrode and a drain electrode, so the ferroelectric domain in the channel layer is polarized and overturned and the conductivity of the channel layer is changed due to the change of the ferroelectric domain. Thus, the synaptic behaviors can be simulated through the change of the conductivity, so it is achieved that one synaptic behavior is simulated by using one transistor or device, the miniaturization and integration of the chip are facilitated, compatibility with the existing silicon-based technology is achieved, and the power consumption can be reduced.

Owner:PEKING UNIV

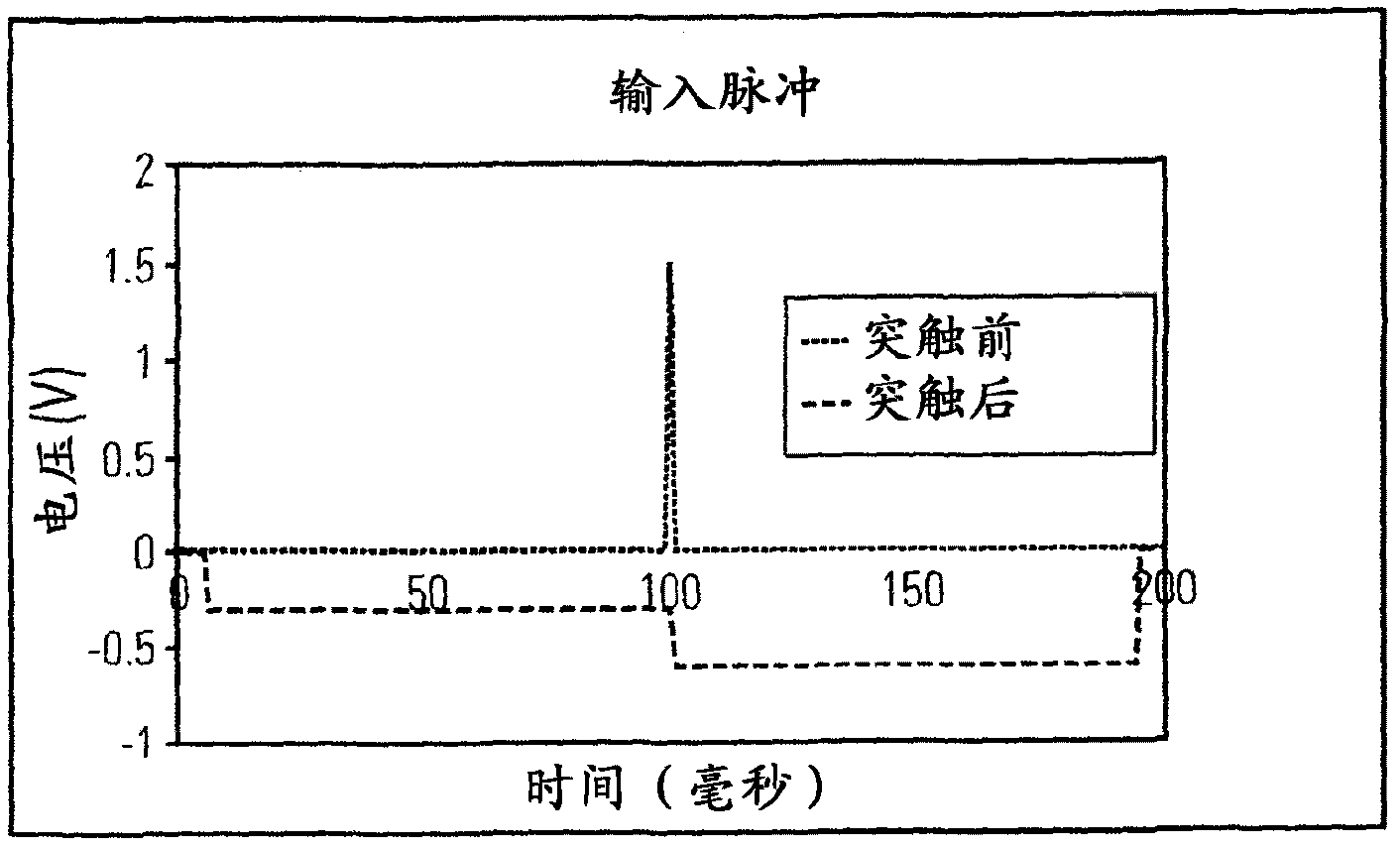

Electronic learning synapse with spike-timing dependent plasticity using unipolar memory-switching elements

According to embodiments of the invention, a system, method and computer program product producing spike-dependent plasticity in an artificial synapse. In an embodiment, a method includes: receiving a pre-synaptic spike in an electronic component; receiving a post-synaptic spike in the electronic component; in response to the pre-synaptic spike, generating a pre-synaptic pulse that occurs a predetermined period of time after the received pre-synaptic spike; in response to the post-synaptic spike, generating a post-synaptic pulse that starts at a baseline value and reaches a first voltage value a first period of time after the post-synaptic spike, followed by a second voltage value a second period of time after the post synaptic spike, followed by a return to the baseline voltage a third period of time after the post-synaptic spike; applying the generated pre-synaptic pulse to a pre-synaptic node of a synaptic device that includes a uni-polar, two-terminal bi-stable device in series with a rectifying element; and applying the generated post-synaptic pulse to a post-synaptic node of the synaptic device, wherein the synaptic device changes from a first conductive state to a second conductive state based on the value of input voltage applied to its pre and post-synaptic nodes, wherein the resultant state of the conductance of the synaptic device after the pre- and post-synaptic pulses are applied thereto depends on the relative timing of the received pre-synaptic spike with respect to the post synaptic spike.

Owner:IBM CORP

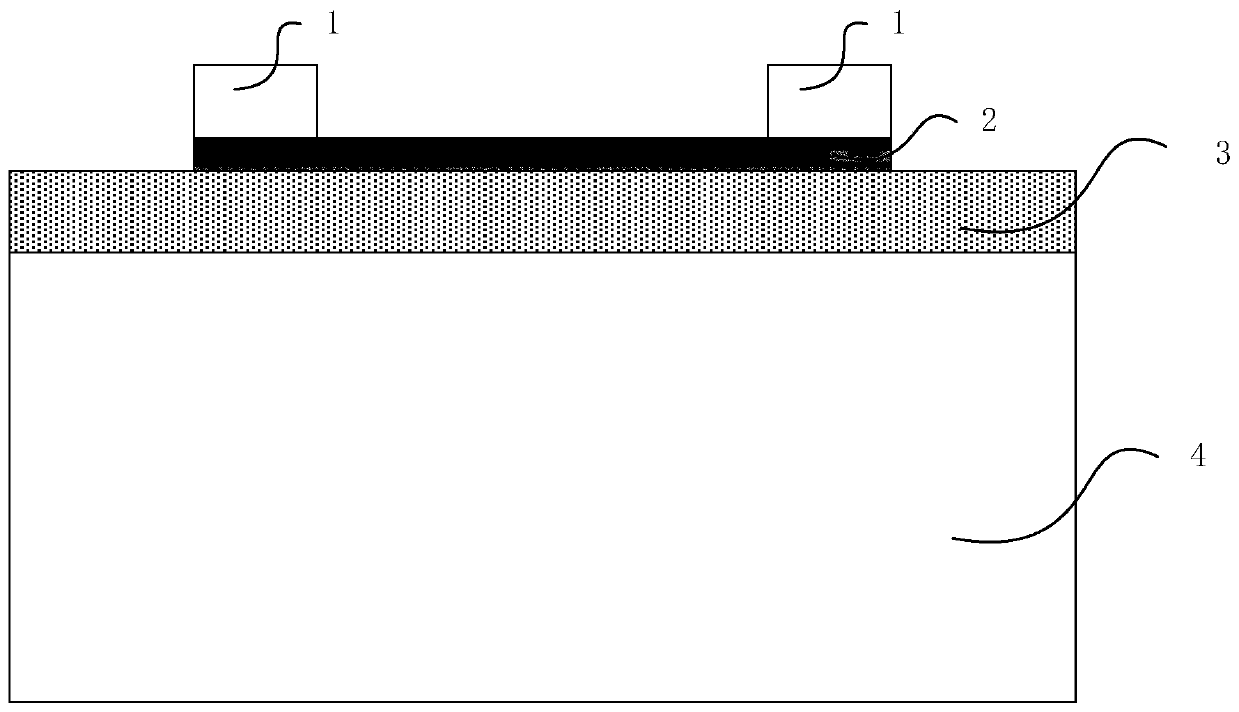

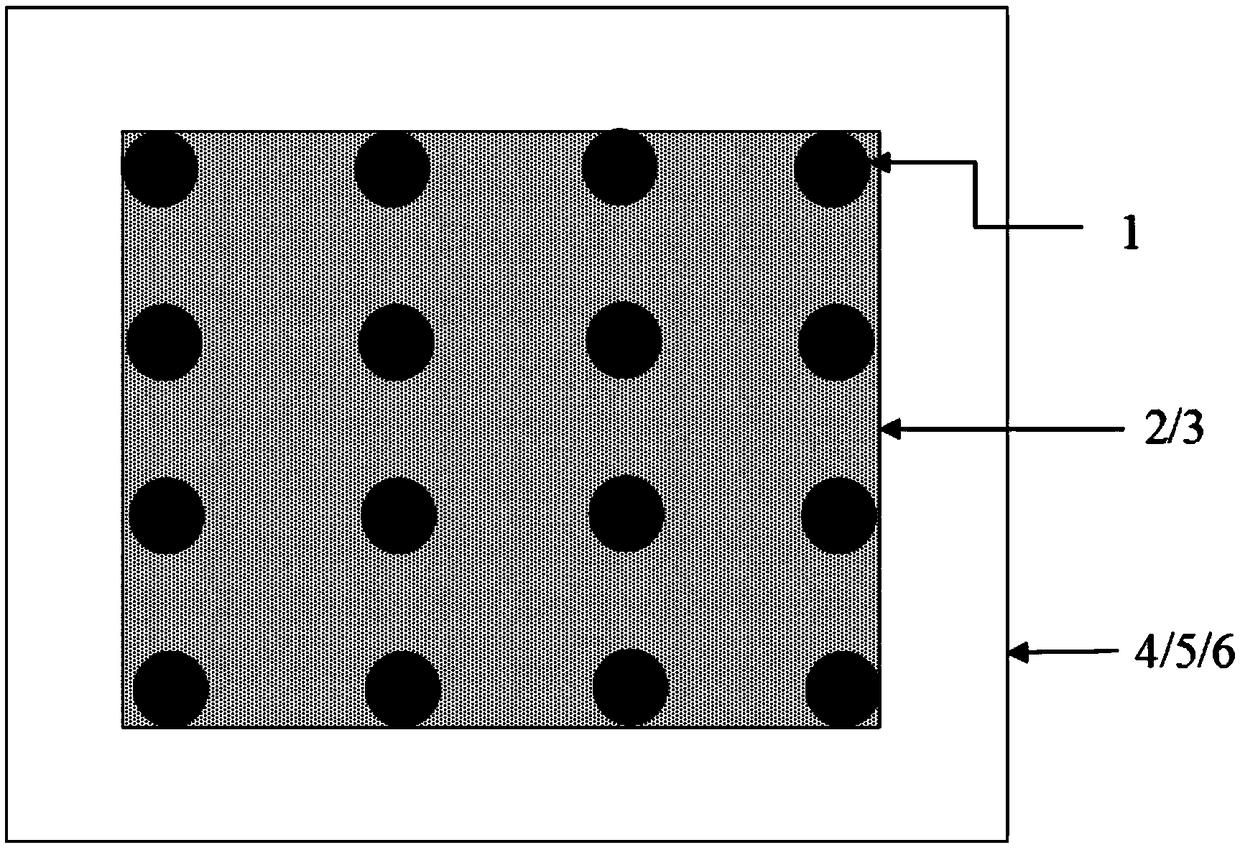

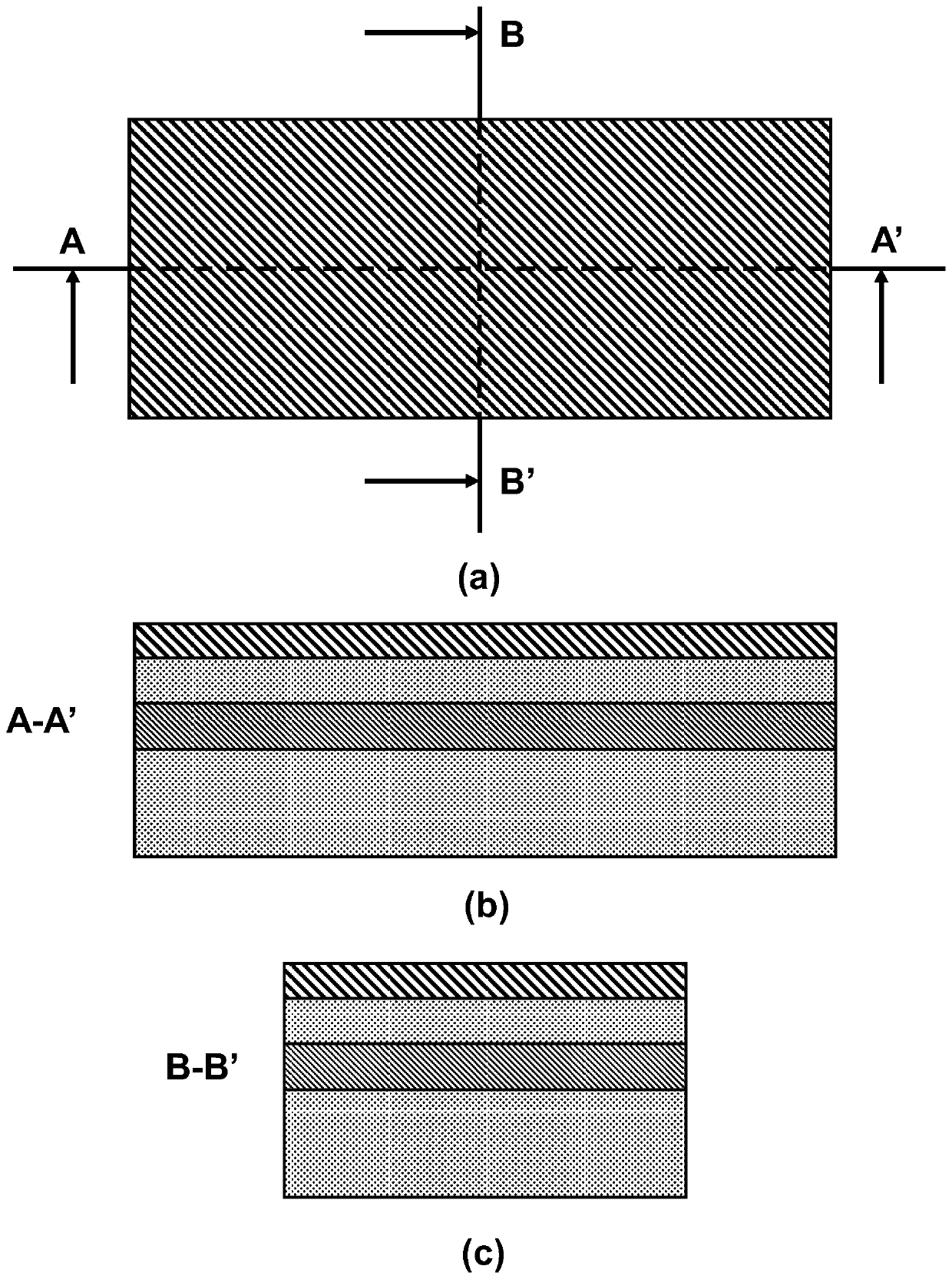

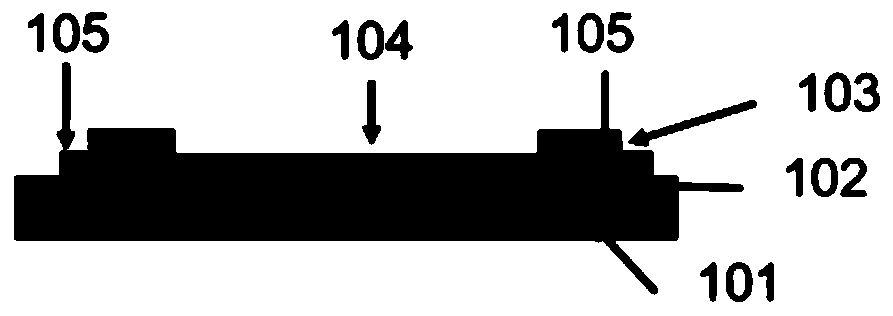

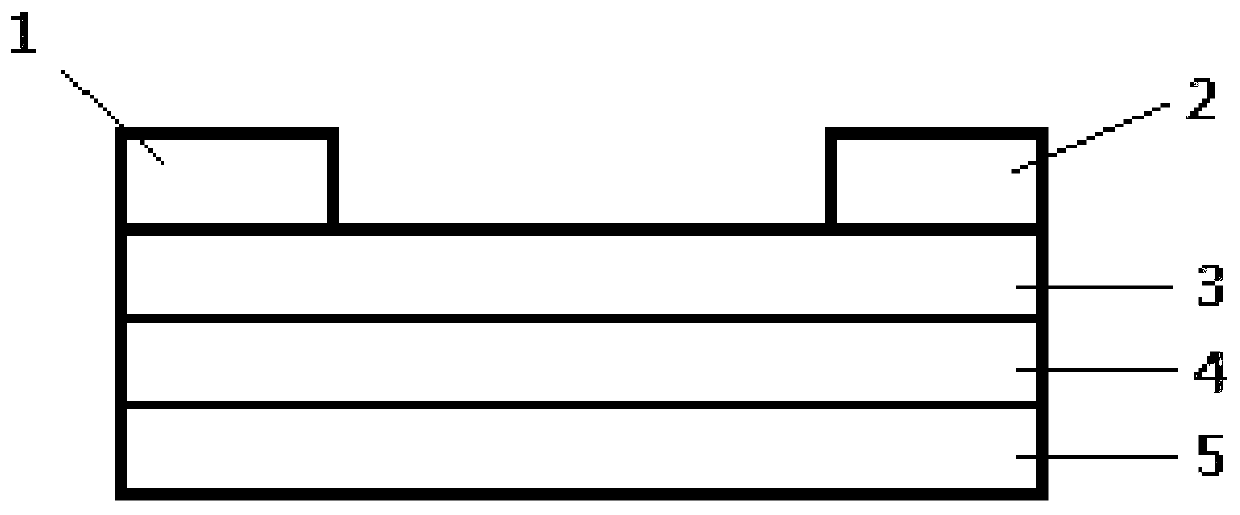

Bionic synaptic device, manufacturing method and application thereof

The invention discloses a bionic synaptic device and a manufacturing method and application thereof. Specifically, the invention relates to the bionic synaptic device with spike-time-dependent plasticity learning behaviors. The bionic synaptic device includes a gate electrode (2), wherein the square resistance of the gate electrode is 30 to 800 omega. The gate electrode is used as the synaptic front end of the bionic synaptic device. The device further includes a gate dielectric layer (3) which comprises a solid electrolyte with a proton conductive property, a channel (4), wherein the channellayer is used as the synaptic rear end of the bionic synaptic device. The device further includes a source (5a) and a drain (5b). According to the bionic synaptic device, different linear spike-time-dependent plasticity learning behaviors can be realized on a single device; the circuit design is greatly simplified; and the device has important application prospects in the fields of neuromorphic devices, artificial intelligence and the like.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

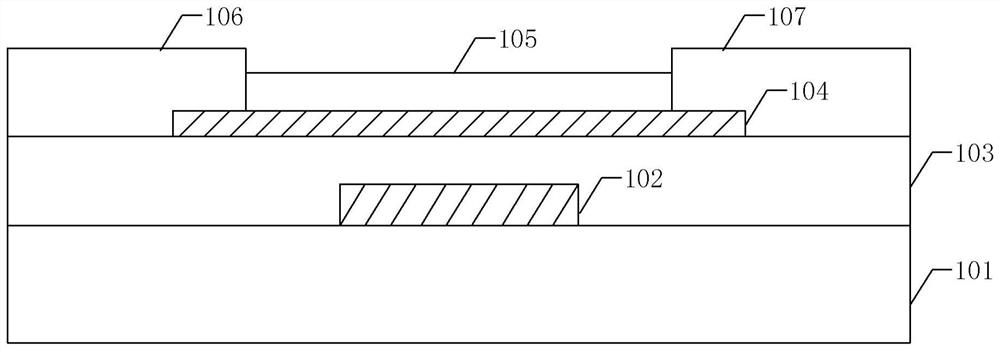

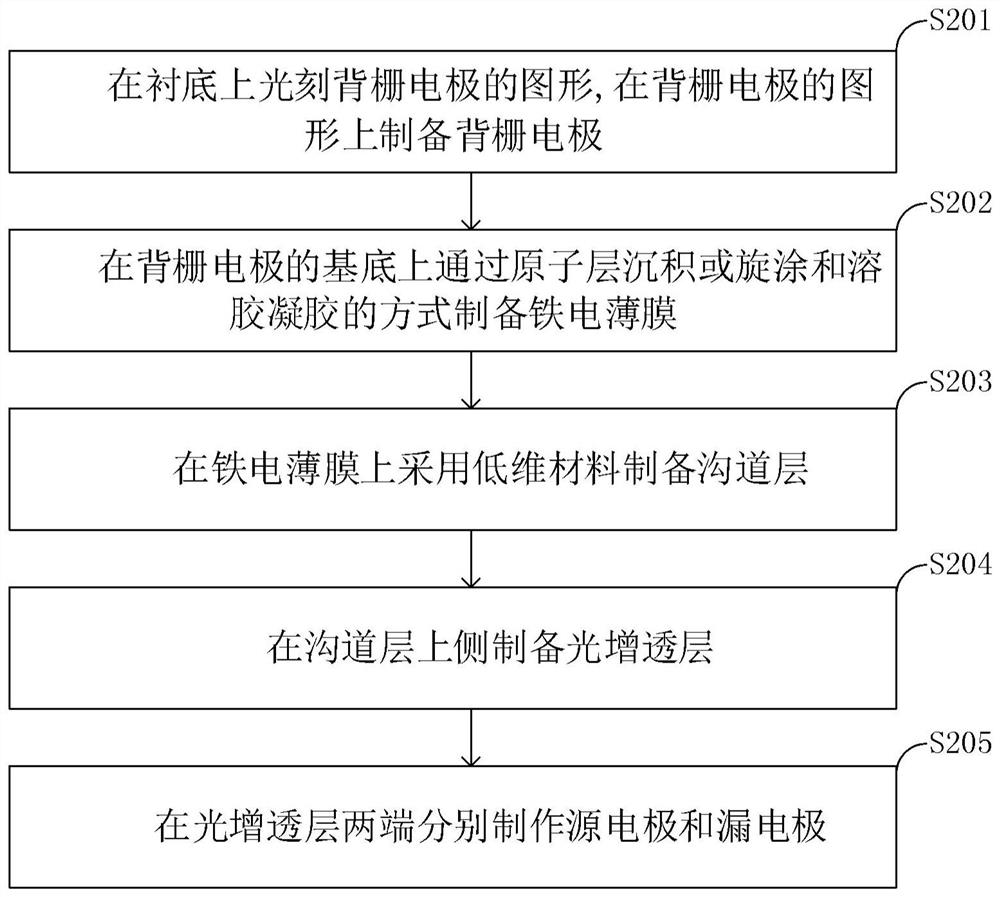

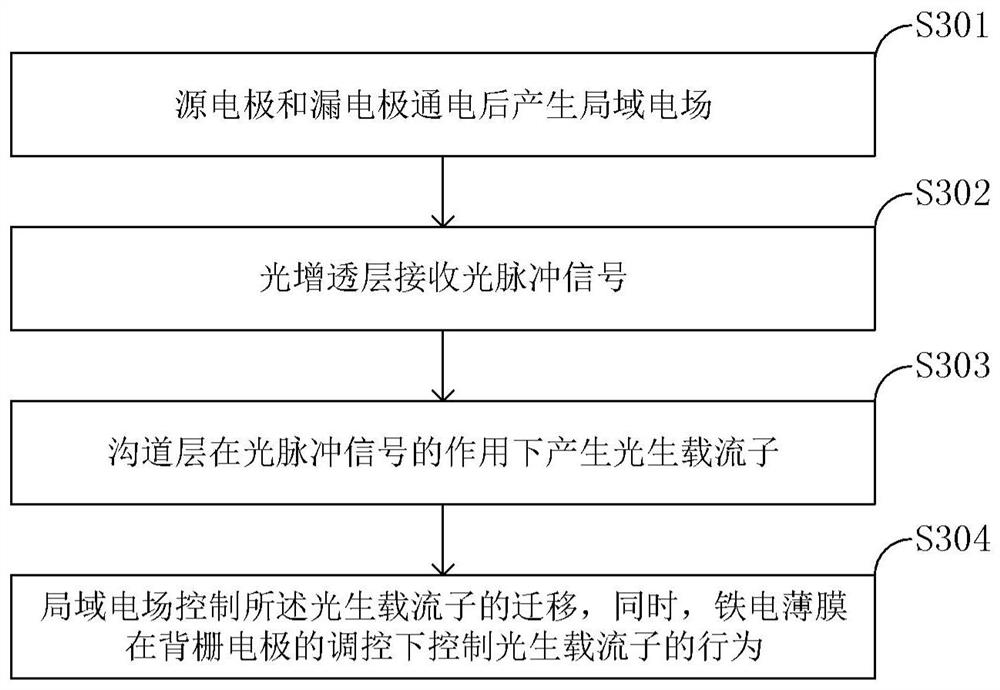

Photoelectric regulation and control nerve synapse transistor and preparation method thereof

PendingCN112542515AControllable Test ParametersImprove stabilitySolid-state devicesSemiconductor/solid-state device manufacturingSynapseAdaptive learning

The invention discloses a photoelectric regulation and control nerve synapse transistor and a preparation method. Thephotoelectric regulation and control nerve synapse transistor comprises a substrate, a back gate electrode, a ferroelectric film, a channel layer and a light anti-reflection layer, wherein a source electrode and a drain electrode are arranged at the two ends of the light anti-reflection layer respectively, the channel layer is made of one or more layers of low-dimensional materials, and at least one layer of low-dimensional materials makes contact with the source electrode and the drain electrode. The low-dimensional material is a two-dimensional material or a one-dimensional material; the ferroelectric film has a ferroelectric polarization effect, and the polarization overturning characteristic is regulated and controlled by the back gate electrode. Through redesigning the structure of the photoelectric regulation and control neural synaptic transistor under the synergistic effect of optical excitation and electric regulation and control and optimizing the material, a cranial nerve-like synaptic device which is easy to regulate and control, low in power consumptionand easy to be compatible with a spiking neural network algorithm is realized; based on the advantages of parallel storage and operation and adaptive learning of the device structure, the functions ofinformation storage and image recognition are improved from the device level.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Three-terminal synapse device and method of operating the same

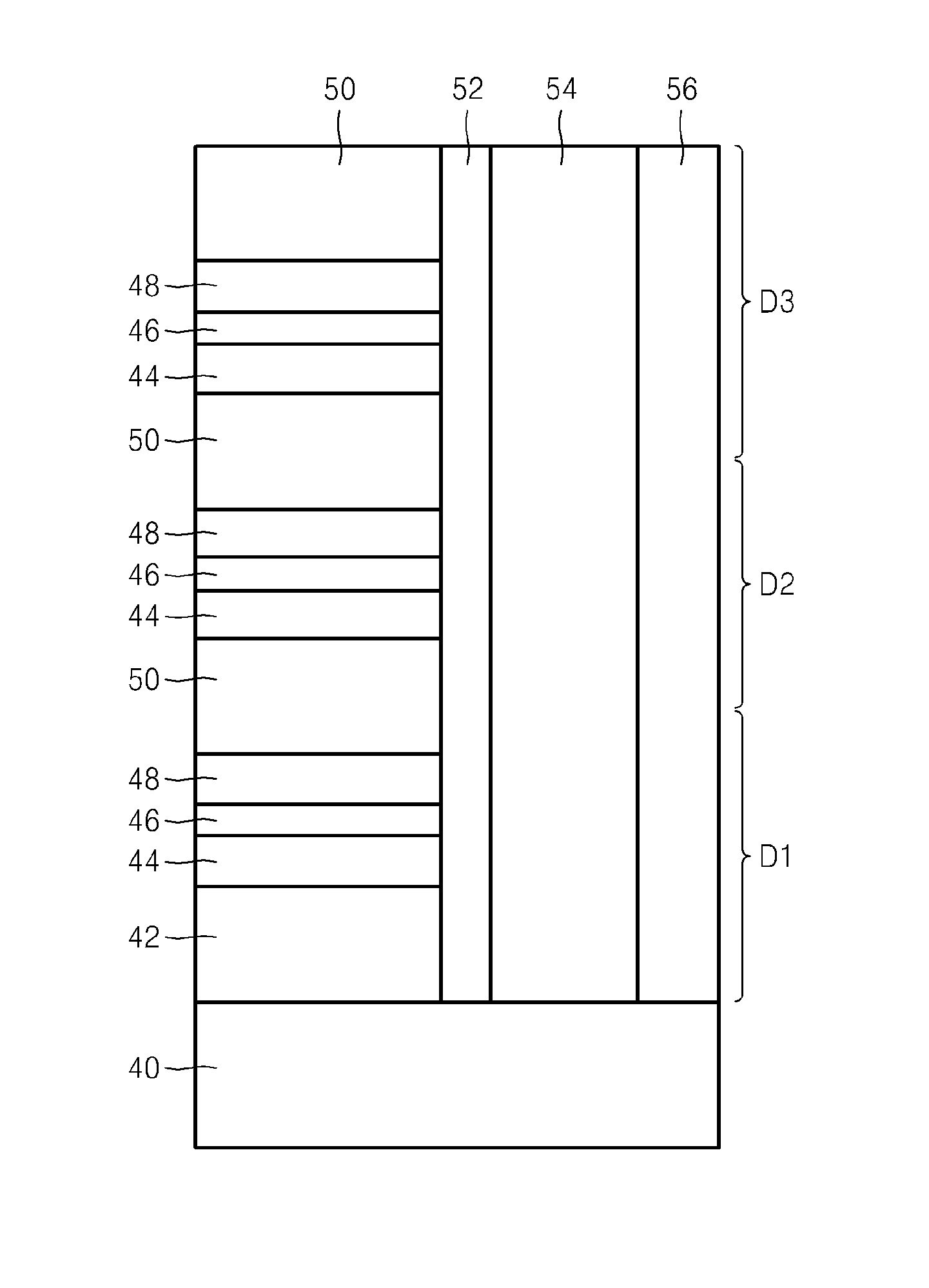

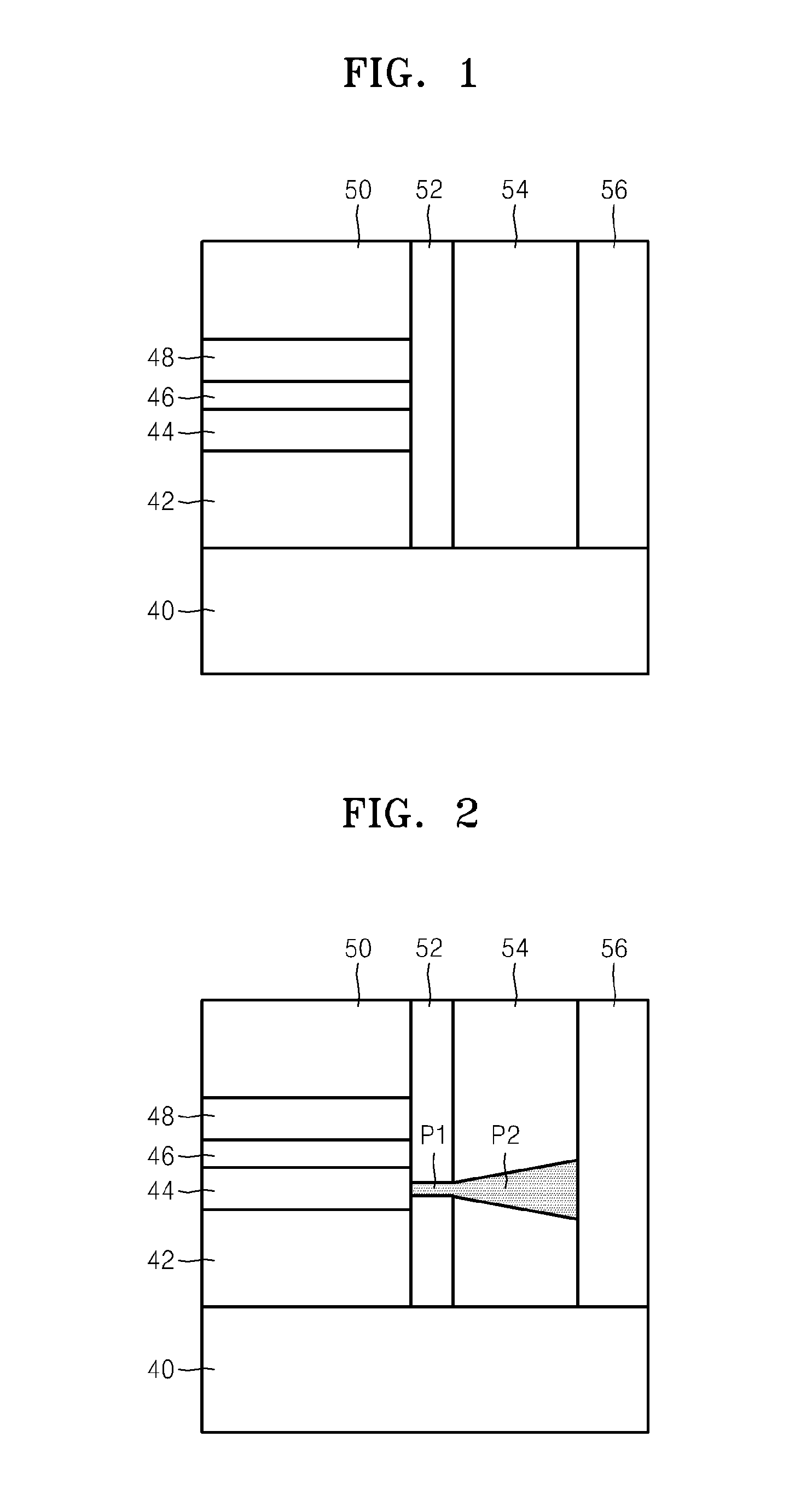

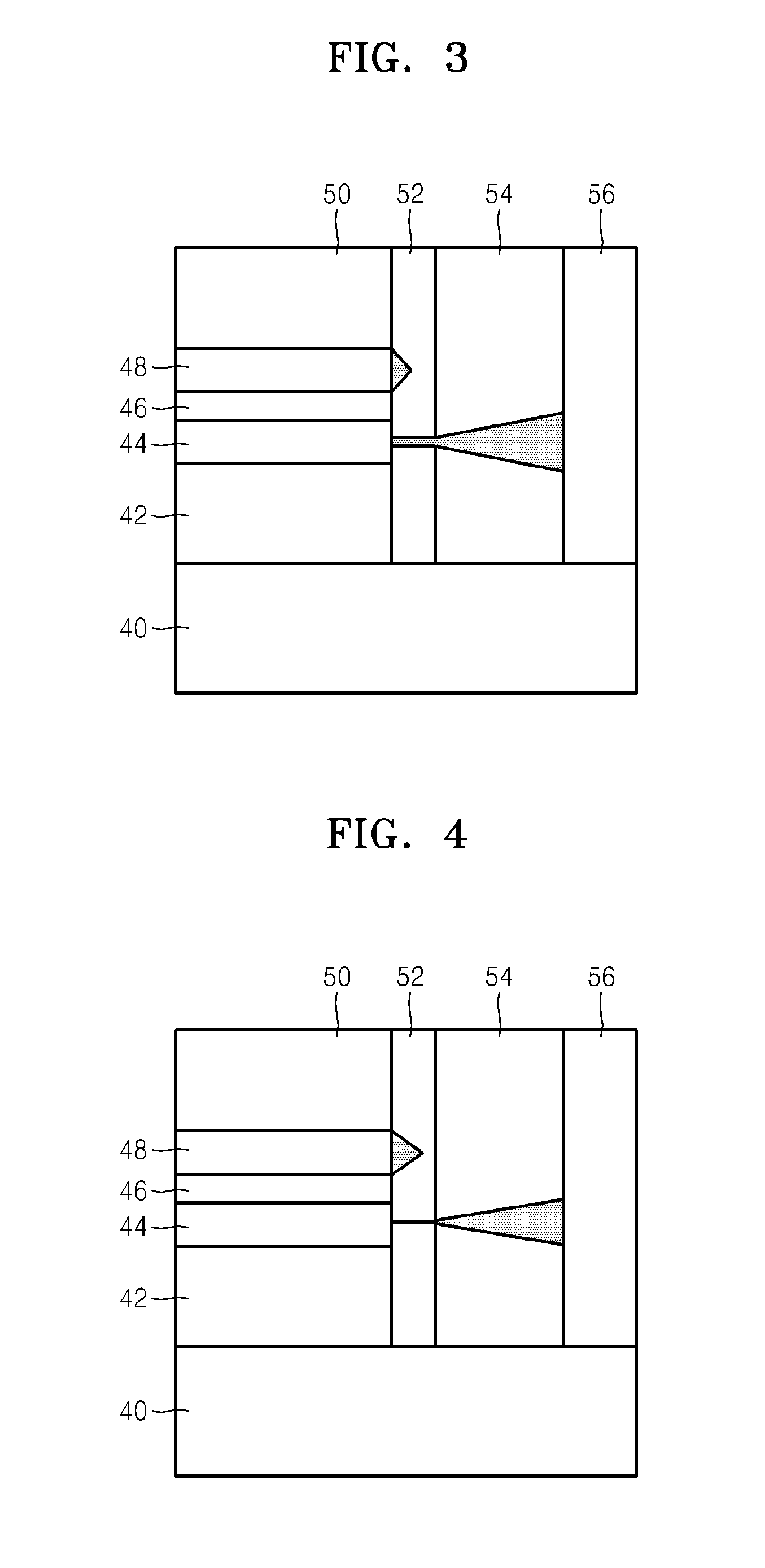

ActiveUS20150117090A1High degreeEasy to operate and controlDigital storageBulk negative resistance effect devicesEngineeringElectrical and Electronics engineering

A three-terminal synapse device may include a drain layer formed on a substrate, a gate layer formed on the drain layer, a source layer vertically stacked on the substrate and facing the drain layer and the gate layer. First and second vertical insulating layers may be formed between the source layer and a stack including the drain layer and the gate layer. The first and second vertical insulating layers have different ion mobilities from each other. The first and second vertical insulating layers may cover side surfaces of the drain layer and the gate layer. The ion mobility of the second vertical insulating layer may be greater than that of the first vertical insulating layer.

Owner:SAMSUNG ELECTRONICS CO LTD +1

SiNx-Based optical reading synaptic device structure and preparation method thereof

ActiveCN107634140ASmall sizeEnables optical readingMaterial nanotechnologyElectrical apparatusElectrical resistance and conductanceSynaptic weight

The present invention provides a SiNx-Based optical reading synaptic device structure and a preparation method thereof. The SiNx-Based optical reading synaptic device structure includes a surface plasmon waveguide of a metal / SiNx / metal structure and a memristor of an upper electrode / dual-resistance varying layer / lower electrode structure; the surface plasmon waveguide is of a vertical three-layerstructure including a second metal layer, a dielectric layer and a first metal layer from top to bottom; the memristor is of a vertical four-layer structure including an upper electrode, a second resistance varying layer, a first resistance varying layer and a lower electrode from top to bottom; and the first resistance varying layer and the second resistance varying layer of the memristor, adopted as optical signal transmission channels, are horizontally connected with the dielectric layer of the surface plasmon waveguide. With the SiNx-Based optical reading synaptic device structure and thepreparation method thereof of the invention adopted, the optical reading of synaptic weight is realized, so that the optical reading synaptic device with the amplitude and phase of optical signals adopted as the synaptic weight has unparalleled advantages compared with a traditional synaptic device with resistance adopted as synaptic weight; and the surface plasmon waveguide can make the optical signals break through diffraction limits and transmitted, and therefore, the further reduction of the size of the device can be facilitated.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

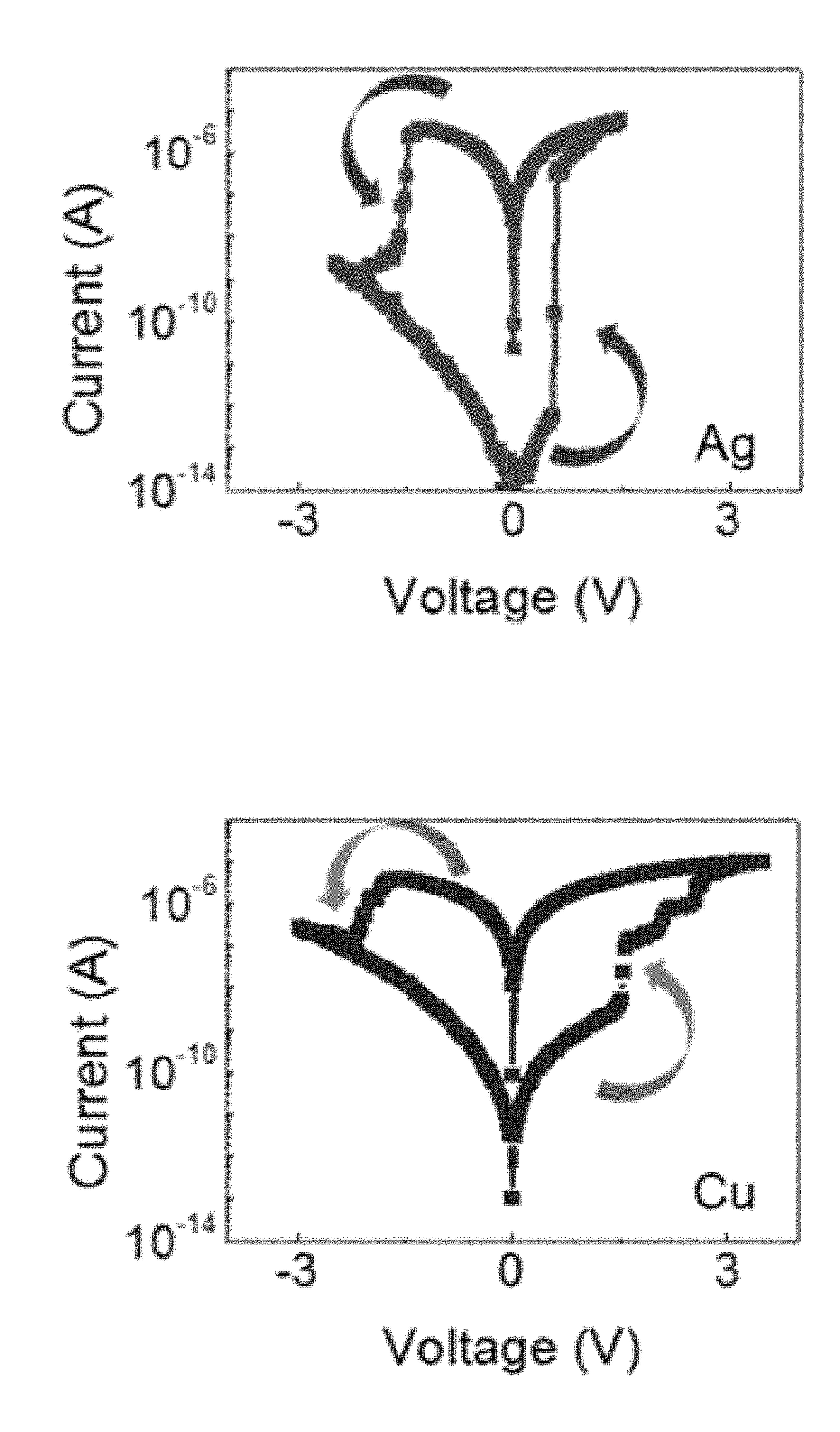

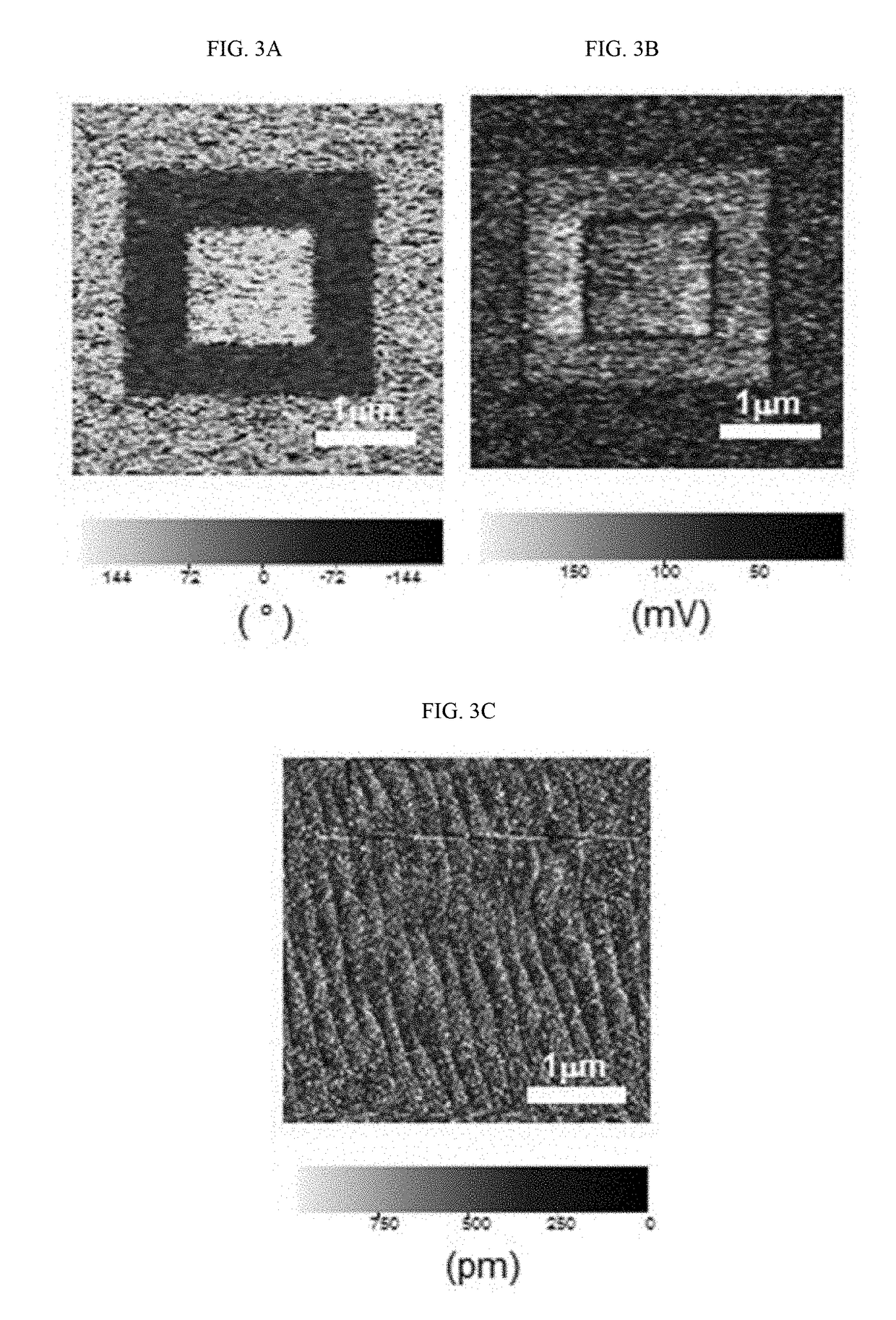

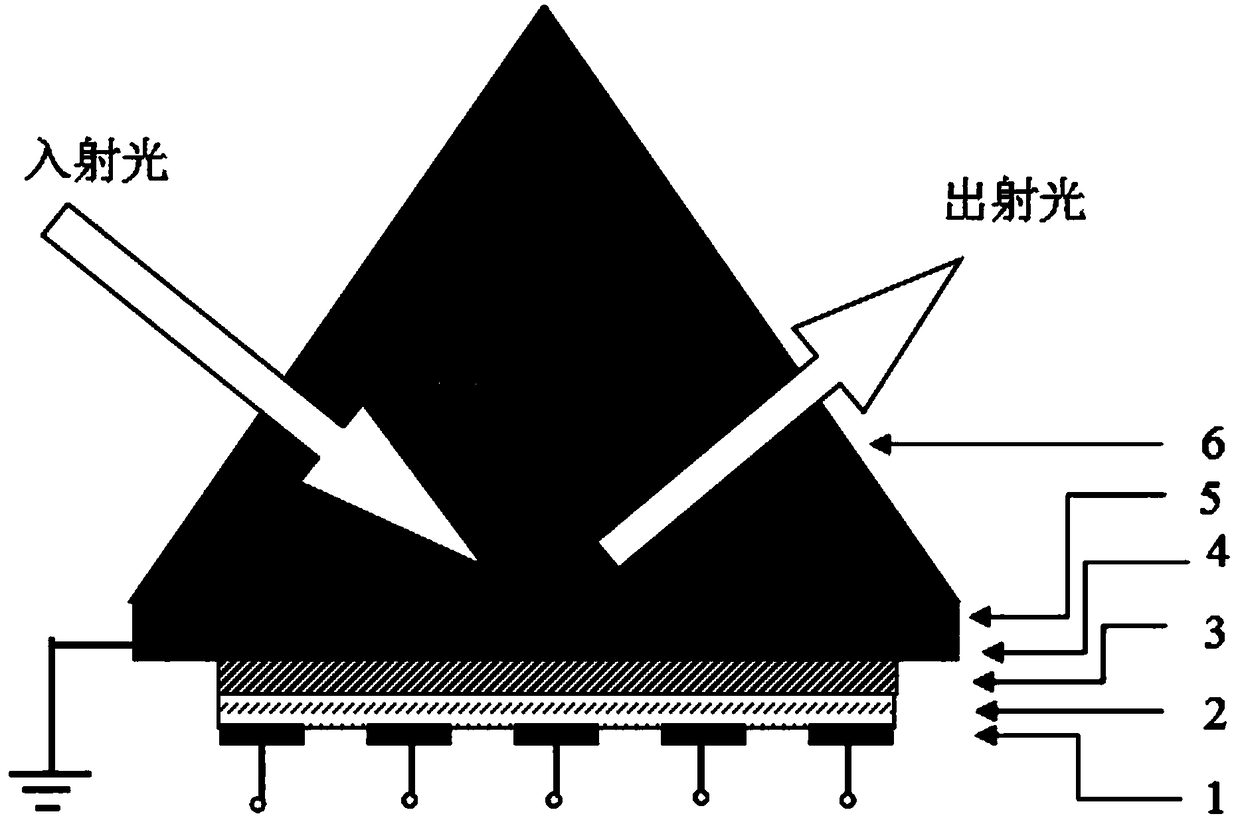

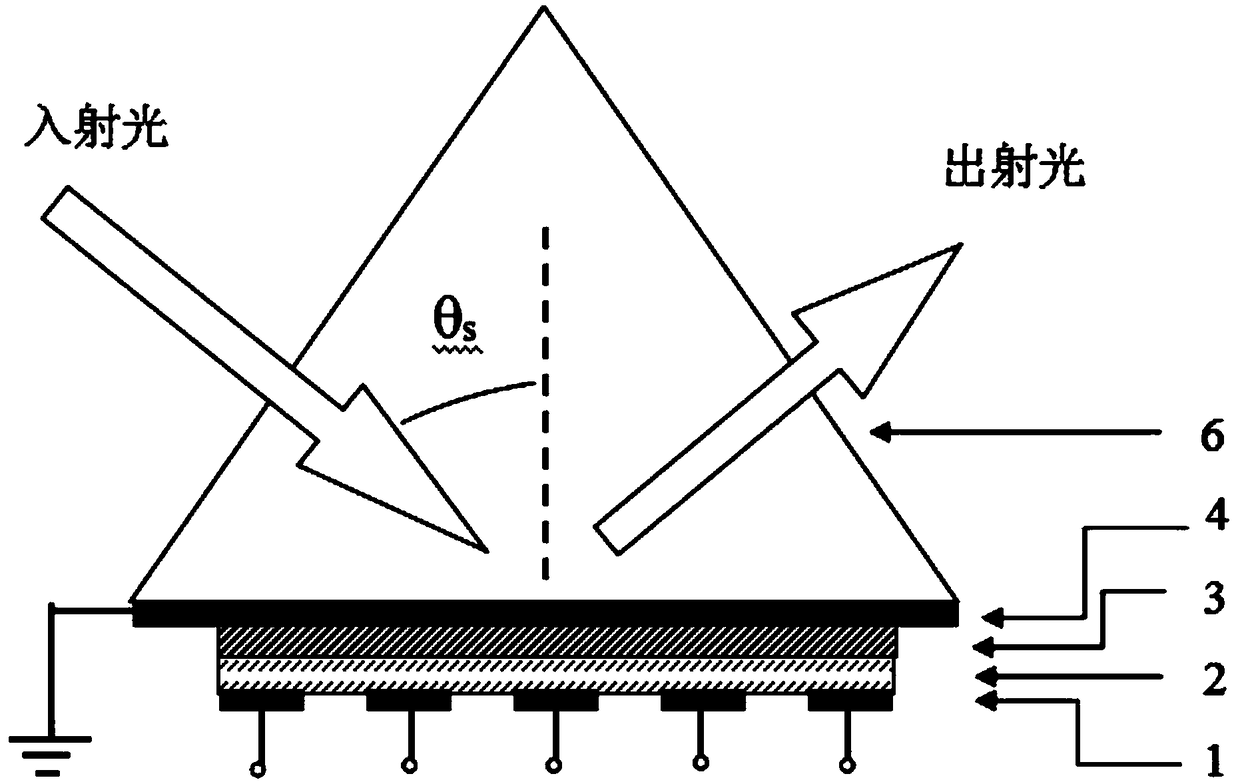

SPR neural synaptic device based on a-SiOx memristor effect and preparation method thereof

ActiveCN109037442AHigh bandwidthLarge signal processing bandwidthElectrical apparatusSynaptic weightEngineering

The invention provides a SPR neural synaptic device based on a-SiOx memristor effect and a preparation method thereof, belonging to the technical field of biomimetic devices. The invention combines K9glass prism with 'top electrode / a-SiOx: metal nanoparticle double resistive layer / bottom electrode' memristor structure coupling, so the optical signal is allowed to be injected into the double resistive layer through the K9 glass prism under the electric modulation, A surface plasmon resonance (SPR) effect is utilize to read that dielectric constant change information of the resistive layer during the working process of the device, thereby realizing the optical read of the synaptic weight of the device. The 'electrically modulated, optically read' synaptic device of the invention has the advantages that the traditional 'electrically modulated, electrically read' synaptic device cannot be compared with, because the synaptic device not only has the characteristics of low energy consumptionand non-volatility of the traditional memristor, but also has the advantages of large signal processing bandwidth and strong electromagnetic interference resistance when the light is used as an information carrier.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

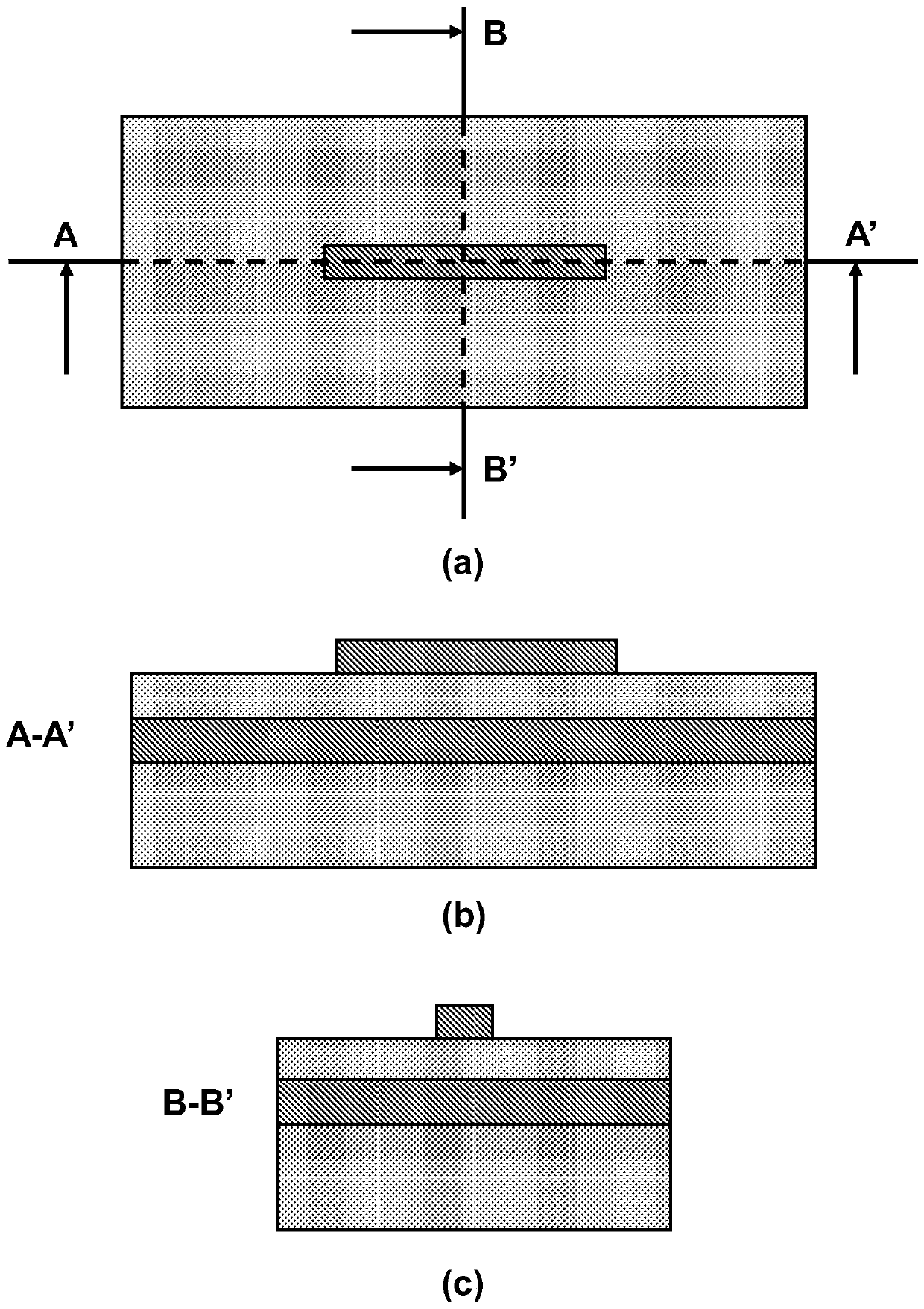

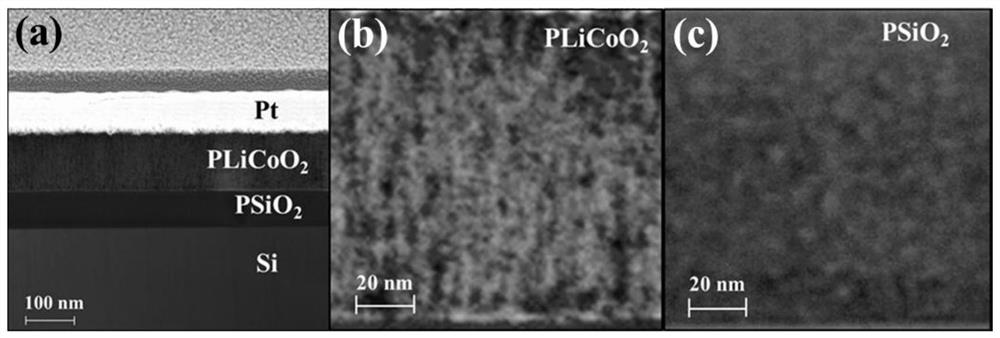

Selectively activated synaptic device with ultrasmall dimension and low power consumption

ActiveUS20180019011A1Solid-state devicesSemiconductor/solid-state device manufacturingFerroelectric thin filmsSynaptic device

Provided herein are a capacitor, a memory device including the capacitor, and a method of manufacturing the capacitor. The capacitor is manufactured by directly depositing a metal electrode having high ion mobility on an ultrathin ferroelectric layer having a certain thickness, and thus may simultaneously use metal cation migration and ferroelectric polarization inversion, and a low-power and high-performance capacitor capable of being selectively activated may be provided by simultaneously controlling an external electric field and an internal electric field caused by polarization of the inside of a ferroelectric thin film.

Owner:KONKUK UNIV IND COOP CORP

Electronic synapse

An electronic synapse device is provided. One embodiment of the invention includes a metastable switching synaptic device. Changing conductance of the metastable switching synaptic device occurs by receiving opposite signed first and second voltage pulses at the metastable switching synaptic device where magnitude of the first voltage pulse and the second voltage pulse each are below a switching voltage magnitude threshold. A magnitude difference between the first voltage pulse and the second voltage pulse exceeds the switching voltage magnitude threshold by an amount, wherein the amount is a function of a relative timing between the first voltage pulse and the second voltage pulse.

Owner:INT BUSINESS MASCH CORP

Producing spike-timing dependent plasticity in a neuromorphic network utilizing phase change synaptic devices

ActiveUS20160224887A1Digital storageNeural architecturesSynaptic deviceSpike-timing-dependent plasticity

Embodiments of the invention relate to a neuromorphic network for producing spike-timing dependent plasticity. The neuromorphic network includes a plurality of electronic neurons and an interconnect circuit coupled for interconnecting the plurality of electronic neurons. The interconnect circuit includes plural synaptic devices for interconnecting the electronic neurons via axon paths, dendrite paths and membrane paths. Each synaptic device includes a variable state resistor and a transistor device with a gate terminal, a source terminal and a drain terminal, wherein the drain terminal is connected in series with a first terminal of the variable state resistor. The source terminal of the transistor device is connected to an axon path, the gate terminal of the transistor device is connected to a membrane path and a second terminal of the variable state resistor is connected to a dendrite path, such that each synaptic device is coupled between a first axon path and a first dendrite path, and between a first membrane path and said first dendrite path.

Owner:INT BUSINESS MASCH CORP

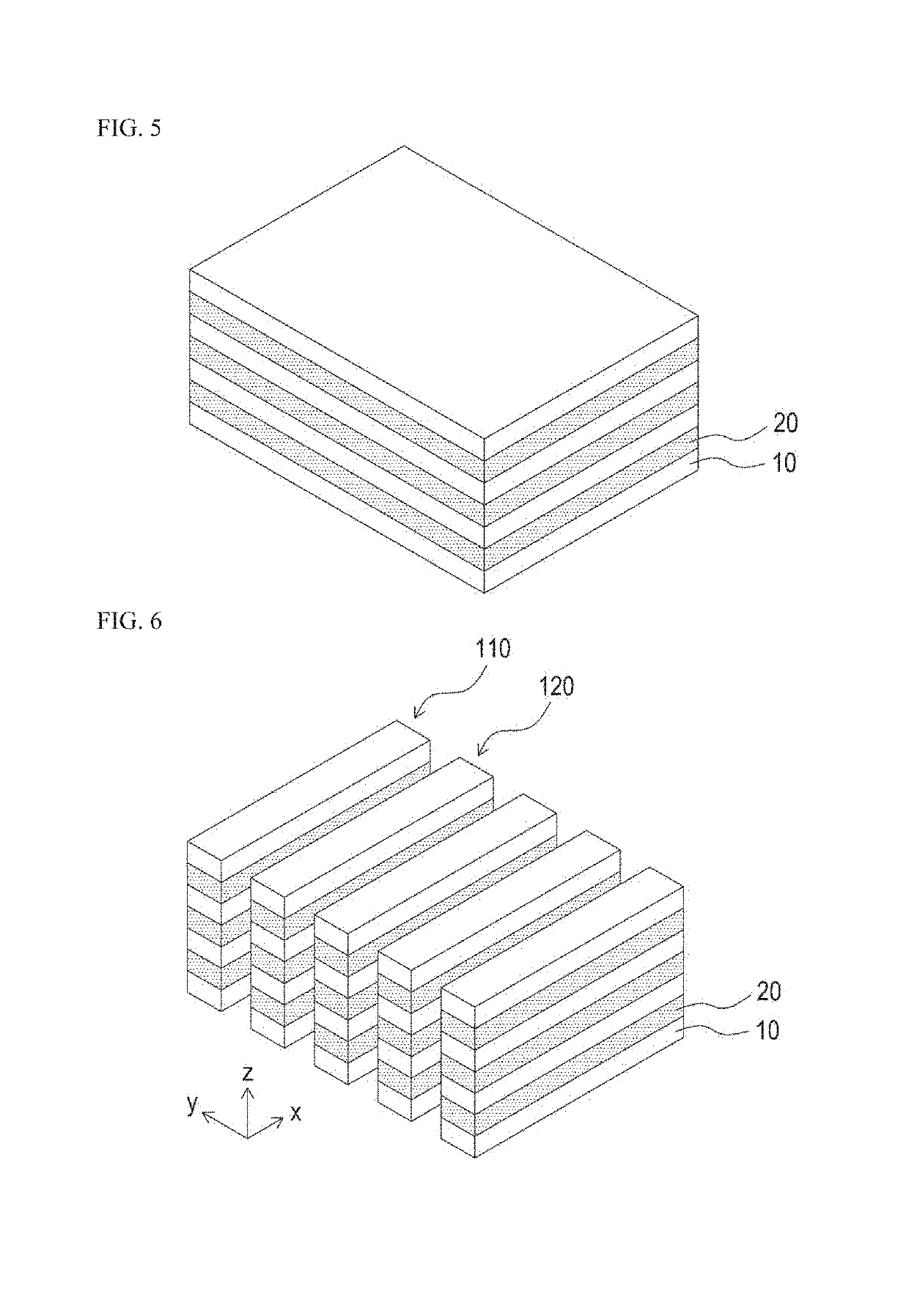

Full memristor neural network and preparation method and application thereof

ActiveCN111275177AHighly integratedImprove scalabilityElectrical apparatusPhysical realisationMiniaturizationEngineering

The invention discloses a full memristor neural network and a preparation method and application thereof. The full memristor neural network forms a memristor synaptic device through a bottom electrode, a first functional layer and an intermediate electrode, then a second functional layer covers the memristor synaptic device, and a top electrode covers the second functional layer to form a memristor neural component, so that the full memristor neural network is constructed. By changing the weight of the synaptic device, the full memristor neural network can realize the functions of pattern recognition, supervised learning and the like. The full-memristor neural network has high integration level and miniaturization, is compatible with a traditional silicon-based CMOS process, is suitable for large-scale production, and has important significance for finally realizing large-scale brain-like computing hardware in the future.

Owner:PEKING UNIV

Low-voltage multifunctional charge trapping synaptic transistor and preparation method thereof

ActiveCN111564499AEnhanced interfacial electric fieldConducive to tunnelingSemiconductor/solid-state device manufacturingSemiconductor devicesNanowireNeural network hardware

The invention discloses a low-voltage multifunctional charge trapping type synaptic transistor and a preparation method thereof, and belongs to the field of synaptic devices oriented to neural networkhardware application. According to the invention, a silicon nitride and hafnium oxide double-capture-layer structure is adopted to simultaneously realize short-long-time synaptic plasticity on a single device, so that the functions of the synaptic device are enriched; a three-gate nanowire structure is beneficial to enhancing an interface electric field, so that the FN tunneling width at the interface is reduced, the tunneling probability at the interface is enhanced, and the operation voltage and the device power consumption are reduced; and the device has complete CMOS material and processcompatibility, and due to the excellent device characteristics, the device has potential to be applied to a future large-scale neural network computing system.

Owner:PEKING UNIV

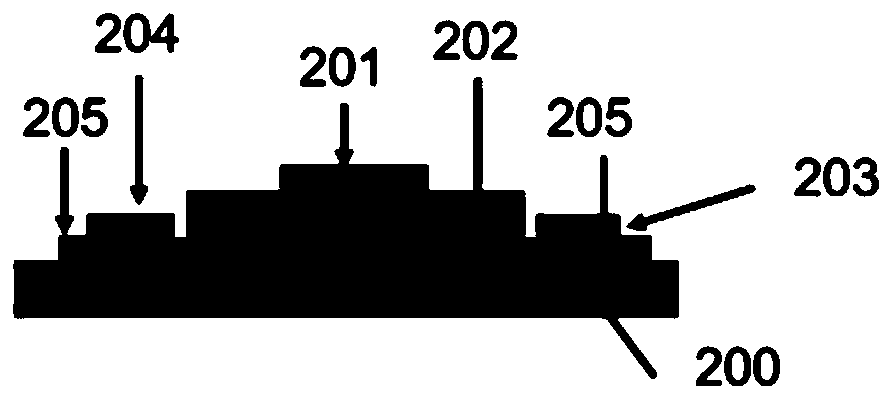

Preparation and modulation method of photoelectric synaptic device

ActiveCN111192938ABroaden the response range of light waveMeet the requirements of complex application scenariosFinal product manufacturePhysical realisationField effectField-effect transistor

The invention discloses a preparation and modulation method of a photoelectric synaptic device. The preparation method comprises the following steps: preparing a field effect transistor structure comprising a gate layer, a dielectric layer, a source electrode and a drain electrode; transferring a graphene thin film over the source electrode and the drain electrode; processing the graphene film into a conductive channel; and preparing a graphdiyne thin film on the surface of the graphene thin film processed into the conductive channel to obtain the photoelectric synapse device of the field effect transistor structure. According to the invention, the graphene film is transferred above the source electrode and the drain electrode, the graphdiyne thin film is prepared on the surface of the graphene thin film to obtain the photoelectric synapse device of the field effect transistor structure, by preparing the graphdiyne thin film on the surface of the graphene thin film, the light wave response range is widened, regulation and control of light signals and electric signals are achieved through the field effect transistor structure, and therefore the requirements under complex applicationscenes are met. The method can be widely applied to the technical field of artificial neural networks.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

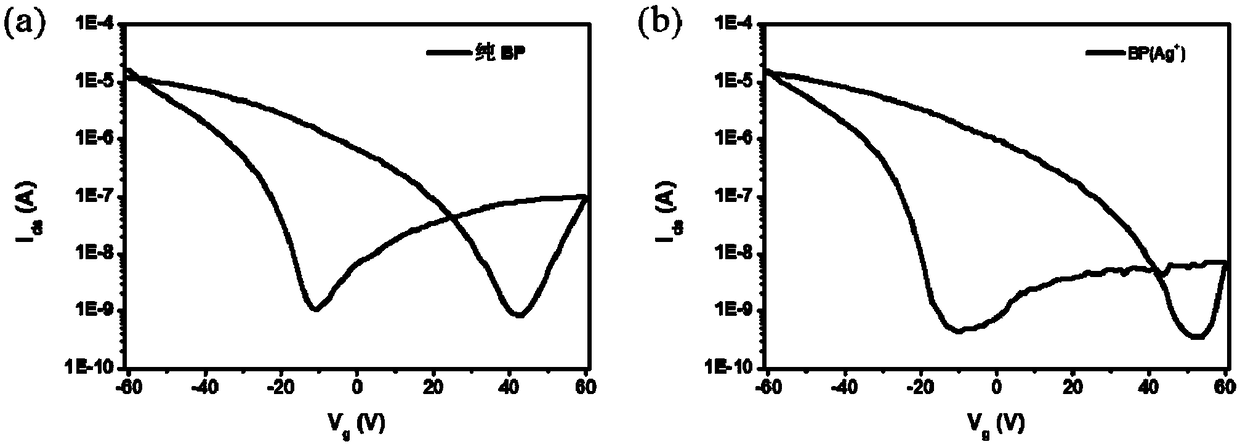

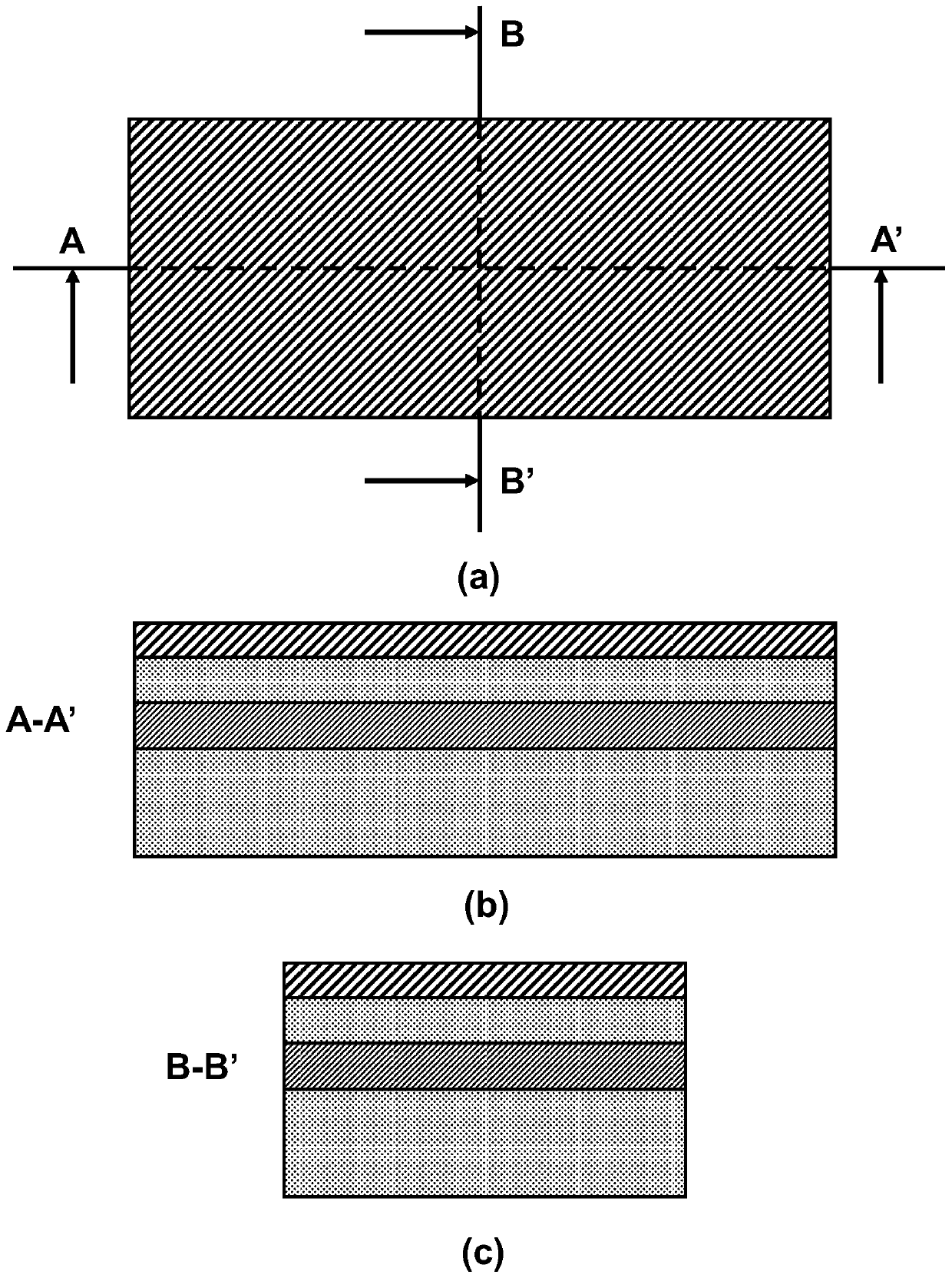

Synaptic device based on metal cation modified black phosphorus and preparation method thereof

ActiveCN108987565AGood environmental stabilityExcellent synaptic performanceElectrical apparatusIsolation layerBlack phosphorus

A metal cation modify black phosphorus-based synaptic device includes a back gate electrode as a front end of the synapse, An isolation layer and a functional layer sequentially arranged on the back gate electrode, and a first electrode as a reference electrode and a second electrode as a synaptic posterior end spaced apart on the functional layer, the channel structure formed between the first electrode and the second electrode exposing a part of the functional layer, the material of the functional layer comprising a metal cation modified black phosphorus sheet. The metal cation modified black phosphorus synaptic device provided by the invention has good environmental stability and excellent synaptic performance, and provides an important component device support with extremely practicalvalue for brain-like calculation. The invention also provides a preparation method of a synaptic device based on metal cation modified black phosphorus, which is simple and easy to operate.

Owner:山东森格姆德激光科技有限公司

Artificial Synapse with Hafnium Oxide-Based Ferroelectric Layer in CMOS Back-End

ActiveUS20190131383A1Solid-state devicesSemiconductor/solid-state device manufacturingCMOSSynaptic device

Artificial synaptic devices with an HfO2-based ferroelectric layer that can be implemented in the CMOS back-end are provided. In one aspect, an artificial synapse element is provided. The artificial synapse element includes: a bottom electrode; a ferroelectric layer disposed on the bottom electrode, wherein the ferroelectric layer includes an HfO2-based material that crystallizes in a ferroelectric phase at a temperature of less than or equal to about 400° C.; and a top electrode disposed on the bottom electrode. An artificial synaptic device including the present artificial synapse element and methods for formation thereof are also provided.

Owner:IBM CORP

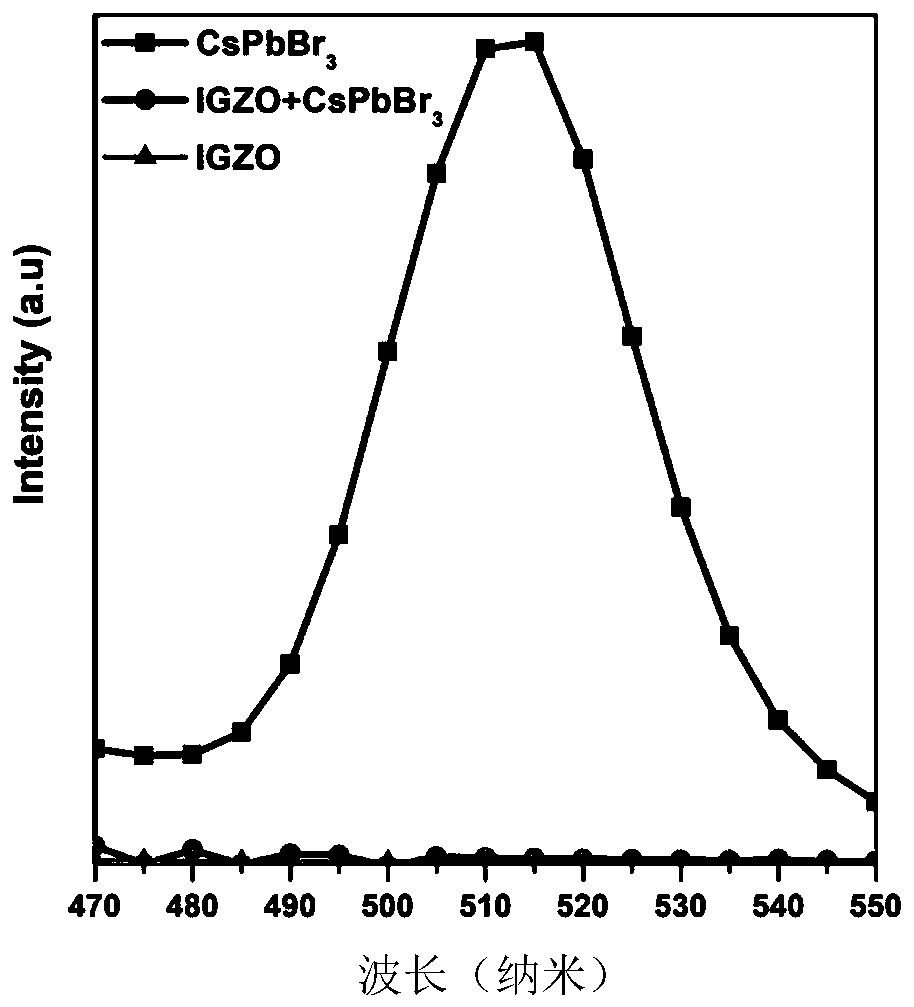

Three-terminal type thin film transistor, preparation method thereof and photosensitive nerve synapse device

InactiveCN111554770AReduce power consumptionEasy to makeFinal product manufacturePhysical realisationOxide thin-film transistorQuantum dot

The invention discloses a three-terminal type thin film transistor, a preparation method thereof and a photosensitive nerve synapse device. The three-terminal type thin film transistor comprises a substrate, a channel, a gate electrode, a source electrode and a drain electrode, wherein the channel is formed by compounding a metal oxide and a quantum dot material, and the quantum dot material is mixed in the metal oxide. The thin film transistor has the characteristics of high visible light response intensity and strong continuous photoconductive effect, so that the response spectrum of the photosensitive nerve synapse is broadened, the use requirements of the photosensitive nerve synapse in the visible light band can be met, and the thin film transistor is more suitable for being used as aphotosensitive nerve synapse device compared with the traditional oxide thin film transistor.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

Near-infrared light regulation synaptic transistor and preparation method thereof

PendingCN110534572ASignificant synaptic plasticity featuresRich choiceSemiconductor/solid-state device manufacturingSemiconductor devicesShort-term memoryPhotonics

The invention discloses a near-infrared light regulation synaptic transistor and a preparation method thereof. The preparation method of the transistor comprises the following steps of: preparing a MoSe2 / Bi2Se3 heterostructure; preparing a chlorobenzene solution of PMMA, and then mixing the MoSe2 / Bi2Se3 heterostructure into the chlorobenzene solution of PMMA; arranging a MoSe2 / Bi2Se3 / PMMA layer onthe Si / SiO2 substrate layer, and performing annealing for 30-50 minutes at the temperature of 100-140 DEG C; arranging a semiconductor layer on the MoSe2 / Bi2Se3 / PMMA layer; arranging a source electrode and a drain electrode on the semiconductor layer. According to the invention, the synaptic device based on the MoSe2 / Bi2Se3 topological insulator material shows an obvious synaptic plasticity characteristic controlled by near-infrared light, regulation and control of the near-infrared light intensity enable the photonic synaptic device to achieve conversion from short-term memory correspondingto the short-term plasticity STP to long-term memory corresponding to the long-term plasticity LTP, and a hardware basis is provided for a light-operated neural architecture and application of the light-operated neural architecture in neuromorphic calculation.

Owner:SHENZHEN UNIV

Nanowire ion grid control synaptic transistor and preparation method thereof

ActiveCN111564489AImprove energy efficiencyGood backend integration featuresSemiconductor devicesCMOSNanowire

The invention discloses a nanowire ion grid control synaptic transistor and a preparation method thereof, and belongs to the field of synaptic devices oriented to neural network hardware application.According to the invention, the advantages of good one-dimensional transport characteristic of fence nanowires and low operating voltage in an ion grid control double-electric-layer system are combined, and compared with the existing planar large-size synaptic transistor based on a two-dimensional material or an organic material, the nanowire ion grid control synaptic transistor of the invention can achieve low power consumption and small area overhead; and due to the excellent device consistency and CMOS rear-end integration characteristic, the nanowire ion grid control synaptic transistor has the potential to be applied to a future large-scale neuromorphic calculation circuit.

Owner:PEKING UNIV

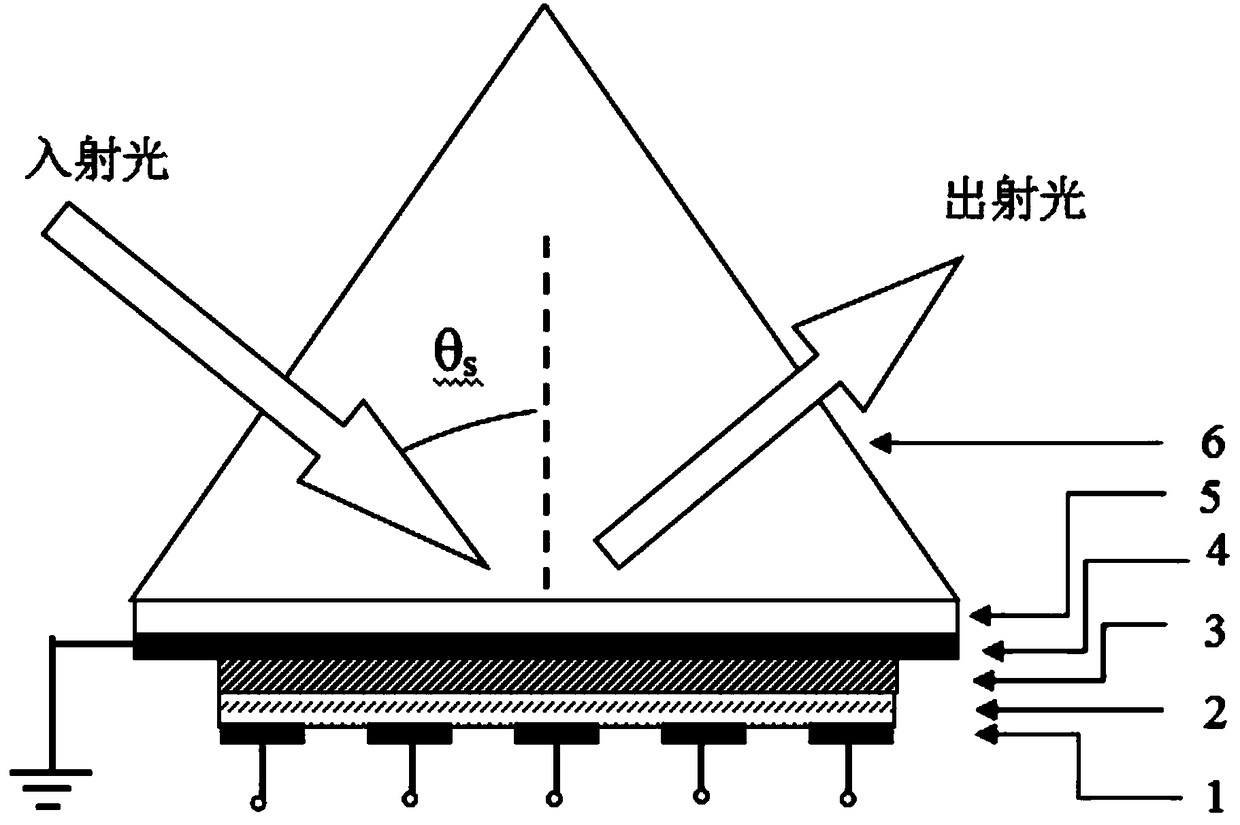

SPR nerve synaptic device based on a-Si memristor effect and preparation method thereof

ActiveCN109065713AHigh bandwidthImprove anti-electromagnetic interference performanceElectrical apparatusSynaptic weightPrism

The invention relates to a SPR nerve synaptic device based on a-Si memristor effect and a preparation method thereof, belonging to the technical field of biomimetic devices. The invention combines thecrystalline silicon prism with the top electrode / a-Si: metal nanoparticle double resistive layer / bottom electrode memristor structure coupling, thereby making the optical signal modulated by the crystal silicon prism into the double resistive layer. A surface plasmon resonance (SPR) effect is utilize to read the dielectric constant change information of the resistive layer dure the working process of the device by the optical signal, thereby realizing the optical read of the synaptic weight of the device. The electrically modulated and optically read synaptic device of the invention has the advantages that the traditional electrically modulated and electrically read synaptic device cannot be compared with, because the synaptic device not only has the characteristics of low energy consumption and non-volatility of the traditional memristor, but also has the advantages of large signal processing bandwidth and strong electromagnetic interference resistance when the light is used as an information carrier.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

SPR neural synaptic device based on a-SiOxNy memristor effect and preparation method thereof

ActiveCN109065714AHigh bandwidthAvoid grazing incidenceElectrical apparatusSynaptic weightEngineering

The present invention relates to a SPR synaptic device with SiOxNy memristor effect and a preparation method thereof, belonging to the technical field of biomimetic devices. The invention combines thecrystalline silicon prism with the top electrode / a-SiOxNy: metal nanoparticle double resistive layer / bottom electrode memristor structure coupling, thereby making the optical signal modulated by thecrystal silicon prism into the double resistive layer. A surface plasmon resonance (SPR) effect is utilize to read the dielectric constant change information of the resistive layer during the workingprocess of the device by the optical signal, thereby realizing the optical read of the synaptic weight of the device. The electrically modulated and optically read synaptic device of the invention hasthe advantages that the traditional electrically modulated and electrically read synaptic device cannot be compared with, because the synaptic device not only has the characteristics of low energy consumption and non-volatility of the traditional memristor, but also has the advantages of large signal processing bandwidth and strong electromagnetic interference resistance when the light is used asan information carrier.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Resistive random access memory device for 3D stack and memory array using the same and fabrication method thereof

ActiveUS20190131523A1Reduce power consumptionReduce voltageElectrical apparatusElectrical resistance and conductanceRandom access memory

The present invention relates to a resistance change memory, that is, a resistive memory device. By forming a bottom electrode from a doped semiconductor different material from a conventional one, it is possible to fabricate the memory device simultaneously with peripheral circuit elements. By having one or more electric field concentration regions in the bottom electrode, it is possible to reduce the power consumption reducing the voltage. The present invention can be also stacked vertically in any small and apply to the synaptic device array recently attracting the great interest as the next generation computing technology for realizing the neural imitation system.

Owner:SEOUL NAT UNIV R&DB FOUND

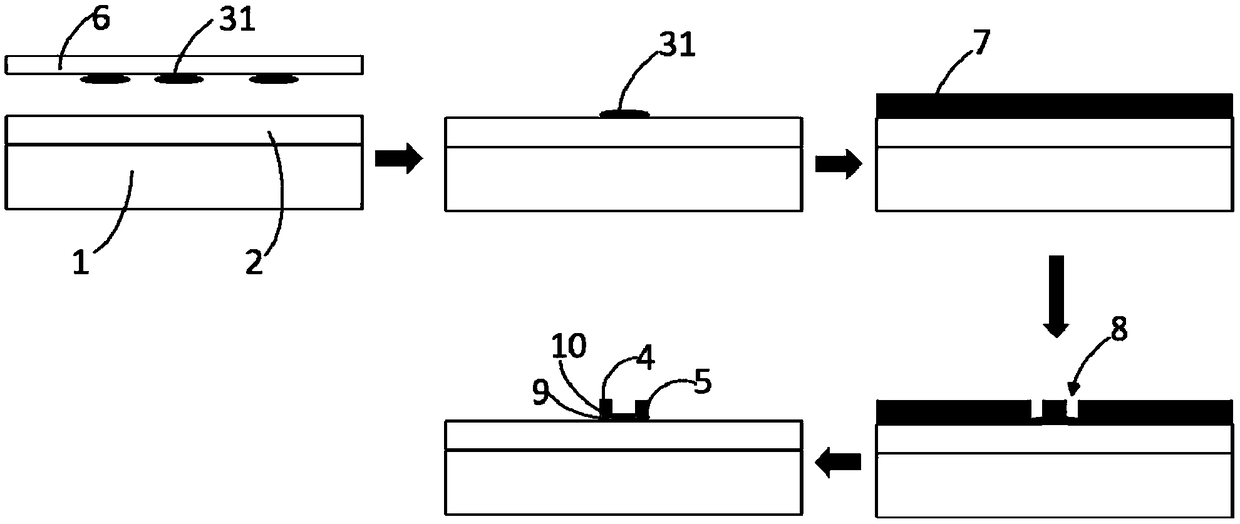

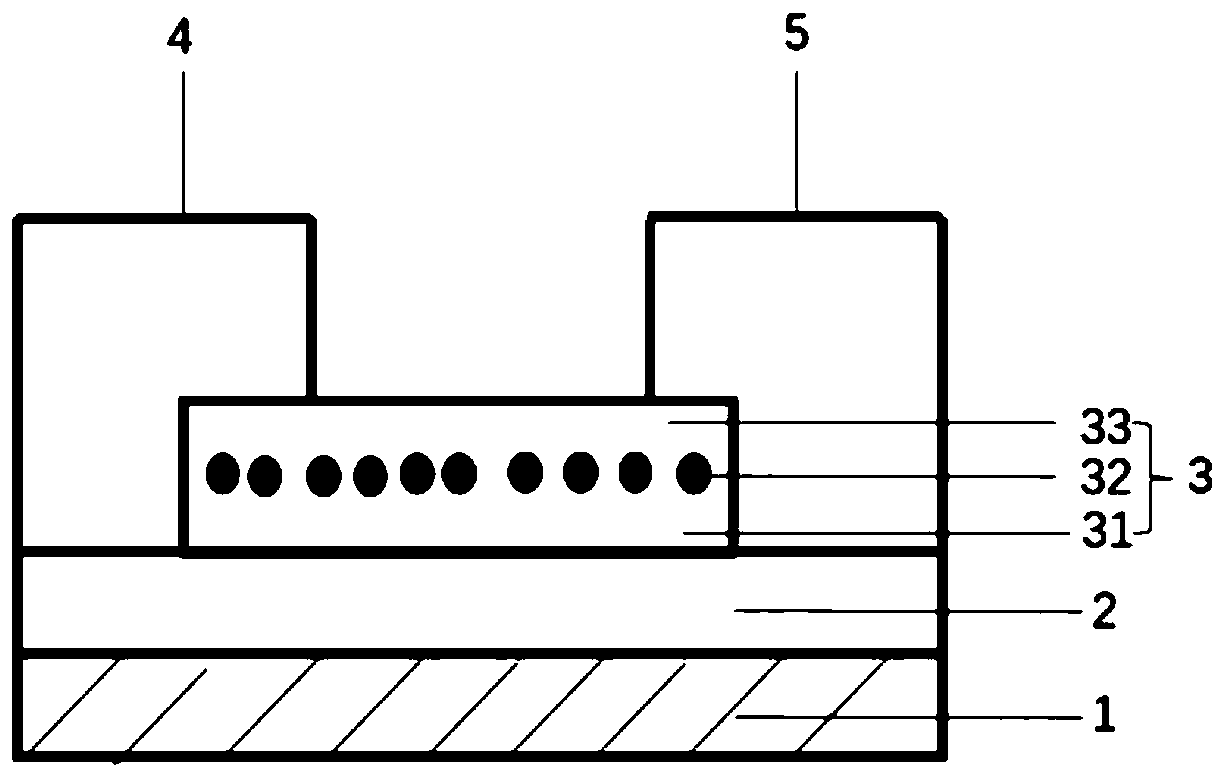

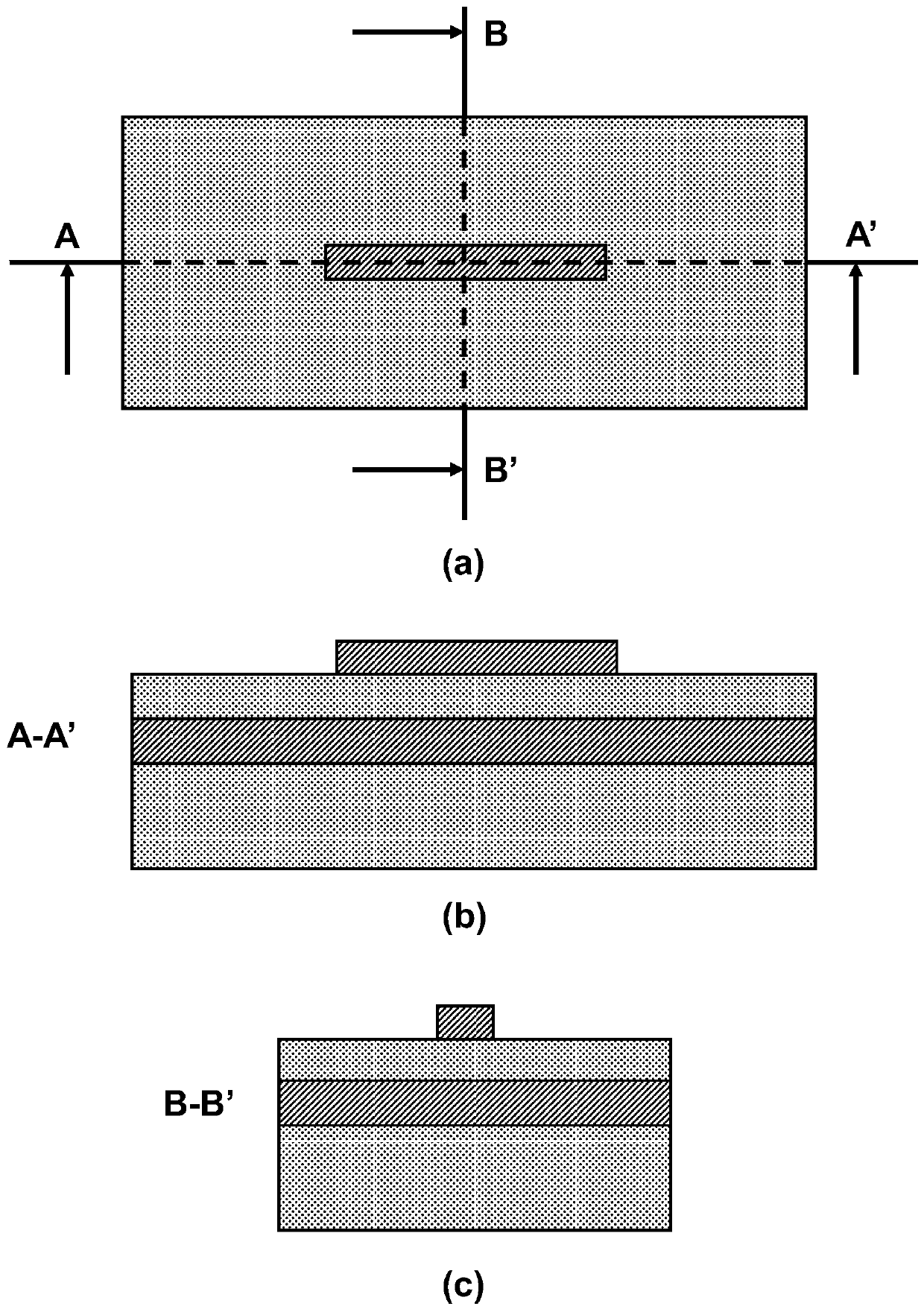

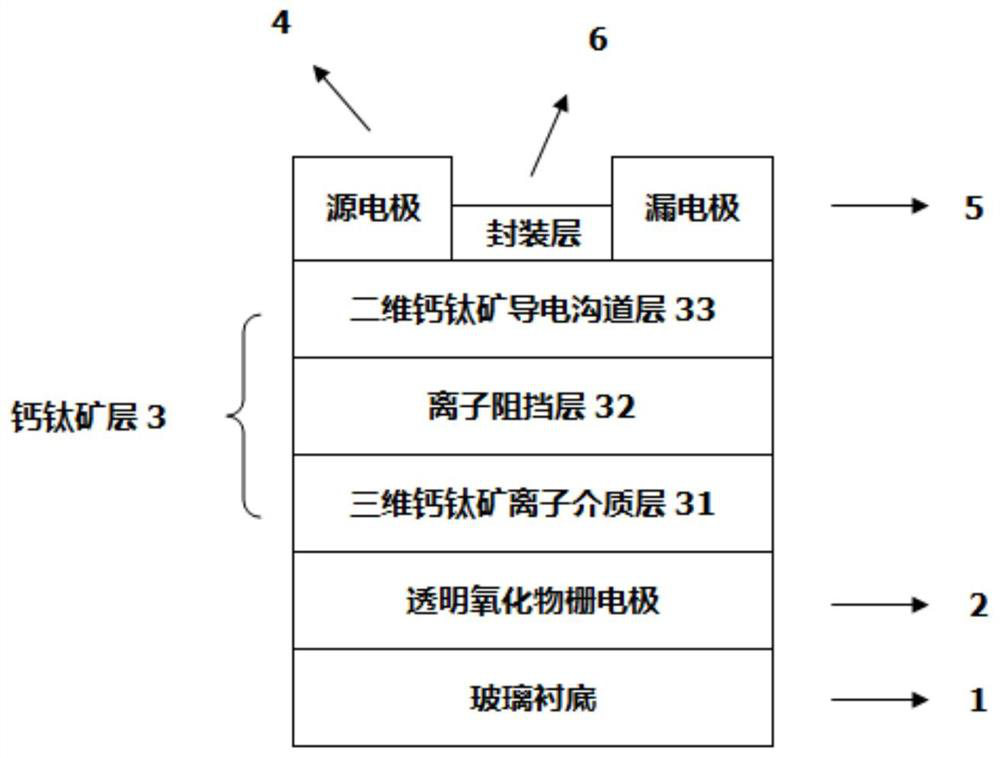

Synaptic transistor based on two-dimensional and three-dimensional perovskite composite structure and preparation method of synaptic transistor

ActiveCN111628078ARealize transmissionRealize regulationFinal product manufactureSolid-state devicesNeural network systemPerovskite (structure)

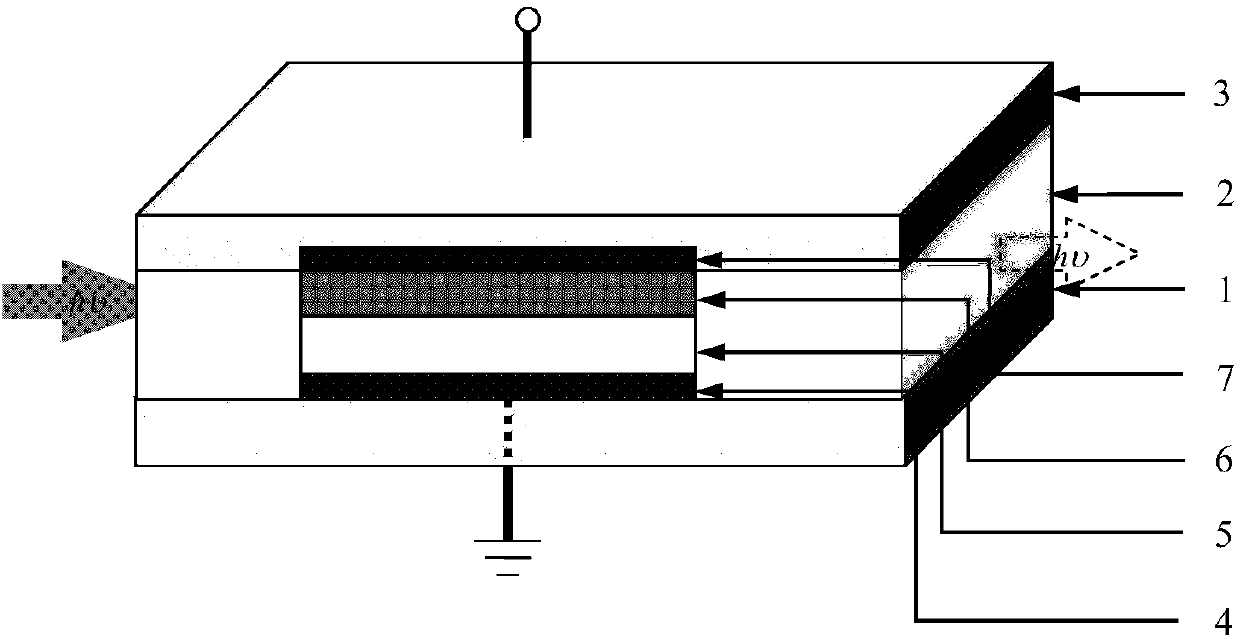

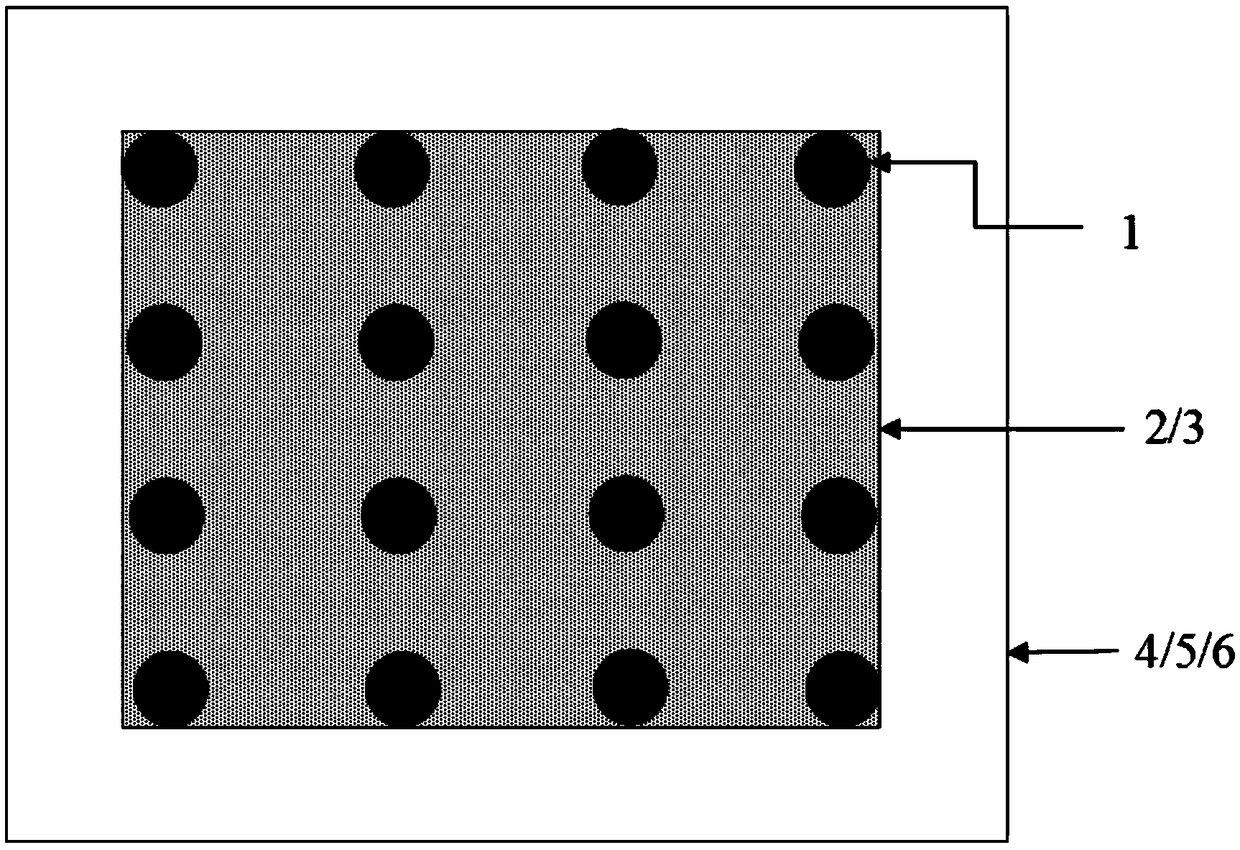

The invention discloses a synaptic transistor based on a two-dimensional and three-dimensional perovskite composite structure and a manufacturing method of the synaptic transistor, and mainly solves the problem that an existing two-terminal perovskite synaptic device is inaccurate in synaptic behavior simulation. The synaptic transistor comprises a glass substrate (1), a transparent oxide gate electrode (2), a perovskite mining area (3), a source electrode (4), a drain electrode (5) and a packaging protection layer (6) from bottom to top. An ion dielectric layer is made of a three-dimensionalperovskite material, and a conductive channel layer is made of a two-dimensional perovskite material; carrier transport in the two-dimensional perovskite material is simulated by utilizing an electricfield formed by ion migration in the three-dimensional perovskite material; a device grid simulates a synaptic front film as an input end; and a device source and drain simulate a synaptic back filmto read current after synapsis. According to the invention, the two processes of carrier transport and grid control can be adjusted at the same time, regulation and control of source and drain currents are realized, the accuracy of synaptic behavior simulation of the synaptic transistor is improved, and the synaptic transistor can be used for simulating human neural synapses and constructing a neural network system.

Owner:XIDIAN UNIV

Preparation method of double-layer porous oxide structure based on artificial nerve synaptic function

ActiveCN111725398AImprove performanceImprove featuresElectrical apparatusPhysical realisationCranial nervesSilicon oxide

The invention relates to preparation of a double-layer porous oxide structure based on an artificial nerve synaptic function. A device is composed of a top end electrode, an oxide layer and a bottom end electrode. The preparation method has the advantages that 1, a porous silicon oxide structure with a sponge-like structure is simulated; 2, an ionic / ion-doped porous oxide layer is grown on the surface of the porous silicon oxide to form a double-layer porous oxide structure; and 3, the contact interface of the double-layer porous structure presents a structure that small holes surround large holes. The structure not only shows excellent electrical properties, but also can simulate the basic function of the nerve synapse, and provides a research path for the exploration of a memristive mechanism and the construction of a novel synapse device. The memristor provided by the invention has excellent electrical properties. The preparation method is simple, the performance is excellent, the application in the fields of high-density storage calculation and artificial intelligence is wide, and a new path is provided for exploring a novel cranial nerve-like working mechanism.

Owner:BEIHANG UNIV

Ferroelectric polarization regulated artificial synaptic device and preparation method thereof

InactiveCN111081875AImprove stabilityGood repeatabilitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringLow power dissipation

The invention relates to a ferroelectric polarization regulated artificial synaptic device and a preparation method thereof. The method is characterized in that a two-dimensional semiconductor layer,a source / drain electrode, a ferroelectric functional layer and a gate electrode are sequentially prepared on a substrate to form a ferroelectric polarization regulated artificial synaptic structure, and the two-dimensional semiconductor is a MoS2 or WSe2 transition metal chalcogenide coating; the ferroelectric functional layer is a polyvinylidene fluoride-based ferroelectric polymer film; the preparation of the synaptic device comprises the preparation of an SiO2 / Si layer, the transition metal chalcogenide layer, a back gate structure, a polyvinylidene fluoride layer and a metal top gate electrode. Compared with the prior art, the artificial synaptic device has the advantages of ultra-low power consumption, long service life and the like, the organic ferroelectric transistor synapse has avery good prospect due to the characteristics, a large-scale neural structure network can be promoted to simulate a human brain, and large-scale parallelism and low-power-consumption operation in a human brain algorithm network can be enlightened.

Owner:EAST CHINA NORMAL UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com