Low-voltage multifunctional charge trapping synaptic transistor and preparation method thereof

A charge trapping and transistor technology, applied in the field of charge trapping synaptic transistors, can solve the problems of high operating voltage, single function, lack of simulation of short-term plasticity, etc., and achieve the effect of enhancing the interface electric field and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be described in detail below through specific examples in conjunction with the accompanying drawings.

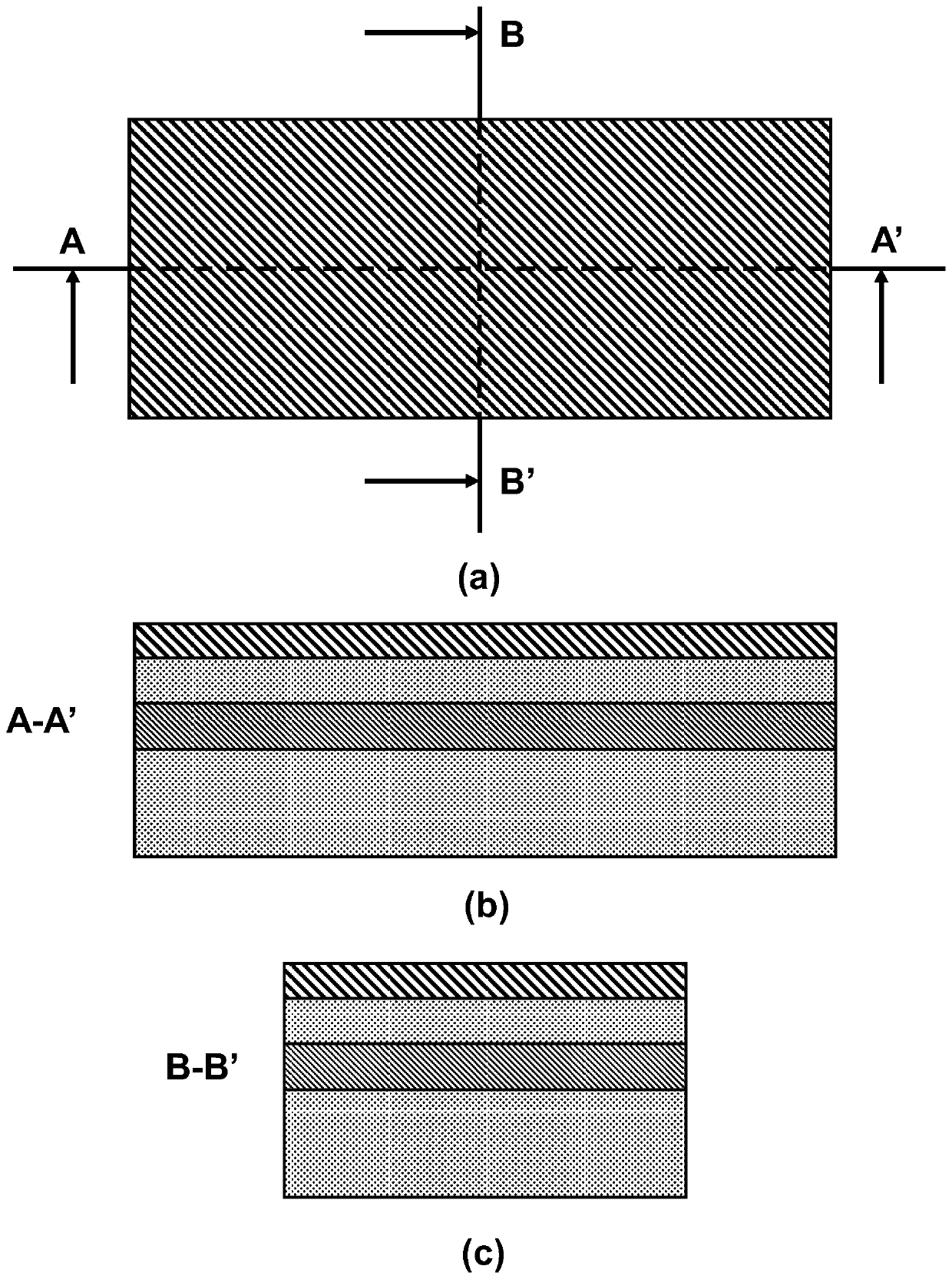

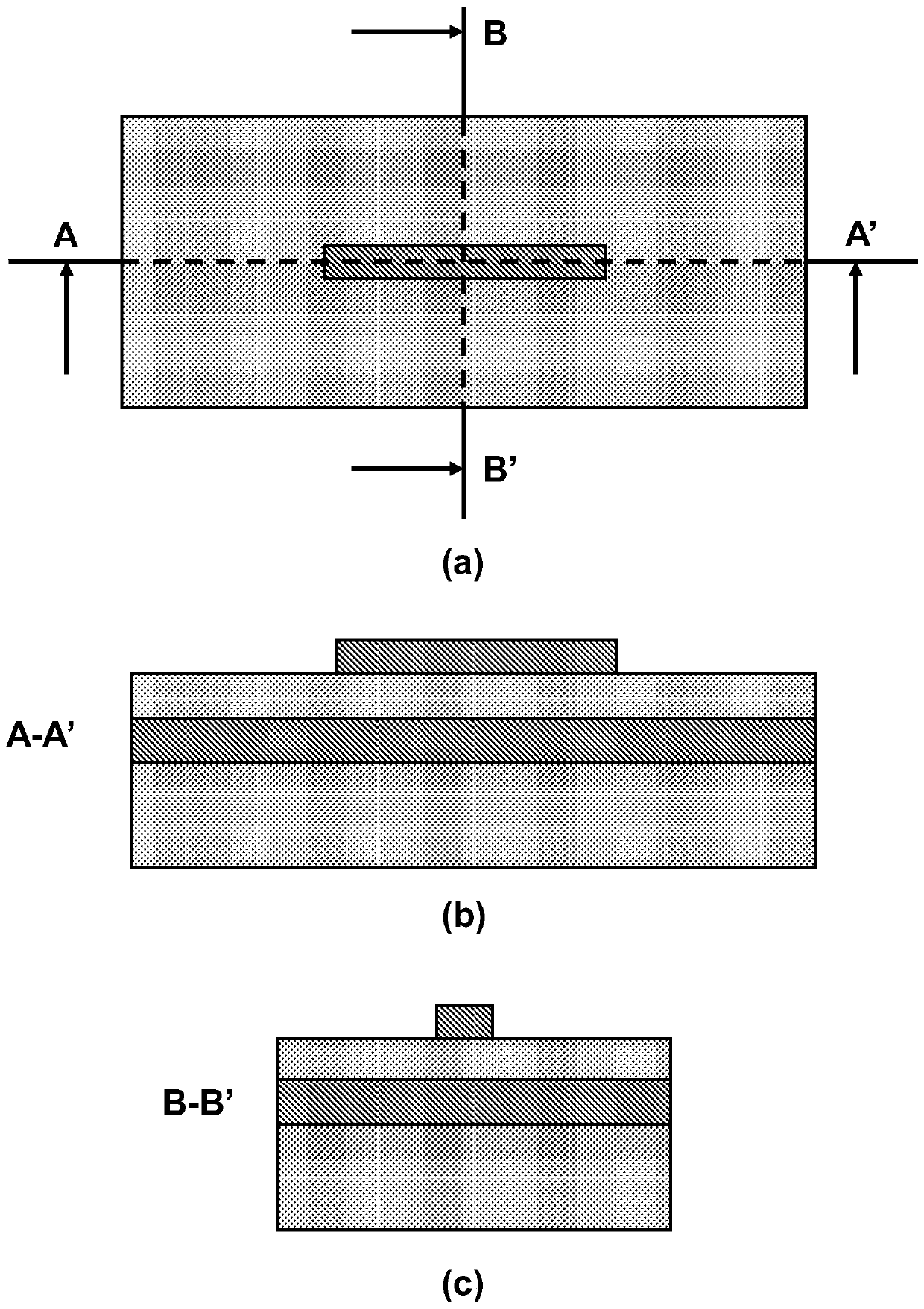

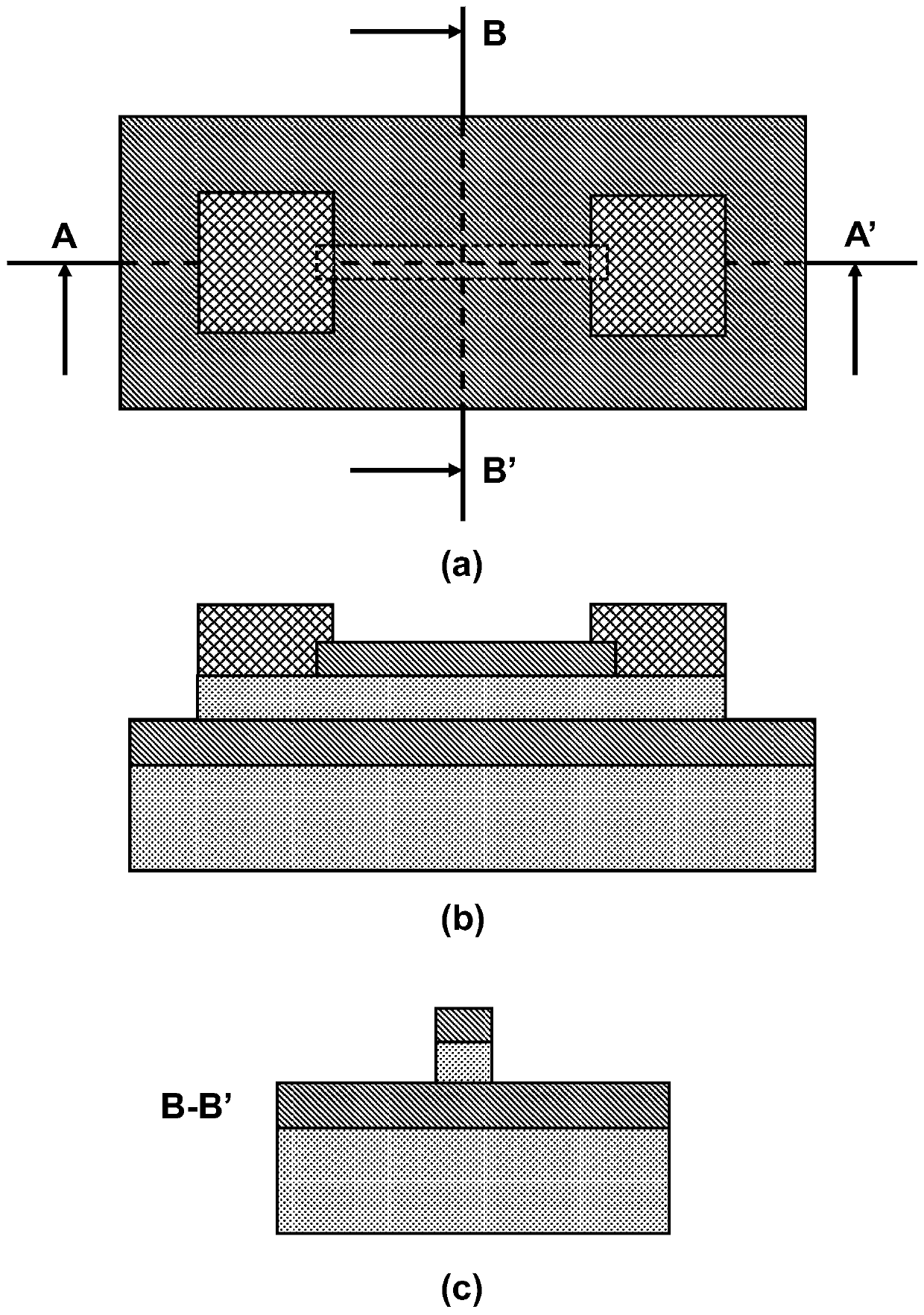

[0043] Such as Figure 1 to Figure 8 As shown, a low-voltage multifunctional charge-trapping synaptic transistor was fabricated according to the following steps:

[0044] 1) Thinning the silicon film of the SOI substrate, the specific operation method is dry oxygen oxidation or hydrogen-oxygen synthesis to oxidize the surface silicon film to form a silicon oxide film, and then rinse the surface silicon oxide film with hydrofluoric acid solution, and then spin Coated with HSQ electron beam glue, such as figure 1 shown. It is also possible to use a bulk silicon substrate, and then deposit a silicon oxide film and a polysilicon film in sequence to form an SOI substrate.

[0045] 2) Using electron beam lithography to define the nanowire mask, the width of the nanowire mask is the line width of the subsequent silicon nanowires, such as figu...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com