Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

178 results about "Synaptic weight" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

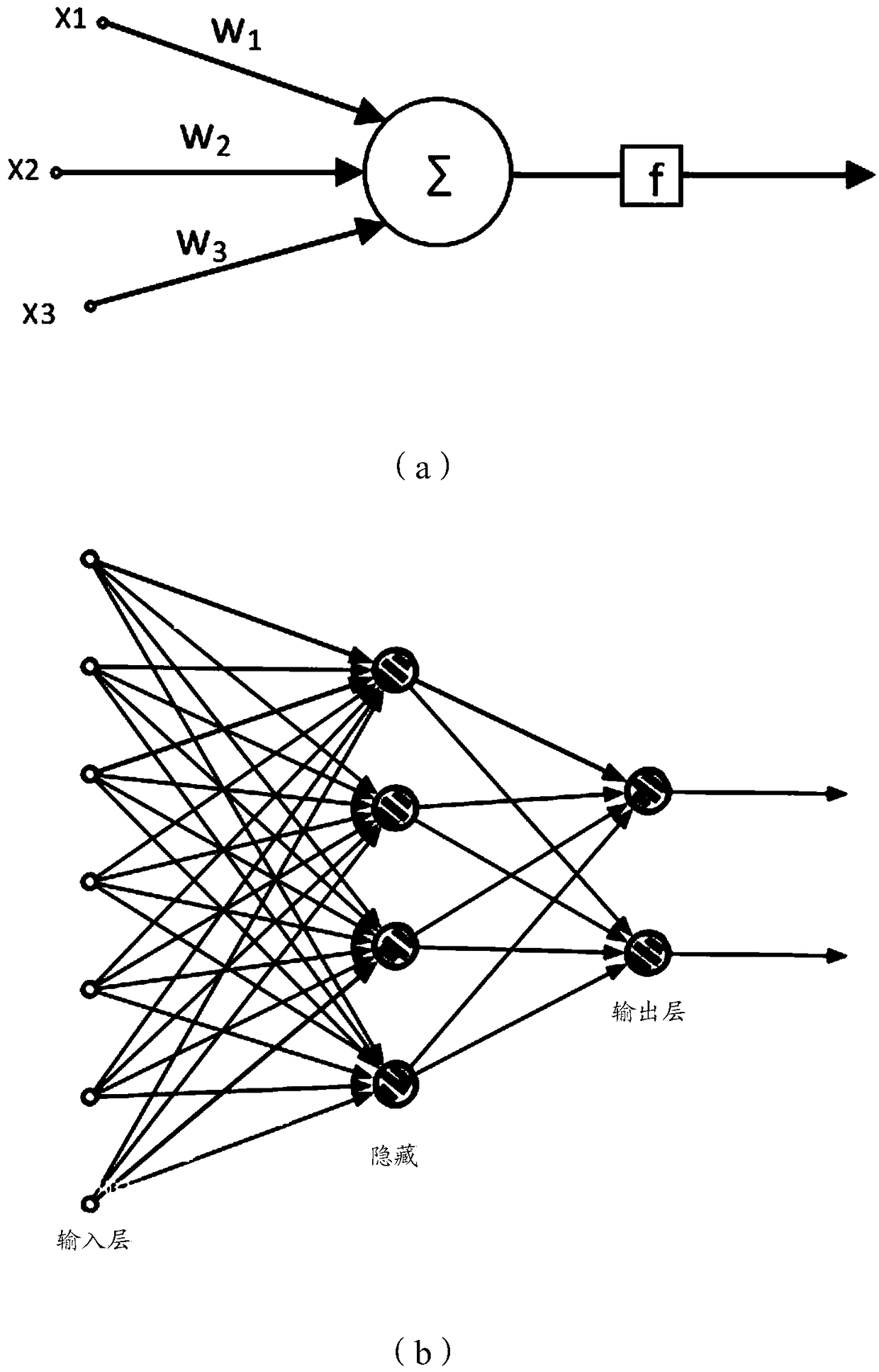

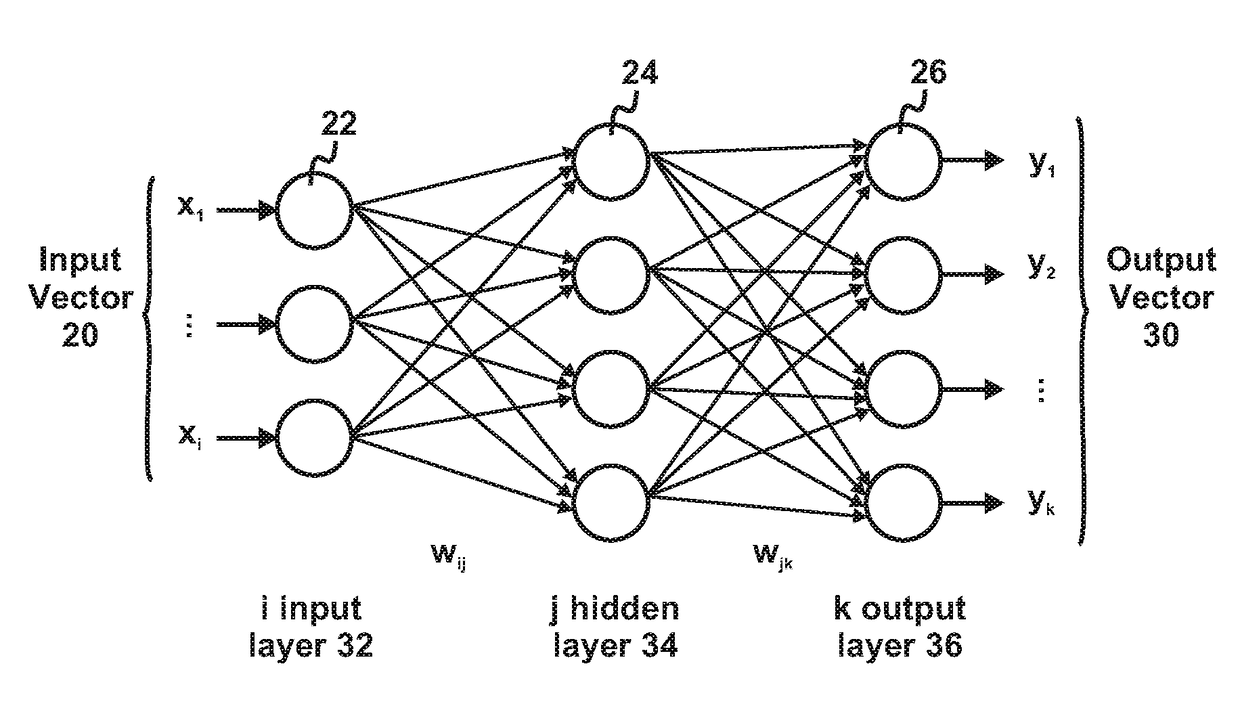

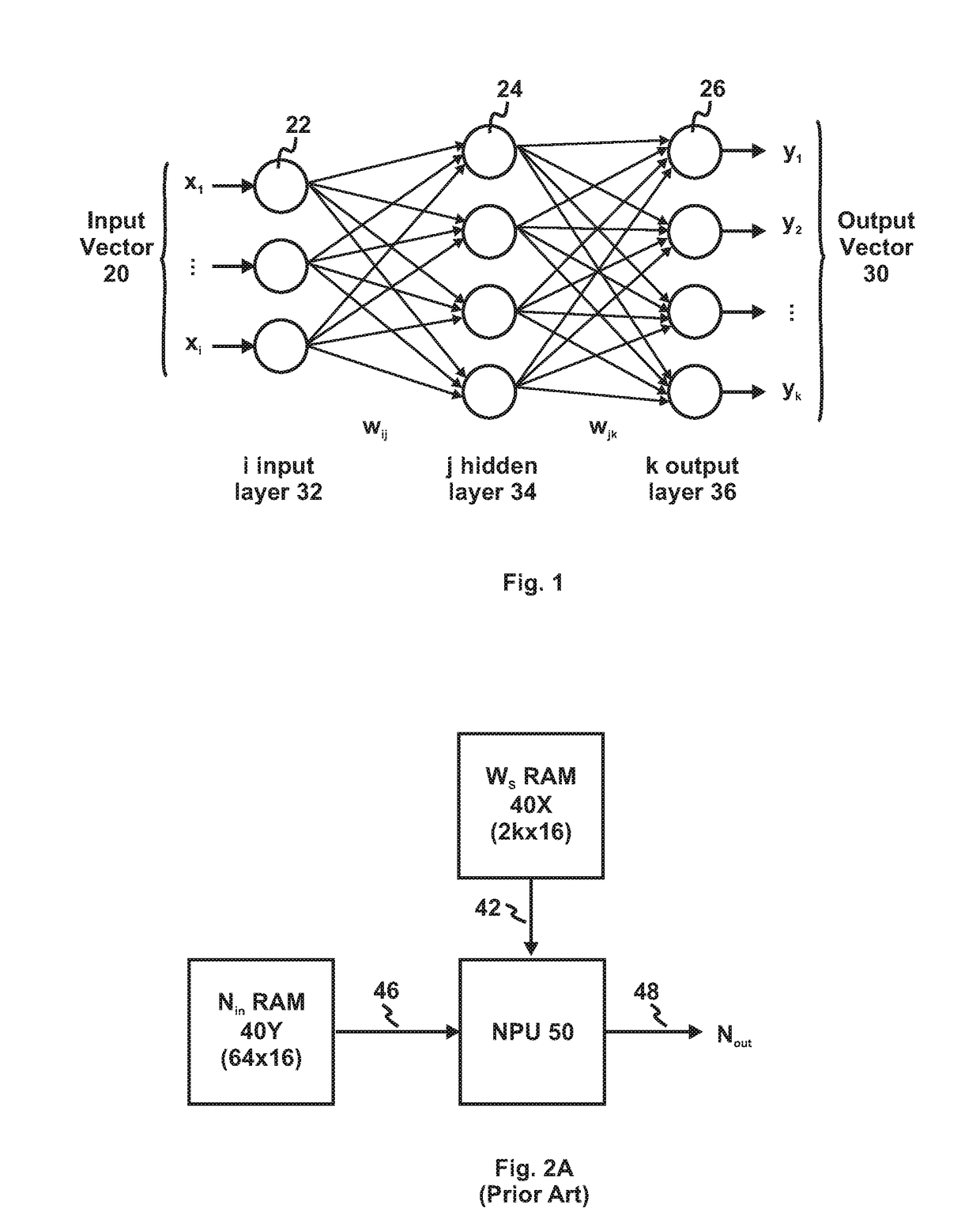

In neuroscience and computer science, synaptic weight refers to the strength or amplitude of a connection between two nodes, corresponding in biology to the amount of influence the firing of one neuron has on another. The term is typically used in artificial and biological neural network research.

Calculation apparatus and method for accelerator chip accelerating deep neural network algorithm

InactiveCN105488565AExtended waiting timeConsume morePhysical realisationNeural learning methodsSynaptic weightNerve network

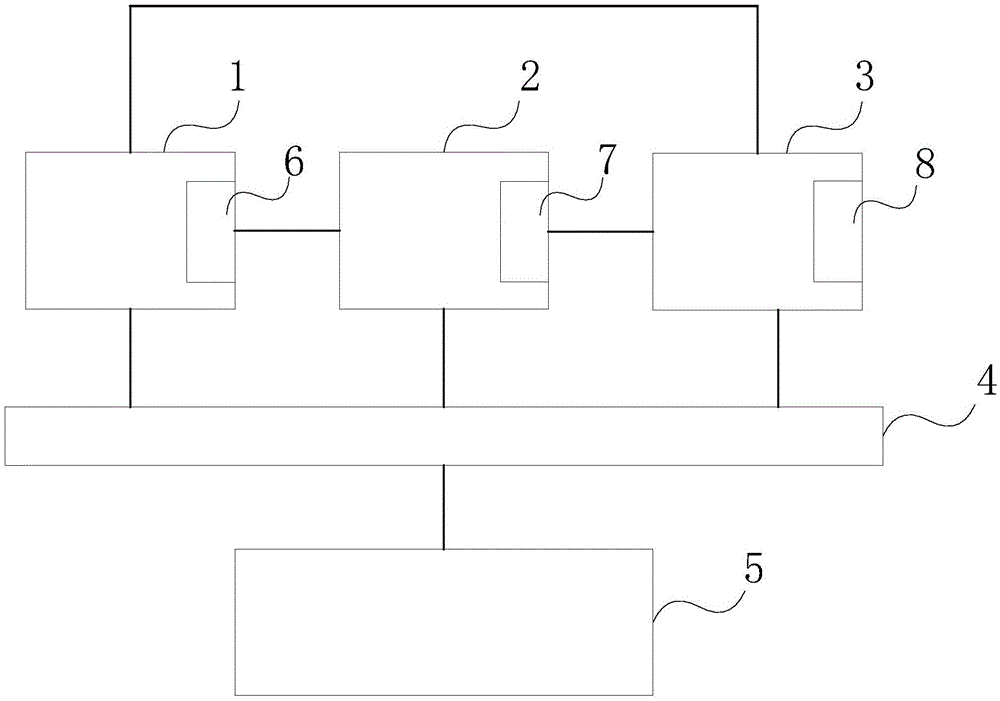

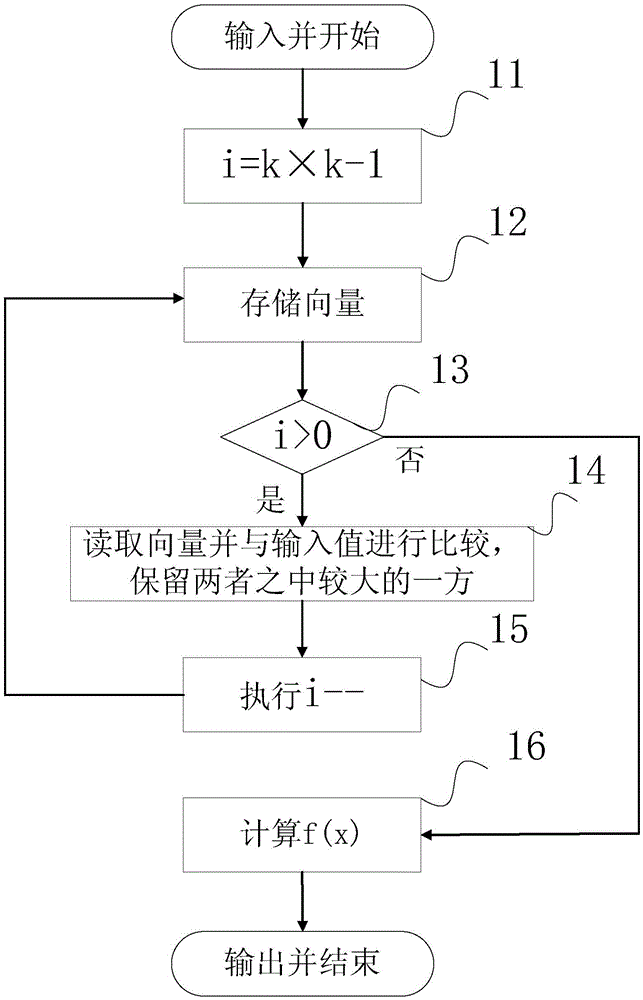

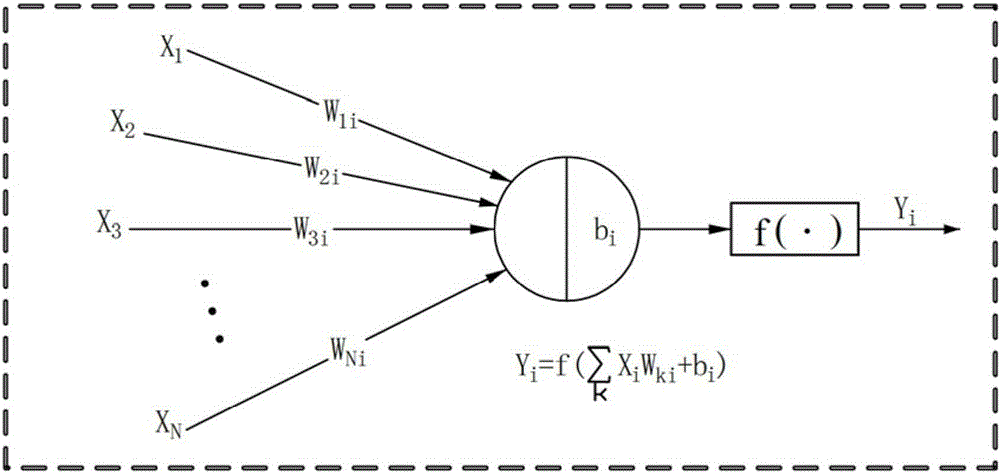

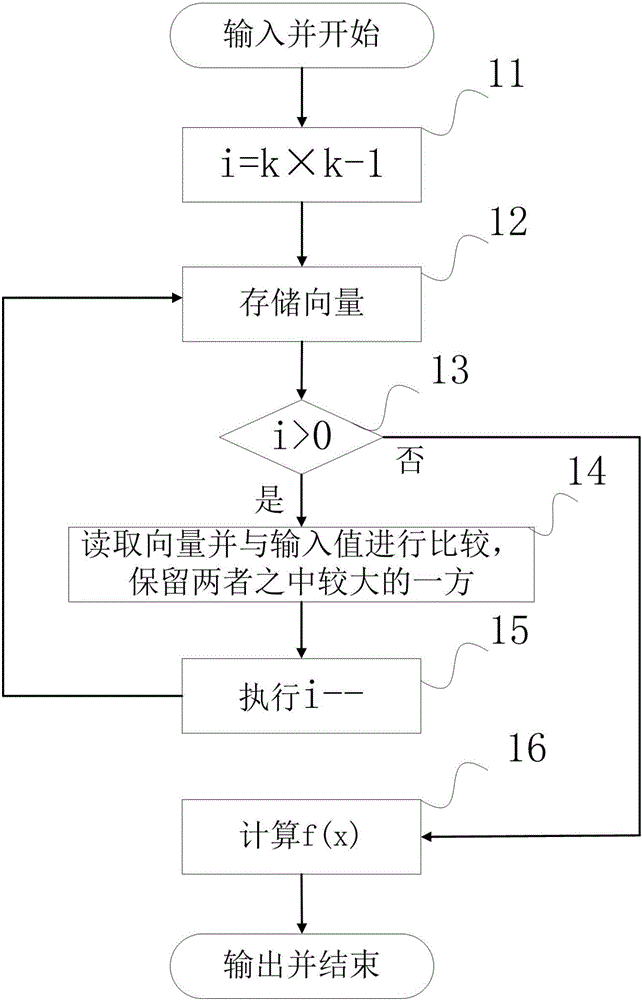

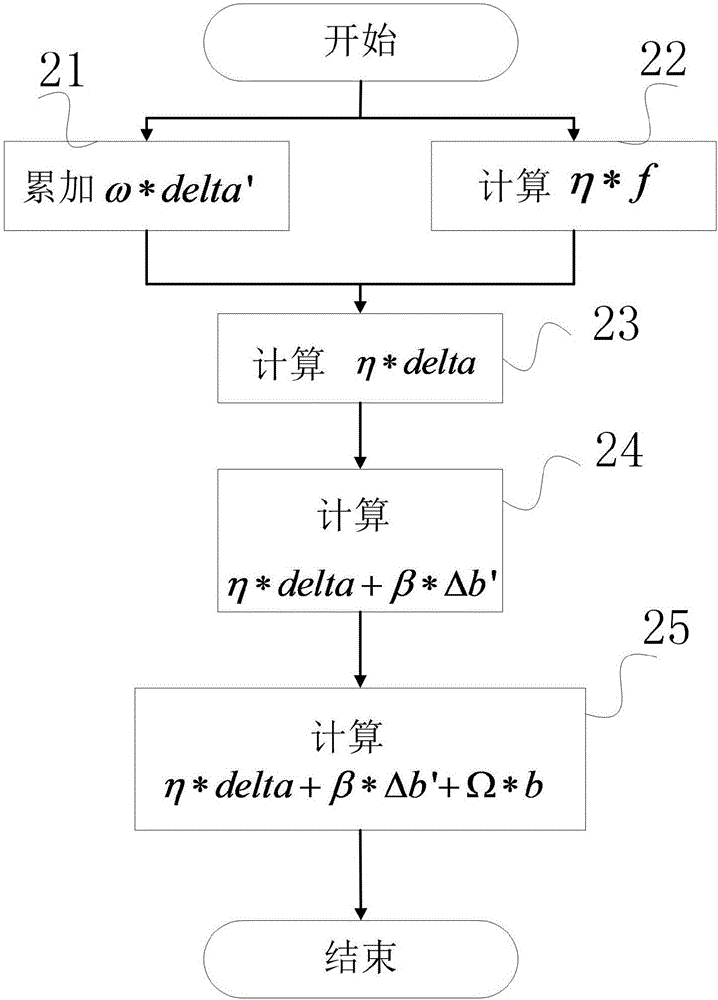

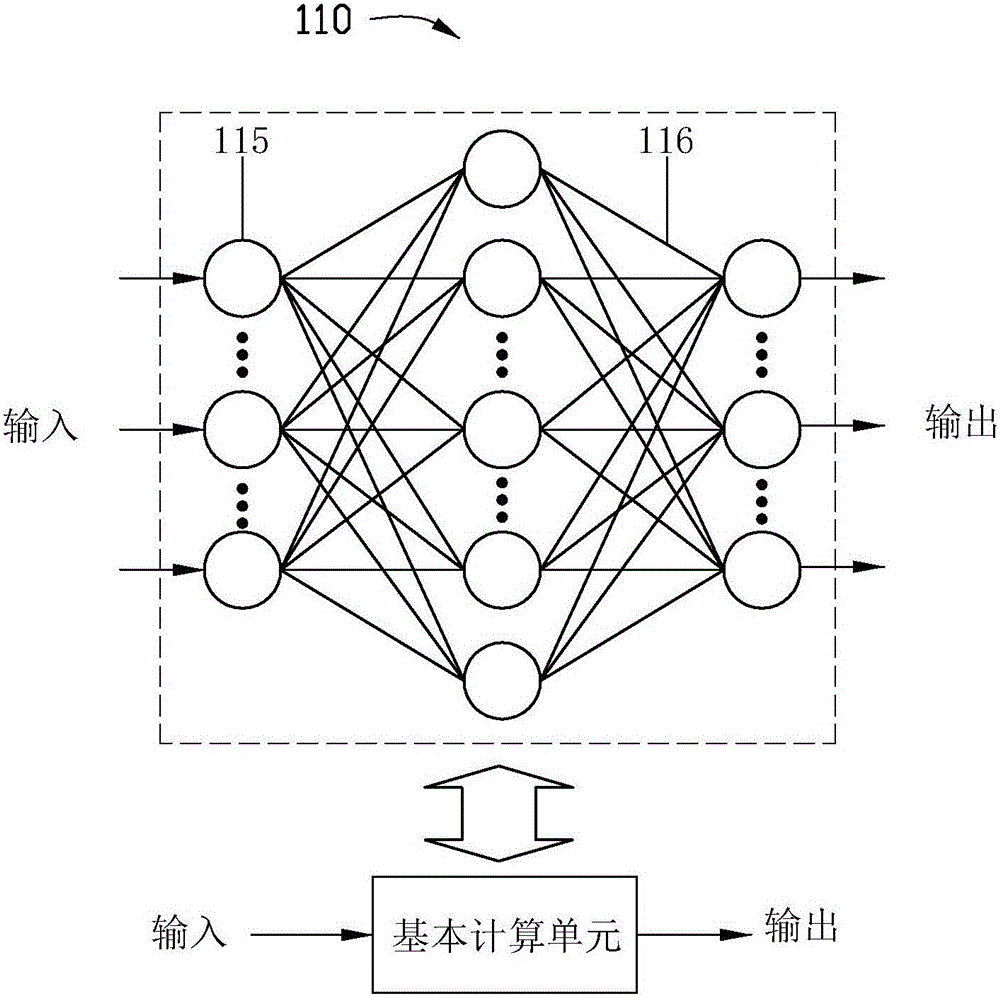

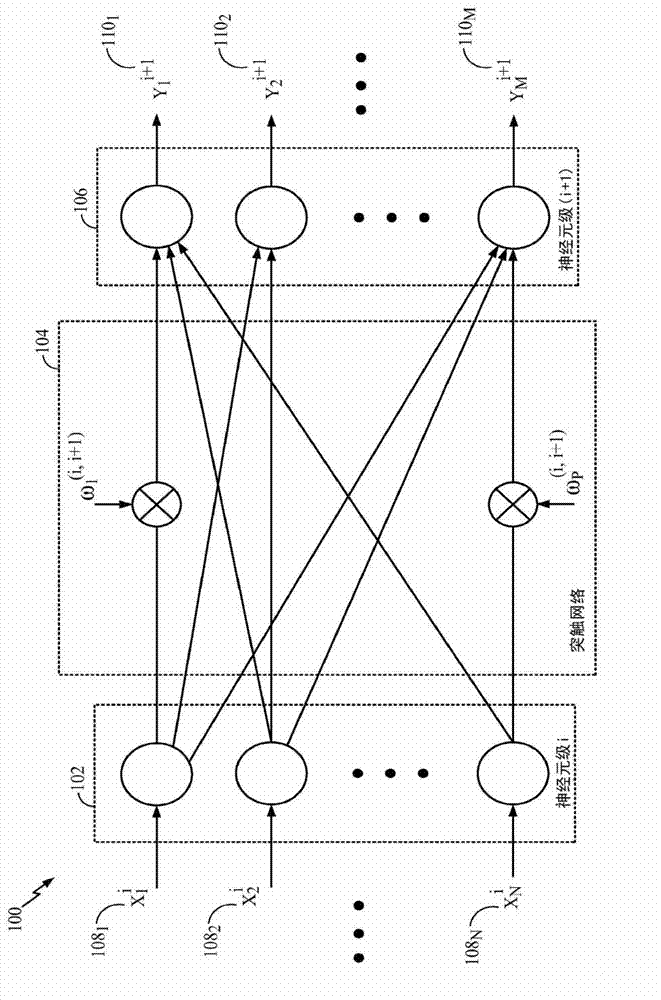

The invention provides a calculation apparatus and method for an accelerator chip accelerating a deep neural network algorithm. The apparatus comprises a vector addition processor module, a vector function value calculator module and a vector multiplier-adder module, wherein the vector addition processor module performs vector addition or subtraction and / or vectorized operation of a pooling layer algorithm in the deep neural network algorithm; the vector function value calculator module performs vectorized operation of a nonlinear value in the deep neural network algorithm; the vector multiplier-adder module performs vector multiplication and addition operations; the three modules execute programmable instructions and interact to calculate a neuron value and a network output result of a neural network and a synaptic weight variation representing the effect intensity of input layer neurons to output layer neurons; and an intermediate value storage region is arranged in each of the three modules and a main memory is subjected to reading and writing operations. Therefore, the intermediate value reading and writing frequencies of the main memory can be reduced, the energy consumption of the accelerator chip can be reduced, and the problems of data missing and replacement in a data processing process can be avoided.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

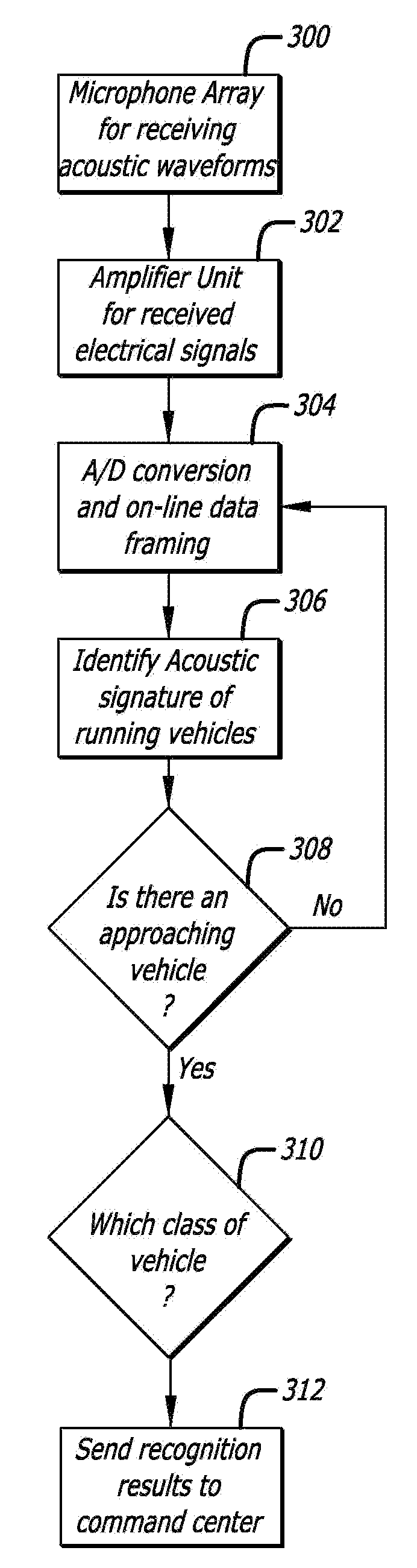

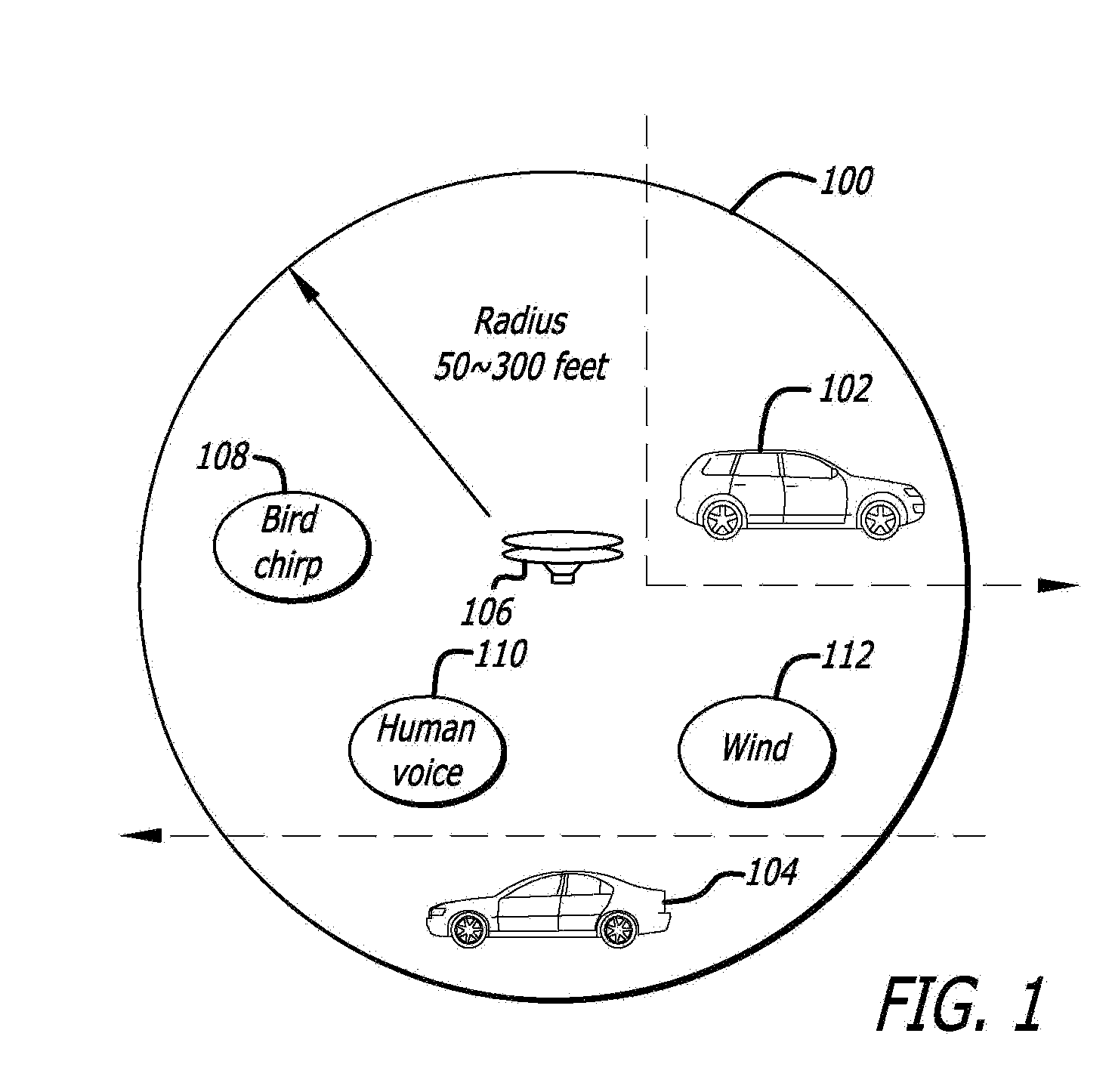

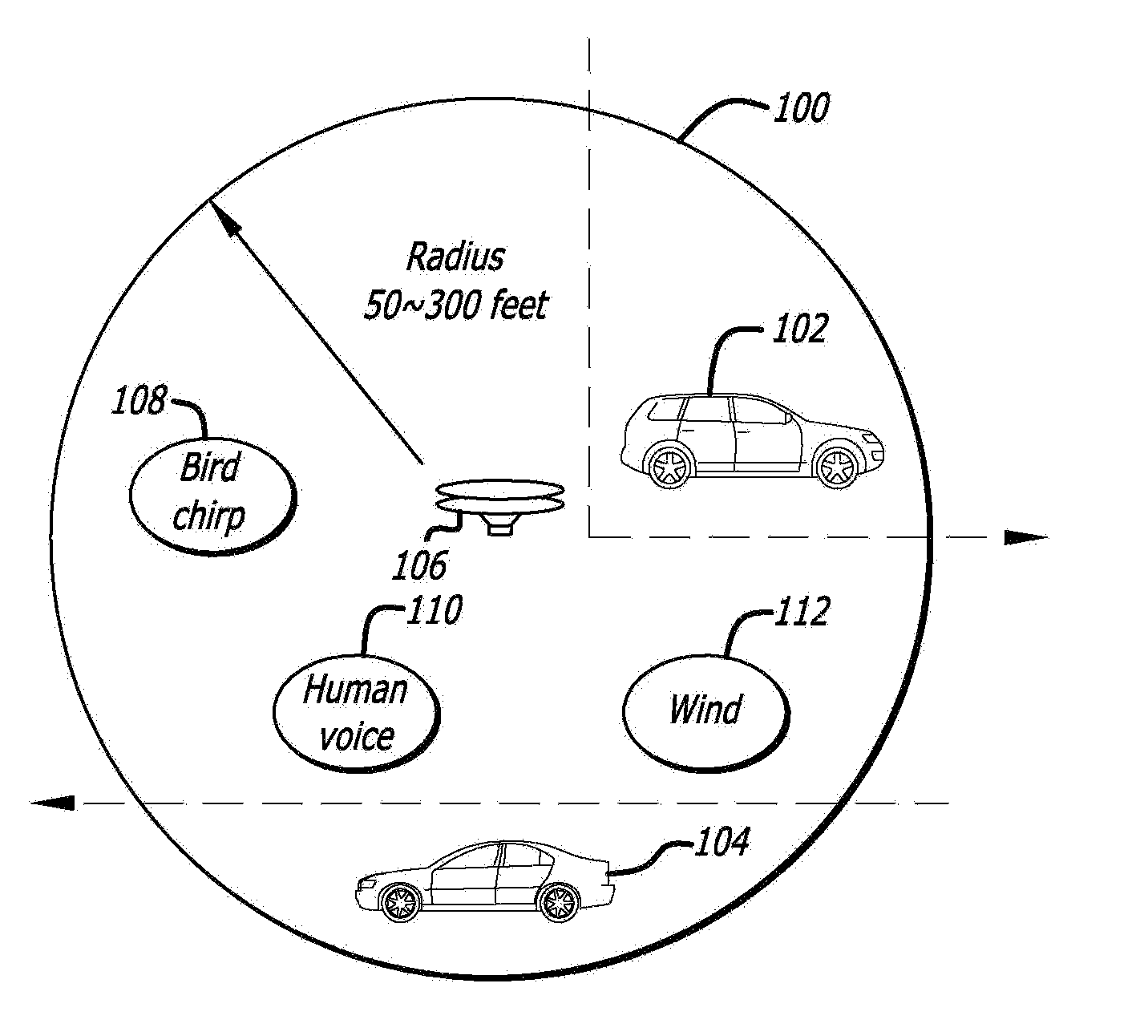

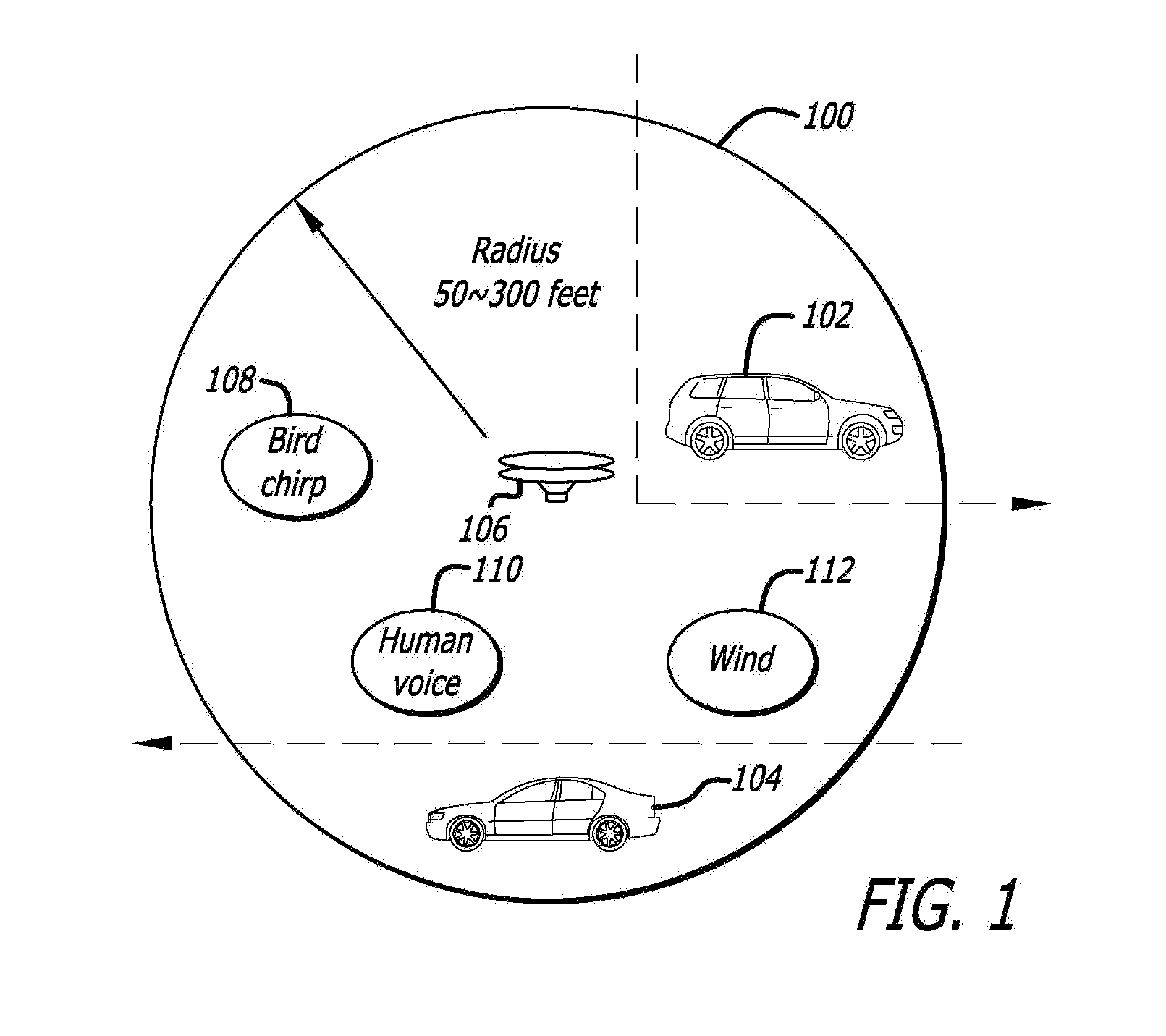

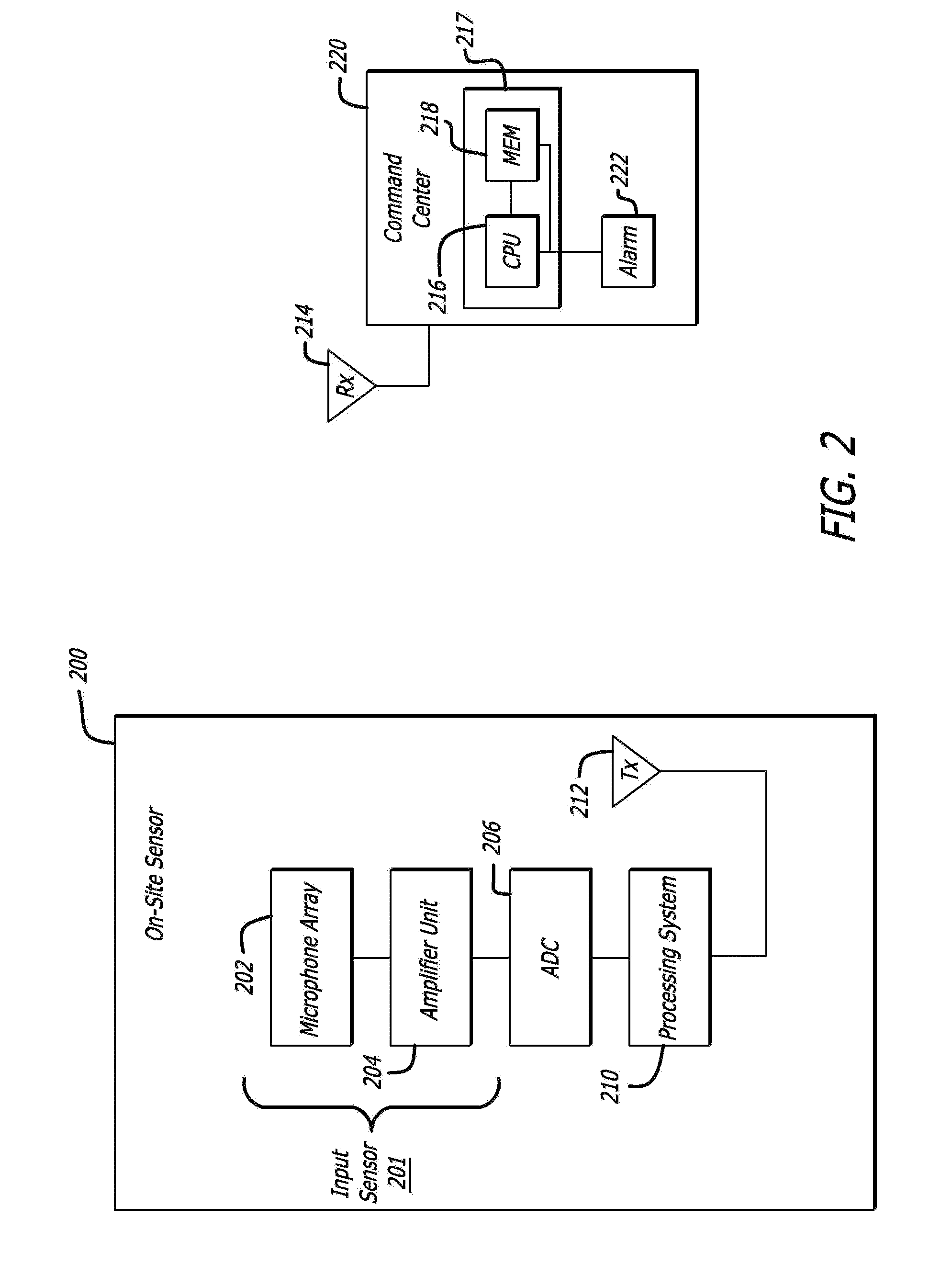

Detection and classification of running vehicles based on acoustic signatures

ActiveUS20090115635A1Analogue computers for vehiclesVibration measurement in fluidFeature vectorSynaptic weight

A method and apparatus for identifying running vehicles in an area to be monitored using acoustic signature recognition. The apparatus includes an input sensor for capturing an acoustic waveform produced by a vehicle source, and a processing system. The waveform is digitized and divided into frames. Each frame is filtered into a plurality of gammatone filtered signals. At least one spectral feature vector is computed for each frame. The vectors are integrated across a plurality of frames to create a spectro-temporal representation of the vehicle waveform. In a training mode, values from the spectro-temporal representation are used as inputs to a Nonlinear Hebbian learning function to extract acoustic signatures and synaptic weights. In an active mode, the synaptic weights and acoustic signatures are used as patterns in a supervised associative network to identify whether a vehicle is present in the area to be monitored. In response to a vehicle being present, the class of vehicle is identified. Results may be provided to a central computer.

Owner:UNIV OF SOUTHERN CALIFORNIA

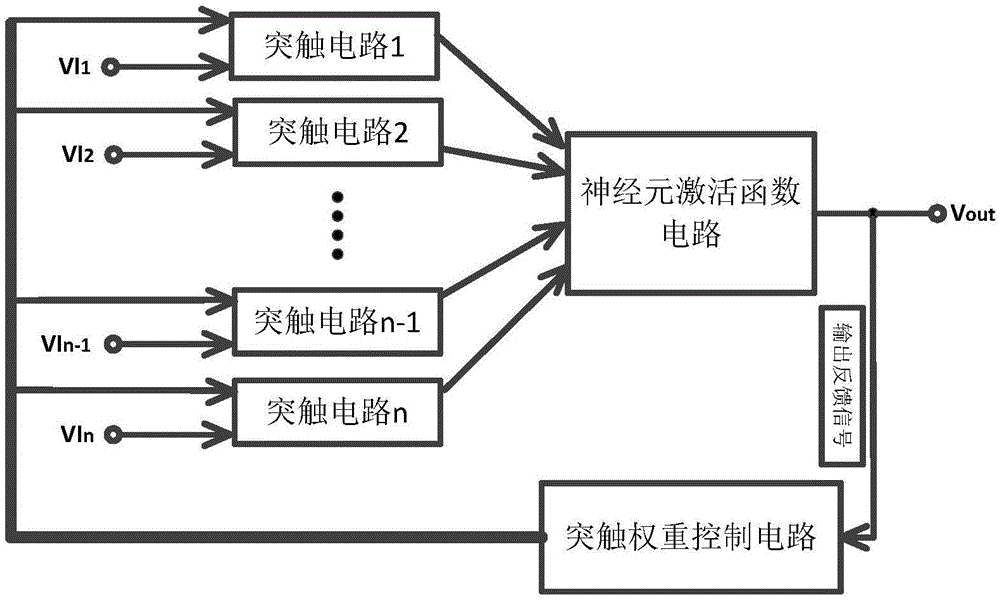

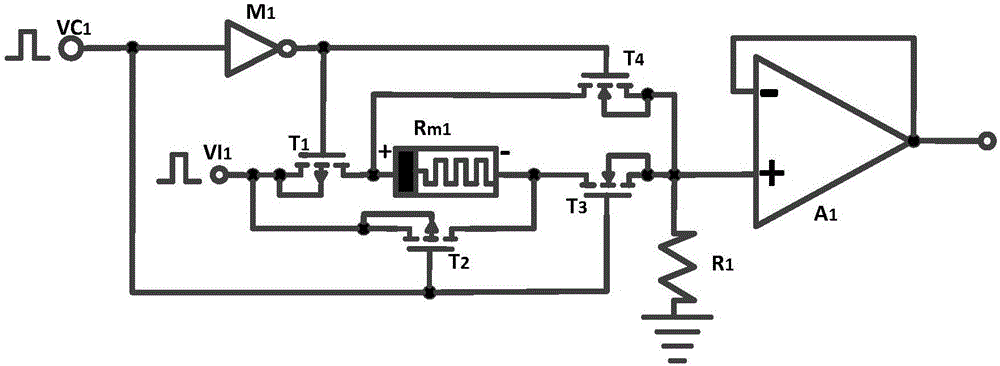

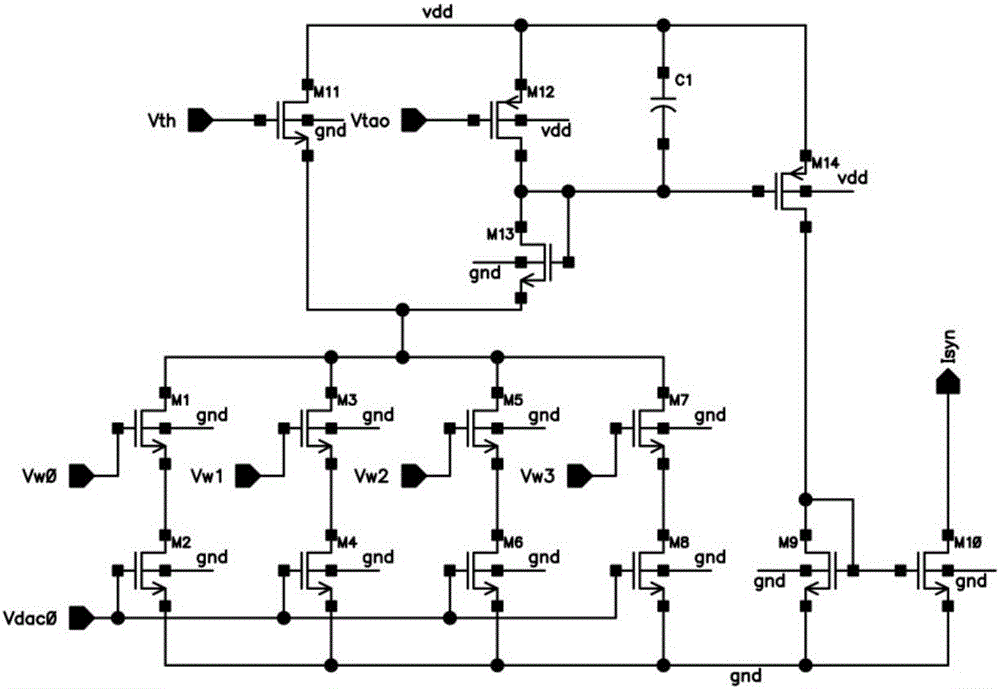

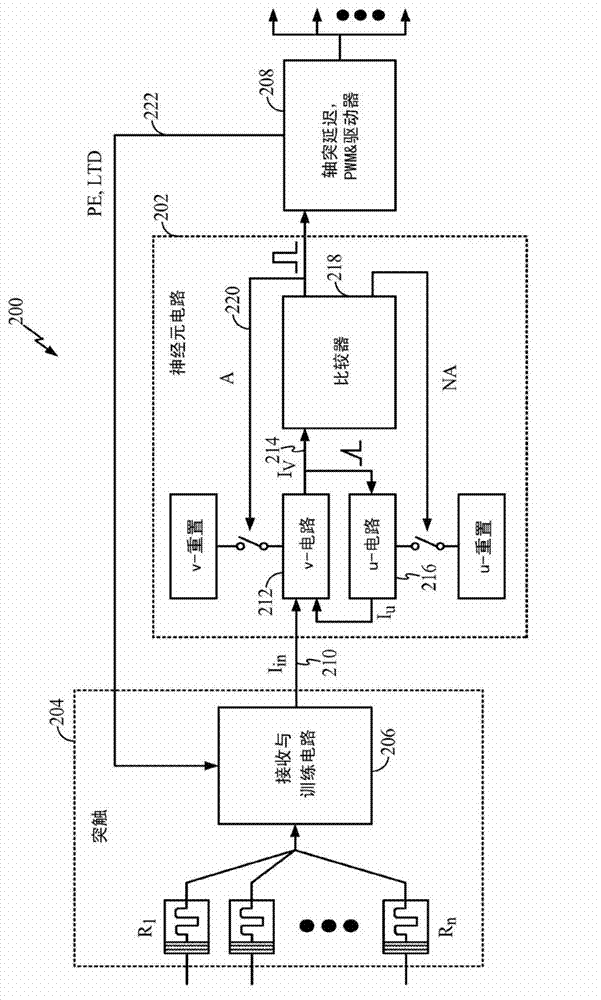

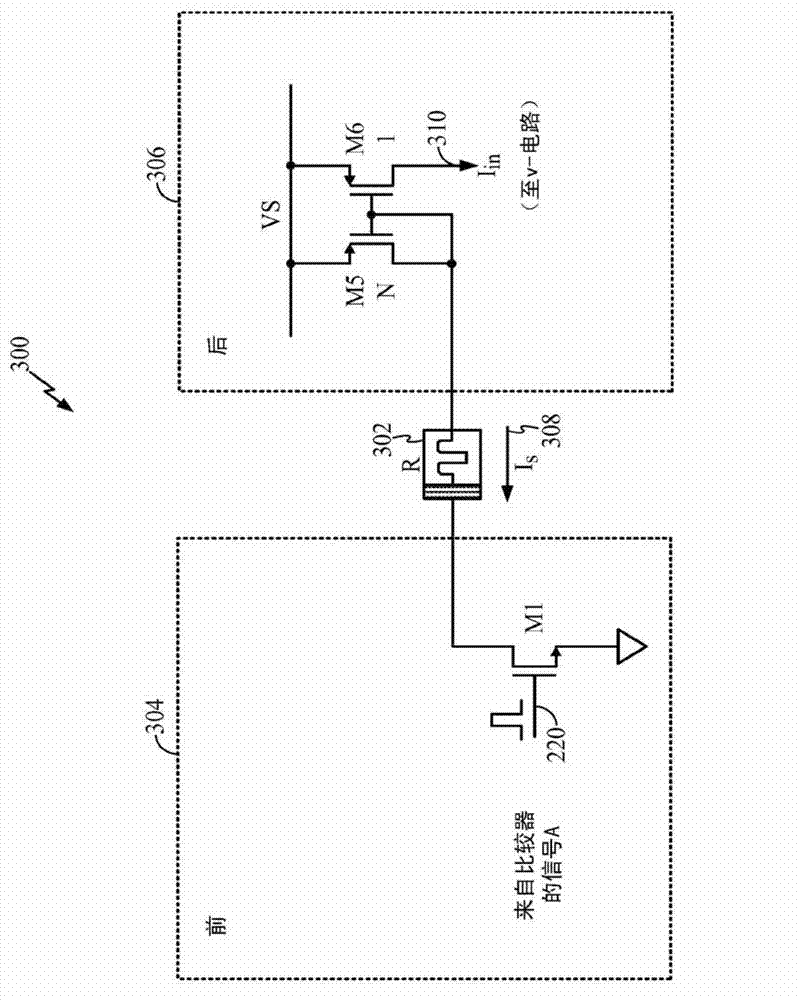

Memristor-based neuron circuit

ActiveCN106815636AGood effectEasy compositionNeural architecturesPhysical realisationActivation functionNerve network

The invention discloses a memristor-based neuron circuit, comprising a synaptic circuit, a neuron activation function circuit and a synaptic weight control circuit. In the synaptic circuit, a memristor, under the control of four MOS tubes, changes the memristor value to simulate the change of the synaptic weight in the neuron network. The designed neuron synaptic circuit is capable of being directly connected with a digital logic electrical level so as to achieve convenient and real-time adjustment to the synaptic weight and through the use of the feature that the output voltage of an operational amplifier is restricted by the power supply voltage, the neuron circuit activation function can be realized as a saturated linear function. The neuron synaptic weight change circuit can utilize the existing CMOS micro-controller and at the same time, the micro-controller can be loaded by the neuron network algorithm to change the synaptic weight to realize corresponding functions. According to the invention, a plurality of neuron circuits could be connected into a large-scale neuron network for complicated functions such as mode identification, signal processing, associated memory and non-linear mapping, etc.

Owner:HUAZHONG UNIV OF SCI & TECH

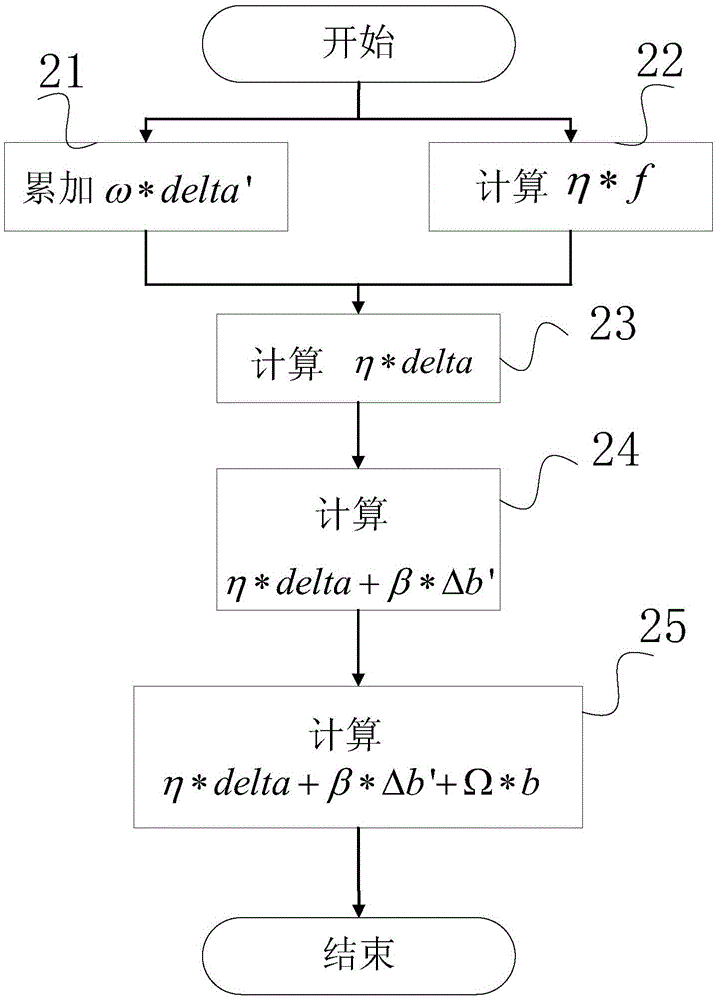

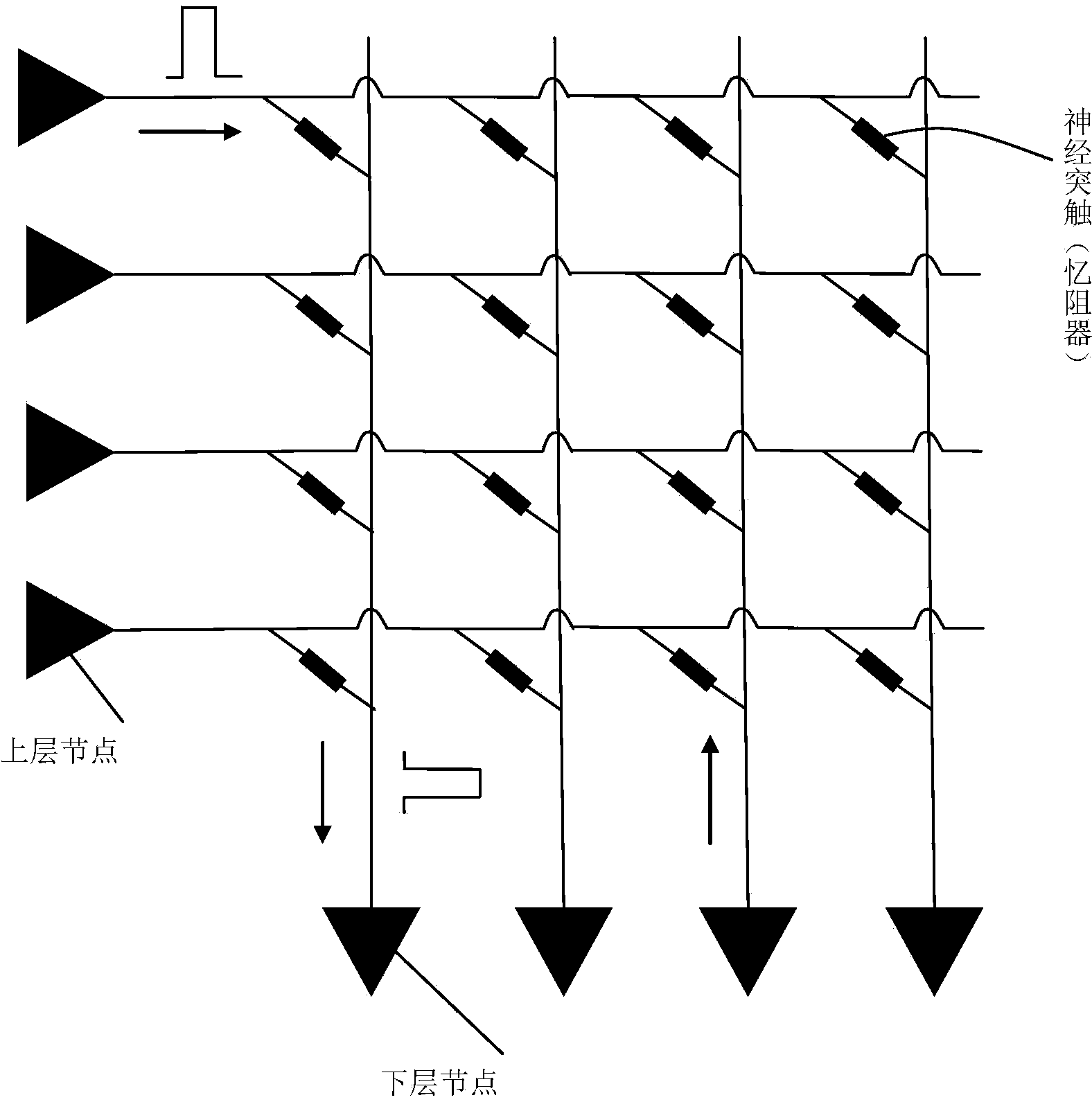

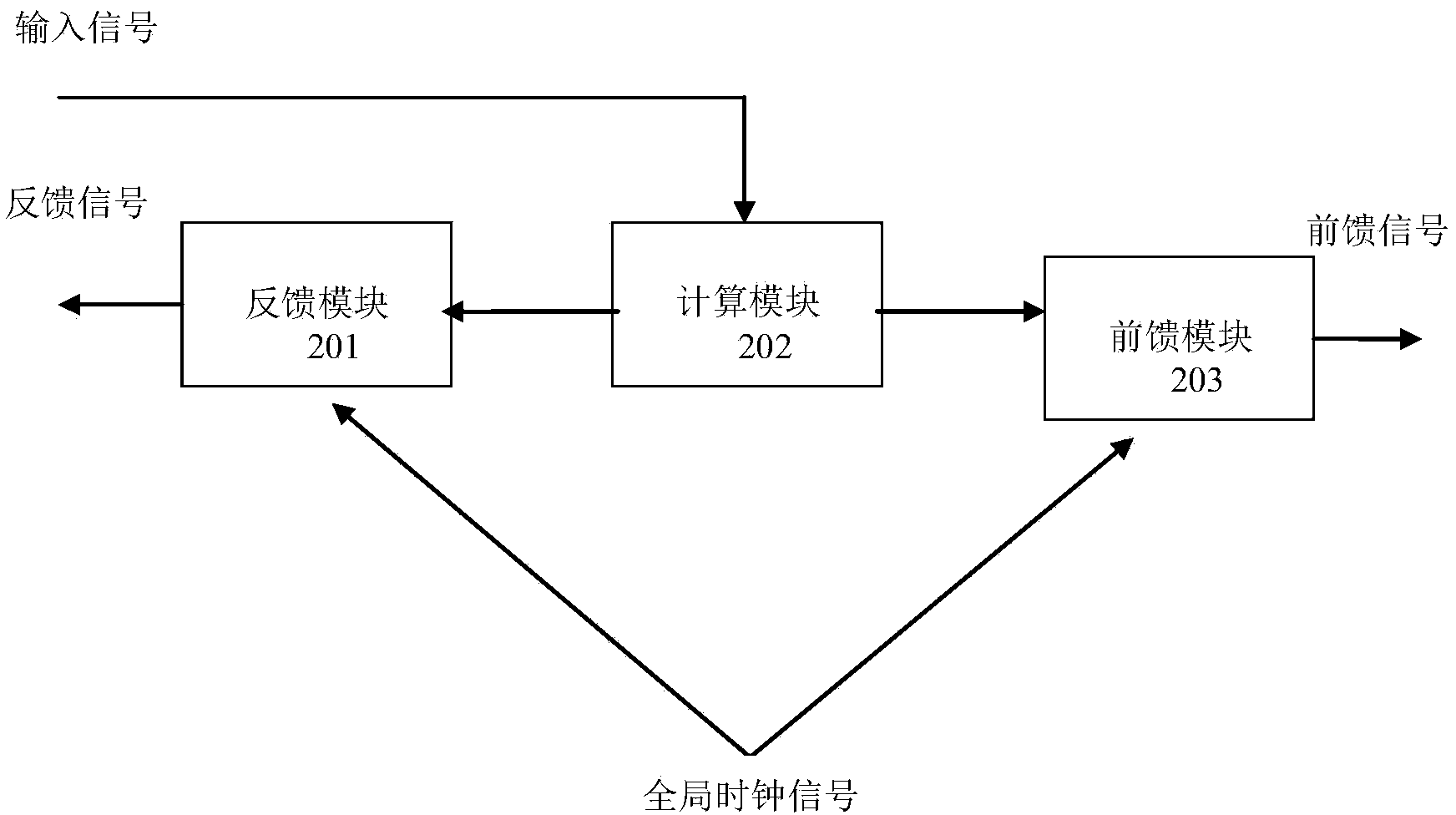

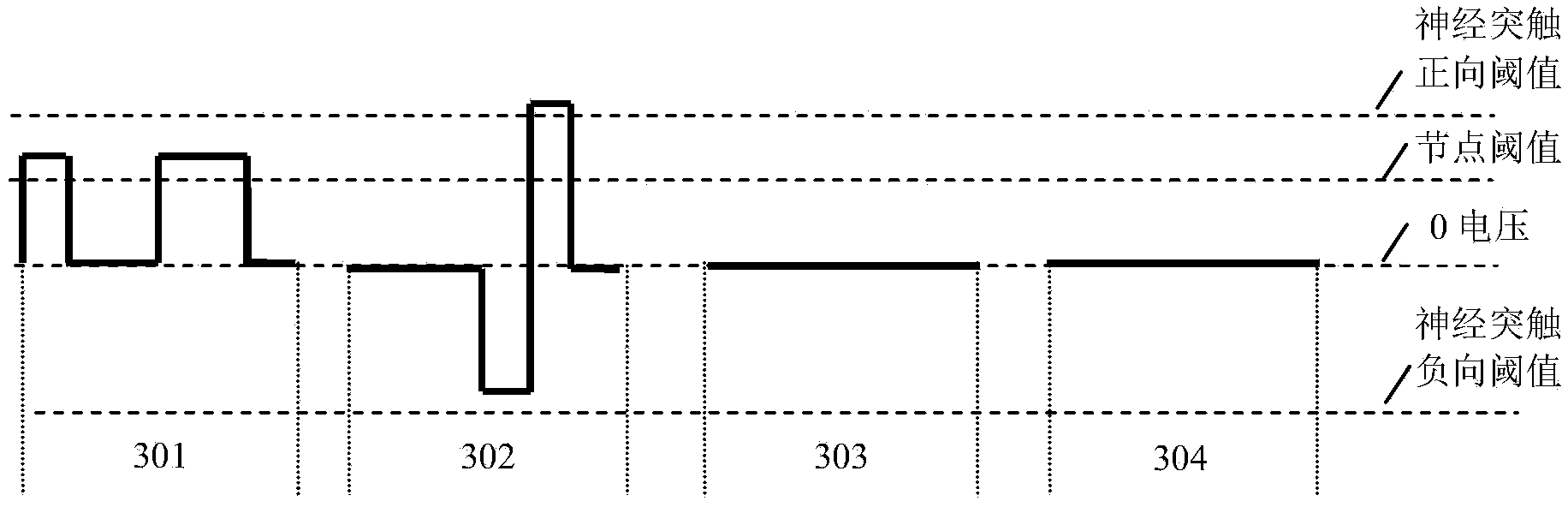

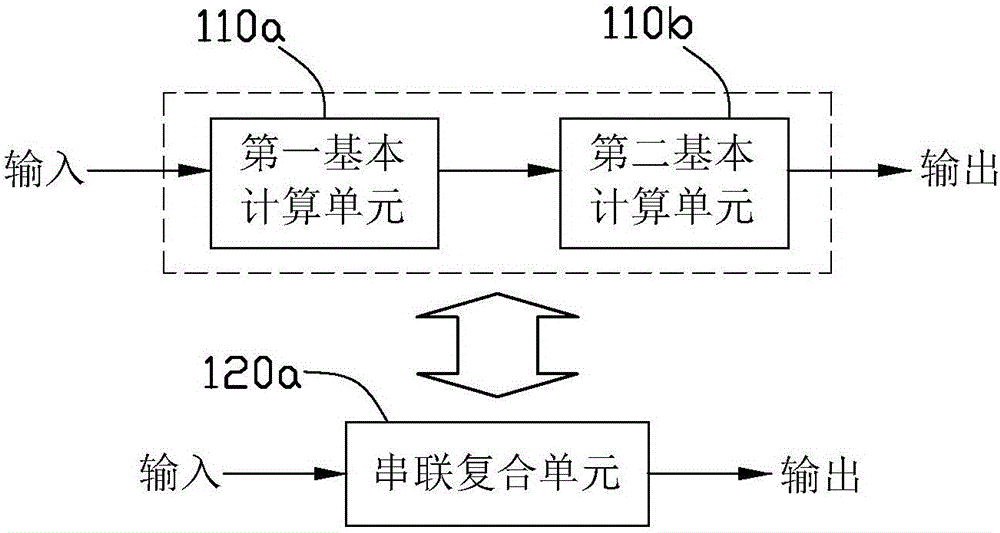

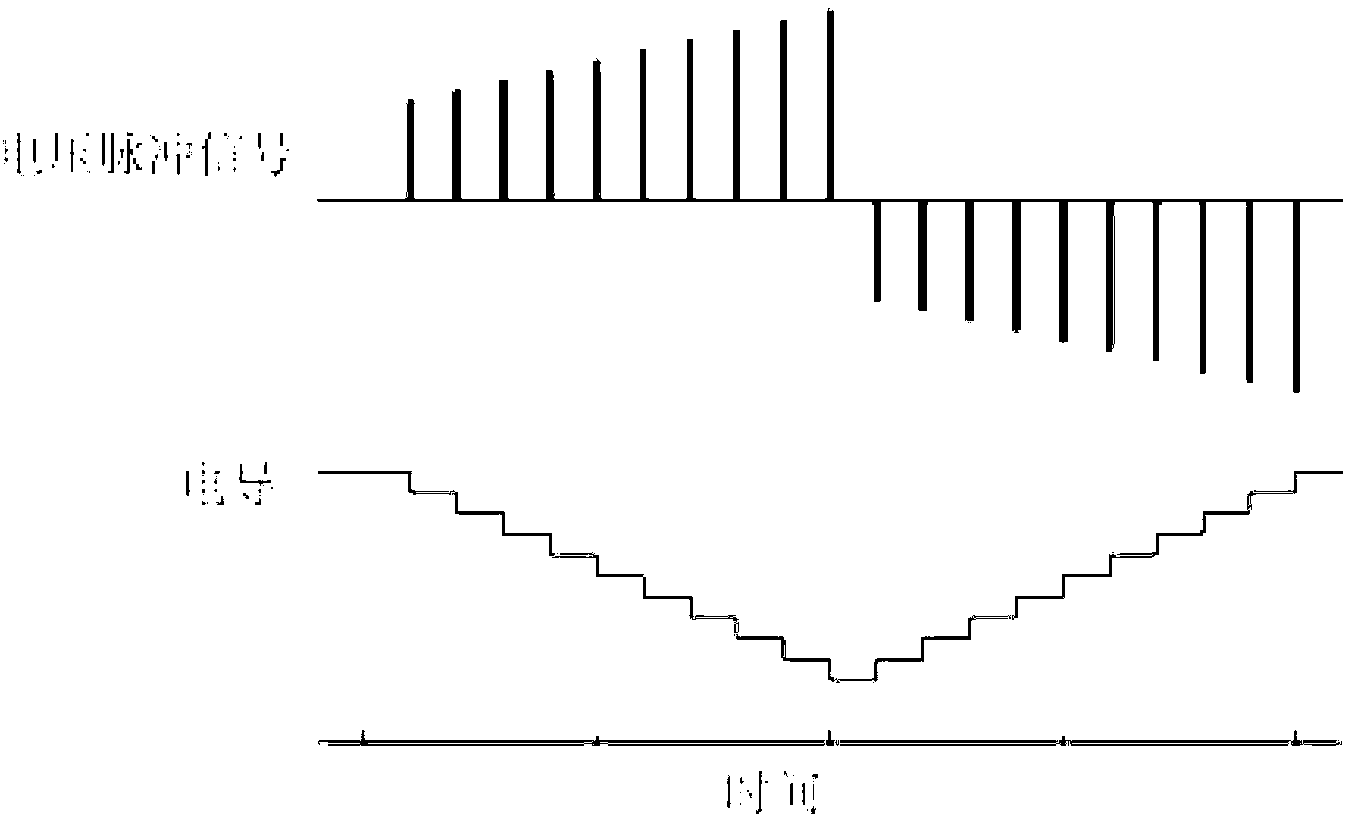

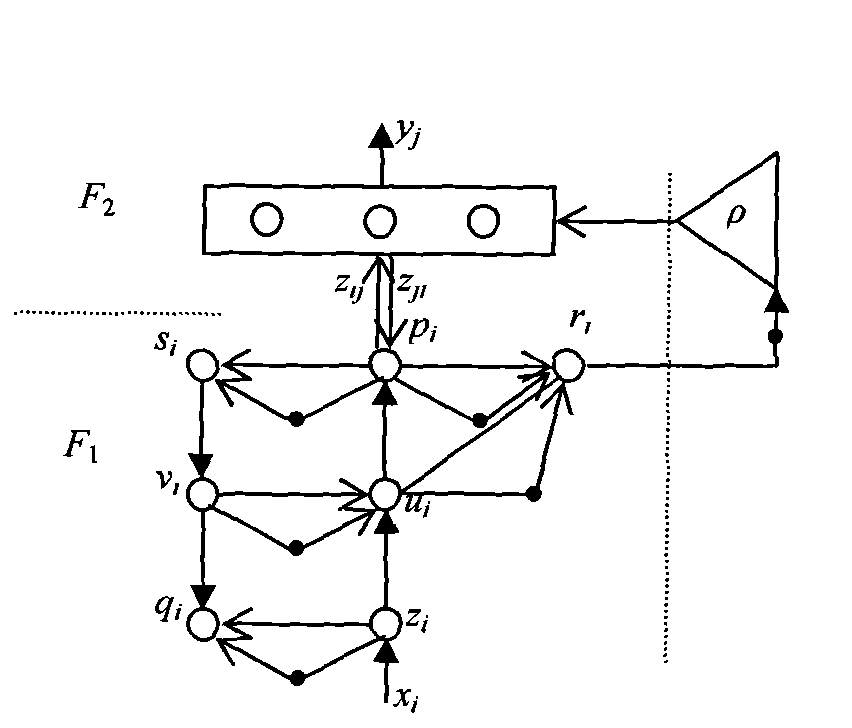

Feedback artificial neural network training method and feedback artificial neural network calculating system

InactiveCN103455843AFast convergenceReduce energy consumptionBiological neural network modelsSynaptic weightNerve network

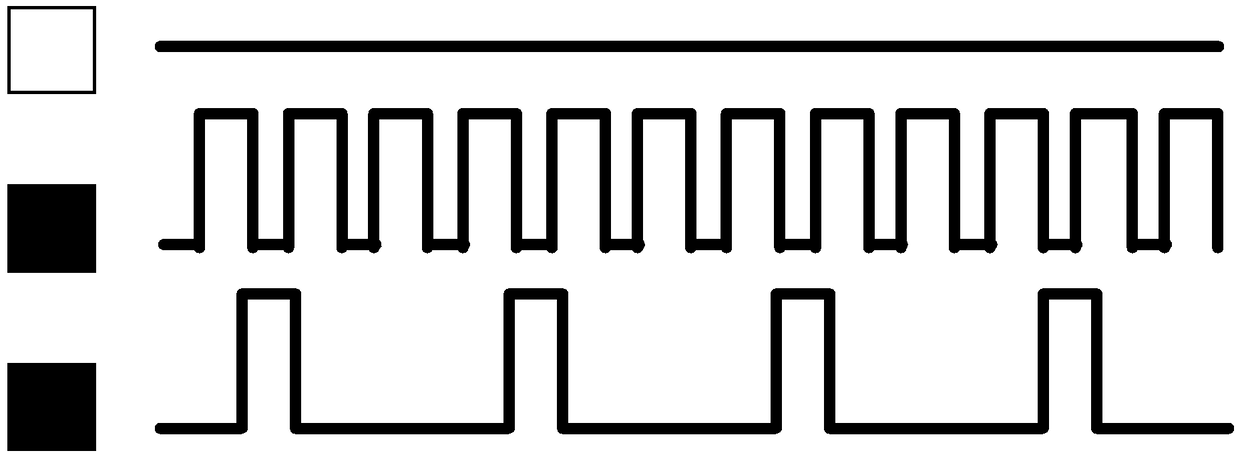

The invention discloses a feedback artificial neural network training method and a feedback artificial neural network calculating system and belongs to the field of calculation of neural networks. According to the artificial neural network training method, the synapse weight is adjusted according to a feedforward signal and a feedback signal at the two ends of each neural synapse; when the signals at the two ends of each neural synapse are an excitation feedforward signal and an excitation feedback signal respectively, the synapse weight is adjusted to the maximum value; when the signals at the two ends of each neural synapse are a tranquillization feedforward signal and an excitation feedback signal respectively, the synapse weight is adjusted to the minimum value. According to the feedback artificial neural network calculating system, each node circuit comprises a calculating module, a feedforward module and a feedback module and the node circuits are connected through the neural synapses simulated by memristors, and a series of pulse signals are adopted to achieve the feedback artificial neural network training method. An artificial neural network provided by the system and the method is high in rate of convergence, and the artificial neural network calculating system is few in control element, low in energy consumption and capable of being applied to data mining, pattern recognition, image recognition and other respects.

Owner:HUAZHONG UNIV OF SCI & TECH

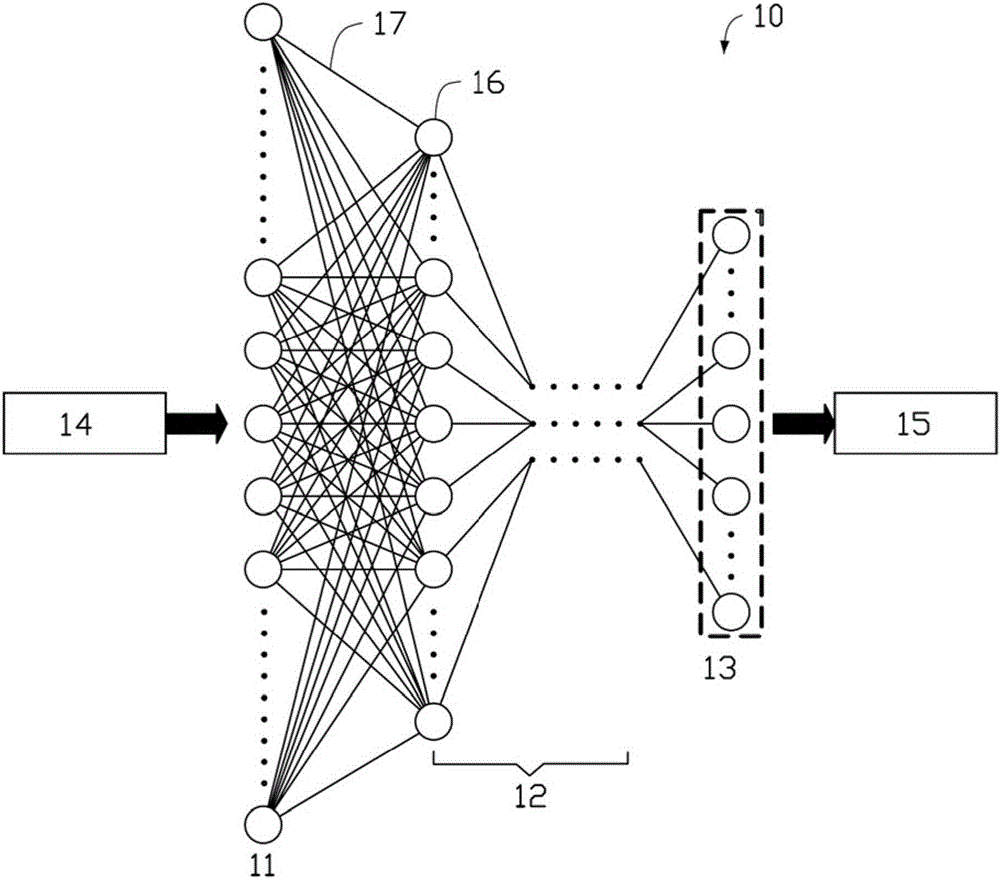

Deep neural network system based on memristor

ActiveCN105224986AIncrease computing speedHigh densityNeural architecturesInformation processingNerve network

The invention provides a deep neural network system based on a memristor, which comprises an input layer, an output layer and multiple hidden layers, wherein the input layer receives an external information input mode, the external information input mode is calculated and converted layer by layer, and an external output result is generated finally by the output layer. A synaptic weight of the deep neural network adopts the memristor for simulation, and the feature that resistance of the memristor changes along with applied electric signals is used to simulate a connection strength behavior of a connection synapse between neural networks. The invention further provides an information processing system for the deep neural network system based on the memristor.

Owner:TSINGHUA UNIV

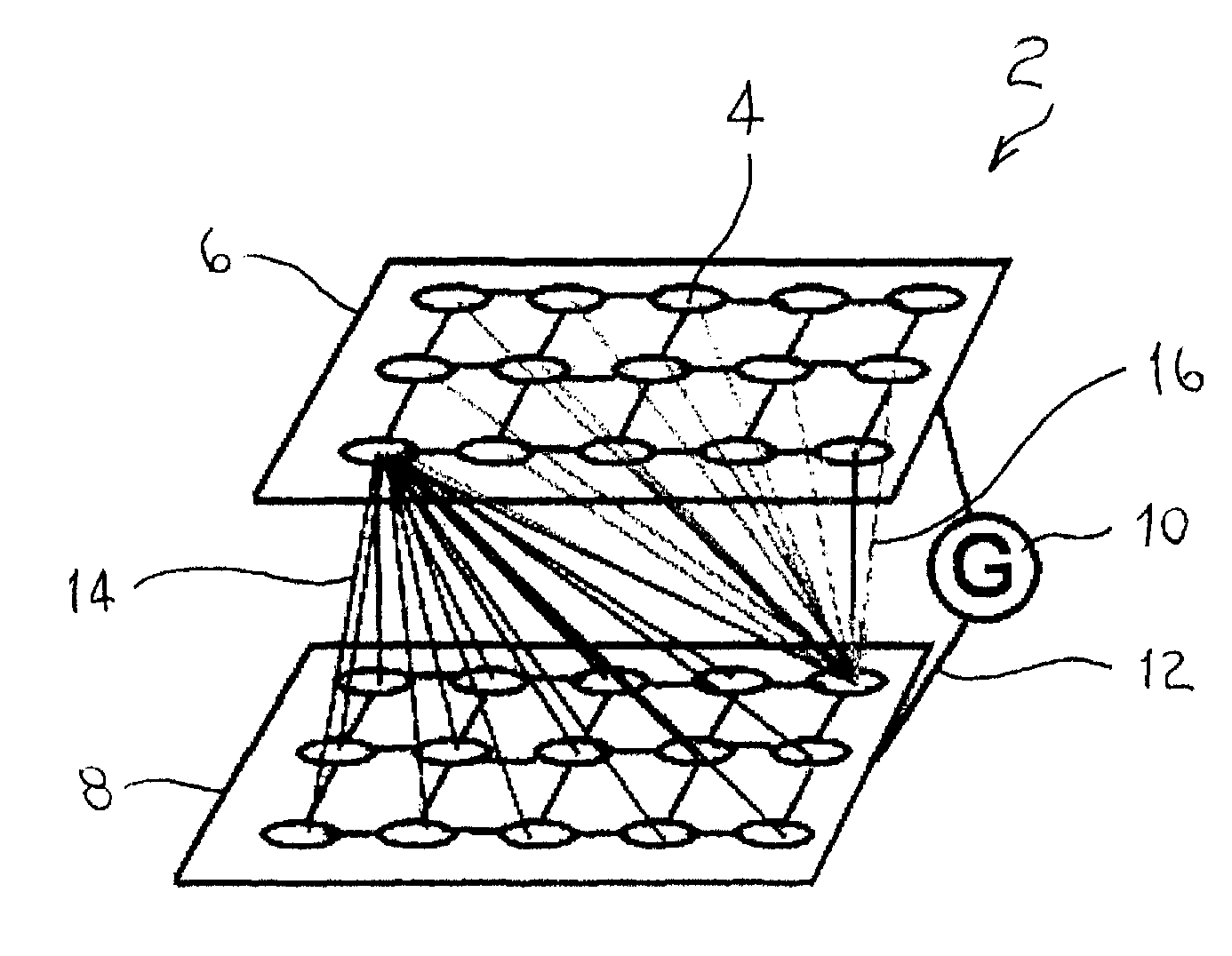

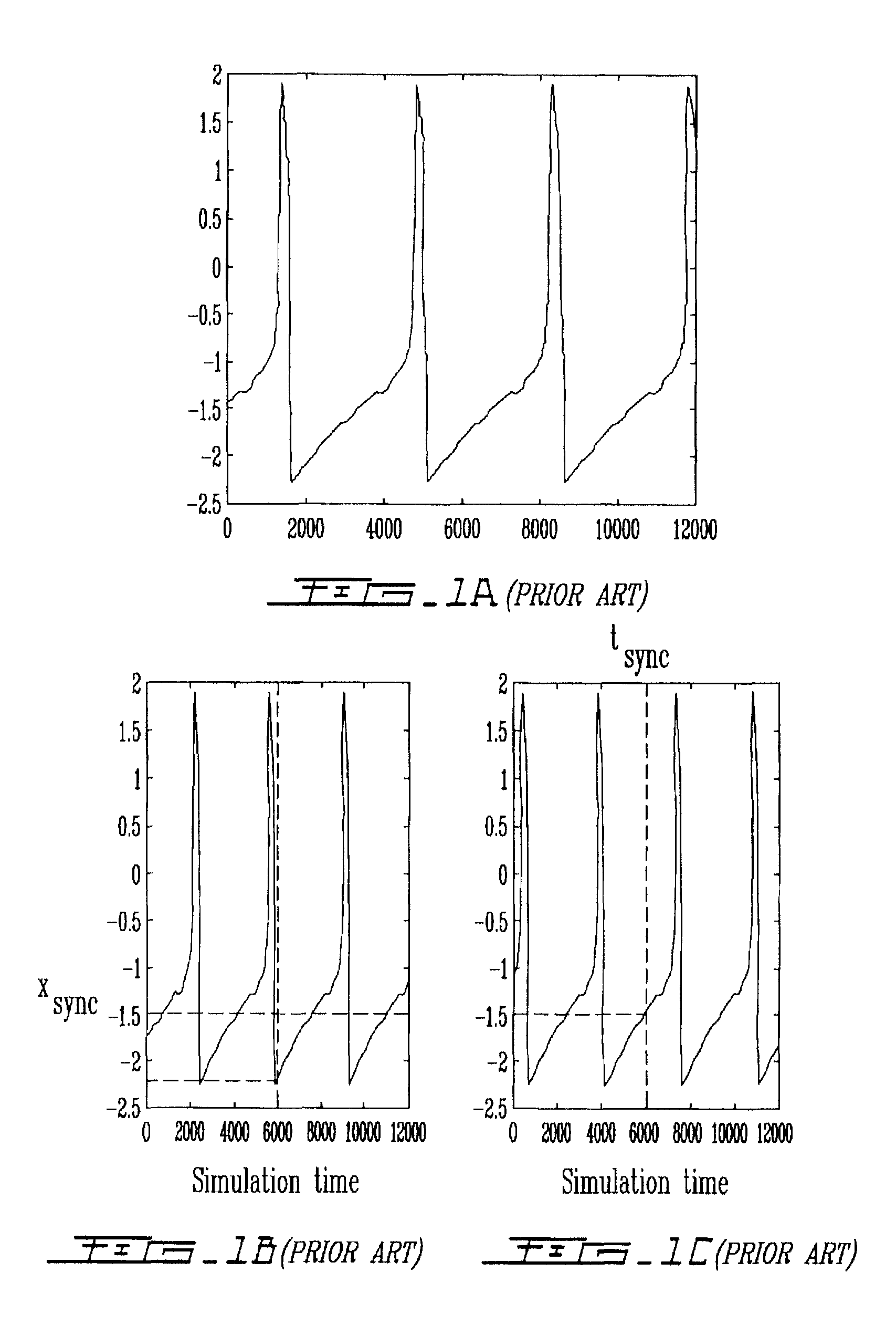

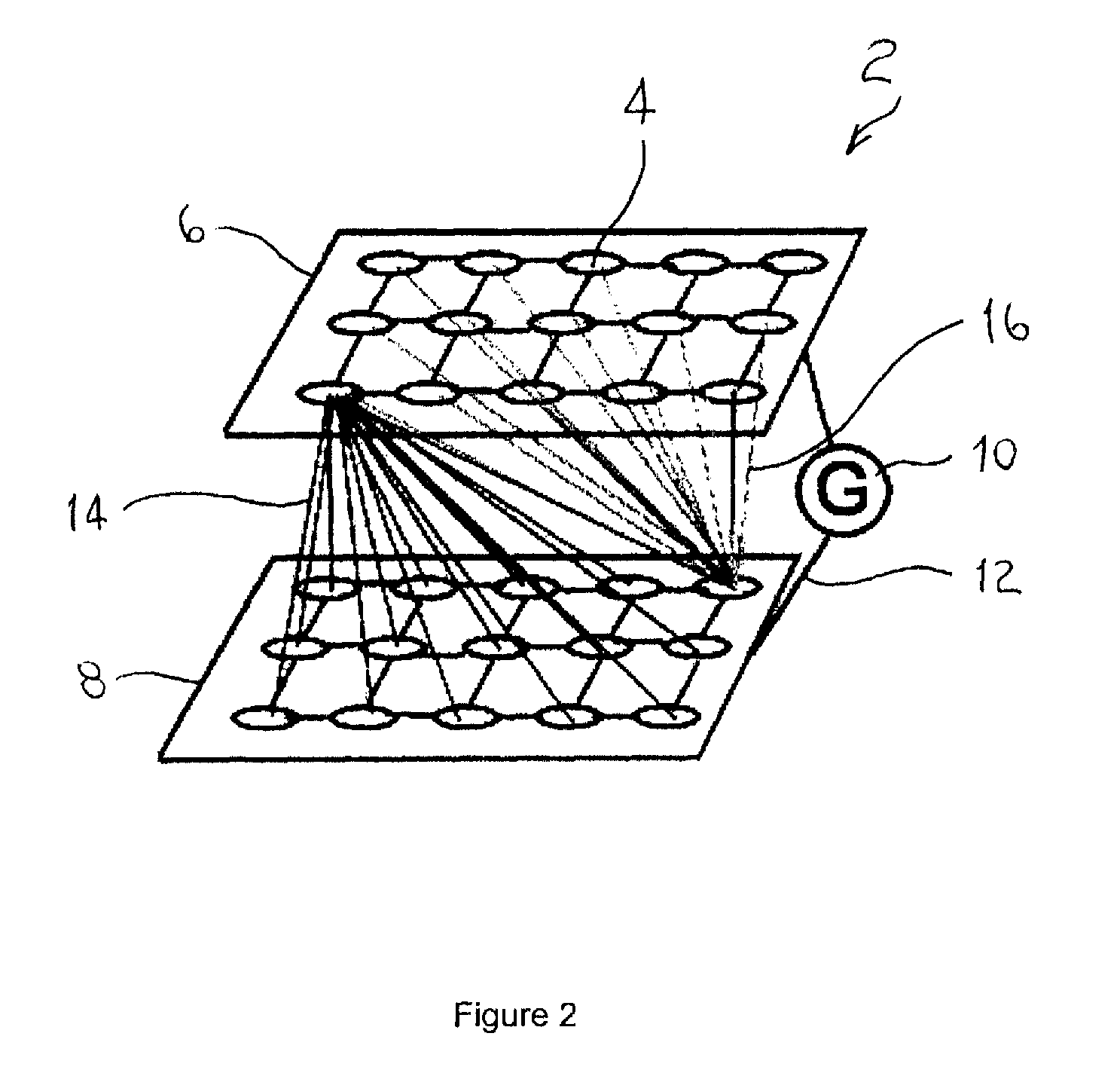

Spatio-temporal pattern recognition using a spiking neural network and processing thereof on a portable and/or distributed computer

ActiveUS8346692B2Digital computer detailsCharacter and pattern recognitionSynaptic weightSpiking neural network

A spiking neural network has a layer of connected neurons exchanging signals. Each neuron is connected to at least one other neuron. A neuron is active if it spikes at least once during a time interval. Time-varying synaptic weights are computed between each neuron and at least one other neuron connected thereto. These weights are computed according to a number of active neurons that are connected to the neuron. The weights are also computed according to an activity of the spiking neural network during the time interval. Spiking of each neuron is synchronized according to a number of active neurons connected to the neuron and according to the weights. A pattern is submitted to the spiking neural network for generating sequences of spikes, which are modulated over time by the spiking synchronization. The pattern is characterized according to the sequences of spikes generated in the spiking neural network.

Owner:ROUAT JEAN +2

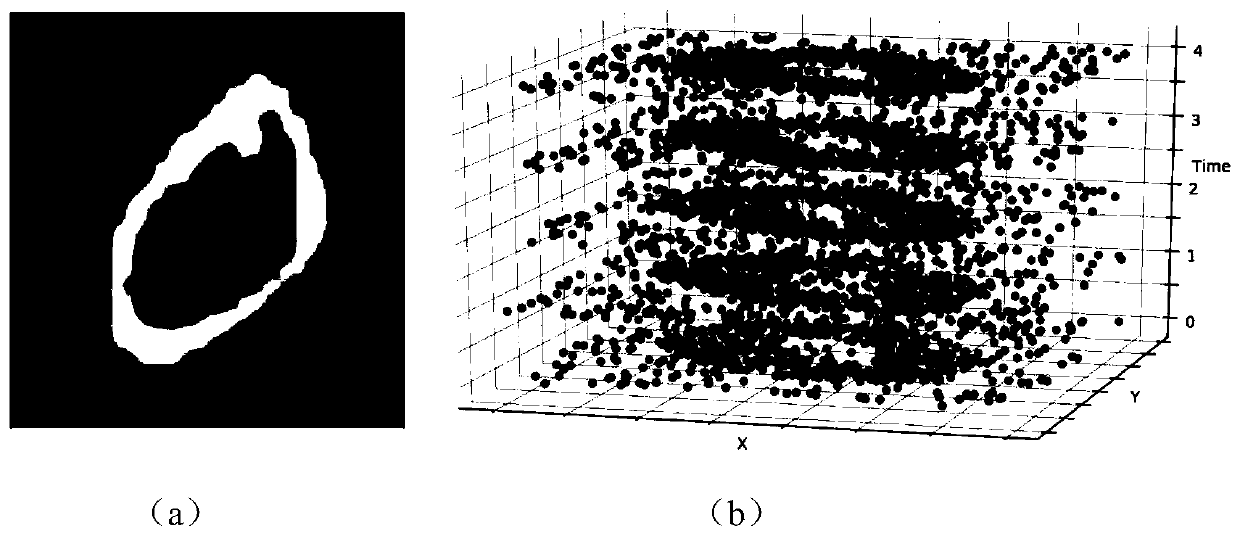

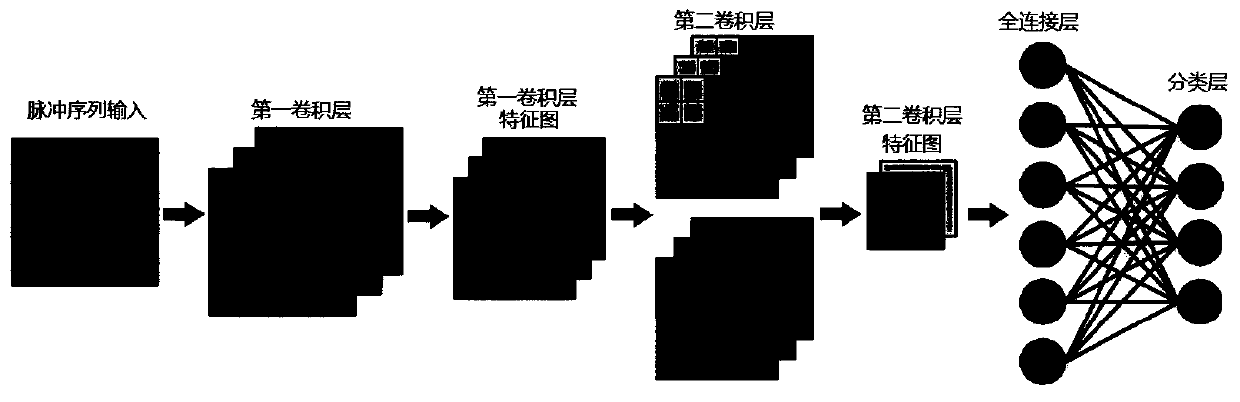

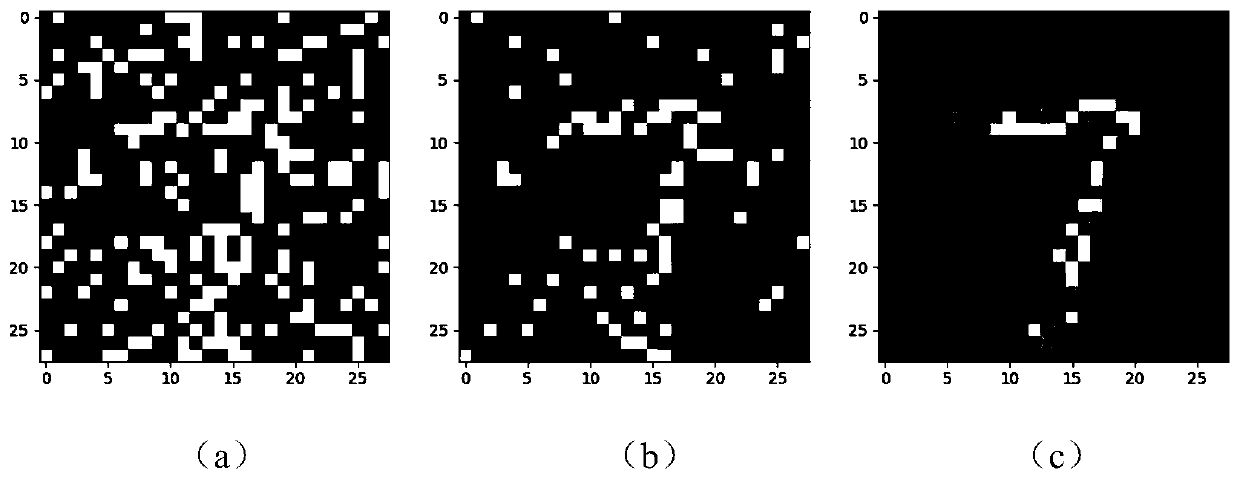

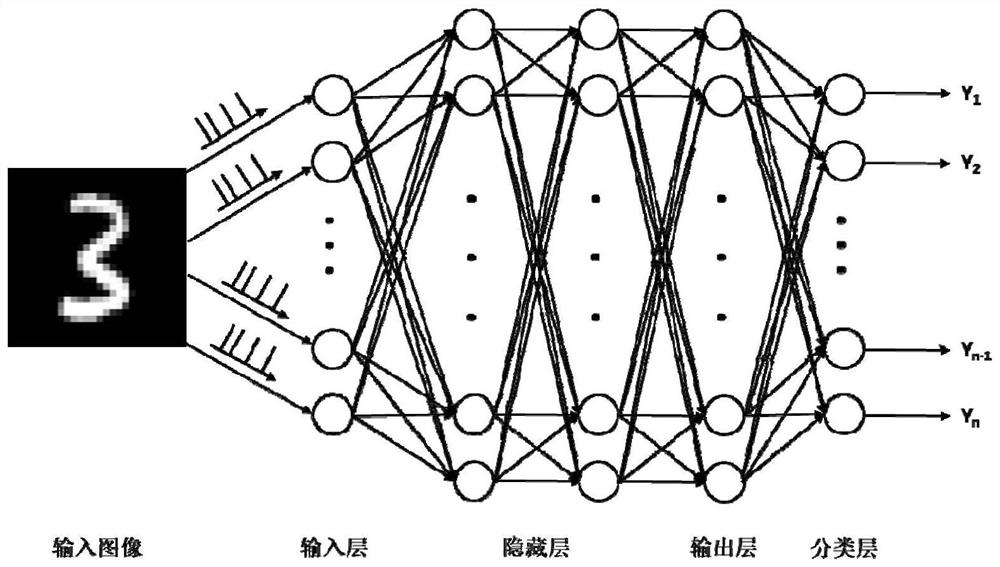

Method for learning and recognizing image pulse data space-time information based on Spike cube SNN

ActiveCN110210563ARealize identificationCharacter and pattern recognitionTime informationPattern recognition

The invention discloses a method for carrying out joint learning on space-time information of an image pulse sequence and an image recognition method. The method comprises the following steps of establishing a pulse sequence unit Spike cube and LIF neuron model on the basis of the pulse neural network, and learning synaptic weights and excitation thresholds, which are connected with each other, ofneurons of the pulse neural network by adopting an STDP mechanism; and using the trained model to carry out image classification and identification. The invention provides a new technical scheme forstructural design and learning of a pulse neural network and image pulse sequence learning and recognition, and also provides a new processing method for pulse data output by a DVS and other bionic vision cameras.

Owner:PEKING UNIV

Operation device and method of accelerating chip which accelerates depth neural network algorithm

ActiveCN106529668AExtended waiting timeConsume morePhysical realisationNeural learning methodsSynaptic weightAlgorithm

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

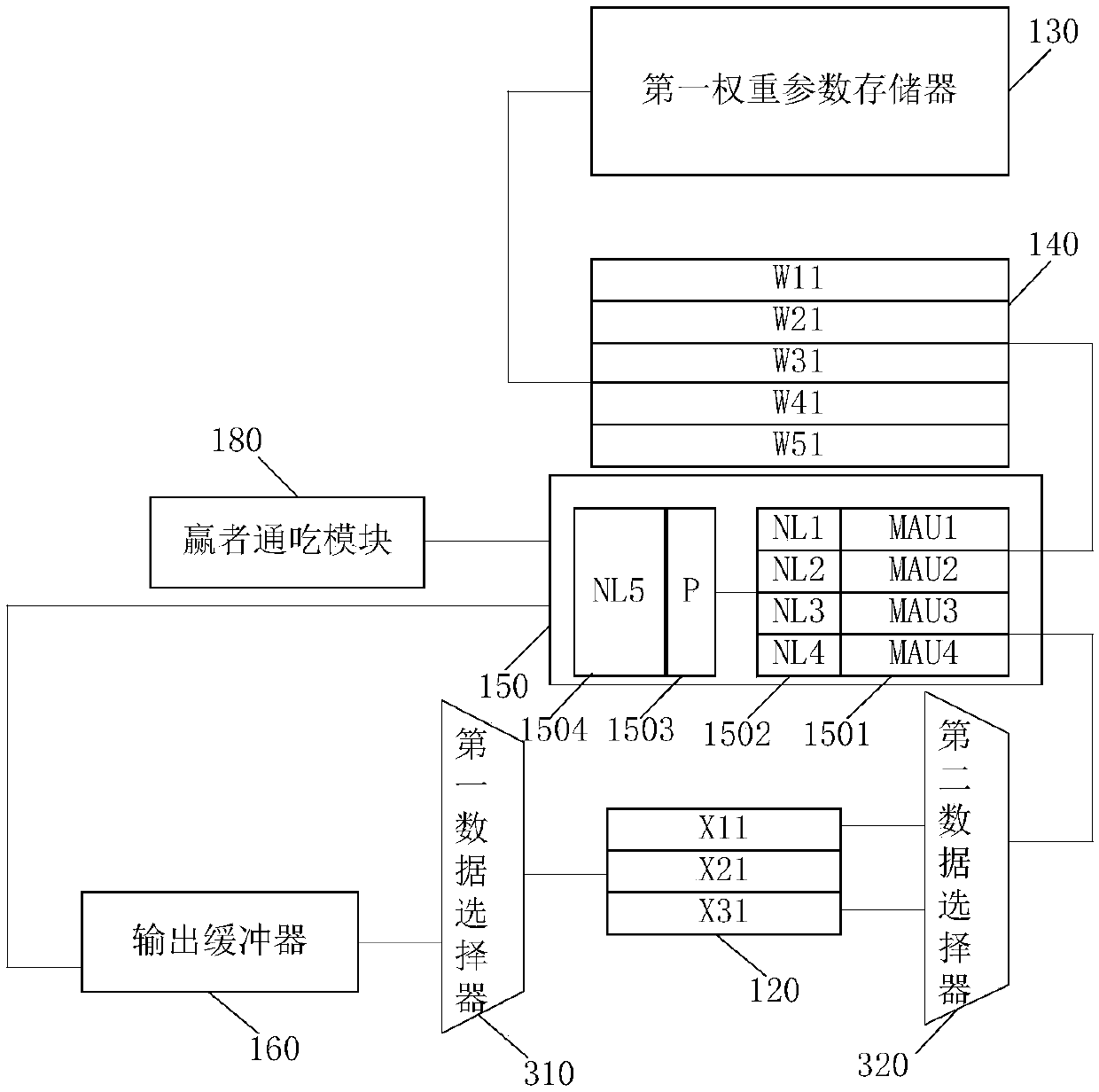

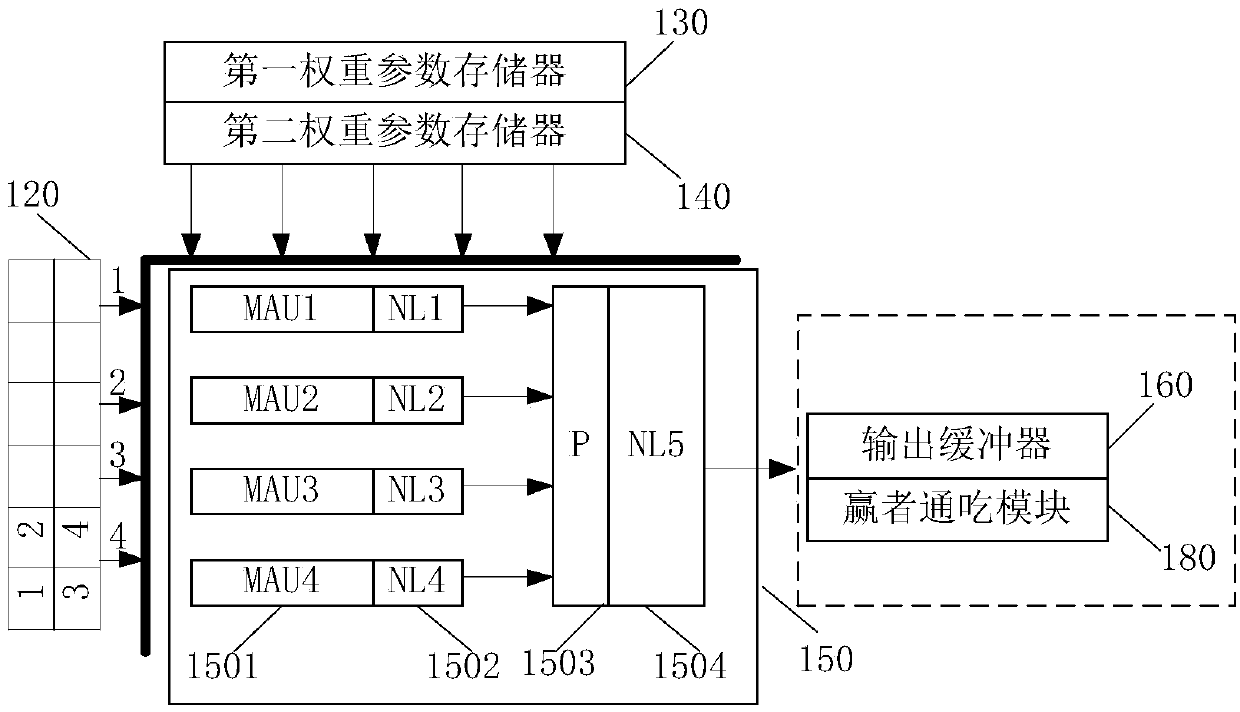

Multi-mode neural morphological network core

ActiveCN105095967AReal-time computingGuaranteed accuracyPhysical realisationNerve networkSynaptic weight

Provided in the invention is a multi-mode neural morphological network core comprising a mode register, an axon input unit, a synaptic weight storage unit, a dendrite unit and a neuron computing unit. According to the multi-mode neural morphological network core, both artificial neural network computing and impulsive neural network computing can be carried out; and switching between an artificial neural network operation mode and an impulsive neural network operation mode can be realized according to demands.

Owner:LYNXI TECH CO LTD

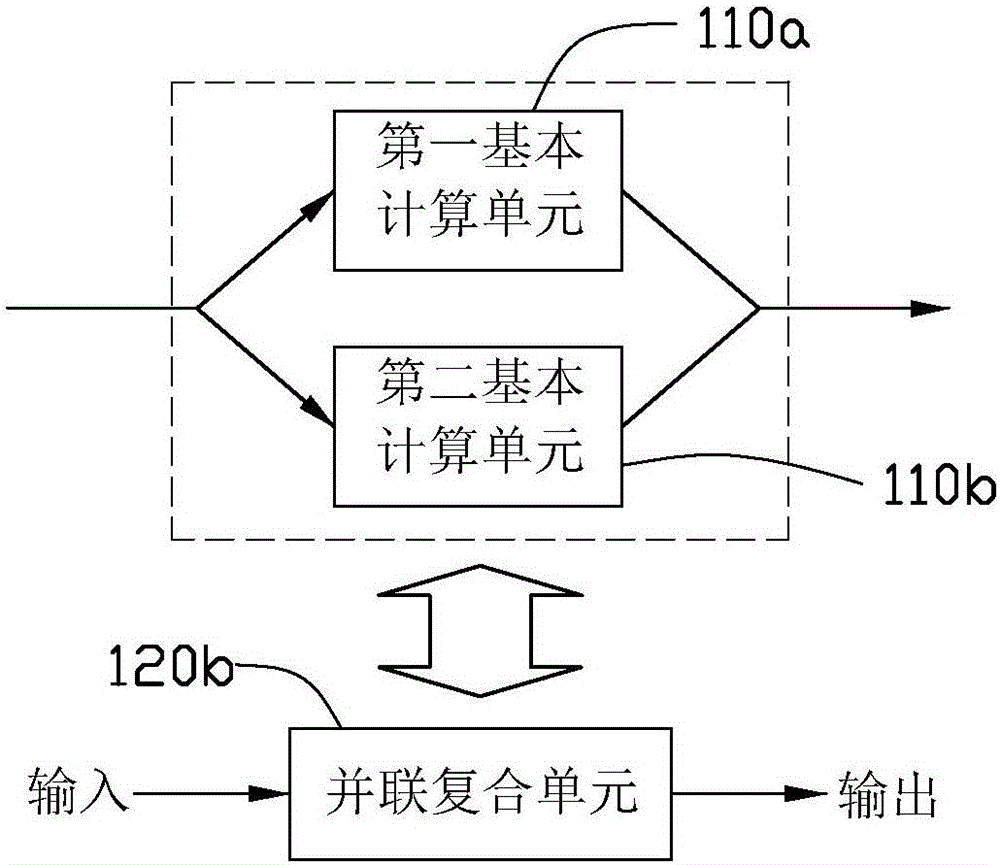

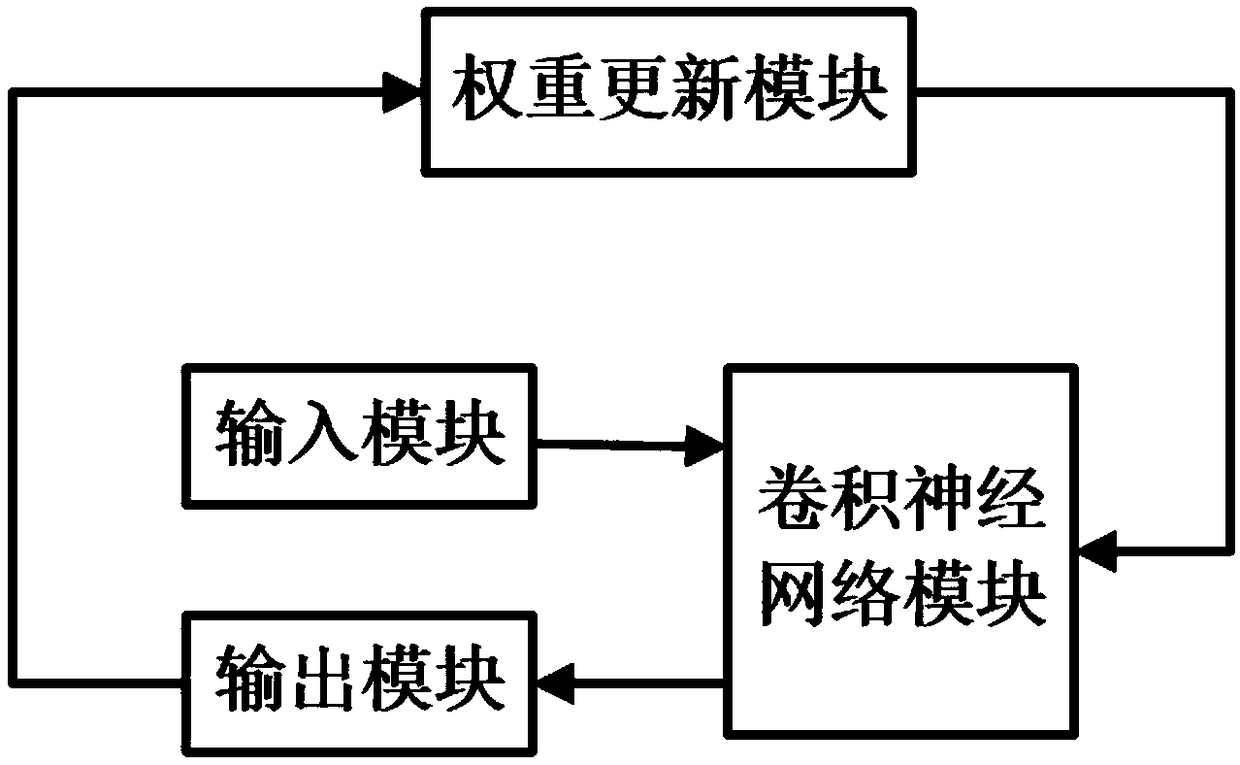

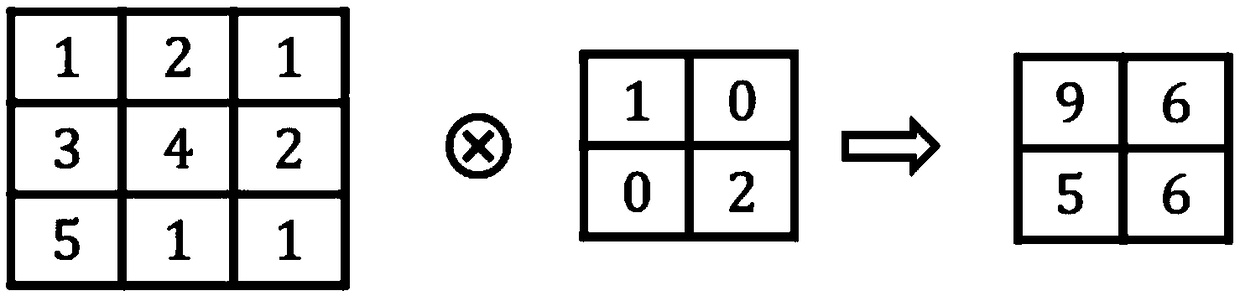

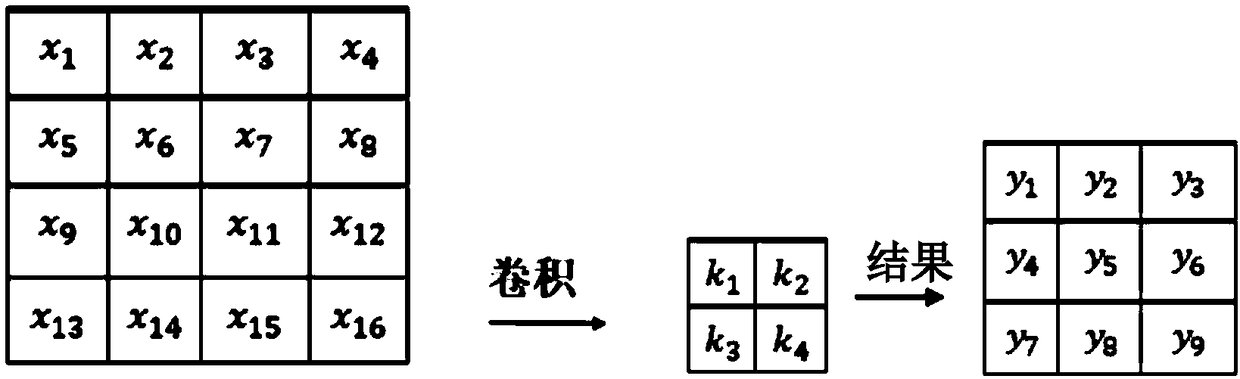

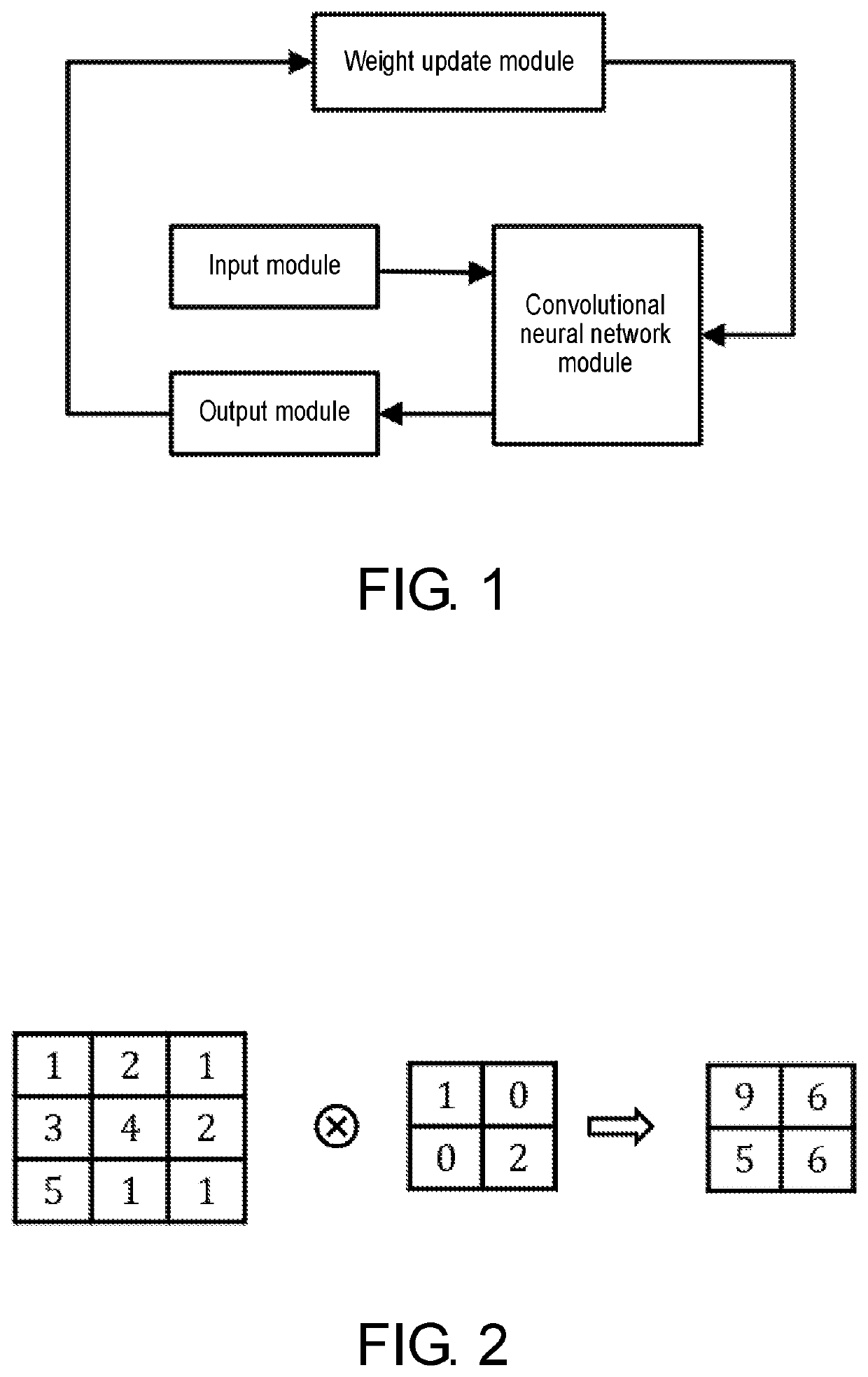

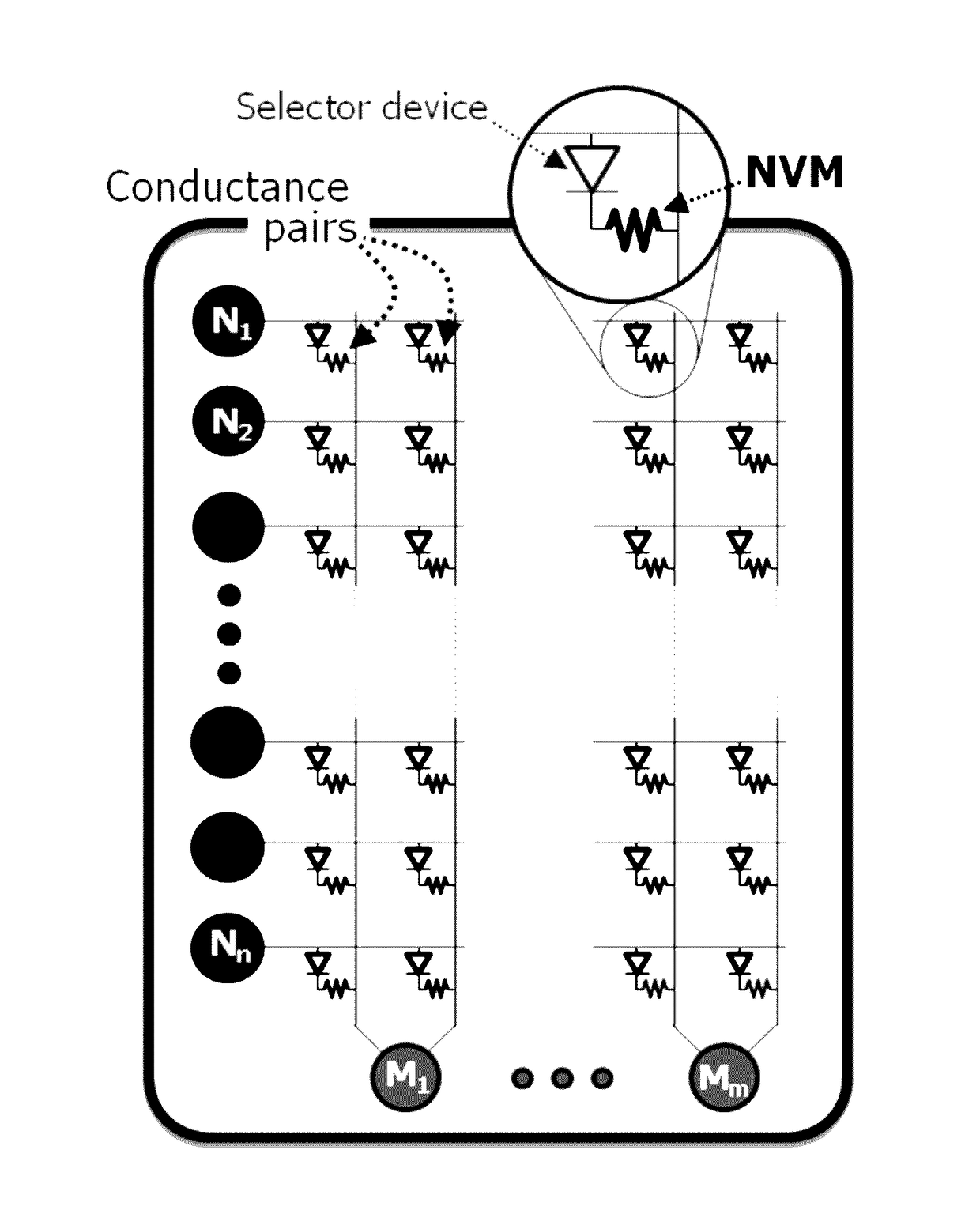

A convolution neural network-on-chip learning system based on nonvolatile memory

ActiveCN109460817AAchieve energy consumptionAvoid disadvantagesNeural architecturesPhysical realisationSynaptic weightSignal transition

The invention discloses a convolution neural network on-chip learning system based on non-volatile memory, comprising an input module, a convolution neural network module, an output module and a weight update module. The on-chip learning of the convolution neural network module utilizes the characteristic that the conductance of the memristor changes with the applied pulse to realize the synapticfunction, and the convolution kernel value or the synaptic weight value is stored in the memristor unit. The input module converts the input signal into the voltage signal required by the convolutional neural network module. The convolutional neural network module transforms the input voltage signal layer by layer and transmits the result to the output module to get the output of the network. Theweight updating module adjusts the conductance value of the memristor in the convolutional neural network module according to the result of the output module, and updates the convolution core value orsynaptic weight value of the network. The invention aims at realizing the on-chip learning of the convolution neural network, realizing the on-line processing of the data, and realizing the requirements of high speed, low power consumption and low hardware cost based on the high parallelism of the network.

Owner:HUAZHONG UNIV OF SCI & TECH

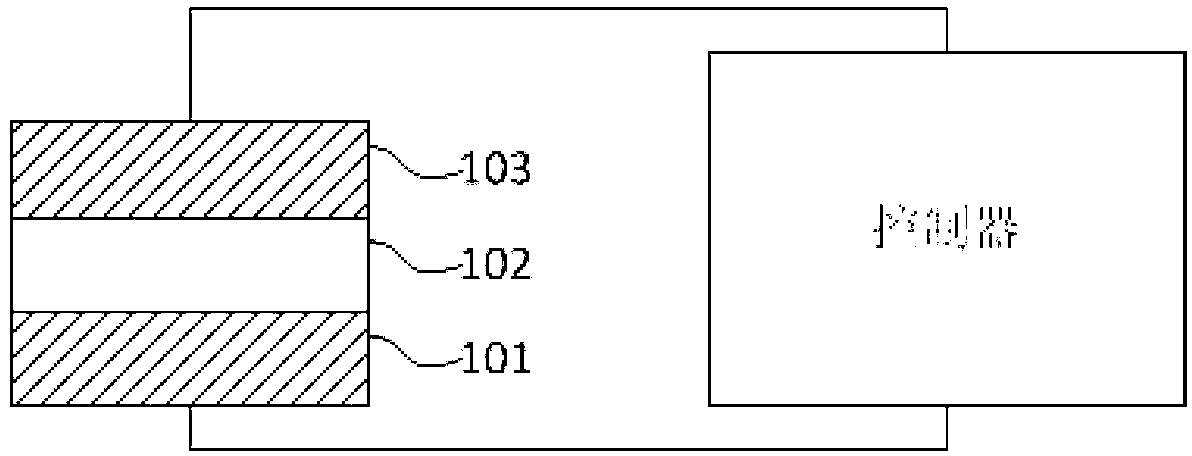

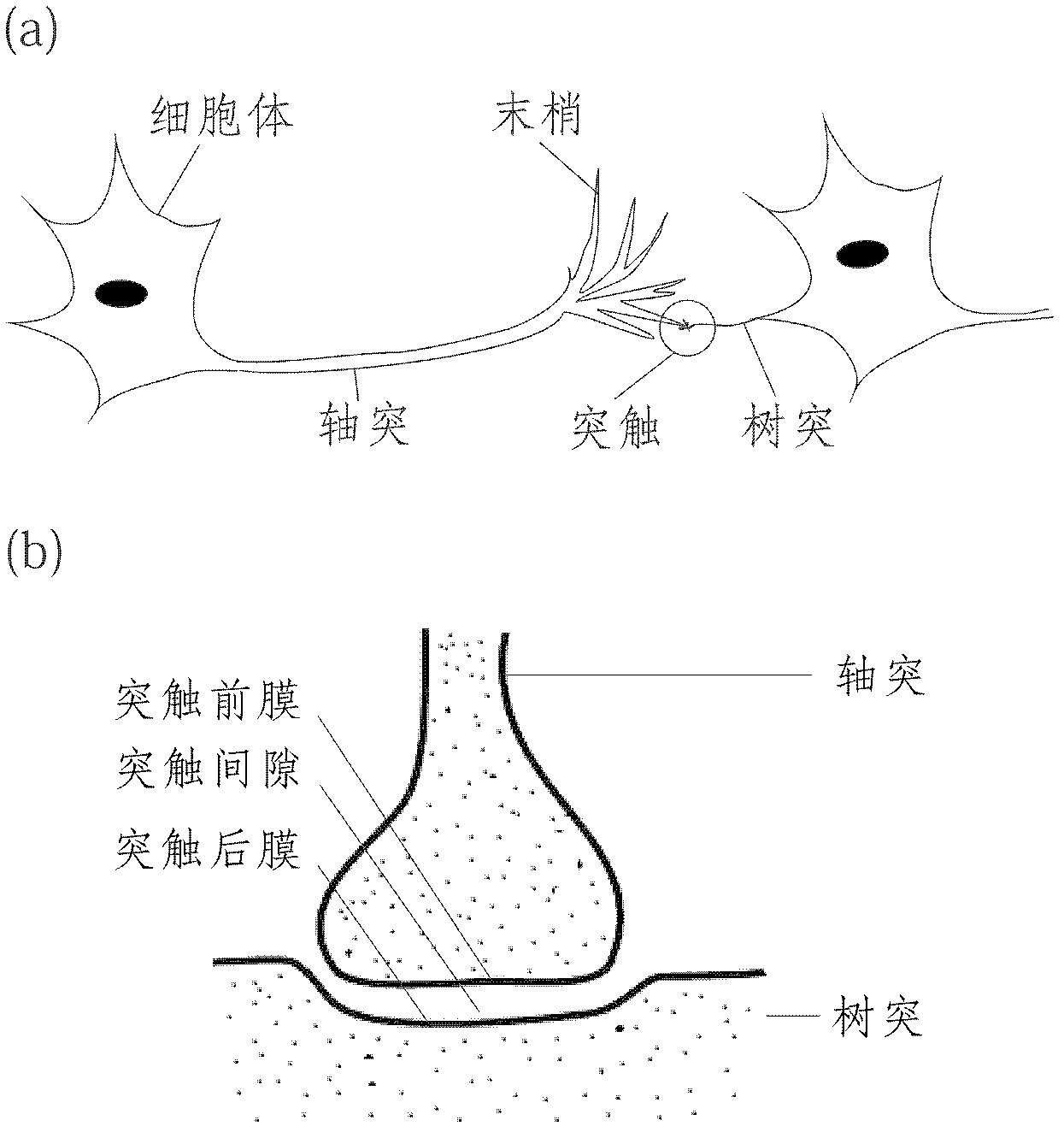

Unit, device and method for simulating biological neuron and neuronal synapsis

ActiveCN103078054AReduce power consumptionSmall sizeElectrical apparatusNeural architecturesHigh resistanceSynaptic weight

The invention discloses a unit, a device and a method for simulating biological neuron and neuronal synapsis on the basis of chalcogenide compounds. The unit comprises a first electrode layer, a function material layer and a second electrode layer. During the neuron simulation, a device receives the stimulation of one or a plurality of electric pulses, the resistance of the function material is changed into the low resistance state from the high resistance state, the simulated neuron is changed into an excitation state from a resting state, and the threshold value excitation and energy accumulation excitation functions are realized. During the neuronal synapsis simulation, the electric conductance of the function material layer of the device can be gradually changed according to input signals, and the synapsis weight regulating function is realized, the ynapsis weight is changed according to time differences of signals input at two ends, and the STDP (spike timing dependent plasticity) function of synapsis is realized. The basic device forming the artificial neural network can be provided.

Owner:HUAZHONG UNIV OF SCI & TECH

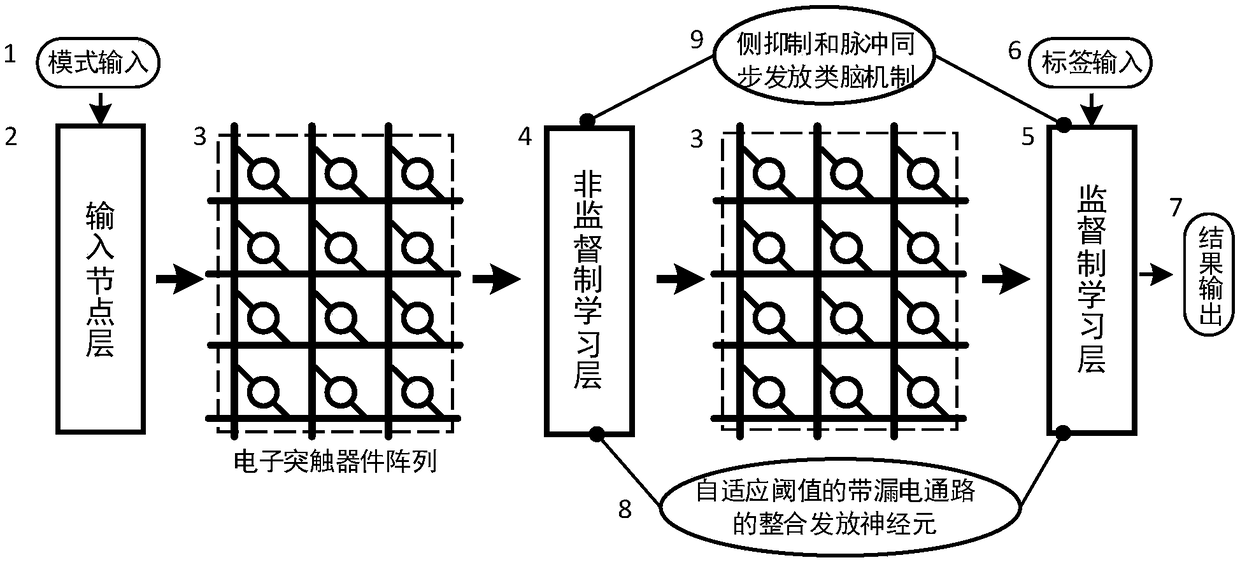

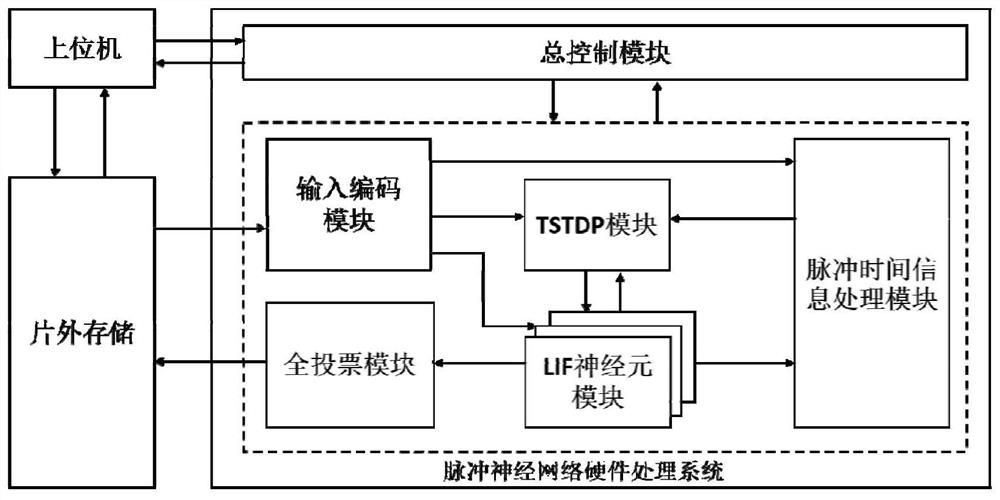

A hardware impulse neural network system

ActiveCN108985447AEasy to identifyImprove robustnessPhysical realisationNeural network systemSynaptic weight

The invention discloses a hardware impulse neural network system, comprising: an input node layer and an unsupervised learning layer are connected through a synaptic connection unit in a neuron full connection mode; the unsupervised learning layer and the supervised learning layer are connected through another synaptic connection unit in a neuron full connection mode; the input node layer and theunsupervised learning layer are connected through a synaptic connection unit in a synaptic connection mode. The input node layer realizes the information input under different coding modes, the non-supervisory learning layer adopts the non-supervisory learning mode, and the supervisory learning layer adopts the supervisory learning mode. A synaptic connection unit is realized by an electronic synaptic device, so that that synaptic connection unit has a pulse time dependent plasticity STDP. The synaptic array unit receives as presynaptic pulses the stimulation signals from the neurons in the front layer and the postsynaptic pulses the action potential pulses excited by the neurons in the back layer. The time difference between the presynaptic pulses and the postsynaptic pulses determines the synaptic weight adjustment amount of the synaptic connection unit. The neural network system provided by the invention has a wide application value.

Owner:HUAZHONG UNIV OF SCI & TECH

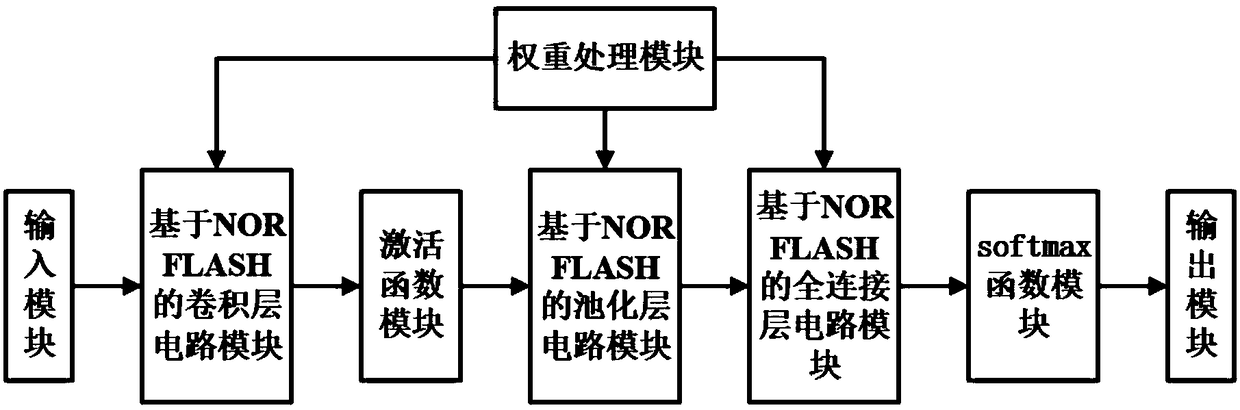

Memory-based convolutional neural network system

ActiveCN108805270ACharacter and pattern recognitionNeural architecturesSynaptic weightReal-time data

The invention discloses a memory-based convolutional neural network system, comprising an input module, a convolutional layer circuit module, a pooling circuit module, an activation function module, afully connected layer circuit module and an output module, wherein a convolution kernel value or a synaptic weight value is stored in a NOR FLASH unit; the input module converts an input signal intoa voltage signal required by a convolutional neural network; the convolutional layer circuit module performs an convolution operation on the voltage signal corresponding to the input signal and the convolution kernel value and transmits the result to the activation function module; the activation function module activates the signal; the pooling layer circuit performs a pooling operation on the activated signal; and the fully connected layer circuit module multiplies the signal subjected to pooling operation with the synaptic weight value to perform classification, and a softmax function module normalizes the classification result to a probability value and takes the classification result as the output of the entire network. The system disclosed by the invention can satisfy the requirements of real-time data processing, and has a low hardware cost.

Owner:HUAZHONG UNIV OF SCI & TECH

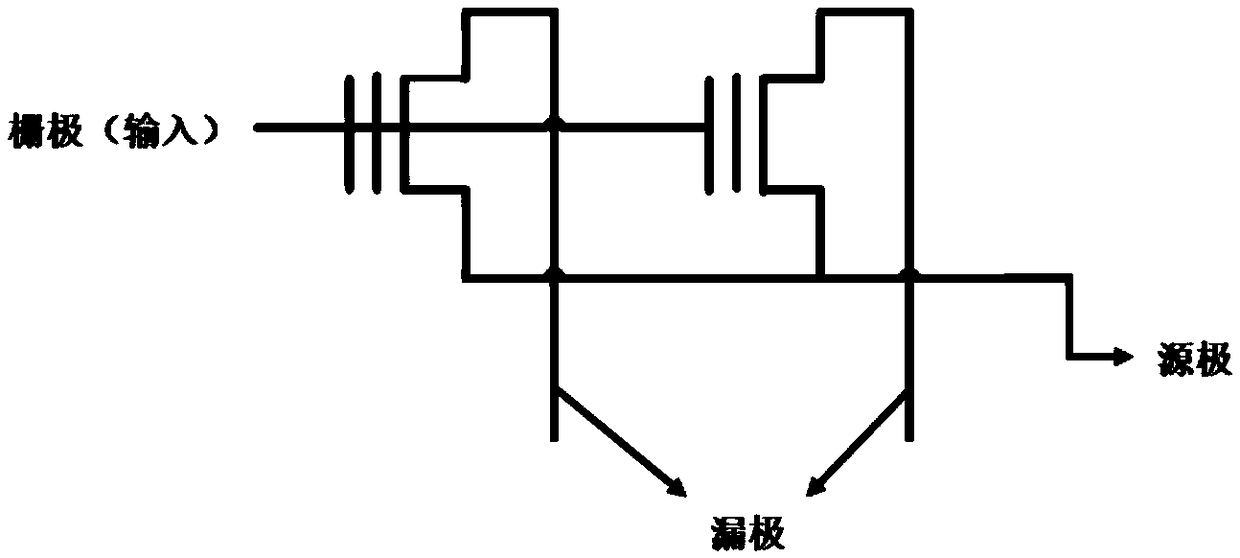

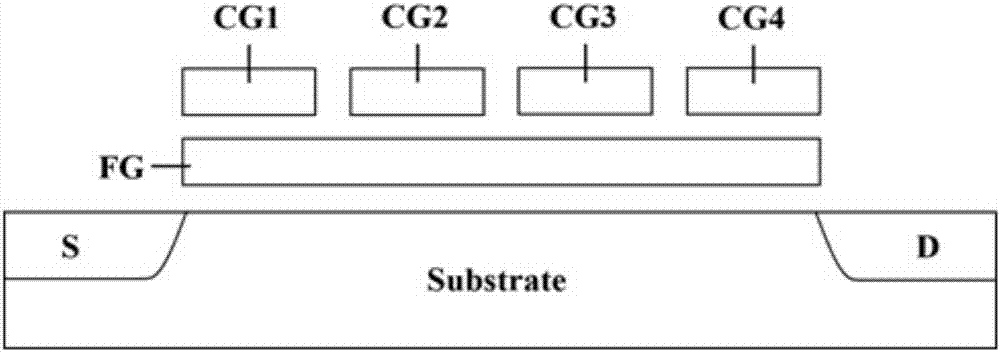

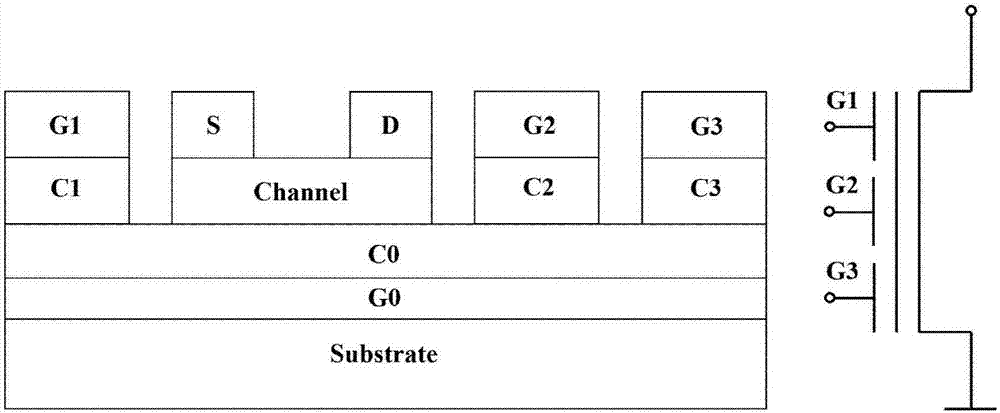

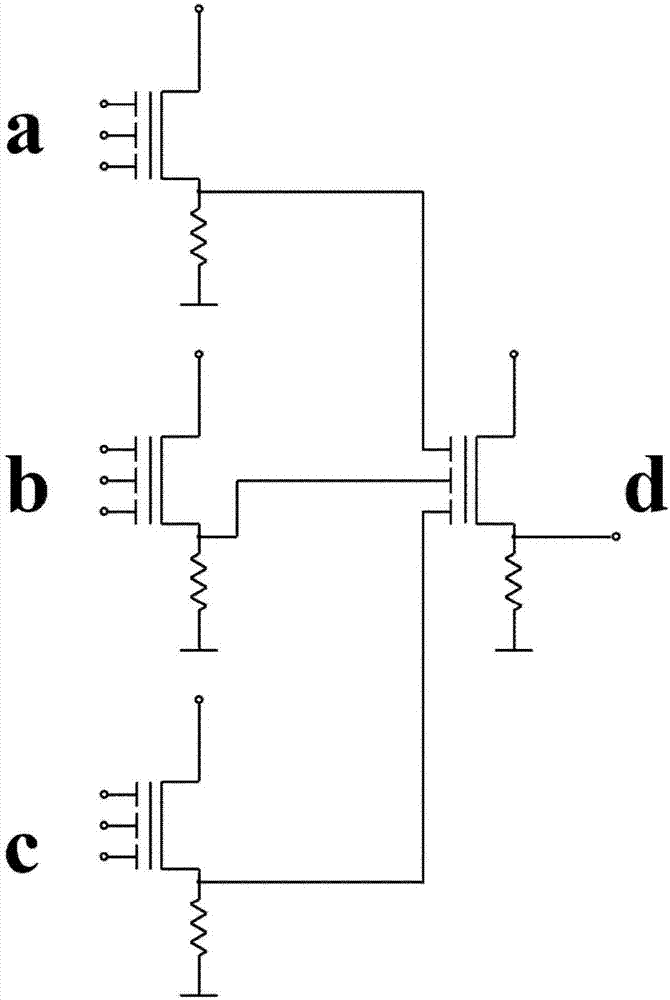

Multiple grid electrode neuron transistor, manufacturing method therefor and formed nerve network

ActiveCN106910773AImprove space utilizationSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceElectricity

The invention discloses a multiple grid electrode neuron transistor comprising source and drain electrodes, a channel, gate media, a floating gate electrode, a plurality of input grid electrodes and capacitance memory layers among the input grids and the gate media. All of the input grid electrodes and the gate media are jointly coupled onto the floating gate electrode via the capacitance memory layers, the channel is coordinately controlled to output a current, and a weighted computation function of neurons is simulated. The capacitance memory layers change in capacitance volume along with history of input grid voltage signals, and therefore plasticity of synaptic weight can be simulated. The invention also puts forward a manufacturing method for the multiple grid electrode neuron transistor and a nerve network which is formed via electric interconnection among a number of grid electrode neuron transistors. The multiple grid electrode neuron transistor is simple in structure and is convenient to manufacture and integrate, and the multiple grid electrode neuron transistor can hopefully be applied to the field of brain-like intelligent chips and the like.

Owner:NANJING UNIV

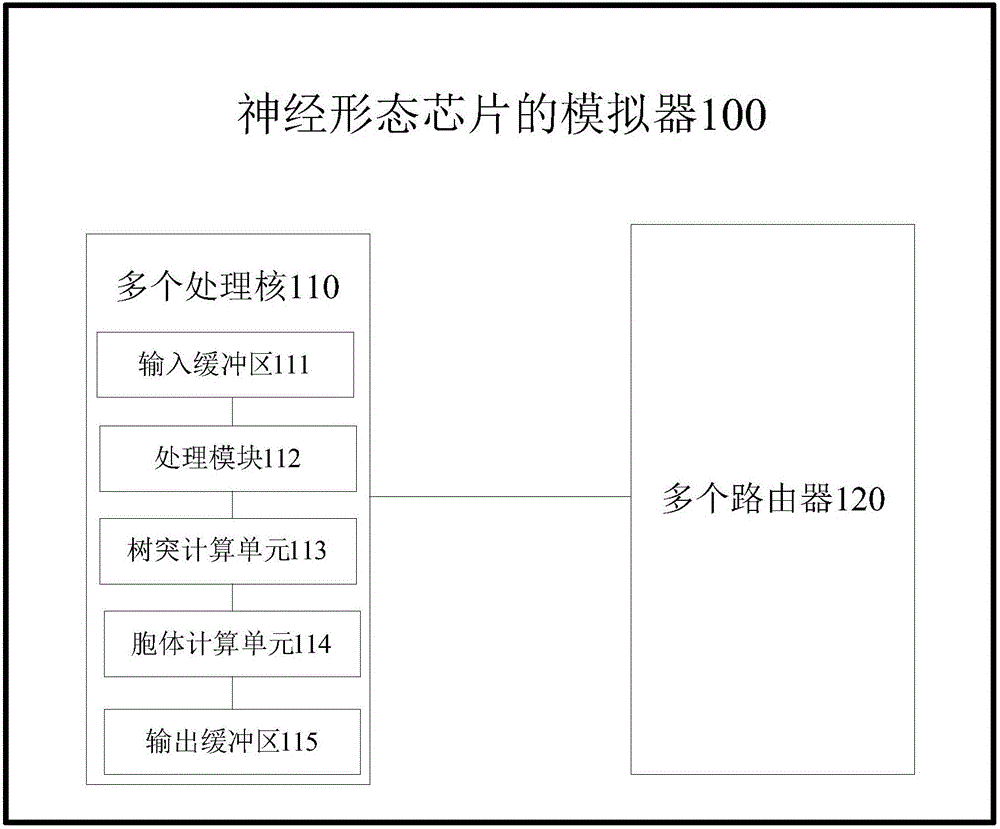

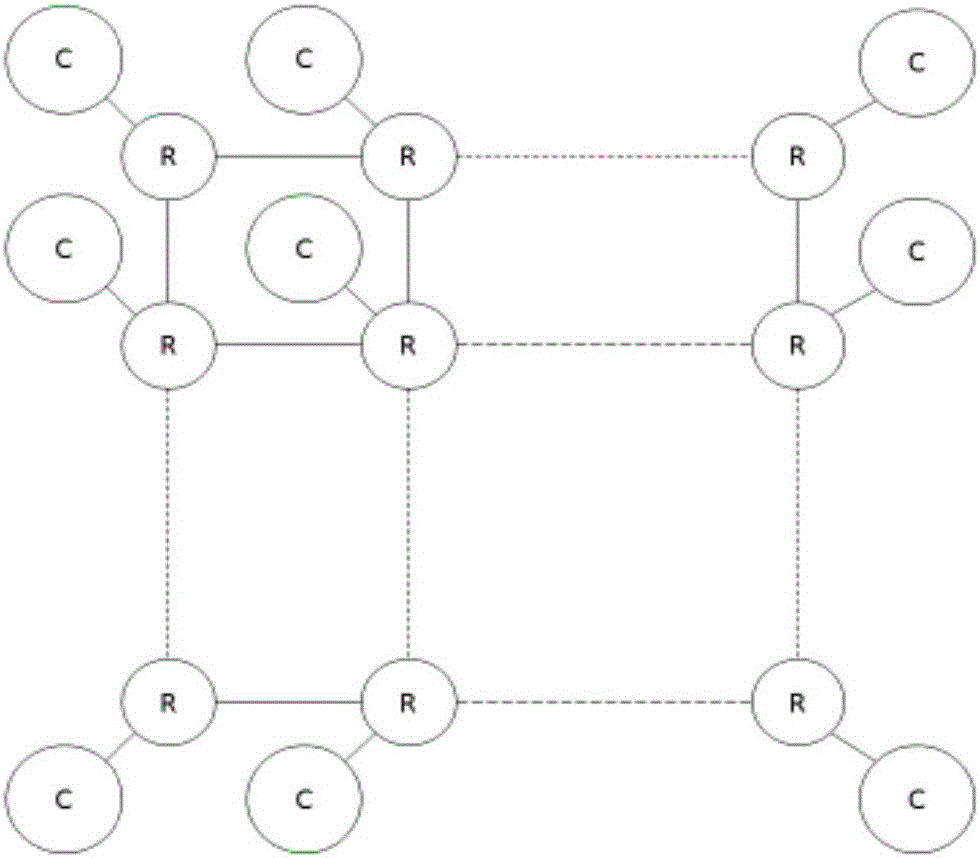

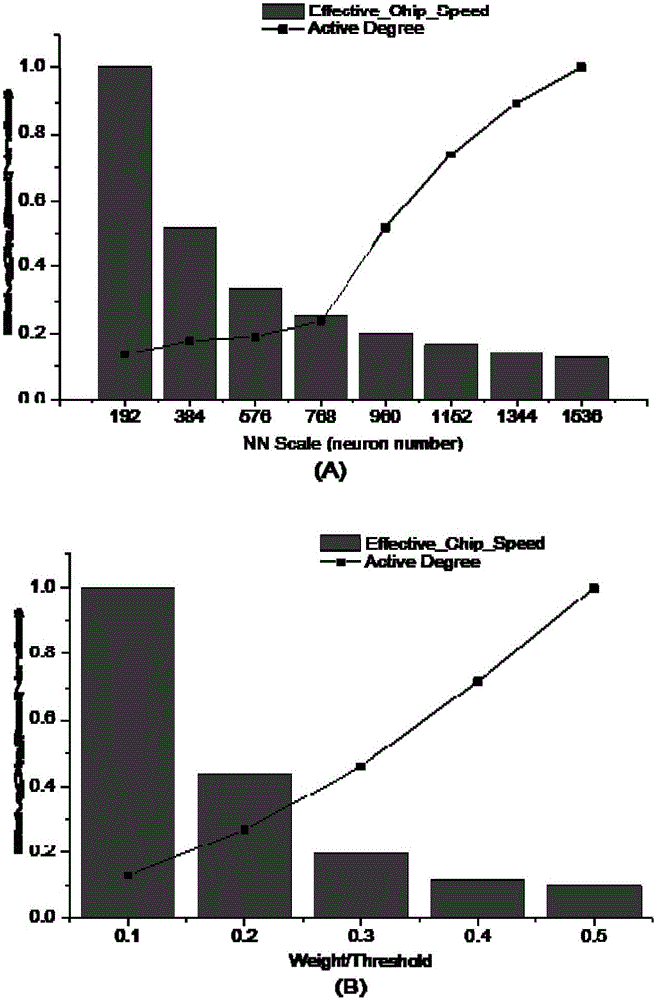

Neuromorphic chip simulator

InactiveCN106201651ARapid designQuality assurancePhysical realisationSoftware simulation/interpretation/emulationSynaptic weightProcessing core

The invention proposes a neuromorphic chip simulator. The simulator comprises a plurality of processing cores and a plurality of routers. Each processing core comprises an input buffer area, a processing module, a dendritic calculation unit, a cell body calculation unit and an output buffer area. The dendritic calculation unit comprises a memory array and N simulated neurons; each simulated neuron comprises M axon inputs; and the dendritic calculation unit performs multiplication on the axon input of each position on each simulated neuron and a synaptic weight of a corresponding position, accumulates multiplication results, and combines accumulated results obtained by all the simulated neurons as output data of the dendritic calculation unit. The cell body calculation unit comprises N simulated neurons; each simulated neuron performs accumulation on a result obtained by multiplication and addition in the dendritic calculation unit and a numerical value accumulated by the previous simulated neuron; and pulses are generated when an accumulated numerical value exceeds a preset threshold. The output buffer area stores pulse-containing data packets. According to the simulator, the quality and efficiency of a neuromorphic chip design process can be ensured and designers can design neuromorphic chips with higher quality more quickly.

Owner:鄞州浙江清华长三角研究院创新中心

Convolutional neural network on-chip learning system based on non-volatile memory

PendingUS20200342301A1Improve operation speed and densityHigh degree of parallelismNeural architecturesPhysical realisationSynaptic weightEngineering

Disclosed by the disclosure is a convolutional neural network on-chip learning system based on non-volatile memory, comprising: an input module, a convolutional neural network module, an output module and a weight update module. The on-chip learning of the convolutional neural network module implements a synaptic function by using a characteristic which the conductance of a memristor changes according to an applied pulse, and the convolutional kernel value or synaptic weight value is stored in a memristor unit; the input module converts an input signal into a voltage signal required by the convolutional neural network module; the convolutional neural network module converts the input voltage signal level by level, and transmits the result to the output module to obtain an output of the network; and the weight update module adjusts the conductance value of the memristor in the convolutional neural network module according to the result of the output module to update a network convolutional kernel value or synaptic weight value.

Owner:HUAZHONG UNIV OF SCI & TECH

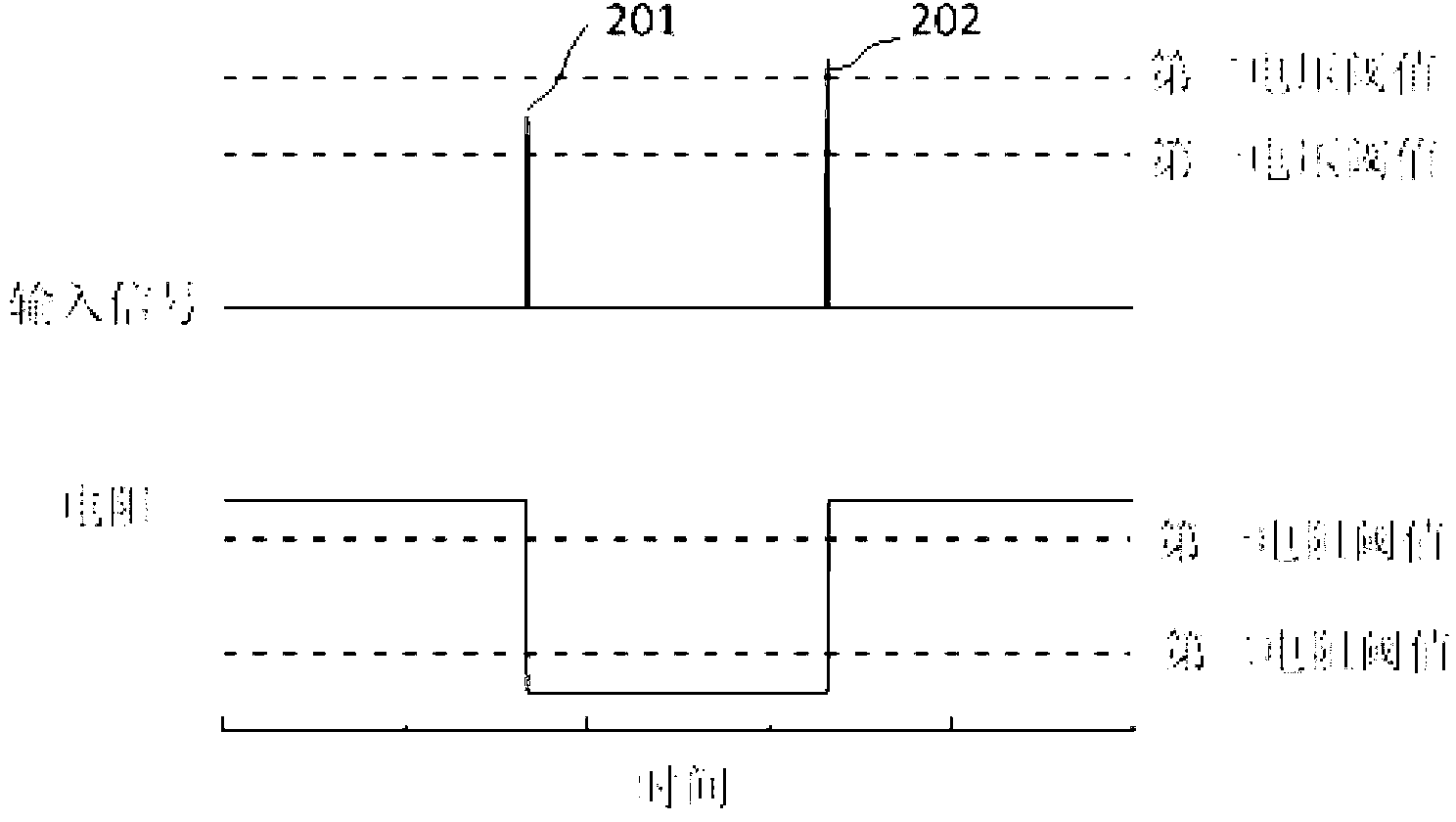

Unit, device and method for simulating biological neuronal synapsis

ActiveCN103078055AHighly integratedReduce power consumptionElectrical apparatusNeural architecturesSynaptic weightDevice form

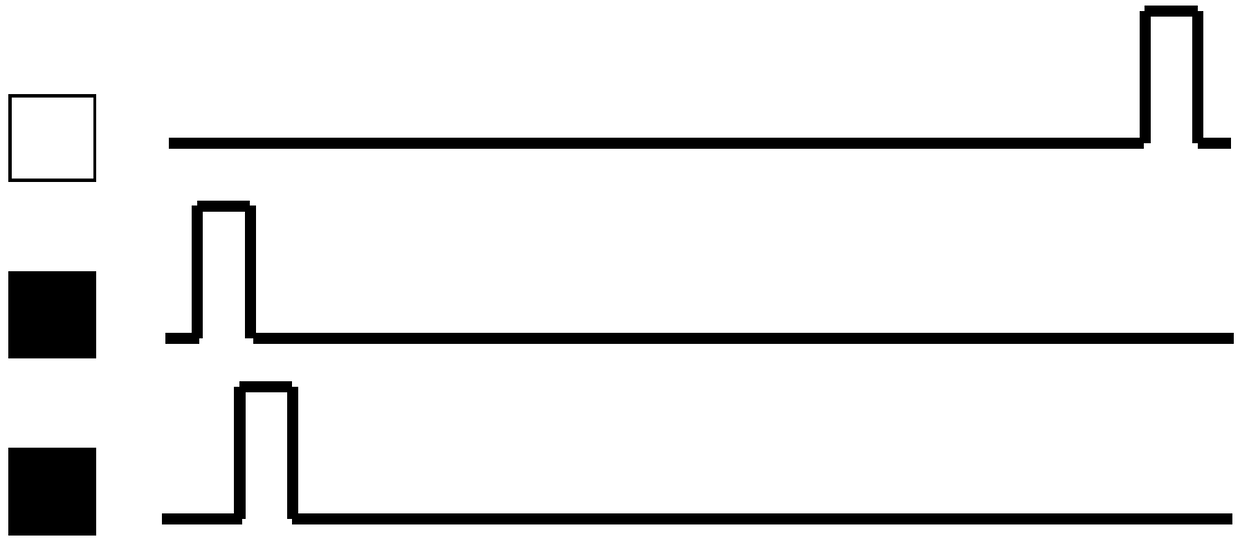

The invention discloses a unit, a device and a method for simulating biological neuronal synapsis on the basis of chalcogenide compounds. The unit comprises a first electrode layer, a function material layer and a second electrode layer, wherein the first electrode layer receives first pulse signals, and the second electrode layer receives second pulse signals. A device can change electric conductance simulation synapsis weight changes according to input signals. When the difference value between the frequency of the first pulse signals and the frequency of the second pulse signals is plus or minus, the electric conductance is changed , and the simulation of the pulse frequency dependent synaptic plasticity function of the biological neuronal synapsis is realized. When the signal difference peak value between the first pulse signals and the second pulse signals is plus or minus, the electric conductance is changed, and the simulation of the pulse time dependent synaptic plasticity function of the biological neuronal synapsis is realized. The unit, the device and the method have the advantages that the basic function of the biological neuronal synapsis can be realized on single inorganic devices, the basic device forming the artificial neural network can be provided, and the effects of integration degree improvement and power consumption reduction can be obtained.

Owner:HUAZHONG UNIV OF SCI & TECH

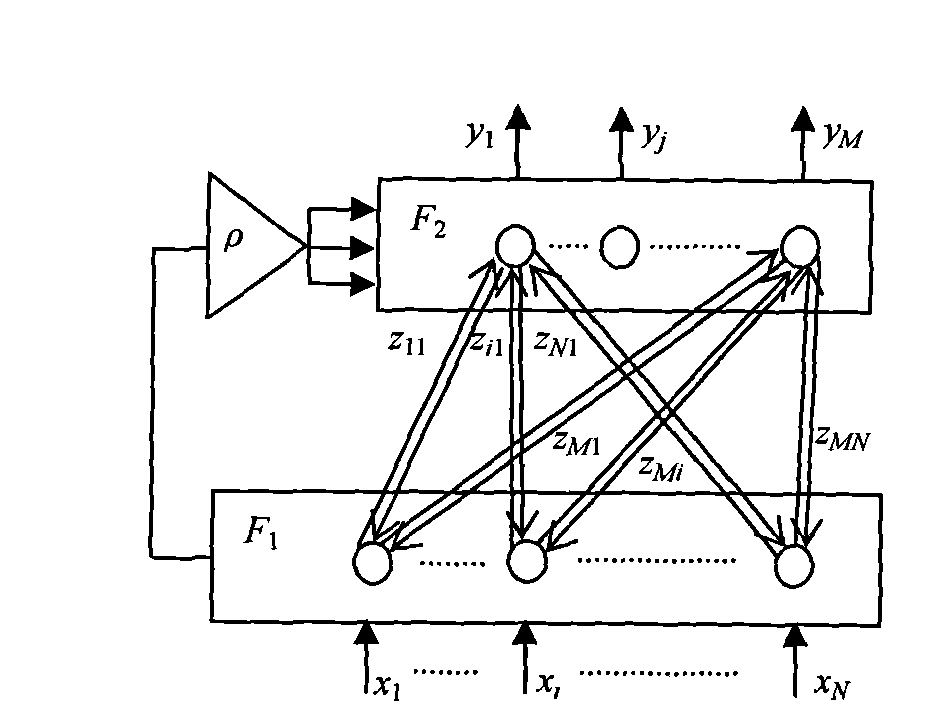

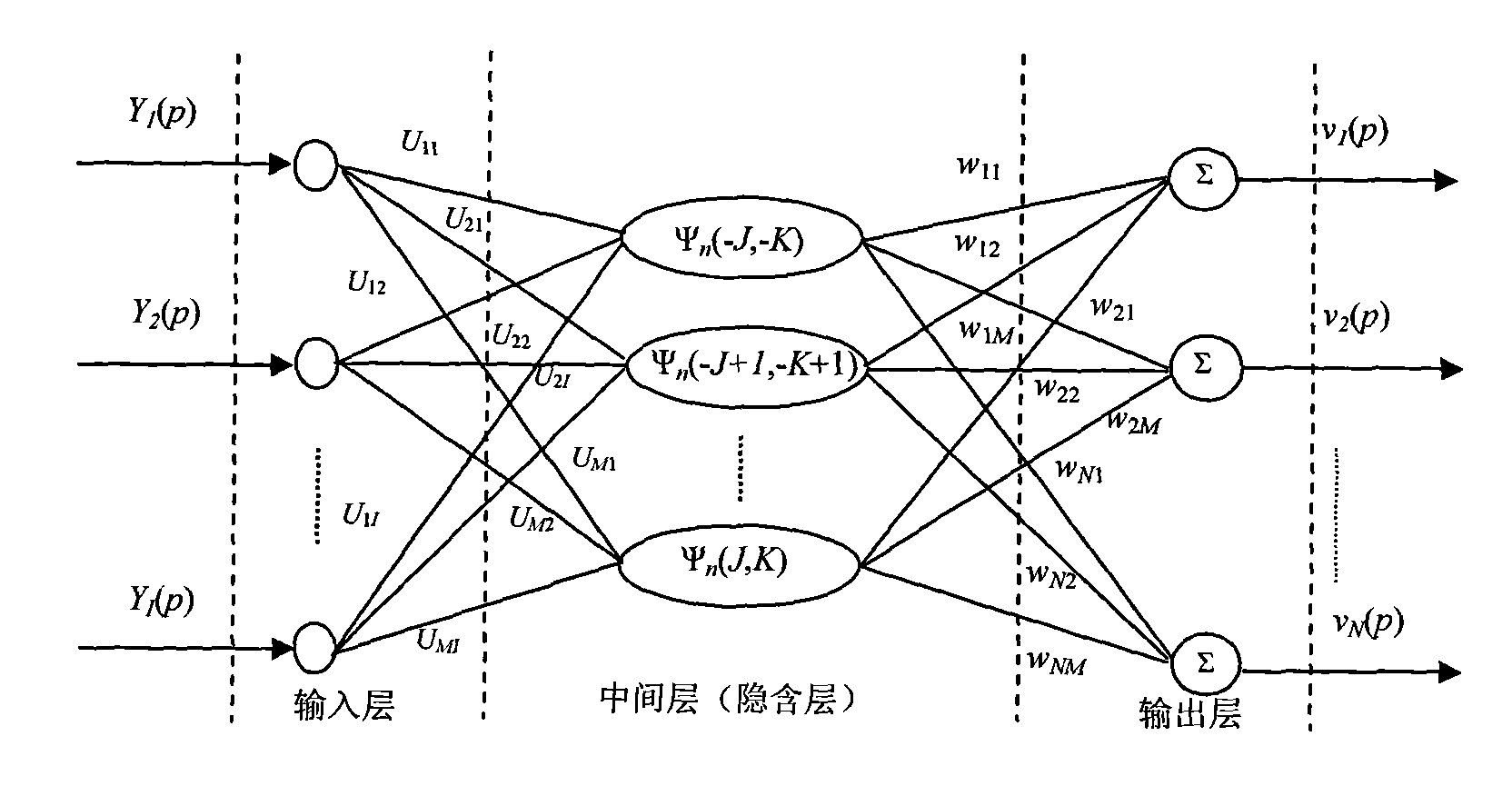

Classification and identification method for communication signal modulating mode based on ART2A-DWNN

InactiveCN101667252ASimple calculationAccurate identificationModulated-carrier systemsCharacter and pattern recognitionTime domainNerve network

The invention relates to a classification and identification method for a communication signal modulating mode based on ART2A-DWNN, belonging to the field of classification and identification of communication signal modulating modes and solving the problem that single neural network has long period and low accuracy for classifying and identifying communication signals. In the method, an ART2A-E algorithm based on an ART2A network is taken as a first layer of a combined neural network, and similar modes is roughly classified by selecting relatively smaller vigilance parameters; a DWNN is directly connected with the output layer with the corresponding type of the ART2A network, Morlet mother wavelet Phi(x) with higher resolution in frequency domain and time domain are adopted, learning is carried out by utilizing error back-propagation algorithm, a synaptic weight can be modified with a conjugate gradient method till output is within the error range, and the number of modes in each typeis reduced after rough ART2-E classification, so that the DWNN can quickly converge. The invention is used for classification and identification of communication signals.

Owner:HARBIN INST OF TECH

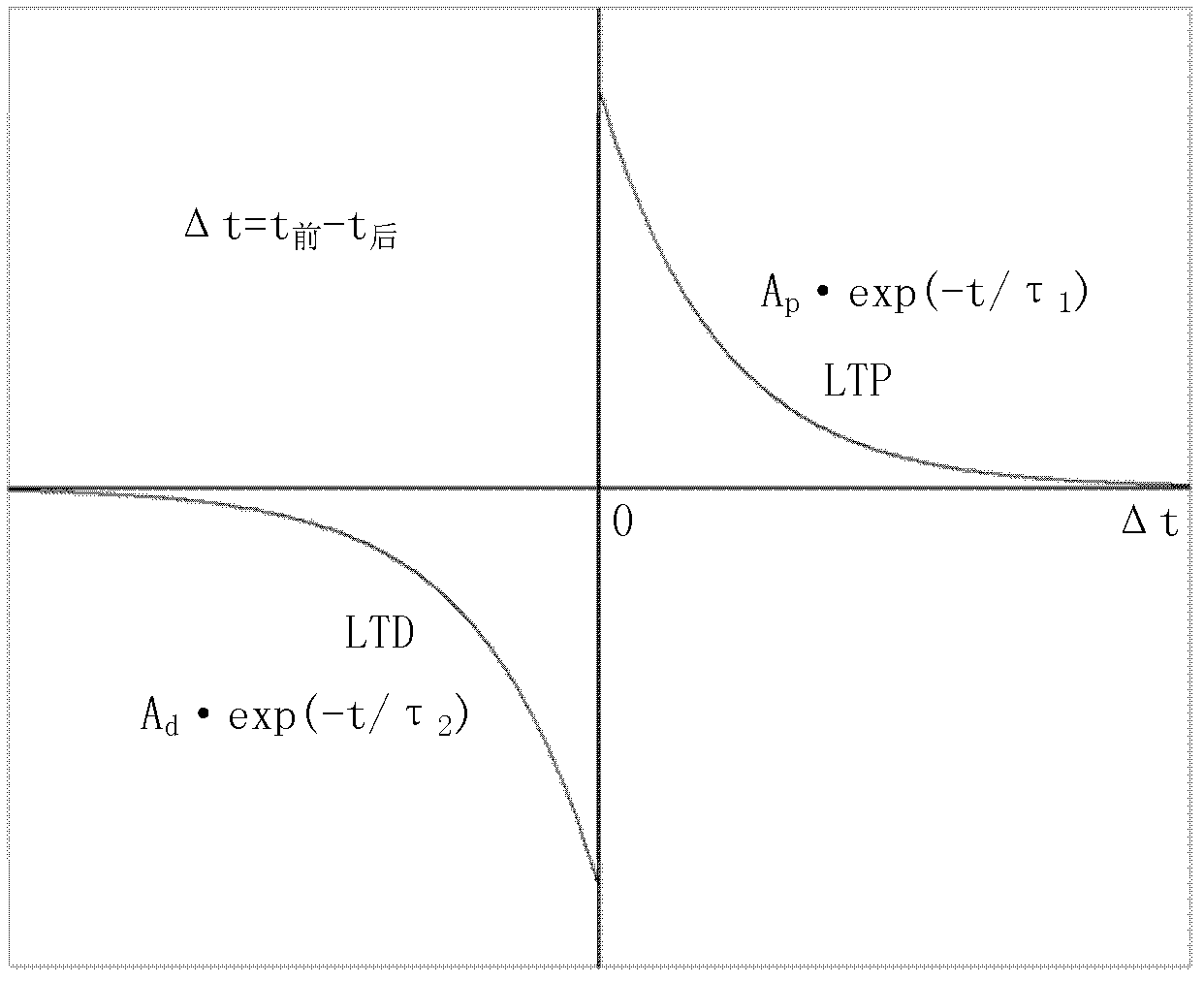

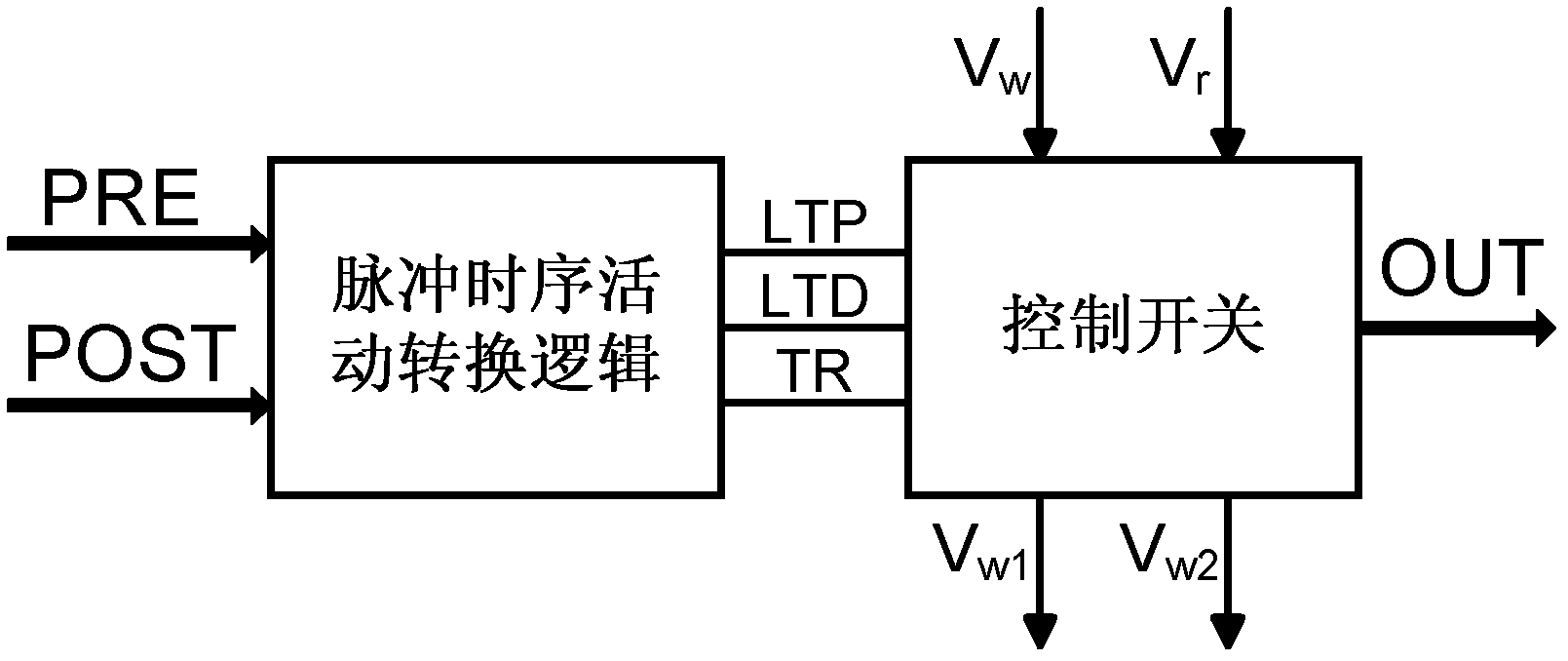

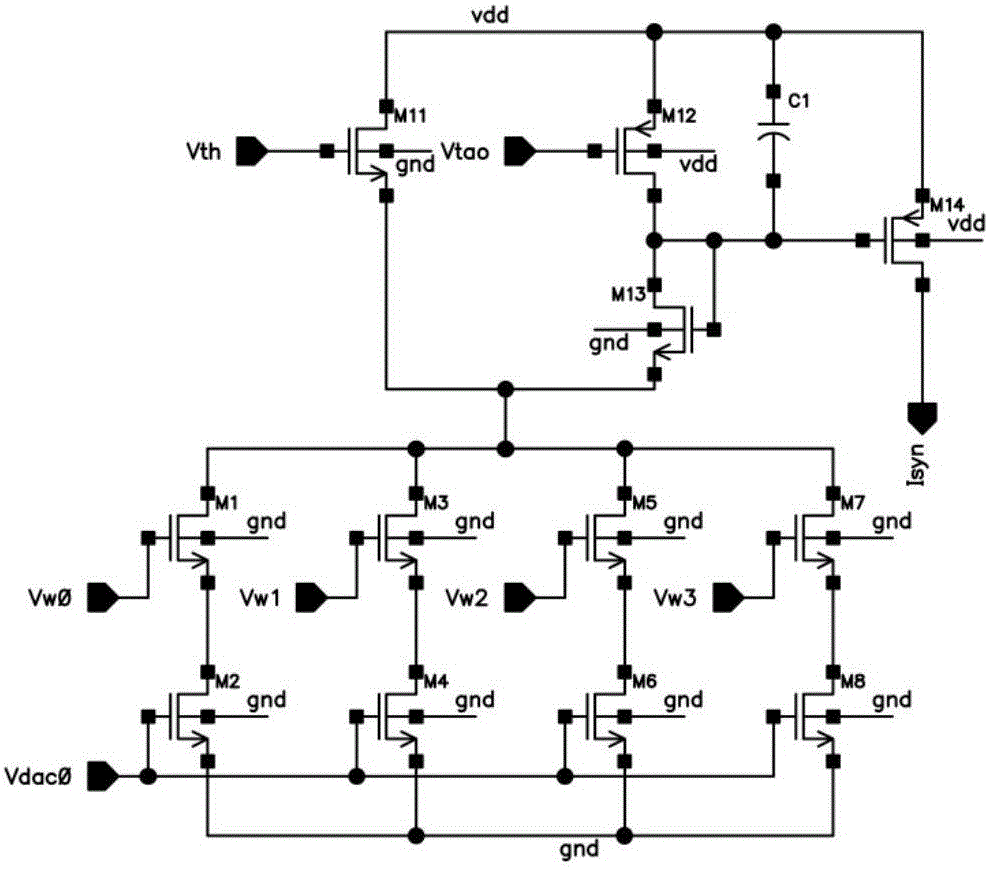

Spike timing activity conversion circuit

The invention relates to a principle about the connection among neurons in neural networks in integrated circuits and biology. A spike timing activity conversion circuit is composed of spike timing activity conversion logic and a control switch. The spike timing activity conversion logic receives a signal (PRE) and a signal (POST) which are treated to generate a long term potentiation (LTP) signal, a long term depression (LTD) signal or a transmission control (TR) signal. The three signals are output to the control switch, which is in connection with write operation voltage (Vw) and read operation voltage (Vr) of a resistive synapse. Under the control of the TR, LTP and LTD signals, output (OUT) of transinformation can be generated, or proper voltage can be output to Vw1 and Vw2 which are voltages respectively added to the two ends of the resistive synapse. The invention provides a conversion circuit, which can convert a spike timing activity relation into corresponding LTP and LTD spikes for output according to an STDP (spike timing dependent plasticity) rule, thus realizing the function of an STDP model. Therefore, the conversion circuit can be conveniently applied in neural networks, electronic synaptic weight adjustment and other circuits.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

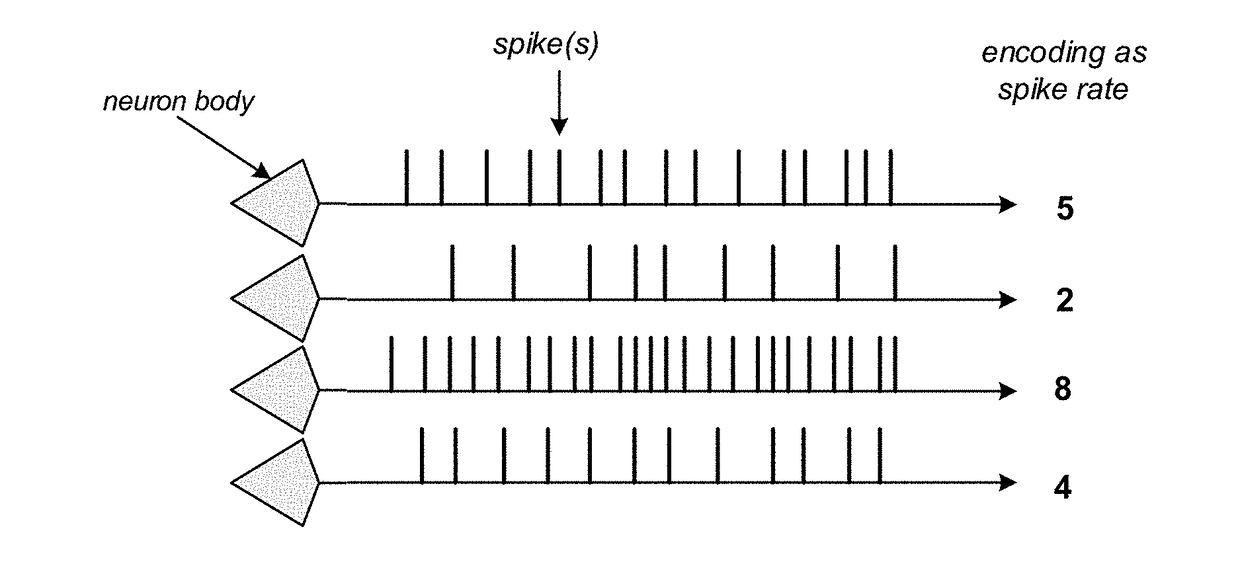

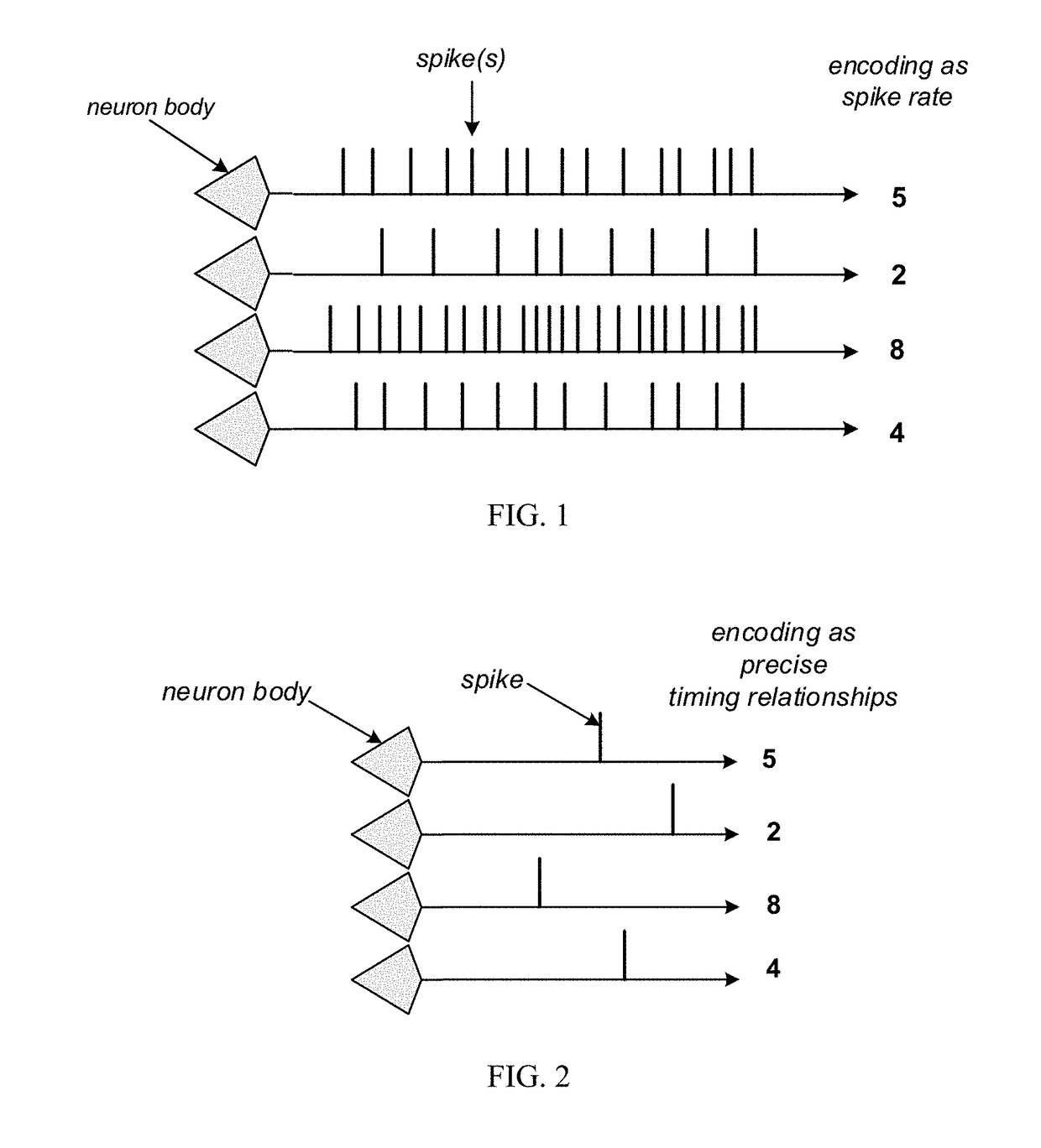

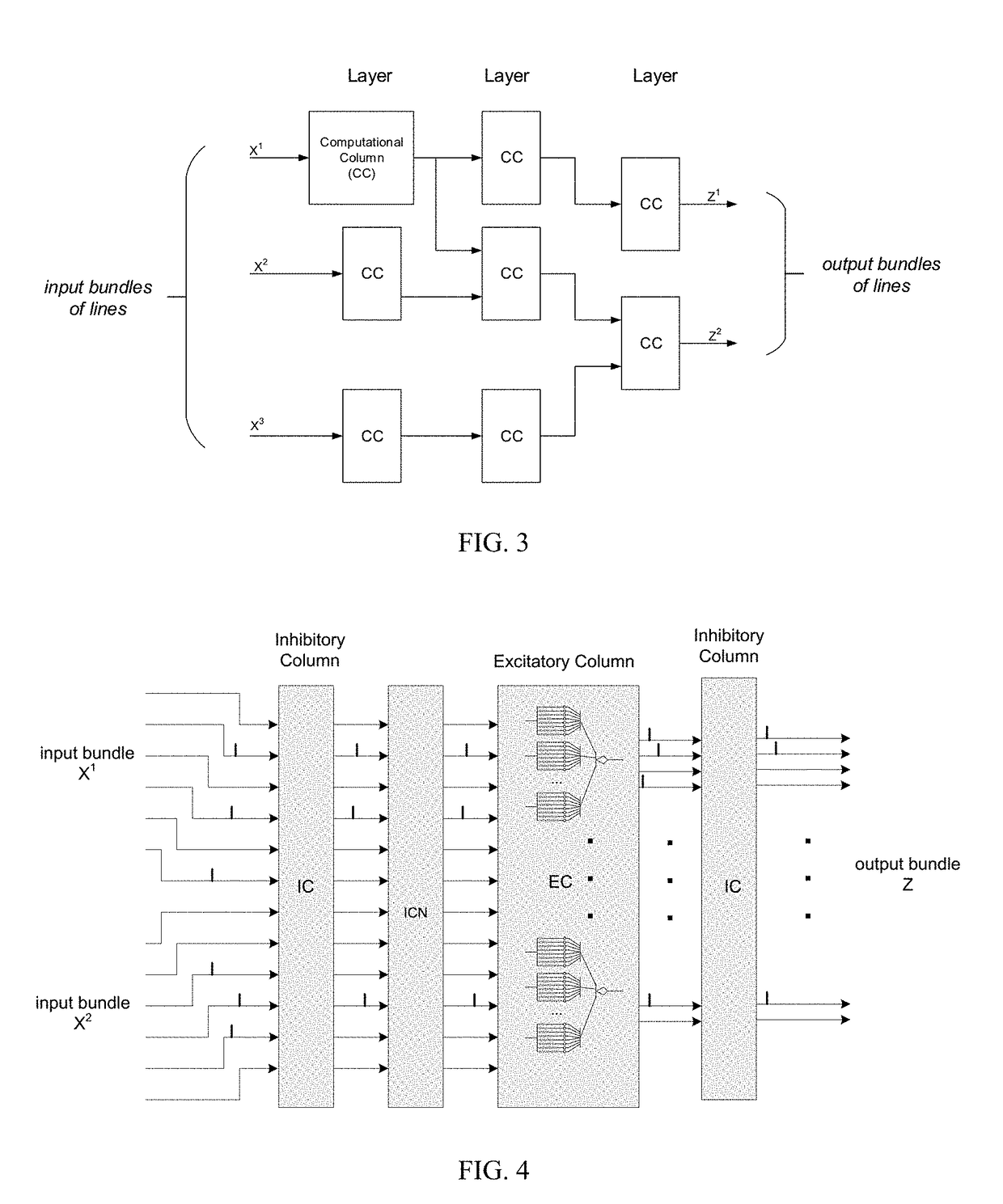

Cognitive Neural Architecture and Associated Neural Network Implementations

InactiveUS20170286828A1Eliminate spikesFaster and computationally far more efficientNeural architecturesNeural learning methodsNerve networkSynaptic weight

A spiking neural network in which communication and computation is performed on data represented as points in actual time. Such neural networks provide new ways of performing computation in human-engineered computing systems that employ the same basic paradigm as the mammalian neocortex. Information is encoded based on the relative timing of individual voltage spikes produced, consumed, and computed upon by groups of neurons. Component and interconnection delays are an integral part of the computation process. Multi-connection paths between pairs of neurons are modeled as a single compound path. Multi-layer networks are trained from the input layer proceeding one layer at a time to the output layer. Training involves a computation that is local to each synapse, and synaptic weights are determined by an averaging method. The action of inhibitory neurons is modeled as a bulk process, rather than with individual neurons.

Owner:SMITH JAMES EDWARD

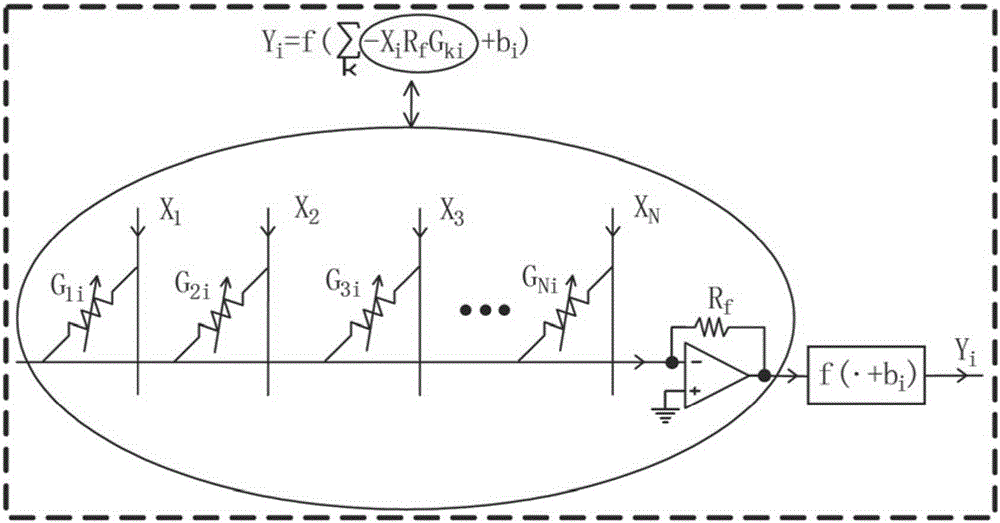

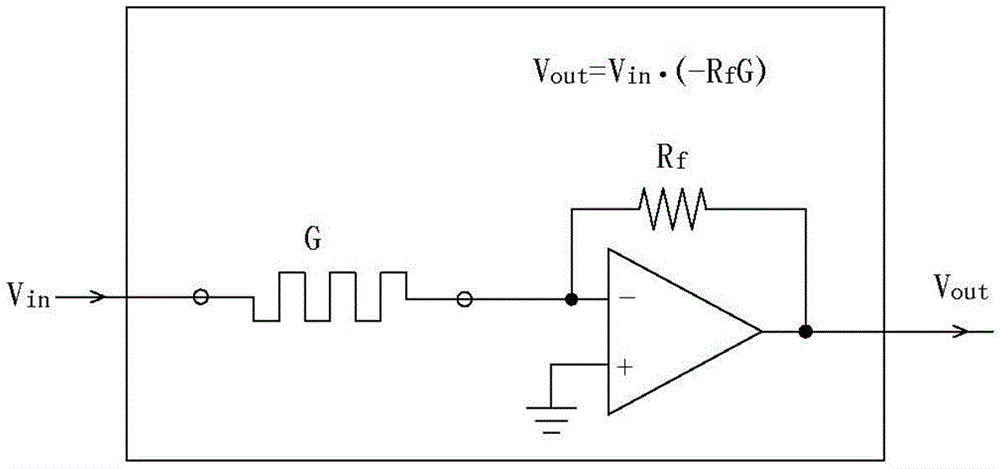

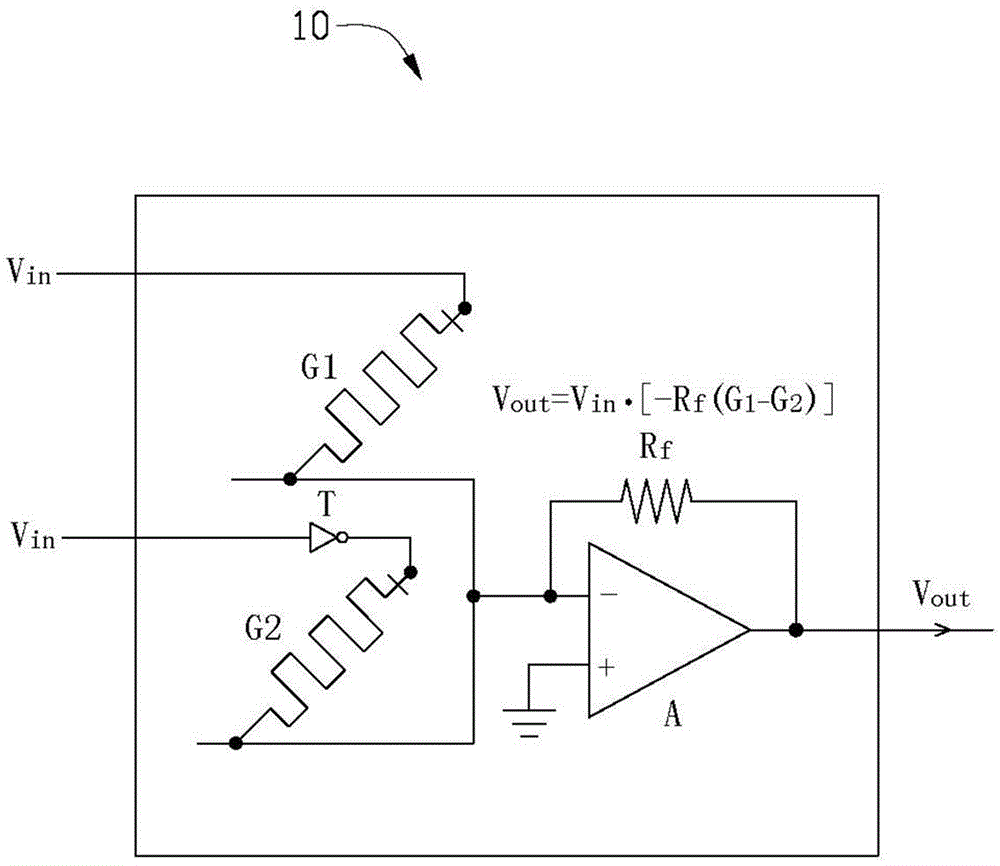

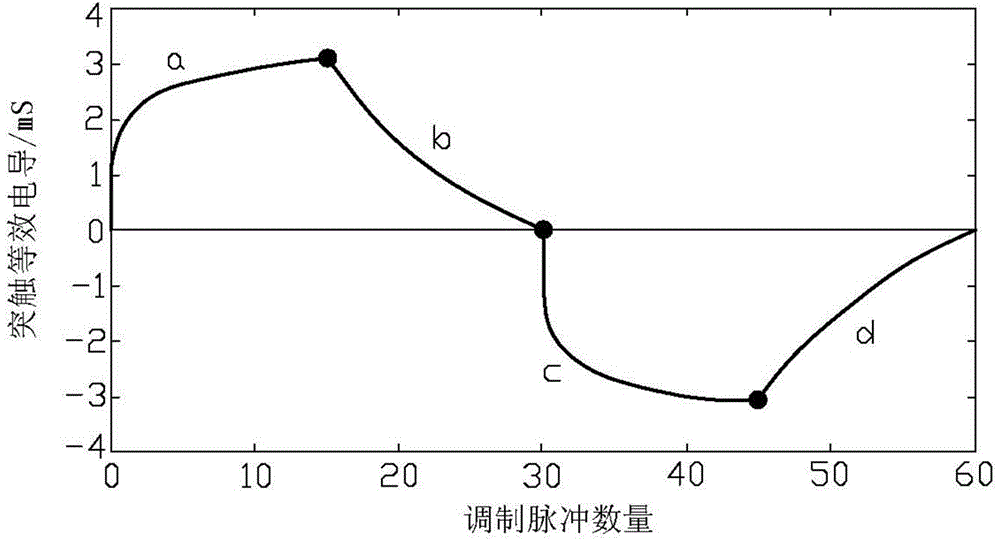

Neural network synapse structure based on memristive devices and synaptic weight building method

ActiveCN104916313ARealize Unique Path ModulationDigital storageLogic circuitsSynaptic weightAudio power amplifier

The invention provides a neural network synapse structure based on memristive devices. The neural network synapse structure comprises a first memristive device, a second memristive device, a voltage inverter, an operational amplifier and a feedback resistor, wherein the second memristive device is serially connected with the voltage inverter to form a serial connection structure, and the serial connection structure is in parallel connection with the first memristive device to form a parallel connection structure; and one end of the parallel connection structure is connected with an input voltage, and the other end of the parallel connection structure is connected with the reverse input end of the operational amplifier and the feedback resistor is bridged between the output end and the reverse input end of the operational amplifier.

Owner:LYNXI TECH CO LTD

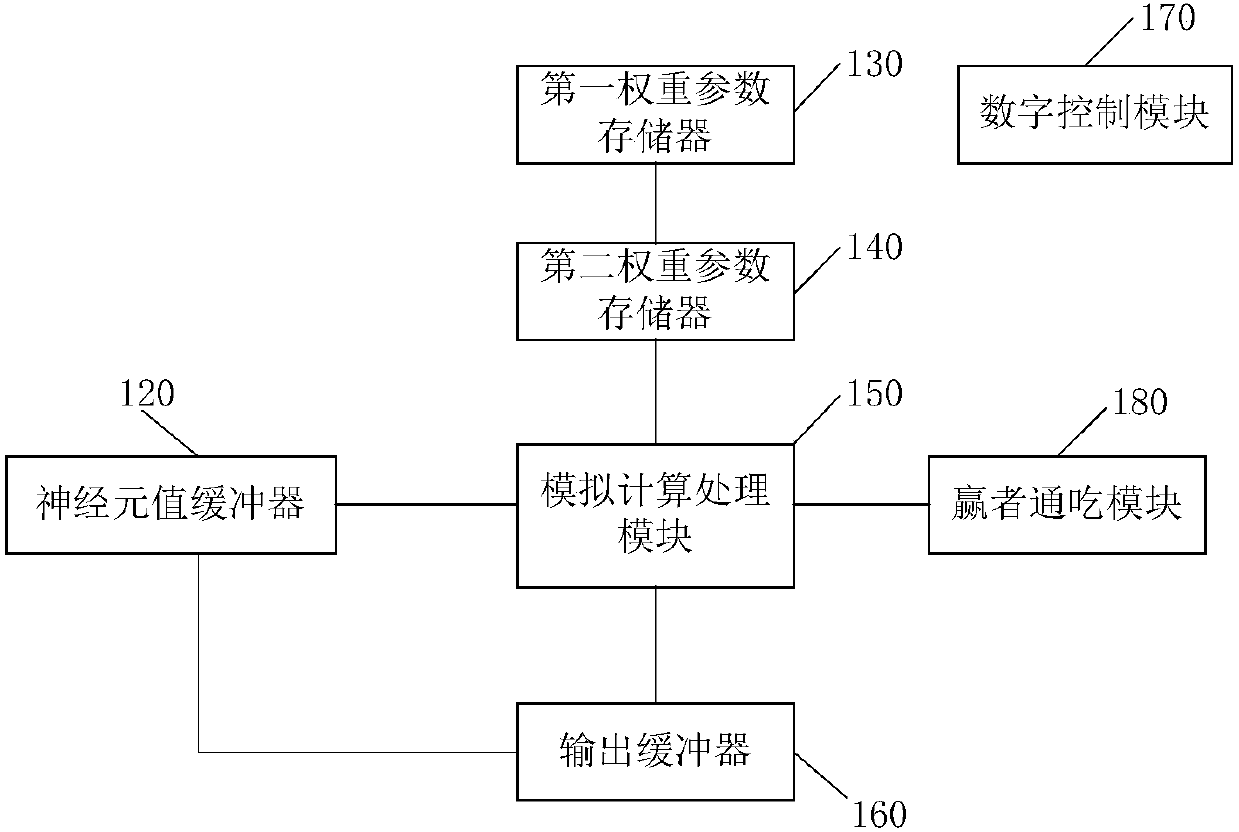

Neural network algorithm oriented analog perception computing architecture

ActiveCN107679622AReduce conversion modulesReduce energy consumptionNeural architecturesPhysical realisationSynaptic weightNerve network

The invention discloses a neural network algorithm oriented analog perception computing architecture which comprises a neuron value buffer configured to cache the sample parameters of an object to beanalyzed, a synaptic weight buffer configured to store synaptic weights corresponding to the sample parameters, and an analog computation processing module configured to extract and classify the features of the object to be analyzed in the analog domain according to the synaptic weights and the sample parameters. According to the invention, the features of the object to be analyzed can be extracted and classified, and the sample parameters and the synaptic weights are computed in the analog domain. The architecture has the characteristics of high efficiency. Moreover, the cost of analog-to-digital and digital-to-analog conversion modules is reduced, and the energy consumption is reduced.

Owner:TSINGHUA UNIV

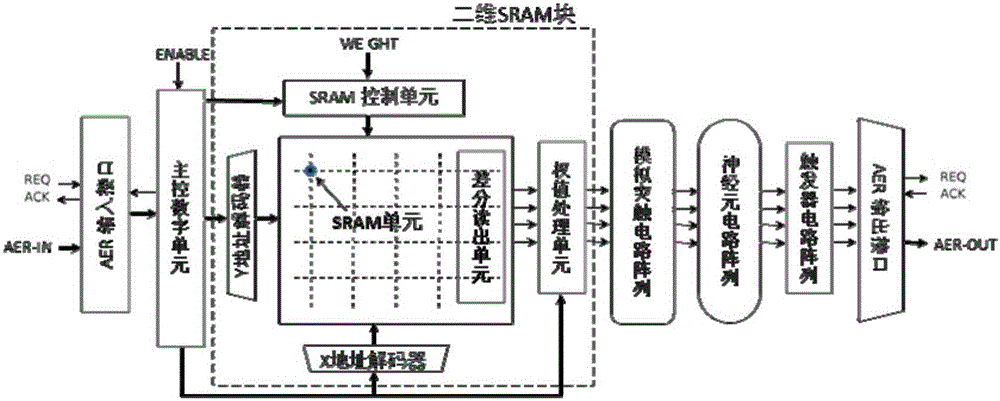

Digital-analog hybrid neural network chip architecture

The invention discloses a digital-analog hybrid neural network chip architecture. The architecture comprises a two-dimensional SRAM module, an analog synaptic circuit, a nerve cell circuit, an AER communication module, and a master control digital unit. The two-dimensional SRAM module is taken as a storage unit of neural network connection relation and a synaptic weight value. The analog synaptic circuit and the nerve cell circuit respectively consist of an MOSFET circuit working in a subthreshold section. The AER communication module serves as the input and output interfaces of a chip, and employs an AER protocol for communication. All control circuits in the architecture are synchronous digital circuits. The architecture is low in power consumption, is high in degree of parallelism, and can achieve a neural network algorithm in a reasonable chip area, wherein the neural network algorithm is more complex in nerve cell functions, is larger in network scale, and is more flexible in connection.

Owner:ZHEJIANG UNIV

Acoustic signature recognition of running vehicles using spectro-temporal dynamic neural network

InactiveUS20110169664A1Vibration measurement in fluidDetection of traffic movementFeature vectorDynamic neural network

Owner:UNIV OF SOUTHERN CALIFORNIA

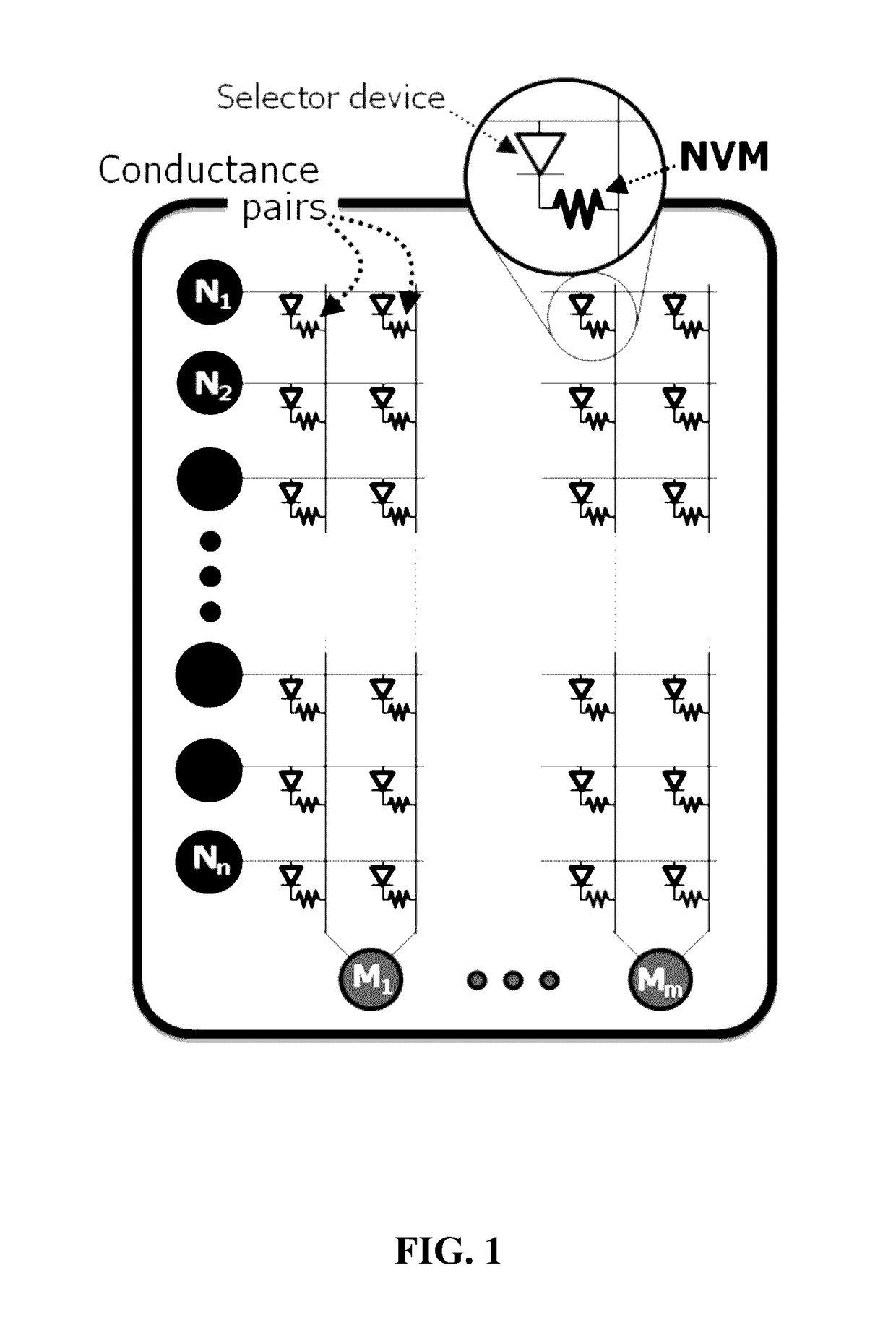

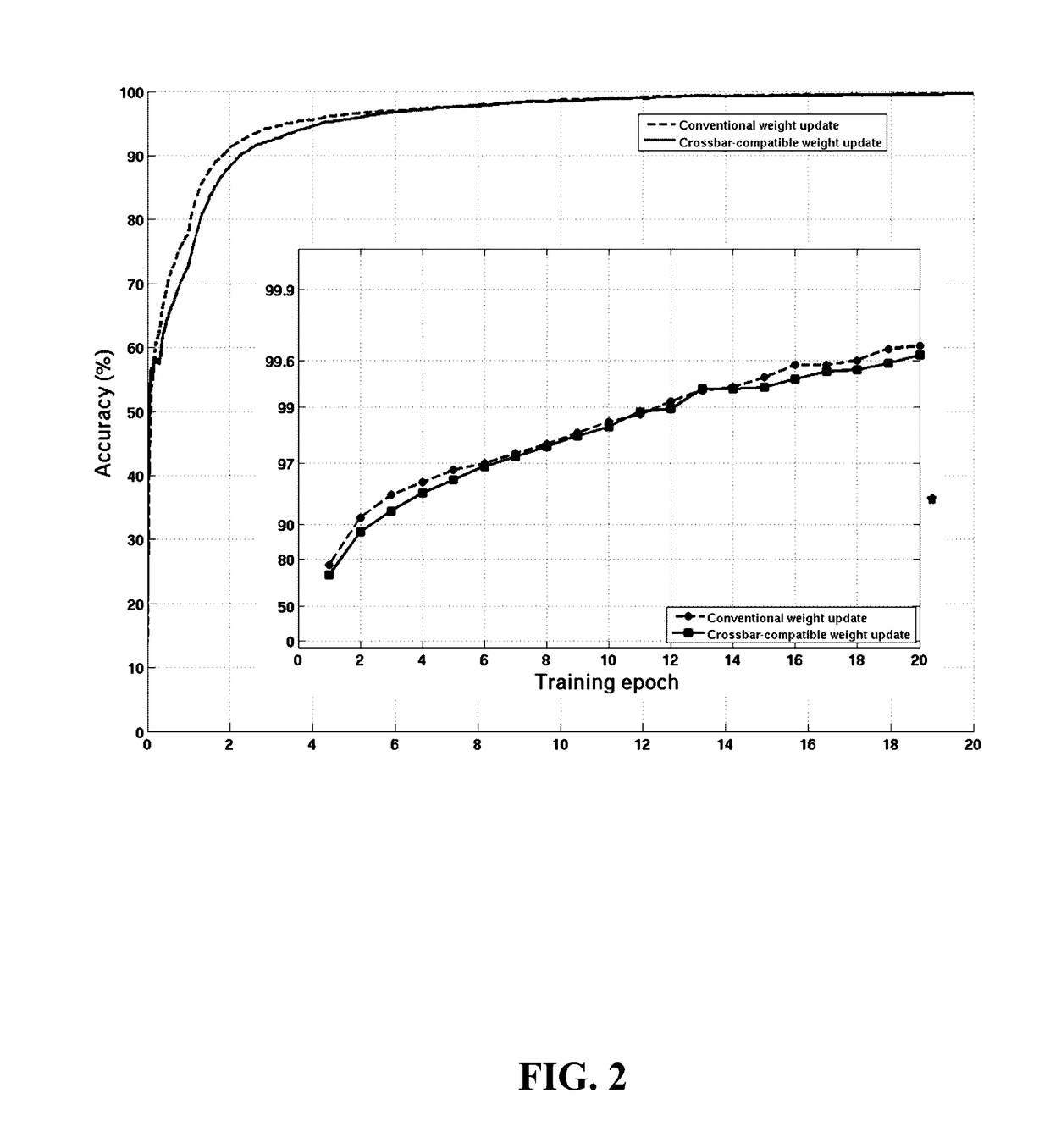

Neuron-centric local learning rate for artificial neural networks to increase performance, learning rate margin, and reduce power consumption

ActiveUS20170154259A1Network degradationInhibitory activityNeural architecturesNeural learning methodsSynaptic weightLocal learning

Artificial neural networks (ANNs) are a distributed computing model in which computation is accomplished using many simple processing units (called neurons) and the data embodied by the connections between neurons (called synapses) and the strength of these connections (called synaptic weights). An attractive implementation of ANNs uses the conductance of non-volatile memory (NVM) elements to code the synaptic weight. In this application, the non-idealities in the response of the NVM (such as nonlinearity, saturation, stochasticity and asymmetry in response to programming pulses) lead to reduced network performance compared to an ideal network implementation. Disclosed is a method that improves performance by implementing a learning rate parameter that is local to each synaptic connection, a method for tuning this local learning rate, and an implementation that does not compromise the ability to train many synaptic weights in parallel during learning.

Owner:IBM CORP

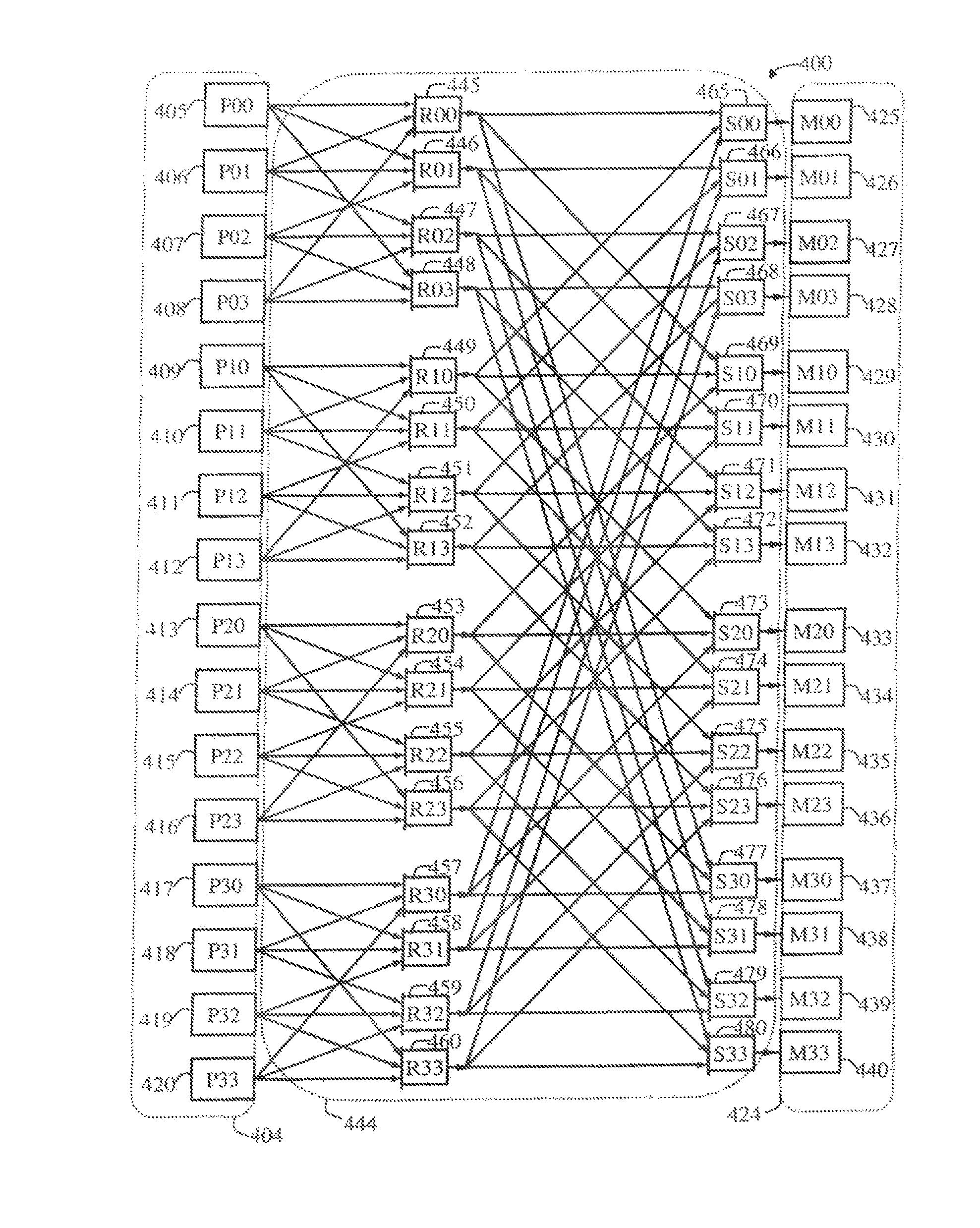

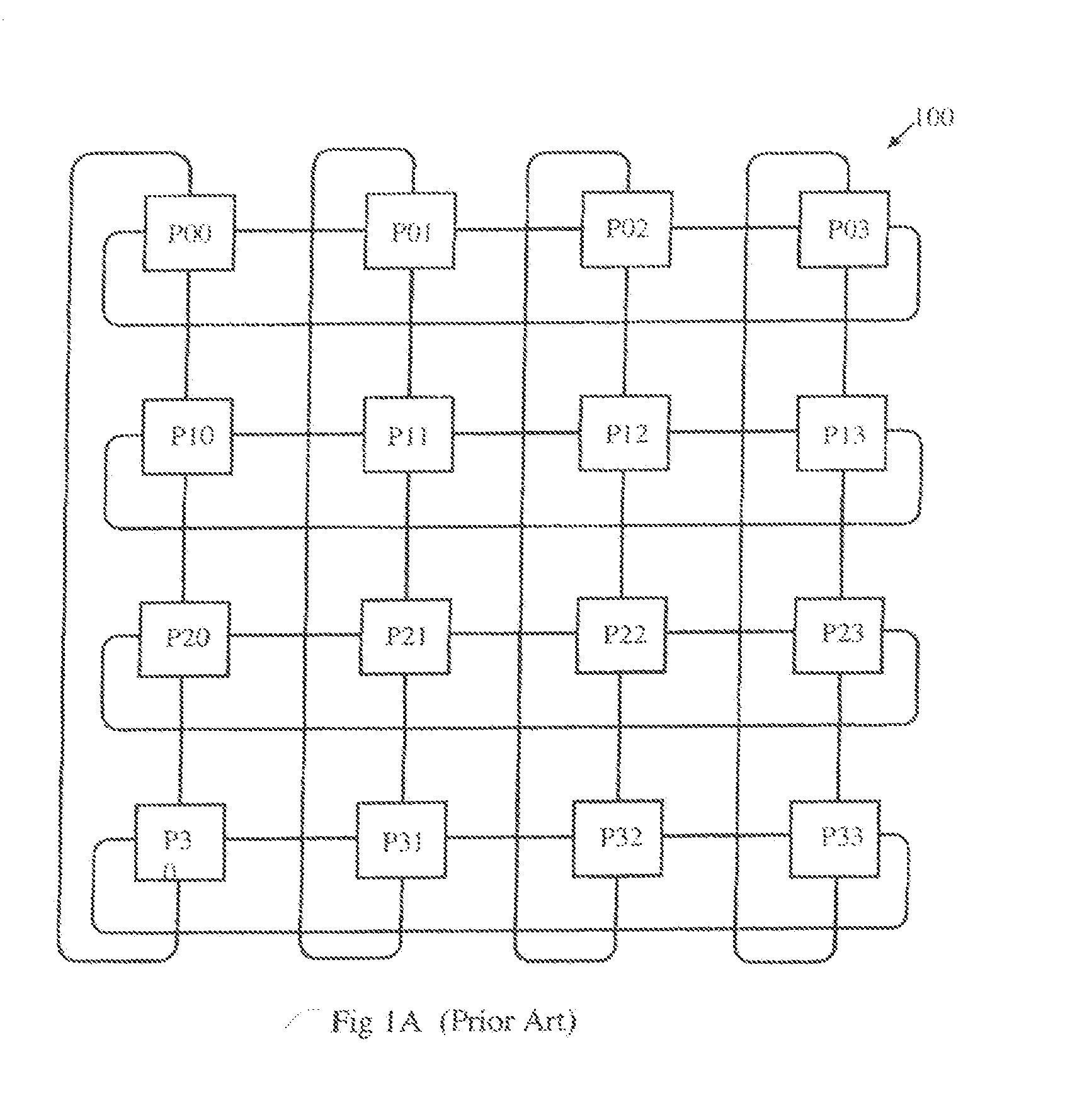

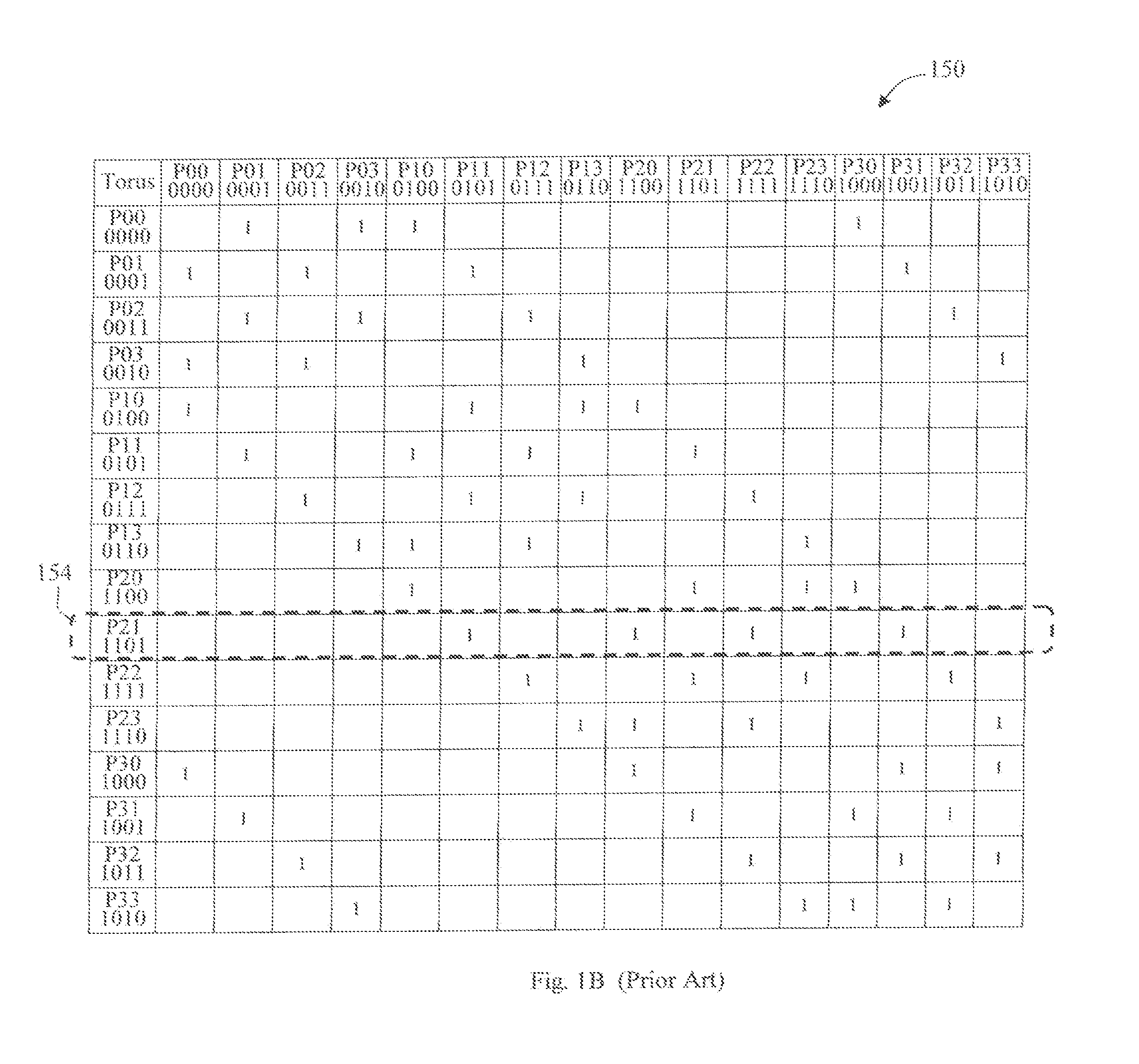

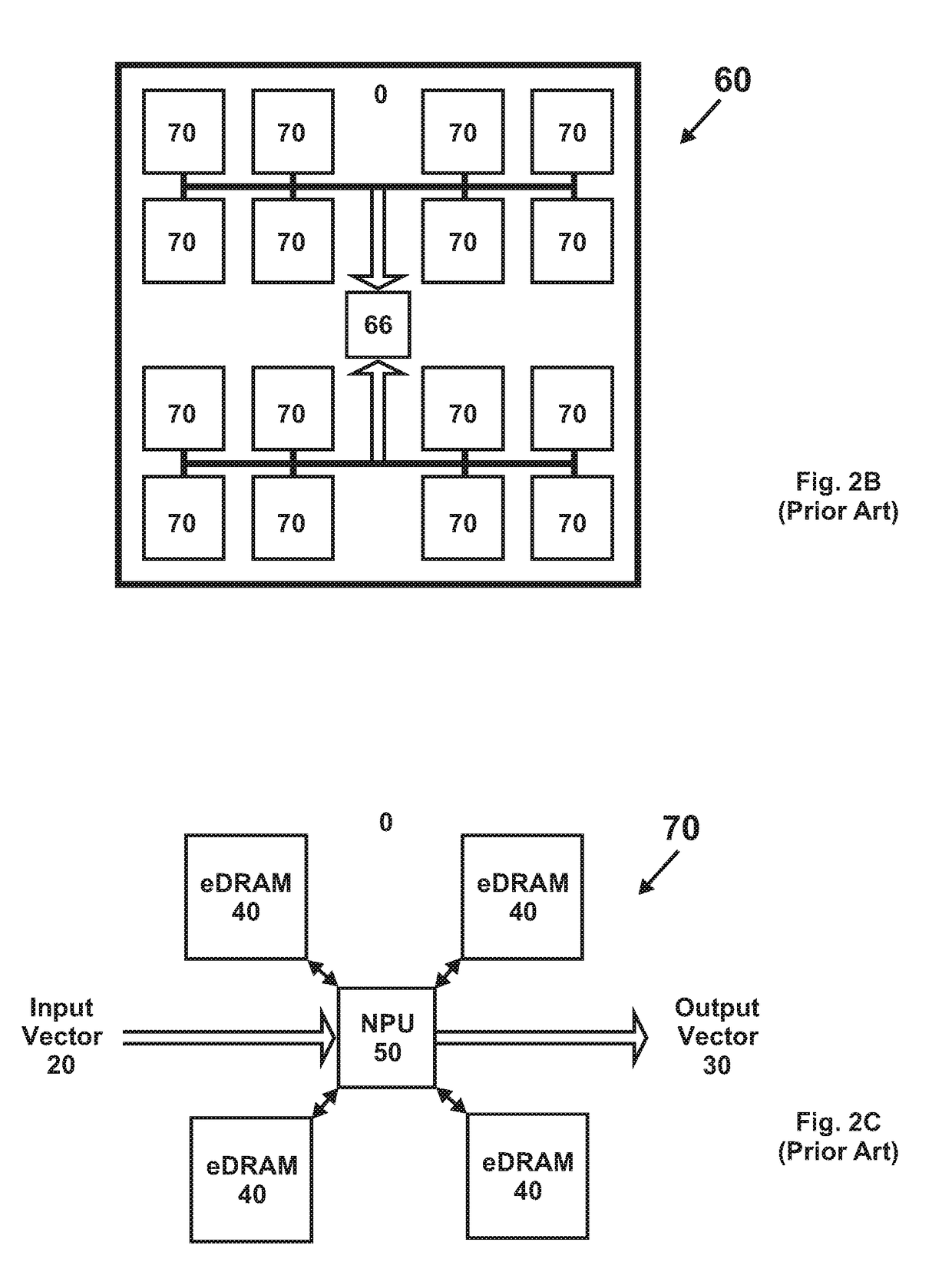

Interconnection network connecting operation-configurable nodes according to one or more levels of adjacency in multiple dimensions of communication in a multi-processor and a neural processor

InactiveUS20130198488A1Single instruction multiple data multiprocessorsInstruction analysisNODALSynaptic weight

A Wings array system for communicating between nodes using store and load instructions is described. Couplings between nodes are made according to a 1 to N adjacency of connections in each dimension of a G×H matrix of nodes, where G≧N and H≧N and N is a positive odd integer. Also, a 3D Wings neural network processor is described as a 3D G×H×K network of neurons, each neuron with an N×N×N array of synaptic weight values stored in coupled memory nodes, where G≧N, H≧N, K≧N, and N is determined from a 1 to N adjacency of connections used in the G×H×K network. Further, a hexagonal processor array is organized according to an INFORM coordinate system having axes at 60 degree spacing. Nodes communicate on row paths parallel to an FM dimension of communication, column paths parallel to an IO dimension of communication, and diagonal paths parallel to an NR dimension of communication.

Owner:PECHANEK GERALD GEORGE

Communication and synapse training method and hardware for biologically inspired networks

Owner:QUALCOMM INC

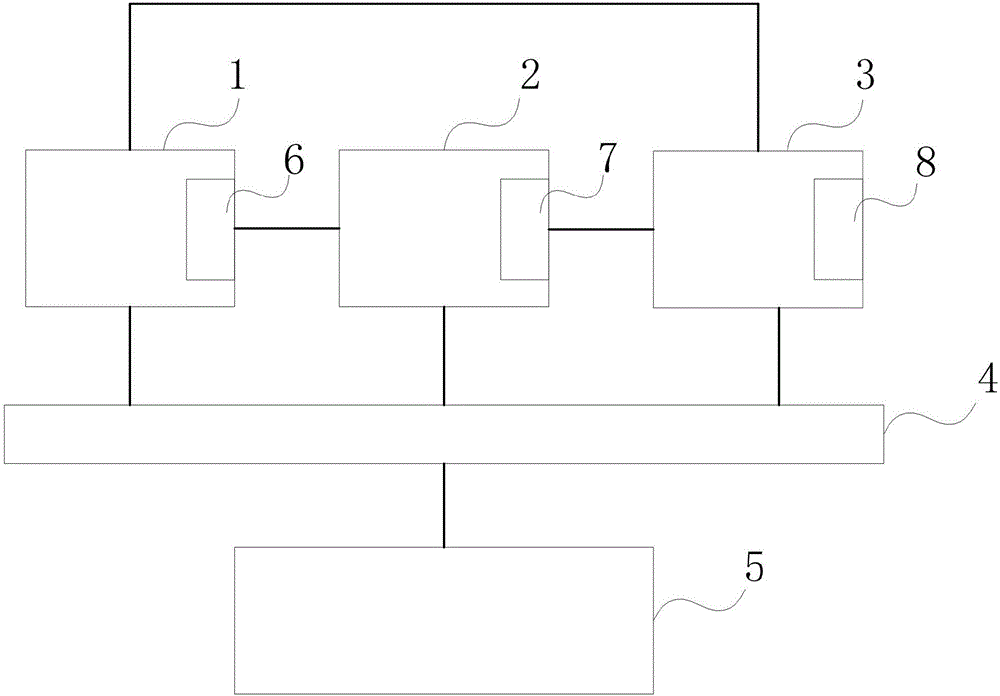

Image recognition system and method based on spiking neural network

PendingCN112784976AAccelerate the lossCharacter and pattern recognitionPhysical realisationTime informationInformation processing

The invention discloses an image recognition system and method based on a pulse neural network. The system comprises an upper computer, an off-chip memory, a master control module, an input coding module, an LIF neuron module, a pulse time information processing module, a TSTDP module and a full voting module. The method comprises the following steps: a training stage: training synaptic weights between an input layer and a hidden layer, between the hidden layers and between the hidden layer and an output layer of the spiking neural network; a benchmarking stage: training a synaptic weight between an output layer of the spiking neural network and a full voting classification layer; in the recognition stage, the output layer votes for the full-voting classification layer by adopting a full-voting mechanism, and image recognition is carried out. The invention provides a full voting output decoding mechanism capable of reducing information loss, and the problem of output decoding information loss of a pulse neural network caused by a traditional voting mechanism is effectively improved. The method can be widely applied to the technical field of artificial neural network and digital circuit design.

Owner:SUN YAT SEN UNIV

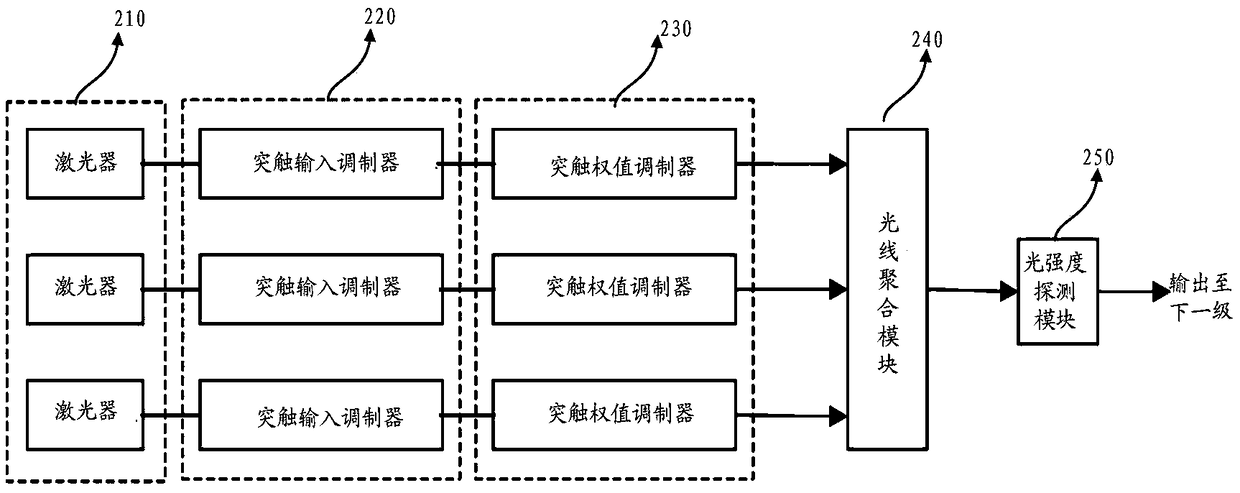

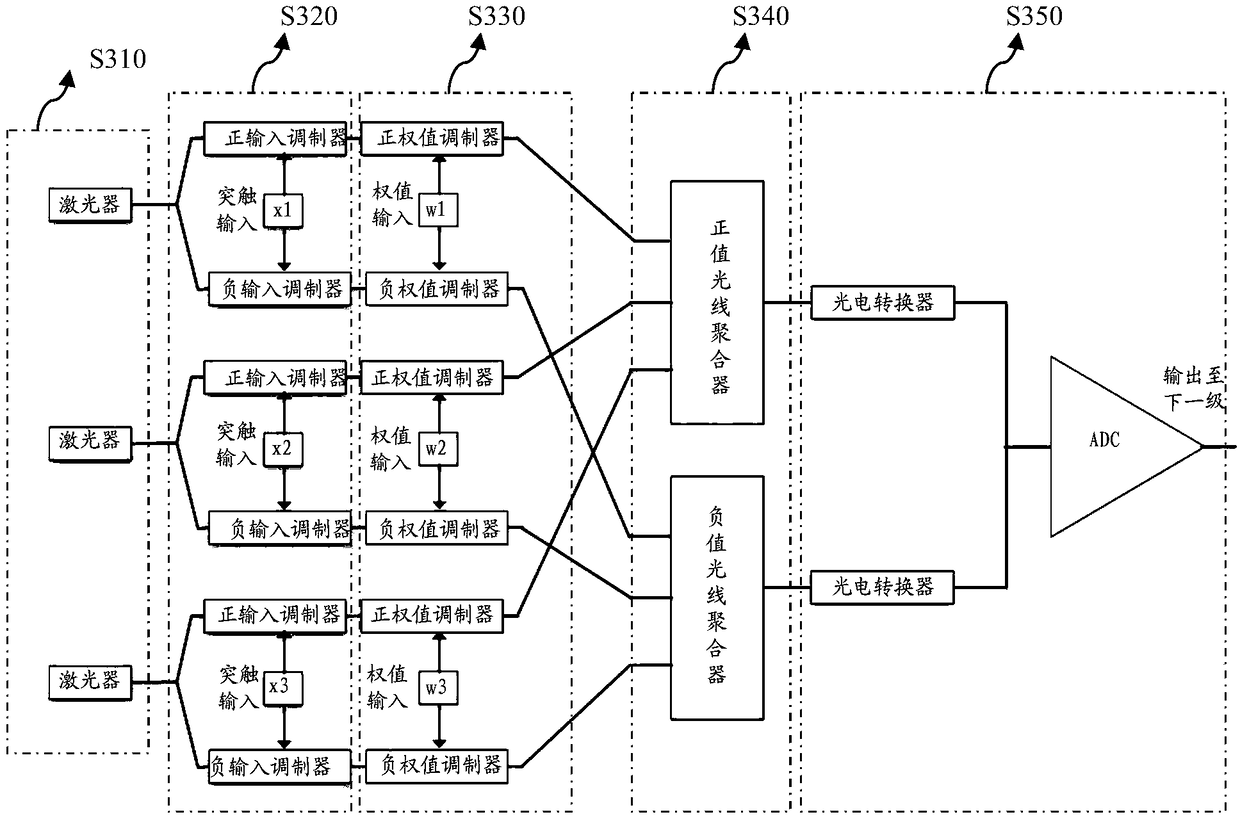

An optical neuron structure and a neural network processing system including the structure

ActiveCN109376855AHigh speedReduce energy consumptionPhysical realisationSynaptic weightNerve network

The present invention provides an optical neuron structure and a neural network processing system including the structure. The neuron structure comprises a synaptic input modulation module, a synapticweight modulation module, a light aggregation module and a light intensity detection module, wherein, the synaptic input modulation module is used for receiving an optical signal and performing optical path modulation under the control of an electrical signal associated with the input neuron; A synaptic weight modulation module for performing modulation of an optical signal of the bearer input neuron under control of an electrical signal associated with the weight; The light aggregation module is used for aggregating the output optical signals of a plurality of synaptic weight modulation modules; The light intensity detection module is configured to convert an output light signal from the light aggregation module into an electrical signal and perform an activation operation. The optical neuron structure of the invention and the neural network processing system including the structure can realize the fast calculation of the neural network.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

Integrated Neuro-Processor Comprising Three-Dimensional Memory Array

ActiveUS20170270403A1Improve artIncreased die areaNeural architecturesPhysical realisationSynaptic weightNeural processing

The present invention discloses an integrated neuro-processor comprising at least a three-dimensional memory (3D-M) array. The 3D-M array stores the synaptic weights, while the neuro-processing circuit performs neural processing. The 3-D integration between the 3D-M array and the neuro-processing circuit not only improves the computational power per die area, but also greatly increases the storage capacity per die area.

Owner:HANGZHOU HAICUN INFORMATION TECH +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com