Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

89 results about "Neural processing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Neural processing originally referred to the way the brain works, but the term is more typically used to describe a computer architecture that mimics that biological function. In computers, neural processing gives software the ability to adapt to changing situations and to improve its function as more information becomes available.

Methods and systems for neural and cognitive processing

ActiveUS20150339570A1Easily customizedScalable performanceDigital computer detailsDigital dataData miningArtificial intelligence

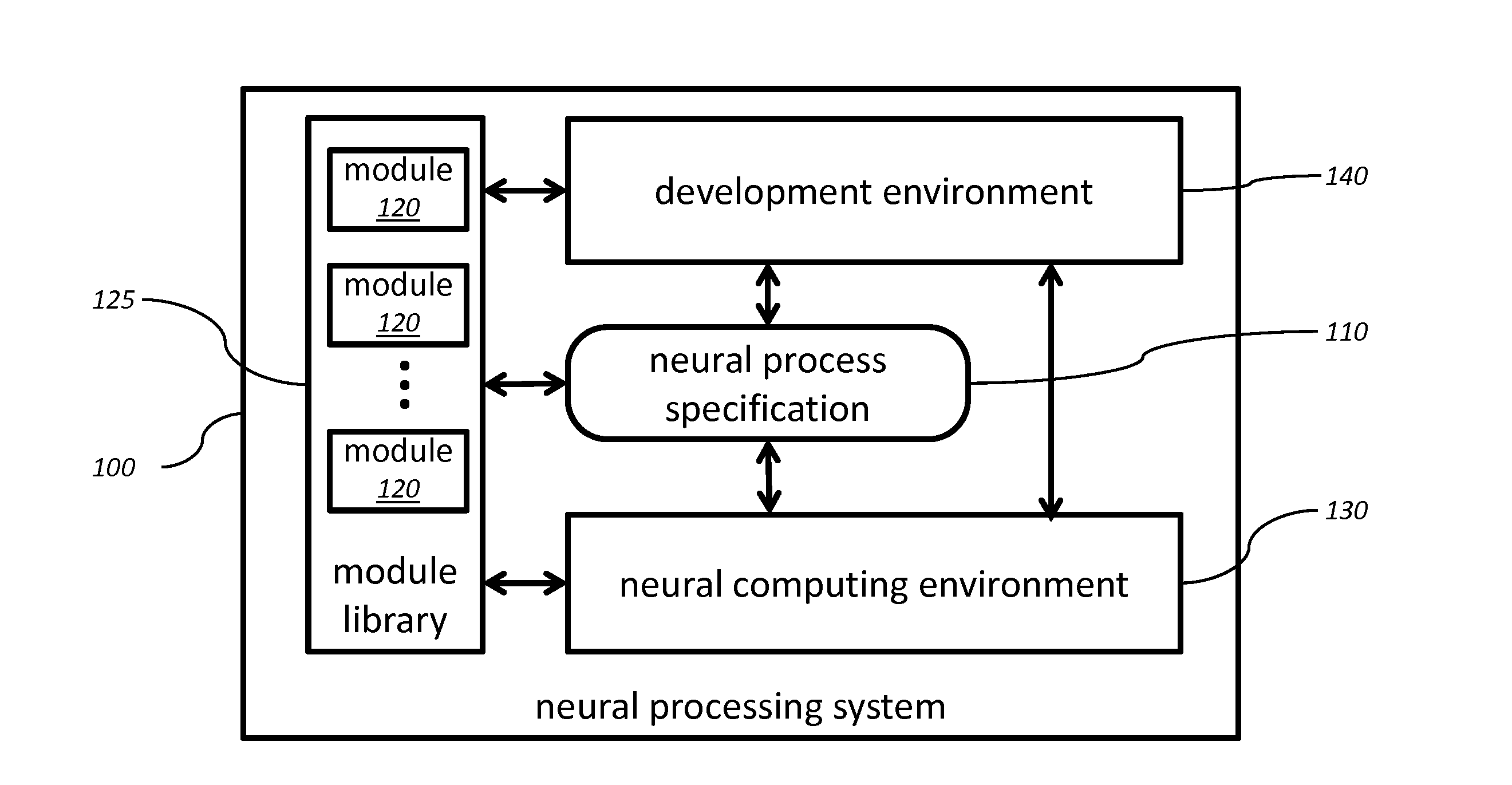

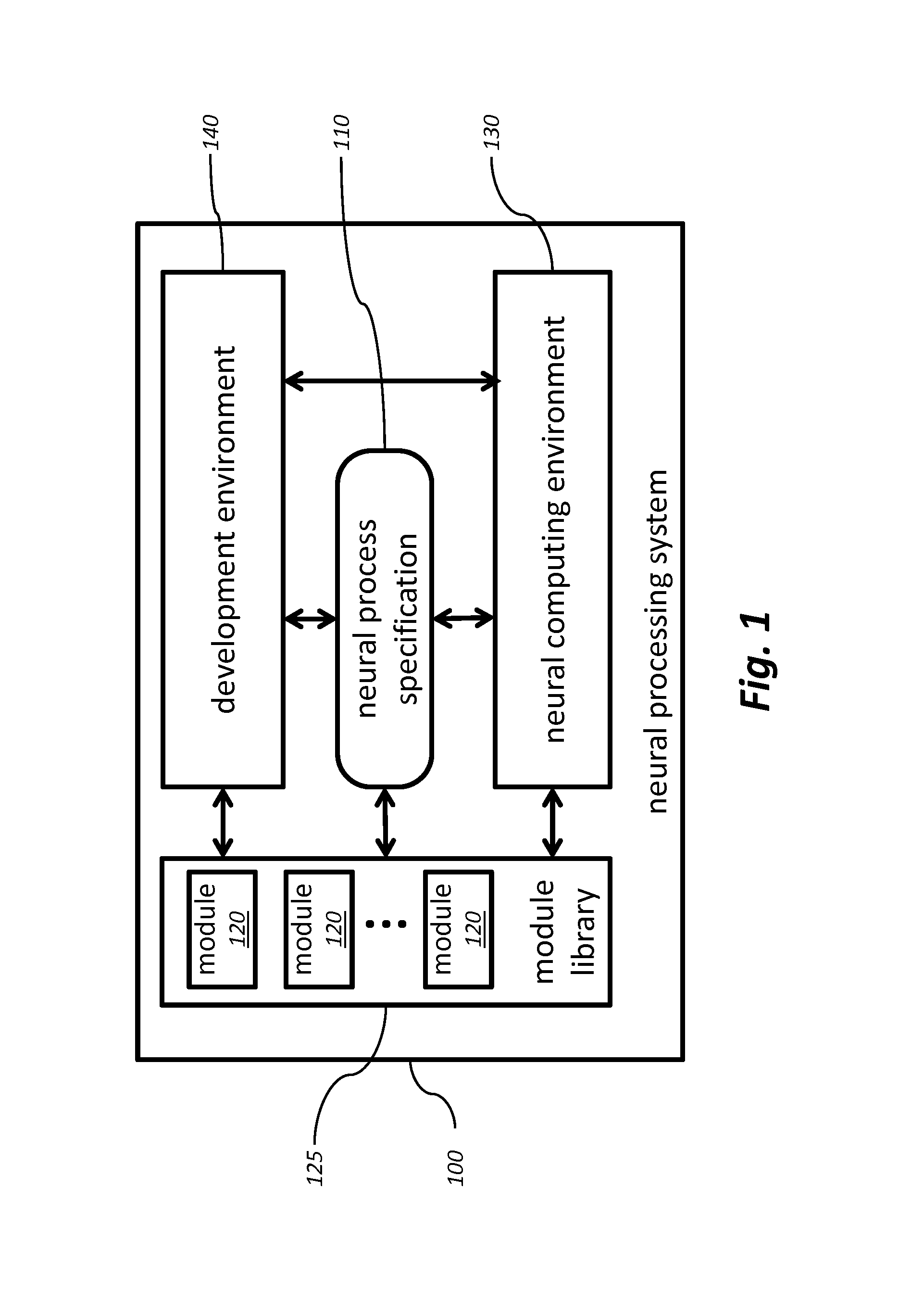

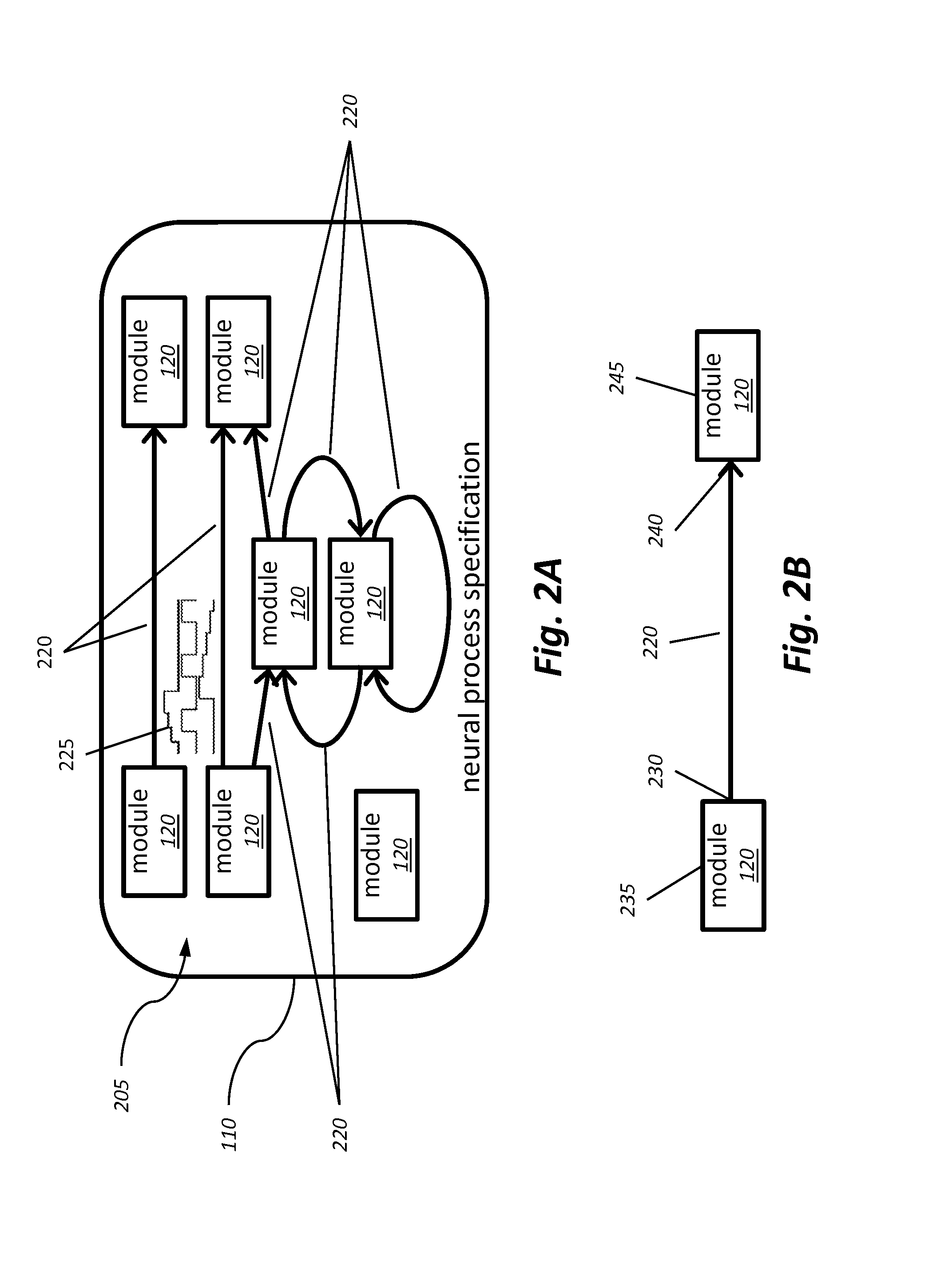

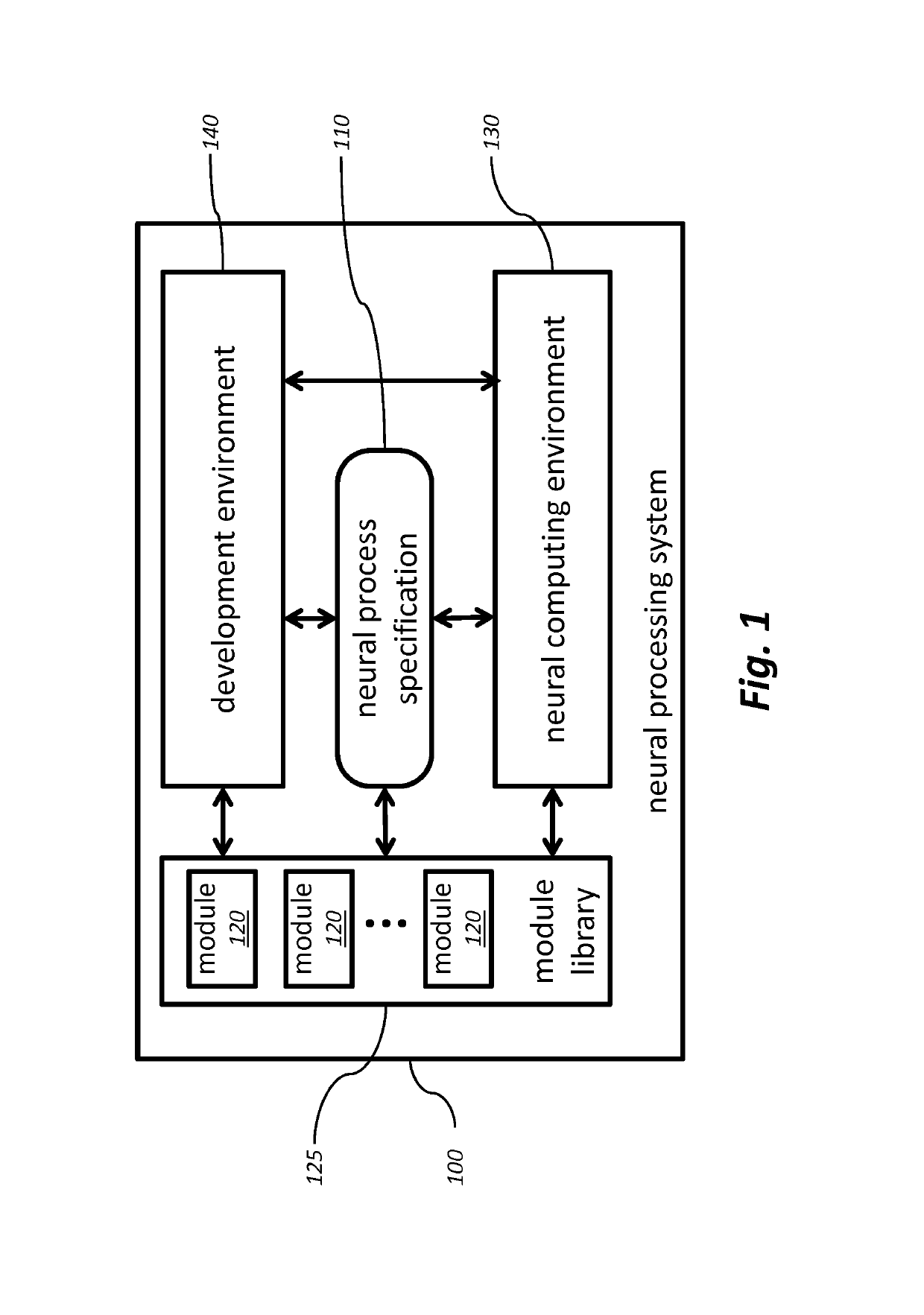

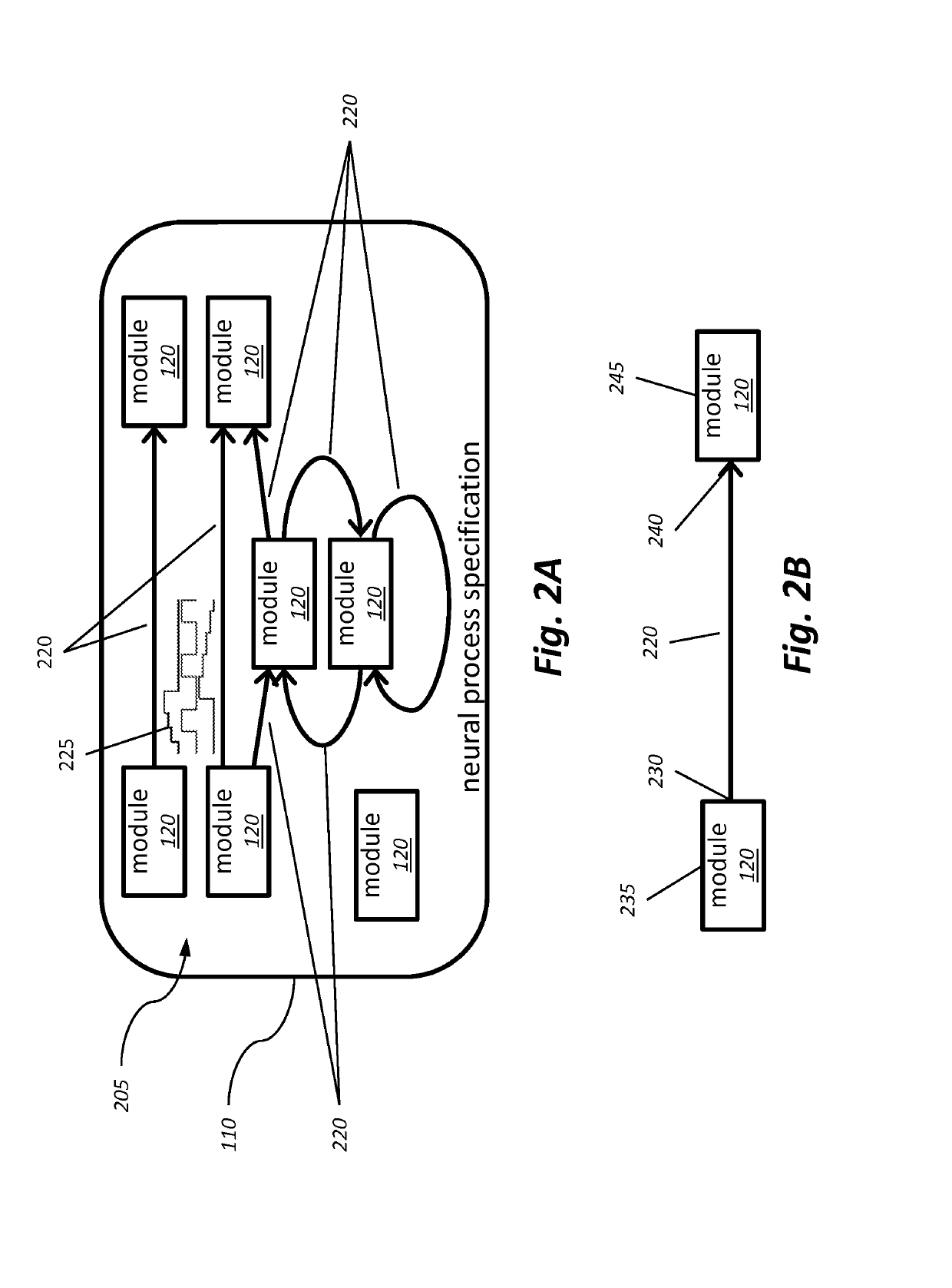

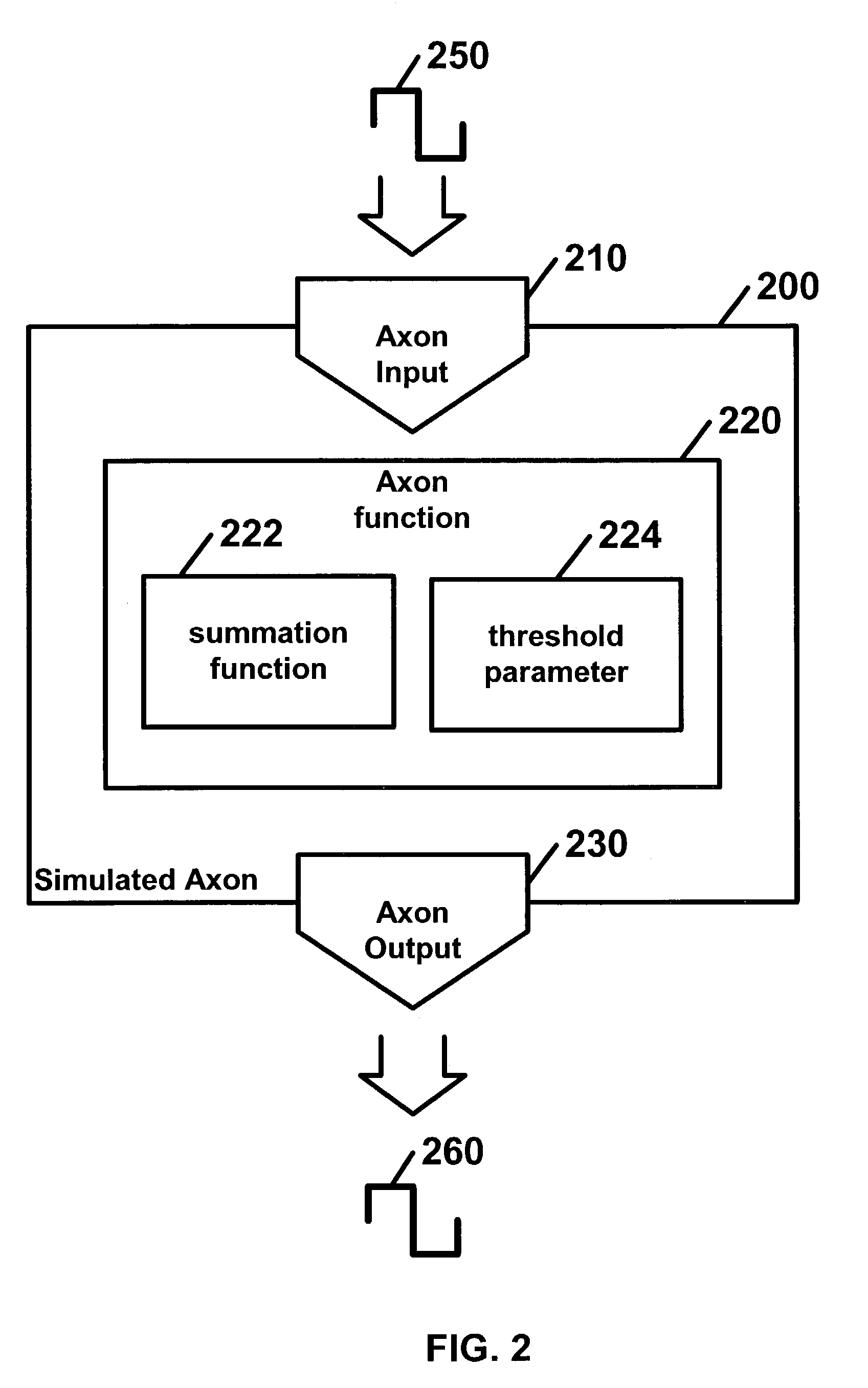

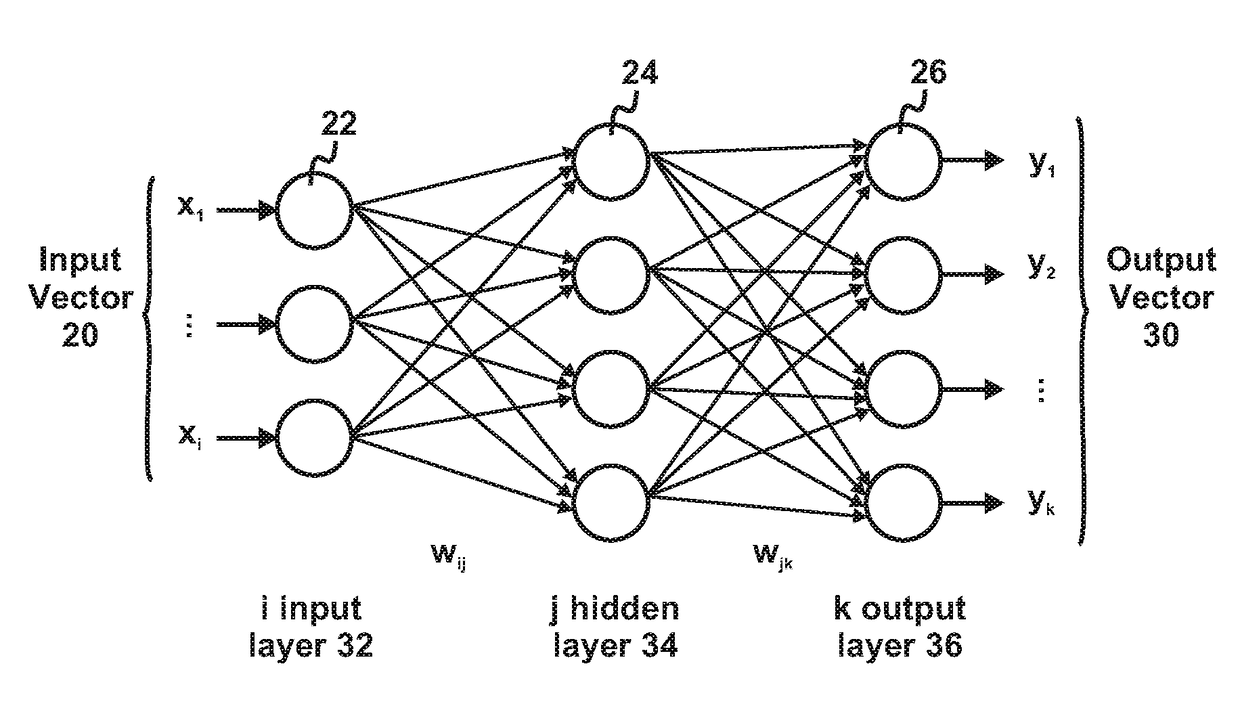

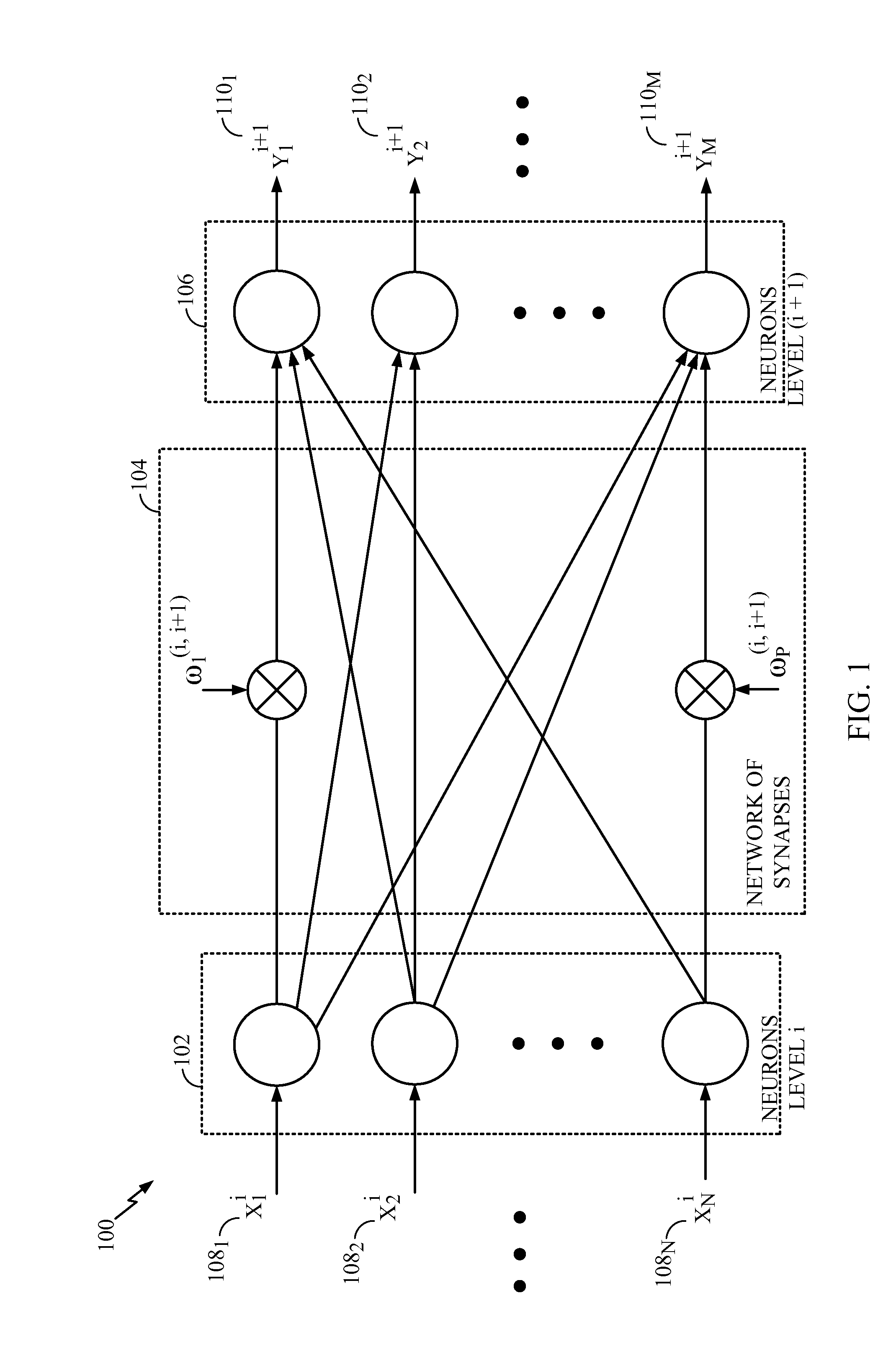

Provided herein is a system for creating, modifying, deploying and running intelligent systems by combining and customizing the function and operation of reusable component modules arranged into neural processing graphs which direct the flow of signals among the modules, analogous in part to biological brain structure and operation as compositions of variations on functional components and subassemblies.

Owner:SCHEFFLER LEE J

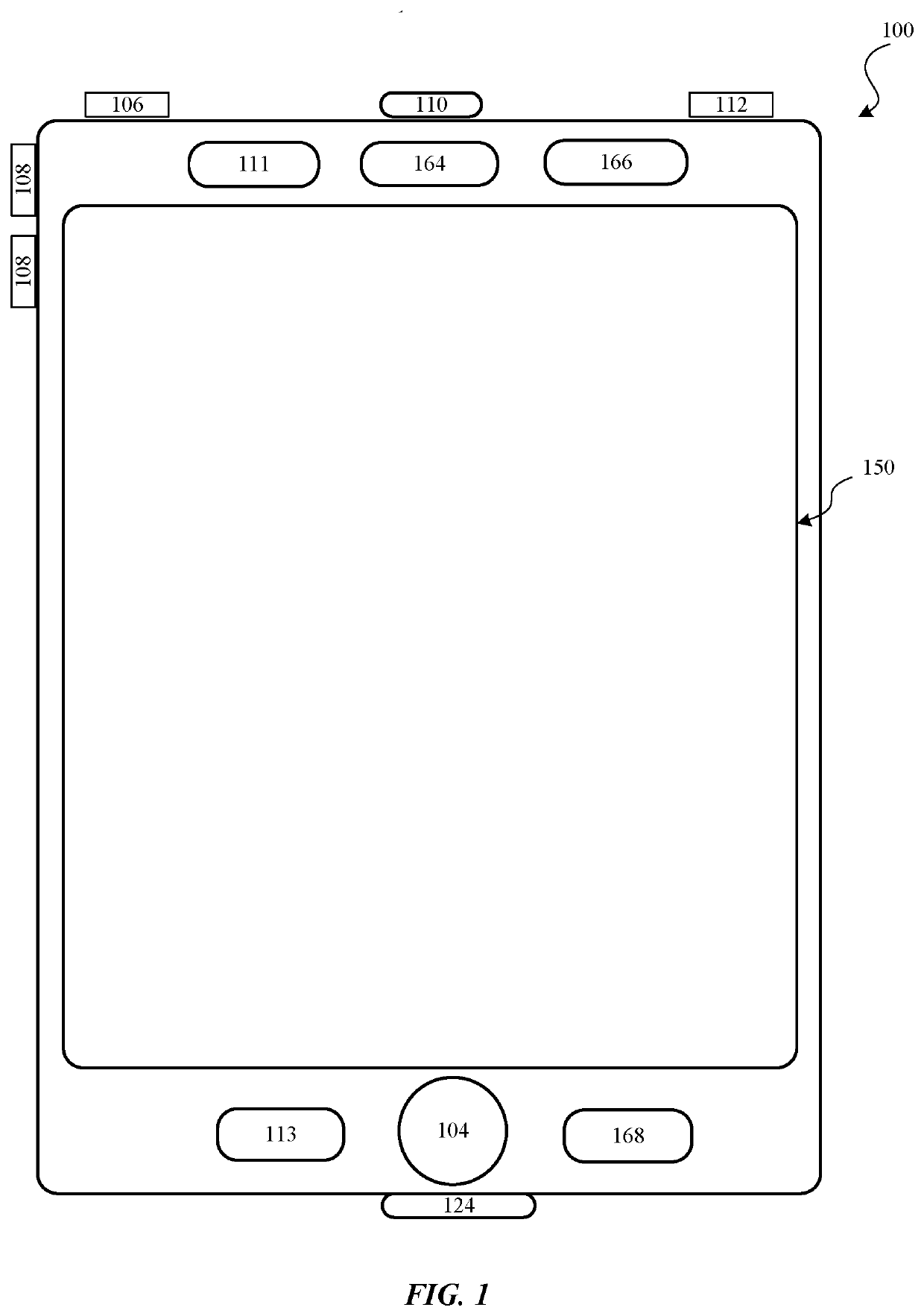

Method and Apparatus for Training Brain Development Disorders

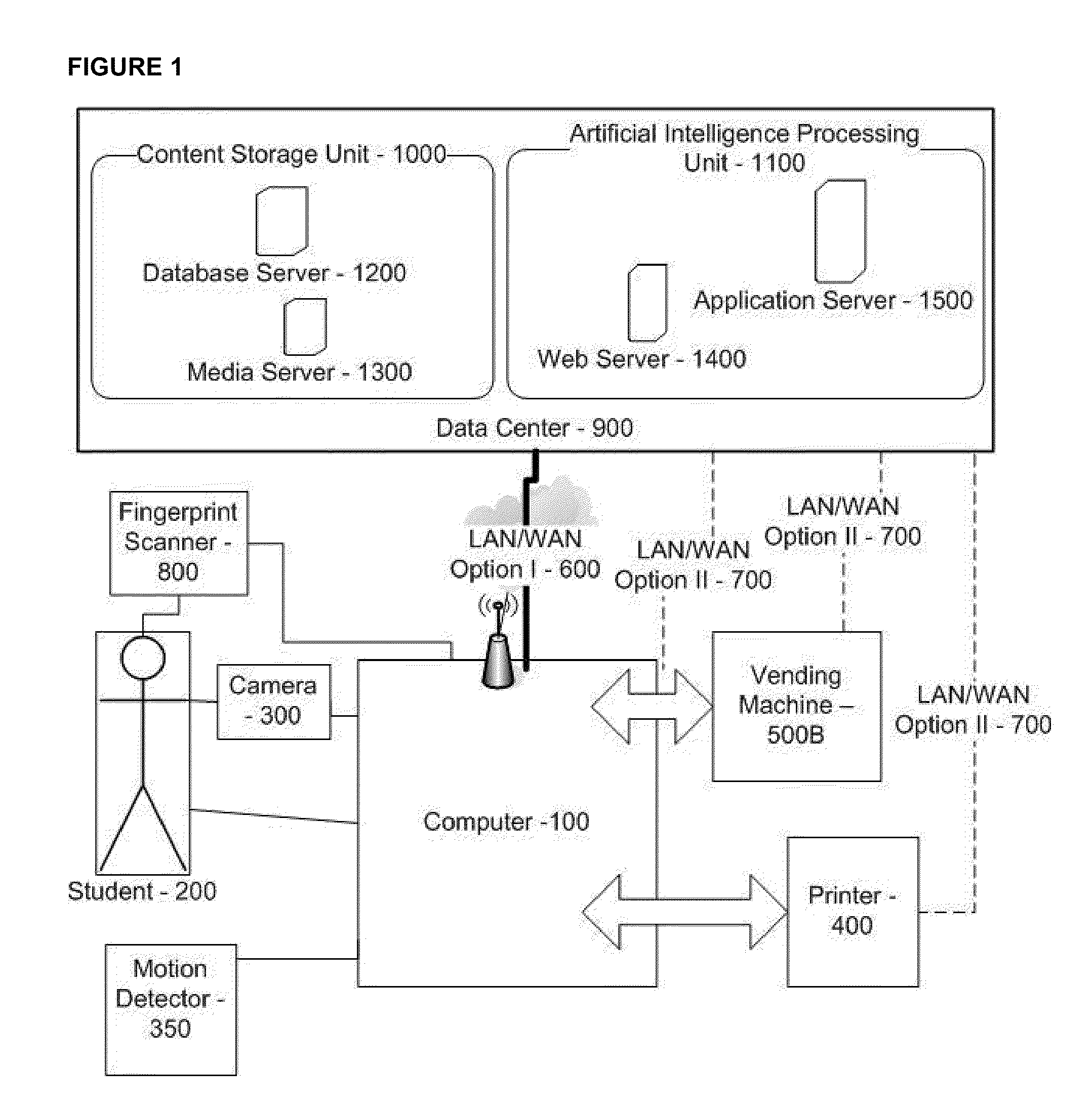

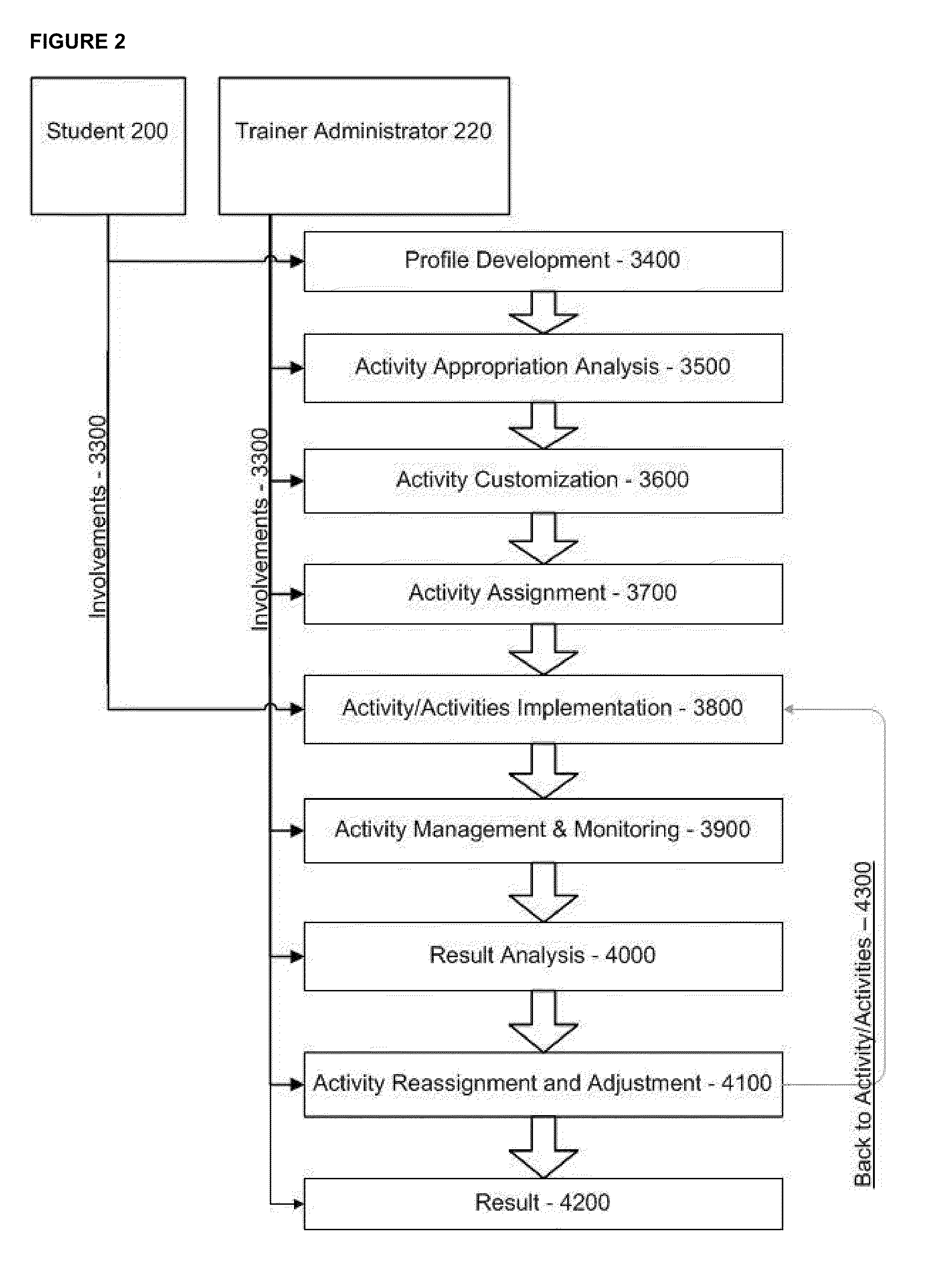

InactiveUS20110229862A1Reduce interactionProvide usageElectrical appliancesTeaching apparatusBrain developmentAnimation

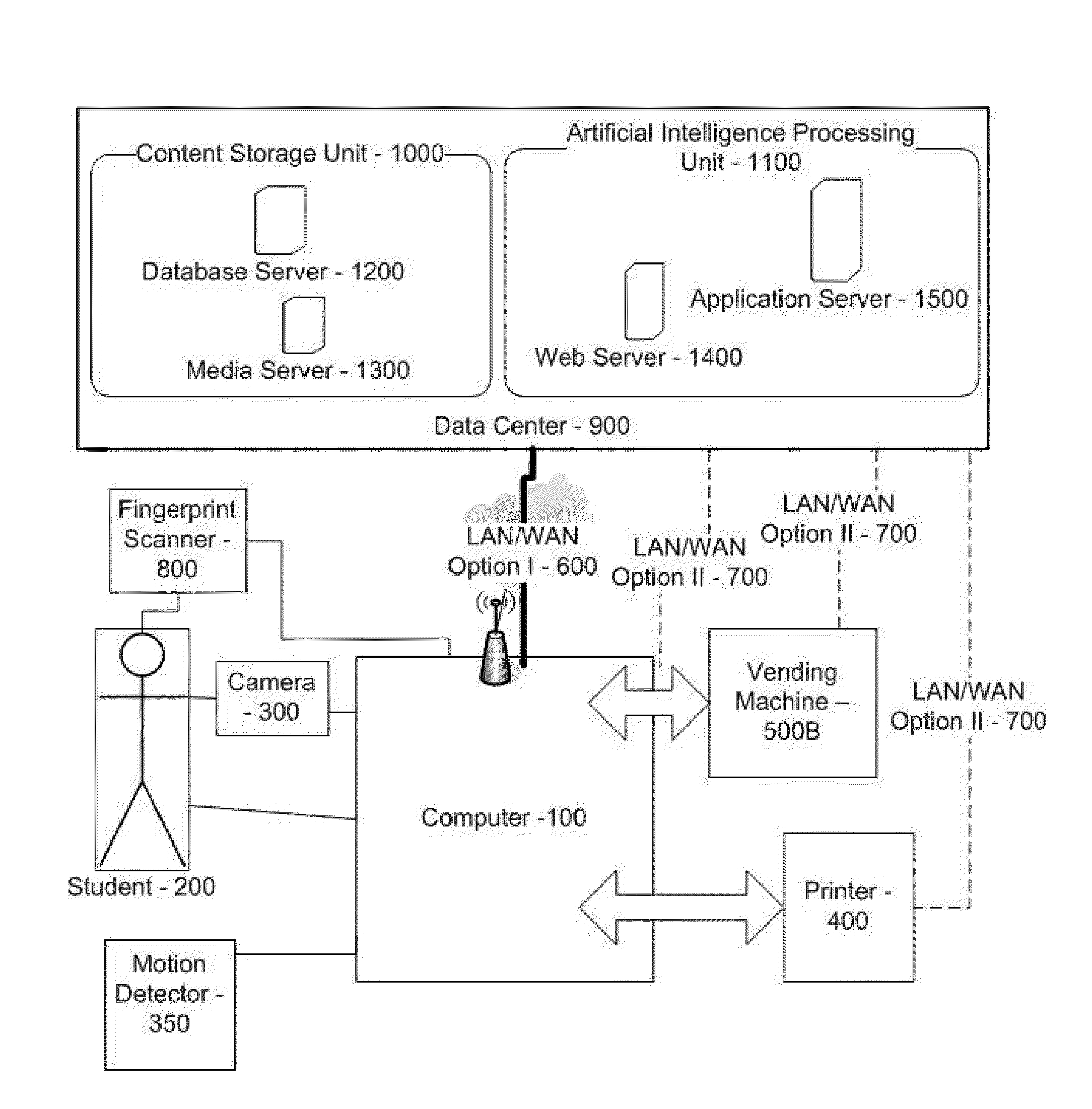

The present invention relates to the field of education of human subjects, and more specifically to a computer program for training the brain development disorder where in human subjects are impaired of social interaction and communication. The program deliver animated content to the subject and varies the size, clarity, colors, background images, animated characters, sound with animation, method of instructions, so they would be more easily distinguished by the subject and thereby gradually improves the subject's neurological processing and memory of the elements through repetitive stimulation. Thus the system, method and apparatus of the present invention maximizes the effectiveness and efficiency of learning by adding a reward delivery system to deliver the object of the student's interest upon achieving the goal set by the trainer. The system includes modules configuration system, user validation system, content delivery system, user response / input system, monitoring system and feedback system. The configuration engine includes a progress module which monitors a user's performance on any of learn, review and test modules and changes the future lessons based on the monitored performance. The content delivery system includes help or instructions screen to provide assistance with any of the learning lessons.

Owner:OHM TECH

Methods and systems for neural and cognitive processing

ActiveUS10417554B2Easily customizedScalable performanceNeural architecturesComputer simulationsData miningArtificial intelligence

Provided herein is a system for creating, modifying, deploying and running intelligent systems by combining and customizing the function and operation of reusable component modules arranged into neural processing graphs which direct the flow of signals among the modules, analogous in part to biological brain structure and operation as compositions of variations on functional components and subassemblies.

Owner:SCHEFFLER LEE J

Neural processor

InactiveUS7174325B1Simple methodLarge structureDigital computer detailsNeural architecturesDendriteNeural processing

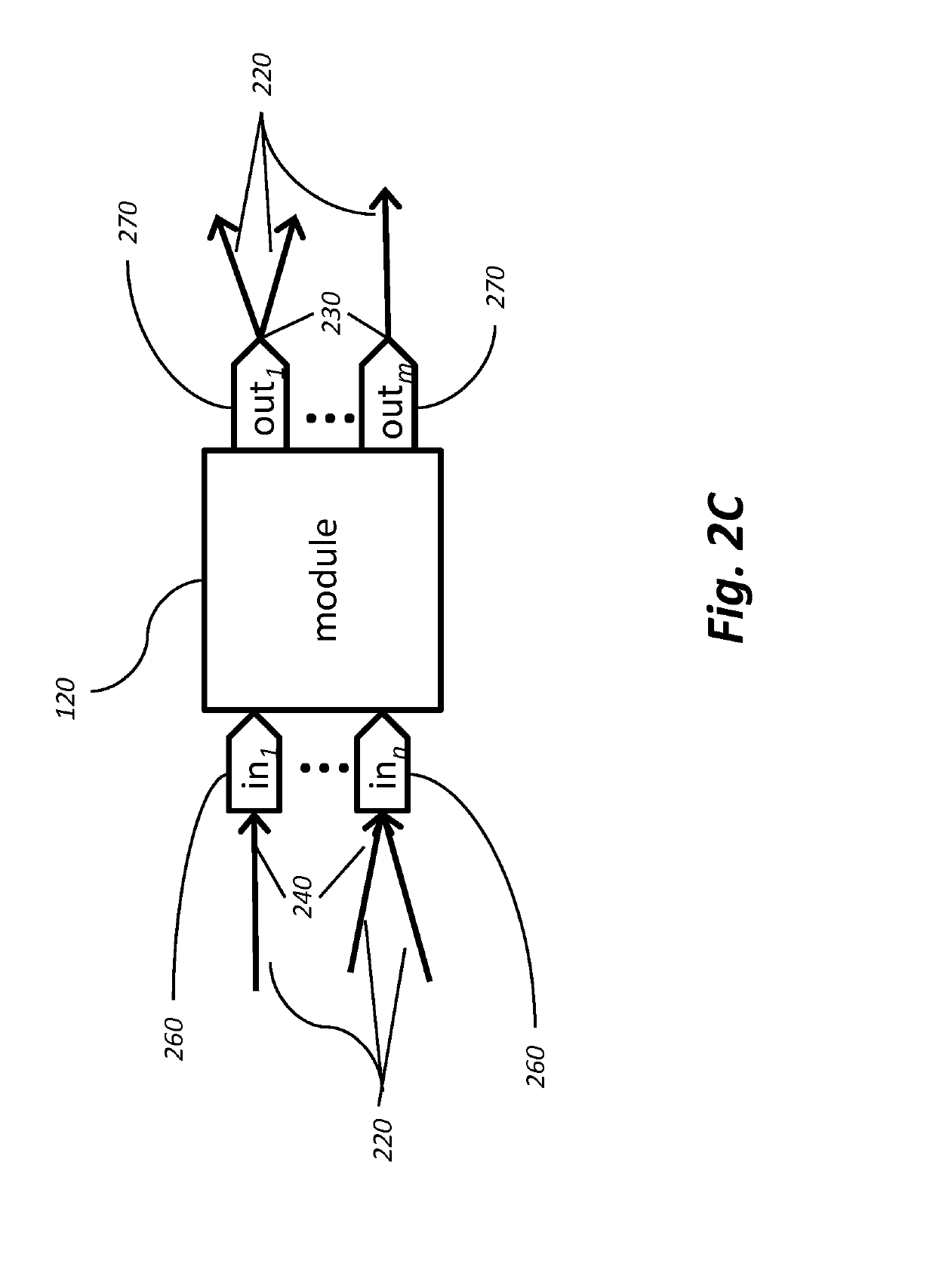

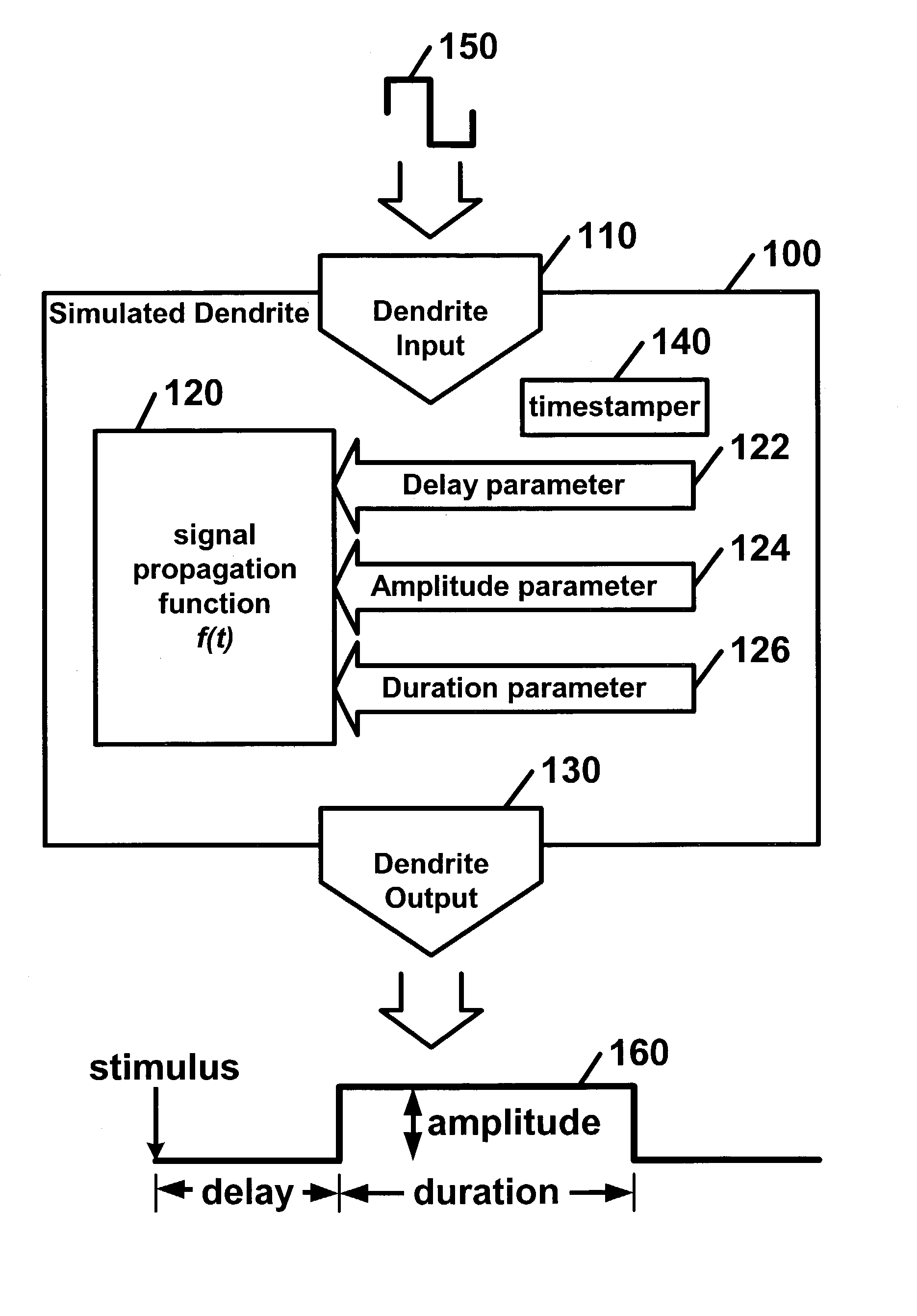

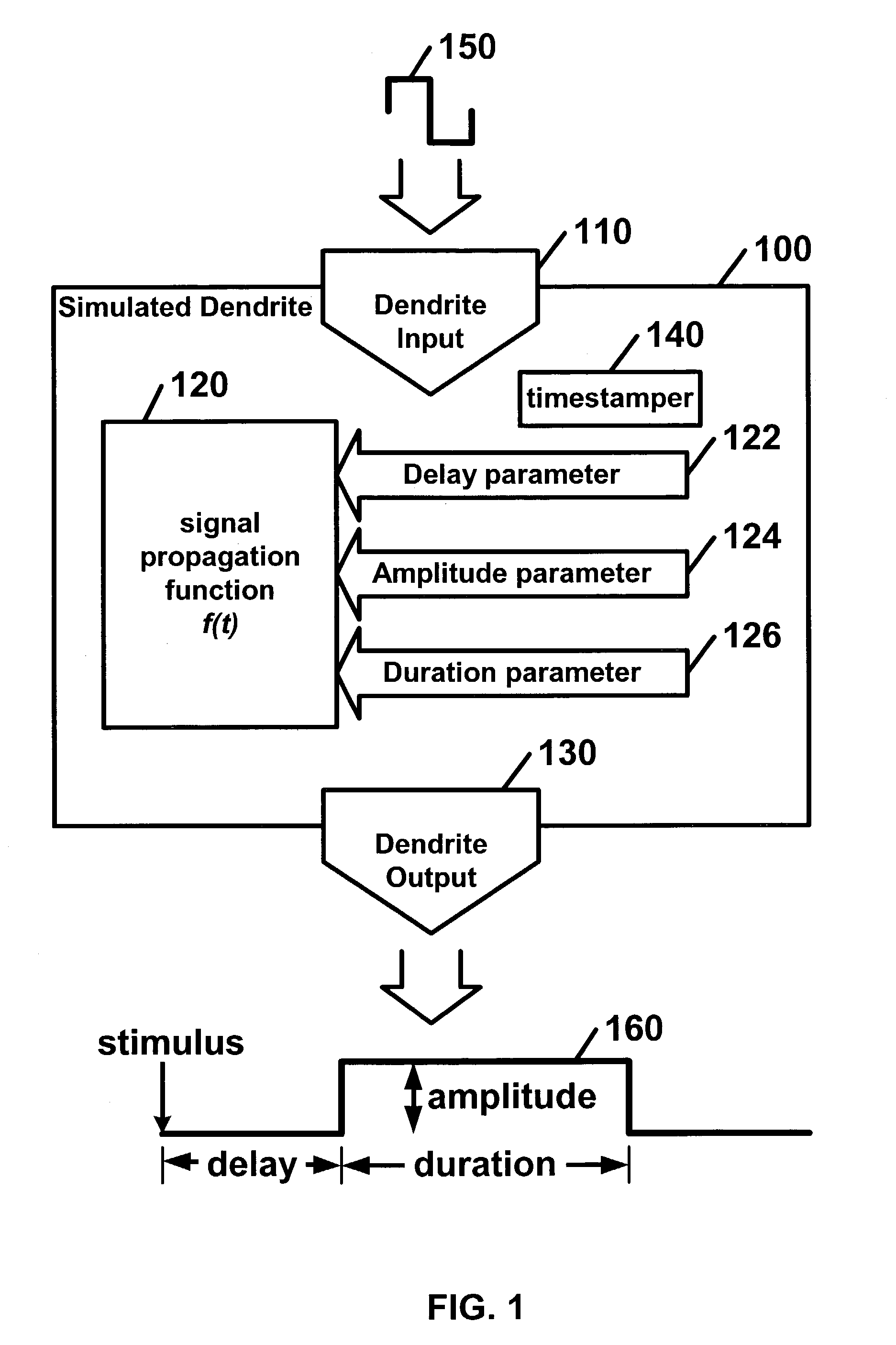

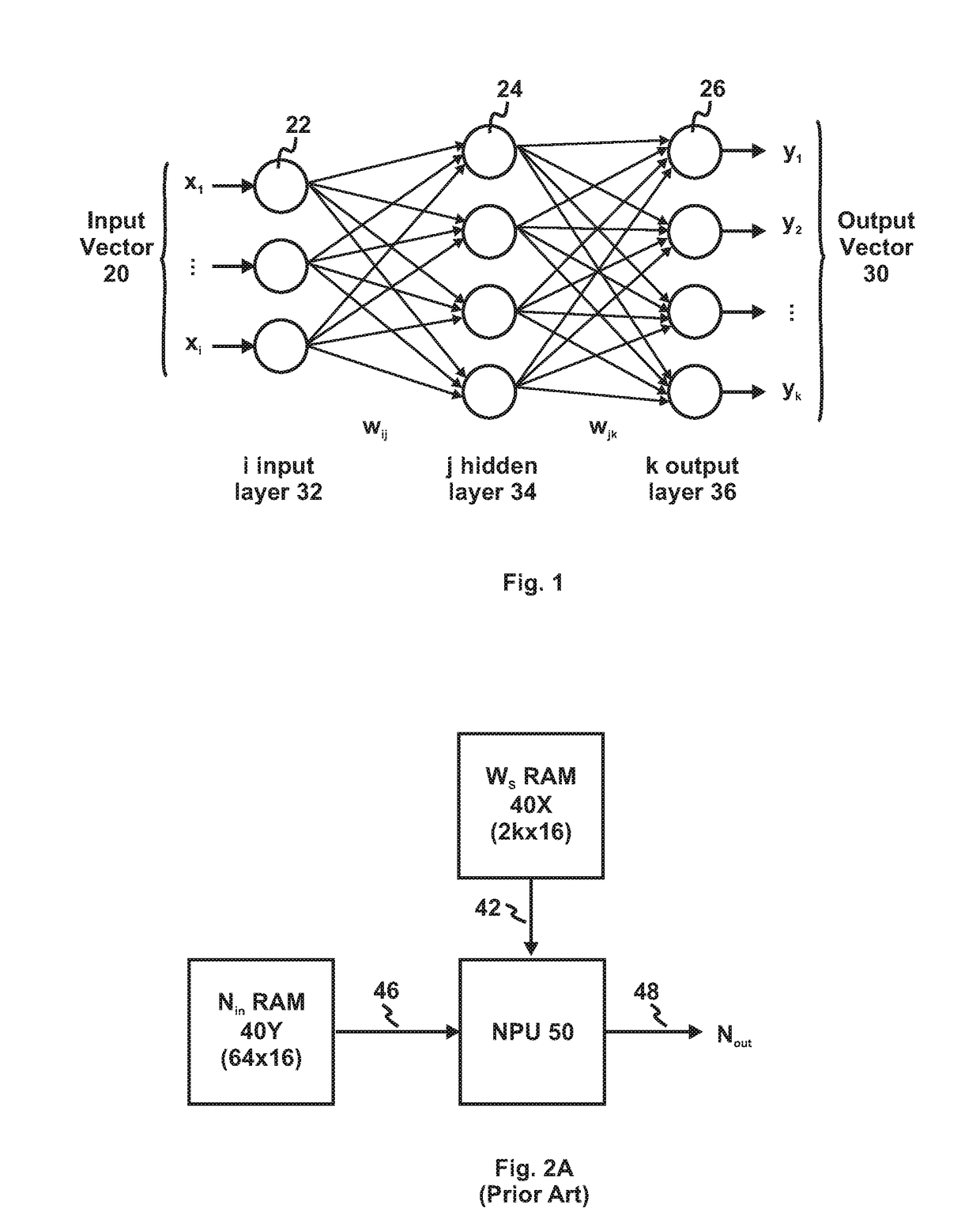

Disclosed is a digital neural processor comprising at least one neural processing element. The neural processing elements including at least one simulated dendrite and a simulated axon. Each of the simulated dendrites may include: a dendrite input capable of receiving at least one dendrite input signal and a dendrite signal propagation function capable of calculating a dendrite output signal in discrete time steps from each dendrite input signal. The signal propagation function may further include a delay parameter; a duration parameter; and an amplitude parameter. The simulated axon includes an axon input capable of receiving dendrite output signals, an axon function, capable of calculating an axon output signal from dendrite output signal(s) and an axon output capable of outputting the axon output signal.

Owner:GEORGE MASON INTPROP INC

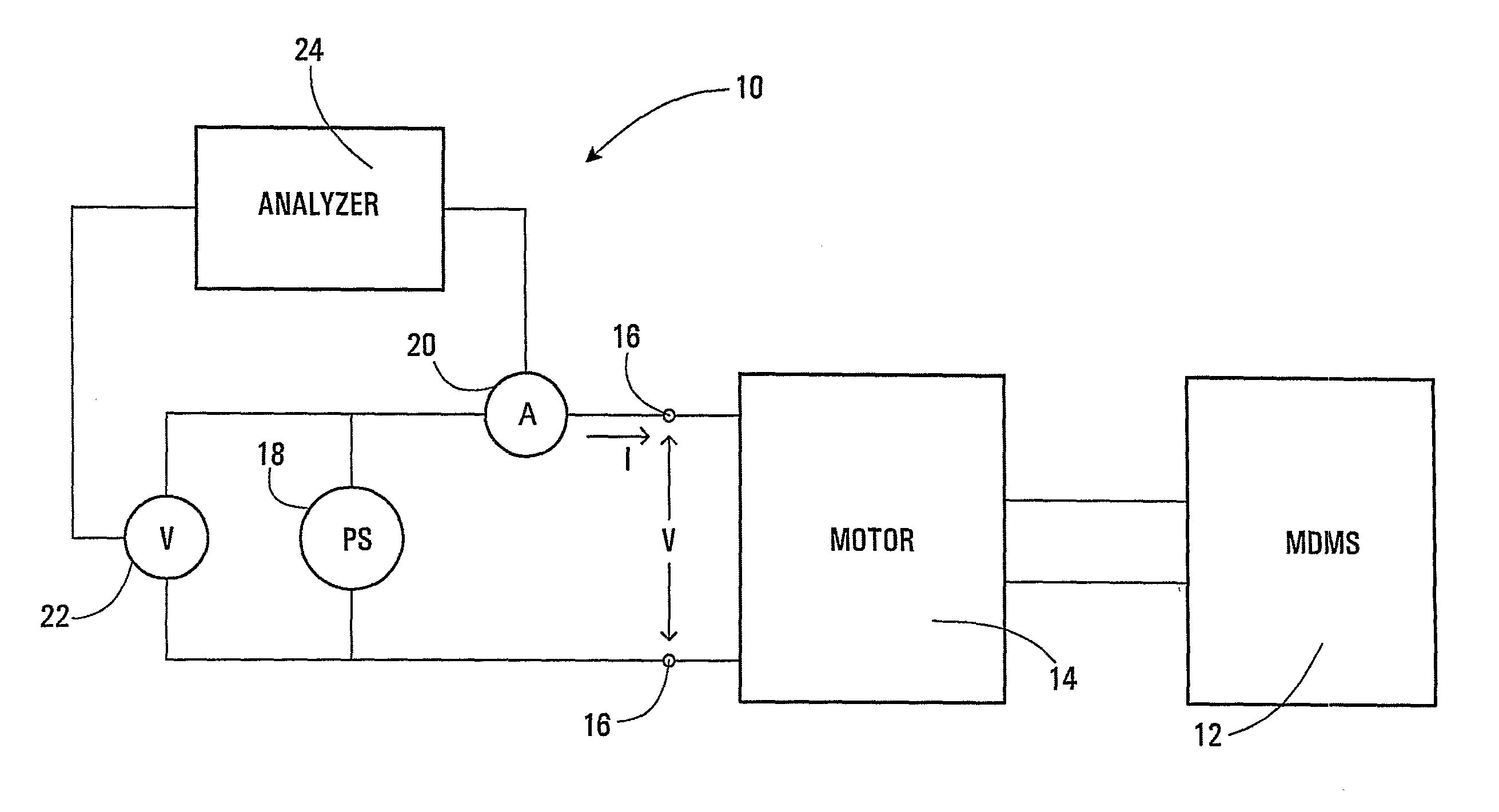

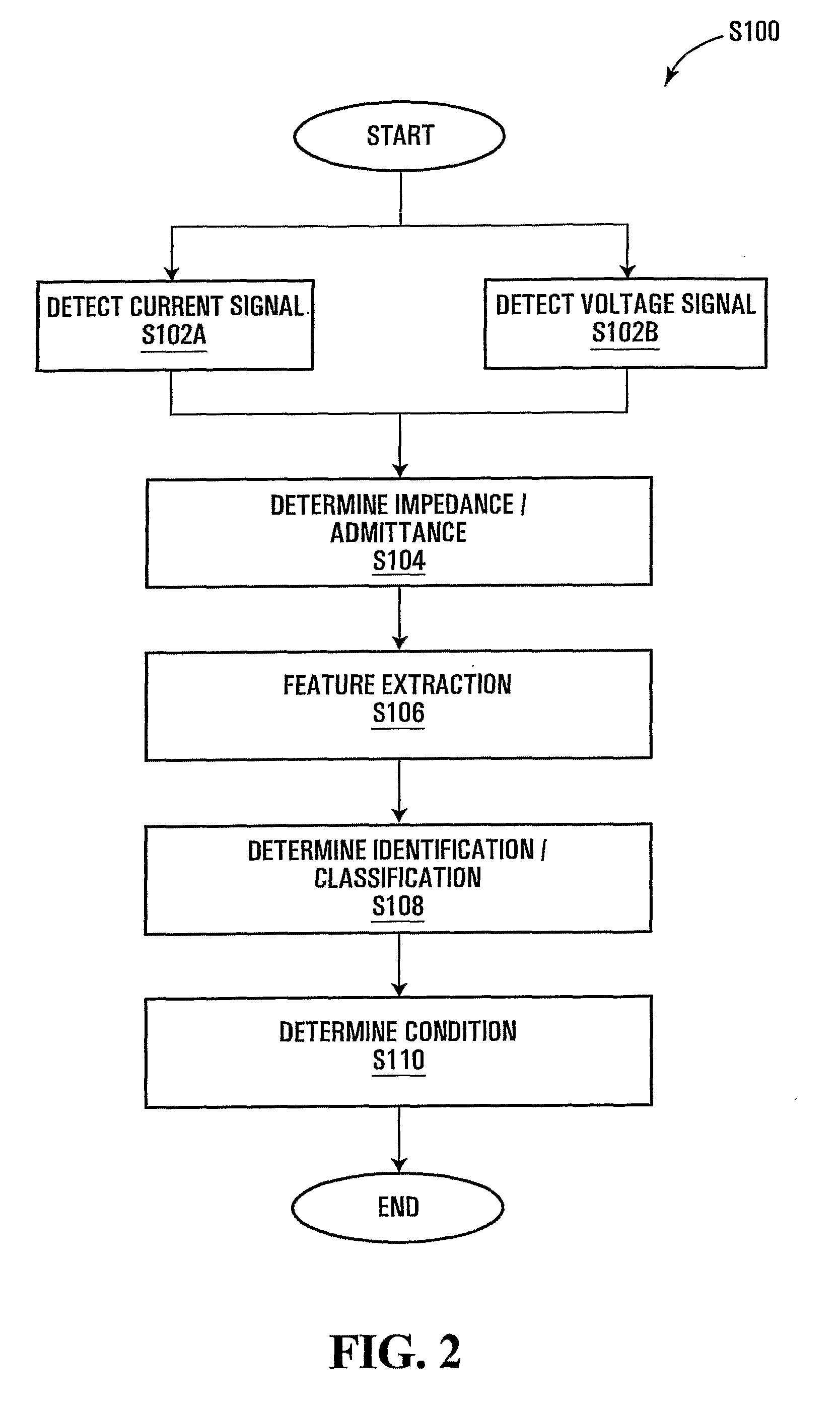

Method and Apparatus for Assessing Condition of Motor-Driven Mechanical System

InactiveUS20070282548A1Reliable indicatorMachine gearing/transmission testingMachine bearings testingMotor driveAdmittance

Conditions of a mechanical system driven (12) by a motor (14) can be assessed by monitoring an admittance or impedance at an input to the motor (14) over a period of time. The admittance or impedance may be determined by measuring the input voltage (22) and current (20). Variations in admittance or impedance are associated with known conditions including faults. An analyser (24) processes the admittance or impedance and provides a warning signal if a known fault condition is determined. The processing may be done using a neural processor.

Owner:NANYANG TECH UNIV

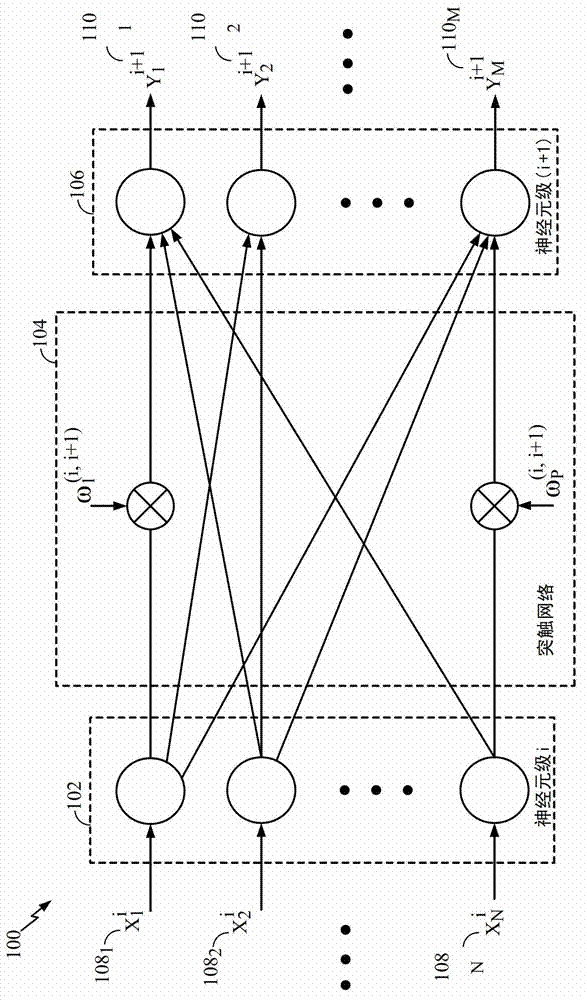

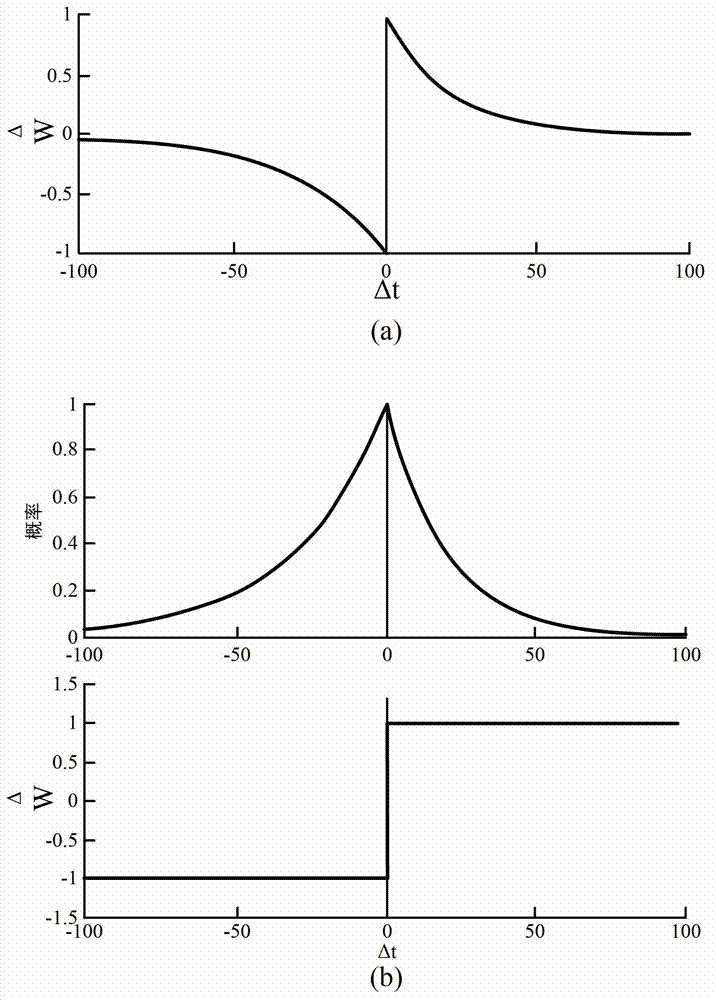

Methods and systems for digital neural processing with discrete-level synapses and probabilistic stdp

Certain embodiments of the present disclosure support implementation of a digital neural processor with discrete-level synapses and probabilistic synapse weight training.

Owner:QUALCOMM INC

Performing multiply and accumulate operations in neural network processor

ActiveUS20190340486A1Computation using non-contact making devicesPhysical realisationVector elementAlgorithm

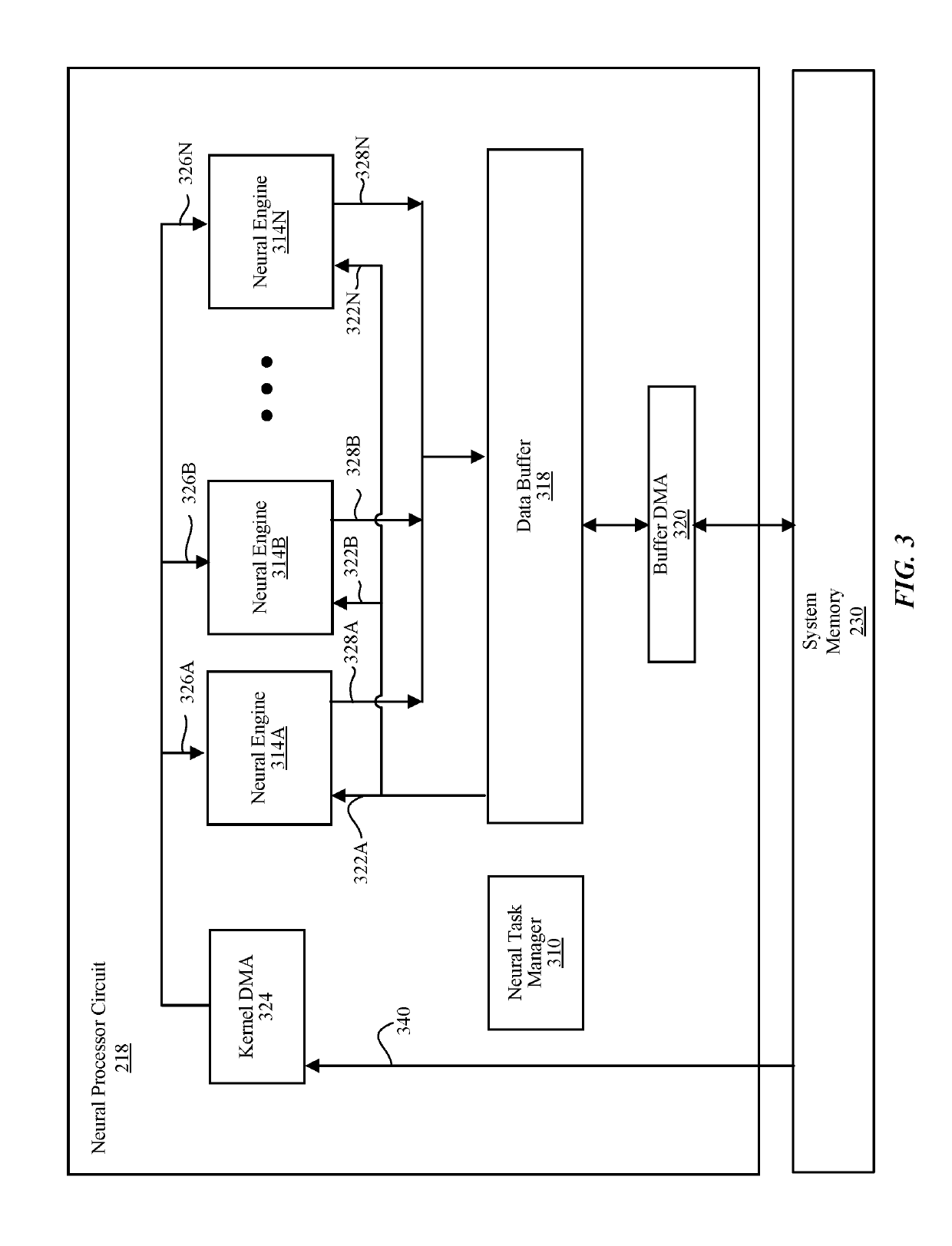

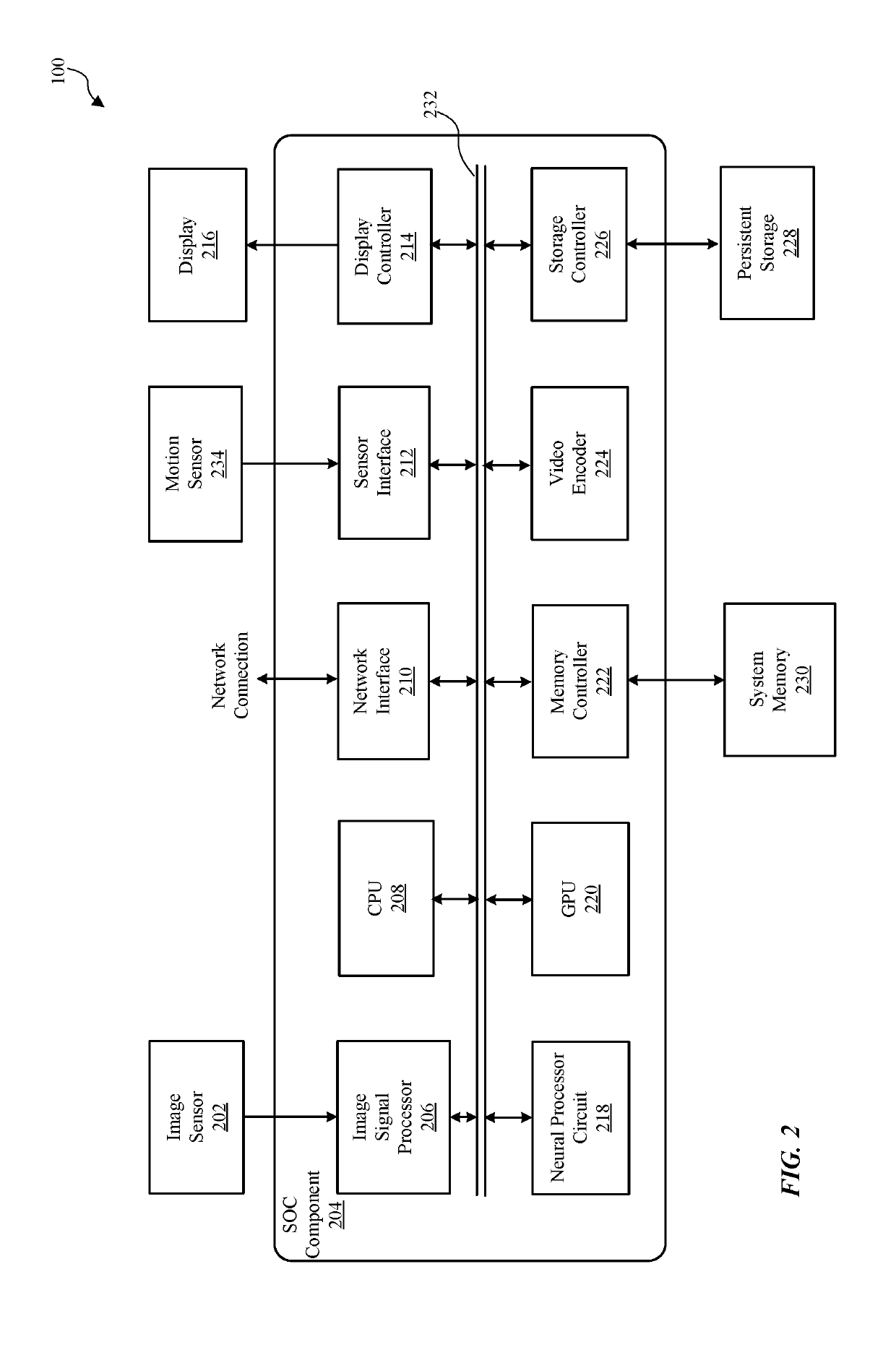

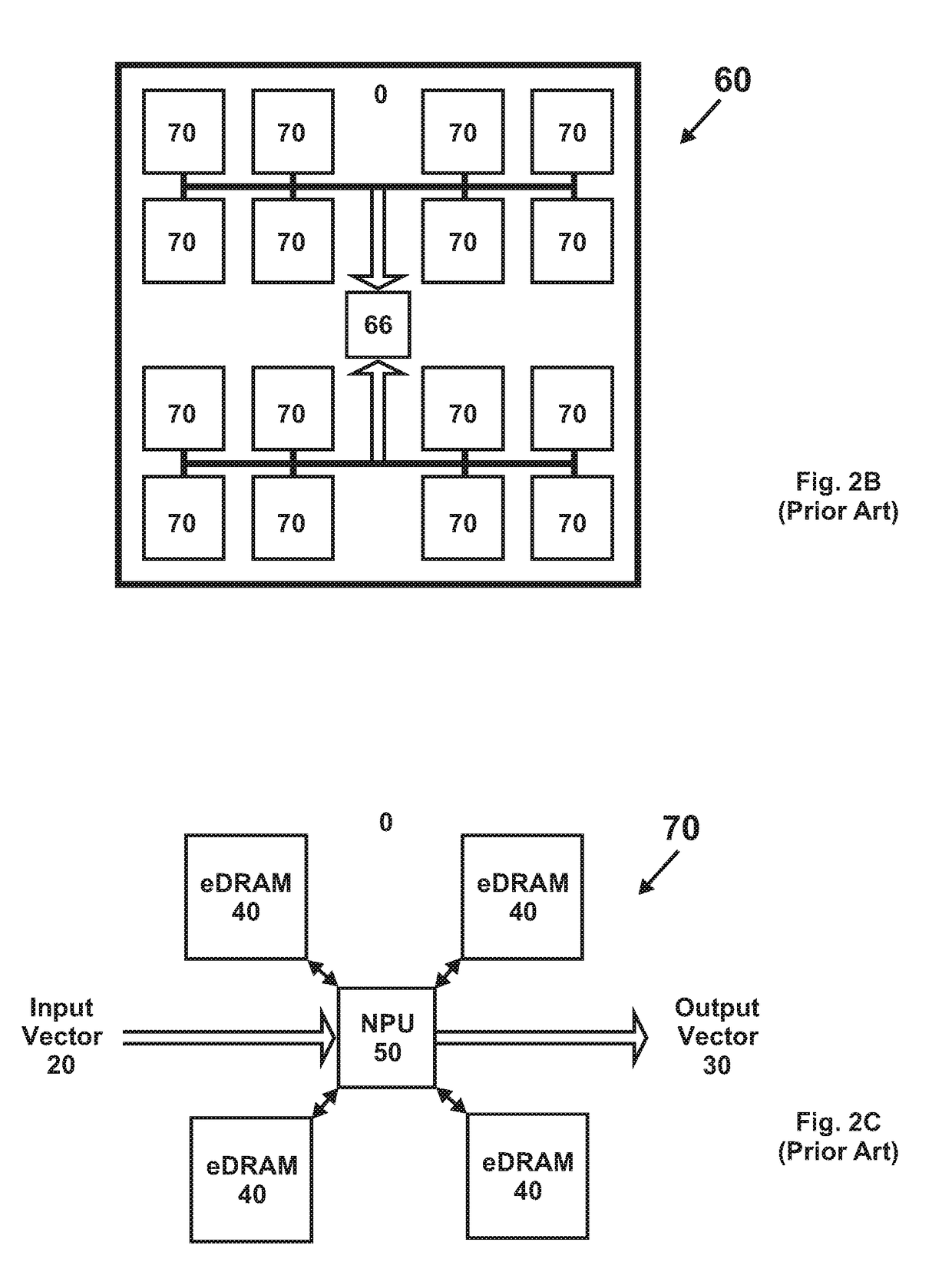

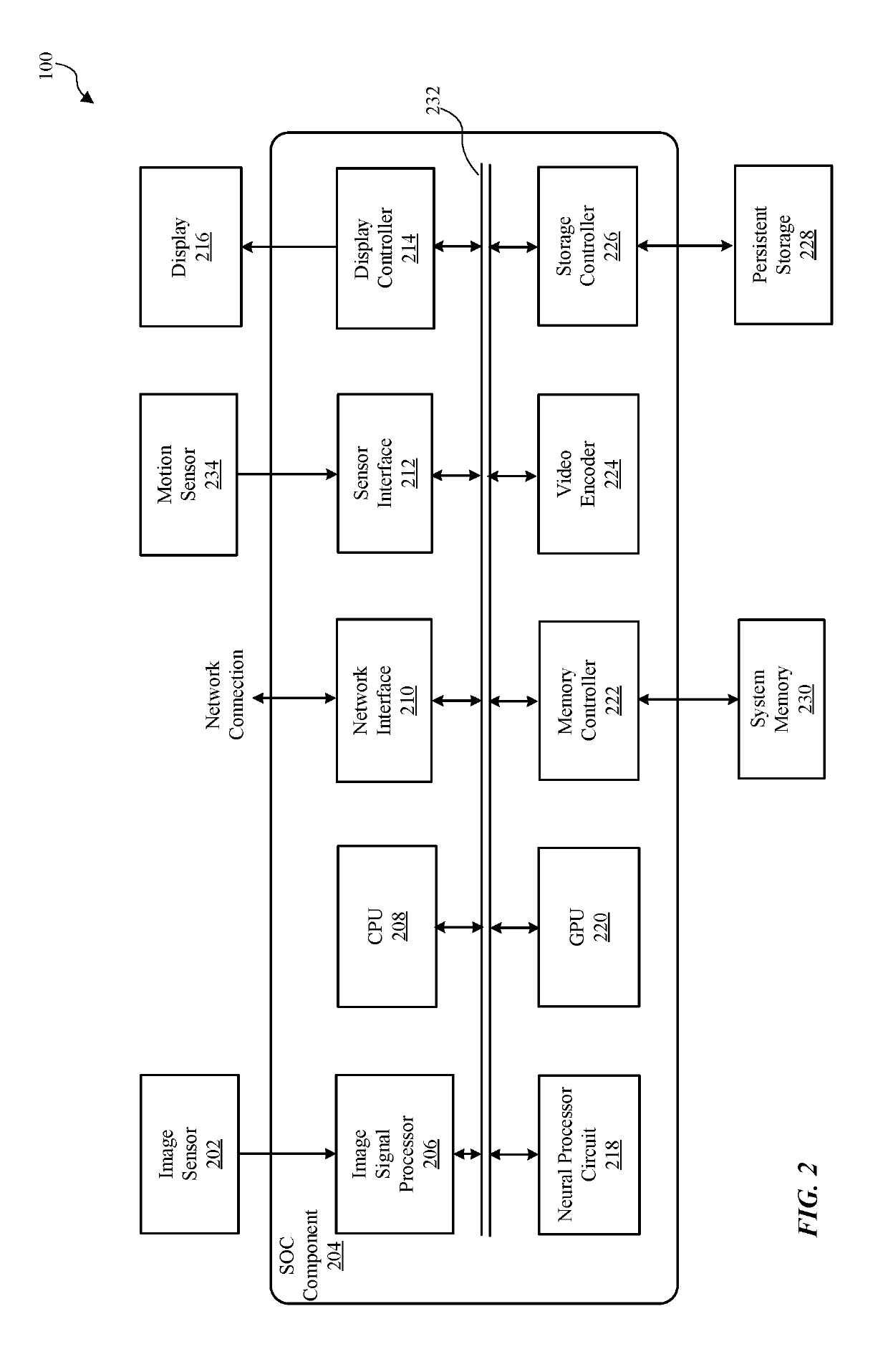

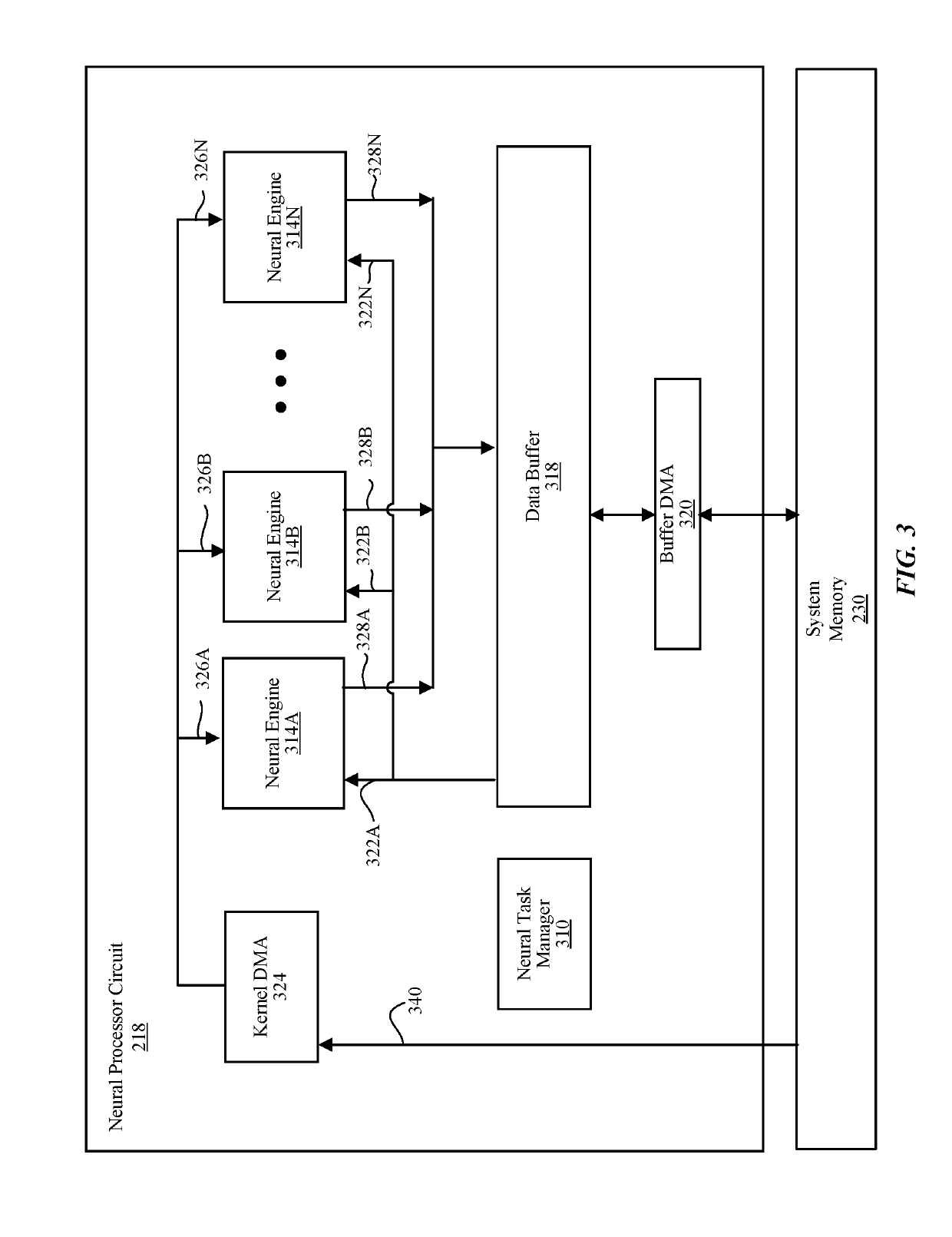

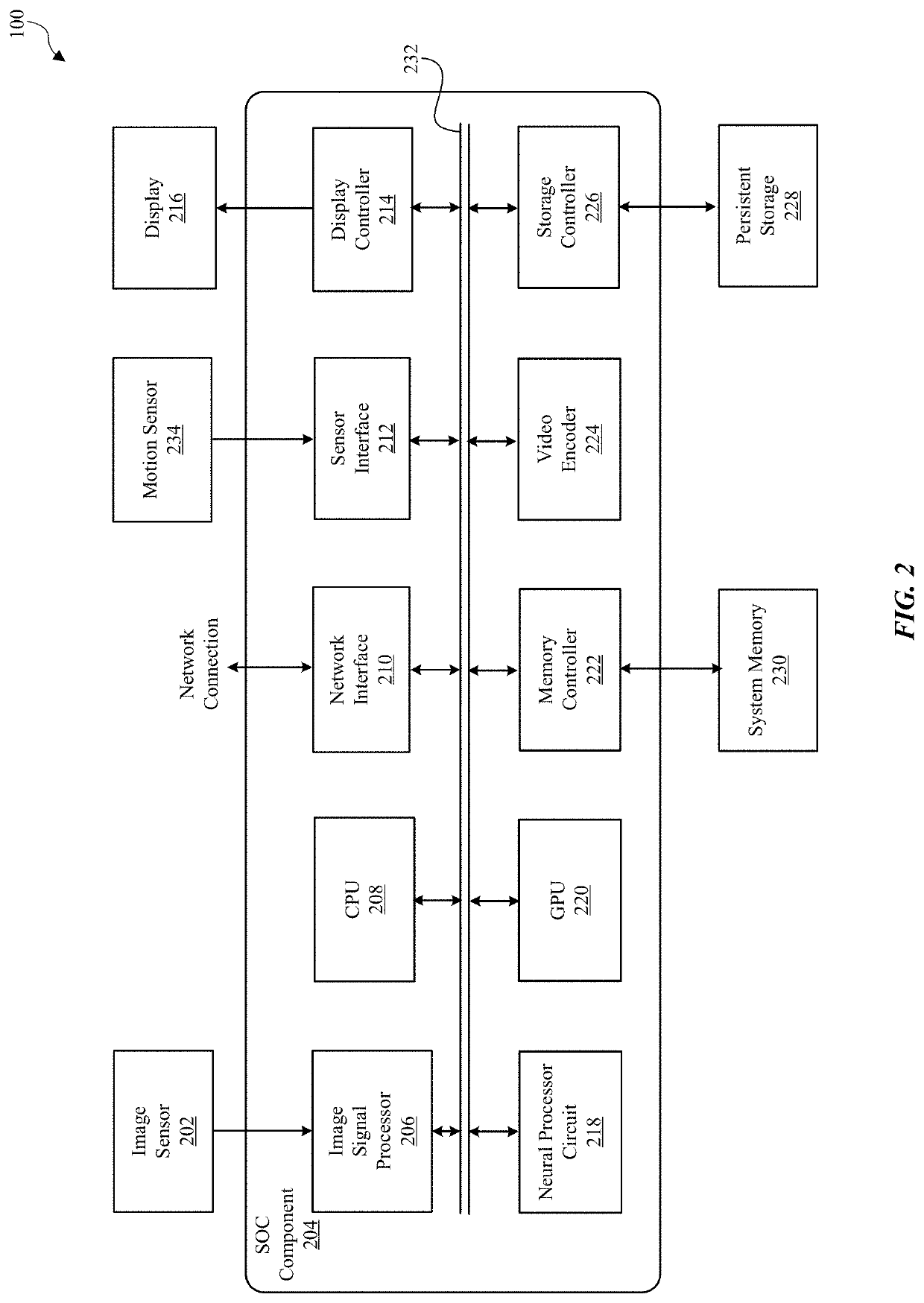

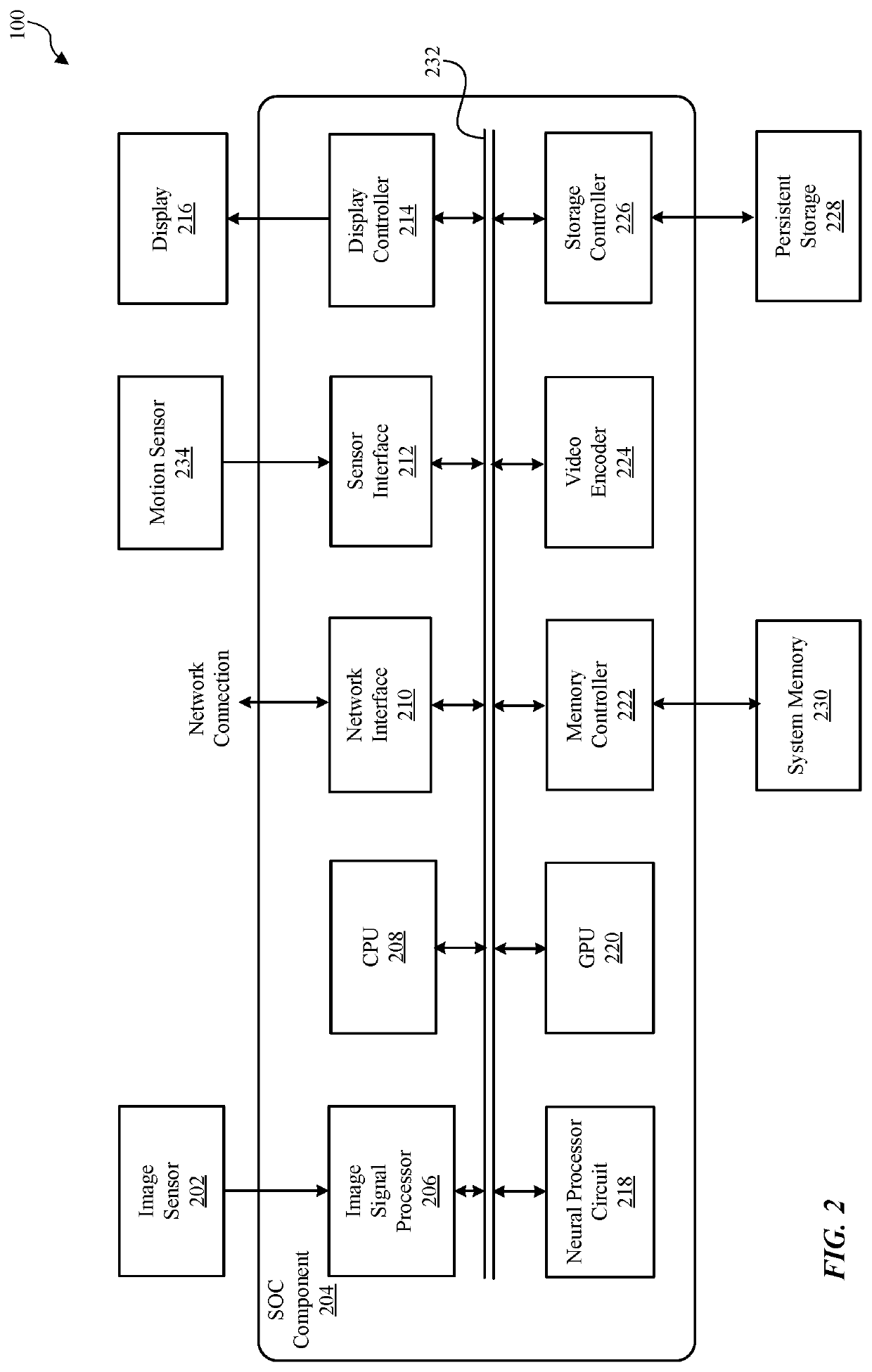

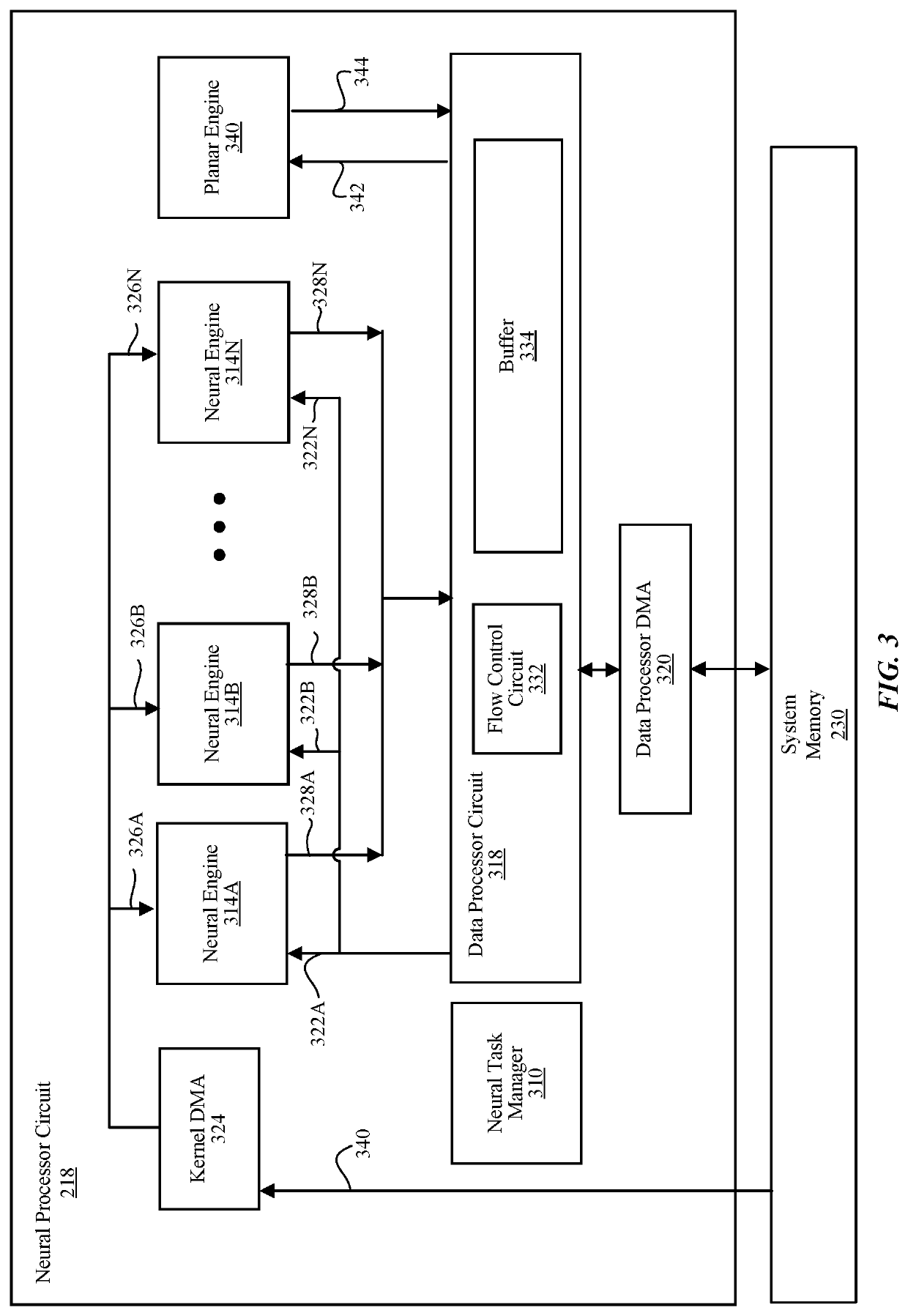

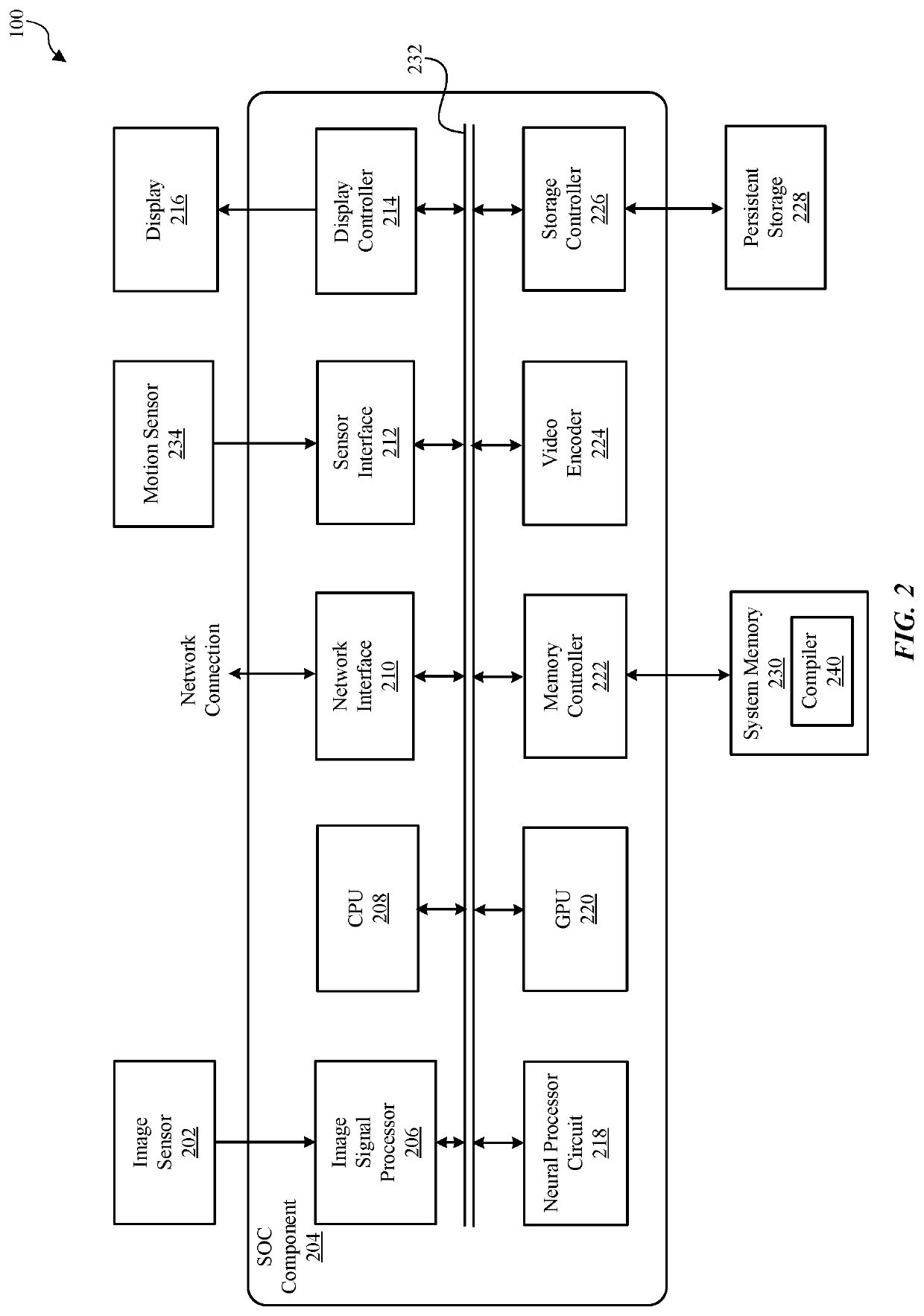

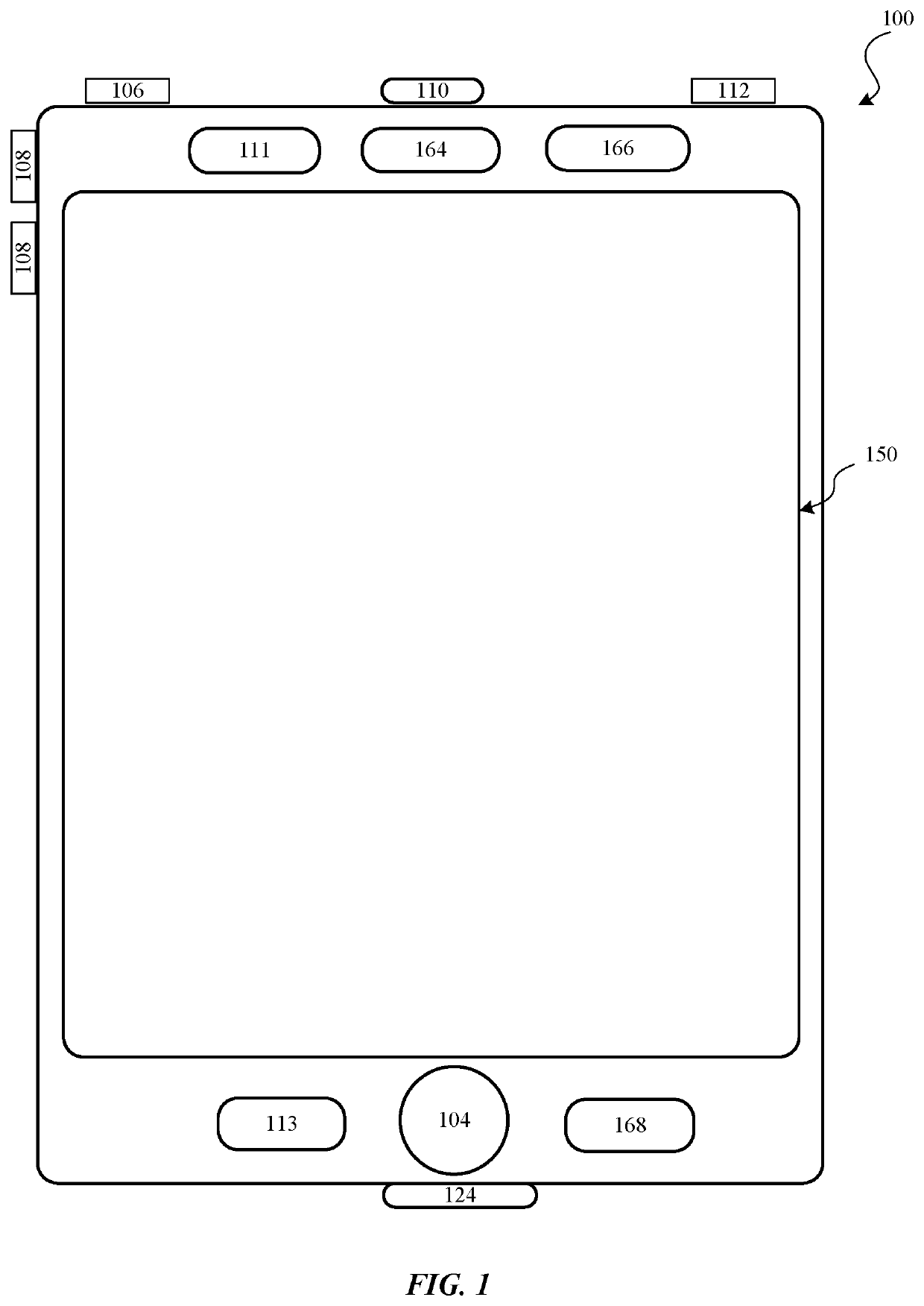

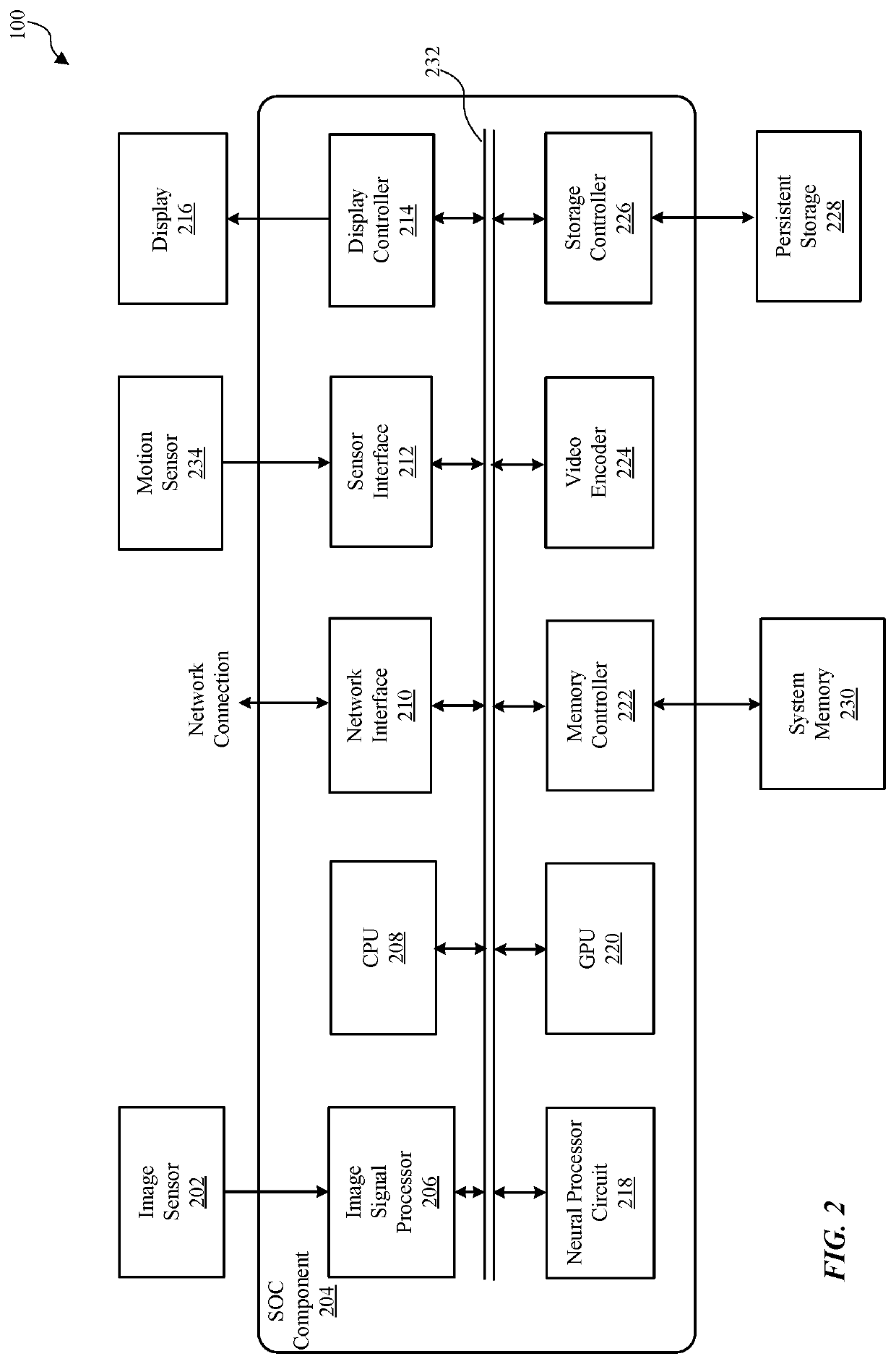

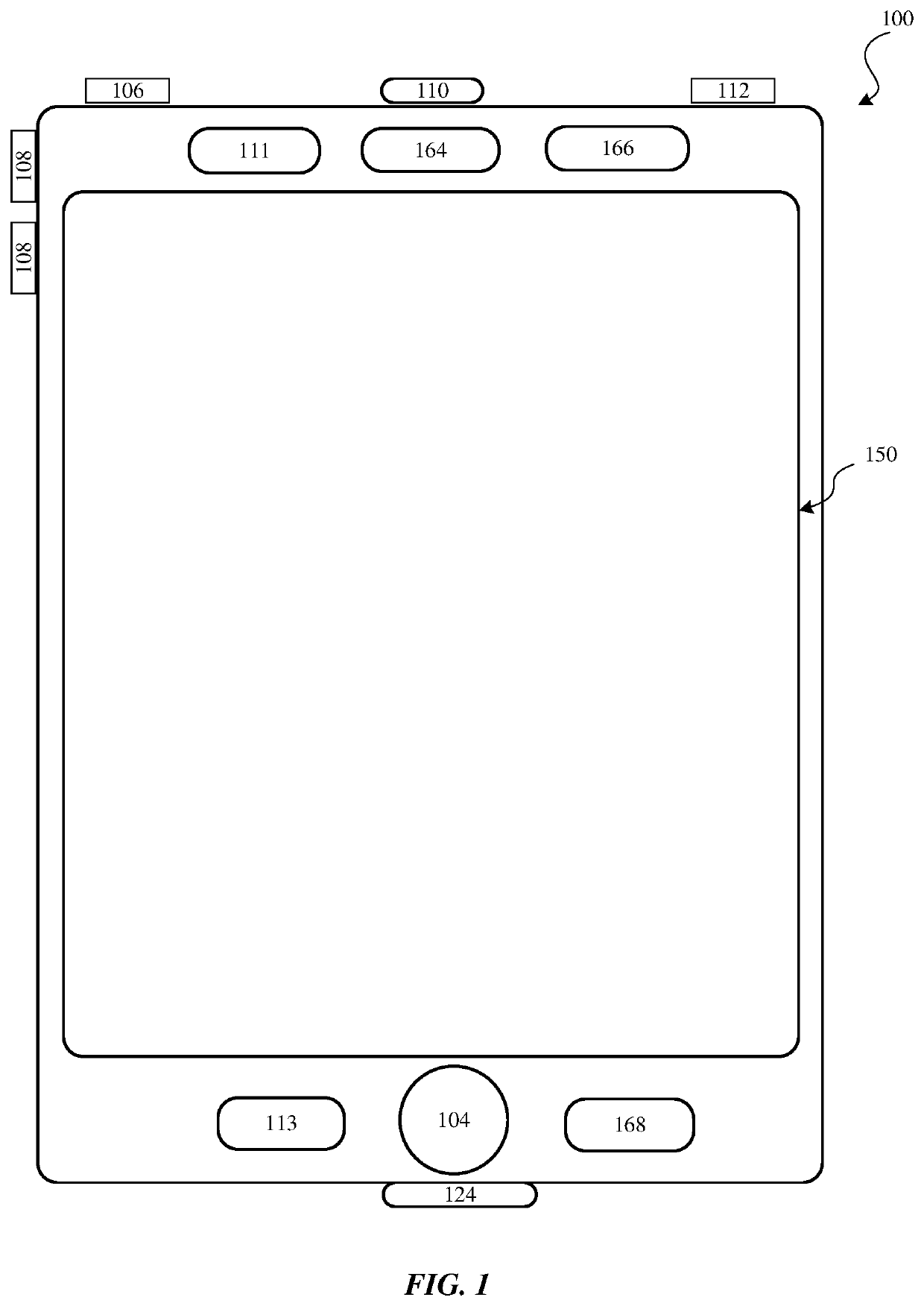

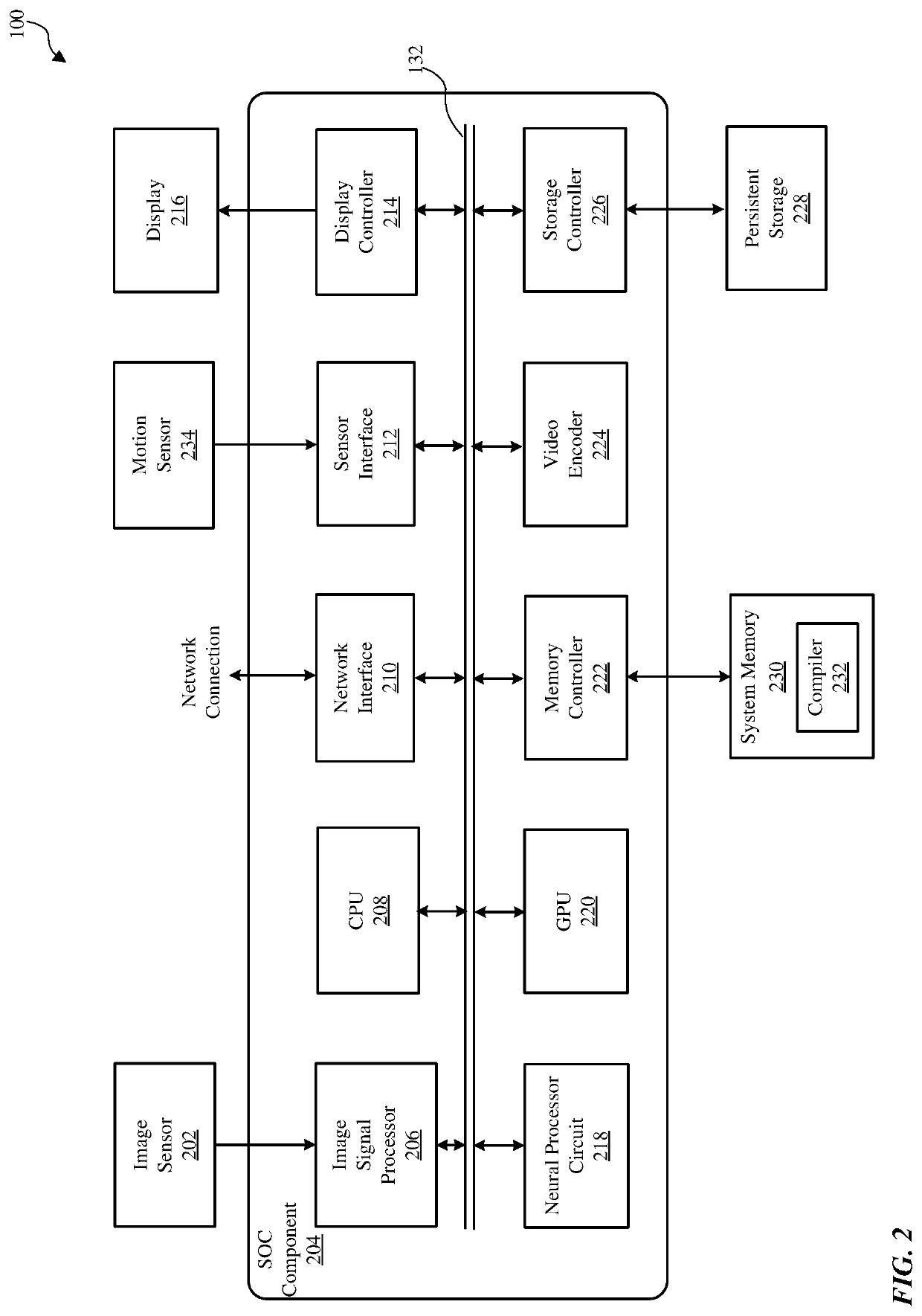

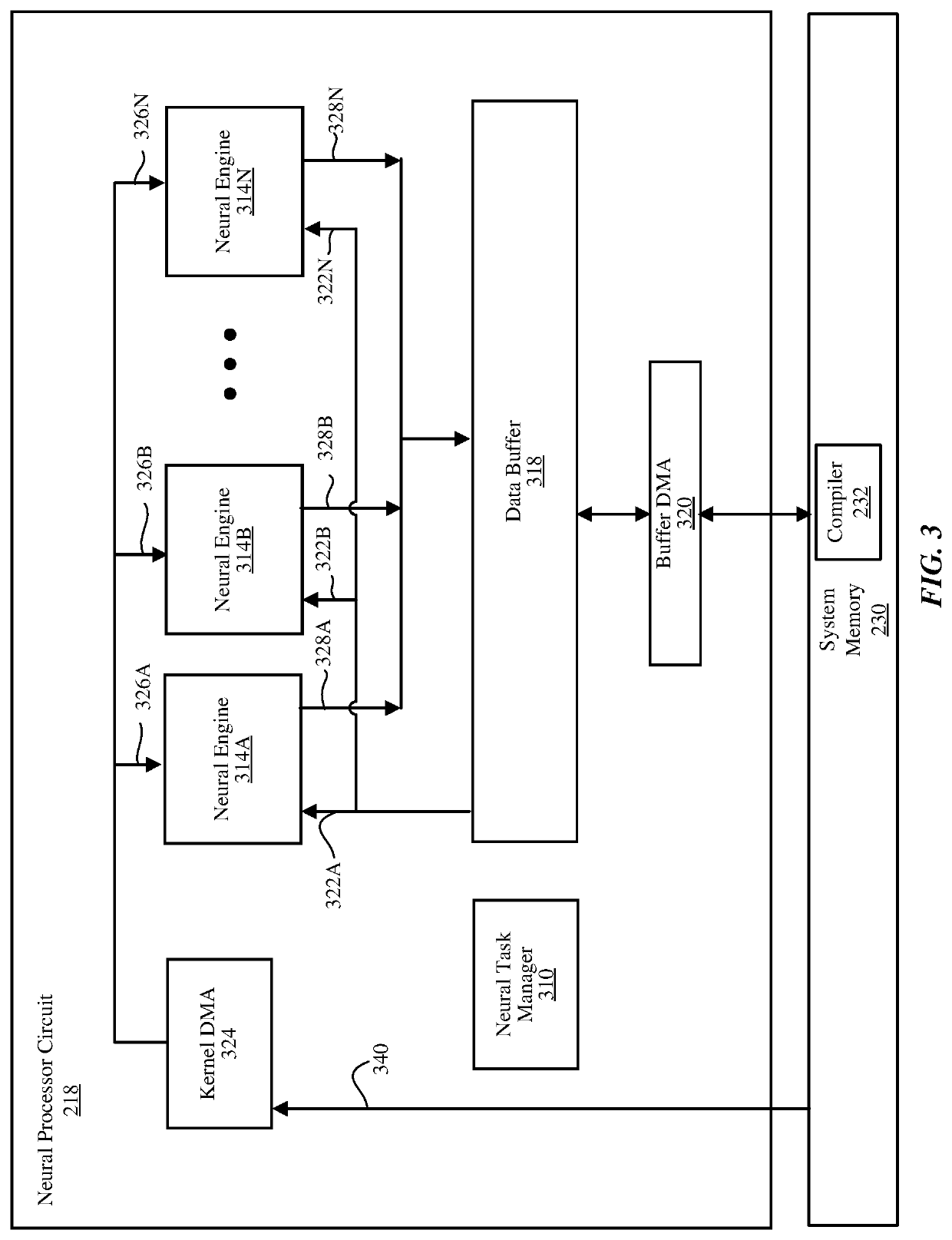

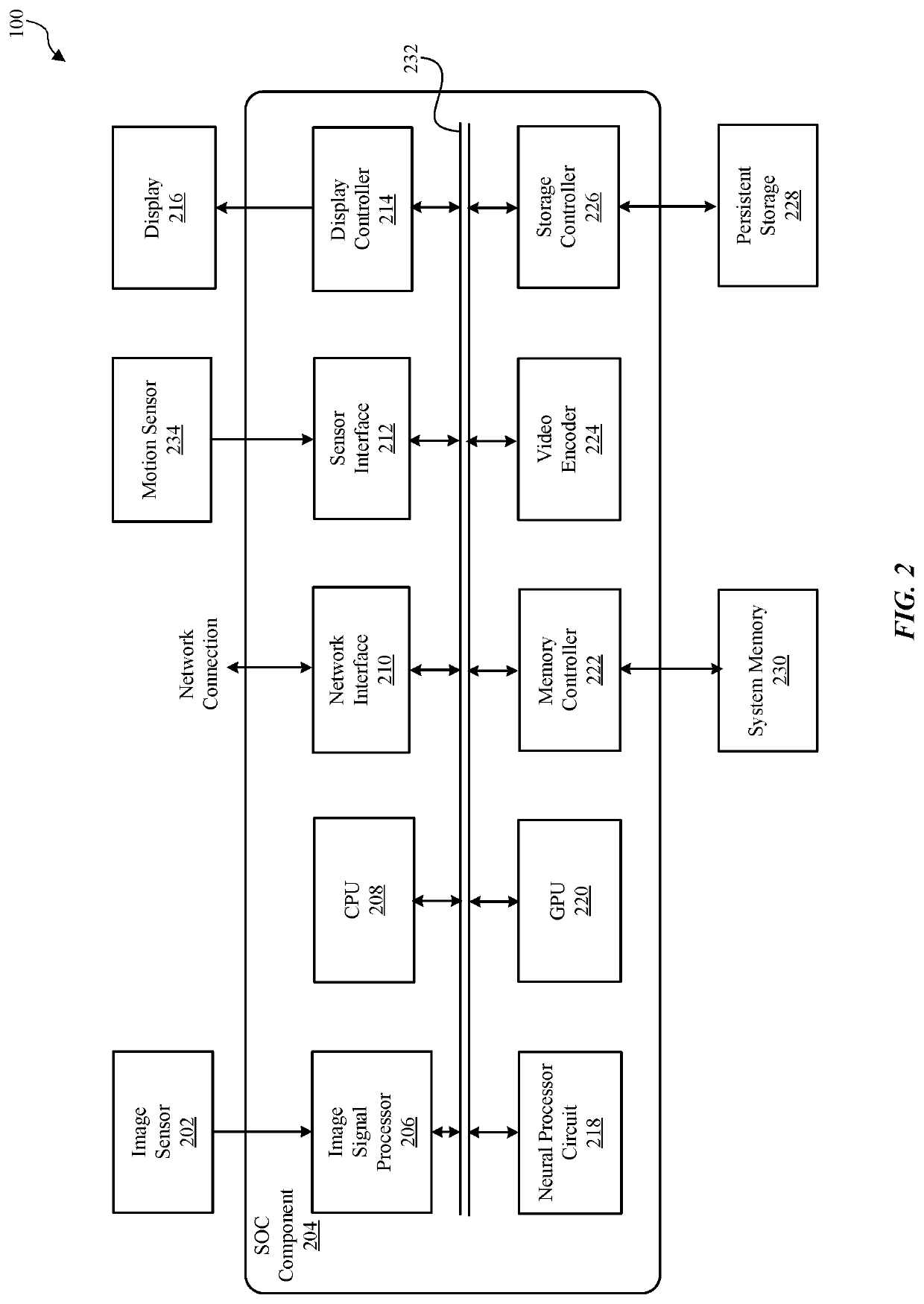

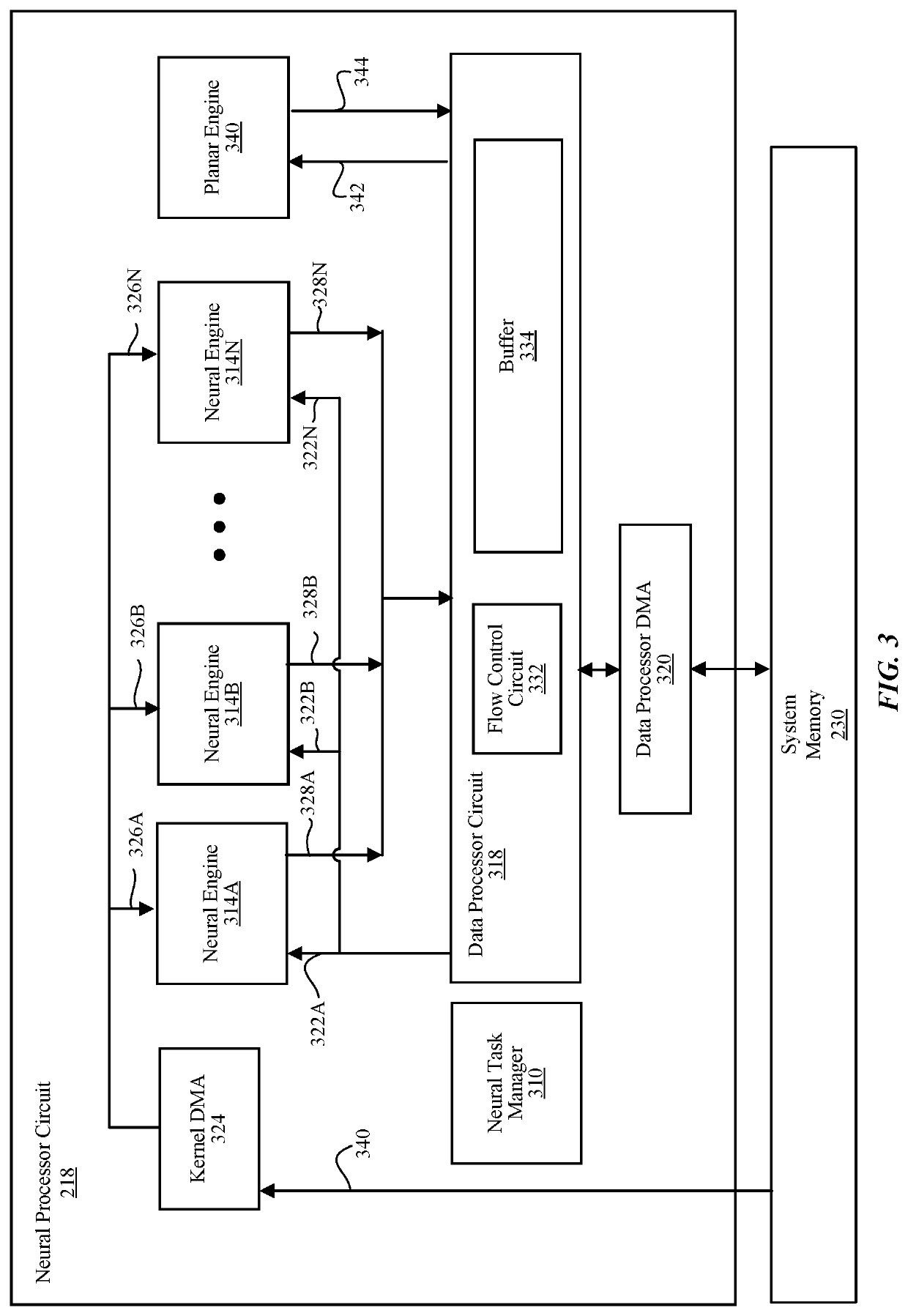

Embodiments relate to a neural processor circuit including a plurality of neural engine circuits, a data buffer, and a kernel fetcher circuit. At least one of the neural engine circuits is configured to receive matrix elements of a matrix as at least the portion of the input data from the data buffer over multiple processing cycles. The at least one neural engine circuit further receives vector elements of a vector from the kernel fetcher circuit, wherein each of the vector elements is extracted as a corresponding kernel to the at least one neural engine circuit in each of the processing cycles. The at least one neural engine circuit performs multiplication between the matrix and the vector as a convolution operation to produce at least one output channel of the output data.

Owner:APPLE INC

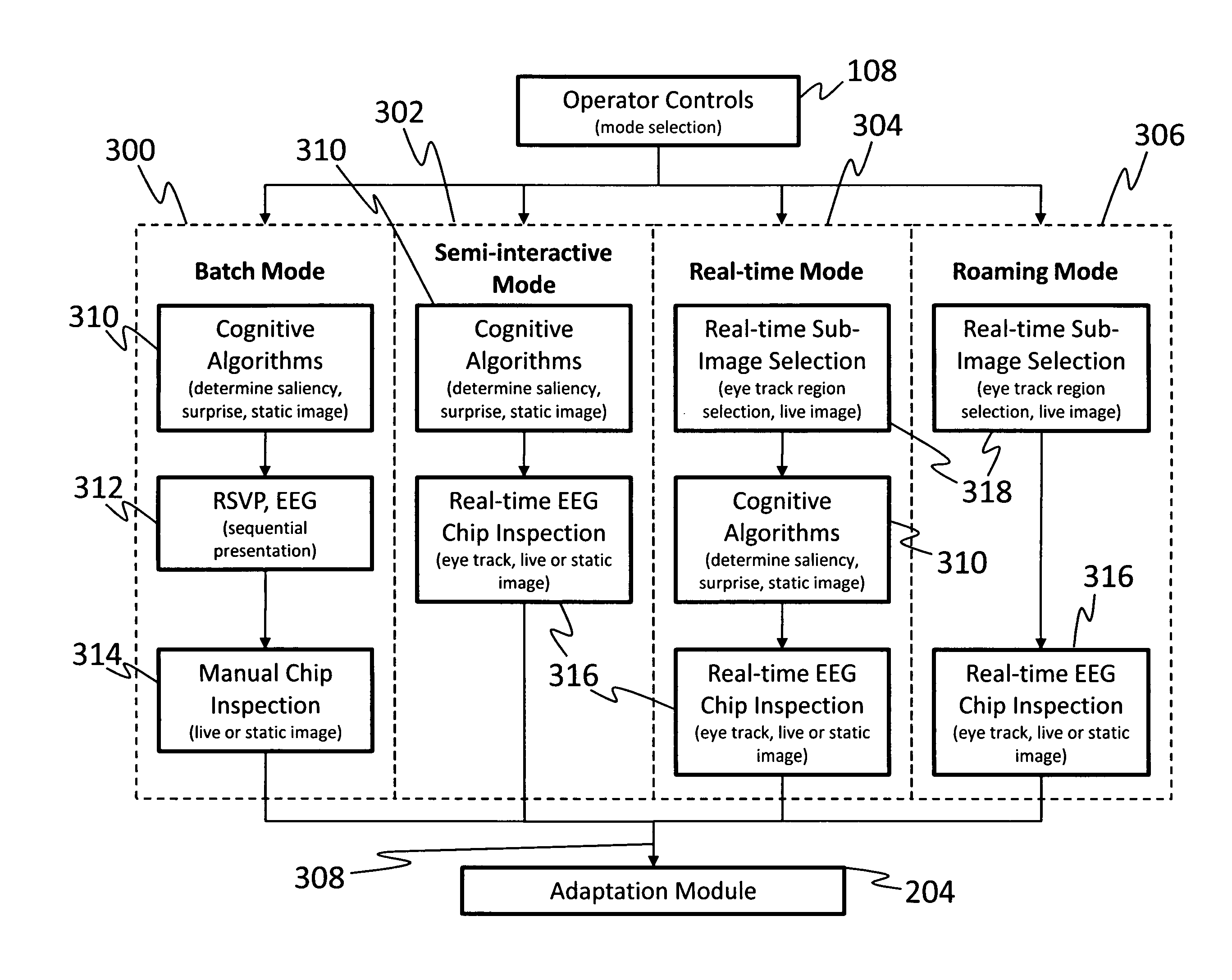

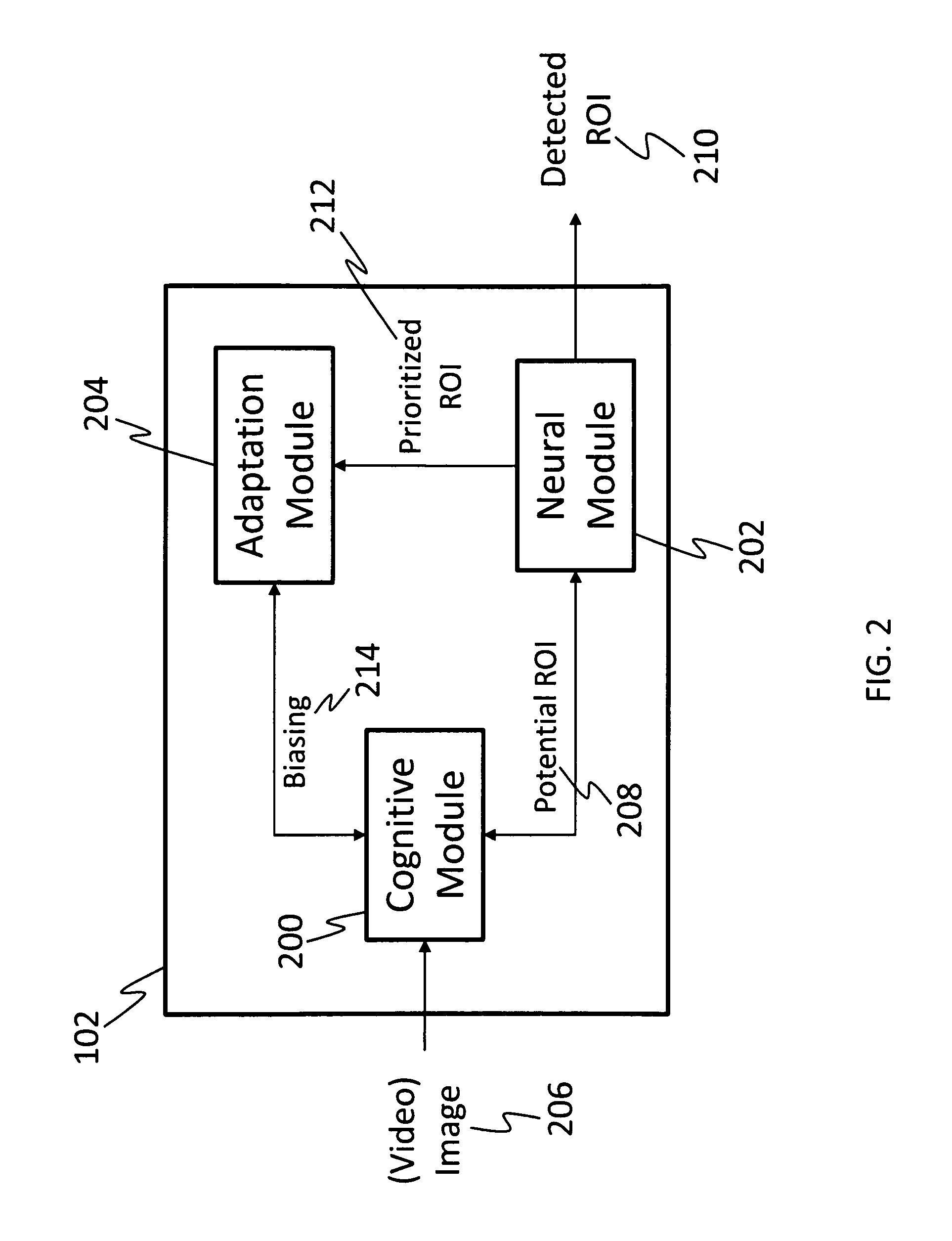

System for intelligent goal-directed search in large volume imagery and video using a cognitive-neural subsystem

ActiveUS8335751B1Improve responseDigital computer detailsCharacter and pattern recognitionSimulationInformation gain

A system for intelligent goal-directed search in large volume visual imagery using a cognitive-neural subsystem is disclosed. The system comprises an imager, a display, a display processor, a cognitive-neural subsystem, a system controller, and operator controls. The cognitive-neural subsystem comprises a cognitive module, a neural module, and an adaptation module. The cognitive module is configured to extract a set of regions of interest from the image using a cognitive algorithm. The neural module is configured to refine the set of regions of interest using a neural processing algorithm. The adaptation module is configured to bias the cognitive algorithm with information gained from the neural module to improve future searches. The system functions in a plurality of operating modes, including: batch mode, semi-interactive mode, real-time mode, and roaming mode.

Owner:HRL LAB

Compression of kernel data for neural network operations

Owner:APPLE INC

Integrated Neuro-Processor Comprising Three-Dimensional Memory Array

ActiveUS20170270403A1Improve artIncreased die areaNeural architecturesPhysical realisationSynaptic weightNeural processing

The present invention discloses an integrated neuro-processor comprising at least a three-dimensional memory (3D-M) array. The 3D-M array stores the synaptic weights, while the neuro-processing circuit performs neural processing. The 3-D integration between the 3D-M array and the neuro-processing circuit not only improves the computational power per die area, but also greatly increases the storage capacity per die area.

Owner:HANGZHOU HAICUN INFORMATION TECH +1

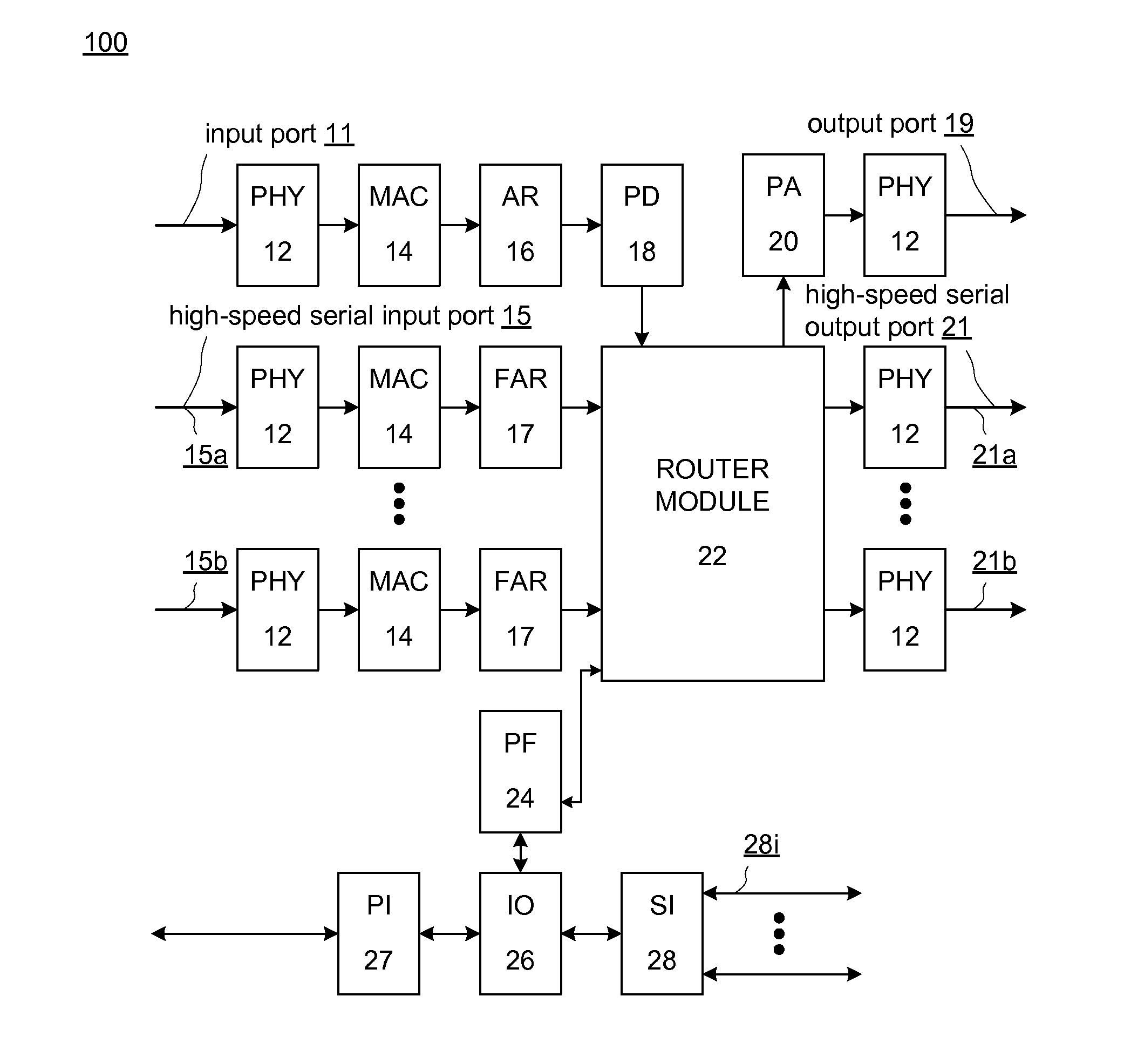

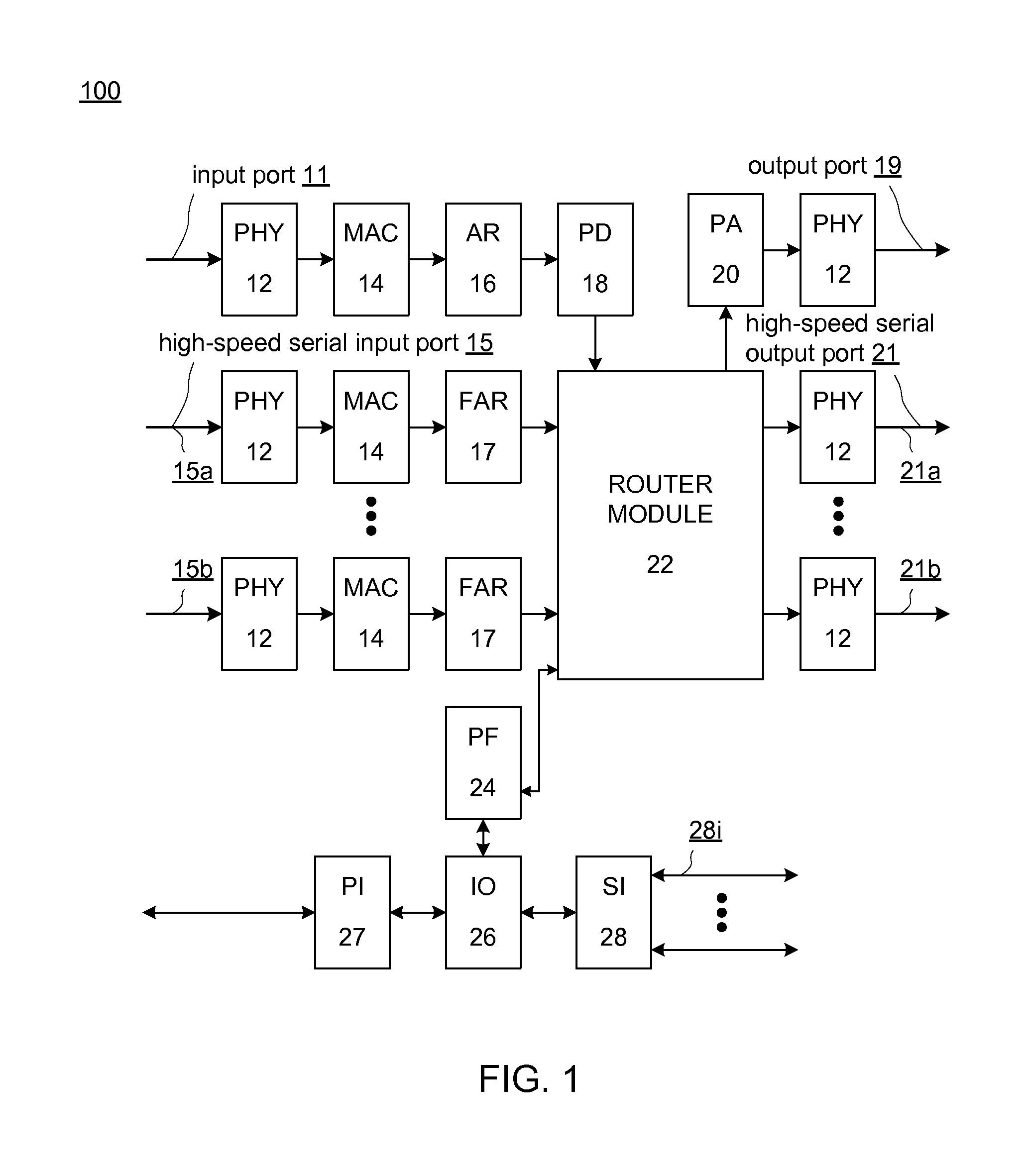

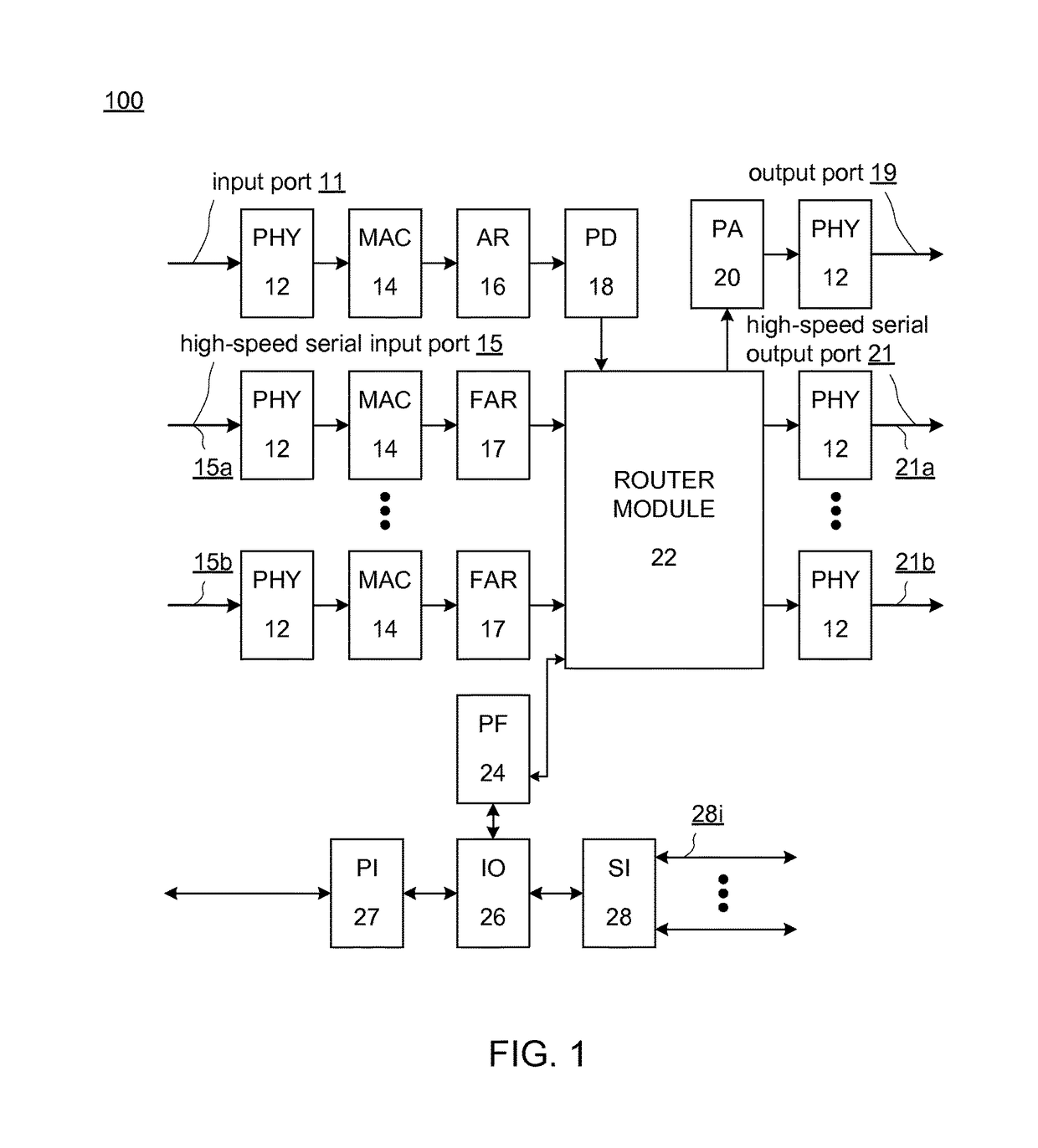

I/O data interface for packet processors

InactiveUS8848726B1Efficient and simple and flexible and scalableTime-division multiplexData switching by path configurationInformation processingProtocol for Carrying Authentication for Network Access

Systems and methods to process packets of information use an on-chip information processing system configured to receive, resolve, convert, and / or transmit packets of different packet-types in accordance with different protocols. A first packet-type may use a protocol for wired local-area-networking (LAN) technologies, such as Ethernet. A second packet-type may use a proprietary protocol. The proprietary protocol may be used to exchange information with one or more packet processing engines, such as neural processing engines.

Owner:FRIDAY HARBOR LLC

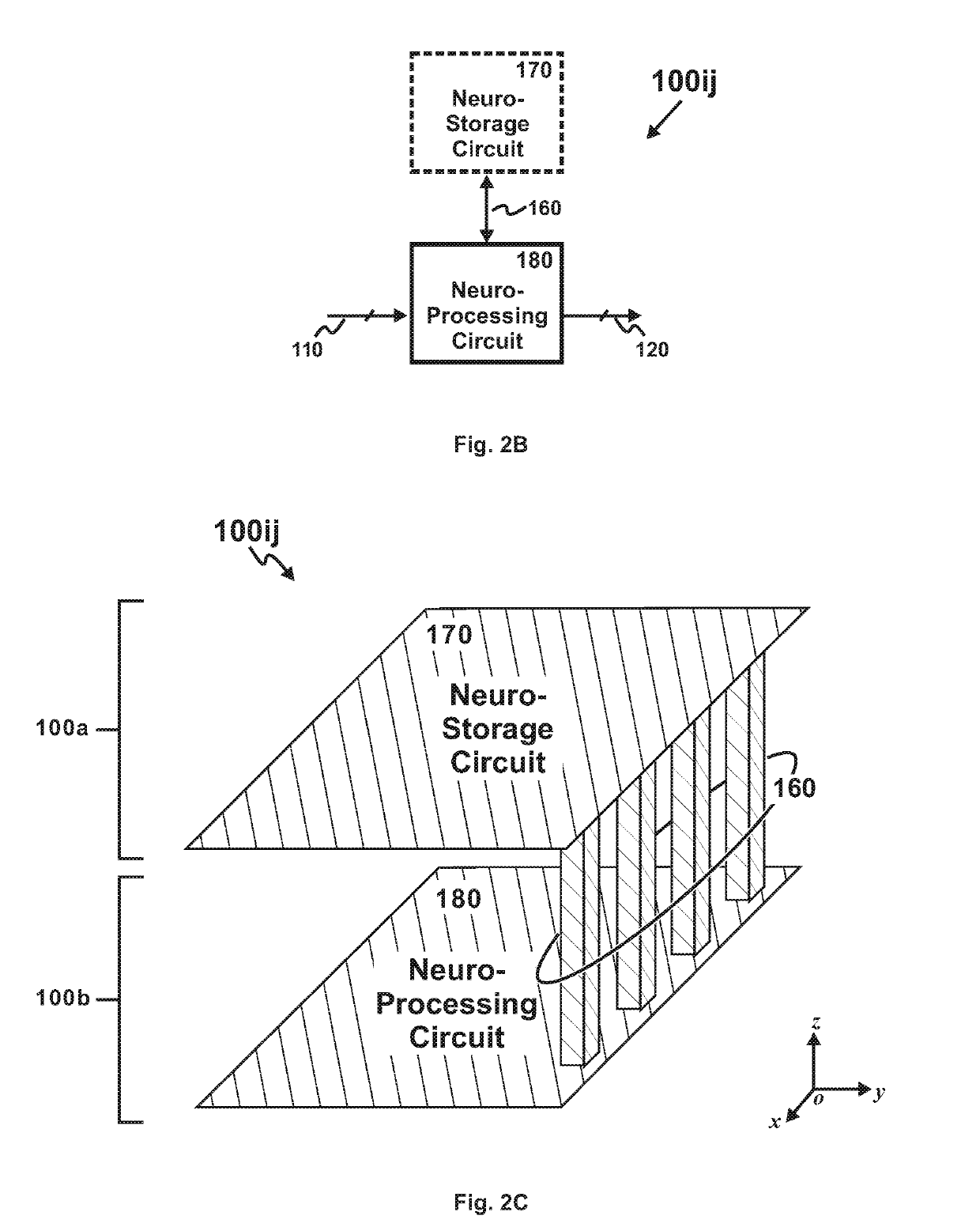

Vertically Integrated Neuro-Processor

ActiveUS20190164038A1Improve artIncrease speedSolid-state devicesDigital storageSynaptic weightProcessing element

A vertically integrated neuro-processor comprises a plurality of neural storage-processing units (NSPU's). Each NSPU comprises at least a neuro-storage circuit and a neuro-processing circuit. The neuro-storage circuit comprises a memory array for storing at least a synaptic weight, while the neuro-processing circuit performs neural processing with the synaptic weight. The memory array and the neuro-processing circuit are vertically stacked and communicatively coupled by a plurality of inter-level connections.

Owner:HANGZHOU HAICUN INFORMATION TECH +1

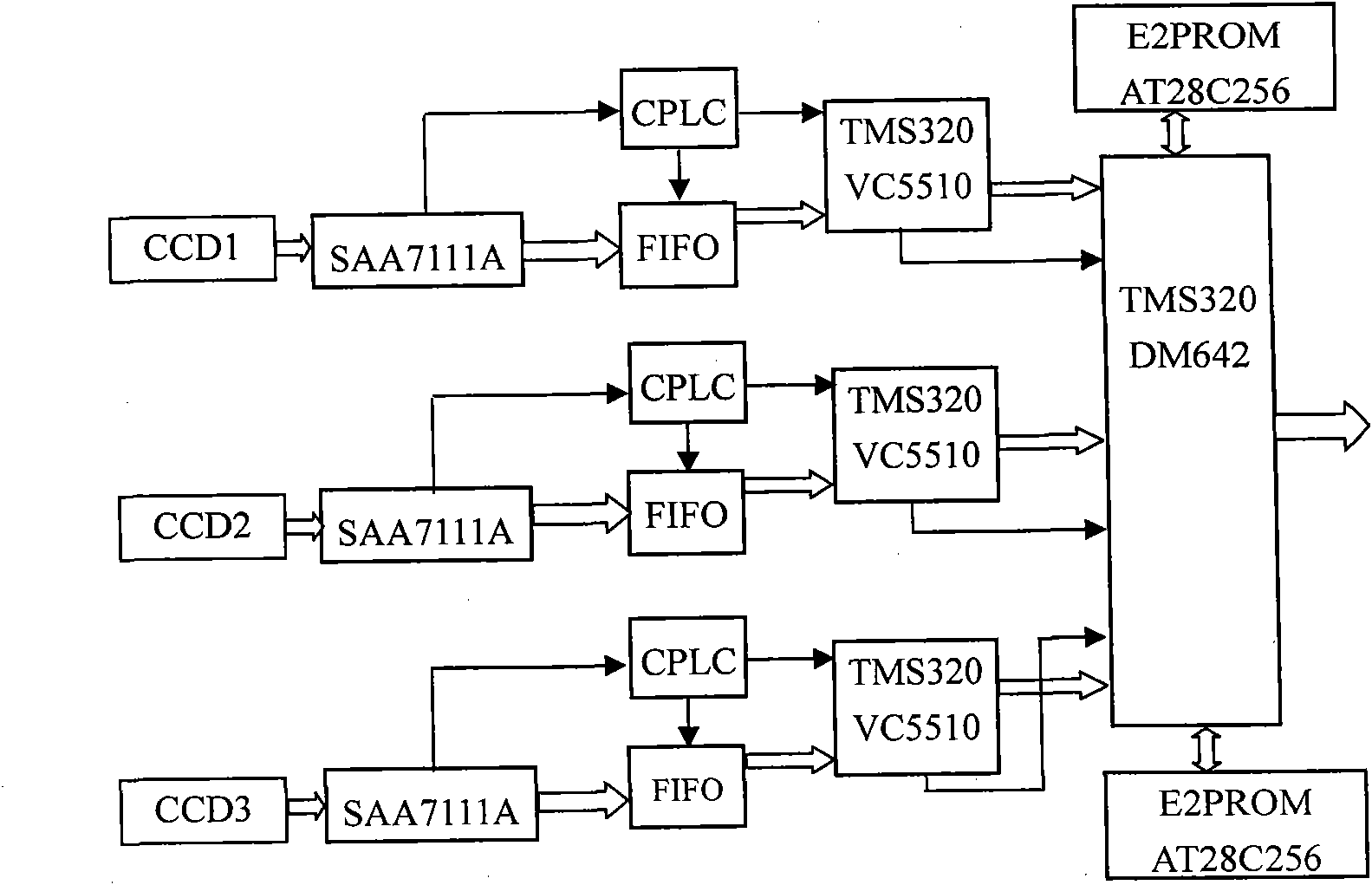

Multi-charge coupled device group self-adaptive imaging instrument of cambered optical structure and method thereof

InactiveCN101867828AHigh brightness sensitivityBreak through the limitations of poor daytime imagingTelevision system detailsClosed circuit television systemsAdaptive imagingNeural processing

The invention relates to a multi-charge coupled device group self-adaptive imaging instrument of a cambered optical structure and a method thereof, belonging to a field of the image information acquisition and processing. By imitating an ommateum to adjust the nerve conduction mode with the change of the illumination under the condition of day alternates with night to obtain a self-adaptive imaging effect principle, the instrument uses a plurality of common charge coupled devices (CCD), corresponding auxiliary circuits and a neural processing algorithm to construct a biomimic self-adaptive adjustment imaging instrument. The imaging instrument has an imaging function of self adjusting fusion modes with the change of illumination conditions, can acquire a high-contrast image under a normal illumination condition, and also can acquire a high-brightness sensitive image under a weak illumination condition. The invention realizes high-definition surveillance and monitoring under the condition of day alternates with night, belonging to the image information acquisition and processing field.

Owner:NANJING INST OF TECH

Time-varying brain network reconstruction method facing dynamic video target detection

ActiveCN112641450ACharacter and pattern recognitionDiagnostic recording/measuringPattern recognitionNeural information processing

The invention belongs to the technical field of electroencephalogram recognition, and particularly relates to a time-varying brain network reconstruction method facing dynamic video target detection. The method comprises the following steps that a scalp electroencephalogram signal of a testee under an acquired dynamic video is mapped to a cortex space, and a cortex signal with high temporal-spatial resolution is reconstructed; and an interested brain area is selected from the cortex space to serve as a network analysis node, and a cortex time-varying brain network connection graph reflecting the cognitive processing process is obtained by analyzing the neural information processing process from target search to target discovery according to cortex signal. According to the method, a neural processing mechanism of the process from search to discovery of a dynamic visual target is expanded, scalp electroencephalogram with the high temporal-spatial resolution is selected to be mapped into cortex electroencephalogram with the high temporal-spatial resolution, a finer brain activity diagram can be obtained, the brain neural information processing process is further explored through a time-varying network analysis method, the application of a brain-computer interface in an actual environment is facilitated, and the application prospect is good.

Owner:PLA STRATEGIC SUPPORT FORCE INFORMATION ENG UNIV PLA SSF IEU

Ternary mode of planar engine for neural processor

A neural processor includes one or more neural engine circuits and a planar engine circuit. The neural engine circuits can perform convolution operations of first input data with one or more kernels to generate a first output. The planar engine circuit receives second input data that corresponds to a version of the first input data. The planar engine circuit also receives third input data that includes fourth input data and fifth input data stored together in a dimension of third input data. The planar engine circuit performs a first elementwise operation between a version of the second input data and a version of the fourth input data to generate intermediate data. The planar engine circuit performs a second elementwise operation between the intermediate data and a version of the fifth input data to generate a second output.

Owner:APPLE INC

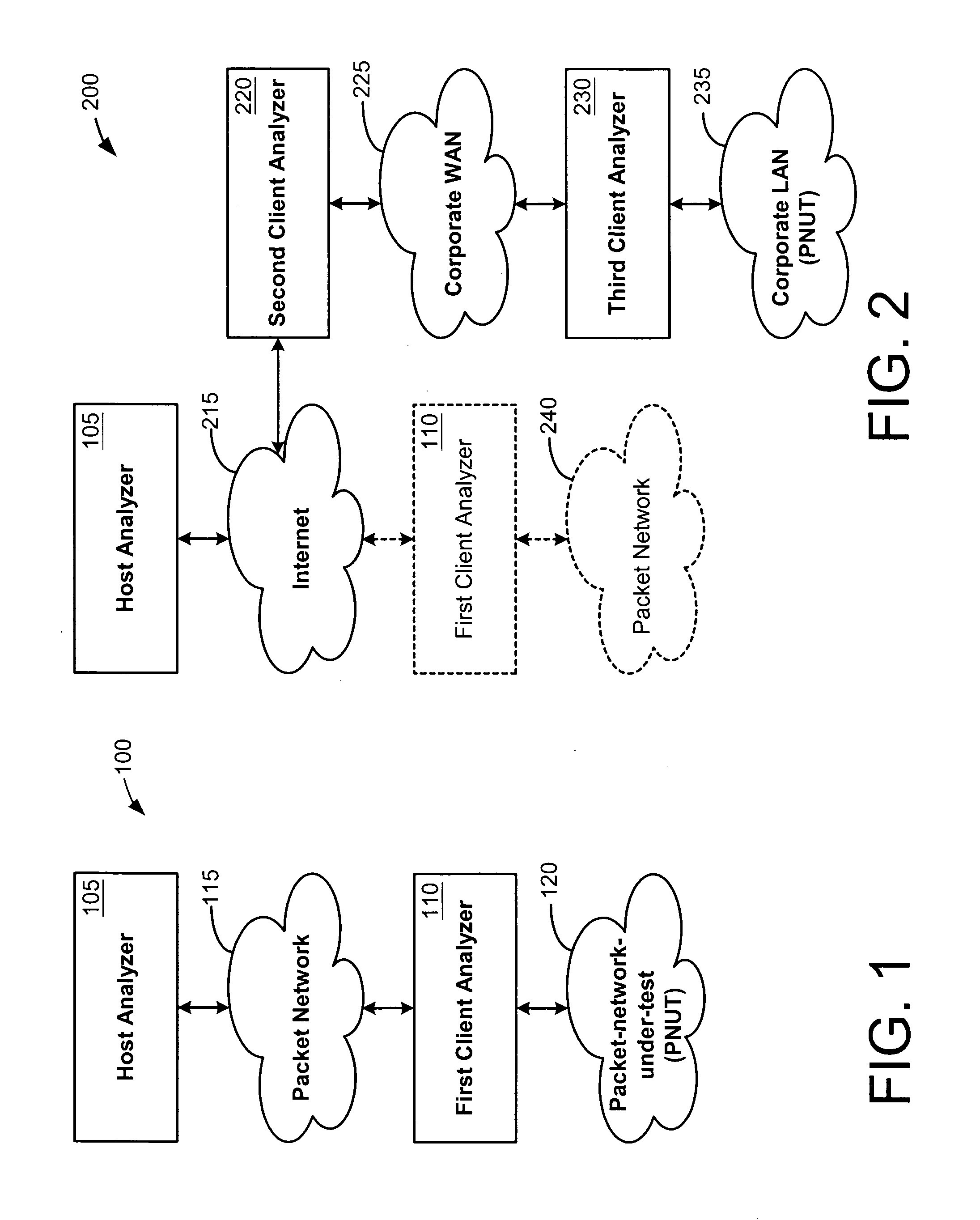

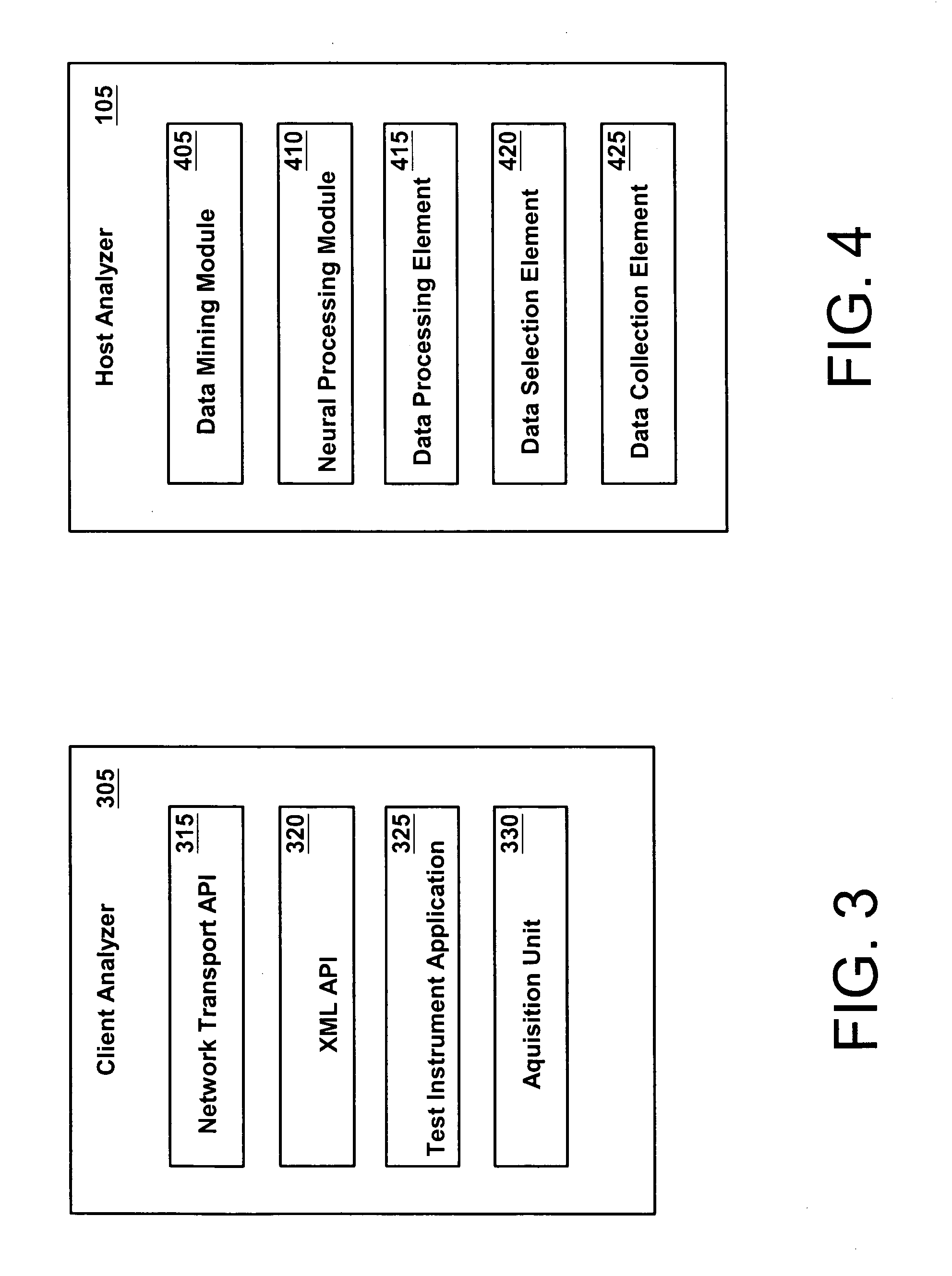

Systems and methods for characterizing packet-switching networks

A packet-network analyzer system for characterizing network conditions of a packet-network-under-test is provided. In this regard, one such system can be broadly summarized by a representative analyzer system that incorporates a data collection element to receive the raw digital data from a host analyzer, a data selection element to generate a selected data set from the raw digital data, a data processing element to process the selected data set to generate a normalized data set, a neural processing module to process the normalized data set to generate a set of rules and relationships, and a data mining module that uses the rules and relationships to generate a mined data set from the selected data set, the mined data set being used to characterize a packet-network-under-test. Another embodiment can be described as a method for analyzing a packet-network-under-test, comprising the steps of receiving raw digital data that is derived from a packet-network-under-test; generating a selected data set from the received raw digital data; generating a normalized data set from the selected data set; processing the normalized data set in a neural network to generate a set of rules and relationships; using the set of rules and relationships for mining the selected data set to generate a mined data set; and using the mined data set to characterize the packet-network-under-test.

Owner:VIAVI SOLUTIONS INC

Splitting of input data for processing in neural network processor

Embodiments of the present disclosure relate to splitting input data into smaller units for loading into a data buffer and neural engines in a neural processor circuit for performing neural network operations. The input data of a large size is split into slices and each slice is again split into tiles. The tile is uploaded from an external source to a data buffer inside the neural processor circuit but outside the neural engines. Each tile is again split into work units sized for storing in an input buffer circuit inside each neural engine. The input data stored in the data buffer and the input buffer circuit is reused by the neural engines to reduce re-fetching of input data. Operations of splitting the input data are performed at various components of the neural processor circuit under the management of rasterizers provided in these components.

Owner:APPLE INC

Reduction mode of planar engine in neural processor

Embodiments relate to a neural processor that includes one or more neural engine circuits and planar engine circuits. The neural engine circuits can perform convolution operations of input data with one or more kernels to generate outputs. The planar engine circuit is coupled to the plurality of neural engine circuits. A planar engine circuit can be configured to multiple modes. In a reduction mode, the planar engine circuit may process values arranged in one or more dimensions of input to generate a reduced value. The reduced values across multiple input data may be accumulated. The planar engine circuit may program a filter circuit as a reduction tree to gradually reduce the data into a reduced value. The reduction operation reduces the size of one or more dimensions of a tensor.

Owner:APPLE INC

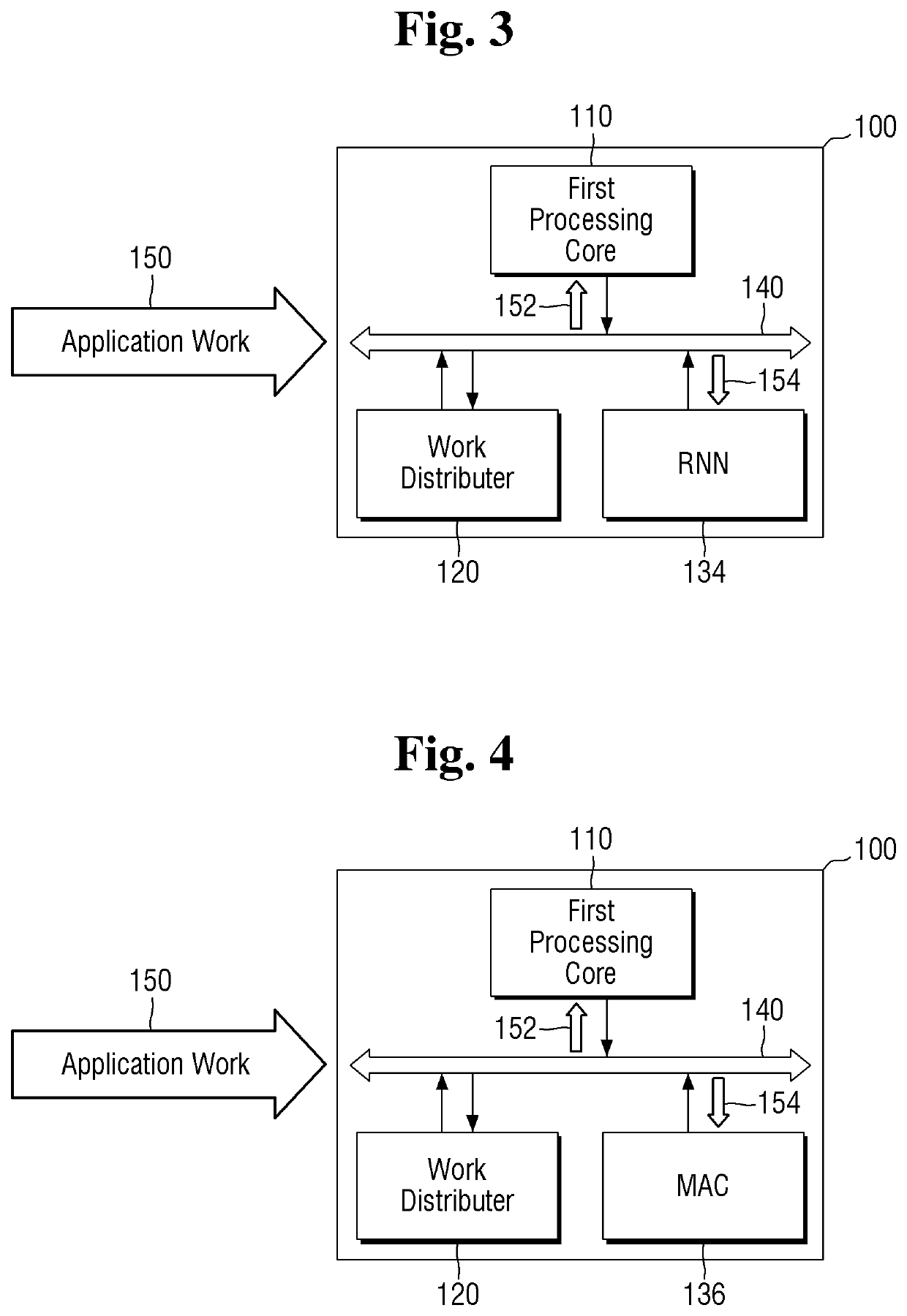

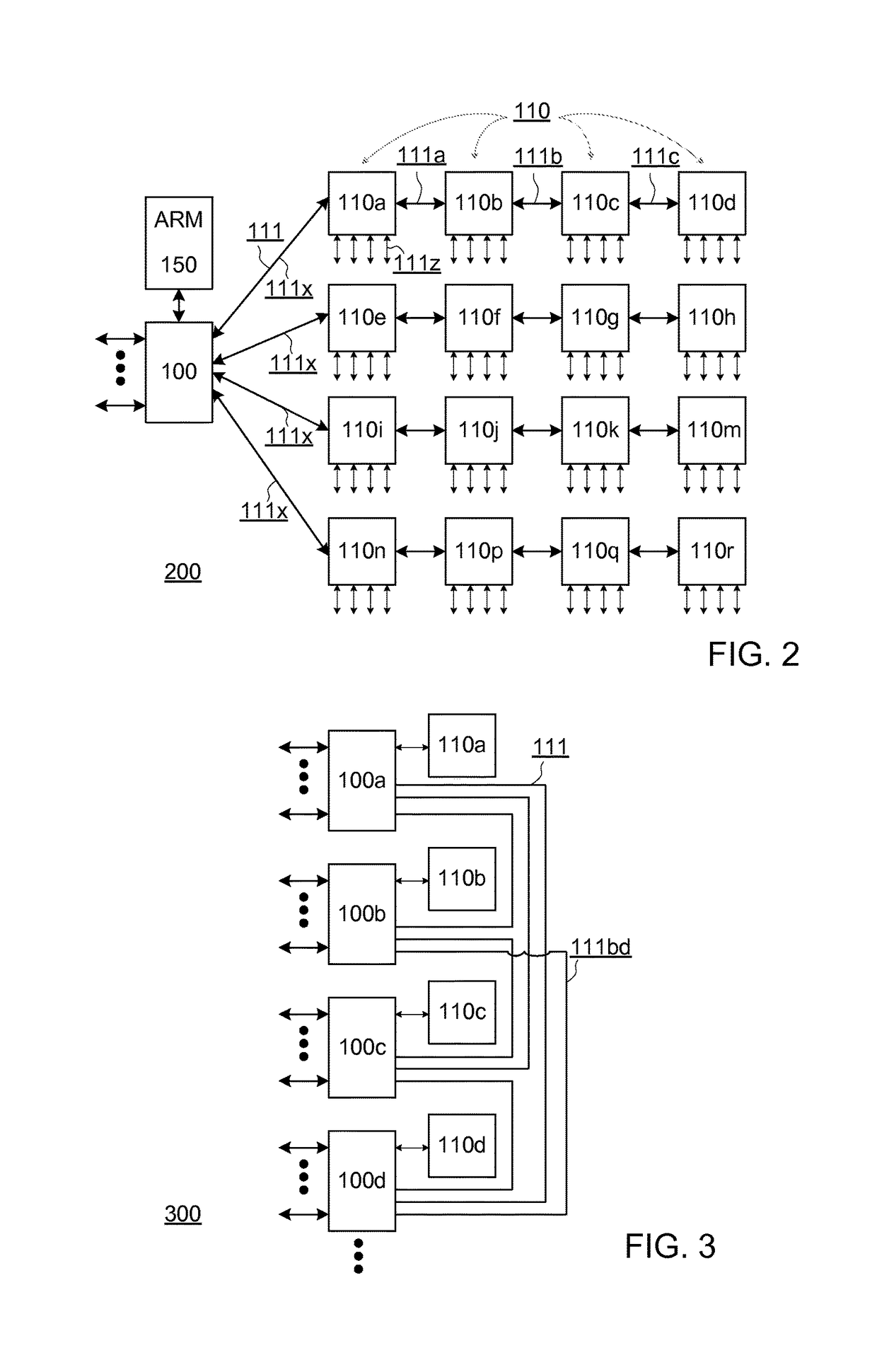

Neural processing unit, neural processing system, and application system

ActiveUS20200151549A1Easy to handlePrevent and reduce resource wasteDigital data processing detailsNeural architecturesProcessing coreProcessing element

Provided is a neural processing unit that performs application-work including a first neural network operation, the neural processing unit includes a first processing core configured to execute the first neural network operation, a hardware block reconfigurable as a hardware core configured to perform hardware block-work, and at least one processor configured to execute computer-readable instructions to distribute a part of the application-work as the hardware block-work to the hardware block based on a first workload of the first processing core.

Owner:SAMSUNG ELECTRONICS CO LTD

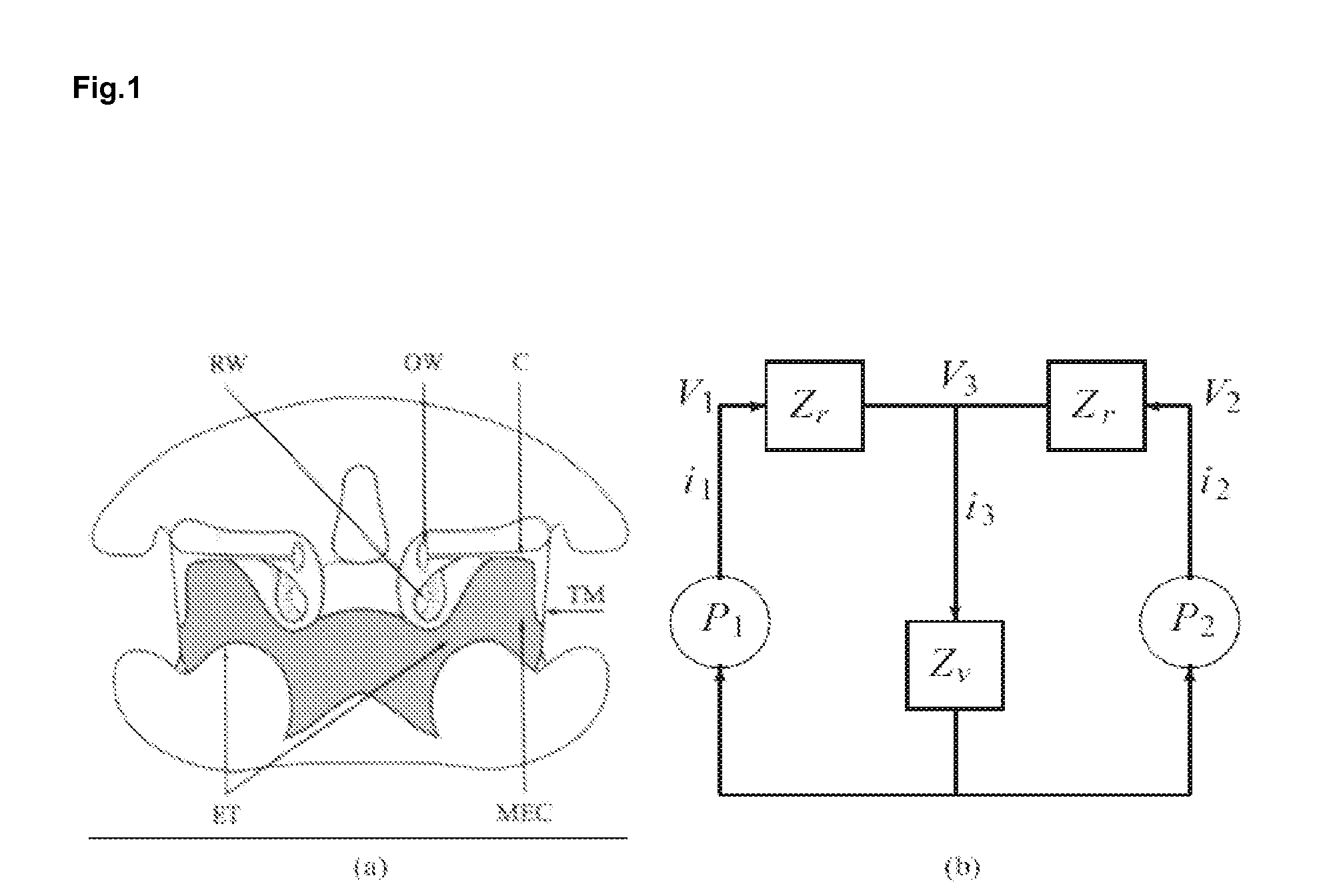

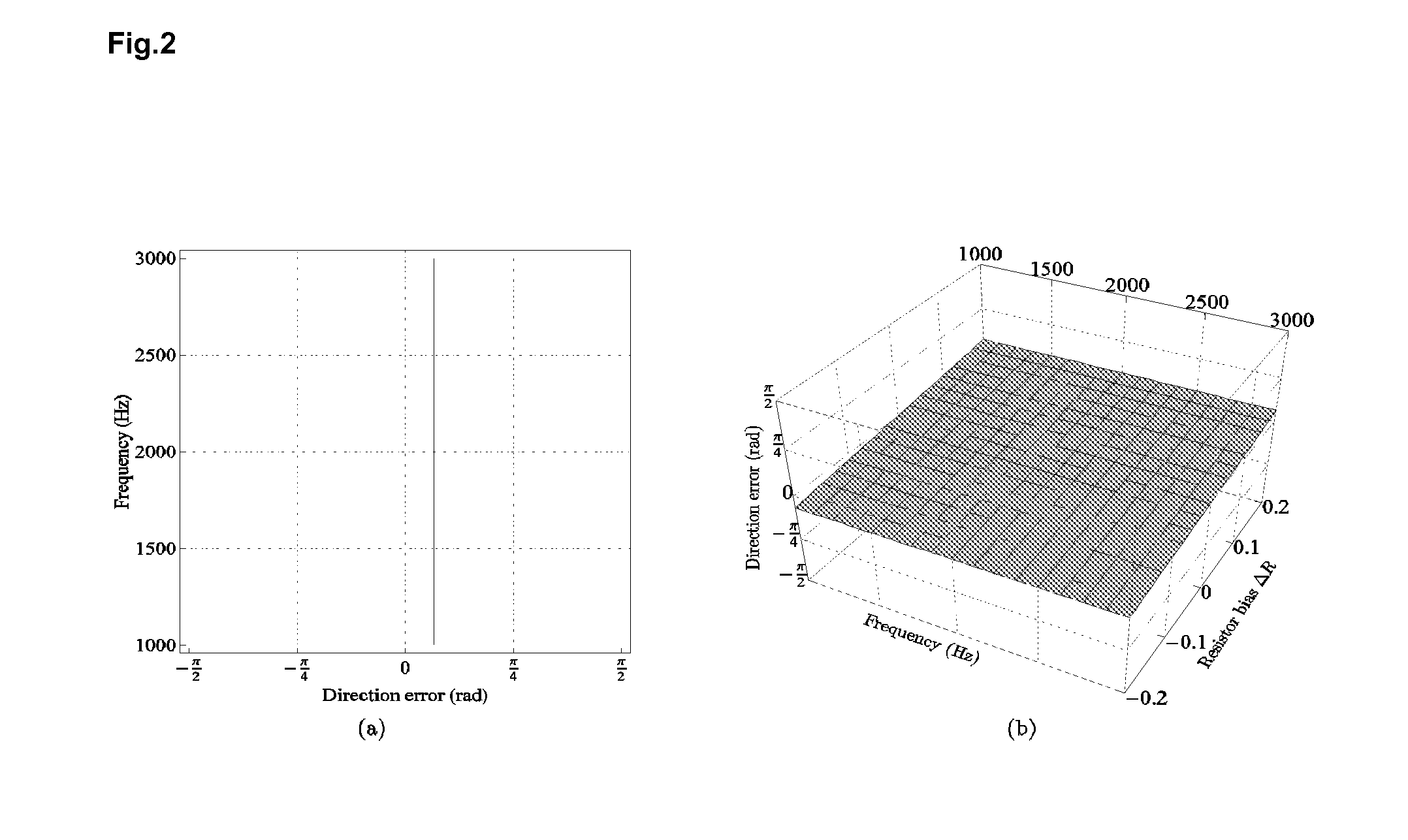

Sound localizing robot

InactiveUS20120109375A1Enhancing auditory localisation cuesMicrophones signal combinationDirection/deviation determination systemsNervous systemBand-pass filter

There is provided a biomimetic robot modelling the highly directional lizard ear. Since the directionality is very robust, the neural processing is very simple. This mobile sound localizing robot can therefore easily be miniaturized. The invention is based on a simple electric circuit emulating the lizard ear acoustics with sound input from two small microphones. The circuit generates a robust directionality around 2-4 kHz. The output of the circuit is fed to a model nervous system. The nervous system model is bilateral and contains a set of band-pass filters followed by simulated EI-neurons that compare inputs from the two ears. This model is implemented in software on a digital signal processor and controls the left and right-steering motors of the robot. Additionally, the nervous system model contains a neural network that can self-adapt so as to auto-calibrate the device.

Owner:LIZARDTECH

Piecewise linear neuron modeling

InactiveUS20140143191A1Reduce complexityAccurate modelingDigital computer detailsDigital dataMain processing unitNervous system

Methods and apparatus for piecewise linear neuron modeling and implementing one or more artificial neurons in an artificial nervous system based on one or more linearized neuron models. One example method (for implementing a combination of a plurality of neuron models in a system of neural processing units) generally includes loading parameters for a first neuron model selected from the plurality of neuron models into a first neural processing unit, determining a first state of the first neural processing unit based at least in part on the parameters for the first neuron model, and determining a second state of the first neural processing unit based at least in part on the parameters for the first neuron model and on the first state. This method may also include updating the plurality of neuron models (e.g., by adding, deleting, or adjusting parameters for the first neuron model or another neuron model).

Owner:QUALCOMM INC

Chained neural engine write-back architecture

Owner:APPLE INC

I/O data interface for packet processors

ActiveUS9614785B1Efficient and simple and flexible and scalableData switching networksInformation processingData interface

Systems and methods to process packets of information use an on-chip information processing system configured to receive, resolve, convert, and / or transmit packets of different packet-types in accordance with different protocols. A first packet-type may use a protocol for wired local-area-networking (LAN) technologies, such as Ethernet. A second packet-type may use a proprietary protocol. The proprietary protocol may be used to exchange information with one or more packet processing engines, such as neural processing engines.

Owner:FRIDAY HARBOR LLC

Multi-Mode Planar Engine For Neural Processor

Embodiments relate to a neural processor that include a plurality of neural engine circuits and one or more planar engine circuits. The plurality of neural engine circuits can perform convolution operations of input data of the neural engine circuits with one or more kernels to generate outputs. The planar engine circuit is coupled to the plurality of neural engine circuits. The planar engine circuit generates an output from input data that corresponds to output of the neural engine circuits or a version of input data of the neural processor. The planar engine circuit can be configured to multiple modes. In a pooling mode, the planar engine circuit reduces a spatial size of a version of the input data. In an elementwise mode, the planar engine circuit performs an elementwise operation on the input data. In a reduction mode, the planar engine circuit reduces the rank of a tensor.

Owner:APPLE INC

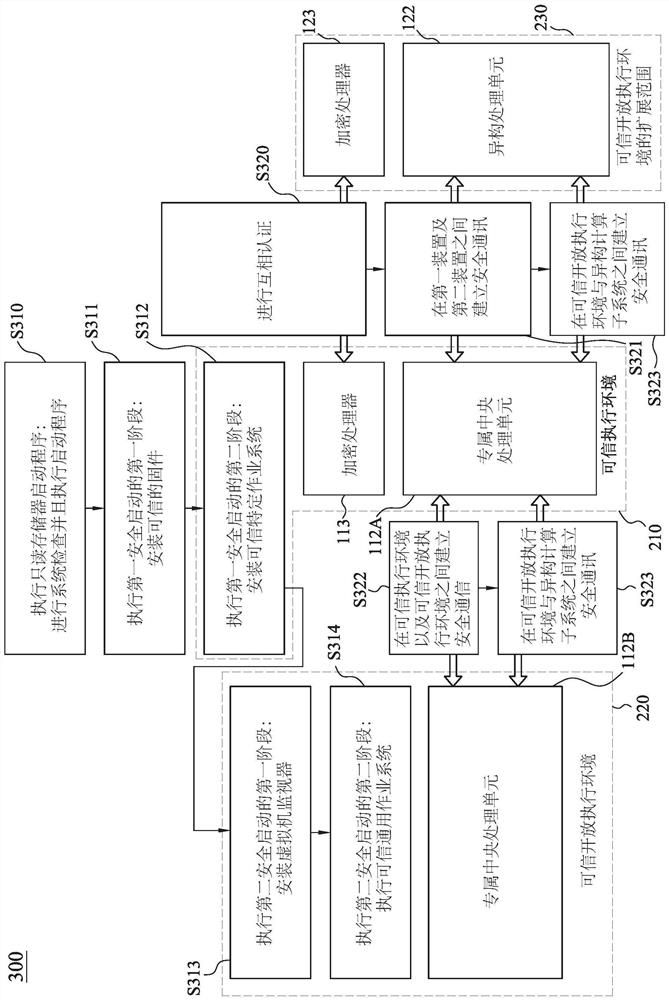

Trusted operation system and method with remote authentication and information independence of heterogeneous processor through open connector

PendingCN114600108AInternal/peripheral component protectionPlatform integrity maintainanceNetwork processing unitConfidentiality

A system and method for securing a heterogeneous processing unit (e.g., an image processing unit; a GPU (Graphics Processing Unit), a neural network processing unit (Neural Processing Unit; nPU (Network Processing Unit) and a visual processing unit (Video Processing Unit; ) and a central processing unit (Central Processing Unit, VPU, etc. Programs, parsing modules and processing data executed by a standard open-type connector (such as Ethernet, universal serial bus and sequence peripheral interface), such as a CPU (central processing unit), are ensured in authenticity, confidentiality and integrity.

Owner:FIDUCIAEDGE TECH CO LTD

Dynamic variable bit width neural processor

Embodiments relate to an electronic device that includes a neural processor having multiple neural engine circuits that operate in multiple modes of different bit width. A neural engine circuit may include a first multiply circuit and a second multiply circuit. The first and second multiply circuits may be combined to work as a part of a combined computation circuit. In a first mode, the first multiply circuit generates first output data of a first bit width by multiplying first input data with a first kernel coefficient. The second multiply circuit generates second output data of the first bit width by multiplying second input data with a second kernel coefficient. In a second mode, the combined computation circuit generates third output data of a second bit width by multiplying third input data with a third kernel coefficient.

Owner:APPLE INC

Processing group convolution in neural network processor

Embodiments relate to a neural processor circuit including neural engines, a buffer, and a kernel access circuit. The neural engines perform convolution operations on input data and kernel data to generate output data. The buffer is between the neural engines and a memory external to the neural processor circuit. The buffer stores input data for sending to the neural engines and output data received from the neural engines. The kernel access circuit receives one or more kernels from the memory external to the neural processor circuit. The neural processor circuit operates in one of multiple modes, at least one of which divides a convolution operation into multiple independent convolution operations for execution by the neural engines.

Owner:APPLE INC

Compiling and scheduling transactions in neural network processor

Embodiments relate to a compiler. The compiler decreases data fetch and read associated with storing data in a data buffer of a neural processor circuit to or from a system memory. The data buffer can store an input slice of data for processing by a neural engine(s) of the neural processor circuit, an output slice of data output from the neural engine(s), and / or an intermediate data slice of data.

Owner:APPLE INC

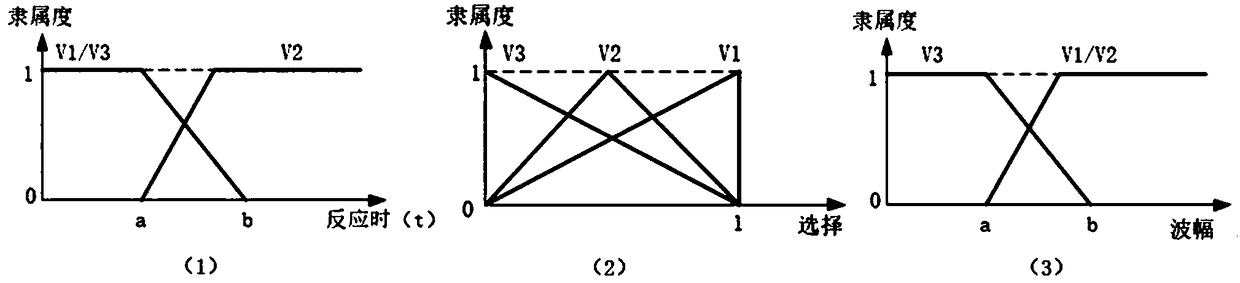

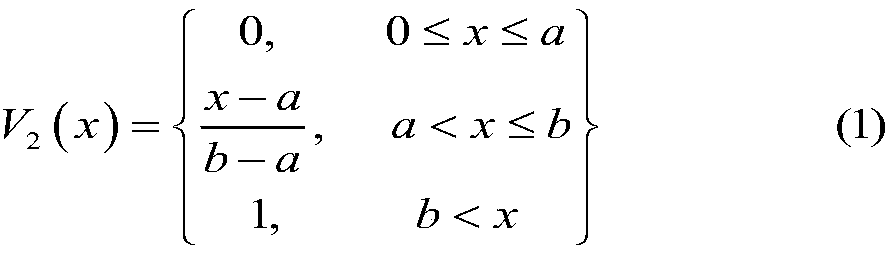

A product image recognition method based on EEG signal and fuzzy inference

InactiveCN109271894AInput/output for user-computer interactionCharacter and pattern recognitionPattern recognitionFuzzy inference

The invention relates to a product image recognition method based on EEG signal and fuzzy inference. The method comprises the following steps: 1) image evaluation is carried out on the product image which needs to be recognized by using EEG signal acquisition device; 2) the classification number of perceptual image vocabulary pair is set, and the image words of the pictures are judged; 3) according to the image reasoning model, the required behavior and EEG data are statistically analyzed; 4) that fuzzy matrix is substituted into the calculation to carry on the comprehensive evaluation. The invention has the beneficial effects that: the invention starts from the neural processing mechanism, searches for the mapping relationship between the image and the EEG, reasoning the product image byusing the EEG experiment combined with fuzzy evaluation, and constructs a new product image quantitative reasoning method; The product image reasoning model based on EEG can directly calculate the semantic value of the subjective image of the product samples through the objective data (the selection rate of the subjects, reaction time and N400 amplitude) rather than subjective evaluation, which can provide methodological support for the future systematic image acquisition.

Owner:ZHEJIANG UNIV CITY COLLEGE

Circuit for performing pooling operation in neural processor

Embodiments relate to a denominator circuit that determines the number of valid elements of a data surface covered by a kernel depending on various locations of the kernel relative to the data surface. The denominator circuit includes a first circuit and a second circuit that have the same structure. The first circuit receives numbers representing different horizontal locations of a reference point in the kernel and generates a first matrix with first output elements corresponding to the different horizontal locations. The second circuit receives numbers representing different vertical locations of a reference point in the kernel and generates a second matrix with second output elements corresponding to the different vertical locations. A matrix multiplication of the first matrix and the second matrix is performed to obtain an array of valid elements covered by the kernel.

Owner:APPLE INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com