Three-terminal type thin film transistor, preparation method thereof and photosensitive nerve synapse device

A thin-film transistor and oxide thin-film technology, which is applied in the field of optoelectronic devices, can solve the problems that photosensitive synapses do not have obvious advantages and the oxide band gap is large, and achieve the effects of low power consumption and simple preparation methods

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

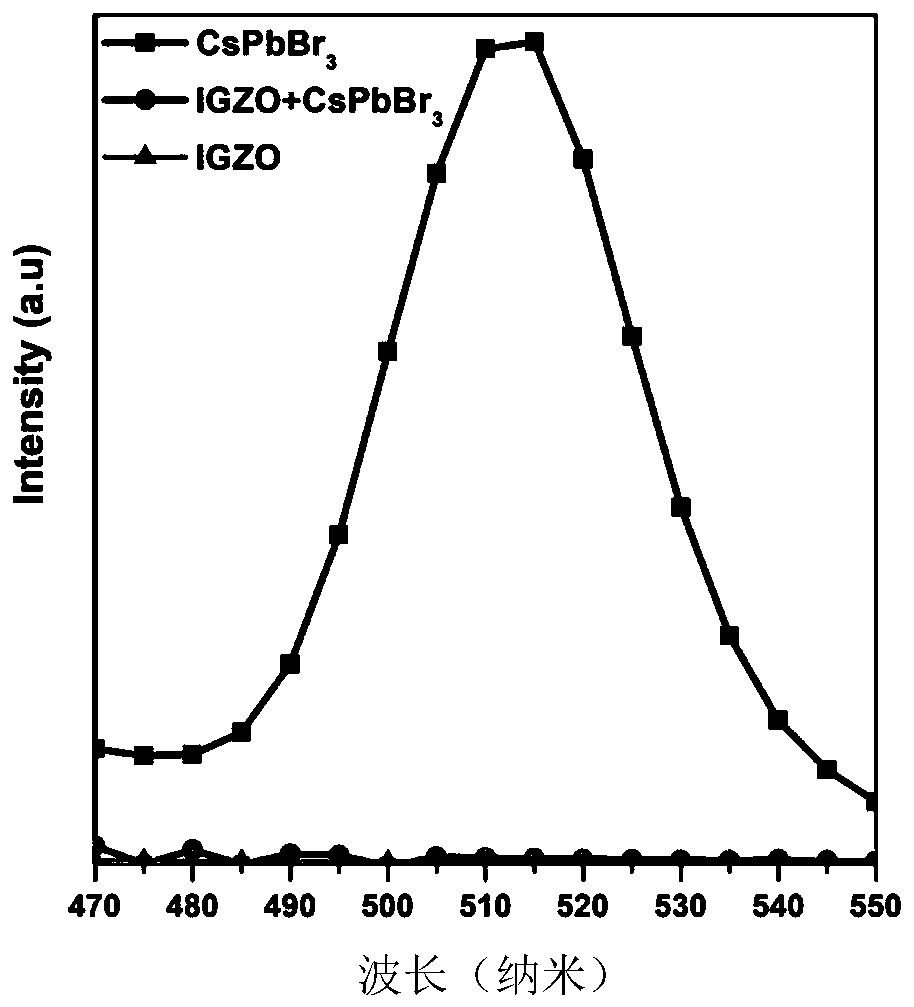

[0040] Spin-coat CsPbBr with toluene as solvent on quartz glass plate A 3 -QDs solution, then heated to volatilize toluene to obtain CsPbBr with a thickness of 20nm 3 -QDs quantum dot layer;

[0041] Using radio frequency magnetron sputtering technology, grow an indium gallium zinc oxide film (IGZO film) with a thickness of 50 nm on the quartz glass sheet B;

[0042] First, an IGZO film with a thickness of 20 nm was grown on a quartz glass sheet C by radio frequency magnetron sputtering technology, and then CsPbBr with toluene as a solvent was spin-coated on the IGZO film. 3 -QDs solution, heated to volatilize toluene to obtain CsPbBr with a thickness of 20nm 3 -QDs layer, finally in CsPbBr by RF magnetron sputtering 3 - growing an IGZO thin film with a thickness of 30 nm on the QDs layer to obtain a composite thin film layer of IGZO thin film / quantum dots.

[0043] The three types of samples on the quartz glass sheets A, B, and C were analyzed and characterized by a fluores...

Embodiment 2

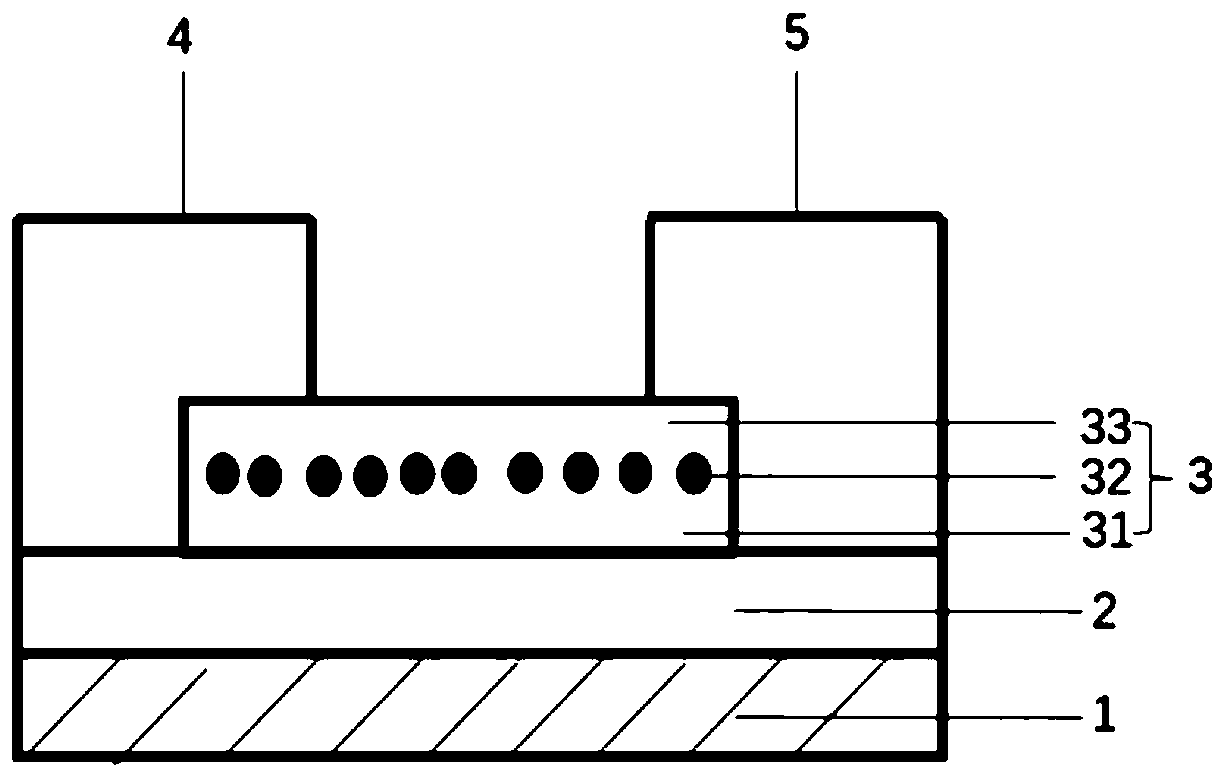

[0045] Thin film transistor structures such as figure 1 As shown, it includes a substrate, a channel layer 3 , a gate electrode, a source electrode 4 and a drain electrode 5 . Wherein, the gate electrode is located in one layer of the channel layer, and the source electrode 4 and the drain electrode 5 are located in the other layer of the channel layer 3, forming a dislocation structure.

[0046] In this embodiment, a p-type doped Si material 1 (p+Si for short) is selected as the substrate and the gate electrode, and SiO grown by thermal oxidation is arranged between the channel layer 3 and the gate electrode. 2 as the gate insulating layer 2.

[0047] In this embodiment, the material of the source electrode 4 is an alloy of Ti and Au, and the material of the drain electrode 5 is an alloy of Ti and Au.

[0048] In this embodiment, the channel layer 3 is made of the first indium gallium zinc oxide thin film layer 31 (first IGZO thin film layer 31), CsPbBr 3 Quantum dot layer...

Embodiment 3-9

[0060] In Examples 3-9, the structure of the thin film transistor is basically the same as that in Example 2, and the different thicknesses of the first IGZO thin film layer and the second IGZO thin film layer are shown in the table below.

[0061] In the embodiment 3-9, the preparation method of the thin film transistor is basically the same as the preparation method of the thin film transistor in the embodiment 2, and the different sputtering time when preparing the first IGZO thin film layer and the second IGZO thin film layer is shown in the following table .

[0062] Table 1

[0063]

[0064]

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com