Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

850 results about "Single crystal silicon wafer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

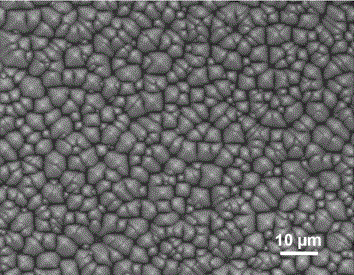

Alcohol-free alkaline texturing solution for mono-crystalline silicon wafer, texturing method for mono-crystalline silicon wafer, solar cell and manufacturing method for solar cell

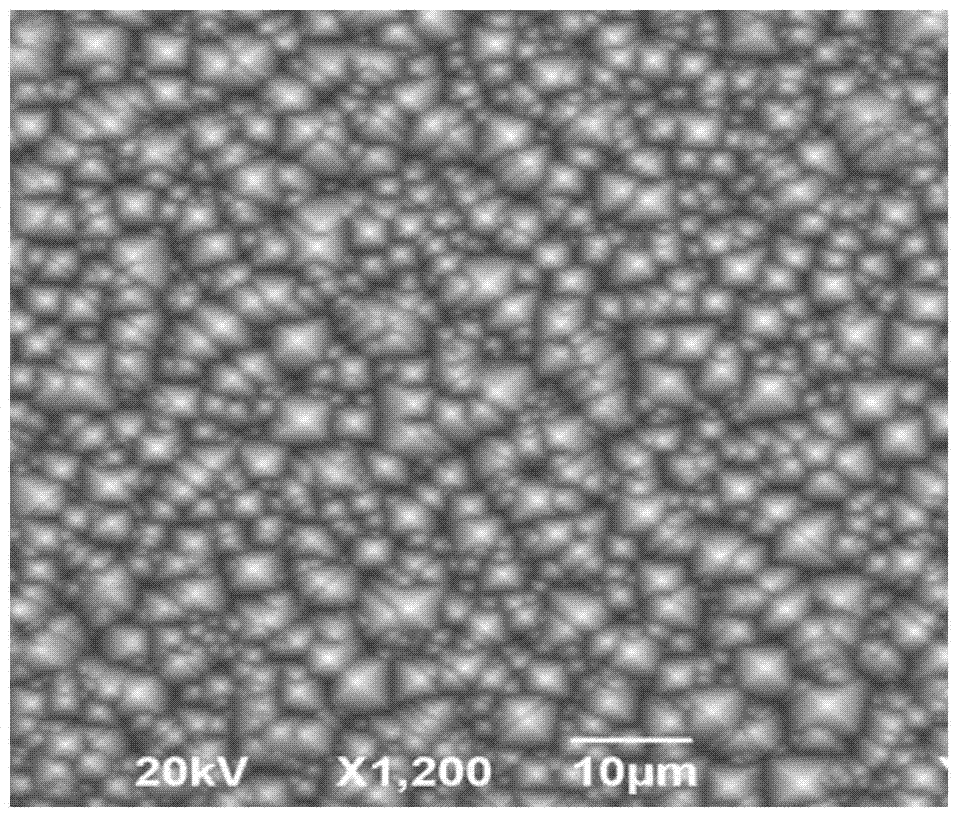

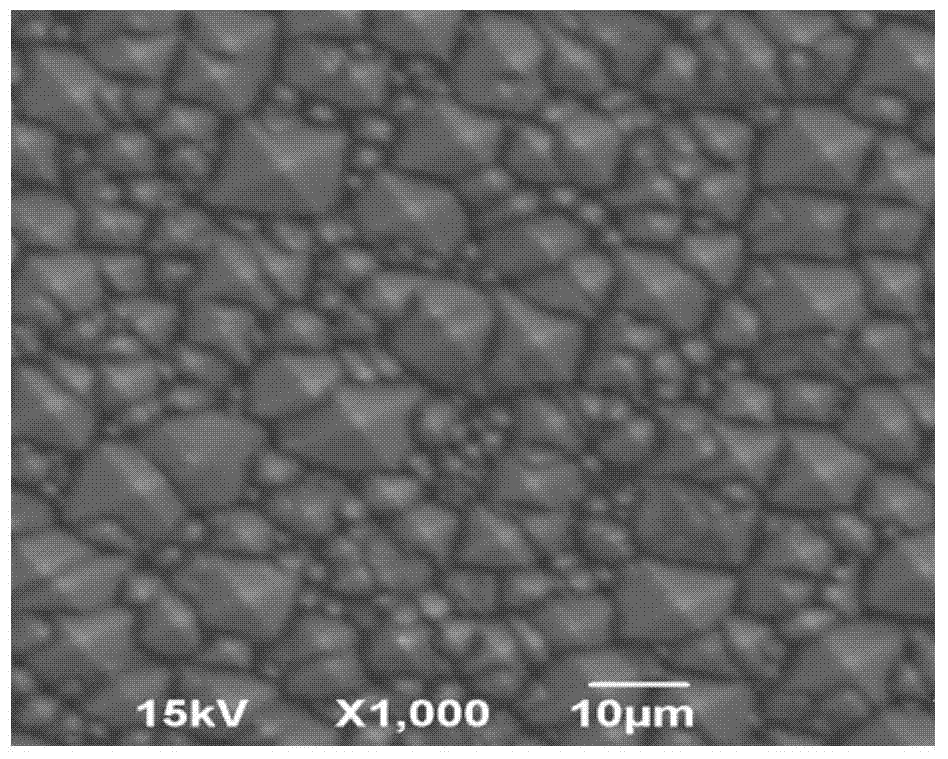

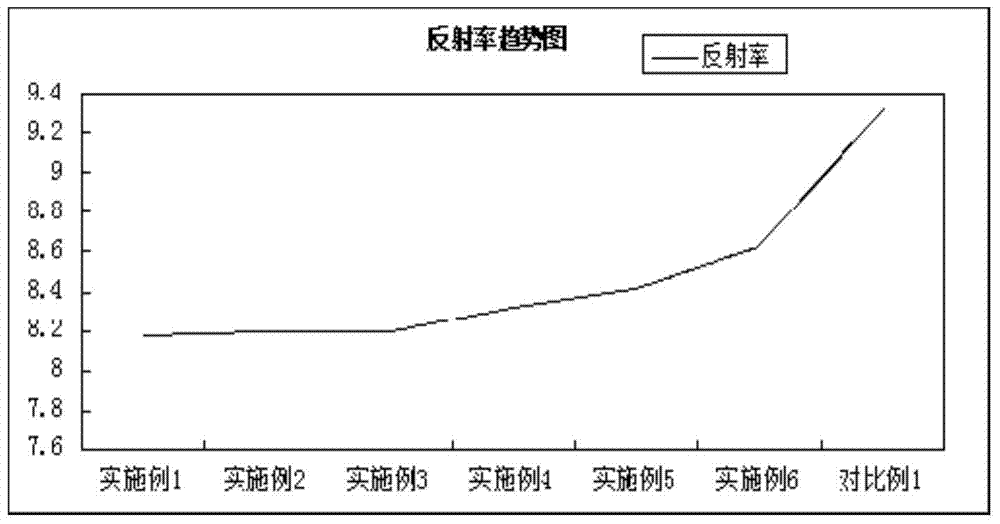

InactiveCN103614778AReduce reflectivityIncreased anisotropyAfter-treatment detailsFinal product manufactureAlcohol freeAbsorption capacity

The invention discloses an alcohol-free alkaline texturing solution for a mono-crystalline silicon wafer, a texturing method for the mono-crystalline silicon wafer, a solar cell and a manufacturing method for the solar cell. The alcohol-free alkaline texturing solution for the mono-crystalline silicon wafer comprises an alkaline solution and a texturing additive, wherein the texturing additive is an alcohol-free additive. According to the alcohol-free alkaline texturing solution, isopropanol which is harmful to human bodies and the environment adopted in the conventional alkaline texturing solution is abandoned; the corrosion depth of the surface of a silicon wafer can be controlled within the range of 5 to 7.5 mu m easily by performing surface texturing on the mono-crystalline silicon wafer obtained by performing linear cutting on a diamond by only adopting the alcohol-free alkaline texturing solution consisting of the alkaline solution and the alcohol-free additive; meanwhile, the corrosion speed is guaranteed; the anisotropy of corrosion is enhanced; pyramid structures on the surface of the silicon wafer obtained after the texturing are small and uniform in size, so that the reflectivity of the surface of the silicon wafer is reduced by about 1 percent; the light absorption capacity of the surface of the silicon wafer is increased; the conversion efficiency of the solar cell is improved.

Owner:YINGLI ENERGY CHINA

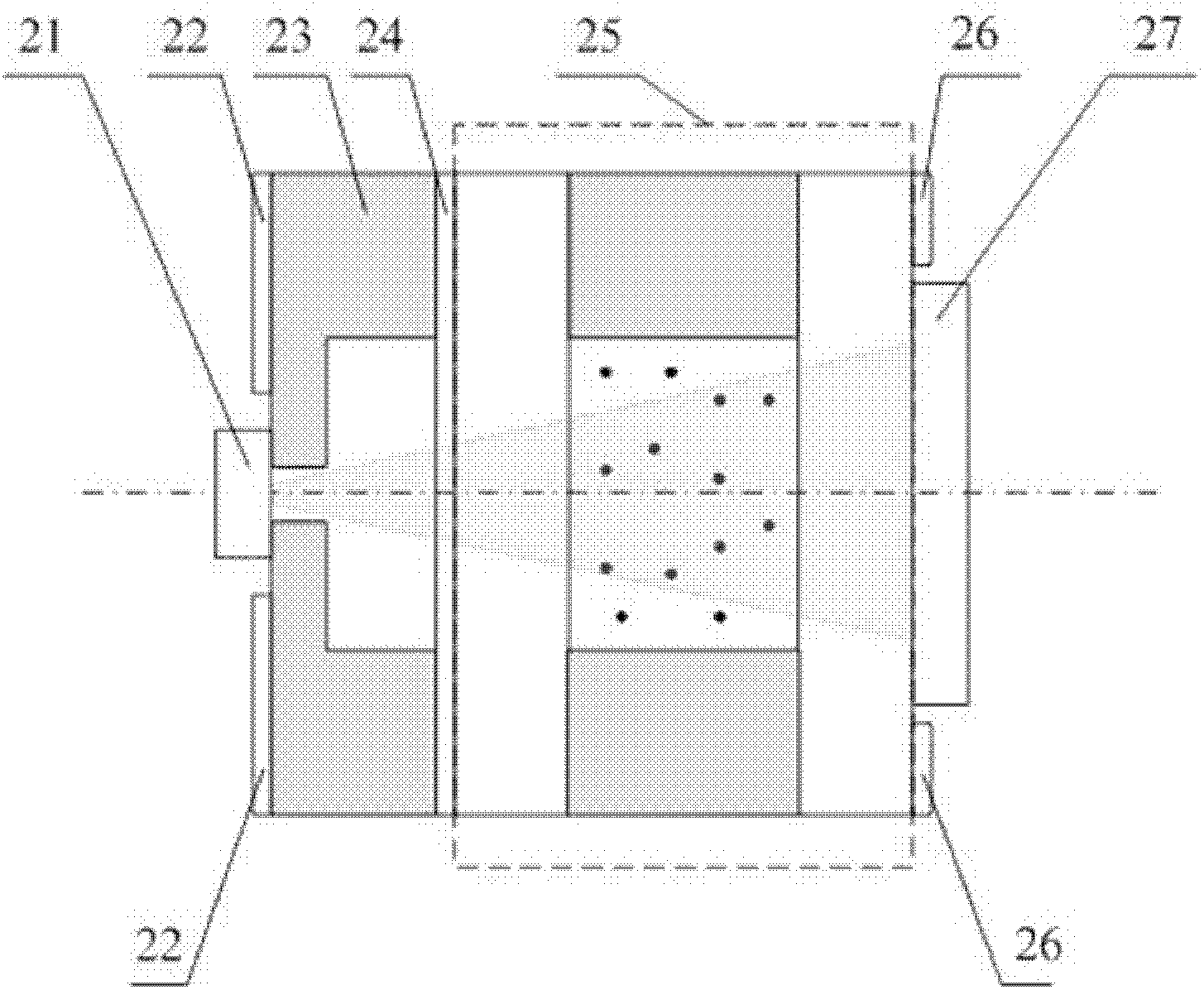

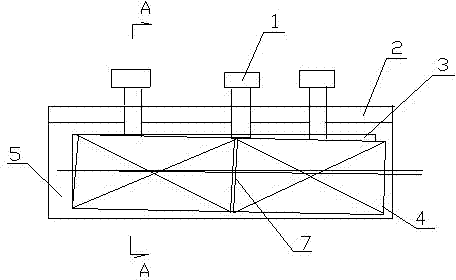

Groove type atomic gas cavity and atomic clock physical system formed by same

ActiveCN102323738ALower working temperatureUnlimited thicknessApparatus using atomic clocksCrystal planeParticle physics

The invention relates to a groove type atomic gas cavity produced by applying MEMS technology and an atomic clock physical system formed by the same. The cavity is characterized in that the cavity is formed in such a manner that a silicon wafer with a groove and Pyrex glass sheets define a cavity structure through bonding; the cavity structure is used for alkali metal atom vapor and buffer gases to fill in; the cross section of the groove is in a shape of inverted trapezoid; and the groove comprises a bottom surface and side walls forming included angles with the bottom surface. The cavity is manufactured based on MEMS (micro-electro-mechanical system) technology. The silicon groove is formed through anisotropic etching of the (100) monocrystalline wafer. The groove type cavity is manufactured through silicon-glass anode bonding. The side walls of the cavity are {111} crystal planes of the silicon wafer. The cavity and the system have the following beneficial effects: by utilizing the cavity, the distance between two reflectors in the cavity is easy to enlarge through atomic cavity dimension design, thus increasing the length of the interaction space between laser and atomic gas, enhancing the signal to noise ratio of the CPT (coherent population trapping) signal and being beneficial to improvement of the frequency stability of the micro CPT atomic clock.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

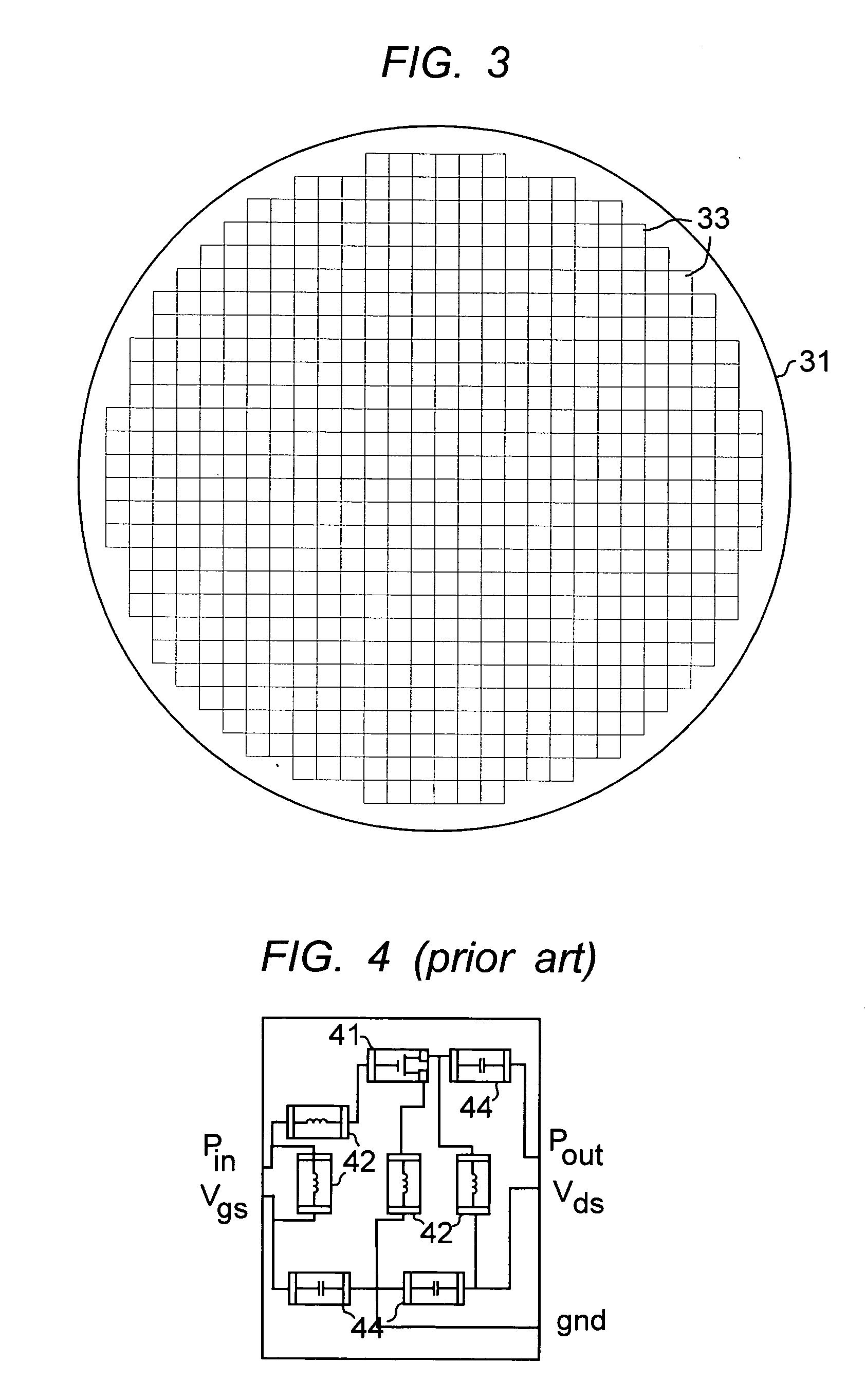

Integrated passive devices

InactiveUS20050253255A1Easy to processEasy to handleSemiconductor/solid-state device detailsSolid-state devicesProduction lineWafering

Owner:SYCHIP

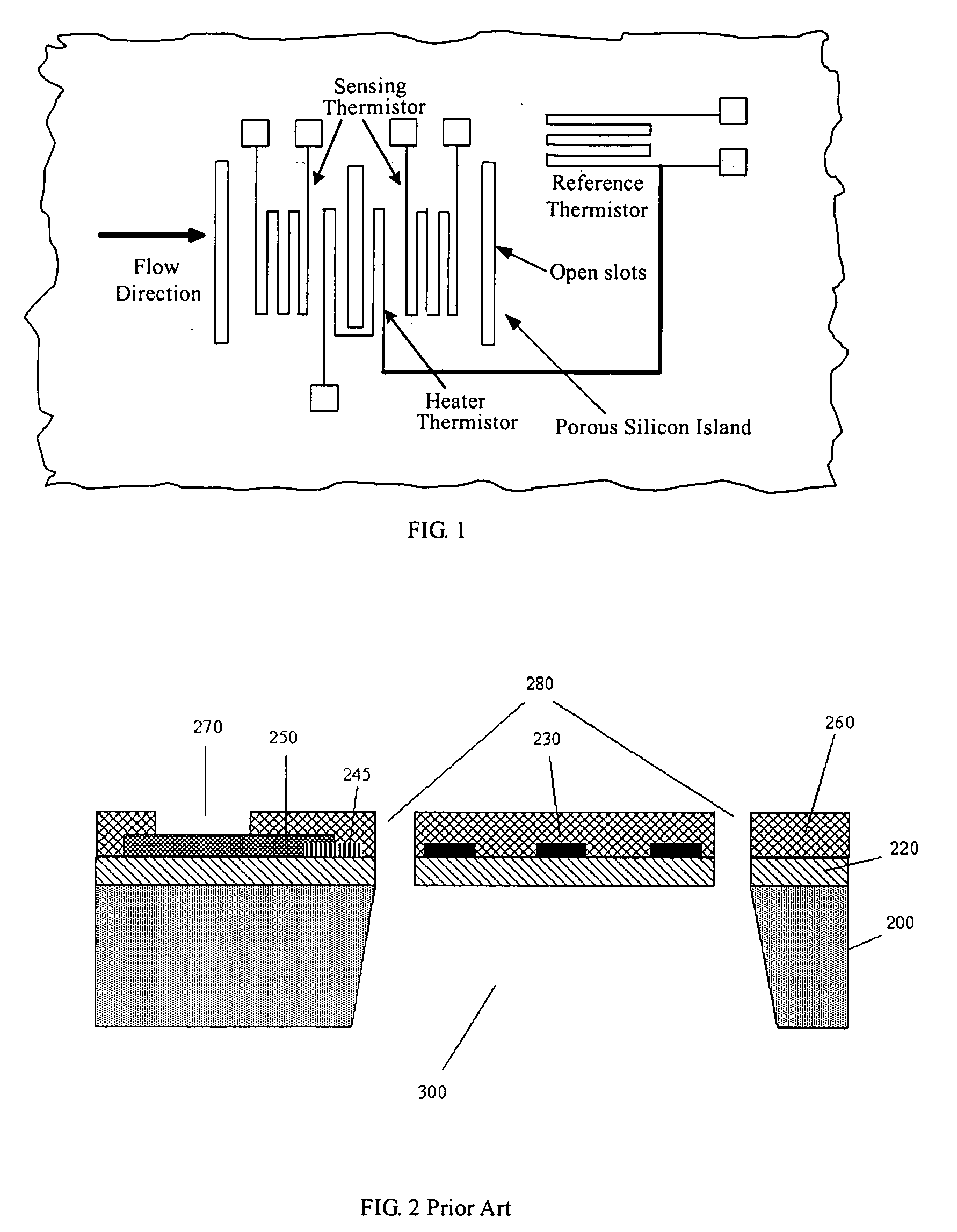

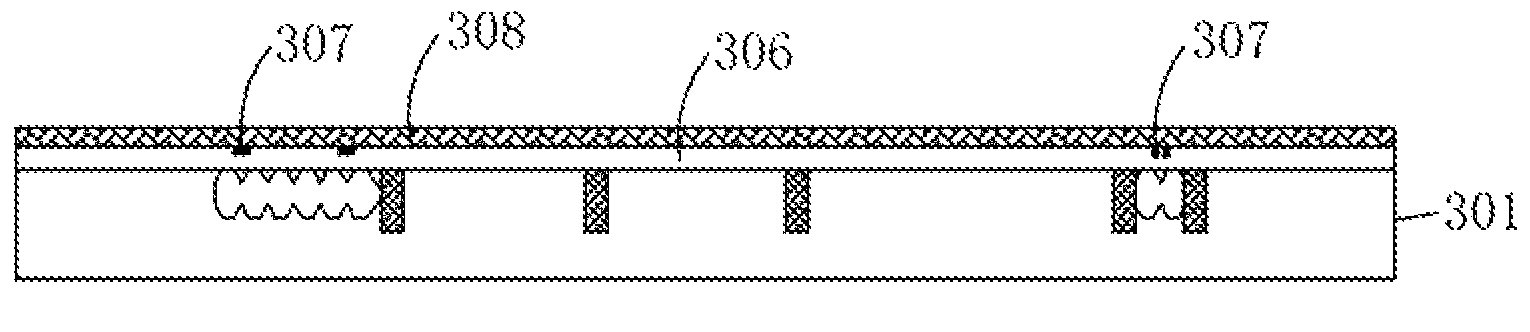

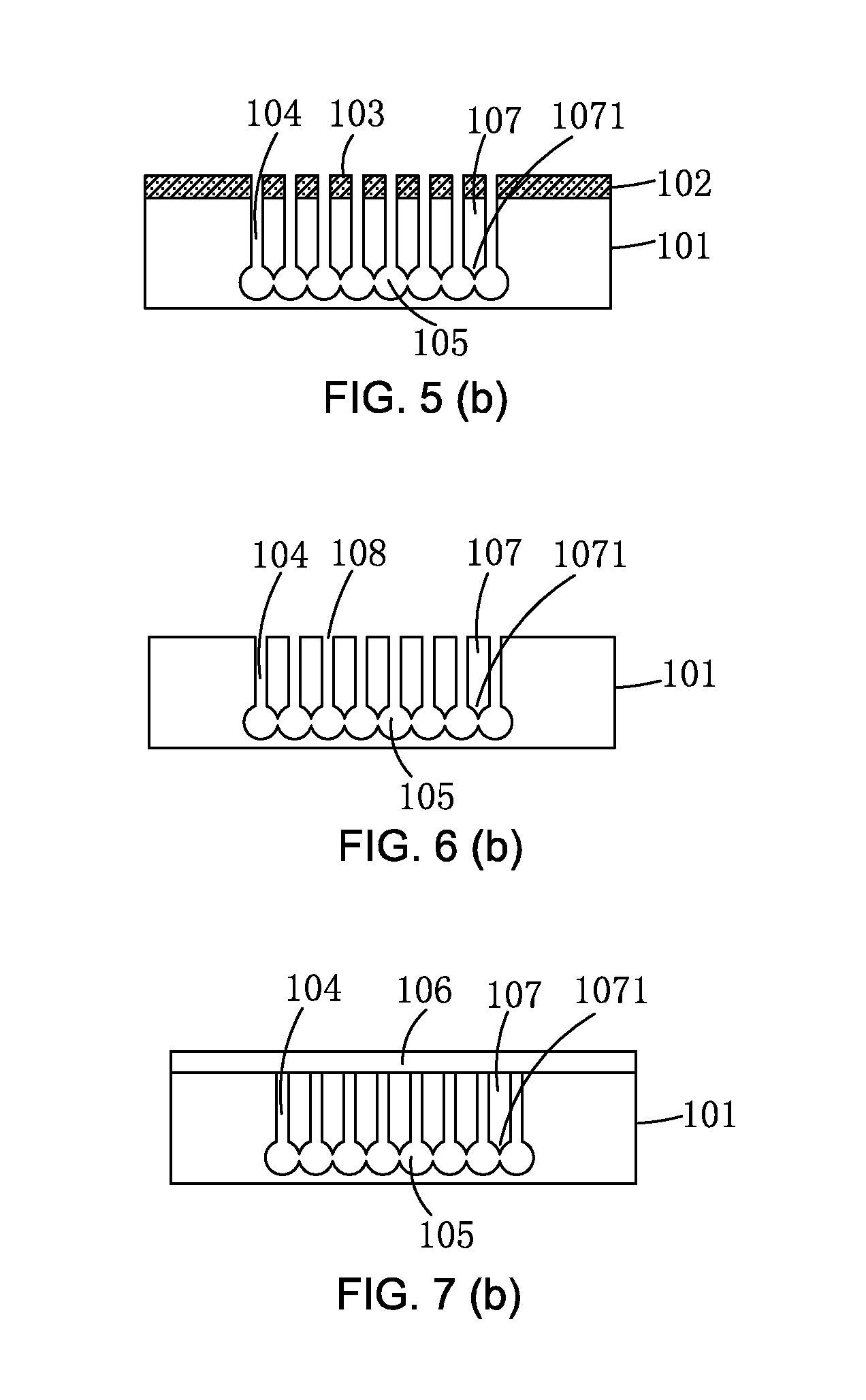

Micromachined Thermal Mass Flow Sensor With Self-Cleaning Capability And Methods Of Making the Same

ActiveUS20090158859A1Improve performanceRobust self-cleanedLiquid surface applicatorsVolume/mass flow by thermal effectsForeign matterThermal isolation

The current invention generally relates to Micro Electro Mechanical Systems (MEMS) thermal mass flow sensors for measuring the flow rate of a flowing fluid (gas / liquid) and the methods of manufacturing on single crystal silicon wafers. The said mass flow sensors have self-cleaning capability that is achieved via the modulation of the cavity of which the sensing elements locate on the top of the cavity that is made of a silicon nitride film; alternatively the sensing elements are fabricated on top of a binary silicon nitride / conductive polycrystalline silicon film under which is a porous silicon layer selective formed in a silicon substrate. Using polycrystalline silicon or the sensing elements as electrodes, an acoustic wave can be generated across the porous silicon layer which is also used for the thermal isolation of the sensing elements. The vibration or acoustic energy is effective to remove foreign materials deposited on top surface of the sensing elements that ensure the accuracy and enhance repeatability of the thermal mass flow sensing.

Owner:M TECH INSTR HLDG

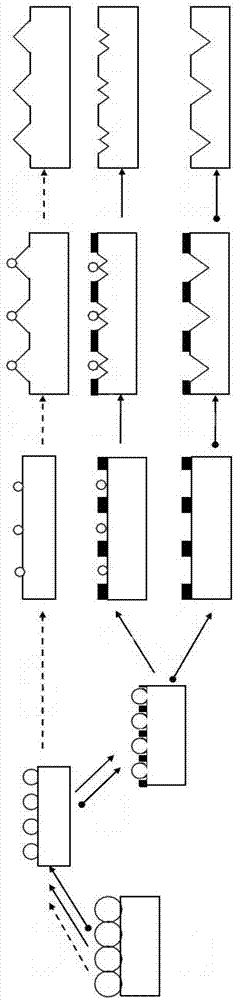

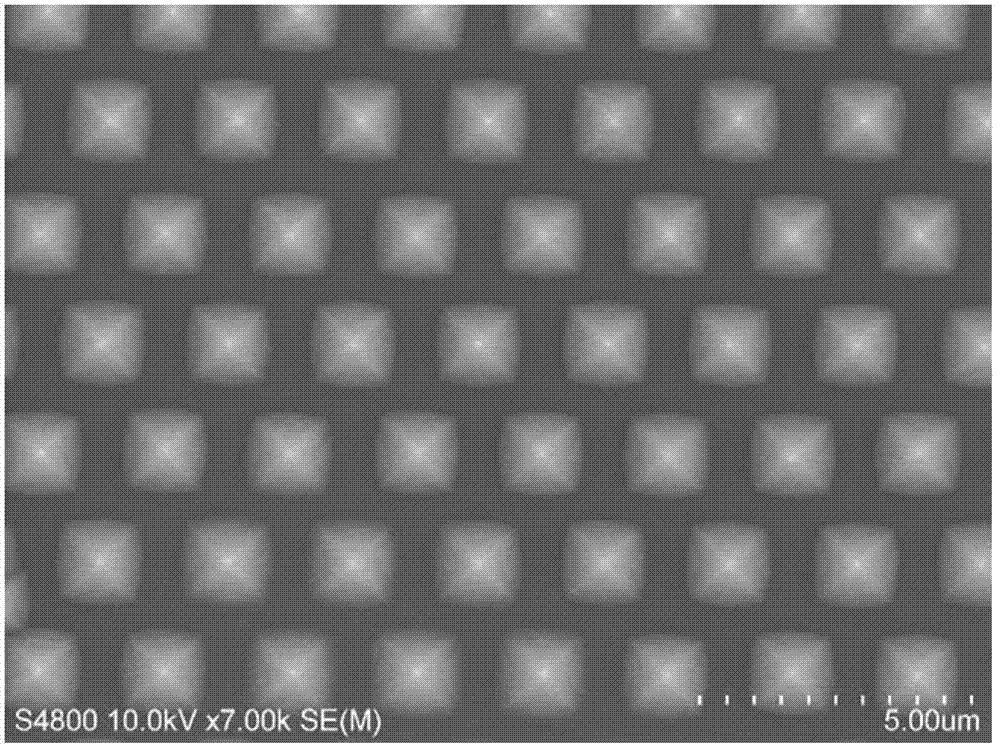

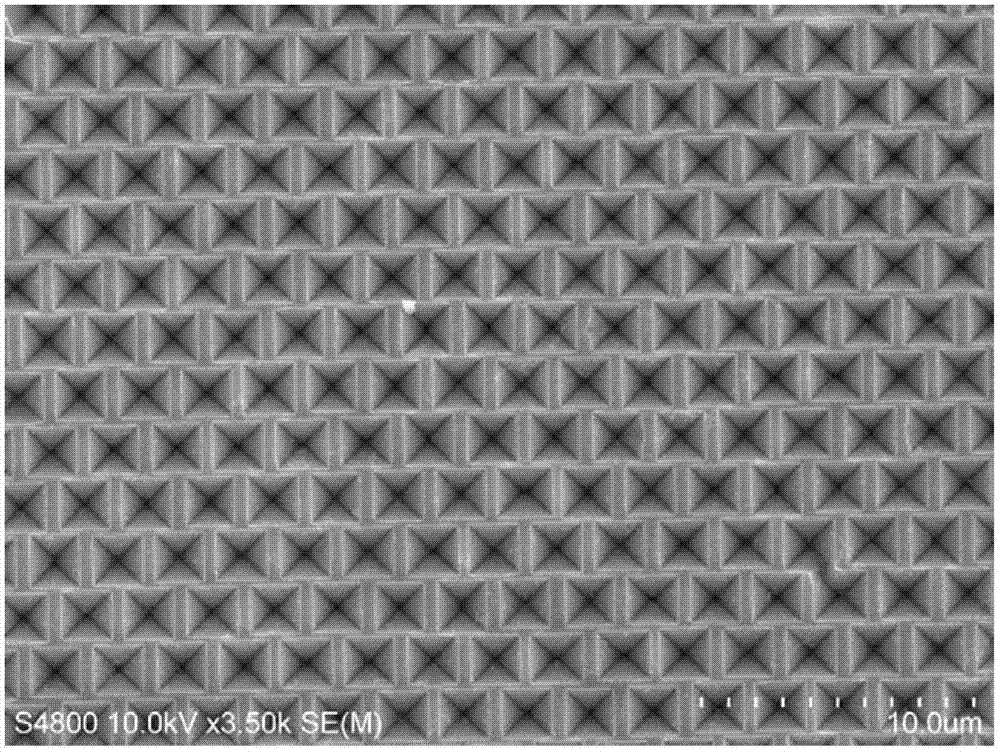

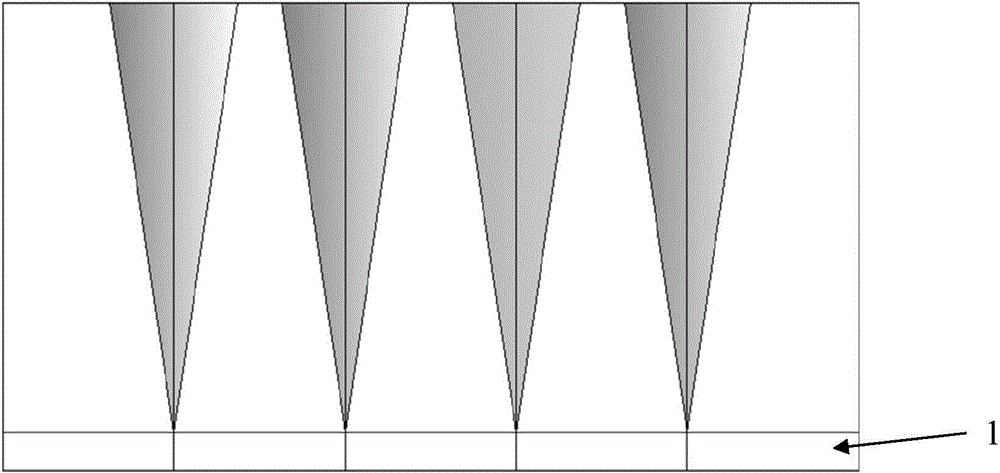

Method for preparing pyramid array on monocrystalline silicon substrate

ActiveCN103112816ALow costEasy to operateDecorative surface effectsChemical vapor deposition coatingMicrosphereGas phase

The invention relates to a method for preparing a pyramid array on a monocrystalline silicon substrate, and belongs to the technical field of manufacture of photovoltaic and semiconductor devices. The method comprises the following steps of: covering microballons in periodic arrangement on the surface of a monocrystalline silicon piece, and annealing near the glass transition temperature point of the microballoon; in oxygen atmosphere, obtaining a microballoon array in separation arrangement after etching by use of inductive coupling plasma; depositing a metallic titanium membrane on the monocrystalline silicon piece uniformly by a physical vapor deposition manner; and putting a silicon wafer with a masking film into an alkaline solution containing a surfactant for corrosion so as to obtain the pyramid array in order arrangement. The method is simple in process, short in preparation period and mature in technology; and three structures such as a positive pyramid array, an inverted pyramid array and a positive and inverted pyramid combined array can be obtained by a method for preparing a template through selecting and fine turning. The method has wide application value in the fields of photovoltaic, magnetic memory devices, nano photoelectric devices, nano sensors, surface raman enhancement and surface plasma effect and the like.

Owner:HUANGSHAN AKENT SEMICON TECH

Method of forming one or more nanopores for aligning molecules for molecular electronics

InactiveUS20030116531A1Less sensitiveDecorative surface effectsNanoinformaticsMolecular arrayMolecular electronics

A technique is provided for forming a molecule or an array of molecules having a defined orientation relative to the substrate or for forming a mold for deposition of a material therein. The array of molecules is formed by dispersing them in an array of small, aligned holes (nanopores), or mold, in a substrate. Typically, the material in which the nanopores are formed is insulating. The underlying substrate may be either conducting or insulating. For electronic device applications, the substrate is, in general, electrically conducting and may be exposed at the bottom of the pores so that one end of the molecule in the nanopore makes electrical contact to the substrate. A substrate such as a single-crystal silicon wafer is especially convenient because many of the process steps to form the molecular array can use techniques well developed for semiconductor device and integrated-circuit fabrication.

Owner:HEWLETT PACKARD DEV CO LP

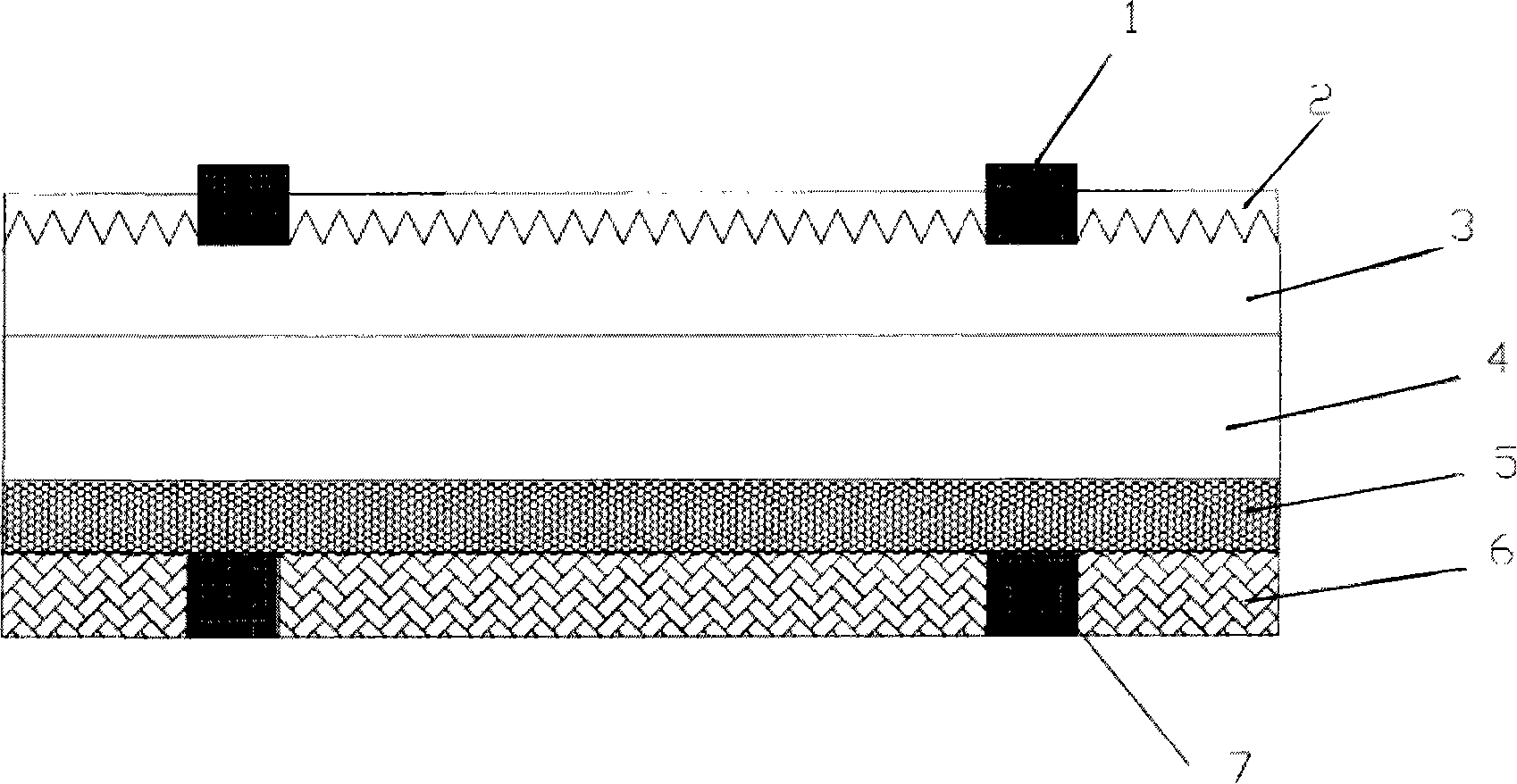

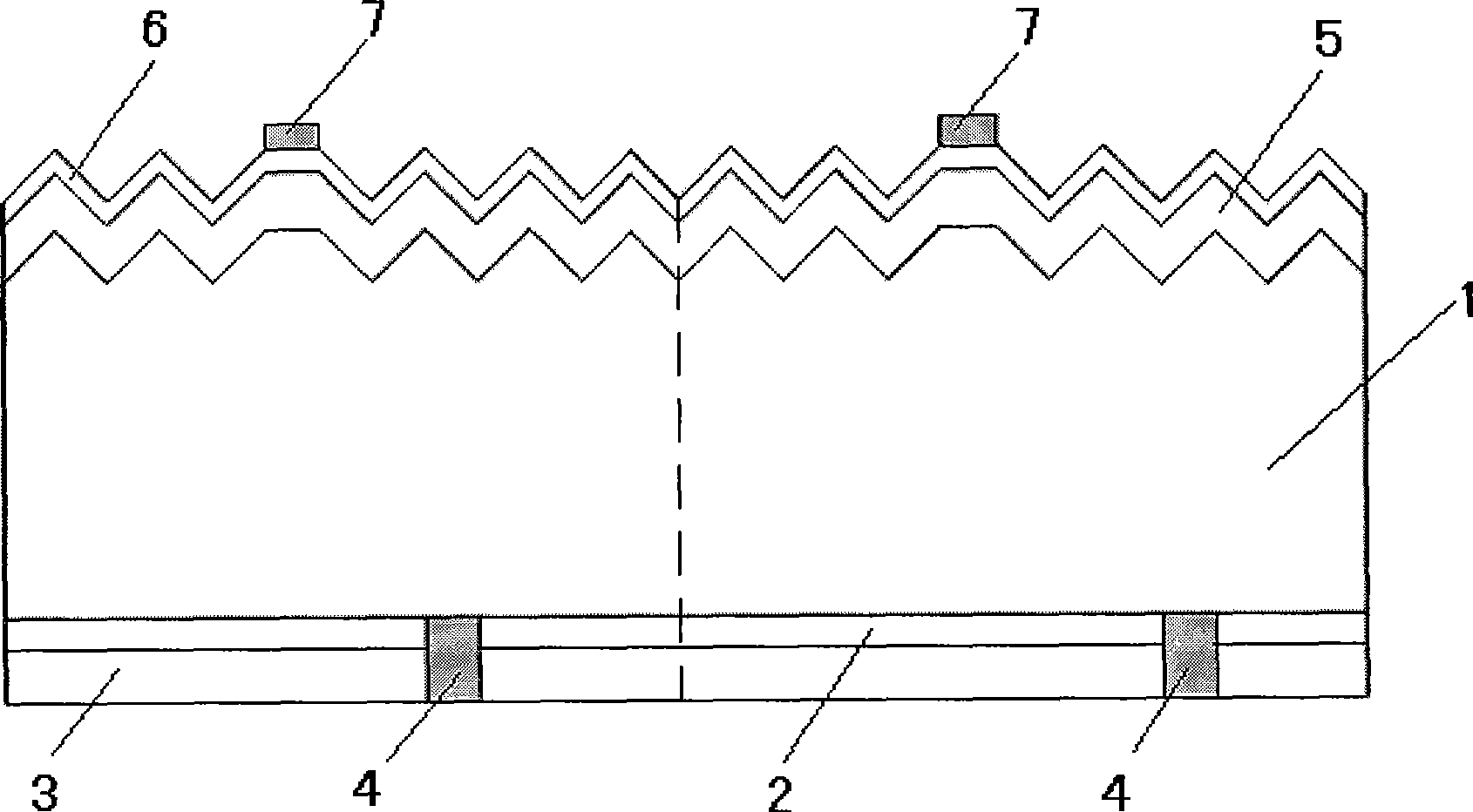

Novel aluminum emitter junction N type single crystal silicon solar battery

ActiveCN101150148ASolderabilitySolve problems that cannot be solved by firmness problemsFinal product manufacturePhotovoltaic energy generationScreen printingGrating

This invention provides a new type of type-N monocrystal silicon solar cells of Al back emission junction including: 1, Ag grating positive electrode, 2, SiNx reduction reflection layer of 80nm thick, 3, a positive N+phosphor diffusion layer of 0.3-0.5um thick, 4, type-N monocrystal silicon chip with the resistivity of 0.2-15ohmcm, 5, a P+ Al-Si alloy layer, 6,a back Al electrode, 7, a back AgAl master grating elctrode, in which, sintering of AlSi alloy and that of the back electrode are separated by two times of silk screen printing Al slurry and two times of sintering.

Owner:NINGBO ULICA SOLAR SCIENCE & TECHNOLOGY CO LTD

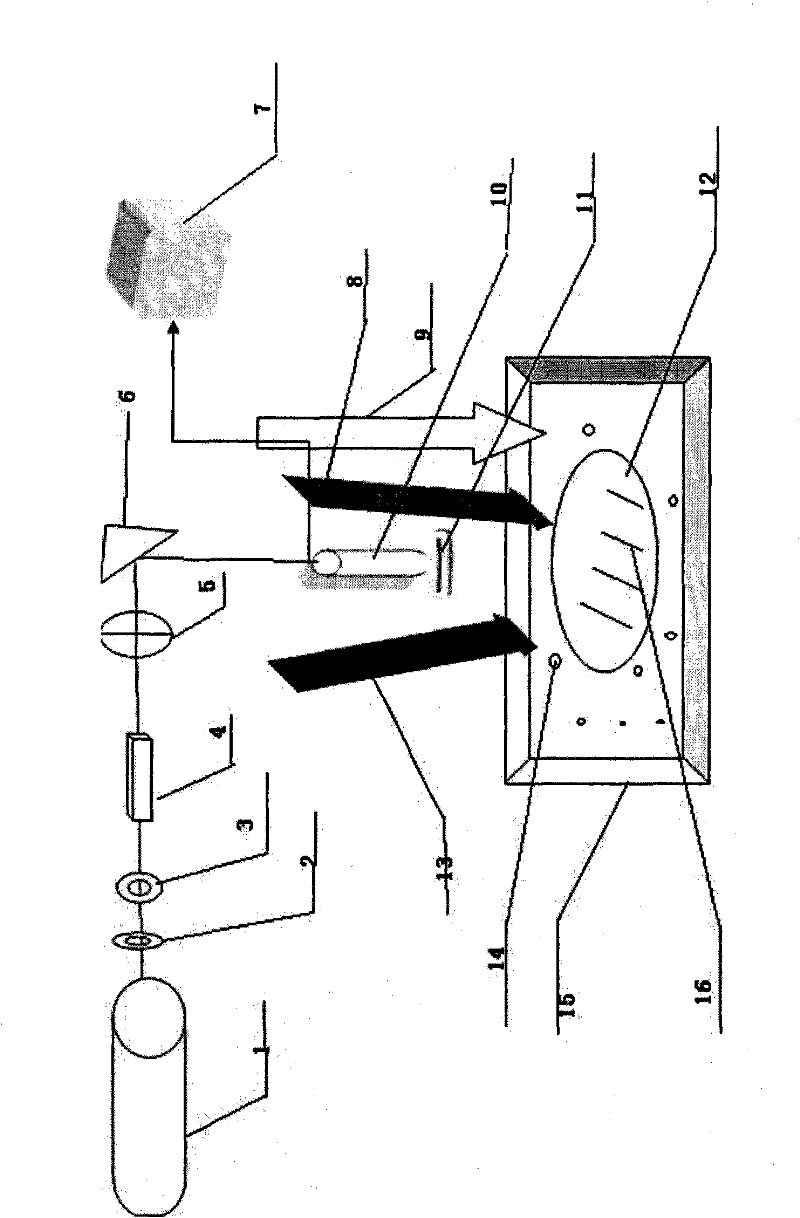

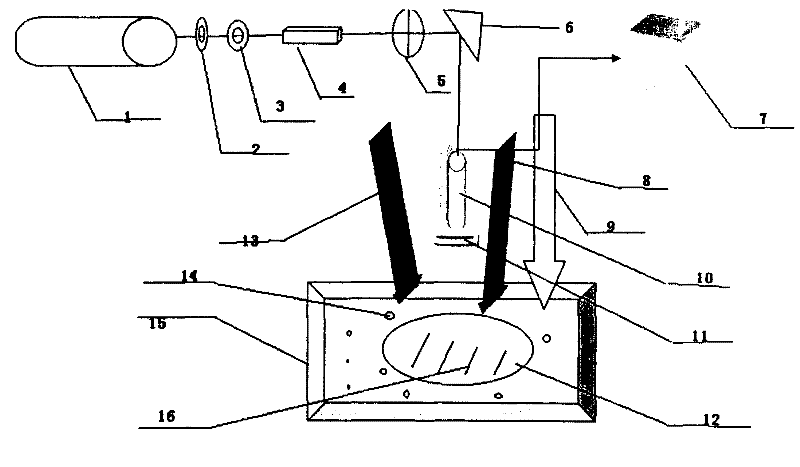

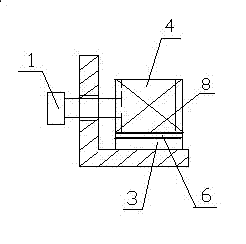

High-speed precision crystal silicon laser etching apparatus and method

InactiveCN102201493AEasy to controlNo pollution in the processLaser beam welding apparatusSemiconductor devicesHeat-affected zoneAutomatic control

The invention provides a high-speed precision crystal silicon laser etching apparatus and method. The method comprises the following steps: (A) placing a single crystal silicon wafer or a polycrystalline silicon wafer on a four-dimensional precision moving platform for laser processing by using a specific manipulator, with the aid of an observation and monitoring CCD system; (B) precisely focusing a laser beam on the surface of the silicon wafer, scanning the surface of the silicon wafer at a high speed by using a three-dimensional dynamic focusing vibration mirror in cooperation with a specific telecentric field lens, rising the surface etching temperature of the silicon wafer, and feeding phosphorous paste or phosphoric acid to a high-speed laser etching line at the same time; and (C) removing the manipulator for the silicon wafer and fixing next silicon wafer at the same time, and repeating the above drilling mode at. The method has the following advantages: laser has the characteristics of non-contact, no environment pollution and easy controllability, and can achieve the automatic control; since the laser focusing spot is in a micrometer size or smaller, thereby achieving high silicon wafer etching accuracy, small heat affected zone at the edge, and little damage to the substrate; and the power generation efficiency of the crystal silicon is further improved, and the production cost is further reduced.

Owner:周明

Method for preparing silicon nanowire array membrane electrode

InactiveCN101719543AImprove performanceEasy to makeElectrode manufacturing processesElectrode carriers/collectorsSingle crystal silicon waferLithium electrode

The invention discloses a method for preparing a lithium ion battery anode with high performance, i.e. a method for preparing a silicon nanowire array membrane electrode, comprising the following steps of: catalyzing corroded silicon wafers by a metal, and corroding a monocrystalline silicon piece into a silicon nanowire array membrane completely consisting of the silicon nanowire through corrosion twice; and preparing into the electrode by using two different techniques, wherein two different techniques are as follows: 1, plating an aluminum membrane at the back side of the silicon nanowire array membrane by using a method of vacuum thermal evaporation; annealing to form an Si-Al alloy which is used as a current collector; and 2, covering a carbon aerogel on the surface of the silicon nanowire array membrane, pyrolyzing the carbon aerogel into the carbon through vacuum sintering and using the carbon aerogel as a current collector. The silicon nanowire array membrane is used as the lithium ion battery assembled with the anode and has the advantages of large lithium storage capacity, high Kulun efficiency, favorable circulation stability, convenient operation, and favorable repeatability without complicated apparatus.

Owner:TSINGHUA UNIV

Monocrystalline silicon wafer alcohol-free texturing process and texturing additive

ActiveCN104576831AReduce CODReduce the cost of cashmereAfter-treatment detailsFinal product manufactureAlcohol freePotassium hydroxide

The invention relates to a monocrystalline silicon wafer alcohol-free texturing process and a texturing additive. Firstly, a silicon wafer is placed in preprocessing liquid so as to be preprocessed for 60 s to 300 s, and the silicon wafer is then placed in texturing liquid for texturing. The monocrystalline silicon texturing process includes the steps that deionized water is heated to 70 DEG C to 90 DEG C, sodium hydroxide or potassium hydroxide is added, and monocrystalline silicon texturing corrosive liquid is acquired. When the texturing additive is adopted for texturing, isopropanol or ethyl alcohol is not needed, tiny, even and dense pyramid texturing faces can be acquired, texturing cost is reduced, and environmental pollution is avoided. The preprocessing process is added before the texturing step, the silicon wafer acquired after texturing can be cleaner, rework caused by white spot fingerprints and the like can be reduced, and certain practical value is achieved.

Owner:JIANGSU SHUNFENG PHOTOVOLTAIC TECH CO LTD

Cleaning process of monocrystalline silicon wafer

InactiveCN102327882AImprove work efficiencyEasy to cleanCleaning using liquidsMegasonic cleaningSilicon chip

The invention relates to a cleaning process of a monocrystalline silicon wafer. The cleaning process comprises the following steps: (1) pre-flushing: orderly cleaning the monocrystalline silicon wafer in four grooves of a four-groove degumming machine; (2) degumming: manually degumming the pre-flushed silicon wafer; (3) ultrasonic wave cleaning: immersing the degummed silicon wafer in a six-groove type ultrasonic wave cleaning machine; (4) whirling: centrifugally whirling the cleaned silicon wafer on a centrifugal whirling device; (5) checking; detecting the appearance of the whirled silicon wafer, entering the other processes when the detection is qualified. The cleaning process has good cleaning effect, the yield is greatly improved, and the working efficiency of the machine is greatly improved.

Owner:无锡尚品太阳能电力科技有限公司

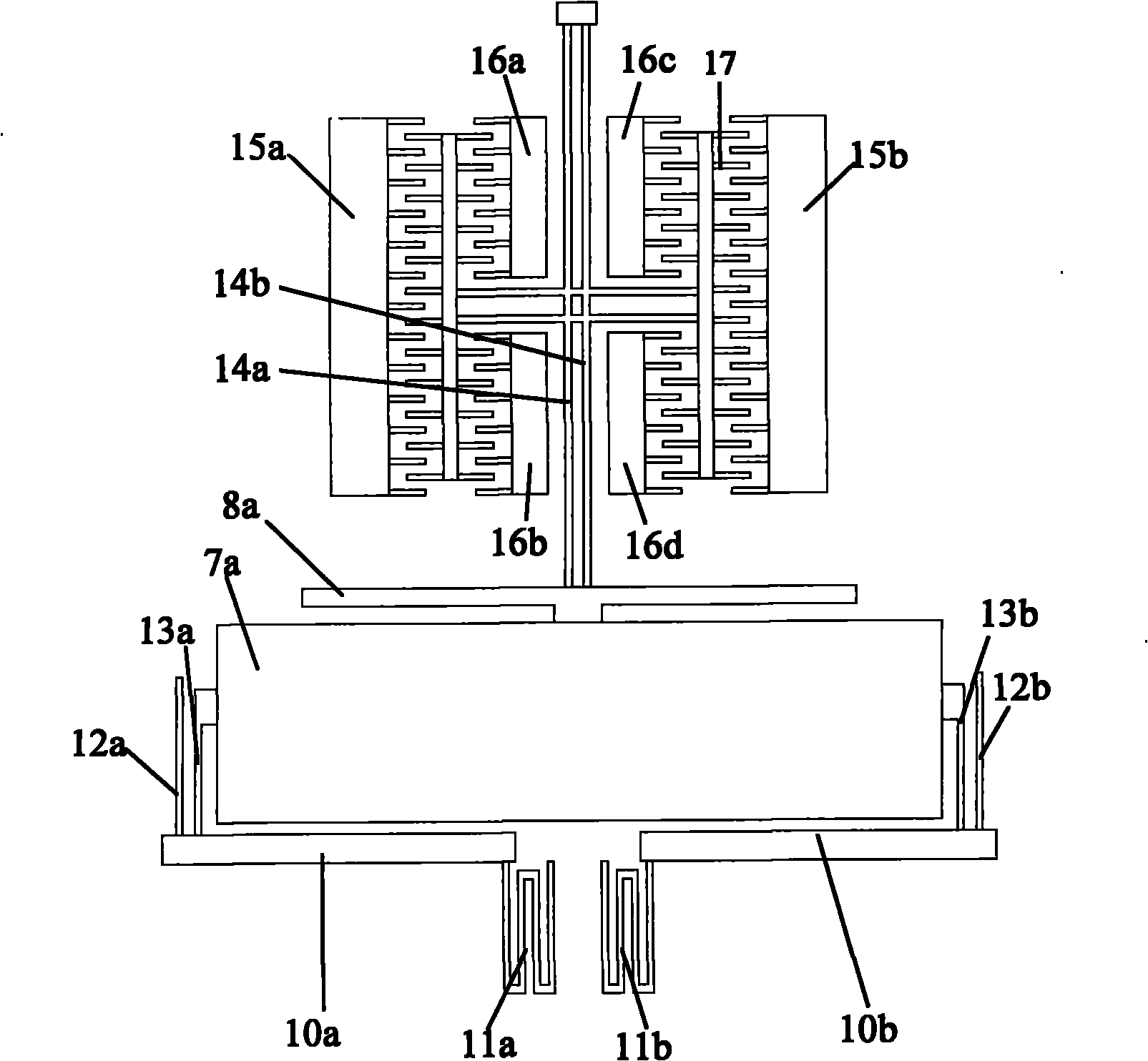

Silicon micro-resonant accelerometer

ActiveCN101963624AImprove stabilityIncrease stiffnessAcceleration measurementPiezoelectric/electrostrictive devicesAccelerometerWorking environment

The invention discloses a silicon micro-resonant accelerometer which comprises an upper layer and a lower layer, wherein the upper layer is an accelerometer mechanical structure manufactured on a single-crystal silicon wafer, the lower layer is a signal lead manufactured on a glass substrate, the accelerometer mechanical structure comprises a mass block, an outer frame, two resonators, four primary leverage amplification mechanisms, two rigid rods and two guide mechanisms, a first resonator and a second resonator are symmetrically arranged at the upper side and the lower side of the mass block, one end of either resonator is connected with the outer frame, and the other end is connected with the guide mechanism; and the mass block is connected with the outer frame by four multi-folded beams, and the outer frame enables the mechanical structure part at the upper layer to suspend above the glass substrate part at the lower part by means of four fixed bases which are symmetrical with the center of the mass block. The invention greatly reduces the influence of residual machining stress and heat stress produced by the temperature change of the working environment on the vibration frequency of the structure, improves the stability of the resonant frequency of the resonator and reduces the temperature coefficient of frequency.

Owner:NANJING UNIV OF SCI & TECH

Texturing method of quasi-single crystal silicon wafer

InactiveCN102468371AReduce dosageReduce consumptionAfter-treatment detailsFinal product manufactureCrystal orientationSingle crystal

The invention relates to a texturing method of a quasi-single crystal silicon wafer. The texturing method is characterized in that the method comprises the following steps that: a wet etching method is employed to remove a mechanical damage layer on a quasi-single crystal silicon wafer that based on crystal grain crystal grains; and according to a proportion for which the crystal grains account, plasma etching and reactive ion etching are employed to carry out single crystal texturing. Therefore, there is no need for deionized water to carry out the plasma etching and the reactive ion etching; and less chemical reagent dosages are required. Meanwhile, pollution of reaction product discharging is low as well as safety and environmental-friendly performances are realized. Moreover, reflectivity of the textured quasi-single crystal silicon wafer is less than 15%; the surface light tripping effect is good; and the cell slice gives full play to advantages of the quasi-single crystal silicon wafer; the textured surface texturing is independent of conditions of the crystal orientation and the substrate; and advantages of high reliability, easiness for control and less silicon chip consumption are realized; and the utilization of the method is beneficial for application of thin silicon chips.

Owner:SUZHOU TALESUN SOLAR TECH CO LTD

Monocrystalline silicon wafer texture surface making additive and application

ActiveCN106119977ATexture fastFast response to texturingPolycrystalline material growthAfter-treatment detailsEtherPyramid

The invention provides a monocrystalline silicon wafer texture surface making additive. The monocrystalline silicon wafer texture surface making additive comprises the following components in percentages by mass: 0.1%-3% of a component A, 0.01%-10% of a component B and the balance of water. The component A is selected from one or more of crown ether, crown ether derivatives and alkali metal complex of the crown ether; and the component B is alcohol ether. The invention further provides texture surface making liquid for monocrystalline silicon wafer texture surface making. The texture surface making liquid contains an alkali solution and the monocrystalline silicon wafer texture surface making additive. The invention further provides a monocrystalline silicon wafer texture surface making method. Texture surface making on a monocrystalline silicon wafer is carried out by the texture surface making liquid. The additive is added in the monocrystalline silicon wafer texture surface making liquid, so that texture surface making reaction becomes fast, quick texture surface making on the monocrystalline silicon wafer cut by a diamond wire can be carried out, the capacity is improved, uniform and compact texture surface pyramids can be obtained, the reflectivity is reduced, and the efficiency of a battery is improved.

Owner:CHANGZHOU SHICHUANG ENERGY CO LTD

A single crystal short rod splicing method using diamond wire cutting

InactiveCN102294757AIncrease profitThere will be no pull-out phenomenonFine working devicesWire cuttingEngineering

The invention discloses a single crystal short rod splicing method using diamond wire cutting. First, the end face of the single crystal silicon short rod is detected, and the flatness of the end face is required to be less than 0.3mm, and then the short rod is bonded by coating the end face with glue. After bonding, it is pressurized and solidified, and then the splicing rods are squared, end-face ground, and rolled. After passing the inspection, the splicing rods are cut into single-crystal silicon wafers in the slicing cabin. Make full use of all short monocrystalline silicon rods, greatly improve the utilization rate of short monocrystalline silicon rods, and reduce production costs. Since the splicing rods are not perpendicular to the diamond wire, the diamond wire does not need Adjusting the position of the wire cutting device can make the diamond wire never appear empty when cutting the splicing rod. The splicing rod method of the present invention can make full use of the single crystal silicon short rod to be processed into silicon wafers, which improves the round silicon The utilization rate of rods reduces the processing cost.

Owner:江西金葵能源科技有限公司

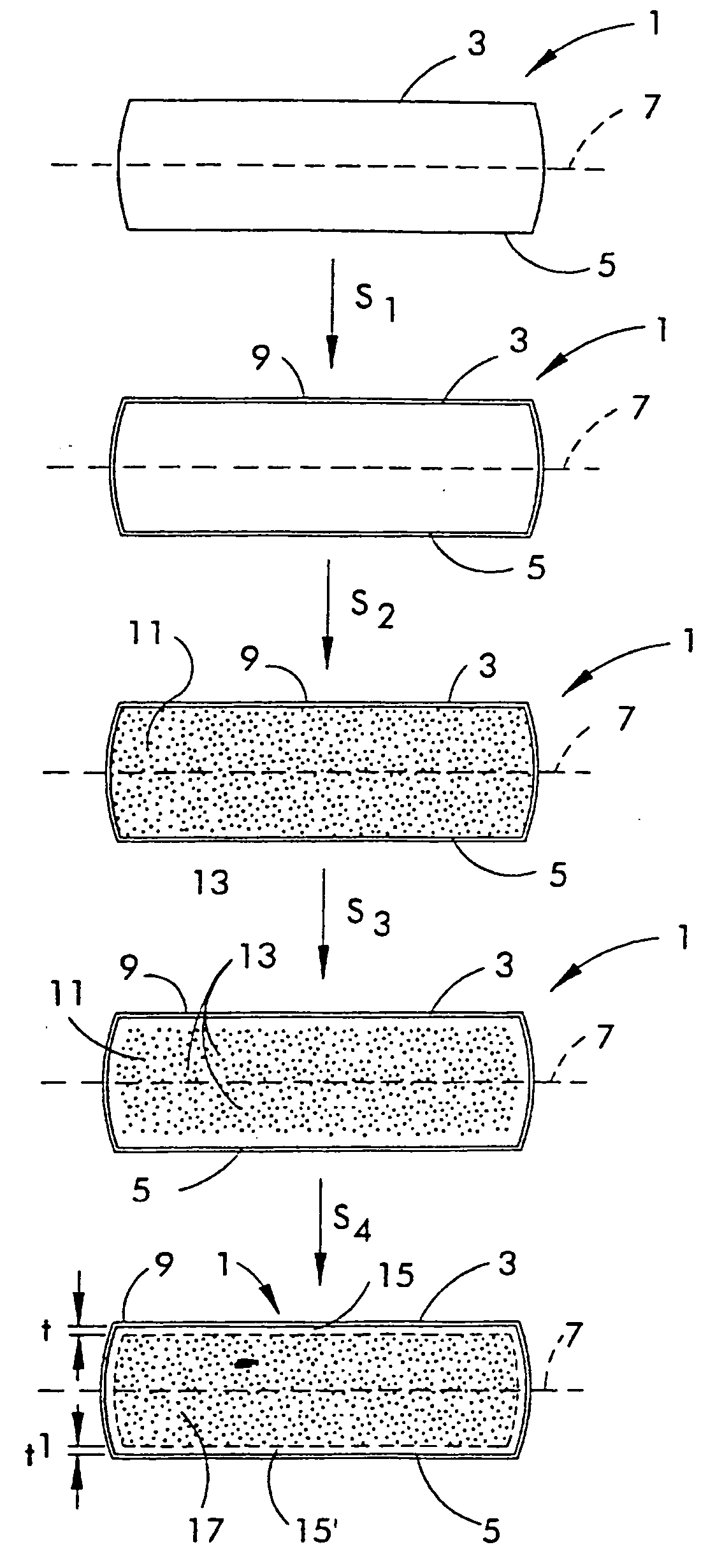

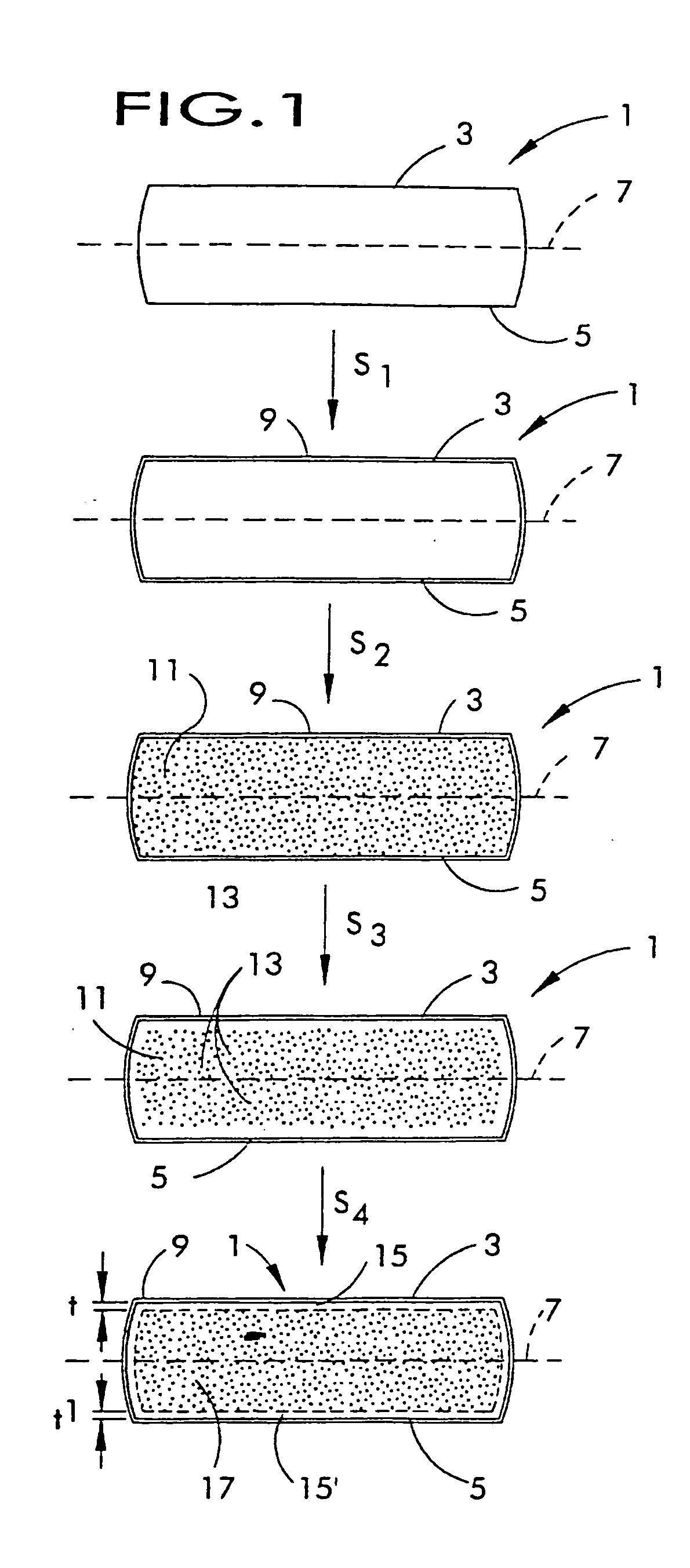

Silicon Heterojunction Solar Cells

InactiveUS20130180578A1Improve device performanceCostSemiconductor/solid-state device manufacturingPhotovoltaic energy generationCell fabricationSolar cell

Methods are described for fabricating HIT solar cells, including double heterojunction and hybrid heterojunction-homojunction solar cells, with very thin single crystal silicon wafers, where the silicon wafer may be less than 80 microns thick, and even less than 50 microns thick. The methods overcome potential issues with handling these very thin wafers by using a process including epitaxial silicon deposition on a growth substrate, partial cell fabrication, attachment to a support substrate and then separation from the growth substrate. Some embodiments of the present invention may include a solar cell device architecture comprising the combination of a heterostructure on the front side of the device with a homojunction at the rear of the device. Furthermore, device performance may be enhanced by including a dielectric stack on the backside of the device for reflecting long wavelength infrared radiation.

Owner:SVAGOS TECHNICK INC

Method for detecting microdefects of quasi monocrystalline silicon sheets

InactiveCN104900758AGood casting processImprove conversion efficiencyFinal product manufactureSemiconductor devicesCooking & bakingMicroscopic observation

The invention discloses a method for detecting microdefects of quasi monocrystalline silicon sheets. The method includes a manually and mechanically polishing step of manually and mechanically polishing aquasi monocrystalline silicon sheet to be etched and flushing the quasi monocrystalline silicon sheet with deionized water; a chemical etch polishing step of chemically etching and polishing the silicon sheet subjected to the mechanical polishing and rinsing the silicon sheet with deionized water; a preferential microdefect etching step of carrying out preferential microdefect etching on the silicon sheet subjected to the chemically etching and polishing, rinsing the silicon sheet with deionized water and drying the silicon sheet in a baking oven; and a microdefect observation process of carrying out minority carrier lifetime and iron-boron opposite scanning for the etched silicon chip, observing the minority carrier lifetime scanning color distribution by a metallographic microscope, accurately positioning the microdefect positions, classifying the defect types, positioning and cutting the silicon chip into pieces, and marking the pieces. The method is rapid, accurate, energy-saving, environmental-friendly, pollution-free and highly practical.

Owner:连云港市产品质量监督检验中心

Miniature solid or hollow silicon needle, silicon needle array and preparing method thereof

InactiveCN101244303AReduce thicknessStable structureDecorative surface effectsMicroneedlesCrystal orientationHollow core

The invention discloses a miniature solid or hollow silicon needle, a silicon needle array and the manufacture method, belonging to the medical service and hairdressing apparatus and micro machining technical field. The lower end of the miniature silicon needle head is column. The upper needle point of the needle head is provided with at least one arc sharp corner to form the peak. A through hole is arranged on the peak and is connected with the inverse triangle groove at the bottom. By micro-electronics craft, at the positive and the back surfaces of the (110) crystal orientation monocrystalline silicon wafer, two kinds of inverse triangle grooves are processed in batches which are formed by six silicon (111) surfaces, using the anisotropism self-stop wet corrosion. Then the silicon needle and a through hole are manufactured by the DRIE method. The through hole is connected with the back inverse triangle groove. The invention has the advantages that: the solid or hollow silicon needle array can be manufactured in batches with low cost, high productivity and firm structure; the invention has a wider potential application in the transdermal drug delivery, micro body fluid extraction and other biomedical field.

Owner:TSINGHUA UNIV

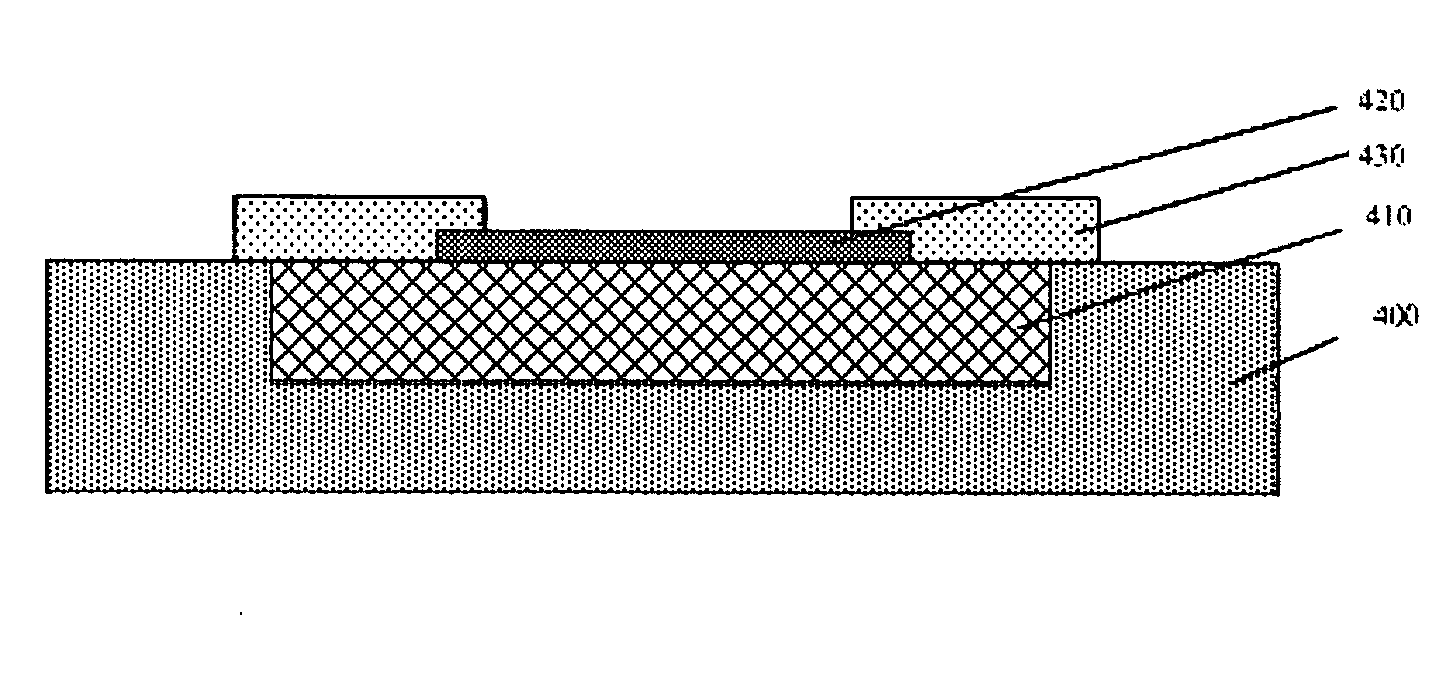

Methods for manufacturing MEMS sensor and thin film and cantilever beam thereof with epitaxial growth process

ActiveUS7972888B1Easy to controlControl thicknessFluid pressure measurement by electric/magnetic elementsSemiconductor/solid-state device manufacturingWaferingMems sensors

A method for manufacturing a MEMS sensor and its thin film and cantilever beam includes steps of etching a top surface of a single-crystal silicon wafer in combination of a deposition process, an outer epitaxial growth process, a wet etching process and a back etching process in order to form a pressure-sensitive single-crystal silicon film, a cantilever beam, a mass block, a front chamber, a back chamber and trenches connecting the front and the back chambers. The single-crystal silicon film is prevented from etching so that the thickness thereof can be well controlled. The method of the present invention can be used to replace the traditional method which forms the back chamber and the pressure-sensitive single-crystal silicon film from the bottom surface of the silicon wafer.

Owner:MEMSENSING MICROSYST SUZHOU CHINA

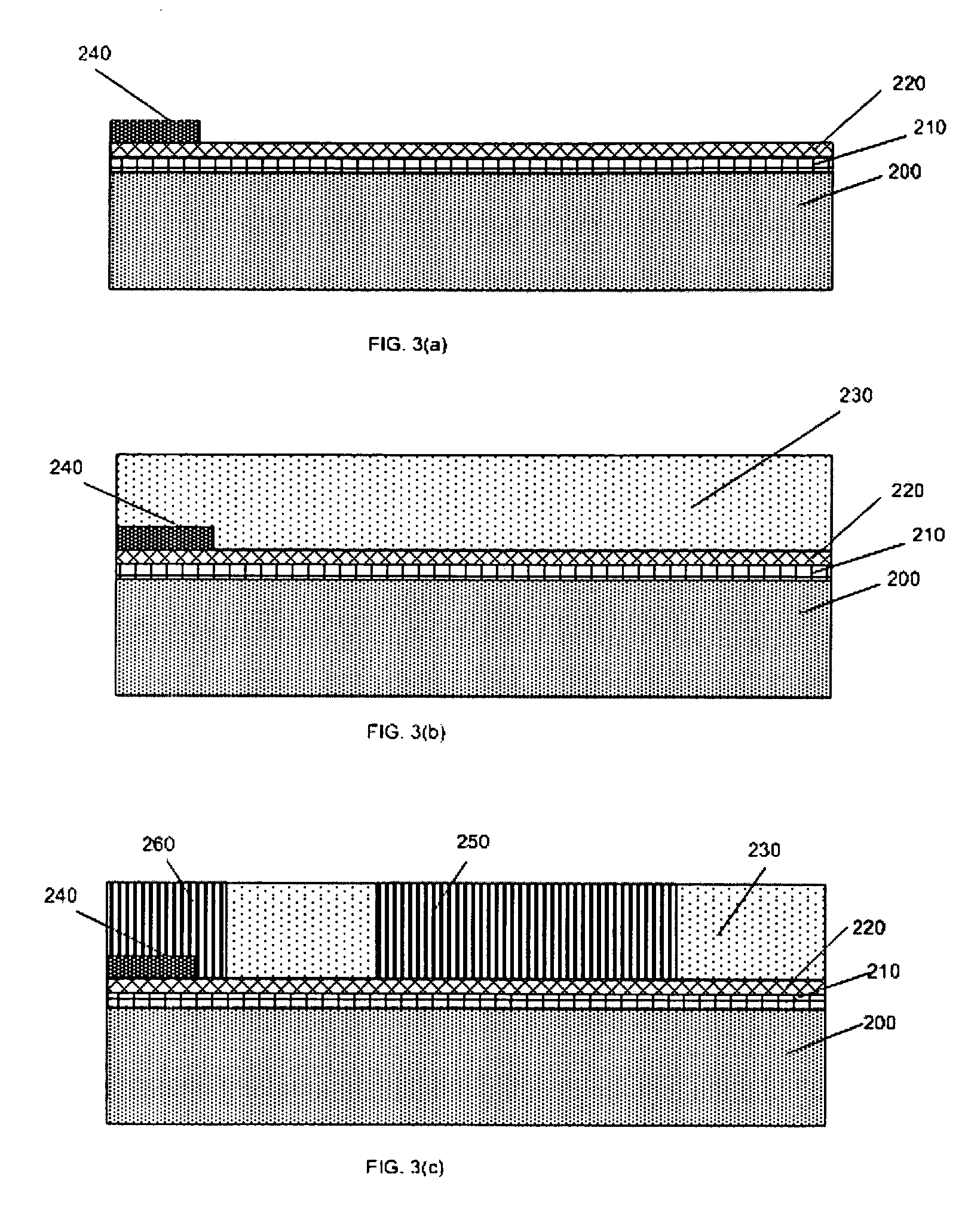

Wavelength converter, manufacturing method thereof and related wavelength conversion device

The embodiment of the invention discloses a wavelength converter, a manufacturing method thereof and a related wavelength conversion device. The manufacturing method of the wavelength converter comprises the steps of forming a mask layer with a mask-free region on a first surface of a monocrystalline silicon wafer of which the first surface is a <100> crystal face or a <110> crystal face, putting the monocrystalline silicon wafer in predetermined etching solution for etching to form a micro structure array on the first surface, and sequentially forming a reflective layer and a wavelength conversion layer on the surface of the micro structure array. The invention can provide a manufacturing method for a wavelength converter has a smooth-surface micro structure array.

Owner:APPOTRONICS CORP LTD

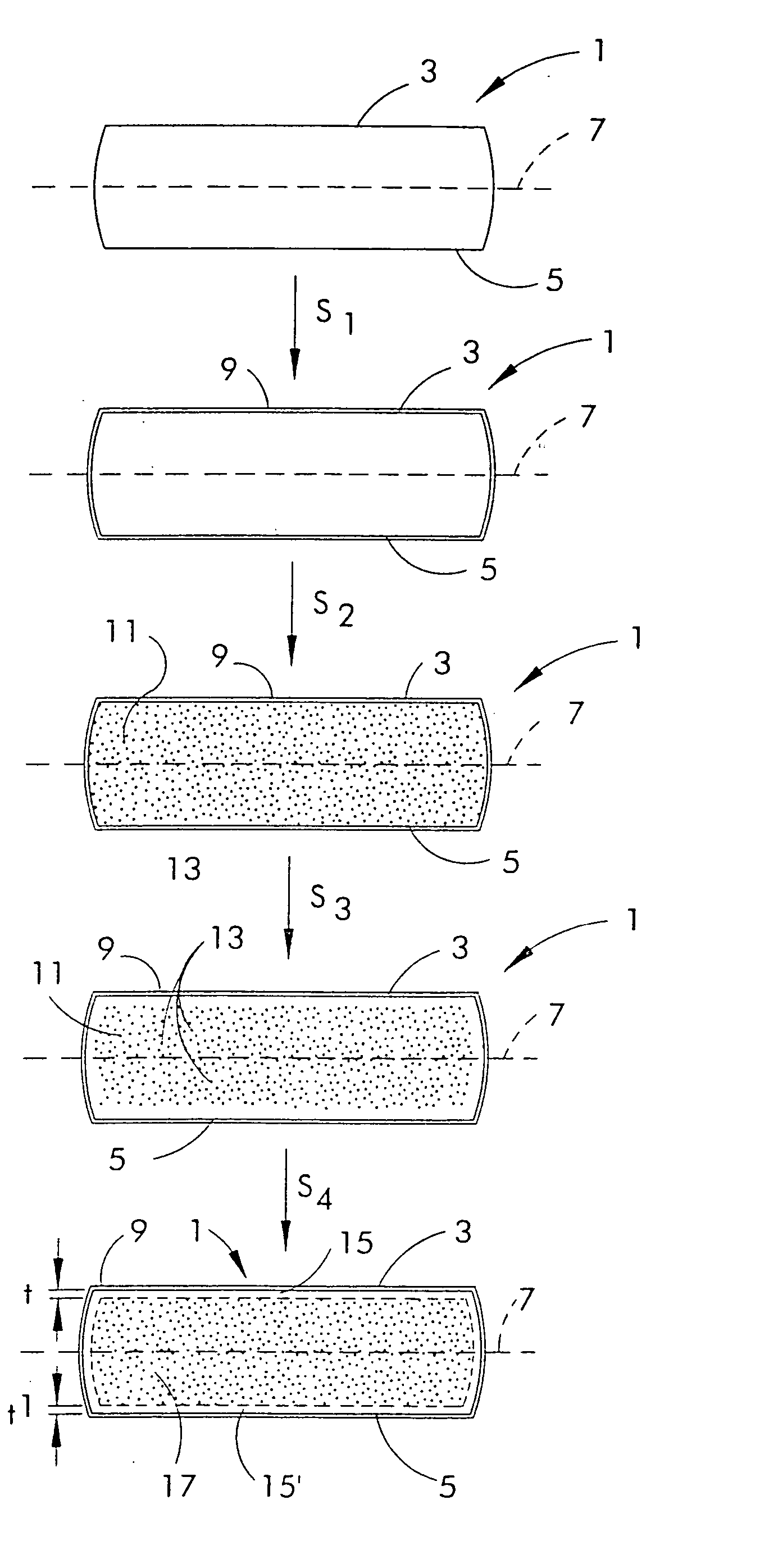

Process for making silicon wafers with stabilized oxygen precipitate nucleation centers

A process for imparting controlled oxygen precipitation behavior to a single crystal silicon wafer. Specifically, prior to formation of the oxygen precipitates, the wafer bulk comprises dopant stabilized oxygen precipitate nucleation centers. The dopant is selected from a group consisting of nitrogen and carbon, and the concentration of the dopant is sufficient to allow the oxygen precipitate nucleation centers to withstand thermal processing, such as an epitaxial deposition process, while maintaining the ability to dissolve any grown-in nucleation centers.

Owner:SUNEDISON SEMICON LIMITED UEN201334164H

Fabrication method of P-type back-surface tunneling oxide passivation contact solar cell

InactiveCN110233180AAvoid secondary diffusionEasy to operateFinal product manufacturePhotovoltaic energy generationOperabilitySilicon thin film

The invention provides a fabrication method of a P-type back-surface tunneling oxide passivation contact solar cell. The method comprises the steps of performing previous process processing on a frontsurface and a back surface of a P-type single-crystal silicon wafer; oxidizing the back surface to form an ultrathin tunneling oxide layer and fabricate a boron-doping silicon thin film layer; performing phosphorus diffusion on the front surface of the single-crystal silicon wafer, and fabricating a selective emitter; and printing metal electrodes on surfaces of a first passivation anti-reflection layer on the back surface and a second passivation anti-reflection layer on the front surface of the single-crystal silicon wafer, and forming favorable contact between the metal electrodes and thesingle-crystal silicon wafer, thereby obtaining P-type back-surface tunneling oxide passivation contact of the solar cell. The invention provides a complete and practical P-type tunneling oxide passivation contact solar fabrication process circuit, a process method of first back-surface boron-doping poly-silicon thin film and then front-surface phosphorus diffusion, secondary phosphorus diffusioncan be effectively prevented, so that a phenomenon that square resistance is not matched is generated, and the operability is high.

Owner:SUZHOU TALESUN SOLAR TECH CO LTD

Process for implementing oxygen into a silicon wafer having a region which is free of agglomerated intrinsic point defects

InactiveUS20050130394A1Improve inhalation effectPolycrystalline material growthSemiconductor/solid-state device testing/measurementSilicon on insulatorSingle crystal silicon wafer

The present invention relates to a process for the preparation of a silicon on insulator wafer. The process includes implanting oxygen into a single crystal silicon wafer which is substantially free of agglomerated vacancy-type defects. The present invention further relates to a process for the preparation of a silicon on insulator wafer wherein oxygen is implanted into a single crystal silicon wafer having an axially symmetric region in which there is a predominant intrinsic point defect which is substantially free of agglomerated intrinsic point defects. Additionally, the present invention relates to a silicon on insulator (“SOI”) structure in which the device layer is substantially free of agglomerated intrinsic point defects.

Owner:MEMC ELECTONIC MATERIALS INC

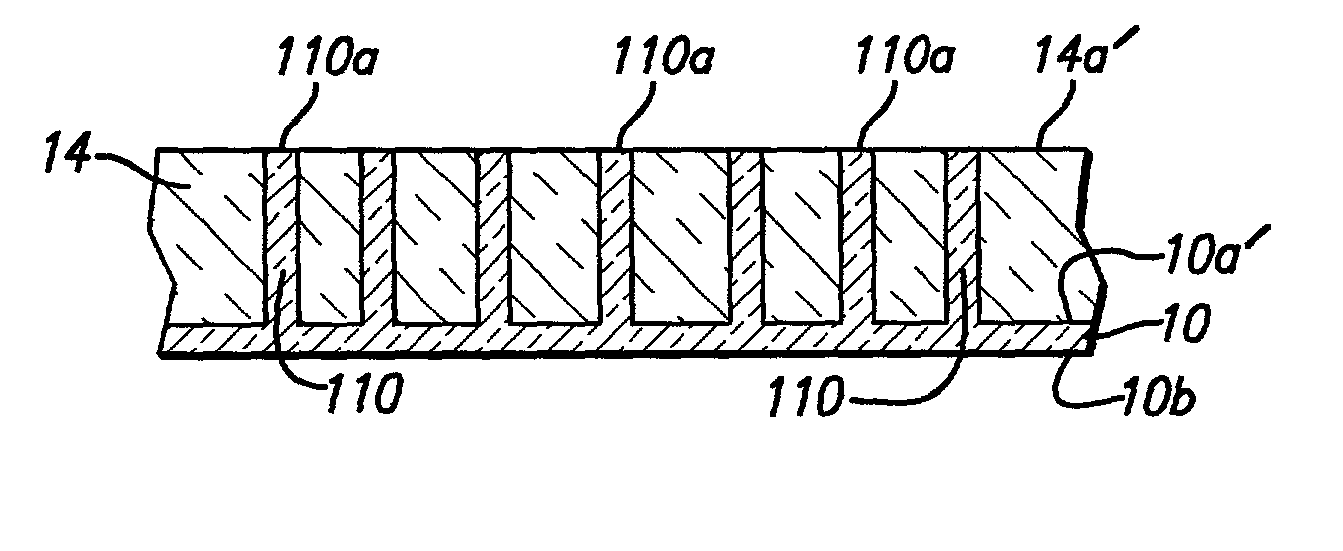

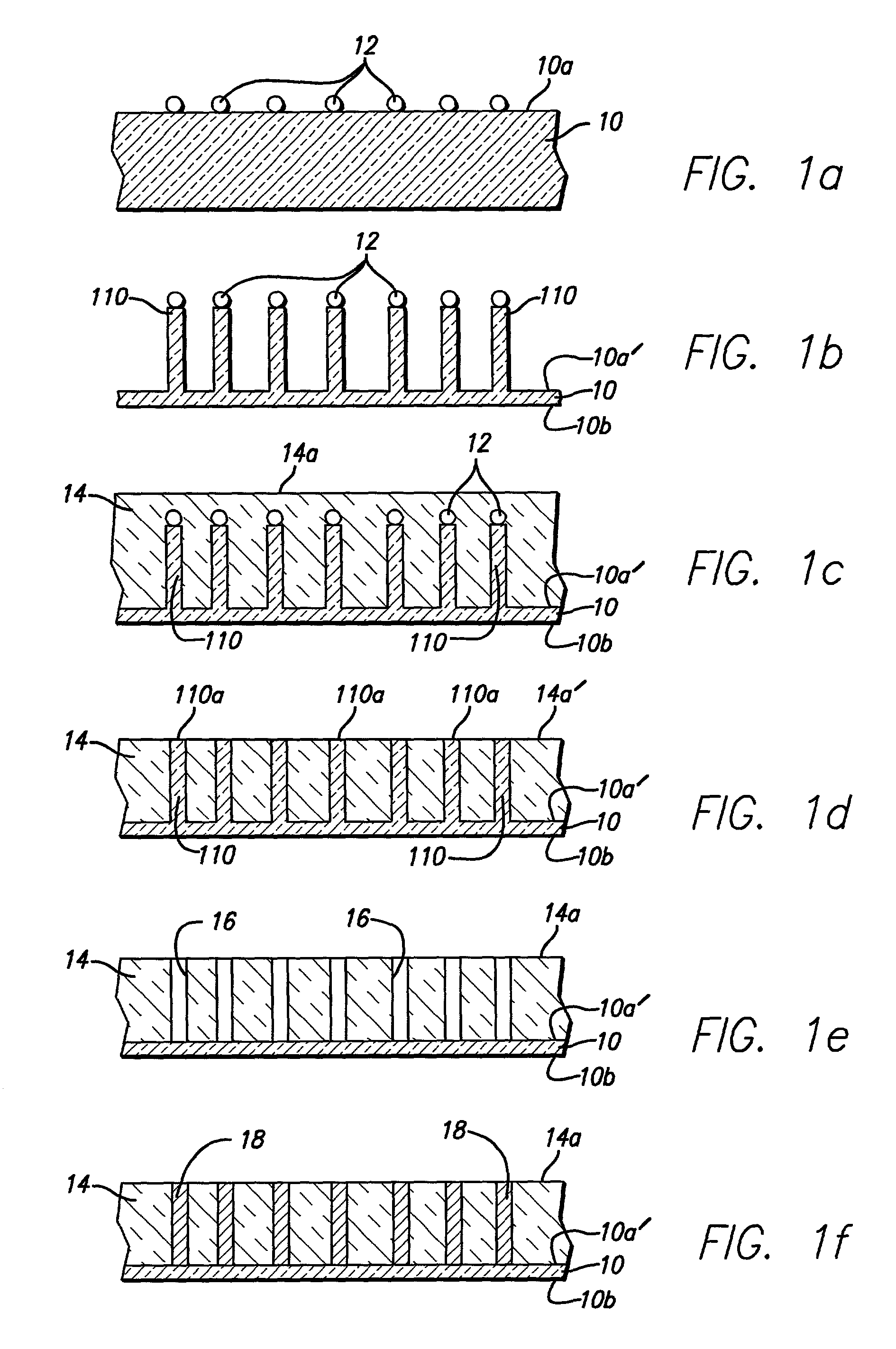

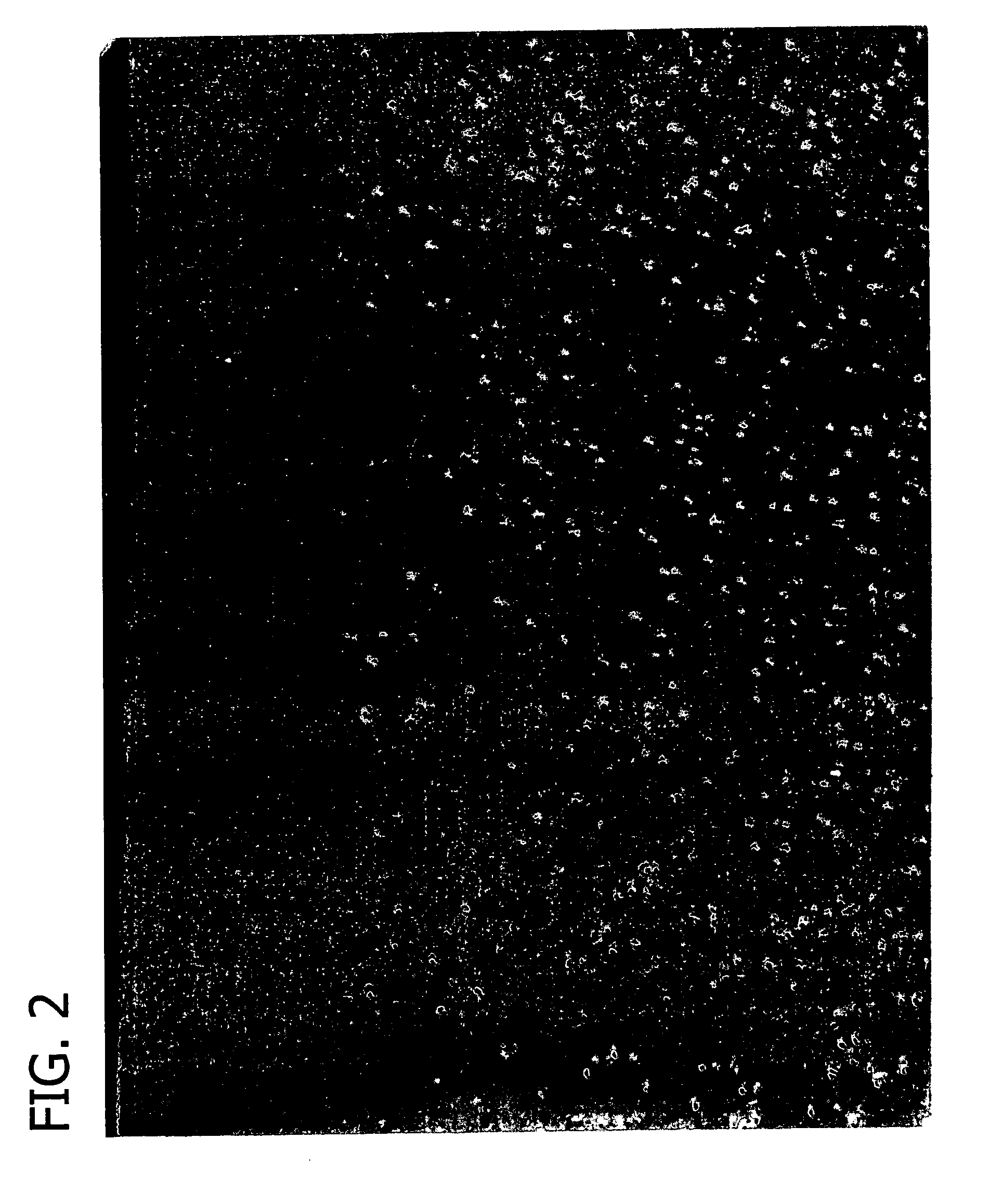

Integrated passive devices

InactiveUS7259077B2Facilitate processing handlingHigh resistivitySemiconductor/solid-state device detailsSolid-state devicesProduction lineWafering

The specification describes an integrated passive device (IPD) that is formed on a polysilicon substrate. A method for making the IPD is disclosed wherein the polysilicon substrate is produced starting with a single crystal handle wafer, depositing a thick substrate layer of polysilicon on one or both sides of the starting wafer, forming the IPD on one of the polysilicon substrate layers, and removing the handle wafer. In a preferred embodiment the single crystal silicon handle wafer is a silicon wafer rejected from a single crystal silicon wafer production line.

Owner:SYCHIP

Methods for manufacturing MEMS sensor and thin film thereof with improved etching process

ActiveUS7998776B1Fluid pressure measurement by electric/magnetic elementsSemiconductor/solid-state device manufacturingEngineeringMems sensors

A method for manufacturing a MEMS sensor and a thin film thereof includes steps of etching a top surface of a single-crystal silicon wafer in combination of a deposition process, an isotropic DRIE process, a wet etching process and a back etching process in order to form a pressure-sensitive single-crystal silicon film, a cantilever beam, a mass block, a front chamber, a back chamber and trenches connecting the front and the back chambers. The single-crystal silicon film is prevented from etching so that the thickness thereof can be well controlled. The method of the present invention can be used to replace the traditional method which forms the back chamber and the pressure-sensitive single-crystal silicon film from the bottom surface of the silicon wafer.

Owner:MEMSENSING MICROSYST SUZHOU CHINA

Test method of residual stress of silicon single crystal piece

ActiveCN102435361AEasy to pressImprove the quality of workmanshipForce measurementSingle crystalStrain gauge

The invention discloses a test method of residual stress of a silicon single crystal piece. Main test steps comprise preparing a three-dimensional strain rosette, a strain gauge, a detected silicon single crystal piece and the like, pasting the three-dimensional strain rosette, testing an initial value of each resistor of the three-dimensional strain rosette and recording the value, cutting a silicon chip to release a stress, testing each data of the three-dimensional strain rosette again and recording the data, processing the data, and analyzing and discussing a result. According to the invention, the three-dimensional strain rosette is taken as a strain sensor, a cutting method is employed to release a residual stress of the silicon chip, through employing an YE2539 high speed static strain indicator to measure reverse direction strain of the strain rosette tightly pasted on the silicon chip, size and direction of a residual stress of each point on the silicon chip can be calculated, and a unique test operation process of the silicon chip is formed. Test precision is high, speed is fast, and cost is low. A test result analysis shows that: total residual stress of a monocrystalline silicon piece is small, a residual stress at a circumference edge is large relative to an internal measuring point, a maximum residual stress of an unprocessed monocrystalline silicon piece is large relative to a processed monocrystalline silicon piece.

Owner:扬州晶新微电子有限公司

Ant-apex contact heterojunction solar battery and preparation method thereof

InactiveCN101447518AImprove photoelectric conversion efficiencyLow costPhotovoltaic energy generationSemiconductor devicesHeterojunctionSingle crystal

The invention relates to an ant-apex contact heterojunction solar battery and a preparation method thereof. The ant-apex contact heterojunction solar battery is characterized in that a plurality of units are included; each unit adopts a P-type or N-type single crystal silicon as a silicon substrate which is used as a base region of the battery; a passivation layer and an aluminium layer are sequentially prepared on the back surface of the silicon substrate from inside to outside, and a point contact base electrode is formed on the surface of the aluminium layer; an amorphous layer used as an emitter region of the battery is deposited on the right surface of the silicon substrate; a transparent conductive film and an emitter region electrode arranged on the transparent conductive film are arranged on the surface of the amorphous layer; and when in use, the base electrode and the emitter region electrode of each unit are respectively connected with an anode and a cathode of electrical equipment through leads. In the ant-apex contact heterojunction solar battery and the preparation method thereof, because the point contact base electrode which is realized through the laser heating technique is adopted on the back surface of the silicon substrate, the effect for passivating and reducing ohmic contact of the electrode can be achieved, the complex process of high sintering in a conventional battery is avoided, the demand to the environment cleanliness is low, the demand to the substrate is thus not high, and a conventional single crystal wafer sold in the market can be adopted.

Owner:JIANGSU AIDE SOLAR ENERGY TECH CO LTD

Paving method of seed crystals, pseudo-single crystal silicon wafer and preparation method of pseudo-single crystal silicon wafer

InactiveCN104131332AReduce the chance of dislocationsReduce dislocationPolycrystalline material growthFrom frozen solutionsCrucibleDislocation

The invention provides a paving method of seed crystals for casting a pseudo-single crystal silicon wafer. The paving method comprises the following steps: providing a crucible; paving target seed crystals at the bottom of the crucible; reserving a gap between two adjacent target seed crystals and filling the gap with an anisotropic seed crystal, wherein the target seed crystals and the anisotropic seed crystals are tightly contacted and fill the bottom of the crucible to obtain a seed crystal layer; the anisotropic seed crystal comprises a first side face and a second side face which are respectively contacted with the side faces of the two adjacent target seed crystals, the types of crystal boundaries respectively formed by the first and second side faces and the side faces contacted with the adjacent target seed crystals are consistent, and the growth faces of the anisotropic seed crystals is high index crystal faces relative to the growth faces of the target seed crystals. By filling the anisotropic seed crystals in the gaps between two adjacent target seed crystals, dislocation and proliferation of dislocation preferably occur in the anisotropic seed crystals, so that the probability of generating dislocation of the target seed crystals is reduced, and the problem that the pseudo-single crystal prepared in the prior art is more in dislocation is solved.

Owner:JIANGXI SAI WEI LDK SOLAR HI TECH CO LTD

A novel method of diffused layer removal on the single surface

InactiveCN101217173AImprove conversion efficiencySimple processFinal product manufactureSemiconductor devicesLayer removalProtection layer

The invention provides a novel method for removing a diffusion layer on a single surface, the method is that a front surface on an N-type single crystal silicon wafer substrate is firstly formed with an N<PLUS> layer by phosphorus diffusion, a silicon nitride thin film protection layer is deposited at the front surface, and a back surface uses the strong base corrosion for removing the back surface diffusion layer; the invention can significantly improve the conversion efficiency of an N-type single crystal silicon solar cell and reduce the cost, the process is simple, the operation is convenient; the invention is applicable to large-scale production, particularly simplifies the technology of removing the back N-type diffusion layer, thus greatly improving production efficiency.

Owner:NINGBO ULICA SOLAR SCIENCE & TECHNOLOGY CO LTD

Silicon wafers by epitaxial deposition

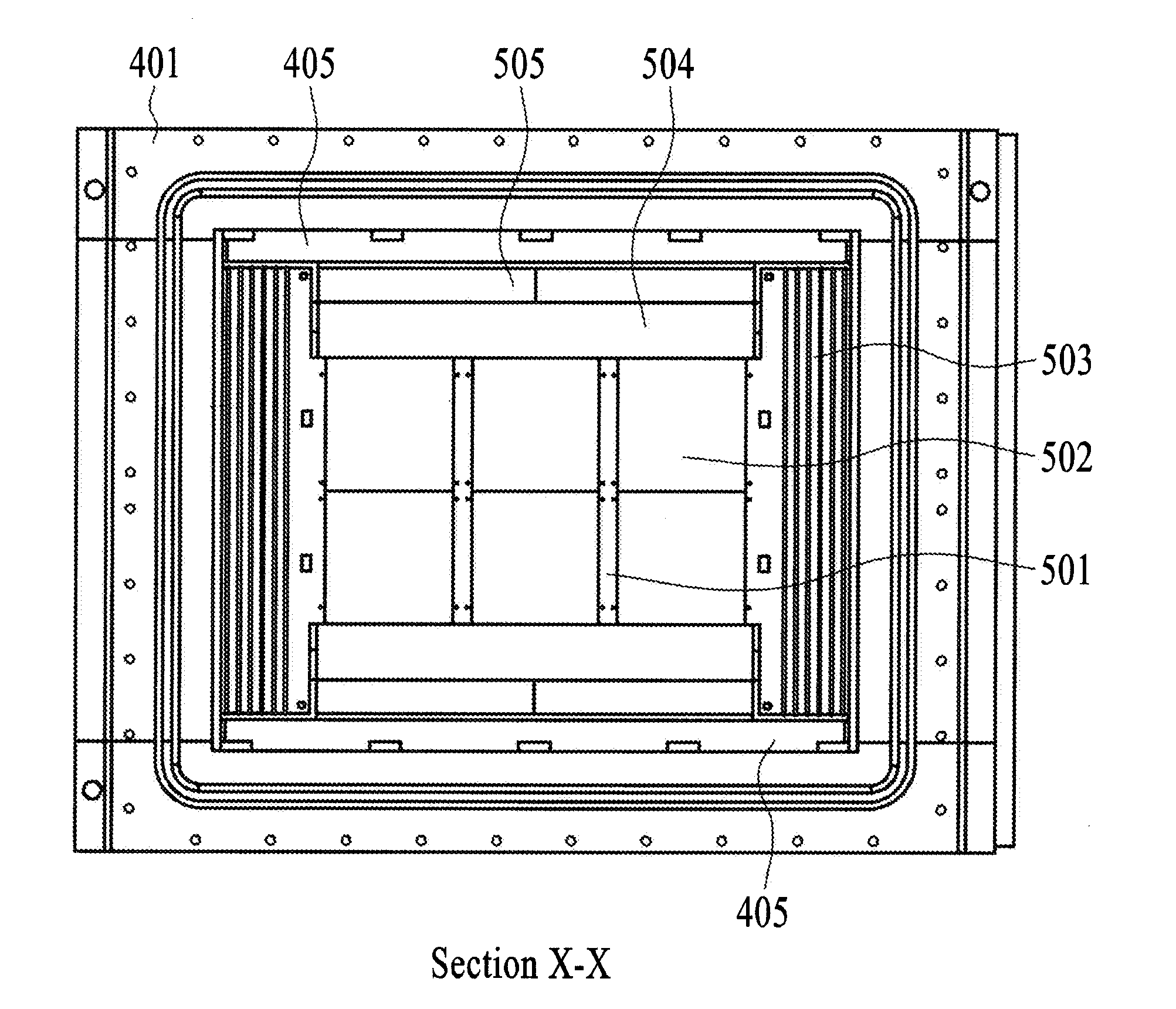

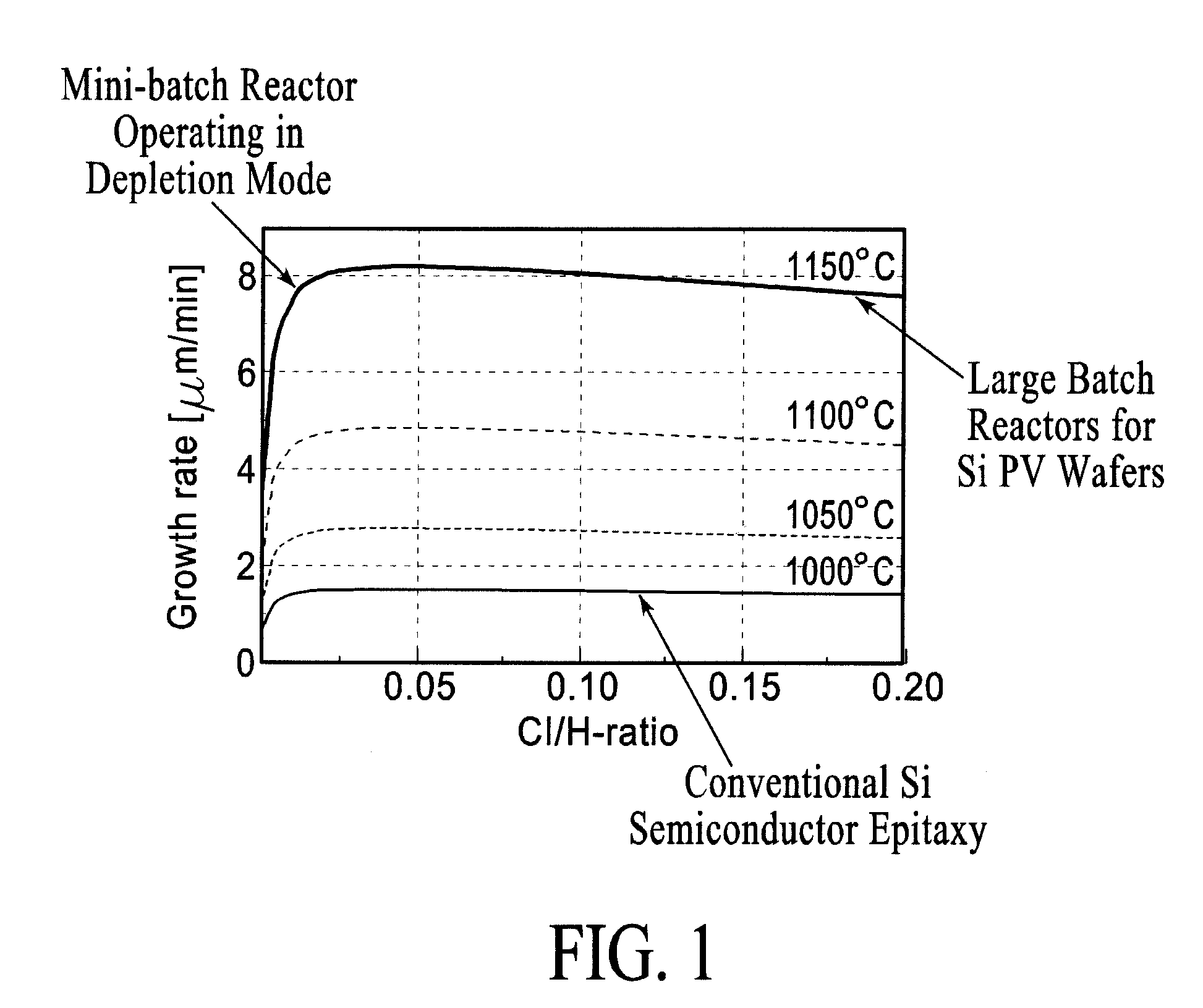

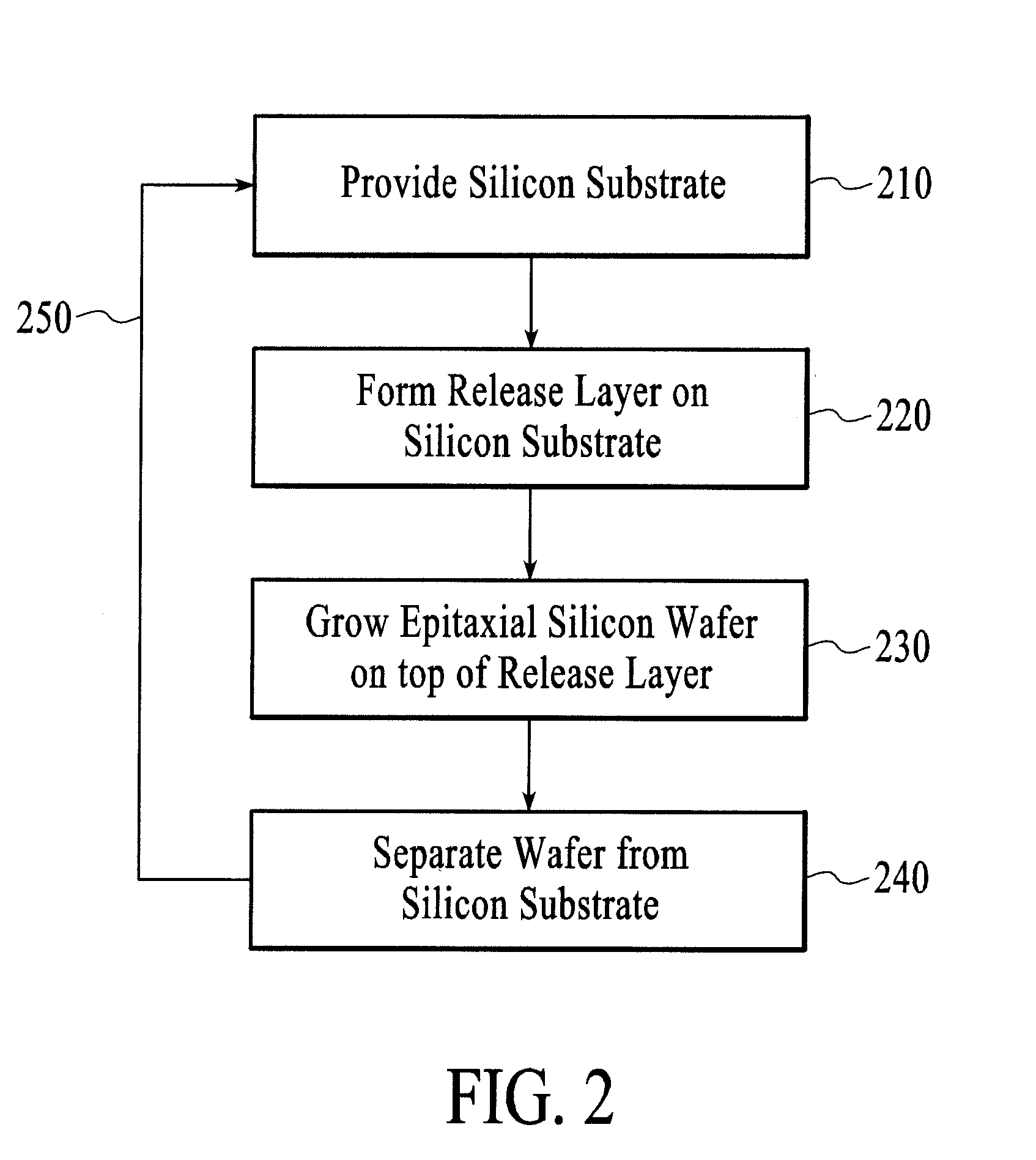

InactiveUS20130032084A1Reduce manufacturing costImprove efficiencyPolycrystalline material growthSemiconductor/solid-state device manufacturingTemperature controlEmissivity

A system for depositing thin single crystal silicon wafers by epitaxial deposition in a silicon precursor depletion mode with cross-flow deposition may include: a substrate carrier with low total heat capacity, high emissivity and small volume; a lamp module with rapid heat-up, efficient heat production, and spatial control over heating; and a manifold designed for cross-flow processing. Furthermore, the substrate carrier may include heat reflectors to control heat loss from the edges of the carrier and / or heat chokes to thermally isolate the carrier from the manifolds, allowing independent temperature control of the manifolds. The carrier and substrates may be configured for deposition on both sides of the substrates—the substrates having release layers on both sides and the carriers being configured to have equal process gas flow over both surfaces of the substrate. High volume may be addressed by a deposition system comprising multiple mini-batch reactors.

Owner:SVAGOS TECHNICK INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com