Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

78results about How to "Good hole filling ability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Porefilling electroplating leveling agent, preparation method and electroplating liquid using leveling agent

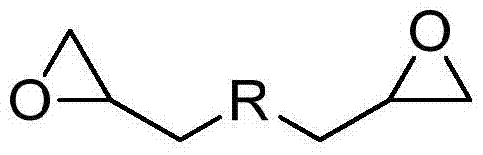

The invention discloses a porefilling electroplating leveling agent, a preparation method thereof and an electroplating liquid using the porefilling electroplating leveling agent, and relates to the technical field of electroplating. The porefilling electroplating leveling agent comprises ingredients: 3-(dimethylamino)-1- propanethiol, piperazine and binary epoxy compound, wherein the molar mass ratio of the 3-(dimethylamino)-1- propanethiol, the piperazine and the binary epoxy compound is 1-3: 2-4: 4-6; and the binary epoxy compound has the following structural formula (see in the specification), wherein R is a linking group of a non-epoxy group. According to the porefilling electroplating leveling agent, a functional group containing sulfur atoms is added into leveling agent molecules, so that the interaction between the leveling agent molecules and an accelerator and an inhibitor is improved, the leveling agent, the accelerator and the inhibitor can better interwork, and the prepared electroplating liquid has an excellent porefilling performance.

Owner:SHENZHEN BANMING SCI & TECH CO LTD

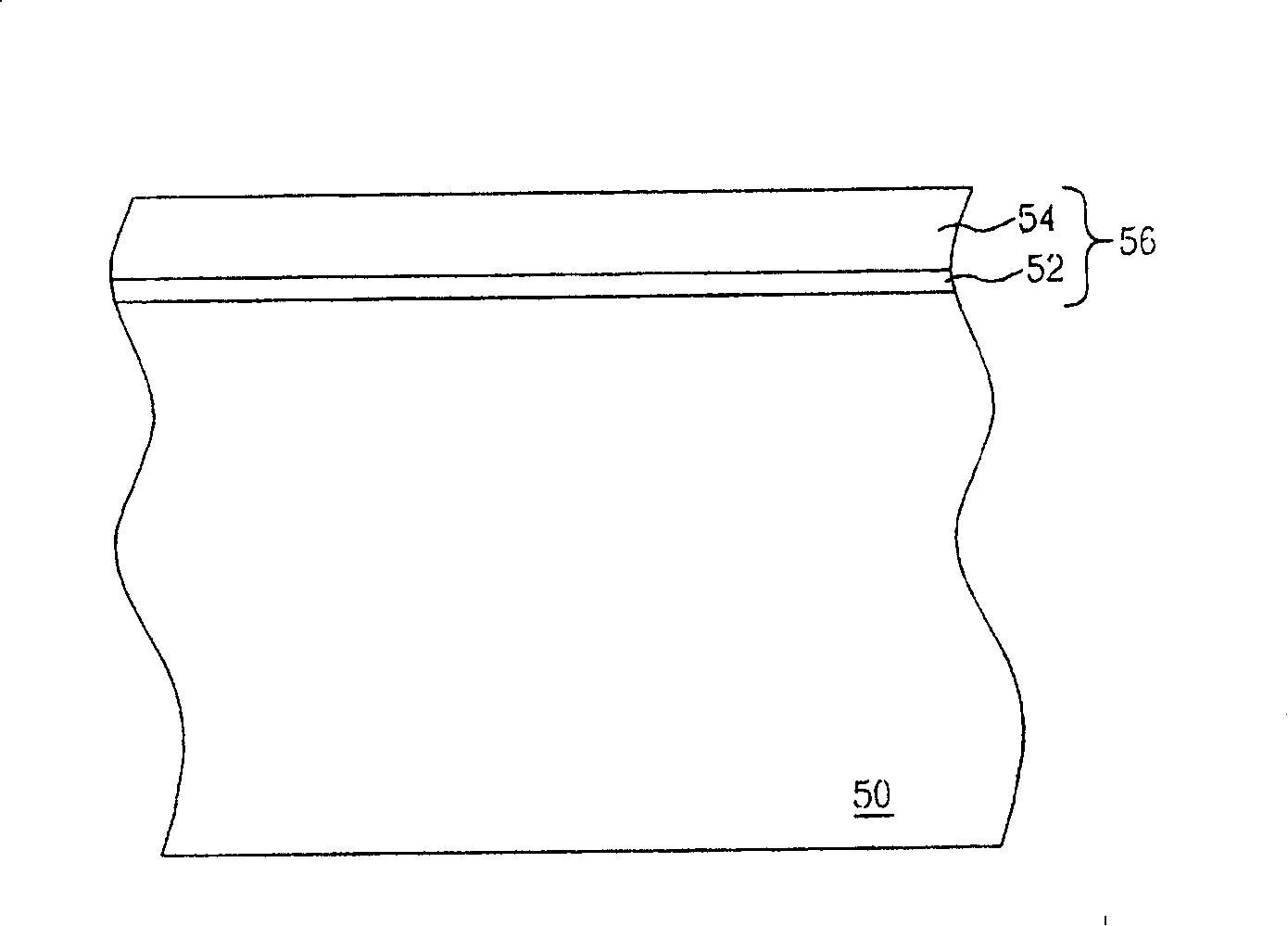

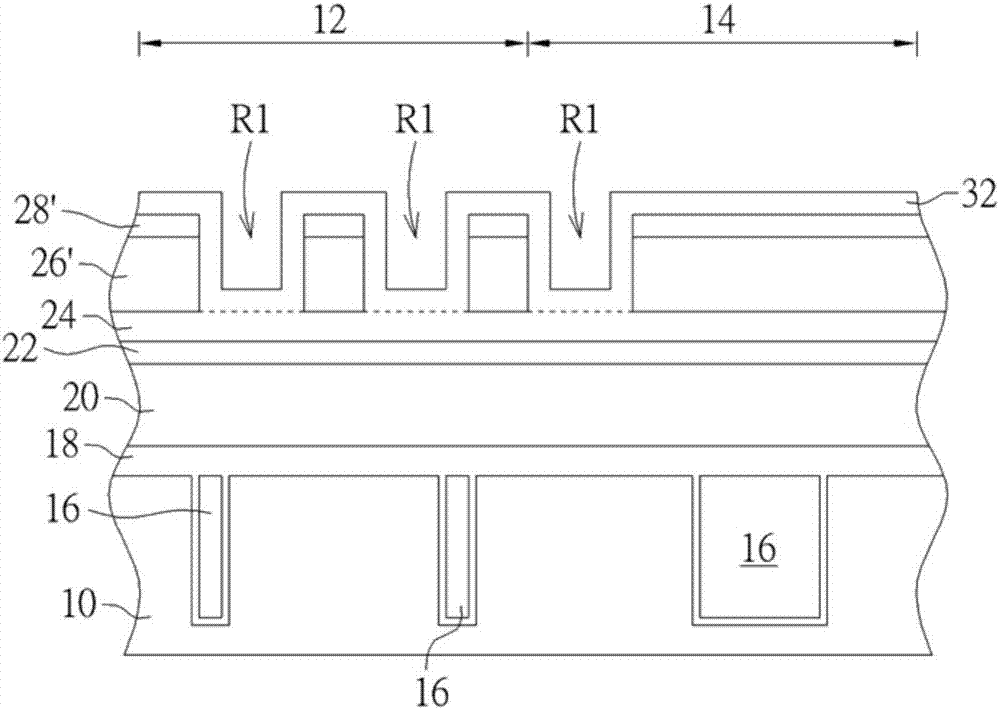

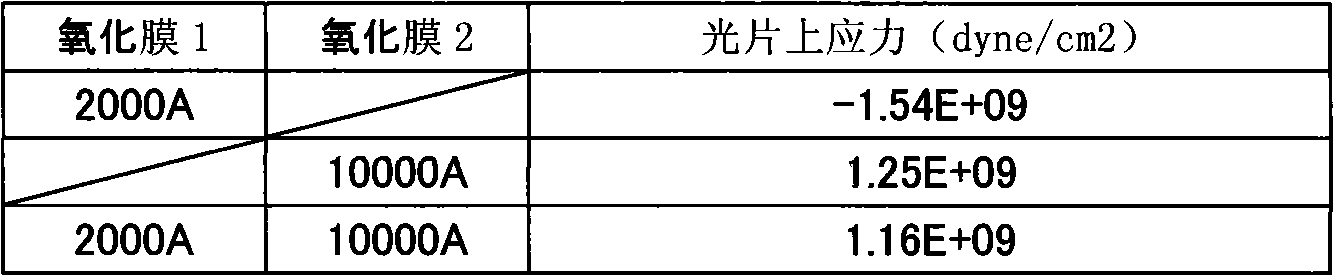

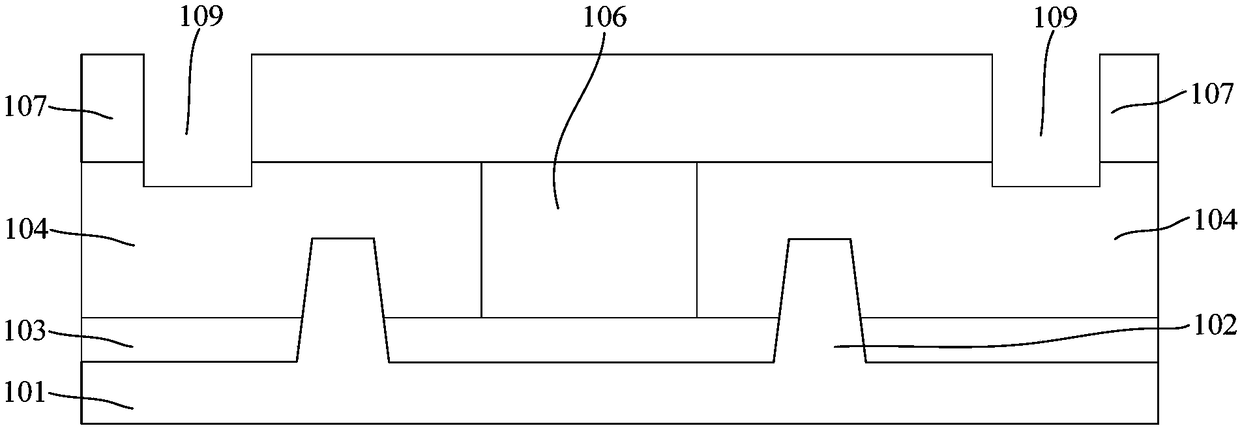

Shallow groove isolation layer of semiconductor element and manufacturing method thereof

ActiveCN101231967AImprove qualityGood hole filling abilitySolid-state devicesSemiconductor/solid-state device manufacturingIsolation layerEngineering

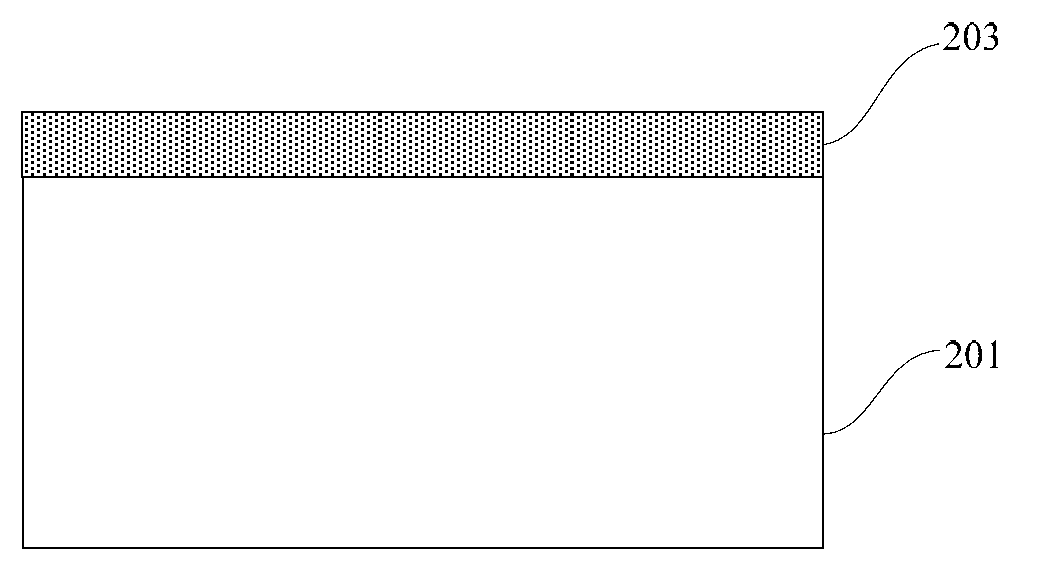

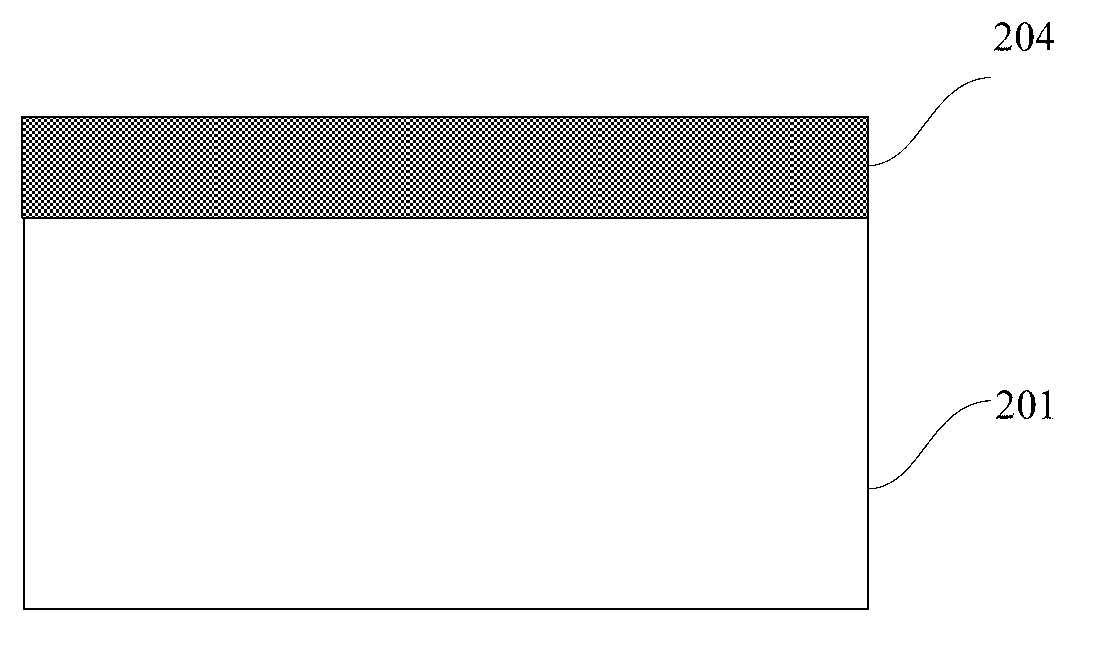

The invention provides a method for filling silica layers in grooves. Firstly, a subbase comprising a plurality of grooves is provided; a reactant gas with a first O3 / TEOS flow ratio is provided for a first sedimentation process so that a first silica layer is formed on the surface of the subbase and in the grooves all sidedly. The reactant gas with a second O3 / TEOS flow ratio is provided for a second sedimentation process so that a second silica layer is formed on the surface of the subbase. In addition, the second O3TEOS flow ratio is less than the first O3 / TEOS flow ratio.

Owner:UNITED MICROELECTRONICS CORP

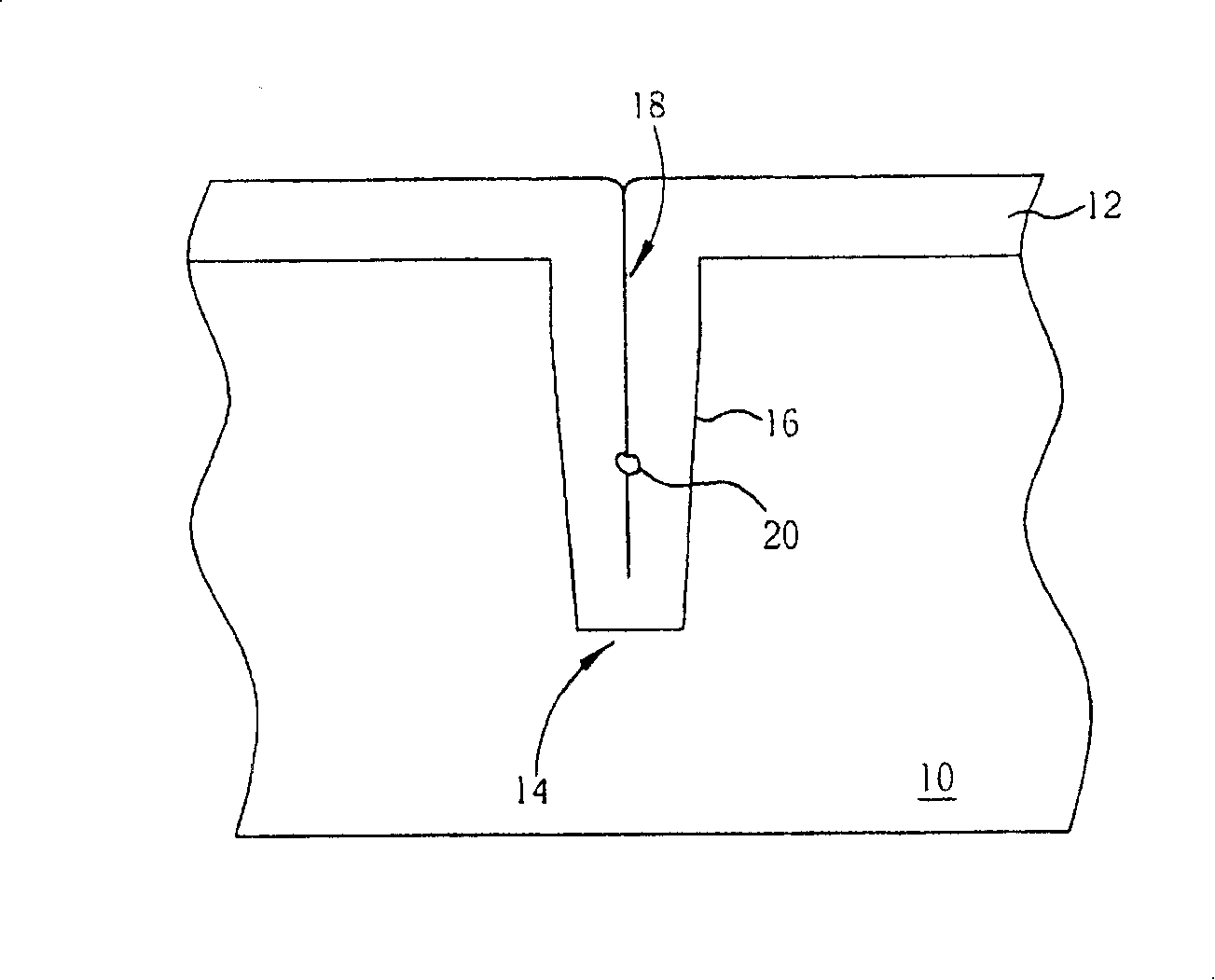

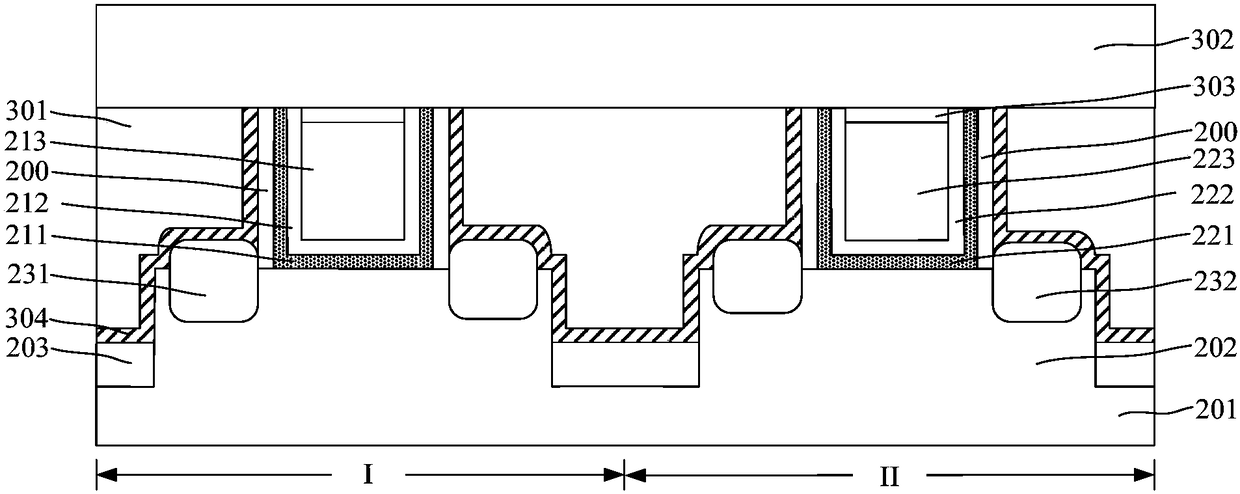

Damascene process for chemically vapor depositing titanium nitride and copper metal layer

InactiveCN1426092AExcellent hole fillingGood adhesionSemiconductor/solid-state device manufacturingCrystalliteTantalum nitride

The present invention relates to Damascene process of chemically vapor depositing TiN layer and Cu metal layer. Inside one multiple-cavity vacuum equipment, TiN diffusing barrier layer and Cu metal film are first deposited successively and then heat annealed quickly in H2-N2 atmosphere to obtain TiSiN barrier layer and Cu metal film with homogeneously distributed crystal size and resistance. The present invention has excellent filling property and form retention, good adhesion to insulating medium and stable and simple technological process. When combined with chemical and mechanical polishing of Cu, may be manufactured Cu metal Damascene interconnection wiring structure suitable for deep submicron superlarge scale ICs.

Owner:SHANGHAI HUA HONG GROUP +1

Electroplating solution for surface pore filling of plate parts and electroplating method thereof

ActiveCN104131319AGood hole filling abilityPrinted element electric connection formationConcentration polarizationElectron transfer

The invention discloses an electroplating solution for surface pore filling of plate parts and an electroplating method thereof. The electroplating solution contains 0.1-200g / L tetravalent vanadium and 0.2-15g / L pentavalent vanadium. The tetravalent vanadium and the pentavalent vanadium which are added to the electroplating solution are capable of forming a quasi-reversible redox system, and in the redox system, the pentavalent vanadium is superior to bivalent copper in reduction. Compared with the bivalent iron / trivalent iron system in the prior art, the charge number of the pentavalent vanadium is far higher than that of trivalent ferric irons so that the radius of the pentavalent vanadium hydrated ion can be greater than that of the trivalent ferric hydrated iron. The case that the metal ions of high titanium oxide are difficult to supplement by the way of electron transfer due to concentration polarization is avoided, so that more excellent pore-filling effect can be achieved.

Owner:上海天承化学有限公司

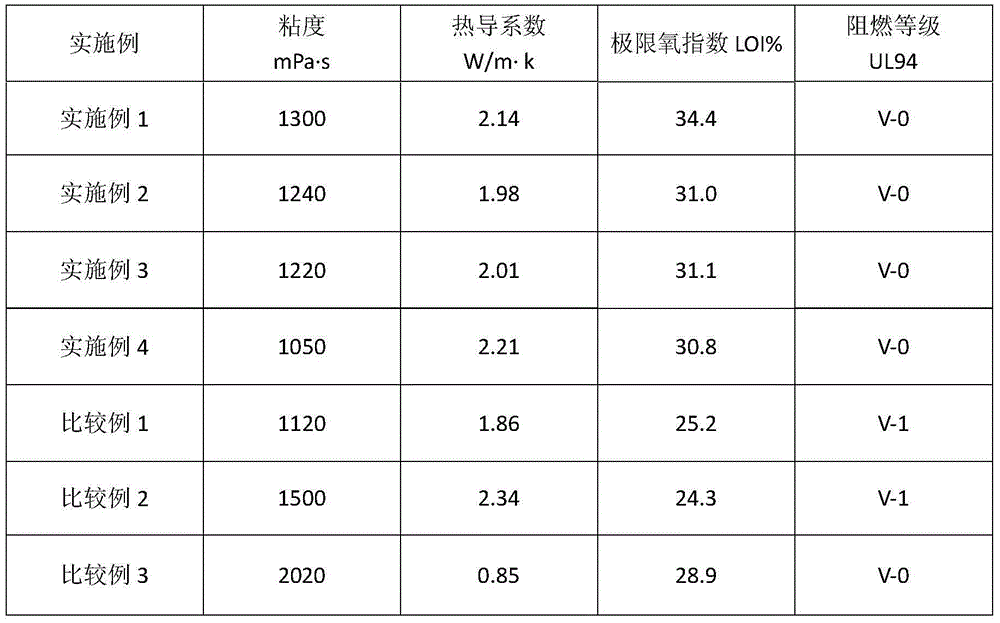

Environment-friendly flame-retardant heat-conducting glue and preparation method thereof

ActiveCN104559890AHigh softening pointImprove flame retardant performanceNon-macromolecular adhesive additivesEpoxy resin adhesivesEpoxyHeat conducting

The invention discloses environment-friendly flame-retardant heat-conducting glue and a preparation method thereof. The preparation method comprises the following steps: diluting a coupling agent by using absolute ethyl alcohol, regulating the pH value of the diluted solution, adding a heat-conducting filler, and mechanically stirring; centrifuging, washing, and drying, thereby obtaining a component A; uniformly mixing an epoxy resin, a curing agent and a curing accelerator by using a high-speed dispersion machine, thereby obtaining a low-viscosity component B; and uniformly grinding and mixing the component A, the component B, an organic phosphorus flame retardant and aluminum hydroxide, vacuumizing, heating the mixture at the temperature of 80-90 DEG C, and heating at the temperature of 130-150 DEG C, thereby obtaining the environment-friendly flame-retardant heat-conducting glue. The environment-friendly flame-retardant heat-conducting glue is low in viscosity, high in heat conductivity coefficient, good in mechanical property and high in acid-base resistance and corrosion resistance, the flame-retardant level reaches UL94V-0, the heat dissipation problem of a general electronic component can be solved; because the heat-conducting glue has good flame-retardant property, when the heat-conducting glue is applied to high-voltage and high-temperature electrical equipment, the on-fire potential safety hazard of the electronic component is effectively reduced.

Owner:中山沃硅化工科技有限公司

Semiconductor device and forming method thereof

ActiveCN107958872AImprove electrical performanceImprove protectionTransistorSemiconductor/solid-state device manufacturingGate dielectricWork function

A semiconductor device and a forming method thereof are provided. The forming method includes the following steps: providing a substrate including an NMOS region, wherein an interlayer dielectric layer is formed on the substrate, and an N region opening penetrating the interlayer dielectric layer is formed in the interlayer dielectric layer of the NMOS region; forming a high-k gate dielectric layer on the bottom and sidewall of the N region opening; forming an N-type work function layer on the high-k gate dielectric layer; forming a diffusion barrier layer on the N-type work function layer; hydrogenating the diffusion barrier layer; and after hydrogenation, forming a metal gate filling the N region opening on the diffusion barrier layer. The ability of the diffusion barrier layer to protect the N-type work function layer is improved, and therefore, the electrical performance of a semiconductor device formed is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

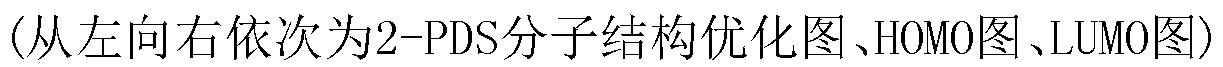

New purpose of 2,2'- dithiopyridine, electroplating hole filling additive with same and electroplating method adopting additive

ActiveCN109972180AShorten the timeImprove flatnessPrinted element electric connection formationPolymer scienceElectroplating

The invention discloses a new purpose of 2,2'- dithiopyridine, an electroplating hole filling additive with the same and an electroplating method adopting the additive, specifically, the purpose of 2,2'- dithiopyridine serving as the electroplating hole filling leveling agent, and belongs to the technical field of electroplating leveling agent. The additive is composed of 200 to 300 ppm of an inhibitor, 5 to 11 ppm of an accelerating agent and 7 to 15 ppm of 2,2'- dithiopyridine. The application of the 2,2'- dithiopyridine to the electroplating hole filling leveling agent is provided, and the2,2'- dithiopyridine is used for electroplating hole filling of a circuit board.

Owner:BOMIN ELECTRONICS CO LTD +1

Titanium-antimony-tellurium phase-changing material depositing method and preparation method of phase-changing storage unit

ActiveCN103000807APrecise and controllable thicknessImprove compactnessElectrical apparatusHigh densityTitanium

The invention provides a titanium-antimony-tellurium phase-changing material depositing method and a preparation method of a phase-changing storage unit. The titanium-antimony-tellurium phase-changing material depositing method includes: depositing a Ti precursor which comprises one or more than one of (R1)4Ti, (R1R2N)4Ti, (R1O)4Ti, ((R1)3Si)4Ti and TiM4, wherein R1 and R2 are linear chains, branched chains or annular alkyls containing 1-10 carbons, and M is Cl, F or Br; depositing a Te precursor which comprises one or more than one of (R1)2Te, (R1R2N)2Te and ((R1)3Si)2Te, wherein R is selected from a linear chain, a branched chain or an annular alkyl or alkenyl containing 1-10 carbons; and depositing Sb precursors which comprise one or more than one of (R1)3Sb, (R1R2N)3Sb, (R1O)3Sb, ((R1)3Si)3Sb and SbM3, wherein R1 and R2 are linear chains, branched chains or annular alkyls containing 1-10 carbons, and M is Cl, F or Br. The TiSbTe phase-changing materials prepared by the titanium-antimony-tellurium phase-changing material depositing method have the advantages of being accurate and controllable in thickness, good in thin film compactness and strong in pore filling capability. Phase-changing thin films prepared by the titanium-antimony-tellurium phase-changing material depositing method can be applied to a storer, so that high-density storing can be achieved, and simultaneously low-energy-consumption devices can be obtained.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

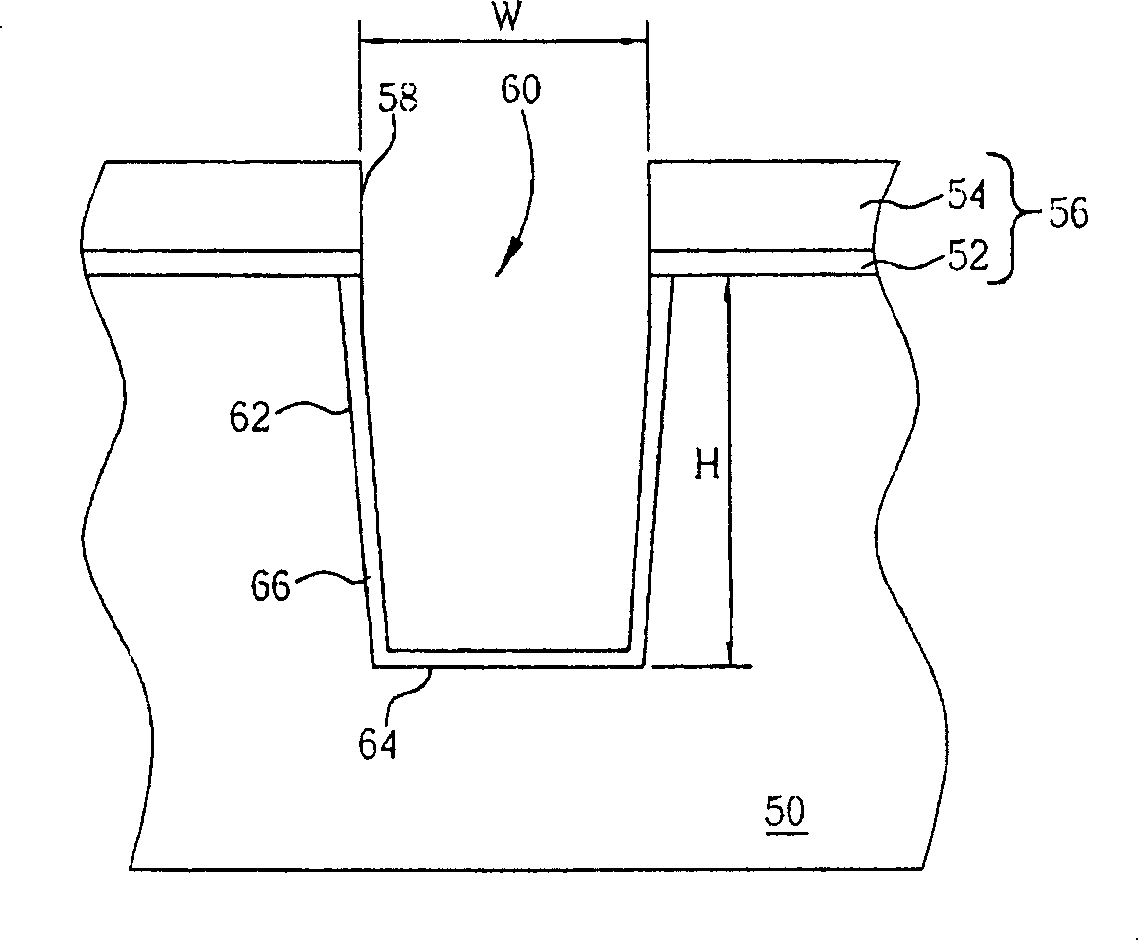

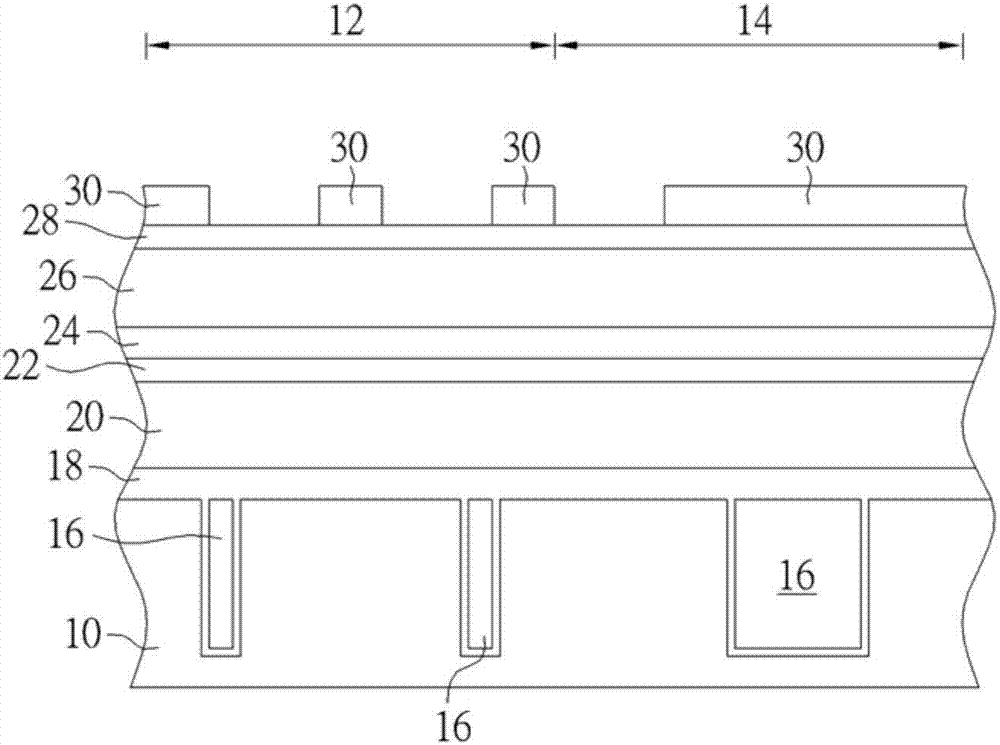

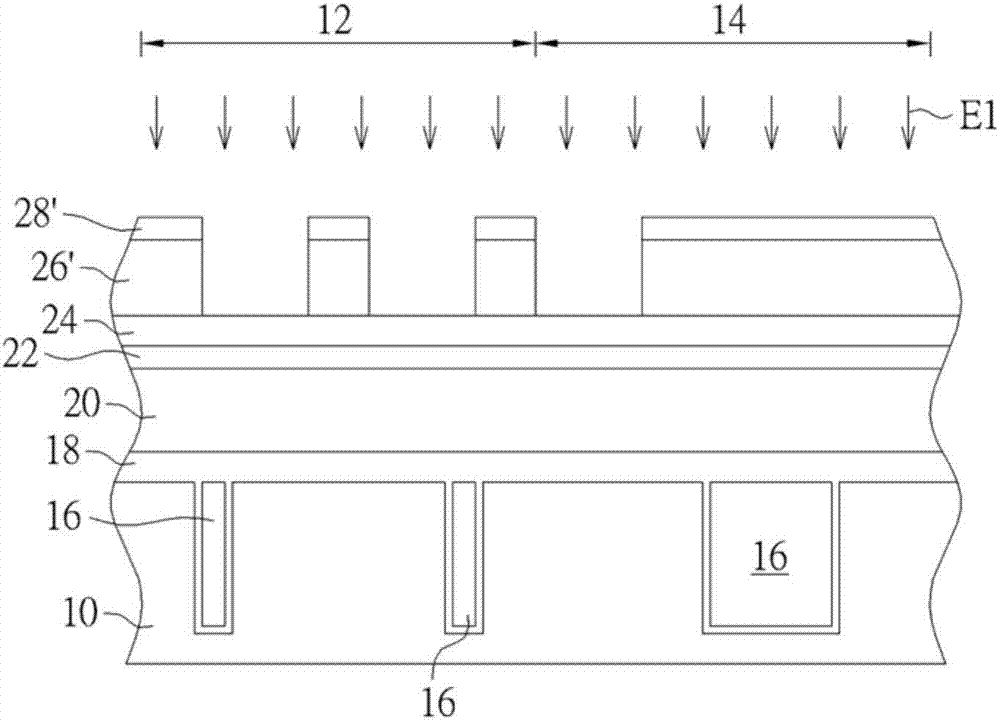

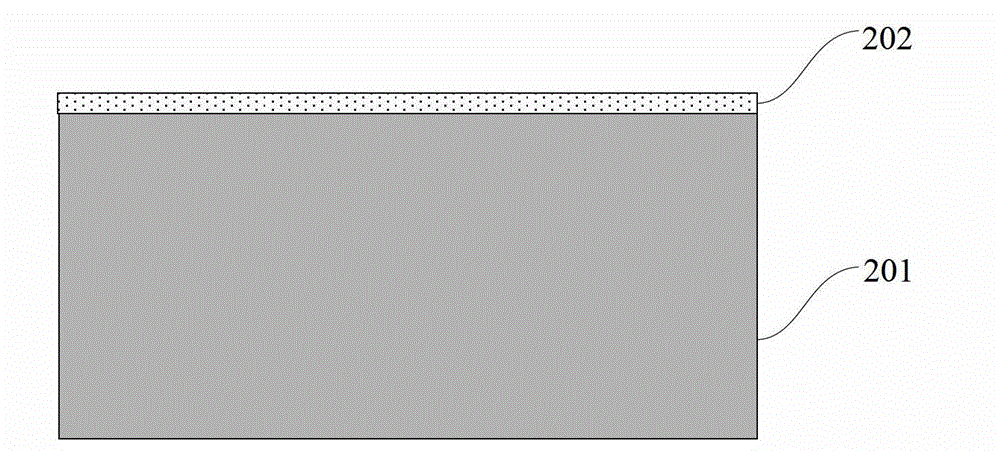

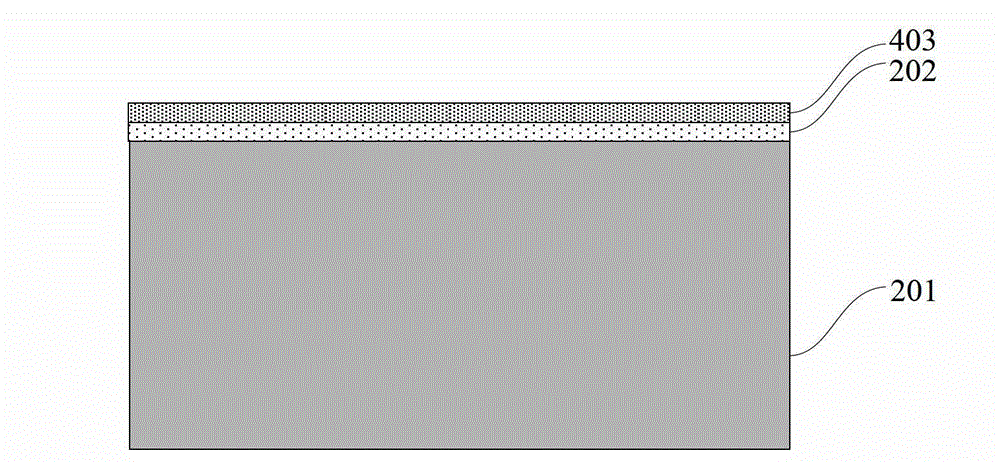

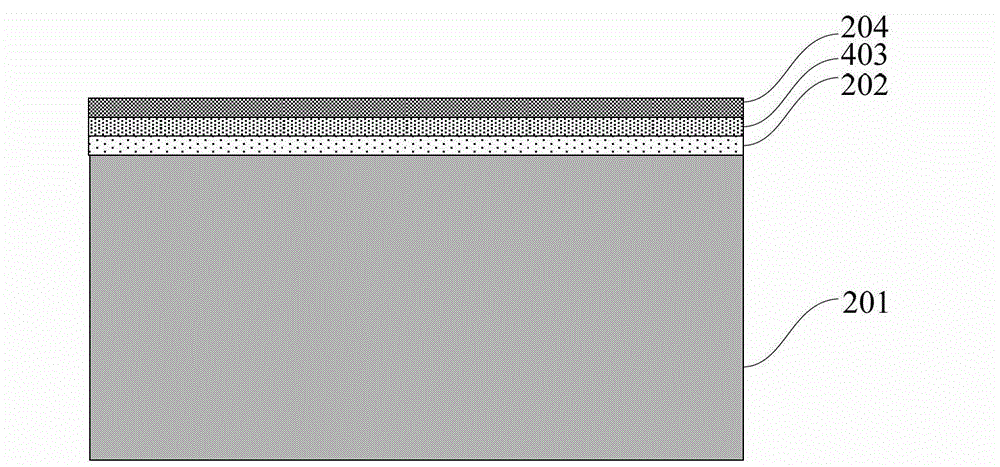

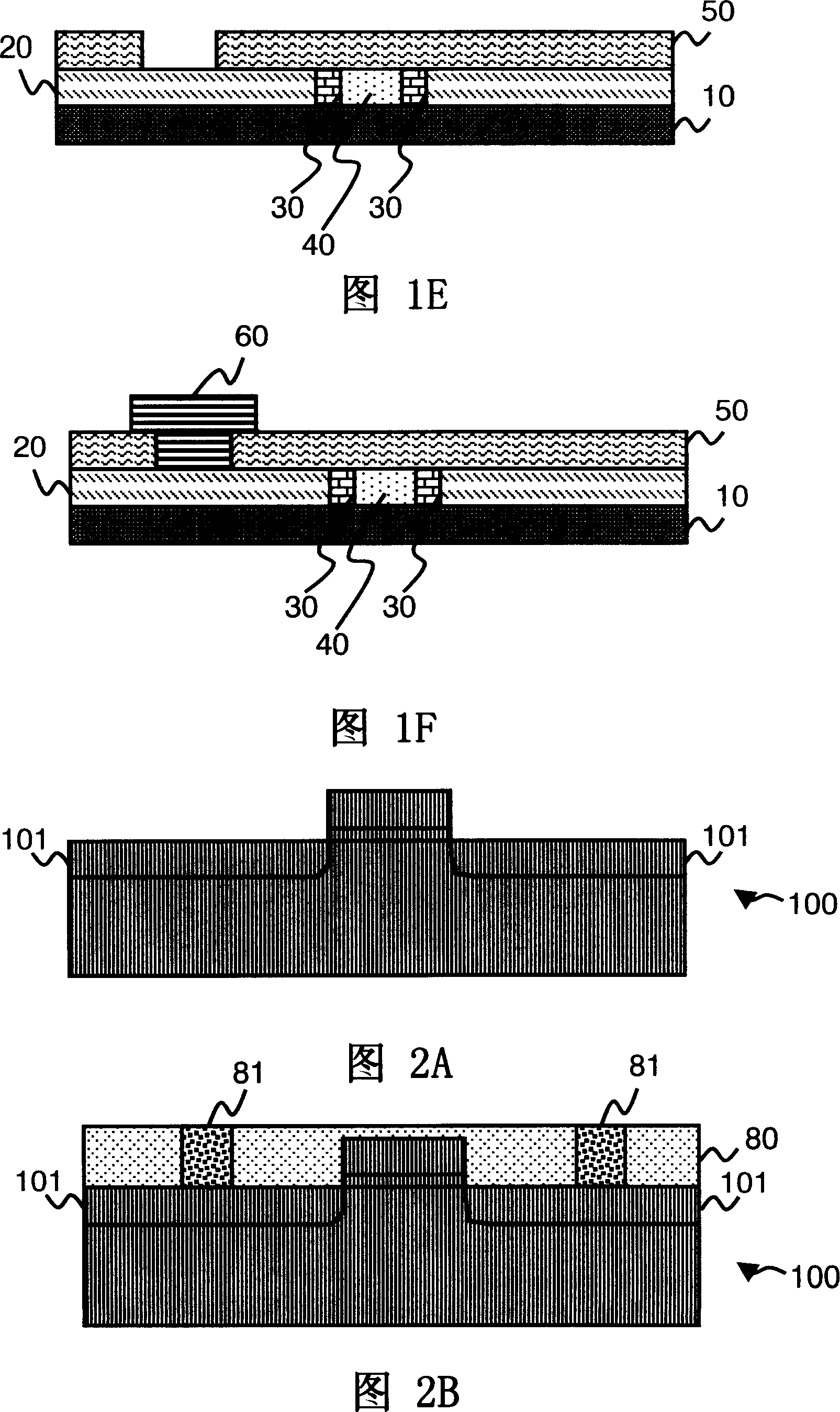

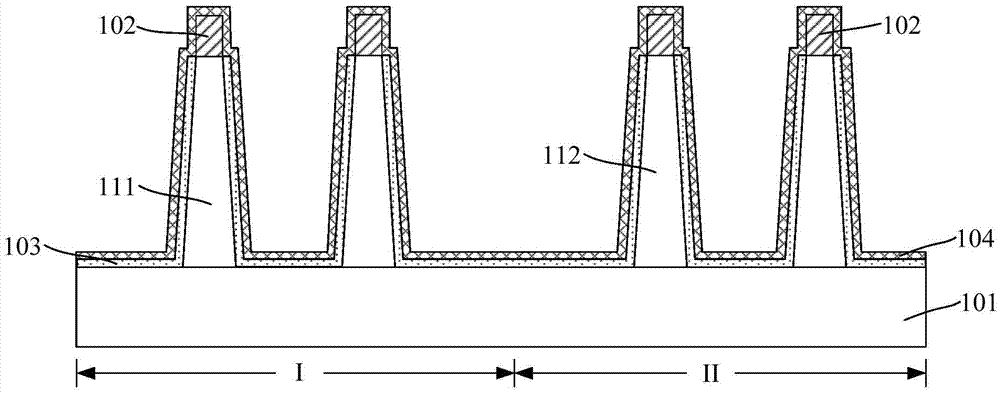

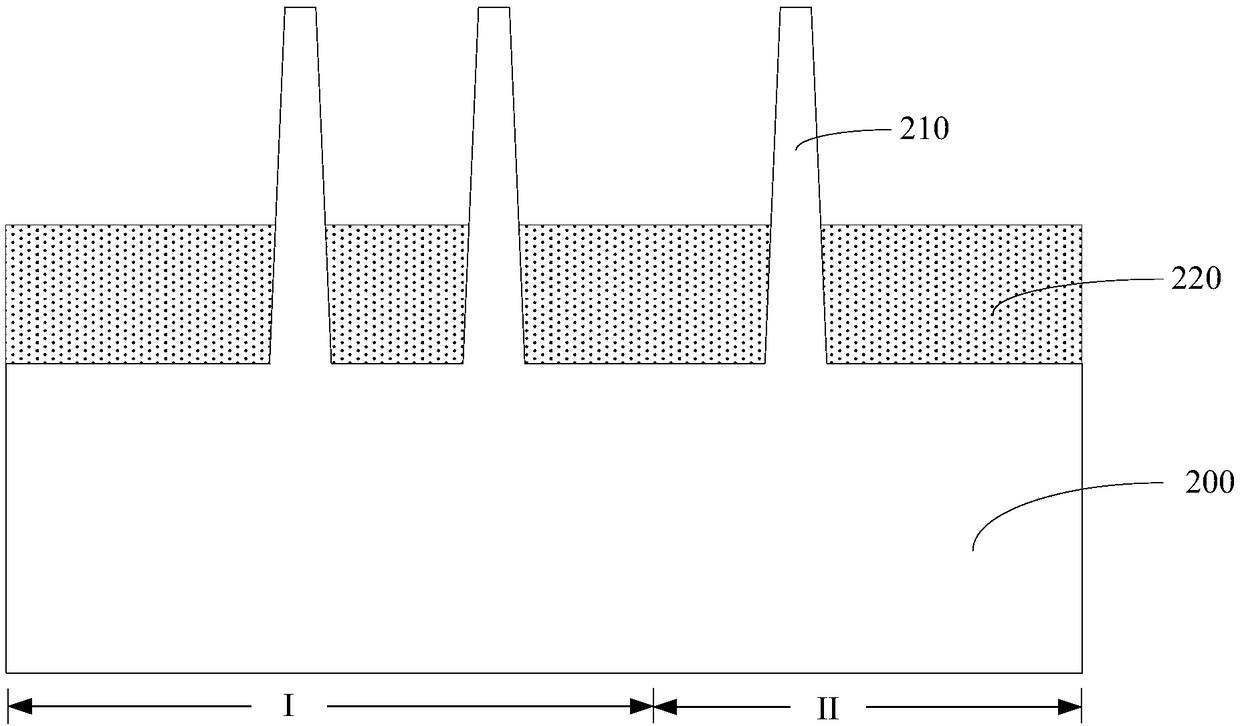

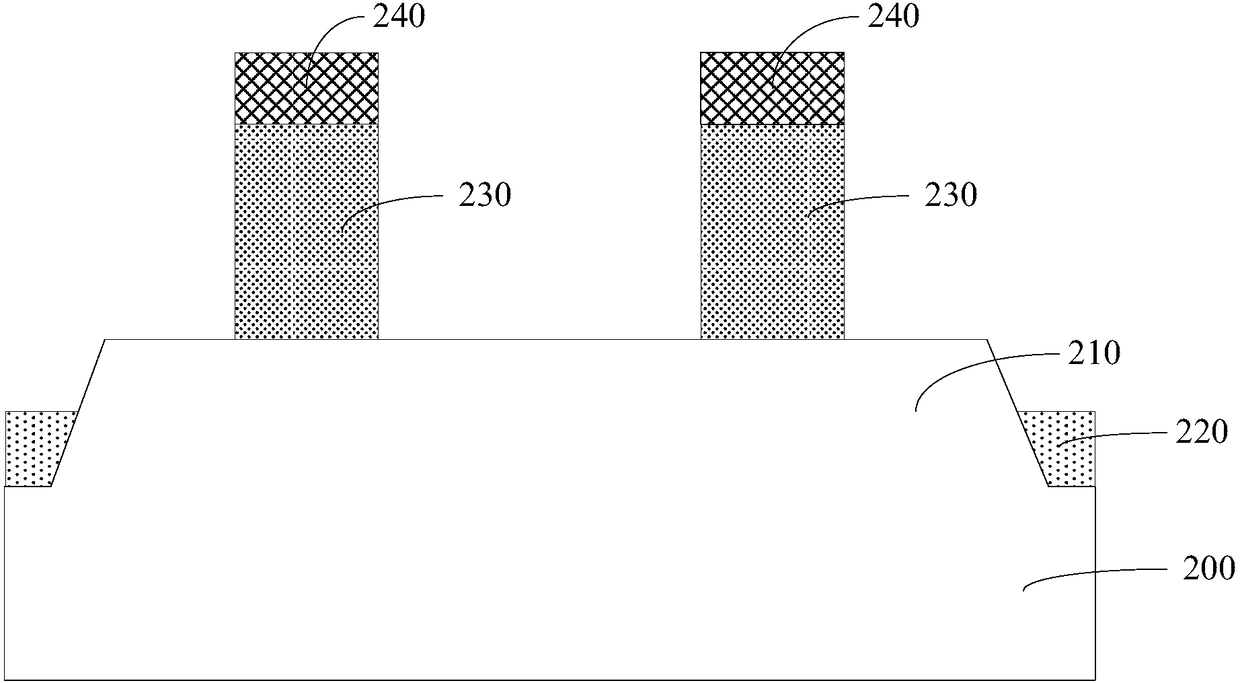

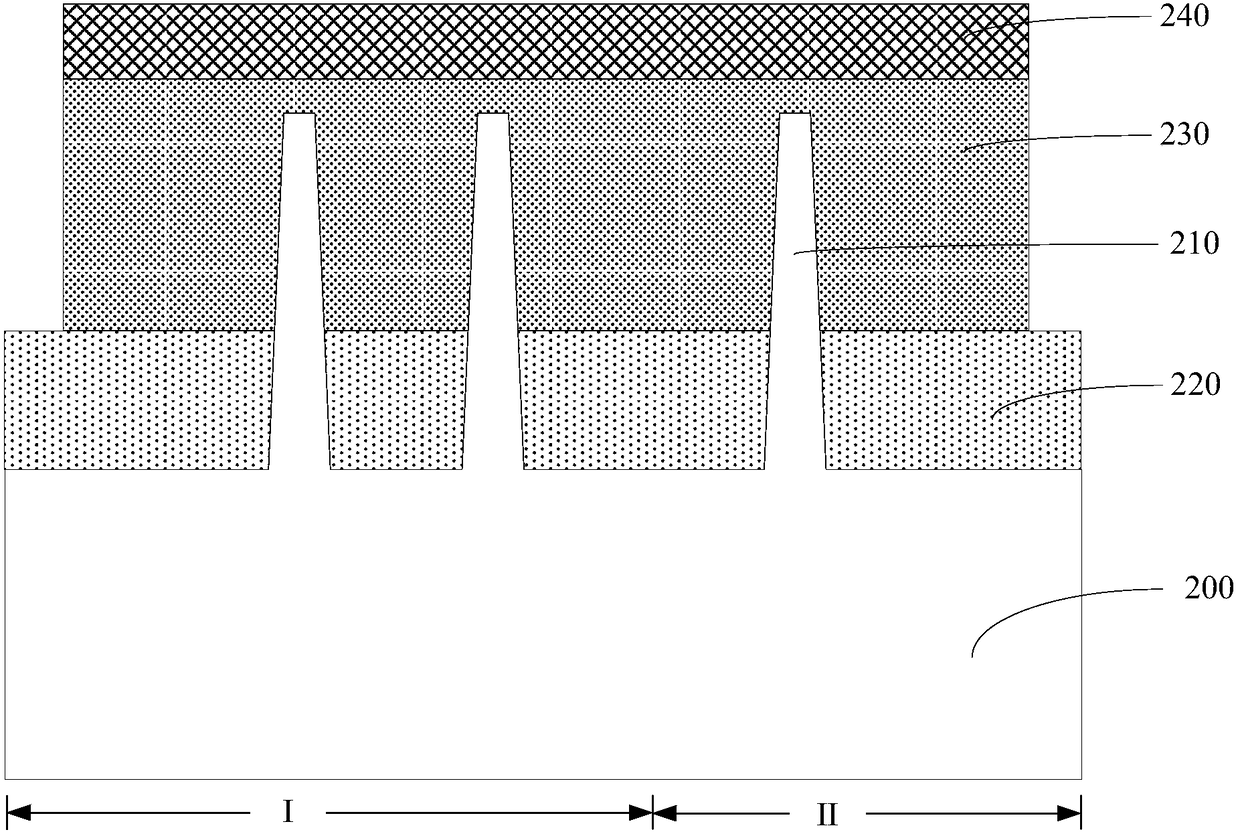

Manufacturing method of buried word line

ActiveCN107968073ASave materialGood hole filling abilityTransistorSemiconductor/solid-state device manufacturingEngineeringMask layer

The invention discloses a manufacturing method of a buried word line. The manufacturing method comprises the steps of providing a substrate firstly, wherein the substrate comprises a plurality of shallow trench isolation parts; next, forming a plurality of first patterned material layers which are positioned above the substrate, wherein a first groove is included between any two adjacent first patterned material layers; next, forming at least one second patterned material layer which is positioned in the first groove; by taking each first patterned material layer and the second patterned material layer as a mask layer, performing a first etching step; and forming a plurality of second grooves at least in the shallow trench isolation parts and the substrate.

Owner:UNITED MICROELECTRONICS CORP +1

Method for preparing titanium-stibium-tellurium (Ti-Sb-Te) phase change material and method for preparing phase change storage unit

ActiveCN102978588APrecise and controllable thicknessGood film densityElectrical apparatusChemical vapor deposition coatingHigh density storageComposite material

The invention provides a method for preparing a titanium-stibium-tellurium (Ti-Sb-Te) phase change material and a method for preparing a phase change storage unit. The method for preparing the Ti-Sb-Te phase change material comprises the following steps: 1) introducing a precursor SbCl3 pulse of Sb to a substrate, washing away unabsorbed SbCl3, then introducing a precursor (R3Si)2Te pulse of Te and washing away the unabsorbed (R3Si)2Te and by-products of reaction; 2) introducing a TiCl4 pulse of Ti to the substrate, washing away the residual TiCl4, then introducing the precursor (R3Si)2Te pulse of Te and washing away the residual (R3Si)2Te and by-products of reaction; and 3) introducing a precursor SbCl3 pulse of Sb to the substrate, washing away the residual SbCl3, then introducing a (R3Si)3Sb of Sb and washing away the unabsorbed (R3Si)3Sb and by-products of reaction. The Ti-Sb-Te phase change material prepared by using the method has the characteristics of accurately controllable thickness, good film compactness and strong pore-filling capability. A phase change film prepared by using the method can realize high-density storage when applied to a memorizer, and meanwhile a low power-cost device can be obtained.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

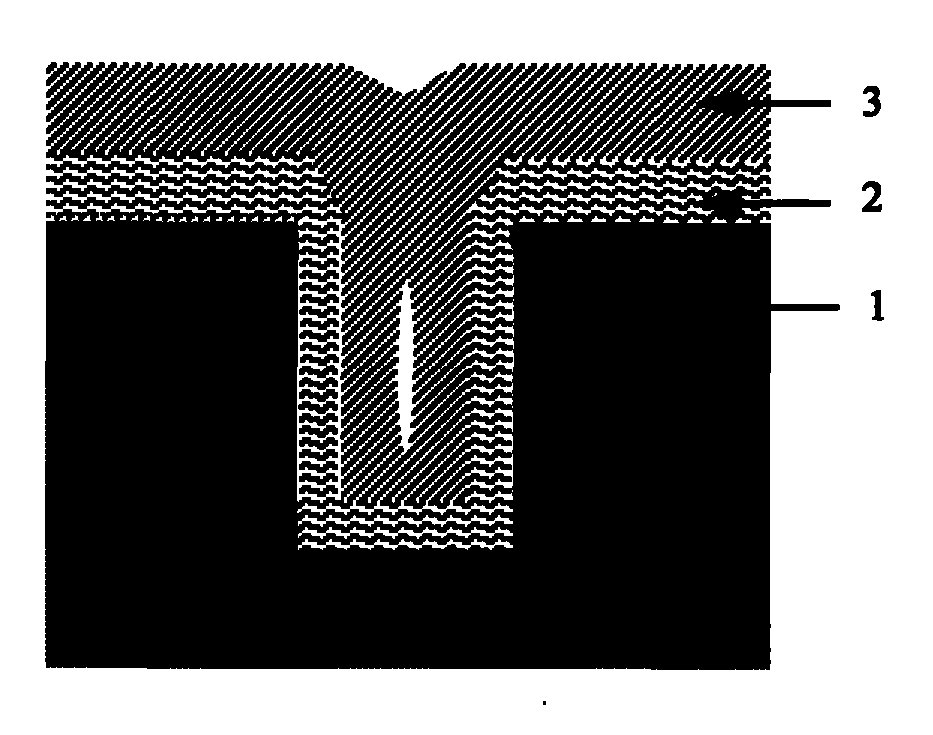

Method for filling deep trench

ActiveCN101887852AReduce tensile stressGood step coverageSemiconductor/solid-state device manufacturingChemical vapor deposition coatingEngineeringDeep trench

The invention discloses a method for filling a deep trench, which comprises the following steps: when the deep trench is filled, firstly depositing a first compression stress film layer, and then depositing a second tensile stress film layer using TEOS-O3-based AP / SA CVD to complete filling of the deep trench. In the invention, by adopting deposition of films with different performances for twice, the method for filling the deep trench achieves good step coverage and good pore filling performance, and the filling films have smaller tensile strength to prevent generating defects or cracks in the films or on the interface.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Gas wall electrode side connection phase shift storage and its producing method

InactiveCN1988200AEasy to operateReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryPhase shifted

This invention discloses a clearance wall electrode side connected phase change memory and its manufacturing method including applying a conductor electrode with rather low resistivity to combine with clearance wall electrode of high resistivity and forming the phase change material layer between the clearance wall electrodes so as to reduce the contact area between the phase change material layer and the wall electroce and reduce the volume of the material to further reduce the operation current and power loss of the phase change memory.

Owner:IND TECH RES INST

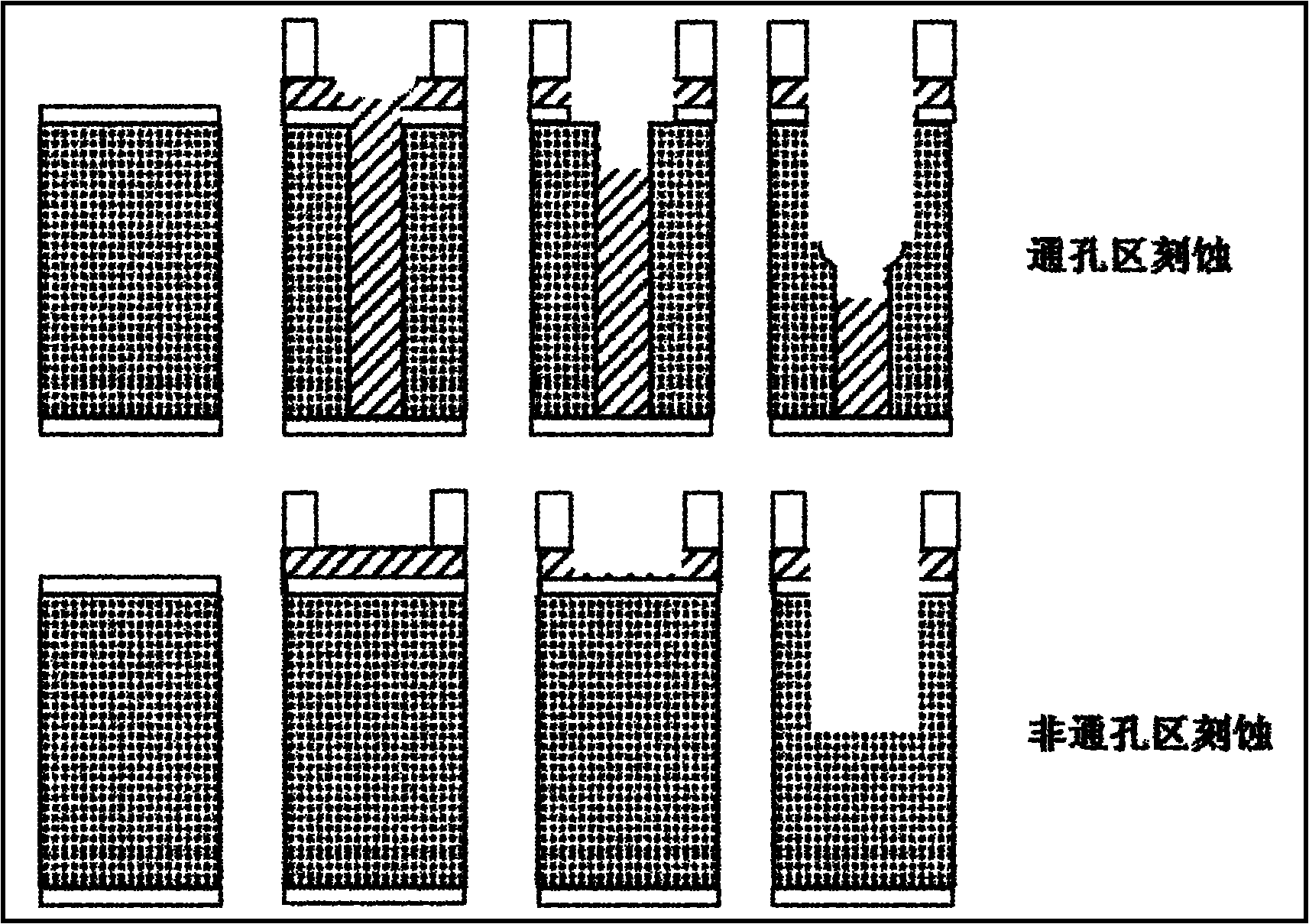

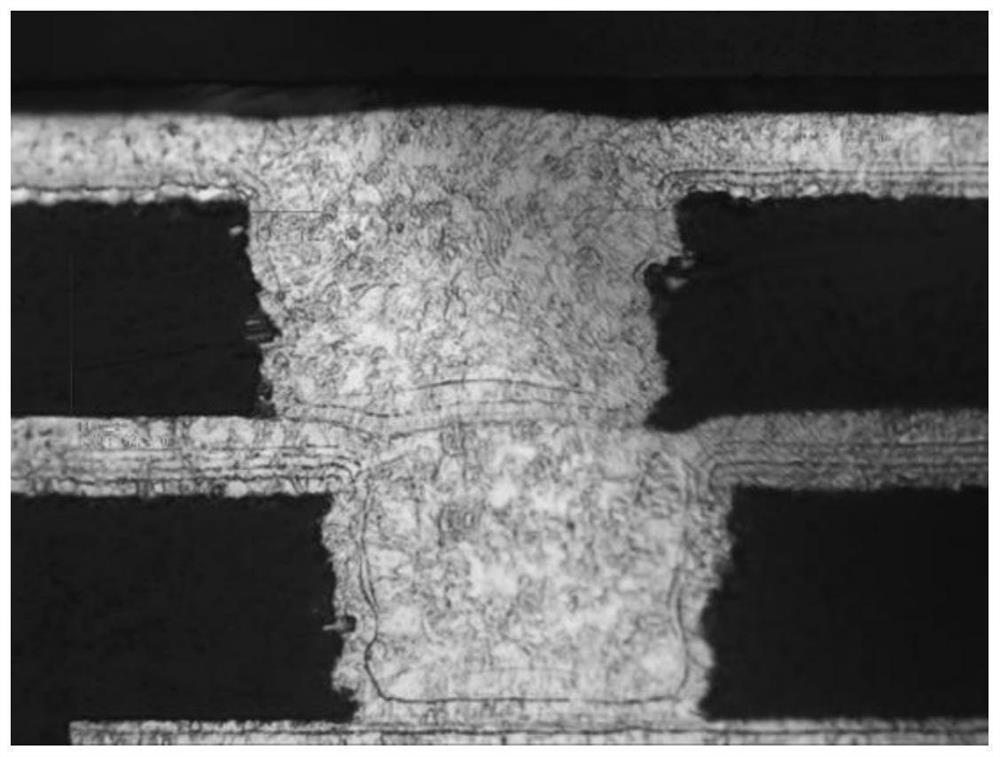

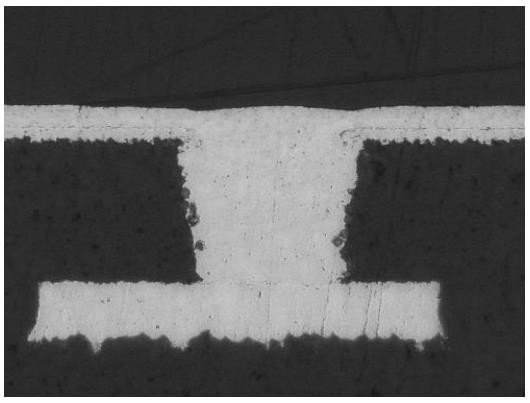

Copper filling process for blind holes of circuit board

InactiveCN106132116AShort production processImprove uniformityPrinted element electric connection formationElectroplatingCopper deposition

The invention provides a copper filling process for blind holes of a circuit board. The copper filling process sequentially comprises the following steps of (1) outer-layer board lamination; (2) laser drilling to obtain the blind holes; (3) mechanical drilling to obtain through holes; (4) copper deposition flash plating: carrying out copper deposition flash plating on the blind holes and the through holes; and (5) vertical continuous electroplating (VCP vertical hole filling), carrying out hole filling on the blind holes after copper deposition flash plating. By the production technology, mixed plating of the through holes and the blind holes can be achieved, i.e., the production flow is optimized into mixed plating of the through holes and the blind holes, so that the production efficiency is improved; and the production cost is reduced.

Owner:GUANGZHOU MEADVILLE ELECTRONICS

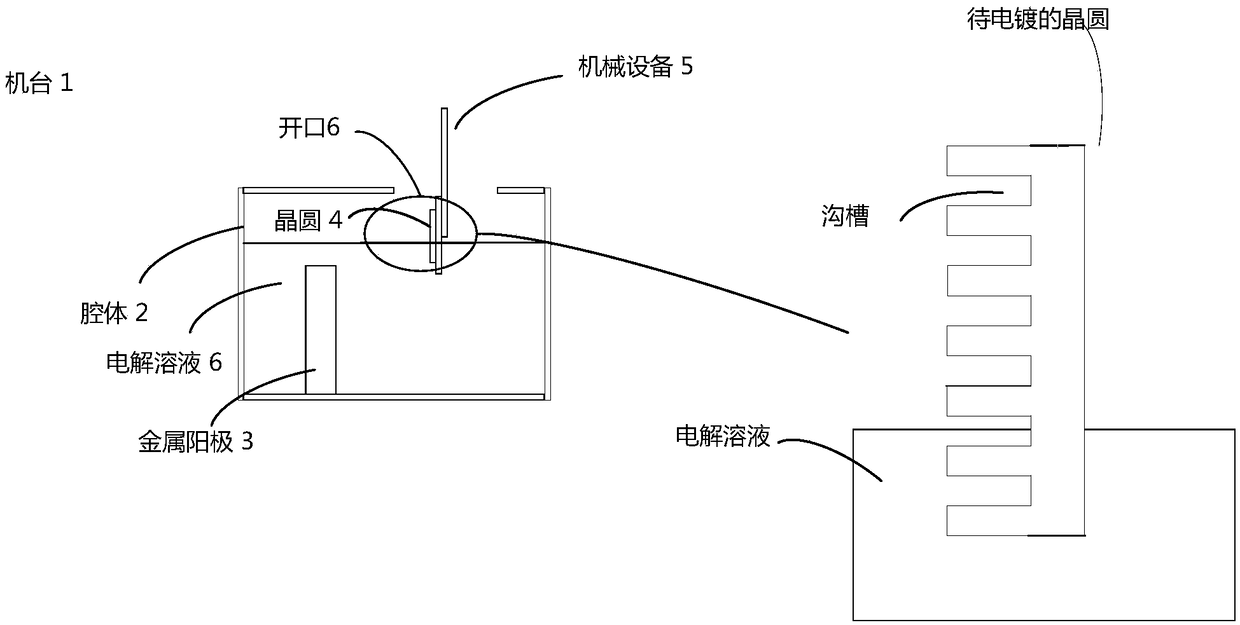

Equipment and method for reducing defects of wafer holes

InactiveCN108118377AImprove contact effectGood hole filling abilityElectrolysis componentsSemiconductor devicesMetalMaterials science

The application relates to a machine board for electroplating a wafer. The machine board comprises a cavity, wherein an opening is formed in the surface of the cavity and used for receiving the waferso as to feed the wafer into the cavity; a metal anode is arranged in the cavity and can be filled with an electrolytic solution; the metal anode is basically perpendicular to the liquid level of theelectrolytic solution.

Owner:HUAIAN IMAGING DEVICE MFGR CORP

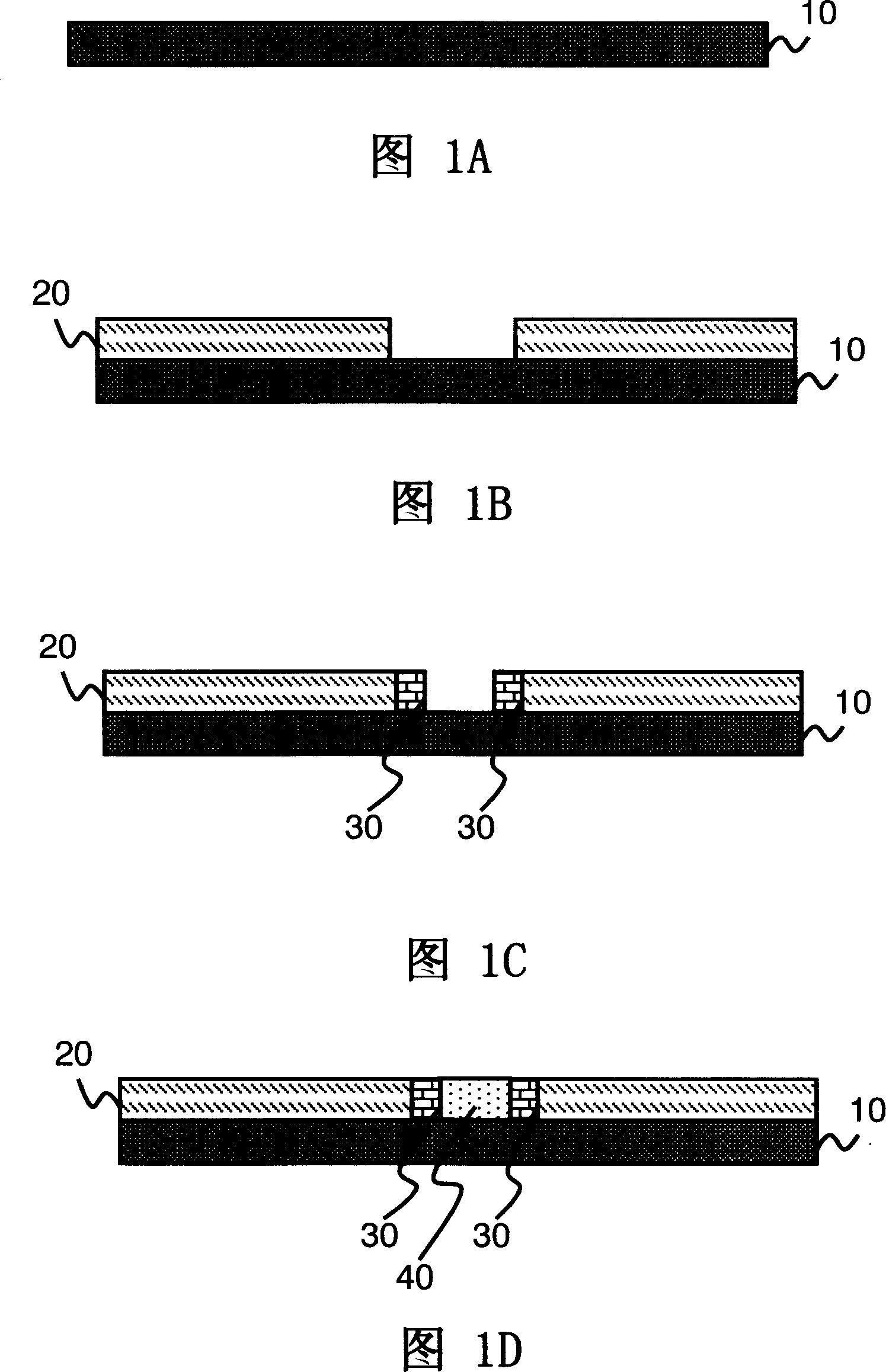

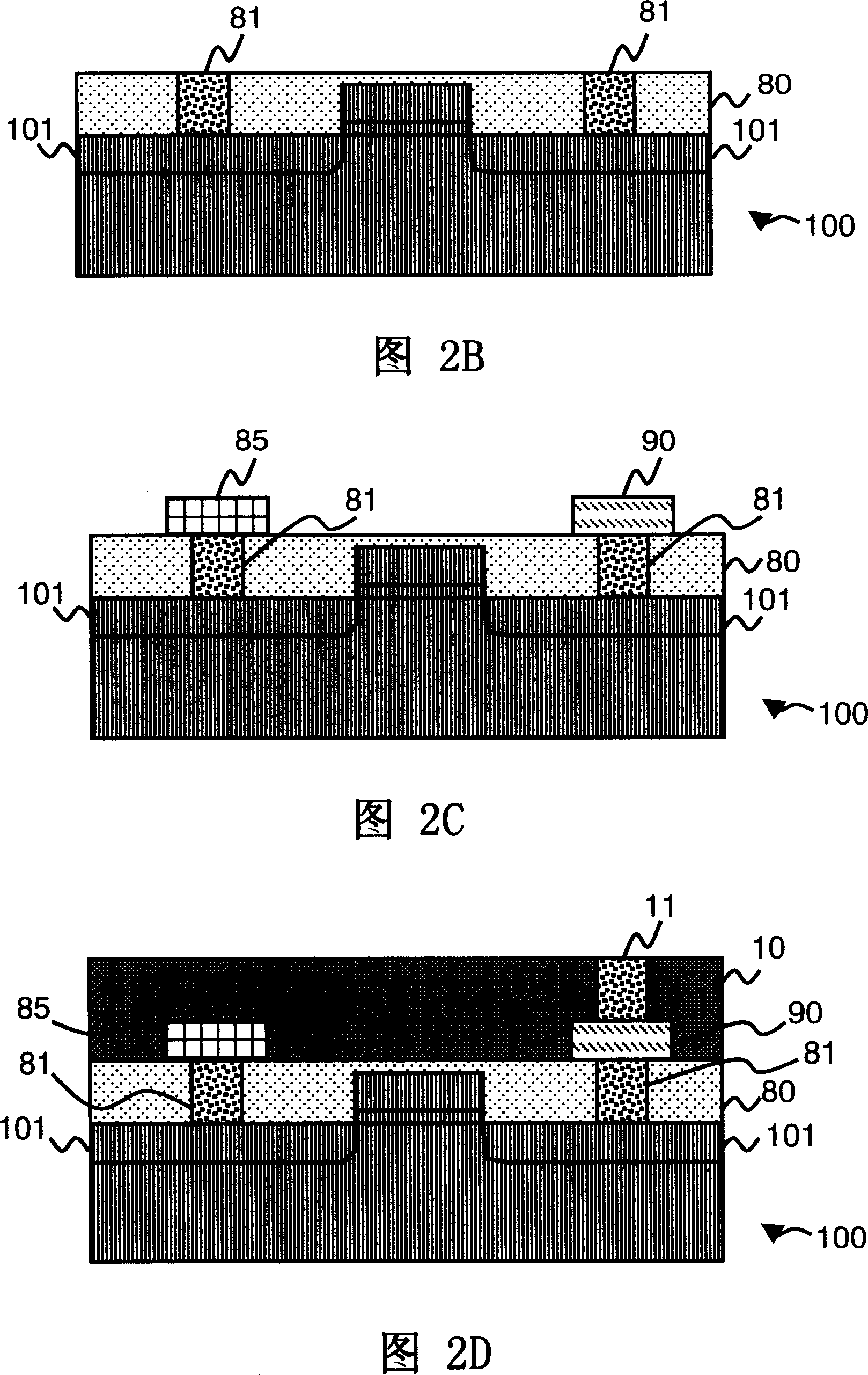

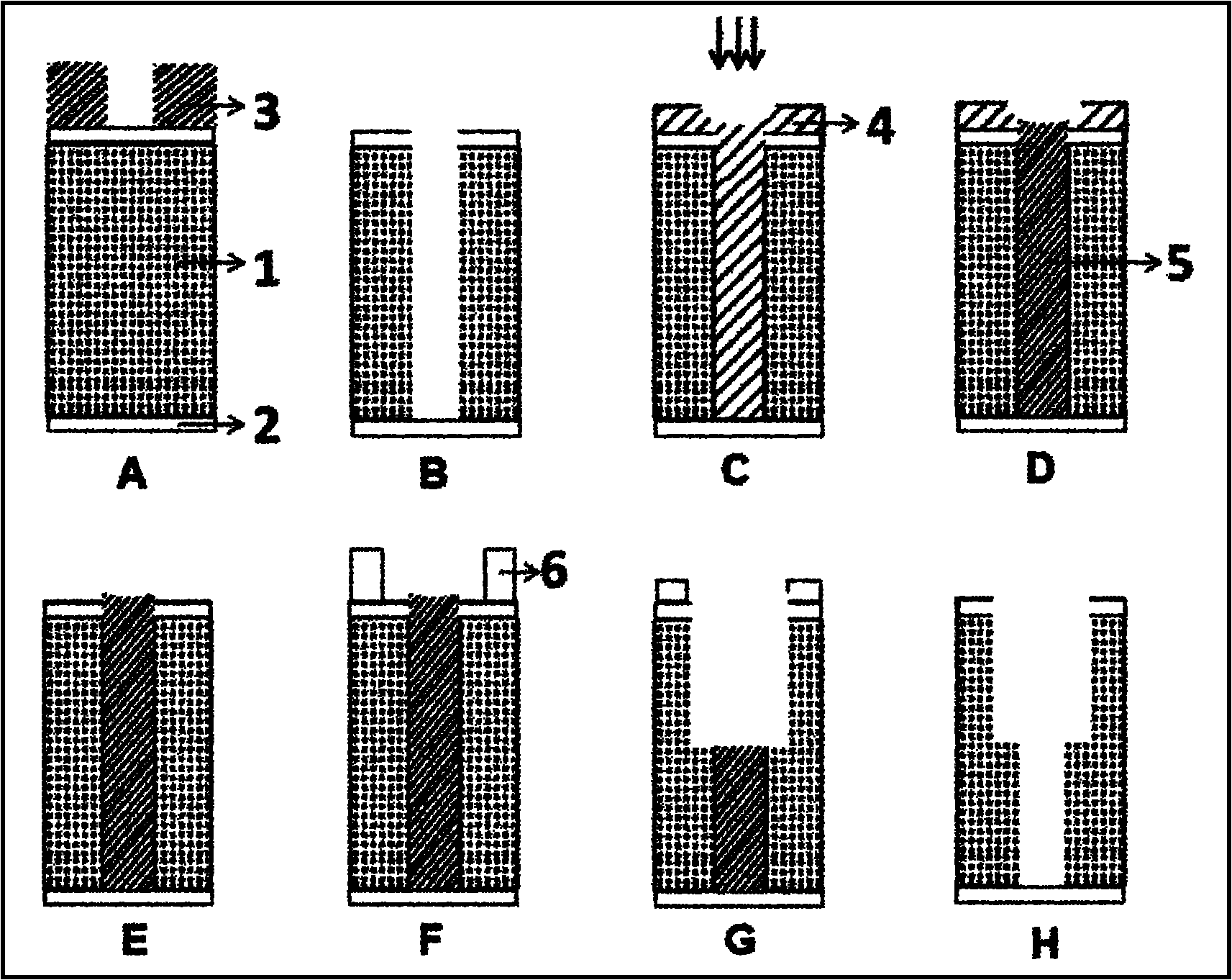

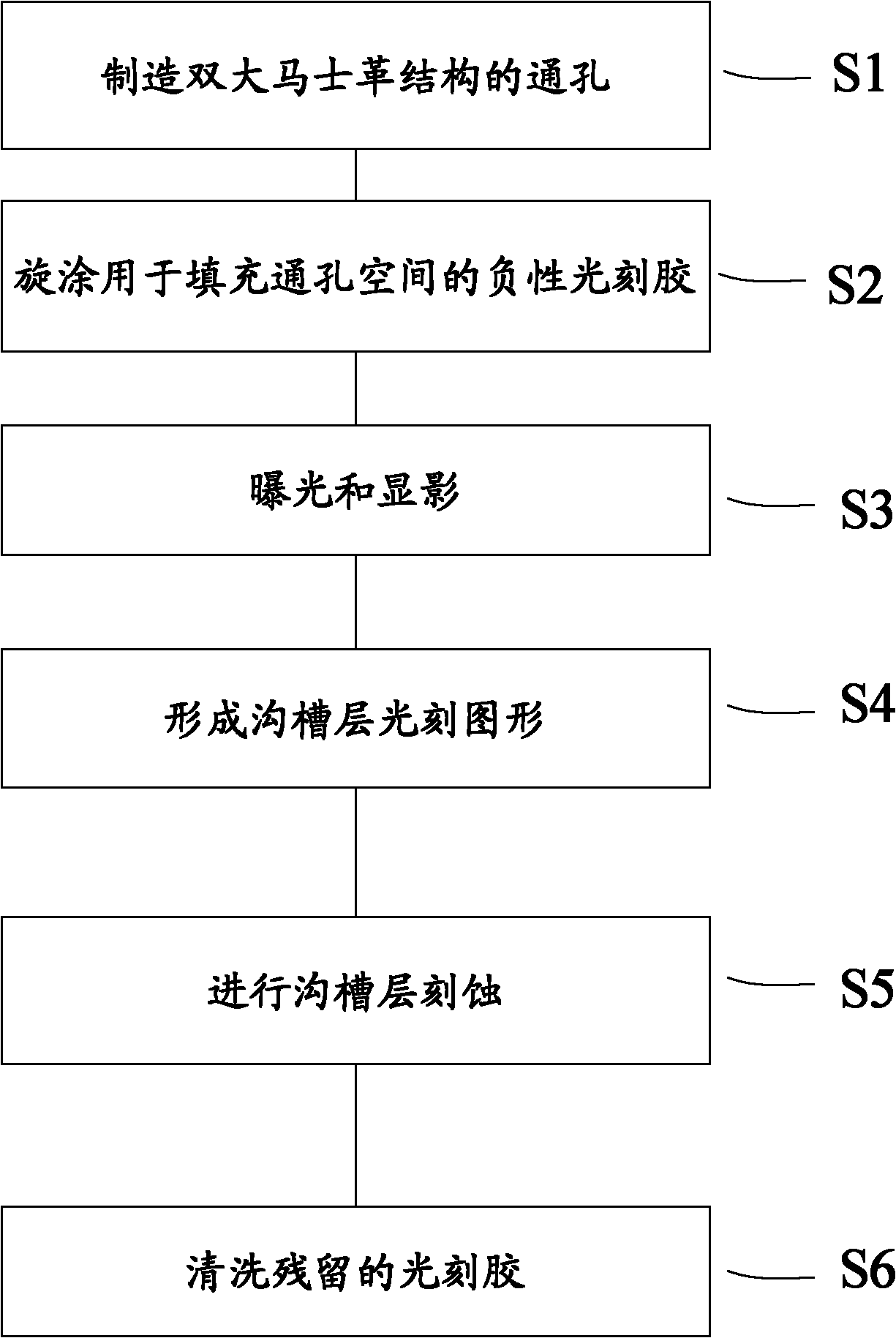

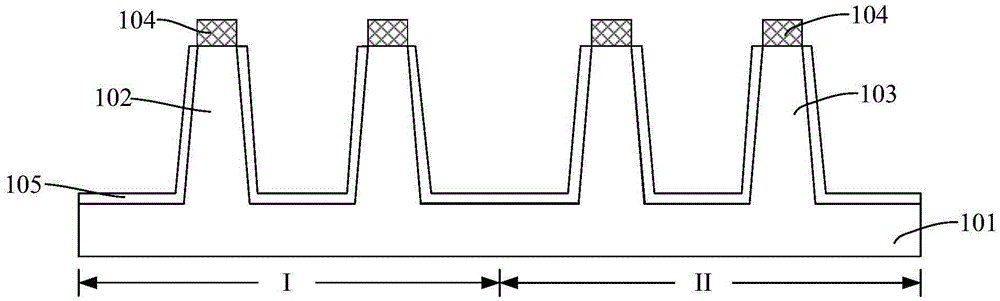

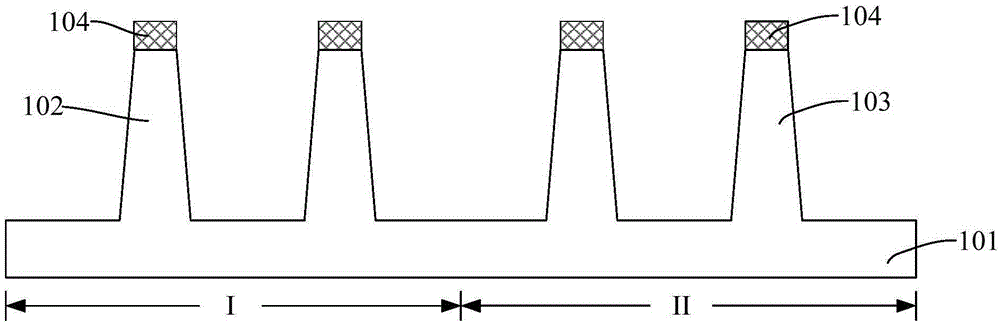

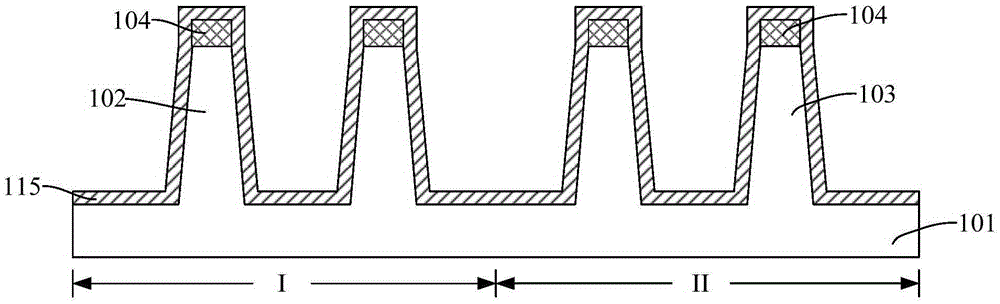

Manufacturing methods for dual damascene process and integrated circuit

InactiveCN102142395AImprove the shape of beveled facetsImprove stability andPhotomechanical apparatusSemiconductor/solid-state device manufacturingPhotoresistIntegrated circuit

The invention provides manufacturing methods for a dual damascene process and an integrated circuit. The manufacturing method for the dual damascene process comprises: a through hole forming step, in which a through hole is formed by a photomask; a through hole filling step, in which the through hole formed in the through hole forming step is filled by a negative photoresist; a through hole area exposing and developing step, in which a filled through hole area is exposed and developed by the photomask which is the same as a through hole layer after the through hole filling step; and a groove forming step, in which a groove is formed after the through hole filling step. According to the methods, a space of the etched through hole is filled by the negative photoresist with good hole filling performance, so that good filling of the space of the through hole is guaranteed, the good flatness of a surface of a silicon wafer is recovered, and the appearance of an oblique etched face of the etched groove is improved.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

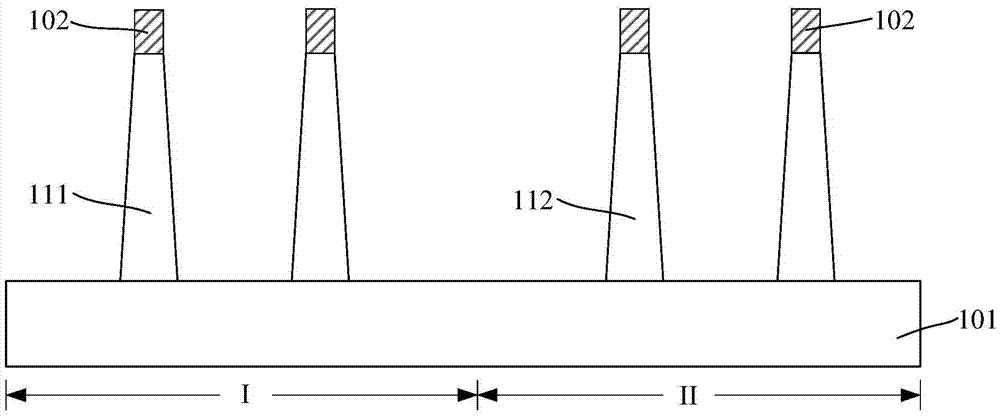

Method for forming fin field effect transistor

ActiveCN106571339AGood lookingImprove lattice qualitySemiconductor/solid-state device manufacturingSemiconductor devicesElectrical performanceField-effect transistor

A method for forming a fin field effect transistor comprises the following steps: forming a first fin on the surface of the substrate in a NMOS region and forming a second fin on the surface of the substrate in a PMOS region; forming a first doping layer covering the sidewall surface of the first fin, wherein the first doping layer contains first anti-punchthrough ions; forming a second doping layer on the sidewall surface of the second fin, wherein the second doping layer contains second anti-punchthrough ions; forming a dielectric layer on the surface of the substrate, wherein the top of the dielectric layer is lower than the top of the first fin and the top of the second fin; removing the first doping layer higher than the top of the dielectric layer; removing the second doping layer higher than the top of the dielectric layer; subjecting the remaining first doping layer and the remaining second doping layer to annealing to diffuse the first anti-punchthrough ions into the first fin to form a first anti-punchthrough layer and to diffuse the second anti-punchthrough ions into the second fin to form a second anti-punchthrough layer. The method improves the electrical performance of the formed fin field effect transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Synthesis method and application of over-speed hole-filling copper plating leveling agent

ActiveCN114381769AImprove fill rateImprove ductilityElectrical connection printed elementsCopper platingMetallurgy

The invention discloses a synthesis method and application of an overspeed porefilling copper plating leveling agent. The invention provides a copper plating technology capable of filling blind holes of substrates such as circuit boards, semiconductor support plates, organic material substrates, ceramic plates and the like in an over-speed manner. In particular to a synthesis method of a leveling agent for blind hole over-speed hole-filling electro-coppering and an application of the leveling agent in PCB (printed circuit board) copper plating. The leveling agent is composed of a quaternary ammonium salt type leveling agent and an IMEP type leveling agent. According to the electroplating solution obtained by matching the leveling agent with other additives, an insoluble anode is adopted, the temperature of the electroplating solution is increased to 30-50 DEG C, the electroplating solution has good hole filling capacity and excellent surface copper control capacity when the current density range is 3 ASD-5 ASD, the hole filling rate of obtained blind holes is high, and a copper plating layer is compact, flat, free of cavities and good in ductility. Compared with a common hole filling technology, the electroplating efficiency is improved, and the capacity of a client side is greatly improved.

Owner:广州市慧科高新材料科技有限公司

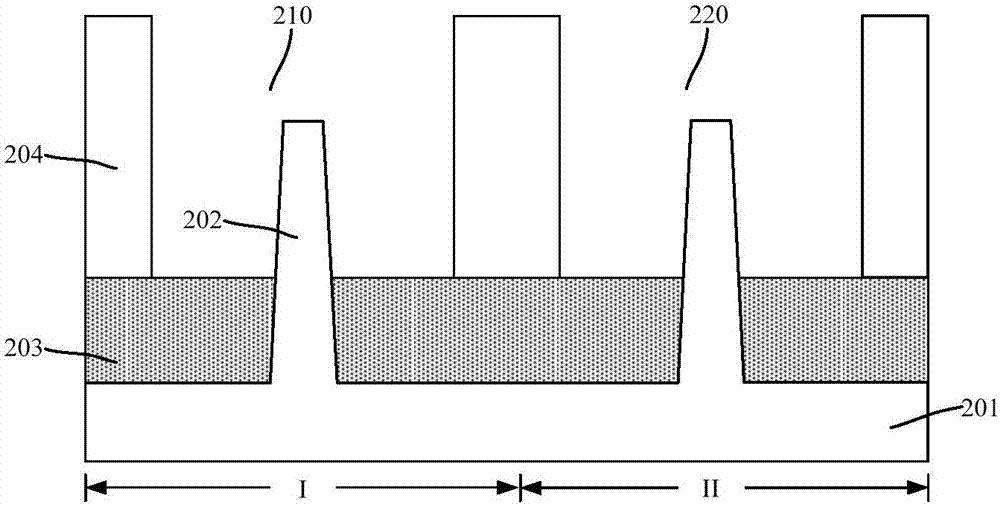

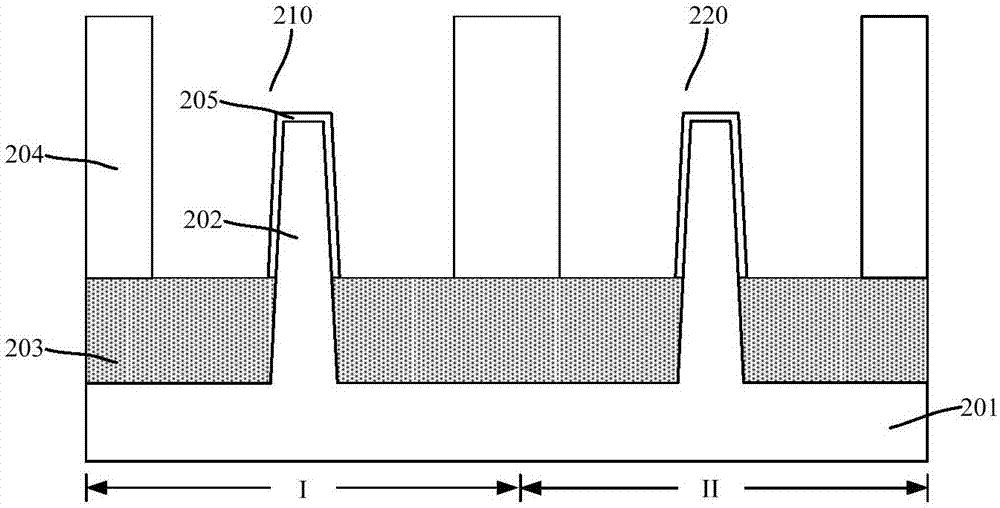

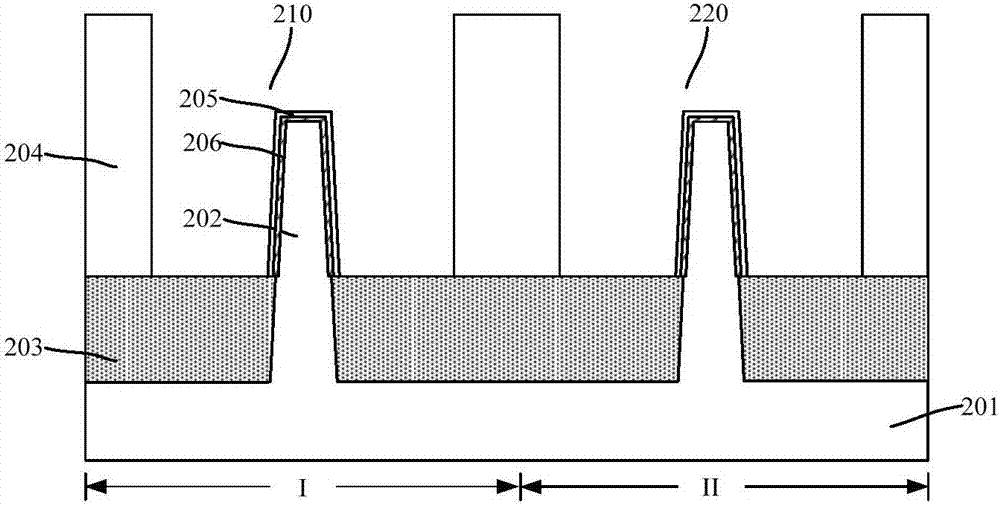

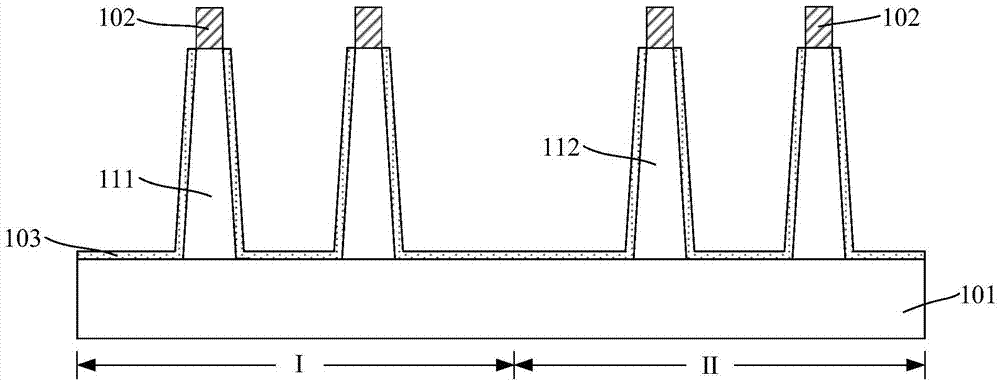

Formation method of fin field-effect transistor

ActiveCN106952873AImproved design redundancyPlay a blocking roleSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerIsolation layer

A formation method of a fin field-effect transistor comprises the steps of forming lining oxide layers on a surface, a surface of a side wall of a first fin part and a surface of a side wall of a second fin part; forming an insulation blocking layer on a surface of the lining oxide layer on a first region; depositing a precursor material layer on a surface of the insulation blocking layer and a surface of the lining oxide layer on a second region; performing curing and annealing on the precursor material layer under a H2O-containing atmosphere, and converting the precursor material layer to an insulation layer, wherein during the curing and annealing process, the side wall of the first fin part is oxidized to form a first oxide layer, the side wall of the second fin part is oxidized to form a second oxide layer, and the thickness of the first oxide layer is smaller than the thickness of the second oxide layer; and removing the insulation layer in a partial thickness to form an isolation layer, and also removing the lining oxide layer, the insulation blocking layer, the first oxide layer and the second oxide layer which are higher than the top of the isolation layer. After the isolation layer is formed, the critical dimension of the first fin part is larger than the critical dimension of the second fin part, and the process is simple in step.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

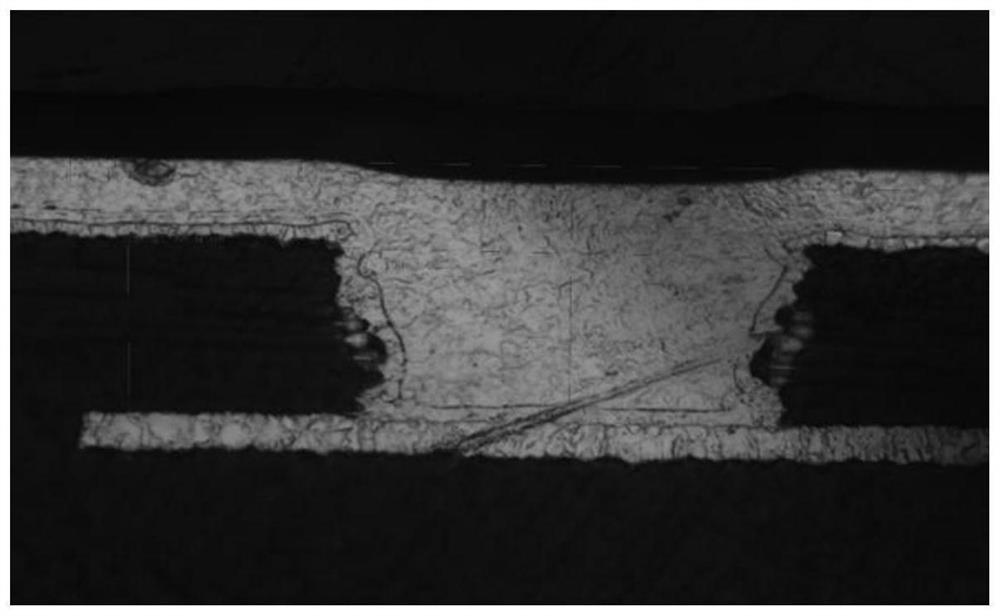

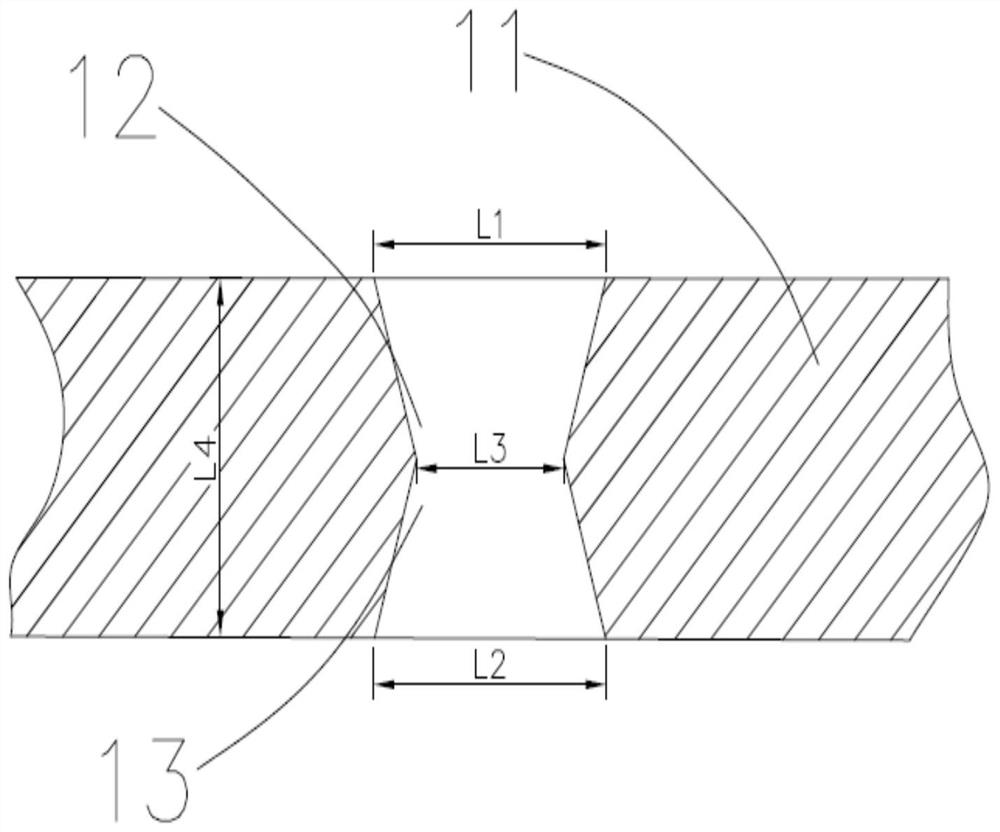

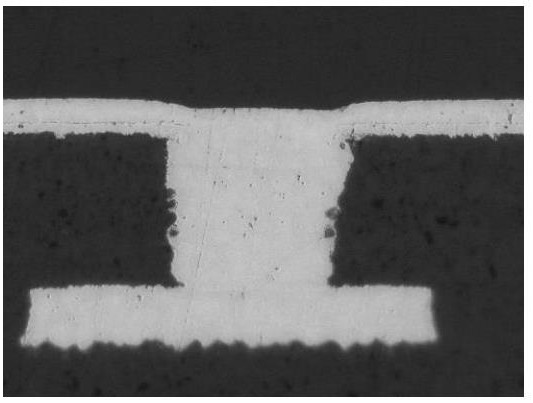

Method for improving electroplating hole filling process of circuit board

InactiveCN112423480AImproving the electroplating and filling processImprove reliabilityPrinted element electric connection formationLaser processingEngineering

The invention relates to the technical field of circuit boards, and in particular, relates to a method for improving an electroplating hole filling process of a circuit board, wherein the method comprises the following steps: (1) taking a circuit board substrate to be drilled, and drilling a first hole channel in the front surface of the circuit board substrate and a second hole channel in a backsurface area of the corresponding circuit board substrate by adopting laser processing; and communicating the first hole passage and the second hole passage to form a through hole; and (2) carrying out electrocoppering hole filling on the circuit board substrate drilled with the through hole. Laser drilling is carried out on the front face and the back face of the circuit board substrate at the same time, the through hole is formed after the holes drilled in the front face and the back face of the circuit board substrate are communicated, and the thin circuit board substrate can be used for machining the through hole and can also be used for hole filling. The method is simple and easy to operate and control, high in production efficiency and low in production cost, a plating layer on the surface of the substrate is uniform after the holes are filled with the electroplated metal, the quality problem of an etched circuit is avoided, and the product yield, the product reliability and theproduction efficiency of the circuit board are improved.

Owner:东莞市科佳电路有限公司

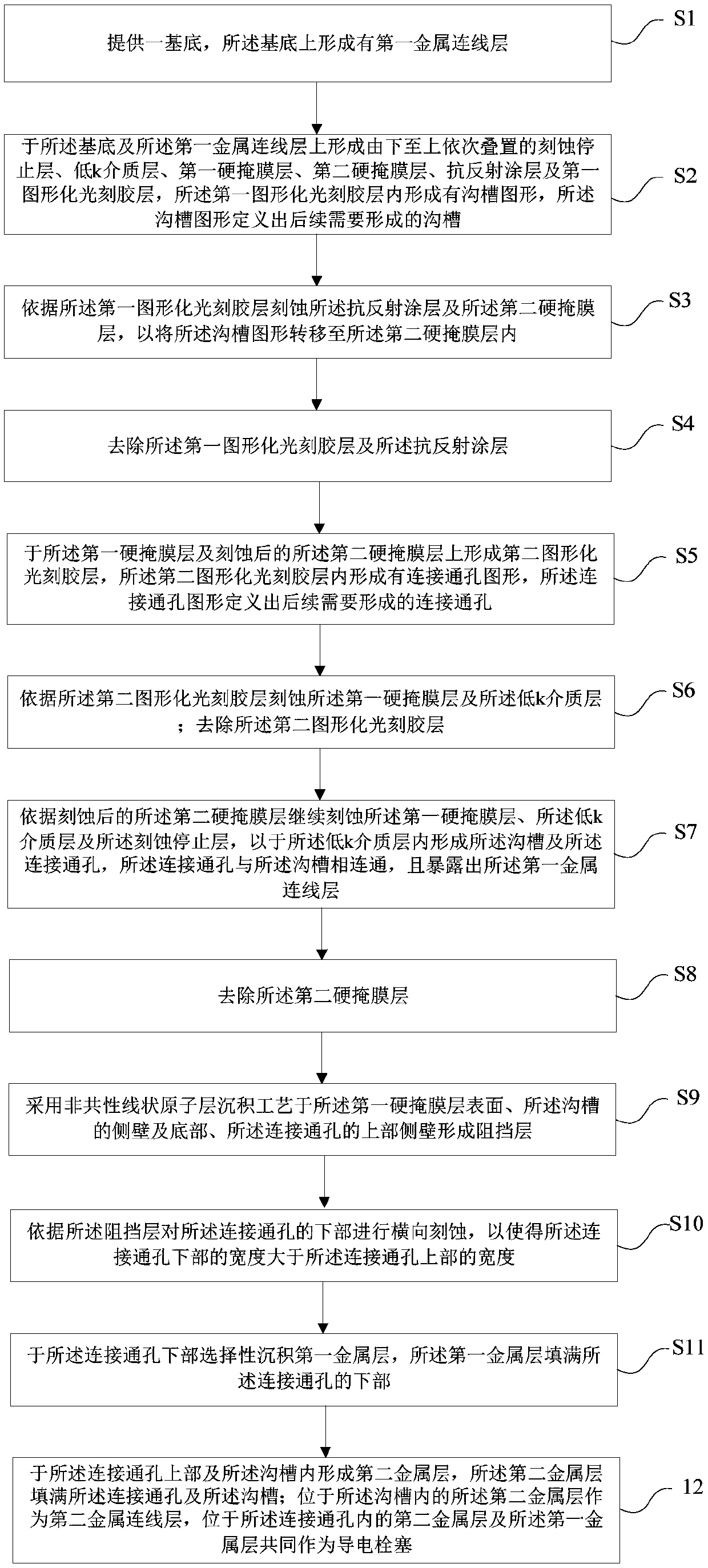

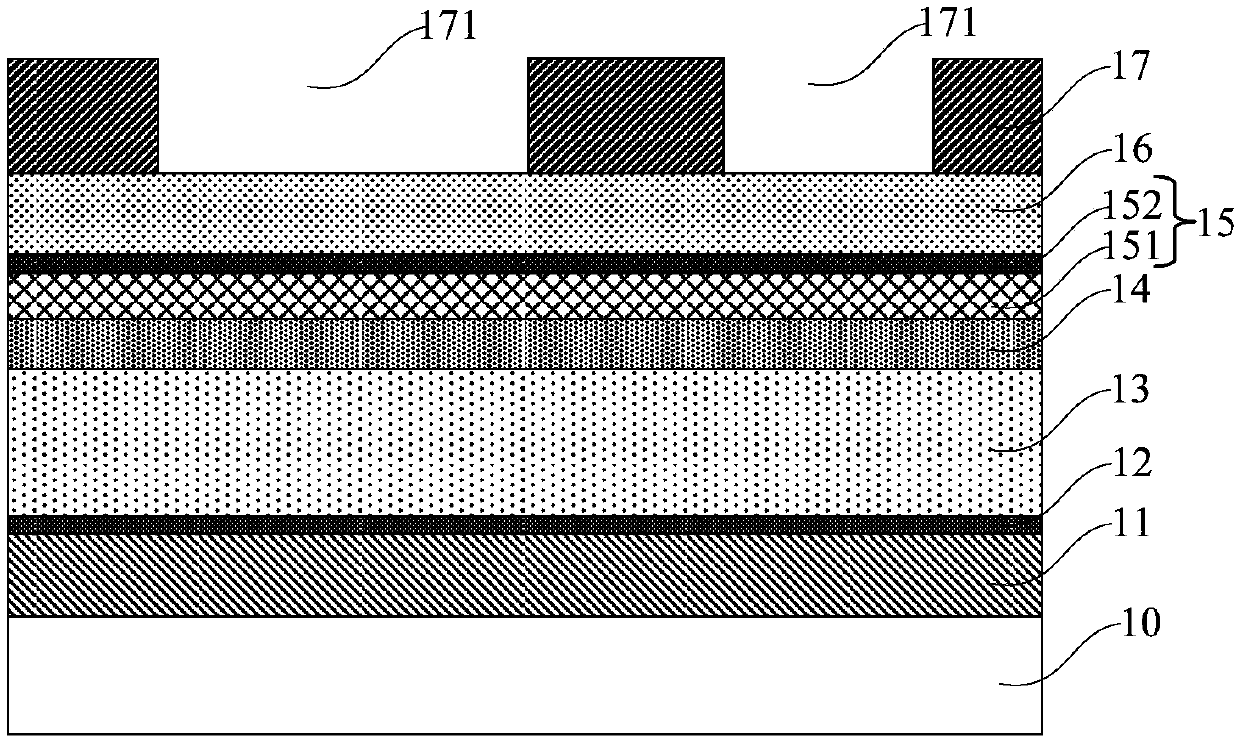

Semiconductor interconnection structure and preparation method thereof

InactiveCN110931423AIncrease contact surfaceReduce contact resistanceSemiconductor/solid-state device detailsSolid-state devicesAnti-reflective coatingEngineering

The invention provides a semiconductor interconnection structure and a preparation method thereof, and the method comprises the steps: 1), providing a substrate which is provided with a first metal connecting line layer; 2) forming an etching stop layer, a low-k dielectric layer, a first hard mask layer, a second hard mask layer, an anti-reflection coating and a first graphical photoresist layer on the substrate and the first metal connecting line layer; 3) etching the anti-reflection coating and the second hard mask layer; 4) removing the first graphical photoresist layer and the anti-reflection coating; 5) forming a second graphical photoresist layer; 6) etching the first hard mask layer and the low-k dielectric layer; 7) continuously etching the first hard mask layer, the low-k dielectric layer and the etching stop layer to form a groove and a connecting through hole; 8) removing a second hard mask layer; 9) forming a barrier layer; 10) transversely etching the lower portion of theconnecting through hole; (11) selectively depositing a first metal layer on the lower portion of the connecting through hole, and (12) forming a second metal layer. The preparation method can reduce contact resistance between the conductive plug and the first metal connecting line layer.

Owner:SIEN QINGDAO INTEGRATED CIRCUITS CO LTD

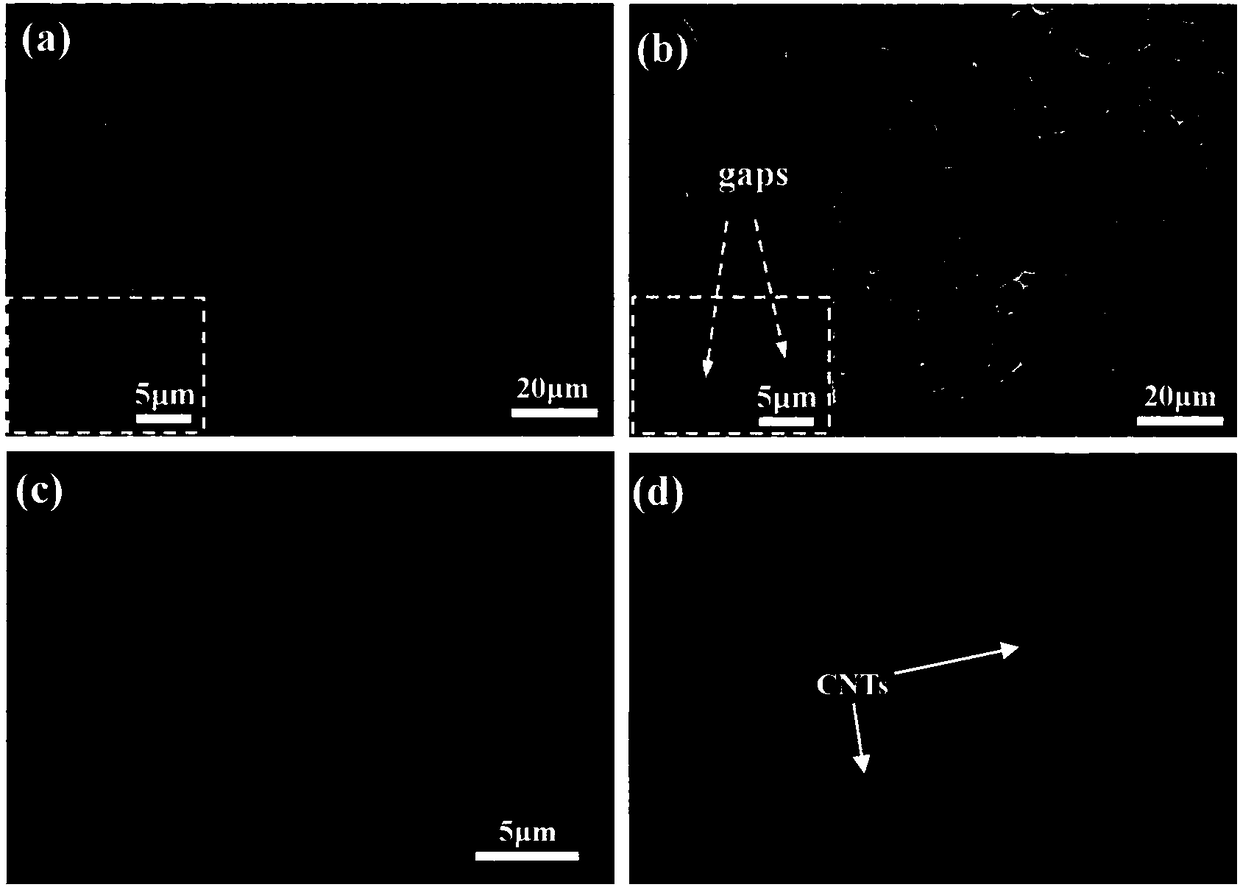

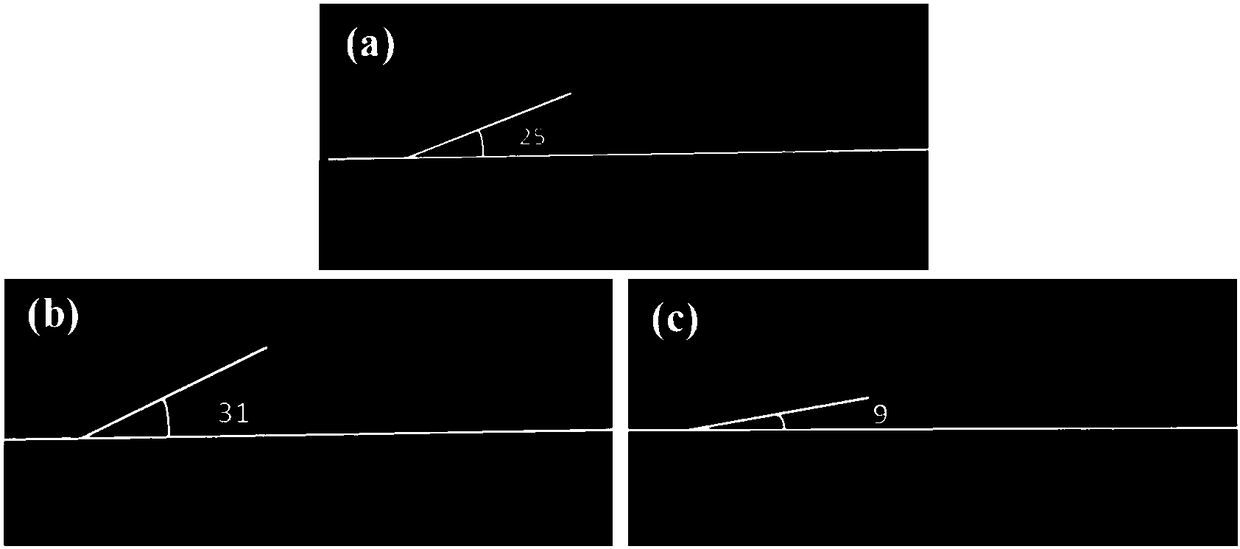

Method for improving wettability of brazing filler metal based on surface modification of carbon-carbon composite

The invention discloses a method for improving the wettability of brazing filler metal based on surface modification of a carbon-carbon composite. Carbon nanotubes grow in situ in a hole formed afteroxidation pretreatment of the carbon-carbon composite and are used as a bridge to promote liquid brazing filler metal to be wetted and spread in a brazing process and improve the capacity of filling the hole. The carbon nanotubes grow on the surface of the carbon-carbon composite by selecting a chemical vapor deposition method, and the carbon-carbon composite is brazed or brazed together with metal by selecting the brazing filler metal capable of wetting the carbon-carbon composite after the carbon-carbon composite is subjected to surface modification. By using the method, the surface of the carbon-carbon composite which is not brazed is subjected to high-temperature oxidation, and CNTs grow on the surface of the carbon-carbon composite which is not brazed, an infiltration interface structure is formed between a brazinrg seam and the carbon-carbon composite, and the spreading and filling capacity of the liquid brazing filler metal is improved, so that the reaction of the brazing fillermetal and the carbon-carbon composite is more sufficient, and the method has important significance in reducing residual stresses in joints and improving the connection performance of the joints.

Owner:TIANJIN UNIV

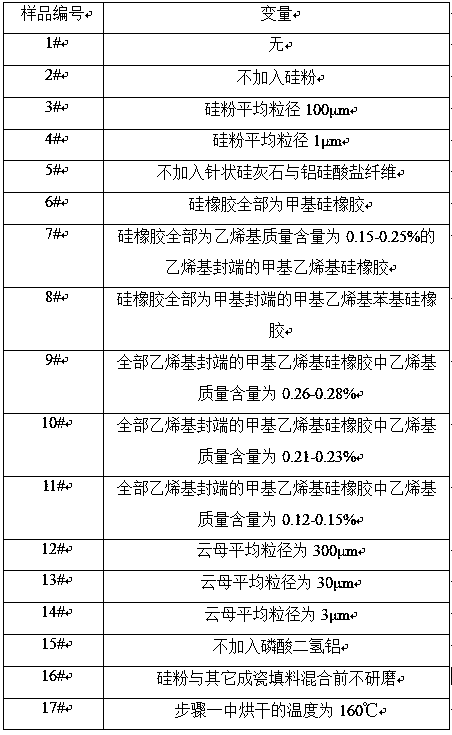

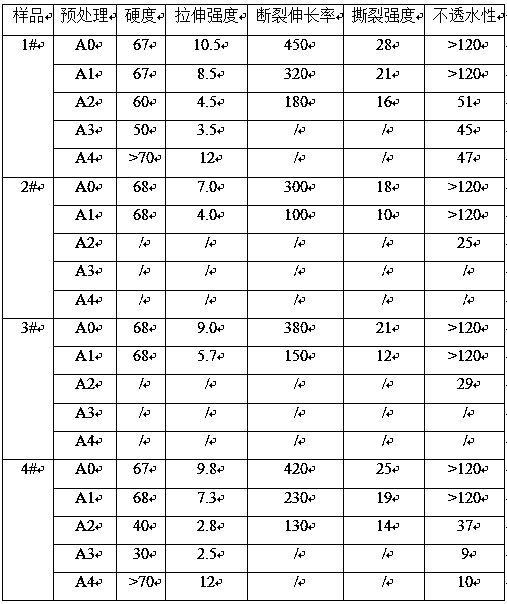

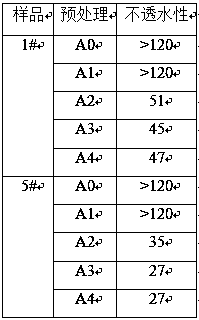

Waterproof ceramicized silicon rubber material and preparation method and application thereof

InactiveCN108948744ADenseImprove waterproof performanceApparatus for joining/termination cablesCable glandPolymer science

The invention discloses a waterproof ceramicized silicon rubber material comprising a ceramic-forming filler, silicone rubber, silicone oil, boron oxide, a coupling agent and a vulcanizing agent; andthe ceramic-forming filler comprises silicon powder, mica and silicon dioxide. A preparation method comprises the following steps: (1) grinding the silicon powder, mixedly grinding the silicon powderand other ceramic-forming filler components, and drying to obtain the pretreated ceramic-forming filler; (2) blending all components excluding the ceramic-forming filler and the vulcanizing agent, mixing and performing mixing under vacuum to obtain organosilicone rubber compound; (3) mixing the pretreated ceramic-forming filler with the organosilicone rubber compound; and (4) adding the vulcanizing agent for mixing. The waterproof ceramicized silicone rubber has good mechanical properties at normal temperature, and has a low ceramic-forming temperature to avoid cracking at ambient temperatureof 300 to 400 DEG C, so that a ceramic body transformed after ceramic-forming has a dense structure and good waterproof performance. The waterproof ceramicized silicon rubber material can be used in acable gland with a refractory layer made of the waterproof ceramicized silicon rubber material, and the cable gland is mechanically stable and still has water resistant at high temperature.

Owner:BEISIT ELECTRIC TECH HANGZHOU CO LTD

Fin field-effect transistor and forming method thereof

InactiveCN108807378AQuality improvementImprove electrical performanceTransistorSolid-state devicesEngineeringField-effect transistor

The invention provides a fin field-effect transistor and a forming method thereof. The forming method comprises: providing a substrate, the substrate including a first device region and a second device region, and the substrate having a plurality of discrete fins; forming a dummy grid electrode across the fins; forming an interlayer dielectric layer on the fins exposed the dummy grid electrode, the interlayer dielectric layer exposing the dummy grid electrode; removing a first opening of the dummy grid electrode, the first opening formed in the interlayer dielectric layer; forming an initial metal grid electrode fully filling the first opening; performing graphical processing on the initial metal grid electrode, to form a second opening in the initial metal grid electrode, on the directionvertical to a substrate surface, the second opening penetrating the initial metal grid electrode; forming a first metal grid electrode in the first device region and forming a second metal grid electrode in the second device region. Electrical properties of the fin field-effect transistor are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

A kind of hole-filling electroplating leveling agent, preparation method and electroplating solution using the leveling agent

The invention discloses a hole-filling electroplating leveling agent, a preparation method thereof and an electroplating solution using the hole-filling electroplating leveling agent, and relates to the technical field of electroplating. The hole-filling electroplating leveling agent includes ingredients 3-(dimethylamino)-1-propanethiol, piperazine, binary epoxy compound, and the 3-(dimethylamino)-1-propanethiol The molar mass ratio of mercaptan, piperazine and binary epoxy compound is 1~3:2~4:4~6; described binary epoxy compound has the following structural formula: wherein, R is the connection of non-epoxy group group. The hole-filling electroplating leveling agent of the present invention improves the interaction between the leveling agent molecule and the accelerator and inhibitor by introducing a sulfur atom-containing functional group into the leveling agent molecule, so that the three types of additives can better cooperate with each other , so that the prepared electroplating solution can achieve excellent hole filling performance.

Owner:SHENZHEN BANMING SCI & TECH CO LTD

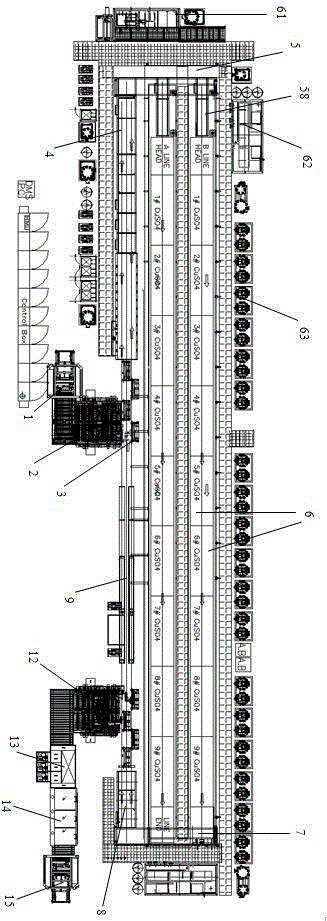

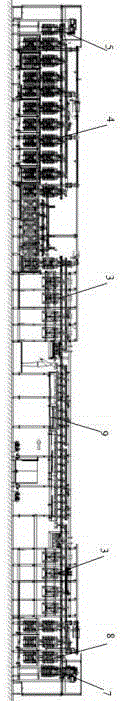

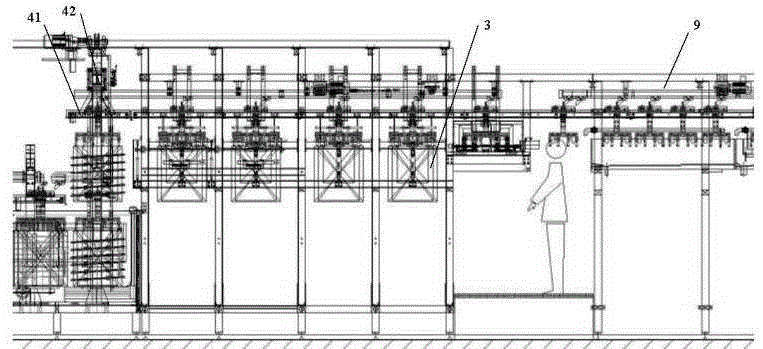

Vertical continuous electroplating hole filling line

PendingCN106637371AGood hole filling abilityGood bindingSemiconductor devicesPre treatmentEngineering

The present invention provides a vertical continuous electroplating hole filling line for PCB board processing. The vertical continuous electroplating hole filling line comprises a plurality of sub-lines arranged in a side-by-side manner, and is characterized in that each sub-line comprises a material feeding mechanism, a pretreatment device, a front shifting device, an electroplating pretreatment device, a multi-stage electroplating copper cylinder, a rear shifting device, a post-treatment device and a deplating device, wherein the material feeding mechanism, the pretreatment device, the front shifting device, the electroplating pretreatment device, the multi-stage electroplating copper cylinder, the rear shifting device, the post-treatment device and the deplating device are sequentially connected, the material inlet end of the material feeding mechanism is connected to an automatic plate feeding device, the material inlet end of the automatic plate feeding device is provided with a plate feeding conveying belt, and the material outlet end of the post-treatment device is sequentially connected to a central positioning machine, a corner turning machine, a horizontal plate drying machine and an automatic plate collection device. According to the present invention, with the vertical continuous electroplating hole filling line, the thickness uniformity of the plating layer at blind holes, buried holes and other hole filling positions of the high density circuit board, the deep plating ability, the hole filling ability and the bonding force are good, the shape is beautiful, the consistency of the hole wall plating layer and the plate surface plating layer is good, the operation, the maintenance and the repair are convenient, the structure is compact, the occupation space is small, the generated waste gas is less, and the environmental protection advantage is provided.

Owner:DONGGUAN CRAY AUTOMATION TECH

Composite electroplating brightener and preparation method thereof

InactiveCN111058065ATo achieve a bright effectIncrease brightnessNitrogenous heterocyclic compoundThiourea

The invention discloses a composite electroplating brightener. Every liter of an electroplating solution comprises the following raw materials in parts by volume: 7 to 12 mL / L of copolymer of 2,2-dimethyl-1,3-propanediol and 1,2-ethylene glycol, 7 to 12 mL / L of sodium phenyldithiopropane sulfonate, 3 to 6 mL / L of diphenylamine thiourea, 6 to 10 mL / L of triethanolamine, 1.2 to 2.2 mL / L of sodium polydithiodipropane sulfonate and 14-17 mL / L of a nitrogenous heterocyclic compound. The composite electroplating brightener can be suitable for various electroplating processes such as copper plating,zinc plating, copper-zinc alloy plating and the like, has multiple functions, achieves the brightening effect, and also has remarkable improvement effects on the current efficiency, the elongation, the tensile strength and other properties of a plating layer; and the electroplating brightener has a good hole filling effect on the surface of an electroplated (such as electrocoppering or electrogalvanizing) base material, the surface gloss of the plating layer is high, and the brightening effect is good.

Owner:浙江金欣新材料科技股份有限公司

Preparation process of deep submicron integrated circuit Cu barrier

InactiveCN1414613ALow resistivityReduced via contact resistanceSemiconductor/solid-state device manufacturingInterconnectionRapid thermal annealing

A preparing process for Cu blocking layer of integrated circuit in deep submicron uses the IPVD process to deposite TaSiN as a blocking layer to Cu diffusing and to select Ta as an adjacent blocking layer material of Cu metal. In chemical electroplating of Cu, the alternating electric field and electroplating additives are applied. The heat treatment for Cu with annealing in fast heating and the chemicomechanical polishing for Cu is carried out to grind off the unnecessary Cu metal and blocking layer in addition to connection wire and through hole to realize the Cu interconnection wiring technology of Damascus. The process raises the ability of antidiffusing for Cu and F, improves the sticking ability with Cu metal film and insulation media, is suitable to be used in the interconnection technology of Cu metal and low dielectric material.

Owner:SHANGHAI HUA HONG GROUP +1

Semiconductor structure and forming method thereof

ActiveCN108666267AEfficient removalRemove completelySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureMetal silicide

The invention discloses a semiconductor structure and a forming method thereof. The forming method comprises the following steps of: forming a first through hole that penetrates through a dielectric layer and exposes a surface of a source-drain doping region; forming a second through hole that penetrates through the dielectric layer and exposes a top of a gate structure; depositing cap layers on abottom and sidewalls of the first through hole and a bottom and sidewalls of the second through hole; performing a first cleaning process on the bottom of the first through hole and the bottom of thesecond through hole to remove cap layers located on the bottom of the first through hole and the bottom of the second through hole; performing a second cleaning process on the source-drain doping region exposed at the bottom of the first through hole and the gate structure exposed at the bottom of the second through hole after the first cleaning process; forming metal layers on the bottom and thesidewalls of the first through hole, the bottom and the sidewalls of the second through hole and a top of the dielectric layer after the second cleaning process; and performing an annealing process on the metal layers to convert the metal layer located on the source-drain doping region into a metal silicide layer. According to the invention, the electrical properties of the formed semiconductor structure can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Application of circuit board hole-filling electroplating leveling agent

ActiveCN113430597AGood hole filling abilityPrinted element electric connection formationThioureaPhysical chemistry

The invention provides application of a circuit board hole-filling electroplating leveling agent, and relates to the technical field of hole-filling electroplating. The circuit board hole-filling electroplating leveling agent is thioureido imidazoline quaternary ammonium salt, namely thioureido is introduced into leveling agent molecules, and when the leveling agent is added into an electroplating solution system for hole-filling electroplating, the surface copper thickness is small and is smaller than 15 micrometers; and the hole-filling performance is excellent, and the leveling agent can adapt to increasingly fine development of fine circuit processing. An electroplating solution used during electroplating is composed of 40 to 120 g / L of sulfuric acid, 120 to 240 g / L of copper sulfate pentahydrate, 40 to 80 ppm of chloride ions, 2 to 10 ppm of an accelerator, 600 to 1000 ppm of an inhibitor and 3 to 10 ppm of the thioureido imidazoline quaternary ammonium salt, and holes filled through electroplating are one or more of blind holes, through holes and buried holes.

Owner:SHENZHEN BANMING SCI & TECH CO LTD

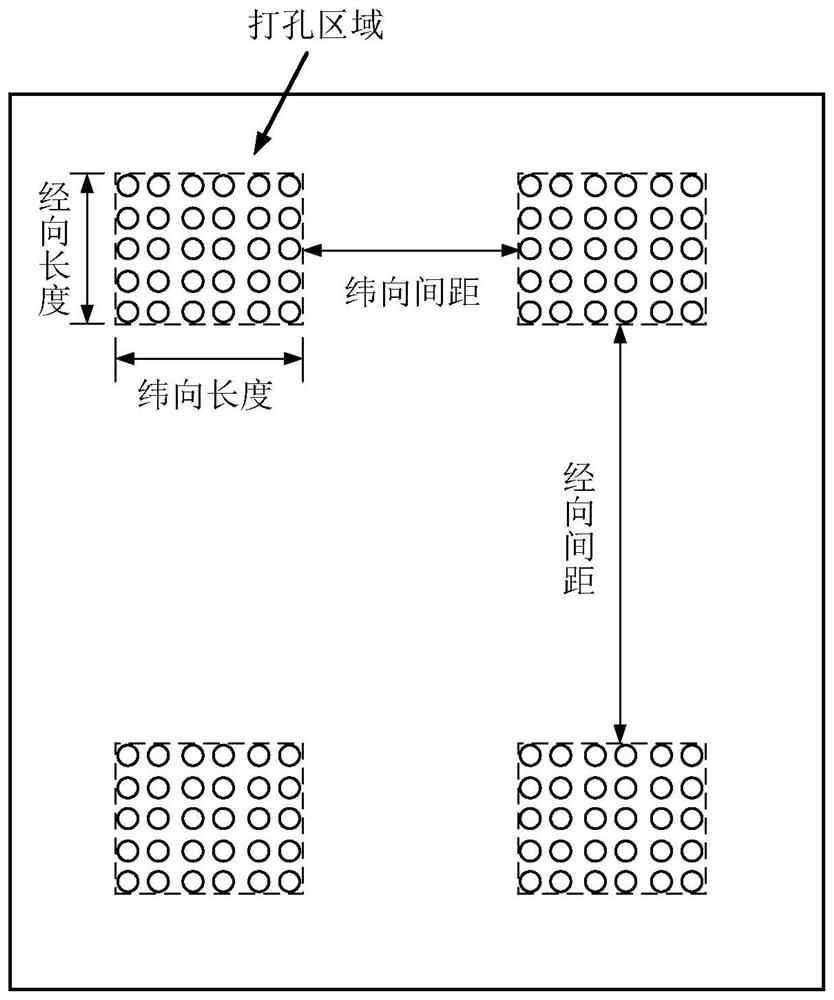

Bonding sheet, preparation method thereof and metal foil-clad laminated board comprising bonding sheet

ActiveCN113045856AReduce intensityImprove cooling effectCircuit susbtrate materialsMetal layered productsPunchingMetal foil

The invention provides a bonding sheet, a preparation method thereof and a metal foil-clad laminated board comprising the bonding sheet. The bonding sheet comprises a reinforcing material and a resin composition for infiltrating and filling the reinforcing material; the reinforcing material is provided with at least one punching area, at least three holes are formed in any punching area, and the diameter of each hole is 0.5-4 mm; and the distance between holes in any one punching area ranges from 0.4 mm to 2 mm, and the minimum distance between every two adjacent punching areas is larger than the distance between the holes. The holes with specific diameters and intervals are formed in the reinforcing material, so that the holes are filled with the resin composition instead of the reinforcing material, the strength of the bonding sheet is not obviously reduced, meanwhile, the heat dissipation performance and the hole filling performance of the punching area of the bonding sheet are improved, and it is ensured that a metal foil-clad laminated board and a circuit board prepared through the bonding sheet have enough rigidity, good local heat dissipation capacity and high interlayer bonding force.

Owner:GUANGDONG SHENGYI SCI TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com