Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

901 results about "Copper deposition" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Process for electroless copper deposition

InactiveUS20070099422A1Solid-state devicesSemiconductor/solid-state device manufacturingCopper platingRuthenium

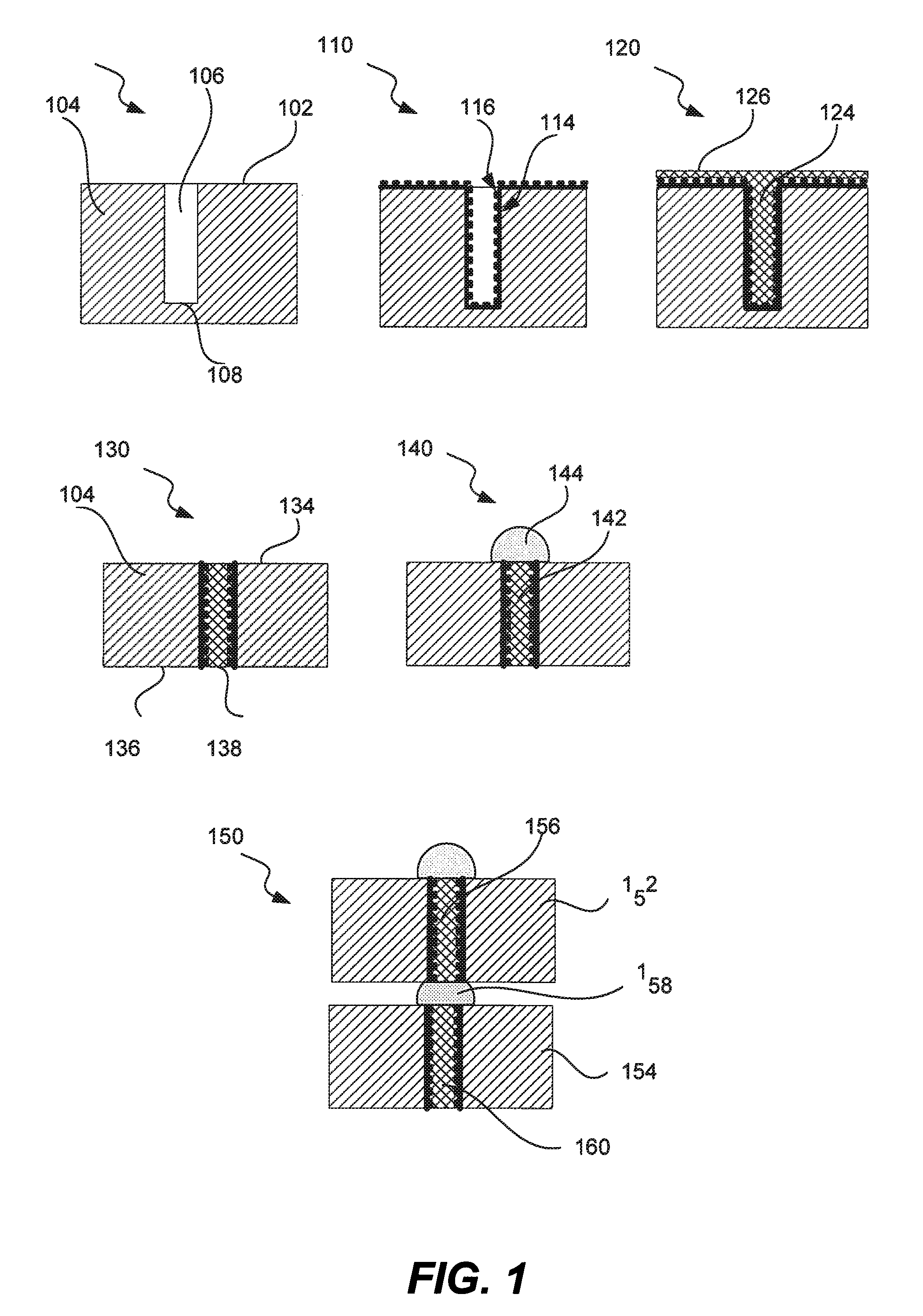

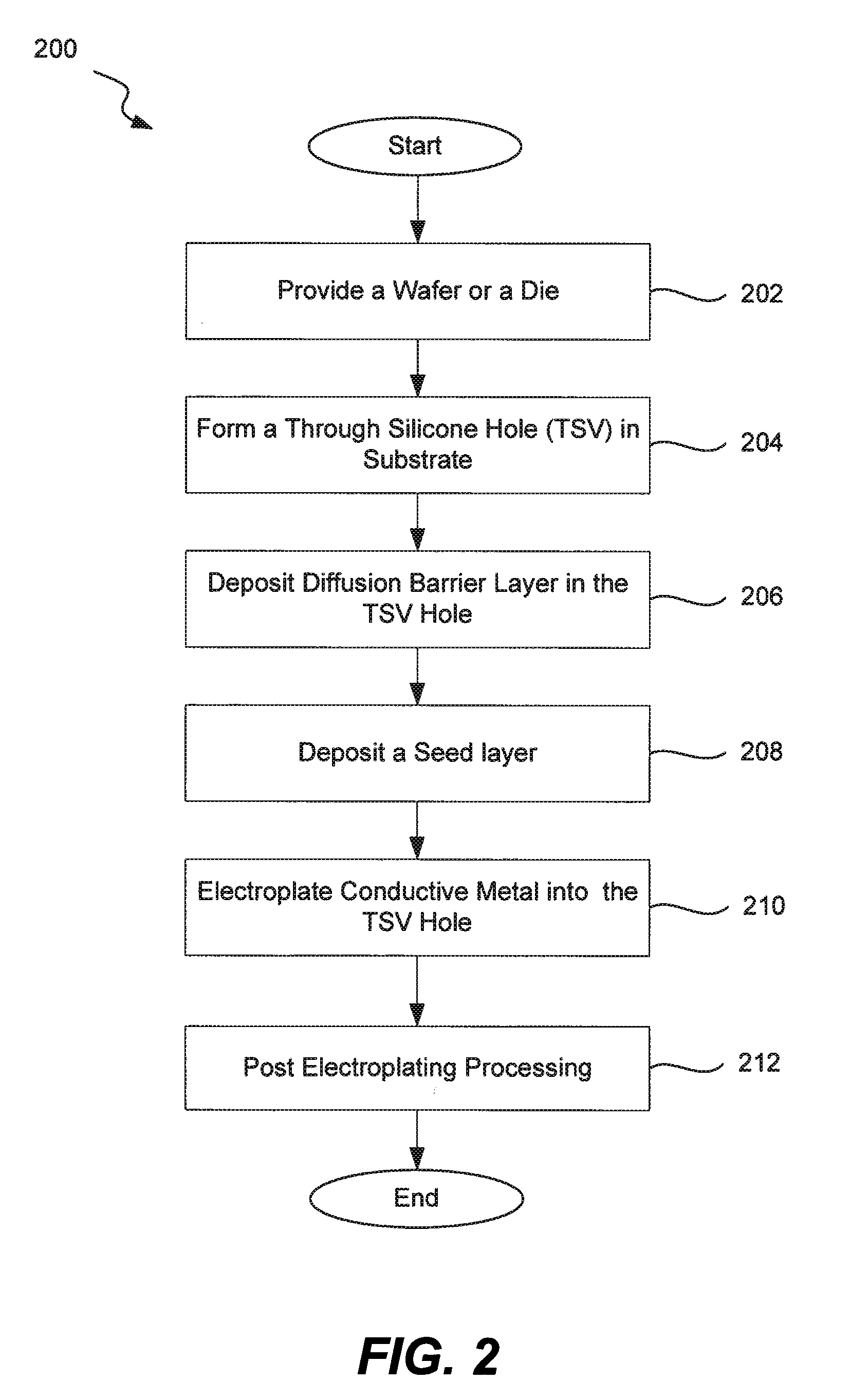

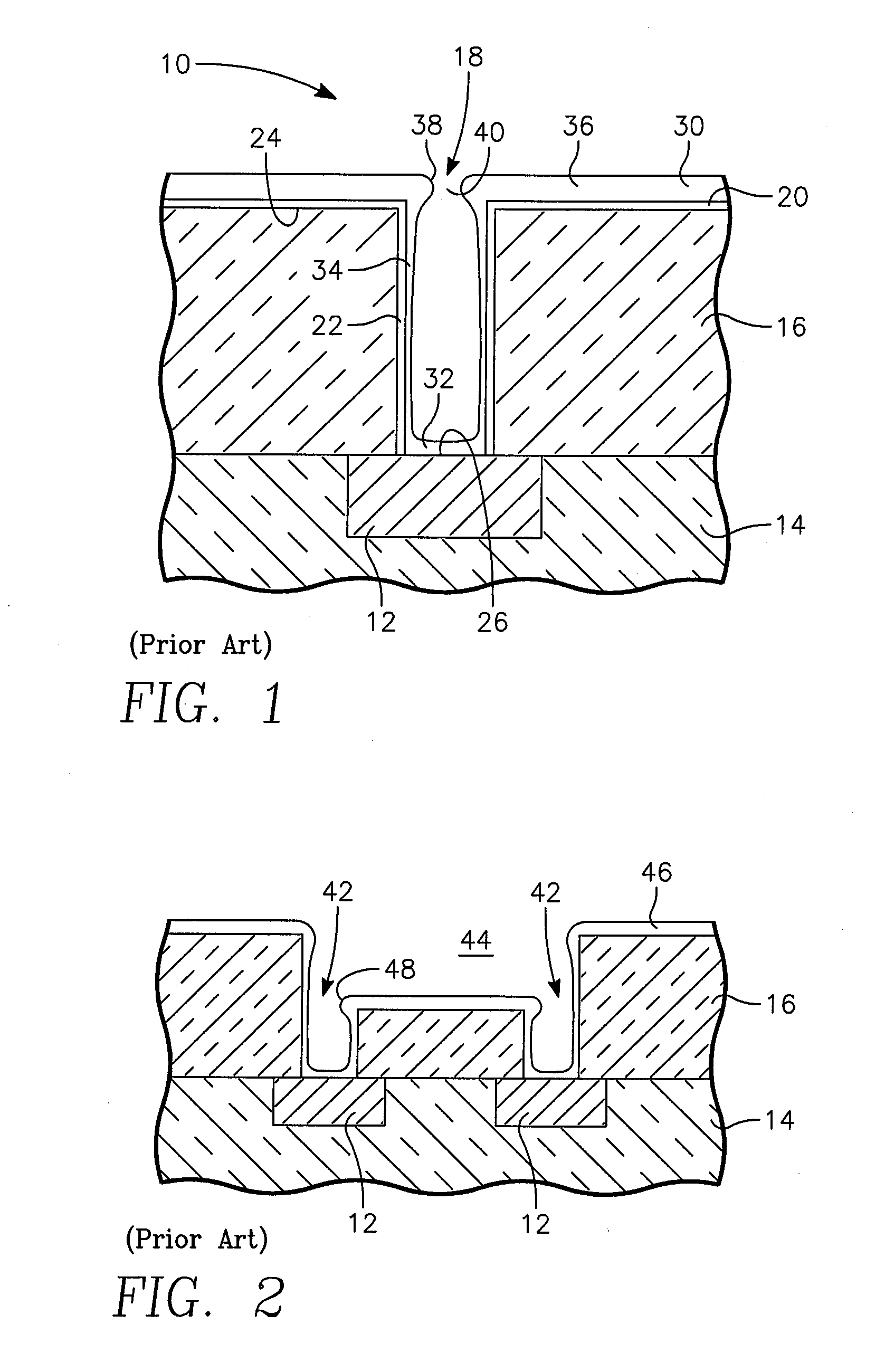

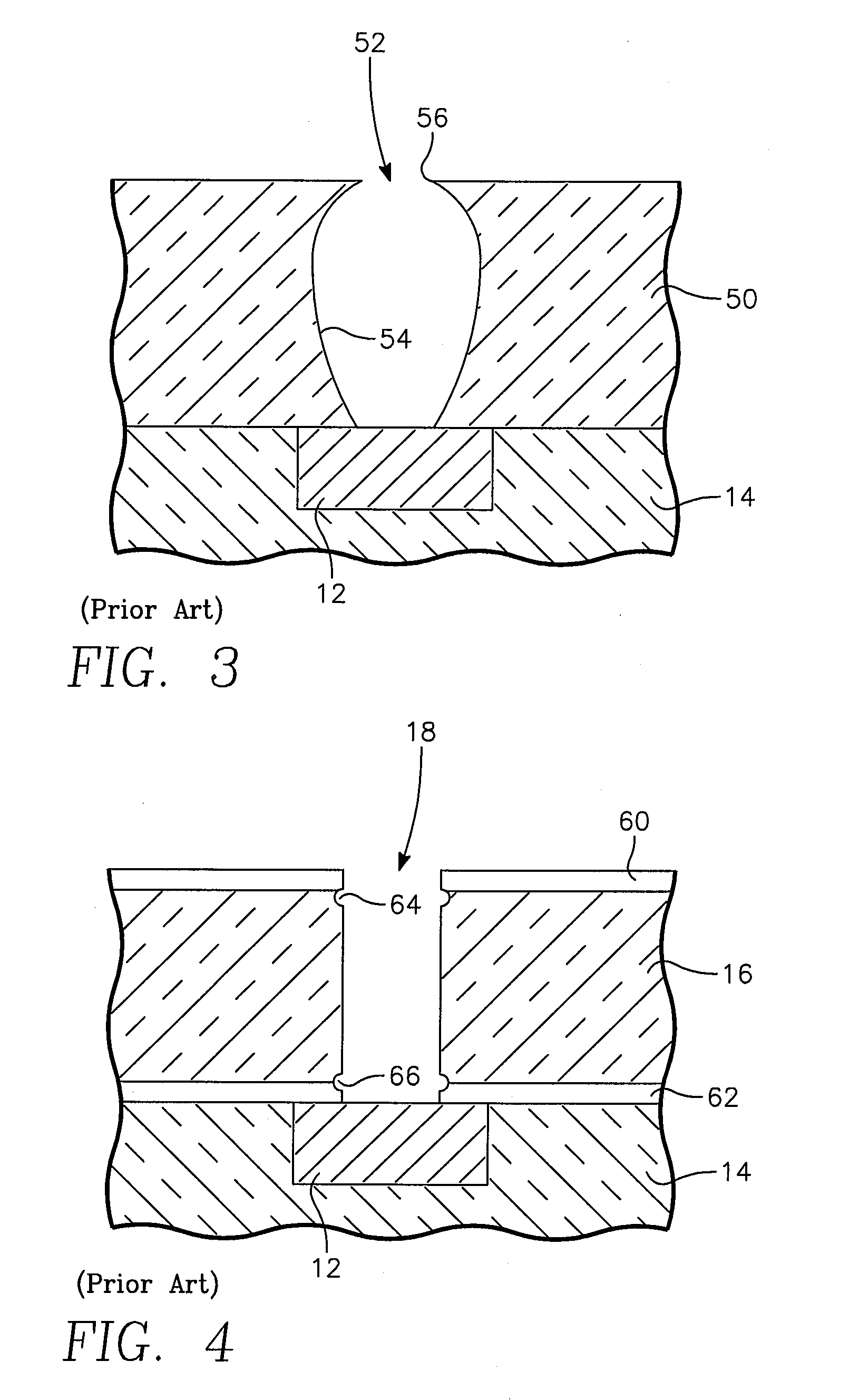

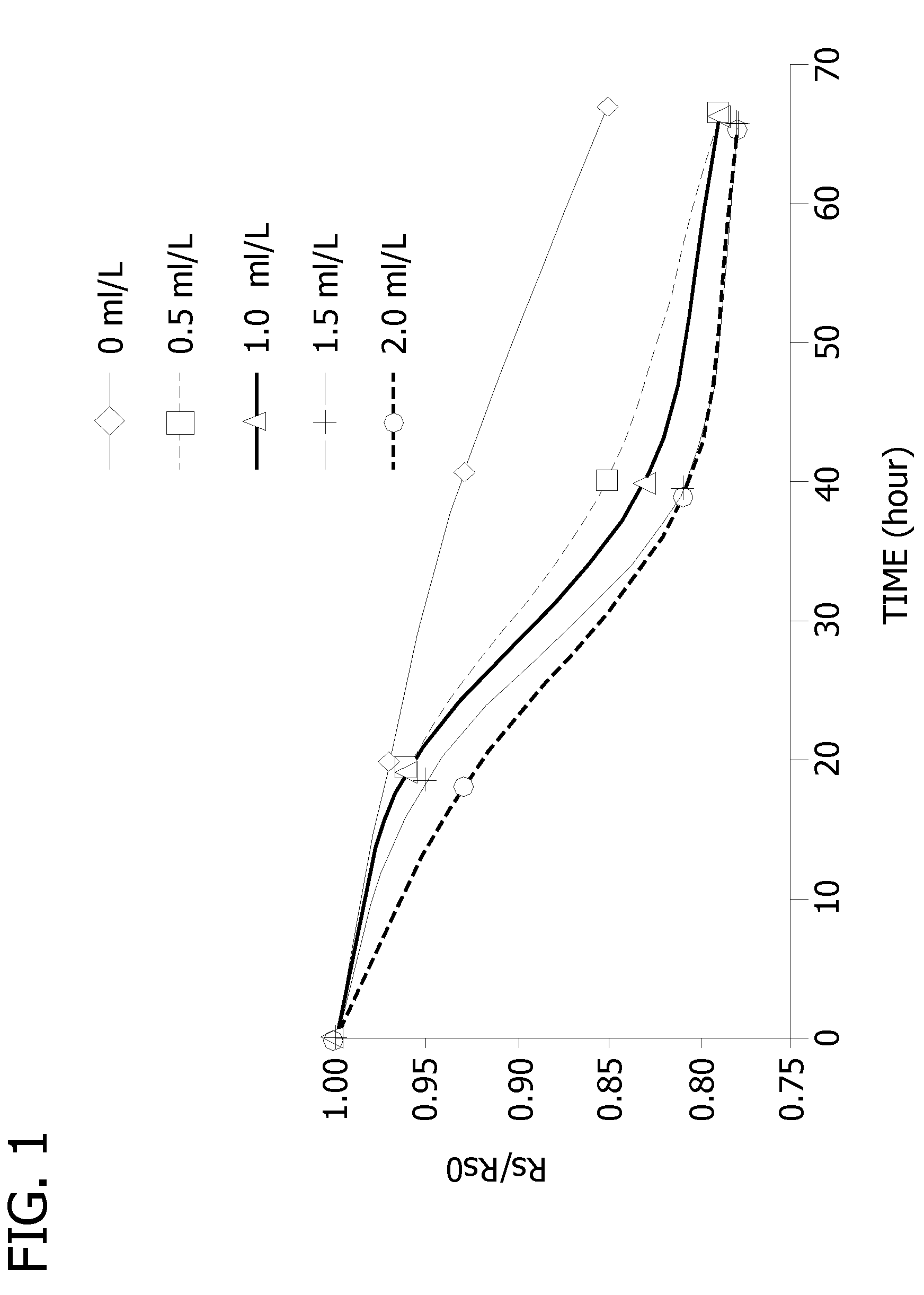

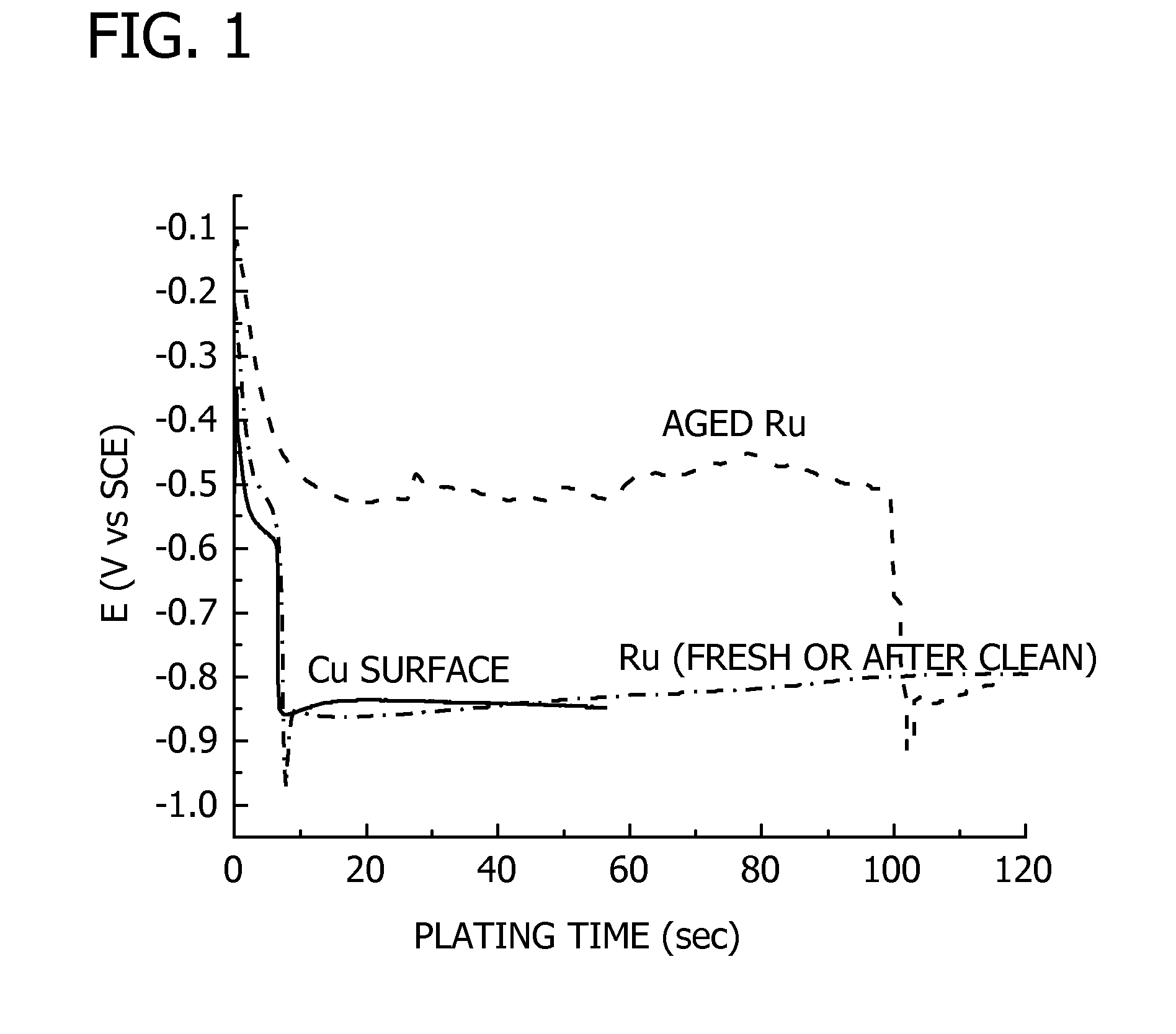

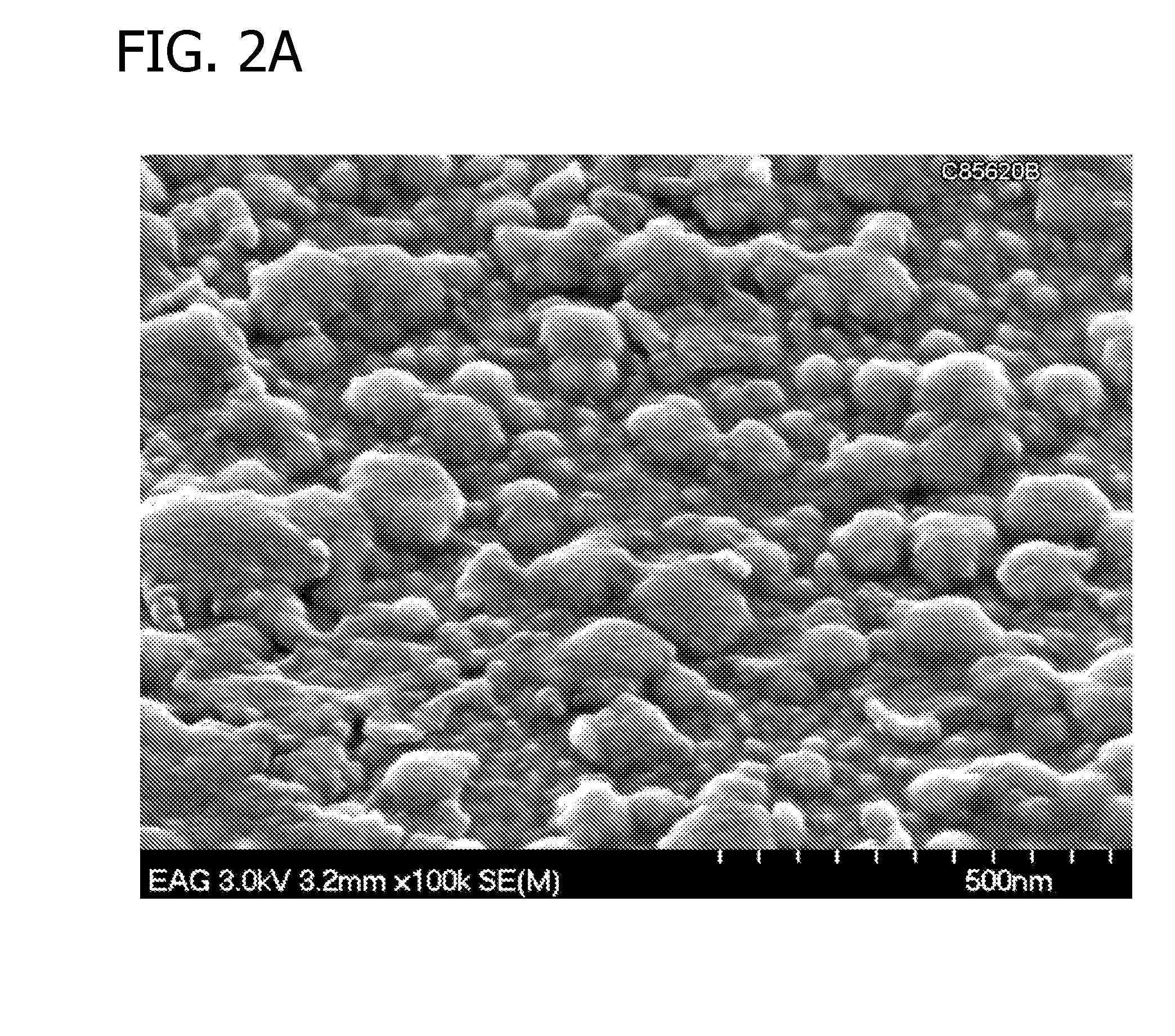

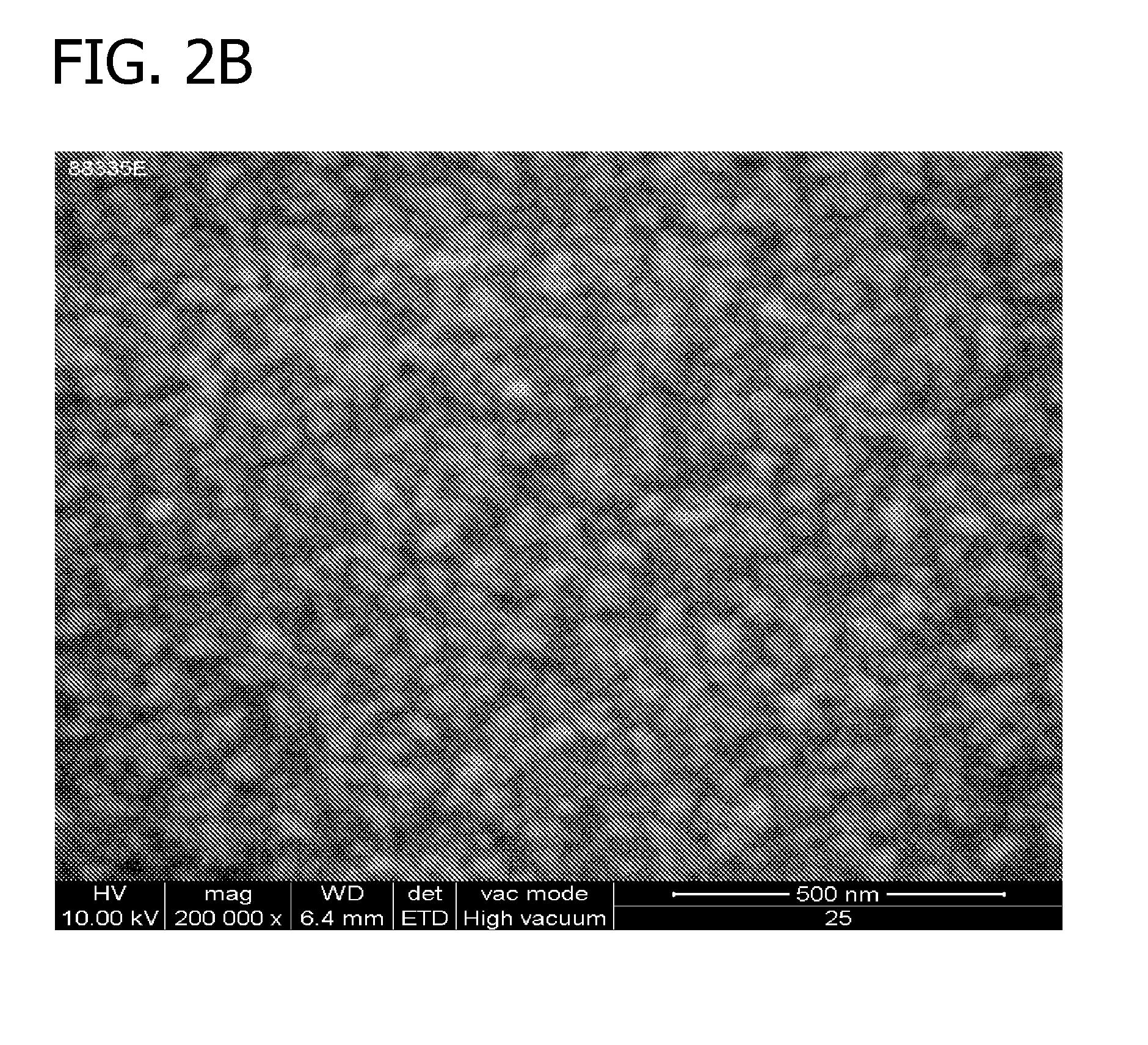

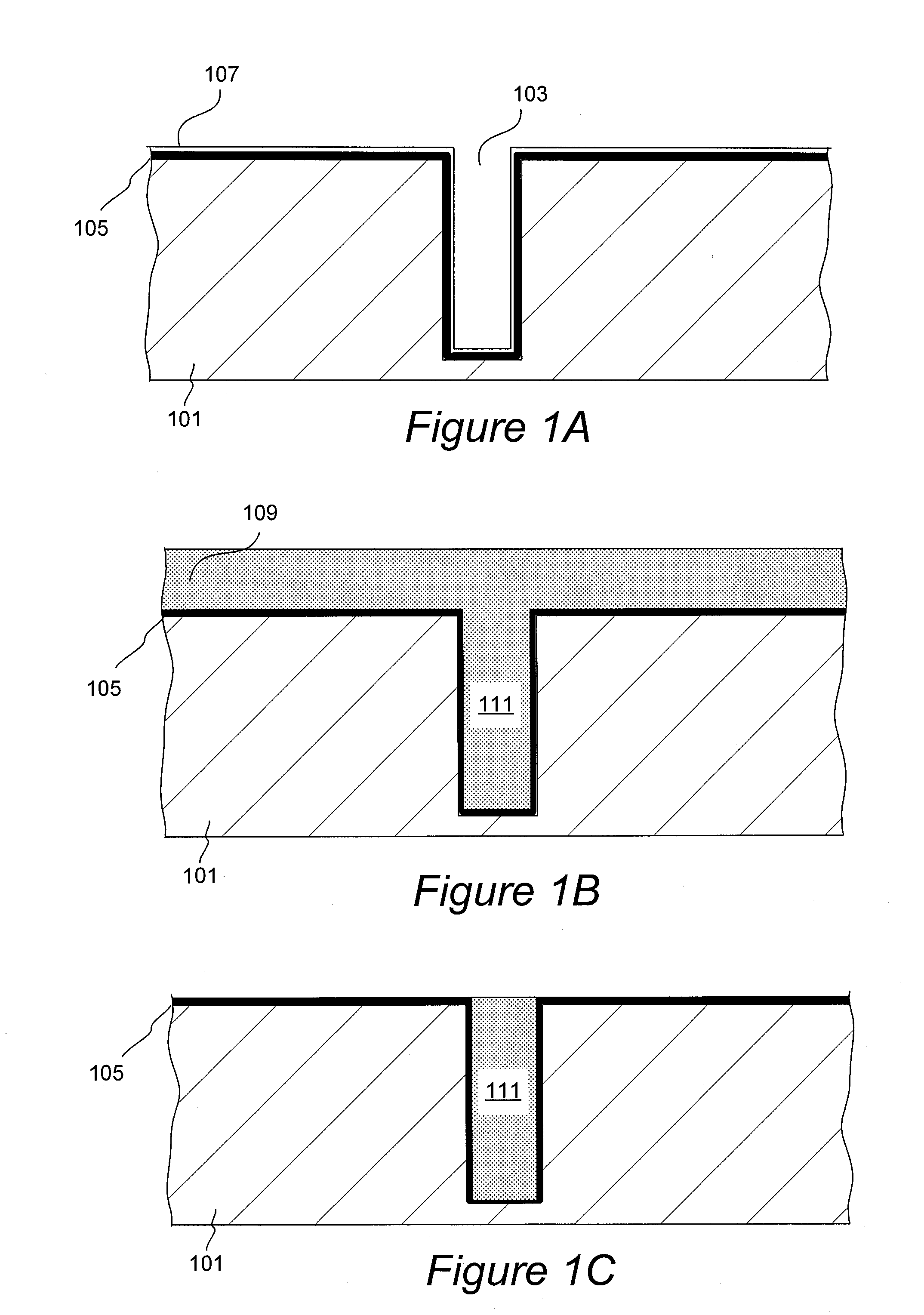

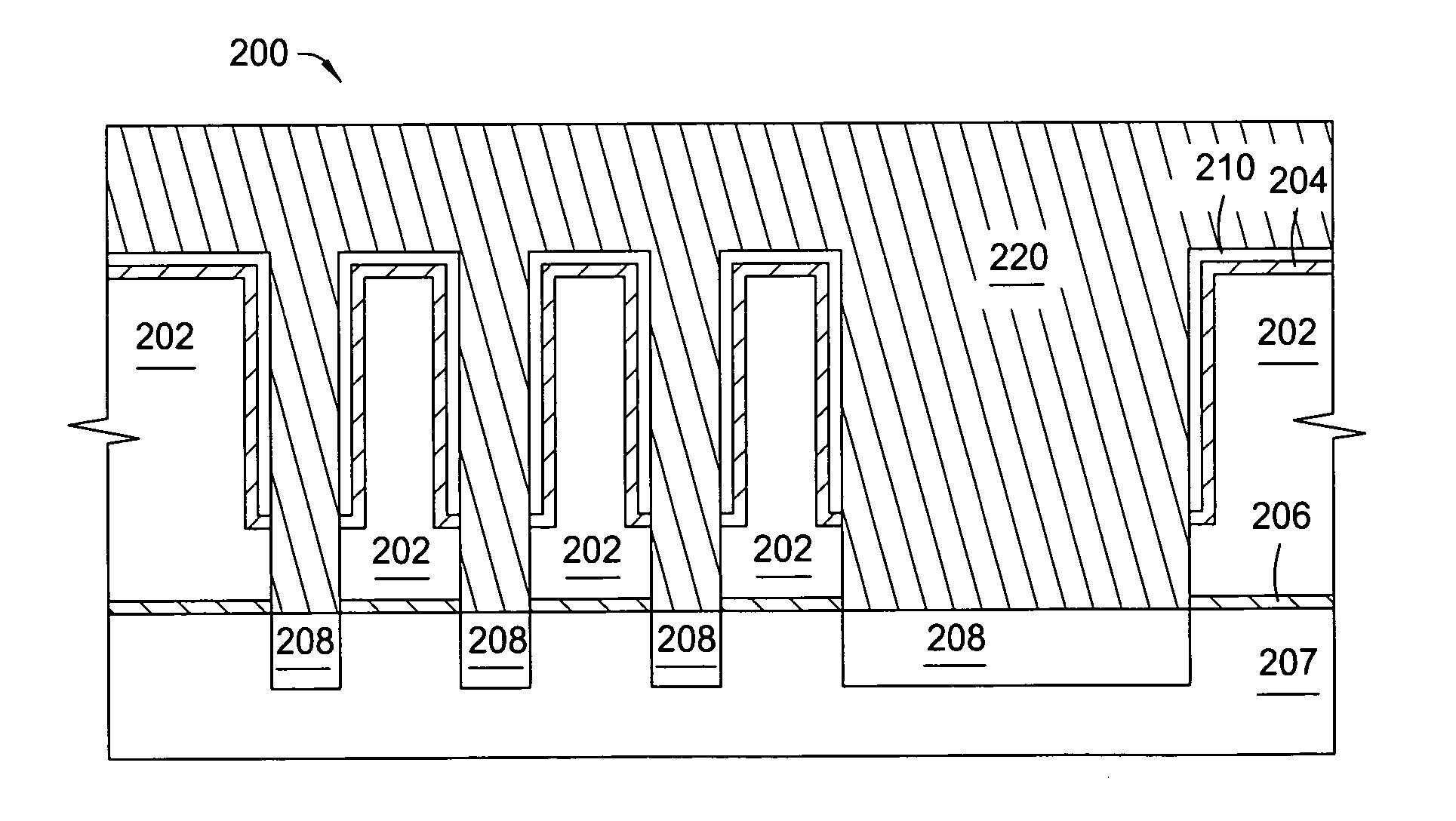

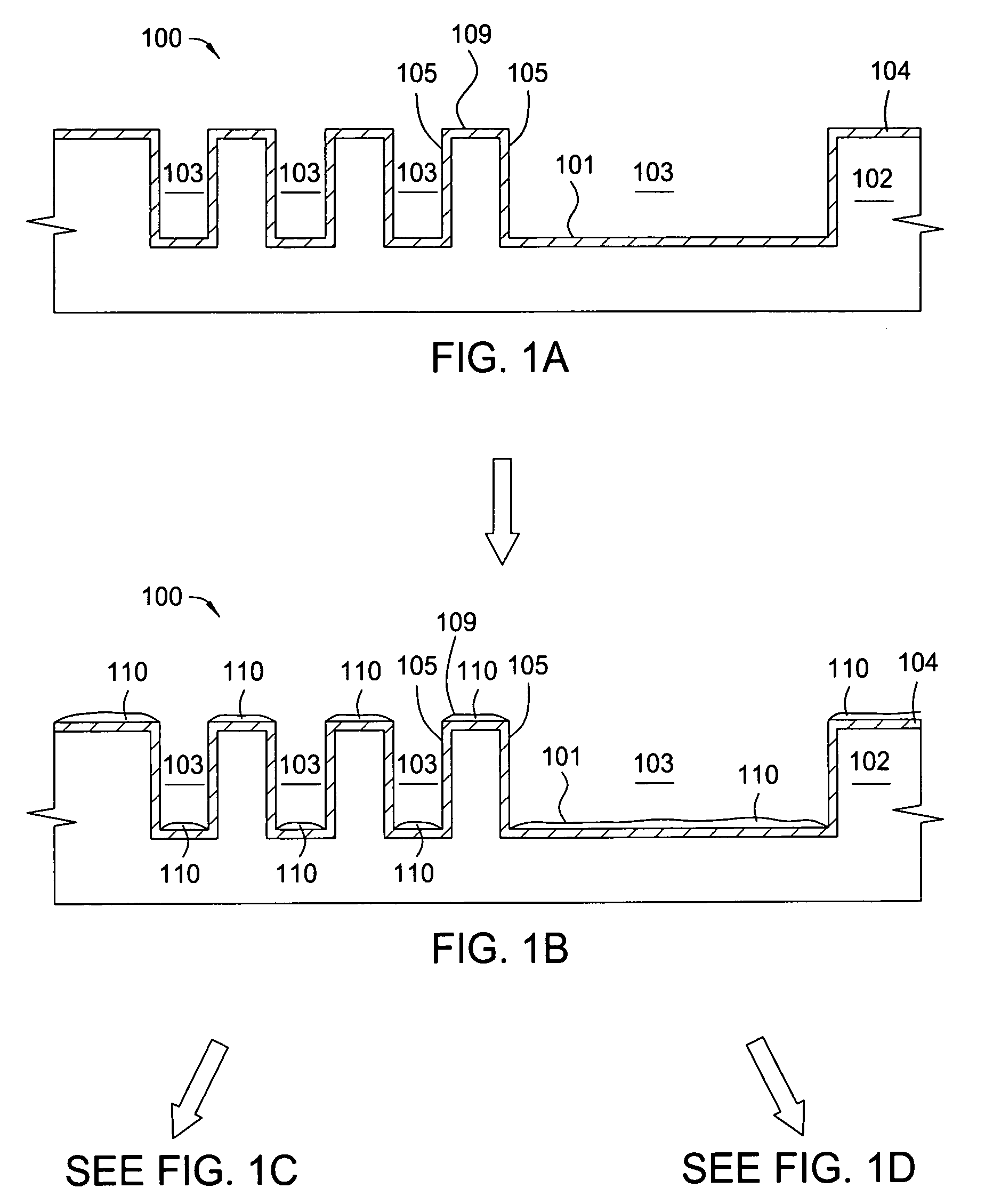

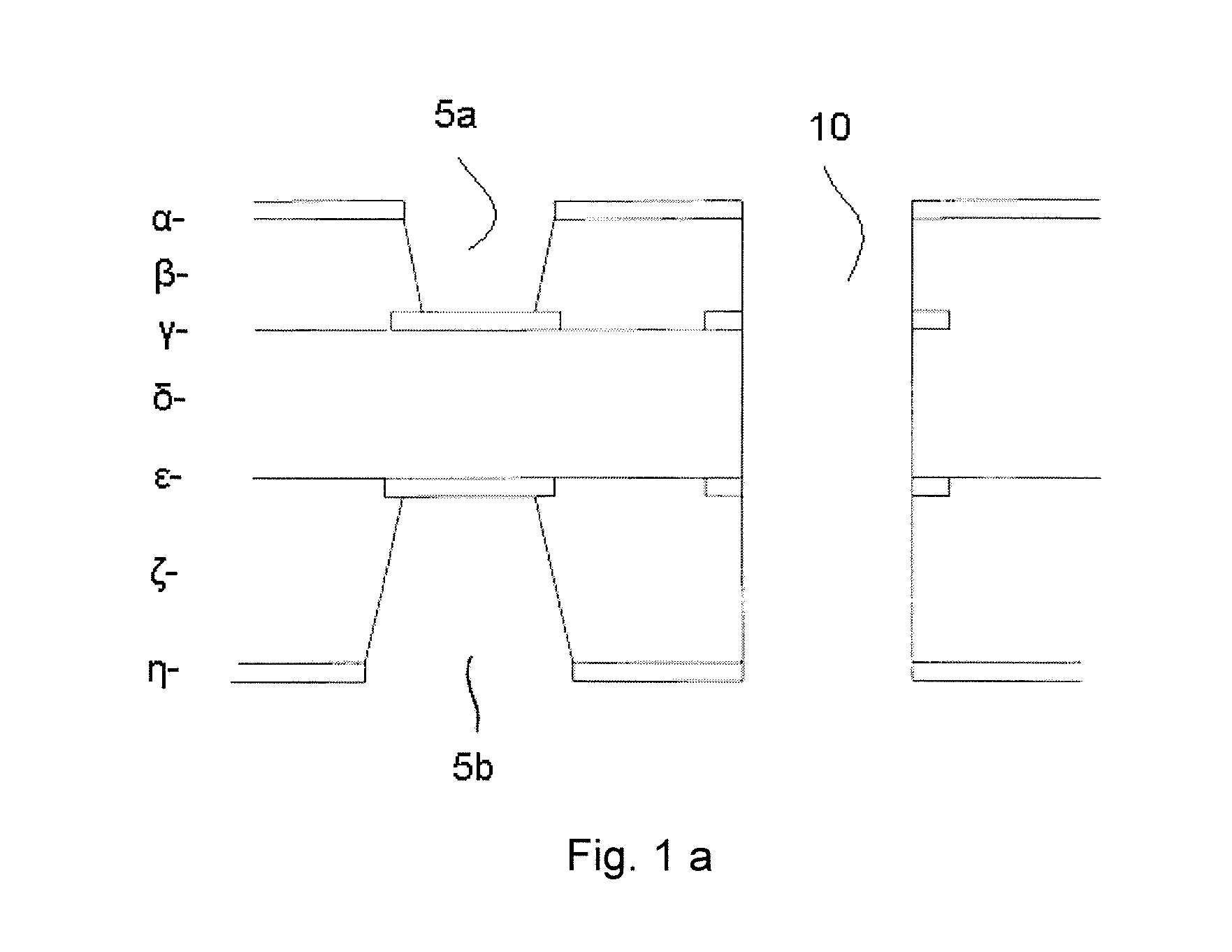

Embodiments of the invention provide a method for depositing a copper material on a substrate by an electroless deposition process and also provide a composition of an electroless deposition solution. In one embodiment, the copper material is deposited from an electroless copper solution that contains an additive, such as an inhibitor, to promote a bottom-up fill process. In one aspect, the field of the substrate may be maintained free of copper material or substantially free of copper material during the electroless deposition process. Prior to the electroless deposition process for forming the copper material, a barrier layer may be deposited on the substrate, and thereafter, a ruthenium layer may be deposited thereon. In one example, the copper material is formed during a bottom-up, electroless deposition process directly on the ruthenium layer. Alternatively, a seed layer may be formed on the ruthenium layer prior to depositing the copper material.

Owner:APPLIED MATERIALS INC

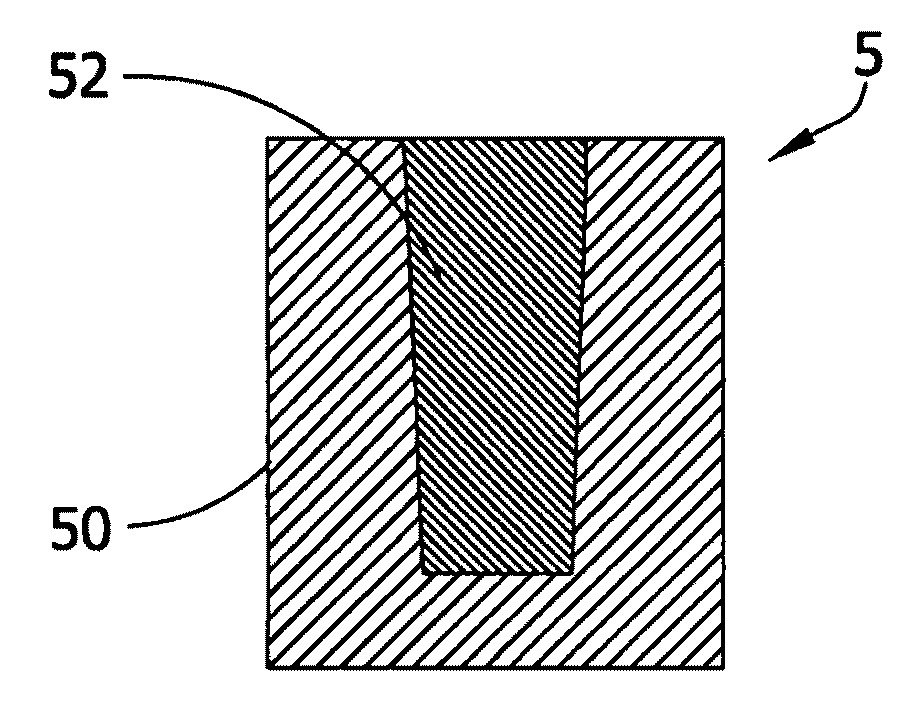

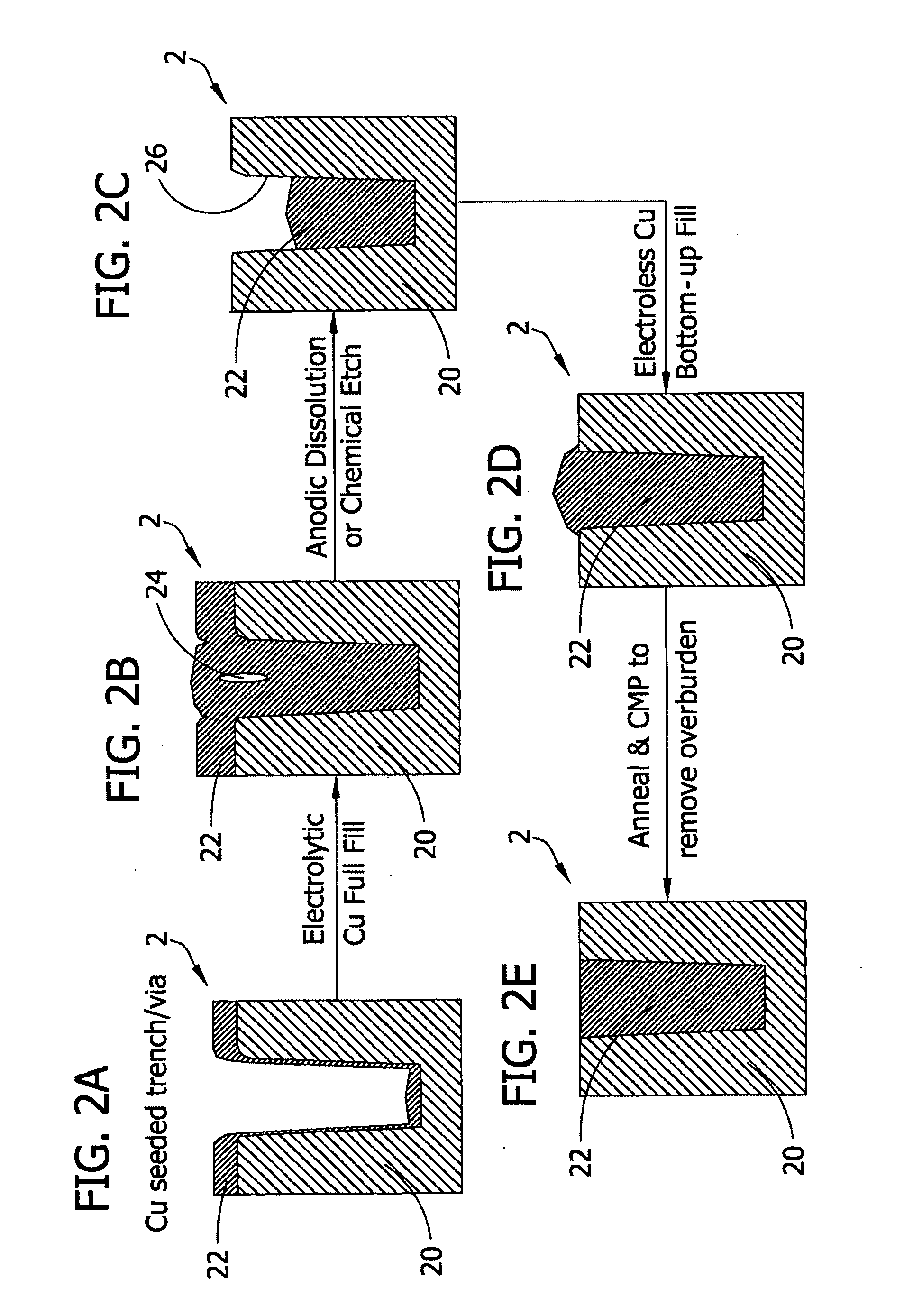

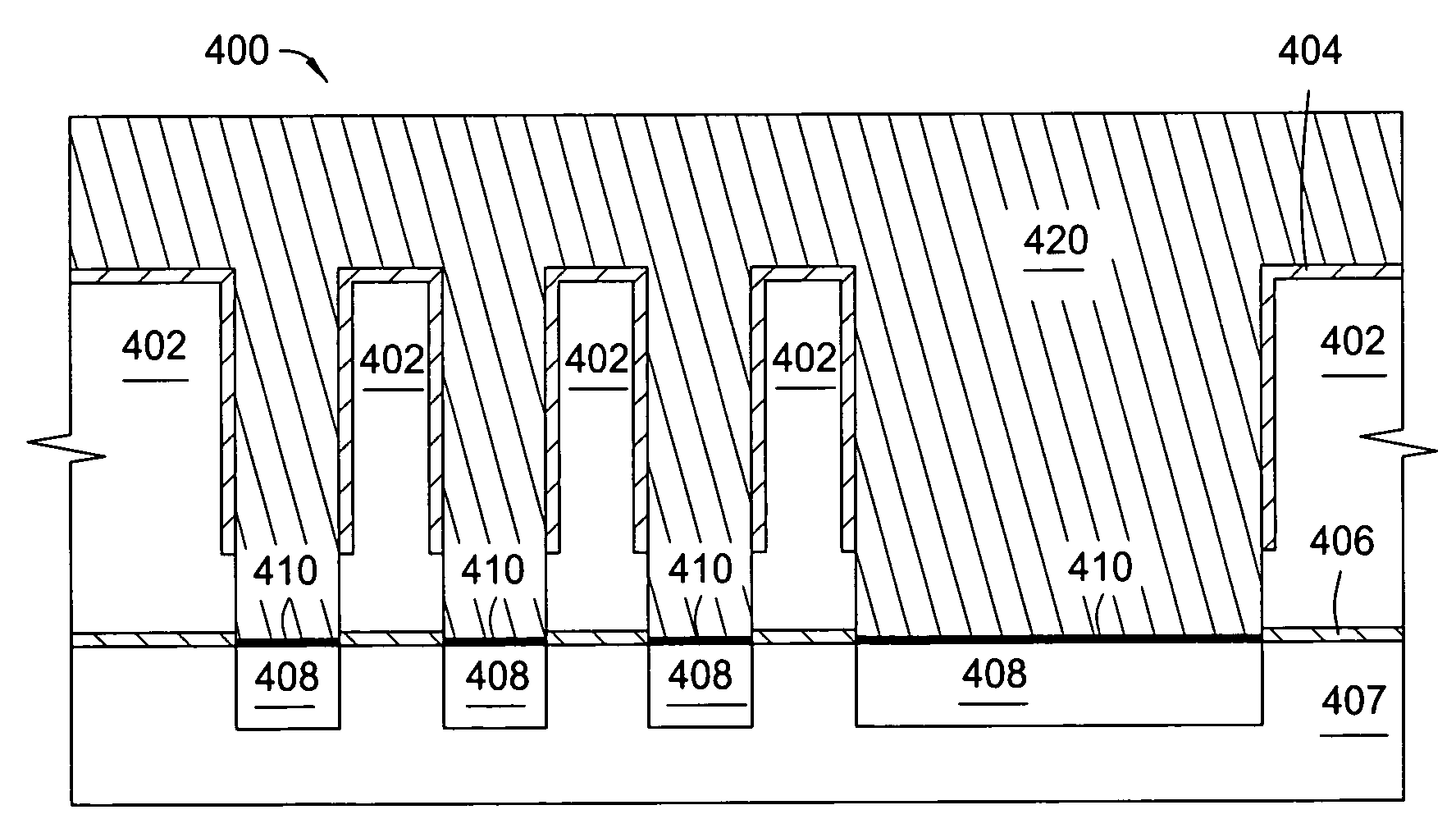

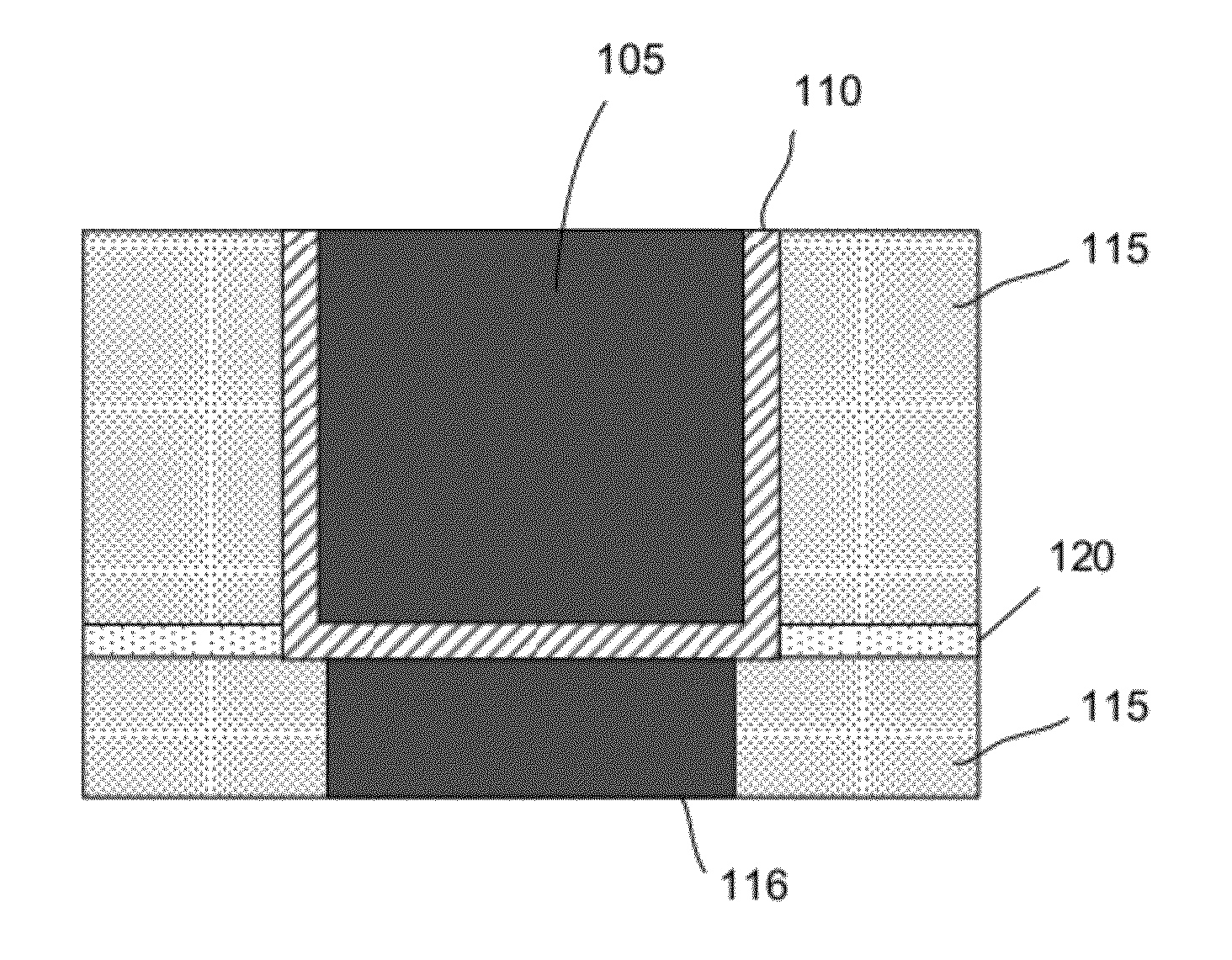

Through silicon via filling using an electrolyte with a dual state inhibitor

ActiveUS20110284386A1Faster rateLittle and depositionCellsMachining electric circuitsElectricityElectroplating

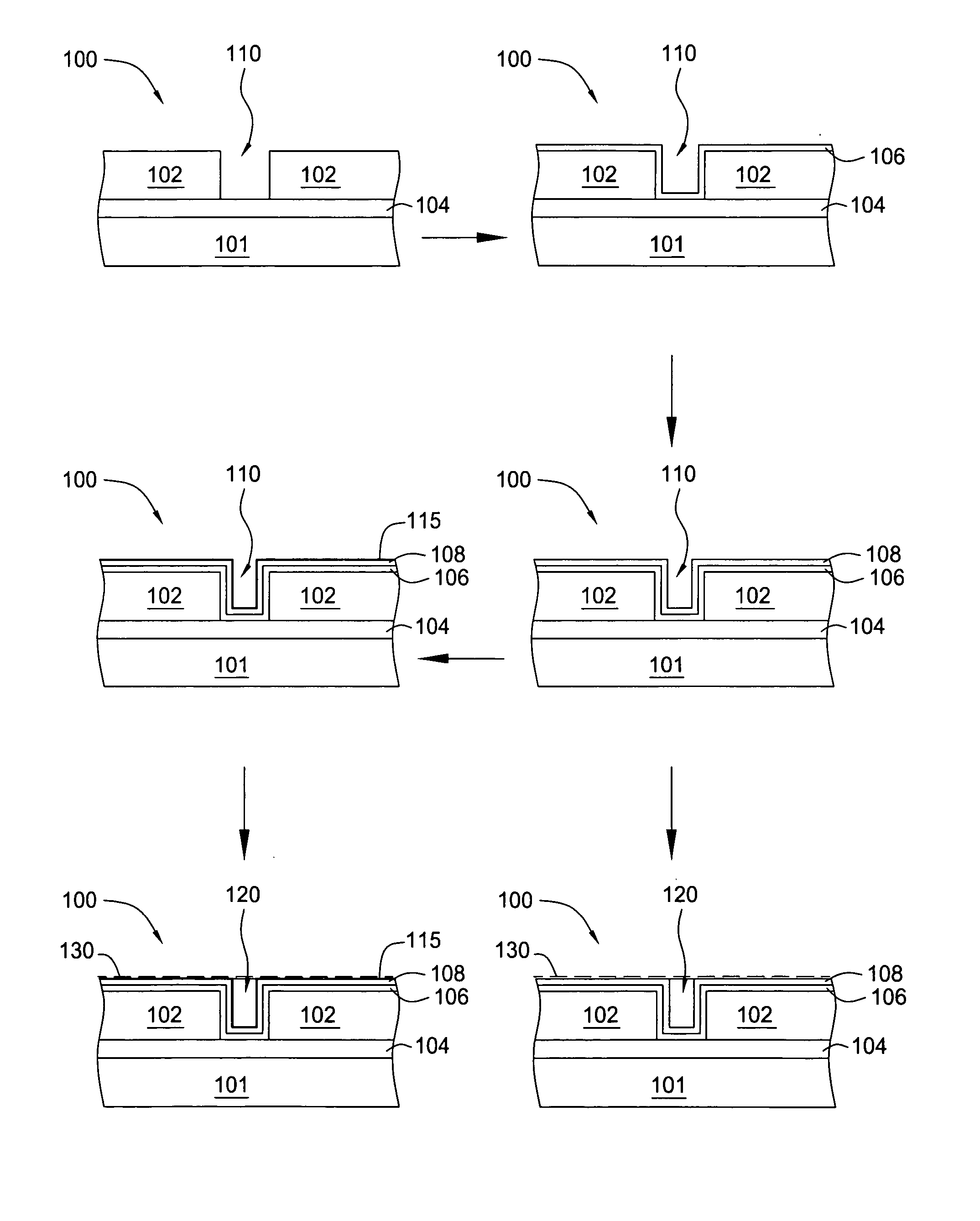

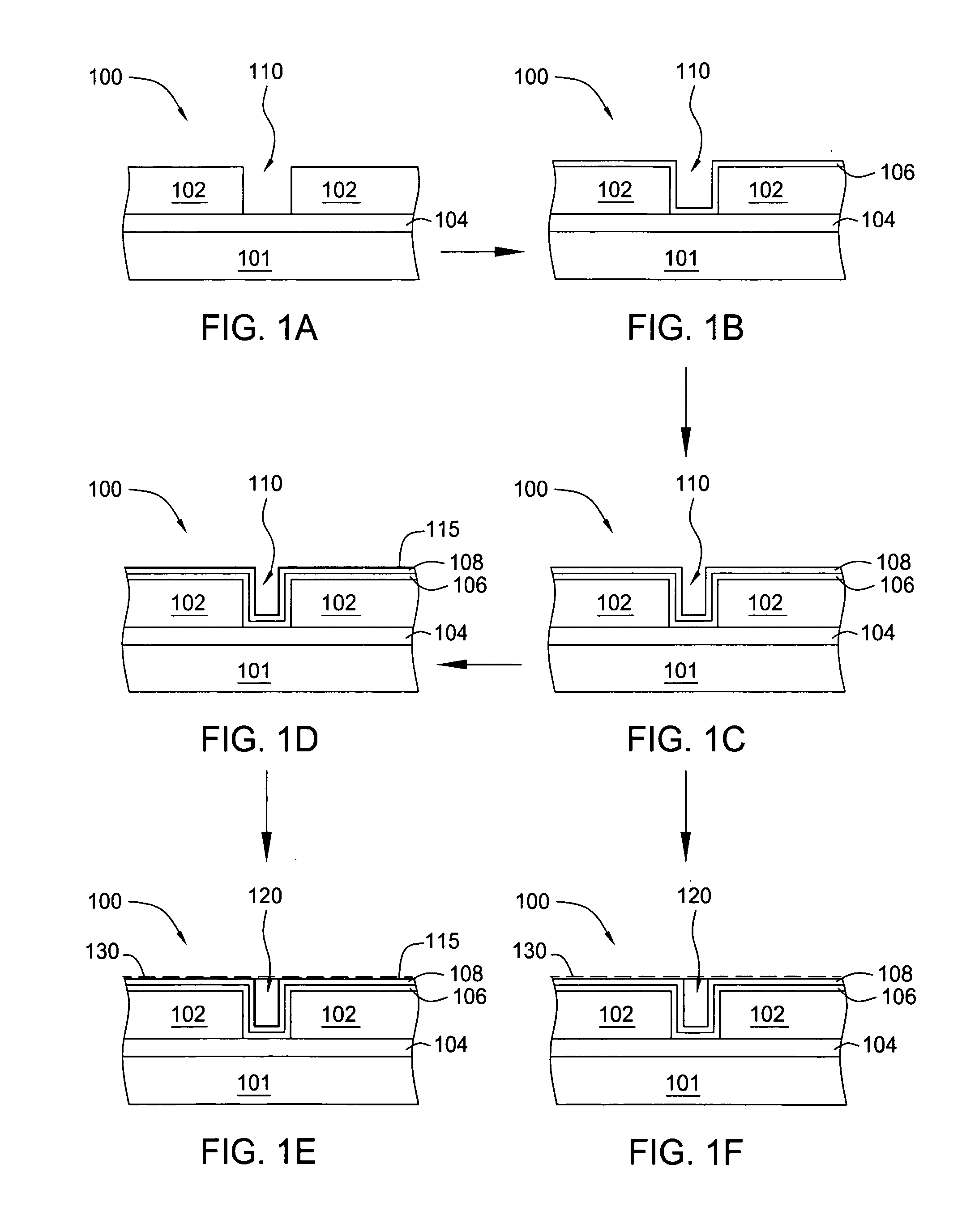

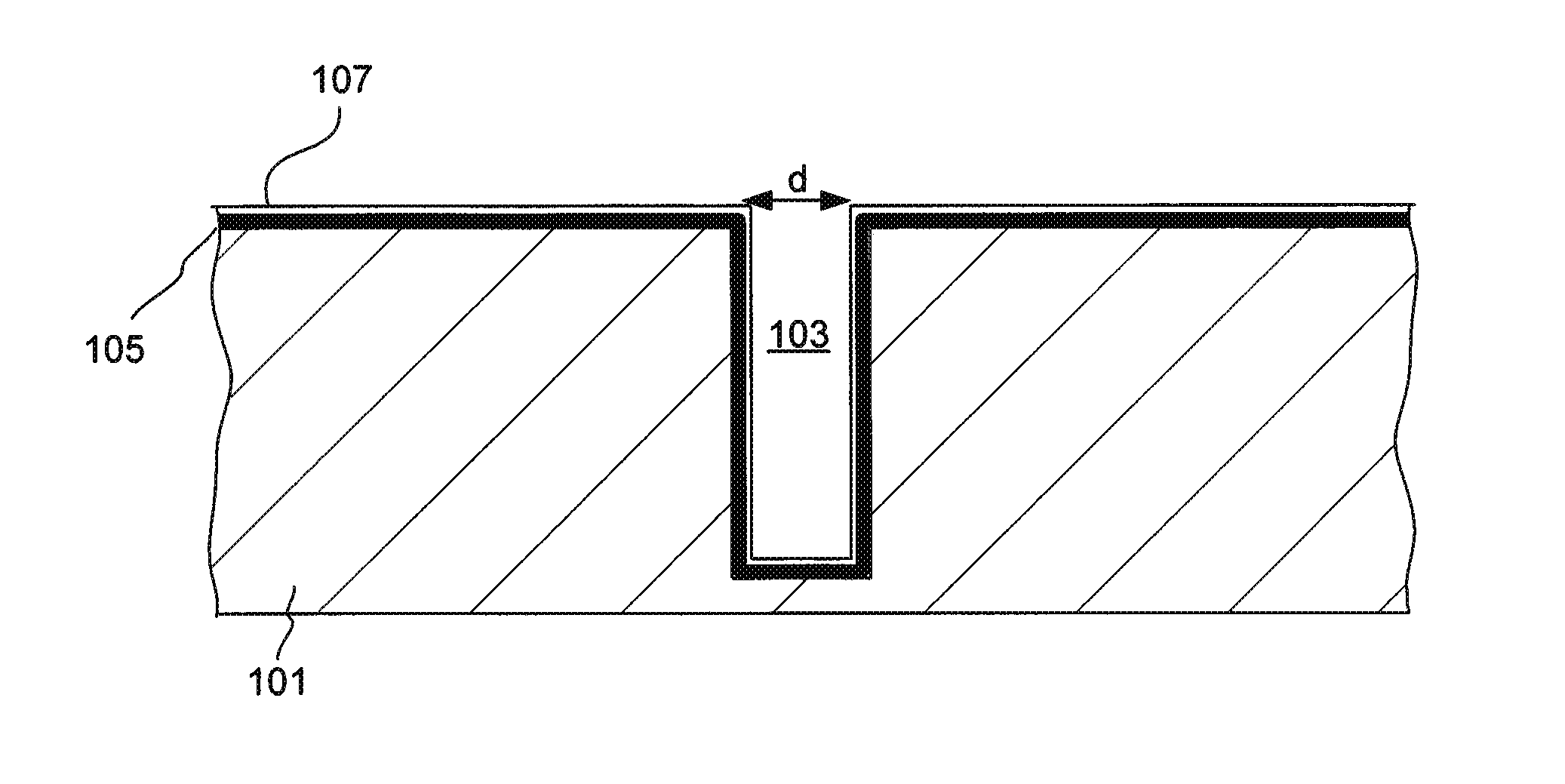

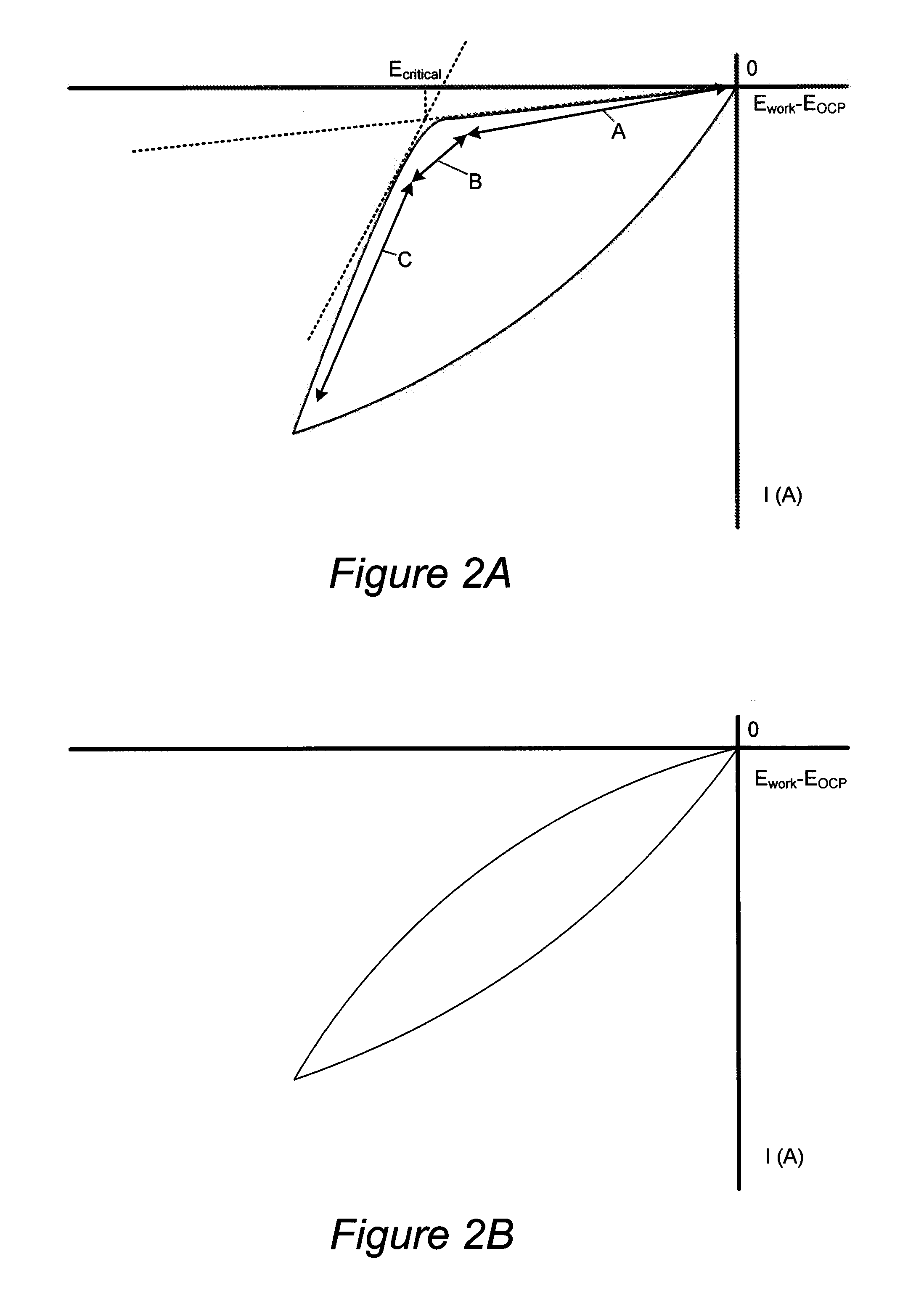

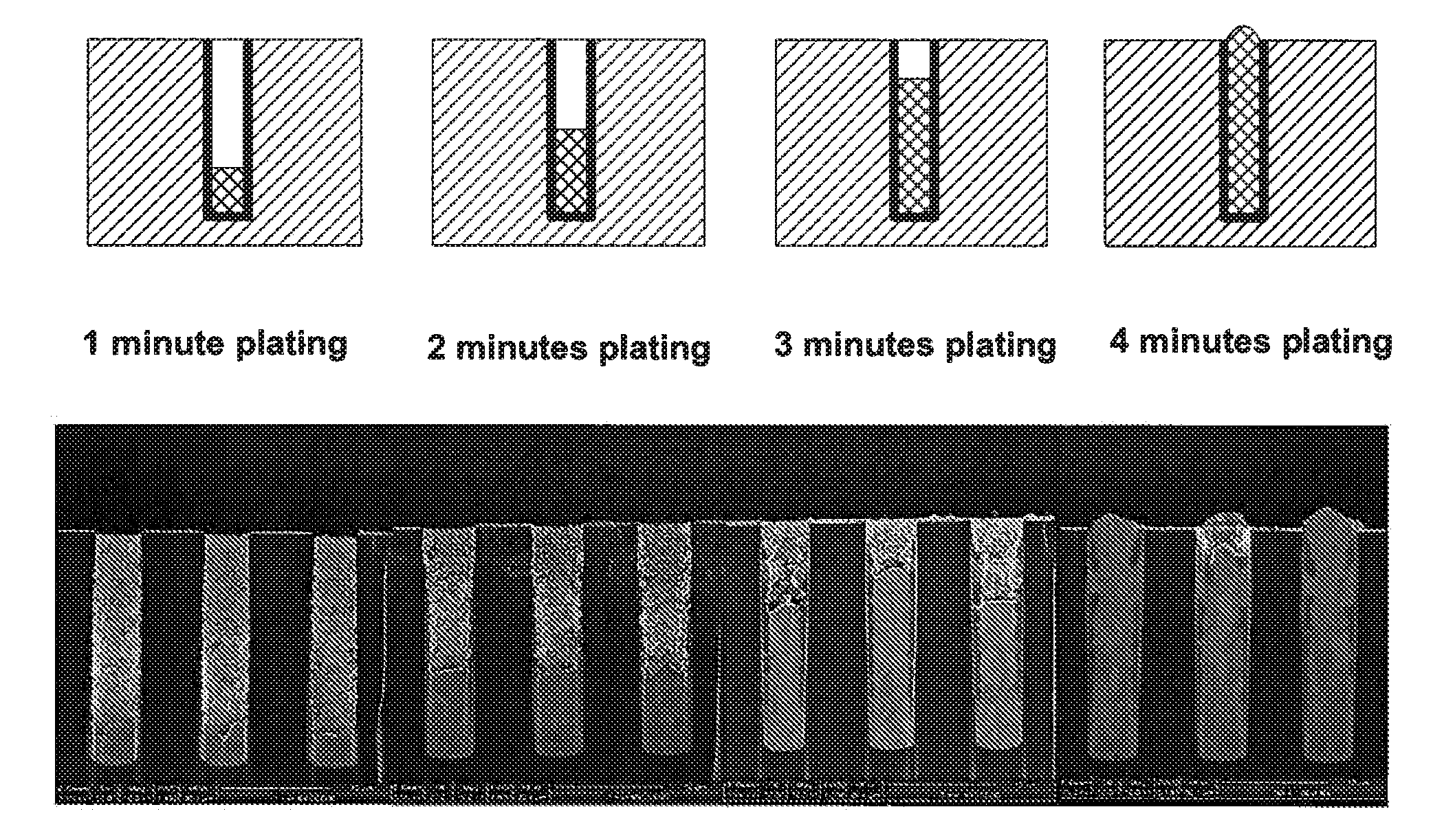

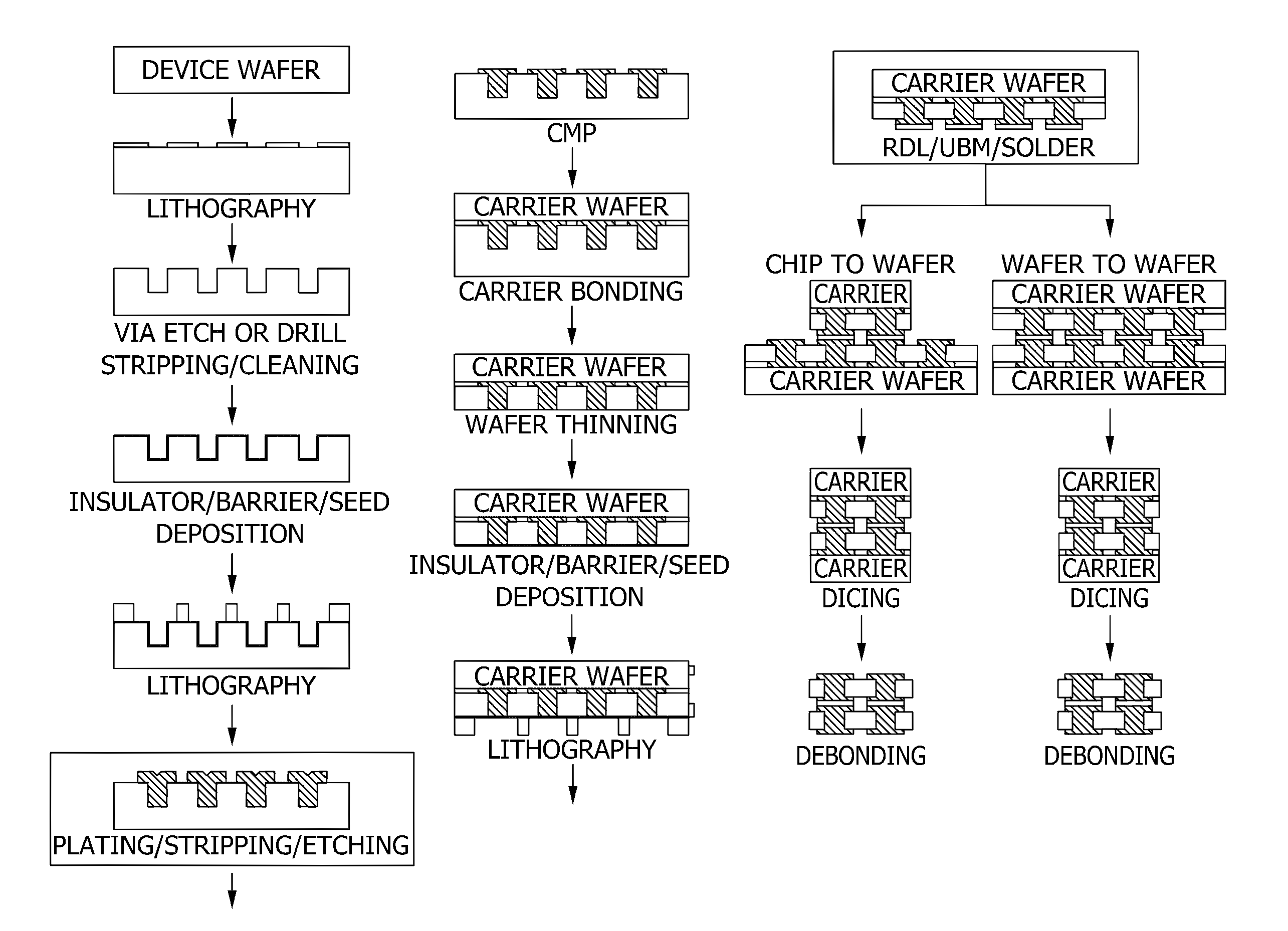

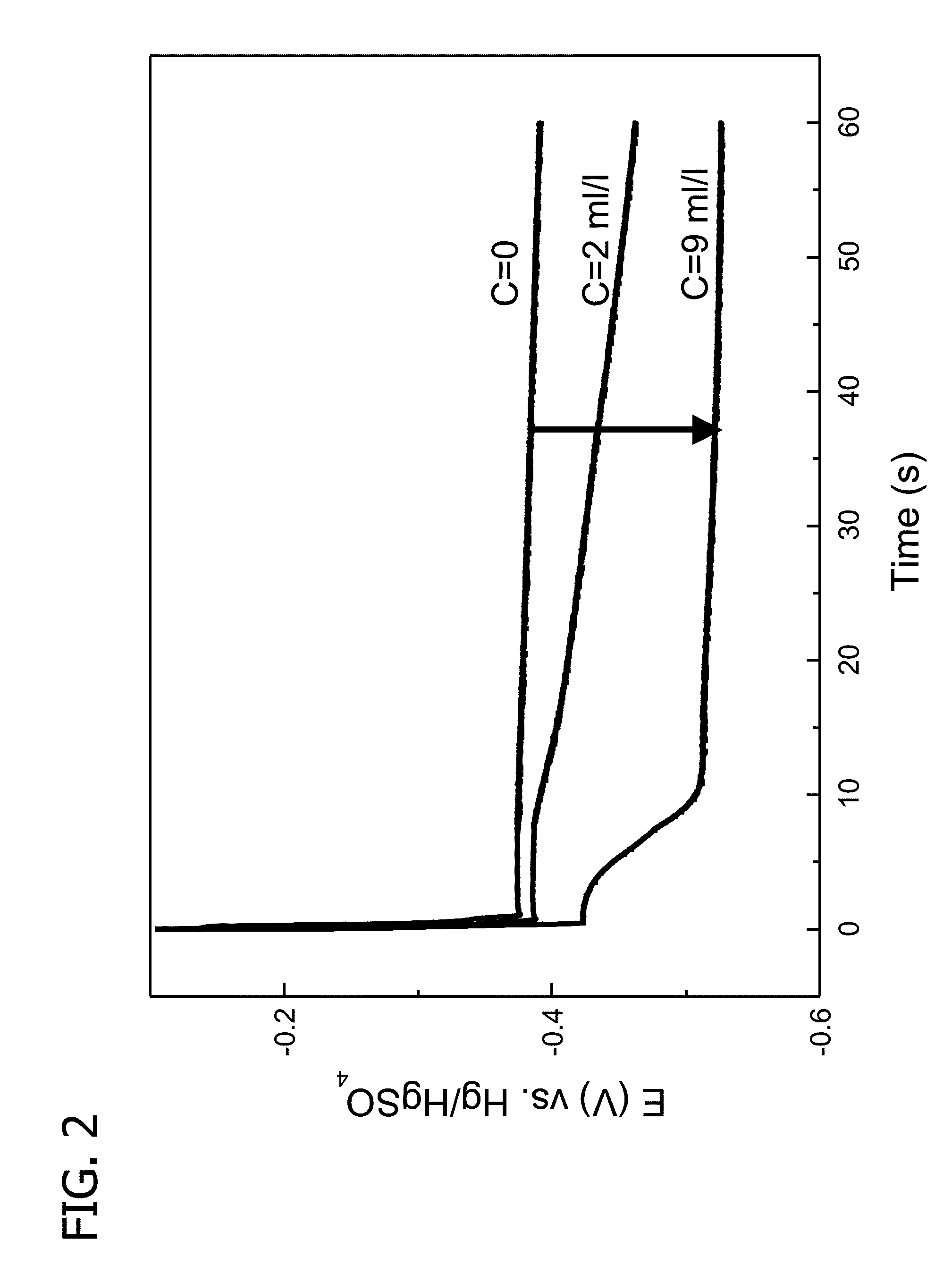

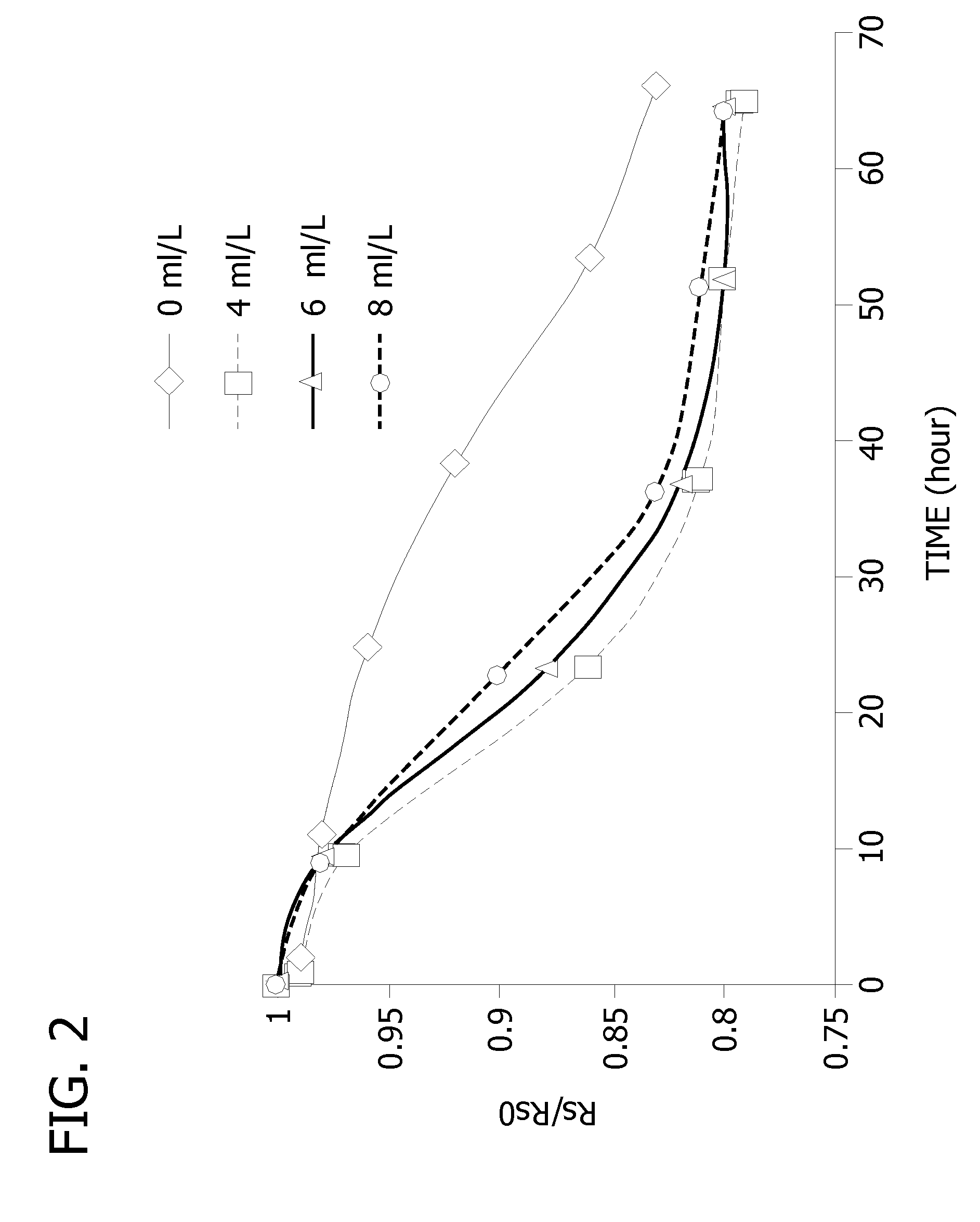

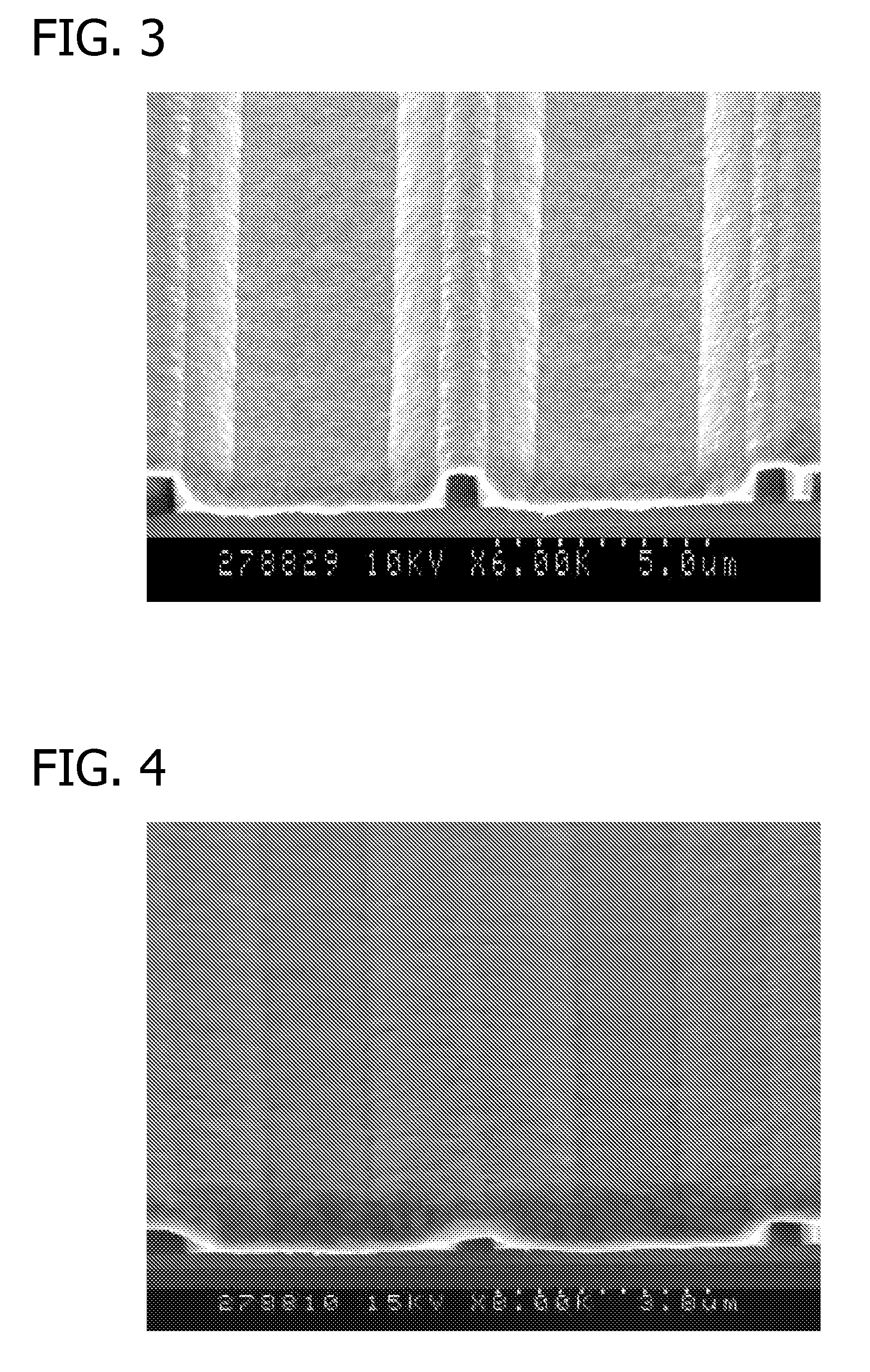

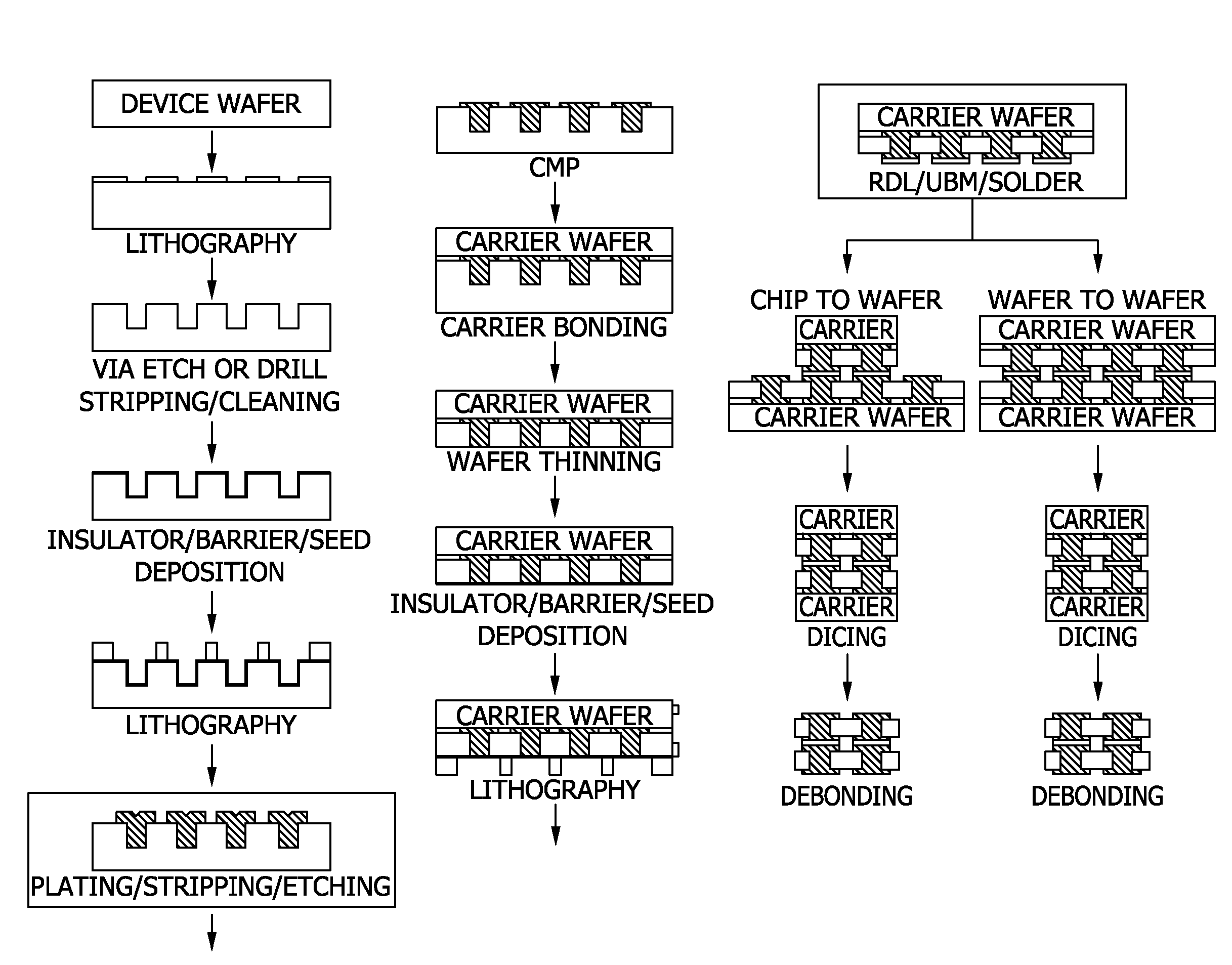

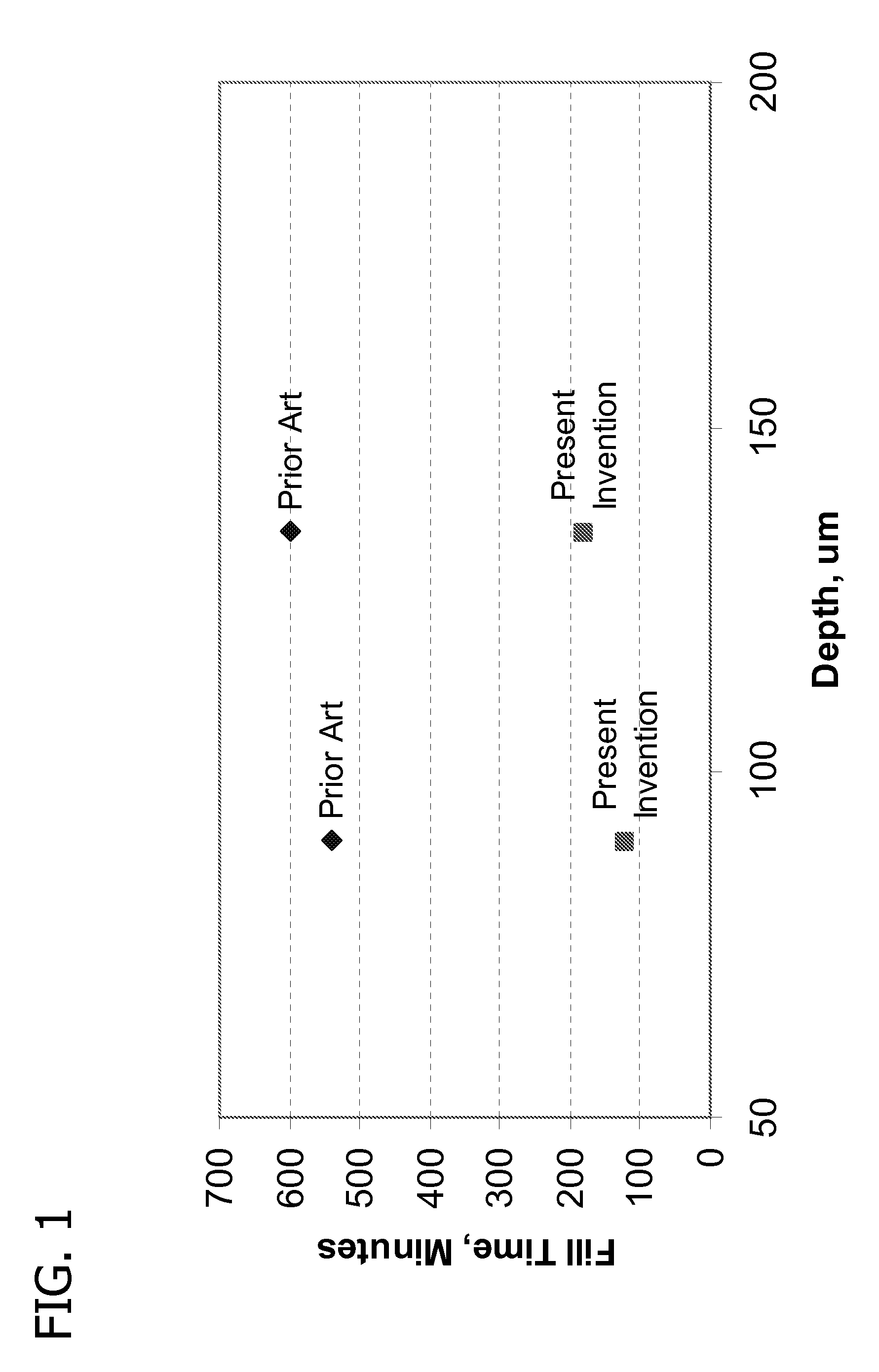

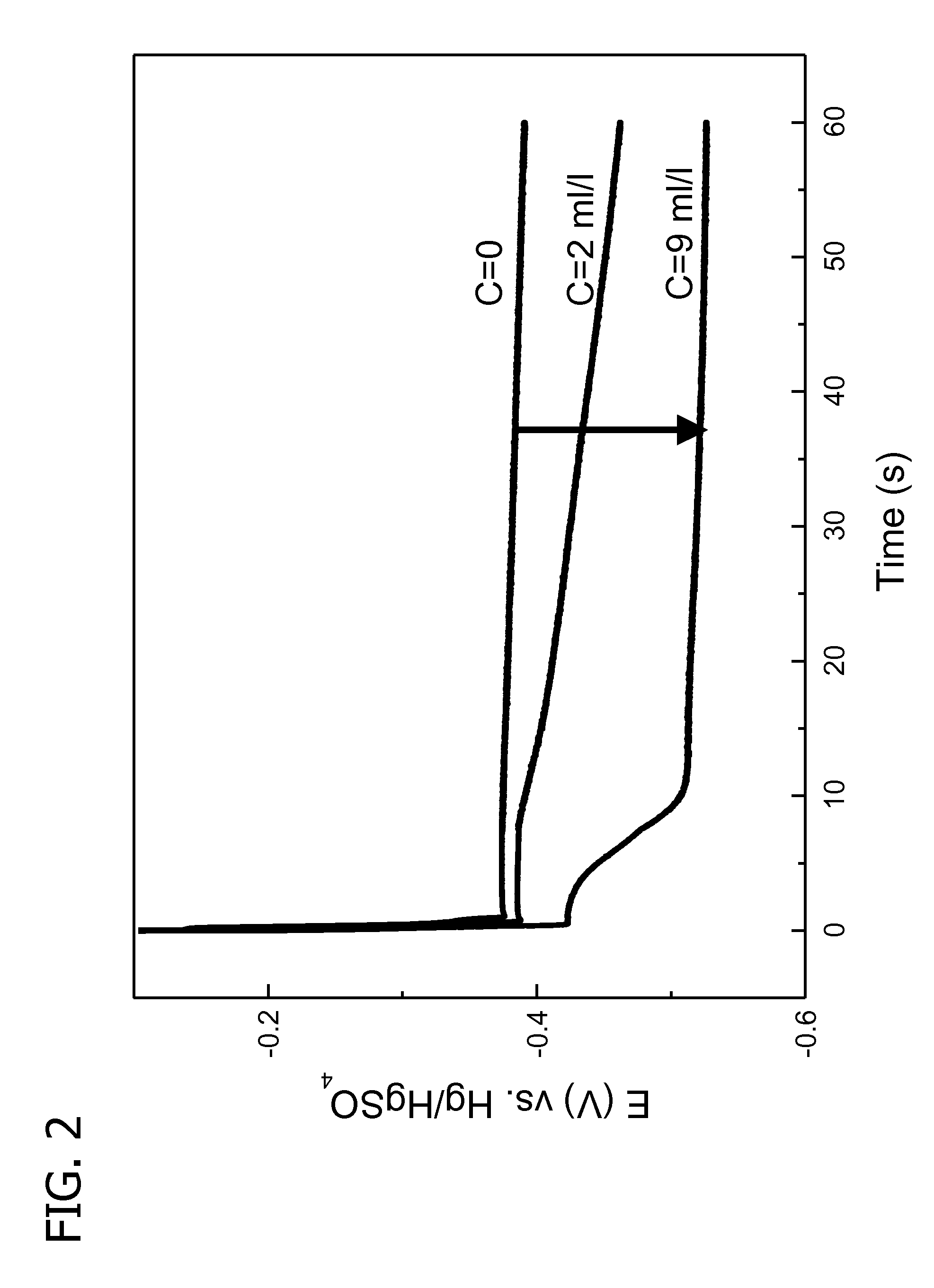

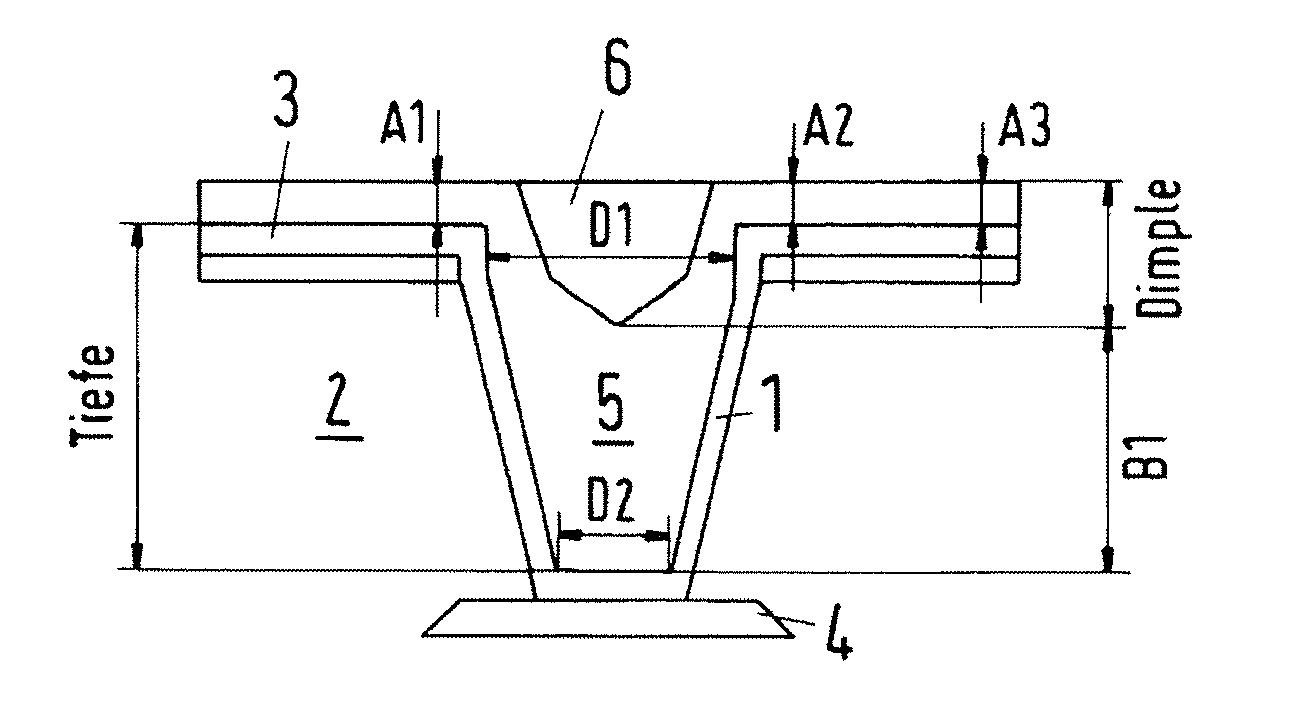

A method for electrofilling large, high aspect ratio recessed features with copper without depositing substantial amounts of copper in the field region is provided. The method allows completely filling recessed features having aspect ratios of at least about 5:1 such as at least about 10:1, and widths of at least about 1 μm in a substantially void-free manner without depositing more than 5% of copper in the field region (relative to the thickness deposited in the recessed feature). The method involves contacting the substrate having one or more large, high aspect ratio recessed features (such as a TSVs) with an electrolyte comprising copper ions and an organic dual state inhibitor (DSI) configured for inhibiting copper deposition in the field region, and electrodepositing copper under potential-controlled conditions, where the potential is controlled not exceed the critical potential of the DSI.

Owner:NOVELLUS SYSTEMS

Process For Through Silicon Via Filing

A semiconductor electroplating process deposits copper into the through silicon via hole to completely fill the through silicon via in a substantially void free is disclosed. The through silicon via may be more than about 3 micrometers in diameter and more that about 20 micrometers deep. Low copper concentration and high acidity electroplating solution is used for deposition copper into the through silicon vias.

Owner:NOVELLUS SYSTEMS

Resputtered copper seed layer

InactiveUS20080190760A1Increase pressureReduce stressElectric discharge tubesVacuum evaporation coatingSputter depositionElectrochemistry

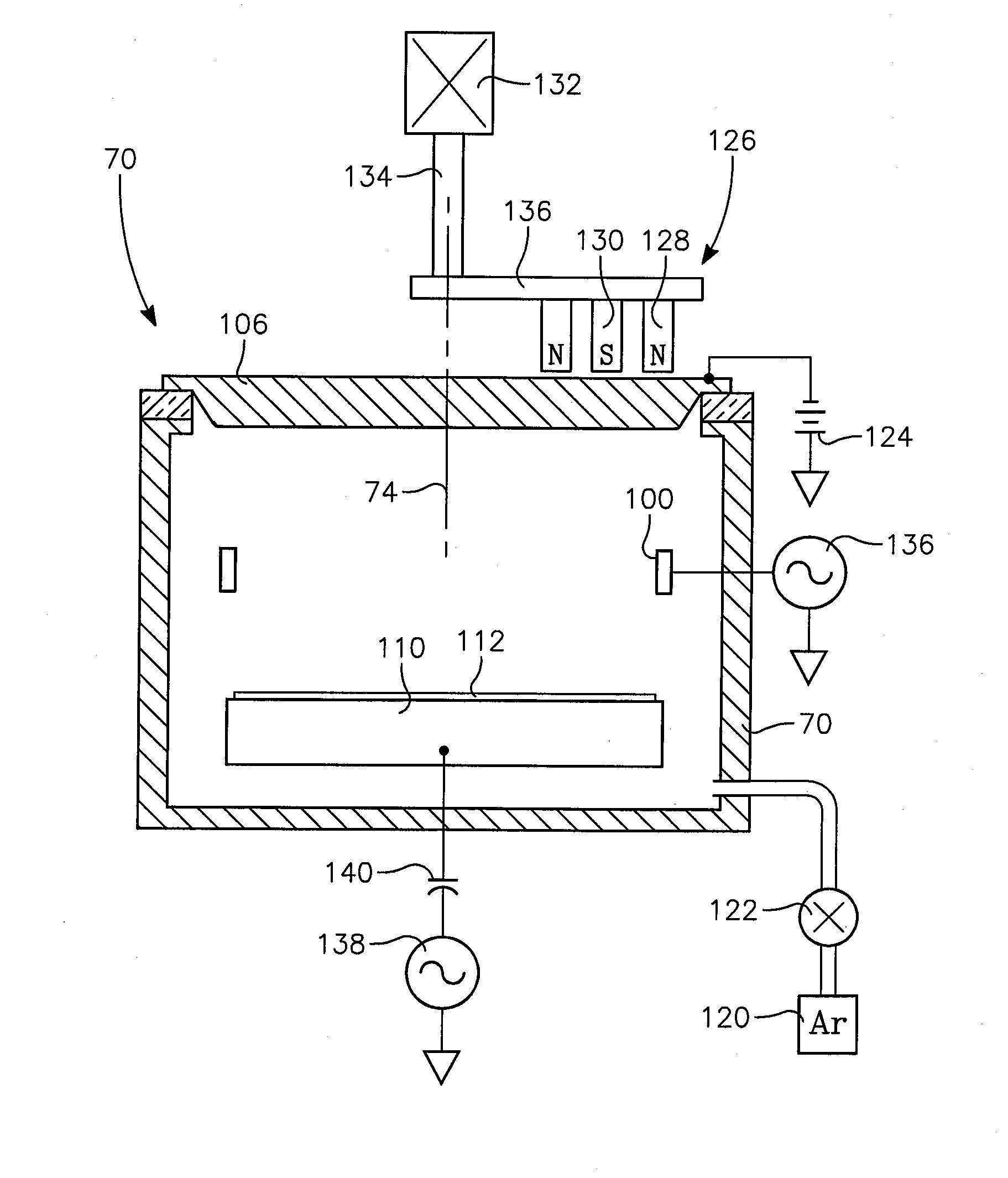

An integrated copper deposition process, particularly useful for forming a copper seed layer in a narrow via prior to electrochemical plating of copper, including at least one cycle of sputter deposition of copper followed by sputter etching of the deposited copper, preferably performed in a same sputter chamber. The deposition is performed under conditions promoting high copper ionization fractions and strong wafer biasing to draw the copper ions into the via. The etching may be done with argon ions, preferably inductively excited by an RF coil around the chamber, or by copper ions, which may be formed with high target power and intense magnetron or by use of the RF coil. Two or more cycles of deposition / etch may be performed. A final flash deposition may be performed with high copper ionization and low wafer biasing.

Owner:APPLIED MATERIALS INC

Copper metallization of through silicon via

ActiveUS7670950B2Advantageous bias towards bottom upSemiconductor/solid-state device manufacturingSemiconductor devicesOrganic sulfonic acidElectrolysis

A method for metallizing a through silicon via feature in a semiconductor integrated circuit device substrate comprising immersing the semiconductor integrated circuit device substrate into an electrolytic copper deposition composition comprising a source of copper ions, an organic sulfonic acid or inorganic acid, or one or more organic compounds selected from among polarizers and / or depolarizers, and chloride ions.

Owner:MACDERMID ENTHONE INC

Ruthenium layer formation for copper film deposition

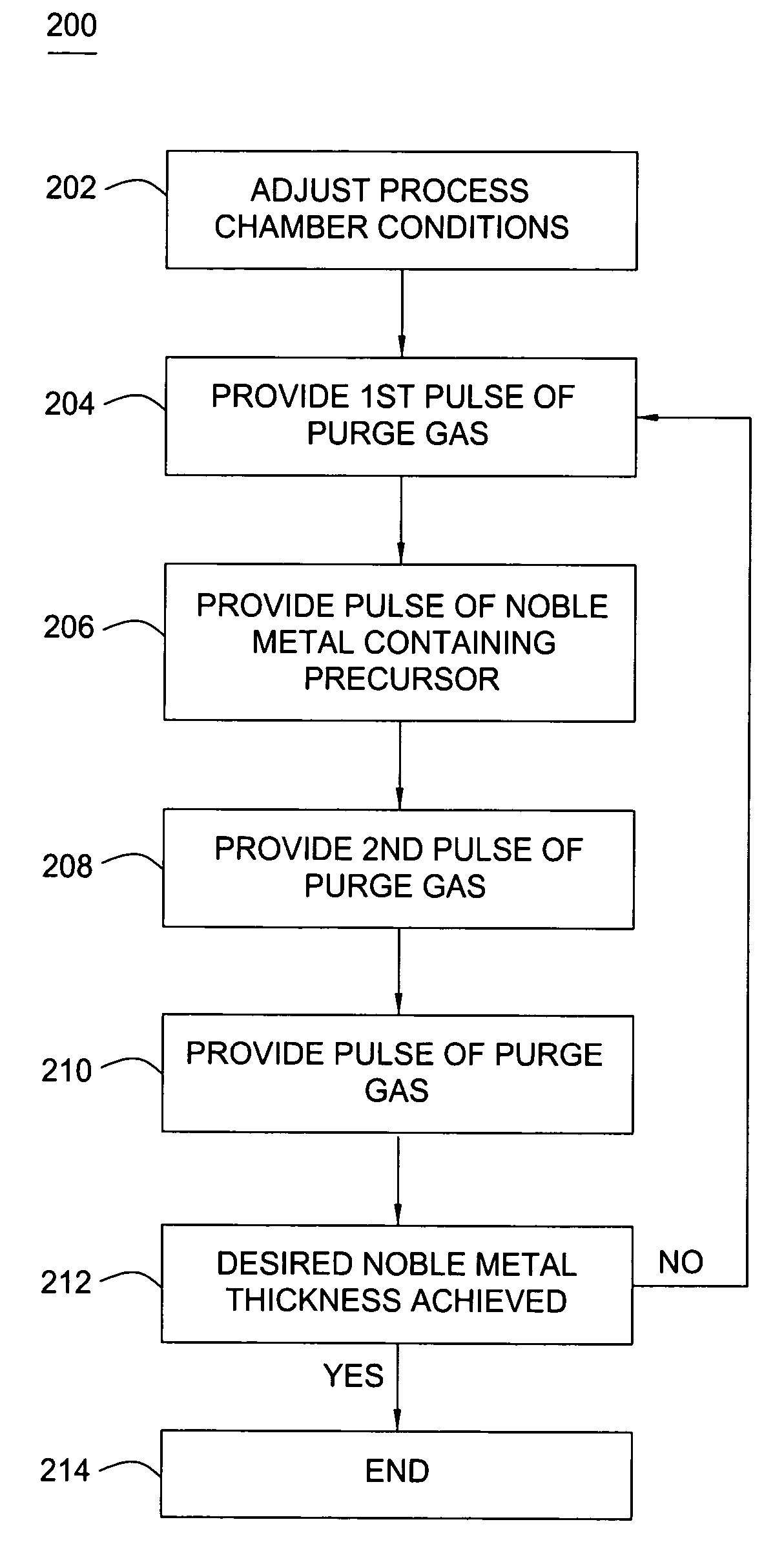

In one embodiment, a method for forming a material on a substrate is provided which includes positioning a substrate containing a dielectric material having vias formed therein within a process chamber, forming a barrier layer within the vias and on the dielectric material during a barrier deposition process, forming a ruthenium layer on the barrier layer during a ruthenium deposition process, and filling the vias with a copper material during a copper deposition process. The copper material may be formed by depositing a copper bulk layer over a copper seed layer. The method further provides that the ruthenium layer may be formed by an atomic layer deposition process (ALD) or a physical vapor deposition (PVD) process and the copper material may be formed by an electroless chemical plating process, an electroplating process, a chemical vapor deposition process, an ALD process and / or a PVD process.

Owner:APPLIED MATERIALS INC

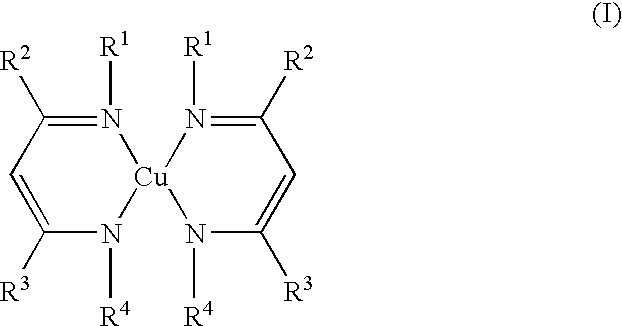

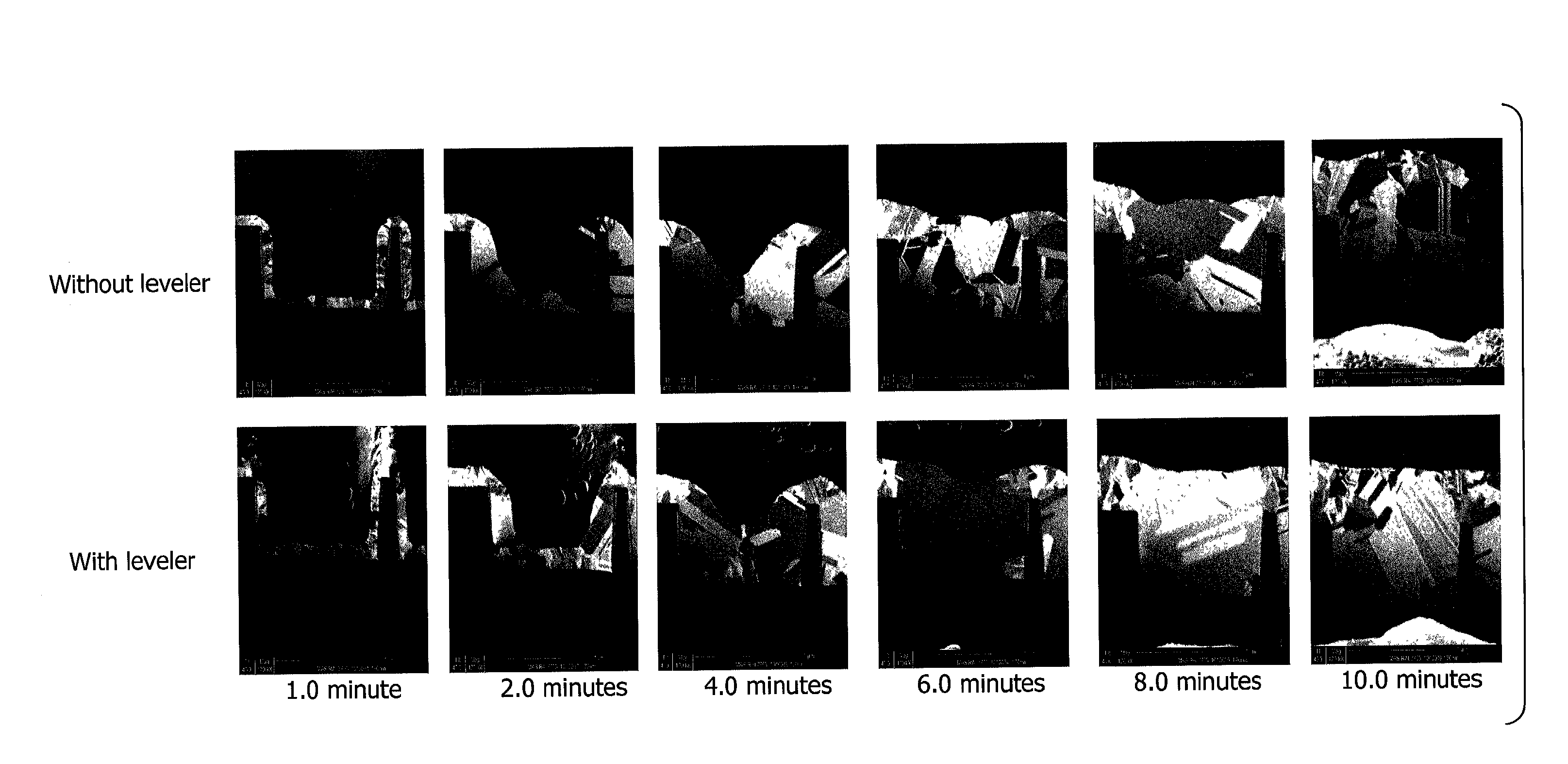

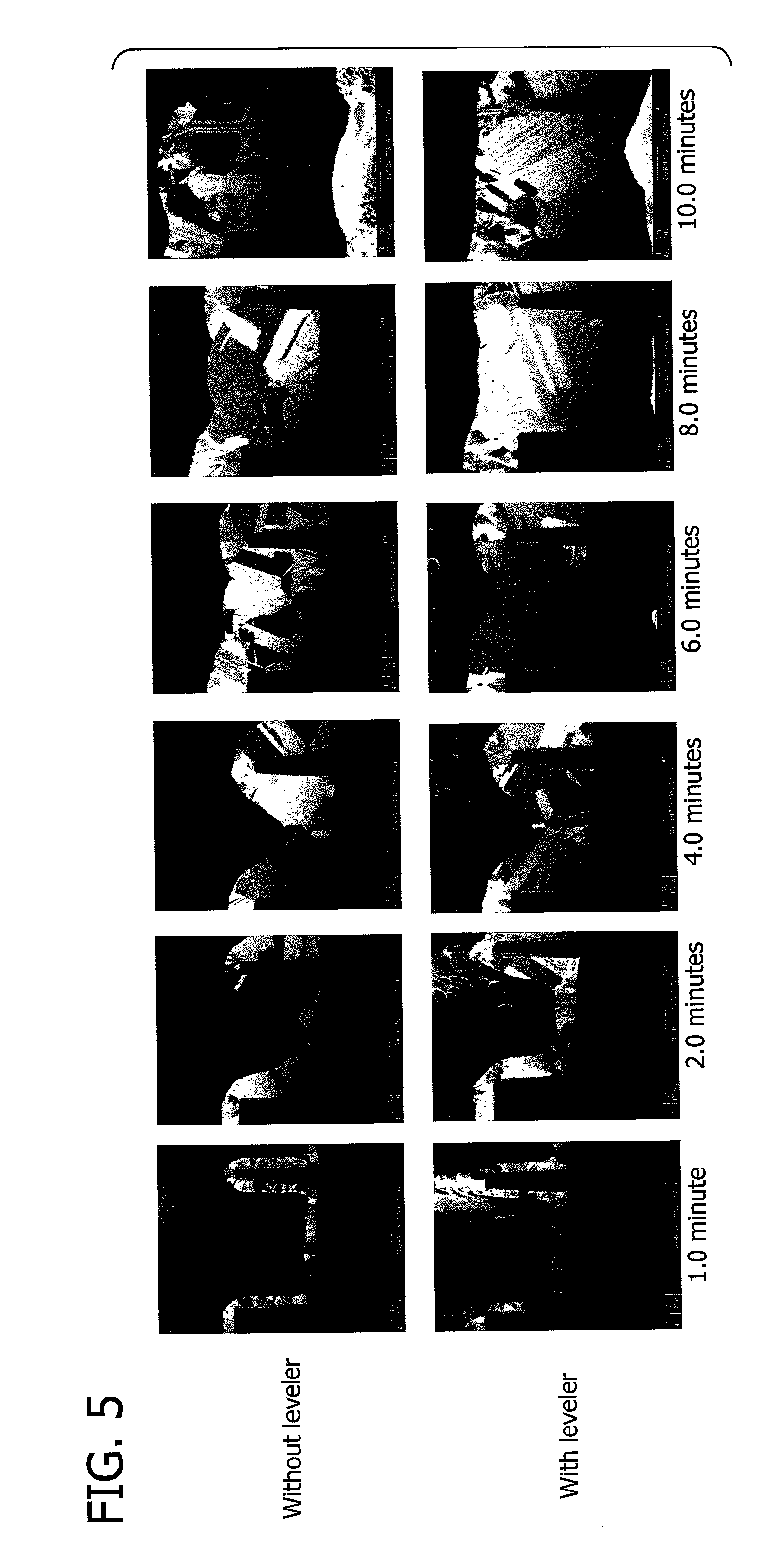

Electrodeposition of copper in microelectronics with dipyridyl-based levelers

ActiveUS20100126872A1Semiconductor/solid-state device detailsSolid-state devicesElectrolysisEngineering

A method for metallizing a via feature in a semiconductor integrated circuit device substrate, wherein the semiconductor integrated circuit device substrate comprises a front surface, a back surface, and the via feature and wherein the via feature comprises an opening in the front surface of the substrate, a sidewall extending from the front surface of the substrate inward, and a bottom. The method comprises contacting the semiconductor integrated circuit device substrate with an electrolytic copper deposition chemistry comprising (a) a source of copper ions and (b) a leveler compound, wherein the leveler compound is a reaction product of a dipyridyl compound and an alkylating agent; and supplying electrical current to the electrolytic deposition chemistry to deposit copper metal onto the bottom and sidewall of the via feature, thereby yielding a copper filled via feature.

Owner:MACDERMID ENTHONE INC

Copper metallization of through silicon via

ActiveUS20090035940A1Advantageous bias towards bottom upSemiconductor/solid-state device manufacturingSemiconductor devicesOrganic sulfonic acidElectrolysis

A method for metallizing a through silicon via feature in a semiconductor integrated circuit device substrate comprising immersing the semiconductor integrated circuit device substrate into an electrolytic copper deposition composition comprising a source of copper ions, an organic sulfonic acid or inorganic acid, or one or more organic compounds selected from among polarizers and / or depolarizers, and chloride ions.

Owner:MACDERMID ENTHONE INC

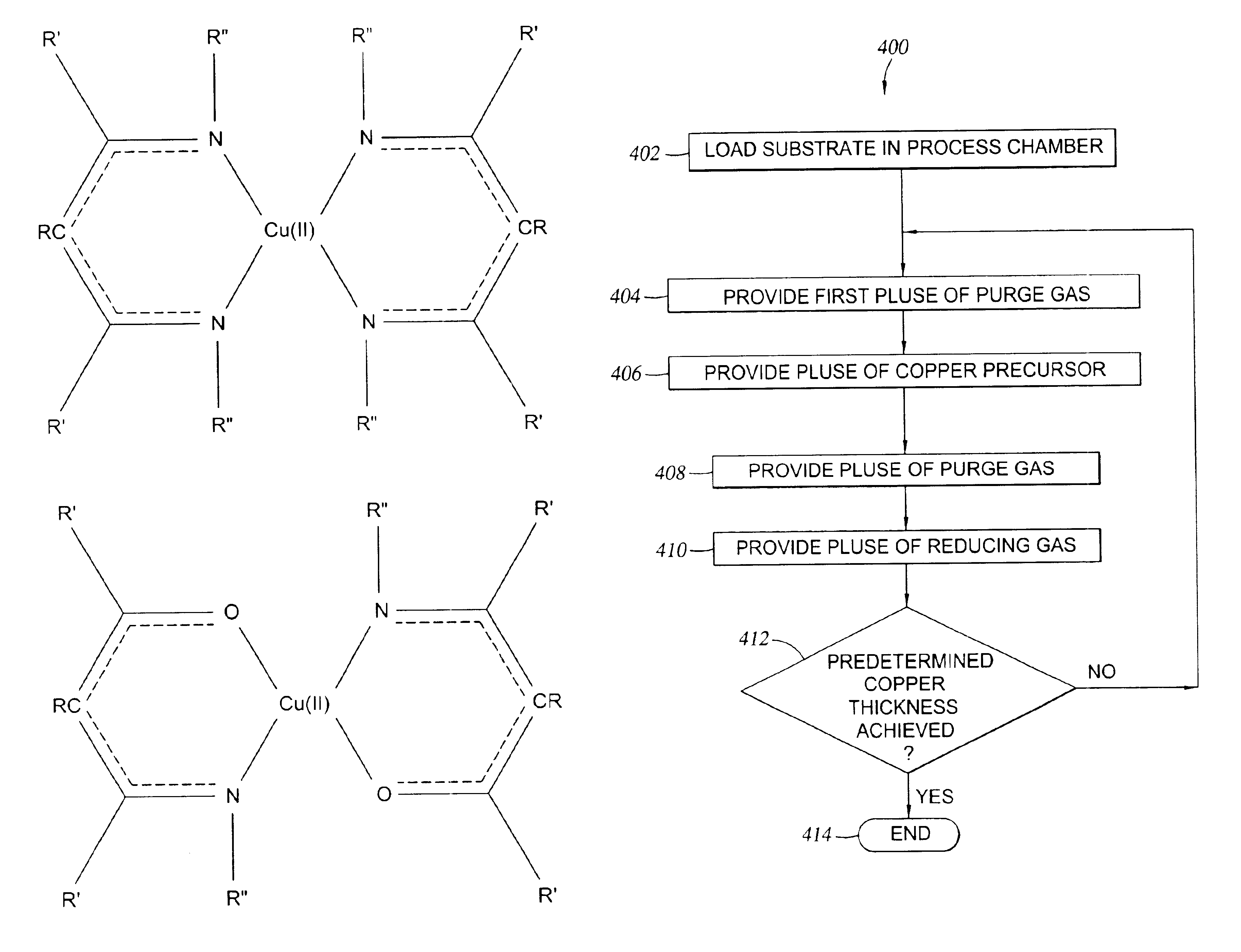

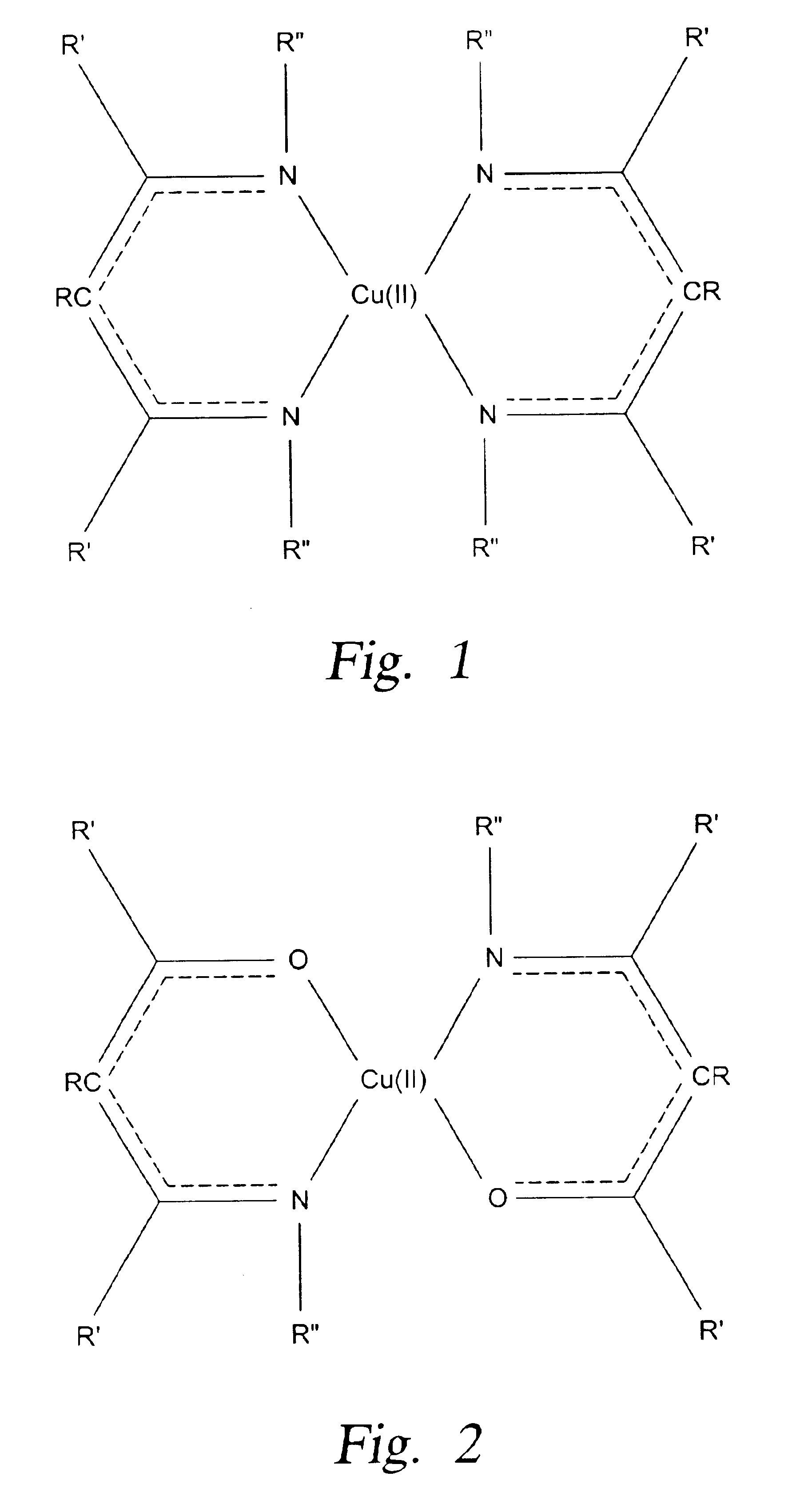

Atomic layer deposition of copper using a reducing gas and non-fluorinated copper precursors

InactiveUS6821891B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingNitrogenProduct gas

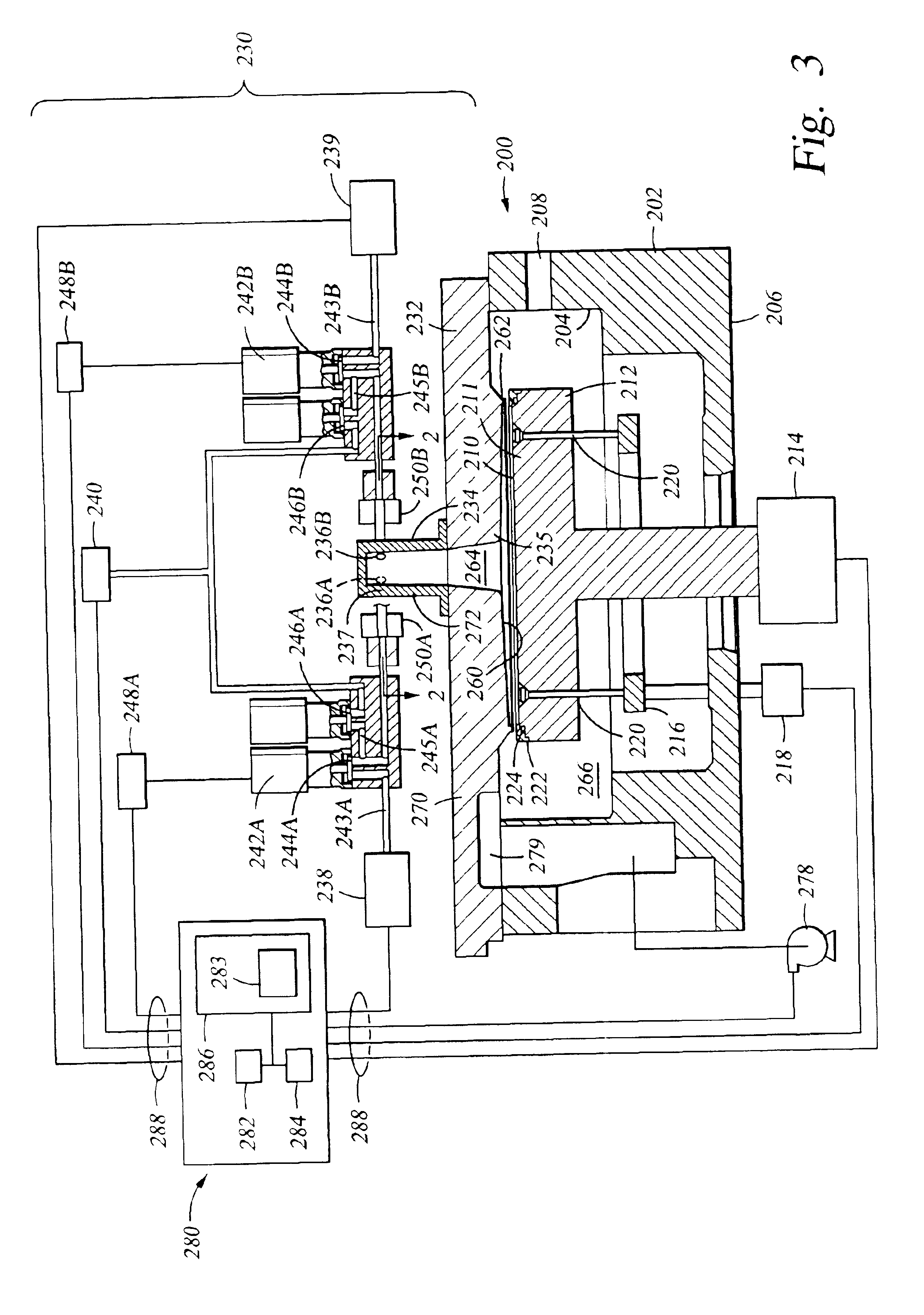

Methods of forming copper films by sequentially introducing and then reacting nitrogen containing analogs of Copper II beta-diketonates which analogs are more stable source reagents for copper deposition. The nitrogen containing analogs replace -O- with -N(R'')- wherein R'' is an alkyl group having from one to four carbon atoms. Replacement of each -O- is preferred although replacement of one -O- per cyclic ring is sufficient to improve stability of the copper source reagents. The source reagent can be purified by sublimation to remove solvents and excess ligands prior to semiconductor processing. The processing chamber is preferably a cyclical deposition chamber maintained at a pressure of less than about 10 Torr and the substrate is maintained at a temperature of about 50 to about 200° C.

Owner:APPLIED MATERIALS INC

Surface preparation process for damascene copper deposition

A method is disclosed for metallizing a substrate comprising an interconnect feature in the manufacture of a microelectronic device, wherein the interconnect feature comprises a bottom, a sidewall, and a top opening having a diameter, D. The method comprises the following steps: depositing a barrier layer on the bottom and the sidewall of the interconnect feature, the barrier layer comprising a metal selected from the group consisting of ruthenium, tungsten, tantalum, titanium, iridium, rhodium, and combinations thereof; contacting the substrate comprising the interconnect feature comprising the bottom and sidewall having the barrier layer thereon with an aqueous composition comprising a reducing agent and a surfactant; and depositing copper metal onto the bottom and the sidewall of the interconnect feature having the barrier layer thereon.

Owner:MACDERMID ENTHONE INC

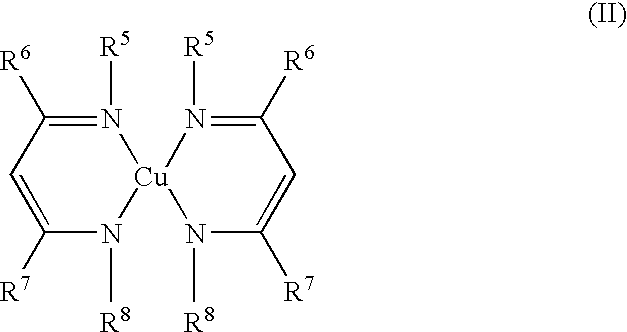

Volatile copper(II) complexes for deposition of copper films by atomic layer deposition

InactiveUS20050003075A1Copper organic compoundsVacuum evaporation coatingDiimineAtomic layer deposition

The present invention relates to novel 1,3-diimine copper complexes and the use of 1,3-diimine copper complexes for the deposition of copper on substrates or in or on porous solids in an Atomic Layer Deposition process. This invention also provides a process for making amino-imines and novel amino-imines.

Owner:EI DU PONT DE NEMOURS & CO

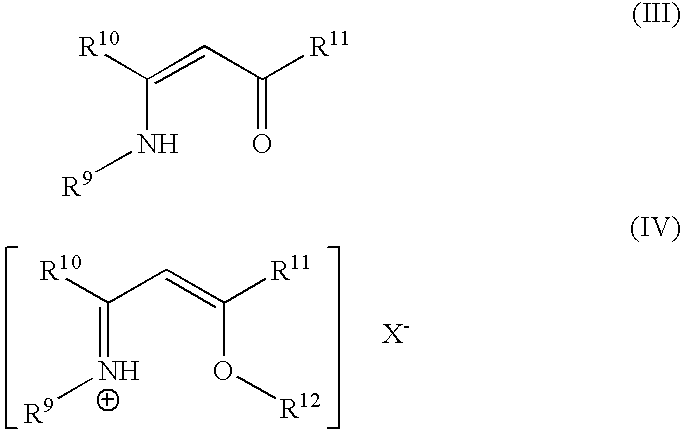

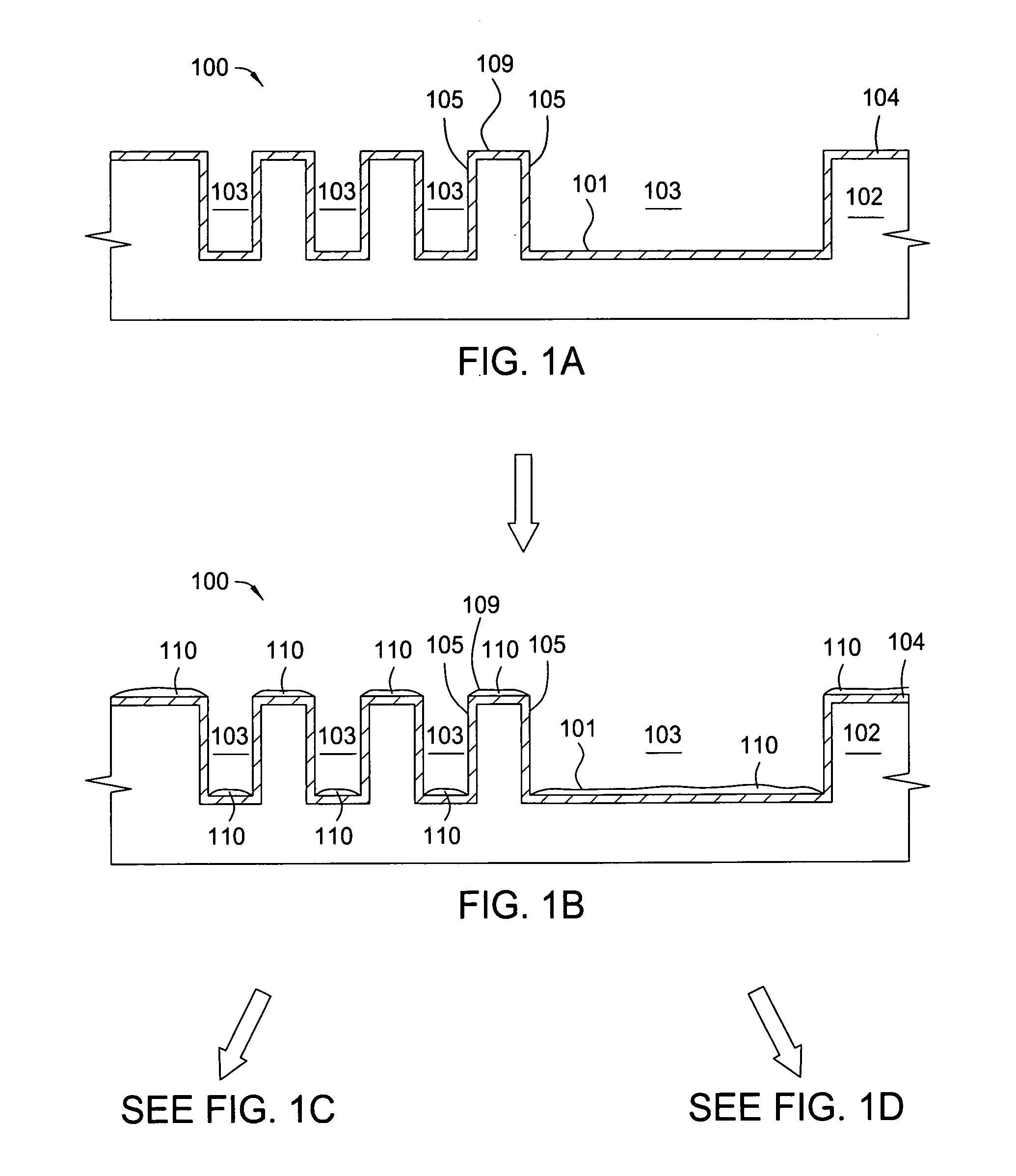

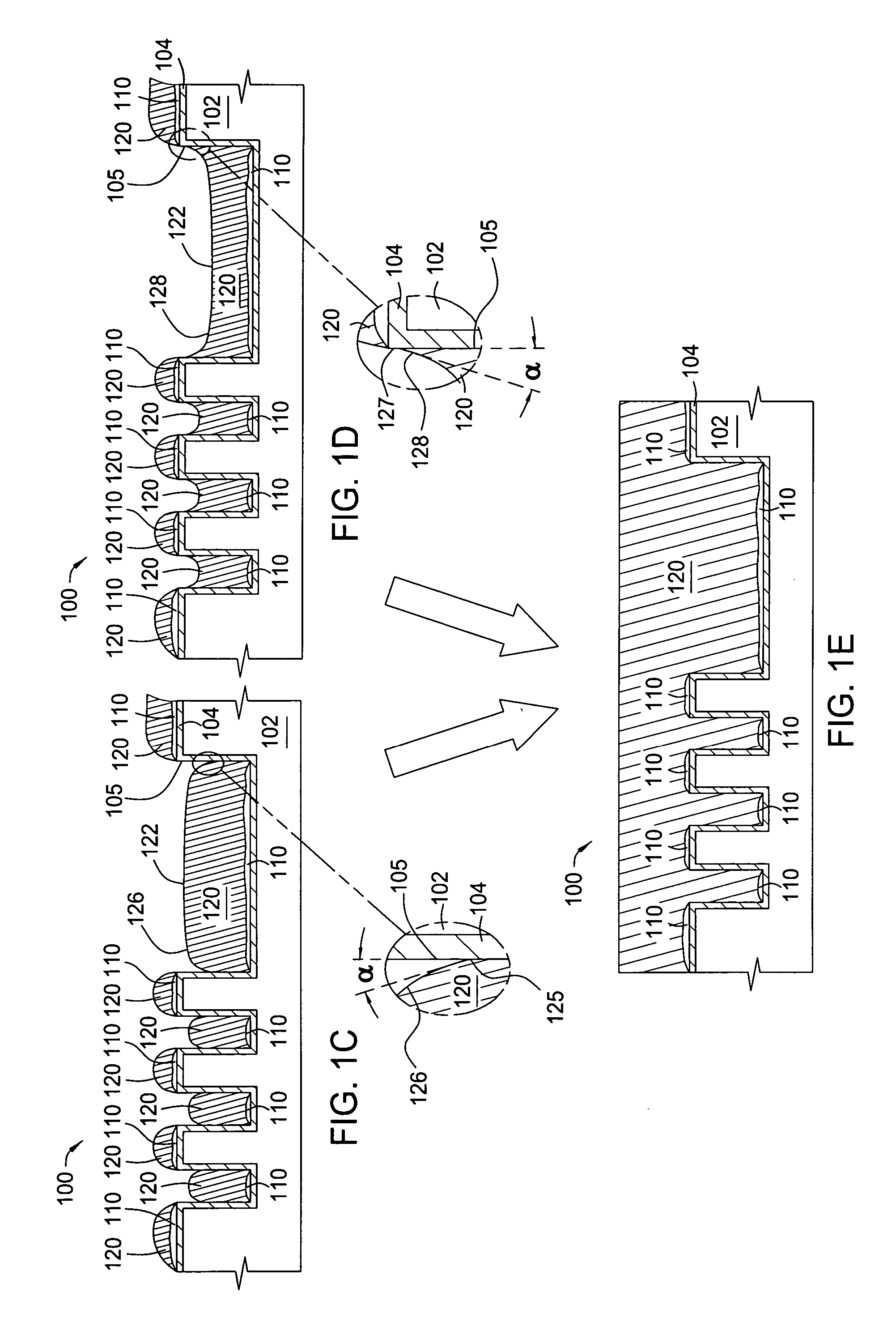

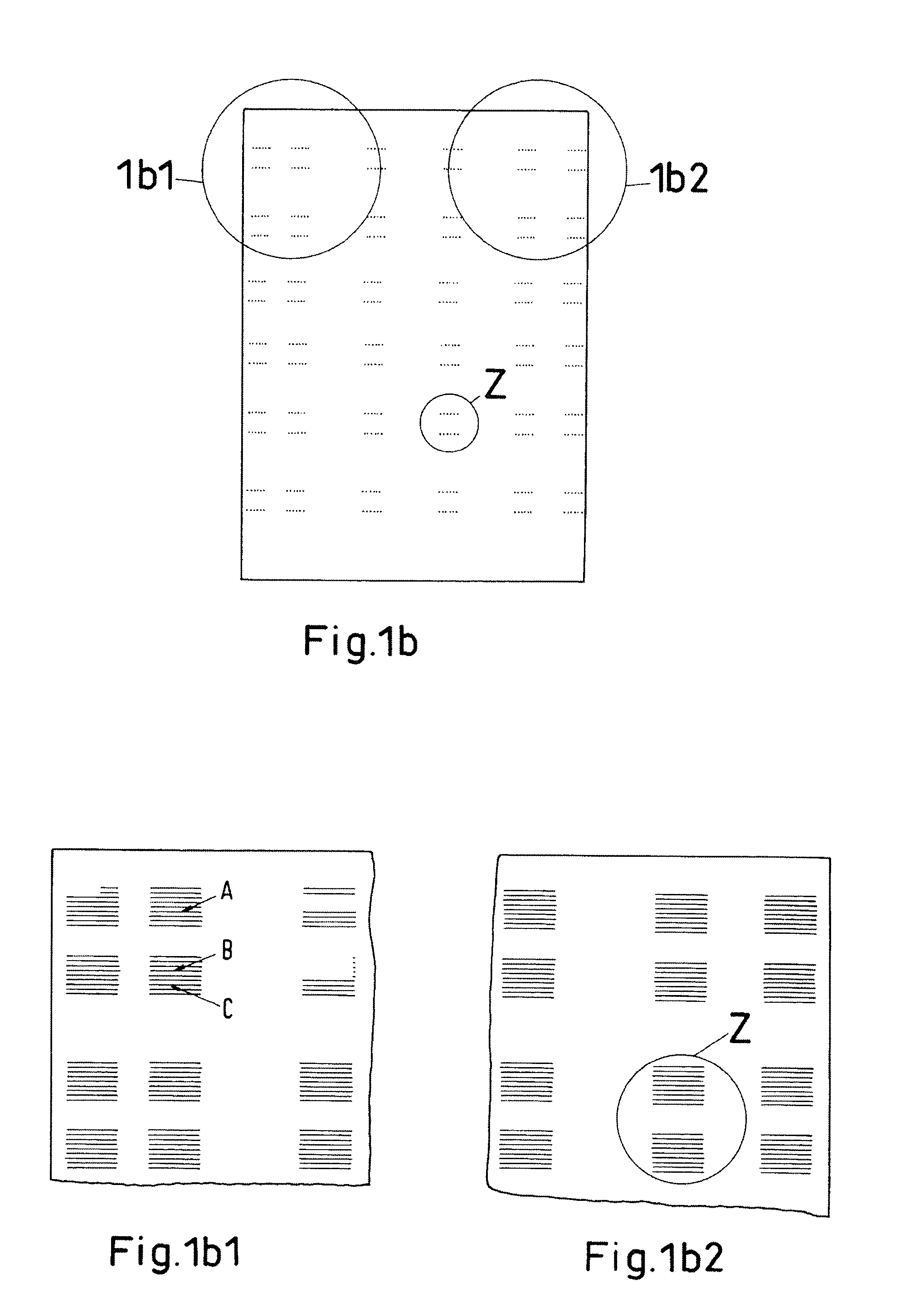

Copper deposition for filling features in manufacture of microelectronic devices

ActiveUS20100285660A1Simplify deposition of copperQuality improvementSemiconductor/solid-state device manufacturingLiquid/solution decomposition chemical coatingElectroplatingSemiconductor

A method for plating copper onto a semiconductor integrated circuit device substrate by forming an initial metal deposit in the feature which has a profile comprising metal on the bottom of the feature and a segment of the sidewalls having essentially no metal thereon, electrolessly depositing copper onto the initial metal deposit to fill the feature with copper. A method for plating copper onto a semiconductor integrated circuit device substrate by forming a deposit comprising a copper wettable metal in the feature, forming a copper-based deposit on the top-field surface, and depositing copper onto the deposit comprising the copper wettable metal to fill the feature with copper.

Owner:MACDERMID ENTHONE INC

Novel manufacturing method for back drilling of PCB (Printed Circuit Board)

InactiveCN101998768AImprove the problem of cloakingProtect from being etchedPrinted circuit manufactureBoring/drilling machinesEngineeringFlying probe

The invention discloses a novel manufacturing method for the back drilling of a PCB (Printed Circuit Board), which comprises the steps of: A) drilling the PCB substrate for the first time after the PCB substrate is subjected to cutting, bonding with a dry film, browning the inner layer and treating with a pressing board; B) carrying out the copper-deposition panel electroplating or added-panel electroplating; C) carrying out the back drilling on holes to be subjected to the back drilling; D) carrying out alkaline etching treatment on the board subjected to the back drilling; and E) carrying out solder stripping treatment on the PCB board, detecting the PCB board subjected to the solder stripping treatment through a flying probe tester and obtaining a finished product when the PCB is detected to be qualified. In the manufacturing method, the pattern tin electroplating is carried out after the external layer dry film on the PCB is made, then the back drilling is carried out on the hole to be subjected to the back drilling, and then etching is carried out so that the burr generated in the course of the drilling can be eliminated and the copper in a part of the hole with the copper can be protected from being etched at the same time.

Owner:SHENZHEN SUNTAK MULTILAYER PCB

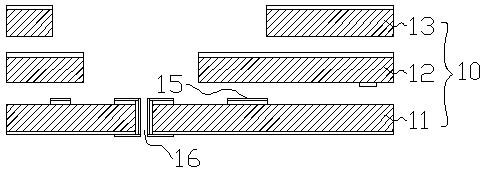

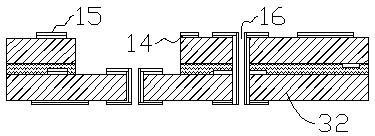

Second-order ladder groove bottom graphical printed board and processing method thereof

The invention relates to the printed circuit board technology field, especially relating to a processing method of a second-order ladder groove bottom graphical printed board. The method comprises the following steps: carrying out a pretreatment on a first daughter board which reserves a plug-in hole, a second daughter board provided with a circuit graph and a third daughter board provided with a circuit graph; pressing the first daughter board and the second daughter board to obtain a first motherboard; carrying out distressing, hole drilling, copper deposition, internal layer figure transfer, and etching resistance metal protective layer plating treatments on the first motherboard to obtain a second motherboard; pressing the third daughter board and the second motherboard to obtain a third motherboard; carrying out distressing, hole drilling, copper deposition, external layer figure transfer treatments on the third motherboard to obtain a finished second-order ladder groove bottom graphical printed board. According to the second-order ladder groove bottom graphical printed board prepared by the method, each ladder can be subjected to wiring and plug-in installation, and a usage scope of a plate is expanded. The invention also relates to the second-order ladder groove bottom graphical printed board.

Owner:珠海杰赛科技有限公司

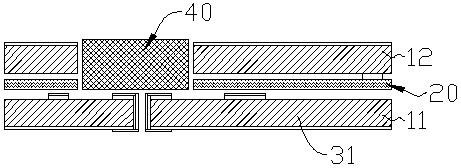

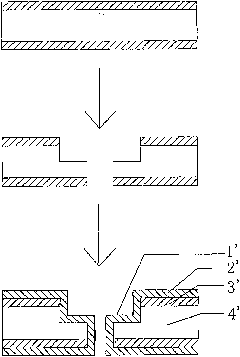

Production method of stepped groove circuit board with through hole, soldermask and circuit graphics at groove bottom

ActiveCN102548258APrevent peelingFrom erosionMultilayer circuit manufactureNon-metallic protective coating applicationGraphicsAdhesive

The invention relates to a production method of a stepped groove circuit board with a through hole, a soldermask and a circuit graphics at a groove bottom, which comprises the following steps that: 1, a sub board is produced, and is provided with the circuit graphics, the soldermask and the metalized through hole; 2, a prepreg and a core board are provided, and a through groove is arranged at the prepreg; 3, packing is carried out, a polytetrafluoroethylene (PTFE) gasket is placed in the through groove, and a polyimide adhesive tape is adhered to one side of the PTFE gasket, which is close to the sub board; 4, lamination is carried out, so a mother board is produced; 5, the through hole is drilled on the mother board, a protective adhesive tape is adhered to the outer end of the metalized through hole, and then copper deposition and electroplating are carried out; 6, the protective adhesive tape is removed, and an outer layer of circuit graphics is produced; 7, the outer layer is subjected to soldermask treatment, the board is milled in a depth control way, and a stepped groove is formed; and 8, the PTFE gasket and the polyimide adhesive tape are taken out, surface treatment is carried out, so the stepped groove circuit board is produced. According to the production method, the stepped groove circuit board of which the through hole at the groove bottom cannot be blocked can be produced, and the soldermask of the groove bottom is good.

Owner:DONGGUAN SHENGYI ELECTRONICS

Manufacturing method for improving accuracy of PCB (printed circuit board) back drilling hole

ActiveCN103533761AAffect accuracyHigh precisionPrinted circuit manufactureWell drillingPrinted circuit board

The invention discloses a manufacturing method for improving accuracy of a PCB back drilling hole. The manufacturing method comprises the steps as follows: A), a circuit board substrate is subjected to front procedure processing, through-hole drilling, copper deposition, board electroplating, outer circuit pattern transferring, pattern electroplating and the like; B), back drilling is performed on a PCB 4, and whether the depth of the back drilling hole is qualified is detected; and C), a well drilled back drilling hole is subjected to alkaline etching and photosensitive welding resistance, and finally a finished product is manufactured. The technical scheme is characterized in that drill file coefficients used in a through-hole drilling procedure are correspondingly corrected according to expansion and contraction data obtained in a technological process from the through-hole drilling procedure to the drilling procedure of the PCB 4 during back drilling, and the drill file data is maintained to be consistent with actual expansion and contraction; a drilling-in surface in the through-hole drilling procedure is consistent with that during the back drilling; and a phenolic aldehyde base plate 6 is additionally paved on the top surface of the PCB 4. With the adoption of the manufacturing method, the depth accuracy and the position accuracy of a back drilling hole of a conventional PCB 4 can be effectively improved, so that the completeness of signal transmission of the PCB 4 is guaranteed.

Owner:广东依顿电子科技股份有限公司

Method for machining PCB with step groove

The invention discloses a method for machining a PCB with a step groove, which comprises the following steps: milling the step groove on the PCB formed after pressing; drilling a plurality of blind holes in the step groove by using laser; performing copper deposition electroplating on the surface of the PCB; performing pattern electroplating on the PCB after copper deposition; and milling a through groove on the surface of the step groove after the pattern electroplating. By designing the metallized laser blind holes on the surface of the step groove, the method for machining the PCB with the step groove can effectively increase the contact area between electroplating copper and a base material, effectively enhance the bonding force between the electroplating copper and the base material, improve the quality of a product, and avoid the phenomenon of poor welding caused by layered peeling of the electroplating copper and the base material; and the through groove is milled after the pattern electroplating, so the board surface is flat when outer layer pattern machining is performed on the PCB, the film sticking effect is good, poor etching can be effectively improved, and the condition of product scrap is reduced.

Owner:SHENNAN CIRCUITS

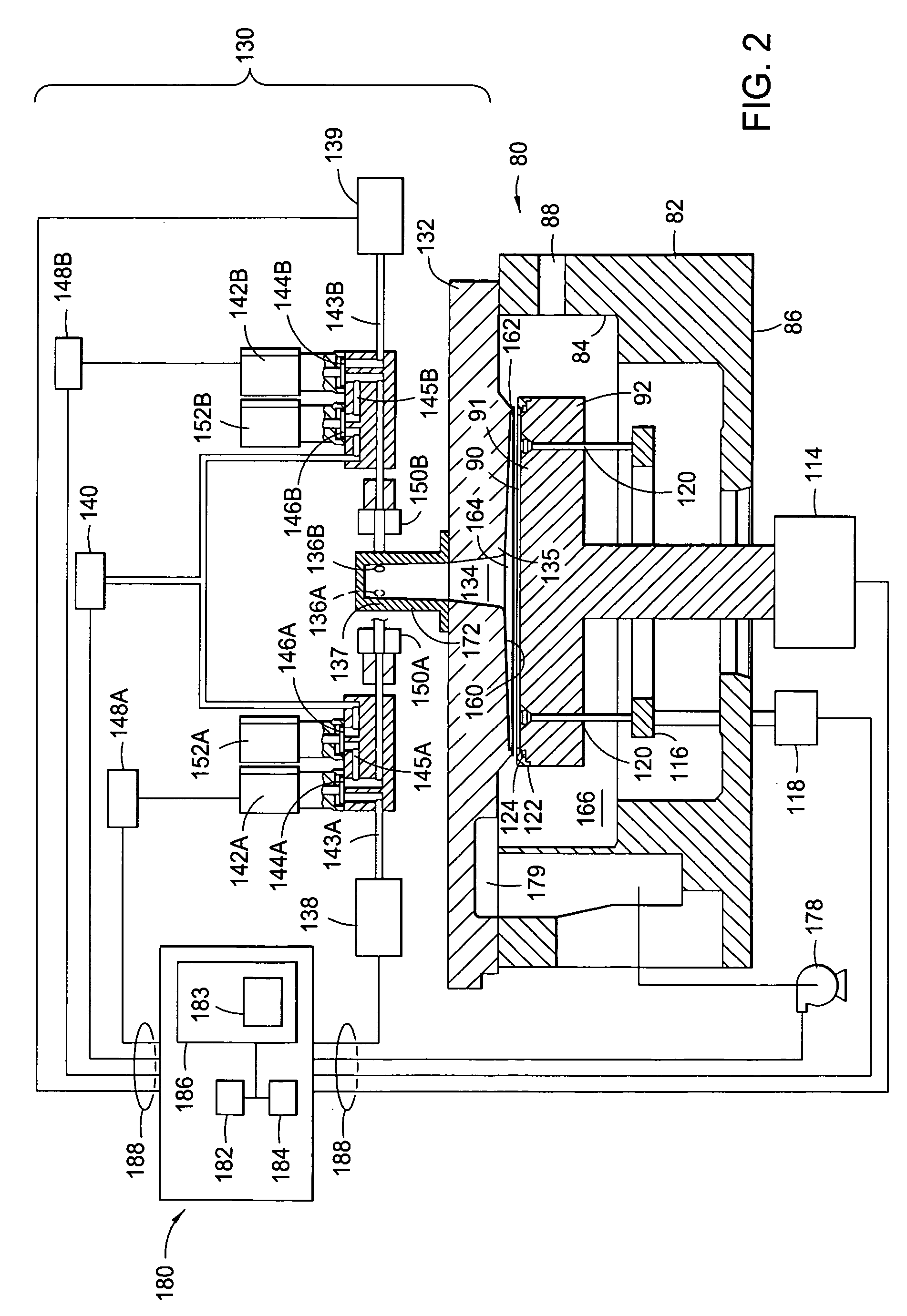

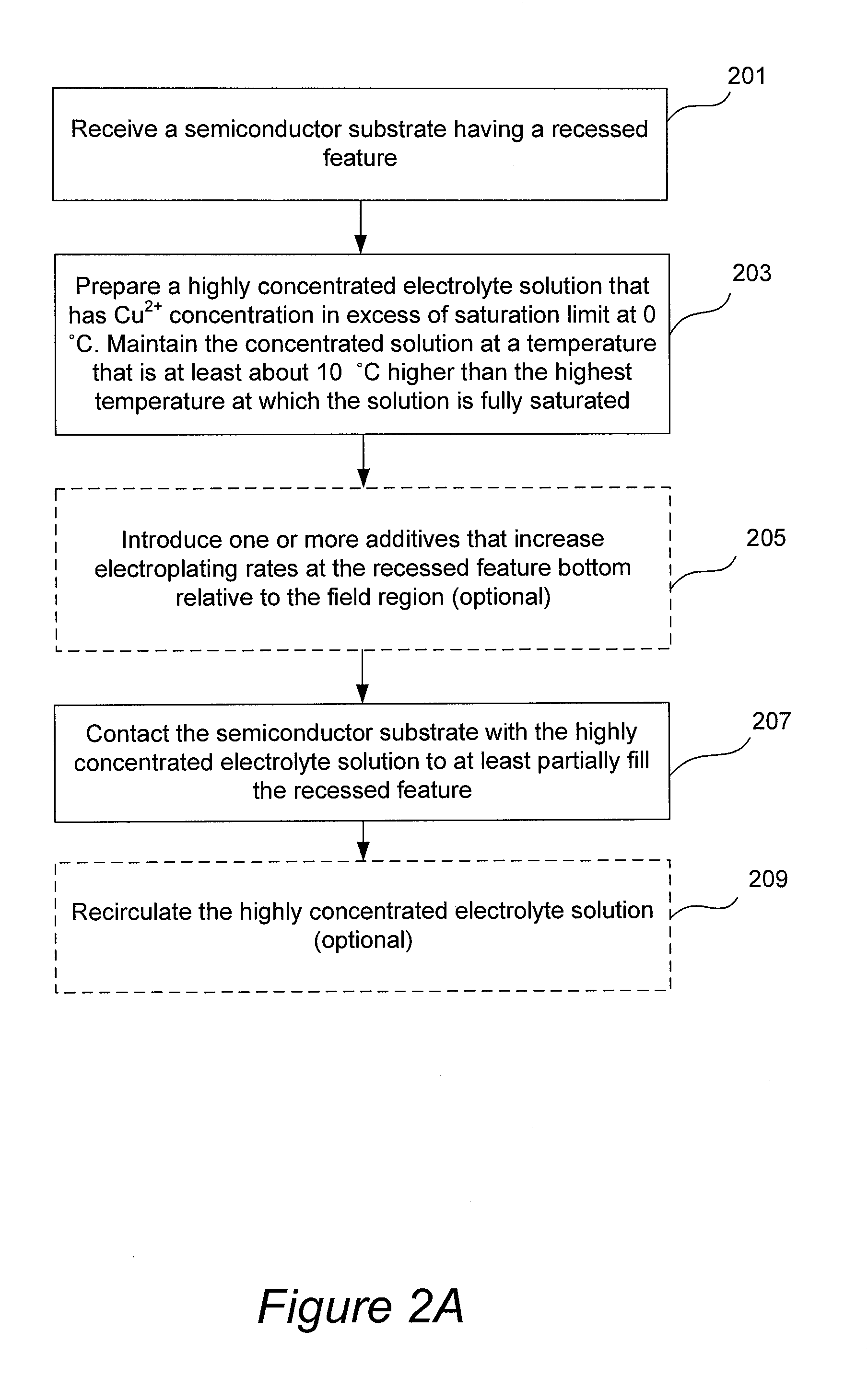

Electrolyte Concentration Control System for High Rate Electroplating

An electroplating apparatus for filling recessed features on a semiconductor substrate includes an electrolyte concentrator configured for concentrating an electrolyte having Cu2+ ions to form a concentrated electrolyte solution that would have been supersaturated at 20° C. The electrolyte is maintained at a temperature that is higher than 20° C., such as at least at about 40° C. The apparatus further includes a concentrated electrolyte reservoir and a plating cell, where the plating cell is configured for electroplating with concentrated electrolyte at a temperature of at least about 40° C. Electroplating with electrolytes having Cu2+ concentration of at least about 60 g / L at temperatures of at least about 40° C. results in very fast copper deposition rates, and is particularly well-suited for filling large, high aspect ratio features, such as through-silicon vias.

Owner:NOVELLUS SYSTEMS

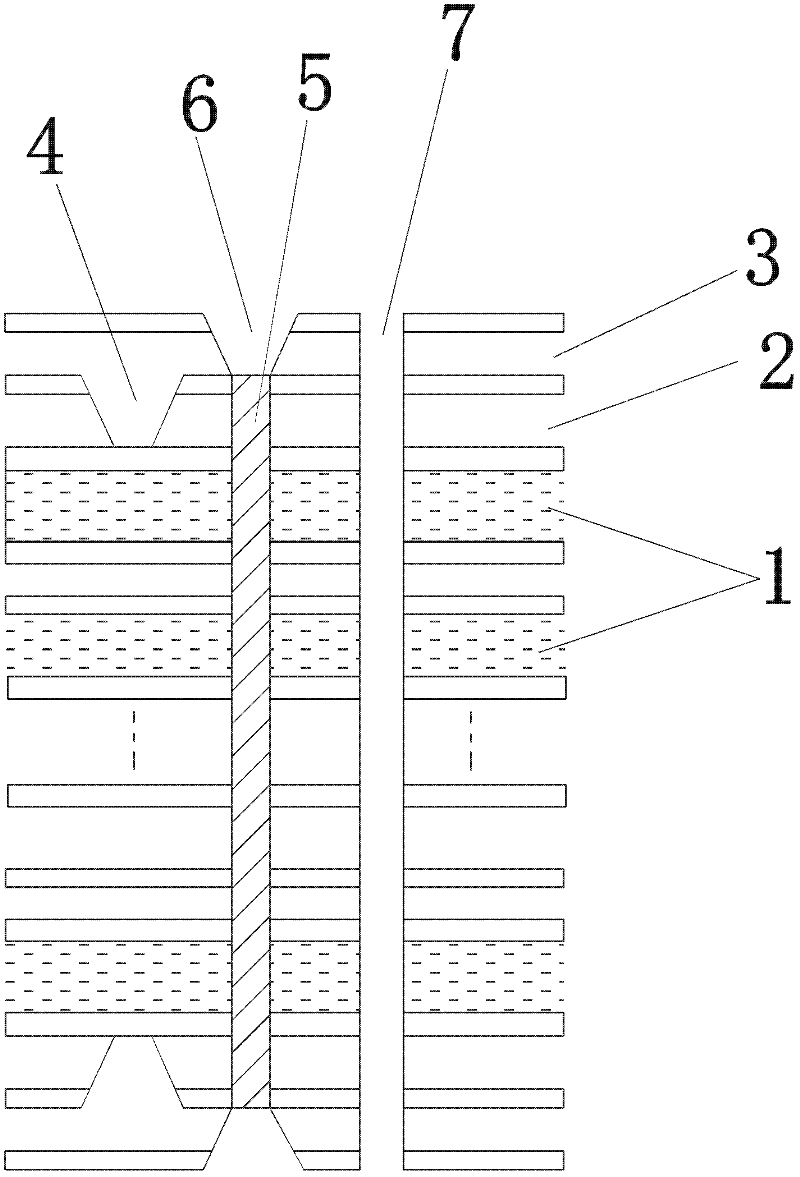

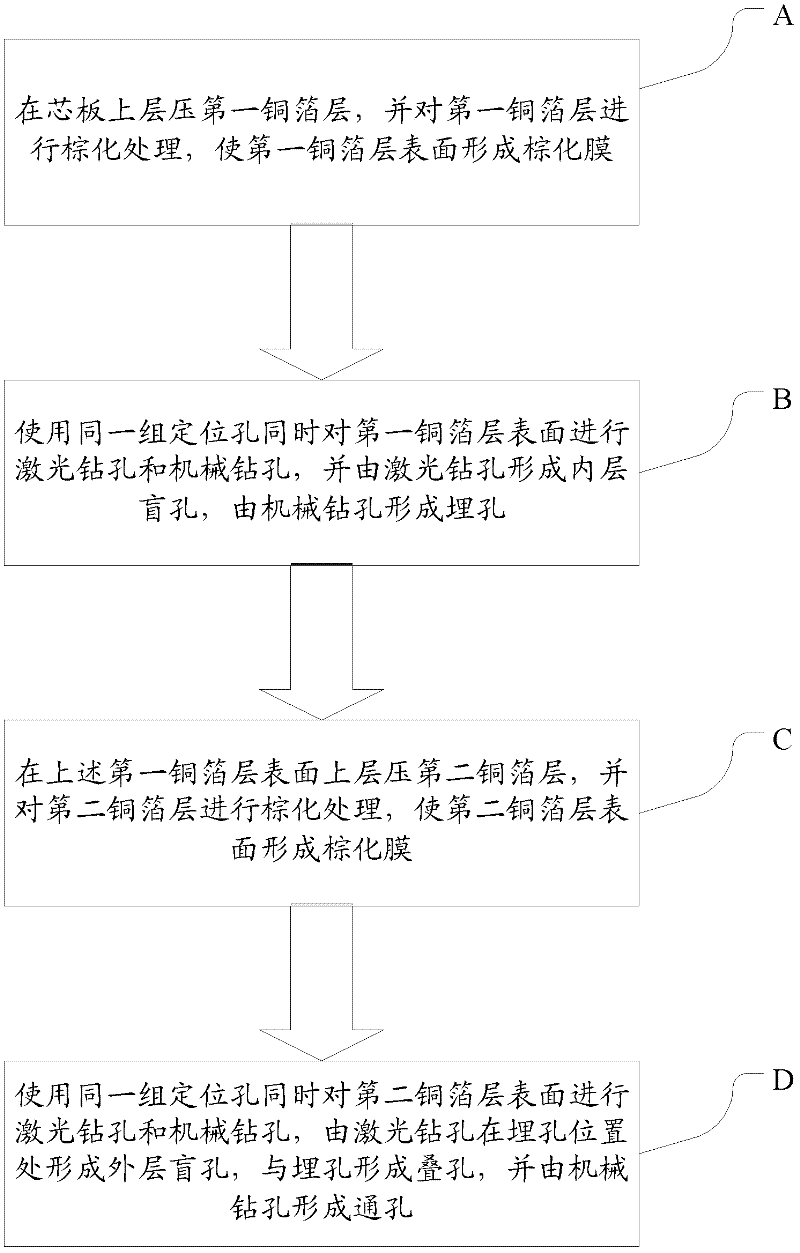

Production method of multi-stage HDI plate

ActiveCN102523704AGood dimensional stabilityAvoid processPrinted circuit aspectsMultilayer circuit manufactureCopper foilElectroplating

The invention discloses a production method of a multi-stage HDI plate. The method comprises the following steps: A. laminating a first copper foil layer on a core plate, carrying out multiband to the first copper foil layer so as to form a brown film on a surface of the first copper foil layer; B. using a same group of location holes to simultaneously carry out laser drilling and mechanical drilling to the surface of the first copper foil layer, forming an internal-layer blind hole through the laser drilling and forming a buried hole through the mechanical drilling; C. laminating a second copper foil layer on the surface of the first copper foil layer, carrying out the multiband to the second copper foil layer so as to form the brown film on the surface of the second copper foil layer; D. using the same group of location holes to simultaneously carry out the laser drilling and the mechanical drilling to the surface of the second copper foil layer, forming an outer-layer blind hole on the position of the buried hole through the laser drilling, forming a folded hole with the buried hole and forming a through hole through the mechanical drilling. At present, the blind hole and the buried hole are drilled separated so that the through hole and the blind hole are not matched with each other. According to the method of the invention, the above problem can be solved; processes of internal layer copper deposition, padpower, an internal layer plating hole graph, porefilling electroplating, film stripping, abrasive-belt grinding plate and the like can be reduced; a production period can be substantially shortened and production cost can be saved.

Owner:SHENZHEN SUNTAK MULTILAYER PCB

Process for electroless copper deposition

ActiveUS20070004201A1Semiconductor/solid-state device manufacturingLiquid/solution decomposition chemical coatingCompound (substance)Conductive materials

Embodiments of the invention provide methods for forming conductive materials within contact features on a substrate by depositing a seed layer within a feature and subsequently filling the feature with a copper-containing material during an electroless deposition process. In one example, a copper electroless deposition solution contains levelers to form convexed or concaved copper surfaces. In another example, a seed layer is selectively deposited on the bottom surface of the aperture while leaving the sidewalls substantially free of the seed material during a collimated PVD process. In another example, the seed layer is conformably deposited by a PVD process and subsequently, a portion of the seed layer and the underlayer are plasma etched to expose an underlying contact surface. In another example, a ruthenium seed layer is formed on an exposed contact surface by an ALD process utilizing the chemical precursor ruthenium tetroxide.

Owner:APPLIED MATERIALS INC

Process for electroless copper deposition

ActiveUS7651934B2Semiconductor/solid-state device manufacturingLiquid/solution decomposition chemical coatingCompound (substance)Electroless deposition

Owner:APPLIED MATERIALS INC

Method of manufacturing a 2-layered flexible substrate

InactiveUS6045713AImprove adhesionDecorative surface effectsVacuum evaporation coatingCopper conductorCopper plating

A method of manufacturing a 2-layered flexible substrate includes forming an underlying metal layer on an insulation film with a deposition layer formed by a dry plating method using at least one of nickel, copper-nickel alloy, chromium and chromium oxide and a copper deposition layer formed by a dry plating method on the noted deposition layer, then forming a primary electric copper plated deposition layer on the underlying metal layer, then applying a treatment using at least one alkaline solution selected from inorganic alkaline solutions and organic alkaline solutions, then forming an electroless copper plated deposition layer as an intermediate metal layer on the primary electric copper plated deposition layer and, finally, forming a secondary electric copper plated deposition layer on the intermediate metal layer, thereby finally forming a copper conductor layer of 1 to 35 mu m thickness on the insulation film.

Owner:SUMITOMO METAL MINING CO LTD

Coppering and porefilling process for circuit board

InactiveCN101951735AImprove grinding effectReduce drum platingPrinted element electric connection formationPower flowSolder mask

The invention discloses a coppering and porefilling process for a circuit board, which comprises the following steps of: A) performing cutting, inner layer multibond and plane pressing on a circuit board substrate, and then drilling the circuit board substrate; B) performing copper deposition and panel plating on the drilled substrate; C) performing image transfer on the substrate subjected to copper deposition and panel plating through a hole plating film; D) performing a coppering and porefilling process on the substrate subjected to image transfer; E) performing circuit image transfer through a circuit film; F) performing silk screen on a solder mask and characters; G) performing a plane immersion Ni / Au process; and H) testing and checking the electrical property and shape of a finished board, and producing the finished product. By using the coppering and porefilling process for the circuit board, a hole is subjected to the image transfer process before the coppering and porefilling process; and after a dry film is stuck, the hole is subjected to exposure and development by the hole plating film, and the hole which needs electroplating and copper filling is exposed; and by using a scheme of low copper low current density plating, the copper concentration in plating solution is controlled to be 50 to 60g / L, and the current density is controlled to be 10 to 14ASF, so that plump plating is reduced to a maximum extent, and the finished product ratio and finished product quality are improved.

Owner:JIANGMEN SUNTAK CIRCUIT TECH

Method for etching outer circuit of PCB product with high aspect ratio

The invention discloses a method for etching an outer circuit of a PCB (printed circuit board) product with high aspect ratio, which comprises the following steps of: A) cutting a circuit board substrate, sticking a dry film, browning the inner layer, treating a pressing board, and then drilling the circuit board substrate; B) performing copper deposition plating on the full board or adding a board for plating; C) performing first film removal treatment on the pattern plated board; D) performing alkali etching treatment on the outer circuit after development; and E) performing tin removal treatment on the PCB obtained in the step D), inspecting qualification, and obtaining a finished product. The method for etching the outer circuit of the PCB product with the high aspect ratio can manufacture the product with aspect ratio of 15:1 to 30:1 or over by sticking the film again after the pattern plating is finished, using hole covering film exposure, covering the dry film on the hole for protection, adopting alkali etching and then removing the film and the tin; and the method has no defect of the PCB with high aspect ratio manufactured by prolonging the tin plating time or increasing the tin plating current density in the prior art.

Owner:DALIAN CHONGDA CIRCUIT

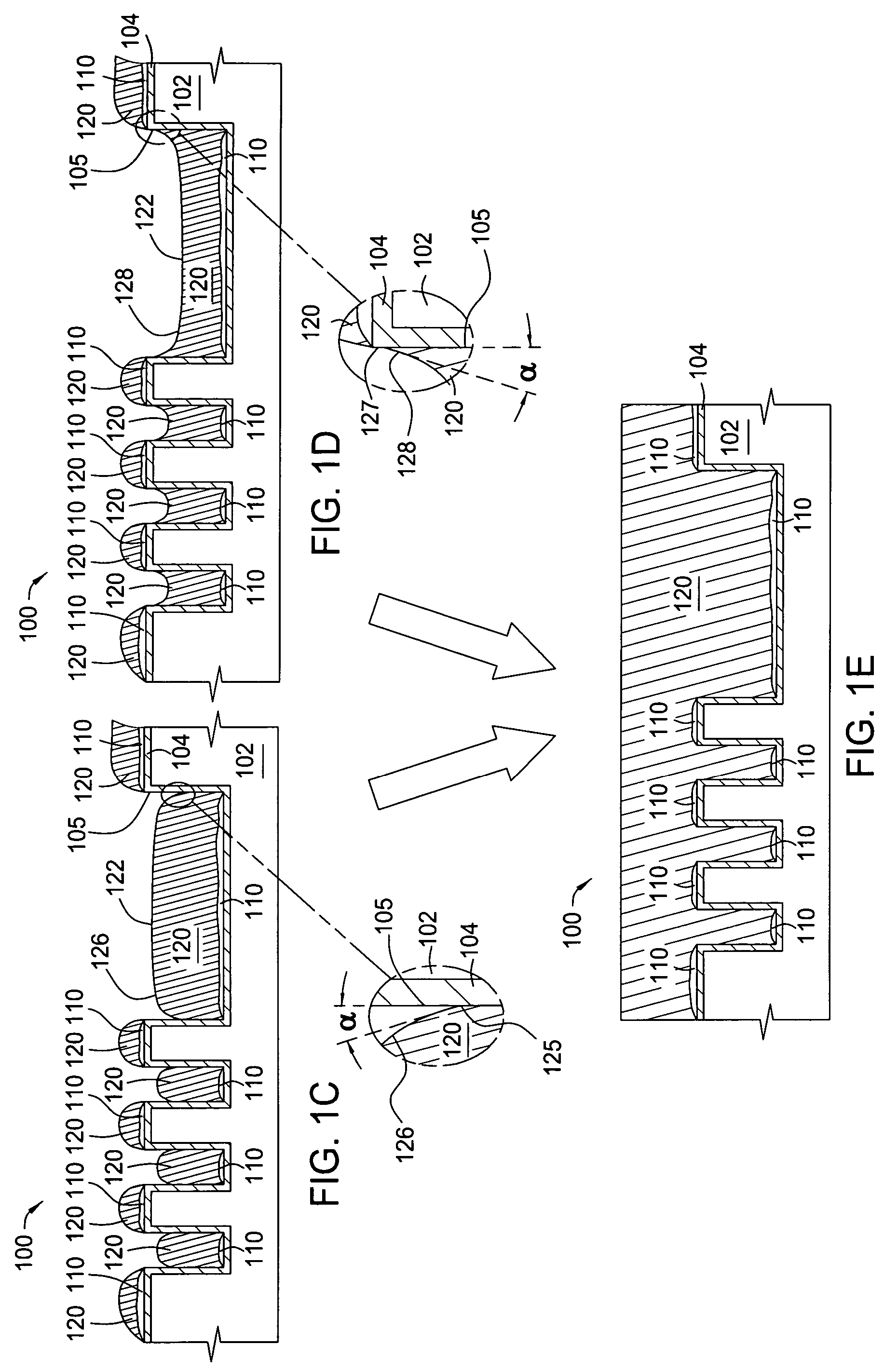

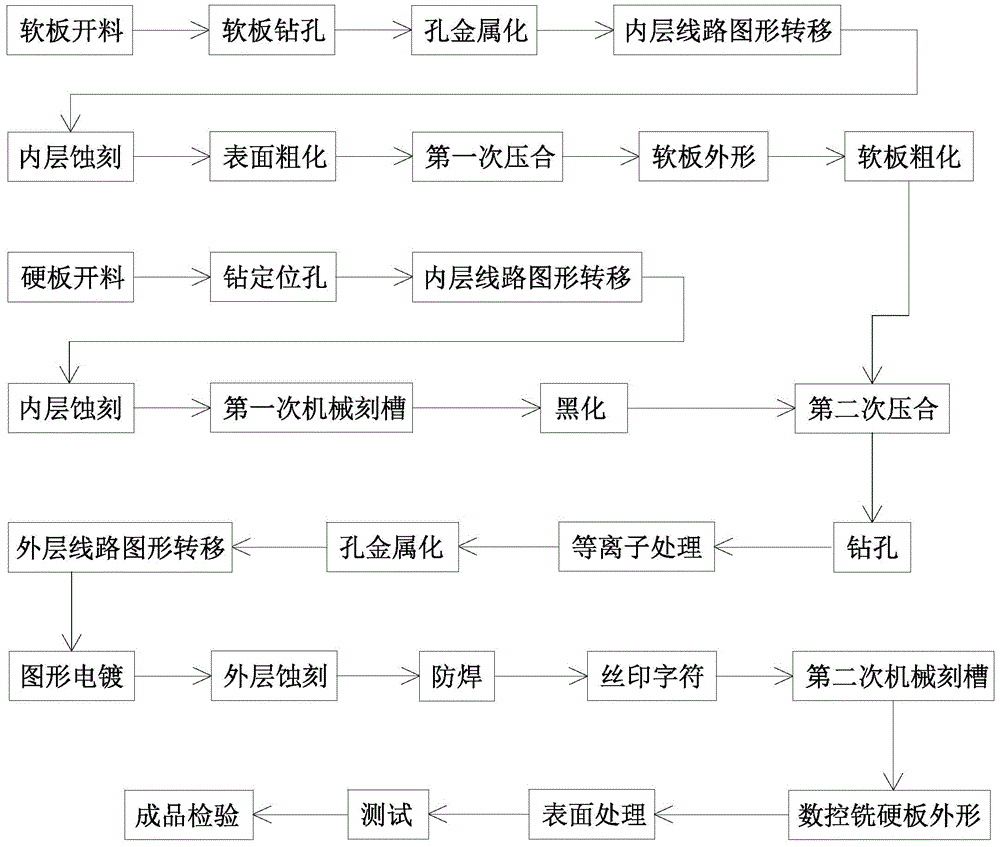

Fabrication method for rigid-flex printed combination board of covering membrane window

InactiveCN104135823AImprove reliabilityImprove manufacturing yieldPrinted circuit assemblingEtchingSurface roughness

The invention provides a fabrication method for a rigid-flex printed combination board of a covering membrane window. The fabrication method comprises the steps of soft board treatment, hard board treatment and treatment after a soft board and a hard board are combined, wherein the step of soft board treatment comprising surface roughening, in which the surface of the soft board is roughened; lamination for a first time, in which a covering membrane is pressed onto the surface of the soft board; soft board appearance, in which the appearance of the soft board is subjected to shaping; and soft board roughening, in which the soft board after being subjected to shaping is roughened; the step of hard board treatment comprises inner layer etching; mechanical groove carving for the first time, in which grooves are carved on the part of a flexible region of the hard board; and blackening, in which the surface roughness of copper foils at an inner layer is enhanced; and the step of treatment after the soft board and the hard board are combined comprises lamination for a second time, in which the roughened soft board and the blackened hard board are laminated to form the soft and hard combination board. Lamination is performed for twice in the fabrication method, the lamination reliability and the fabrication yield can be improved, and plasma treatment is adopted prior to copper deposition, the reliability of a hole wall can be ensured.

Owner:东莞市五株电子科技有限公司

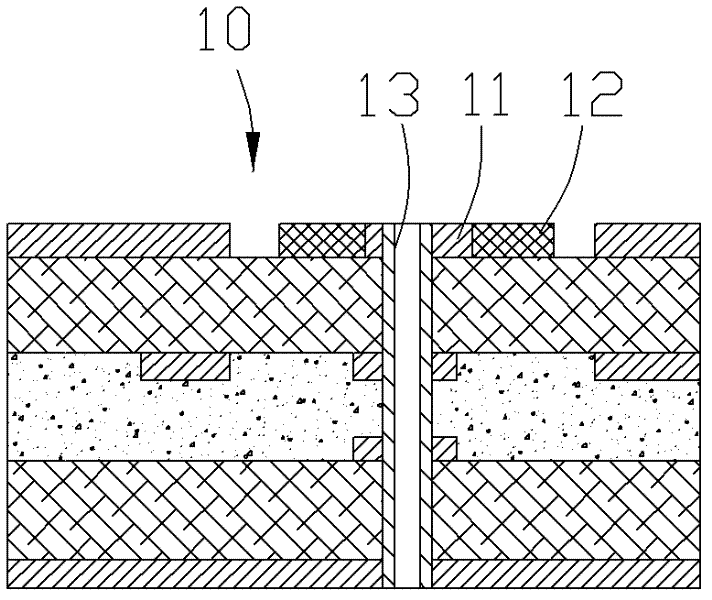

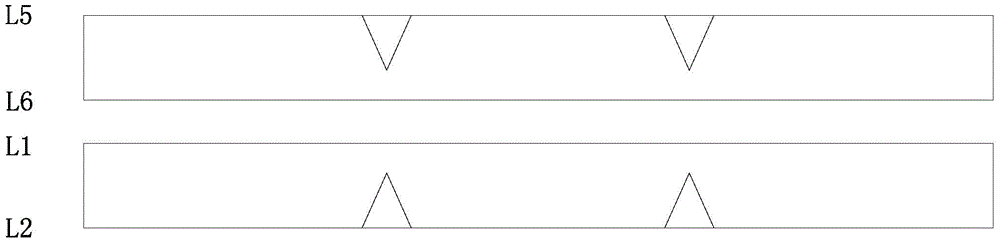

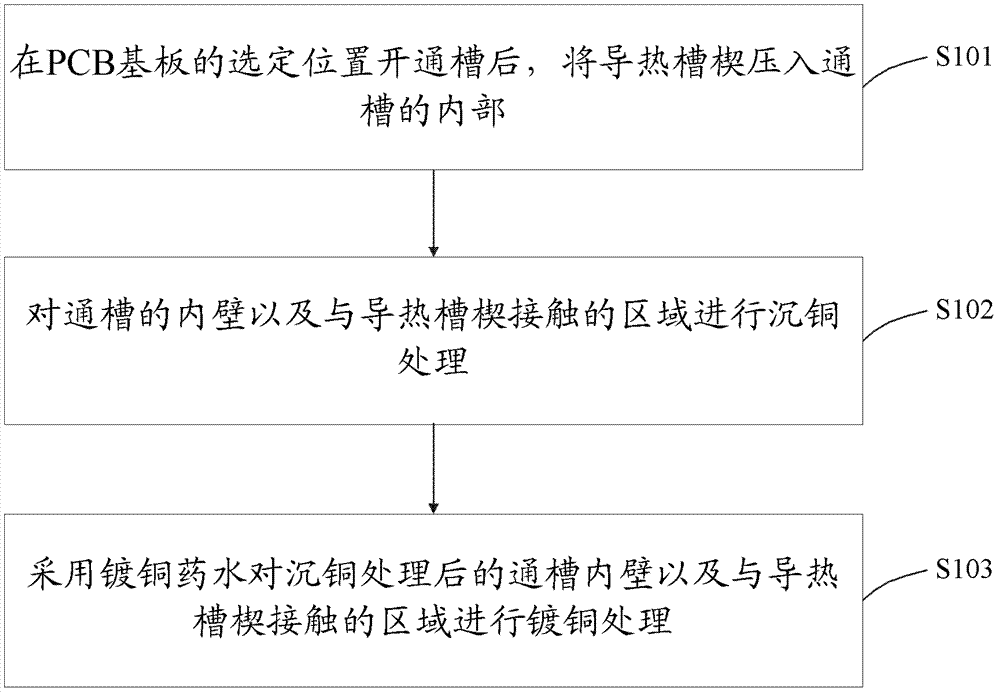

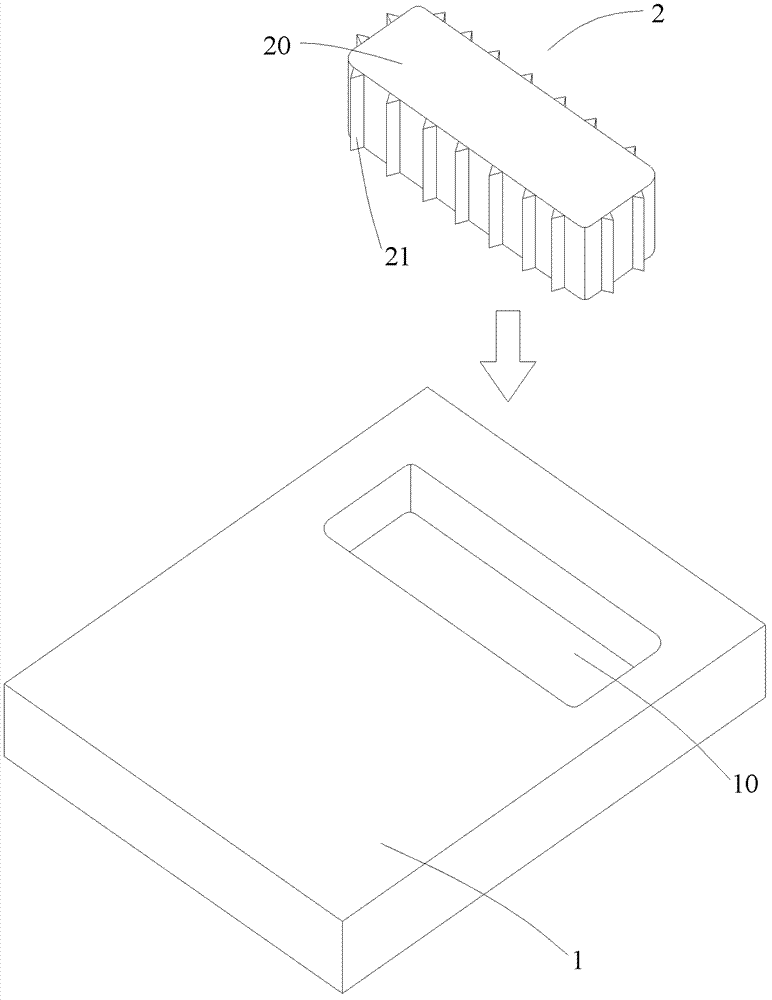

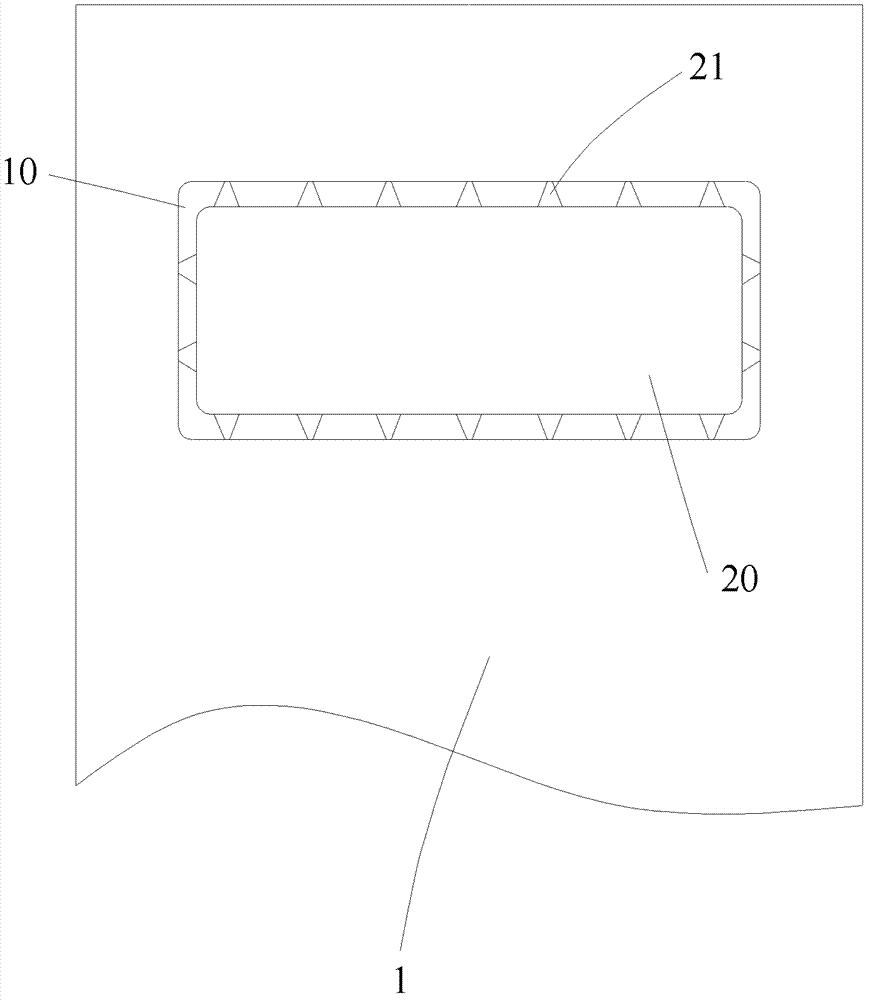

Press-in type high thermal conductive printed circuit board (PCB) and manufacture method thereof

ActiveCN103096638AShort processMake electrical connectionsPrinted circuit assemblingState of artCopper plating

The invention relates to the technical field of printed wiring board manufacture, in particular to a press-in type high thermal conductive printed circuit board (PCB) and manufacture method of the press-in type high thermal conductive PCB. The press-in type high thermal conductive PCB and the manufacture method of the press-in type high thermal conductive PCB are mainly used for solving the problems in the prior art that the connection between a press-in copper block and a PCB base plate is not firm, and looseness and even falling off of the press-in copper block is easy to happen in copper deposition and electroplating. The manufacture method of the press-in type high thermal conductive PCB comprises the steps: a through groove is formed in a chosen position of the PCB base board, a heat conductive slot wedge is pressed inside the through groove, copper deposition is conducted to the inner wall of the through groove and the contact area of the inner wall of the through groove and the heat conductive slot wedge, and copper plating is conducted to the inner wall of the through groove and the contact area of the inner wall of the through groove and the heat conductive slot wedge after copper deposition through copper plating liquid medicine. By means of the press-in type high thermal conductive PCB and the manufacture method of the press-in type high thermal conductive PCB, the technological process in high thermal conductive PCB manufacture is shortened, and the heat conductive slot wedge in a completed PCB is not easy to loosen.

Owner:NEW FOUNDER HLDG DEV LLC +1

Electroplating copper plughole process of circuit board

ActiveCN101873770AMeets high current connection requirementsImprove performancePrinted element electric connection formationCopper platingPhotographic plate

The invention discloses an electroplating copper plughole process of a circuit board. The process comprises the following steps of: manufacturing a substrate inner layer circuit: arranging an inner layer circuit on a material plate coated with a copper layer, overlapping a plurality of plates and laminating, and drilling a through hole on the multi-layer plate; electroplating the surface of a copper deposition plate: arranging the multi-layer plate in the copper deposition liquid to plate a conductive thin copper layer on the wall of the hole and the external surface of the multi-layer plate; transferring a special plating hole pattern, i.e., transferring the photographic plate image to the multi-layer plate; electroplating the through hole: electroplating the multi-layer plate to fill the through hole with the plated copper; reducing copper and etching: the through hole plated with copper partially exposing out of the plate surface, removing copper exposing out of the plate surface; arranging outer layer circuit: carrying out the arrangement of the outer layer circuit of the multi-layer plate; electroplating pattern; reducing film and etching: removing the dry film and etching; and printing green oil on the naked copper plate and work character, and baking to produce the finished plate.

Owner:广东兴达鸿业电子有限公司

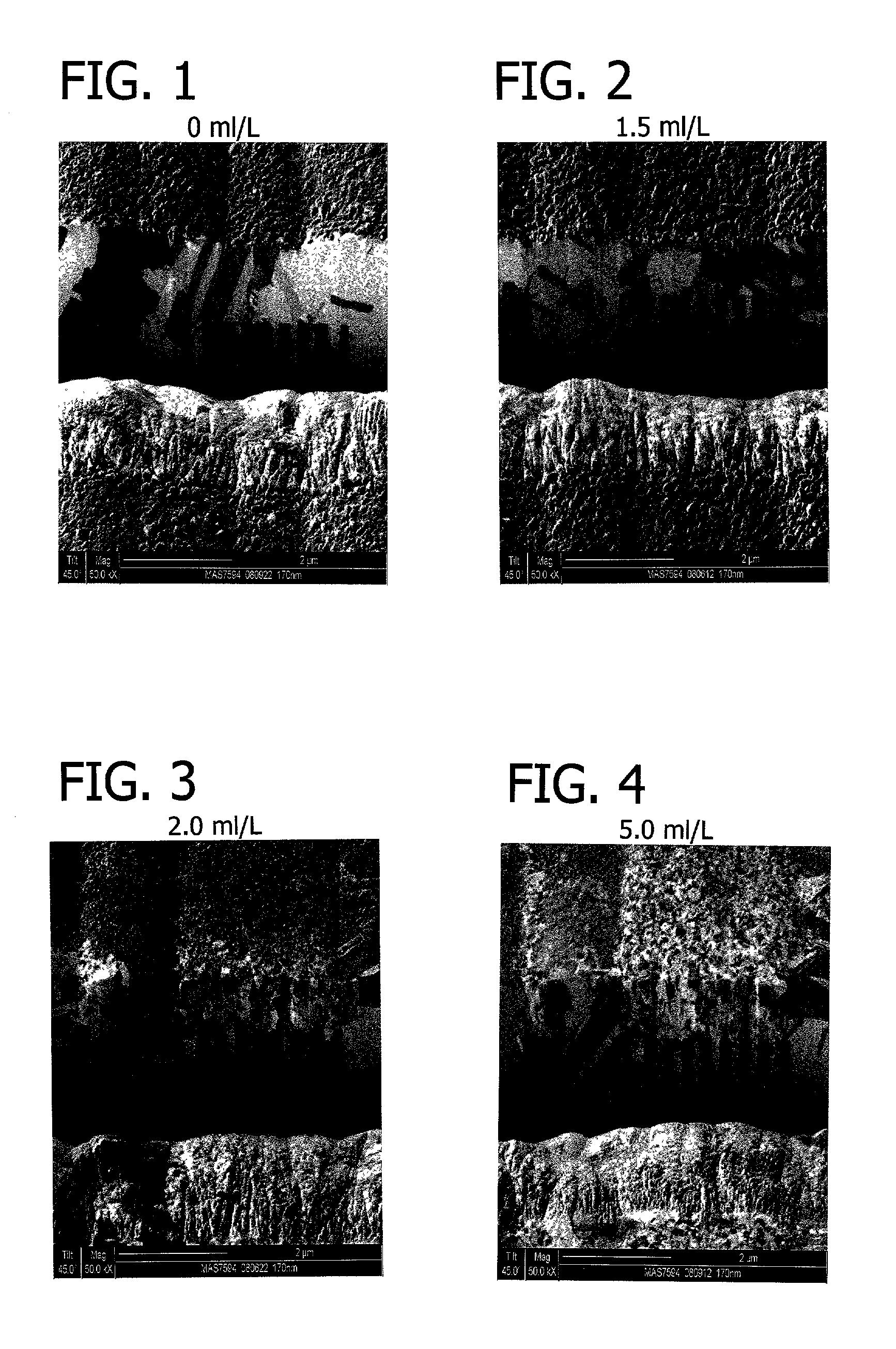

Defect reduction in electrodeposited copper for semiconductor applications

InactiveUS7316772B2Improve surface morphologyFew defectSemiconductor/solid-state device manufacturingPrinted circuit manufactureWaferingMetallurgy

A method for electroplating a copper deposit onto a semiconductor integrated circuit device substrate having submicron-sized features, and a concentrate for forming a corresponding electroplating bath. A substrate is immersed into an electroplating bath formed from the concentrate including ionic copper and an effective amount of a defect reducing agent, and electroplating the copper deposit from the bath onto the substrate to fill the submicron-sized reliefs. The occurrence of protrusion defects from superfilling, surface roughness, and voiding due to uneven growth are reduced, and macro-scale planarity across the wafer is improved.

Owner:MACDERMID ENTHONE INC

Cobalt metal barrier layers

InactiveUS20120161320A1Semiconductor/solid-state device detailsSolid-state devicesCobalt metalDopant

Electrical interconnects for integrated circuits and methods of fabrication of interconnects are provided. Devices are provided comprising copper interconnects having metal liner layers comprising cobalt and a metal selected from the group consisting of Ru, Pt, Ir, Pd, Re, or Rh. Devices having barrier layers comprising ruthenium and cobalt are provided. Methods include providing a substrate having a trench or via formed therein, forming a metal layer, the metal being selected from the group consisting of Ru, Pt, Ir, Pd, Re, and Rh, onto surfaces of the feature, depositing a copper seed layer comprising a cobalt dopant, and depositing copper into the feature.

Owner:INTEL CORP

Aqueous, Acid Bath and Method for the Electrolytic Deposition of Copper

ActiveUS20110011746A1Control roughnessEasy to drillAnodisationPrinted circuit manufactureElectrolysisCopper

To generate a very uniform copper deposit in particular in blind micro vias (BMVs) and trenches, an aqueous, acid bath for the electrolytic deposition of copper is provided, said bath containing at least one copper ion source, at least one acid ion source, at least one brightener compound and at least one leveler compound, wherein at least one leveler compound is selected from the group comprising synthetically produced non-functionalized peptides and synthetically produced functionalized peptides and synthetically produced functionalized amino acids.

Owner:ATOTECH DEUT GMBH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com