Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

71results about How to "Good retention properties" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

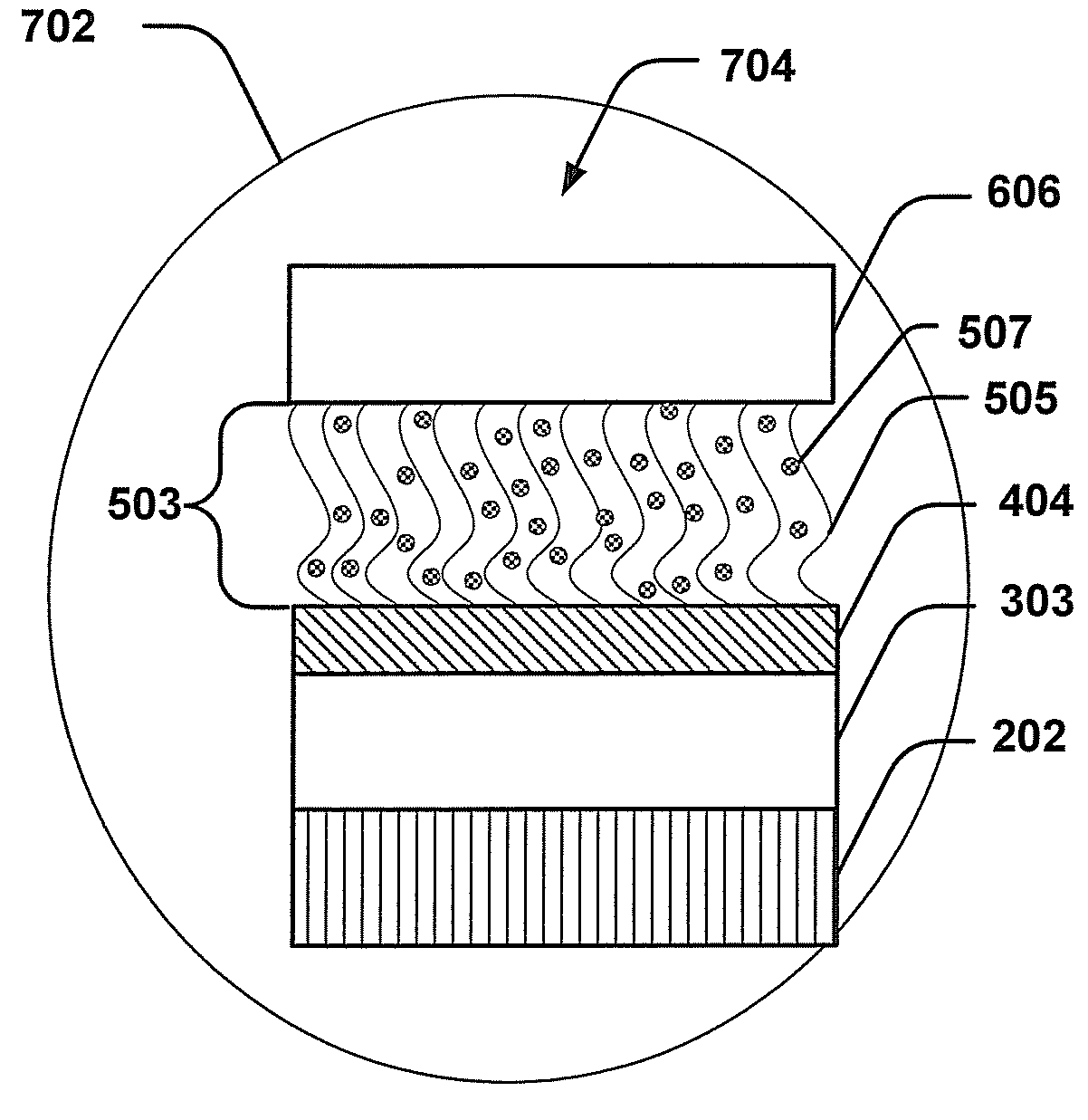

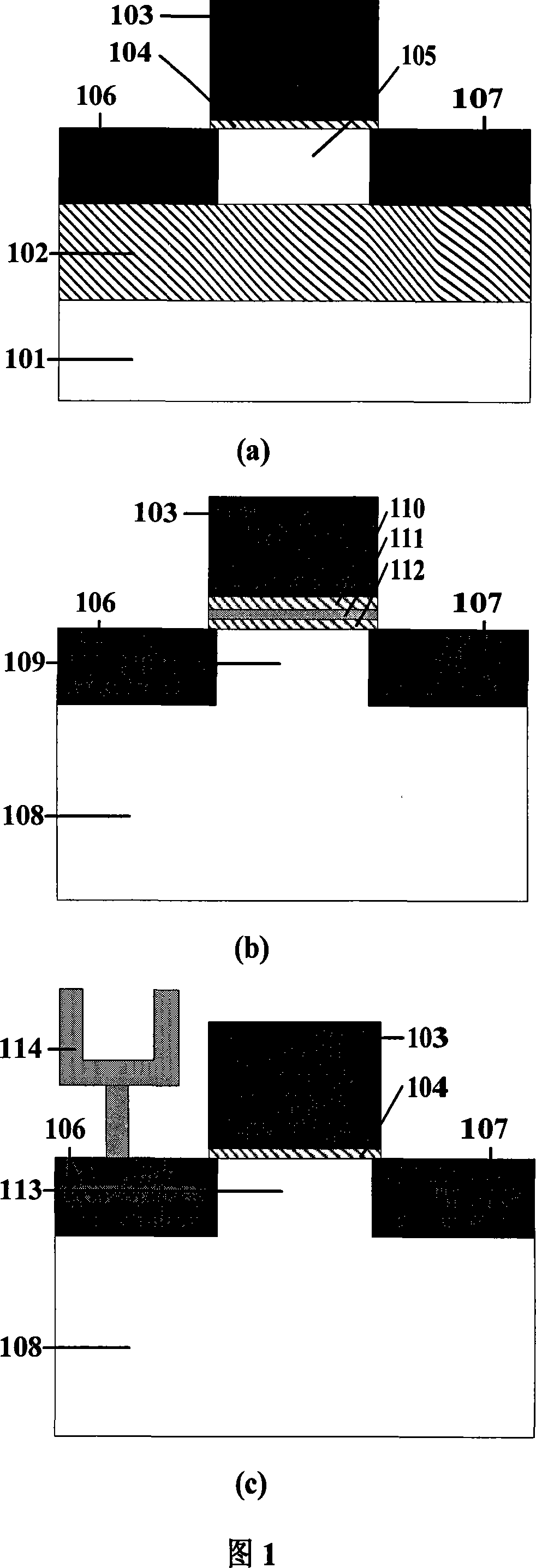

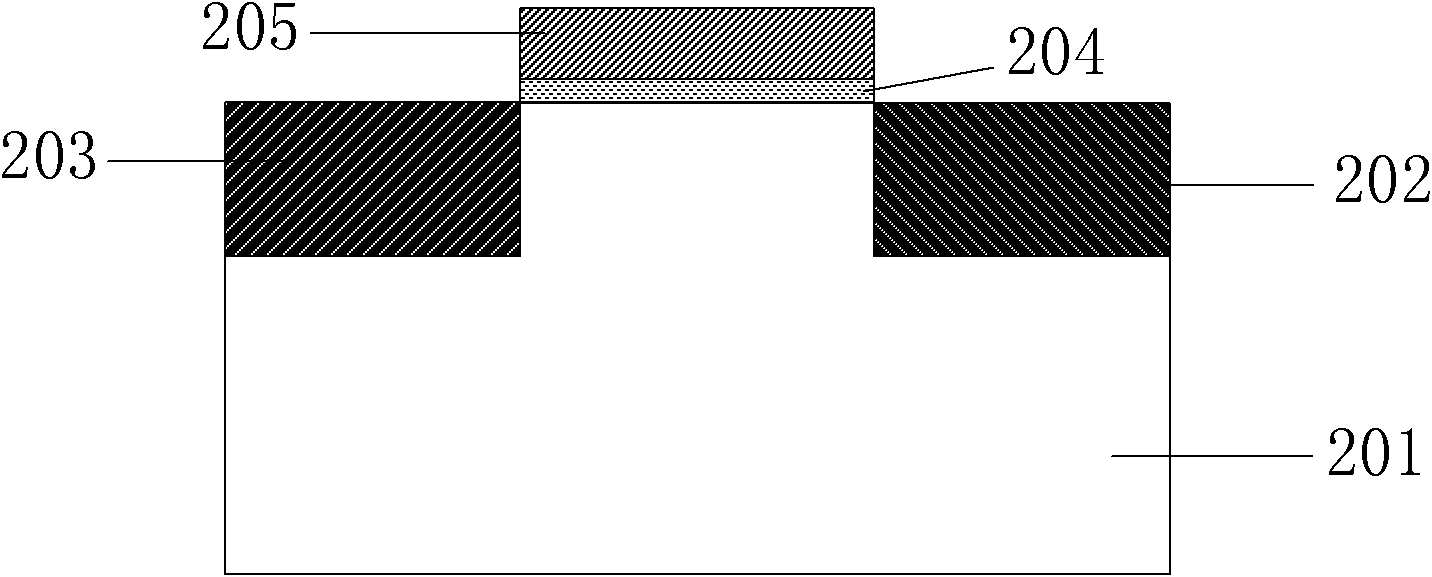

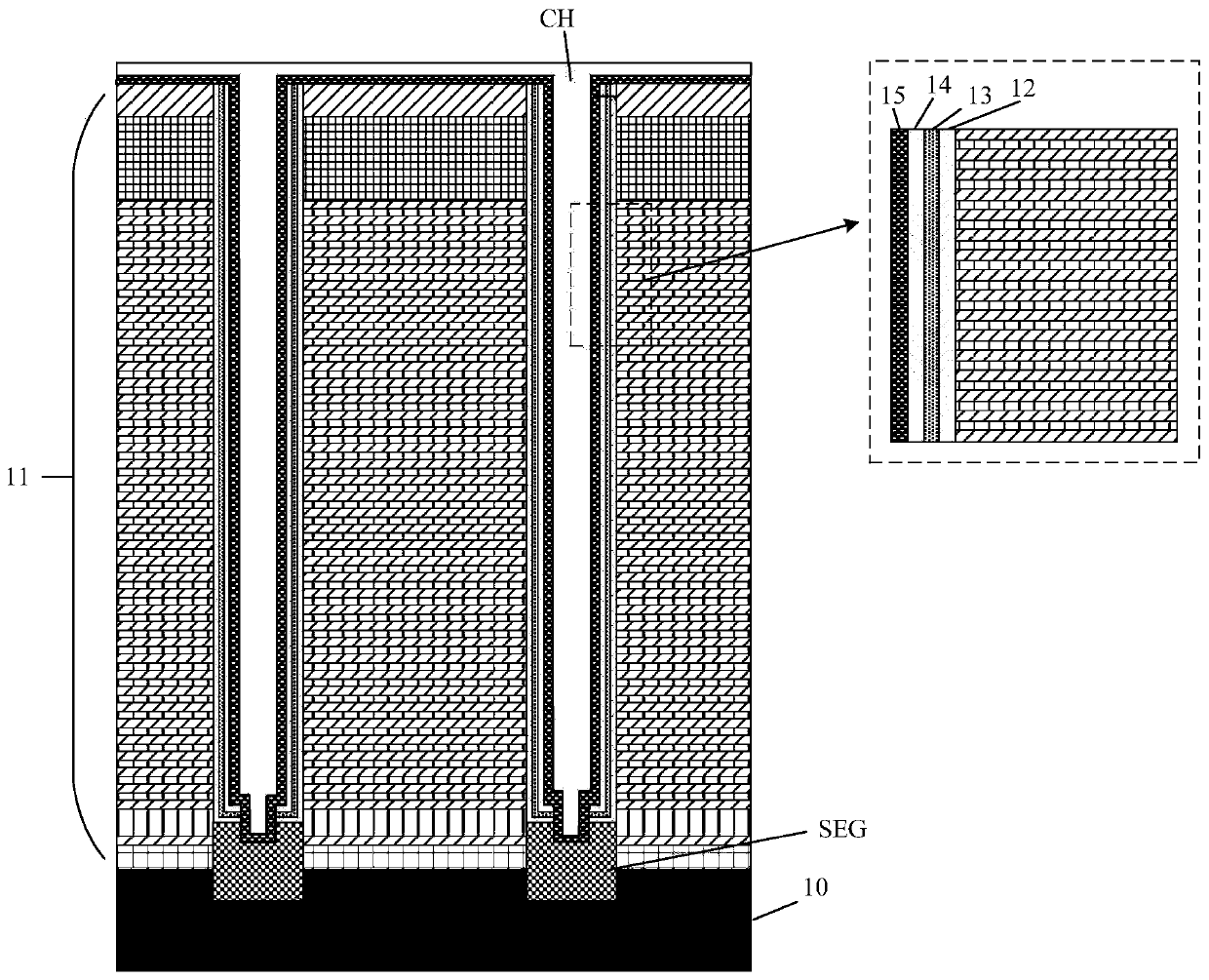

Three-dimensional semiconductor device and production method of three-dimensional semiconductor device

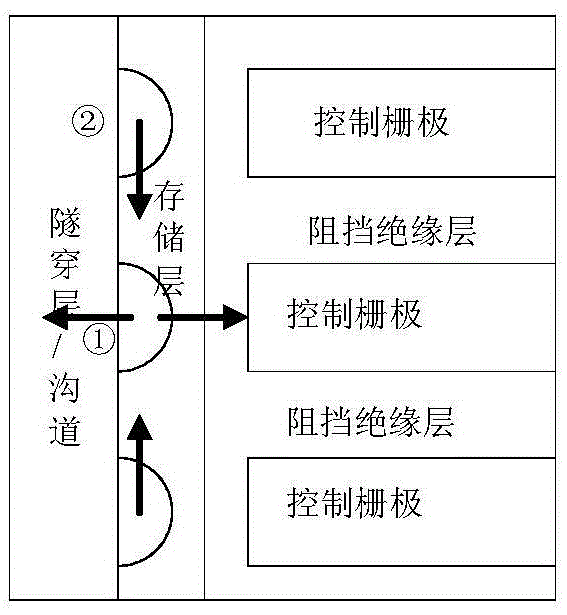

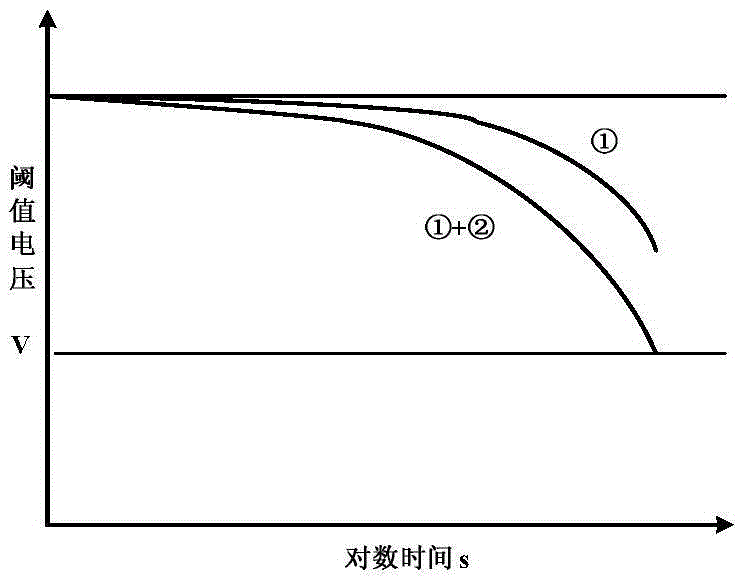

ActiveCN105679761AGood retention propertiesImprove featuresSolid-state devicesSemiconductor devicesEngineeringBlocking layer

The invention discloses a production method of a three-dimensional semiconductor device. The method comprises following steps of forming a mask layer stack composed of multiple alternate first and second mask layers on a substrate; etching the mask stack to form channel holes, thus exposing the top of the substrate and the side walls of the first and second mask layers; removing one part of the second mask layers to form hollows; conformally forming blocking layer in the channel holes and the hollows; forming storage layers on the blocking layers; selectively etching so as to remove one part of the storage layers; and conformally forming tunneling layers in the channel holes and the hollows. According to the three-dimensional semiconductor device and the production method of the three-dimensional semiconductor device provided by the invention, the transversely diffused accesses are cut off by utilizing separated storage layer structures; and the data hold characteristic is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

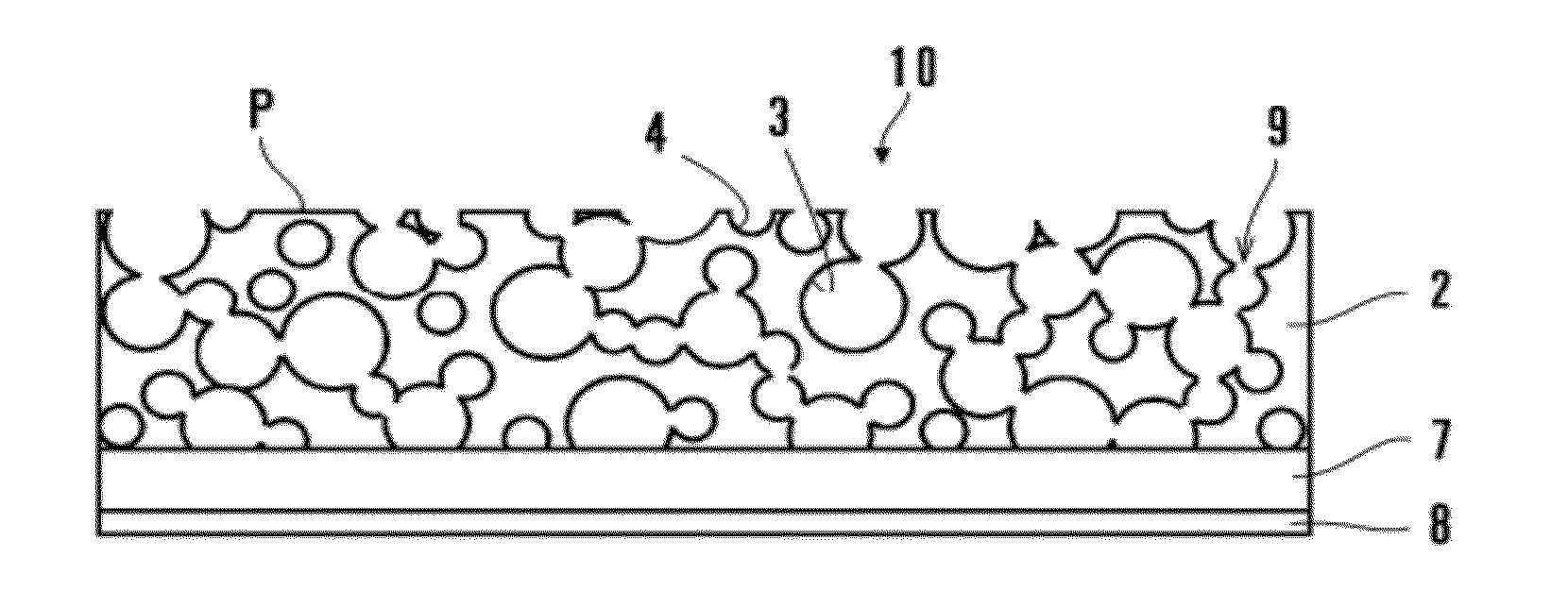

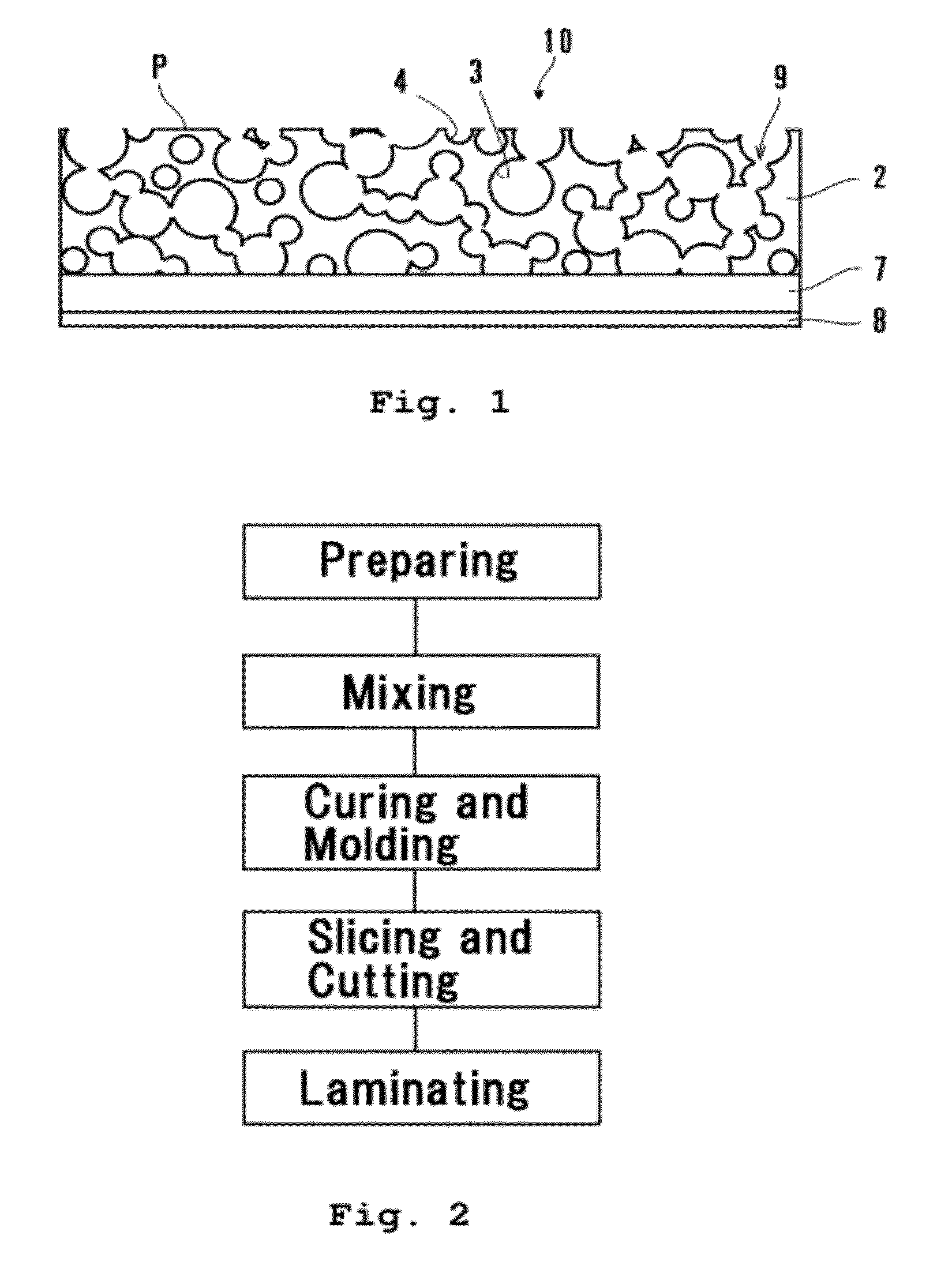

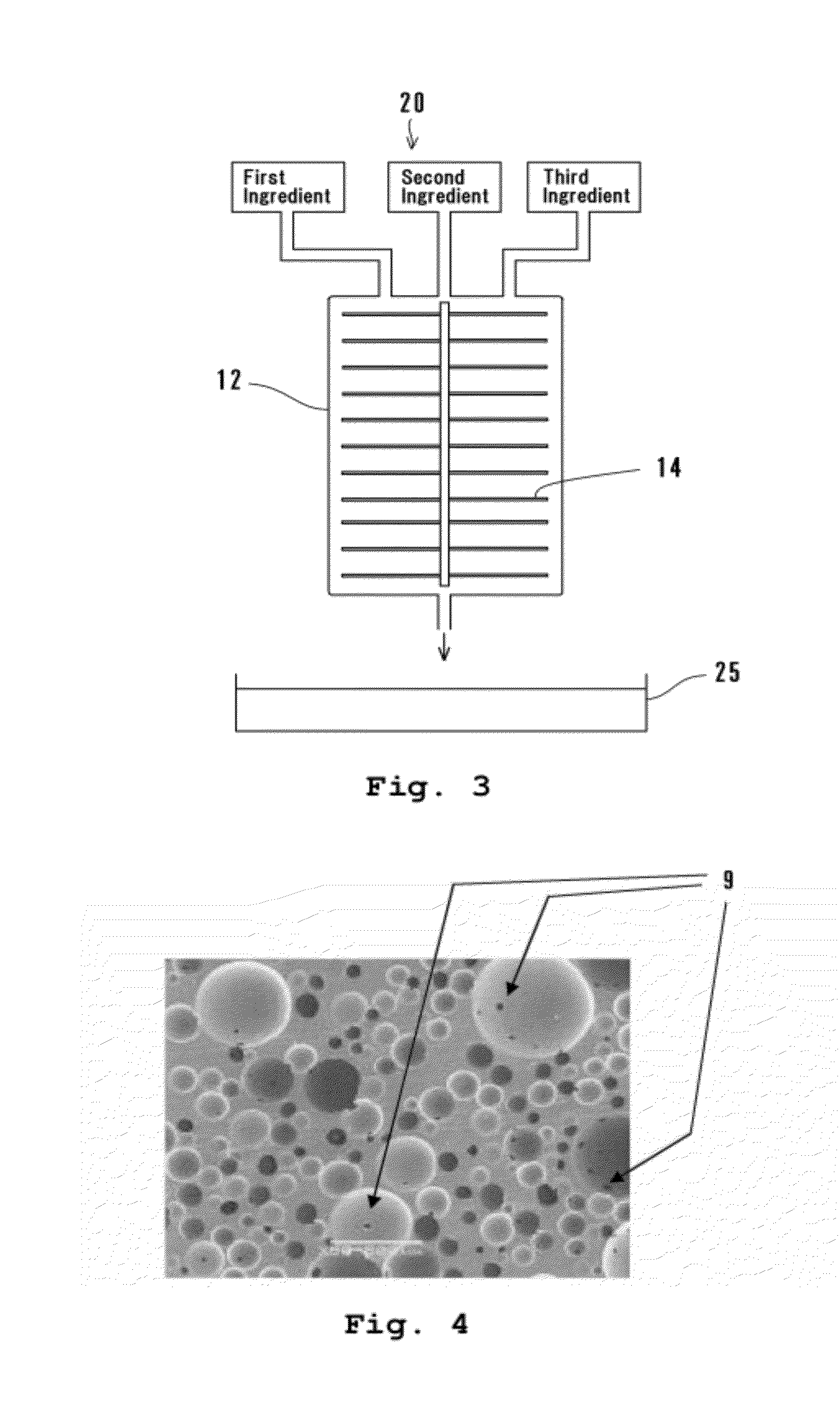

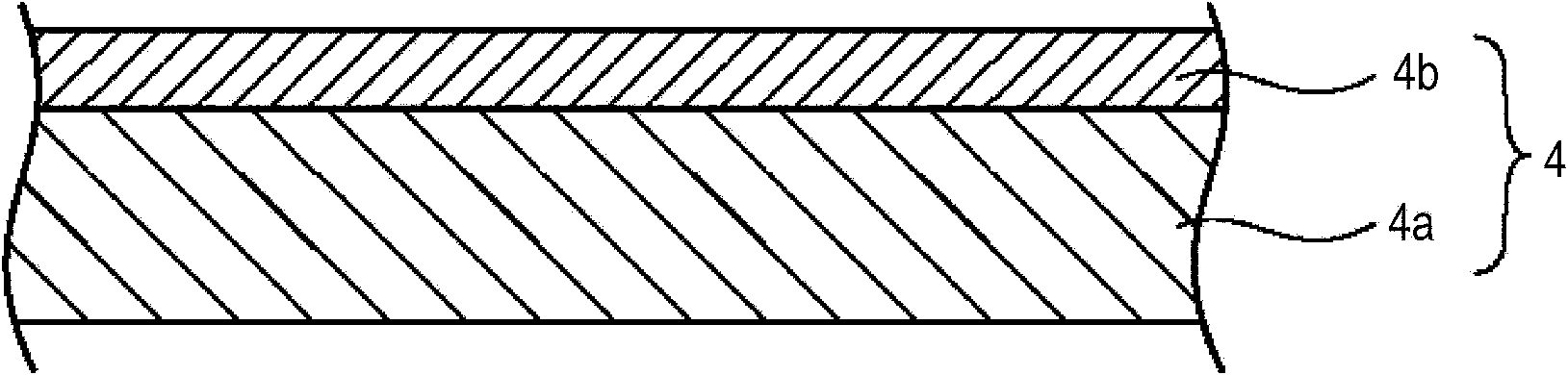

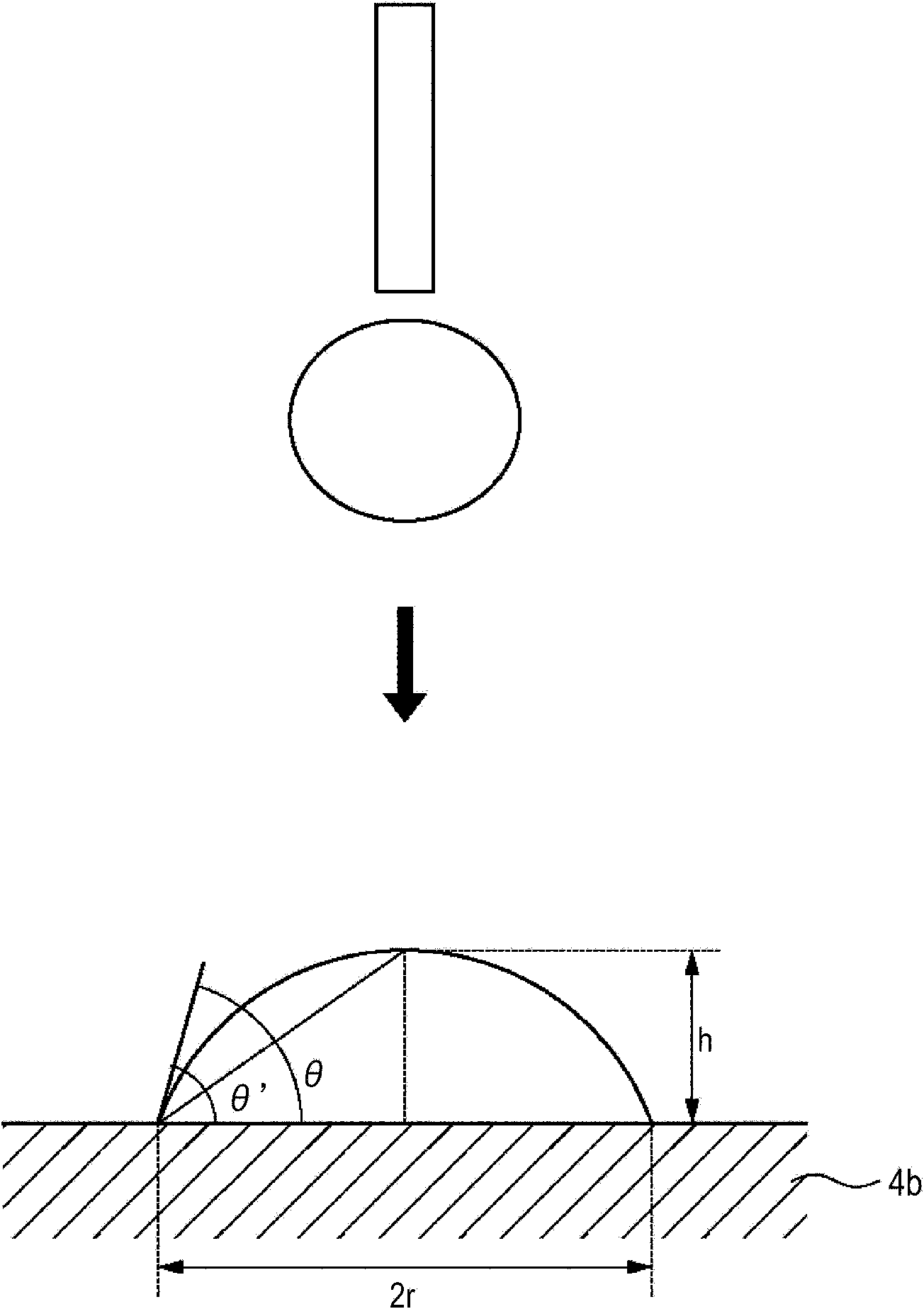

Polishing pad, manufacturing method thereof and polishing method

ActiveUS20120100783A1High affinityImprove polishing effectAbrasion apparatusSemiconductor/solid-state device manufacturingPolyamine CompoundFOAM CONTROL

A polishing pad capable of improving an affinity to polishing liquid and stabilizing polishing performance is provided. A polishing pad 10 is equipped with a urethane sheet 2. The urethane sheet 2 has a polishing surface P for polishing an object to be polished. The urethane sheet 2 is formed by a dry molding method and is formed by slicing a polyurethane foamed body which is obtained by reacting and curing mixed liquid in which an isocyanate-group containing compound, water, a foam control agent and a polyamine compound are mixed. Foams 3 are dispersed approximately uniformly inside the urethane sheet 2. Opened pores 4 which are opened parts of the foams 3 are formed at the polishing surface P. Inside the urethane sheet 2, the foams 3 formed adjacently to each other are communicated by communication holes 9, and the communication holes 9 are formed at a ratio of 800 holes / cm2 or more when observed from a side of the polishing surface P. Polishing liquid moves via the communication holes 9 and the foams 3.

Owner:FUJIBO HLDG +1

Double-fin type channel double-grid multifunction field effect transistor and producing method thereof

ActiveCN101068029AIncrease the on-state drive currentImprove DC characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesOxideEngineering

This invention provides a double-fin channel double-grid multifunction field effect transistor and its preparation method, in which, the field effect transistor has a silicon substrate, the channel is two same fins with rectangular sections to form a double-fin channel, the outside of each is oxygen grid and front grid, the inside of which is tunnel through oxidation layer, a SiN4 trap layer, a block oxidation layer and a back grid to form a double-grid structure, two ends of the double-fin channel is connected with a common n+source and n+drain, the front and back grids are aligned covering little part of the n+source and n+drain, a thick SiO2 insulation layer is set just under the channel and the silicon substrate connected with the n+source and the n+drain to form a structure with the double-fin channel on the insulation layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Diaphragm and nonaqueous electrolyte battery

ActiveCN102130315ADoes not impair ionic conductivityImprove featuresNon-aqueous electrolyte accumulatorsCell seperators/membranes/diaphragms/spacersInorganic oxideElectrolyte

The present invention provides a diaphragm and a nonaqueous electrolyte battery. The diaphragm according to the invention comprises a functional resin layer which comprises a resin material and an inorganic oxide filler. Furthermore the functional resin layer is provided with a porous interconnecting structure in which a plurality of holes are connected with one another and has a contact angle that is not larger than 11 DEG relatively to an electrolyte.

Owner:MURATA MFG CO LTD

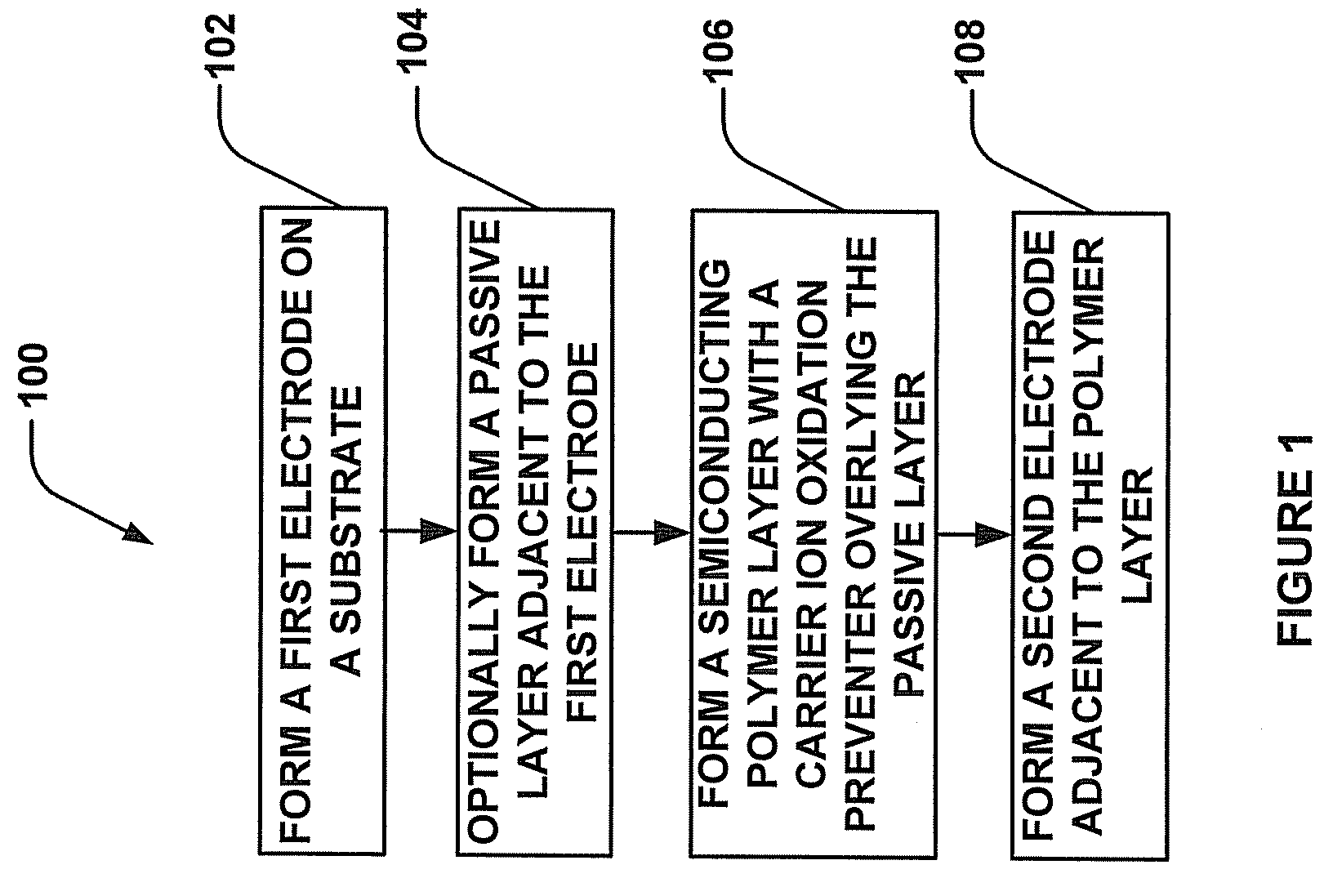

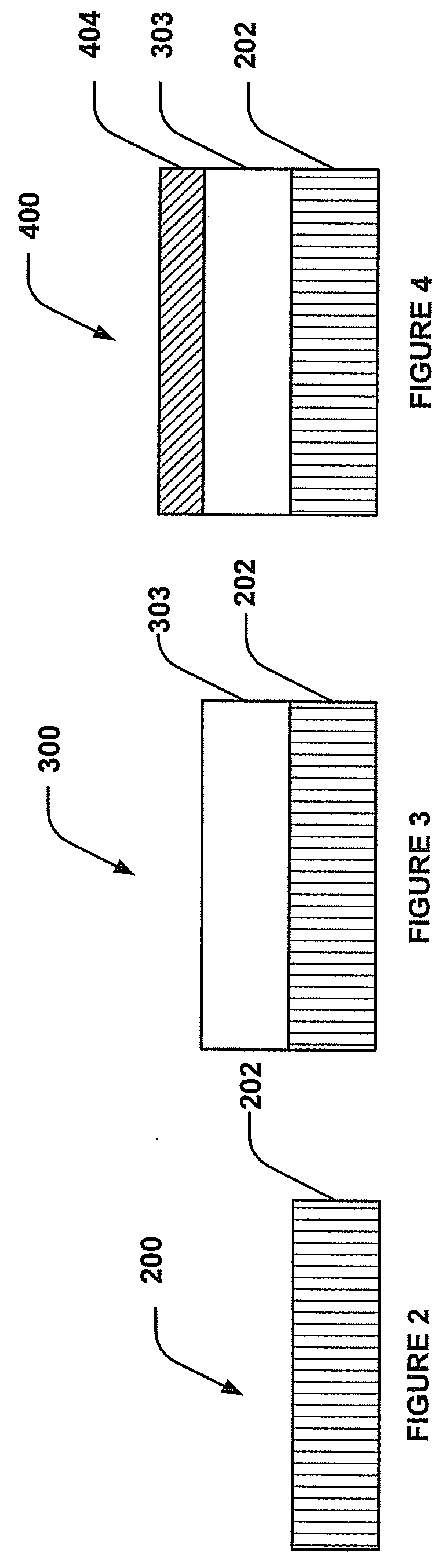

Prevention of oxidation of carrier ions to improve memory retention properties of polymer memory cell

ActiveUS20080135834A1Improve retentionImprove practicalitySolid-state devicesSemiconductor/solid-state device manufacturingMemory retentionMemory cell

Improving memory retention properties of a polymer memory cell are disclosed. The methods include providing a semiconducting polymer layer containing at least one organic semiconductor and at least one of a carrier ion oxidation preventer and an electrode oxidation preventer. The oxidation preventers may contain at least one of 1) an oxygen scavenger, 2) a polymer with oxidizable side-chain groups which can be preferentially oxidized over the carrier ions / electrodes, and 3) an oxidizable molecule that can be preferentially oxidized over the carrier ions / electrodes.

Owner:MONTEREY RES LLC

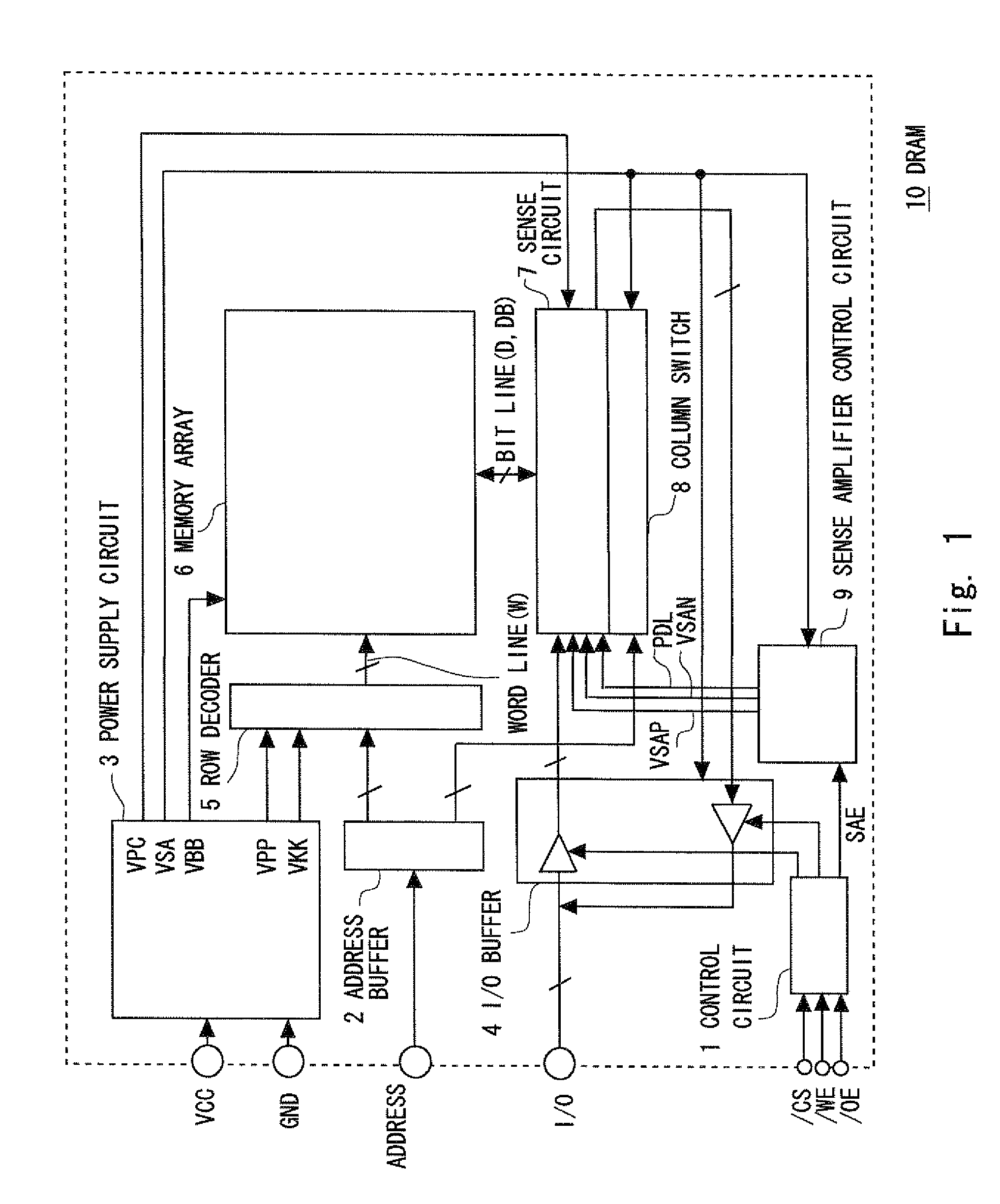

Semiconductor device and dram controller

InactiveUS20090080234A1Good retention propertiesHigh speedDigital storageAudio power amplifierChip size

According to a semiconductor device of the present invention, a differential potential between a sense amplification level and a precharge level of a sense amplifier is set to a power supply potential (VCC-GND) so as to improve resistance against degradation of hold characteristics. Further, low power consumption can be realized along with the improvement. Additionally, the precharge level is set to a power supply of GND or VCC so as to realize a stable supply of the precharge level. Further, a chip size can be reduced since a power supply circuit for precharge is not needed.

Owner:RENESAS ELECTRONICS CORP

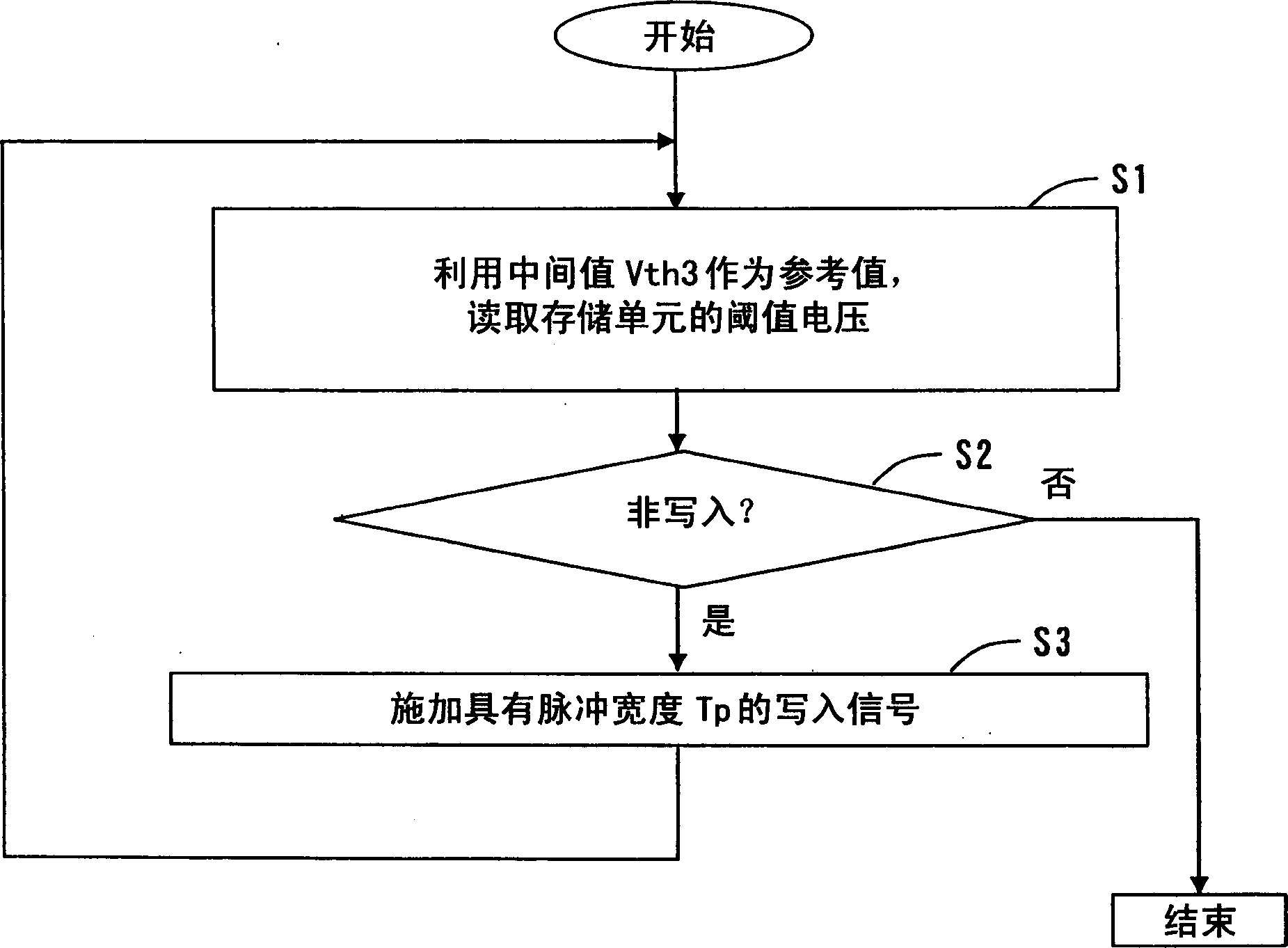

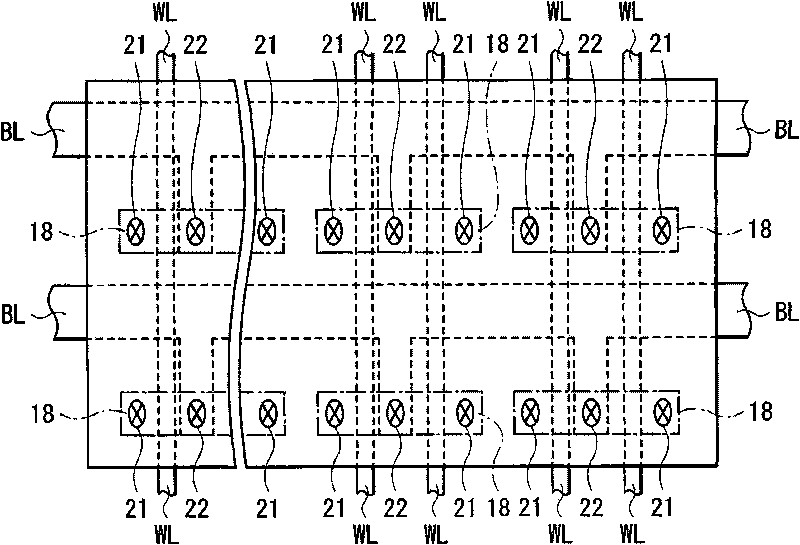

Non-volatile semiconductor memory device and rewriting method

InactiveCN1492446ASave operating timeGood retention propertiesRead-only memoriesDigital storageValue setVoltage range

A non-volatile semiconductor memory device is provided, which comprises a memory array comprising memory cells, in which each memory cell is capable of storing data values depending on the voltages thereof, the data values include a first data value corresponding to a first voltage range and a second data value corresponding to a second voltage range, and the first data is written in a memory cell of the memory cells, a determination section for determining whether a voltage value of the memory cell is higher or lower than a reference value set between a maximum value and a minimum value of the first voltage range, and a rewrite section for rewriting the first data into the memory cell based on a determination result of the determination section so that a margin between the first voltage range and the second voltage range in the memory cell is enlarged.

Owner:SHARP KK

Storage element and storage device

ActiveCN101765914AGood retention propertiesImproved resistance value retention characteristicsSolid-state devicesDigital storageHigh resistanceElectrical resistance and conductance

The invention provides a resistance variation type storage device improved in ability to hold resistance values in writing and erasure states. A storage layer 5 comprising a high resistance layer 2 and an ionization layer 3 is provided between a lower electrode 1 and an upper electrode 4. The ionization layer 3 contains Zr (zirconium) and Al (aluminum) as metal elements to be cationized as well as an ion conductive material (anion element) such as S (sulfur), Se (selenium), and Te (tellurium) (chalcogenide element). An equivalent ratio represented by equivalent ratio=(valence of cations*number of moles) / (valence of anions*number of moles) is 0.5 to 1.5, and consequently holding characteristics of writing and erasure states are improved.

Owner:SONY CORP

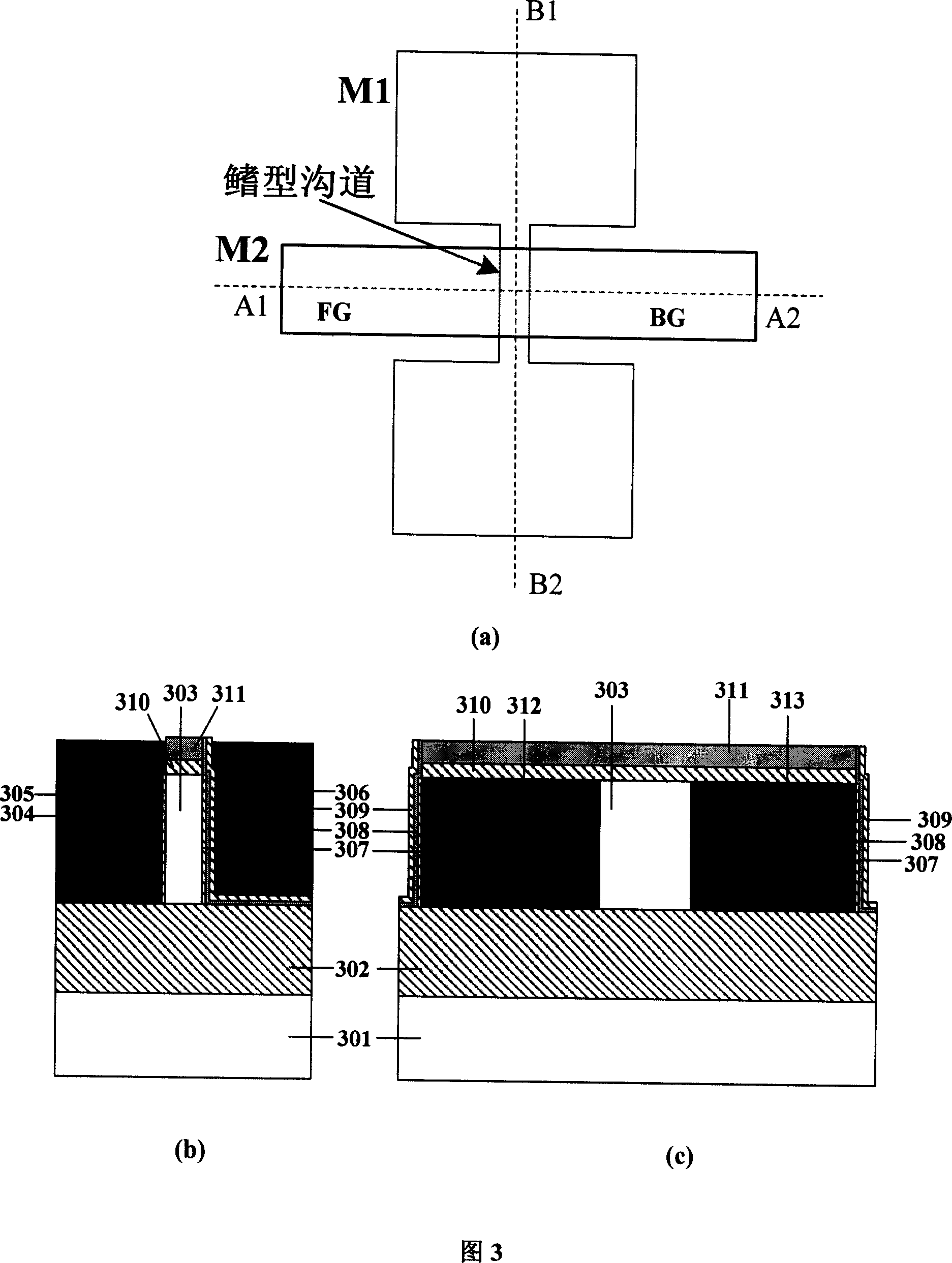

Fin channel dual-bar multi-function field effect transistor and its making method

ActiveCN101079450AGood retention propertiesInhibit redistributionSemiconductor/solid-state device manufacturingSemiconductor devicesUnderlayMOSFET

The invention provides a fin type channel dual-grid multifunctional field effect transistor and preparing method in metallic oxide semi-conductor field effect transistor technique field of the grand scale integration. The flied effect transistor is based on SOI underlay, the cross section of channel is rectangular fin along the vertical direction of the channel and forms the fin channel; a side of the channel is the grid oxide and the front grip, the other side is the tunnel oxide layer as the silicon nitride trap layer, the barrier oxide layer and the back grip of the charge storage layer and forms dual-grid structure; two edges of the fin channel are connected with the common n+ source and n+ leakage, the front grid aligns the back grid, the n+ source and the n+ leakage are covered less; the device achieves the channel section, the source section and the leakage section on the insulating layer based on SOI underlay. The invention is provided with high-effective MOSFET logical device function, the function of high-speed storage and the function of no condenser type DRAM.

Owner:PEKING UNIV +1

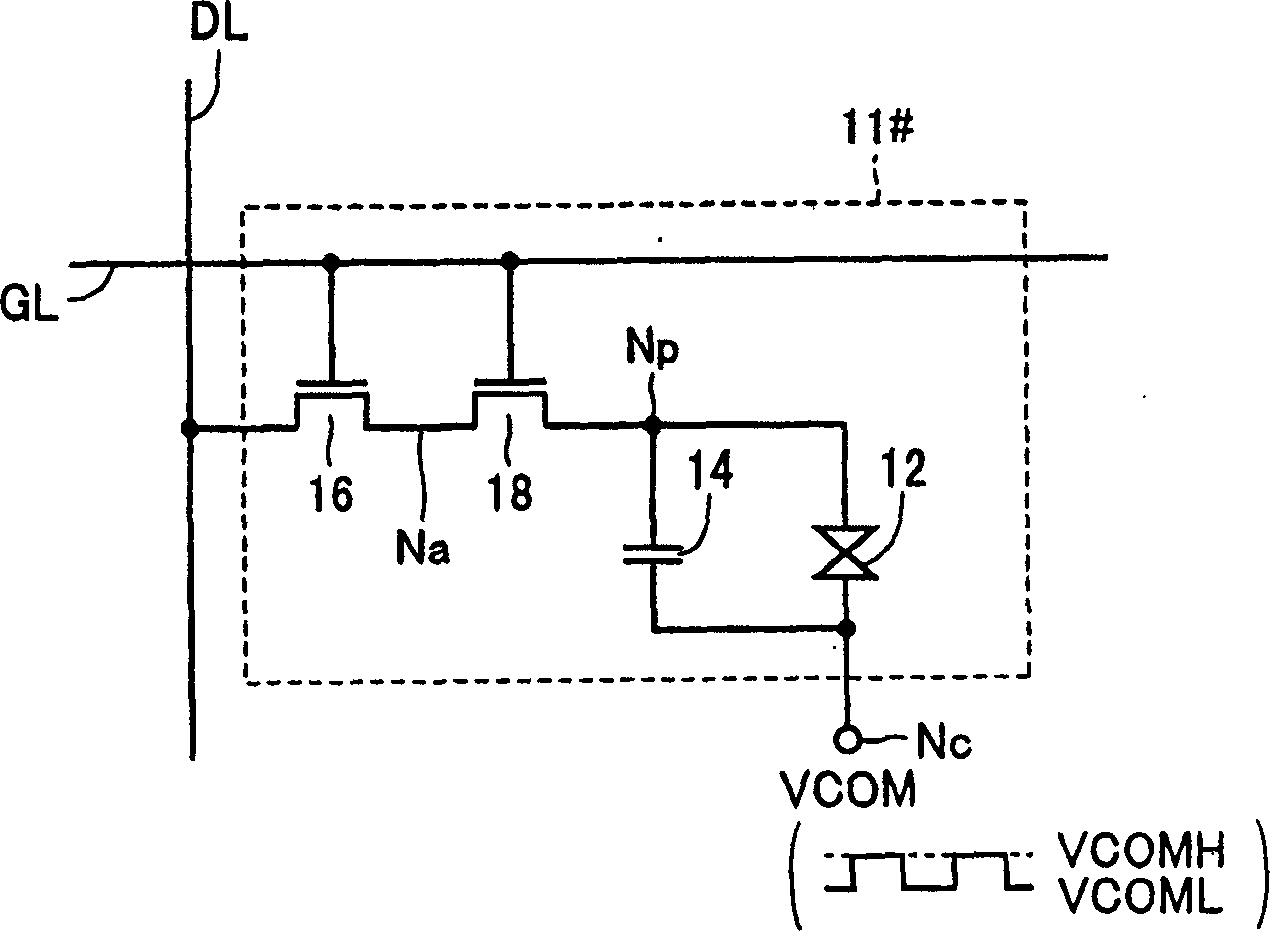

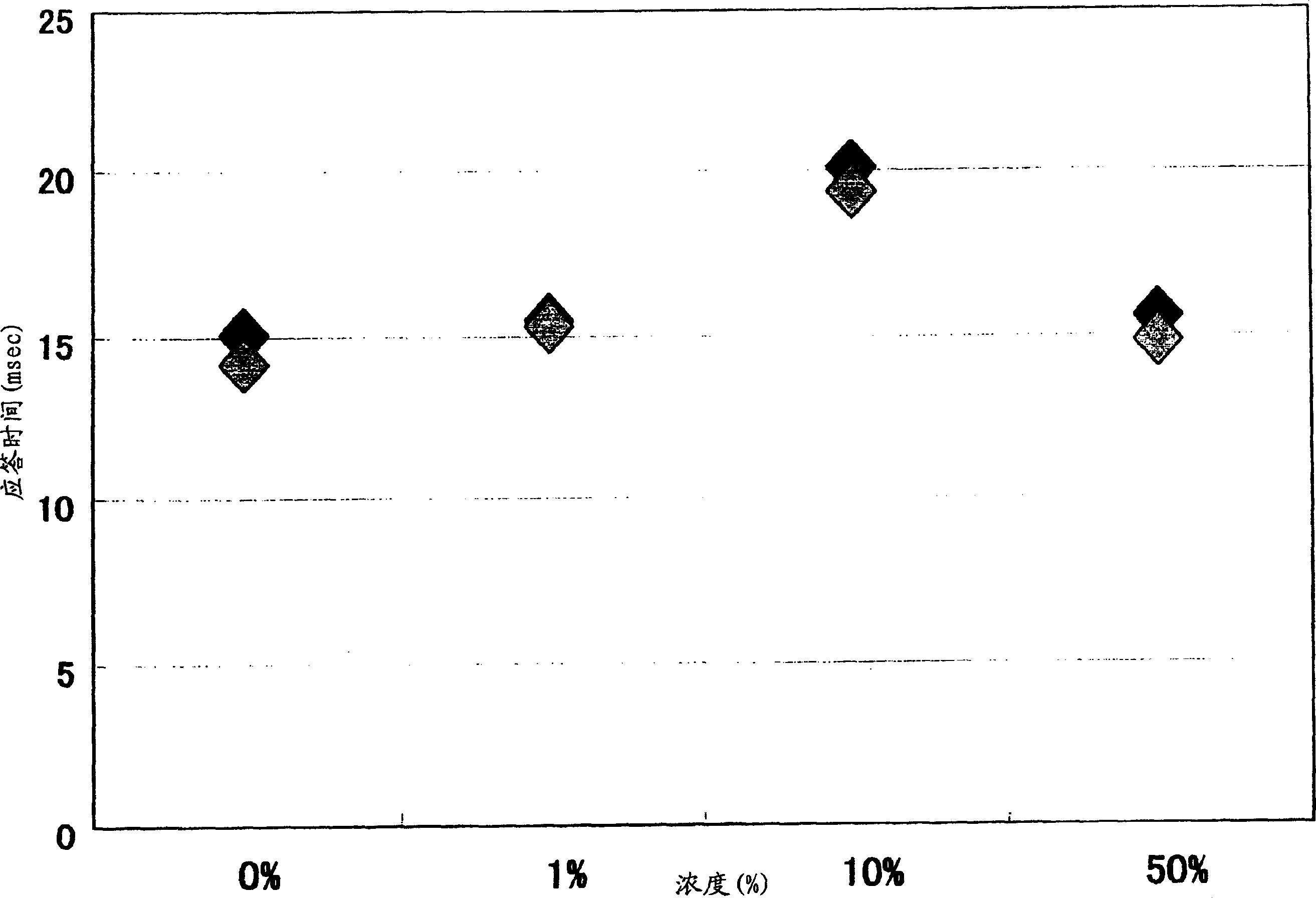

Liquid crystal display device with pixel of small leakage current

InactiveCN1517967AGood retention propertiesSuppression of off-leakage currentCathode-ray tube indicatorsNon-linear opticsLiquid-crystal displayLow voltage

A pixel (10) has N type TFT elements (16, 18, 19) which are connected in series between a data line (DL) and a pixel electrode node (Np). While the gates of the TFT elements (16 and 18) are connected to a gate line (GL), the gate of the TFT element (19) is connected to a gate line (GL#). The gate lines (GL and GL#) in a selected state are set to a high voltage with which the TFT elements (16, 18, 19) can sufficiently be turned on. The gate line (GL) in an unselected state is set to a low voltage with which the TFT elements (16 and 18) can sufficiently be turned off and the gate line (GL#) in the unselected state is set to an intermediate voltage between the highest voltage and the lowest voltage which are applied through the data line (DL).

Owner:MITSUBISHI ELECTRIC CORP

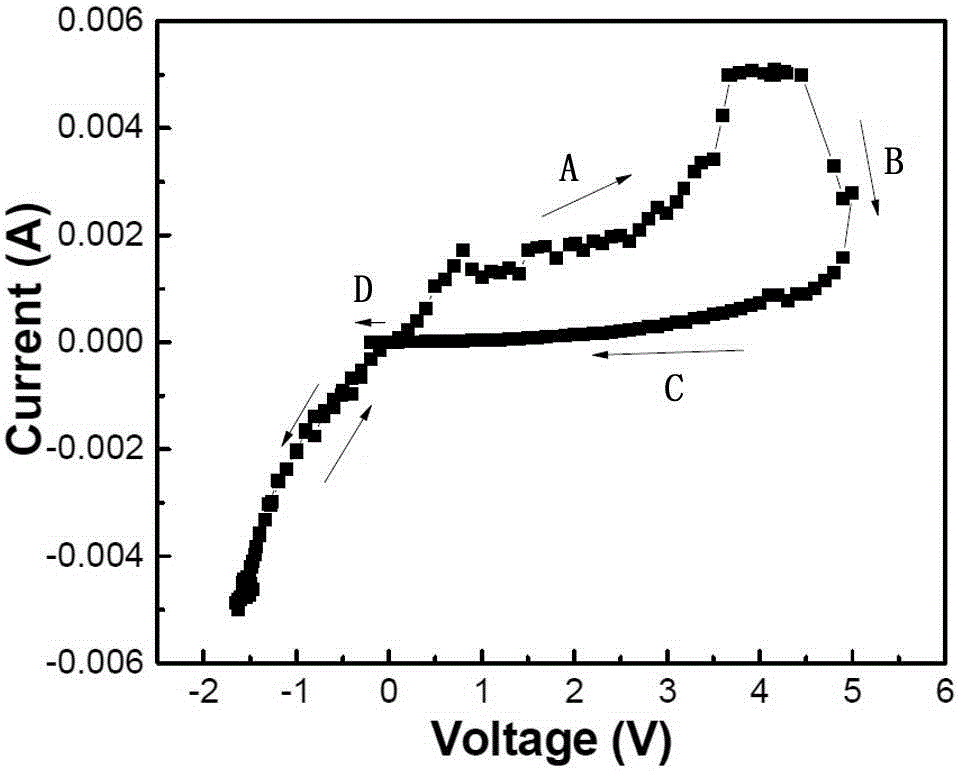

Method for preparing metal oxide thin-film resistive random access memory through plasma processing

ActiveCN106098937AEasy to prepareReaction conditions are easy to controlSemiconductor/solid-state device manufacturingHigh resistanceControllability

The invention provides a method for preparing a metal oxide thin-film resistive random access memory through plasma processing, wherein the method belongs to the technical field of electronic films and components. The memory comprises the components of a substrate, a lower electrode, a fluorine-doped metal oxide and an upper electrode. According to the method, a relatively novel plasma processing method is utilized for conveniently and controllably preparing a metal oxide resistive random access functional layer with uniform defect distribution. The metal oxide resistive random access functional layer can conveniently and quickly realize switching between formation and switching-off of a conductive channel under the function of an electric field, namely switching between a low-resistance state and a high-resistance state of the device. Furthermore, the method has an ultralow working voltage. The upper electrode is prepared through a mask method, thereby greatly reducing device dimension and improving integration density. Through testing, the metal oxide thin-film resistive random access memory prepared according to the method has excellent performance. In one word, the invention realizes the method for preparing the metal oxide thin-film resistive random access memory with advantages high performance and small dimension, wherein the method has advantages of simple operation, effective controllability, high efficiency and low cost. Furthermore relatively high performance consistency is realized. The method is suitable for batch resistive random access array production in future, and furthermore has good application prospect.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

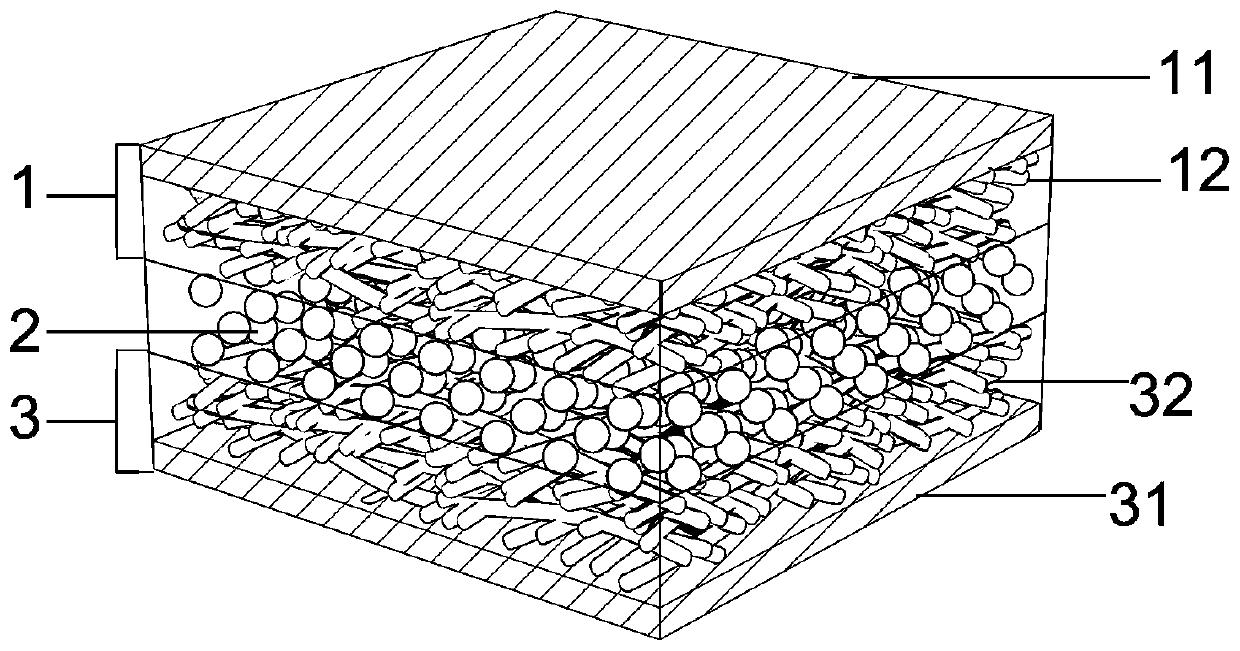

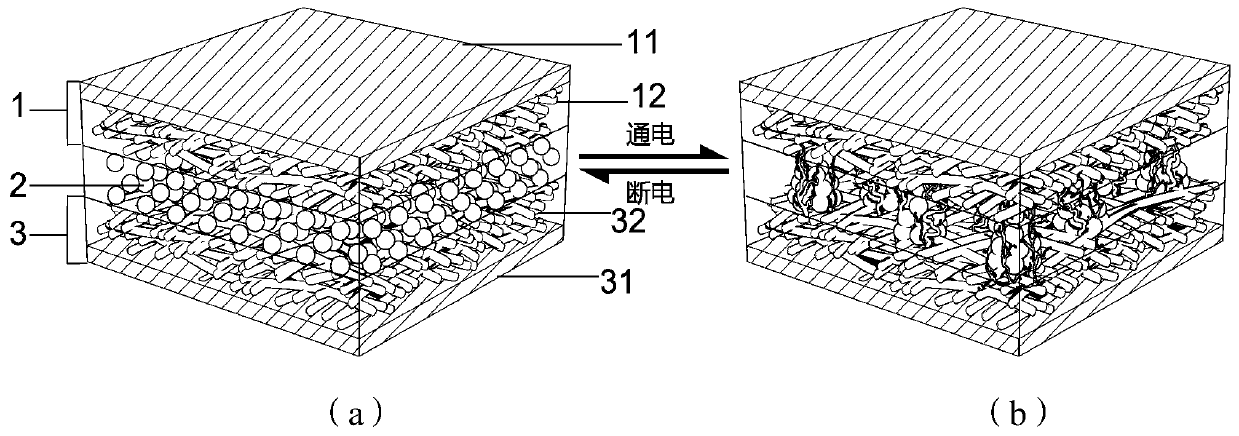

Organic material resistance random access memory element and manufacturing method thereof

ActiveCN105185909AStrong fatigue resistanceSimple structureSolid-state devicesSemiconductor/solid-state device manufacturingRandom access memoryOptoelectronics

The invention provides an organic material resistance random access memory element and a manufacturing method thereof. The structure of the memory element comprises a lower electrode layer, a resistance random dielectric layer, and an upper electrode layer arranged in sequence from bottom to top. The lower electrode layer is an ITO layer. The resistance random dielectric layer is CH3NH3PbI(3-x)Cl3 layer. The upper electrode layer is an Ag layer or an Al layer. The manufacturing method for the organic material resistance random access memory element comprises: using a sol-gel method to form the CH3NH3PbI(3-x)Cl3 layer on the ITO layer of ITO glass, and then performing annealing treatment, and then using a vacuum evaporation method to deposit Ag or Al upper electrode layer on the CH3NH3PbI(3-x)Cl3 layer, and finally a resistance random access memory element whose heterostructure form is Ag or Al / CH3NH3PbI(3-x)Cl3 / ITO is formed. The organic material resistance random access memory element is stable in performance, and has relatively good fatigue resistance and holding property.

Owner:HEBEI UNIVERSITY

Wire-coating composition based on new polyester amide imides and polyester amides

InactiveCN101243148AImprove general performanceGood to maintain regular performanceInsulatorsPolyamide coatingsPolyesterImide

Wire-coating composition containing resins with nucleophilic groups as well as possibly amide group-containing resins which are capable of crosslinking with one another, comprising (A) 5 to 95% by weight of at least one resin with nucleophilic groups selected from the group consisting of OH, NHR, SH, carboxylate and CH-acidic groups, (B) 0 to 70% by weight of at least one amide group-containing resin and (C) 5 to 95% by weight of at least one organic solvent, wherein the resins of either component (A) or component (B) contain a-carboxy-ss-oxocycloalkyl carboxylic acid amide groups and the percent by weight of (A) - (C) adds up to 100 percent. The wire-coating compositions according to the invention allow a significant increase in the enamelling speed without losing the positive properties of standard wire enamels.

Owner:EI DU PONT DE NEMOURS & CO

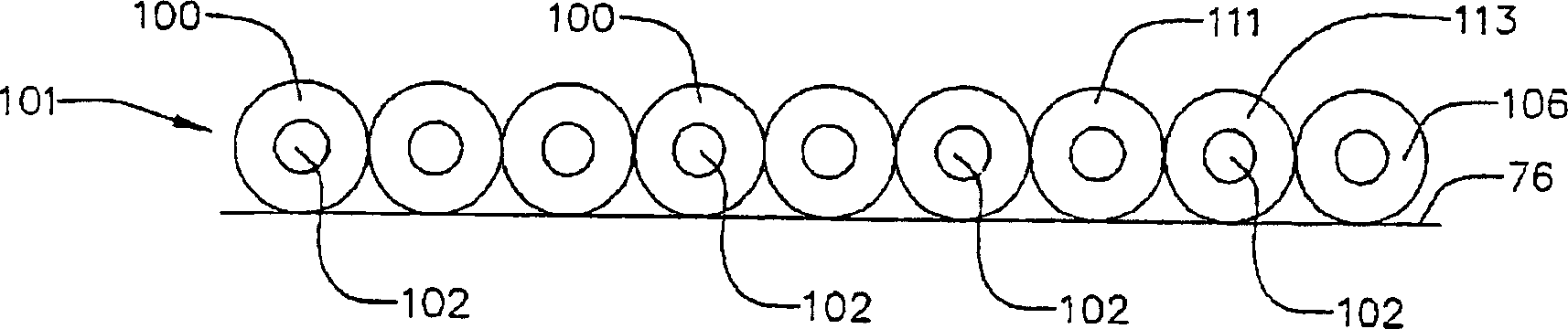

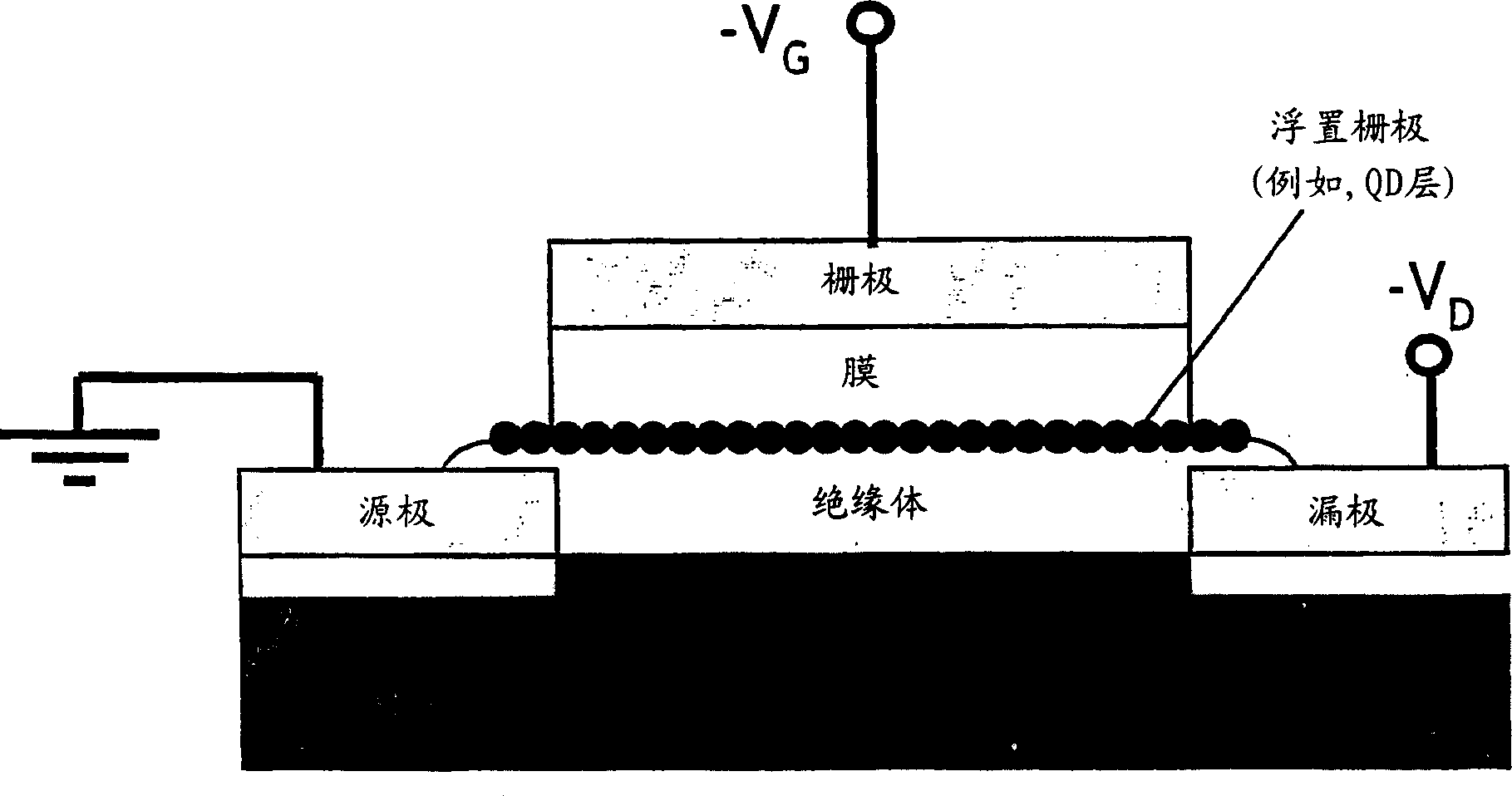

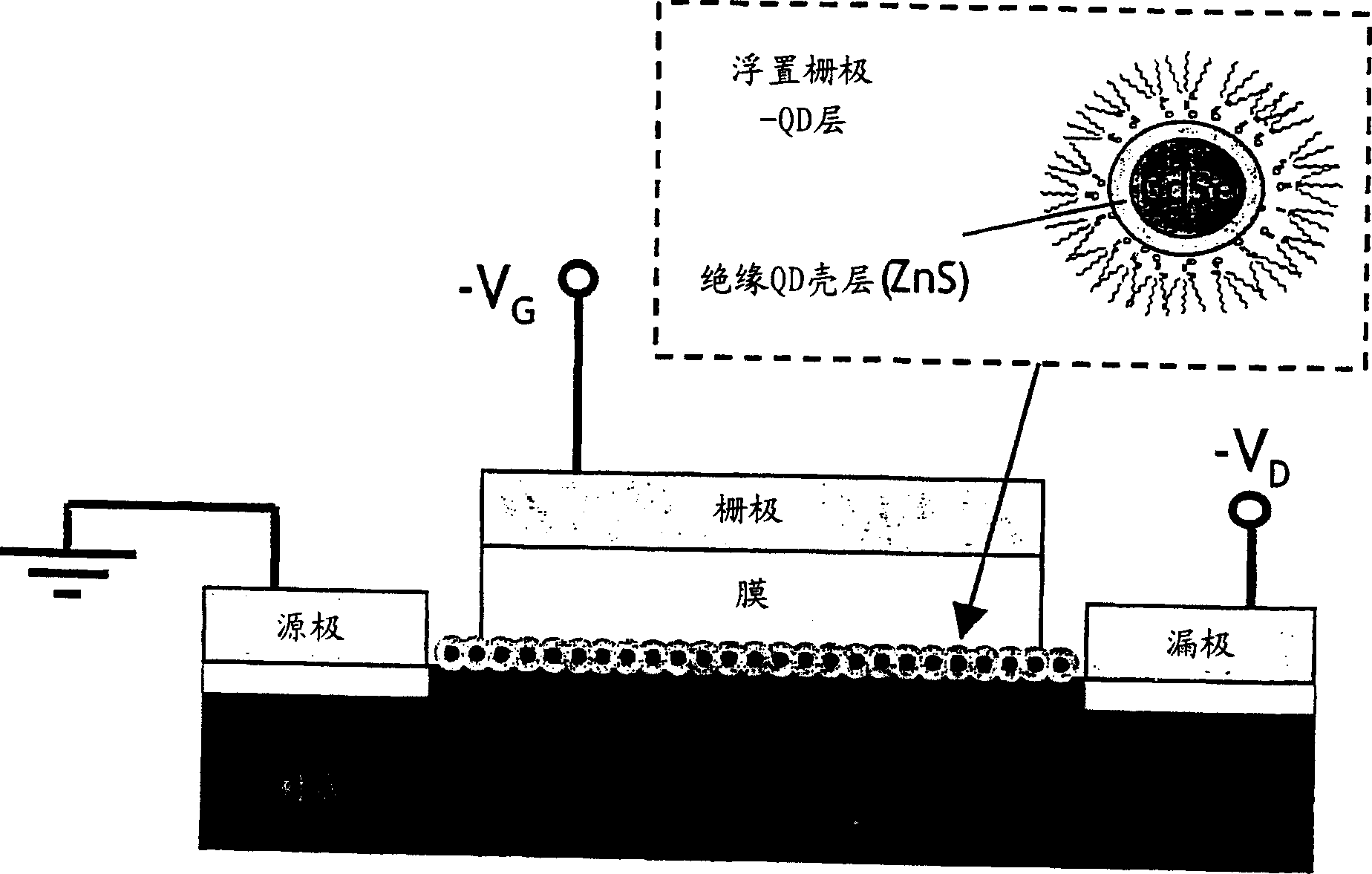

Non-volatile memory device

InactiveCN1864253AEasy to manufactureLow costTransistorMaterial nanotechnologyNanoparticleActive layer

A memory device can include an active layer that has a selectable lateral conductivity. The layer can include a plurality of nanoparticles.

Owner:MASSACHUSETTS INST OF TECH

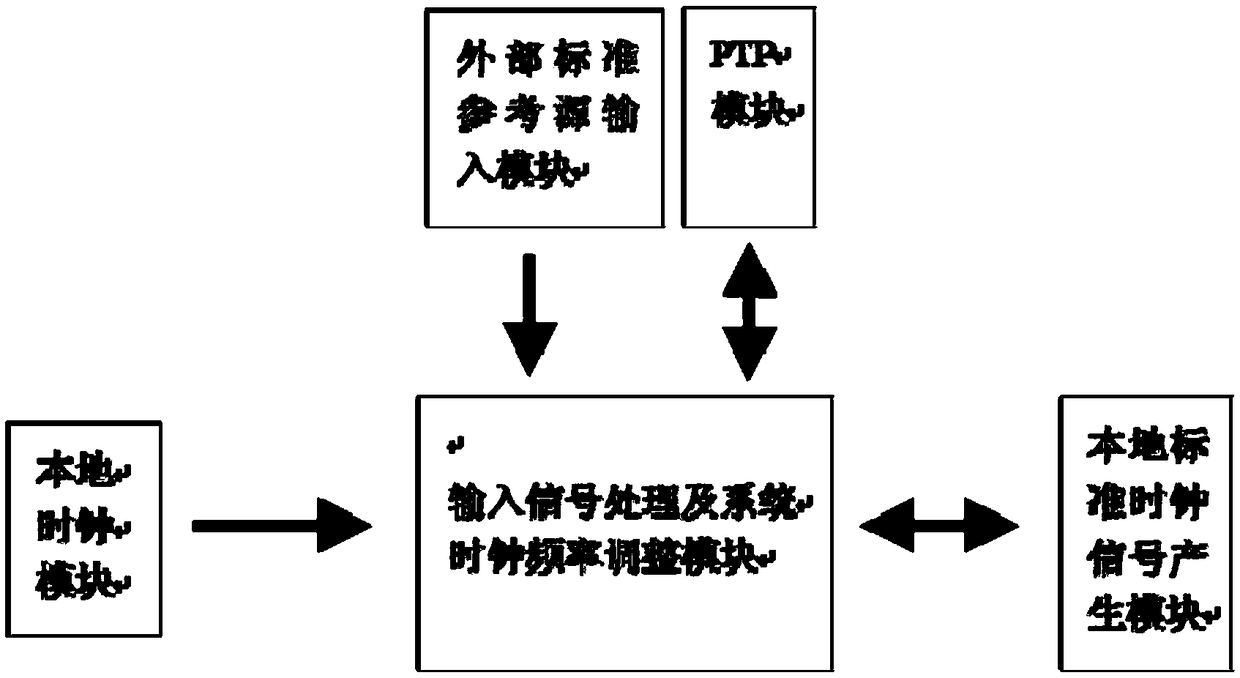

System for recovering PTP slave clock

InactiveCN109495203AFlexible configurationGood retention propertiesTime-division multiplexTimestampTime delays

The invention provides a system for recovering a PTP slave clock. The system is characterized by comprising a PTP module, an input signal processing and system clock frequency adjusting module and a local clock module, wherein the PTP module marks a timestamp on a PTP data packet at a PHY layer (physical layer); when the system is configured as a main clock source, a high-precision and high-stability PTP is output, a PTP synchronization request is responded in a hardware level, and hardware automatically and regularly sends a PTP synchronization packet; when the system is configured as a slaveclock, a PTP synchronization event message and a general message can be received or sent, an optimal PTP main clock source is selected according to an optimal main clock source selection algorithm, and a time delay of a PTP synchronization line and a clock deviation between local and PTP main clock sources are calculated; the input signal processing and system clock frequency adjusting module isused for adjusting the frequency of a system clock signal, so that the system clock frequency is locked to an external standard reference signal or a PTP input; and the local clock module is used forproviding a local reference clock for the system to serve as a basis of system precision.

Owner:浙江赛思电子科技有限公司

Memristor-based neurosynaptic bionic device and a preparation method thereof

ActiveCN109802035AEffective control over migrationImprove performanceElectrical apparatusFinal product manufactureSputteringOptoelectronics

The invention discloses a memristor-based neurosynaptic bionic device and a preparation method thereof. The bionic device comprises: a flexible lower electrode layer, a copper nanoparticle-doped silicon oxynitride film layer deposited on the flexible lower electrode layer, and a flexible upper electrode layer over the copper nanoparticle-doped silicon oxynitride film layer. The flexible lower electrode layer includes a first flexible substrate and a first silver nanowire transparent electrode over the first flexible substrate. The flexible upper electrode layer includes a second flexible substrate and a second silver nanowire transparent electrode under the second flexible substrate. The lower electrode layer and the upper electrode layer are both prepared by spraying the flexible substrate with silver nanowire ink to form a silver nanowire wet film, and performing a constant-heat treatment in a sealed container. The copper nanoparticle-doped silicon oxynitride film layer is prepared by applying a copper piece to a silicon nitride target by radiofrequency reaction magnetron sputtering and introducing oxygen. The neurosynaptic bionic device of the present invention is capable of efficiently simulating a neurosynaptic function and has short-term plasticity.

Owner:BEIJING INSTITUTE OF GRAPHIC COMMUNICATION

Method for grafting sabina chinensis on platycladus orientalis stock

The invention discloses a method for grafting sabina chinensis on a platycladus orientalis stock. The method is characterized by including the steps that (1) a healthy sabina chinensis scion is picked; (2) a one-year strong platycladus orientalis seedling is picked as the stock; (3) the two sides of a sabina chinensis branch are cut, one side is long, the other side is short, the branch is of a wedge shape, and the length of the branch is identical to the depth of a notch of the platycladus orientalis; the short side of the cut sabina chinensis branch is inserted in the portion close to platycladus orientalis bark, and the long side is close to a platycladus orientalis wood part; (4) after being grafted, the branch is tied tightly through thin film or jute skin; (5) after grafting, planting is conducted; (6) the branch is cut; (7) fertilizer is applied; (8) normal management is conducted.

Owner:ANJI ZHONGKE LANDSCAPING ENG

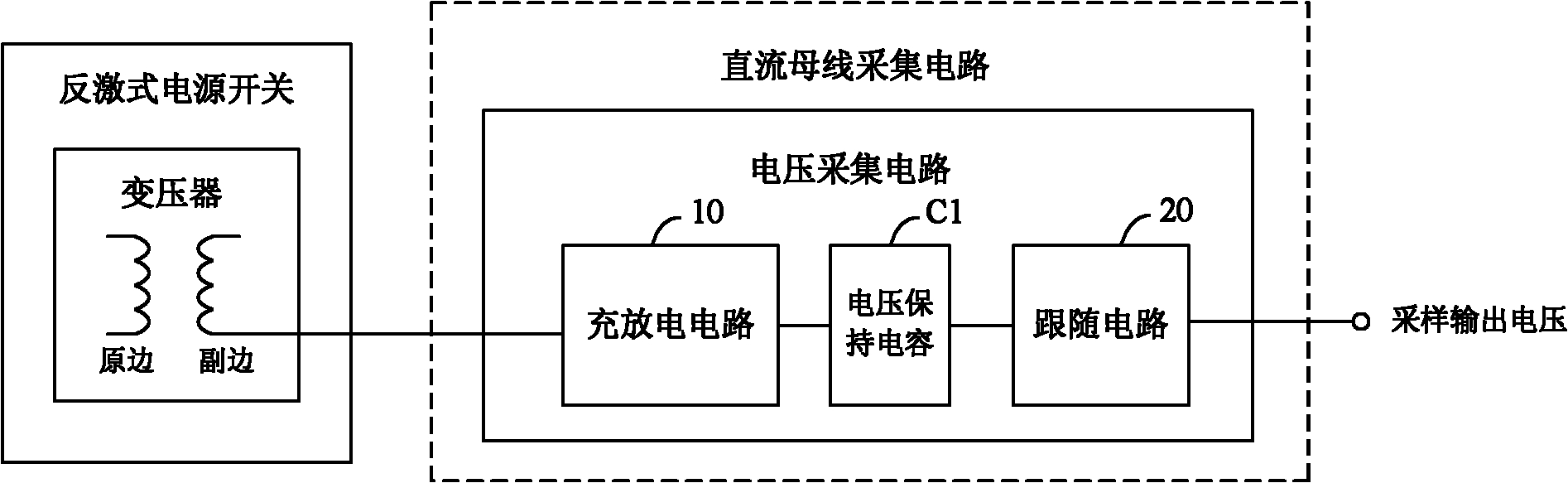

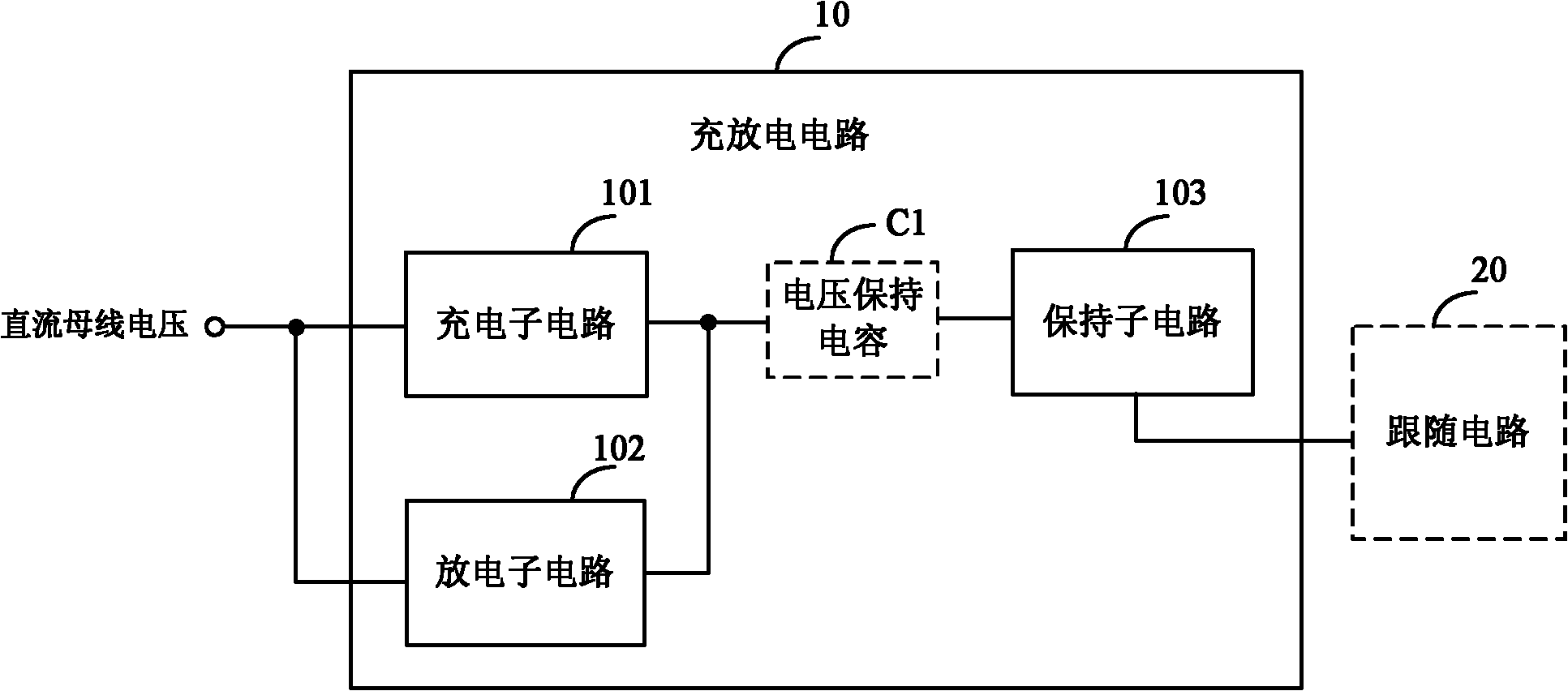

Collecting circuit for direct current bus

ActiveCN101873075AImprove real-time performanceGood retention propertiesBatteries circuit arrangementsCurrent/voltage measurementCharge and dischargeCapacitance

The invention relates to a collecting circuit for a direct current bus, which is used for collecting direct current bus voltage of a flyback converter. The collecting circuit for the direct current bus comprises a voltage collecting circuit which is connected to a secondary coil of a transformer of the flyback converter by adopting a forward mode, wherein the voltage collecting circuit comprises a voltage sustaining capacitor, a charge and discharge circuit and a follower circuit. In a forward period of the flyback converter, the charge and discharge circuit charges the voltage sustaining capacitor according to the collected direct current bus voltage, and simultaneously, the voltage sustaining capacitor discharges to realize quick charging and quick discharging and improve the real-time of voltage collection; and in a flyback period of the flyback converter, the charge and discharge circuit stops discharging of the voltage sustaining capacitor, and the voltage sustaining capacitor cannot discharge without a discharge circuit, so that excellent sustaining characteristic can be realized, and the sampling accuracy of sample voltage can be improved.

Owner:SHENZHEN SUNFAR ELECTRIC TECH

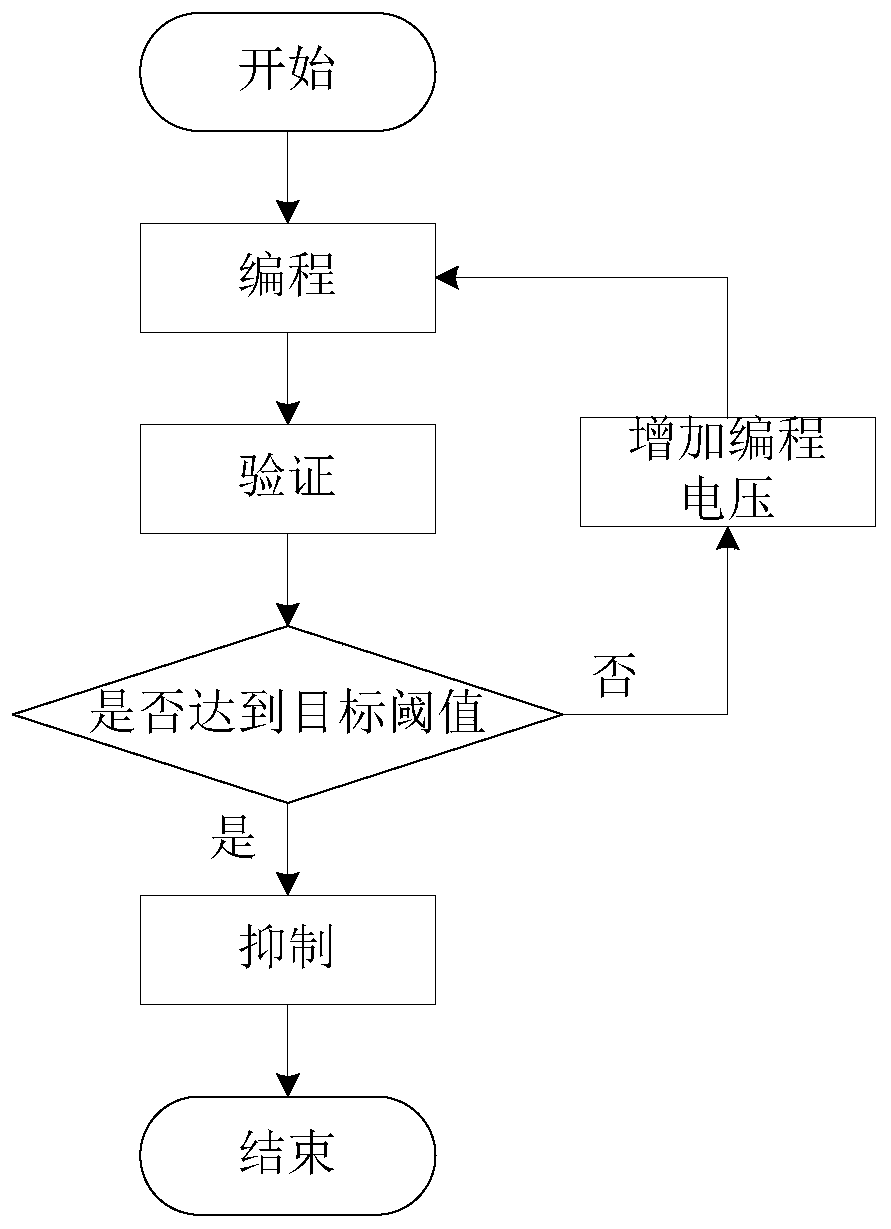

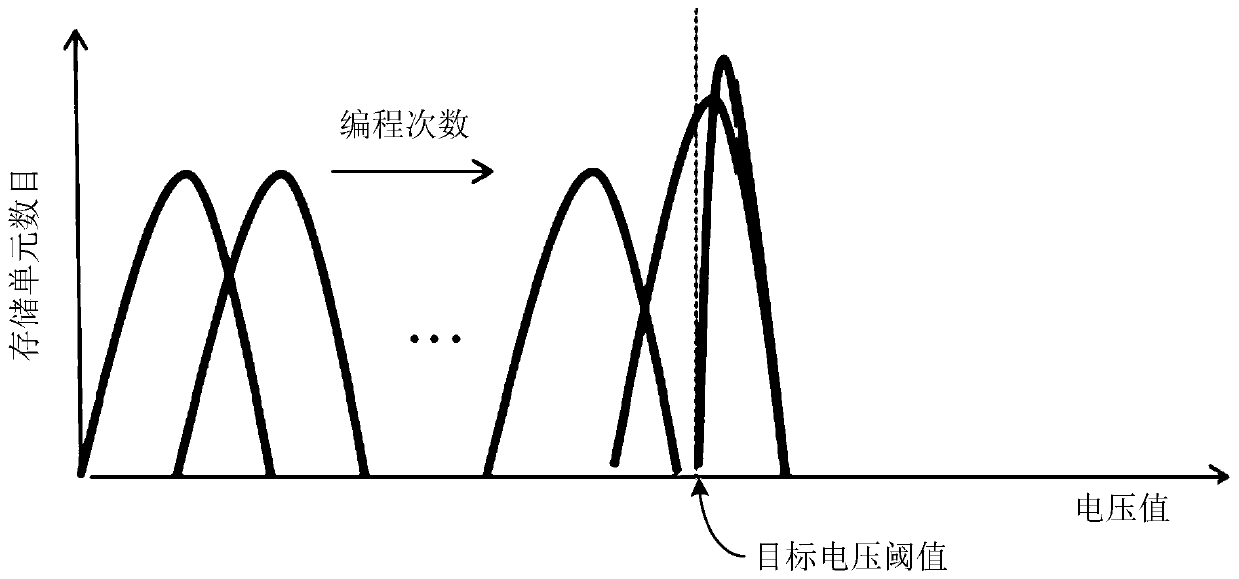

Nonvolatile memory and programming method thereof

The present invention relates to a nonvolatile memory, comprising a memory cell array and a controller. The memory cell array comprises a plurality of memory cells. The controller is configured to apply a first programming signal to a first memory cell of the plurality of memory cells; verify whether the threshold voltage of the first memory cell reaches a first threshold voltage or not; when thevoltage of the first memory cell reaches a first threshold voltage, verify whether the threshold voltage of the first memory cell reaches a second threshold voltage, wherein the second threshold voltage is greater than the first threshold voltage; and when the threshold voltage of the first memory cell does not reach the second threshold voltage, apply a second programming signal to the first memory cell. The threshold voltage of the memory cell located on the lower boundary of the threshold voltage distribution is improved, so that the distribution of each programming state is narrower, the width of the reading window is increased, and the tolerance of the nonvolatile memory to the reduction of the reading window caused by charge loss is improved.

Owner:YANGTZE MEMORY TECH CO LTD

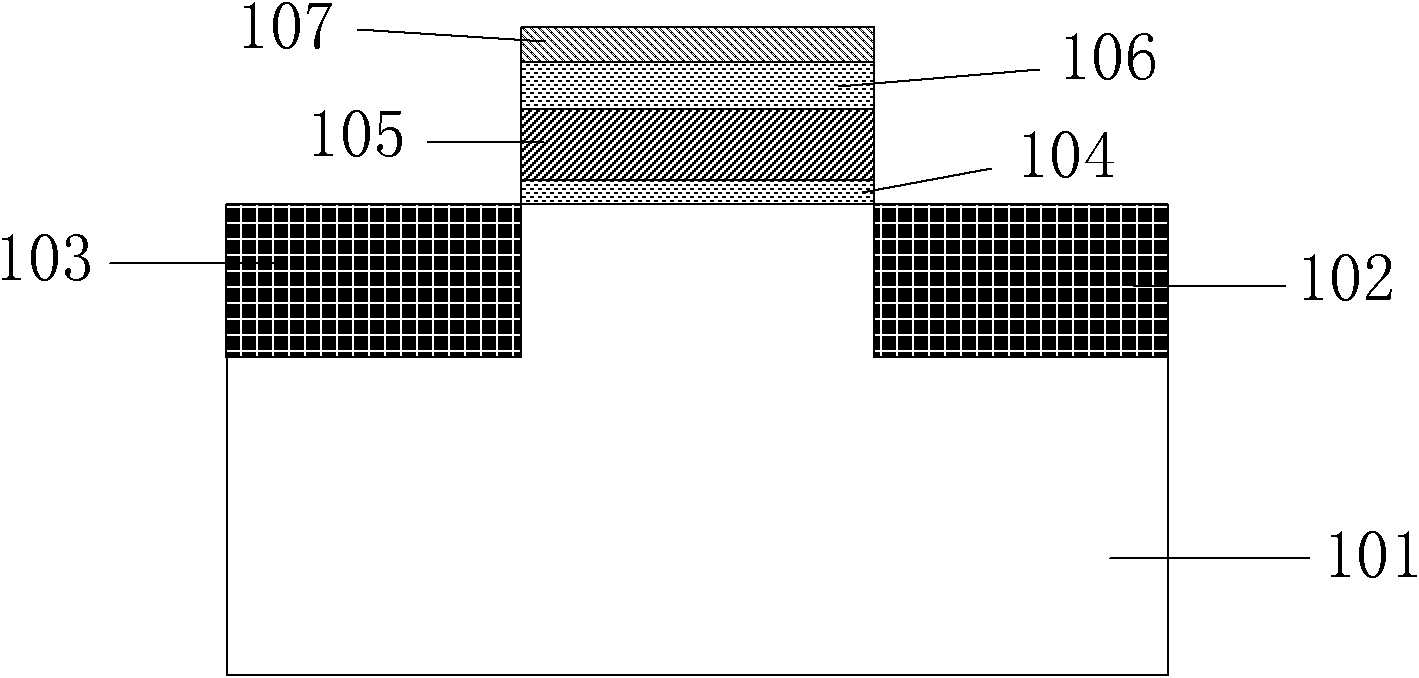

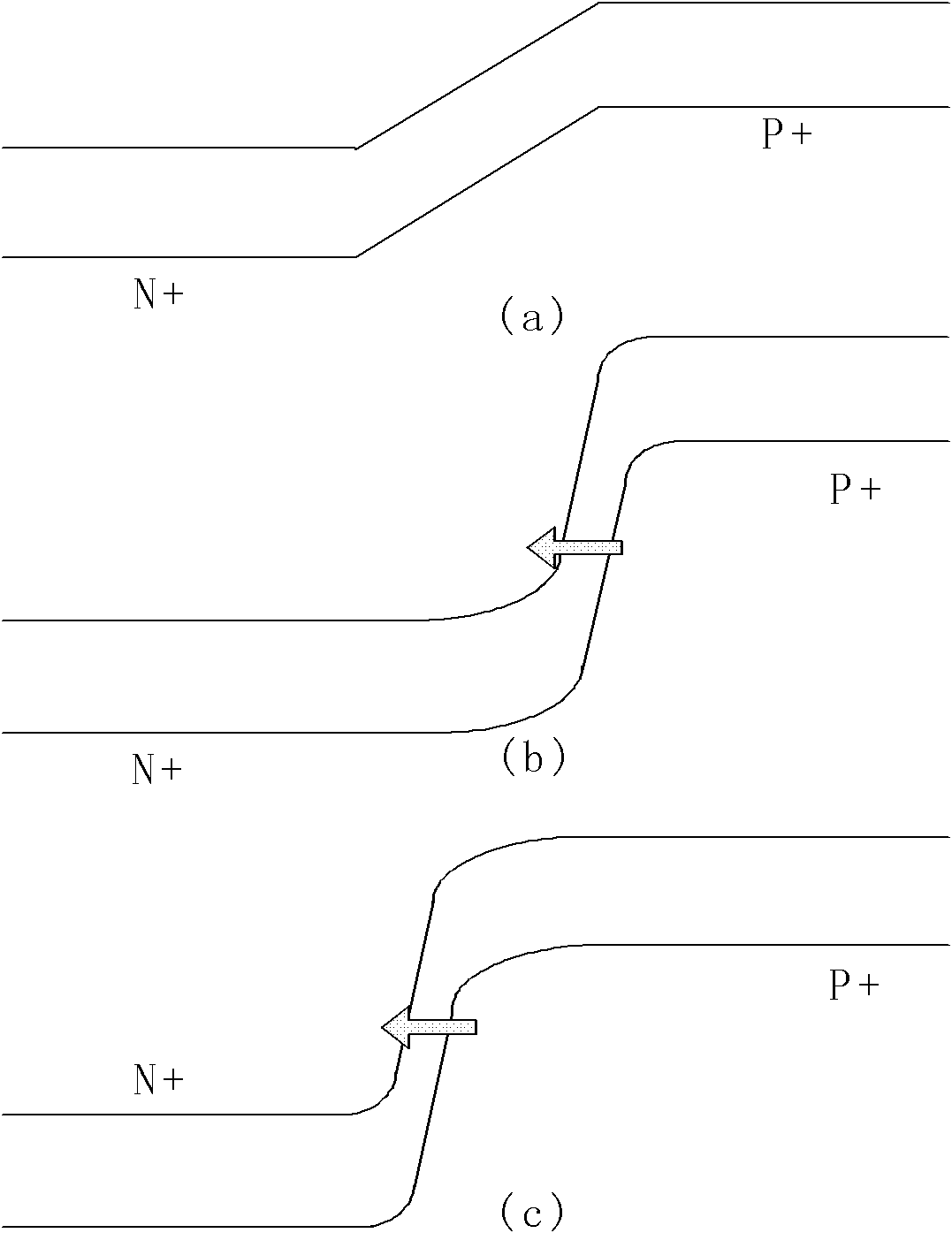

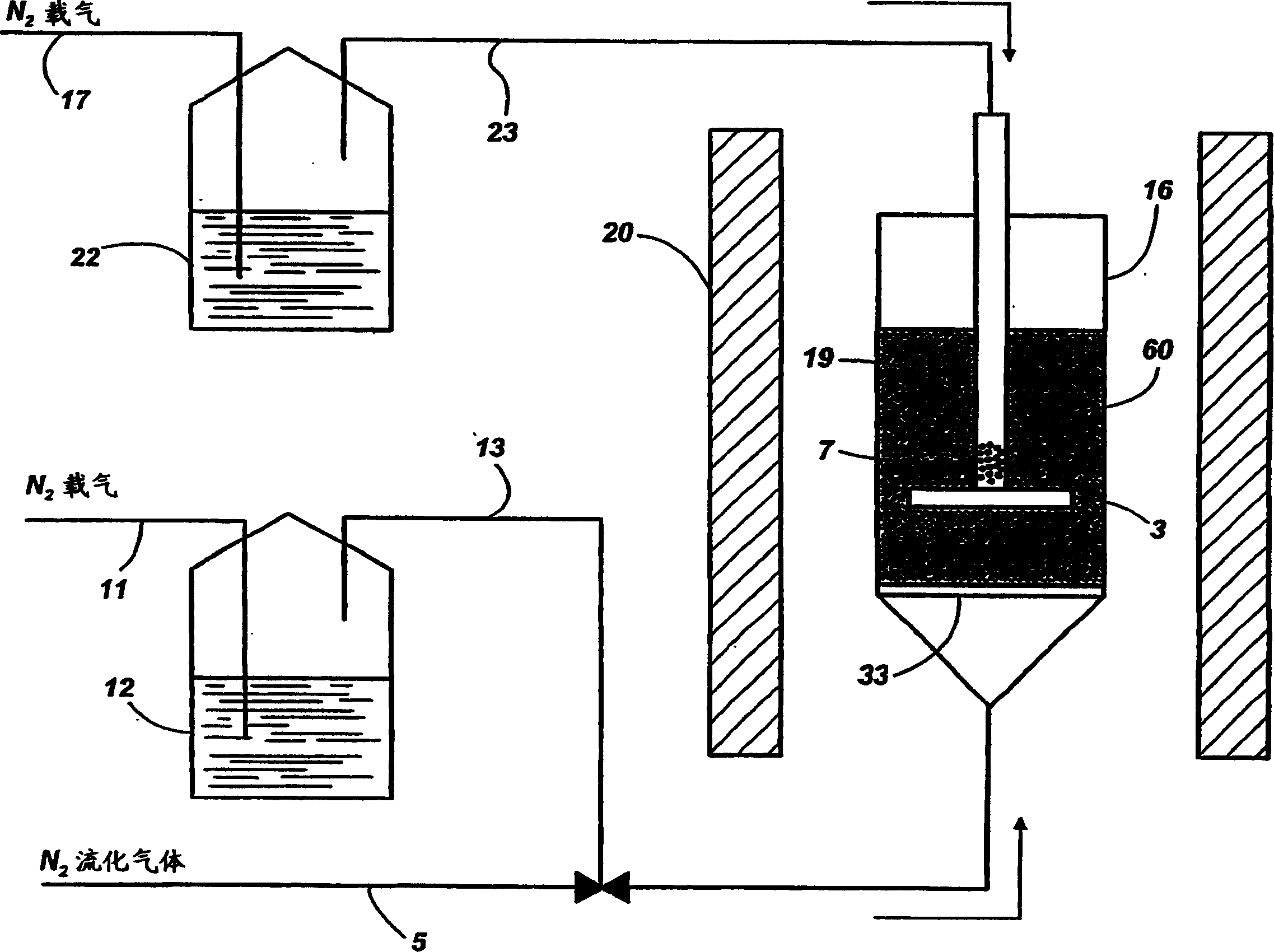

SONOS flash memory, preparation method thereof, and operation method thereof

ActiveCN102738244AGood retention propertiesImprove programming efficiencyRead-only memoriesSemiconductor/solid-state device manufacturingCMOSPolycrystalline silicon

The invention discloses a SONOS flash memory, a preparation method thereof, and an operation method thereof. The flash memory comprises a substrate, a source drain and a groove, wherein a tunneling oxide layer, a silicon nitride trap layer, a block oxide layer and a polysilicon control grid are positioned on the groove in order. The flash memory is characterized in: that the substrate is lightly doped silicon; and the source drain comprises different doped types consisting of a P+ region and an N+ region. Compared with the prior standard CMOS technologies, the flash memory has better compatibility. As common SONOS flash memories, the flash memory in the invention is provided with good maintenance characteristics. Meanwhile, the flash memory of the invention has an ideal small size and can effectively improve programming efficiency, reduce power consumption, and inhibit the tunneling effects.

Owner:PEKING UNIV

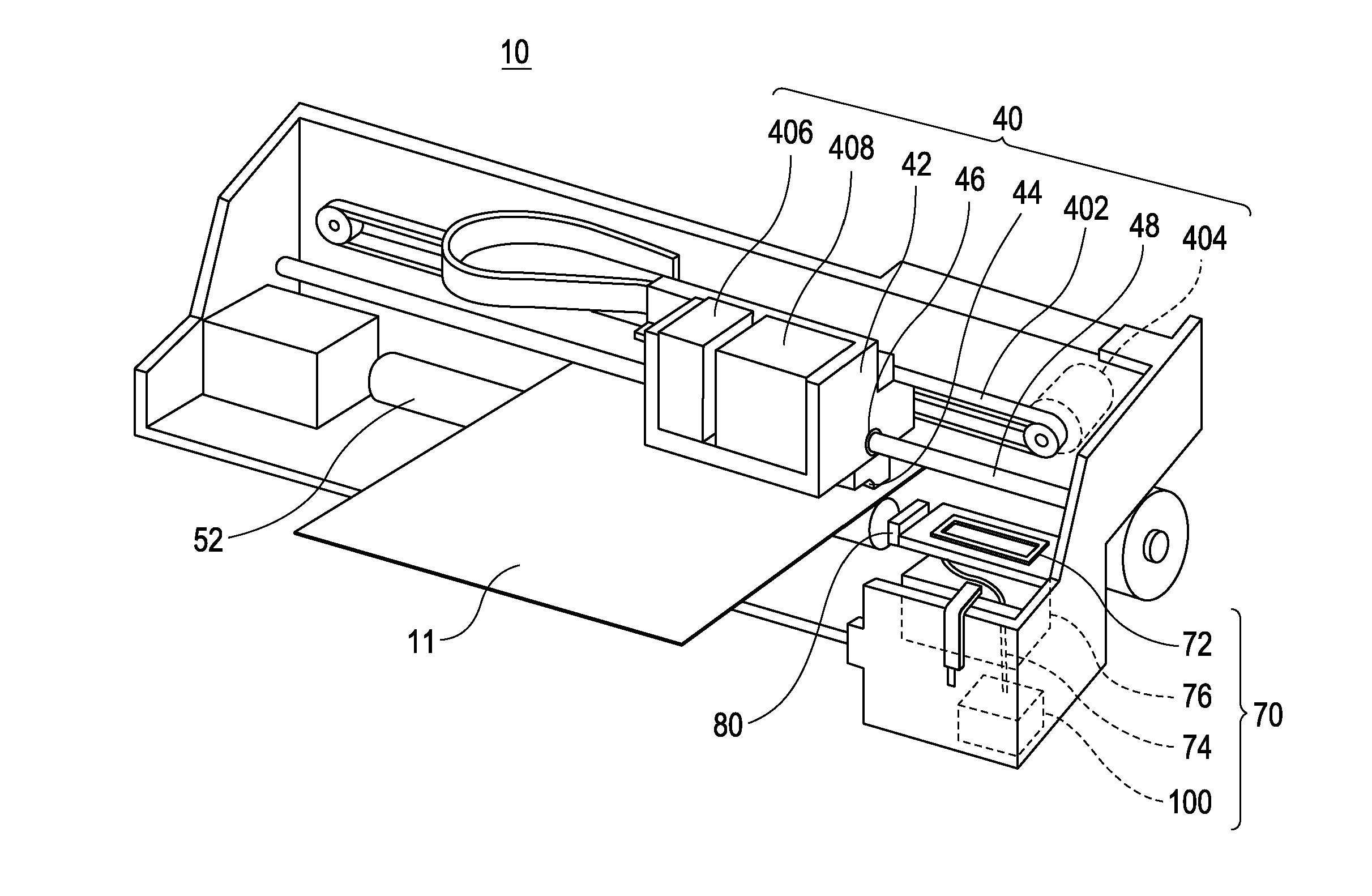

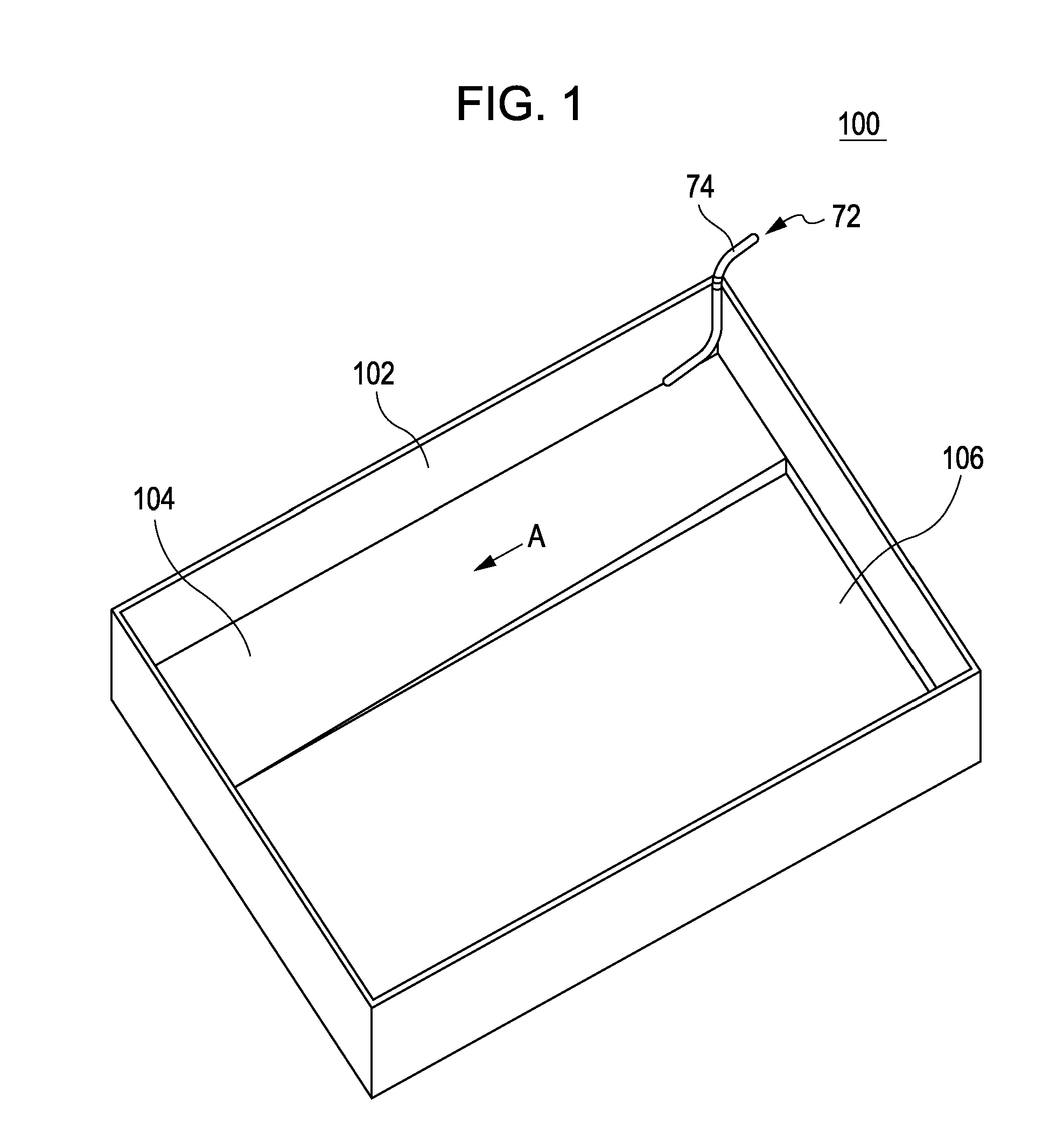

Waste ink absorber and ink jet recording device incorporating the same

InactiveUS20070229585A1Avoid foamingExcellent ink-absorbingOther chemical processesPrintingSolventWaste management

The invention describes a waste ink absorber for an ink jet recording device, wherein the ink is a non-aqueous ink, including a porous plastic prepared by sinter-molding plastic particles; and an oily solvent impregnated into the porous plastic. The invention also describes an ink jet recording device, wherein the ink is a non-aqueous ink, including a waste ink tank including a waste ink diffusing-chamber and an absorber-retaining chamber, and the waste ink absorber, wherein the waste ink absorber is retained in the absorber-retaining chamber and not the waste ink diffusing-chamber.

Owner:SEIKO EPSON CORP

Three-dimensional memory and preparation method thereof

ActiveCN110491880AReduce thicknessUniform qualitySolid-state devicesSemiconductor devicesDielectric layerMaterials science

The embodiment of the invention discloses a three-dimensional memory and a preparation method thereof, and the method comprises the following steps: providing a laminated structure which comprises a plurality of dielectric layers and sacrificial layers, wherein the dielectric layers and the sacrificial layers are alternately laminated, and a channel through hole CH passing through the laminated structure; forming a pre-storage layer on the side wall of the CH; removing the sacrificial layers, and exposing the pre-storage layer; and oxidizing the pre-storage layer at the position where the sacrificial layers are removed so as to form a barrier layer which is relatively close to the outer side and a storage layer which is relatively close to the inner side along the radial direction of the CH.

Owner:YANGTZE MEMORY TECH CO LTD

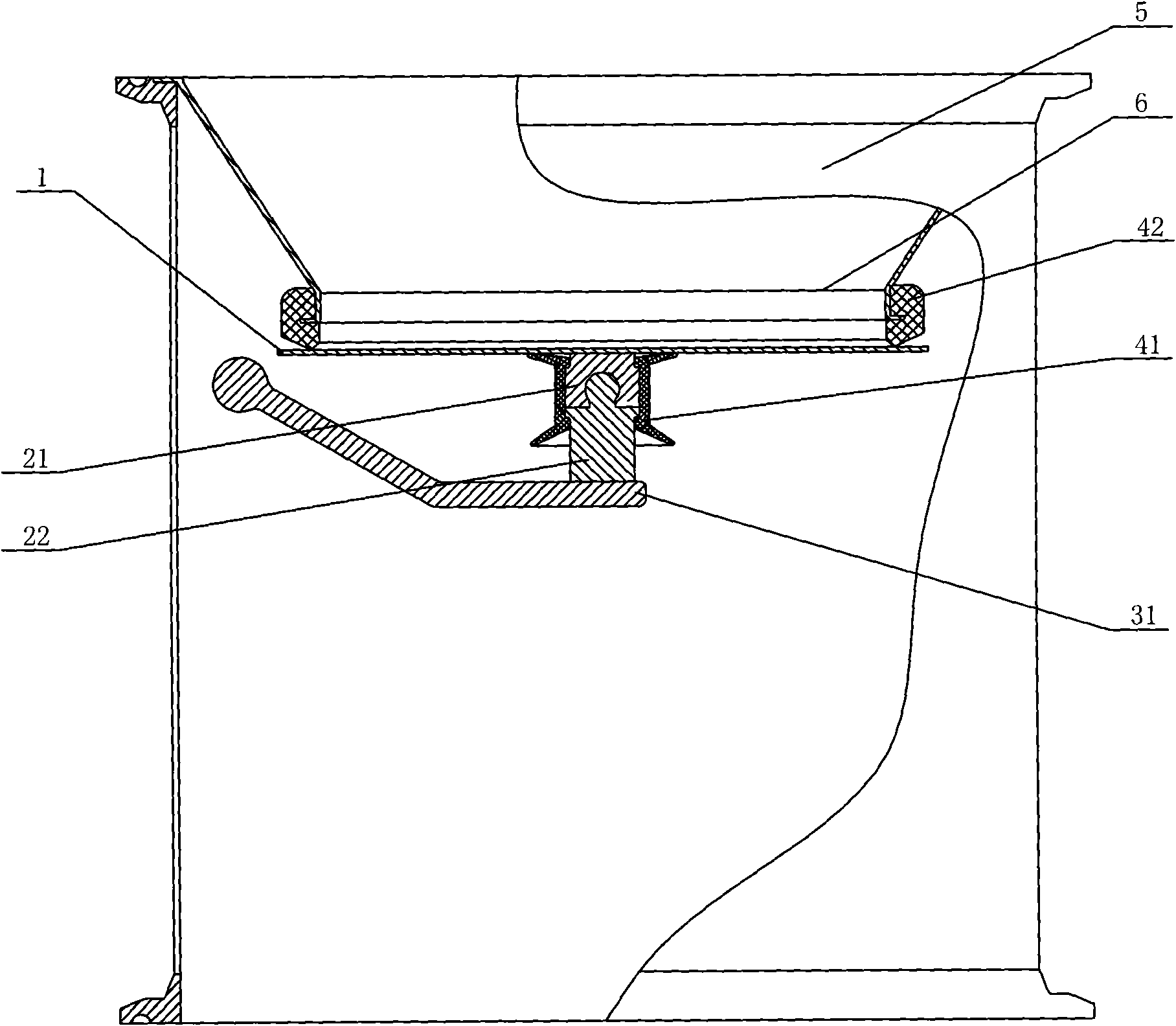

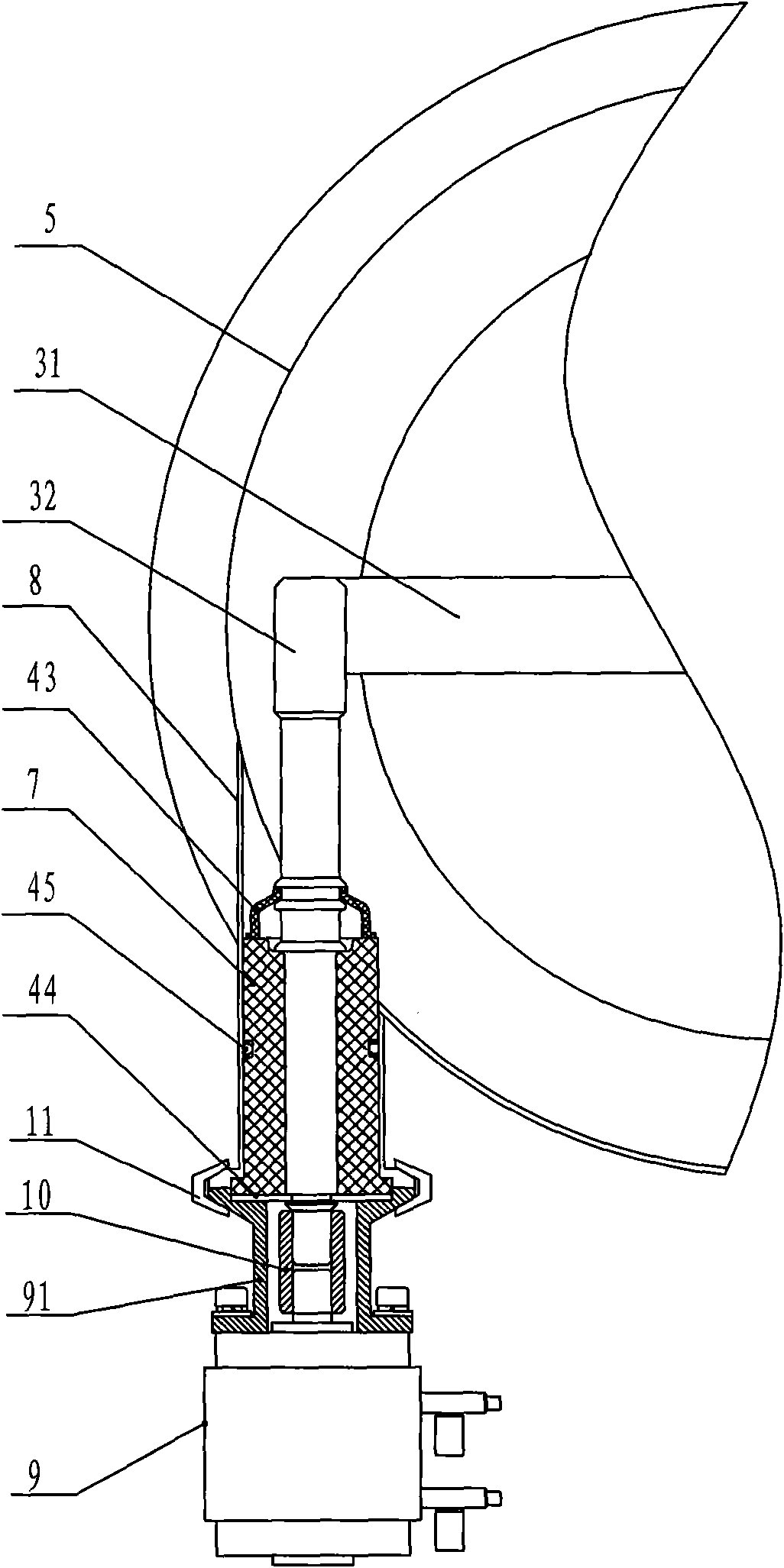

Discharge gate mechanism

ActiveCN101555946AGood retention propertiesMaintain propertiesOperating means/releasing devices for valvesLift valveRubber CupEngineering

The invention relates to a discharge gate mechanism. The mechanism comprises a discharge gate which rests against a discharge hopper port inside a discharge bin, a coupler, an L-shaped connecting lever, an axial supporting device of the L-shaped connecting lever, a drive unit of the L-shaped connecting lever and a sealing member for sealing a connecting part of the parts; the coupler consists of a pin boss and a pin inserted into the same, and is externally provided with a matching sealing rubber sleeve; one arm of the L-shaped connecting lever is connected with the discharge gate by the coupler, and the other arm is provided with a stepped section which hermetically passes through a discharge bin shell and is connected with the drive unit, and the stepped section is sequentially sheathed with a sealing rubber cup, a supporting casing and a retaining ring of the axial supporting device; the sealing rubber cup, the supporting casing and the retaining ring are arranged inside a supporting sleeve, one end of the supporting sleeve is fixedly arranged outside the discharge bin shell, and the other end of the supporting sleeve is fixedly connected with the drive unit; and a sealing ring is arranged between the supporting casing and the supporting sleeve. The discharge gate mechanism has the advantages of good tightness, convenient opening and closing and easy assembly and disassembly for cleaning.

Owner:BEIJING GOLDENTEAM TECH

A method to encapsulate phosphor via chemical vapor deposition

InactiveCN1791702APrevent penetrationGood retention propertiesLayered productsChemical vapor deposition coatingAluminateHigh intensity

Owner:OSRAM SYLVANIA INC

Directional film and liquid crystal display device using the same directional film

InactiveCN1637526AAvoid passingOrientation has no effectNon-linear opticsLiquid-crystal displayViscosity

The present invention aims to provide an alignment film that prevents deterioration due to impurity ions in liquid crystal, and a liquid crystal display using the alignment film. The alignment film 10 of the present invention provides an alignment film composed of a resin composition comprising a polyimide resin or a polyamide resin and a low molecular weight thermosetting resin having a viscosity of 1 to 3000 poise at 25°C. The impurity ions 14 in the liquid crystal 12 are prevented from reaching the pixel electrodes 16 by using the alignment film 10 in which the monomer thermosetting resins are mixed. The liquid crystal display of the present invention provided with this alignment film has improved retention characteristics in a reliability test, and is excellent in operating characteristics even when a liquid crystal with high dielectric anisotropy is used.

Owner:INNOLUX CORP

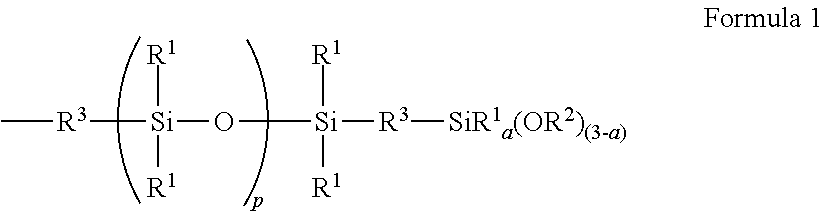

Laminate, method of manufacturing the same, and method of manufacturing electronic component

InactiveUS20200164613A1Improve heat resistanceLow elastic modulusSemiconductor/solid-state device detailsSynthetic resin layered productsSilicone GelsPolymer science

Provided is a laminate having, on a substrate, a gel layer which is excellent in heat resistance, has low elastic modulus, low stress and is excellent in stress buffering properties and flexibility, is soft and excellent in holding property of electronic components before curing, and after curing, the gel layer is changed to a hard cured layer which is higher in shape retention and excellent in mold releasability than before curing, and a method for manufacturing the same. Also provided is a method for manufacturing an electronic component in which use of the laminate makes it difficult to cause problems such as deposits of silicone gel or a cured product thereof to a substrate or an electronic component, and makes it difficult to cause problems of defects or defective products of the electronic component. The laminate includes a curing reactive silicone gel layer on at least one type of substrate.

Owner:DOW TORAY CO LTD

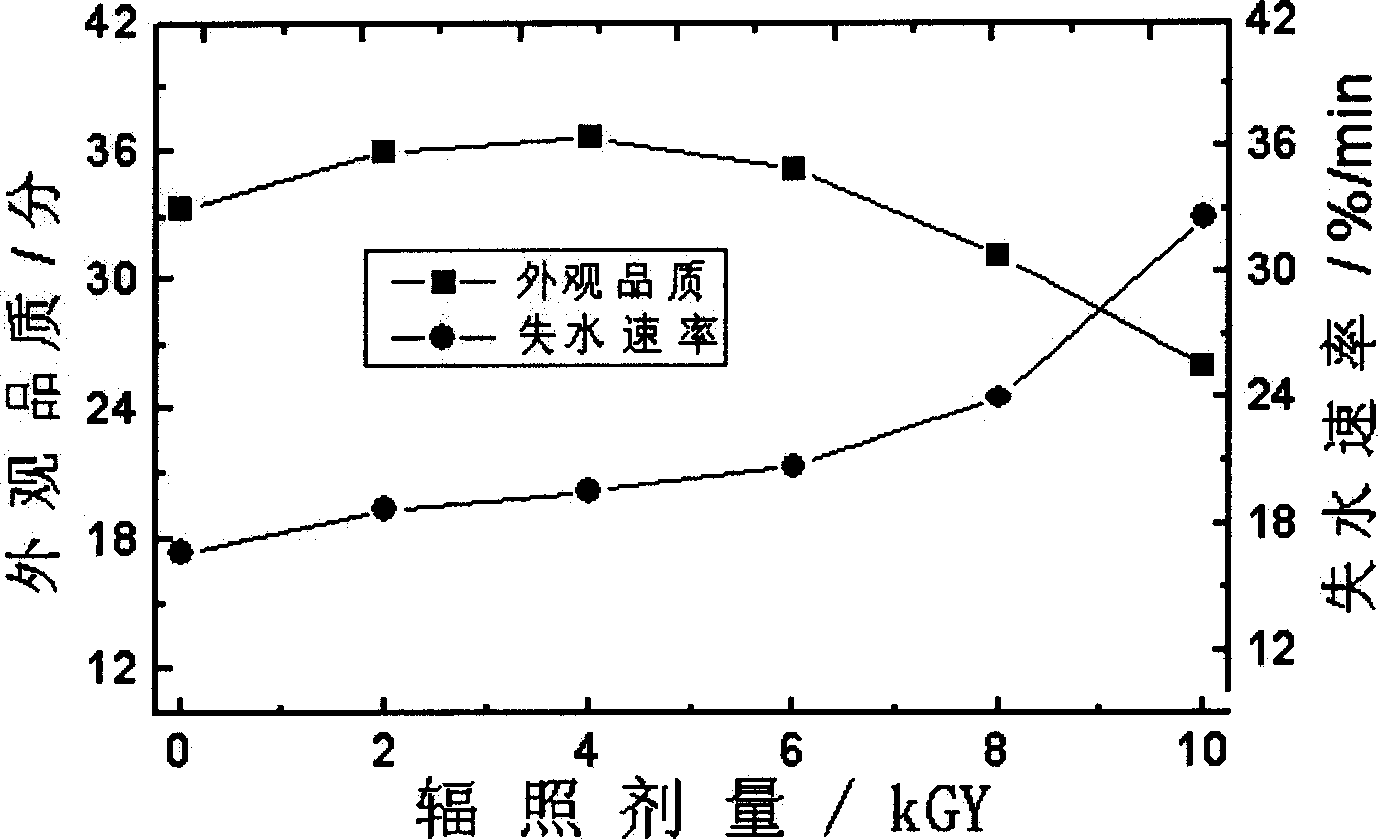

Irradiation pretreatment process for producing dry fruits and vegetalbe

InactiveCN1452894AHigh electrical conductivityImprove permeabilityFood preservationFood preparationMildewPlastic film

The producing process of dry fruit and vegetable product includes the following steps: sorting, washing and draining fruit and vegetable, sealing with plastic film and packing in paper box; irradiation with Co-60 ray of dosage 1-10 KGy for 2 hr; slicing, drying with hot blast at 60-70 deg.c temperature and 1 m / s blast speed within 1 hr after irradiation. The process of the present invention can sterilize, killing insects, prevent rot and mildew and has the features of fast speed, low power consumption and high dry product quality.

Owner:ZHEJIANG UNIV

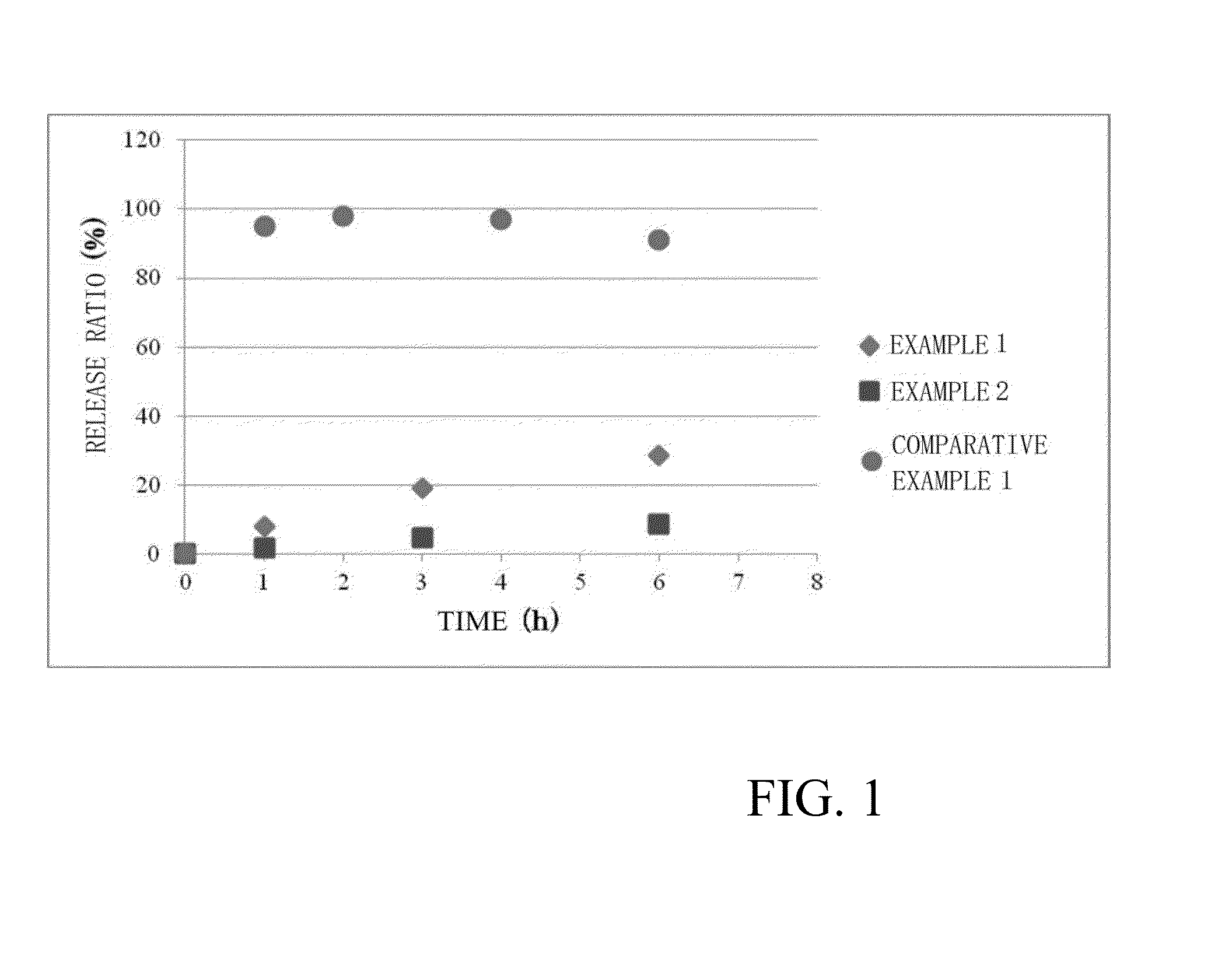

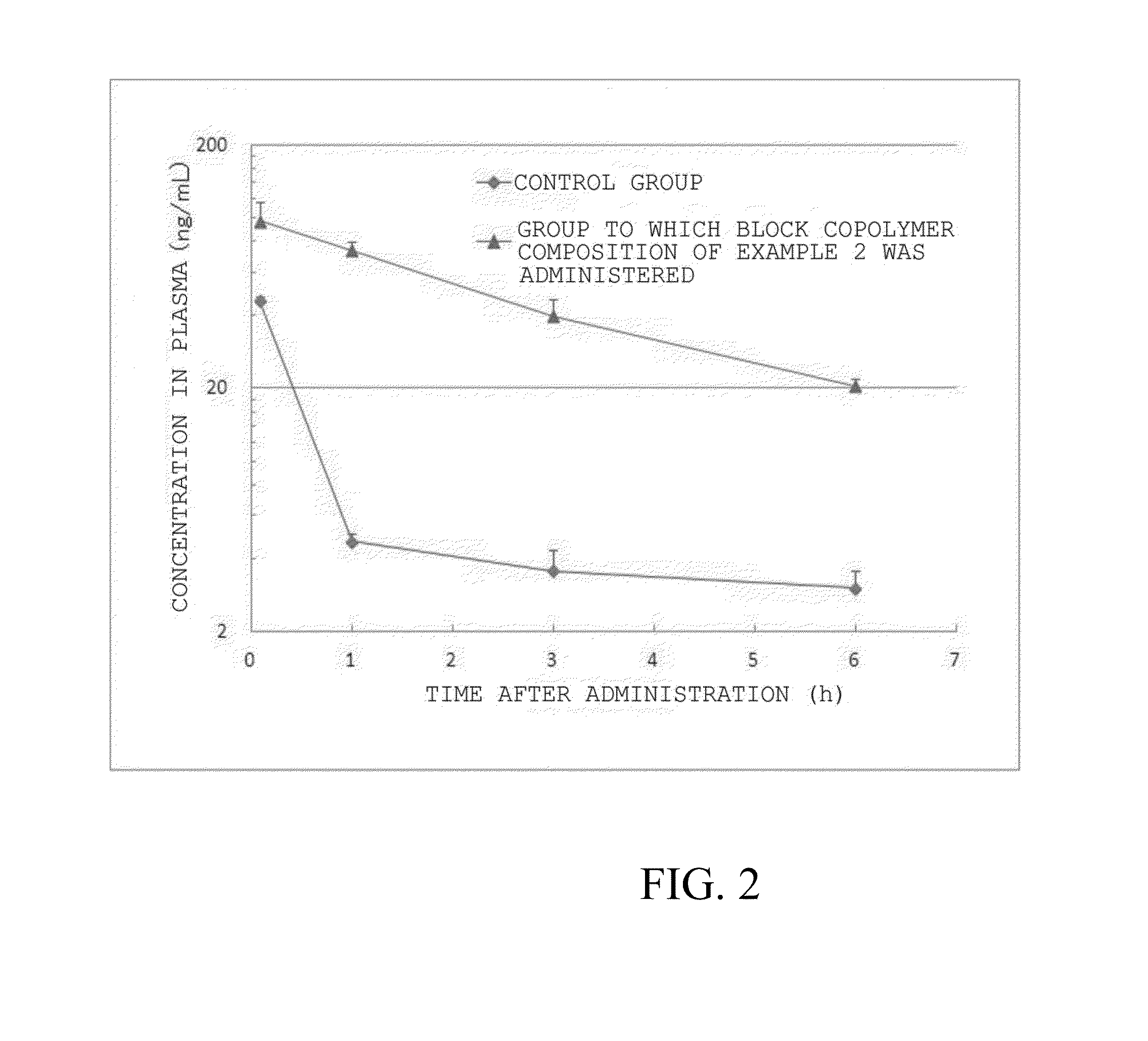

Pharmaceutical composition containing block copolymer comprising boric acid compound

InactiveUS20140017192A1Stable retention propertyImprove retentionBoron compound active ingredientsPharmaceutical non-active ingredientsOxygen atomChemistry

A pharmaceutical composition includes a block copolymer having a hydrophilic segment, a hydrophobic segment, and a boronic acid compound bound to a side chain of the hydrophobic segment via a linker moiety that includes a heterocyclic structure. The heterocyclic structure contains a cyclic skeleton that includes a boron atom of the boronic acid compound, one or two atom(s) X bound to the boron atom and selected from an oxygen atom and a nitrogen atom, and one or two carbon atom(s) (respectively) bound to the atom(s) X. The block copolymer further includes at least one organic group bound to the carbon atom(s). The organic group(s) contain(s) an aromatic group or cyclic alkyl group that sterically protects a boronic acid ester bond and / or a boron amide bond resulting from bonding between the boron atom and the atom(s) X.

Owner:NANOCARRIER

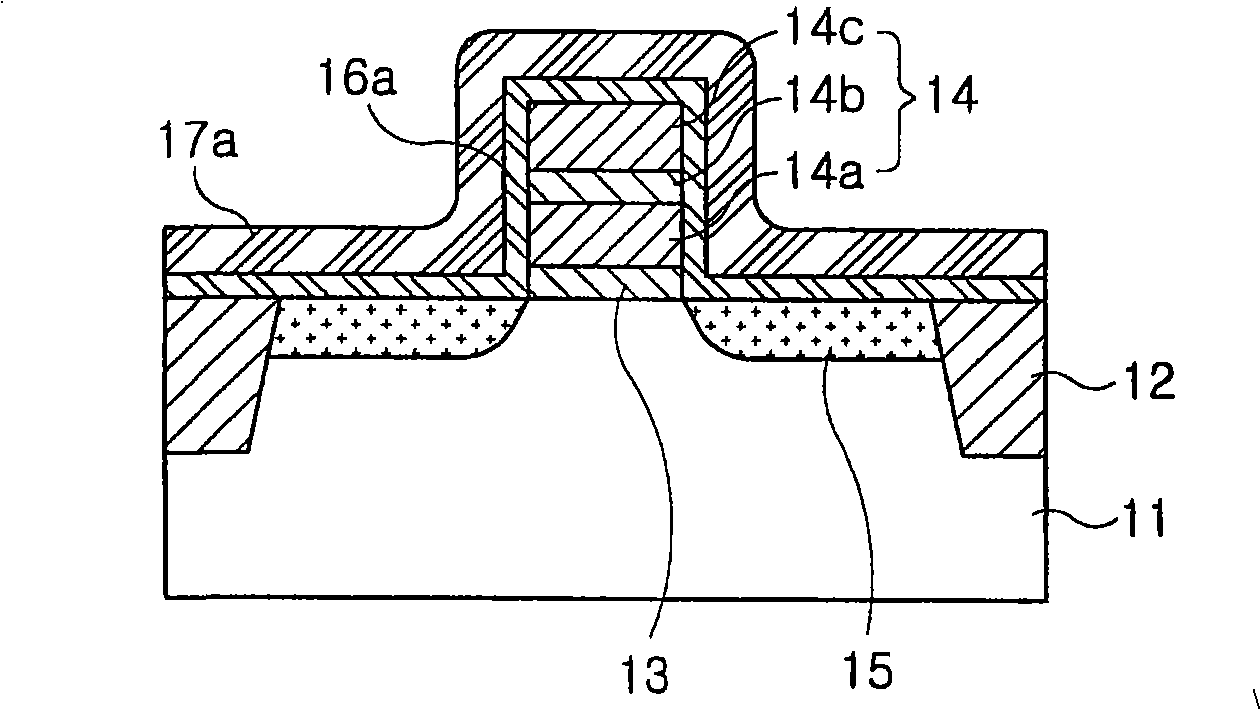

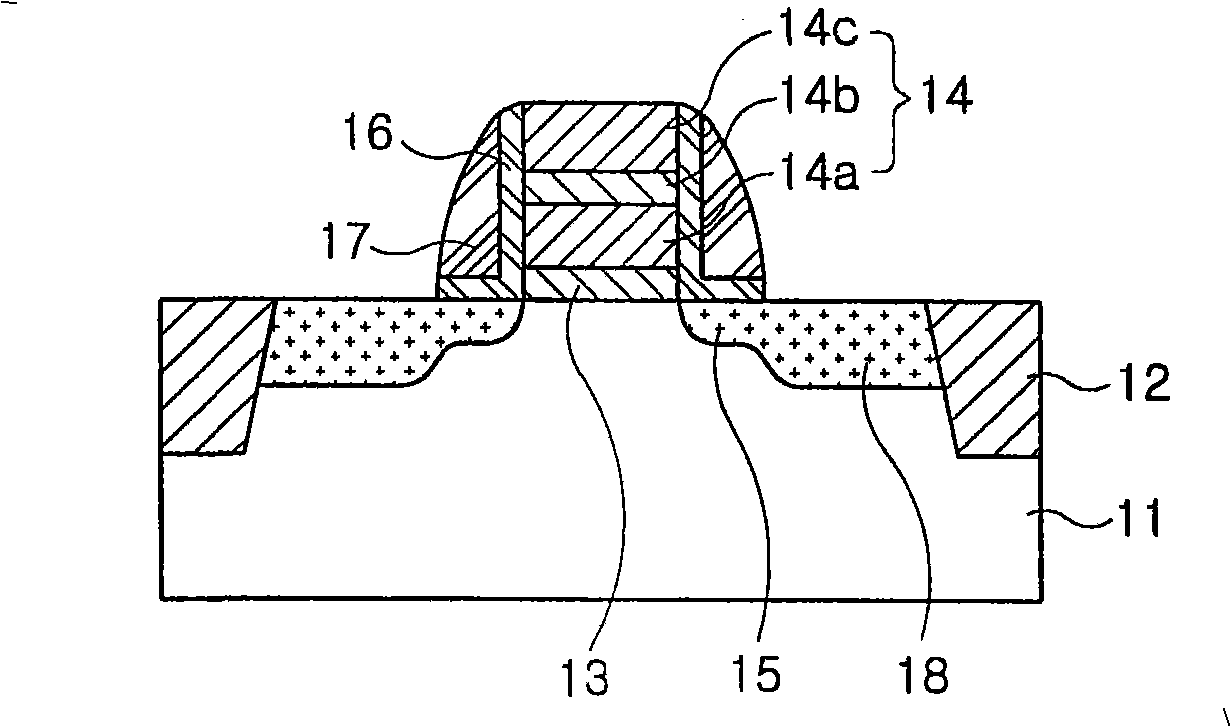

Semiconductor device and method of fabricating the same

InactiveCN101350310APrevent movementLoss minimizationSemiconductor/solid-state device manufacturingSemiconductor devicesCharge lossNitride

A method of fabricating a semiconductor device includes forming first spacers formed of a TEOS layer and second spacers formed of a first nitride layer on sidewalls of a gate electrode formed on a semiconductor substrate, and then forming source / drain regions in the semiconductor substrate using the first and second spacers and the gate electrode as masks, and then removing the second spacers, and then depositing a second nitride layer on an entire surface of the semiconductor substrate, and then implanting ions into the second nitride layer to generate compressive stress, and then etching the second nitride layer to form barrier nitride layers on the side walls of the first spacers. Because the barrier nitride has compressive stress, it is possible to prevent the movement of mobile ions, minimize influence on charge loss and charge gain in a flash memory device, and enhance a retention characteristic.

Owner:DONGBU HITEK CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com