Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

51 results about "Resonance tunneling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

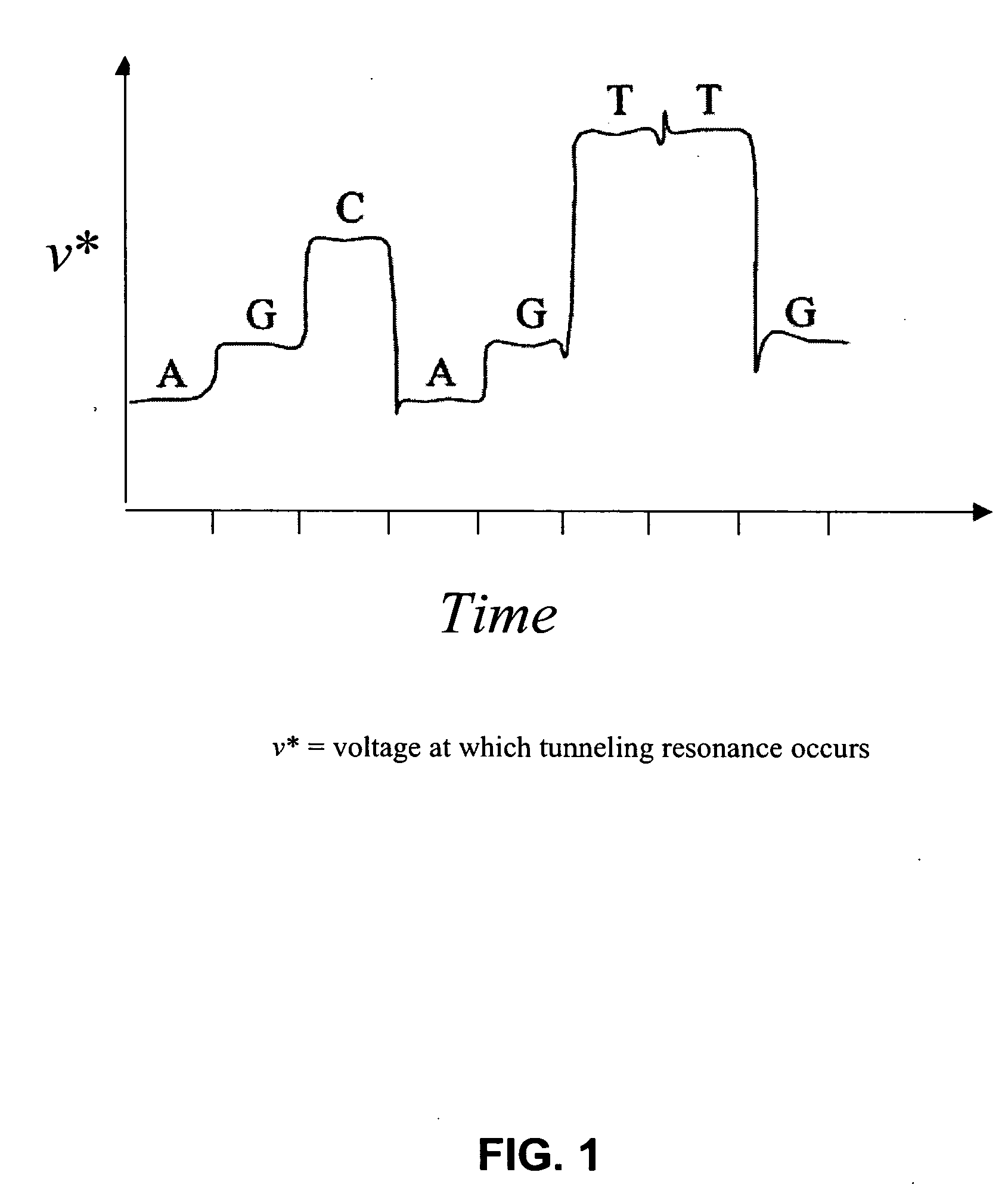

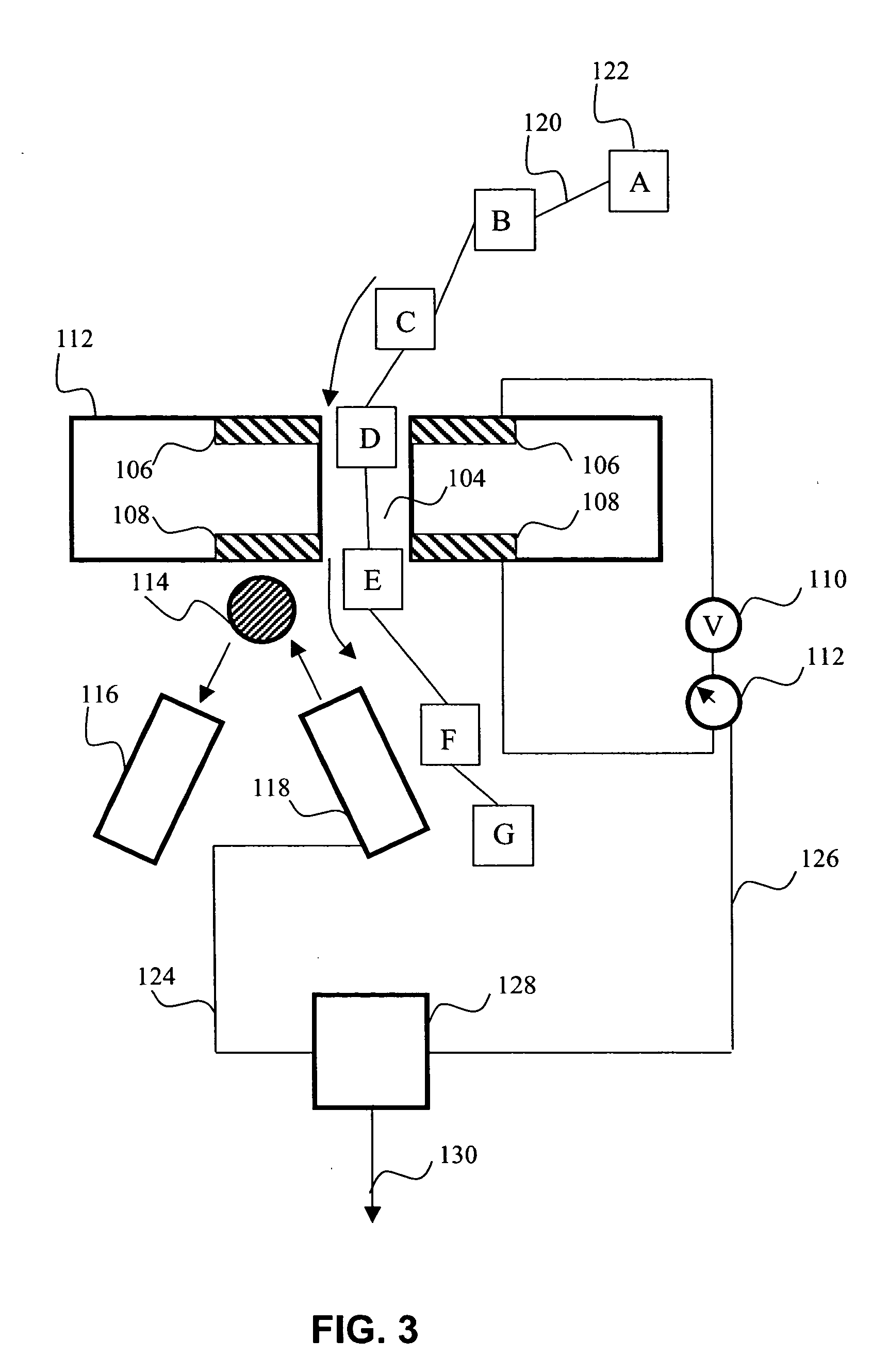

Characterization of biopolymers by resonance tunneling and fluorescence quenching

InactiveUS20060019259A1Bioreactor/fermenter combinationsBiological substance pretreatmentsFluorescenceBiopolymer

The present invention provides a method and apparatus for determining the identity of a monomeric residue of a biopolymer. The apparatus comprises a substrate having a nanopore, a potential-producing element for producing a ramped potential across electrodes adjacent to the nanopore, and a quenchable excitable moiety adjacent to the nanopore. As a biopolymer passes through the nanopore, the identity of monomeric residues of a biopolymer may be determined by detecting changes in (a) current across the electrodes and (b) a signal of the quenchable excitable molecule. The subject method and apparatus find use in determining the identity of a plurality of monomeric residues of a biopolymer, and, as such, may be employed in a variety of diagnostic and research applications.

Owner:AGILENT TECH INC

Metastable state assistant quantum dot resonance tunneling diode and working condition

InactiveCN100580957CIncrease working temperatureSimple structureDiodeWorking temperatureSingle electron tunneling

The invention provides a semiconductor quantum-dot metastable resonant tunneling diode structure and the working conditions. The structure includes: a substrate and a growth collector, a second tunnel barrier layer, quantum dots which are coupled between an emitter and the collector, a first tunnel barrier layer and the emitter which are sequentially arranged on the substrate. The working conditions include working temperature, working bias voltage and the obtainment of the metastable state of the quantum dots. The invention can eliminate the impact of the neighboring sub-level of the quantum dots on the metastable single-electron tunneling so as to achieve the purpose of improving the working temperature of the diode.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

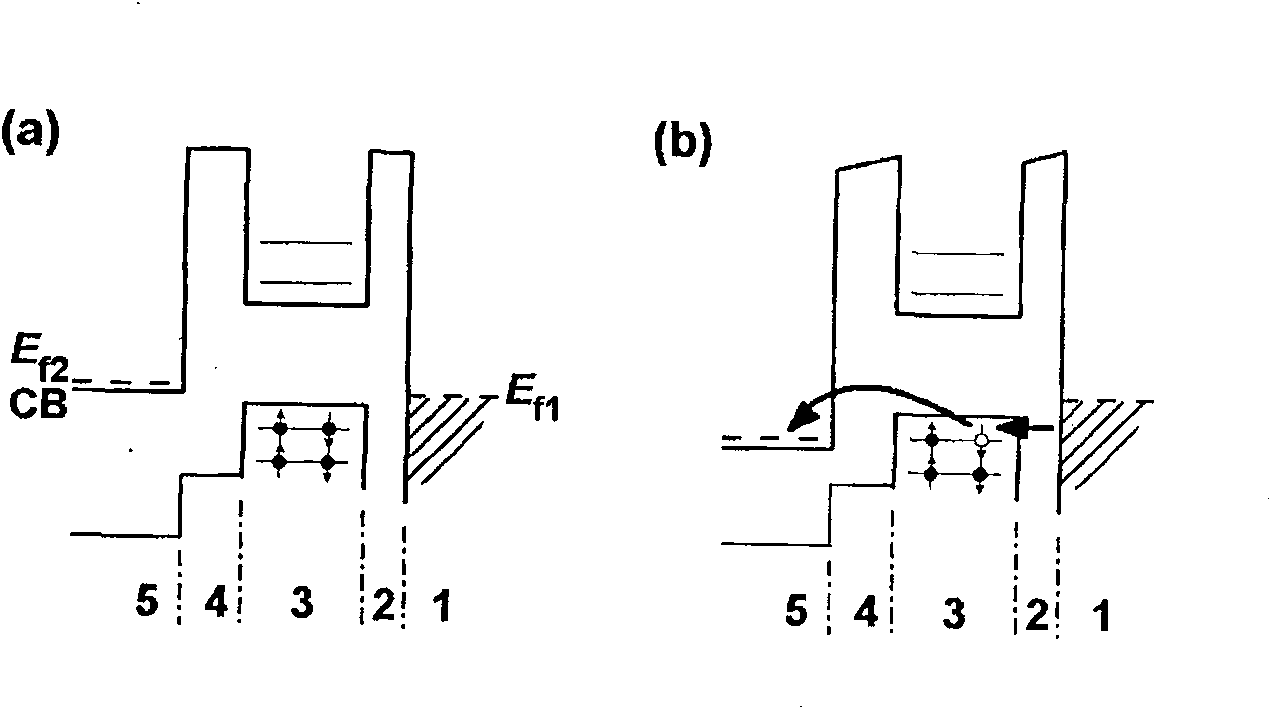

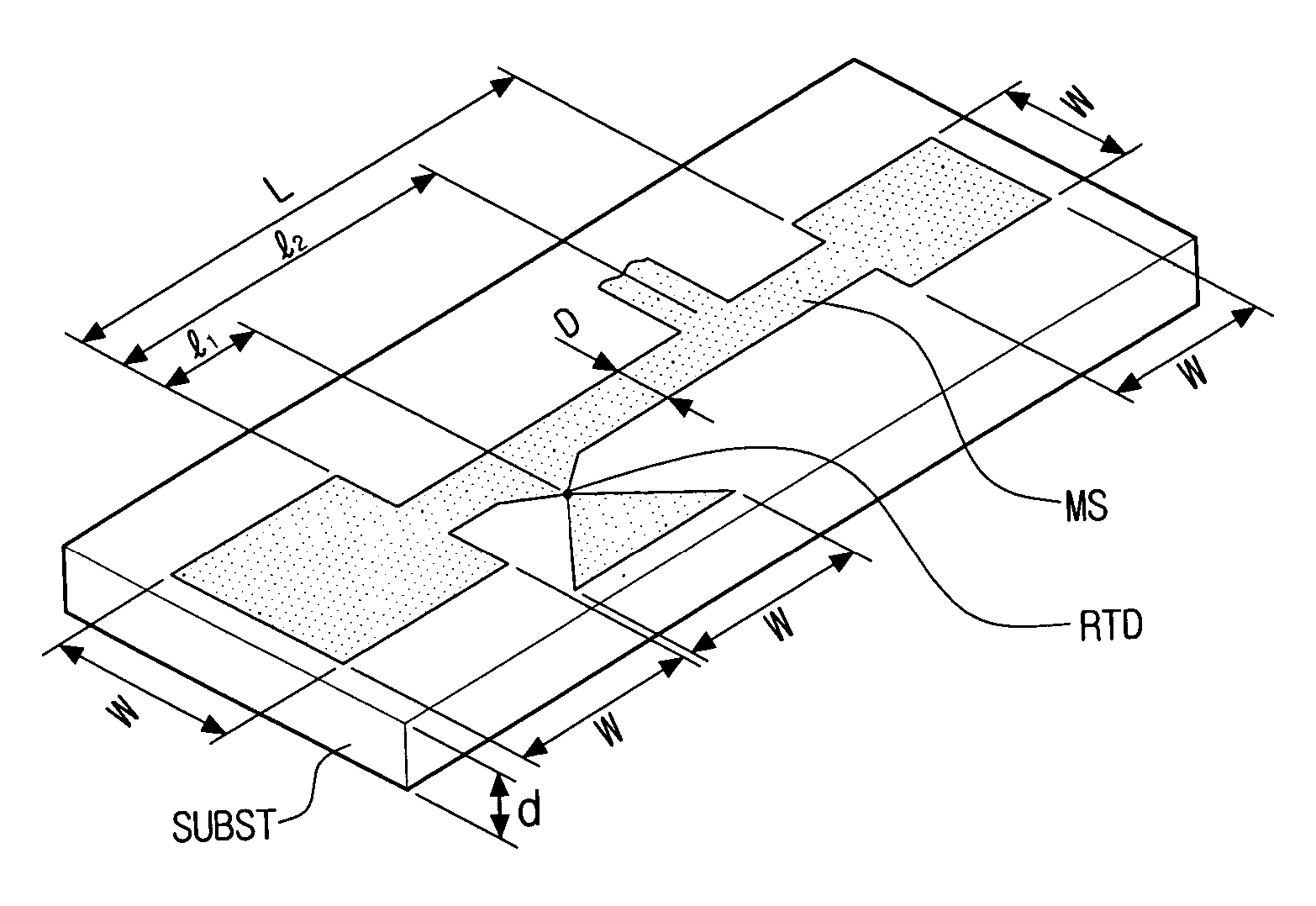

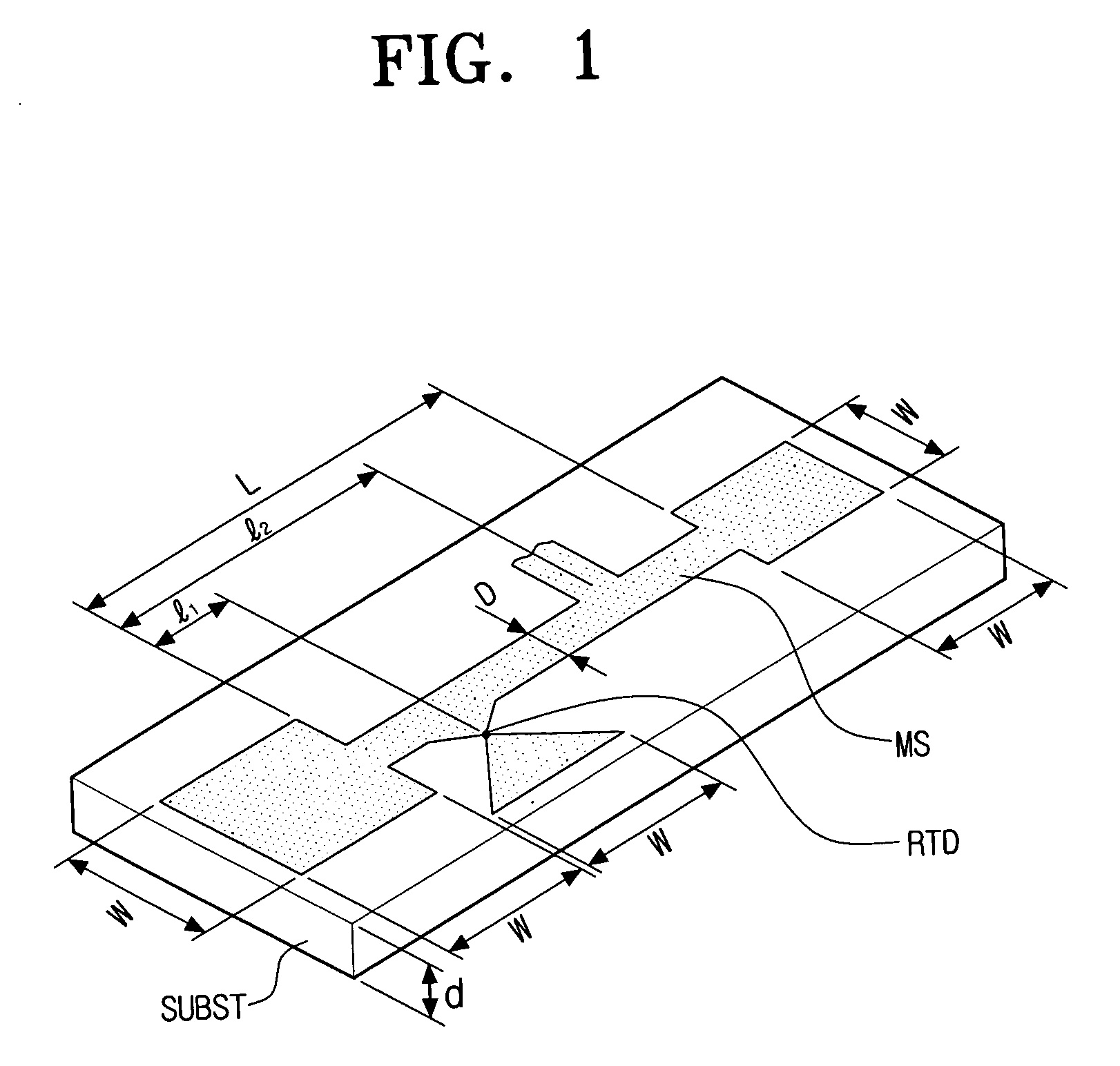

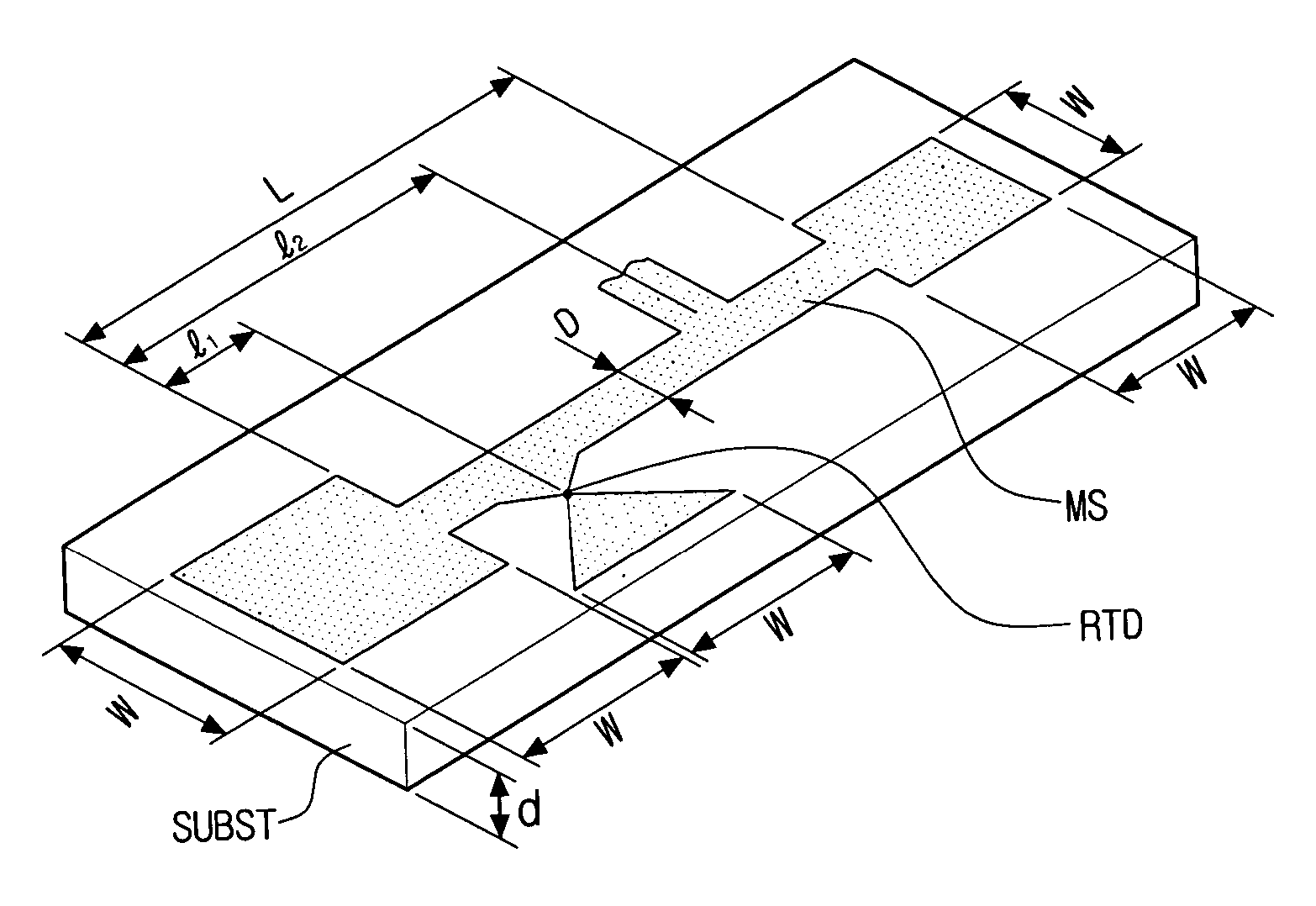

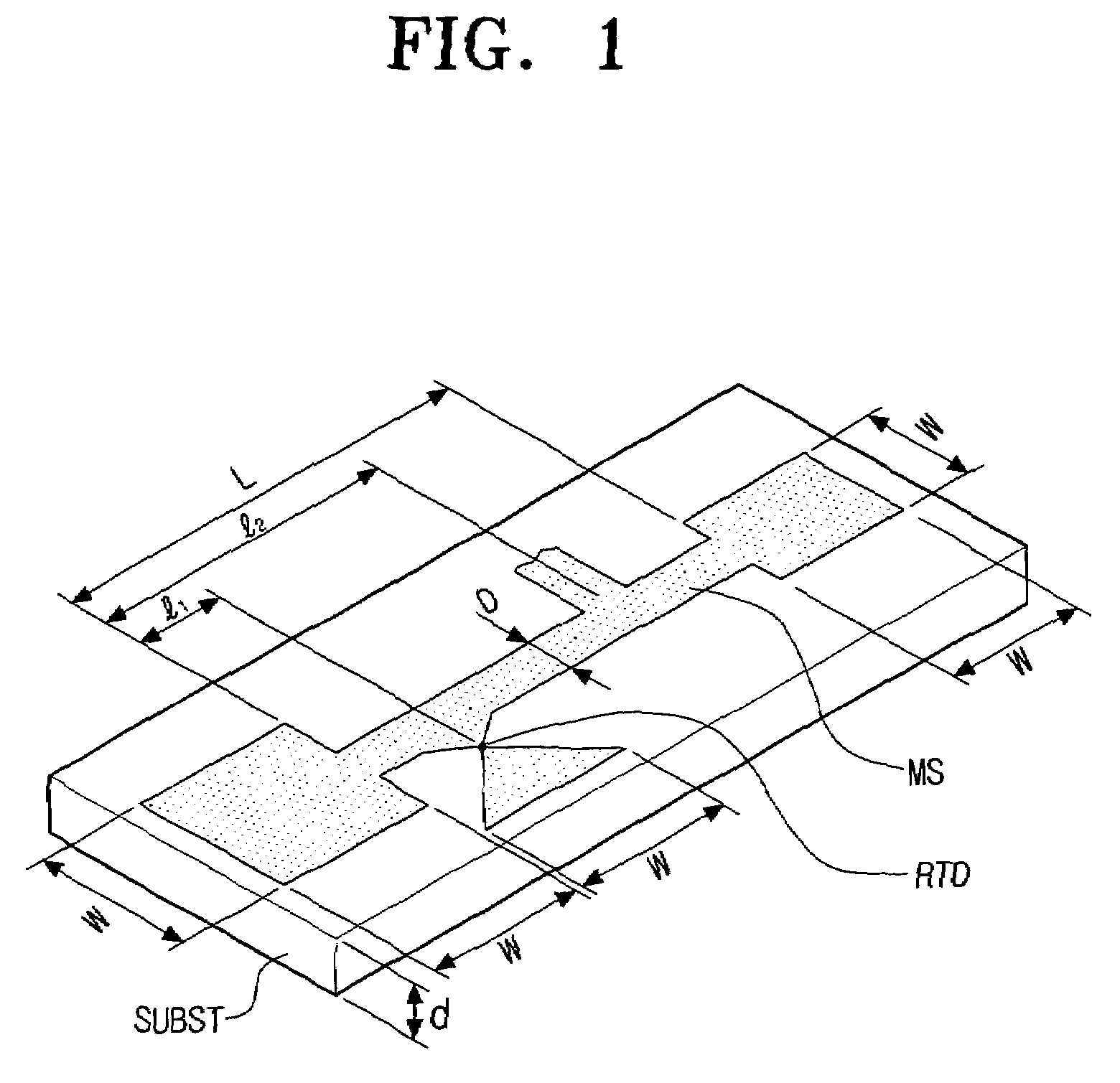

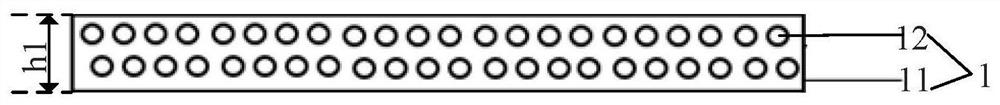

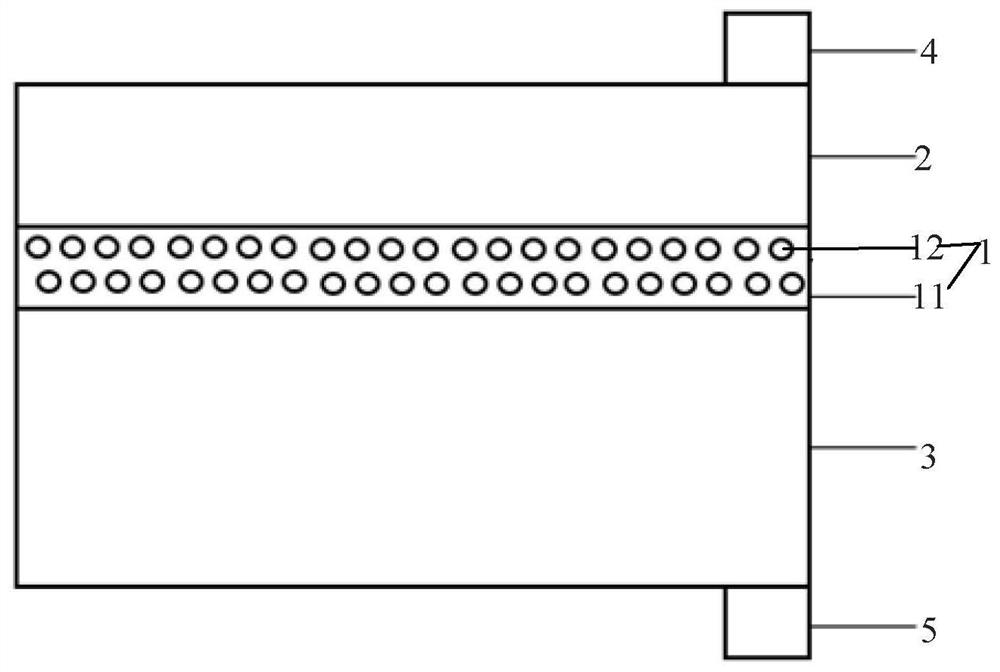

Microstrip stablized quantum well resonance-tunneling generator for millimeter and submillimeter wavelength range

ActiveUS20060055476A1Increase the oscillation frequencyIncrease speedSemiconductor/solid-state device detailsNanoinformaticsSemiconductor quantum wellsTunnel diode

A microstrip stabilized quantum well resonance-tunneling generator which generates electromagnetic waves for millimeter and submillimeter wavelength range is provided The generator includes a resonant tunneling semiconductor quantum well diode, and a microstrip resonator. The resonant tunneling diode, the microstrip resonator and interconnecting lines and junctions are fabricated as a monolithic integrated device on a common substrate. As a result, the monolithic integrated device provides the expansion of the operation frequency range toward the terahertz region as a result of reduction of the parasitic inductance as well as of minimizing the other parasitic parameters of the electric circuitry connecting the resonant tunneling diode and resonator.

Owner:SAMSUNG ELECTRONICS CO LTD +1

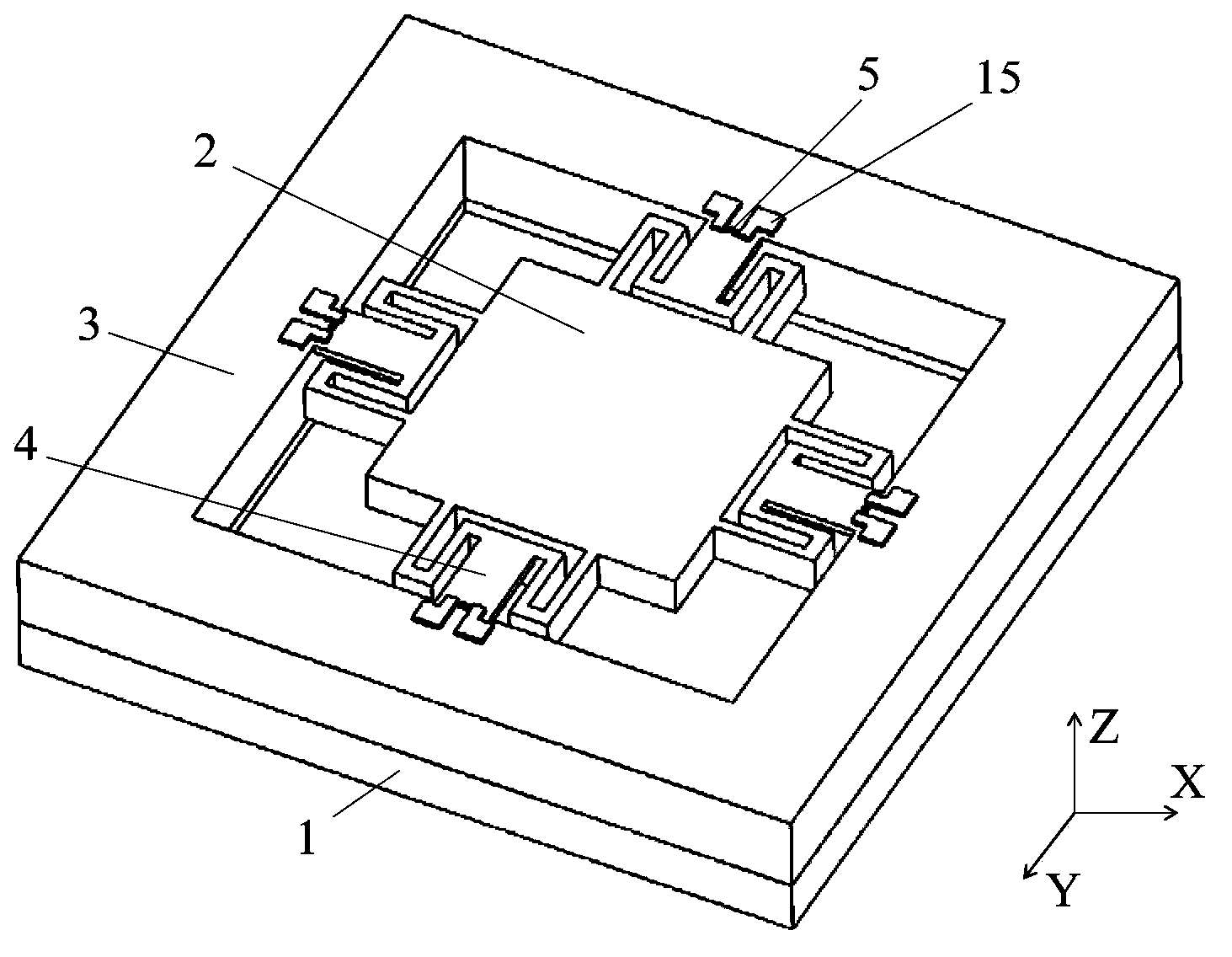

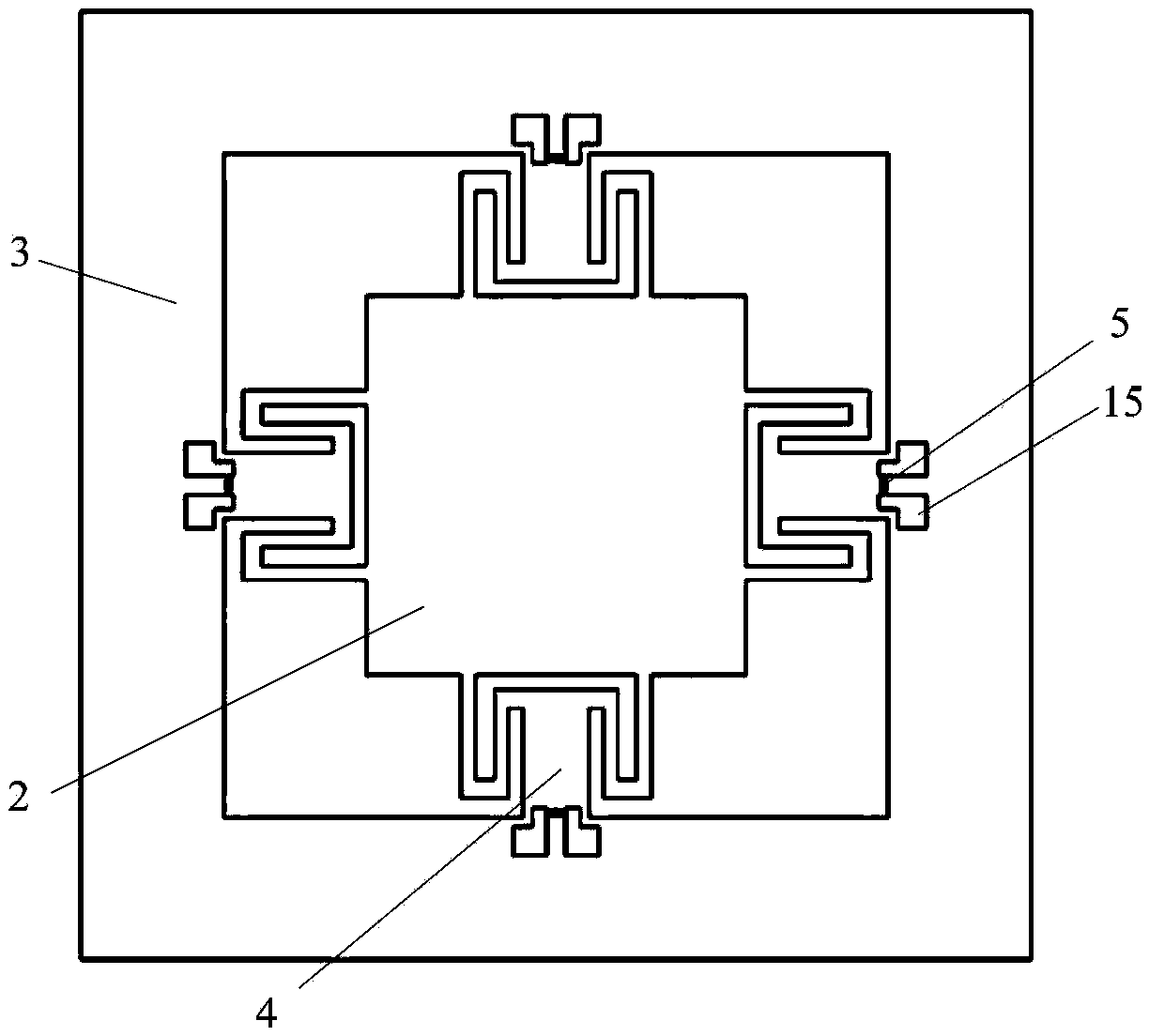

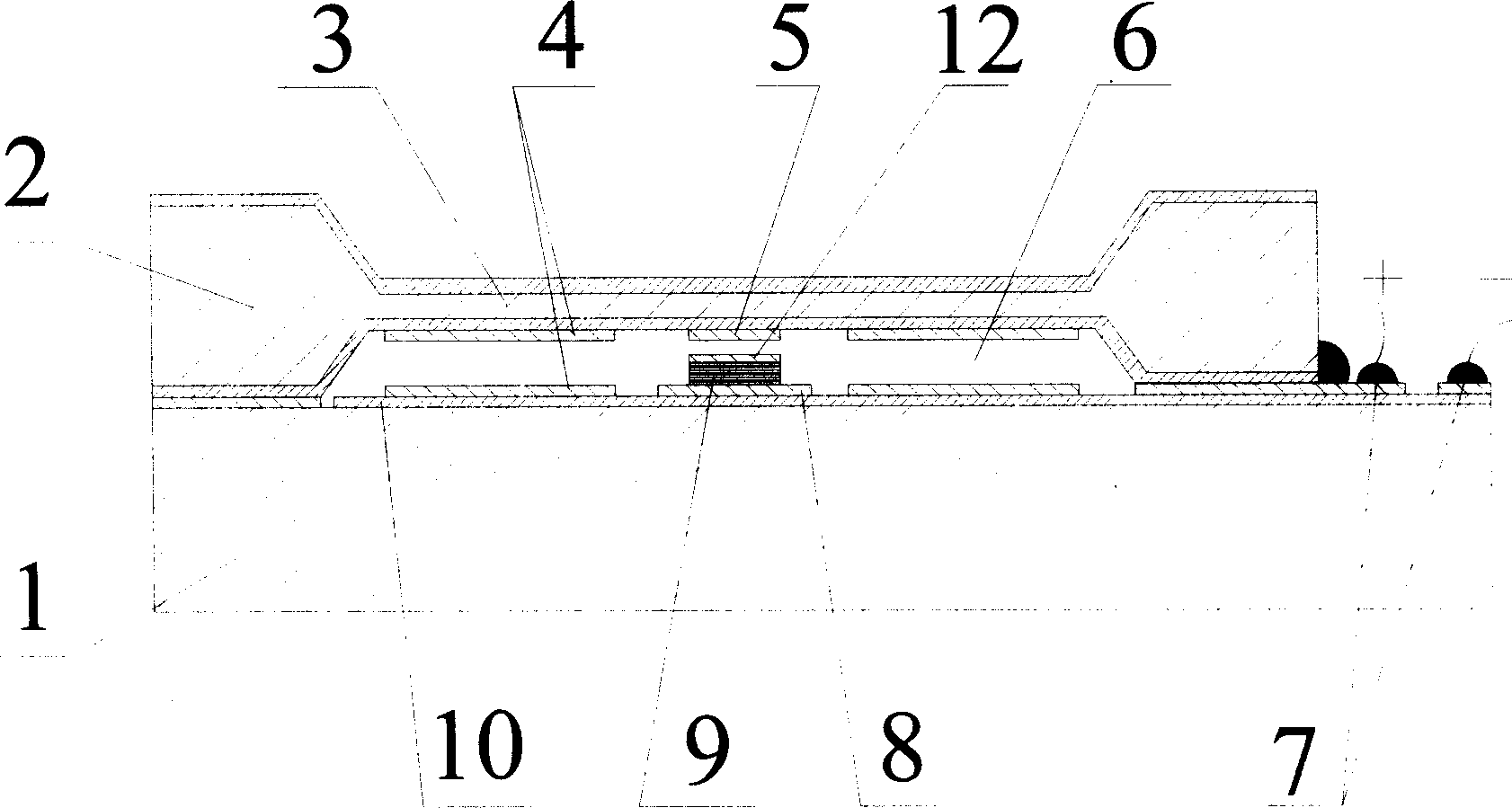

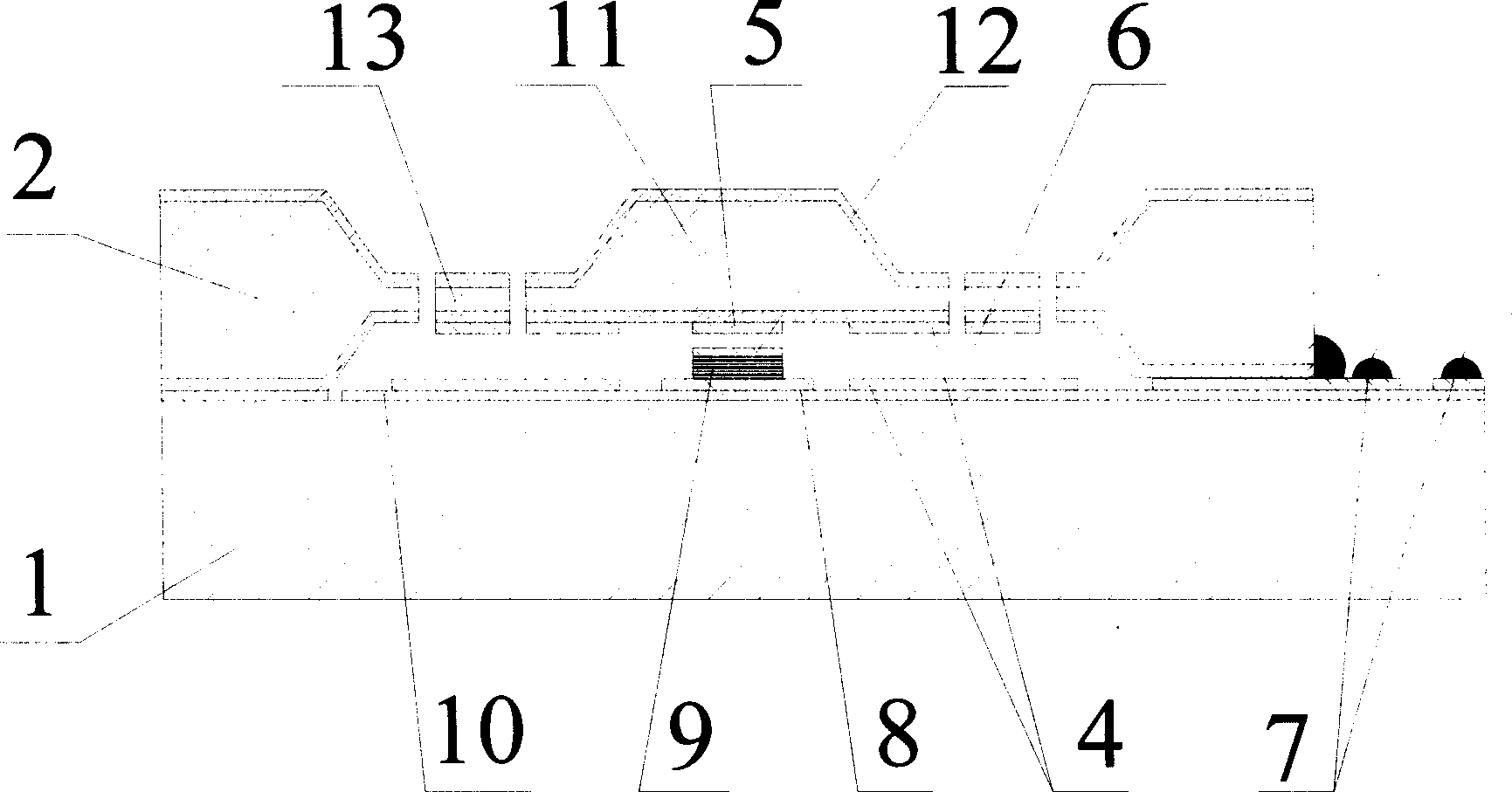

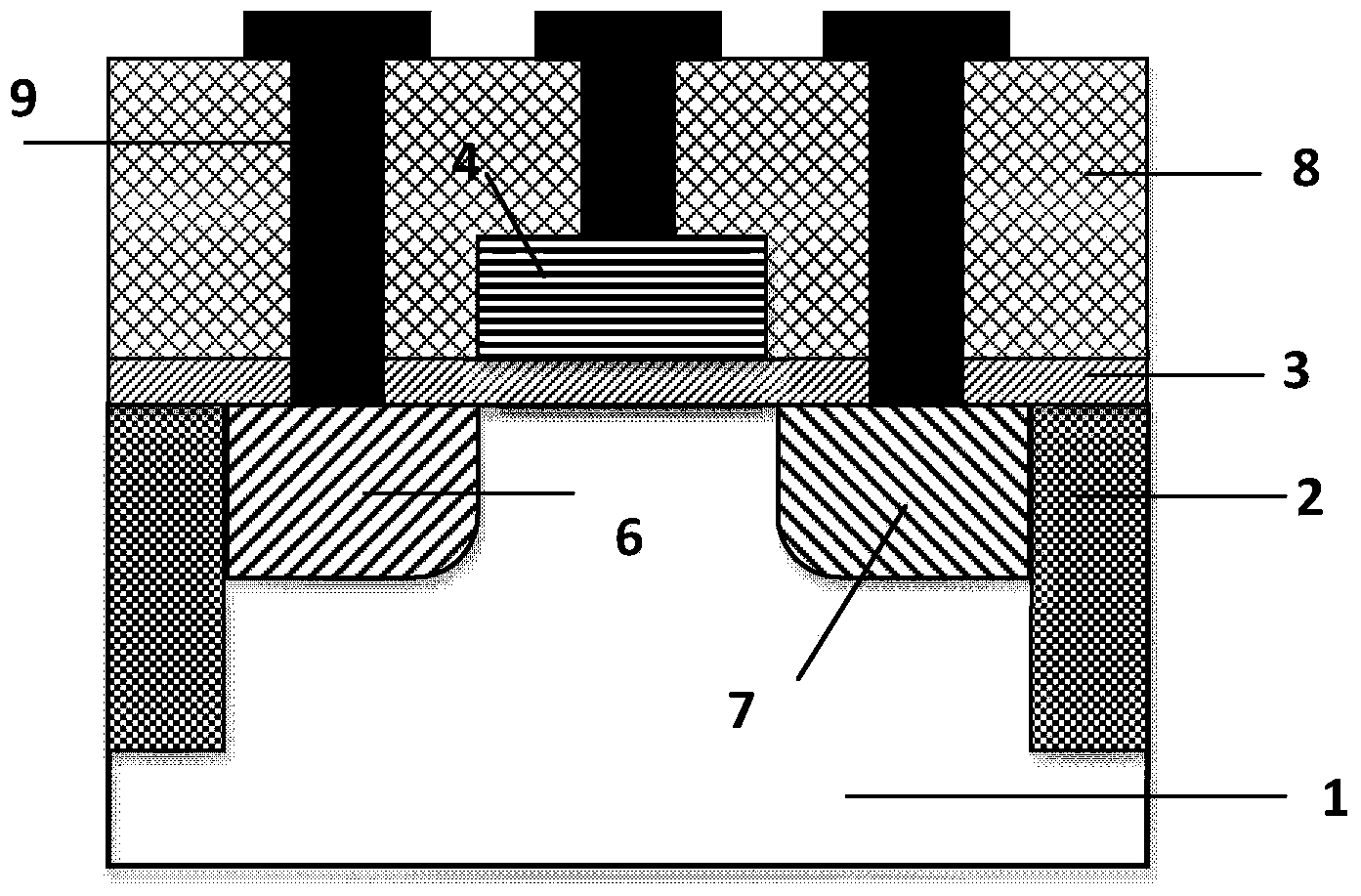

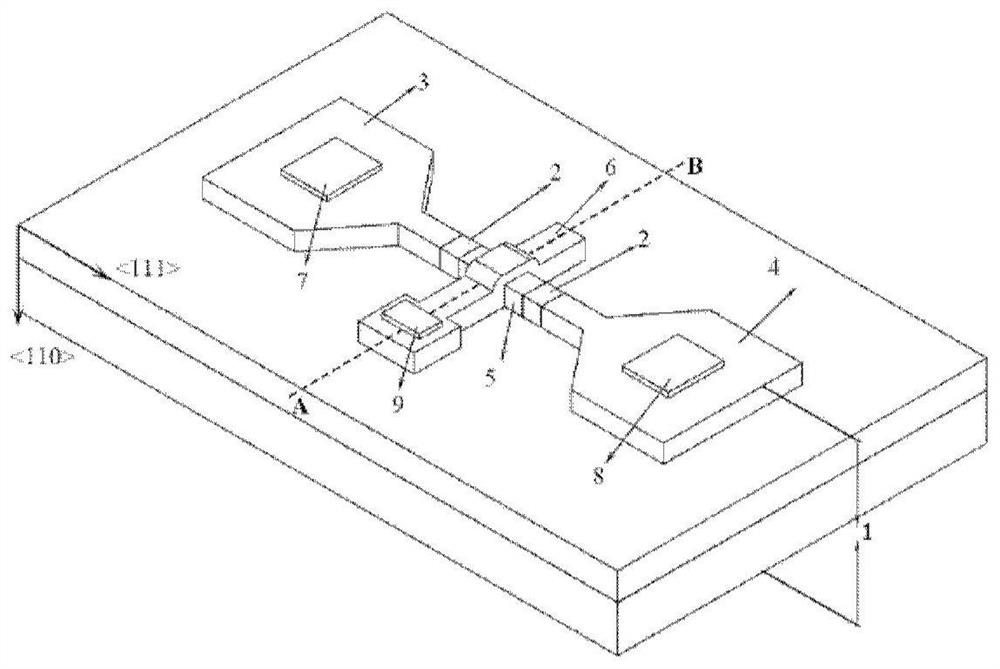

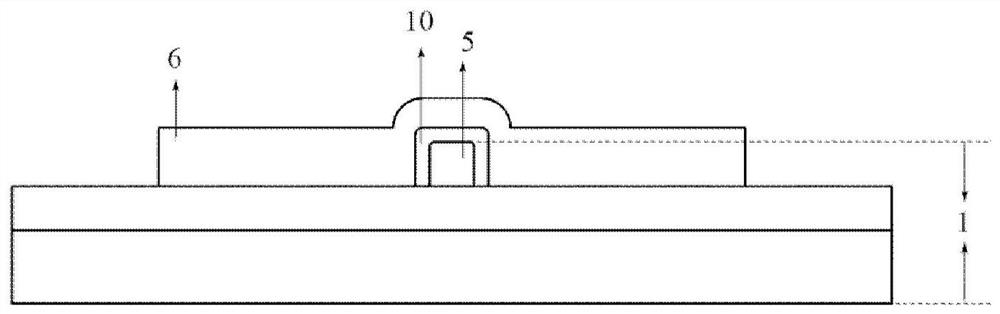

Novel micro-accelerometer based on mesoscopic piezoresistive effect

InactiveCN103364585AReasonable structural designHigh detection sensitivityAcceleration measurement using interia forcesAccelerometerThin membrane

A novel micro-accelerometer based on the mesoscopic piezoresistive effect is mainly and structurally composed of a bonding substrate, a sensitive mass block, a supporting frame body, resonant tunneling devices and combined beams. Each resonant tunneling deice is composed of a resonant tunneling material thin film layer, a resonant tunneling device positive pole and a resonant tunneling device negative pole. Each combined beam is composed of a detection beam, a connection block and a transverse buffering beam. The bonding substrate serves as a carrier, the supporting frame body is bonded on the bonding substrate, the center position of each of the four edges of the supporting frame body is connected with one combined beam, one combined beam is connected to the center position of each of the four edges of the sensitive mass block, the other sides of the combined beams are connected with the supporting frame body, and each combined beam is composed of the detection beam, the connection block and the transverse buffering beam. Each resonant tunneling material thin film layer is of a multi-potential-barrier voltage-sensitive structure and can enable the sensitivity of a silicon piezoresistive device to be improved by 1-2 orders of magnitude. The novel micro-accelerometer based on the mesoscopic piezoresistive effect is reasonable and compact in structure, convenient to detect, high in precision, good in reliability and suitable for miniaturization, and has strong lateral resistance.

Owner:ZHONGBEI UNIV

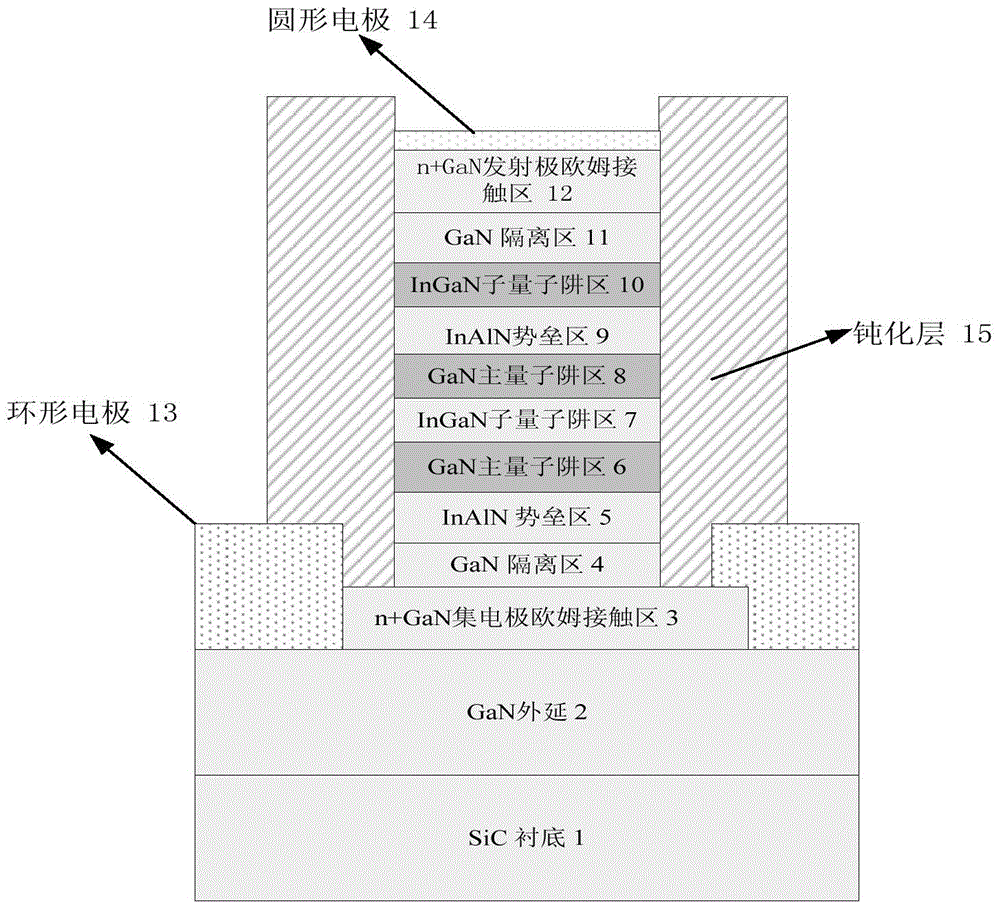

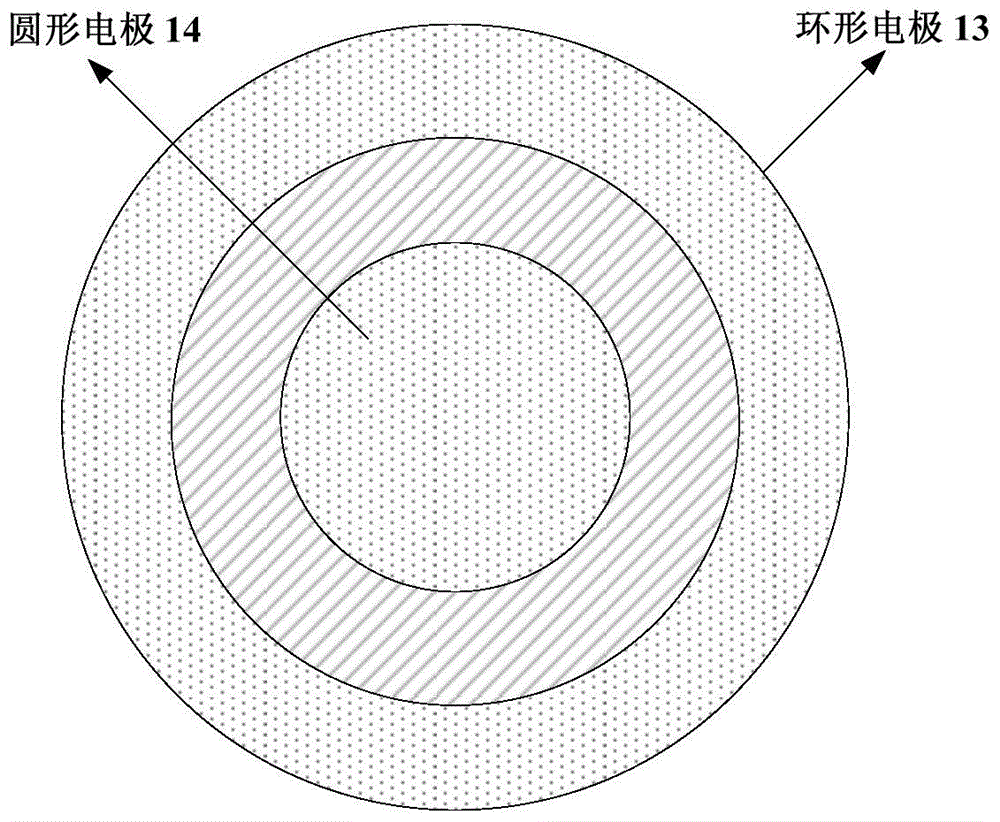

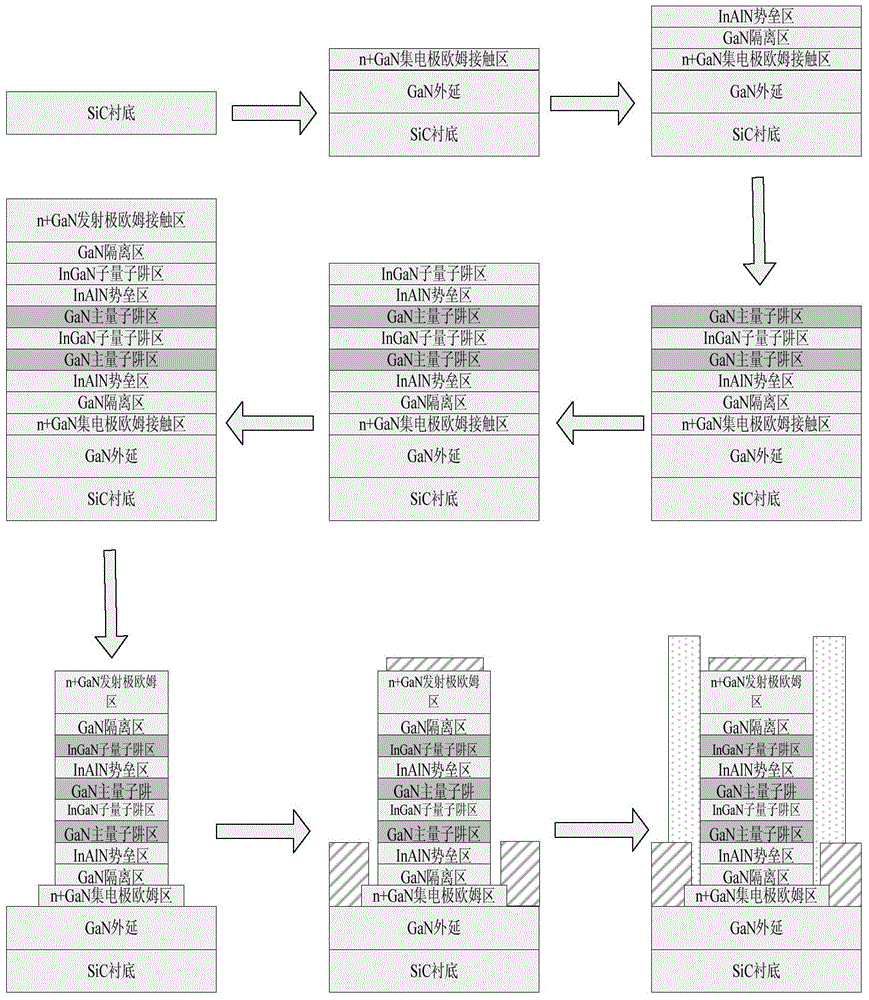

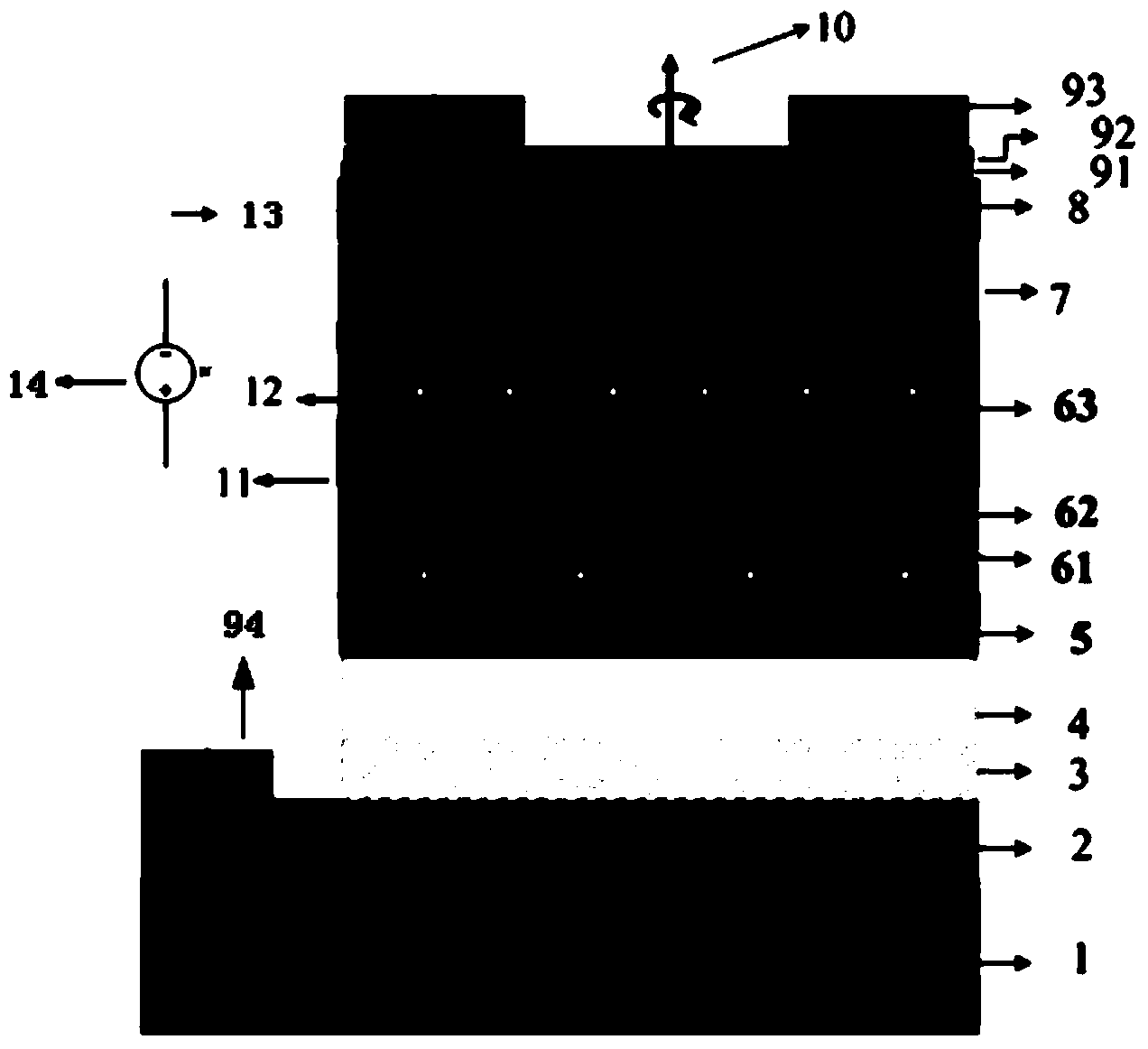

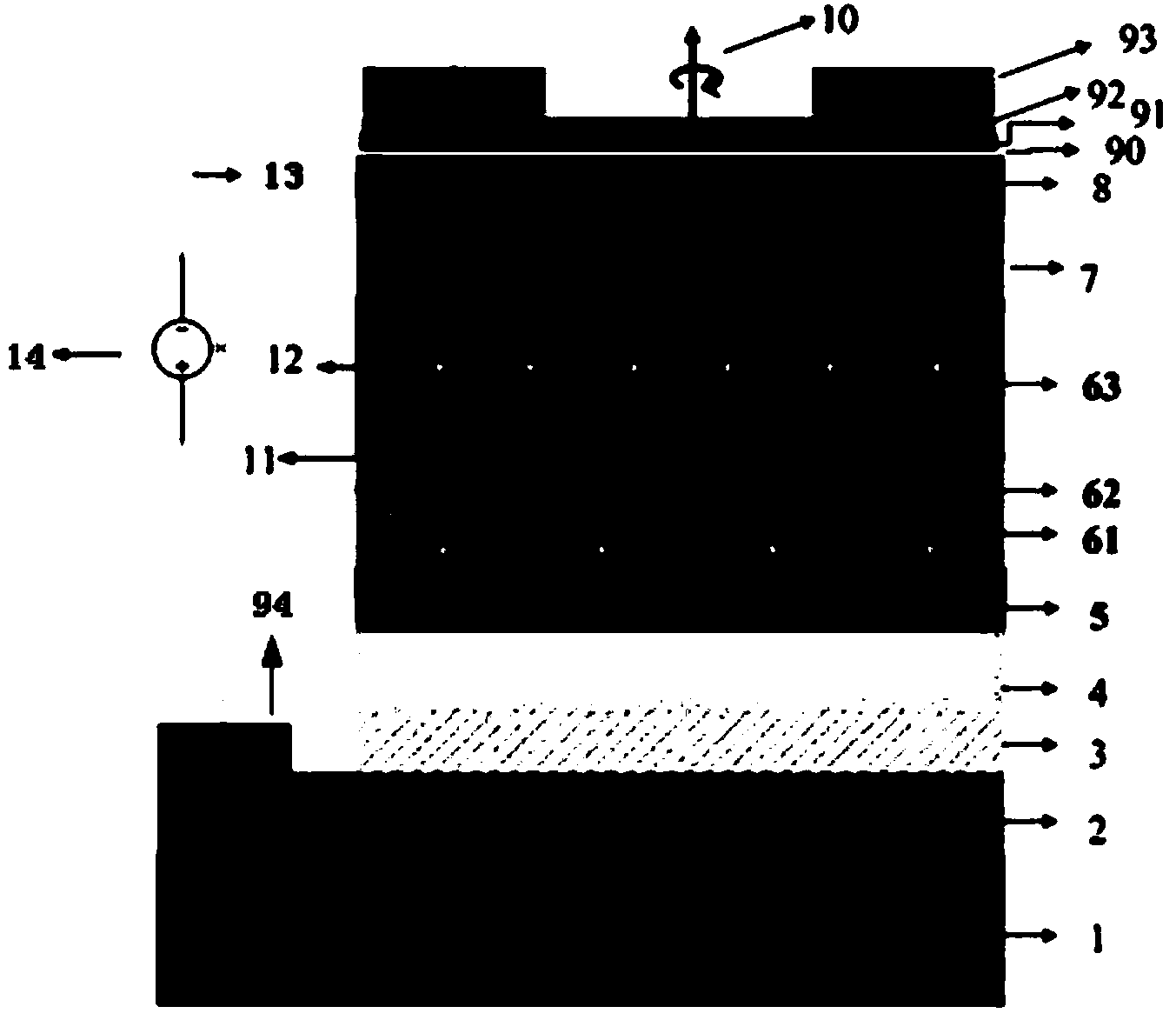

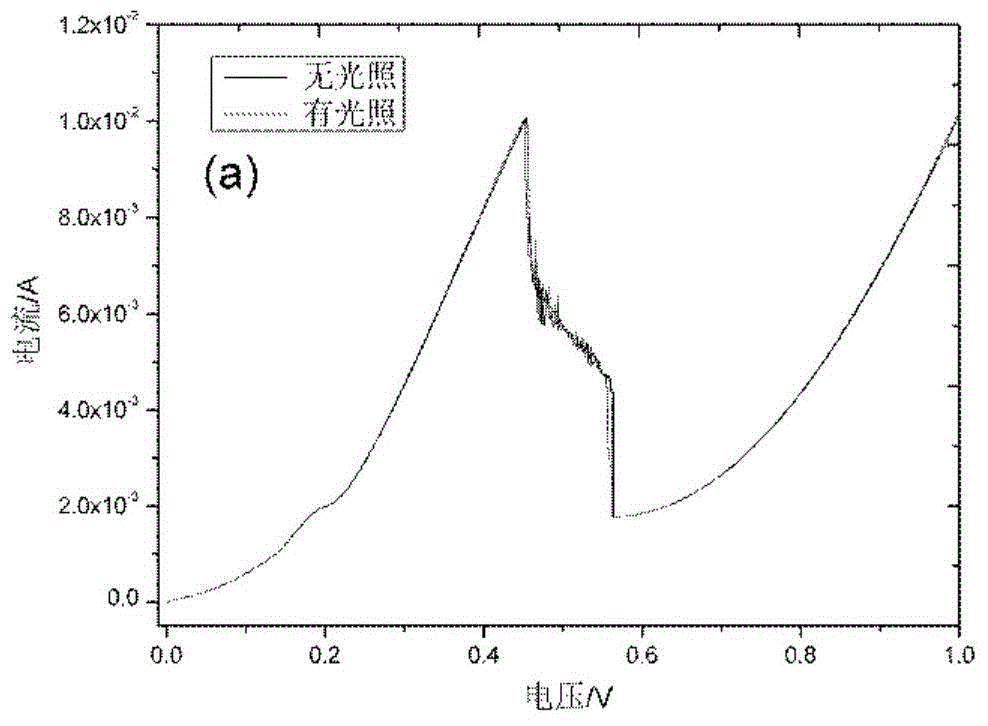

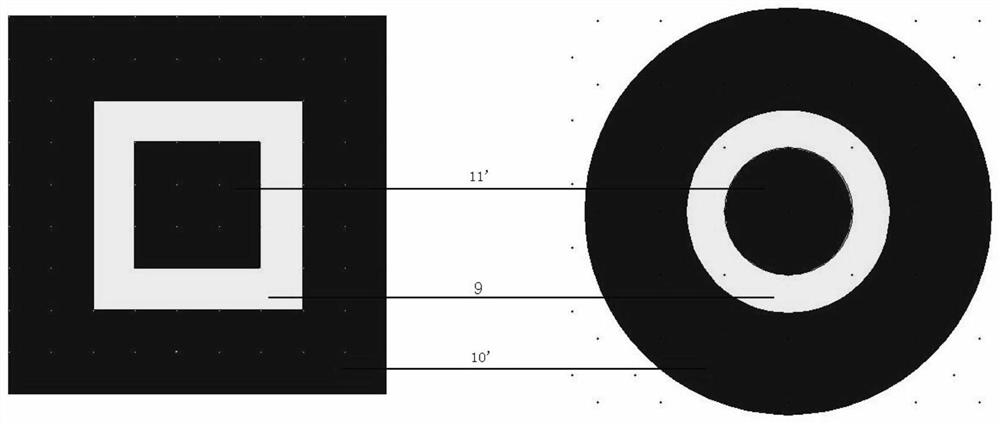

Resonance tunneling diode with double InGaN sub quantum wells and manufacturing method thereof

ActiveCN104465913AIncrease peak currentReduce power consumptionSemiconductor devicesPower flowTerahertz radiation

The invention discloses a resonance tunneling diode with double InGaN sub quantum wells. The resonance tunneling diode mainly solves the problems that an existing device is small in tunneling current and poor in I-V character repeatability. The resonance tunneling diode comprises a main body and an auxiliary body, the main body is divided into a SiC substrate layer, a GaN epitaxial layer, an n+GaN collector ohmic contact layer, a first GaN isolating layer, a first InAlN barrier layer, a first GaN main quantum well layer, a second GaN main quantum layer, a second InAlN barrier layer, a second GaN isolating layer and an n+GaN emitter diode ohmic contact layer from bottom to top, and the auxiliary part is provided with an annular electrode, a round electrode and a passivation layer. The annular electrode is arranged above the n-GaN collector ohmic contact layer, the round electrode is arranged above the n+GaN emitter ohmic contact layer, and the passivation layer is arranged above the annular electrode and the round electrode. The resonance tunneling diode can effectively improve the power of the device, reduce power consumption and improve the repeatability and is suitable for the terahertz radiation frequency band work.

Owner:晋江三伍微电子有限公司

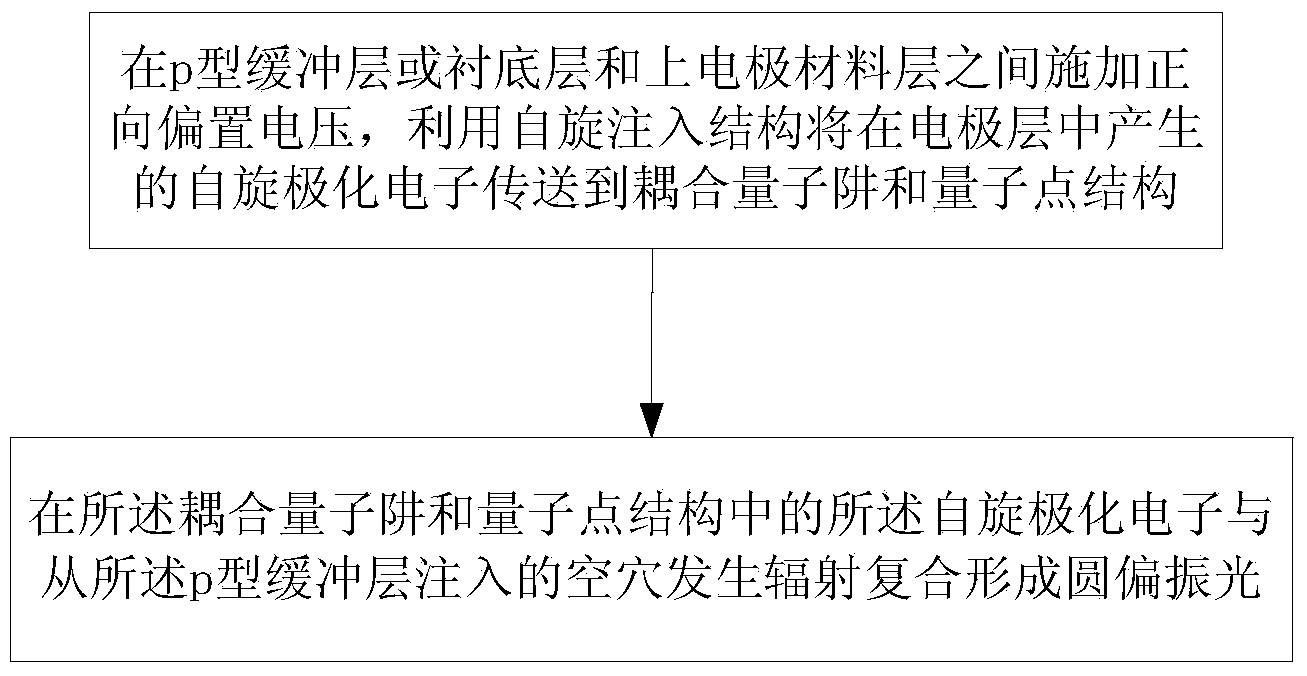

Spin-photoelectron device and spin injection method thereof

InactiveCN103779463ASolve the problem of extremely low spin injection efficiencySolve the problem of severe spin lossSemiconductor devicesContact layerTunnel junction

The invention provides a spin-photoelectron device and a spin injection method of the spin-photoelectron device. According to the method, spin-polarized electrons generated by a magnetic metal layer are conveyed to a coupled quantum well and quantum dot structure through a spin injection structure formed by an n-type contact layer and an electrode layer, an M-S Schottky junction or M-O-S tunnel junction is preferentially selected as the spin injection structure, and therefore the problem of extremely-low spin injection efficiency caused by conductivity mismatching of magnetic metal and a semiconductor in the prior art is solved. The growth sequence of the coupled quantum well and quantum dot structure is as follows: a quantum dot layer, a spacing layer and a quantum well layer, the resonance-tunneling effect between the ground state level of ground-state electrons of a quantum well and the excited state level of quantum dots can be achieved by adjusting components of the quantum dot layer of a semiconductor, components of the quantum well layer of the semiconductor, the thickness of the spacing layer and other parameters, the problem of spin loss caused by energy relaxation is solved, and the spin-polarized electrons can be efficiently injected into the quantum dots of the semiconductor very fast.

Owner:苏州强明光电有限公司

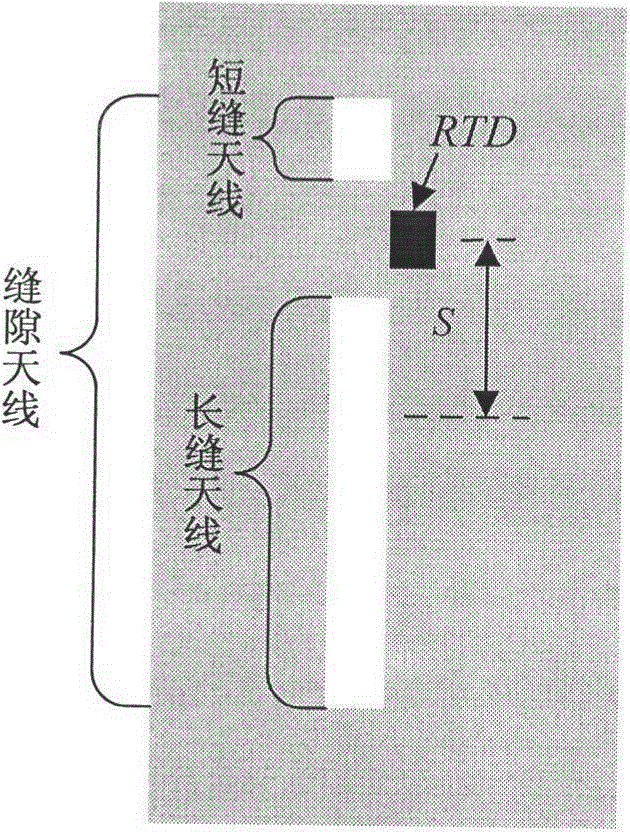

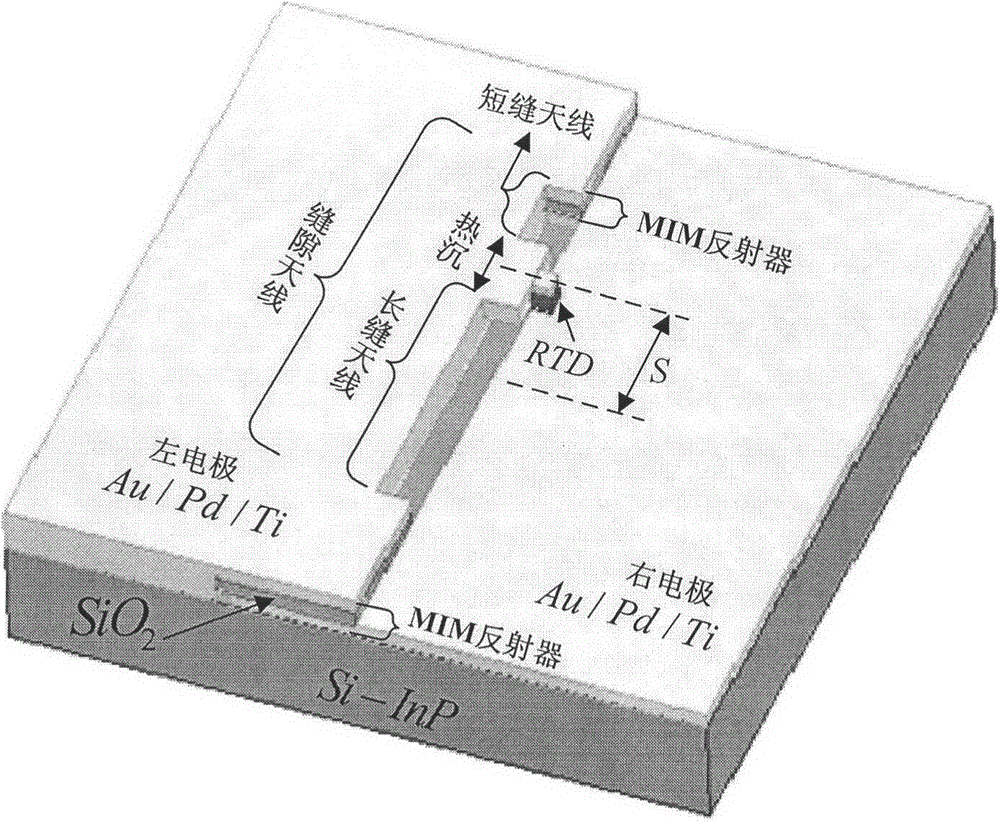

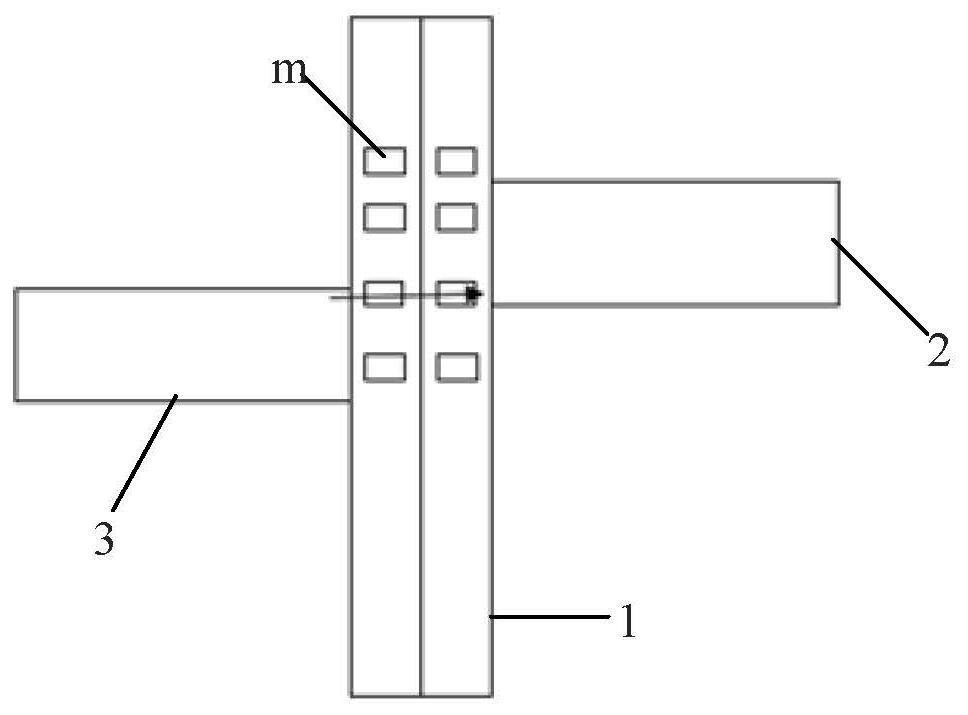

Detuning feed slot antenna based on resonance tunneling mechanism

The invention discloses a detuning feed slot antenna based on a resonance tunneling mechanism, and belongs to the field of antennas. The detuning feed slot antenna based on the resonance tunneling mechanism comprises a detuning feed slot antenna body and a RTD. The resonance tunneling diode serves as an excitation device and is used for generating terahertz waves, and the detuning feed slot antenna body serves as an electromagnetic wave transmitting device and is used for transmitting the terahertz waves generated by the resonance tunneling diode out. The top electrode of the RTD is connected with a left electrode of the detuning feed slot antenna body through a heat sink, and the bottom electrode of the RTD is connected with the right electrode of the detuning feed slot antenna body. The detuning feed slot antenna based on the resonance tunneling mechanism has important application in the fields of superspeed data link transmission, wireless communication, military and national defense and the like.

Owner:TIANJIN POLYTECHNIC UNIV

Resonant tunneling micro mechanical force sensor and method for manufacturing the same

InactiveCN1632486AHigh sensitivityReduce power consumptionTelevision system detailsAcceleration measurement using interia forcesSemiconductor materialsConductive materials

It is resonance tunneling micro mechanical force sensor and its process method, which belongs to micro mechanical system and sensor technique field. This invention discloses a resonance tunneling micro mechanical force sensor, which mainly comprises upper and down silicon pad, wherein, the upper silicon pad has grown tunneling positive electrode on down surface; the down silicon pad has grown tunneling negative electrode in the upper surface at relative position area. The tunneling negative electrode surface grows multiple thin films of tunneling knots. The multiple structures is formed by isolation layer material and metal material alternately or by different gap semi-conductive material. This invention also discloses the process method of the said micro mechanical force sensor.

Owner:TSINGHUA UNIV

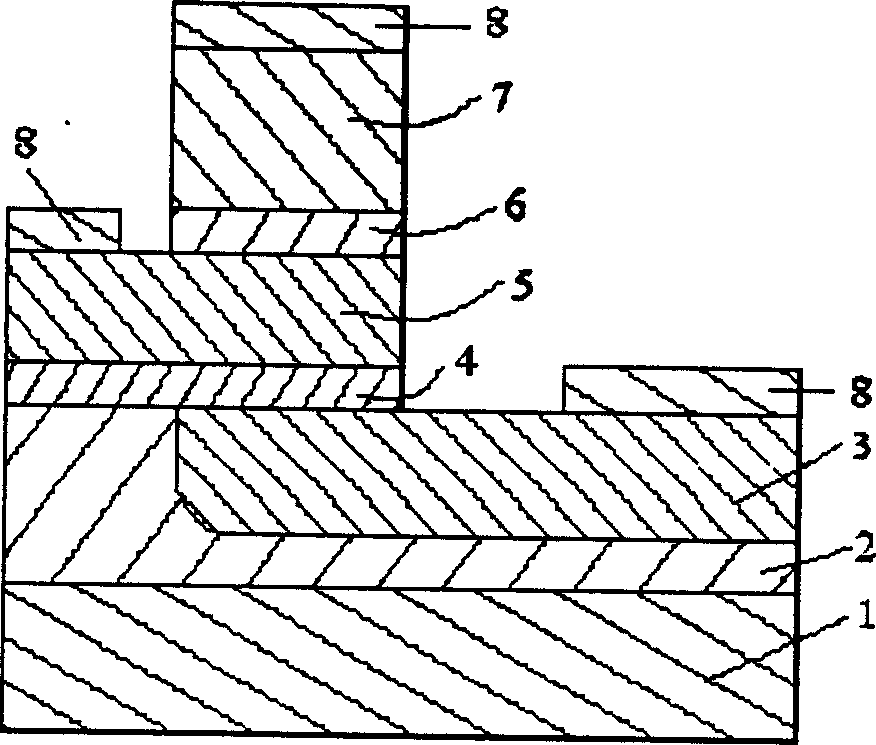

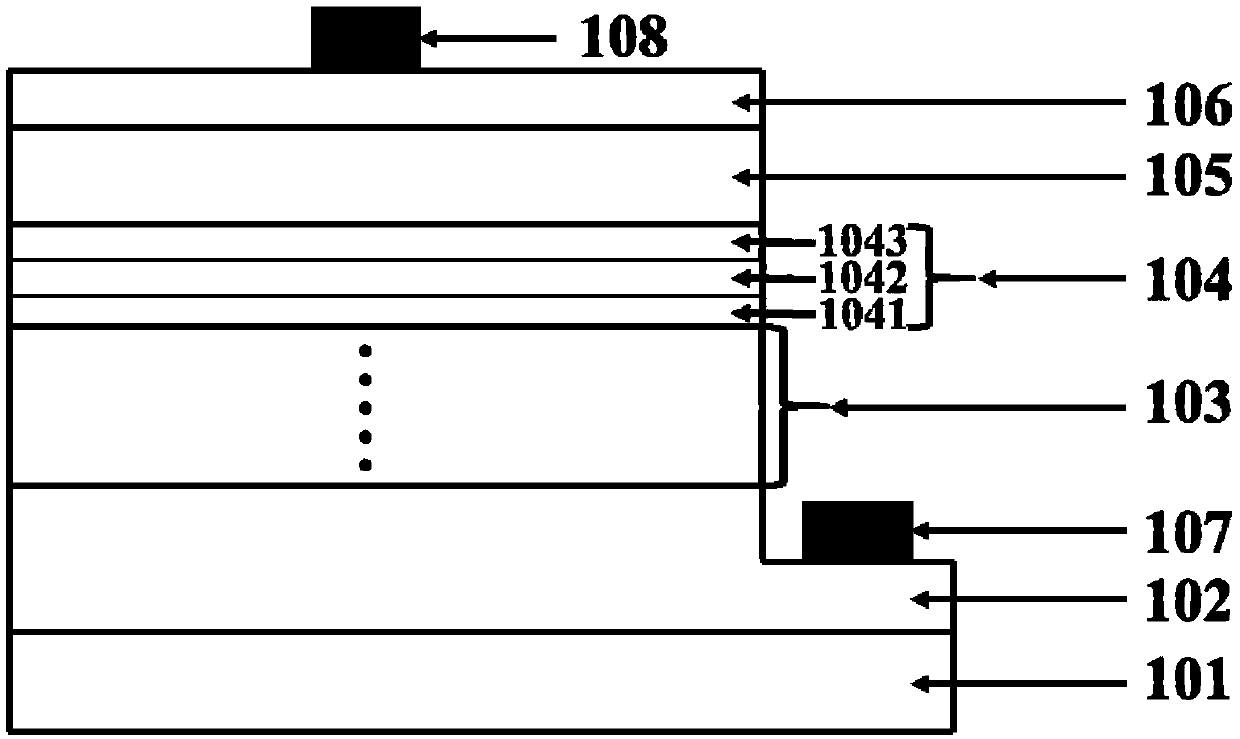

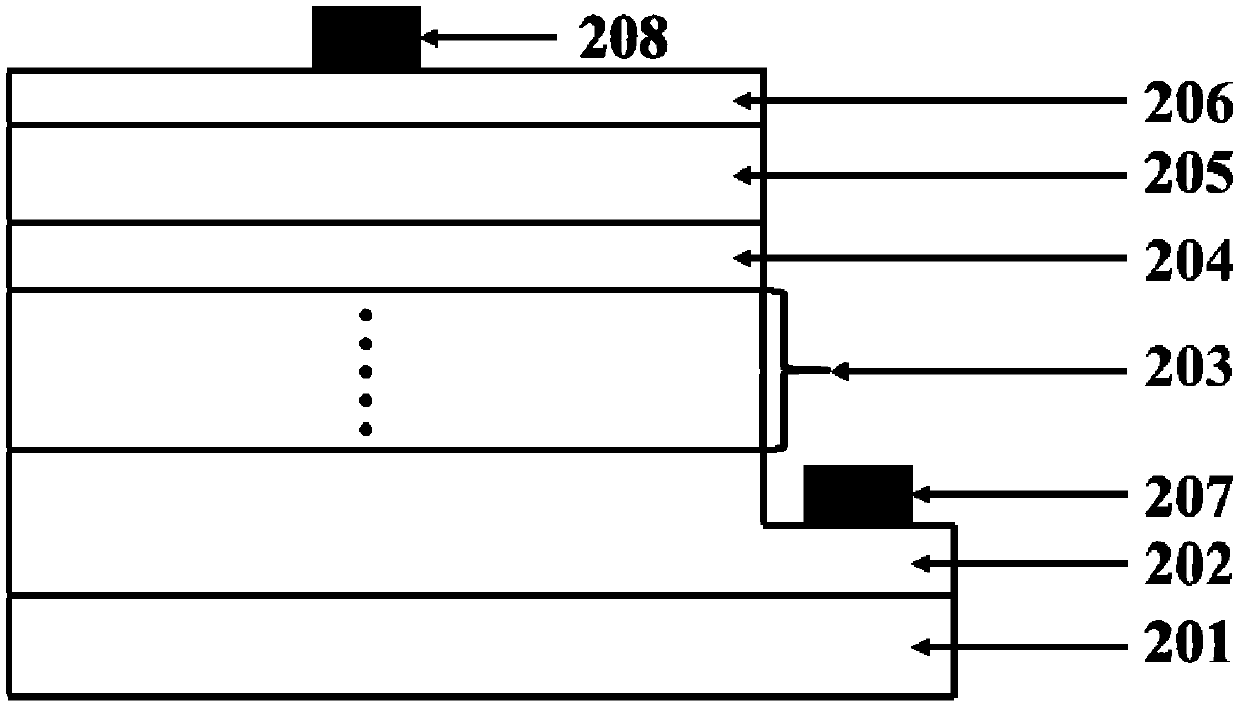

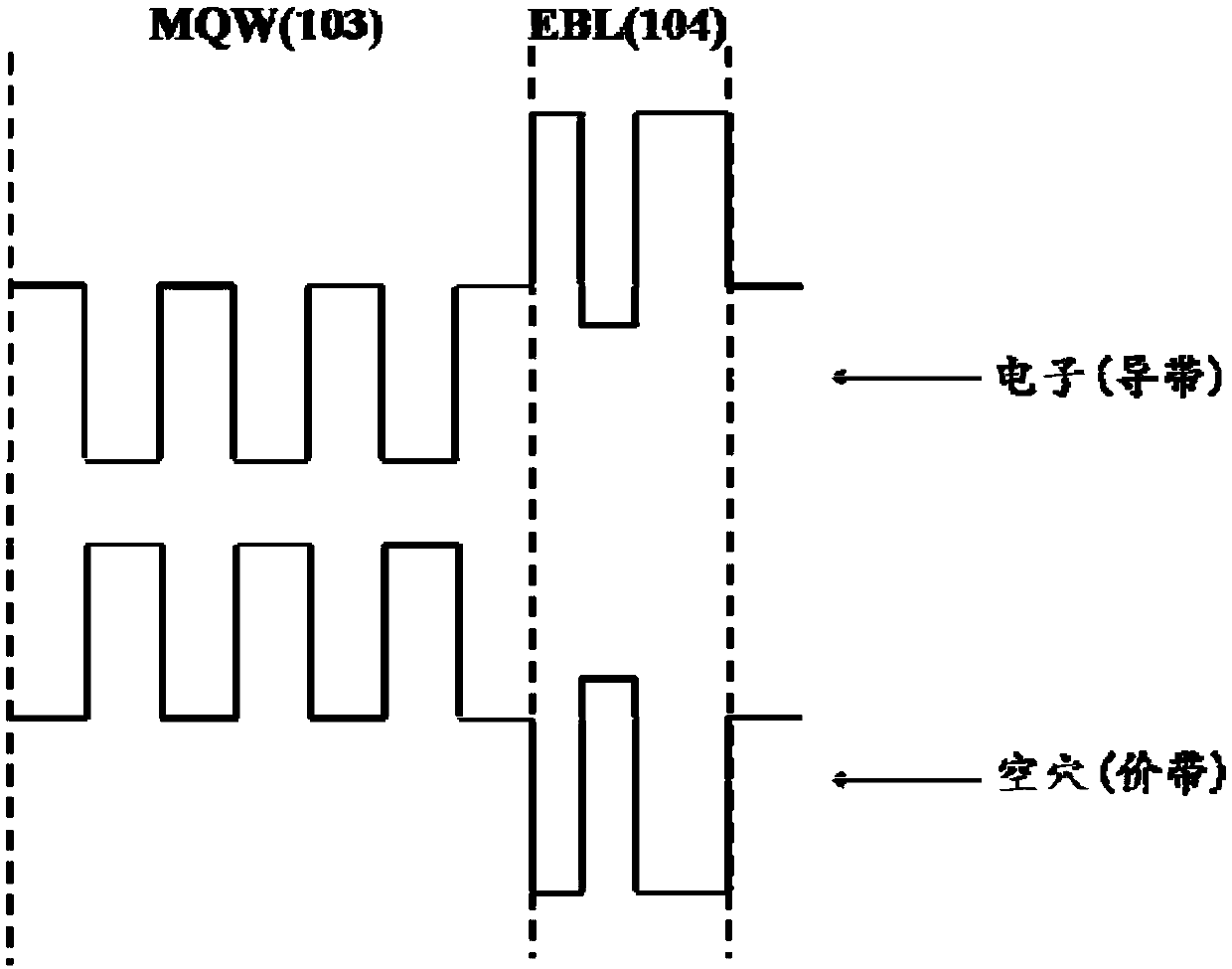

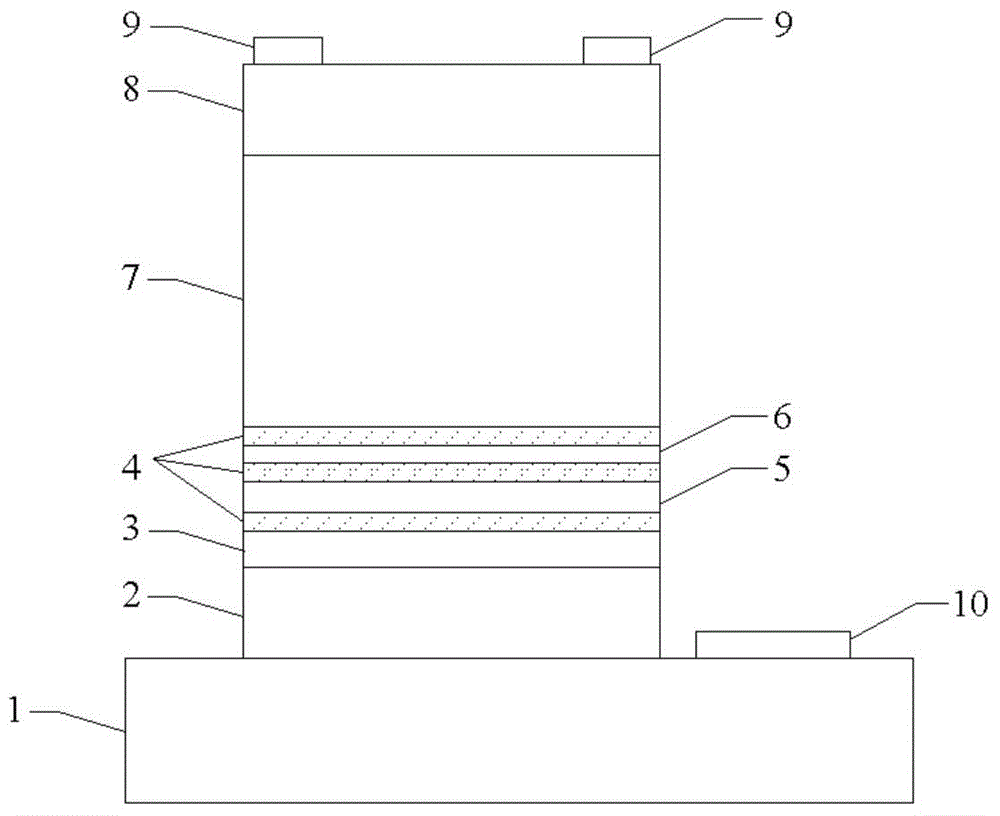

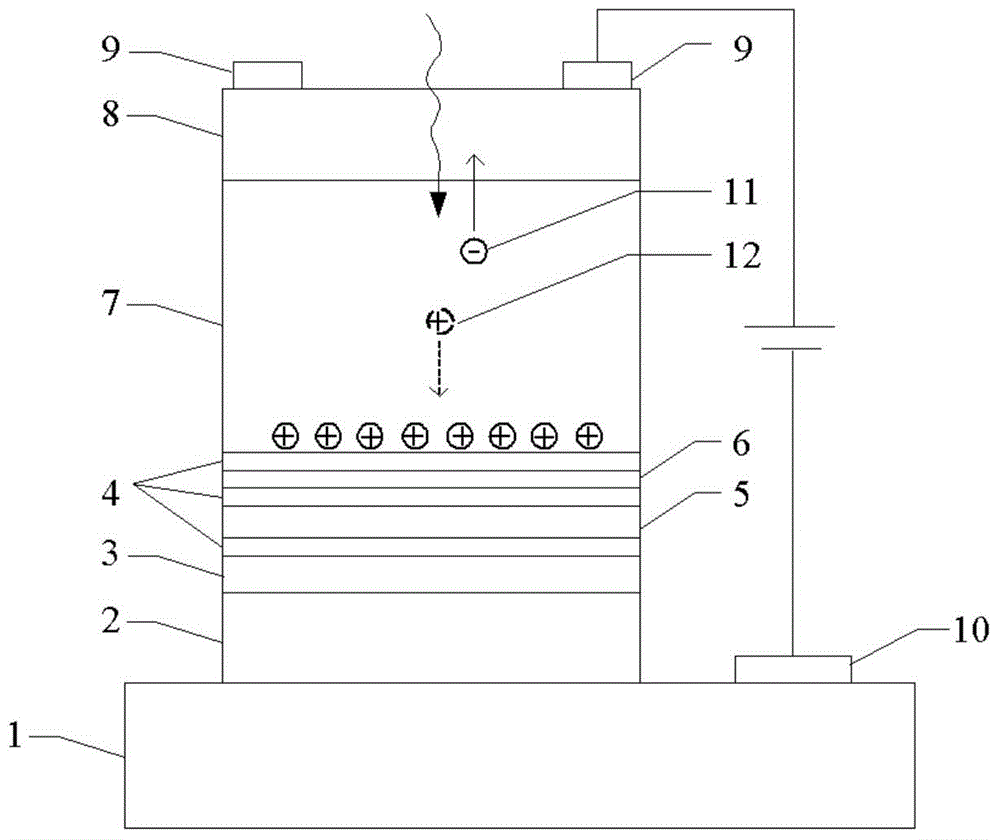

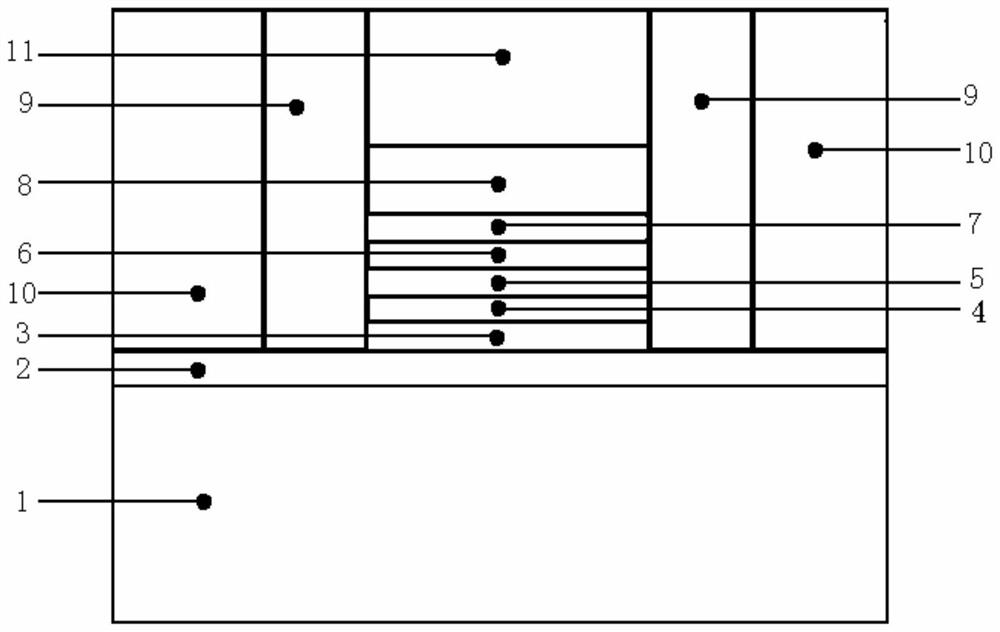

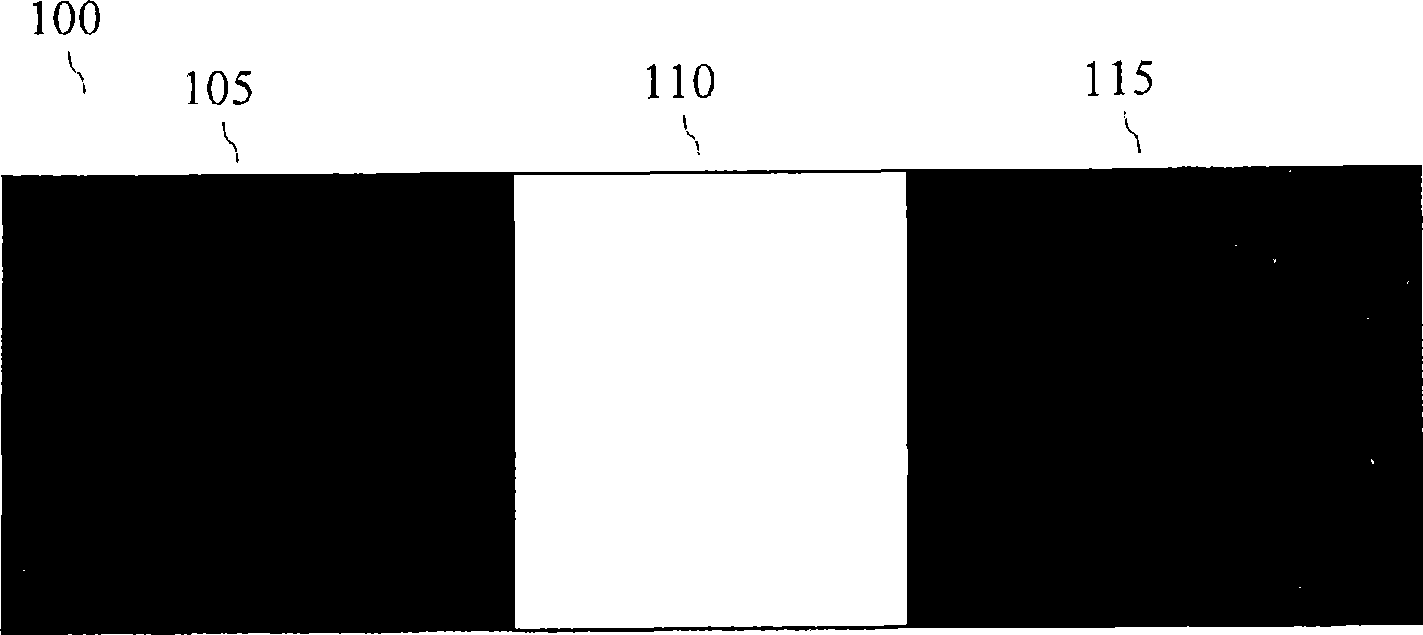

Light emitting diode with electron blocking layer in resonant tunneling structure

ActiveCN107195746AImprove the blocking effectIncreased efficiency of injection into the active regionSemiconductor devicesPotential wellOhmic contact

The invention discloses a light emitting diode with an electron blocking layer in a resonant tunneling structure. The light emitting diode comprises a substrate, an n-type nitride layer, a multiple quantum well layer, the electron blocking layer, a p-type nitride layer and a p-type nitride ohmic contact layer, an n-type electrode which is arranged on the n-type nitride layer, and a p-type electrode which is arranged on the p-type nitride layer, wherein the substrate, the n-type nitride layer, the multiple quantum well layer, the electron blocking layer, the p-type nitride layer and the p-type nitride ohmic contact layer are arranged in order from the bottom up. The electron blocking layer is composed of a p-type doped nitride barrier layer, a non-doped nitride potential well layer, and a non-doped barrier layer which increases the hole transmittance through a resonance tunneling effect, wherein the p-type doped nitride barrier layer, the non-doped nitride potential well layer and the non-doped barrier layer are arranged in order from bottom to top. The light emitting diode provided by the invention has the advantages that electrons are effectively prevented from passing through an active region into a p-type region, which increases the injection efficiency of a hole into the active region through the electron blocking layer; a good electronic blocking effect is realized through a simple growth mode and less layer structures; and the hole injection efficiency significantly higher than a traditional electronic blocking layer structure is acquired.

Owner:SOUTHEAST UNIV

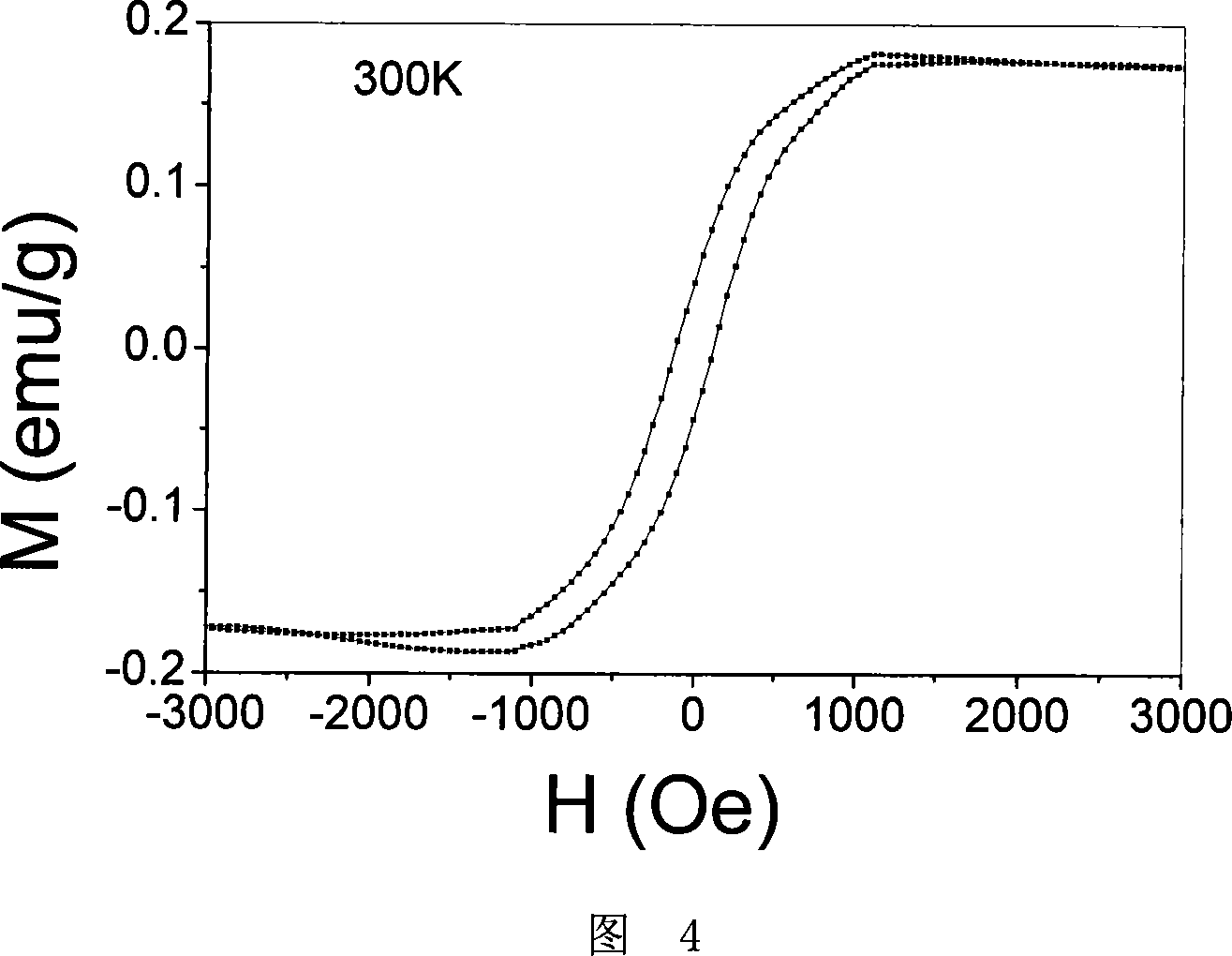

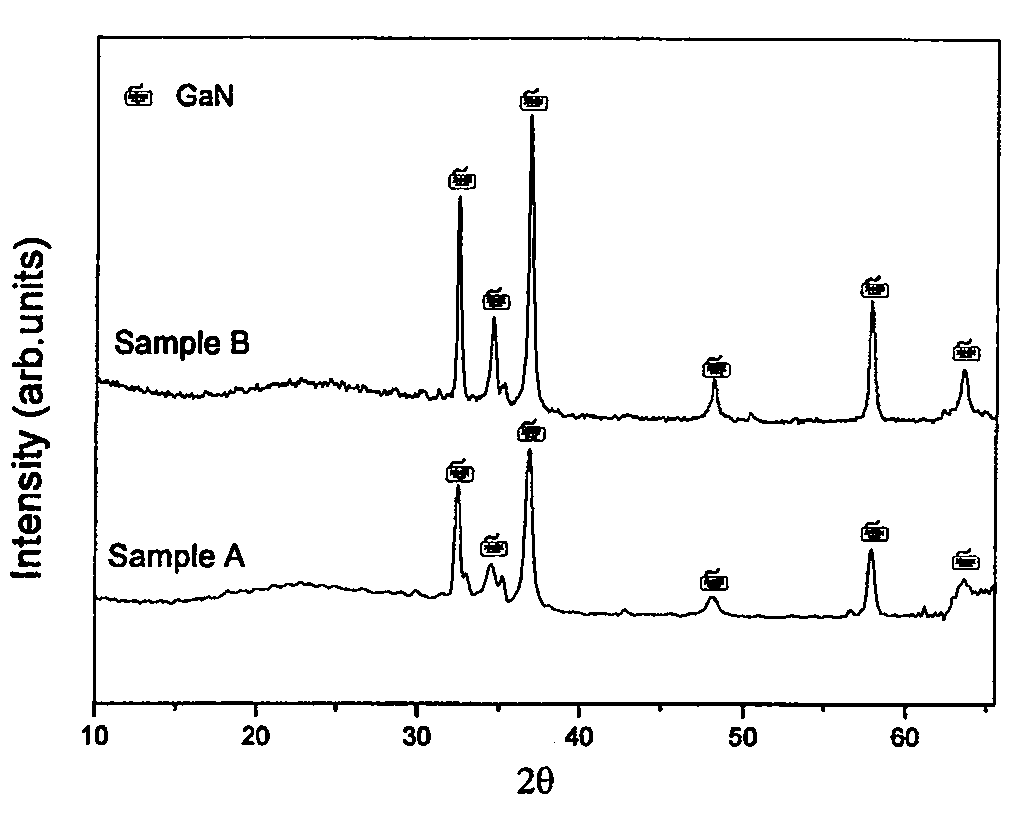

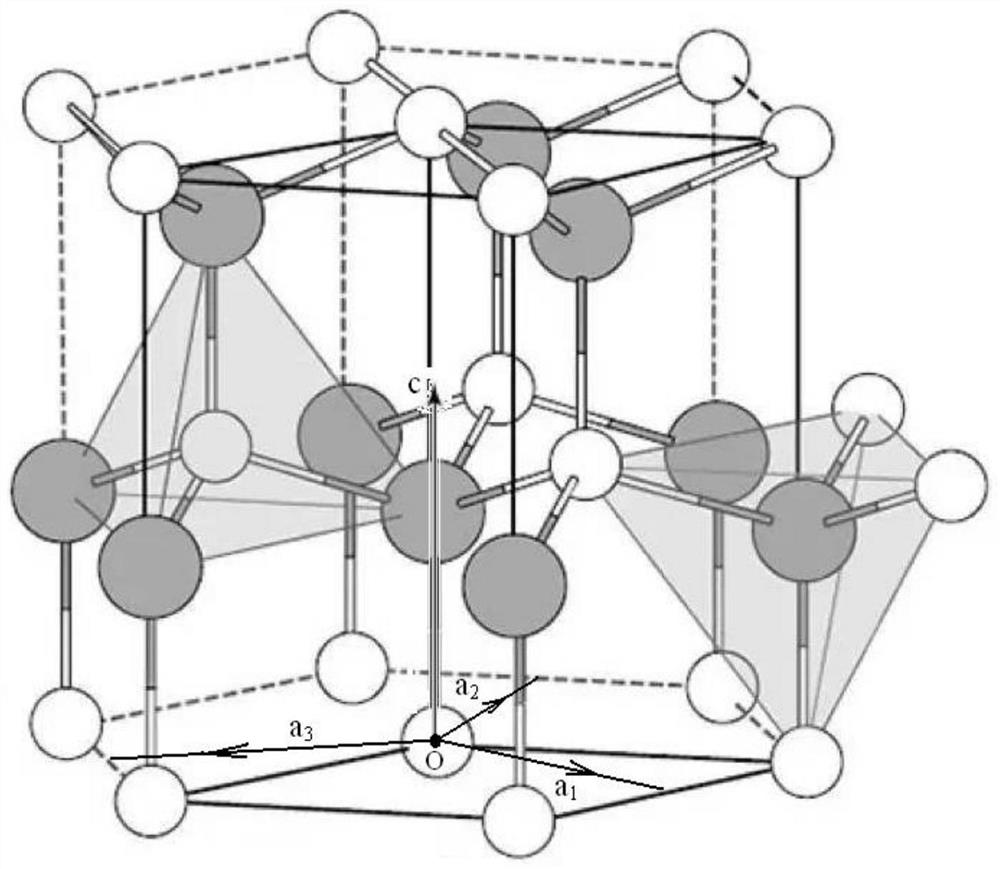

A method for making GaMnN sparse magnetic semiconductor nano wire

InactiveCN101127303AStrong ferromagnetismIncrease productionSemiconductor/solid-state device manufacturingNanowireCurie temperature

The utility model discloses a method for preparing the GaMnN diluted magnetic semiconductor nanowire, comprising the following steps: 1) Mn doping: Mn is in-situ doped on the Ga2O3 nanowire; 2) ammonification: the Ga2O3 nanowire doped with the Mn is aminated in the ammonia atmosphere to obtain the GaMnN diluted magnetic semiconductor nanowire. The utility model has the advantages of simple method, low requirement for the equipment, strong ferromagnetism of the prepared GaMnN nanowire, higher Curie temperature than the ambient temperature, controllable magnetic doping concentration, high purity of the nanowire, high output and controllable linear (the nanowire with diameter varying from tens of nanometer to hundreds of nanometer is prepared through adjusting the growing parameters such as air pressure). The utility model is applied for producing the nanometer spin electronic devices, such as spin field effect transistor (spin-FET), spin light emitting diode (spin-LED) and spin resonance tunneling device (spin-RTD) and has broad application prospect.

Owner:PEKING UNIV

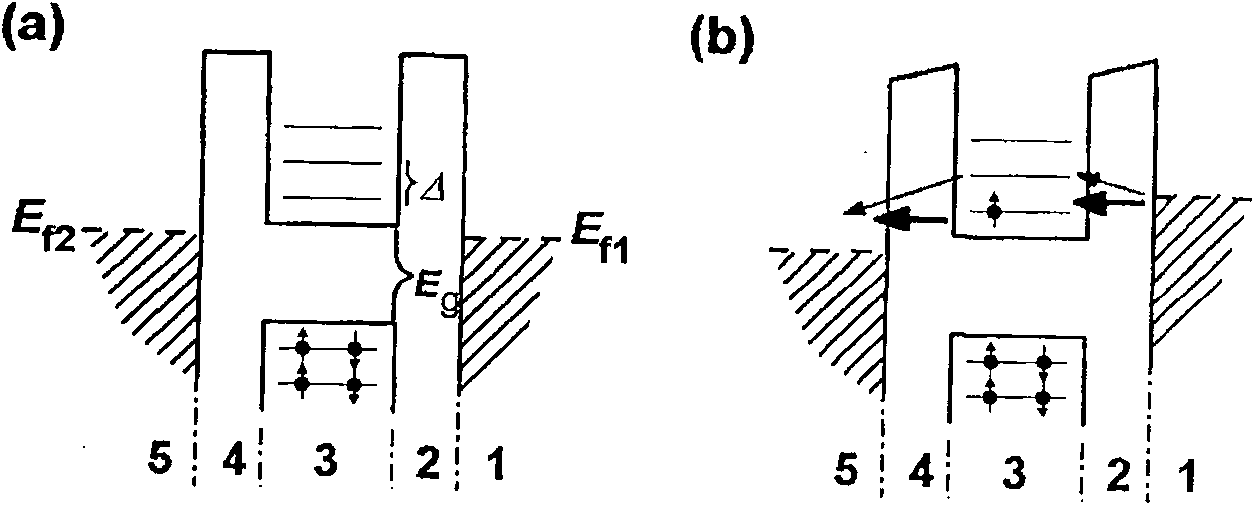

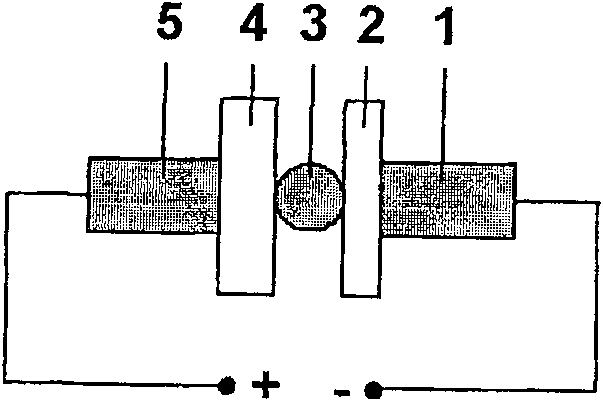

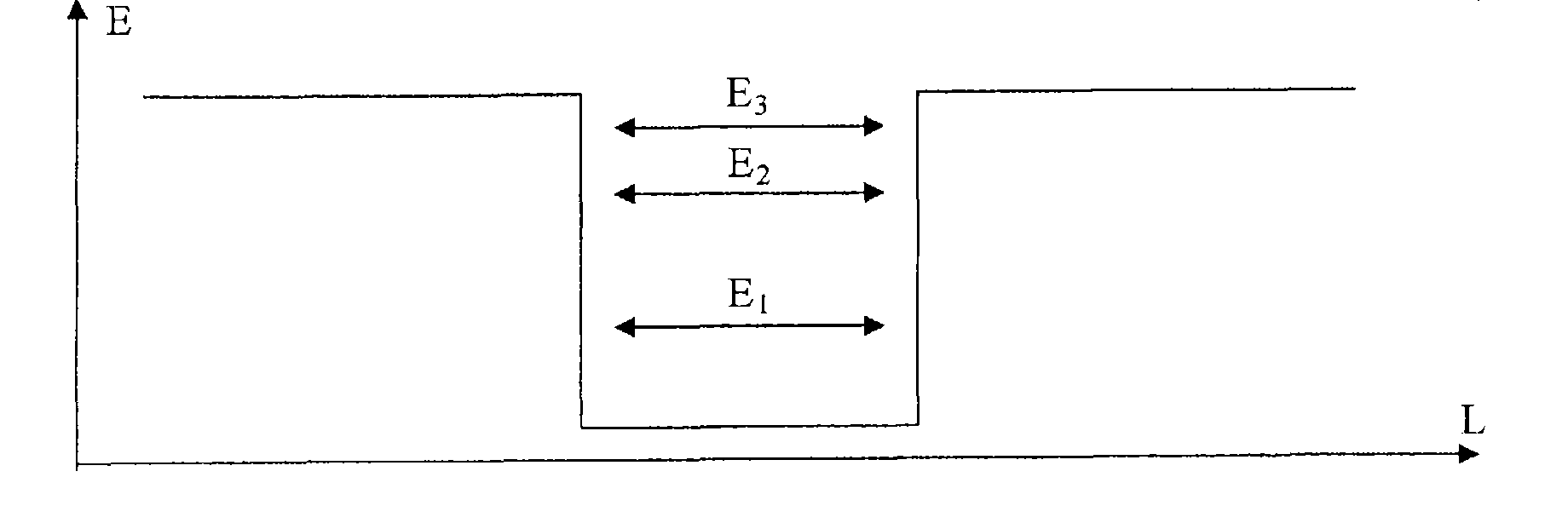

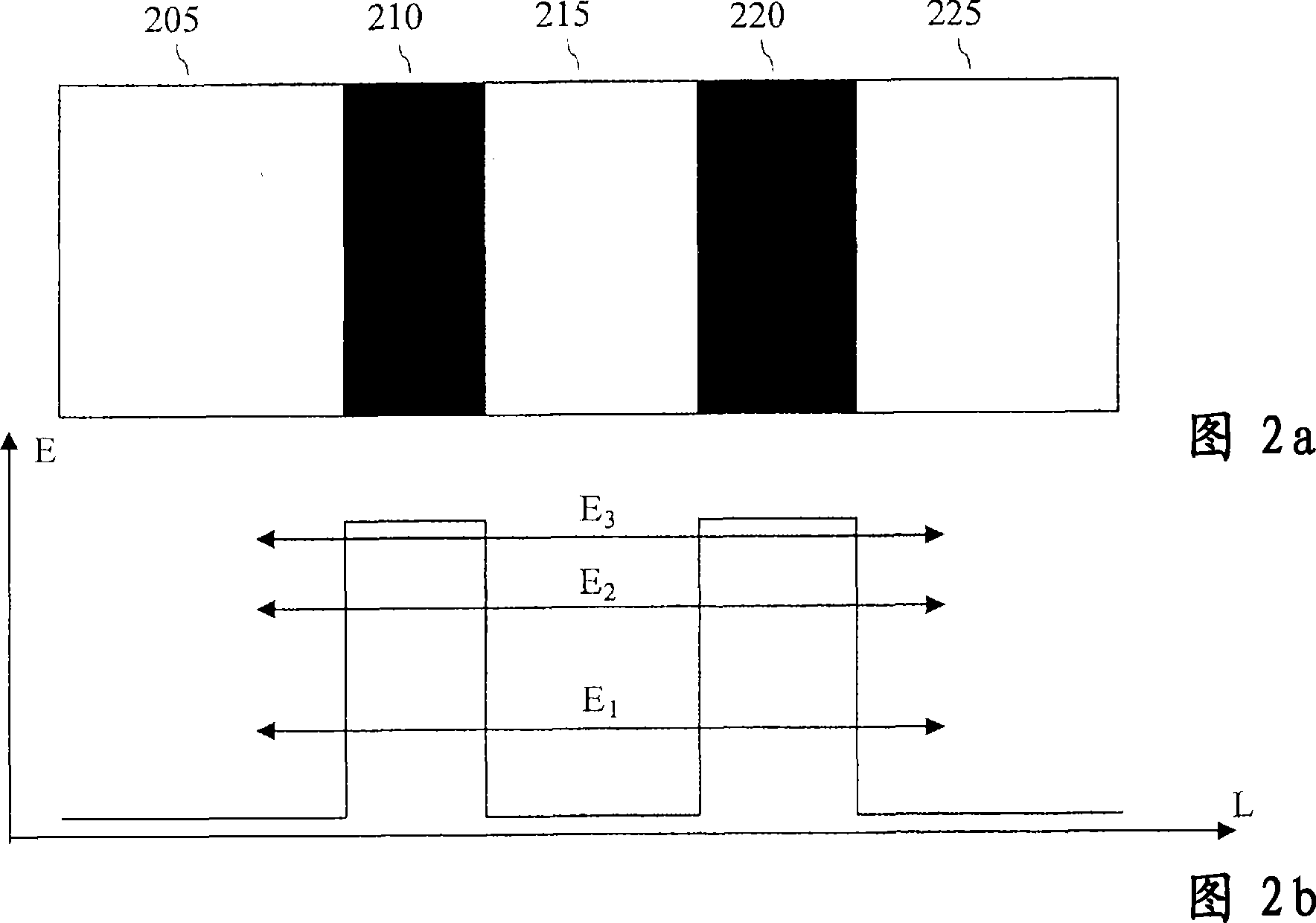

Transistor based on bibarrier tunnel junction resonance tunneling effect

ActiveCN1753187AReduce leakage currentLarge collector currentTransistorDiodeSchottky barrierSignal on

The invention relates to a transistor based on the resonance tunneling effect of double-barrier tunnel junction, comprising: substrate, emitter, base, collector, and first and second tunnel barrier layers, where the first one is arranged between the emitter and base and the second one is between the base and collector; and the areas of tunnel junctions formed between the emitter and base and between the base and collector are 1 sq um-10,000 sq um; thickness of the base is comparable with free stroke of electrons of its material; only one of the emitter, base and collector has a free magnetization direction. Because of double barrier structure, the invention overcomes Schottky barrier generated between the base and collector, where the base current is modulation signal, and makes modulation modes of collector signal and base current similar by changing the magnetization direction of the base or collector, thus making the resonance tunneling effect, and can obtain an amplified signal on proper conditions.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

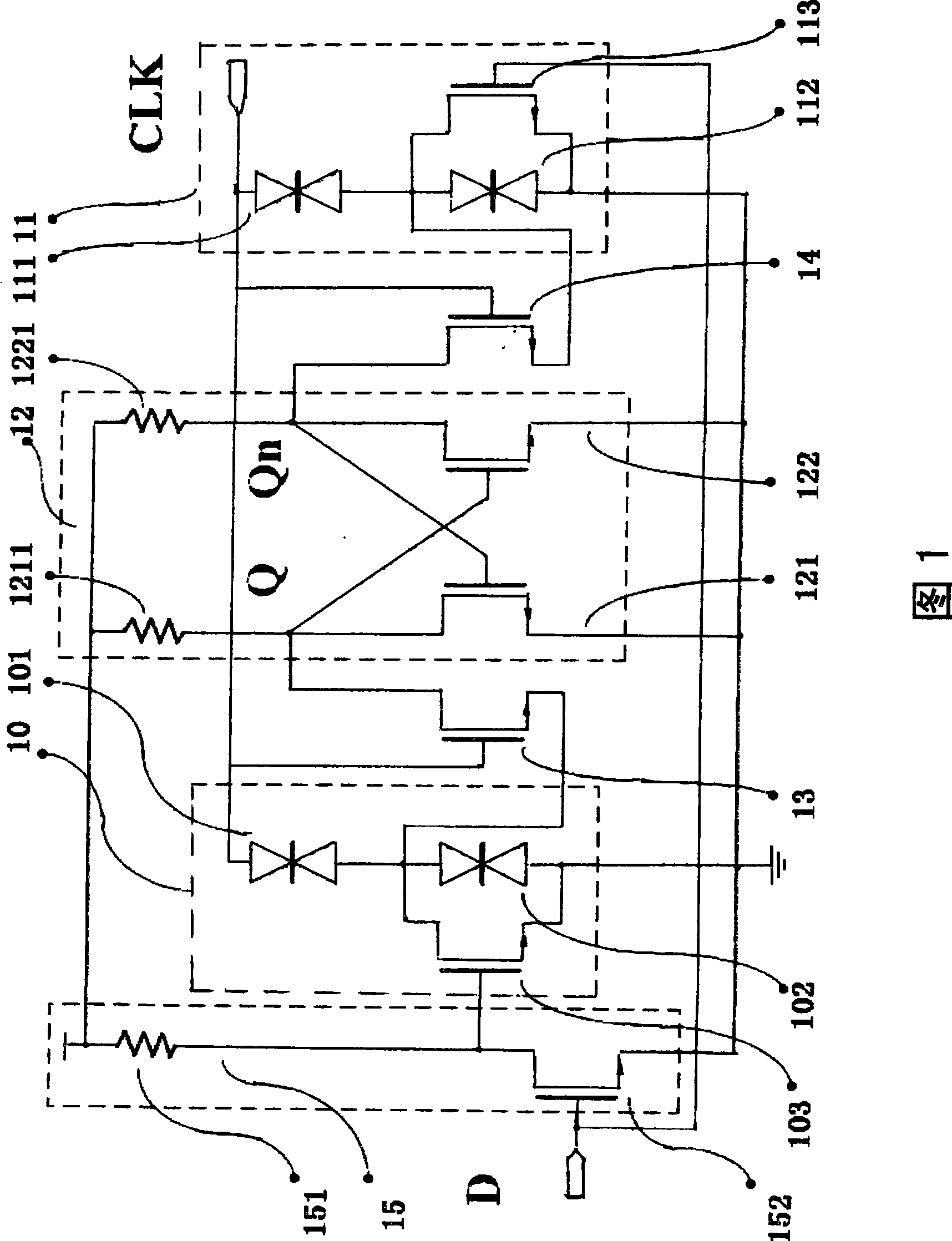

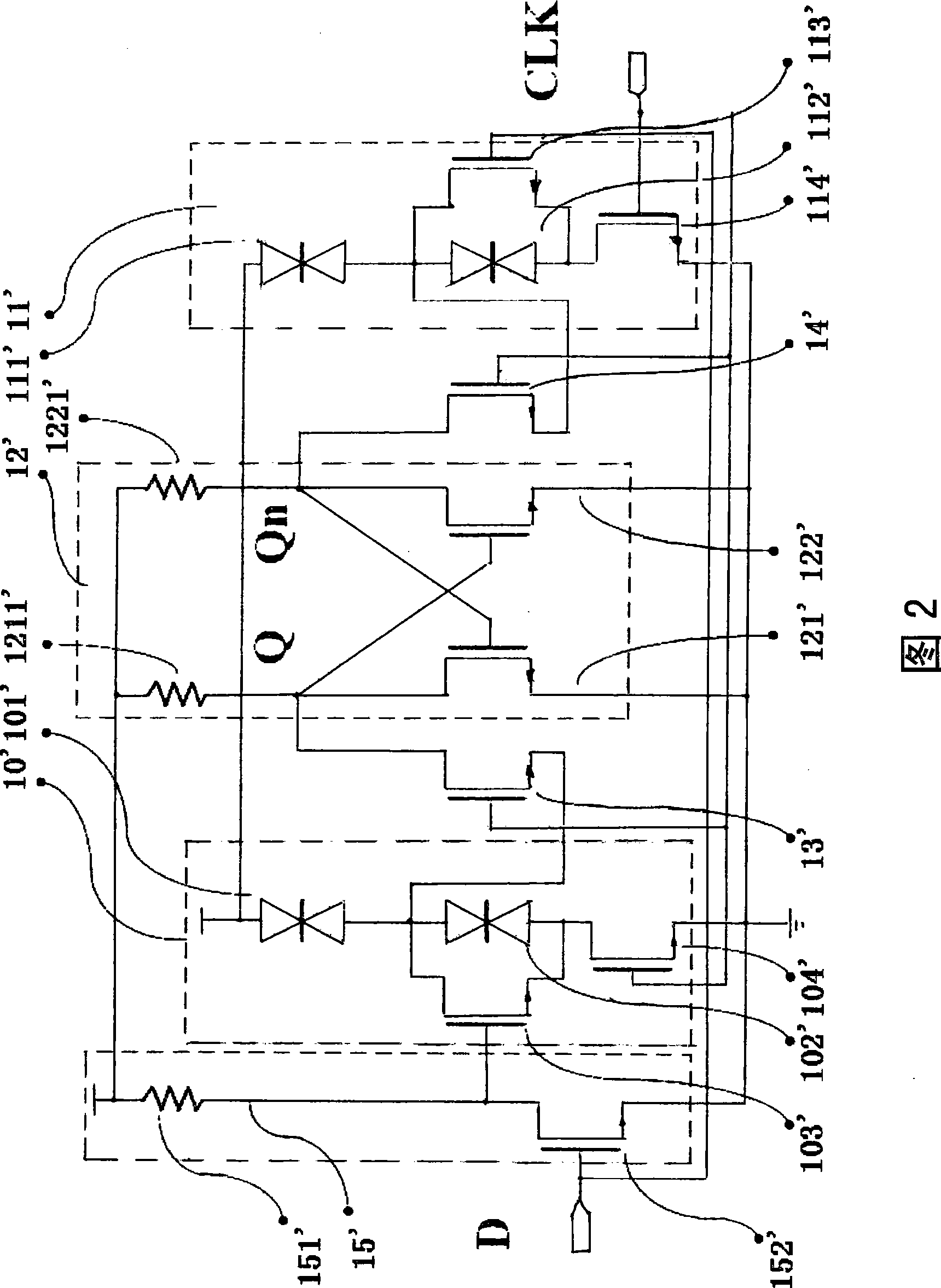

D trigger for resonance tunnel-through diode

The invention relates to a resonance tunneling dioxide D trigger, which comprises a first monostability-bistability conversion logic unit, a second monostability-bistability conversion logic unit, a latch unit, a transmission gate, a second transmission gate and a phase inverter, wherein the latch unit consists of a first phase inverter and a second phase inverter; the output of the first phase inverter is connected with the input end of the second phase inverter; the output of the second phase inverter is connected with the input end of the first phase inverter; the input end of the first transmission gate is connected with the output end of the first monostability-bistability conversion logic unit, while the output end is connected to the input end of the latch unit; the input end of the second transmission gate is connected with the output end of the second monostability-bistability conversion logic unit, while the output end is connected with the input end of the latch unit; and the output end of the phase inverter is connected with the input end of the first monostability-bistability conversion logic unit, one end of the phase inverter is earthed, and the input end of the phase inverter is connected to the input end of the second monostability-bistability conversion logic unit.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

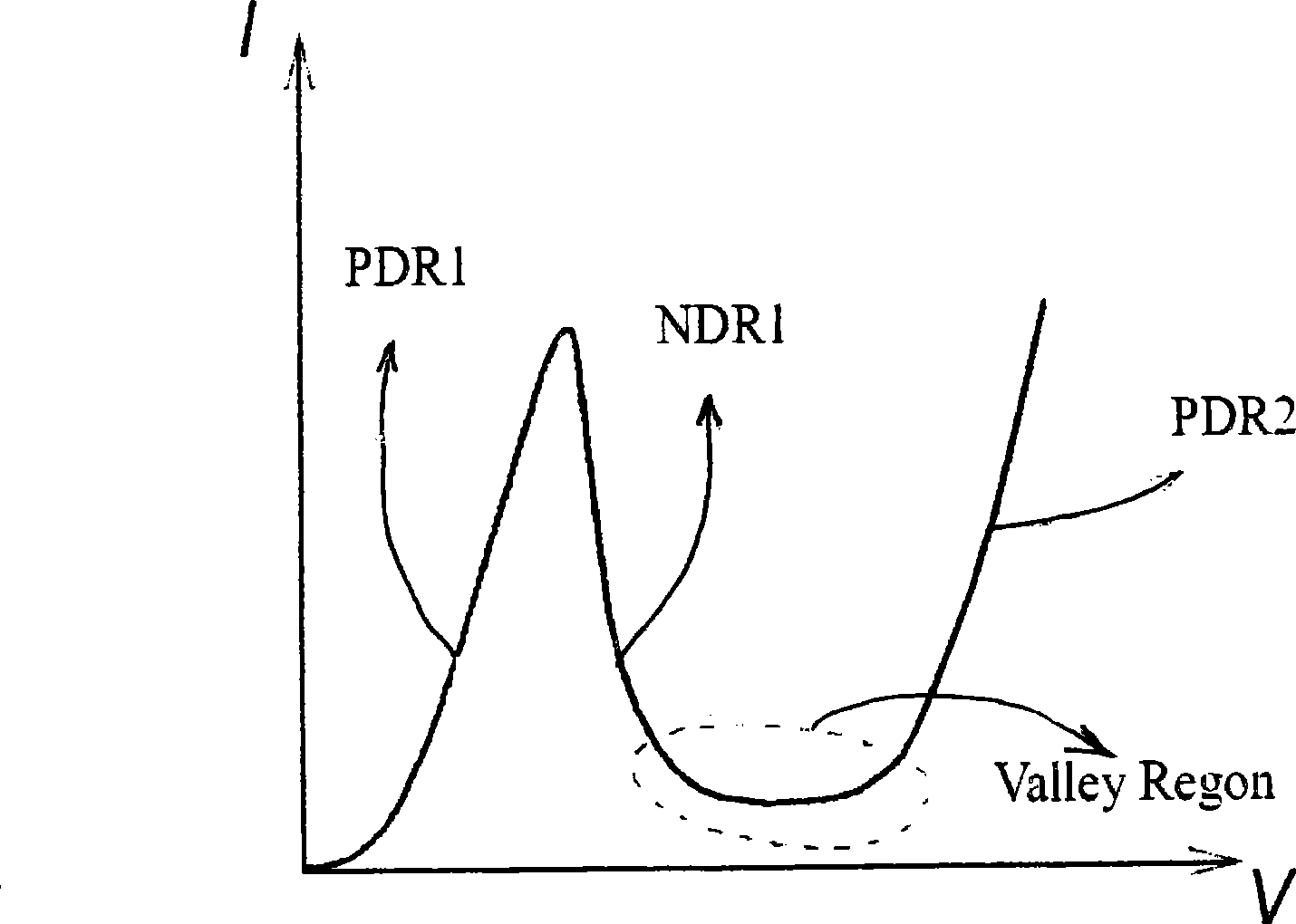

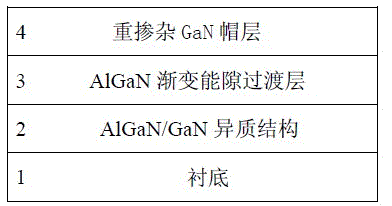

Method for manufacturing nitride gradient energy gap resonance tunneling ohmic contact

ActiveCN103337461AReduce exposureChange 2D propertiesSemiconductor/solid-state device manufacturingHeterojunctionOhmic contact

The invention discloses a method for manufacturing nitride gradient energy gap resonance tunneling ohmic contact. According to the method, an AlGaN / GaN heterostructure 2, an AlGaN gradient energy gap depletion layer 3 and a heavy doping GaN cap layer 4 are sequentially grown on a substrate 1 so as to manufacture the ohmic contact; the heavy doping GaN cap layer 4 can reduce the contact barrier of a metal-semiconductor; the gradient energy gap depletion layer 3 forms a middle trap to reduce the resistance of the ohmic contact through the resonance tunneling. According to the invention, by the design of the middle trap of the a gradient energy gap, the metal-semiconductor contact barrier generated in the high-temperature alloy process is separated from the heterojunction barrier, and energy bands of double-barrier and single-trap heterostructures are optimally designed respectively, so that the tunneling current is obviously increased, and the ohmic contact is reduced. Meanwhile, with the design of the heavy doping GaN cap layer, the high-temperature alloy process is omitted; the surface appearance, the device performance and the reliability of the contact are improved.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

Microstrip stabilized quantum well resonance-tunneling generator for millimeter and submillimeter wavelength range

ActiveUS7274263B2Increase speedLoss levelingSemiconductor/solid-state device detailsNanoinformaticsSemiconductor quantum wellsTunnel diode

A microstrip stabilized quantum well resonance-tunneling generator which generates electromagnetic waves for millimeter and submillimeter wavelength range is provided The generator includes a resonant tunneling semiconductor quantum well diode, and a microstrip resonator. The resonant tunneling diode, the microstrip resonator and interconnecting lines and junctions are fabricated as a monolithic integrated device on a common substrate. As a result, the monolithic integrated device provides the expansion of the operation frequency range toward the terahertz region as a result of reduction of the parasitic inductance as well as of minimizing the other parasitic parameters of the electric circuitry connecting the resonant tunneling diode and resonator.

Owner:SAMSUNG ELECTRONICS CO LTD +1

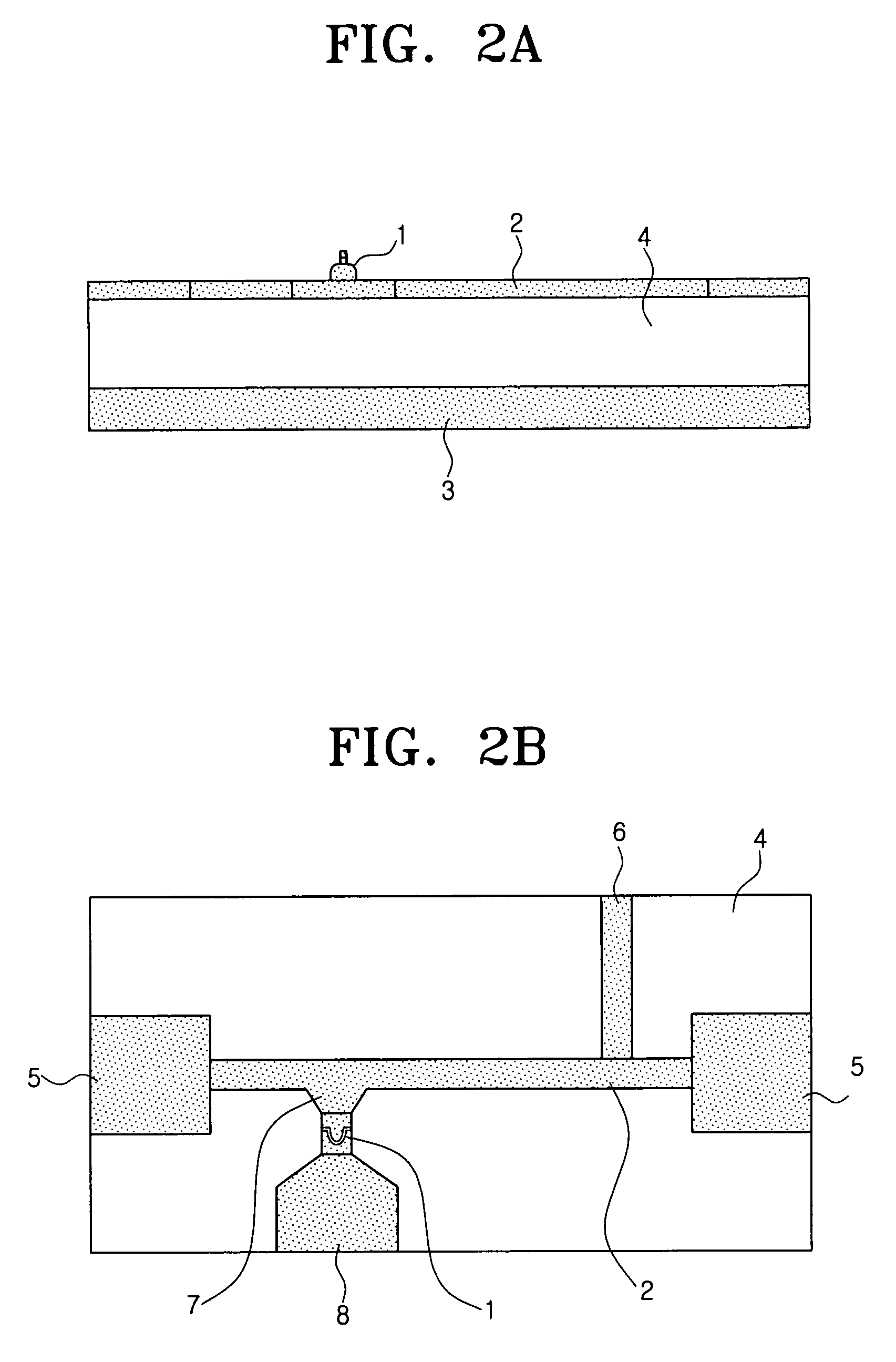

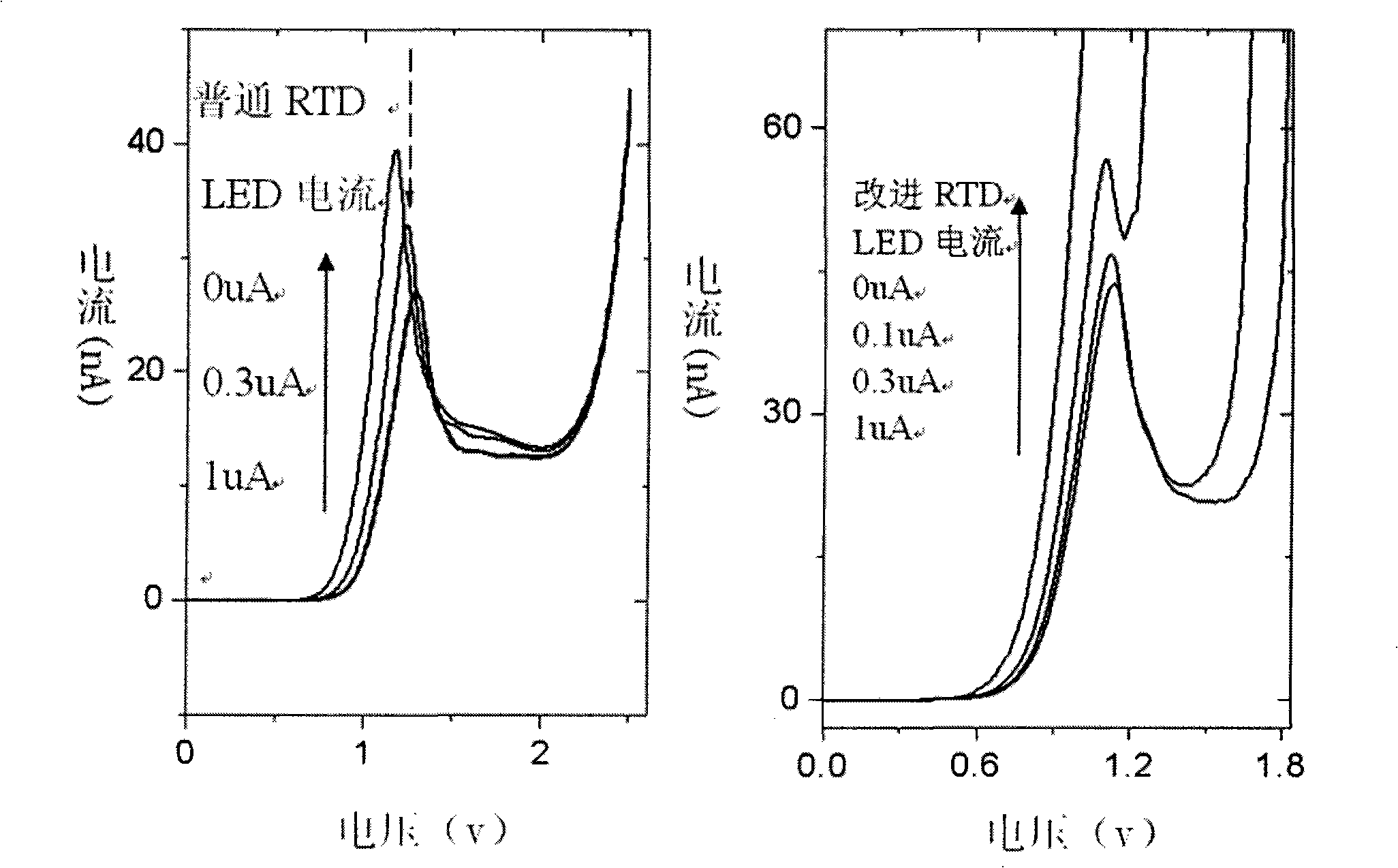

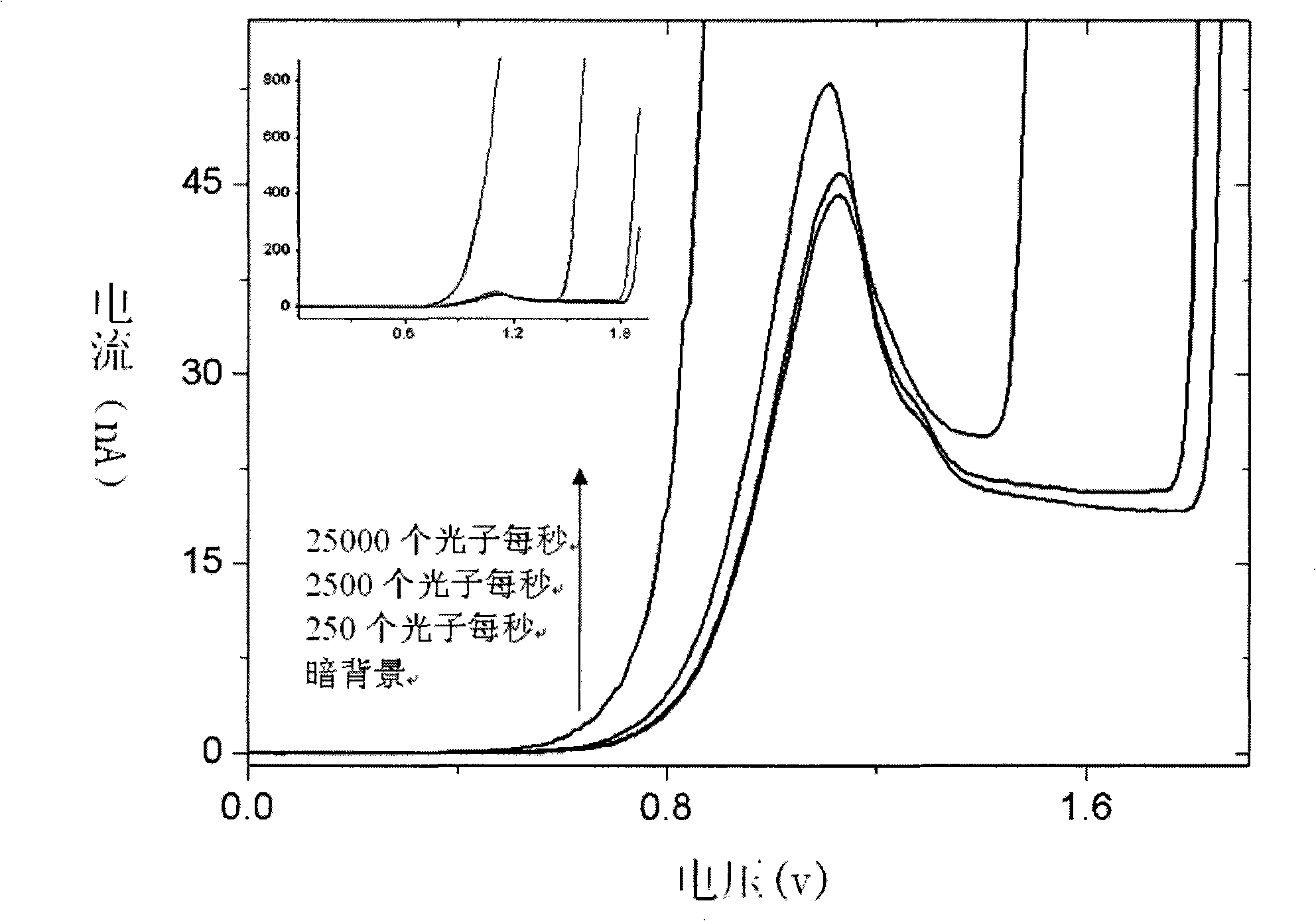

Method for enhancing dynamic range of quantum dot resonance tunneling diode photodetector

InactiveCN101335309AProlonged rapid thermal annealing timeExtended thermal annealing timeFinal product manufactureSemiconductor devicesPhotodetectorAbsorption layer

The invention discloses a method for increasing the dynamic range of a quantum dot resonance tunneling diode photodetector, and the hardcore of the structure thereof comprises a GaAs or InGaAs incident photon absorption layer, InAs self-assembly quantum dots with order of magnitude being 10<10>cm<-2> to 10<11>cm<-2> and an AlGaAs / GaAs double-potential-barrier structure layer; the core of the technology thereof is improved to extend the annealing time of the technique of the crisscross bridge resonance tunneling diode device so as to lead ohmic contact to diffuse to the double-potential-barrier structure layer; the core inventive point of the detecting approach thereof is that a longitudinal current branch of an original tunneling diode which is sensitive to small photons is kept, simultaneously, another transverse current which consists of two-dimensional electron gas is educed from a quantum well and can reflect the continuous variation of incident light intensity when suffering intensive modulation from a quantum dot electric field. The device of the invention has the advantages that the improvement of both the structure and the technology of the device can be compatible with the original equipment while the multiphoton detection sensitivity is greatly improved compared with the original device.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

A light-emitting diode with a resonant tunneling structure electron blocking layer

ActiveCN107195746BImprove the blocking effectIncreased efficiency of injection into the active regionSemiconductor devicesPotential wellOhmic contact

The invention discloses a light emitting diode with an electron blocking layer in a resonant tunneling structure. The light emitting diode comprises a substrate, an n-type nitride layer, a multiple quantum well layer, the electron blocking layer, a p-type nitride layer and a p-type nitride ohmic contact layer, an n-type electrode which is arranged on the n-type nitride layer, and a p-type electrode which is arranged on the p-type nitride layer, wherein the substrate, the n-type nitride layer, the multiple quantum well layer, the electron blocking layer, the p-type nitride layer and the p-type nitride ohmic contact layer are arranged in order from the bottom up. The electron blocking layer is composed of a p-type doped nitride barrier layer, a non-doped nitride potential well layer, and a non-doped barrier layer which increases the hole transmittance through a resonance tunneling effect, wherein the p-type doped nitride barrier layer, the non-doped nitride potential well layer and the non-doped barrier layer are arranged in order from bottom to top. The light emitting diode provided by the invention has the advantages that electrons are effectively prevented from passing through an active region into a p-type region, which increases the injection efficiency of a hole into the active region through the electron blocking layer; a good electronic blocking effect is realized through a simple growth mode and less layer structures; and the hole injection efficiency significantly higher than a traditional electronic blocking layer structure is acquired.

Owner:SOUTHEAST UNIV

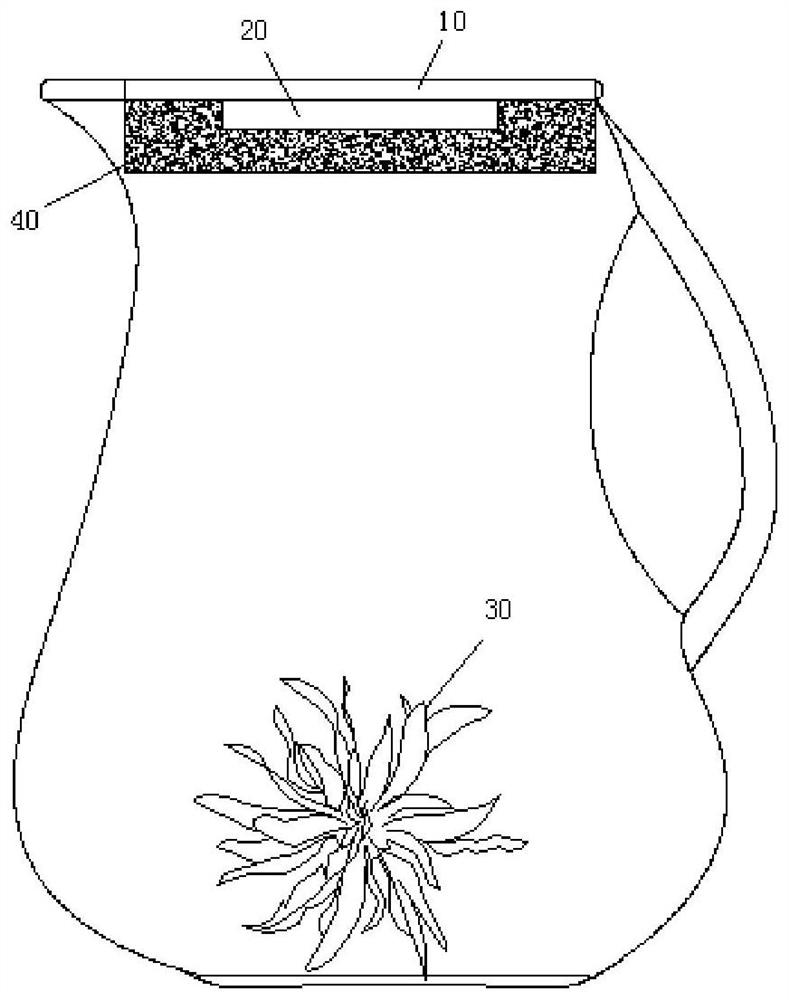

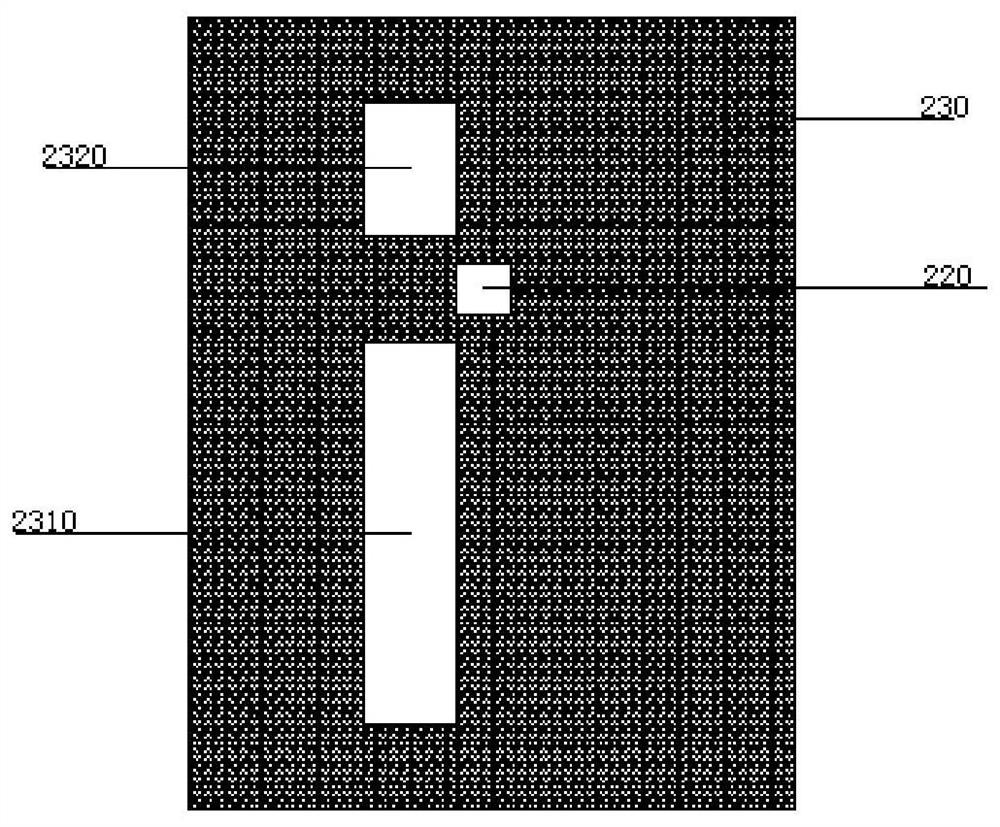

Terahertz water quality enhancement activation instrument

InactiveCN112266118AMaintain active stateActivation state maintenanceWater/sewage treatment by irradiationMultistage water/sewage treatmentHigh activationLiquid water

The invention belongs to the technical field of small molecular diagram water, and particularly relates to a terahertz water quality enhancement activation instrument. The instrument comprises a watercontainer and an activation device, the activation device is arranged on the water container and can activate liquid water contained in the water container by emitting terahertz waves; the activationdevice comprises a control unit, at least one resonance tunneling diode and a peripheral circuit corresponding to the resonance tunneling diode. The resonance tunneling diode can form an oscillationloop with the peripheral circuit under the control of the control unit so as to generate the terahertz waves. The terahertz water quality enhancement activation instrument not only can efficiently activate liquid water through the terahertz waves, but also can maintain the activation state of the water body through infrared radiation, mineral element bonding or molecular low-frequency resonance and other methods, and has the technical effects of high activation efficiency, good activation effect, high safety coefficient and the like.

Owner:深圳新青春科技发展有限公司

A method for making GaMnN sparse magnetic semiconductor nano wire

InactiveCN100557770CRoom temperature ferromagneticStrong ferromagnetism at room temperatureSemiconductor/solid-state device manufacturingLinear controlNanowire

The invention discloses a method for preparing GaMnN dilute magnetic semiconductor nanowires. The method of the present invention comprises the following steps: 1) Mn doping: in-situ doping Mn on Ga2O3 nanowires; 2) ammoniation: ammoniating Ga2O3 nanowires doped with Mn under an ammonia atmosphere to obtain GaMnN dilute Magnetic semiconductor nanowires. The method of the invention is simple and requires less equipment, the prepared GaMnN nanowire has strong ferromagnetism, the Curie temperature is higher than room temperature, and its magnetic doping concentration is controllable, the nanowire has high purity, large output, and linear shape control (adjustment of growth parameters such as air pressure can prepare nanowires with a diameter of tens of nanometers to hundreds of nanometers), and can be used for spin field effect transistors (spin-FETs), spin light-emitting diodes (spin-LEDs), and spin resonance The fabrication of nano-spintronic devices such as spin-RTD has broad application prospects.

Owner:PEKING UNIV

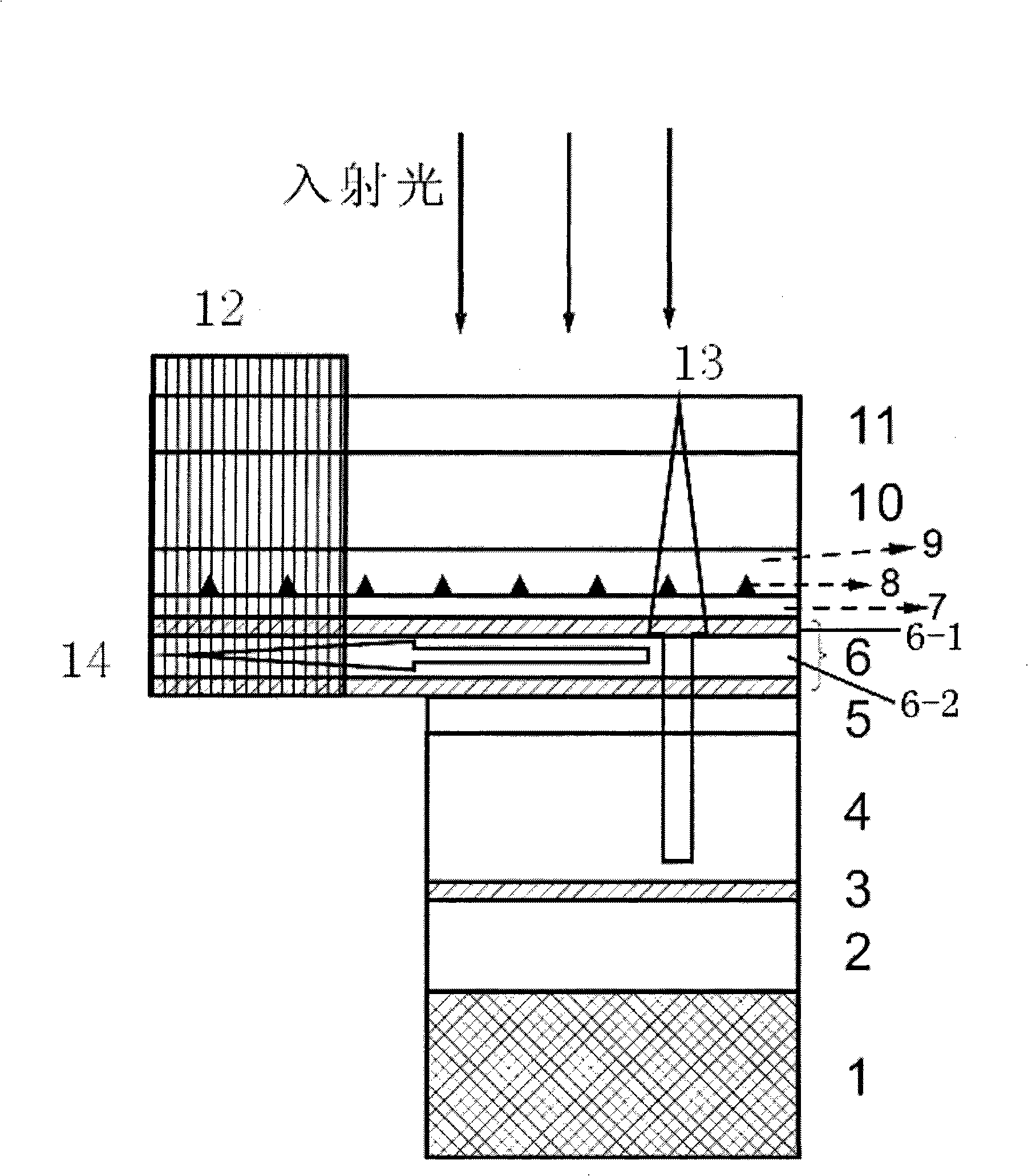

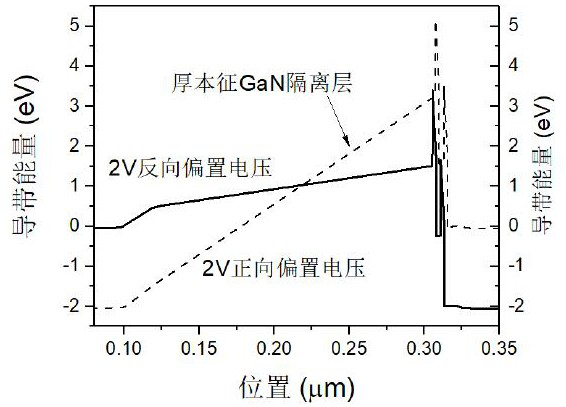

Nitride resonance tunneling diode structure suitable for ultraviolet light detection

ActiveCN112151639AEnhancing the Quantum Efficiency of Ultraviolet Light DetectionRealize resonant tunneling transportSemiconductor devicesUltraviolet lightsPeak current

The invention discloses a nitride resonance tunneling diode structure suitable for ultraviolet light detection, and solves the problems that a conventional nitride resonance tunneling diode structureis not suitable for a thick light absorption layer and cannot perform ultraviolet light detection with high quantum efficiency. According to the invention, a double-barrier resonance tunneling structure is arranged in a p type doped nitride epitaxial layer / intrinsic nitride epitaxial layer / n type doped nitride epitaxial layer, and a built-in polarization electric field of a nitride heterojunctionis counteracted by using the built-in electric field of the p-i-n structure, so that the problem of energy band uplift of the GaN thick light absorption layer is solved, and the nitride resonance tunneling diode structure of the thick light absorption layer can generate resonance tunneling; and an AlGaN / GaN superlattice structure is introduced, and the alignment of a quantum well energy level anda light absorption layer conduction band energy level is adjusted by using the polarization field of the superlattice structure, so that the peak current of resonance tunneling is enhanced.

Owner:INST OF ELECTRONICS ENG CHINA ACAD OF ENG PHYSICS

Near infrared detector based on resonance tunneling effect

InactiveCN105047725AReduce shot noiseImprove responsivenessSemiconductor/solid-state device manufacturingDiodeDouble barrierShot noise

The invention provides a near infrared detector based on a resonance tunneling effect. The major structure of the near infrared detector is a resonance tunneling diode, yet a double-barrier structure frequently used by the resonance tunneling diode is changed to a three-barrier structure, so that shot noise of the detector is inhibited, and an absorption layer is grown in an epitaxial mode between the three-barrier structure and a collector electrode. According to the invention, positive bias is applied when the detector works, near infrared light is incident from the collector electrode, a photoproduction electron-hole pair is generated at the absorption layer, and a photoproduction hole drifts towards the direction of the three-barrier structure under the effect of an electric field and is accumulated at the interface between the double-barrier structure and the absorption layer, such that electric potential at the two sides of the three-barrier structure is changed. The detector provided by the invention has quite high responsibility at a room temperature.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI +1

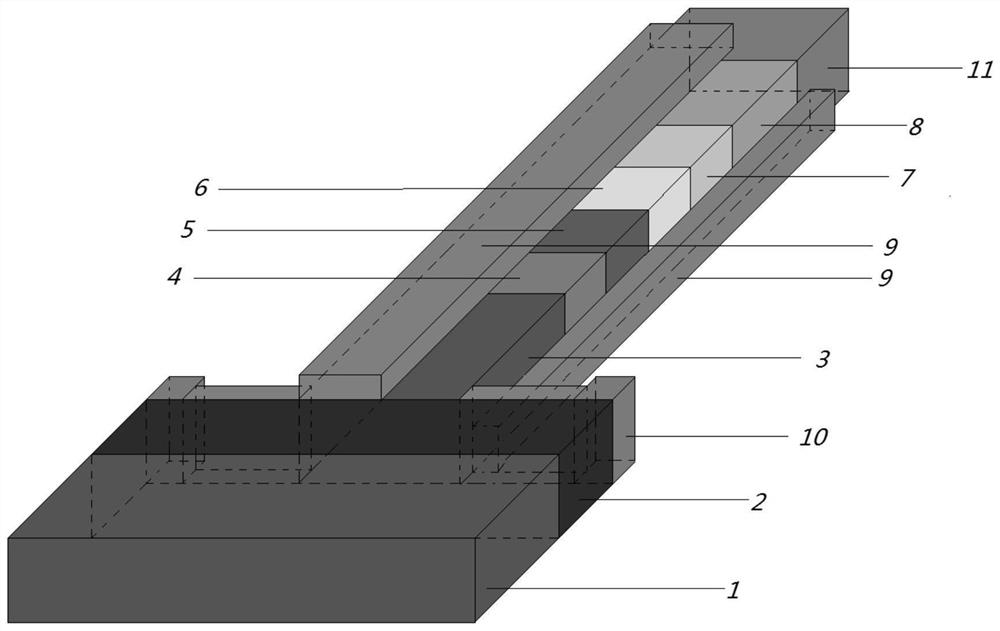

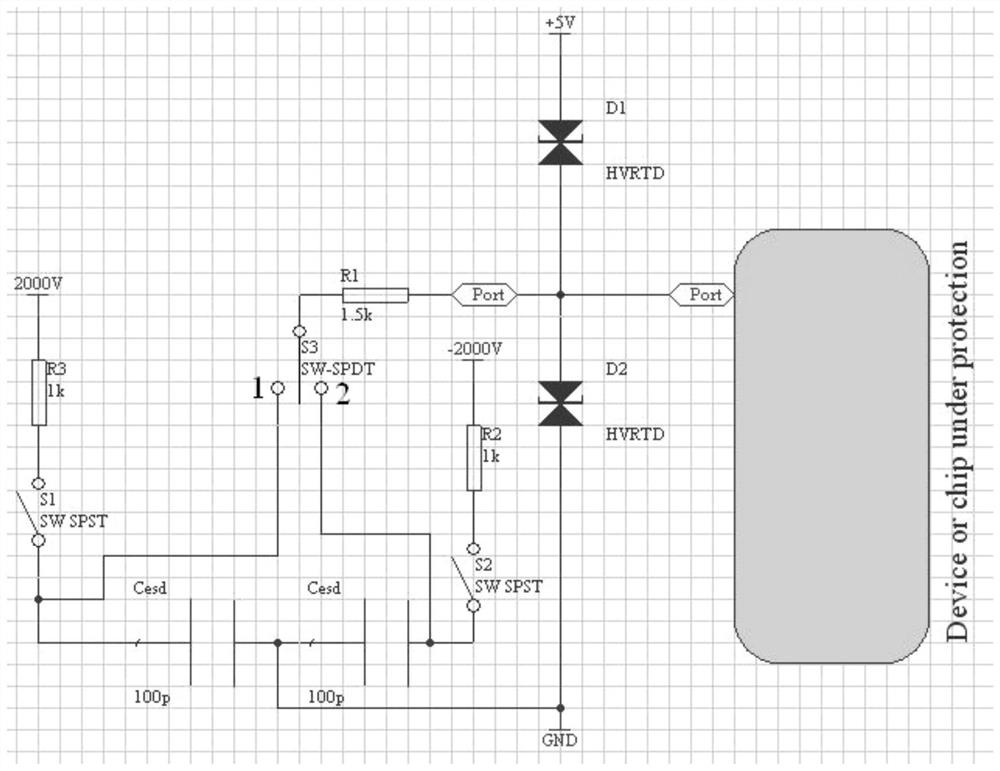

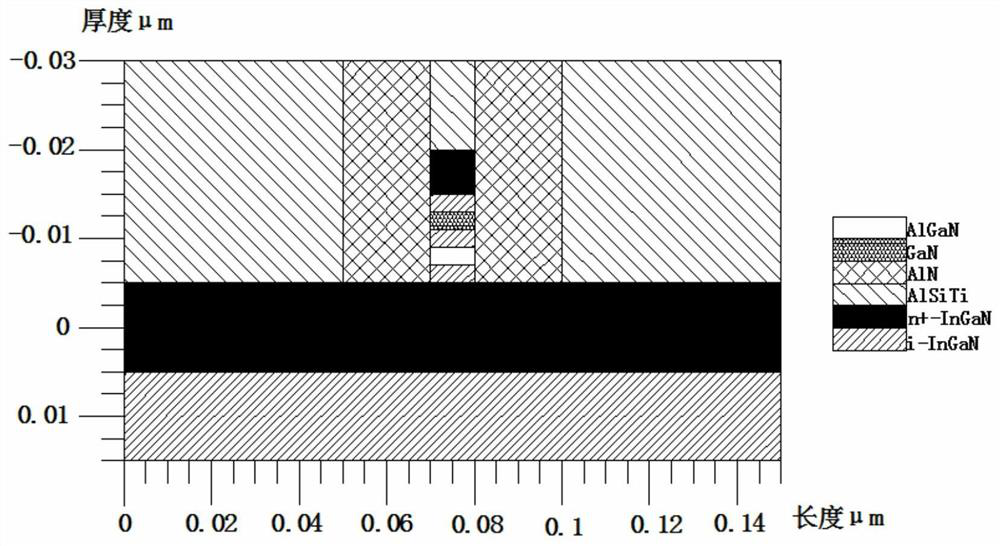

A Gan-based High Voltage Rectifier Resonant Tunneling Diode

The invention relates to a GaN-based high-voltage rectification resonant tunneling diode. The present invention includes planar GaN substrates, n + -In 0.07 Ga 0.93 N collector layer, i‑In 0.07 Ga 0.93 N first spacer layer, AlGaN first barrier layer, i‑In 0.14 Ga 0.86 N quantum well layer, GaN second barrier layer, i‑In 0.21 Ga 0.89 N second isolation layer, n + -In 0.21 Ga 0.89 N emitter layer, passivation layer, collector metal electrode pins and emitter metal electrode pins. This kind of GaN-based high-voltage resonant tunneling diode—HVRTD has volt-ampere characteristics of high forward blocking voltage and reverse ultra-low resistivity, and its manufacturing process is compatible with GaN-based integrated devices and circuits (including circuits, optical circuits, magnetic circuits, It is compatible with the micro-nano integrated manufacturing process of gas circuit, mechanical circuit and composite circuit, and is very suitable for ESD protection applications of GaN-based integrated devices and circuits. It can withstand ±2000V ESD within an approximately ideal time of 840ns to ensure GaN-based integrated devices and The road is not damaged.

Owner:SHANGRAO NORMAL UNIV

A New Voltage Domain Oscillating Diode

Owner:SHANGRAO NORMAL UNIV

Middle series connection layer and production method thereof, laminated photovoltaic device and preparation method thereof

PendingCN113990959AImprove tunneling efficiencyIncrease the open circuit voltageFinal product manufacturePhotovoltaic energy generationQuantum dotEngineering

The invention provides a middle series connection layer and a production method thereof, and a laminated photovoltaic device and a preparation method thereof, and relates to the technical field of photovoltaics. The middle series connection layer comprises a potential barrier layer and quantum dot structures dispersed in the potential barrier layer. The quantum dot structure dispersed in the barrier layer depends on the quantum confinement effect, a controllable tunneling channel is established in the barrier layer, the controllable tunneling channel can assist carriers of corresponding energy levels in high-efficiency resonance tunneling, the tunneling efficiency of the corresponding carriers is improved, tunneling current is greatly improved, contact resistance is reduced, the reverse barrier heights of the two sides of the middle series connection layer are reduced, the reduction degree of the overall open-circuit voltage of the laminated photovoltaic device is further reduced, and the overall open-circuit voltage and efficiency of the laminated photovoltaic device are improved. Meanwhile, by means of a discrete energy level structure established in the barrier layer, the contact resistance is effectively controlled, so that the series resistance is relatively low.

Owner:LONGI GREEN ENERGY TECH CO LTD

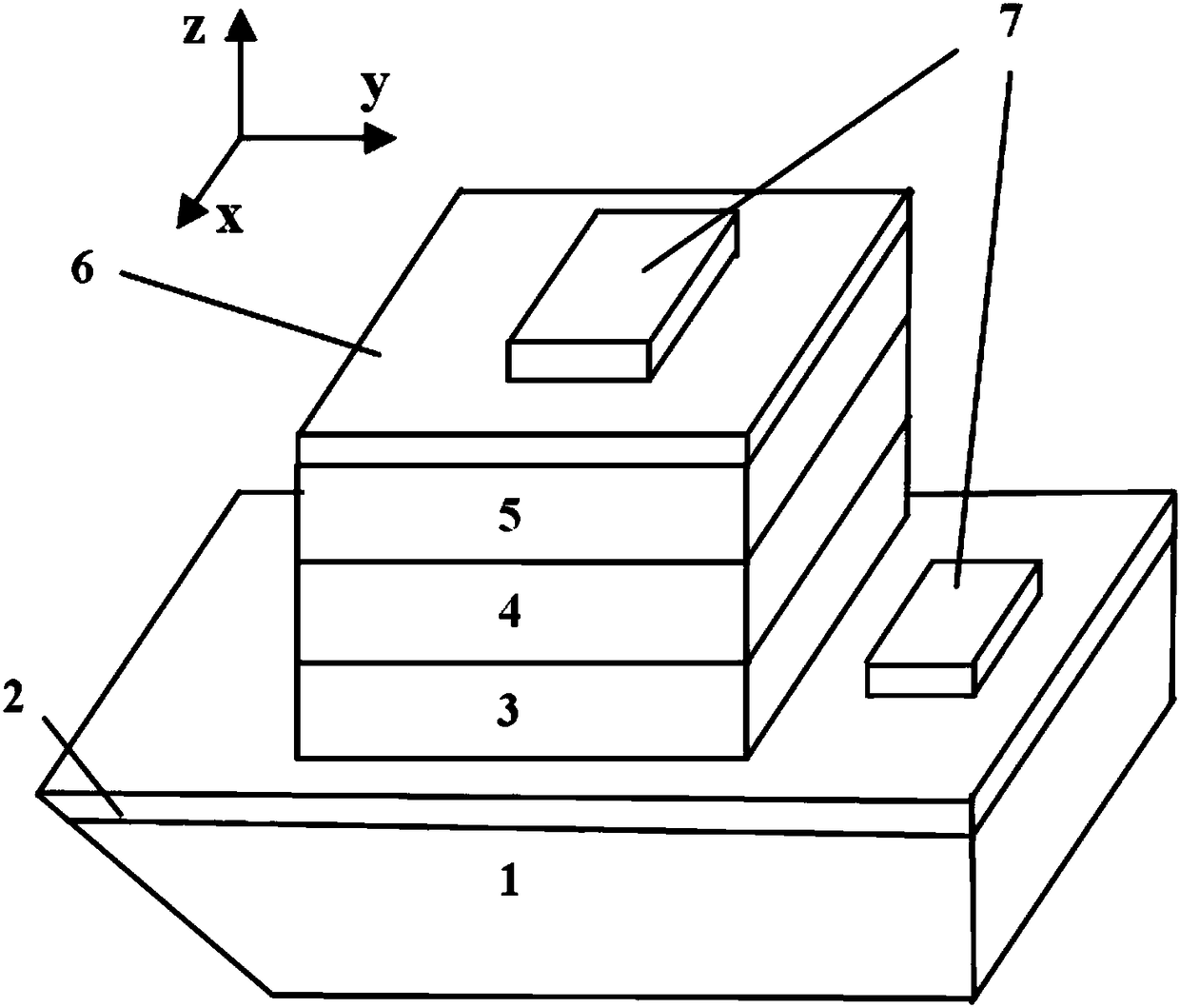

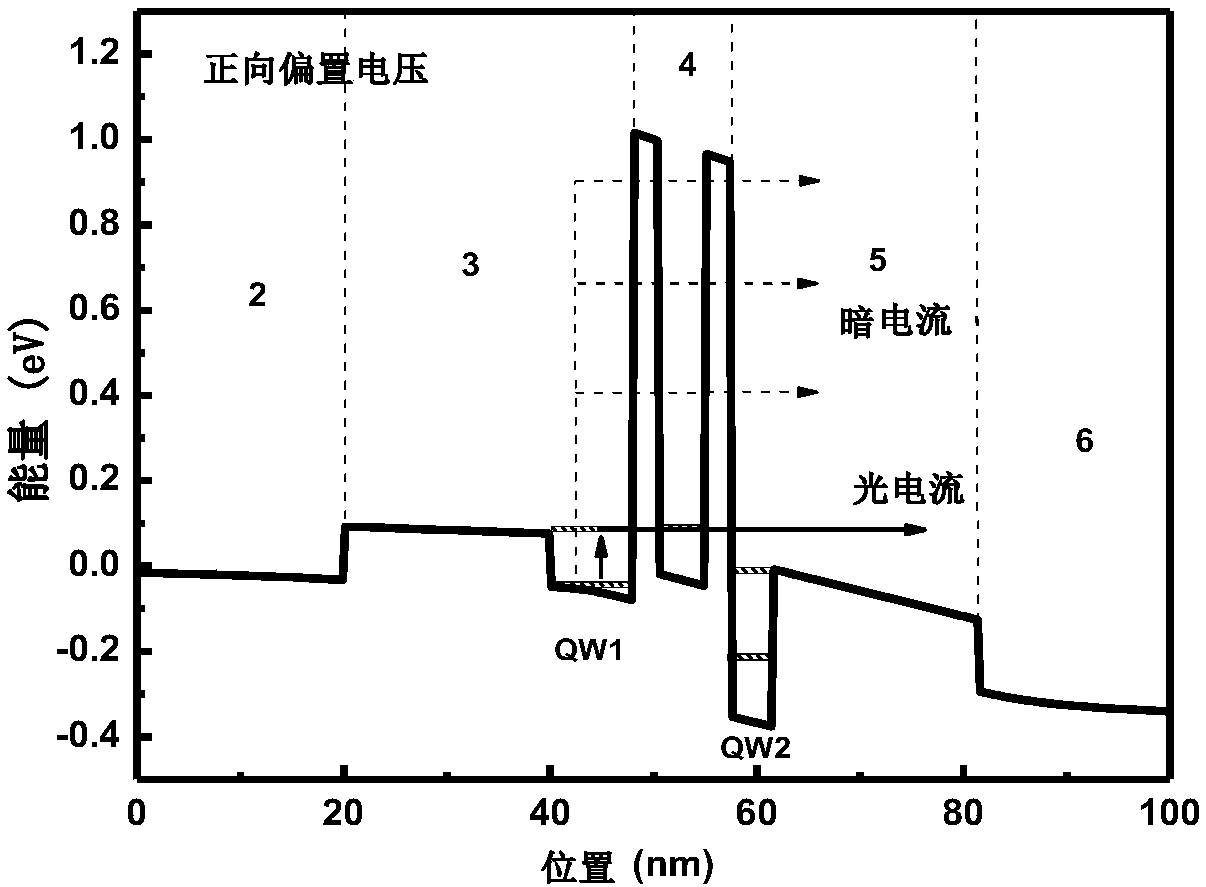

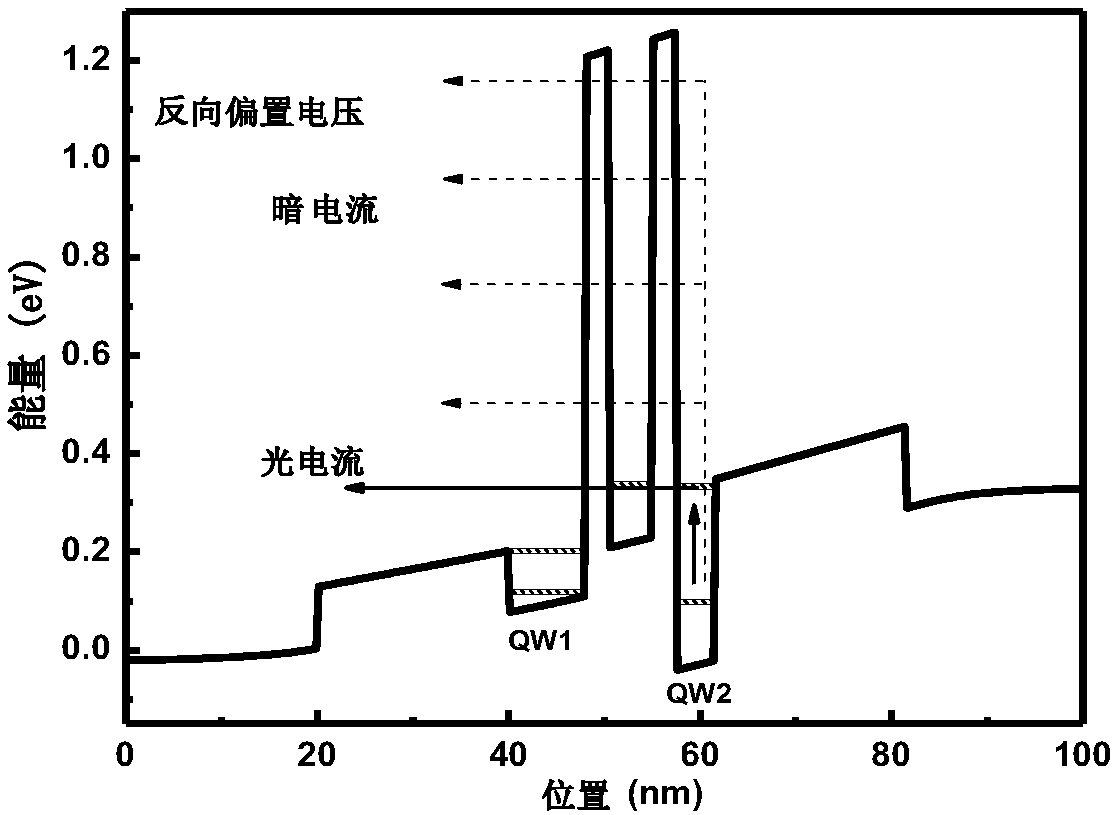

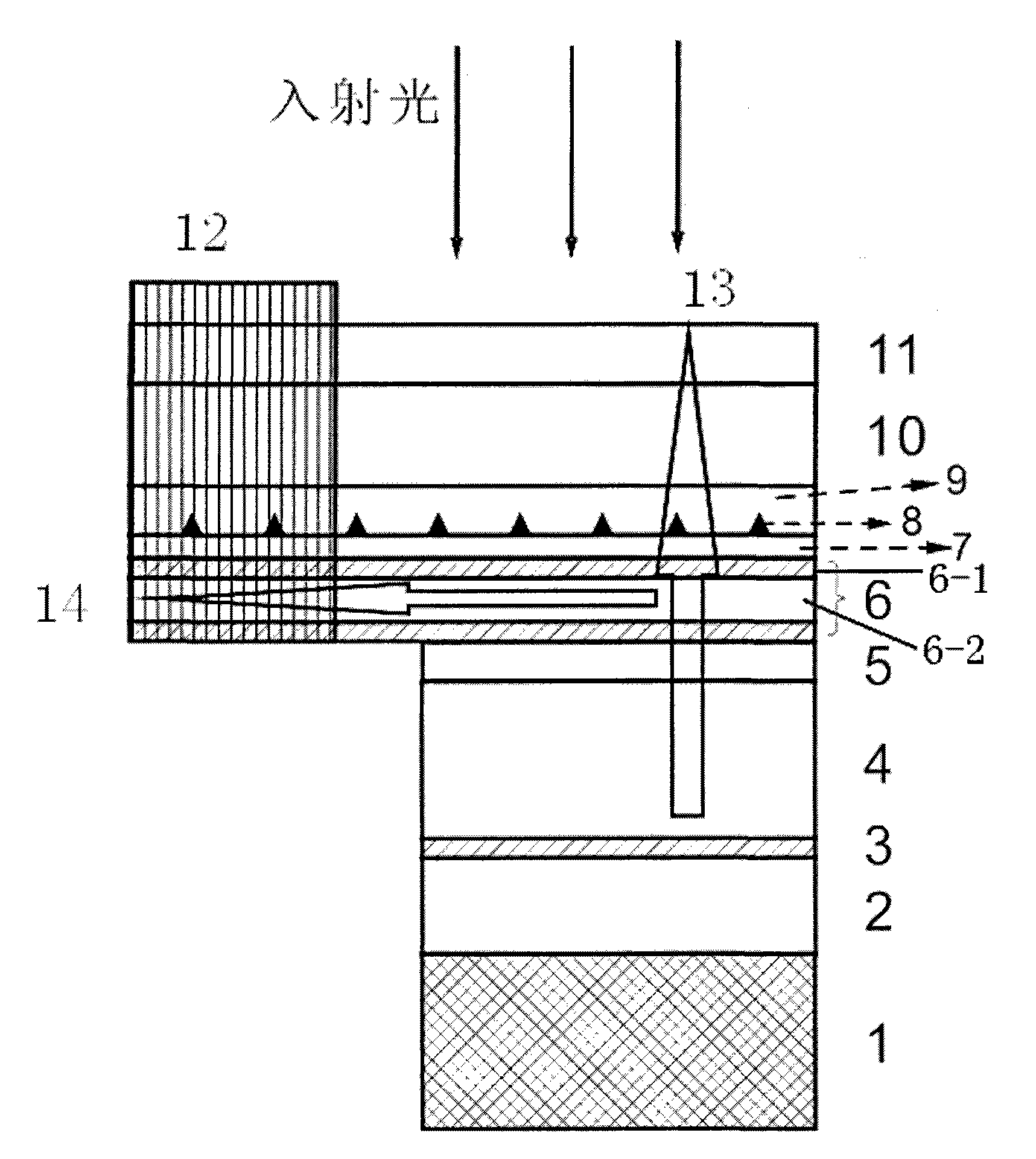

GaAs-base bi-color quantum well infrared detector based on resonance tunneling effect

PendingCN108520904APromote growthBlock dark currentFinal product manufactureSemiconductor devicesTunnel diodeQuantum well

The invention discloses a GaAs-base bi-color quantum well infrared detector based on a resonance tunneling effect. The detector is prepared by sequentially growing a lower electrode layer, an active region layer and an upper electrode layer on a GaAs substrate by virtue of a molecular beam epitaxy measure, wherein the active region layer is formed by clamping a resonance tunneling diode structurebetween two different quantum wells. When a specific positive or negative bias is applied to the detector, two waveband light currents produced through the response of quantum wells with different widths selectively run through a resonance tunneling diode so as to form a response loop. Compared with current traditional bi-color quantum well detectors, the GaAs-base bi-color quantum well infrared detector has the advantages that the bi-color detection can be realized through adjusting the direction and size of the applied bias, and the working temperature of the device can be increased; and besides, the preparation process of the detector is relatively simple, and the detector has the important signature to the development of bi-color infrared quantum well detectors.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

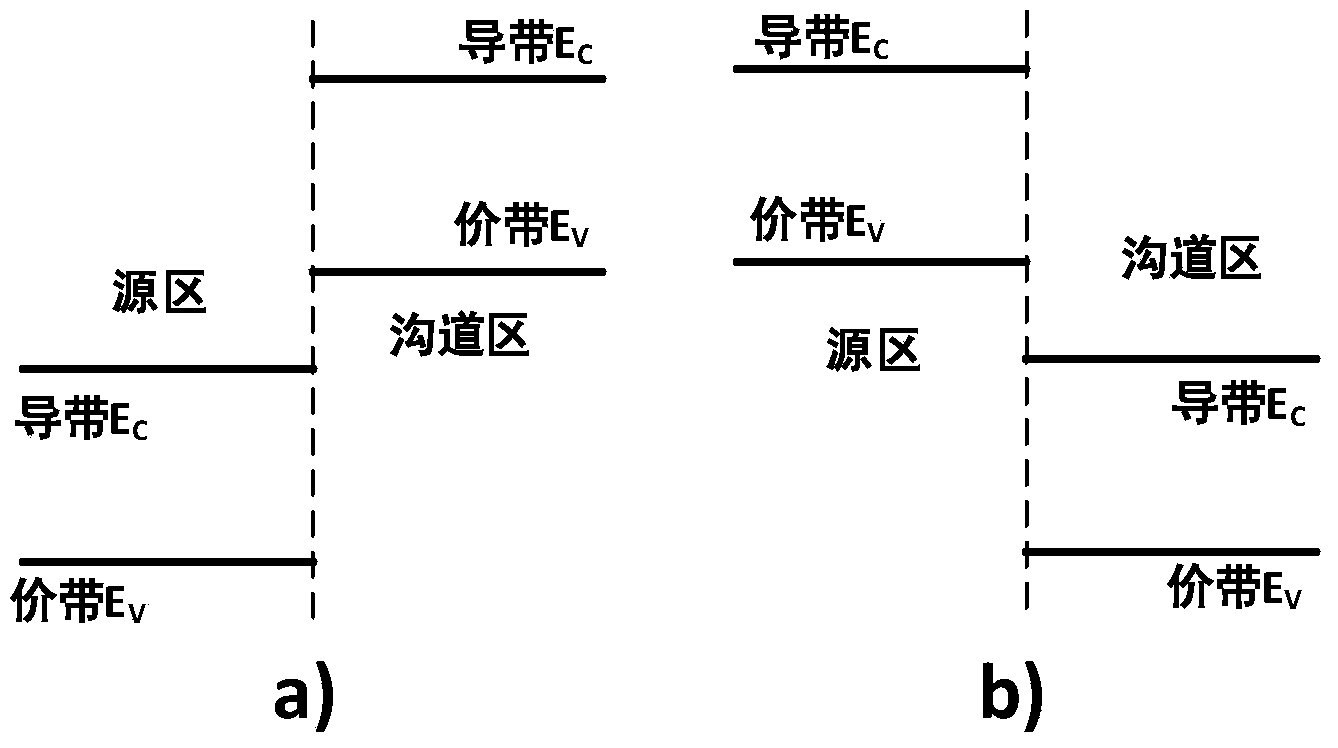

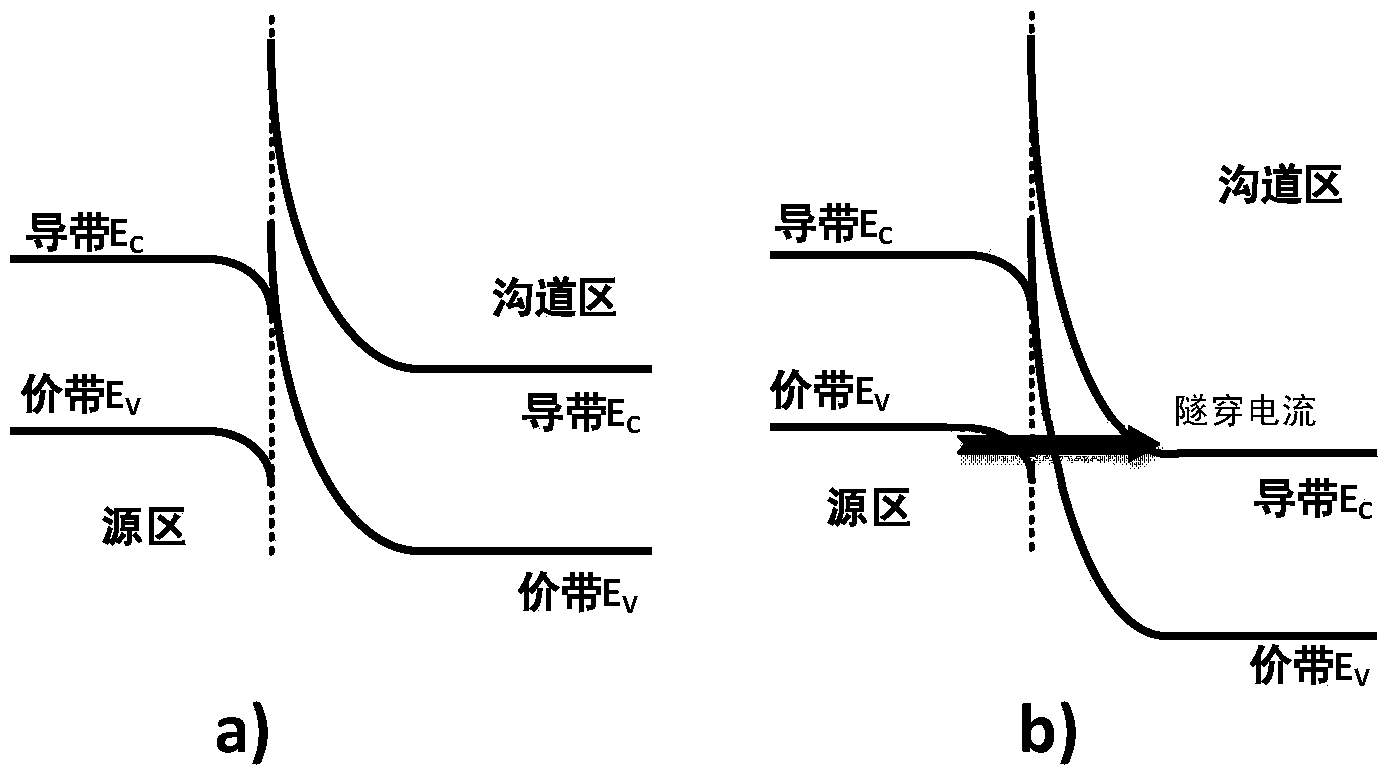

Anti-staggered-layer heterojunction resonance tunneling field-effect transistor (TFET) and preparation method thereof

ActiveCN104241373AIncrease the on-state currentSuppresses off-state currentSemiconductor/solid-state device manufacturingDiodeHeterojunctionValence band

The invention discloses an anti-staggered-layer heterojunction resonance tunneling field-effect transistor (TFET) and a preparation method thereof. The TFET comprises a tunneling source region, a channel region, a drain region and a control grid located above the channel region, wherein an electronic band structure of a heterogeneous tunneling junction of the tunneling source region and an electronic band structure of a heterogeneous tunneling junction of the channel region are respectively an anti-staggered-layer heterojunction. If the TFET is an N type device, the bottom of a conduction band of the tunneling source region is located below the valence band top of the channel region at the juncture surface of the heterogeneous tunneling junction of the tunneling source region and the heterogeneous tunneling junction of the channel region; if the TFET is a P type device, the valence band top of the tunneling source region is located above the bottom of a conduction band of the channel region. Thus, on-state currents of the TFET can be remarkably increased; meanwhile, off-state currents of the device are effectively suppressed, and a steep subthreshold slope is maintained. According to the preparation method of the TFET, a low-power dissipation integrated circuit formed by TFETs is prepared by effectively using a standard process, production cost is greatly reduced, and the process is simple.

Owner:PEKING UNIV

Method for enhancing dynamic range of quantum dot resonance tunneling diode photodetector

InactiveCN101335309BProlonged rapid thermal annealing timeExtended thermal annealing timeFinal product manufactureSemiconductor devicesPhotodetectorAbsorption layer

The invention discloses a method for increasing the dynamic range of a quantum dot resonance tunneling diode photodetector, and the hardcore of the structure thereof comprises a GaAs or InGaAs incident photon absorption layer, InAs self-assembly quantum dots with order of magnitude being 10<10>cm<-2> to 10<11>cm<-2> and an AlGaAs / GaAs double-potential-barrier structure layer; the core of the technology thereof is improved to extend the annealing time of the technique of the crisscross bridge resonance tunneling diode device so as to lead ohmic contact to diffuse to the double-potential-barrier structure layer; the core inventive point of the detecting approach thereof is that a longitudinal current branch of an original tunneling diode which is sensitive to small photons is kept, simultaneously, another transverse current which consists of two-dimensional electron gas is educed from a quantum well and can reflect the continuous variation of incident light intensity when suffering intensive modulation from a quantum dot electric field. The device of the invention has the advantages that the improvement of both the structure and the technology of the device can be compatible with the original equipment while the multiphoton detection sensitivity is greatly improved compared with the original device.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

A nanowire transistor based on resonant tunneling and its preparation method

InactiveCN110491940BImprove gate control abilityTunneling transportSemiconductor/solid-state device manufacturingSemiconductor devicesNanowireContact resistance

The invention discloses a nanowire transistor based on resonance tunneling. The nanowire transistor comprises an SOI substrate, a tunneling barrier structure, a source region, a drain region, nanowires, a grid electrode, a source electrode, a drain electrode, a grid electrode and an insulating dielectric layer. The tunneling barrier structure is located on the buried oxide layer of the SOI substrate. The source region, the drain region and the nanowire are formed by etching top silicon of the SOI substrate; the nanowire is positioned between the source region and the drain region; wherein thesource region, the drain region and the nanowire are not directly connected and are connected through a tunneling barrier structure, the insulating dielectric layer is formed on the surfaces of the source region, the drain region and the nanowire, the grid electrode is formed on the insulating dielectric layer above the nanowire, the source electrode is formed on the source region, the drain electrode is formed on the drain region, and the grid electrode is formed on the grid electrode. According to the nanowire transistor structure based on resonance tunneling and the preparation method of the nanowire transistor structure, the sub-threshold slope is reduced, and large conduction current and small source-drain contact resistance can be achieved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

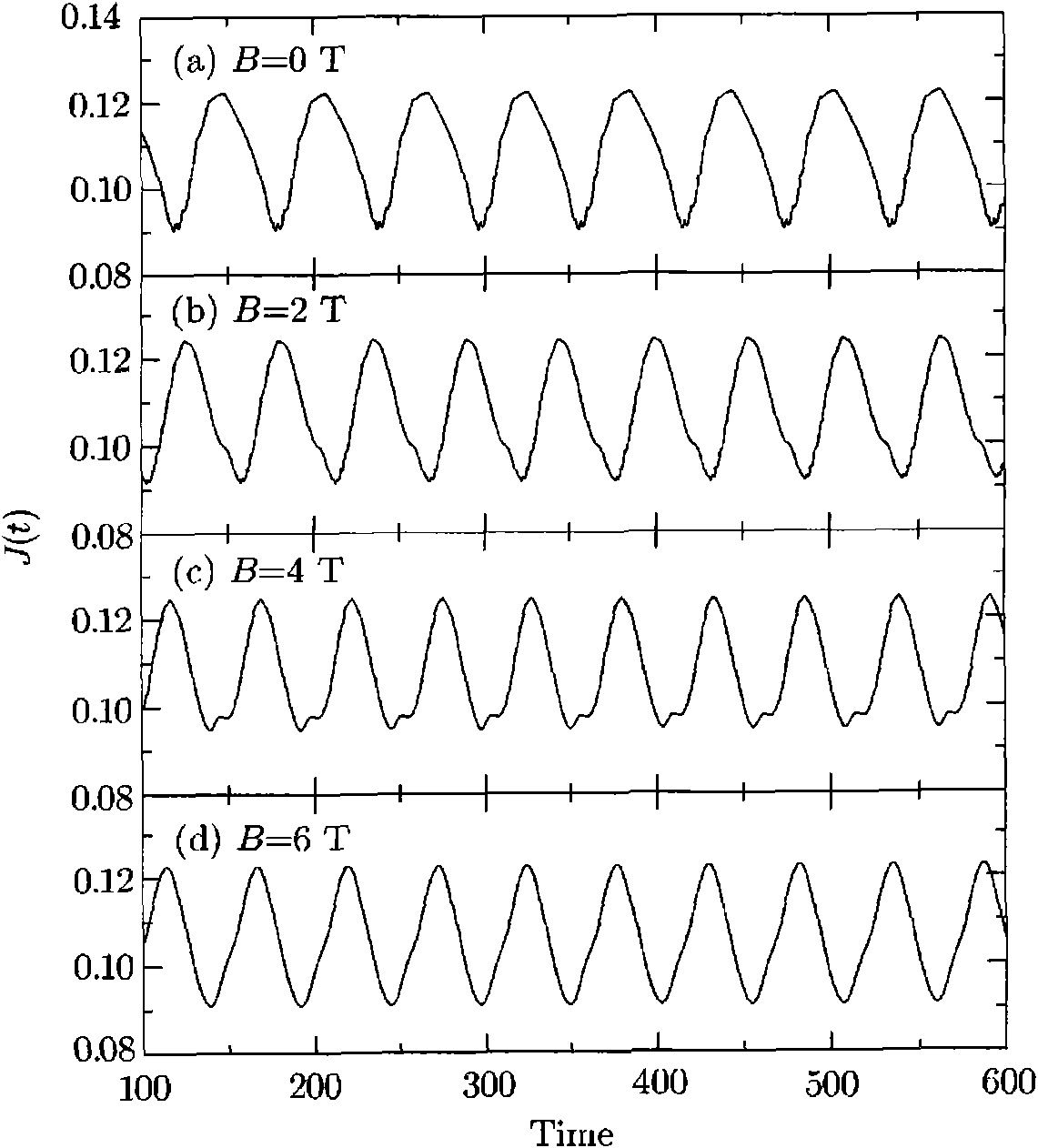

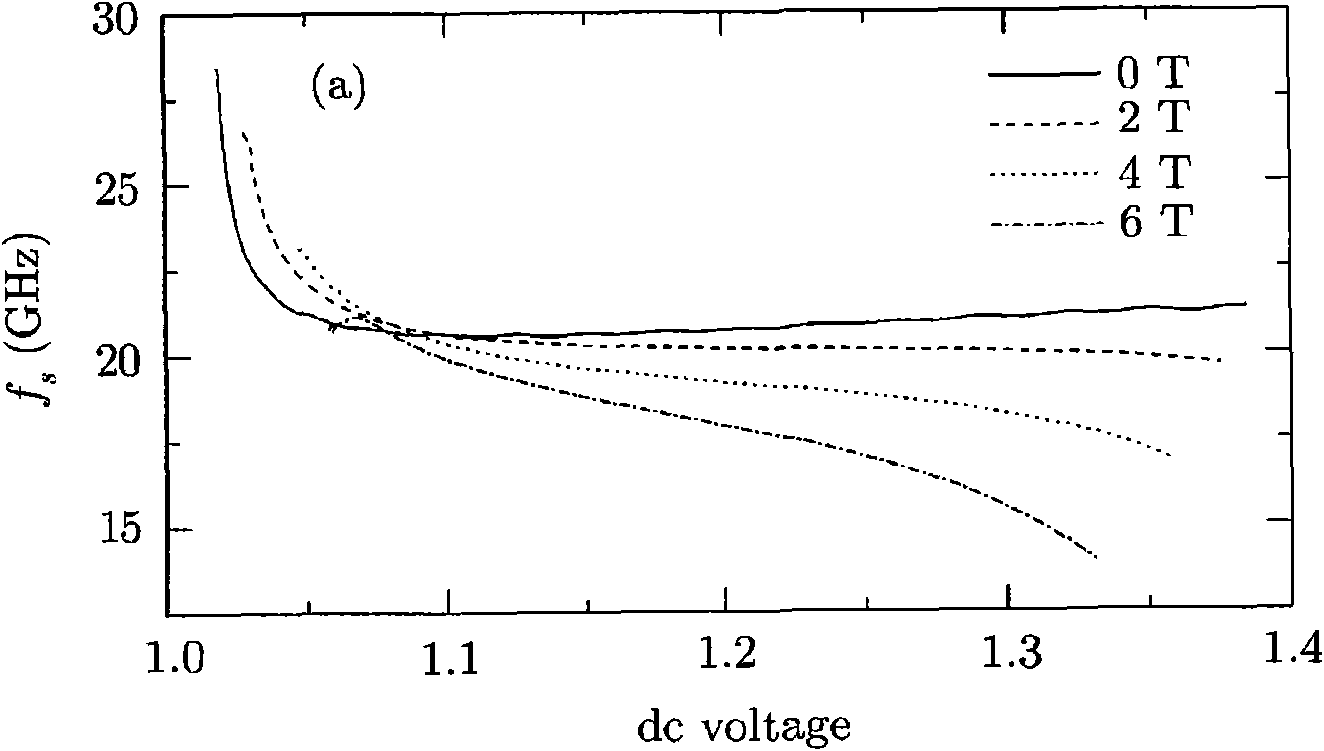

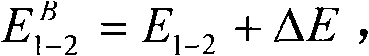

Realization method of tunable superlattice oscillator

The invention relates to a realization method of a tunable superlattice oscillator. The realization method is characterized in that (1) a current oscillation mode and an oscillation frequency in a superlattice oscillator are regulated by utilizing an externally-added magnetic field and an electric field, wherein, the superlattice oscillator is a weak coupling superlattice based on a resonance tunneling mechanism of a current carrier; (2) the direction of the externally-added magnetic field is vertical to that of the superlattice, the electric field is direct current bias voltage, and the direct current bias is along the growth direction of the superlattice; (3) the direct current bias voltage is fixed on the superlattice oscillator to produce zero damping oscillation current, and then the resonance frequency of the superlattice oscillator is continuously regulated by regulating the externally-added magnetic strength. To sum up, the invention can realize continuous change of the oscillation frequency of the superlattice oscillator by utilizing the regulation of the externally-added magnetic field and the electric field.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

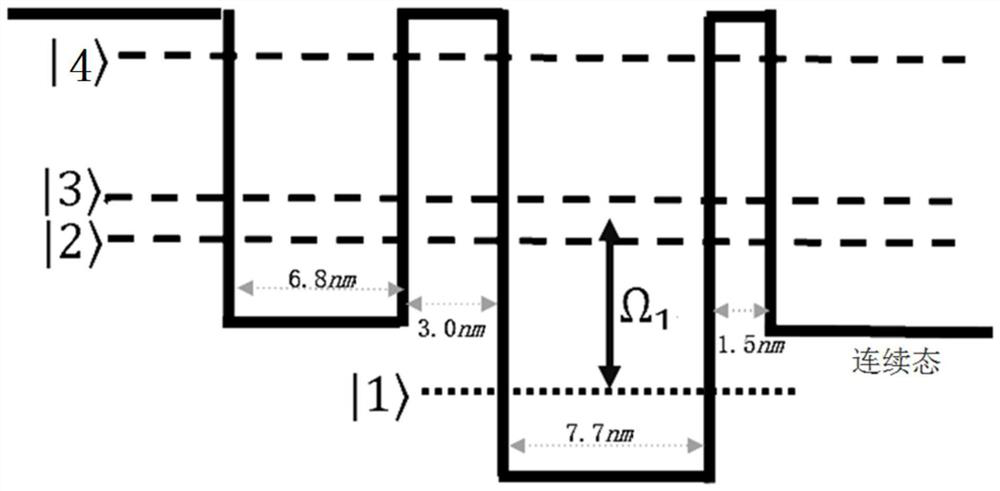

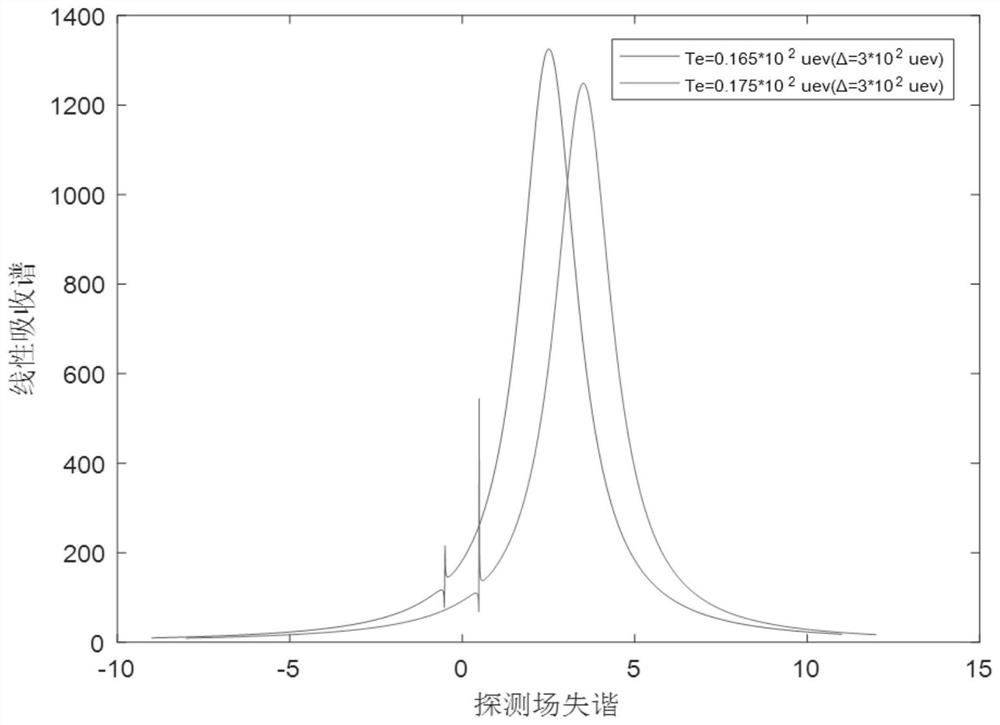

A method for measuring tunneling characteristics between double wells based on fano resonance effect

InactiveCN109164071BAccurate measurementHigh precisionAnalysis by material excitationExternal biasPhotodetector

The invention discloses a method for measuring tunneling between double wells based on the Fano resonance effect. The specific steps are: S1: adjust an external bias source to make the double quantum well structure achieve resonant tunneling. Under the excitation of the probe light, pass The photodetector detects the distance between the double peaks of the absorption spectrum, and roughly determines the size of the tunneling characteristic; S2: Adjust the external bias source again to find a suitable tunneling detuning of the double quantum well structure, and detect the absorption spectrum again through the photodetector The asymmetry of , is the appropriate tunneling detuning, Δ is the energy level interval between the representative states; S3: Utilize the polarizability of the double quantum well structure to determine the absorption spectrum, the absorption spectrum A=c*Im(χ (1) ), where c is a constant coefficient, Im(χ (1) ) to take χ (1) The imaginary part of ; S4: numerically fitting the relationship between the asymmetry of the absorption spectrum and the variation of the tunneling characteristic, and obtained that the size of the tunneling characteristic of the double quantum well structure is inversely proportional to the asymmetry of the absorption spectrum. The invention can realize the precise measurement of the tunneling characteristic and improve the measurement accuracy.

Owner:SHANDONG UNIV OF SCI & TECH

Solid state cooling or power generating device and method of fabricating the same

InactiveCN101438106AImprove efficiencyReduce productionEnergy efficient heating/coolingSolid-state devicesVacuum gapQuantum well

The present invention relates to a solid state cooling / power generating device is provided comprising a first and second electrode separated by a vacuum gap. According to the present invention at least one of the electrodes is provided with a nanoscaled semiconductor heterostructure 301, which comprises at least one quantum well which in combination with the vacuum gap 315 forms a double barrier resonance structure providing conditions which allows resonant tunneling between the first and second electrode.

Owner:BEAKON TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com