Anti-staggered-layer heterojunction resonance tunneling field-effect transistor (TFET) and preparation method thereof

A field effect transistor and resonant tunneling technology, applied in the field of field effect transistor logic devices, can solve the problems of low on-state current, inability to meet system integration application requirements, low band-band tunneling efficiency, etc. The effect of suppressing the off-state current of the device and reducing the production cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The present invention will be further described through specific embodiments below in conjunction with the accompanying drawings.

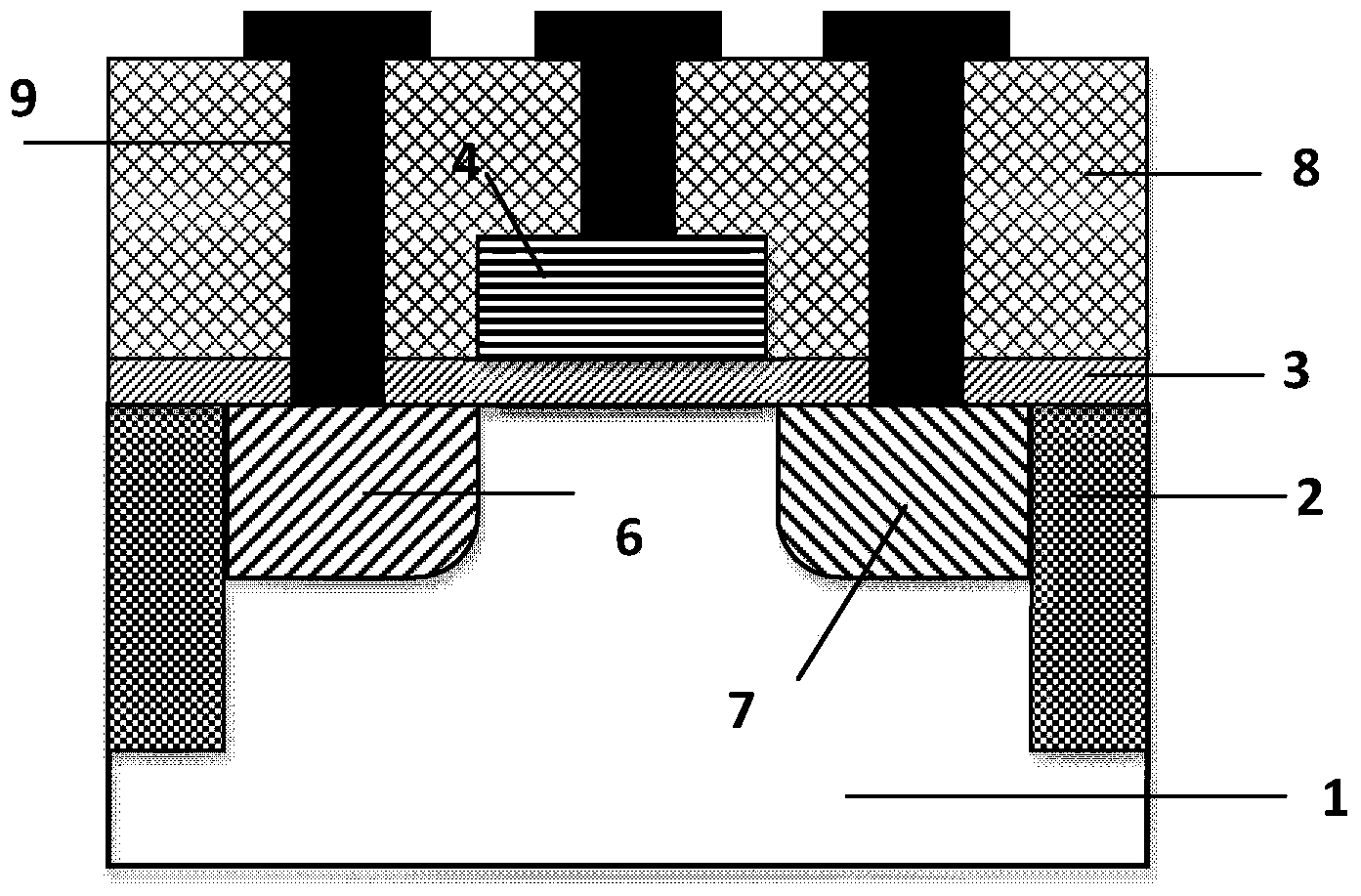

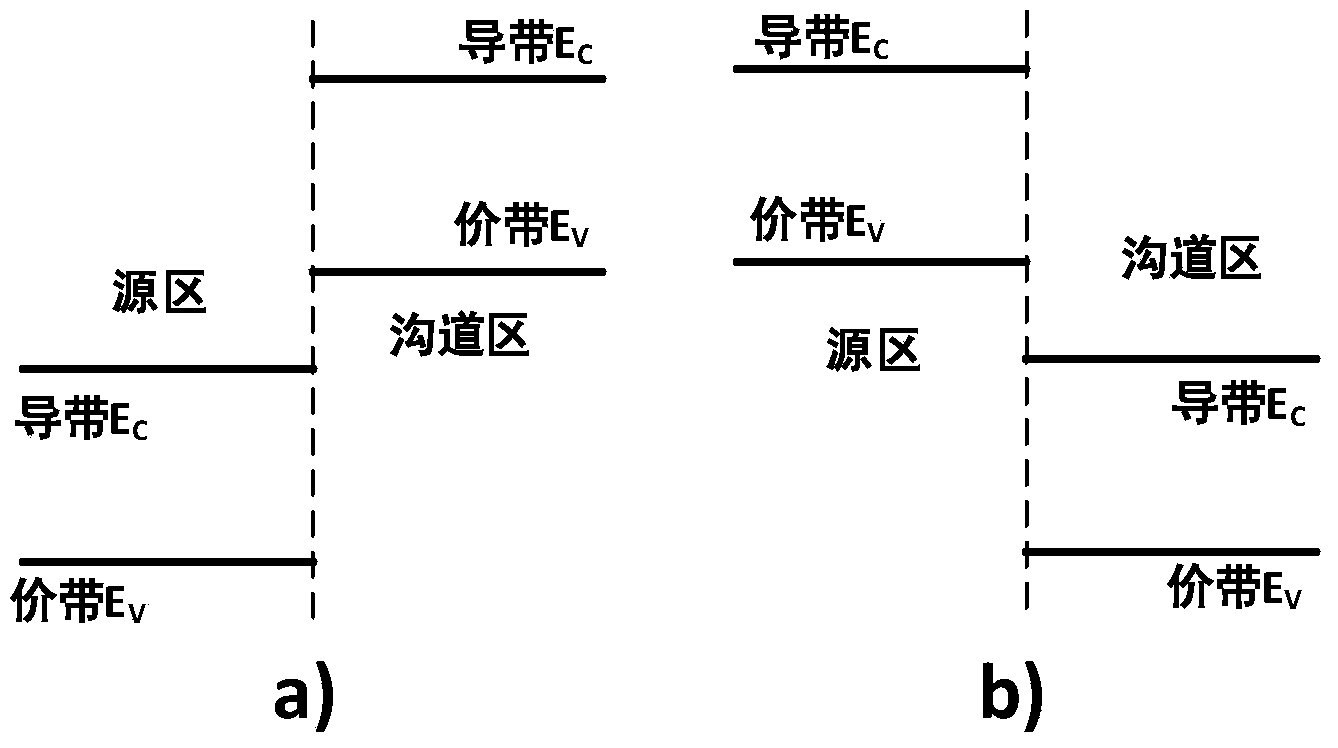

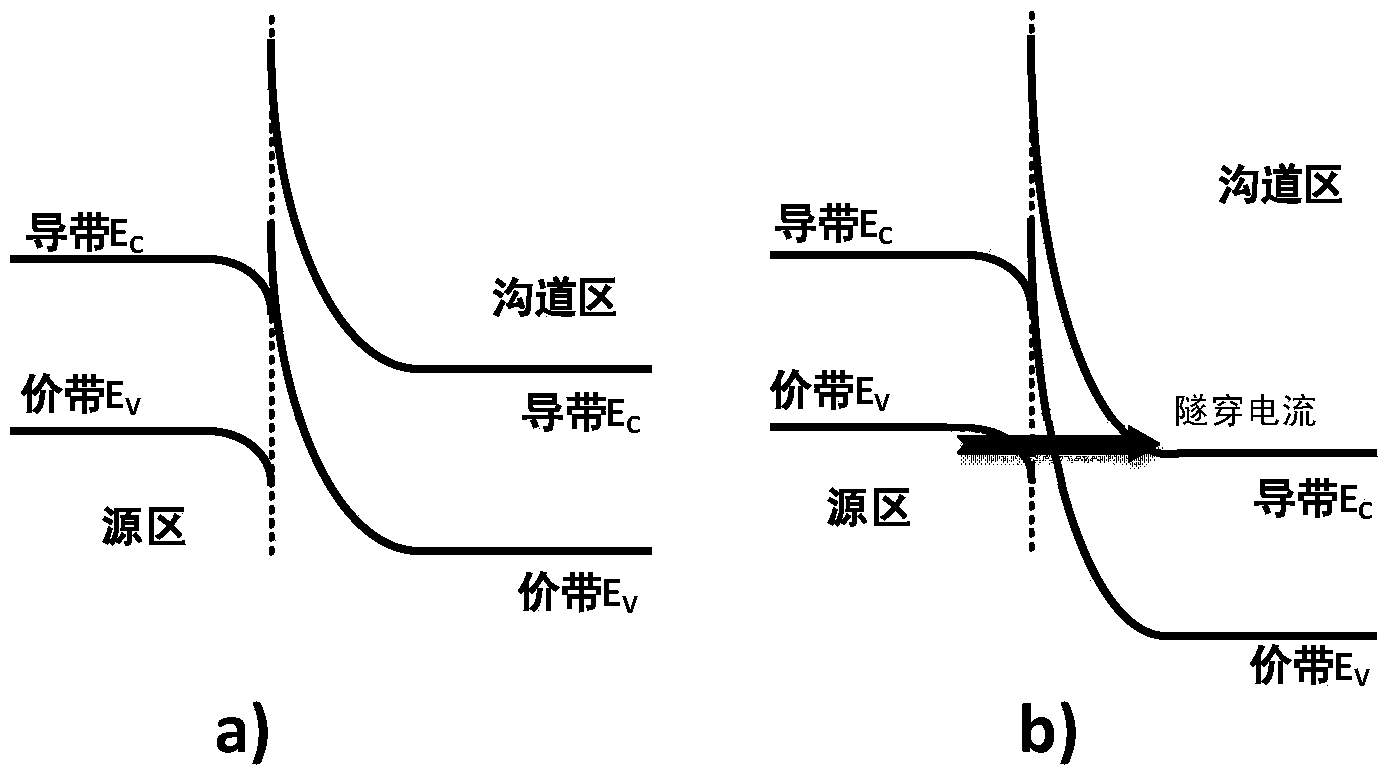

[0049] The anti-staggered layer type heterojunction resonant tunneling field effect transistor provided by the present invention has a structure such as figure 1 As shown, it includes a tunneling source region 6, a channel region 1, a drain region 7 and a control gate 4 located above the channel region 1, wherein the energy of the heterogeneous tunneling junction between the tunneling source region 6 and the channel region 1 The band structure is an anti-staggered layered heterojunction, such as Picture 1-1 , where: a) is the energy band structure of the N-type anti-staggered layer type heterojunction resonant tunneling transistor; b) is the P-type anti-staggered layer type heterojunction resonant tunneling transistor Tunneling junction anti-staggered layered energy band structure;.

[0050] The aforementioned anti-staggered layer hetero...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com