Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

86 results about "Amorphous silicon nitride" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

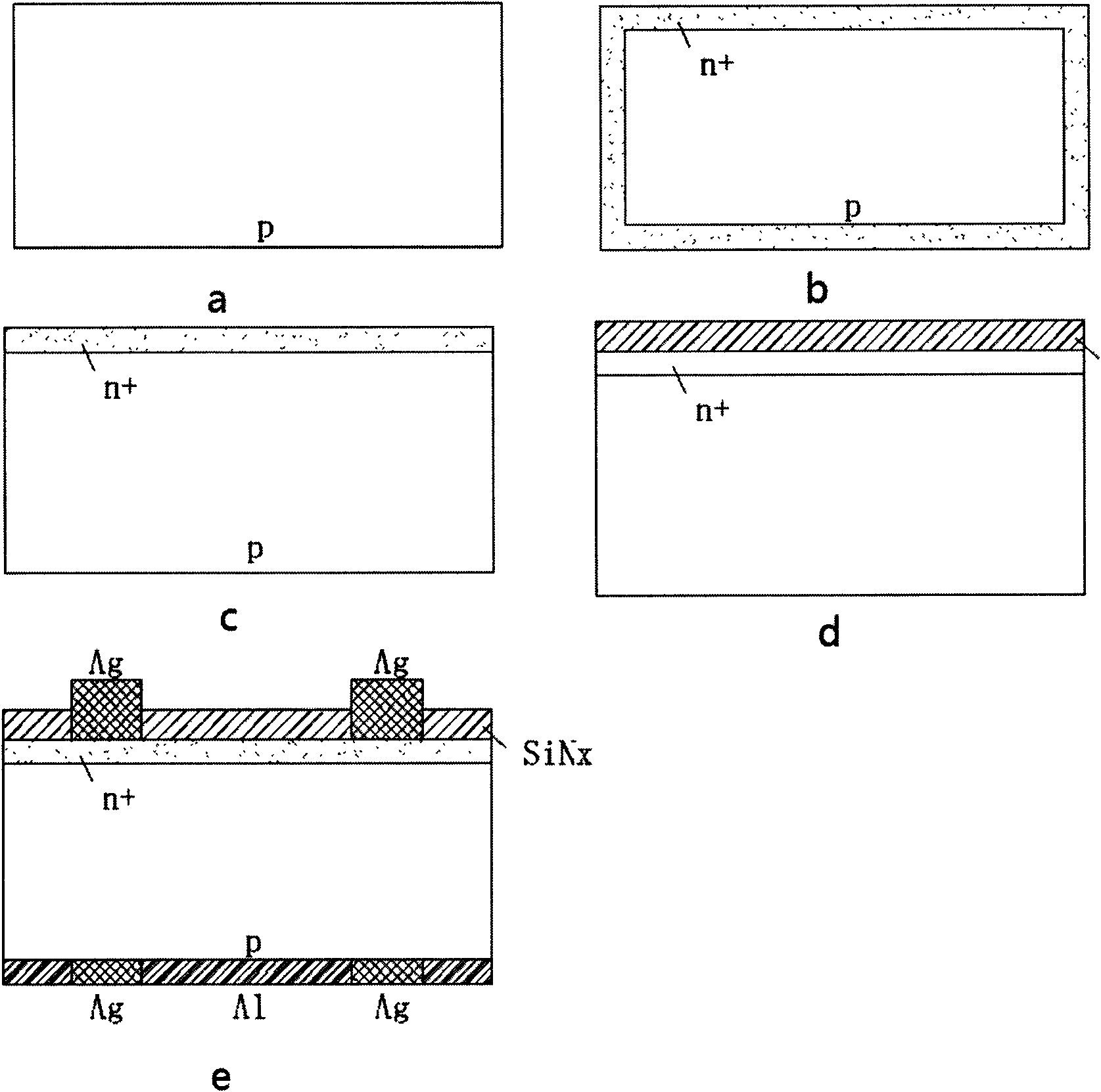

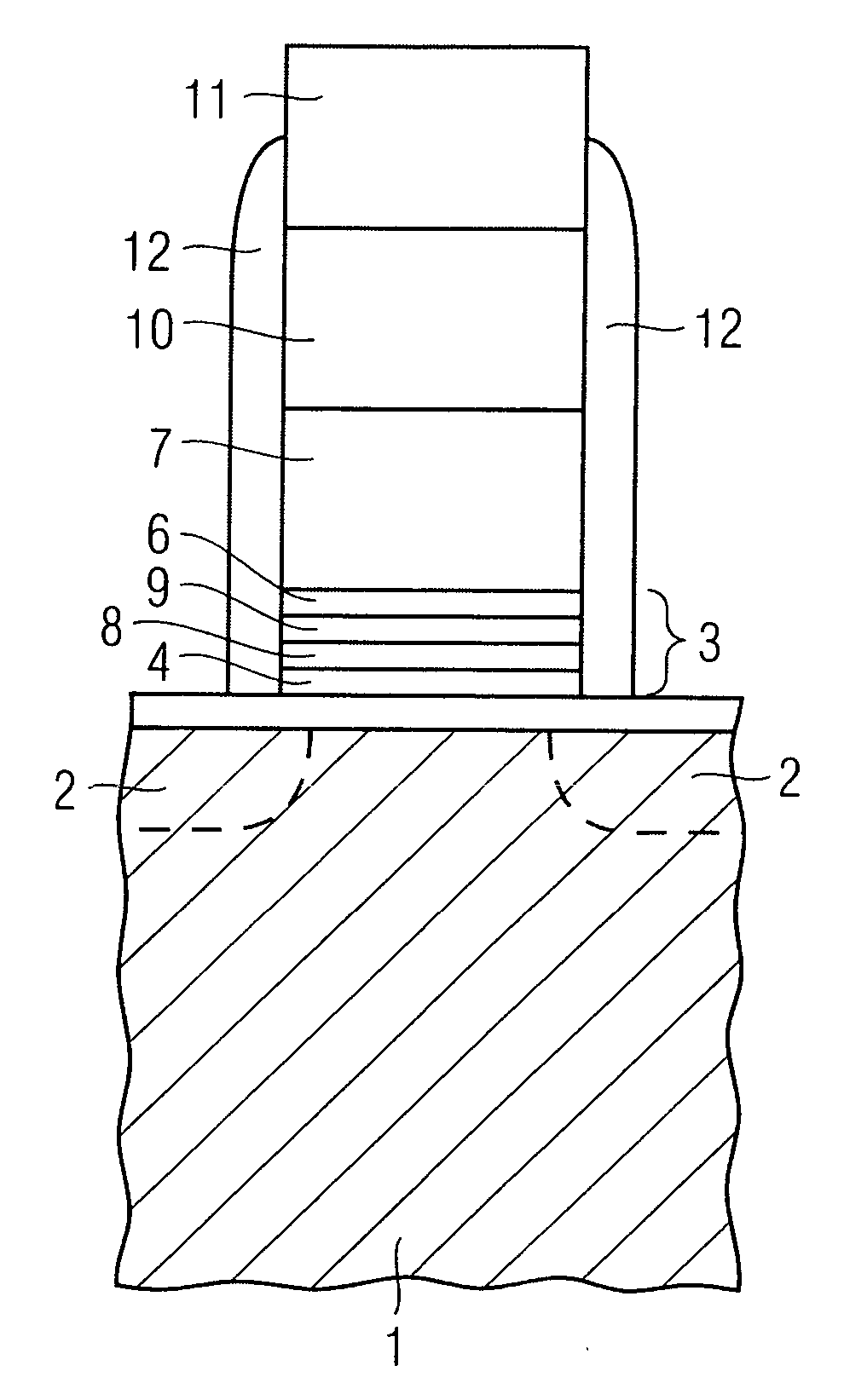

Photovoltaic cell and method of fabricating the same

ActiveUS7199395B2Significant to useLow costPhotovoltaic energy generationSemiconductor devicesAmorphous siliconOptoelectronics

An i-type amorphous silicon film and an anti-reflection film made of amorphous silicon nitride or the like are formed in this order on a main surface of an n-type single-crystalline silicon substrate. On a back surface of the n-type single-crystalline silicon substrate are provided a positive electrode and a negative electrode next to each other. The positive electrode includes an i-type amorphous silicon film, a p-type amorphous silicon film, a back electrode, and a collector electrode formed in this order on the back surface of the n-type single-crystalline silicon substrate. The negative electrode includes an i-type amorphous silicon film, an n-type amorphous silicon film, a back electrode, and a collector electrode formed in this order on the back surface of the n-type single-crystalline silicon substrate.

Owner:SANYO ELECTRIC CO LTD

Microbolometer for infrared detector or Terahertz detector and method for manufacturing the same

InactiveUS20110315981A1Improve business performanceLow costSemiconductor/solid-state device manufacturingPyrometry using electric radation detectorsComposite filmMicrobolometer

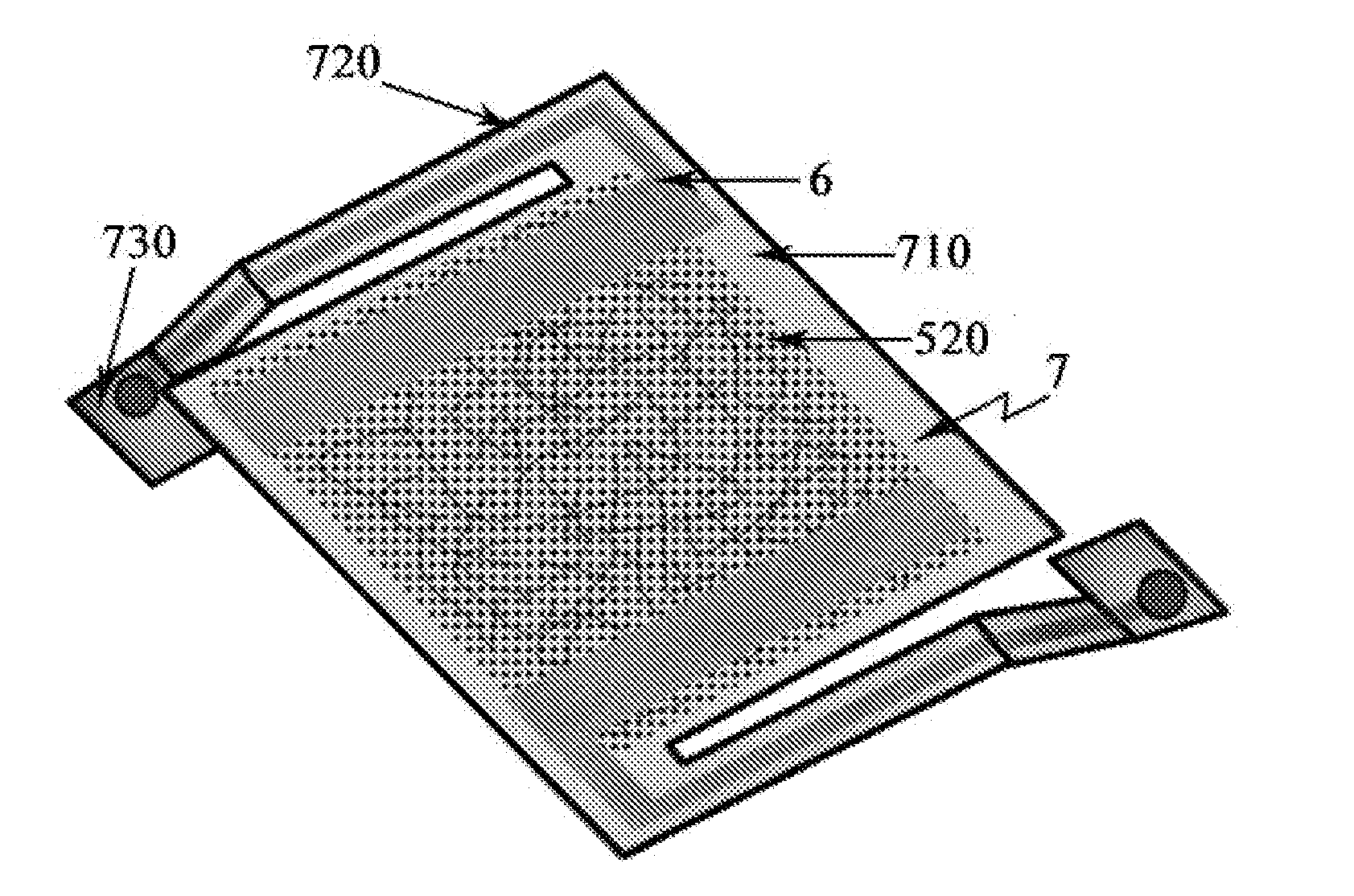

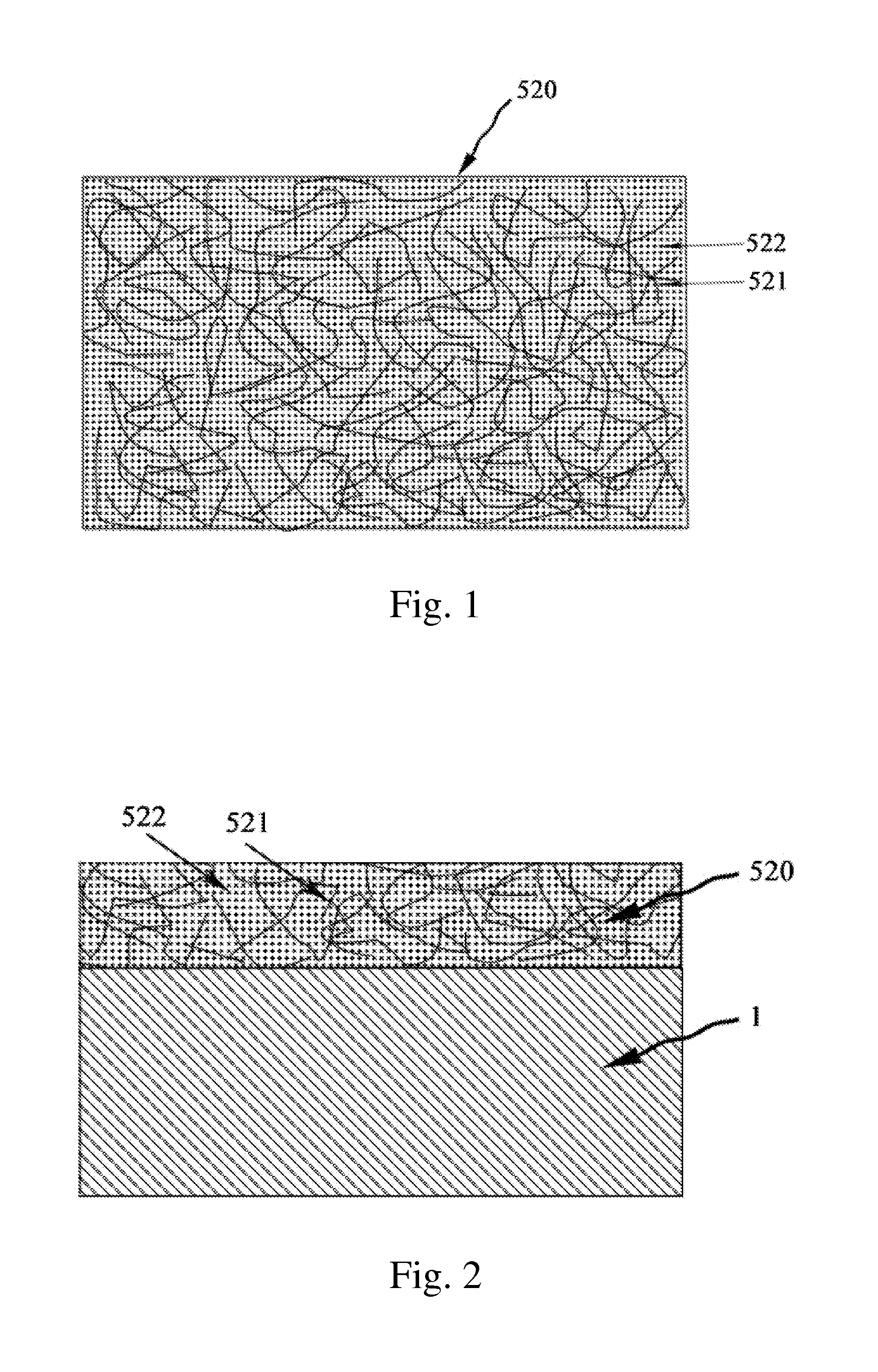

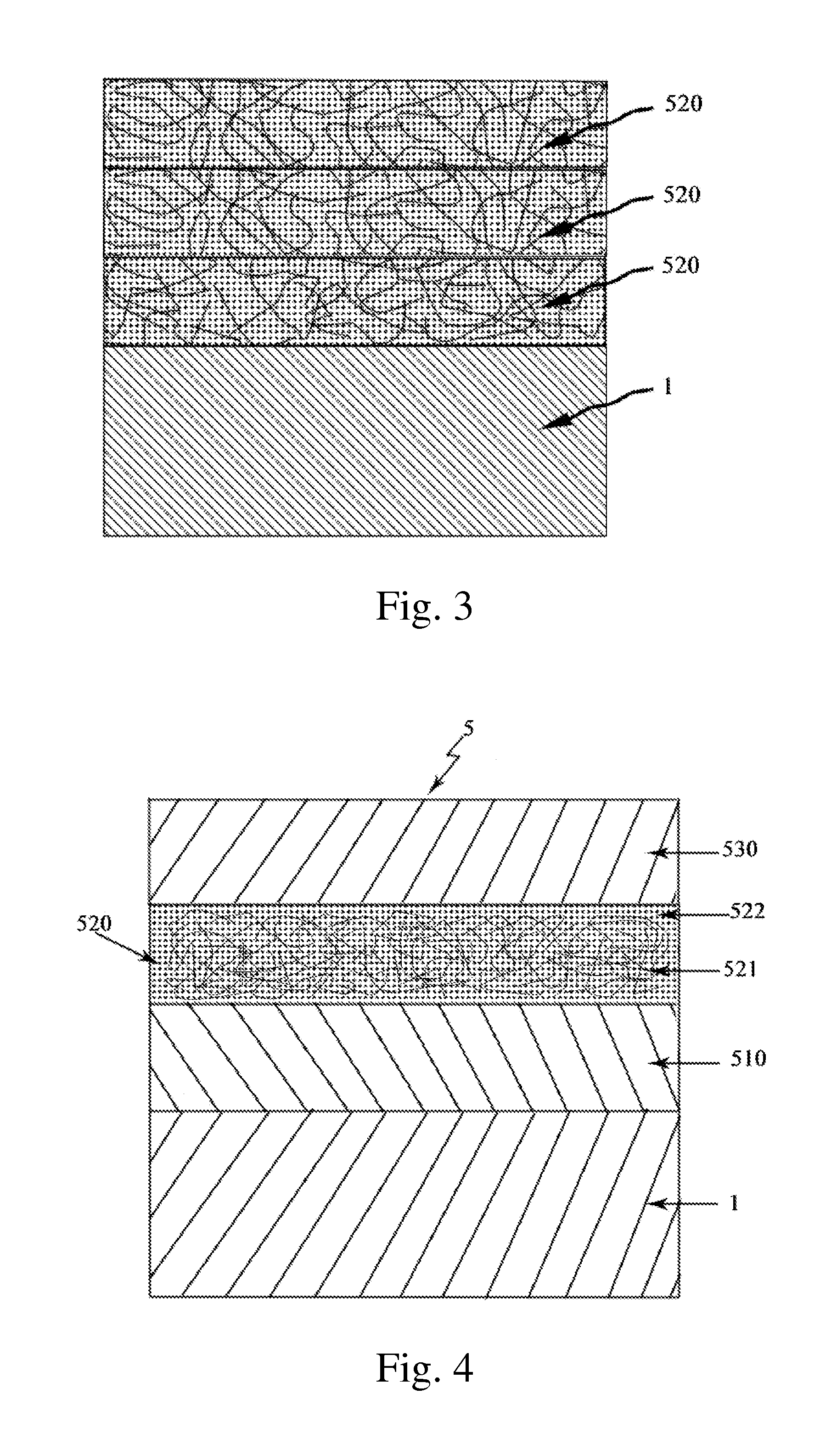

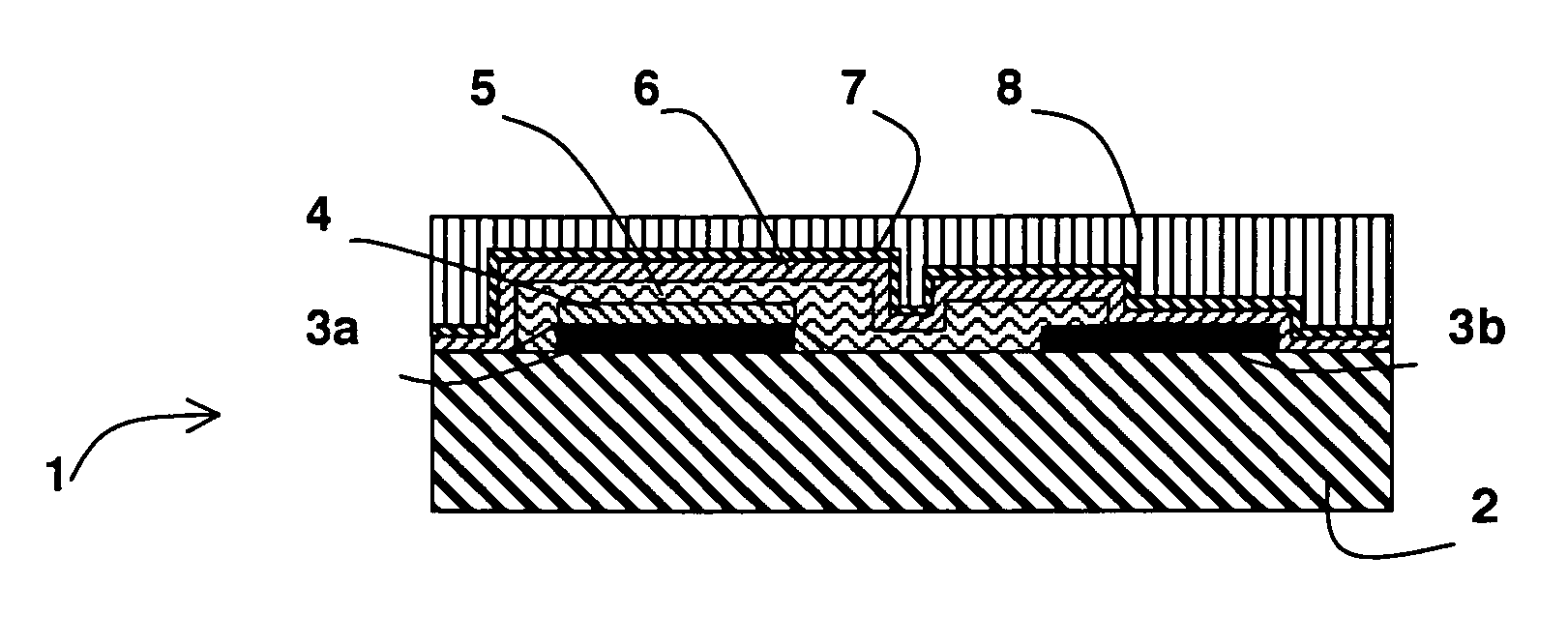

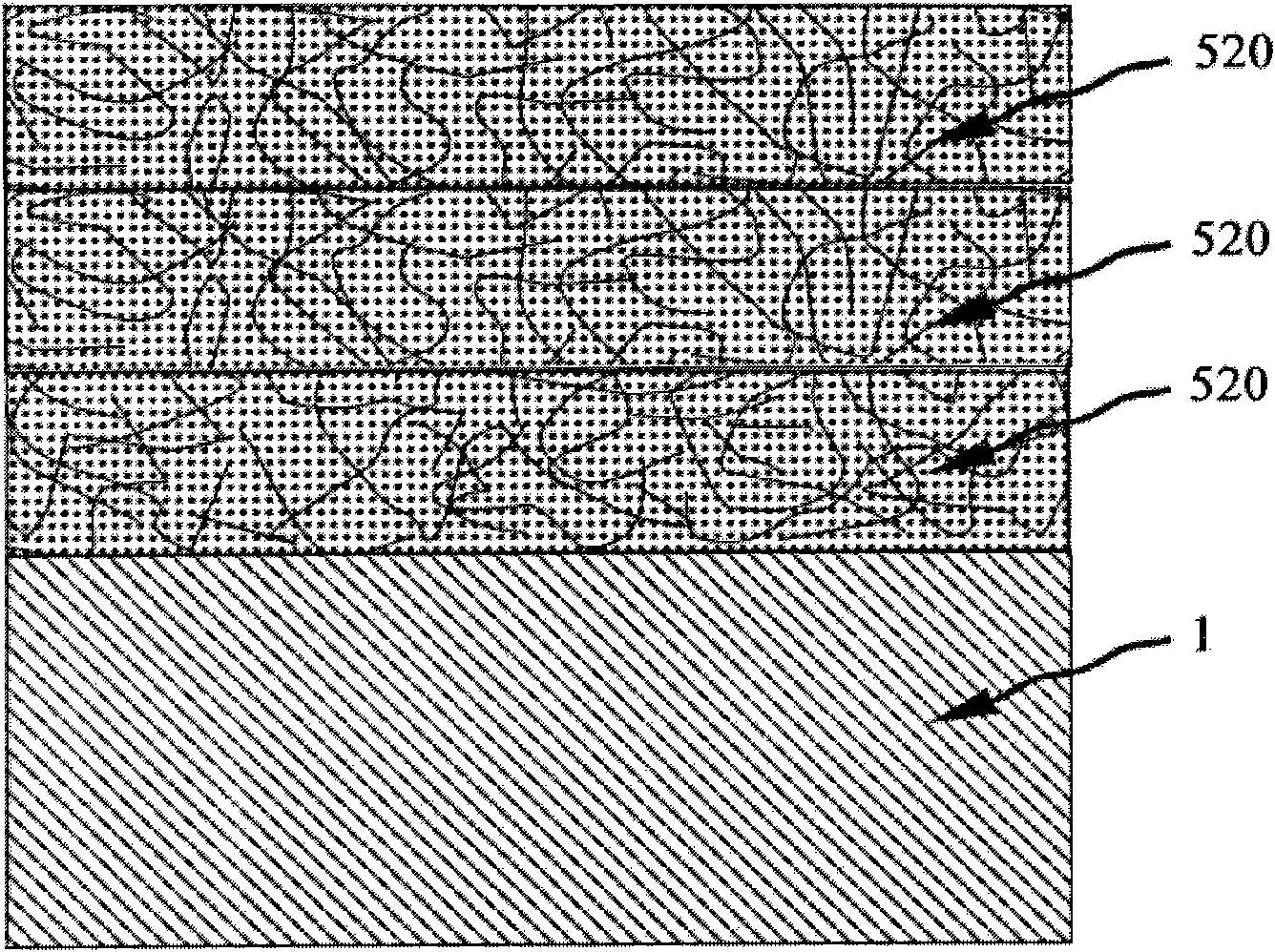

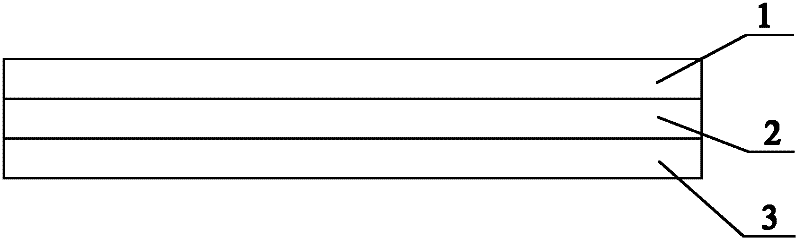

A microbolometer includes a micro-bridge structure for uncooling infrared or terahertz detectors. The thermistor and light absorbing materials of the micro-bridge structure are the vanadium oxide-carbon nanotube composite film formed by one-dimensional carbon nanotubes and two-dimensional vanadium oxide film. The micro-bridge is a three-layer sandwich structure consisting of a layer of amorphous silicon nitride base film as the supporting and insulating layer of the micro-bridge, a layer or multi-layer of vanadium oxide-carbon nanotube composite film in the middle of the micro-bridge as the heat sensitive and light absorbing layer of the microbolometer, and a layer of amorphous silicon nitride top film as the stress control layer and passivation of the heat sensitive film. The microbolometer and method for manufacturing the same can overcome the shortcomings of the prior art, improve the performance of the device, reduce the cost of raw materials and is suitable for large-scale industrial production.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

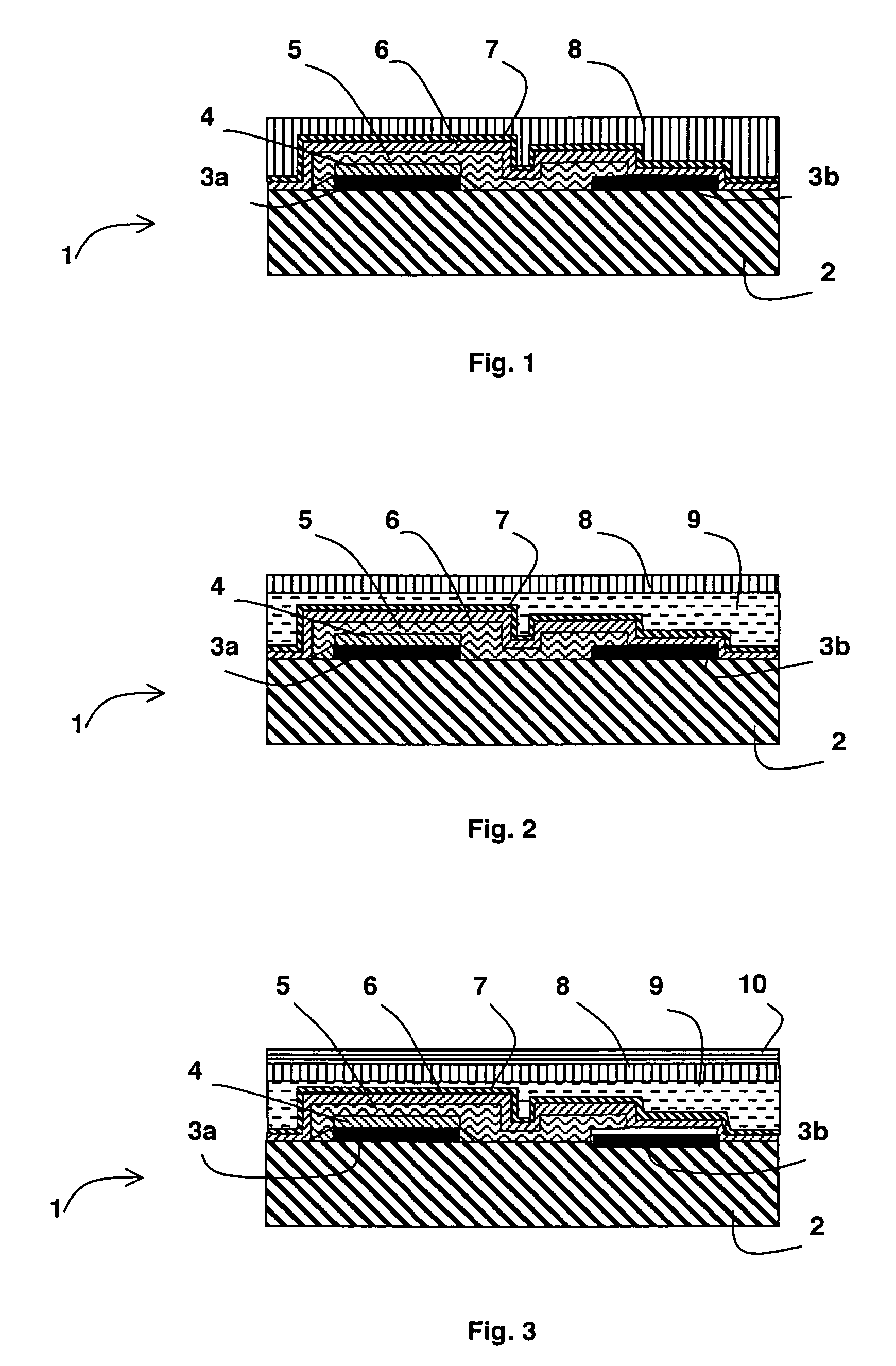

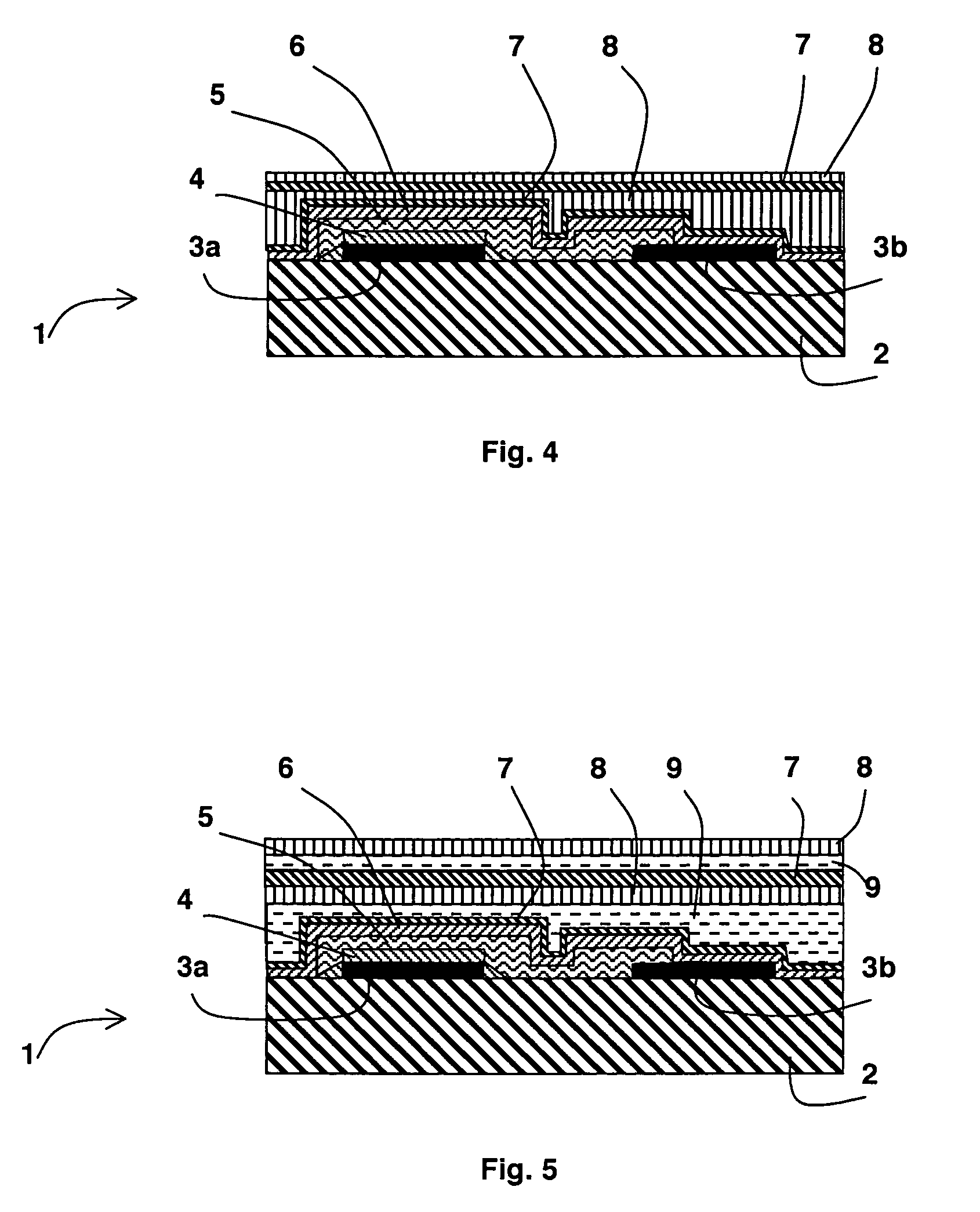

Lithium microbattery provided with a protective envelope, and method for producing one such microbattery

InactiveUS20070048604A1Easily compatibleEasy to implementPrimary cellsElectrode carriers/collectorsMetallic lithiumCarbide

A lithium microbattery comprises a substrate on which at least one stack is arranged successively comprising a cathode, an electrolyte containing lithium and an anode consisting of metallic lithium. A protective envelope comprising at least first and second distinct superposed layers covers the stack to protect the same against external contamination. The first layer, deposited on the whole of the anode, comprises at least one material that is chemically inert with regard to lithium, selected from the group consisting of a hydrogenated amorphous silicon carbide, a hydrogenated amorphous silicon oxycarbide, hydrogenated amorphous carbon, fluorinated amorphous carbon and hydrogenated amorphous silicon. The second layer comprises a material selected from the group consisting of a hydrogenated amorphous silicon carbonitride, a hydrogenated amorphous silicon nitride and a fluorinated amorphous carbon.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

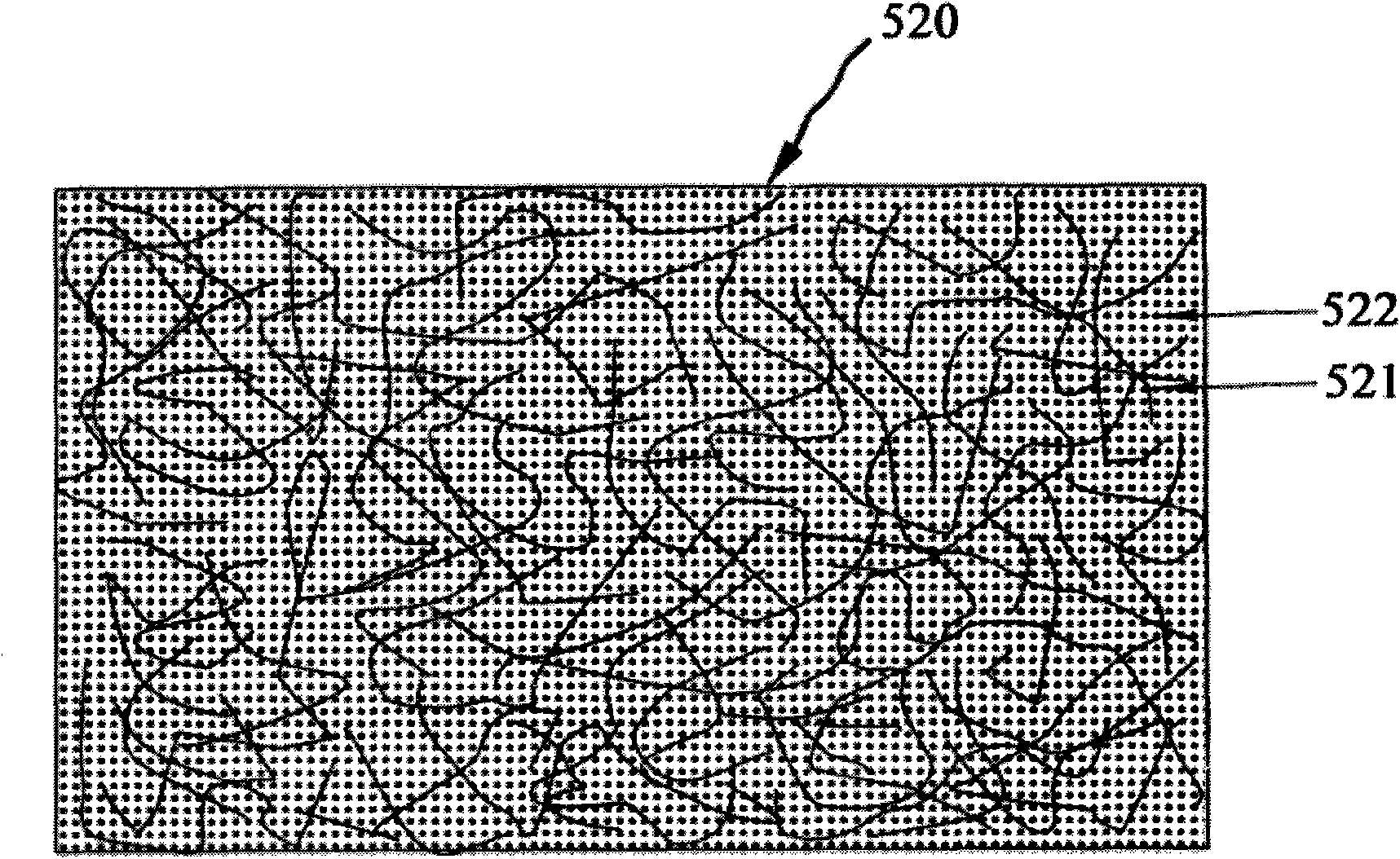

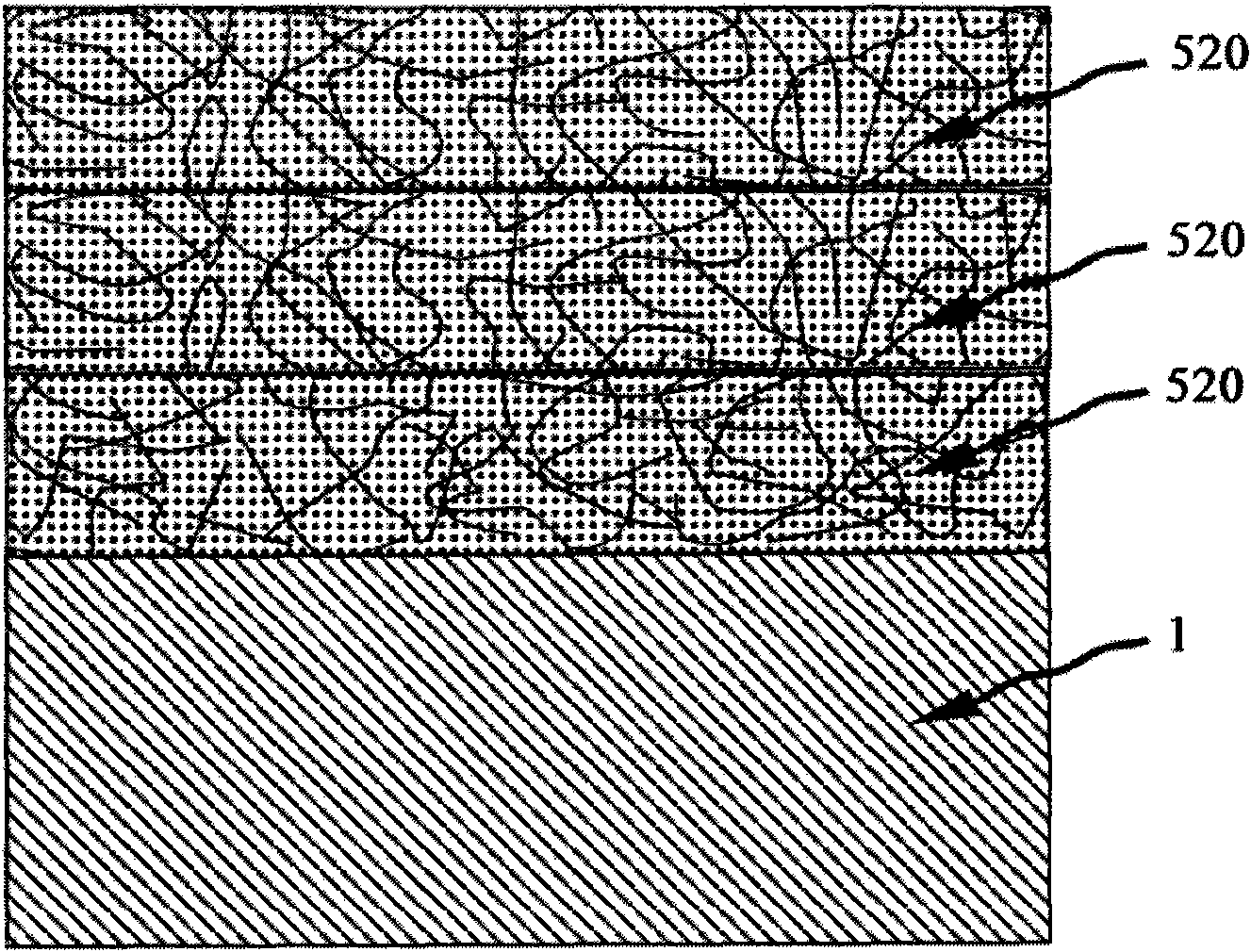

Uncooled microbolometer and preparation method thereof

InactiveCN101881667AImprove performanceReduce residual stressDecorative surface effectsChemical vapor deposition coatingCarbon nanotubeHeat sensitive

The invention discloses an uncooled microbolometer, which comprises a microbolometer microbridge structure used for an uncooled detector, wherein the thermistor material and the light absorbing material in the microbridge structure are vanadium oxide-carbon nano tube composite membranes, the vanadium oxide-carbon nano tube composite membranes are formed by compounding one-dimensional carbon nano tubes and two-dimensional vanadium oxide membranes, and the microbridge structure is in a three-layer sandwich structure: the bottom layer is provided with an amorphous silicon nitride membrane which is used as the supporting and insulating material of the microbridge, the middle layer is provided with one or more layers of vanadium oxide-carbon nano tube composite membranes which are used as the heat sensitive layer and the light absorbing layer of the microbolometer; and the surface layer is provided with another layer of amorphous silicon nitride membrane which is used as the passivation layer of the heat sensitive membrane and a stress control layer. The microbolometer and the preparation method thereof can overcome the defects of the prior art, improve the working performance of devices, reduce the cost of raw materials, and are suitable for large-scale industrial production.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

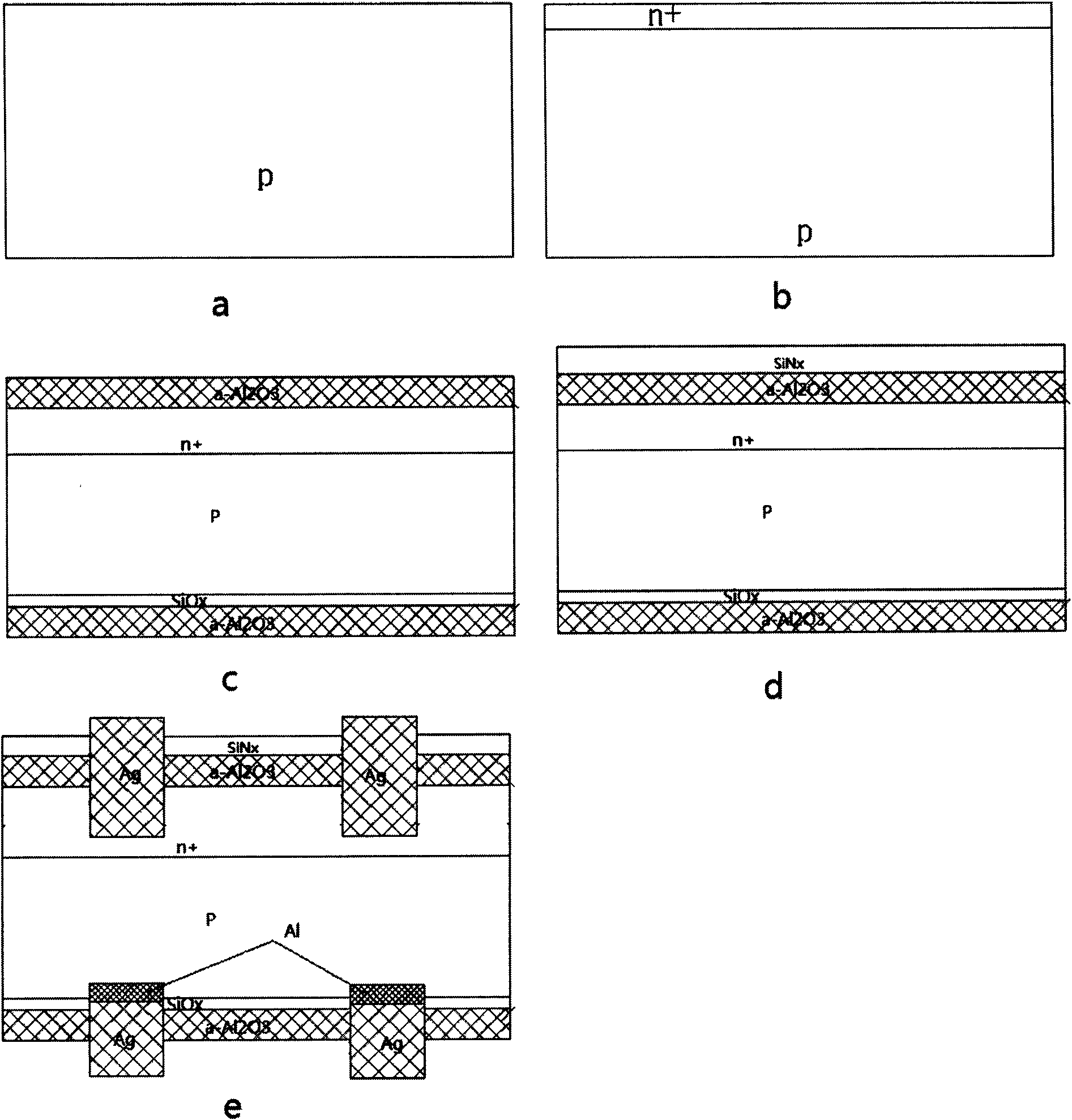

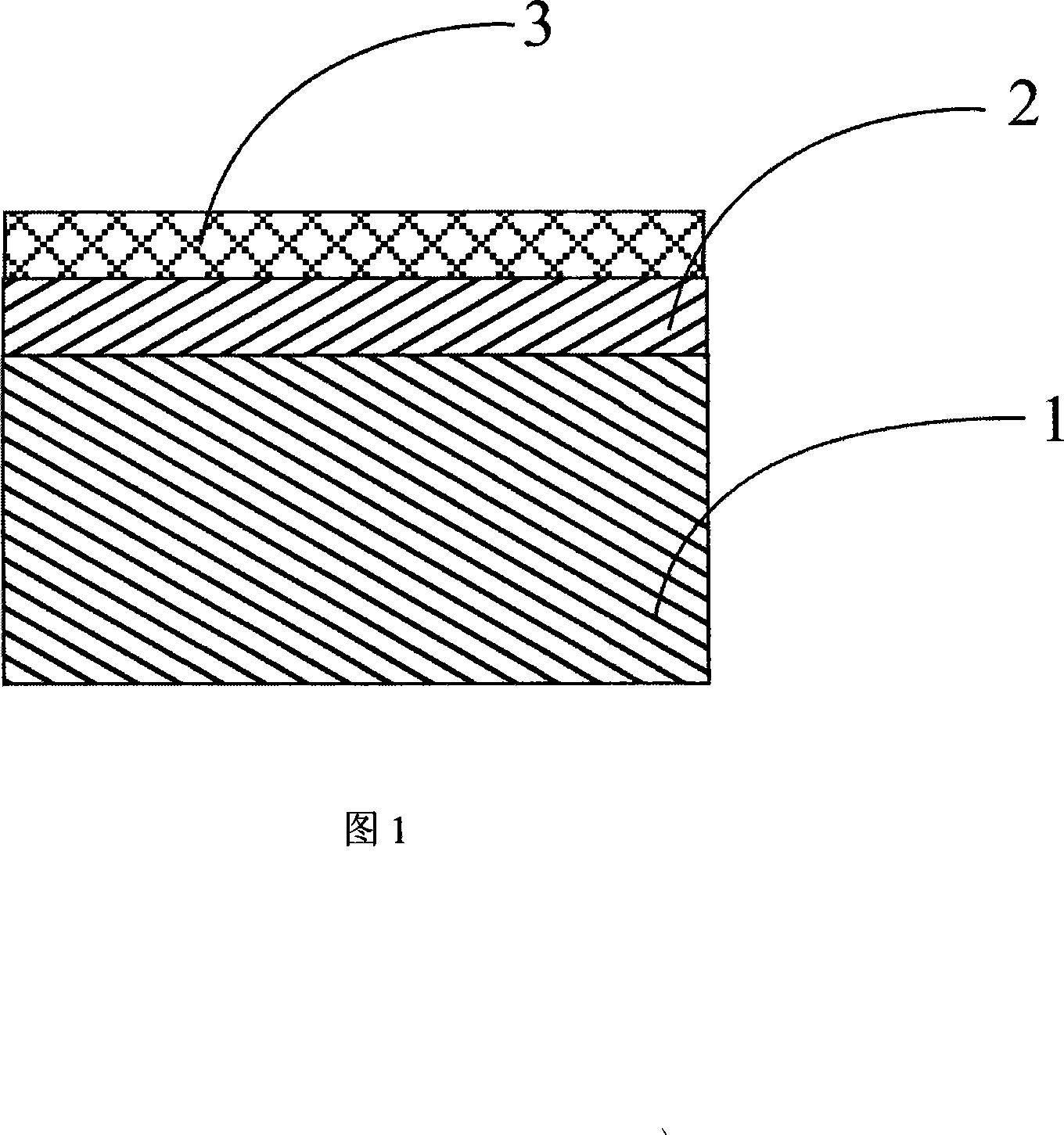

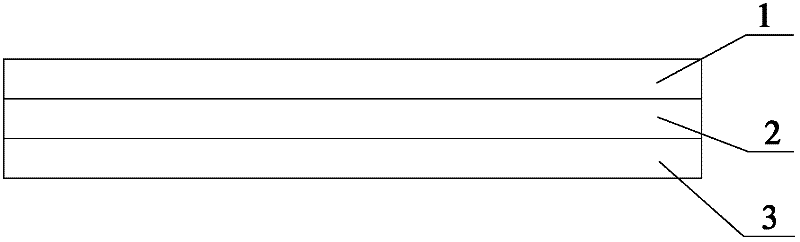

Composite passivated anti-reflection film used for crystalline silicon solar battery and preparation method thereof

InactiveCN102157570AImprove anti-reflection effectImprove passivation effectFinal product manufactureChemical vapor deposition coatingElectrical batteryEngineering

The invention discloses a composite passivated anti-reflection film used for a crystalline silicon solar battery and a preparation method thereof. The composite passivated anti-reflection film consists of a silicon oxide (SiO2) layer, an amorphous alumina (a-Al2O3) layer and an amorphous silicon nitride (a-Si1-xNx) layer which are arranged on the emitter on a light receiving surface of the crystalline silicon solar battery in turn. The preparation method comprises the following steps of: preparing an a-Al2O3 layer on the emitter on the light receiving surface of the crystalline silicon solar battery by a plasma enhanced chemical vapor deposition (PECVD) process or an atomic layer deposition (ALD) process; forming the SiO2 layer between the emitter layer and the a-Al2O3 layer by an annealing process; and preparing the a-Si1-xNx layer on the a-Al2O3 layer by the PECVD process. The composite passivated anti-reflection film has the advantages that: the a-Si1-xNx anti-reflection film has a good anti-reflection effect; the a-Al2O3 / SiO2 composite passivated film has double effects of chemical passivation and field passivation and has a good passivation effect; the a-Si1-xNx / a-Al2O3 / Si2O composite passivated anti-reflection film has high thermal stability and is compatible with a subsequent battery preparation process; and the anti-ultraviolet (UV) performance is high.

Owner:上海太阳能电池研究与发展中心

Microbolometer and preparation method thereof

InactiveCN101774530AImprove performanceReduce residual stressTelevision system detailsNanostructure manufactureComposite filmControl layer

The invention relates to a microbolometer, which comprises a microbridge structure, wherein a thermosensitive resistance material and an infrared absorption material layer in the microbridge structure are of a carbon nanometer tube-amorphous silicon composite film, the carbon nano tube-amorphous silicon composite film is formed by compounding an one-dimension carbon nano-tube and a two-dimensional amorphous silicon film, and the microbridge structure is of a three-layer sandwich structure; the most bottom layer is of a amorphous silicon nitride film which is used as a supporting and insulation material of the microbridge; the intermediate layer is of one layer or multiple layers of carbon nano-tube-amorphous composite film, the stress is opposite to the nature of the bottom layer silicon nitride film, and the carbon nano-tube-amorphous composite film is used as the thermosensitive layer and the infrared absorption layer of the microbolometer; and the surface layer is of an amorphous silicon nitride film, the stress of the amorphous silicon nitride film is opposite to the nature of the intermediate carbon nano-tube-amorphous composite film, and the amorphous silicon nitride film is used as a passivation layer of the inforared sensing film and a control layer of the stress. The microbolometer and the preparation method can overcome the weaknesses of the prior art, improves the working performance of the part, reduces the cost of the raw material and are applicable to the industrialized mass production.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

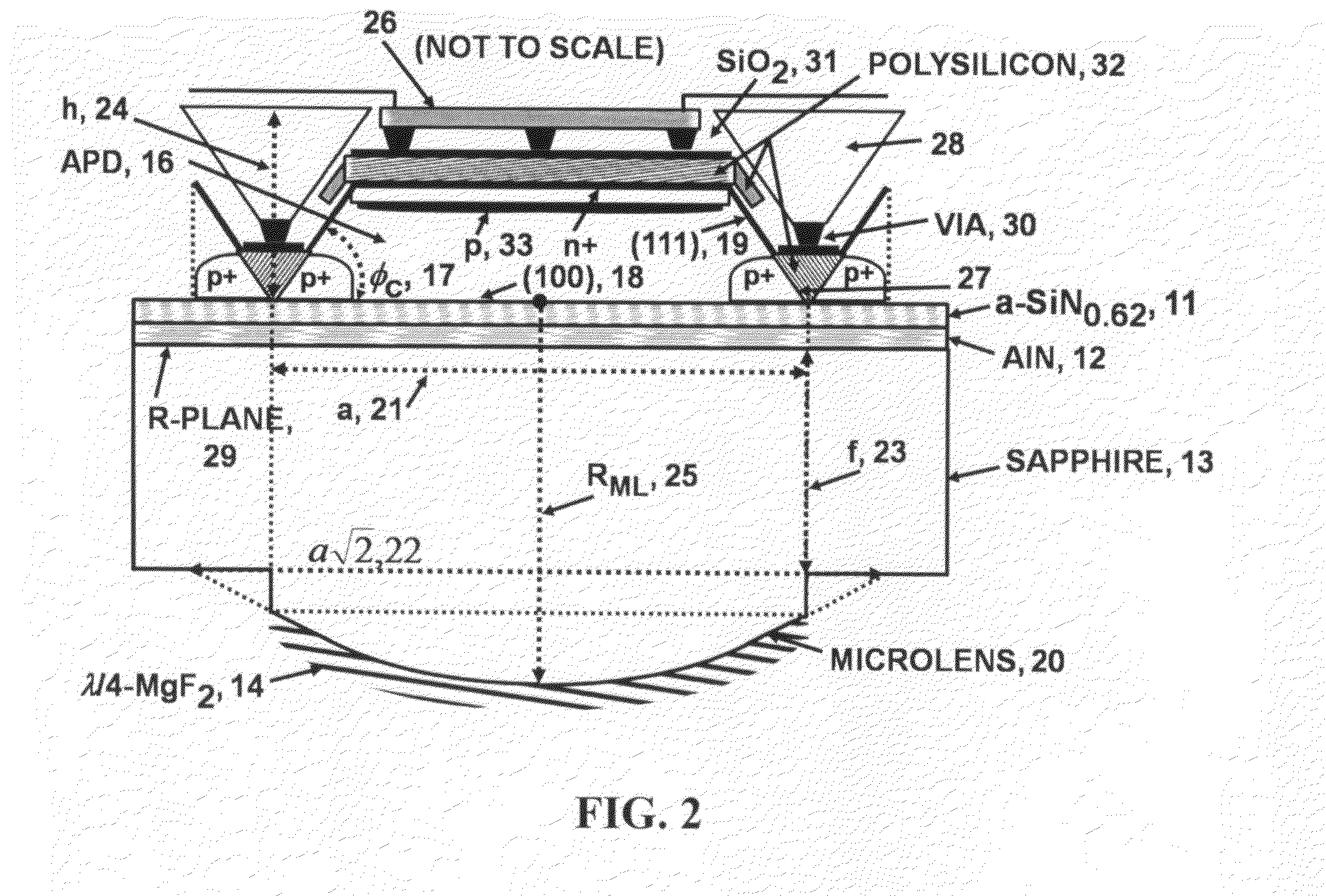

Thin, very high transmittance, back-illuminated, silicon-on-saphire semiconductor substrates bonded to fused silica

InactiveUS20120299143A1High light transmittanceSuppression problemSolid-state devicesSemiconductor/solid-state device manufacturingSingle crystalSilicon dioxide

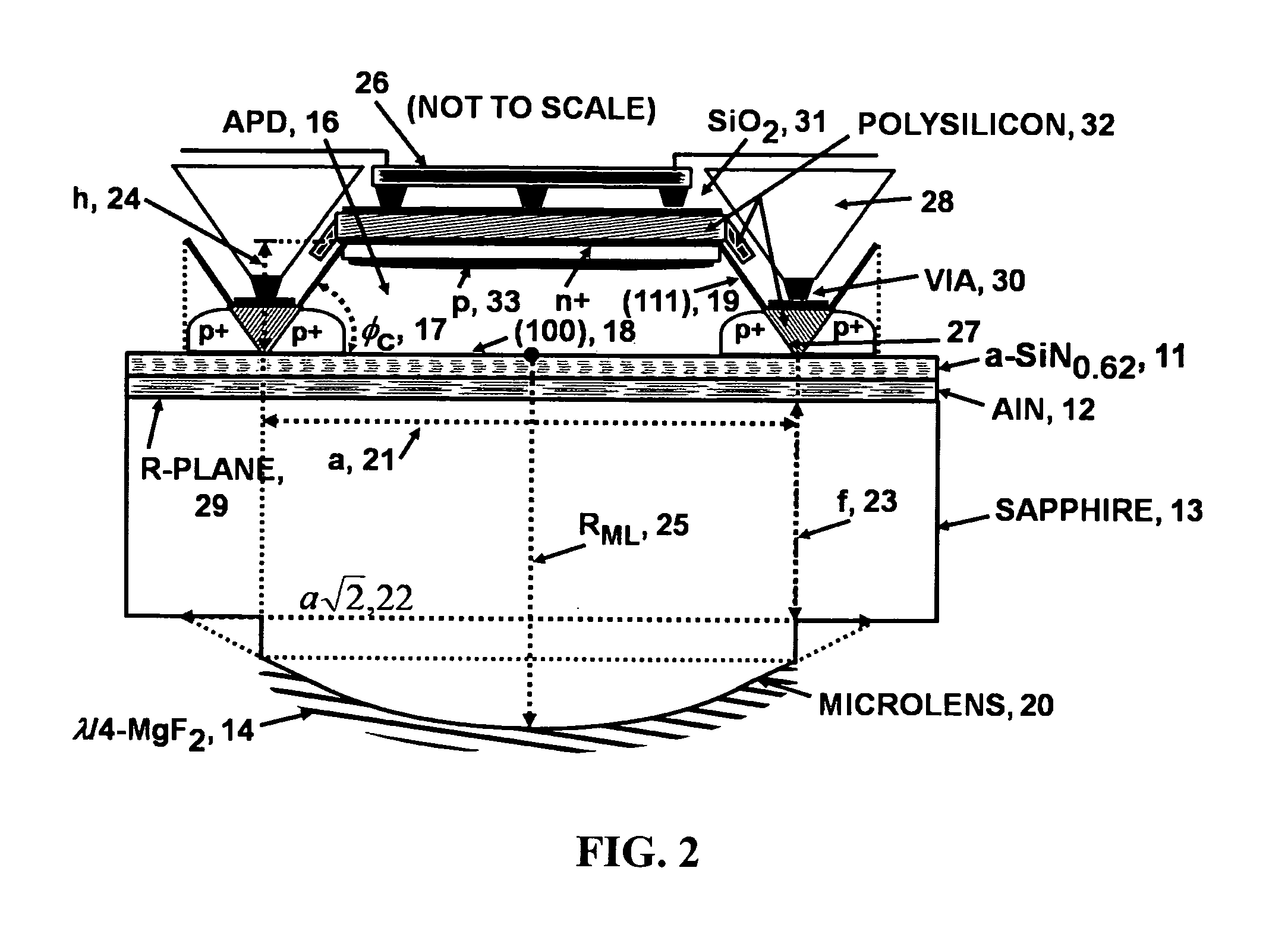

A very high transmittance, back-illuminated, silicon-on-thin sapphire-on-fused silica wafer substrate design is presented for enabling high quantum efficiency and high resolution, silicon or silicon-germanium avalanche photodiode detector arrays with improved indirect optical crosstalk suppression. The wafer substrate incorporates a stacked antireflective bilayer between the sapphire and silicon, comprised of single crystal aluminum nitride (AlN) and non-stoichiometric, silicon rich, amorphous silicon nitride (a-SiNX<1.33), as well as a one quarter wavelength, magnesium fluoride (λ / 4-MgF2) back-side antireflective layer which is bonded to a fused silica wafer. The fused silica provides mechanical support, allowing the sapphire to be thinned to optimal thickness below 50 μm, for improved optical transmittance and in conjunction with monolithic sapphire microlenses, suppression of indirect optical crosstalk from multiple reflections of APD emitted light. After solid-state device fabrication, the silicon can be coated with photoresist and the fused silica dissolved in buffered hydrogen fluoride (HF) to recover the thin Si—(AlN / a-SiNX<1.33)-sapphire-(MgF2).

Owner:STERN ALVIN GABRIEL

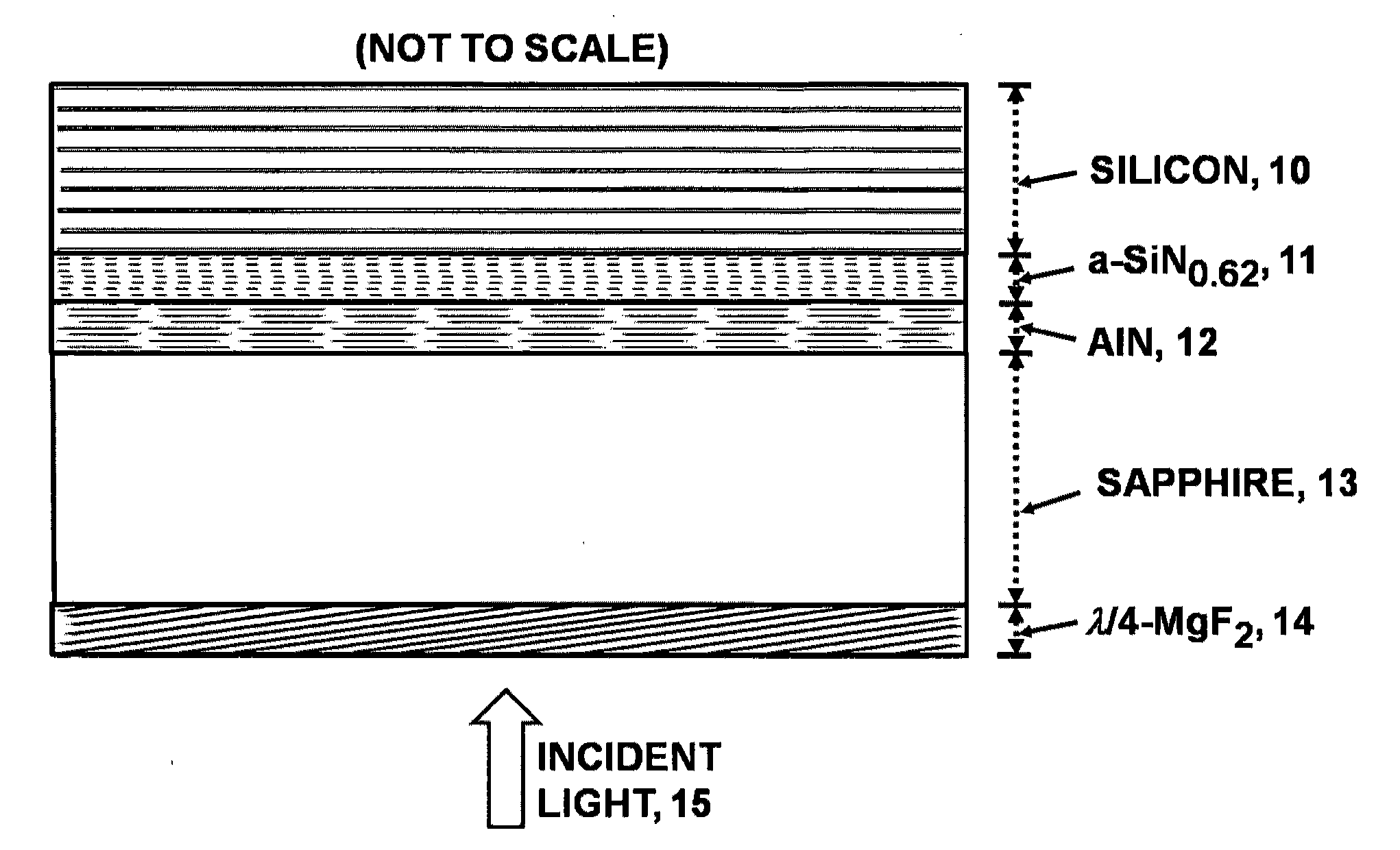

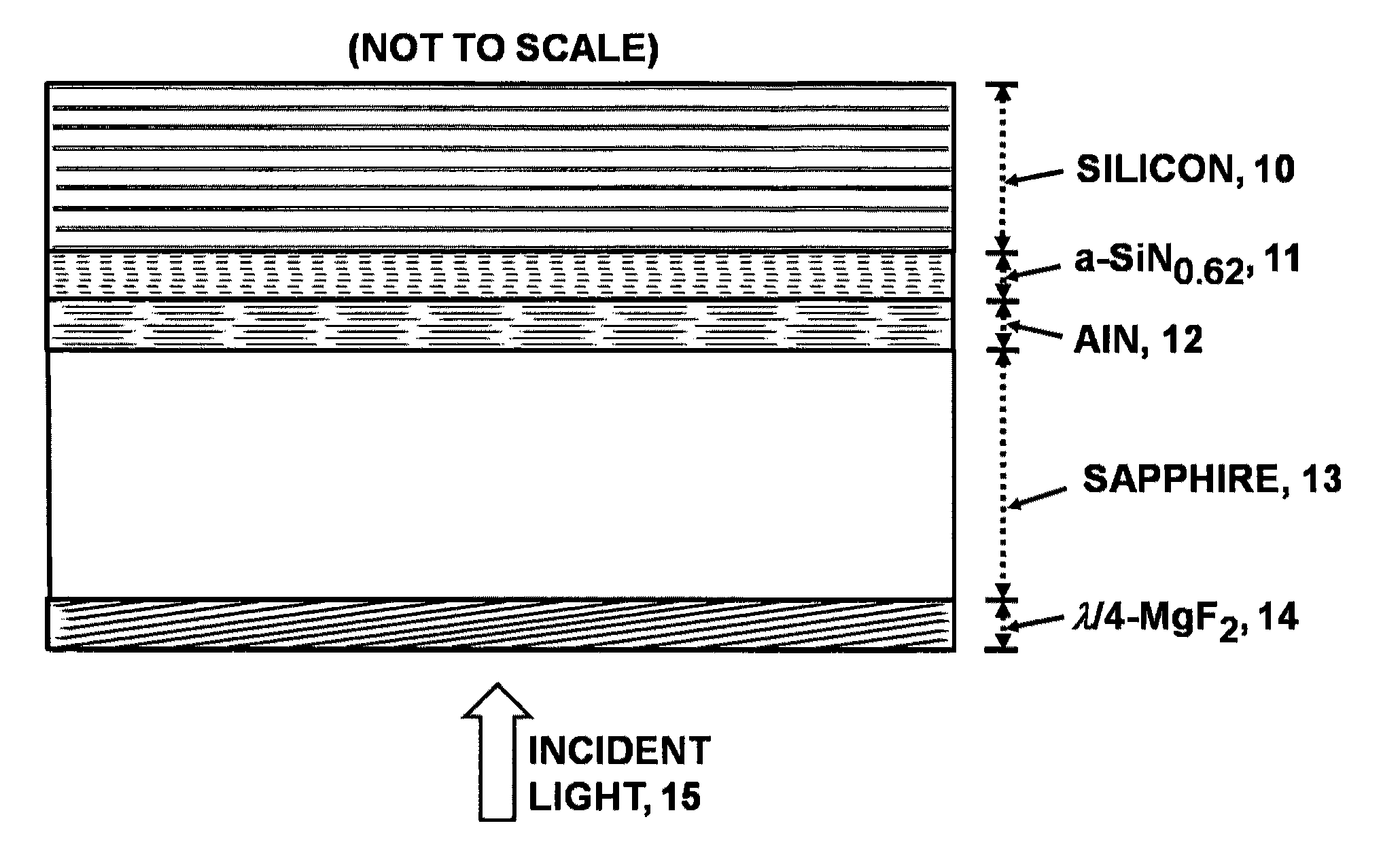

Very high transmittance, back-illuminated, silicon-on-sapphire semiconductor wafer substrate for high quantum efficiency and high resolution, solid-state, imaging focal plane arrays

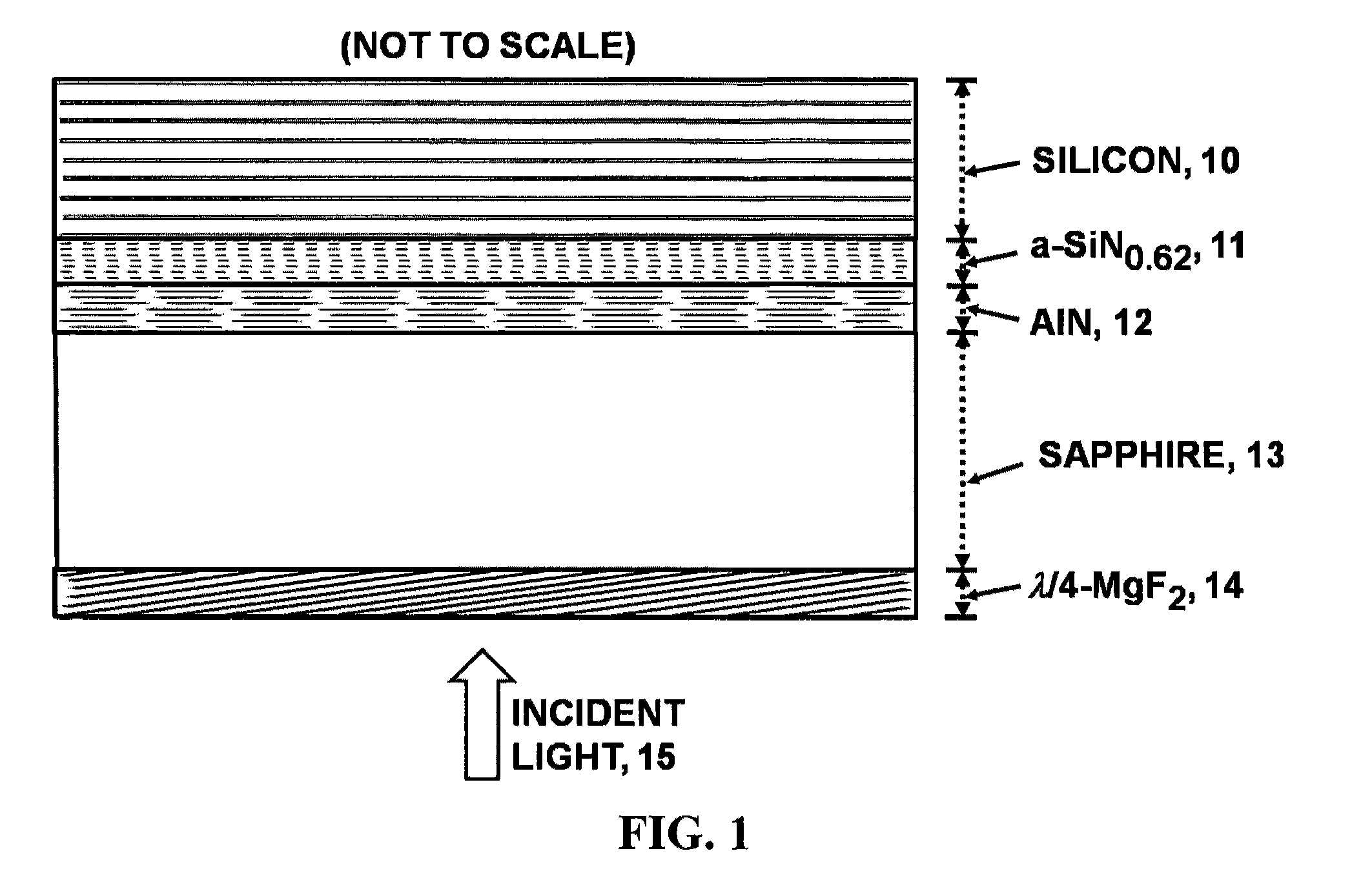

InactiveUS20120193636A1High light transmittanceImprove quantum efficiencyLaser detailsSolid-state devicesSingle crystalRefractive index matching

An advanced, very high transmittance, back-illuminated, silicon-on-sapphire wafer substrate design is presented for enabling high quantum efficiency and high resolution, silicon or silicon-germanium avalanche photodiode detector arrays. The wafer substrate incorporates a stacked antireflective bilayer between the sapphire and silicon layers, comprised of single crystal aluminum nitride (AlN) and non-stoichiometric, silicon rich, amorphous silicon nitride (a-SiNX<1.33), that provides optimal refractive index matching between sapphire and silicon. A one quarter wavelength, magnesium fluoride (λ / 4-MgF2) antireflective layer deposited on the back surface of the thinned sapphire provides refractive index matching at the air-sapphire interface. Selecting a composition of x=0.62 for a-SiNX, tunes an optimal refractive index for the layer. Selecting design thicknesses of 52 nm for single crystal AlN, 30 nm for a-SiN0.62, and 120 nm for λ / 4-MgF2 yields a back-illuminated optical transmittance T>50% for 250-300 nm, T>70% for 300-400 nm and T>90% for 400-1100 nm.

Owner:STERN ALVIN GABRIEL

Very high transmittance, back-illuminated, silicon-on-sapphire semiconductor wafer substrate for high quantum efficiency and high resolution, solid-state, imaging focal plane arrays

InactiveUS8354282B2High light transmittanceGreat index of refractionLaser detailsSolid-state devicesSingle crystalRefractive index matching

An advanced, very high transmittance, back-illuminated, silicon-on-sapphire wafer substrate design is presented for enabling high quantum efficiency and high resolution, silicon or silicon-germanium avalanche photodiode detector arrays. The wafer substrate incorporates a stacked antireflective bilayer between the sapphire and silicon layers, comprised of single crystal aluminum nitride (AlN) and non-stoichiometric, silicon rich, amorphous silicon nitride (a-SiNX<1.33), that provides optimal refractive index matching between sapphire and silicon. A one quarter wavelength, magnesium fluoride (λ / 4-MgF2) antireflective layer deposited on the back surface of the thinned sapphire provides refractive index matching at the air-sapphire interface. Selecting a composition of x=0.62 for a-SiNX, tunes an optimal refractive index for the layer. Selecting design thicknesses of 52 nm for single crystal AlN, 30 nm for a-SiN0.62, and 120 nm for λ / 4-MgF2 yields a back-illuminated optical transmittance T>50% for 250-300 nm, T>70% for 300-400 nm and T>90% for 400-1100 nm.

Owner:STERN ALVIN GABRIEL

High-hardness antibacterial TiSiN/Ag nano composite functional coating and preparation method and application thereof

ActiveCN105861988AHigh hardnessImprove antibacterial propertiesVacuum evaporation coatingSputtering coatingComposite functionTitanium nitride

The invention relates to a high-hardness antibacterial TiSiN / Ag nano composite functional coating and a preparation method and application thereof. Specifically, the coating comprises a nano composite layer and an optional transition layer, amorphous silicon nitride serves as a substrate of the nano composite layer, and titanium nitride nanocrystalline particles and silver nanocrystalline particles are embedded into the substrate. Optionally, the coating further comprises a substrate used for supporting the coating, and the transition layer is positioned between the nano composite layer and the substrate. The high-hardness antibacterial TiSiN / Ag nano composite functional coating is high in hardness and excellent in antibacterial performance, thereby being capable of well meeting requirements on abrasion resistance and antibacterial protection. The preparation method is simple in process and easy for large-scale popularization.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

Preparation method of improved type back surface tunnel oxidization and passivation contact efficient battery

InactiveCN107845692AIncrease the open circuit voltageHigh process feasibilityFinal product manufactureSemiconductor devicesSurface concentrationElectricity

The invention relates to a preparation method of an improved type back surface tunnel oxidization and passivation contact efficient battery. The preparation method comprises the steps of performing texturing after a silicon wafer damage layer is removed; next, forming a low surface concentration B doped P<+> emitting junction; after performing edge insulating and back surface polishing, enabling ultra-thin tunnel oxide layer SiO<2> and P-doped polysilicon layer to be grown on the back surface of a silicon wafer; depositing an aluminium oxide layer on the surface of the P<+> emitting junction;enabling a hydrogenated amorphous silicon nitride passivated antireflection layer to be grown on the front surface of the silicon wafer; forming partial heavy doping on the back surface of the siliconwafer by adopting a laser doping or wet etching method; enabling the hydrogenated amorphous silicon nitride passivated antireflection layer to be grown on the back surface of the silicon wafer; and finally, printing Ag / Al paste on the front surface of the silicon wafer, and printing Ag paste on the back surface. By adoption of the layer of the ultra-thin tunnel oxide layer SiO<2>, one layer of phosphorus P-doped silicon layer and the P-doped region partial heavy doping, the metal-semiconductor surface compounding on the back surface can be greatly lowered; and the preparation method has the most obvious advantage of capability of greatly improving electrical performance on the basis of compatibility with the conventional battery manufacturing process.

Owner:SHANGHAI SHENZHOU NEW ENERGY DEV

Crystalline silicon solar cell and preparation method thereof

ActiveCN102122674APromote passivationImprove anti-reflection abilityFinal product manufacturePhotovoltaic energy generationSilver electrodeSilicon oxide

The invention discloses a crystalline silicon solar cell and a preparation method thereof, and the crystalline silicon solar cell comprises a pn plus junction silicon substrate, wherein a first amorphous alumina layer and an amorphous silicon nitride layer are arranged on the surface of an n plus emitter, a silver electrode penetrates the amorphous silicon nitride layer and the first amorphous alumina layer and is connected with the n plus emitter, a composite passivation medium layer is arranged on the surface of a p type substrate, the p type substrate comprises a silicon oxide layer and a second amorphous alumina layer, and a p type substrate is in contact with a back electrode. The preparation method comprises the special preparation of the composite passivation medium layer, nitric acid and hydrogen peroxide solution are adopted for processing the surface of the p type substrate, the sol-gel process is adopted for preparing the second amorphous alumina layer, and the composite passivation medium layer (4) is formed after annealing. The crystalline silicon solar cell has the advantages of simple process, low equipment investment, good passivation and anti-reflection performances of the front surface, excellent passivation effect of the composite passivation medium layer on the back surface, capability of improving the utilization efficiency of long waves, and the like.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

A preparation method of a high-efficiency N-type double-sided battery with double-sided tunneling oxidation passivation

InactiveCN109216498ARaise VocExcellent selective tunneling effectFinal product manufacturePhotovoltaic energy generationGas phaseSingle crystal

The invention relates to a preparation method of a double-sided tunneling oxidation passivation high-efficient N-type double-sided battery, which comprises the following steps: cutting silicon wafer to remove damage layer for velveting; doping high-temperature vapor phase boron source to form p + emitting junction; growing ultra-thin tunnel oxide layer SiO2 and P-doped polycrystalline silicon layer on the back of the silicon wafer; Frontal tunneling oxidation passivation structure is formed on the p + emitting junction surface by thermal oxidation and polycrystalline deposition. A local heavily dope region is formed on that back side of the silicon wafer by laser doping or wet patterning etch method, and a hydride amorphous silicon nitride passivation antireflection layer is deposited on the front side / back side of the battery. At last, that front and back electrode metallize ohmic contact is formed by screen printing electrode grid line. A metal on that back of the battery is minimizeby the invention. Semiconductor surface recombination can obtain Voc enhancement of about 35mV, and the technology route is compatible with the existing traditional single crystal battery preparationprocess to improve the battery efficiency.

Owner:SHANGHAI SHENZHOU NEW ENERGY DEV +1

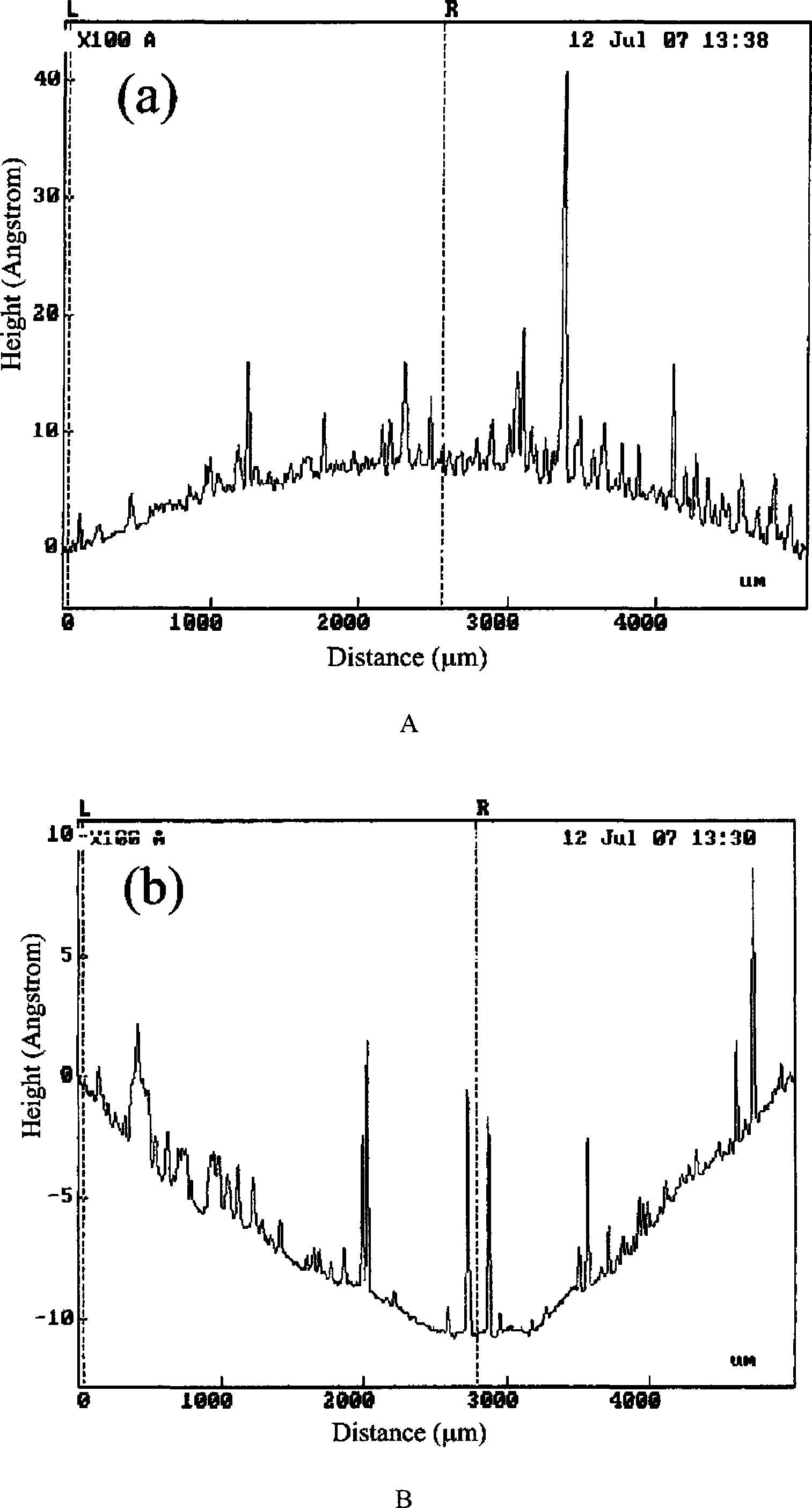

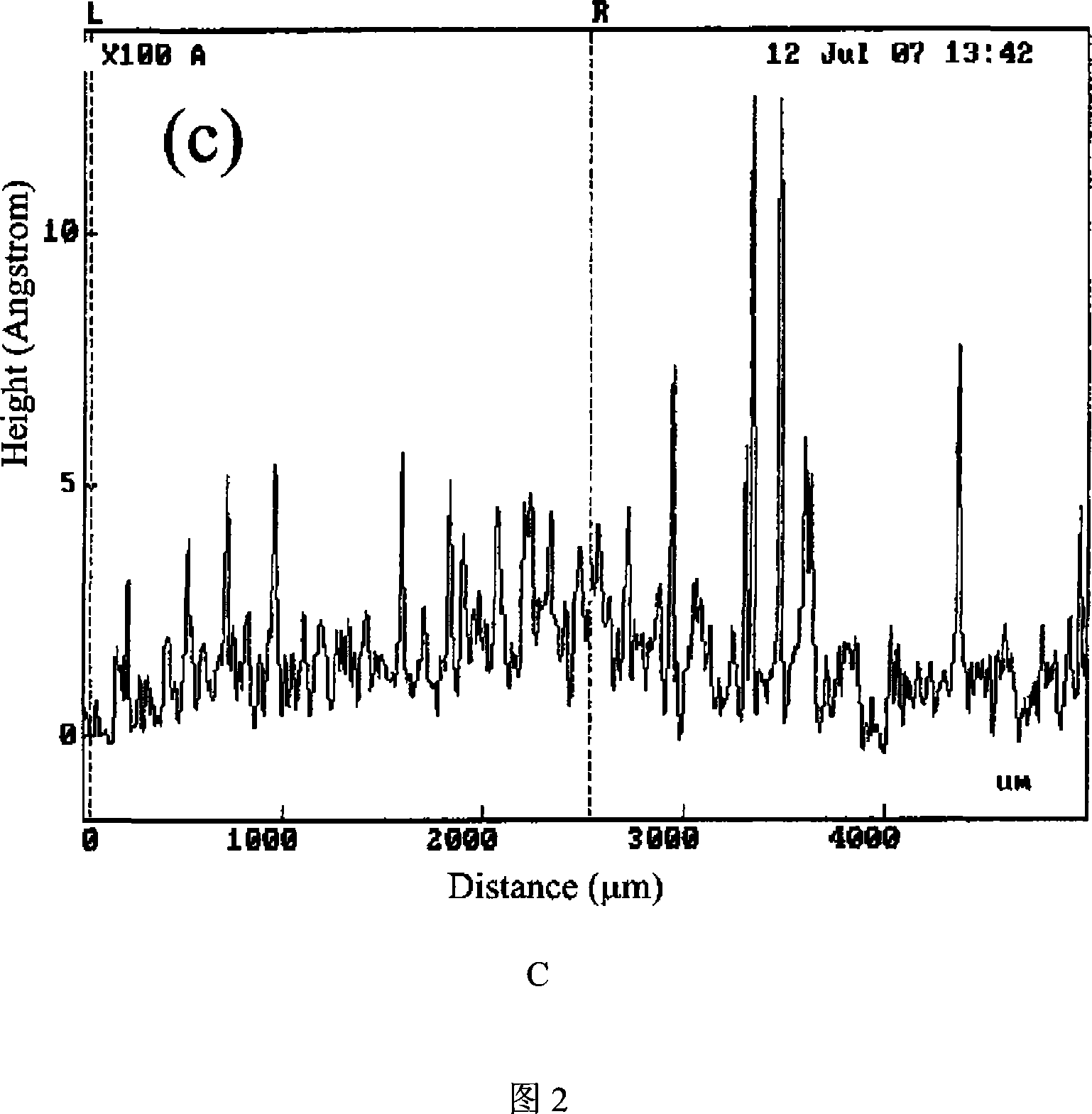

Method for altering mechanical and optical performance of thin film

InactiveCN101197278AControl physical propertiesChange physical propertiesSemiconductor/solid-state device manufacturingRefractive indexYoung's modulus

The invention discloses a method for changing the mechanics and optical performances of membrane, which is characterized in that an amorphous silicon dioxide transition layer with pressing stress is arranged on a substrate, and then an amorphous silicon nitrogen membrane with tension stress is arranged on the transition layer. The method overcomes the drawback in the prior art and improves original cragged stress grads by simple overlapping of common membrane with similar characteristic and opposite stress, thereby increasing the light reflection rate of amorphous silicon nitrogen membrane by reducing the tension stress of the membrane, and correspondingly reducing hardness and young modulus of the membrane, so that the stress of special membrane can be effectively controlled. A low stress silicon nitrogen membrane with low internal stress can be prepared, thus improving the working performance of the membrane, reducing cost of raw material and being suitable for large-scale industrialized production.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Charge trapping semiconductor memory element with improved trapping dielectric

ActiveUS20060197141A1Easy to chargeImprove retentionTransistorSolid-state devicesDielectricGate dielectric

A semiconductor memory element, which can be controlled via field effect, includes a semiconductor substrate of a first conduction type, a first doping region of a second conduction type provided in the semiconductor substrate, a second doping region of the second conduction type provided in the semiconductor substrate, a channel region located between the first and second doping regions, a multilayer gate dielectric which is arranged adjacent to the channel region and has a charge trapping memory layer, and a gate terminal provided above the gate dielectric. The charge trapping memory layer includes at least one sequence of adjacent layers, wherein the sequence of adjacent layers comprises an amorphous silicon carbide layer and an amorphous silicon nitride layer.

Owner:INFINEON TECH AG

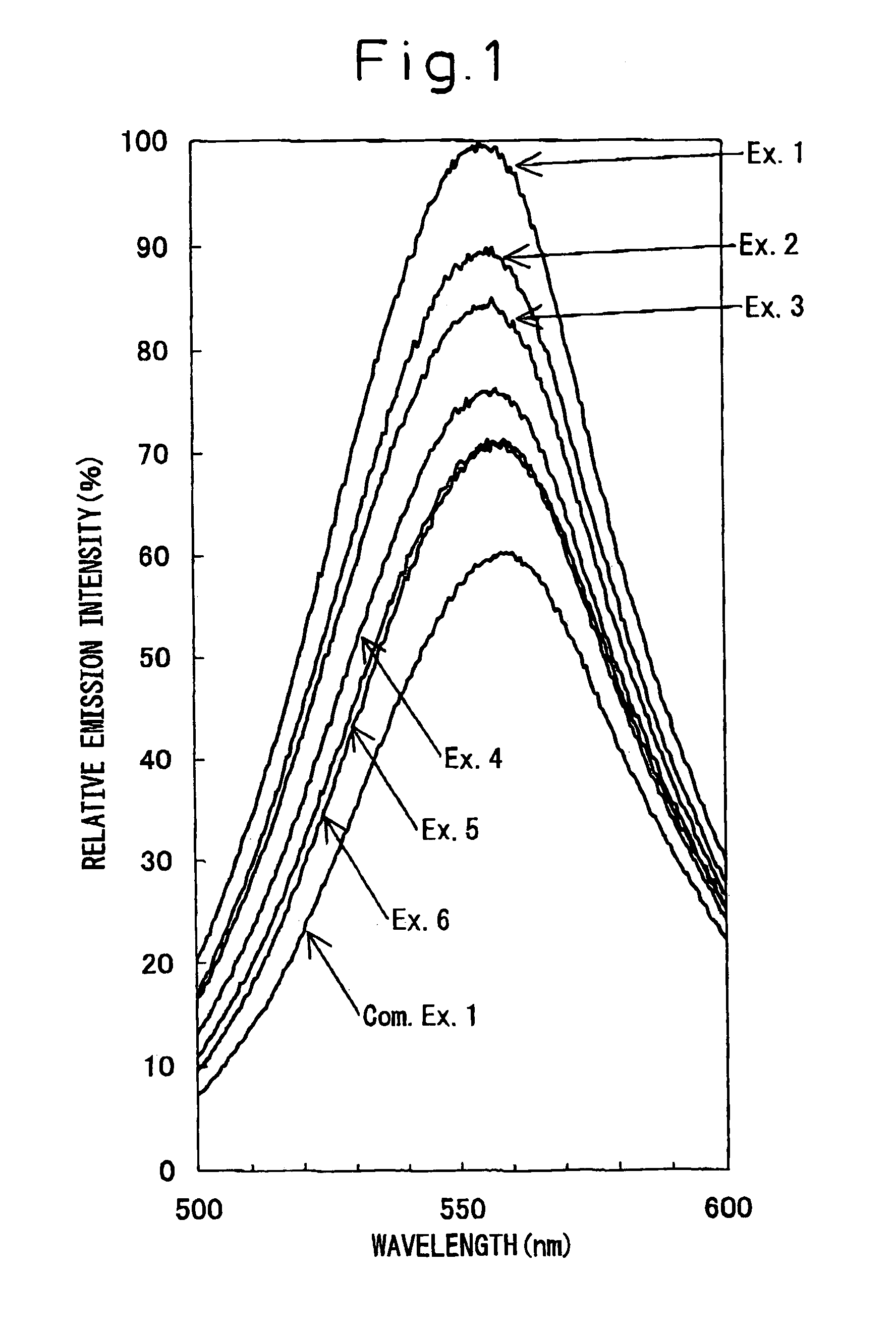

Production method of sialon-based phosphor, and sialon-based phosphor

ActiveUS7258818B2Prevent excessive aggregationSemiconductor/solid-state device manufacturingLuminescent compositionsPhotoluminescenceLanthanide

To provide a sialon-based phosphor capable of forming a thin film by mixing it with a resin, and giving a uniform photoluminescent light with high light emission intensity, and to provide a method for producing a sialon-based phosphor not having excessively large agglomerated particles and a wide particle size distribution, there is provided a method for producing an α-sialon based phosphor represented by the formula:MxLnySi12−(m+n)Al(m+n)OnN16−nwherein M is at least one metal selected from Ca, Mg, Y and Li, Ln is at least one lanthanide metal selected from Eu, Dy, Er, Tb, Yb and Ce, ax+by=m (assuming that the valence of metal M is a and the valence of lanthanide metal Ln is b), 0<x≦1.5, 0.3≦m≦4.5, and 0<n<2.25), wherein the silicon nitride raw material used as the raw material is a silicon nitride raw material powder comprising amorphous silicon nitride and crystalline silicon nitride.

Owner:UBE CORP

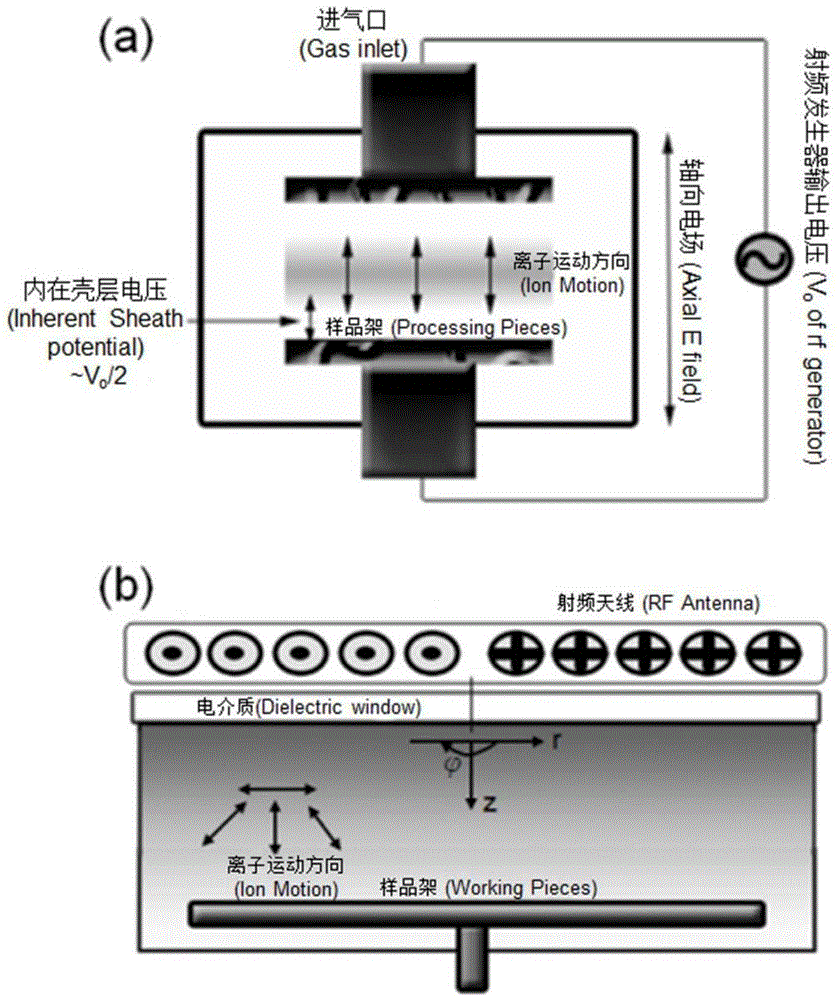

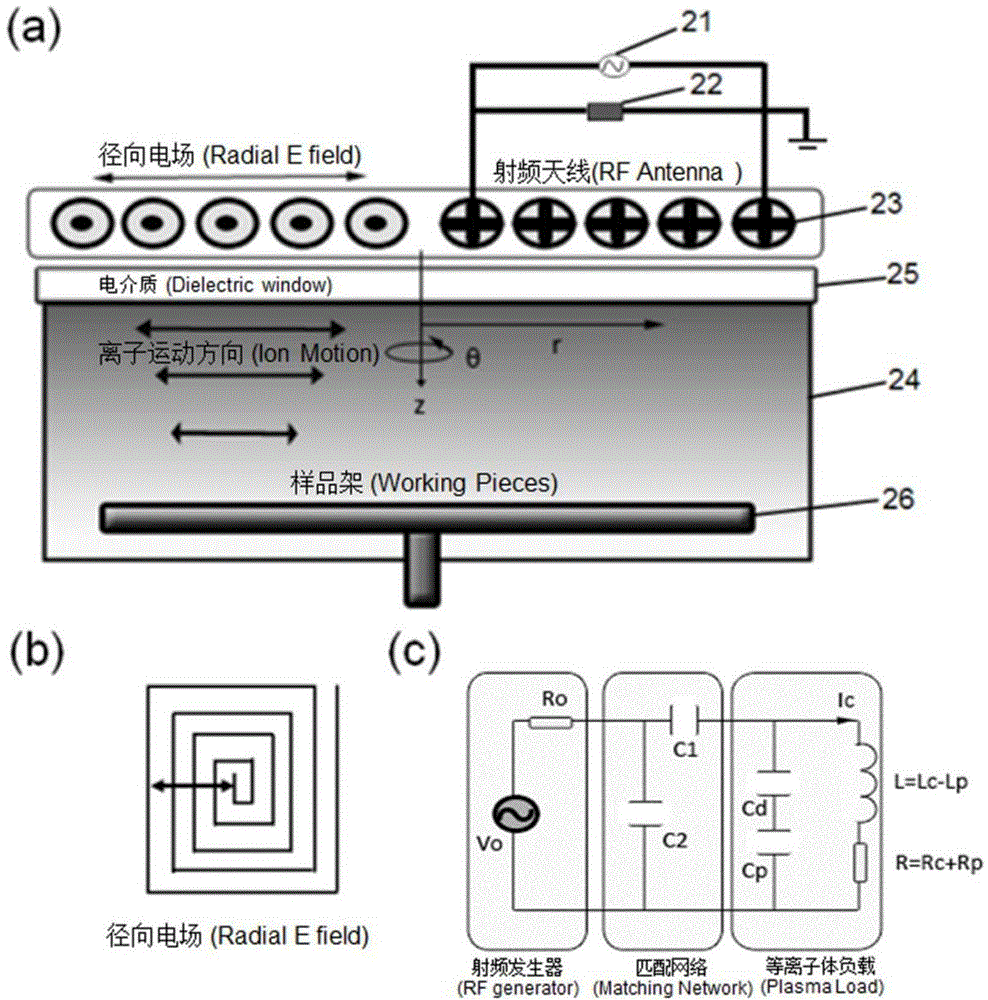

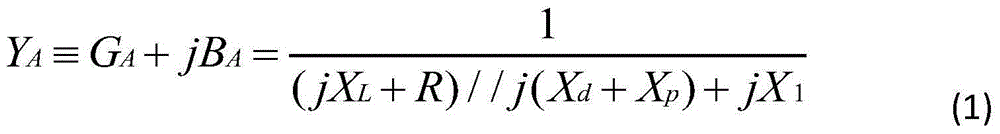

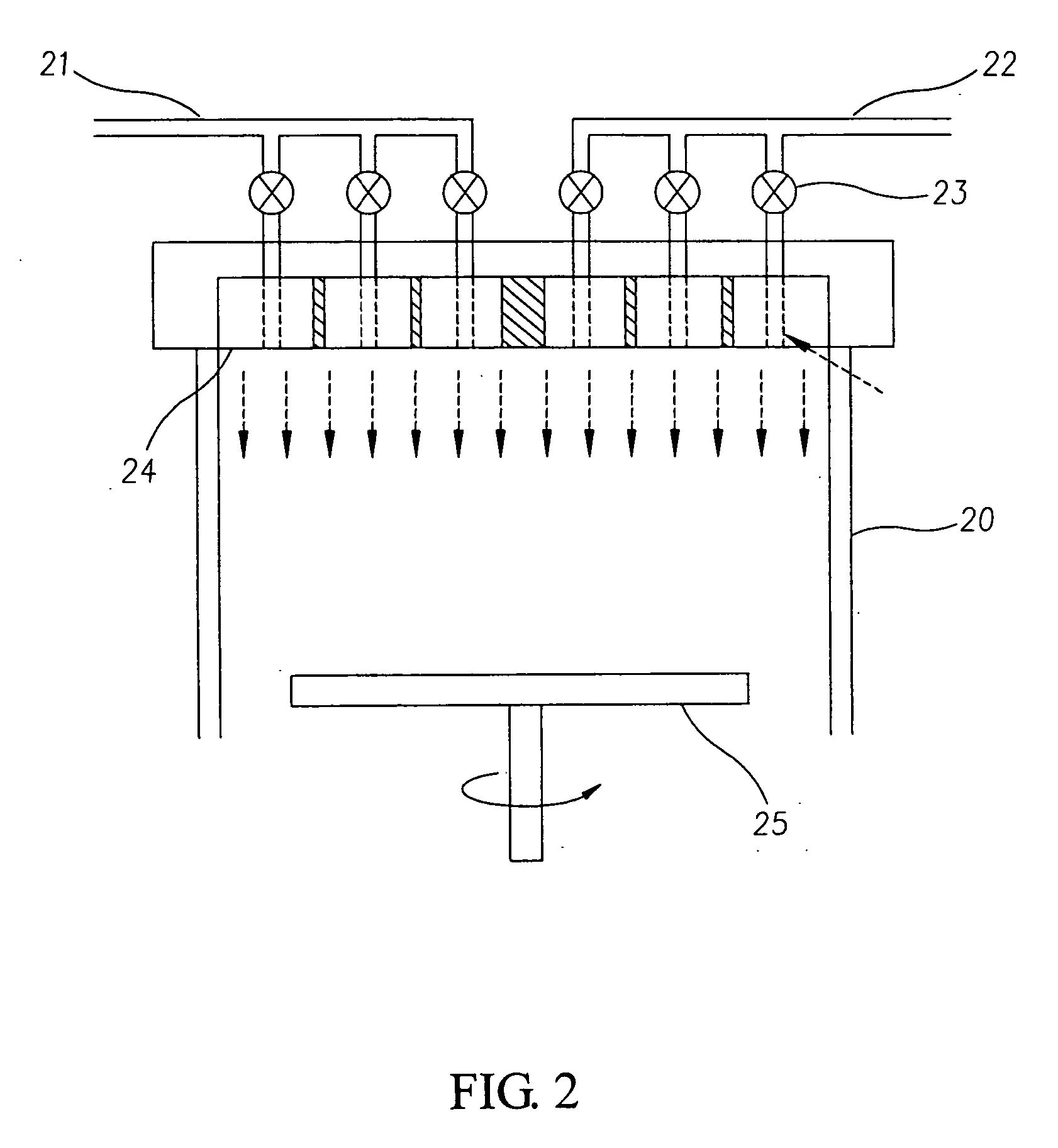

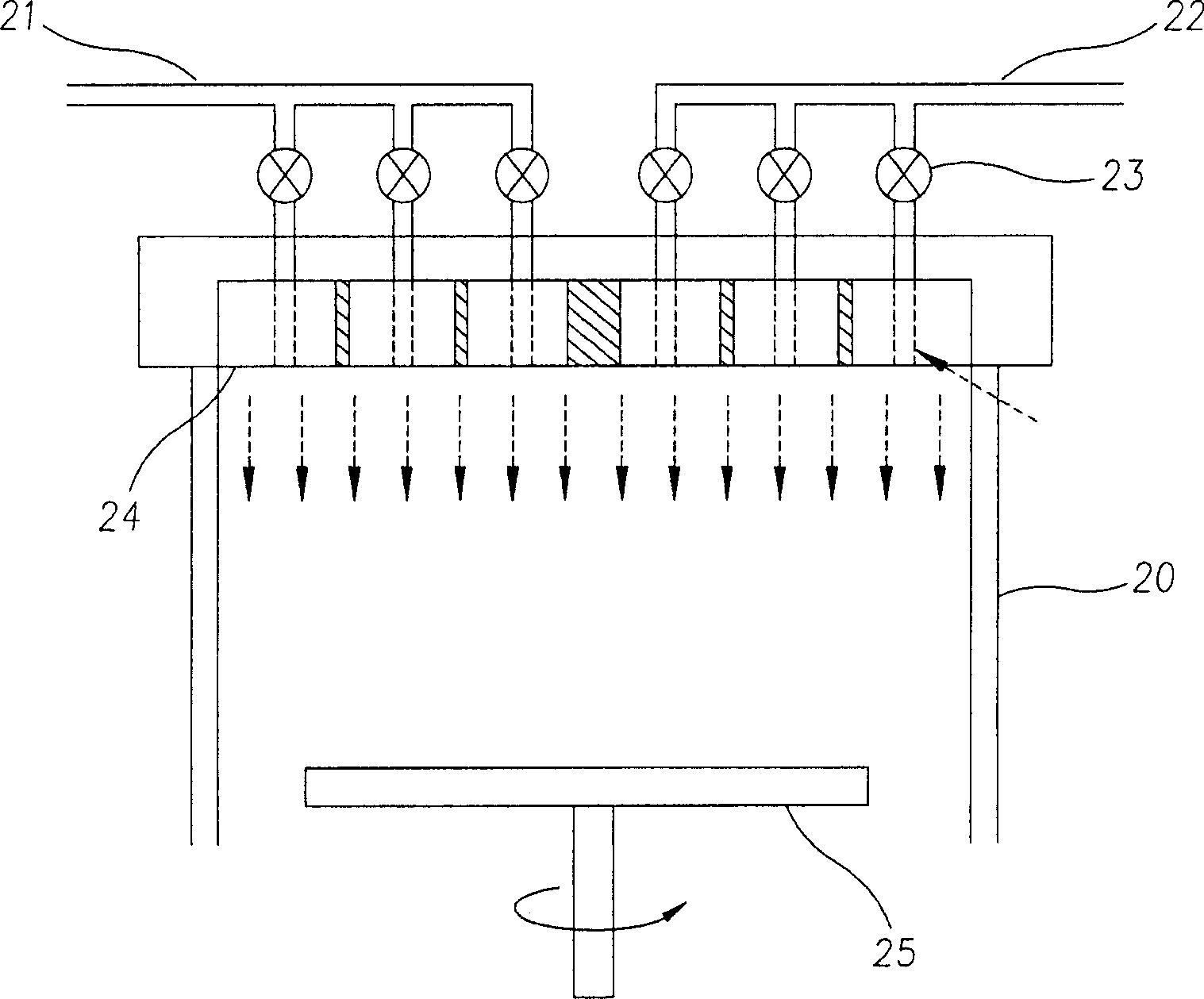

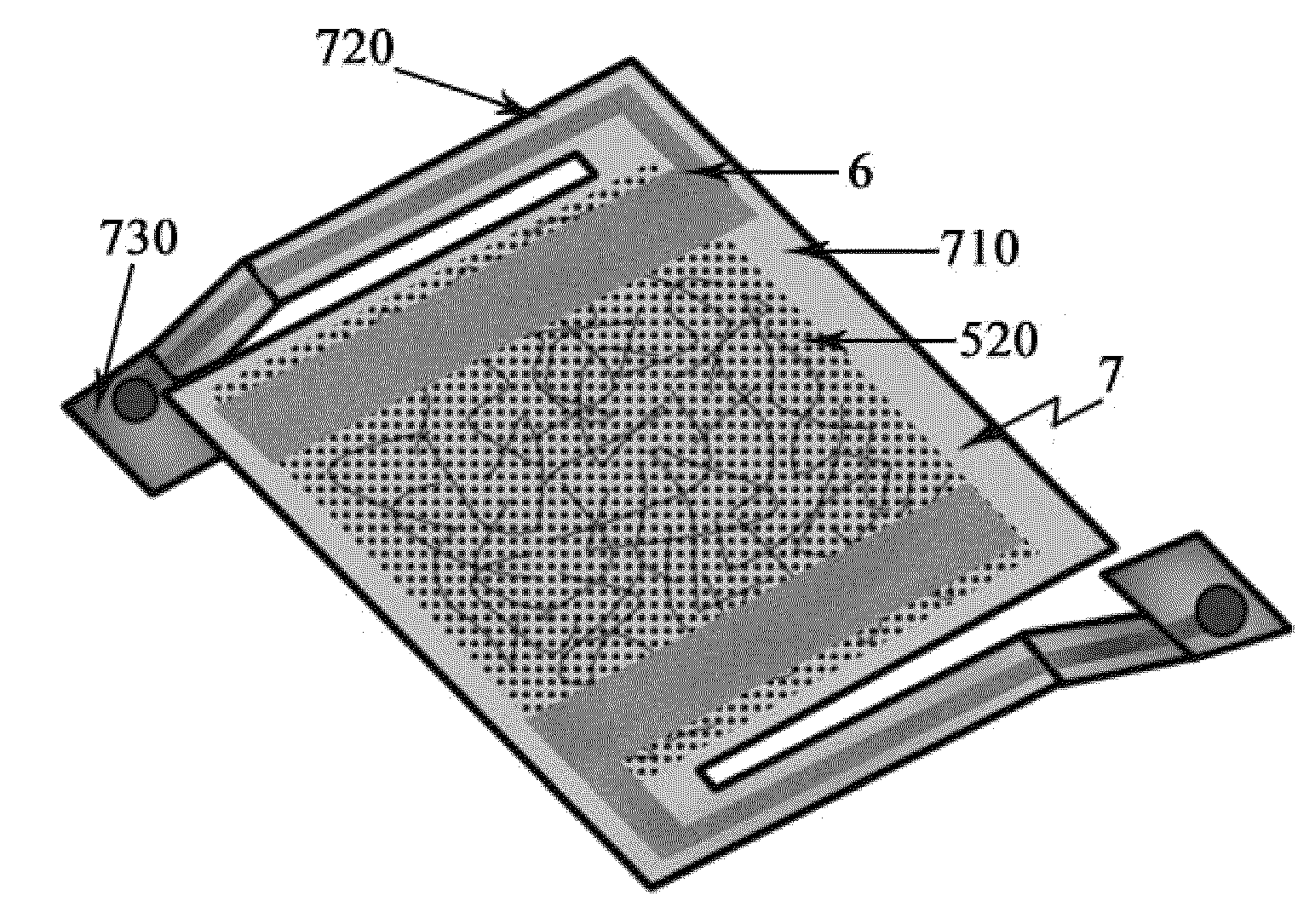

Non-parallel plate type capacitive coupled plasma chemical vapor deposition method

ActiveCN104694906ALow ionization rateAvoid cross contaminationChemical vapor deposition coatingCapacitancePlasma density

The invention relates to a film deposition method, and particularly relates to a non-parallel plate type capacitive coupled plasma chemical vapor deposition method. The method adopts the following components: a planar rectangular spiral inductive antenna, a low-frequency power generator, an impedance matching network, a columnar vacuum chamber, quartz glass and a lining bracket. By controlling radio frequency input power and tuning matched capacitance, the method disclosed by the invention can be used for realizing stable capacitive coupled discharging in the vacuum chamber; the plasma is relatively low in density; a radial electrostatic field which is parallel to the surface of a lining and built by potential difference of the two ends of a coil plays a leading role, so that the motion of positive ions is limited in a direction parallel to the surface of the lining. Therefore, the method disclosed by the invention commences in two aspects, namely reduction of the plasma density and limitation on motion direction of the positive ions, so that bombardment caused by the positive ions to the film surface during a chemical vapor deposition can be remarkably inhibited, and surface damages are reduced. The system can be used for preparing various necessary passivation layers such as non-crystalline silicon and non-crystalline silicon nitride for a high-efficiency crystalline silicon solar cell.

Owner:JIANGNAN UNIV

Yttrium modified chromium aluminium carbonitride/silicon nitride nano composite coating and deposition method thereof

ActiveCN103436841AHigh bonding strengthGood heat matchingLayered productsVacuum evaporation coatingRare-earth elementAlloy

The invention relates to a yttrium modified chromium aluminium carbonitride / silicon nitride nano composite coating and a deposition method thereof. Chromium aluminium carbonitride and silicon nitride are subjected to nano composite design to form a nano composite structure with nanocrystal chromium aluminium carbonitride implanted into amorphous silicon nitride, so that the rigidity of the coating is improved; the toughness of the coating and bonding strength of the coating and a matrix are both considered; a rare earth element Y is introduced simultaneously, so that the mechanical property and high-temperature oxidation resistance of the coating are further improved; and the nano composite coating which is strong in bonding force, high in rigidity, good in toughness, low in friction coefficient and prominent in thermostability and is used for high-speed steel and hard alloy cutters and molds is obtained. The coating comprises a chromium-aluminum-yttrium bonding layer, a chromium-aluminum-yttrium nitride transition layer and a nano composite layer; the membrane / matrix bonding strength of the obtained coating reaches 40-90N; the surface composite strength under 10g load reaches 40-65 GPa; and the friction coefficient is 0.2-0.5 when matched with GCr15.

Owner:JIANGXI SCI & TECH NORMAL UNIV

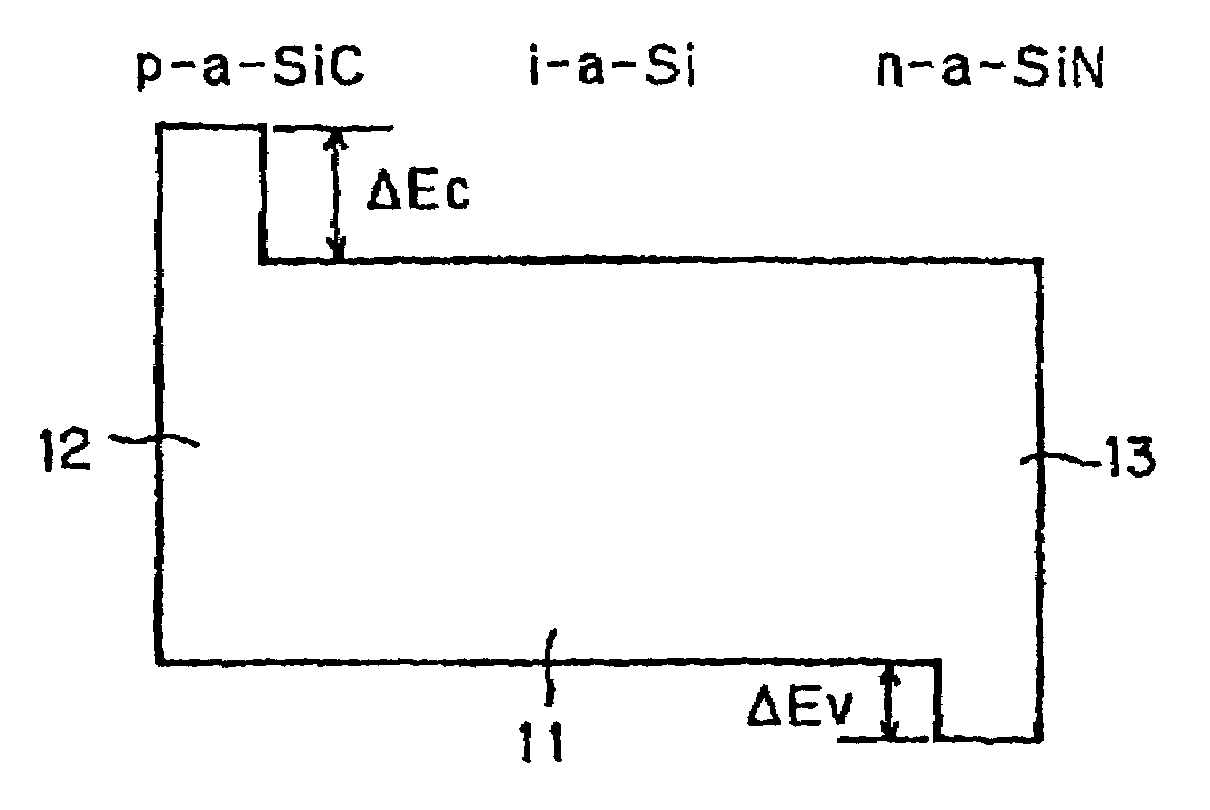

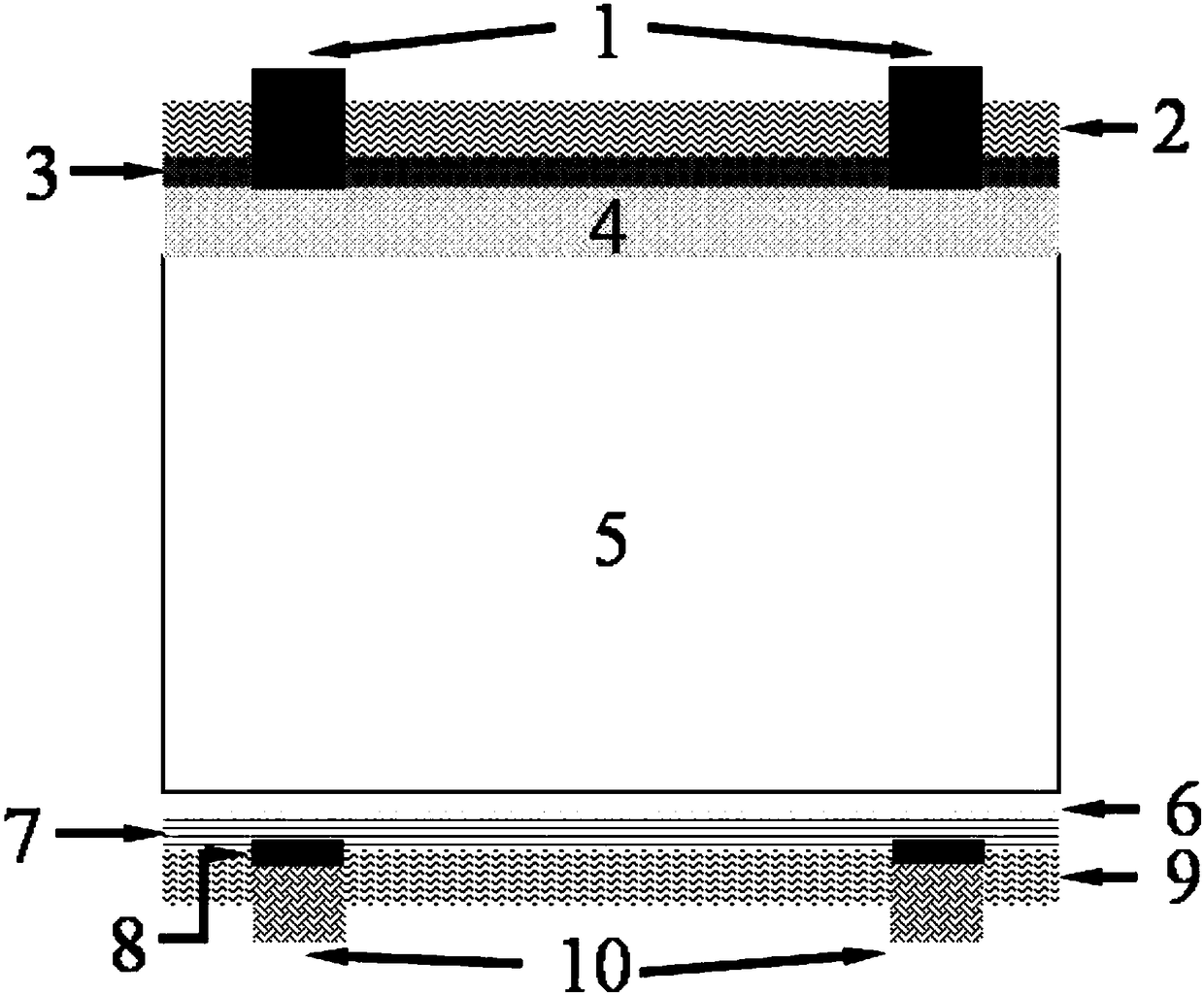

Photoelectric conversion device and solid-state image sensing device using the same

InactiveUS6936806B1Prevent electronInhibit injectionSolid-state devicesMaterial analysis by optical meansElectron injectionCharge carrier

Disclosed is a photoelectric conversion device having a multiplying function and an image sensing device using the same. The photoelectric conversion device essentially comprises three layered structure: a carrier generation / multiplication layer composed of amorphous silicon to have both the function of absorbing light and generating carriers through optical excitation and the function of multiplying the generated carriers; an electron injection inhibiting layer composed of an amorphous silicon carbide of the p-type conductivity to inhibit injection of electrons into the carrier generation / multiplication layer; and a hole injection inhibiting layer composed of an amorphous silicon nitride of the n-type conductivity to inhibit injection of holes into the carrier generation / multiplication layer. The said carrier generation / multiplication layer is provided between said electron injection inhibiting layer and said hole injection inhibiting layer.

Owner:MINOLTA CO LTD

Fabrication method of frontal emitter junction tunneling oxidation passivation battery base on single crystal PERC

InactiveCN109216499AWith selective tunnelingBoost battery VocFinal product manufactureSemiconductor devicesEtchingSingle crystal

A method for manufacture a front emitter junction tunnel oxidation passivation battery based on a single crystal PERC, comprises a single crystal silicon wafer dedamaged layer, surface polishing, single sided velvet making, A sup thin tunneling oxide lay SiO2 and a P-doped polycrystalline silicon layer are prepared on that pile surface of a silicon wafer to form an N + emit junction, the phosphorus-doped polycrystalline silicon layer on the back side is removed by wet selective etching, A high-temperature anneal process activate that phosphorus-doped polycrystalline silicon layer on the frontsurface, Al2O3 layer is deposited on the back of the battery, and hydride amorphous silicon nitride passivation antireflection layer is deposited on the front / back of the battery. The back passivationlayer is selectively patterned and opened by ns laser. Finally, the back aluminum paste / back electrode and the front metal electrode grid line are printed on the screen to form the metallized ohmic contact of the front and back electrodes. As that selective tunnel capability is adopted, the metal on the surface of the emit junction is reduced. Semiconductor surface recombination and process technology route compatible with the existing high-efficiency single crystal PERC battery fabrication process is conducive to reduce equipment investment costs.

Owner:SHANGHAI SHENZHOU NEW ENERGY DEV +1

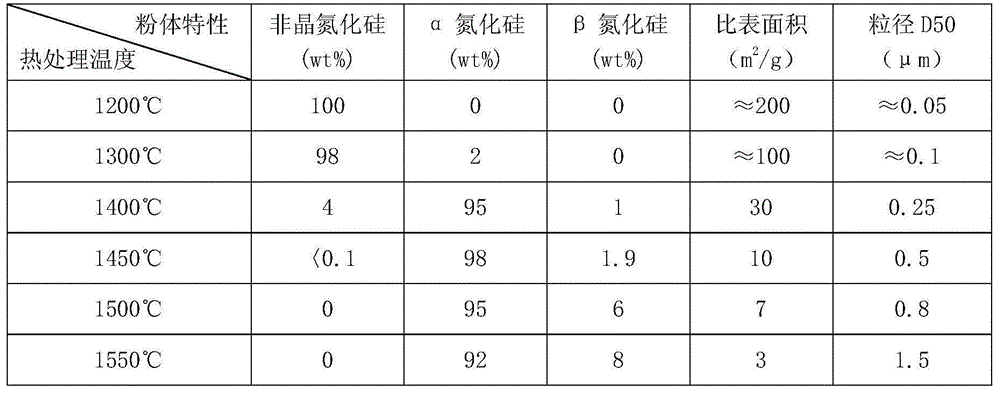

Method for preparing micrometer/nanometer spherical silicon nitride powder

ActiveCN105236363AAvoid pollutionControl contentMaterial nanotechnologyNitrogen compoundsImpurityHeat treated

The invention discloses a method for preparing micrometer / nanometer spherical silicon nitride powder. The method comprises that liquid silicon tetrachloride is added into liquefied ammonia and an organic solution in a quartz glass reactor, the mixture undergoes a reaction to obtain a yoghourt-type mixture, after deposition, liquid ammonia in an upper layer is drawn, clean liquid ammonia is added into the mixture, the mixture is stirred and precipitated, impurity ammonium chloride is extracted, the reactor and silicam are transferred into a heating furnace, the organic solution is stirred and dried and then is heated to produce amorphous silicon nitride powder, and the amorphous silicon nitride powder is transferred into a silicon carbide or silicon nitride container and then is roasted to form crystalline silicon nitride powder. Silicam powder is prepared by a low temperature reaction, is washed and extracted by liquid ammonia, is purified by ammonium chloride and is subjected to multitime heat treatment to form high-purity micrometer / nanometer spherical silicon nitride powder. The method has a fast preparation rate, a high yield and a high recovery rate, easily controls and improves silicon nitride powder purity and realizes industrial large-scale production.

Owner:陕西阳乐陶瓷材料科技有限公司

Group iii nitride semiconductor device and its method of manufacture

ActiveUS20050082563A1Avoid crackingRelieve pressurePolycrystalline material growthFinal product manufactureLattice constantSilicon

Disclosed is a Group III nitride semiconductor device comprising a stress-absorbing layer having: an amorphous silicon nitride layer, an aluminum interlayer, an amorphous aluminum nitride pre-layer and a polycrystalline Group III nitride layer containing aluminum. The stress-absorbing layer is located between a silicon substrate and a Group III nitride semiconductor, for alleviating stress resulted from different lattice constants between the Group III nitride substance and the silicon substrate, thereby preventing cracking of the Group III nitride semiconductor due to the stress. Further disclosed is a method of manufacturing Group III nitride semiconductor device.

Owner:EPISTAR CORP

Method for producing silicon nitride powder

The invention discloses a method for producing silicon nitride powder. The method comprises the following steps: 1) reacting silicon tetrachloride and ammonia which are used as raw materials in order to synthesize a silicon nitride precursor Si(NH)2 solid, and obtaining pure Si(NH)2 powder; 2) transferring the Si(NH)2 into a high temperature furnace, and calcining the Si(NH)2 to obtain amorphous silicon nitride powder; and 3) refining and briquetting the obtained silicon nitride powder, transferring the briquetted powder into a high temperature crystallization furnace, and performing calcination to obtain crystalline silicon nitride powder. The method can continuously synthesize the silicon nitride precursor, and can flexibly control the particle size, the shape and the phase composition of the final product silicon nitride powder by adopting two calcination treatments which are low temperature decomposition of the Si(NH)2 and high-temperature crystallization of the amorphous silicon nitride powder; no organic solvents participate in the whole process, so carbon impurities in the silicon nitride powder are avoided; and the raw materials used for the product are produced in large scale in China, so low-cost production of high-purity sub-micron isometric silicon nitride powder is achieved.

Owner:JIANGSU ZHONGNENG POLYSILICON TECH DEV

Method for preparing silicon nitride powder through atomization reaction process

InactiveCN105129750AHigh purityHigh alpha phase contentNitrogen compoundsSilicon tetrachlorideCrystallization

Owner:SHANDONG SINOCERA FUNCTIONAL MATERIAL CO LTD

Manufacture method of high-efficiency cell with front emission junction and backside tunneling oxidation and passivation contact

InactiveCN106784128AReduce surface recombinationImprove electrical performance parametersFinal product manufactureSemiconductor devicesElectricitySurface concentration

The invention relates to a manufacture method of a high-efficiency cell with a front emission junction and backside tunneling oxidation and passivation contact. Texturing is carried out after removing a damage layer of a silicon chip, a B-doped P+ emission junction of a low surface concentration is formed, an ultrathin tunneling oxide layer SiO2 and a P-doped polysilicon layer are grown in the back side of the silicon chip after edge insulation and backside polishing, an alumina layer is deposited in the surface of the P+ emission junction, a hydrogenated amorphous silicon nitride passivation antireflection layer is grown in the front side of the silicon chip in a PECVD or magnetron sputtering method, a Ag / Al slurry is printed in the front side of the silicon chip, a full aluminum backfield Al-BSF structure is formed in the back side of the silicon chip, and a drying furnace is used to implement drying. Compared with the prior art, the ultrathin tunneling oxide SiO2 layer (<2nm) and the P-doped silicon layer are used to reduce metal-semiconductor surface combination in the backside greatly, and the manufacture method has the obvious advantage that electric performance parameters can be improved greatly on the basis that the method is compatible with a traditional cell manufacturing technology.

Owner:SHANGHAI SHENZHOU NEW ENERGY DEV

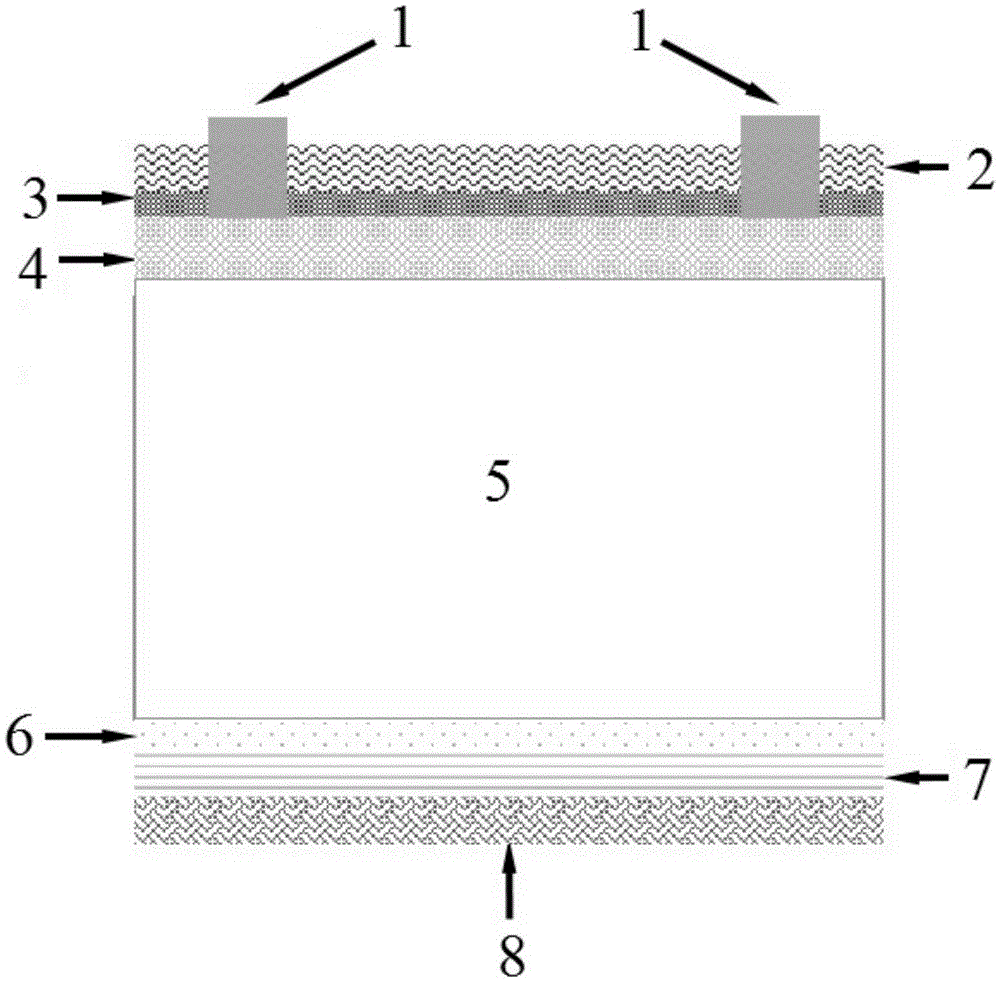

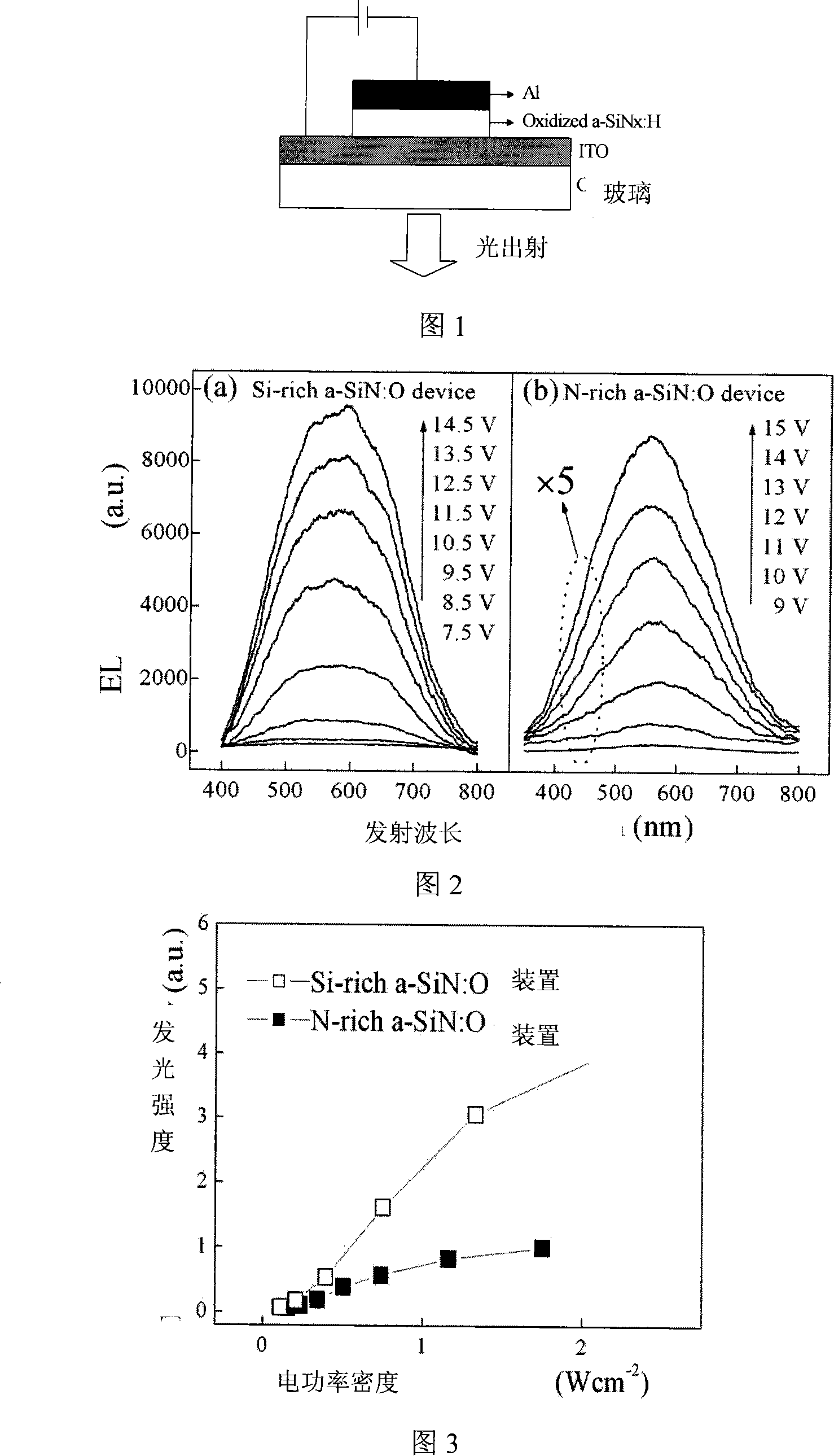

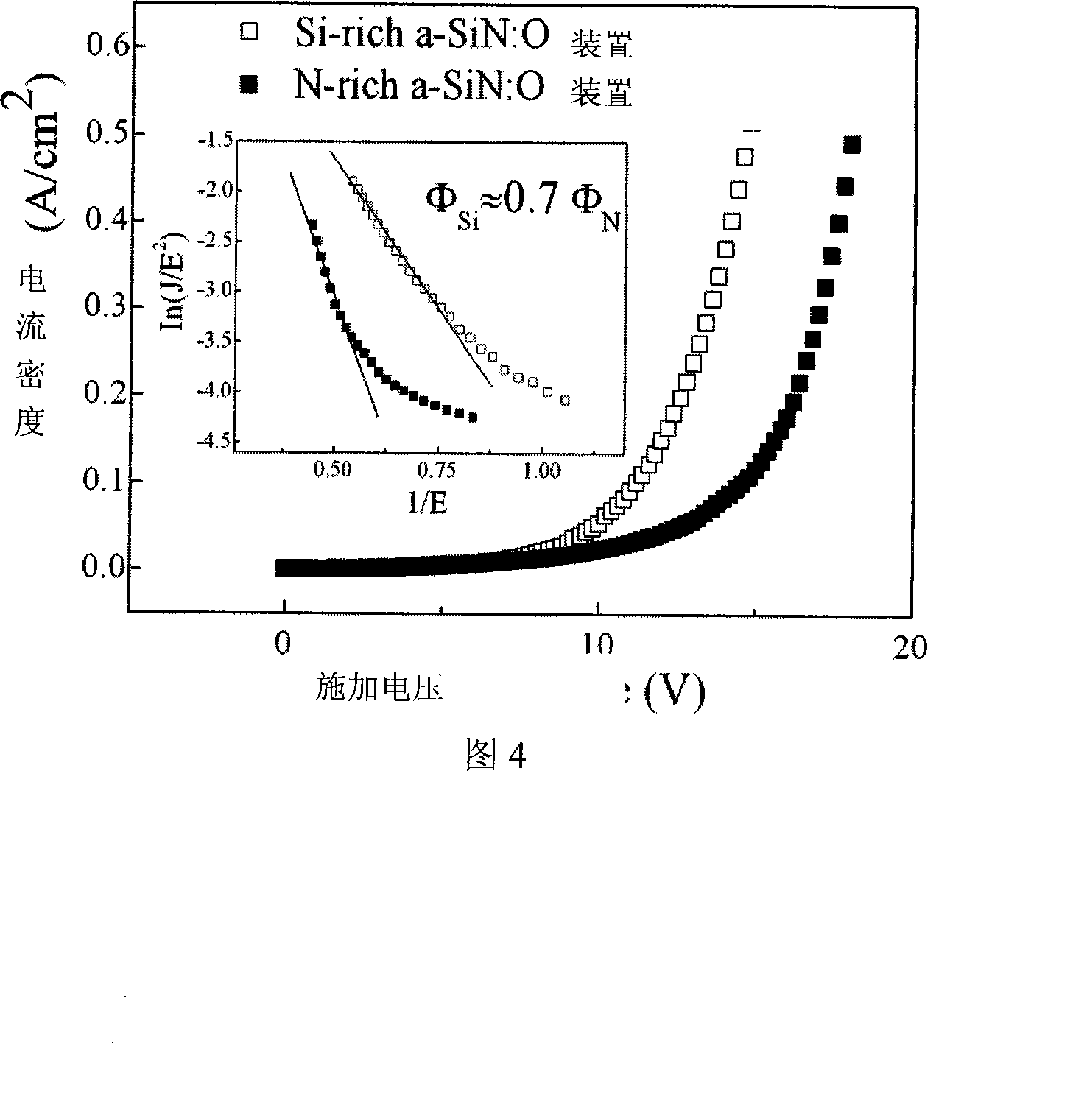

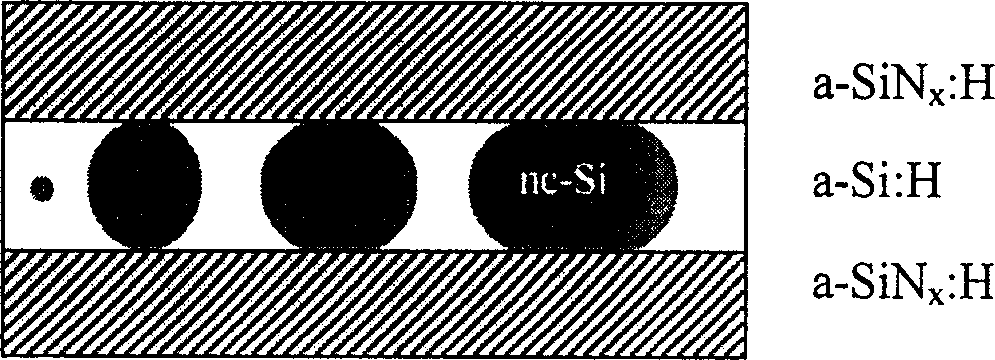

Method for improving luminous efficiency of oxygen silicon base doped nitride thin-film electroluminescent device

InactiveCN101132042AHigh strengthImprove efficiencySemiconductor devicesOxygen plasmaRoom temperature

Method for promoting the efficiency of luminescence of electroluminescence device made of oxygen-doped silicon-rich nitride thin-film. Te procedures are: (1), growth, under room temperature, of silicon-rich amorphous silicon nitride film (a-SiNx), using SiH4 and NH3 (with flow rode ratio of 0.5-1) as gas by plasma vapour phase reaction source, deposition of a-SiNx film onto ITO glass substrate with its thickness of 60-100nm; (2), at the temperature of the substrate being of 95-105deg.C, by using PECVD technique, oxygen plasma resource oxidizing above-mentioned a-SiNx film for 10-30 min, to produce this inventive silicon-rich oxygen-doped a-SiNx film, used for layer of electroluminescence device.

Owner:NANJING UNIV

Positive dielectric film of sandwich structure suitable for RIE (reactive ion etching) texture and manufacturing method thereof

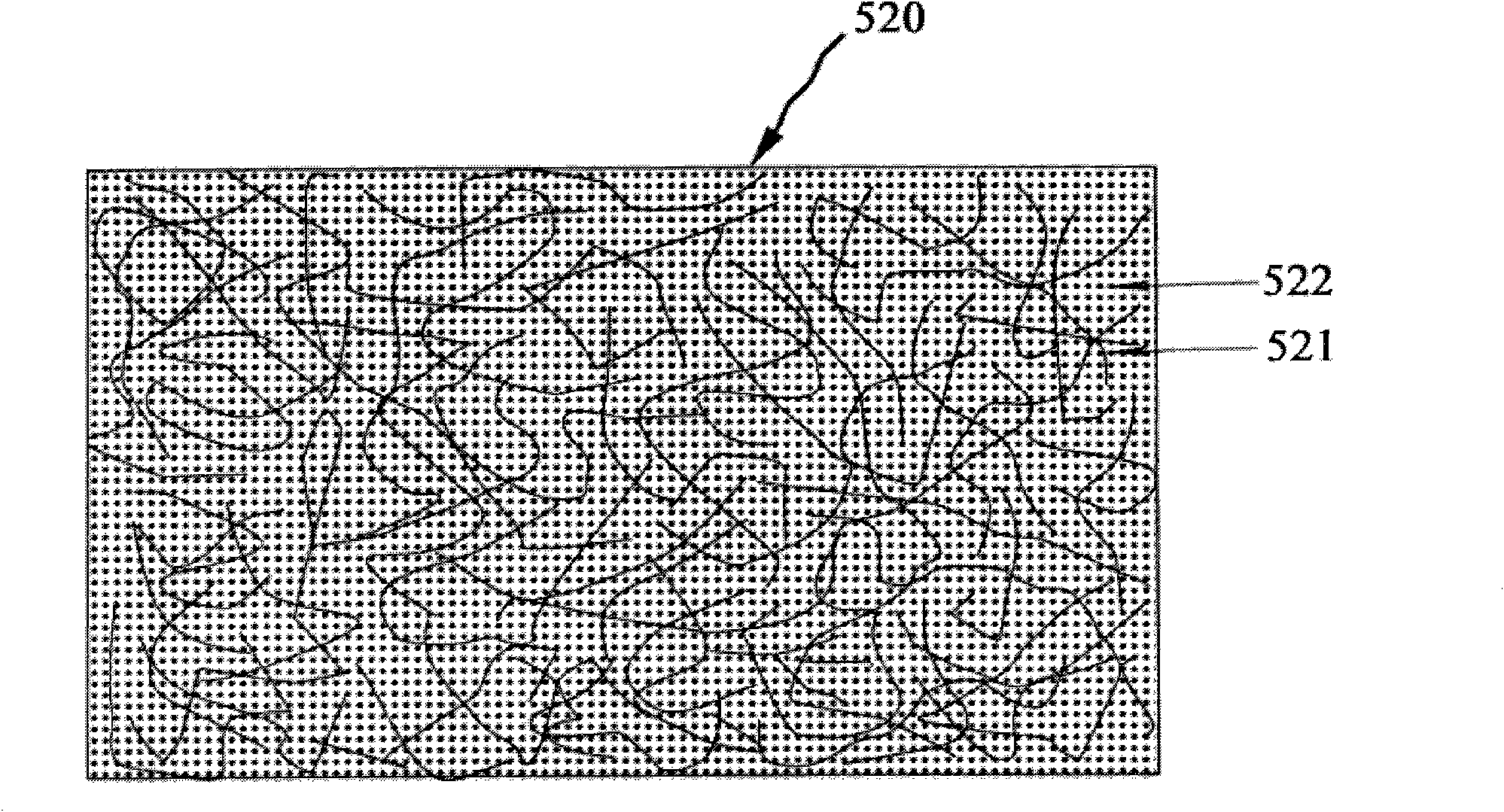

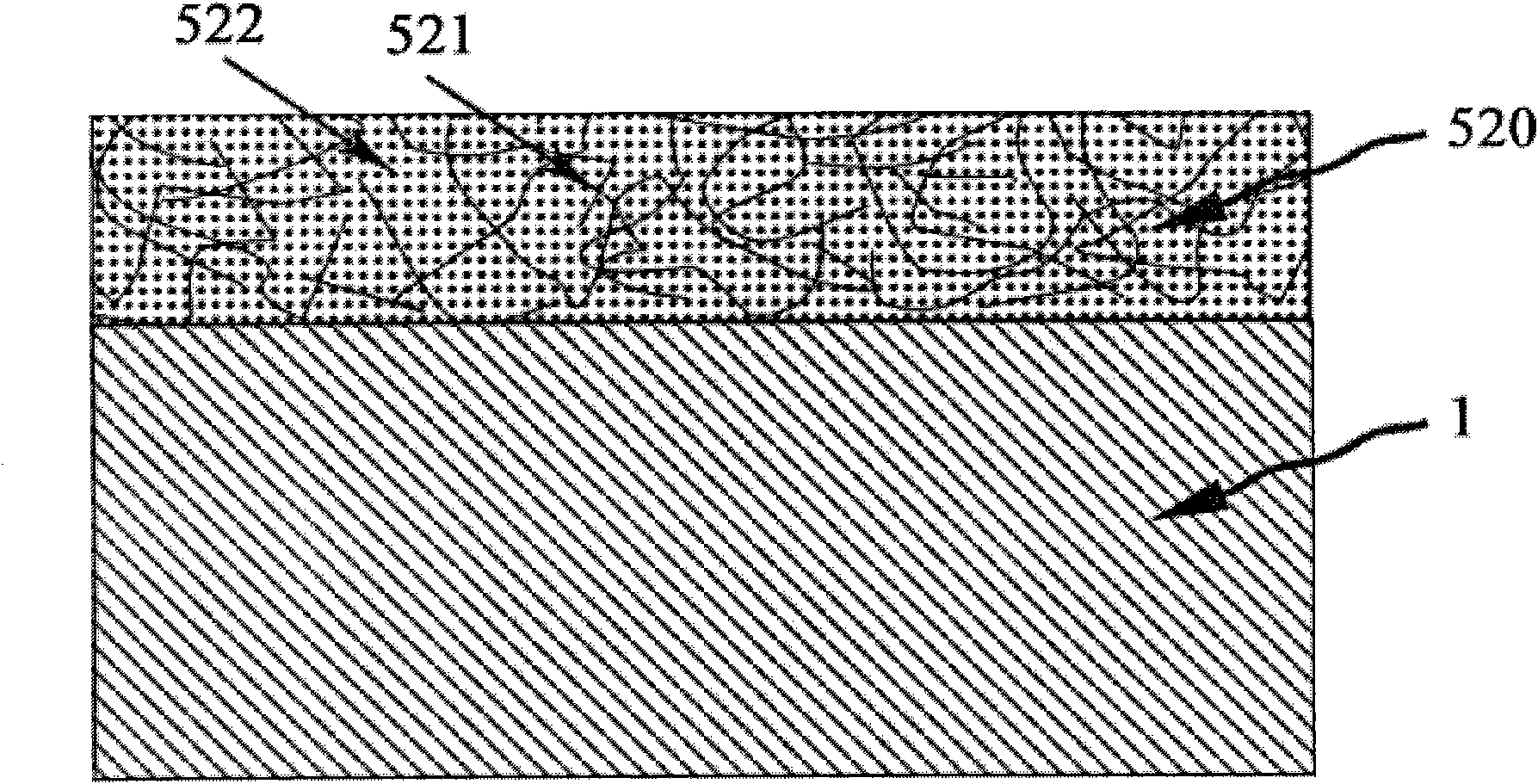

ActiveCN102339871AHigh positive charge densityReduce compound ratePhotovoltaic energy generationSemiconductor devicesDielectricInter layer

The invention relates to the technical field of crystalline silicon solar cell technologies, and in particular relates to a positive dielectric film of a sandwich structure suitable for an RIE (reactive ion etching) texture and a manufacturing method thereof. The positive dielectric film comprises a SiO2 (silicon dioxide) film at a bottom layer, wherein a SiNx (amorphous silicon nitride) film at an intermediate layer is covered on the surface of the SiO2 film at the bottom layer; and a SiO2 film at a surface layer is covered on the surface of the SiNx film at the intermediate layer. The manufacturing method of the positive dielectric film comprises the following steps of: 1, using a dry-oxygen oxidation method to grow a SiO2 film layer on a silicon texture; 2, adopting a PECVD (plasma enhanced chemical vapor deposition) method to deposit a SiNx film layer rich in silicon; and 3, adopting the PECVD method to deposit a SiO2 film. According to the invention, a crystalline silicon cell textured by RIE can be passivated effectively, the open-circuit voltage of the cell can be increased by 3-5mV, and the conversion efficiency of the cell can be increased by 0.2%-0.4%.

Owner:TRINA SOLAR CO LTD

III-nitride semiconductor element and manufacturing method thereof

Disclosed a structure of III group nitride semi-conductor device and its manufacturing method comprises a stress release layer formed by an amorphous silicon nitride layer, a metal aluminous medium layer, an amorphous nitride aluminous preposition layer and a multiple-crystal III group nitride layer containing aluminous element, is arranged between the silicon base plate and the III group nitride semi-conductor, for releasing the stress caused by the difference of lattice parameters and the coefficients of thermal expansion between the III group nitride material and the silicon base plate, which also can avoid the breakage caused by the stress.

Owner:EPISTAR CORP

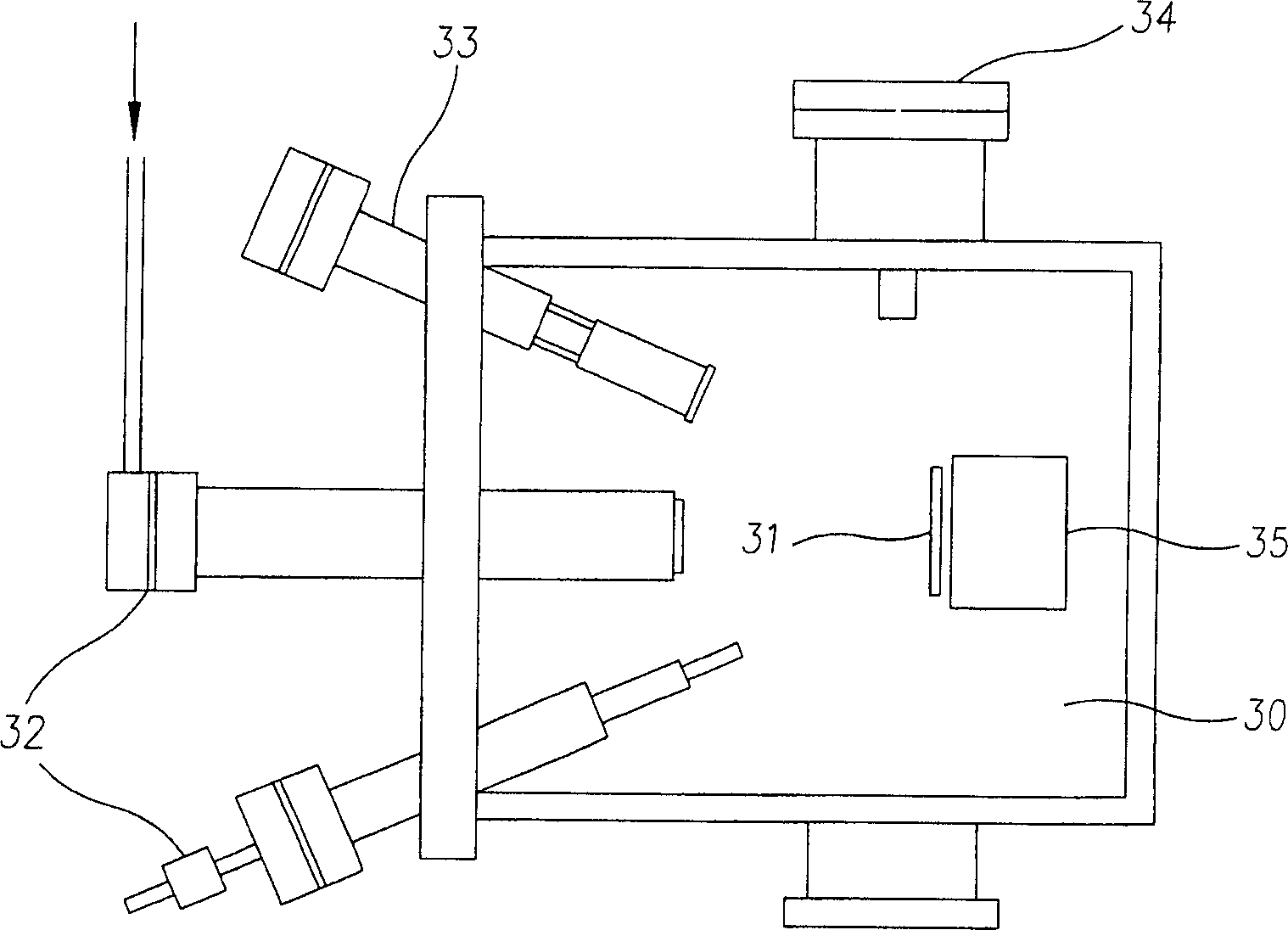

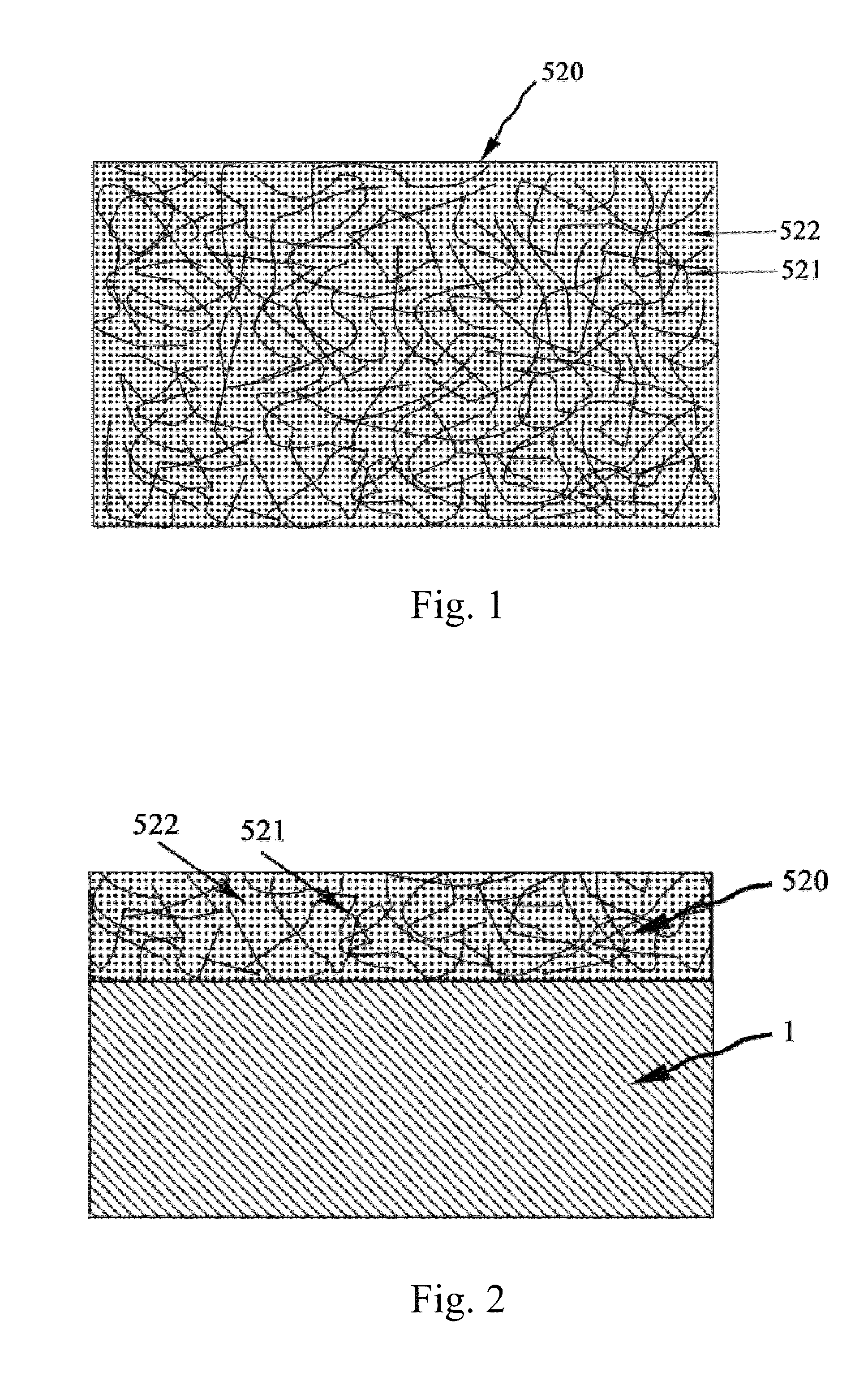

Laser-inducing preparation of size-controllable high-density nano silicon quanta array of points

InactiveCN1438168AAvoid heat treatmentEffective passivation protectionMaterial nanotechnologyPolycrystalline material growthSilicon dioxideMaterials science

The method for preparing size-controllable high-density nano silicon quantum point array by laser induction includes: firstly, preparing multilayer modulated structure; using plasma reinforced chemical vapor-phase sedimentation techinque to prepare amorphous silicon orgermaium / amorphous silicon nitride or silicon dioxide single-layer or multilayer modulated structure, in which a-Si:H sublayer thickness is basically in accord with laser crystallized desired quantum point size; then using laser to induce crystallization; the substrate temp. is 150-250 deg.C.

Owner:NANJING UNIV

Microbolometer for infrared detector or terahertz detector and method for manufacturing the same

InactiveUS9212950B2Improve business performanceLow costSemiconductor/solid-state device manufacturingPyrometry using electric radation detectorsComposite filmMicrobolometer

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com