Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

80results about How to "Reduced ohmic contact resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

AlGaN/GaN high electron mobility transistor devices

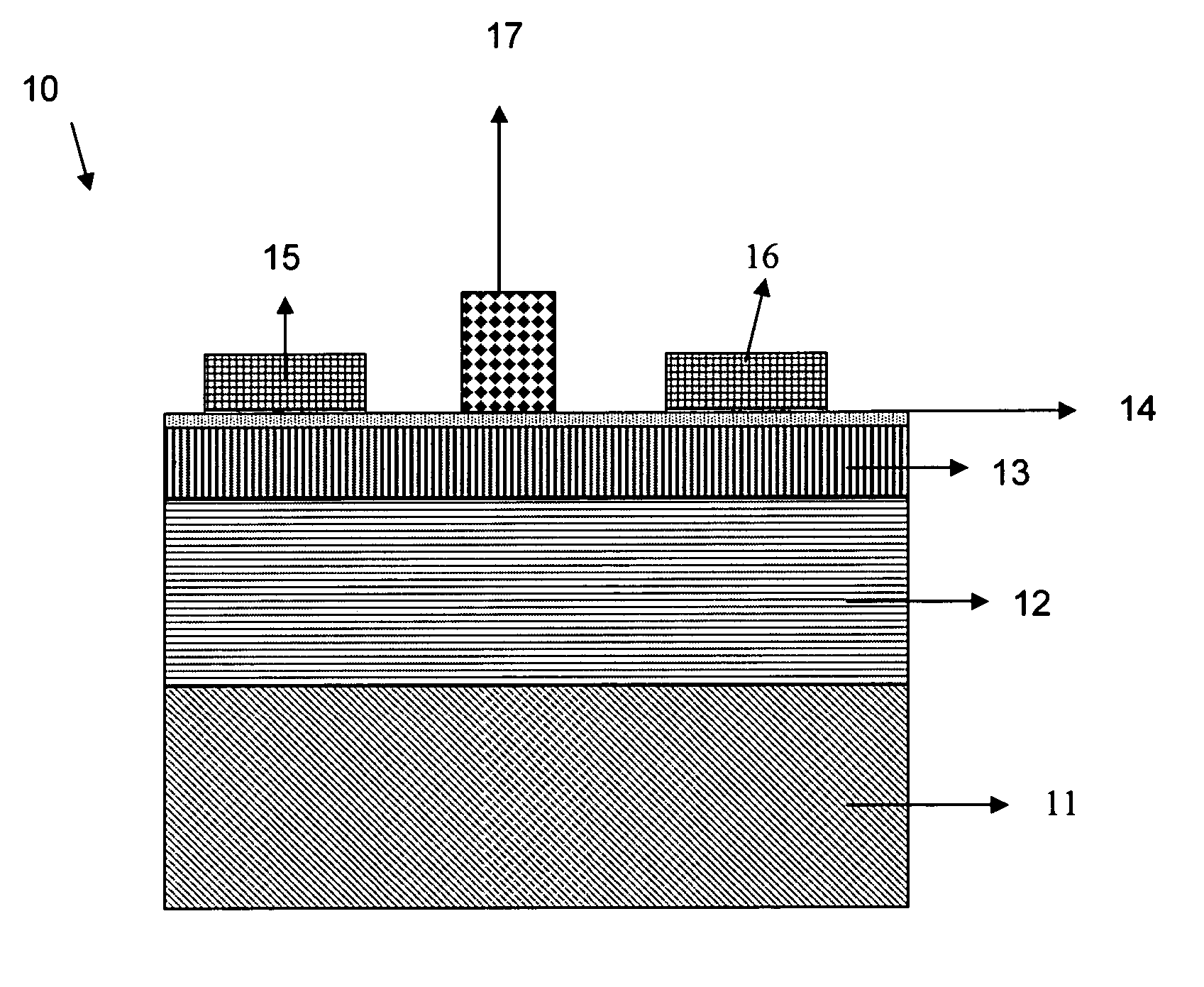

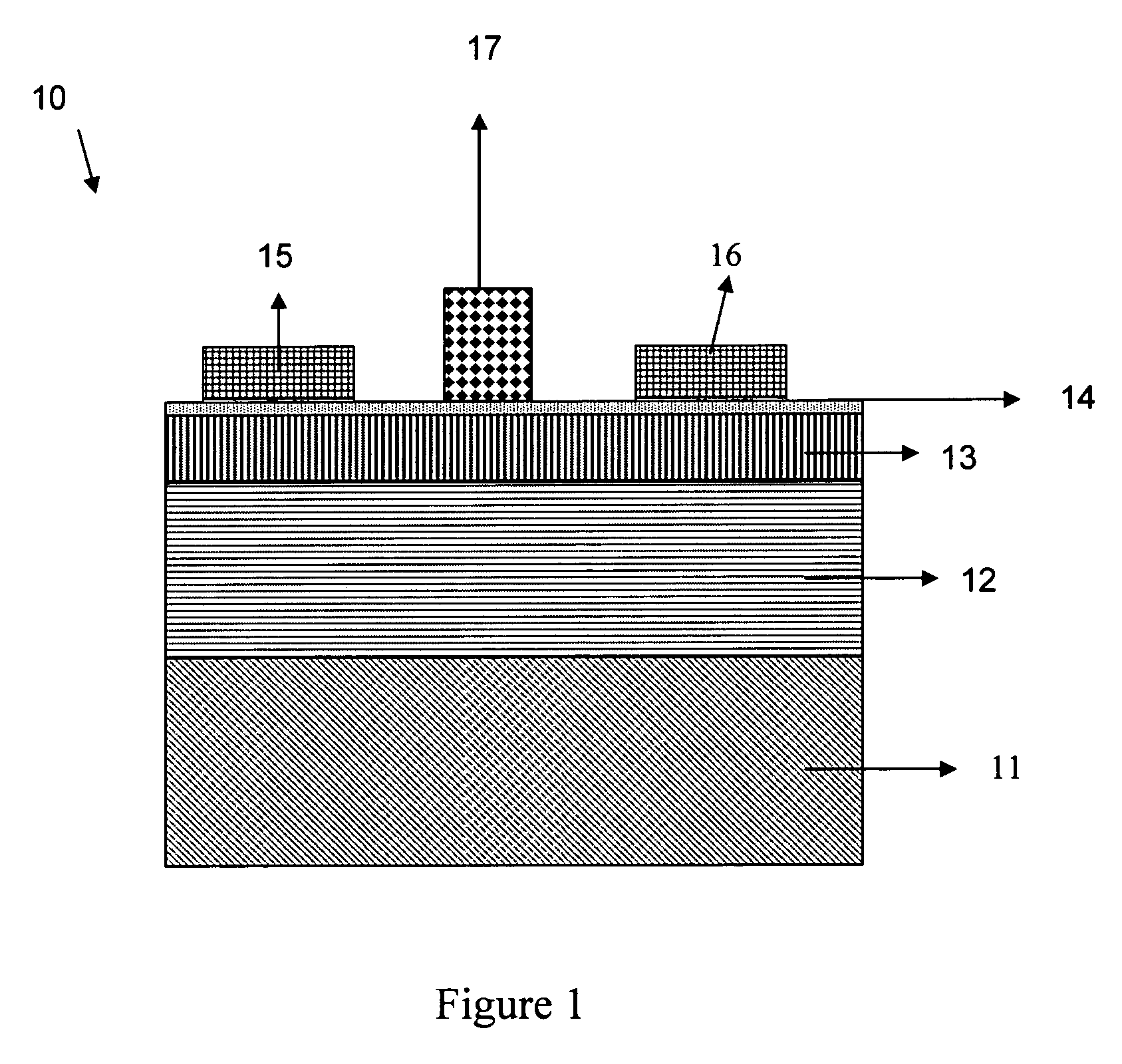

ActiveUS20060006414A1Avoid crackingReduce the appearance of cracksSolid-state devicesSemiconductor/solid-state device manufacturingMESFETCooling down

The present invention recites a new method for manufacturing Group III-N field-effect devices, such as HEMT, MOSHFET, MISHFET devices or MESFET devices, grown by Metal-Organic Vapor Phase Expitaxy, with higher performance (power), by covering the surface with a thin SiN layer on the top AlGaN layer, in the reactor where the growth takes place at high temperature, prior cooling down the structure and loading the sample out of the reactor, as well as a method to produce some HEMT transistors on those heterostructures, by depositing the contact on the surface without any removal of the SiN layer by MOCVD. The present invention recites also a device.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Nitride semiconductor device and manufacturing method thereof

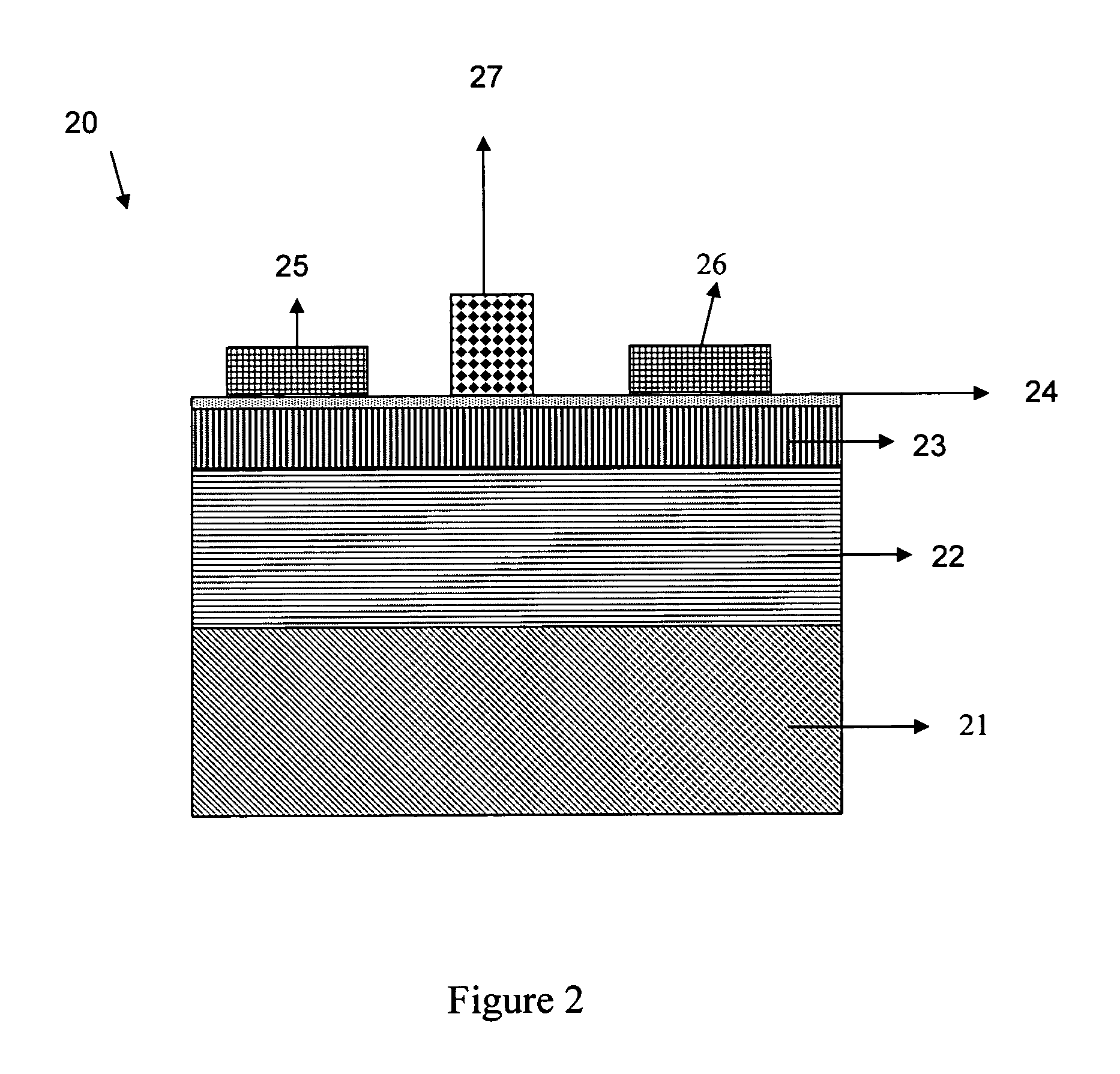

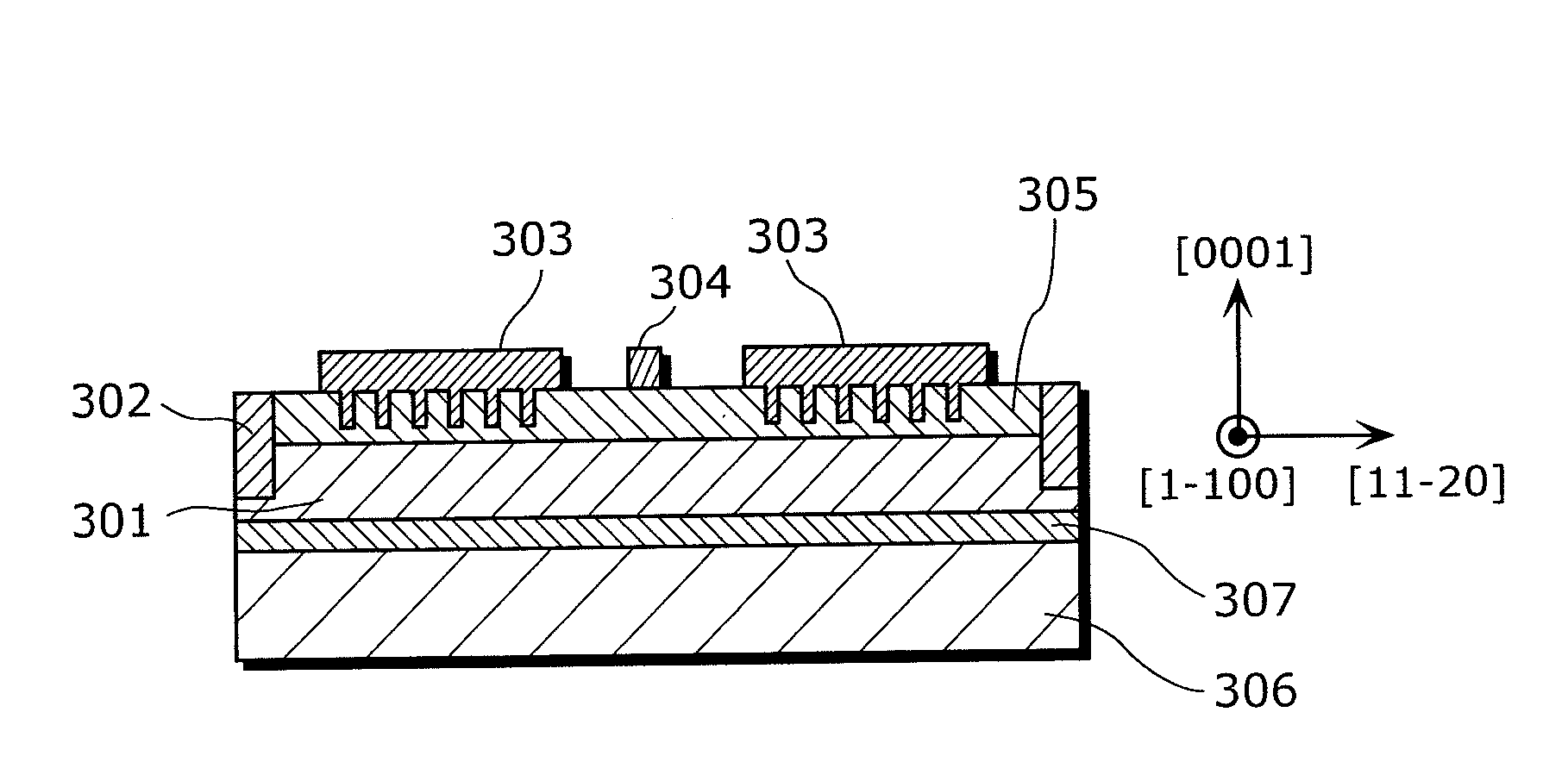

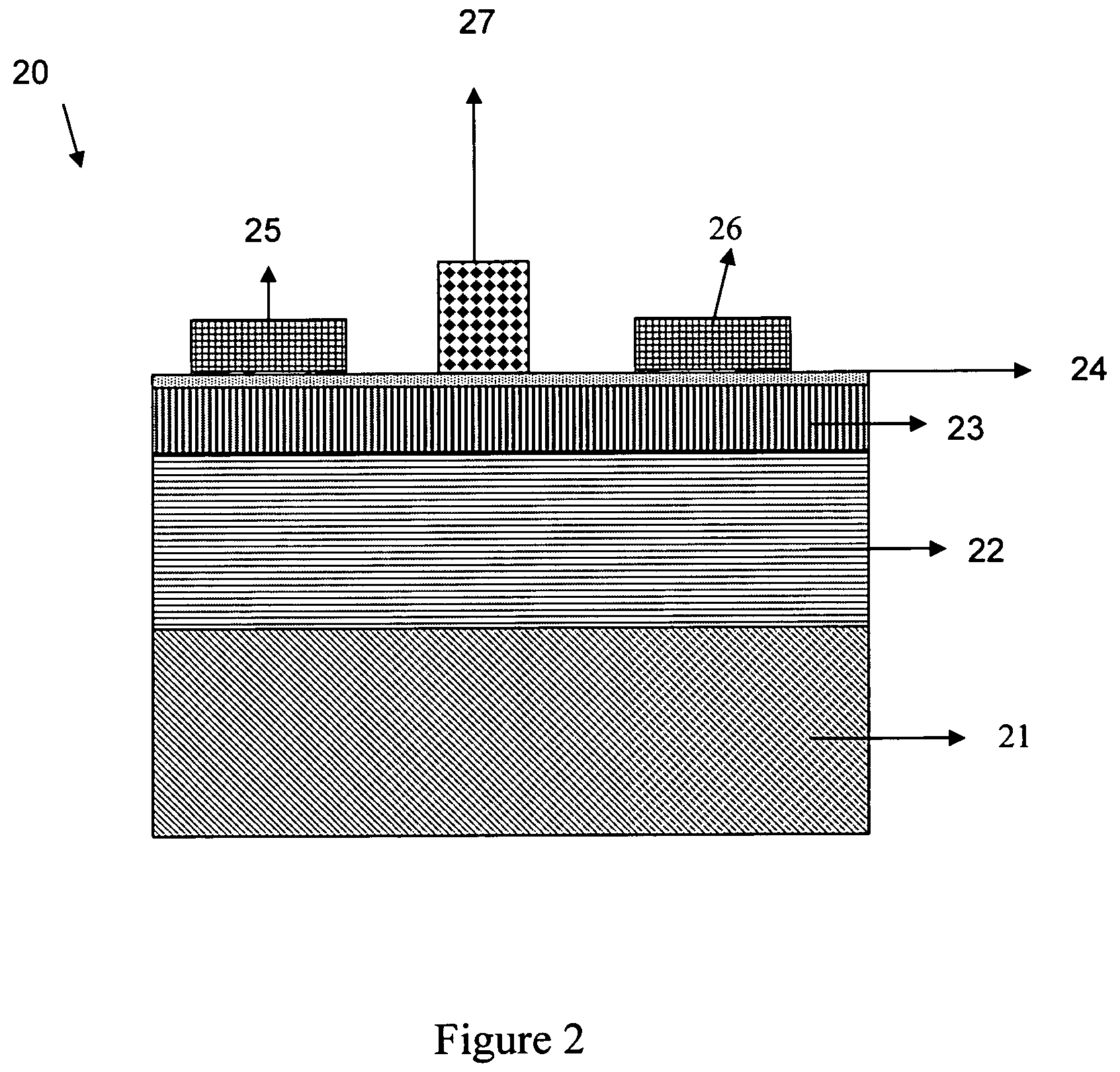

ActiveUS20080217625A1Reduce parasitic resistanceLower barrier heightSemiconductor/solid-state device manufacturingSemiconductor devicesCheckerboard patternIsolation layer

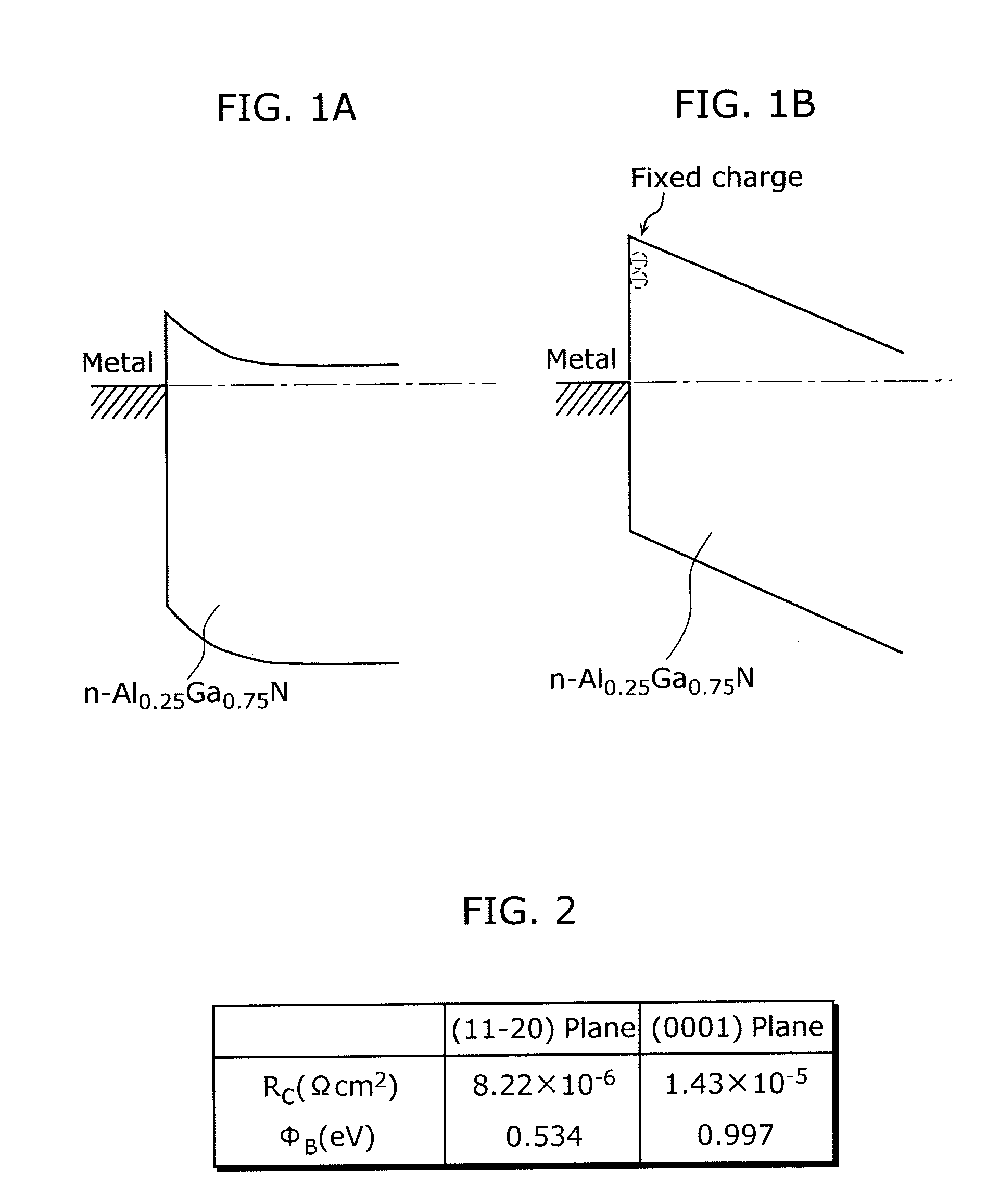

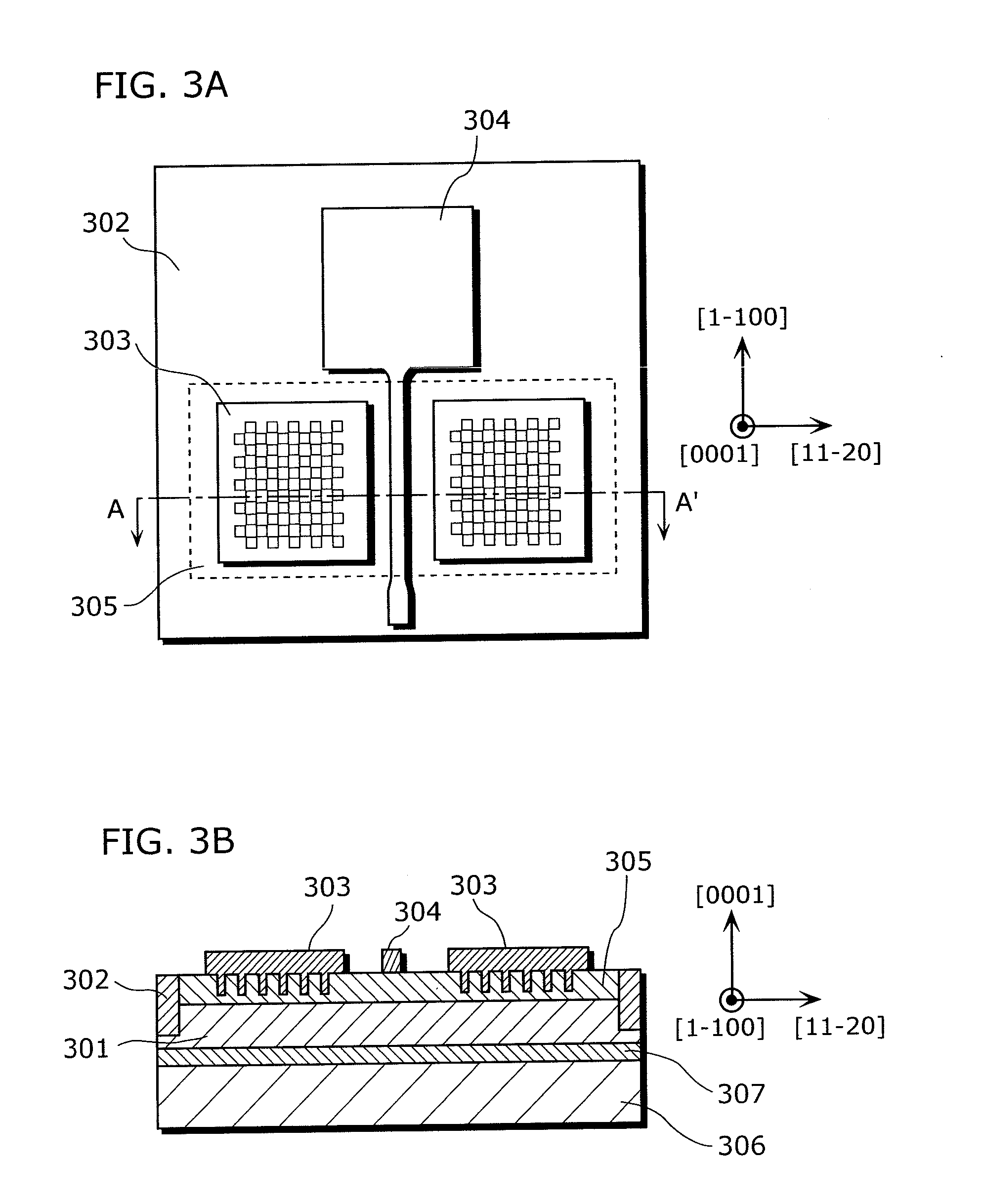

It is an object of the present invention to provide a nitride semiconductor device with low parasitic resistance by lowering barrier height to reduce contact resistance at an interface of semiconductor and metal. The nitride semiconductor device includes a GaN layer, a device isolation layer, an ohmic electrode, an n-type Al0.25Ga0.75N layer, a sapphire substrate, and a buffer layer. A main surface of the n-type Al0.25Ga0.75N layer is on (0001) plane as a main surface, and concaves are arranged in a checkerboard pattern on the surface. The ohmic electrode contacts the sides of the concaves of the n-type Al0.25Ga0.75N layer, and the sides of the concaves are on non-polar surfaces such as (11-20) plane or (1-100) plane.

Owner:PANASONIC CORP

Lead-free aluminum paste for solar battery

InactiveCN101789456AMeet environmental protection requirementsStrong adhesionFinal product manufactureNon-conductive material with dispersed conductive materialAluminium powderSolar battery

The invention provides a lead-free aluminum paste for a solar battery, which is mainly used for producing a conductive electrode for a solar battery. The lead-free aluminum paste mainly comprises the following components by weight percent: 70 to 80 percent of aluminum powder, 19 to 30 percent of organic bond, 0.1 to 5 percent of inorganic glass powder and 0.1 to 2 percent of a first additive. The organic bond comprises the following components by weight percent: 40 to 60 percent of terpineol, 1 to 5 percent of ethylcellulose, 1 to 5 percent of lecithin and 20 to 50 percent of a second additive. The lead-free aluminum paste for the solar battery mainly solves the technical problems that the existing aluminum paste for the solar battery has poor electrical conductivity and low photoelectric conversion efficiency. The lead-free aluminum paste has the advantages of good electric conductivity, high photoelectric conversion efficiency and the like.

Owner:西安宏星电子浆料科技股份有限公司

Nitride semiconductor device and manufacturing method thereof

ActiveUS7777305B2Reduce parasitic resistanceLower barrier heightSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerElectrode Contact

It is an object of the present invention to provide a nitride semiconductor device with low parasitic resistance by lowering barrier height to reduce contact resistance at an interface of semiconductor and metal. The nitride semiconductor device includes a GaN layer, a device isolation layer, an ohmic electrode, an n-type Al0.25Ga0.75N layer, a sapphire substrate, and a buffer layer. A main surface of the n-type Al0.25Ga0.75N layer is on (0 0 0 1) plane as a main surface, and concaves are arranged in a checkerboard pattern on the surface. The ohmic electrode contacts the sides of the concaves of the n-type Al0.25Ga0.75N layer, and the sides of the concaves are on non-polar surfaces such as (1 1 −2 0) plane or (1 −1 0 0) plane.

Owner:PANASONIC CORP

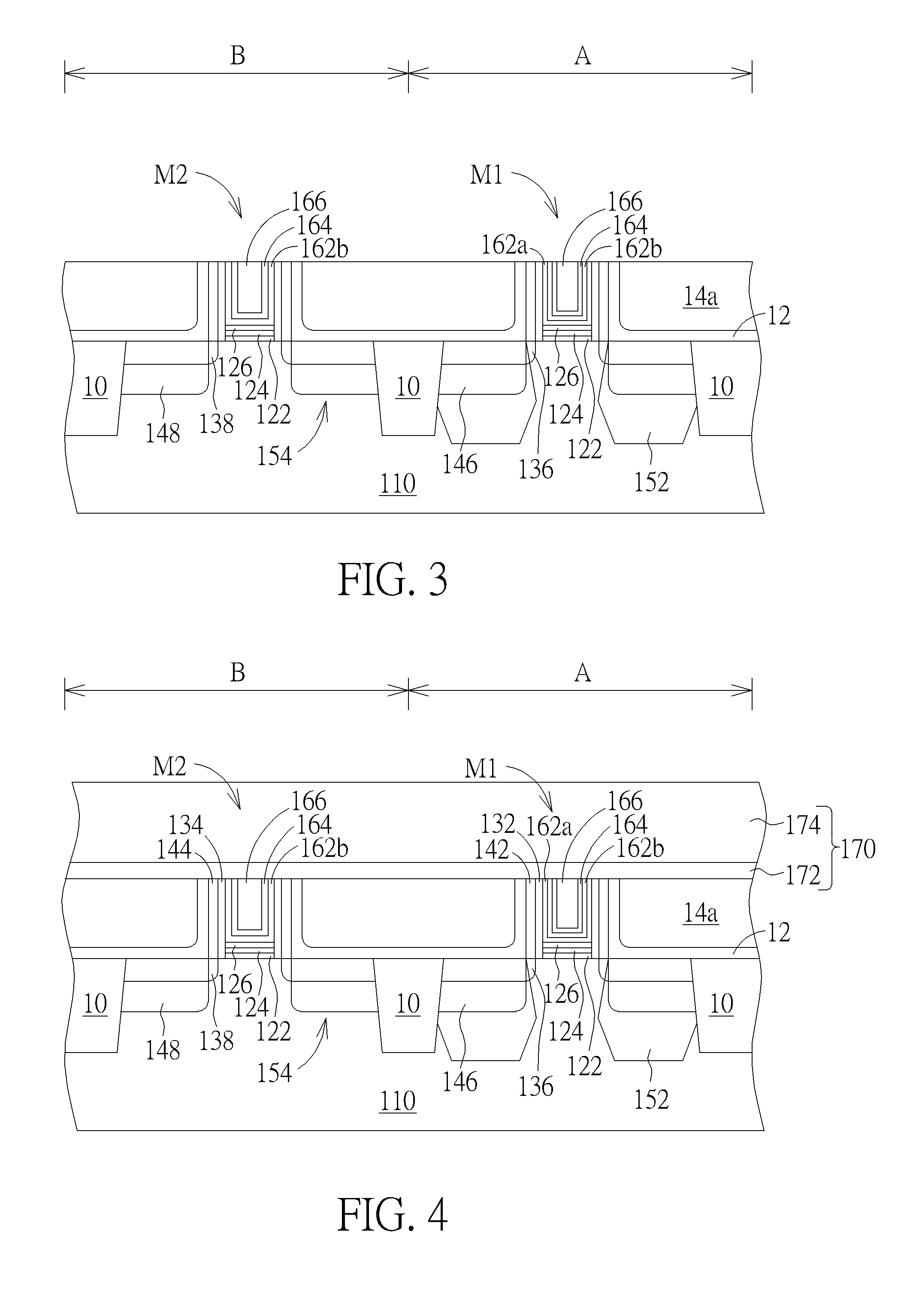

Semiconductor device and manufacturing method of the same

InactiveUS20080237639A1Increase productionImprove breakdown voltageSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSemiconductor

The objective of the present invention is to provide a semiconductor device of a hetero-junction field effect transistor that is capable of obtaining a high output and a high breakdown voltage and a manufacturing method of the same.The present invention is a semiconductor device of a hetero-junction field effect transistor provided with an AlxGa1-xN channel layer with a composition ratio of Al being x (0<x<1) formed on a substrate, an AlyGa1-yN barrier layer with a composition of Al being y (0<y≦1) formed on the channel layer, and source / drain electrodes and a gate electrode formed on the barrier layer, wherein the composition ratio y is larger than the composition ratio x.

Owner:MITSUBISHI ELECTRIC CORP

AlGaN/GaN high electron mobility transistor devices

ActiveUS7547928B2Avoid crackingReduce the appearance of cracksSolid-state devicesSemiconductor/solid-state device manufacturingMESFETCooling down

The present invention recites a new method for manufacturing Group III-N field-effect devices, such as HEMT, MOSHFET, MISHFET devices or MESFET devices, grown by Metal-Organic Vapor Phase Expitaxy, with higher performance (power), by covering the surface with a thin SiN layer on the top AlGaN layer, in the reactor where the growth takes place at high temperature, prior cooling down the structure and loading the sample out of the reactor, as well as a method to produce some HEMT transistors on those heterostructures, by depositing the contact on the surface without any removal of the SiN layer by MOCVD. The present invention recites also a device.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

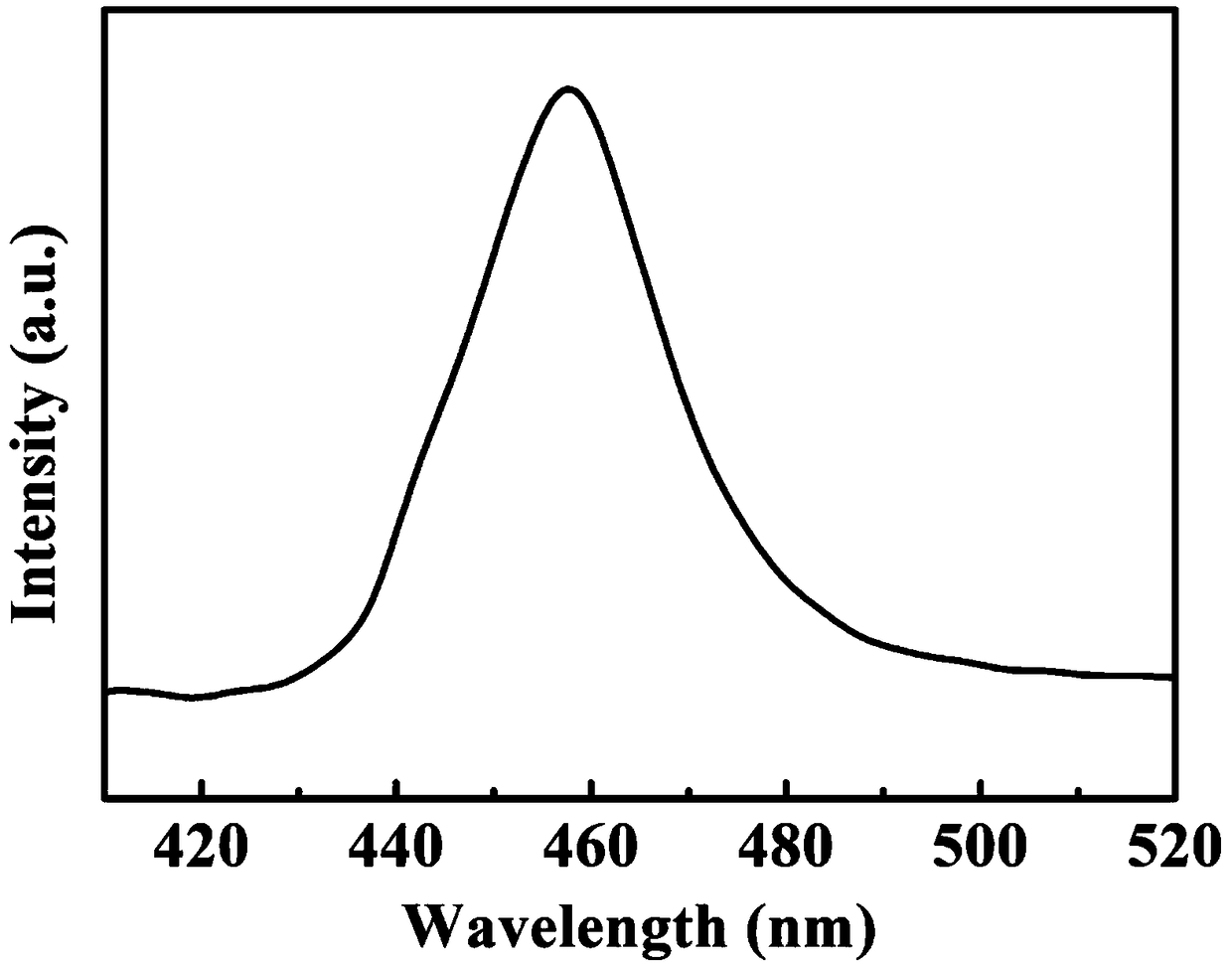

Light-emitting diode of photonic crystal structure and application thereof

ActiveCN102945902AImprove light extraction efficiencyReduced ohmic contact resistanceSemiconductor devicesCrystal structurePhotonic crystal structure

The invention provides a light-emitting diode of a photonic crystal structure. The light-emitting diode is provided with a substrate (101), a buffer layer (102), an n-type GaN epitaxial layer (103), an active luminescent layer (105) with InGaN / GaN multiple quantum wells, a p-type GaN epitaxial layer (106), a p-type super-lattice structure (107), a transparent conducting layer (109) and a passivation layer (110) in sequence from bottom to top, wherein an n-type electrode (104) is further arranged on the n-type GaN epitaxial layer (103); a p-type electrode (111) is further arranged on the transparent conducting layer (109); and a photonic crystal structure (108) is prepared in the p-type super-lattice structure (107). The light-emitting diode is applicable to a GaN-based LED (Light-emitting Diode), and is also applicable to other photo-electronic apparatuses which need to improve reflectivity of a certain wave band.

Owner:SOUTHEAST UNIV

Aluminum paste for solar energy battery and preparation method thereof

ActiveCN102592704AStrong adhesionReduced ohmic contact resistanceNon-conductive material with dispersed conductive materialCable/conductor manufactureMuffle furnaceThermal insulation

The invention discloses an aluminum paste for a solar energy battery. The aluminum paste for solar energy battery comprises an aluminum powder, a copper powder, a non-leaded glass powder and organic carriers, wherein the organic carriers are composed of organic solvents and organic addition agents, the aluminum powder is of sphere and / or of squamelliform, the aluminum powder has thick grains andthin grains; and the non-leaded glass powder adopts the glass system of lanthanum, boron and zinc. The preparation method includes uniformly mixing the raw materials of the non-leaded glass powder, subjecting the powder to heating and thermal insulation in a high temperature muffle furnace, then quenching the melted glass powder grains and grinding the grains; mixing and uniformly stirring the organic solvents and organic addition agents in proportion; weighing the aluminum powder, the copper powder, the non-leaded glass powder and the organic carriers, uniformly stirring the mixture in a container, then subjecting the mixture to grinding in a three-roll grinder and finally obtaining the uniform aluminum paste for the solar energy battery. On the premise of meeting the requirement of electrical properties of the solar energy battery, the requirement of non-leaded environmental protection can also be met.

Owner:JIANGSU RUIDE NEW ENERGY TECH

Gallium nitride devices having low ohmic contact resistance

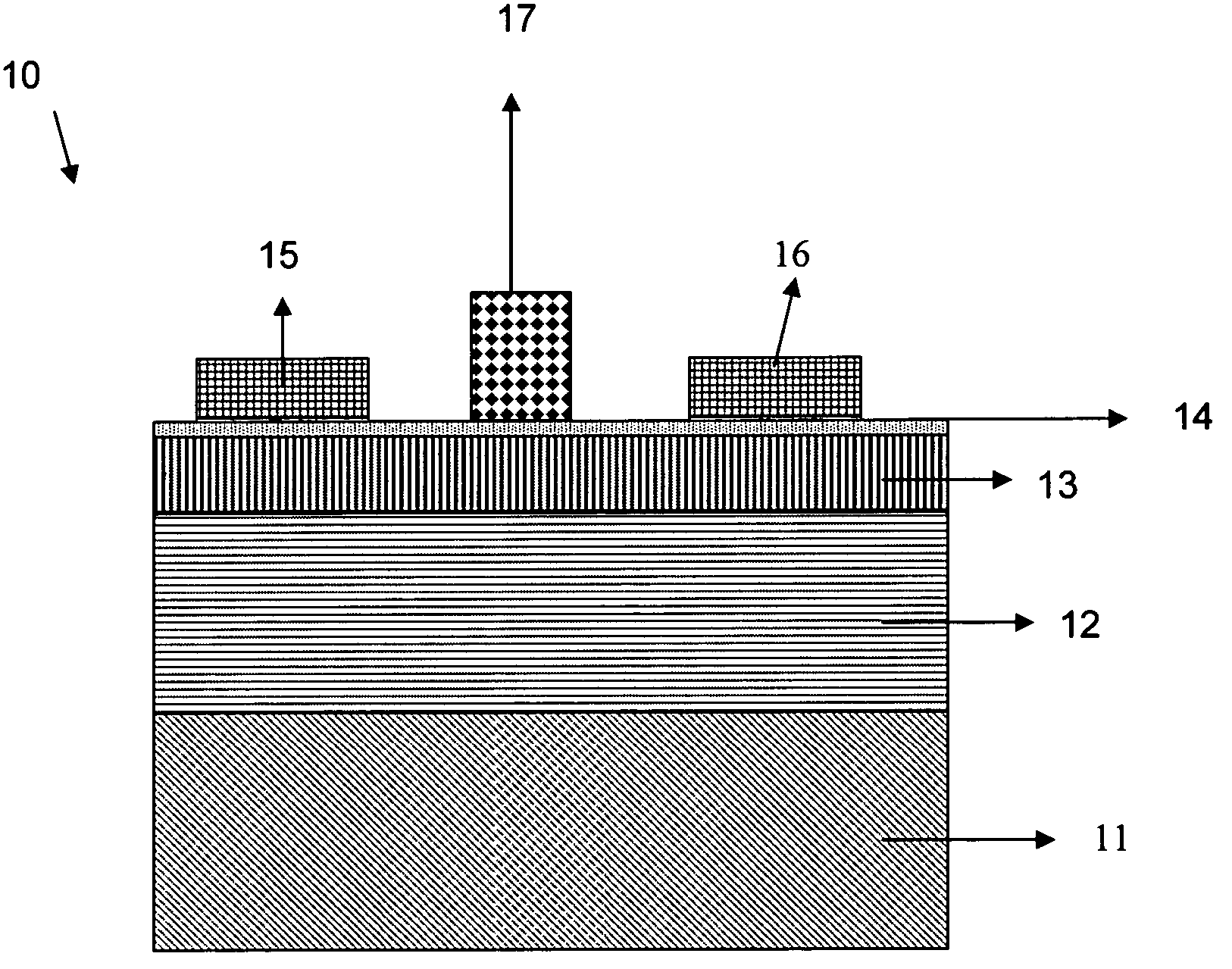

ActiveUS8772786B2Reduce contact resistanceHigh electron mobilitySemiconductor devicesSemiconductor structureOhmic contact

A semiconductor structure having mesa structure comprising: a lower semiconductor layer; an upper semiconductor layer having a higher band gap than, and in direct contact with, the lower semiconductor layer to form a two-dimension electron gas (2DEG) region between the upper semiconductor layer. The 2DEG region has outer edges terminating at sidewalls of the mesa. An additional electron donor layer has a band gap higher than the band gap of the lower layer disposed on sidewall portions of the mesa structure and on the region of the 2DEG region terminating at sidewalls of the mesa. An ohmic contact material is disposed on the electron donor layer. In effect, a sideway HEMT is formed with the electron donor layer, the 2DEG region and the ohmic contact material increasing the concentration of electrons (i.e., lowering ohmic contact résistance) all along the contact between the lower semiconductor layer and the electron donor layer.

Owner:RAYTHEON CO

Semiconductor process for treating metal gate

ActiveUS20170032975A1ReduceOhmic contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPlasma treatmentConductive materials

A semiconductor process for treating a metal gate includes the following steps. A metal gate including a main conductive material on a substrate is provided. A H2 / N2 plasma treatment process is performed to reduce the main conductive material.

Owner:UNITED MICROELECTRONICS CORP

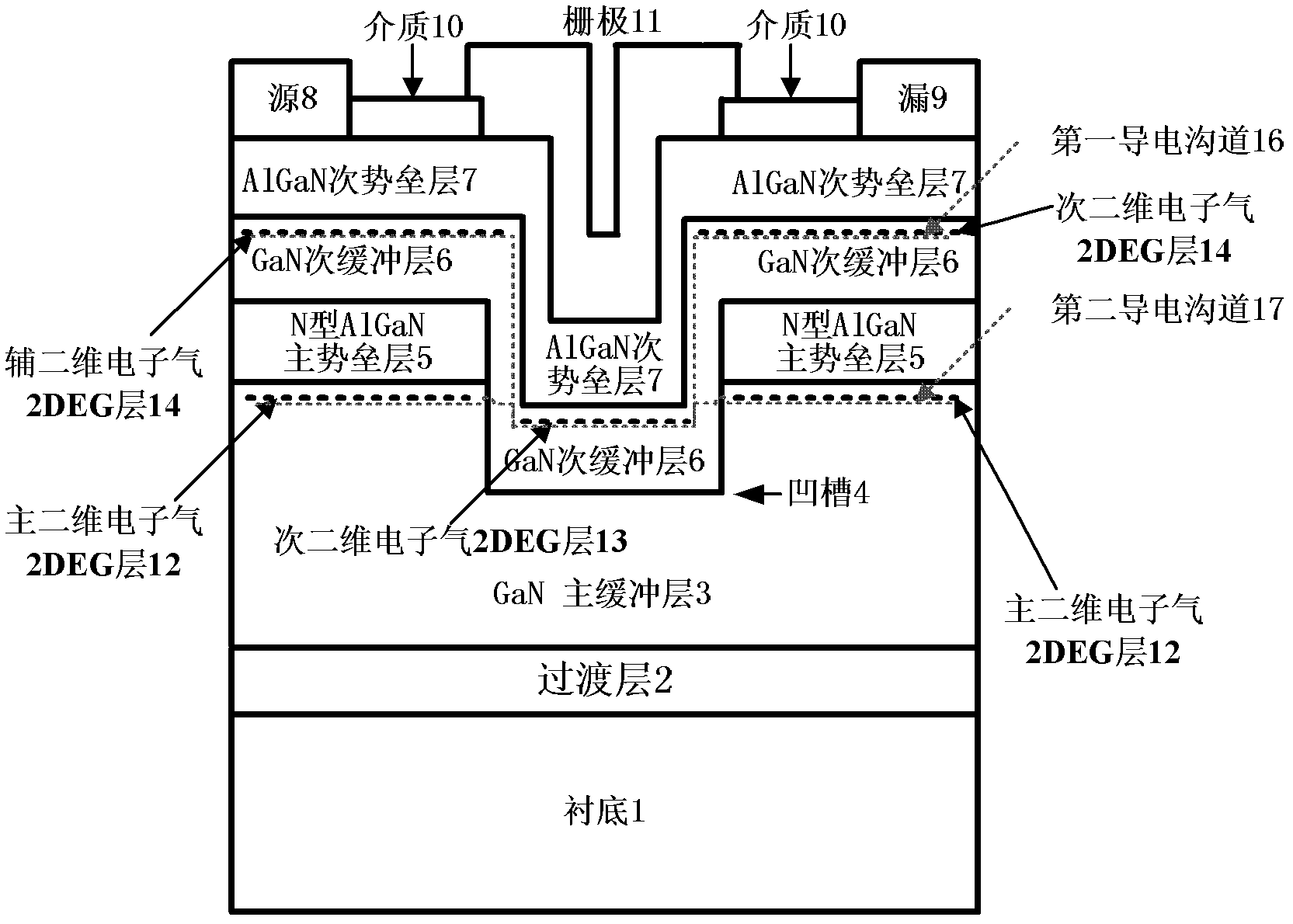

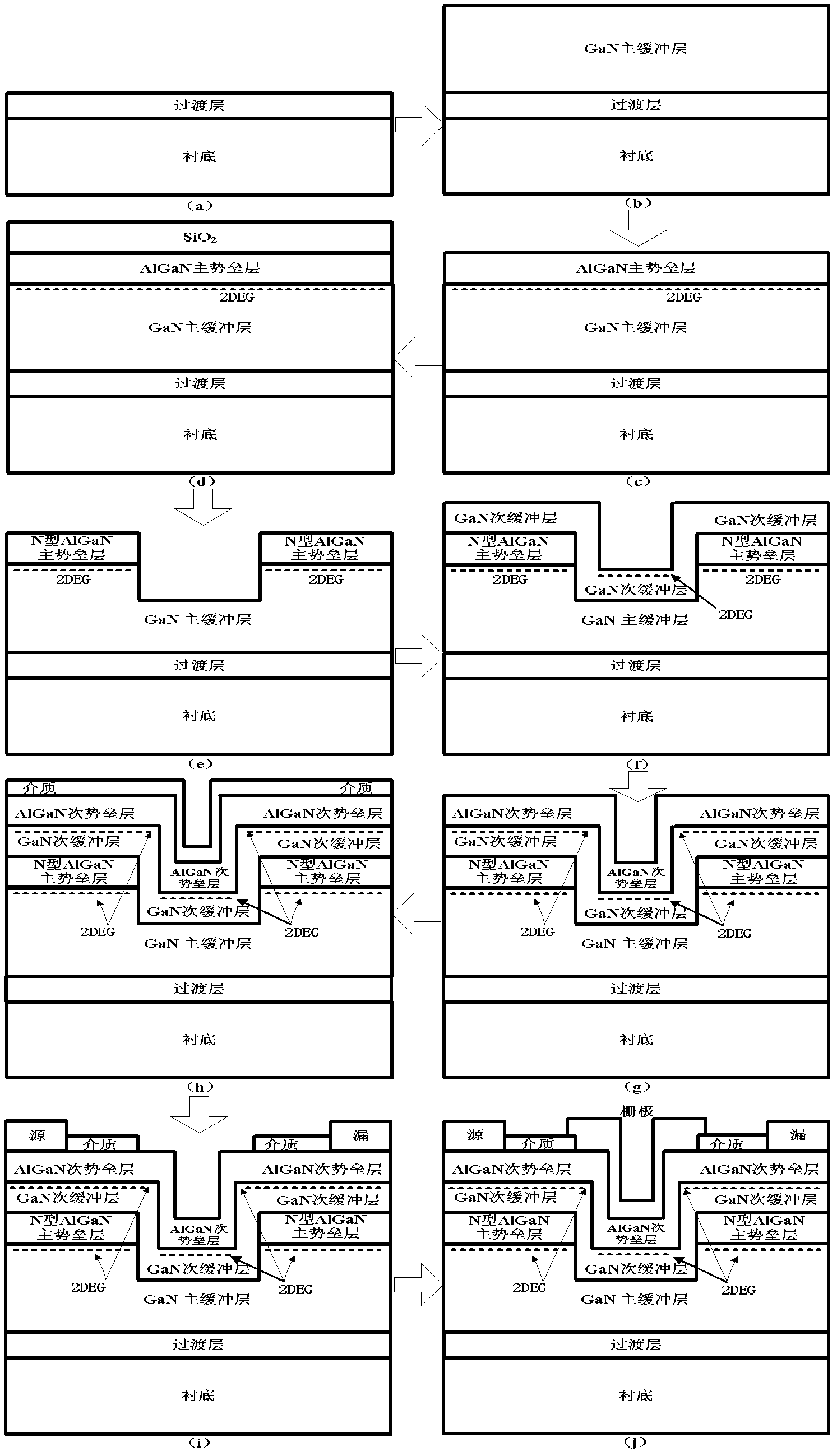

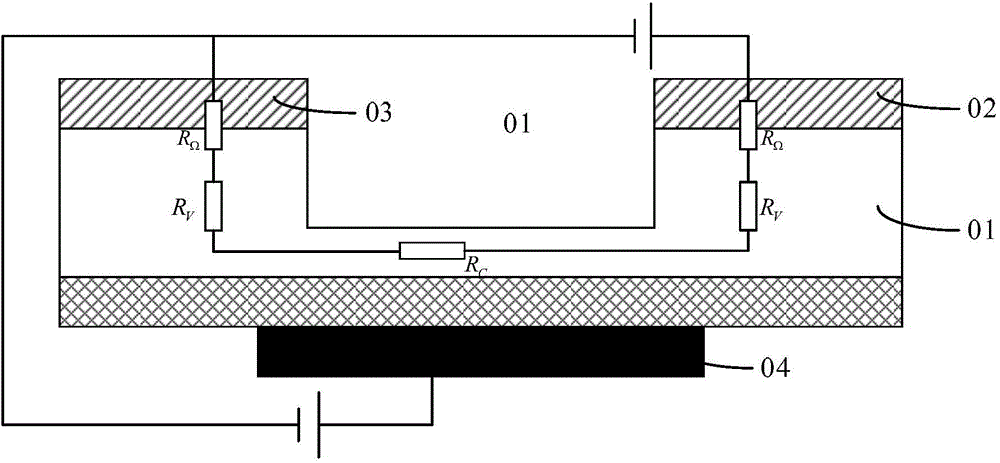

GaN-based MS grid enhancement type high electron mobility transistor and manufacture method thereof

ActiveCN102683406AReduce concentrationReduced polarization effectsSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowOptoelectronics

The invention discloses a GaN-based MS grid enhancement type high electron mobility transistor and a manufacture method thereof which mainly resolve the problems of low current density and poor reliability of a GaN-based enhancement type device. The structure of the device is that a transition layer (2) and a GaN main buffer layer (3) are sequentially arranged on a lining (1), a groove (4) is etched in the middle of the GaN main buffer layer, an AlGaN main barrier layer (5) is respectively arranged above the GaN mian buffer layer (3) on two sides of the groove, and a GaN auxiliary buffer layer (6) and an AlGaN auxiliary barrier layer (7) are sequentially arranged on the inner wall of the groove and the surface of the AlGaN main barrier layer (5) on two sides of the groove. A source electrode (8), a drain electrode (9), a grid electrode (11) and a medium layer (10) are arranged on the AlGaN secondary barrier layer (7). The source electrode (8) and the drain electrode (9) are respectively located on two sides above the AlGaN auxiliary barrier layer (7), the grid electrode (11) is located in the middle above the AlGaN auxiliary barrier layer (7), and the medium layer (10) is distributed on an area outside the source electrode, the drain electrode and the grid electrode. The transistor has the advantages of being good in enhancement type characteristic, high in current density, high in breakdown voltage, simple and mature in manufacture process and high in reliability, thereby being capable of being used in high temperature switch devices and digital circuits.

Owner:云南凝慧电子科技有限公司

Nitride semiconductor heterojunction field effect transistor having wide band gap barrier layer that includes high concentration impurity region

InactiveUS8035130B2Increase productionLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationDevice material

The objective of the present invention is to provide a semiconductor device of a hetero-junction field effect transistor that is capable of obtaining a high output and a high breakdown voltage and a manufacturing method of the same. The present invention is a semiconductor device of a hetero-junction field effect transistor provided with an AlxGa1-xN channel layer with a composition ratio of Al being x (0<x<1) formed on a substrate, an AlyGa1-yN barrier layer with a composition of Al being y (0<y≦1) formed on the channel layer, and source / drain electrodes and a gate electrode formed on the barrier layer, wherein the composition ratio y is larger than the composition ratio x.

Owner:MITSUBISHI ELECTRIC CORP

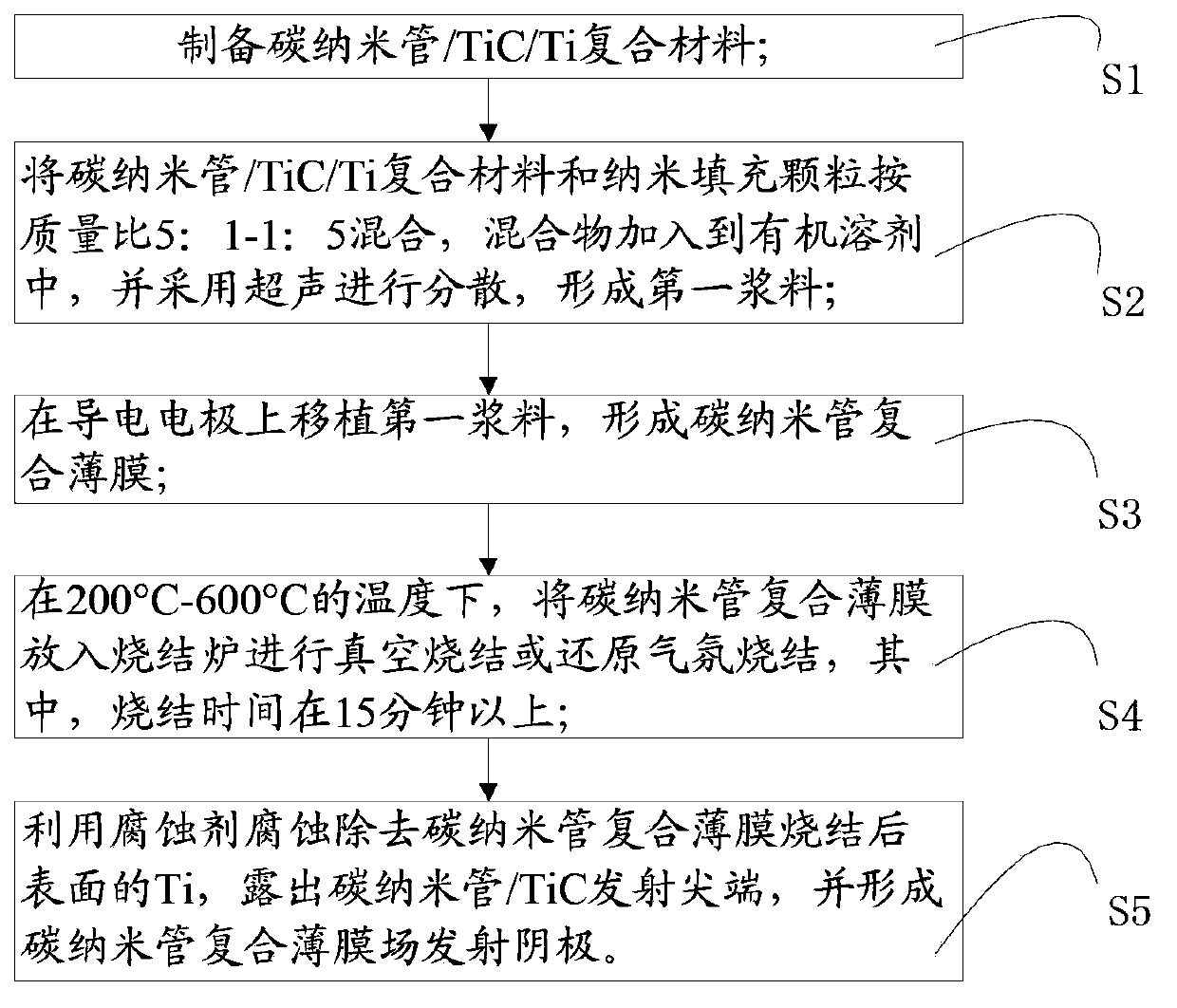

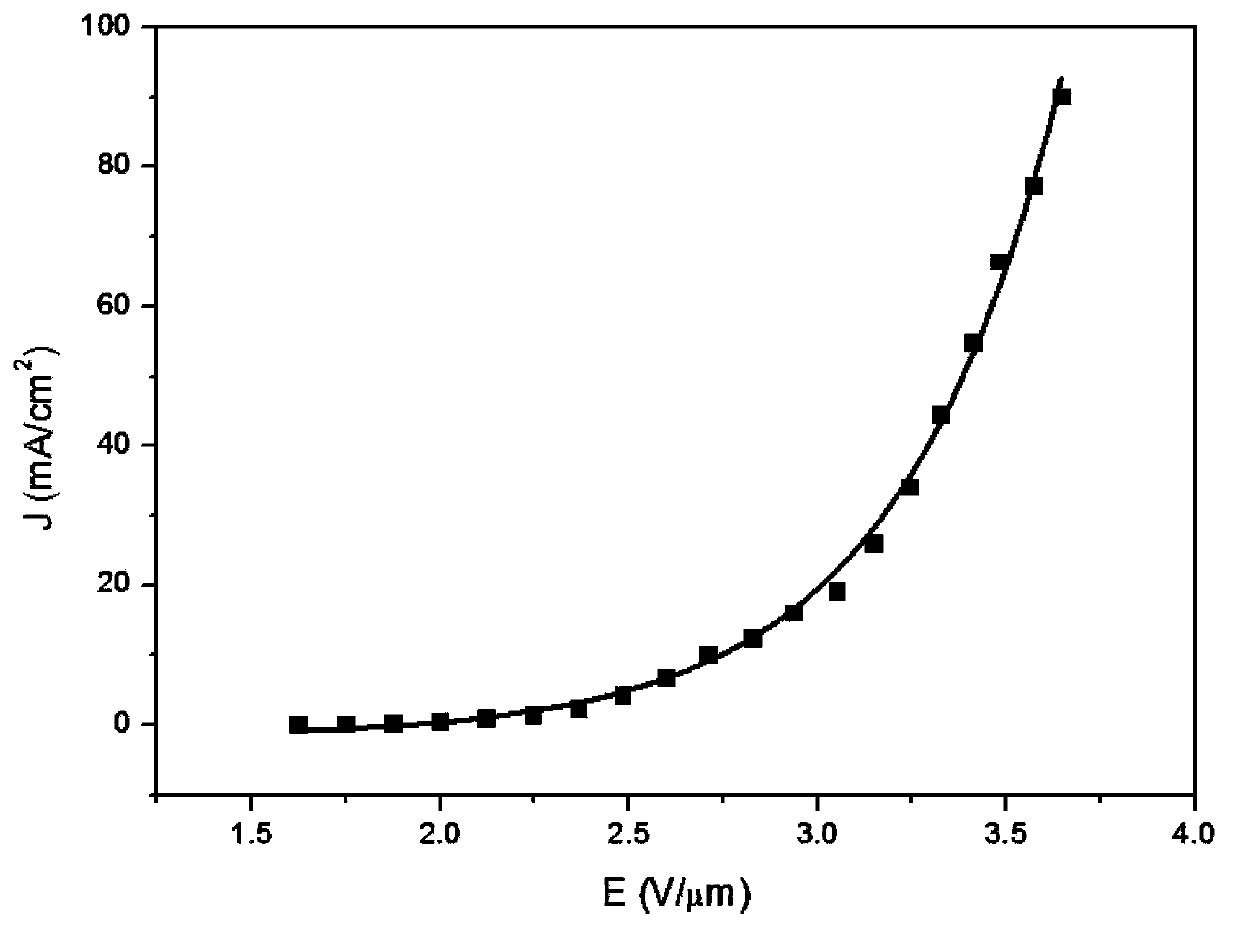

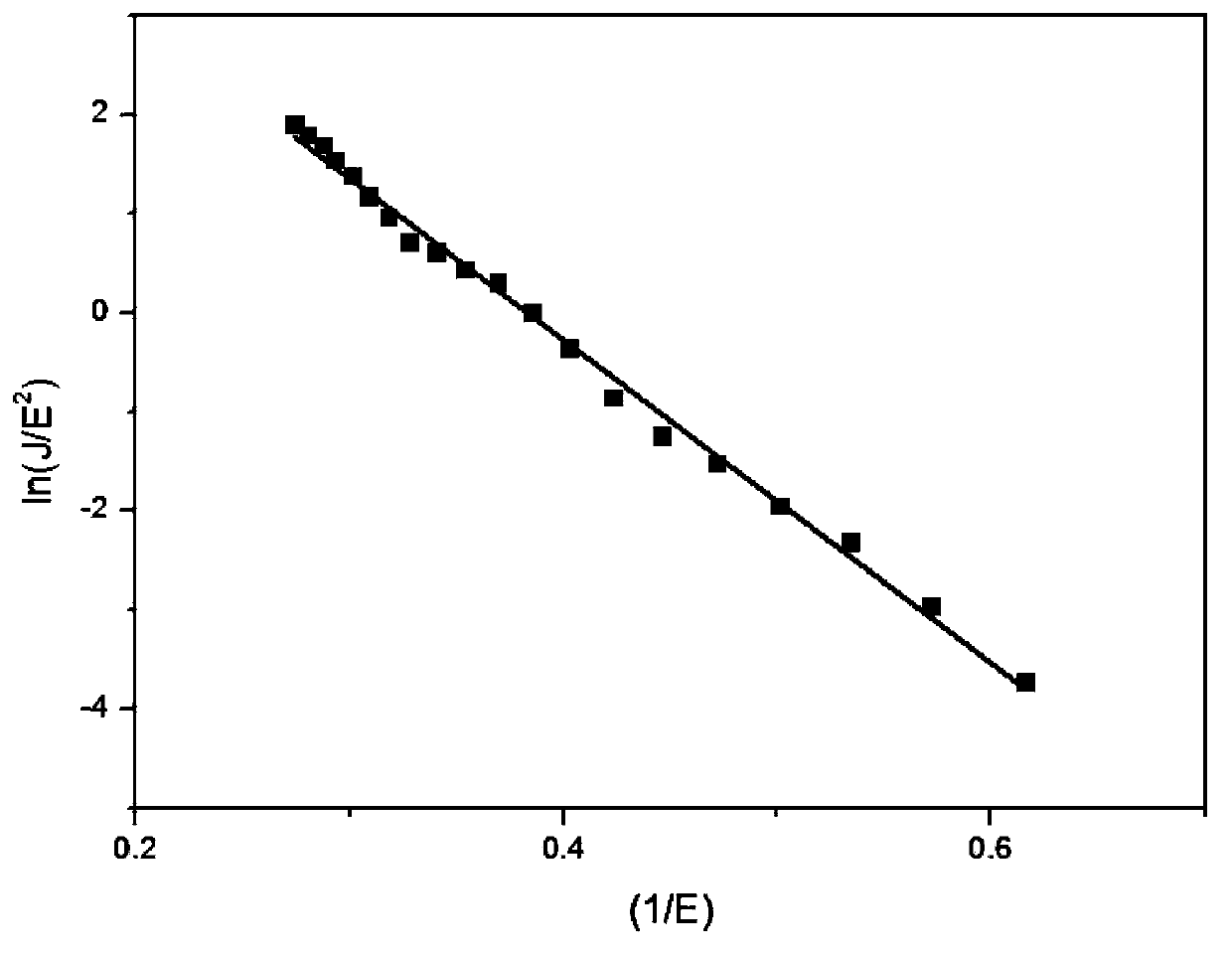

Carbon nanotube composite thin film field emission cathode preparation method

ActiveCN103871802AOvercoming the Schottky BarrierIncrease contact areaMaterial nanotechnologyCold cathode manufactureComposite filmSilver electrode

The invention provides a carbon nanotube composite thin film field emission cathode preparation method. The carbon nanotube composite thin film field emission cathode preparation method includes the following steps that: S1, nanotube / TiC / Ti composite materials are prepared; S2, the nanotube / TiC / Ti composite materials and nano filling particles are mixed according to at the mass ratio of 5:1 to 1:5, and the mixture is added to an organic solvent, and ultrasound is adopted to perform dispersion, and a first slurry can be formed; S3, the first slurry is transplanted on a silver electrode, and a nanotube composite film can be formed; S4, the nanotube composite film is put into a sintering furnace so as to be subjected to vacuum sintering or reducing atmosphere sintering for more than 15 minutes under temperature from 200 DEG C to 600 DEG C; S5, Ti on the surface of the sintered carbon nanotube composite film is corroded and removed through using a corrodent, and a carbon nanotube / TiC emission tip is exposed, and a carbon nanotube composite thin film field emission cathode can be formed. With the carbon nanotube composite thin film field emission cathode prepared by the invention adopted, adhesion and electrical contact between the emitter and the base of a carbon nanotube can be improved, and field emission performance can be improved.

Owner:SHENZHEN INST OF ADVANCED TECH CHINESE ACAD OF SCI

Solar cell and manufacturing method thereof

ActiveCN102916087AImprove photoelectric conversion efficiencyReduce compoundingFinal product manufactureSemiconductor devicesState of artElectrical resistance and conductance

The invention provides a solar cell and a manufacturing method thereof. The manufacturing method comprises the following steps of: providing a substrate, wherein the substrate comprises a body layer and a diffusion layer covering the front surface of the body layer; carrying out partial heavy doping on the diffusion layer to form a first secondary grid line; forming a refraction-reducing layer on the front surface of the substrate; forming a discontinuous second secondary grid line above the first secondary grid line; forming a continuous main grid line and a third secondary grid line above the second secondary grid line; and sintering the substrate. According to the solar cell and the manufacturing method thereof provided by the invention, the third secondary grid line does not contact the substrate, and the second secondary grid line and the substrate are in point contact, so that the compounding of current carriers on the surface of the substrate is reduce; in addition, the partial heavy doping is carried out on the diffusion layer to realize the partial heavy doping at a partial optical contact part of a front electrode and the substrate, so that ohmic contact resistance between the front electrode of the solar cell and the substrate is reduced as compared with that in the prior art, and the photoelectric conversion efficiency of the solar cell is improved.

Owner:上饶捷泰新能源科技有限公司

Method of reducing GaN HEMT device ohm contact resistance

ActiveCN105118780AReduced ohmic contact resistanceImprove ohmic contact metal surface and edge morphologySemiconductor/solid-state device manufacturingNanotechnologyEtchingOhm

The invention discloses a method of reducing GaN HEMT device ohm contact resistance. The method comprises the following steps of Si3N4 and SiO2 composite dielectric layer growing on a GaN heterojunction material; (2) ohm area thin layer Ni evaporating and stripping; (3) Ni metal nanocluster making and SiO2 dielectric layer etching; (4) photoresist mask layer making; (5) photoresist mask layer etching through oxygen plasma; (6) Si3N4 and SiO2 composite dielectric layer etching; (7) GaN heterojunction micropore making; (8) evaporating / stripping / annealing to form ohm contact. By means of the method, problems of high GaN ohm contact resistivity and a bad metal morphology are solved. The method has the following advantages that (1) the ohm alloy temperature can be lowered; the ohm metal surface and edge morphology can be improved; (2) the micro channel dimension can be controlled through nanodots; the dimension can reach a nanometer level; an electron beam technical preparation way is not required; the technical time consumption is low; (3) and low ohm contact resistance can be acquired.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

A method for reducing the ohmic contact resistance of a wide band gap semiconductor device

PendingCN109216171AImprove performanceIncrease contact areaNanotechnologySemiconductor devicesSemiconductor materialsOhmic contact

The invention discloses a method for reducing the ohmic contact resistance of a wide band gap semiconductor device, wherein the material of the wide band gap semiconductor device is III- V-group wide-band gap semiconductor material that comprises a substrate, a buffer lay, a channel layer and an alloy barrier layer sequentially arranged from bottom to top. That method comprise the following steps:depositing a passivation layer; 2, coating photoresist and forming a photoresist window; 3, etching that passivation layer and for a window of the passivation layer; 4, coating a nano ball; 5, forming a nano groove; 6, coating photoresist and forming a photoresist window; 7, evaporating the electron beam or magnetron sputtering the multi-layer metal; Step 8, peeling off the multi-layer metal; Step 9: Rapidly carrying out thermal annealing to form ohmic contact. The method of the invention greatly increases the contact area between the electrode metal and the wide band gap semiconductor, reduces the ohmic contact resistance of the wide band gap semiconductor device, enhances the device performance, improves the process efficiency, and reduces the process cost.

Owner:NAT UNIV OF SINGAPORE +2

Low-pressure diffusion process applied to polycrystalline black silicon solar cells

ActiveCN108321255ASame concentration distributionImprove uniformityFinal product manufactureSemiconductor/solid-state device manufacturingLow temperature depositionThin oxide

The invention relates to a low-pressure diffusion process applied to polycrystalline black silicon solar cells, which comprises the following steps: (1) allowing a silicon wafer to entering a tube; (2) performing constant temperature processing; (3) performing low temperature oxidation, generating a thin oxide layer on a surface of the silicon wafer to make the subsequent phosphorus source deposition more uniform; (4) performing low temperature deposition, uniformly depositing a phosphorus source on the surface of the silicon wafer; (5) performing high temperature propulsion, allowing the phosphorus source to diffuse into the silicon wafer, wherein during high temperature propulsion, the temperature is 820-850 DEG C, the nitrogen flow rate is 1000-3000sccm, the dry oxygen is 0-1000sccm, the furnace pressure is 50-150mbar, and the time is 10-20 minutes; (6) performing secondary diffusion, wherein during the secondary diffusion, the temperature is 800-850 DEG C, the nitrogen flow rate is1000-3000sccm, the source nitrogen is 0-400sccm, the dry oxygen is 0-1000sccm, the furnace pressure is 50-150mbar, the time is 2-10 minutes; (7) performing cooling; (8) performing nitrogen filling, allowing the pressure inside the pipe to reach the atmospheric pressure so that a furnace door is opened; and (9) performing discharging. The present invention improves the uniformity of the square resistance after diffusion of polycrystalline black silicon.

Owner:WUXI SUNTECH POWER CO LTD

Light-emitting diode of photonic crystal structure and application thereof

ActiveCN102945902BImprove light extraction efficiencyReduced ohmic contact resistanceSemiconductor devicesPhotonic crystal structureCrystal structure

The invention provides a light-emitting diode of a photonic crystal structure. The light-emitting diode is provided with a substrate (101), a buffer layer (102), an n-type GaN epitaxial layer (103), an active luminescent layer (105) with InGaN / GaN multiple quantum wells, a p-type GaN epitaxial layer (106), a p-type super-lattice structure (107), a transparent conducting layer (109) and a passivation layer (110) in sequence from bottom to top, wherein an n-type electrode (104) is further arranged on the n-type GaN epitaxial layer (103); a p-type electrode (111) is further arranged on the transparent conducting layer (109); and a photonic crystal structure (108) is prepared in the p-type super-lattice structure (107). The light-emitting diode is applicable to a GaN-based LED (Light-emitting Diode), and is also applicable to other photo-electronic apparatuses which need to improve reflectivity of a certain wave band.

Owner:SOUTHEAST UNIV

GaN transistor and manufacturing method thereof

InactiveCN107230625AReduced ohmic contact resistanceIncreasing device currentSemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideSilicon nitride

The invention provides a GaN transistor and a manufacturing method thereof. The method comprises the steps of forming a non-doped GaN layer on a surface of a silicon substrate, and forming an AlGaN layer on a surface of the non-doped GaN layer; depositing a layer of silicon nitride on the surface of the AlGaN layer to form a dielectric layer; etching the dielectric layer, the AlGaN layer and the non-doped GaN layer to form a drain contact hole and a source contact hole; and growing N-type doped GaN layers in the drain contact hole and the source contact hole, forming a drain on the N-type doped GaN layer in the drain contact hole, and forming a source on the N-type doped GaN layer in the source contact hole. With the GaN transistor and a manufacturing method thereof, provided by the invention, the ohmic contact resistance can be reduced, the device current is increased, and the integral performance of the device is improved.

Owner:PEKING UNIV +2

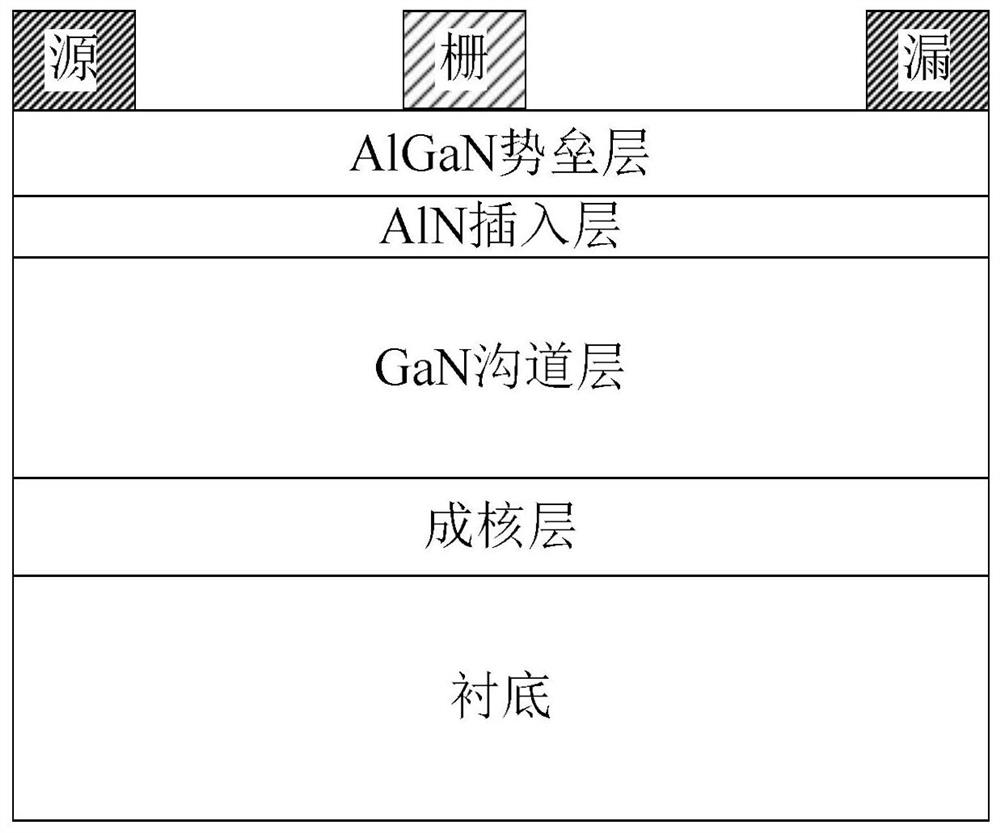

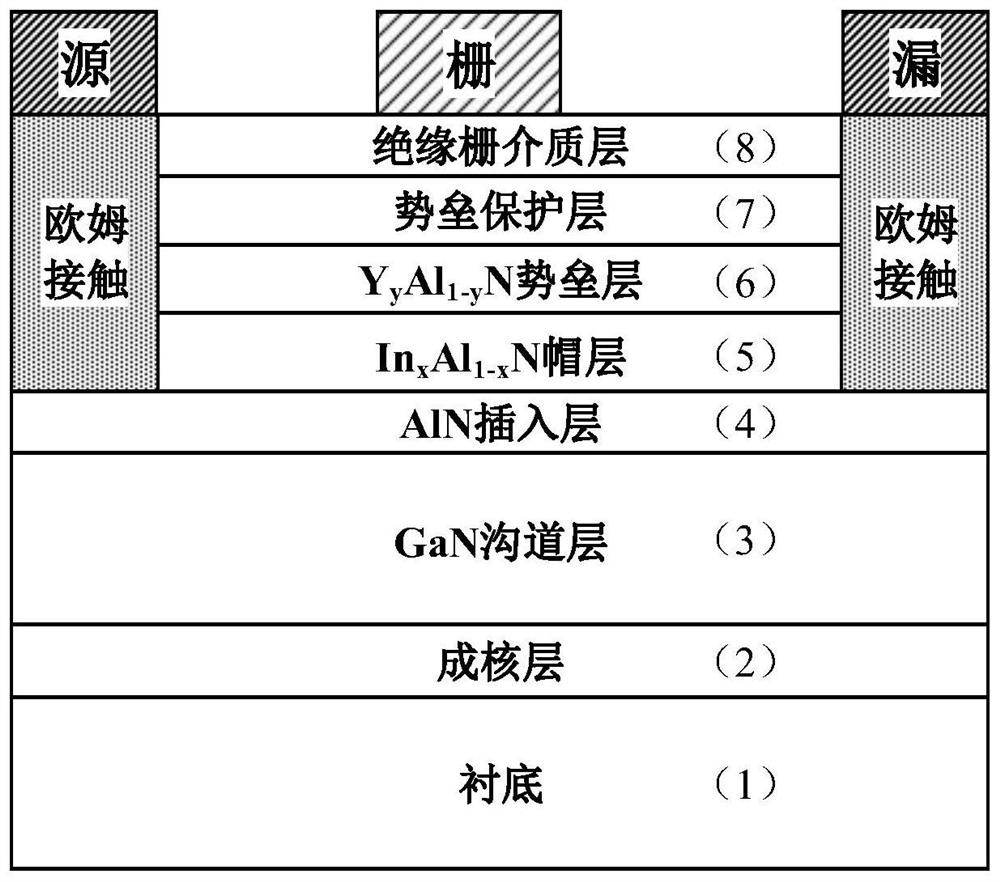

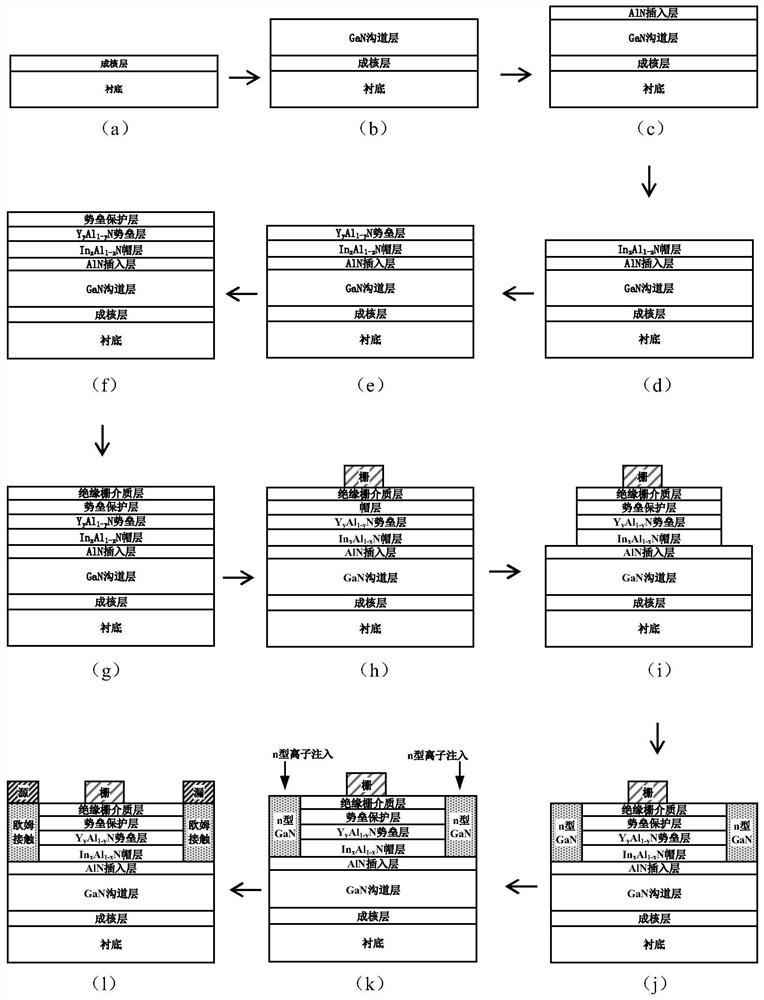

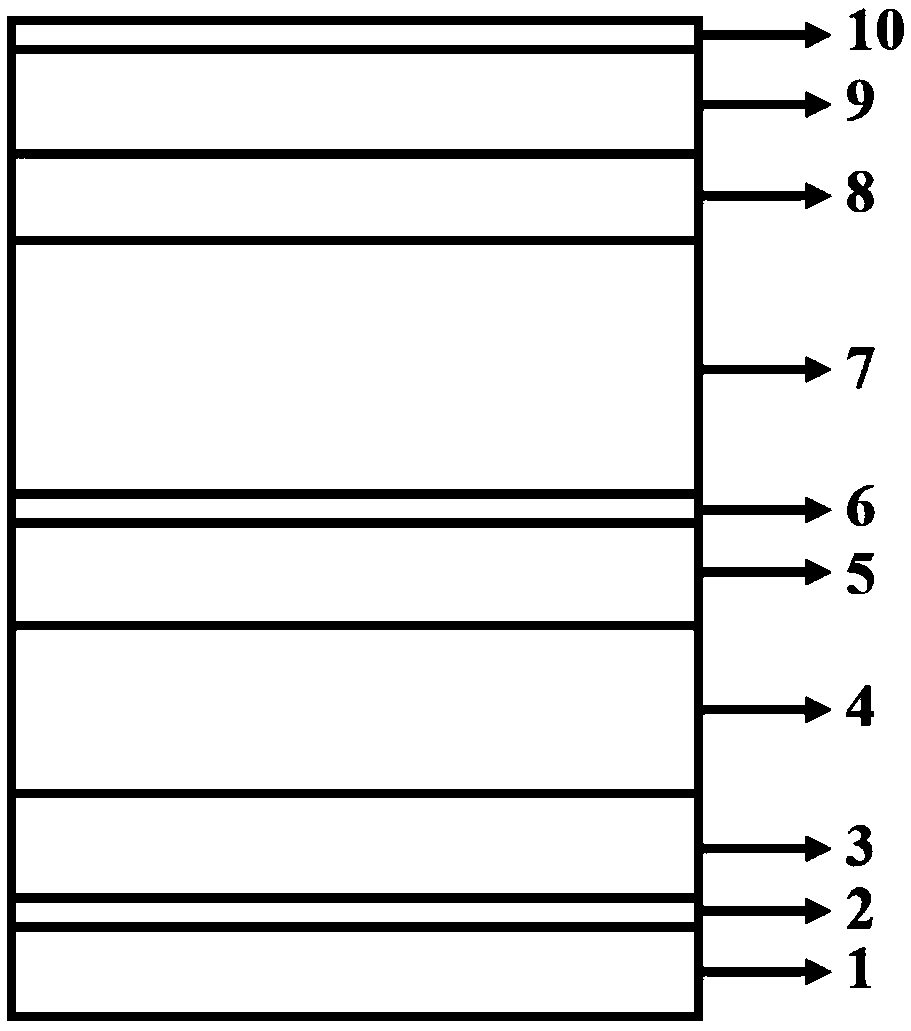

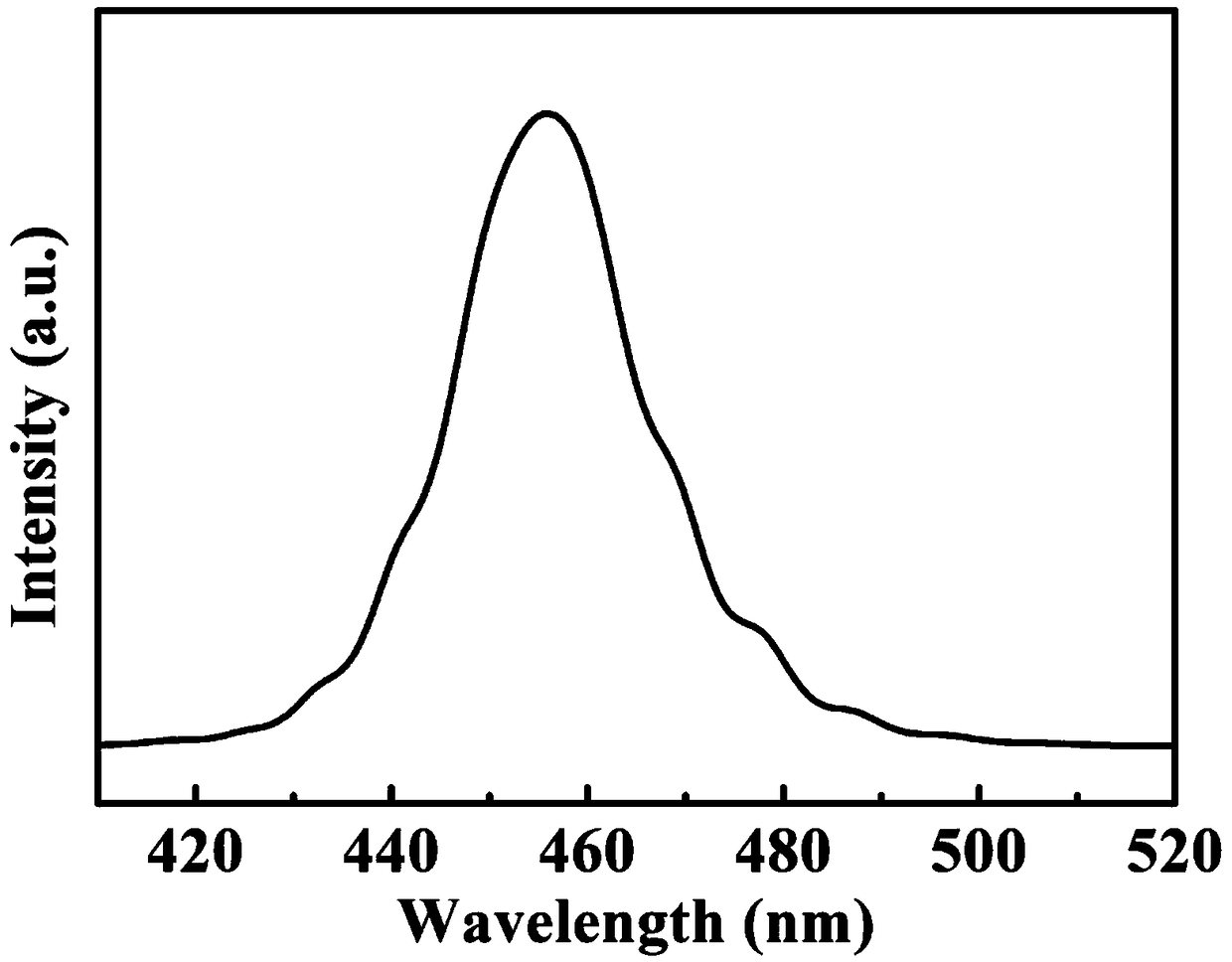

YAlN/GaN high-electron-mobility transistor and manufacturing method thereof

ActiveCN112736131AEffective protectionImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricOhmic contact

The invention relates to a YAlN / GaN high-electron-mobility transistor and a manufacturing method thereof, and mainly solves the problems of low working frequency and high material dislocation density of an existing nitride microwave power device. The transistor comprises a substrate, a nucleating layer, a GaN channel layer, an AlN insertion layer and a YAlN barrier layer from bottom to top, wherein an InAlN cap layer is arranged between the insertion layer and the barrier layer; a barrier protection layer and an insulated gate dielectric layer are sequentially arranged at the upper part of the barrier layer, and ohmic contact regions for manufacturing a source electrode and a drain electrode are arranged on two sides from the InAlN cap layer to the insulated gate dielectric layer. A nucleating layer, a GaN channel layer, an AlN insertion layer and an InAlN cap layer in the structure are grown by adopting MOCVD; and the YAlN barrier layer and the barrier protection layer are grown by adopting MBE. The material is high in polarization intensity, high in device working frequency, high in reliability, simple in manufacturing process and high in consistency, and can be used for a high-frequency microwave power amplifier and a microwave millimeter wave integrated circuit.

Owner:XIDIAN UNIV

Manufacturing method of low-temperature ohmic contact of III group nitride electronic device

InactiveCN105390382AIncreased chance of electron tunnelingReduced ohmic contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactMetal

The invention discloses a manufacturing method of low-temperature ohmic contact of a III group nitride electronic device. The manufacturing method comprises the steps of: injecting N type impurities in a III group nitride ohmic contact region; depositing ohmic metal on the III group nitride ohmic contact region injected with the N type impurities; and adopting a microwave annealing technology to achieve ohmic contact at low temperature. After the N type impurities are injected to the III group nitride ohmic contact region, the manufacturing method further comprises the step of adopting the microwave annealing technology to activate the injected N type impurities. The microwave annealing technology utilizes the microwave annealing technology to achieve the low-temperature activation of the injected N type impurities in III group nitrides, so as to form an N type heavily-doped layer, increase electronic tunnelling probability, and reduce ohmic contact resistance; furthermore, the manufacturing method can enhance the interface reaction between the ohmic metal and the III group nitride semiconductor, reduce contact-potential barrier, improve ohmic contact area, and further reduce the contact resistance.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Manufacturing method of ohmic contact electrode based on AlGaN/GaN HEMT

InactiveCN106373874AImprove reliabilityReduced ohmic contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactOptoelectronics

The invention provides a manufacturing method of an ohmic contact electrode based on an AlGaN / GaN HEMT. The method comprises the following stesp: successively depositing a silicon nitride passivation layer and a tetraethoxysilane oxide layer above an aluminum gallium nitride barrier layer; etching the silicon nitride passivation layer and the tetraethoxysilane oxide layer at a left-side area and a right-side area to form ohmic etching holes; performing cleaning processing on the aluminum gallium nitride barrier layer below the ohmic etching holes successively by use of a DHF solution, an SC1 solution and an SC2 solution; in the ohmic etching holes, depositing an ohmic electrode metal layer above the ohmic etching holes and the tetraethoxysilane oxide layer, and performing annealing processing on the AlGaN / GaN HEMT with the ohmic electrode metal layer deposited thereon; and performing photoethcing and etching on the ohmic electrode metal layer at an intermediate area above the tetraethoxysilane oxide layer so as to form the ohmic contact electrode. According to the invention, good ohmic contact is formed between the ohmic electrode contact layer and the aluminum gallium nitride barrier layer, and thus ohmic contact resistance of a device is effectively reduced.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

Electronic device

InactiveUS7199476B2Reduced ohmic contact resistanceEfficient transferSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor chip

An electronic device has at least one semiconductor chip, which has mutually opposing contact sides, of which one first contact side is electroconductively surface-bonded via a first, solid soldering-agent layer to at least one first metallic conductor part. The semiconductor chip is electroconductively surface-bonded on its second contact side facing opposite the first contact side via a second soldering-agent layer to at least one second metallic conductor part. The softening temperature of the second soldering-agent layer is adapted to an operating temperature that occurs in this soldering-agent layer during operation of the device in such a way that the second soldering-agent layer is doughy or liquid at the operating temperature. The second soldering-agent layer is laterally bounded by a flow-off protection device.

Owner:SCHAEFFLER TECH AG & CO KG

Method for manufacturing diamond device

ActiveCN103915338AImprove performanceEasy to prepareSemiconductor/solid-state device manufacturingSemiconductor devicesSurface layerOhmic contact

The invention discloses a method for manufacturing a diamond device, and relates to the technical field of semiconductor devices. The method includes the following steps: (1) an active area on a diamond surface layer with conducting channels is covered with photoresist; (2) the conducting channels in the positions, outside the active area, of the diamond are removed, and the photoresist is removed; (3) the positions outside the source position and the drain position are covered with the photoresist; (4) graphene is transferred to cover the surface of the diamond; (5) ohmic contact metal is deposited on the grapheme; (6) stripping is carried out to form a source and a drain; (7) a grid is manufactured. The manufacturing method is simple, a graphene layer is arranged between the diamond channels and source and drain metal, the graphene can be in good ohmic contact with the diamond and in good ohmic contact with the source and drain metal, the ohmic contact resistance of the diamond device can be greatly reduced, and the performance of the diamond device can be improved.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

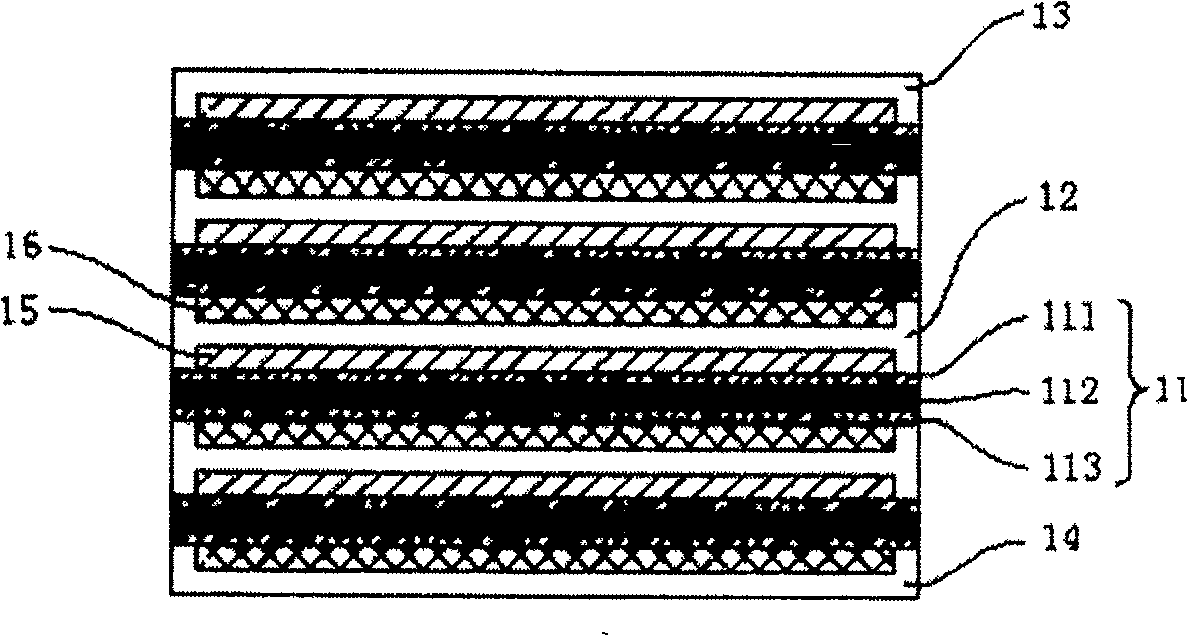

Large-power vertical structure LED epitaxial structure and preparation method thereof

ActiveCN108807627AImproved current scaling performanceImprove conductivityNanotechnologySemiconductor devicesQuantum wellGas phase

The invention discloses a large-power vertical structure LED epitaxial structure. The large-power vertical structure LED epitaxial structure includes a pre-paved Al layer, an AlN buffer layer, an AlGaN buffer layer, a u-type GaN layer, a first graphene layer, an n-type GaN layer, a multi-quantum well, a p-type GaN layer, and a second graphene layer, wherein all the above layers and the multi-quantum well are grown on an Si substrate; and the first graphene layer and the second graphene layer are formed by vapor deposition. The large-power vertical structure LED epitaxial structure has better photoelectric performance and has wide application.

Owner:HEYUAN CHOICORE PHOTOELECTRIC TECH CO LTD

Back passivation solar cell and preparation method thereof

ActiveCN107452830AImprove life expectancyImprove passivation effectFinal product manufacturePhotovoltaic energy generationPower flowMicrosecond

The invention relates to a solar cell. The solar cell comprises a silicon wafer, a front-surface electrode, an aluminum layer and a back electrode, wherein the front-surface electrode is arranged on a light surface of the silicon wafer, the aluminum layer and the back electrode are arranged on a backlight surface of the silicon wafer, the aluminum layer is arranged on a surface of the backlight surface of the silicon wafer, the back electrode is arranged on a surface of the aluminum layer, and minority carrier lifetime of backlight surface of the silicon wafer in contact with the aluminum layer is 3-10 microseconds. The invention also provides a preparation method of a back passivation solar cell. The solar cell prepared by the method is simple in process and good in passivation effect, the series resistance of the battery is greatly reduced, the filling factor of the battery is obviously increased, and the photoelectric conversion efficiency is also improved; and compared with the solar cell only comprising the aluminum layer on the backlight surface, the short-circuit current and the open-circuit voltage of the battery both can be increased to a great extent, the series resistance is also reduced, and thus, the conversion efficiency of the battery is remarkably improved.

Owner:BYD CO LTD

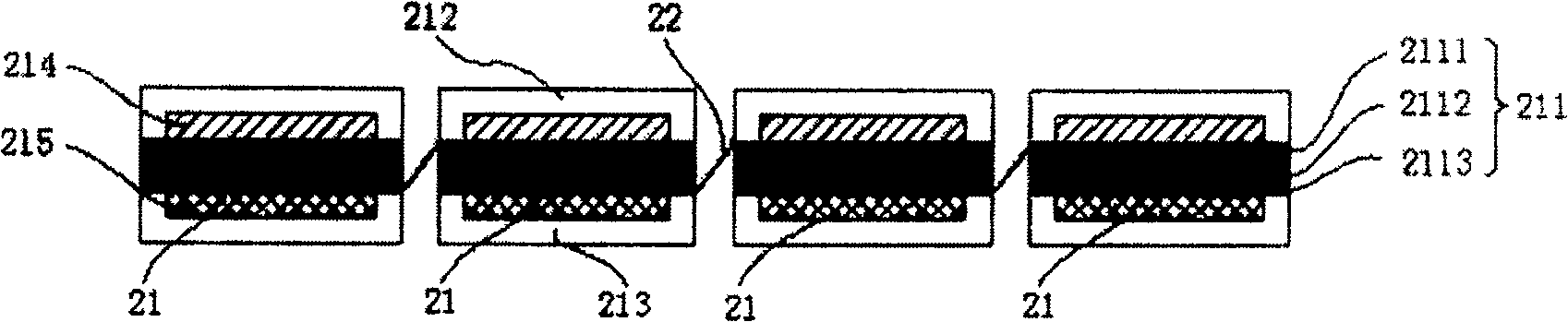

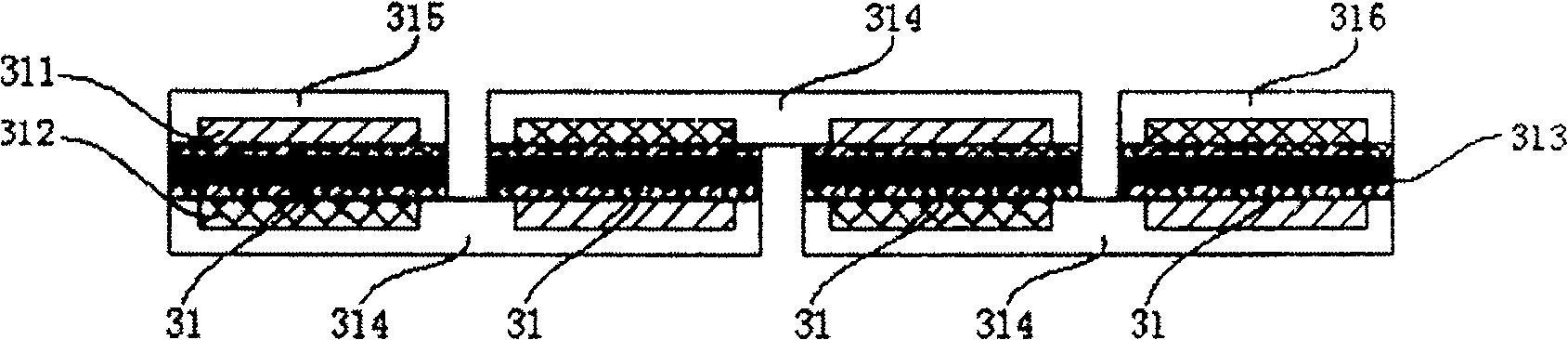

Silicon base plane fuel cell group and its preparing method

InactiveCN100421294CLower resistanceSolve supply difficultiesFuel cells groupingFinal product manufactureFuel cellsOutput device

This invention provides a silicon-base plane fuel cell set and its manufacturing method, in which, the cell set is composed of a cell body part made up of multiple fuel cell units, a supply device for reactants, an electric energy output device and a fastening device, the cell units in the body are arrayed orderly along a same plane, the supply device for reactants surrounds the body, the electric energy output device is led out from the body, passes through the supply device to reach outside of the cell set and the fastening device is mounted on the supply device.

Owner:HARBIN INST OF TECH

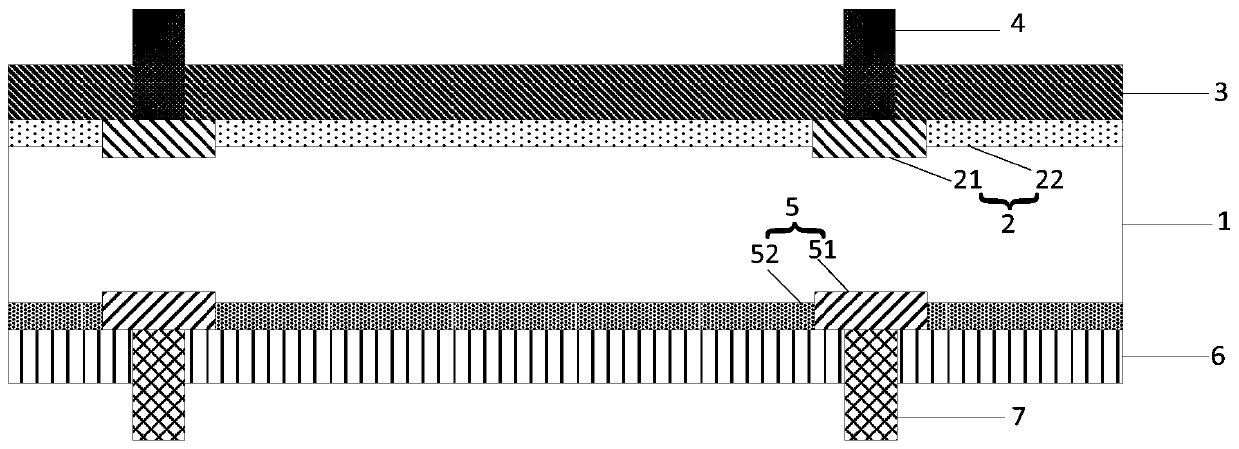

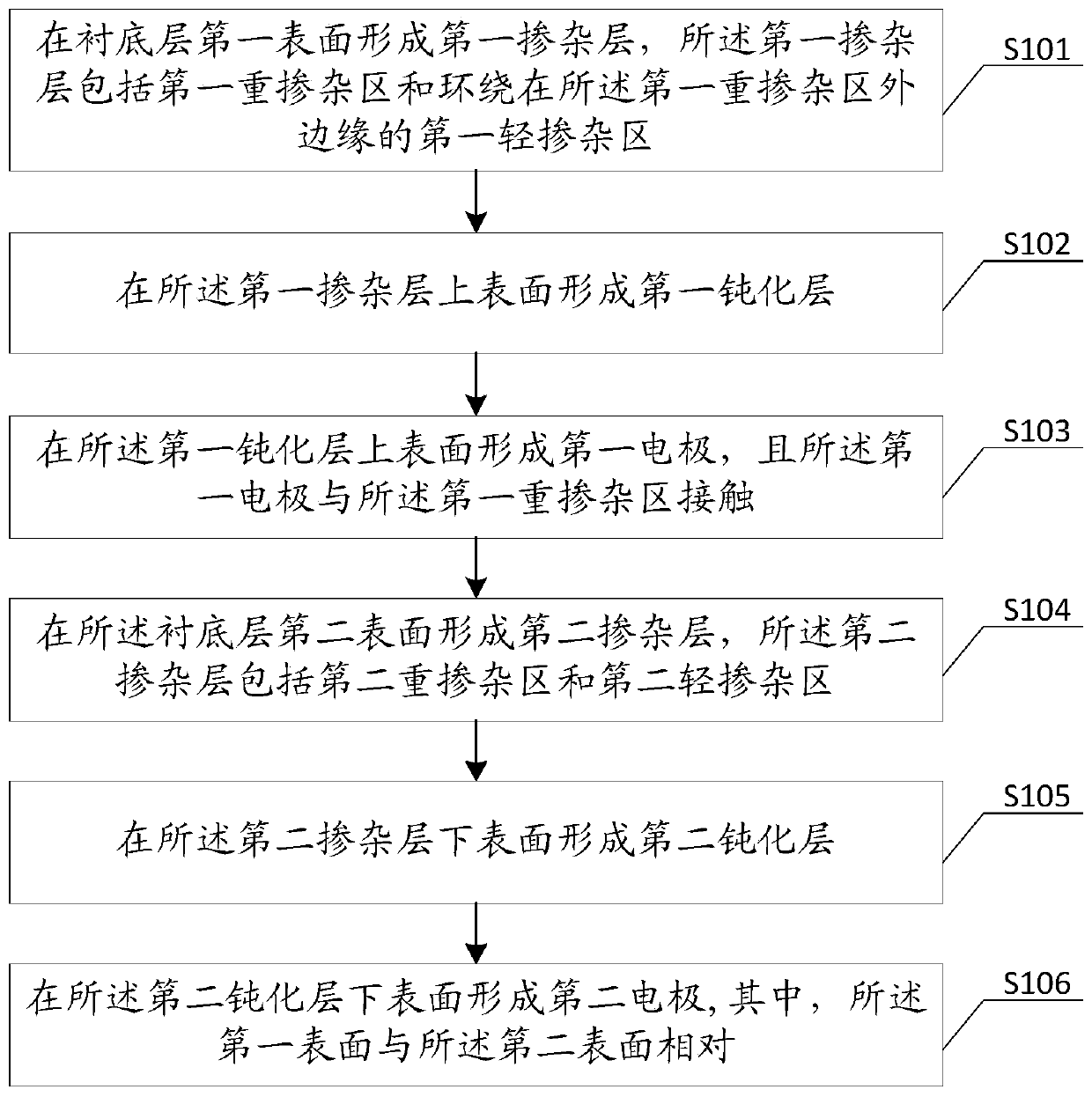

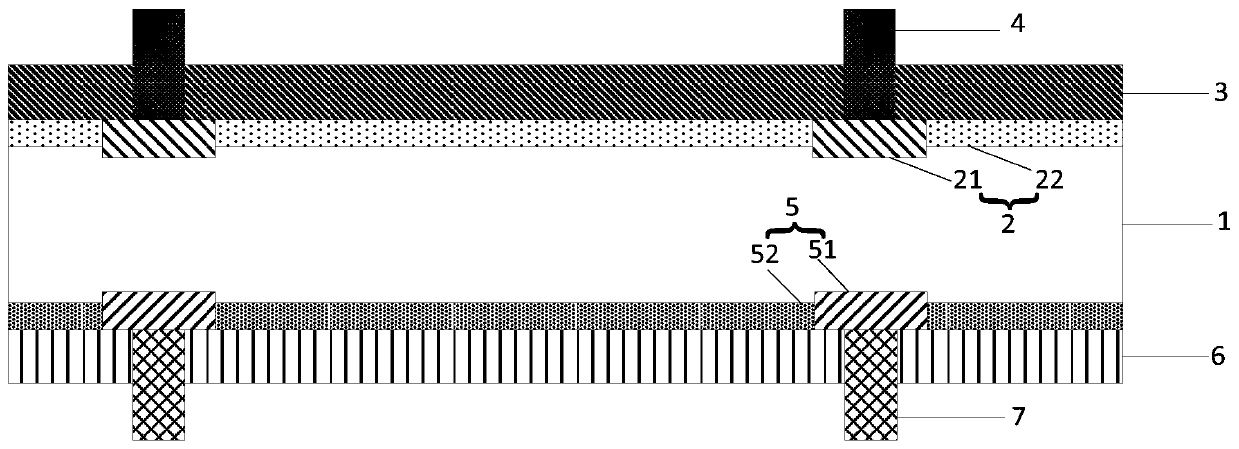

Double-faced solar cell and preparation method thereof

InactiveCN110021673AImprove passivation effectReduced ohmic contact resistanceFinal product manufacturePhotovoltaic energy generationPhotovoltaic conversion efficiencyElectrode

The invention discloses a double-faced solar cell. The double-faced solar cell comprises a P-type substrate layer, a first doping layer, a first passivation layer, a first electrode, a second doping layer, a second doping layer, a second passivation layer and a second electrode, wherein the first doping layer is positioned on the first surface of the P-type substrate layer; the first doping layercomprises a first heavily doped region and a first lightly doped region surrounding the outer edge of the first heavily doped region; the first passivation layer is positioned on the upper surface ofthe first doping layer; the first electrode is positioned on the upper surface of the first passivation layer, and the first electrode is in contact with the first heavily doped region; the second doping layer is positioned on the second surface of the P-type substrate layer, and the second doping layer comprises a second heavily doped region and a second lightly doped region; the second passivation layer is positioned on the lower surface of the second doping layer; the second electrode is positioned on the lower surface of the second passivation layer; and the first surface is opposite to the second surface. According to the double-faced solar cell disclosed by the invention, the first surface and the second surface of the cell adopt selective emitting electrode technology respectively,so that the photovoltaic conversion efficiency is further promoted. Moreover, the invention provides a preparation method with the advantages.

Owner:SUZHOU TALESUN SOLAR TECH CO LTD

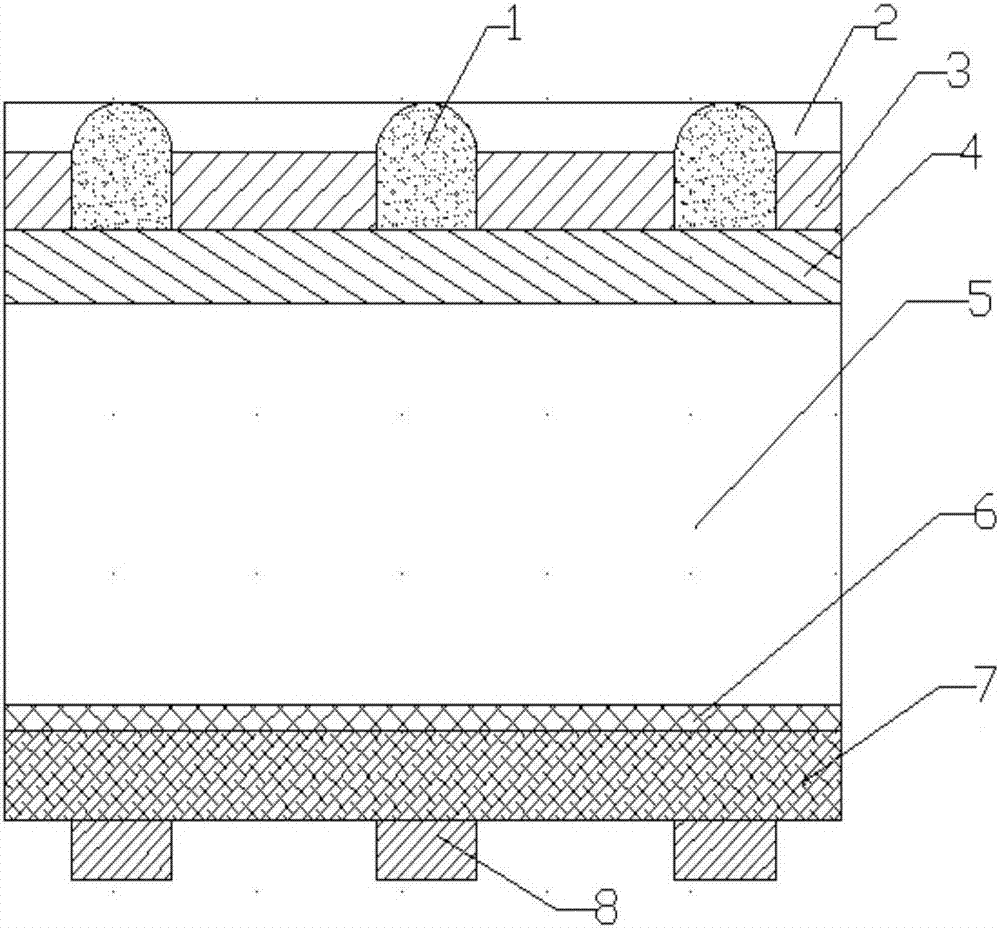

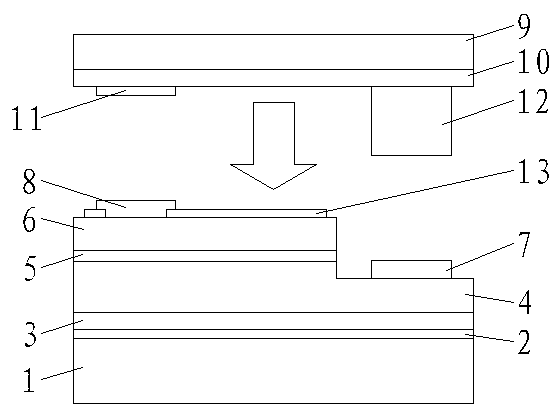

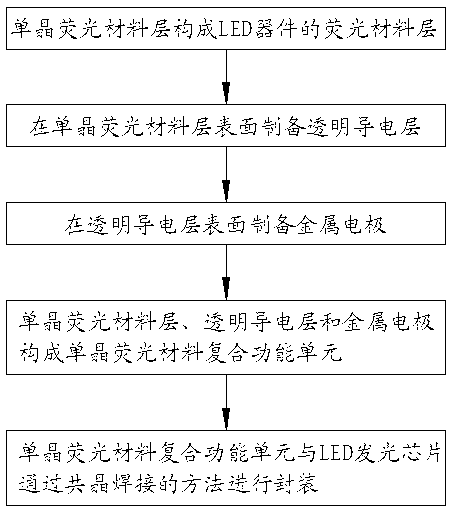

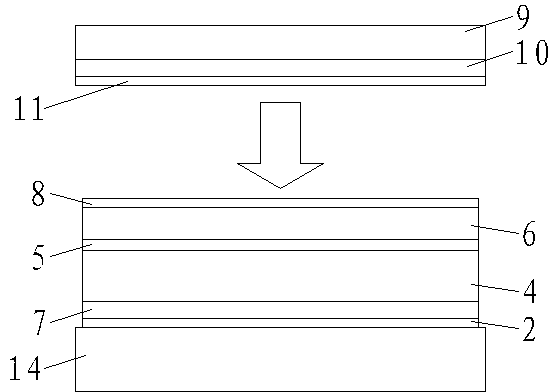

White light light-emitting diode device and encapsulation method without gold thread

InactiveCN103137824AImprove cooling effectImprove light extraction efficiencySemiconductor devicesMetallic electrodeEngineering

The invention discloses a white light emitting diode (LED) device which comprises a compound functional unit of monocrystal fluorescent materials and an LED shining chip. The compound functional unit of monocrystal fluorescent materials is arranged on one side of the LED shining chip, and comprises a monocrystal fluorescent material layer, a transparent conducting layer and a metal electrode. The monocrystal fluorescent material layer is arranged at one end of the transparent conducting layer, the metal electrode is arranged at the other end of the transparent conducting layer. Provided is an encapsulation method without gold thread. Technical processes including beating the gold line and fluorescent powder coating are unnecessary. The technical process is simple and efficient. Defects caused by the LED device gold thread are overcome.

Owner:KUSN KAIWEI ELECTRONICS

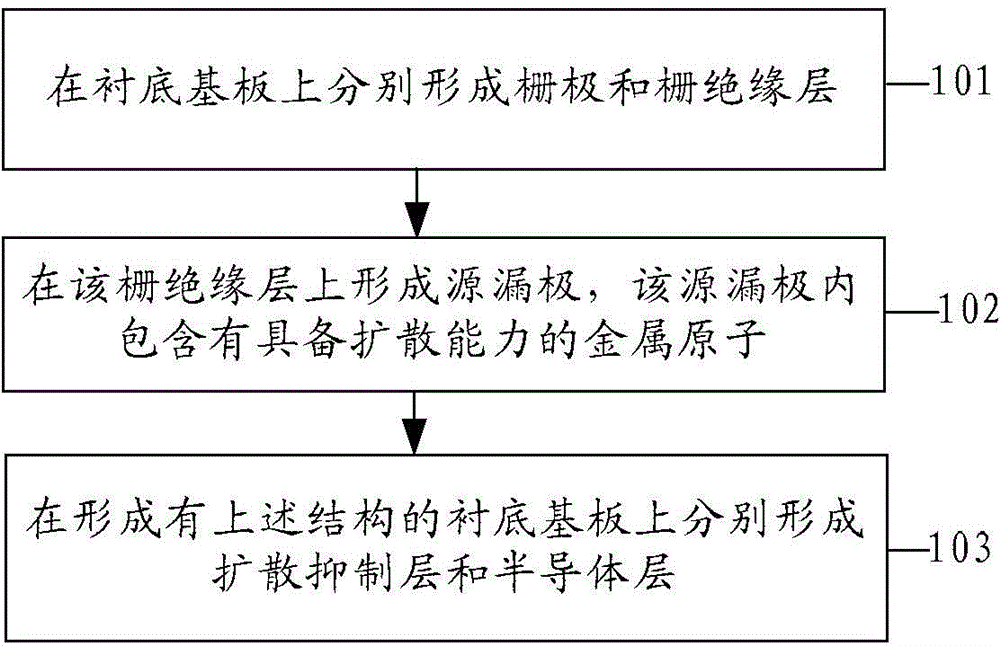

Film transistor, array substrate, manufacturing method for array substrate, and display device

InactiveCN104882488ASmall on-state resistanceIncrease the on-state currentTransistorSolid-state devicesSalicideOhmic contact

The embodiment of the invention provides a film transistor, an array substrate, a manufacturing method for the array substrate, and a display device, and relates to the technical field of electronics. The ohmic contact resistance formed between an active layer and source-drain electrodes is reduced. The method comprises a step of forming a diffusion inhibition layer which is used for lowering the capability of diffusion of metal atoms in the source-drain electrodes to a semiconductor layer, wherein the step is operated between a step of forming the source-drain electrode and a step of forming a non-crystalline silicon semiconductor layer. The method also comprises a step of enabling the metal atoms diffused from the diffusion inhibition layer to react with amorphous silicon in a part, close to the source-drain electrode, of the semiconductor layer, and a step of generating a metal transition layer containing metal silicide. The method can be used for the manufacturing of the film transistor.

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com