Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

60results about How to "Reduce saturation current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor device

InactiveCN103828060AReduced turn-on voltage increasesReduce voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceGate voltage

Owner:DENSO CORP

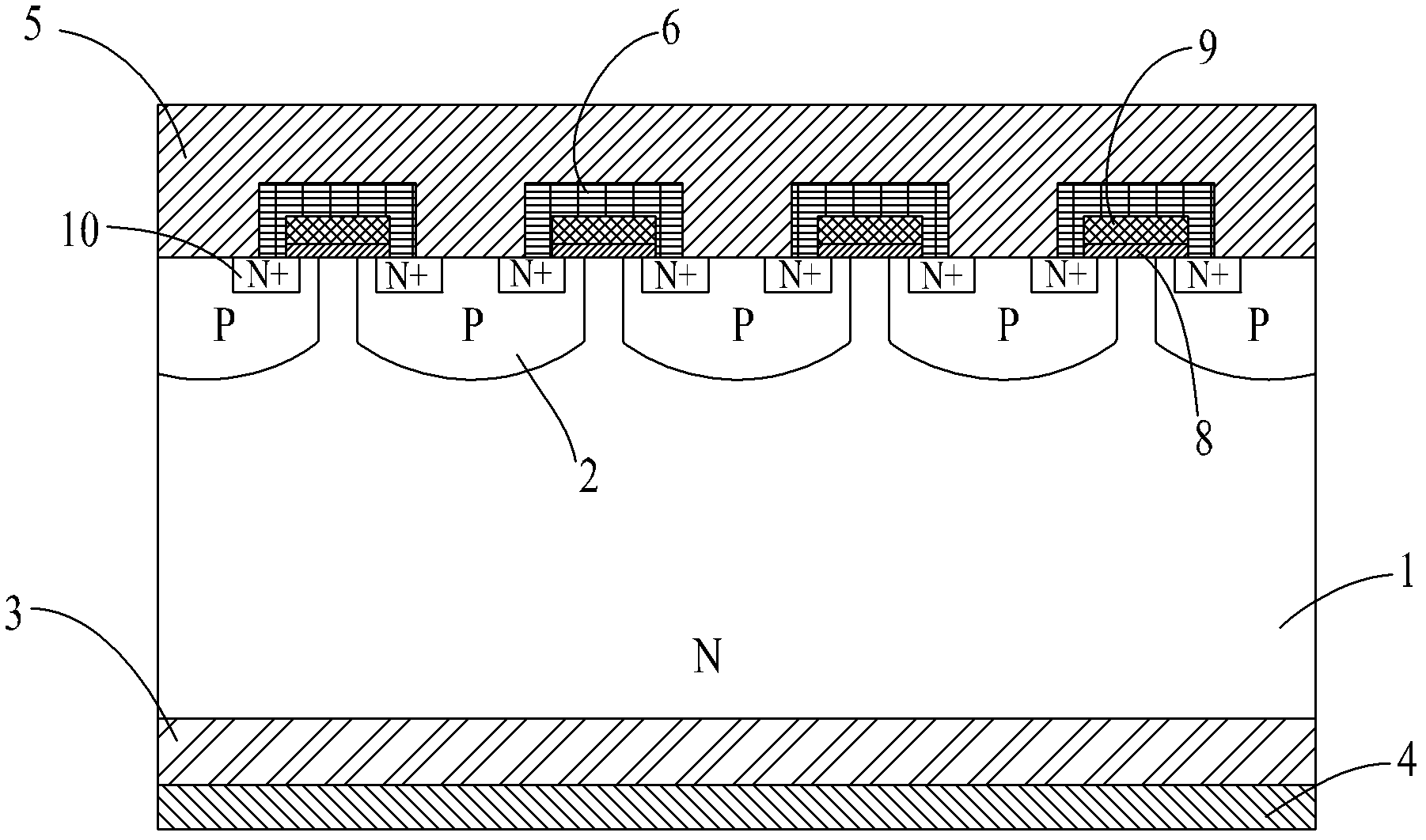

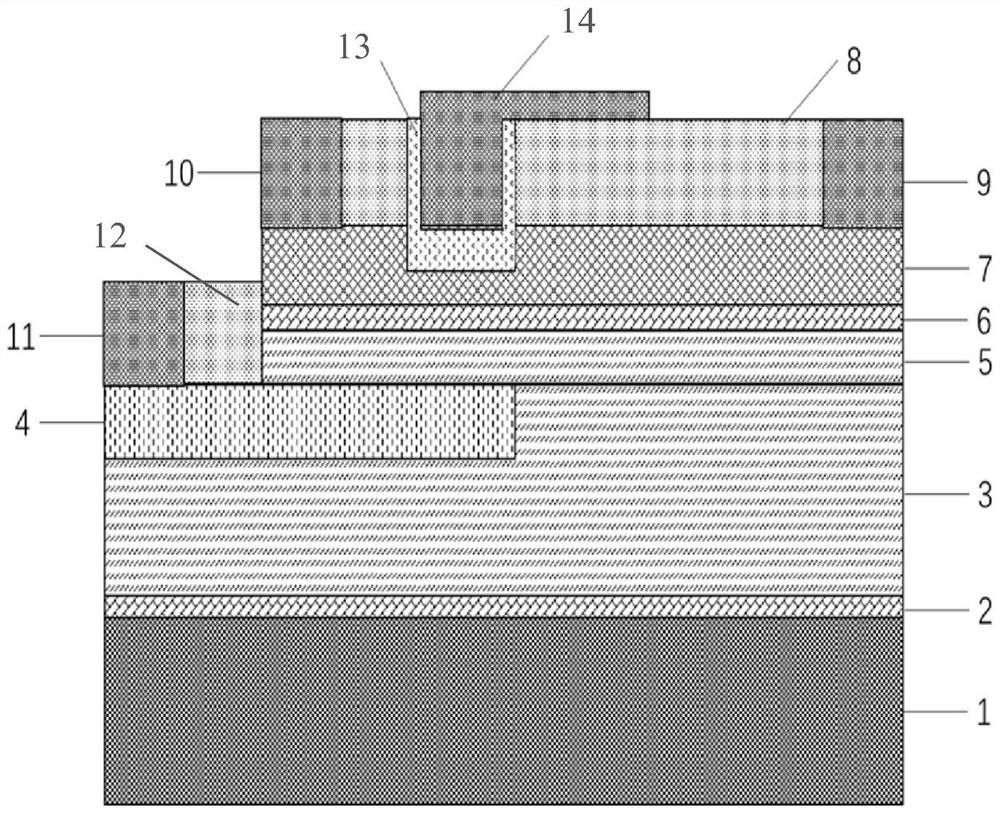

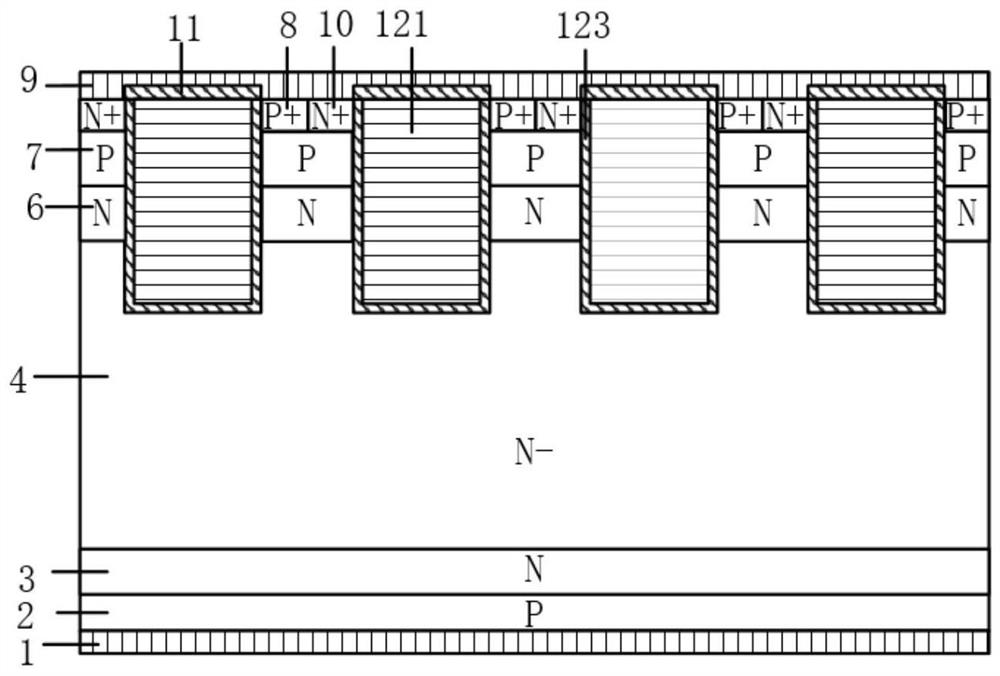

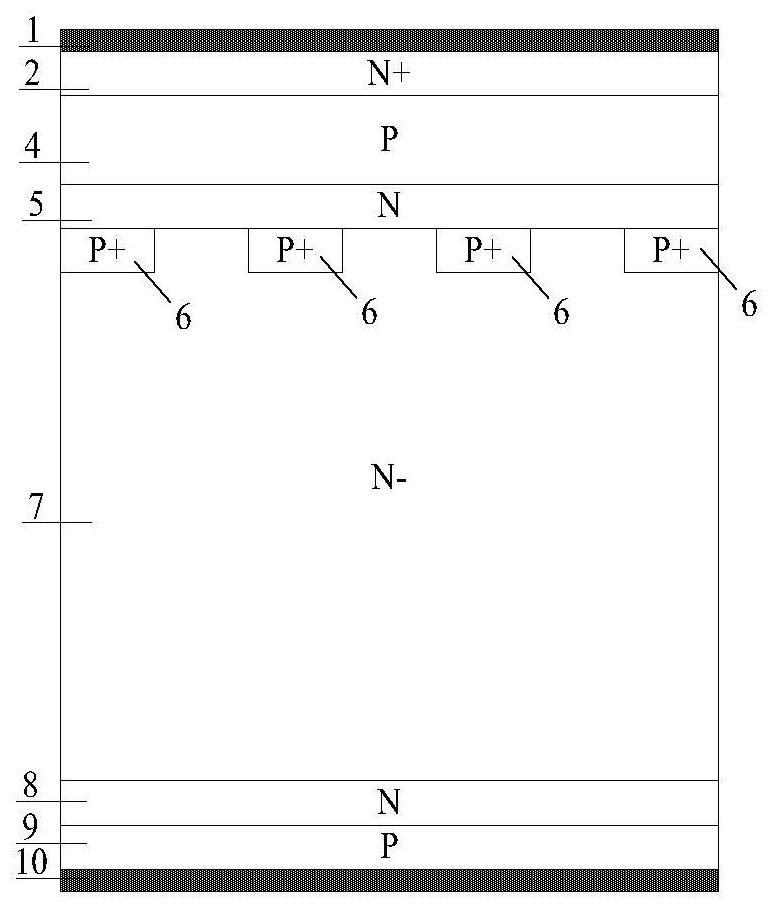

Insulated gate bipolar transistor (IGBT) with low-conductivity saturation voltage drop and manufacturing method for IGBT

ActiveCN102569373AIncrease pressure dropLow resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringMedia layer

The invention relates to an insulated gate bipolar transistor (IGBT) with low-conductivity saturation voltage drop and a manufacturing method for the IGBT. A second conductive type layer is arranged in an active region and partitioned into a plurality of second conductive type layer first regions and a second conductive type layer second regions by conductive polysilicon and insulated gate medium layers; an insulation medium layer is covered on the first main surface of a semiconductor substrate; first conductive type injection regions are symmetrically arranged in the second conductive type layer first regions and contacted with the corresponding insulated gate medium layers; emitter contact holes are formed above the second conductive type layer second regions, pass through the insulation medium layer and extend to the first main surface; emitter metal layers are filled in the emitter contact holes and covered on the insulation medium layer; and the emitter metal layers are in ohm contact with the second conductive type layer first regions. The IGBT has relatively low saturation voltage drop Vcesat and relatively high impact resistance.

Owner:WUXI NCE POWER

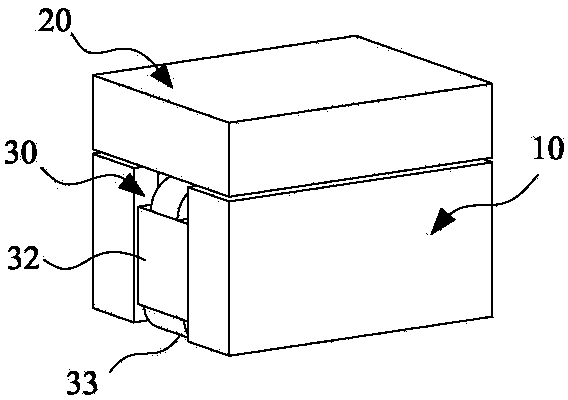

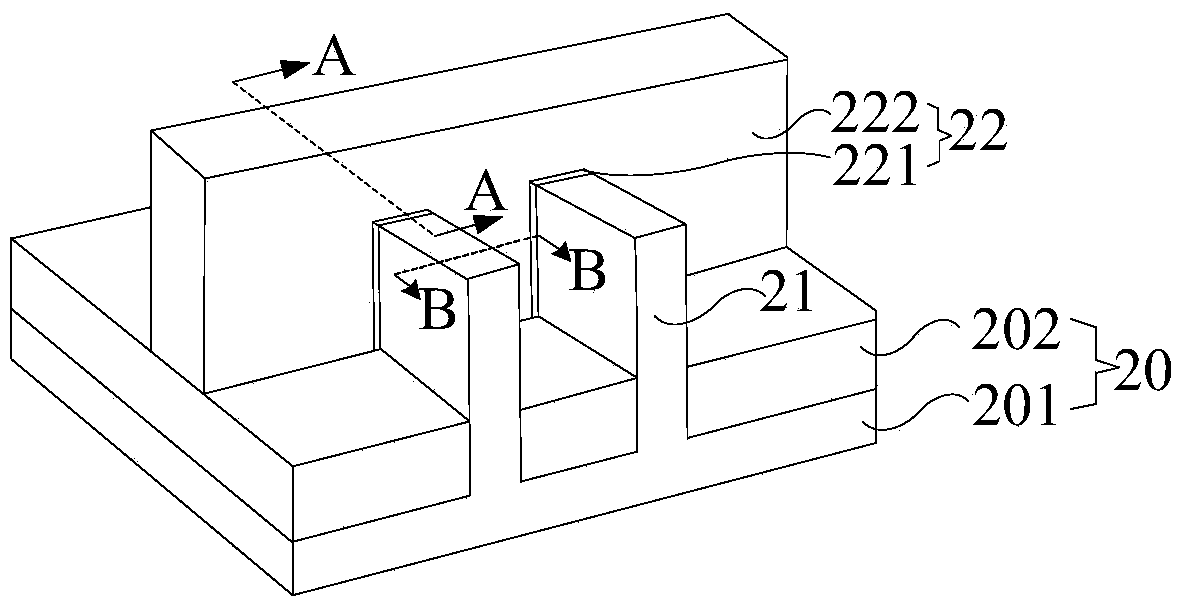

Flat coil inductor, flat coil and manufacture method of flat coil

ActiveCN103680861ASmooth linesEasy to fold and processTransformers/inductances coils/windings/connectionsCoils manufactureEngineeringInductor

The invention discloses a flat coil inductor, a flat coil and a manufacture method of the flat coil. The flat coil inductor comprises a magnetic core, a magnetic cover covering the magnetic core and the flat coil coiled on the magnetic core, wherein the magnetic core is provided with, at least, a first groove and a second groove. The flat coil comprises, at least, the top end base portion and two side edge flattening portions, wherein the base portion is larger than the side edge flattening portions in thickness, the side edge flattening portions are larger than the base portion in width, the base portion is embedded into the first groove, and the side edge flattening portions are embedded into the second groove. The side edge flattening portions are formed by locally flattening the flat coil of the inductor, so that different thicknesses are obtained, the side edge flattening portions are larger than the base portion in width but are smaller than the base portion in thickness, and a magnetic core accommodating space defined by the flat coil is increased. The magnetic core can be matched and assembled with a large corresponding magnetic core, so that the direct-current resistance of the inductor in a limited size range is decreased, the saturation current is increased, and the inductor can obtain the best electrical characteristics.

Owner:DONGUAN PULSE ELECTRONICS CO LTD

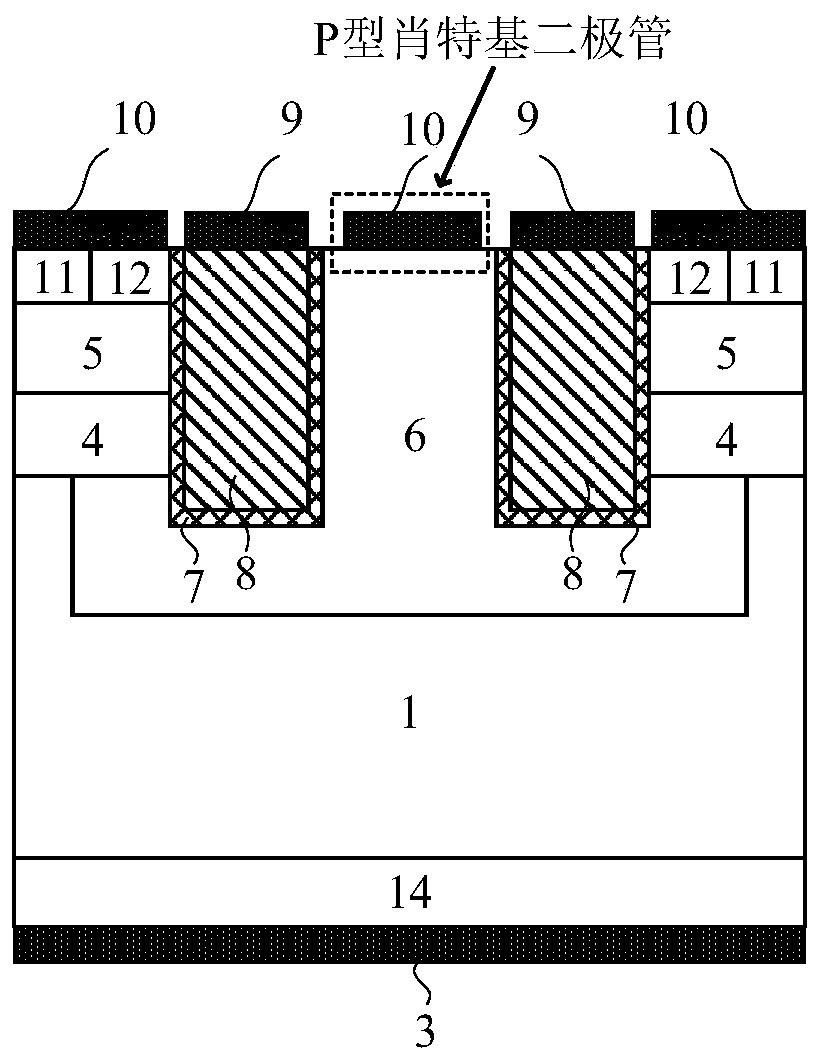

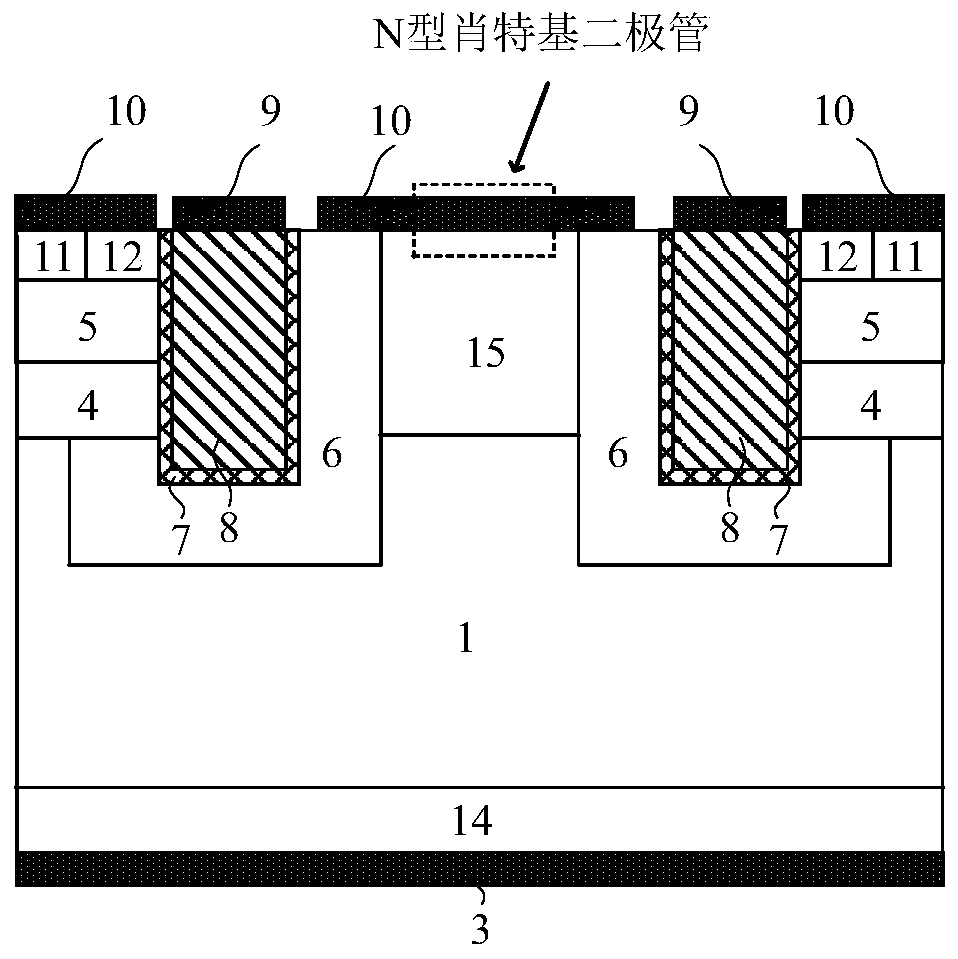

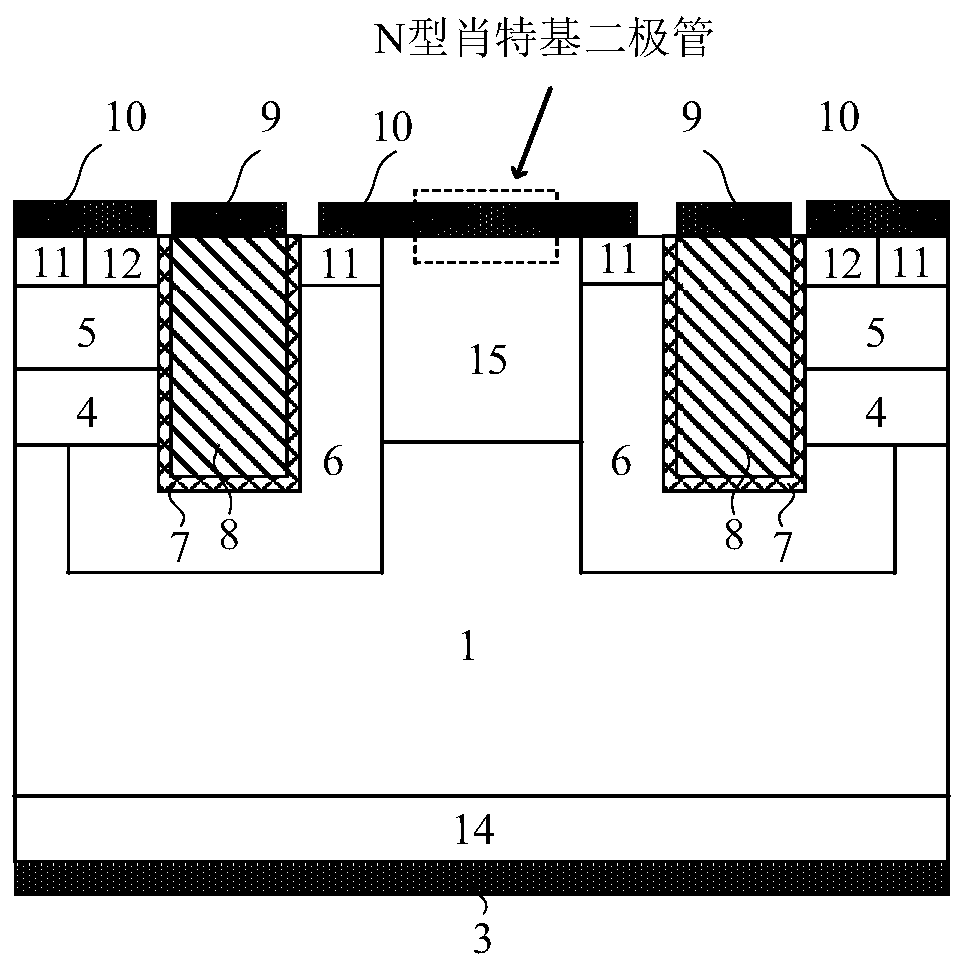

SiC power device

ActiveCN110767753ASmall pressure dropEliminate minority carrier injection effectDiodeHeterojunction diodeMinority carrier injection

The invention belongs to the field of power semiconductors, and particularly provides a SiC power device. The SiC power device comprises a SiC MOSFET and a SiC IGBT. For the SiC MOSFET device integrated with a PN junction body diode, the reverse recovery charge and related loss of the body diode can be greatly reduced, the reverse recovery peak current is reduced, and the EMI noise is reduced; forthe SiC MOSFET device integrated with an N-type Schottky diode or an integrated heterojunction diode, the voltage drop during reverse conduction of the MOSFET can be reduced, and the minority carrierinjection effect is eliminated, so that the conduction loss and reverse recovery loss of the diode are reduced; for the reverse conduction type SiC IGBT device integrated with the PN junction body diode, the reverse recovery charge and related loss of the body diode can be greatly reduced, the reverse recovery peak current is reduced, and the EMI noise is reduced; and moreover, for the reverse conduction type SiC IGBT device integrated with the N-type Schottky diode or the heterojunction diode, the voltage drop during reverse conduction of the reverse conduction IGBT can be reduced, the minority carrier injection effect is eliminated, and the conduction loss and reverse recovery loss of the diode are reduced.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Double-staggered flyback photovoltaic grid-connected micro inverter and control method thereof

ActiveCN102931678AImprove efficiencyLow costSingle network parallel feeding arrangementsPhotovoltaic energy generationCapacitanceTransformer

The invention discloses a double-staggered flyback photovoltaic grid-connected micro inverter and a control method thereof. The double-staggered flyback photovoltaic grid-connected micro inverter comprises a direct-current-side capacitor, a double-flyback converter, a converter bridge and an output filter, wherein two high-frequency transformers of the double-staggered flyback converter respectively have a double-secondary winding structure, so a system can work in a staggered flyback mode at any time, and requirements of the system on the saturation current of the high-frequency transformers, magnetic cores, input output capacitance and the rated current of a power metal oxide semiconductor field effect transistor (MOSFET) are reduced; the converter bridge consists of two thyristors; and by using an active conversion method, the quality of grid-connected current waveform is ensured on the premise that the reliability of the system is ensured. The double-staggered flyback photovoltaic grid-connected micro inverter can efficiently convert and transmit energy without pollution, and has the characteristics of compact structure, low cost, reliability and practicability.

Owner:CENT SOUTH UNIV

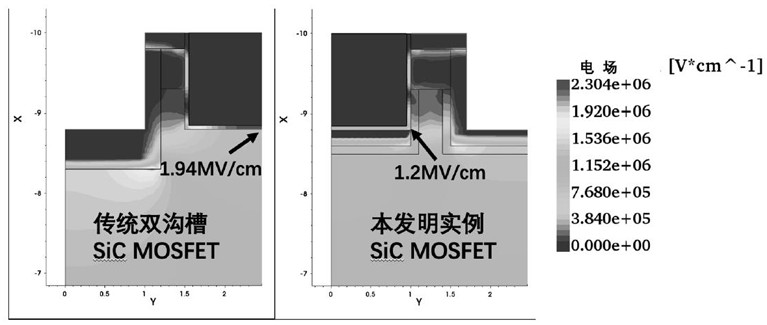

Low-power-consumption and high-reliability trench silicon carbide MOSFET device

ActiveCN110518065AReduce switching lossesImprove short circuit performanceSemiconductor devicesDiodeCapacitanceMOSFET

The invention provides a low-power-consumption and high-reliability trench silicon carbide MOSFET device which comprises an N-type substrate, an N-type epitaxial layer, a first P-Body region, first P+ contact region, a first N + contact region, a second P- body region, a second P + contact region, a second N + contact region, an oxide layer, a groove grid, a metal electrode and drain electrode. According to the SiC MOSFET device, the on-resistance can be significantly reduced through the parallel connection of four channels, and the reliability of the oxide layer of the device can be enhancedand partial gate leakage capacitance can be shielded through wrapping and protection of the second P- body to the groove grid so that the switching loss of the device can be reduced. When the deviceis short-circuited, the JFET region formed by the first P- body region and the Second P- body region is cut off so as to reduce the saturation current of the device and improve its short-circuit capability.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

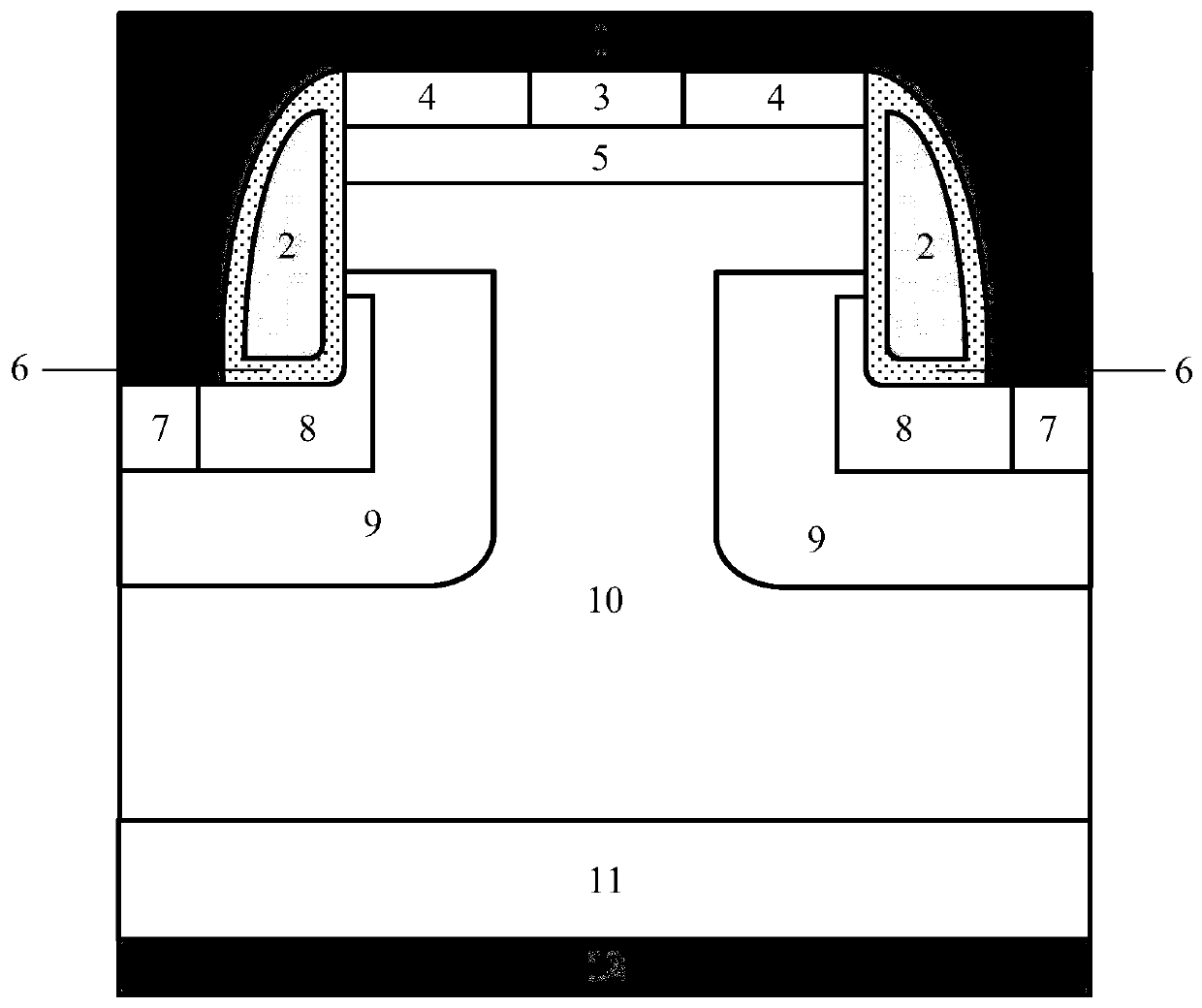

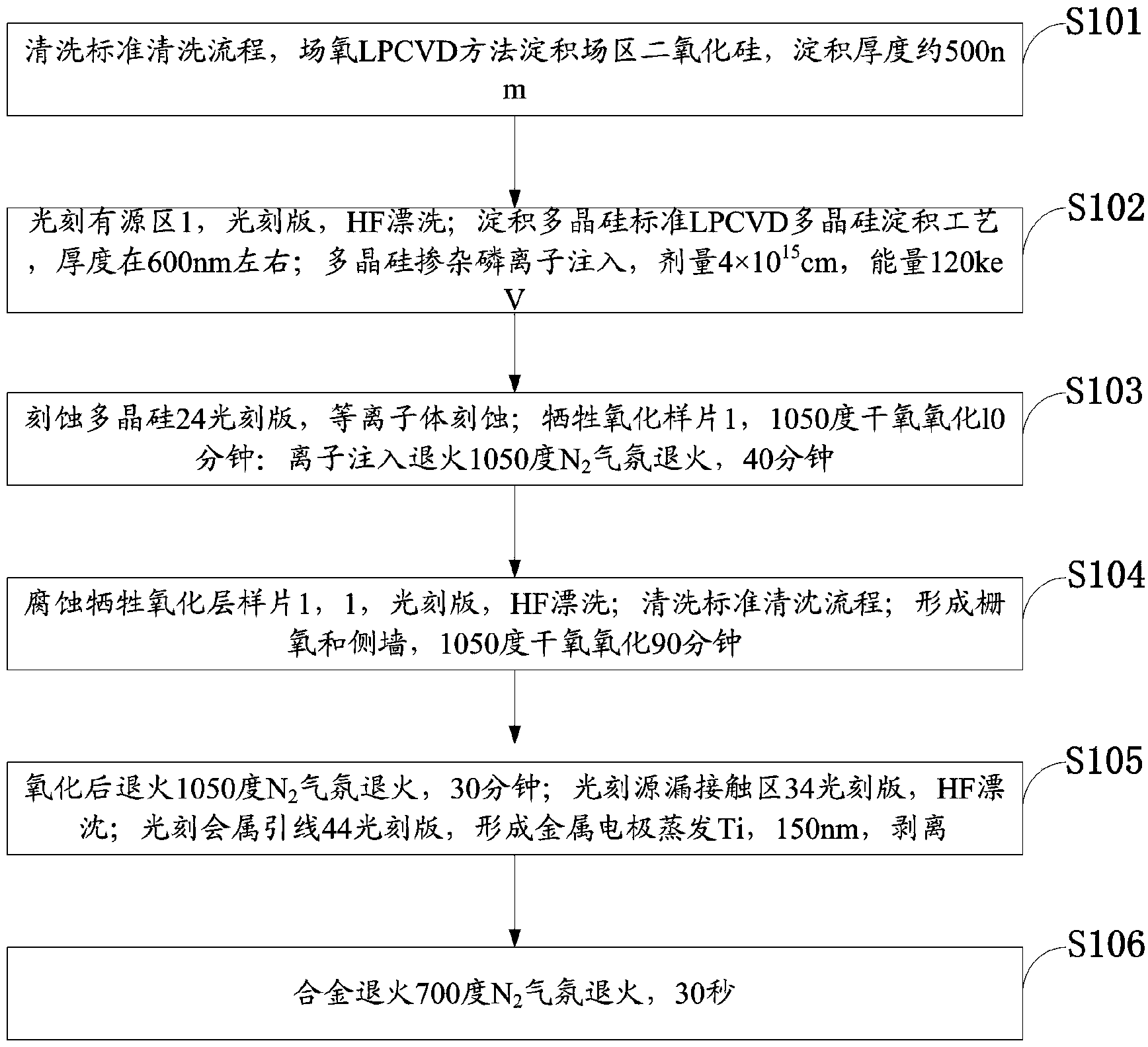

4H-SiC Schottky barrier source/drain MOSFET device with field plate terminal protection and manufacturing method thereof

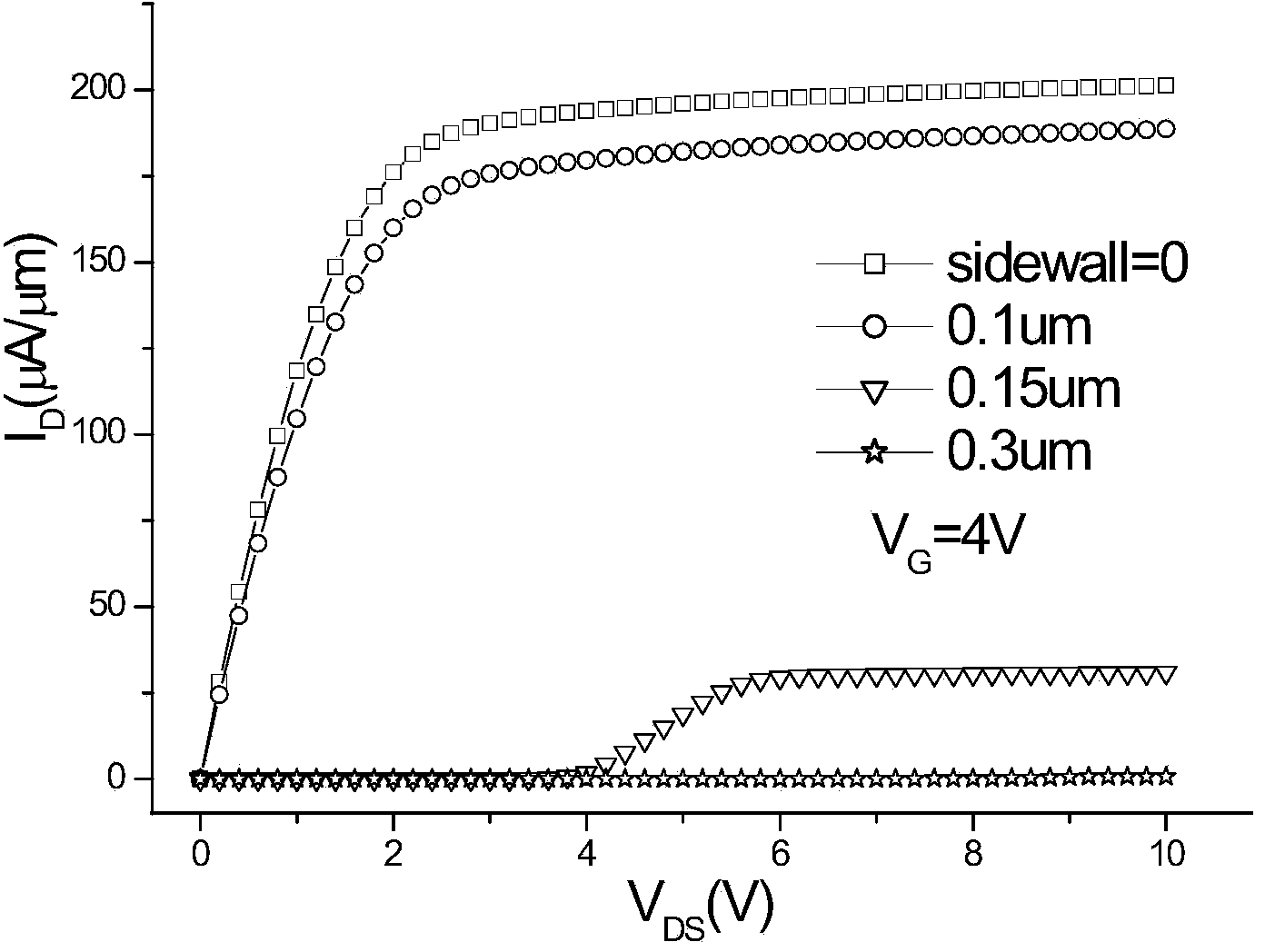

InactiveCN103560087AReduce saturation currentLower transconductanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSchottky barrier

The invention discloses a 4H-SiC Schottky barrier source / drain MOSFET device with field plate terminal protection and a manufacturing method thereof. The manufacturing method includes the steps of performing a standard cleaning process, depositing field area silicon dioxide through a field oxide LPCVD method, performing photoetching on an active area, performing HF bleaching, depositing polycrystalline silicon through a standard LPCVD polycrystalline silicon deposition process, doping the polycrystalline silicon, injecting phosphorus ions, etching the polycrystalline silicon, etching plasmas, sacrificing an oxidized sample 1, performing ion injection annealing, performing 1050 DEG C N2 atmosphere annealing, corroding and sacrificing an oxidation layer sample 1, performing HF bleaching, performing the standard cleaning process to form gate oxide and a side wall, performing annealing to 1050 DEG after oxidization, performing N2 atmosphere annealing, performing photoetching on a source / drain contact area, performing HF bleaching, performing photoetching on a metal lead to form 150nm metal electrode evaporation Ti, performing peeling, performing alloy annealing, and performing 700 DEG C N2 atmosphere annealing, wherein the device comprises a substrate and an epitaxial layer. According to the 4H-SiC Schottky barrier source / drain MOSFET device with field plate terminal protection and the manufacturing method of the 4H-SiC Schottky barrier source / drain MOSFET device with field plate terminal protection, the problem that transconductance and conductance resistance output characteristics of the device become poor due to the fact that 4H-SiC MOSFET is too low in inversion layer mobility ratio is better solved.

Owner:CENTRAL SOUTH UNIVERSITY OF FORESTRY AND TECHNOLOGY

IGBT device and forming method thereof

ActiveCN103855197AReduce the saturation conduction voltage dropReduce saturation currentTransistorSemiconductor/solid-state device manufacturingPower flowVoltage drop

The embodiment of the invention discloses an IGBT device and a forming method thereof. The IGBT device comprises a semiconductor substrate, a base region, a gate structure, an emitter and a collector. The gate structure includes a U-shaped part and a horizontal part, wherein the U-shaped part of the gate structure penetrates through the base region, the horizontal part of the gate structure covers part of the upper surface of the base region, and the horizontal part and the U-shaped part of the gate structure form an integral structure. The emitter is formed in positions, respectively on the two sides of the U-shaped part of the gate structure, in the base region, and is not in contact with the U-shaped part of the gate structure. Therefore, the IGBT device provided by the invention has the advantages of low difficulty of production technology, low saturated conduction voltage drop, high latch-resistant capability, low saturation current and the like.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +2

High-voltage-resistant bigrid transverse HEMT device and preparation method thereof

ActiveCN113113469AIncrease saturation currentImprove breakdown voltageFinal product manufactureSemiconductor/solid-state device manufacturingHeterojunctionLow leakage

The invention relates to a high-voltage-resistant bigrid transverse HEMT device, which comprises a buffer layer positioned on a substrate, and a laminated layer consisting of a GaN channel layer, an AlN insertion layer and an AlGaN barrier layer which are sequentially laminated on the buffer layer, and also comprises a p-type buried layer, a grid positioned on the p-type buried layer, and a source / drain electrode and an inverted L-shaped grid which are positioned on the barrier layer; in the thickness direction, the p-type buried layer extends by a certain depth from the surface, close to the channel layer, of the buffer layer to the side, away from the channel layer, of the buffer layer; the source and the drain are located on the surface of the barrier layer; a gate groove is formed between the source electrode and the drain electrode, and the inverted L-shaped gate is located in the gate groove and extends towards one side of the drain electrode; and in the length direction, the p-type buried layer extends from the position below the grid electrode to the position below the grid groove. Through the introduction of the p-type buried layer and the structural arrangement of double gates combined with the AlGaN / AlN / GaN heterojunction, the HEMT device with low on-resistance, high saturation current, high breakdown voltage and low leakage current is obtained.

Owner:SOUTH CHINA NORMAL UNIVERSITY

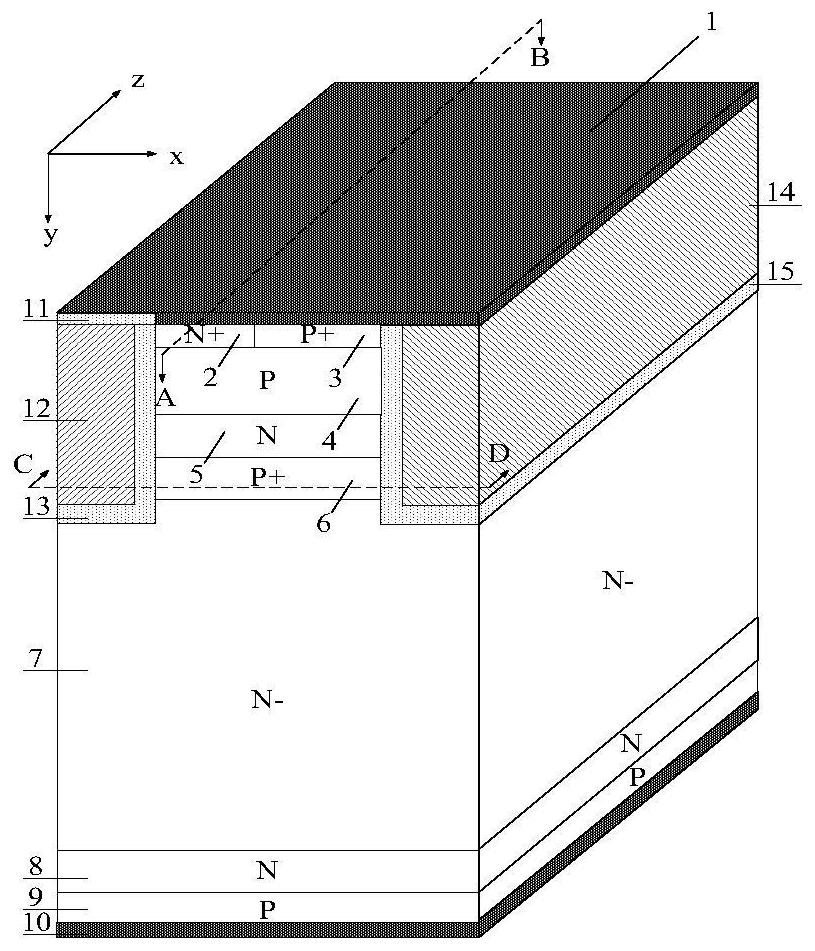

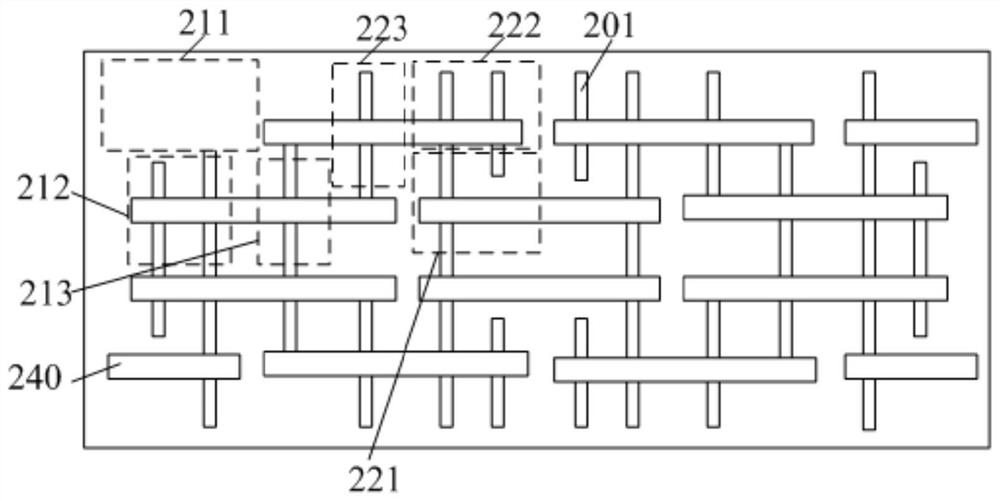

Hybrid cell type integrated IGBT device

InactiveCN109801911ATurn-on voltage dropIncrease current densityTransistorSemiconductor/solid-state device manufacturingCell regionEngineering

The invention relates to a hybrid cell type integrated IGBT (Insulated Gate Bipolar Transistor) device. The device comprises an active region. The active region of the hybrid cell type integrated IGBTdevice comprises a groove cell region (2) and a plane cell region (3). The groove cell region is composed of groove type IGBT cells, and the plane cell region is composed of plane type IGBT cells. According to the hybrid cell type integrated IGBT device, a groove type IGBT cell structure and a plane type IGBT cell structure are arranged in a single chip at the same time. The hybrid cell type integrated IGBT device is provided with two independent control gates. The advantages of the two control gates are combined, and a better device performance is achieved.

Owner:上海擎茂微电子科技有限公司

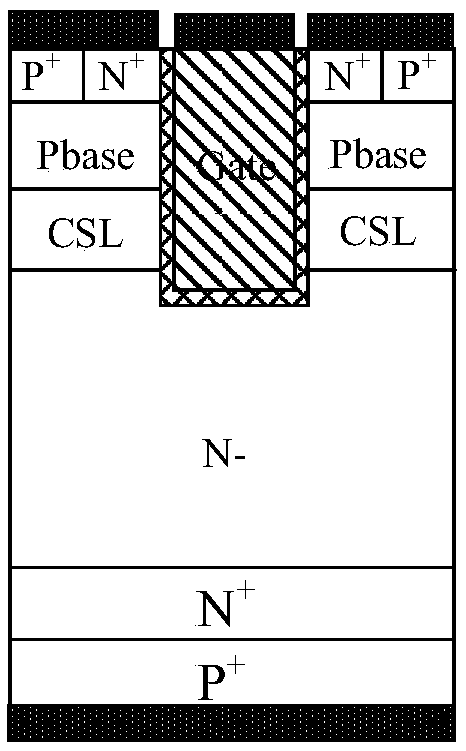

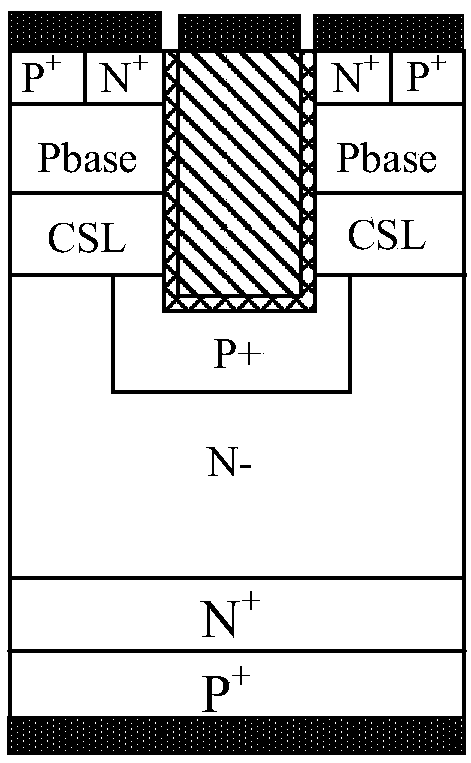

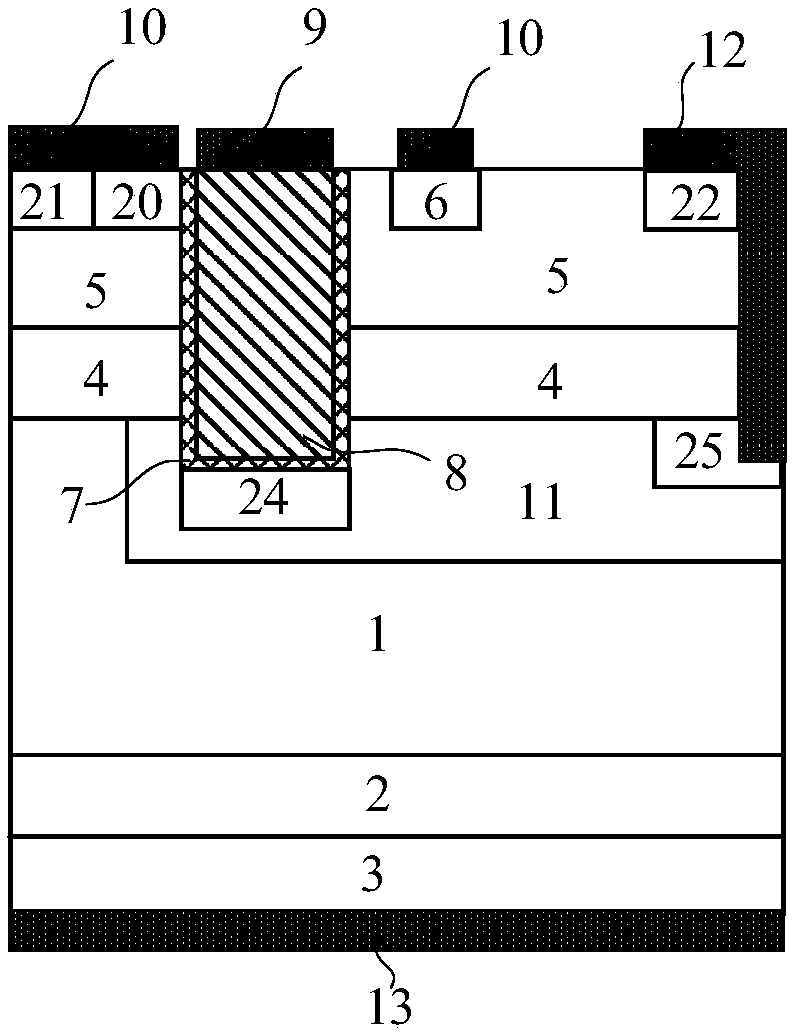

Double-groove type SiC MOSFET cellular structure, device and manufacturing method

InactiveCN114267739AImprove shielding effectReduce gate-to-drain capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCapacitance

The invention discloses a double-groove type SiC MOSFET cellular structure and device and a manufacturing method thereof, the double-groove type SiC MOSFET cellular structure comprises an N + + type SiC substrate, an N-type SiC drift layer, a P type base region and an N + type source region, the N-type SiC drift layer is located above the N + + type SiC substrate and is provided with a source electrode groove and a grid electrode groove, and the bottom of the source electrode groove is provided with an N type hole blocking layer and a source electrode P + type shielding layer; an N-type current conducting layer and a grid P + type shielding layer are arranged at the bottom of the grid groove, and a grid dielectric layer and a grid electrode are arranged in the grid groove; the P-type base region and the N + type source region are located on the N-type SiC drift layer between the source trench and the gate trench and are arranged from bottom to top. Shielding of the drain voltage is further enhanced, the electric field peak value and the gate-drain capacitance of the gate dielectric layer are reduced, the reliability of the gate dielectric layer and the working frequency of the device are improved, the on-resistance of the device can be reduced, and the short-circuit capability of the device can be enhanced.

Owner:北京昕感科技有限责任公司

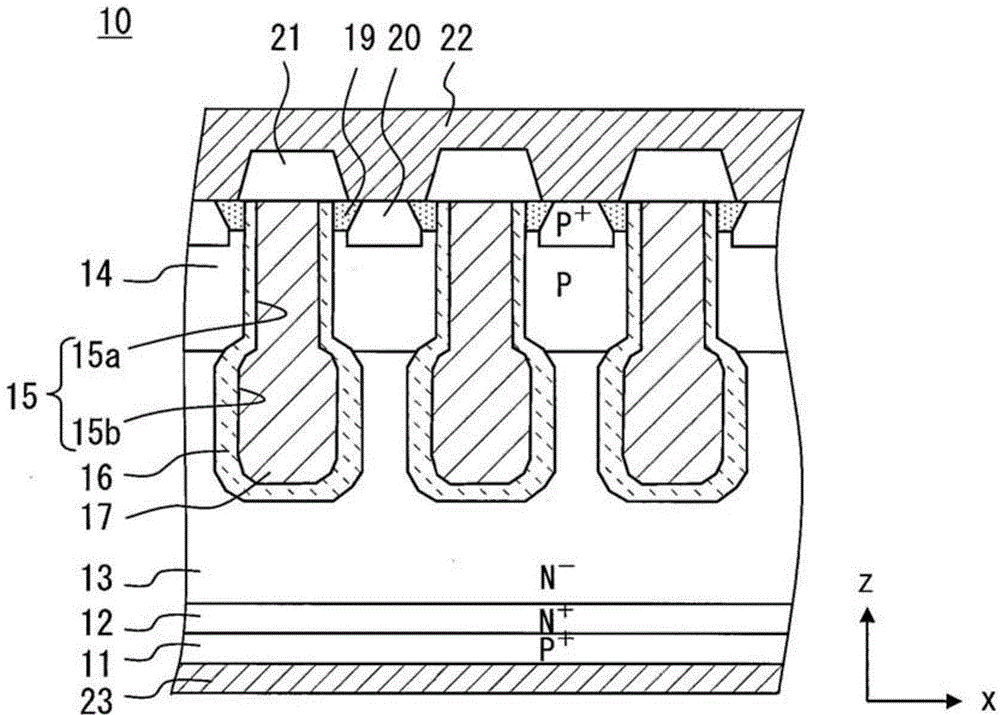

Trench gate IGBT device with carrier storage layer

This invention relates to the power semiconductor field, providing a trench gate IGBT device with carrier storage which is used for solving the problems of high saturation voltage, small short circuitsafe working area and limited concentration of the existing trench gate IGBT device with carrier storage layer, and put forward a novel trench gate IGBT device with carrier storage layer. The trenchgate IGBT device with carrier storage layer directly integrates a plurality of series diodes on the surface of silicon wafers to clamp the potential of the electric field shielding layer in the P region, thereby breaking the concentration limit of CSL on the basis of trench gate IGBT process, greatly improving the injection efficiency of IGBT emitter and greatly improving the trade-off relation between forward voltage drop and turn-off loss of IGBT. Meanwhile, due to the clamping effect of the diode, the drain near the IGBT nMOS channel is clamped at a lower voltage under high voltage and large current, thereby greatly reducing the saturation current of the novel IGBT and improving the short circuit safe working area of IGBT.

Owner:杭州朋声科技有限公司

IGBT device with carrier storage layer using diode clamping

ActiveCN109686787AInhibit onPrevent breakdownTransistorSolid-state devicesSaturation voltageSemiconductor

The invention relates to the field of power semiconductors, provides an IGBT device with a carrier storage layer using diode clamping, and solves the problems that the saturation voltage of an existing groove gate IGBT with the carrier storage layer (CSL) is high, a short circuit safe working area is smaller, and the CSL concentration is limited. The IGBT device with the carrier storage layer using diode clamping has the advantages that the IGBT directly integrates one or more series diodes on the surface of a silicon wafer through a groove gate IGBT process for clamping electric potential ofan electric field shielding layer of a P region, on the basis of the groove gate IGBT process, the limitation of the CSL concentration is broken through, the injection efficiency of an IGBT emitting electrode is greatly improved, thereby greatly improving the tradeoff relationship between conduction voltage drop and turn-off loss of the IGBT; due to the clamping action of a diode, a drain electrode near an nMOS channel of the IGBT is clamped at a lower voltage under the high voltage and large current, so that saturation current of the novel IGBT is reduced to a great extent, thereby enlargingthe short circuit safe working area of the IGBT.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

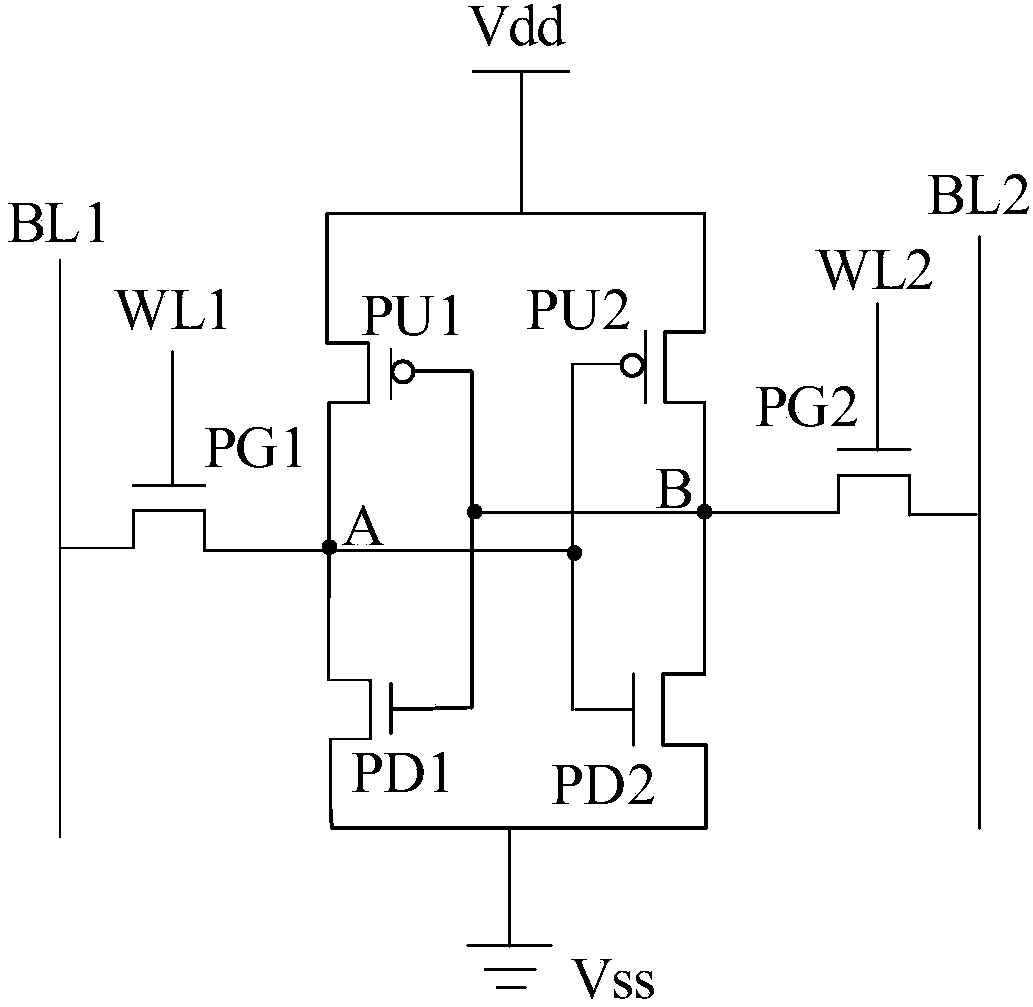

Memory structure and forming method thereof

ActiveCN108281425ARead Noise Capacitance ImprovementImprove write performanceSolid-state devicesSemiconductor devicesIonEngineering

The invention provides a memory structure and a forming method thereof. The memory structure comprises a first transmission transistor and a second transmission transistor, wherein the first transmission transistor comprises a first transmission drain region and a first transmission source region; the first transmission source region and the first transmission drain region are provided with firstdoped ions; the concentration of the first doped ions in the first transmission drain region is different from that in the first transmission source region; the second transmission transistor comprises a second transmission drain region and a second transmission source region; the second transmission source region and the second transmission drain region are provided with second doped ions; and the concentration of the second doped ions in the second transmission drain region is different from that in the second transmission source region. The writing ability of a memory can be improved whilethe noise reading capacity of the memory is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Separated gate CSTBT with self-biased PMOS and manufacturing method thereof

ActiveCN113838920AIncrease the doping concentrationImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceChannel density

The invention relates to a separated gate CSTBT with a self-biased PMOS and a manufacturing method of the separated gate CSTBT, and belongs to the technical field of power semiconductor devices. According to the present invention, on the basis of the traditional CSTBT, a separated gate electrode equipotential with the emitter and a P-type buried layer are introduced, the influence of an N-type charge storage layer on the breakdown characteristic of a device can be effectively shielded through charge compensation, and the compromise relation between the forward conduction voltage drop Vce (on) and the turn-off loss Eoff of the device can be improved. In addition, the separated gate electrode and a gate electrode are located in a same groove, so that the channel density can be reduced; the saturation current density is effectively reduced by turning on a parasitic PMOS to clamp the potential of the N-type charge storage layer, and the short-circuit safe working capability of the device is improved. Meanwhile, the gate capacitance can be reduced, the switching speed of the device is improved, and the switching loss of the device is reduced. In addition, the current uniformity in a chip can be improved, the current concentration is avoided, and the reliability and a reverse bias safety working area of the device are improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Semiconductor device and manufacturing method thereof, and electronic apparatus

ActiveCN105206577AImprove stabilityReduce saturation currentSolid-state devicesSemiconductor/solid-state device manufacturingNon symmetricEngineering

The invention provides a semiconductor device and a manufacturing method thereof, and an electronic apparatus. The manufacturing method includes: a semiconductor substrate is provided, front devices of a plurality of memory cells are formed on the semiconductor substrate, each memory cell comprises at least two pull-up transistors, at least two pull-down transistors, and at least two pass-gate transistors, wherein the pull-up transistors, the pull-down transistors, and the pass-gate transistors all comprise grid electrodes and grid electrode sidewalls, and asymmetric pocket ion implantation is performed for the two pass-gate transistors of each memory cell. According to the manufacturing method for the semiconductor device, the pass-gate transistors in asymmetric pocket areas with different doping concentrations are formed, the conflict between the writability and the reading stability of an SRAM unit can be effectively balanced, the writability and the reading stability of the SRAM unit are improved, and the reliability of the SRAM unit is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

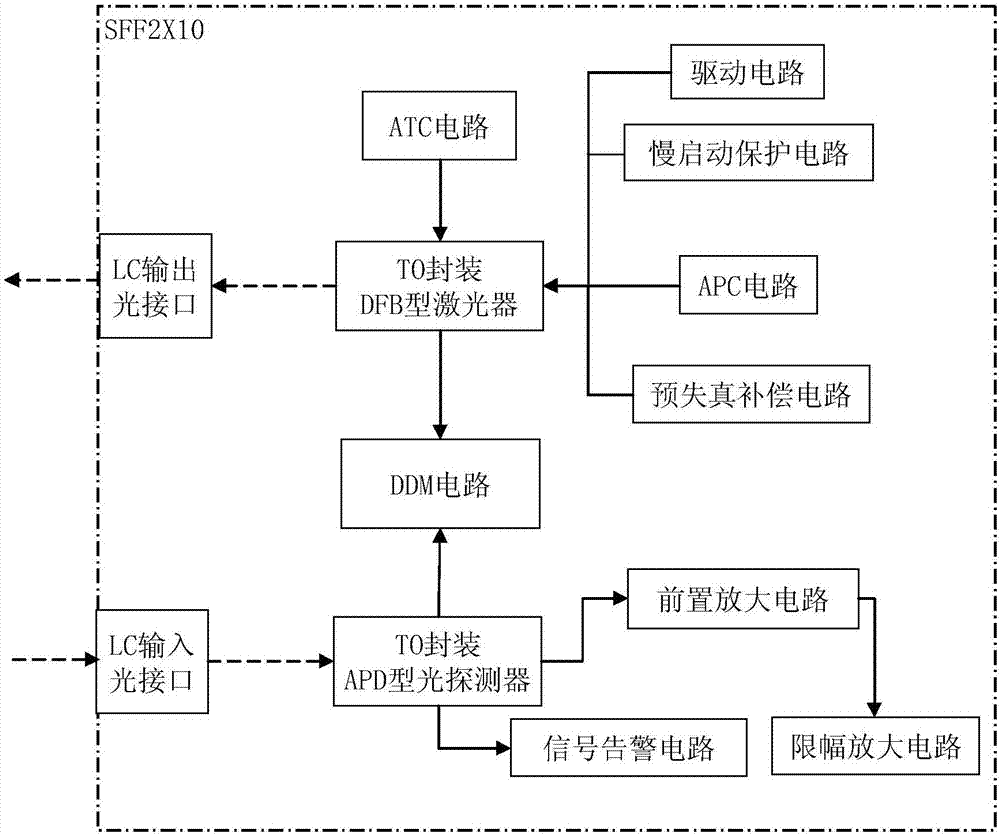

Small-sized welding packaging high power simulation optical module

InactiveCN106959492ALow sensitivity to light receptionLarge dynamic rangeCoupling light guidesEngineeringLinearity

The invention discloses a small-sized welding packaging high power simulation optical module. A simulation laser source inner core, the superfluous external circuit of which is stripped, is disposed in a TO case in a packaged manner, and an optical detector is disposed in another TO case, and the simulation laser and the optical detector are respectively connected with an input optical interface and an output optical interface. A functional circuit comprises a driving circuit and a pre-amplification and limiting-amplification circuit. A transmitting and receiving optoelectronic device, the functional circuit, and the optical interfaces are disposed on the same circuit board, and are disposed in an SFF2*10 for welding and packaging. Welding pins are connected with the corresponding functional pins of the optoelectronic device and the functional circuit. The simulation laser is connected with an automatic power control circuit, a pre-distortion compensation circuit, and an automatic temperature control circuit device. The simulation laser and the optical detector are connected with a digital diagnosis monitoring circuit, and the optical detector is also connected with a signal alarming circuit. The linearity, the spectral characteristic, the temperature stability performance, and the modulation characteristic of the small-sized welding packaging high power simulation optical module are better than that of a digital laser, and the small-sized welding packaging high power simulation optical module has advantages of high optical power, large dynamic range, small packaging, stable linear range, and high reliability.

Owner:NO 34 RES INST OF CHINA ELECTRONICS TECH GRP +1

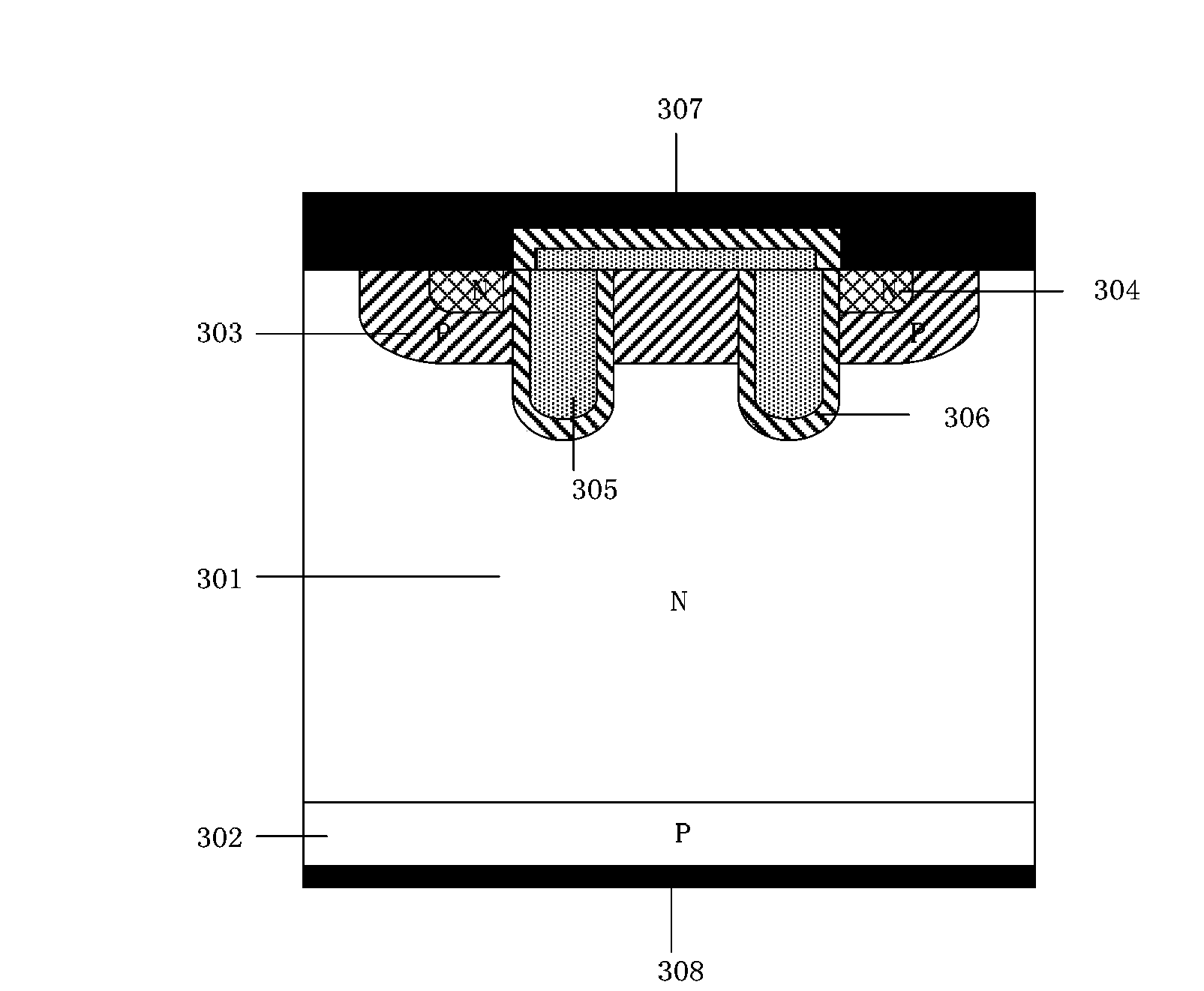

Silicon carbide MOS device with groove type JFET and preparation process thereof

PendingCN111509037AReduce the problem of excessive JFET resistanceReduce excessive resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconJFET

The invention discloses a silicon carbide MOS device with a groove type JFET and a preparation process of the silicon carbide MOS device. The silicon carbide MOS device with the groove type JFET comprises a silicon carbide substrate, the doping type of the silicon carbide substrate material is a first conductive type, a first conductive type semiconductor epitaxial layer and a drain electrode arerespectively arranged on a front surface and a back surface of the silicon carbide substrate, wherein a JFET region is arranged on an active region of the first conductive type semiconductor epitaxiallayer, a first surface, a second surface and a third surface are arranged on the JFET region, and a first conductive type source region and a second conductive type base region are arranged on the first surface and the second surface respectively from outside to inside, a source electrode is arranged above the first surface, a gate medium and a gate electrode are arranged above the third surface,a second conductive type injection body region is arranged between the second conductive type base region and the source electrode, and an inter-electrode isolation medium is arranged between the source electrode and the gate electrode.

Owner:PN JUNCTION SEMICON HANGZHOU CO LTD

Insulated gate bipolar transistor (IGBT) with low-conductivity saturation voltage drop and manufacturing method for IGBT

ActiveCN102569373BIncrease pressure dropLow resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesParasitic bipolar transistorEngineering

The invention relates to an insulated gate bipolar transistor (IGBT) with low-conductivity saturation voltage drop and a manufacturing method for the IGBT. A second conductive type layer is arranged in an active region and partitioned into a plurality of second conductive type layer first regions and a second conductive type layer second regions by conductive polysilicon and insulated gate medium layers; an insulation medium layer is covered on the first main surface of a semiconductor substrate; first conductive type injection regions are symmetrically arranged in the second conductive type layer first regions and contacted with the corresponding insulated gate medium layers; emitter contact holes are formed above the second conductive type layer second regions, pass through the insulation medium layer and extend to the first main surface; emitter metal layers are filled in the emitter contact holes and covered on the insulation medium layer; and the emitter metal layers are in ohm contact with the second conductive type layer first regions. The IGBT has relatively low saturation voltage drop Vcesat and relatively high impact resistance.

Owner:WUXI NCE POWER

Junction field-effect transistor and manufacturing method thereof

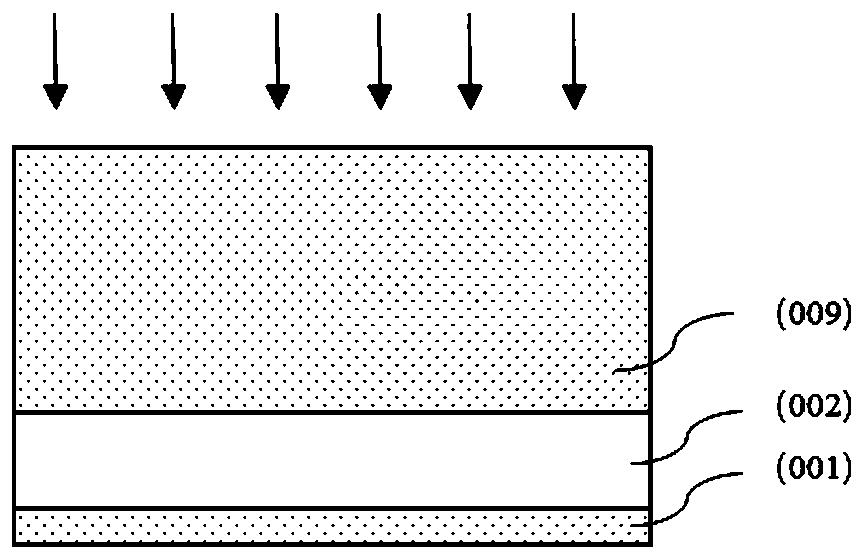

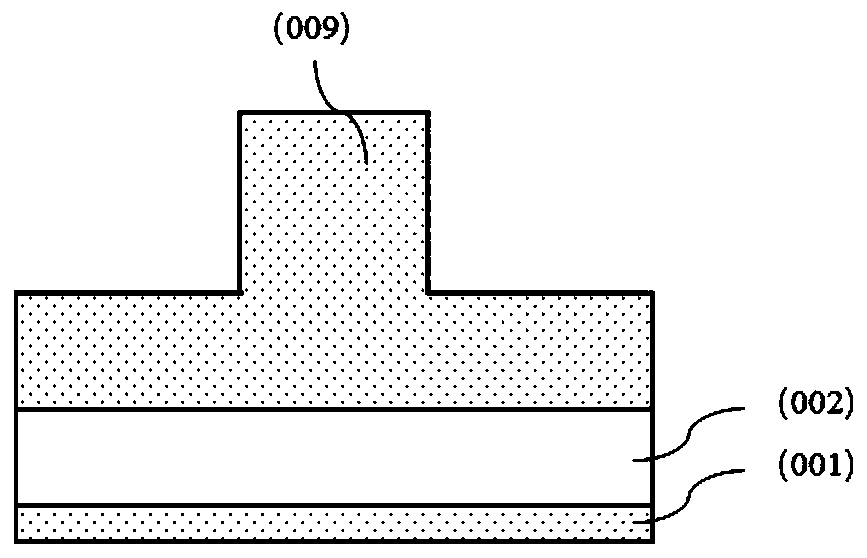

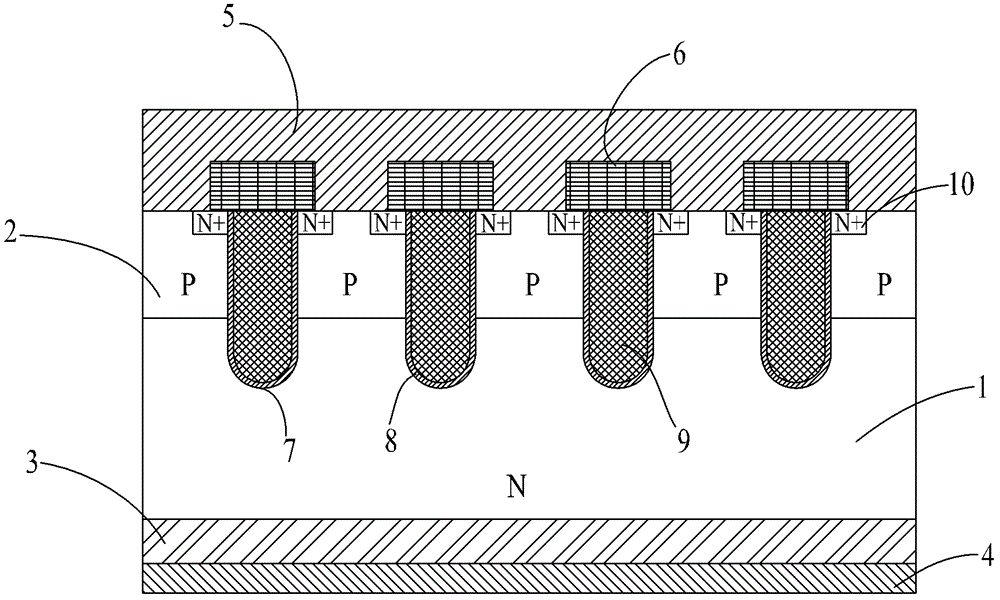

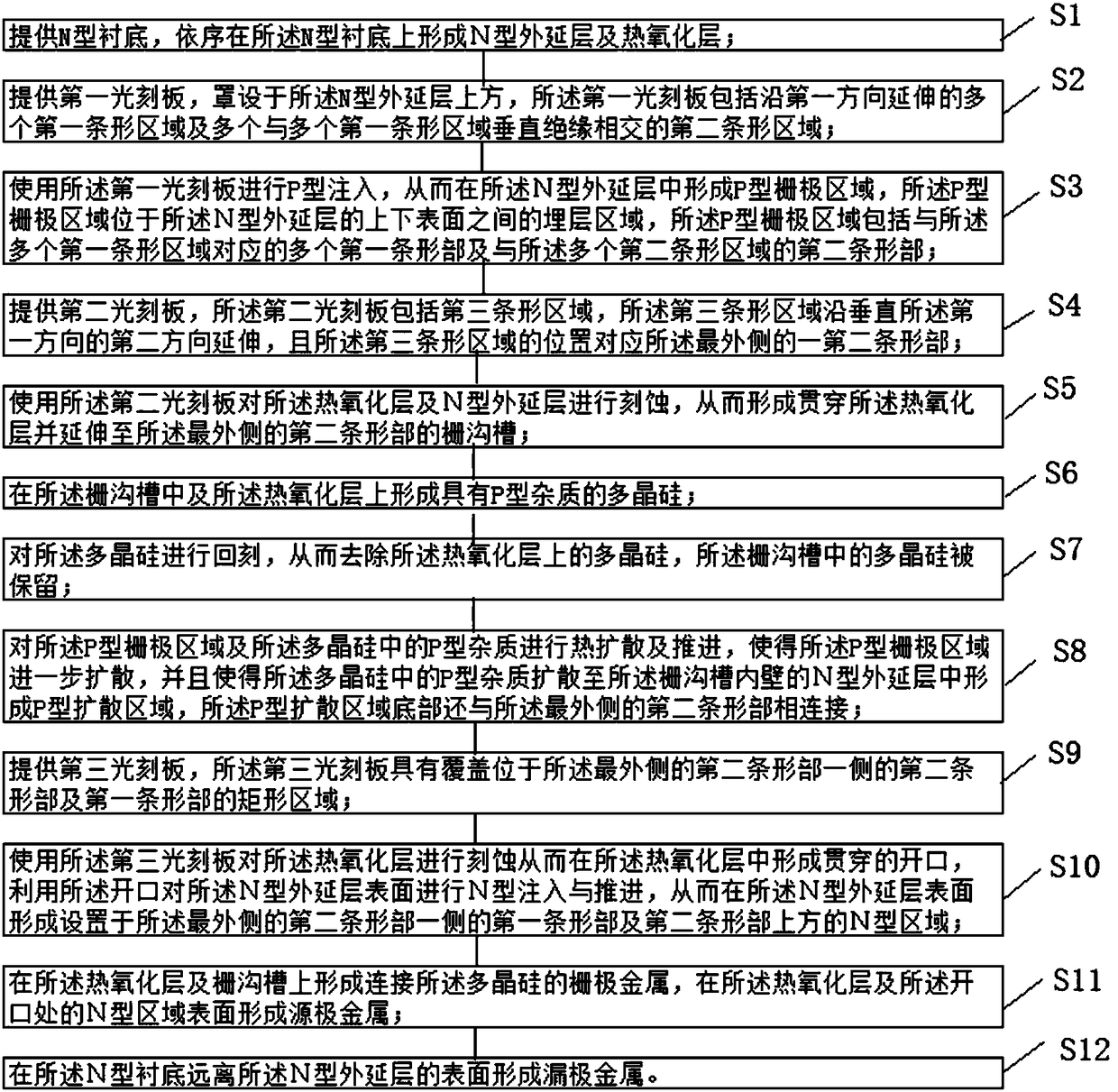

InactiveCN108091575ALow propulsion temperatureShort advance timeSemiconductor/solid-state device manufacturingSemiconductor devicesPolycrystalline siliconOxide

The invention relates to a junction field-effect transistor and a manufacturing method thereof. The junction field-effect transistor obtained by the manufacturing method includes an N-type substrate,an N-type epitaxial layer, a buried P-type gate region formed in the N-type epitaxial layer, an oxide layer, a gate trench penetrating through the oxide layer and extending to the P-type gate region,a P-type diffusion region formed on the inner wall of the gate trench and connected to the P-type gate region, polysilicon formed in the gate trench, an N-type region formed on the surface of the N-type epitaxial layer, an opening penetrating through the oxide layer and corresponding to the N-type region, gate metal formed on the oxide layer and the gate trench and connected to the polysilicon, source metal, and drain metal. The P-type gate region includes a plurality of first parallel bar portions and a plurality of second bar portions perpendicularly intersecting with the first bar portions,the outermost second bar portion being in contact with the gate trench and the P-type diffusion region, and the first bar portion at one side of the outermost second bar portion and the second bar portion being located below the N-type region.

Owner:眉山国芯科技有限公司

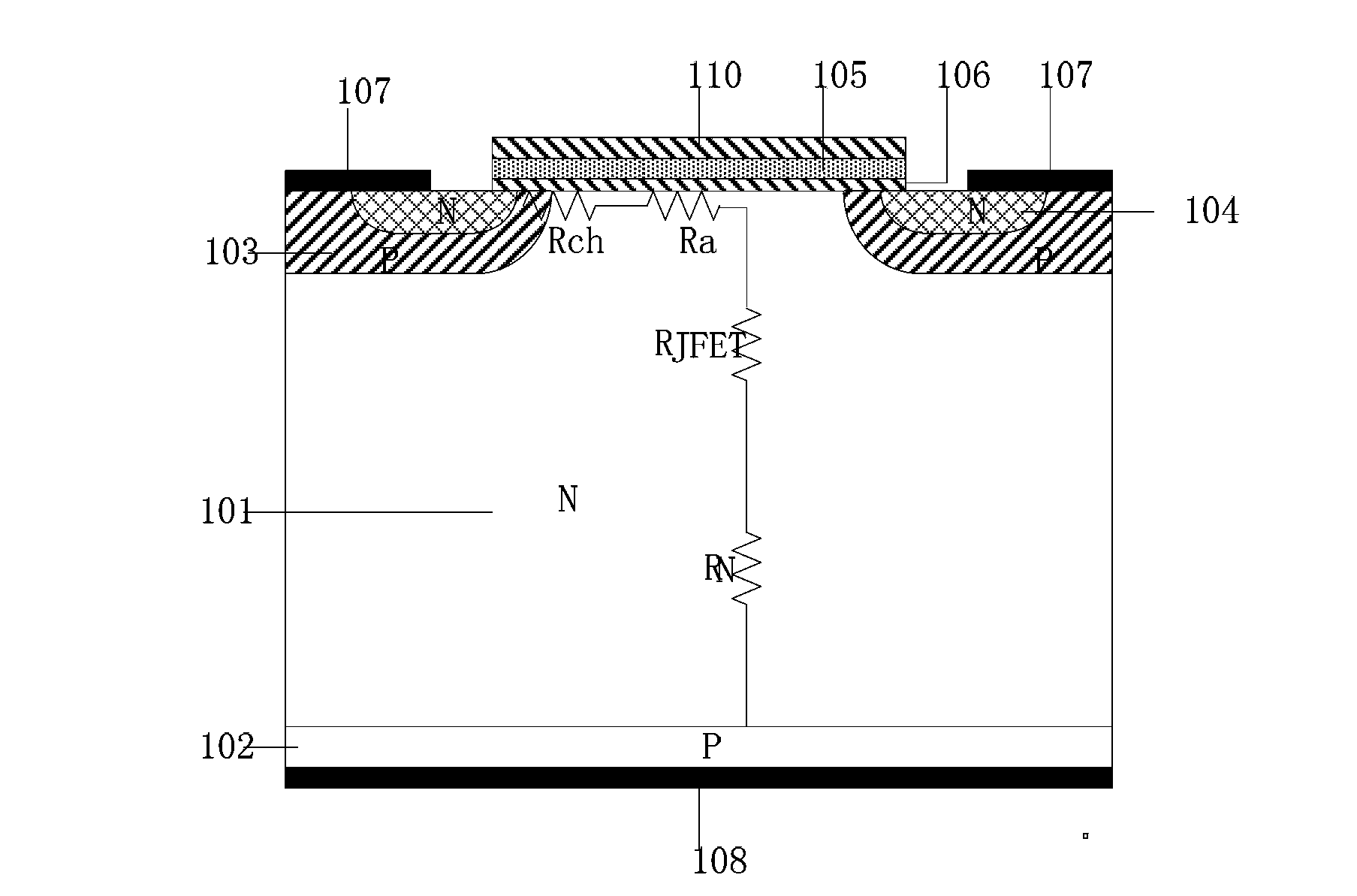

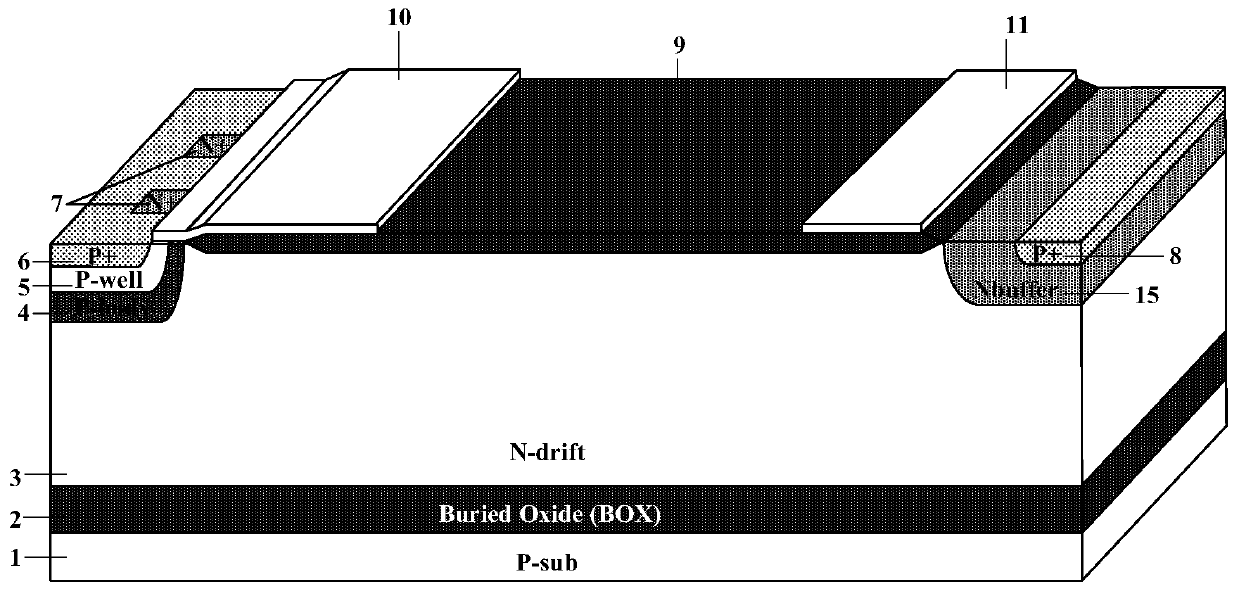

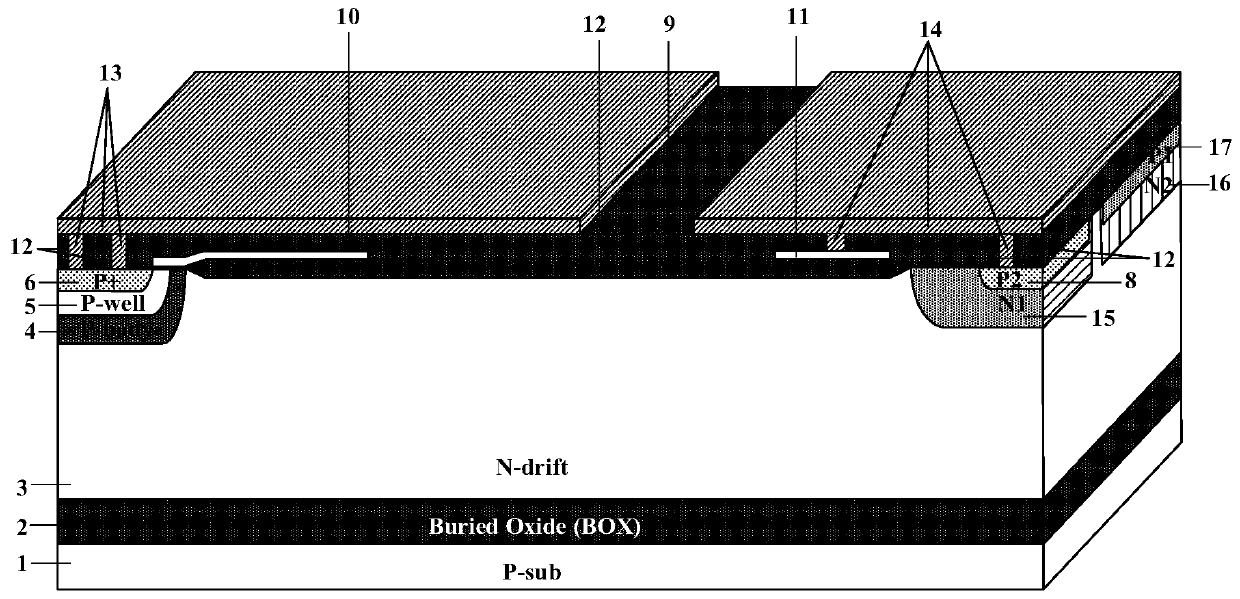

Silicon-on-insulator transverse insulated gate bipolar transistor with low saturation current

ActiveCN111430454ALarge linear currentReduced injection efficiencySemiconductor devicesPhysical chemistryEngineering

The invention discloses a silicon-on-insulator transverse insulated gate bipolar transistor with low saturation current. The According to the semiconductor is provided with:, a semiconductor substrate; wherein a buried oxide layer is arranged on the a P-type substrate; an N-type drift region is arranged above on the buried oxide layer; , wherein a P-type body region, a field oxide layer and a collector region are arranged on the N-type drift regionsubstrate; connected P traps are arranged in the P-type body region; a P-type emitter region is arranged in the P traps; an N-type emitter region isarranged on the P-type emitter region; an oxide layer is arranged above on the P-type body region, the P traps, the P-type emitter region, the field oxide layer and the collector region; a polysilicon gate is arranged between the field oxide layer and the oxide layer and extends to the upper part of the P traps; a gate oxide layer is arranged among the P traps, the P-type body region and the polysilicon gate,; wherein the collector region comprises a heavily-doped N-type collector region and a lightly-doped N-type collector region which are arranged in the N-type drift region and isolated bythe N-type drift region, a lightly-doped P-type collector region is arranged in the heavily-doped N-type collector region, and a heavily-doped P-type collector region is arranged in the lightly-dopedN-type collector region.

Owner:SOUTHEAST UNIV

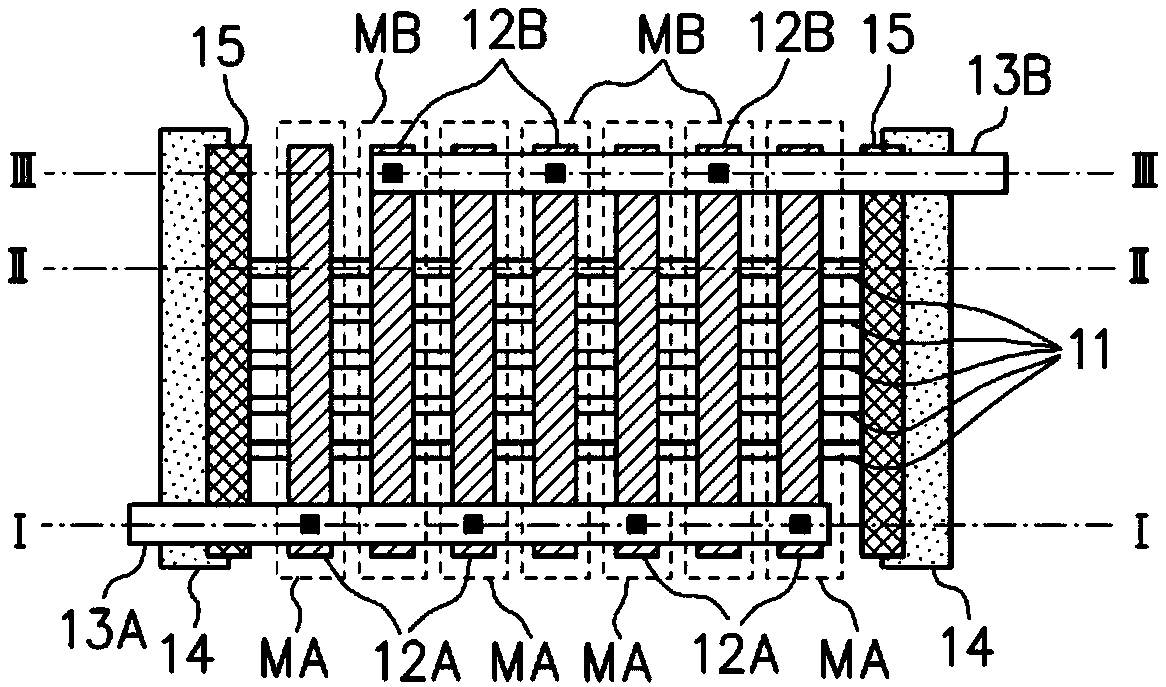

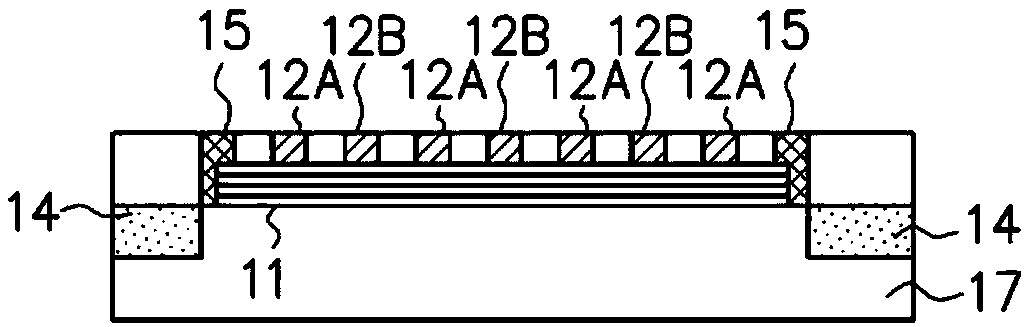

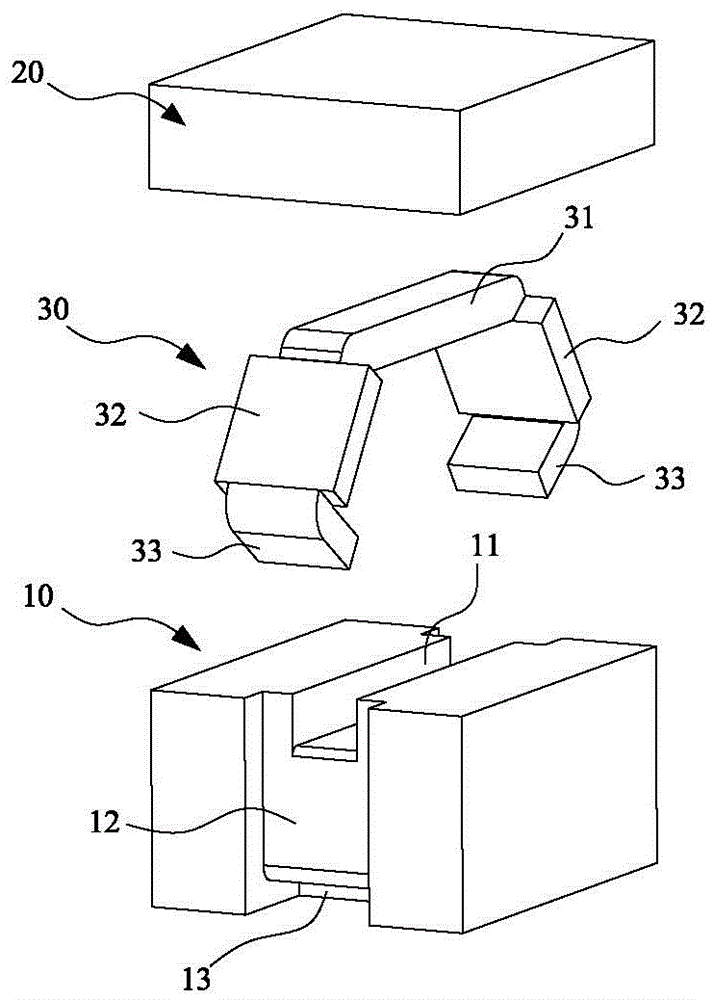

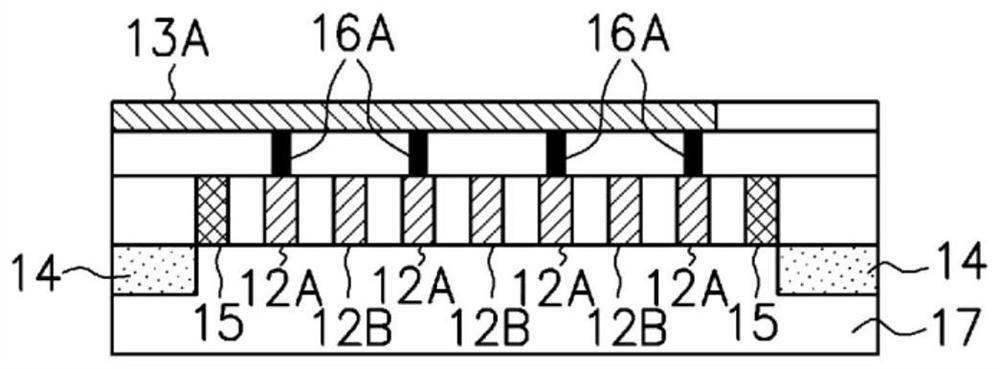

Semiconductor device and semiconductor integrated circuit

ActiveCN109417033AReduce saturation currentReduce feverSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSemiconductor

The present invention provides a semiconductor device and a semiconductor integrated circuit, comprising: element isolation regions (14); projected semiconductor regions (11); a plurality of first gate electrodes (12A) which are formed between a pair of opposing ends of the element isolation regions and each of which is formed on both side surfaces and the top surface of a part of the projected semiconductor region; at least one second gate electrode (12B) which is formed between a pair of the plurality of first gate electrodes in the same layer as the plurality of first gate electrodes, and to which voltage to turn a transistor to an off state is applied; and source regions and drain regions formed in the projected semiconductor regions on both sides of the first gate electrode and the second gate electrode. By disposing, between transistors having the first gate electrodes, a transistor having the second gate electrode to which voltage to turn the transistor to an off state is applied, heat generated in the transistors is reduced without reducing the saturation current of the transistors.

Owner:SOCIONEXT INC

SOI LIGBT device integrated with Zener diode

ActiveCN111834450AImprove compromiseReduced Miller CapacitanceSemiconductor devicesCapacitanceZener diode

The invention belongs to the technical field of power semiconductors, and particularly relates to an SOI LIGBT device integrated with a Zener diode. Compared with a traditional LIGBT, the Zener diodeis introduced into a P well region at an emitter end of a new device, the P-type region of the Zener diode is electrically connected with the emitter of the device, and the N-type region of the Zenerdiode is electrically connected with the P well region through floating ohmic metal. When the voltage of a collector electrode is continuously increased, the Zener diode is reversely broken down and conducted, so that the potential of the P well region is clamped, the gate capacitance of the device can be reduced, the saturation current can be reduced to improve the short-circuit capability of thedevice when the device is conducted, and a hole extraction path can be provided in the turn-off process to reduce the turn-off time and the turn-off loss. Compared with a traditional LIGBT structure,the novel LIGBT structure provided by the invention has the advantages that a better compromise relationship between conduction voltage drop and turn-off loss is obtained, and the short-circuit resistance of the device is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Segmented injection self-clamping IGBT device and manufacturing method thereof

PendingCN113838913AReduce saturation currentImprove affordabilitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsTrench igbt

The invention provides a segmented injection self-clamping IGBT and a manufacturing method thereof. A trench structure equipotential with an emitter is introduced to the right side of a cell, the P-type doped buried layers are introduced below an N-type charge storage layer, and the high-concentration P-type buried layers are distributed at intervals by changing an opening of a mask plate, so that the adverse effect of the high-concentration P-type buried layers on the threshold voltage when a device is conducted is improved, and the on-resistance is reduced. When the device is saturated, a self-biased PMOS structure is opened, and the electric potential of a CS layer is clamped at a lower value, so that the saturation current of the IGBT is reduced. The high-concentration P-type buried layers distributed at intervals can ensure that the PMOS structure is normally started under high collector voltage so as to clamp the potential of the CS layer, the saturation current is reduced, and the short-circuit capability of the device is improved. On the basis of a traditional trench IGBT process method, the P+ buried layers distributed in a segmented mode in a z direction can be achieved only by adding one mask, the process complexity is not increased, and implementation is easy.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

Cable temperature and load current measuring wireless device based on induction power taking

PendingCN113847952AHigh permeabilityReduce saturation currentTransmission systemsCircuit arrangementsPhysicsRogowski coil

The invention belongs to the technical field of cable measuring, and particularly relates to a cable temperature and load current measuring wireless device based on induction power taking, which comprises a shell and a power taking and current measuring ring, and is characterized in that the shell comprises an upper shell, a middle shell and a lower shell which are detachable; a main control board and a wireless communication module are fixed in the middle shell; the power taking and current measuring ring is fixedly arranged on the shell and penetrates through a measured cable; the power taking and current measuring ring comprises a detachable annular soft magnetic alloy belt and a Rogowski coil; and and a temperature probe is fixed below the lower shell. The soft magnetic alloy belt is adopted to take power, and the soft magnetic alloy belt is soft and can be easily installed on measured objects in different shapes. The Rogowski coil is used for current measuring, large current does not generate heat, the measuring range is wide, the size is small, the weight is light, and the opening is easy to install. The device is easy to install, Rogowski coils and soft magnetic alloy belts of different sizes can be replaced for measured objects of different sizes, and adaptability and universality are high.

Owner:GUANGXI POWER GRID ELECTRIC POWER RES INST +1

Method of forming a fin field effect transistor

ActiveCN106298529BThe overall thickness is thinIncrease resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideOptoelectronics

A forming method of a fin type field effect transistor comprises the steps of supplying a substrate which comprises a first area with first fin parts; forming a first gate structure which bestrides the first fin parts; forming a first source electrode material layer and a first drain electrode material layer on the first fins at two sides of the first gate structure; forming a first dielectric layer on the substrate, the first gate structure, the first source electrode material layer and the first drain electrode material layer; forming a first source electrode through hole and a first drain electrode through hole in the first dielectric layer; forming a first metal layer on the source electrode material layer and the first drain electrode material layer; performing first annealing processing on the first metal layer for forming a first high-impedance-phase metal silicide layer; performing ion implantation on the first high-impedance-phase metal silicide layer; and performing second annealing processing on the first high-impedance-phase metal silicide layer after ion implantation, thereby forming a first source electrode metal silicide layer and a first drain electrode metal silicide layer. The forming method can improve performance of a subsequently formed transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Flat coil inductor, flat coil and manufacturing method of flat coil

ActiveCN103680861BLarge DC resistanceSize DC resistanceTransformers/inductances coils/windings/connectionsCoils manufactureEngineeringInductor

The invention discloses a flat coil inductor, a flat coil and a method for manufacturing a flat coil. The inductor includes a magnetic core, a magnetic cover covering the magnetic core, and a flat coil wound on the magnetic core. The core is at least provided with first and second grooves, and the flat coil at least includes a top base and two side flattened parts, the thickness of the base is greater than the thickness of the side flattened parts, and the width of the side flattened parts is greater than that of the base Width, the base is embedded in the first groove, and the flattened parts on both sides are embedded in the second groove. By partially flattening the flat coil of the inductor to form a side flattened part to obtain different thicknesses, the width of the side flattened part is larger than the width of the base part, and the thickness is smaller than the thickness of the base part, so that the flattened part surrounded by the flat coil The space for synthetically accommodating the magnetic core becomes larger, and it is assembled with the corresponding larger magnetic core, which makes the DC resistance of the inductor smaller and the saturation current larger within a limited size range, so that the inductor can obtain the best electrical performance. characteristic.

Owner:DONGUAN PULSE ELECTRONICS CO LTD

Memory structure and method of forming the same

ActiveCN108281425BRead Noise Capacitance ImprovementImprove write performanceSolid-state devicesSemiconductor devicesEngineeringComputational physics

The present invention provides a memory structure and its formation method. Among them, the memory structure includes: the first transmission transistor, which includes the first transmission leakage area and the first transmission source area, the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area and the first transmission source area.There is a first doped ion in the transmission leakage area, which is different from the first doped ion concentration in the first transmission leakage area.The second transmission transistor includes the second transmission leakage area and the second transmission source area. The second transmission source area and the second transmission leakage area have a second doped ionThe concentration of the doped ion is different from the second doped ion concentration in the second transmission source area.The memory can improve the memory writing ability while increasing the read noise capacity of the memory.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor device and semiconductor integrated circuit

ActiveCN109417033BReduce saturation currentReduce feverSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

Owner:SOCIONEXT INC

Semiconductor device

ActiveCN102751329BLower turn-on voltageMiniaturizationSolid-state devicesSemiconductor devicesField-effect transistorSemiconductor

Owner:MITSUBISHI ELECTRIC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com