Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

202results about How to "Reduce DC resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

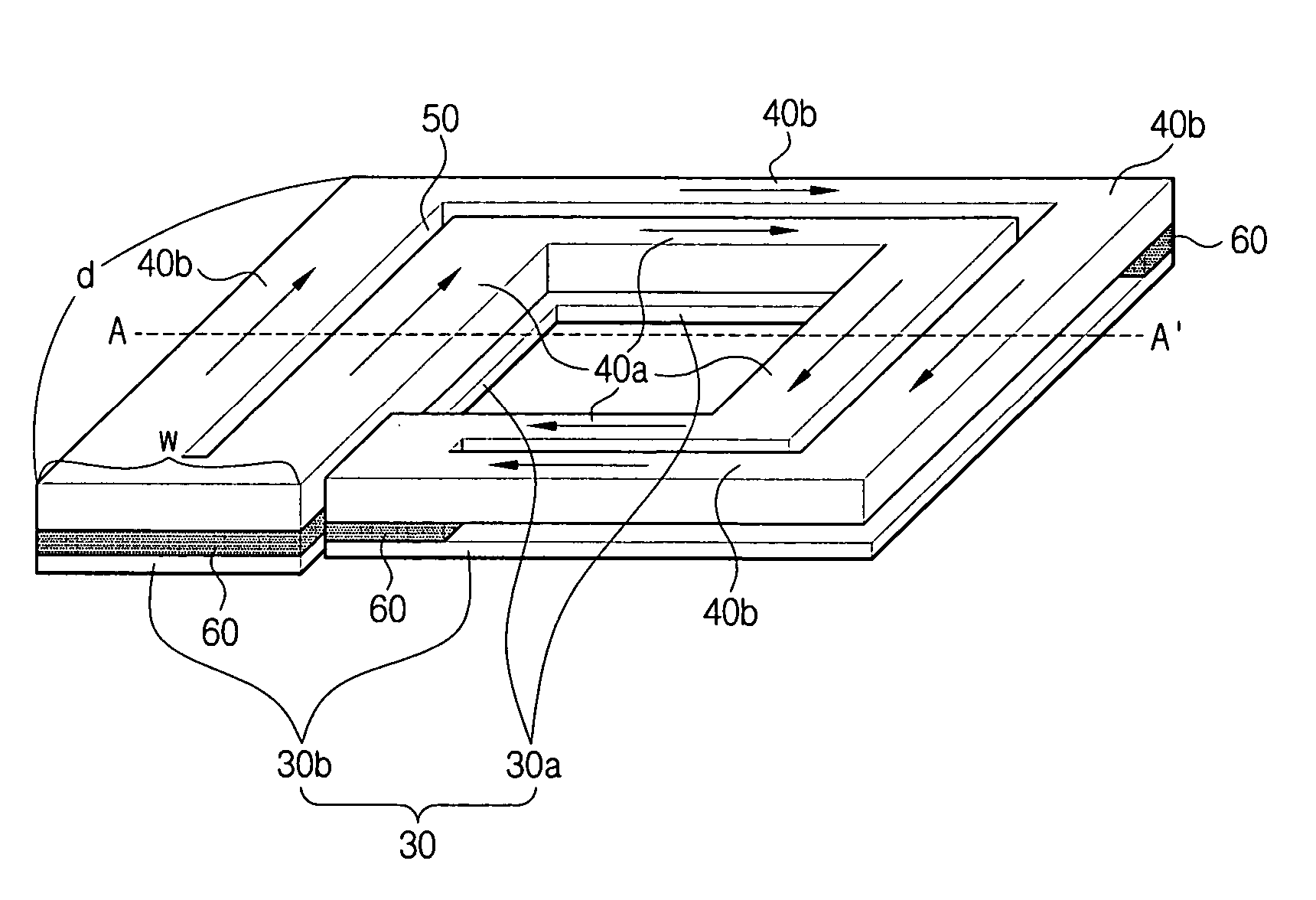

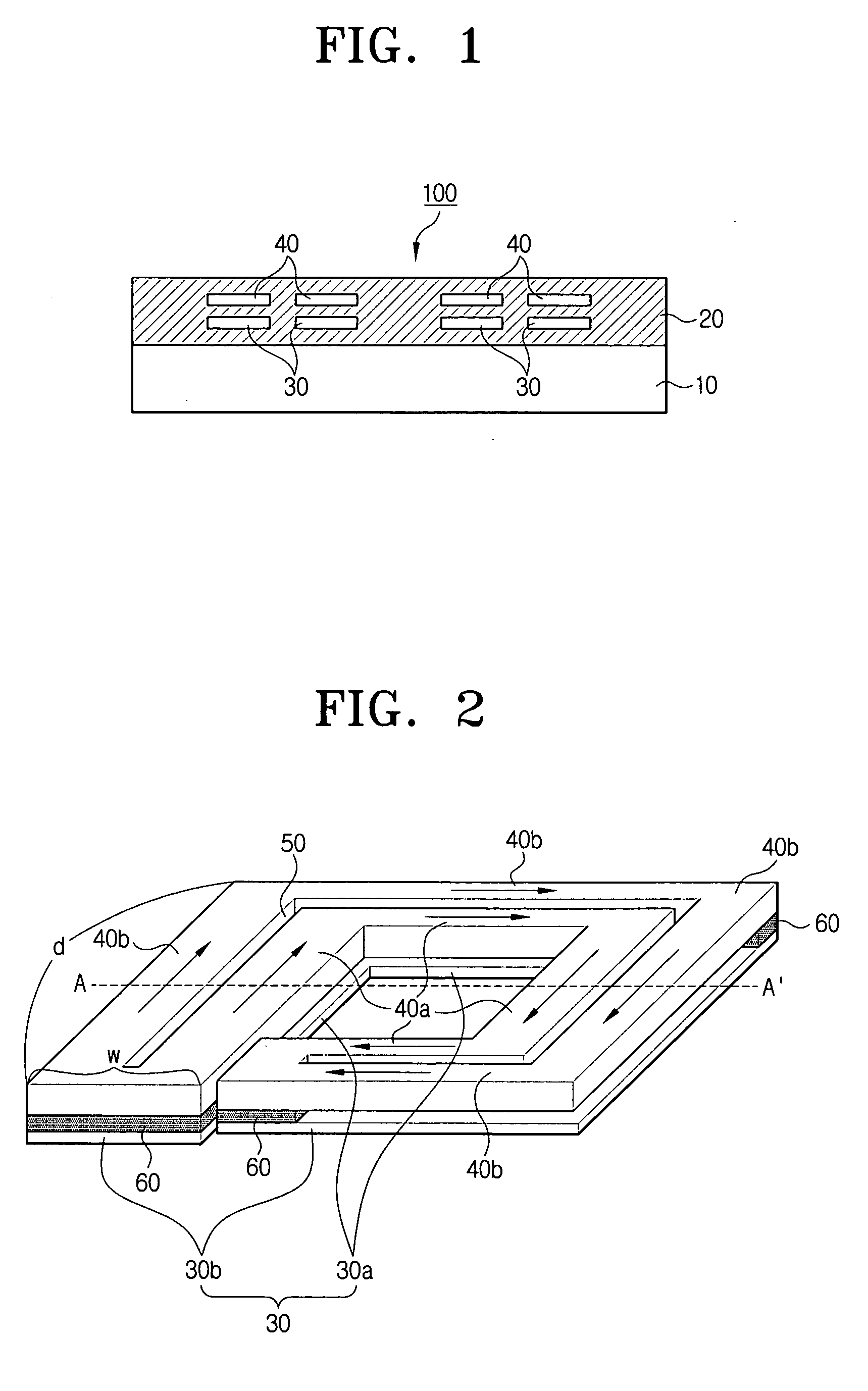

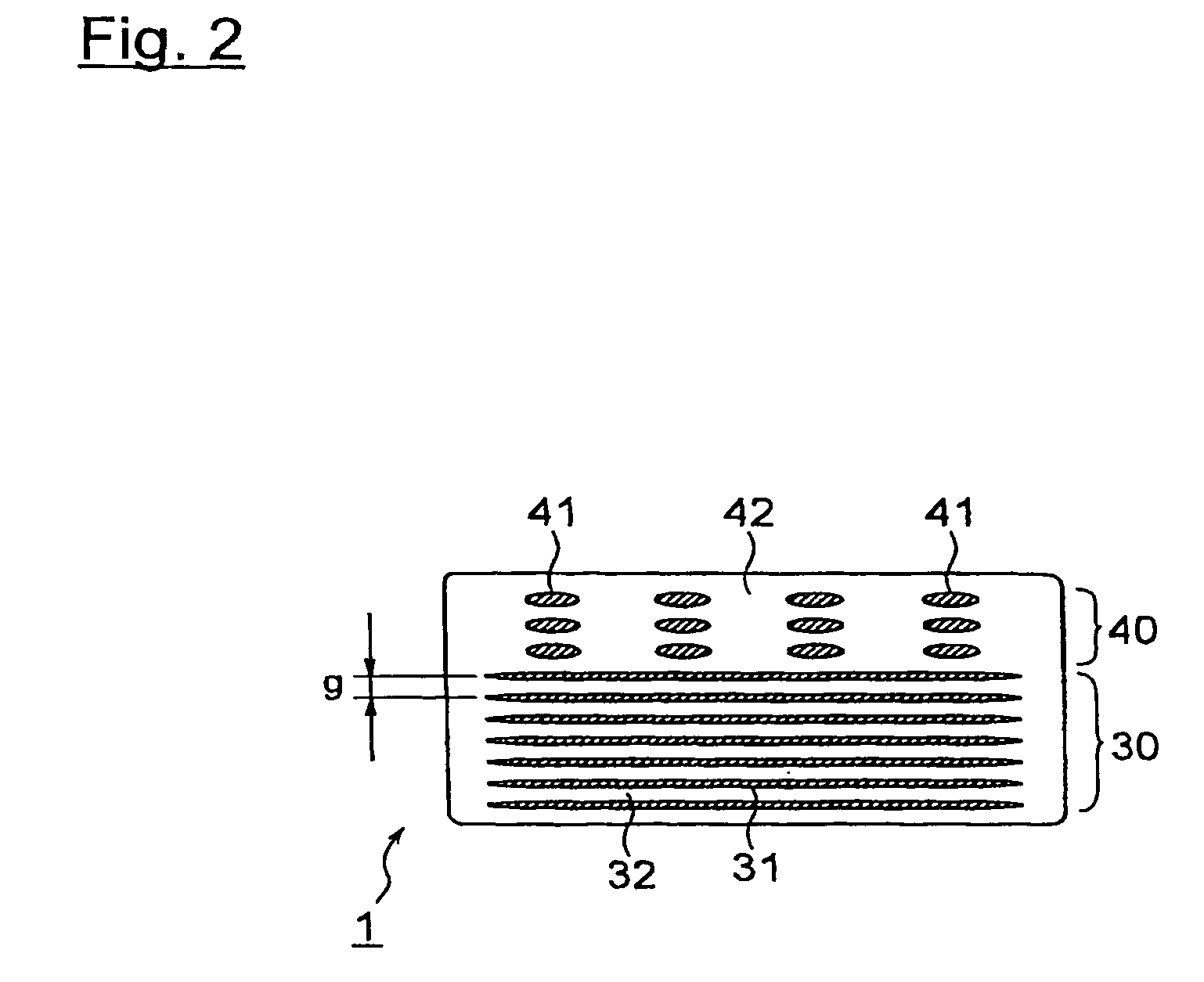

Shredded parallel stacked inductor

ActiveUS20060192645A1Minimizing skin effectReduce DC resistanceUnwanted magnetic/electric effect reduction/preventionPrinted inductancesOptoelectronicsInductor

A shredded parallel stacked inductor is provided. The shredded parallel stacked inductor includes a substrate, an oxide film formed on the substrate, metallic layers spirally formed within the oxide film, and vias formed in regions of the metallic layers to join the metallic layers in parallel, thus forming a spiral cavity in a center part of the metallic layers.

Owner:SAMSUNG ELECTRONICS CO LTD

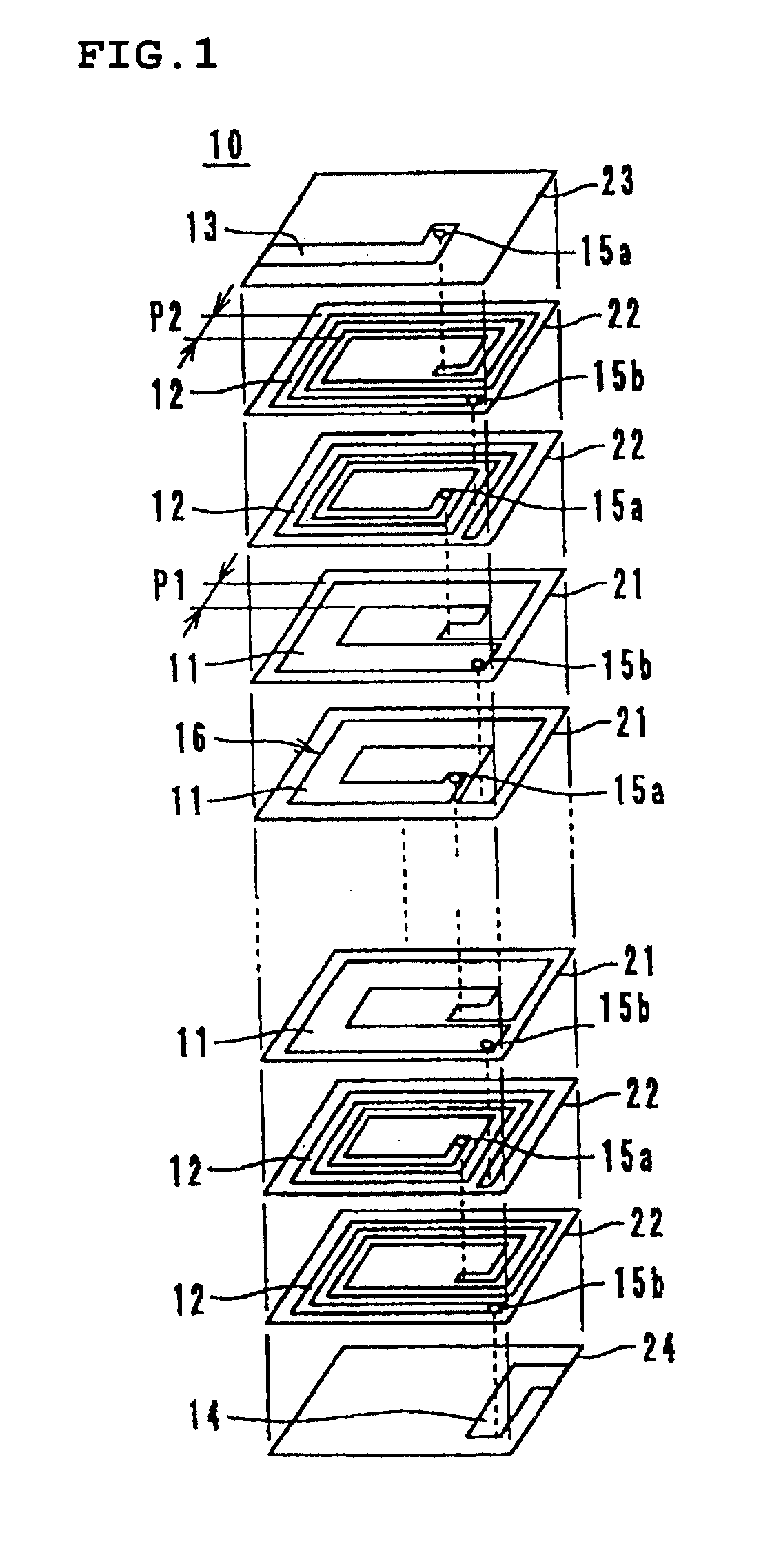

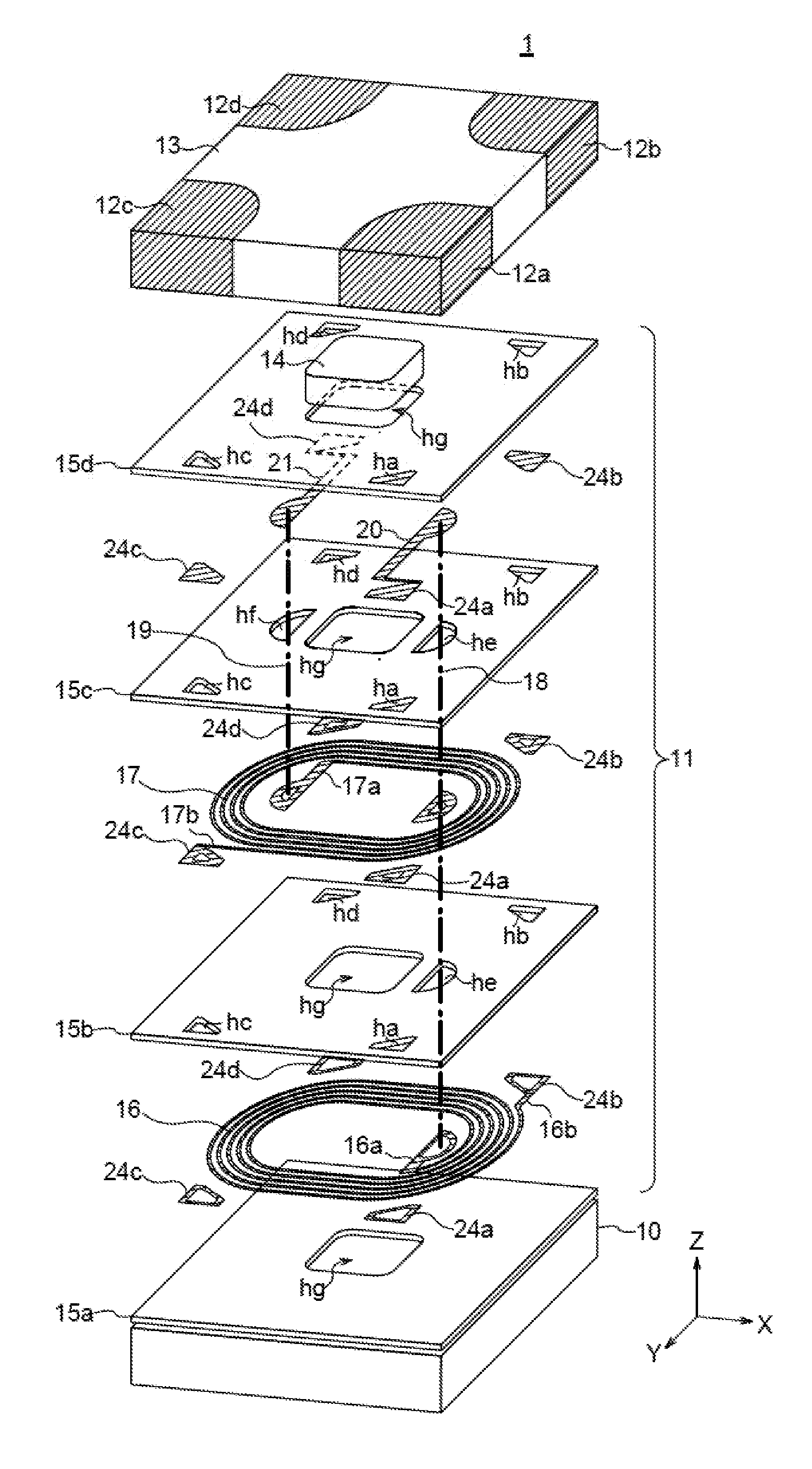

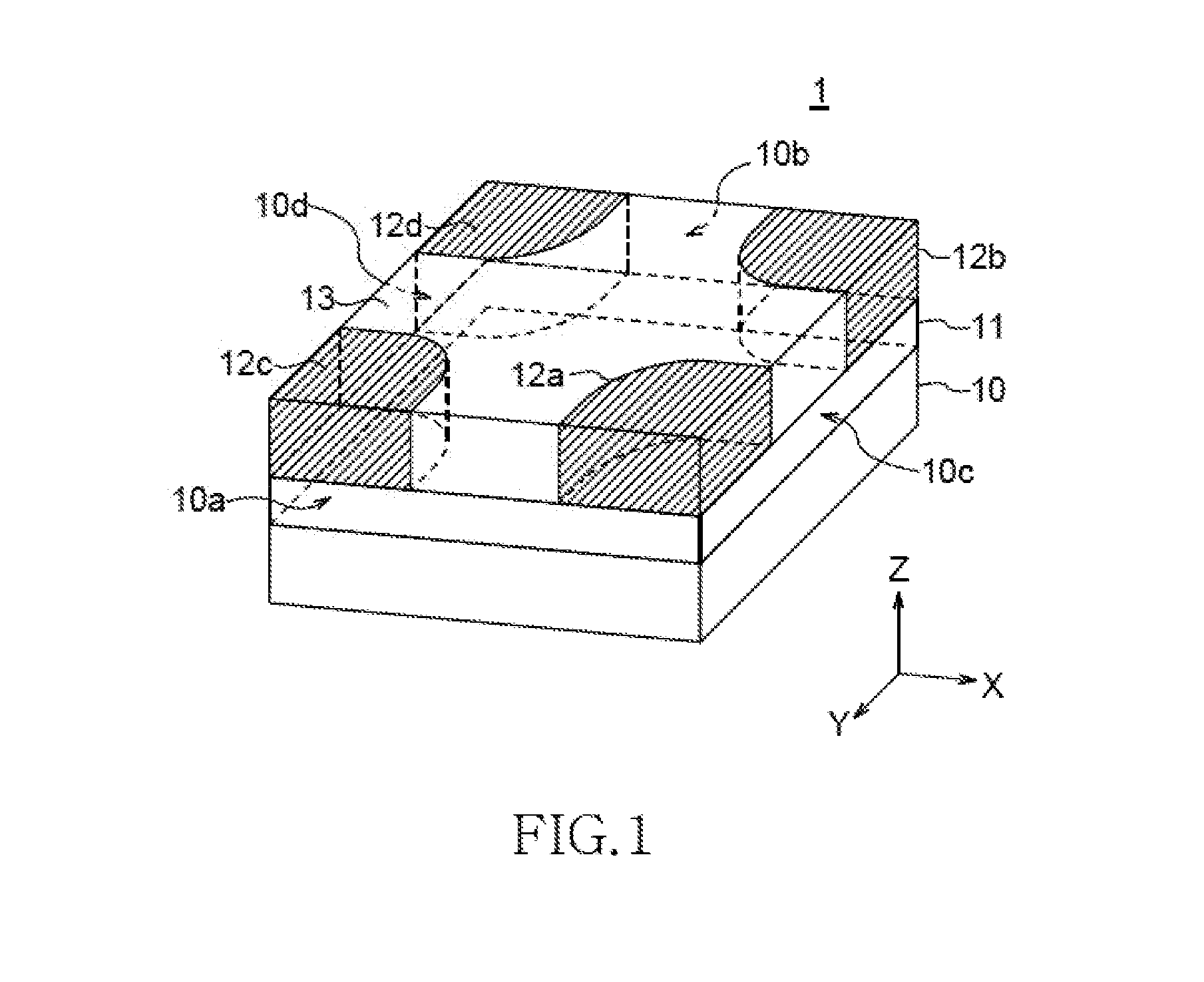

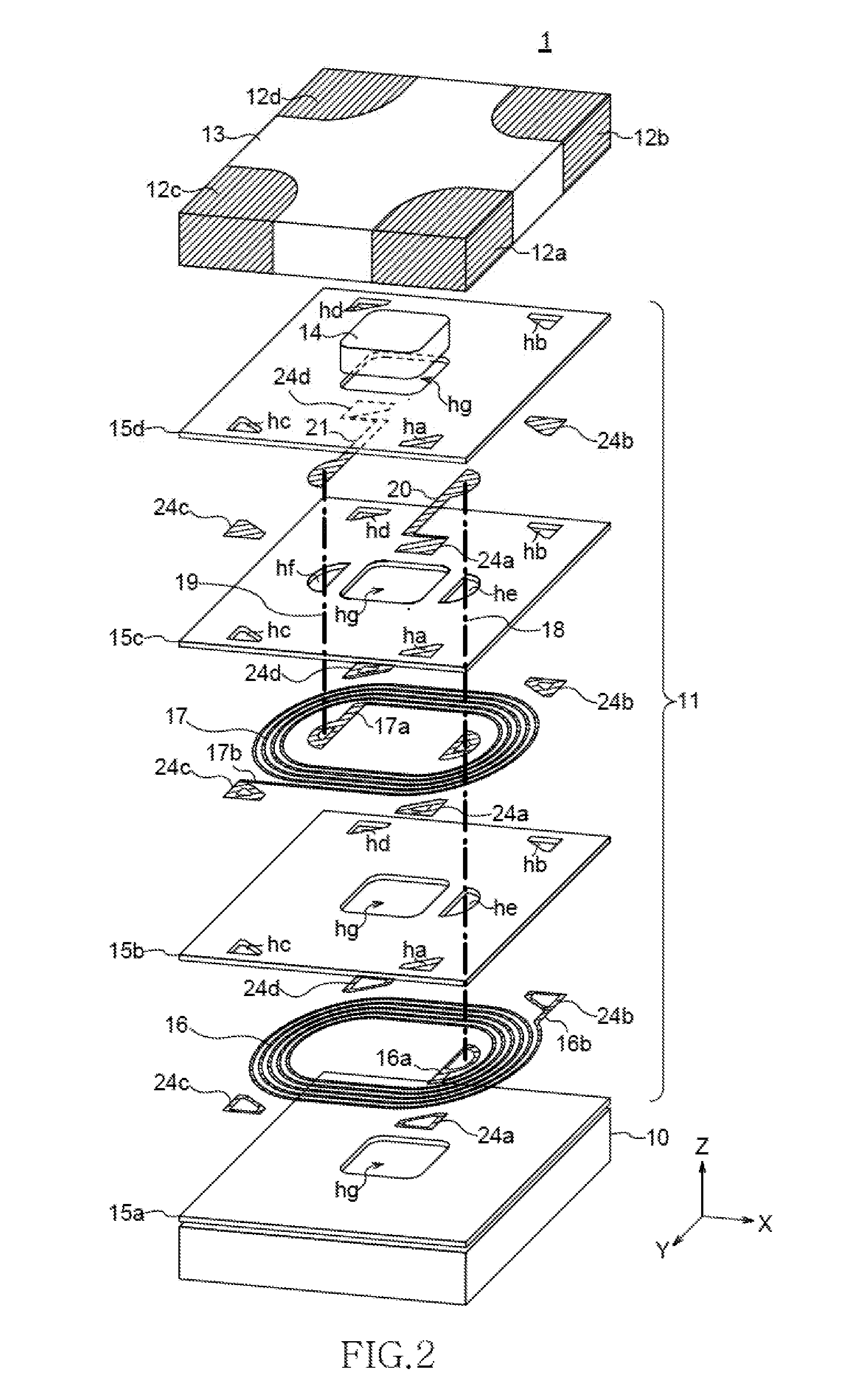

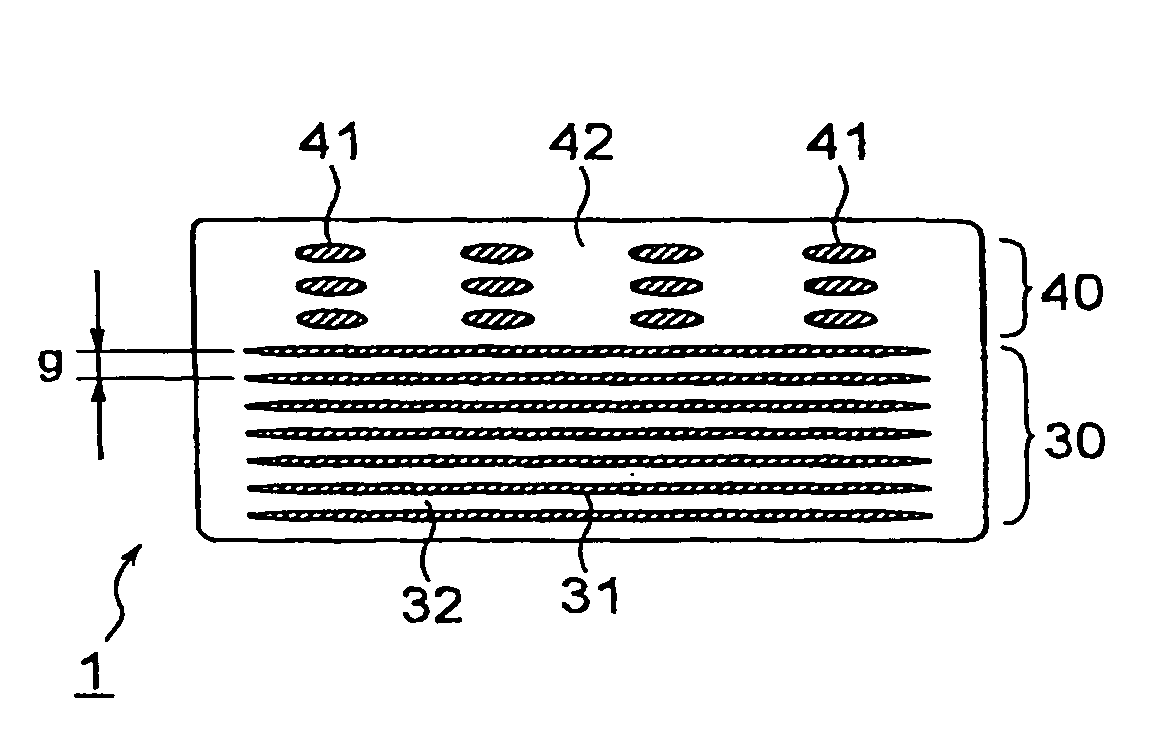

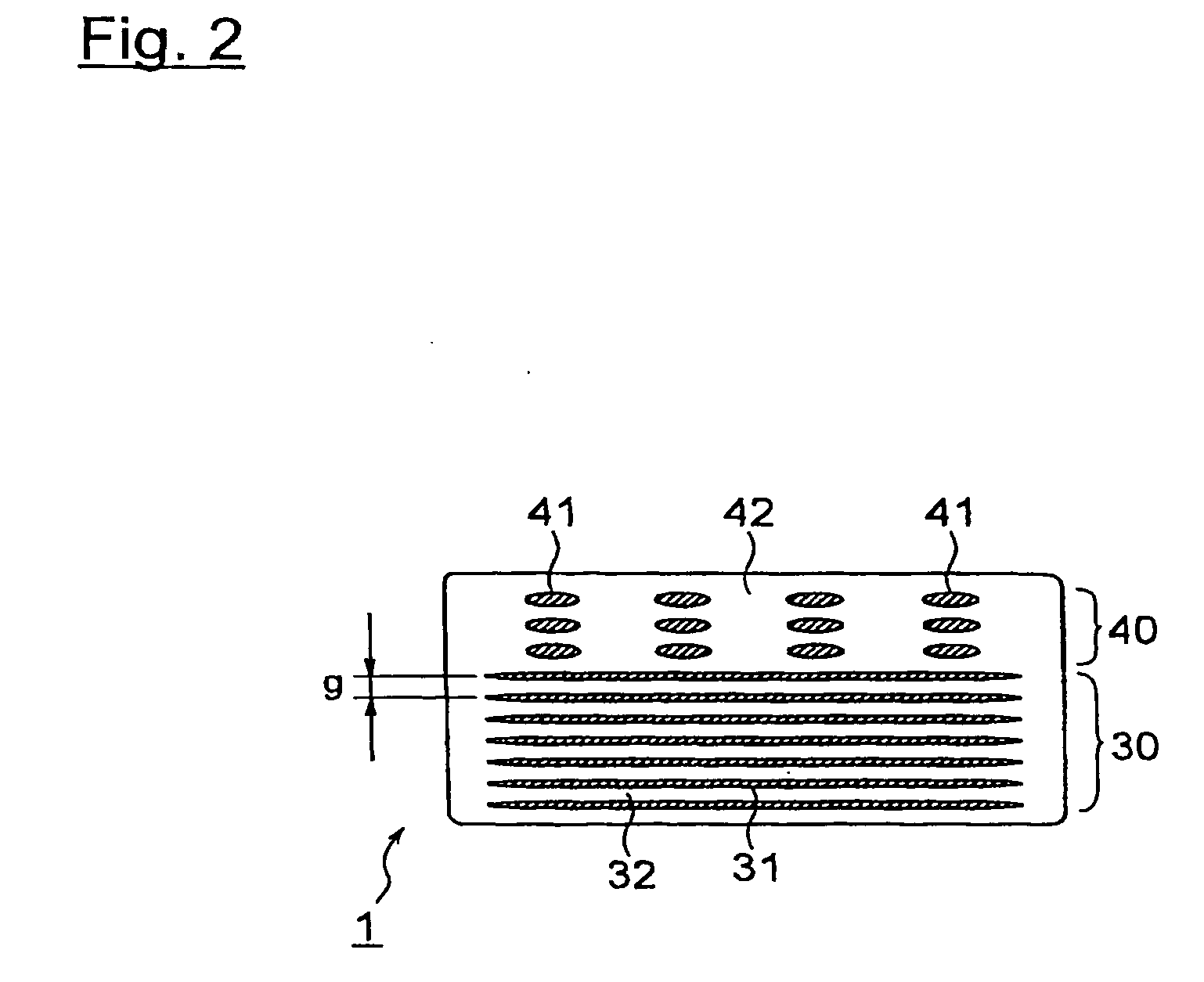

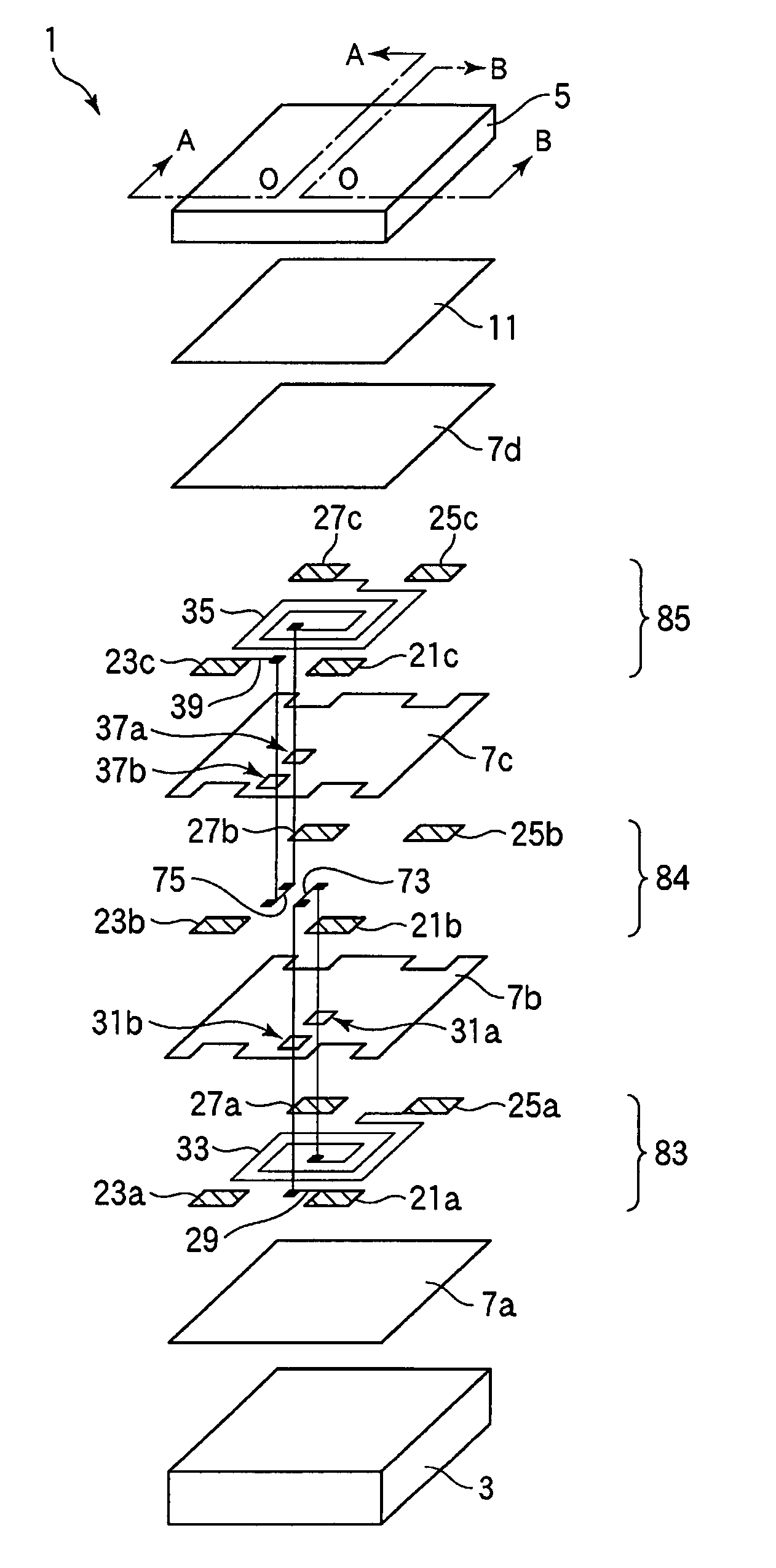

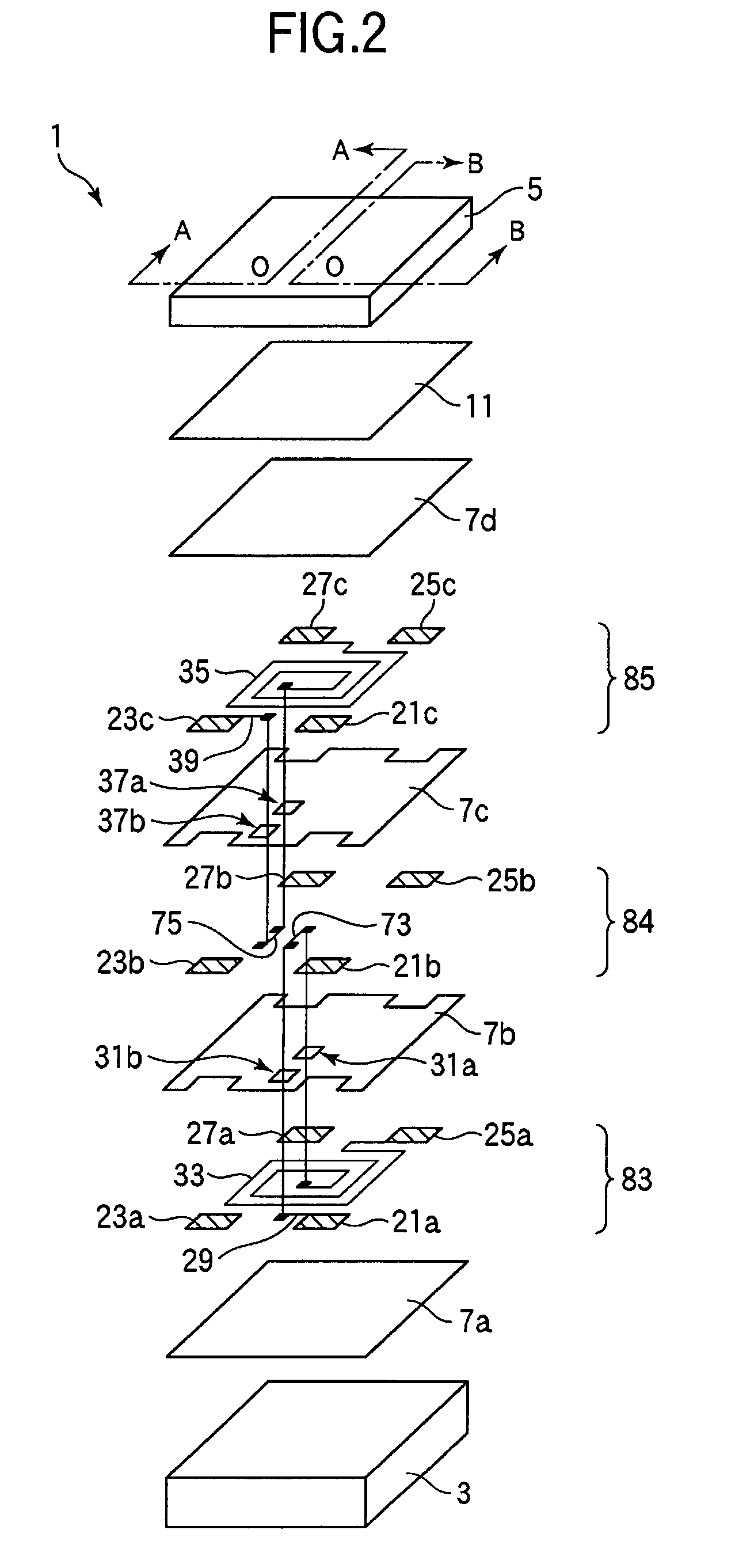

Laminated inductor

InactiveUS7046114B2Increase freedomHigh design freedomTransformers/inductances casingsTransformers/inductances coils/windings/connectionsElectrical conductorInductor

A laminated inductor includes ceramic sheets provided with spiral coil conductor patterns of one turn, ceramic sheets provided with spiral coil conductor patterns of two turns, and ceramic sheets provided with lead-out conductor patterns, which are laminated together. The coil conductor patterns are successively electrically connected in series in regular order through via holes. The via holes are disposed at fixed locations in the ceramic sheets.

Owner:MURATA MFG CO LTD

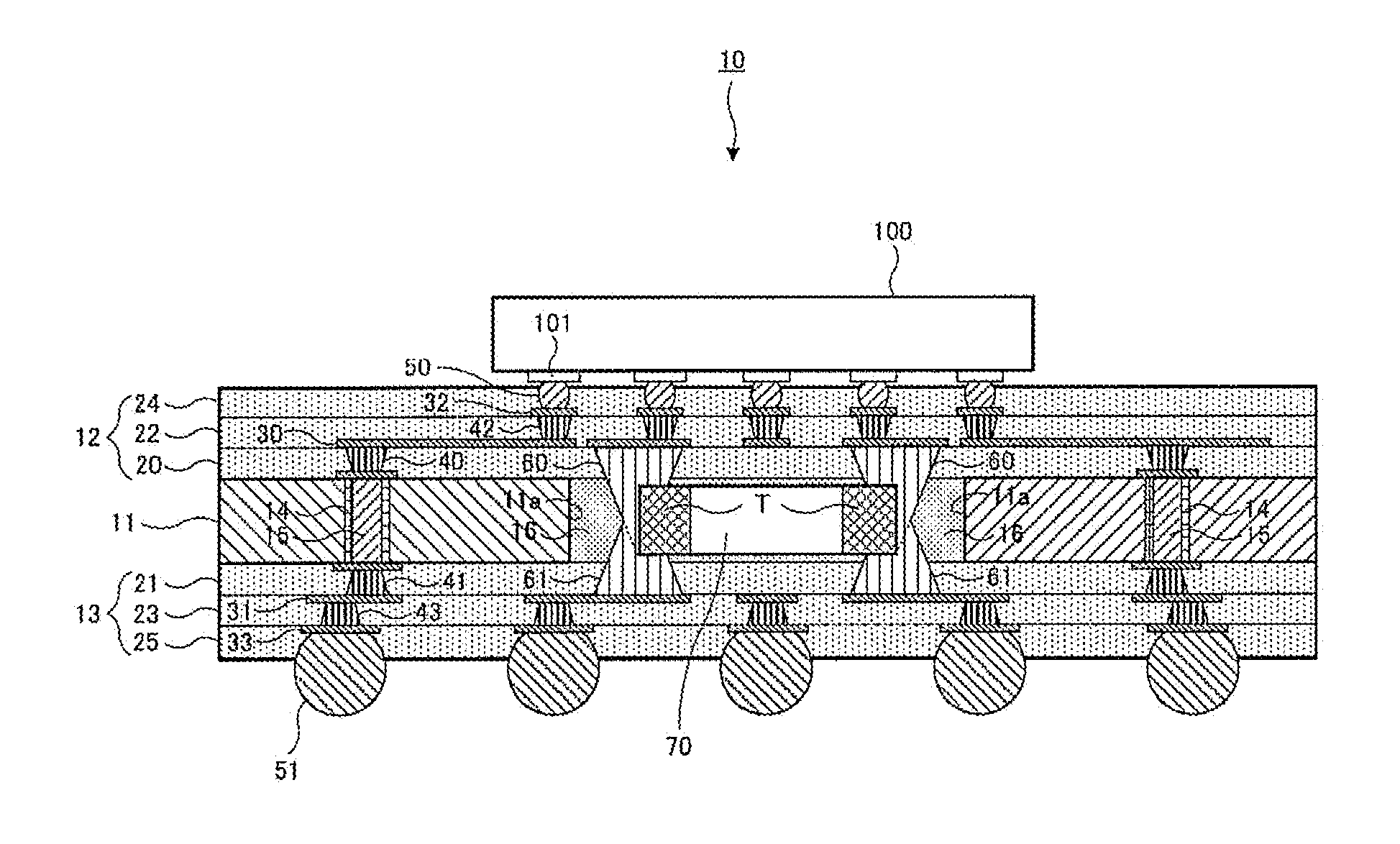

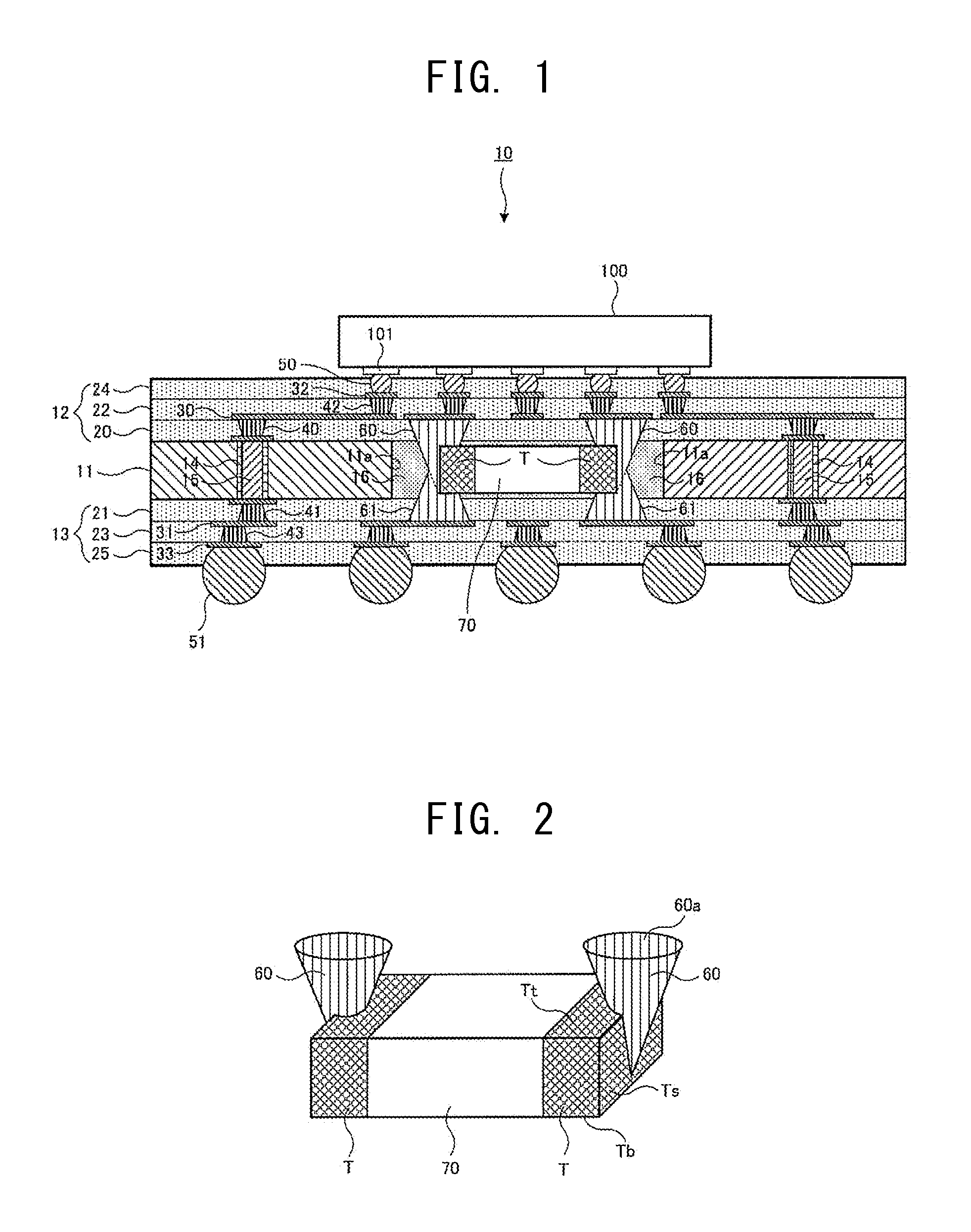

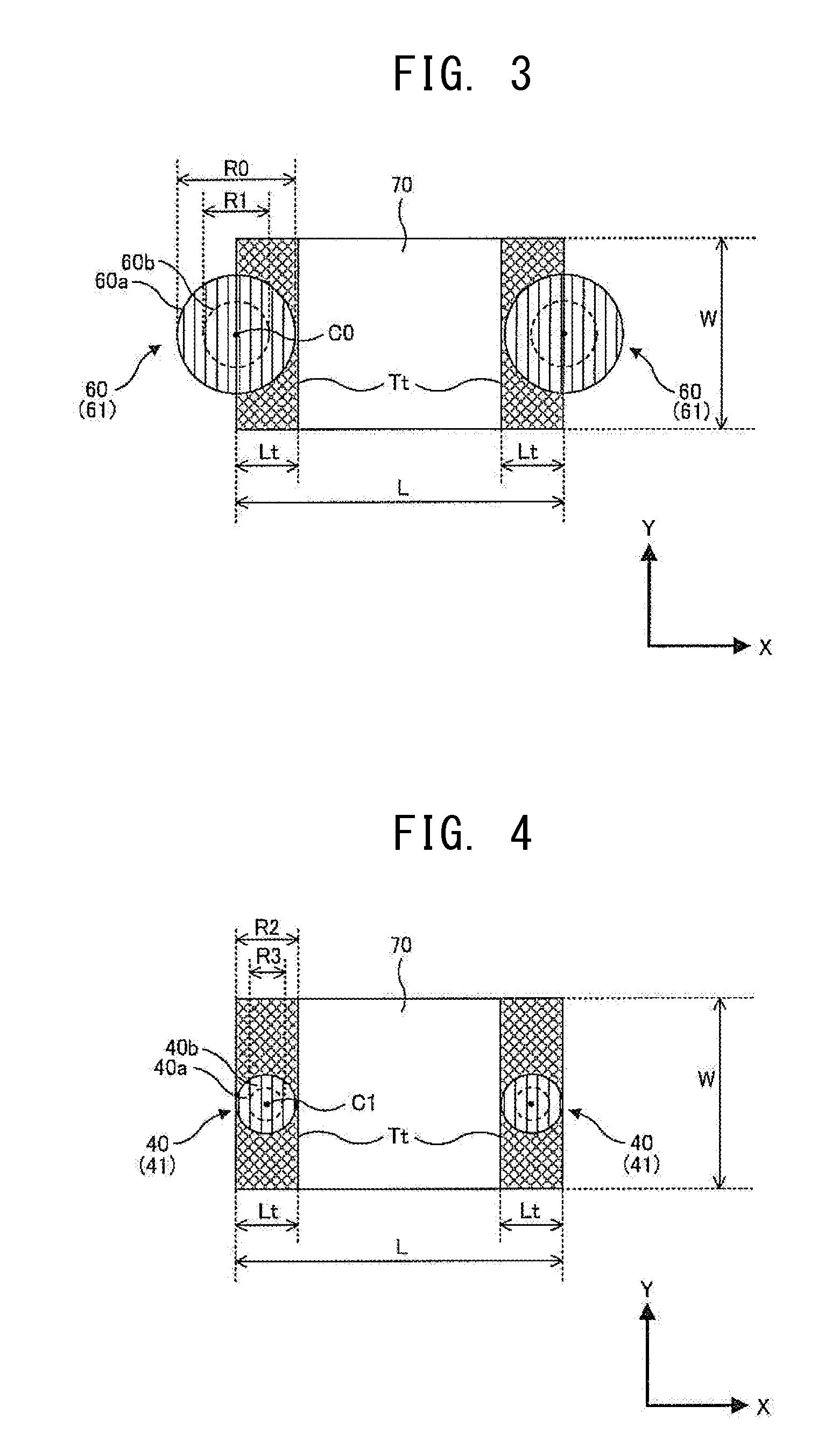

Component-incorporated wiring substrate and method of manufacturing the same

InactiveUS20130048361A1Wide connectionReduce DC resistancePrinted circuit assemblingFinal product manufactureElectrical conductorInsulation layer

A component-incorporated wiring substrate is provided. Some embodiments include a plate-like component incorporated in a core substrate and a build-up layer having an insulation layer and a conductor layer disposed in alternating layers. The component has terminal electrodes formed at its opposite ends having a side surface and a main surface. An insulation layer disposed on the main surface of the component has via conductors formed therein which are connected to the side surfaces and the main surfaces of the respective terminal electrodes. The via conductors are tapered, such that their via diameter decreases in a direction toward the terminal electrode, and their via diameter at a position where they connect to the main surface is greater than a length of the main surface. Accordingly, the area of connection between the via conductors and the corresponding terminal electrodes is increased, improving connection reliability through enhancement of tolerance for positional deviation.

Owner:NGK SPARK PLUG CO LTD

Negative electrode material and preparation method thereof, negative electrode plate and lithium ion battery

PendingCN107946561AImprove cycle performanceReduce usageNegative electrodesSecondary cellsInternal resistanceCarbon nanotube

The invention discloses a negative electrode material of a lithium ion battery. The negative electrode material comprises the following components in parts by mass: 88-105 parts of active material, 0.01-0.1 parts of single-wall carbon nanotubes, 0.01-0.5 parts of graphene nanobelt, one or less parts of super conductive carbon black, one or less parts of less-wall or multi-wall carbon nanotubes, 0.05-0.5 parts of dispersing agent, 1-3 parts of thickening agent, 1-4 parts of binder and 25-60 parts of solvent; the active material comprises a silicon oxide material SiO<x> and synthetic graphite, wherein x is greater than 0 and less than 2; and the silicon element in the negative electrode material is less than or equal to 3.5mass%. The invention provides the negative electrode material comprising the silicon oxide material and the low-dimensional carbon conductive material of the lithium ion battery; by virtue of the negative electrode material of the lithium ion battery, the problems of capacity fading and increasing internal resistance caused by losing of effective electron channels due to low electrical conductivity and an expansion effect in the use process of a silicon oxide negative electrode active material can be solved; and meanwhile, the cycle performance of the lithium ion battery applying the negative electrode material is improved.

Owner:SHENZHEN BAK POWER BATTERY CO LTD

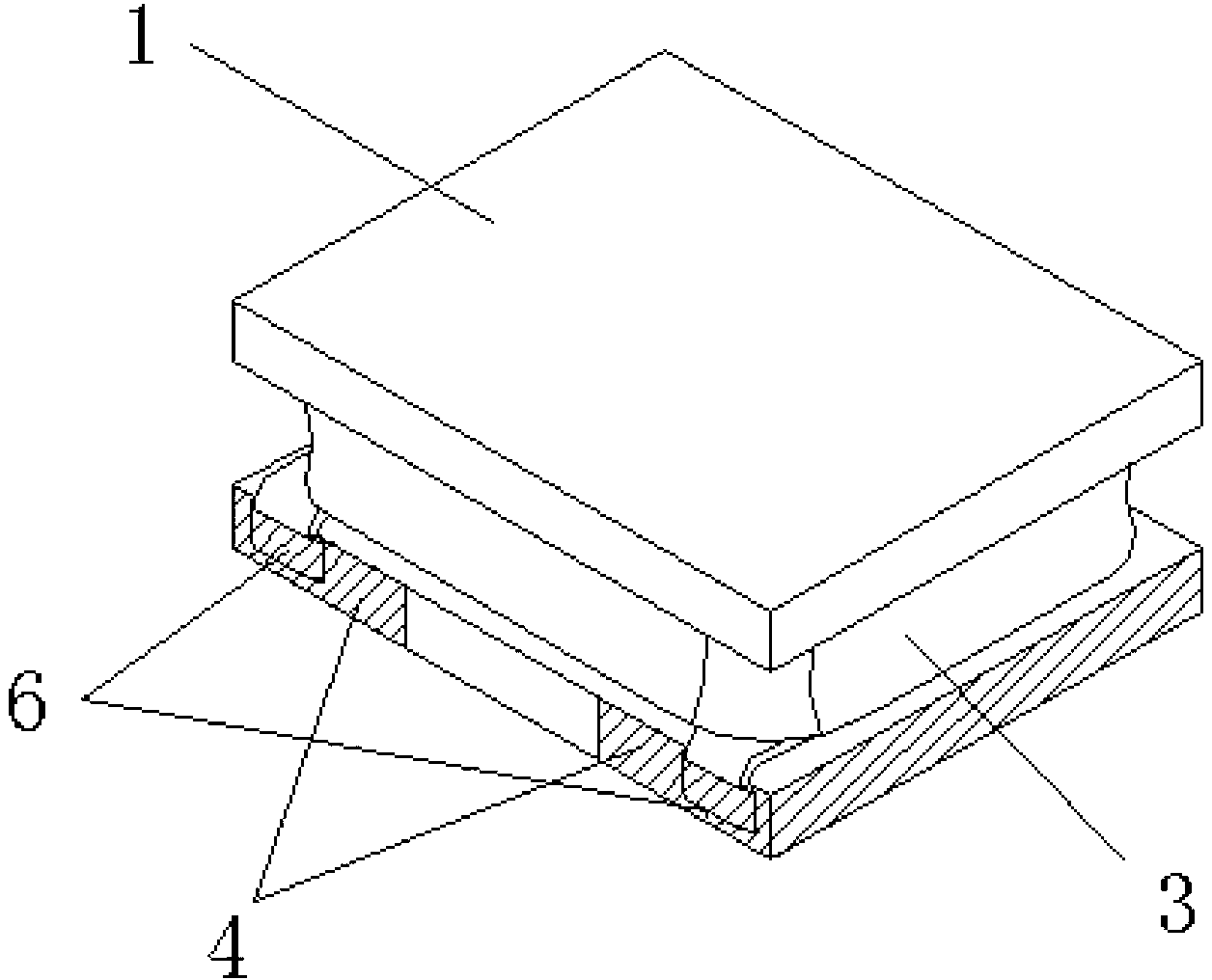

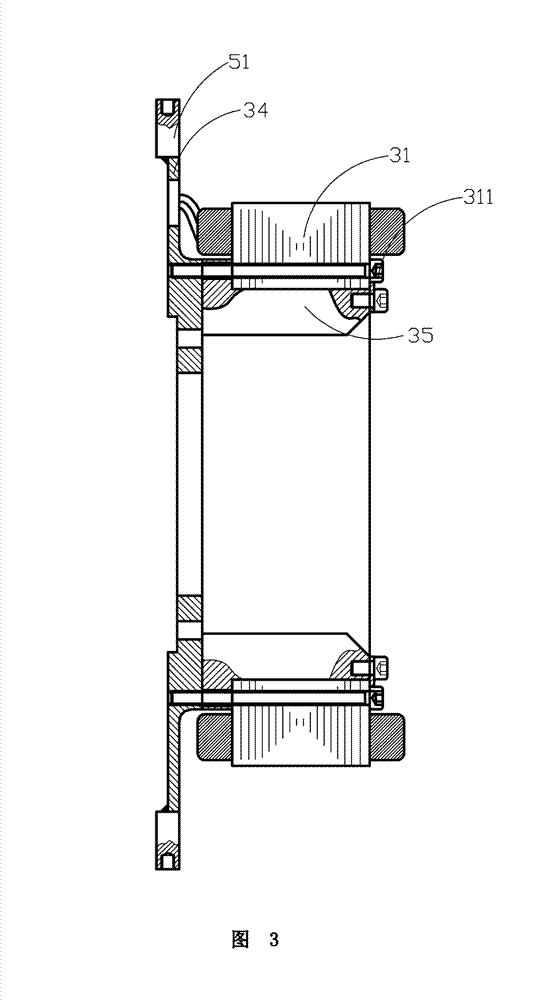

Magnetic element and its manufacture, power supply module therewith

InactiveCN1407564AReduce magnetic lossIncrease the inductance valueTransformers/inductances coils/windings/connectionsEncapsulation/impregnationElectrical conductorComputer module

A magnetic device includes a sheet-type coil including a planar conductive coil and an insulating substance; and a sheet-type first magnetic member disposed on at least one of upper and lower surfaces of the sheet-type coil, where a magnetic permeability of the insulating substance is smaller than a magnetic permeability of the first magnetic member. The magnetic device preferably includes a second magnetic member provided at a predetermined area of the sheet-type coil, the second magnetic member being made of a resin containing a magnetic powder and having a permeability larger than the insulating substance and smaller than the first magnetic member. The predetermined area is at least one position selected from a center portion and a peripheral portion of the sheet-type coil where a conductor constituting the planar conductive coil is not present. Further, a power supply module of the present invention includes the magnetic device according to the present invention.

Owner:PANASONIC CORP

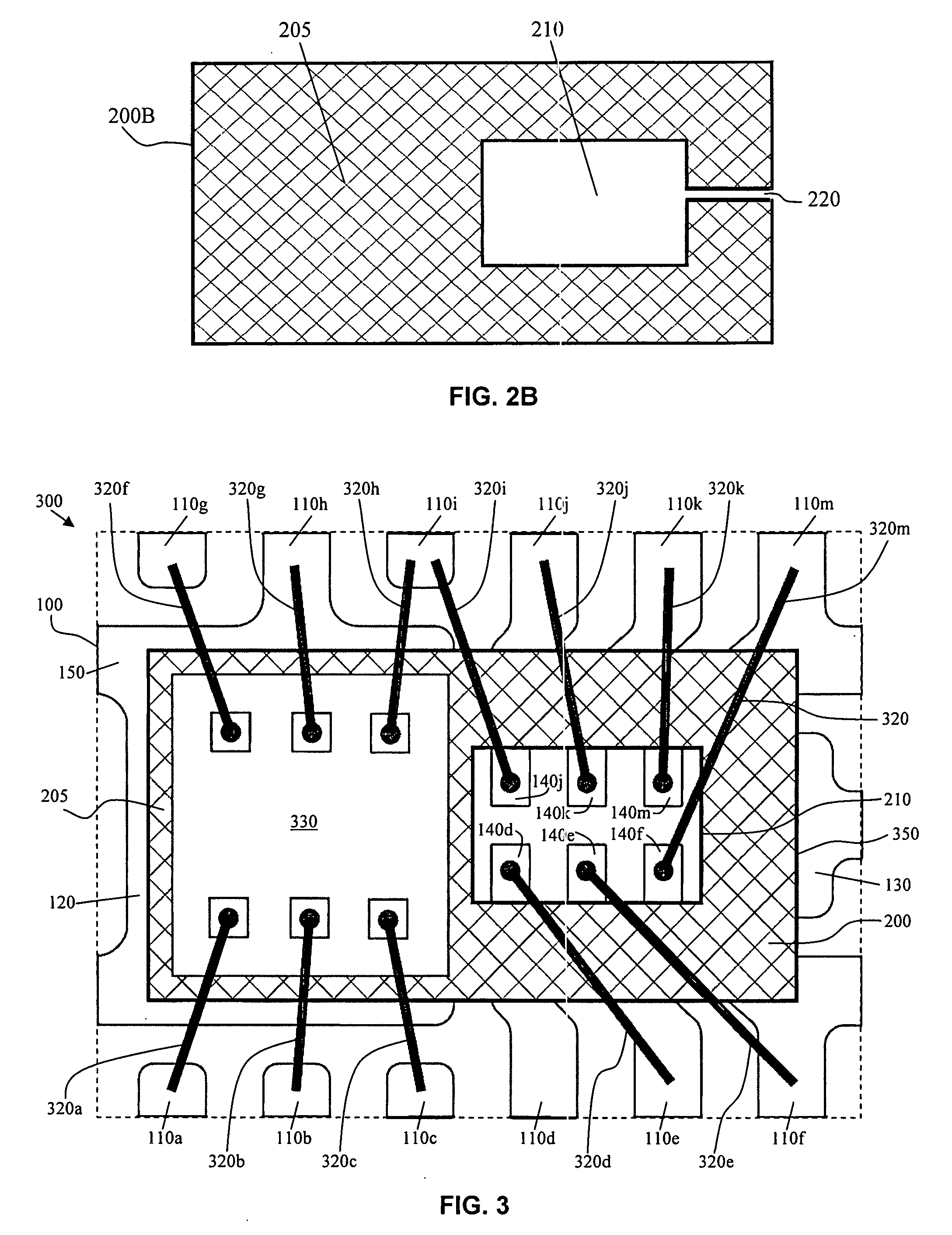

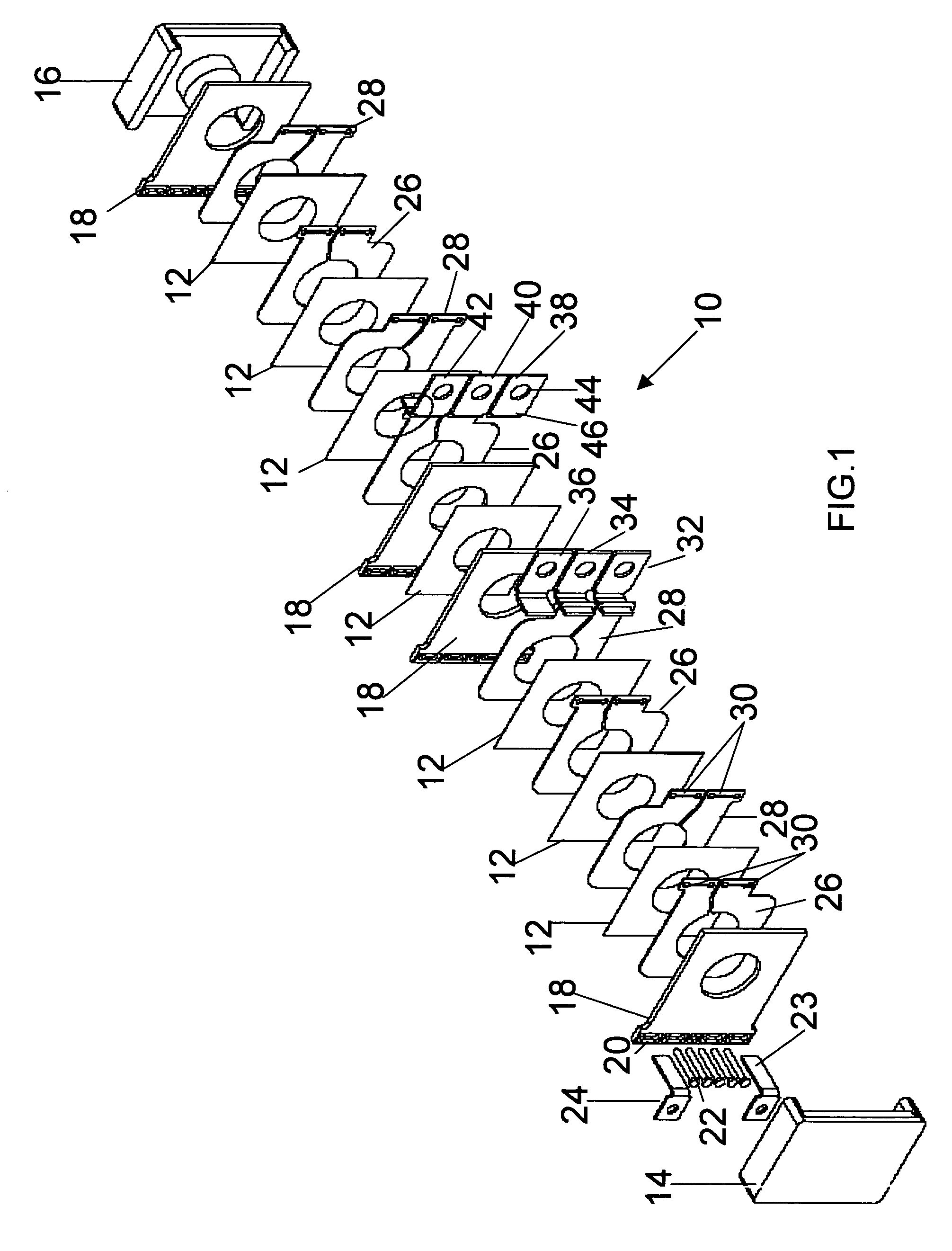

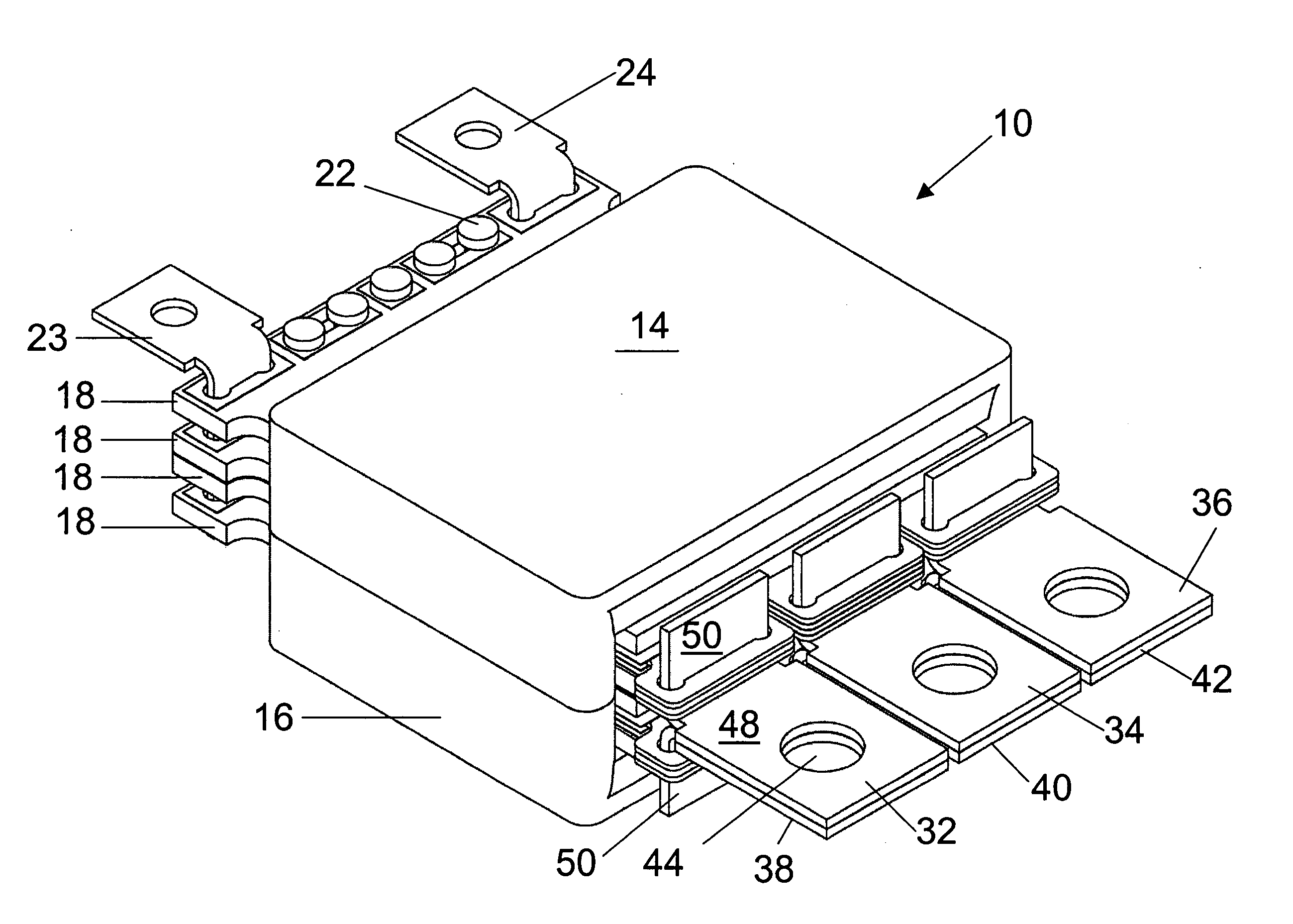

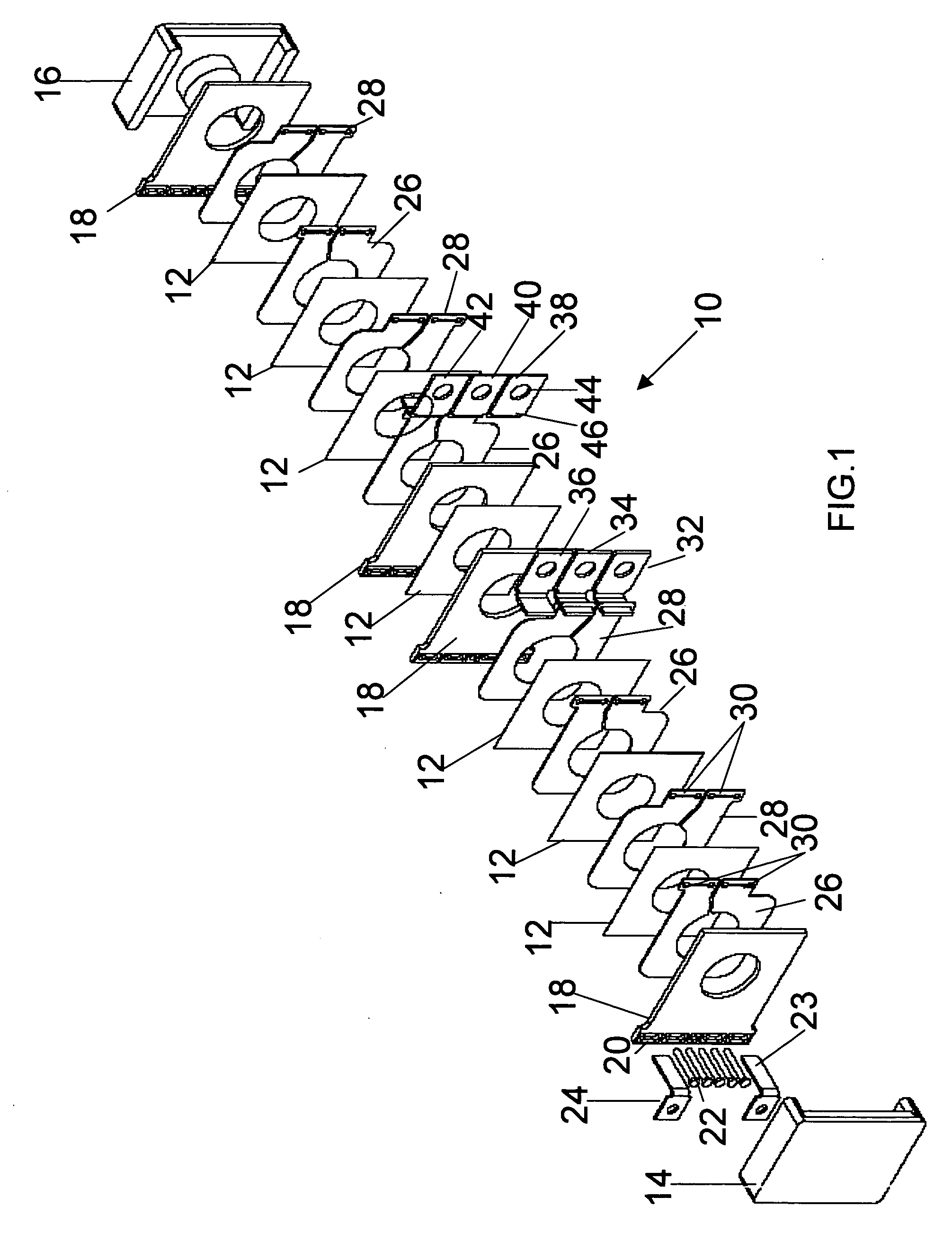

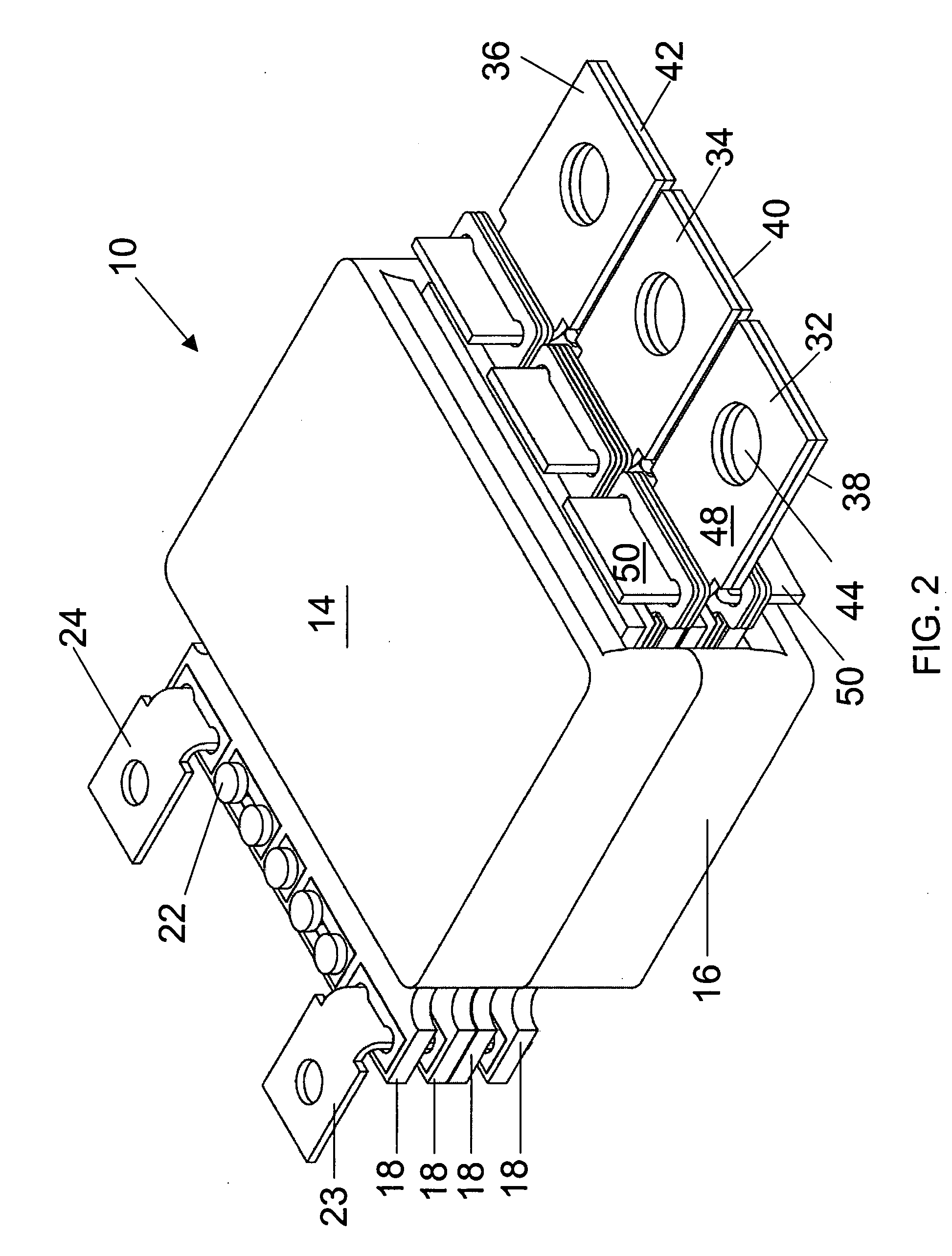

Semiconductor power device package having a lead frame-based integrated inductor

ActiveUS20090134503A1Increase inductanceReduce DC resistanceSemiconductor/solid-state device detailsSolid-state devicesInductorLead frame

A semiconductor power device package having a lead frame-based integrated inductor is disclosed. The semiconductor power device package includes a lead frame having a plurality of leads, a inductor core attached to the lead frame such that a plurality of lead ends are exposed through a window formed in the inductor core, a plurality of bonding wires, ones of the plurality of bonding wires coupling each of the plurality of lead ends to adjacent leads about the inductor core to form the inductor, and a power integrated circuit coupled to the inductor. In alternative embodiments, a top lead frame couples each of the plurality of lead ends to adjacent leads about the inductor core by means of a connection chip.

Owner:ALPHA & OMEGA SEMICON INC

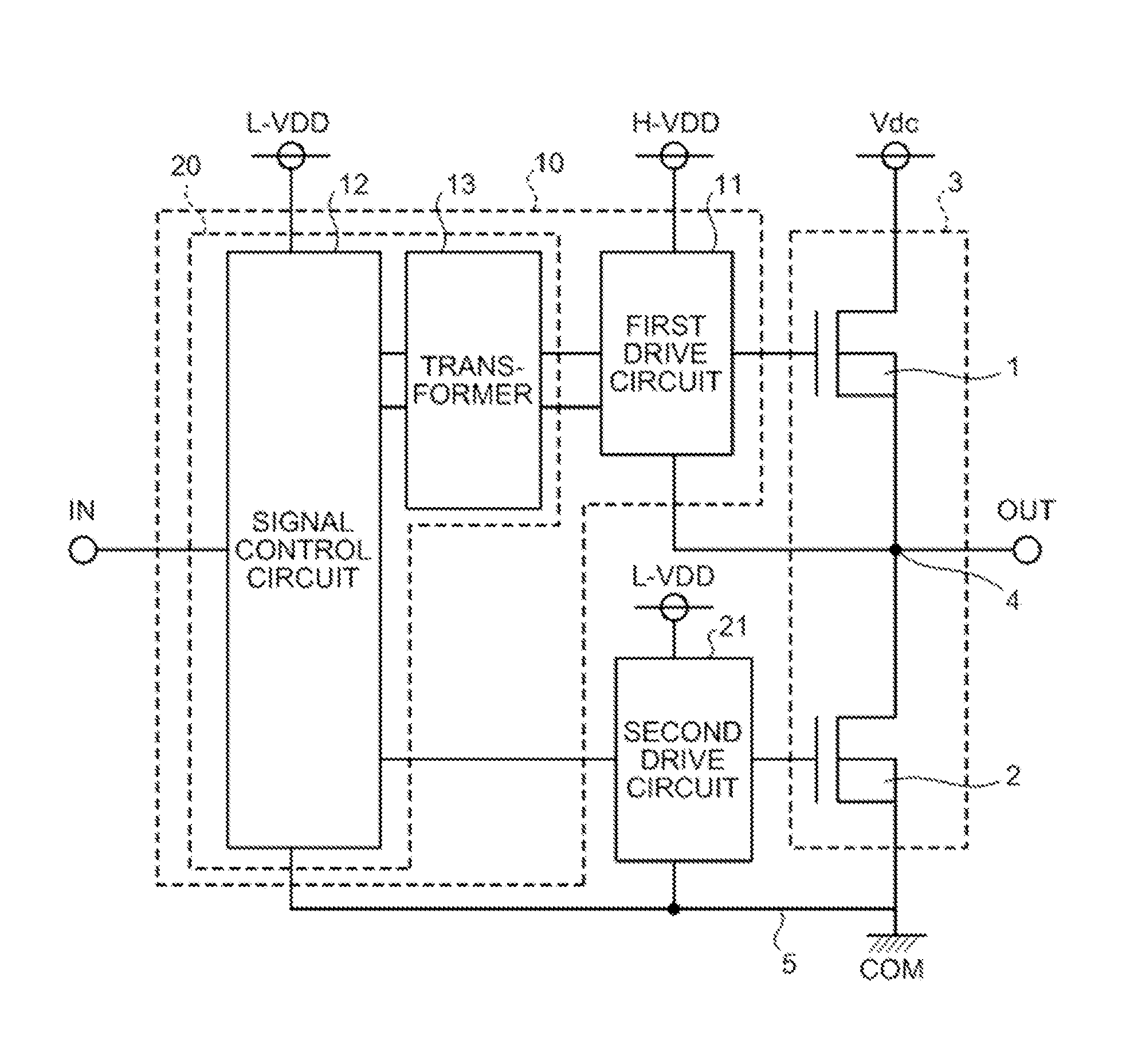

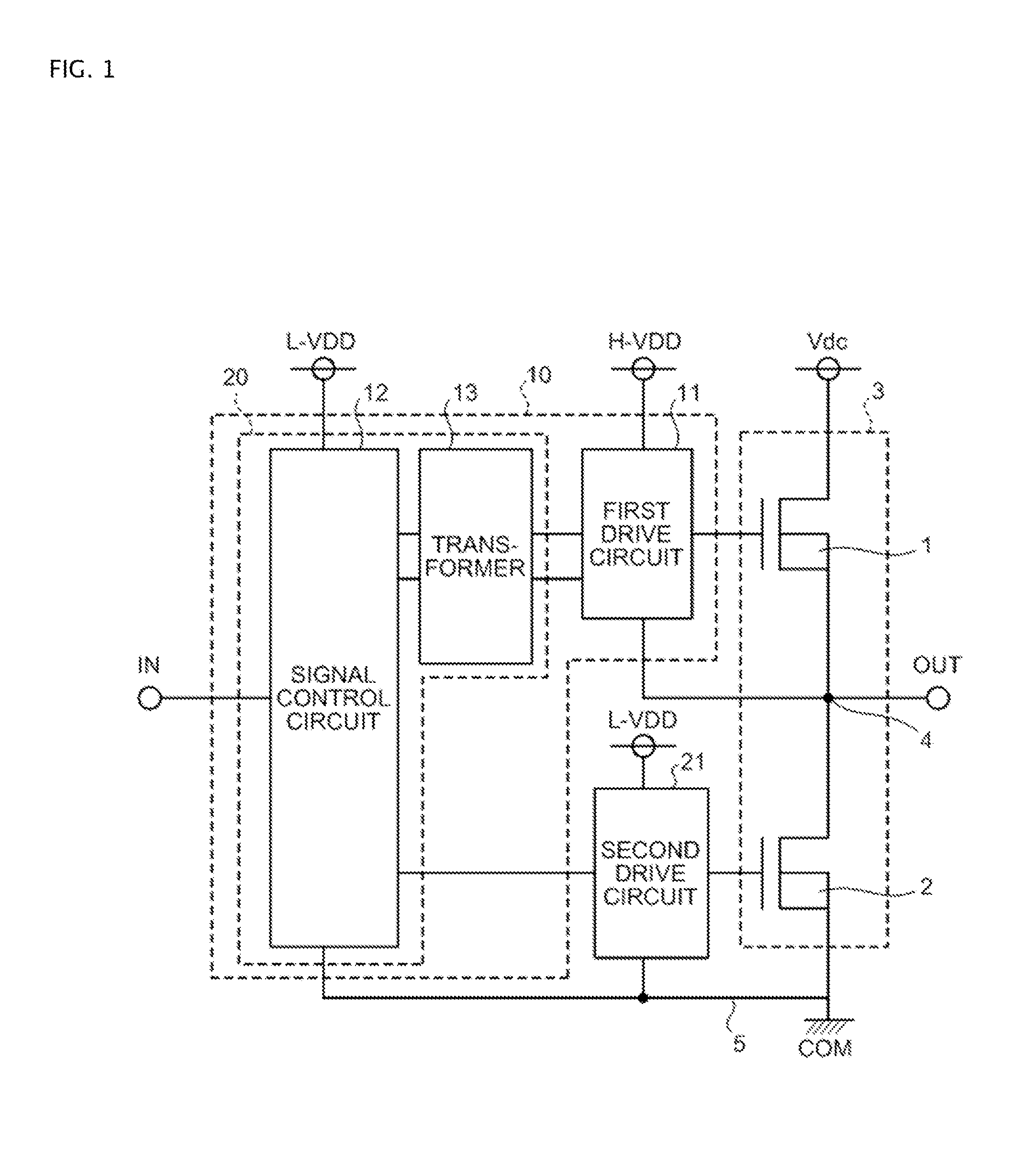

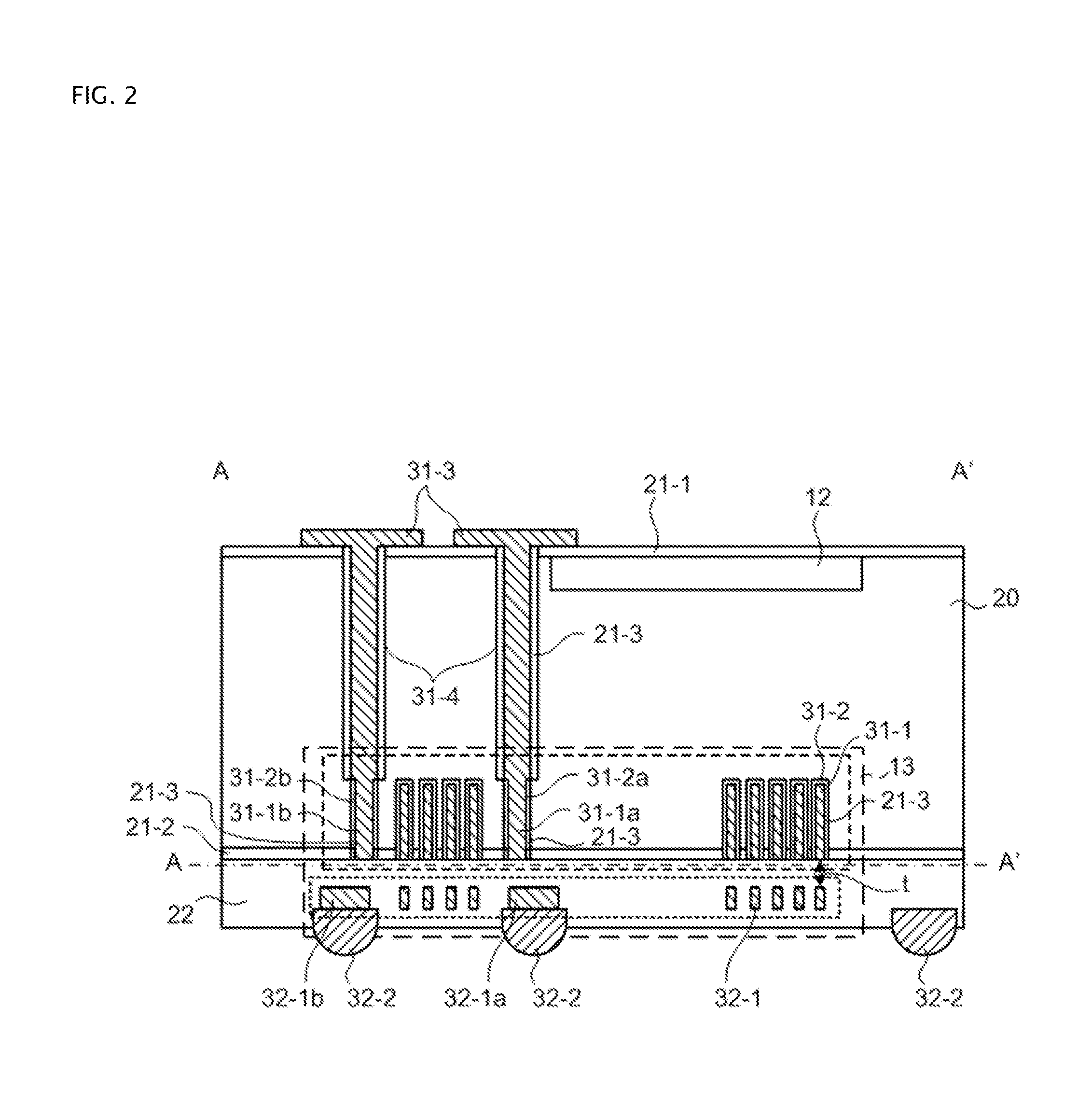

Isolator and isolator manufacturing method

ActiveUS20130321094A1Small sizeEliminate the effects ofSemiconductor/solid-state device detailsSolid-state devicesElectricityAnterior surface

In certain aspects of the invention, an isolator is configured by a reception circuit, a transmission circuit, and a transformer. In some aspects, the transmission circuit is disposed in an anterior surface of a semiconductor substrate. The transformer is disposed in a posterior surface of the semiconductor substrate and transmits in an electrically isolated state to the reception circuit, a signal input from the transmission circuit. The transformer is configured by a primary coil and a secondary coil. The primary coil can be configured by a metal film embedded in an oxide film inside a coil trench. The secondary coil can be disposed inside an insulating film covering the primary coil so as to oppose the primary coil and is insulated from the primary coil by the insulating film.

Owner:FUJI ELECTRIC CO LTD

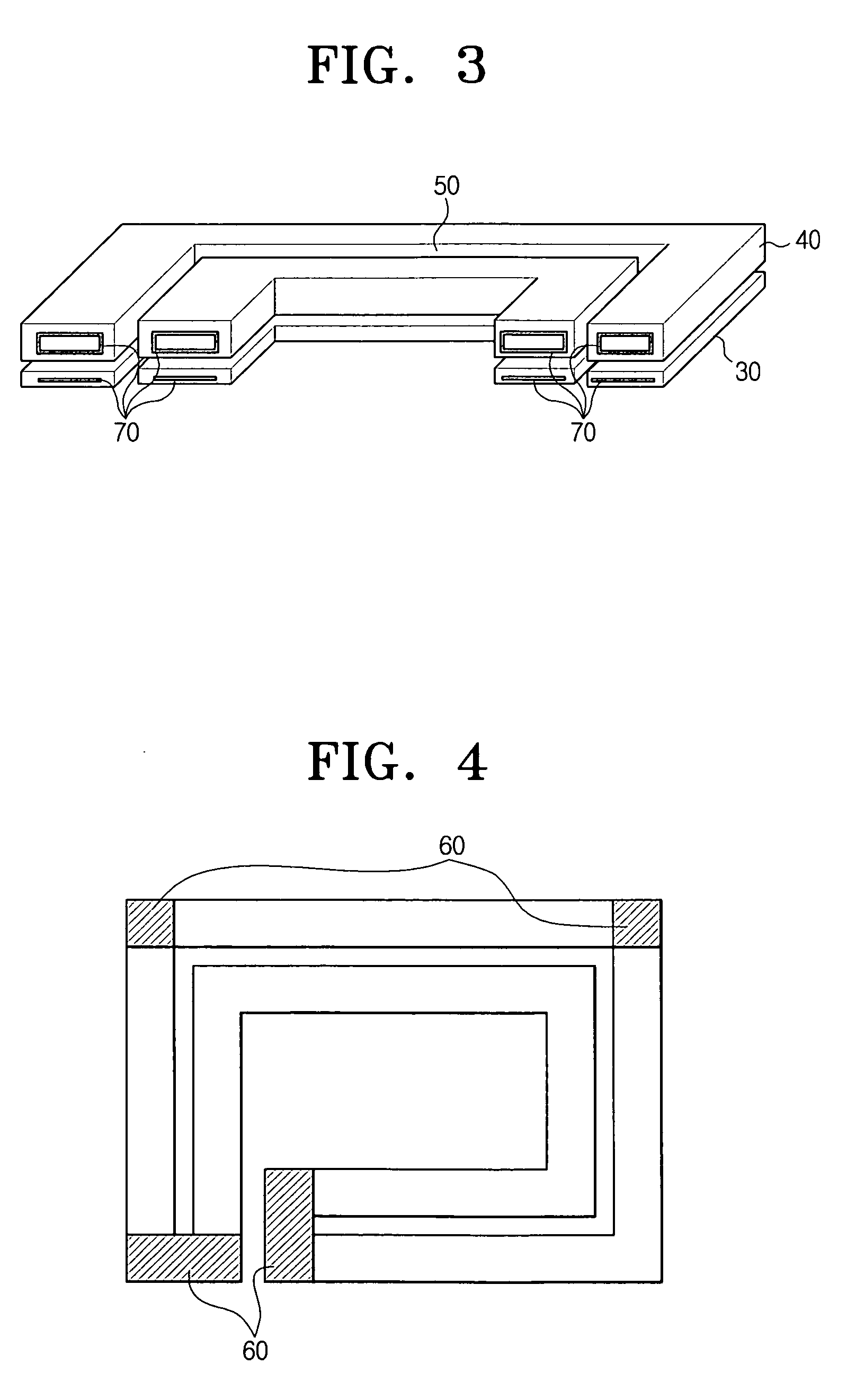

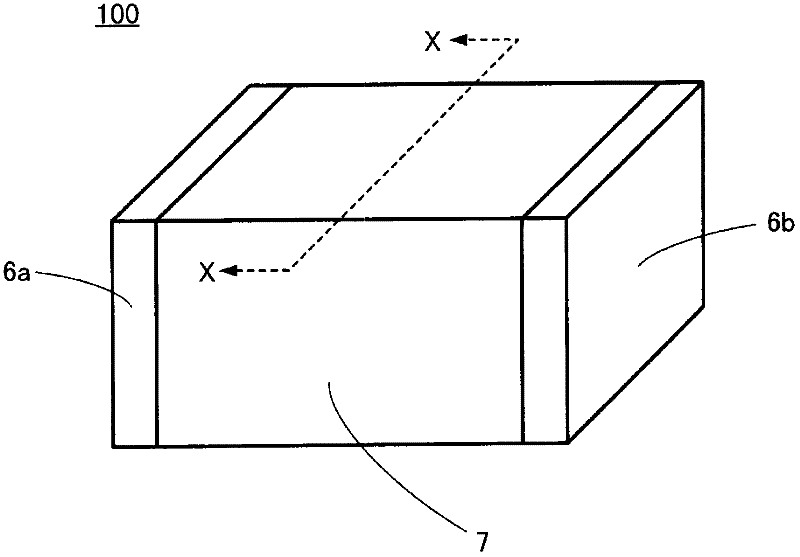

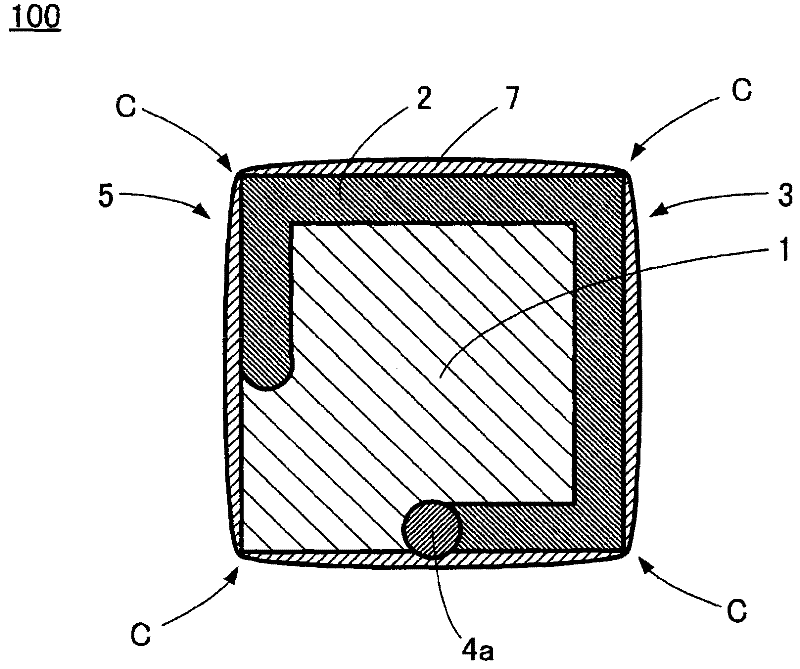

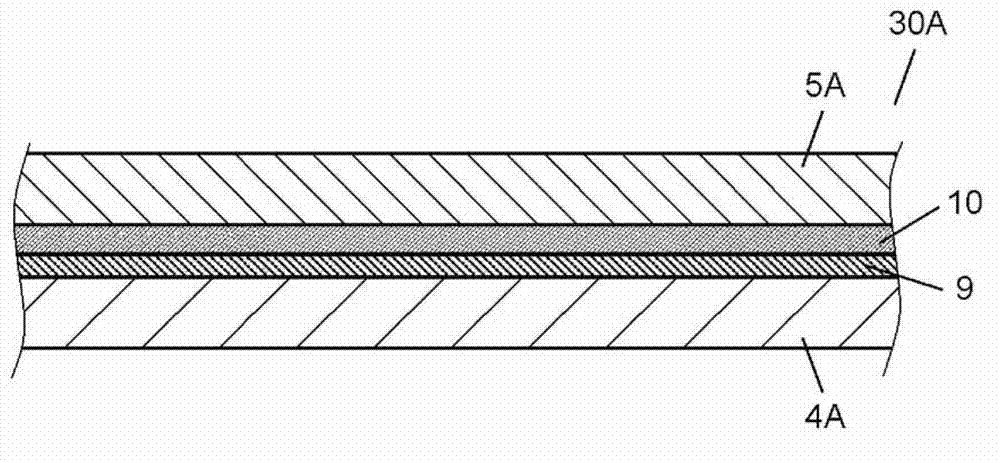

Electronic component and manufacturing method thereof

ActiveUS20140266547A1Joint strengthReduce DC resistanceTransformers/inductances coils/windings/connectionsCoils manufactureElectrical conductorElectronic component

An electronic component includes a first conductor layer including a first conductor pattern P1, a first insulating layer covering the first conductor layer, a first opening h1 passing through the first insulting layer to expose top and side surfaces of the first conductor pattern P1 therethrough, and a second conductor layer formed on the first insulating layer and including a second conductor pattern P2 connected to the first conductor pattern P1 through the first opening h1. A first opening region which is a planar region inside the first opening h1 includes a first region in which the first conductor pattern P1 is formed and a second region in which the first conductor pattern P1 is not formed. The second conductor pattern P2 is embedded in both the first and second regions of the first opening h1.

Owner:TDK CORPARATION

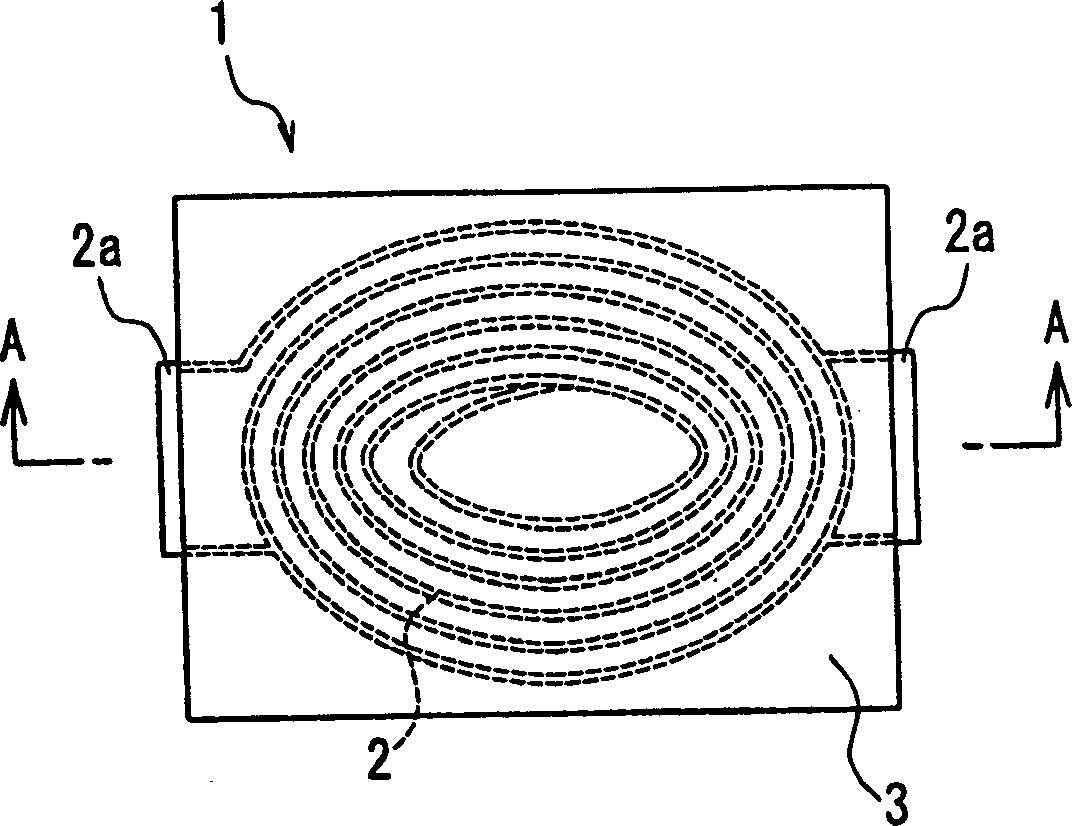

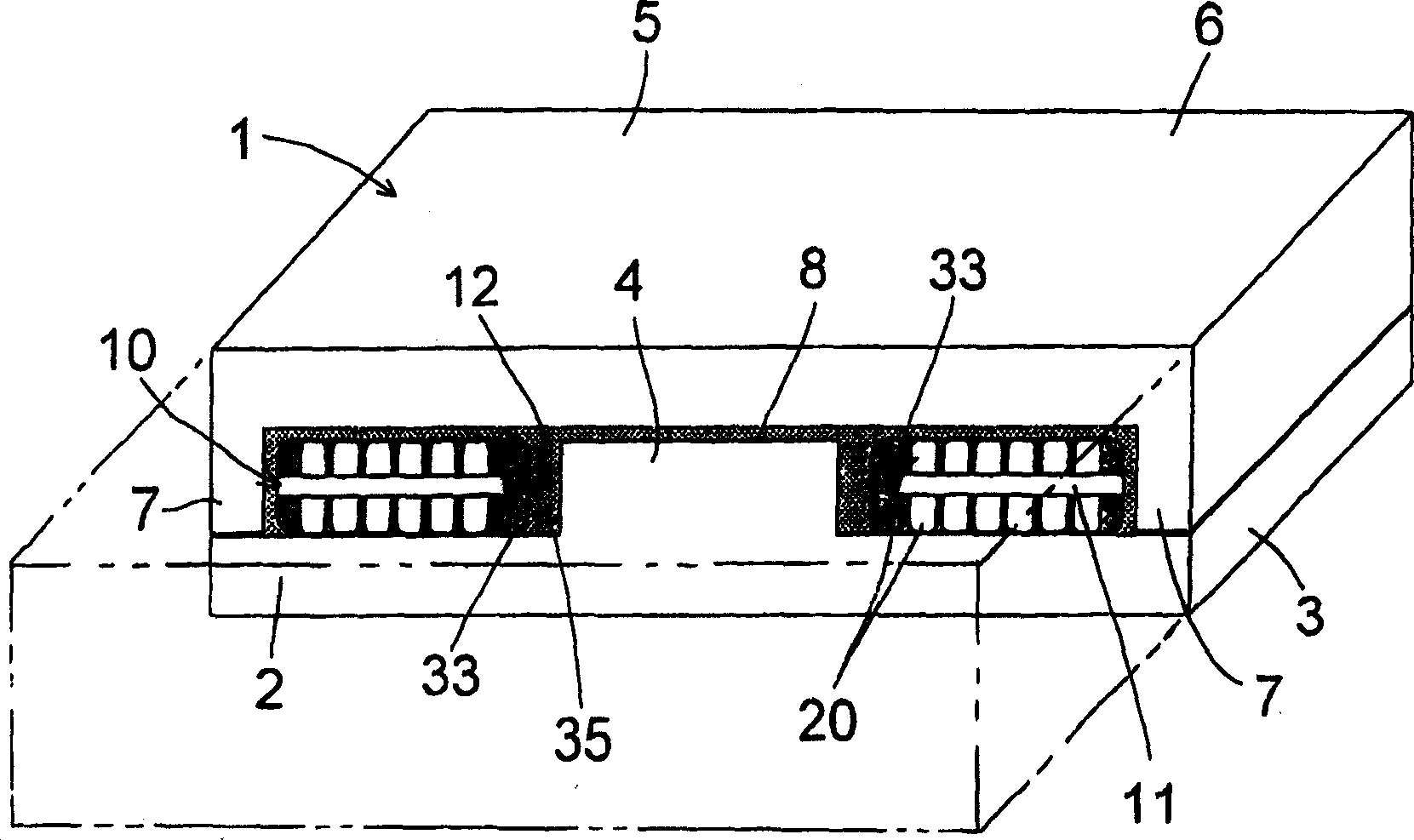

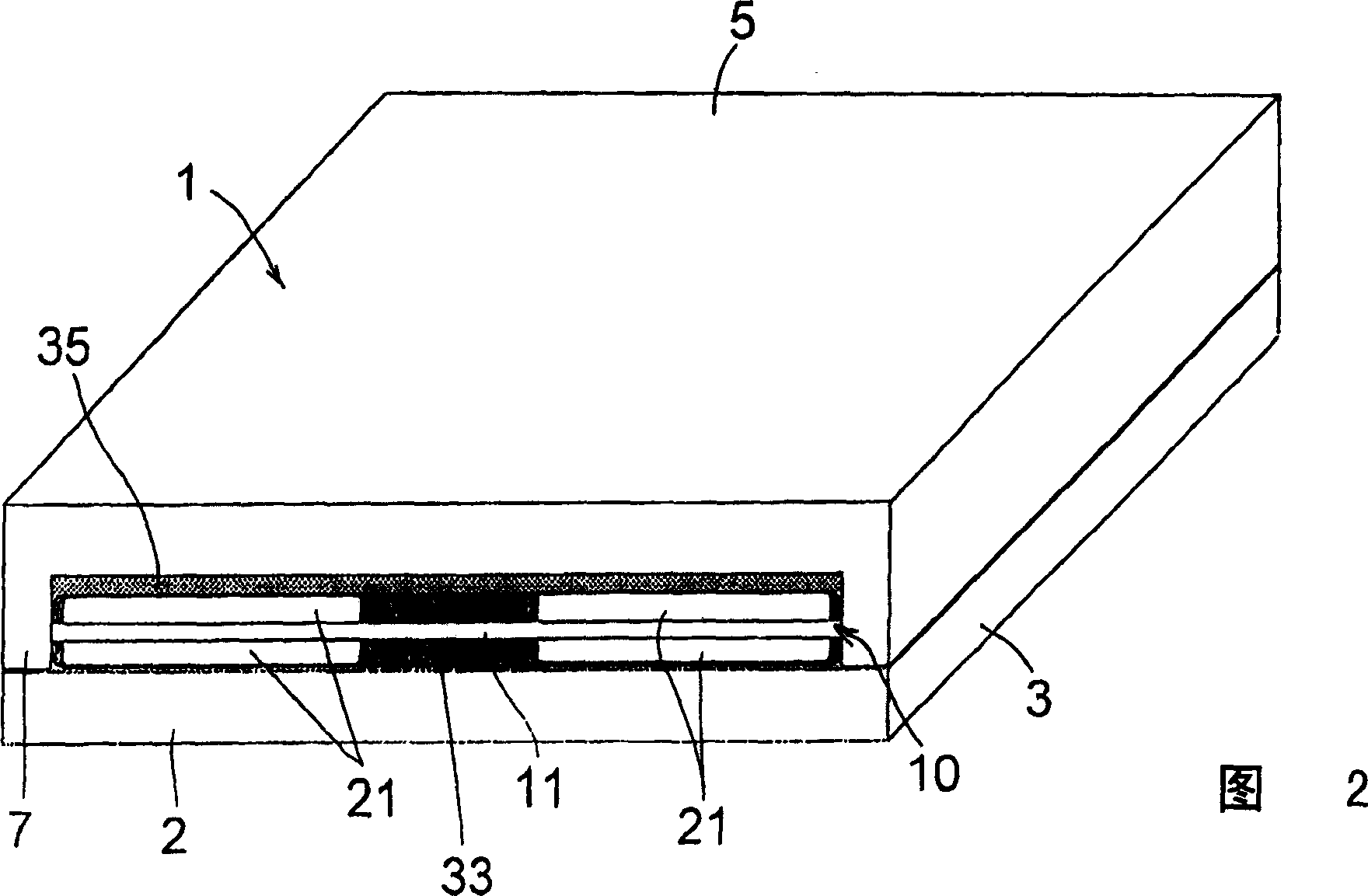

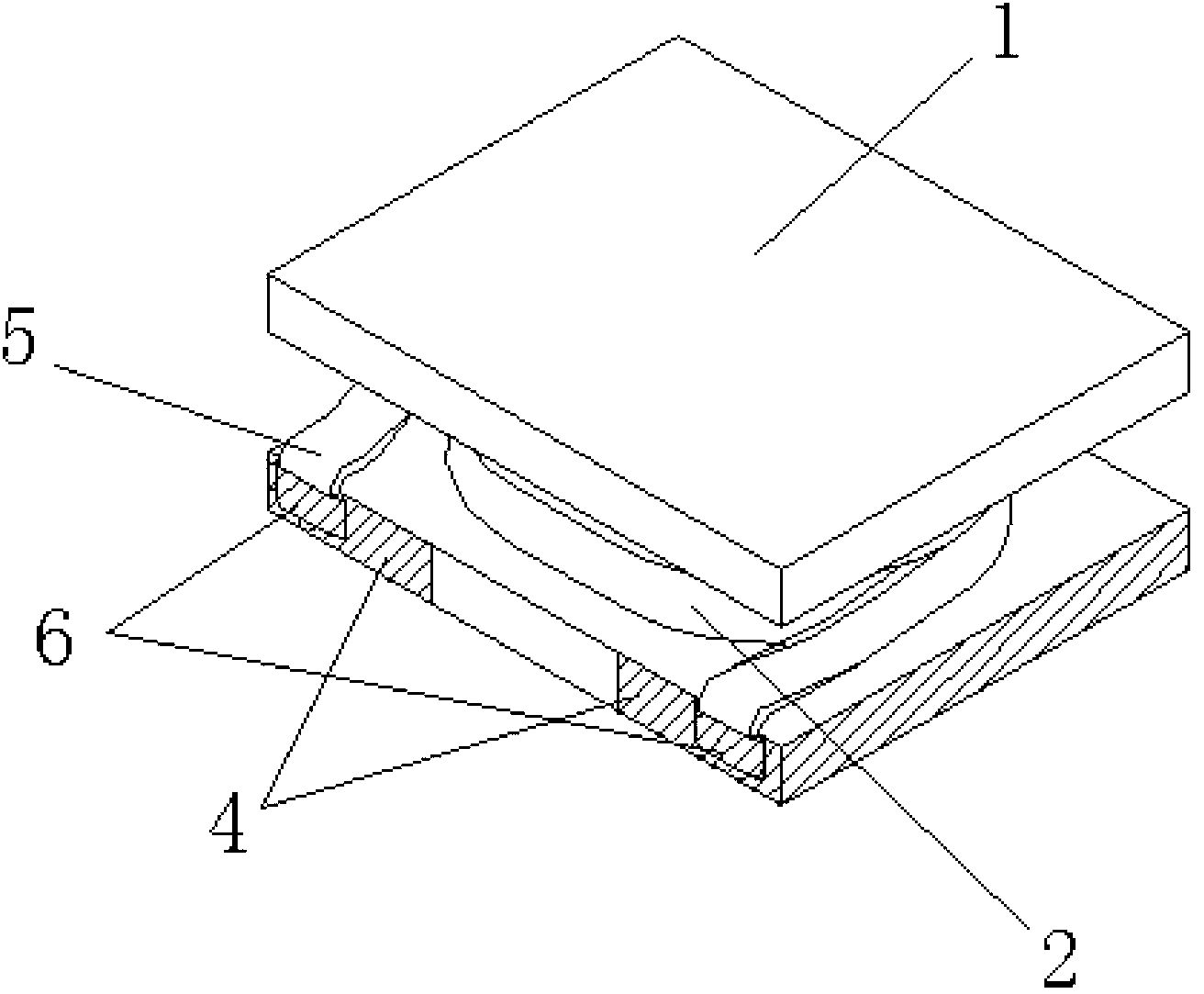

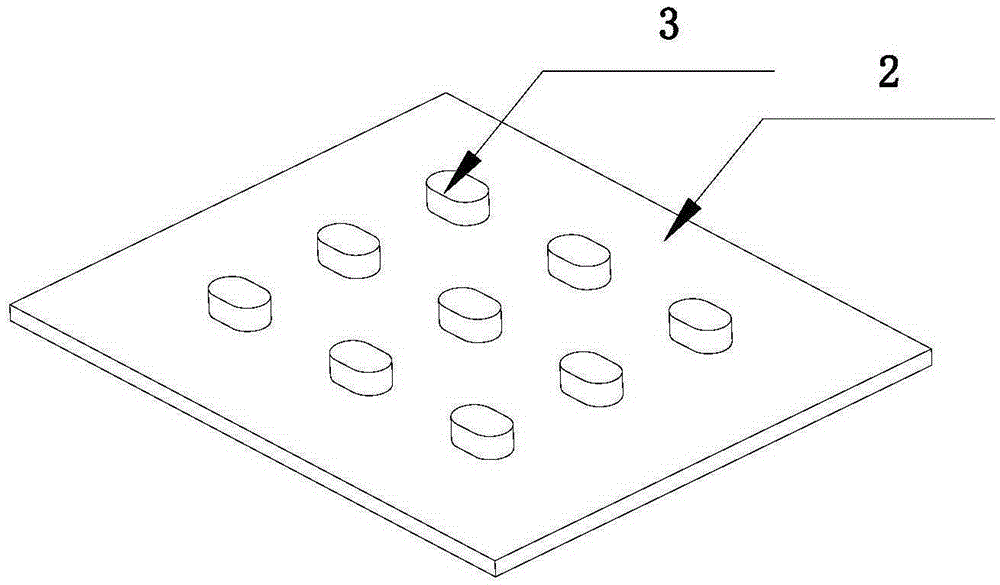

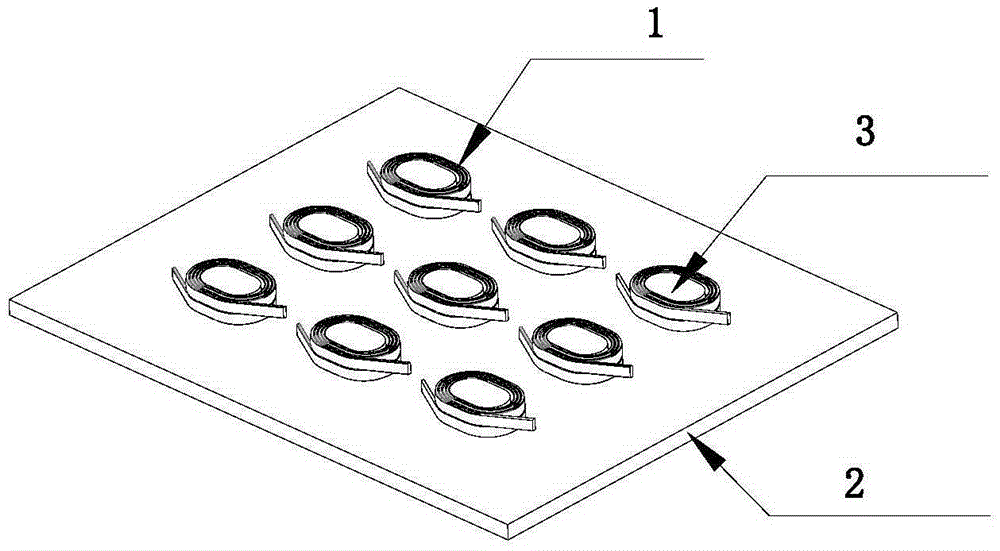

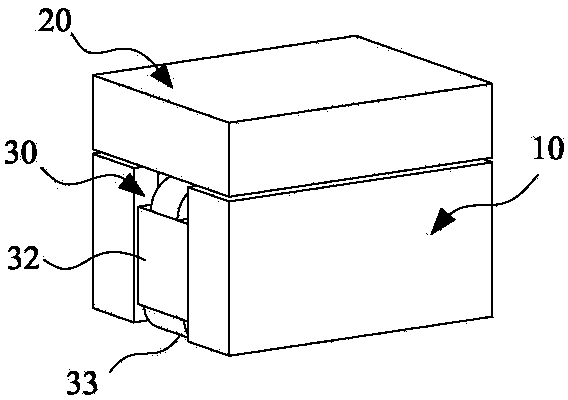

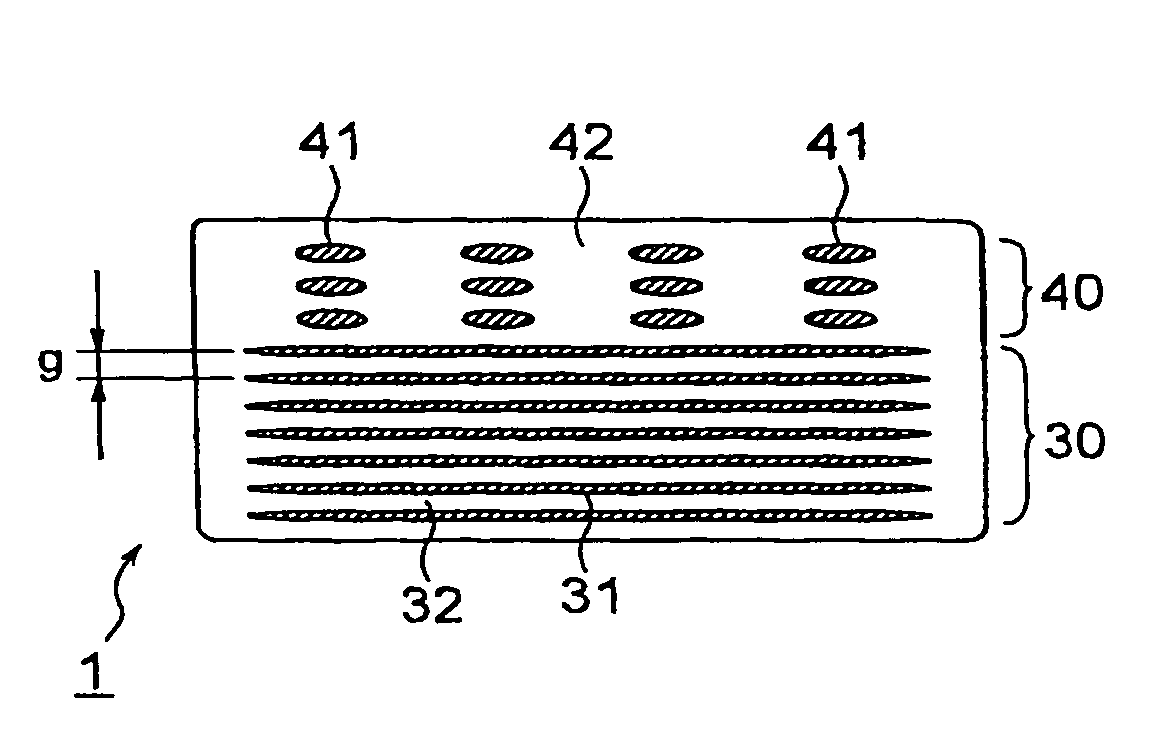

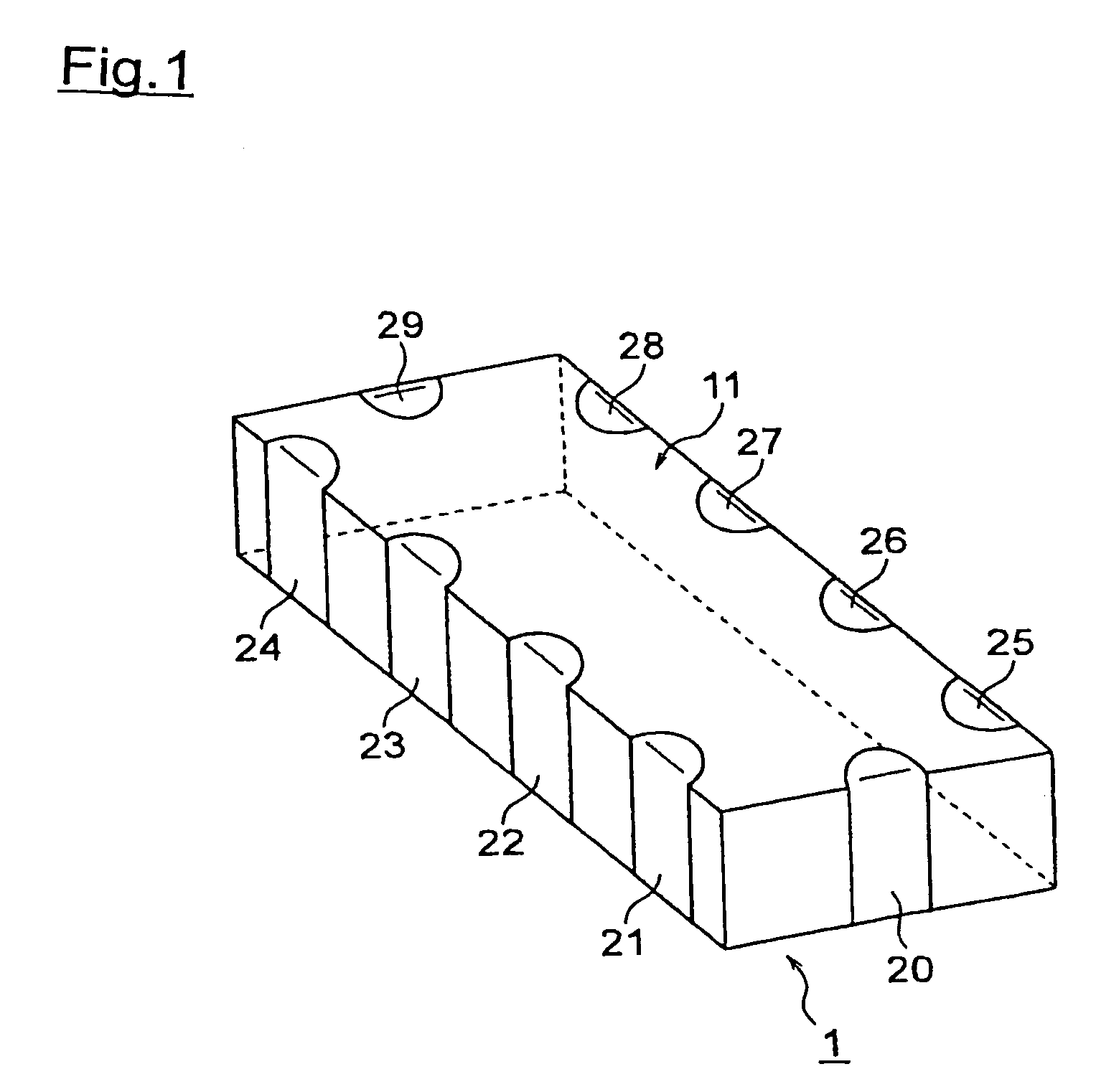

Coil circuit board and surface mounted type coil element

ActiveCN1574128AReduce DC resistanceStrong electrical reliabilityTransformers/inductances coils/windings/connectionsCoils manufactureElectrical conductorSurface mounting

Provided is a coil substrate and a surface mounting type coil element which have higher inductance and low resistance coil conductor and are manufactured with less number of processes. Magnetic cores 2 and 5 are provided face to face. A spiral coil conductor 20 is formed to the front and rear surfaces of a core structure body 1 having an external core closed at both ends and a central leg, and of an insulating plate 11 including a through hole 12 at the center thereof. Moreover, a coil substrate 10 mutually connecting the spiral coil conductors 20 at the front and rear surfaces via the front and rear contacts and an external electrode connected to the coil conductor 20 are also provided. Under the condition that the central leg is inserted into the through-hole 12, the coil substrate 10 is allocated at the internal side of the core structure body 1 and the magnetic cores 2, 5 include a gap at the central leg.

Owner:TDK CORPARATION

Terminal system for planar magnetics assembly

ActiveUS7460002B2Reduce resistanceImprove efficiencyTransformers/inductances coils/windings/connectionsCoilsEngineeringConductor Coil

Owner:STANDEX ELECTRONICS

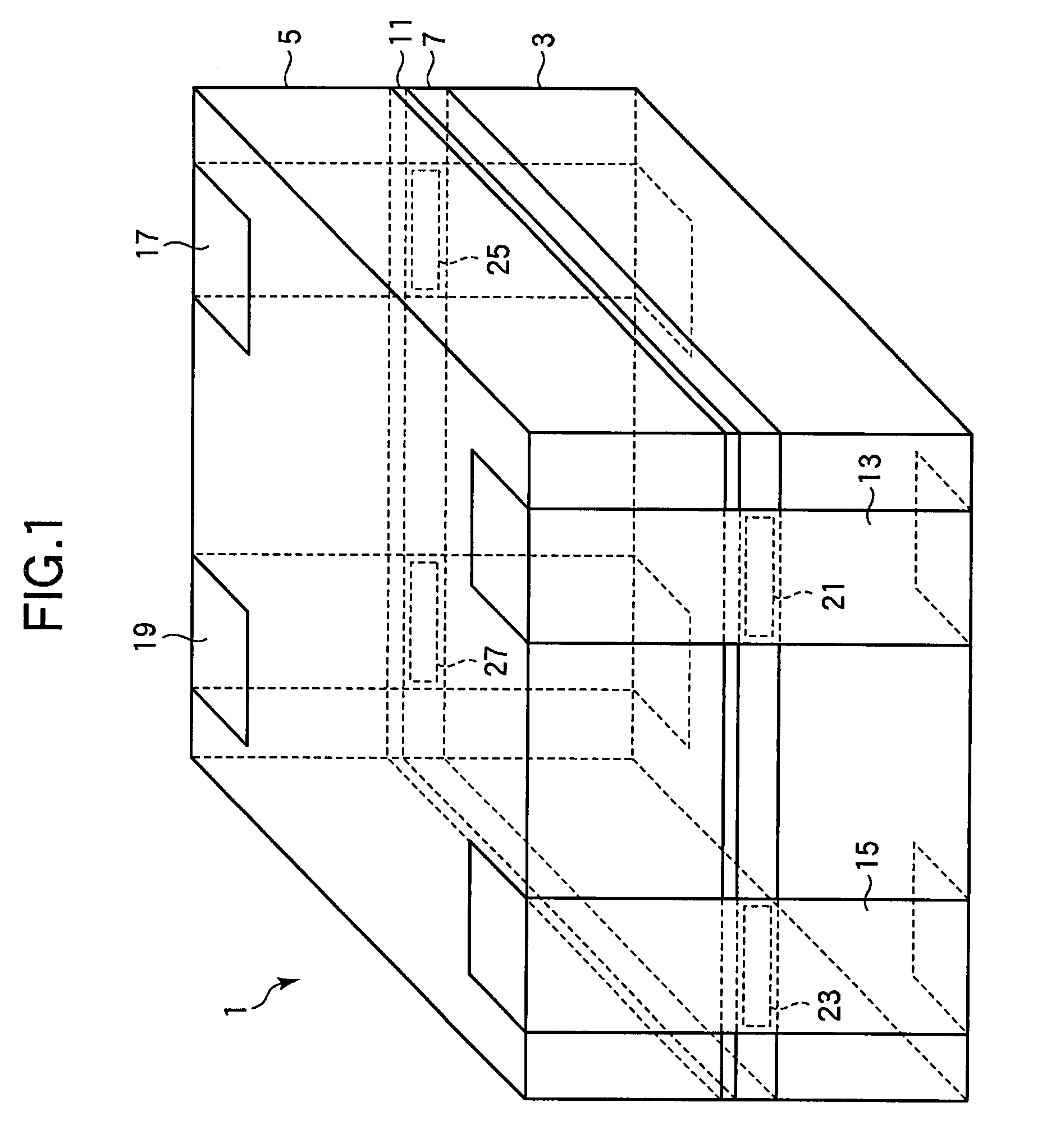

Dielectric ceramic composition, multilayer complex electronic device, multilayer common mode filter, multilayer ceramic coil and multilayer ceramic capacitor

ActiveUS20090278627A1Reduce DC resistanceMaintain good propertiesMultiple-port networksFixed capacitor dielectricCeramic capacitorDielectric permittivity

A dielectric ceramic composition comprises as a main component, Cu oxide, Si oxide and one selected from the group consisting of Zn oxide alone and a combination of Mg oxide and Zn oxide, as a subcomponent, a glass component including B oxide and at least one selected from the group consisting of Si oxide, Ba oxide, Ca oxide, Sr oxide, Li oxide and Zn oxide, and having a glass softening point is 750° C. or less, wherein a content of said glass component is 1.5 to 15 wt % with respect to 100 wt % of said main component.According to the present invention, a dielectric ceramic composition can be provided which is available to be sintered at low temperature (for example, 950° C. or lower) while comparatively decreasing contents of a glass component, which shows good properties (specific permittivity, loss Q value and insulation resistance), and which is available to perform cofiring different materials.

Owner:TDK CORPARATION

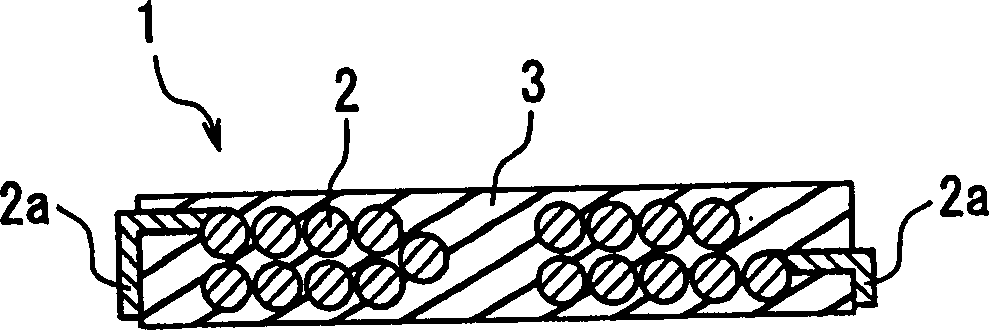

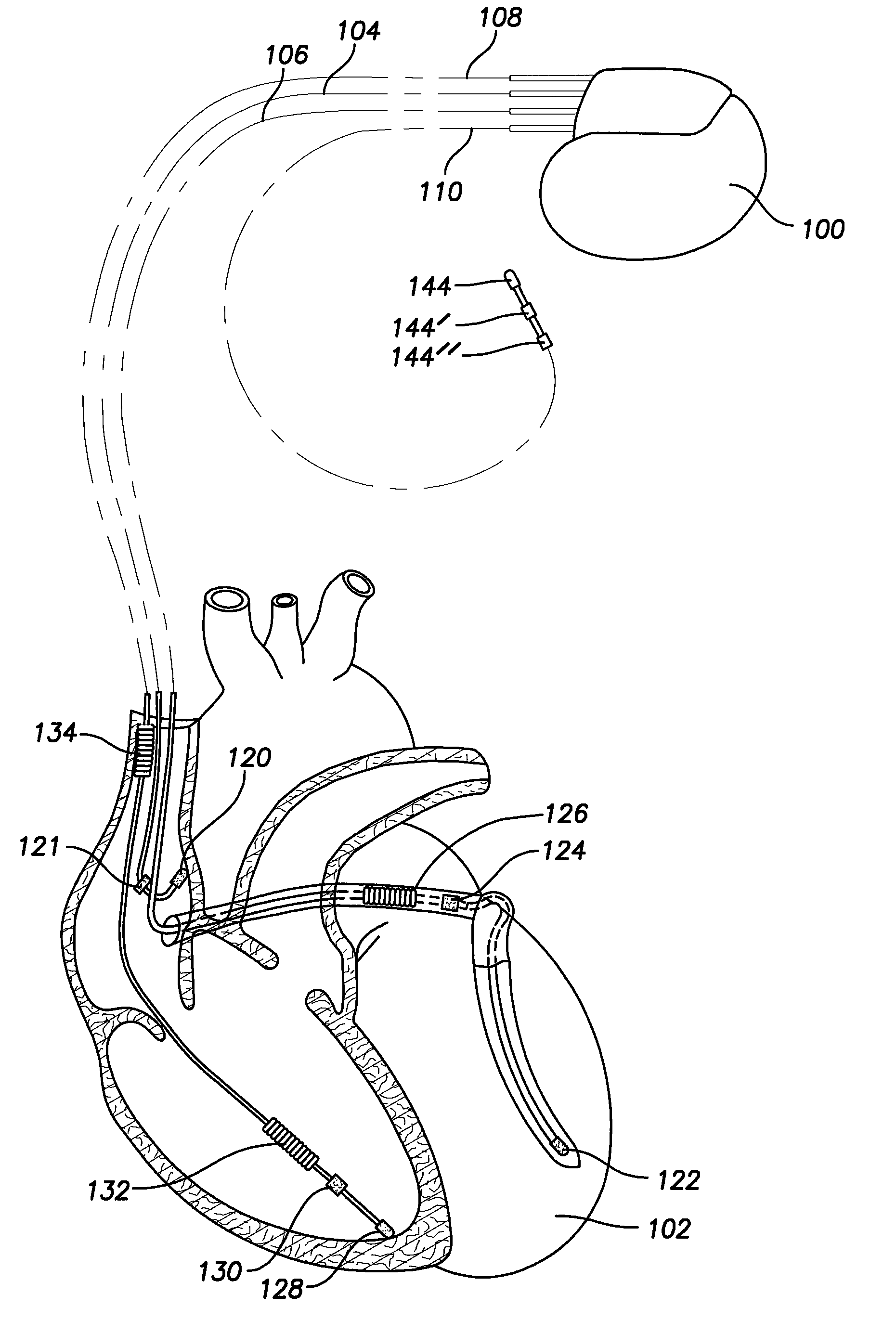

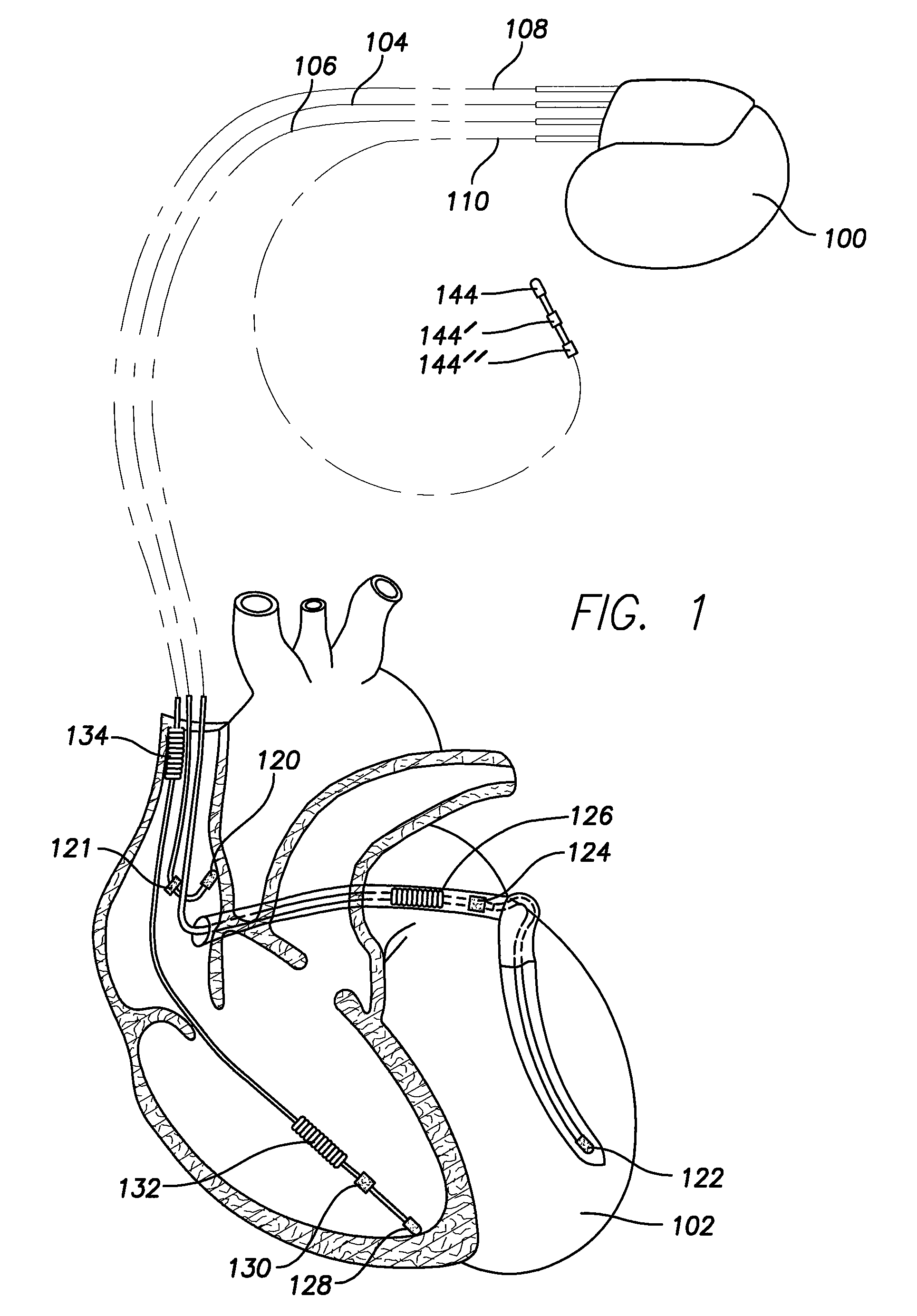

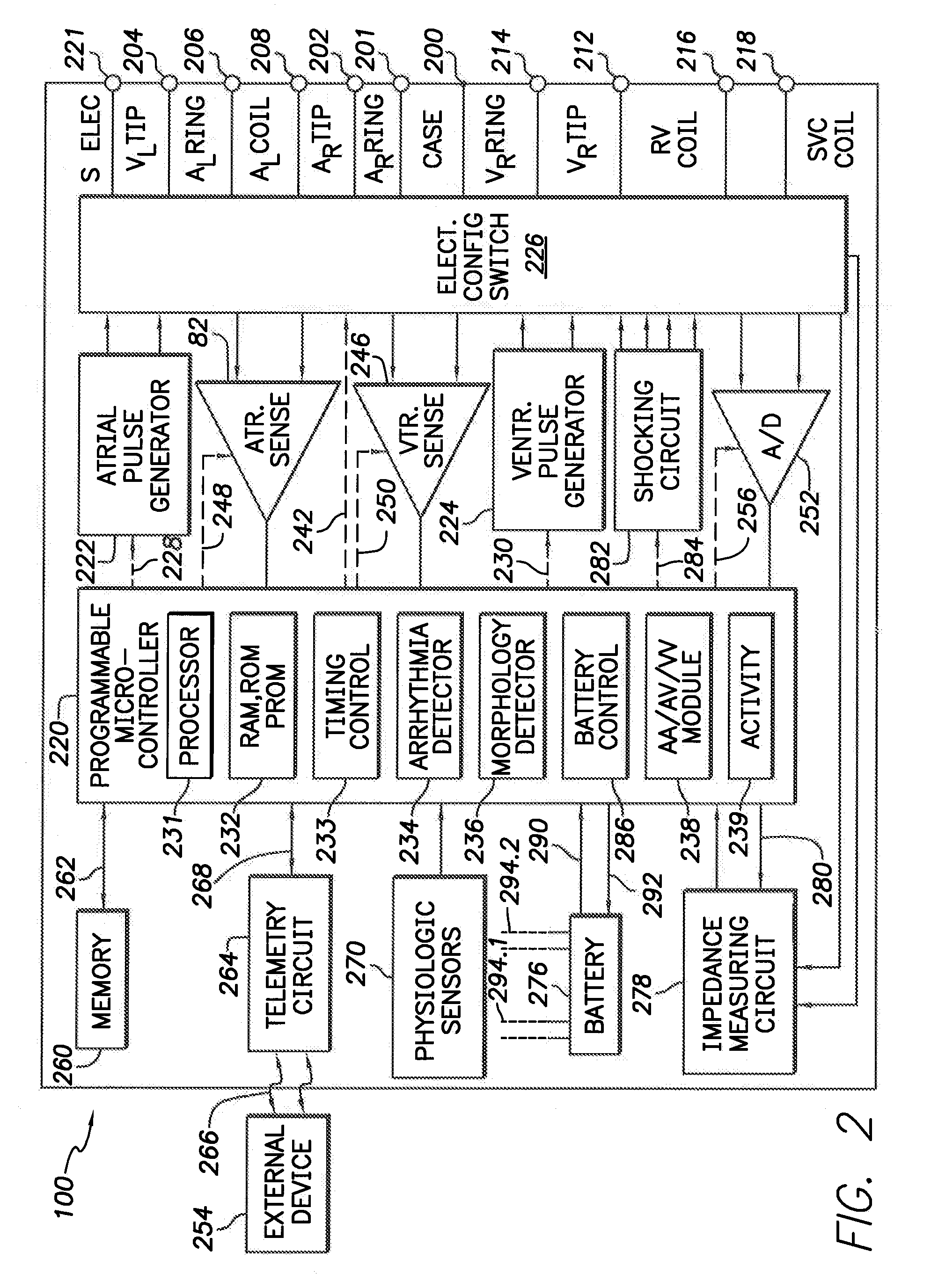

Small caliber implantable biometric leads and cables for same

ActiveUS20100204767A1Optimal mechanical and electrical performanceReduce the overall diameterInternal electrodesInsulated cablesAlloySmall caliber

Implantable medical leads have reduced diameter while providing for optimized mechanical and electrical properties, by reducing the diameters of the conducting cables used within the leads for sensing and delivery of therapeutic electrical stimulation. In an embodiment, conducting filaments within a cable have oval cross-sectional areas. Suitably orienting the oval filaments increases the contact surface between adjacent filaments, broadly distributing the pressure between filaments and reducing fretting fatigue, while the oval cross-sectional area also increases conductivity. In an embodiment, non-conducting coatings around filaments within a cable, or around groups of filaments organized into cable-layers, reduce fretting fatigue. In an embodiment, the cross-sectional area of filaments decreases as the filaments are positioned at increasing radial distances from the center of the cable. In an embodiment, the relative composition of various filament metals and / or alloys is varied in filaments at different radial distances from the center of the cable.

Owner:PACESETTER INC

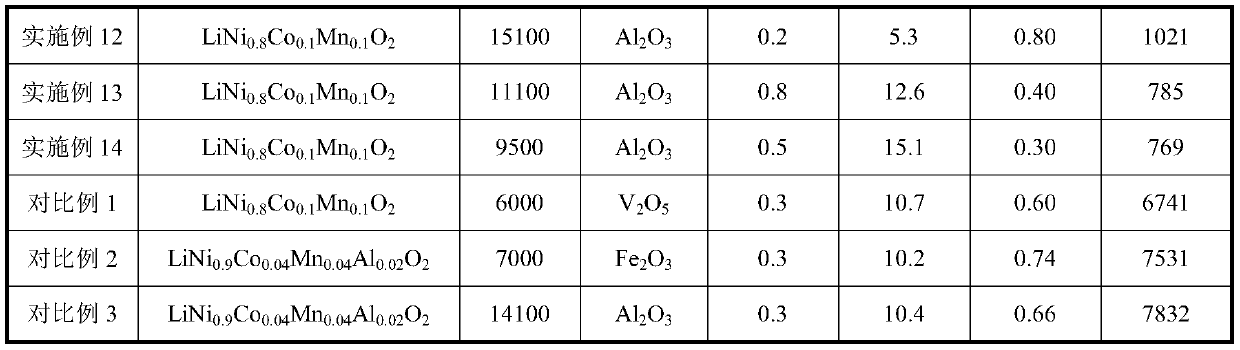

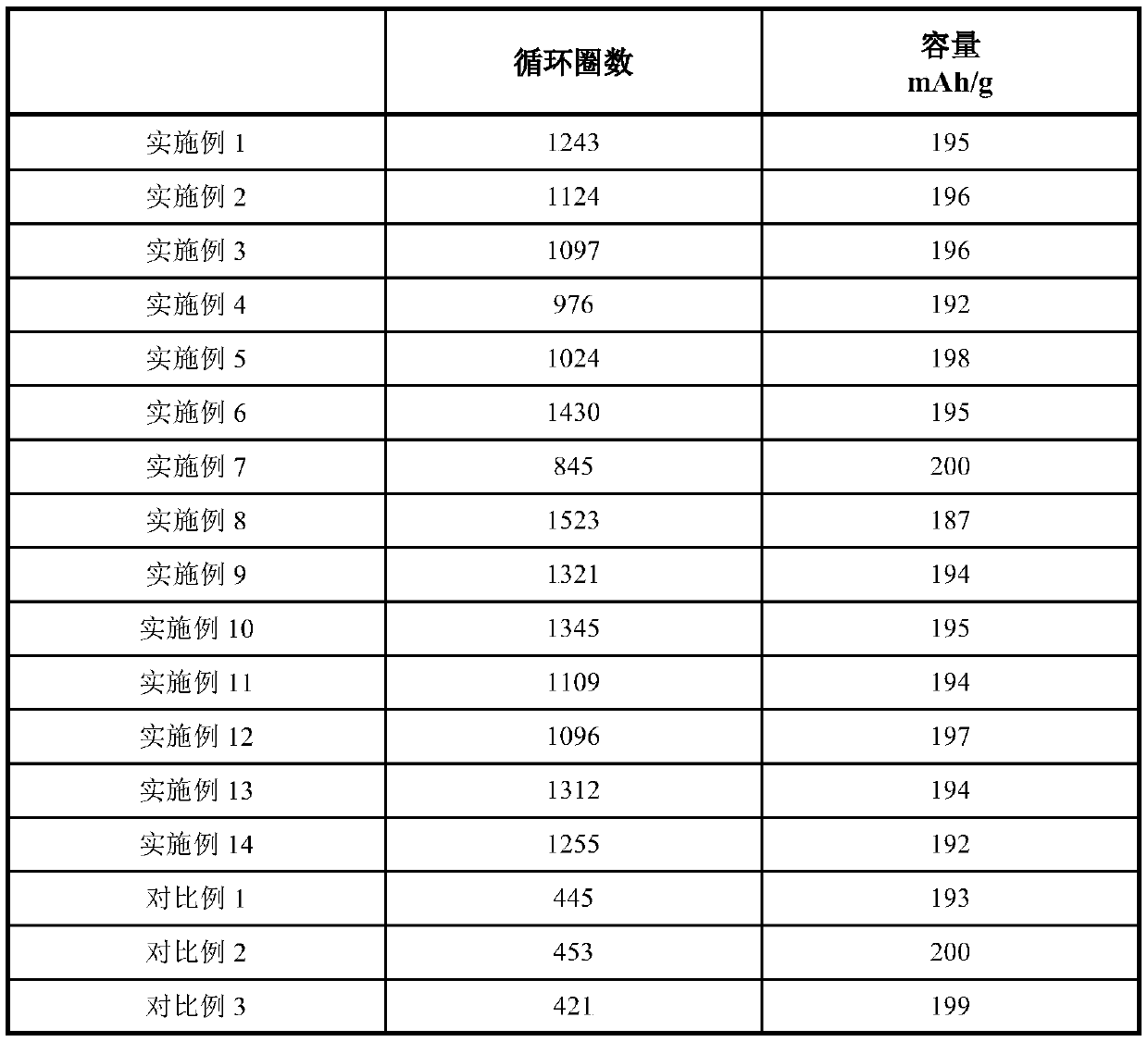

Positive electrode material and preparation method and application thereof

ActiveCN111384377APromote polarizationSmall specific surface areaPositive electrodesSecondary cells servicing/maintenanceComposite materialLithium electrode

The invention relates to the field of electrochemistry, in particular to a positive electrode material as well as a preparation method and application thereof. The invention provides a positive electrode material, which comprises a base material, the base material comprises secondary particles composed of primary particles, and the surface of the base material is provided with an oxide coating layer. According to the positive electrode material disclosed by the invention, doping and surface coating are carried out in a high-nickel base material; the powder resistivity of the positive electrodematerial is controlled within a proper range; and meanwhile, the specific surface area of the positive electrode active material is reduced, the surface miscellaneous lithium amount is reduced, the polarization problem of the positive electrode material is improved, the direct current impedance of the lithium ion battery is reduced, the side reaction between the positive electrode material and anelectrolyte is effectively reduced, the gas production problem of the battery is inhibited, the volume energy density of the battery is improved, and the cycle performance and the rate capability areoptimized.

Owner:CONTEMPORARY AMPEREX TECH CO

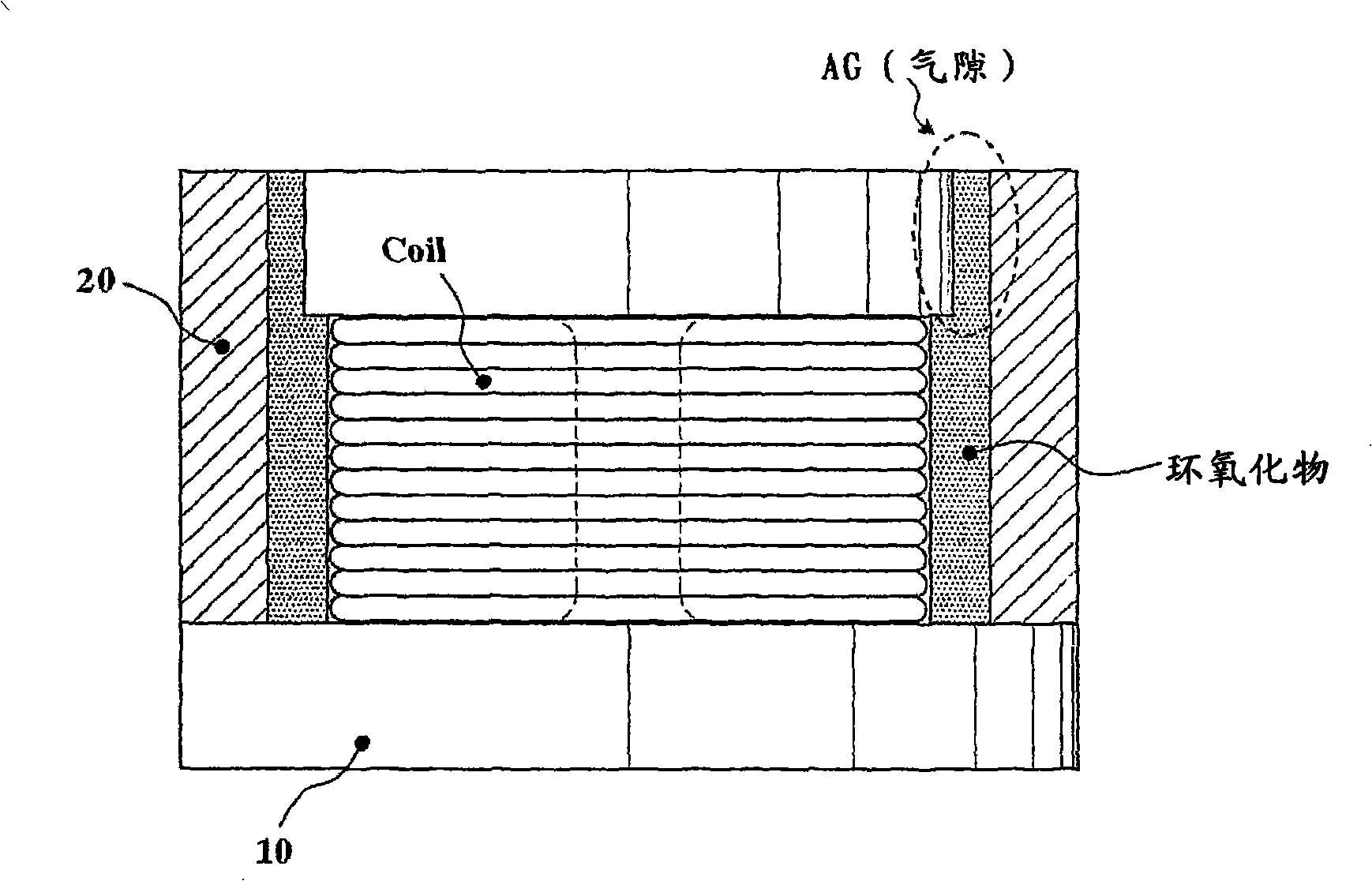

Winding power inductor and production method thereof

ActiveCN103295732AObvious high currentReduce DC resistanceTransformers/inductances coils/windings/connectionsTransformers/inductances magnetic coresEpoxyButt welding

Disclosed are a winding power inductor and a production method thereof. An I-shaped core is made of ferrous alloy soft magnet powder. A coil winding is a butt-wound flat enameled wire winding made by butt-welding flat wires. A glue layer is a magnetic glue layer made of ferrous alloy soft magnet and epoxy resin system. The production method includes: making the I-shaped core of the ferrous alloy soft magnet powder, making an L-shaped sputtered metallized layer on the vane swing side of the I-shaped core by means of sputtering, winding the flat enameled wires on a middle post of the I-shaped core by means of butt welding to make the butt-wound flat enameled wire winding, connecting wire ends of the butt-wound flat enameled wire winding to the L-shaped-section metallized layer by spot welding to form electrodes, and using a glue dispenser to coat the surface of the butt-wound flat enameled wire winding after the wire ends are fused so as to make the magnetic glue layer. The winding power inductor has the advantages of evident high current and low-current impedance, is simple in process, and is convenient for automatic batch production.

Owner:贵阳顺络迅达电子有限公司

Terminal system for planar magnetics assembly

ActiveUS20060279394A1Reduce resistanceImprove efficiencyTransformers/inductances coils/windings/connectionsCoilsConductor CoilTerminal system

Owner:STANDEX ELECTRONICS

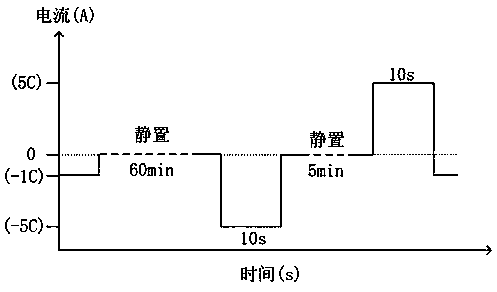

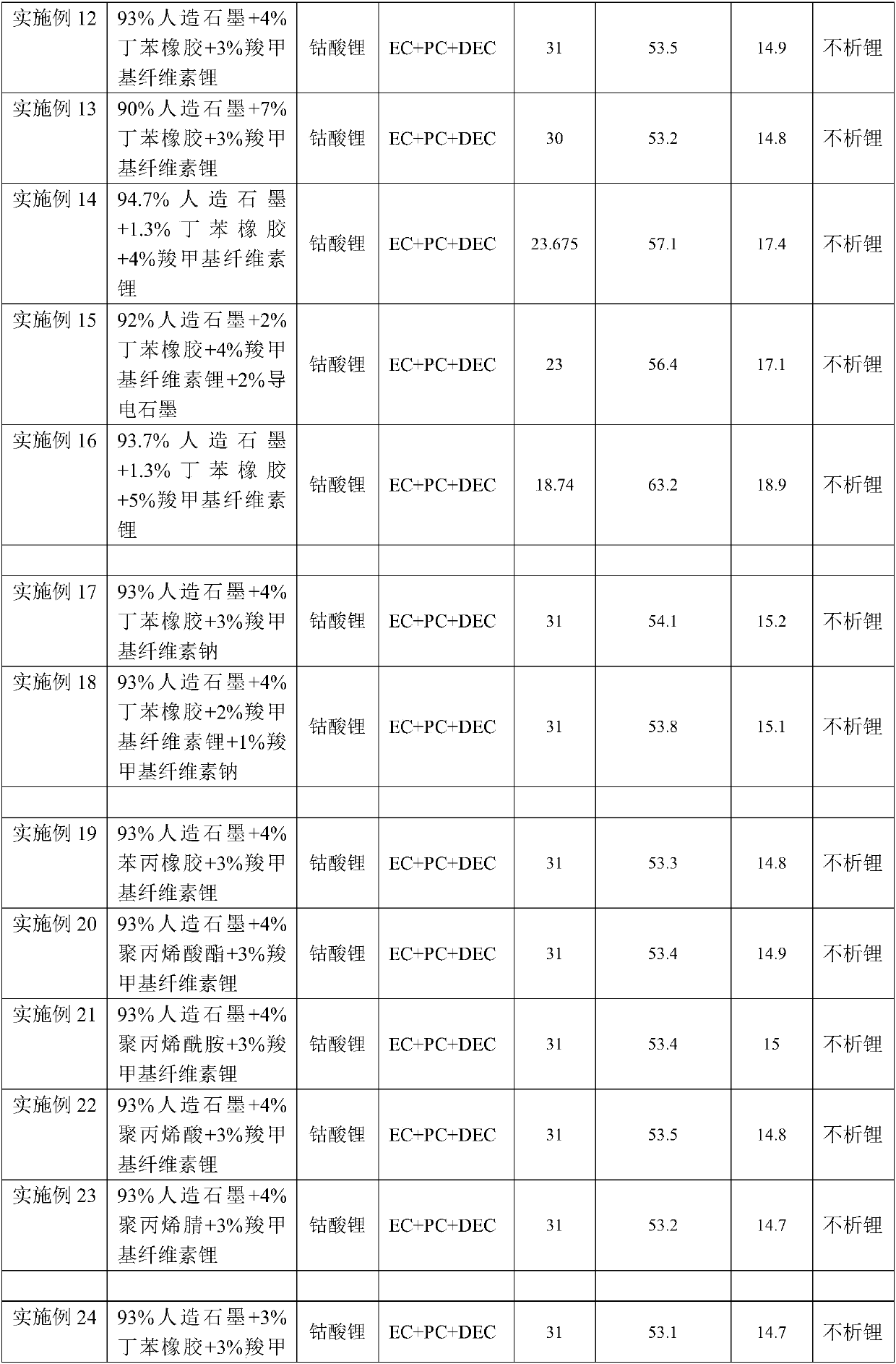

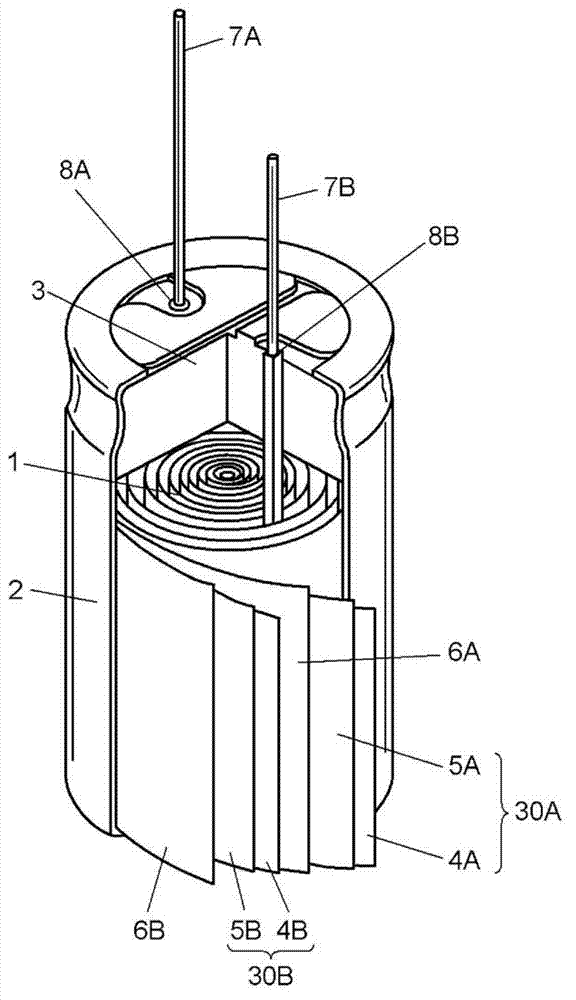

Electrode assembly and lithium ion battery

ActiveCN111384405AReduce oxidation rateIncrease profitFinal product manufactureElectrode carriers/collectorsMetallic lithiumEngineering

The invention provides an electrode assembly and a lithium ion battery. The electrode assembly comprises a positive pole piece, an isolating membrane and a negative pole piece, wherein the negative pole piece comprises a negative current collector and a negative active material layer, and further comprises a metal lithium layer, the metal lithium layer is formed by a plurality of regular or irregular strip-shaped lithium-rich areas, and the plurality of lithium-rich areas are distributed at intervals in the length direction of the negative pole piece in a non-continuous form. The electrode assembly also satisfies the following conditions: the ratio of the negative electrode capacity per unit area to the positive electrode capacity per unit area is 1.2-2.1, and the ratio of the negative electrode capacity per unit area to the sum of the positive electrode capacity per unit area and 80% of the capacity of the metal lithium layer on the surface of the negative electrode active material layer per unit area is greater than or equal to 1.10. The lithium ion battery disclosed by the invention has relatively high lithium supplementing efficiency and relatively low direct-current impedance,and meanwhile, the lithium ion battery also has long cycle life and storage life.

Owner:CONTEMPORARY AMPEREX TECH CO

Surface mounting inductor manufacture method

InactiveCN105355409AImprove pass rateReduce manufacturing costTransformers/inductances coils/windings/connectionsInorganic material magnetismInsulation layerChemical plating

The invention discloses a surface mounting inductor manufacture method comprising the following steps: firstly preparing an inductor body; carrying out insulation treatment for the surface of the inductor body besides an electrode portion; pre-processing the electrode portion of the inductor body; removing an insulation layer on end portions of two lead wires of a coil in the inductor body; depositing one or more layers of metal conductive layers on the surface of the electrode portion of the inductor body through either a physics vapour deposition technology, or chemical vapor deposition or electroplate and chemical plating technology, the metal conductive layers are the electrode, thus obtaining the surface mounting inductor; the advantages are that the electrode position mode is employed to form the electrode, the electrode can directly grow into form on the electrode portion of the inductor body, and the electrode can be directly deposited on the end portion of the lead wires of the coil in a forming process; the electrode and the lead wires are connected through atom combination so as to provide high connecting integration, thus greatly reducing DC resistance between the lead wires of the coil and the electrode; the DC resistance between the lead wires of the coil and the electrode is relatively small, so the performance of the surface mounting inductor is high.

Owner:NINGBO YUNSHENG ELECTRONIC COMPONENTS TECHNOLOGY CO LTD +1

Coil component

ActiveUS7408435B2Reduce DC resistanceImpedence networksTransformers/inductances coils/windings/connectionsElectrical conductorSurface mounting

Owner:TDK CORPARATION

All-solid-state lithium-ion battery and manufacturing method thereof

InactiveCN106532109AReduce DC resistanceImprove ionic conductivityFinal product manufactureElectrolyte accumulators manufactureSolventIon

The invention discloses an all-solid-state lithium-ion battery and a manufacturing method thereof. The manufacturing method comprises the following steps of (1) dissolving a polymer electrolyte into a solvent to prepare a glue solution; (2) fully mixing a positive electrode host material, a conductive agent and the glue solution obtained in the step (1), coating a positive current collector, heating the positive current collector and then carrying out co-curing to obtain a positive electrode plate, fully mixing a negative electrode host material, the conductive agent and the glue solution obtained in the step (1), coating a negative current collector, heating the negative current collector and then carrying out co-curing to obtain a negative electrode roll; (3) carrying out mechanical ball milling on a sulfide electrolyte, dissolving the product into the solvent to prepare slurry, coating the surface of the negative electrode roll, heating the negative electrode roll and then curing the negative electrode roll to obtain a negative electrode plate; and (4) assembling the positive electrode plate and the negative electrode plate by adopting a lamination technology to obtain the all-solid-state lithium-ion battery. Compared with the prior art, the all-solid-state lithium-ion battery disclosed by the invention has relatively low DC resistance, relatively high ionic conductivity and good cycle performance.

Owner:SHANGHAI AEROSPACE POWER TECH

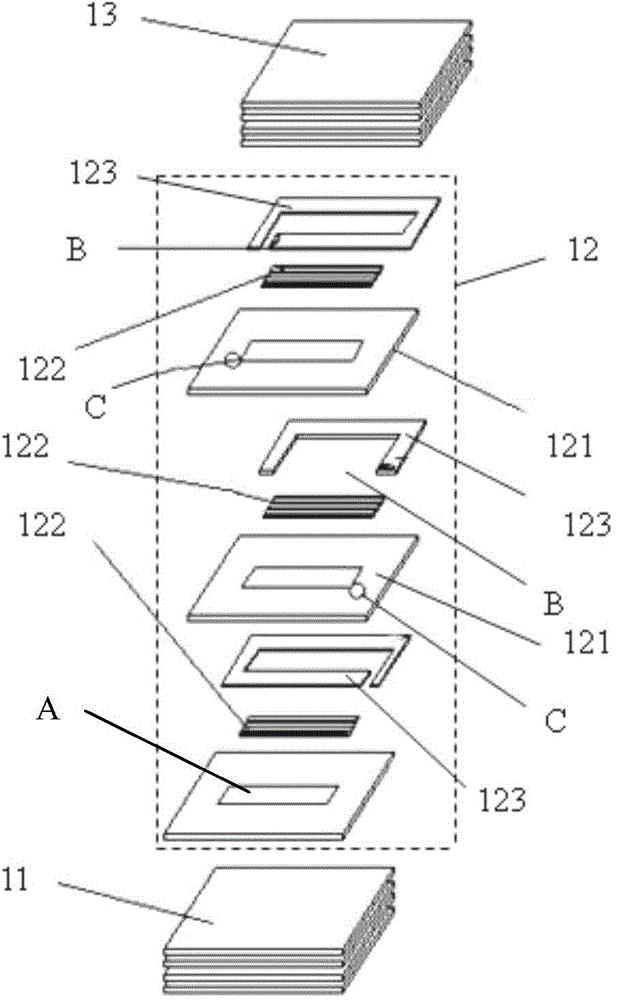

Multilayer coil component and method for manufacturing the same

ActiveCN102007551ASmall characteristic deviationReduce DC resistanceUnwanted magnetic/electric effect reduction/preventionCoils manufactureDc resistanceCeramic

Provided is a highly reliable multilayer coil component wherein migration of Ag constituting an inner conductor is controlled, problem of internal stress is relaxed without forming an air gap between a magnetic ceramic layer and an inner conductor layer, DC resistance is lowered, and disconnection of an inner conductor due to a surge is prevented from occurring easily. A metal film (20) is distributed over the surface of an inner conductor (2), so that an air gap does not exist on the interface (A) of the inner conductor (2) including the metal film (20) and a magnetic ceramic (11) on the periphery of the inner conductor, and the interface (A) of the inner conductor (2) and the magnetic ceramic (11) is in a dissociative state. An acid solution containing a metal is infiltrated from the side surface of a magnetic ceramic element via a side gap portion, i.e. a region between the side portion of the inner conductor and the side surface of the magnetic ceramic element, so as to reach the interface of the inner conductor and the magnetic ceramic on the periphery thereof, and thus the metal is deposited on the surface of the inner conductor.

Owner:MURATA MFG CO LTD

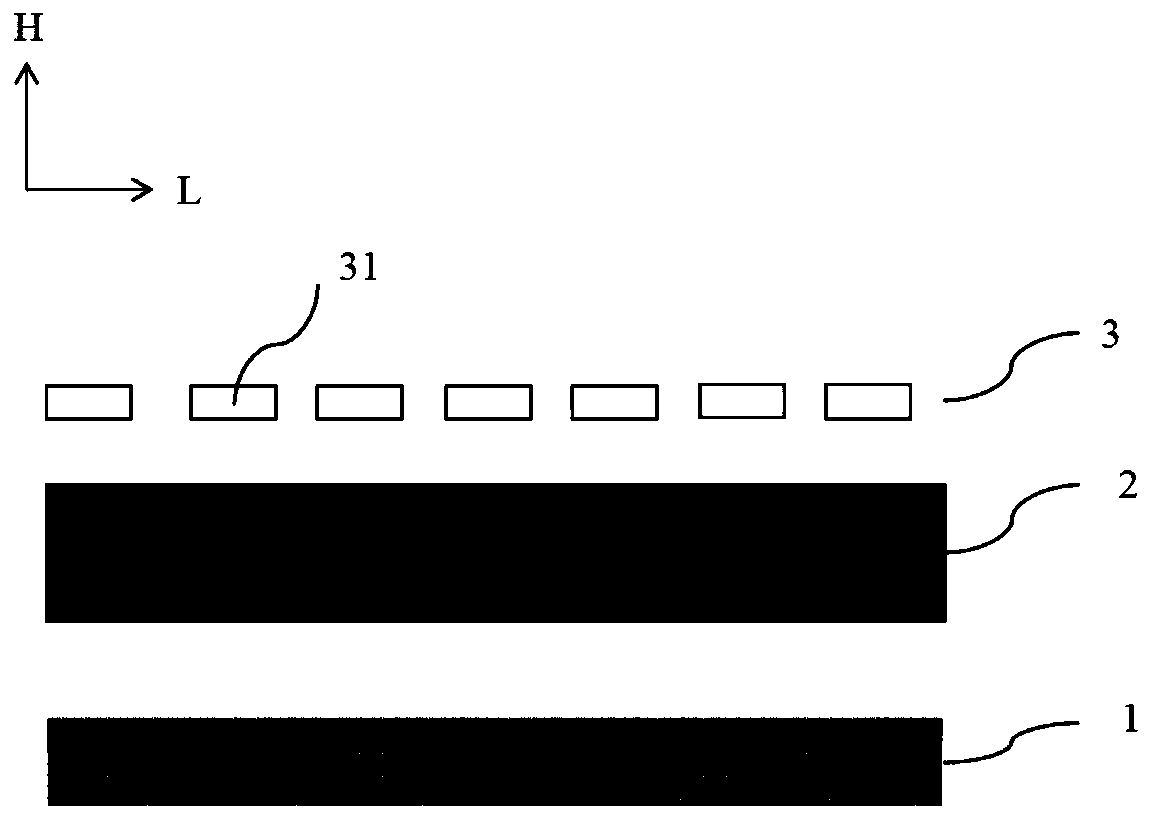

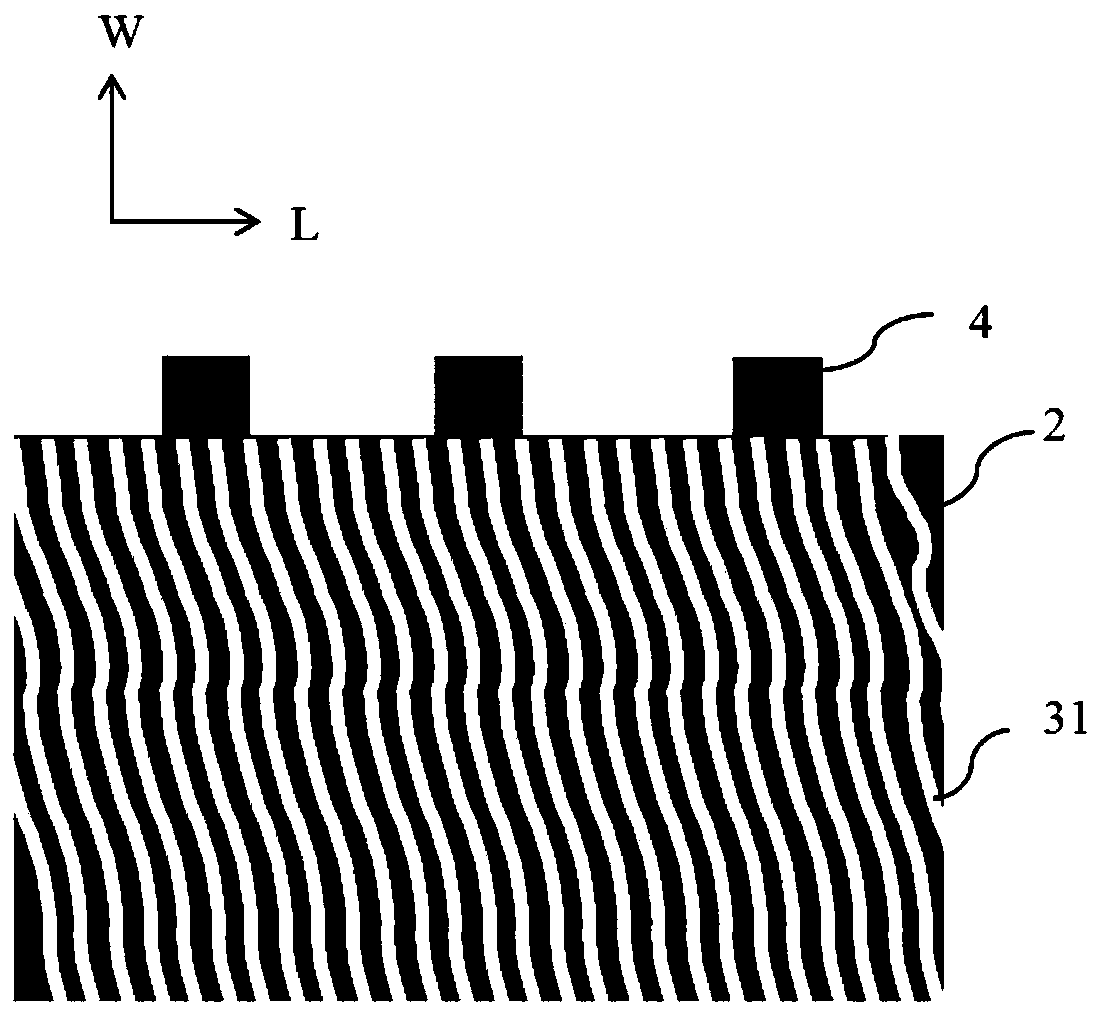

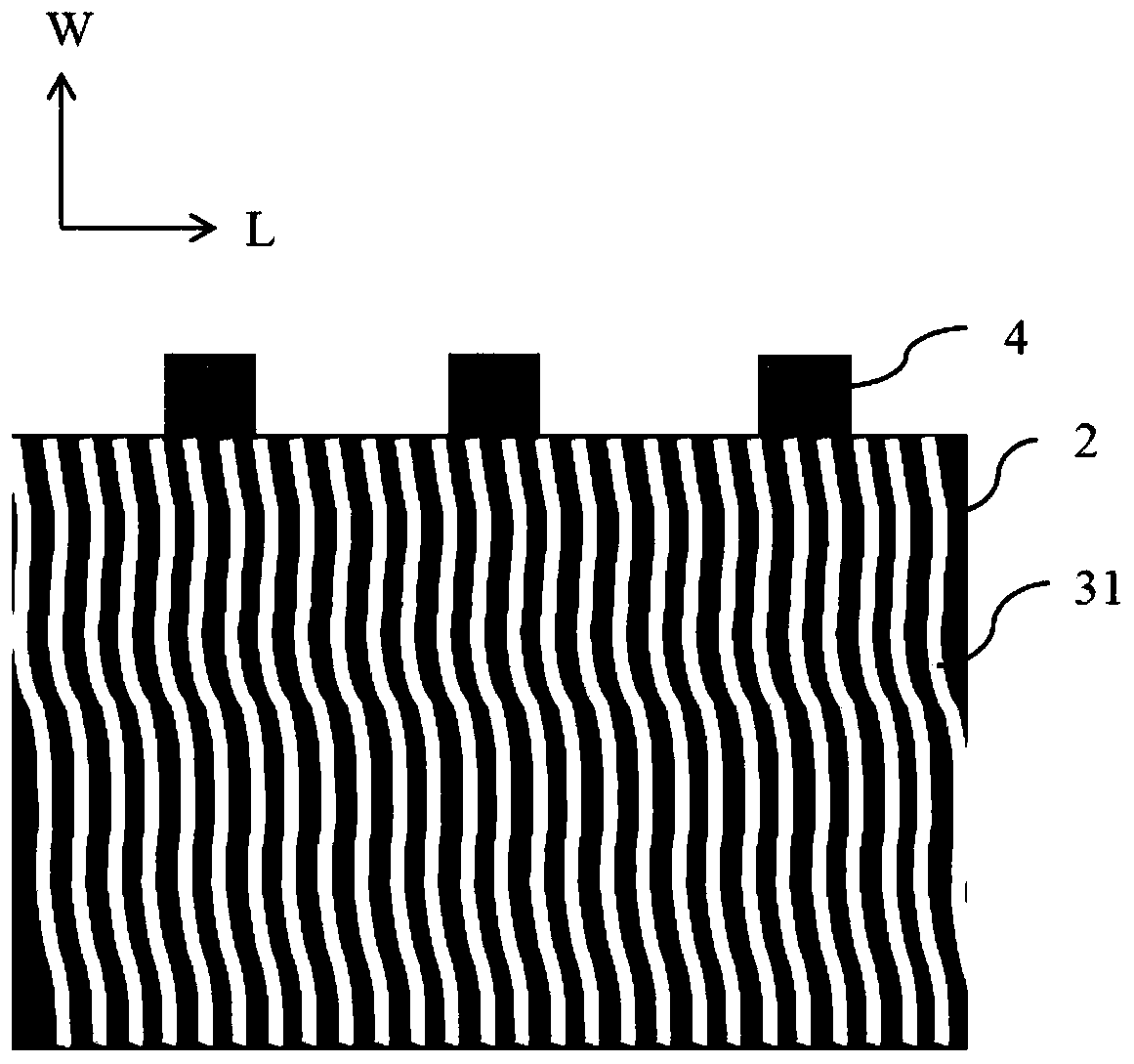

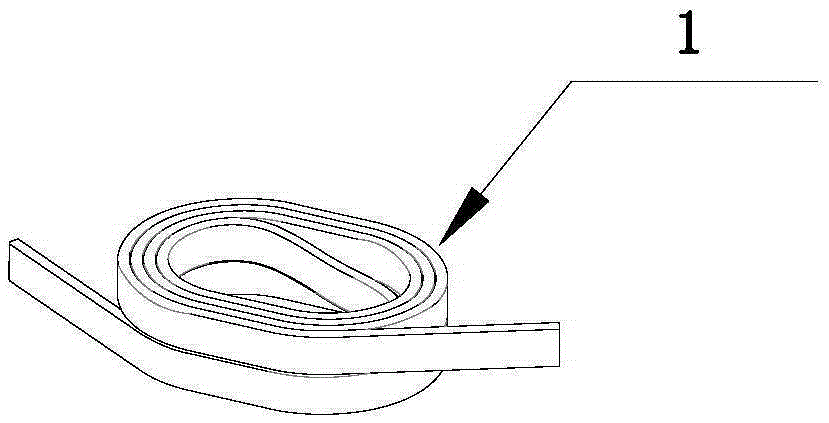

Flat coil inductor, flat coil and manufacture method of flat coil

ActiveCN103680861ASmooth linesEasy to fold and processTransformers/inductances coils/windings/connectionsCoils manufactureEngineeringInductor

The invention discloses a flat coil inductor, a flat coil and a manufacture method of the flat coil. The flat coil inductor comprises a magnetic core, a magnetic cover covering the magnetic core and the flat coil coiled on the magnetic core, wherein the magnetic core is provided with, at least, a first groove and a second groove. The flat coil comprises, at least, the top end base portion and two side edge flattening portions, wherein the base portion is larger than the side edge flattening portions in thickness, the side edge flattening portions are larger than the base portion in width, the base portion is embedded into the first groove, and the side edge flattening portions are embedded into the second groove. The side edge flattening portions are formed by locally flattening the flat coil of the inductor, so that different thicknesses are obtained, the side edge flattening portions are larger than the base portion in width but are smaller than the base portion in thickness, and a magnetic core accommodating space defined by the flat coil is increased. The magnetic core can be matched and assembled with a large corresponding magnetic core, so that the direct-current resistance of the inductor in a limited size range is decreased, the saturation current is increased, and the inductor can obtain the best electrical characteristics.

Owner:DONGUAN PULSE ELECTRONICS CO LTD

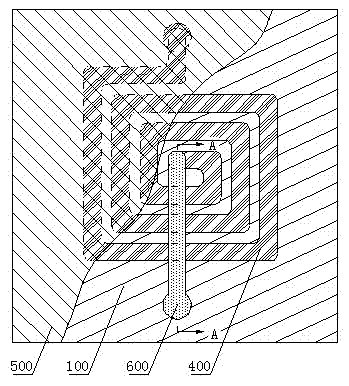

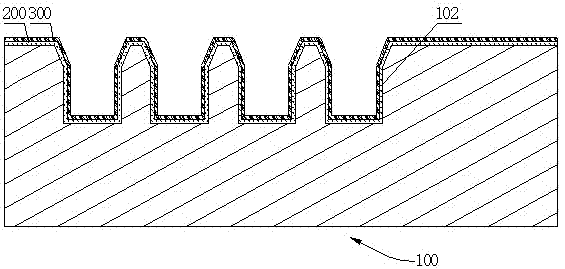

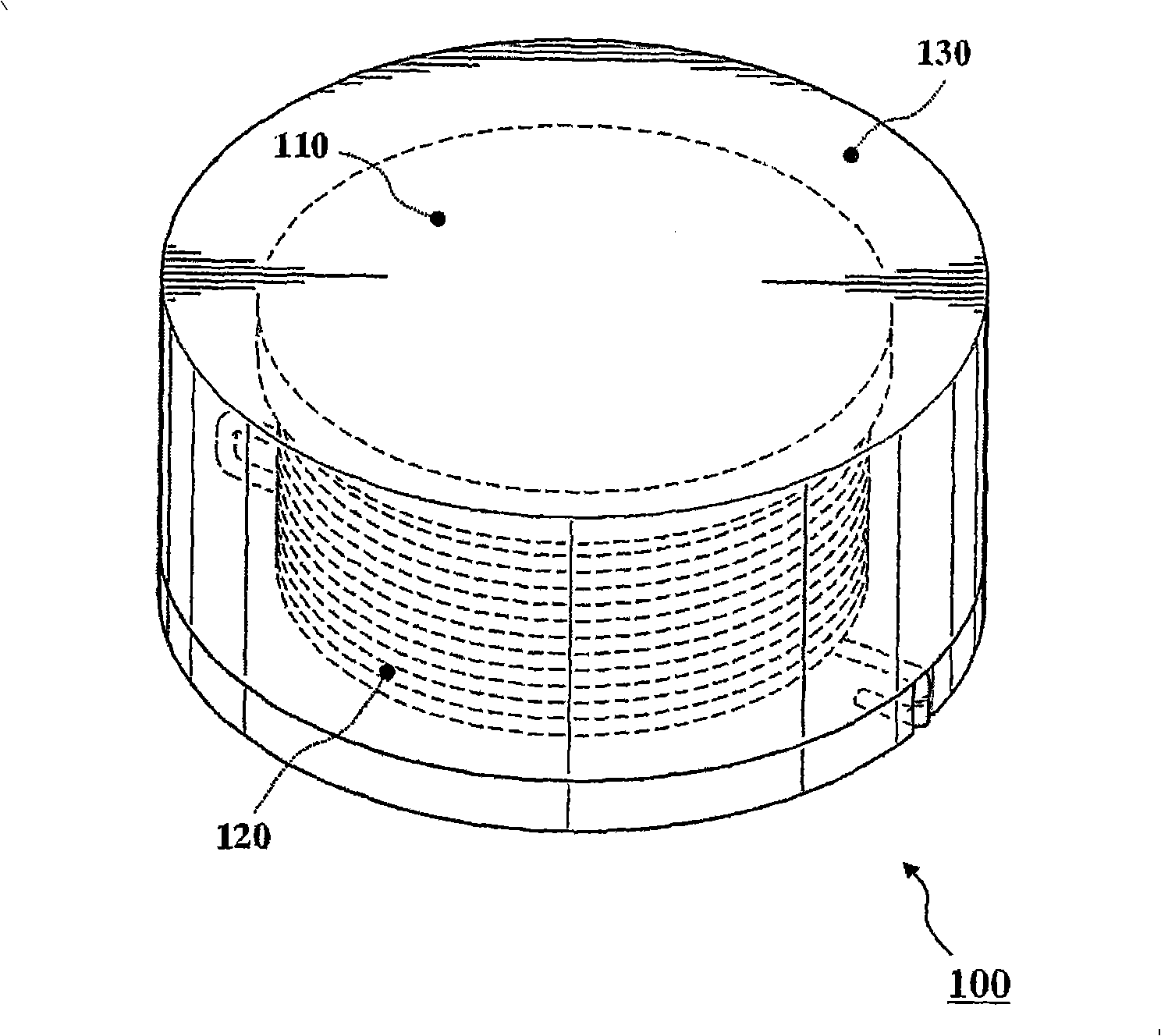

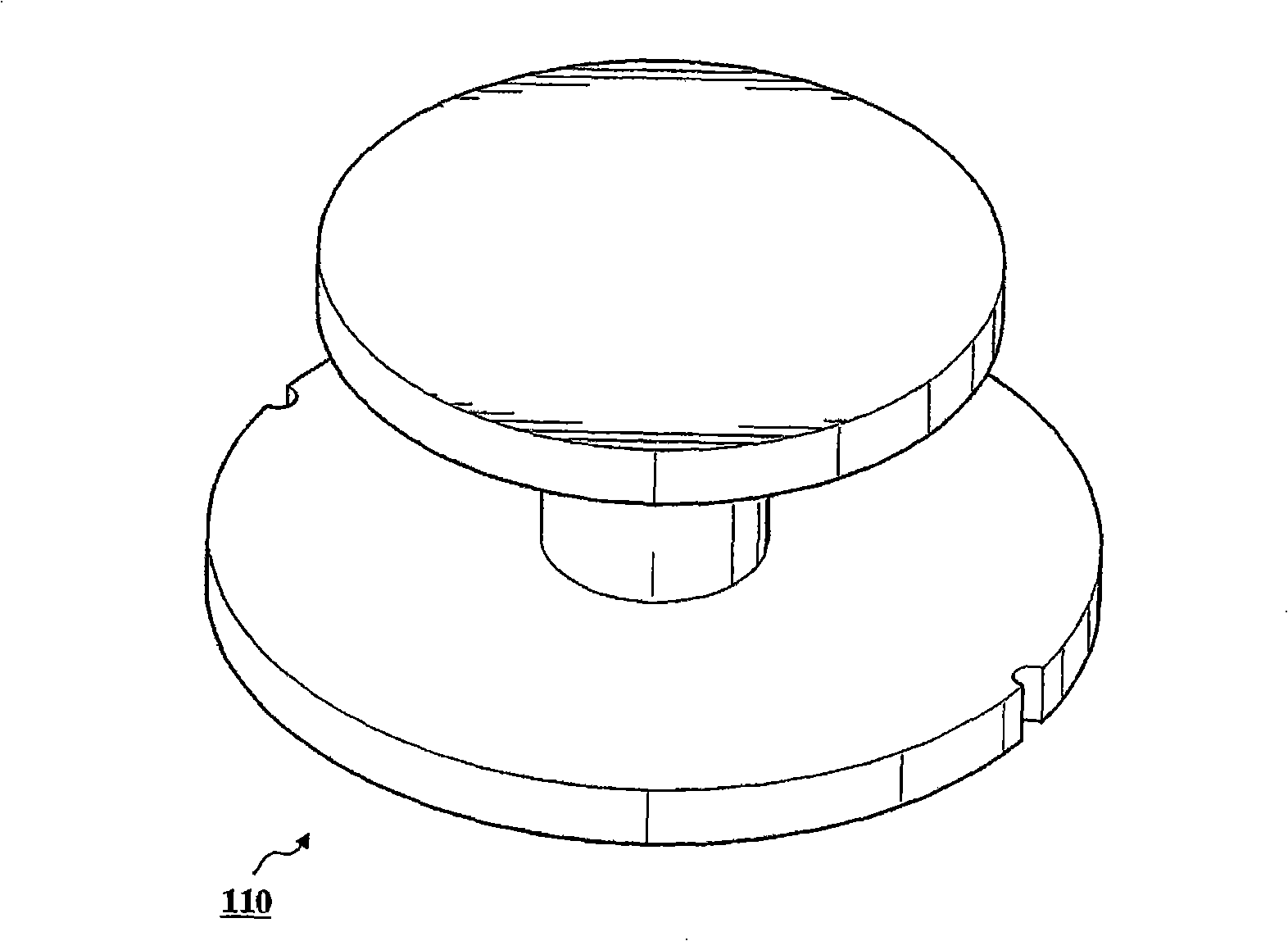

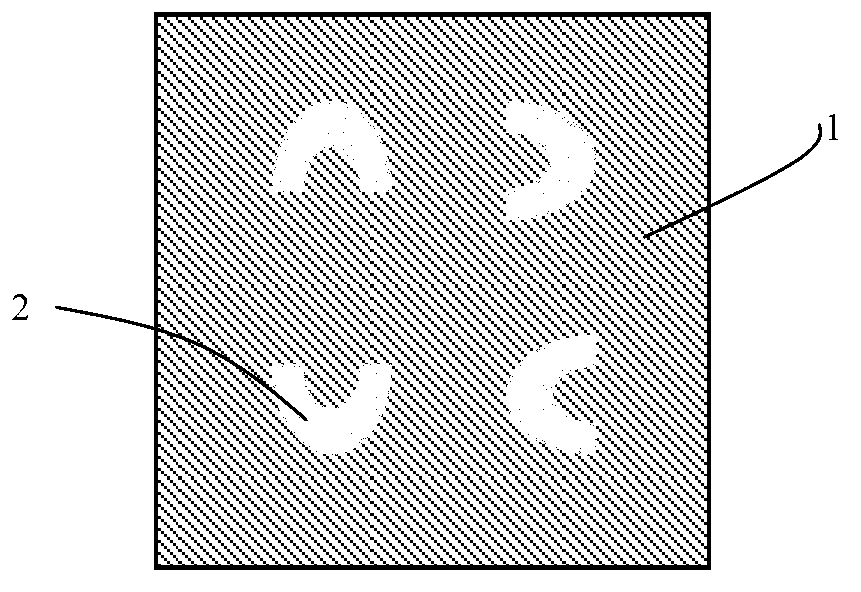

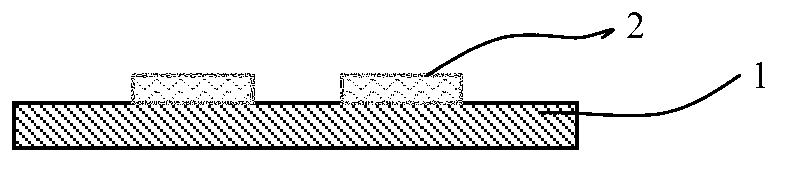

Novel silicon substrate low resistance inductance structure and wafer level encapsulating method thereof

ActiveCN103165571ALower requirementAvoid rewiring methodSemiconductor/solid-state device detailsSolid-state devicesInsulation layerInductor

The invention relates to a novel silicon substrate low resistance inductance structure and a wafer level encapsulating method of the novel silicon substrate low resistance inductance structure, and belongs to the technical field of semiconductor encapsulation. A coil groove (102) is formed in the upper surface of a silicon wafer (100) in an etching mode, an insulation layer (300) is coated inside the coil groove (102), an electroplating seed layer (300) is arranged in a deposit mode through a physical method, a thick copper metal wiring layer (400), namely an inductance coil, is formed in the coil groove (102) in a photoetching imaging mode through an electroplating technology, and finally, a secondary passivating layer (500) and metal leading wires (600) are arranged on the thick copper metal wiring layer (400), and the thick copper metal wiring layer (400) is communicated with the thick copper metal wiring layer (400) through an secondary passivating layer opening (501). According to the novel silicon substrate low resistance inductance structure and a wafer level encapsulating method of the novel silicon substrate low resistance inductance structure, the copper metal wiring layer serving as the inductance coil is embedded into the interior of a silicon substrate body, technological difficulty and technological cost of preparation of the inductance coil are reduced, an encapsulating density is improved, meanwhile direct current resistance of an inductor is reduced by increasing the thickness of coils, and a quality factor of the inductor is improved.

Owner:JIANGYIN CHANGDIAN ADVANCED PACKAGING CO LTD

Surface mounting type power inductor

InactiveCN101351854AReduce the number of turnsReduce DC resistanceTransformers/inductances magnetic coresCores/yokesSurface mountingInductor

Disclosed herein is a surface mount type power inductor which has an outer magnetic capsule integrated with a coil-wound inner core, and which thus has no air gap between the outer magnetic capsule and the inner core, and can maintain a large inductance L in a high current condition. In the inductor, a coil is wound a predetermined number of turns around the inner core formed from ferrite or magnetic metal. An outer magnetic capsule, molded from a magnetic powder, an insulation filler, a binder, and a lubricant, is provided to cover the inner core and the coil.

Owner:TODA ISU

Laminated coil

InactiveCN102403087AImprove featuresNo increase in shapeTransformers/inductances casingsTransformers/inductances coils/windings/connectionsEngineeringElectrical and Electronics engineering

Owner:MURATA MFG CO LTD

Dielectric ceramic composition, multilayer complex electronic device, multilayer common mode filter, multilayer ceramic coil and multilayer ceramic capacitor

ActiveUS8102223B2Improve featuresLow dielectric constantMultiple-port networksFixed capacitor dielectricCeramic capacitorPermittivity

A dielectric ceramic composition comprises as a main component, Cu oxide, Si oxide and one selected from the group consisting of Zn oxide alone and a combination of Mg oxide and Zn oxide, as a subcomponent, a glass component including B oxide and at least one selected from the group consisting of Si oxide, Ba oxide, Ca oxide, Sr oxide, Li oxide and Zn oxide, and having a glass softening point is 750° C. or less, wherein a content of said glass component is 1.5 to 15 wt % with respect to 100 wt % of said main component. According to the present invention, a dielectric ceramic composition can be provided which is available to be sintered at low temperature (for example, 950° C. or lower) while comparatively decreasing contents of a glass component, which shows good properties (specific permittivity, loss Q value and insulation resistance), and which is available to perform cofiring different materials.

Owner:TDK CORPARATION

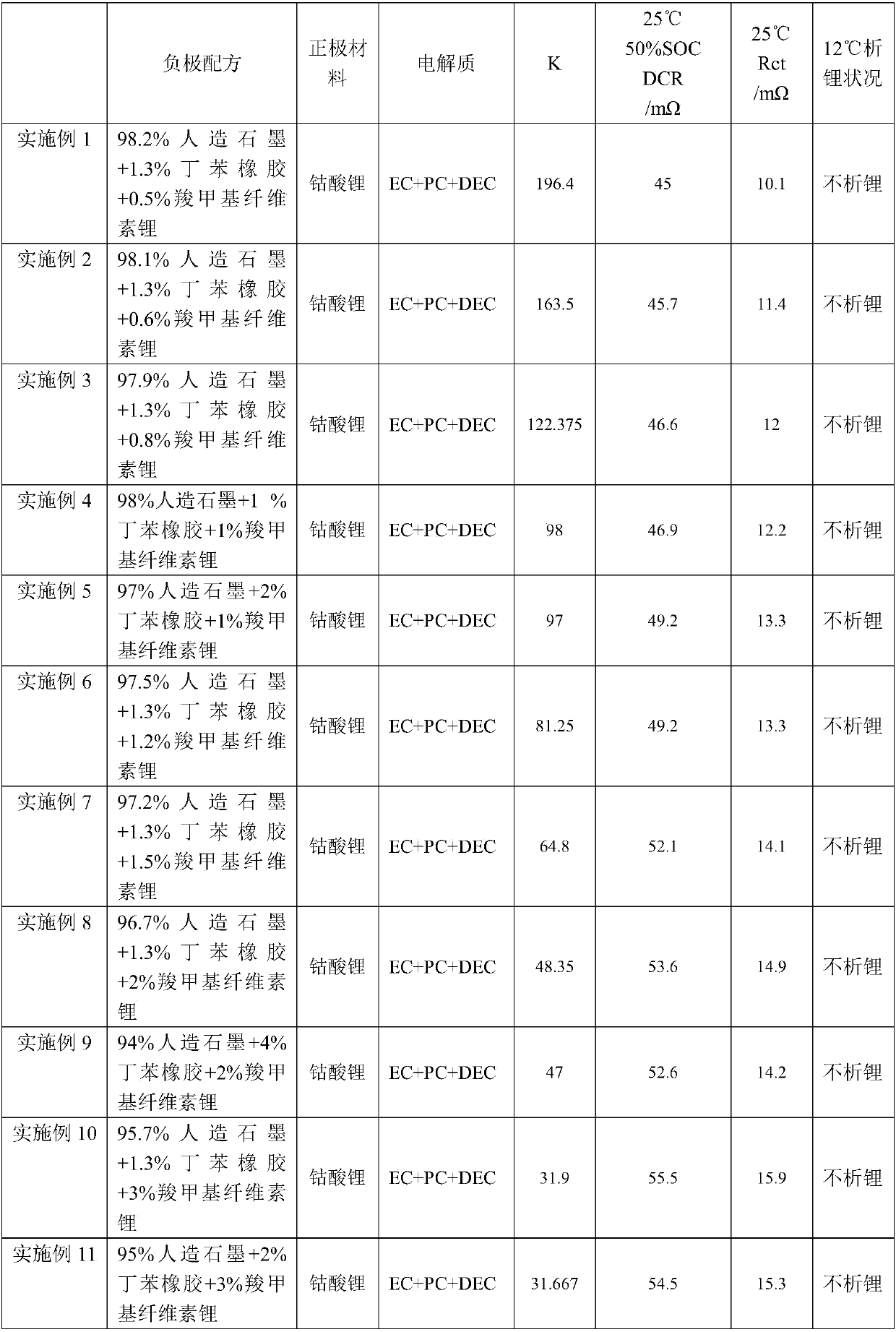

Negative electrode sheet and lithium ion battery including negative electrode sheet

PendingCN110197894ANo loss of energy densityDoes not affect cycle lifeFinal product manufactureNegative electrodesTO-18Carboxymethyl cellulose

The embodiment of the application provides a negative electrode sheet and a lithium ion battery including the negative electrode sheet. The negative electrode sheet includes a negative current collector and a negative active material layer disposed on the negative current collector, wherein the negative active material layer includes a negative active material and a dispersant, the mass ratio of the negative active material and the dispersant is greater than or equal to 18.74, and the dispersant includes lithium carboxymethyl cellulose. The negative electrode sheet, while not losing the energydensity of the lithium ion battery, not affecting the cycle life of the lithium ion battery and not causing cyclic expansion, greatly reduces the DC resistance of the lithium ion battery and the charge transfer resistance of an interface, and avoids lithium deposition of the lithium ion battery during cyclic charge / discharge process.

Owner:NINGDE AMPEREX TECH

Cascading inductor based on metal magnetic slurry and preparation method thereof

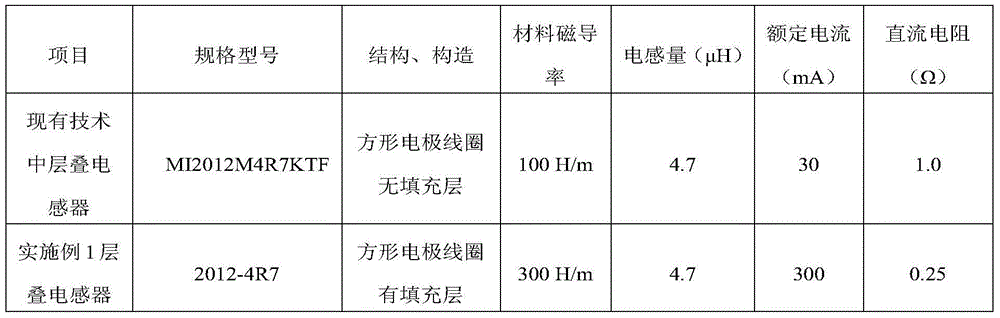

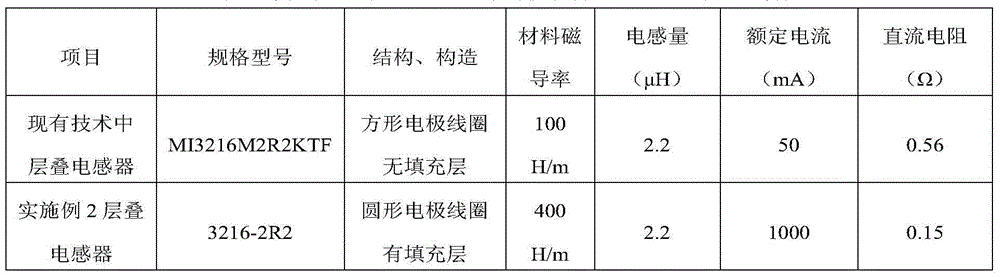

ActiveCN104465020AHigh saturation magnetizationIncrease the rated currentTransformers/inductances detailsInductances/transformers/magnets manufactureInter layerMetal alloy

The invention firstly aims to provide a cascading inductor based on metal magnetic slurry. The cascading inductor comprises a first base body, an interlayer and a second base body, wherein the first base body, the interlayer and the second base body are arranged from bottom to top. The interlayer comprises at least two single-layers arranged from bottom to top. Each single-layer comprises a dielectric layer, a packing layer and a coil electrode, wherein the dielectric layer is provided with a through hole in the vertical direction; the packing layer is arranged at the through hole, and the upper surface of the packing layer is not lower than the upper surface of the dielectric layer; the coil electrode is arranged on the upper surface of the dielectric layer and located around the packing layer; the packing layer comprises inorganic powder bodies composed of metal magnetic powder, lead-free glass powder, organic carriers and auxiliaries. The cascading inductor based on the metal magnetic slurry is simple in overall structure; since the packing layers are made of metal alloy materials with high saturation flux density, the saturation magnetization intensity of the whole cascading inductor is improved, and then the rated current is increased. The invention secondly aims to provide a preparation method of the cascading inductor based on the metal magnetic slurry. By means of the preparation method, the process steps are simple, the cost is low, and the cascading inductor is quite suitable for large-scale batch production.

Owner:SHENZHEN GUDIAN ELECTRONICS

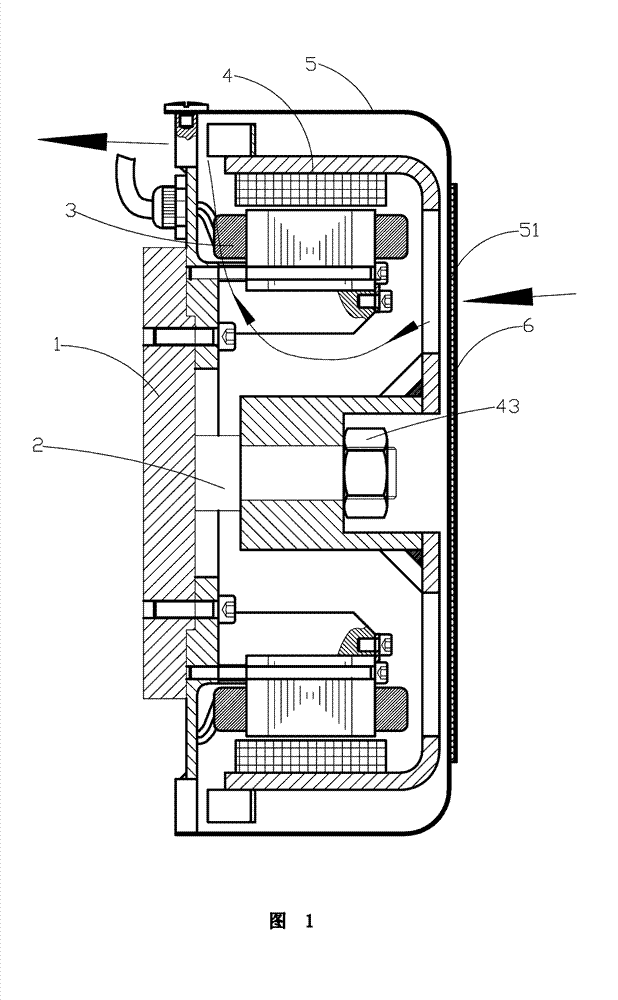

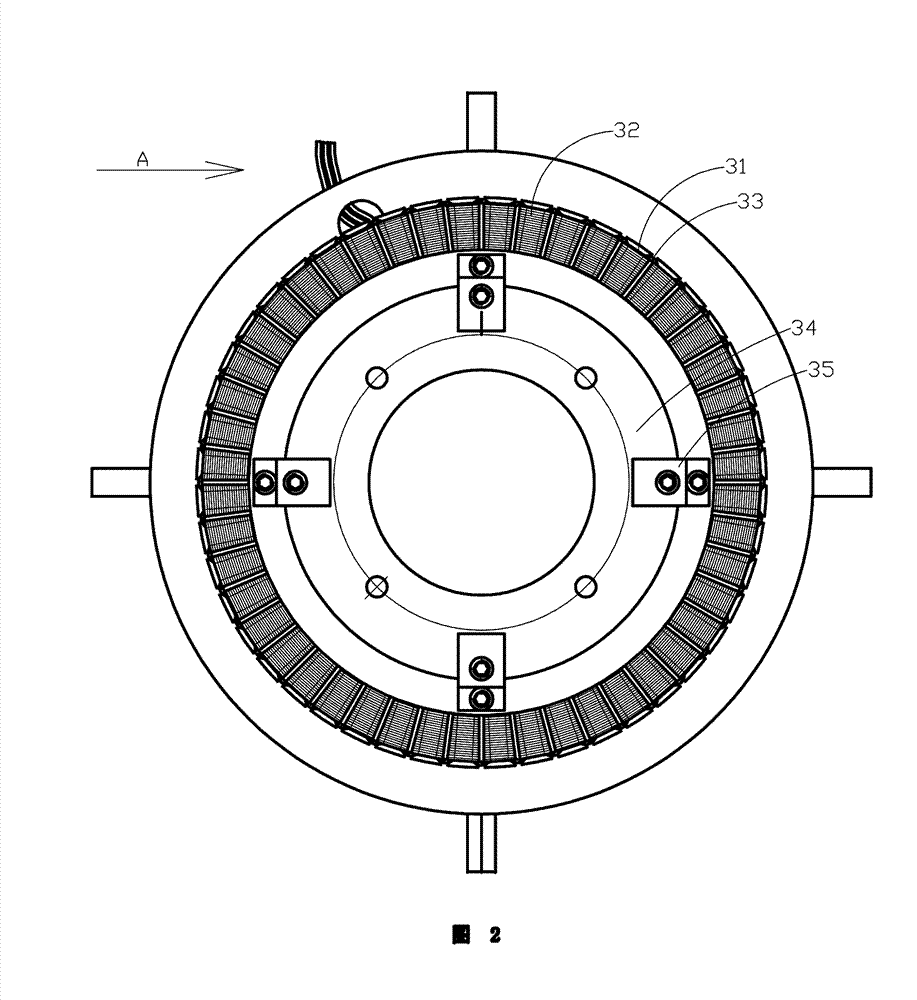

External-rotor intermediate-frequency permanent magnet generator device

InactiveCN102738934AImprove automationSave human effortMagnetic circuit rotating partsMagnetic circuit stationary partsIntermediate frequencyConductor Coil

An external-rotor intermediate-frequency permanent magnet generator device comprises a power interface fixing disc, a power shaft arranged on the power interface fixing disc, an internal stator connected with the power interface fixing disc, an annular external rotor connected with the power shaft and having a magnetic steel, and a protection cover connected with the internal stator and provided with an air inlet. The external rotor of the intermediate-frequency permanent magnet generator device is arranged outside the internal stator; an iron core lamination of the stator is designed to a coil slot shape and is distributed on the external circumference; the winding form is designed to a centralized winding form; and a stator winding coil is wound on the teeth individually in such a manner that one tooth corresponds to one independent coil and both sides of each coil have one pole respectively so as to form a fractional-slot winding. The stator iron core can be conveniently fixed on a stator reinforcement rib because the coil has a short and small end; the rotor is a multi-polar magnetic steel rotor; and the stator and the stator iron core are shorter in comparison with the generator of the same capacity, so that generator can be designed to a flat structure, which can have no rear bearing and of which the front end can be directly connected with an interface of a power oil machine.

Owner:FUJIAN YANAN ELECTRIC MACHINE

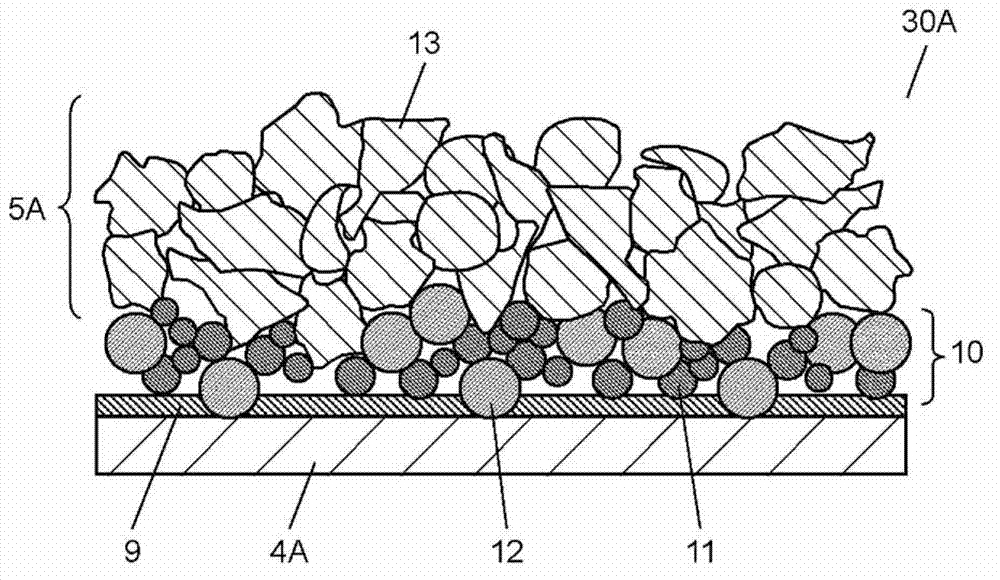

Electrode structure for capacitor, process for producing same, and capacitor including the electrode structure

InactiveCN102822920AReduce DC resistanceLower internal resistanceElectrolytic capacitorsHybrid capacitor electrodesEngineeringProtection layer

Disclosed is an electrode structure for capacitors which comprises a current collector having conductivity, a protective layer formed on the current collector, an anchor coat layer formed on the protective layer, and a polarizable electrode layer formed on the anchor coat layer. The protective layer contains an oxyhydroxide, and the anchor coat layer contains conductive particles.

Owner:PANASONIC INTPROP MANAGEMENT CO LTD

Production method of thick-electrode device

InactiveCN103077779AReduce widthReduce DC resistanceInductances/transformers/magnets manufactureCable/conductor manufactureMetallurgyCeramic substrate

The invention relates to a production method of a thick-electrode device, and the production method comprises the following steps of utilizing screen meshes with the same patterns to be printed with electrode paste on a first ceramic substrate and a film with a releasing function; utilizing the obtained film which is printed with the electrode paste to be laminated onto a second ceramic substrate, and removing the film to obtain the second ceramic substrate with the electrode paste; inverting the first ceramic substrate which is printed with the electrode paste onto the second ceramic substrate with the electrode paste to be aligned and laminated for the electrode patterns to form a third ceramic substrate; discharging the glue; and sintering. Due to the adoption of the production method of the thick-electrode device, the width of the electrode is reduced, while the production of a thick electrode is realized, the direct-current resistance of the device is effectively reduced, and the consumption of the electrode paste can be reduced on the premise of guaranteeing the performance of the device.

Owner:SHENZHEN SUNLORD ELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com