Novel silicon substrate low resistance inductance structure and wafer level encapsulating method thereof

A silicon wafer and silicon-based technology, applied in the field of new silicon-based low-resistance inductance structure and its wafer-level packaging, can solve the problems of limited packaging density, difficult process, easy to have residual glue, etc., to reduce DC resistance, The effect of reducing process difficulty and improving quality factor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

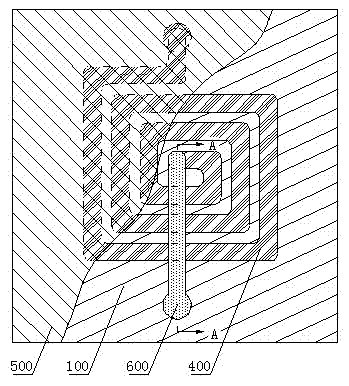

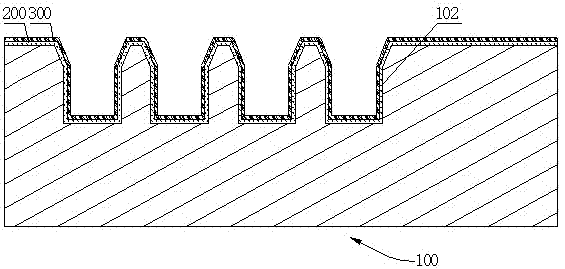

[0050] see figure 1 and figure 2 , the present invention is a novel silicon-based low-resistance inductance structure, including a silicon base body 101, on which a concave coil slot 102 is arranged, and the coil slot 102 can be distributed in a spiral shape. The inclination angle of the side wall of the coil slot 102 is α, the inclination angle of the upper edge of the side wall is β, and α≧β. Preferably, the value range of the inclination angle α of the side wall of the coil slot 102 is: 80°≦α≦90°, and the value range of the inclination angle β along the side wall is: 50°≦α≦70°.

[0051] The bottom and side walls of the coil slot 102 and the upper surface of the silicon base body 101 are coated with an insulating layer 200 of organic material. A single-layer metal or multi-layer electroplating seed layer 300 is disposed on the insulating layer 200 inside the coil slot 102 . A metal wiring layer 400 is provided in the coil slot 102 where the electroplating seed layer 300...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com