Memory structure and method of forming the same

A technology of memory and storage area, which is applied in the direction of semiconductor devices, electric solid state devices, electrical components, etc., and can solve the problems of small reading noise capacity and poor reading and writing ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037]The memory structure of the prior art has many problems, for example, the static noise capacity of the static memory is small, and the anti-interference ability is poor.

[0038]Now combine the memory of the prior art to analyze the reasons for the low static noise capacity of the memory and poor anti-interference ability:

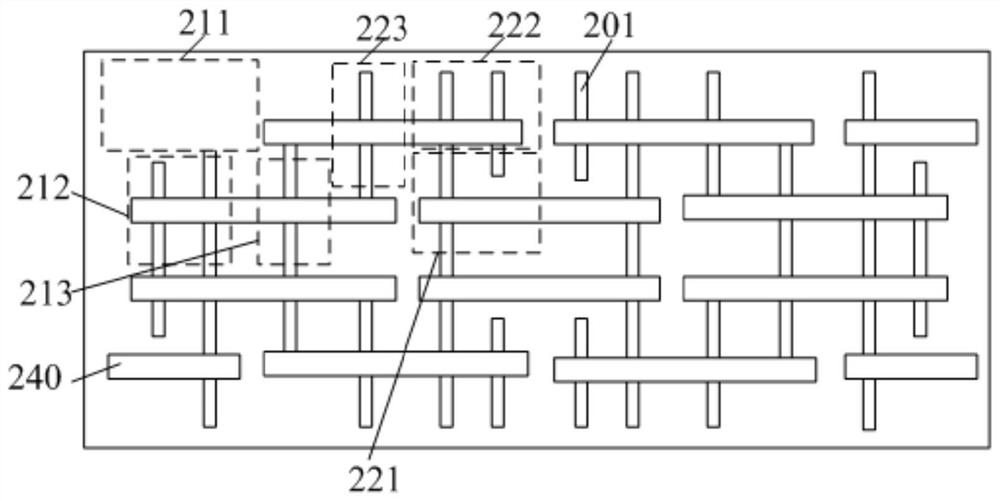

[0039]figure 1 It is a schematic diagram of a static memory structure.

[0040]Please refer tofigure 1 The static memory includes: a first pull-up transistor PU1, a first pull-down transistor PD1, a first transfer transistor PG1, a second pull-up transistor PU2, a second pull-down transistor PD2, and a second transfer transistor PG2. The source of the first pull-up transistor PU1 is connected to the drain of the first pull-down transistor PD1 to form a first storage node A. The source of the second pull-up transistor PU2 is connected to the drain of the second pull-down transistor PD2. The drains are connected to form a second storage node B. The gate of the first ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com