Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

110results about How to "Reduce reverse leakage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

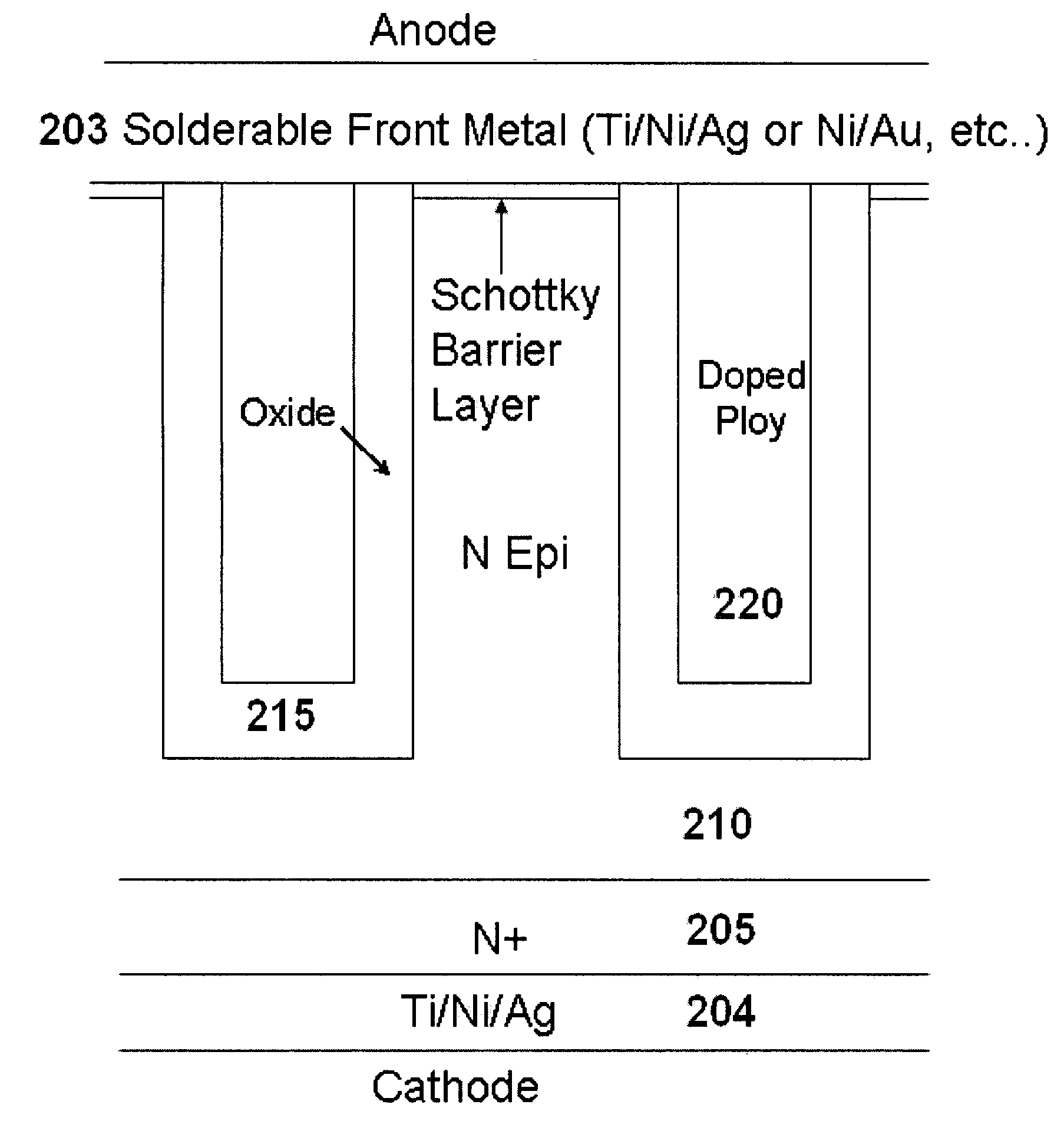

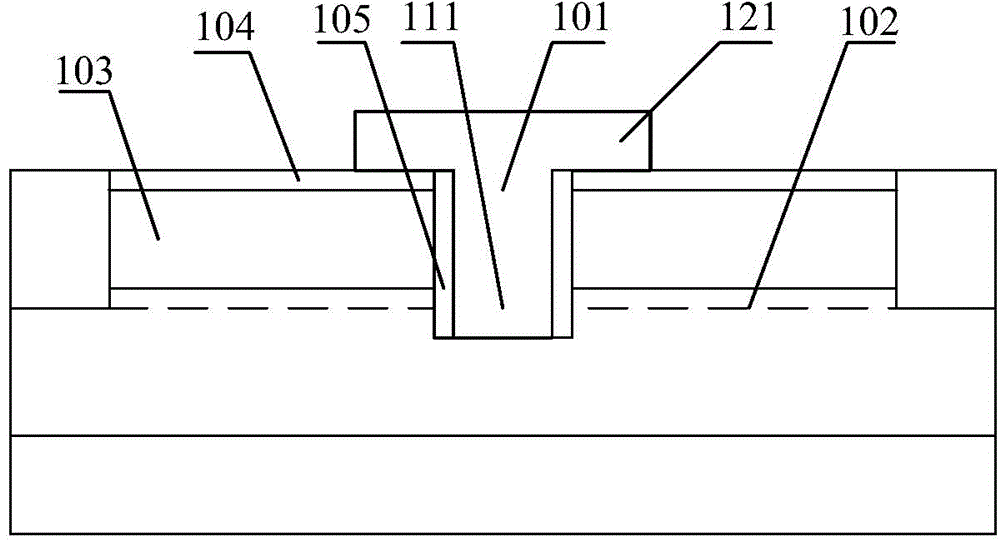

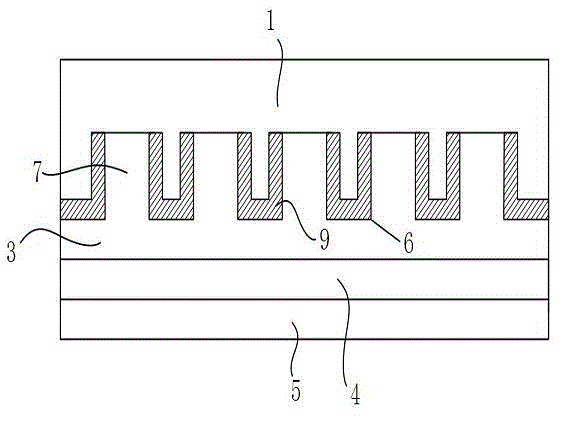

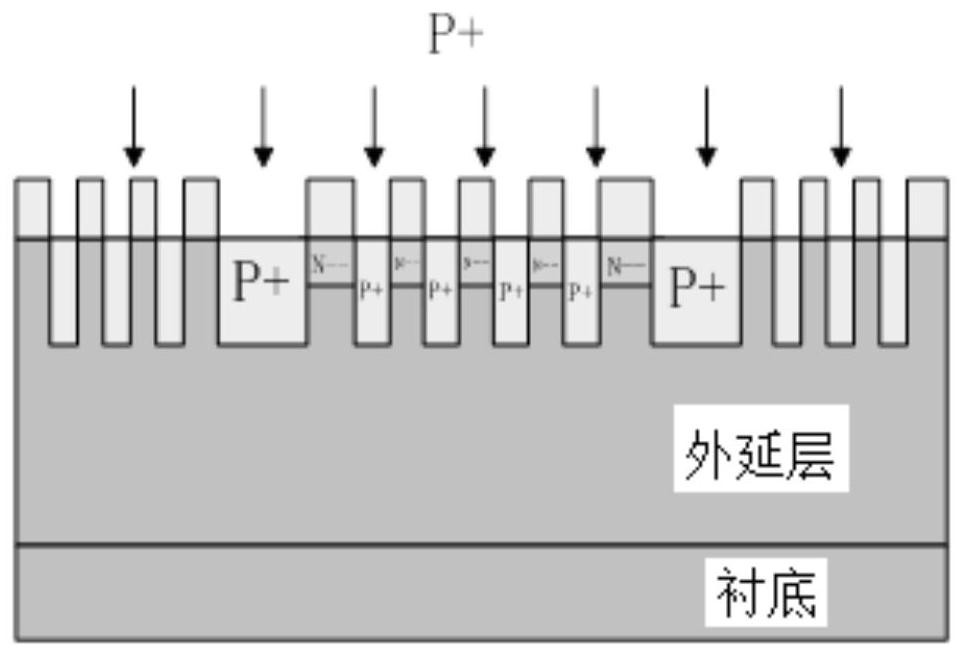

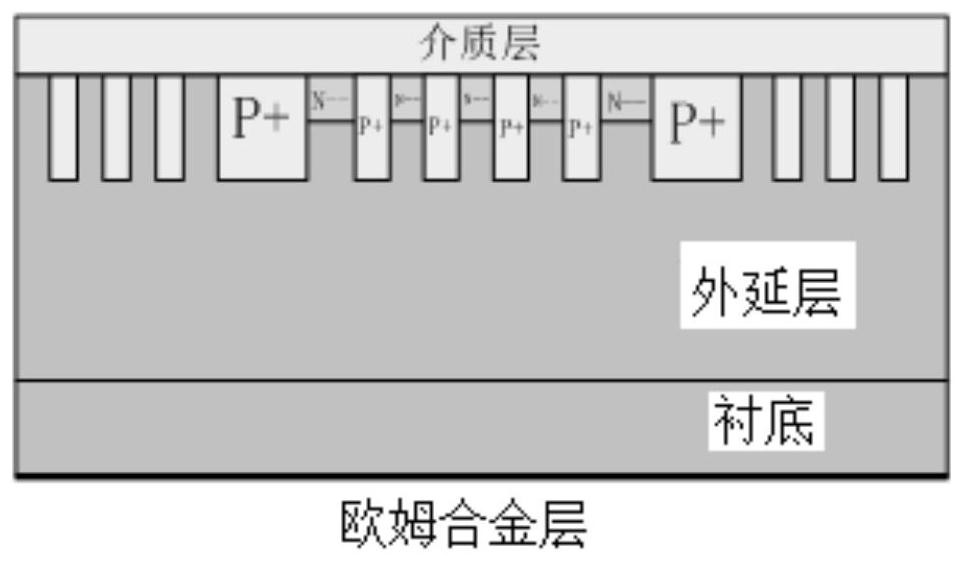

Trench schottky with multiple epi structure

InactiveUS20090309181A1Reduce doping concentrationIncrease the doping concentrationSemiconductor devicesDopantSchottky barrier

A trench Schottky barrier rectifier includes an cathode electrode at a face of a semiconductor substrate and an multiple epitaxial structure in drift region which in combination provide high blocking voltage capability with low reverse-biased leakage current and low forward voltage. The multiple structure of the drift region contains a concentration of first conductivity dopants therein which comprises two or three different uniform value from a Schottky rectifying junction formed between the anode electrode and the drift region. The thickness of the insulating region (e.g., SiO2) in the MOS-filled trenches is greater than 1000 Å to simultaneously inhibit field crowing and increase the breakdown voltage of the device. The multiple epi structure is preferably formed by epitaxial growth from the cathode region and doped in-situ.

Owner:FORCE MOS TECH CO LTD

Schottky diode and manufacturing method for Schottky diode

InactiveCN104134704AIncrease widthReduce concentration effectSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierSchottky diode

The invention provides a Schottky diode and a manufacturing method of the Schottky diode. The Schottky diode has the advantages that due to the fact that a groove structure with the wide upper portion and the narrow lower portion is mainly formed in a semiconductor layer, the concentration of two-dimensional electron gas below the Schottky metal inclined groove face can be effectively modulated, the Schottky barrier width and the Schottky barrier height can be increased, and therefore reverse electric leakage can be reduced; meanwhile, the concentration effect of an electric field at the edge of a groove can be further effectively improved, and the breakdown voltage of a device can be increased.

Owner:GPOWER SEMICON

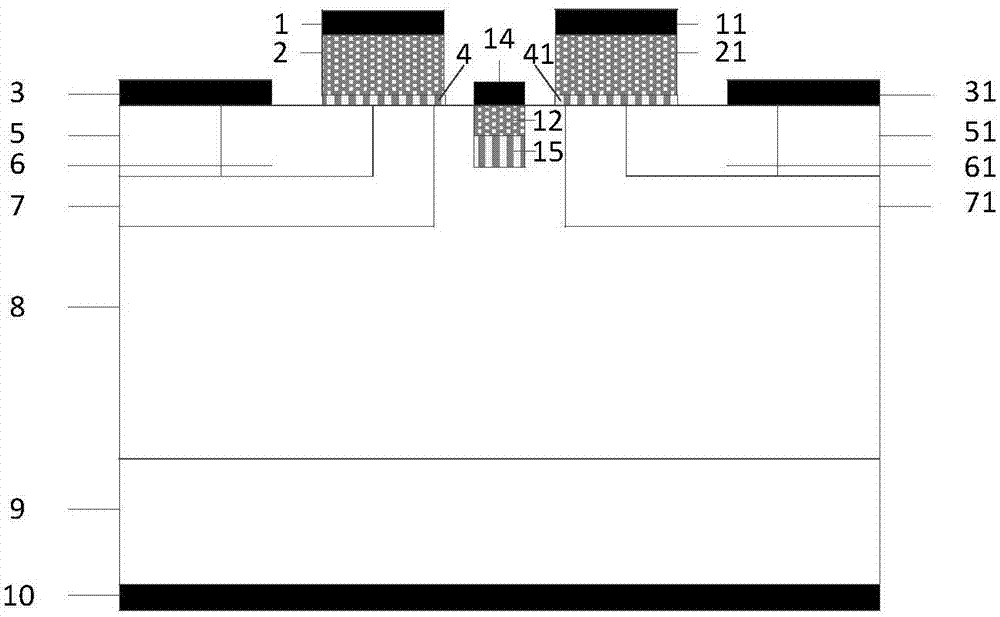

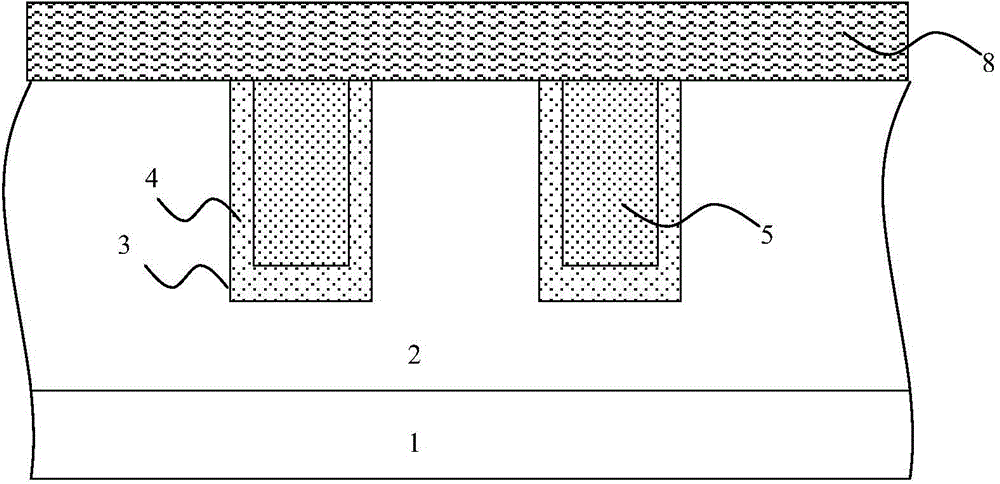

Silicon carbide VDMOS device and manufacturing method thereof

ActiveCN107275407AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingDiodeCapacitanceHeterojunction

The invention discloses a silicon carbide VDMOS device and manufacturing method thereof, and belongs to the technical field of power semiconductors. A trench is etched on a JFET region surface of a traditional silicon carbide VDMOS device, P type doping is introduced into the bottom of the trench, and at the same time, a polycrystalline silicon layer is formed in the trench, so that the polycrystalline silicon layer and a side wall of the trench are in contact to form a Si / SiC heterojunction. A diode is integrated in the device, and the device has the advantages of low conduction voltage drop, fast switching speed and good reverse recovery characteristic in a diode working mode, and has the advantages of high breakdown voltage, small grid capacitance and fast switching speed in an MOS working mode. The proposed device structure optimizes application of the device in the field of inverter circuits, chopper circuits and the like, and has the advantage that the process is simple, and is compatible with a traditional silicon carbide VDMOS device process.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

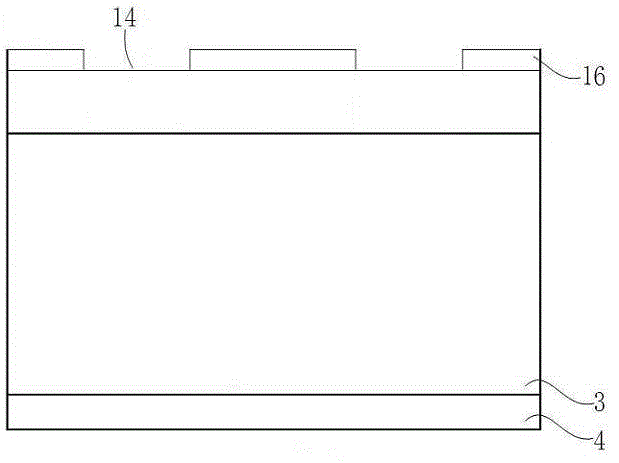

MWT cell with back passive film and preparation method thereof

InactiveCN105304730AImprove conversion efficiencyAvoid destructionFinal product manufacturePhotovoltaic energy generationTectorial membraneHydrofluoric acid

The invention discloses a preparation method of an MWT cell with a back passive film. The preparation method comprises the steps that wet texturing is performed on a provided silicon wafer; phosphorus diffusion or boron diffusion is performed on the silicon wafer; the edge and the back surface emitter of the silicon wafer are etched, and a PSG or a BSG is removed; the silicon wafer is punched; the silicon wafer is cleaned by hydrofluoric acid; the back passive film is deposited on the back surface of the silicon wafer; a protection film is deposited on the back surface of the silicon wafer; an anti-reflection passive film is deposited on the front surface of the silicon wafer; a slot is arranged in the non-emitter electrode printing region of the back surface of the silicon wafer; an emitter electrode and a base contact electrode are printed on the back surface of the silicon wafer, and through holes distributed at the center position of the emitter electrode are filled; and an aluminum back field is printed on the back surface of the silicon wafer, and fine gate lines are printed on the front surface. Correspondingly, the invention also provides the MWT cell prepared by the preparation method. With application of the preparation method, electric leakage around the through holes can be reduced so that photoelectric conversion efficiency of the MWT cell can be substantially enhanced.

Owner:ZHEJIANG ASTRONERGY

Soft fast recovery diode and manufacturing method thereof

ActiveCN103872144AReduce EMIReduce lossSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceControl layer

The invention relates to a soft fast recovery diode and a manufacturing method thereof. The diode comprises an N type intrinsic region, a back N<+> buffer region, an anode metal layer and a cathode metal layer, wherein the back N<+> buffer region is formed on the back face of the N type intrinsic region; a P type emitting region is formed between the front face of the N type intrinsic region and the anode metal layer; mask oxide layers are formed symmetrically at the two ends of the anode metal layer; a P type high-resistance region is formed on the boundary of an active region; a P<+> ohmic contact layer is formed in the center of the active region; an overall lifetime control region is formed on the entire diode, and covers all structural layers of the diode; a localized lifetime control layer is positioned close to the P<+> ohmic contact layer in the P type emitting region along the axial direction of the diode; the localized lifetime control layer is positioned in a plane constructed by the P type emitting region and the P type high-resistance region along a direction which is vertical to the axial direction of the diode. The soft fast recovery characteristic of a device is realized by adopting an overall-localized lifetime control way; by arranging the high-resistance region, the snow slide resistance of the device is improved.

Owner:STATE GRID CORP OF CHINA +2

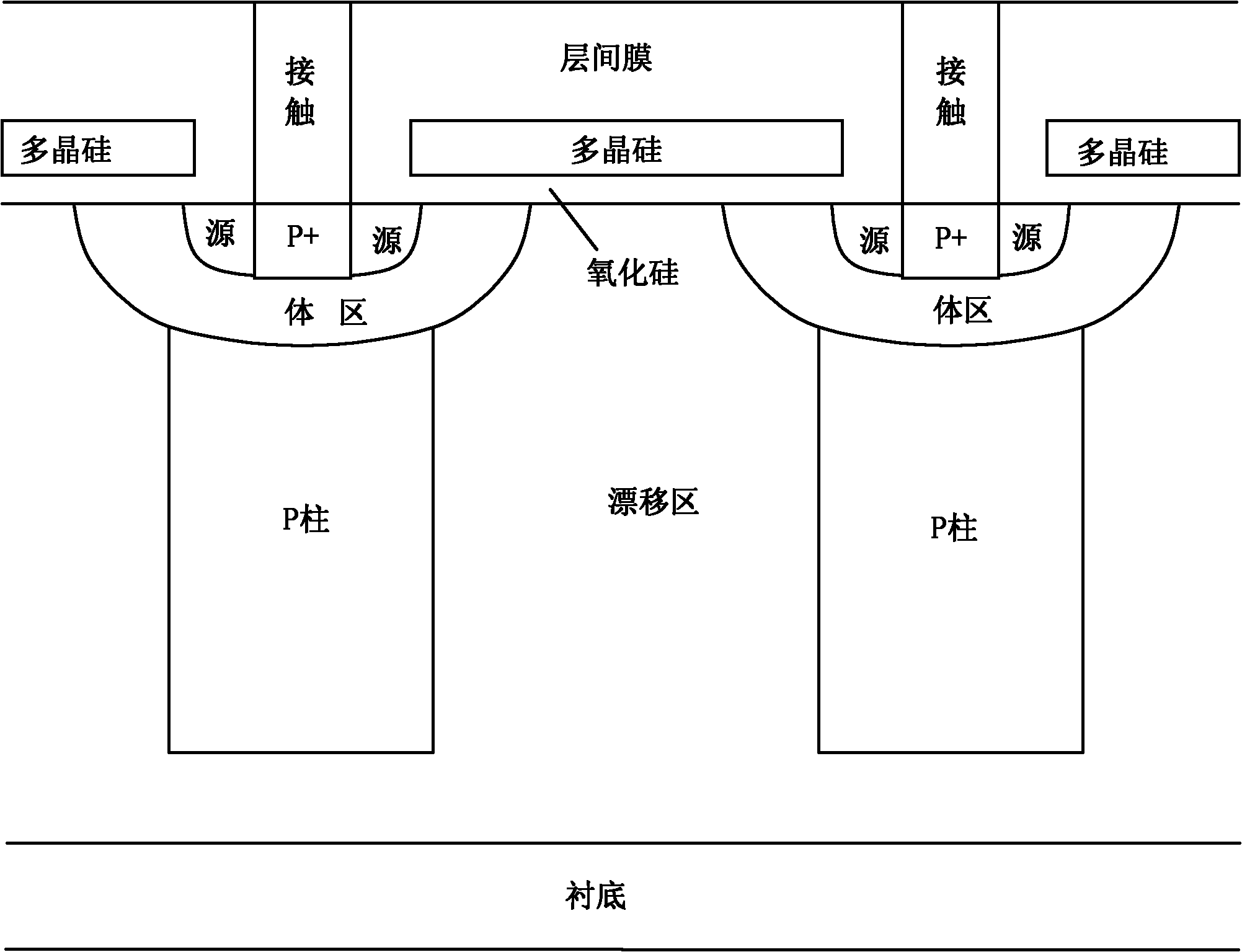

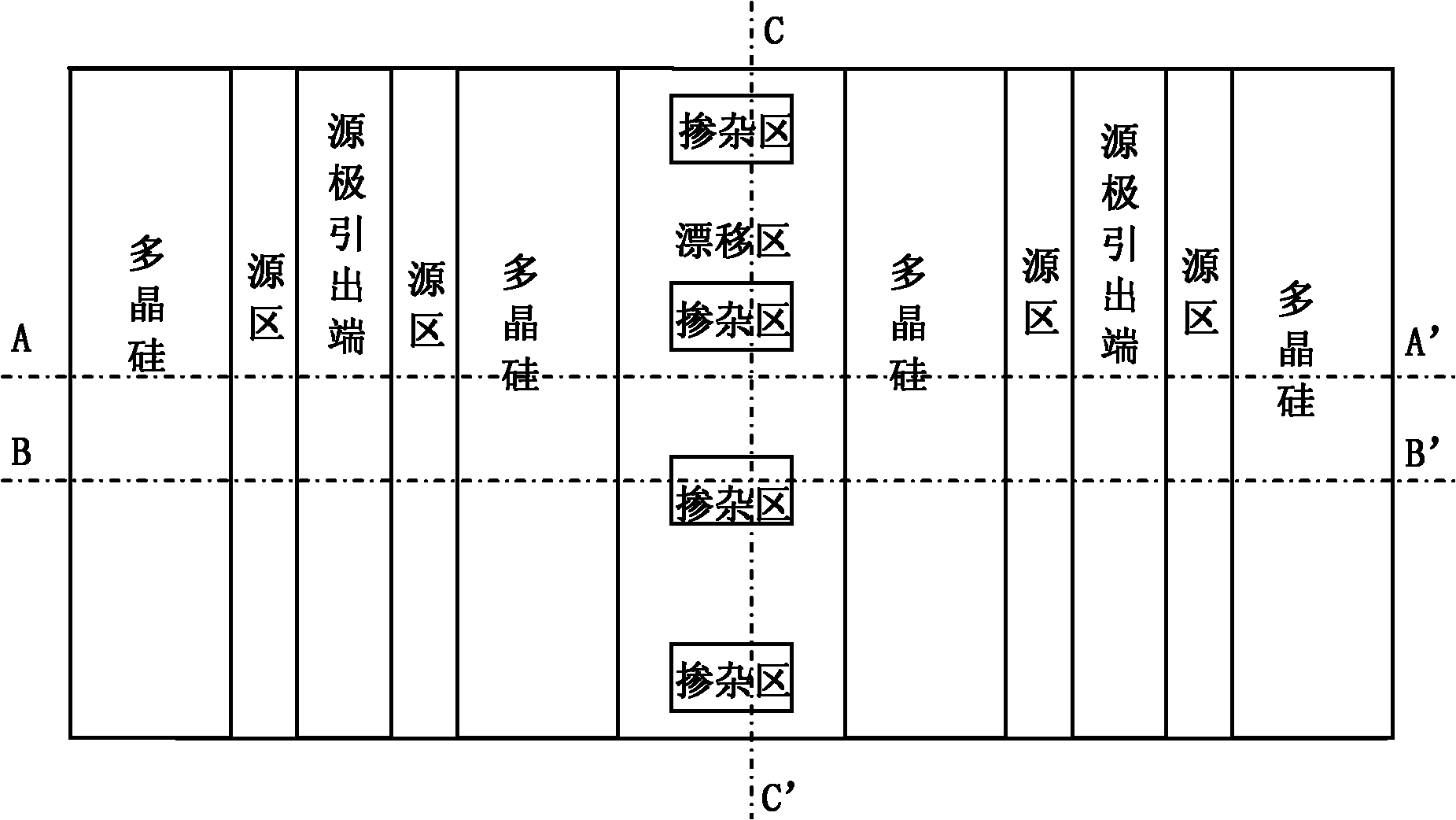

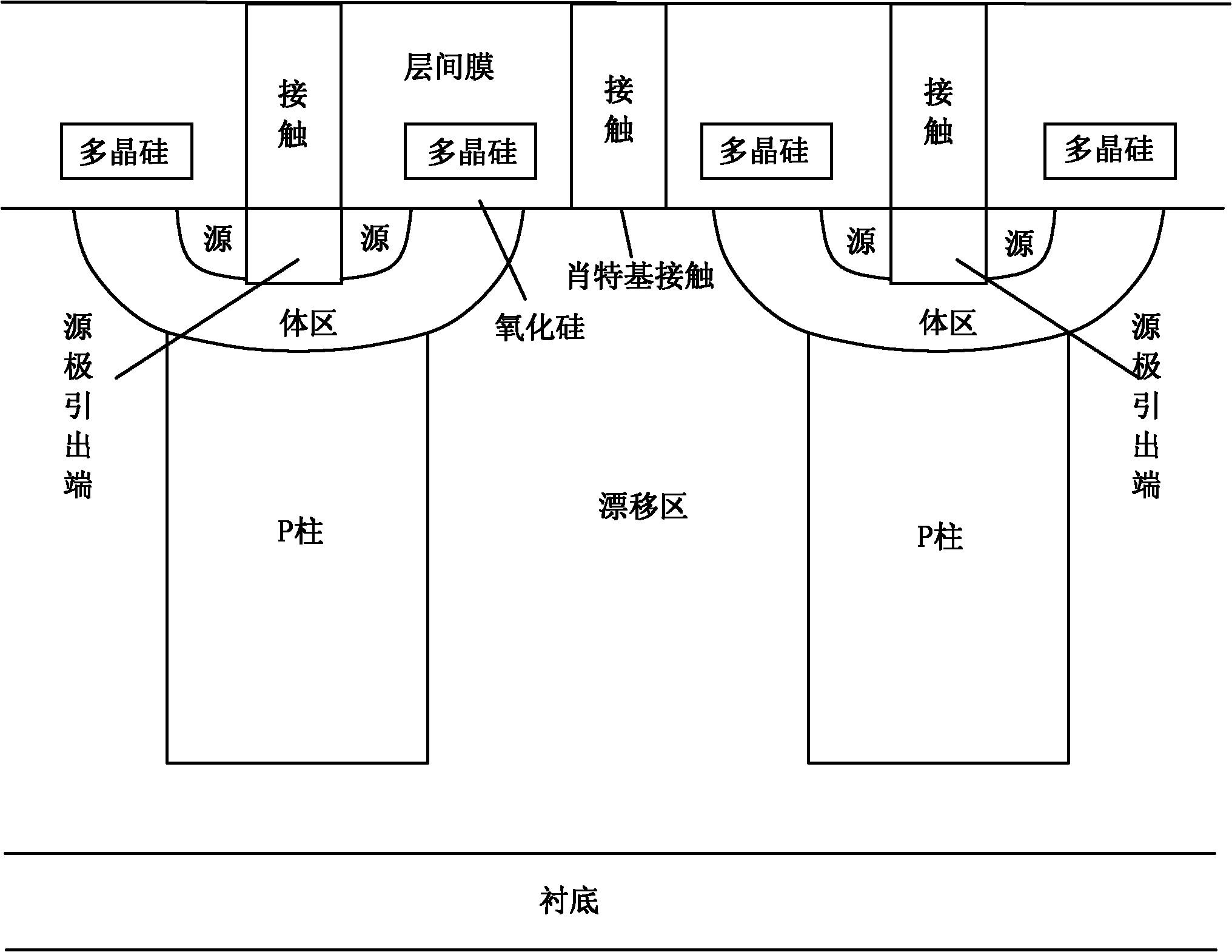

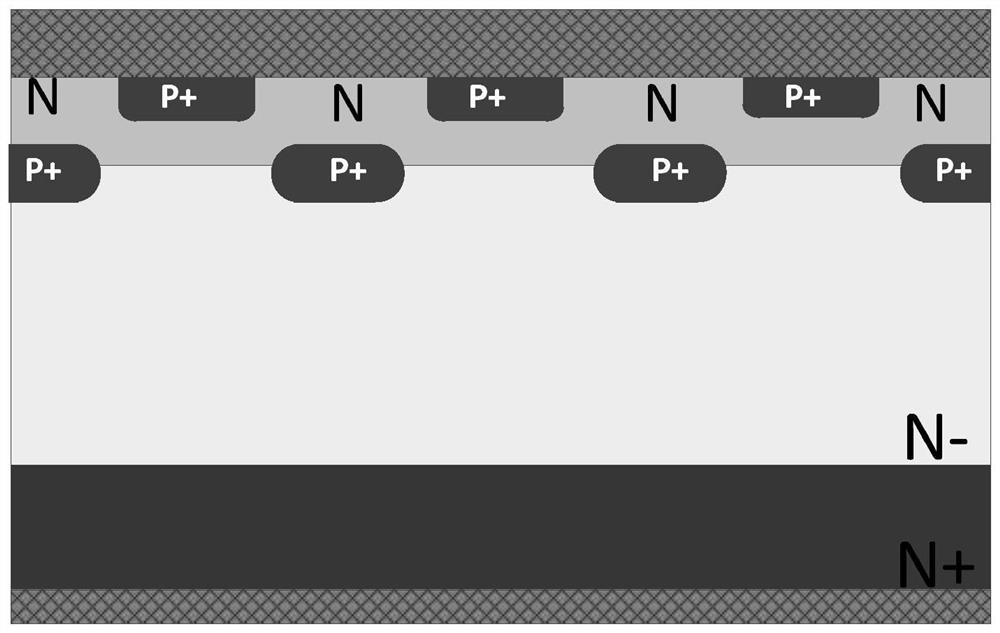

Method for integrating Schottky diode in super-junction MOSFET (metal-oxide-semiconductor field effect transistor)

ActiveCN102610523AReduce reverse leakageReduce intakeSemiconductor/solid-state device manufacturingDiodeMOSFETField-effect transistor

The invention discloses a method for integrating a Schottky diode in a super-junction MOSFET (metal-oxide-semiconductor field effect transistor). In order to connect and combine the Schottky diode consisting of a Schottky contact and a substrate in the super-junction MOSFET in parallel, the anode of the Schottky diode is positioned on a drift area between two body areas at a source end of the super-junction MOSFET element cell area, and is connected with the source end of the super-junction MOSFET; a plurality of doping areas are arranged on the drift area of the anode, the electric conduction types of the doping areas are opposite to the electric conduction type of the drift area, the concentration of impurity is larger than that of impurity in the drift area, and the doping areas are connected with the source end of the super-junction MOSFET; and the cathodes of the Schottky diode share the drain electrode of the super-junction MOSFET. According to the method, the reverse electric leakage amount of the Schottky diode can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

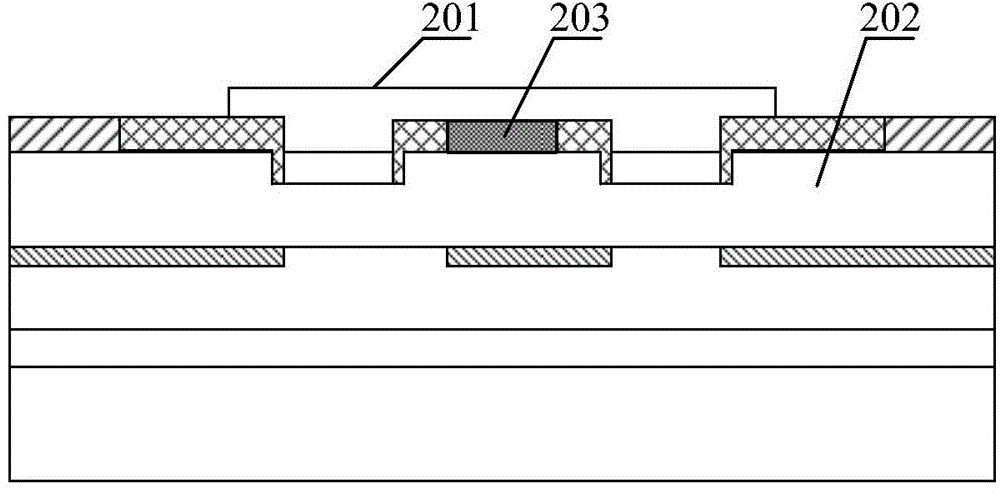

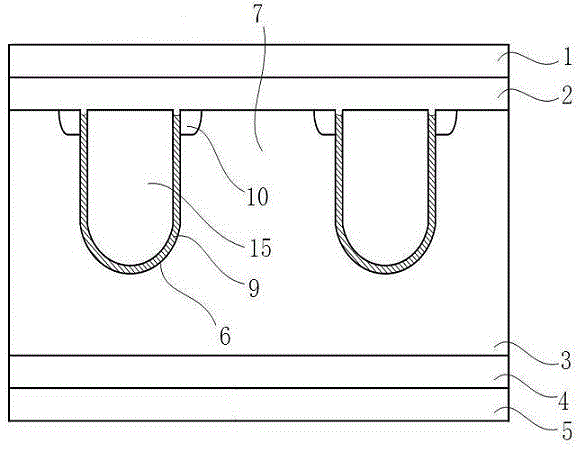

Schottky diode and manufacturing method thereof

ActiveCN104882491AReduce reverse leakageImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor package

The invention discloses a Schottky diode and a manufacturing method thereof. The Schottky diode comprises a substrate, a first semiconductor layer, a second semiconductor layer, a first passivation dielectric layer, a cathode, an anode slot, a low work function anode and a high work function anode, wherein the first semiconductor layer is located on the substrate; the second semiconductor layer is located on the first semiconductor layer, and a two-dimensional electron gas is formed at the at the interface between the first semiconductor layer and the second semiconductor layer; the first passivation dielectric layer is located on the second semiconductor layer, and a part of the second semiconductor layer is exposed out of the first passivation dielectric layer; the cathode is arranged on the exposed part of the second semiconductor layer or extends to the upper surface of the first passivation dielectric layer; the anode slot extends from the first passivation dielectric layer to a region where the two-dimensional electron gas is positioned or exceeds the region where the two-dimensional electron gas is positioned; the low work function anode is arranged on the anode slot and extends to the upper surface of the second semiconductor layer; and the high work function anode covers the low work function anode, and is electrically connected with the low work function anode. The Schottky diode provided by the invention has the advantages of being low in reverse electric leakage, high in breakdown voltage, low in forward threshold voltage and turn-on resistance.

Owner:GPOWER SEMICON

Schottky diode structure

ActiveUS20150001666A1Reduce reverse leakageLower forward voltageSemiconductor devicesSemiconductorSchottky diode

The invention provides a Schottky diode structure. An exemplary embodiment of a Schottky diode structure includes a semiconductor substrate having an active region. A first well region having a first conductive type is formed in the active region. A first doped region having the first conductive type is formed on the first well region. A first electrode is disposed on the active region, covering the first doped region. A second electrode is disposed on the active region, contacting to the first well region. A gate structure is disposed on the first well region. A second doped region, having a second conductive type opposite to the first conductive type, and is formed on the first well region. The gate structure and the second doped region are disposed between the first and second electrodes.

Owner:MEDIATEK INC

Trenched Schottky-barrier diode and manufacturing method thereof

ActiveCN102916055ALower doping concentration is lowReduce reverse leakageSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierOhmic contact

The invention discloses a trenched Schottky-barrier diode, and solves the problems that a conventional trenched Schottky-barrier diode is lower in performance and reliability, high in reverse current leakage and poor in reverse blocking capability. The doping density of an epilayer gradually increases from the top to bottom, a second conduction type non-uniformly doped conductive polycrystalline silicon of which the doping density gradually decreases from the top to bottom is filled in trenches, second conduction type heavily doped lug boss apex angle protection areas are formed at the apex angles on two sides of lug bosses, and a Schottky-barrier metal layer in ohmic contact with the top surfaces of both the conductive polycrystalline silicon and the lug boss apex angle protection areas is added to the bottom surface of an anodal metal layer. The trenched Schottky-barrier diode provided by the invention has the advantages of low reverse current leakage, good voltage reverse blocking capability and excellent reliability. The invention also provides a manufacturing method of the trenched Schottky-barrier diode, which has the advantages of less steps and low manufacturing cost and can effectively isolate areas from damage by the technological process and contamination of impurities due to local impairment of isolating layers.

Owner:HANGZHOU LION MICROELECTRONICS CO LTD

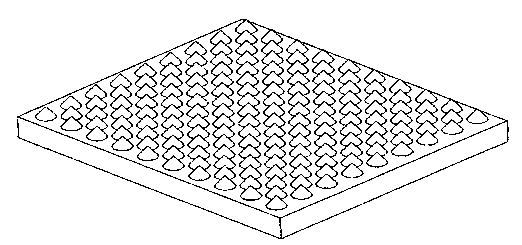

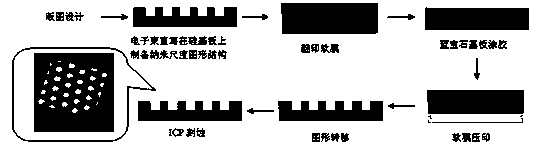

Method for fast preparing sapphire pattern substrate through nanoimprint technology

InactiveCN103840050AUniform graphic sizeReduce processing costsPhotomechanical apparatusSemiconductor devicesPhotoresistAdhesive

The invention discloses a method for fast preparing a sapphire pattern substrate through the nanoimprint technology. The method comprises the following steps: a nanoimprint template is prepared through two methods including the hard template method and the soft template method, an epitaxial layer is grown on a clean sapphire substrate, SiO2 or Cr is evaporated and plated to obtain a target substrate, and then the surface of the target substrate is coated with moderate hot-pressing adhesive, imprinting is performed on the target substrate coated with uniform adhesive and the nanoimprint template, a photoresist surface pattern is transferred to the surface of the target substrate, and after a series of post processes, the required sapphire pattern substrate is obtained. The method of the invention has the following main advantages that the problem of the traditional lithography in the feature size reduction process can be solved, the pattern substrate having the nanometer feature size is prepared, and the size of the pattern substrate is less than 500nm. The method of the invention has the following advantages that the bran-new NPSS substrate industrialization technology can be realized, and at the same time, the substrate machining cost and epitaxy production cost can be reduced, and the LED lighting chip production cost is reduced by 15%.

Owner:SUZHOU NANOJOIN PHOTONICS

Technological method for manufacturing groove type Schottky diodes

ActiveCN104701161AReduce reverse leakageImprove in-plane uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesContact holeSilicon oxide

The invention discloses a technological method for manufacturing groove type Schottky diodes. Contact holes are particularly formed by means of etching by the aid of two-step dry processes. The technological method includes etching silicon surfaces at first when the contact holes are about to be formed; then etching silicon and silicon oxide in grooves together. Selection ratios of the silicon to the silicon oxide in last-step contact hole etching menus are 1:1, the silicon surfaces are etched by depths higher than 1000 angstroms approximately, the silicon oxide in the side walls of the grooves is protruded out of the silicon surfaces, and Schottky contact effects are ultimately realized by the aid of metal. The technological method has the advantages that the technological method aims to solve the problem of high electric leakage of existing groove Schottky diode products, the internal uniformity of the surfaces of products can be improved, the production cost can be reduced, the yield of the products can be increased, and the technological method is suitable for mass production on a large scale.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

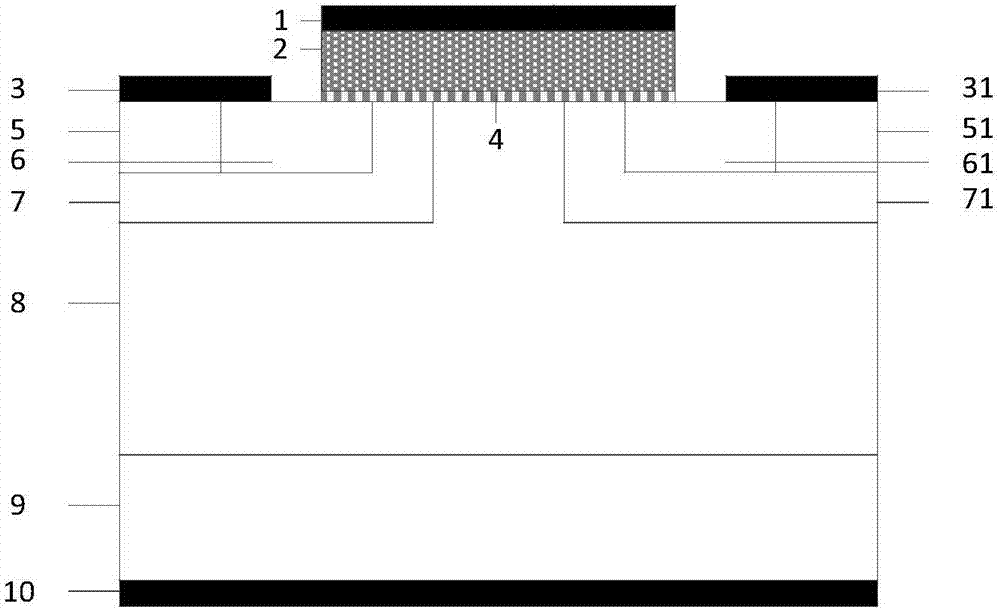

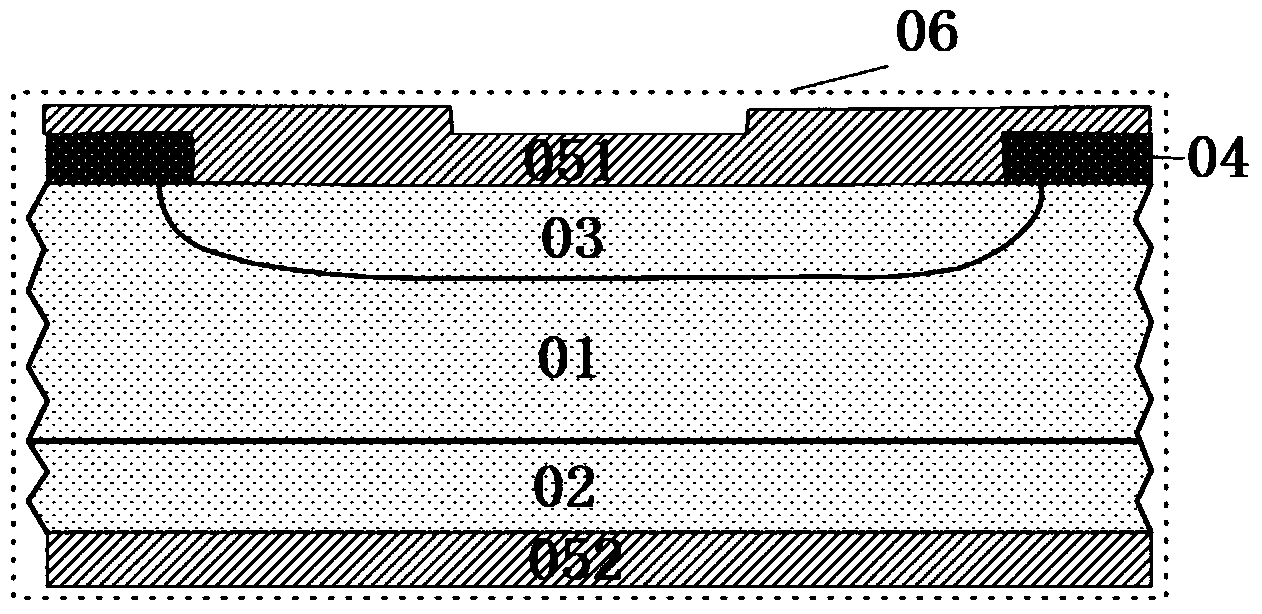

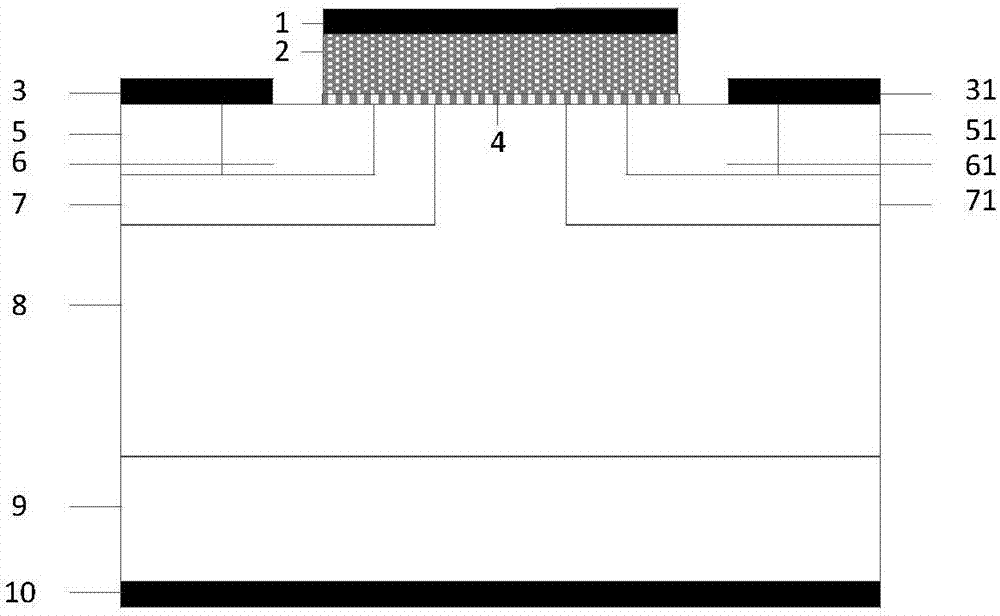

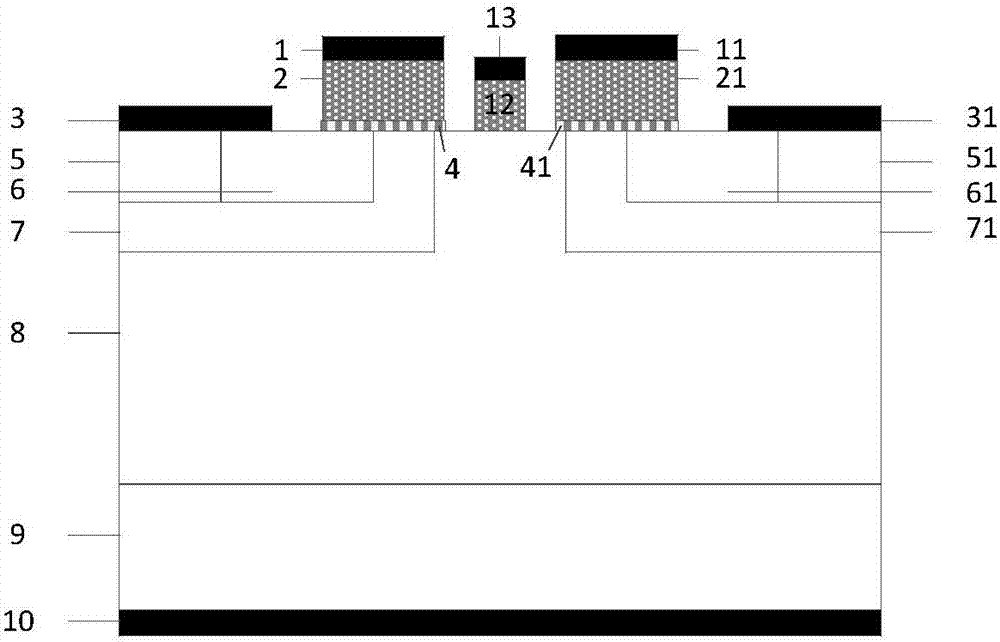

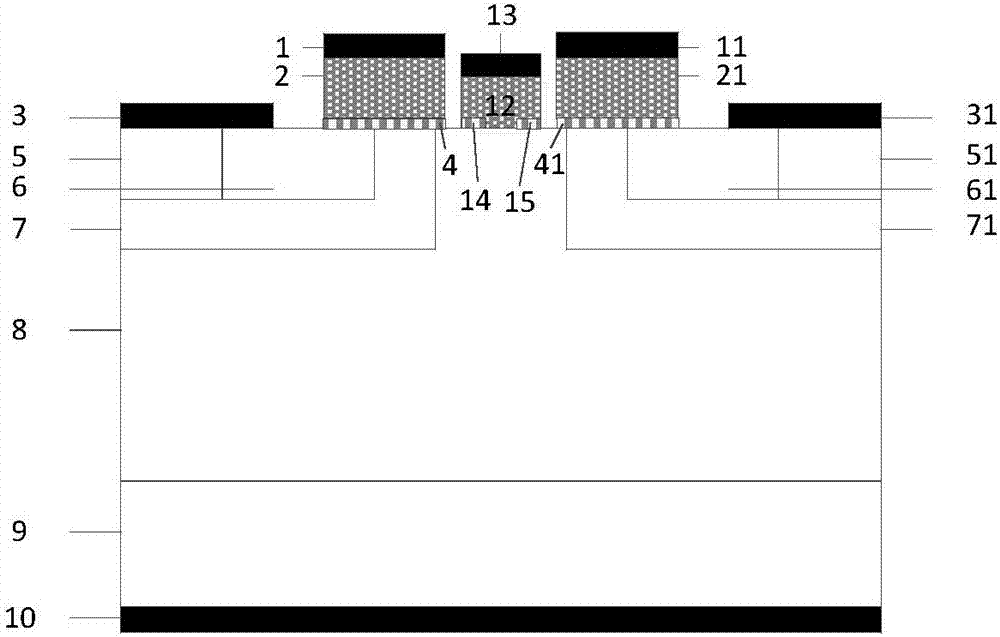

SiC vertical double diffused metal-oxide-semiconductor (VDMOS) device and fabrication method thereof

ActiveCN107248533AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceHeterojunction

The invention discloses a SiC vertical double diffused metal-oxide-semiconductor (VDMOS) device and a fabrication method thereof, and belongs to the technical field of a power semiconductor. A poly-silicon layer is directly deposited on a surface of a junction field-effect transistor (JFET) region of the SiC VDMOS device to form a Si / SiC heterojunction, a diode is further integrated in the device, and the application of the device in the field of an inversion circuit, a chopping circuit and the like is optimized. Compared with the prior art directly employing a VDMOS parasitic SiC diode, the SiC VDMOS device has the advantages of relatively low power loss, relatively fast working speed and relatively high working efficiency, and positive conduction is easier to achieve; compared with the prior art that a fast recovery diode (FRD) is reversely connected with the exterior of the device in parallel, the SiC VDMOS device has the advantages that the usage number of the device is reduced, connection lines between the devices are reduced, and the miniature development of the device is promoted; moreover, the grid width is reduced, the grid capacitance is reduced, and the working speed of the device is further increased; and therefore, the VDMOS device proposed by the invention has wide application prospect in the circuit field of the inversion circuit, the chopping circuit and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

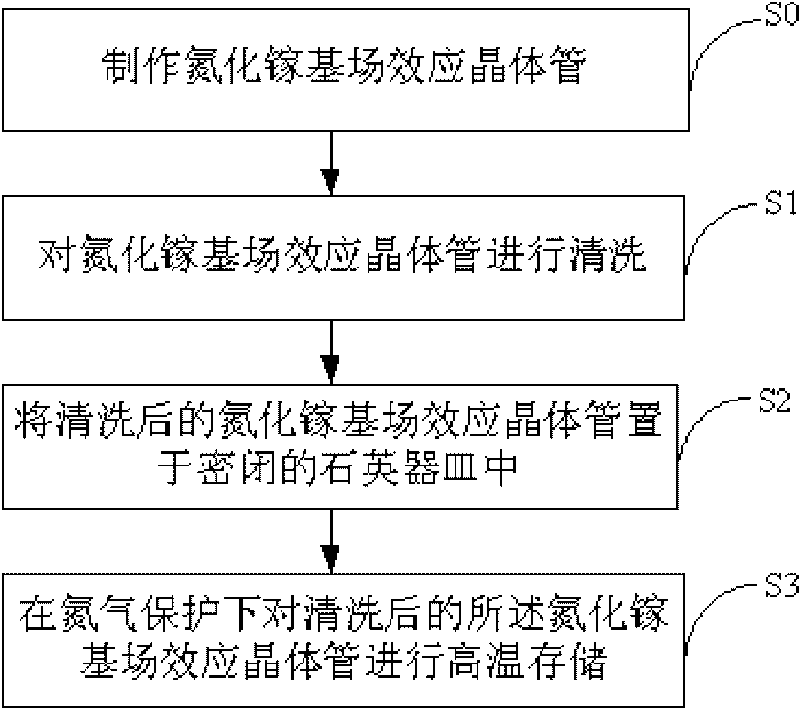

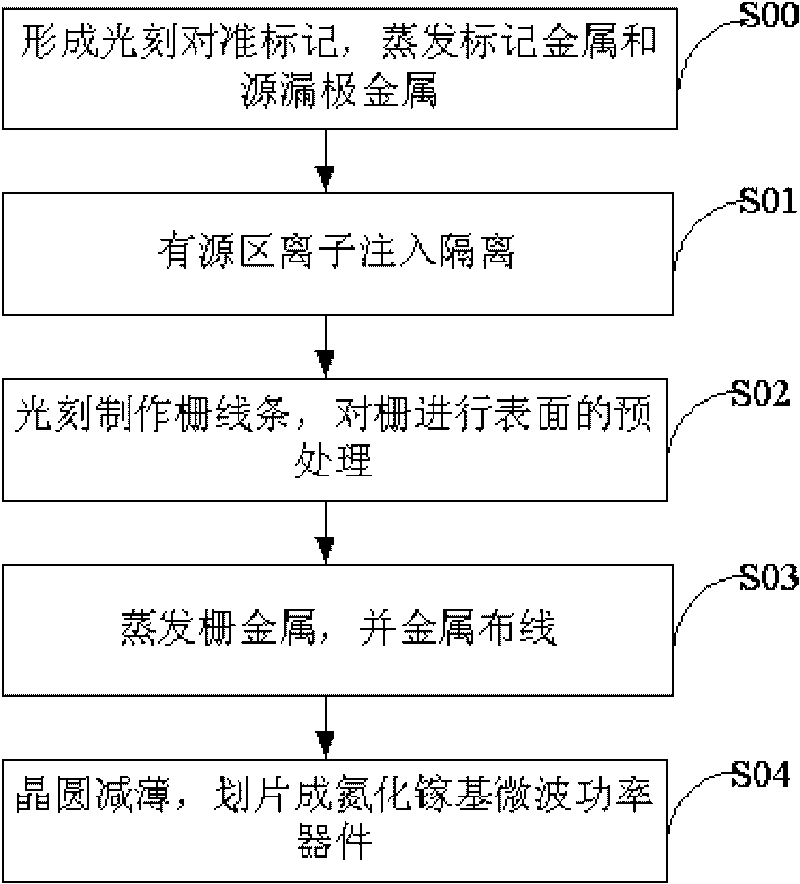

Method for improving Schottky barrier of gallium nitride-based field effect transistor

InactiveCN101707184ARaise the barrier heightImprove stabilitySemiconductor/solid-state device manufacturingSchottky barrierSemiconductor materials

The invention discloses a method for improving a Schottky barrier of a gallium nitride-based field effect transistor, belonging to the technical field of manufacture of semiconductor material device. The method comprises the following steps: cleaning the gallium nitride-based field effect transistor; and storing the cleaned gallium nitride-based field effect transistor under the protection of nitrogen at high temperature. By means of the invention, the height of the Schottky barrier of gallium nitride-based field effect transistor is increased, the reverse leakage f the Schottky barrier of gallium nitride-based field effect transistor is reduced, and the power characteristic and the breakdown characteristic of the gallium nitride-based field effect transistor are improved; therefore, the problem of parameter drift of the gallium nitride-based field effect transistor in the work is solved, and the stability and reliability of the gallium nitride-based field effect transistor are improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Diode anode structure, vertical diode and transverse diode

ActiveCN106298977AImprove efficiencyReduce reverse leakageSemiconductor devicesSchottky barrierSemiconductor package

The embodiment of the invention discloses a diode anode structure, a vertical diode and a transverse diode, and relates to the technical field of semiconductors. The diode anode structure comprises a semiconductor layer, at least two first Schottky metal layers, and at least one second Schottky metal layer, the two first Schottky metal layers are located on the semiconductor layer and forms Schottky contact with the semiconductor layer to obtain a first Schottky barrier height, and the at least one second Schottky metal layer is located on the semiconductor layer and between the first Schottky metal layers, and forms Schottky contact with the semiconductor layer to obtain a second Schottky barrier height. By employing the above technical scheme, two barrier heights are formed at an anode area with a semiconductor, when the diode is turned off in a reverse manner, the first Schottky barrier height can reduce reverse leakage, when the diode is turned on in a forward manner, the second Schottky barrier height can reduce forward turn-on voltage, and the usage efficiency of the diode can be improved by employing the above diode anode structure.

Owner:GPOWER SEMICON

Mesa etching process of high voltage diode silicon blocks

ActiveCN103943496AConsistent corrosion rateReduce reverse leakageSemiconductor/solid-state device manufacturingSemiconductor devicesHigh pressureHigh voltage

The invention relates to a mesa etching process of high voltage diode silicon blocks. The mesa etching process sequentially comprises performing mixed acid preparation; placing the silicon blocks to be treated into a BE plastic film and arranging the BE film with the silicon blocks on a plastic supporting frame; performing mixed acid treatment; performing etching quantity measurement; performing first time washing; performing nitric acid etching cleaning; performing second time washing; performing third time washing; performing dewatering and drying; drying the dry air; performing assembly sintering on the silicon blocks and electrode leads. According to the mesa etching process of the high voltage diode silicon blocks, a novel mixed acid is developed and accordingly the etching speed of cutting surfaces of the silicon blocks is consistent, the difference of the etching quantity is small, and damage layers caused by cut-off are completely removed; hydrofluoric acid cleaning treatment is performed after the mixed acid treatment is performed and accordingly a few oxidation layers on the surface of chip solder are removed and the good sintering soldering of the electrode leads can be convenient; the etching treatment rate is uniform and accordingly the good mesa shapes of the silicon blocks are formed and the difference of the etching quantity is small; the reverse electric leakage of a device is small, the breakdown characteristic is hard, the surge tolerance is large, and the rate of finished products is significantly improved.

Owner:江苏皋鑫电子有限公司

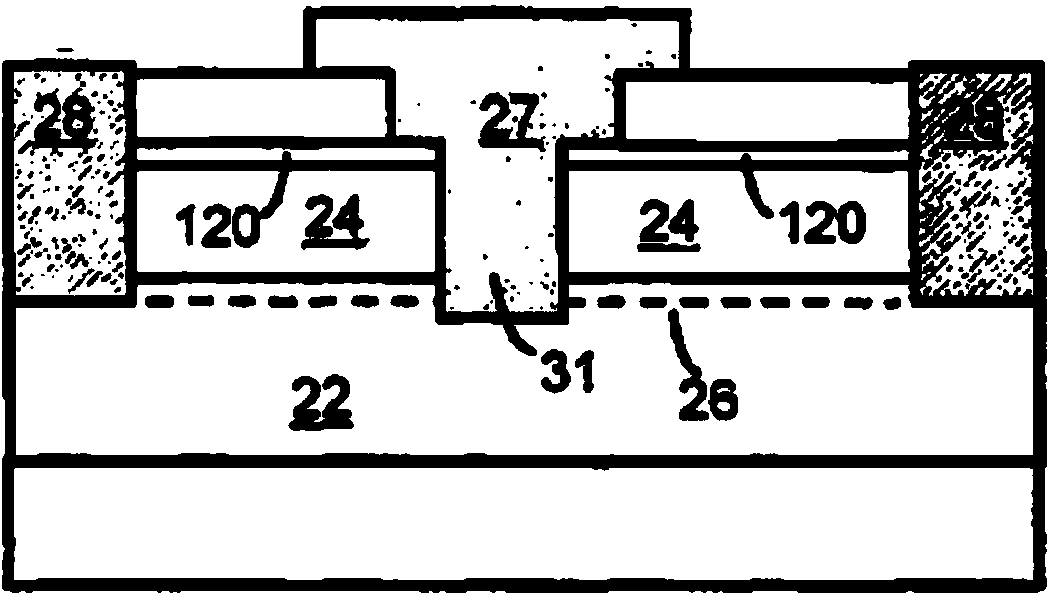

Trench-type Schottky-barrier diode rectifier and preparation method

ActiveCN101901808AOvercoming the tip discharge effectReduce reverse leakageSolid-state devicesSemiconductor/solid-state device manufacturingAluminiumTitanium

The invention provides a trench-type Schottky-barrier diode rectifier and a preparation method. By using the two shoulders of a conducting poly-silicon T-shaped head in the trench and the silica layers on the extended sections to cover the vertex angles of boss structures on two sides of the trench, the invention, based on the existing trench-type Schottky diode rectifiers, overcomes the problems of increase in inverse current leakage and reduction in inverse blocking capacity caused by the tip discharge effect produced by contact of the vertex angles of the boss and an upper metal layer; moreover, by filling the trench with the conducting poly-silicon instead of aluminum, titanium and other conventional materials of the upper metal layer, on one hand, the invention solves the problem that the reliability of the rectifier is influenced by hollow cavities left during trench filling, and on the other hand, the invention provides more flexible design space for the ratio of the opening width to depth of the trench of the diode rectifier.

Owner:SUZHOU SILIKRON SEMICON CO LTD

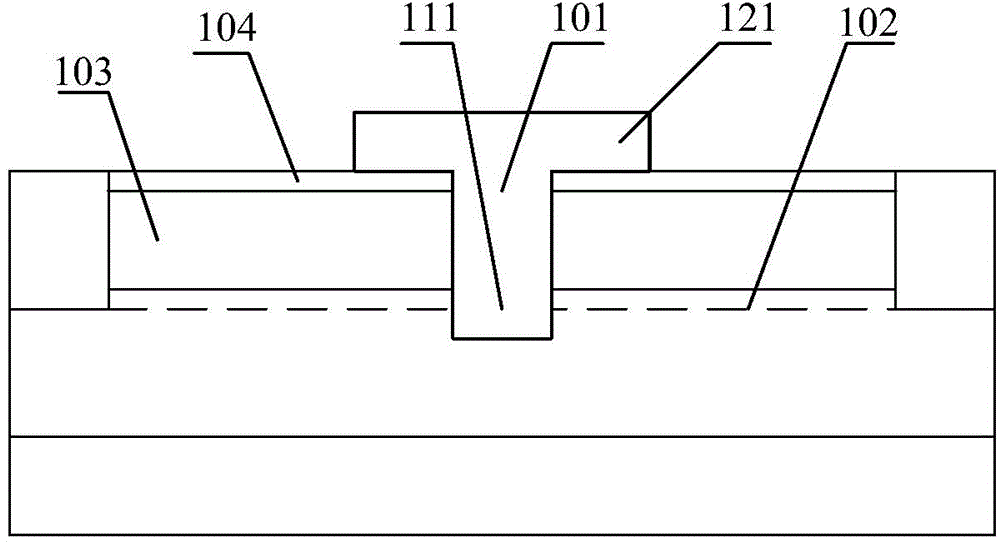

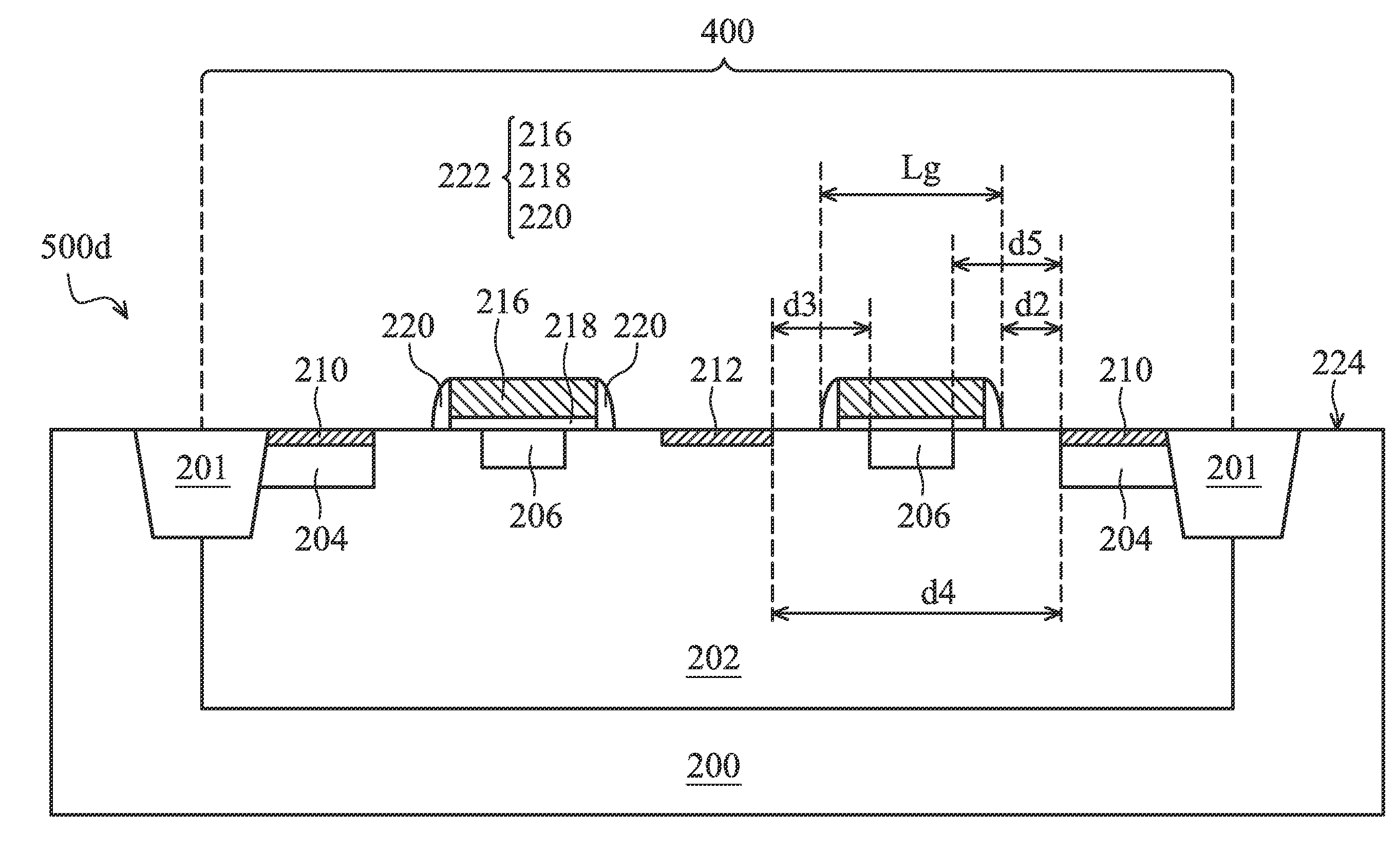

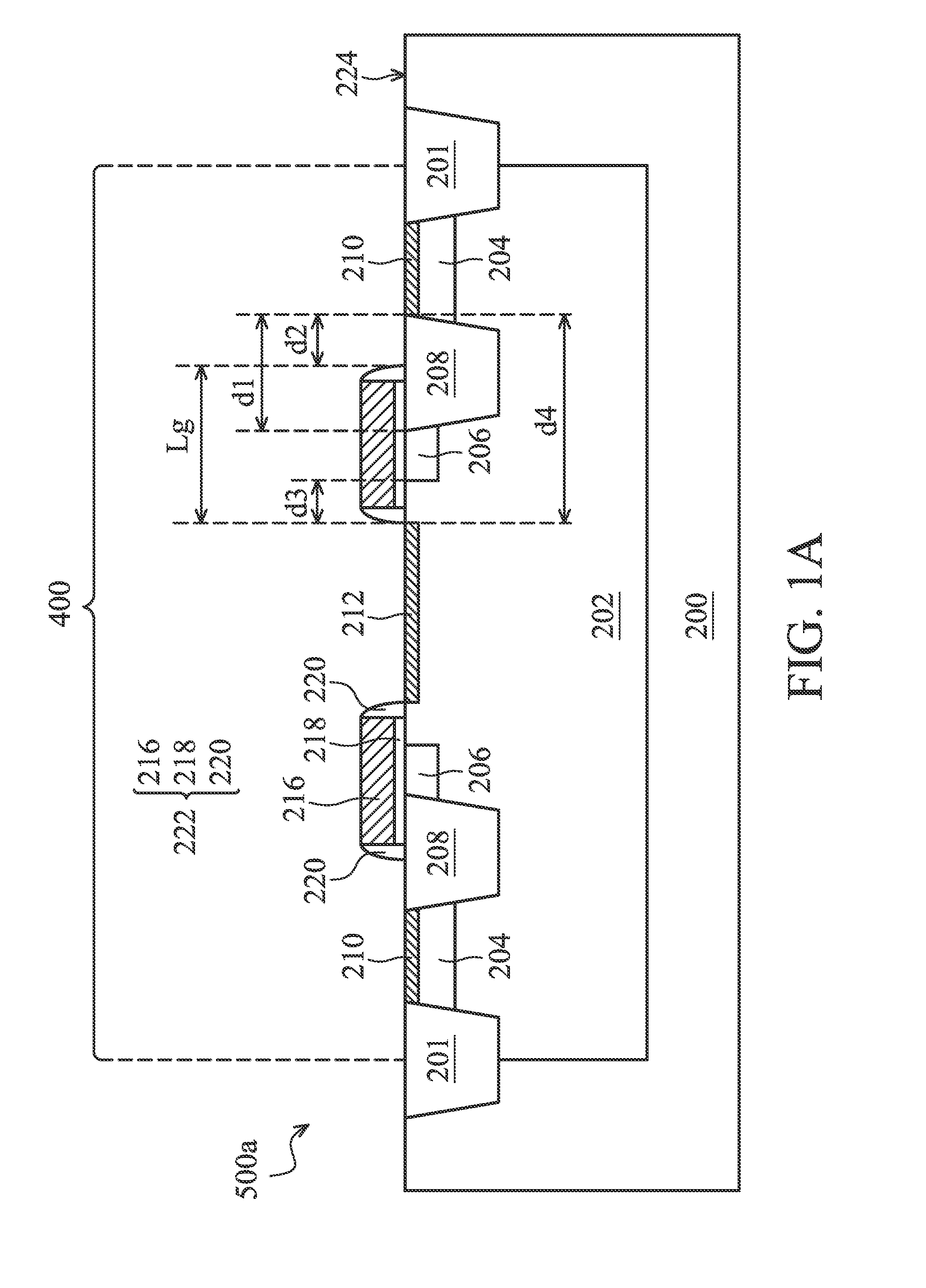

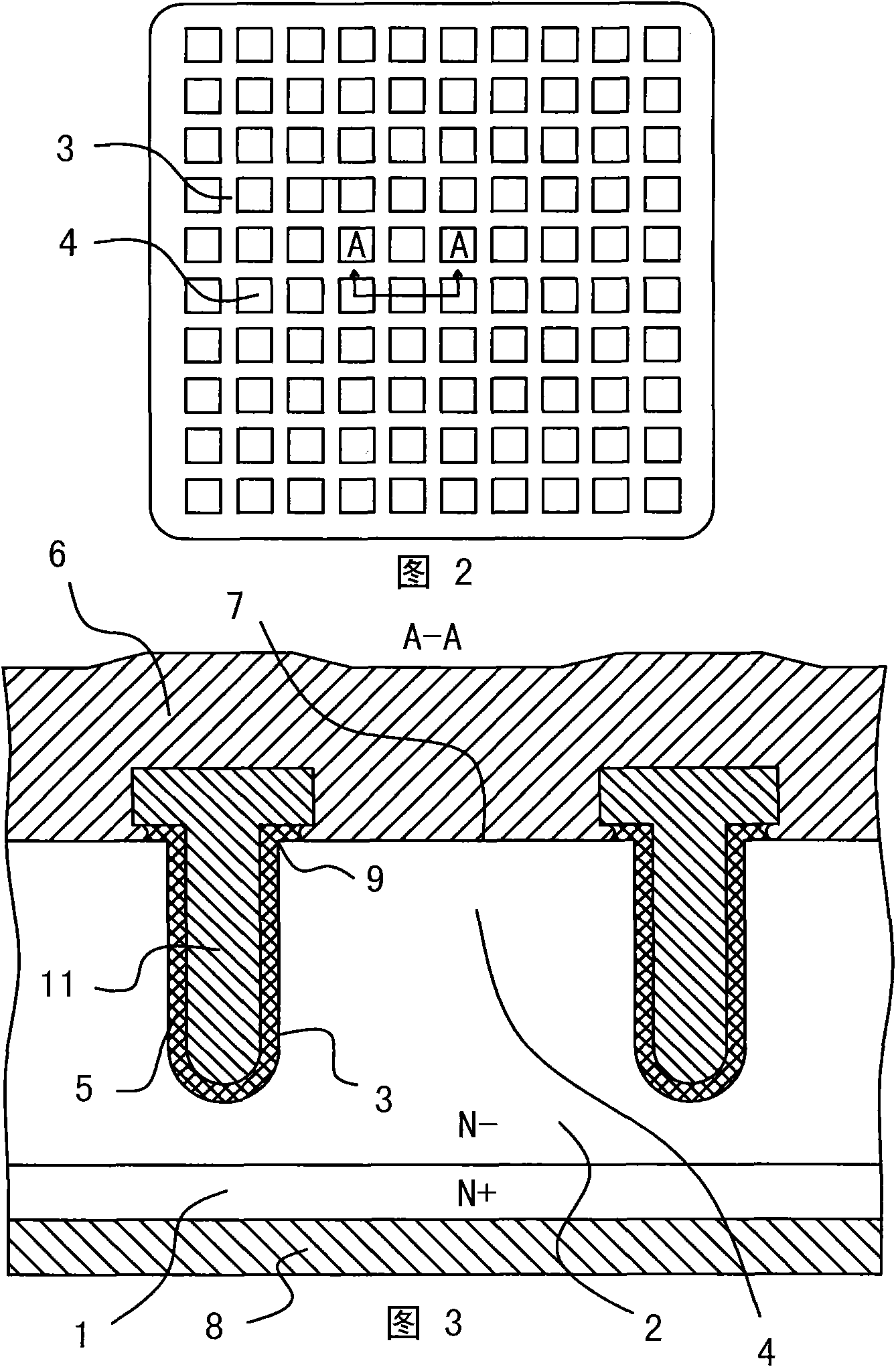

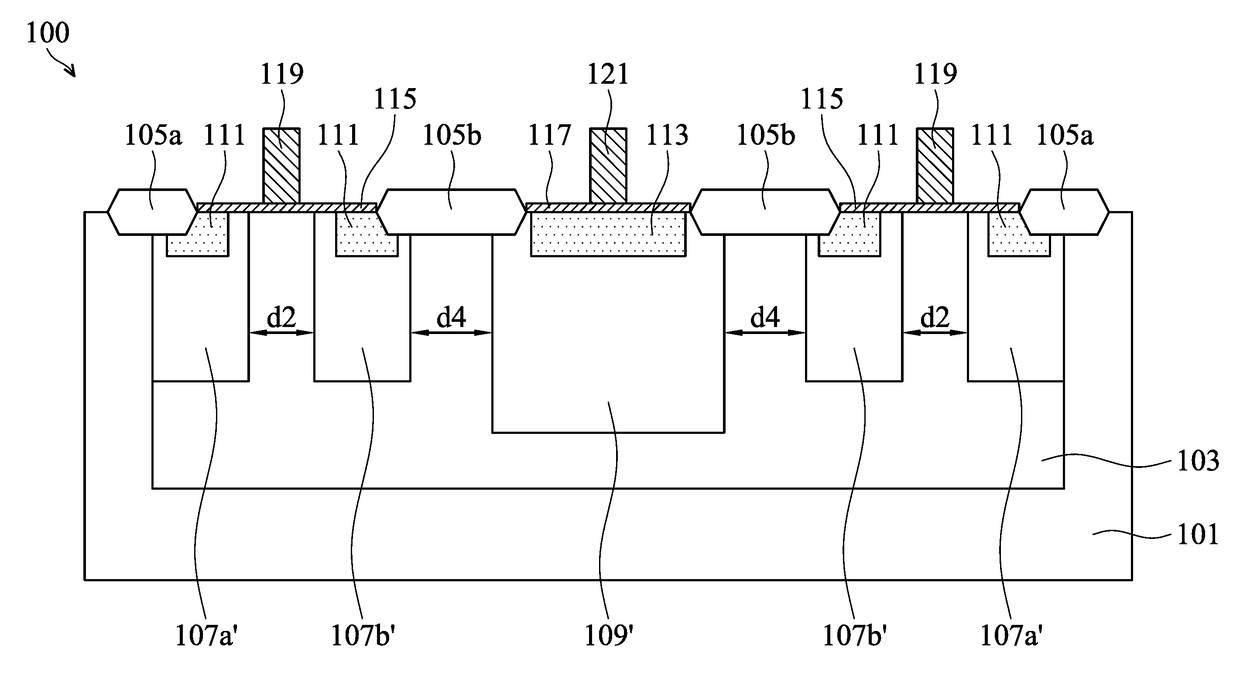

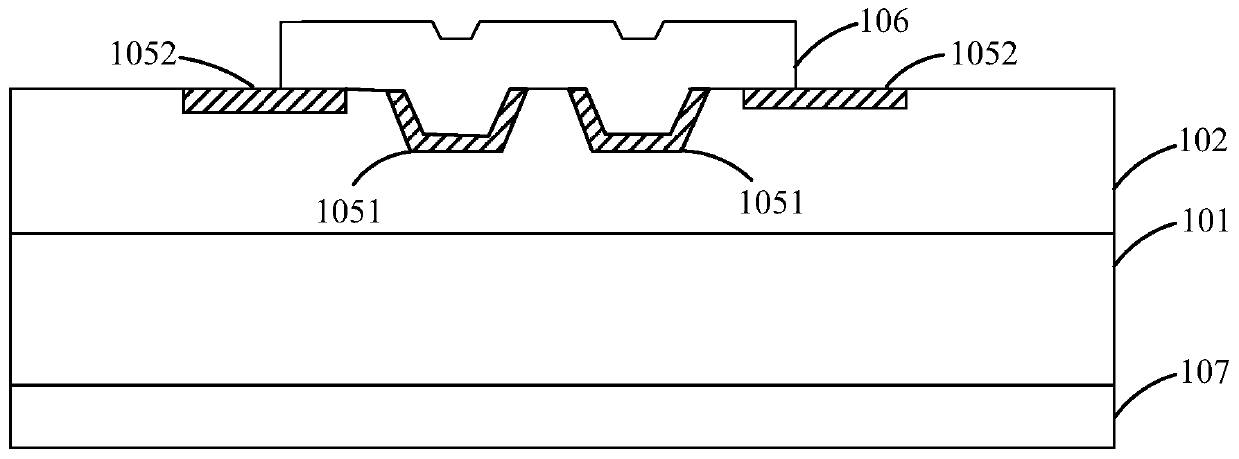

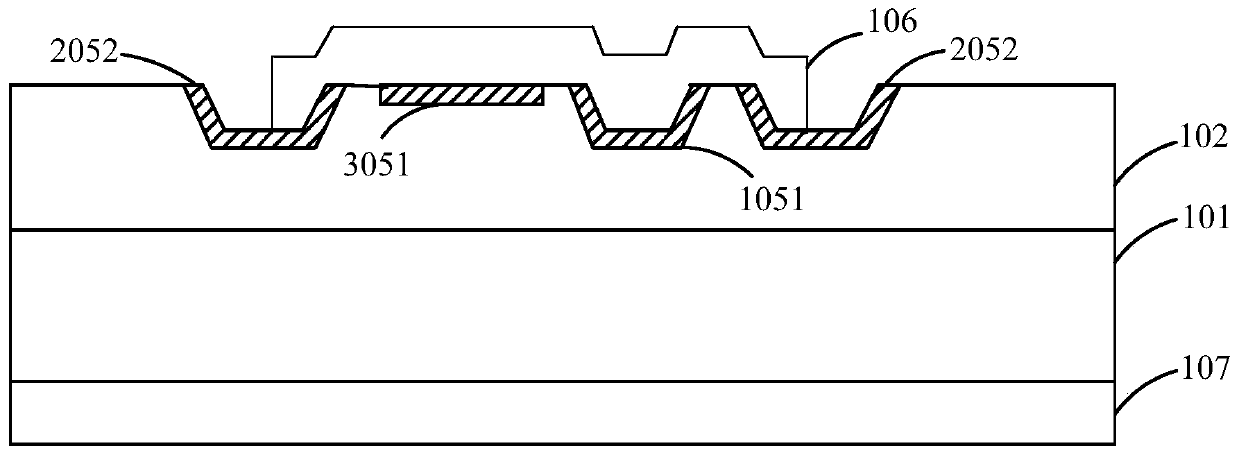

Semiconductor devices and methods for manufacturing the same

ActiveUS20180190493A1DistanceReduce contact areaSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEngineering

A method for manufacturing a semiconductor device includes forming a first well region in a semiconductor substrate, forming isolation structures on the semiconductor substrate, and forming second well regions and a third well region in the first well region, wherein the second well regions are isolated from the third well region by the isolation structures, and two of the adjacent second well regions have a first distance between them. The method also includes performing a rapid thermal annealing process to shorten the first distance to a second distance. The method further includes forming first barrier metal layers on the first well region and covering the second well regions, forming a second barrier metal layer on the first well region and covering the third well region, forming first electrodes on the first barrier metal layers, and forming a second electrode on the second barrier metal layer.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

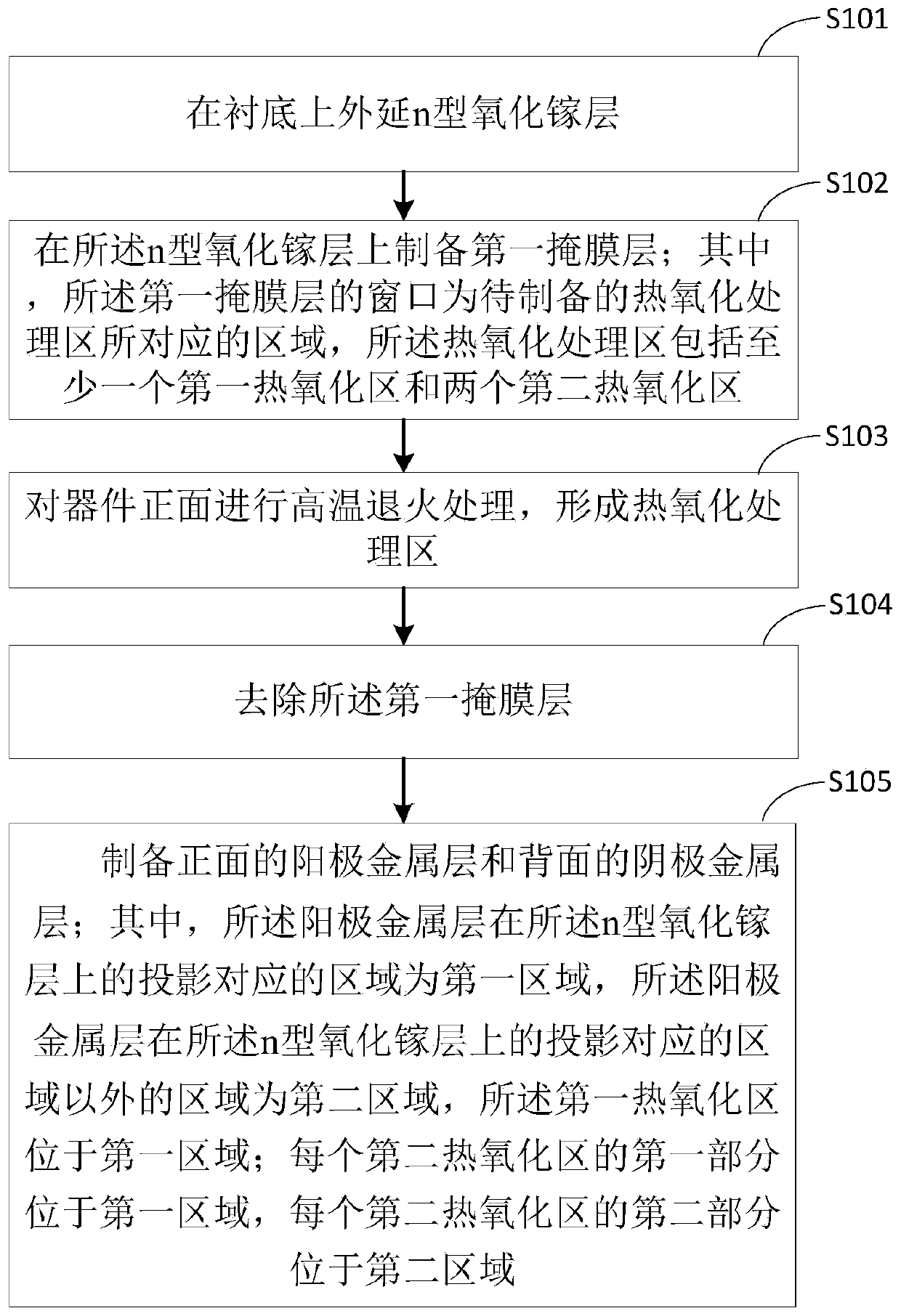

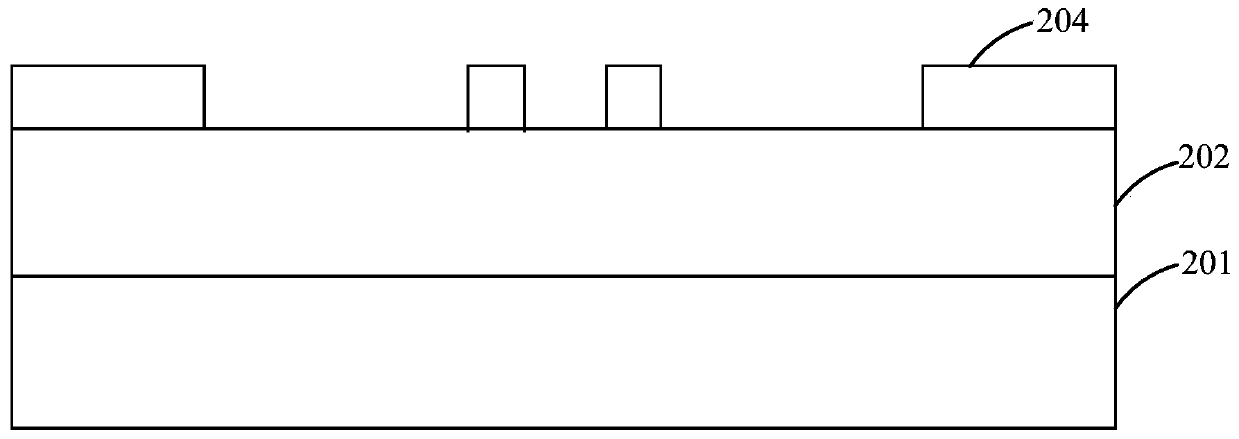

Schottky diode and preparation method thereof

PendingCN111129163AImprove breakdown voltageImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky diodeSemiconductor

The invention relates to the field of semiconductors, and particularly relates to a Schottky diode and a preparation method thereof. The method comprises the steps of extending an n-type gallium oxidelayer on a substrate; preparing a first mask layer on the n-type gallium oxide layer, wherein a window of the first mask layer is an area corresponding to a thermal oxidation treatment area to be prepared, and the thermal oxidation treatment area comprises at least one first thermal oxidation area and two second thermal oxidation areas; performing first high-temperature annealing treatment on thefront surface of the device to form a thermal oxidation treatment region; removing the first mask layer; preparing an anode metal layer on the front surface and a cathode metal layer on the back surface, the first thermal oxidation region is located below the anode metal, and each second thermal oxidation region is partially located below the anode metal. According to the method, the terminal structure can be formed through thermal oxidation, and the electric fields below the anode metal and in the edge region are reduced, so that anode reverse electric leakage is reduced, and breakdown and conduction characteristics are improved.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

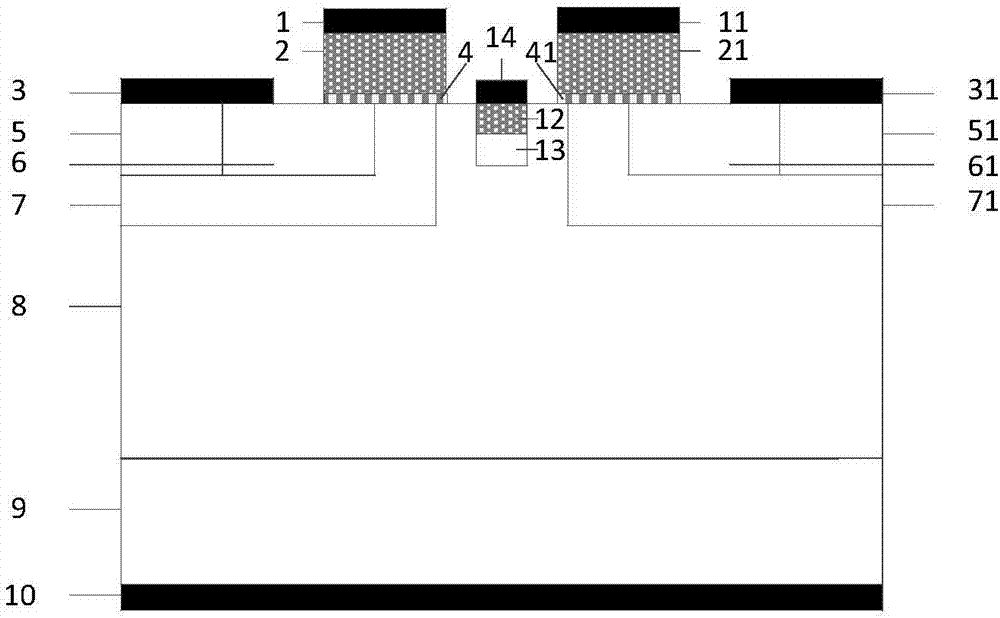

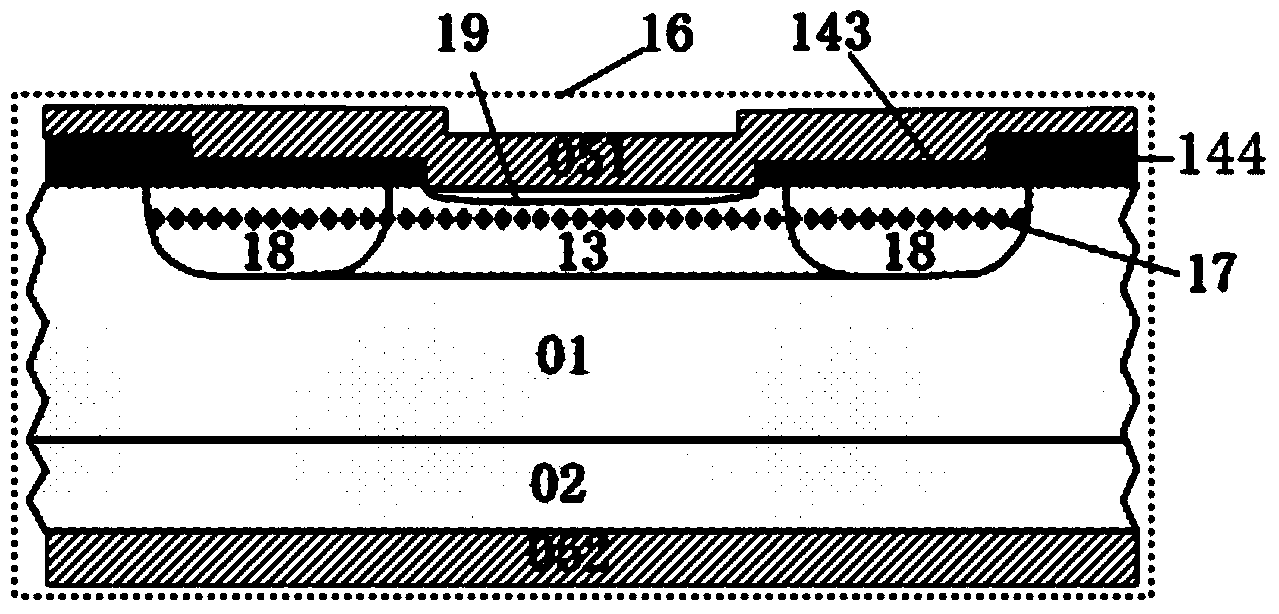

Silicon carbide power diode device and manufacturing method thereof

ActiveCN107256884AReduce process stepsForward voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionHigh concentration

The invention discloses a silicon carbide power diode device and a manufacturing method thereof, belonging to the technical field of power semiconductors. A trench structure is formed in the surface drift region of a conventional silicon carbide device, a high concentration doped region opposite to the drift region in the doping type is formed at the bottom of the trench, and a polysilicon layer opposite to the drift region in the doping type is arranged in the trench, so that the polysilicon layer and the trench side wall form an Si / SiC heterojunction, and furthermore, a diode is integrated inside the device. According to the invention, the forward voltage drop of the device is reduced, meanwhile, as the conduction mode of the device is converted from the silicon carbide PIN diode bipolar conduction into majority carrier conduction, thereby improving the reverse recovery characteristic of the device and improving the device switching speed; and the device further has the advantages of low PIN diode reverse leakage, high breakdown voltage and good device temperature stability. In addition, the device manufacturing method has the advantages of simple process, fewer process step, and low cost.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

SiC SBD device with semi-floating structure, and preparation method thereof

ActiveCN112687750AIncreased injection areaLimit the surface electric field changeSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical field strengthReverse bias

The invention discloses a SiC SBD device with a semi-floating structure, and a preparation method thereof. The SiC SBD device comprises an active region and a non-active region, wherein the active region and the non-active region comprise a SiC substrate of a first doping type, a SiC epitaxial layer of the first doping type grown on the substrate, a surface trap of a second doping type formed by injection on the surface of the epitaxial layer, an anode and a cathode; a JFET region of the first doping type is arranged between the adjacent second doping type wells of the active region, and a floating doping region of the second doping type is arranged below the JFET region; and a second doping type surface trap and a floating doping region are arranged at the lower position between the adjacent second doping type traps of the non-active region and are communicated with the interior of the corresponding region in the active region. The SiC SBD device with the semi-floating structure can limit the electric field intensity of the Schottky contact surface during reverse bias, so reverse electric leakage of the SiC SBD device is reduced.

Owner:FUDAN UNIV

Clamp diode, layout structure thereof and manufacturing method thereof

InactiveCN103811560AImproved reverse leakage characteristicsLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceMetal silicide

The invention discloses a clamp diode comprising an N type well region on a P type substrate, P type high resistance regions at the upper part of the N type well region, a P type low resistance region between the P type high resistance regions, insulated regions at the outer sides of the P type high resistance regions, N+ deposed regions between the two insulated regions at the same side of P type high resistance regions, polysilicon layers on the insulated regions adjacent to the P type high resistance regions, and metal silicide on the P type low resistance region and the N+ deposed regions. The P type high resistance regions and the P type low resistance region are led out through the metal silicide to form the anode of the clamp diode, the N+ deposed regions are led out through the metal silicide to form the cathode of the clamp diode, and the polysilicon layers and an anode lead-out end are in short circuit connection. The invention also provides the layout structure of the clamp diode and a manufacturing method of the clamp diode. The function of a BGR circuit in a high precision voltage requirement application can be replaced by the clamp diode, the manufacturing cost of a circuit can be reduced at the same time, the integrated chip area is reduced, and the miniaturization of an integrated circuit is facilitated.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

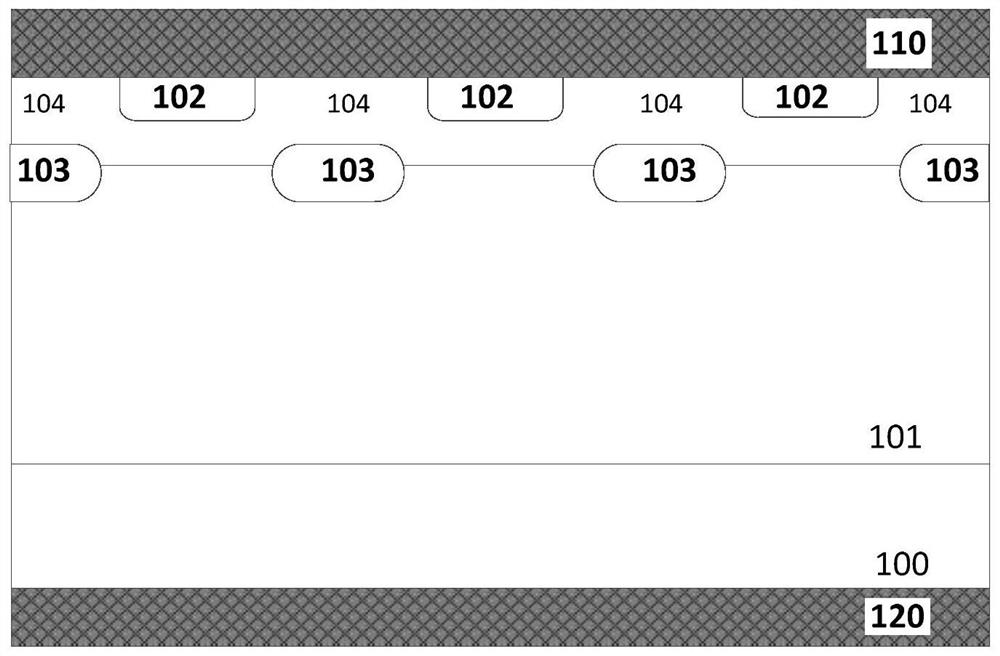

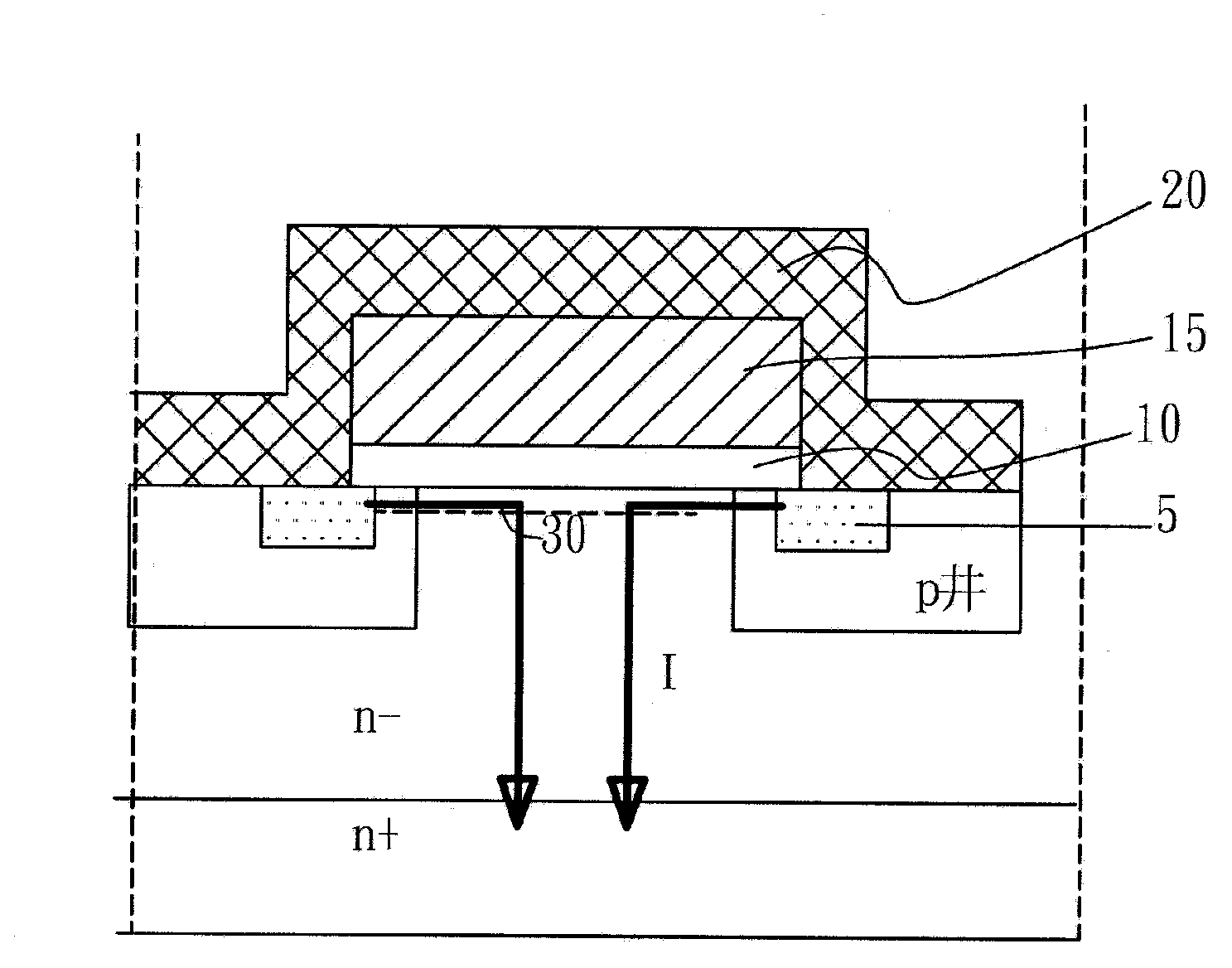

Trench-type MOS rectifier and manufacturing method thereof

ActiveCN103824774ALow forward biasReduce reverse leakageTransistorSemiconductor/solid-state device manufacturingElectricityEngineering

The invention discloses a structure of a trench-type MOS rectifying element structure. The structure includes: a planar MOS rectifying structure is formed on platforms of an active zone and adjacent edges of the platforms are provided with active-zone trenches which are formed in an n- epitaxial layer of a heavily doped n+ semiconductor substrate. In the active-zone trenches, trench gate oxide layers are formed at the bottom parts and side walls of the trenches and p-type doped polycrystalline silicon layers are formed on the trench gate oxide layers. A top-part metal layer is formed on the active zone and connected with a grid electrode and a source electrode of the planar MOS structure and the polycrystalline silicon layers of the active-zone trenches. The invention also discloses a manufacturing method of the trench-type MOS rectifying element structure. The trench-type MOS rectifying element structure and the manufacturing method thereof use the trench-type structure so that the forward bias voltage VF is lower and reverse electricity leakage is smaller.

Owner:CHIP INTEGRATION TECH +1

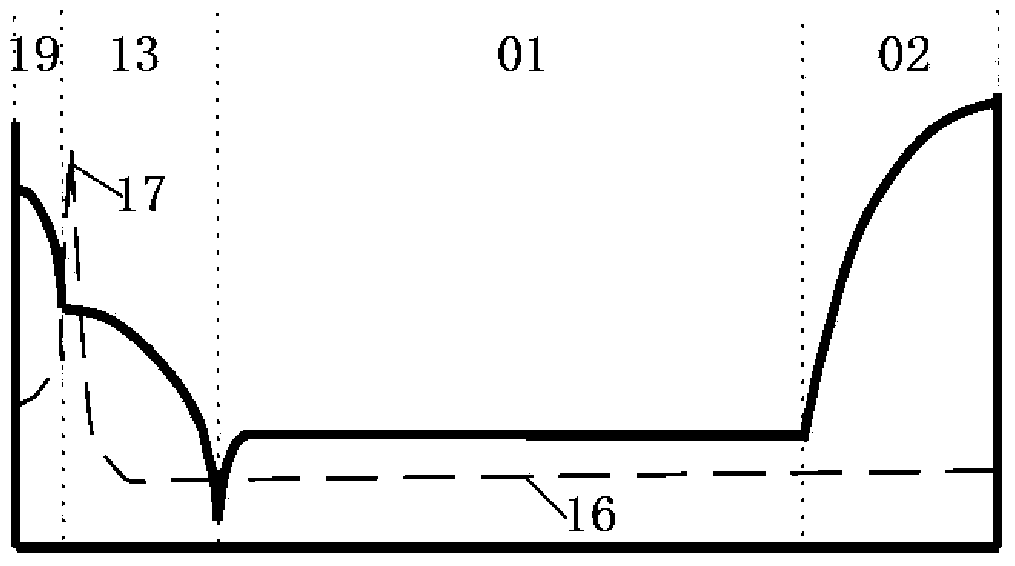

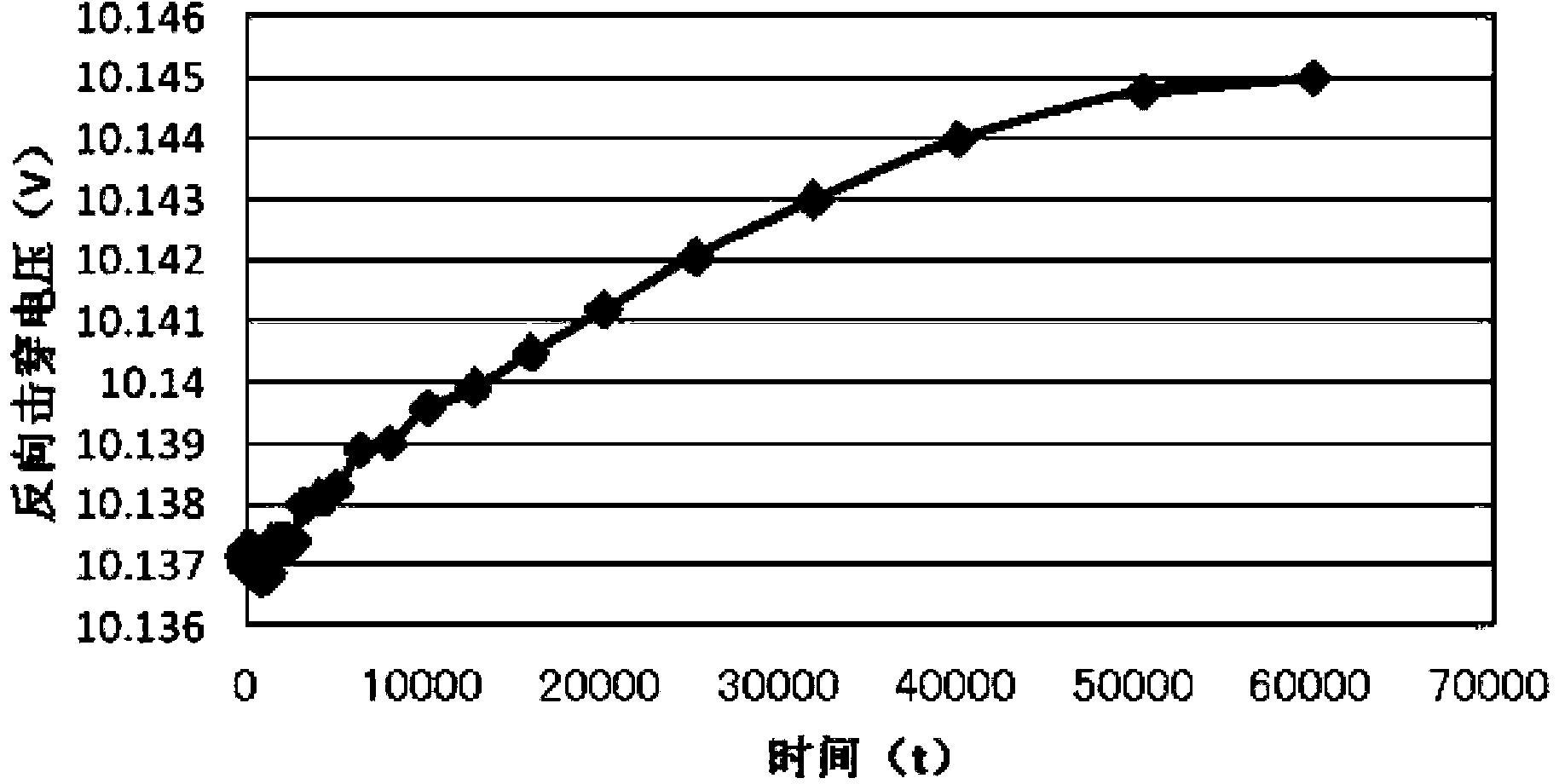

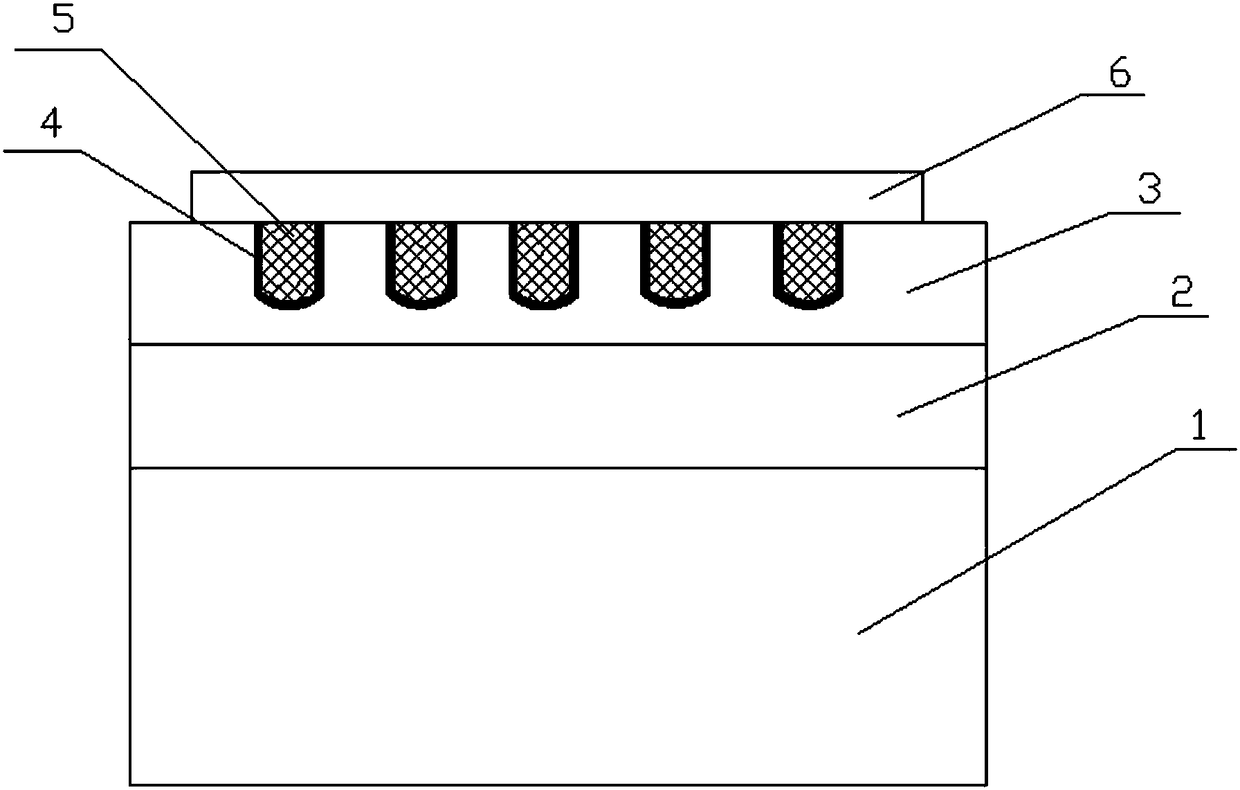

Manufacturing method of trench Schottky

InactiveCN109390233AReduce forward voltage dropReduce reverse leakageSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceVoltage drop

The present invention discloses a manufacturing method of trench Schottky. The method comprises the following steps of: a. performing epitaxy of a buffer layer on an N+ heavily-doped substrate; and b.growing n lightly-doped layers in order on the buffer layer. The buffer layer with relatively high dosage concentration is subjected to epitaxy and is configured to further reduce the forward conduction voltage drop of a device and reduce the resistance of a drifting region on the premise of ensuring the withstand voltage of the device, one or more than one lightly-doped layers with gradually reduced dosage concentration are subjected to epitaxy to gradually increase the electrical resistivity of each layer to effectively reduce the backward electric leakage of the device, achieve the withstand voltage optimization of a barrier region and a trench, achieve the regulation of the epitaxial electrical resistivity, effectively reduce the electric leakage and conduction voltage drop of the trench Schottky products and further improve the device performances; the substrate materials employ a multi-layer epitaxy mode to improve the performances of the device with no need for extra increasingof special processes, and compared to the complete compatibility in the prior art, the processing cost is reduced.

Owner:TIANJIN HUANXIN TECH DEV

Preparation method of trench type Schottky diode

InactiveCN107346733AWon't hurtReduce reverse leakageSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierReverse current

The present invention provides a preparation method of a trench type Schottky diode. The method includes the following steps that: photoetching and etching are performed on a semiconductor silicon substrate of which the surface is sequentially provided with a silicon oxide layer and a silicon nitride layer, so that etching windows can be formed; by means of the etching windows, the N type epitaxial layer of the semiconductor silicon substrate is etched, so that silicon trenches can be formed; the silicon nitride layer is removed, so that a gate oxide layer can be formed on the surface of the entire device; a first polycrystalline silicon layer is deposited on the surface of the entire device, the first polycrystalline silicon layer is etched, so that a second polycrystalline layer is formed in the silicon trenches; and a dielectric layer and a metal layer are sequentially formed on the surface of the entire device. The N type epitaxial layer among adjacent silicon trenches can well contact with the metal layer, so that the contact performance of a Schottky barrier formed between the N type epitaxial layer among the adjacent silicon trenches and the metal layer can be excellent; and since the Schottky barrier is good, the reverse current leakage of the trench type Schottky diode can be decreased, and the performance of the trench type Schottky diode can be improved.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

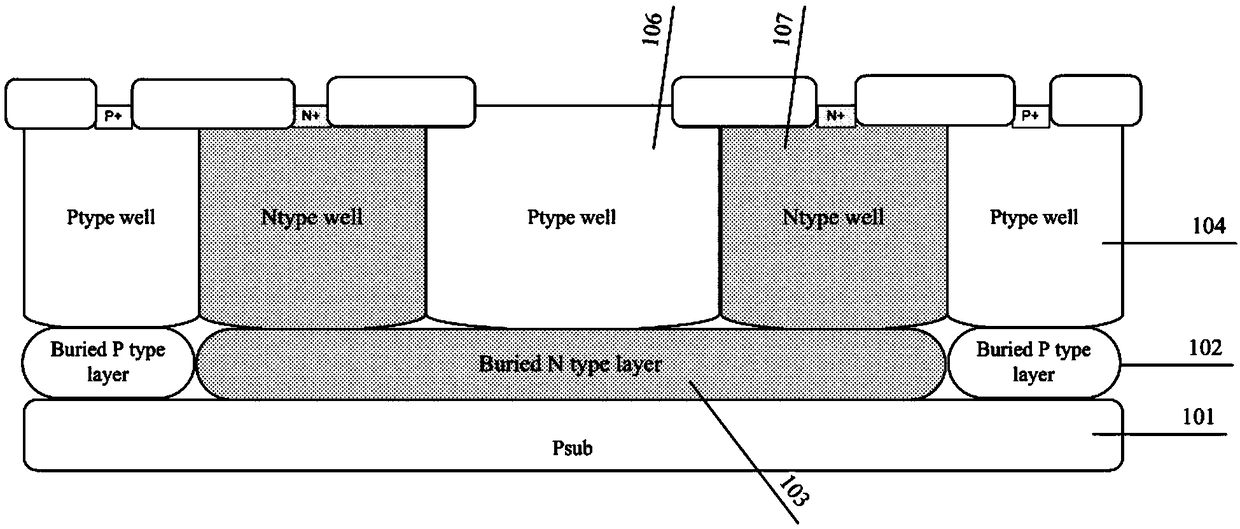

Bidirectional interlayer isolation well with low power consumption and high reliability

PendingCN109494247AHighlight substantive featuresSignificant progressSemiconductor devicesEngineeringHorizontal and vertical

The present invention provides a bidirectional interlayer isolation well with low power consumption and high reliability. The bidirectional interlayer isolation well comprises a substrate and a longitudinal isolation well region and a first buried layer arranged on the substrate, the first buried layer is arranged around the longitudinal isolation well region, the longitudinal isolation well region is provided with a first well region and a transverse isolation well region, the transverse isolation well region is arranged around a first well region, a second well region is arranged on the first buried layer and arranged around the transverse isolation well region, the first well region, the transverse isolation well region and the second well region commonly form two transverse PNP structures, the first well region, the longitudinal isolation well region and the substrate commonly form two longitudinal PNP structures, when the first well region encounters a high voltage, the two transverse PNPs and the two longitudinal PNPs cannot be subjected to amplification and bias due to the same-potential arrangement of the transverse isolation well region so as to effectively weaken the leakage currents in horizontal and vertical directions. The bidirectional interlayer isolation well with low power consumption and high reliability is scientific in design, high in isolation, low in reverse leakage and high in reliability.

Owner:WUXI LINLI SCI & TECH CO LTD

Vertical high-voltage MOSFET device and manufacturing method thereof

ActiveCN110120425AImprove breakdown voltageReduce reverse leakageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringHigh voltage mosfet

The invention discloses a vertical high-voltage MOSFET device and a manufacturing method thereof, and mainly solves the problems that a vertical MOSFET device in the prior art is low in breakdown voltage and is large in leakage current. The device comprises a drain electrode, a substrate and epitaxial layers from bottom to top, wherein shallow grooves with the depth being less than 300 nm is formed in the surface of the upper epitaxial layer. A source electrode is arranged in the shallow grooves, and deep grooves which are greater than 500 nm in depth and penetrate through the two epitaxial layers to the surface of the substrate are formed between the shallow grooves in the surface of the upper epitaxial layer; insulated gate media and gate electrodes are arranged in the deep grooves, andthe substrate is made of n-type Ga2O3 materials, wherein the number of the epitaxial layers is two, and the materials are sequentially p-type GaN with the hole concentration of 1,017-1018cm<-3> and n-type Ga2O3 with the electron concentration of 1,018-1019cm<-3> from bottom to top in sequence. The device improves the breakdown voltage, reduces the reverse leakage and static power consumption, reduces the manufacturing cost and difficulty, and can be used for power devices and high-voltage switching devices.

Owner:XIDIAN UNIV

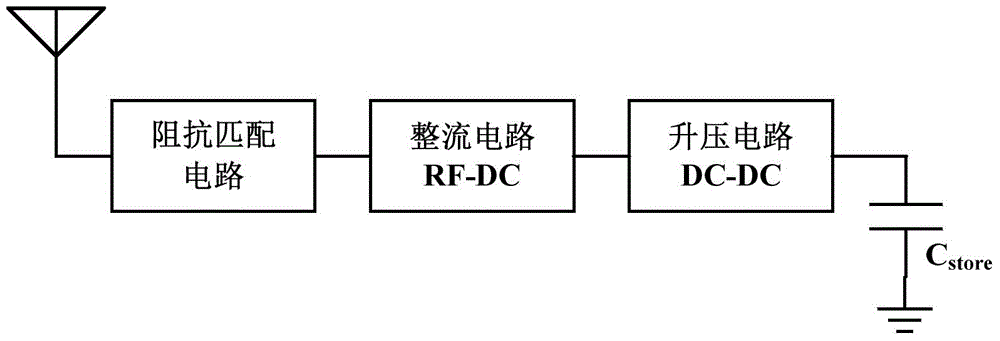

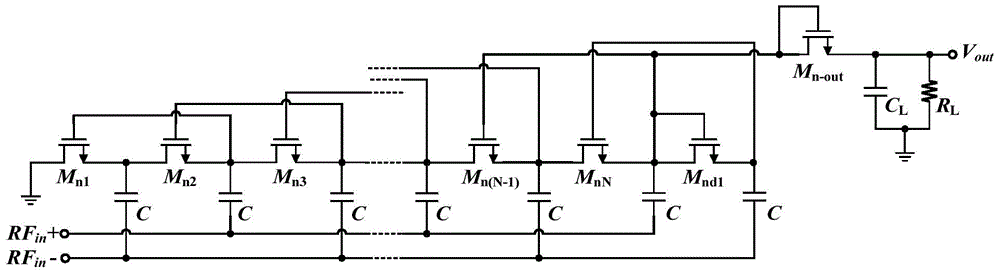

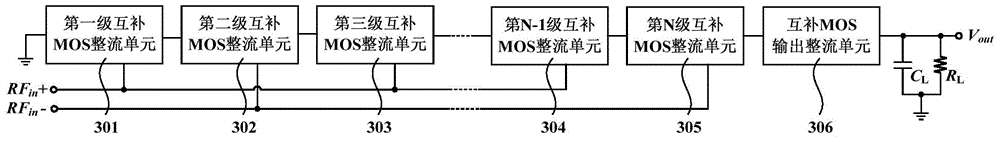

Threshold compensation rectifying circuit

ActiveCN105991047AReduce reverse leakageLower threshold voltageAc-dc conversionLoad resistanceCapacitance

The invention discloses a threshold compensation rectifying circuit. The threshold compensation rectifying circuit includes N grades of complementary MOS rectifying units, a complementary MOS output rectifying unit, a load capacitor, and a load resistor, wherein each grade of complementary MOS rectifying unit is provided with a first input end, a second input end and an output end; the first input end of the current grade of complementary MOS rectifying unit is connected with the output end of the former-grade of complementary MOS rectifying unit; the second input end of the current grade of complementary MOS rectifying unit is connected with a first input signal or a second input signal; the output end of the current grade of complementary MOS rectifying unit is connected with the first input end of the next-grade of complementary MOS rectifying unit; the first input end of the first-grade of complementary MOS rectifying unit is connected with the ground; the output end of the last-grade of complementary MOS rectifying unit is connected with the input end of the complementary MOS output rectifying unit; the complementary MOS output rectifying unit is provided with an input end and an output end, and the output end is connected with an output signal; one end of the load capacitor is connected with the output signal, and the other end of the load capacitor is connected with the ground; and one end of the load resistor is connected with the output signal, and the other end of the load resistor is connected with the ground.

Owner:锐立平芯微电子(广州)有限责任公司

Semiconductor device and preparation method thereof

InactiveCN108767017AReduce leakageLower turn-on voltageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDrain current

A semiconductor device and a preparation method are provided. Due to the fact that the composite anode structure of the first anode Ohmic junction and the second anode MIS junction is adopted to replace a traditional Schottky junction anode, and the rectification characteristic of a traditional Schottky junction is replaced by the channel regulation characteristic of the MIS junction, the two parameter indexes of the reverse leakage current (IR) and the forward opening voltage (VoN) of the semiconductor device are simultaneously improved. Meanwhile, in the preparation method disclosed by the invention, the technical scheme and conditions used in the whole manufacturing process can be realized through the standard Fab technology, the process is simple, and the number of times of windowing when optimizing the design of traditional semiconductor device terminals is reduced.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

High-barrier SiC JBS device and preparation method thereof

PendingCN112310227AReduce manufacturing costHigh electron affinitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryDielectric layer

The invention discloses a high-barrier SiC JBS device and a preparation method thereof. The device comprises a first electrode layer, a SiC substrate, an N-SiC epitaxial layer, a second electrode layer, a dielectric layer and a PI layer which are arranged from top to bottom. According to the SiC device, a JBS structure and a surface low-concentration structure are formed on the epitaxial layer, sothat the barrier height of the device is increased, and meanwhile, the electric leakage characteristic of the device is reduced.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Schottky diode and preparation method thereof

PendingCN111146294AReduce reverse leakageImprove breakdown characteristics and conduction characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsAnode

The invention relates to the field of semiconductors, in particular to a Schottky diode and a preparation method thereof. The Schottky diode comprises: a substrate; an n-type gallium oxide layer formed on the substrate, wherein the n-type gallium oxide layer comprises at least one first thermal oxidation region and two second thermal oxidation regions; an anode metal layer which is formed on the n-type gallium oxide layer; the first thermal oxidation region located below the anode metal layer, wherein the second thermal oxidation regions are partially located below the anode metal layer; a cathode metal layer which is formed on the back surface of the substrate, wherein at least one first thermal oxidation region is provided with a groove structure. Compared with an existing Schottky diode, the Schottky diode has the advantages that the electric field at the anode junction is better, and the high-voltage resistance characteristic and the conduction characteristic are better.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com