Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

39 results about "Surface trap" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

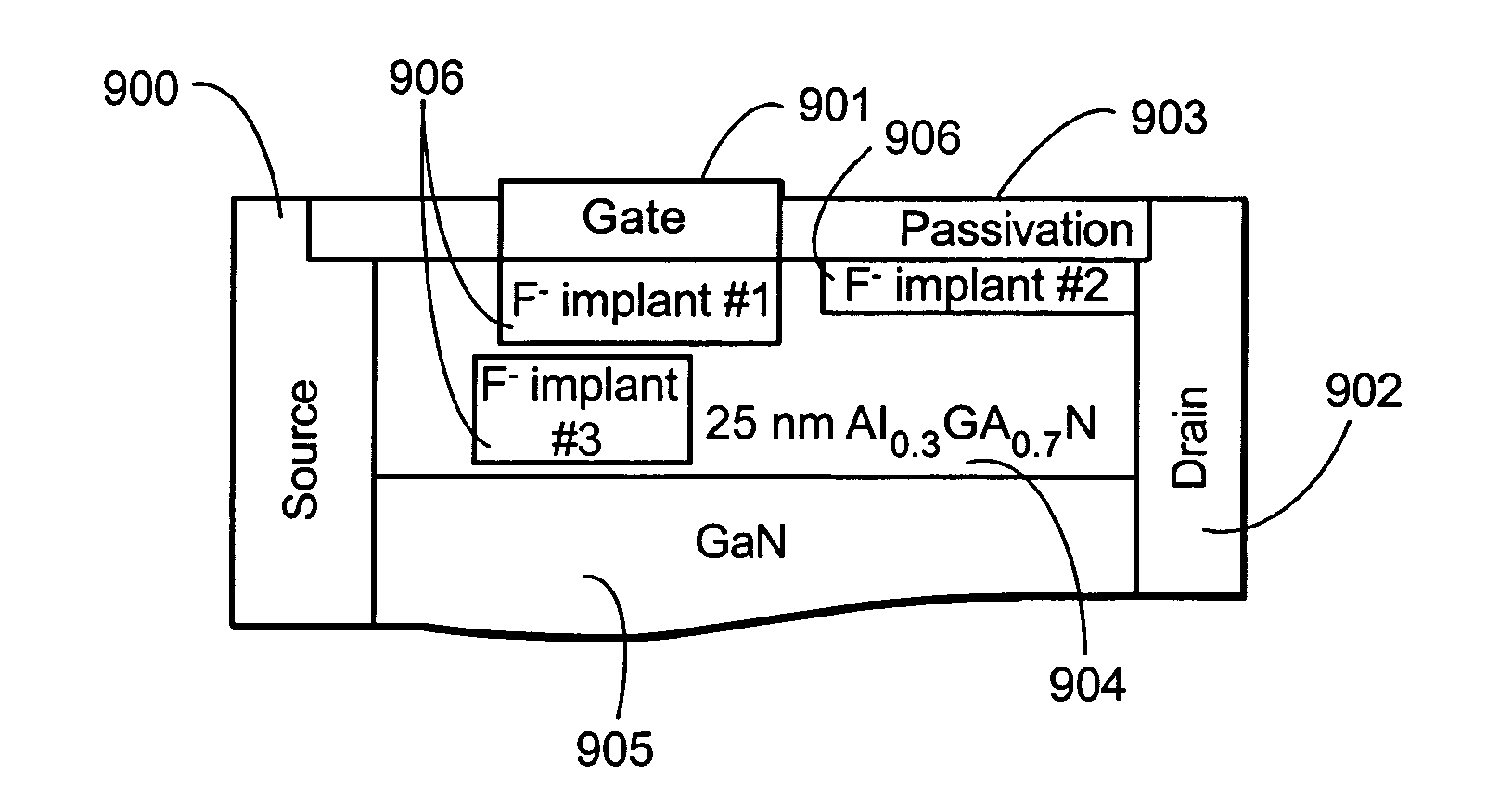

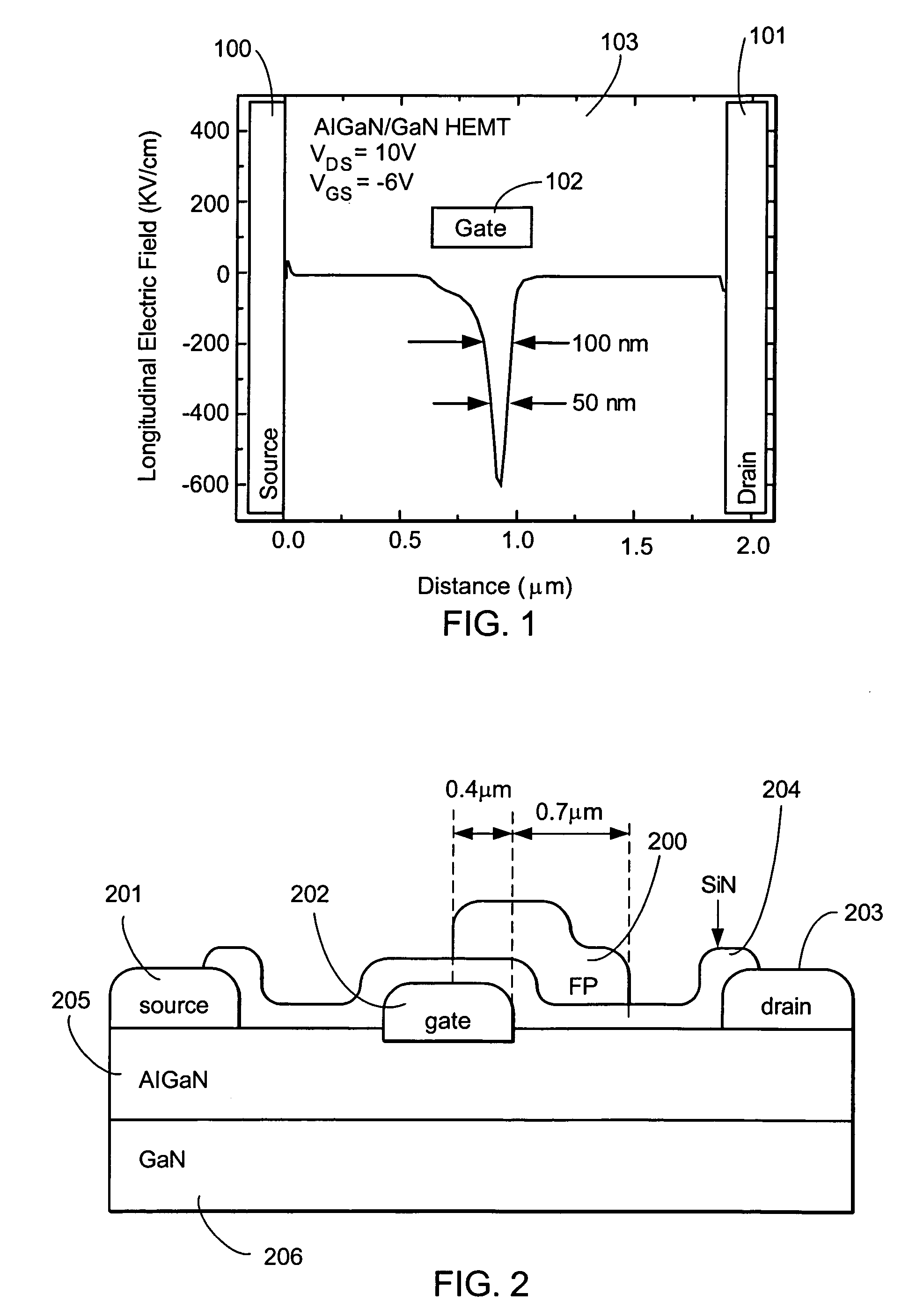

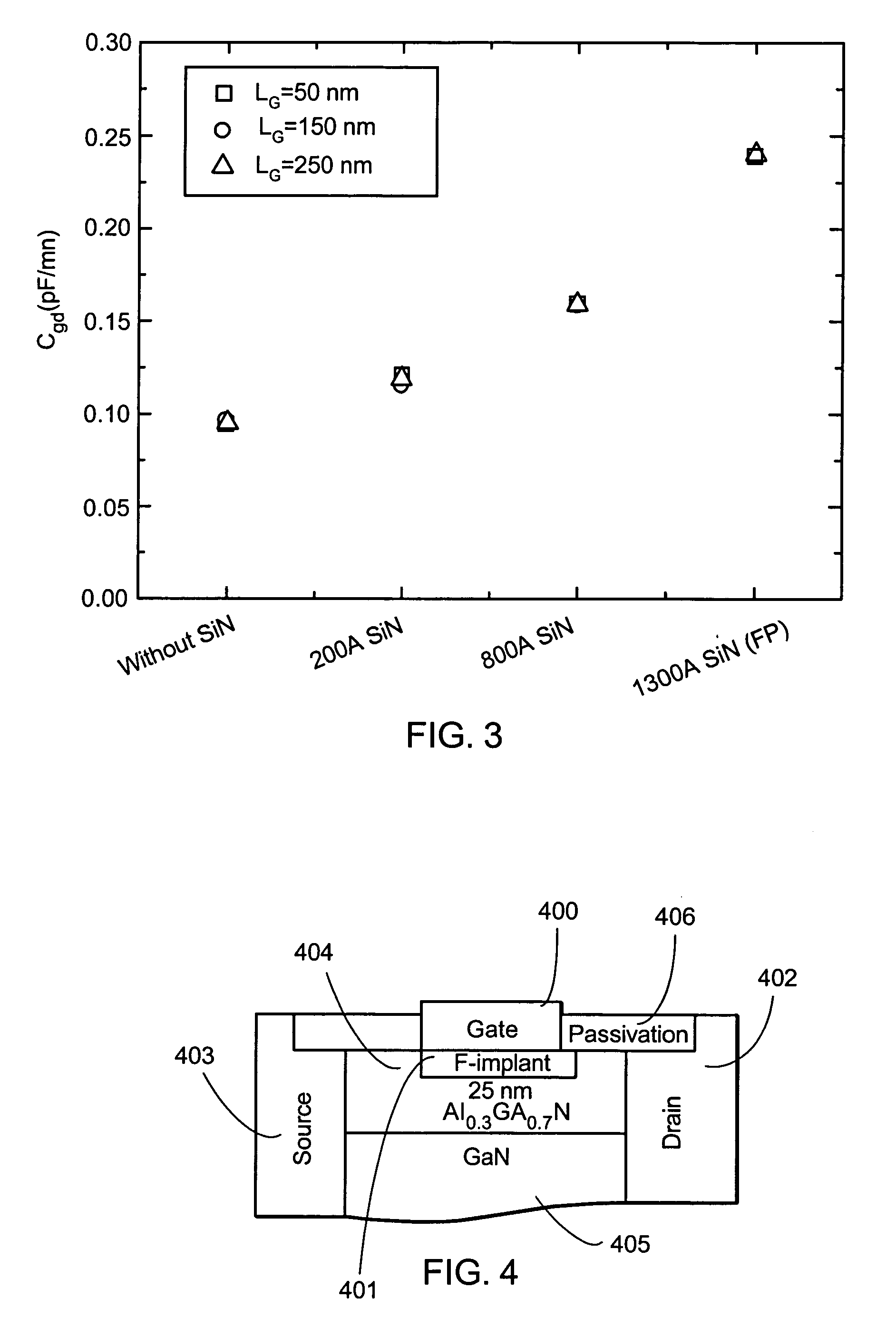

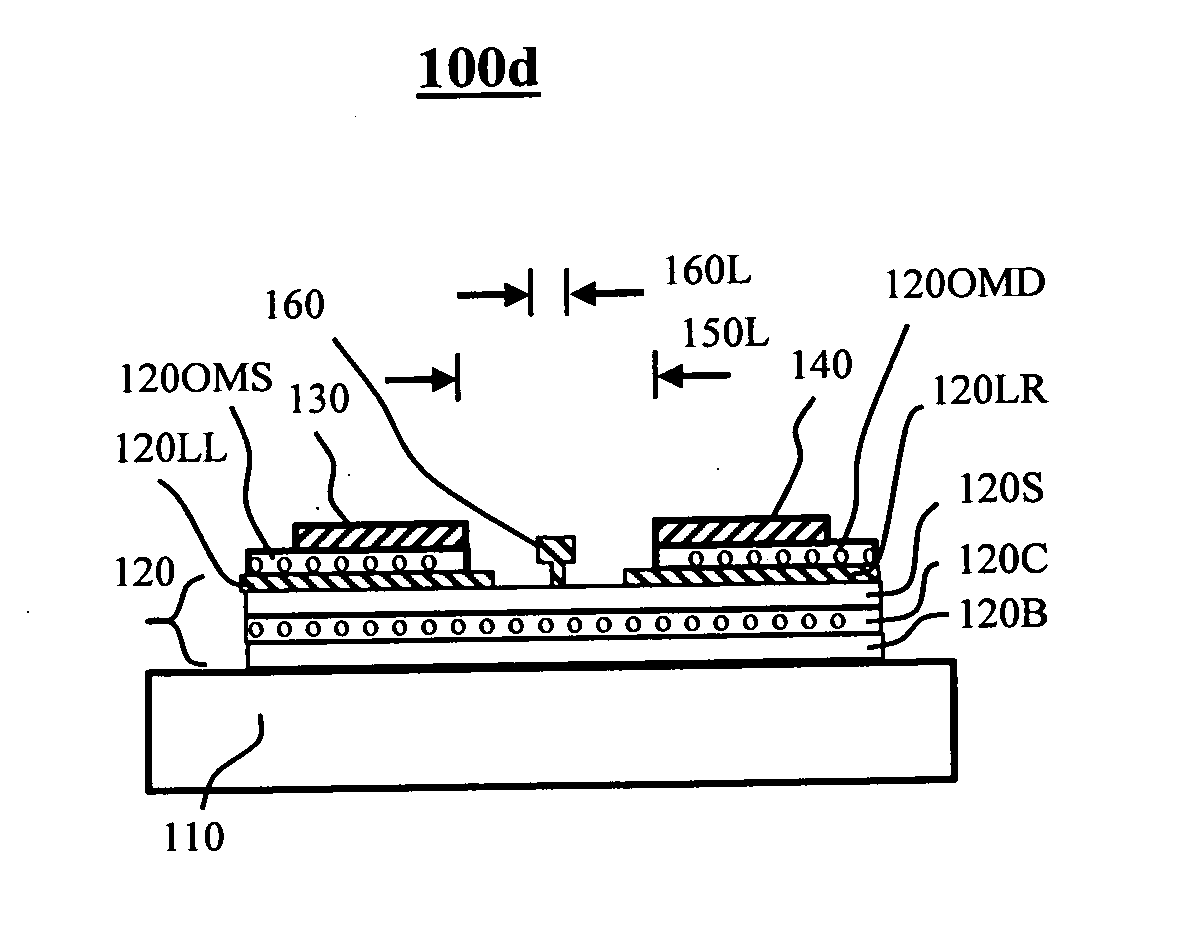

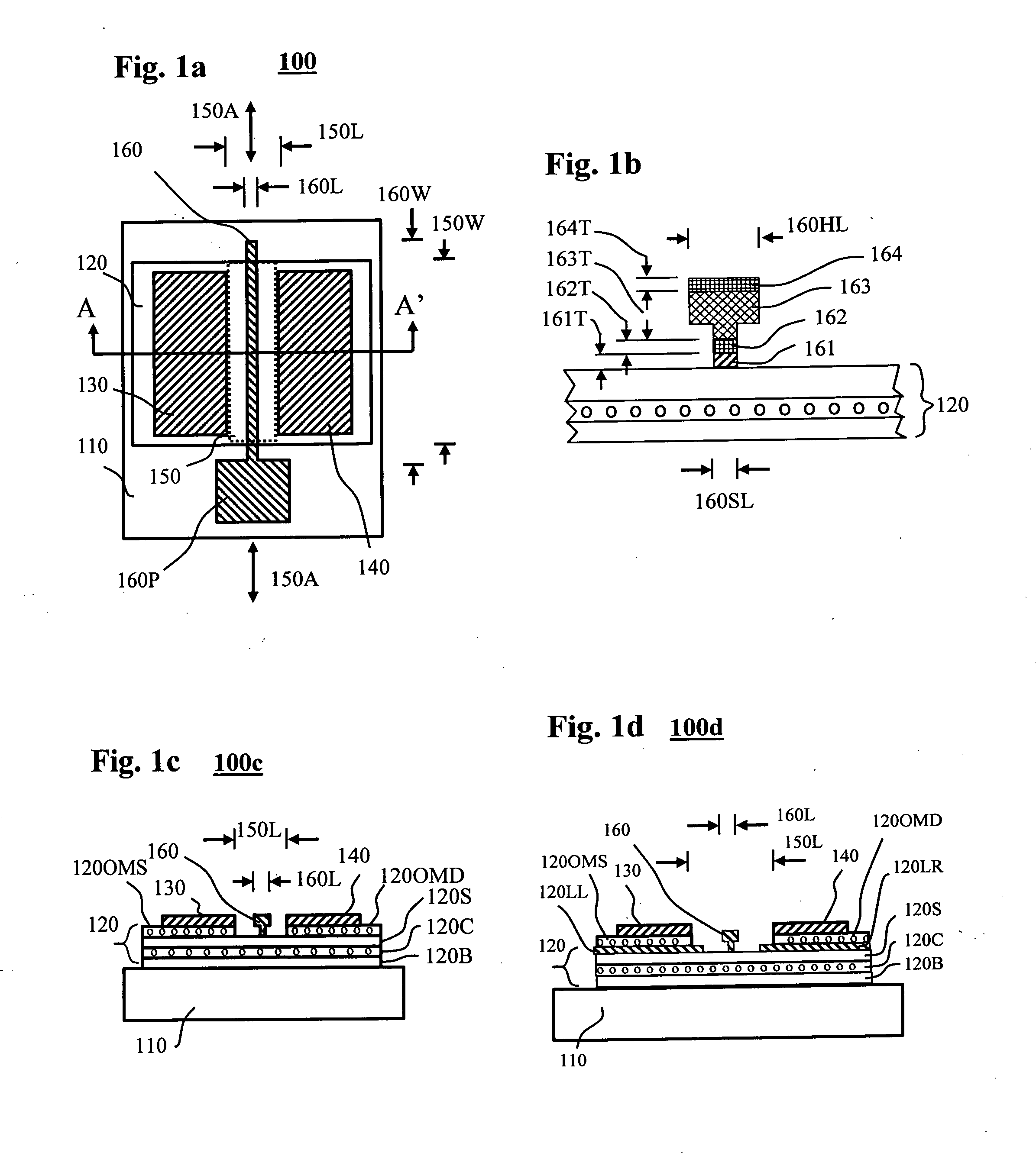

Methods to shape the electric field in electron devices, passivate dislocations and point defects, and enhance the luminescence efficiency of optical devices

ActiveUS20070224710A1Increase output powerReduce gate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueDislocation

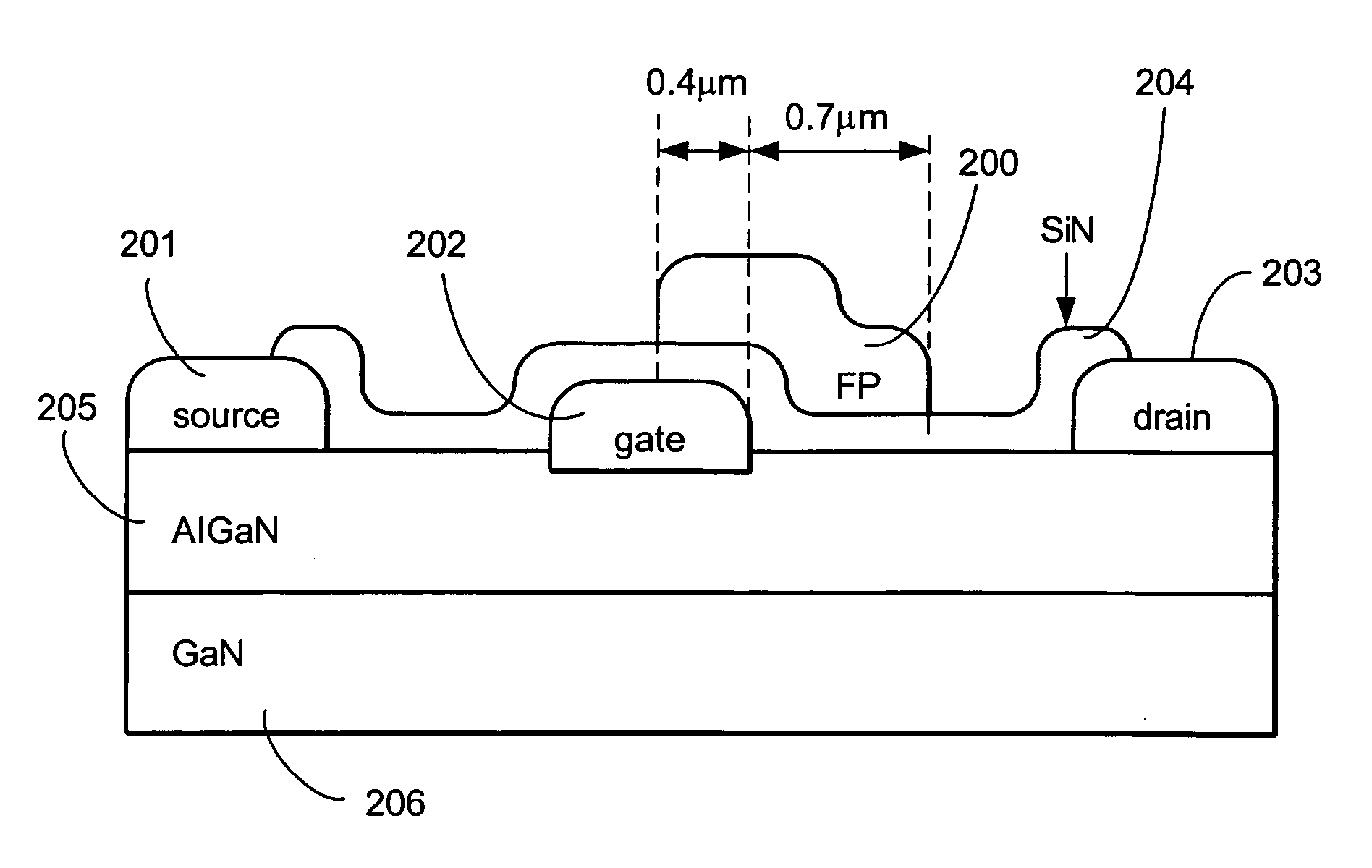

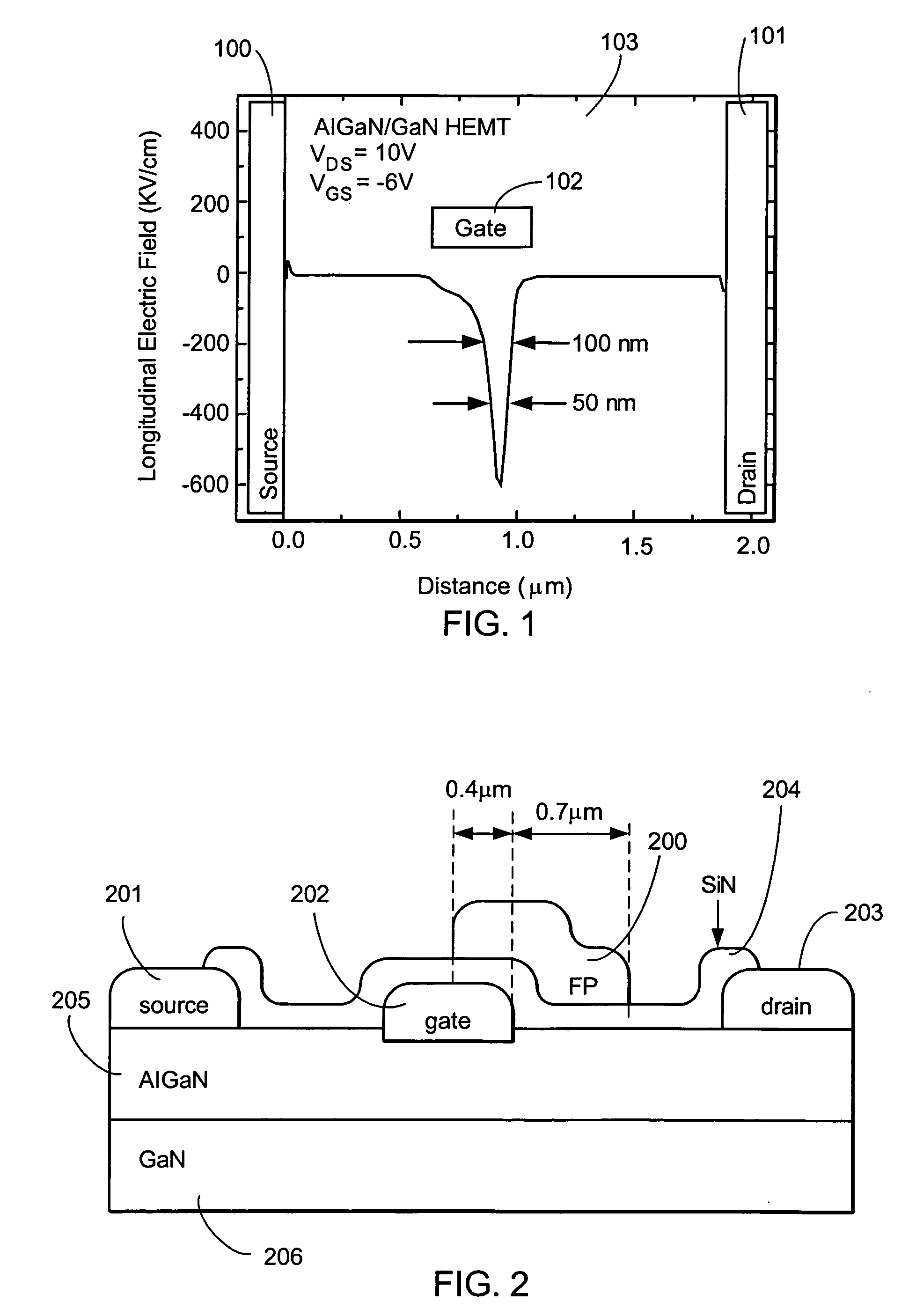

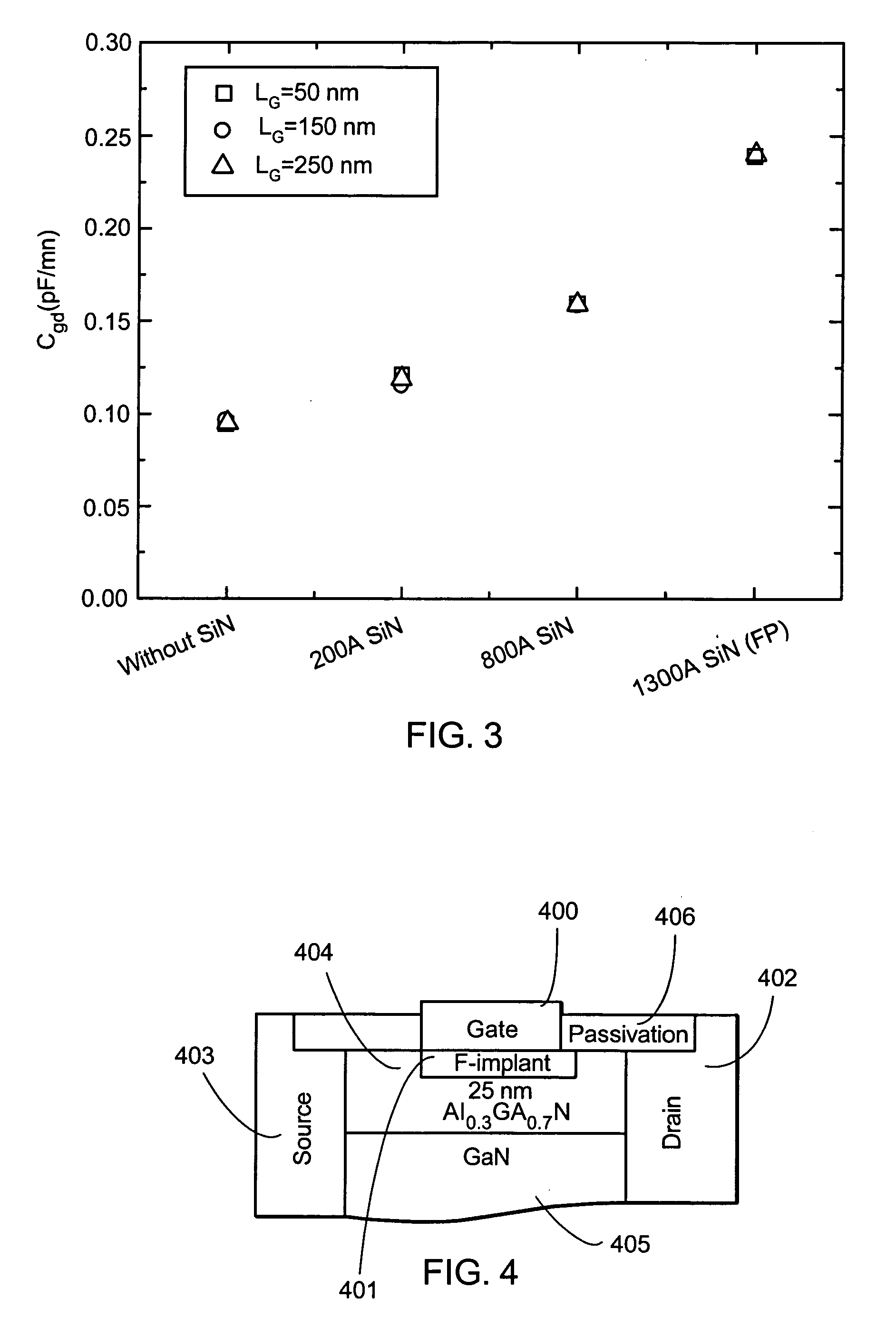

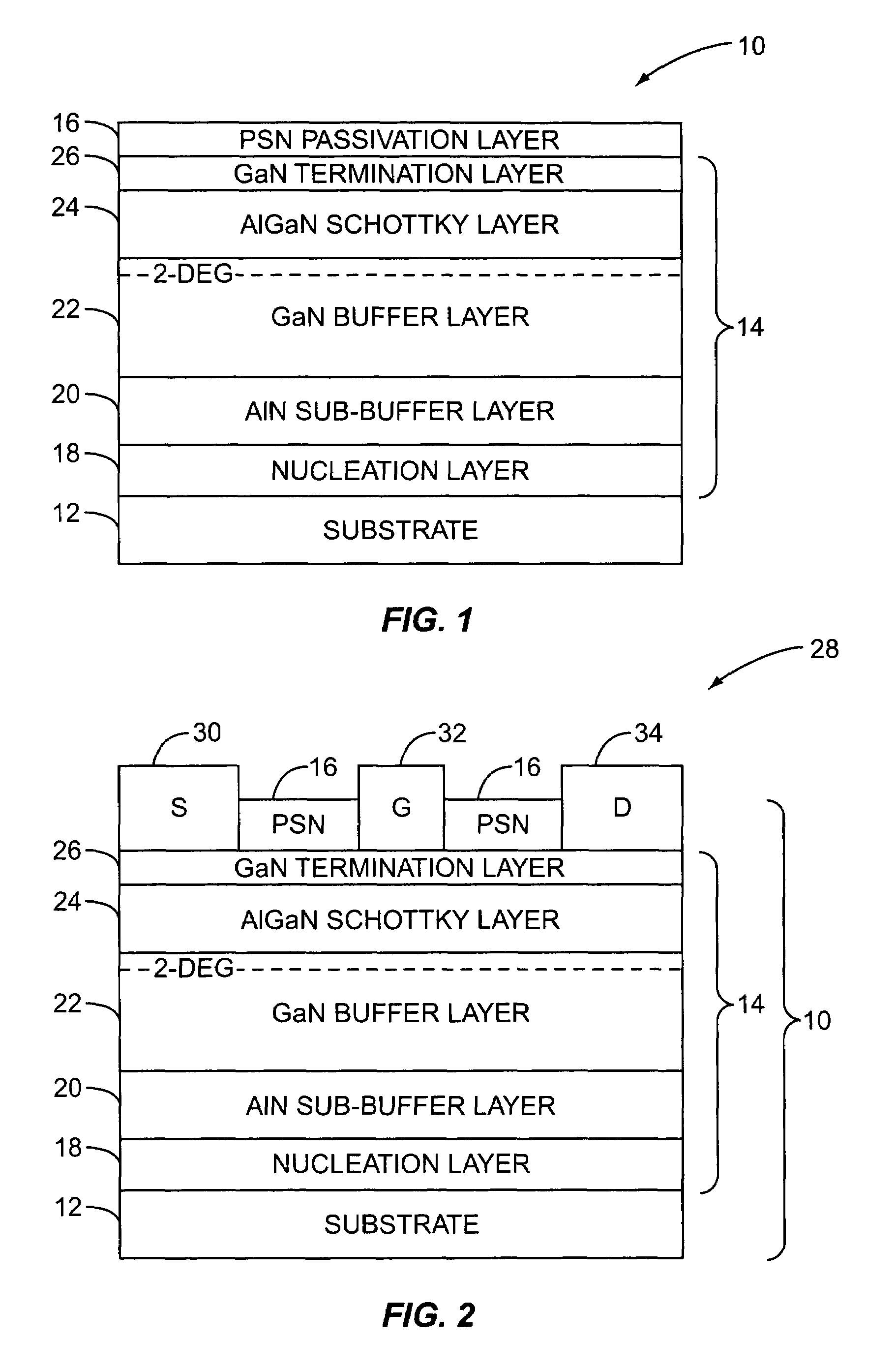

A fluorine treatment that can shape the electric field profile in electronic devices in 1, 2, or 3 dimensions is disclosed. A method to increase the breakdown voltage of AlGaN / GaN high electron mobility transistors, by the introduction of a controlled amount of dispersion into the device, is also disclosed. This dispersion is large enough to reduce the peak electric field in the channel, but low enough in order not to cause a significant decrease in the output power of the device. In this design, the whole transistor is passivated against dispersion with the exception of a small region 50 to 100 nm wide right next to the drain side of the gate. In that region, surface traps cause limited amounts of dispersion, that will spread the high electric field under the gate edge, therefore increasing the breakdown voltage. Three different methods to introduce dispersion in the 50 nm closest to the gate are described: (1) introduction of a small gap between the passivation and the gate metal, (2) gradually reducing the thickness of the passivation, and (3) gradually reducing the thickness of the AlGaN cap layer in the region close the gate.

Owner:RGT UNIV OF CALIFORNIA

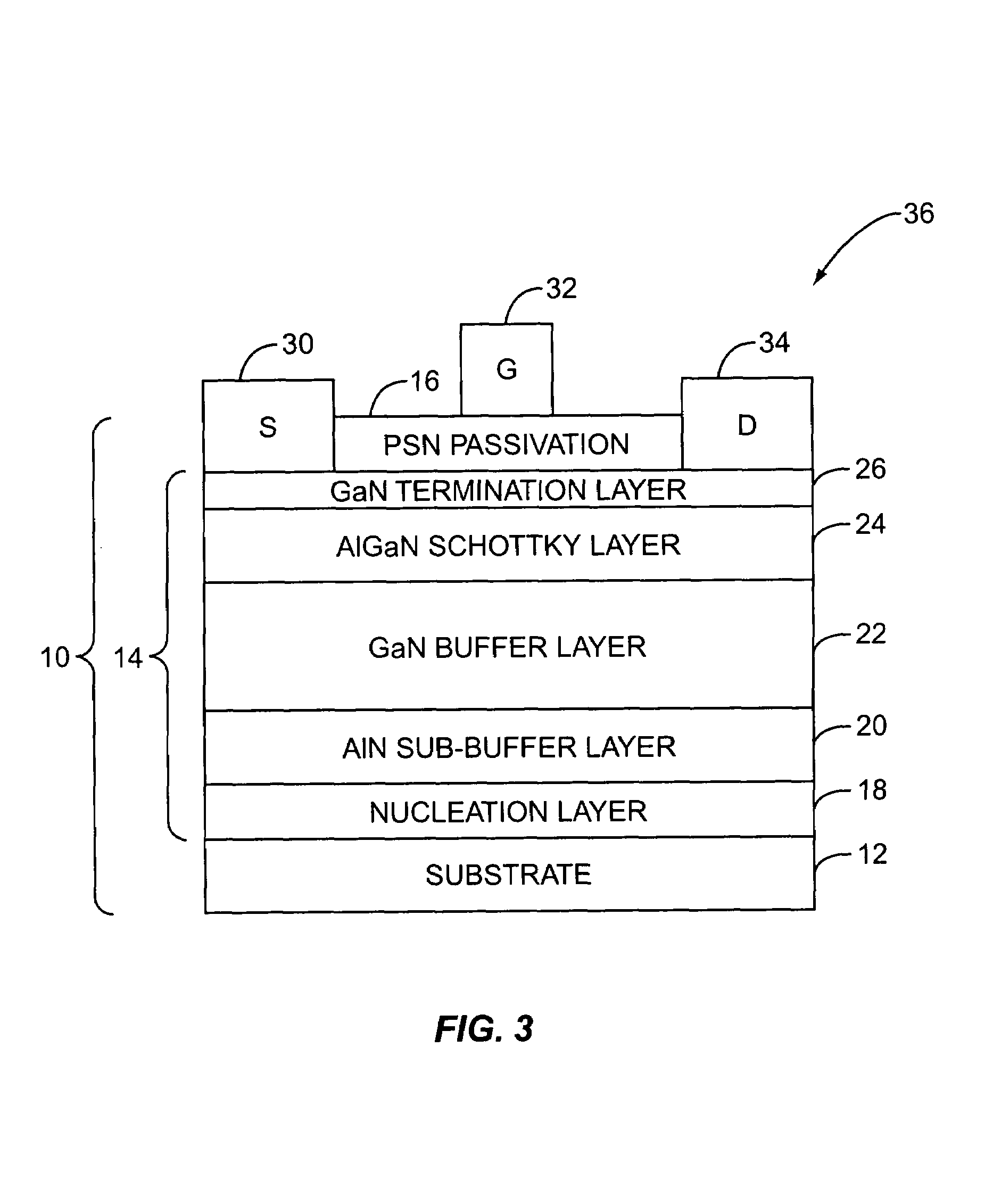

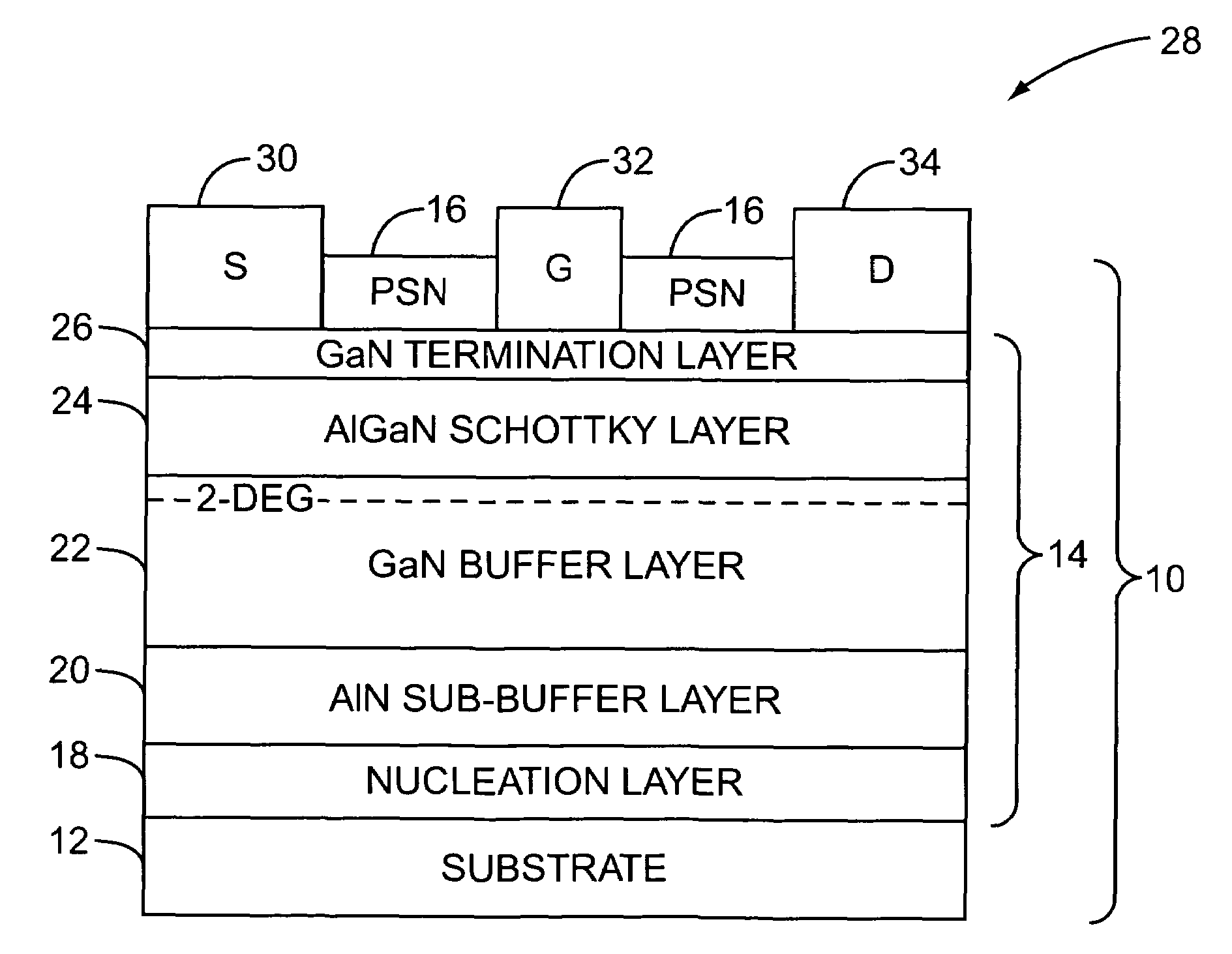

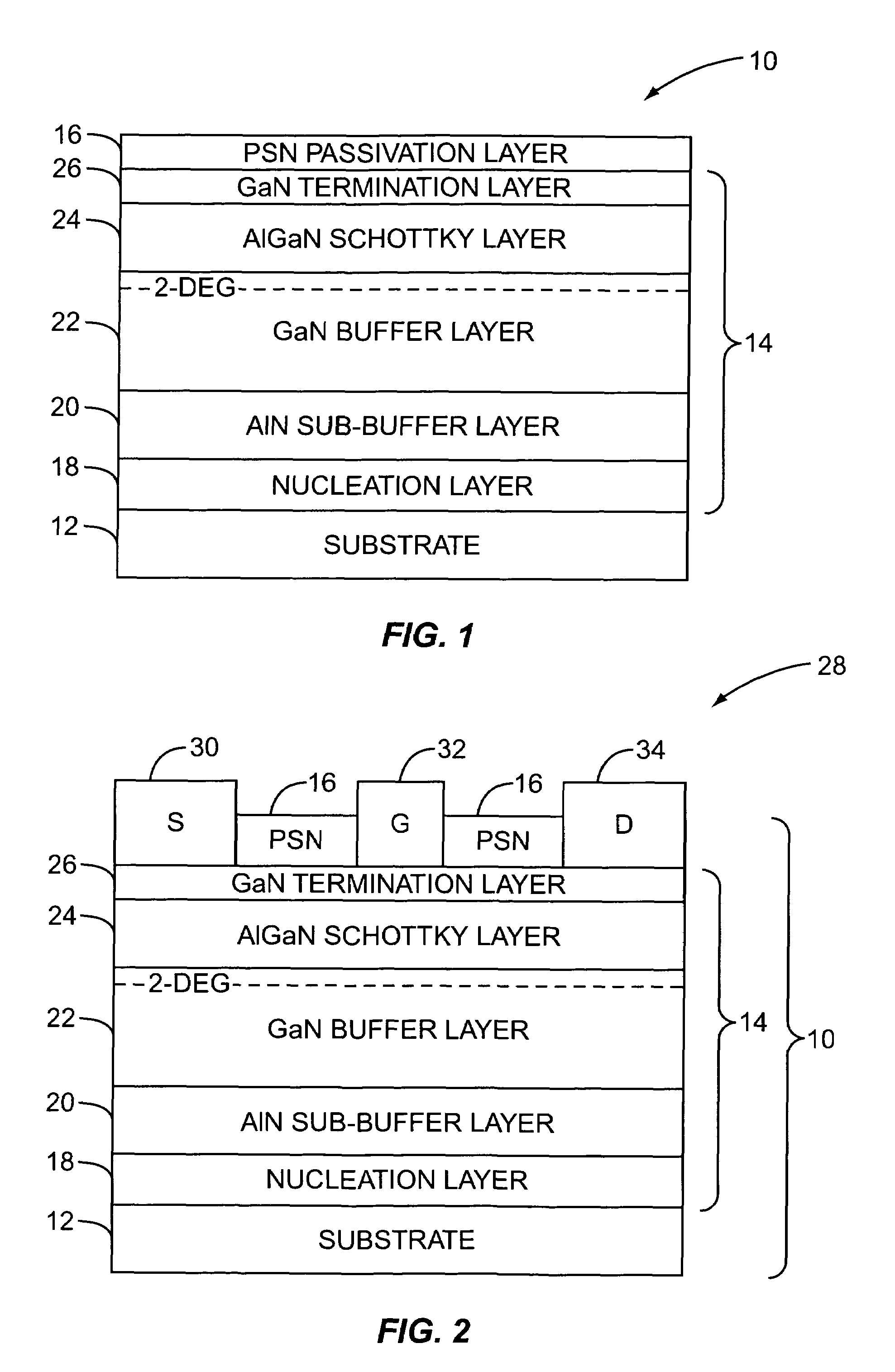

Surface passivation of GaN devices in epitaxial growth chamber

InactiveUS7052942B1Eliminate degradation of operationSemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideSurface trap

The present invention relates to passivation of a gallium nitride (GaN) structure before the GaN structure is removed from an epitaxial growth chamber. The GaN structure includes one or more structural epitaxial layers deposited on a substrate, and the passivation layer deposited on the structural epitaxial layers. In general, the passivation layer is a dielectric material deposited on the GaN structure that serves to passivate surface traps on the surface of the structural epitaxial layers. Preferably, the passivation layer is a dense, thermally deposited silicon nitride passivation layer.

Owner:QORVO US INC

Methods to shape the electric field in electron devices, passivate dislocations and point defects, and enhance the luminescence efficiency of optical devices

ActiveUS8114717B2Reduction in a peak electric fieldImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPeak value

A fluorine treatment that can shape the electric field profile in electronic devices in 1, 2, or 3 dimensions is disclosed. A method to increase the breakdown voltage of AlGaN / GaN high electron mobility transistors, by the introduction of a controlled amount of dispersion into the device, is also disclosed. This dispersion is large enough to reduce the peak electric field in the channel, but low enough in order not to cause a significant decrease in the output power of the device. In this design, the whole transistor is passivated against dispersion with the exception of a small region 50 to 100 nm wide right next to the drain side of the gate. In that region, surface traps cause limited amounts of dispersion, that will spread the high electric field under the gate edge, therefore increasing the breakdown voltage. Three different methods to introduce dispersion in the 50 nm closest to the gate are described: (1) introduction of a small gap between the passivation and the gate metal, (2) gradually reducing the thickness of the passivation, and (3) gradually reducing the thickness of the AlGaN cap layer in the region close the gate.

Owner:RGT UNIV OF CALIFORNIA

Surface passivation of GaN devices in epitaxial growth chamber

ActiveUS7408182B1Eliminate degradation of operationSolid-state devicesSemiconductor/solid-state device manufacturingGallium nitrideSurface trap

The present invention relates to passivation of a gallium nitride (GaN) structure before the GaN structure is removed from an epitaxial growth chamber. The GaN structure includes one or more structural epitaxial layers deposited on a substrate, and the passivation layer deposited on the structural epitaxial layers. In general, the passivation layer is a dielectric material deposited on the GaN structure that serves to passivate surface traps on the surface of the structural epitaxial layers. Preferably, the passivation layer is a dense, thermally deposited silicon nitride passivation layer.

Owner:QORVO US INC

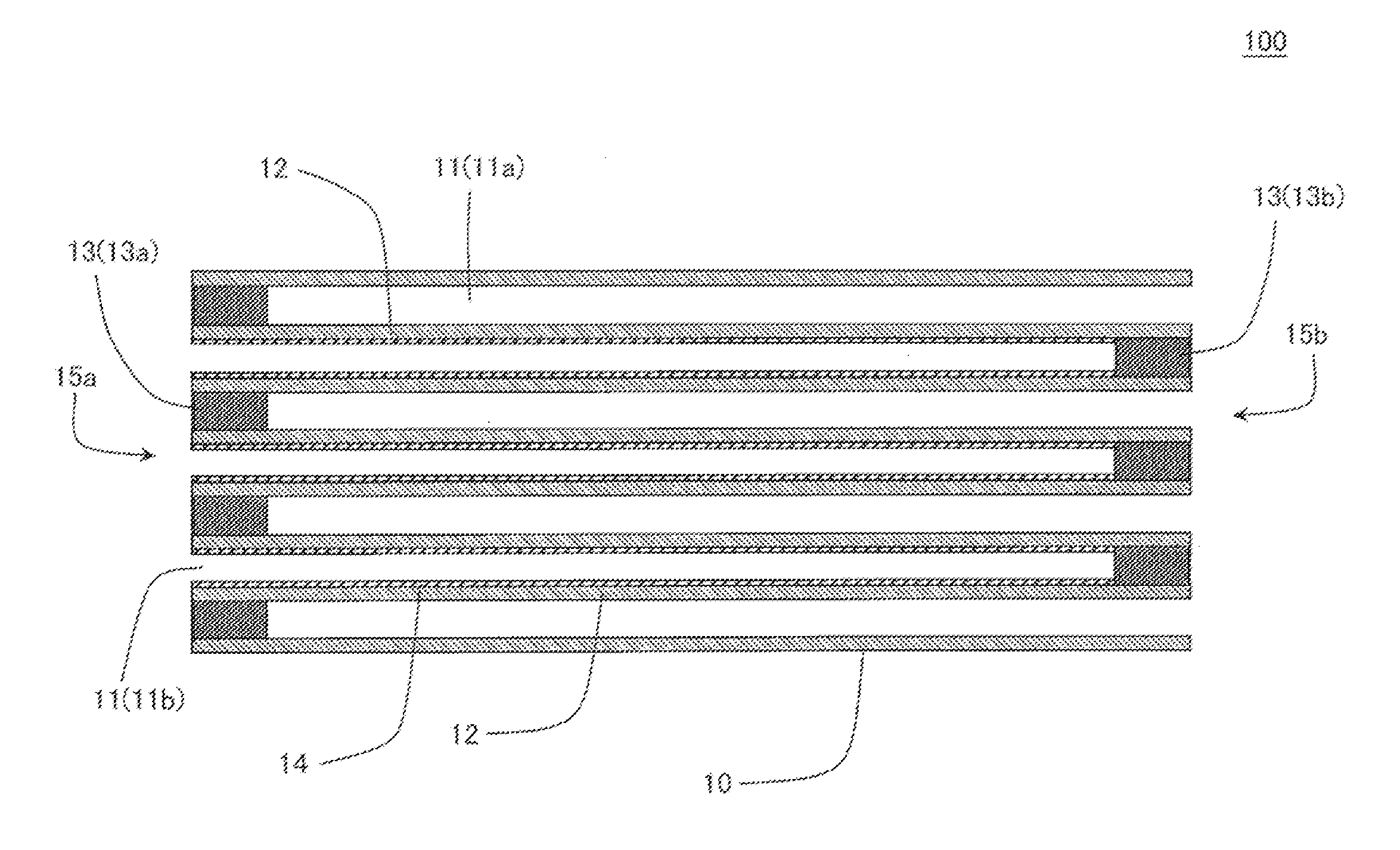

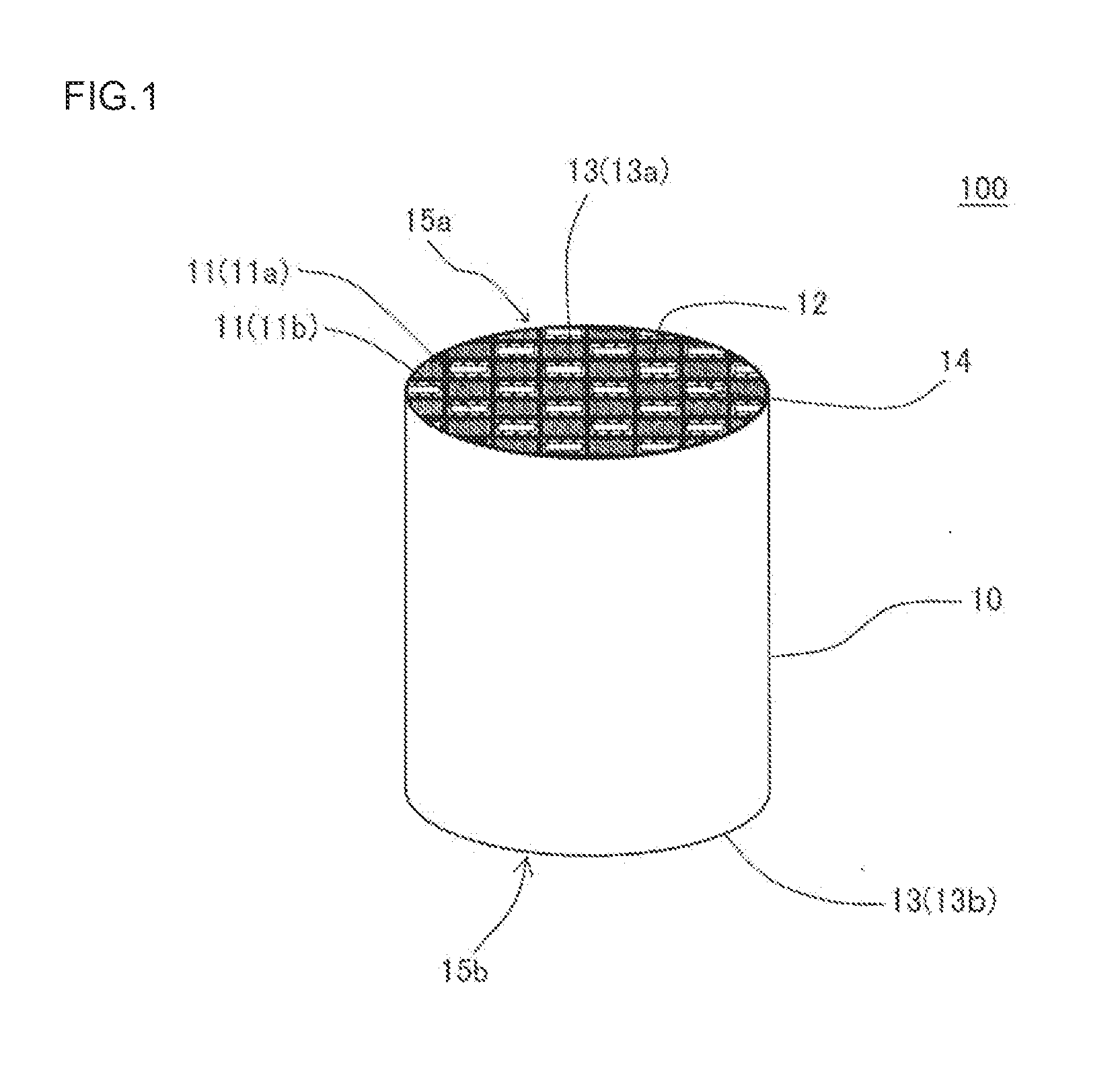

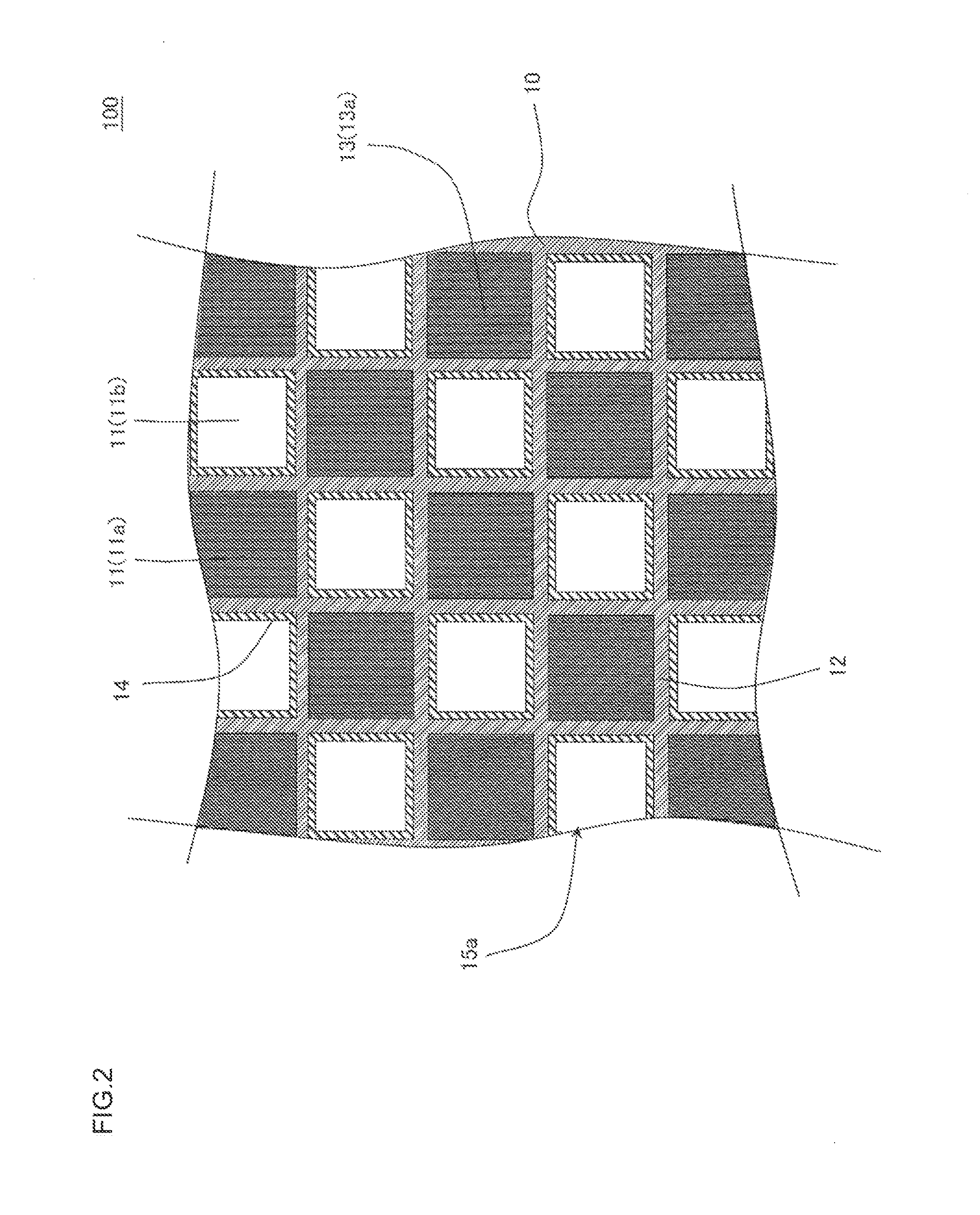

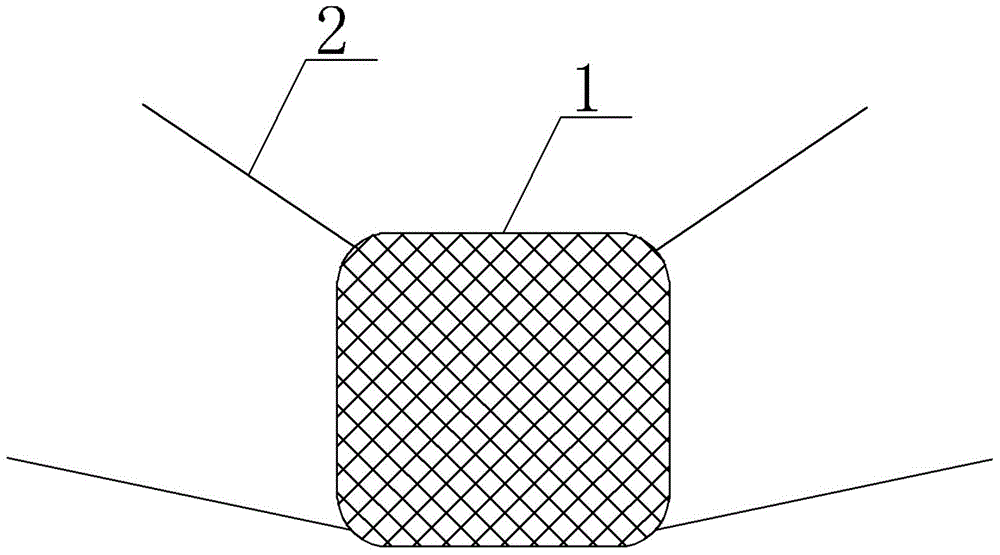

Exhaust gas purification filter

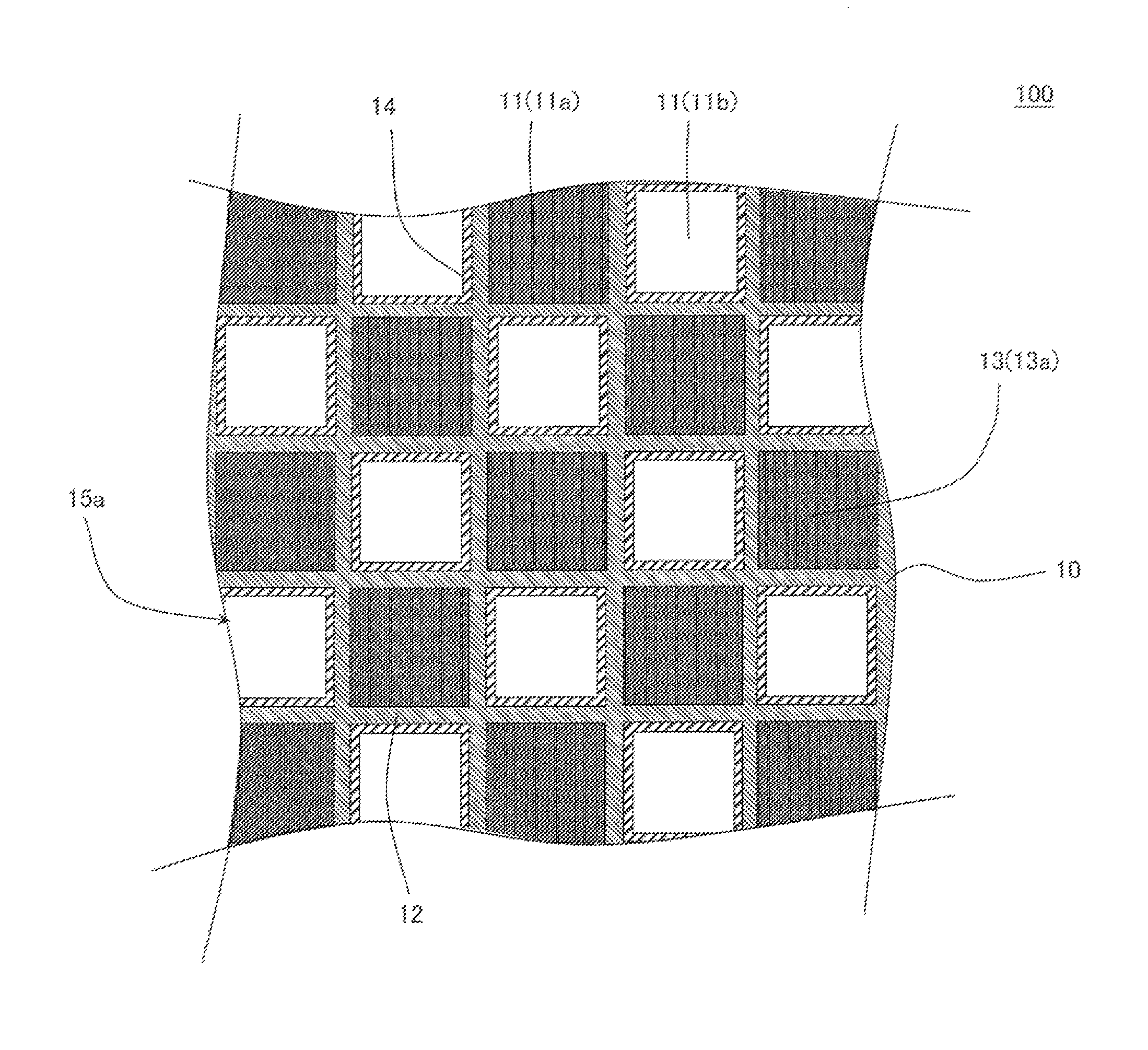

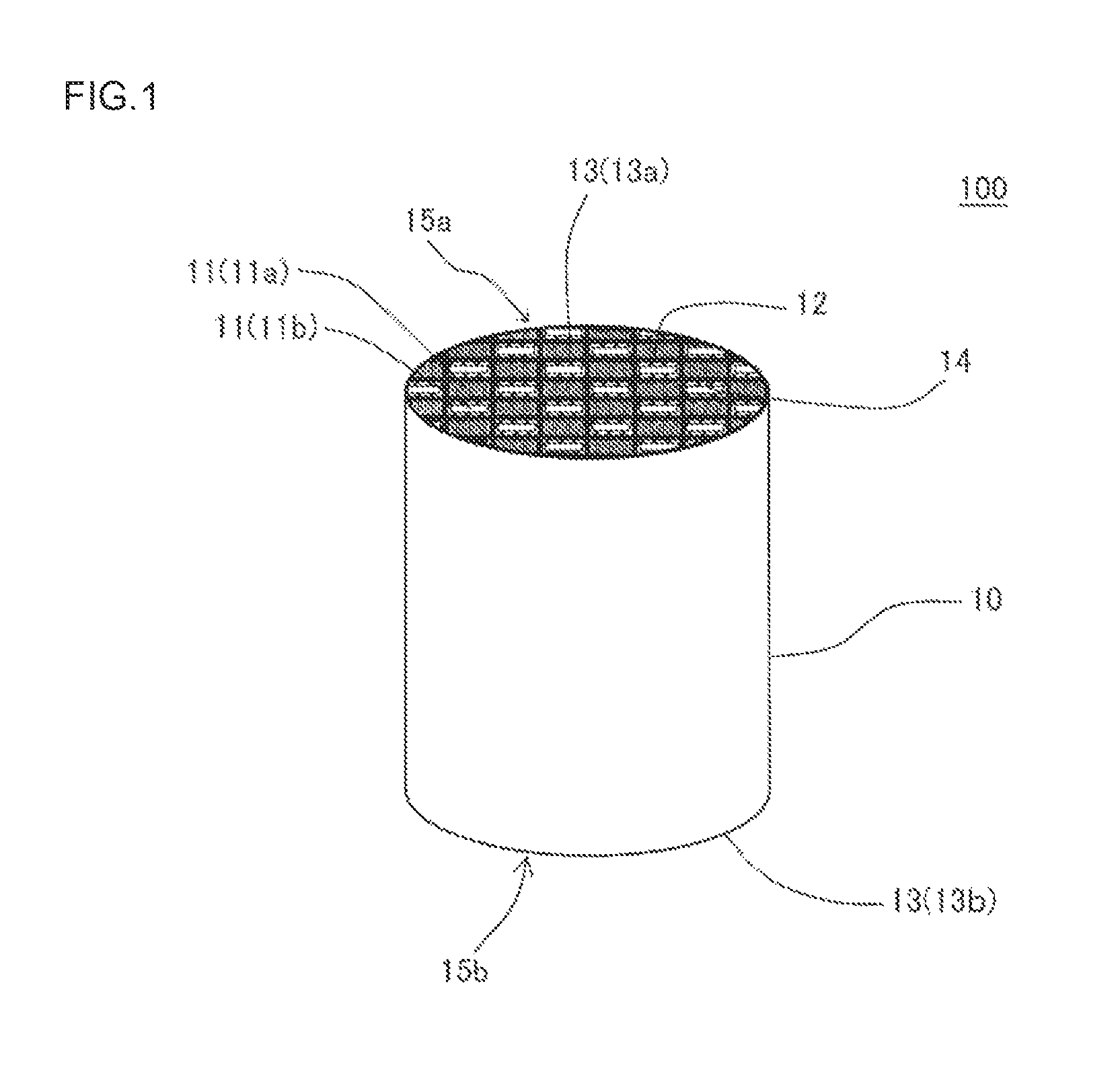

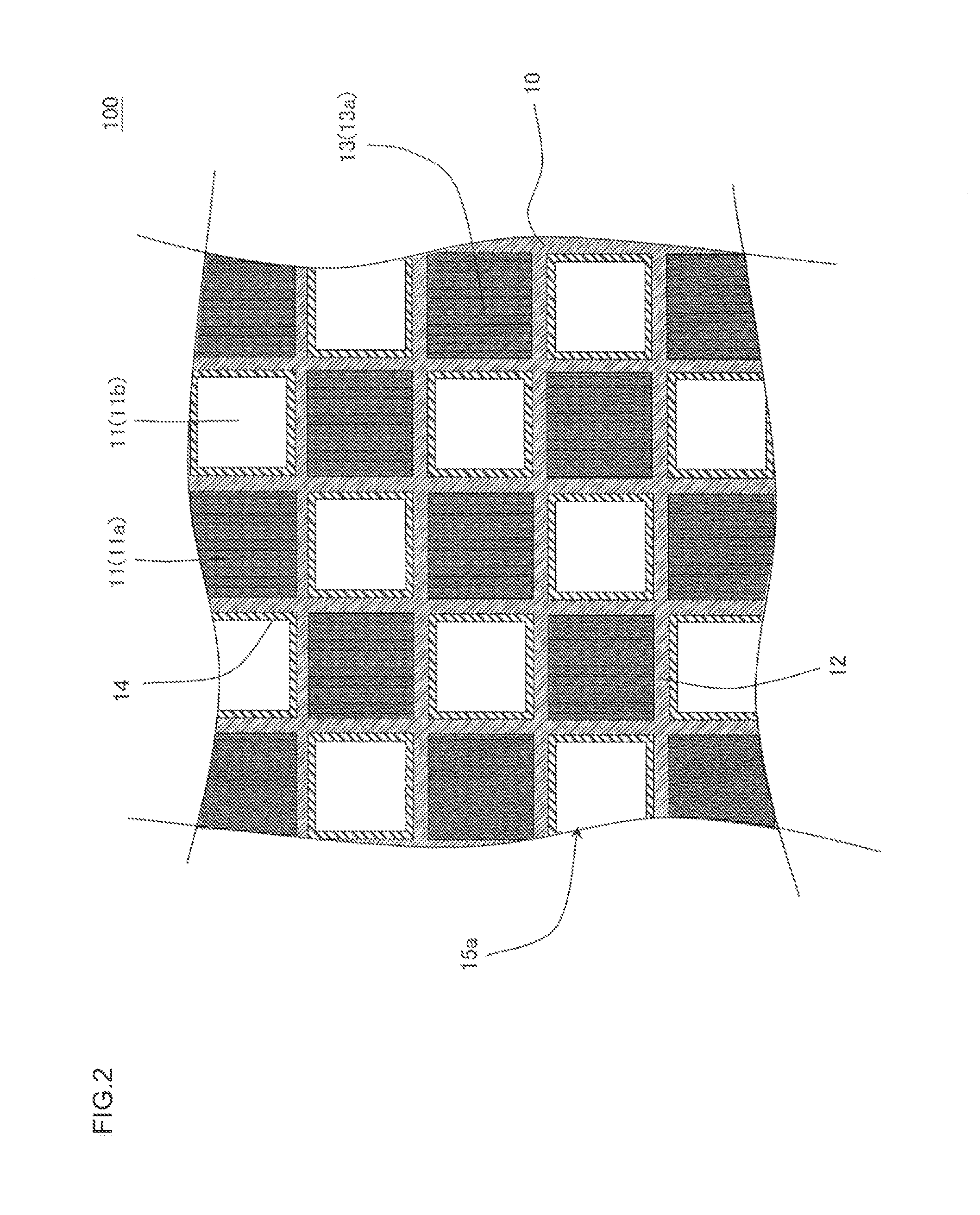

ActiveUS20120317946A1Reduce the amount requiredIncreased pressure lossDispersed particle filtrationTransportation and packagingPorosityHoneycomb structure

An exhaust gas purification filter 100 includes: a honeycomb structure 10 having partition walls 12, plugging portions 13, and a surface trapping layer 14 having an average pore size of 0.1 μm or more and 5 μm or less, a porosity of 50% or more and 80% or less, and a thickness of 1 μm or more and 50 μm or less. The partition walls 12 have a thickness of 0.05 mm or more and 0.18 mm or less and an average pore size of 10 or more and 18 μm or less, and the proportion of the volume of the pores having a size of twice the average pore size or more in the entire pore volume in a pore size distribution of the partition walls 12 is 5% or more and 40% or less.

Owner:NGK INSULATORS LTD

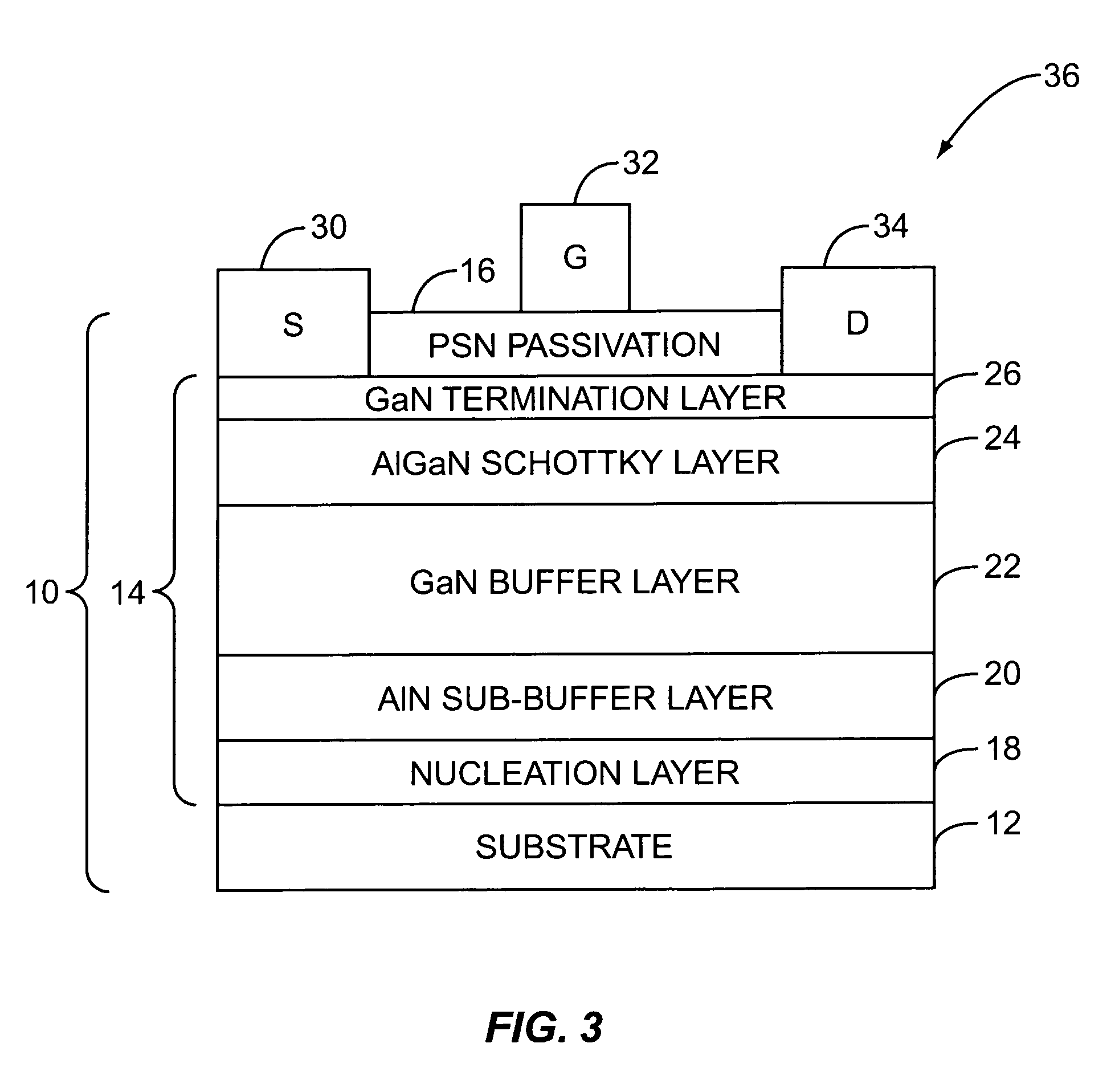

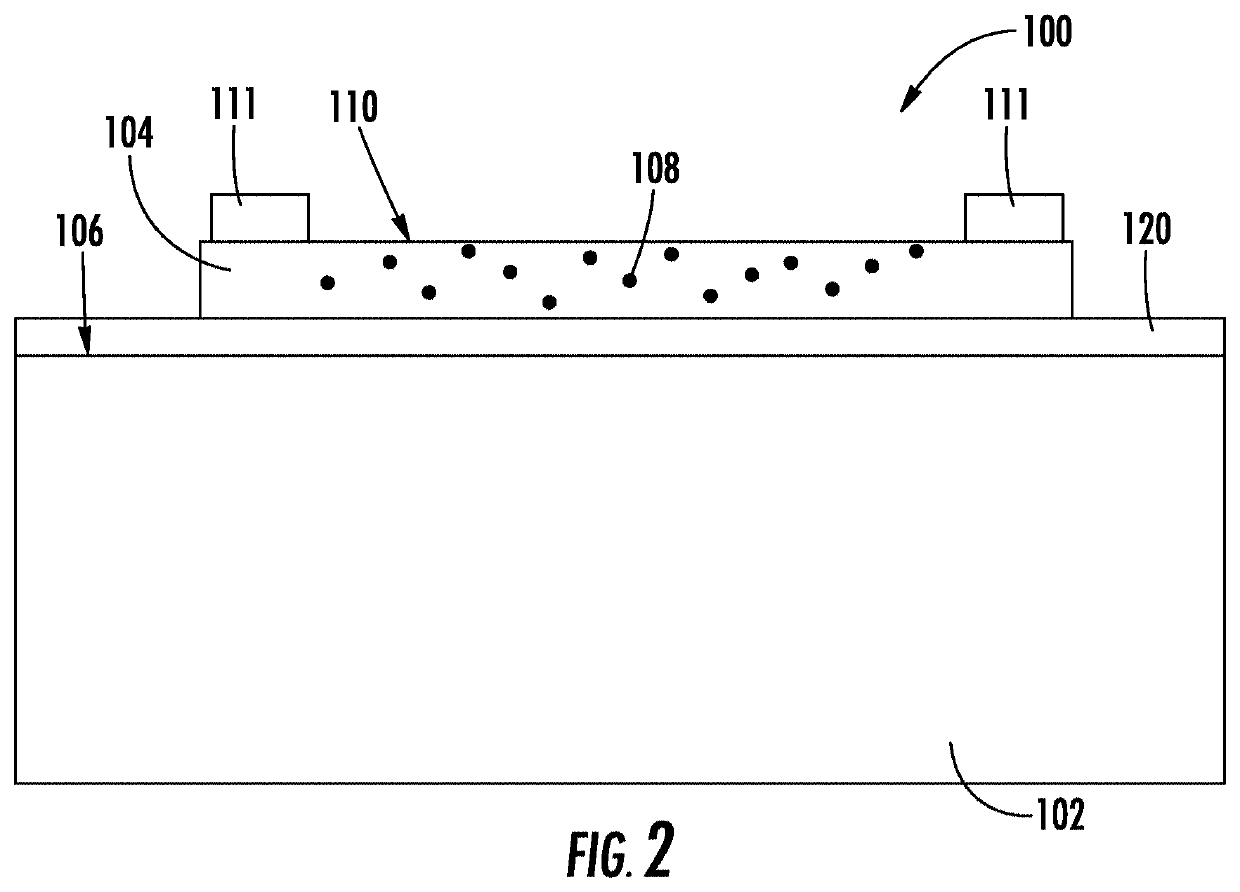

High electron mobility transistors with improved gates and reduced surface traps

InactiveUS20150263116A1Minimize impactImprove adhesionSemiconductor/solid-state device manufacturingSemiconductor devicesMicrowavePower switching

The present invention is related to high electron mobility transistors for power switching and microwave amplification and switching. More specifically, it related to a high electron mobility transistor with an improved gate to enhance the performance. When fabricating a high electron mobility thin film transistors, a first gate metal layer made of chromium alloy or tungsten alloy is deposited to reduce surface traps and to enhance the stability and integrity of the gates.

Owner:QIU CHUNONG +4

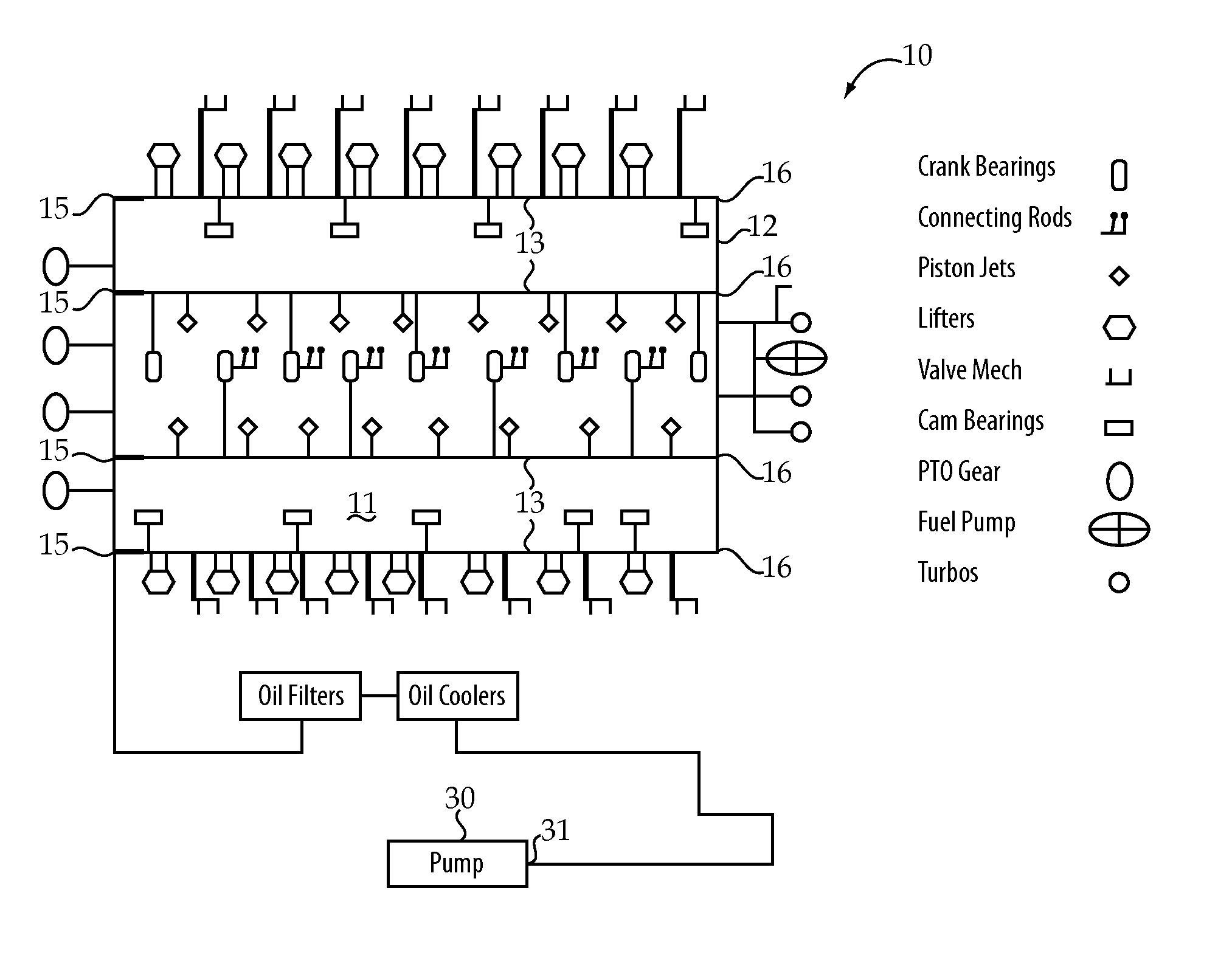

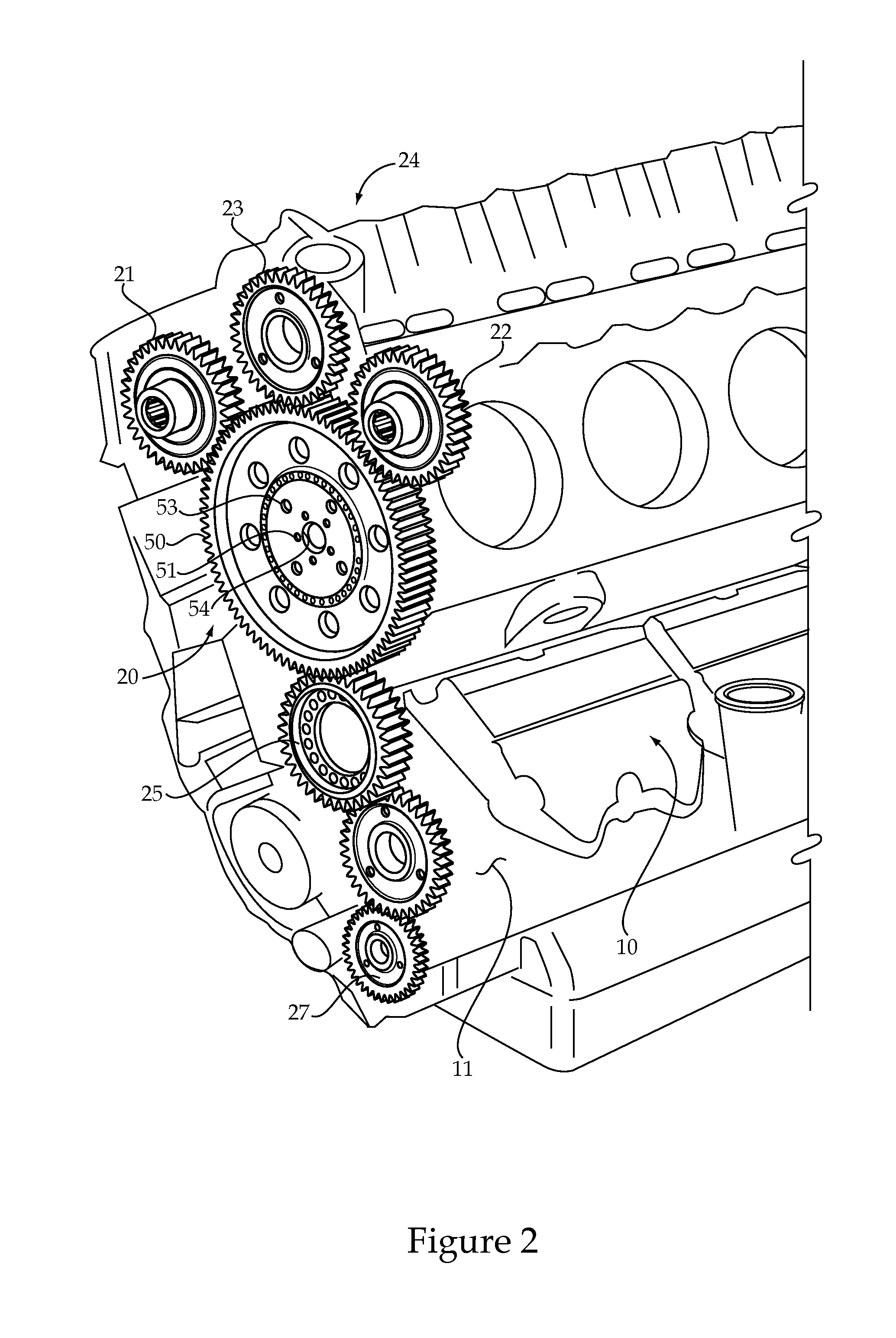

Cam Shaft/Cam Gear Assembly And Thrust Strategy For Engine Using Same

An engine includes a camshaft supported in a housing for rotation about an axis of rotation. A cam gear is attached to one end of the camshaft and includes a first thrust bearing surface. A thrust ring is attached to the cam gear and includes a second thrust bearing surface. A thrust ring retainer is attached to the housing with a plurality of bolts and includes a pair of thrust surfaces trapped between the first thrust bearing surface of the cam gear and a second thrust bearing surface of the thrust ring. The thrust ring retainer also defines a portion of a lubrication connection passage that facilitates pressure equalization among a plurality of lubrication galleries arranged in parallel adjacent the camshaft.

Owner:CATERPILLAR INC

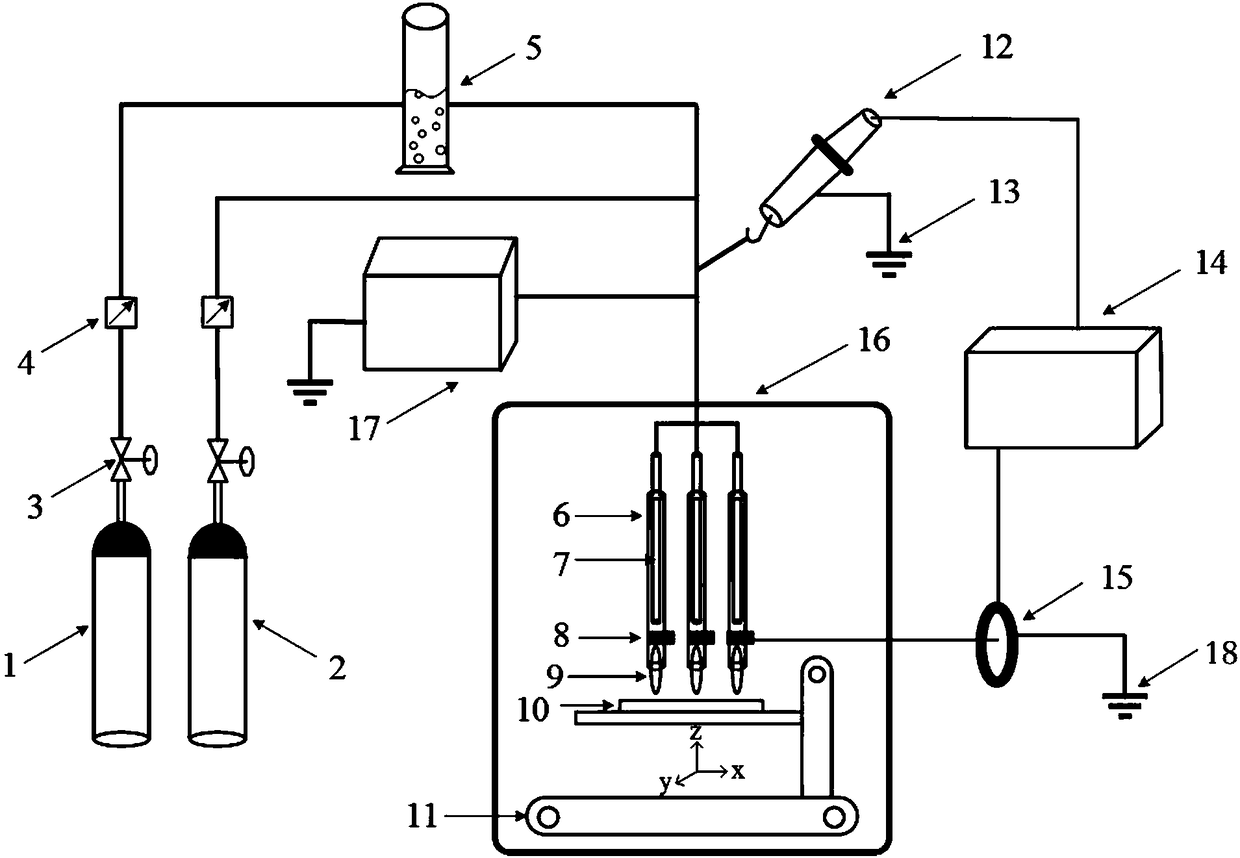

Plasma jet deposition film device and method of shallowing surface trap level

InactiveCN108130524AAvoid errorsLarge discharge areaChemical vapor deposition coatingPlasma jetGas cylinder

The invention discloses a plasma jet deposition film device and a method of shallowing a surface trap level. The device comprises a plasma jet array, a bubbling bottle, a second air cylinder and a power supply. The plasma jet array is arranged in a tempered glass cavity and comprises a quartz tube, a hollow metal capillary tube, a copper foil and a three-dimensional mobile platform, wherein the hollow metal capillary tube is interspersed into the quartz tube, and the outer wall of the hollow metal capillary tube is not in contact with the inner wall of the quartz tube; the copper foil is arranged in the bottom of the quartz tube for grounding; the three-dimensional mobile platform is arranged right below the quartz tube to regulate movement of a sample; one end of the bubbling bottle is connected to a first air cylinder while the other end is connected to the upper orifice of the hollow metal capillary tube; the second air cylinder is connected to the upper orifice of the hollow metalcapillary tube; and the power supply is connected to the hollow metal capillary tube.

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

Exhaust gas purification filter

ActiveUS8734558B2Reduce the amount requiredIncreased pressure lossCombination devicesDispersed particle filtrationPorosityHoneycomb structure

An exhaust gas purification filter 100 includes: a honeycomb structure 10 having partition walls 12, plugging portions 13, and a surface trapping layer 14 having an average pore size of 0.1 μm or more and 5 μm or less, a porosity of 50% or more and 80% or less, and a thickness of 1 μm or more and 50 μm or less. The partition walls 12 have a thickness of 0.05 mm or more and 0.18 mm or less and an average pore size of 10 or more and 18 μm or less, and the proportion of the volume of the pores having a size of twice the average pore size or more in the entire pore volume in a pore size distribution of the partition walls 12 is 5% or more and 40% or less.

Owner:NGK INSULATORS LTD

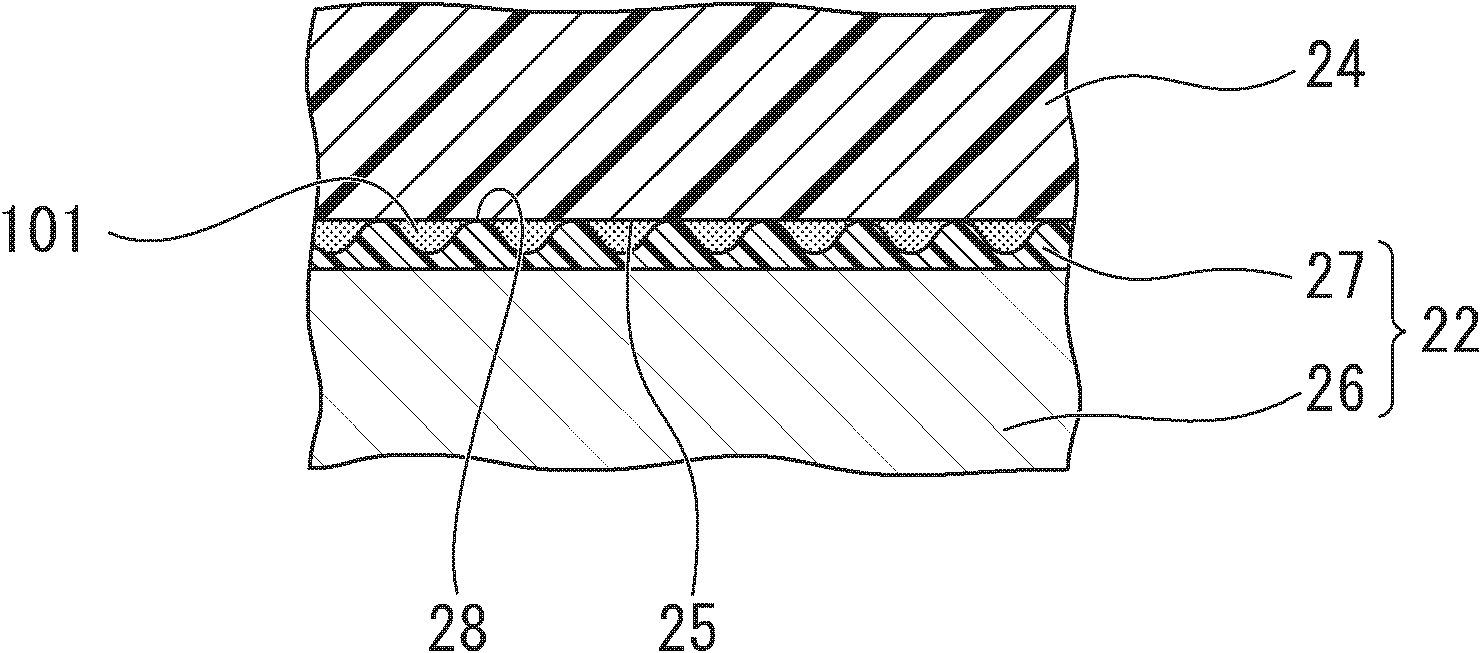

Slide structure, support structure and seismically isolated structure

InactiveCN102422050AWill not be enlargedLow costRotary bearingsLinear bearingsSkin surfaceYoung's modulus

Provided are a slide structure, a support structure and a seismically isolated structure wherein a slide member (21) has a first sliding surface (25) of a sliding body (24) made of synthetic resin and a counter member (22) has a second surface (28) covered with a skin (27) made of synthetic resin that has more than twice as large Young's modulus as that of the first sliding surface. The skin surface is roughened such that the maximum height Rz of roughness is more than 3[mu]m. Small pits on the roughened surface trap lubricant thereby preventing the lubricant from flowing out and thereby providing a stable and low friction state.

Owner:NIPPON STEEL & SUMIKIN ENG CO LTD

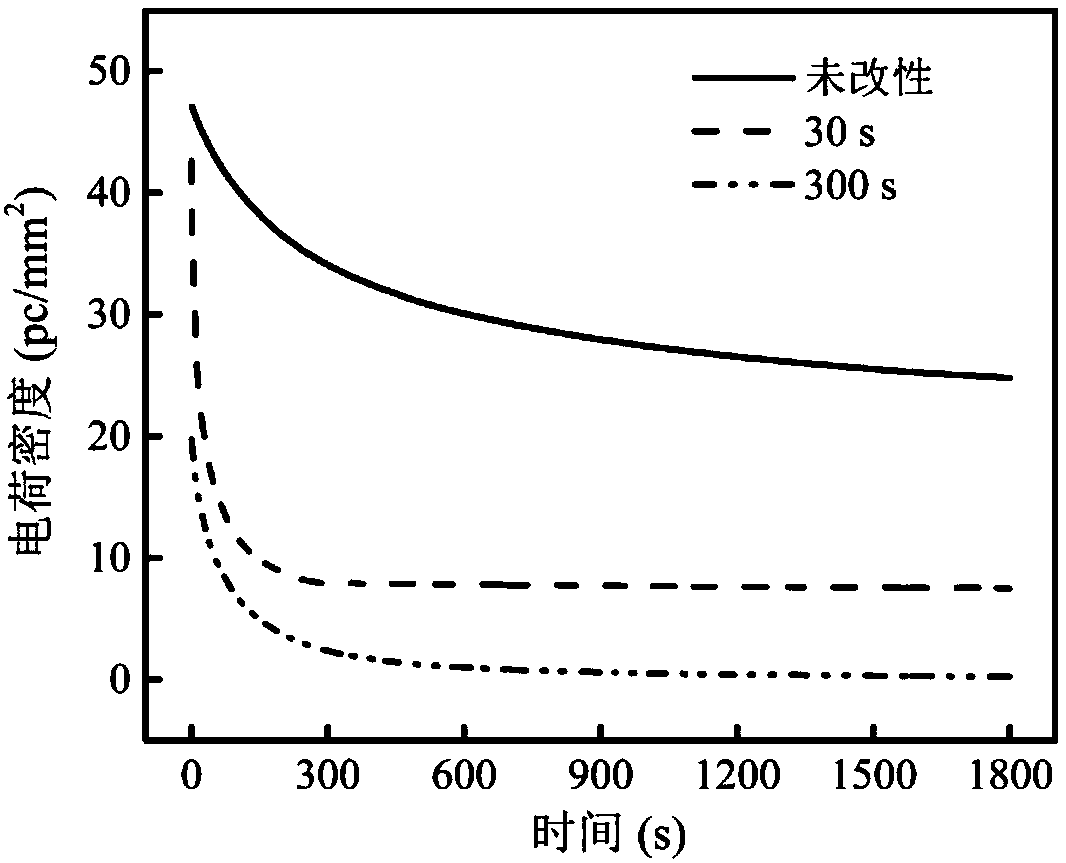

Method of increasing vacuum surface flashover voltage of insulating dielectric material and modified insulating dielectric material

ActiveCN106409450ASimple and fast operationReduce process complexityInsulating bodiesSurface conductivityAlternating current

The invention discloses a method of increasing a vacuum surface flashover voltage of an insulating dielectric material and a modified insulating dielectric material. The method comprises the steps of modifying the surface of a solid insulating dielectric material by adopting ozone, to be specific, putting the to-be-processed solid insulating dielectric material in a sealed cavity, vacuumizing the sealed cavity and then inletting ozone for ozone treatment to obtain the modified insulating dielectric material. The surface conductivity, the surface trap level and the trap density of the insulating dielectric material after the ozone treatment are changed; the surface conductivity is increased obviously, the surface trap level is reduced and the trap density is increased. The method can obviously increase the vacuum alternating current surface flashover voltage of the solid insulating dielectric material; and the method is simple and convenient to operate, has low complexity of the implementation process, relatively good repeatability and strong environmental friendliness, and can be widely applied to the surface treatment of the solid insulating dielectric material in the technical field of high-voltage insulation.

Owner:PINGGAO GRP +2

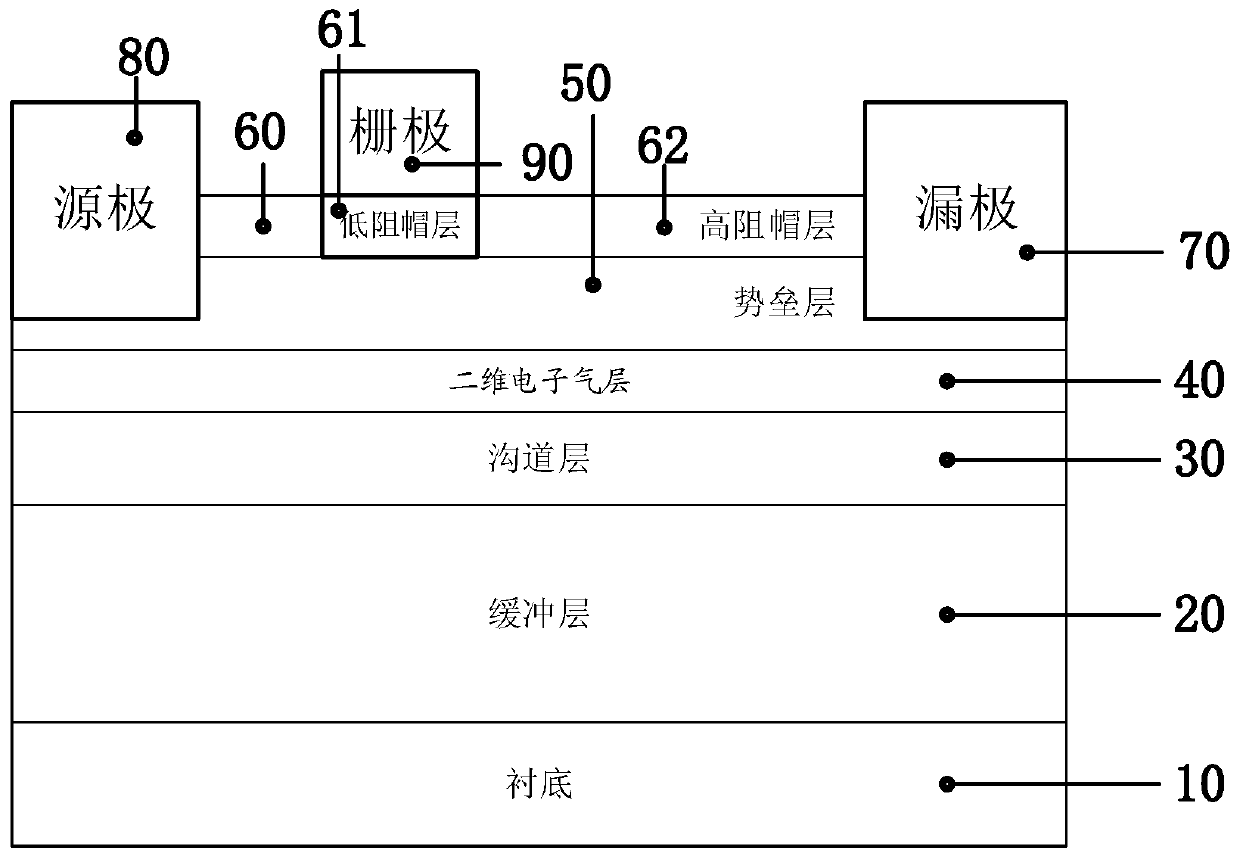

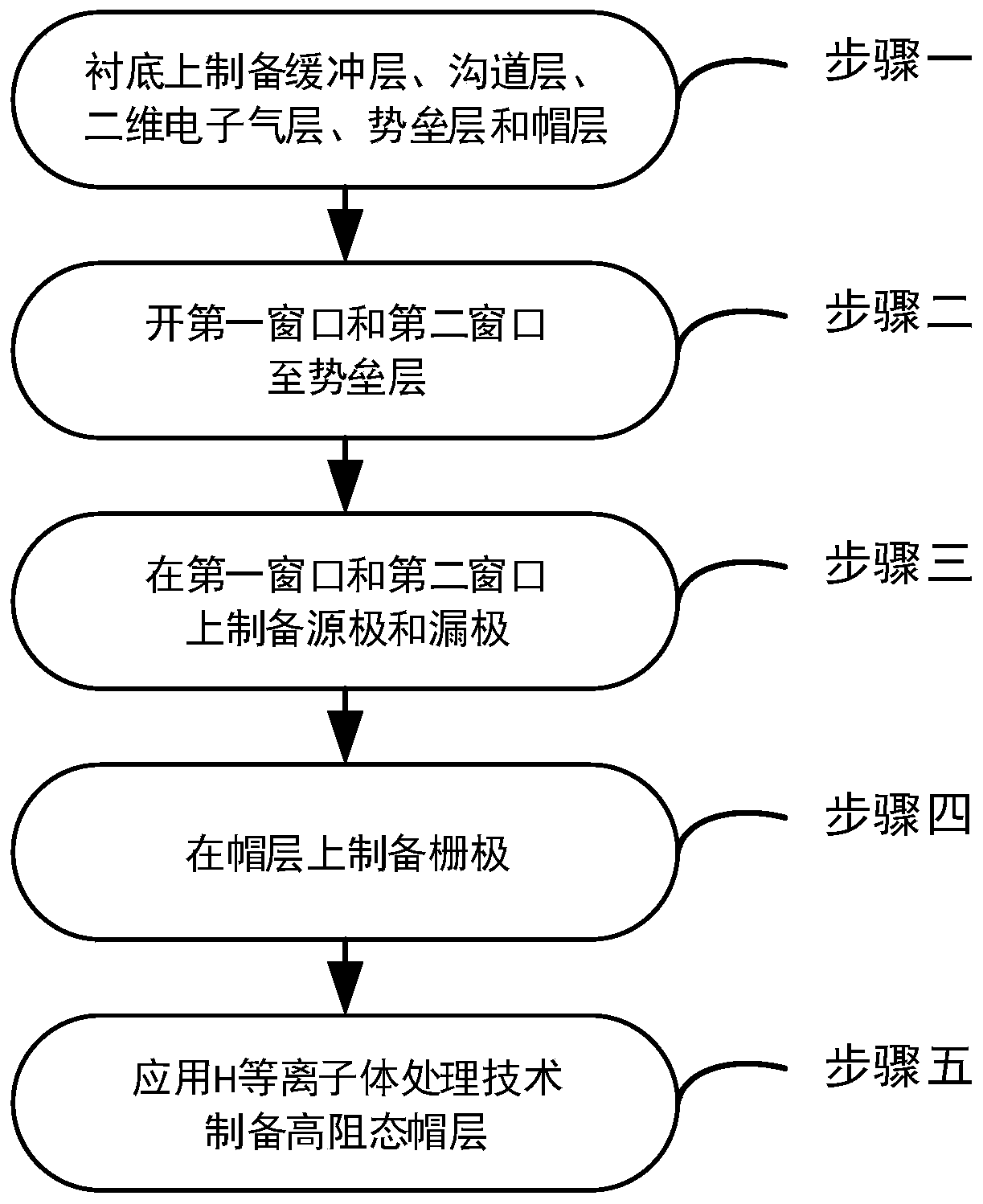

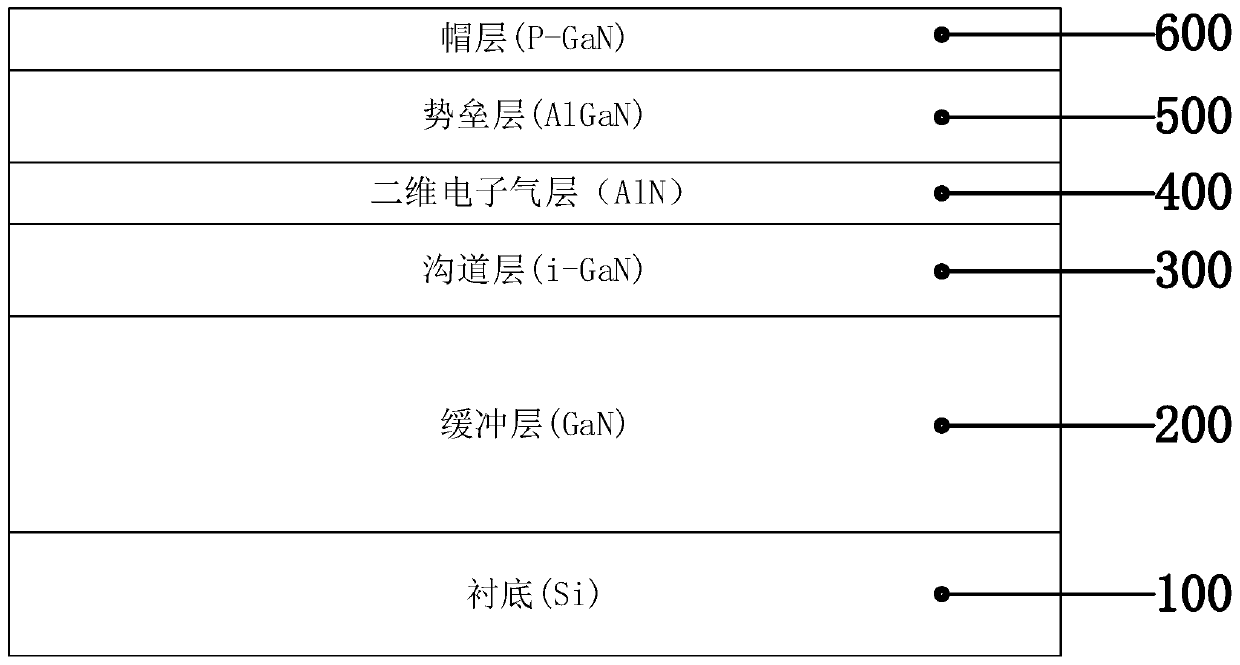

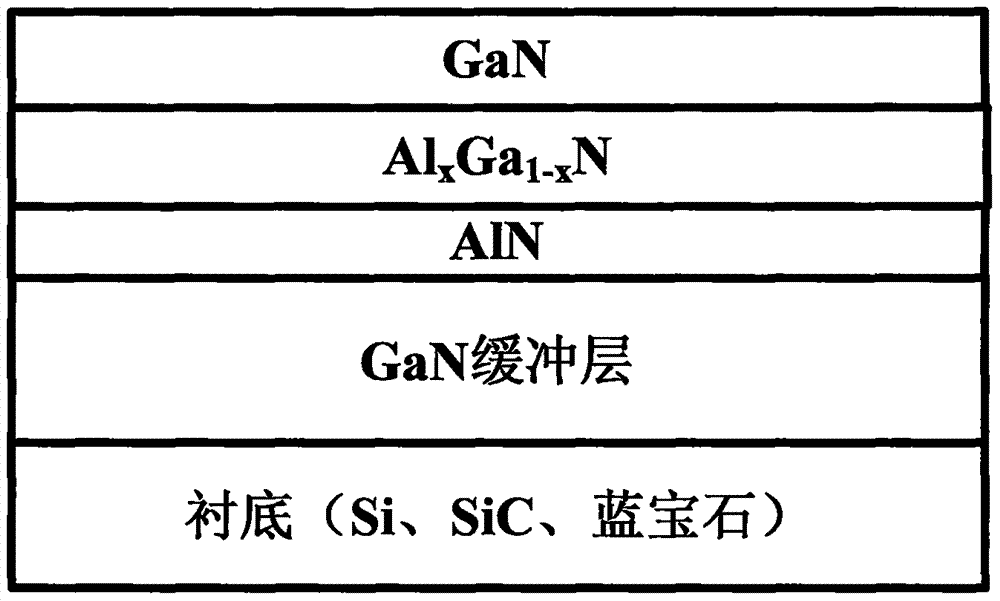

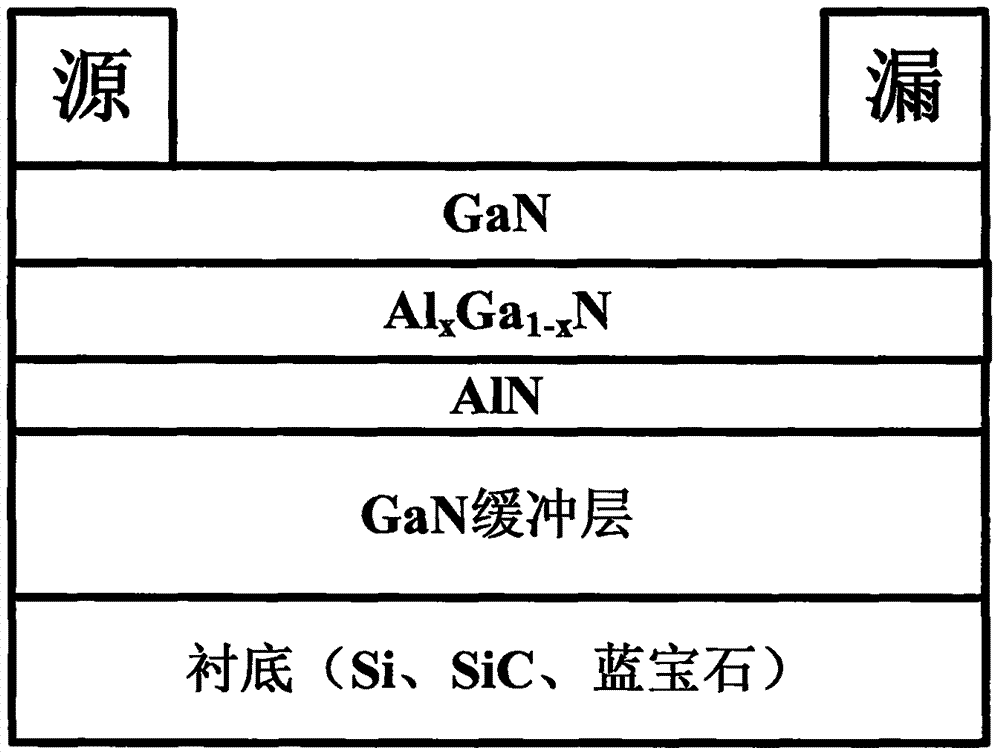

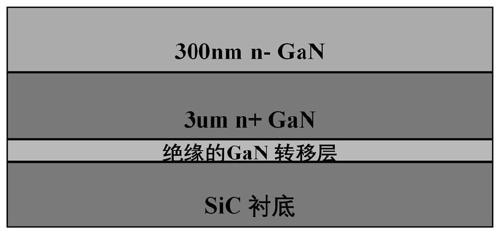

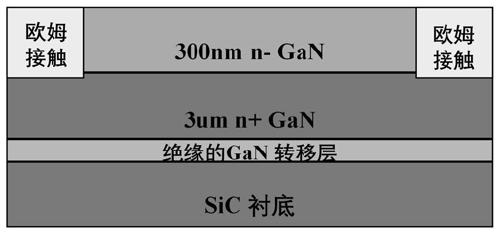

GaN-based HEMT device and preparation method thereof

InactiveCN109742142AReduce the collapse effectSemiconductor/solid-state device manufacturingSemiconductor devicesElectric fieldMaterials science

The invention discloses a GaN-based HEMT device and a preparation method thereof. The GaN-based HEMT device comprises a substrate, a buffering layer, a channel layer, a potential barrier layer, a caplayer, a source electrode, a grid electrode and a drain electrode. Due to the fact that an H plasma processing technology is applied to prepare the cap layer to a high-impedance state to optimize theinternal electric field distribution of the GaN-base HEMT device in the preparation process of the GaN-base HEMT device, the influence of surface traps on the property of the device is reduced.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

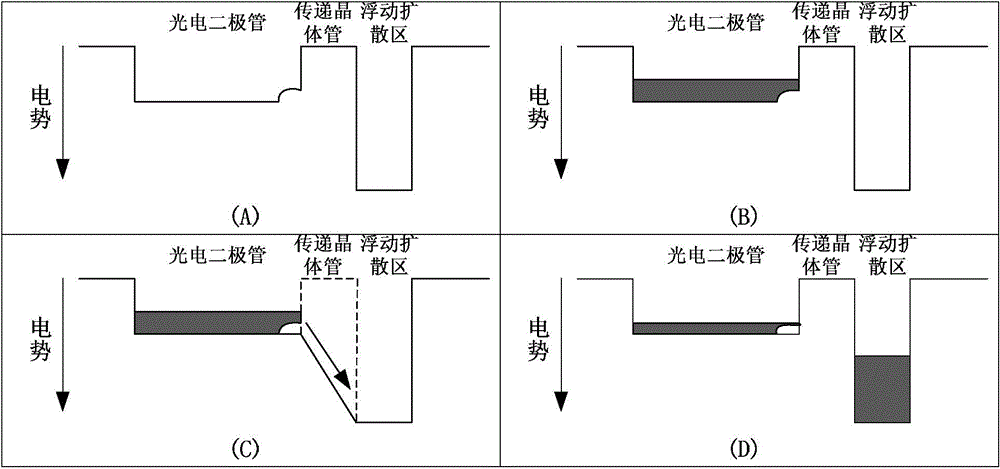

Silicon-based CMOS image sensor and method of the silicon-based CMOS image sensor for restraining photon-generated carrier surface trap recombination

InactiveCN103915457AImprove transfer efficiencyLow surface trap recombination rateRadiation controlled devicesEngineeringFloating diffusion

The invention belongs to the technical field of micro-electronics, and particularly relates to a silicon-based CMOS image sensor and a method of the silicon-based CMOS image sensor for restraining photon-generated carrier surface trap recombination. The silicon-based CMOS image sensor has the advantages of achieving high transfer efficiency of photon-generated carriers and being low in surface recombination rate, and particularly comprises a photodiode (PPD), a floating diffusion region (FD), a transmission transistor (TX), a shallow trench isolation region (STI), an anti-penetration through injection region (APT) and a surface trap restraining layer, wherein the surface trap restraining layer is formed by injecting ions in a local region in a self-aligned mode, and different numbers of the ions with different types of energy are injected at different positions two times. Meanwhile, the high transfer efficiency of the photon-generated carriers and the low surface trap recombination rate are achieved.

Owner:FUDAN UNIV

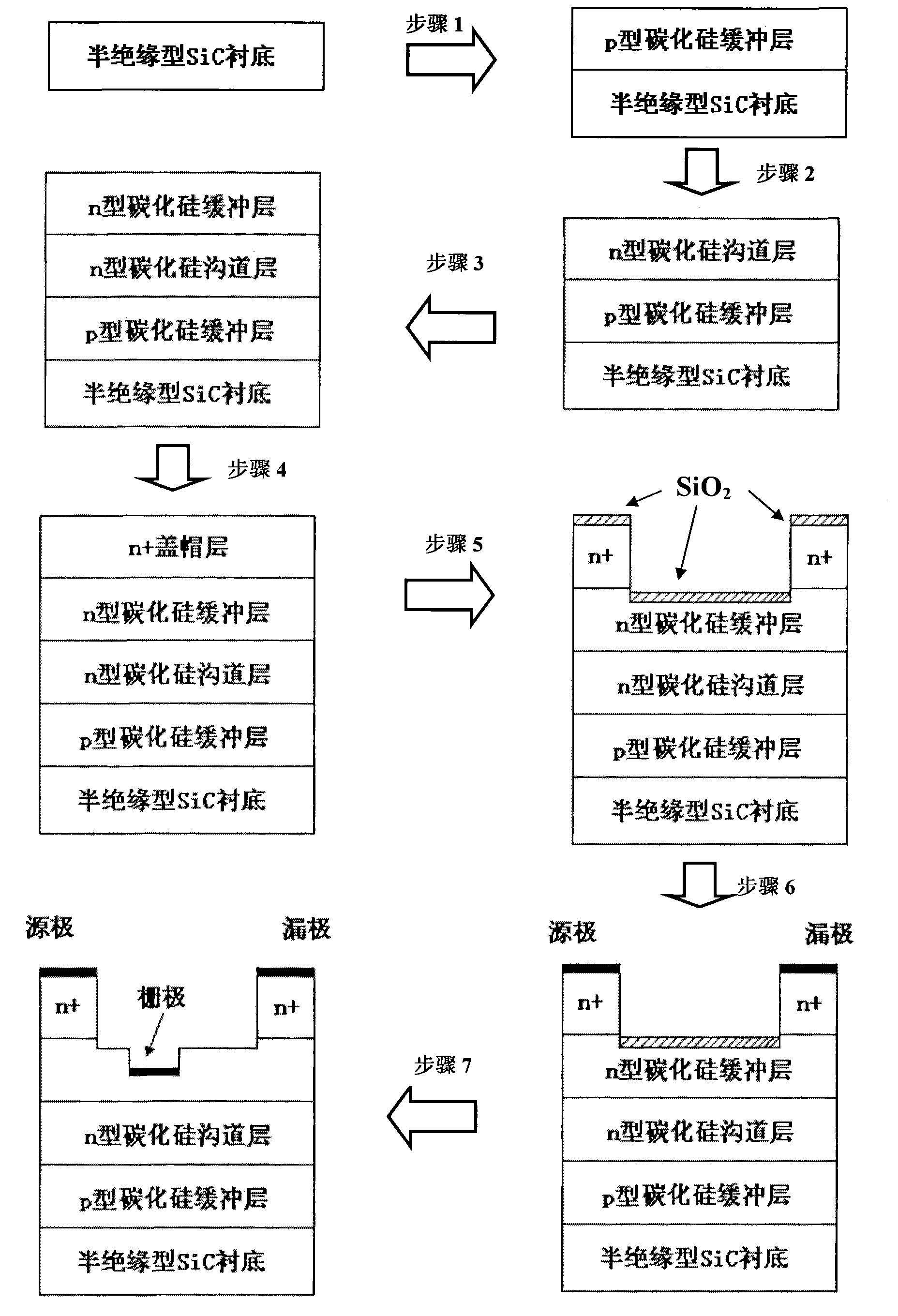

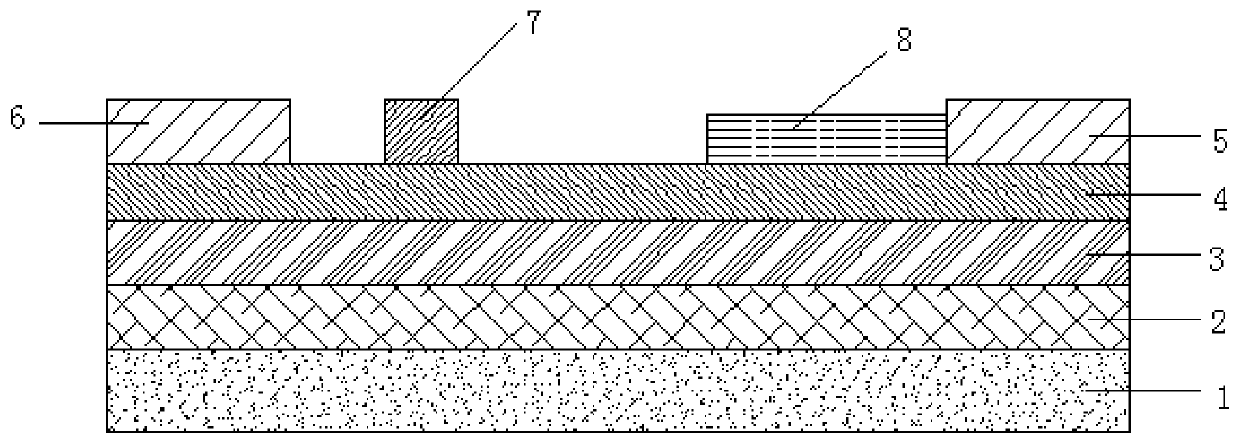

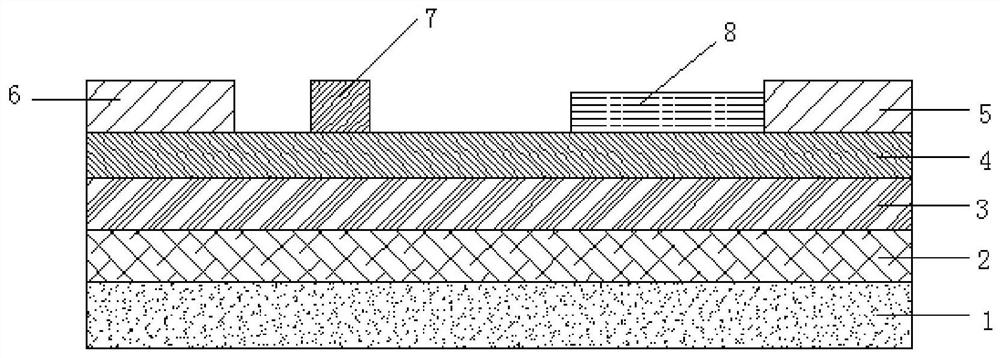

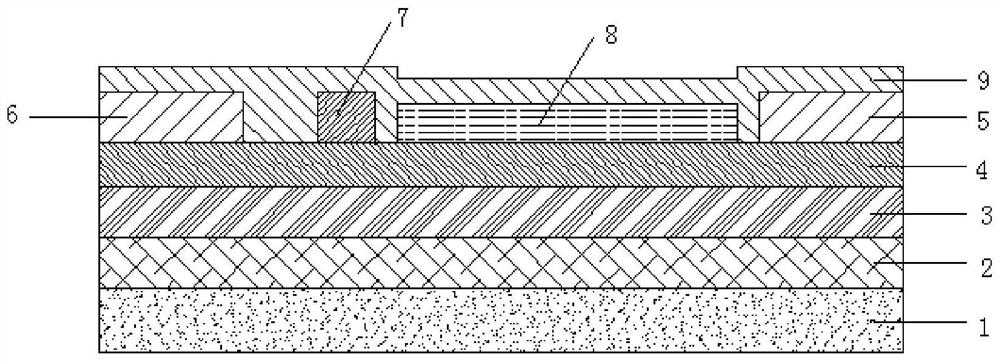

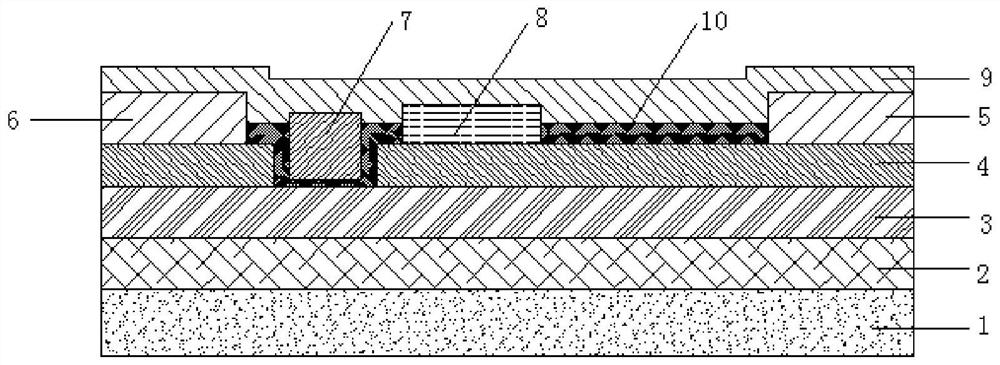

Metal-semiconductor field effect transistor and production method thereof

InactiveCN101552286AWeaken or eliminate the influence ofReduce the impactSemiconductor/solid-state device manufacturingSemiconductor devicesP type siliconMaterials science

The invention discloses a metal-semiconductor field effect transistor formed in silicon carbide, mainly solving the problem of surface trap formed on the surface when making a component. The transistor comprises a semi-insulating silicon carbide substrate (1), a p-type silicon carbide buffer layer (2), a n-type silicon carbide conducting channel layer (3), a n+ capping layer (5), a source electrode (7) and a drain electrode (8), wherein a n-type silicon carbide buffer layer (4) is arranged between the n-type silicon carbide conducting channel layer (3) and the n+ capping layer (5); and a grid electrode (6) are buried inside the buffer layer to form a buried-channel and buried-grid structure. The process of making the component comprises the following steps of: epitaxially growing the p-type silicon carbide buffer layer, the n-type silicon carbide channel layer, the n-type silicon carbide buffer layer and n+ capping layer in sequence; etching grid recession windows on the n+ capping layer and carrying out sacrificial oxidation; and forming the source electrode, the drain electrode and the grid electrode by evaporating metal and peeling. The metal-semiconductor field effect transistor can be used for the manufacturing of high-frequency and high-power integrated circuits.

Owner:XIDIAN UNIV

Surface processing technology for improving GaN HEMT passivation effect and reducing current collapse

InactiveCN107154338AAvoid damageImprove processing stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesTrappingOxygen plasma

The present invention discloses a surface processing technology and a method for improving the surface passivation effect of the gallium nitride-based electronic device and reducing the current collapse. The method is mainly applied to the preparation of the gallium nitride-based electronic device, before the conventional passivation layer deposition, ozone, oxygen plasma and other strong oxidants are used on the surface of gallium nitride for oxidation, then hydrochloric acid is used to remove a thin layer of oxide, and the process is repeated for a number of cycles before the surface passivation to completely remove surface defects, so as to get a relatively perfect surface, thereby improving the surface passivation effect, reducing the current collapse caused by the surface trapping effect.

Owner:PEKING UNIV

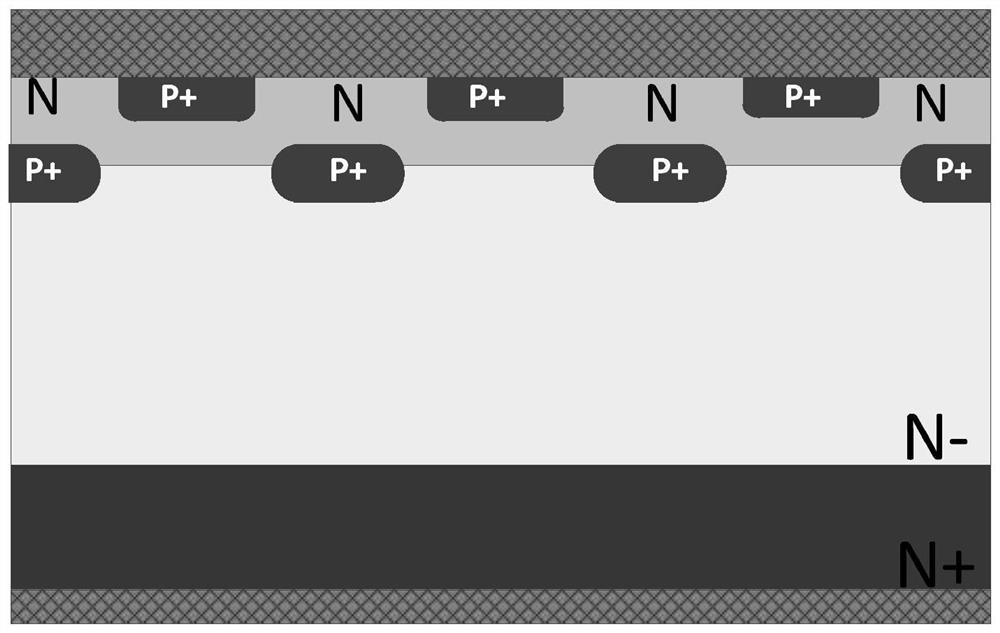

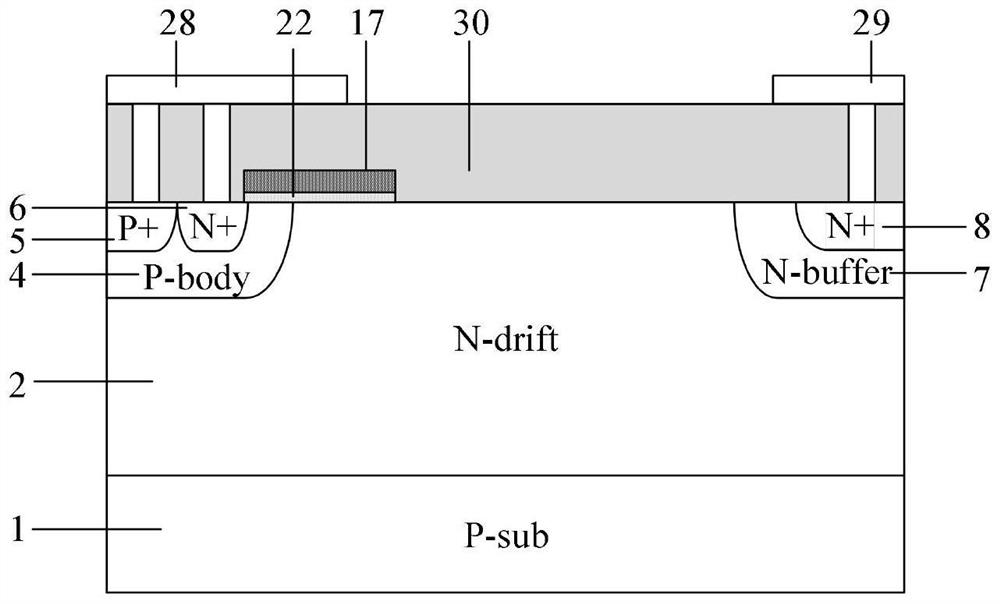

SiC SBD device with semi-floating structure, and preparation method thereof

ActiveCN112687750AIncreased injection areaLimit the surface electric field changeSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical field strengthReverse bias

The invention discloses a SiC SBD device with a semi-floating structure, and a preparation method thereof. The SiC SBD device comprises an active region and a non-active region, wherein the active region and the non-active region comprise a SiC substrate of a first doping type, a SiC epitaxial layer of the first doping type grown on the substrate, a surface trap of a second doping type formed by injection on the surface of the epitaxial layer, an anode and a cathode; a JFET region of the first doping type is arranged between the adjacent second doping type wells of the active region, and a floating doping region of the second doping type is arranged below the JFET region; and a second doping type surface trap and a floating doping region are arranged at the lower position between the adjacent second doping type traps of the non-active region and are communicated with the interior of the corresponding region in the active region. The SiC SBD device with the semi-floating structure can limit the electric field intensity of the Schottky contact surface during reverse bias, so reverse electric leakage of the SiC SBD device is reduced.

Owner:FUDAN UNIV

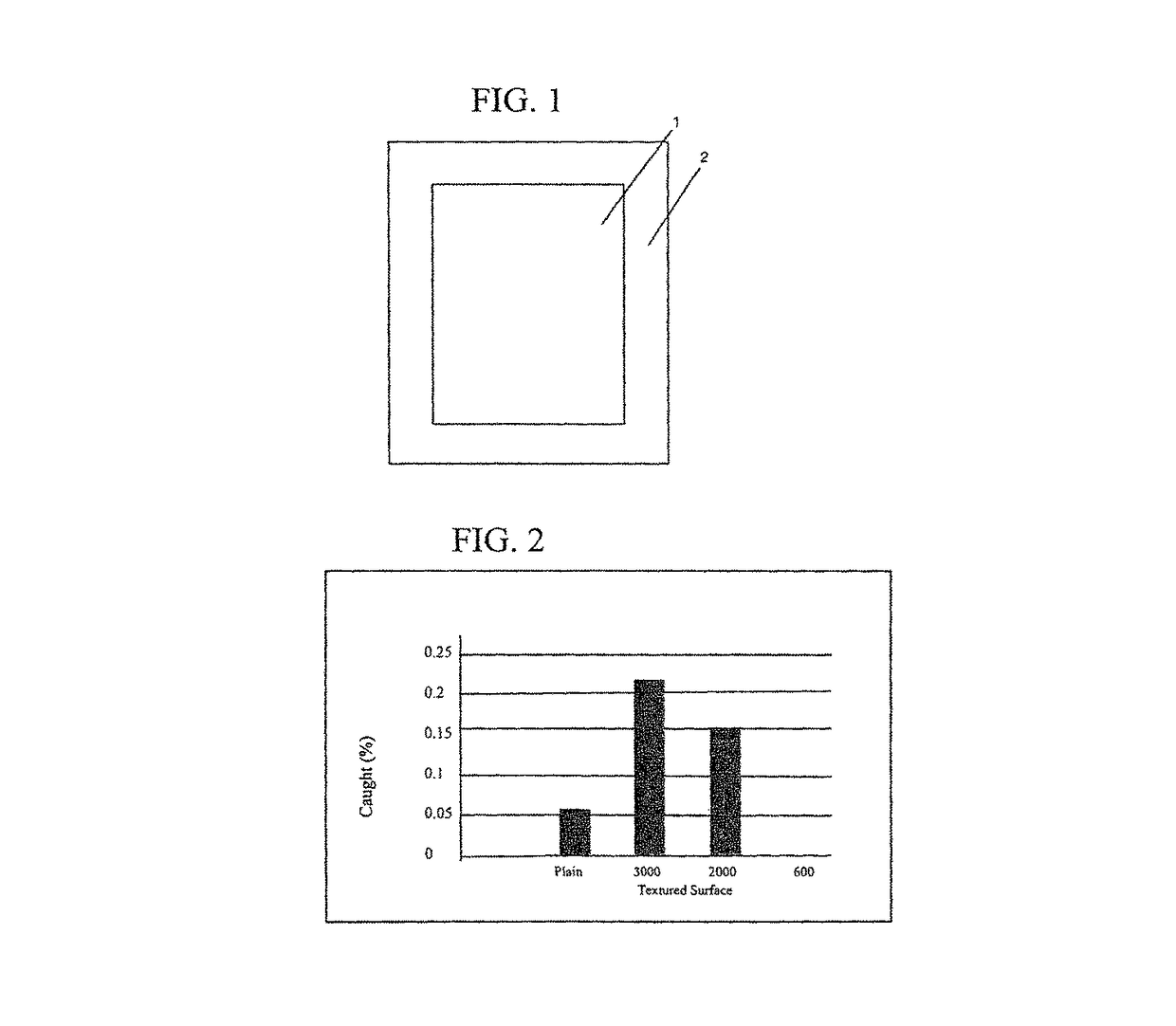

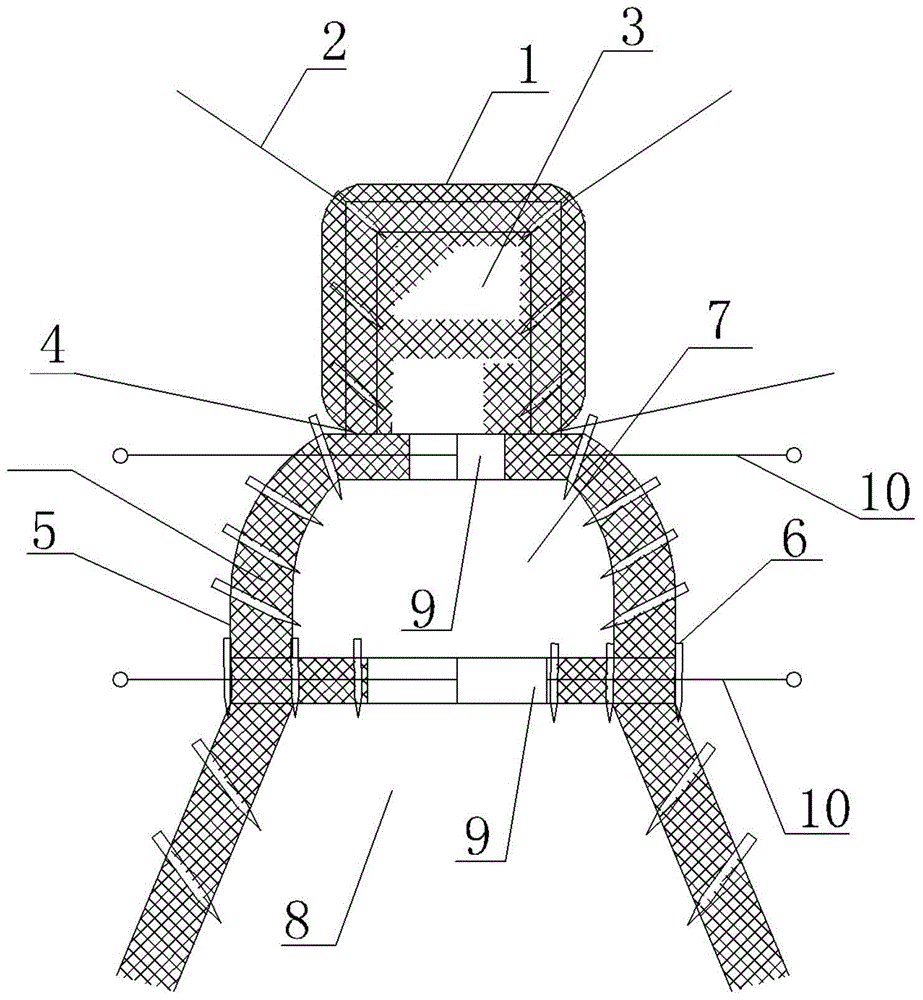

Bed bug sticky trap with specific textured surface

ActiveUS9737065B1Smoothness and roughness qualityRaise the ratioInsect catchers and killersAgainst vector-borne diseasesEngineeringSurface trap

Traps, devices, systems, compositions, and methods for trapping bed bugs, and similar insects with sticky traps having a smooth perimeter surface around the sticky surface, where the smooth perimeter surface can be abraded to a selected texture having both smoothness and roughness qualities. The surfaces are textured so that bed bugs are not able to use the surfaces to pull themselves from the sticky surface, and the textured surface is not so smooth as to cause the bed bugs to avoid the textured surface.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

Dielectric medium trap state measuring and imaging system and method driven by friction nanometer generator

PendingCN113281380ADetection and improvement of micro-nano surface characteristicsWith 2D imagingMaterial analysis by electric/magnetic meansFriction generatorsDielectricNanogenerator

The invention relates to a dielectric medium trap state measuring and imaging system and method driven by a friction nanometer generator, and belongs to the technical field of dielectric media. The system comprises a trap excitation power supply device and a test sample chamber, the trap excitation power supply device comprises an independent layer rotary friction nano generator and a rotary motor, and can output constant charge and high voltage, excite micro-power dielectric barrier uniform discharge on the surface of a dielectric medium, so that electrons are fully sunken and desunken, and desunken current pulses with enough strength and stability are generated; a test sample chamber is used for fixing the dielectric film to be tested and providing controllable filling gas; a test electrode structure is detachable, and electrode groups with different measurement modes can be replaced; and the air gap distance between the upper and lower electrodes can be adjusted. The system has the advantages of being lossless, accurate and capable of achieving two-dimensional imaging, detailed information of trap state distribution on the surface of the high polymer thin film material is further obtained, and detection and improvement of various properties such as insulation, energy storage and micro-nano surface characteristics of the functional material are facilitated.

Owner:CHONGQING UNIV

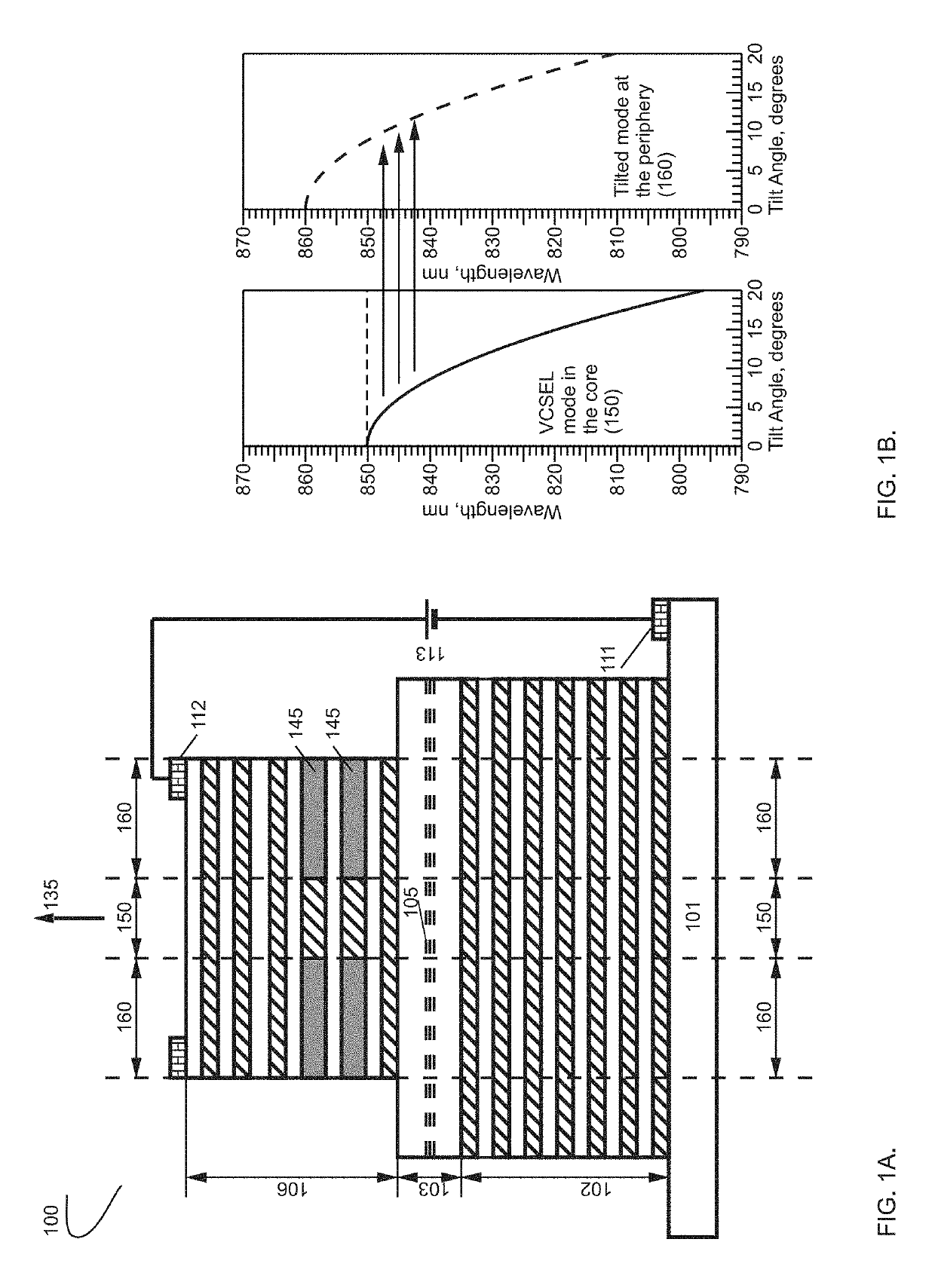

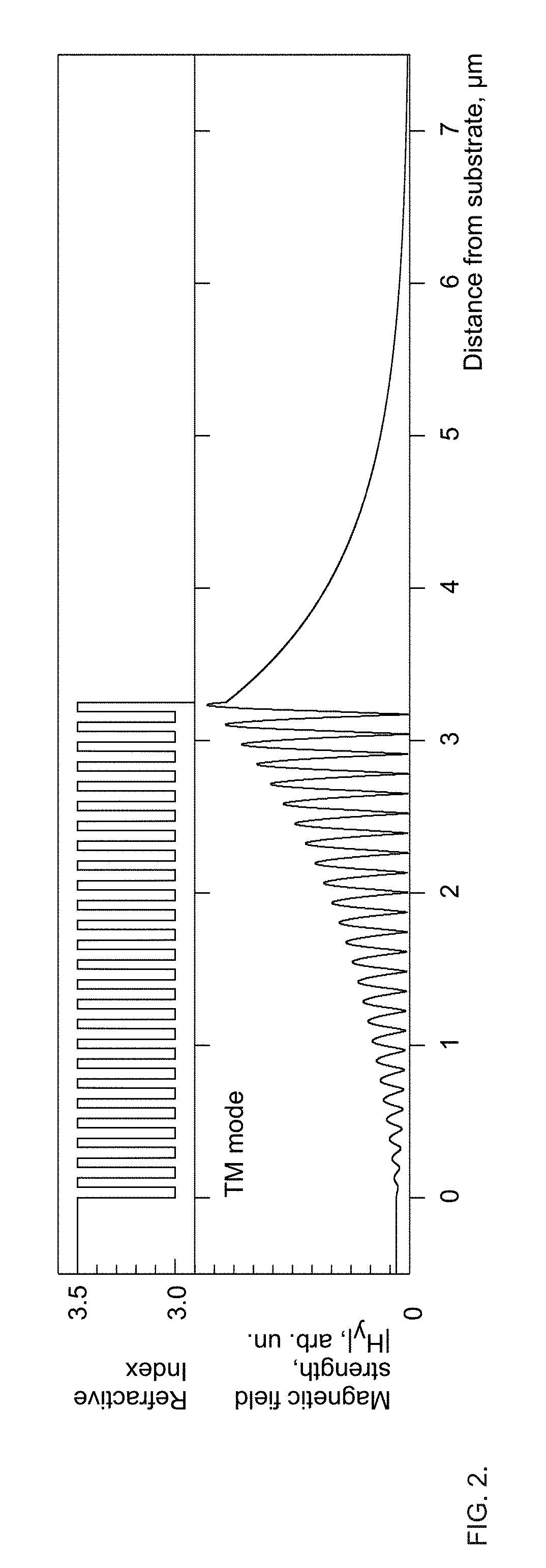

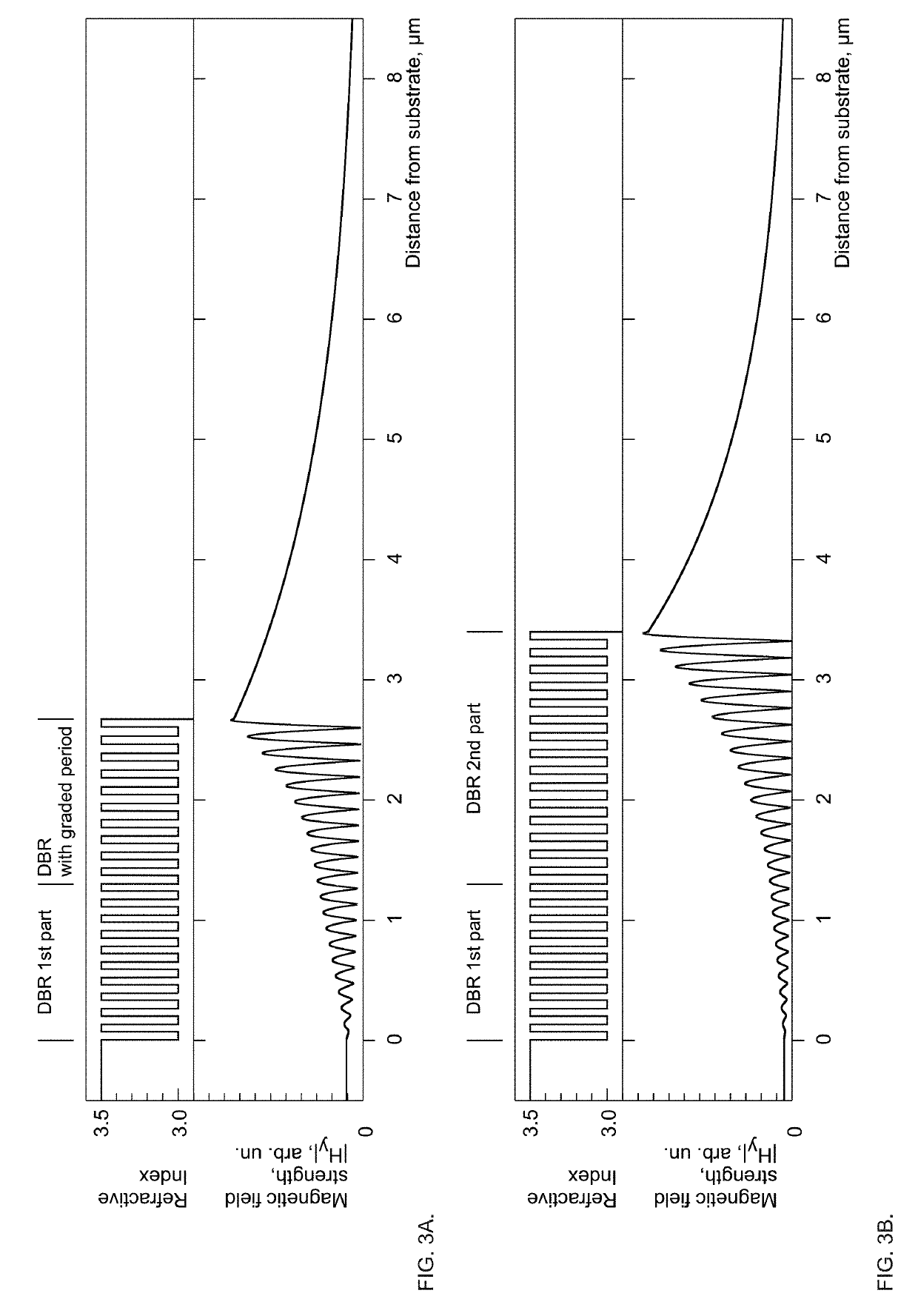

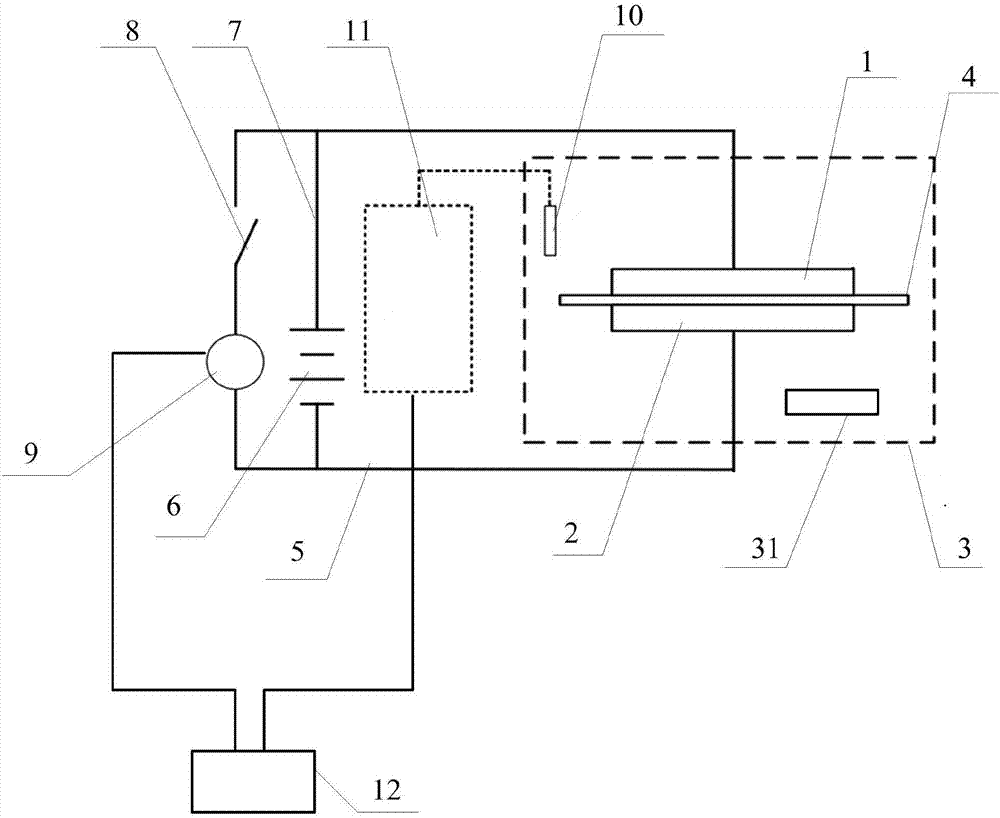

Optoelectronic device based on a surface-trapped optical mode

An optoelectronic device employs a surface-trapped TM-polarized optical mode existing at a boundary between a distributed Bragg reflector (DBR) and a homogeneous medium, dielectric or air. The device contains a resonant optical cavity surrounded by two DBRs, and an additional DBR section on top supporting the surface-trapped mode. Selective chemical transformation, like selective oxidation, etching or alloy composition intermixing form a central core and a periphery having different vertical profiles of the refractive index. Therefore, the longitudinal VCSEL mode in the core is non-orthogonal to the surface-trapped mode in the periphery, and the two modes can be transformed into each other. Such transformation allows fabrication of a number of optoelectronic devices and systems like a single transverse mode VCSEL, an integrated optical circuit operating as an optical amplifier, an integrated optical circuit combining a VCSEL and a resonant cavity photodetector, etc.

Owner:VI SYST GMBH

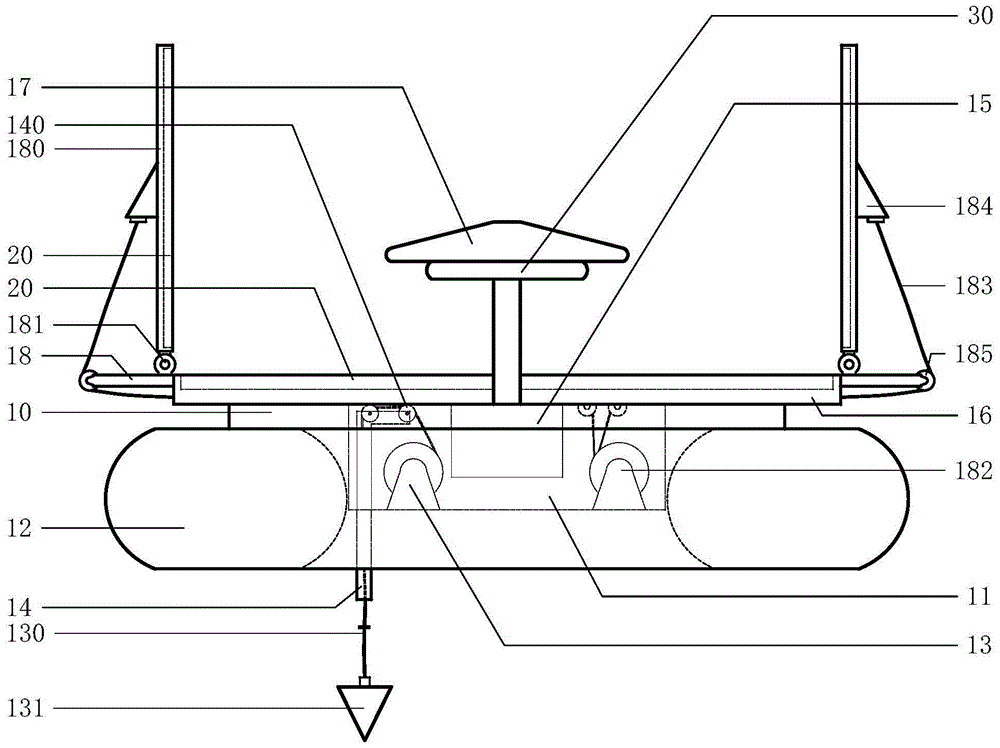

Intelligent sea-surface trapping fishing cage

InactiveCN108040989AAvoid returning empty handedReduce fishing costsProgramme controlComputer controlFishing netSurface trap

The invention provides an intelligent sea-surface trapping fishing cage. The intelligent sea-surface trapping fishing cage comprises a photovoltaic power generator, a floating box, a control processor, a Beidou short message module, a fish school detector, an LED module, a luring box, a lithium battery and a fishing net and is characterized in that an intelligent control mode is used, the fish school detector is used to detect the fish school outside the fishing cage, the control processor precisely controls the LED module and the luring box to lure the fish school, and the Beidou short message module is utilized to transmit information to fishing staff so as to allow the fishing staff to position and collect the fishing cage. A fishing method using the intelligent sea-surface trapping fishing cage greatly lowers fishing cost and fishing labor intensity and increases fishing efficiency, and the situation that the fishing staff return without fishes is avoided.

Owner:HUZHOU GUOXIN MATERIALS

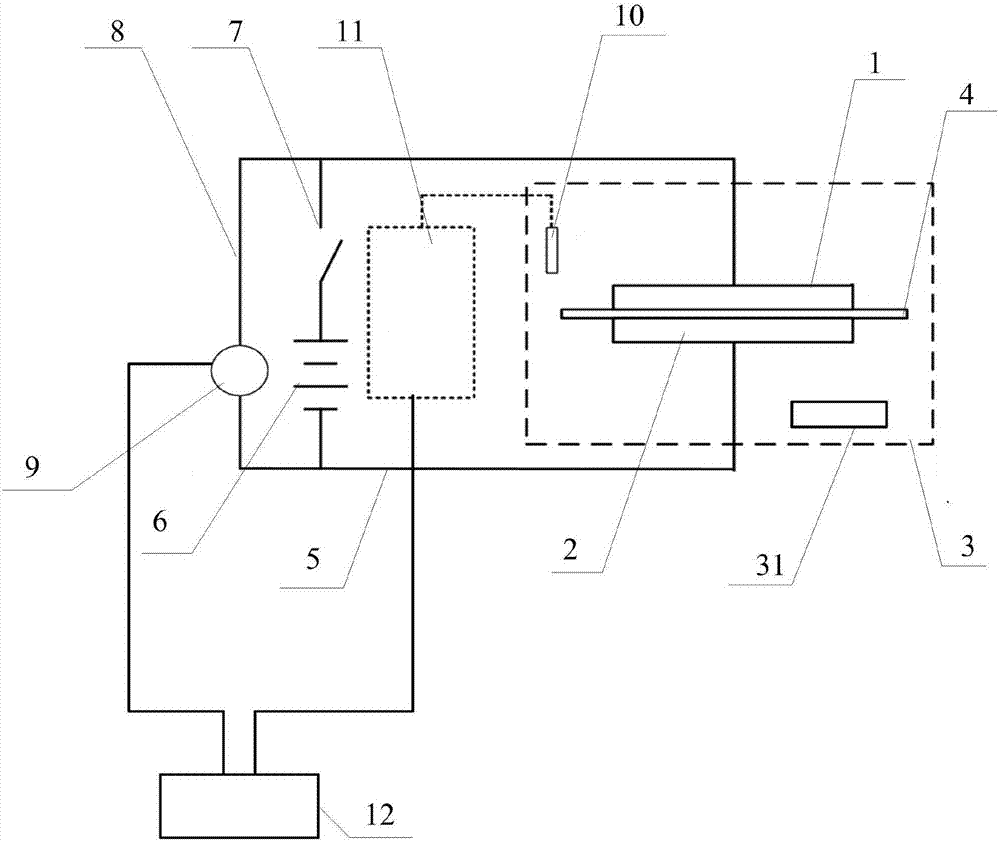

High-field surface trap evaluation system

The embodiment of the invention discloses a high-field surface trap evaluation system. The system comprises an upper electrode plate, a lower electrode plate, a temperature control cavity, an electrode circuit, a temperature probe and a temperature detection device; the upper electrode plate and the lower electrode plate are oppositely arranged in the temperature control cavity, and the space between the upper electrode plate and the lower electrode plate is used for placing samples; a temperature control device is arranged inside the temperature control cavity; the electrode circuit comprises a power supply, a first switch, a second switch and an ammeter; one end of the power supply is connected with one end of the first switch, and the other end of the first switch is connected with the upper electrode plate; the other end of the power supply is connected with the lower electrode plate and one end of the ammeter separately; one end of the second switch is connected with the other end of the ammeter, and the other end of the second switch is connected with the other end of the first switch; the temperature probe is connected with the temperature detection device and located in the temperature control cavity. According to the high-field surface trap evaluation system, the variation rules of the trap characteristics of the samples in a high field can be learned to study the trap characteristics of dielectric materials in the high filed.

Owner:YUNNAN POWER GRID CO LTD ELECTRIC POWER RES INST

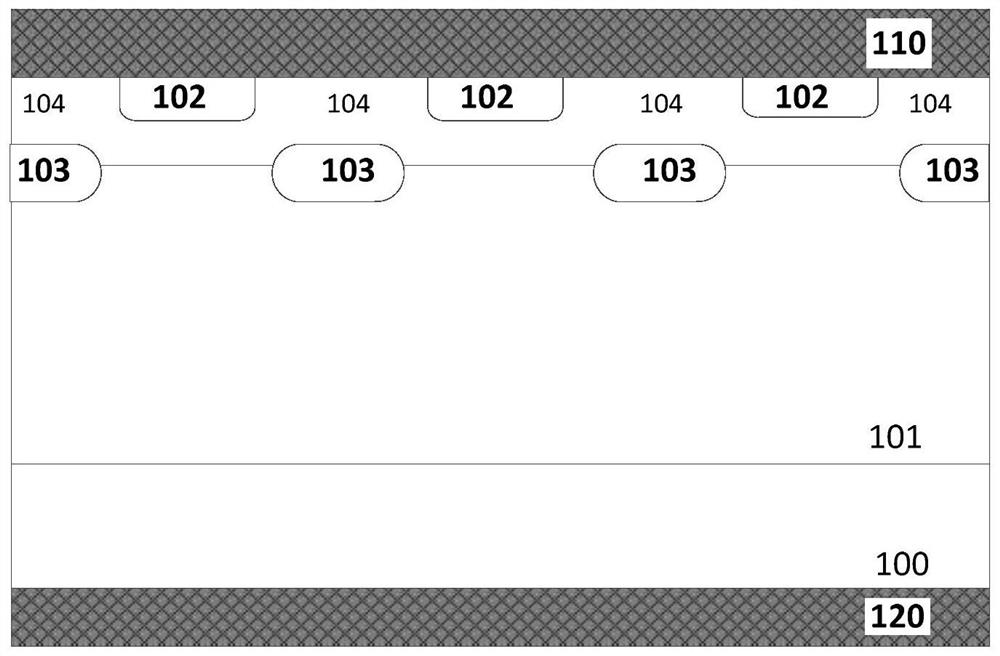

Gallium nitride transistor structure and preparation method thereof

ActiveCN110429127ASuppression of avalanche effectsAlleviate dummy gate effectSemiconductor devicesHeterojunctionGallium nitride

The invention discloses a gallium nitride transistor structure and a preparation method thereof. The gallium nitride transistor structure includes: a substrate 1; a GaN-based buffer layer 2 located onthe substrate 1; an InxAlyGa1-x-yN / GaN heterojunction epitaxial structure positioned on the GaN-based buffer layer 2; a source electrode 6 positioned at one end of the surface of the InxAlyGa1-x-yN / GaN heterojunction epitaxial structure; a drain electrode 5 positioned at the other end of the surface of the InxAlyGa1-x-yN / GaN heterojunction epitaxial structure; and a p-type oxide film and a gate 7which are located at the surface of the InxAlyGa1-x-yN / GaN heterojunction epitaxial structure. The p-type oxide film is arranged between the source electrode 6 and the drain electrode 5 at the surface of the InxAlyGa1-x-yN / GaN heterojunction epitaxial structure to obtain the GaN transistor structure of the p-type oxide intercalation to suppress the current collapse effect, and the virtual gate effect is relieved by neutralizing electrons in the hole in the p-type oxide and captured by surface traps.

Owner:安徽长飞先进半导体有限公司 +1

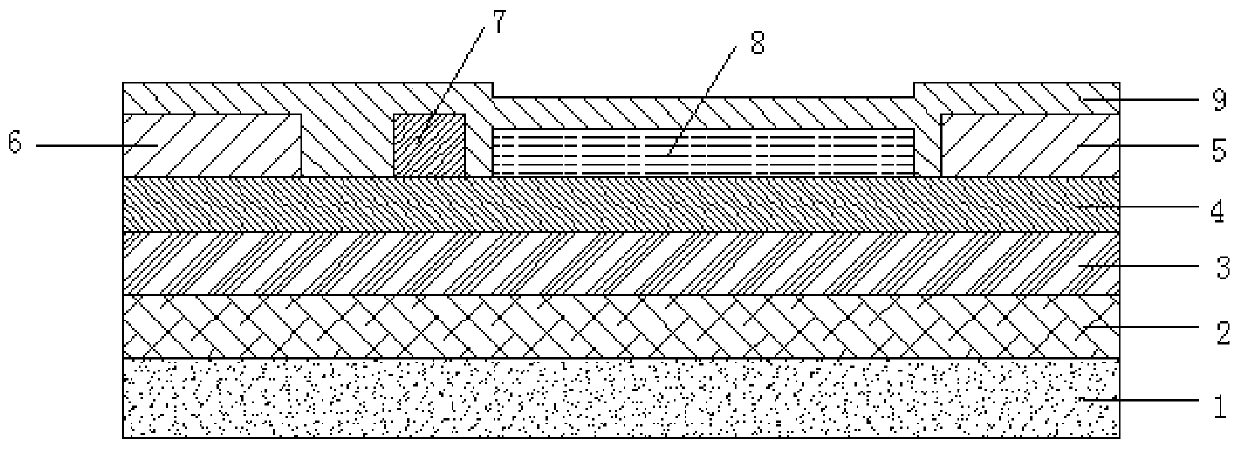

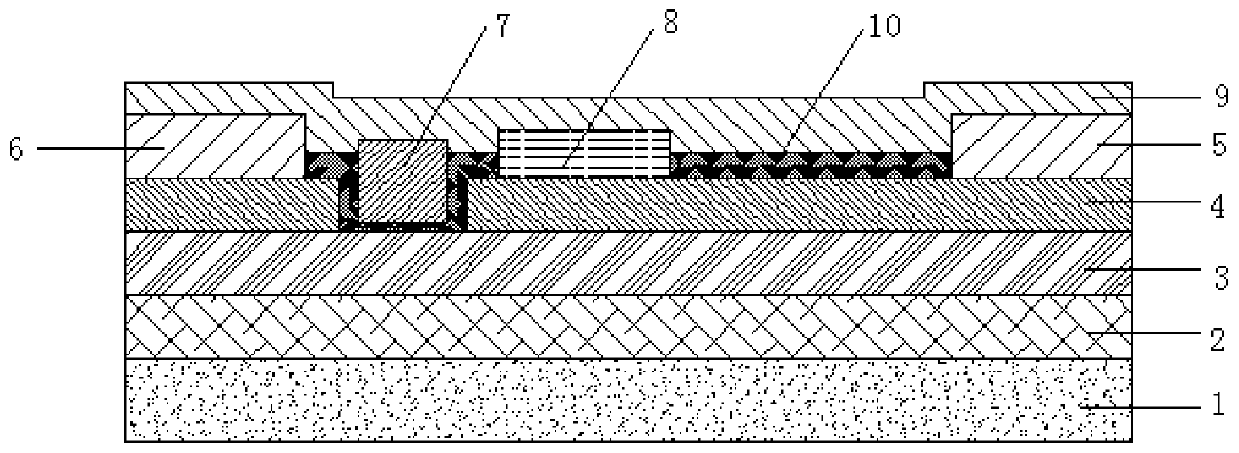

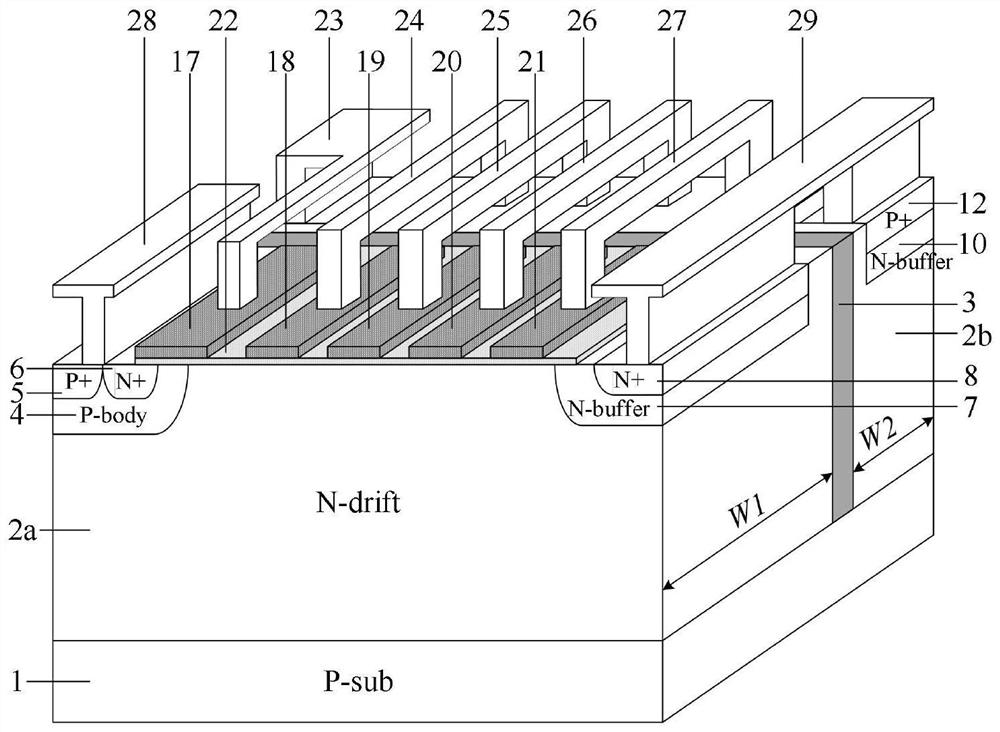

Method and device for improving surface mobility of silicon carbide lateral double-diffusion field effect transistor

ActiveCN112951923AThe breakdown voltage does not dropReduce areaDiodeField-effect transistorPolysilicon gate

The invention discloses a method and device for improving the surface mobility of a silicon carbide lateral double-diffusion field effect transistor. The method comprises the steps: introducing a voltage bias tube, enabling the surface electron concentration of a drift region to be increased when a silicon carbide LDMOS is in forward conduction, enabling the probability that a single electron is captured by a surface trap of an oxide layer above the drift region to be reduced, and enabling the electron mobility to be improved. The device comprises a P-type substrate, which is provided with a P-type isolation layer which divides the device into an LDMOS and a voltage bias tube, the LDMOS comprises a first N-type drift region, a first source region, a first drain region, a gate oxide layer and a polysilicon gate, and is characterized in that four polysilicon field plates which are separated from one another are arranged on the gate oxide layer, the voltage bias tube comprises a second N-type drift region, a second source region and a second drain region, four N+ injection layers are arranged in the second N-type drift region, the polysilicon gate is connected with the second source region, the first drain region is connected with the second drain region, and the four polysilicon field plates are respectively connected with the four N+ injection layers.

Owner:SOUTHEAST UNIV

Nano coating for inhibiting surface charge accumulation of epoxy resin and preparation method

The invention discloses a nano coating for inhibiting surface charge accumulation of epoxy resin and a preparation method. The preparation method comprises the following steps that S1, MMT is weighedand dispersed in deionized water to form a suspension with a mass concentration of 1wt%; S2, PVA and deionized water are added to the suspension prepared in step S1 to enable the PVA mass to account for 40wt%-60wt% of the total solid mass of the PVA and the MMT, and the total solid mass fraction in the solution is 1wt%-2wt%; S3, after complete dissolution of the PVA, a cross-linking agent GA is added, and ultrasonic treatment is performed for 15-30 min under the constant temperature to form a PVA / MMT dispersion system; S4, epoxy resin insulators are treated in the plasmas for 4-8 minutes; andS5, the epoxy resin insulators are vertically immersed into the immersion liquid PVA / MMT dispersion system, and a PVA / MMT two-dimensional nano coating is formed. The coating has a special nano-scale layer structure, can reduce the surface trap level of the epoxy resin insulators from 1.02eV to 0.86eV, and facilitates evacuation of charge carriers along the surface of parallel organic silicate crystal sheet layers; and the surface charge accumulation of the insulators can be reduced, so that the direct current flashover voltage is increased by about 20%.

Owner:XI AN JIAOTONG UNIV +1

Preparation method of GaN-based planar Schottky varactor

ActiveCN111599872ASimple processImprove smoothnessFinal product manufactureSemiconductor/solid-state device manufacturingParasitic capacitorAir bridge

The invention belongs to the field of manufacturing of semiconductor devices, and particularly relates to a preparation method of a GaN-based planar Schottky varactor. The preparation method comprisesthe steps of 1) manufacturing an alignment mark; 2) manufacturing an ohmic electrode; 3) manufacturing a Schottky metal eave structure through primary planarization; 4) conducting Schottky metal evaporation; 5) etching an insulating table; 6) carrying out secondary planarization; and 7) electroplating to form an air bridge, an electrode pad and interconnection metal to obtain the GaN-based planarSchottky varactor. The etching condition of the metal eave structure is effectively improved, the surface quality of the side wall is improved, and trapped charges on the surface of the side wall arereduced, so that the reverse bias characteristic of the device is improved; and errors introduced by the process of the air bridge structure are improved, and parasitic capacitance of the device is effectively reduced.

Owner:NAT SPACE SCI CENT CAS

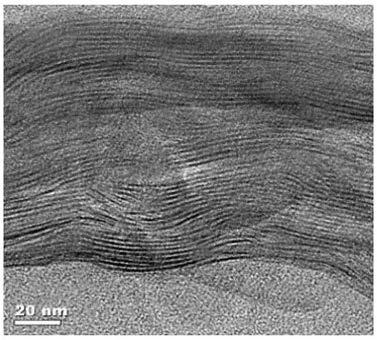

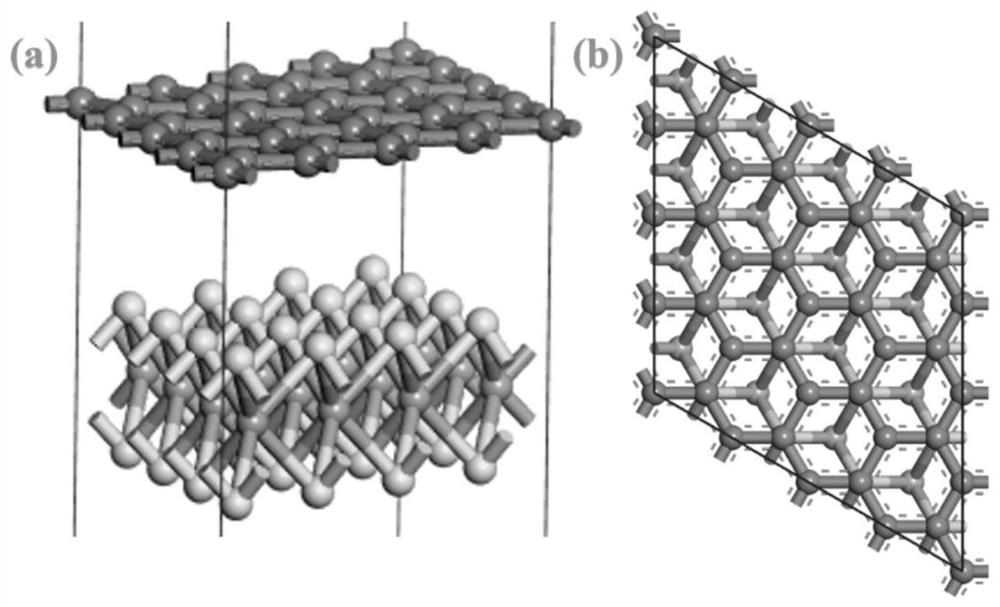

Molybdenum disulfide/graphene composite heterojunction and preparation method thereof

ActiveCN114000103AReduce sulfur vacanciesImprove crystal qualityVacuum evaporation coatingSputtering coatingCarbon filmHeterojunction

The invention discloses a molybdenum disulfide / graphene composite heterojunction and a preparation method thereof. The molybdenum disulfide / graphene composite heterojunction comprises a substrate 1, a molybdenum disulfide layer 2 and a graphene layer 3, wherein the molybdenum disulfide layer 2 is arranged on the substrate 1, and the graphene layer is arranged on the molybdenum disulfide layer 2. According to the preparation method, the sulfur vacancy of the prefabricated thin film is reduced and the crystallization quality of the molybdenum disulfide buffer layer is improved by optimizing the design of the process of preparing the MoS2 / graphene composite heterojunction through magnetron sputtering and combining the annealing process, and meanwhile, the composite heterojunction thin film with high surface roughness is formed on the carbon film through argon ion sputtering; the average collision frequency of the secondary electrons and the surface trap wall can be effectively increased, so that the secondary electron emission phenomenon is inhibited.

Owner:XI AN JIAOTONG UNIV +1

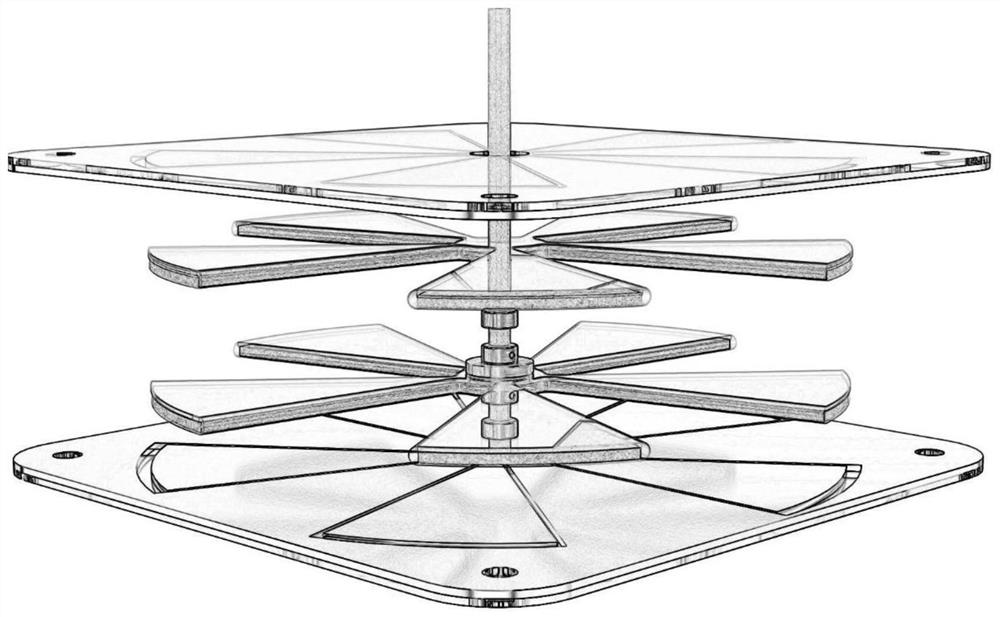

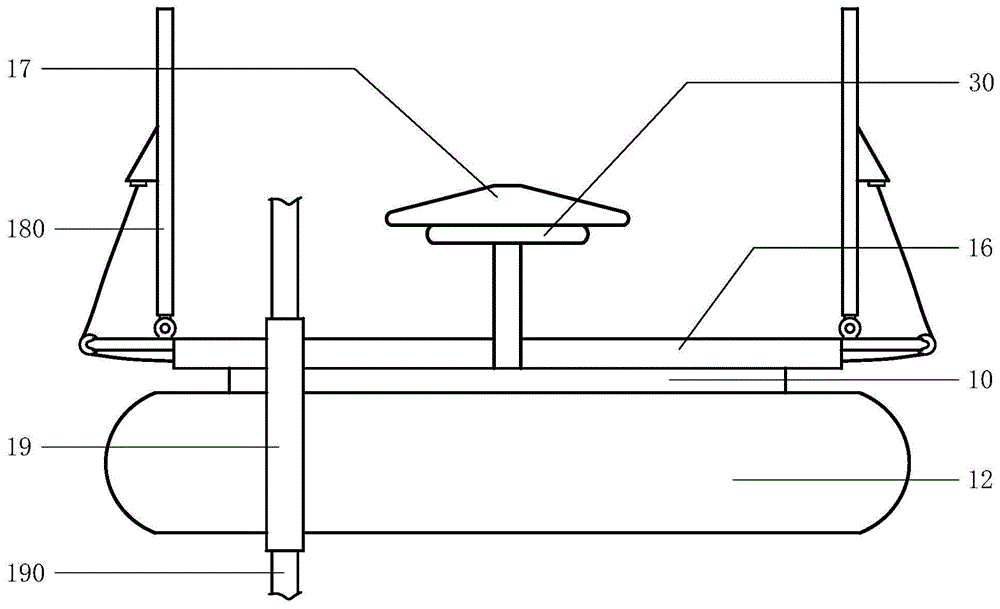

A kind of solar water surface insect trap lamp

ActiveCN104798754BImprove qualityReduce fish farming costsClimate change adaptationAgricultural fishingSolar waterAquatic product

The invention relates to a solar water surface light trap which comprises a water surface positioning bed frame, a solar cell plane and an optical control light trap, wherein the water surface positioning bed frame adopts a frame structure, and a dynamic instrument cabin and frame-shaped floating balls are respectively arranged at the center of the bottom and around the bottom of the frame structure; an anchorage hoist, a drawstring duct and a storage battery are arranged in the dynamic instrument cabin; the solar cell plane is mounted on the top surface of a cell plane platform, and the optical control light trap is mounted in a cover-shaped lamp holder and provided with an optical control switch. The solar cell plane is utilized to absorb solar energy and convert the solar energy into electrical energy, and the optical control light trap is utilized to attract insects to the water surface for feeding fish, so that the fish farming cost is reduced, the quality of fish is improved, moreover, fish farmers can know the growth situation of fish at any time. Therefore, the solar water surface light trap has the advantages of being reasonable in structure and convenient to use and can provide high-quality and pollution-free green aquatic products for people.

Owner:成武县亿昌信息科技有限公司

System and method for mobile ion surface trapping in a gas detection device

A gas detection device is provided having a substrate. A sensing element is coupled to the substrate and constructed and arranged to sense a target gas. A top surface is positioned on the sensing element opposite the substrate. A dopant is disposed within the sensing element. The dopant enhances the ability of the sensing element to sense the target gas. An electric field is applied to the dopant to constrain the dopant at or near the top surface of the sensing element.

Owner:CARRIER CORP

A gallium nitride transistor structure and its preparation method

ActiveCN110429127BSuppression of avalanche effectsAlleviate dummy gate effectSemiconductor devicesHeterojunctionElectron hole

Owner:安徽长飞先进半导体有限公司 +1

Large water surface trapping Wuchang bream device

A large water surface trapping Wuchang bream device comprises a feeding table formed by leaders; the feeding table is surrounding by three leaders in three directions, and provided with an opening; the leader behind the feeding table is connected with a fish gathering box; the leaders in front of / behind the fish gathering box are respectively provided with a front / back push-pull door; two ends of the front / back push-pull door are respectively provided with a push-pull door rope; the front / back push-pull door and the push-pull door ropes are matched to realize open / close of the doors; the leader behind the fish gathering box is connected with a fish taking box in a narrow rectangular box shape; the bottom of the fish taking box is provided with a bottom net connected with a net pulling rope; the bottom net can be pulled out or placed in the fish taking box through the bottom net; the leaders, the feeding table, the fish gather box, the fish taking box and the front / back push-pull doors are mutually connected and fixed through up-down steel ropes and positioning piles.

Owner:XUZHOU YITONG FISHING GEAR

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com