Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

65 results about "Gate effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

“The Gate effect passes only signals whose level exceeds a user-specified threshold. In other words, a Gate effect is a device that allows us to only allow sound through that is above a certain threshold level.

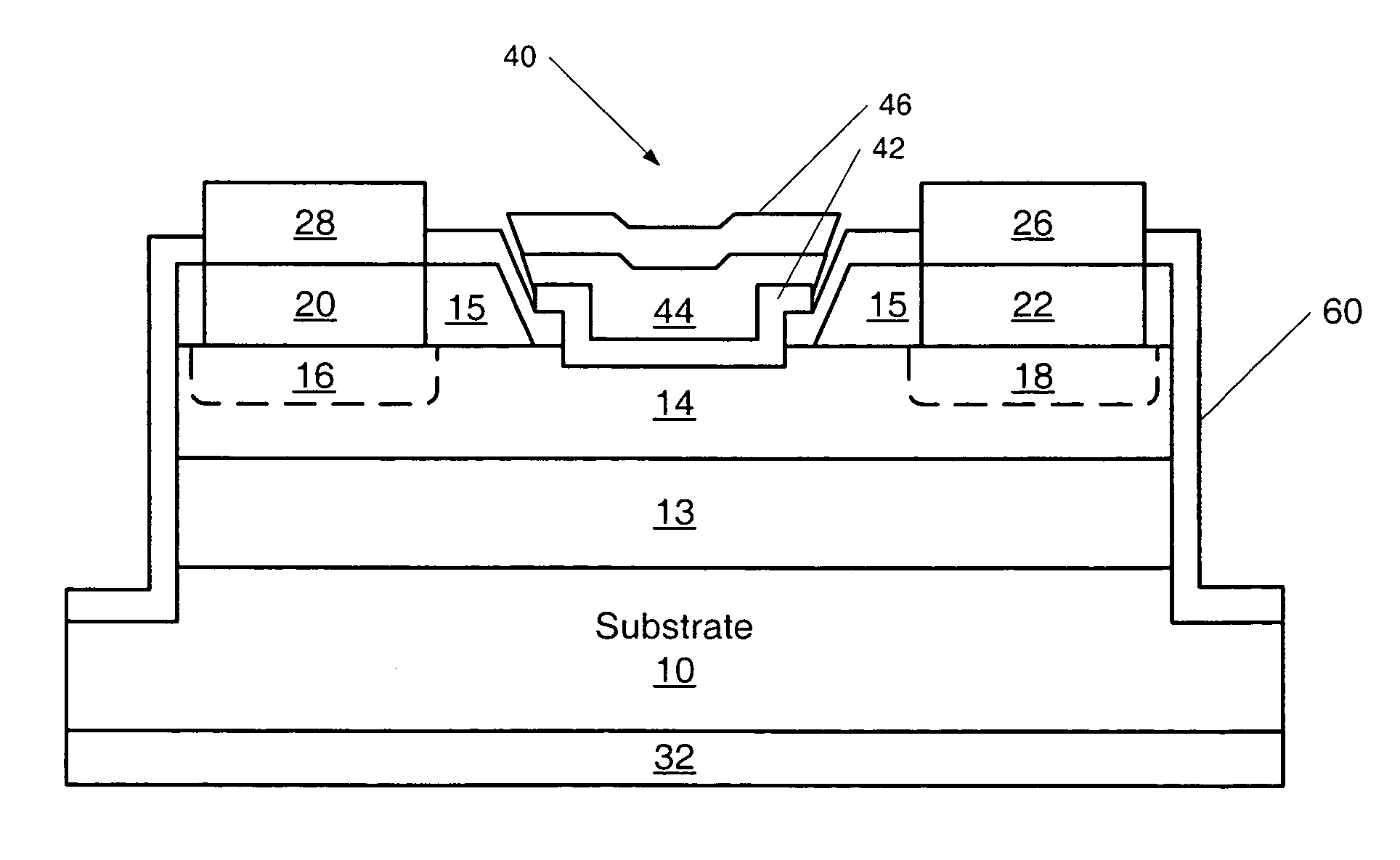

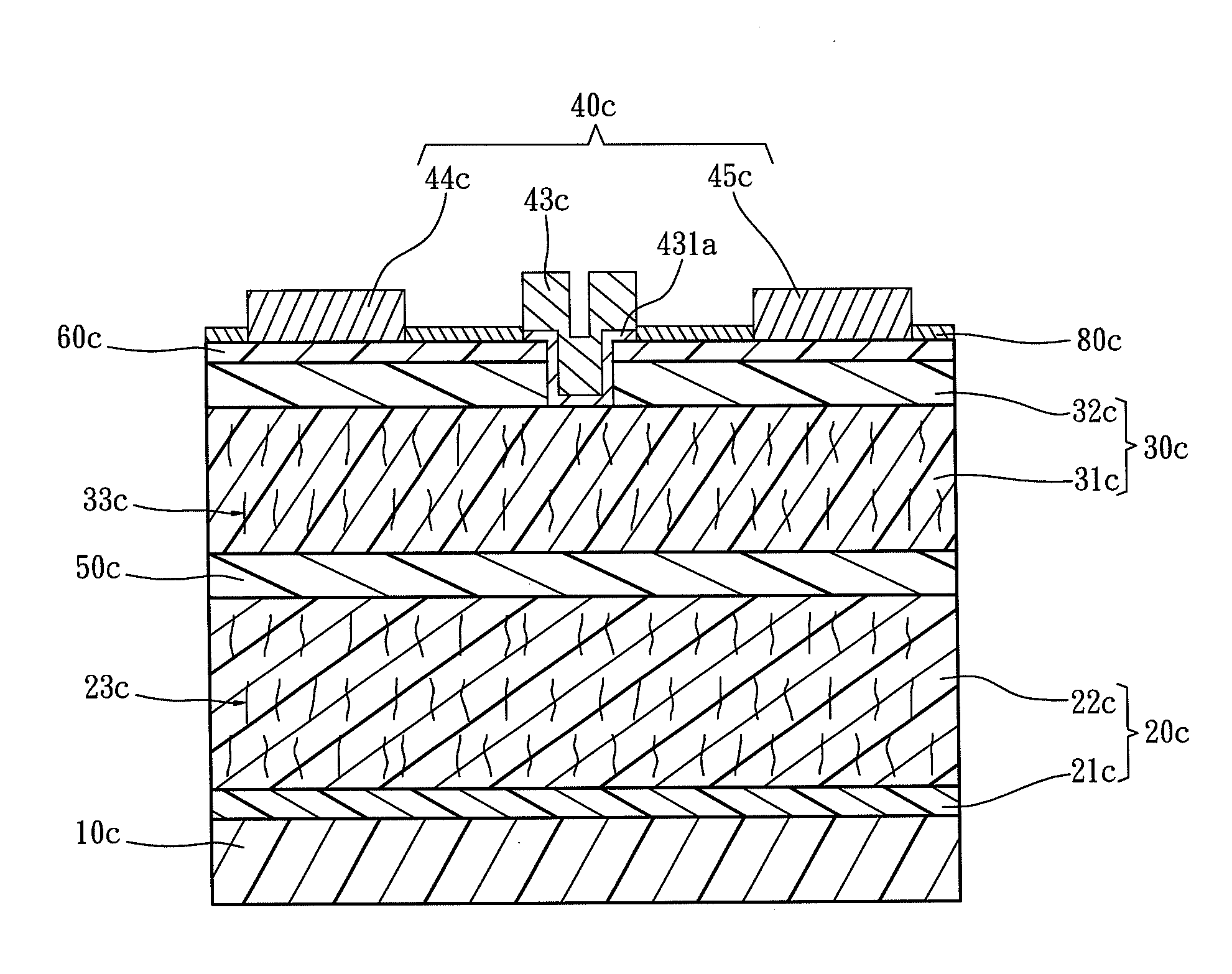

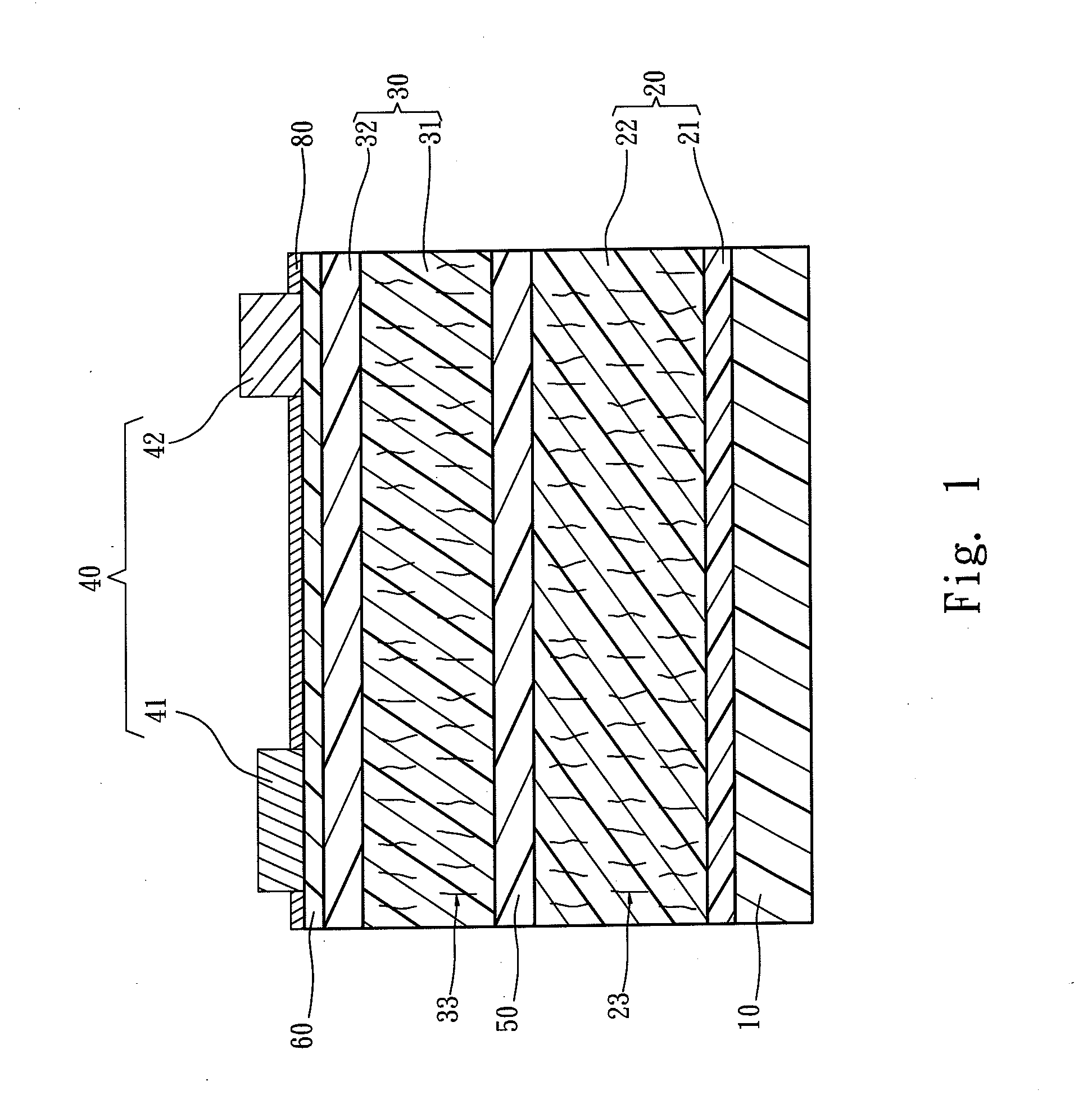

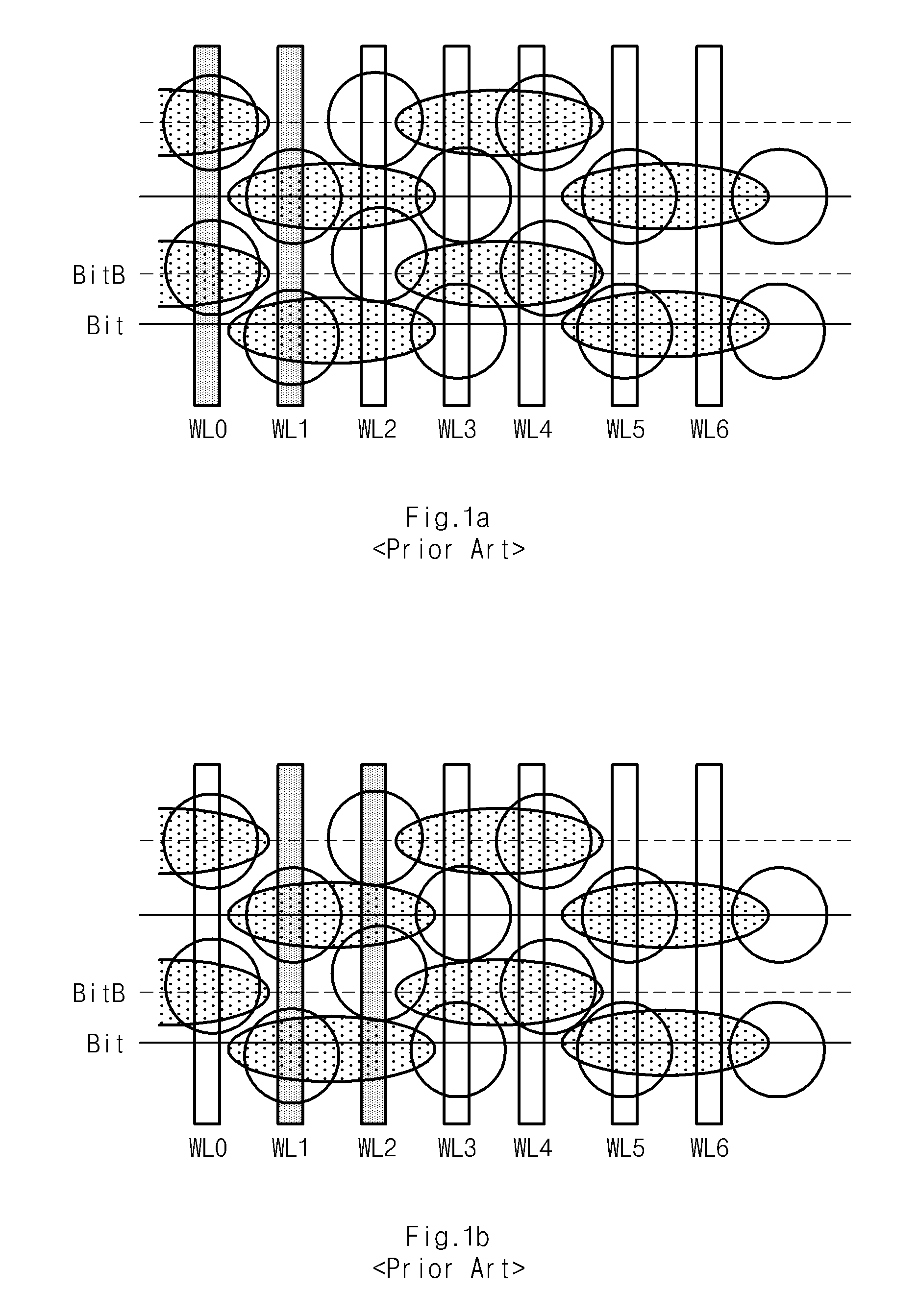

Radiation image pickup device

InactiveUS20060249763A1High sensitivityStable characteristicsTelevision system detailsSolid-state devicesImaging qualityGate effect

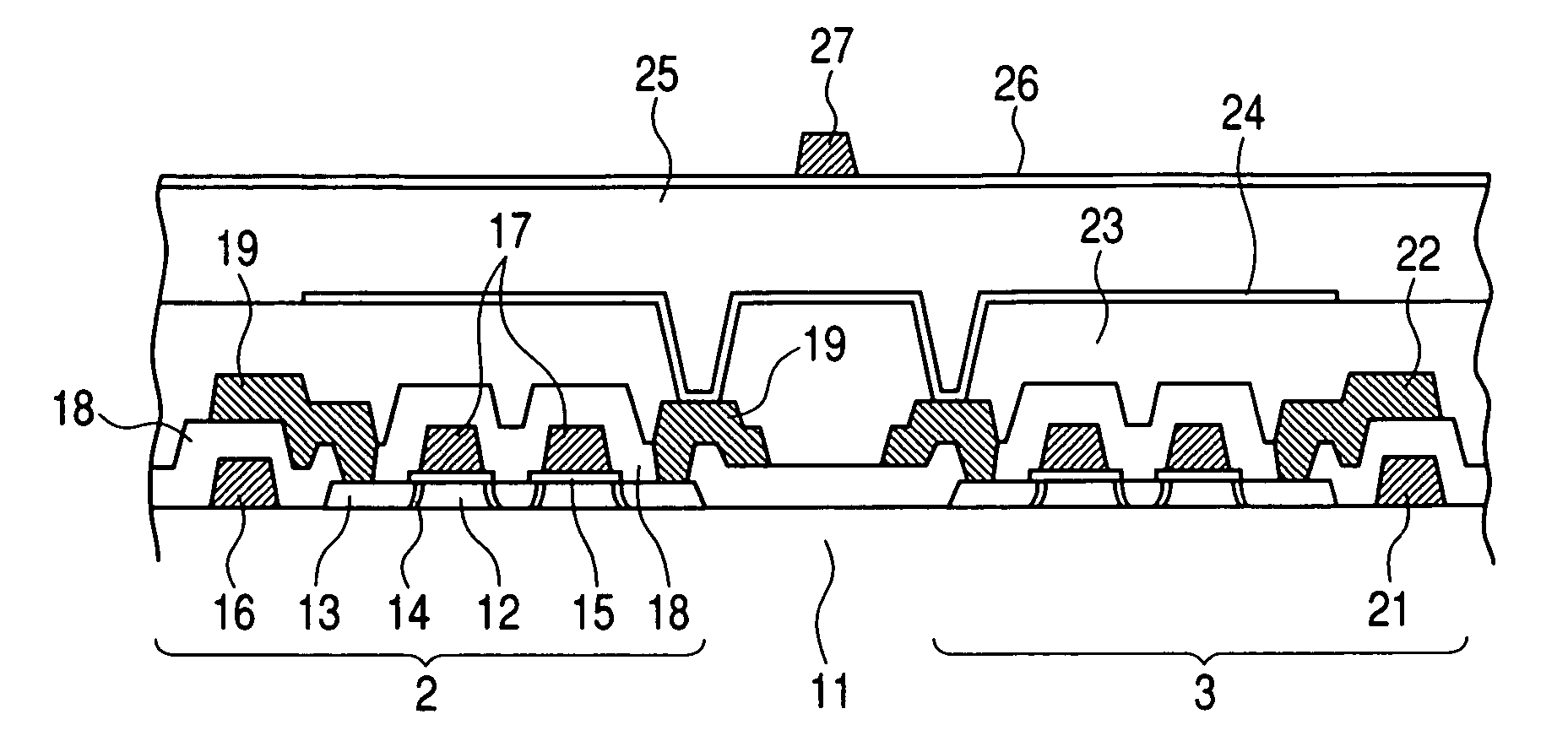

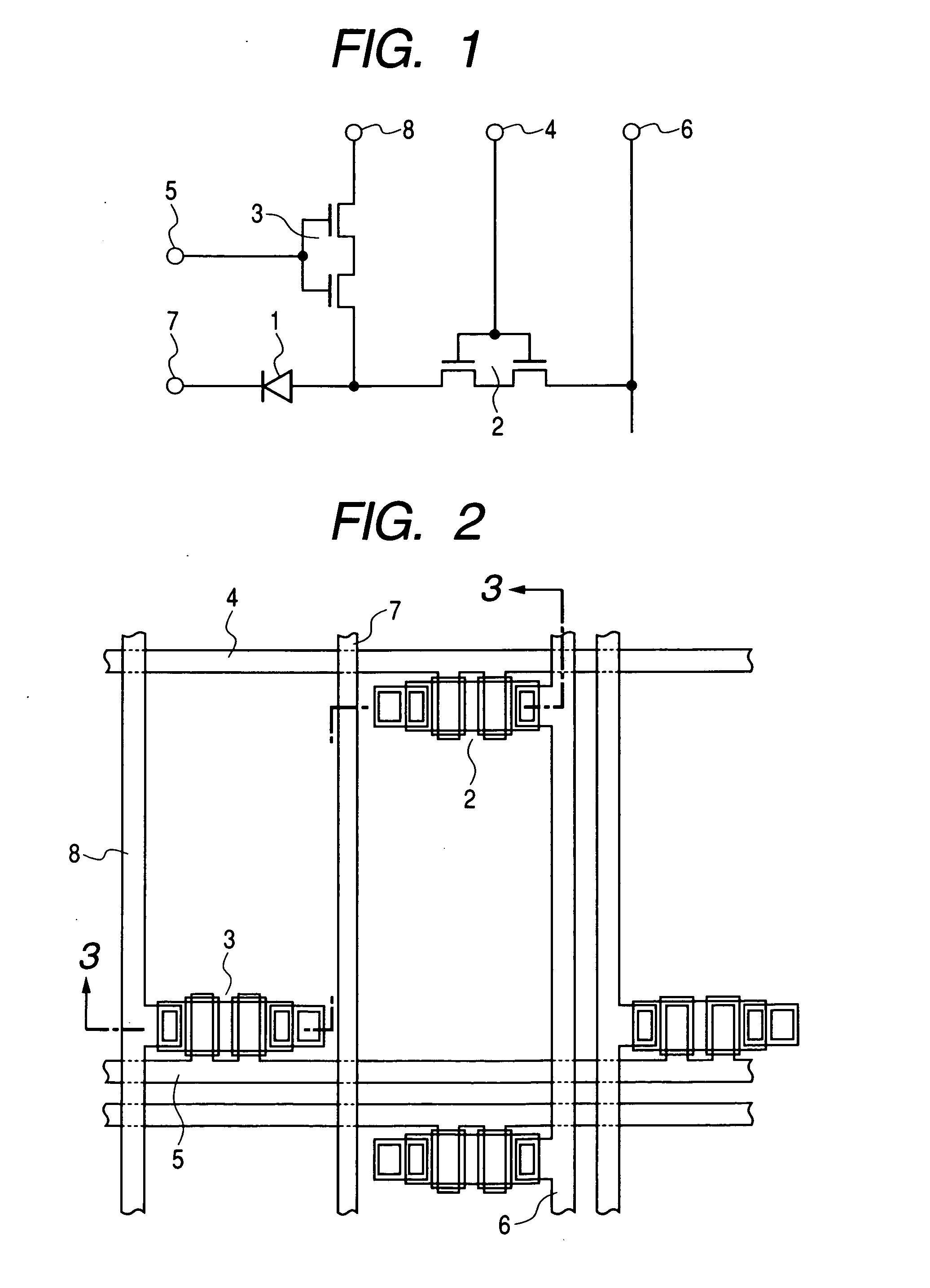

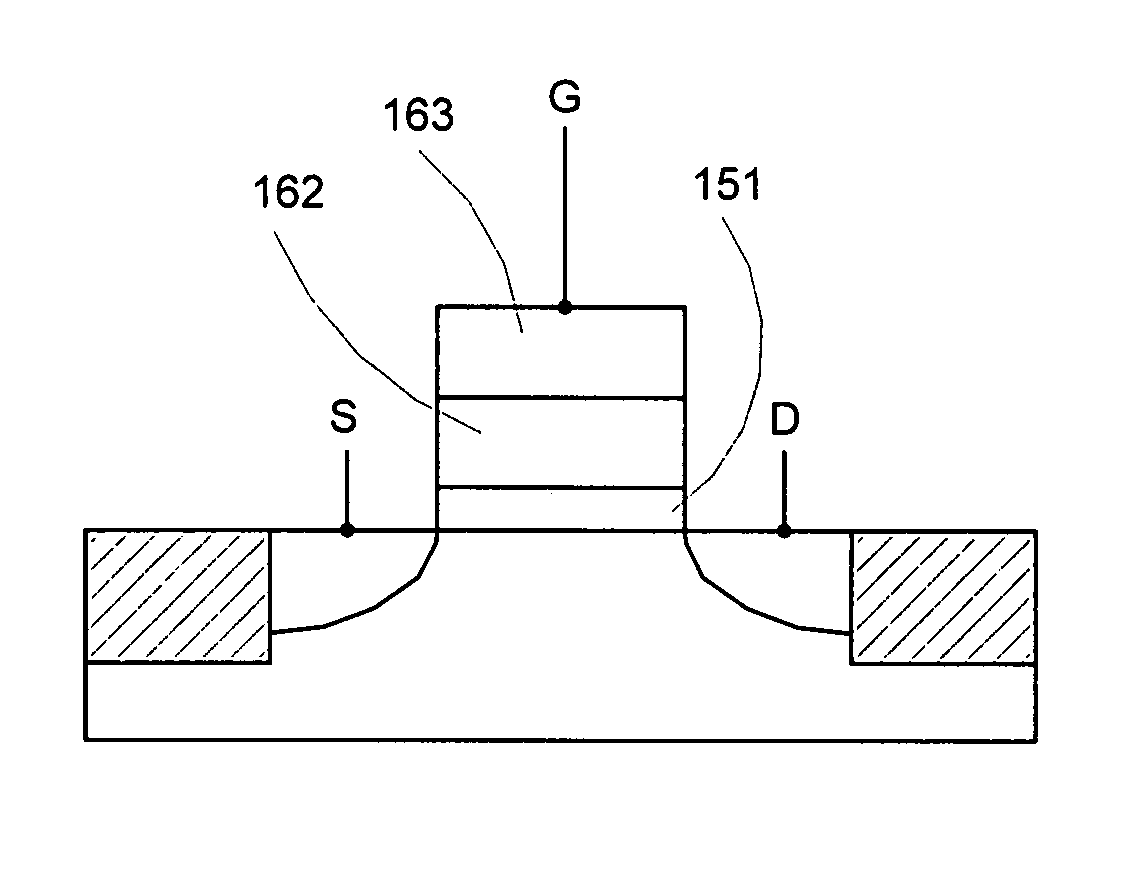

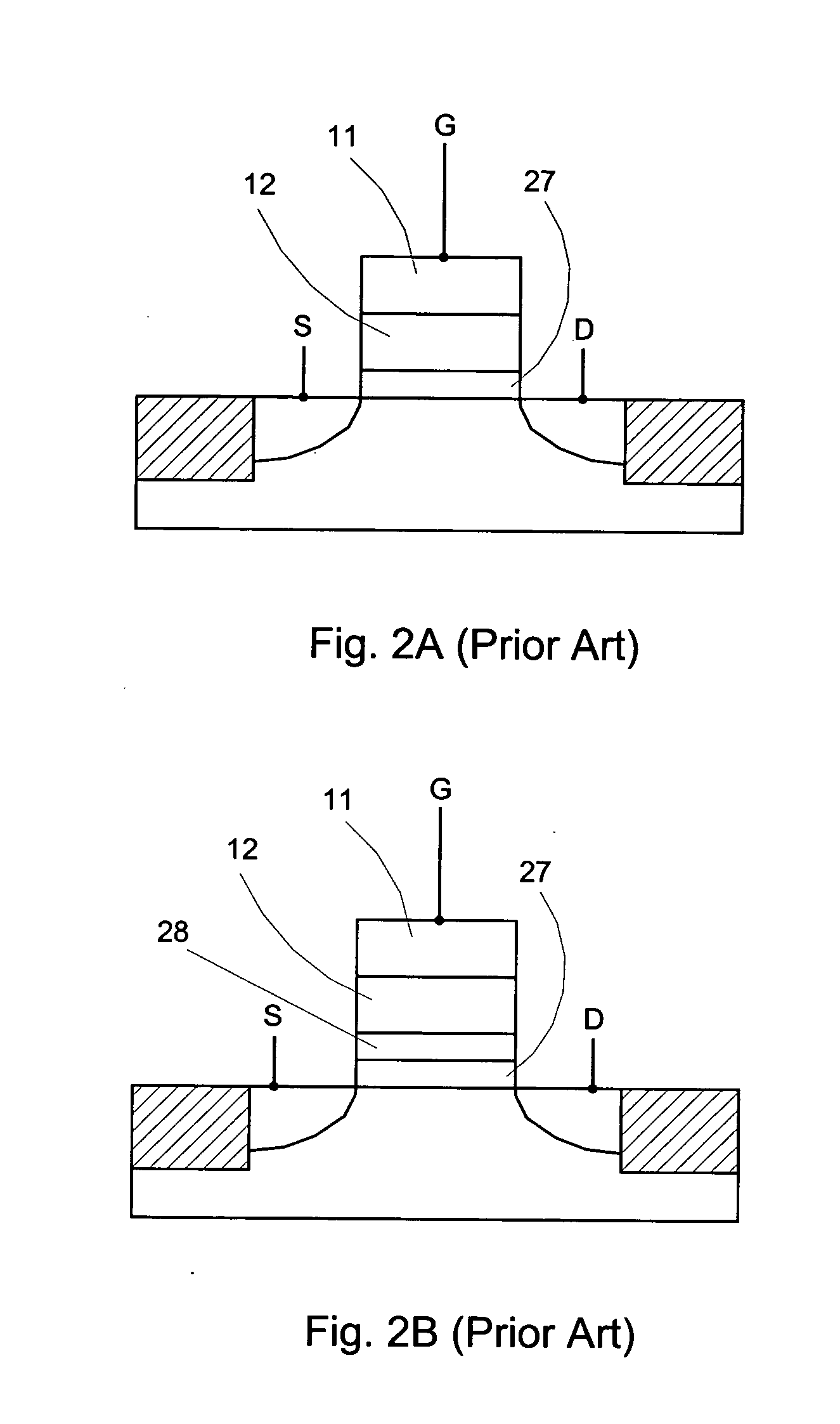

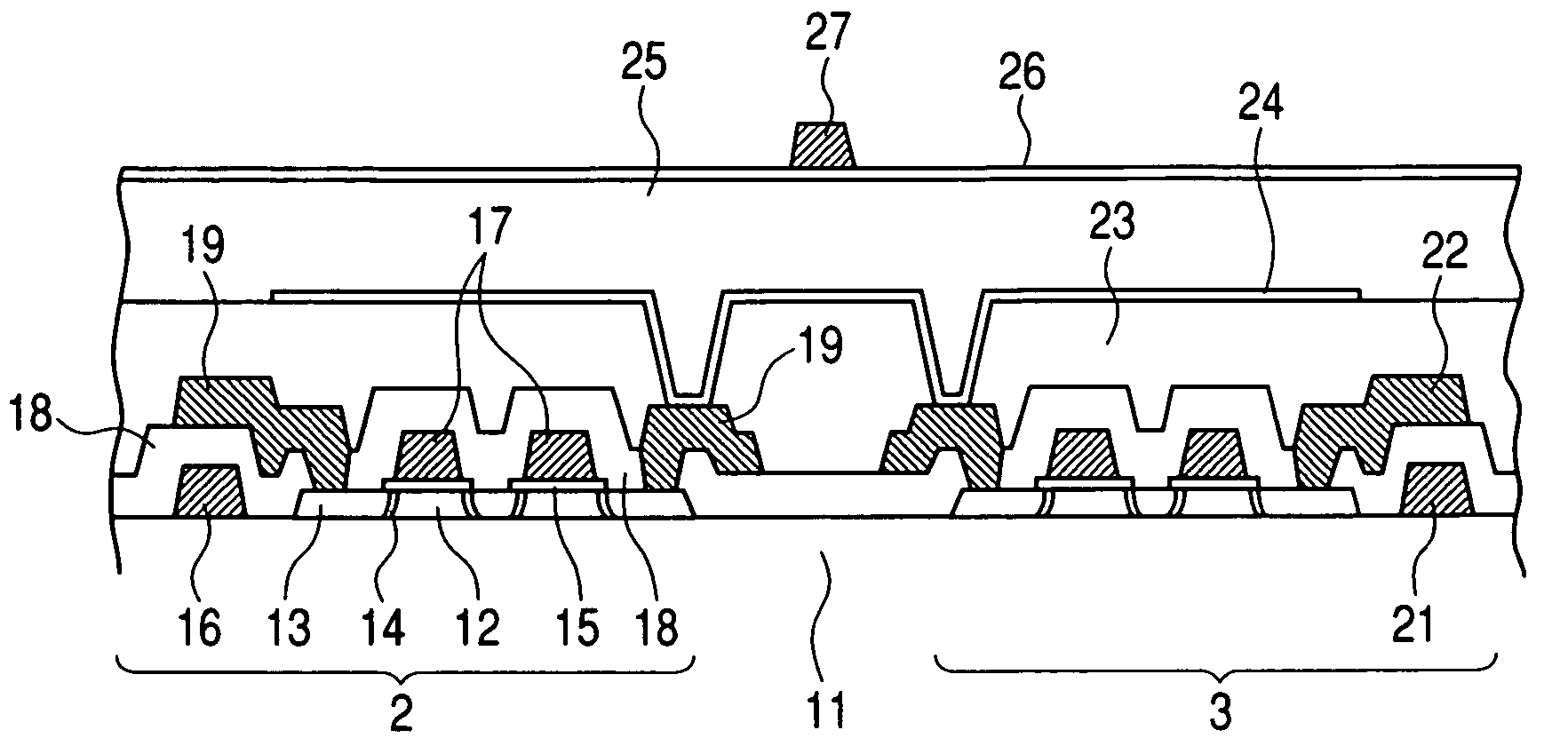

In a radiation image pickup device including: a sensor element for converting radiation into an electrical signal; and a thin film transistor connected to the sensor element, an electrode of the sensor element connected to the thin film transistor is disposed above the thin film transistor, and that the thin film transistor has a top gate type structure in which a semiconductor layer, a gate insulating layer, and a gate electrode layer are laminated in this order on a substrate, so that a channel portion of the thin film transistor is protected by a gate electrode, thereby providing stable TFT characteristics without undesirable turning ON any of the TFT elements due to the back gate effect by the fluctuation in electric potentials corresponding to outputs from the sensor electrodes, and thereby greatly improving image quality.

Owner:CANON KK

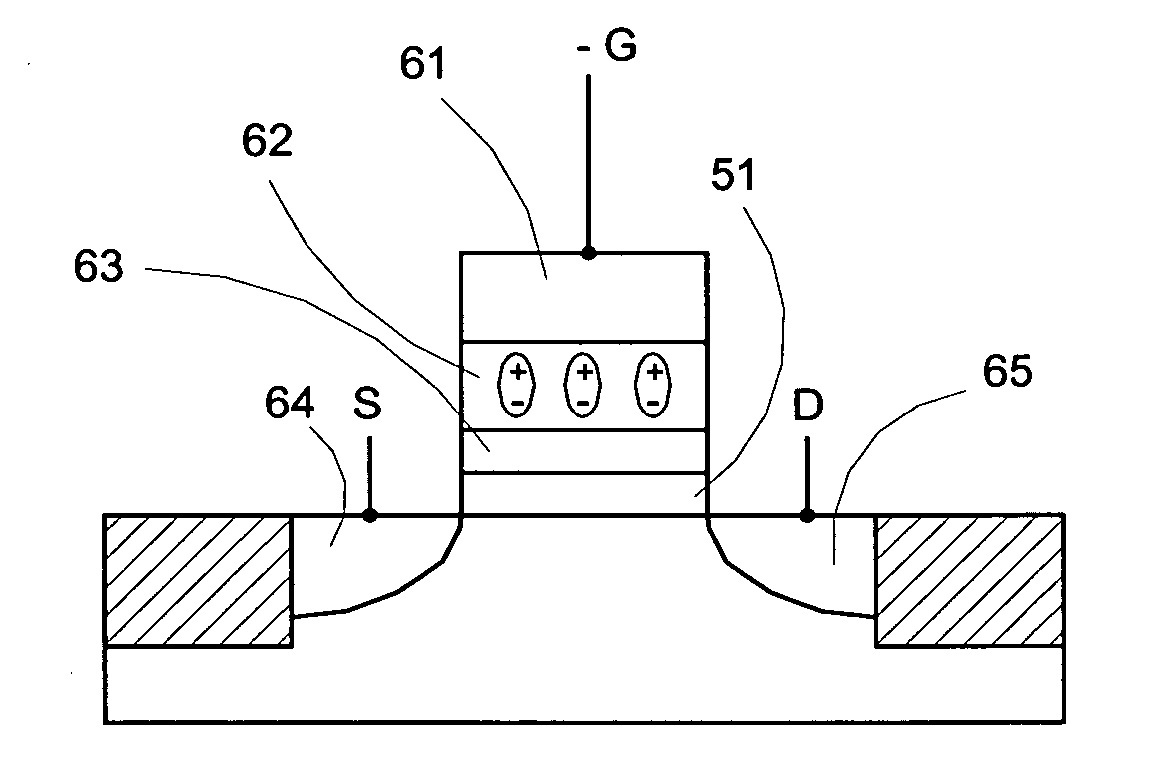

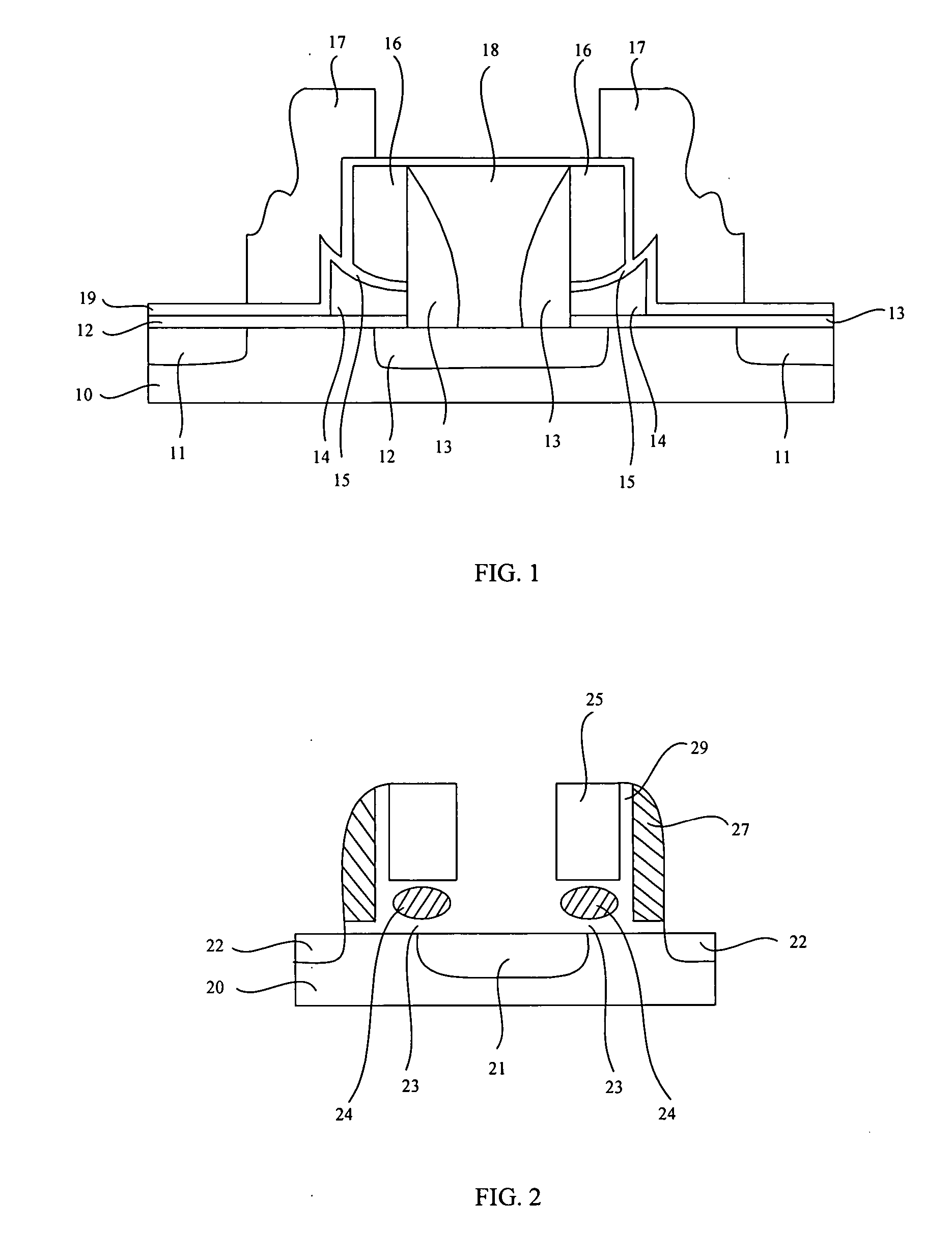

Ferroelectric memory transistor with conductive oxide gate structure

InactiveUS20070272960A1Reduce stepsLow working voltageSolid-state devicesSemiconductor/solid-state device manufacturingMemory retentionGate dielectric

The present invention discloses a ferroelectric transistor having a conductive oxide in the place of the gate dielectric. The conductive oxide gate ferroelectric transistor can have a three-layer metal / ferroelectric / metal or a two-layer metal / ferroelectric on top of the conductive oxide gate. By replacing the gate dielectric with a conductive oxide, the bottom gate of the ferroelectric layer is conductive through the conductive oxide to the silicon substrate, thus minimizing the floating gate effect. The memory retention degradation related to the leakage current associated with the charges trapped within the floating gate is eliminated. The fabrication of the ferroelectric transistor by a gate etching process or a replacement gate process is also disclosed.

Owner:SHARP LAB OF AMERICA INC

Conductive metal oxide gate ferroelectric memory transistor

InactiveUS20050054166A1Reduce stepsEliminate degradationSolid-state devicesSemiconductor/solid-state device manufacturingMemory retentionGate dielectric

The present invention discloses a ferroelectric transistor having a conductive oxide in the place of the gate dielectric. The conductive oxide gate ferroelectric transistor can have a three-layer metal / ferroelectric / metal or a two-layer metal / ferroelectric on top of the conductive oxide gate. By replacing the gate dielectric with a conductive oxide, the bottom gate of the ferroelectric layer is conductive through the conductive oxide to the silicon substrate, thus minimizing the floating gate effect. The memory retention degradation related to the leakage current associated with the charges trapped within the floating gate is eliminated. The fabrication of the ferroelectric transistor by a gate etching process or a replacement gate process is also disclosed.

Owner:SHARP KK

Radiation image pickup device

InactiveUS7541617B2High sensitivityStable characteristicsTelevision system detailsSolid-state devicesImaging qualityGate effect

In a radiation image pickup device including: a sensor element for converting radiation into an electrical signal; and a thin film transistor connected to the sensor element, an electrode of the sensor element connected to the thin film transistor is disposed above the thin film transistor, and that the thin film transistor has a top gate type structure in which a semiconductor layer, a gate insulating layer, and a gate electrode layer are laminated in this order on a substrate, so that a channel portion of the thin film transistor is protected by a gate electrode, thereby providing stable TFT characteristics without undesirable turning ON any of the TFT elements due to the back gate effect by the fluctuation in electric potentials corresponding to outputs from the sensor electrodes, and thereby greatly improving image quality.

Owner:CANON KK

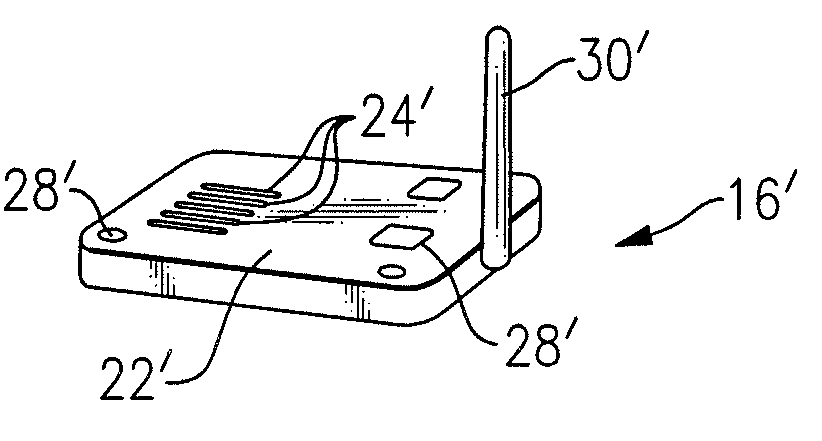

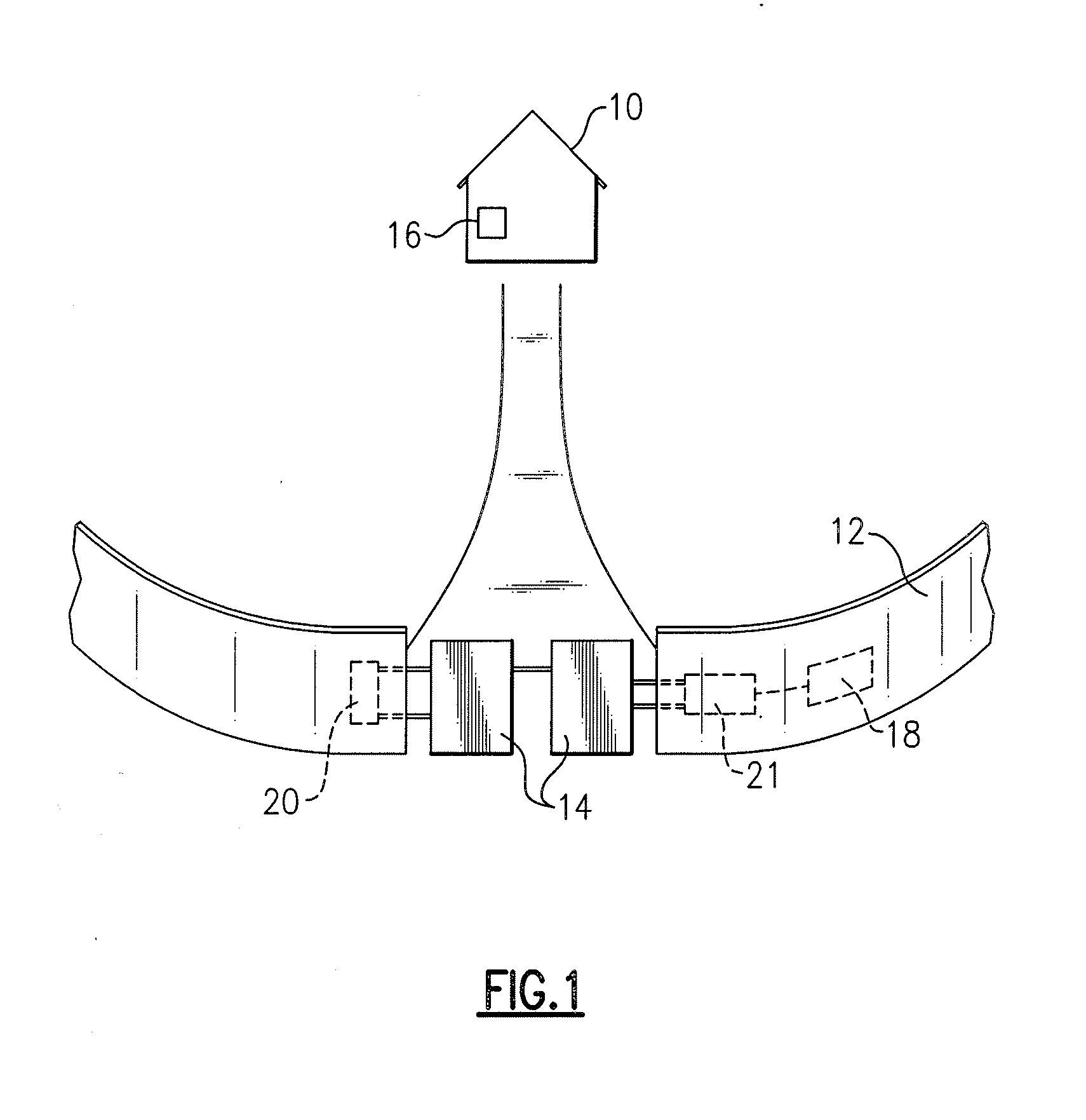

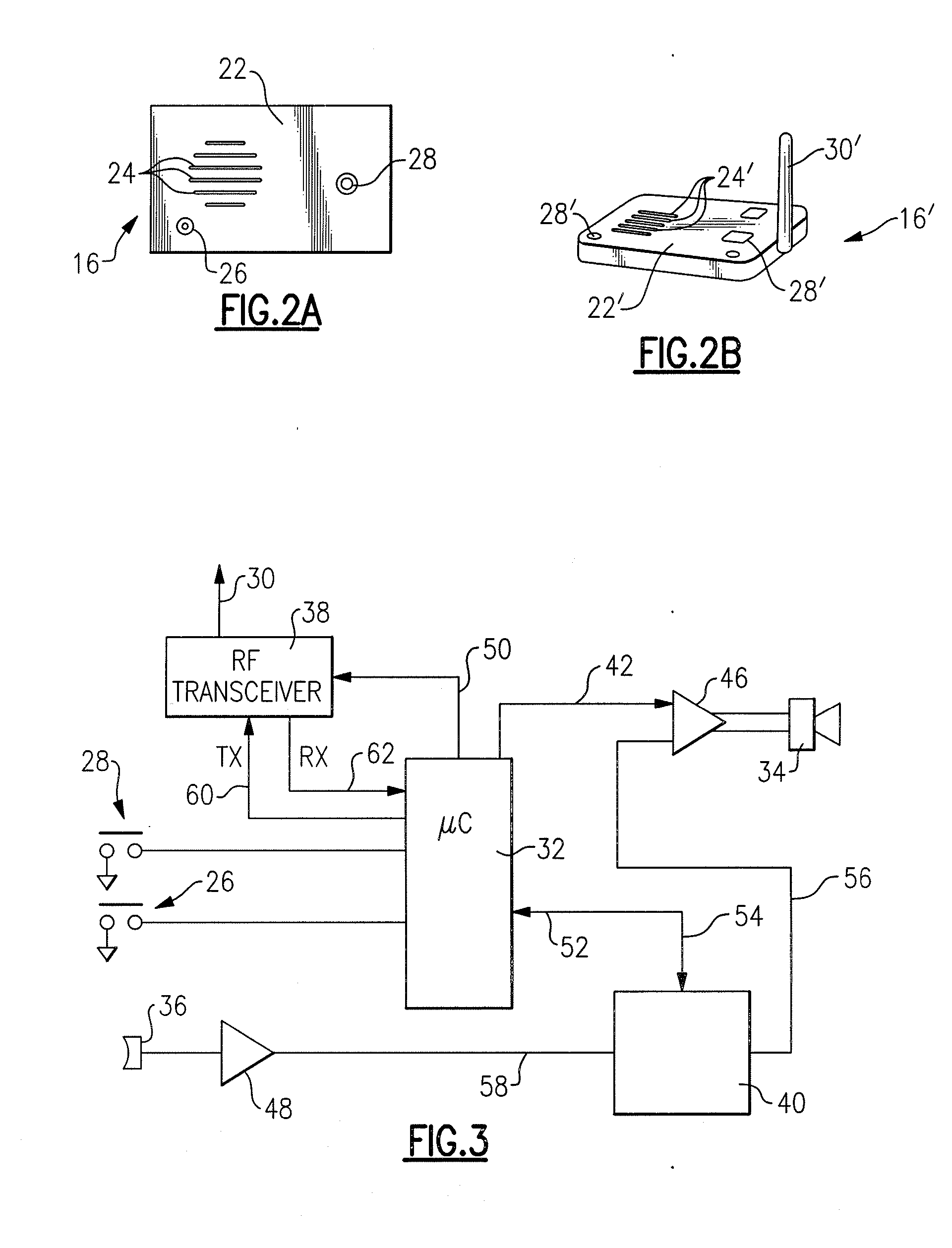

Wireless Gate Control and Communication System

InactiveUS20070229218A1Reduced Power RequirementsPractical operationElectric signal transmission systemsDigital data processing detailsCommunications systemVoice communication

A gate control and communication system of the invention including a base unit located within a premises, a gate receiver unit positioned next to a remotely located gate, and a gate control unit located next to the gate. The base unit provides for voice communications with an individual at the gate and for issuing of commands to control the gate. The gate receiver unit includes a switching device which, in response to commands directs the opening and closing of the gate. The gate control unit includes a call button for initiating voice communication with the base unit and a keypad for entering an identification code or password.

Owner:THE CHAMBERLAIN GRP INC

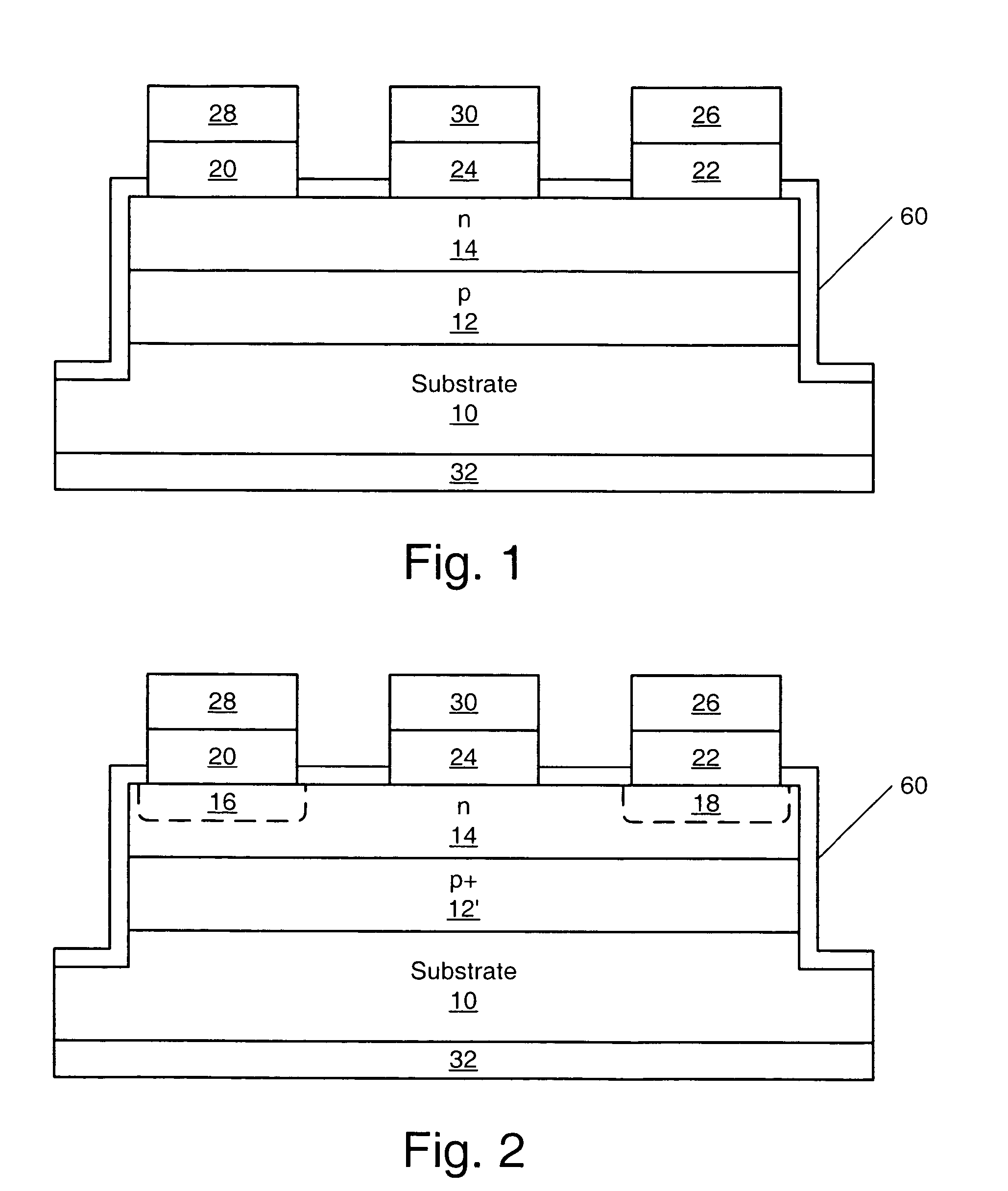

Methods of fabricating silicon carbide metal-semiconductor field effect transistors

InactiveUS7067361B2Improve performanceReduce the impactSemiconductor/solid-state device manufacturingSemiconductor devicesGate effectDeep level

SiC MESFETs are disclosed which utilize a semi-insulating SiC substrate which substantially free of deep-level dopants. Utilization of the semi-insulating substrate may reduce back-gating effects in the MESFETs. Also provided are SiC MESFETs with a two recess gate structure. MESFETS with a selectively doped p-type buffer layer are also provided. Utilization of such a buffer layer may reduce output conductance by a factor of 3 and produce a 3 db increase in power gain over SiC MESFETs with conventional p-type buffer layers. A ground contact may also be provided to the p-type buffer layer and the p-type buffer layer may be made of two p-type layers with the layer formed on the substrate having a higher dopant concentration. SiC MESFETs according to embodiments of the present invention may also utilize chromium as a Schottky gate material. Furthermore, an oxide-nitride-oxide (ONO) passivation layer may be utilized to reduce surface effects in SiC MESFETs. Also, source and drain ohmic contacts may be formed directly on the n-type channel layer, thus, the n+ regions need not be fabricated and the steps associated with such fabrication may be eliminated from the fabrication process. Methods of fabricating such SiC MESFETs and gate structures for SiC FETs as well as passivation layers are also disclosed.

Owner:CREE INC

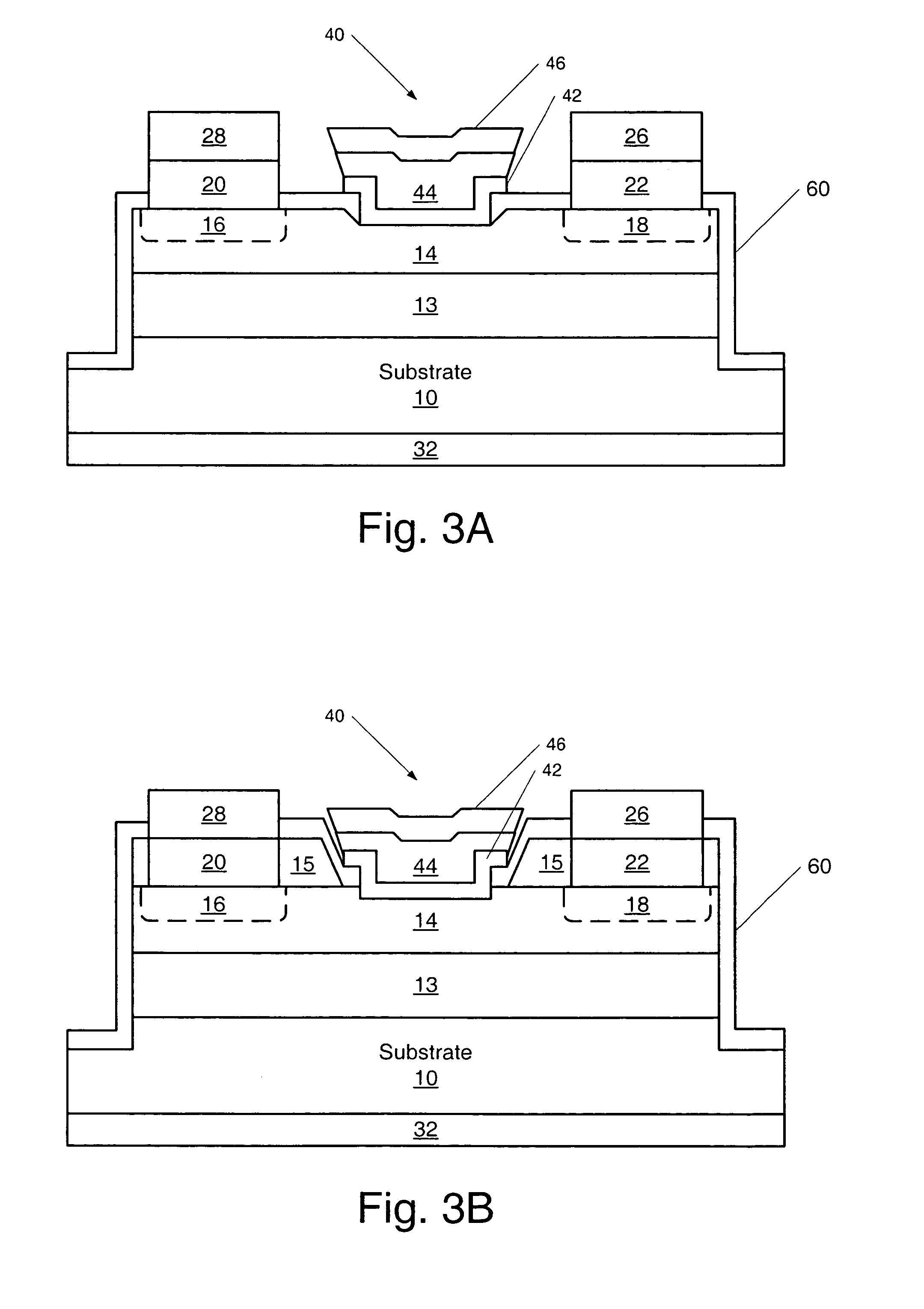

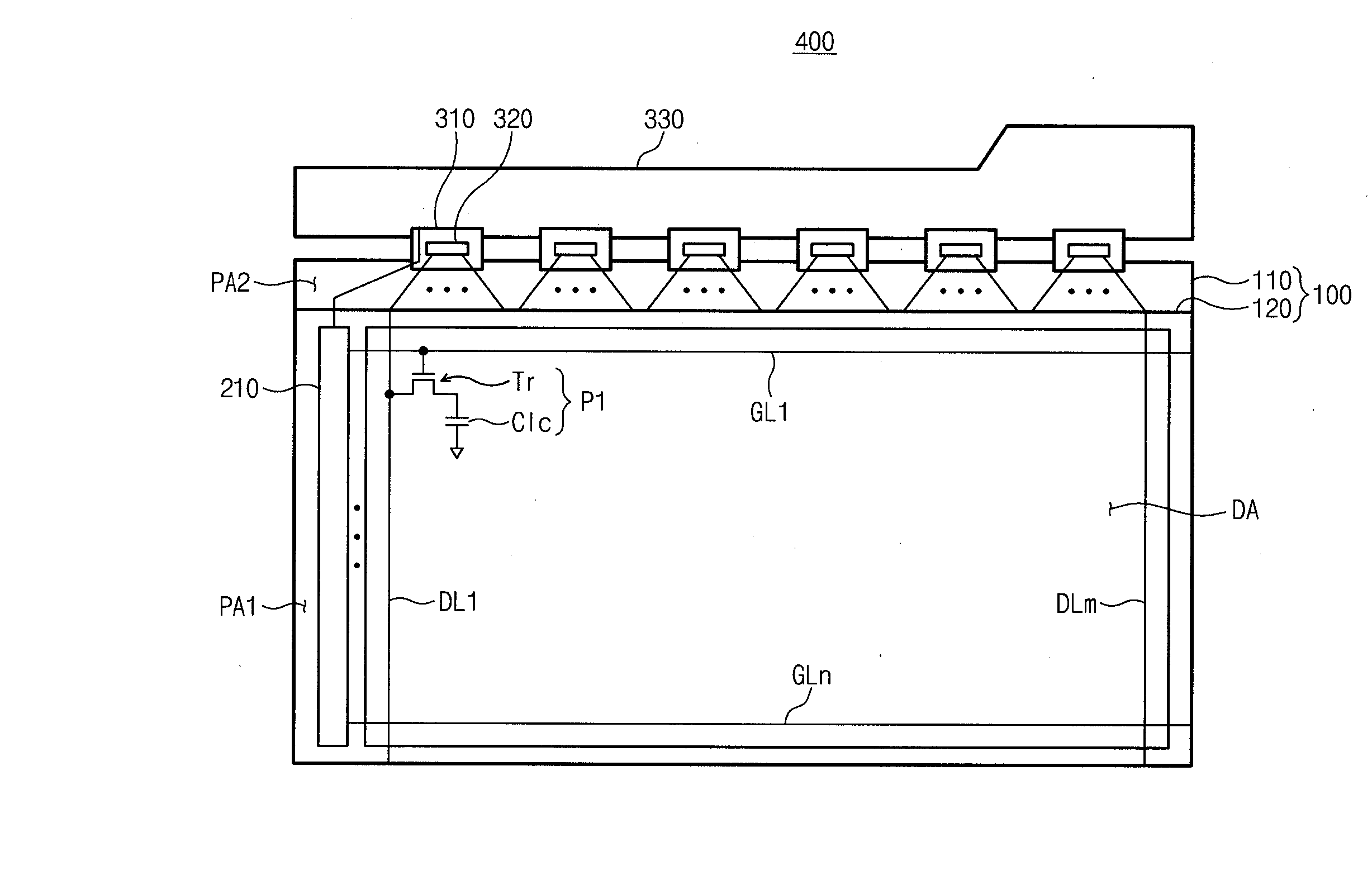

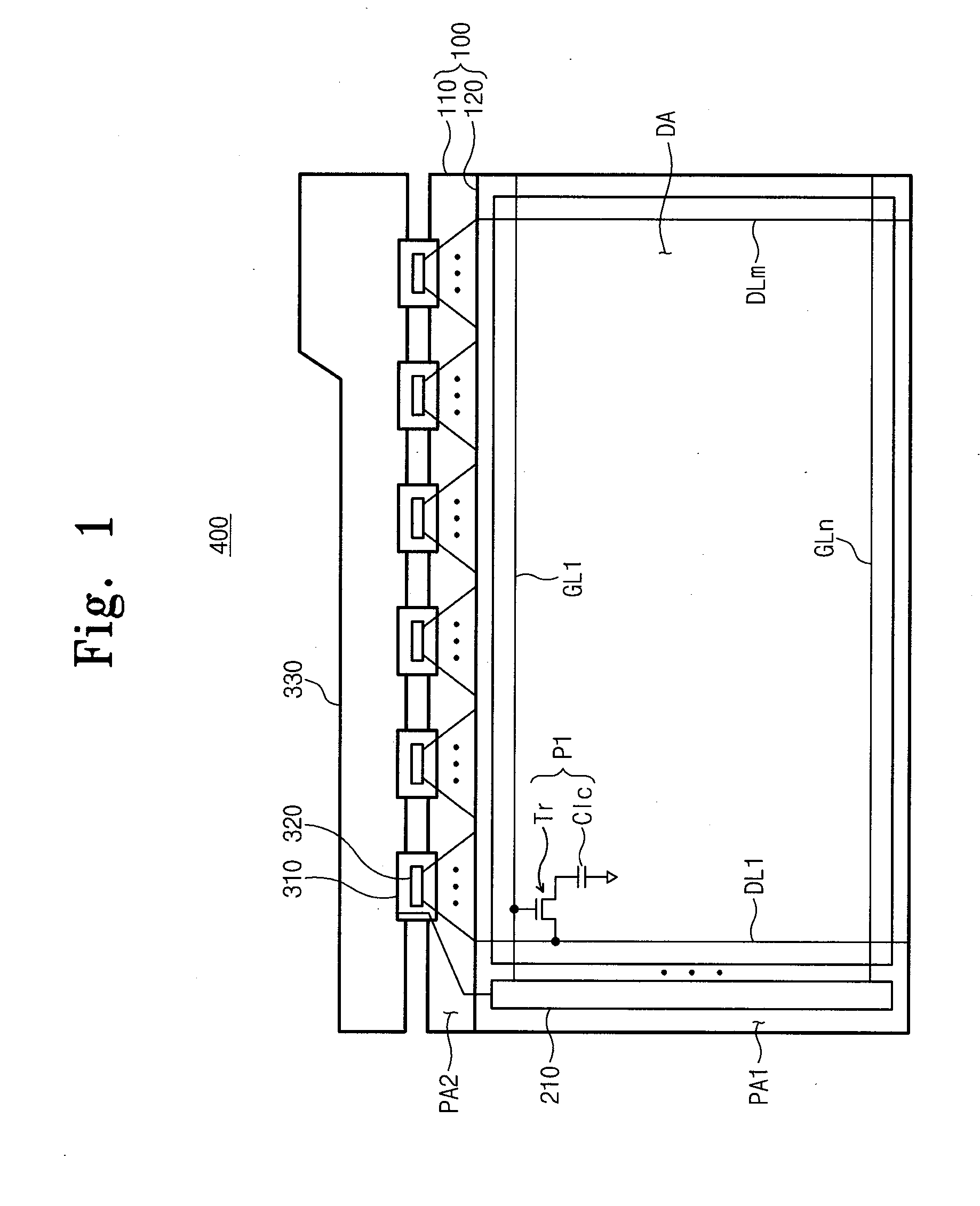

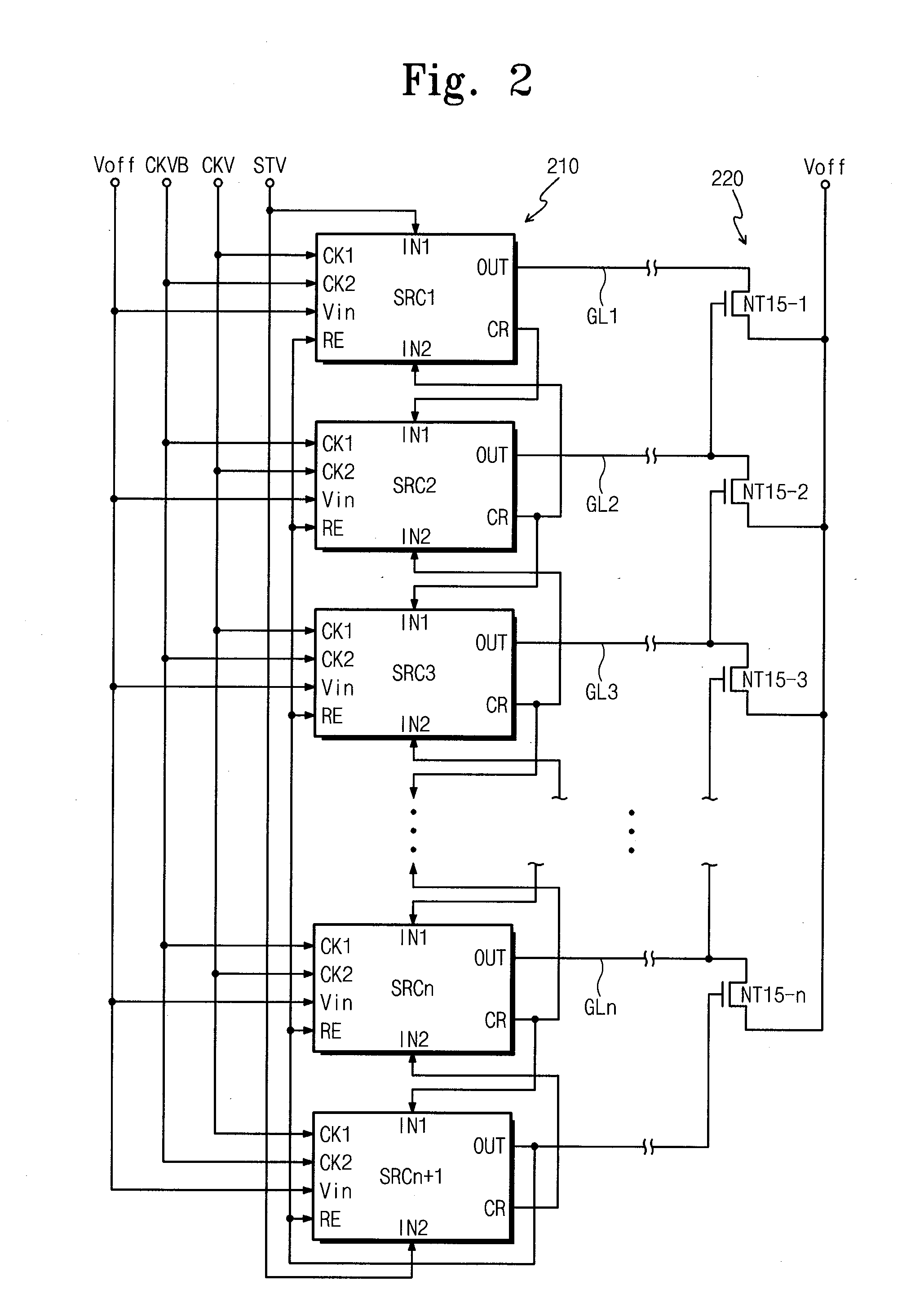

Gate Drive Circuit and Display Apparatus Having the Same

InactiveUS20080074379A1Less distortionAdd reset functionStatic indicating devicesDigital storageDisplay deviceGate effect

A gate drive circuit of a display device includes a plurality of stages, each stage being coupled to at least one other stage. A current stage among the stages includes a gate section, a carry section, a buffer section, and a reset section. The gate section generates a current gate signal and the carry section generates a current carry signal. The buffer section receives a previous carry signal from a previous stage, and then turns on the gate section and the carry section. The reset section receives a next carry signal from next stages, and then turns off the gate section and the carry section. As the current stage is reset in response to the next carry signal, the function of the gate drive circuit is increased.

Owner:SAMSUNG DISPLAY CO LTD

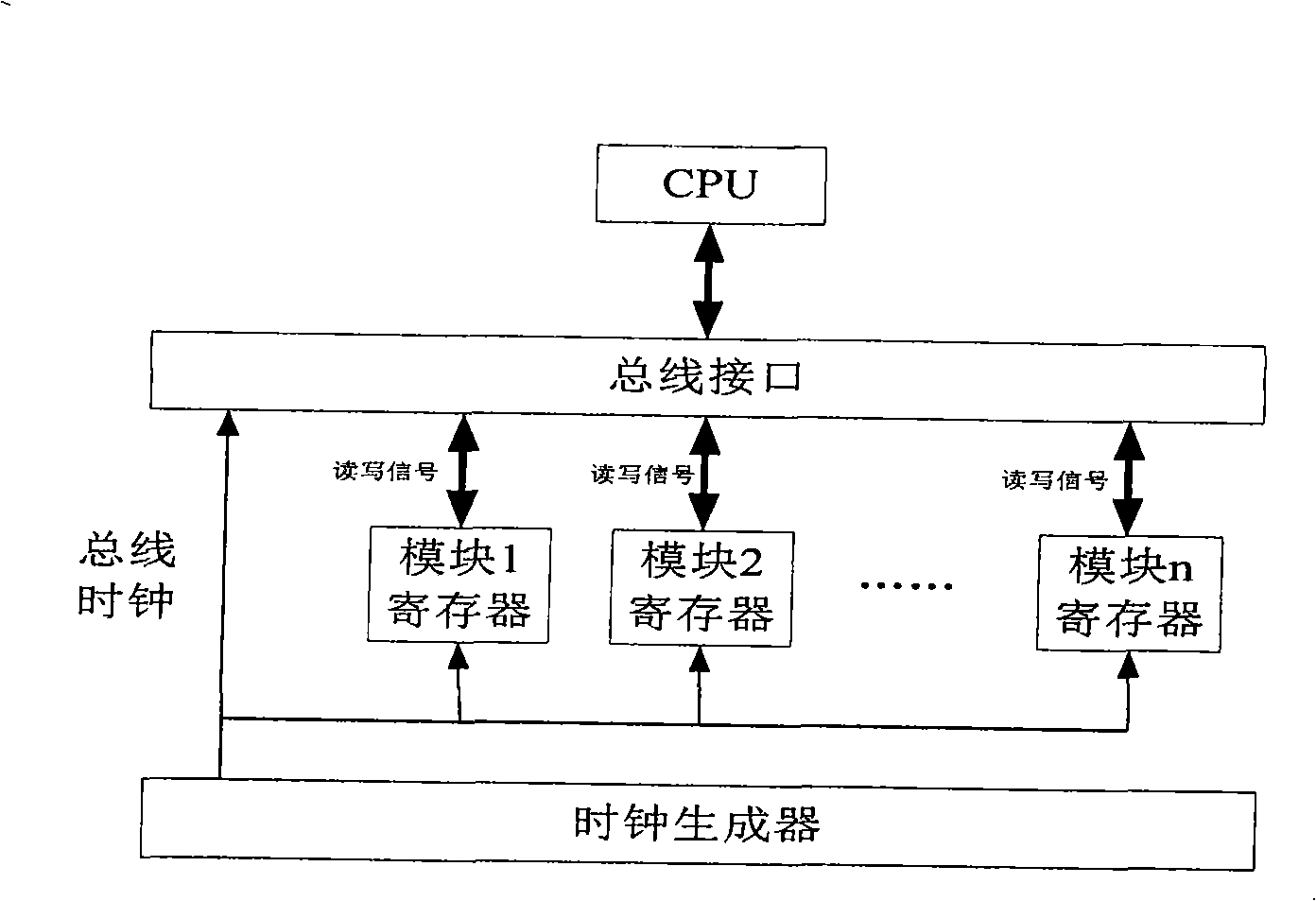

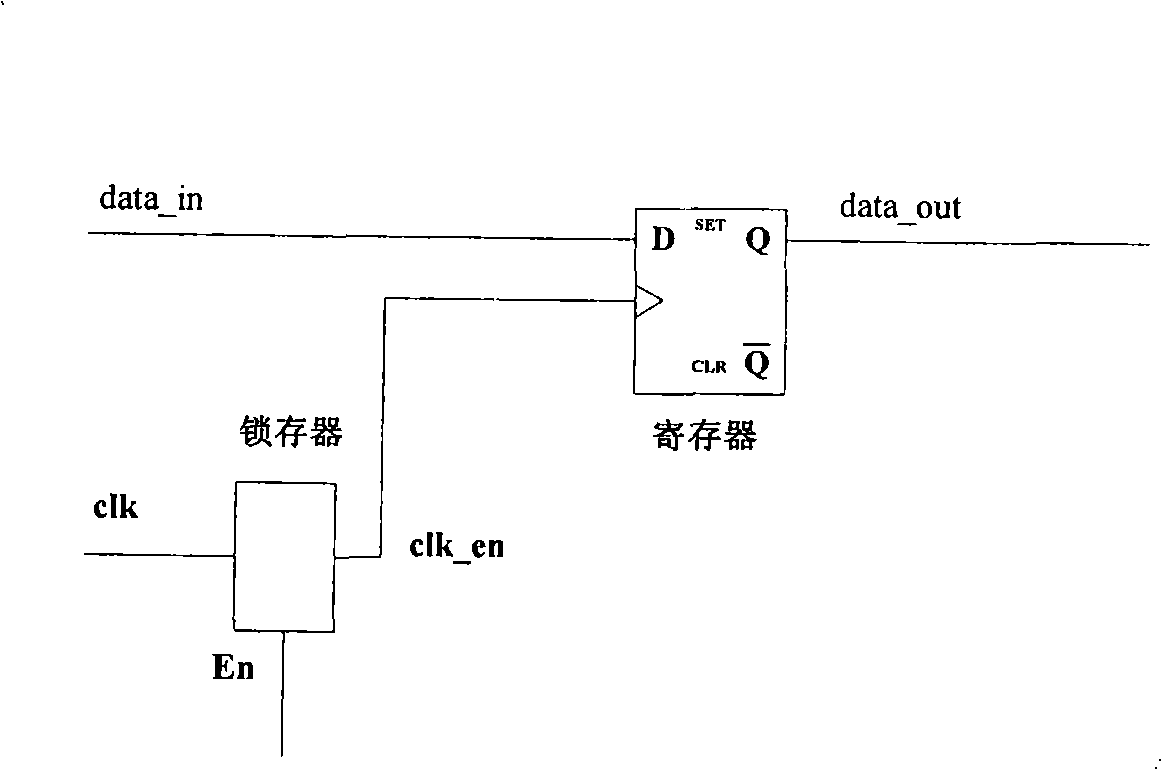

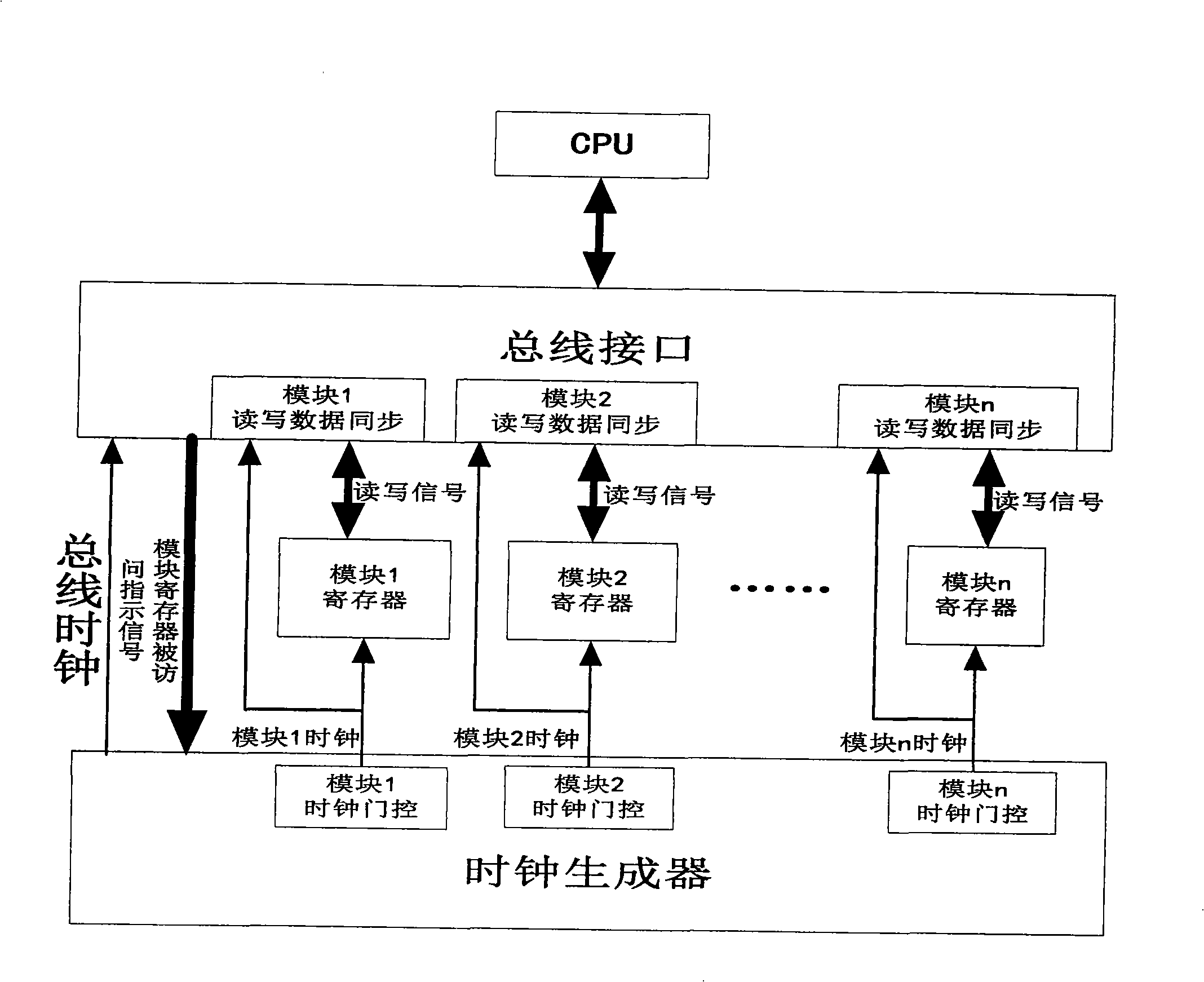

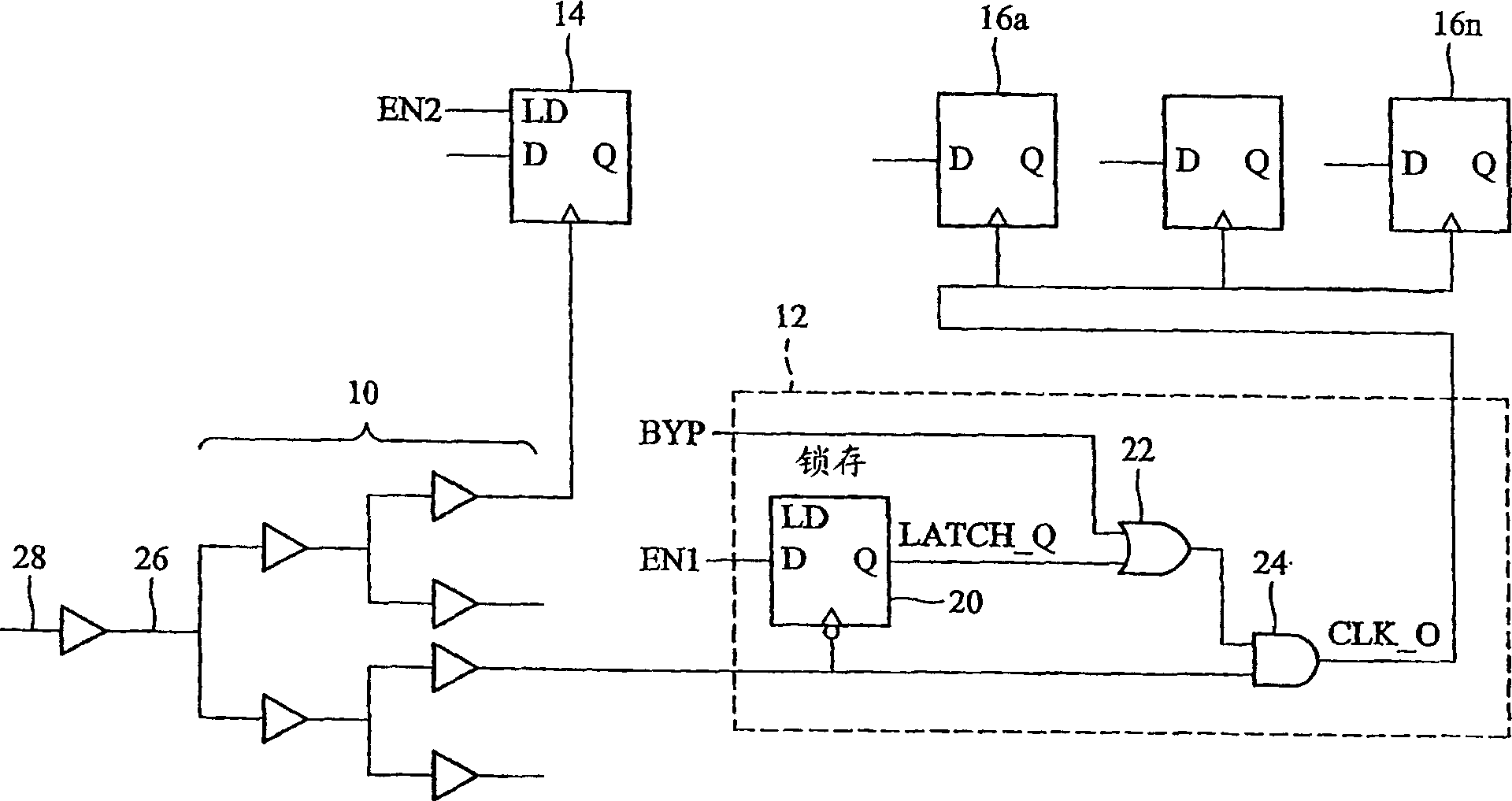

Control system and method of low power consumption read-write register

InactiveCN101329589AEliminate power consumptionReduce power consumptionPower supply for data processingGenerating/distributing signalsData synchronizationControl system

The invention discloses a control system of a low power consumption read / write register. The control system comprises a bus interface, a plurality of register modules and a clock generator, wherein, the clock generator comprises clock gate control units that respectively generate clock signals with the frequency lower than that of a bus clock, the clock signals are output to the corresponding register modules to act as a visit clock of the register; the bus interface comprises a read / write data synchronous unit of the register modules which can respectively realize data reading and writing to different register modules of the bus interface. As the invention improves the clock signal generation method involving the read / write part of the register in the control system, leads the working clocks of different register modules to be mutual-independent, and carries out dynamic gate control according to respective work or idle status, and modifies the position of the gate control unit, therefore, the power consumption of the system is greatly reduced.

Owner:VIMICRO CORP

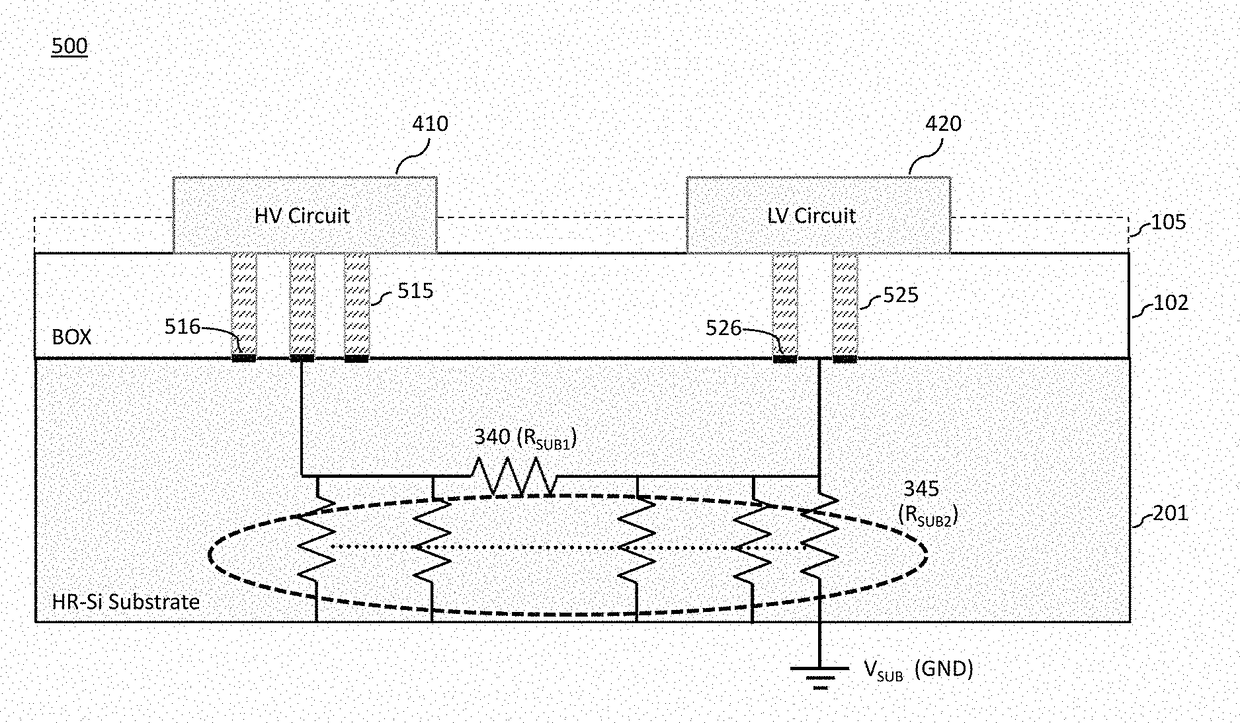

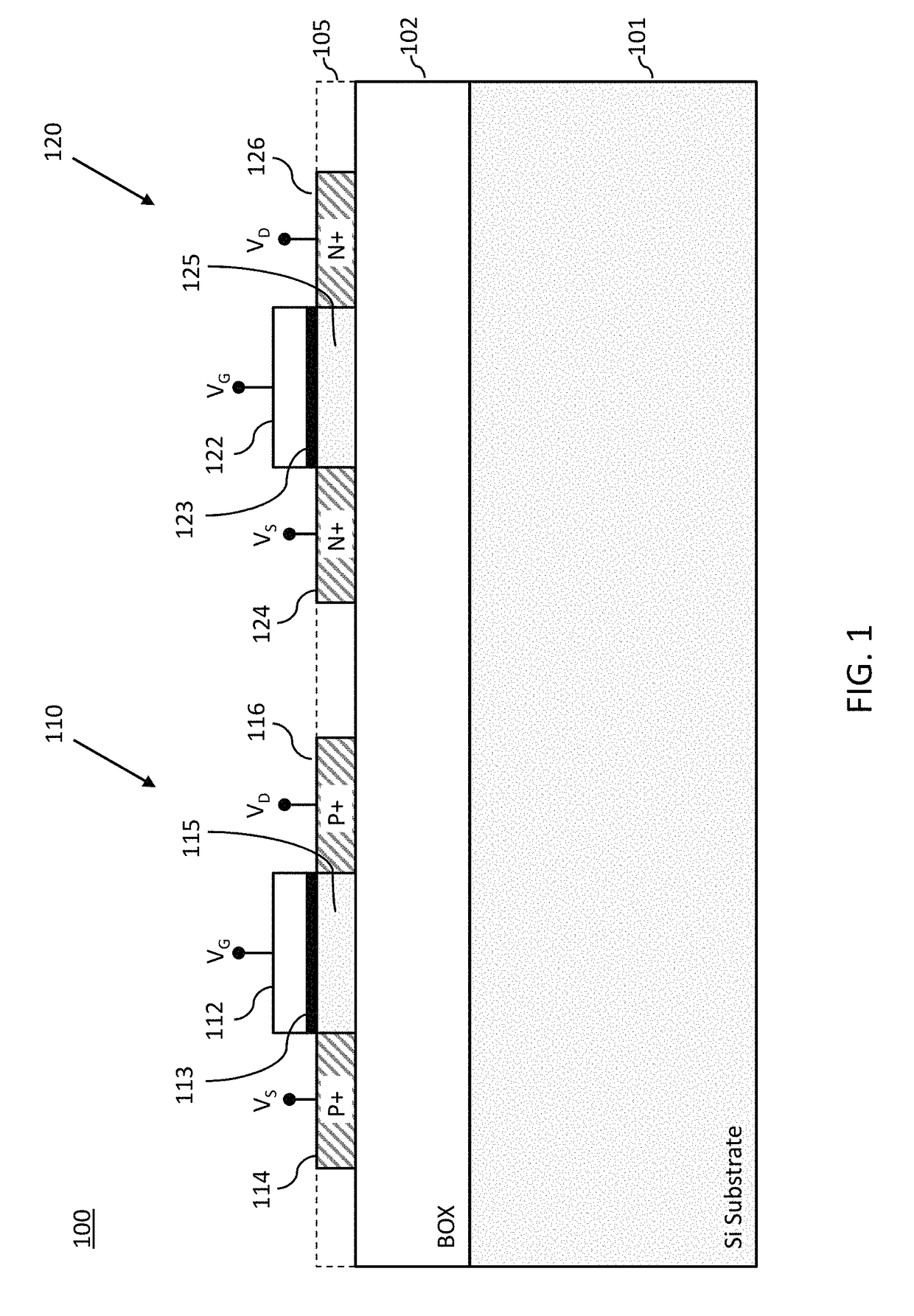

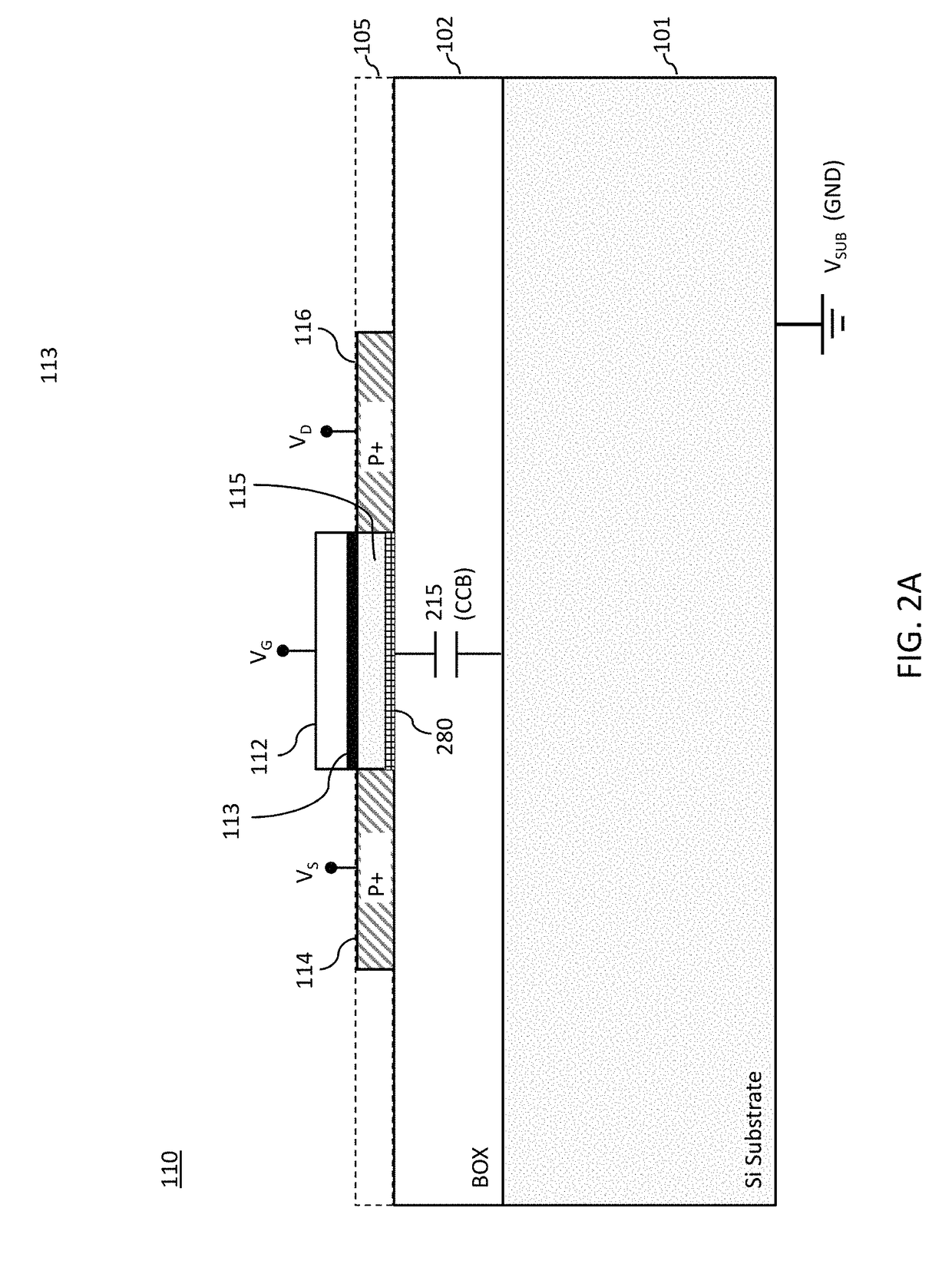

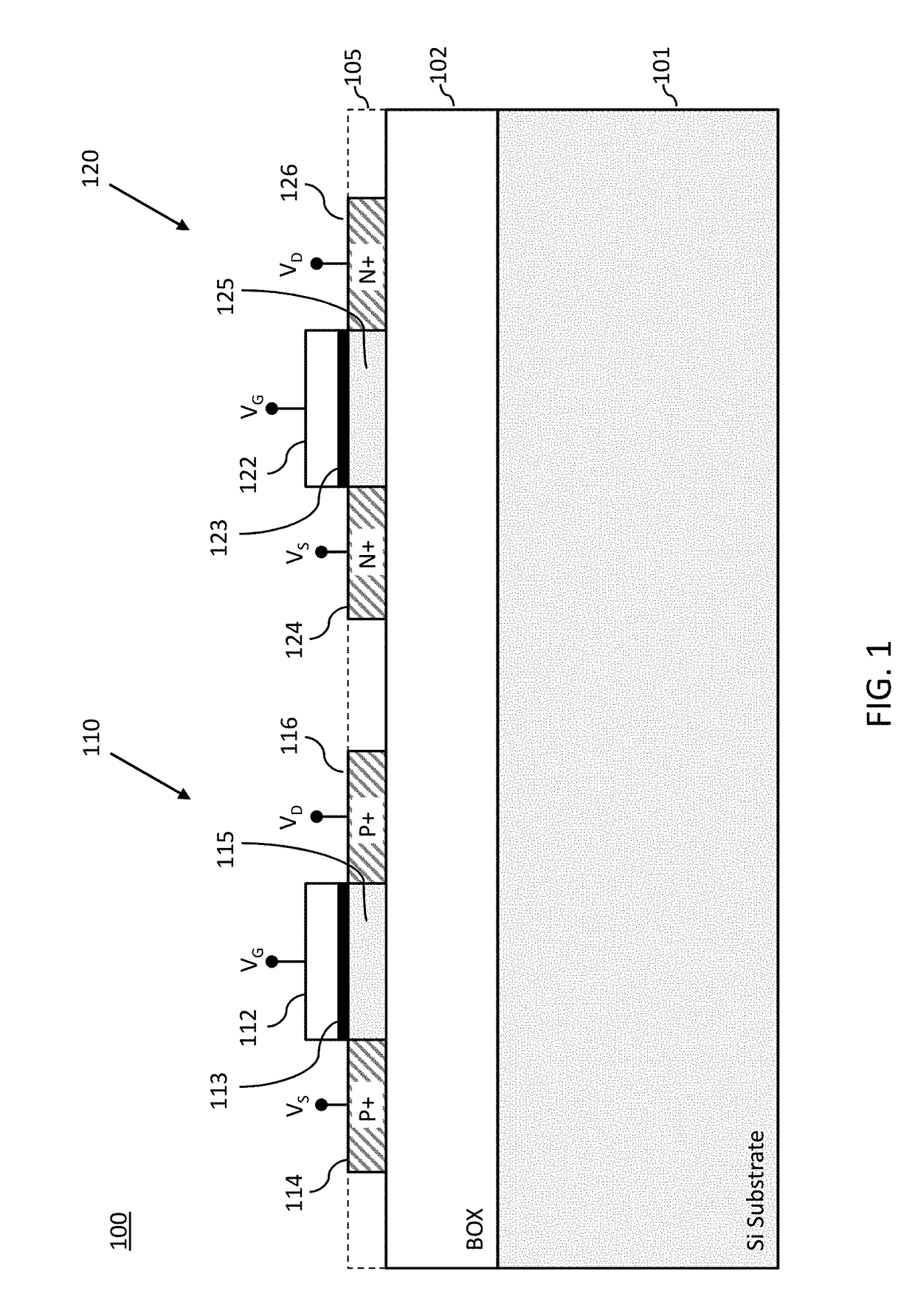

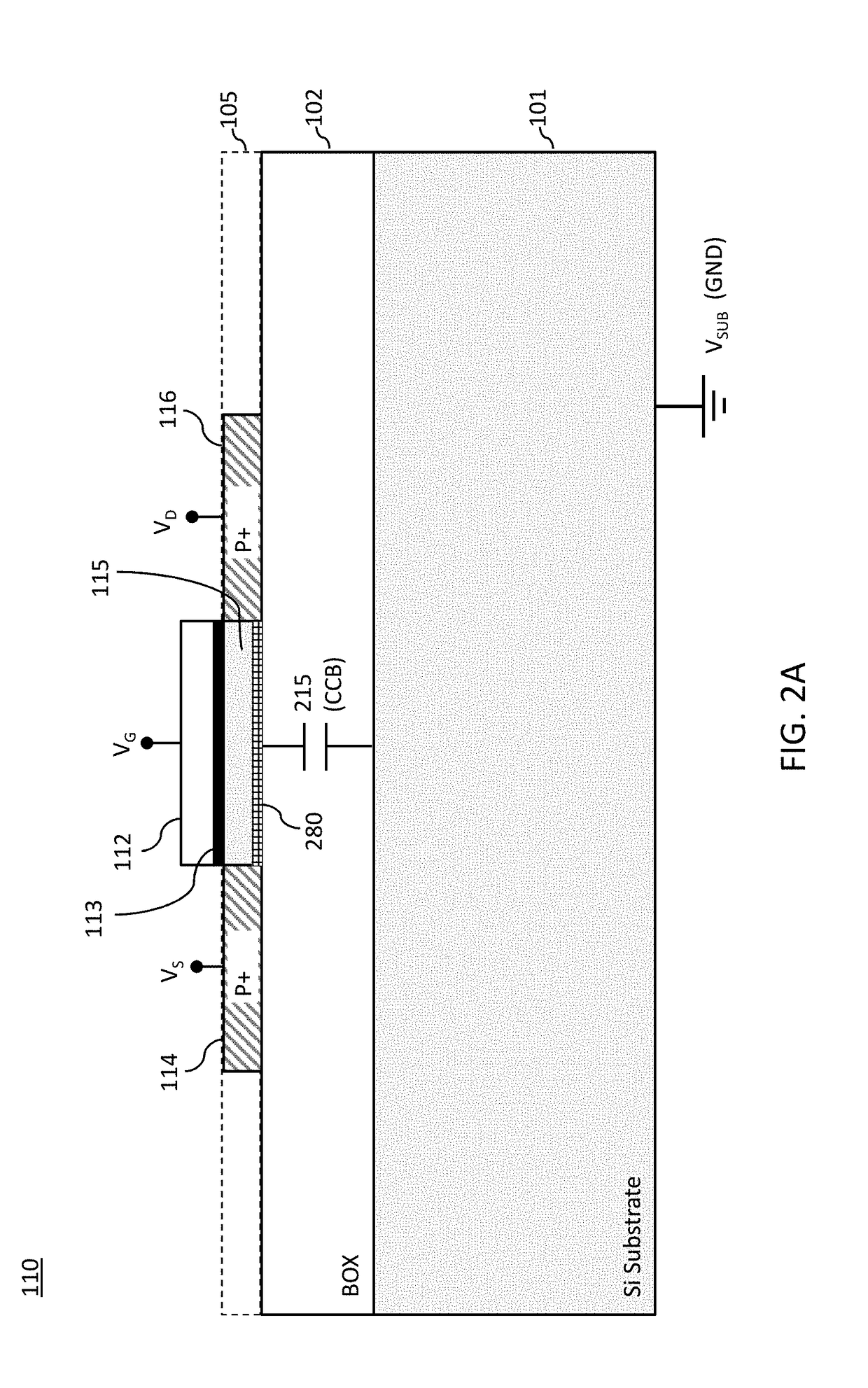

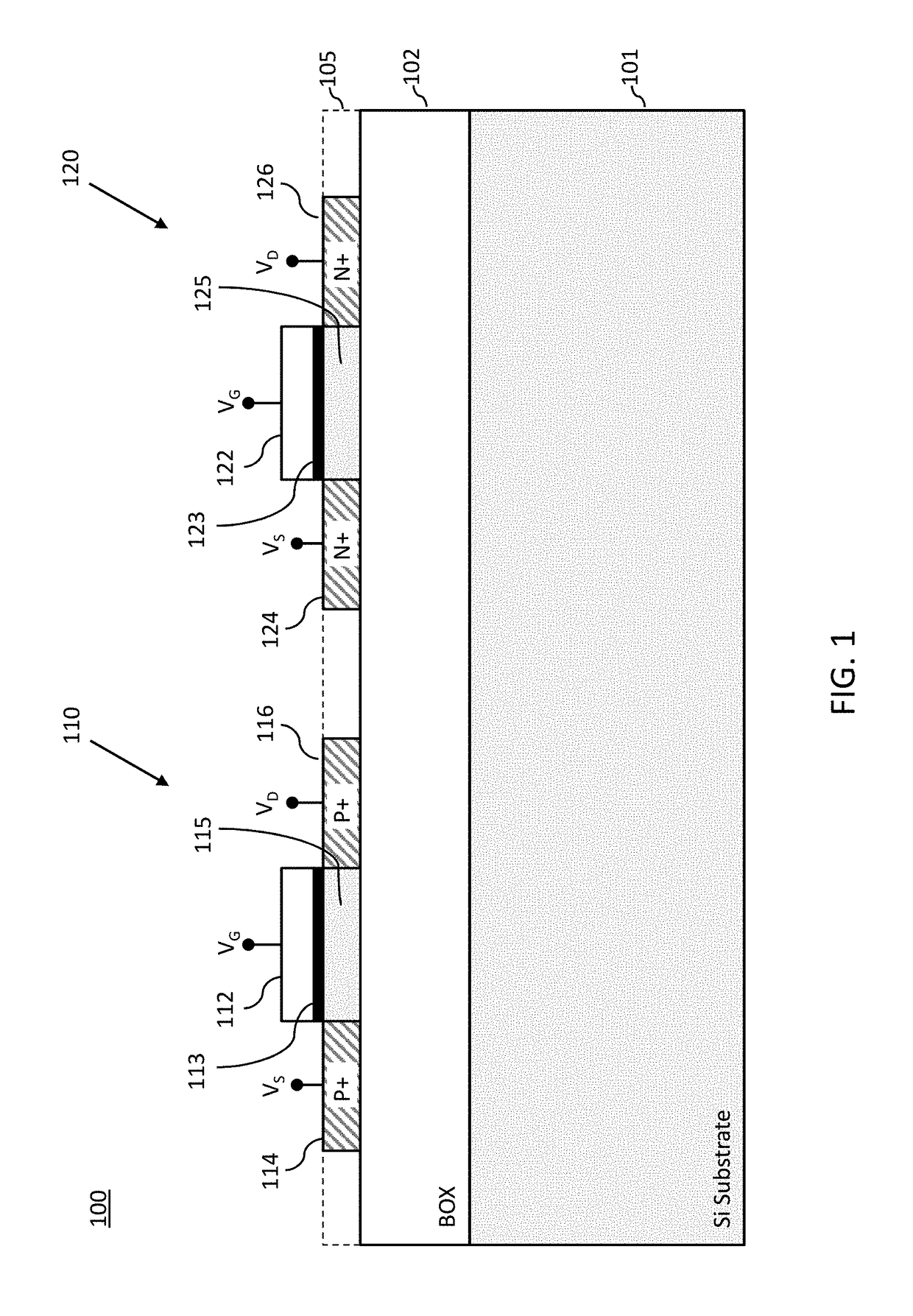

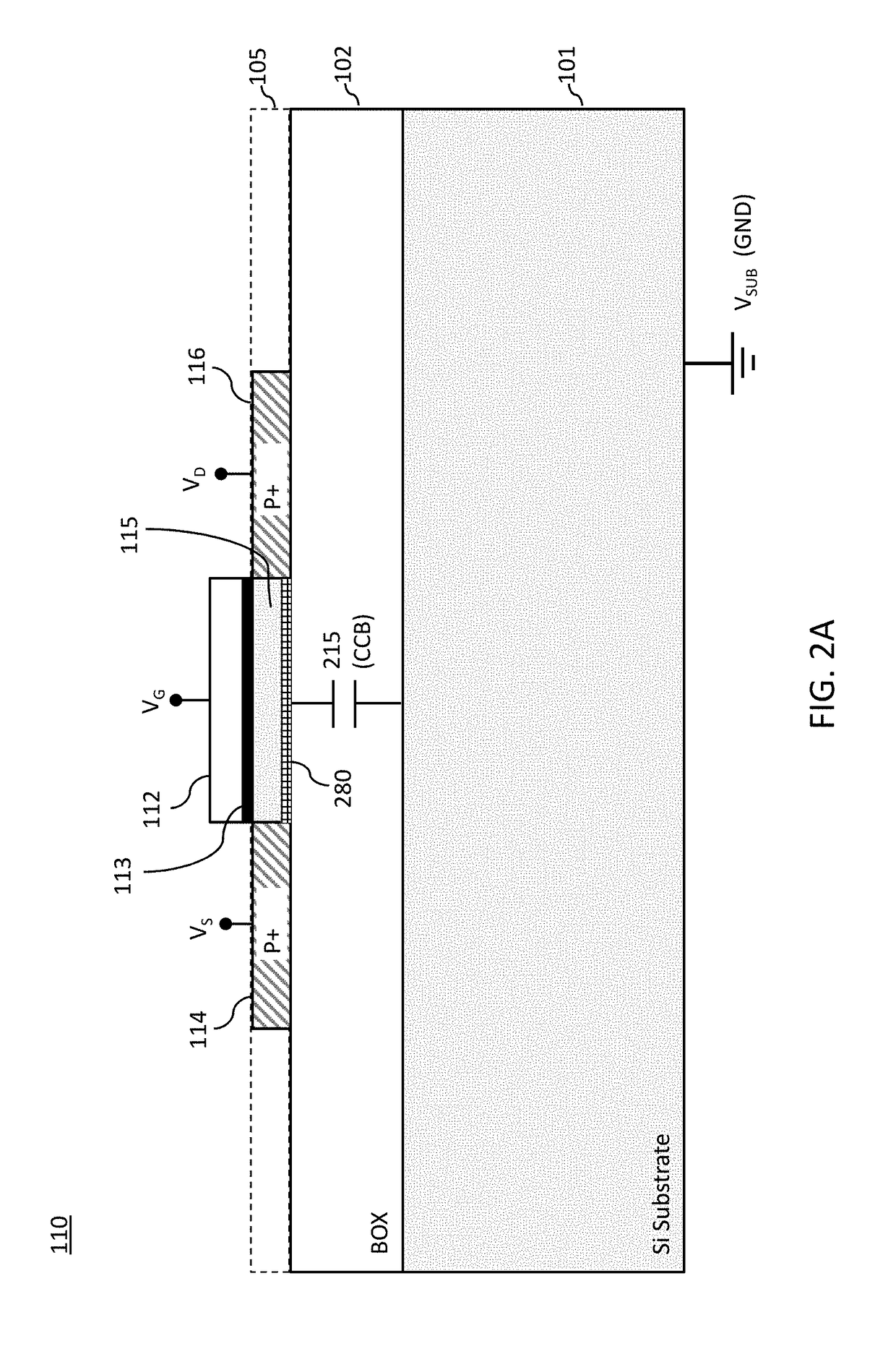

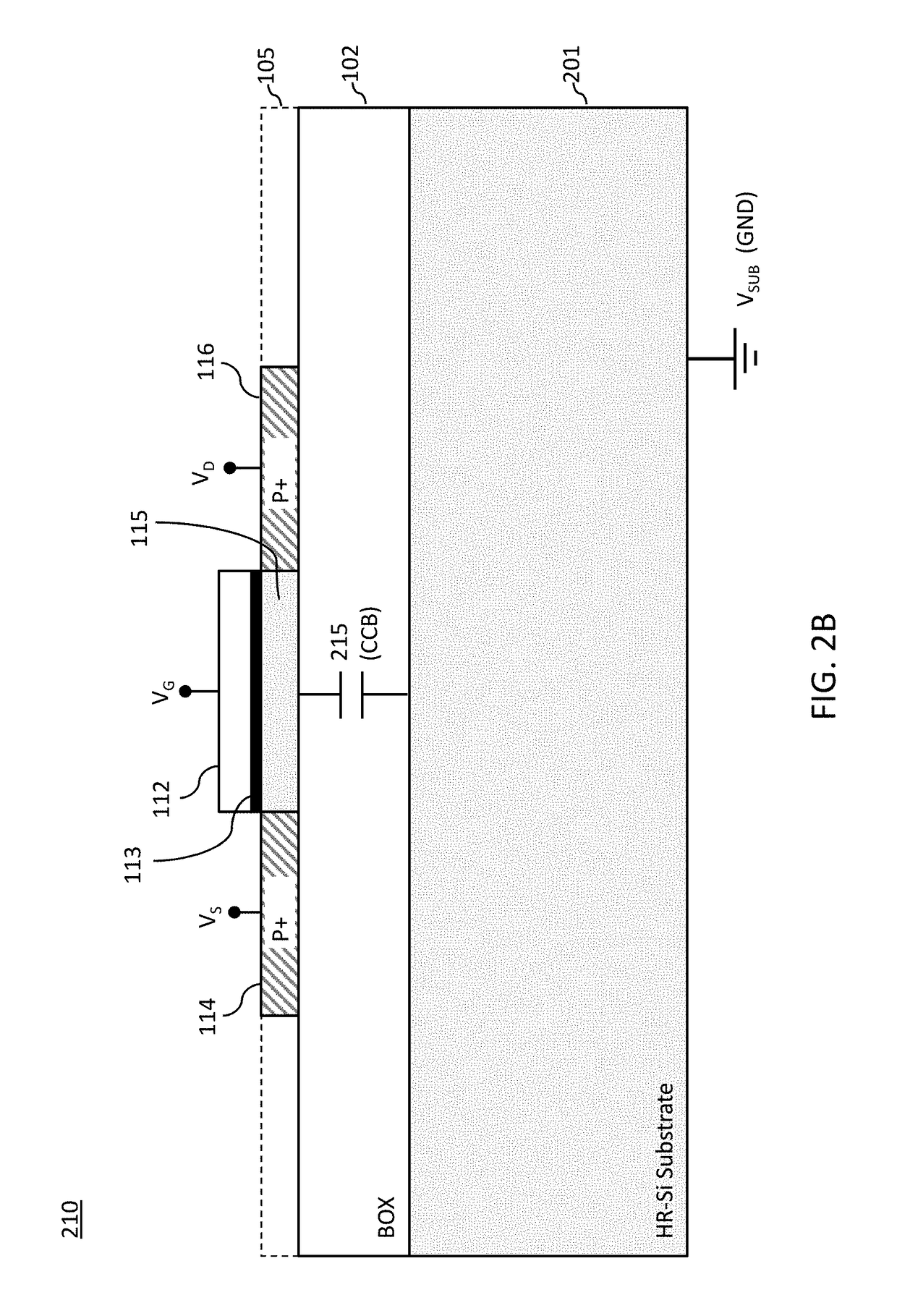

Systems, methods and apparatus for enabling high voltage circuits

ActiveUS9847348B1Reduce the impactReduce impactSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCapacitanceElectrical resistance and conductance

Systems, methods and apparatus for coexistence of high voltage and low voltage devices and circuits on a same integrated circuit fabricated in silicon-on-insulator (SOI) technology are described. In particular, techniques for mitigating back gate effects are described, including using of resistive and / or capacitive couplings to control surface potentials at regions of a substrate used for the SOI fabrication proximate the high voltage and low voltage devices and circuits. In one case, an N-type implant is used to provide a high potential differential with respect to a substrate potential.

Owner:PSEMI CORP

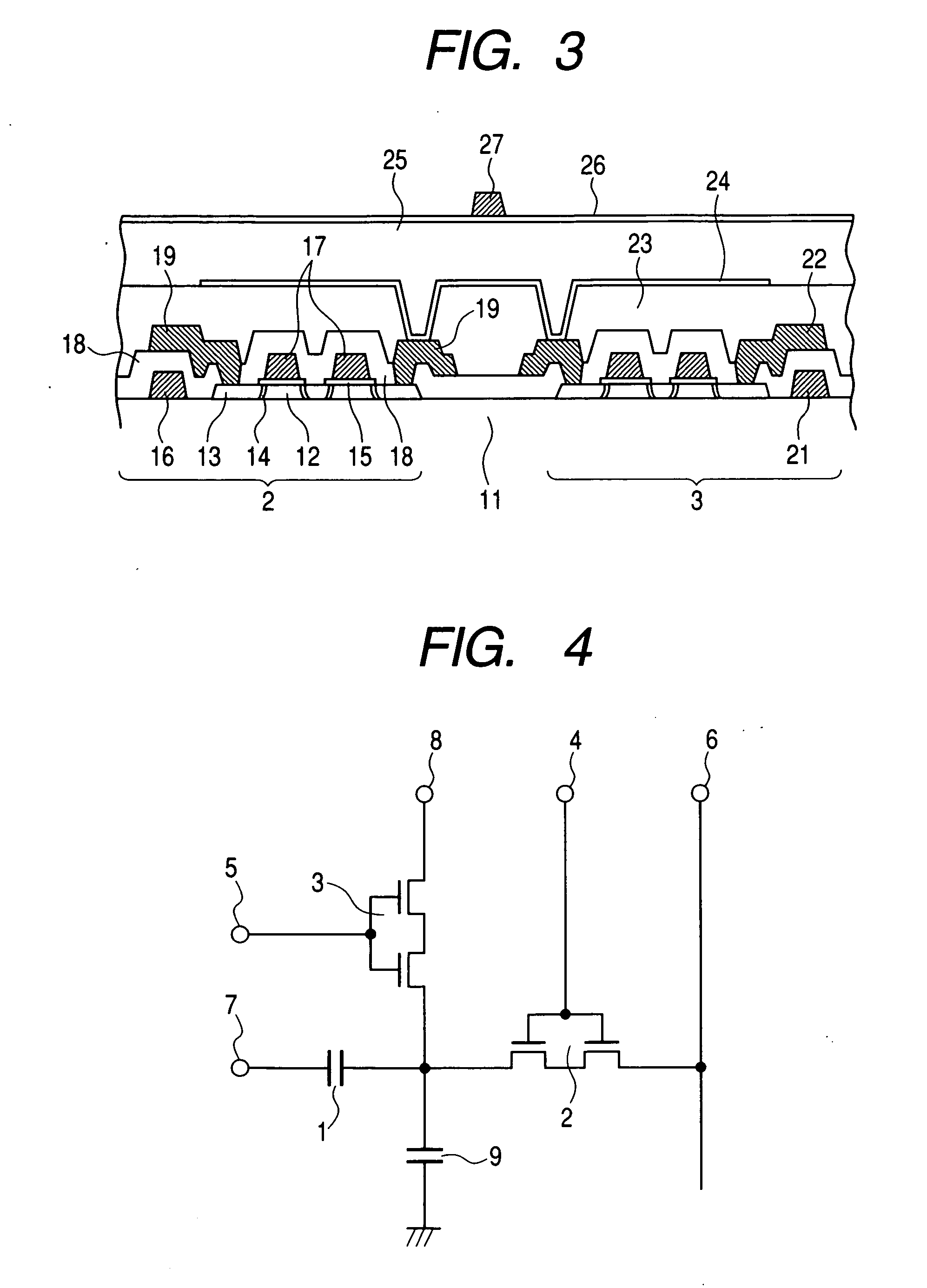

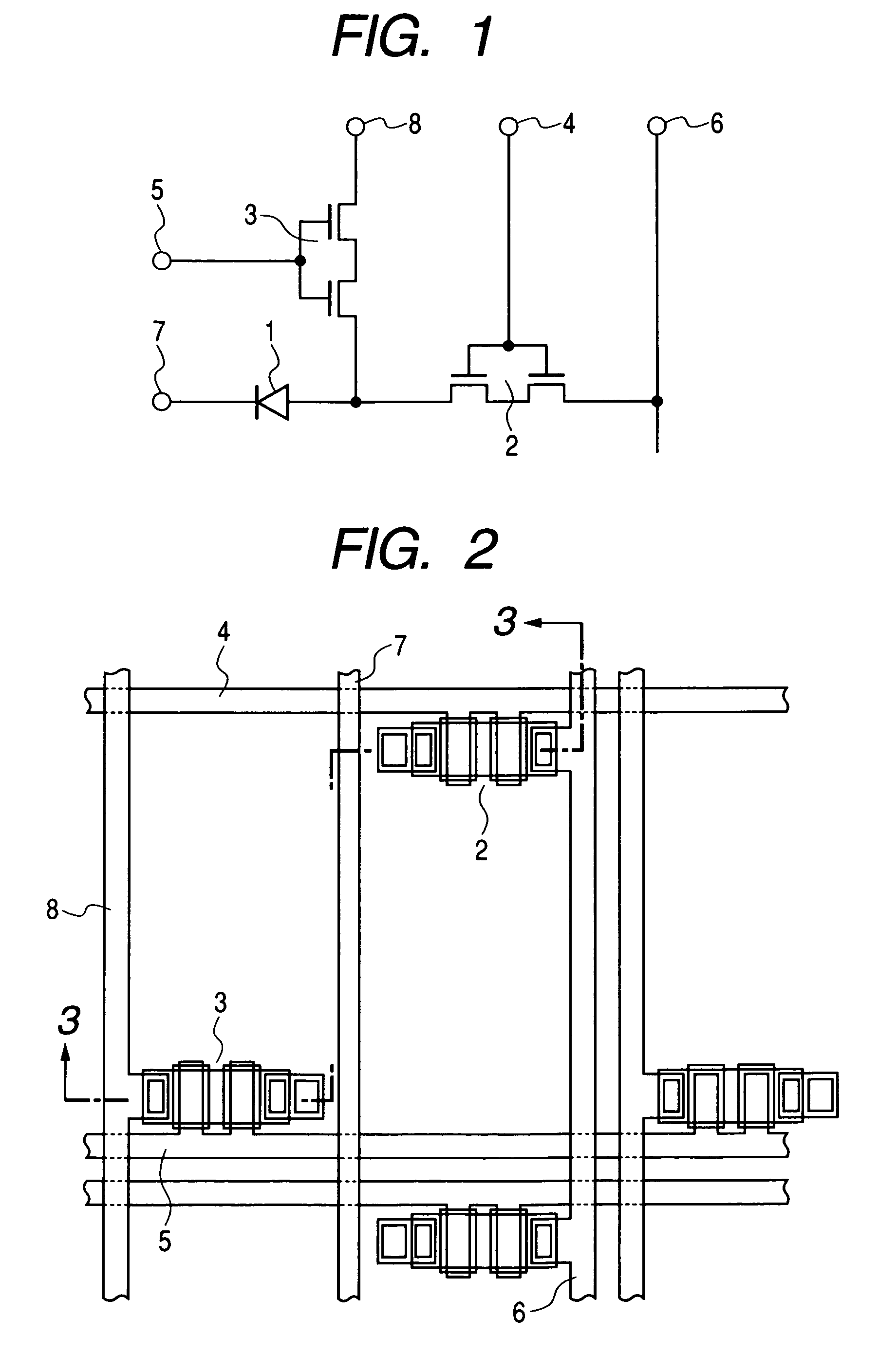

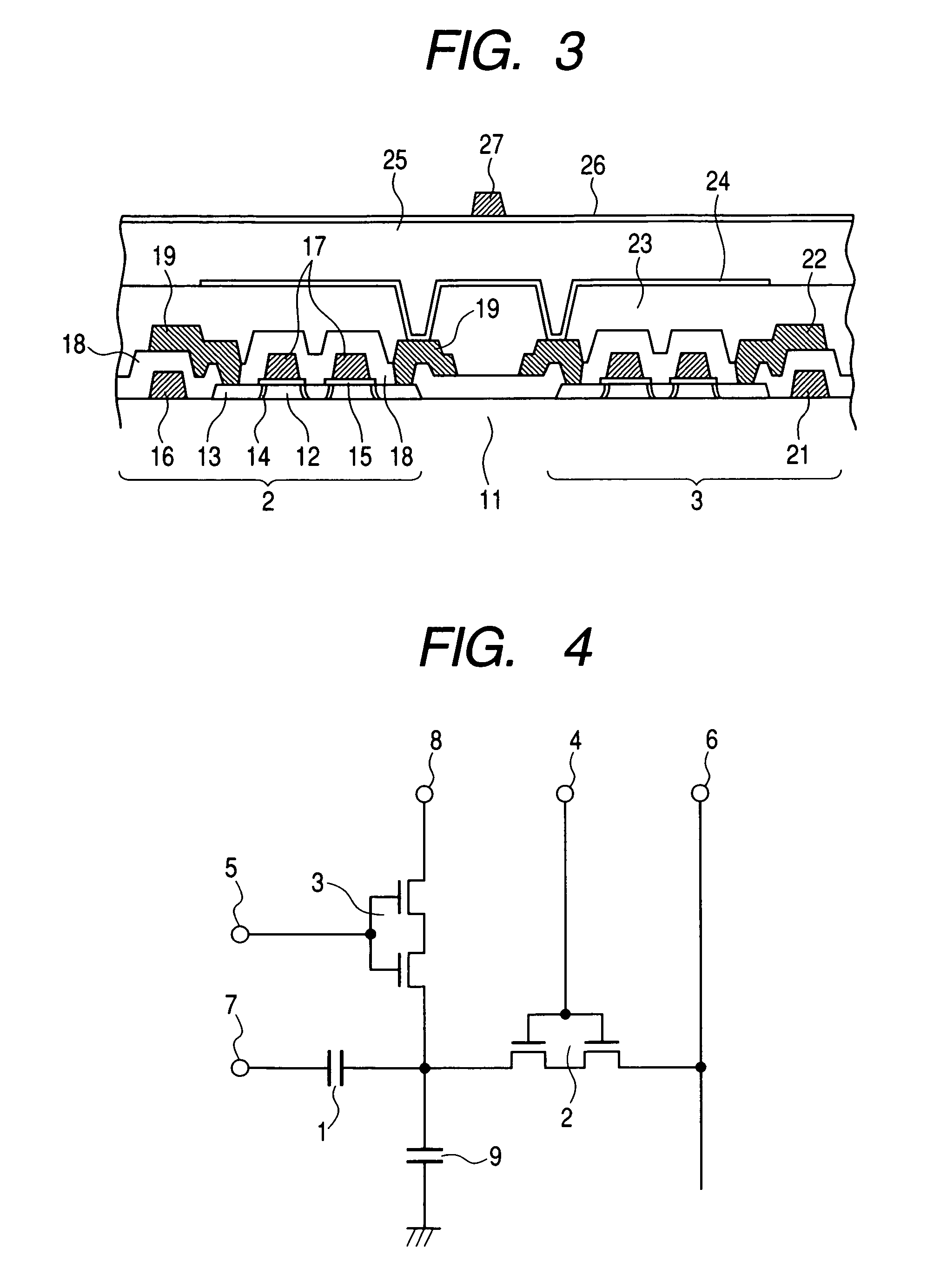

Solid-state image sensor

The present invention provides a solid-state image sensor comprising a source follower amplifier on a single chip capable of preventing a gain loss caused by a back gate effect. In the solid-state image sensor including multi-stage single-chip source follower amplifier, one stage of the multi-stage source follower amplifier has a load transistor 5 whose source and gate are connected to an output signal 3 via a capacitor 7, and a DC voltage 6 is applied via a resistor 8 having a high resistance.

Owner:NEC CORP

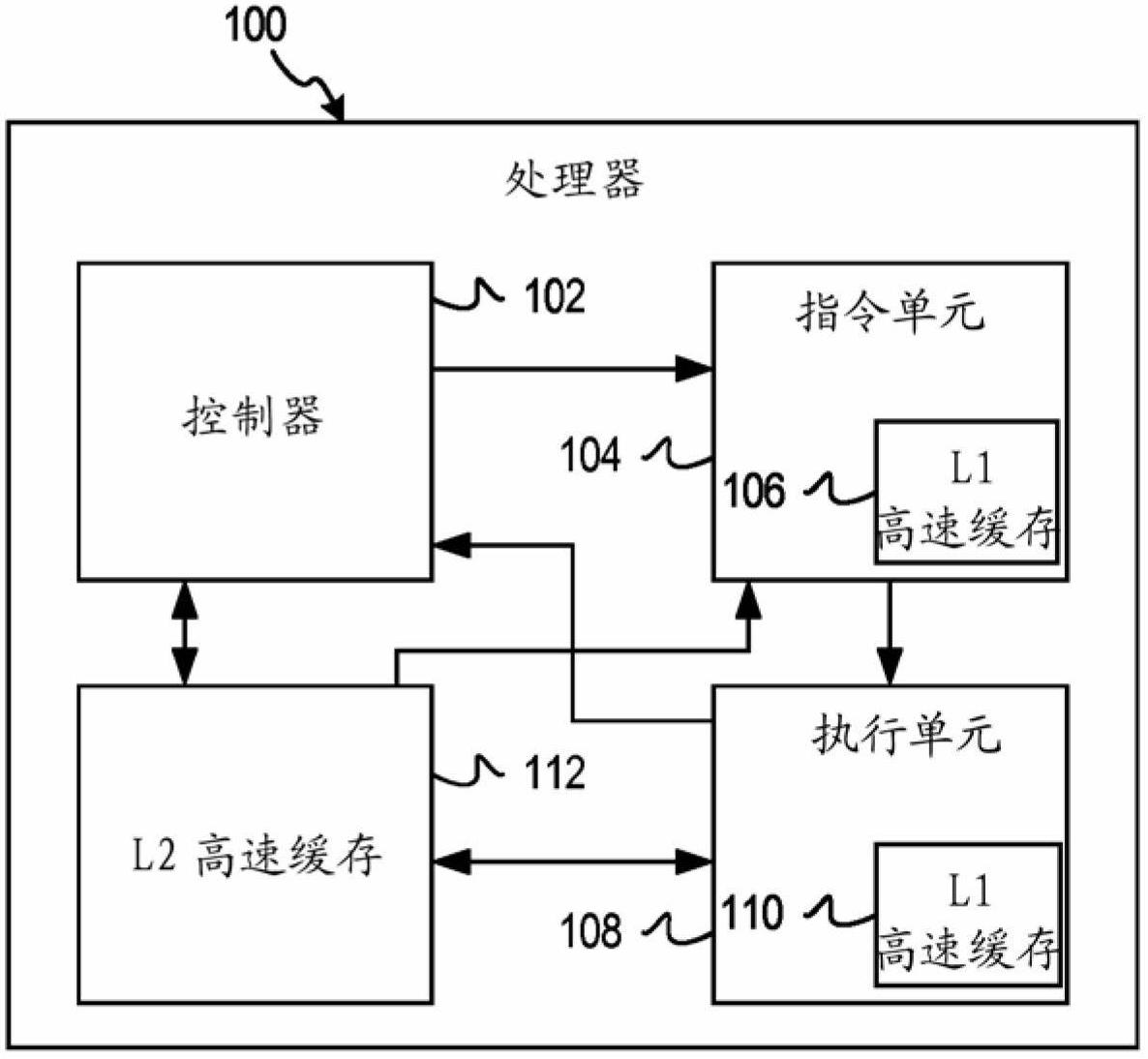

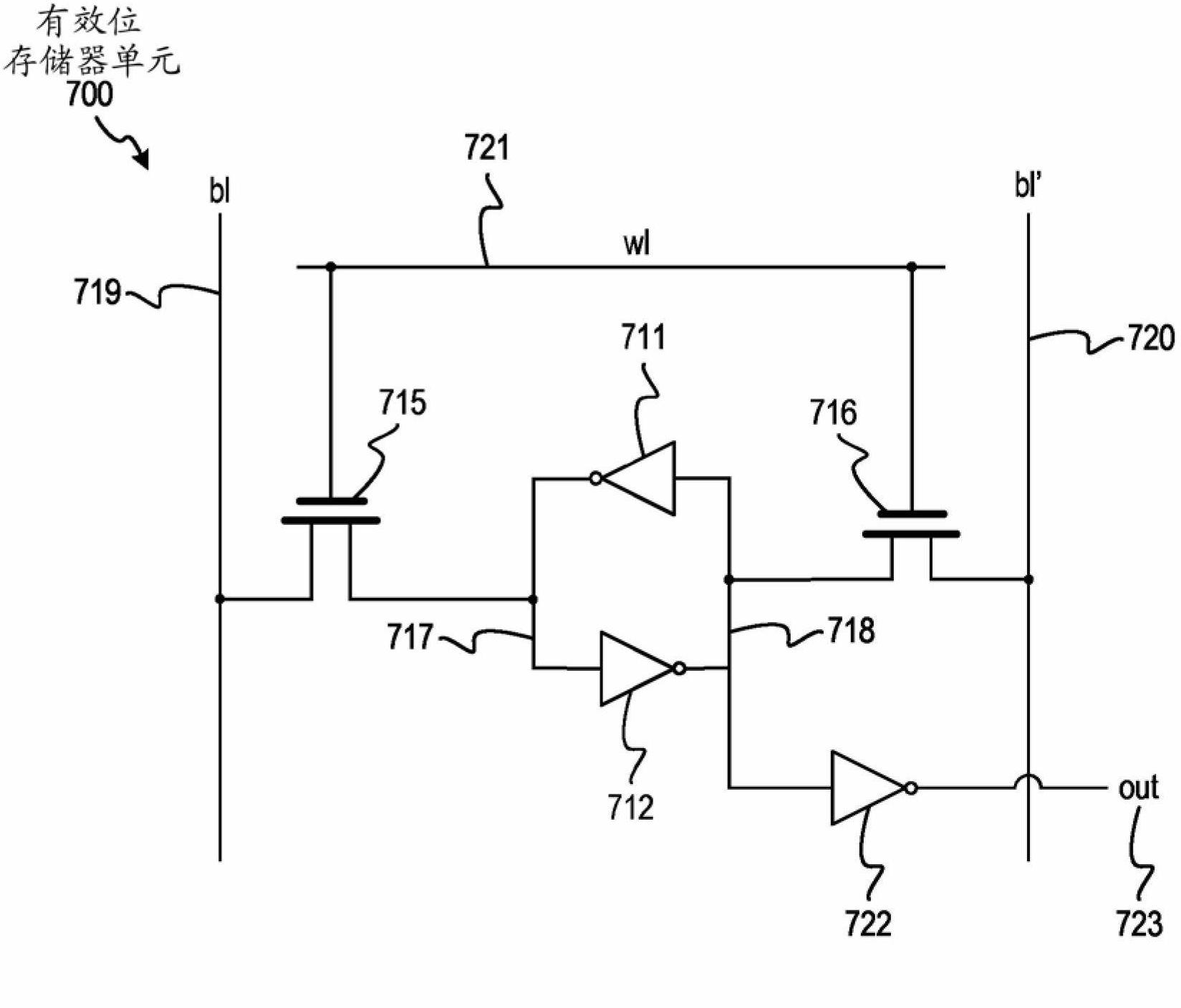

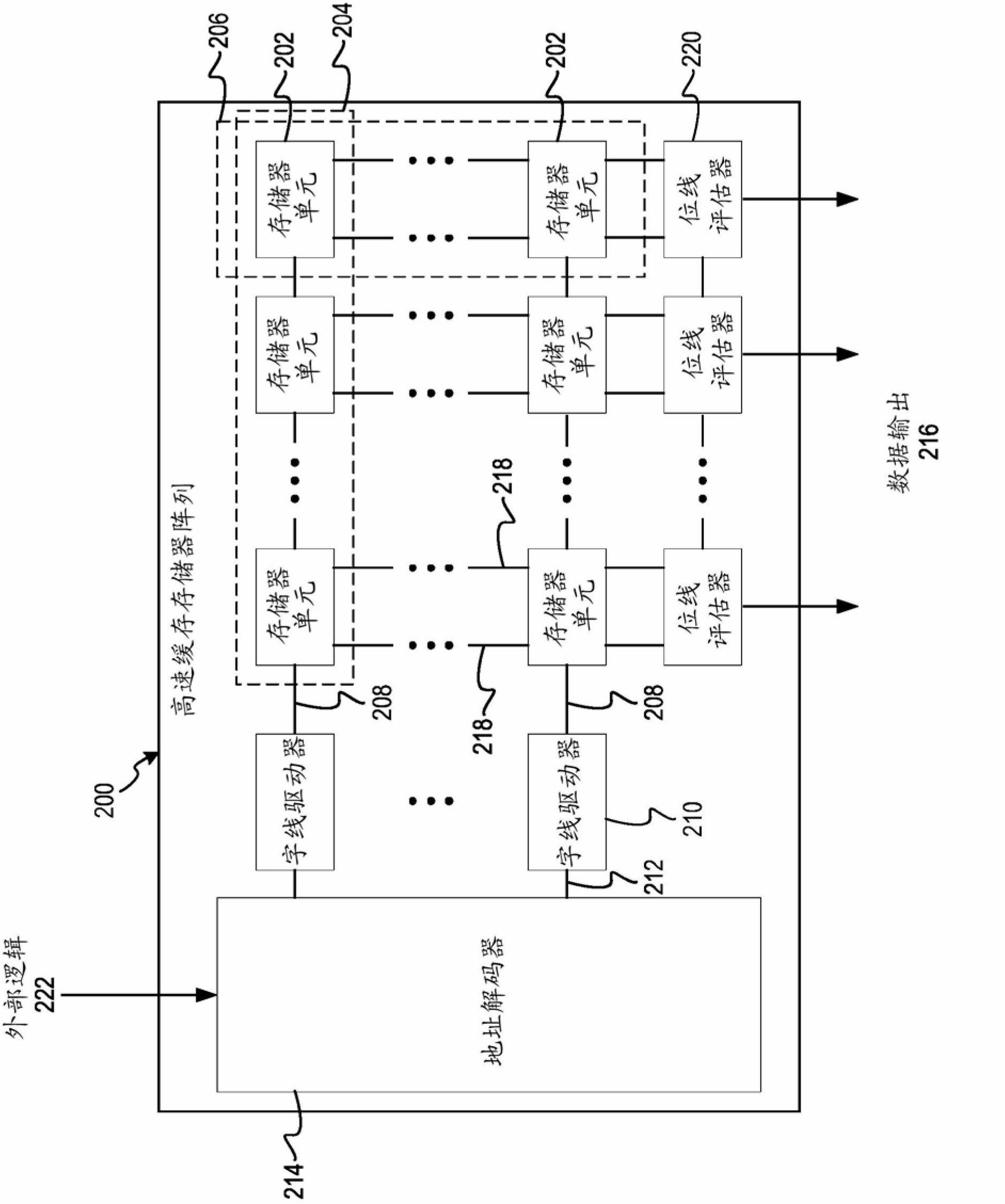

Cache access memory and method

InactiveCN102652311AMemory architecture accessing/allocationMemory adressing/allocation/relocationAddress decoderCache access

A mechanism is provided for gating a read access of any row in a cache access memory that has been invalidated. An address decoder in the cache access memory sends a memory access to a non-gated wordline driver and a gated wordline driver associated with the memory access. The non-gated wordline driver outputs the data stored in a valid bit memory cell to the gated wordline driver in response to the non-gated wordline driver determining the memory access as a read access. The gated wordline driver determines whether the data from the valid bit memory cell from the non-gated wordline driver indicates either valid data or invalid data in response to the gated wordline driver determining the memory access as a read access and denies an output of the data in a row of memory cells associated with the gated wordline driver in response to the data being invalid.

Owner:IBM CORP

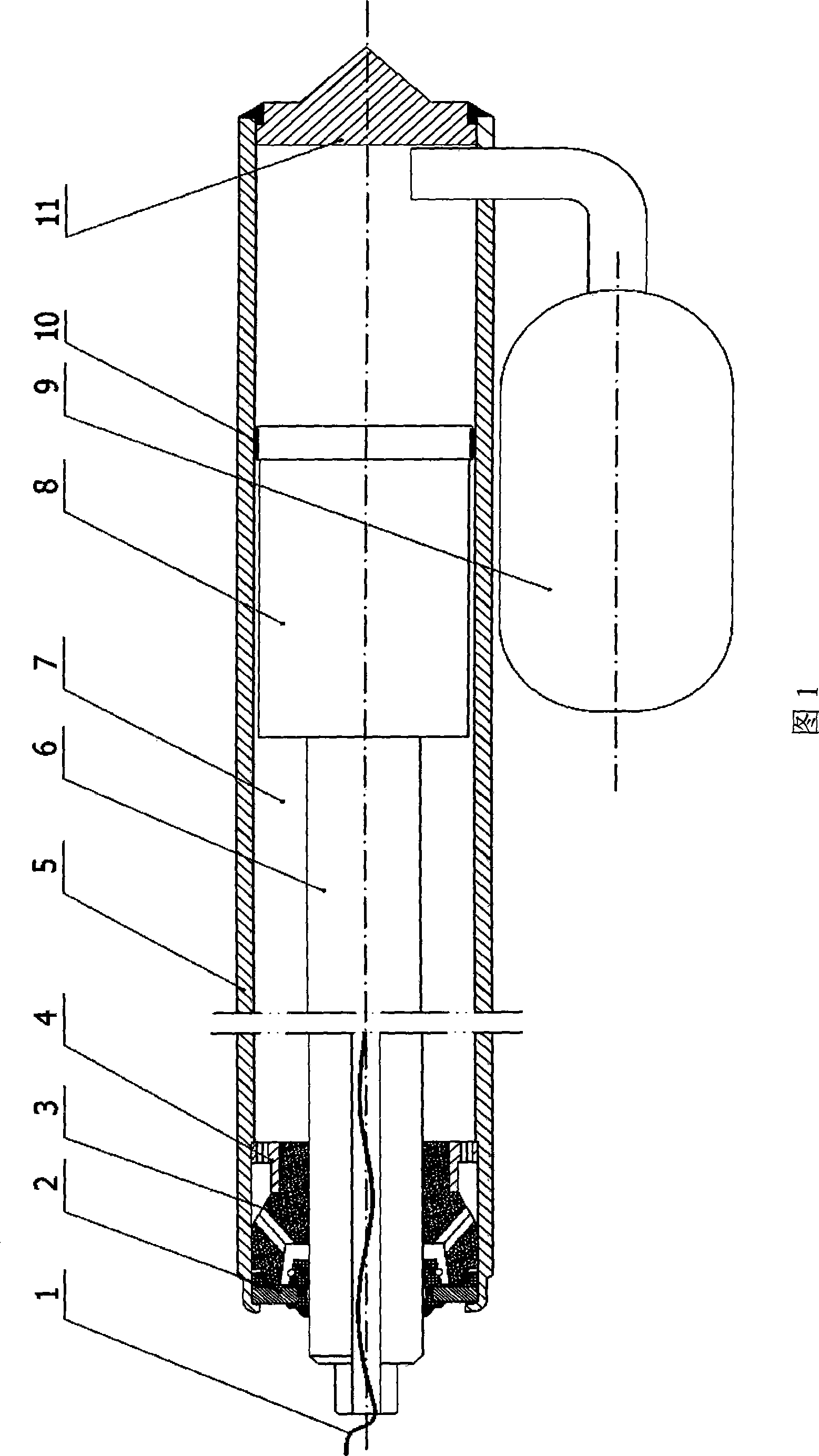

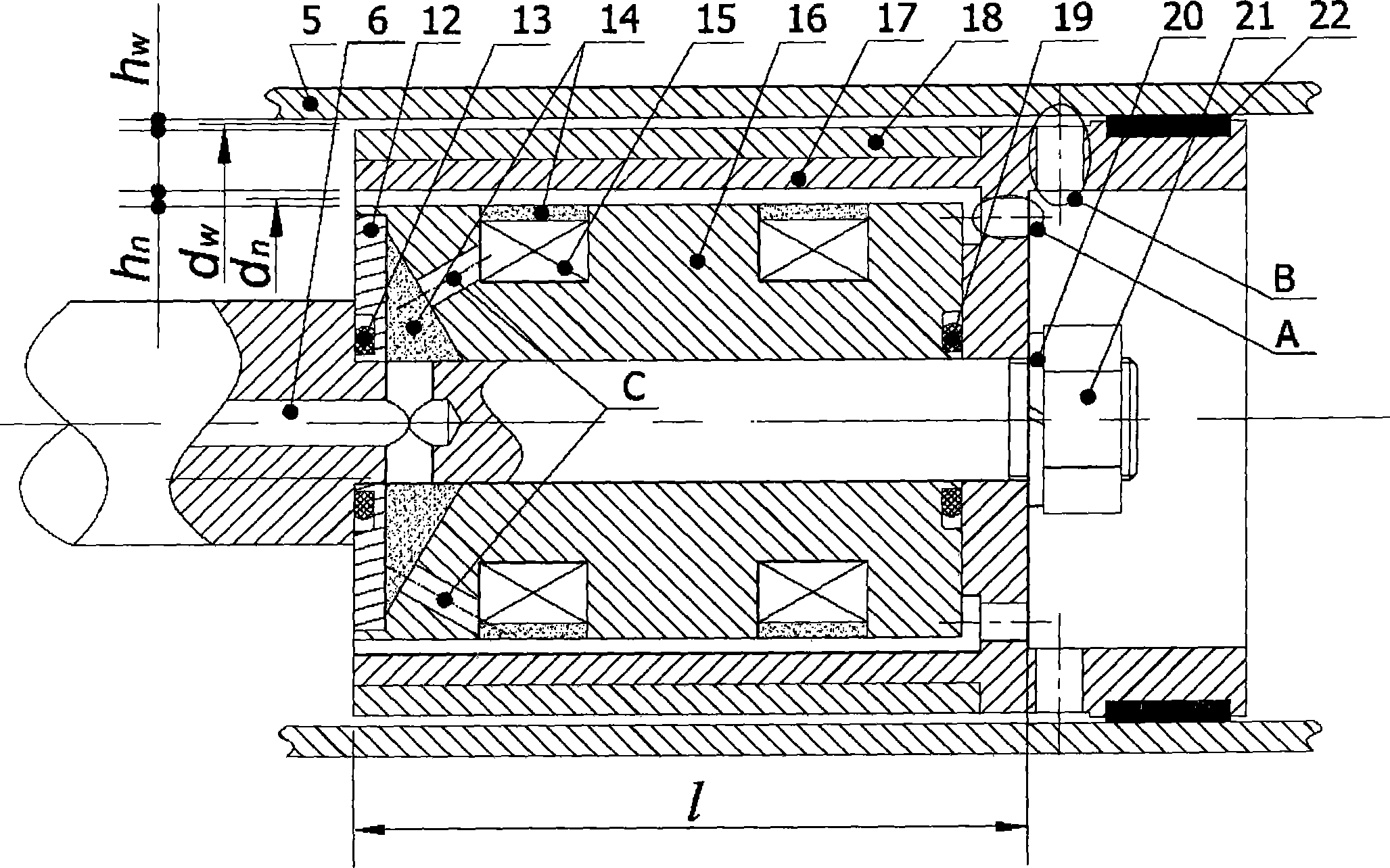

Two-channel magnetorheological damper with passage gating capability

InactiveCN101382177AAchieve serializationAchieving Universal DesignNon-rotating vibration suppressionExcitation currentEngineering

The invention relates to a dual-passage magnetorheological damper with passage gating capability; a working cylinder, a piston body, an excitation component, an magnetic shield sleeve, a piston rod, a guiding ring, a sealing component, a compensating device and the like are jointly compose the whole dual-passage magnetorheological damper; the structural design ensures the realization of passage gating capability of the dual-passage magnetorheological damper and greatly simplifies the design method of the existing magnetorheological damper; the clearance between the piston component and the excitation component forms an internal passage while the clearance between the piston component and the working cylinder forms an external passage; when external excitation current is not applied, the magnetorheological fluid mainly passes through the internal passage and then the damping force is minimum; when the excitation current achieves saturation, the magnetorheological fluid mainly passes through the external passage and then the damping force is maximum. By the passage gating effect of the flowing of the magnetorheological fluid, the stepless change between the minimum value and the maximum value of the damping force is realized.

Owner:CHONGQING UNIV

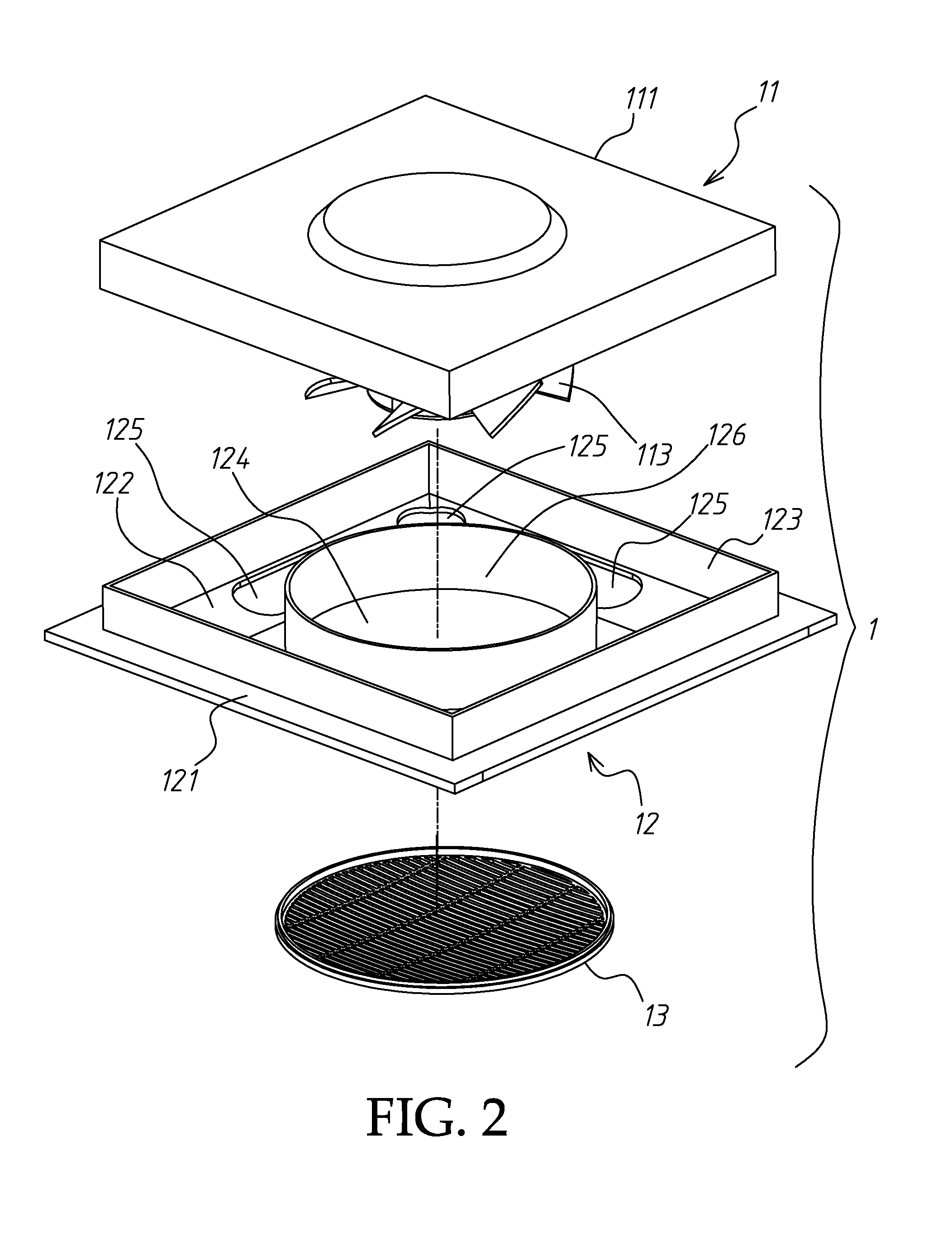

Fan structure for mounting in a light steel structure of a ceiling

InactiveUS20100021294A1Drawback can be obviatedGuaranteed current efficiencyPump componentsStatorsGate effectFan blade

A fan structure is disclosed to include a fan holder holding a fan motor and a fan blade, a bottom cover frame, which has smoothly arched bottom wall, a horizontal mounting flange extending around the smoothly arched bottom wall and mounted in one frame sash of a light steel structure of a ceiling, a vertical connection flange connected to the top cover shell of the fan holder, a circular center opening corresponding to the fan blade, ventilation holes spaced around the circular center opening and a fence disposed above the circular center opening and surrounding the fan blade defining with the top cover shell of the fan holder a space for causing a gate effect during rotation of the fan blade, and a grille mounted in the circular center opening of the bottom cover shell for output of currents of air caused by the fan blade.

Owner:YEH TIEN BAO

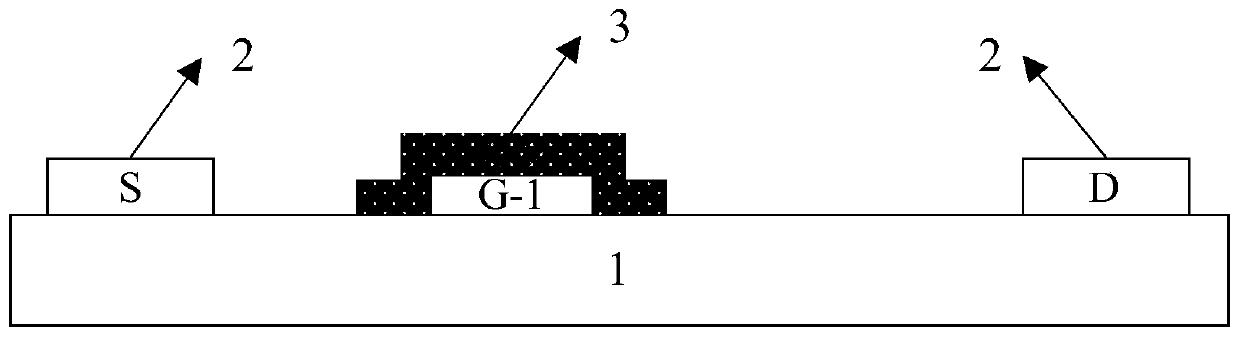

Split gate field effect transistor with a self-aligned control gate

A method of forming a split gate field effect transistor and a structure of the split gate field effect transistor are provided. The method of forming the split gate effect transistor firstly provides a substrate having a pair of floating gates, a first conductive material layer between the pair of floating gates, and a first dielectric layer above the first conductive material layer. Then a control gate is formed. The control gate has a second dielectric layer above the control gate, wherein the control gate is self-aligned to the pair of floating gates by using the first and second dielectric layers as an etching hard mask. Finally, a pair of source / drain regions are formed into said substrate and beside said pair of floating gates and said control gate.

Owner:TAIWAN SEMICON MFG CO LTD

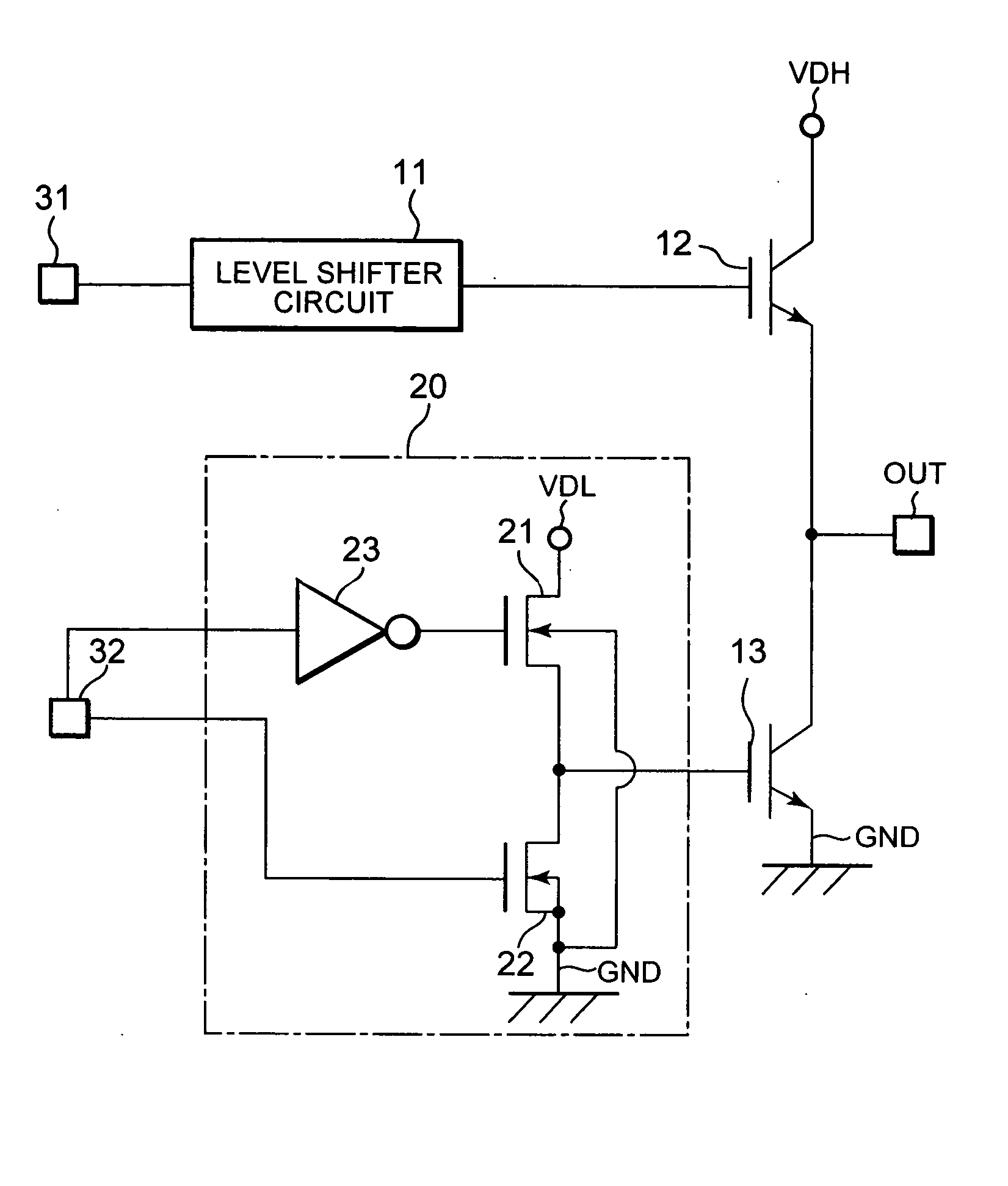

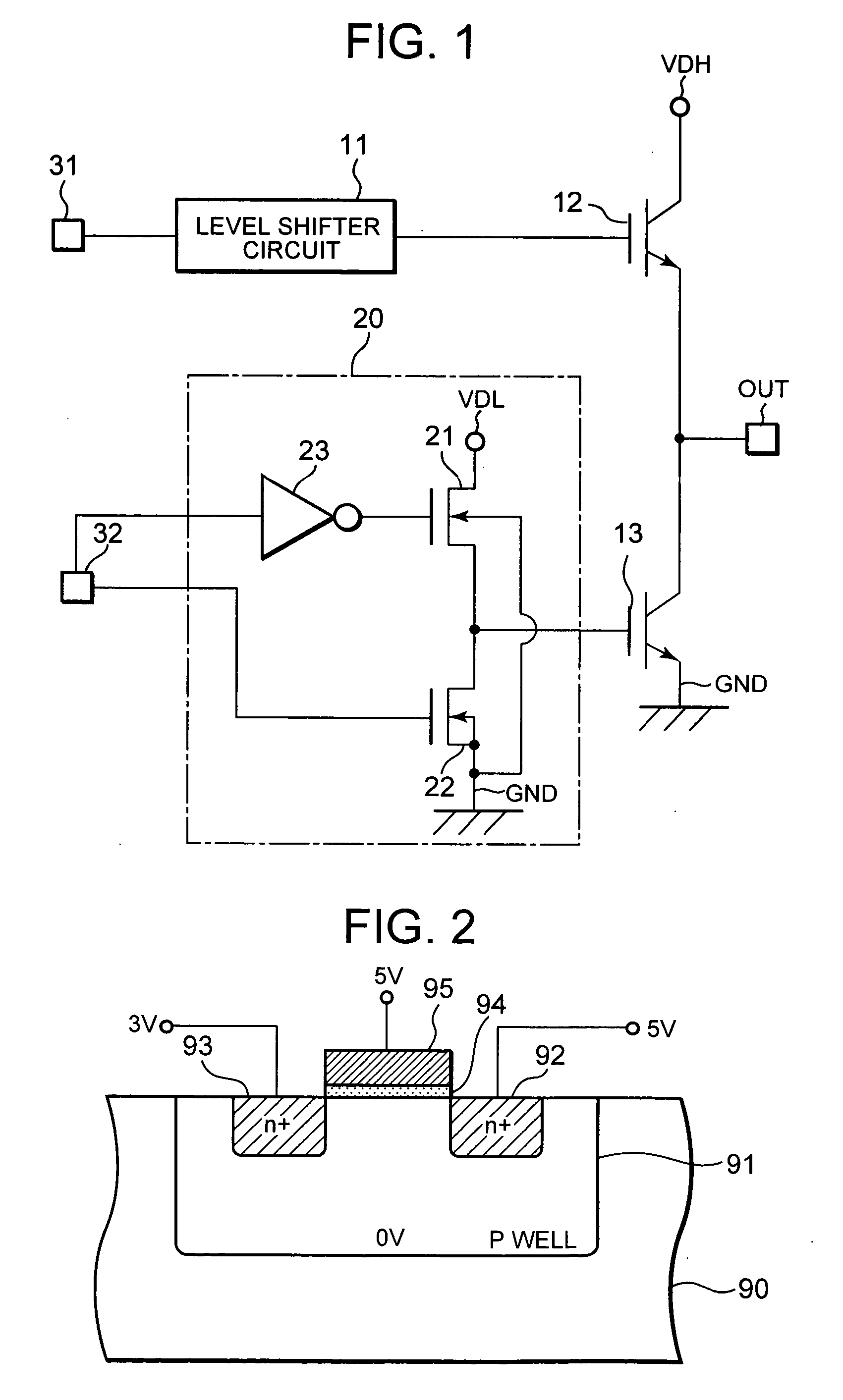

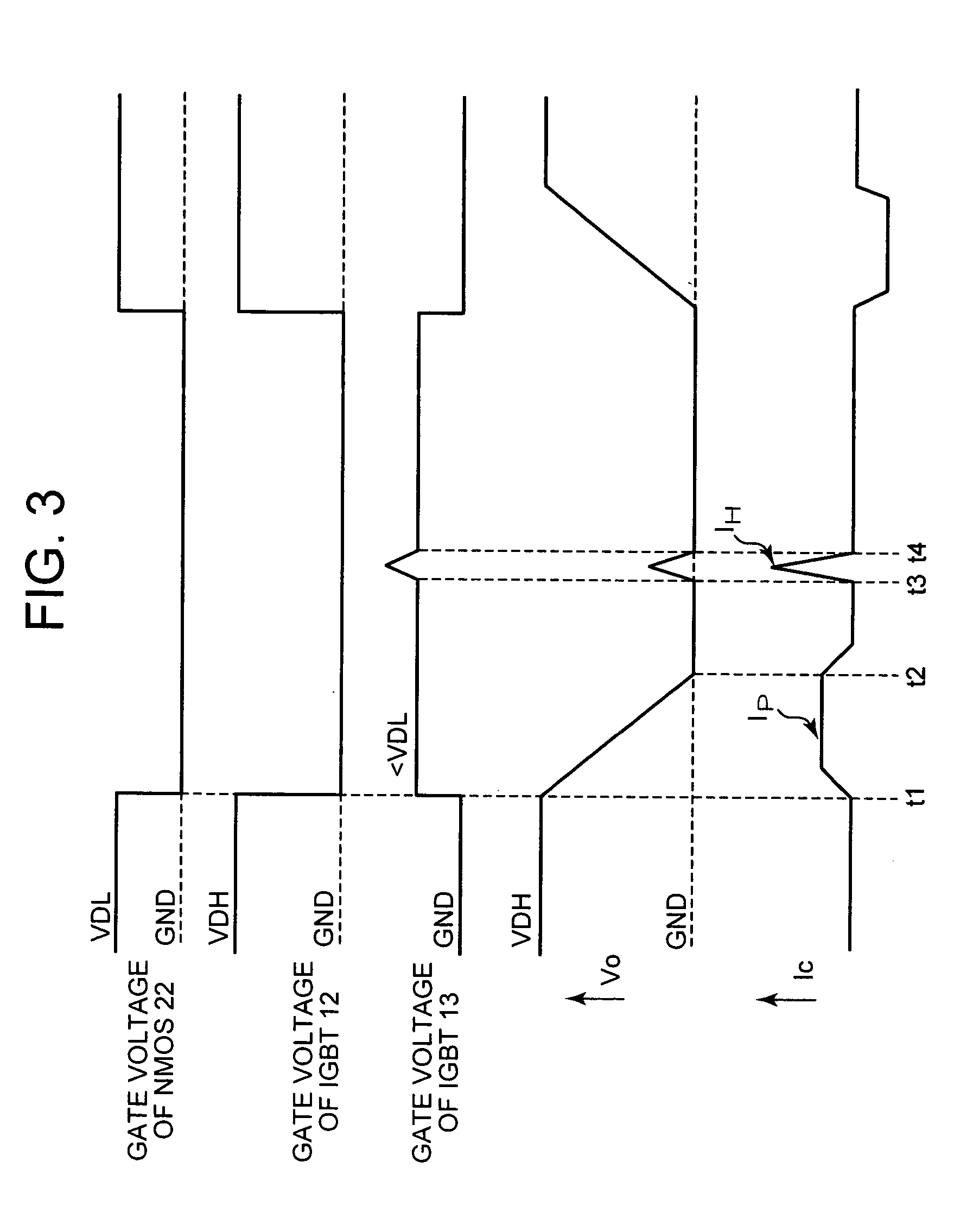

Display apparatus driving circuitry

InactiveUS20050035960A1Avoid noiseBreakage of the device due to an excessive current upon short-circuiting of the output can be preventedCathode-ray tube indicatorsInput/output processes for data processingMOSFETDriver circuit

A display apparatus driving circuitry for driving a plasma display panel. A first transistor is electrically connected between an output terminal and a high-voltage power supply terminal. A second transistor is connected between the output terminal and a reference power supply terminal. A buffer circuit supplies a voltage lower than a low voltage VDL for logic to a gate of the second transistor to make a drop in an output waveform gradual during an address electrical discharge. In a preferred embodiment, during this drop in the output waveform, a p-channel type MOSFET of the buffer circuit is turned on, whereby the VDL is suppressed due to a back gate effect. Therefore, a signal at a potential lower than the VDL is inputted to the gate of the second transistor. As a result, the drop in the second transistor output waveform is gradual, so that noise and damage are prevented.

Owner:FUJI ELECTRIC CO LTD

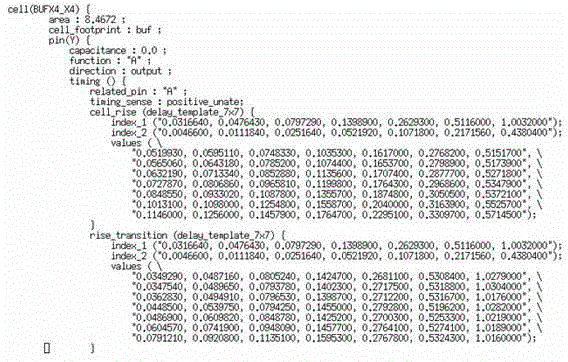

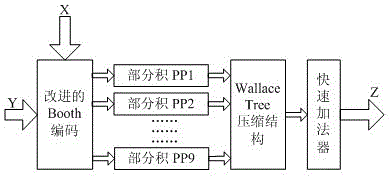

ECO (Engineering Change Order) optimization method of multiplier based on standard cell library extension

InactiveCN102622466AImprove performanceAutomate your designSpecial data processing applicationsPerformance functionCapacitance

The invention relates to an ECO (Engineering Change Order) optimization method of a multiplier based on standard cell library extension. The traditional optimization method is limited in finite drive capability of the standard cells in the library, and cannot realize the shortest path delay. The ECO optimization method comprises the steps as follows: firstly, generating a layout of an extension unit, and characterizing the extension unit to obtain an extension unit library, wherein the characterizing the extension unit comprises characterizing the delay information, characterizing an input port capacitor, characterizing the power consumption, characterizing the area and characterizing a performance function; secondly, performing time series analysis on the multiplier to obtain a key path of the multiplier; and lastly, enabling the gate effects of all stages of the key path of the multiplier to be the same by using the extension unit library so as to obtain the shortest path delay. According to the ECO optimization method, on the premise of not remarkably increasing the design cycle, the key path of the multiplier is analyzed, the shortest path delay is realized, and the performance of the multiplier is improved; in addition, the design automation is conveniently implemented, and the ECO optimization method is also suitable for the rear-end ECO optimization of other digital systems.

Owner:ZHEJIANG UNIV

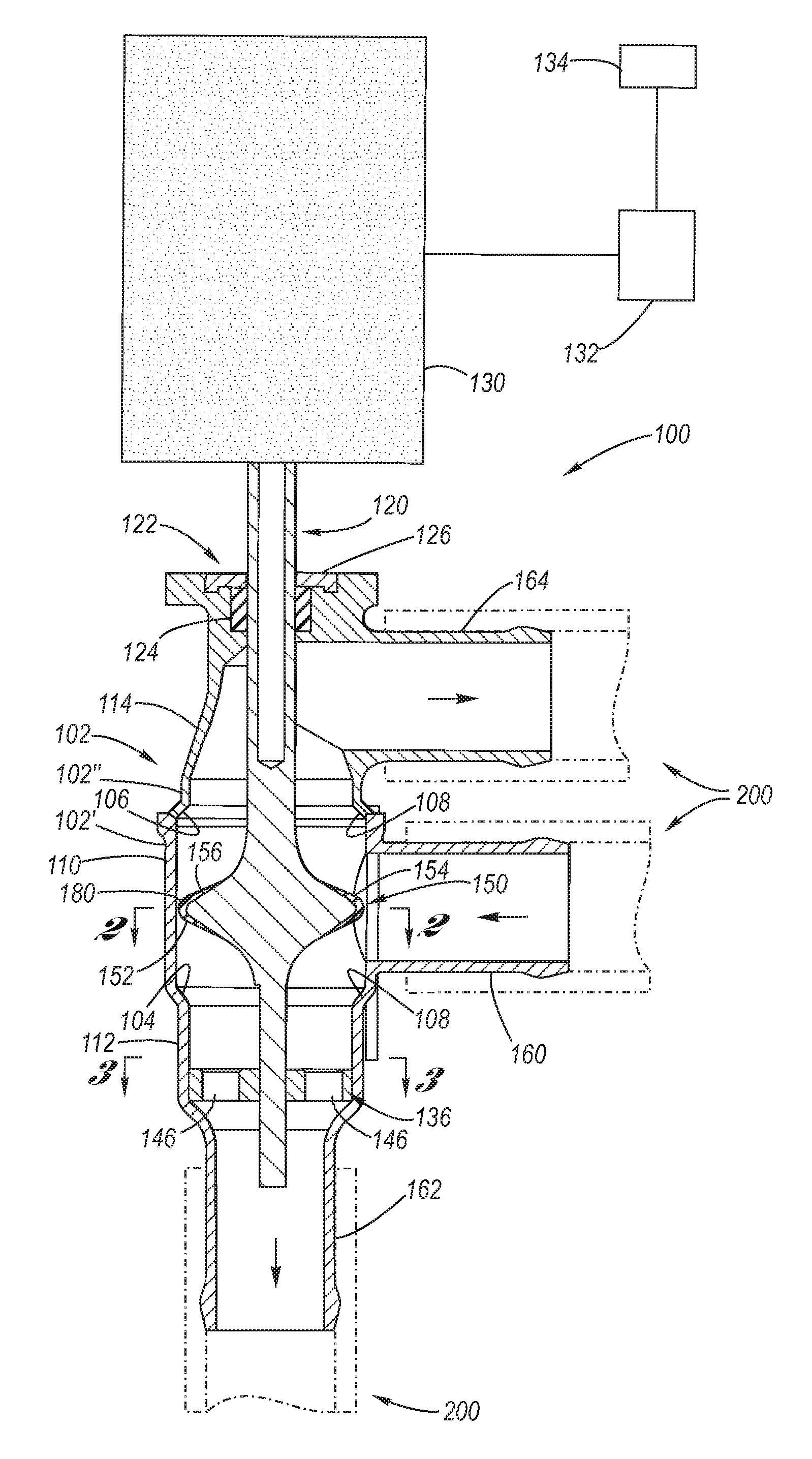

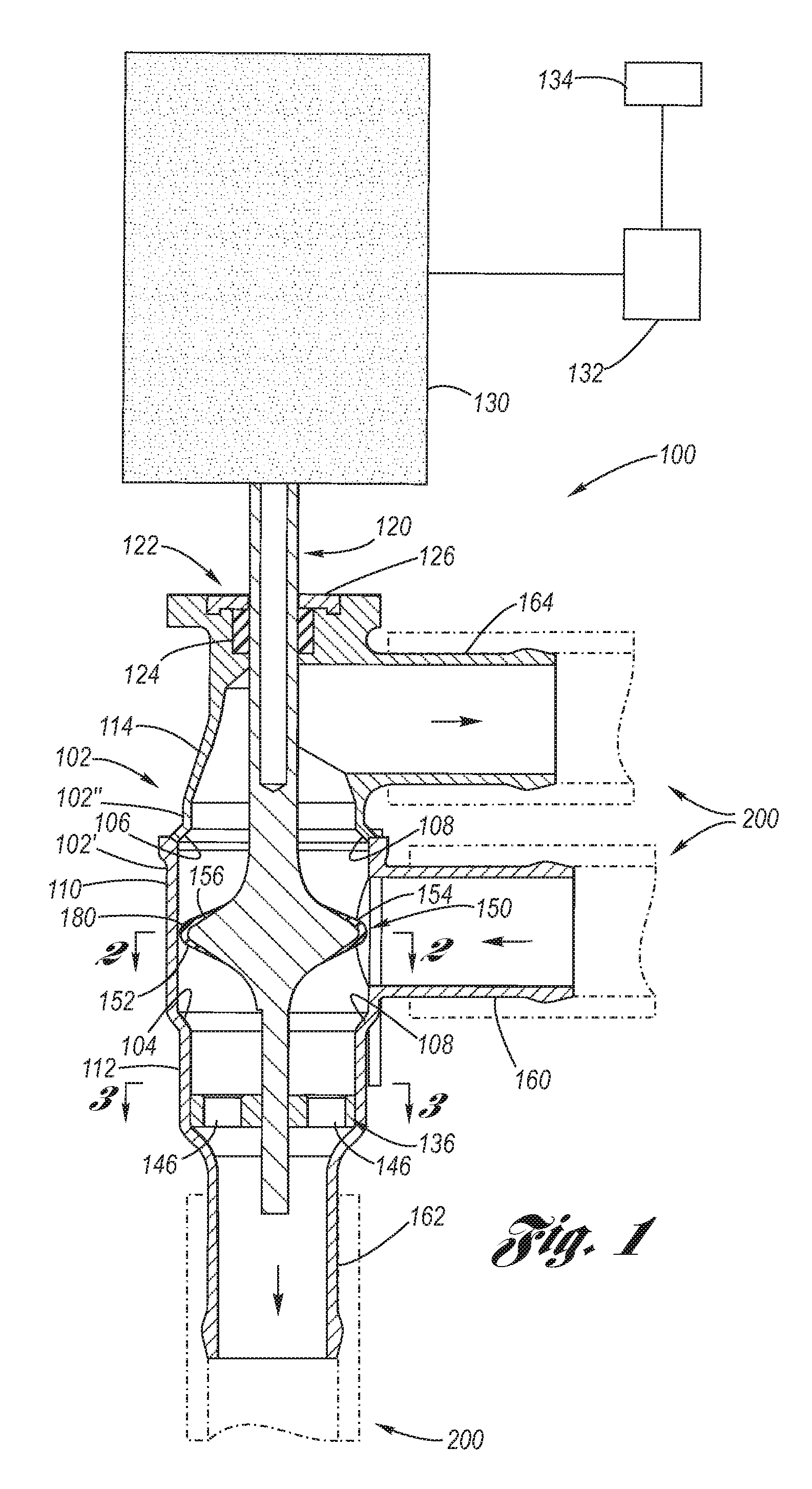

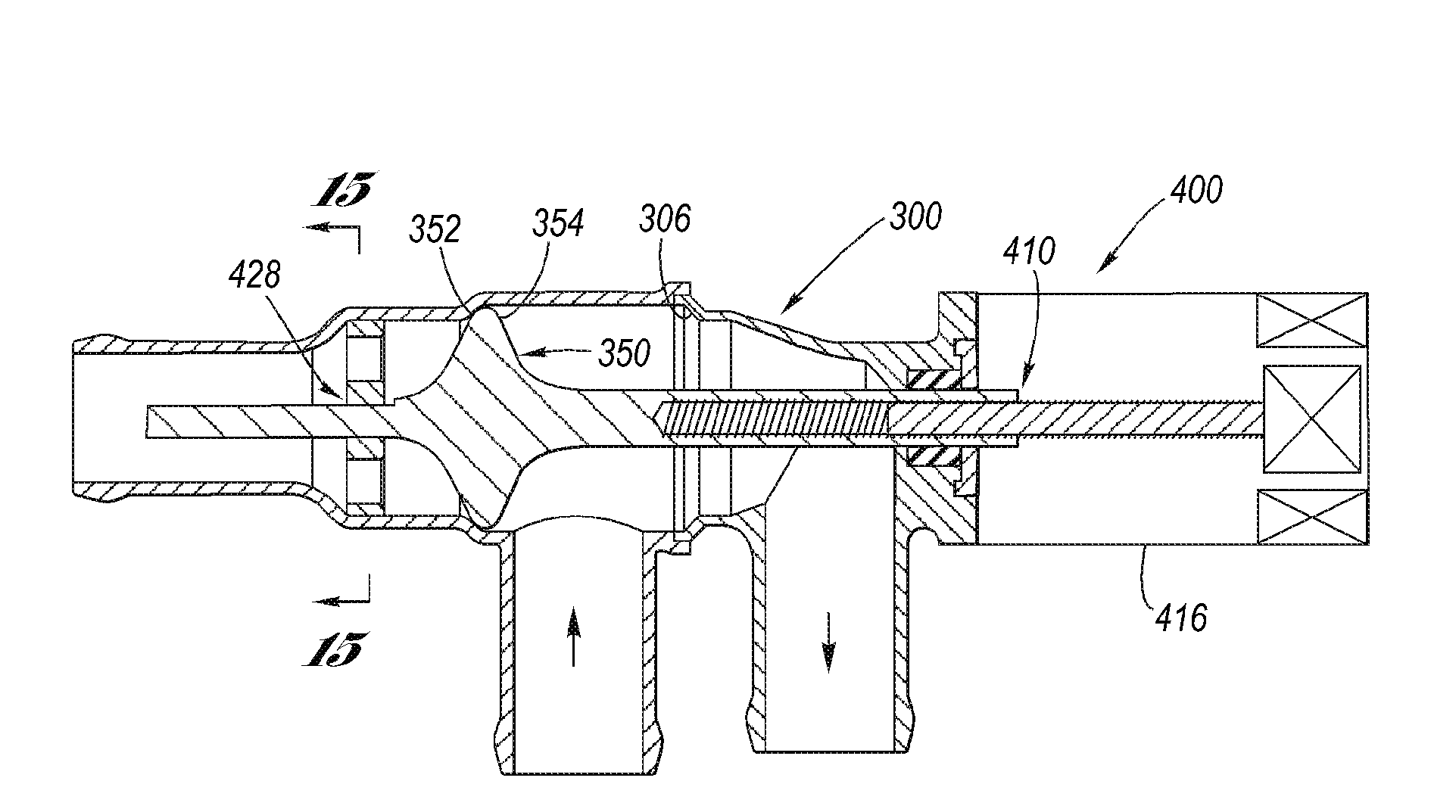

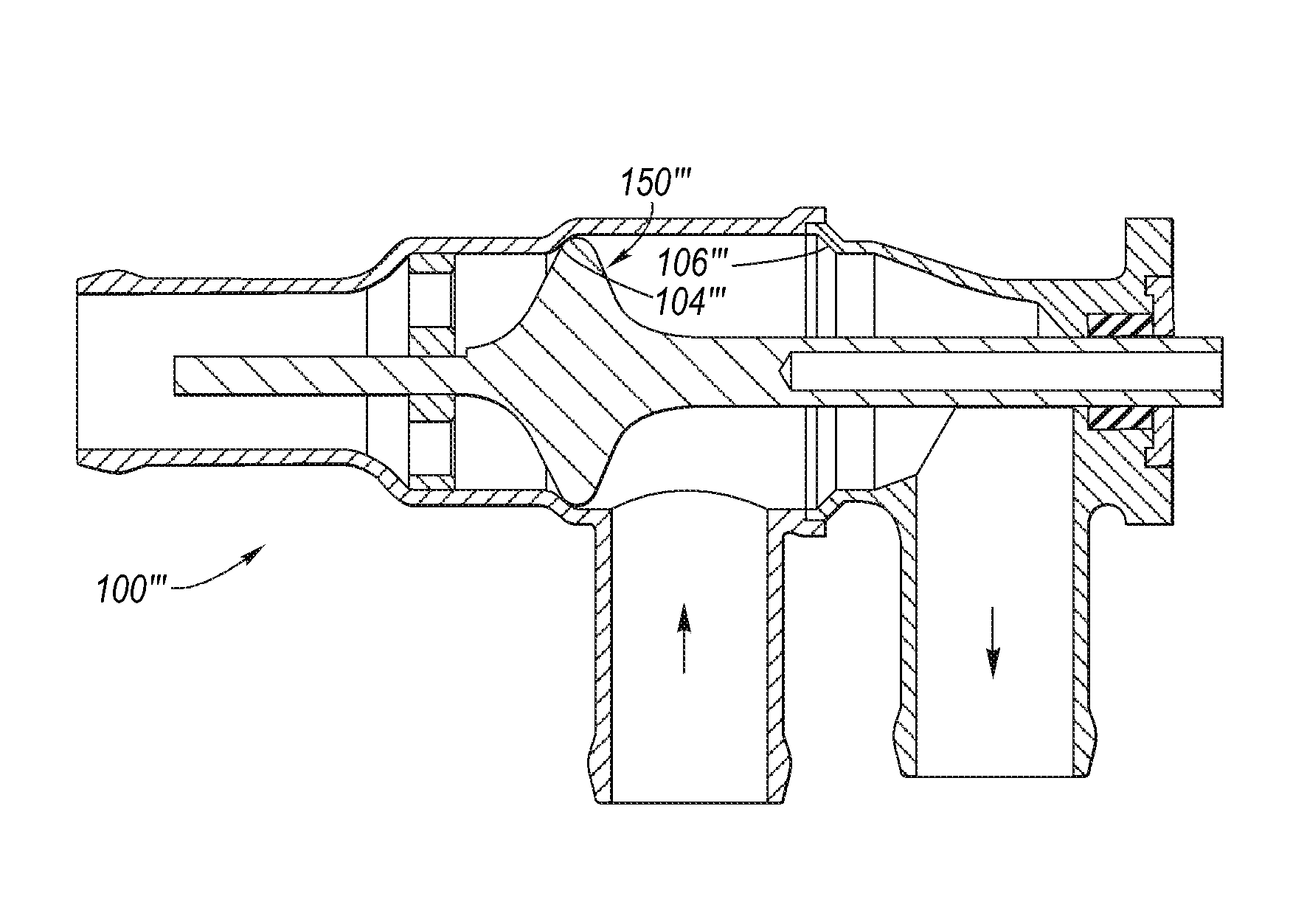

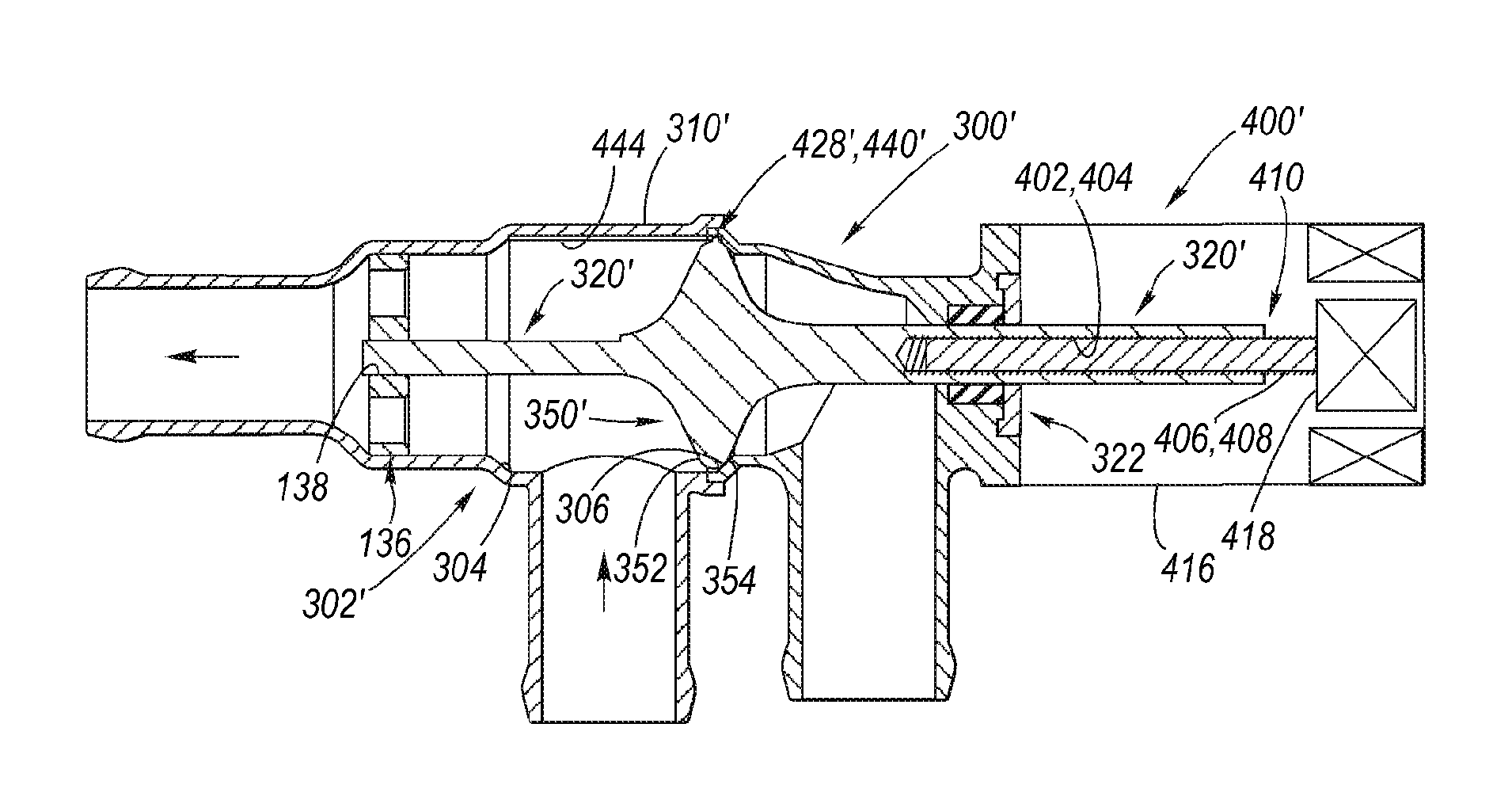

Drive System For An Electro-Mechanical Three-Way Dual Seat Valve

InactiveUS20130105721A1Minimizes seal surfaceReduces and eliminates leakageOperating means/releasing devices for valvesMultiple way valvesReciprocating motionEngineering

A three-way dual seat valve having a valve body including mutually spaced apart annular first and second valve seats. Reciprocally mounted with respect to the valve body is a dual-faced valve stem gate, wherein each gate face thereof is sealingly engageable with a respective valve seat in response to reciprocal movement of the valve stem gate effected via a leadscrew drive system.

Owner:GM GLOBAL TECH OPERATIONS LLC

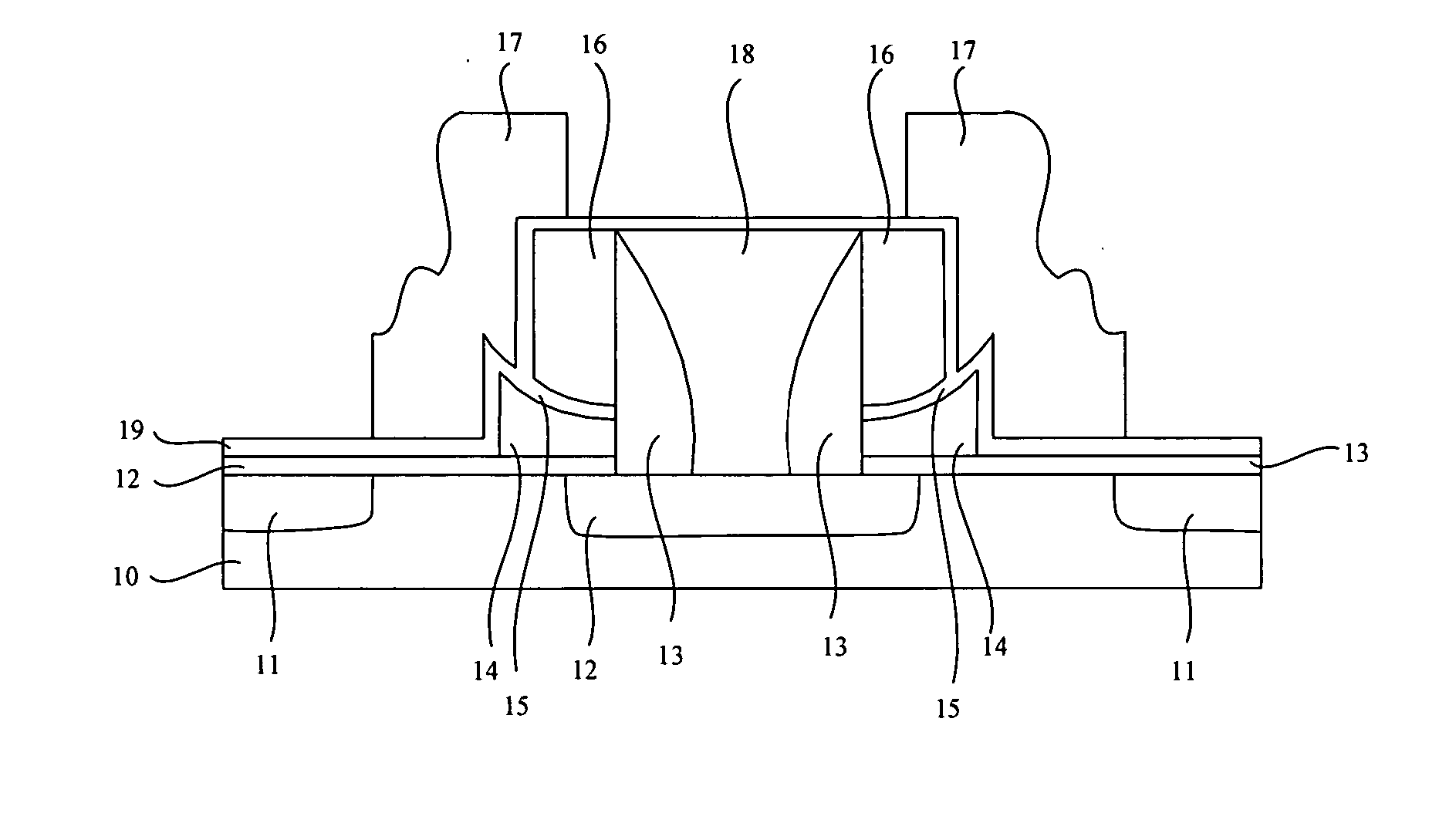

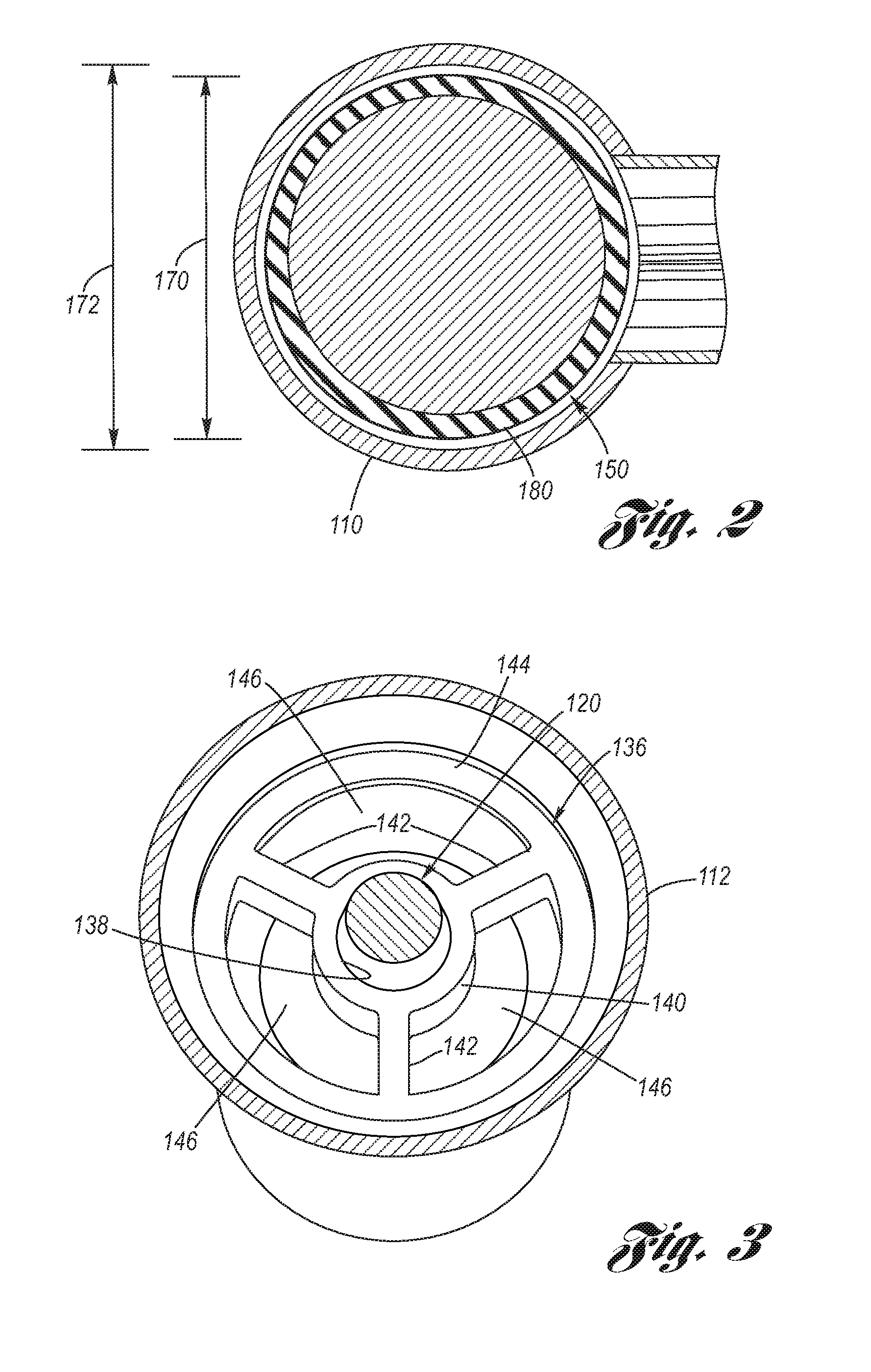

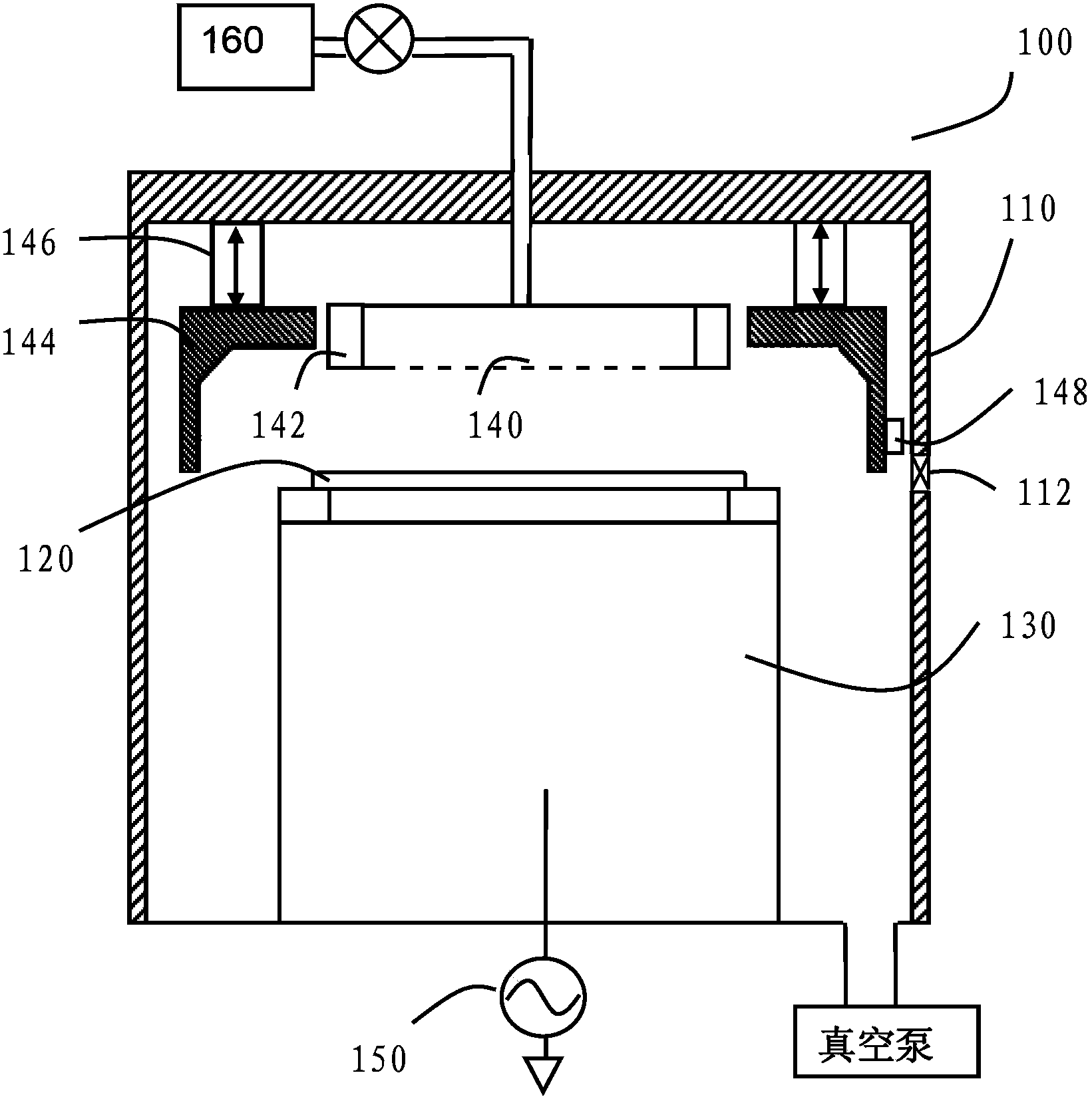

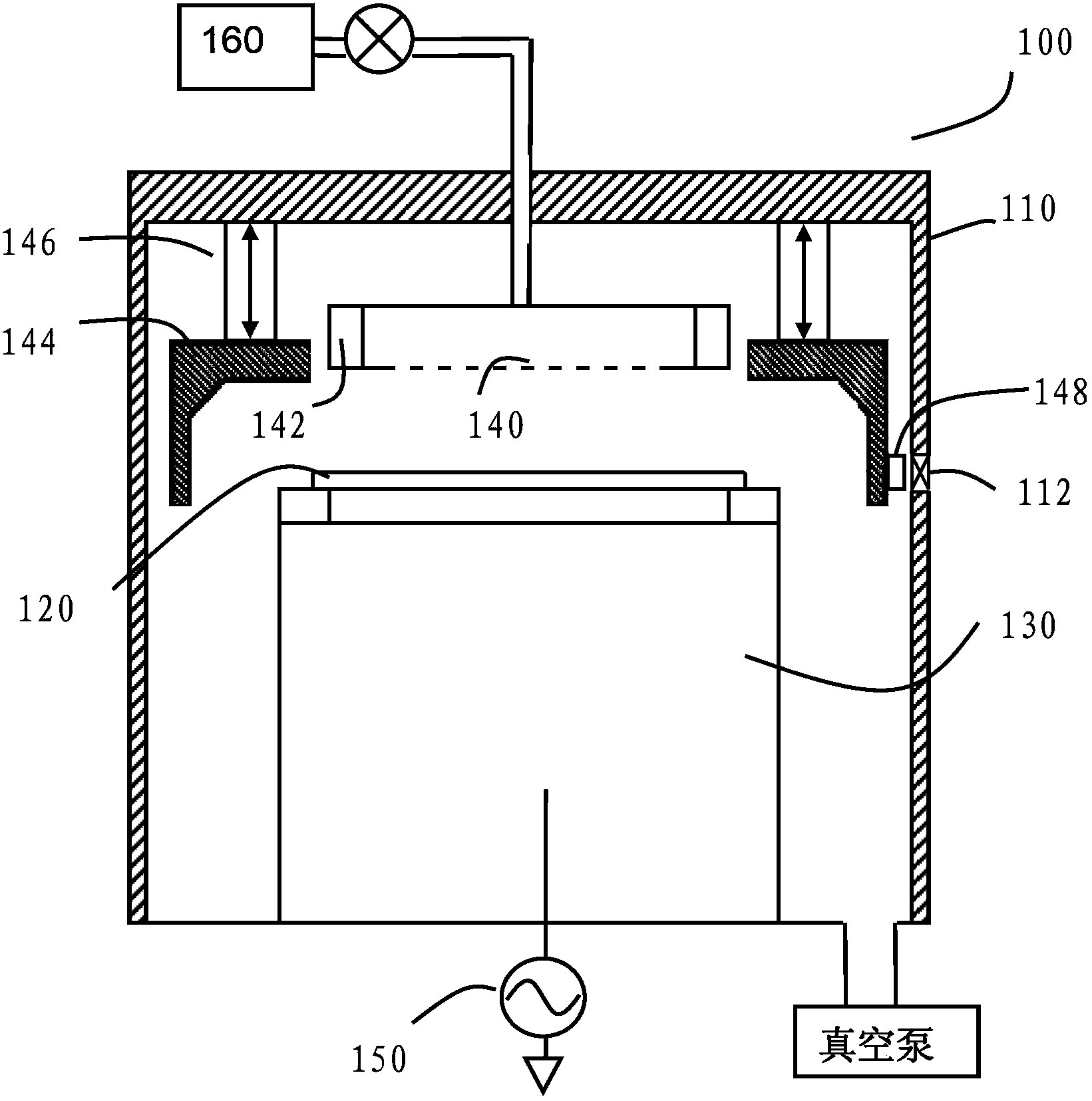

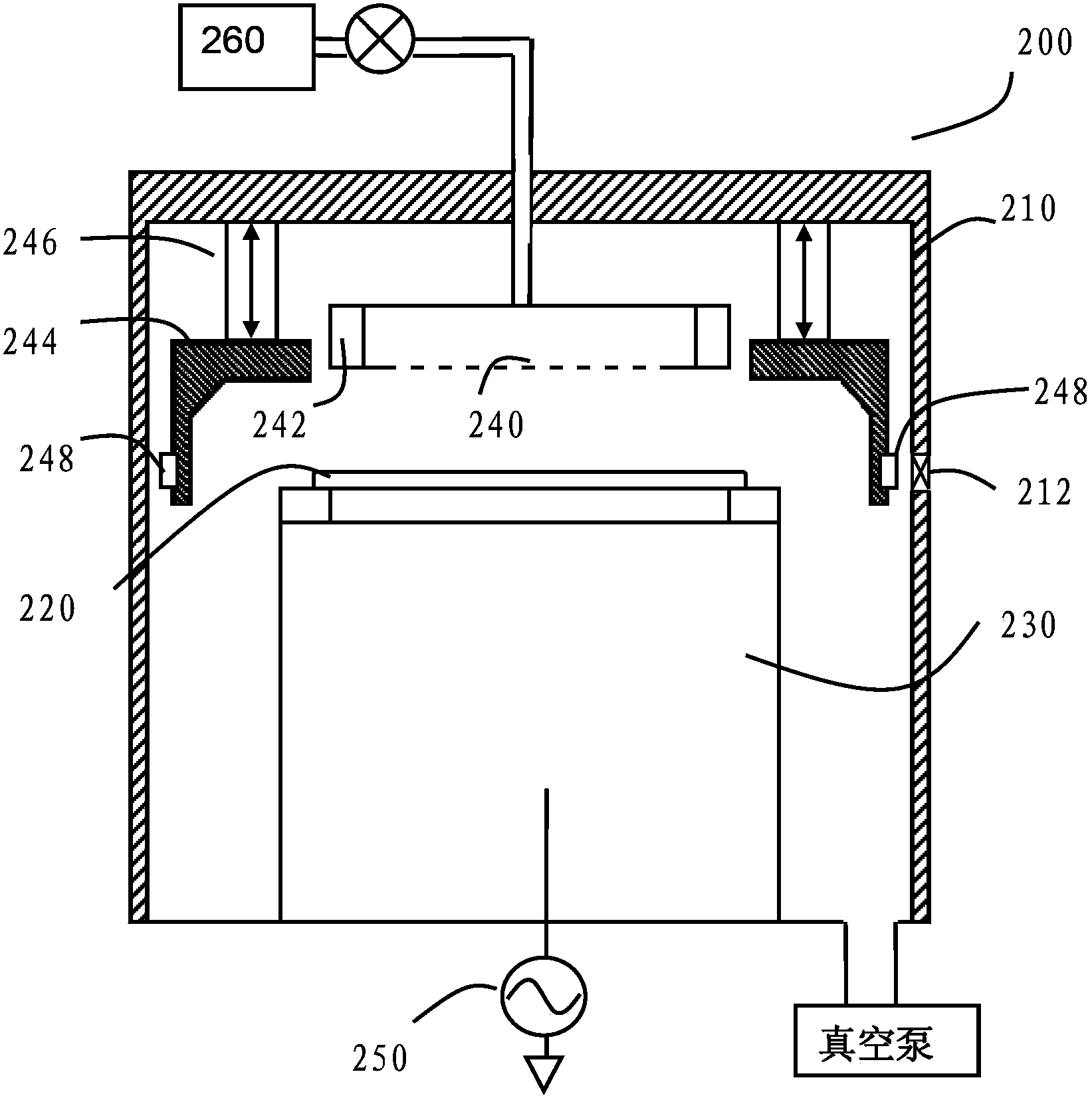

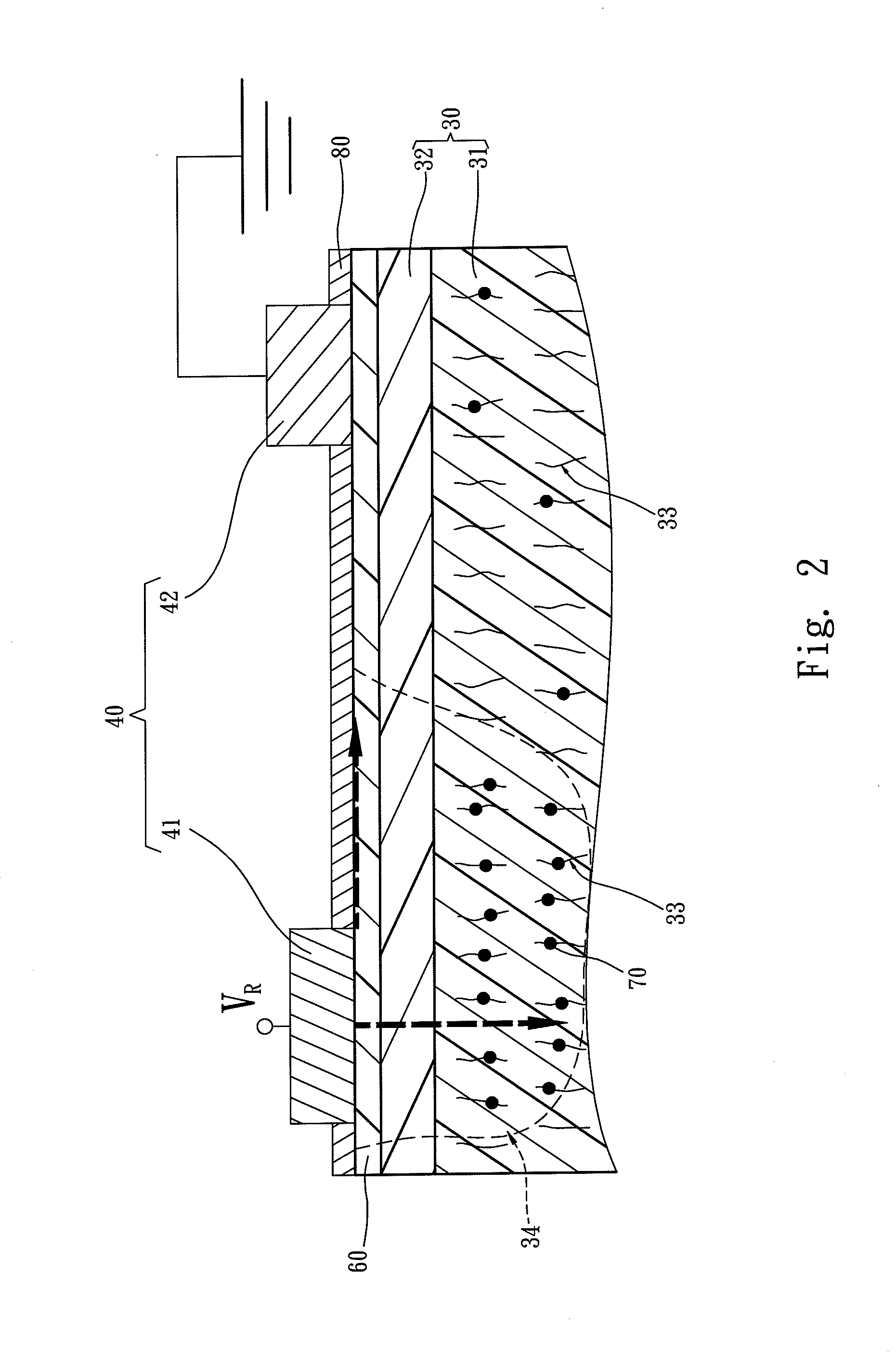

Plasma processing apparatus capable of reducing gate effect

ActiveCN104051210ADistribution regulationSolve the technical problem of uneven electric field distributionElectric discharge tubesEngineeringAluminum metal

The invention discloses a plasma processing apparatus capable of reducing a gate effect. A lifting ring that can move up and down and encircles gas spraying head is arranged in a plasma processing cavity. A metal baffle plate is fixedly arranged at one side, approaching the side wall of the processing cavity, of the lifting ring and preferably, an aluminum metal baffle plate made of the same material as that of the side wall of the processing cavity is used, so that the metal baffle plate can shield a gate opening of the side wall of the processing cavity when the lifting ring descends. Therefore, a technical problem that electrical field distribution in the processing cavity is not uniform due to the gate opening of the side wall of the processing cavity can be solved. According to the technical scheme, the structure of the apparatus is simple. On the basis of the existing lifting ring, the lifting ring and the metal baffle plate are fixedly connected by a bolt or by cutting a groove for embedding the metal baffle plate in one side, approaching the side wall of the processing cavity, of the lifting ring. On the basis of the simple structure, the electric field distribution at the gate opening can be effectively adjusted, thereby effectively adjusting the electric field distribution uniformity in the processing cavity.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

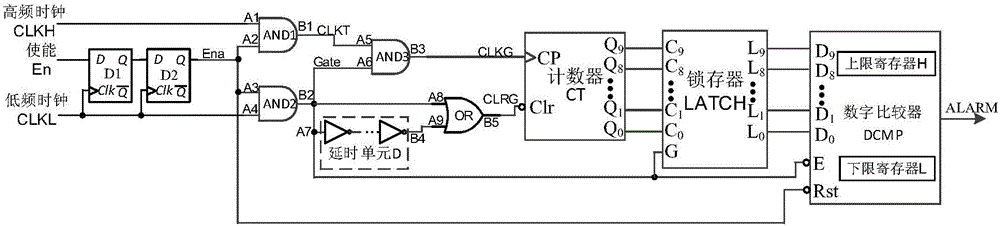

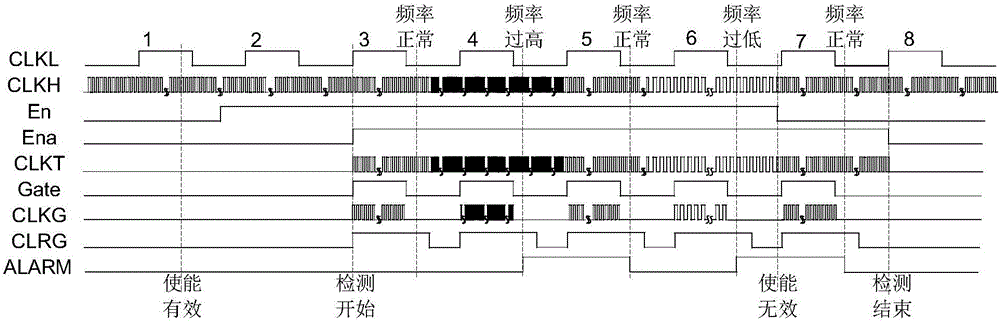

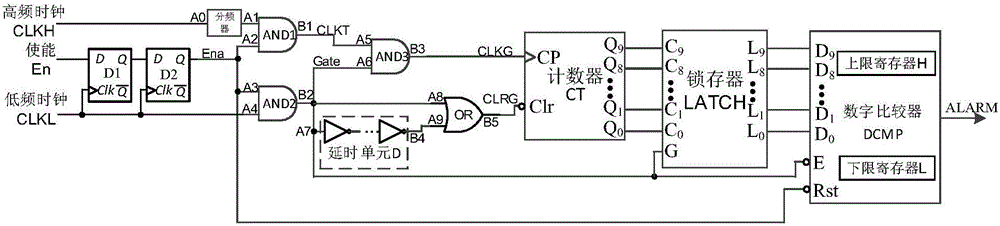

High-frequency clock frequency detection structure for resisting attack chip

ActiveCN106209034AFlexible changeReduce power consumptionPulse train pattern monitoringPlatform integrity maintainanceDelayed timeEngineering

The invention discloses a high-frequency clock frequency detection structure circuit for resisting an attack chip. The circuit comprises two D triggers which are connected in series and are triggered by a rising edge, three two-input AND gate, a delay unit D, an OR gate, a 10-bit asynchronous reset binary addition counter CT, a 10-bit latch and a 10-bit digital comparer DCMP. The two D triggers which are triggered by the rising edge, and the three two-input AND gate form a gate control clock structure. The delay unit D is formed by connecting the even number of phase inverters in series. Delay time is controlled by adjusting the number of the phase inverters. Two 10-bit registers, a frequency upper limit register H and a frequency lower limit register L, are contained in the10-bit digital comparer DCMP. The delay unit D or the OR gate forms a delay reset structure. An internal low-frequency clock is taken as a counting gate, the number of high-frequency clock periods is counted in fixed time, and the high-frequency clock frequency is deduced. When the obtained frequency exceeds a normal working frequency range, an alarm signal is generated.

Owner:TIANJIN UNIV

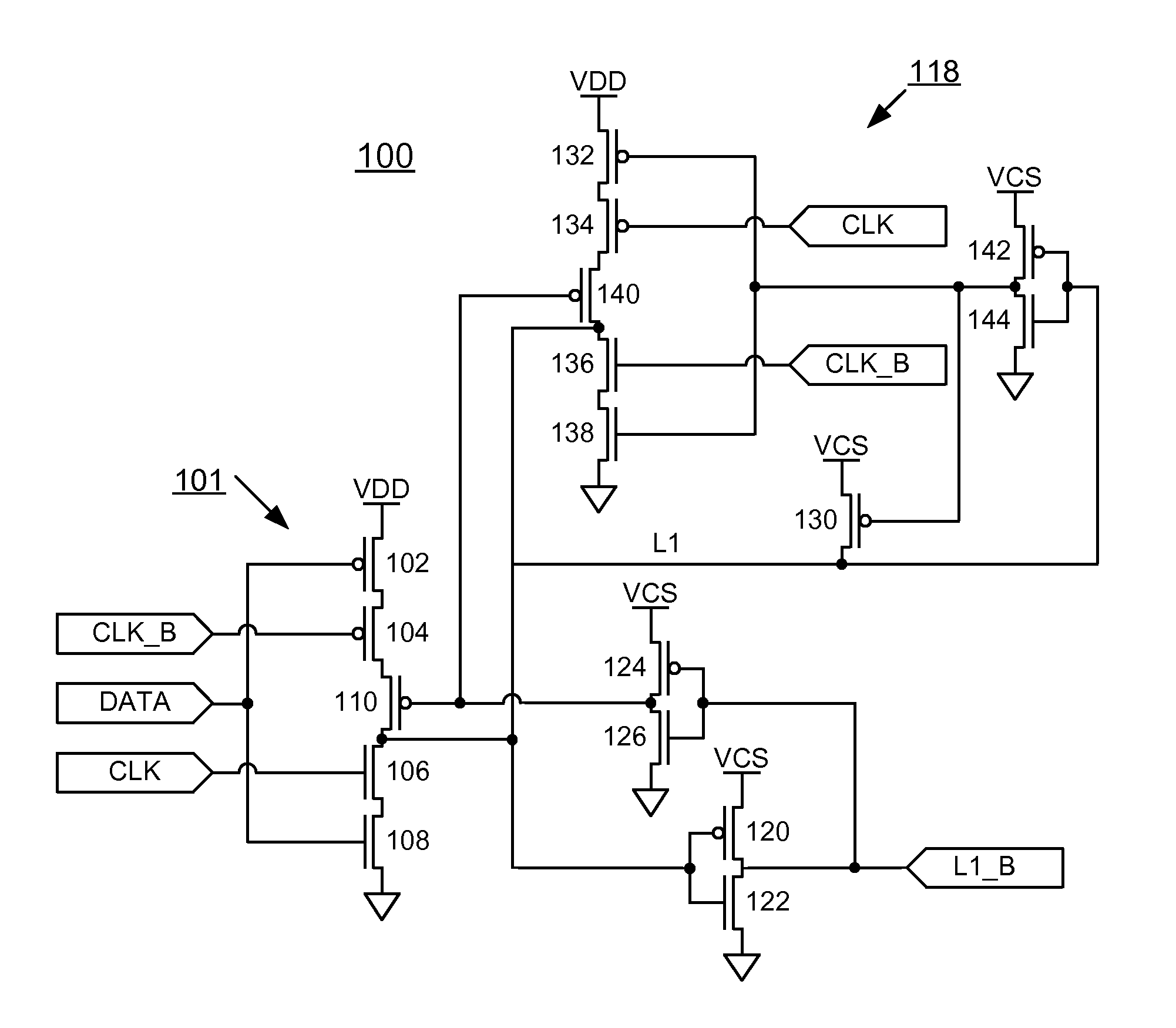

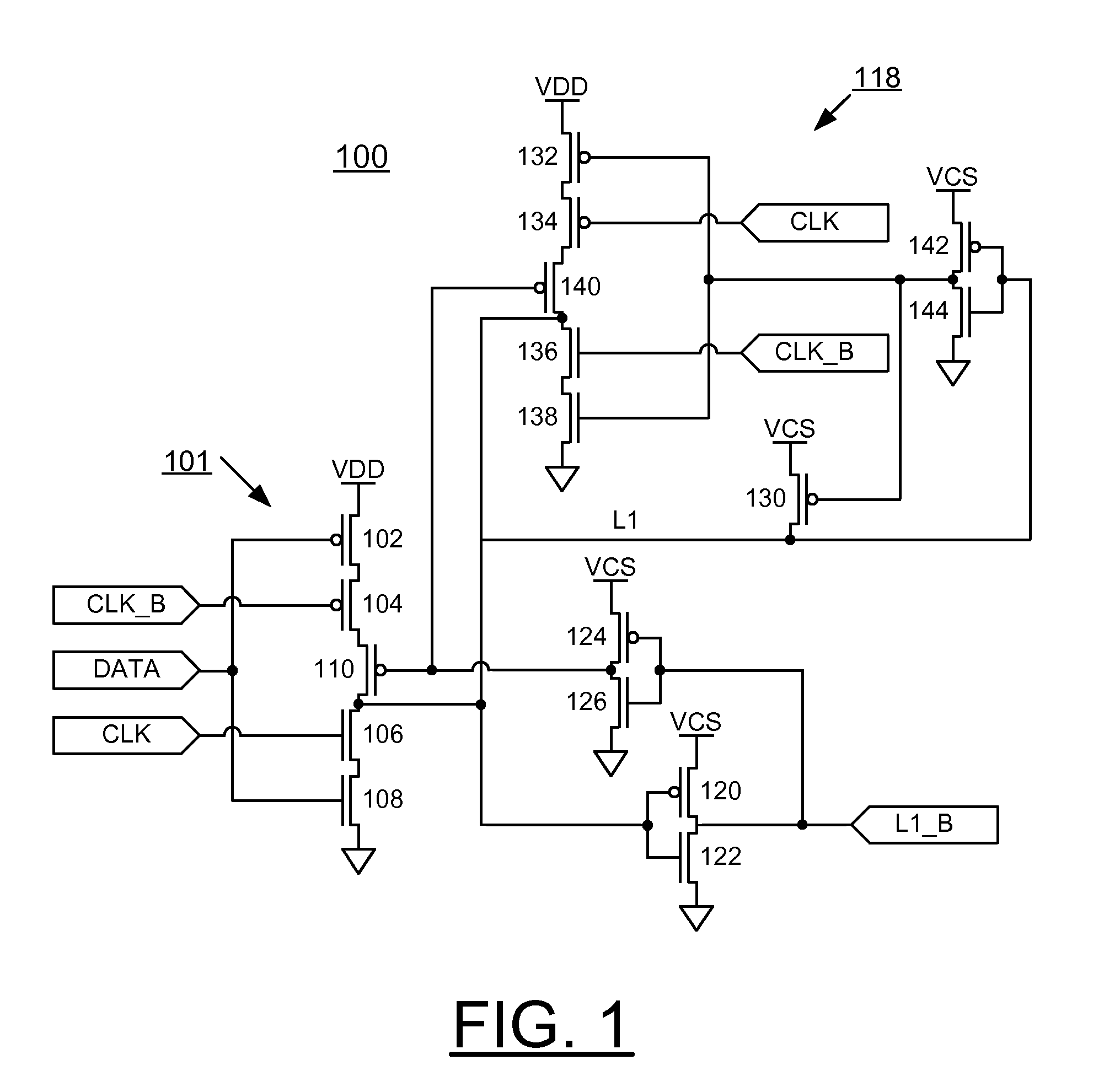

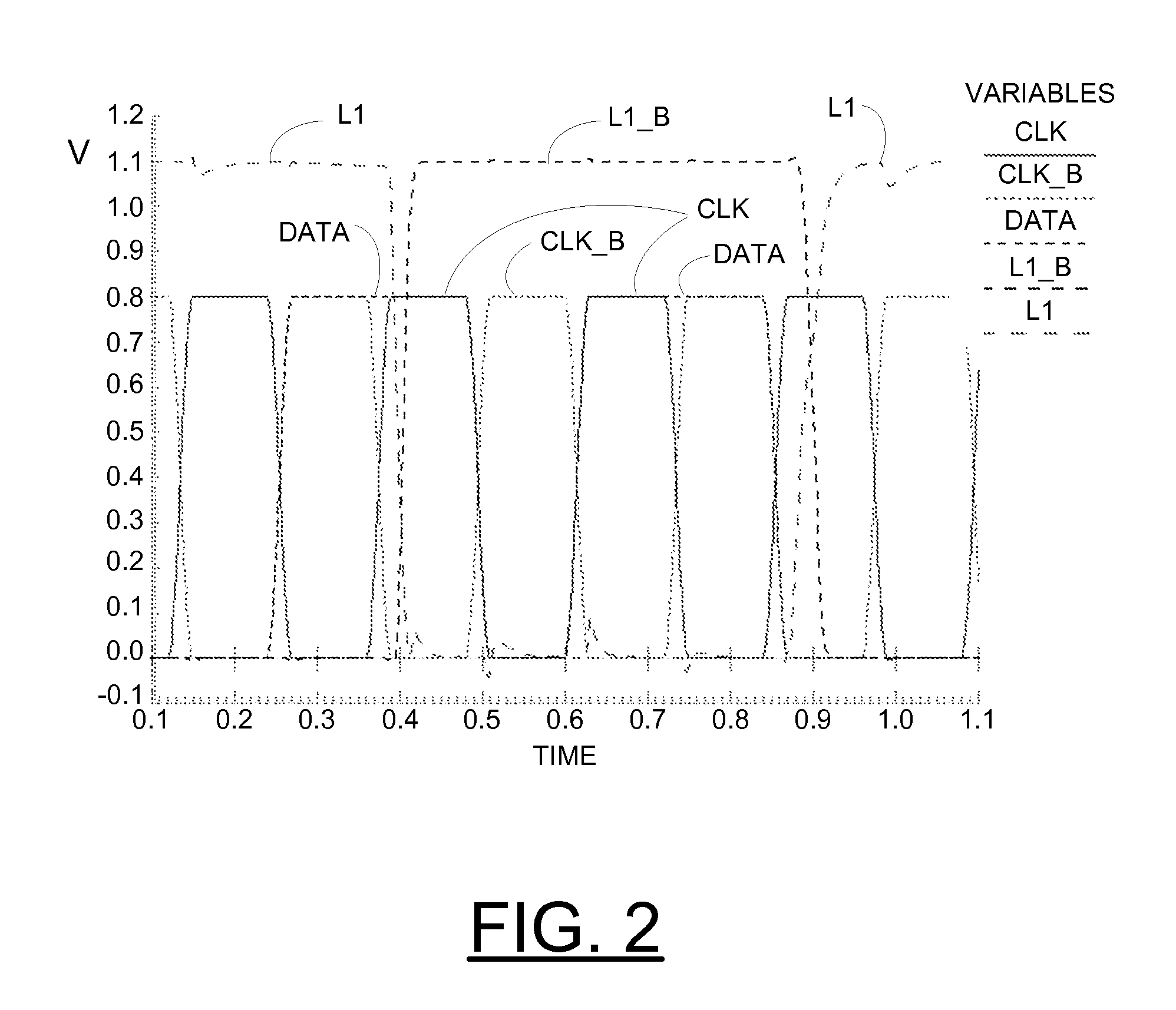

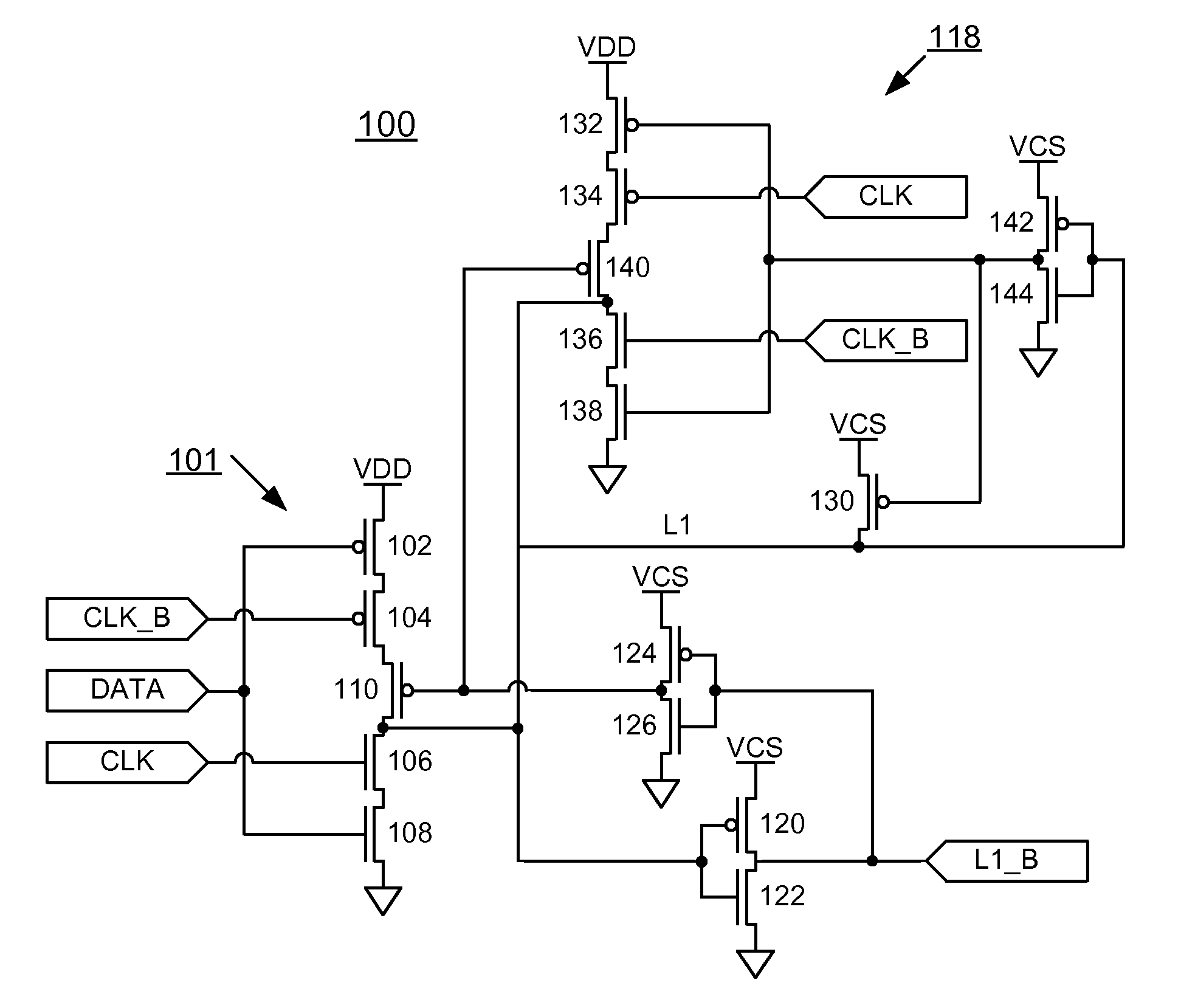

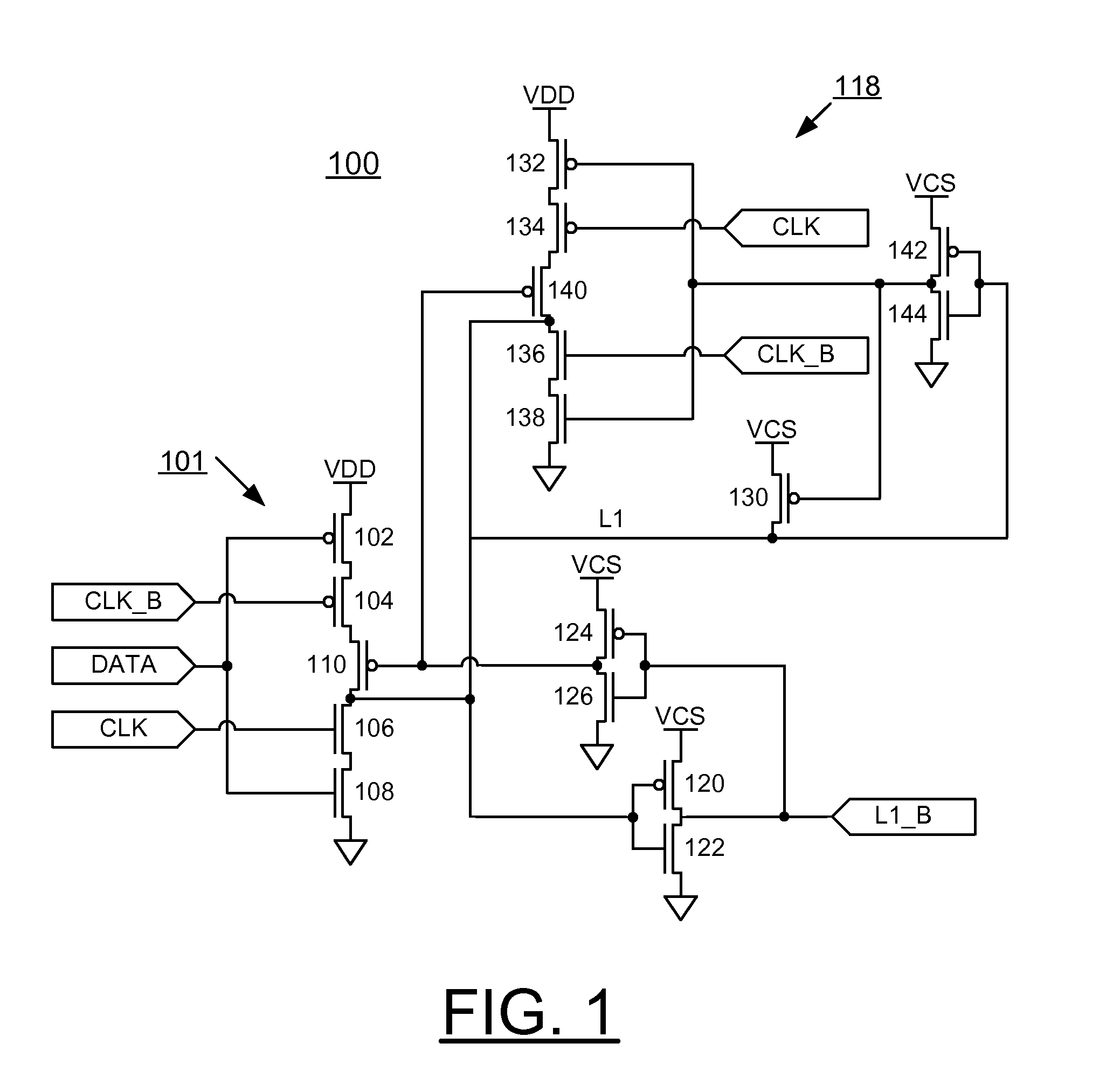

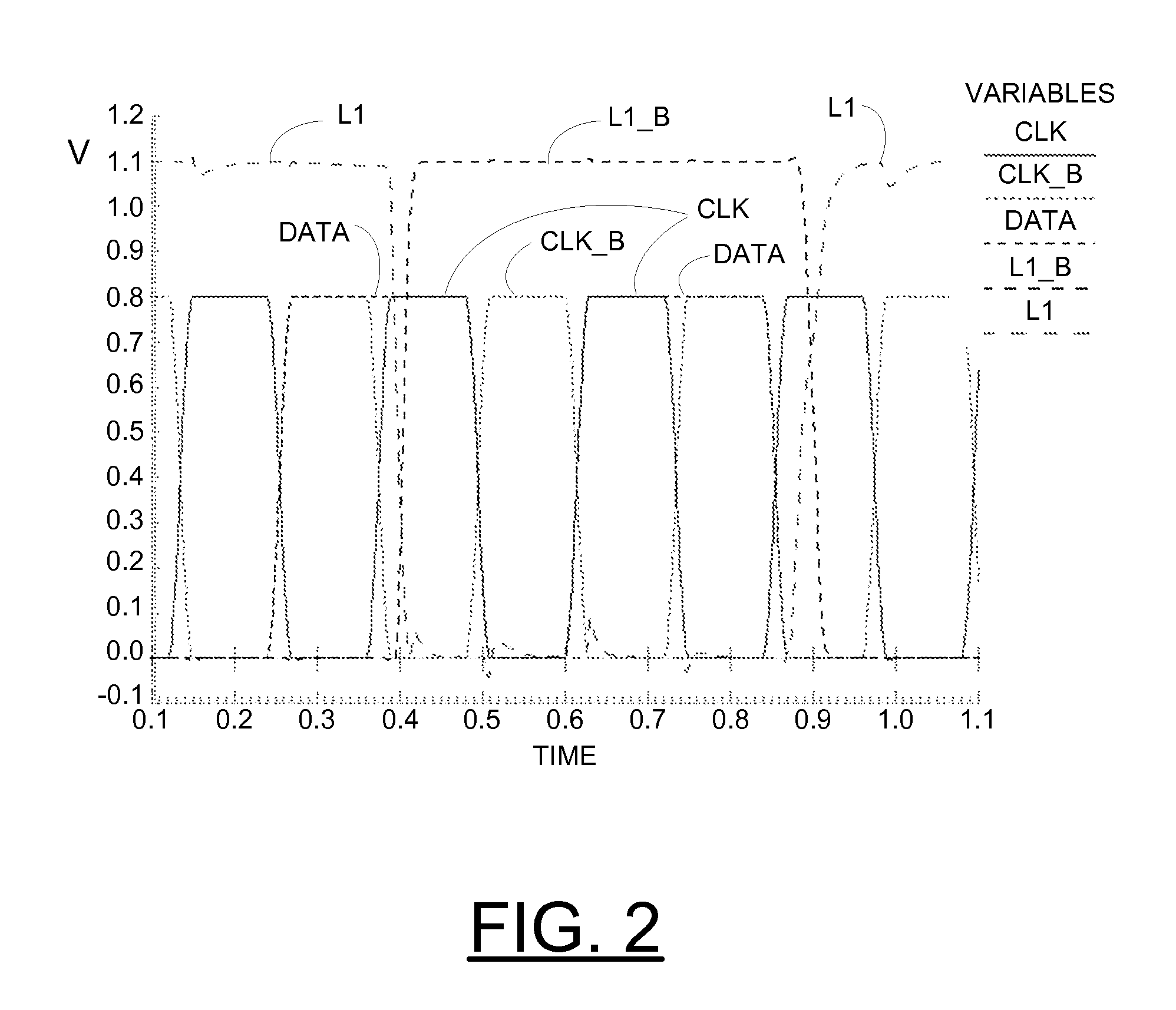

Low power level shifting latch circuits with gated feedback for high speed integrated circuits

Low power level shifter latch circuits with gated feedback for high speed integrated circuits, and a design structure on which the subject circuit resides are provided. A latch input stage operating in a domain of a first voltage supply receives a data input responsive to being enabled by predefined clock signals. A latch storage element coupled to the latch input stage includes a latch output stage operating in a domain of a second voltage supply provides a data output having a voltage level corresponding to the second voltage supply. The latch storage element includes a level shifting device providing level shifting from the first supply level to the second voltage supply level. The latch storage element includes feedback gate devices receiving the predefined clock signals to gate feedback to the latch input stage when data is being written to the latch input stage.

Owner:IBM CORP

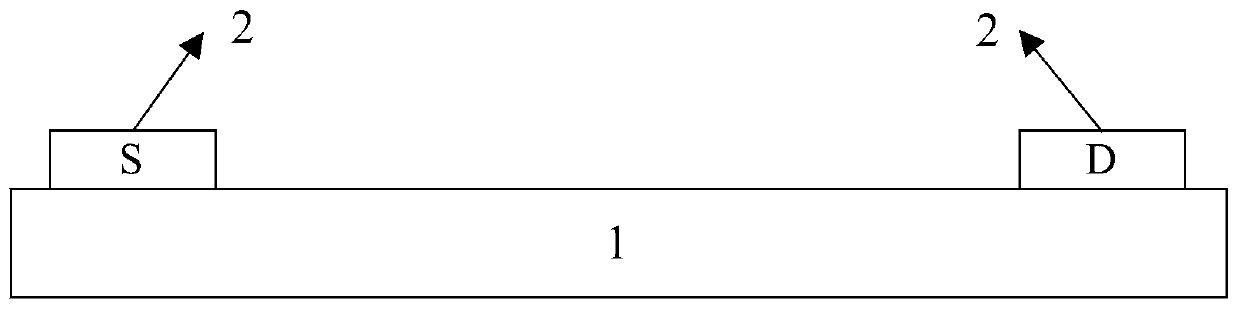

Semiconductor element having high breakdown voltage

InactiveUS20130240895A1Reduce leakage currentImprove breakdown voltageSemiconductor/solid-state device manufacturingDiodeEngineeringGate effect

A semiconductor element having a high breakdown voltage includes a substrate, a buffer layer, a semiconductor composite layer and a bias electrode. The buffer layer disposed on the substrate includes a high edge dislocation defect density area. The semiconductor composite layer disposed on the buffer layer includes a second high edge dislocation defect density area formed due to the first high edge dislocation defect density area. The bias electrode is disposed on the semiconductor composite layer. A virtual gate effect of defect energy level capturing electrons is generated due to the first and second high edge dislocation defect density areas, such that an extended depletion region expanded from the bias electrode is formed at the semiconductor composite layer. When the bias electrode receives a reverse bias, the extended depletion region reduces a leakage current and increases the breakdown voltage of the semiconductor element.

Owner:NAT CENT UNIV

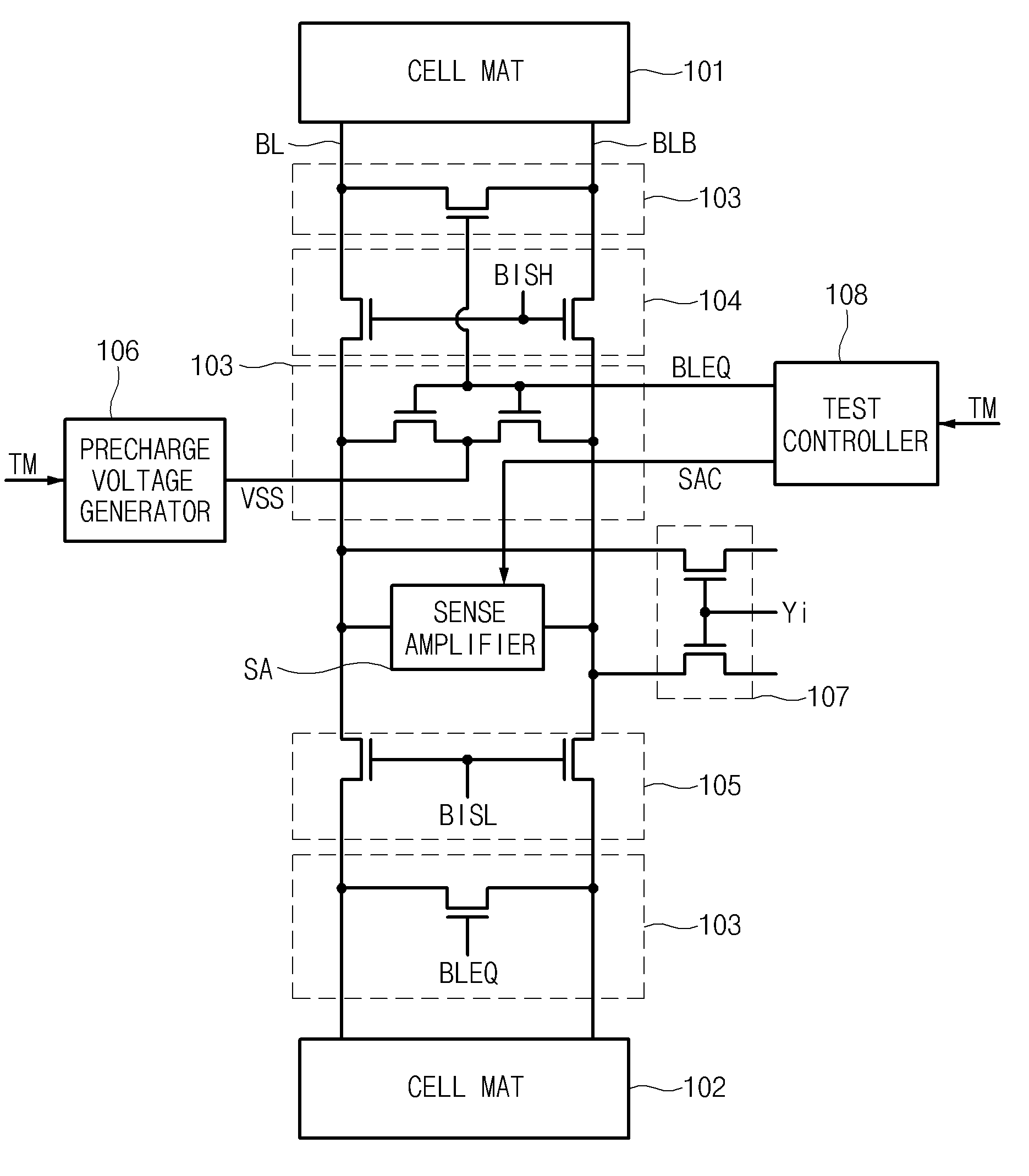

Semiconductor device and method for testing the same

A semiconductor device and a method for testing the same are disclosed, relating to a technology for simultaneously screening an off-leakage-current fail caused by a passing gate effect and a neighbor gate effect. The semiconductor device includes a memory cell configured to read and write data; a sense amplifier configured to sense and amplify cell data received from the memory cell through a pair of bit lines; a bit line precharge unit configured to equalize the pair of bit lines to a level of a ground voltage in response to a bit line equalization signal; a precharge voltage generator configured to provide the ground voltage to the bit line precharge unit during a test mode; and a test controller configured to, during the test mode, maintain an activation state of the bit line equalization signal during a test mode period, and control the sense amplifier to be deactivated.

Owner:SK HYNIX INC

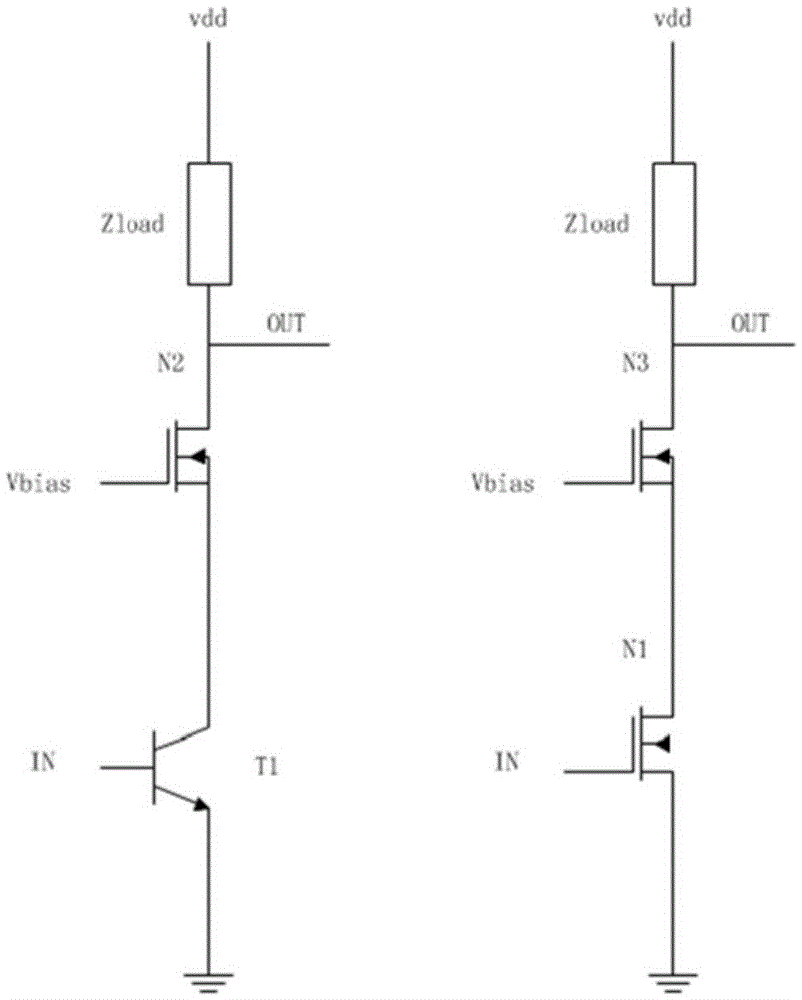

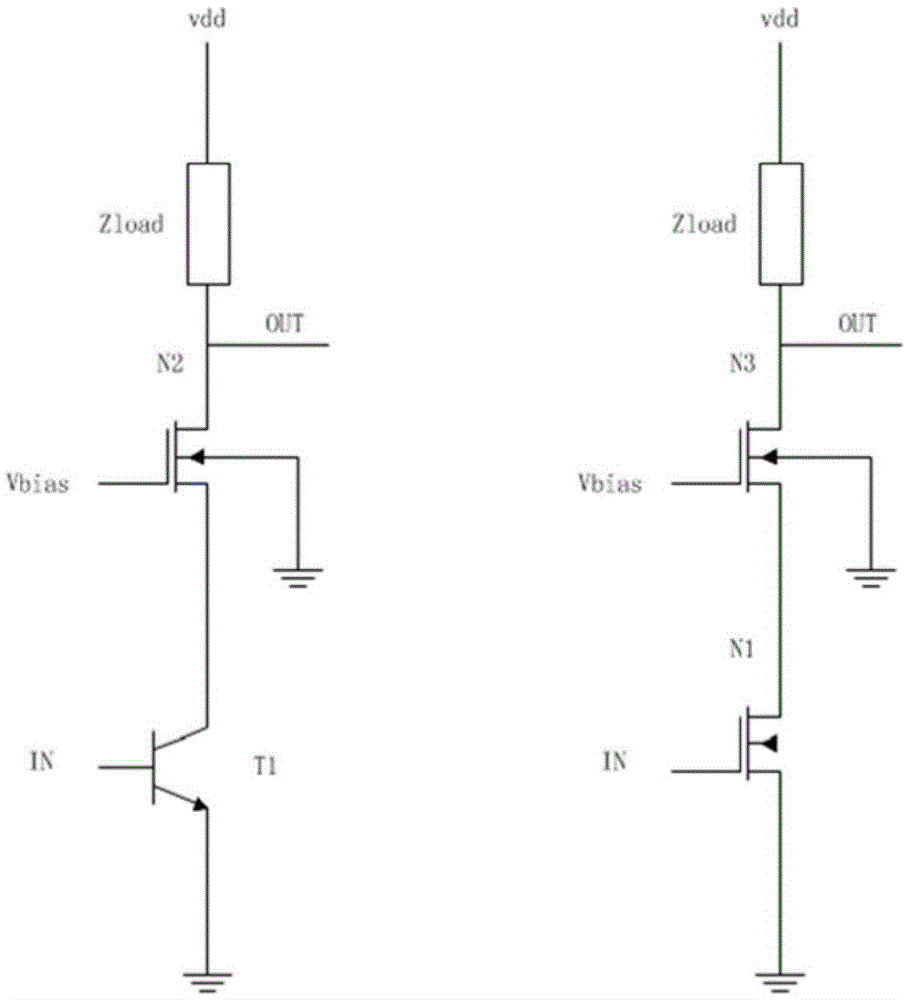

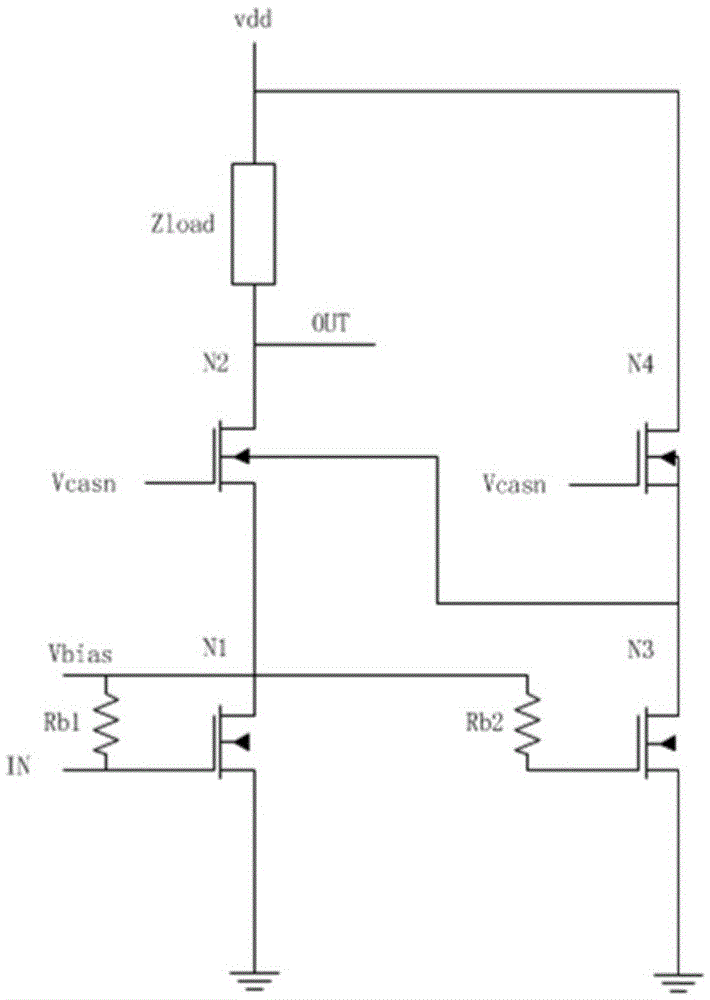

Common-source common-gate amplifier and common-emitter common-gate amplifier

ActiveCN105490646AHigh gainHigh bandwidthPower amplifiersAmplifier modifications to extend bandwidthCascodeEngineering

The present invention discloses a common-source (common-emitter) common-gate amplifier. The common-source (common-emitter) common-gate amplifier comprises a common-source (common-emitter) transistor, a common-gate transistor, an output load and a substrate biasing circuit. The common-source (common-emitter) transistor receives an input signal. The common-gate transistor sends an output signal and is connected to the output load. The amplifier has a substrate end to which the substrate biasing circuit is connected. As compared with the prior art, the present invention realizes a common-source (common-emitter) common-gate amplifier circuit with a separately biased substrate. The back-gate effect of a common-gate device is eliminated so as to improve the amplifier gain, and a direct connection between a source of the common-gate device and the substrate is also avoided so as to increase parasitic capacitance Cgb from the substrate to the gate, thereby improving the bandwidth and the gain of the amplifier. In addition, since the present invention introduces a reconfigurable biasing circuit, the linearity / noise / stray properties of a signal processing channel are balanced during the circuit switching, a good balance between flexibility and complexity is achieved, and significant improvements are made to the power consumption and area.

Owner:GUANGZHOU YIXIN INFORMATION TECH CO LTD

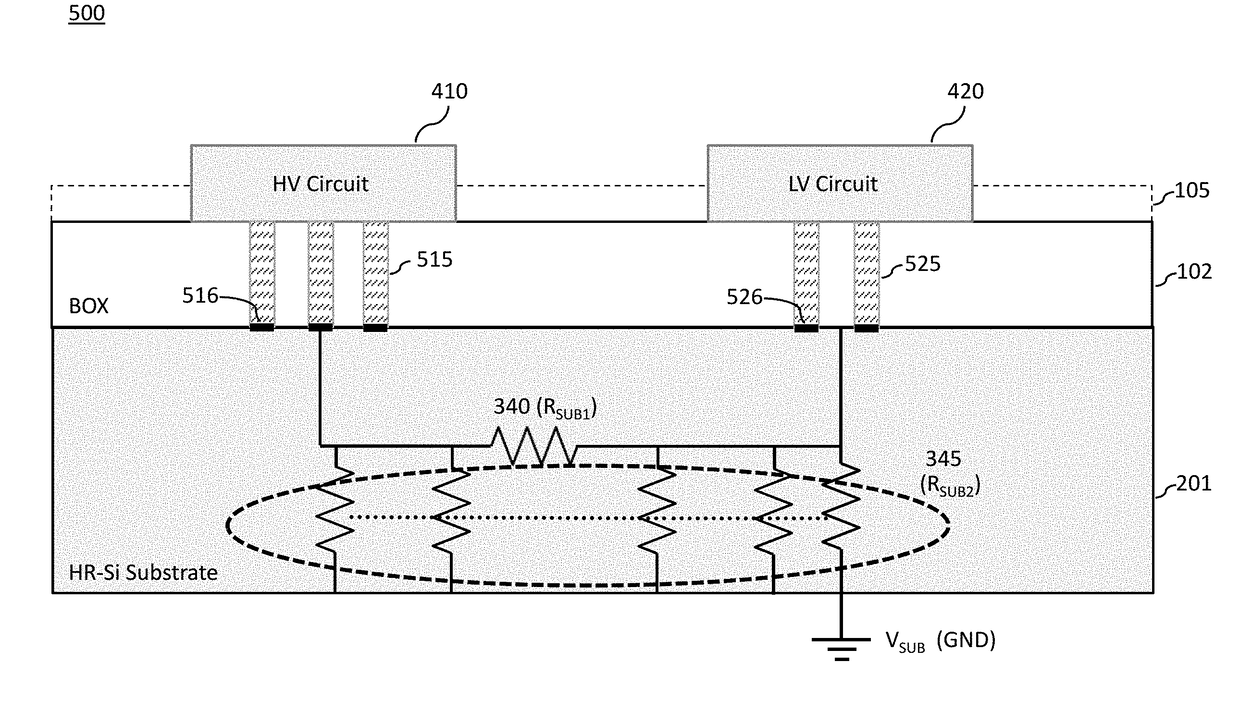

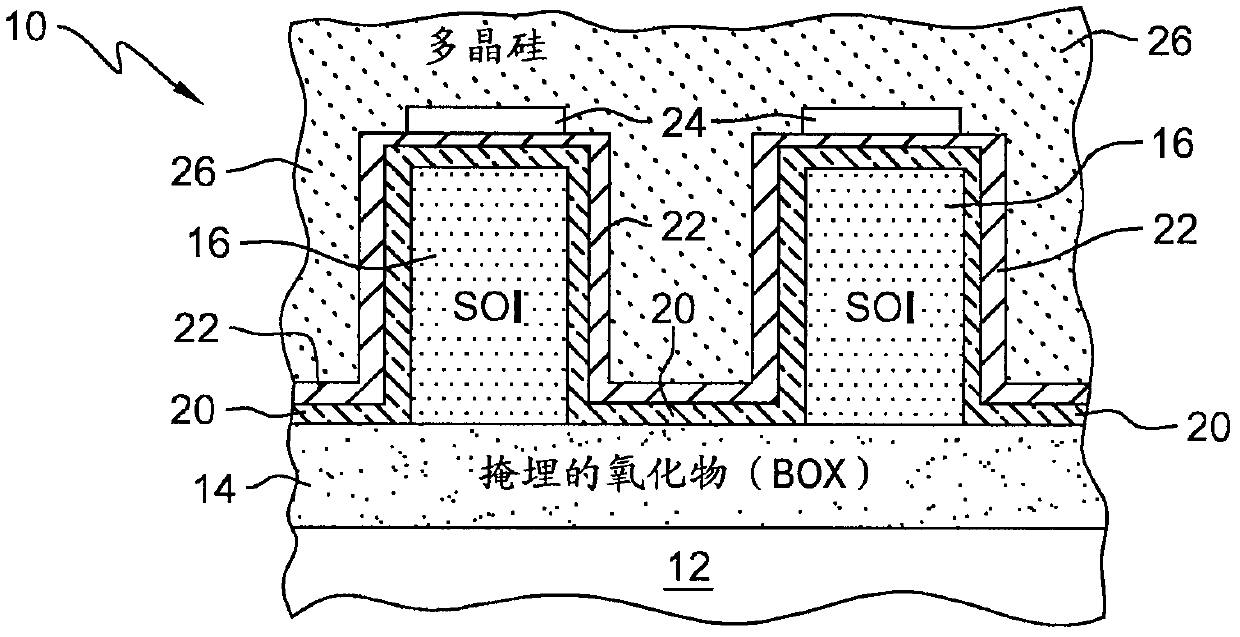

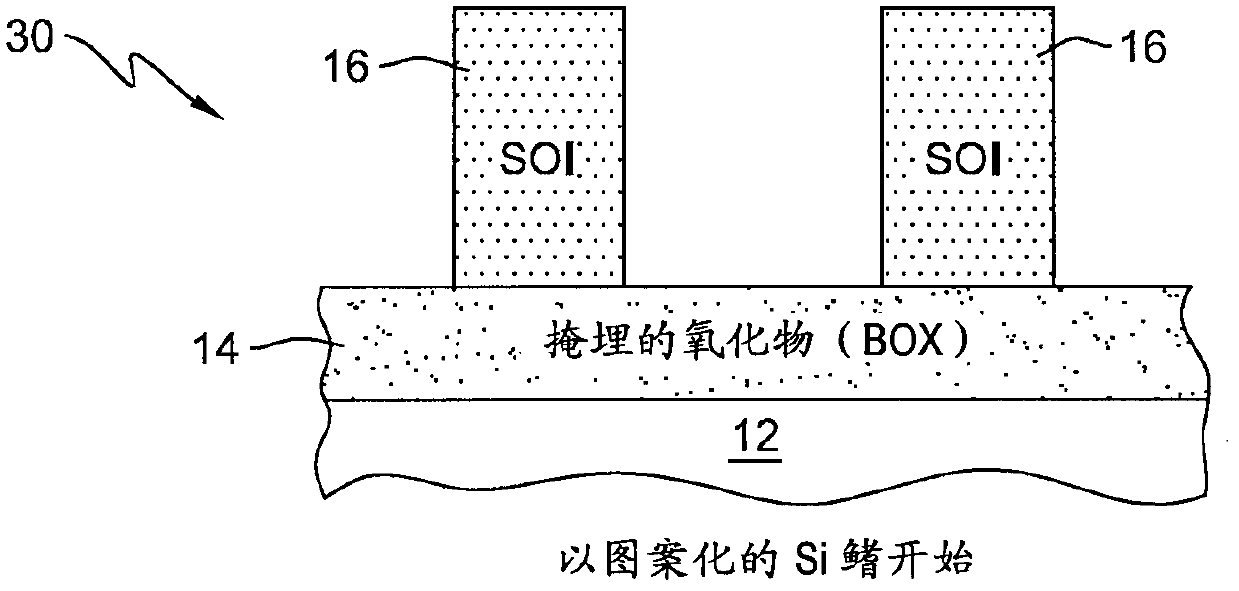

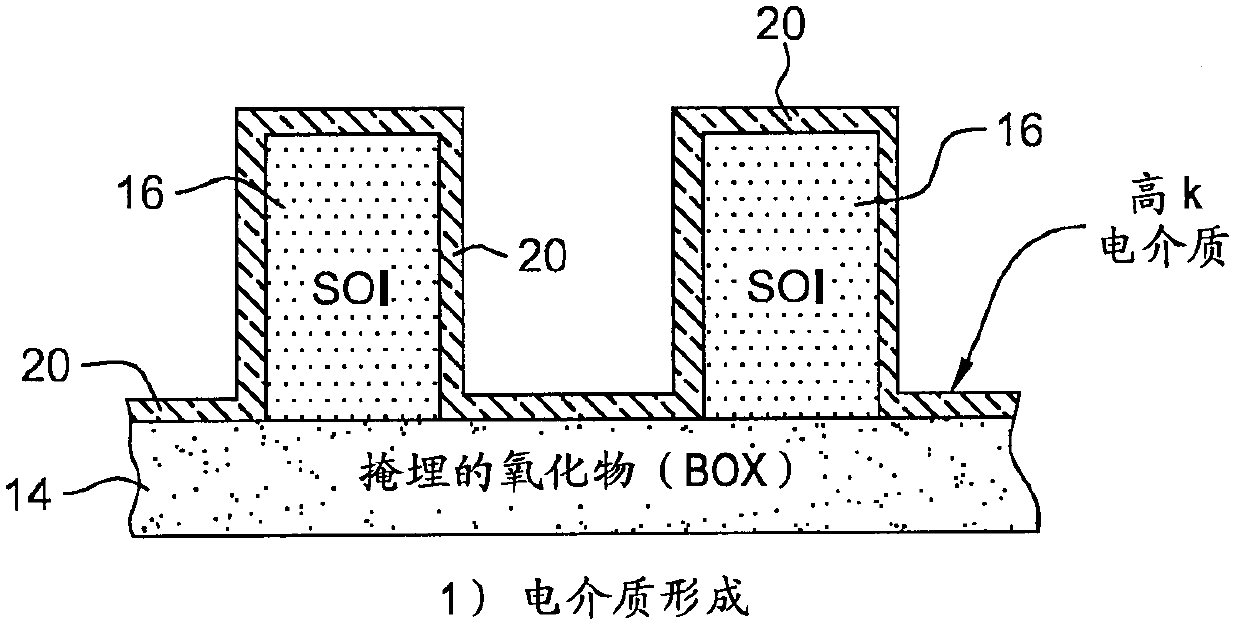

Systems, Methods and Apparatus for Enabling High Voltage Circuits

ActiveUS20180211972A1Reduce impactSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCapacitanceElectrical resistance and conductance

Systems, methods and apparatus for coexistence of high voltage and low voltage devices and circuits on a same integrated circuit fabricated in silicon-on-insulator (SOI) technology are described. In particular, techniques for mitigating back gate effects are described, including using of resistive and / or capacitive couplings to control surface potentials at regions of a substrate used for the SOI fabrication proximate the high voltage and low voltage devices and circuits. In one case, an N-type implant is used to provide a high potential differential with respect to a substrate potential.

Owner:PSEMI CORP

Drive system for an electro-mechanical three-way dual seat valve

InactiveCN103090046AOperating means/releasing devices for valvesMultiple way valvesReciprocating motionEngineering

Owner:GM GLOBAL TECH OPERATIONS LLC

Low Power Level Shifting Latch Circuits With Gated Feedback for High Speed Integrated Circuits

Low power level shifter latch circuits with gated feedback for high speed integrated circuits, and a design structure on which the subject circuit resides are provided. A latch input stage operating in a domain of a first voltage supply receives a data input responsive to being enabled by predefined clock signals. A latch storage element coupled to the latch input stage includes a latch output stage operating in a domain of a second voltage supply provides a data output having a voltage level corresponding to the second voltage supply. The latch storage element includes a level shifting device providing level shifting from the first supply level to the second voltage supply level. The latch storage element includes feedback gate devices receiving the predefined clock signals to gate feedback to the latch input stage when data is being written to the latch input stage.

Owner:IBM CORP

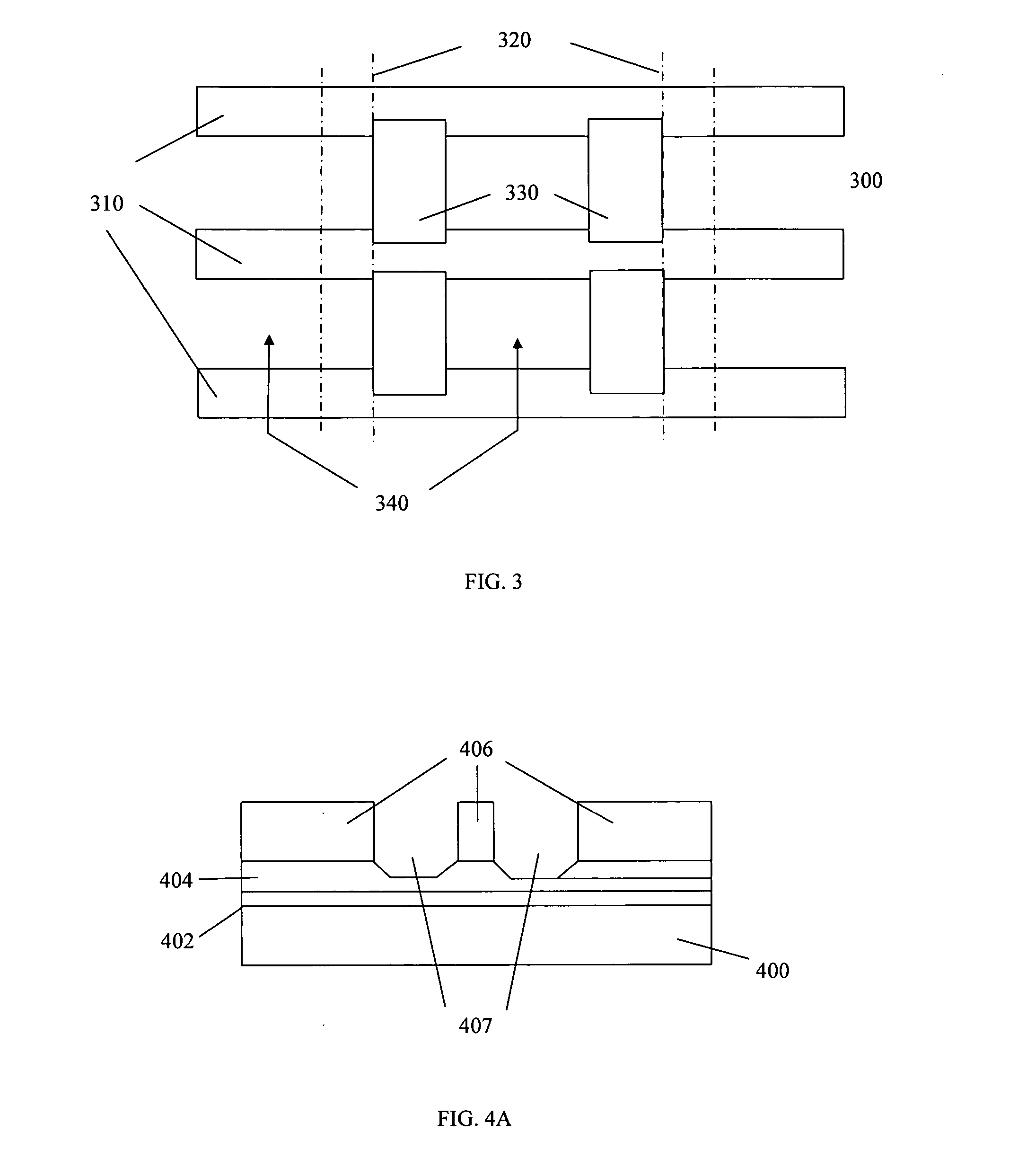

Dual dielectric tri-gate field effect transistor

ActiveCN102498569AImprove operating characteristicsLow gate capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingDielectricField-effect transistor

A dual dielectric tri-gate field effect transistor, a method of fabricating a dual dielectric tri-gate field effect transistor, and a method of operating a dual dielectric tri-gate effect transistor are disclosed. In one embodiment, the dual dielectric tri-gate transistor comprises a substrate, an insulating layer on the substrate, and at least one semiconductor fin. A first dielectric having a first dielectric constant extends over sidewalls of the fin, and a metal layer extends over the first dielectric, and a second dielectric having a second dielectric constant is on a top surface of the fin. A gate electrode extends over the fin and the first and second dielectrics. The gate electrode and the first dielectric layer form first and second gates having a threshold voltage Vt1, and the gate electrode and the second dielectric layer form a third gate having a threshold voltage Vt2 different than Vt1.

Owner:GLOBALFOUNDRIES INC

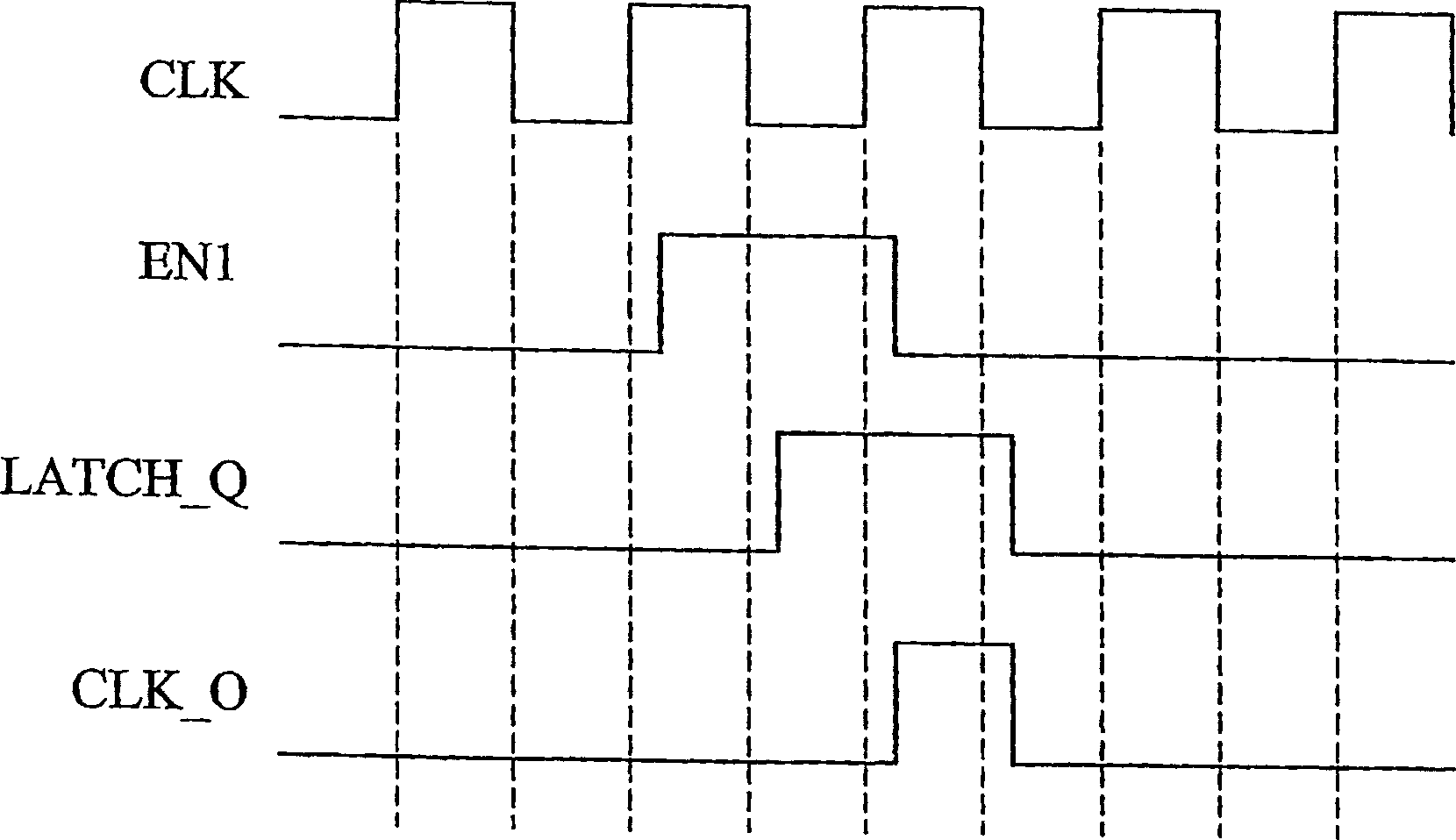

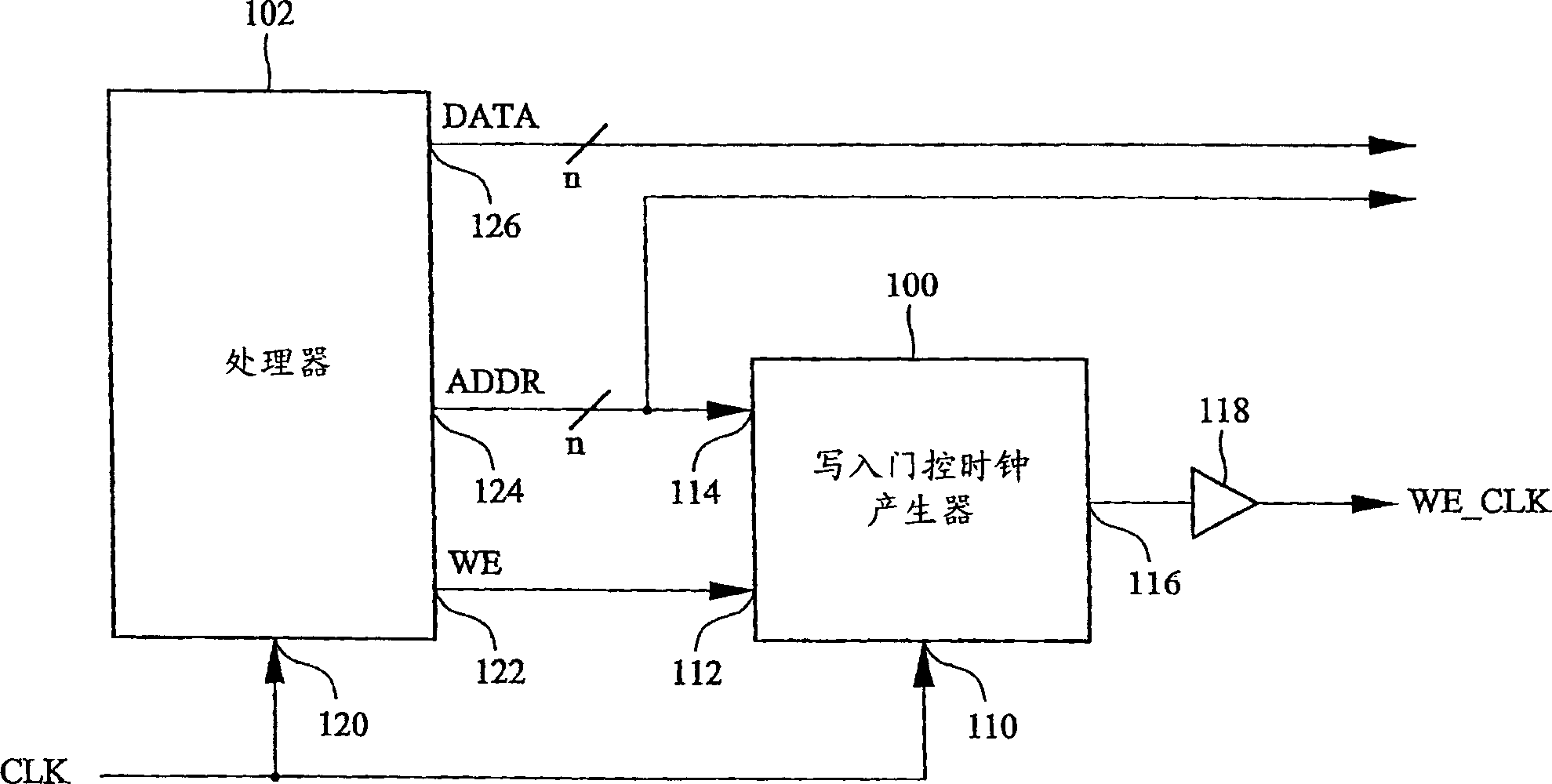

Method and apparatus for producing wirte-in gating clock signal

ActiveCN1667746ASimplified Skew BalanceReduce in quantityDigital storagePower supply for data processingGate effectPulse operation

An apparatus comprising a first circuit and a second circuit. The first circuit may be configured to generate a clock gating signal in response to (i) a write enable signal and (ii) a system clock signal, wherein the clock gating signal is pulsed when the write enable signal operates operate. The second circuit can be configured to generate the above-mentioned write enable signal.

Owner:APPLE INC

HEMT device with multi-metal gate structure and preparation method thereof

PendingCN111403479AImprove breakdown voltageReduces the effects of current collapseSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryEngineering

The invention discloses an HEMT device with a multi-metal gate structure and a preparation method thereof. The device comprises an AlGaN / GaN epitaxy layer; the two ends of the upper surface of the AlGaN / GaN epitaxy layer are connected with a source electrode and a drain electrode respectively; a gate electrode is arranged between the source electrode and the drain electrode at the place close to the source electrode side; and a first layer of metal X of the gate electrode is deposited in an electron beam evaporation mode, a second layer of metal Y of the gate electrode is deposited in a magnetron sputtering mode, the work function of the second layer of metal Y of the gate electrode is higher than that of the first layer of metal X, photoetching is not needed, and a metal structure which is formed after the gate electrode is stripped and makes contact with (Al)GaN is Y / X / Y. The multi-metal gate structure is in contact with (Al)GaN, so that the electric field is redistributed, the peakvalue of the electric field at the gate edge near the drain is reduced, and the breakdown voltage of the device is improved; and meanwhile, the lower electric field peak value of the gate edge weakensgate injection electrons to form a virtual gate effect, so that current collapse of the device is reduced, and the dynamic performance of the device is improved.

Owner:ZHONGSHAN INST OF MODERN IND TECH SOUTH CHINA UNIV OF TECH +1

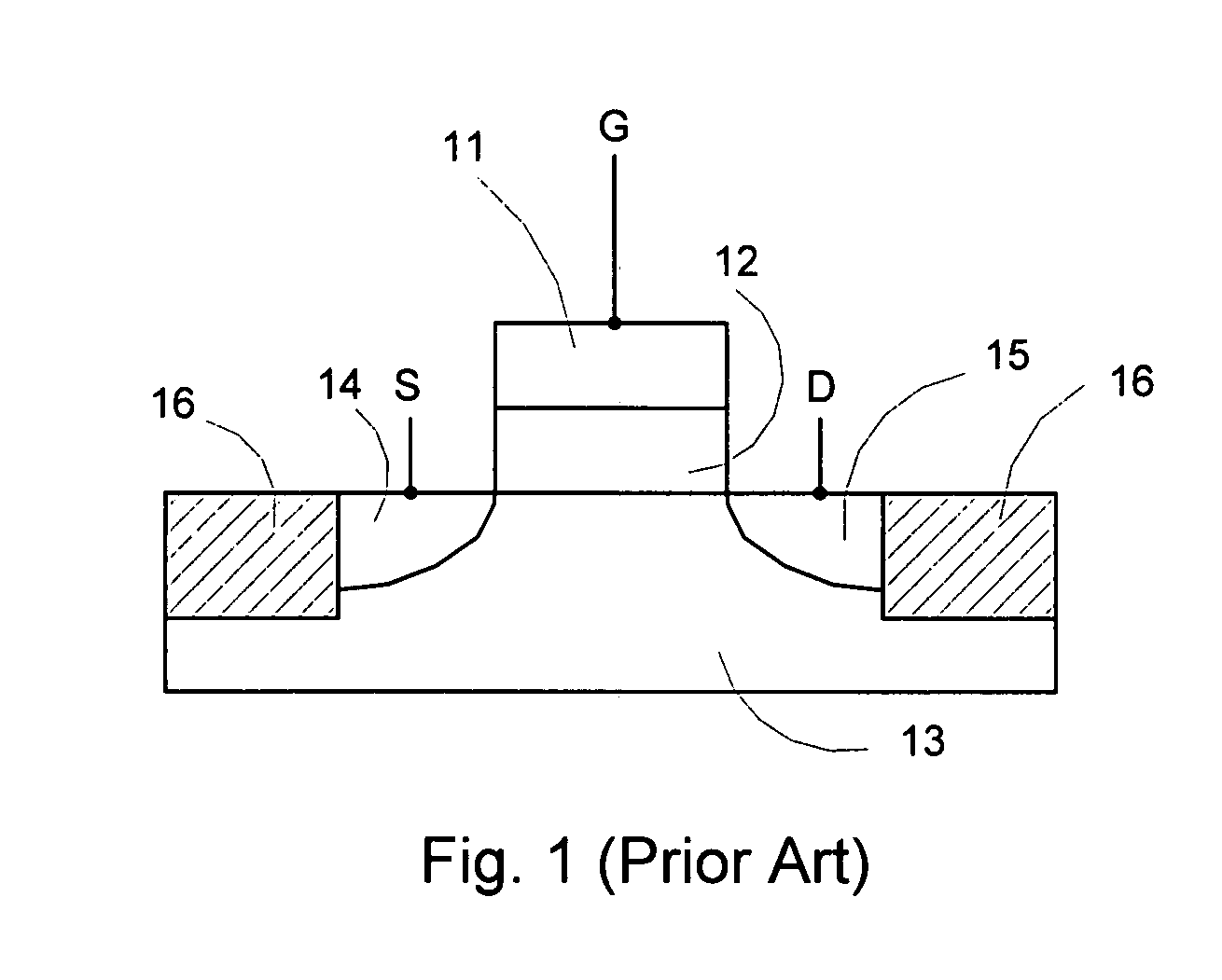

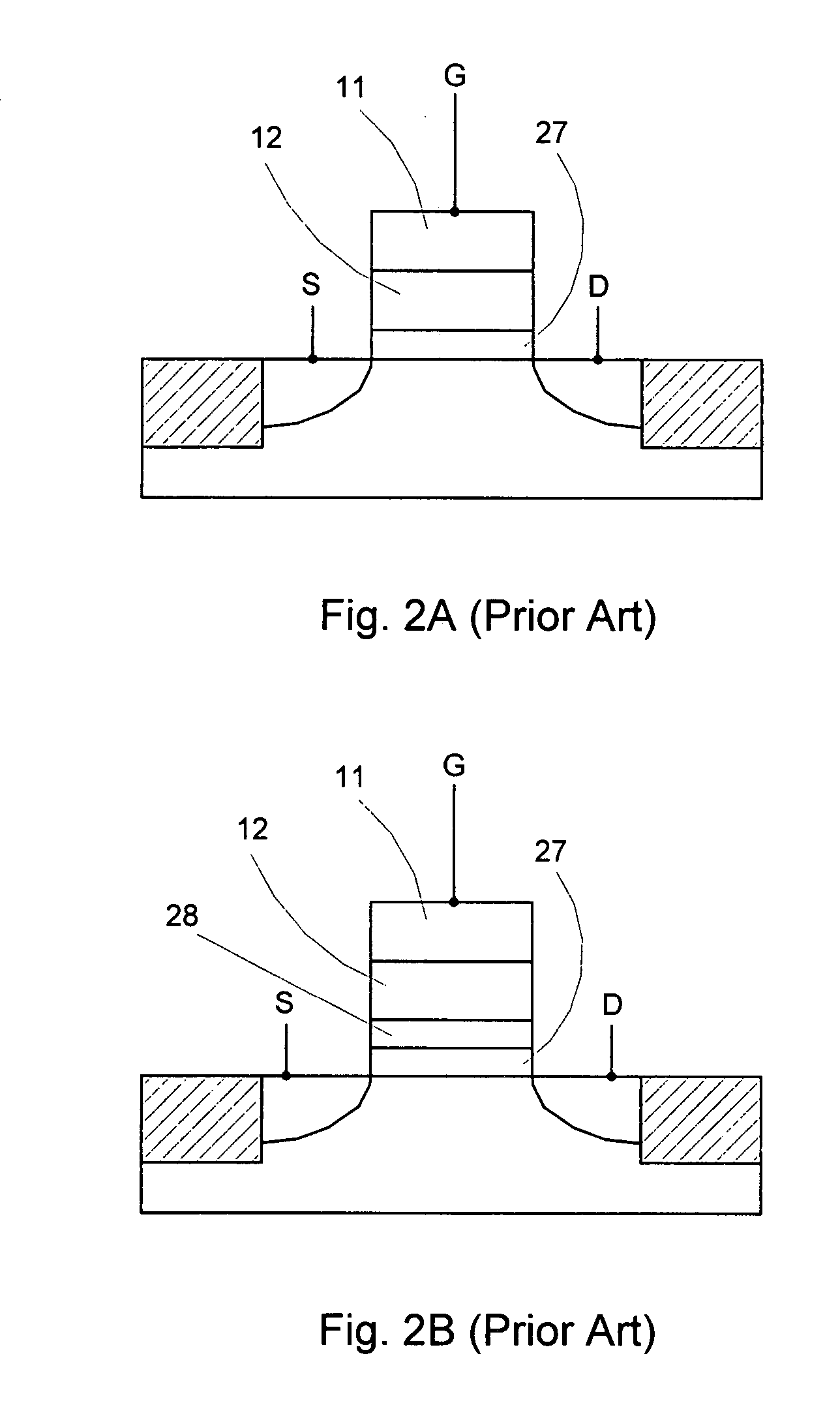

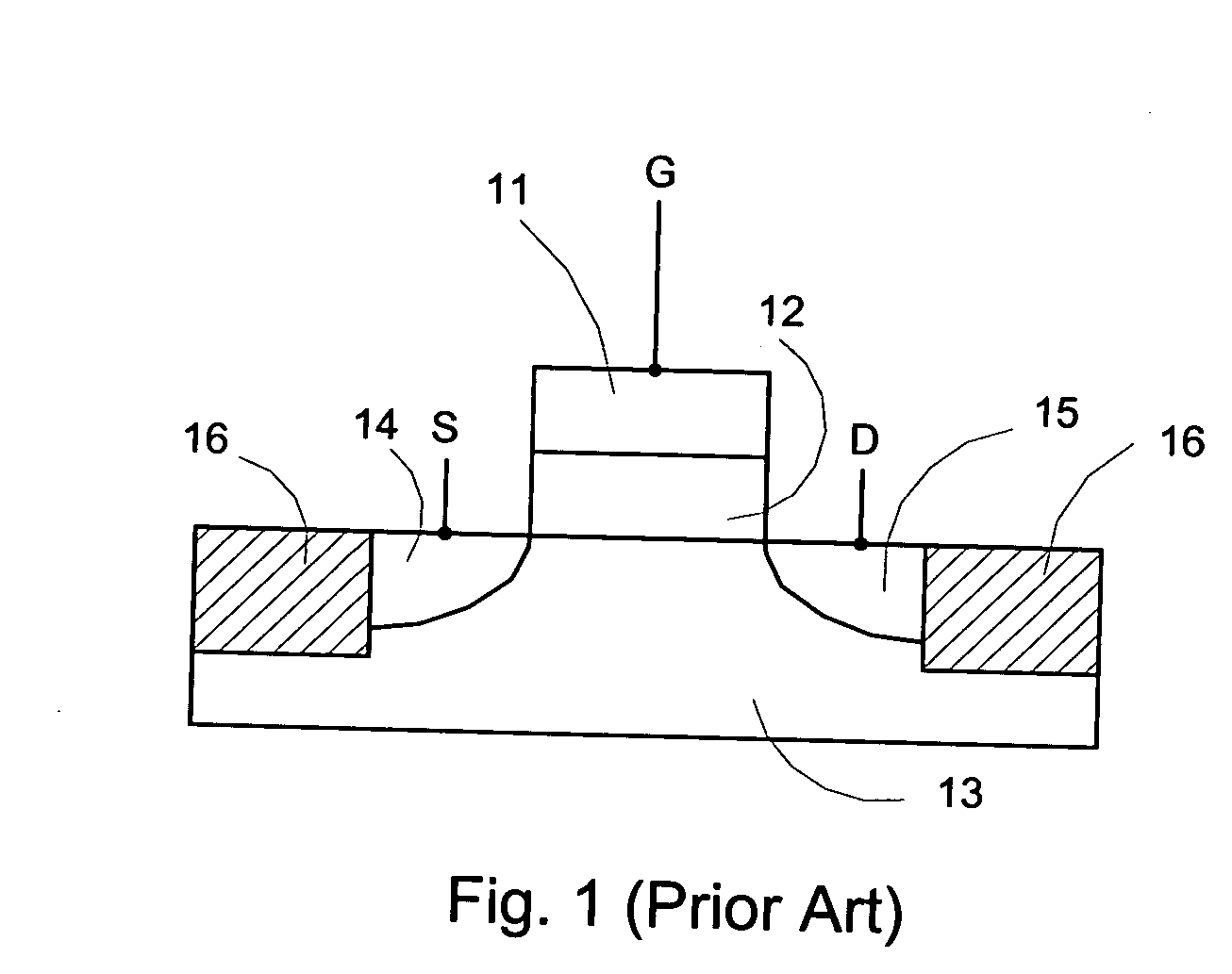

Methods and structures for reducing back gate effect in a semiconductor device

ActiveUS10147740B2Reduce impactSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsResistive couplingElectrical resistance and conductance

Methods and structures for mitigating back gate effects in high voltage and low voltage semiconductor devices of a same integrated circuit fabricated in a silicon-on-insulator technology are described. According to one aspect, one or more resistive couplings are used to control surface potentials at regions of a substrate used for the SOI fabrication proximate the high voltage and low voltage semiconductor devices. According to another aspect, an N-type implant that is biased through a resistive coupling is used to provide a high potential differential with respect to a substrate potential.

Owner:MURATA MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com