Ferroelectric memory transistor with conductive oxide gate structure

a technology of ferroelectric transistor and gate structure, which is applied in the direction of electrical equipment, static storage, instruments, etc., can solve the problems of difficult to form a clean interface, unstable operation of ferroelectric transistor, and difficult to achieve effective transistor operation of the above mfs transistor, etc., to achieve the effect of reducing the operating voltage of the ferroelectric transistor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0026] the present invention is shown in FIG. 3, illustrating an n-channel conductive oxide gate ferroelectric transistor. The gate stack of the present invention comprises a top gate electrode 63, a ferroelectric film 62, a bottom gate electrode 61 and a conductive oxide gate 51, positioning on a p-type silicon substrate 63, and disposed between the source 64 and drain 65 regions having a high concentration of n-type impurity ions. The ferroelectric transistor is isolated by the isolation trenches 66. The gate insulator of the present invention transistor is replaced with a conductive oxide such as InO2 or RuO2 to prevent floating gate effect.

[0027]FIG. 4 show the operation of the above n-channel conductive oxide ferroelectric transistor. In FIG. 4A, when a positive voltage is applied to the gate electrode 63, polarization of the ferroelectric film 62 occurs with electrons are pulled to the top and holes are pulled to the bottom of the ferroelectric film. Electrons are then accumul...

second embodiment

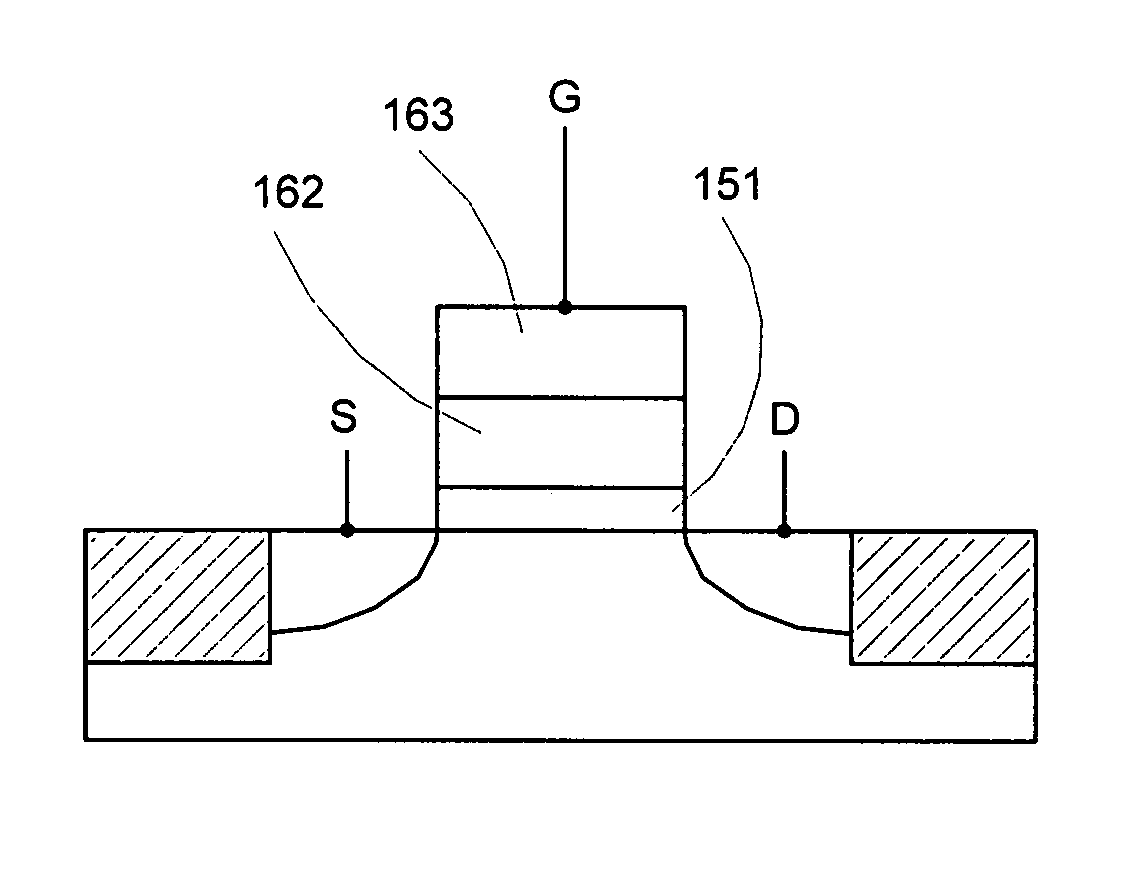

[0030] In the invention, the bottom gate electrode is omitted. Thus gate stack of the conductive oxide gate ferroelectric transistor comprises a top gate electrode 163, a ferroelectric film 162, and a conductive oxide gate 151 as shown in FIG. 5. The conductive oxide in the present invention is preferably a conductive metal oxide, but can be a conductive oxide without any metal components. The conductive oxide can make good interface with the silicon substrate, and can be selected to have a good lattice matching with the deposited ferroelectric film, especially ones having perovskite crystal structures.

[0031] Furthermore, a conductive oxide serving as electrodes for the ferroelectric film may improve the quality of the ferroelectric film, and thus the operation of the ferroelectric transistor. A ferroelectric film is generally formed in an oxidizing ambience such as a deposition process with oxygen as a reactive gas, or an annealing process in an oxygen ambience to improve the stabi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com