Gallium nitride transistor structure and preparation method thereof

A technology of transistors and gallium nitride, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of difficult device technology and small etching selection, achieve high etching selection ratio, alleviate electric field concentration, and simple growth process Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

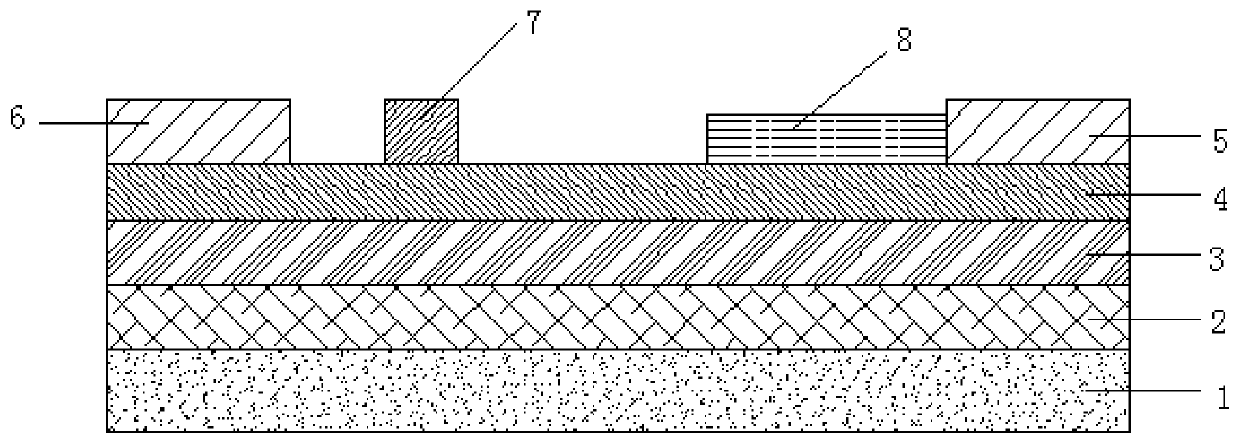

[0040] A gallium nitride transistor structure, comprising a substrate 1, wherein the substrate 1 is a Si, SiC, GaN or sapphire substrate;

[0041] A GaN-based buffer layer 2 located above the substrate 1; a GaN-based channel layer 3 located above the GaN-based buffer layer 2; an In layer located above the GaN-based channel layer 3 x Al y Ga 1-x-y N barrier layer 4, where 0≤x<1, 0≤y<1, and x+y≠0;

[0042] The structure of the GaN-based buffer layer 2 is an AlN nucleation layer, a GaN buffer layer, and an AlGaN buffer layer from bottom to top;

[0043] Located in x Al y Ga 1-x-y The source electrode 6 at one end above the N barrier layer 4; the source electrode 6 is an ohmic contact metal electrode, and the ohmic contact metal electrode is composed of a single layer or multiple layers of metal and In x Al y Ga 1-x-y The N barrier layer 4 forms an ohmic contact electrode;

[0044] Located in x Al y Ga 1-x-y The drain electrode 5 at the other end above the N barrier la...

Embodiment 2

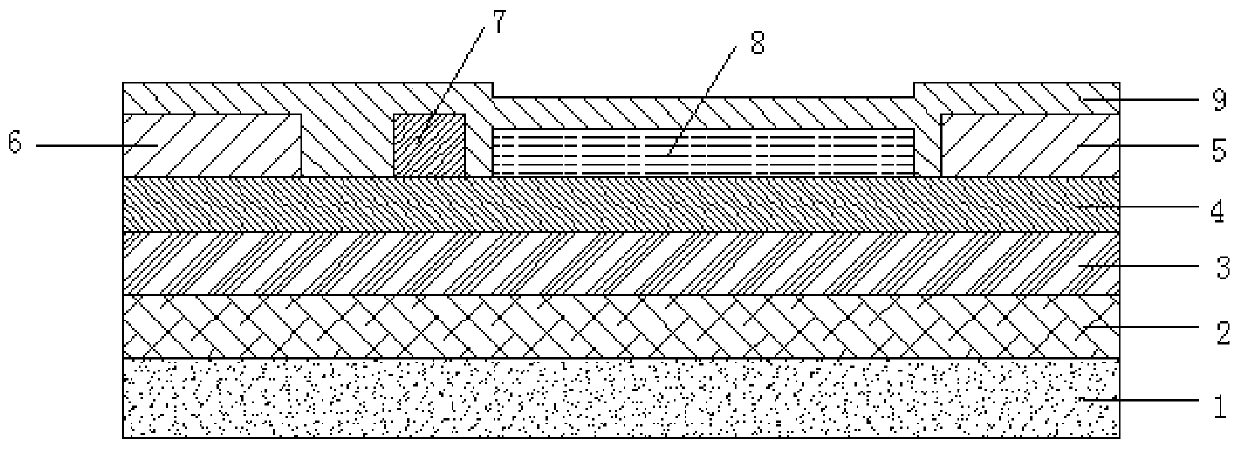

[0055] A gallium nitride transistor structure, the others are the same as in Embodiment 1, except that the uppermost layer of the gallium nitride transistor structure is also covered with a passivation layer 9; the passivation layer 9 includes Si 3 N 4 、Al 2 o 3 , AlN, Y 2 o 3 , La 2 o 3 、 Ta 2 o 5 、TiO 2 , HfO 2 , ZrO 2 single-layer or multi-layer composite structures.

[0056] The preparation method of the gallium nitride transistor is the same as that of Embodiment 1, except that after step (6), a passivation layer 9 deposition step is included, and the passivation layer 9 is deposited by PECVD, MOCVD, ALD or sputtering.

Embodiment 3

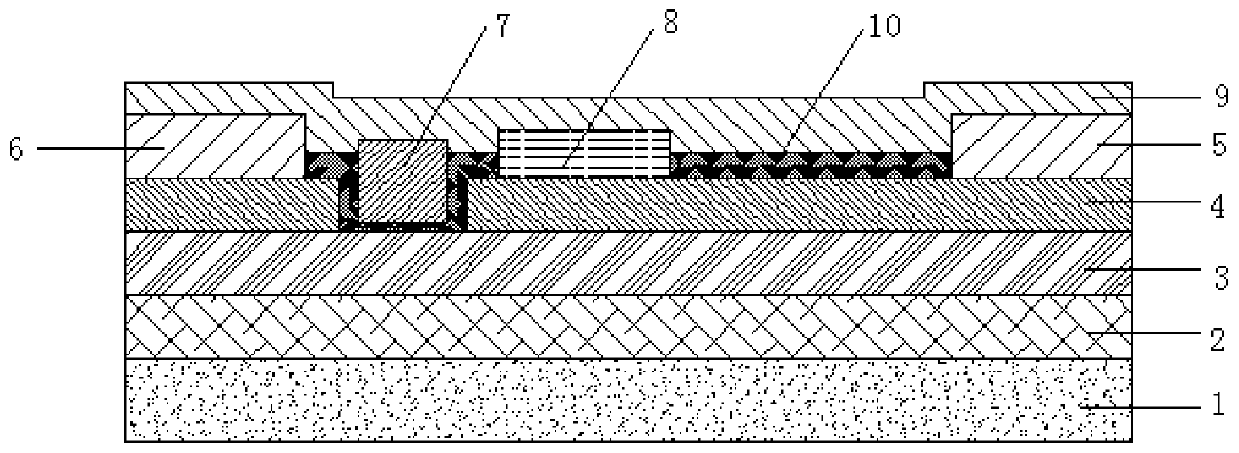

[0058] A gallium nitride transistor structure, comprising a substrate 1, wherein the substrate 1 is a Si, SiC, GaN or sapphire substrate;

[0059] A GaN-based buffer layer 2 located above the substrate 1; a GaN-based channel layer 3 located above the GaN-based buffer layer 2; an In layer located above the GaN-based channel layer 3 x Al y Ga 1-x-y N barrier layer 4, where 0≤x<1, 0≤y<1, and x+y≠0;

[0060] The structure of the GaN-based buffer layer 2 is an AlN nucleation layer, a GaN buffer layer, and an AlGaN buffer layer from bottom to top;

[0061] Located in x Al y Ga 1-x-y The source electrode 6 at one end above the N barrier layer 4; the source electrode 6 is an ohmic contact metal electrode, and the ohmic contact metal electrode is composed of a single layer or multiple layers of metal and In x Al y Ga 1-x-y The N barrier layer 4 forms an ohmic contact electrode;

[0062] Located in x Al y Ga 1-x-y The drain electrode 5 at the other end above the N barrier la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com