Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

145results about How to "Reduce electric field concentration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Polymer matrix composite membrane with high energy density and preparation method thereof

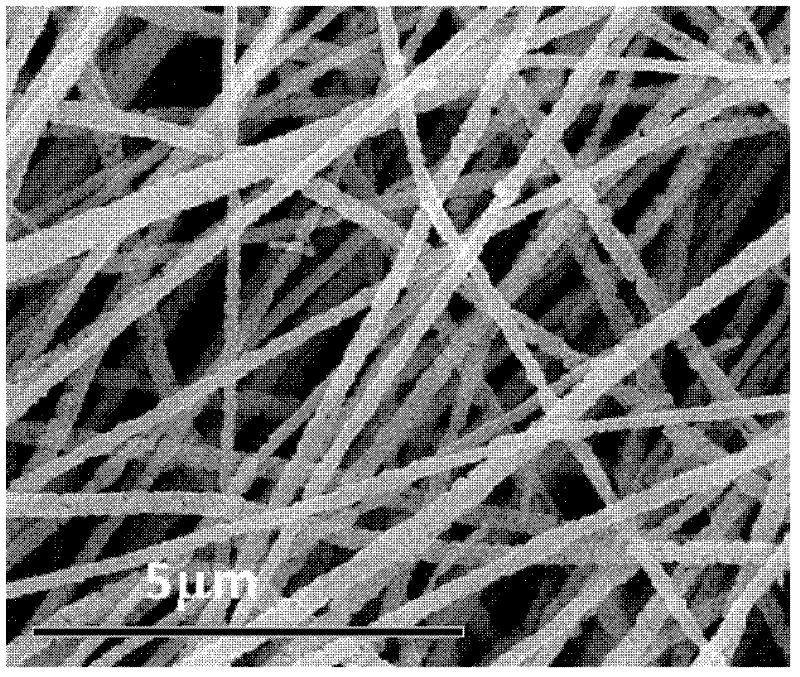

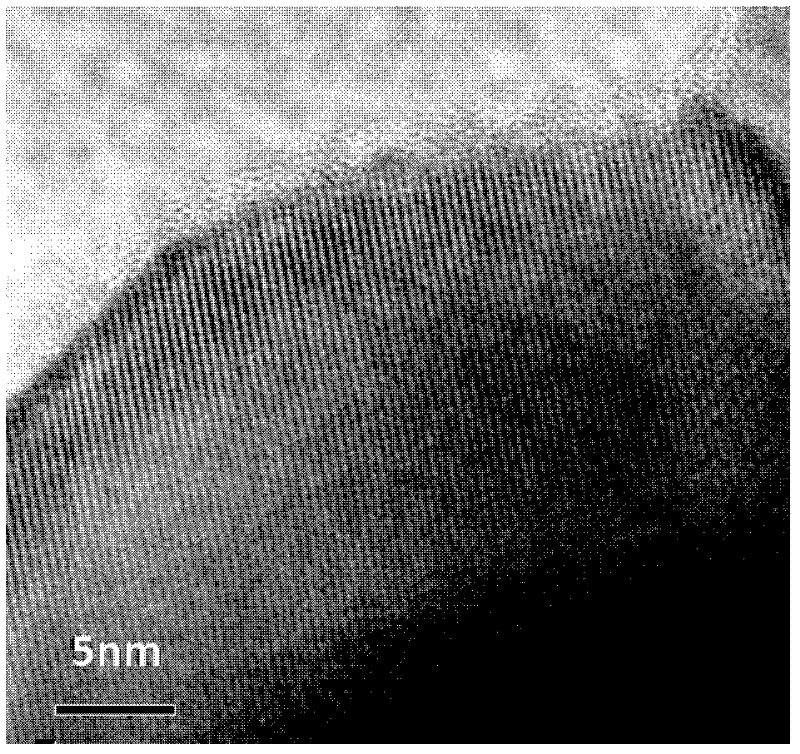

ActiveCN102504449AHigh dielectric constantHigh breakdown field strengthInorganic material artificial filamentsFibre treatmentFiberHigh energy

The invention discloses a high-flexible polymer matrix composite membrane with high energy density and a preparation method thereof. The composite membrane is composed of a polymer matrix and core-shell structured nano-fibre dispersed in the polymer matrix; the core layer of the core-shell structured nano-fibre is ceramic fibre; the shell layer is an organic matter coated layer, wherein the mass percentage of the polymer matrix is 50-95%; and the mass percentage of the core-shell structured nano-fibre is 5-50%. The polymer matrix and the core-shell structured nano-fibre are composited into the membrane by adopting a solution blending and tape casting method or a bidirectional membrane pulling method, so that a flexible polymer matrix composite material having the advantages of being good in dielectric property, high in breakdown field strength and high in energy density is obtained. The dielectric constant of the composite material can be modulated to 10-40 by adjusting the content of nano ceramic fibre; simultaneously, the dielectric loss Tan delta is kept to be less than 5%, the breakdown field strength is more than 210 kV / mm, and the energy density is 2-6 kJ / L; and the composite material is a material which can be used for capacitors and high power static energy storage.

Owner:TSINGHUA UNIV

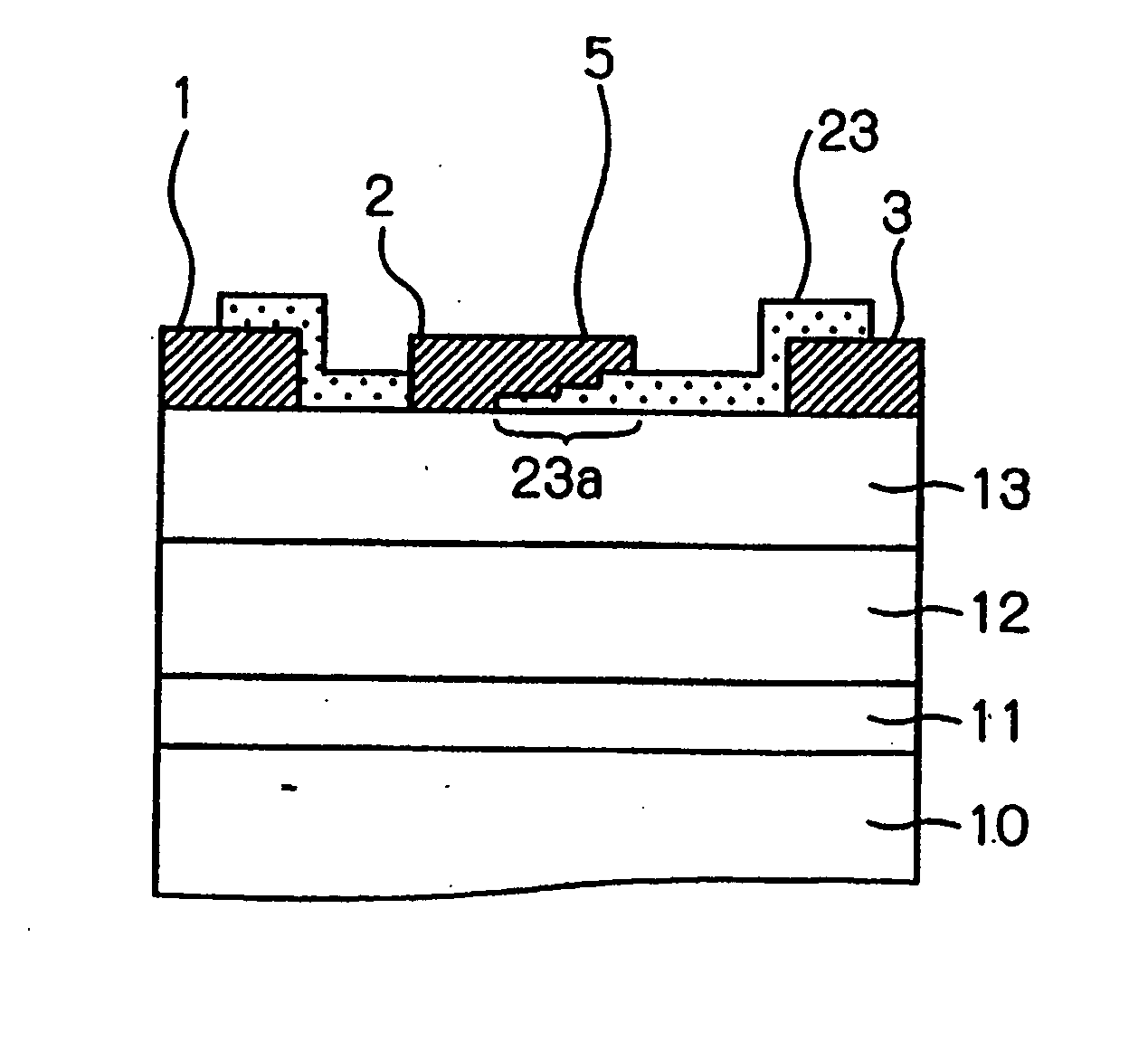

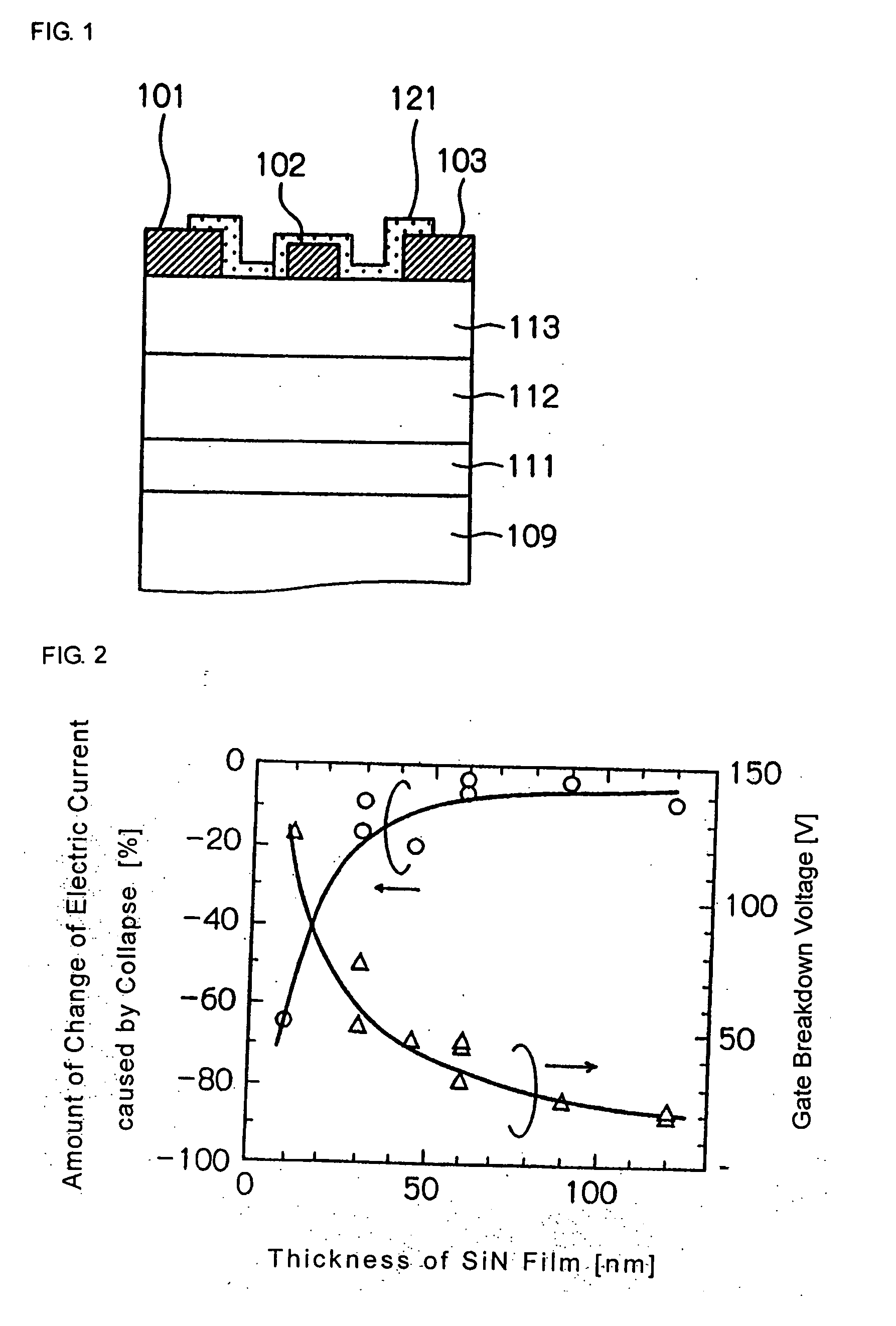

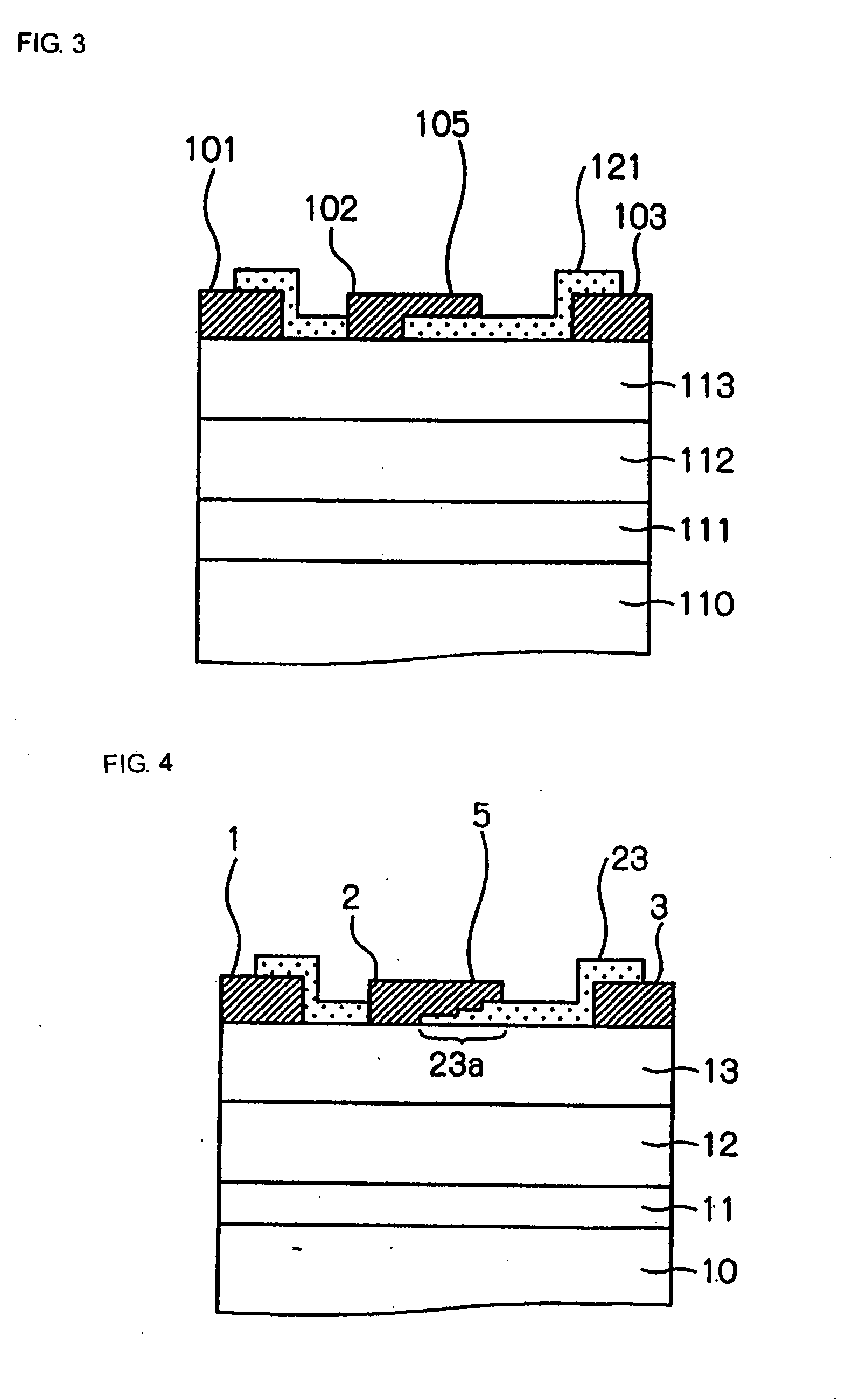

Field effect transistor

InactiveUS20070164326A1Improve gate breakdown voltagePrevent crashSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorCondensed matter physics

A field effect transistor includes a semiconductor layer structure including GaN channel layer 12 and AlGa electron supply layer 13, source electrode 1 and drain electrode 3 which are formed on electron supply layer 13 so as to be separated from each other, gate electrode 2 formed between source electrode 1 and drain electrode 3, and SiON film 23 formed on electron supply layer 13. Gate electrode 2 has a field plate portion 5 that projects toward drain electrode 3 in the form of an eave on SiON film 23. The thickness of a portion (field plate layer 23a) of SiON film 23 lying between field plate portion 5 and electron supply layer 13 gradually increases from gate electrode 2 to drain electrode 3.

Owner:NEC CORP

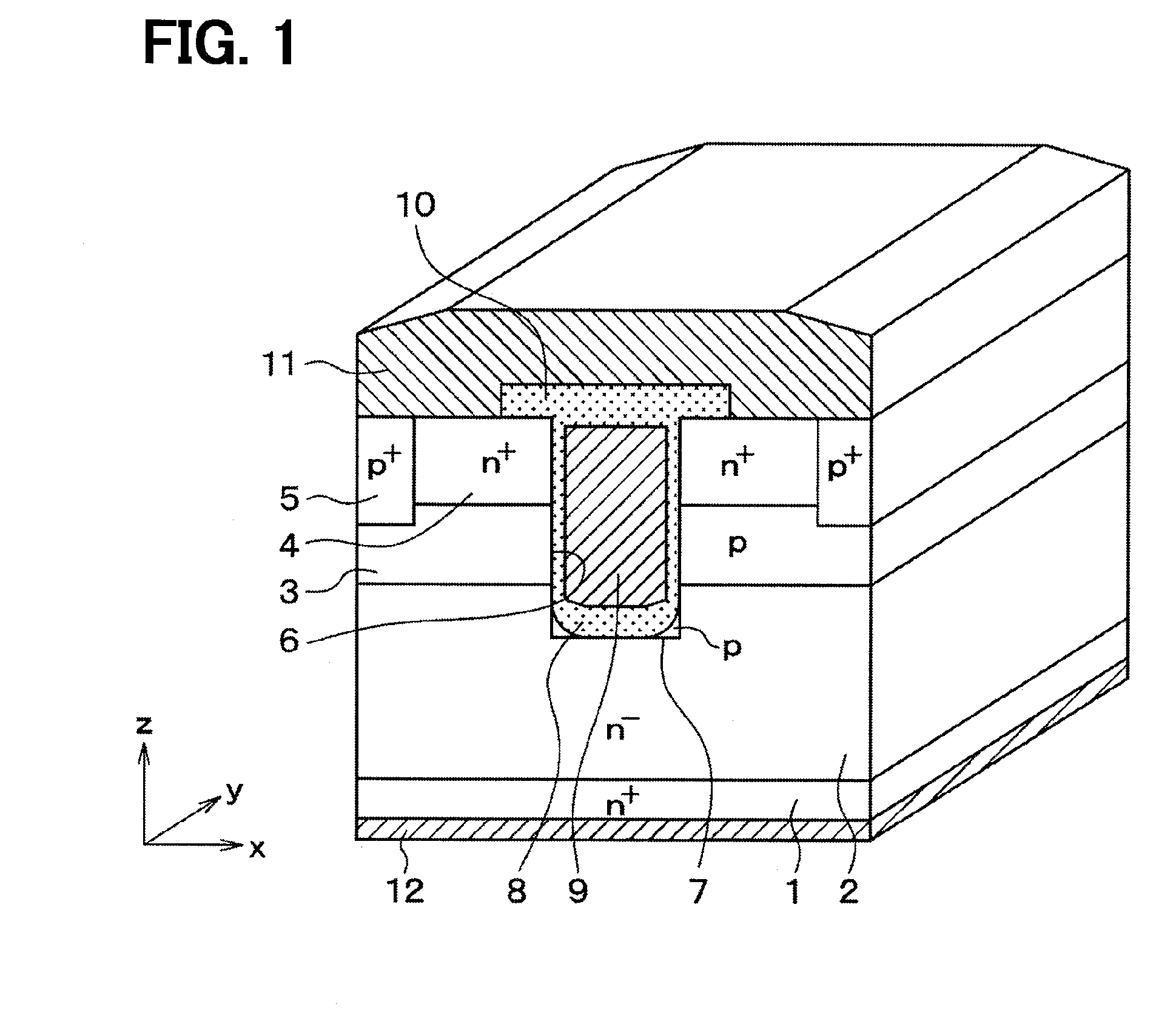

Method of making silicon carbide semiconductor device

ActiveUS20090280609A1Reduce electric field concentrationSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETHigh concentration

In a method of making a silicon carbide semiconductor device having a MOSFET, after a mask is placed on a surface of a first conductivity type drift layer of silicon carbide, ion implantation is performed by using the mask to form a lower layer of a deep layer extending in one direction. A first conductivity type current scattering layer having a higher concentration than the drift layer is formed on the surface of the drift layer. After another mask is placed on a surface of the current scattering layer, ion implantation is performed by using the other mask to form an upper layer of the deep layer at a position corresponding to the lower layer in such a manner that the lower layer and the upper layer are connected together.

Owner:DENSO CORP

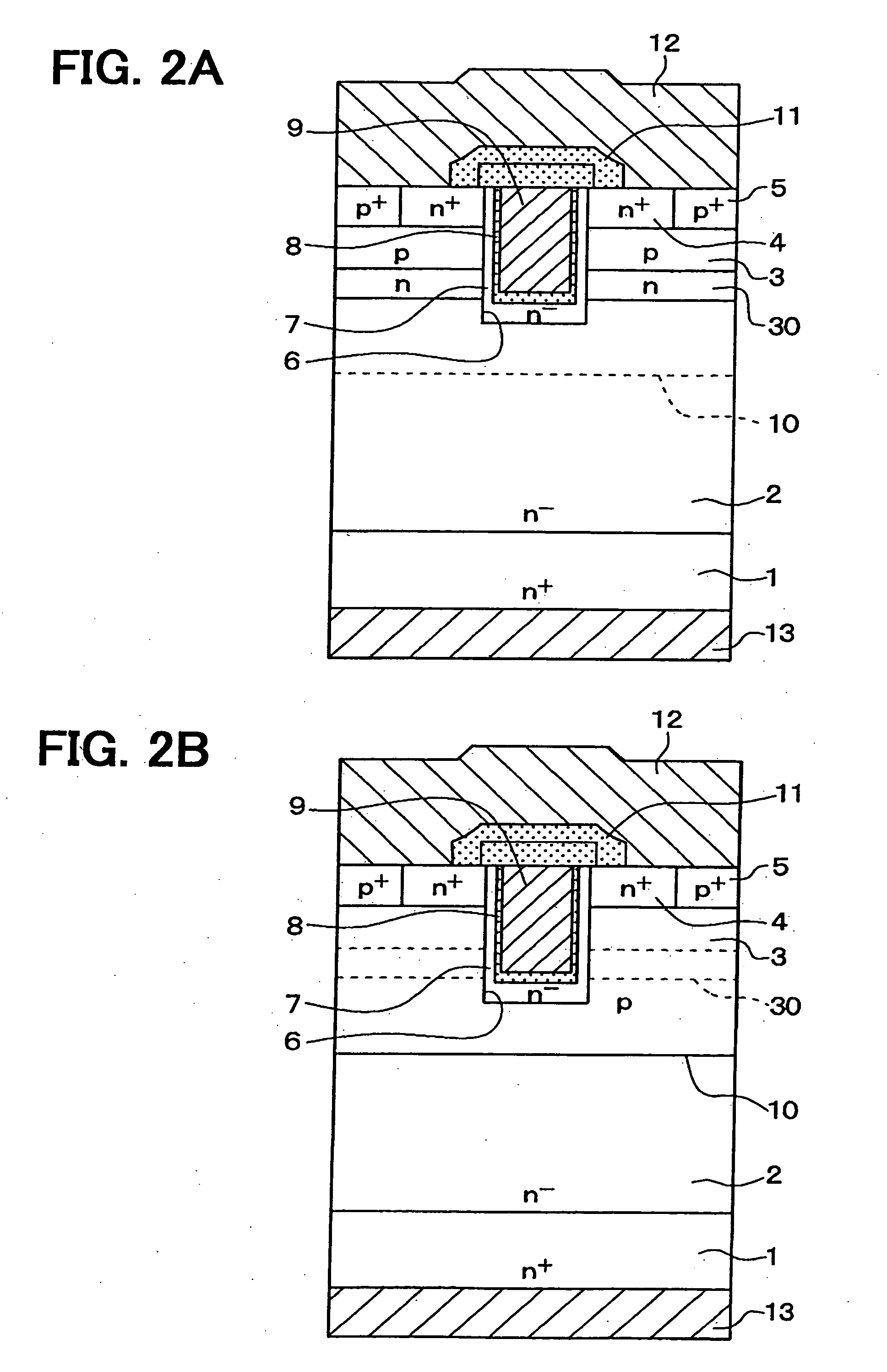

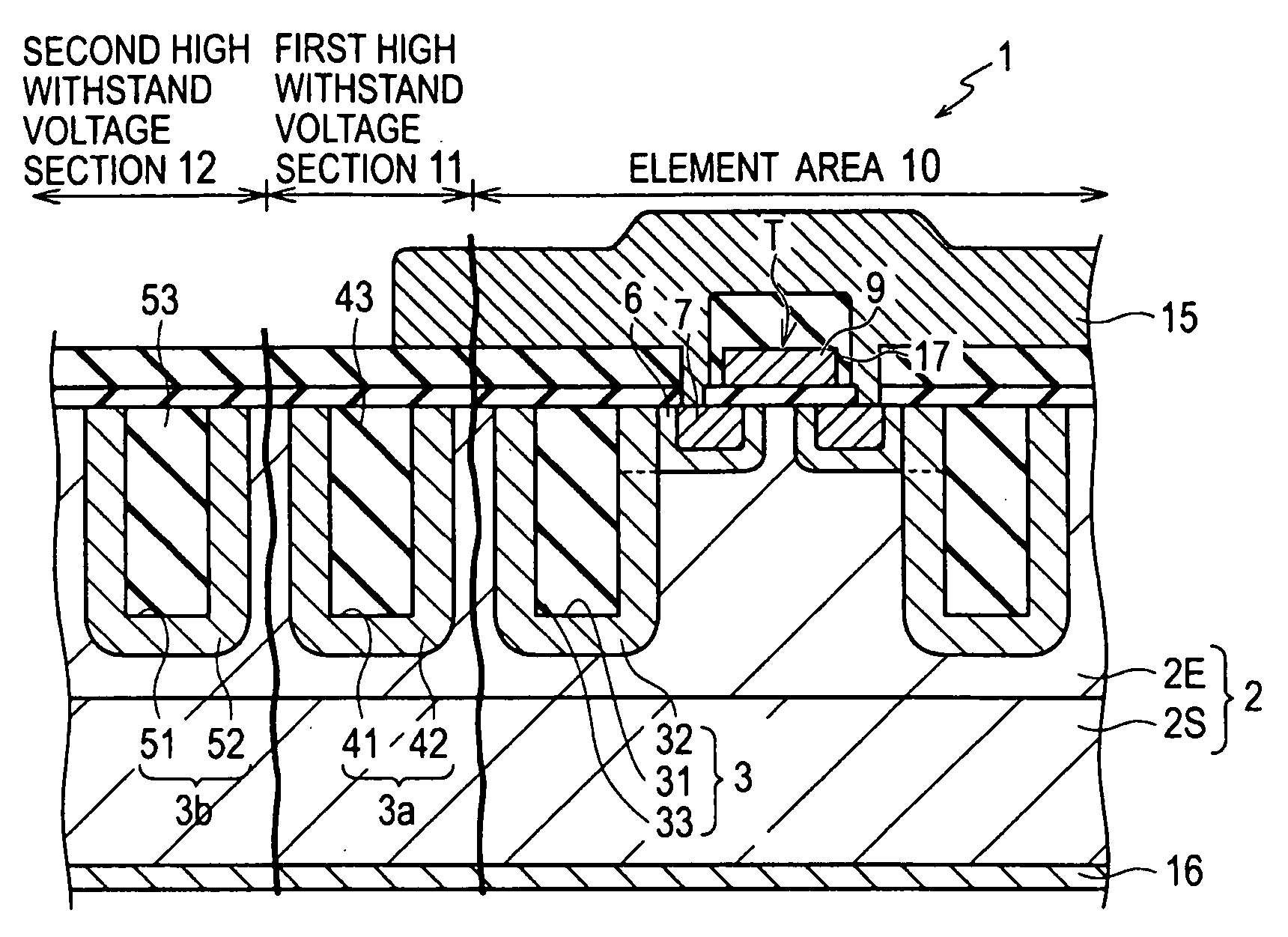

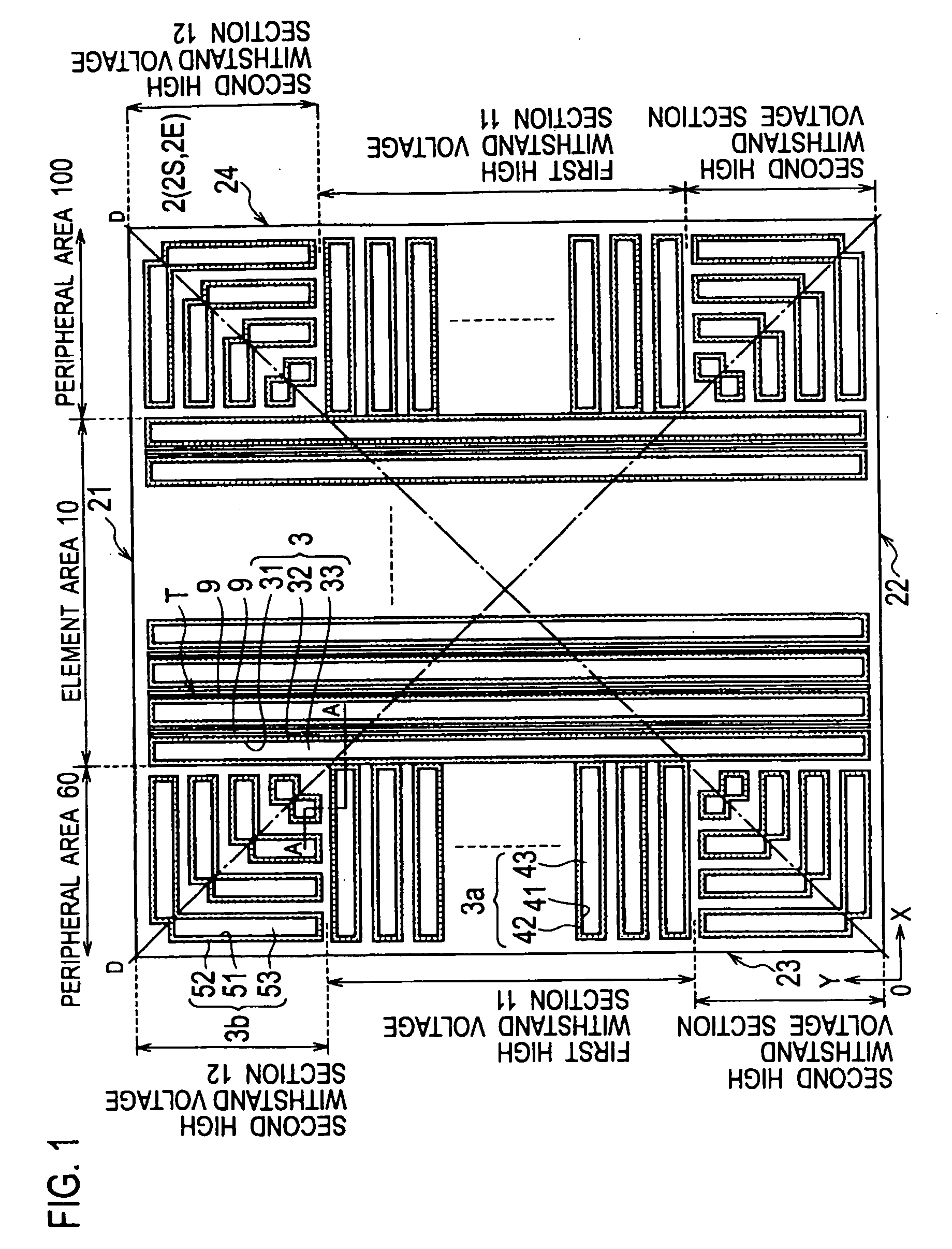

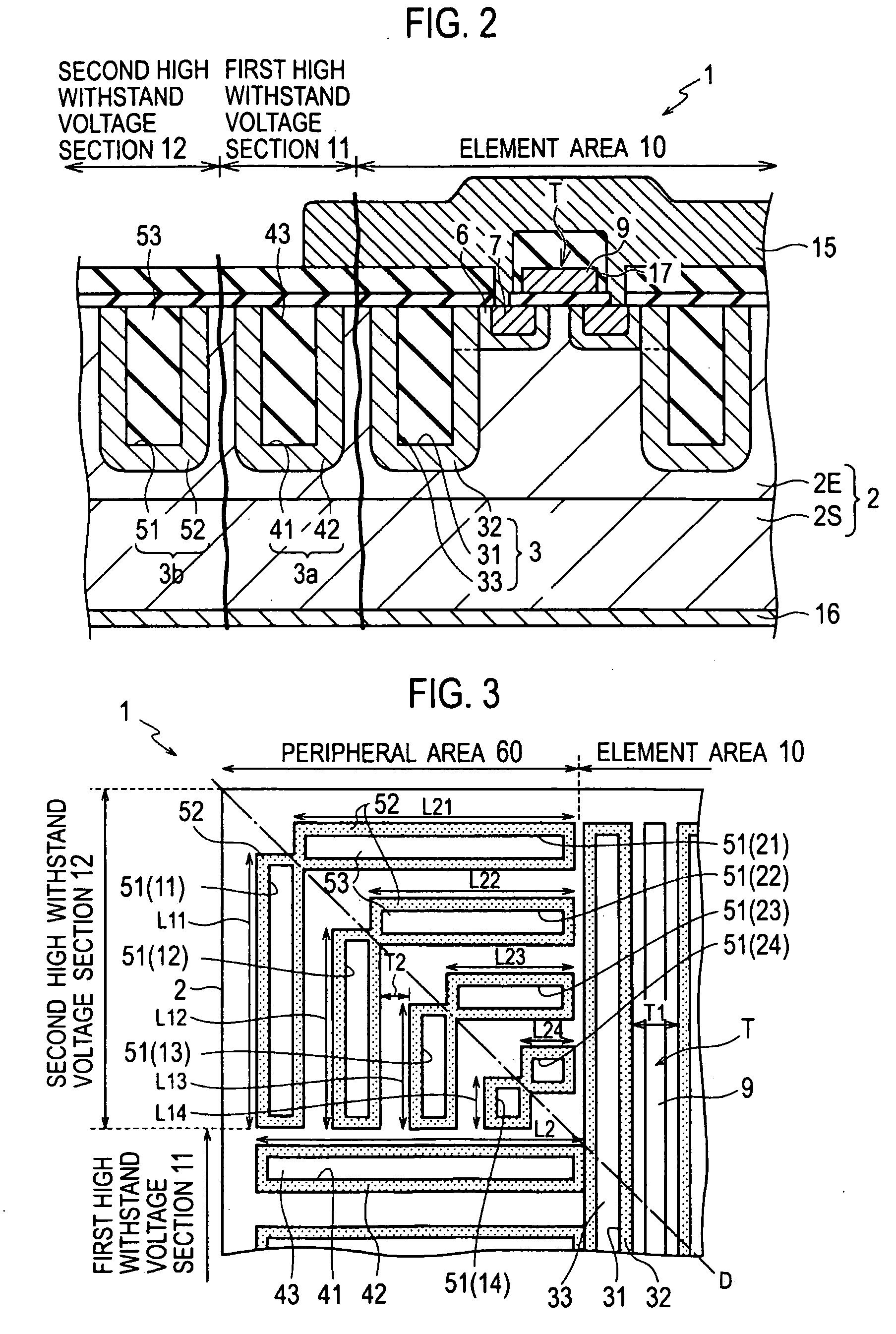

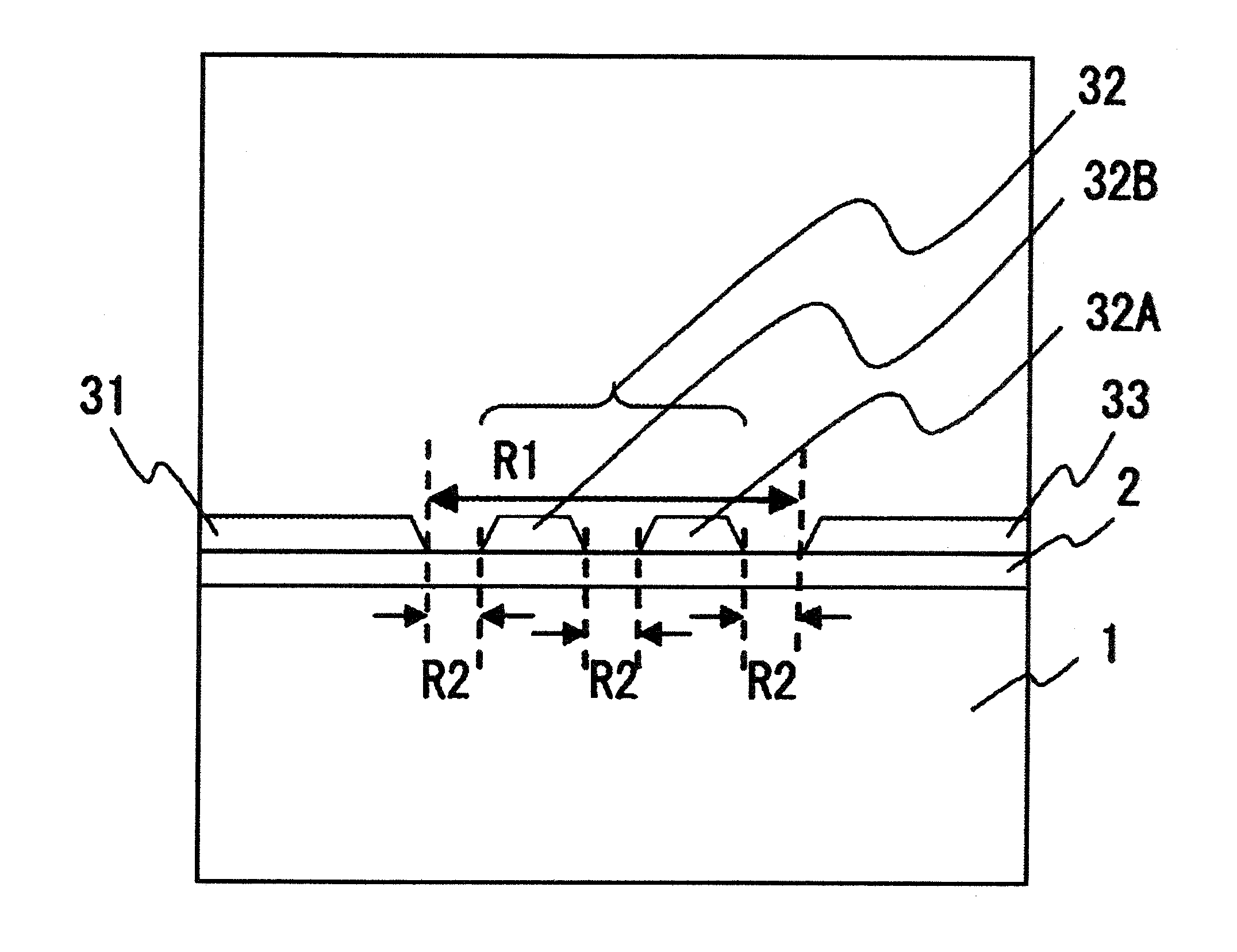

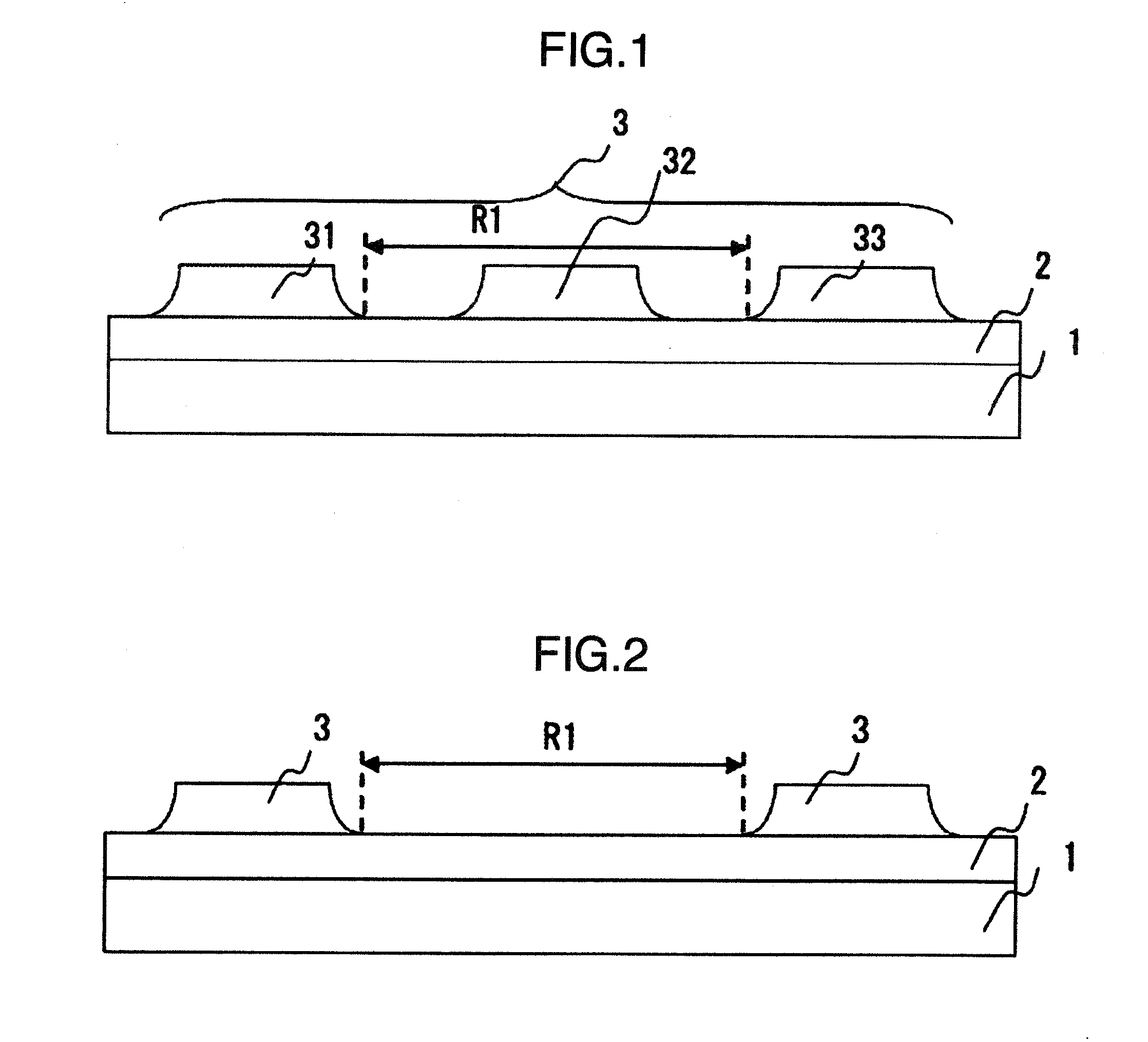

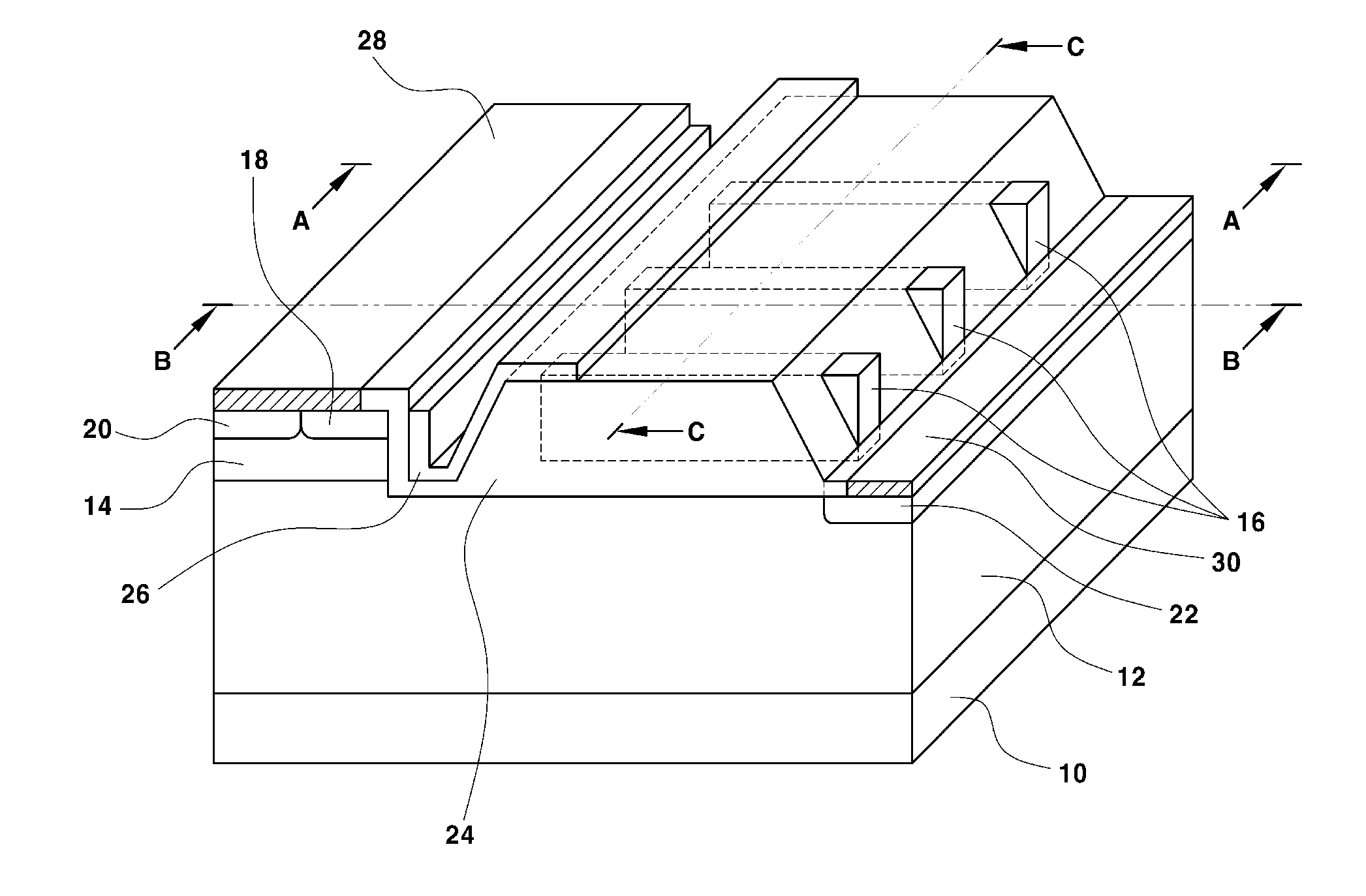

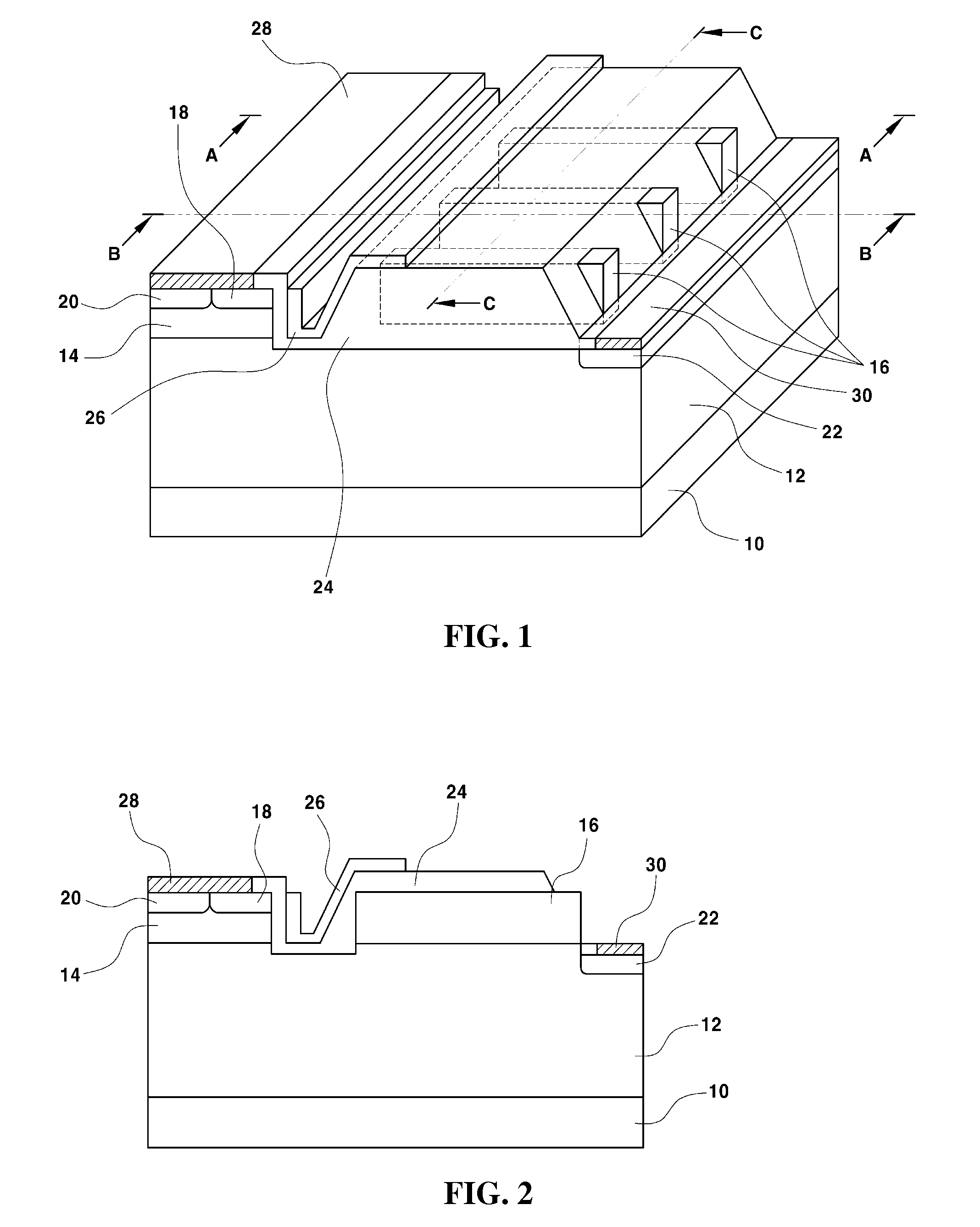

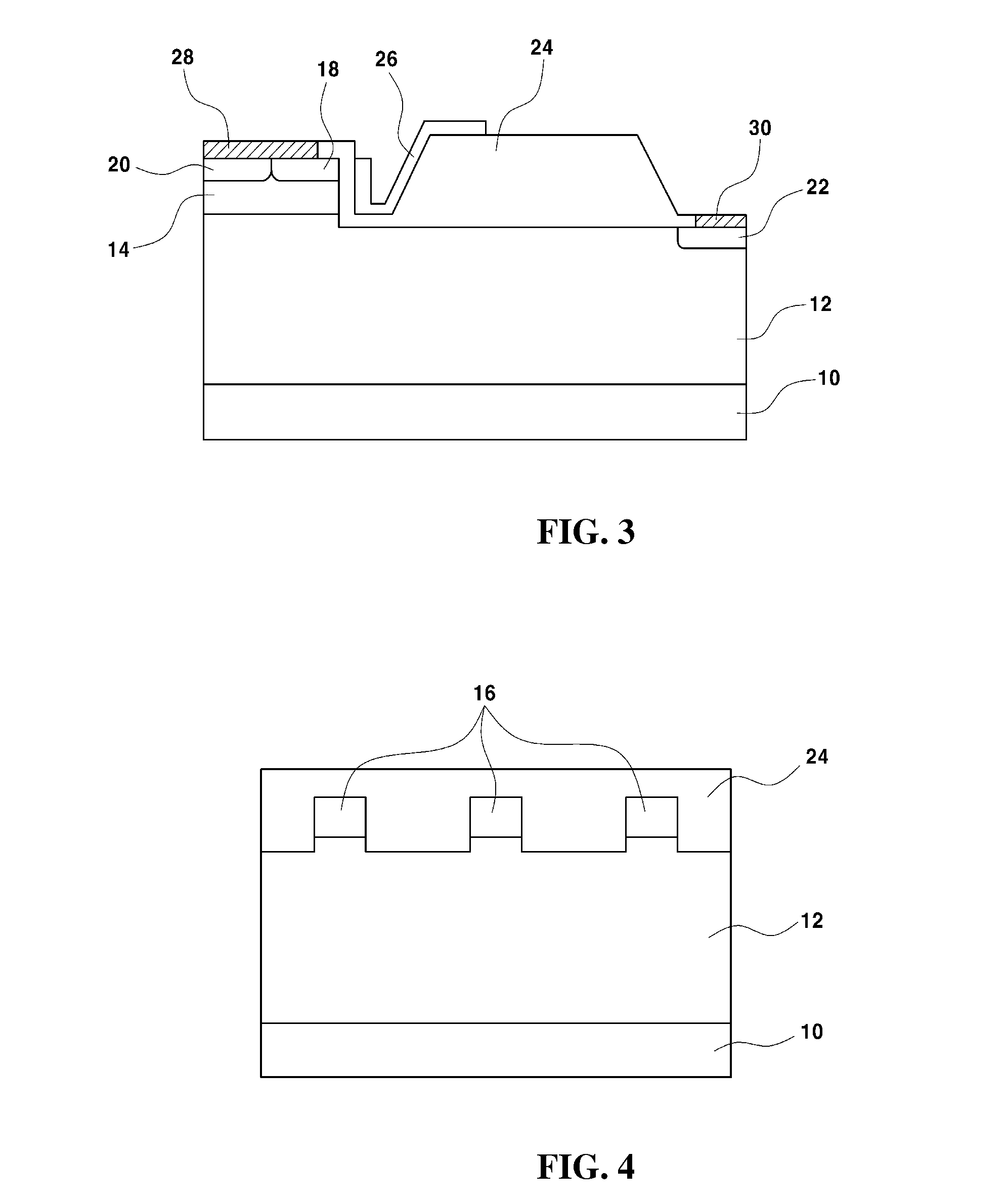

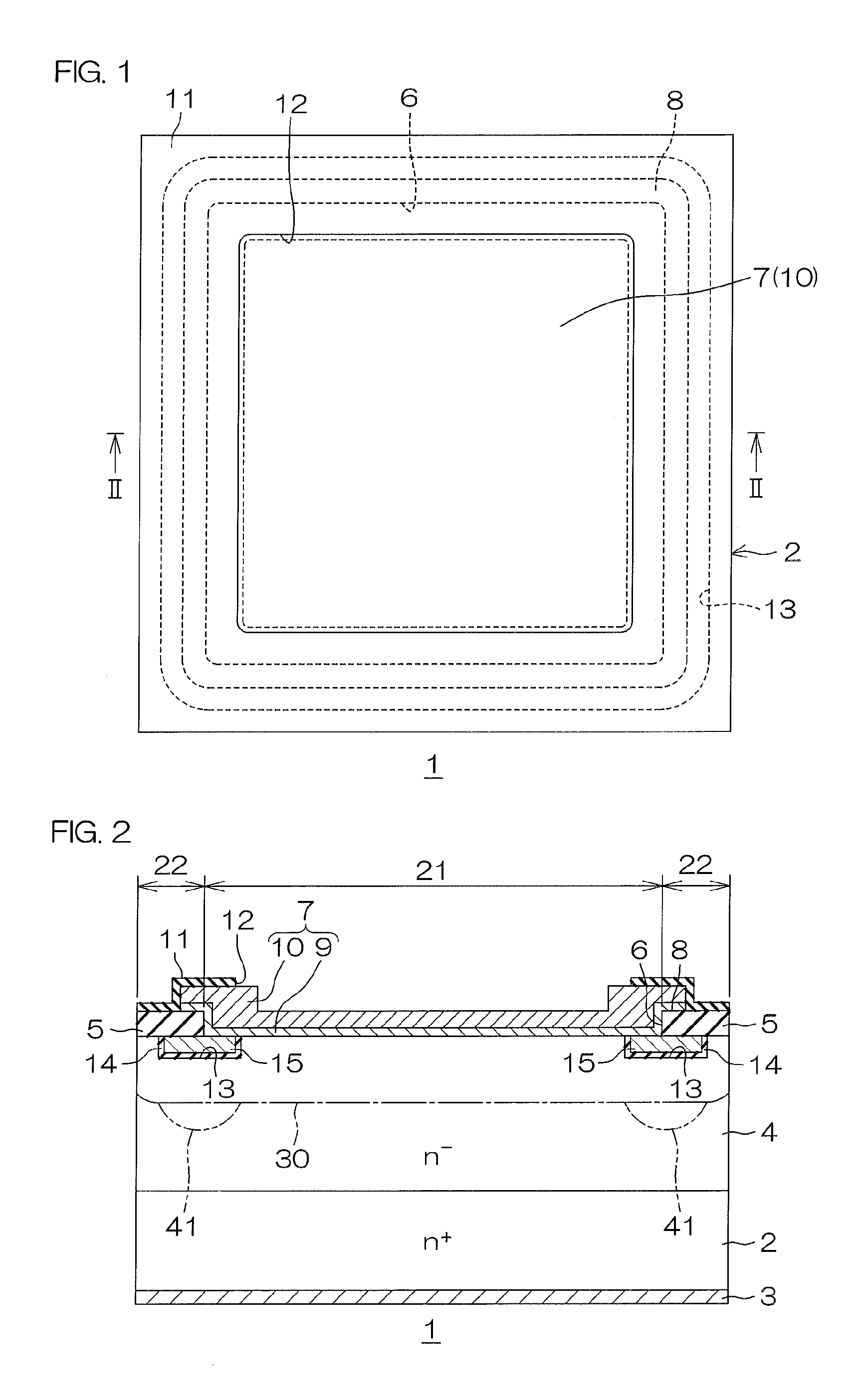

Semiconductor device

InactiveUS20090085146A1Reduce electric field concentrationImprove pressure resistanceTransistorSolid-state devicesDevice materialSemiconductor

A semiconductor device 1 includes a square substrate 2, first RESURF structures 3 in the shape of planar stripes on an element area 10 of a main surface of the substrate 2, a transistor T arranged between the first RESURF structures 3, a first high withstand voltage section 11 constituted by second RESURF structures 3a in the shape of planar strips on a periphery of the main surface of the substrate 2, and a second high withstand voltage section 12 constituted by third RESURF structures 3b which are symmetrically arranged at corners of the substrate 2 with respect to a diagonal line D of the main surface of the substrate 2.

Owner:SANKEN ELECTRIC CO LTD

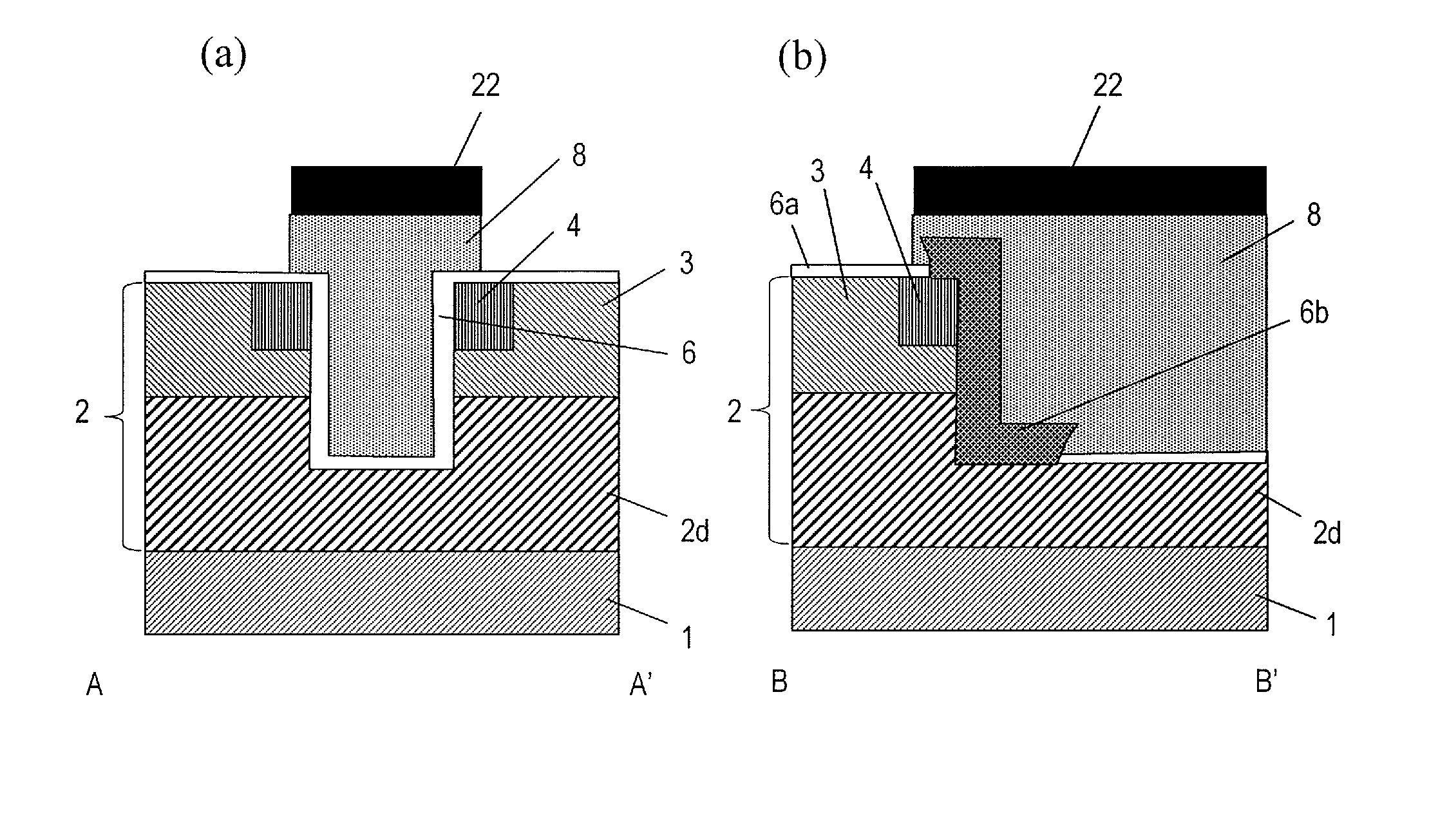

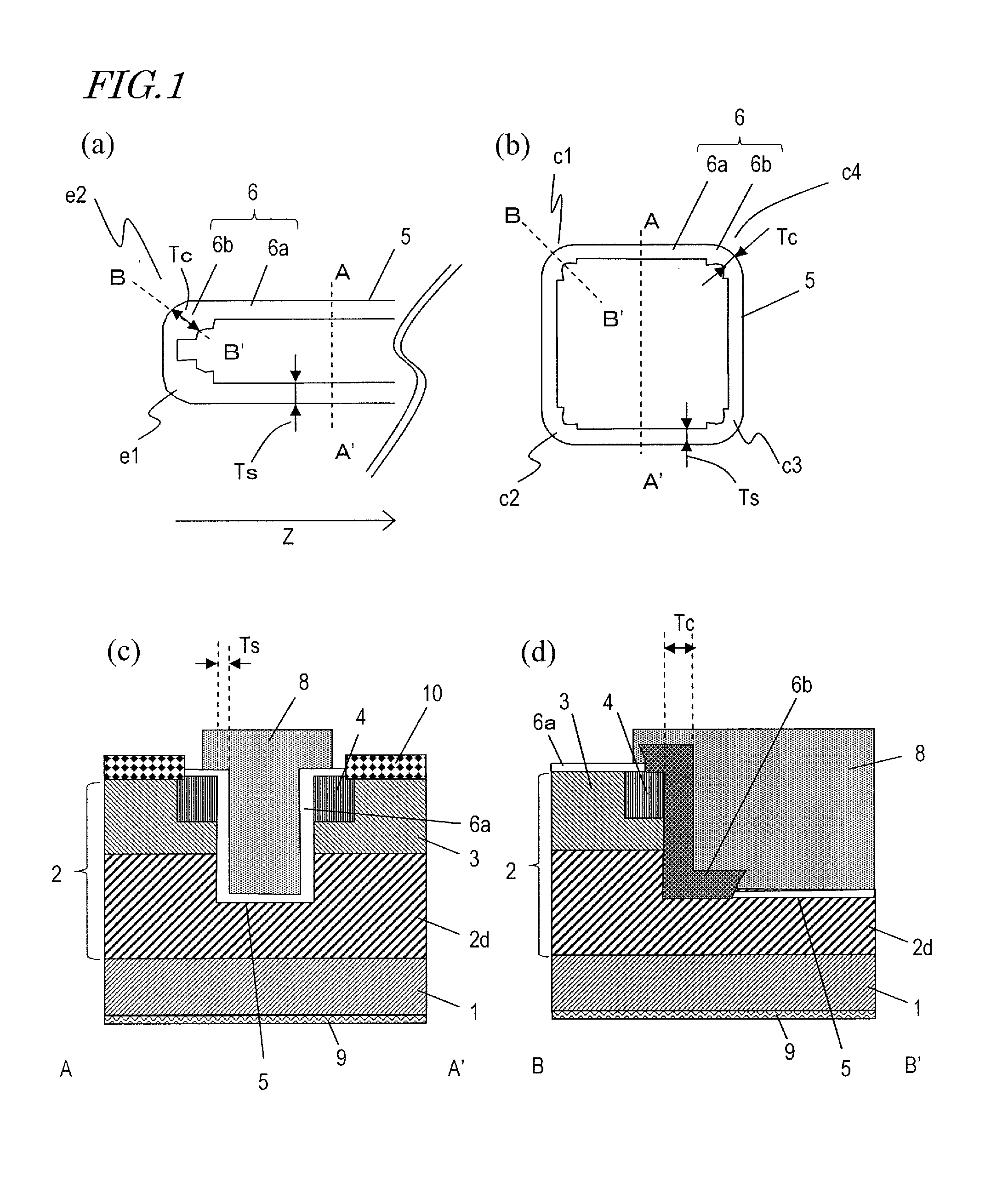

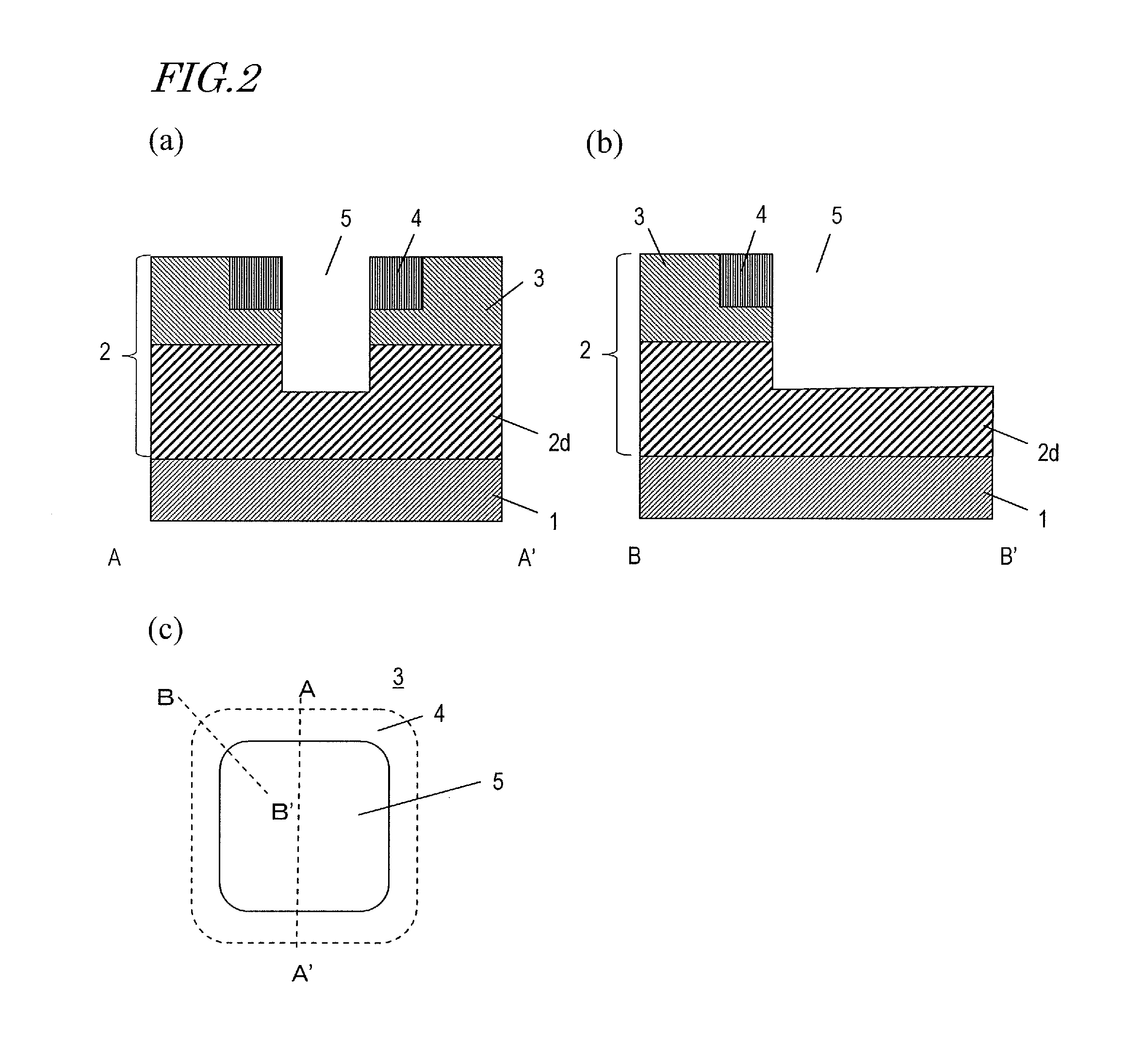

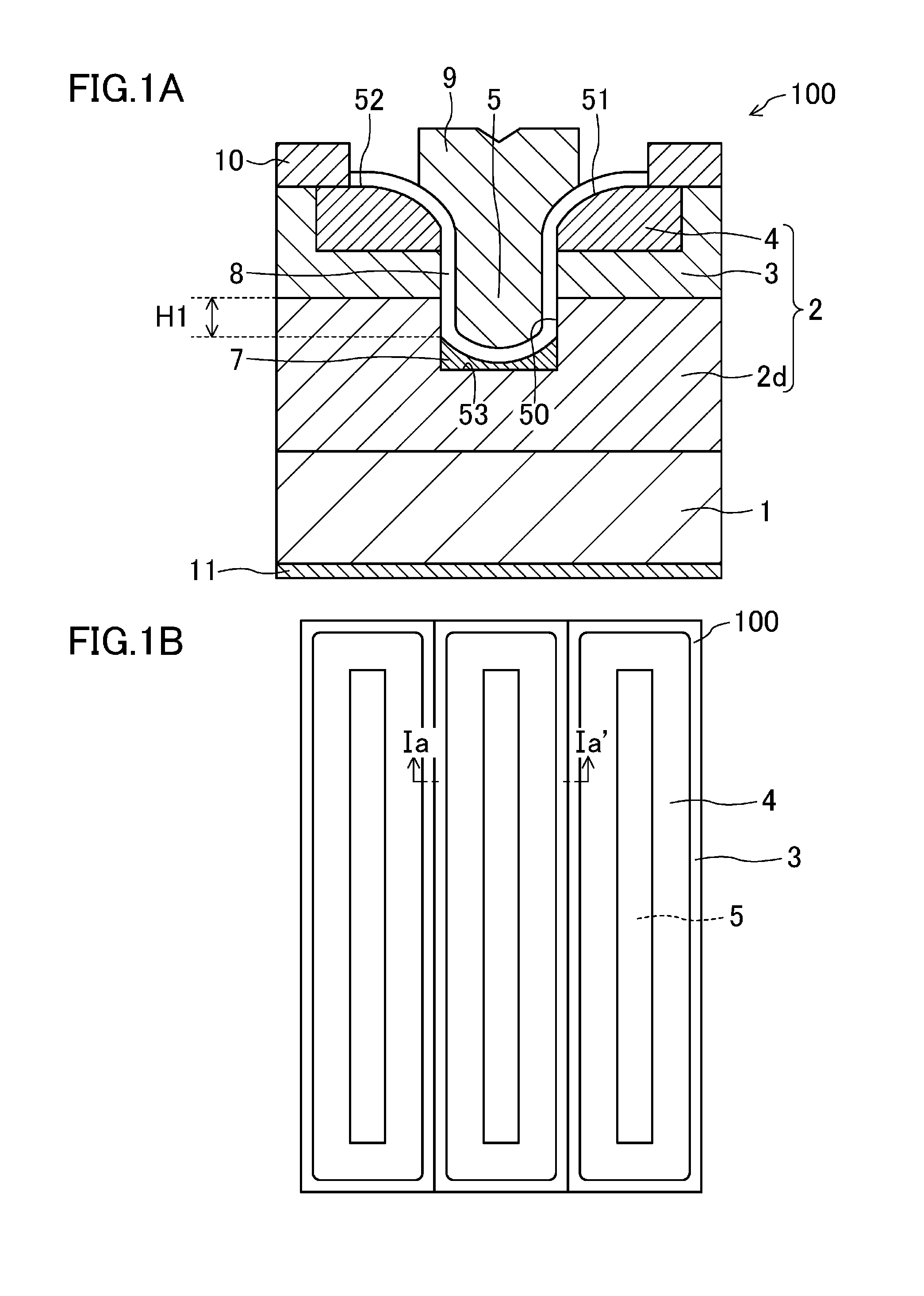

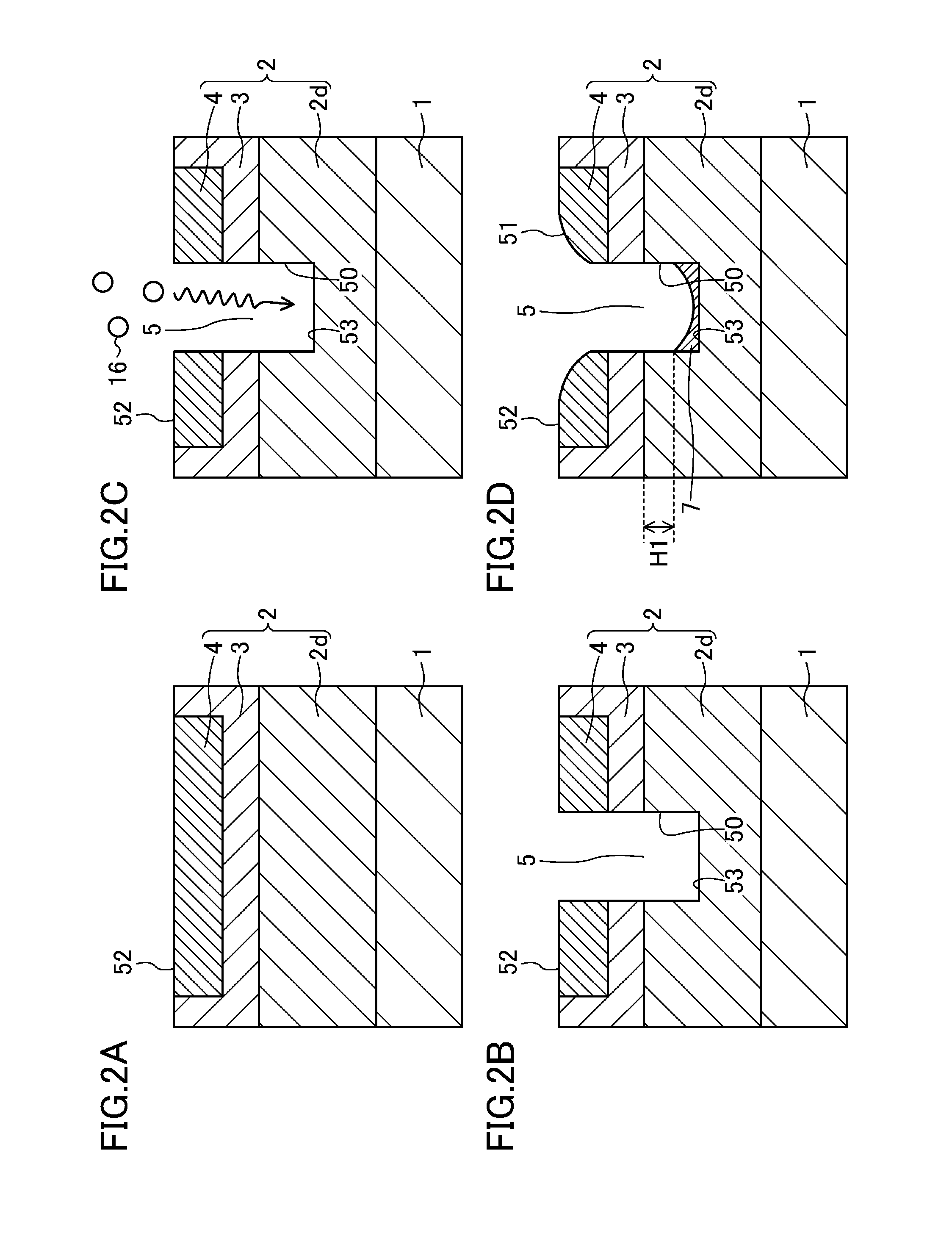

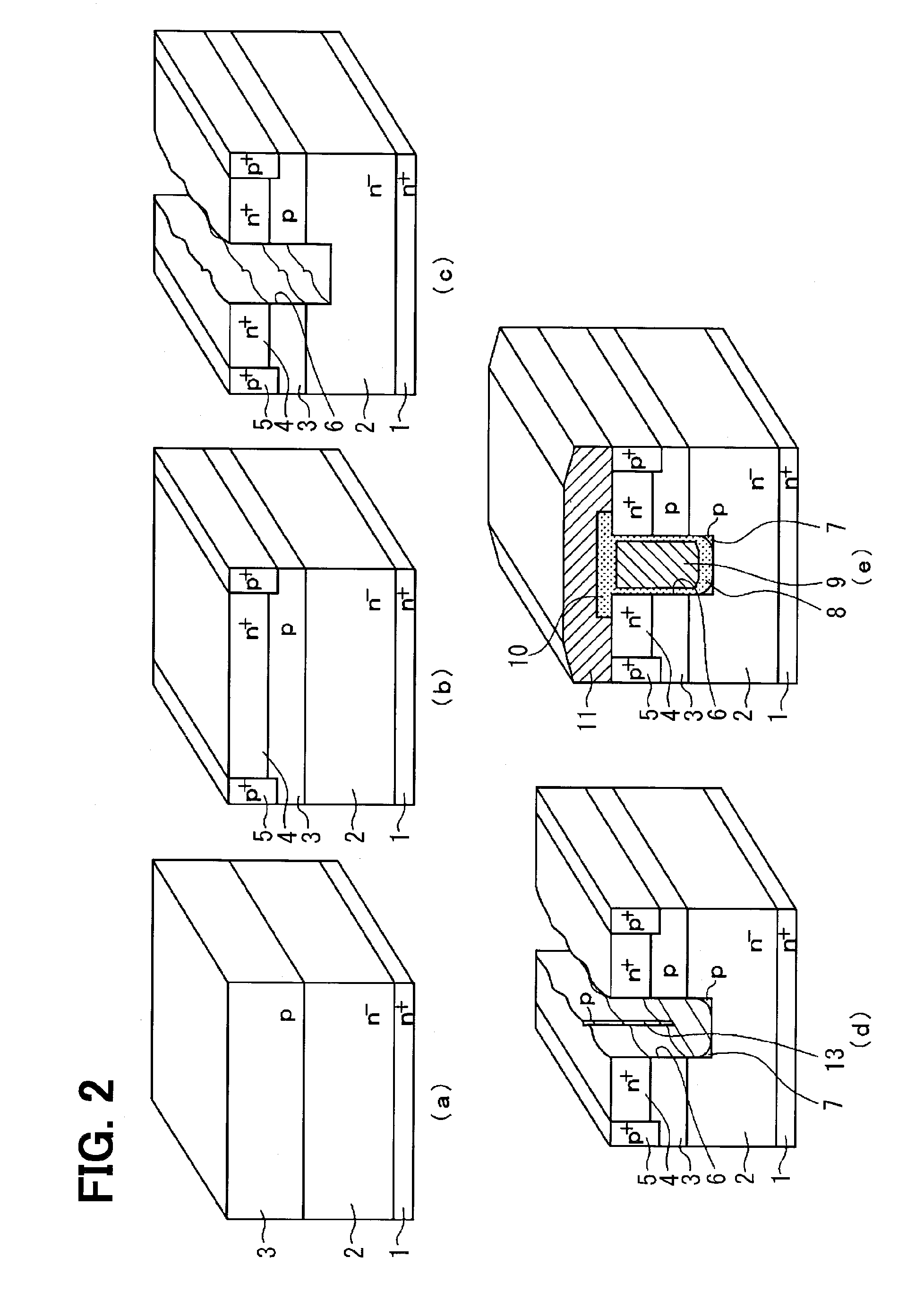

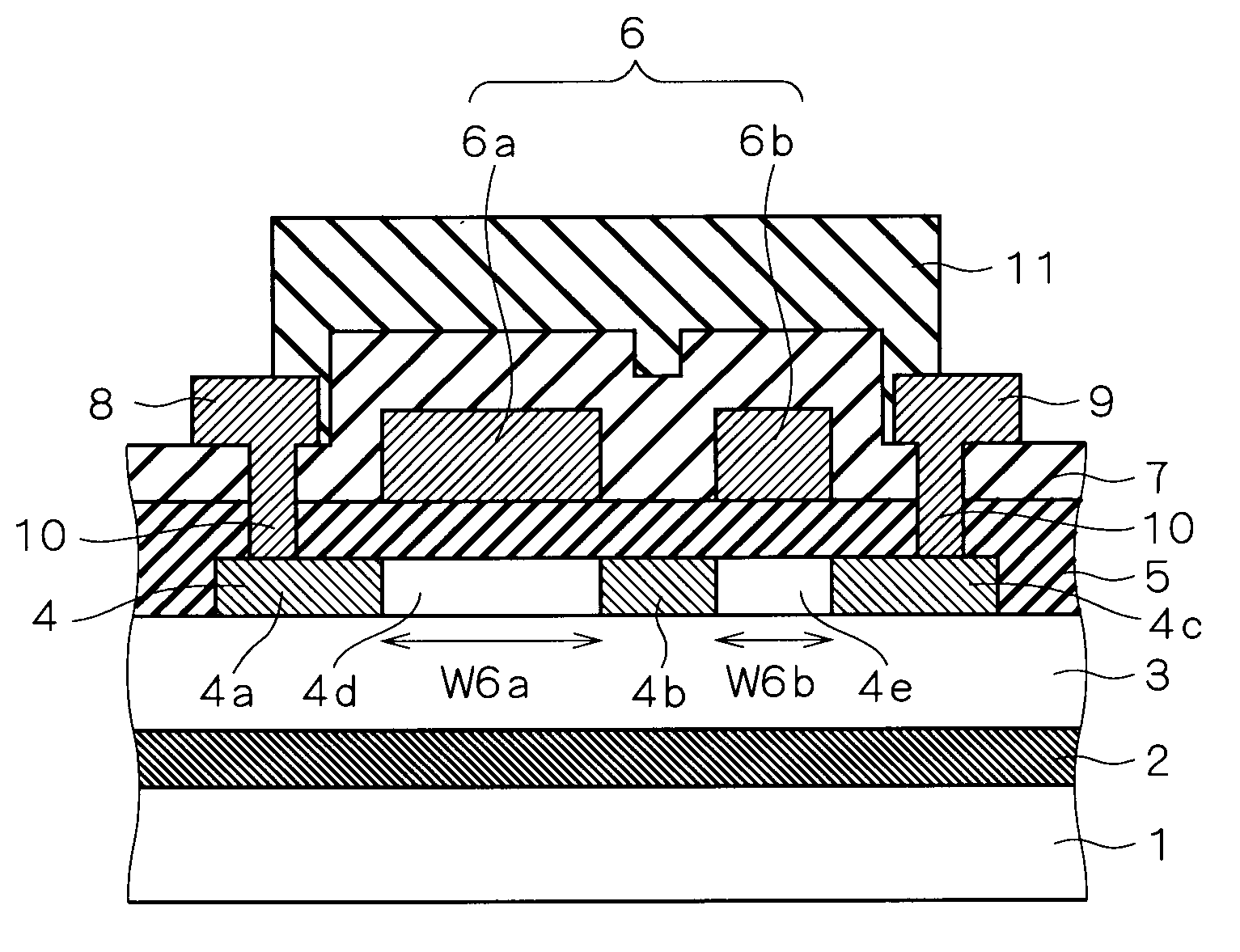

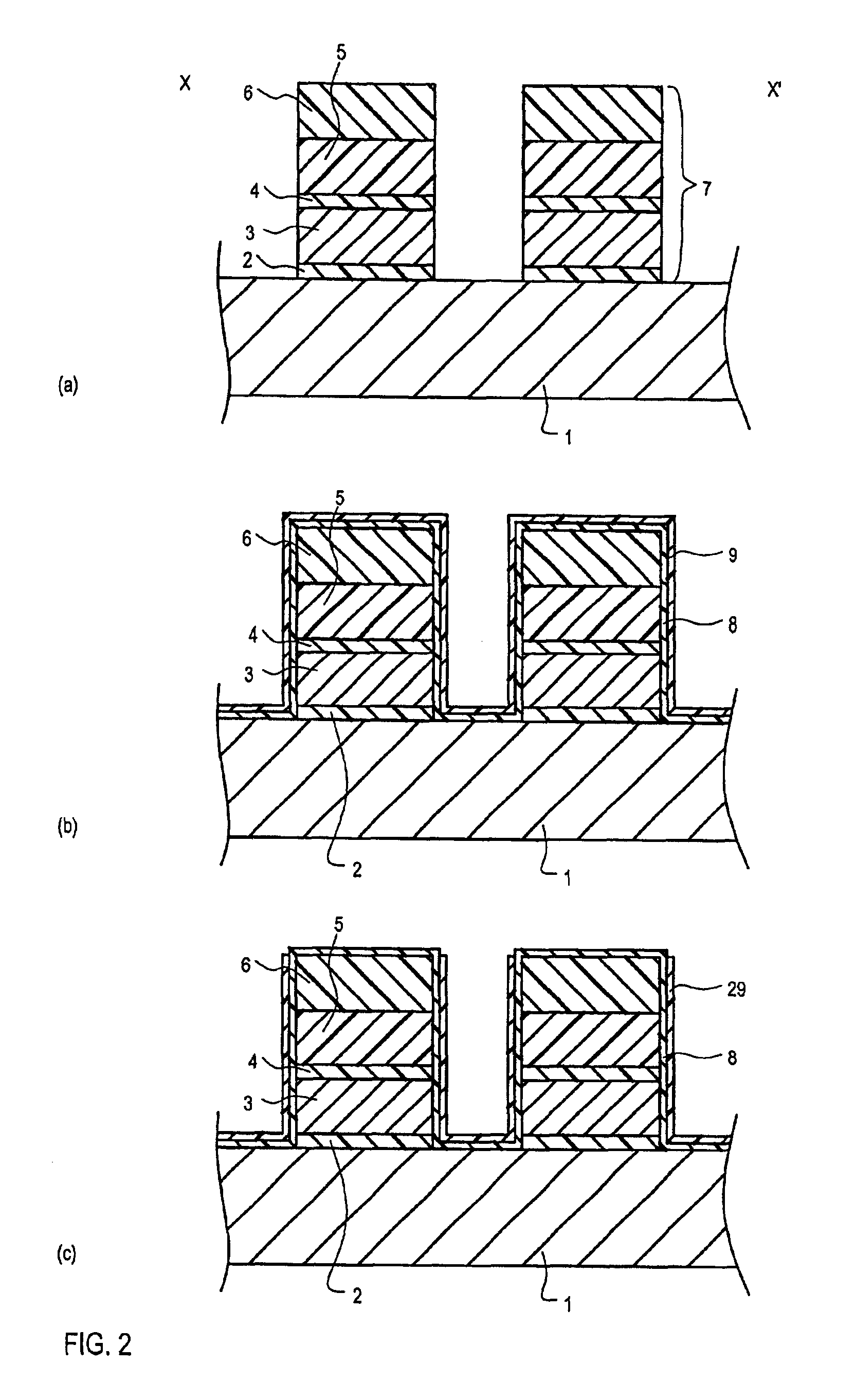

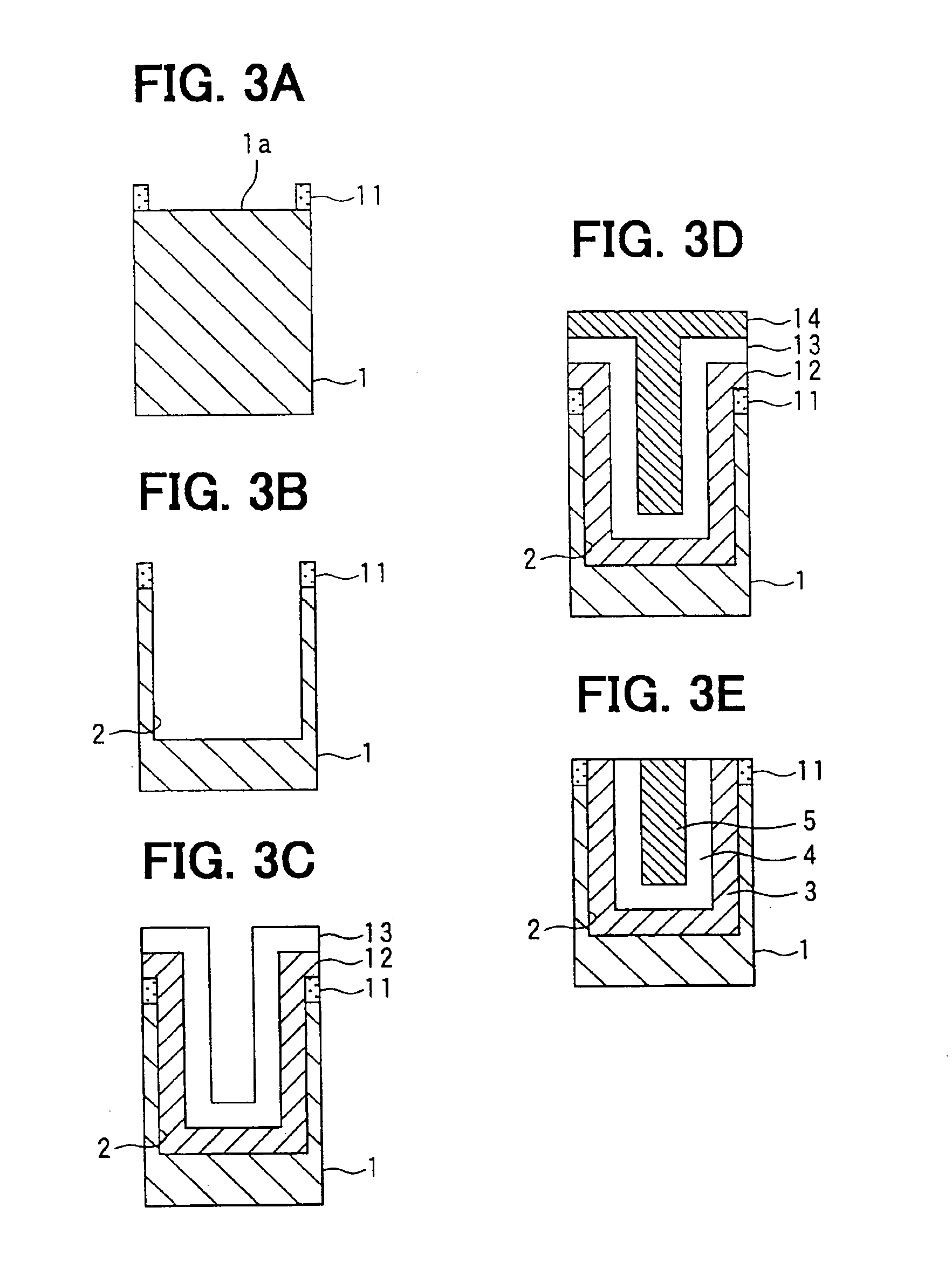

Semiconductor device and method for producing same

InactiveUS20130306982A1Reduce intensityAvoid insulation breakdownTransistorSemiconductor/solid-state device manufacturingDevice materialEngineering

A semiconductor device according to an embodiment of the present invention includes: a semiconductor layer 2 of a wide band gap semiconductor arranged on a principal surface of a substrate 1; a trench 5 arranged in the semiconductor layer and including a bottom surface, a plurality of main side surfaces, and a plurality of corner side surfaces each connecting together two adjacent main side surfaces; a gate insulating film 6 arranged on the bottom surface, the main side surfaces and the corner side surfaces of the trench 5; and a gate electrode 8 arranged in the trench, wherein the semiconductor layer includes a drift region 2d of a first conductivity type, and a body region 3 of a second conductivity type arranged on the drift region; the trench runs through the body region 3 and has the bottom surface inside the drift region; the corner side surfaces of the trench do not have a depressed portion; the gate insulating film 6 is thicker on the corner side surfaces of the trench than on the main side surfaces of the trench; and a portion of the gate insulating film 6 that is located on the corner side surfaces is a first insulating layer 6b, and a portion of the gate insulating film 6 that is located on the main side surfaces is a second insulating layer 6a.

Owner:PANASONIC CORP

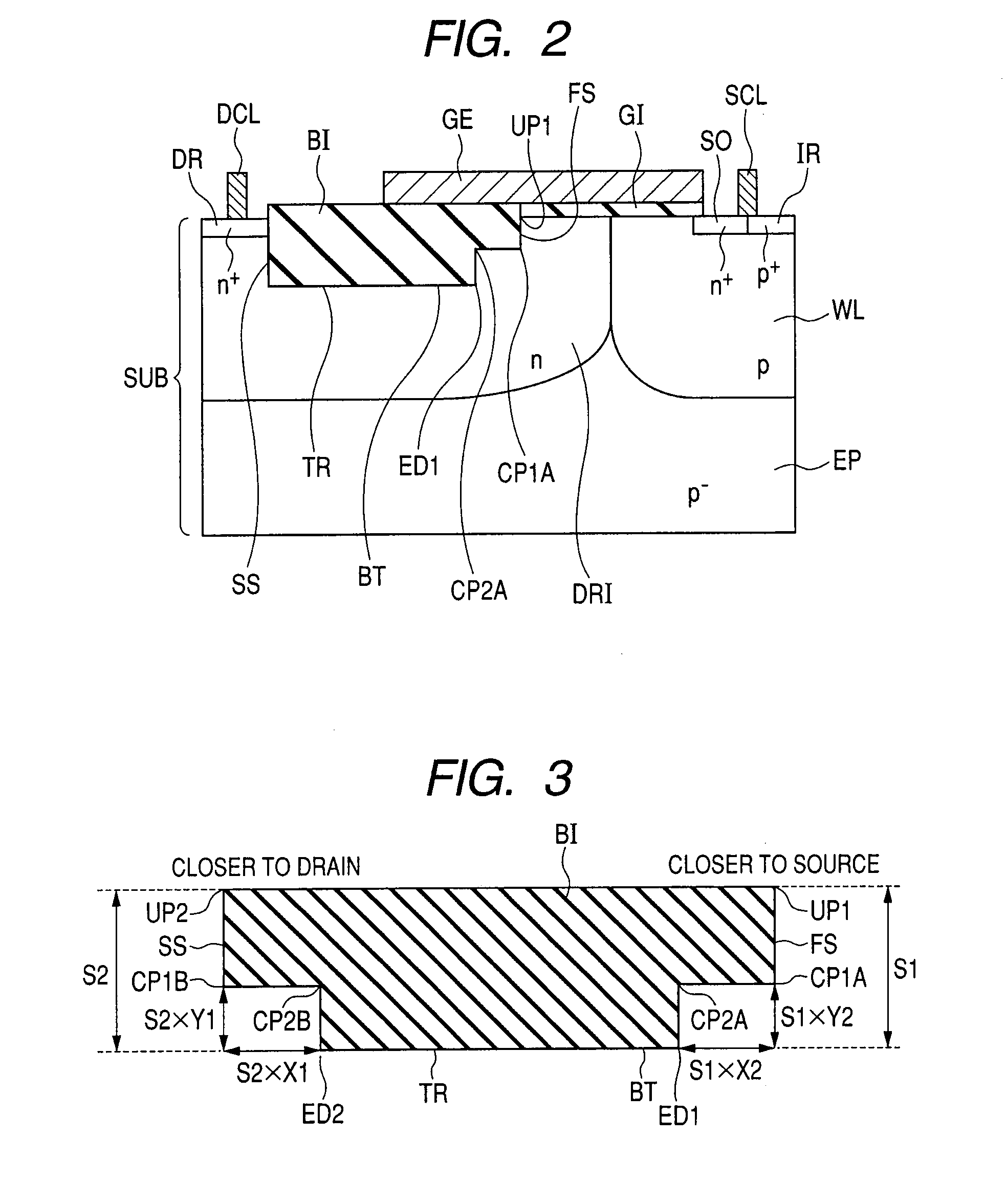

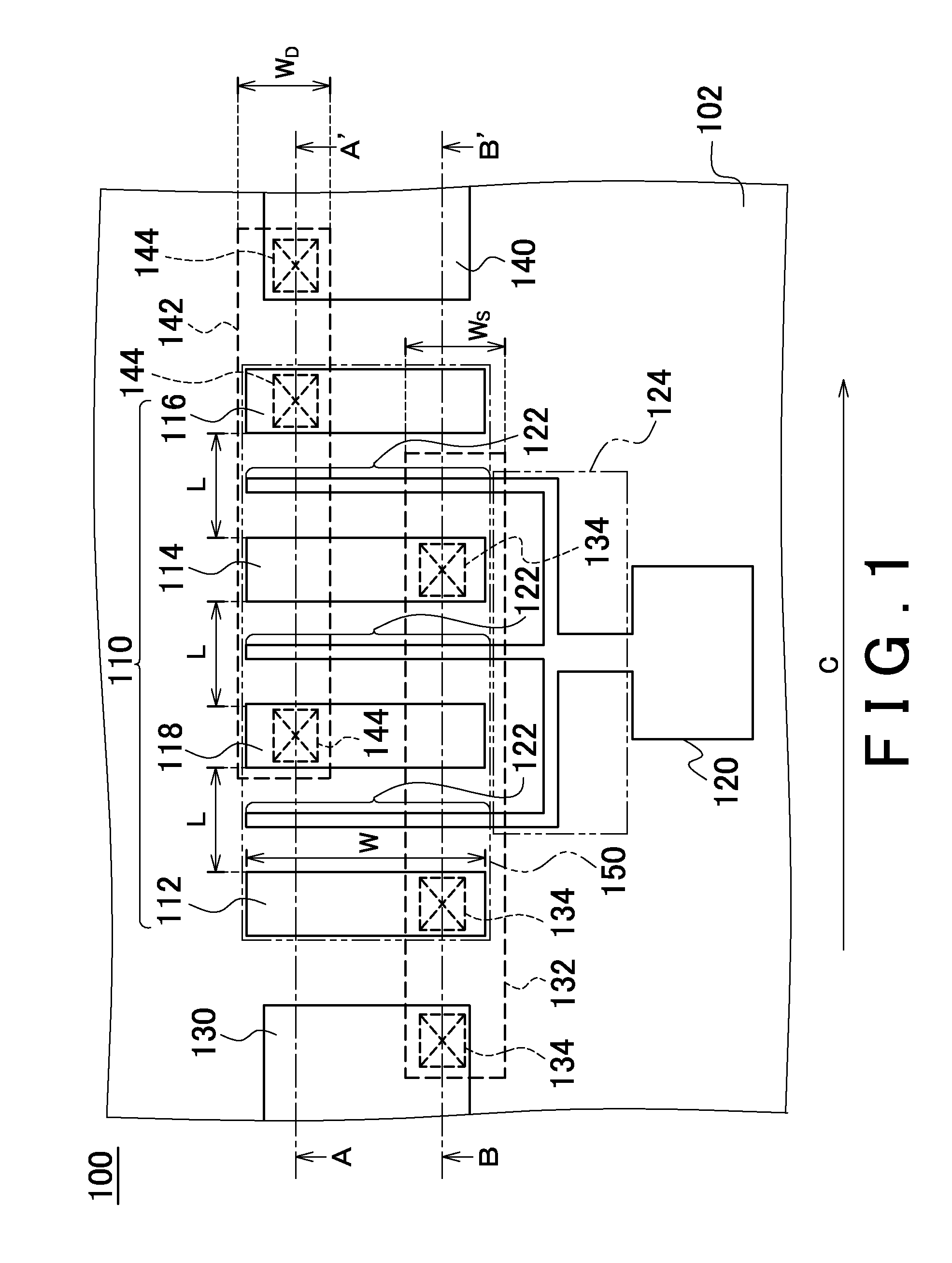

Semiconductor device and method of manufacturing the same

InactiveCN103000673AReduce electric field concentrationIncrease drain withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

The invention provides a semiconductor device and a method of manufacturing the same. The semiconductor device which provides compactness and enhanced drain withstand voltage. The semiconductor device includes: a gate electrode; a source electrode spaced from the gate electrode; a drain electrode located opposite to the source electrode with respect to the gate electrode in a plan view and spaced from the gate electrode; at least one field plate electrode located between the gate and drain electrodes in a plan view, provided over the semiconductor substrate through an insulating film and spaced from the gate electrode, source electrode and drain electrode; and at least one field plate contact provided in the insulating film, coupling the field plate electrode to the semiconductor substrate. The field plate electrode extends from the field plate contact at least either toward the source electrode or toward the drain electrode in a plan view.

Owner:RENESAS ELECTRONICS CORP

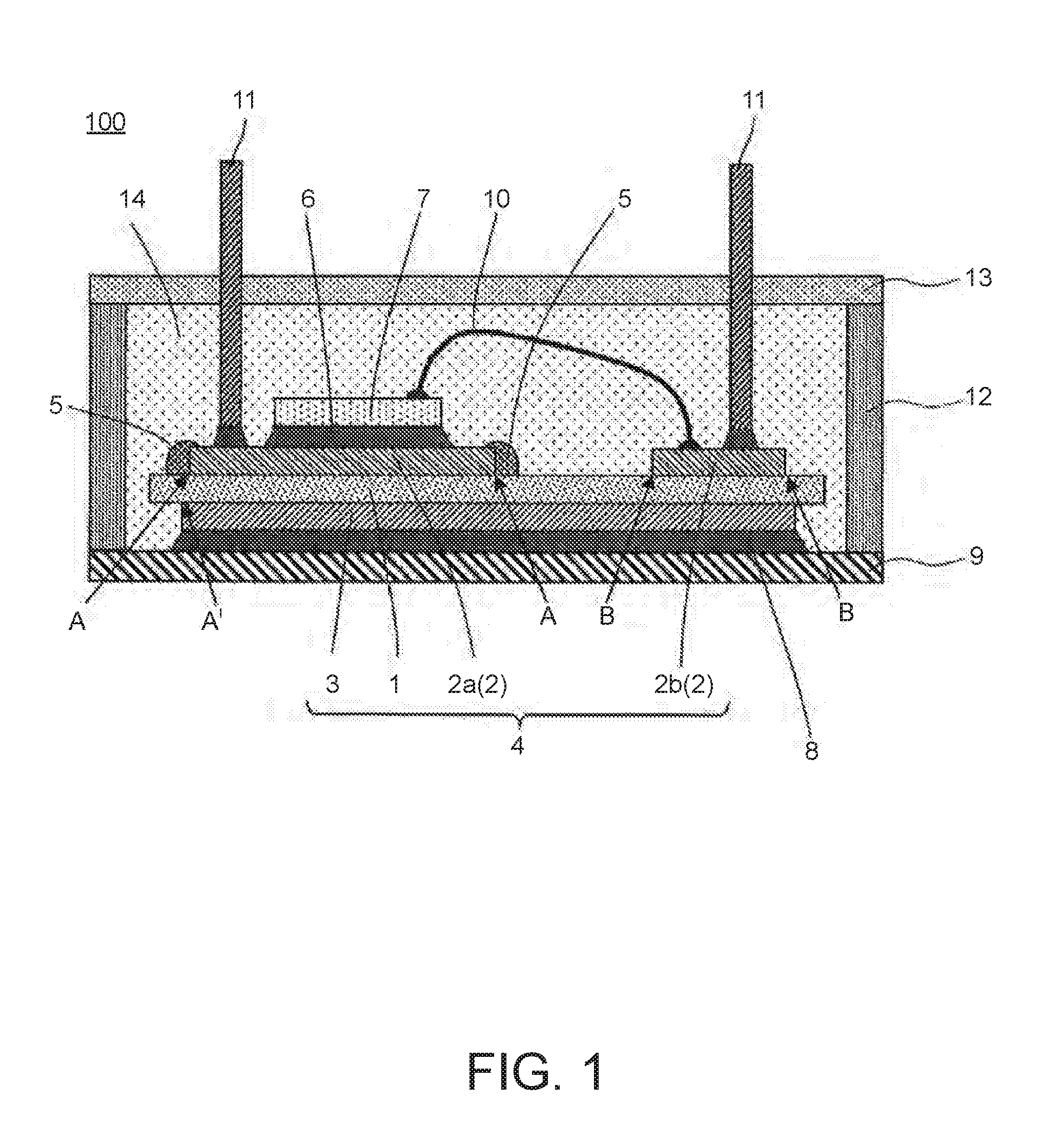

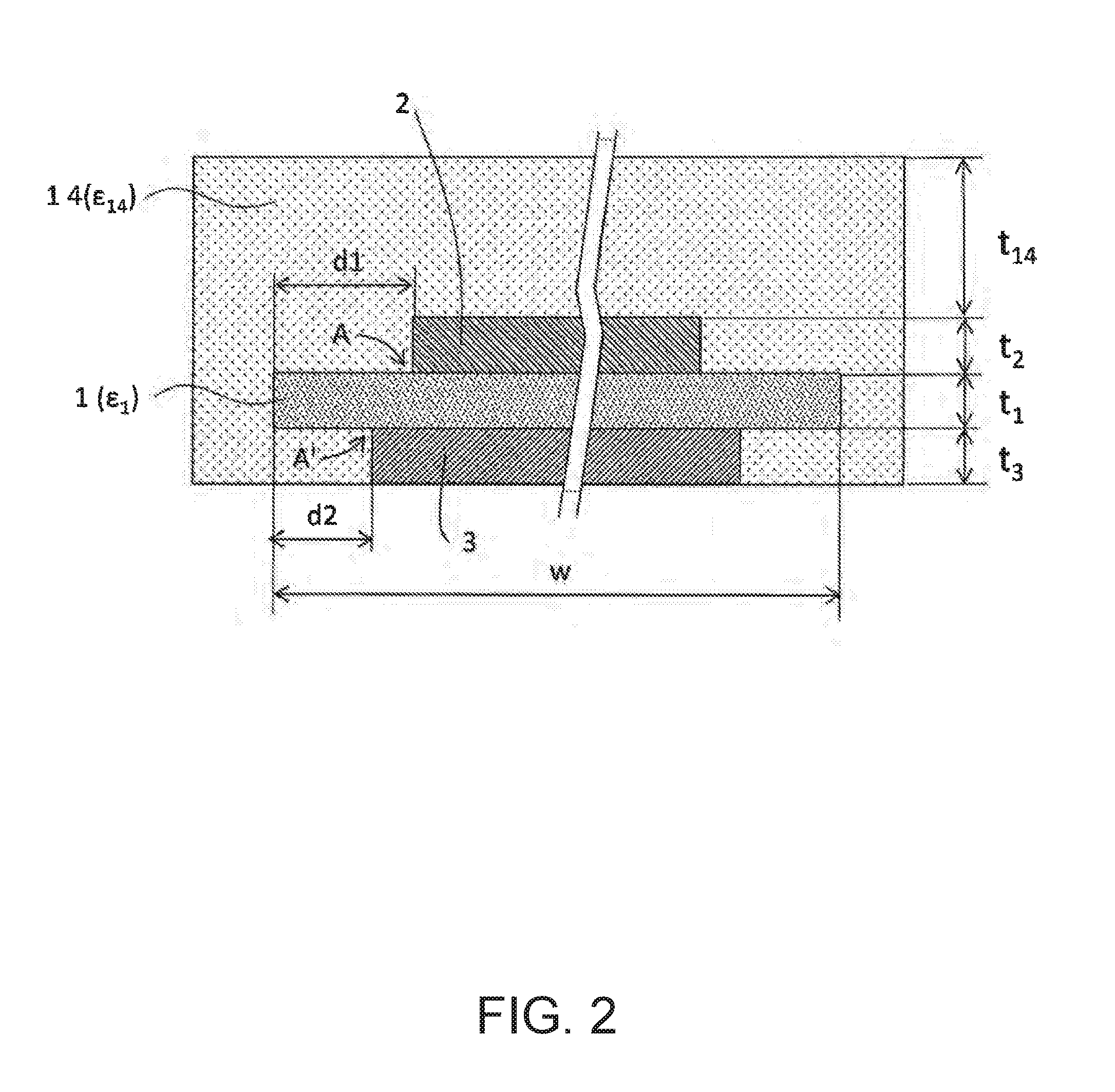

Insulation circuit board, and power semiconductor device or inverter module using the same

ActiveUS20120127684A1Low costImprove featuresConversion constructional detailsSemiconductor/solid-state device detailsInsulation layerElectrical conductor

The invention relates to a high-voltage insulation circuit board which is used in an electric power apparatus such as an electric power converter or the like such as power semiconductor device, inverter module, or the like and provides an insulation circuit board in which electric field concentration at the end sections of a wiring pattern is reduced, partial discharging is suppressed, and a reliability is high. According to the invention, there is provided an insulation circuit board having: a metal base substrate; and wiring patterns which are formed onto at least one of the surfaces of the metal base substrate through an insulation layer, characterized in that between two adjacent wiring patterns in which an electric potential difference exists among the wiring patterns, at least one or more wiring patterns or conductors which are in contact with the insulation layer and have an electric potential in a range of the electric potential difference between the adjacent wiring patterns are arranged. According to the invention, the electric field concentration at the end sections of the wiring pattern to which a high voltage is applied is reduced and partial-discharge-resistant characteristics are improved.

Owner:HITACHI LTD

Semiconductor device and method for manufacturing same

ActiveUS20150333175A1Reduce electric field concentrationIncrease the on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesImpuritySemiconductor

A method for manufacturing a semiconductor device includes the steps of: forming, on a principal face of a substrate, a semiconductor layer including a first semiconductor region of a first conductivity type; and forming, in the semiconductor layer, a trench having a bottom located in the first semiconductor region. The method further includes a step of forming a trench bottom impurity region being of a second conductivity type and covering the bottom of the trench by performing annealing to cause part of the semiconductor layer corresponding to an upper corner portion of the trench to move to be placed on the bottom of the trench.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

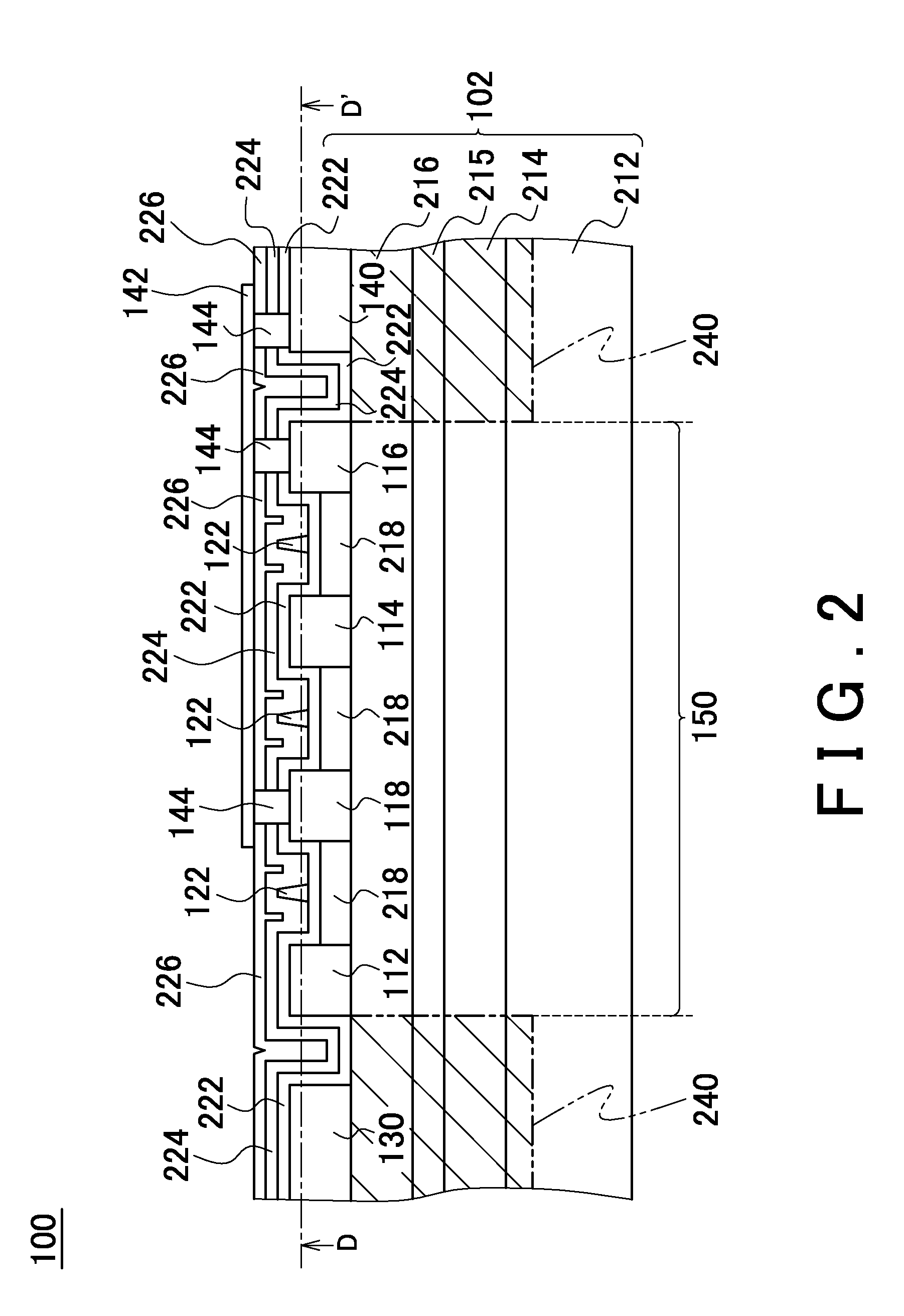

Silicon carbide semiconductor device and method for manufacturing the same

ActiveUS20150048382A1Reduce deteriorationResistant to breakageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETPhysics

In a silicon carbide semiconductor device, a p-type SiC layer is disposed in a corner of a bottom of a trench. Thus, even if an electric field is applied between a drain and a gate when a MOSFET is turned off, a depletion layer in a pn junction between the p-type SiC layer and an n− type drift layer greatly extends toward the n− type drift layer, and a high voltage caused by an influence of a drain voltage hardly enters a gate insulating film. Hence, an electric field concentration within the gate insulating film can be reduced, and the gate insulating film can be restricted from being broken. In this case, although the p-type SiC layer may be in a floating state, the p-type SiC layer is formed in only the corner of the bottom of the trench. Thus, the deterioration of the switching characteristic is relatively low.

Owner:DENSO CORP +1

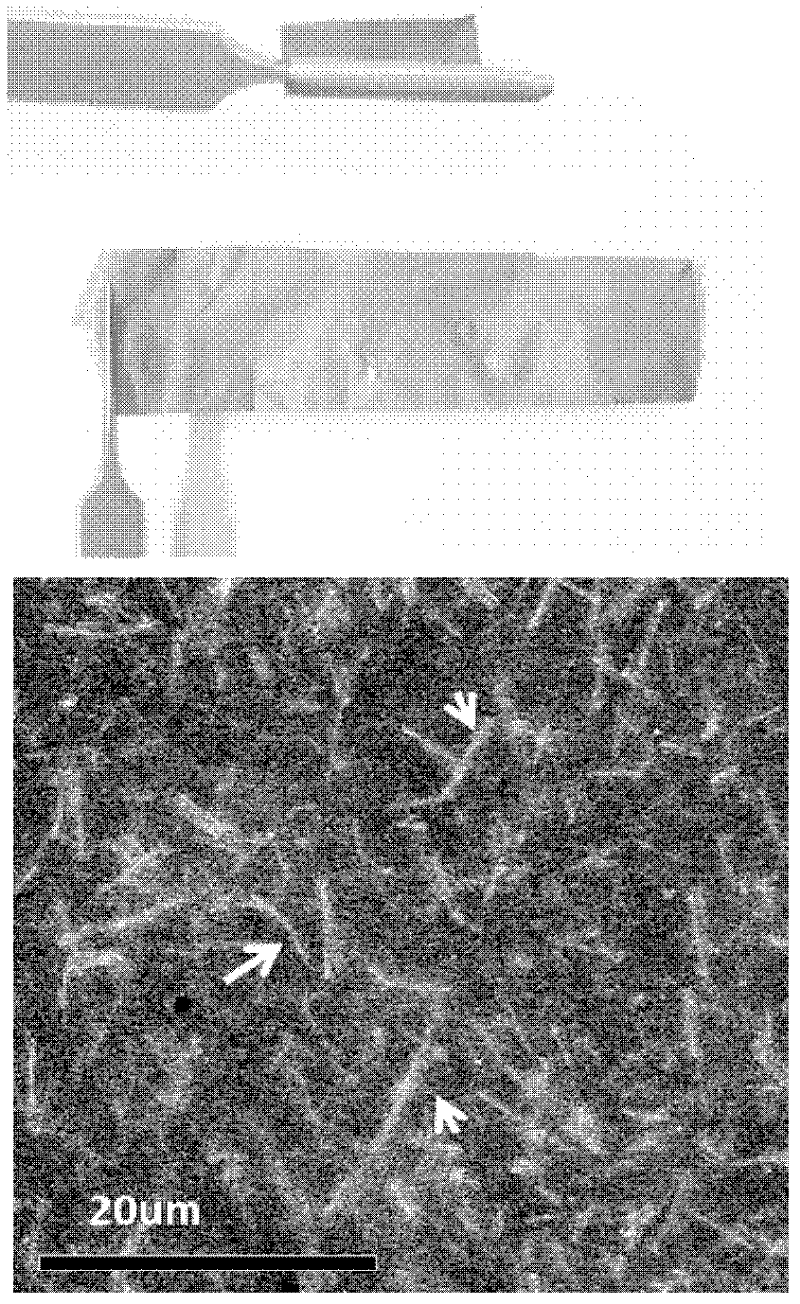

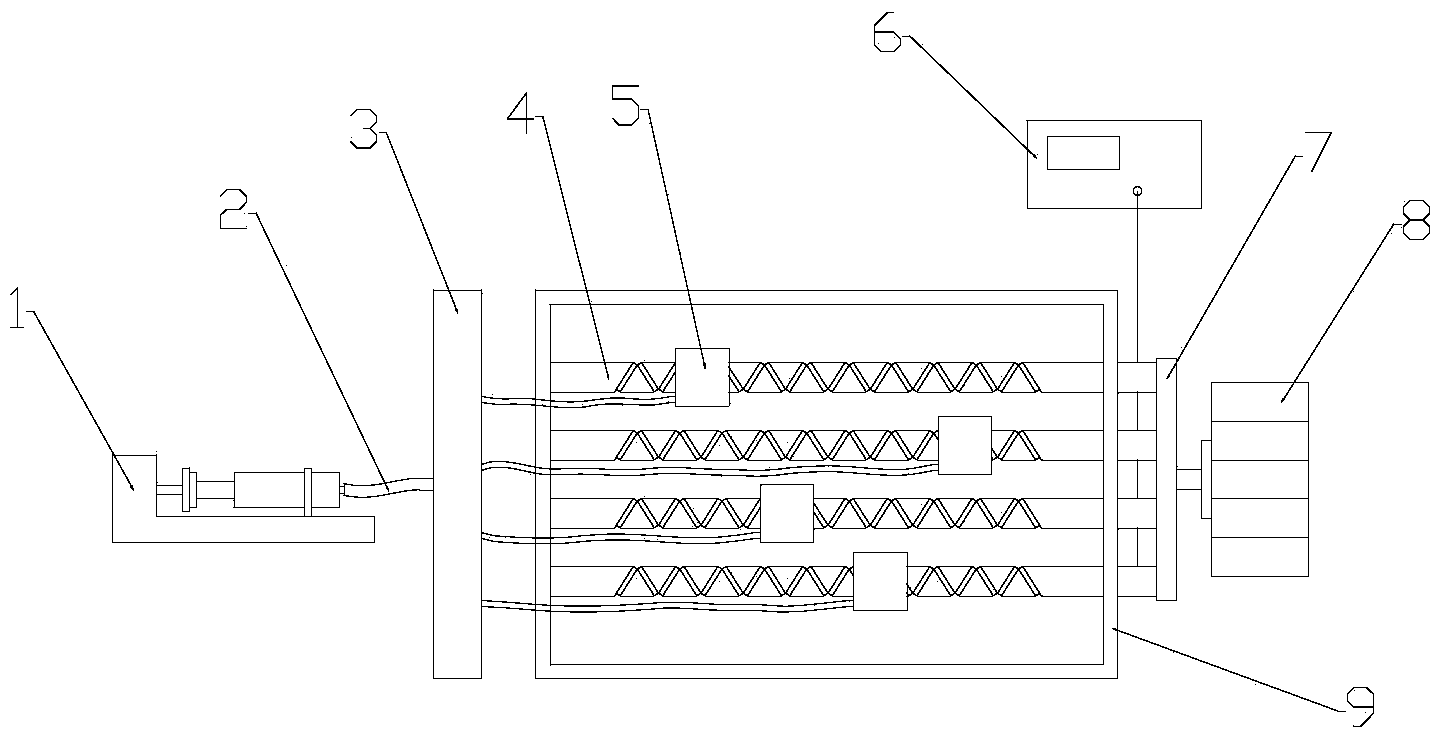

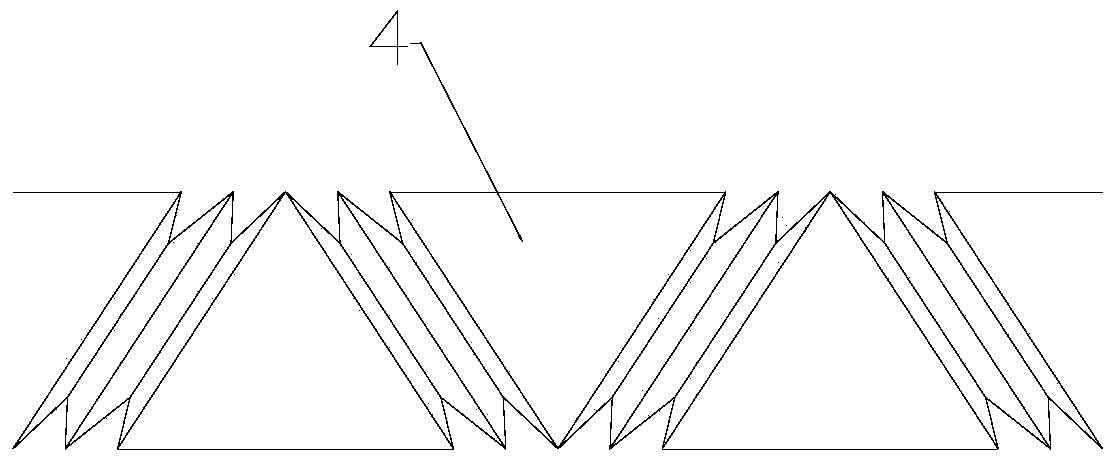

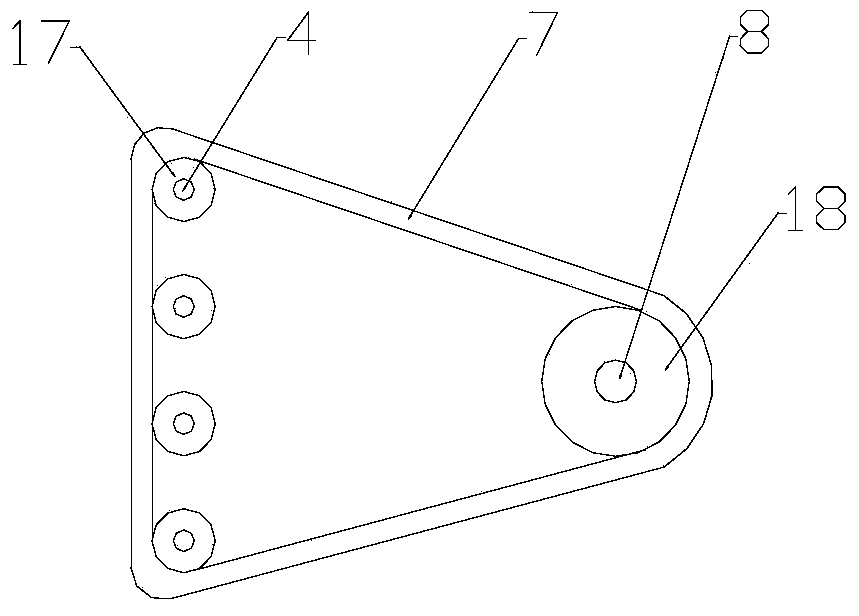

Bidirectional spiral electrostatic spinning device

ActiveCN104032383AJet stabilityImprove thickness uniformitySpinning head liquid feederFilament/thread formingFiberElectrospinning

The invention discloses a bidirectional spiral electrostatic spinning device, and relates to an electrostatic spinning device. The bidirectional spiral electrostatic spinning device is provided with bidirectional threaded guide rods, liquid storage sliders, vertical slide bars, guide rails, a framework, a controllable injection device, a liquid guide pipe, a liquid distributing device, a high-voltage power source, air pumps, pressure regulating valves, air guide pipes, partition plates, motors, driven belt pulleys, driving belt pulleys, V-shaped belts, air hole arrays and collecting devices. The bidirectional spiral electrostatic spinning device has the advantages that large-area and multi-jet injection effects can be realized by the aid of the bidirectional threaded guide rods, so that the electrostatic spinning efficiency further can be improved, phenomena of electrostatic interference among spinning jets and electric field concentration can be reduced, uniform distribution of nano-fibers on collecting plates can be promoted, the thickness uniformity of collected nano-fiber membranes can be improved, the quality of the nano-fiber membranes can be enhanced, the multiple jets can be assuredly stably and quickly injected, and large-area uniform nano-membranes can be collected; the bidirectional spiral electrostatic spinning device is applicable to injection devices with different bidirectional threaded guide rods and different thread shapes, and the lengths, the quantities and the shapes of the bidirectional threaded guide rods of the injection devices can be different from one another.

Owner:XIAMEN UNIV

Semiconductor module and method of manufacturing semiconductor module

ActiveUS20170025344A1Weakening rangeIncrease production costSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A semiconductor module includes an insulated circuit board that includes an insulating substrate, a first conductive plate arranged on a first principal surface of the insulating substrate and within the outer edges of the insulating substrate, and a second conductive plate arranged within the outer edges of the insulating substrate on a second principal surface of the insulating substrate that faces the first principal surface. Furthermore, boundary edges between the first principal surface of the insulating substrate and the side faces of the first conductive plate are covered by an ion gel that contains an ionic liquid.

Owner:FUJI ELECTRIC CO LTD

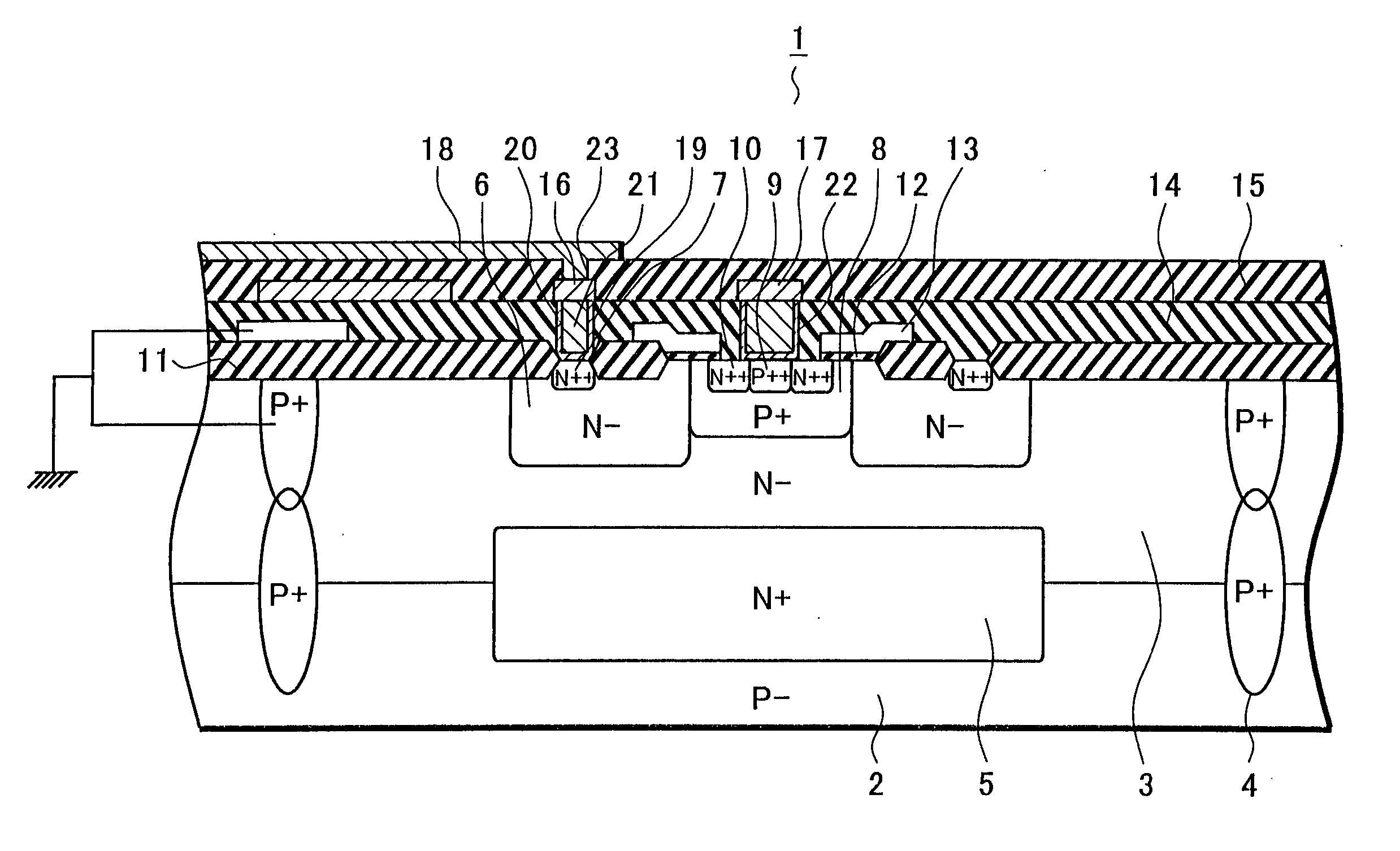

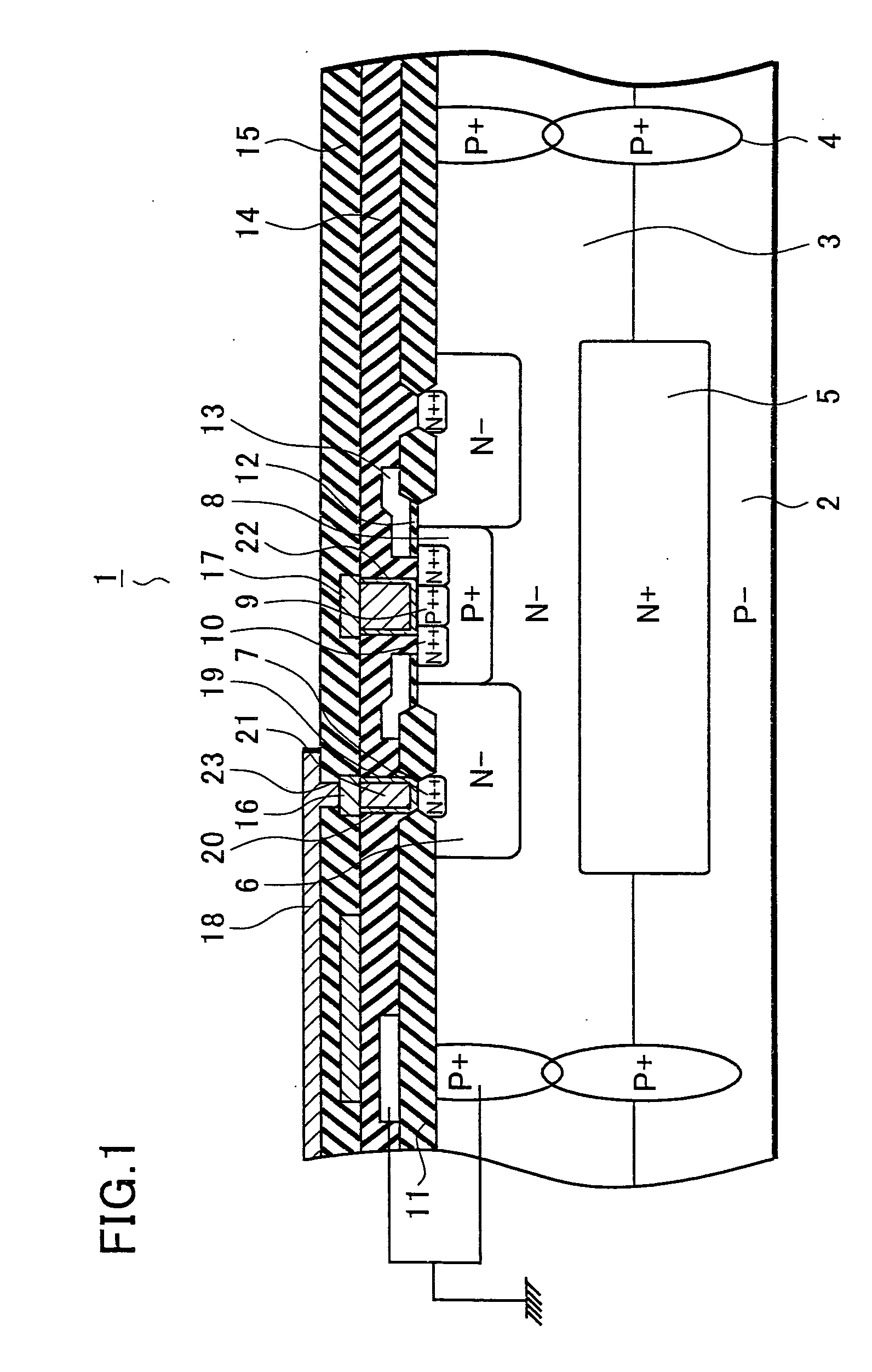

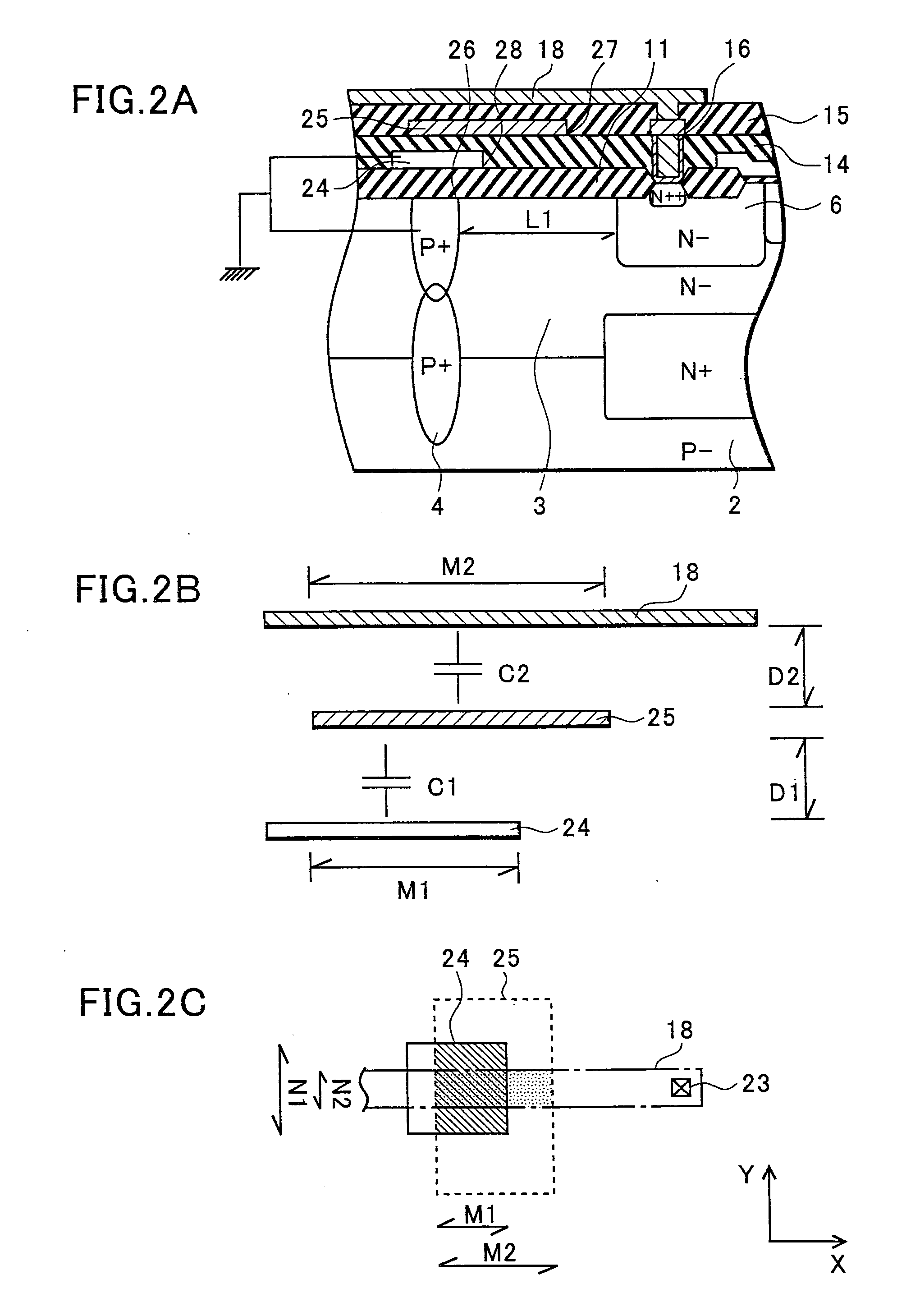

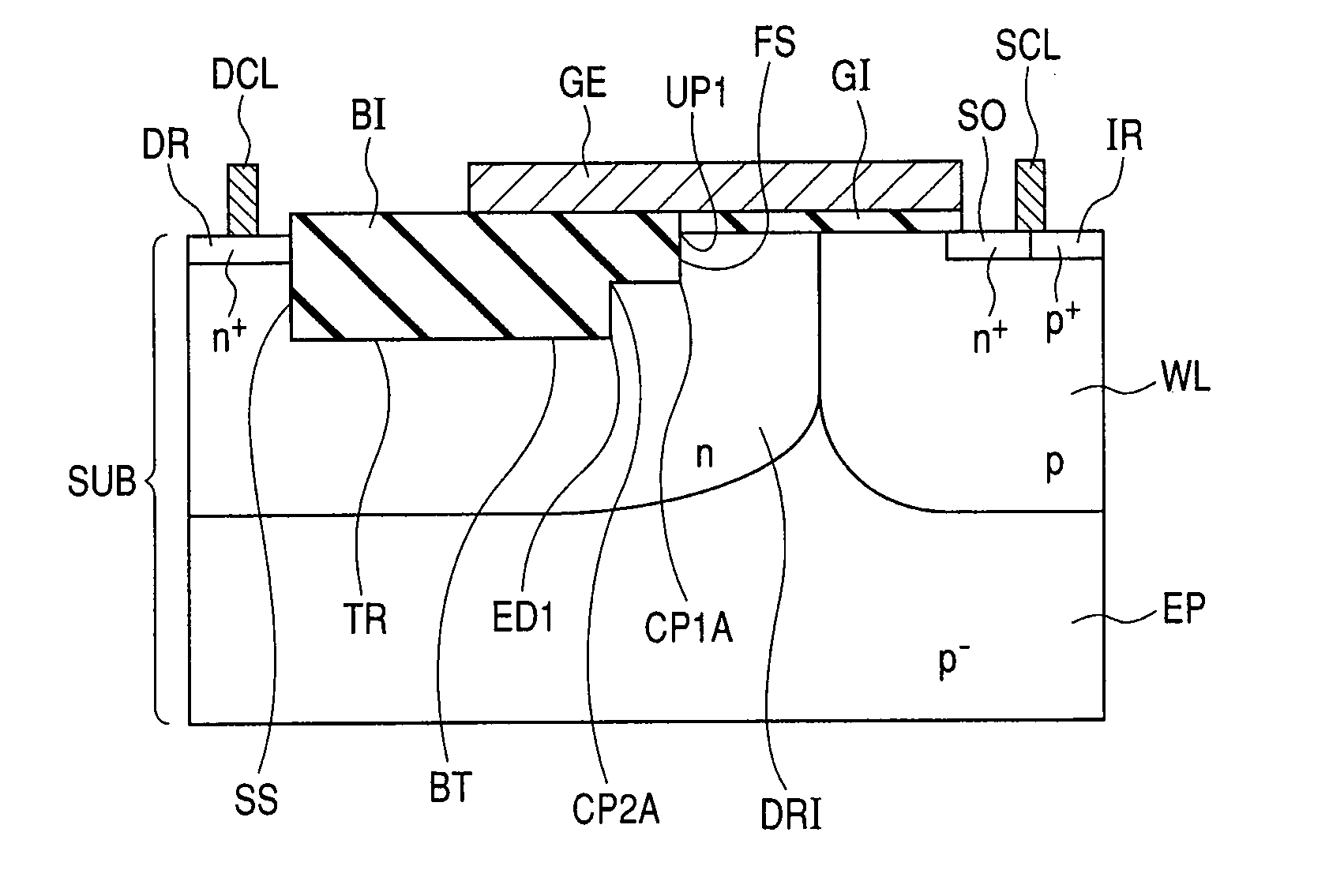

Semiconductor device

ActiveUS20060220099A1Reduce electric field concentrationImprove withstand voltage characteristicsTransistorSolid-state devicesElectric fieldEngineering

In a conventional semiconductor device, there has been a problem that, in a region where a wiring layer to which a high electric potential is applied traverses a top surface of an isolation region, the withstand voltage is deteriorated. In a semiconductor device of the present invention, an epitaxial layer is deposited on a substrate, and an LDMOSFET is formed in one region divided by an isolation region. In a region where a wiring layer connected to a drain electrode traverses a top surface of the isolation region, a conductive plate having a ground electric potential and another conductive plate in a floating state are formed under the wiring layer. With this structure, electric field is reduced in the vicinity of the isolation region under the wiring layer, whereby a withstand voltage of the LDMOSFET is increased.

Owner:SEMICON COMPONENTS IND LLC

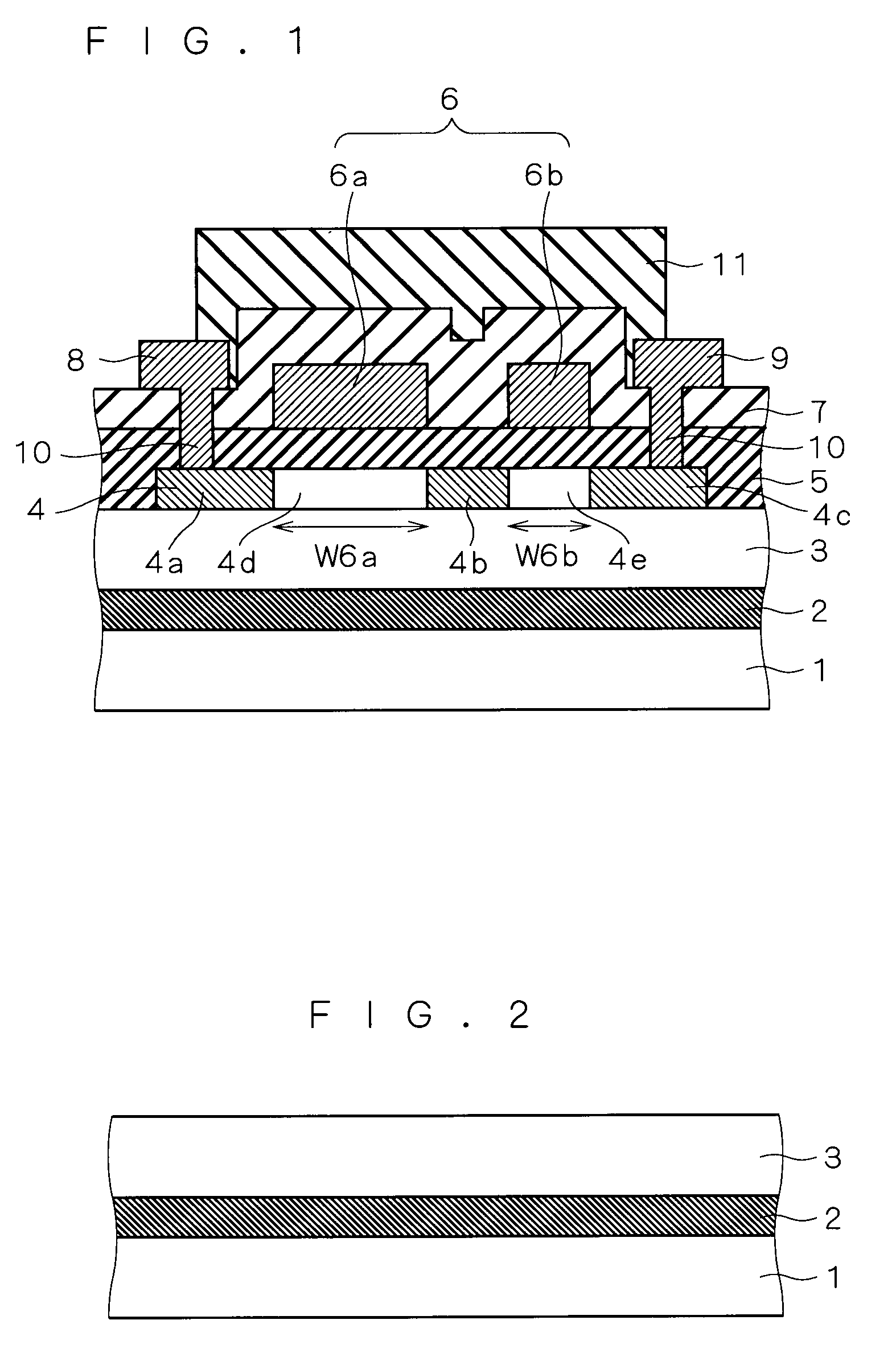

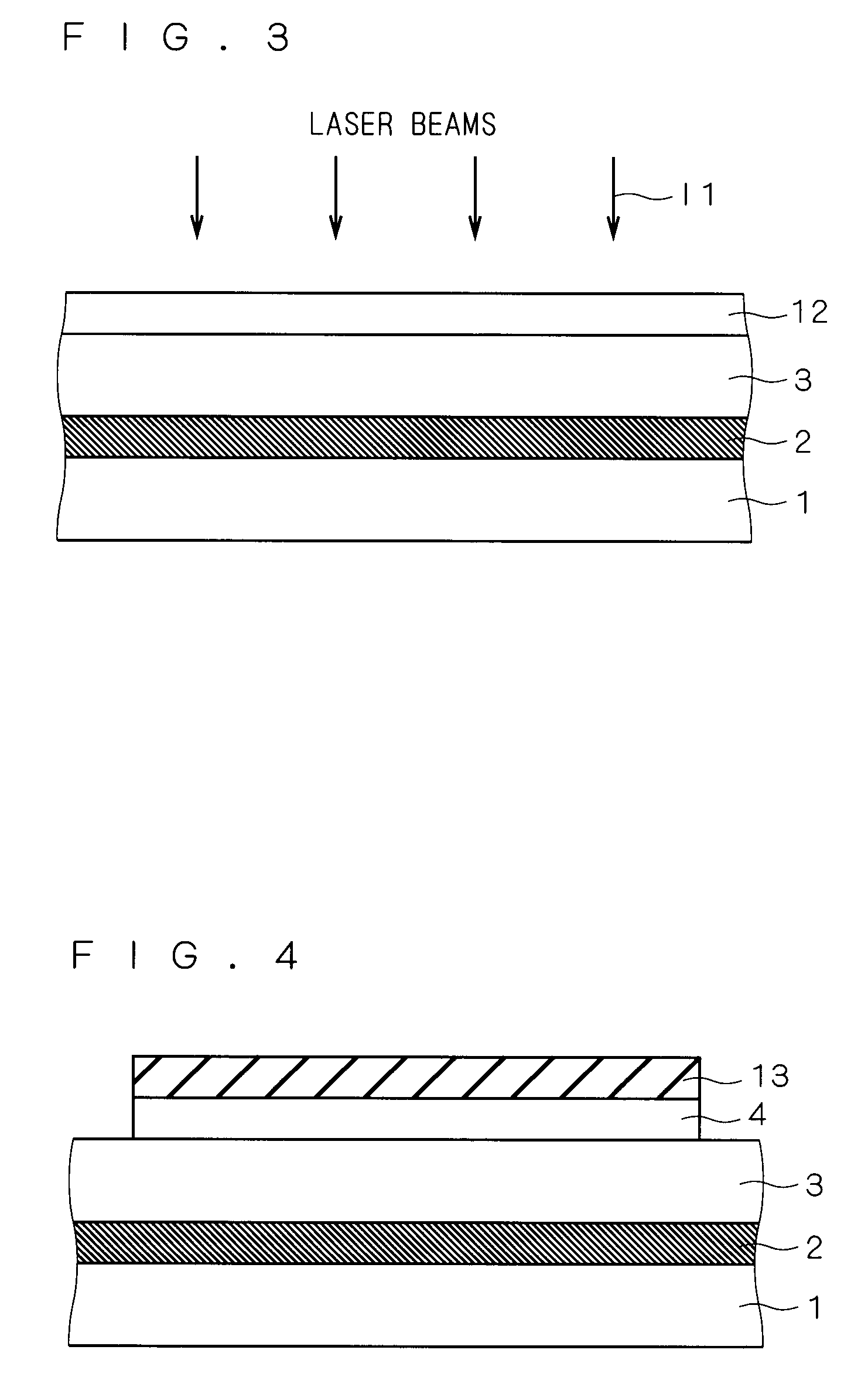

Thin film transistor

InactiveUS20070241336A1Reduce the impactReduce impactSolid-state devicesSemiconductor devicesChannel length modulationElectric field

In first and second gate electrodes constituting a gate electrode, the gate length of the second gate electrode is set shorter than the gate length of the first gate electrode and short enough to produce the short channel effect. The threshold voltage of a second transistor corresponding to the second gate electrode can thereby be made lower than the threshold voltage of a first transistor corresponding to the first gate electrode. When the same voltage is applied to the first and second gate electrodes, an electric field concentration at the channel edge on the drain side is reduced. This in result reduces the channel length modulation effect.

Owner:MITSUBISHI ELECTRIC CORP

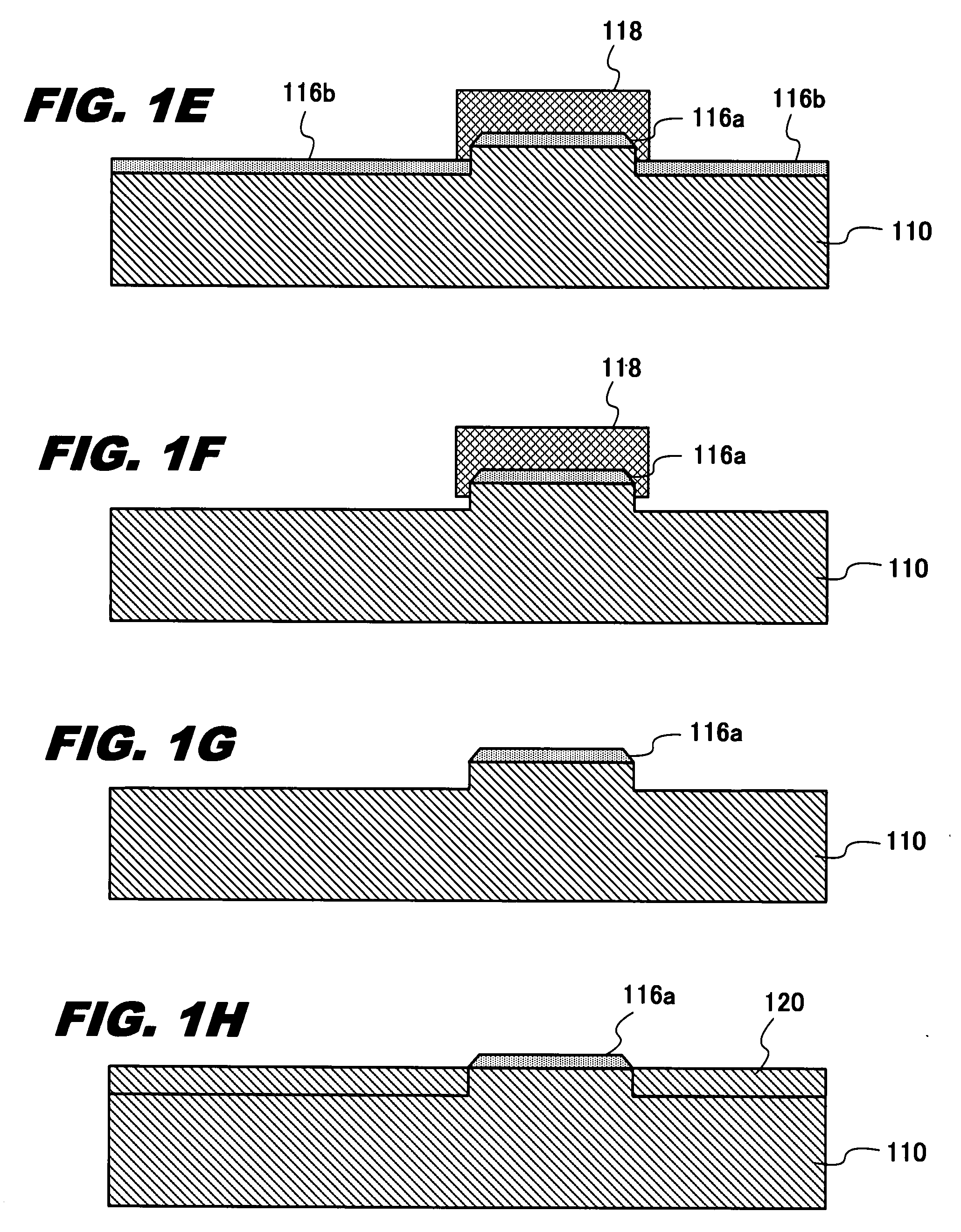

Semiconductor Device and Method of Manufacturing Same

InactiveUS20080128809A1Reduce electric field concentrationPrevent contactTransistorSolid-state devicesWet oxidationSemiconductor components

An object is to reduce the adverse influence which a portion of a gate insulating layer where the thickness has decreased, that is, a step portion, has on semiconductor element characteristics so that the reliability of the semiconductor element is improved. A semiconductor layer is formed over an insulating surface; a side surface of the semiconductor layer is oxidized using wet oxidation to form a first insulating layer; a second insulating layer is formed over the semiconductor layer and the first insulating layer; and a gate electrode is formed over the semiconductor layer and the first insulating layer with the second insulating layer interposed therebetween.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method of manufacturing the same

ActiveUS20100270616A1Reduce electric field concentrationPrevent degradationSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

There is provided a semiconductor device in which the degradation of electric characteristics can be inhibited. A semiconductor substrate has a main surface, and a trench in the main surface. A buried insulating film is buried in the trench. The trench has one wall surface and the other wall surface which oppose each other. A gate electrode layer is located over at least the buried insulating film. The trench has angular portions which are located between the main surface of at least either one of the one wall surface and the other wall and a bottom portion of the trench.

Owner:RENESAS ELECTRONICS CORP

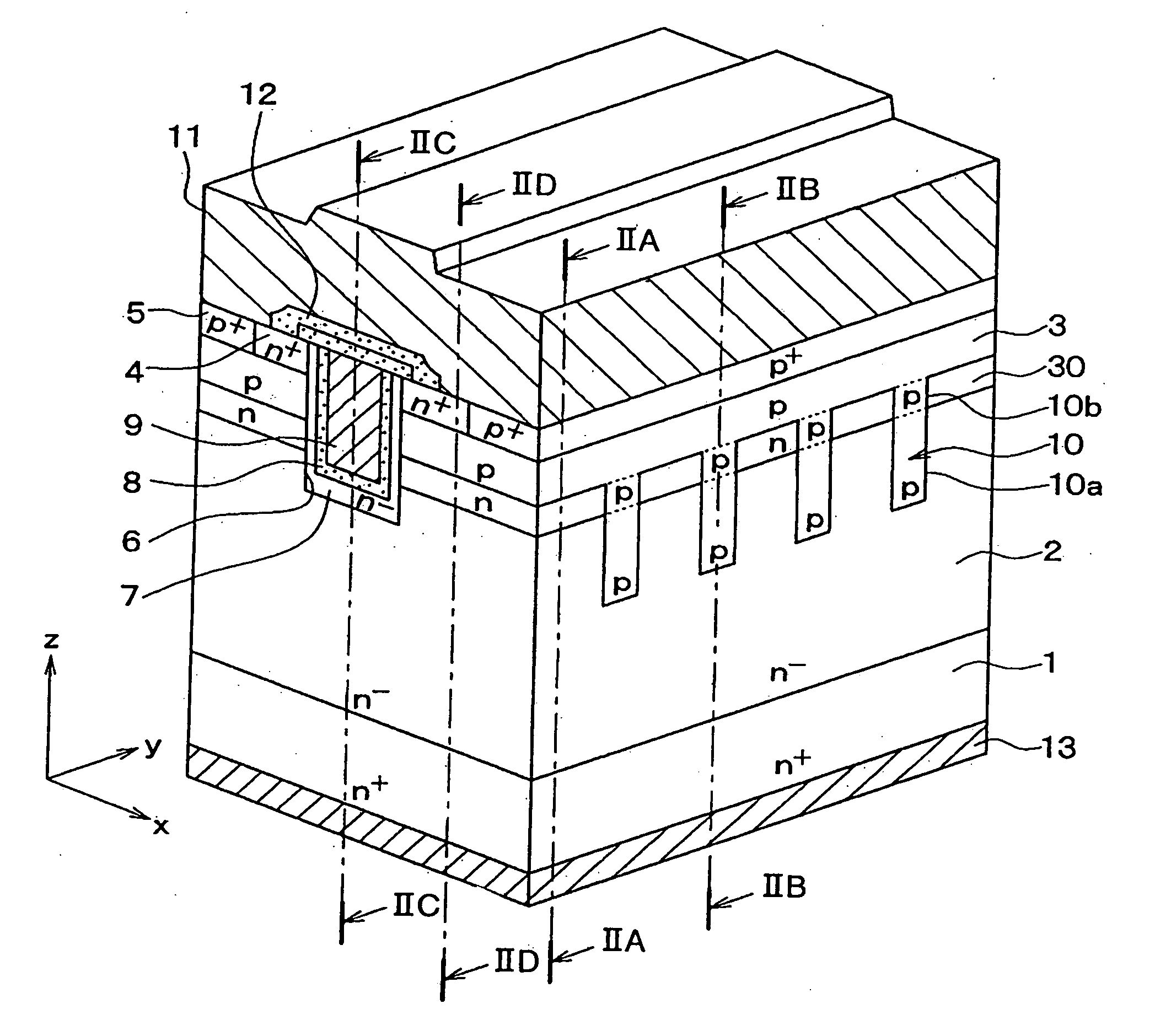

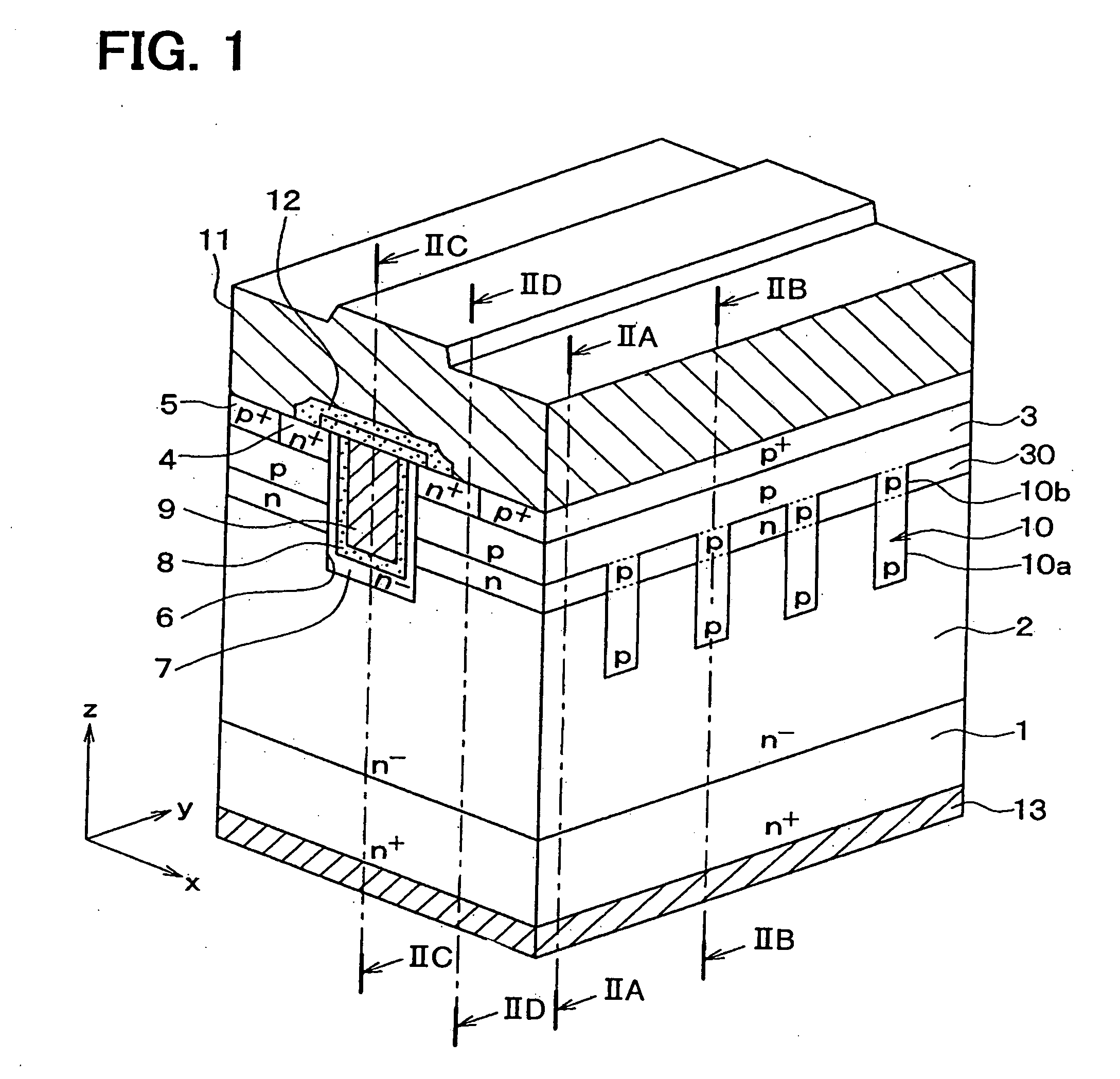

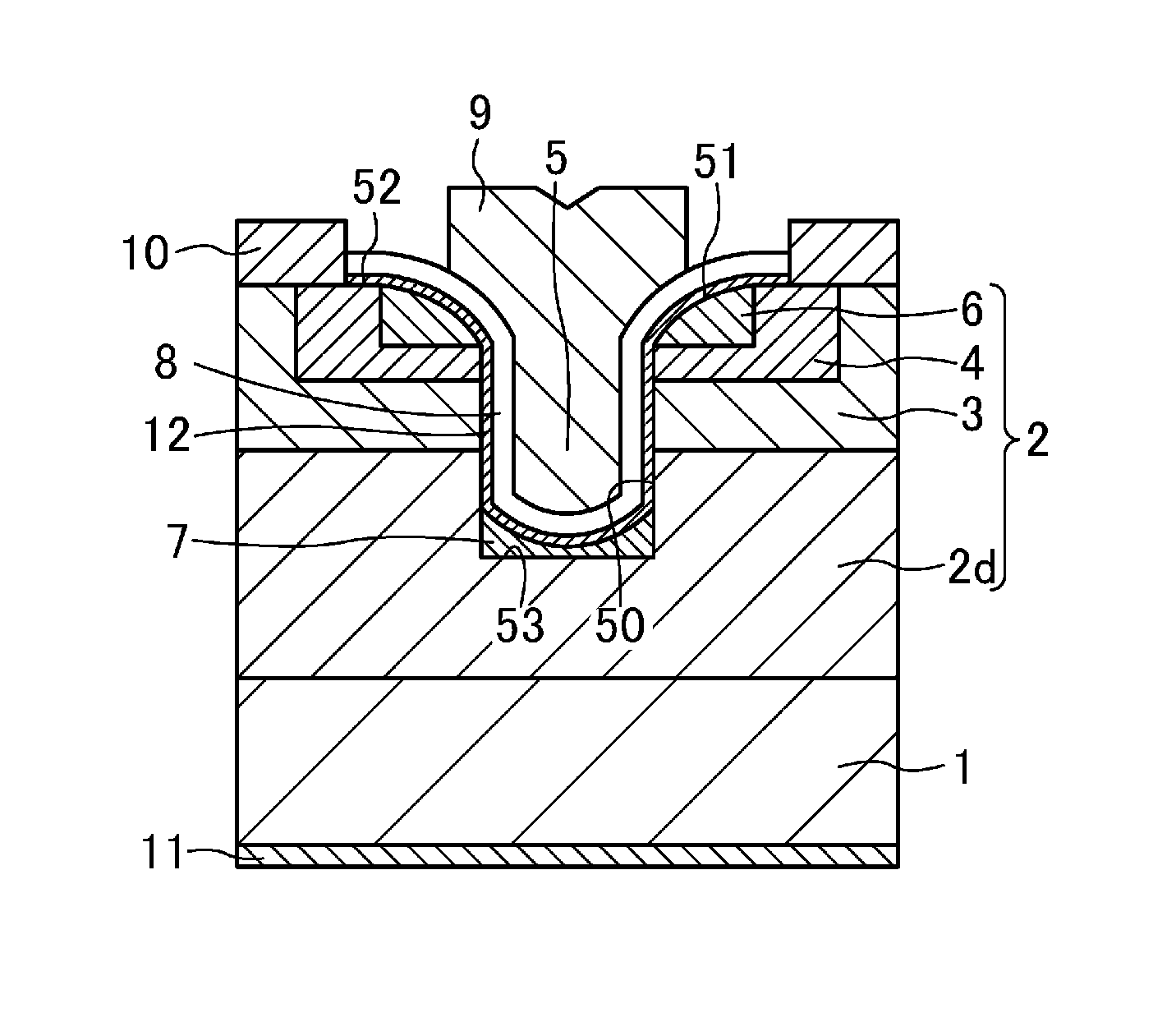

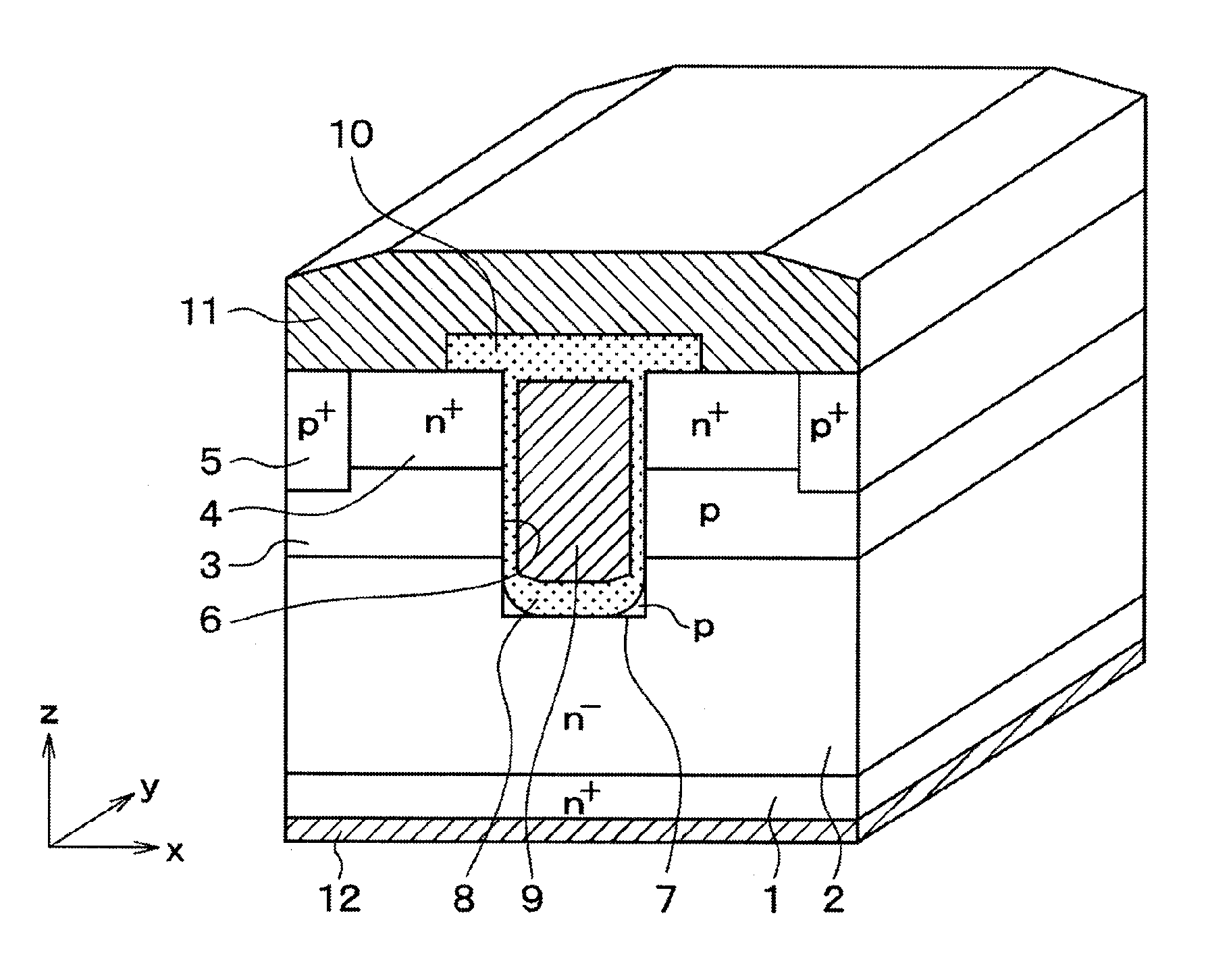

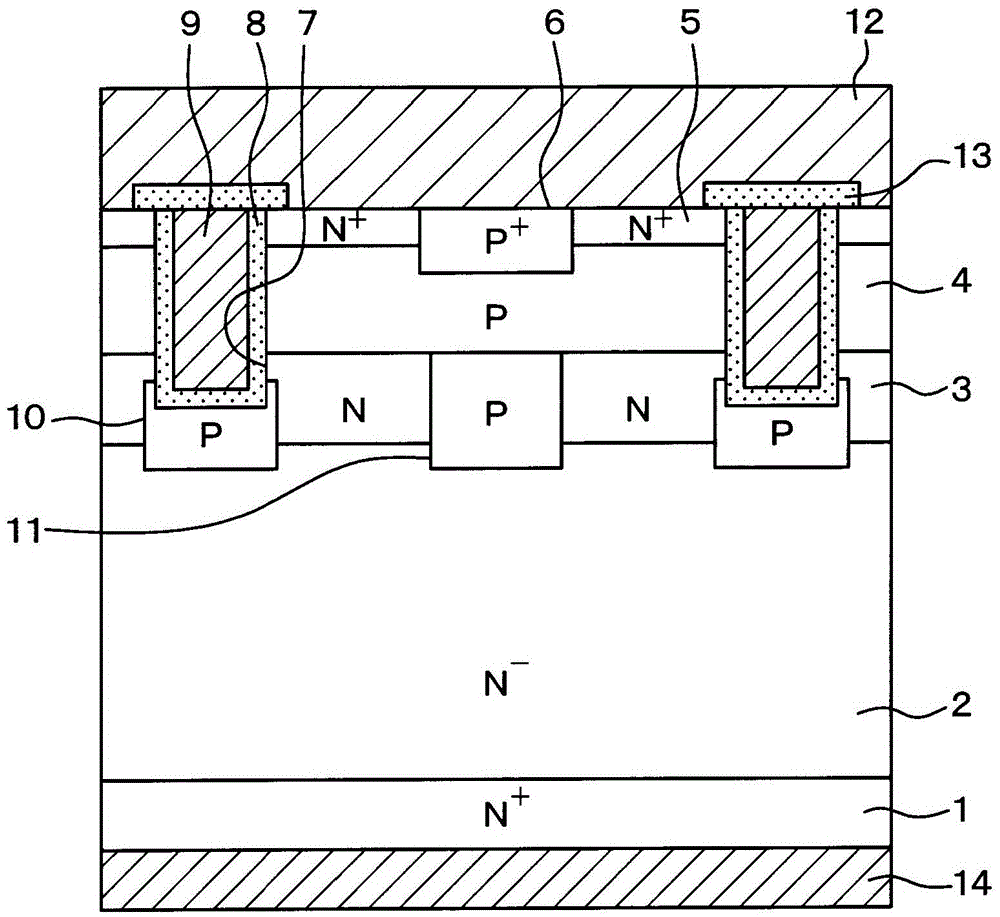

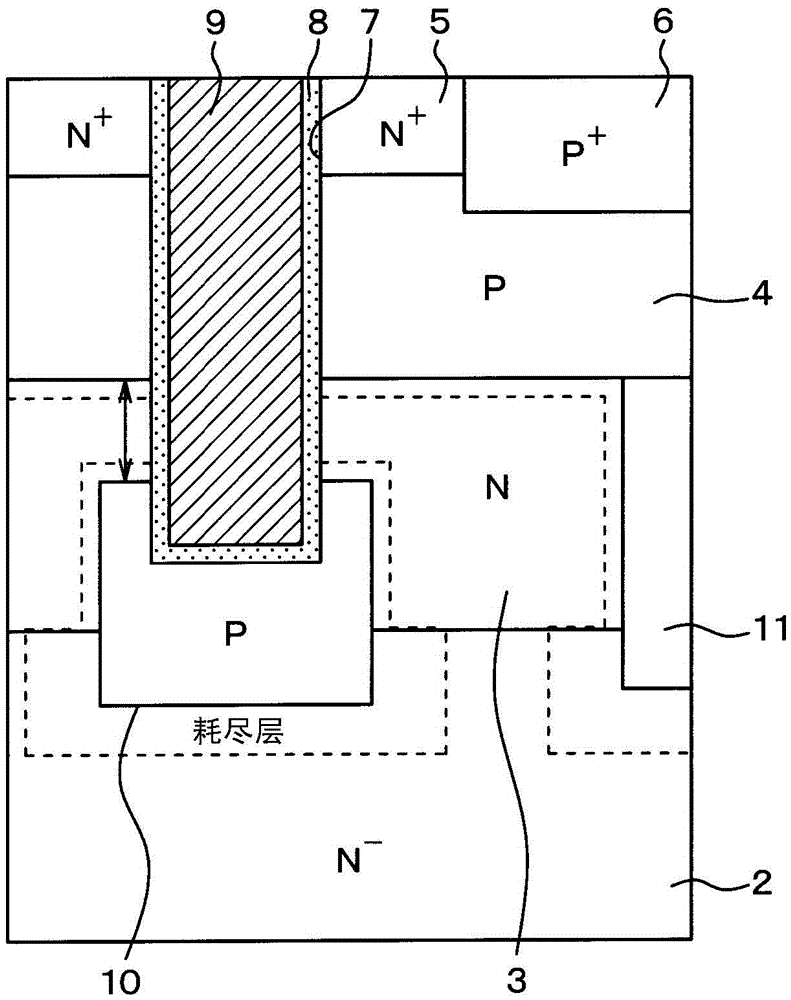

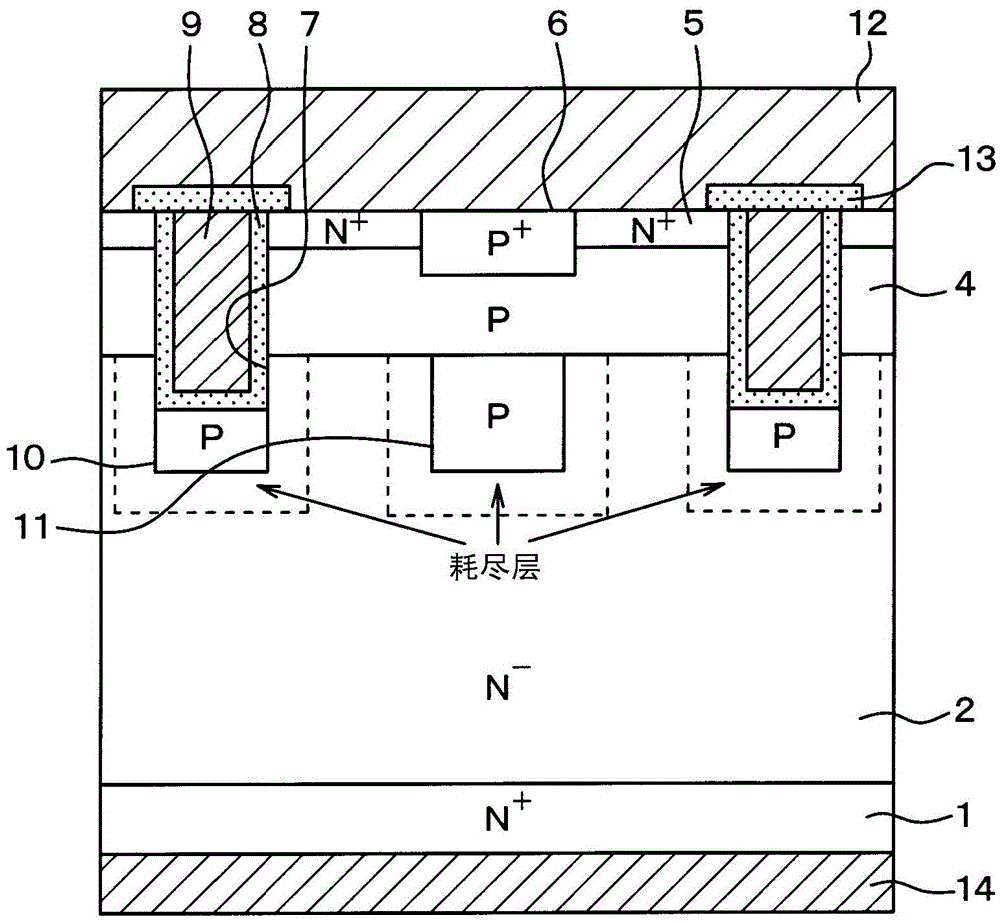

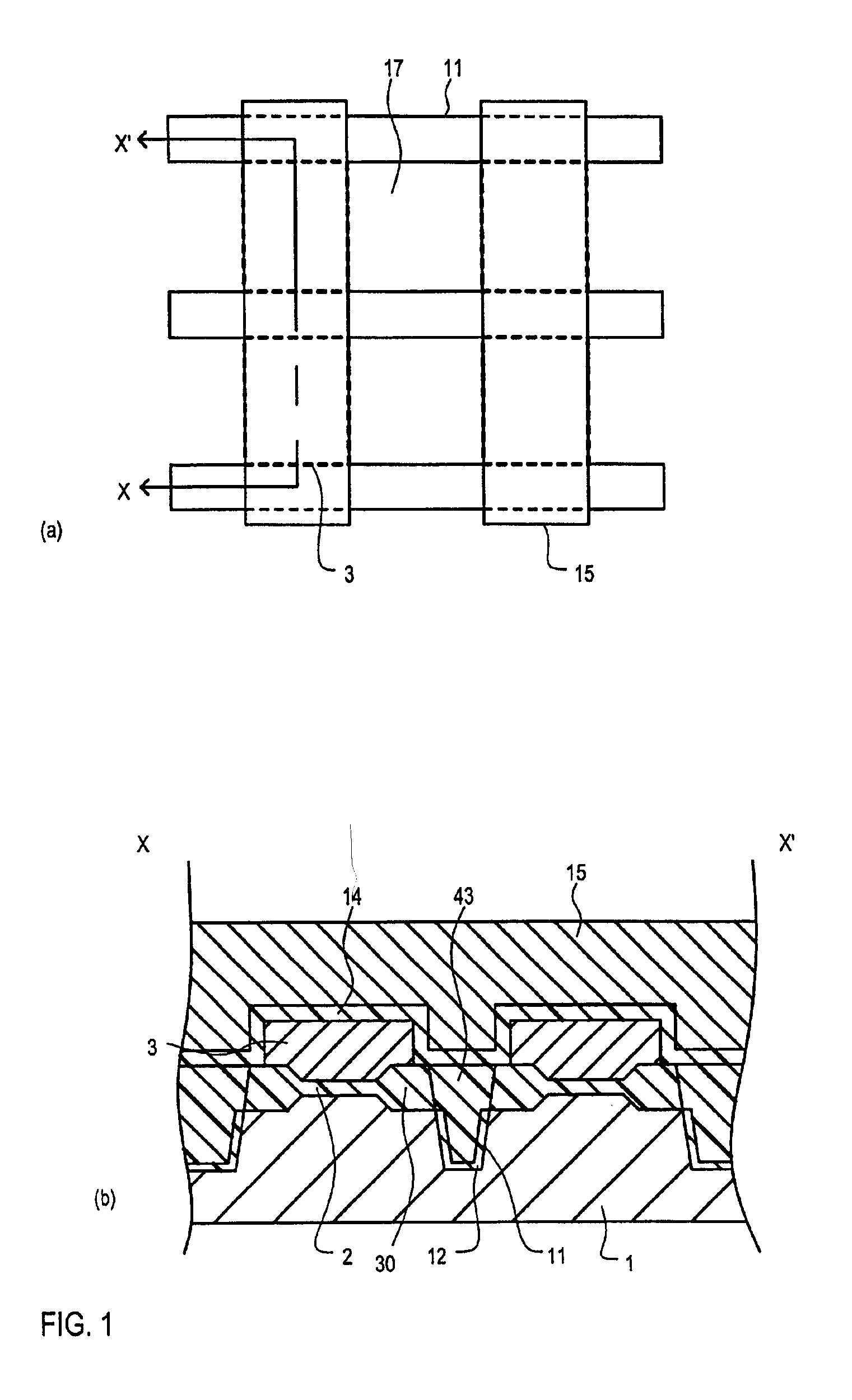

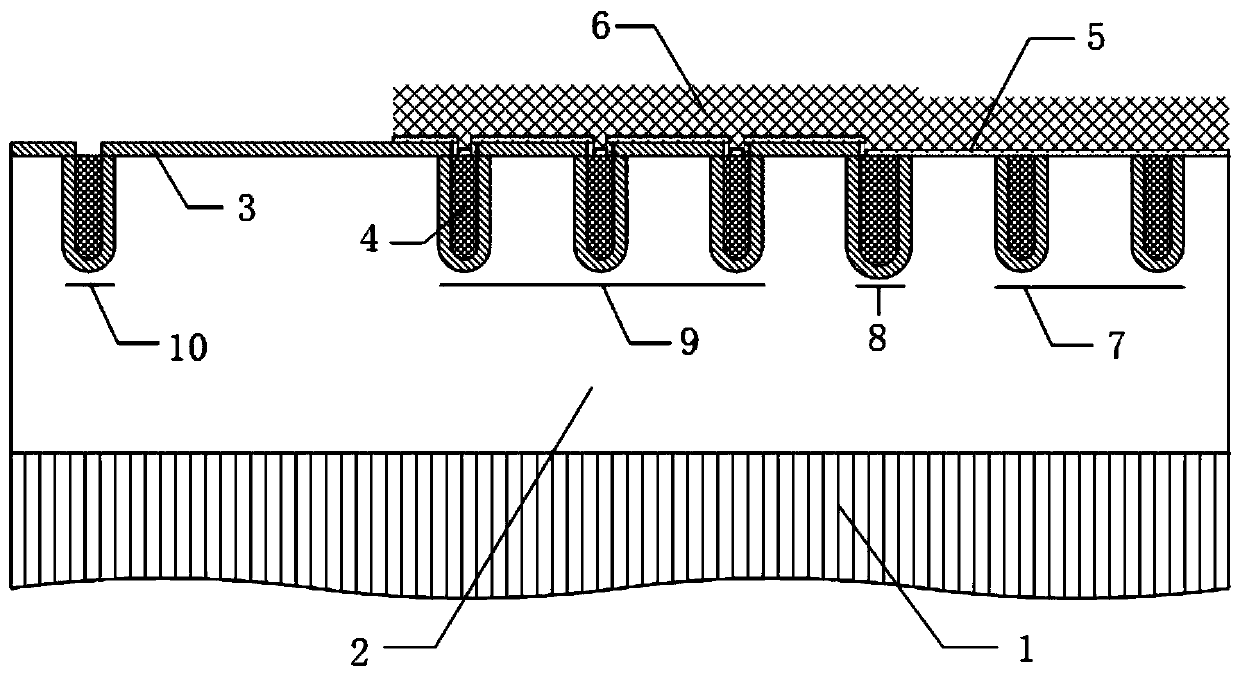

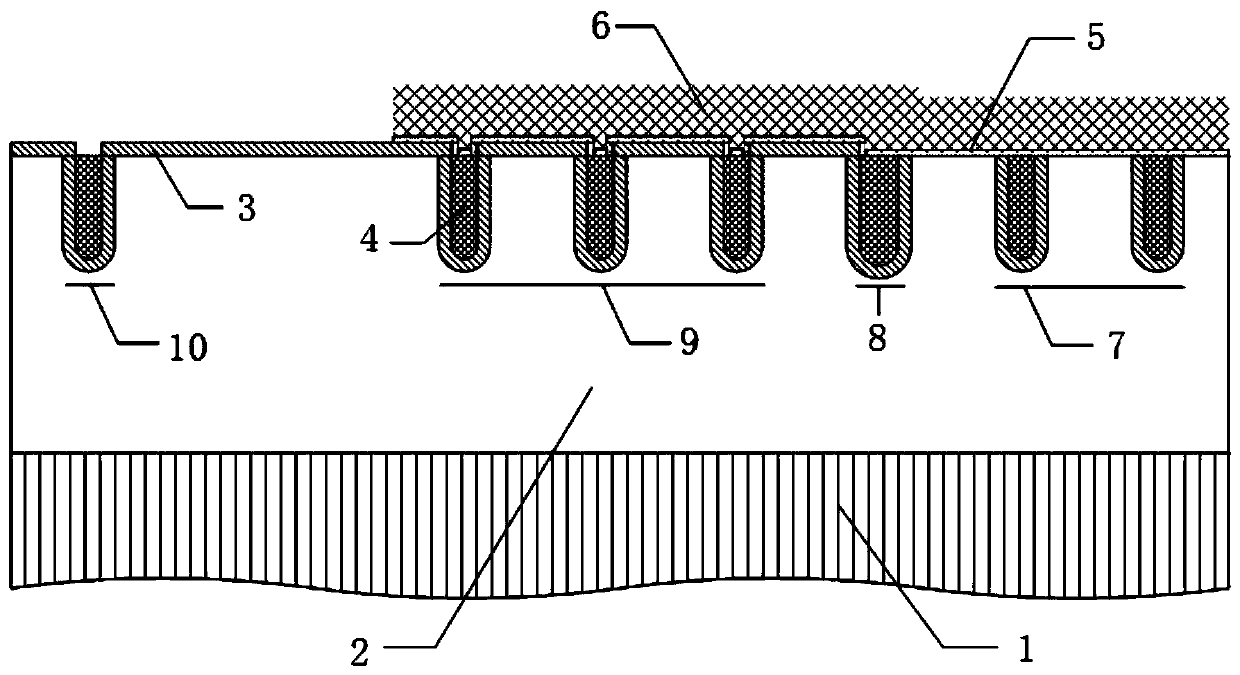

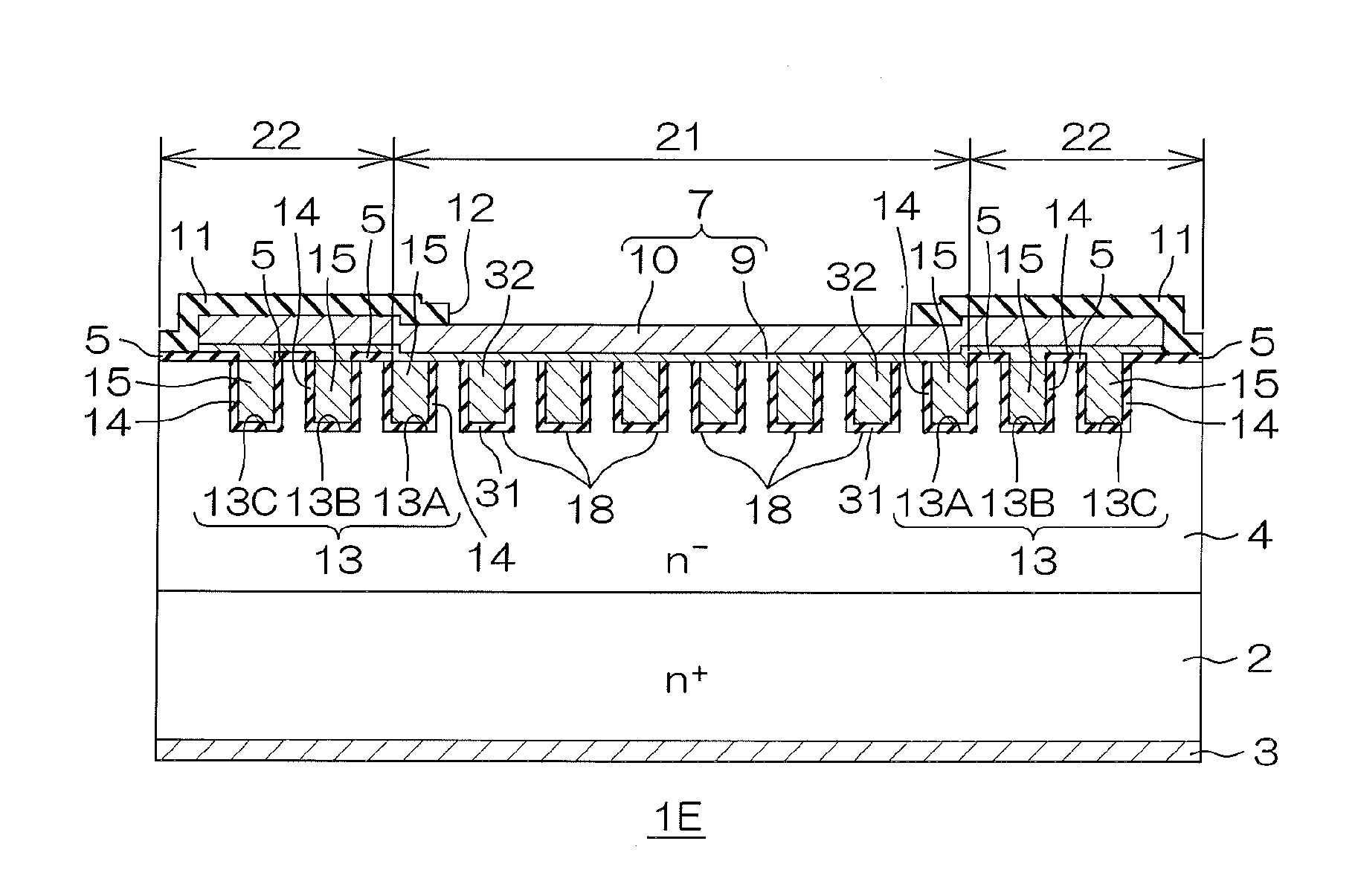

Silicon carbide semiconductor device

ActiveCN105593996AReduce electric field concentrationPrevent breakdownTransistorPower flowSemiconductor

This silicon carbide semiconductor device has a substrate (1), drift layer (2), current dispersion layer (3), base region (4), source region (5), trench (7), gate insulating film (8), gate electrode (9), source electrode (12), drain electrode (14), and bottom layer (10). The current dispersion layer is formed on the drift layer, and has a first conductivity-type impurity concentration set higher than that of the drift layer. The bottom layer has a second conductivity type, is disposed below the base region, covers a bottom portion of the trench, including corner portions of the bottom portion of the trench, and has more depth than the current dispersion layer.

Owner:DENSO CORP +1

Semiconductor device

ActiveUS20130328120A1Large electric field relaxing regionImprove breakdown voltageSemiconductor devicesTectorial membraneSemiconductor

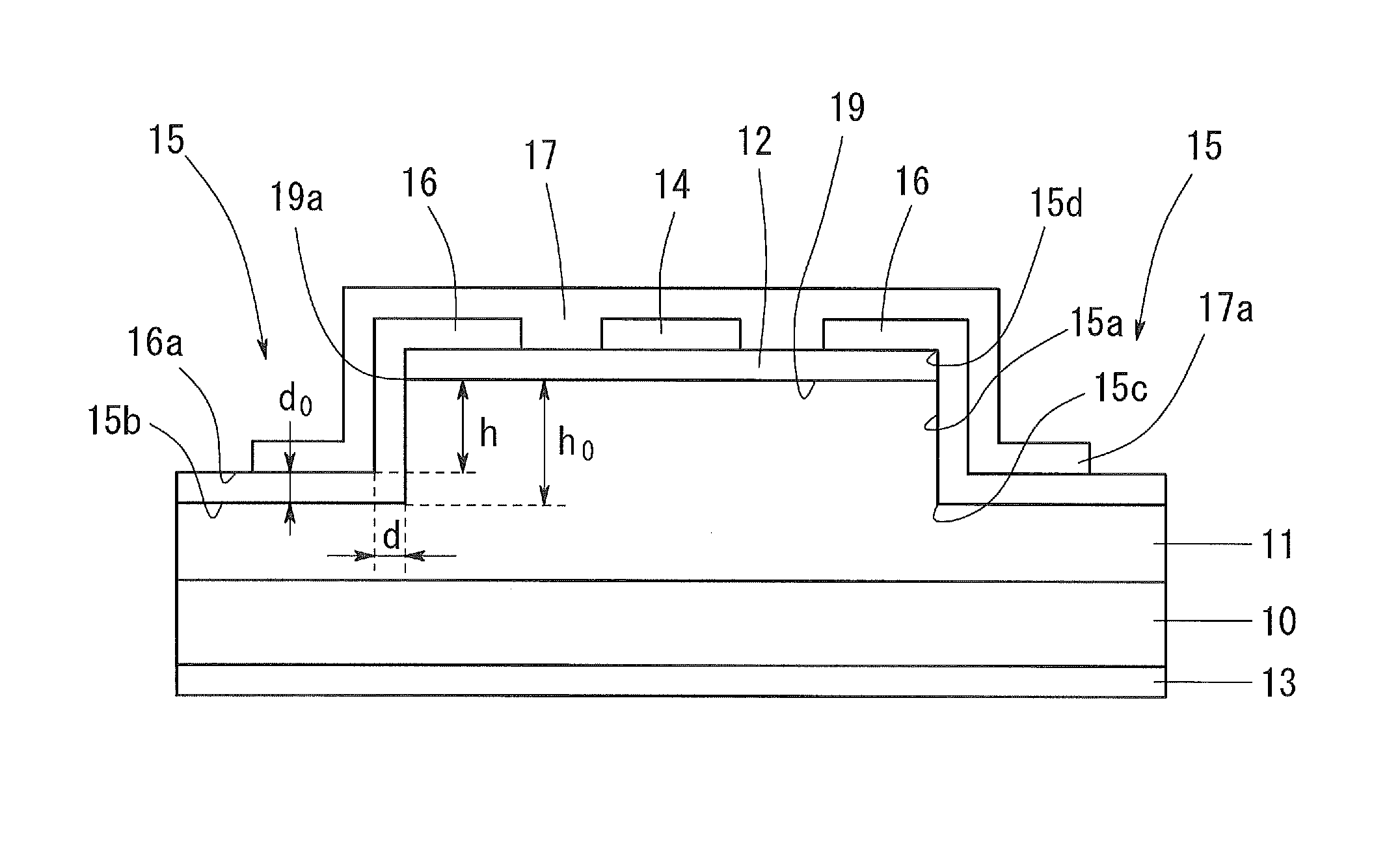

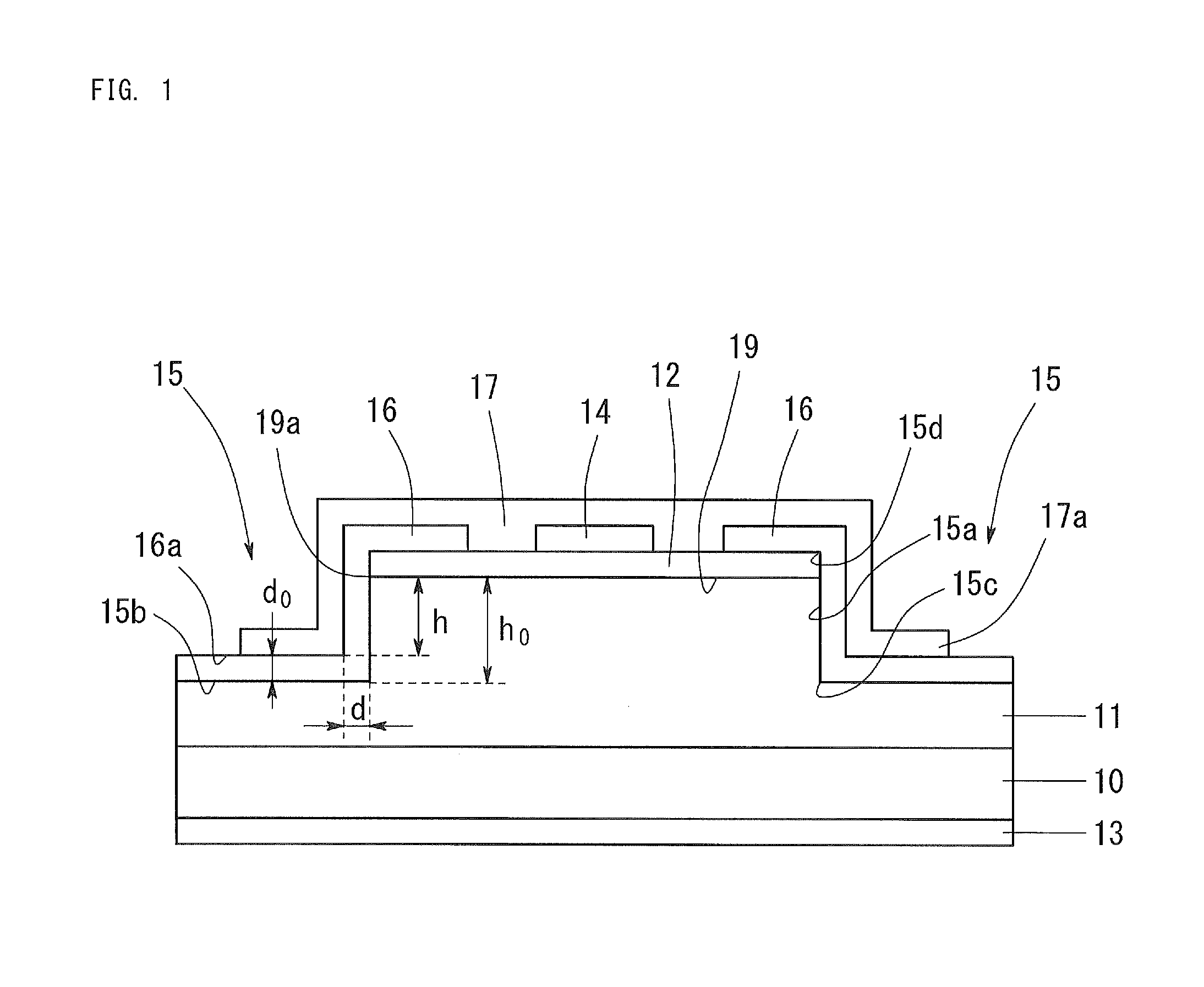

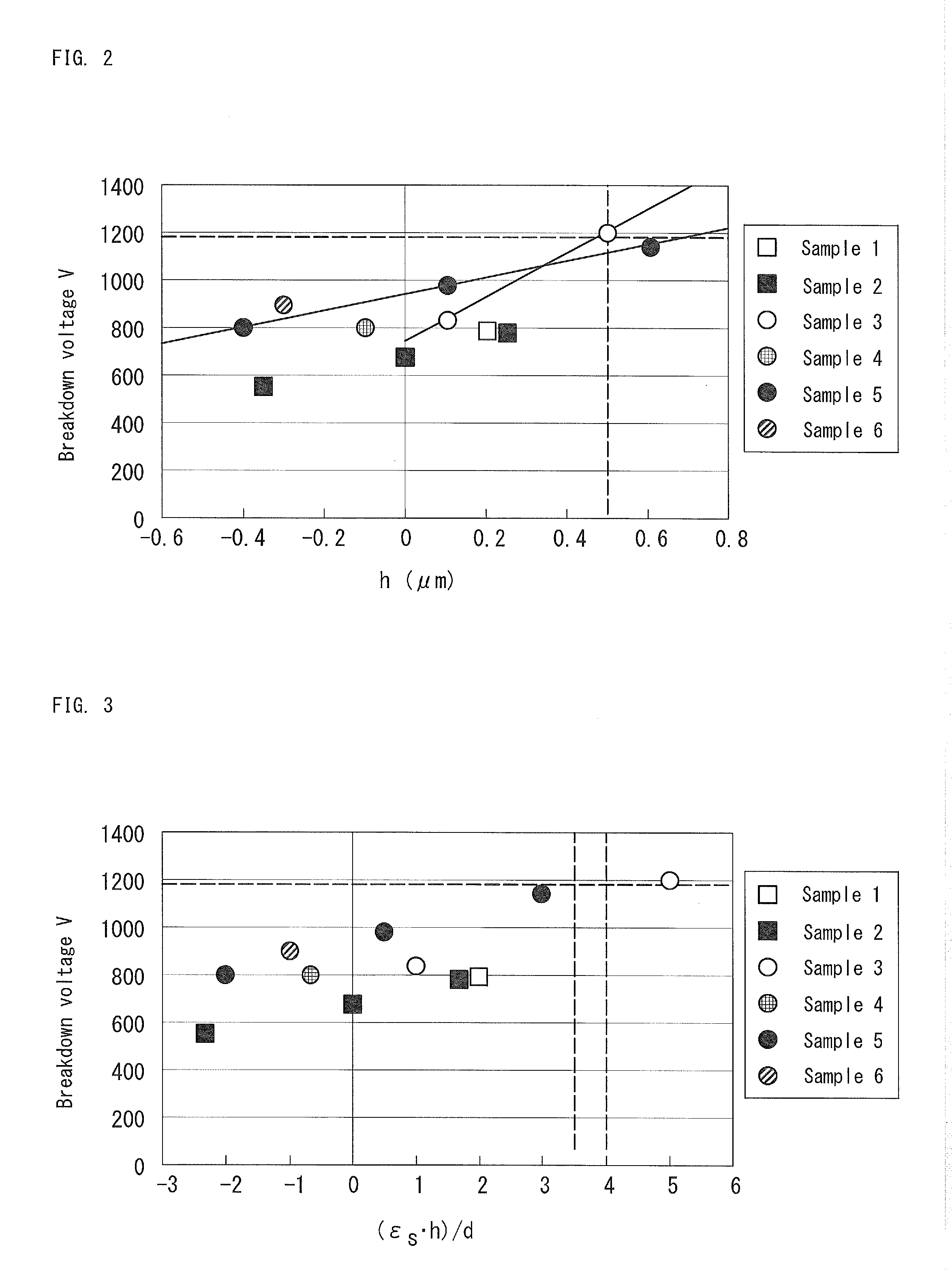

A device comprises a substrate, an n-layer and a p-layer, an n-electrode, and a p-electrode. A step is formed at an outer circumference of the device. A protective film is formed so as to continuously cover a side surface and a bottom surface of the step. A field plate electrode connected with the p-electrode is formed on the protective film. When a distance from the pn junction interface to the surface of the protective film on the bottom surface of the step is defined as h (μm), a dielectric constant of the protective film is defined as ∈s, and a thickness of the protective film at the pn junction interface on the side surface of the step is defined as d (μm), (∈s·h) / d is 4 or more, and ∈s / d is 3 (1 / μm) or more.

Owner:TOYODA GOSEI CO LTD

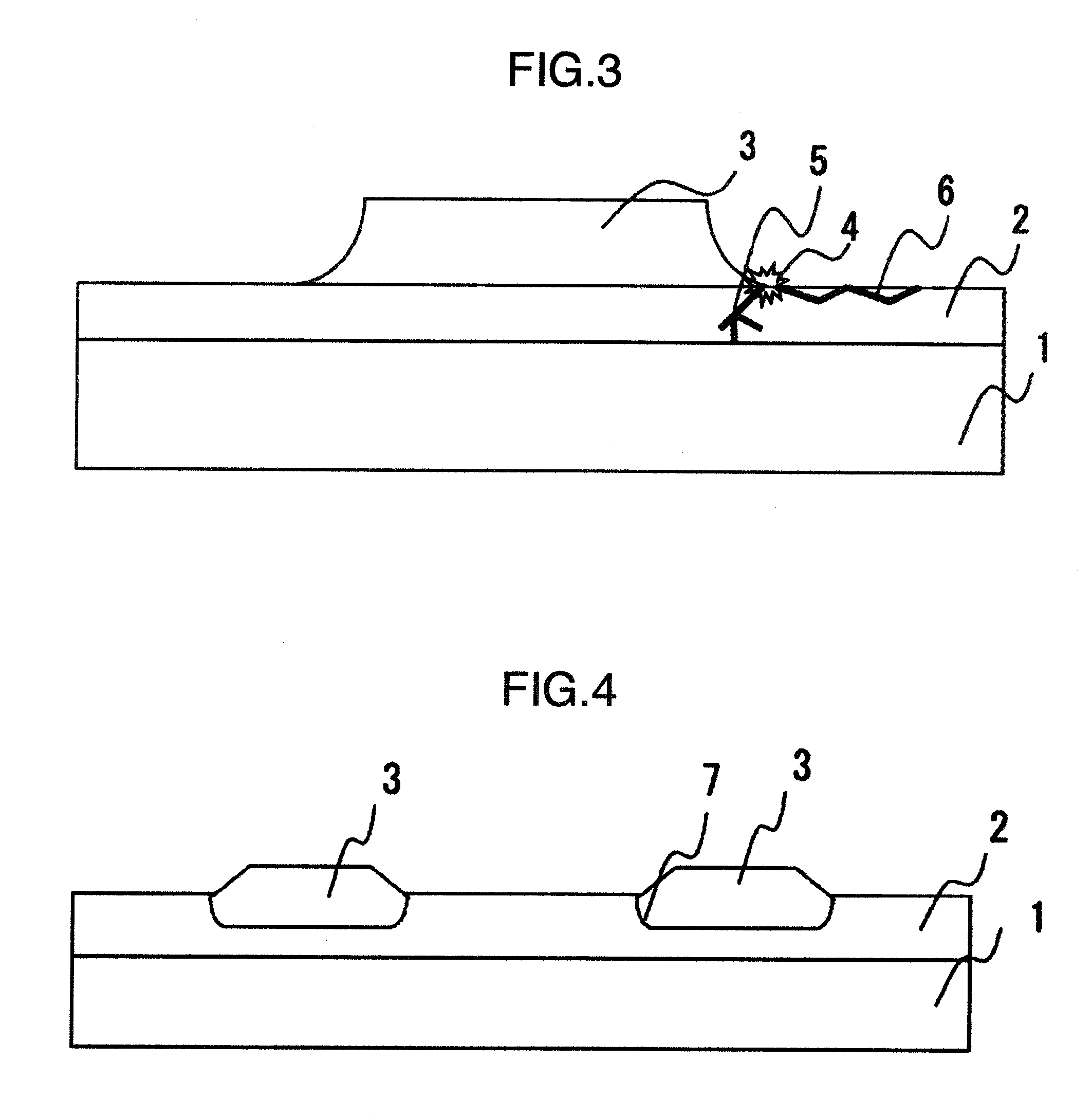

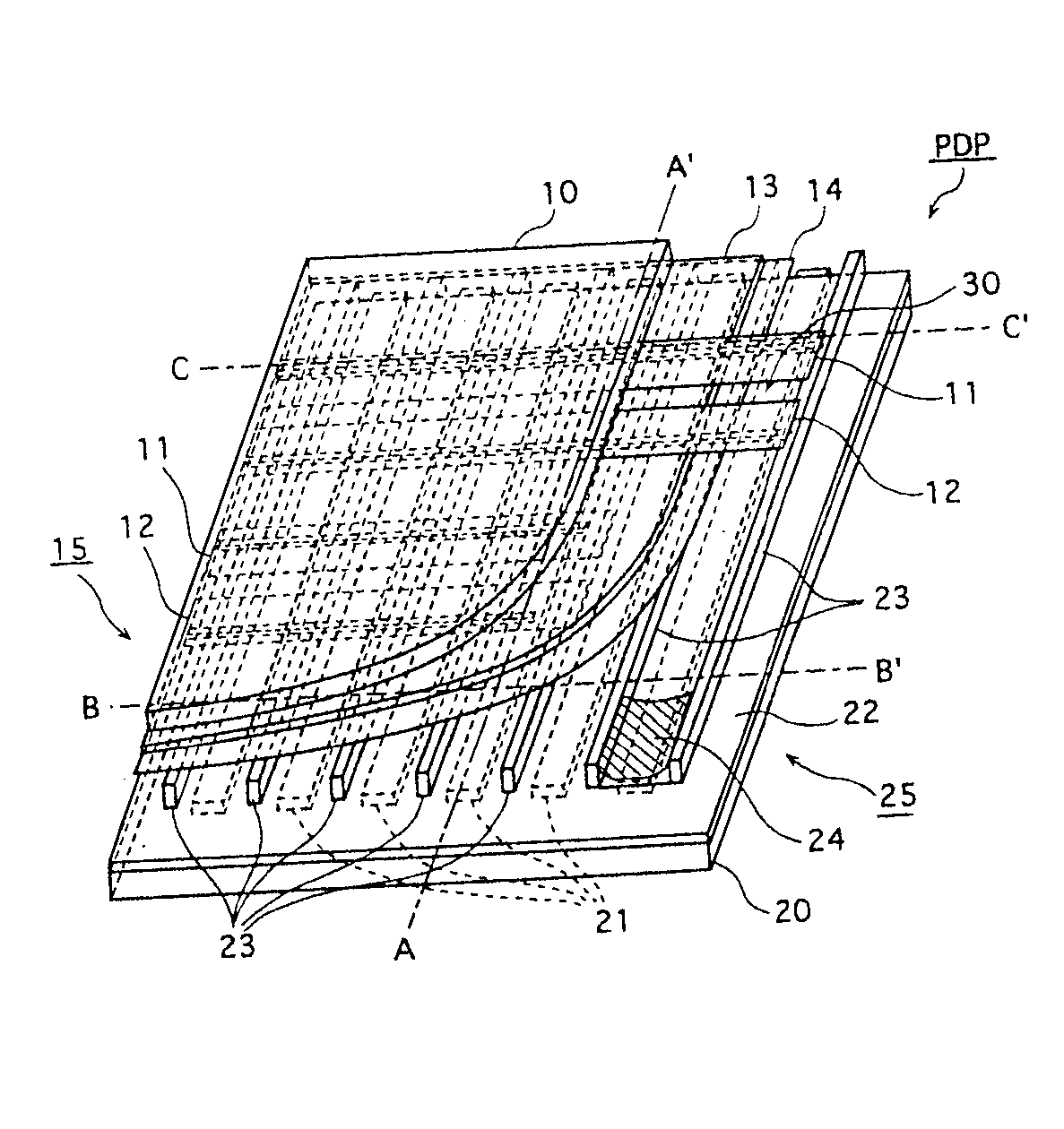

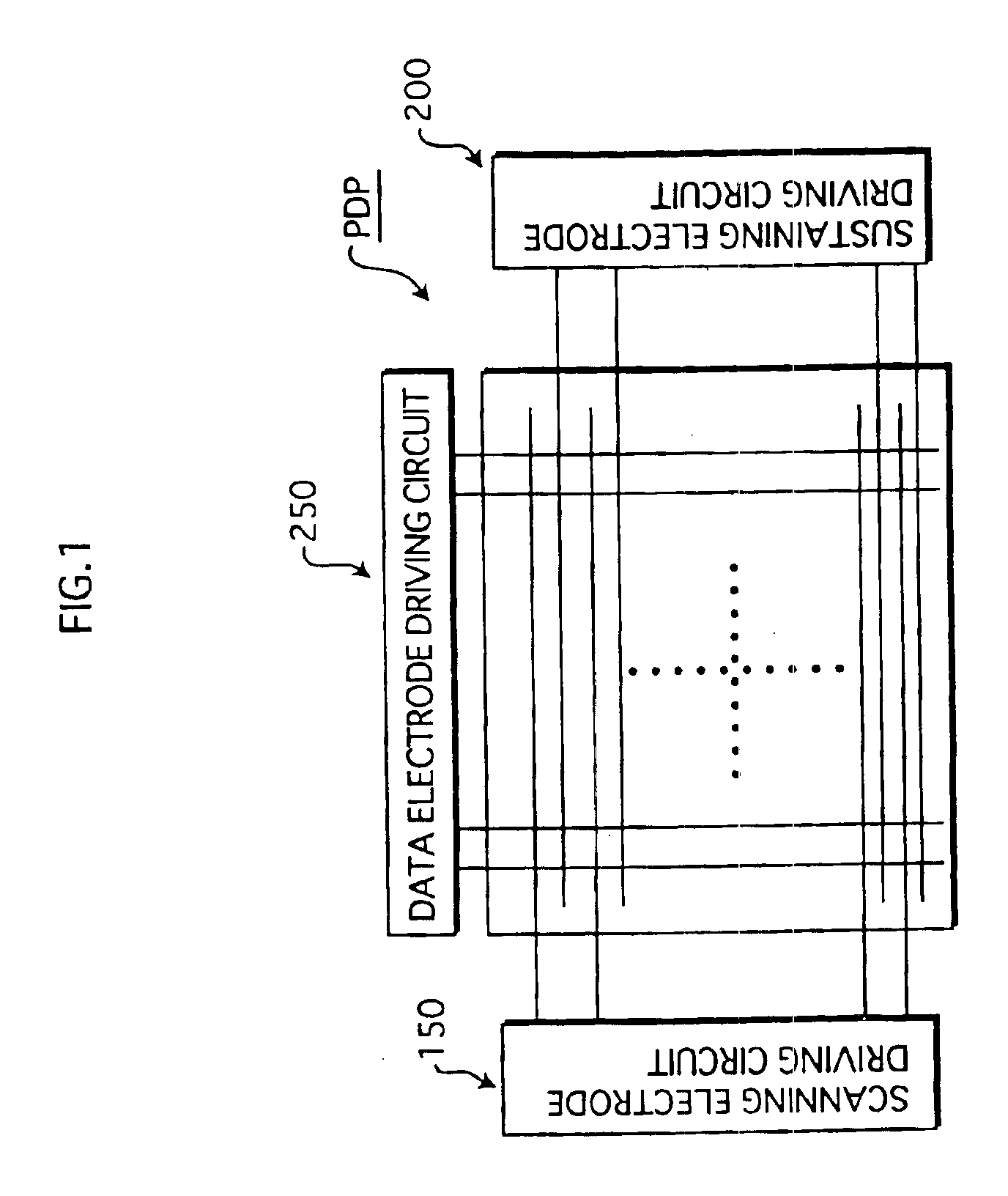

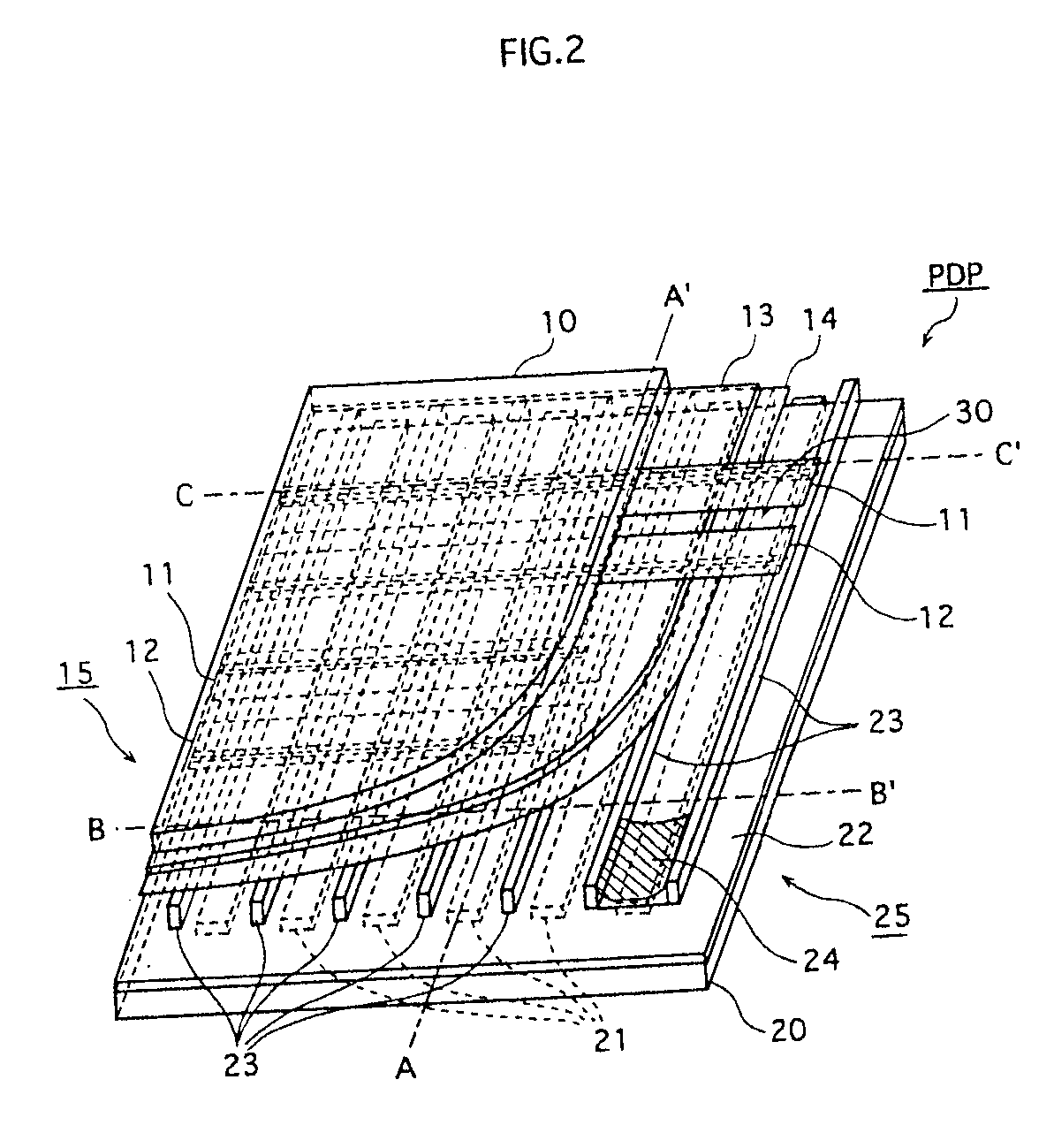

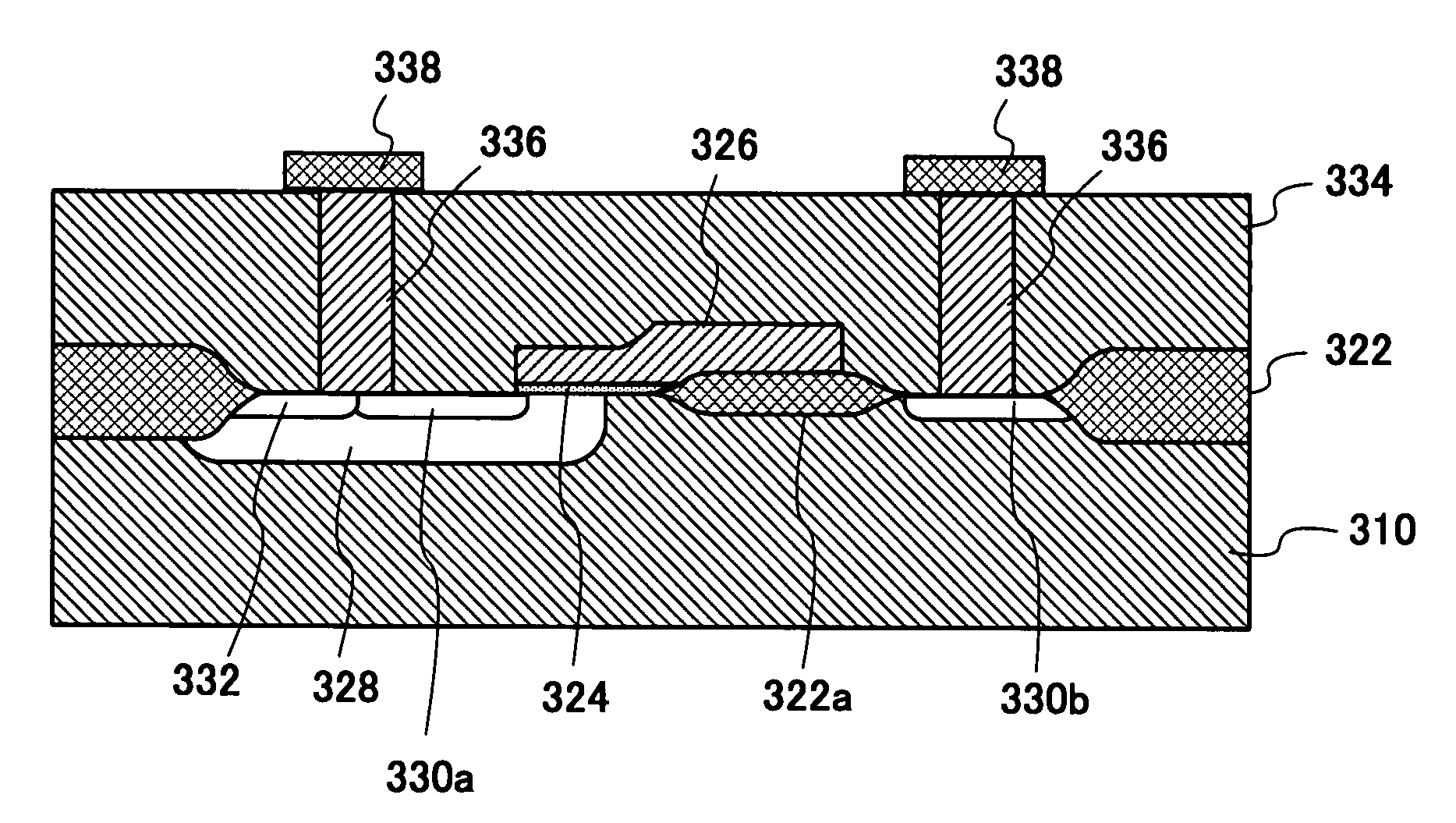

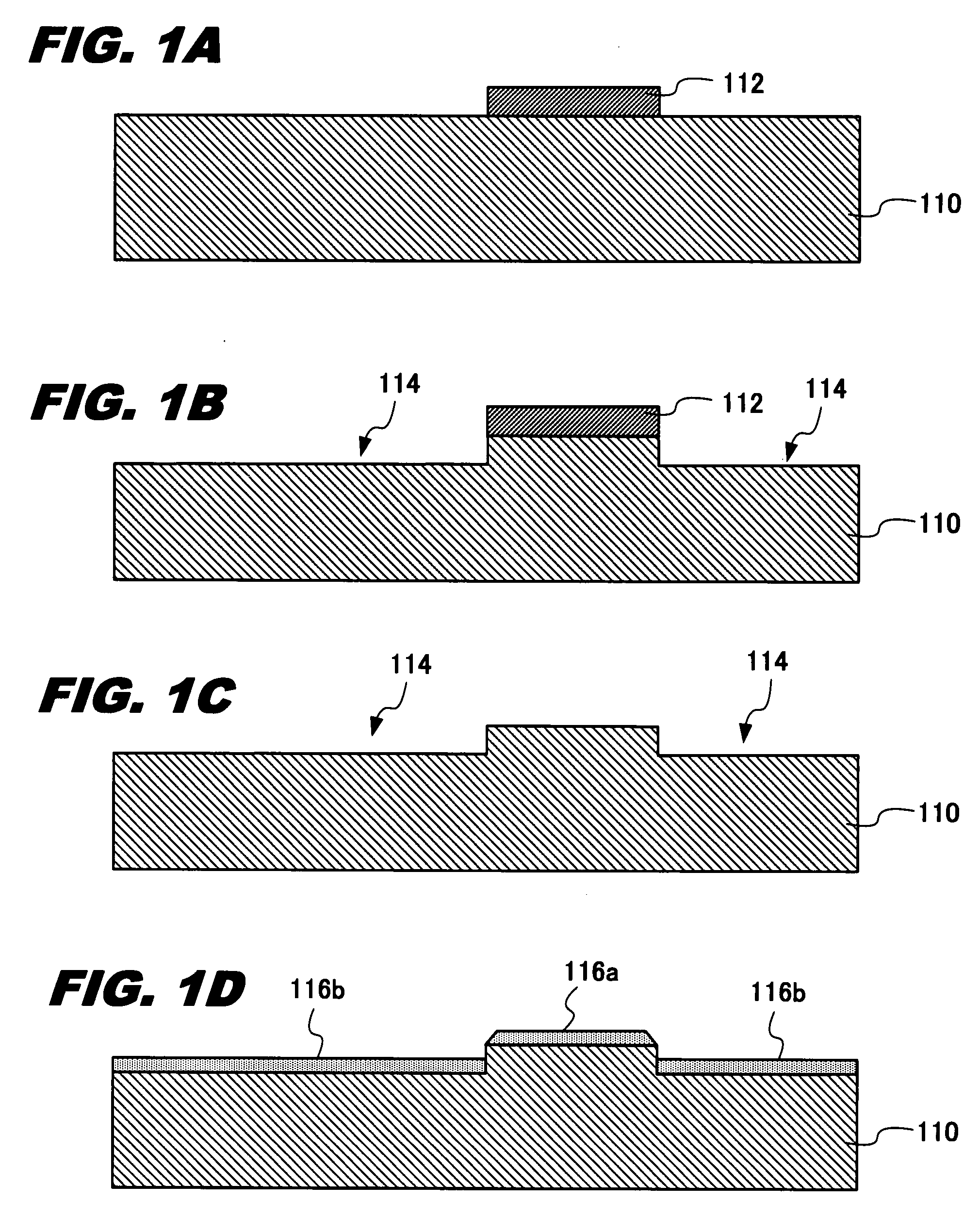

Plasma display unit and production method thereof

InactiveUS6891331B2Avoid high pressureReduced Linearity RequirementsSustain/scan electrodesAlternating current plasma display panelsCooking & bakingDissolution

An object of the present invention is to provide a method for manufacturing electrodes that can effectively suppress edge-curl when metal electrodes such as bus electrodes and data electrodes are patterned mainly by a photolithography method.In order to achieve the above object, in the manufacturing method in the present invention, an amount of undercut generated by difference in a degree of dissolution caused by developing solution is controlled, and baking is performed at a temperature such that glass in a protrusion formed at side edges becomes soft so as to touch a substrate by gravity. With such method for manufacturing, it becomes possible to make the side edges rounded whose curvature changes continuously.

Owner:PANASONIC CORP

Semiconductor device

InactiveUS20080073746A1Control concentrationReduce electric field concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorSemiconductor device

According to the present invention, there is provided a semiconductor device having a gate field plate structure, which includes a semiconductor substrate; a gate insulation film formed on the semiconductor substrate; a protective insulation film formed on the semiconductor substrate; a gate electrode formed on the gate insulation film; and a field plate electrode of the same electric potential as that of the gate electrode, formed on the protective insulation film. The protective insulation film is formed on the surface of the semiconductor substrate, and is not formed inside the substrate.

Owner:LAPIS SEMICON CO LTD

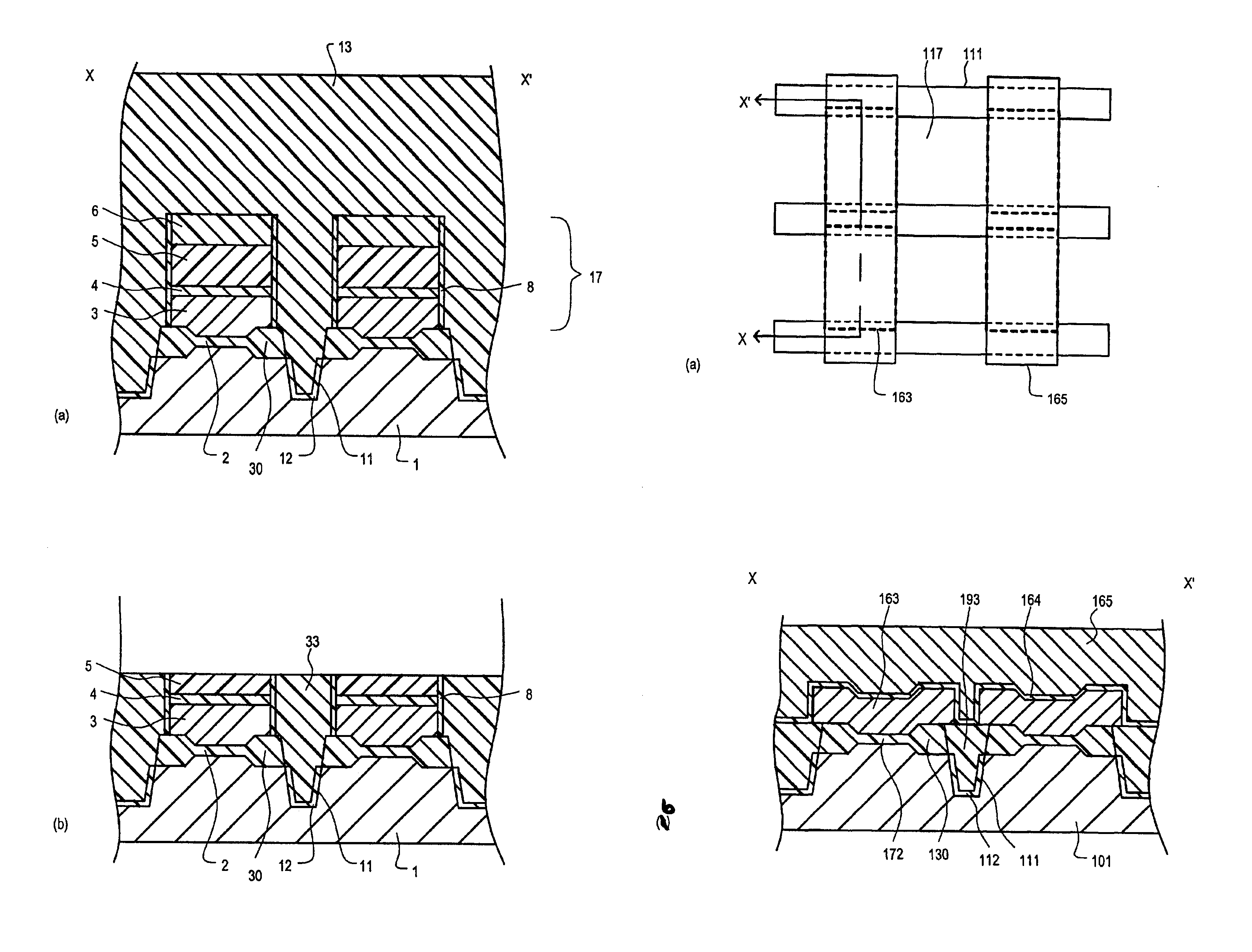

Semiconductor device and its manufacturing method

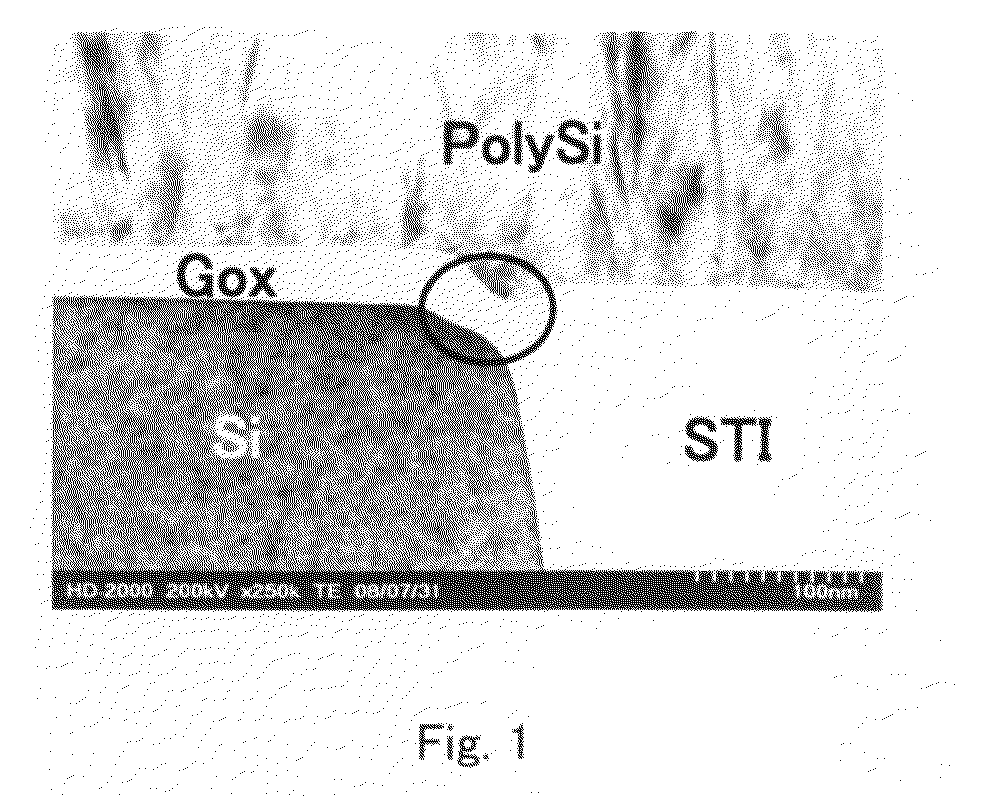

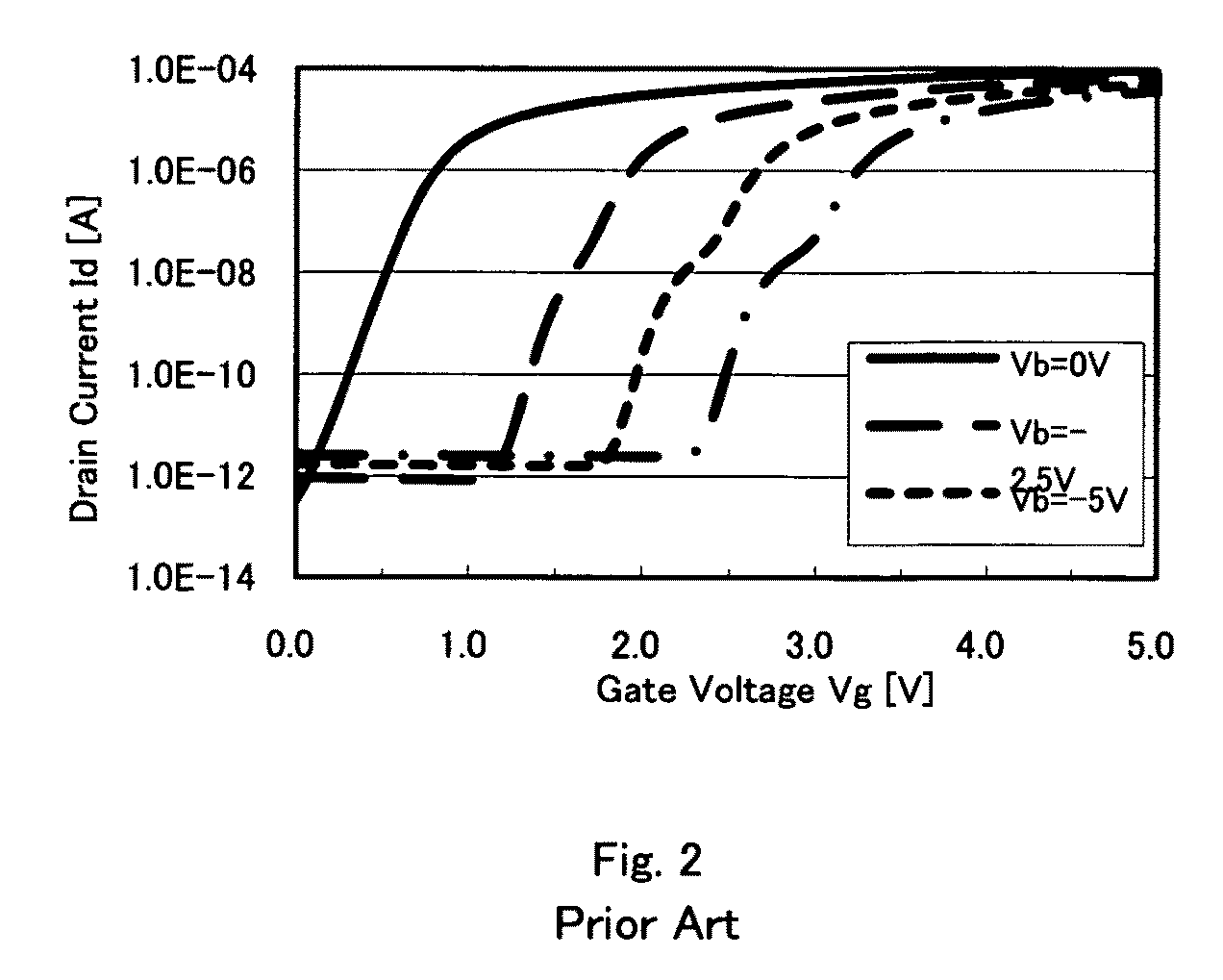

InactiveUS6869849B2DistanceReduce electric field concentrationTransistorSolid-state devicesGate oxideSemiconductor

A semiconductor device including memory cells isolated by a trench that may be self aligned with a stacked film pattern (7) has been disclosed. The memory cells may be flash memory cells having an active gate film (2) that may be thinner than a gate oxide film (30). The active gate film (2) may be located in a central portion under of a gate electrode (3). The gate oxide film (30) may be located under end portions of the gate electrode (3). In this way, a distance between a shoulder portion of a trench (11) and a gate electrode (3) may be increased. Thus, an electric field concentration in the shoulder portion of the trench (11) may be decreased and memory cell characteristics may be improved.

Owner:RENESAS ELECTRONICS CORP

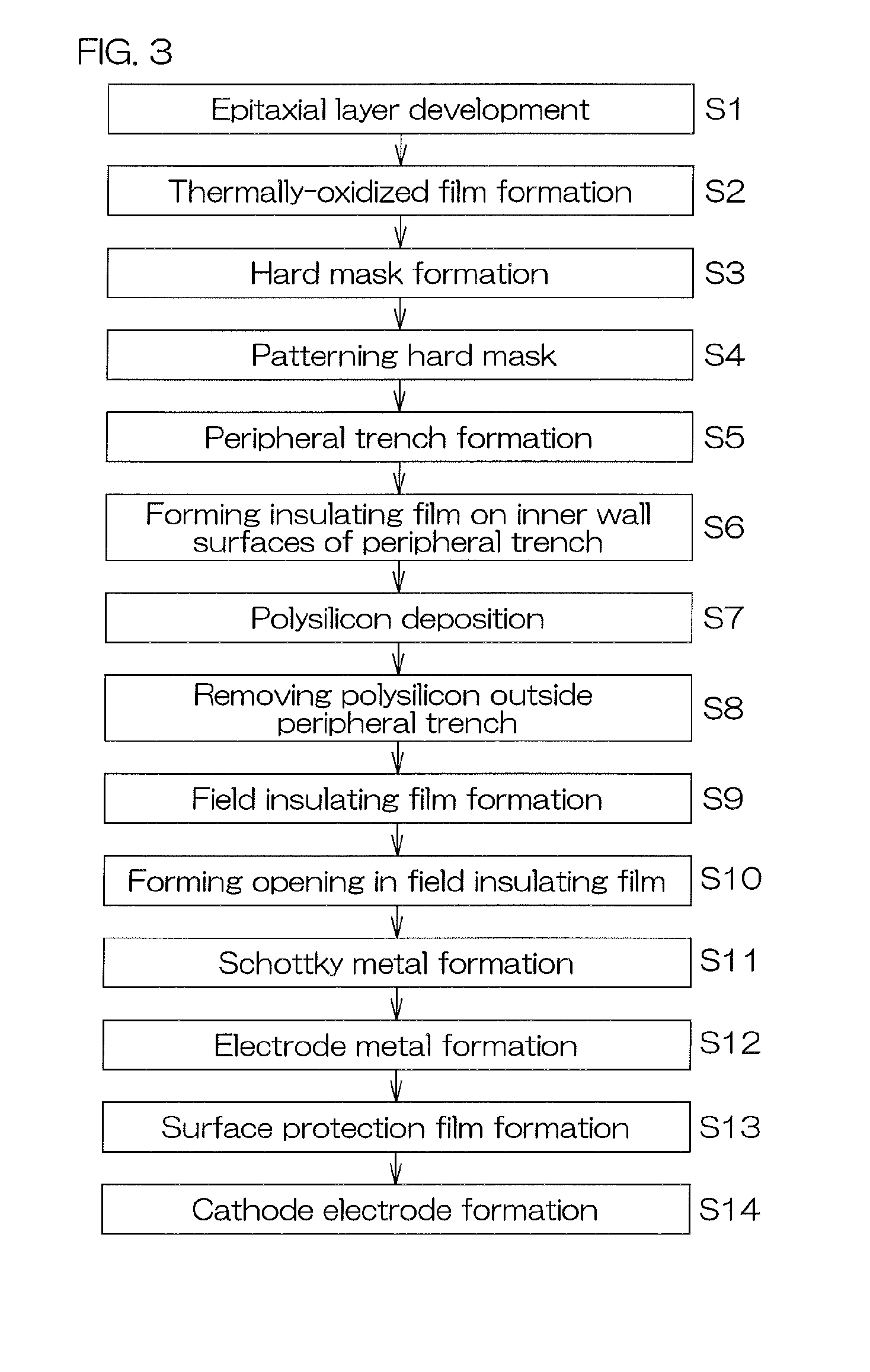

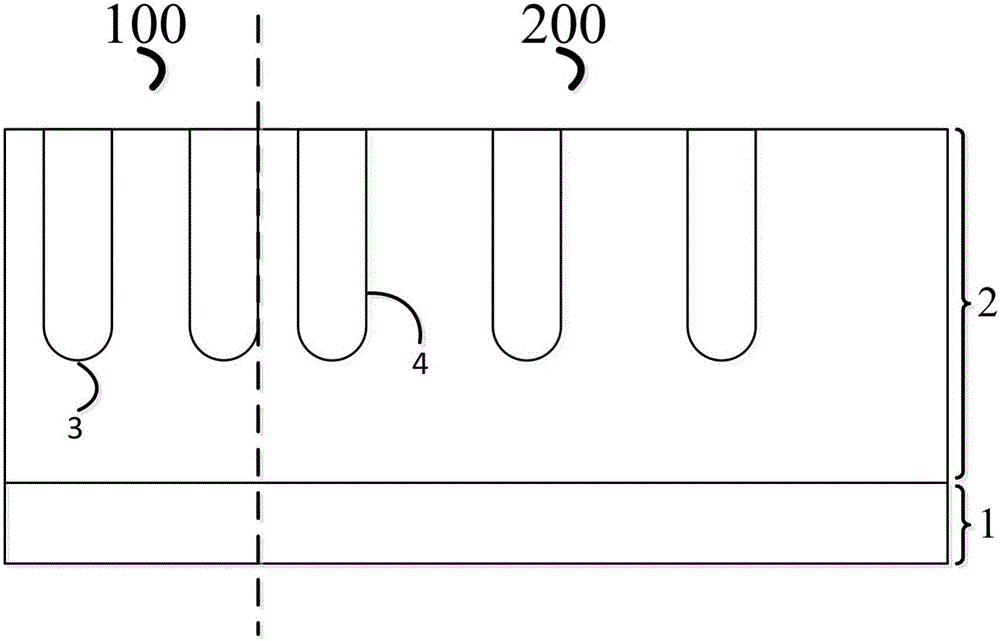

Low-cost TMBS device structure and manufacturing method

InactiveCN110047944AIncrease the expansion areaIncrease the areaSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierCondensed matter physics

The invention relates to a low-cost TMBS device structure and a manufacturing method, and belongs to the technical field of integrated circuit or discrete device manufacturing. The low-cost TMBS device structure comprises a heavily doped silicon substrate, wherein a lightly doped silicon epitaxial layer is arranged on the heavily doped silicon substrate; a silicon groove array is arranged on the lightly doped silicon epitaxial layer; a SiO2 layer is arranged on the inner side wall of the silicon groove array; the silicon groove array is filled with a heavily doped Poly; a Schottky barrier metal layer is arranged on the silicon groove array; and an electrode metal layer is arranged on the Schottky barrier metal layer. The silicon groove array comprises a primitive cell trench unit, a primitive cell large trench, an extension trench and a cut-off trench, Schottky barrier metal layers are arranged on the upper surfaces of the primitive cell trench unit and the primitive cell large trench,and a SiO2 layer and a Schottky barrier metal layer are arranged on the lightly doped silicon epitaxial layer between the primitive cell large trench and the extension trench. According to the invention, the process steps are reduced, the terminal structure is optimized, the terminal electric field distribution is more uniform, and the breakdown voltage is improved; and the forward voltage drop of the device is reduced.

Owner:江苏新顺微电子股份有限公司

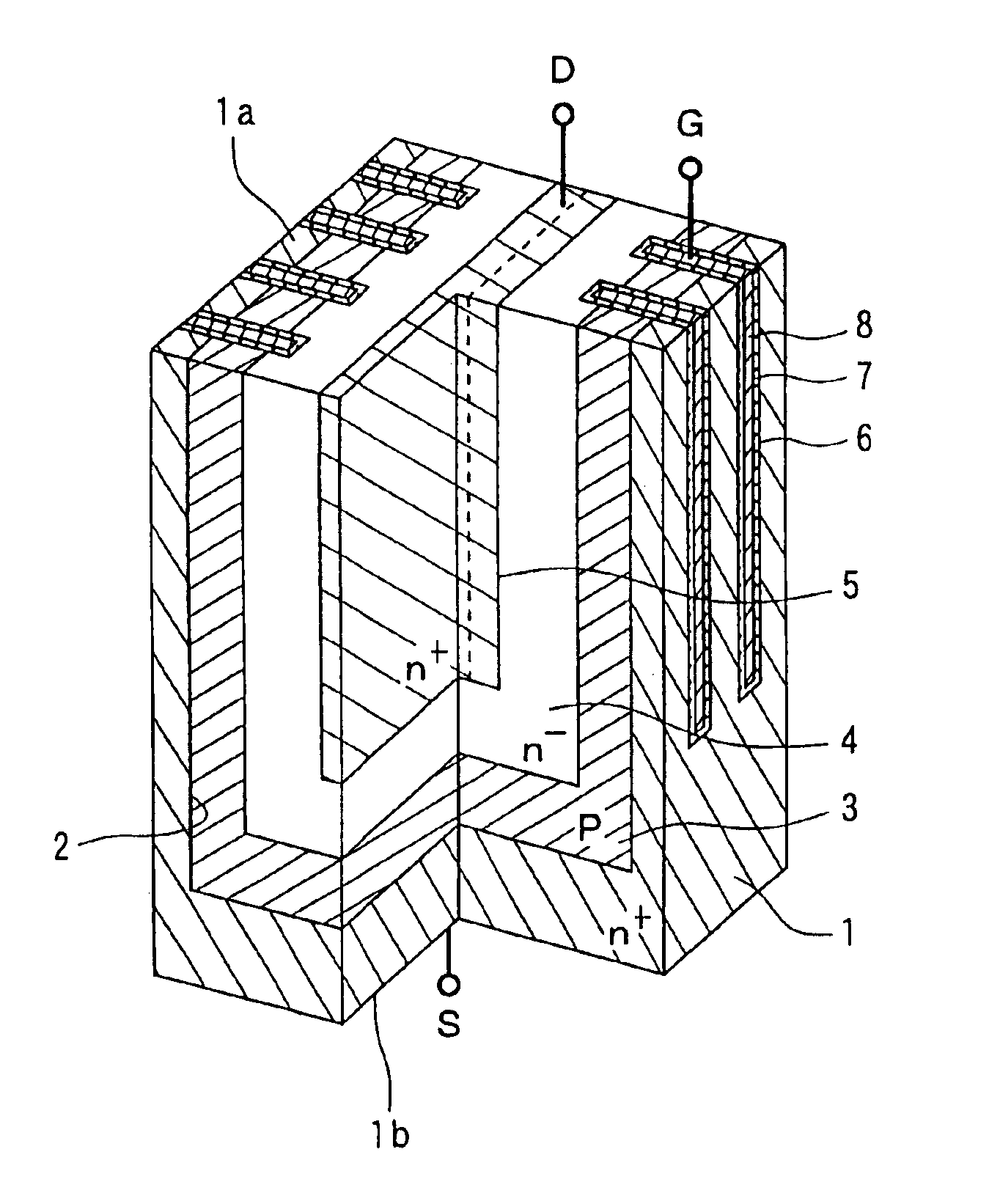

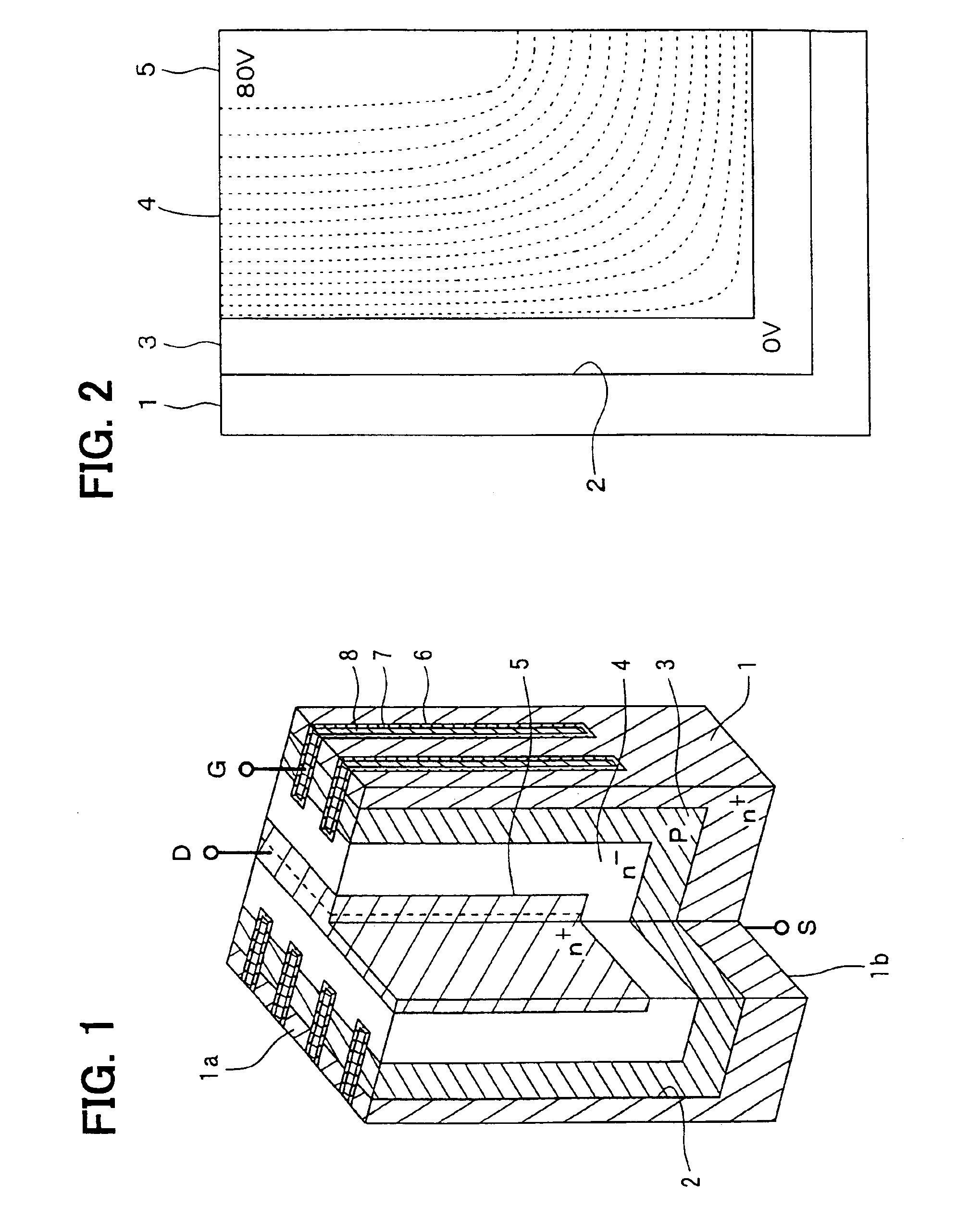

Semiconductor device having high breakdown voltage without increased on resistance

A first trench is formed in a surface of an n+-type semiconductor substrate that forms a source region. A p-type base region, an n−-type drift region, and an n+-type drain region are deposited in this order in the first trench using epitaxial growth. A second trench extending from the source region to the drift region through the base region is formed in the surface. A gate insulating film and a gate electrode are formed on a surface defining the second trench. The n+-type drain region has a location where growing surfaces come together in epitaxial growth and where a defect is likely to occur, and the gate electrode lacks such a location and thus avoids an increase in normalized ON resistance. Therefore, the breakdown voltage remains high without increasing the ON resistance.

Owner:DENSO CORP

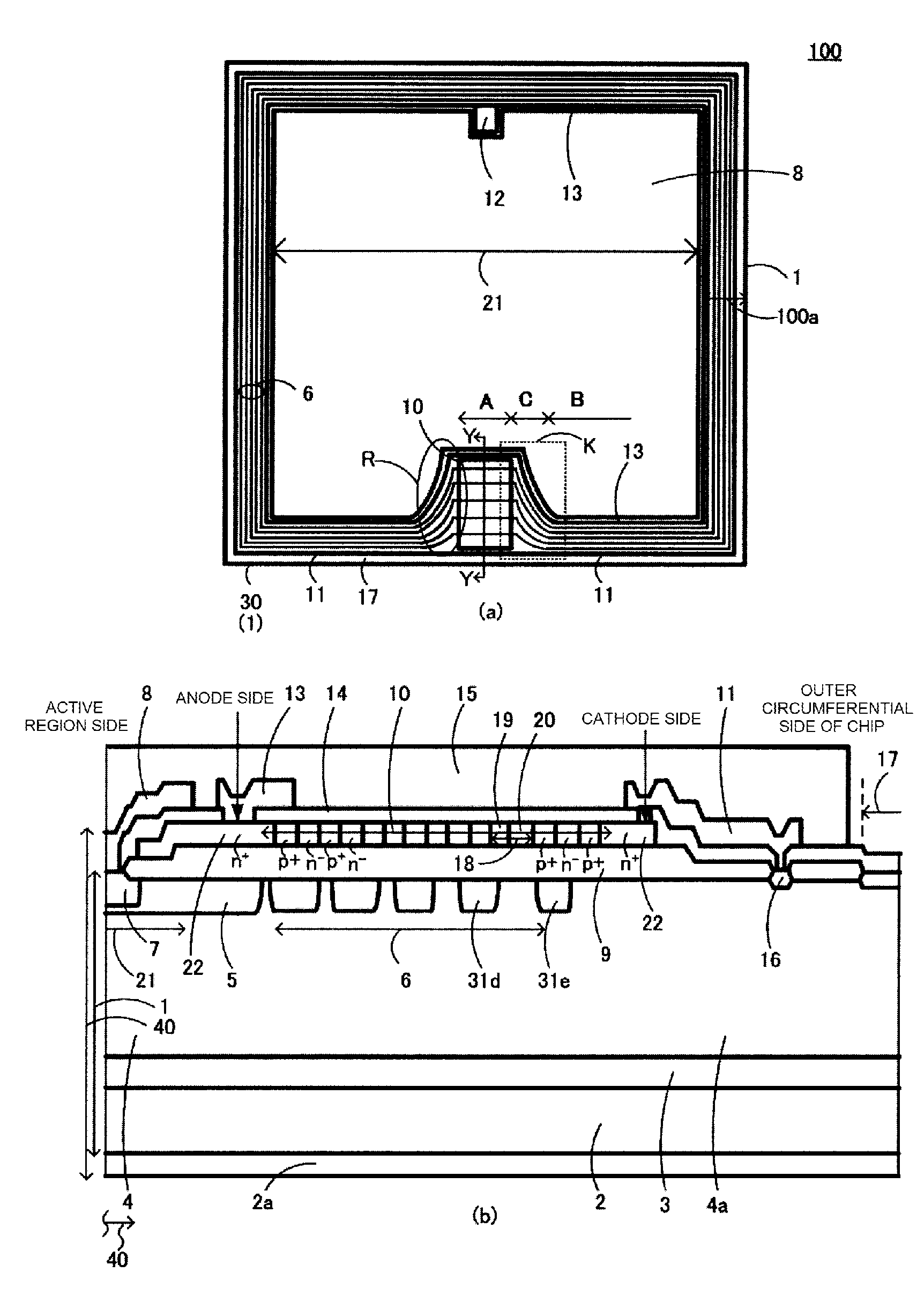

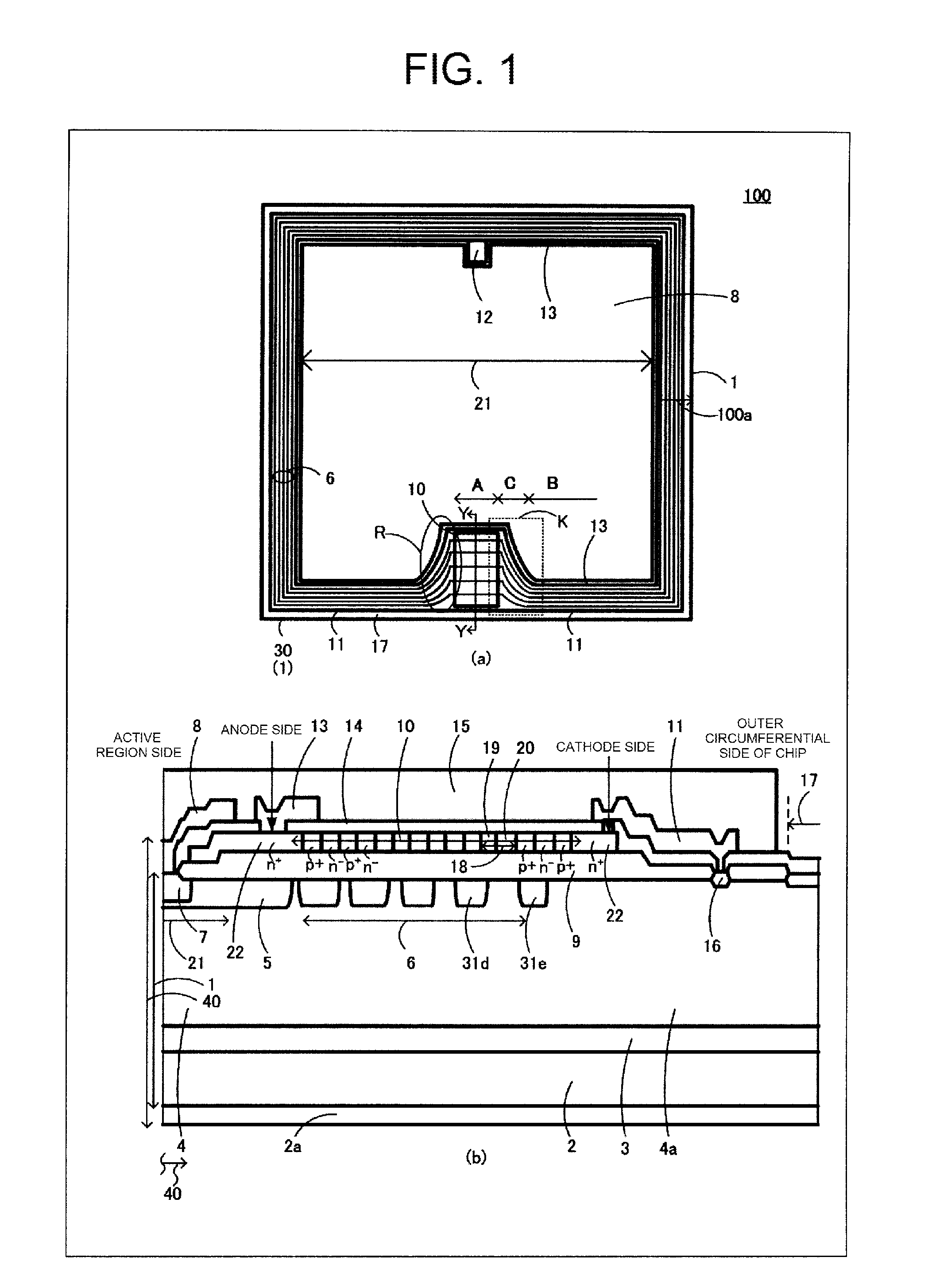

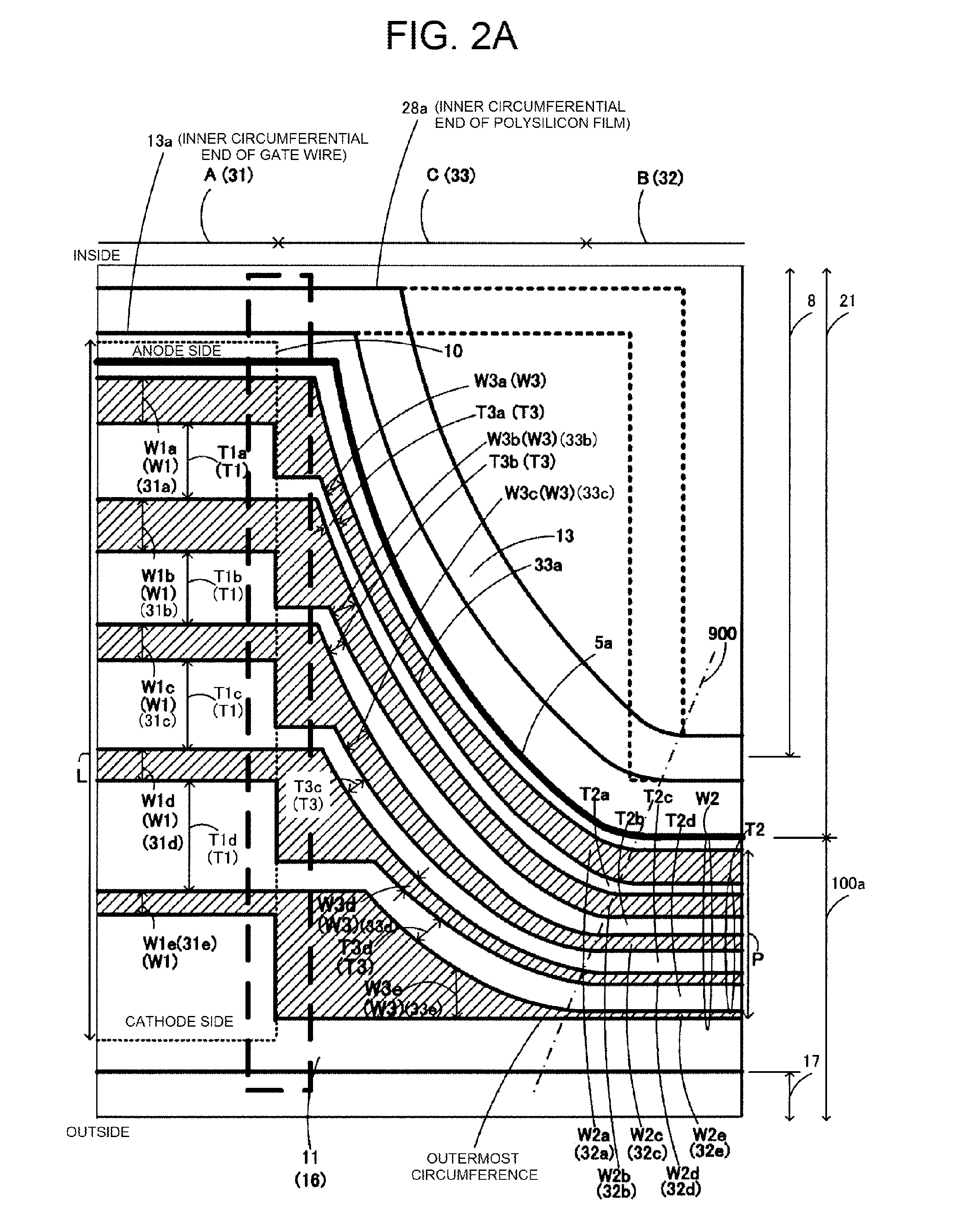

Semiconductor device

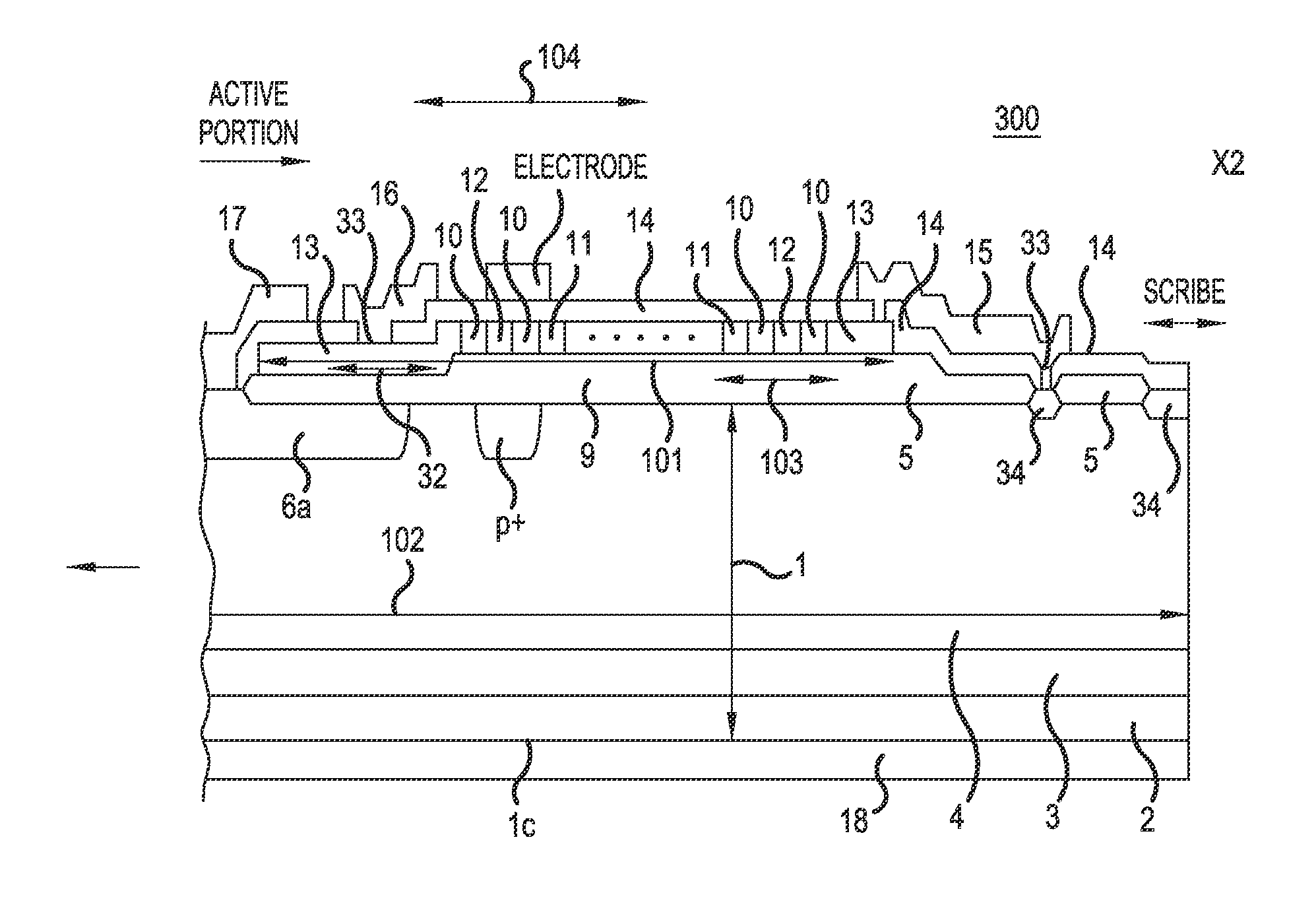

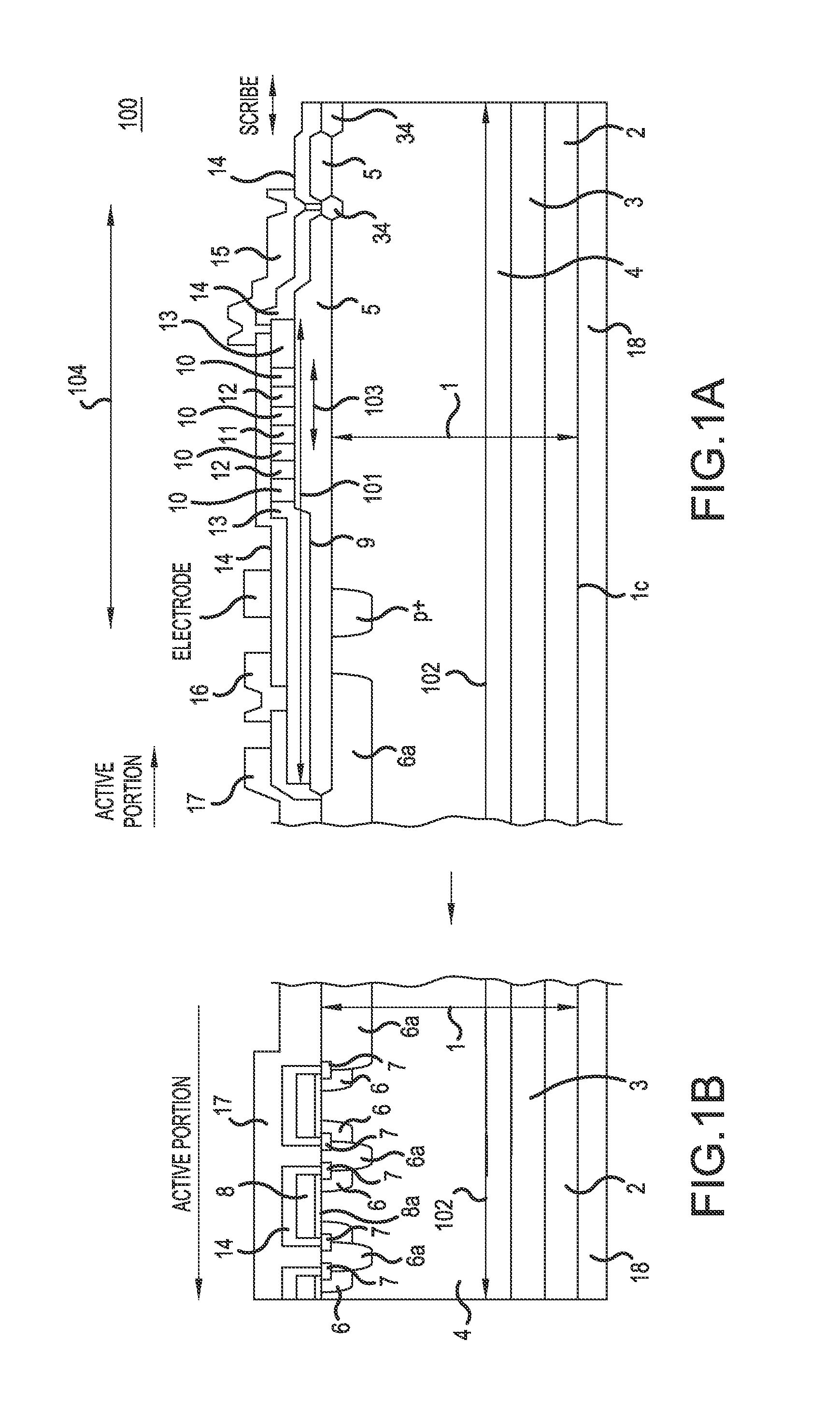

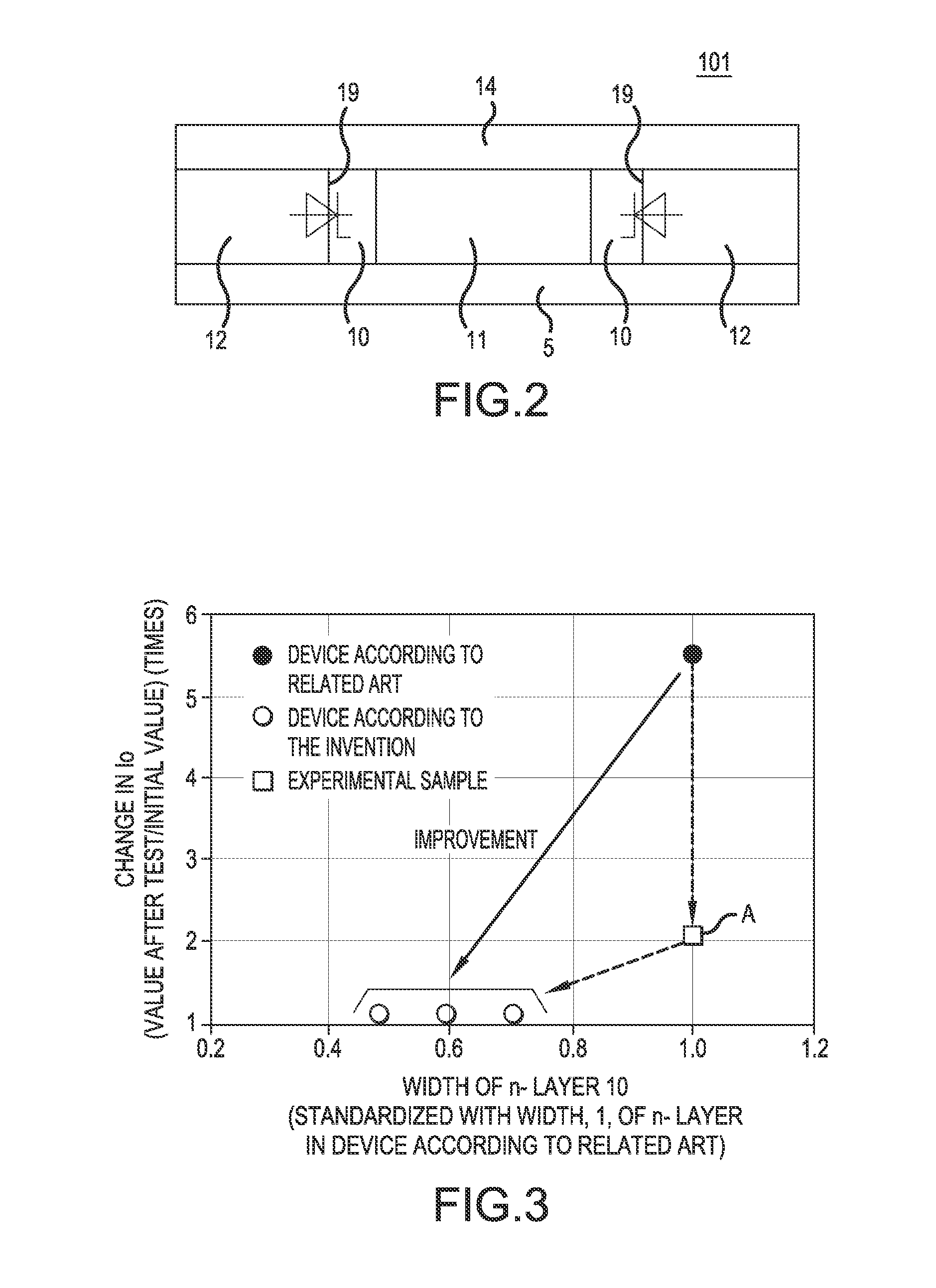

ActiveUS20150340356A1Avoid reliabilityReduce adverse effectsSolid-state devicesSemiconductor/solid-state device manufacturingZener diodePolyimide membrane

A protective diode is provided above a first guard ring region which surrounds an active region, with a field oxide film interposed there between. The protective diode may include a series pn zener diode in which a p+ layer and an n− layer are adjacent to each other. In a semiconductor device having the first guard ring region provided below the protective diode, cracks in the surface protective film may be prevented by providing a surface protective film that may be a polyimide film. The first guard ring region is provided below the protective diode and is connected to a second guard ring region that is provided in a portion other than the portion provided below the protective diode through a third guard ring region which is an intermediate region (R). Thus, when a surge voltage is applied, concentration of electric field on the outermost guard ring may be reduced.

Owner:FUJI ELECTRIC CO LTD

Lateral double diffusion metal-oxide semiconductor device and method for manufacturing the same

ActiveUS20130126969A1Reduce complexityIncrease the doping concentrationSemiconductor devicesLDMOSDouble diffusion

Disclosed is an LDMOS device, which is configured to reduce an electric field concentrated to a gate oxide film and lower an ON-resistance produced when the device conducts a forward action, and a method for manufacturing the same. More specifically, when an n-drift region is formed on a P-type substrate, a p-body is formed on the n-drift region through an epitaxial process, and then the p-body region is partially etched to form a plurality of p-epitaxial layers, so that when the device executes an action for blocking a reverse voltage, depletion layers are formed between the junction surfaces of the p-epitaxial layers and the n-drift region including the junction surfaces between the n-drift region and the p-body.

Owner:HYUNDAI MOTOR CO LTD

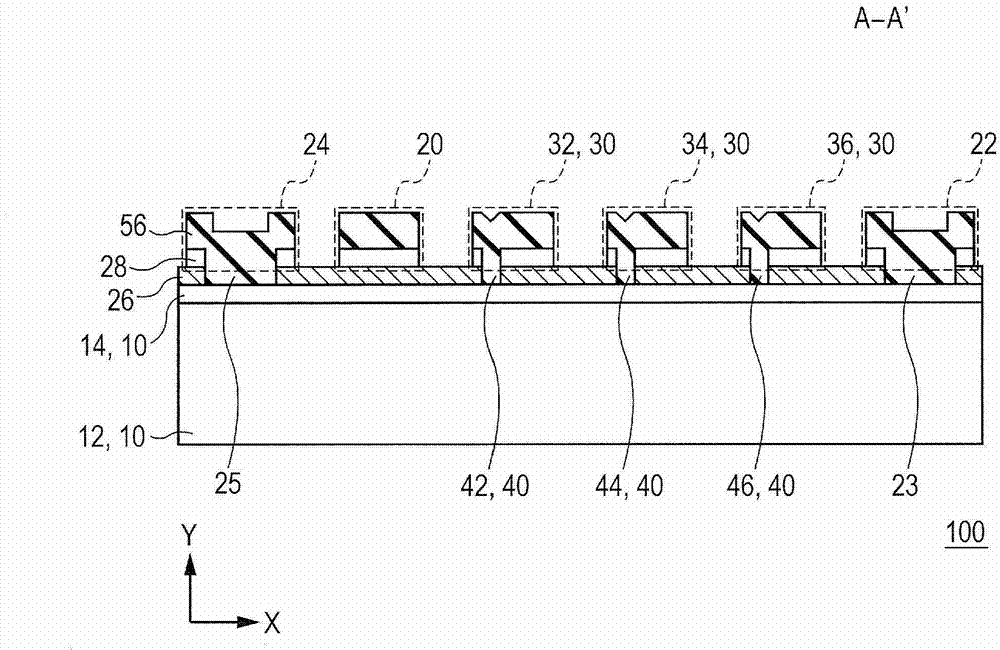

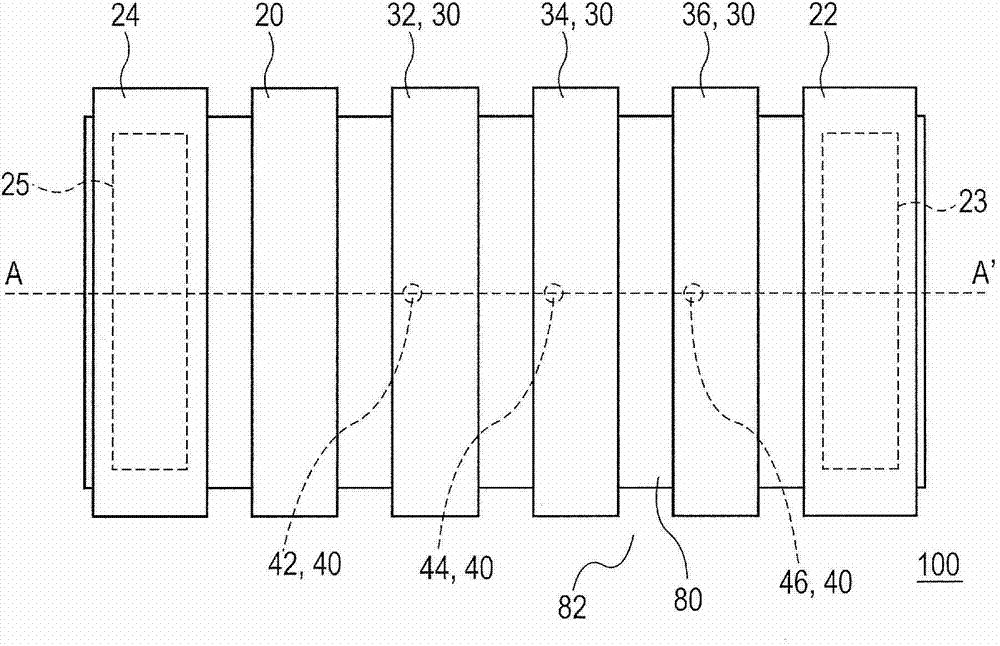

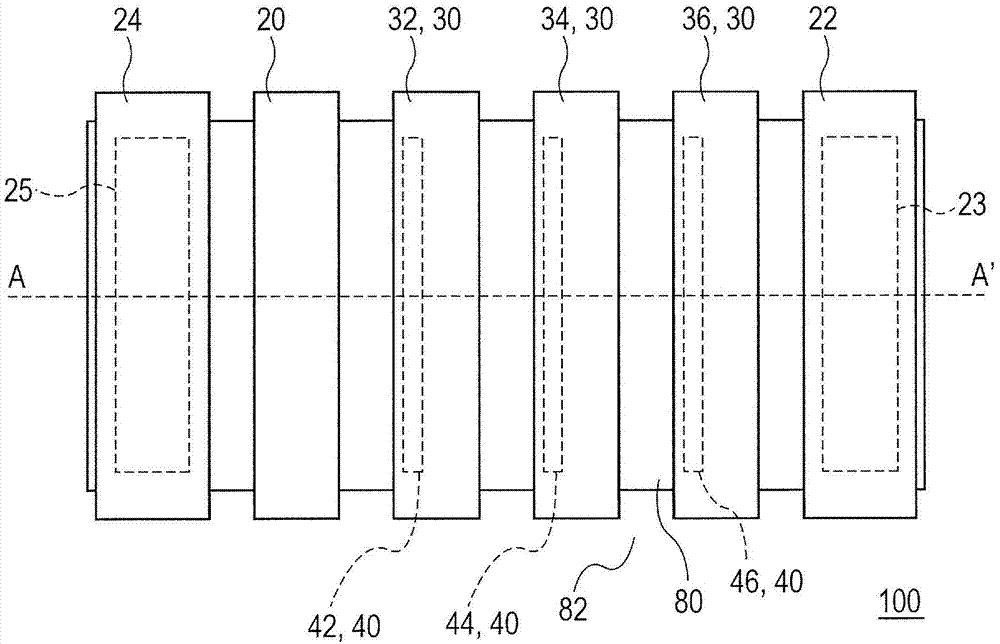

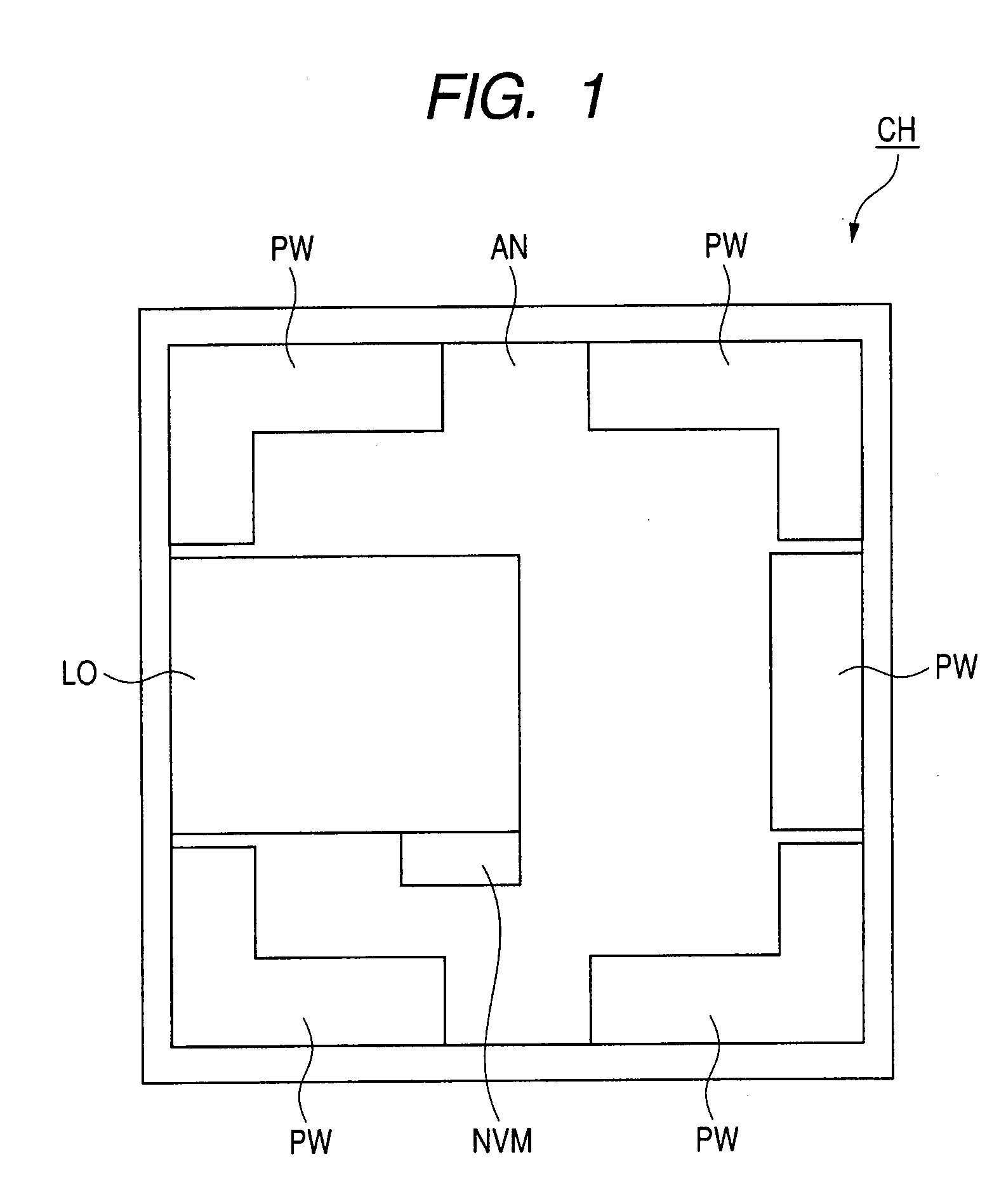

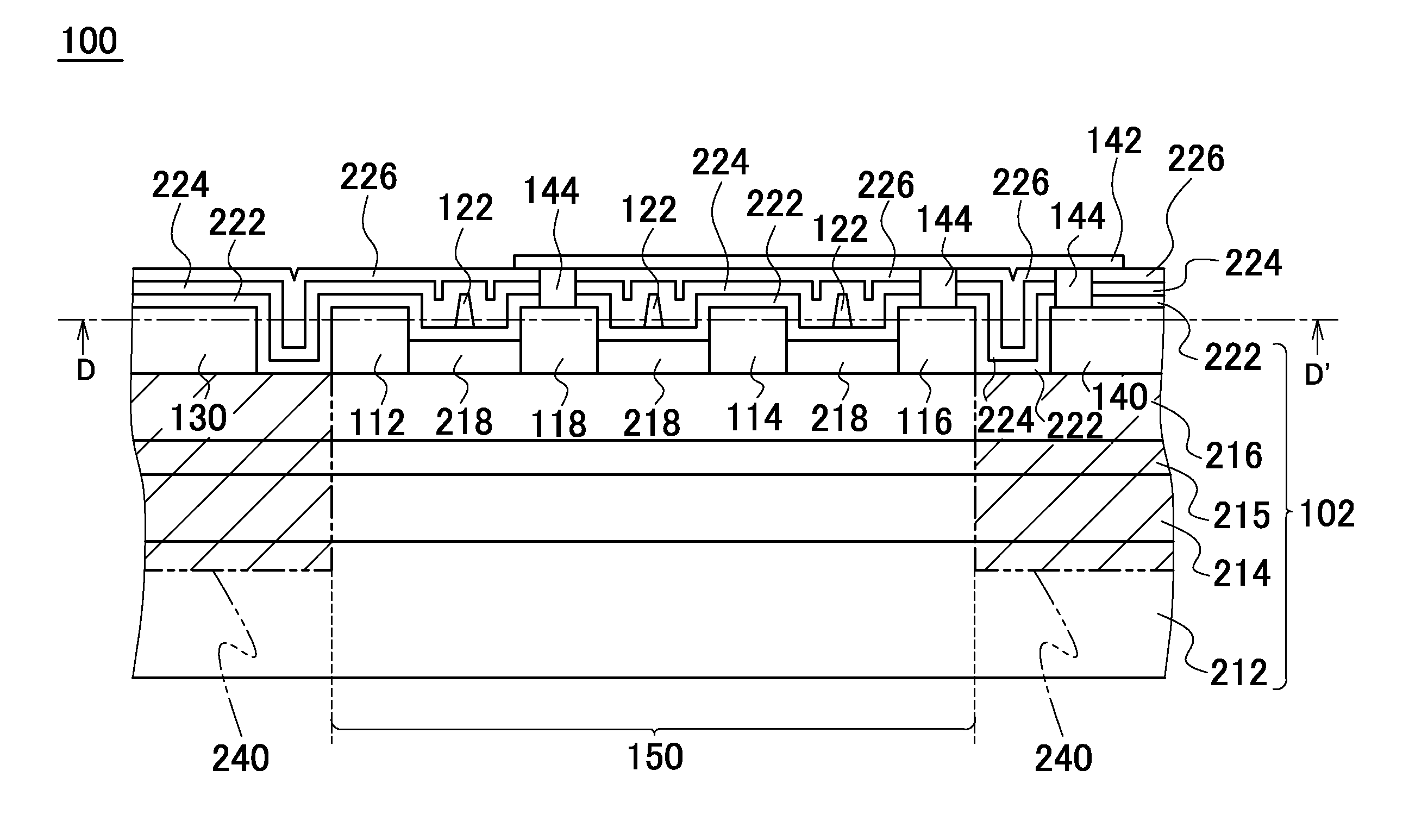

Semiconductor device, method for manufacturing of semiconductor device, and switching circuit

ActiveUS20120074577A1Reduce electric field concentrationSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

It is an objective to provide a semiconductor device with low leak current. The semiconductor device includes a plurality of ground side electrodes and a plurality of signal side electrodes arranged on a semiconductor substrate in an alternating manner; a plurality of control electrodes arranged respectively between each pair of a ground side electrode and a signal side electrode; a ground side electrode connecting section that connects the ground side electrodes to each other; a signal side electrode connecting section that connects the signal side electrodes to each other; and ground side lead wiring and signal side lead wiring that extend respectively from a region near one end and a region near another end of an arranged electrode section, in which the ground side electrodes and the signal side electrodes are arranged in an arrangement direction, away from the arranged electrode group in the arrangement direction.

Owner:ADVANTEST CORP

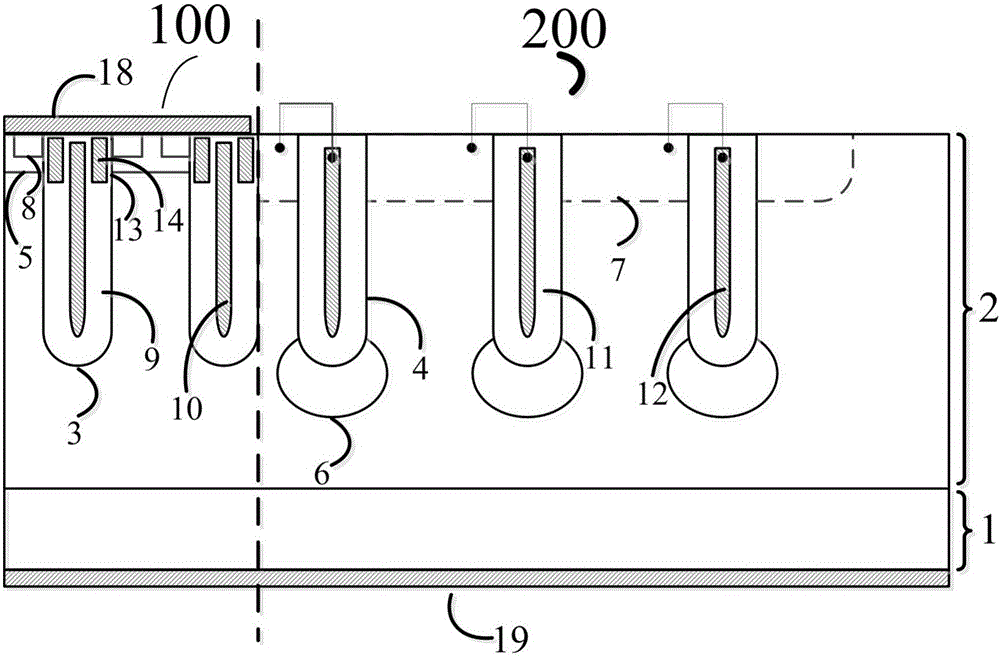

Schottky barrier diode

ActiveUS20150228809A1Reduce leakage currentImprove the immunitySemiconductor devicesSurface layerSchottky barrier

A Schottky metal 9 is in Schottky-contact with a center portion of a surface of an epitaxial layer 4. A peripheral trench 13 is formed by digging from the surface of the epitaxial layer 4 on a boundary portion between an active region 21 where the Schottky metal 9 is in Schottky-contact with the surface of the epitaxial layer 4 and a peripheral region 22 outside of the active region in a surface layer portion of the epitaxial layer 4. An insulating film 14 is formed on an entire area of inner wall surfaces of the peripheral trench 13. There is provided with a conductor 15 which is connected to the Schottky metal 9 and is opposed to the entire area of the inner wall surfaces of the peripheral trench 13 via the insulating film 14 in the peripheral trench 13.

Owner:ROHM CO LTD

Semiconductor structure suitable for charge coupled device and manufacturing method of semiconductor structure

InactiveCN105679810AIncrease exhaustEnhanced depletionSemiconductor/solid-state device manufacturingSemiconductor devicesElectricitySemiconductor structure

The present invention relates to a semiconductor structure suitable for a charge-coupled device and a manufacturing method thereof. On the cross section of the semiconductor device, a second well region of a second conductivity type is provided in a first conductivity type drift region of a terminal protection region, The second well region of the second conductivity type is located in the upper part of the drift region of the first conductivity type, and a plurality of terminal trenches are arranged in the terminal protection zone, and the terminal trenches are located in the second well region of the second conductivity type, and the depth extends to into the drift region of the first conductivity type under the second well region of the second conductivity type; the termination dielectric body and the terminal conductor are filled in the termination trench, and the termination conductor is the same as the adjacent active region outside the termination trench The second conductivity type second well region on the side is electrically connected. The invention has a compact structure, can effectively improve the high-voltage resistance characteristic of the device, is compatible with the existing technology, reduces the cost, has wide application range, and is safe and reliable.

Owner:WUXI NCE POWER

Semiconductor device and method for manufacturing semiconductor device

ActiveUS20150048450A1Reduce areaSuppress concentration of electric fieldSemiconductor/solid-state device manufacturingDiodeDepth directionImpurity

A protective diode has a basic structure including an n+ layer, an n− layer, a p+ layer, and an n− layer in this order. A p-type layer forming the protective diode is the p+ layer with high impurity concentration. Therefore, the spreading of a depletion layer is suppressed and it is possible to reduce the area of the protective diode. In addition, phosphorus ions with a large diffusion coefficient are implanted to form the n− layer with low impurity concentration in the polysilicon layer forming the protective diode. A heat treatment is performed at a temperature of 1000° C. or higher to diffuse the phosphorus ions implanted into the polysilicon layer. Therefore, the impurity profile of the n− layer in the depth direction can be uniformized in the depth direction.

Owner:FUJI ELECTRIC CO LTD

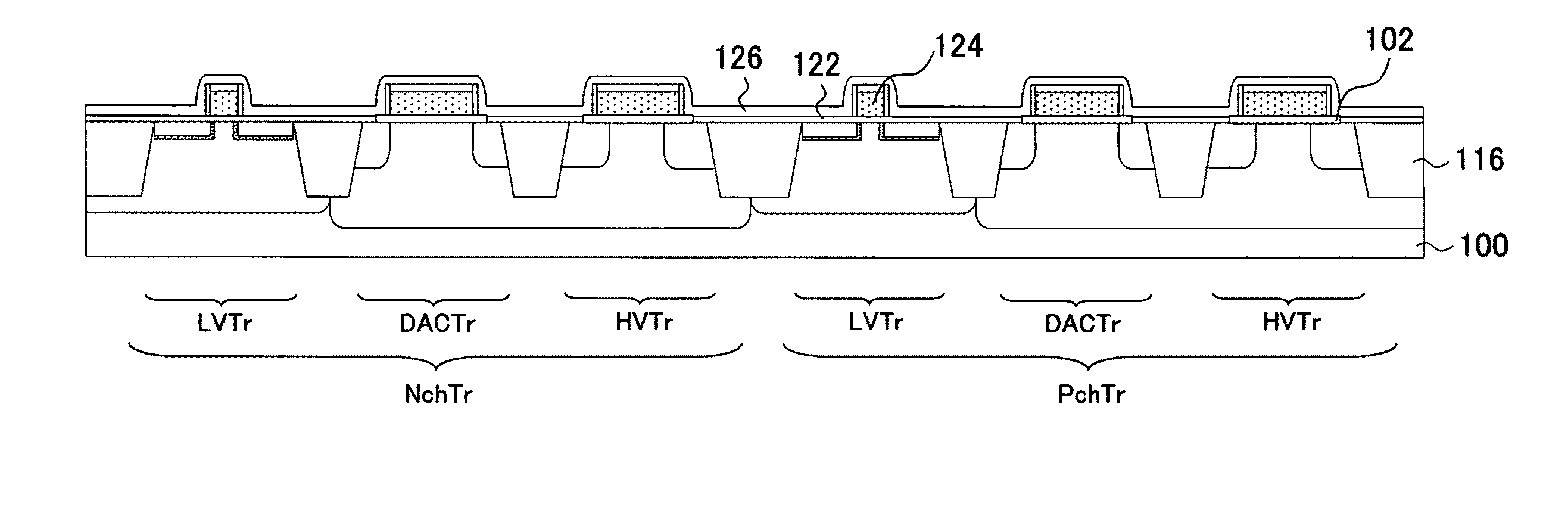

Semiconductor device manufacturing method and semiconductor device

ActiveUS20110042730A1High dielectric strengthImprove image displaySemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceHigh voltage transistors

A formation method of an element isolation film according to which a high-voltage transistor with an excellent characteristic can be formed is provided. On a substrate, a gate oxide film is previously formed. A CMP stopper film is formed thereon, and thereafter, a gate oxide film and a CMP stopper film are etched. The semiconductor substrate is etched to form a trench. Further, before the trench is filled with a field insulating film, an liner insulating film is formed at a trench interior wall, and a concave portion at the side surface of the gate oxide film under the CMP stopper film is filled with the liner insulating film. In this manner, formation of void in the element isolation film laterally positioned with respect to the gate oxide film can be prevented.

Owner:SHARP KK

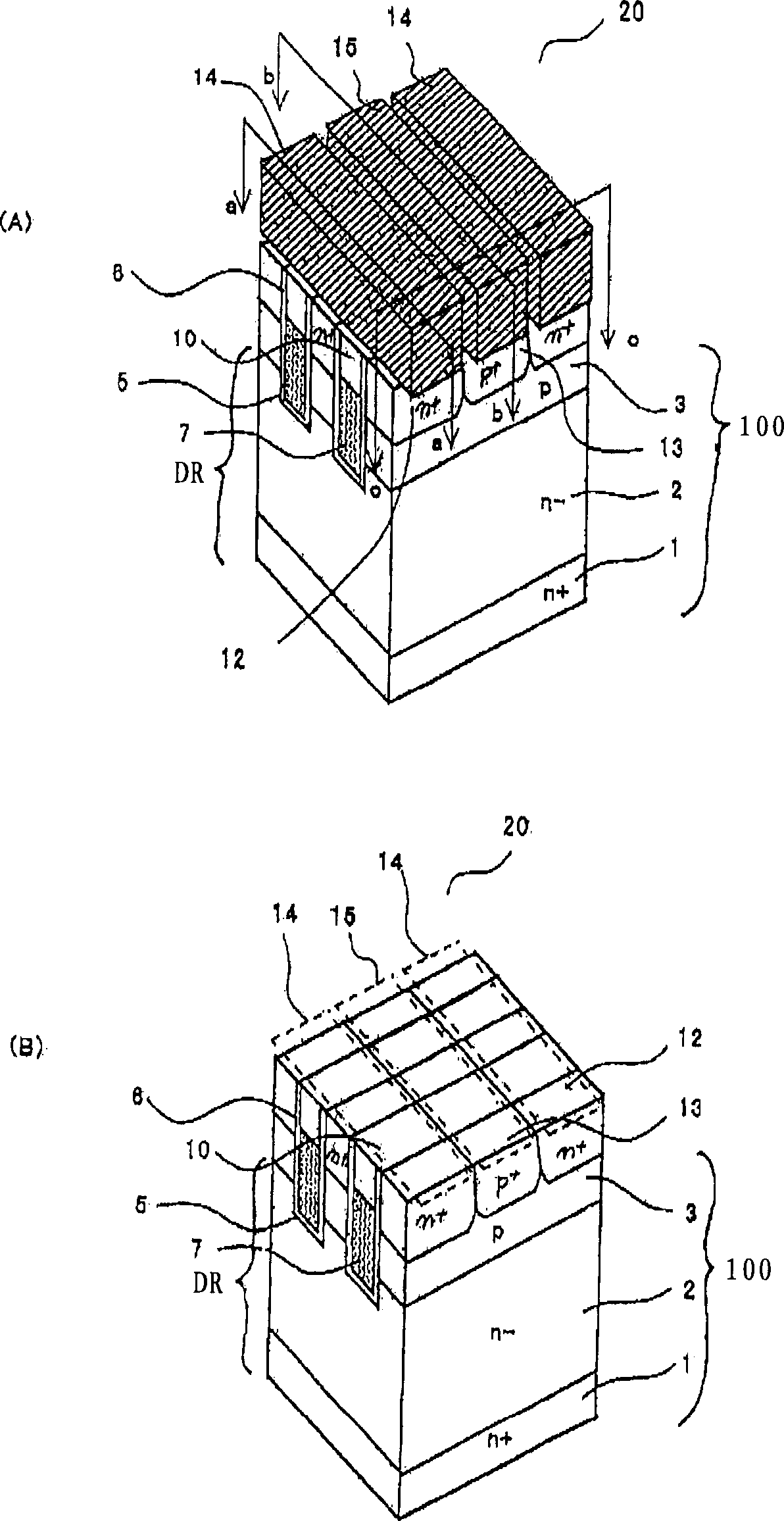

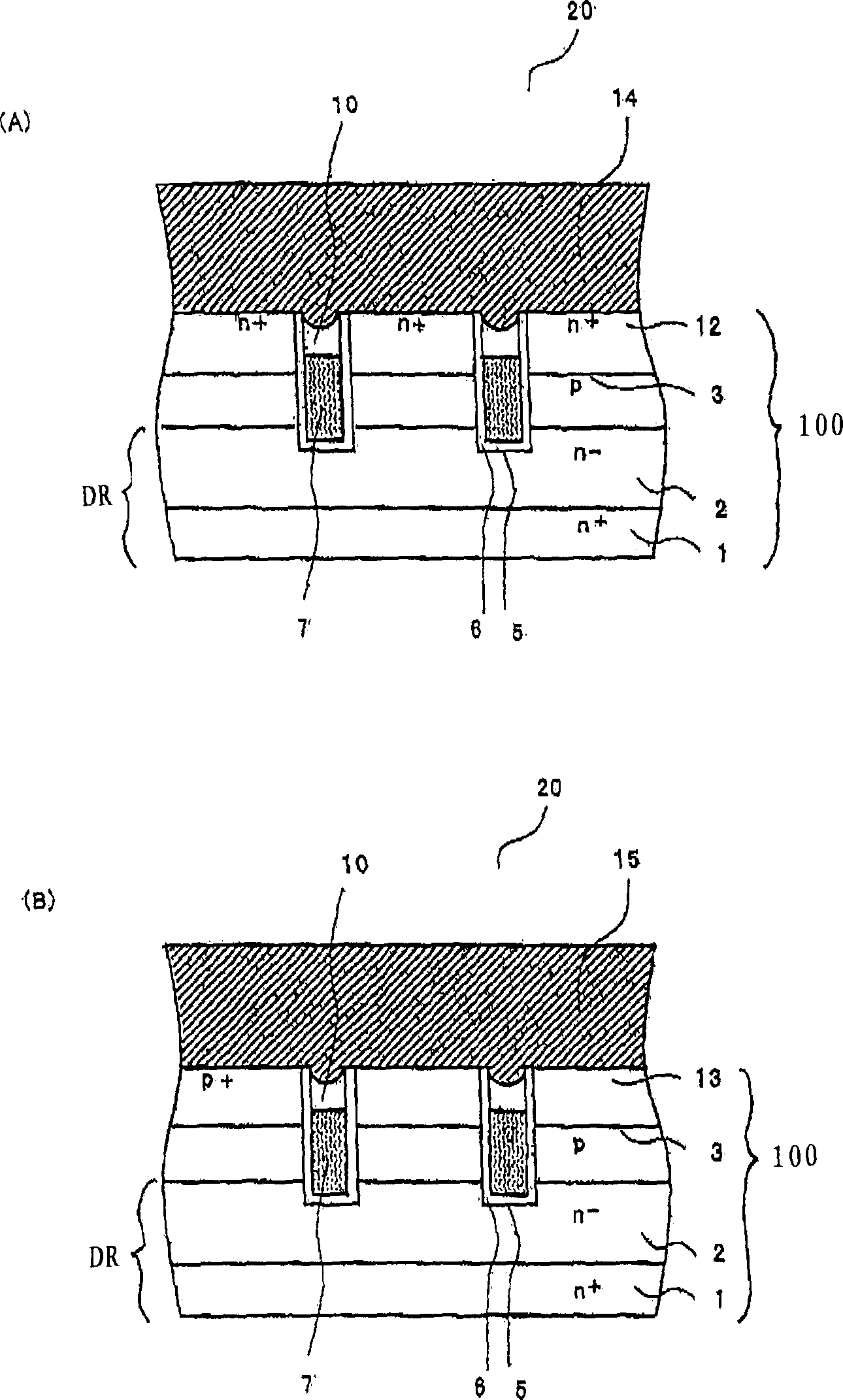

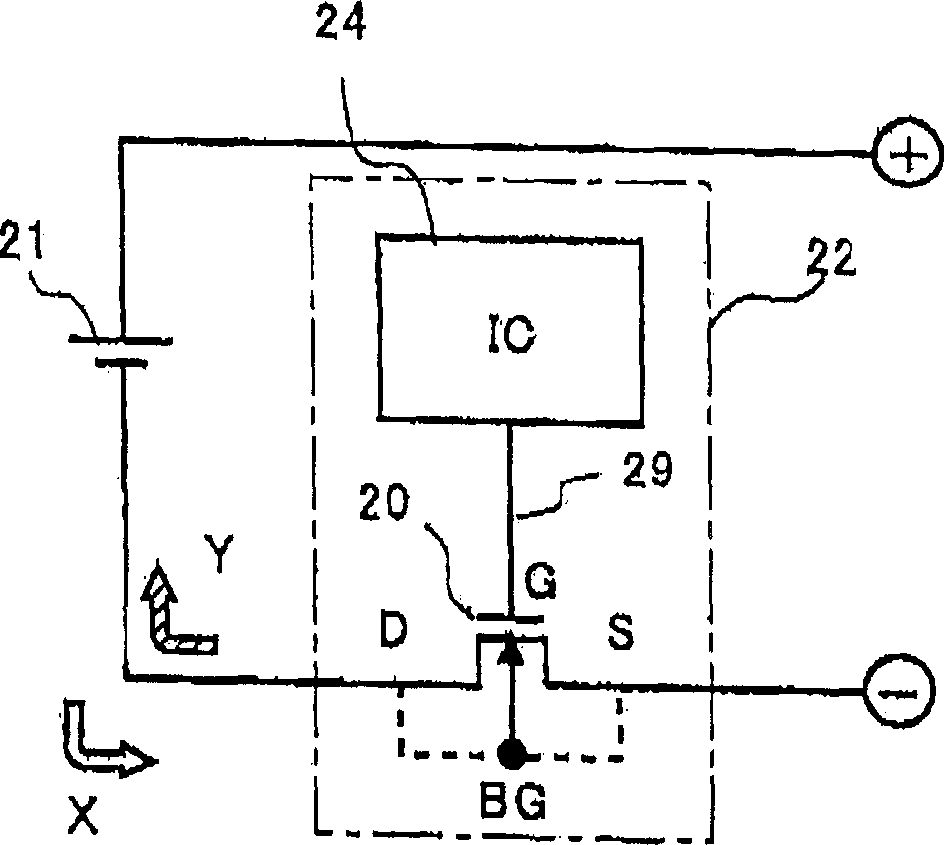

Insulated gate semiconductor device, protection circuit and their manufacturing method

InactiveCN1885561APrevent backflowAchieve planarizationTransistorSolid-state devicesMOSFETPower semiconductor device

A first electrode layer (14), which comes into contact with a source region (12), and a second electrode layer (15), which comes into contact with a body (back gate) region (13), are provided. The first and second electrode layers (14, 15) are insulated from each other and are extended in a direction different from an extending direction of a trench (5). It is possible to individually apply potentials to the first and second electrode layers (14, 15), and to perform control for preventing a reverse current caused by a parasitic diode. Therefore, a bidirectional switching element can be realized by use of one MOSFET.

Owner:SANYO ELECTRIC CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com