Silicon carbide semiconductor device

A silicon carbide and semiconductor technology, applied in the field of silicon carbide semiconductor devices, can solve problems such as narrow current paths and increased on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

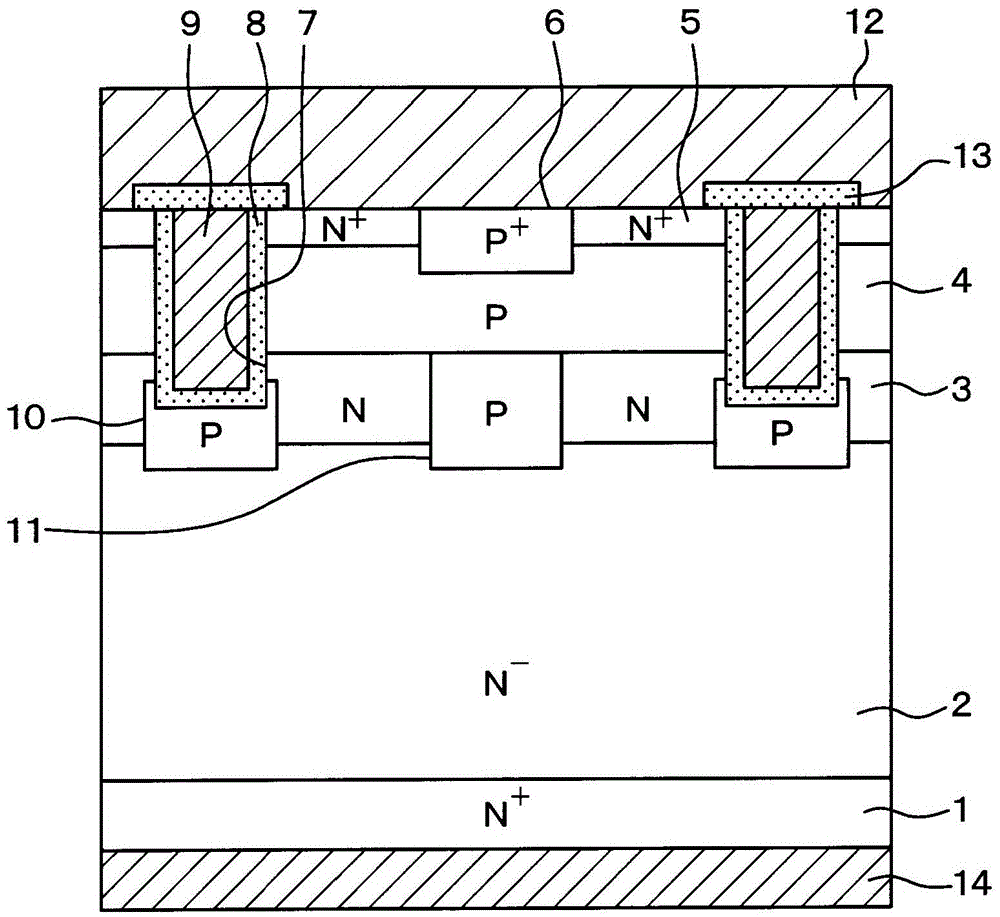

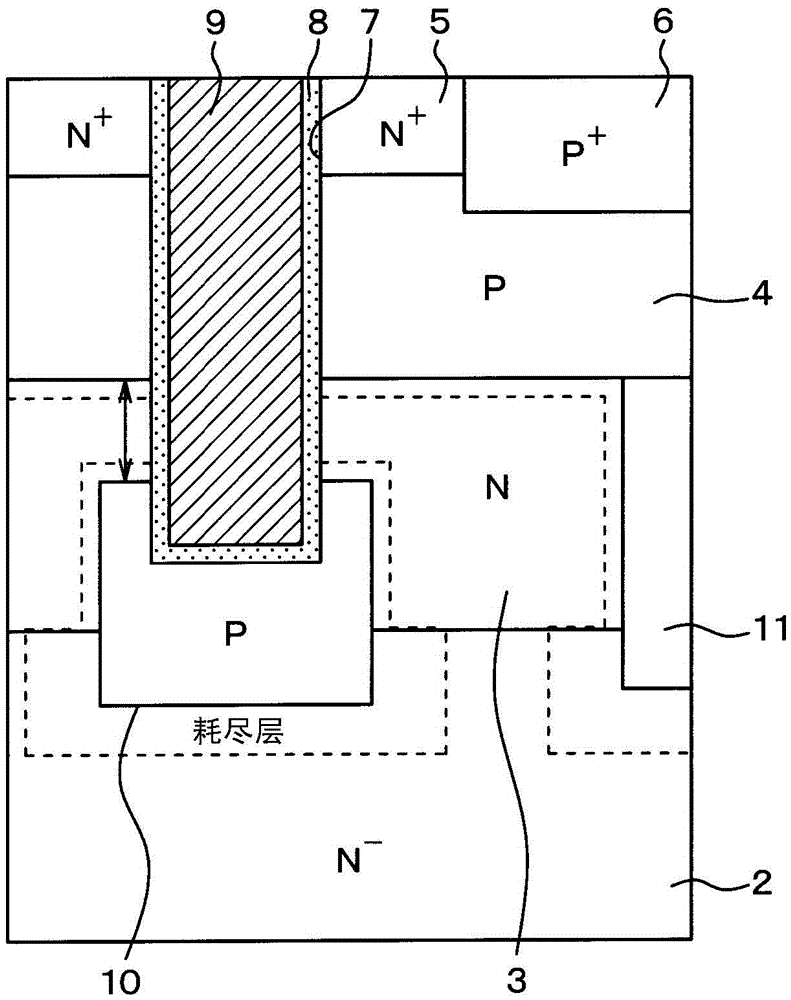

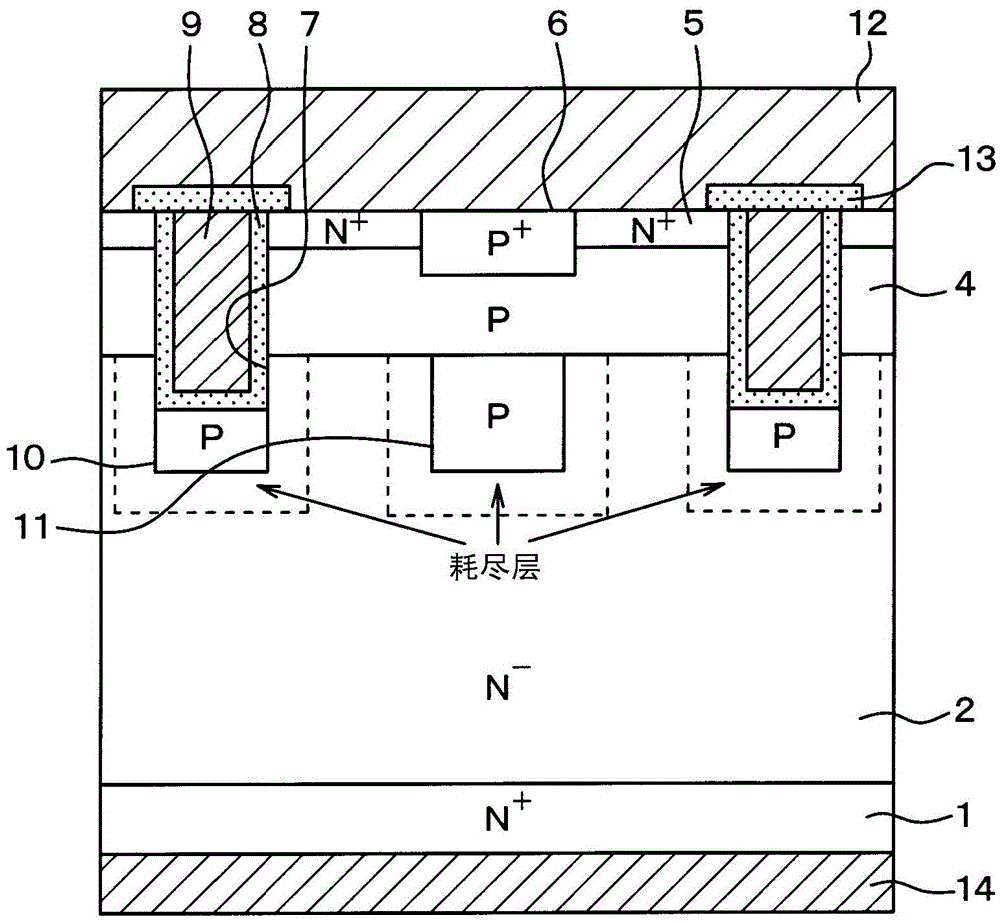

[0028] The first embodiment of the present invention will be described. Here, as an element included in the SiC semiconductor device, a MOSFET with an inverted trench gate structure will be described.

[0029] First, refer to figure 1 The cross-sectional structure of the trench gate structure MOSFET of this embodiment will be described. This figure corresponds to the structure of the MOSFET with 2 cells extracted. Although the figure only shows two-unit MOSFET, it is different from figure 1 In the illustrated MOSFETs, MOSFETs having the same structure are arranged adjacently in multiple columns.

[0030] figure 1 The MOSFET shown uses n + The type layer 1 is formed. n + The type layer 1 is set such that the concentration of n-type impurities such as phosphorus is, for example, 5.0×10 18 ~1.0×10 20 / cm 3 , The thickness is 100~400μm, here the n-type impurity concentration is set to 1.0×10 19 / cm 3 , Set the thickness to 100μm. At that n + On the surface of the type layer 1, n - T...

no. 2 Embodiment approach

[0085] The second embodiment of the present invention will be described. In this embodiment, the structure of the n-type current diffusion layer 3 is changed from the first embodiment, and the rest is the same as the first embodiment, so only the differences from the first embodiment will be described.

[0086] Such as Picture 9 As shown, in this embodiment, the p-type base region 4 arranged on the n-type current dispersion layer 3 is constituted by a first layer 4a and a second layer 4b having different concentrations. The first layer 4a is the surface side, that is, the p-type base region 4 is located at n + Type 5 and p + The p-type impurity concentration is set to be lower in the portion on the side of the type contact layer 6 than in the second layer 4b. For example, the first layer 4a is set such that the depth to the surface is 0.95 μm, and the p-type impurity concentration is 5.0×10 16 / cm -3 . Since n is formed on the first layer 4a with a depth of 0.5 μm to the surfa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com