Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

109results about How to "Reduce forward voltage drop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

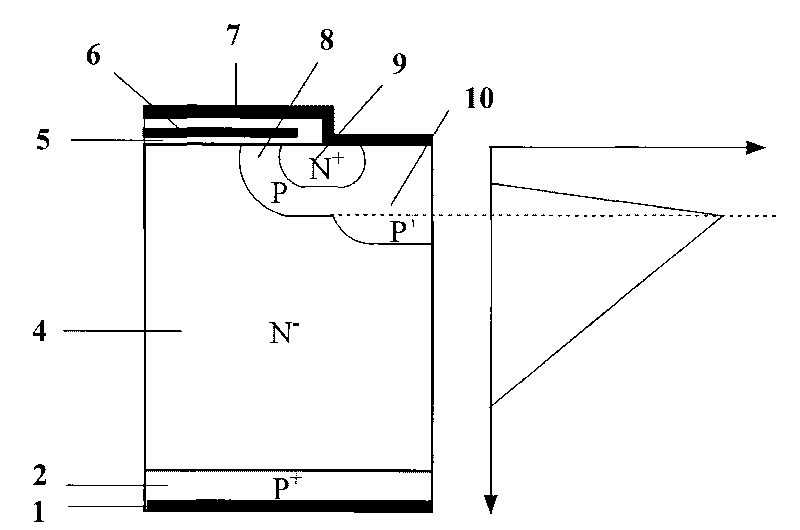

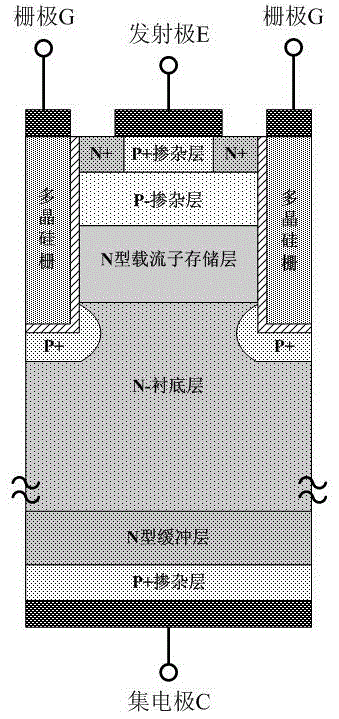

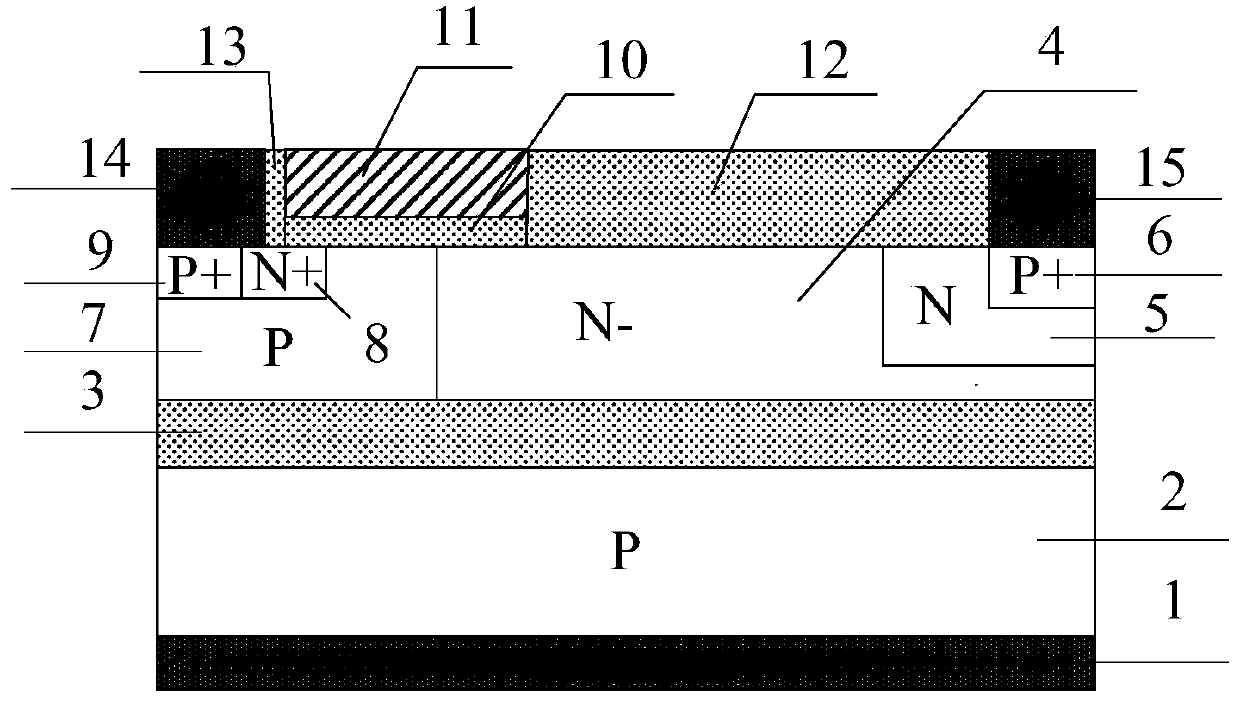

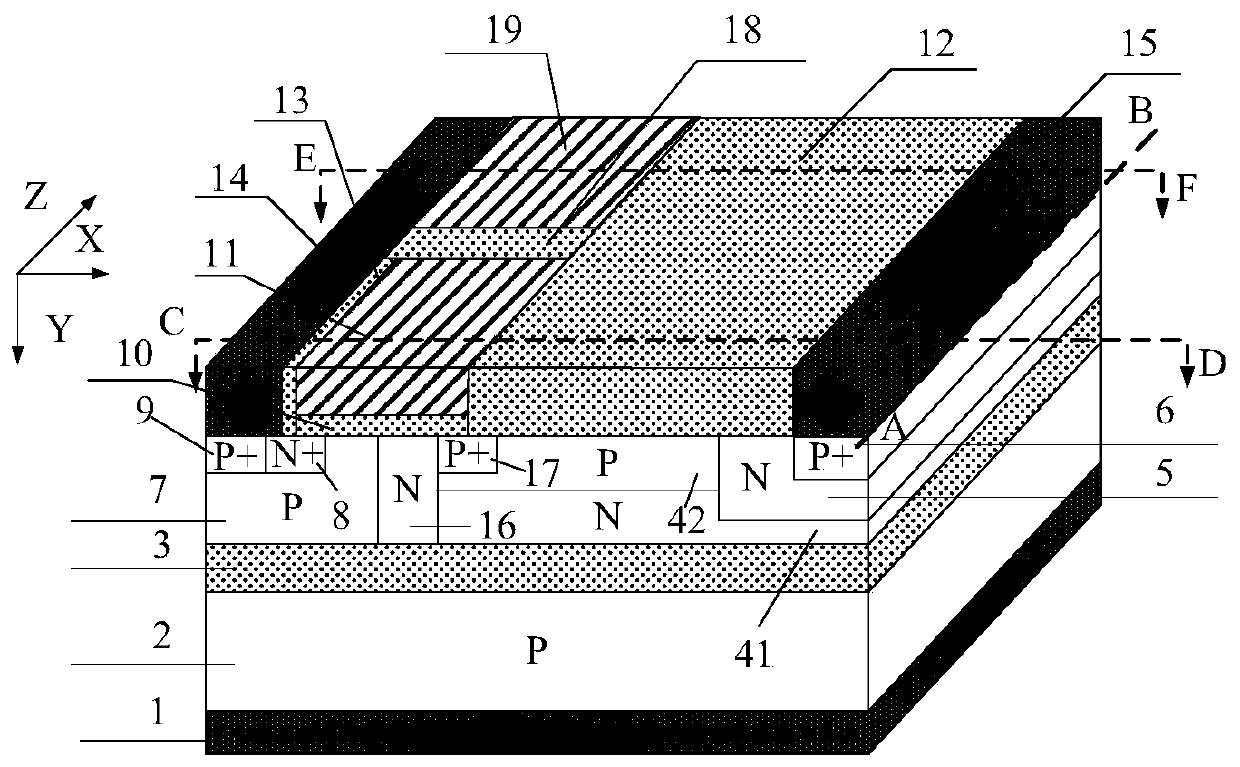

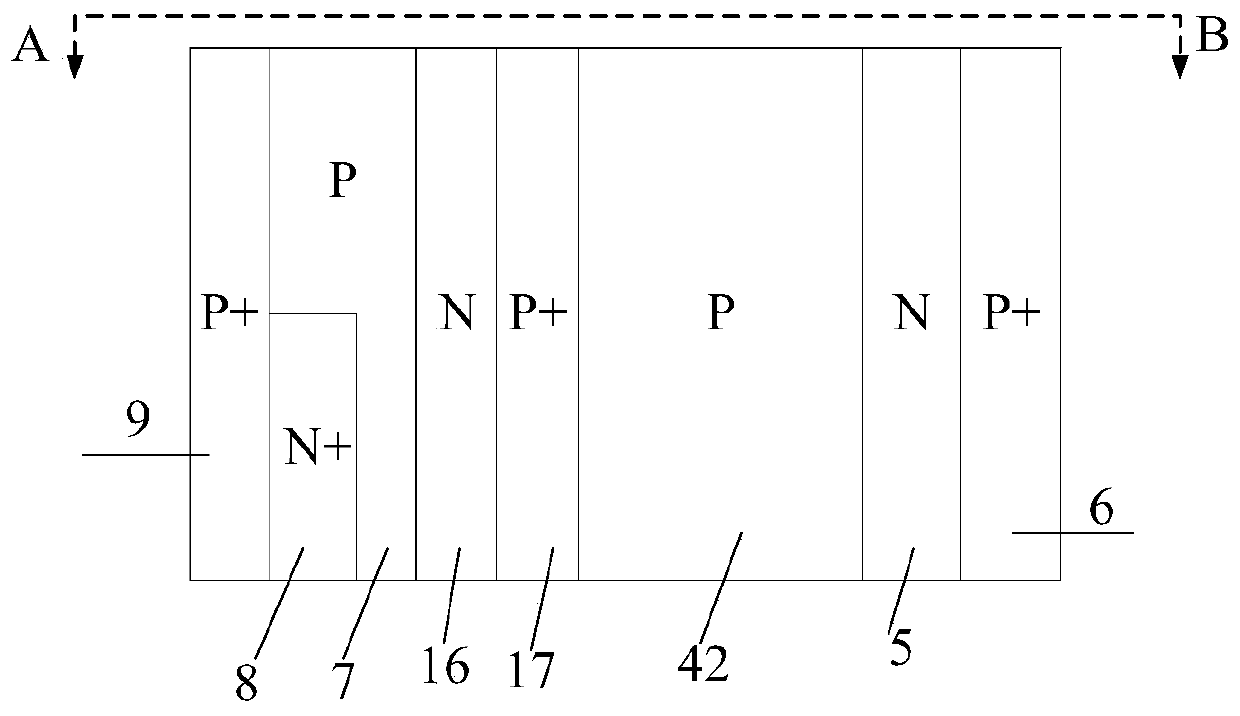

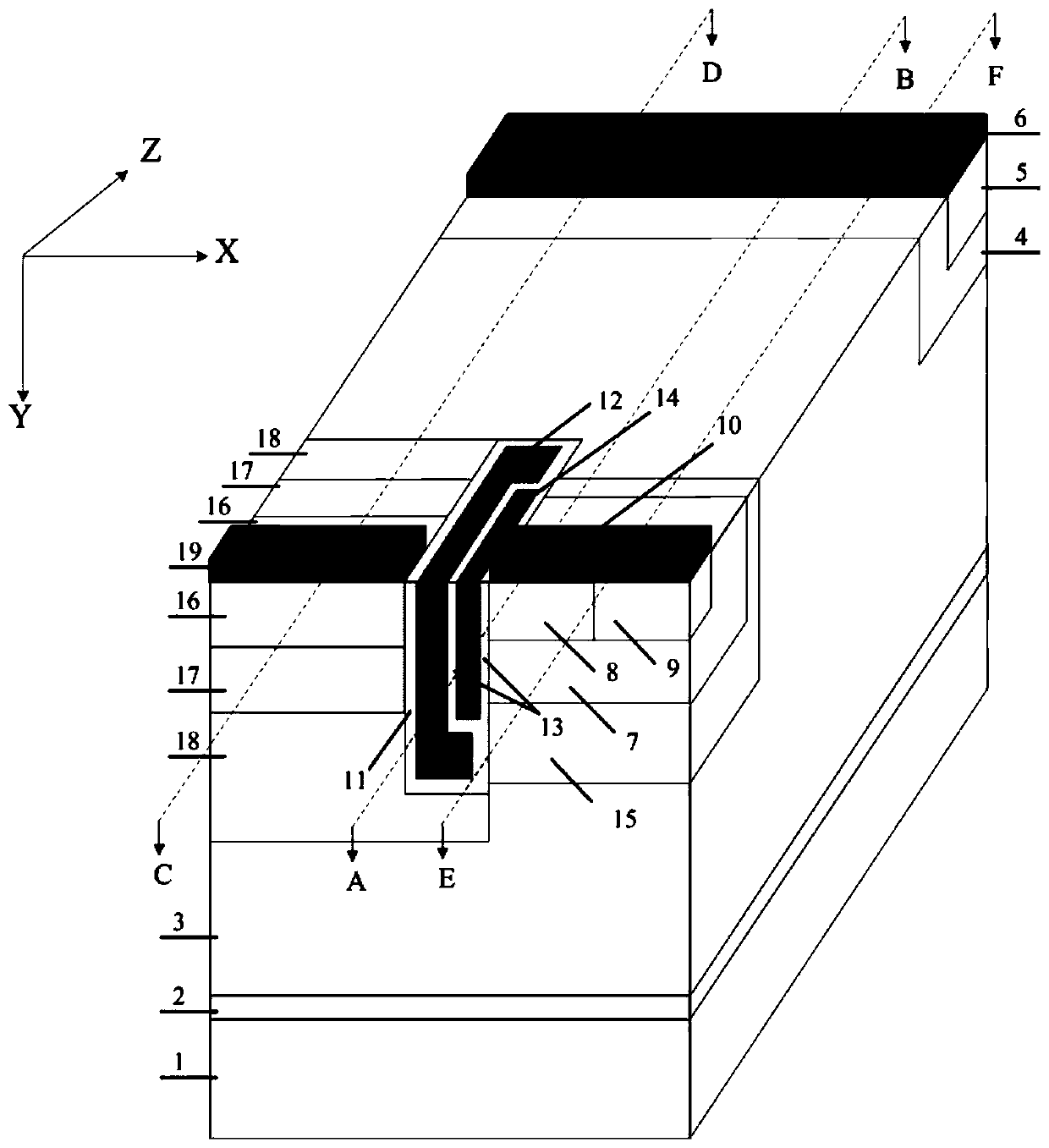

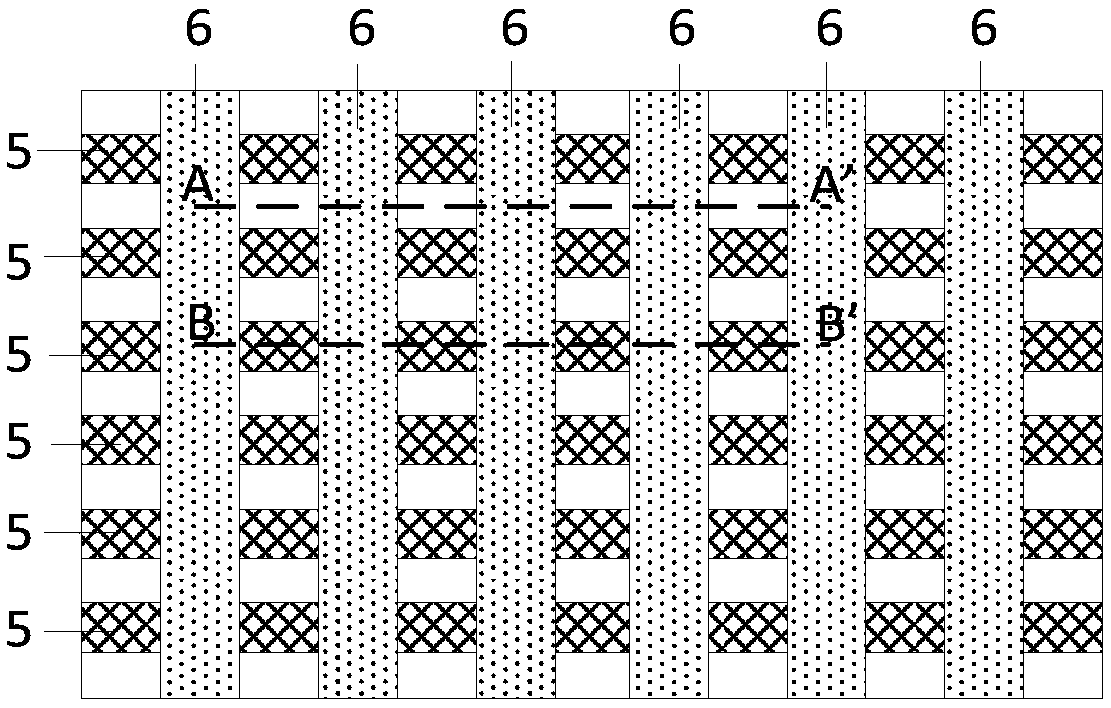

Carrier-storing grooved gate IGBT with P-type floating layer

InactiveCN101694850AReduce forward voltage dropImprove breakdown voltageSemiconductor devicesJFETHigh concentration

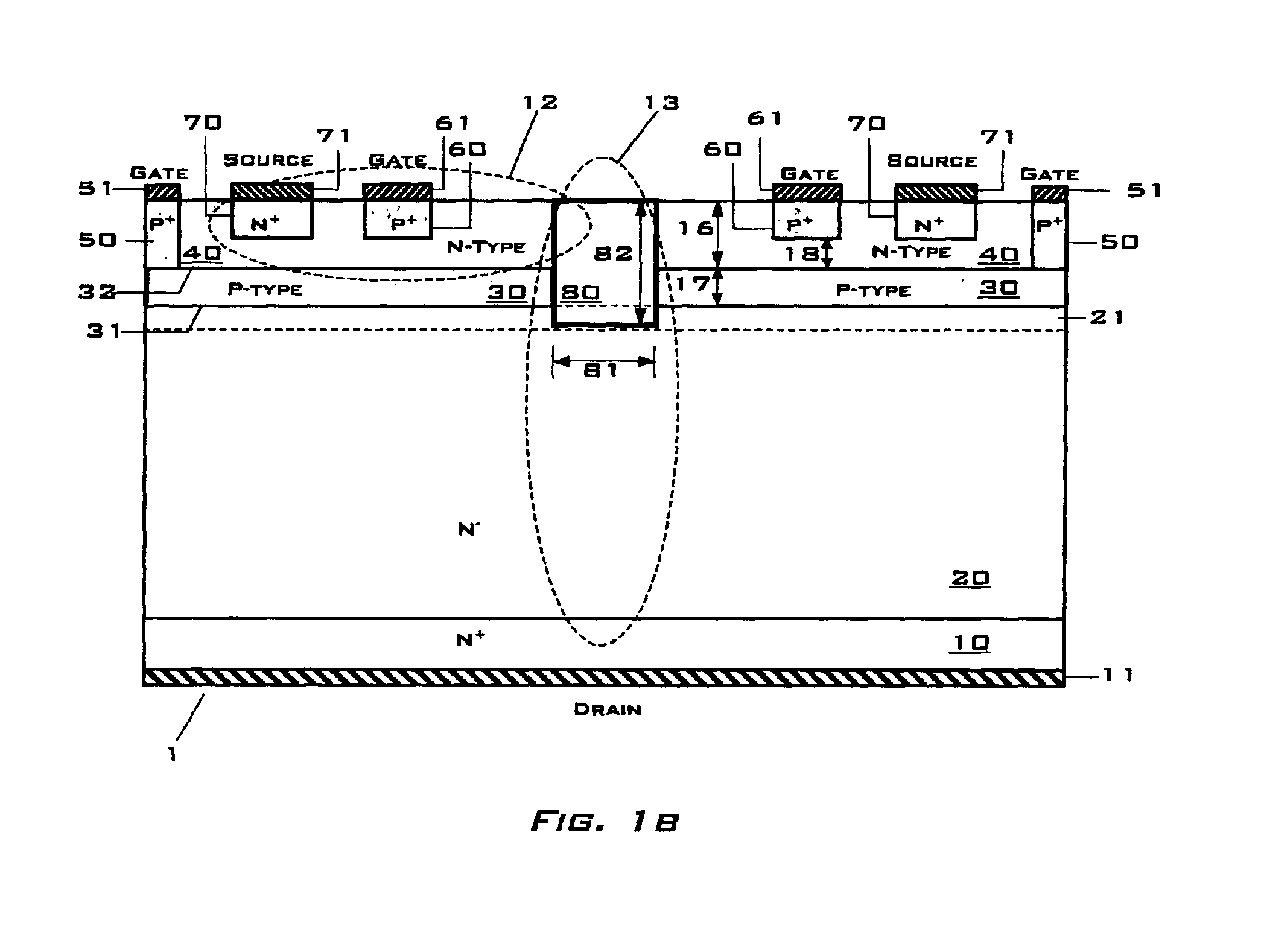

The invention relates to a carrier-storing grooved gate IGBT with a P-type floating layer, belonging to the technical field of semiconductor power devices. On a basis of the prior carrier-storing grooved gate bipolar transistor, a P-type floating layer (13) is introduced to almost free a carrier-storing layer from bearing a withstanding voltage and decrease a forward conducted voltage drop; and the P-type floating layer (13) also improves the electric-field integration effect of the bottom of the grooved gate, thereby effectively decreasing an electric filed with a maximum peak value, preventing the bottom of the grooved gate and the vicinity of the high-concentration carrier-storing layer from being broken down by an overhigh electric field and greatly increasing the breakdown voltage of the device. A JFET zone is introduced due to the existence of the P-type floating layer. When the device is forwardly conducted, the resistance of the JFET zone continuously increases along with the continuously increasing voltage of a collector so that the saturation current of the device is decreased, and a lower conducted voltage drop is obtained while maintaining a greater short-circuit safety operation area (SCSOA).

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

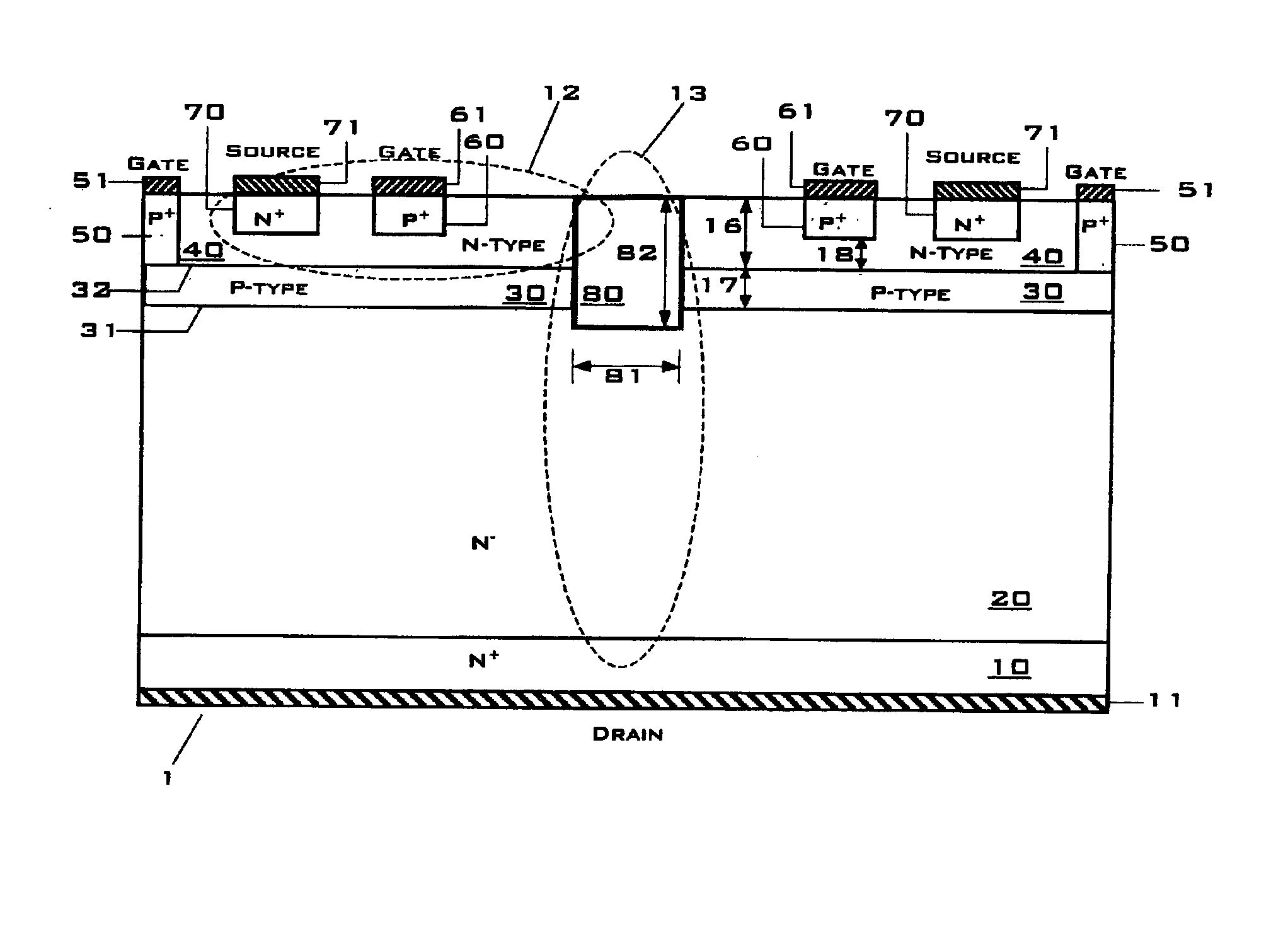

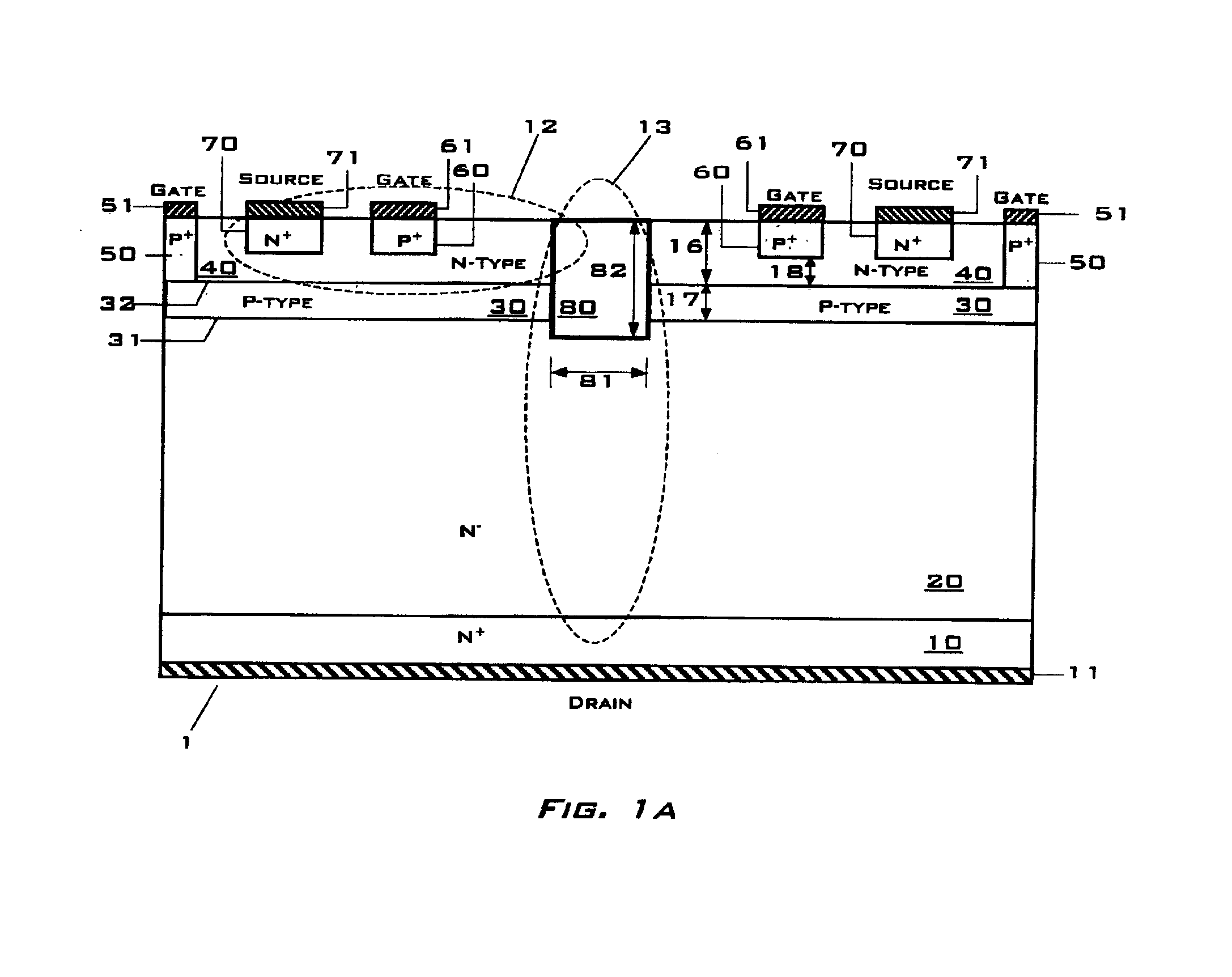

Double-gated vertical junction field effect power transistor

The present invention is a power semiconductor switch having a monolithically integrated low-voltage lateral junction field effect transistor (LJFET) controlling a high-voltage vertical junction field effect transistor (VJFET). The low-voltage LJFET conducting channel is double-gated by p+n junctions at opposite sides of the lateral channel. A buried p-type epitaxial layer forms one of the two p+n junction gates. A p+ region created by ion implantation serves as the p+ region for the second p+n junction gate. Both gates are electrically connected by a p+ tub implantation. The vertical channel of the vertical JFET is formed by converting part of the buried p-type epitaxial layer into n+ channel via n-type ion implantation.

Owner:RUTGERS THE STATE UNIV

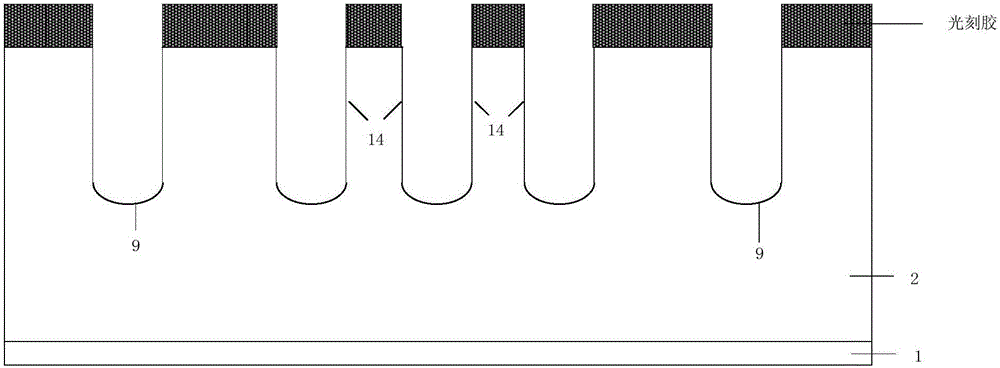

Grooved semiconductor rectifier and manufacturing method thereof

InactiveCN101783345AReduce forward voltage dropReduce reverse leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingVoltage dropEngineering

The invention relates to a grooved semiconductor rectifier and a manufacturing method thereof. The grooved semiconductor rectifier comprises a semiconductor baseplate, a first conduction type substrate and a first conduction type drift region, wherein one or more grooves extend from the first main plane to the first conduction type drift region, one or more mesa parts are limited at the upper part of the first conduction type drift region, and the upper part of the mesa part is provided with a first conduction type injection layer; the inner wall of the groove is covered with an insulation oxide layer, and a first electrode is deposited in the groove covered with the insulation oxide layer; the first conduction type drift region is provided with a second conduction type enclosure layer corresponding to the bottom of the groove, and the bottom of the groove is coated by the second conduction type enclosure layer; a first metal layer corresponding to the upper part of the first plane is deposited on the semiconductor baseplate; and the second plane of the semiconductor baseplate is covered with a second metal layer. The invention has the advantage of low manufacturing cost, and reduces the reverse leakage current and the forward conduction voltage drop of the Schottky rectifier.

Owner:无锡新洁能功率半导体有限公司

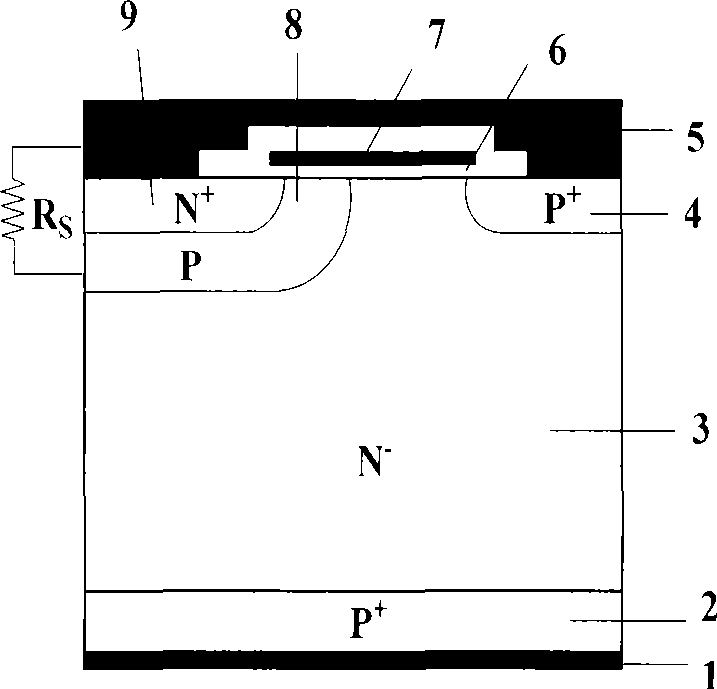

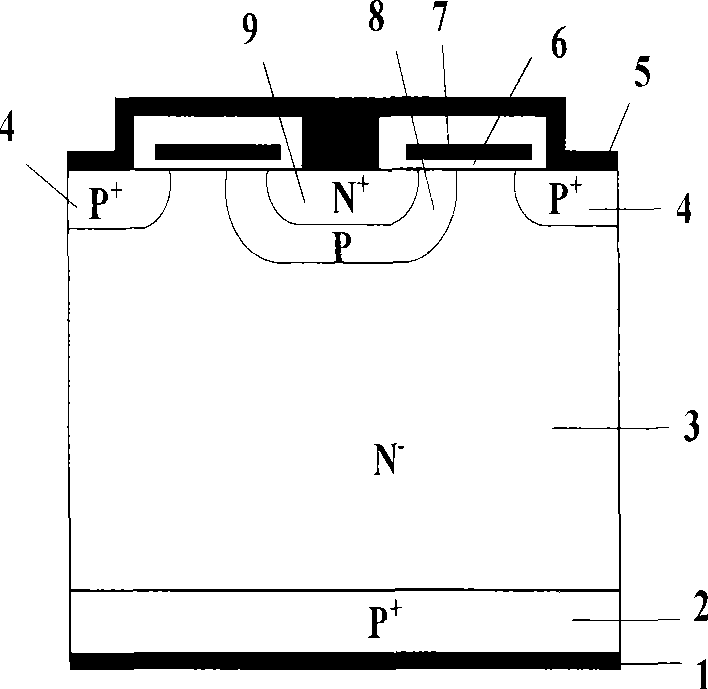

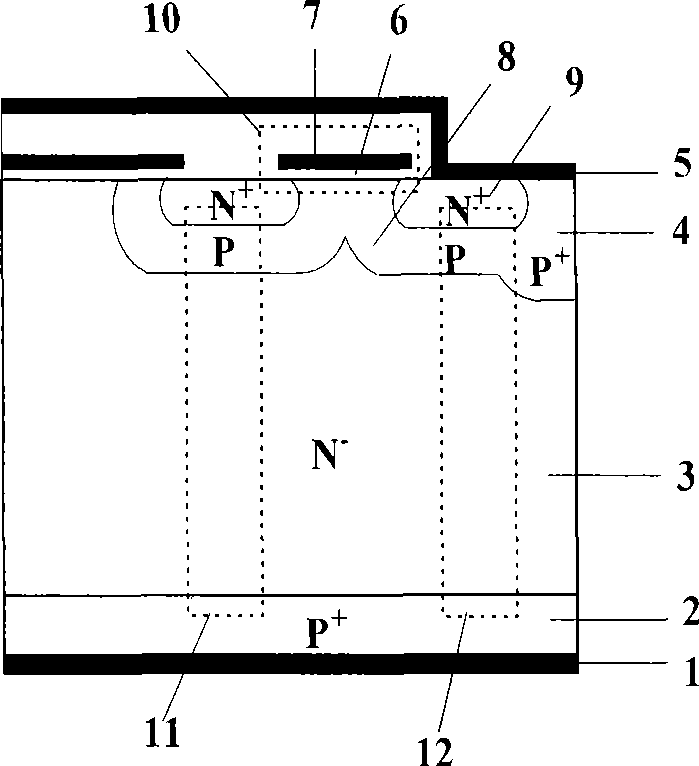

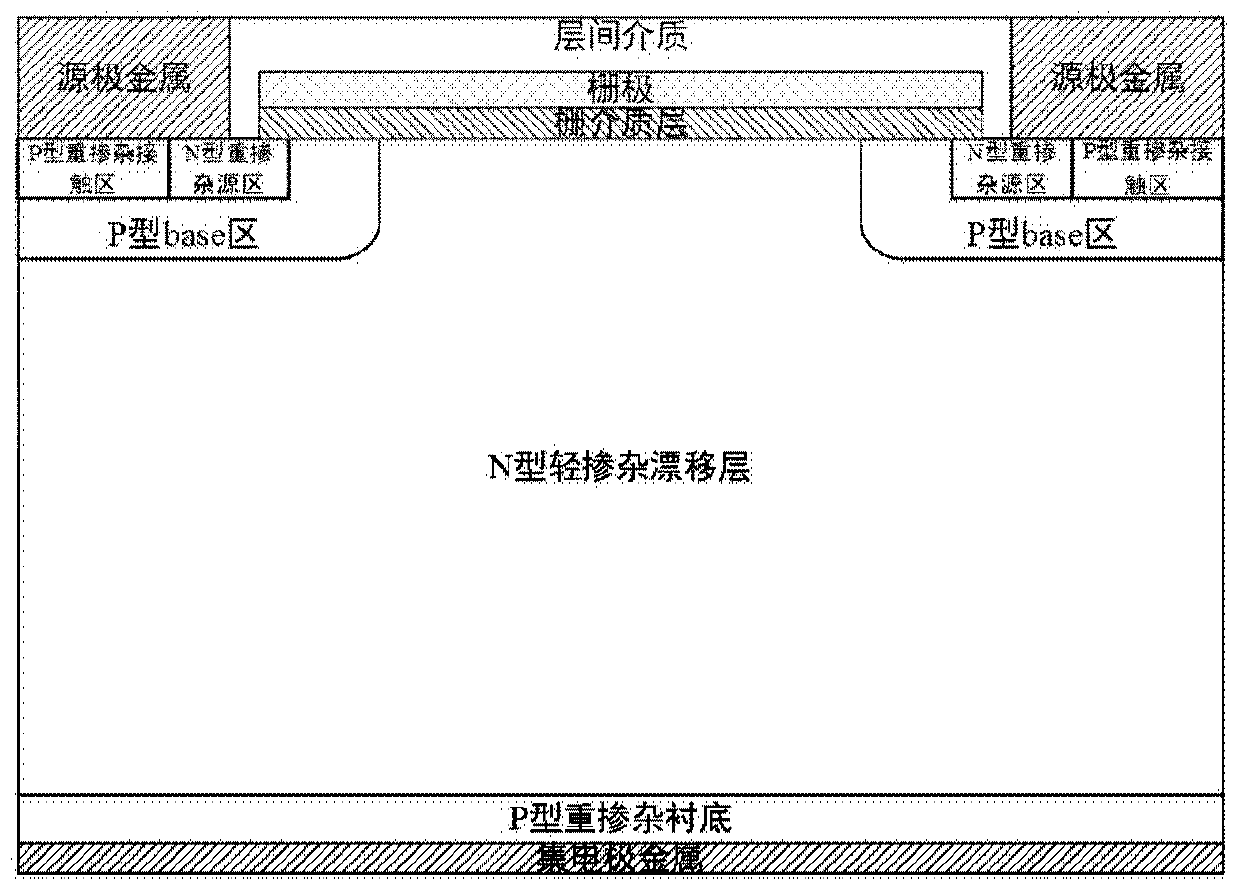

VDMOS device

InactiveCN101404292AReduce forward voltage dropIncrease the cross-sectional areaSemiconductor devicesElectronic systemsReverse recovery

A VDMOS device belongs to the technical field of semiconductor power devices. A doped layer is introduced into a conventional VDMOS device; for an N-channel VDMOS device, the doped layer is an N<+> layer (7) positioned between a P-typed base region (5) and an N<-> drift region (6); for a P-channel VDMOS device, the doped layer is a P<+> layer (7') positioned between an N-typed base region (5') and a P<-> drift region (6'). Compared with the conventional VDMOS device, sectional area where the electrons flow passes through is enlarged by adding the doped layer between the base region and the drift region, thus obtaining lower conduction loss, optimizing positive conduction voltage drop and reverse recovery property of a VDMOS intrinsic diode, and reducing the reverse recovery time to a certain extent while reducing the positive conduction voltage drop. The VDMOS device also has the advantages of simple fabrication process and lower process difficulty. Compared with the conventional VDMOS devices, the VDMOS device satisfies the application requirement of power electronic systems more easily.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

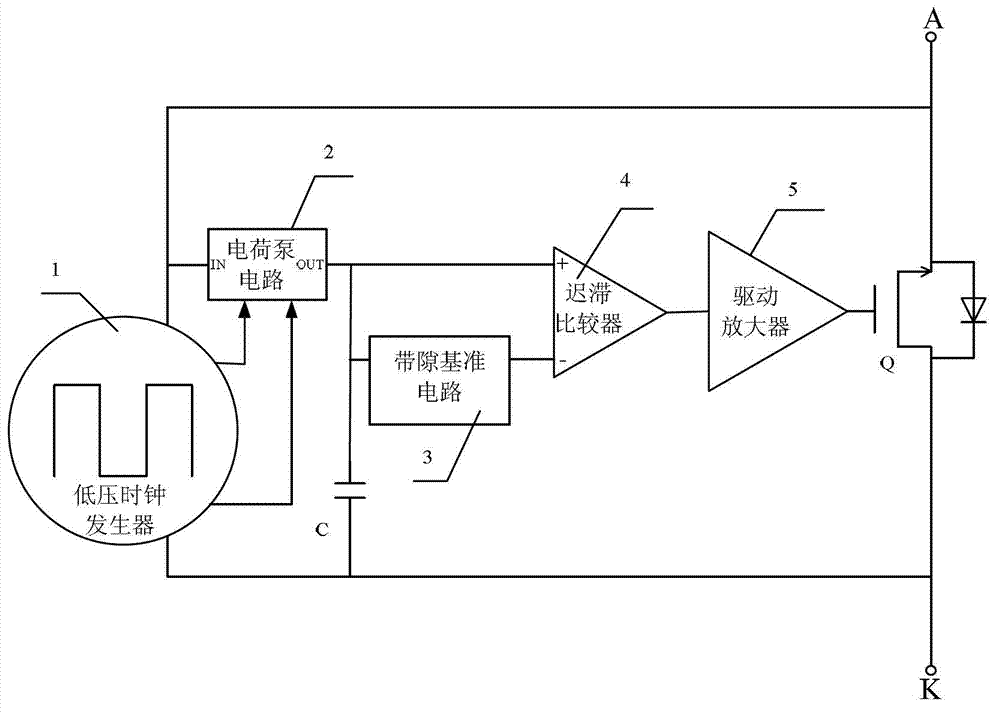

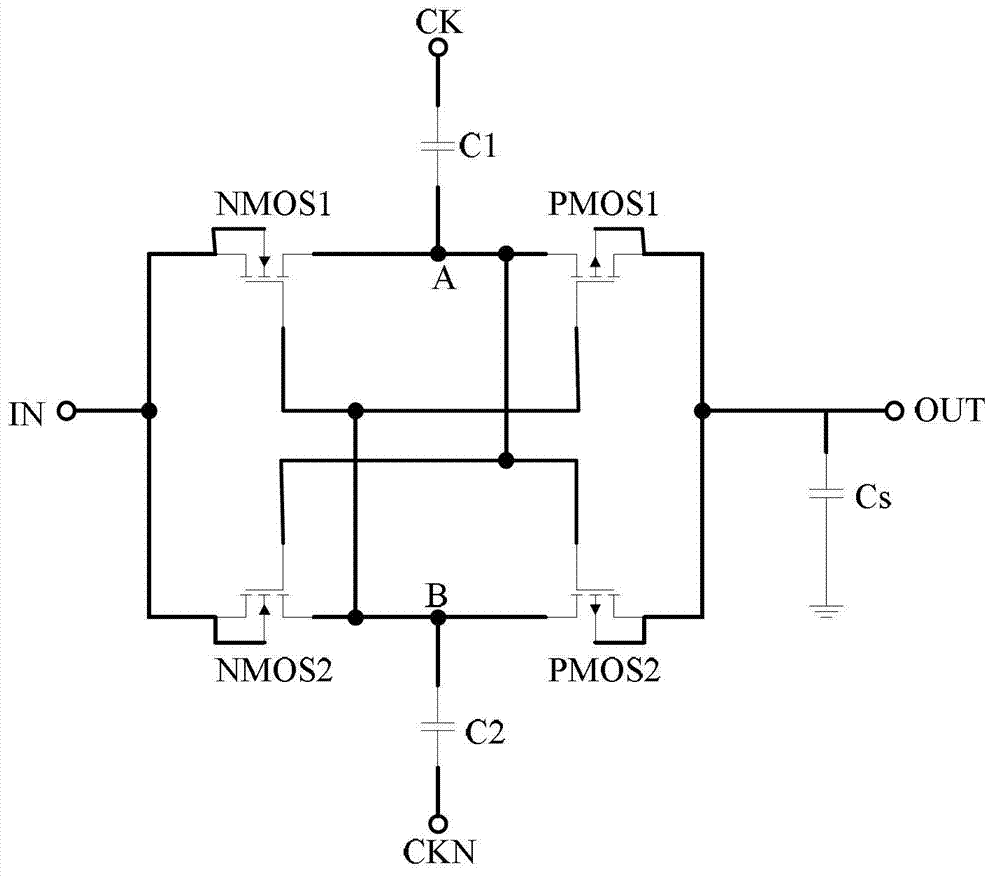

High-performance rectifier diode replaced circuit

ActiveCN102904421AReduce forward voltage dropSolve excessive power consumptionAc-dc conversionApparatus without intermediate ac conversionAudio power amplifierLow voltage

The invention discloses a high-performance rectifier diode replaced circuit which comprises a capacitor, a low-voltage clock generator, a charge pump circuit, a band-gap reference circuit, a hysteresis comparator, a driving amplifier and a power metal oxide semiconductor (MOS) pipe and is characterized in that the low-voltage clock generator detects voltages at two ends of a diode pipe and generates clock signals to drive the charge pump circuit; the charge pump circuit detects the voltages at two ends of the diode pipe and stores the charges in the capacitor after the charges are amplified; the voltage stored on the capacitor and the standard voltage output by the band-gap reference circuit are respectively output to the hysteresis comparator for comparison; and when the voltage stored in the capacitor is larger than the standard voltage output by the band-gap reference circuit, the hysteresis comparator outputs starting signals which are amplified by the driving amplifier and then output to the power MOS pipe to drive the power MOS pipe to be conducted. The high-performance rectifier diode replaced circuit can achieve equivalent diode working characteristics through a pulse working mode and can totally replace original selective beacon radar (SBR) devices in performance and dimension.

Owner:CHONGQING SOUTHWEST INTEGRATED CIRCUIT DESIGN

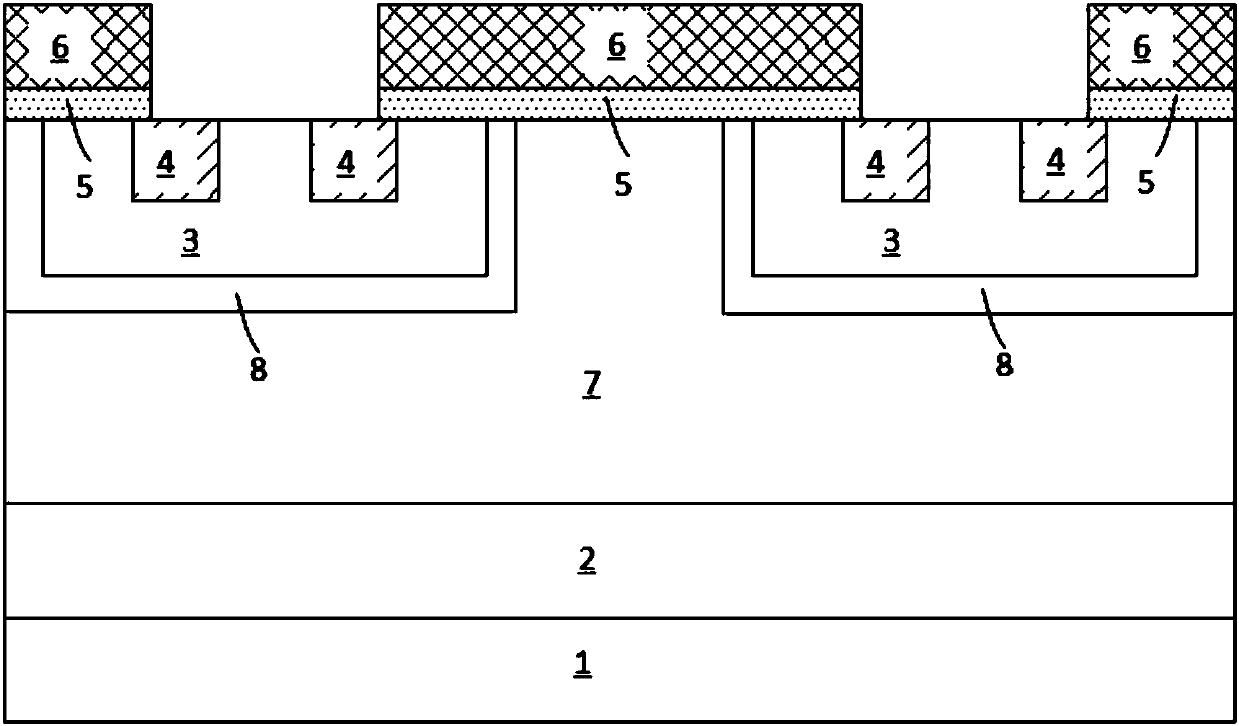

SOI-RC-LIGBT device and preparation method thereof

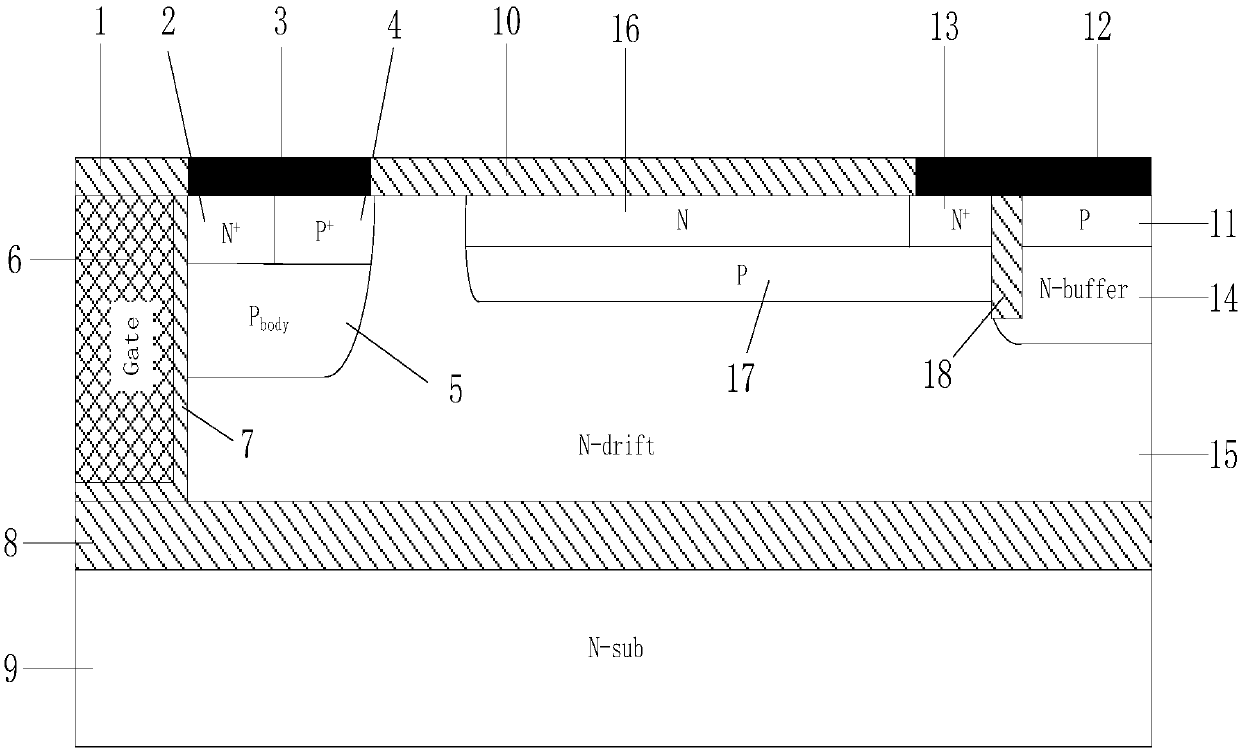

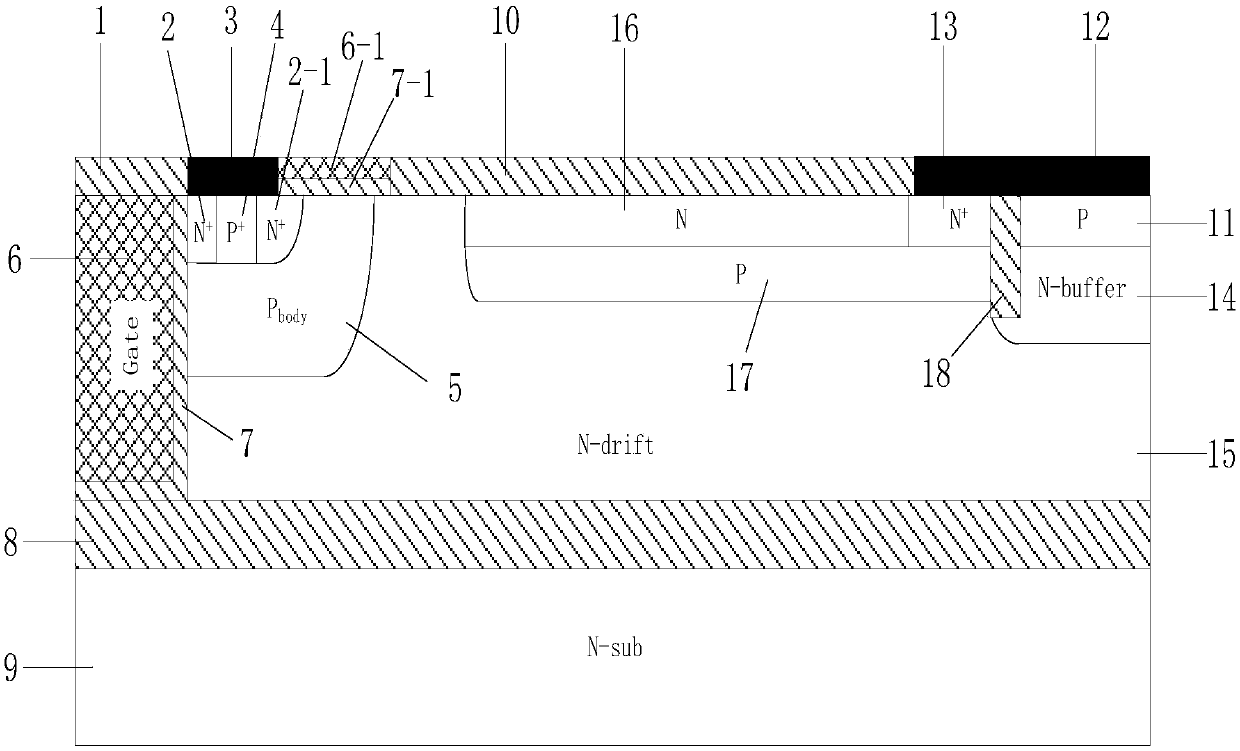

ActiveCN107785415AImprove breakdown voltageLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryVoltage drop

The invention provides an SOI-RC-LIGBT device and a preparation method thereof. The SOI-RC-LIGBT device comprises an N-type substrate, a buried oxide layer, an N-type drift region, a trench gate structure, a P-type base region, an N+ source region, a P+ contact region, an emitting electrode, an oxide layer, an N-type buffer region and a P-type collector region; an N-type strip is arranged on the surface of the portion, between the P-type base region and the N-type buffer region, of the N-type drift region, and a P-type buried layer is arranged in the portion, below the N-type strip, of the drift region; a medium trench structure is arranged between the right sides of the N-type strip and the P-type buried layer and the left sides of the N-type buffer region and the P-type collector region;an N+ collector region is arranged between the N-type strip and the medium trench structure. According to the SOI-RC-LIGBT device, while the IGBT conduction characteristic snapback phenomena are eliminated, the breakdown voltage of the device is improved, the forward conduction voltage drop of the device is reduced, the shutoff speed is increased, the shutoff loss is reduced, and meanwhile, the reverse recovery characteristics of an integrated free-wheeling diode are improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

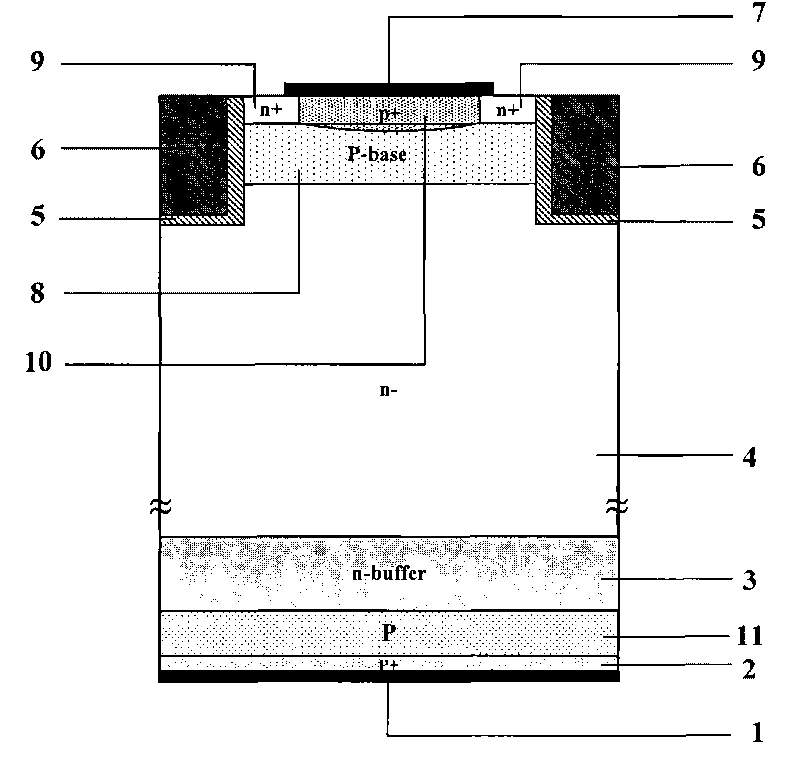

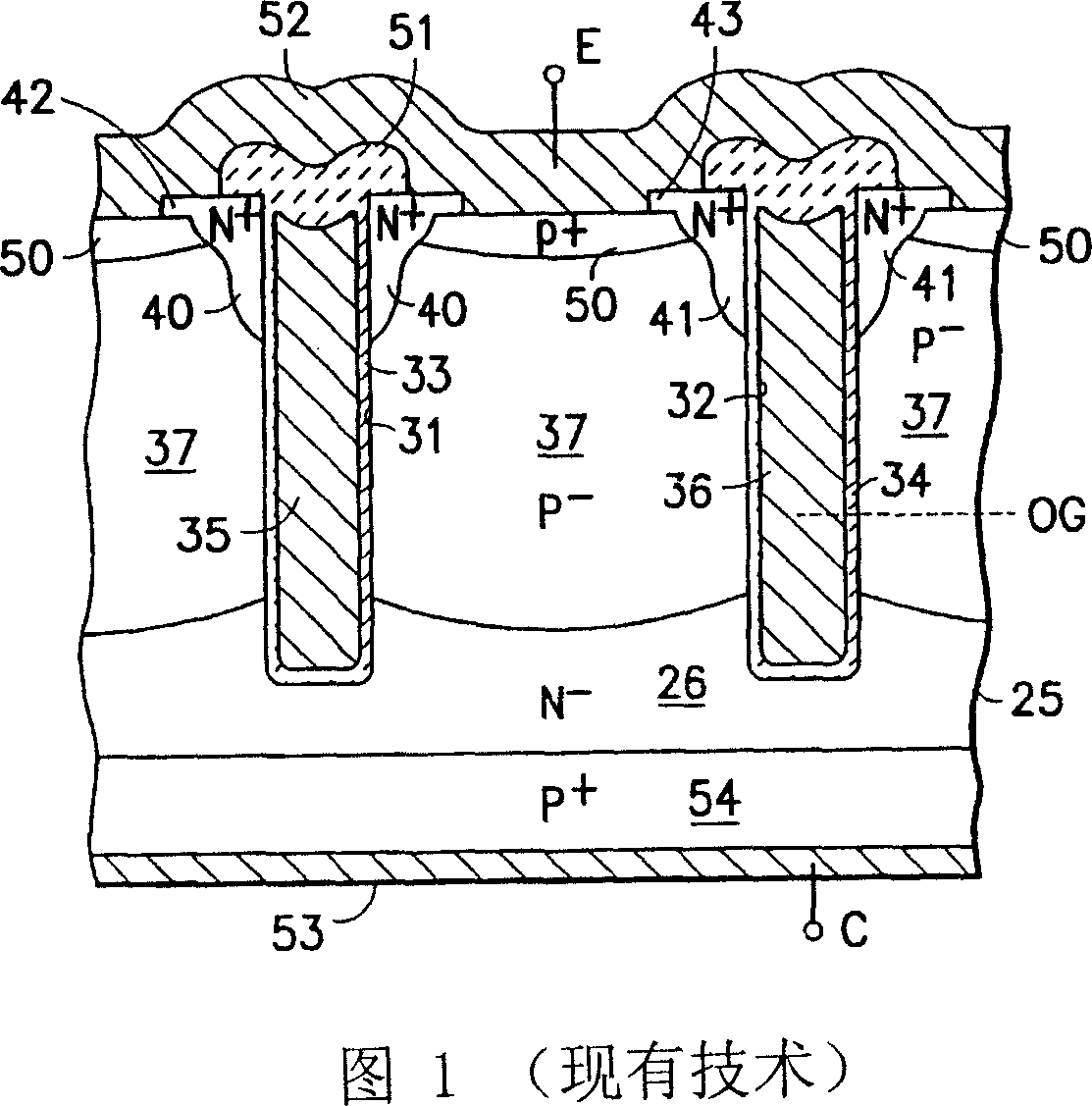

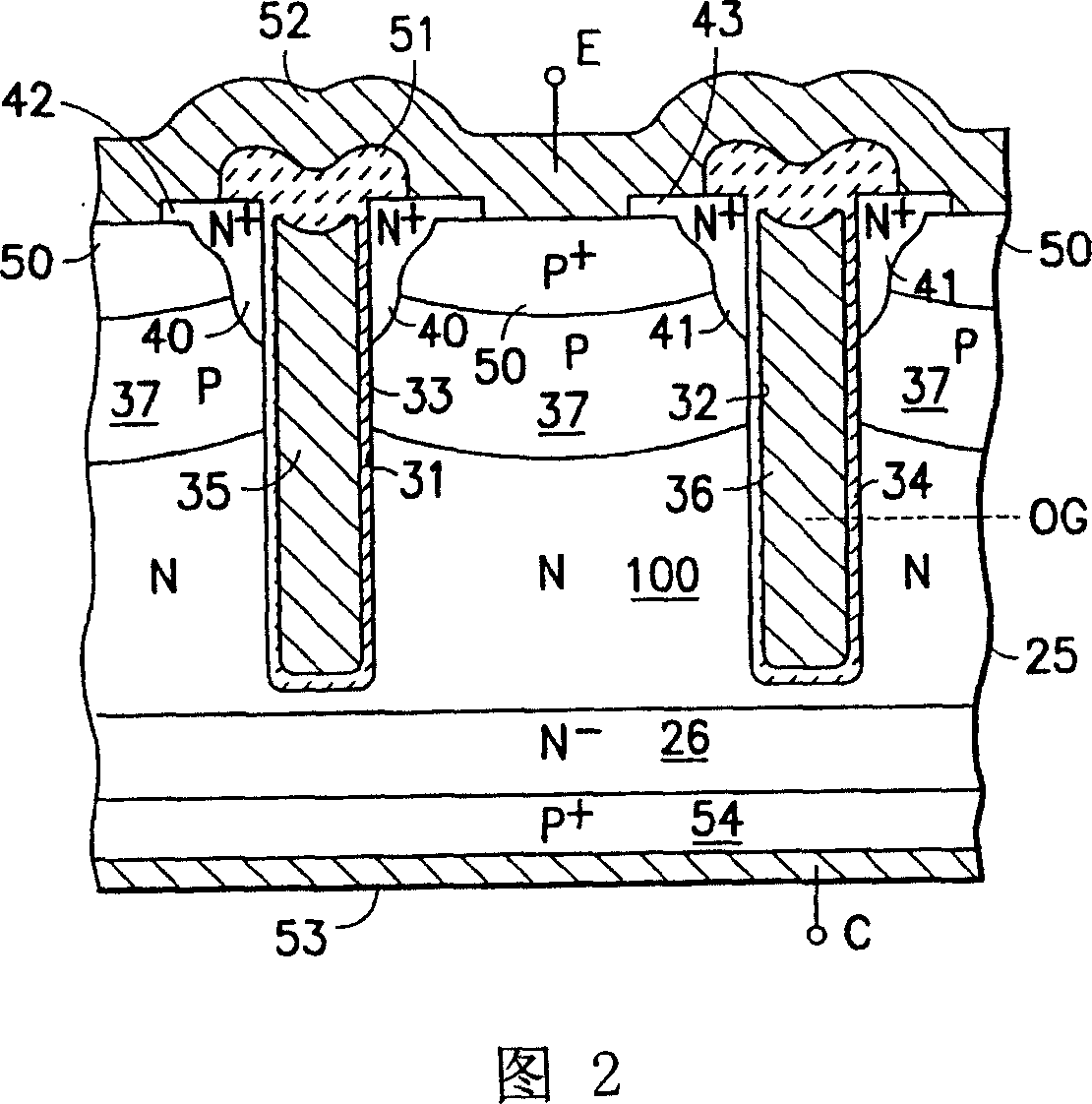

Deep N diffusion for trench IGBT

InactiveCN1921146ALower forward voltageReduce forward voltage dropTransistorTrench igbtHigh concentration

The present invention relates to a deep N diffusion for trench IGBT. An increased conductivity deep diffusion of the same conductivity type as that of the drift region is provided between adjacent trenches of a trench type IGBT and below the trenches to reduce the on resistance components of the drift region resistance and spreading resistance to current flow when the device is turned on. The deep diffusion has a higher concentration than that of the drift region, and has a width of from 4 to 10 microns. The wafer or die has a total width (or thickness) of about 70 to about 300 microns.

Owner:INTERNATIONAL RECTIFIER COEP

Schottky barrier semiconductor rectifier and manufacturing method therefor

ActiveCN105789334AReduced series resistanceReduce forward voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesContact formationSchottky barrier

The invention discloses a schottky barrier semiconductor rectifier. The schottky barrier semiconductor rectifier comprises a schottky barrier metal layer, an epitaxial layer and a first trench, wherein an isolating layer and a silicon dioxide gate-oxide layer are arranged in the first trench; the silicon dioxide gate-oxide layer extends upwards to form a dielectric wall; conductive polysilicon side walls are arranged on the two sides of the dielectric wall; a second trench is formed between the upper part of the epitaxial layer and the conductive polysilicon side walls; a transverse uniform doping region and a gradient doping region are arranged at the upper part of the epitaxial layer; a channel is formed between the gradient doping region and the silicon dioxide gate-oxide layer; spacer regions are arranged among the lower part of the epitaxial layer, the transverse uniform doping region, the gradient doping region and the silicon dioxide gate-oxide layer; a third trench is formed in the second trench; and the schottky barrier metal layer is positioned on the inner side surface of the third trench, and in contact with the epitaxial layer to form the schottky barrier. The schottky barrier semiconductor rectifier has good forward conduction characteristic and high device reliability. The invention also discloses a manufacturing method for the schottky barrier semiconductor rectifier; and the manufacturing method is large in process window, easy to control, low in photoetching number of times, and low in manufacturing cost.

Owner:HANGZHOU LION MICROELECTRONICS CO LTD

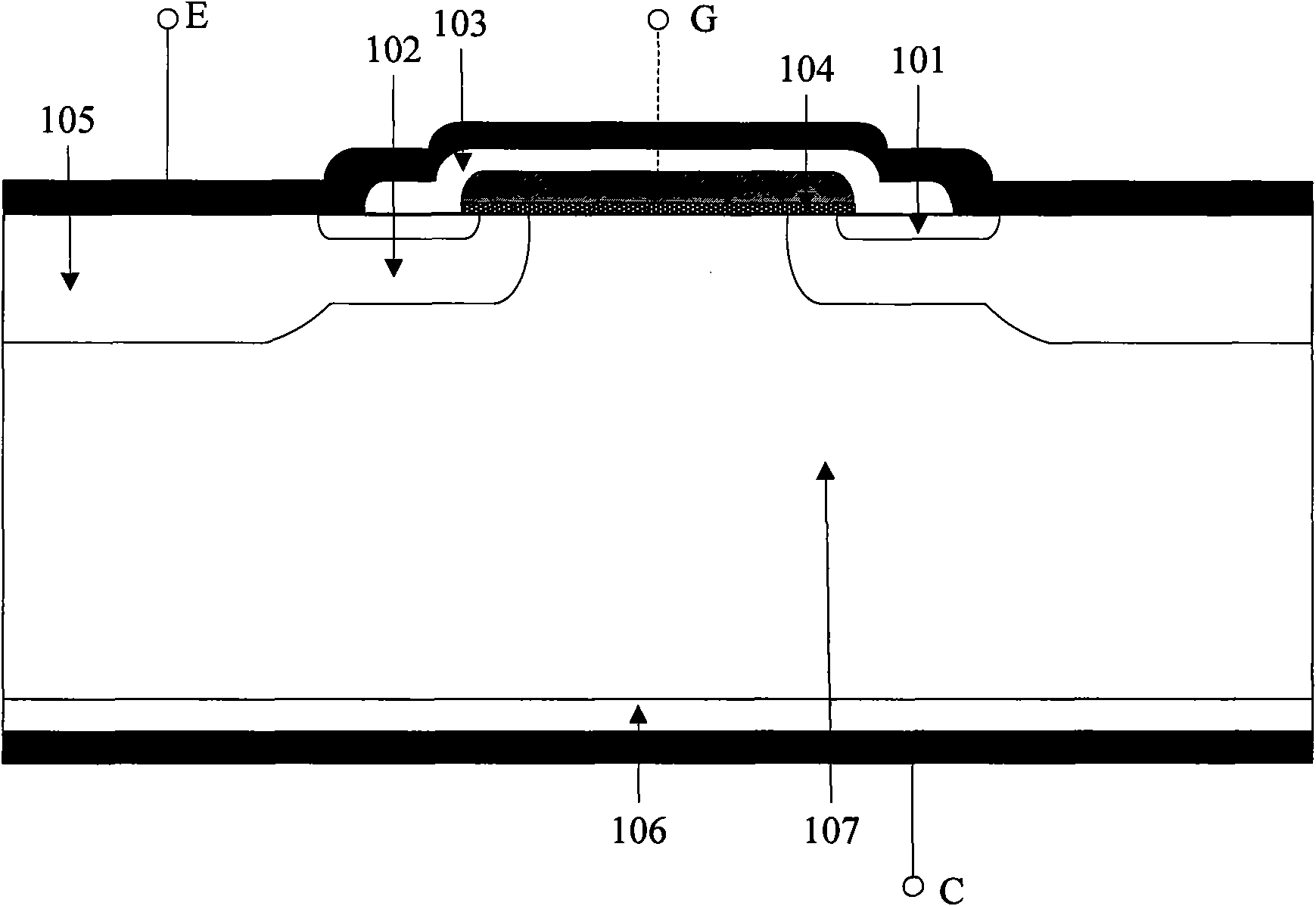

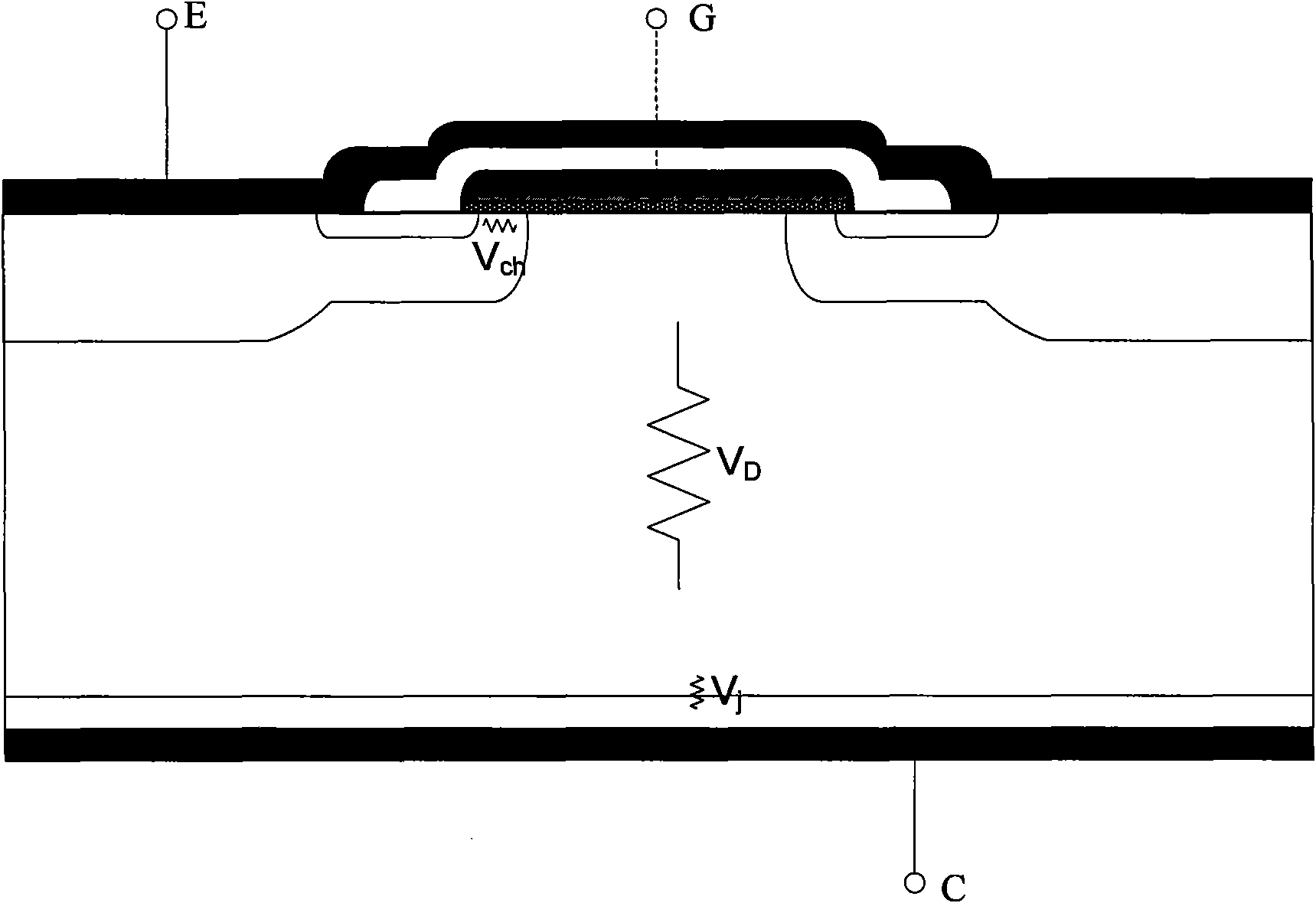

IGBT power device and manufacturing method thereof

InactiveCN110137249AAdjust the position of the electric field peakReduce forward voltage dropThyristorSemiconductor/solid-state device manufacturingPeak valueEngineering

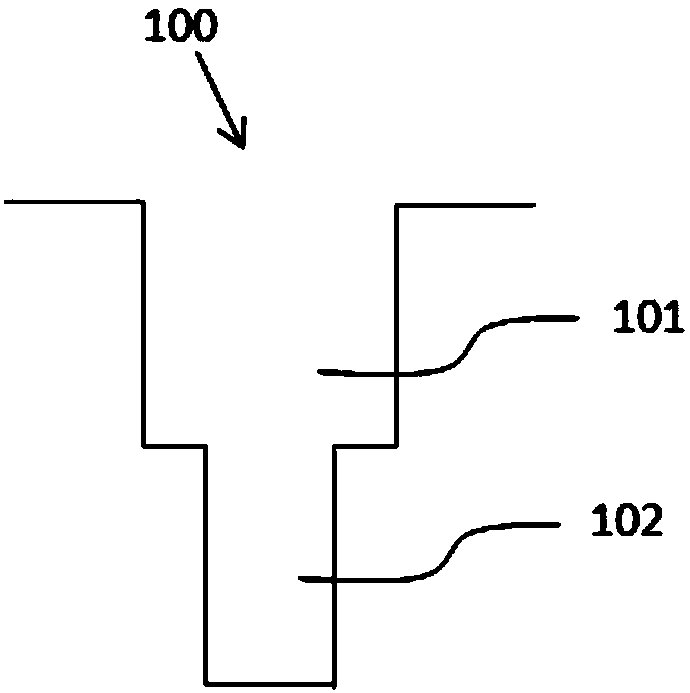

The invention belongs to the technical field of semiconductor power devices, and particularly discloses an IGBT (Insulated Gate Bipolar Transistor) power device. The device comprises: a p-type collector region; an n-type field stop region located on the p-type collector region; an n-type drift region located on the n-type field stop region; a plurality of first grooves, a second groove is arrangedat the lower portion of each first groove; gate structures located in the first grooves and the second grooves; p-type body regions located between adjacent first grooves; n-type emitter regions located in the p-type body regions; and n-type hole charge barrier regions located between the n-type drift region and the p-type body regions. The position of the electric field peak value of the IGBT power device in the reverse bias state can be regulated to allow the IGBT power device to have the smaller forward conduction voltage drop and the shorter turn-off time under the same breakdown voltage.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

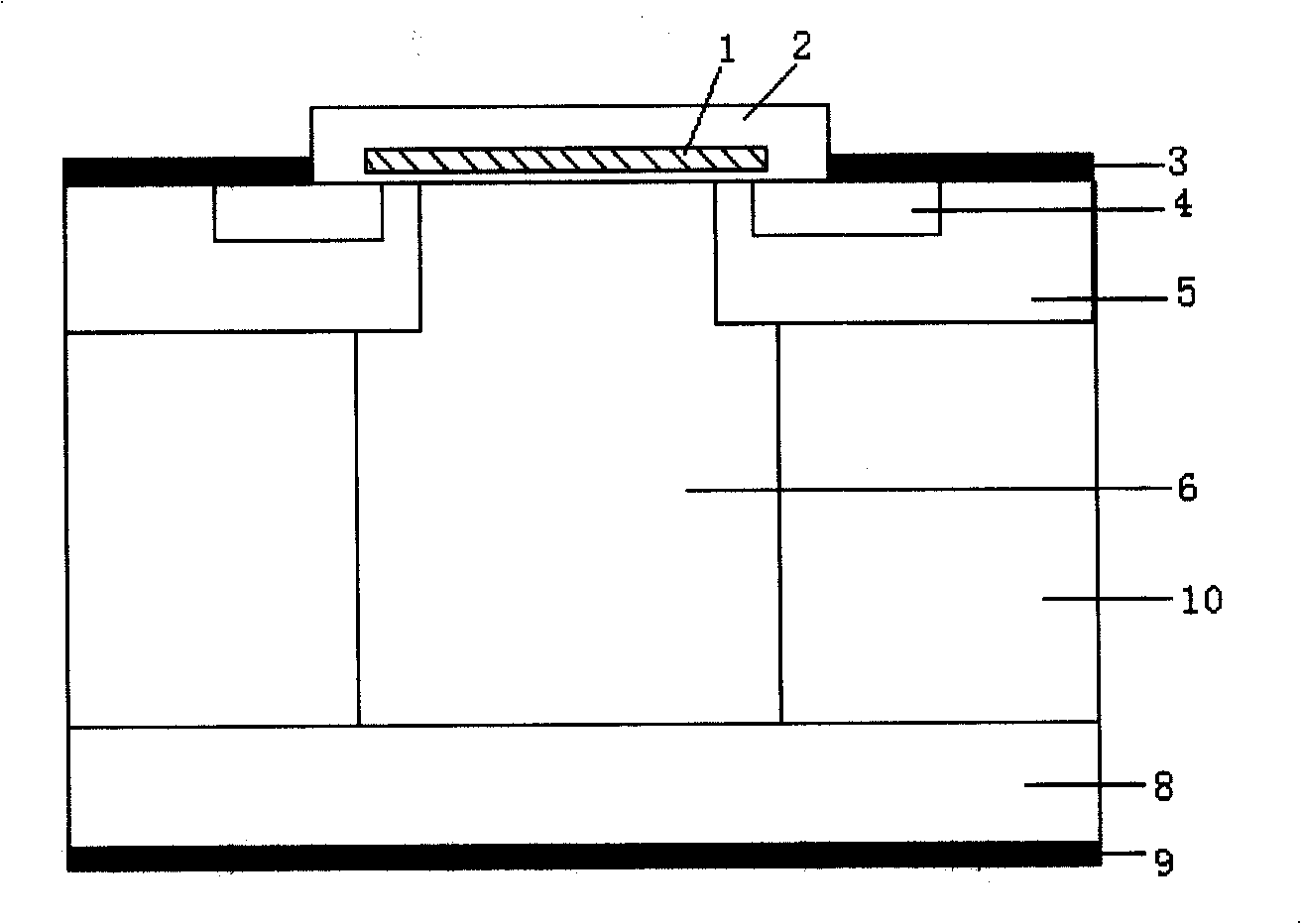

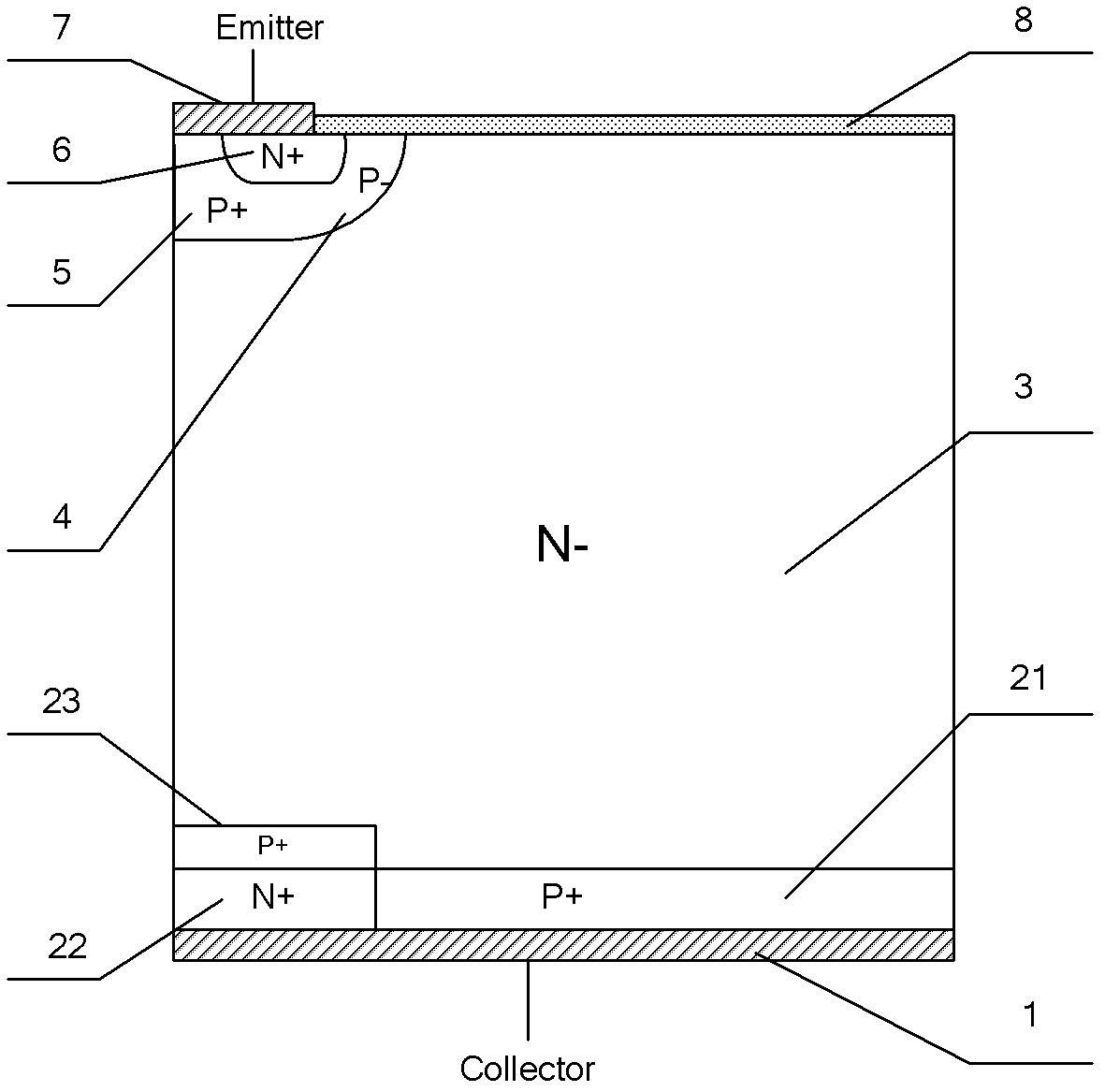

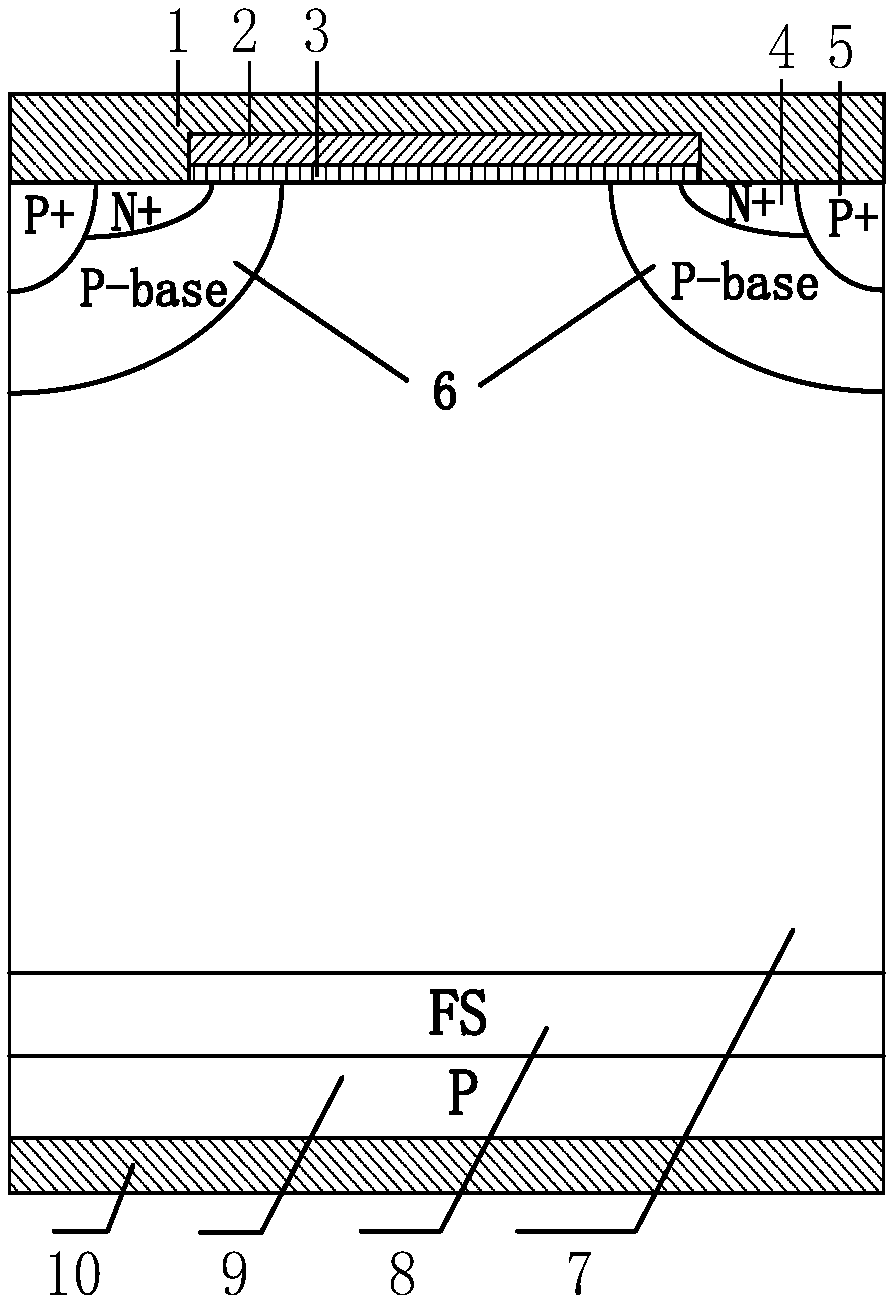

IGBT with back reinforcing structure and fabrication method thereof

InactiveCN102386220AReduce forward voltage dropSmall pressure dropSemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropEngineering

The invention provides an insulated gate bipolar translator (IGBT) with a back reinforcing structure, and belongs to the transistor structure field. The uniform P+ typed collector regions of the traditional IGBT provided by the invention are changed into convex and concave structures, and the surfaces for contacting the P+ typed collector regions with N- typed shift regions are of convex and concave structures; the corresponding P+ typed collector regions and the collectors are also of convex and concave structures. In addition, the invention further discloses a fabrication method of IGBT with the back reinforcing structure. In the invention, as the surfaces of IGBT for contacting the N- typed shift regions and the P+ typed collector regions are of convex and concave structures, and the corresponding P+ typed collector regions and the collectors are also of convex and concave structures, the sizes of P and N junctions in the collector regions are enlarged and the purpose of reducing the positive connection voltage drop is achieved.

Owner:BYD CO LTD

Reverse conducting insulated gate bipolar transistor (RC-IGBT) device

InactiveCN103383957AWeaken the snap-back phenomenonReduce forward voltage dropSemiconductor devicesPower semiconductor deviceVoltage drop

The invention relates to an RC-IGBT device and belongs to the technical field of power semi-conductor devices. Variable-component mixed crystals are used for producing a collector region of the IGBT to form an energy band structure with gradually variable forbidden bandwidth. The forbidden bandwidth is small at the junction of the collector region and a drift region, built-in electrical potentials of the collector region and the drift region are reduced, and the phenomenon of snap-back is relieved; meanwhile, the gradually variable forbidden bandwidth is formed due to the variable-component materials of the collector region, and a retarding field of minority carriers is generated in the collector region, so that injection of the minority carriers to the collector region by the drift region is reduced, the injection efficiency of the collector region to the drift region is improved, the strong conductivity modulation effect can be obtained, and the forward conducting voltage drop of the IGBT is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

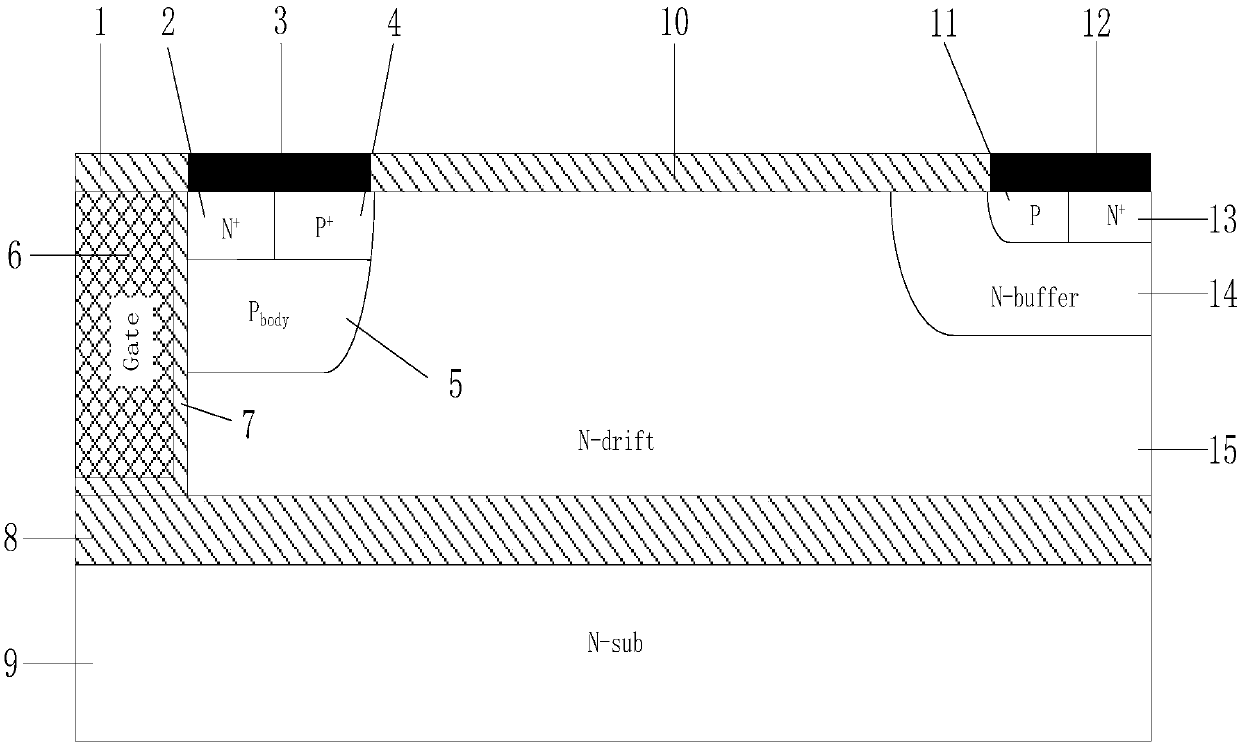

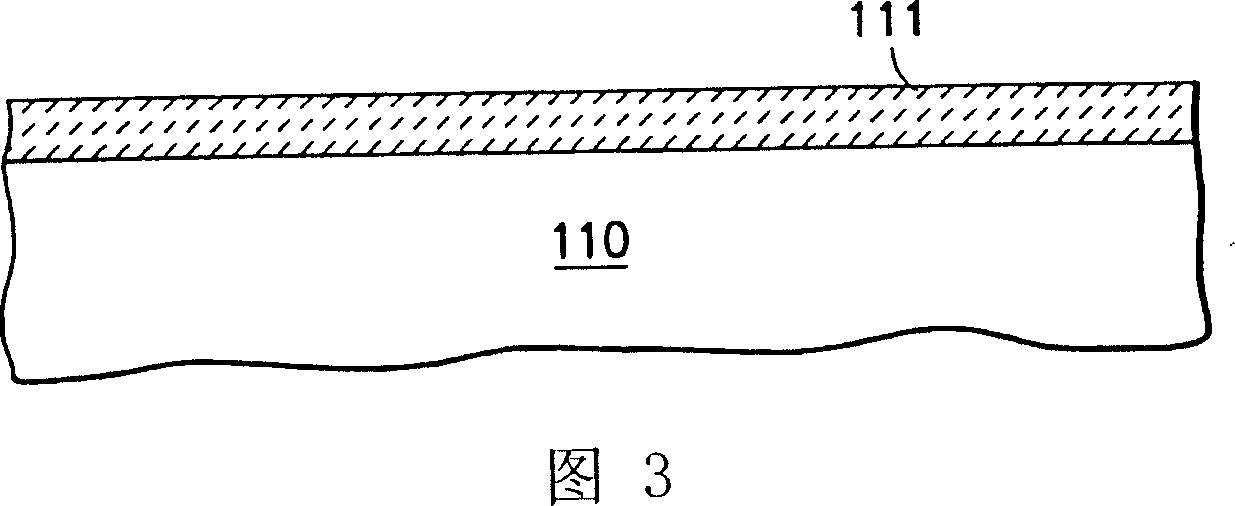

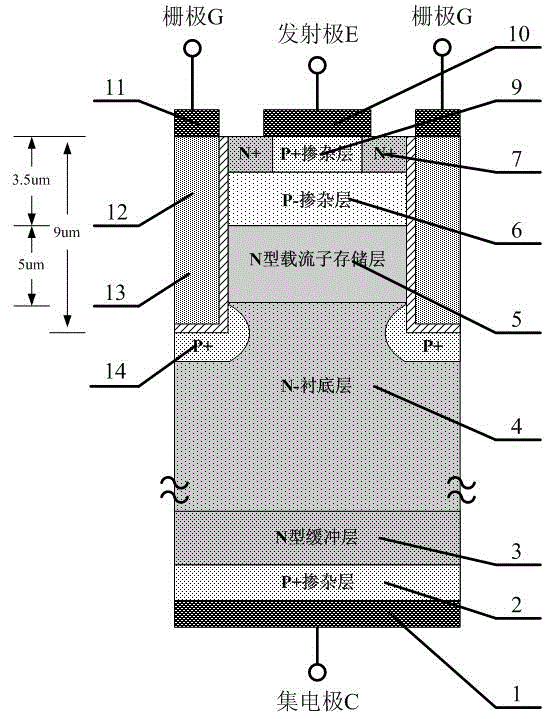

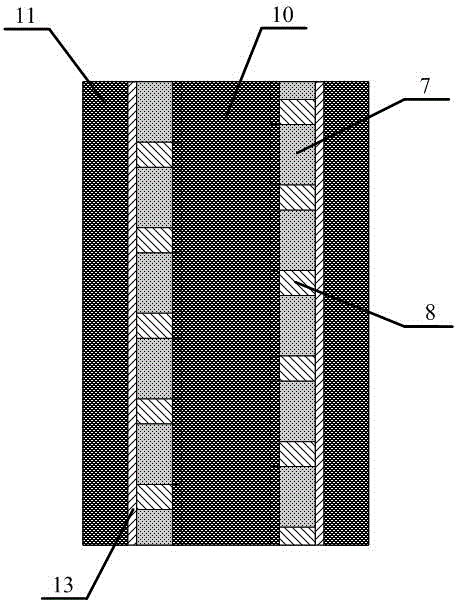

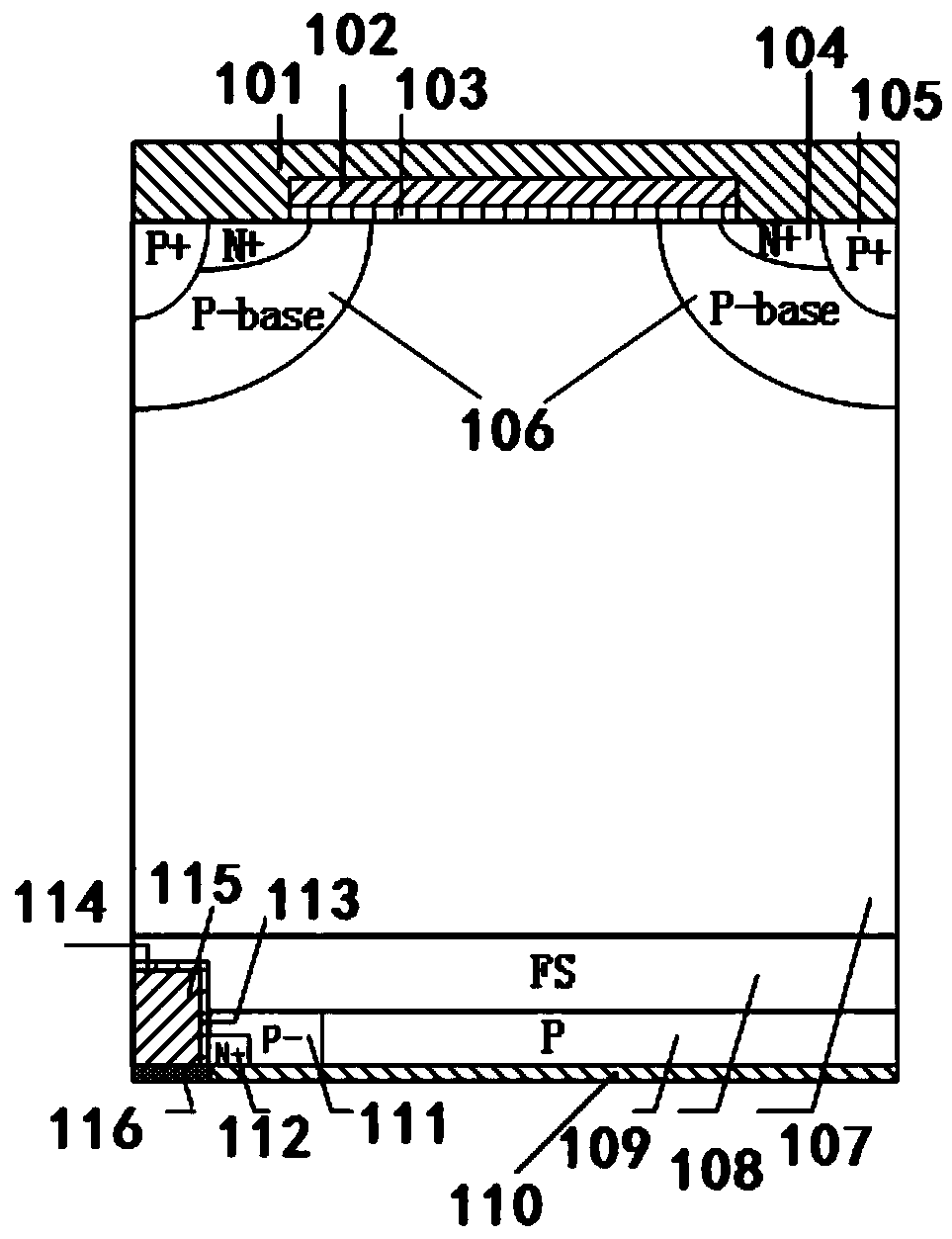

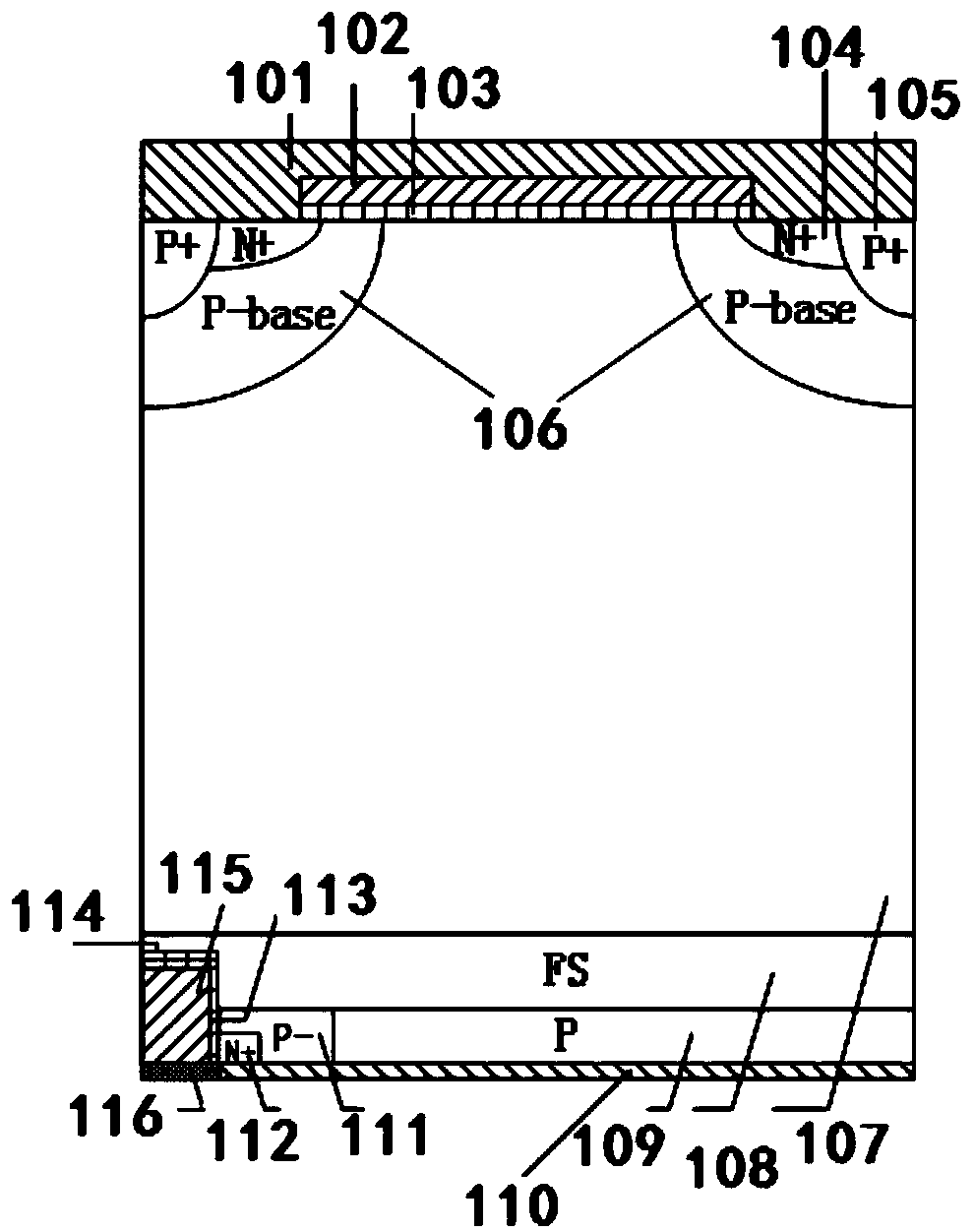

Preparation method of novel light break-through IGBT device

ActiveCN105047700AImprove short circuit safe operating areaGuaranteed working lifeSemiconductor devicesBlocking layerOperating life

The invention relates to the field of power semiconductor devices, and discloses a preparation method of a novel light break-through IGBT device. According to the IGBT device prepared by the preparation method, the structure of an N-type carrier storage layer and a P+ type floating layer is integrated, the IGBT device has advantages of high breakdown voltage, low forward conduction voltage drop and low turn-off loss, and the structure of N+ doping block layers and insulating block layers which are arranged in a staggered and spacing way side by side is arranged between a second P+ doping layer and a gate oxide layer so that the resistance value of an internal emission electrode integrated resistor can be greatly increased, increasing of internal saturation current can be effectively suppressed, the short circuit safe operating area of the IGBT device is expanded, and thus generation of high current impact can be avoided and the operating life of the device can be ensured.

Owner:四川广义微电子股份有限公司

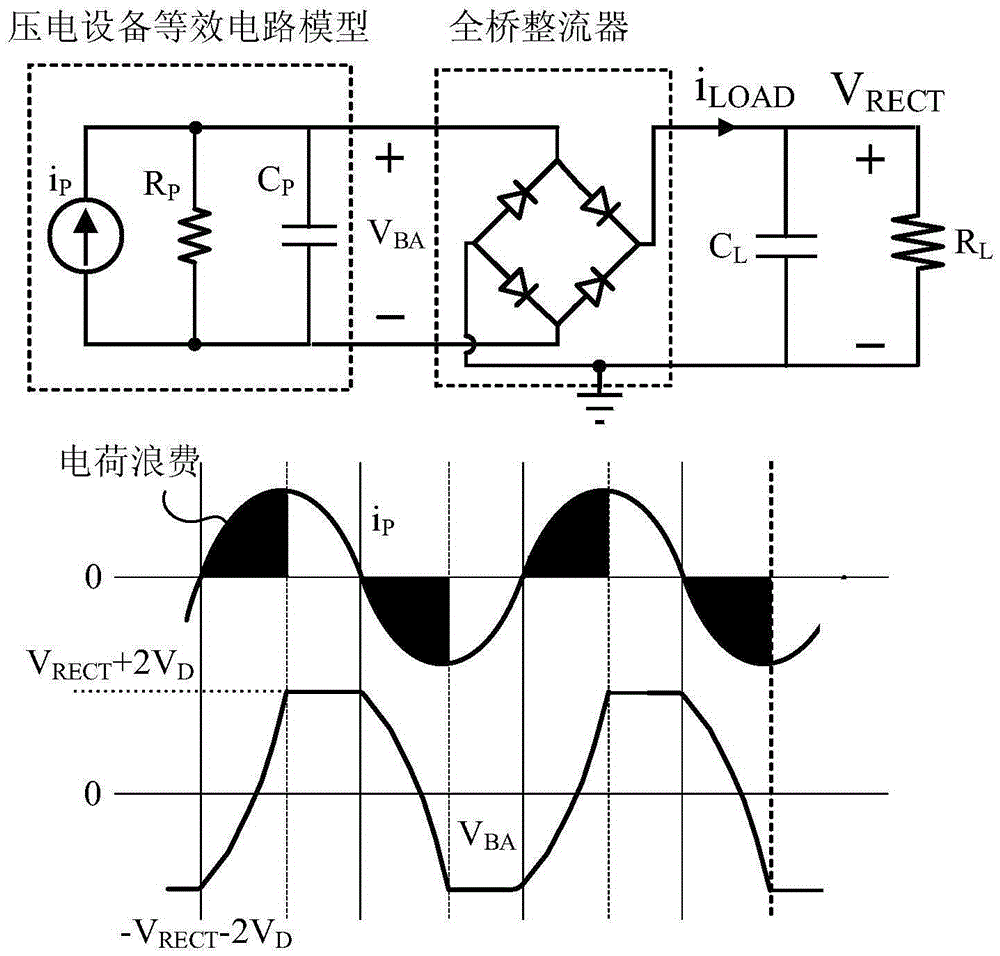

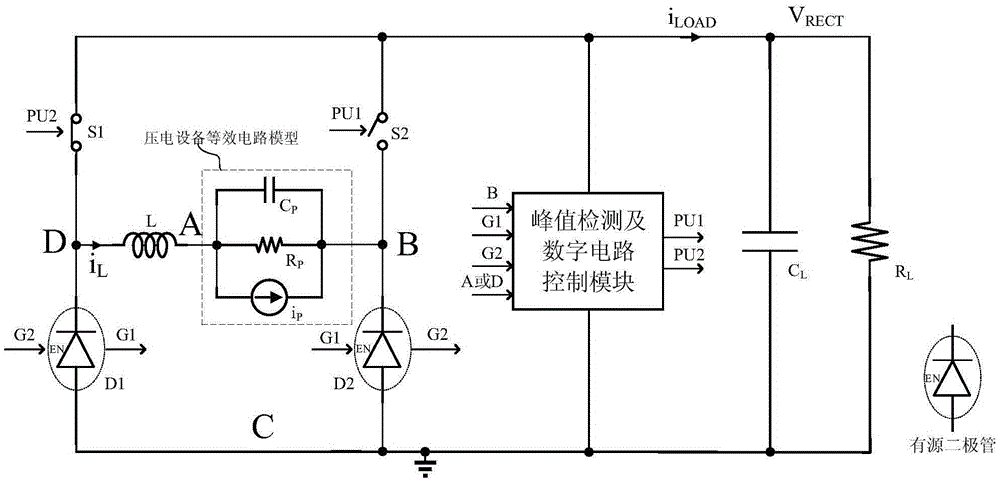

Piezoelectric energy collection rectifier for open-circuit type optimization of turnover time

InactiveCN105634300ALow costReduce forward voltage dropAc-dc conversion without reversalPiezoelectric/electrostriction/magnetostriction machinesCapacitor voltageEngineering

The invention discloses a piezoelectric energy collection rectifier for open-circuit type optimization of turnover time. The piezoelectric energy collection rectifier comprises two active diodes, two switches, an inductor and a peak detection and digital circuit control module, wherein a pair of active diodes carries out complementary conduction / stop operation; once one diode detects a zero crossing point flowing through a current from a positive electrode to a negative electrode, the diode is turned off and opposite the other diode is turned on; each active diode outputs a corresponding on-off state signal; the peak detection and digital circuit control module receives the on-off state signal of each active diode, detects a voltage peak of a cathode of the active diode and outputs a pulse signal of the optimized pulse width; the two switches receive the pulse signal of the peak detection and digital circuit control module and carry out on / off operation; and the inductor is connected with a piezoelectric device in series, and is connected to an input end of the rectifier. Under the control of the peak detection and digital circuit control module, the capacitor voltage of the piezoelectric device is optimally turned over; and meanwhile, the energy is transmitted to a load.

Owner:HUNAN UNIV

Insulated gate bipolar translator (IGBT) device with two short-circuit positive electrodes

InactiveCN102544084AAnode Structure ImprovementReduce forward voltage dropSemiconductor devicesConductivity modulationSilicon dioxide

The invention discloses an insulated gate bipolar translator (IGBT) device with two short-circuit positive electrodes, and belongs to the technical field of semiconductor power devices. A positive electrode structure of the device is a two-positive-electrode short-circuit structure. The IGBT device comprises a first P+ hole emission layer, a second P+ hole emission layer, a metal collector and a silicon dioxide barrier layer, wherein the silicon dioxide barrier layer is positioned on the back face of the first P+ hole emission layer; the metal collector is positioned on the side face of the first P+ hole emission layer and below the second P+ hole emission layer, and the two P+ hole emission layers are contacted with each other; the second P+ hole emission layer is positioned at the bottom of an N- drift region and staggered in parallel with the first P+ hole emission layer; and an electronic trench is formed between the first P+ hole emission layer and the second P+ hole emission layer. The positive electrode structure of the IGBT device is improved, so that the hole injection efficiency is improved, the current carrier concentration distribution in the drift region is optimized, the conductivity modulation performance in the device body is improved, a negative differential resistance (NDR) region is eliminated effectively, the cut-off loss of the IGBT device is reduced effectively, and finally, compromise optimization for conductivity pressure drop and cut-off loss is realized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

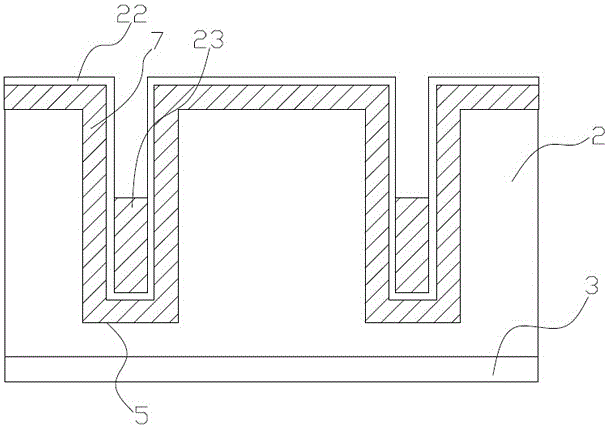

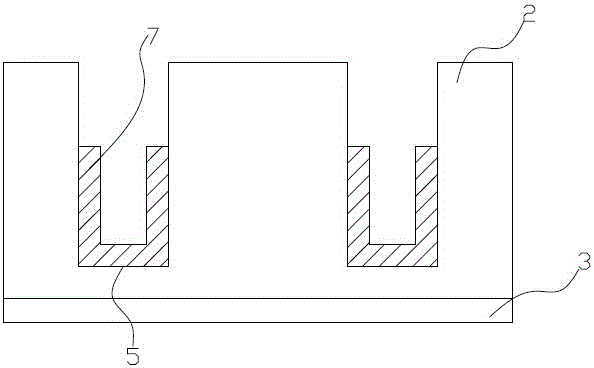

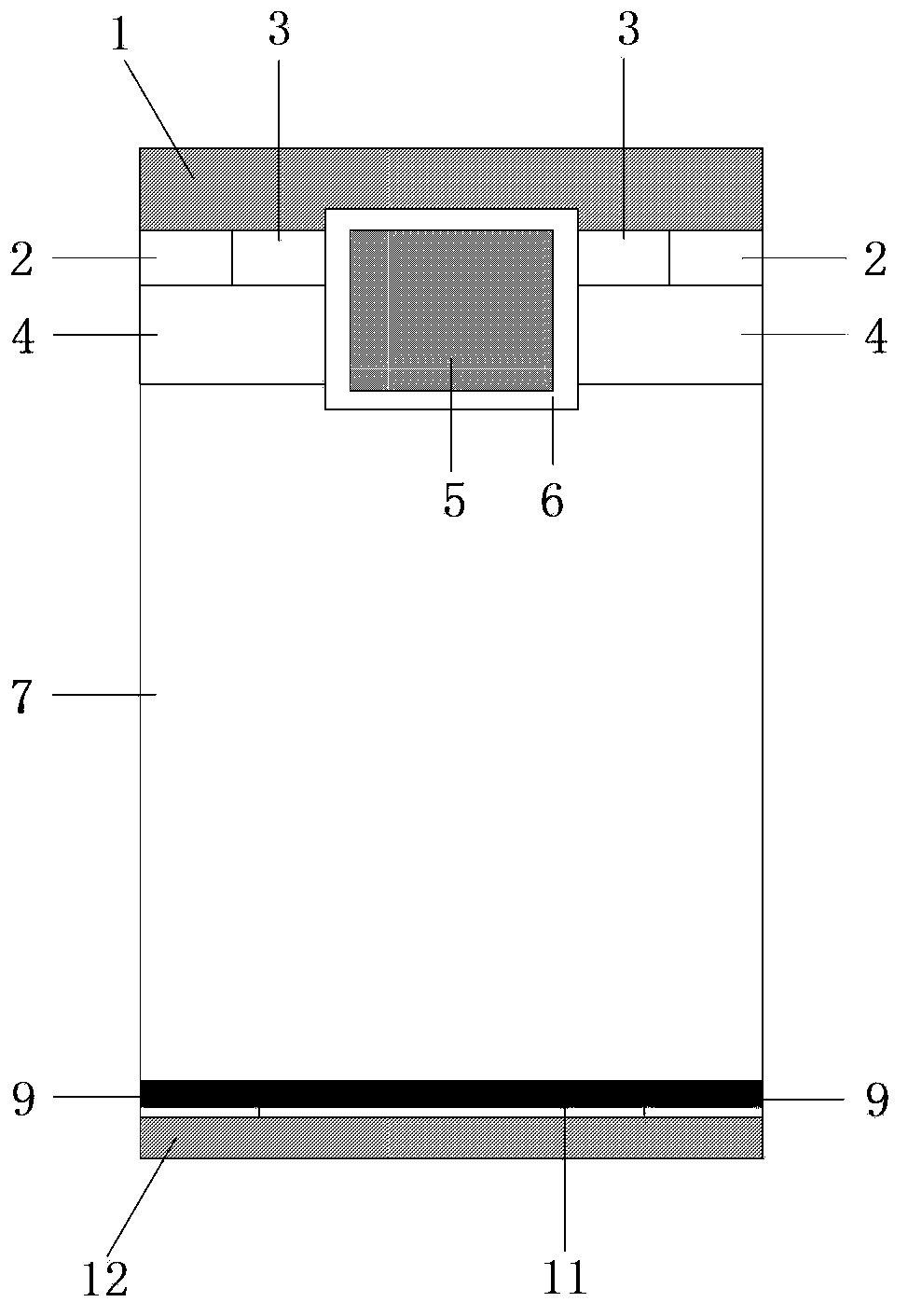

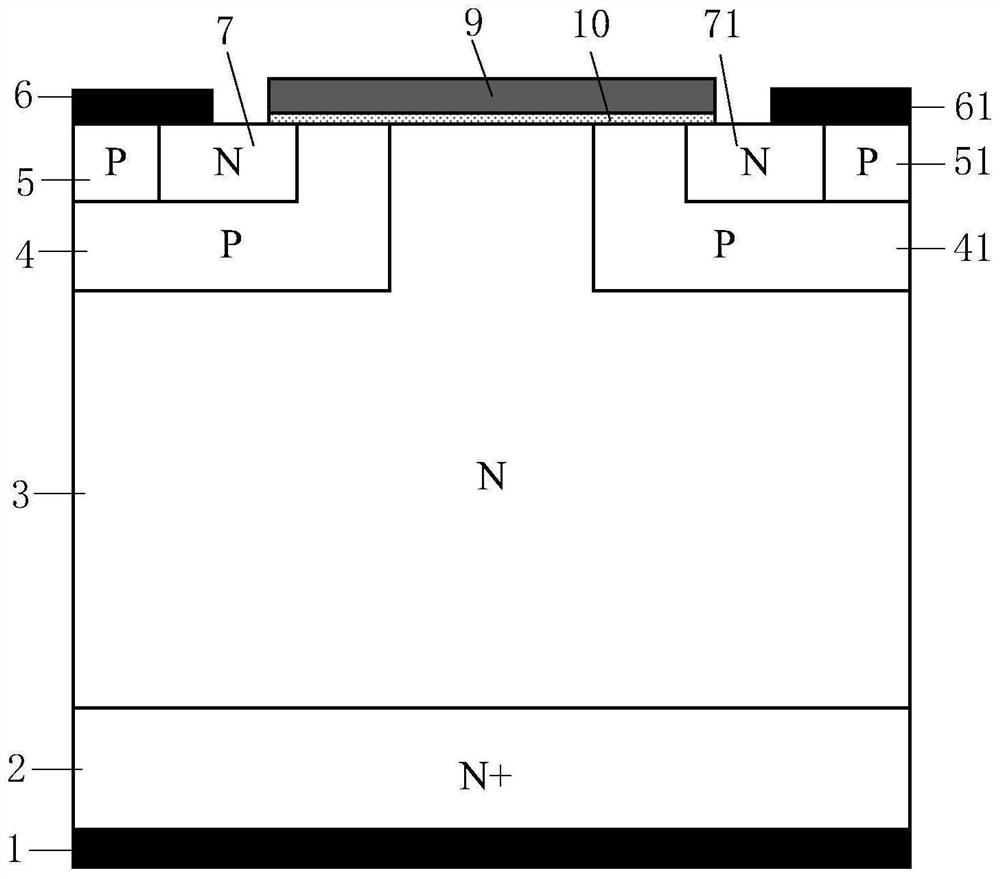

Thin SOI LIGBT device with carrier storage layer

ActiveCN107482058AReduce forward voltage dropReduced turn-off lossSemiconductor devicesHigh densityCharge carrier

The invention belongs to the technical field of power semiconductors, and specifically relates to a thin SOI LIGBT device with a carrier storage layer. The device is mainly characterized in that the device employs two trench gates and one plane gate structure, and the carrier storage layer is introduced between the two trench gates and below a plane gate. During forwarding conduction, the side walls of the trench gates block a hole loop, thereby achieving an effect of injection enhancement, and reducing the forwarding conduction voltage drop of a device. Meanwhile, the N-type carrier storage layer plays a role in hole blocking, promotes the electrons to be injected into a drift region, improves the electric conduction modulation effect, and further reduces the forwarding conduction voltage drop. During forwarding blocking, the trench gates play a role in using up the carrier storage layer, and enable the device to maintain a high withstand voltage under the high density of the storage layer. The beneficial effects of the invention are that the device, compared with a conventional LIGBT structure, is lower in forwarding conduction voltage drop, is higher in switching-off speed, and is lower in switching-off loss.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Semiconductor rectifying device and manufacturing method thereof

InactiveCN101789400AImprove reliabilityAvoid it happening againSolid-state devicesSemiconductor/solid-state device manufacturingOhmic contactEngineering

The invention discloses a semiconductor rectifying device and a manufacturing method thereof. The device is composed of an equivalent diode and a vertical MOS tube which are connected in parallel and comprises the following components: a) a semiconductor substrate with two relative major surfaces, which belongs to a first conduction type; wherein a first major surface is N-epitaxial layer and a second major surface is N+silicon base; b) a protective ring which is located on the first major surface for defining an active region, the protective ring is doped by a second conduction type; c) a gate oxide layer arranged below a polysilicon gate electrode; d) a second conduction type tagma is formed all round the gate oxide layer and on the epitaxial layer, a horizontal expansion region is arranged below the gate oxide layer, the horizontal expansion region serves as a channel region: e) an ohmic contact region of the second conduction type is formed on the surface of the tagma; in the invention, the problem that the existing technology is complex and reliability of device is poor is solved and a semiconductor rectifying device and a manufacturing method thereof featuring simple technology and high reliability are realized.

Owner:SUZHOU SILIKRON SEMICON CO LTD

Thyristor controlled by accumulation layer

An accumulation layer controlled thyristor, which belongs to the technical field of semiconductor power devices, is characterized in that the on / off of the thyristor can be controlled by stopping electron circulation through an electron barrier of an internal electric field formed in a P bypass region and an N depletion region. When a positive voltage is applied on a gate, an accumulation layer is formed at the interface between the N depletion region (33) and a gate oxide layer (6); an electron inversion channel is formed in a P-type base region (8); and electrons pass through an N active region (9), the accumulation layer, an N layer (200), and the electron inversion channel to the an N base region (3), thereby controlling the normal operation of the device. The accumulation layer controlled thyristor as the substitute of the conventional gate controlled thyristors, such as MOS controlled thyristors, has the advantages of lower conduction voltage drop, larger saturation current density, no parasitic effect, and greatly improved safety operation area, and can overcome the disadvantages of the conventional gate-controlled thyristors, such as the deficiency of current saturation characteristic and poor turn-off capability.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

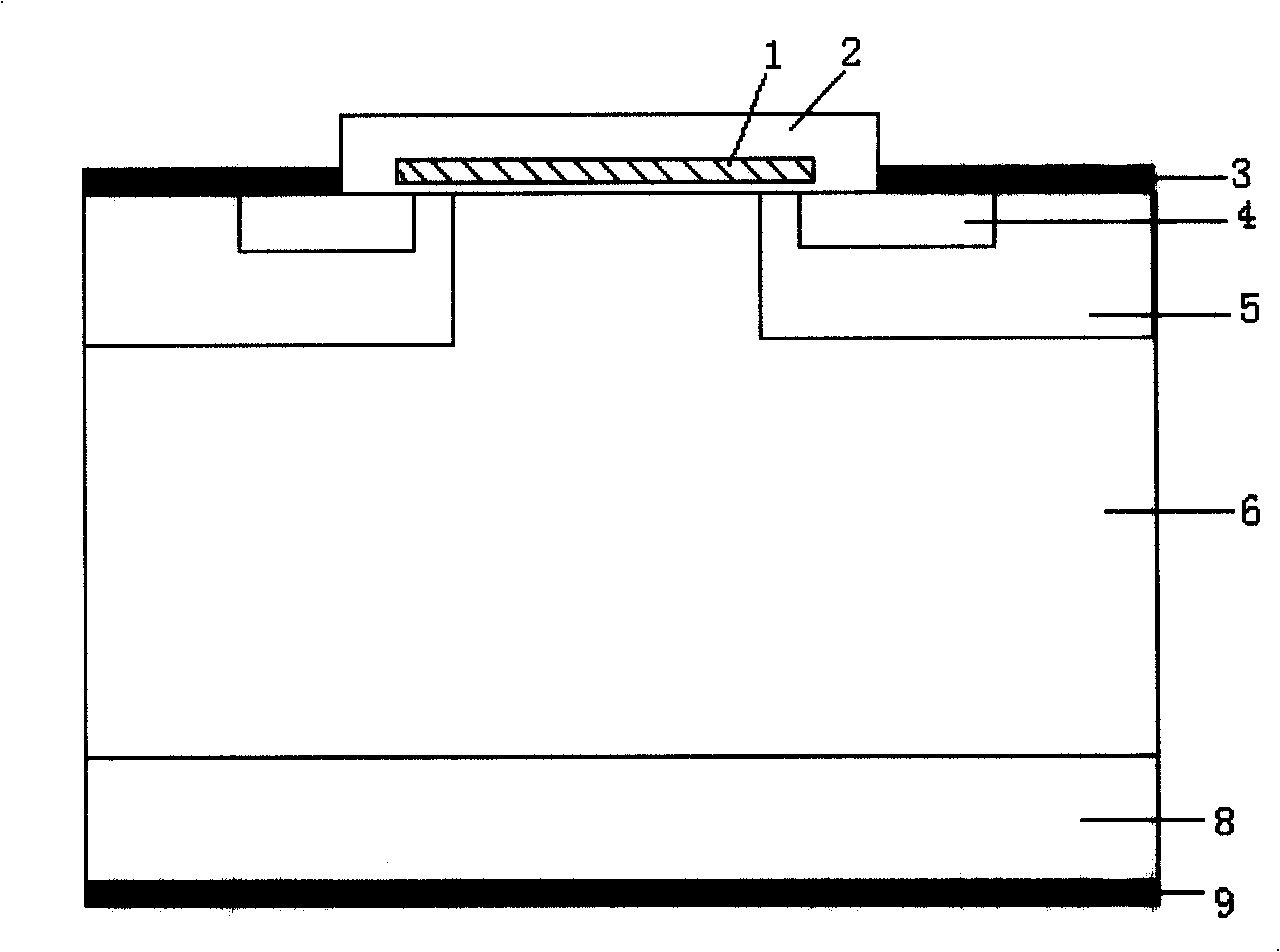

A bipolar power semiconductor device and a preparation method thereof

ActiveCN109065607AReduce forward voltage dropLow Average Forward Voltage DropSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceReverse recovery

The invention relates to a bipolar power semiconductor device and a preparation method thereof, belonging to the technical field of semiconductor power devices. When the cathode structure of the conventional bipolar power semiconductor device is kept unchanged, by introducing an anode trench gate structure and a source region and / or a base region into the anode region of the device, the forward conduction voltage drop of the anode diode is bypassed by controlling the anode trench gate structure without affecting the normal operation and opening of the device, so that the effect of reducing theforward conduction voltage drop of the power semiconductor device is achieved. After the anode diode is bypassed, the minority carrier injection from the anode region to the drift region decreases, and the reverse recovery time of the device is shortened when the device is turned off, which improves the turn-off speed of the device and reduces the switching loss. The invention improves the carrier concentration distribution of the whole N-type drift region and the compromise between the positive conduction voltage drop and the switching loss. Moreover, the fabrication method of the device does not require additional process steps, and is compatible with the traditional device fabrication method.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Silicon carbide insulated gate bipolar transistor and manufacturing method thereof

InactiveCN111048580AMasking complexityOptimize static and dynamic characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconGate dielectric

The invention provides a silicon carbide insulated gate bipolar transistor comprising an N-type heavily doped first field stop layer; an N-type heavily doped second field stop layer which is formed onthe N-type heavily doped first field stop layer; an N-type lightly doped drift layer which is formed on the N-type heavily doped second field stop layer; a regulation and control P-type Base region which is formed in the N-type lightly doped drift layer; an N-type heavily doped source region which is formed in the regulation and control P-type Base region; source metal which is formed in the partial region of the regulation and control P-type Base region and the partial upper surface of the N-type heavily doped source region and forms ohmic contact with the upper surface and the side wall ofthe N-type heavily doped source region; a gate dielectric layer which is formed on the N-type lightly doped drift layer; a grid electrode which is formed on the grid dielectric layer; an interlayer dielectric which is formed on the grid electrode and the two sides of the grid electrode so as to isolate the grid electrode from the source metal; and a P-type heavily doped collector region which is formed on the back surface of the N-type heavily doped first field stop layer. The double-layer field stop layer structure is formed so that the characteristics of the device are optimized and the robustness is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

High withstand voltage and low loss super junction power device

ActiveCN110416294AReduce forward voltage dropHigh forward blocking voltageSemiconductor devicesVoltageSemiconductor

The invention belongs to the technical field of power semiconductors, and in particular relates to a high withstand voltage and low loss super junction power device. The device provided by the invention is characterized in that a pinch-off structure is arranged on a P-type drift region; the pinch-off structure is composed of pinch-off grooves and a P-type body contact region between the pinch-offgrooves; during forward conduction, the pinch-off structure pinches the middle P-type drift region, suppressing the collection of holes by the P-type drift region and improving the storage effect of carriers in the drift region; when the device is turned off, the P-type drift region is connected with an emitter through the P-type body contact region to be used as a hole extraction path to reduce the turn-off loss; when forward withstand voltage is applied, the P-type drift region contacts the emitter through the P-type body contact region, and the potential is 0; the P-type drift region has abetter auxiliary depletion effect; and the device has higher withstand voltage. Compared with a conventional super junction IGBT device, the device provided by the invention has lower on-voltage dropand better Von-Eoff discount. Compared with a P-column floating super junction IGBT device, the super junction IGBT device provided by the invention have higher forward withstand voltage.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

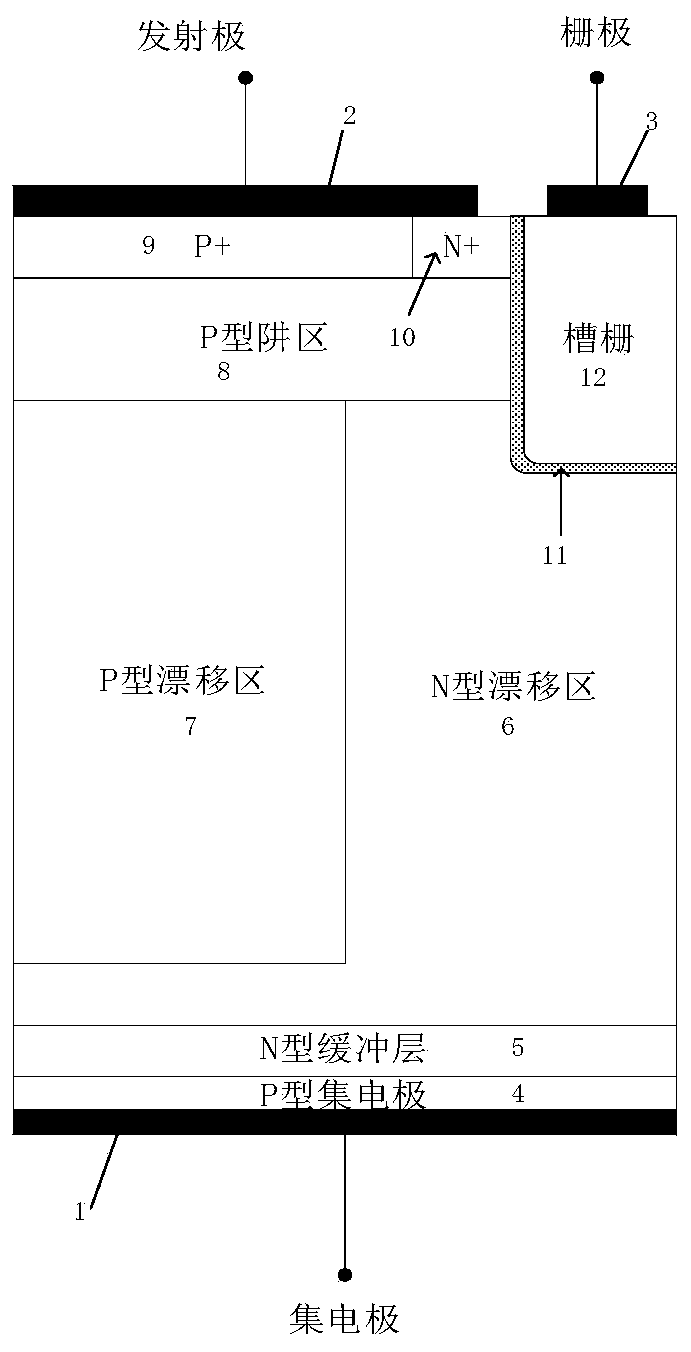

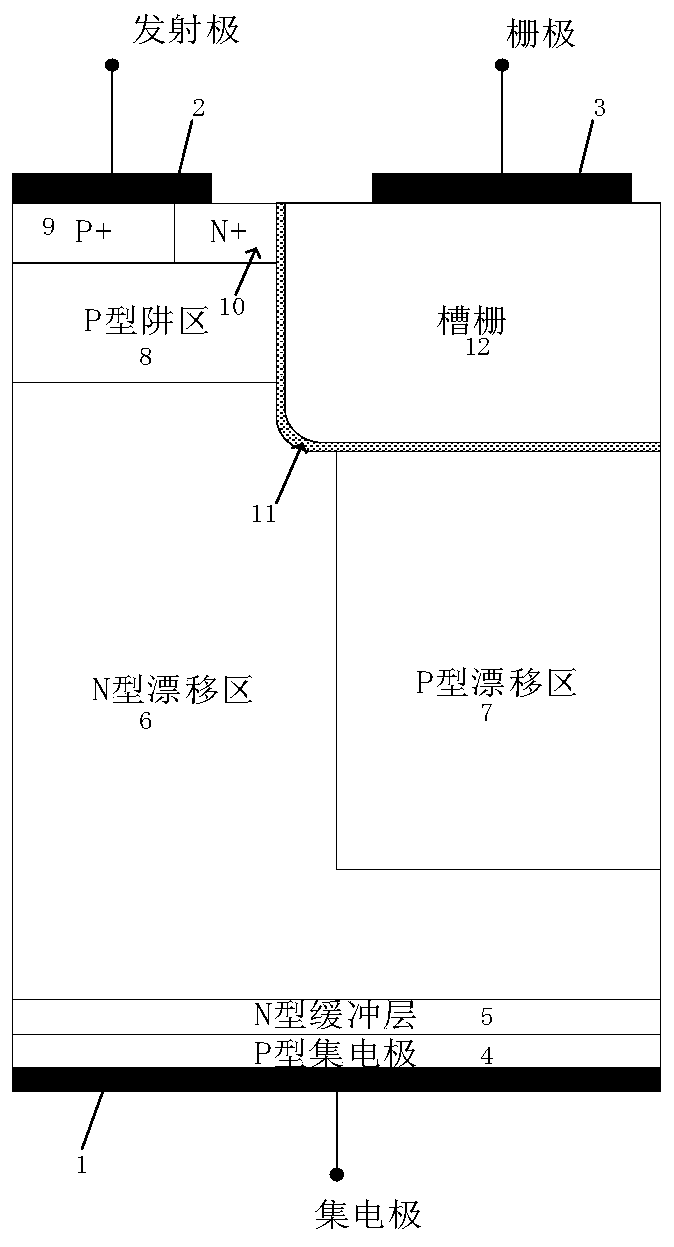

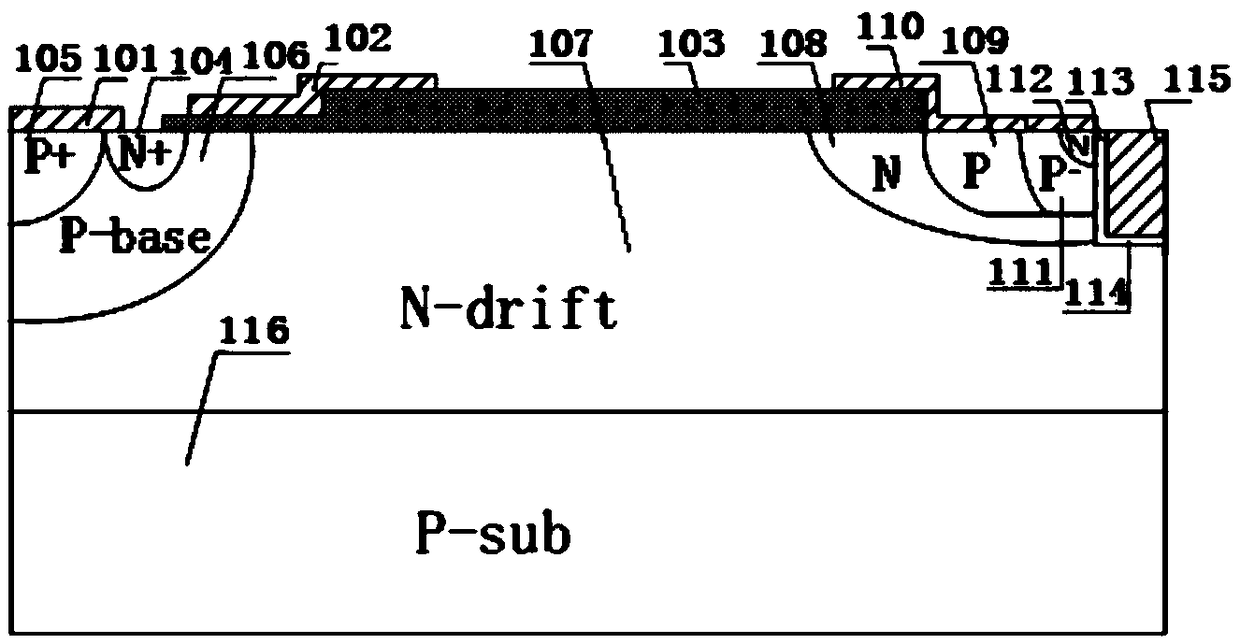

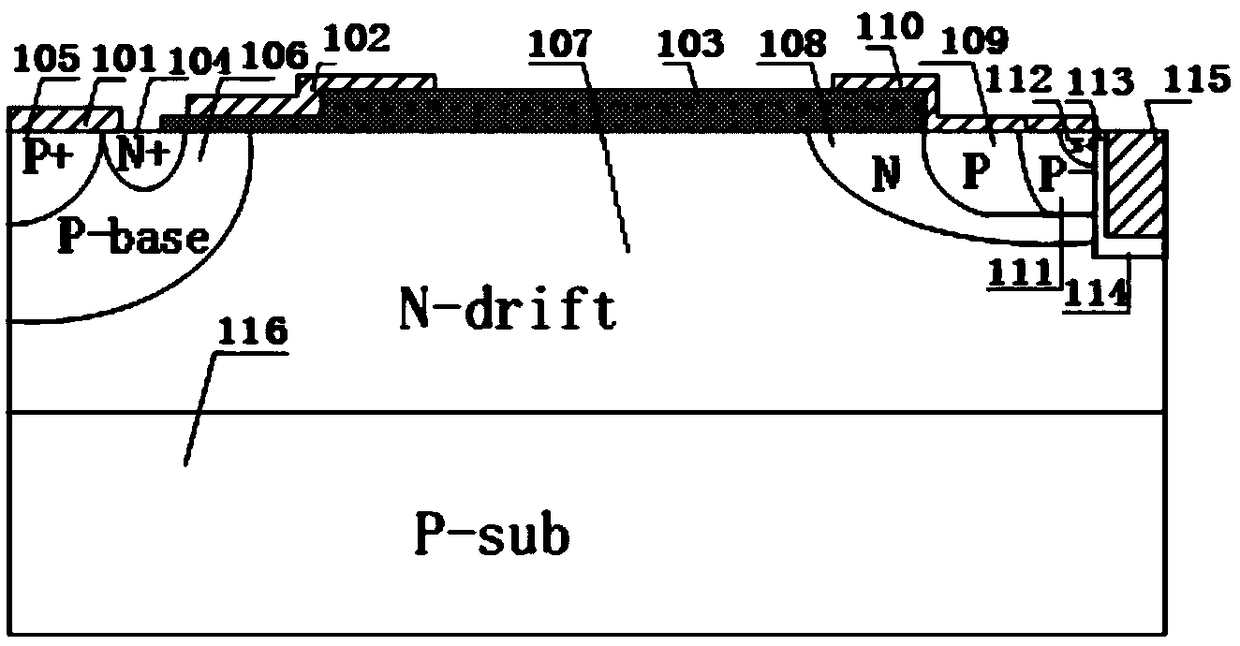

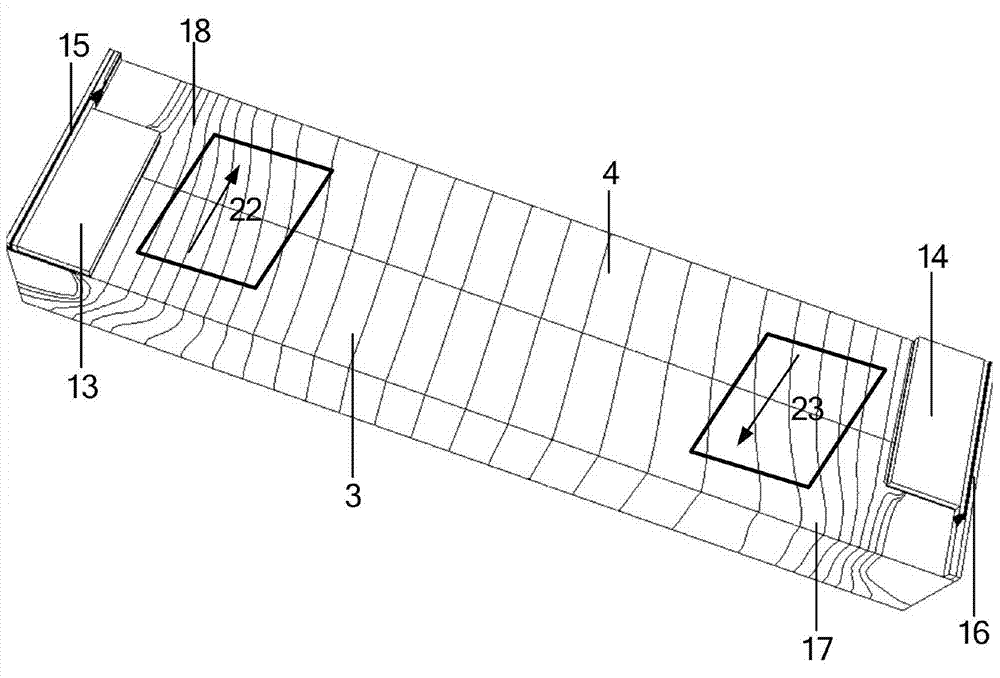

Lateral IGBT and manufacturing method thereof

ActiveCN110473917AReduce conduction voltage dropReduce saturation currentSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceCapacitance

The invention belongs to the technical field of power semiconductor devices and relates to a lateral IGBT and a manufacturing method thereof. A superjunction structure is introduced into the three-dimensional direction on the basis of a conventional lateral IGBT, thereby reducing the on-resistance of the device without affecting the breakdown voltage of the device. The introduced N-type charge storage layer can improve the carrier concentration distribution in the drift region in order to further reduce the on-state voltage drop of the device. The introduction of a split gate structure can effectively shield the influence of the N-type charge storage layer on the breakdown voltage of the device and reduces the gate capacitance, especially the Miller capacitance, thereby increasing the switching speed of the device. The introduction of a PMOS structure can increase the carrier extraction speed of the device in an off state, increases the turn-off speed of the device, and reduces the switching loss of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

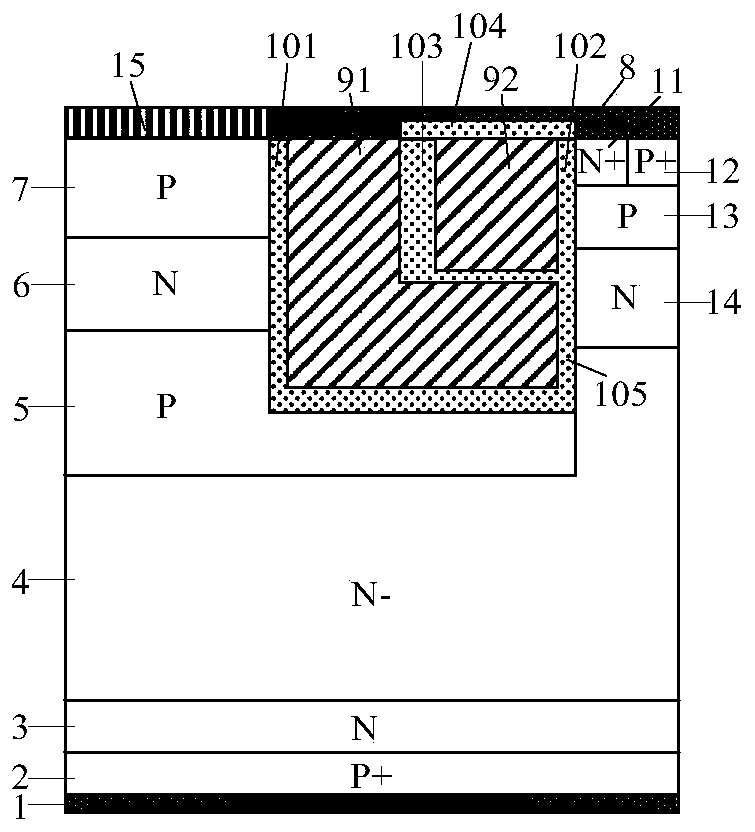

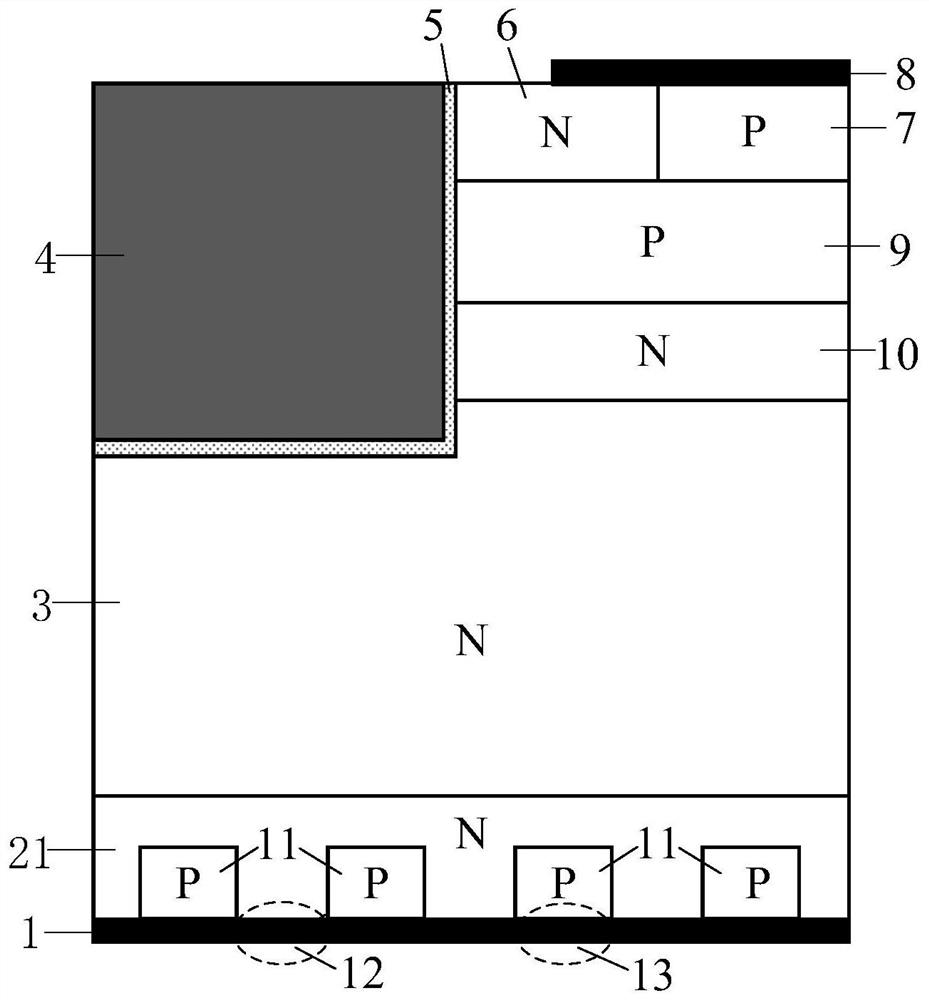

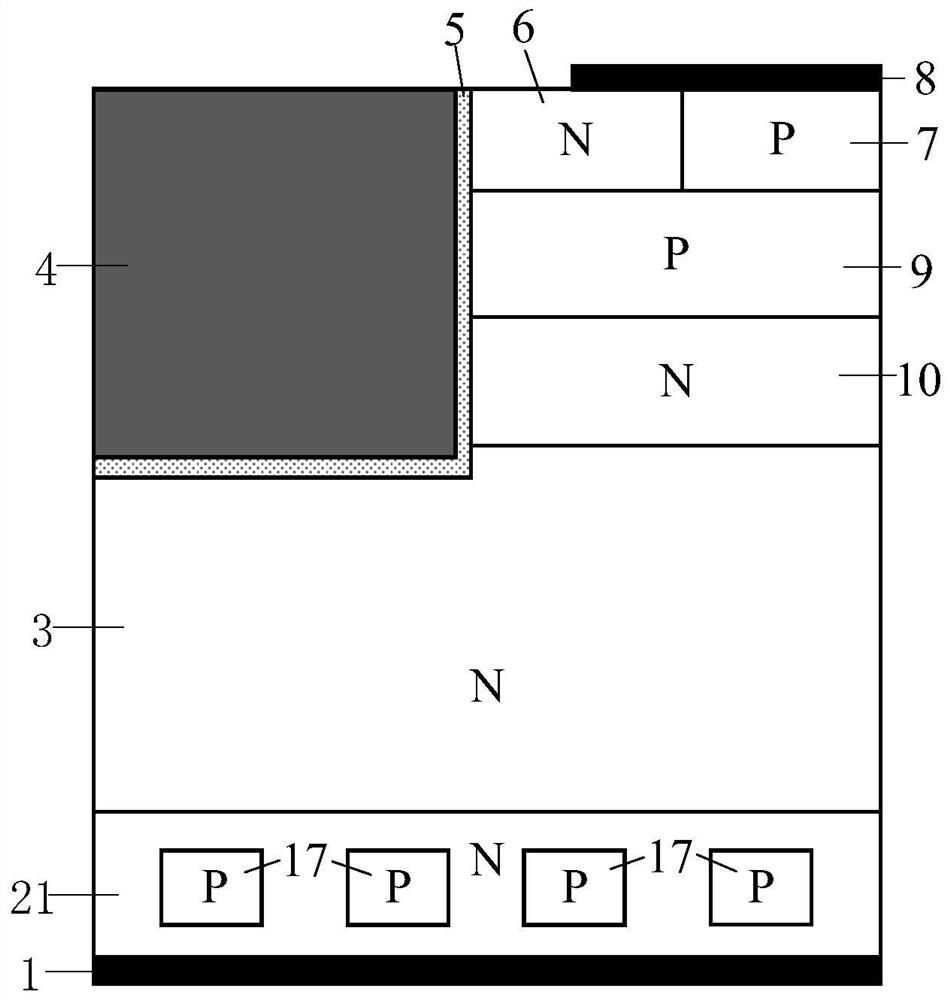

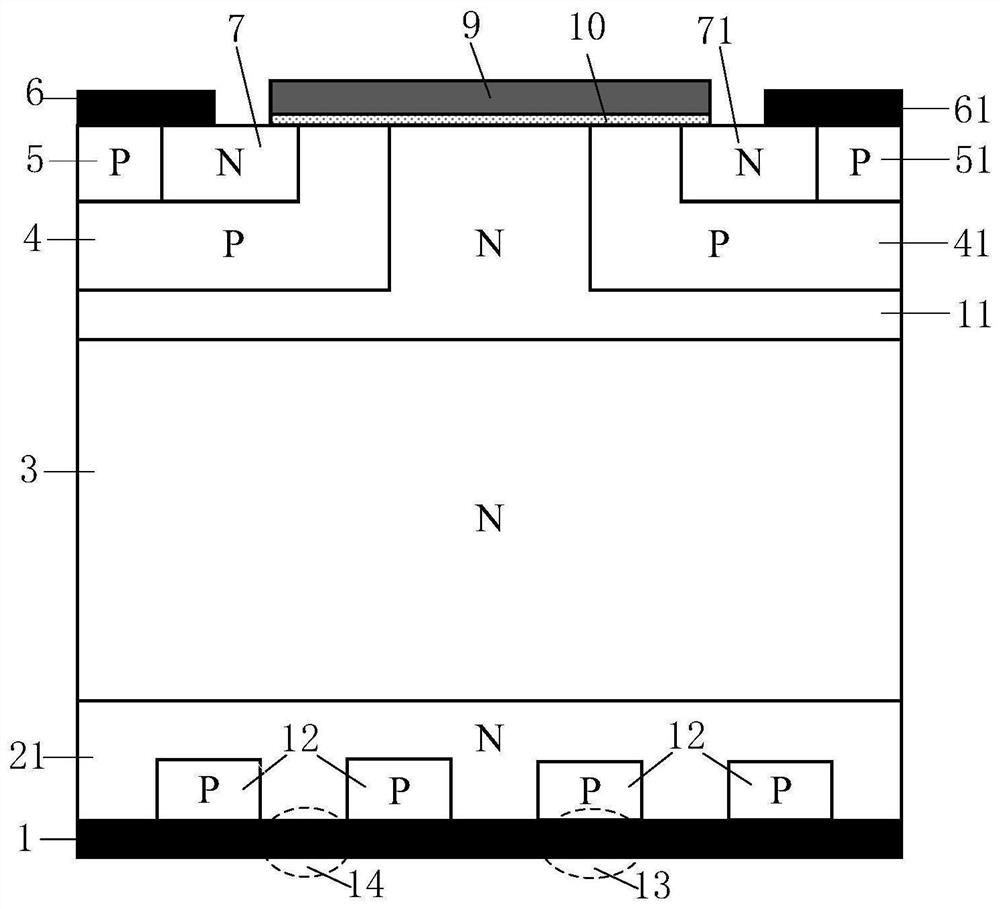

Split gate CSTBT with PMOS current clamping and manufacturing method of split gate CSTBT

ActiveCN110600537AImprove saturation currentImprove doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceCapacitance

The invention belongs to the technical field of a power semiconductor device and relates to a split gate CSTBT with PMOS current clamping and a manufacturing method of the split gate CSTBT. A PMOS structure is introduced on the basis of a traditional CSTBT, a saturation current during forward conduction of a device is effectively improved, the short-circuit safe working capability of the device isimproved, moreover, the influence of an N-type charge storage layer 14 on the breakdown characteristic of the device is eliminated, therefore, the doping concentration of the N-type charge storage layer 14 can be improved to improve carrier distribution during forward conduction of the device, so the conductivity modulation capability of a drift region is improved, forward conduction voltage dropof the device is reduced, the gate capacitance, especially the Miller capacitance, of the device is reduced by an L-shaped separated gate structure, the switching speed of the device is improved, switching loss of the device is reduced, since a separation gate and the gate structure are integrated in the same groove, the area of a chip is saved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

MOSFET (Metal Oxide Semiconductor Field Effect Transistor) integrated with trench Schottky

InactiveCN105957865AIncrease the areaReduce forward voltage dropSolid-state devicesDiodeMOSFETPower flow

The invention belongs to a semiconductor technology, and particularly relates to an MOSFET (Metal Oxide Semiconductor Field Effect Transistor) integrated with trench Schottky. The MOSFET integrated with the trench Schottky is characterized in that a Schottky diode formed by Schottky contact and a substrate is integrated in the MOSFET; a Schottky junction is provided with a planar Schottky junction positioned on a surface and a trench Schottky junction positioned in a body; and the area of the Schottky junction is increased under the condition of occupying the same chip area, so that higher current can be carried. A plurality of P-type heavily-doped rings are further arranged below the trench Schottky junction, and a Schottky diode is switched on at a relatively low voltage to form a conductive path when a body diode is switched on; and when the voltage is boosted to be over 0.5V, the P-type heavily-doped rings below the trench Schottky junction inject minority carriers into an N-type drift region, so that forward break-over voltage drop of the Schottky junction is reduced, and a conductivity modulation effect is achieved. Through adoption of the method, body diode break-over loss of the MOSFET can be reduced, and reverse electric leakage of the Schottky diode is reduced through the P-type heavily-doped rings at the same time.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Trench type silicon carbide reverse blocking MOSFET device and production method thereof

ActiveCN112687743APrevent extensionLarge positive and negative symmetrical withstand voltageEfficient power electronics conversionSemiconductor/solid-state device manufacturingMOSFETCapacitance

The invention belongs to the technical field of power semiconductor devices, and particularly relates to a trench type silicon carbide reverse blocking MOSFET device and a production method thereof. Compared with a traditional trench type silicon carbide MOSFET, by using the device of the invention, an N-type silicon carbide substrate is removed, a first N-type silicon carbide buffer layer is introduced to one side of a device source region, a second N-type silicon carbide buffer layer is introduced to one side of a device drain region, and a junction Schottky barrier diode structure is introduced to one side of the device drain region. The device structure can enable the trench type silicon carbide MOSFET to obtain a large forward and reverse symmetrical withstand voltage and to have small forward conduction voltage drop at the same time. In addition, in order to further solve the reliability problem of a gate oxide layer of the device and the problem of a large gate-drain capacitance, several corresponding derivative structures are provided.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

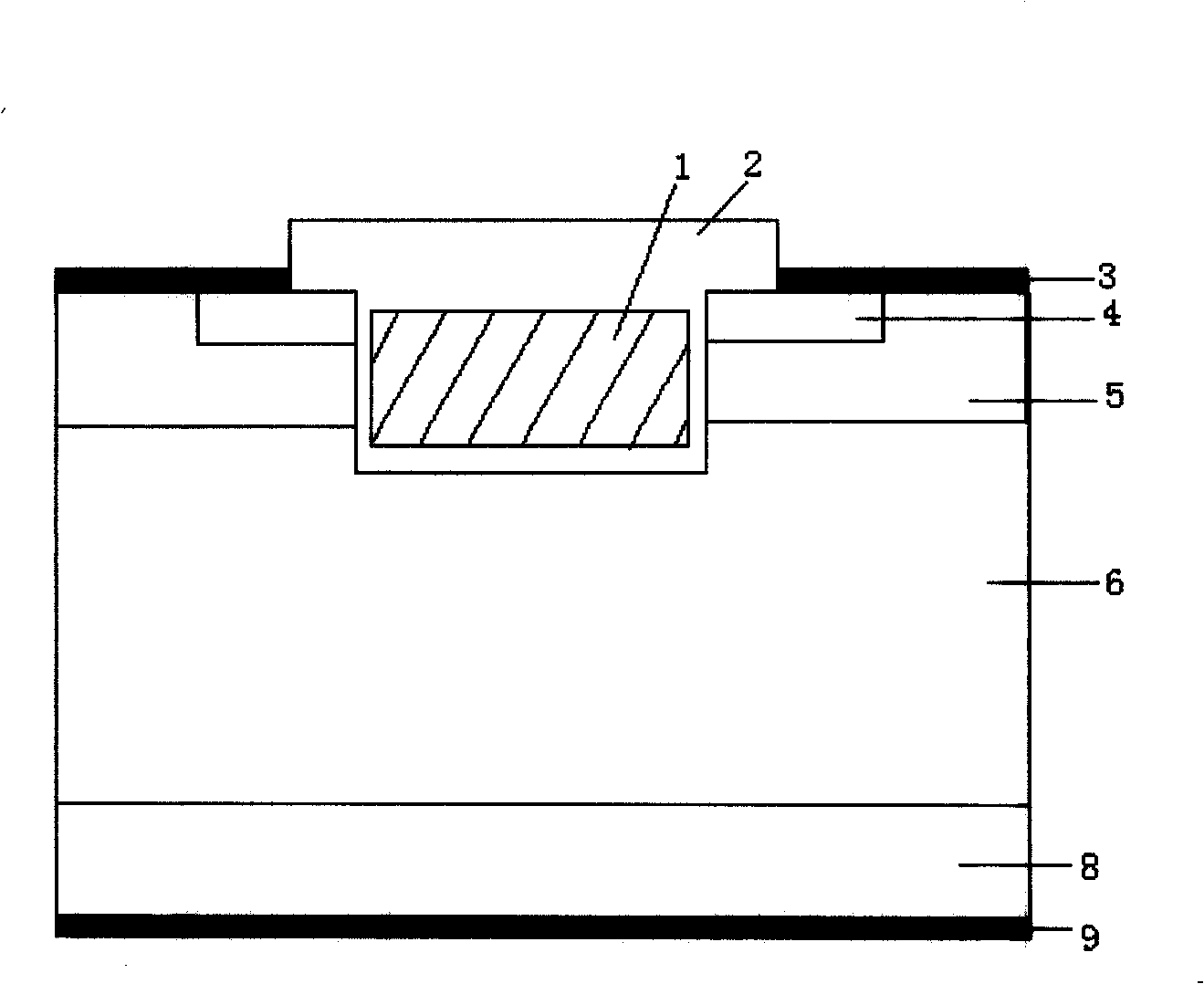

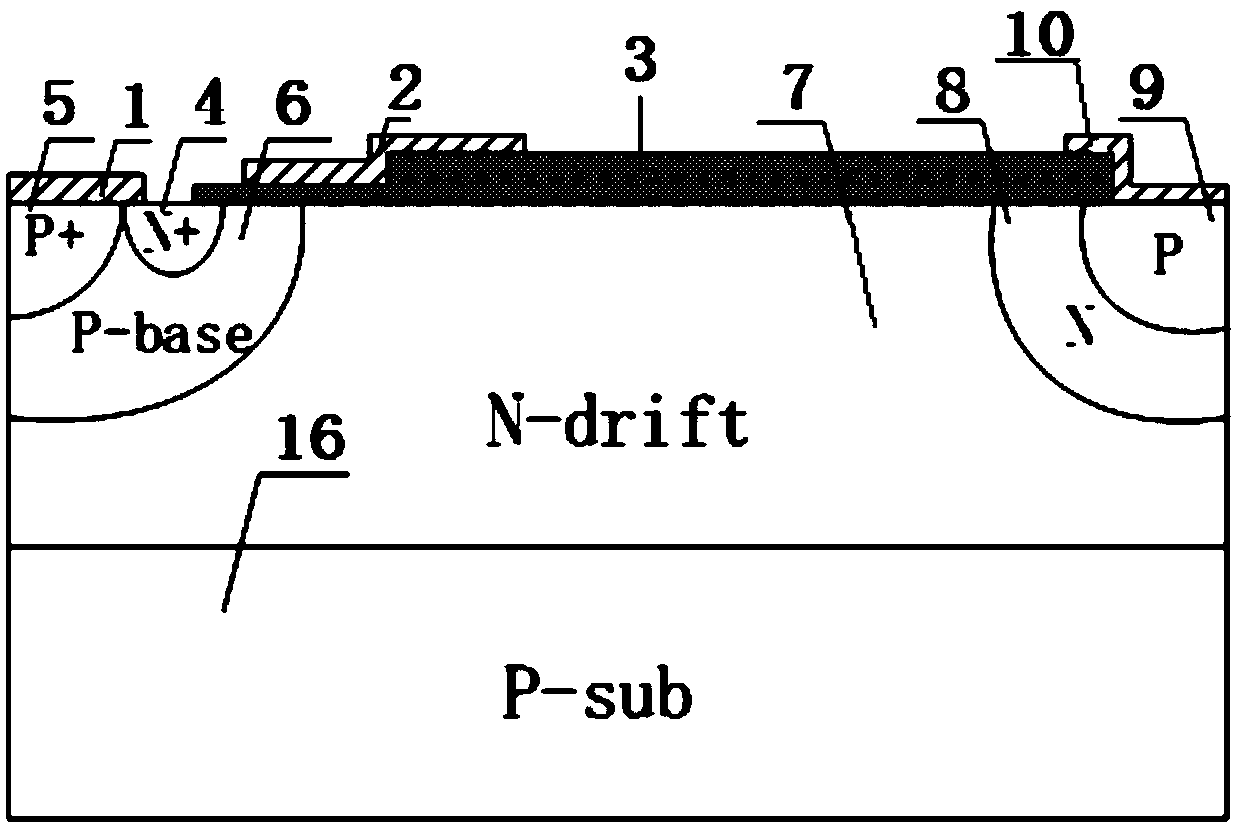

A lateral bipolar power semiconductor device and a manufacturing method thereof

ActiveCN109065608AReduce forward voltage dropLow Average Forward Voltage DropSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceReverse recovery

A lateral bipolar semiconductor power device and a preparation method thereof belong to the technical field of semiconductor power device. When the cathode structure of the conventional bipolar powersemiconductor device is kept unchanged, by introducing an anode trench gate structure and a source region and / or a base region into the anode region of the device, the forward conduction voltage dropof the anode diode is bypassed by controlling the anode trench gate structure without affecting the normal operation and opening of the device, so that the effect of reducing the forward conduction voltage drop of the power semiconductor device is achieved. After the anode diode is bypassed, the minority carrier injection from the anode region to the drift region decreases, and the reverse recovery time of the device is shortened when the device is turned off, which improves the turn-off speed of the device and reduces the switching loss. The invention improves the carrier concentration distribution of the whole N-type drift region and the compromise between the positive conduction voltage drop and the switching loss. Moreover, the fabrication method of the device does not require additional process steps, and is compatible with the traditional device fabrication method.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

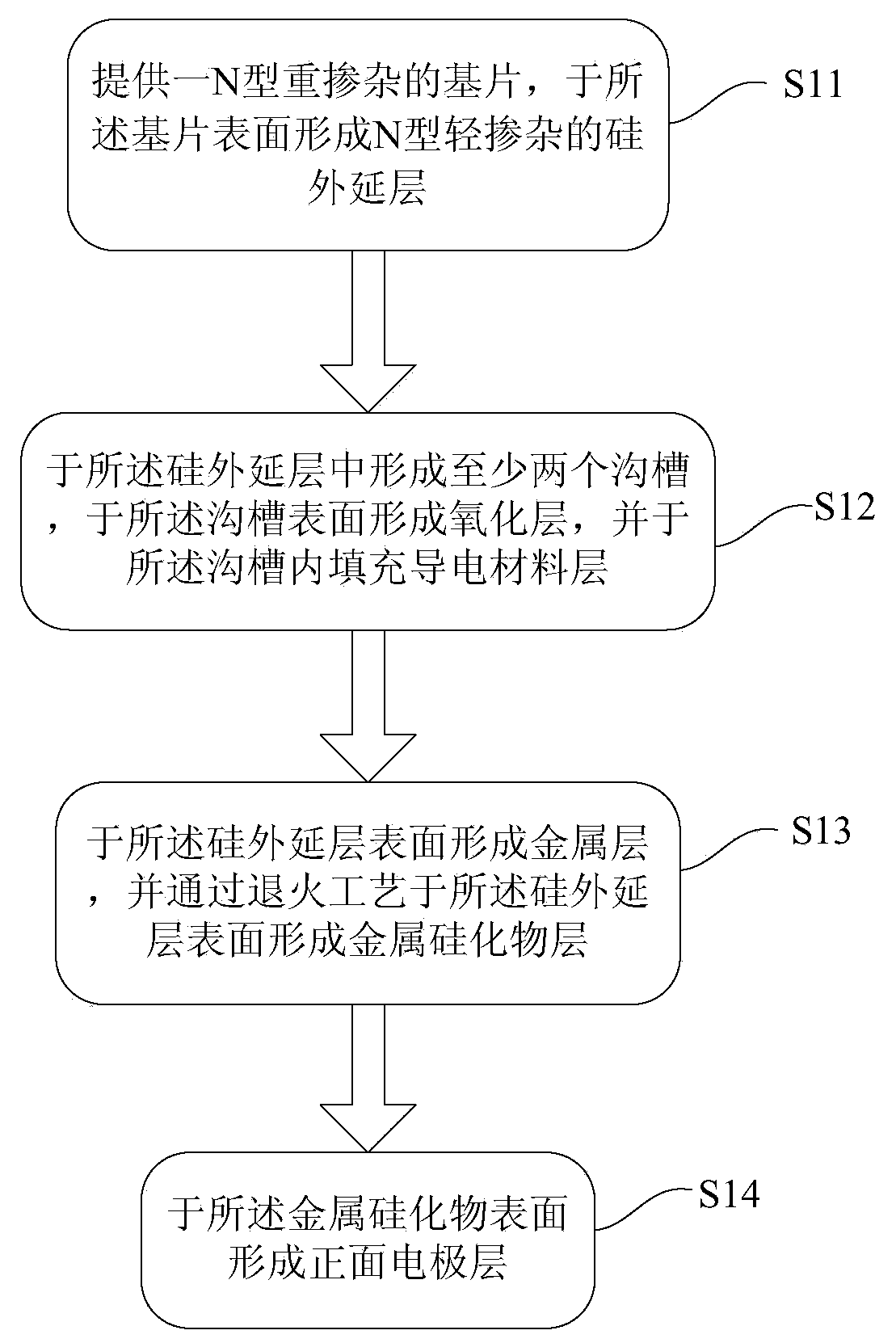

Groove-type Schottky power device structure and method for manufacturing same

ActiveCN103456796ALower forward voltageReduce forward voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideMetal silicide

The invention provides a groove-type Schotty power device structure and a method for manufacturing the groove-type Schotty power device structure. The groove-type Schotty power device structure comprises an N-type heavily doped substrate, an N-type slightly doped silicone epitaxial layer, at least two grooves, conductive material layers, a metal silicide layer and a positive electrode layer, wherein the N-type slightly doped silicone epitaxial layer is arranged on the surface of the N-type heavily doped substrate in a combining mode, the grooves are formed in the silicone epitaxial layer, oxide layers are formed on the surfaces of the grooves, the conductive material layers are filled into the grooves, the metal silicide layer is formed on the surface of the silicone epitaxial layer and the positive electrode layer is formed on the surface of the metal silicide layer. The positive electrode layer is composed of a TiN layer, an AlSiCu layer, a Ti layer, a TiN layer, a Ti layer, an Ni layer and an Ag layer sequentially from bottom to top in an overlapped mode, or composed of a TiN layer, an AlSi layer, a Ti layer, a TiN layer, a Ti layer, an Ni layer and an Ag layer sequentially from bottom to top in an overlapped mode, or composed of a TiN layer, an Al layer, a Ti layer, a TiN layer, a Ti layer, an Ni layer and an Ag layer sequentially from bottom to top in an overlapped mode. According to the groove-type Schotty power device structure, a Schotty junction is formed by metal silicide and slightly doped N-type silicone, the groove MOS structure is adopted to be used as a leakage protection ring of a unit Schotty structure, and the low-leakage Schotty power diode device is formed; improvement to the positive electrode structure greatly lowers the forward conductive pressure drop, and the tolerance, to wave impact, of the device and the anti-static capacity of the device are improved.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

Lateral trench insulated gate bipolar translator (IGBT) having self-biased positive channel metal oxide semiconductor (PMOS) and its preparation method

ActiveCN110504260AReduce conduction voltage dropLower performance requirementsSolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorTurn off time

The invention belongs to the technical field of power semiconductor devices and relates to a lateral trench insulated gate bipolar translator (IGBT) having a positive channel metal oxide semiconductor(PMOS) and its preparation method. Based on a lateral IGBT (LIGBT) device structure, a current carrier storage layer is added to the lateral-trench IGBT having the self-biased PMOS to enhance the conductivity modulation effect, and reduce the device conduction pressure drop; a side face of a grid electrode is wrapped by a sorting grid to reduce the Miller capacitance, reduce the turn-off time, reduce the turn-off loss, and improve the compromise between the forward conduction voltage drop and the turn-off loss; in the meanwhile, the gate charge of a device can be reduced, and drive loss is reduced; the compromise characteristic between a current decline rate (di / dt) and the conduction loss (Eon) is improved; automatic turn-on of a metal-oxide-semiconductor field-effect transistor (MOSFET)is self-biased during forward conduction, a voltage of a charge storage area is clamped, a saturation current is reduced and a short-circuit safe working area is optimized; the turn-on of the MOSFETself-biased in a preliminary stage is turned off, extraction of remaining current carriers of a drift region is accelerated, and the turn-off loss is reduced; a buried layer on a left side of trench gate can assist voltage resistance, and a blocking voltage is increased; and a thin gate oxide layer can reduce a threshold voltage of the device, and reduce the current densify of a latch.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

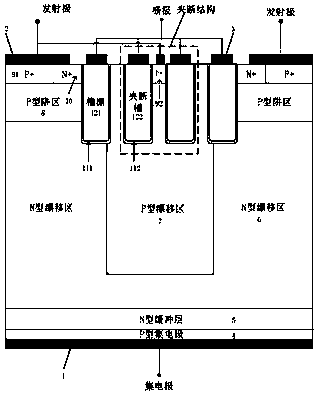

Reverse-conducting double-insulated-gate bipolar transistor

ActiveCN103928507AReduce forward voltage dropIncreased current capabilitySemiconductor devicesParasitic bipolar transistorGate oxide

The invention provides a semiconductor capable of improving the current rebounding phenomenon of a reverse-conducting double-insulated-gate bipolar transistor, improving the turn-off speed and improving voltage resistance. The semiconductor is structurally characterized in that a buried oxide is arranged on a P-type substrate and provided with a drift region, the drift region comprises a first N-type drift region, a first P-type drift region, a second N-type drift region and a second P-type drift region, the first N-type drift region and the first P-type drift region are arranged in an opposite-angle mode, and the second N-type drift region and the second P-type drift region are arranged in an opposite-angle mode; a P-type region is arranged in the first N-type drift region and the second P-type drift region, an N-type emitter region, a P-type collector region and cathode metal connecting the N-type emitter region with the P-type collector region are arranged in the P-type region, and a cathode gate oxide and a cathode polycrystalline silicon layer are arranged on the upper surface of the P-type region; an N-type region is arranged in the first P-type drift region and the second N-type drift region, an N-type collector region, a P-type emitter region and anode metal connecting the N-type collector region with the P-type emitter region are arranged in the N-type region, and an anode gate oxide and an anode polycrystalline silicon layer are arranged on the upper surface of the N-type region.

Owner:SOUTHEAST UNIV

Planar silicon carbide reverse-blocking MOSFET device and preparation method thereof

ActiveCN112687744APrevent extensionLarge positive and negative symmetrical withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconPower semiconductor device

The invention belongs to the technical field of power semiconductor devices, and particularly relates to a planar silicon carbide reverse-blocking MOSFET device and a preparation method thereof. Compared with a traditional planar silicon carbide MOSFET, the planar silicon carbide reverse-blocking MOSFET device in the invention has the following advantages: an N-type silicon carbide substrate is removed, a first N-type silicon carbide buffer layer is introduced to one side of a source region of the device, a second N-type silicon carbide buffer layer is introduced to one side of a drain region of the device, and a junction Schottky barrier diode structure is introduced to one side of the drain region of the device. According to the above device structure, planar silicon carbide MOSFET has relatively small forward conduction voltage drop while obtaining large forward and reverse symmetrical withstand voltage. In addition, in order to further improve the withstand voltage and conduction characteristics of the device, several corresponding derivative structures are provided.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A silicon carbide Schottky diode with high withstand voltage and a method for manufacturing the same

PendingCN109037356AImprove breakdown voltageReduce electric field strengthSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing technologyPower flow

The invention belongs to the technical field of manufacturing semiconductor devices, the invention relates to a silicon carbide Schottky diode with high withstand voltage, A semiconductor substrate comprises an N-type silicon carbide substrate and an N-type silicon carbide epitaxial layer, the upper part of the N-type silicon carbide epitaxial layer is provided with a plurality of spaced apart strip-shaped first P-type well regions and strip-shaped first N-type well regions, A plurality of stripe-shaped second P-type well regions and stripe-shaped second N-type well regions are arranged belowor on the lower surface of the stripe-shaped first P-type well region and the stripe-shaped first N-type well region respectively, and the stripe-shaped first P-type well region and the stripe-shapedsecond P-type well region are respectively at angles of 30 degrees to 90 degrees; A stripe-shaped second P-type well region with a certain angle with the stripe-shaped first P-type well region is arranged below the stripe-shaped first P-type well region, and the doping concentration of the stripe-shaped N-type well region in the stripe-shaped P-type well region is increased at the same time, the breakdown voltage of the device is greatly increased, and the surge current capability of the device is improved.

Owner:WUXI NCE POWER

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com