Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

120results about How to "Increased process complexity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

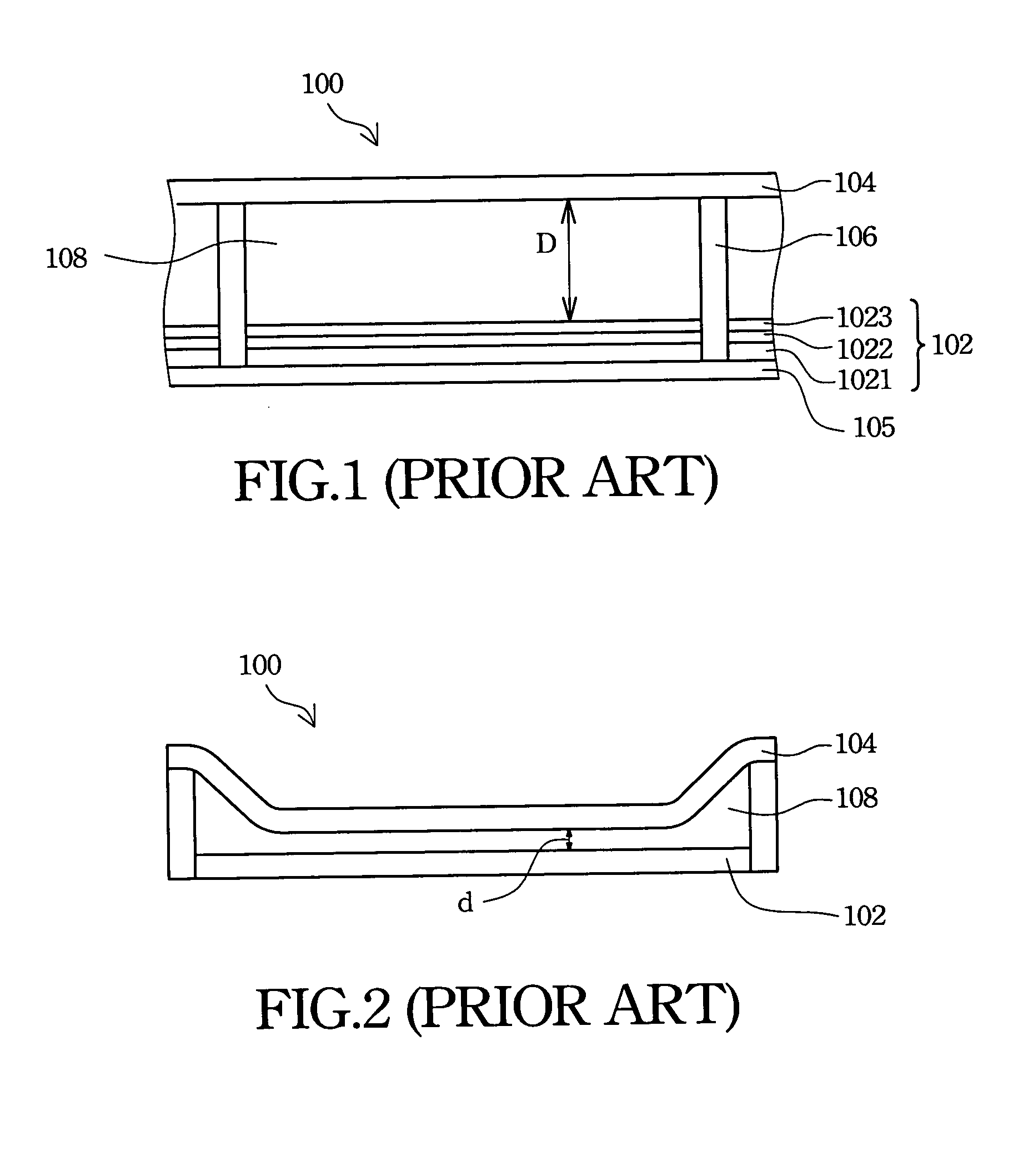

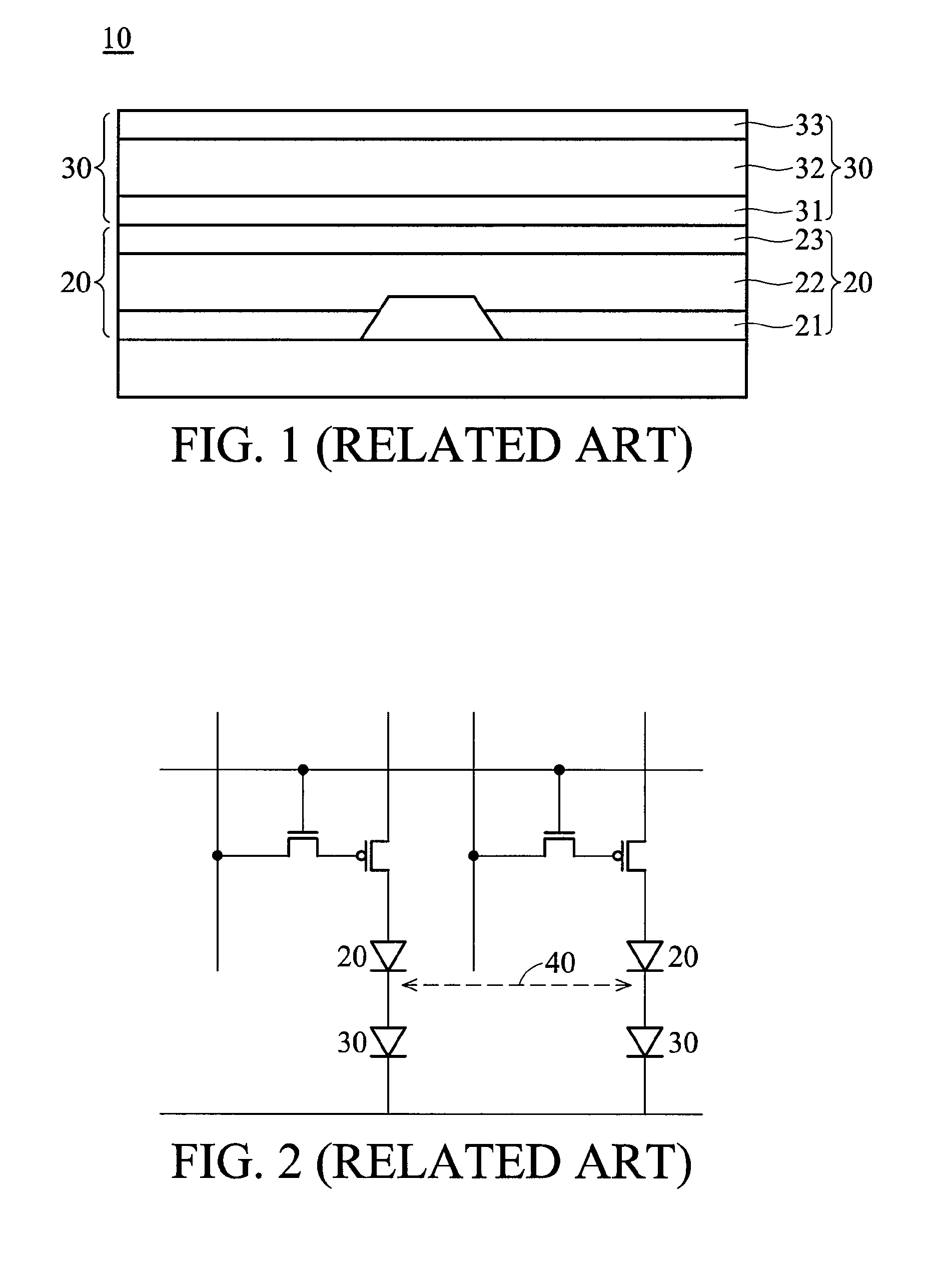

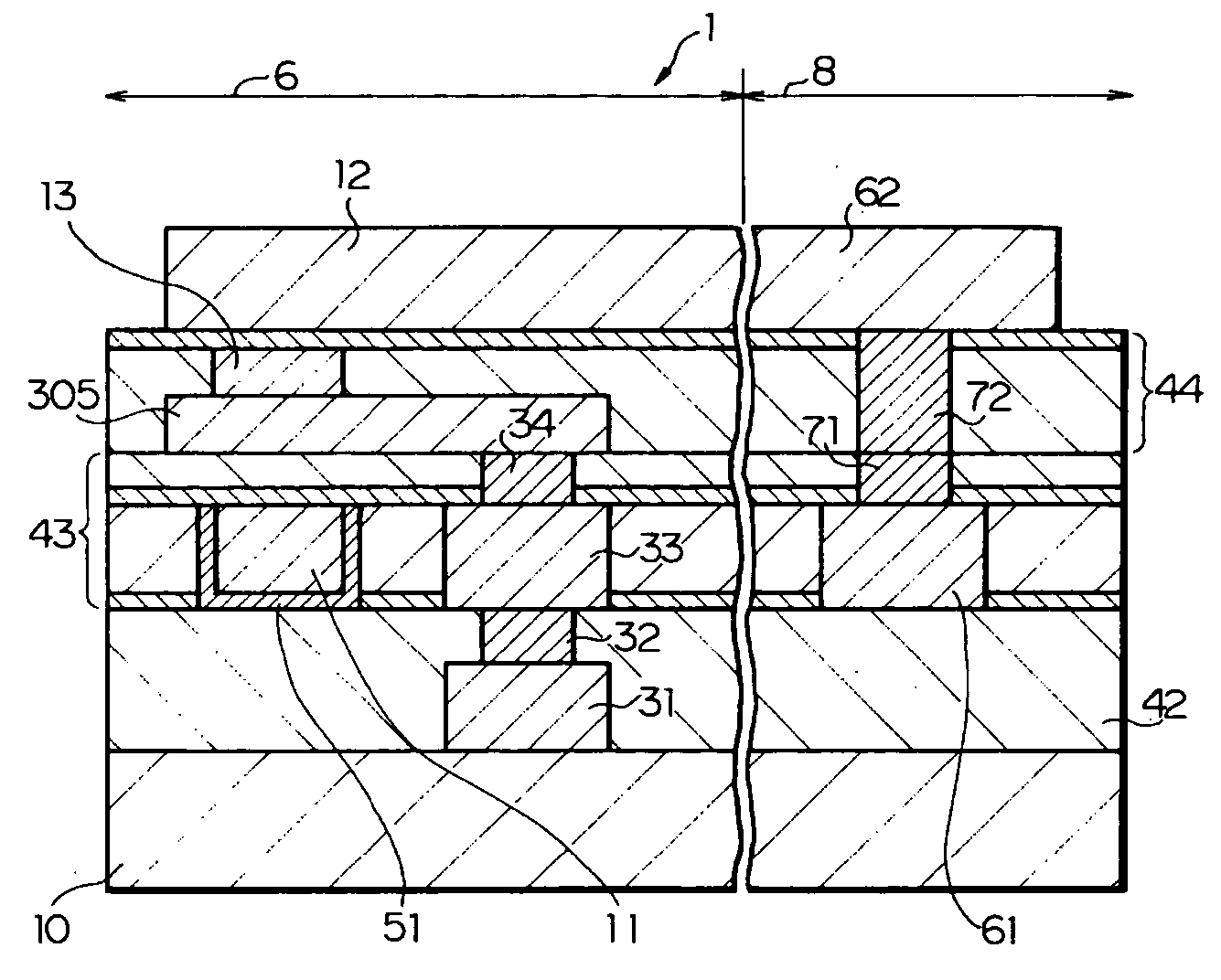

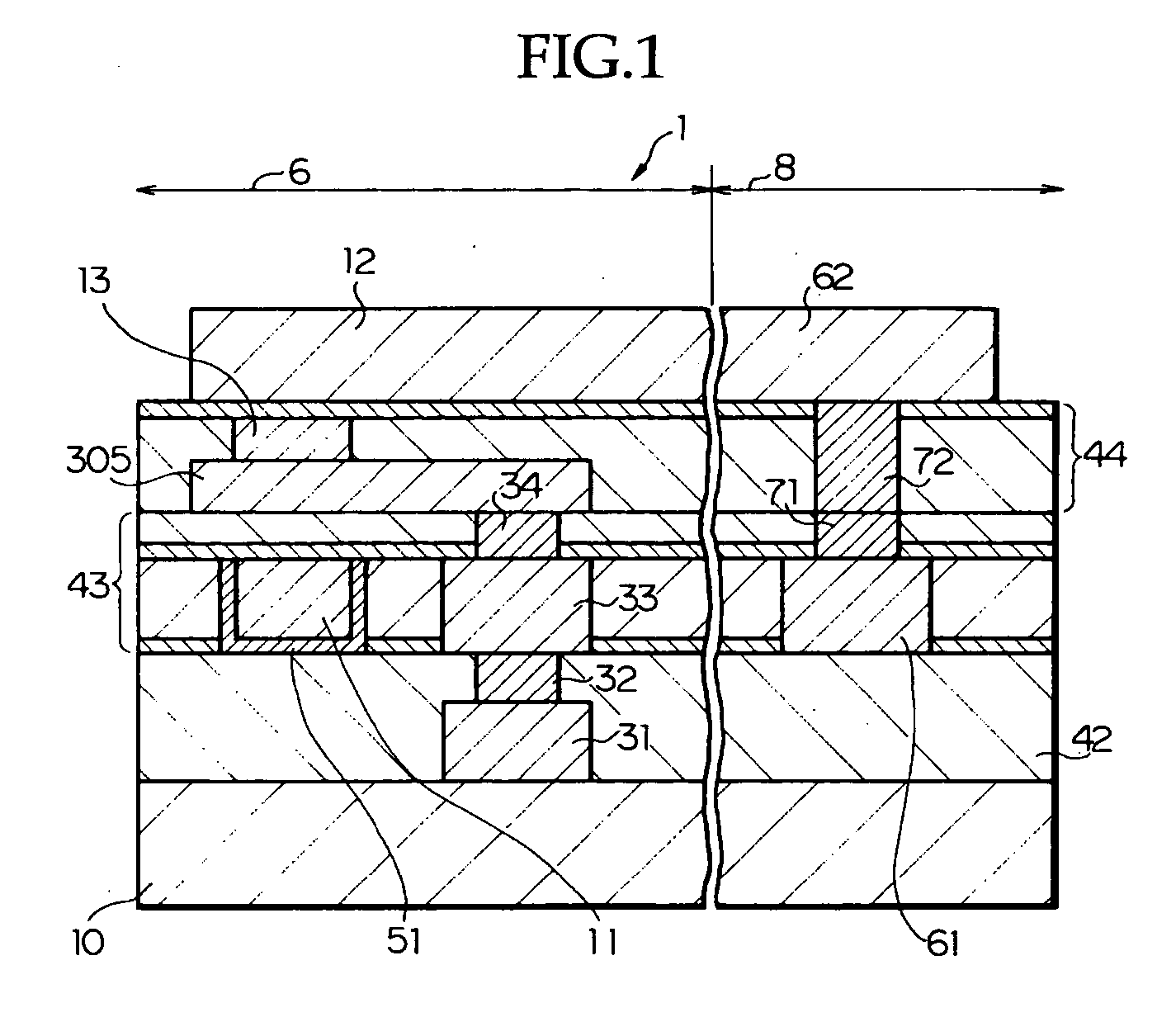

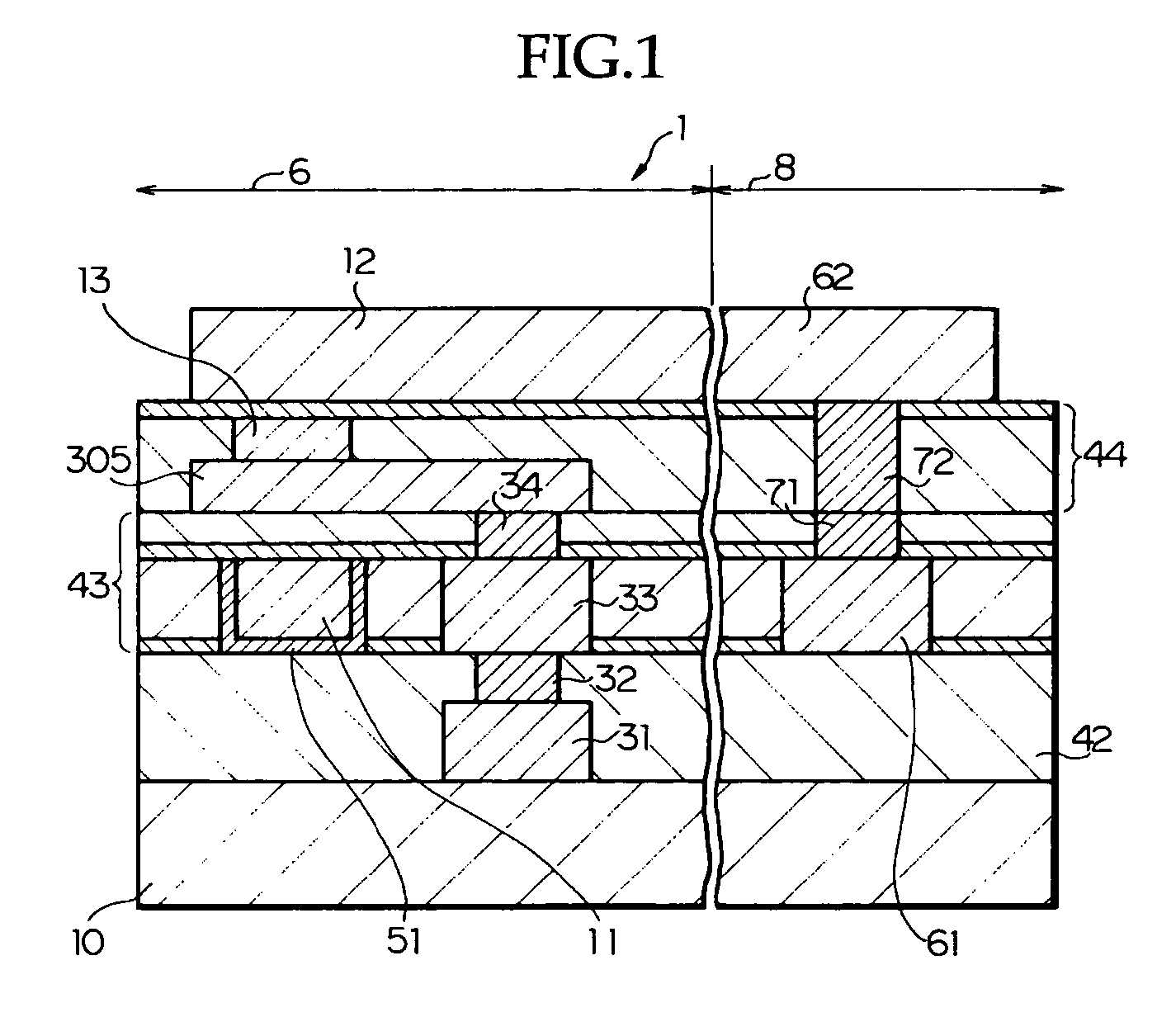

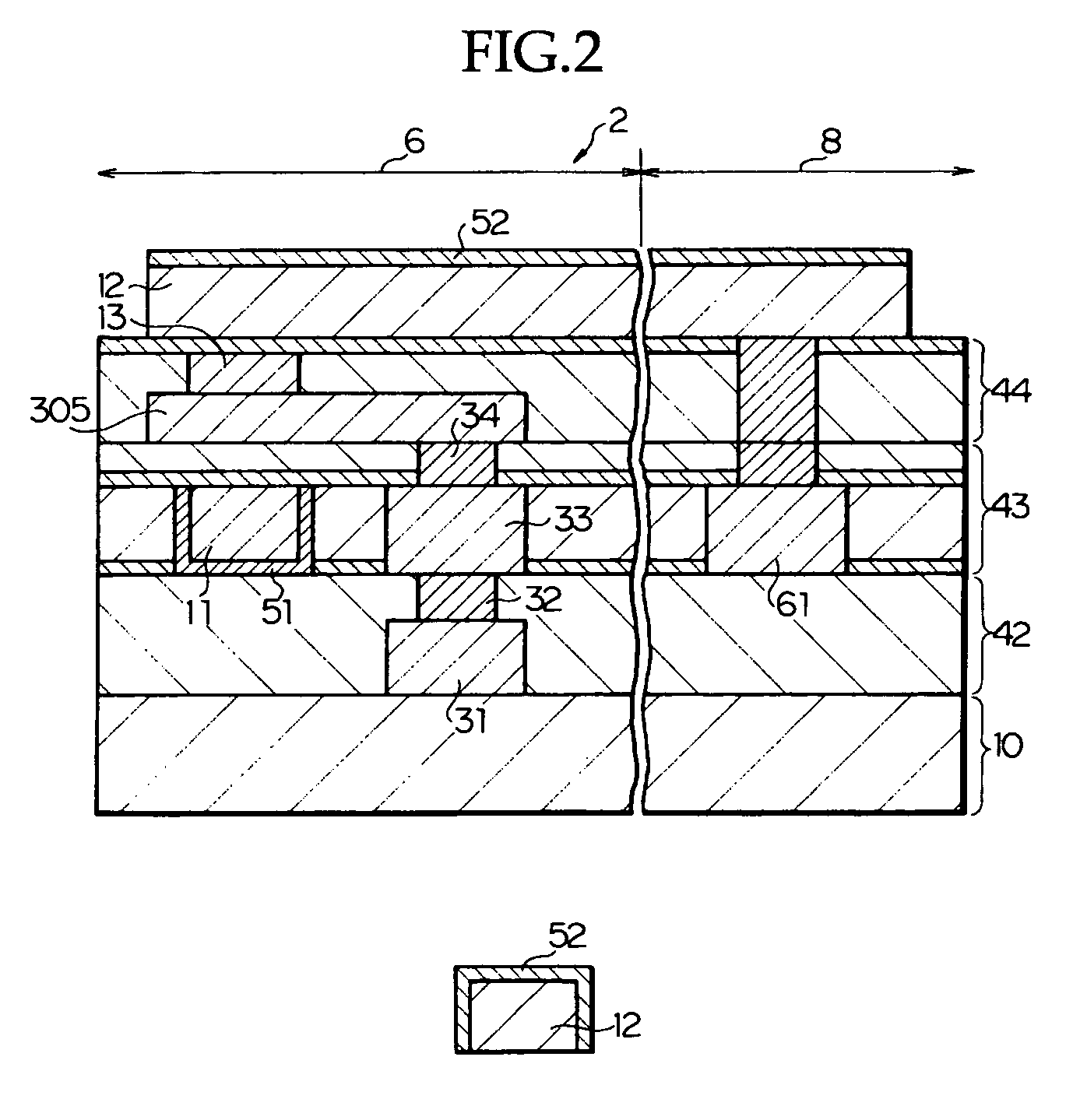

Structure of an optical interference display unit

InactiveUS6958847B2Avoid pollutionIncreased process complexityTelevision system detailsColor television detailsLight reflectionReflective layer

Owner:SNAPTRACK

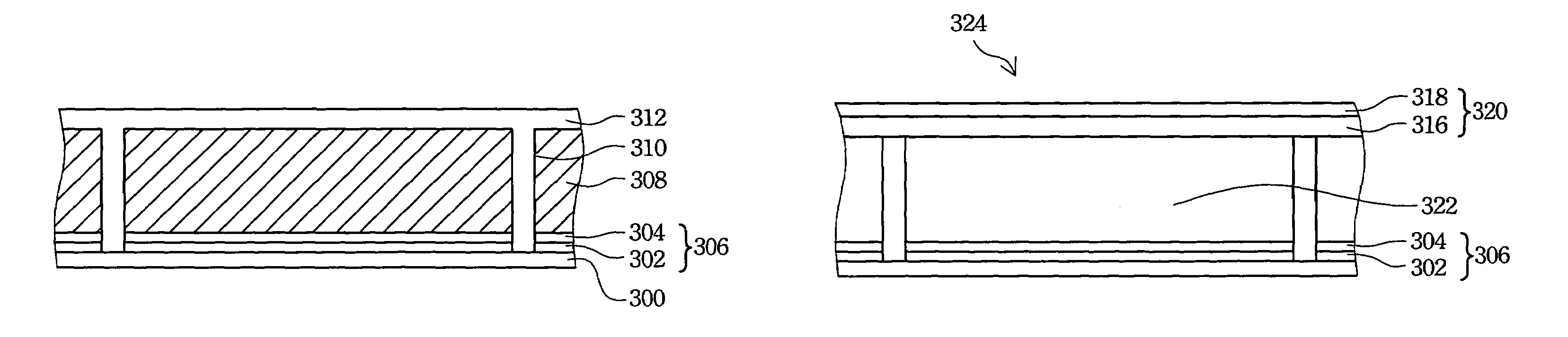

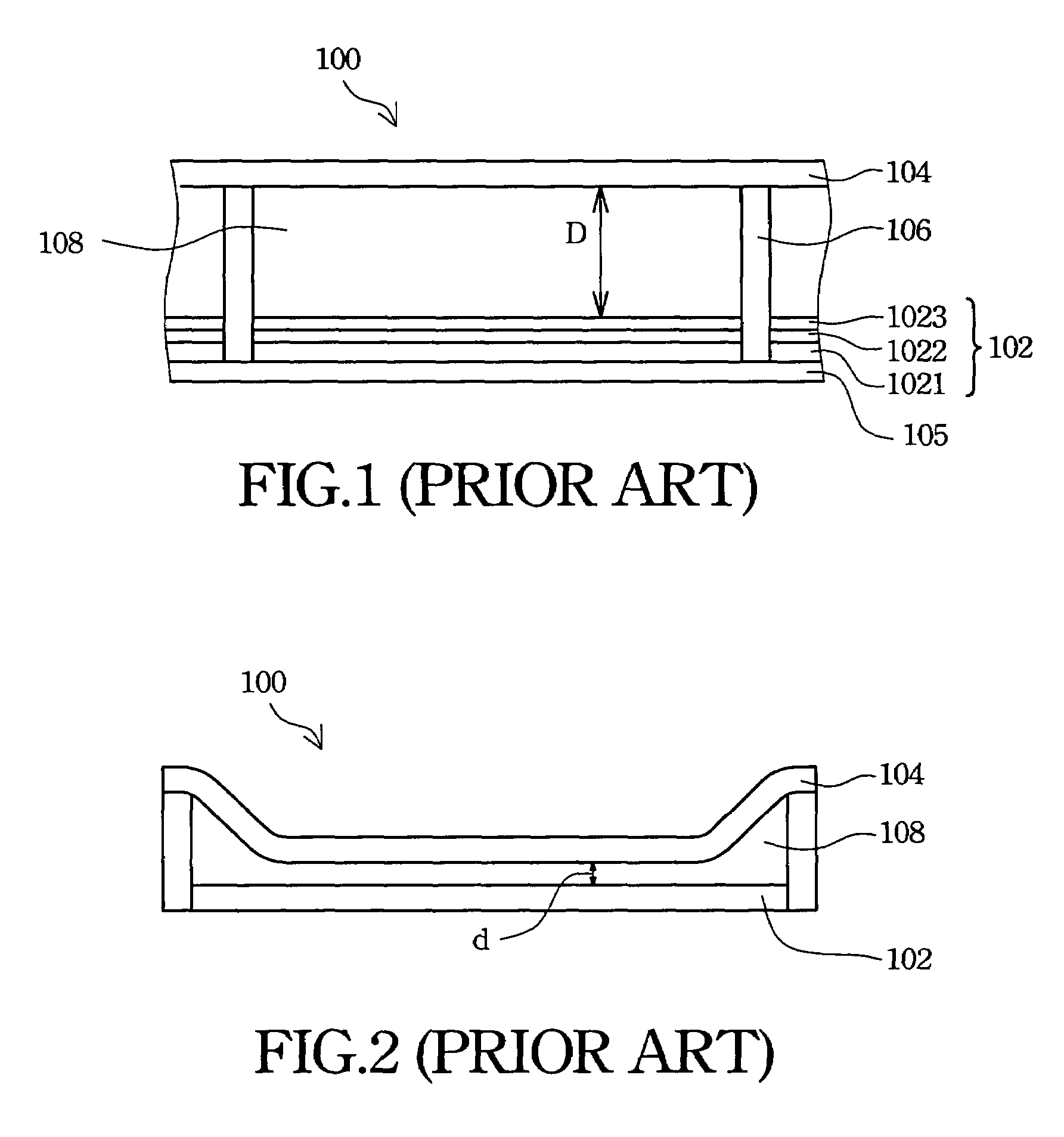

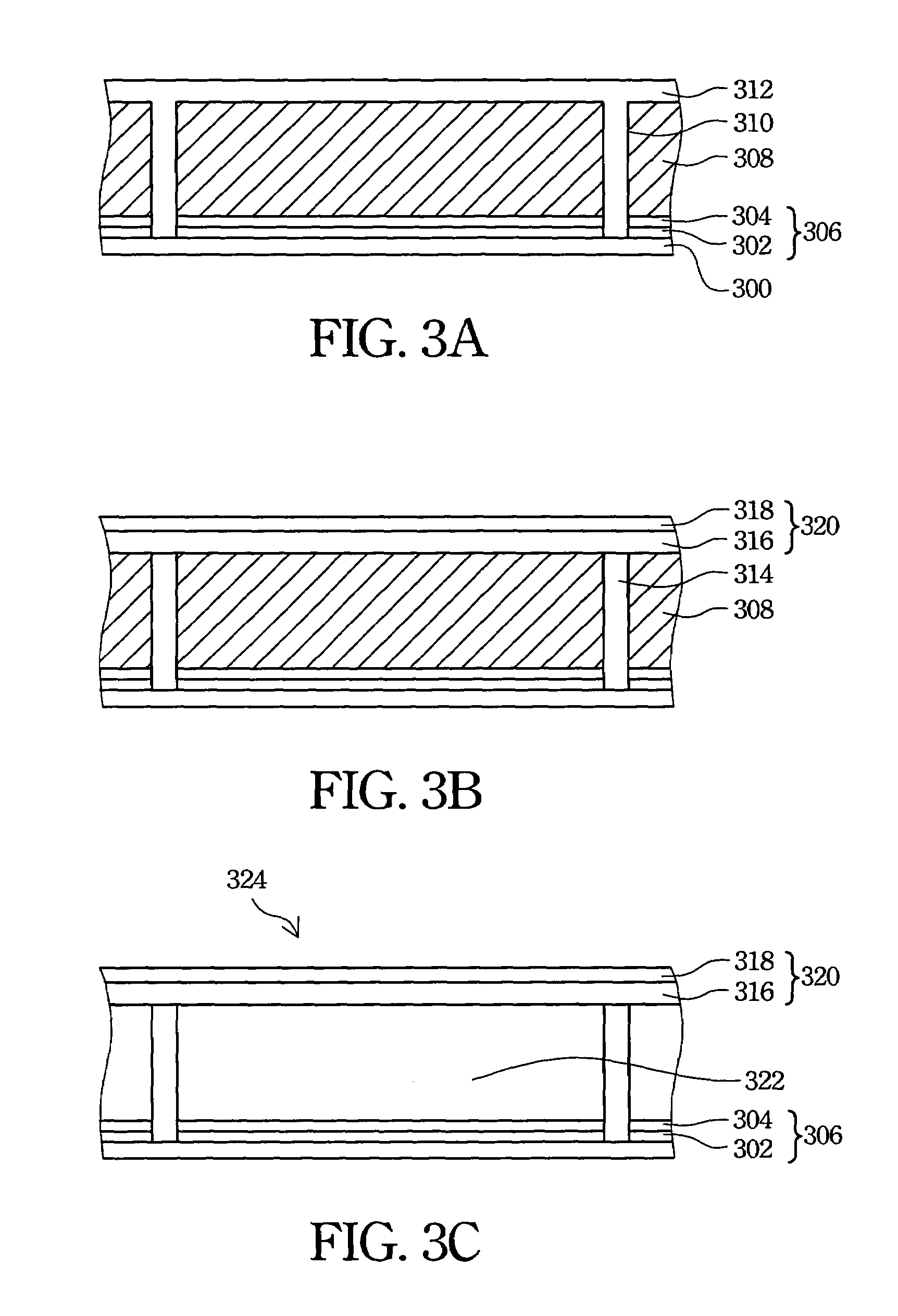

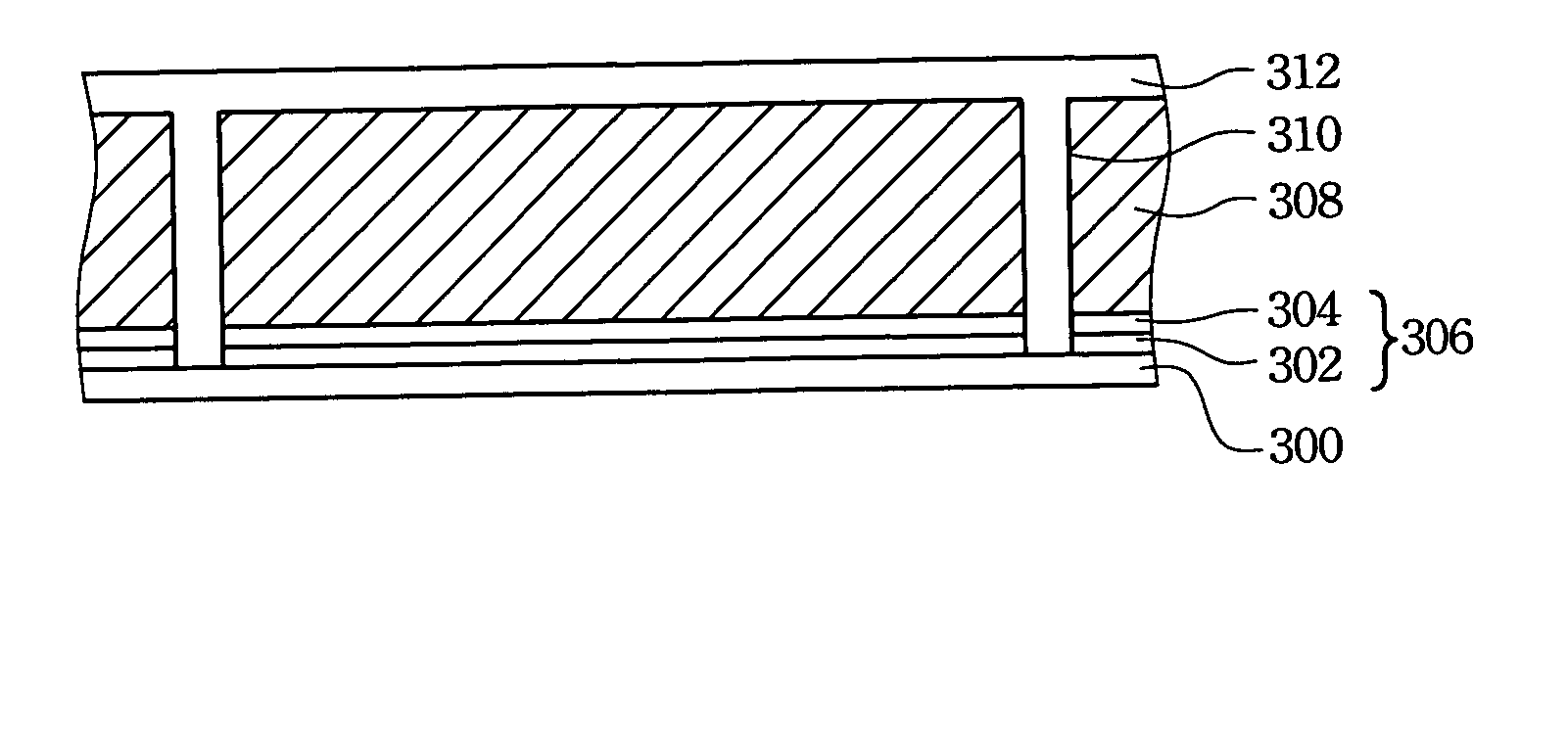

Structure of an optical interference display unit

InactiveUS20050157364A1Good uniformity and qualityIncrease mechanical stressTelevision system detailsColor television detailsLight reflectionReflective layer

An optical interference display unit, at least comprises a light-incidence electrode and a light-reflection electrode located on a transparent substrate. The light-incidence electrode at least comprises a transparent conductive layer and a dielectric layer. The light-reflection electrode at least comprises an absorption layer and a reflective layer.

Owner:SNAPTRACK

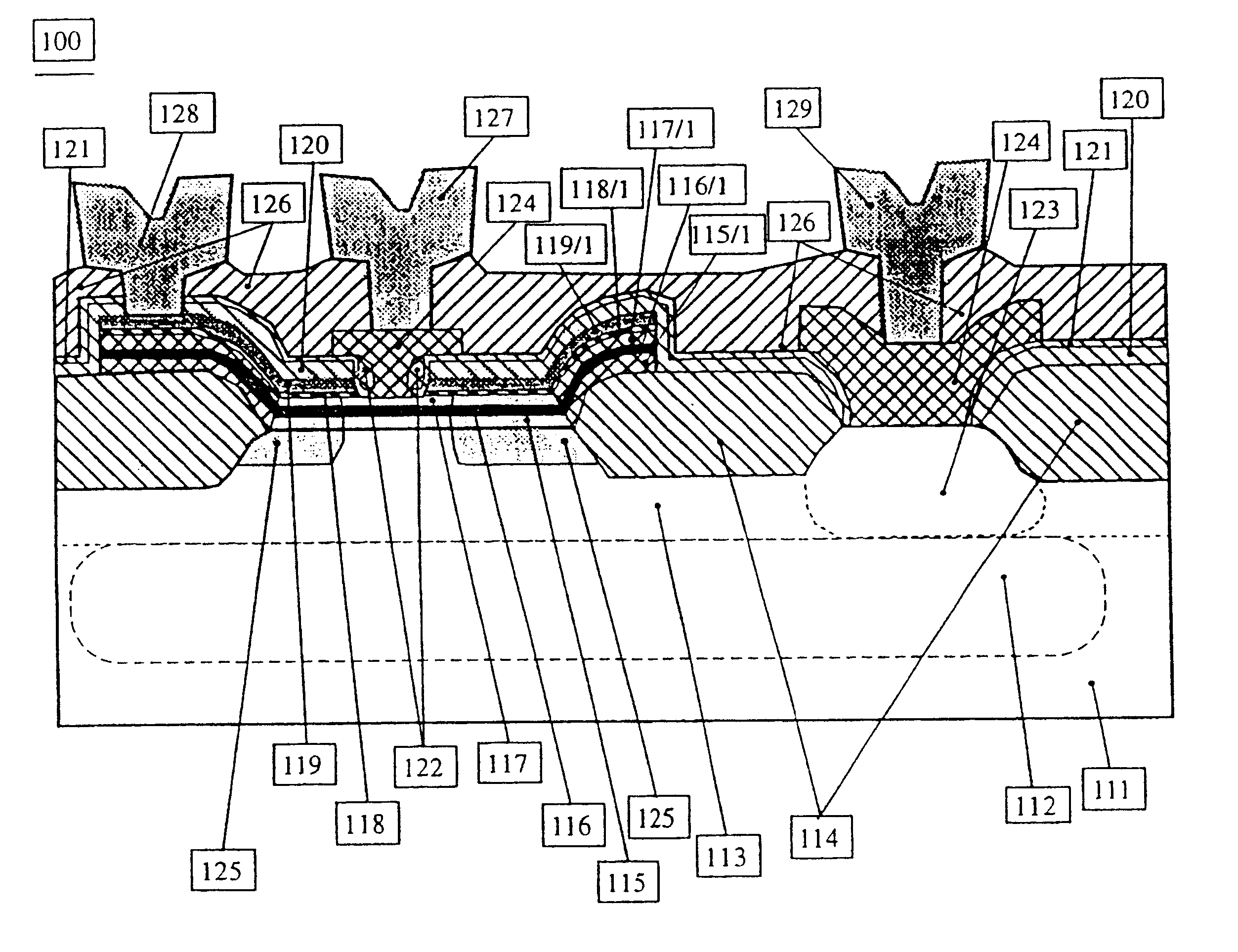

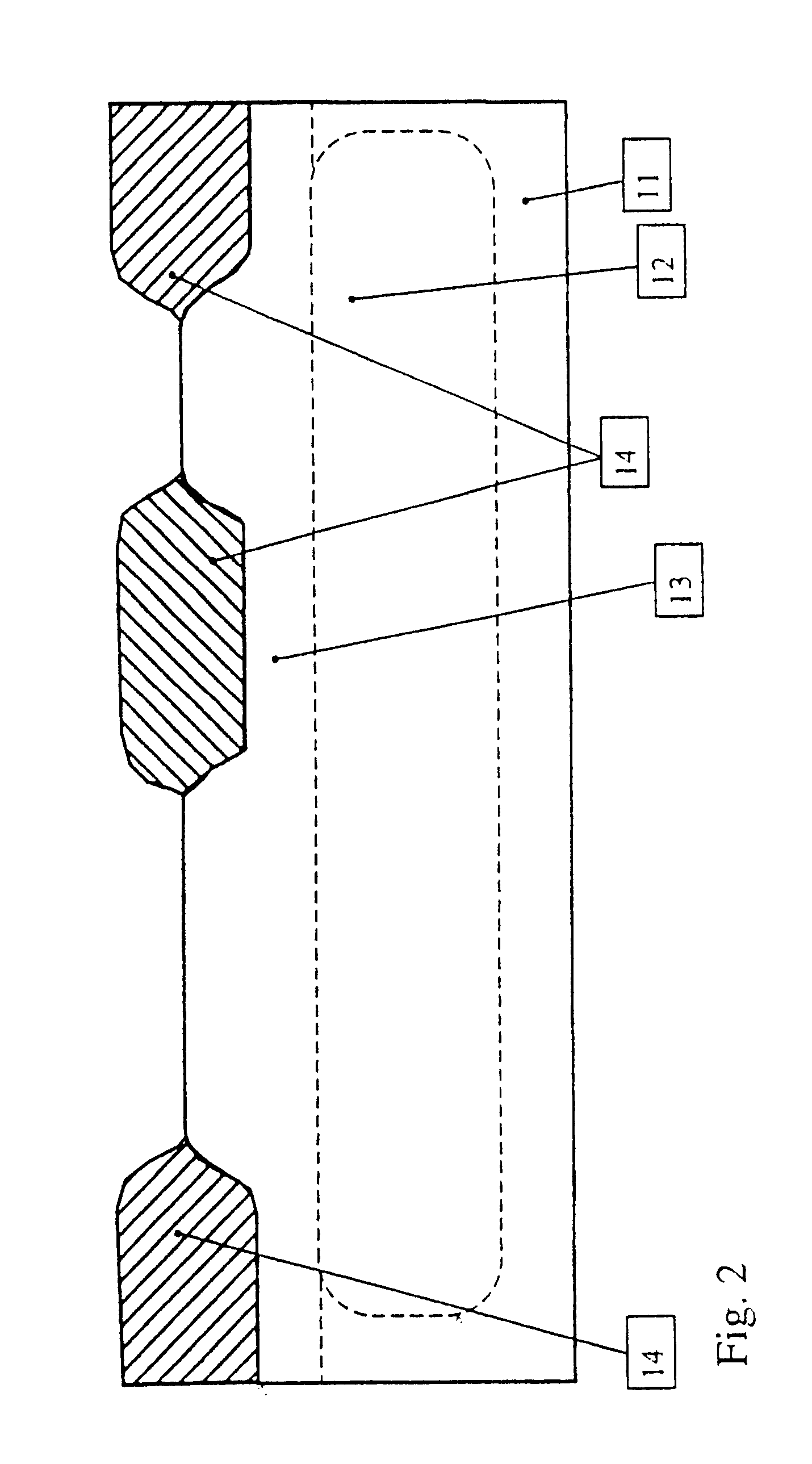

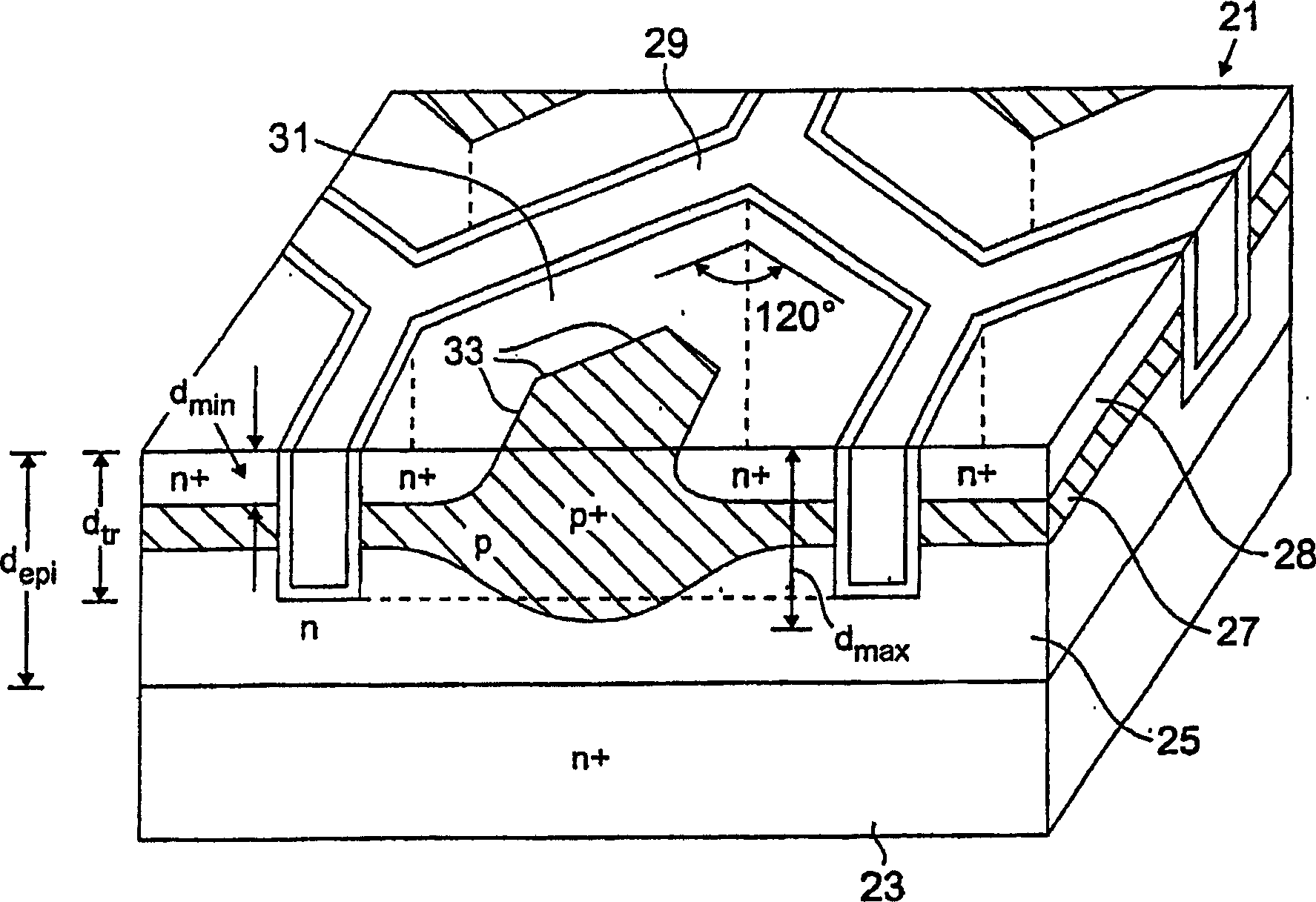

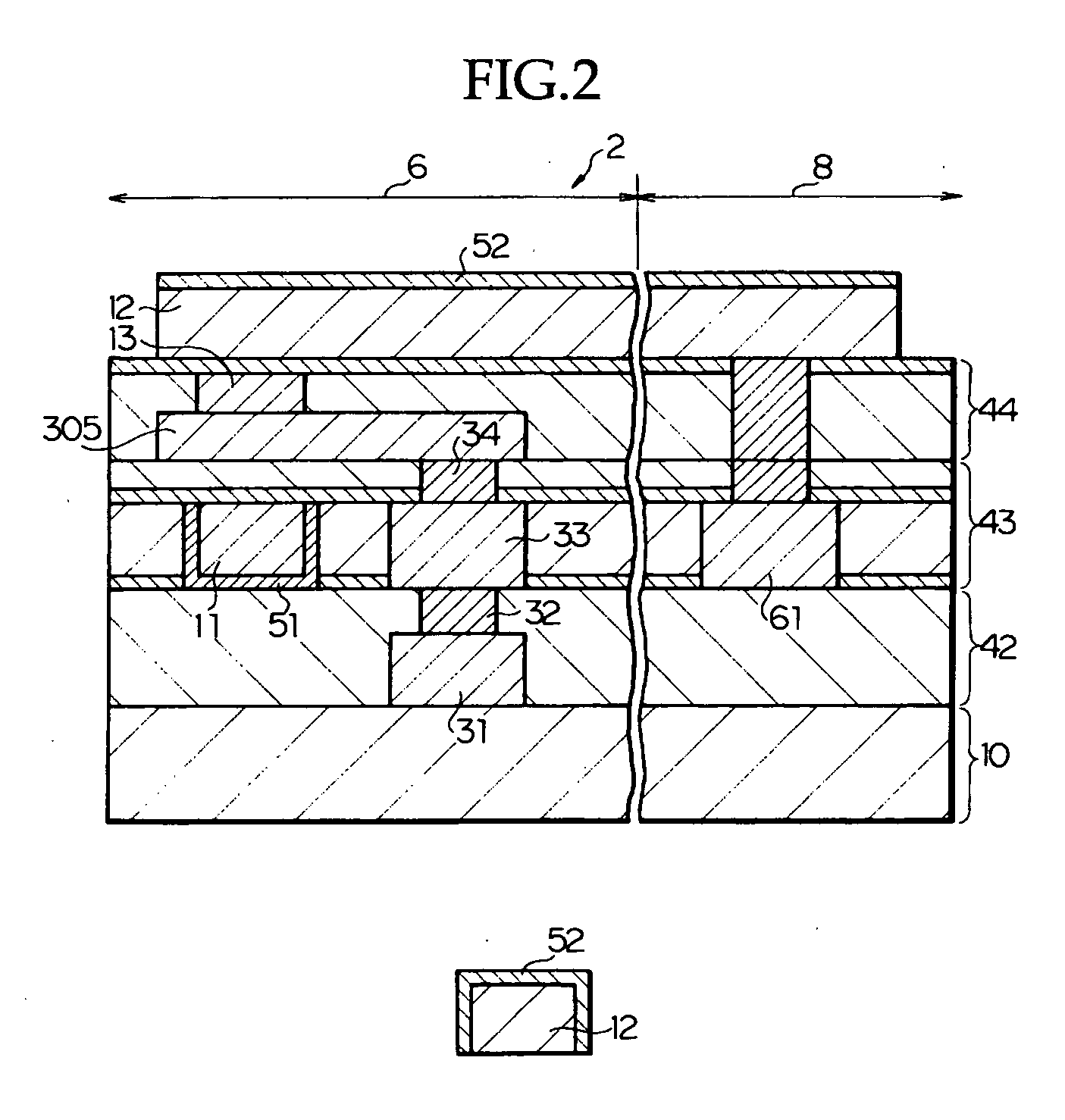

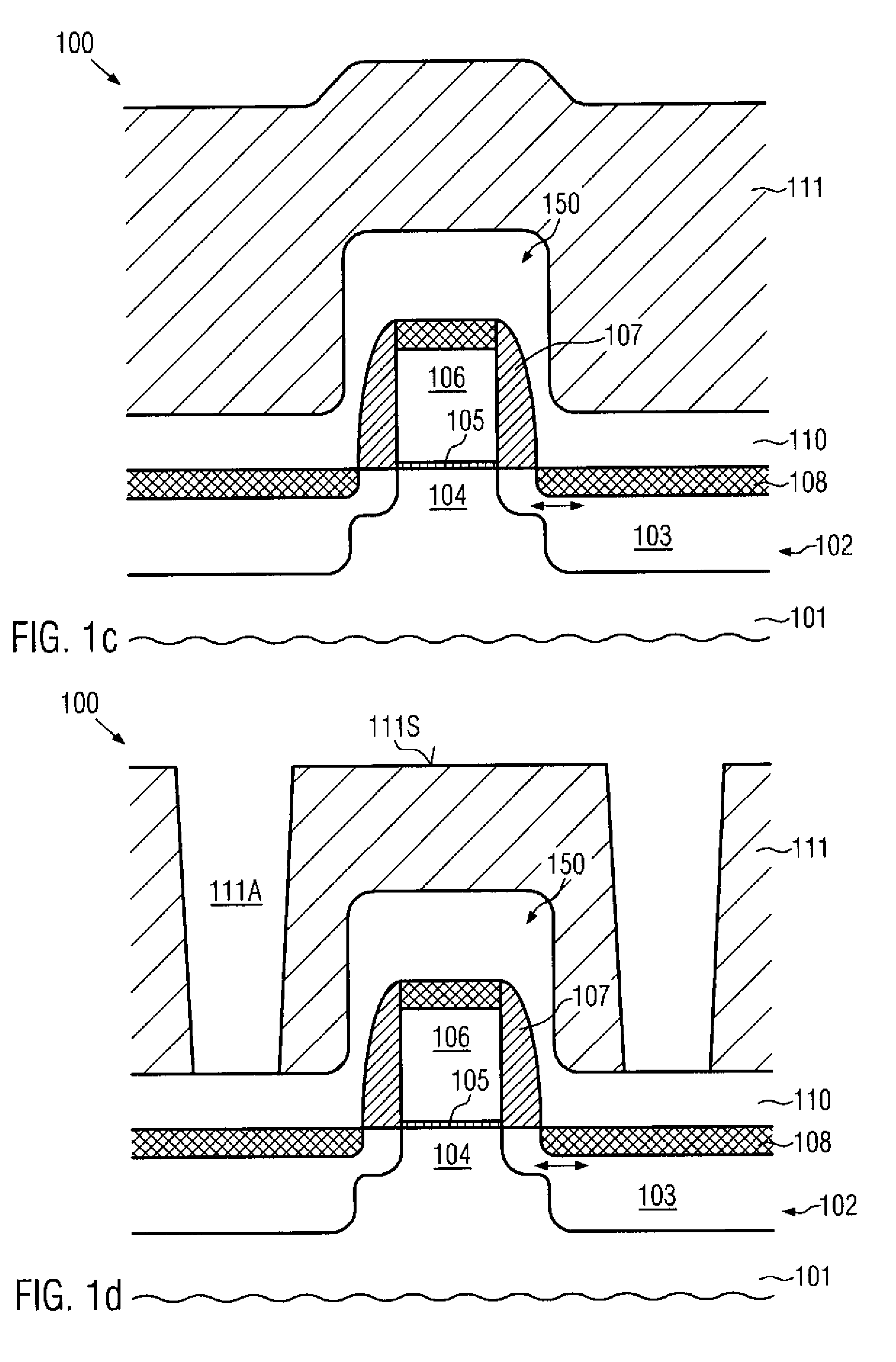

Bipolar transistor and method for producing same

InactiveUS6642553B1Reduced external base resistanceReduce capacitanceTransistorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceSingle process

The invention relates to a bipolar transistor and a method for producing same. The aim of the invention is to provide a bipolar transistor and a method for producing same, which during the use of a single-process poly-silicon technology with differential epitaxis for the production of bases overcomes the disadvantages of conventional systems, so as notably further to improve the high-speed properties of a bipolar transistor, provide the most conductive connections possible between the metal contacts and the active (internal) transistor region as well as a minimized passive transistor surface, while at the same time avoiding greater process complexity and increased contact resistances. To this end a surface relief is produced in the active emitter region by a wet-chemical process. A single-process poly-silicon bipolar transistor having a base produced by epitaxis in accordance with the invention permits a reduction in external base resistance without causing a deterioration in emitter properties. Because the internal and external base regions are deposited continuously no interface problems arise during connection of the base. Base-collector capacity can also be lowered.

Owner:INST FUR HALBLEITERPHYSIK FRFURT ODER

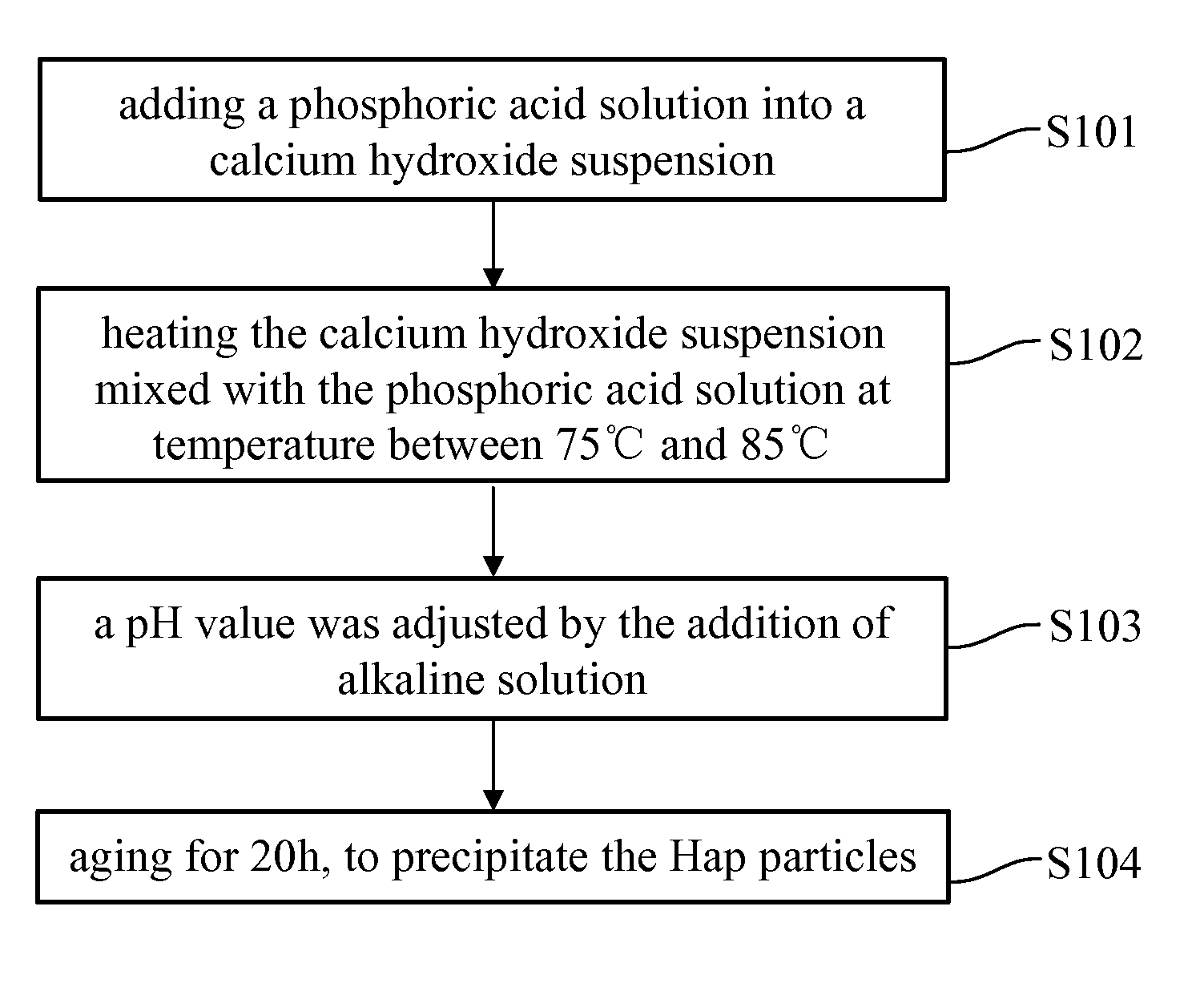

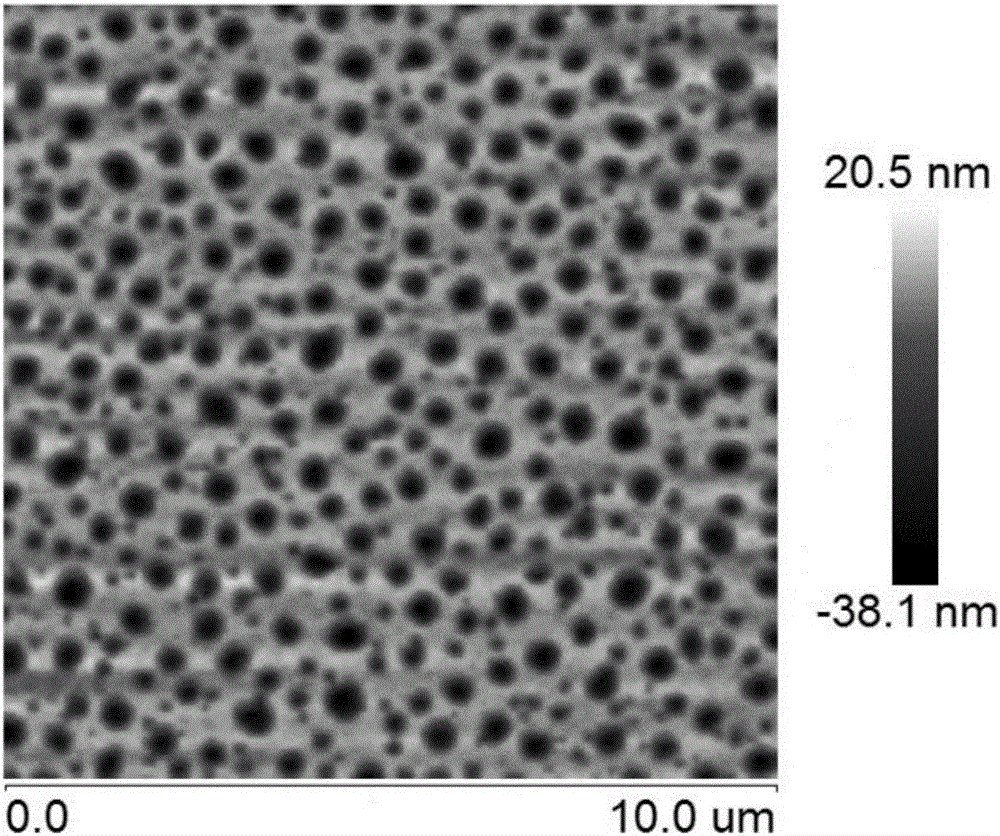

Superparamagnetic nanoparticles IN MEDICAL THERAPEUTICS and manufacturing method THEREOF

InactiveUS20110135577A1Safe and effectiveAvoid problemsBiocidePeptide/protein ingredientsDelivery vehicleMagnetite

The successful transfer of therapeutic agents such as genetic materials (e.g. nucleic acid) or drug into living cells is the most important issue depending on the development of the delivery carrier. A method for manufacturing superparamagnetic nanoparticles in medical therapeutics is described to develop nano-sized calcium phosphate (CaP) mineral was rendered magnetic as delivery vehicle. The CaP-based magnetized nanoparticles (NPs) were possessed superparamagnetic property by hetero-epitaxial growth of magnetite on the CaP crystallites and also showed no harm to the cultured cells and elicited no cytotoxicity. The magnetized CaP was demonstrated to have good plasmid DNA binding affinity or drug carrying capacity. It significantly increased the expression of gene transfection and efficiency in delivery to mesenchymal stem cells (MSCs) under exogenous magnetic field. According to the above facts, this newly-synthesized magnetized CaP NPs has great potential as a novel non-viral targeted delivery vehicle to be applied for medical applications.

Owner:NAT TAIWAN UNIV

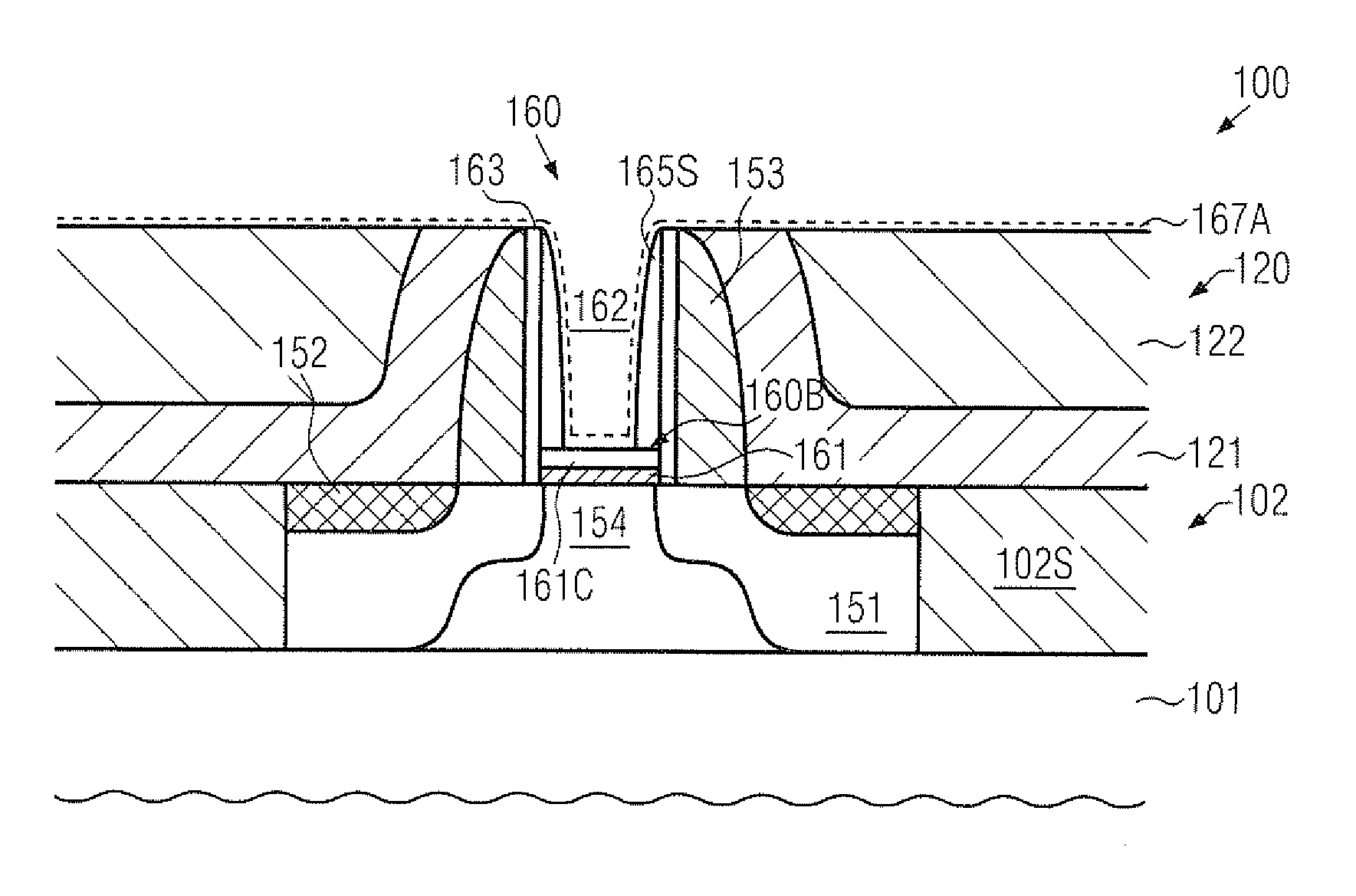

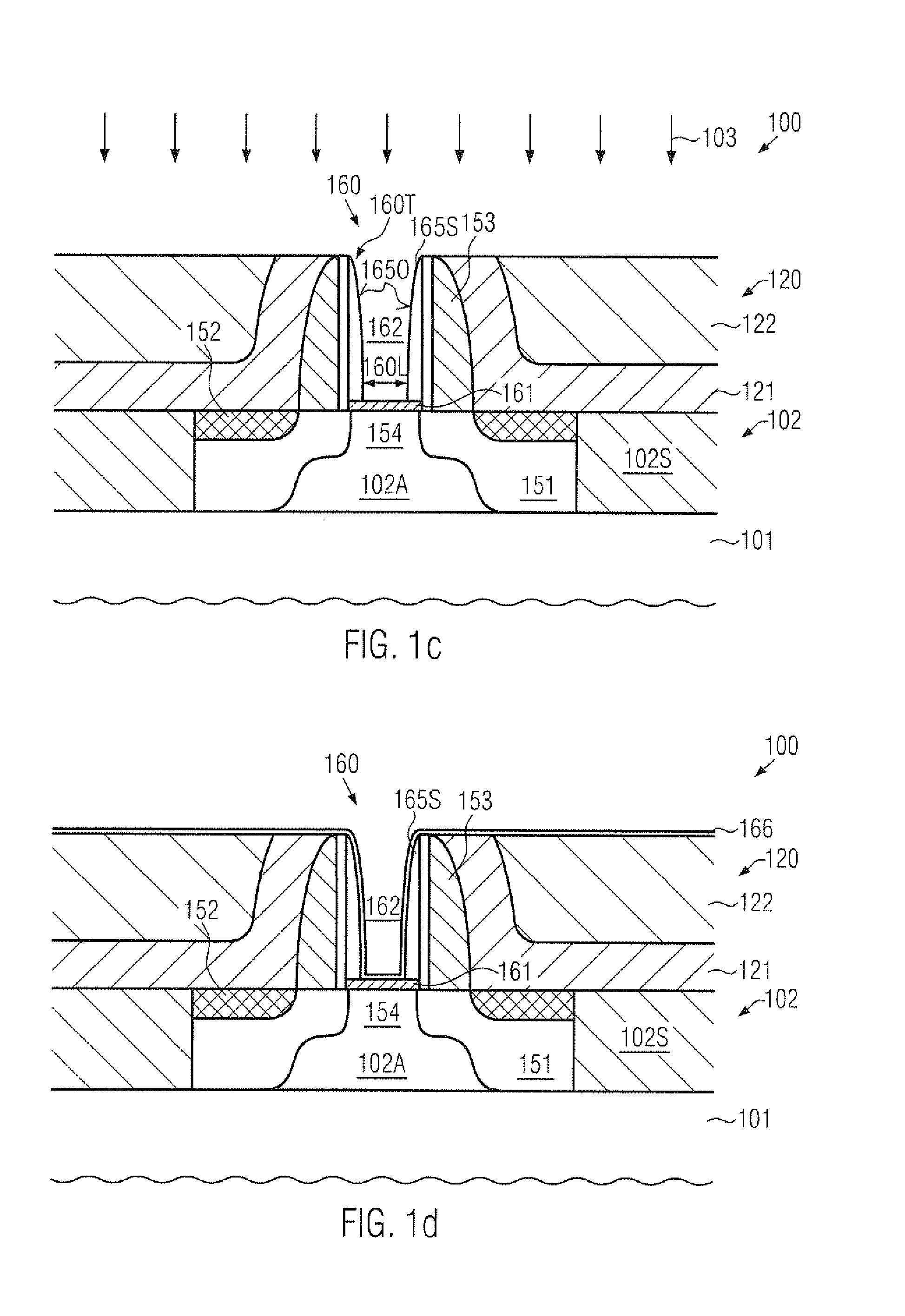

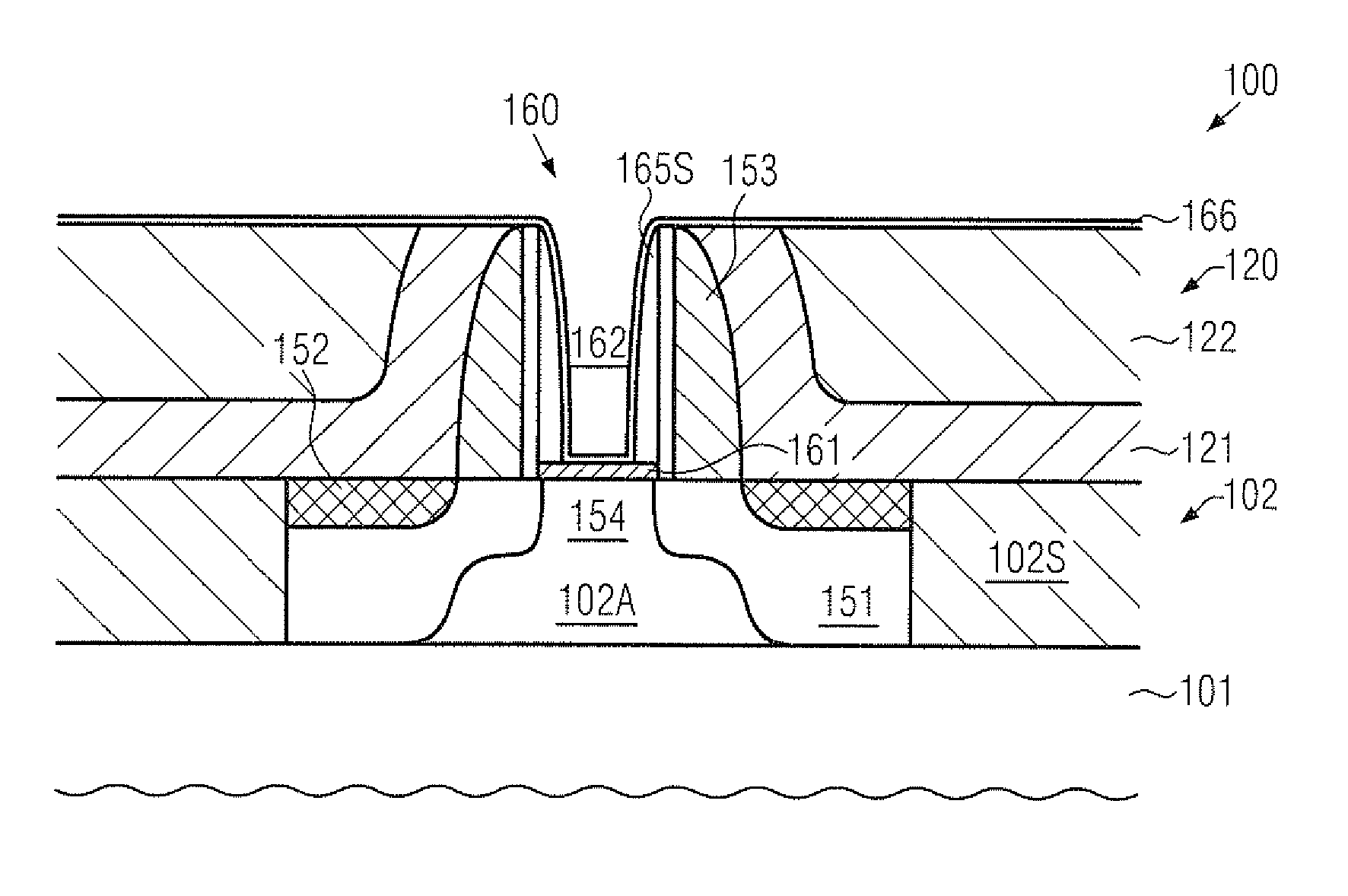

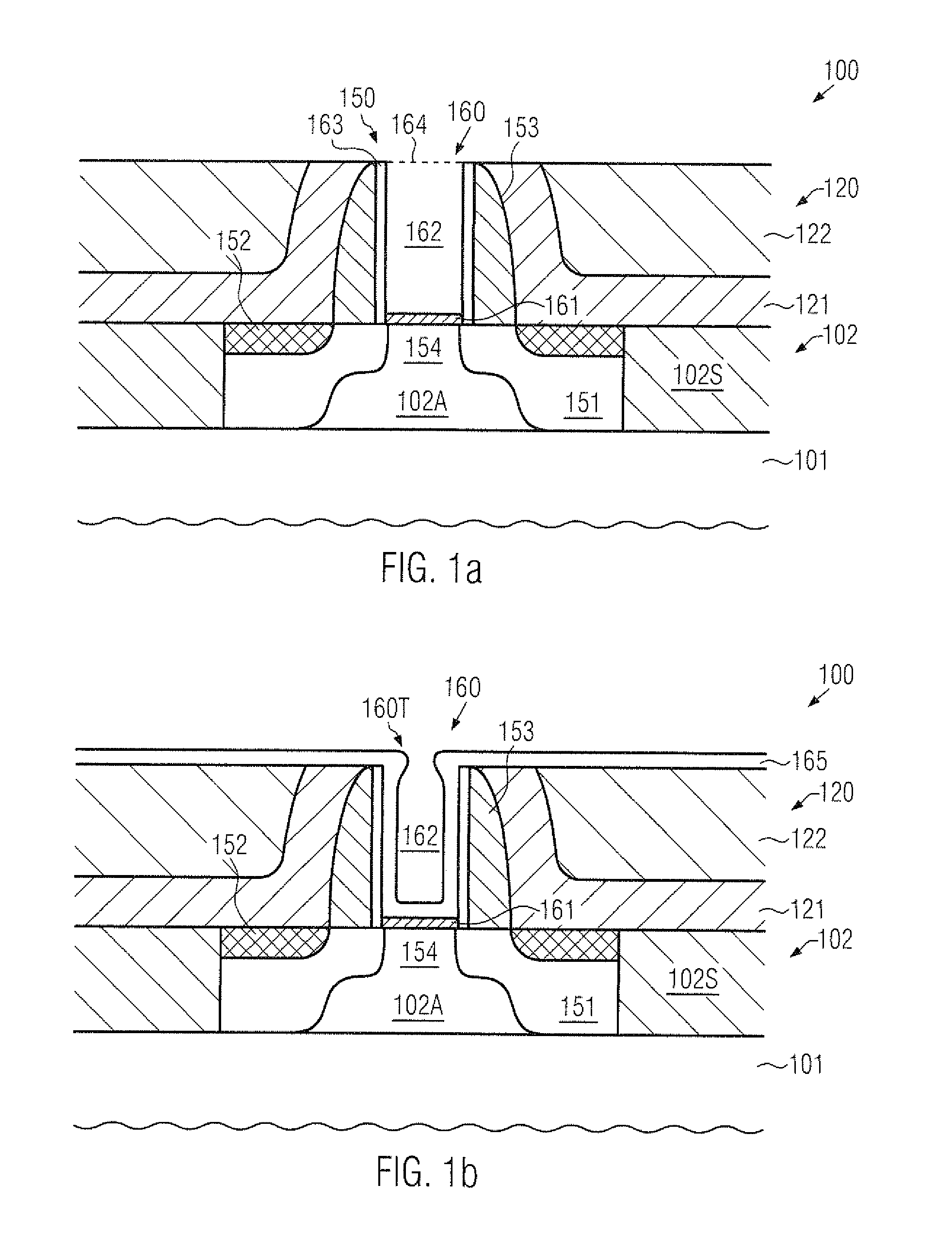

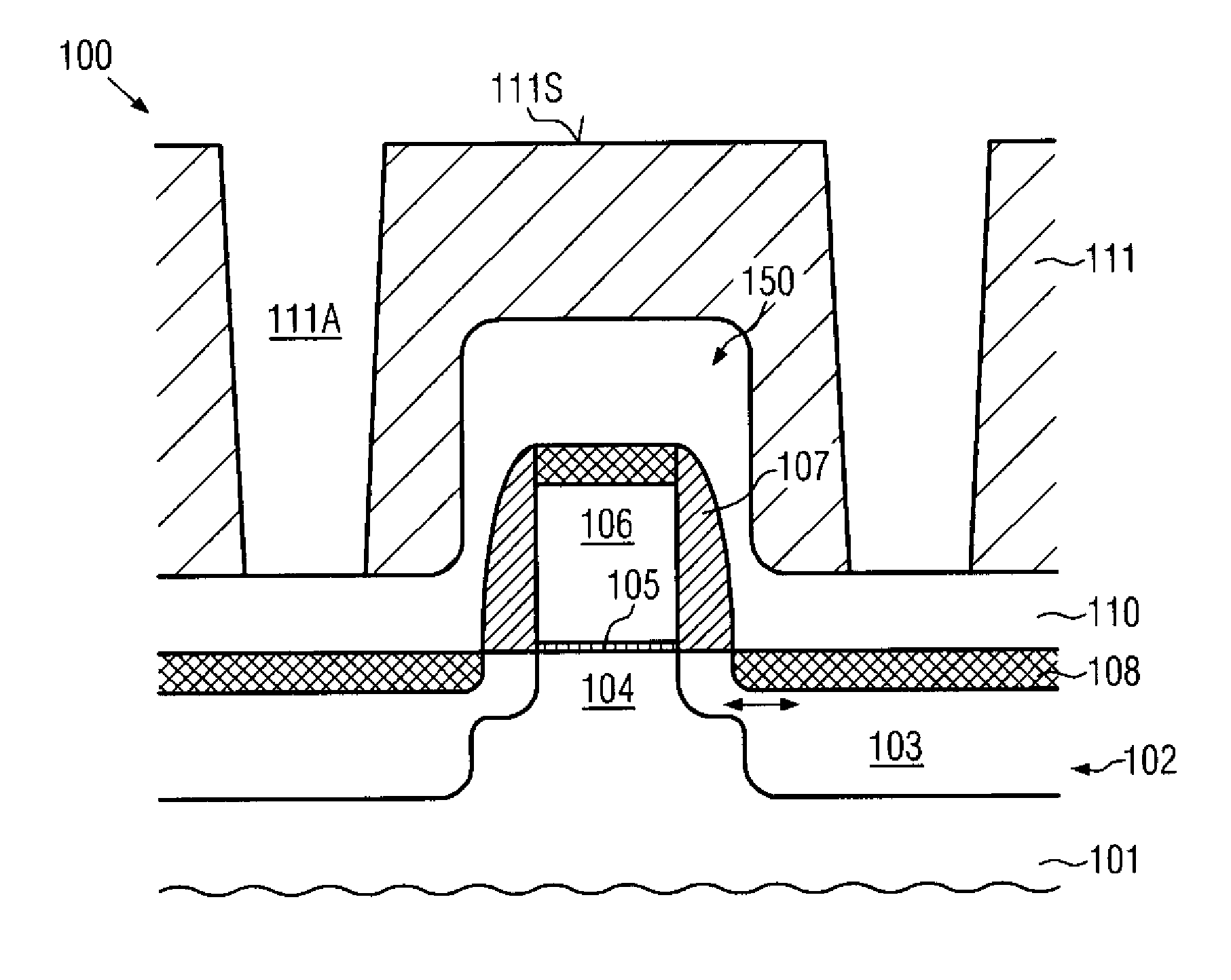

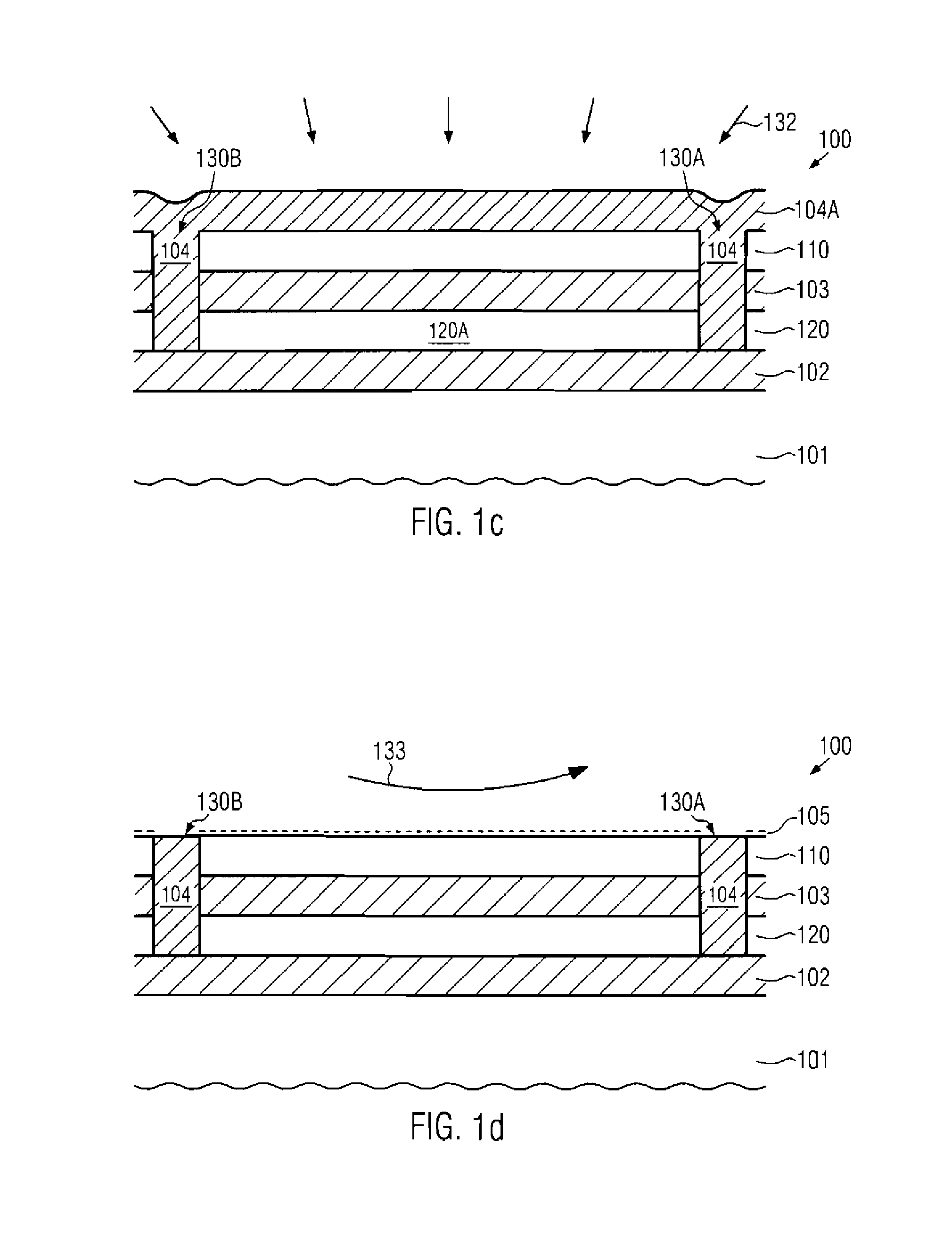

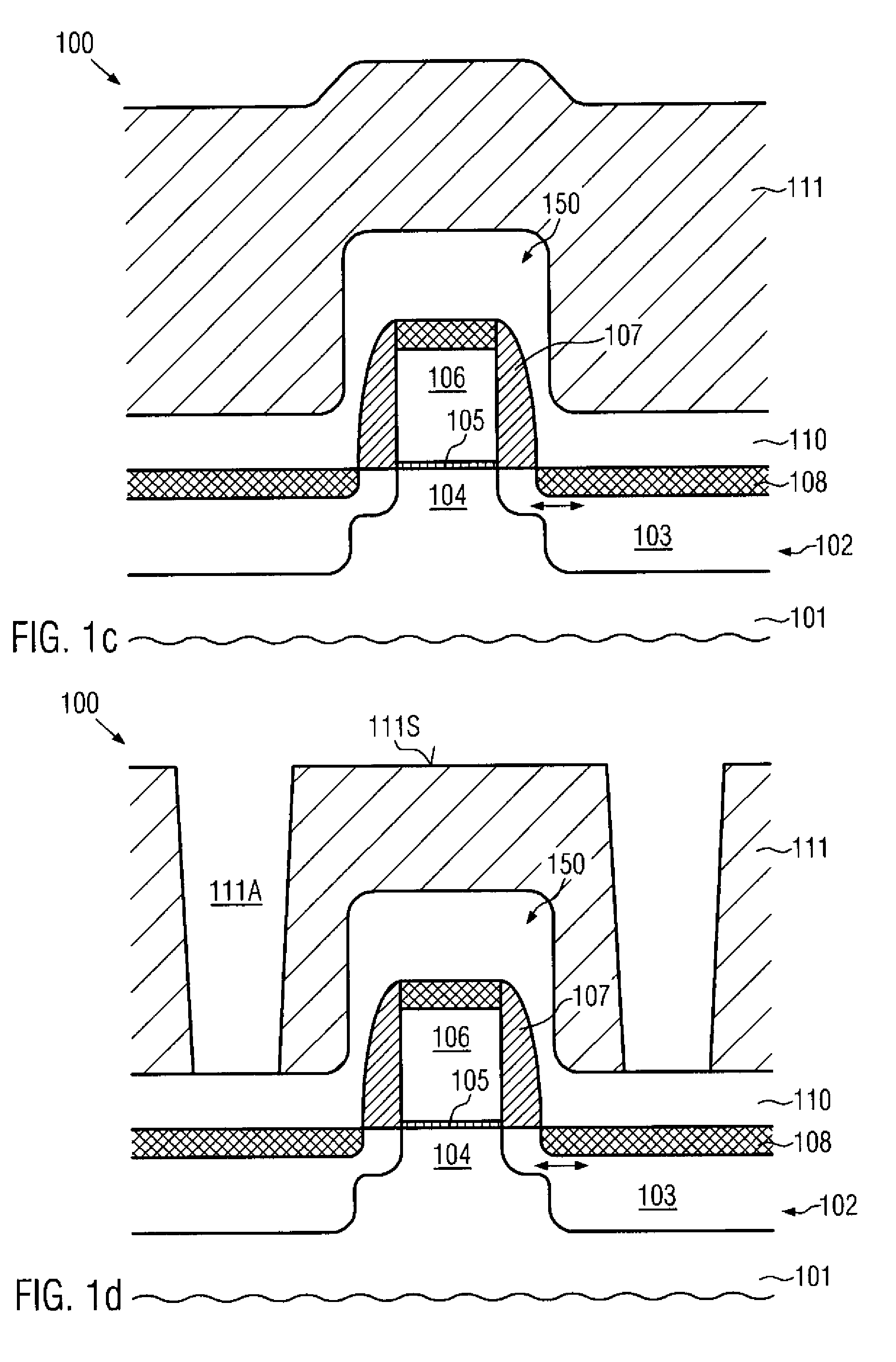

Replacement gate approach based on a reverse offset spacer applied prior to work function metal deposition

ActiveUS20110186915A1Reduce horizontal sizeEffective regulationTransistorSemiconductor/solid-state device manufacturingWork functionEngineering

In a replacement gate approach, a spacer may be formed in the gate opening after the removal of the placeholder material, thereby providing a superior cross-sectional shape upon forming any electrode metals in the gate opening. Moreover, the spacer may be used for reducing the gate length, while not requiring more complex gate patterning strategies.

Owner:GLOBALFOUNDRIES US INC

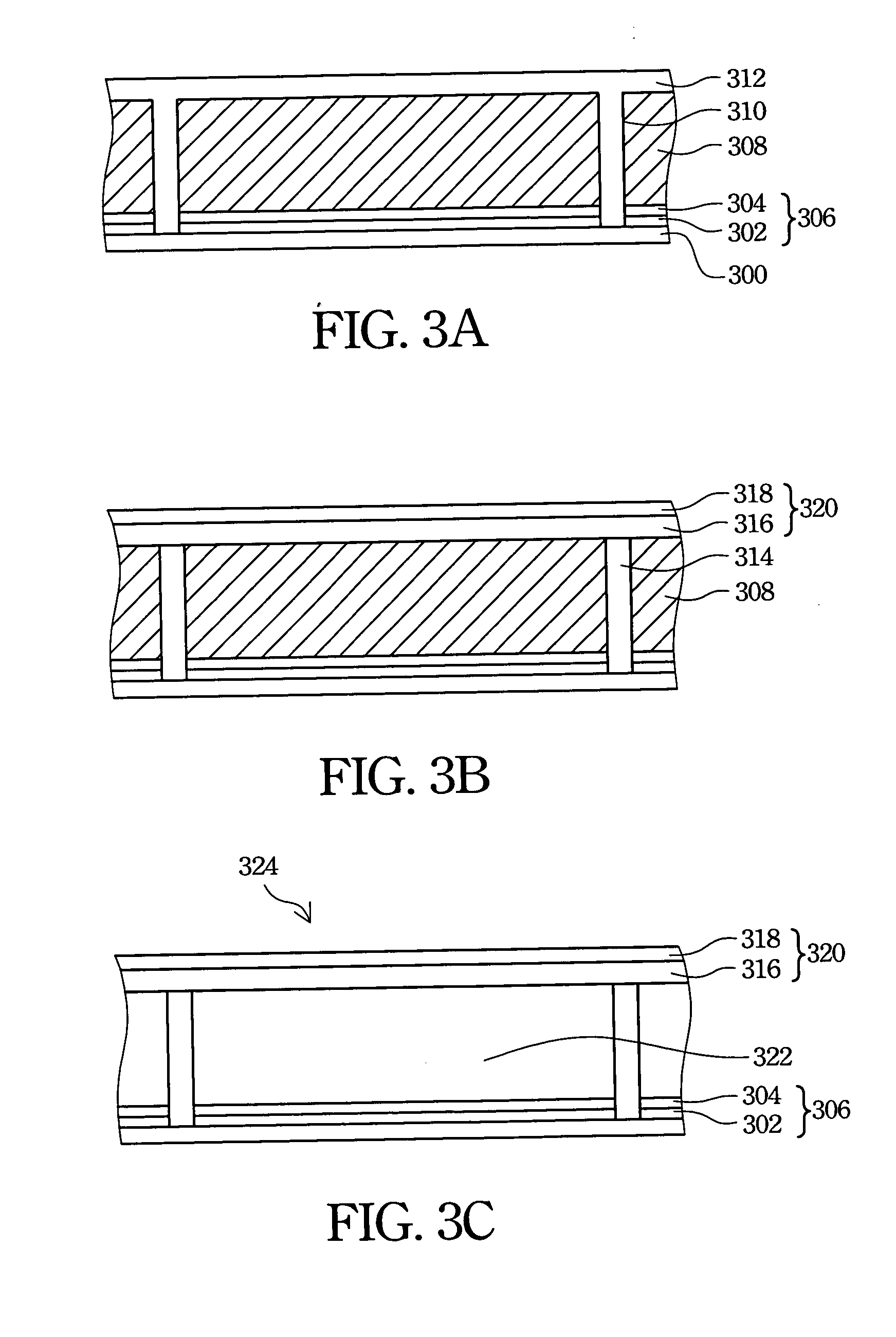

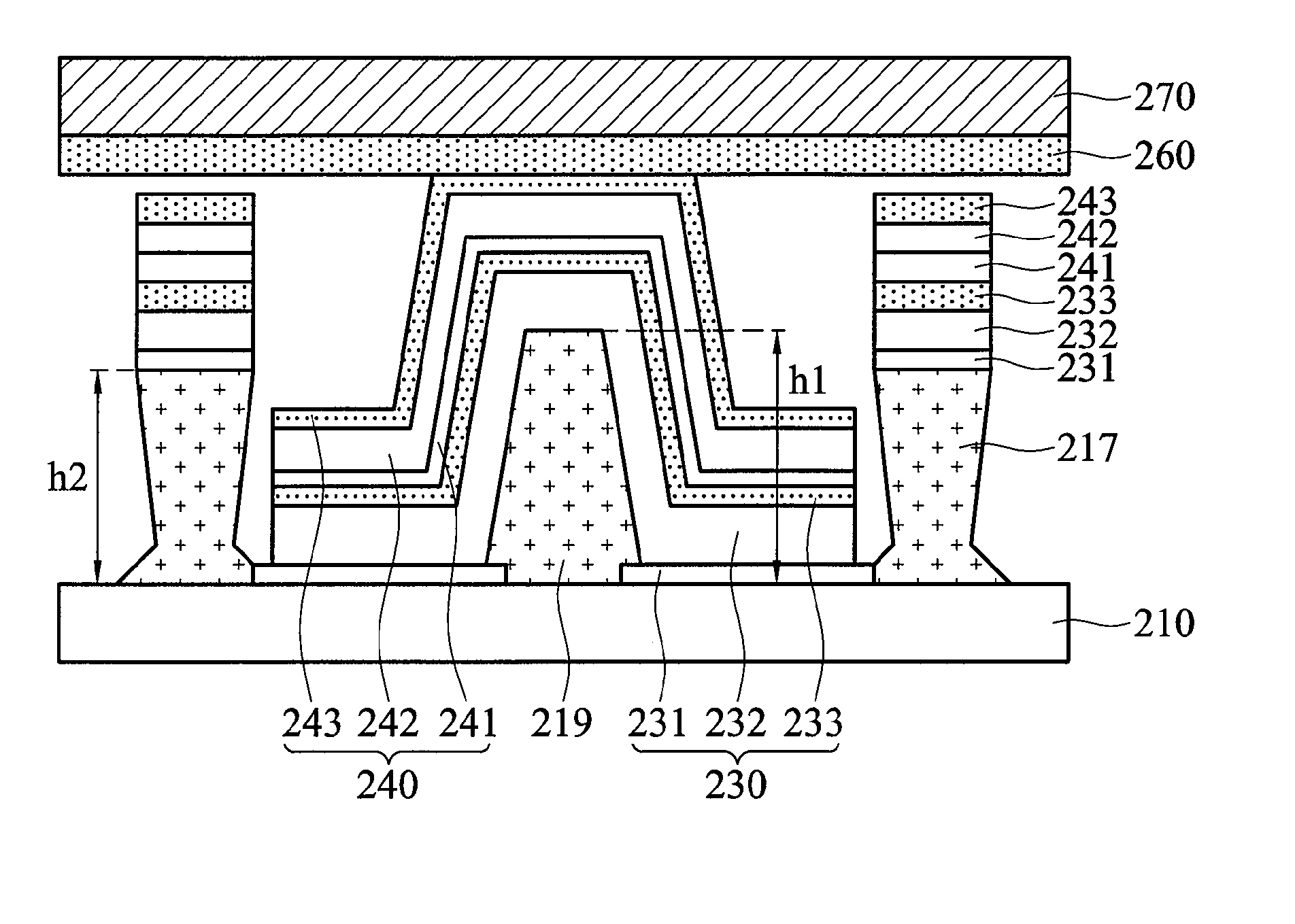

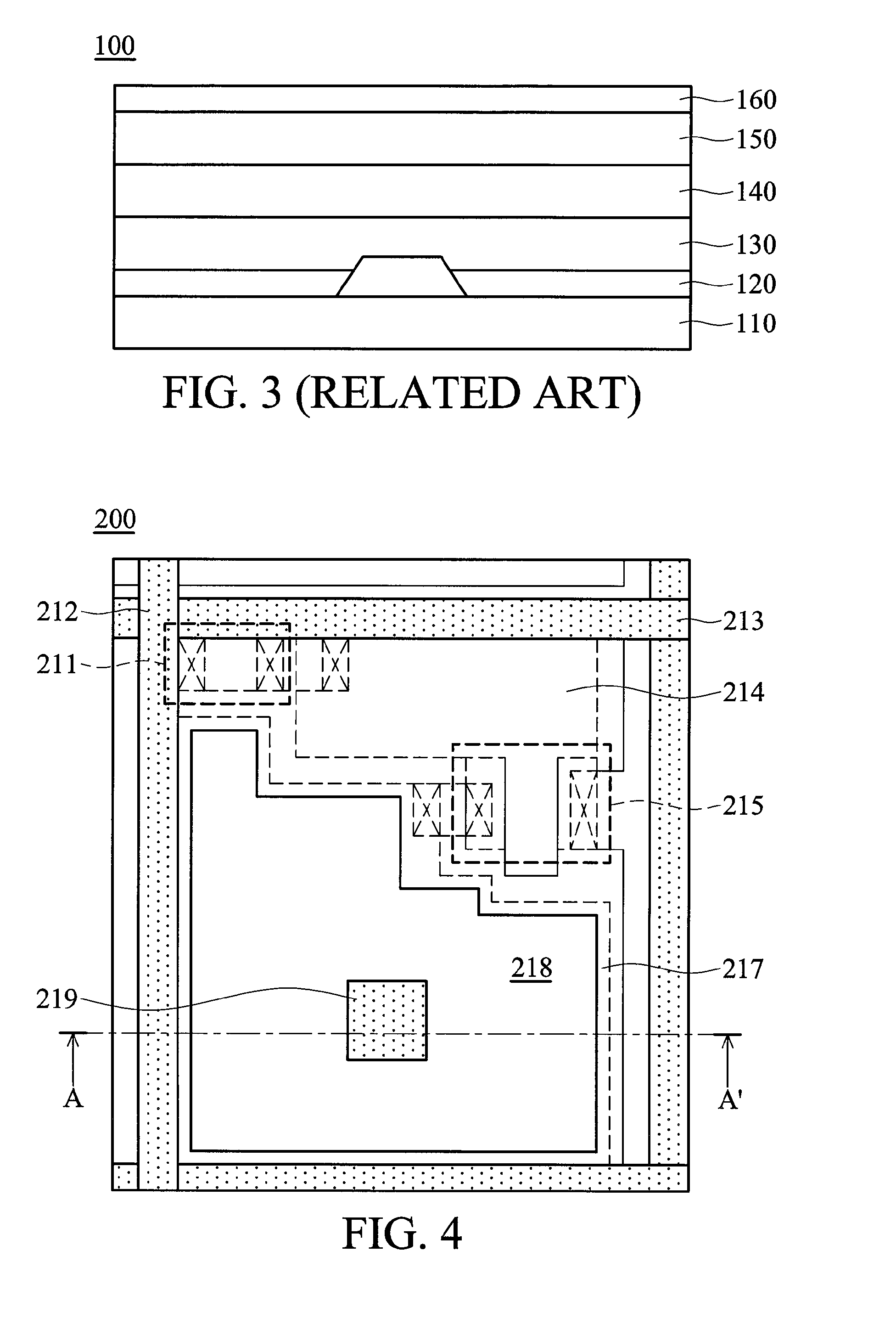

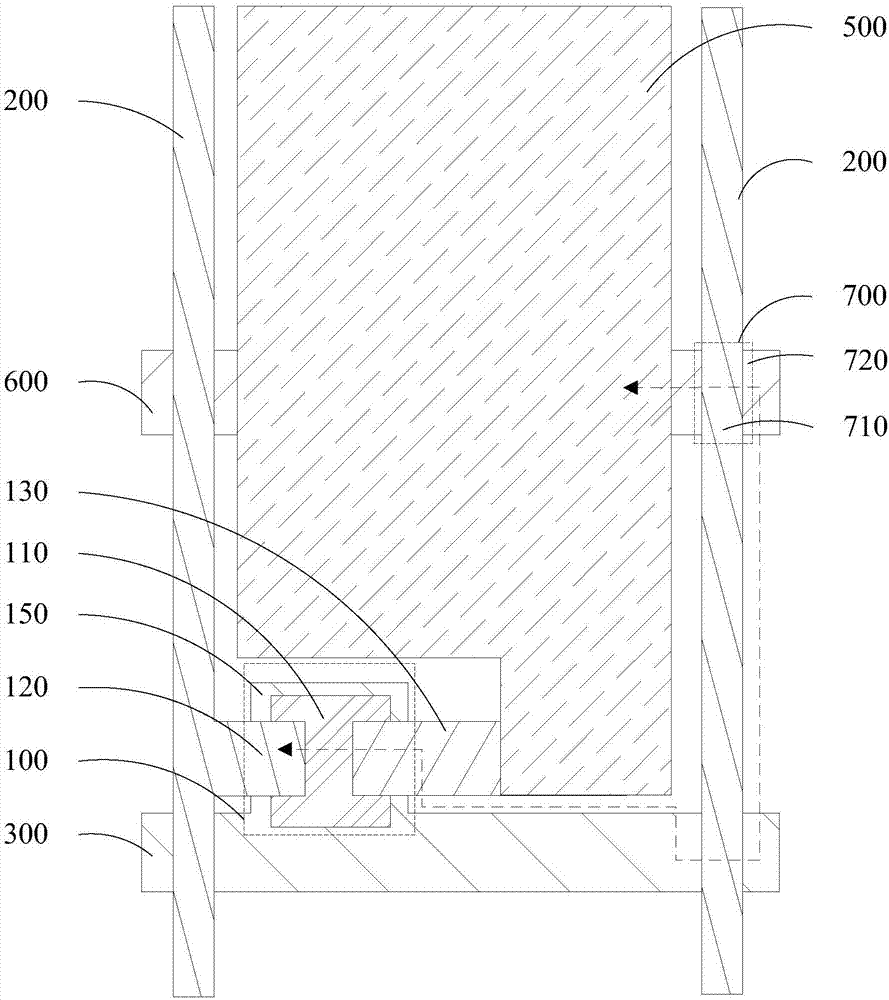

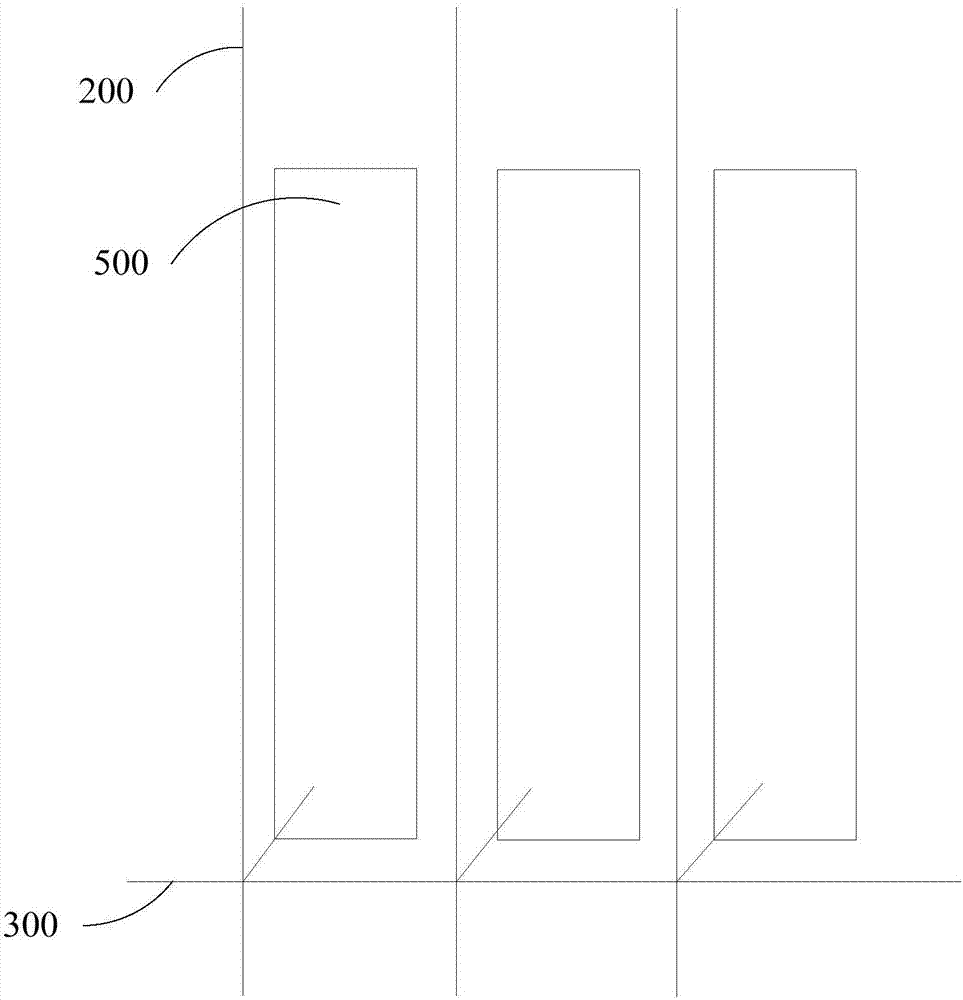

Tandem organic electroluminescent device

ActiveUS20070252524A1Increased process complexityDischarge tube luminescnet screensElectroluminescent light sourcesOrganic electroluminescenceLight-emitting diode

A tandem organic electroluminescent device. The tandem organic electroluminescent device comprises a substrate having a pixel thin film transistor. A rib with chambered corners is formed on the substrate, surrounding a display region. A protrusion is formed in the display region. A plurality of organic light emitting diodes is stacked vertically in the display region, covering the protrusion, wherein each organic light emitting diode comprises a top electrode, an organic electroluminescent layer, and a bottom electrode. The bottom electrode of the bottommost organic light emitting diode is electrically connected to the pixel thin film transistor. A common electrode electrically connected to the top electrode of the topmost organic light emitting diode directly over the protrusion.

Owner:AU OPTRONICS CORP

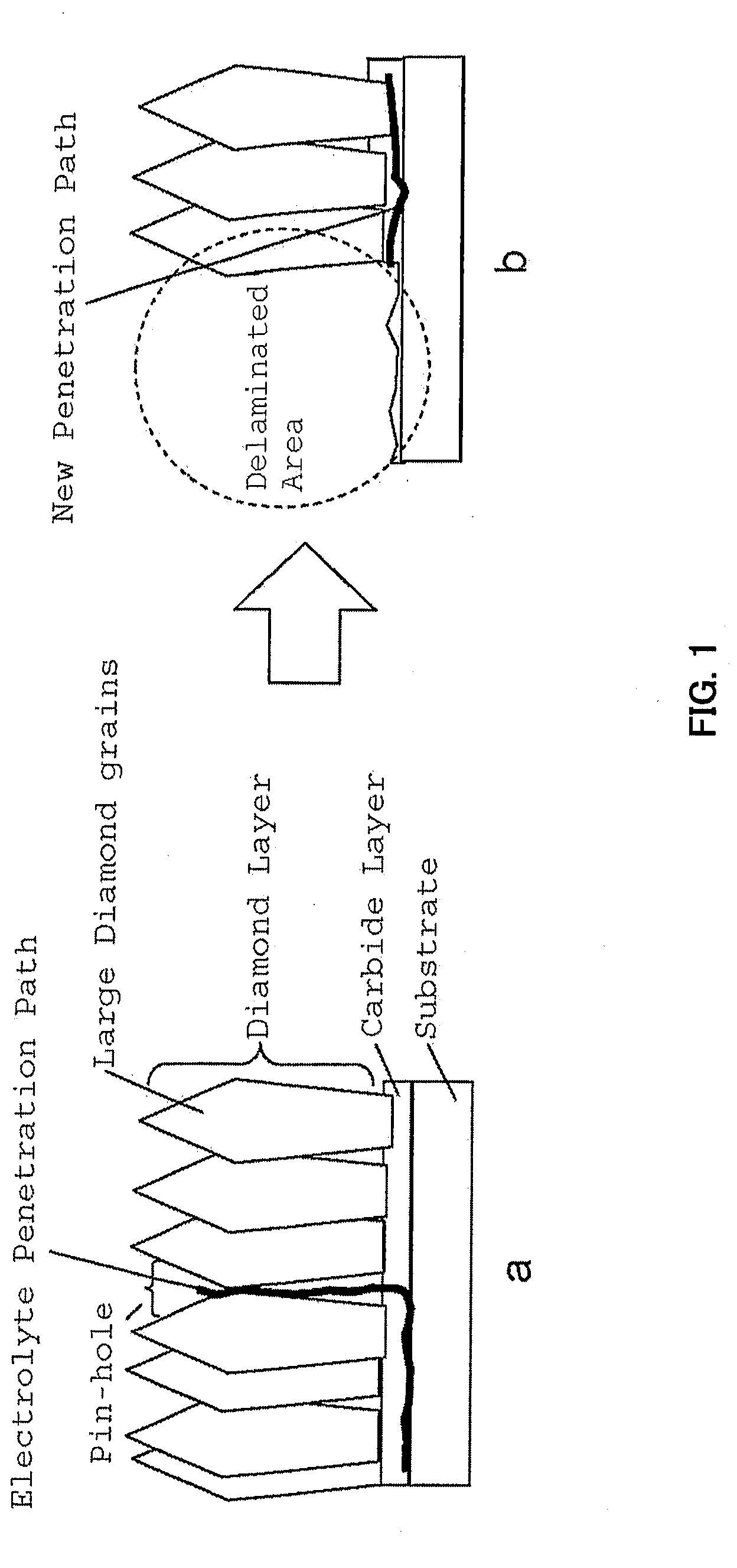

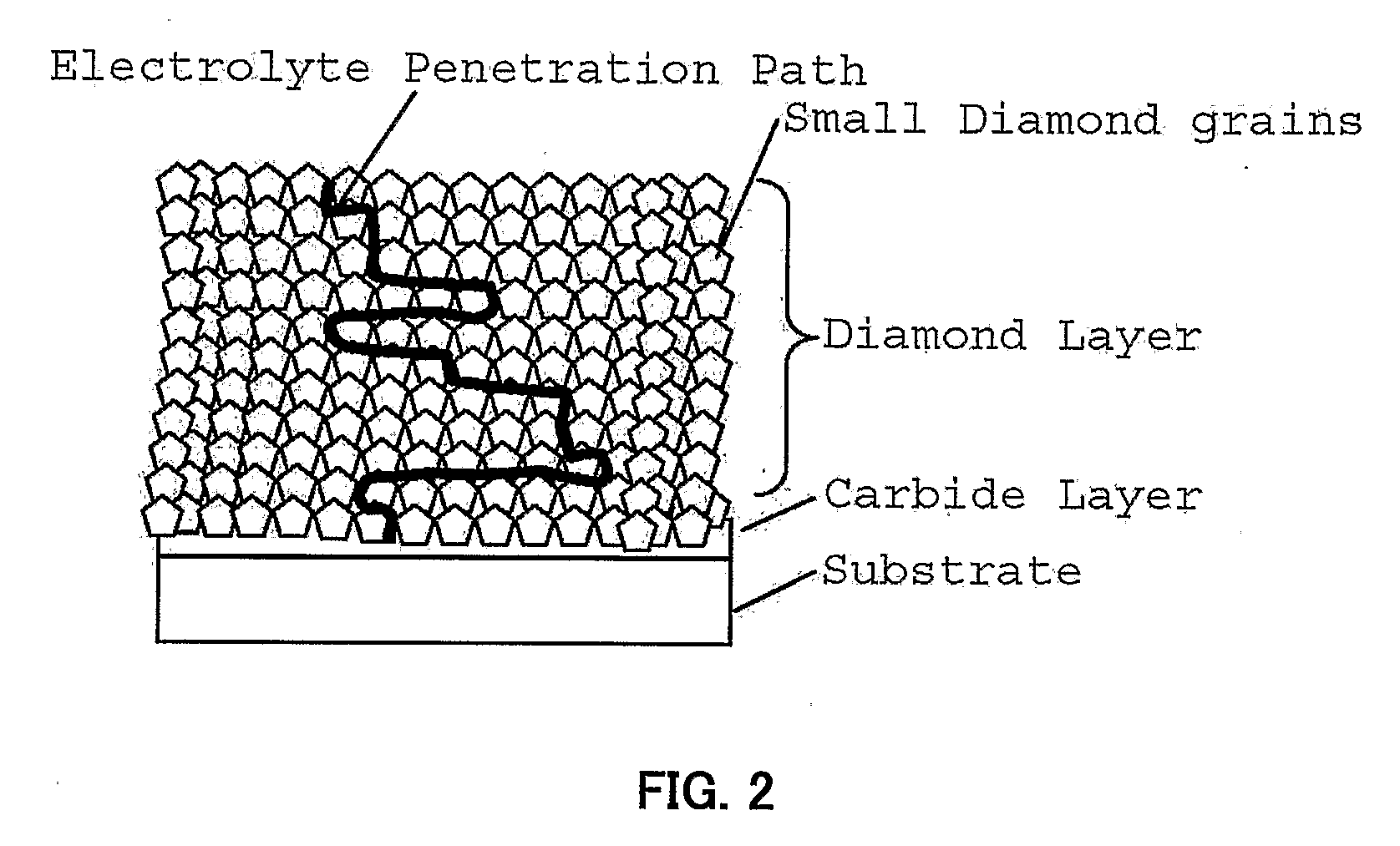

Method for production of diamond electrodes

InactiveUS20090324810A1Reduced stabilityReduced life-timeSpecial surfacesChemical vapor deposition coatingElectrochemical responseDiamond electrodes

The invention is related to the method for production of diamond electrode with improved stability for use in electrochemical reaction. The method concerns to the production of diamond electrodes where the diamond layer is composed of small sized grain, avoiding the delamination problems found in conventional diamond electrodes.

Owner:EBARA CORP +1

Method for manufacturing radio frequency tags with hot and cold stamping technology

ActiveCN102339402AWide range of useFast hot stampingAntenna supports/mountingsRadiating elements structural formsHot stampingInsulation layer

The invention discloses a manufacturing method of radio frequency tags, and the radio frequency tags are manufactured with a hot and cold stamping technology; the process method has the steps that: polyvinyl chloride (PVC), polypropylene (PP), polyethylene terephthalate (PET), paper, plastics and the like are adopted as base materials, and electro-metal stamping foils are stamped on the base materials by a stamping machine through a hot stamping or cold stamping technology, then waste is discharged from other parts of the metal foils, and antenna patterns are obtained; and if coil antennas are to be manufactured, insulation layers need to be paved on coils, the electro-metal stamping foils are stamped on the insulation layers and are connected with the ends of the antennas to form bridges, i.e. radio frequency antennas. Finally, chips are reversely pasted on the antenna bridges, coated and packaged, and radio frequency tags are obtained. A traditional radio frequency tag process has the disadvantages of too high cost, complicated process, long production time, certain pollution to the environment and the like, and the method for manufacturing radio frequency tags with the hot and cold stamping technology can effectively reduce the radio frequency tag manufacturing cost, simplify the complicated process, and meet the market demand for the low-cost radio frequency tags.

Owner:哈尔滨大东方新材料科技股份有限公司

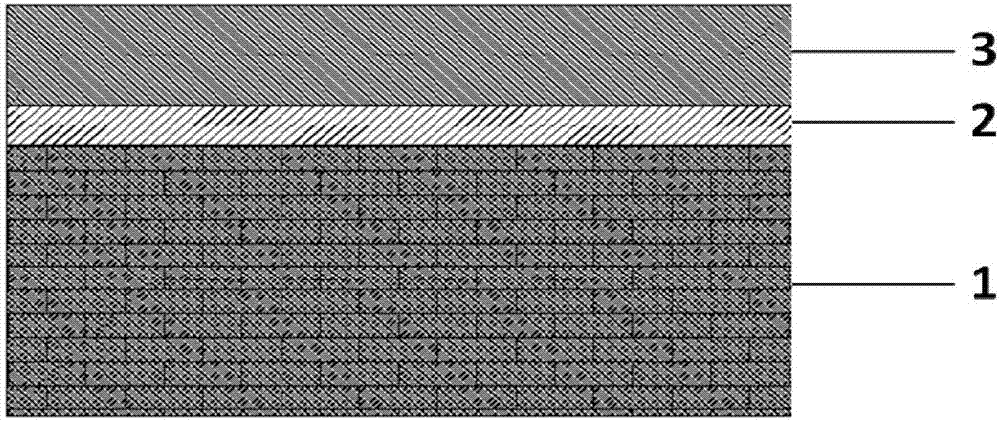

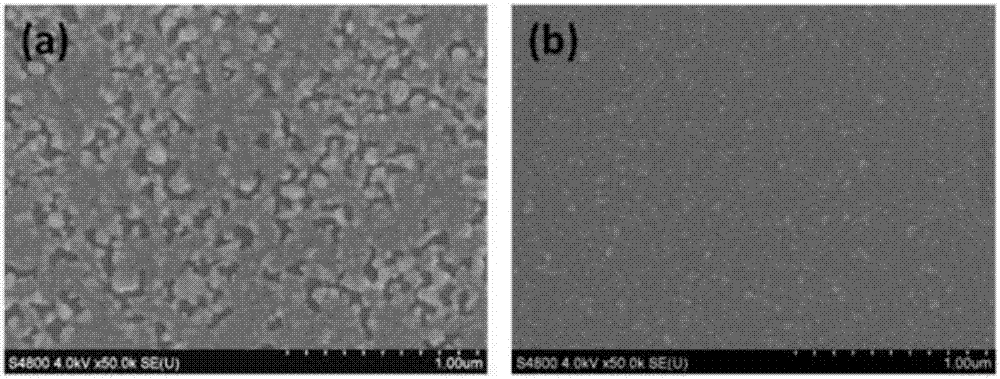

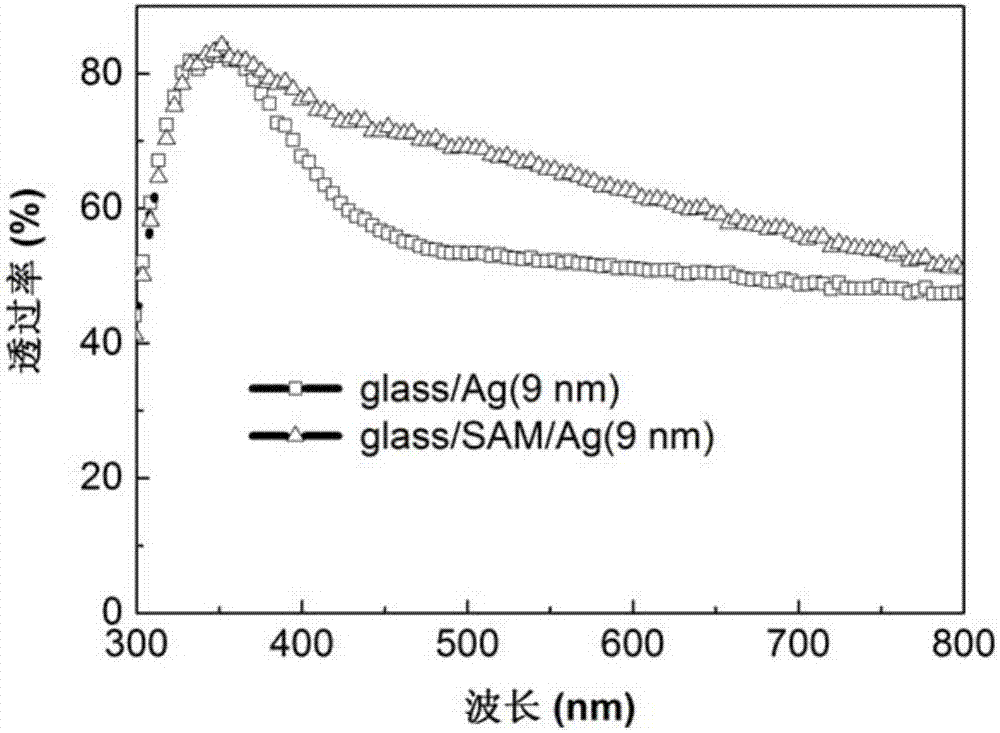

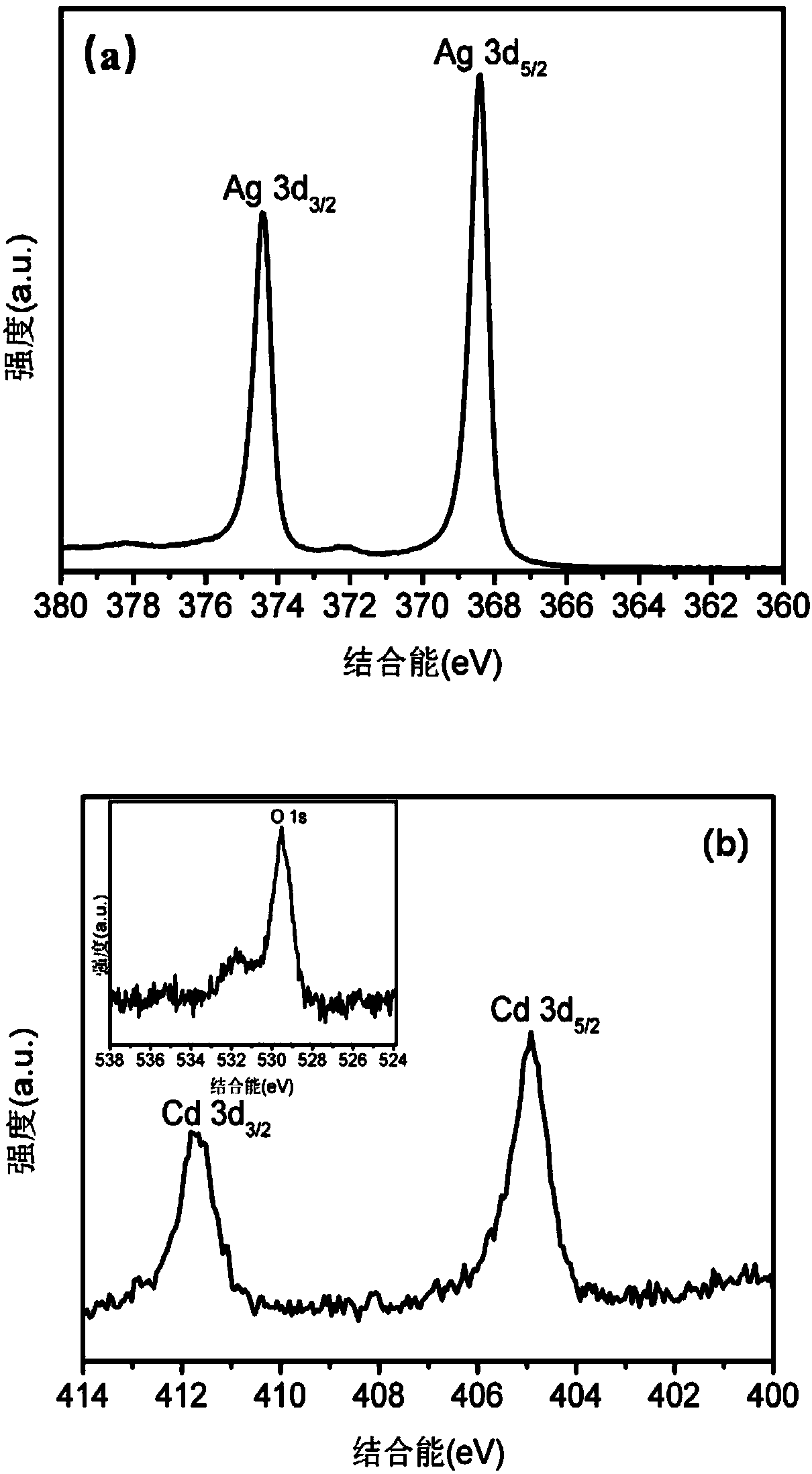

Transparent electrode based on ultra-thin metallic film and preparation method and application thereof

ActiveCN107393979AGood optical performanceControl conductivityFinal product manufactureSemiconductor devicesThin metalSystem structure

The invention discloses a transparent electrode based on an ultra-thin metallic film. The transparent electrode orderly comprises a transparent substrate, a metal layer and a metal oxide layer from bottom to top, wherein the thickness of the metal layer is 3 to 12nm. The substrate is modified by a monomolecular self-assembled layer; an ultra-thin metal layer is directly deposited on the substrate, and the continuity and conductivity of the ultra-thin metallic film are improved through the function of the monomolecular self-assembled layer; or through the co-deposition of metals, the continuous growth of the ultra-thin metallic film is realized directly on the substrate; and a metal oxide layer is deposited on the substrate as an antireflection layer, then a double-layer film system structure is obtained, and through the design and optimization of the double-layer film system structure, the maximization of transmittance is realized. The invention further discloses a preparation method of the transparent electrode based on the ultra-thin metallic film and an application thereof in photoelectric devices, wherein the transparent electrode can have good conductivity and high transmittance at the same time.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

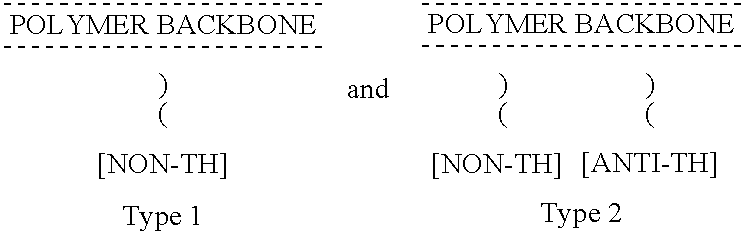

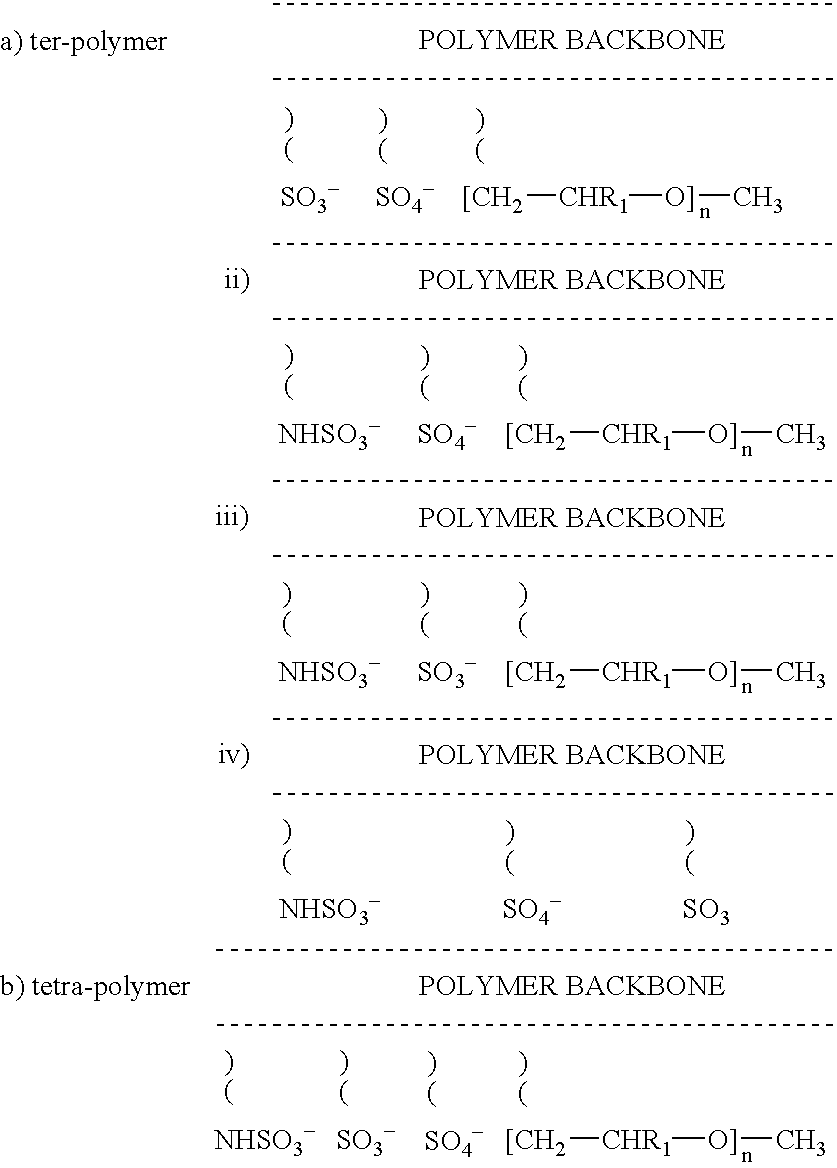

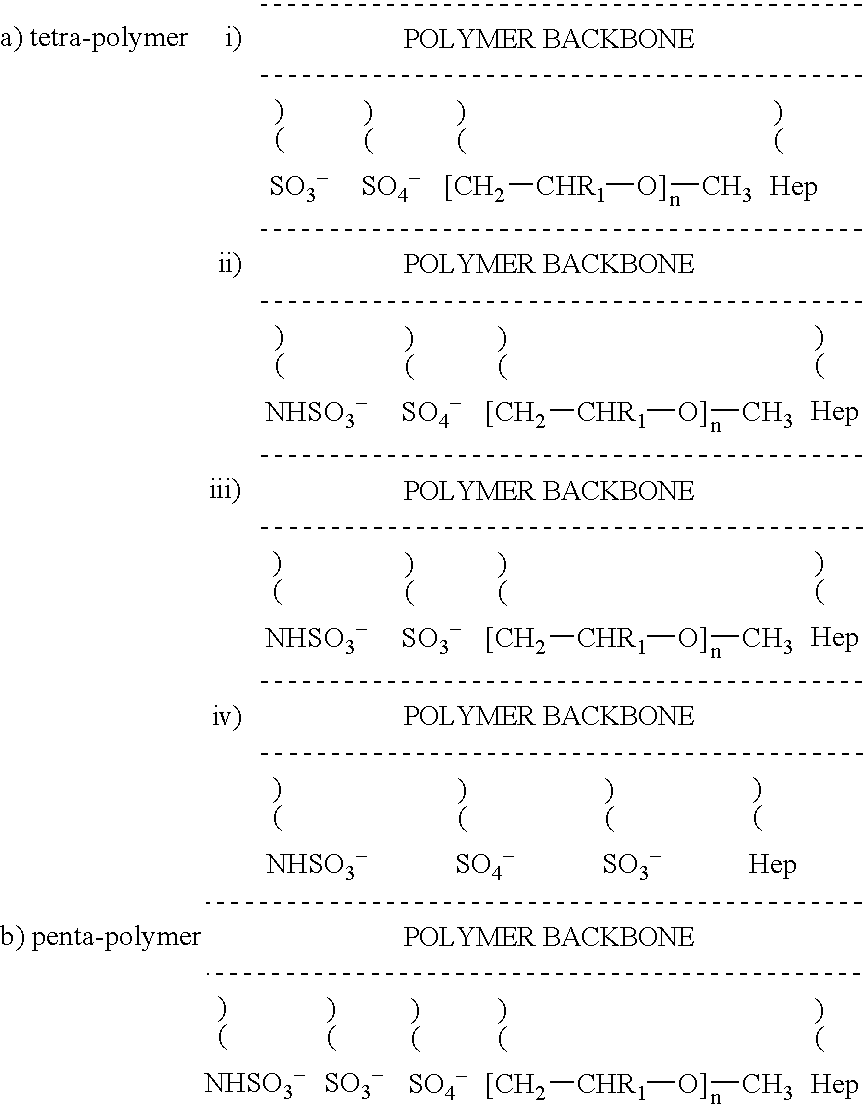

Non-thrombogenic and anti-thrombogenic polymers

InactiveUS7034061B1Improve attachment stabilityPreferential ionic bondingPeptide/protein ingredientsPharmaceutical non-active ingredientsWarfarinPolymer science

Polymers having non-thrombogenic properties can be prepared by copolymerizing monomers of at least three classes selected from (a) monomers having sulphate groups, (b) monomers having sulphonate groups, (c) monomers having sulphamate groups, (d) monomers having polyoxyalkylene ether groups, and (e) monomers having zwitterionic groups. The polymers can additionally be provided with anti-thrombogenic properties by including an additional comonomer having a pendant heparin (or hirudin, warfarin or hyaluronic acid) group. The polymers can be used as coating materials for medical devices, such as tubing or connectors, in order to provide them with non-thrombogenic, and optionally anti-thrombogenic, properties.

Owner:BIOINTERACTIONS

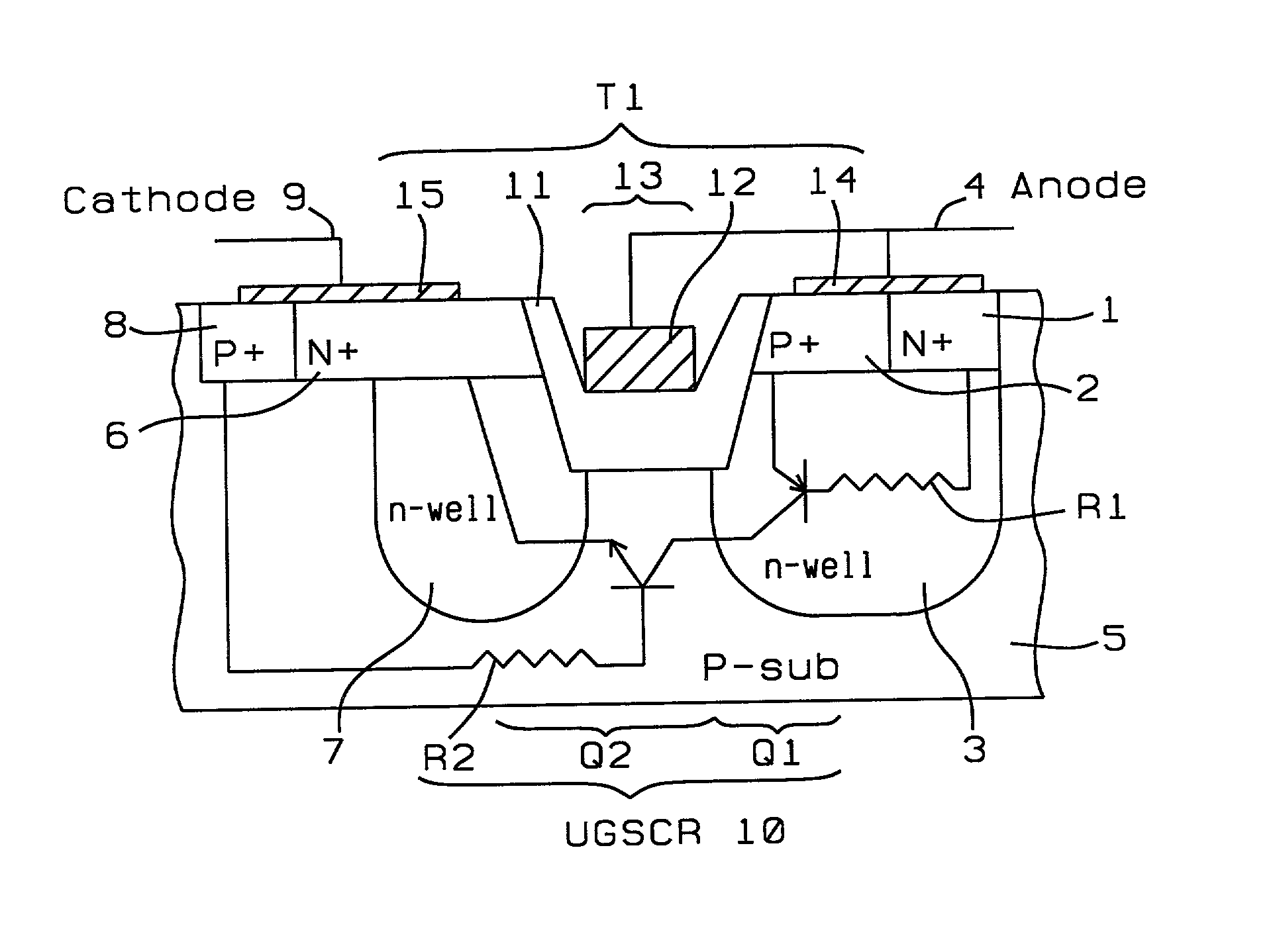

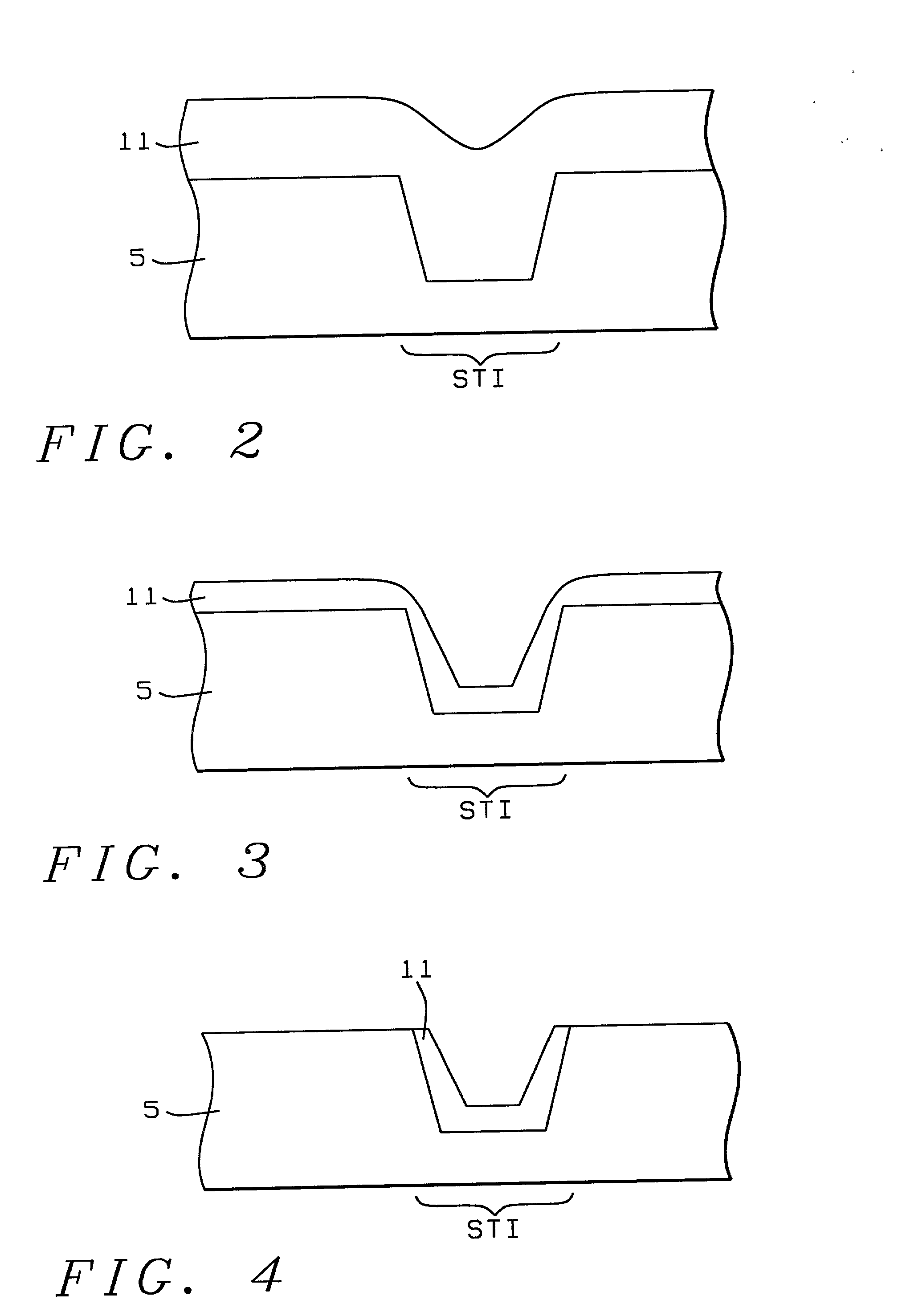

Novel UMOS-like gate-controlled thyristor structure for ESD protection

InactiveUS20020130365A1Increase costIncreased process complexityTransistorThyristorSalicideManufacturing technology

Described is a MOS gate-controlled SCR (UGSCR) structure with a U-shaped gate (UMOS) for an ESD protection circuit in an IC device which is compatible with shallow trench isolation (STI) and self-aligned suicide (salicide) fabrication technology. The UMOS gate is located in a p-substrate and is surrounded by an n-well on either side. Adjacent to one side of the UMOS gate, a first n+ diffusion is formed which straddles the first n-well. The n+ diffusion together with a p+ pickup diffused next to it form the cathode of the SCR (thyristor). Adjacent to the other side of the UMOS gate, a second n+ and p+ diffusion are formed in a second n-well. The second n+ and p+ diffusion together with the UMOS gate form the anode of the SCR and the input terminal of the circuit to be protected. The SCR is formed by the first n+ diffusion / n-well (cathode), the p-substrate, the second n-well and the second p+ / n+diffusion (anode). A latchup immune circuit is achieved by creating a U-shaped gate structure which is lined with a thick gate oxide--similar to a field oxide--under the poly gate.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

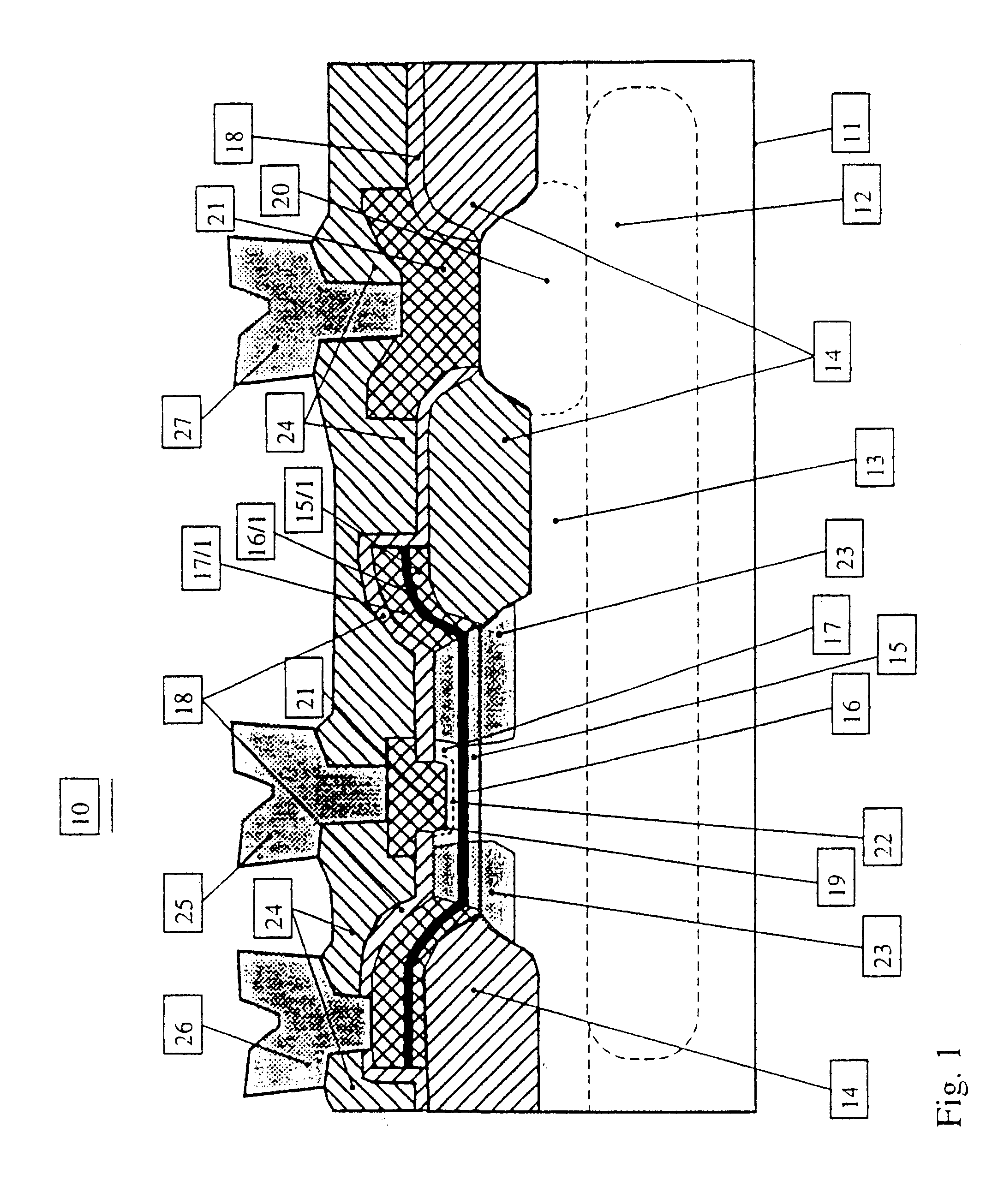

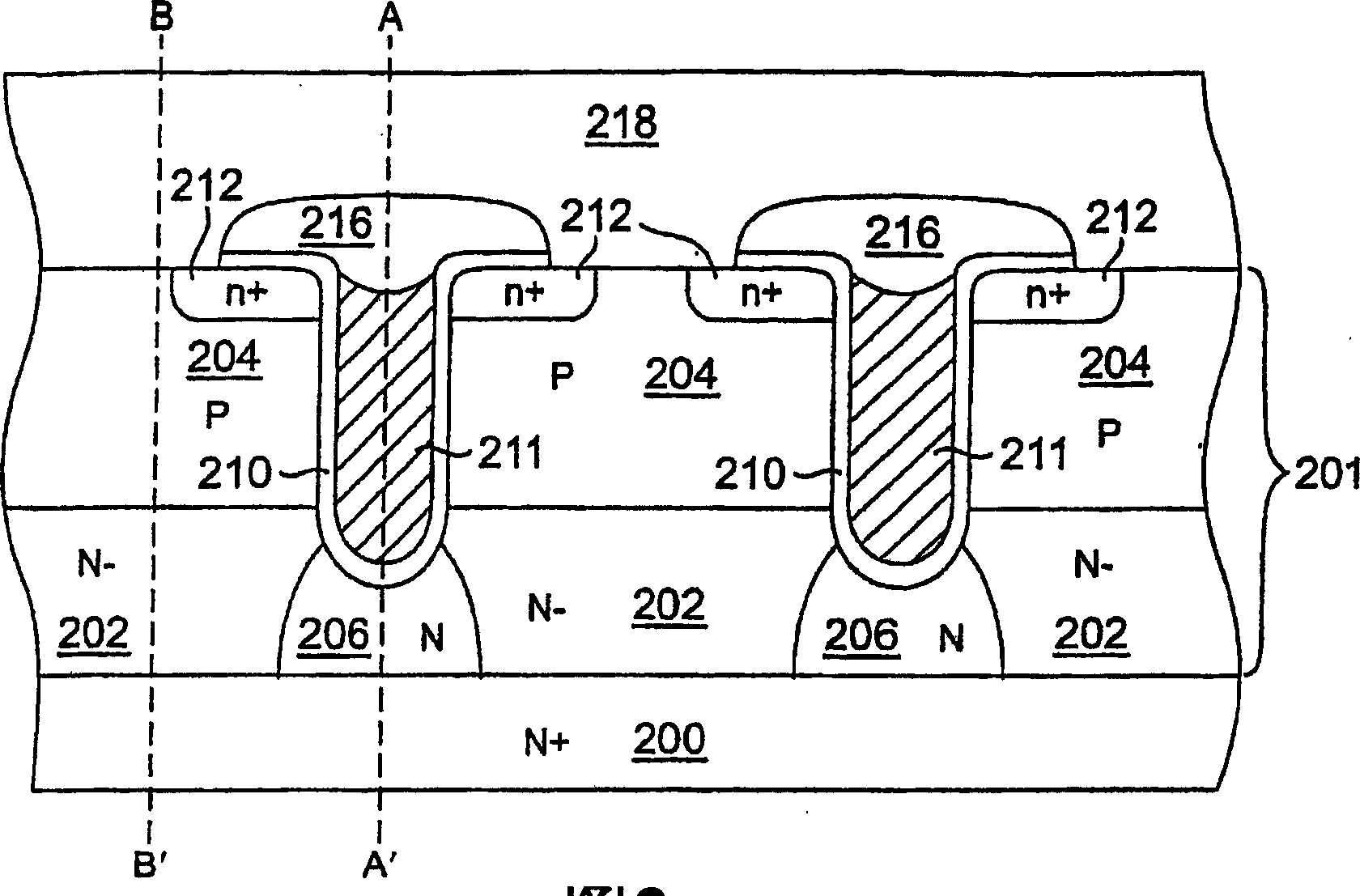

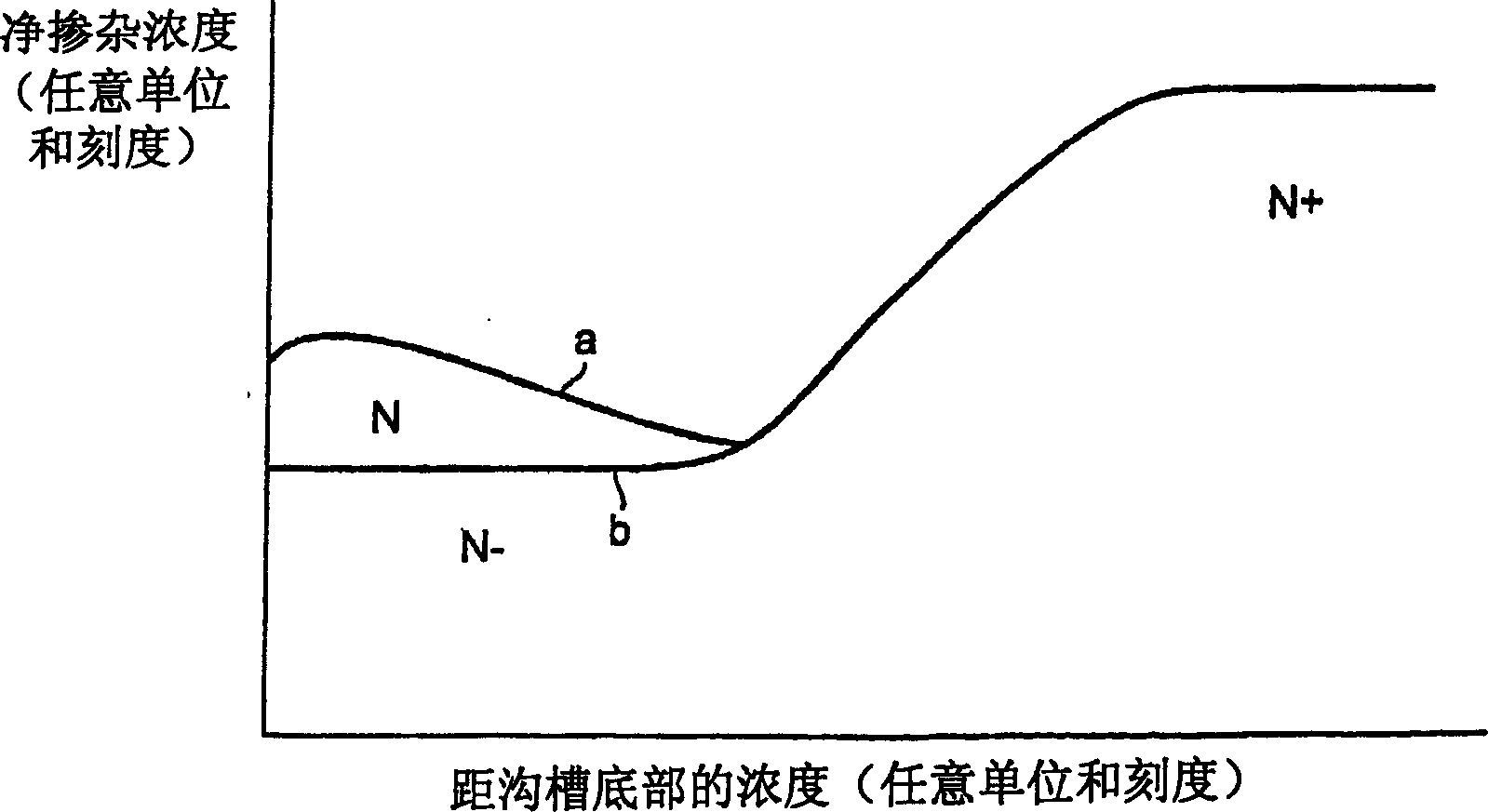

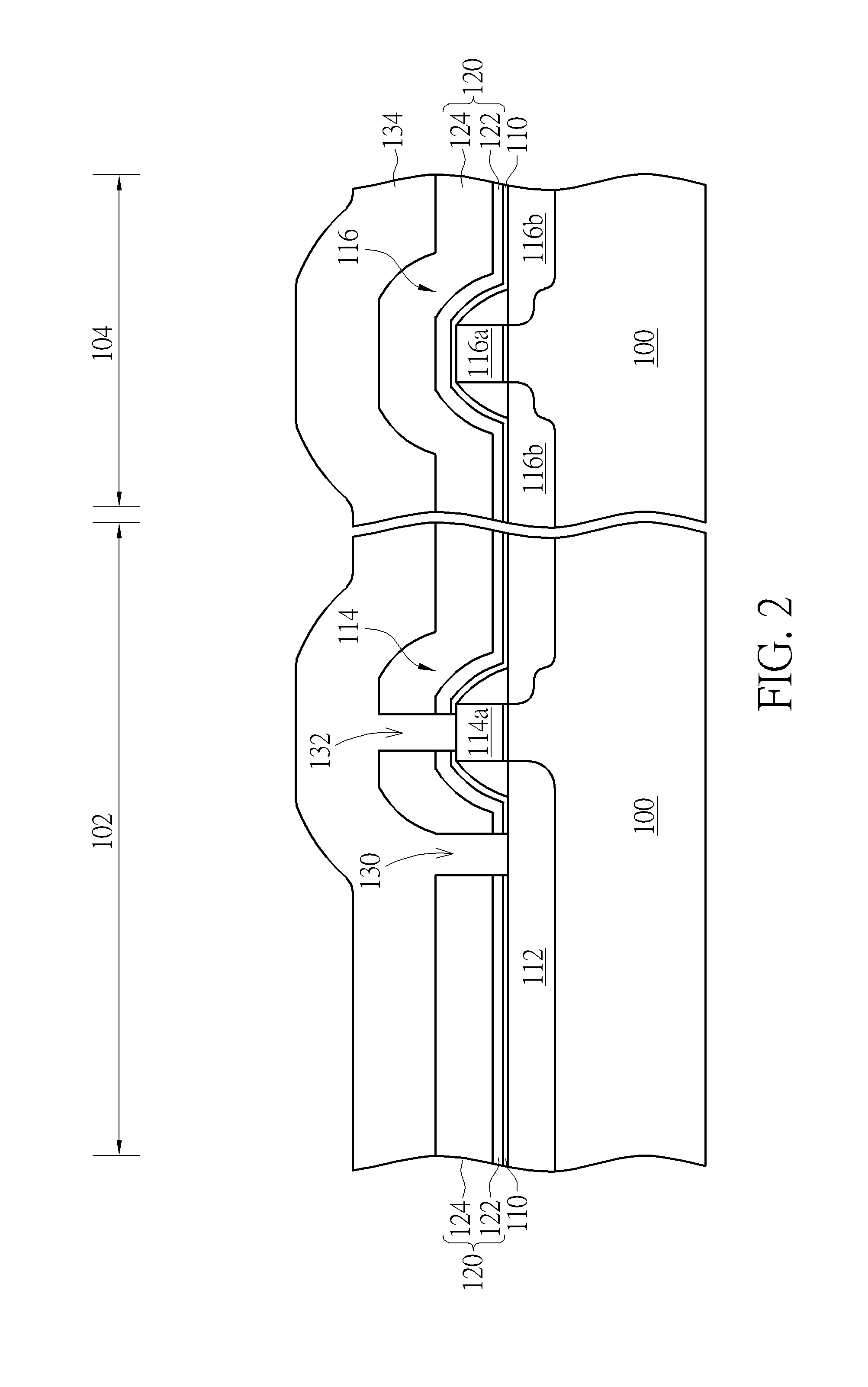

Trench MOSFET device with improved on-resistance

InactiveCN1695252AIncrease design complexityIncreased process complexityThyristorSolid-state devicesTrench mosfetBody region

A trench MOSFET device comprises: a substrate 200 of a first conductivity type, an epitaxial layer of the first conductivity type wherein the epitaxial layer has a lower impurity concentration than the substrate, a trench extending into the epitaxial layer, an insulated conductive region 211 within the trench, a doped region 206 of the first conductivity type formed within the epitaxial layer between a bottom portion of the trench and the substrate, wherein the doped region has an impurity concentration that is lower than that of the substrate and higher than that of the epitaxial layer, a body region 204 of a second conductivity type formed within an upper portion of the epitaxial layer and adjacent trench wherein the body region extends to a lesser depth from the upper surface of the epitaxial layer than does the trench and a source region 212 within the body region.

Owner:GEN SEMICON

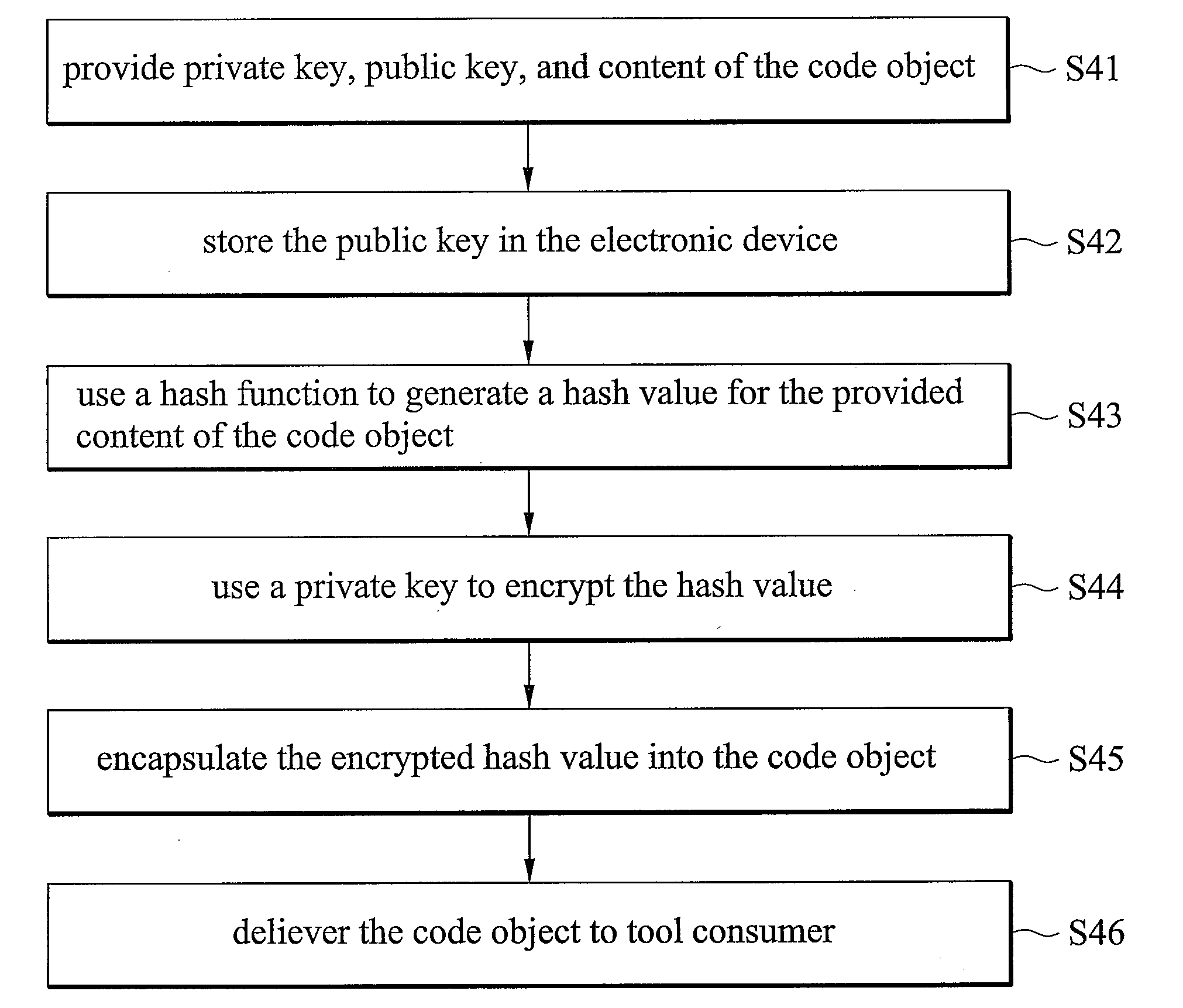

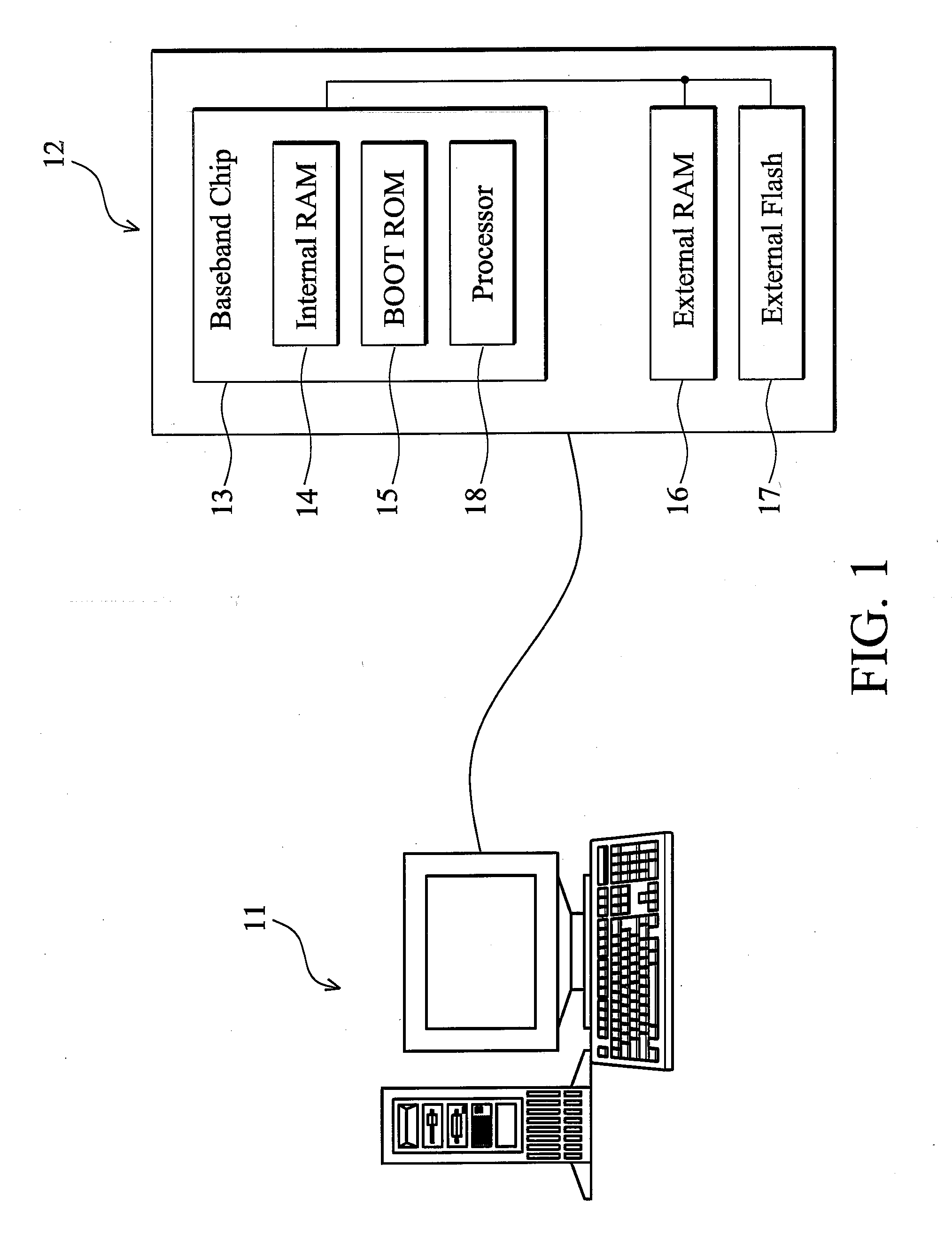

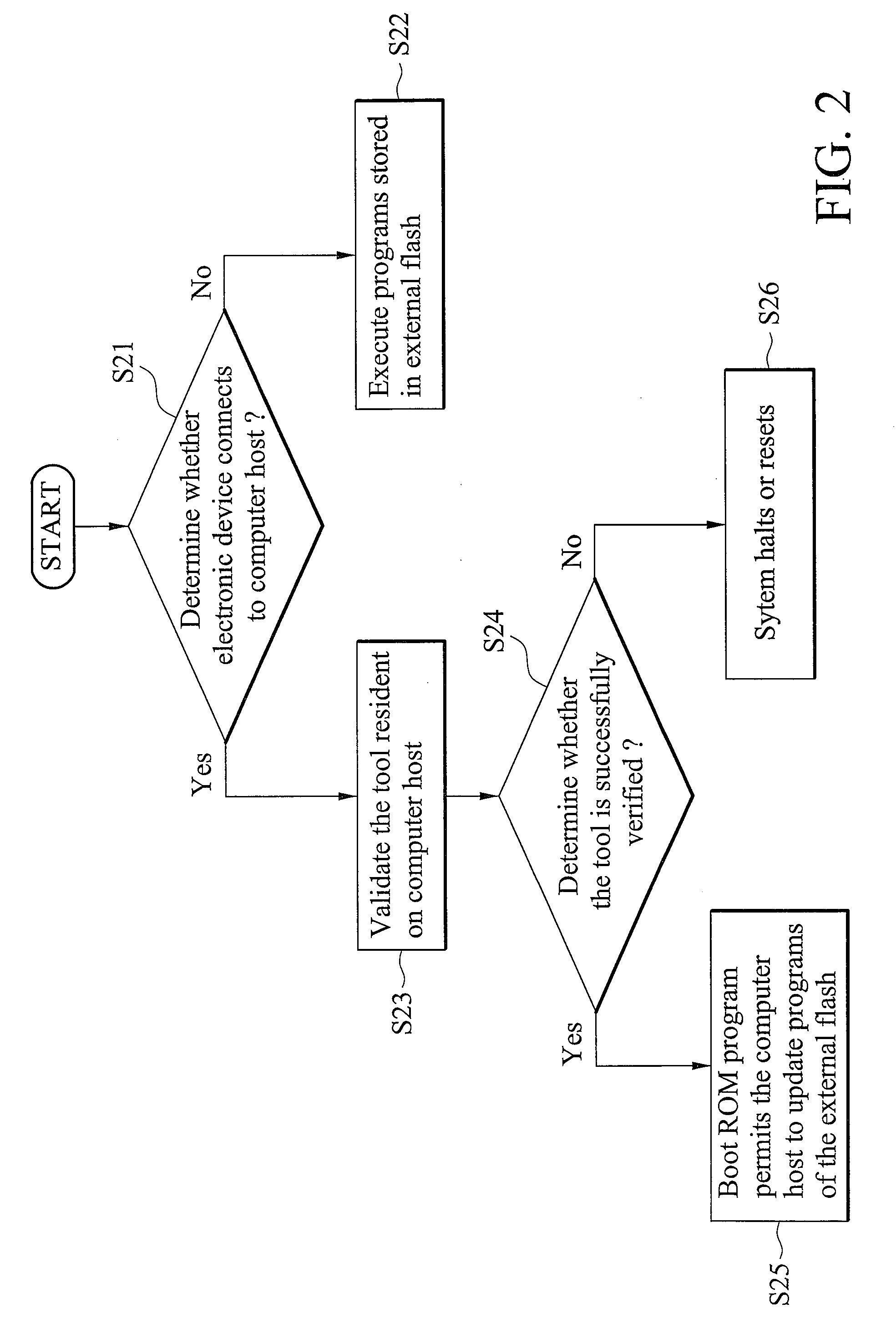

Methods for program verification and apparatuses using the same

InactiveUS20080301466A1Easy to replacePromote cloningUnauthorized memory use protectionHardware monitoringProgram validationFormal verification

An embodiment of an apparatus for downloading and / or executing programs from a tool resident on a computer host is disclosed. The apparatus comprises an external flash memory storing a program, and a processor for validating the tool when detecting that the computer host connects to the apparatus. The processor permits the computer host to update the program of the external flash memory after determining that the tool has been successfully verified.

Owner:MEDIATEK INC

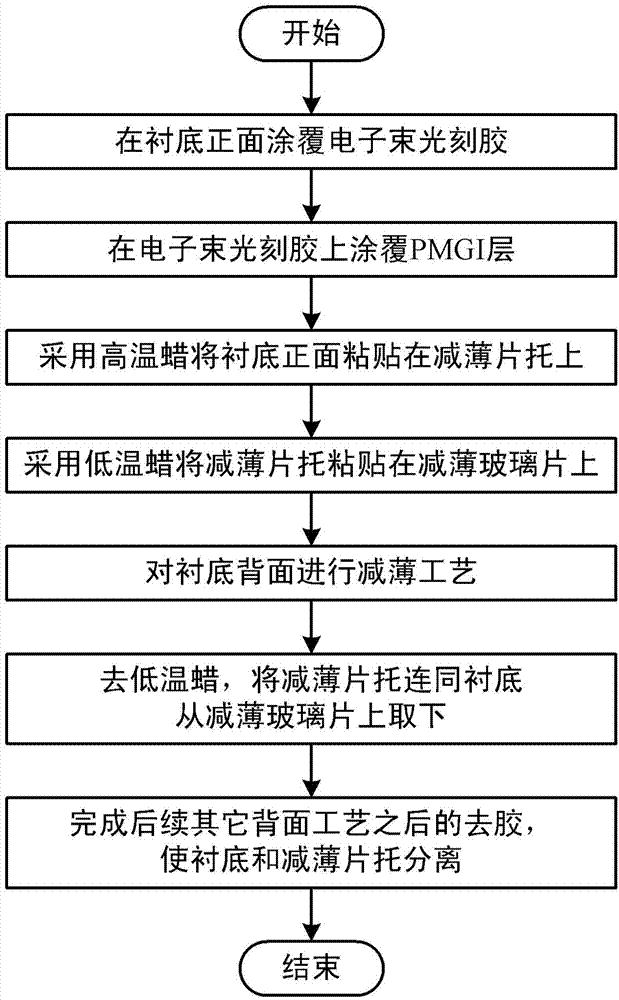

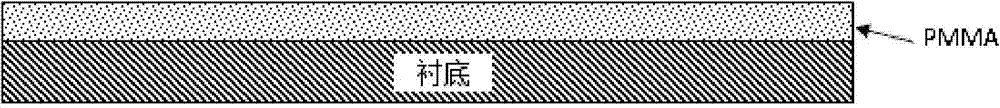

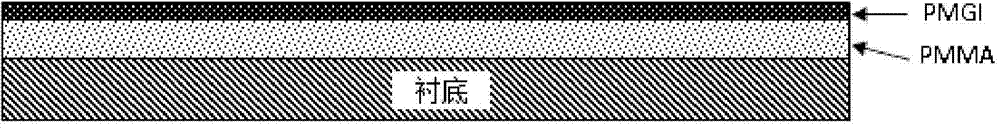

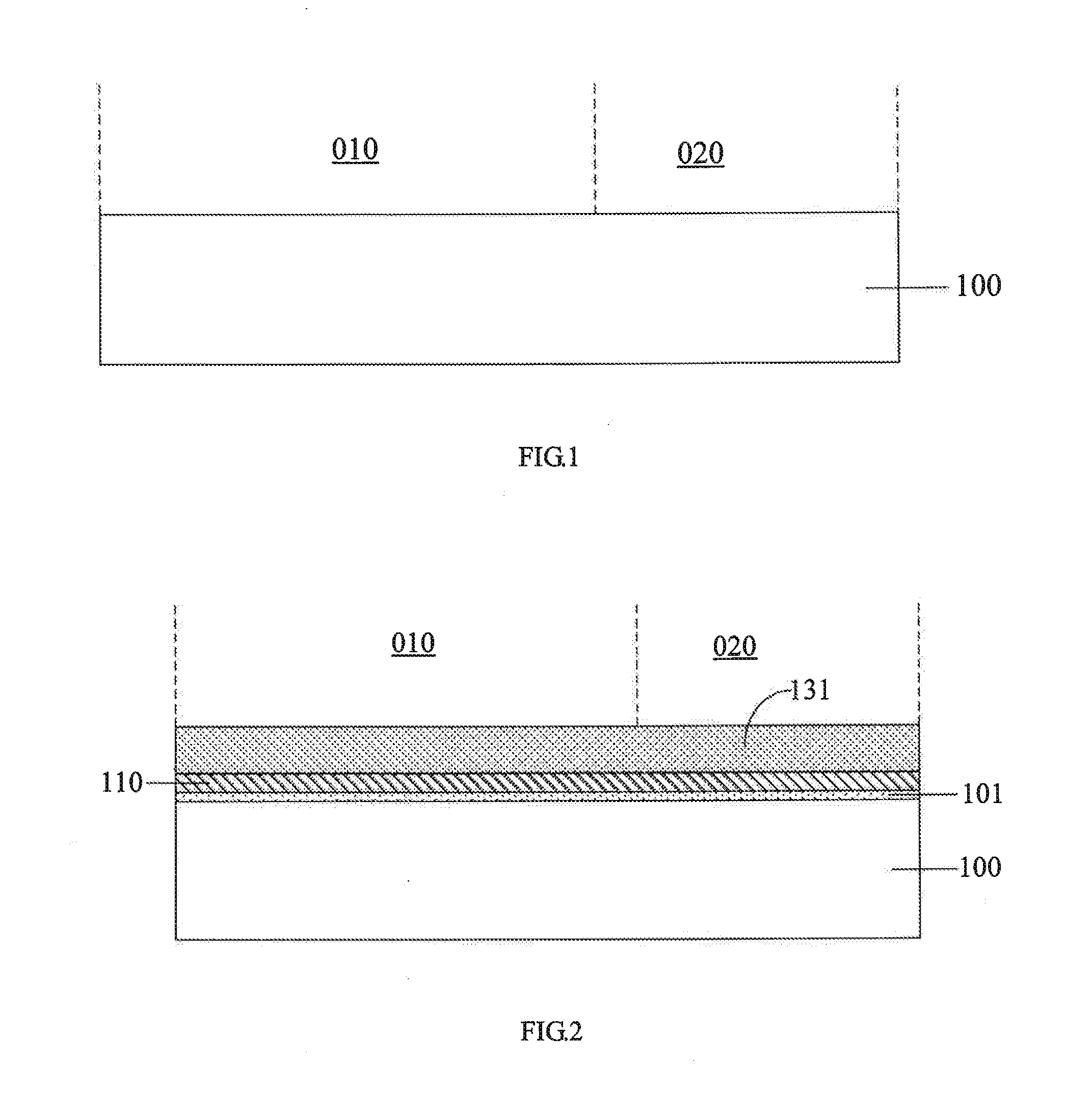

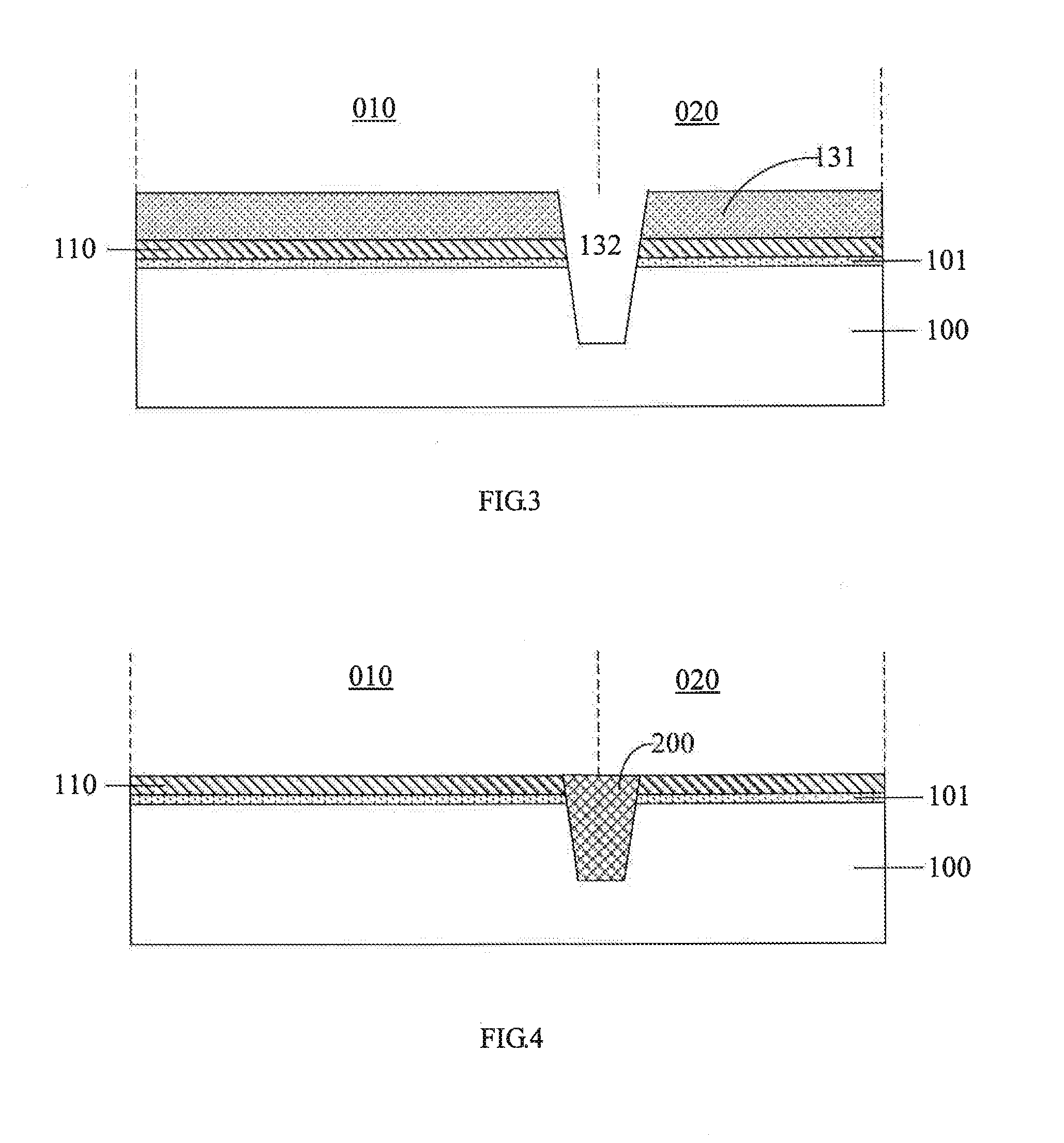

Sheet bonding method in substrate thinning technique

InactiveCN103489755AAvoid integration problemsImprove processing efficiencySolid-state devicesSemiconductor/solid-state device manufacturingWaxOptoelectronics

The invention discloses a sheet bonding method in a substrate thinning technique, which comprises the following steps: coating an electron beam photoresist on the front surface of a substrate; coating a PMGI layer on the electron beam photoresist; bonding the front surface of the substrate onto a thinning sheet support by using high temperature wax; bonding the thinning sheet support onto a thinning glass sheet by using low temperature wax; carrying out thinning technique on the back surface of the substrate; removing the low temperature wax, and taking the thinning sheet support with the substrate off the thinning glass sheet; and completing subsequent photoresist removal after other back surface techniques, and separating the substrate from the thinning sheet support. The method effectively solves the problem of mutual solubility between the photoresist and high temperature wax, and enhances the technical efficiency and technical yield of the thinning technique.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Replacement gate approach based on a reverse offset spacer applied prior to work function metal deposition

ActiveUS8409942B2Effective regulationCritical deposition processTransistorSemiconductor/solid-state device manufacturingWork functionEngineering

Owner:GLOBALFOUNDRIES U S INC

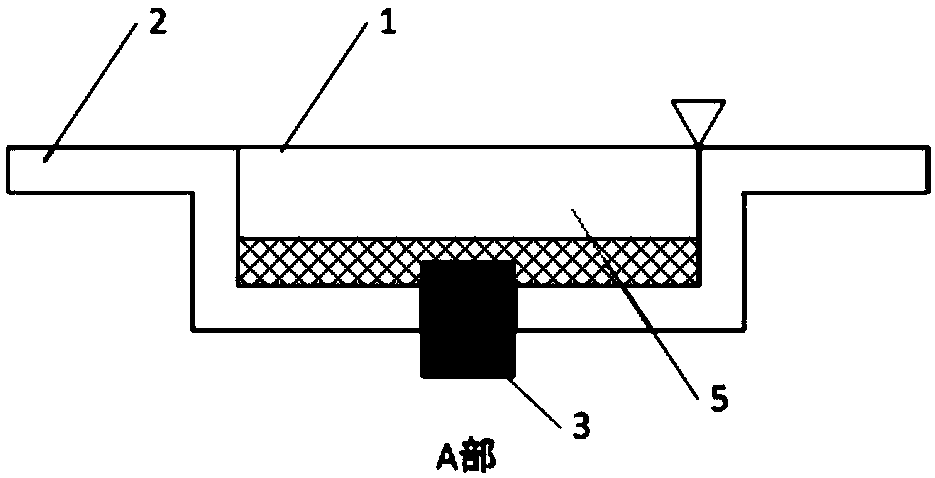

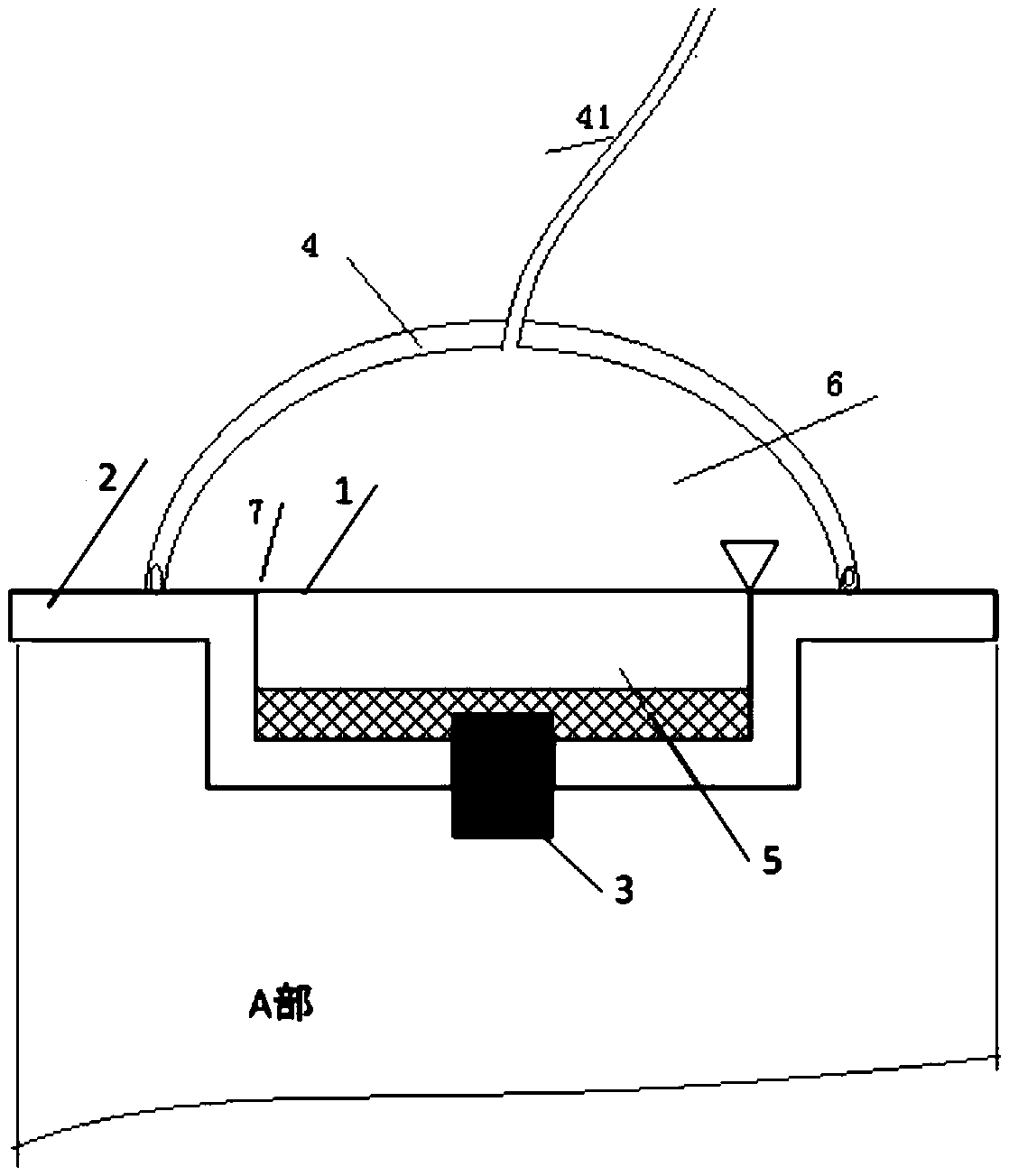

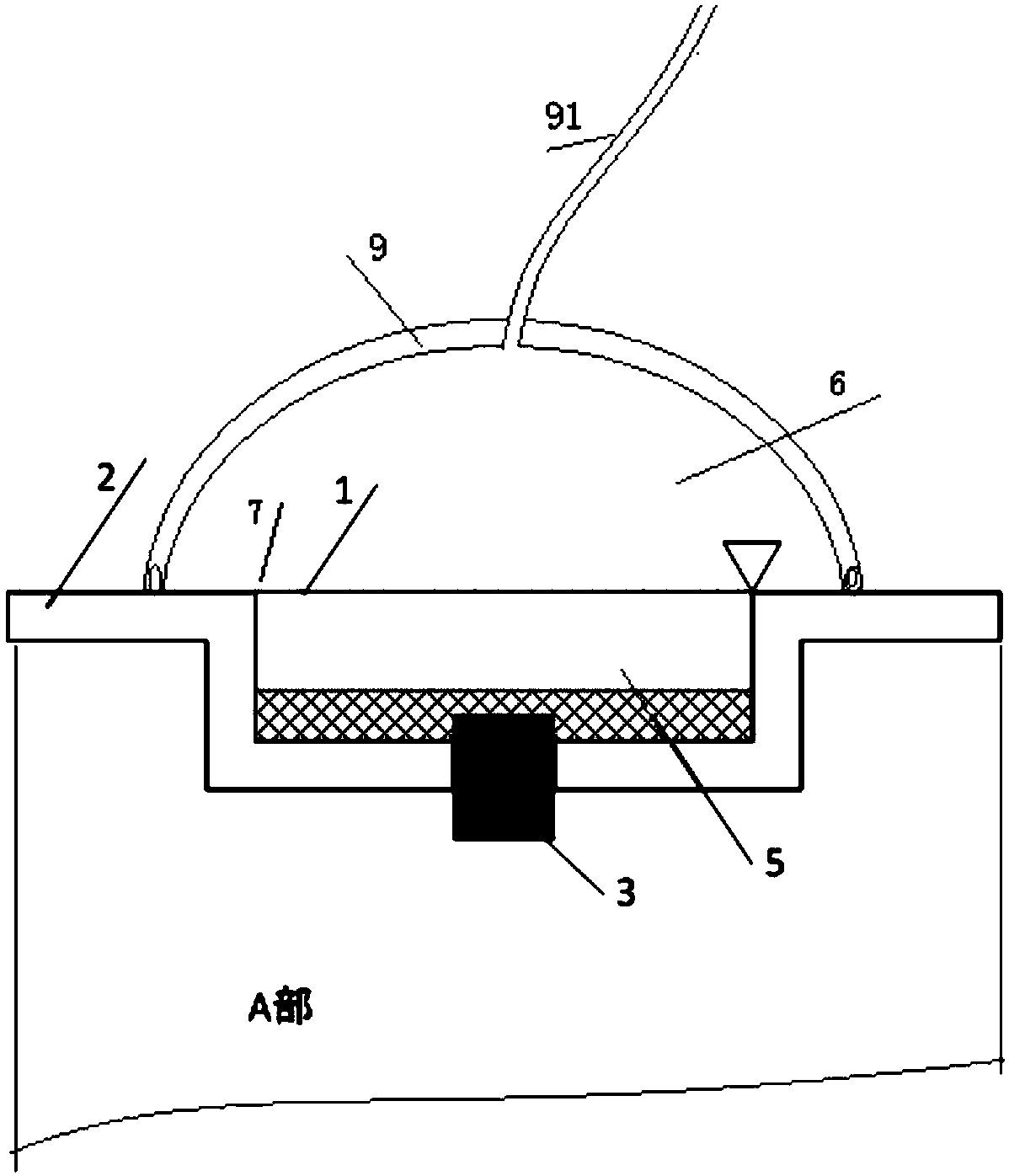

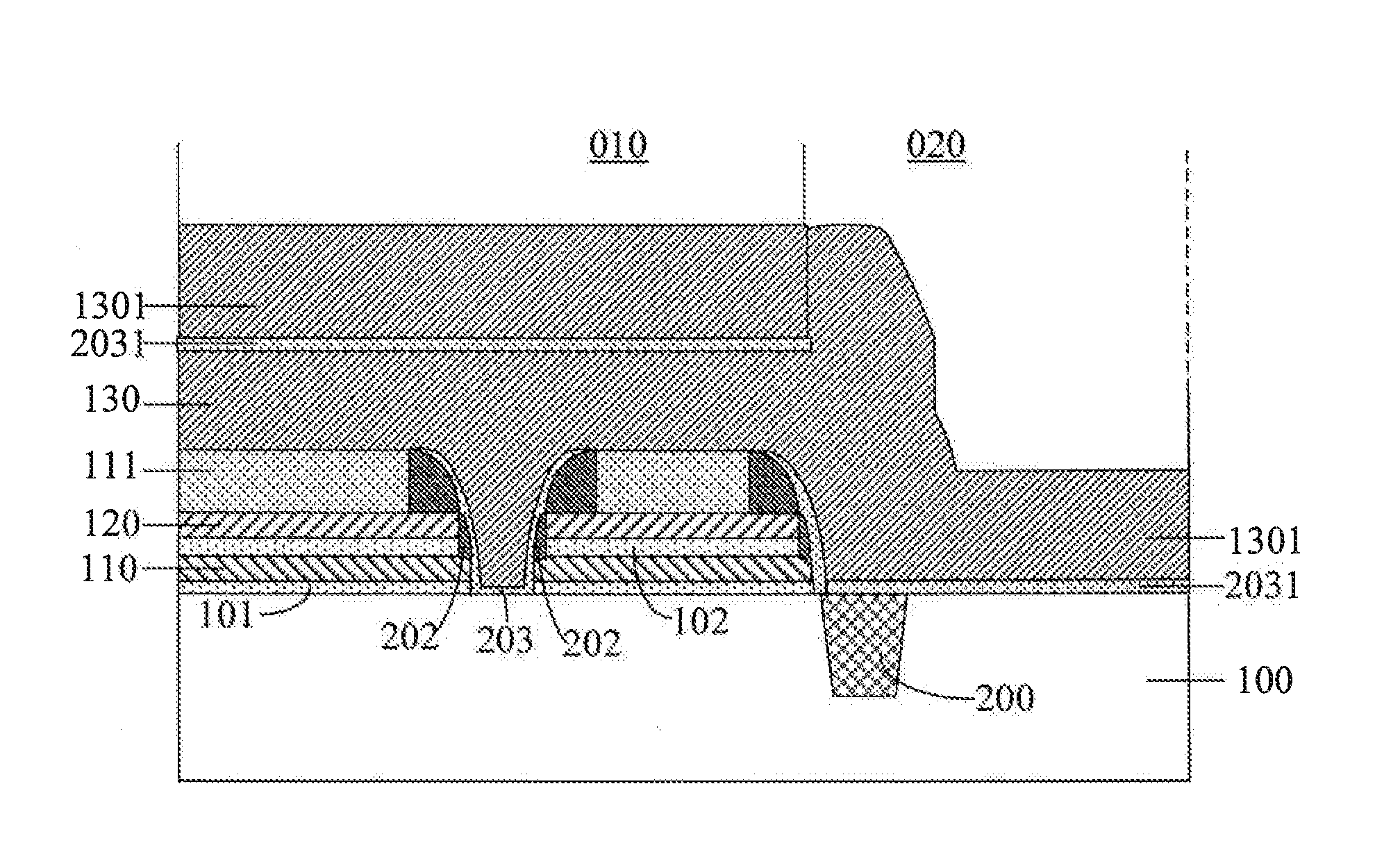

OLED display device

ActiveCN110071150AIncrease the screen ratioImprove AssemblabilitySolid-state devicesSemiconductor devicesDisplay deviceTransmission line

The invention provides an OLED display device comprising a display panel and a camera component, wherein the display panel comprises a base substrate and a display film layer, the camera component comprises a sensor, a signal module and a lens, the sensor is disposed on a recess of the base substrate, the height of the sensor is greater than the depth of the recess, the upper end of the sensor andthe signal module extend into the TFT layer of the display film layer, the TFT layer is internally provided with a camera signal transmission line electrically connected to the signal module, and thelens is disposed in the opening of the display film layer correspondingly located to the upper part of the sensor. The OLED display device provided by the invention respectively builds the sensor andlens of the camera component into the display panel structure relatively independently such that the assembly of the camera component is during the manufacturing process of the display panel, therebyimproving the degree of integration of the display panel and the camera component, realizing the high-integration assembly of the OLED display device with the design of the under-screen camera, and effectively improving the screen ratio and the assemblability of the display device.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

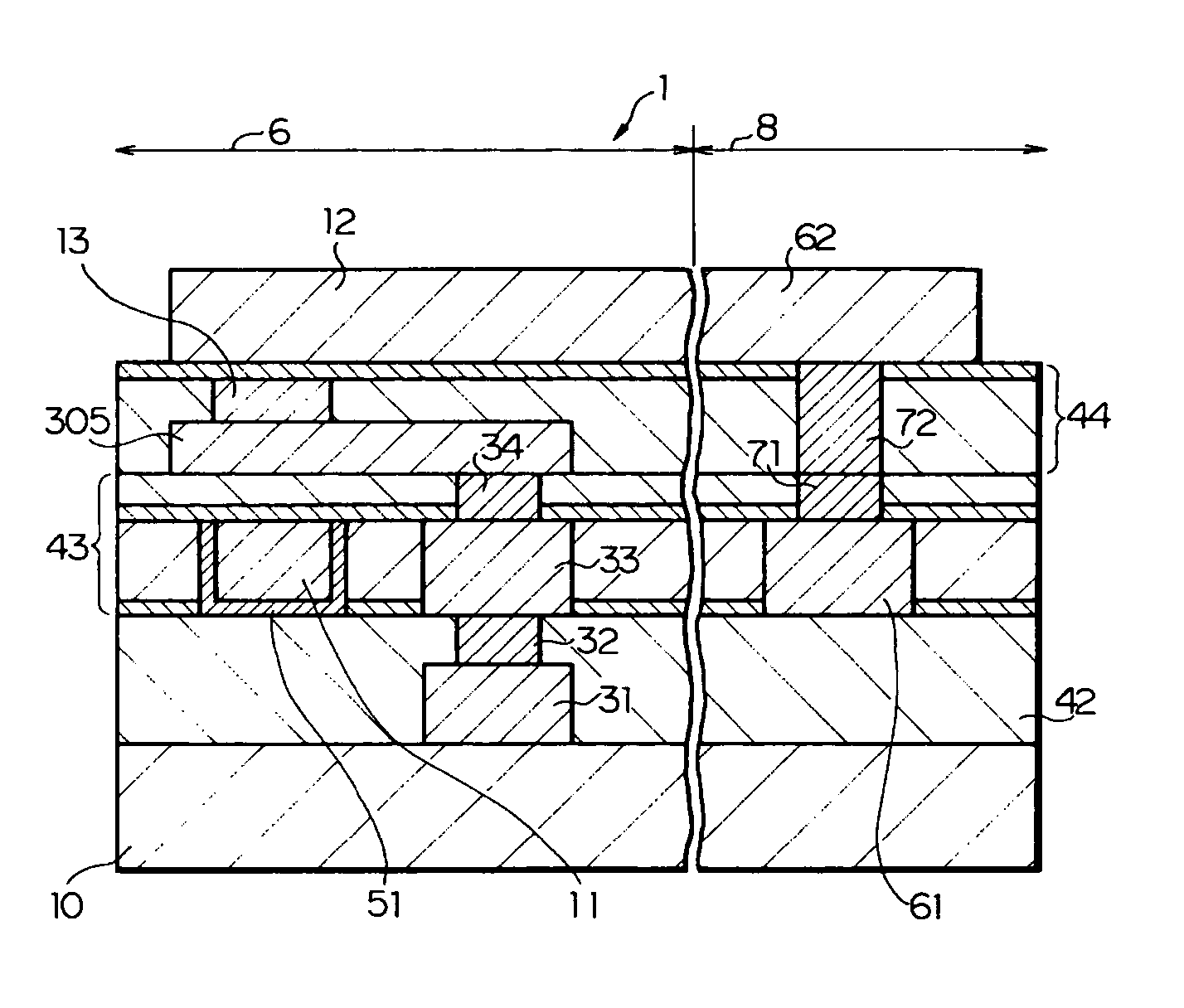

Magnetic memory apparatus and method of manufacturing magnetic memory apparatus

InactiveUS20050030821A1Reduce the valueReduced wiring areaSemiconductor/solid-state device detailsMagnetic-field-controlled resistorsMagnetic memoryEngineering

A magnetic memory apparatus including a memory cell region and a peripheral circuitry region mounted on a substrate is provided. The memory cell region includes first wiring, second wiring that three-dimensionally intersects with the first wiring, and a magnetoresistance effect type memory device disposed in an intersecting region of the first and the second wiring for storing and reproducing information of a magnetic spin. The peripheral circuitry region includes first wiring that is in the same wiring layer as that of the first wiring in the memory cell region, and second wiring that is in the same wiring layer as the second wiring in the memory cell, and a magnetic material layer including a high magnetic permeability layer is formed on both side surfaces of the first wiring only within the memory cell region and on a surface opposite to a surface facing the memory device.

Owner:SONY CORP

Radio frequency micro-strip structure for Ti/Ni/Ag material system

PendingCN108448217AImprove performanceLow costSemiconductor/solid-state device detailsSolid-state devicesHigh resistancePunching

The invention discloses a radio frequency micro-strip structure for the punching and non-punching structures of a Ti / Ni / Ag material system, and a manufacturing method thereof. According to the invention, a punching structure is composed of a through hole, a W covering layer, a passivation layer, a front surface Ti / Ni / Ag metal laminated layer, a Si substrate and a back metal laminated layer. A non-punching structure is composed of a passivation layer, a front surface Ti / Ni / Ag metal laminated layer, a Si substrate and a back metal laminated layer. The front surface Ti / Ni / Ag metal laminated layeris provided with patterns. The Si substrate is made of the high-resistance Si material. According to the invention, the pollution problem of the front metal on IC process lines when the front metal is Au can be avoided. Meanwhile, the complex problem of the technological process caused by the front metal of Cu can also be avoided. The process compatibility of the manufacturing process and the ICprocess is met. At the same time, Ag, lower in resistivity than Au and Cu, is introduced into the material system, so that the radio frequency micro-strip structure is smaller in transmission loss. Inaddition, the passivation layer can be added, so that the electromigration of Ag can be effectively prevented. Finally, during the punching process, the punching structure does not completely penetrate the substrate. The adsorption leakage of the substrate during the subsequent IC process is avoided.

Owner:SOUTHWEAT UNIV OF SCI & TECH

Porous structure organic field effect transistor photosensitive memory and preparation method thereof

InactiveCN105810820ASimple methodSimple processSolid-state devicesSemiconductor/solid-state device manufacturingOrganic field-effect transistorPolymer thin films

The invention relates to a porous structure organic field effect transistor photosensitive memory and a preparation method thereof, and belongs to the field of semiconductor industry memory technologies and biofilm technologies. The memory comprises source and drain electrodes, an organic photosensitive semiconductor, a porous polymer film layer and a gate insulating layer which are arranged from top to bottom in sequence. The polymer film layer of a porous structure is arranged between the organic photosensitive semiconductor and the gate insulating layer. The source and drain electrodes and the organic photosensitive semiconductor are totally or partially of a porous structure which grows periodically. According to the invention, a spin-coating method is adopted to prepare the polymer film layer of the porous structure on a gate insulating layer substrate, and the polymer film layer is used as a porous template layer, the organic photosensitive semiconductor and the metal source and drain electrodes are induced to form the periodic porous growing features. The storage performance and the photosensitive performance of the device are improved by simple process means, the storage capacity, the switching speed and the light response capability are substantially improved, the preparation cost is lowered, and the popularization and the application are facilitated.

Owner:NANJING UNIV OF POSTS & TELECOMM

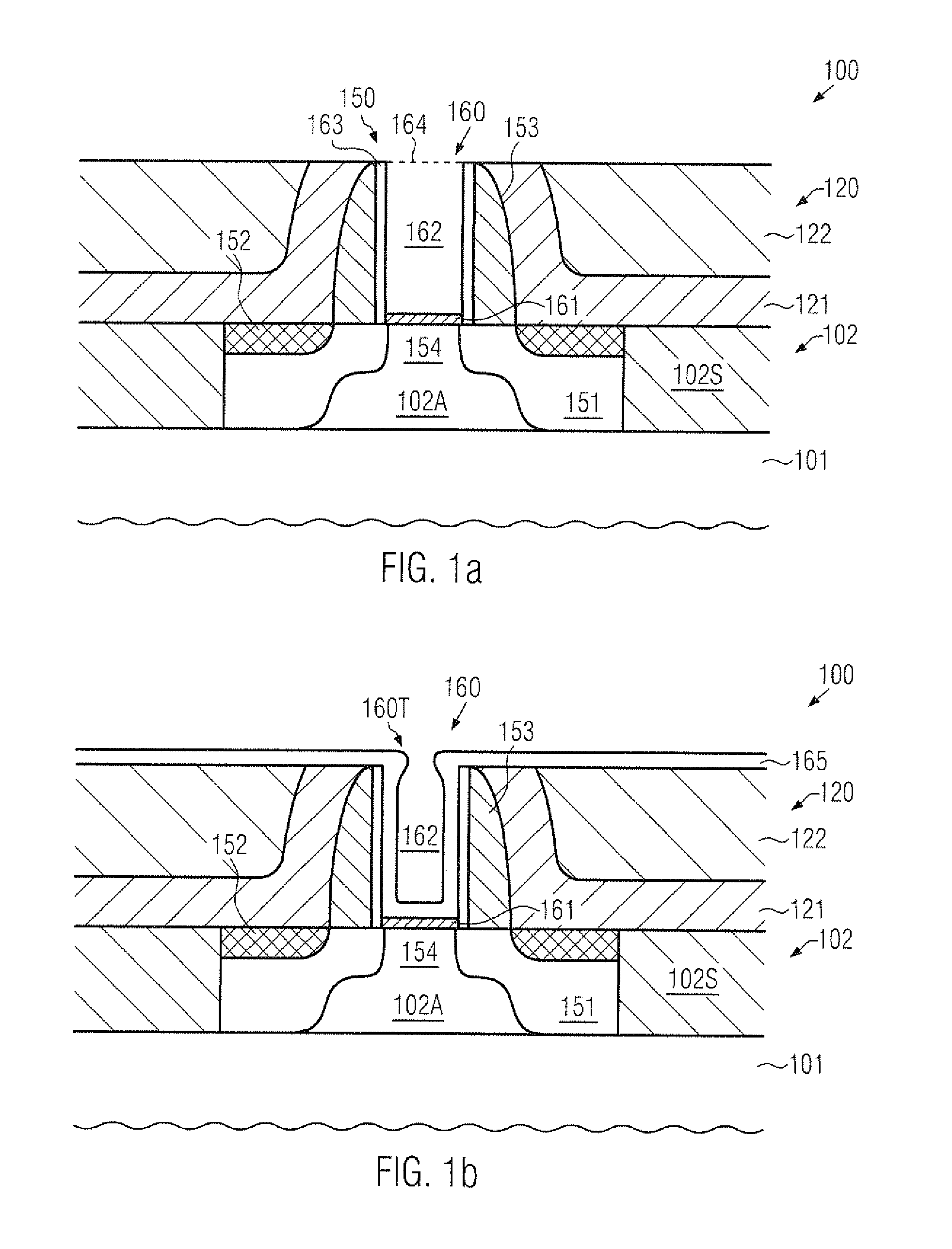

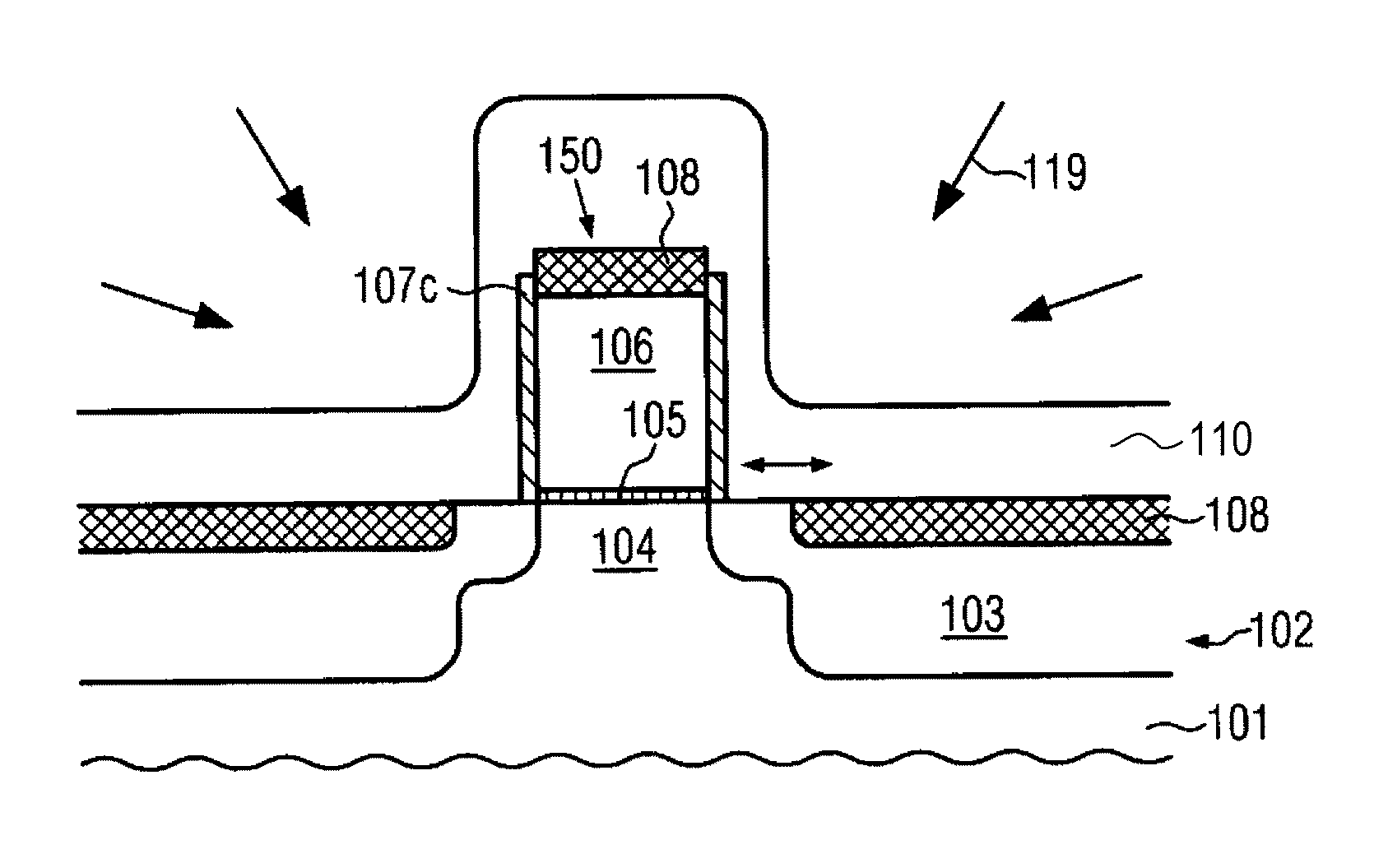

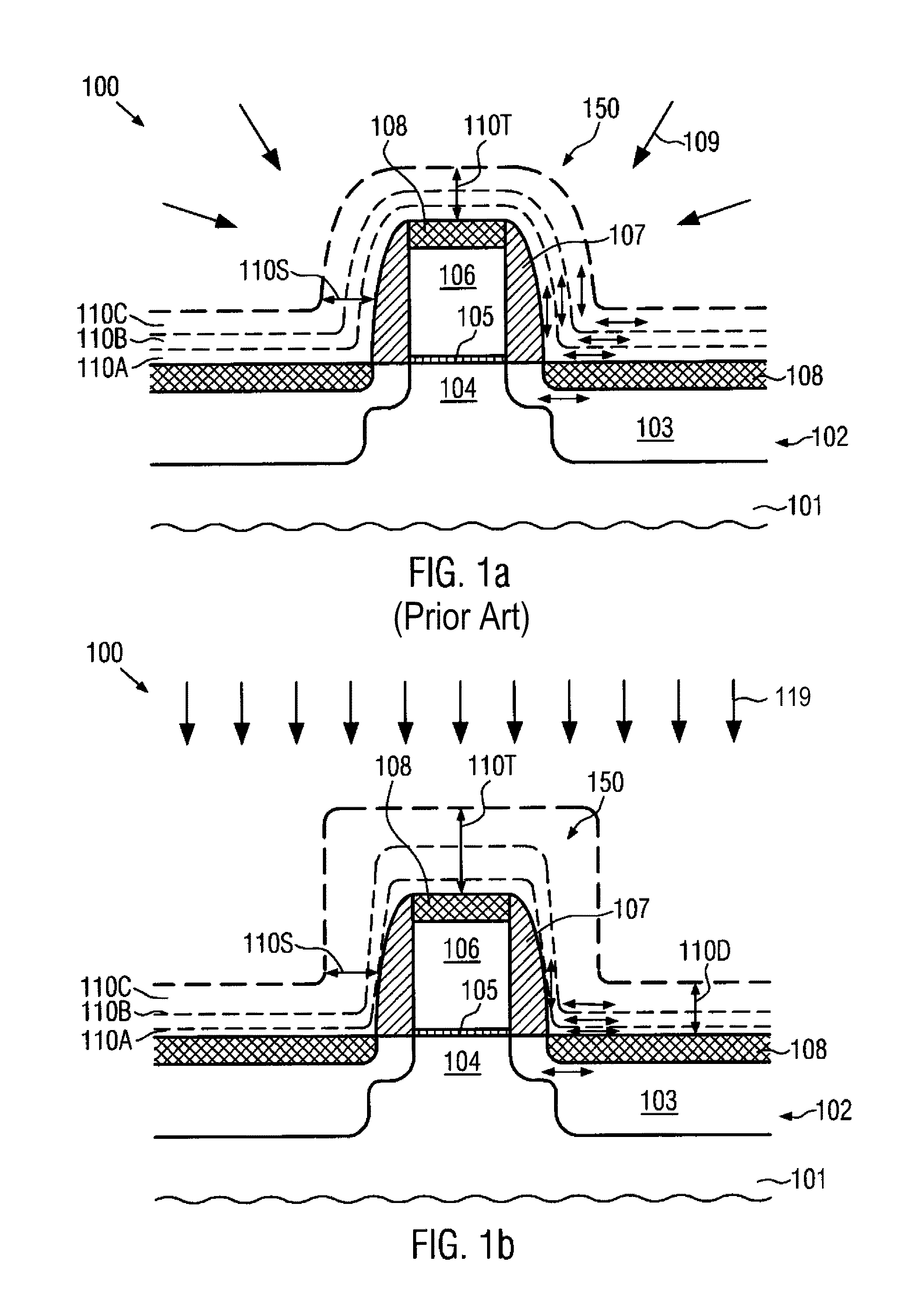

Field effect transistor having a stressed contact etch stop layer with reduced conformality

ActiveUS20080054314A1Improve efficiencyHigh degree of non-conformalityTransistorSemiconductor/solid-state device manufacturingStress conditionsField-effect transistor

By forming a highly non-conformal stressed overlayer, such as a contact etch stop layer, the efficiency of the stress transfer into the respective channel region of a field effect transistor may be significantly increased. For instance, non-conformal PECVD techniques may be used for forming highly stressed silicon nitride in a non-conformal manner, thereby achieving higher transistor performance for otherwise identical stress conditions.

Owner:FULLBRITE CAPITAL PARTNERS

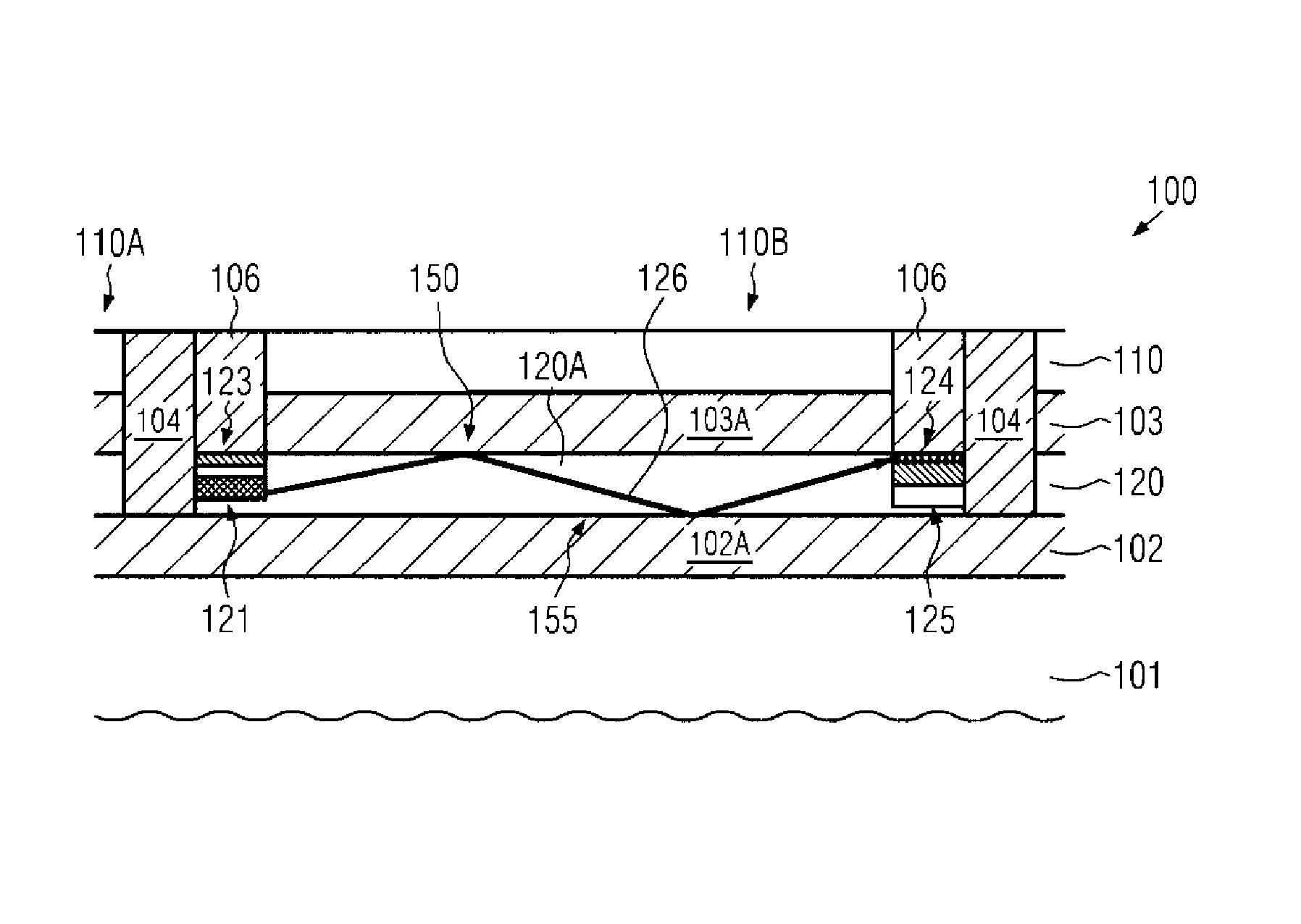

Optical signal transfer in a semiconductor device by using monolithic opto-electronic components

ActiveUS8508008B2Increased process complexityIncrease flexibilitySolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceEngineering

In a semiconductor device, optical signal transfer capabilities are implemented on the basis of silicon-based monolithic opto-electronic components in combination with an appropriate waveguide. Thus, in complex circuitries, such as microprocessors and the like, superior performance may be obtained in terms of signal propagation delay, while at the same time thermal requirements may be less critical.

Owner:GLOBALFOUNDRIES US INC

Sealing performance detection method for battery liquid injection port sealing structure

ActiveCN108692888AIncreased process complexityEasy to operateMeasurement of fluid loss/gain rateHeliumBattery cell

The invention proposes a sealing performance detection method for a battery liquid injection port sealing structure, i.e., the detection of whether the sealing of a welding part of a sealing plate atthe battery liquid injection port sealing structure and a battery housing is qualified or not. After pressurizing the welding part and a cavity between the sealing plate and the battery housing and injecting helium gas, it indicates that there is no sealing if the helium gas flowing out of the cavity is detected to exceed a certain threshold value / a first threshold value. If the helium gas flowingout of the cavity is detected to be the certain threshold value / the first threshold value but the helium gas can be detected to exceed a second threshold value under the vacuum condition, it indicates that the sealing is not qualified; if the helium gas does not exceed the second threshold value under the vacuum condition, it indicates that the sealing is qualified. A detection method for detecting the sealing performance of a battery cell without the advanced injection of helium is innovatively designed. The quality that helium is active gas, the method can achieve the inspection of sealingperformances through a conventional helium detection instrument. The method provided by the invention is simple in operation, is high in accuracy, and facilitates the industrial large-scale application.

Owner:广舜检测技术(上海)有限公司

Field effect transistor having a stressed contact etch stop layer with reduced conformality

ActiveUS7932166B2Improve efficiencyHigh degree of non-conformalityTransistorSemiconductor/solid-state device manufacturingStress conditionsEngineering

By forming a highly non-conformal stressed overlayer, such as a contact etch stop layer, the efficiency of the stress transfer into the respective channel region of a field effect transistor may be significantly increased. For instance, non-conformal PECVD techniques may be used for forming highly stressed silicon nitride in a non-conformal manner, thereby achieving higher transistor performance for otherwise identical stress conditions.

Owner:FULLBRITE CAPITAL PARTNERS

Transparent conductive film with single layer structure, preparation method and application thereof

ActiveCN108385072AImprove thermal stabilityImprove heat and humidity stabilityConductive layers on insulating-supportsVacuum evaporation coatingDirect current magnetron sputteringMaterial consumption

The invention discloses a transparent conductive film with a single layer structure, a preparation method and application thereof. The preparation includes: putting a cleaned substrate into a vacuum chamber of a vacuum magnetron sputtering device, filling argon when the vacuum degree of the chamber is 1*10<-4>-7*10<-4>Pa, and controlling the total air pressure at 0.16Pa, adjusting the sputtering power of a target material to 10-60W, then opening a sample baffle plate, and employing direct current magnetron sputtering technique for deposition on the substrate surface to obtain the transparent conductive film. The transparent conductive film is composed of silver and a metal oxide. By direct sputtering of an alloy target composed of silver and the metal oxide or co-sputtering of silver and ametal oxide target, the transparent metal conductive film with good continuity and stability under a small thickness can be prepared, thereby reaching the purposes of lowering the structural complexity and reducing material consumption.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

Magnetic memory apparatus and method of manufacturing magnetic memory apparatus

InactiveUS7088610B2Solution value is not highImprove magnetic field efficiencySemiconductor/solid-state device detailsMagnetic-field-controlled resistorsMagnetic memoryStorage cell

A magnetic memory apparatus including a memory cell region and a peripheral circuitry region mounted on a substrate is provided. The memory cell region includes first wiring, second wiring that three-dimensionally intersects with the first wiring, and a magnetoresistance effect type memory device disposed in an intersecting region of the first and the second wiring for storing and reproducing information of a magnetic spin. The peripheral circuitry region includes first wiring that is in the same wiring layer as that of the first wiring in the memory cell region, and second wiring that is in the same wiring layer as the second wiring in the memory cell, and a magnetic material layer including a high magnetic permeability layer is formed on both side surfaces of the first wiring only within the memory cell region and on a surface opposite to a surface facing the memory device.

Owner:SONY CORP

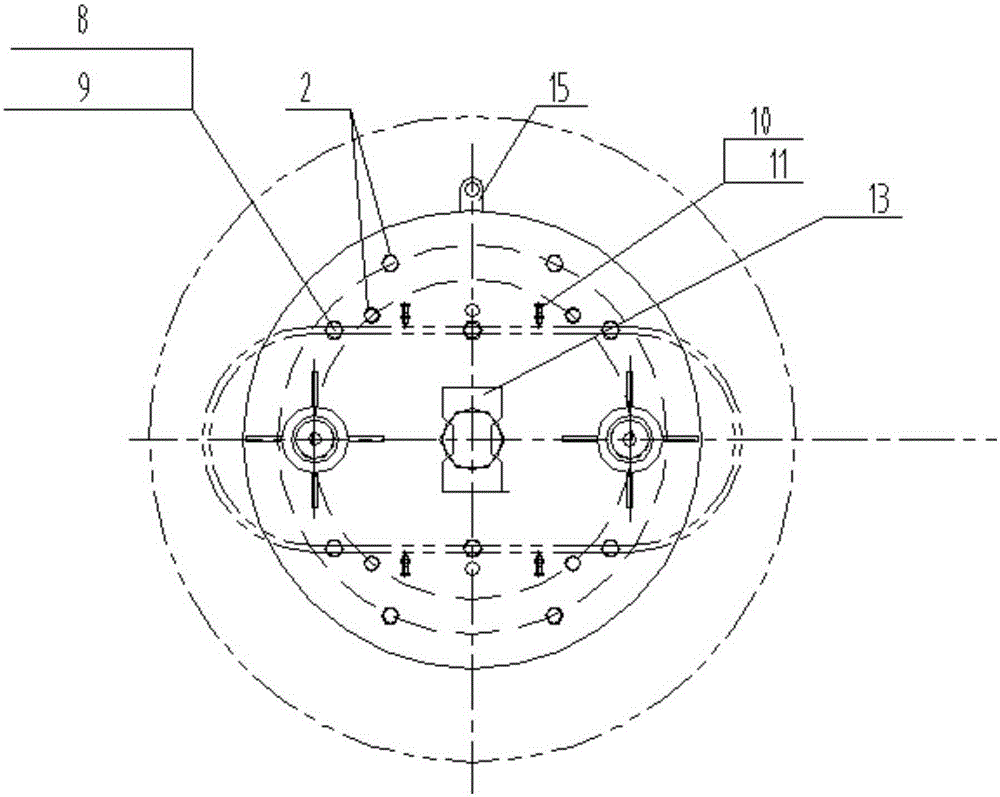

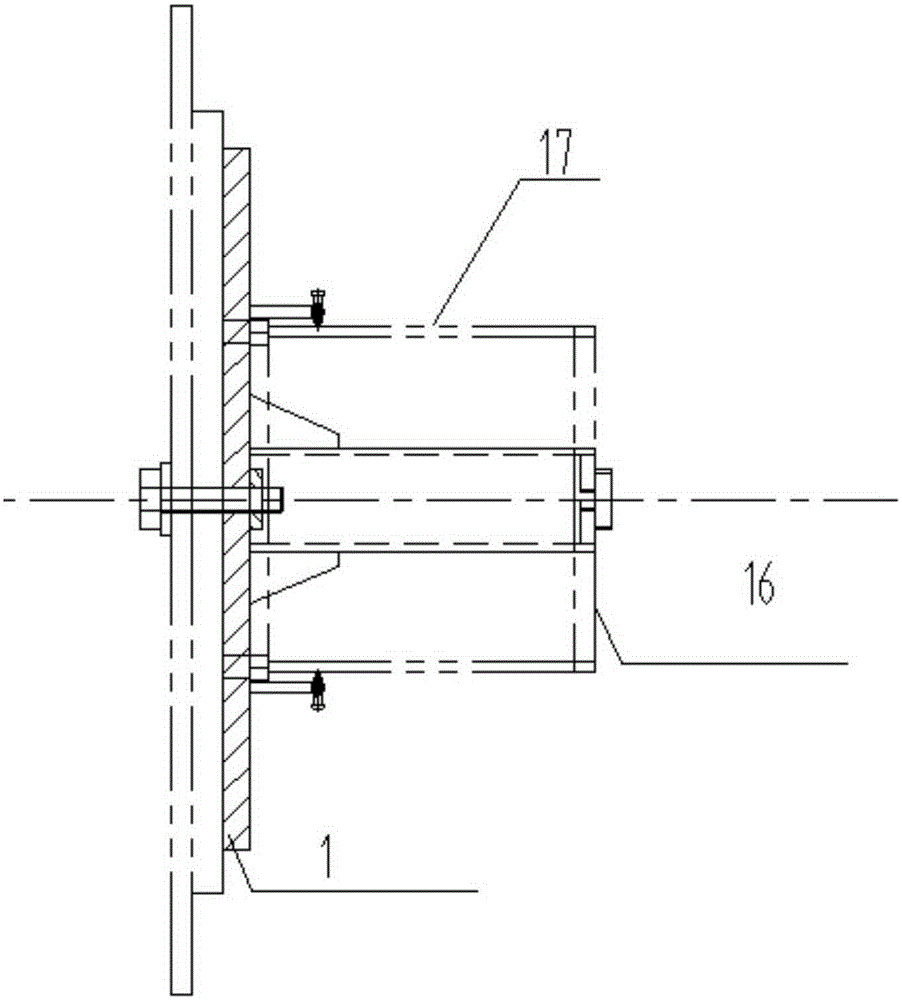

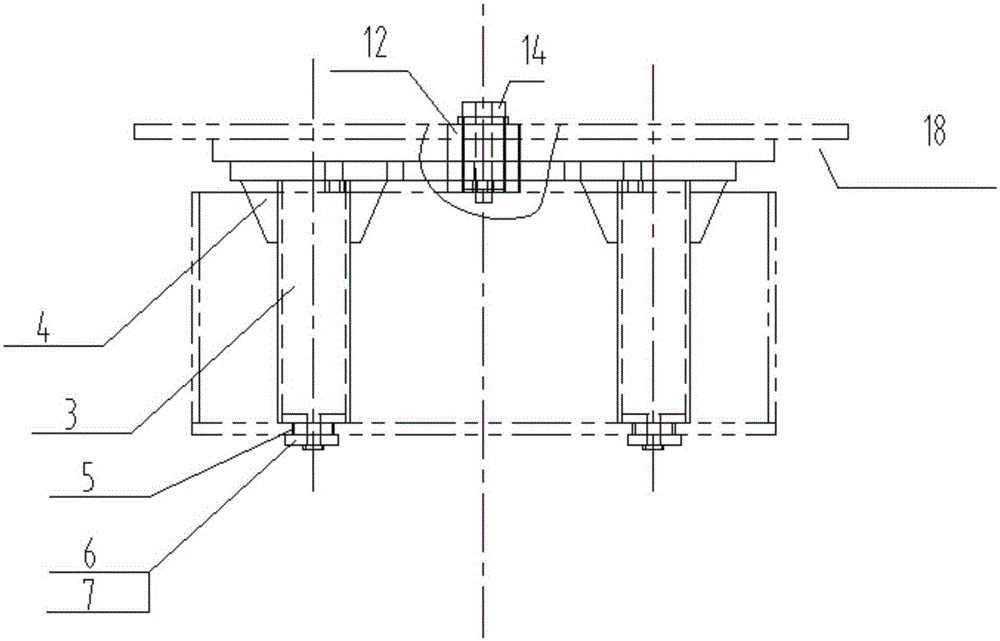

Locomotive sleeper kidney-shaped enclosure plate mechanical welding and positioning tool and welding method implemented through tool

ActiveCN105171319ANo looseningNo displacementWelding/cutting auxillary devicesAuxillary welding devicesMedial axisEngineering

The invention discloses a locomotive sleeper kidney-shaped enclosure plate mechanical welding and positioning tool and a welding method implemented through the tool. The tool comprises a bottom plate fixed to a base plate of a welding device through connection bolts. The bottom plate is further provided with a supporting device, the supporting device comprises two supporting columns symmetric about the medial axis of the tool, the root portions of the supporting columns are provided with crossed auxiliary supporting plates, and positioning rings, cover plates and positioning bolts are arranged on the tops of the supporting columns. The tool has the advantages that installation is convenient, the structure is firm, a sleeper kidney-shaped enclosure plate can be effectively fixed in the welding process, welding defects caused because the base plate of the welding device rotates and accordingly a welding gun head and a weld joint deviate are avoided, and the welding effect is improved.

Owner:CRRC ZIYANG CO LTD

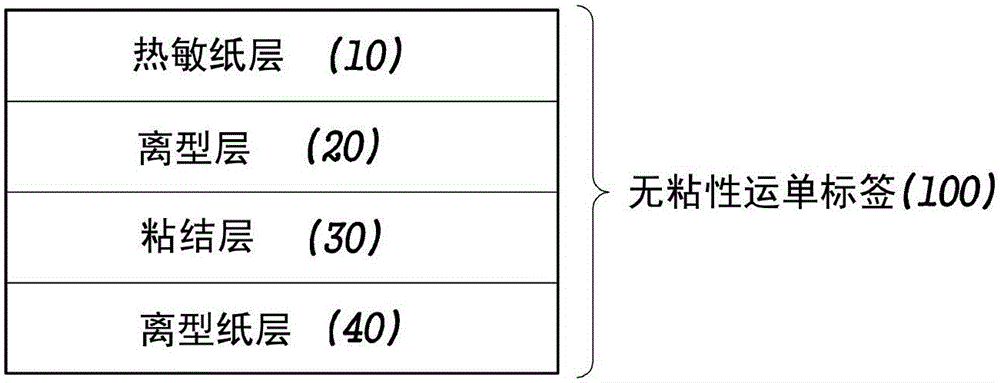

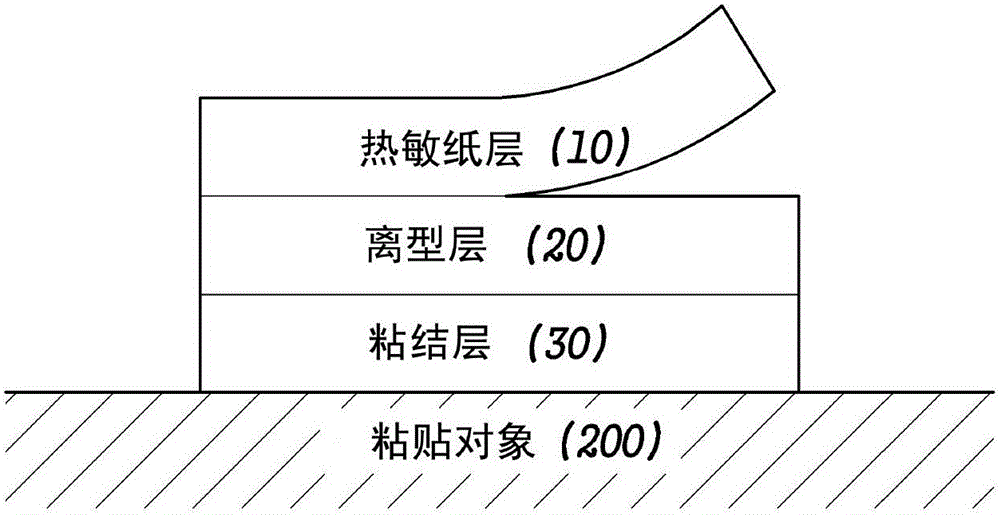

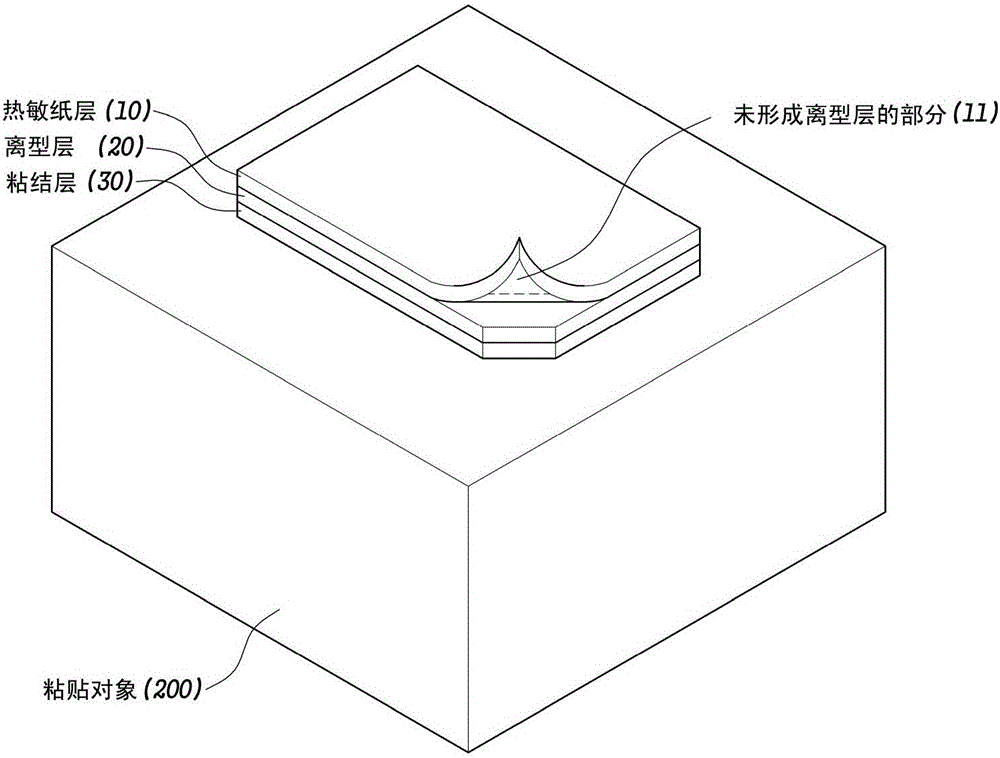

Non-sticking invoice label and manufacturing method thereof

InactiveCN105985744AStickiness will not haveProper adhesionFilm/foil adhesivesPolyether coatingsBiochemical engineeringInvoice

The invention relates to a non-sticking invoice label and a manufacturing method thereof, particularly an invoice label used for express delivery including a surface printable thermo-sensitive paper layer, a sticking layer formed on the back of the thermo-sensitive paper layer, and a release paper layer stuck to the back of the sticking layer. The non-sticking invoice label also comprises a release layer. The release layer is between the back of the thermo-sensitive paper layer and the surface of the sticking layer and is formed by coating a release liquid consisting polyethylene glycol, polyethylene, an emulsifier and water. The release layer is separated from the back of the thermo-sensitive paper layer when the thermo-sensitive paper layer is removed and is left over the surface of the sticking layer, and the part left over the surface of the sticking layer is non-sticking.

Owner:金银铁

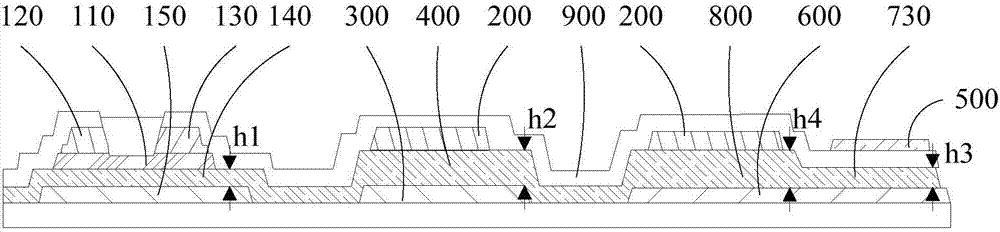

Display panel and preparation method therefor

InactiveCN107507838AExtend in the same directionImprove control effectStatic indicating devicesSolid-state devicesCapacitanceCommon line

The invention discloses a display panel and a preparation method therefor. The display panel comprises subpixels, and each subpixel comprises a drive transistor which comprises a gate medium layer. Each subpixel also comprises a storage capacitor which comprises a capacitor medium layer; a first insulating layer which is disposed between a data line of the display panel and a scanning line of a display panel; and a second insulating layer which is disposed between the data line and a common line of the display panel. The gate medium layer, the first insulating layer, the capacitor medium layer and the second insulating layer are integrated through a halftone mask or the gray scale masking technology to form insulating films with different thicknesses. The thickness of the gate medium layer is less than the thickness of the first insulating layer. The technical scheme of the invention improves the performance of the display panel.

Owner:HKC CORP LTD

Method of manufacturing semiconductor device

ActiveUS20130330894A1Eliminate the issue of “over-erasure”Increase array densitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialGate oxide

A semiconductor device fabrication method particularly suitable for the fabrication of a 90 nm embedded flash memory is disclosed. The method includes: forming a dielectric layer having a first thickness over a first device region and forming a dielectric layer having a second thickness different from the first thickness over a second device region, the dielectric layer having a first thickness serving as a tunnel oxide layer of a split-gate structure, the dielectric layer having a second thickness serving as a gate oxide layer of a MOS transistor. The method enables the fabrication of a MOS transistor including a gate oxide layer with a desired thickness.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

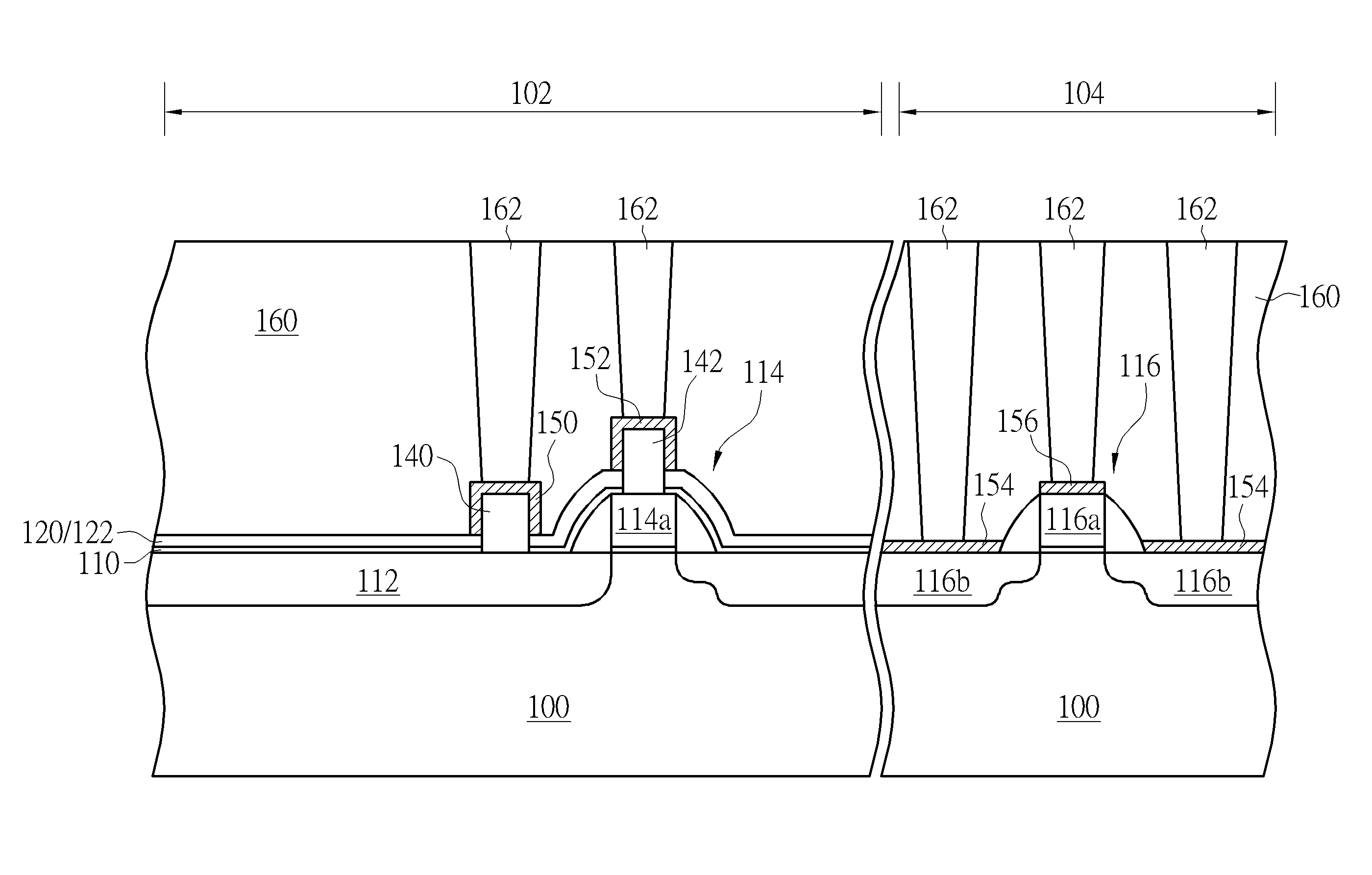

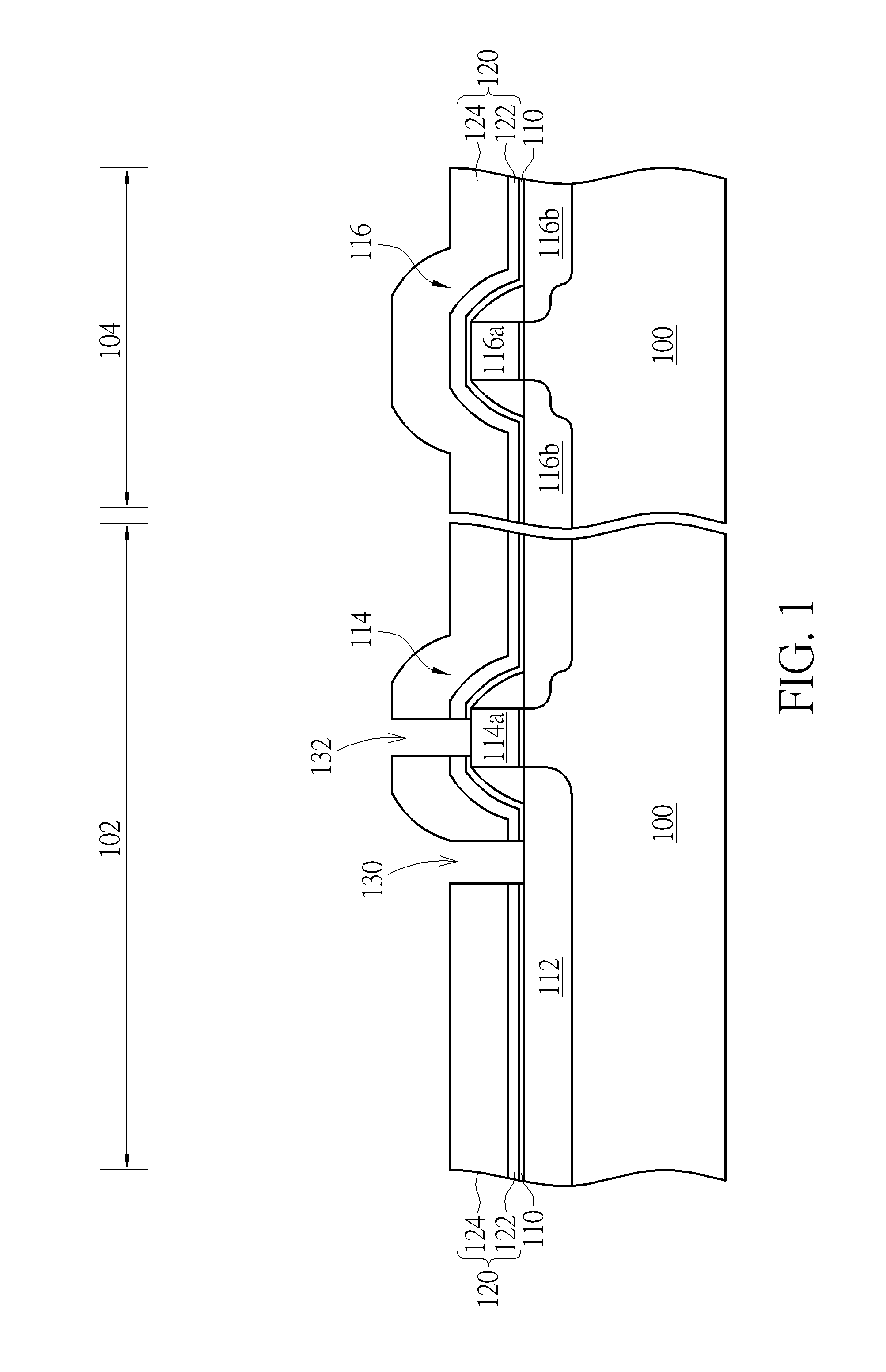

Complementary metal-oxide-semiconductor image sensor and manufacturing method thereof

ActiveUS9537040B2Improve electrical performanceAvoid Metal ContaminationSolid-state devicesDiodeSalicideEngineering

A method for manufacturing semiconductor devices includes following steps. A substrate having a pixel region and a periphery region defined thereon is provided, and at least a transistor is formed in the pixel region. A blocking layer is formed on the substrate, and the blocking layer includes a first opening exposing a portion of the substrate in the pixel region and a second opening exposing a portion of the transistor. A first conductive body is formed in the first opening and a second conductive body is formed in the second opening, respectively. The first conductive body protrudes from the substrate and the second conductive body protrudes from the transistor. A portion of the blocking layer is removed. A first salicide layer is formed on the first conductive body and a second salicide layer is formed on the second conductive body, respectively.

Owner:UNITED MICROELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com