Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

91results about How to "Improve process tolerance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

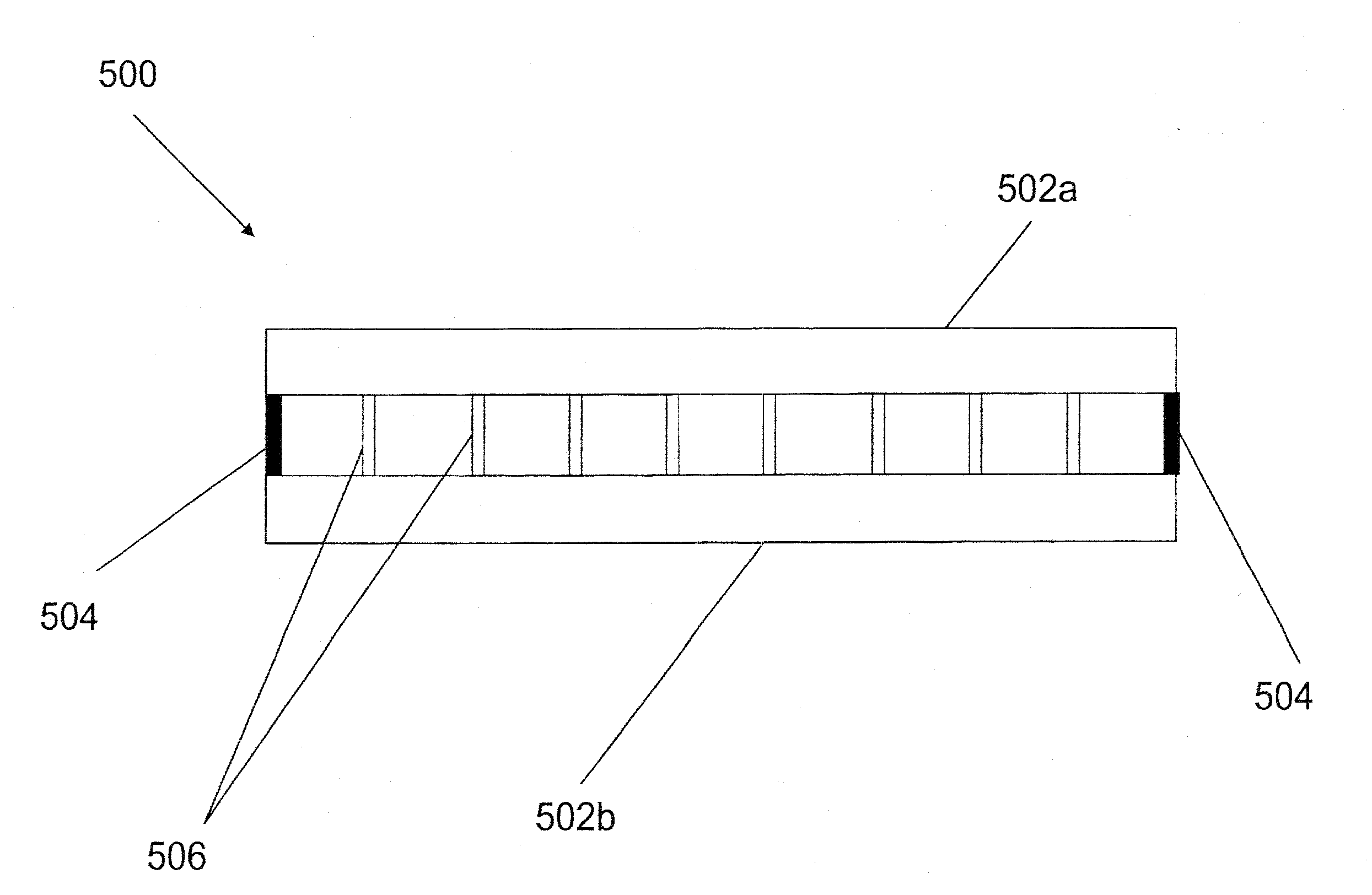

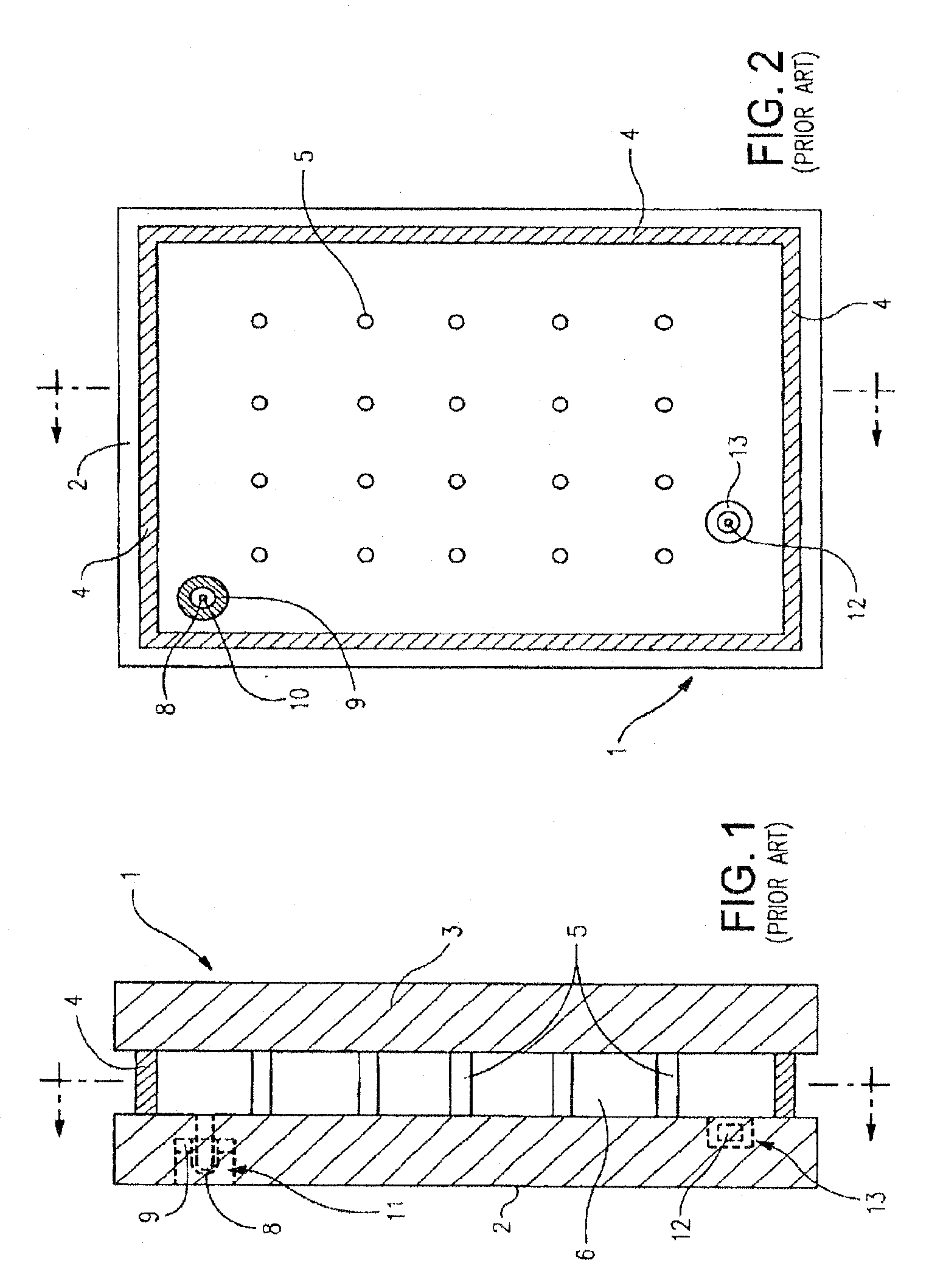

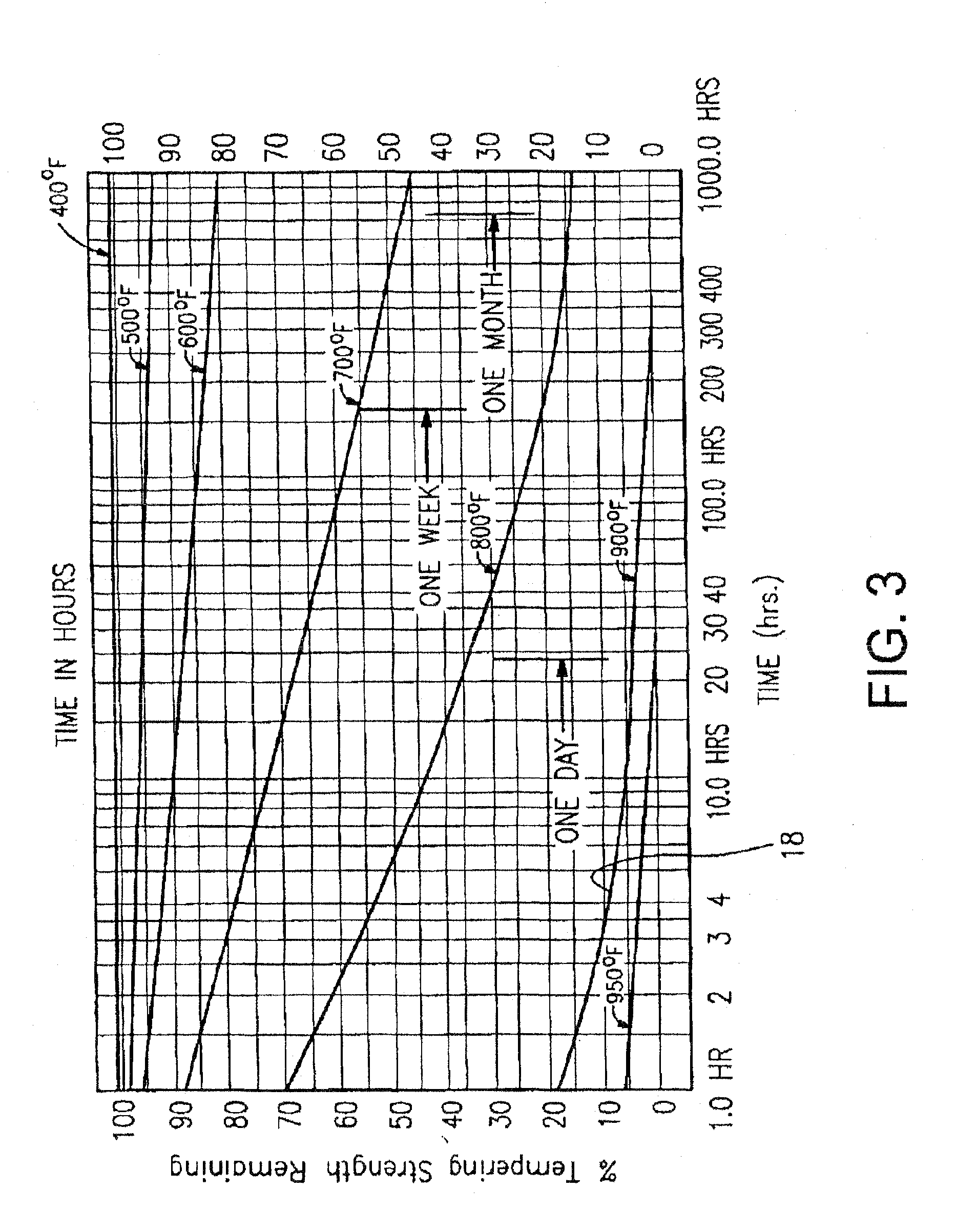

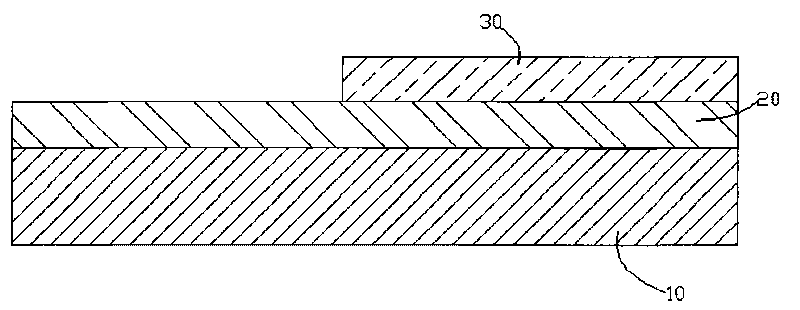

Coefficient of thermal expansion filler for vanadium-based frit materials and/or methods of making and/or using the same

ActiveUS20120213954A1Improve sealingReduce sealClimate change adaptationWindows/door improvementMetal chlorideFrit

Certain example embodiments relate to seals for glass articles. Certain example embodiments relate to a composition used for sealing an insulted glass unit. In certain example embodiments the composition includes vanadium oxide, barium oxide, zinc oxide, and at least one additional additive. For instance, another additive that is a different metal oxide or different metal chloride may be provided. In certain example embodiments, a composition may be combined with a binder solution that substantially or completely burns out by the time the composition is melted. In certain example embodiments, a CTE filler is included with a frit material. In certain example embodiments, a vacuum insulated glass unit includes first and second glass substrates that are sealed together with a seal that includes the above-described composition.

Owner:GUARDIAN GLASS LLC

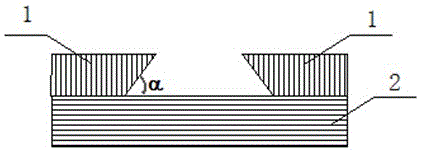

Semiconductor high-voltage terminal structure and production method thereof

ActiveCN101752208ASmall sizeImprove process toleranceSemiconductor/solid-state device detailsSolid-state devicesHigh pressureOblique angle

The invention provides a semiconductor high-voltage terminal structure and a production method thereof. The method comprises the steps of: firstly providing a silicon baseplate, forming a field oxide layer on the silicon baseplate and introducing an easily corroded layer in the field oxide layer; identifying a high-voltage terminal structure area by using a photomask; and then corroding the fieldoxide layer by using a wet method to form a ramp oxide layer with an oblique angle; carrying out ion implantation by using the ramp oxide layer as a self-aligned mask to introduce initial impurities diffusing horizontally; and finally forming a high-voltage protection ring with a horizontal doping gradient at the starting end of the ramp oxide layer; and forming a ramp field plate by depositing high-doping polycrystalline silicon or metal on the ramp oxide layer. The semiconductor high-voltage terminal structure comprises the silicon baseplate, the ramp oxide layer arranged on the silicon baseplate, the high-voltage protection ring with a horizontal doping gradient which is injected by taking the ramp oxide layer as the self-aligned mask, and the high-doping polycrystalline silicon or metal ramp field plate deposited on the ramp oxide layer.

Owner:商海涵

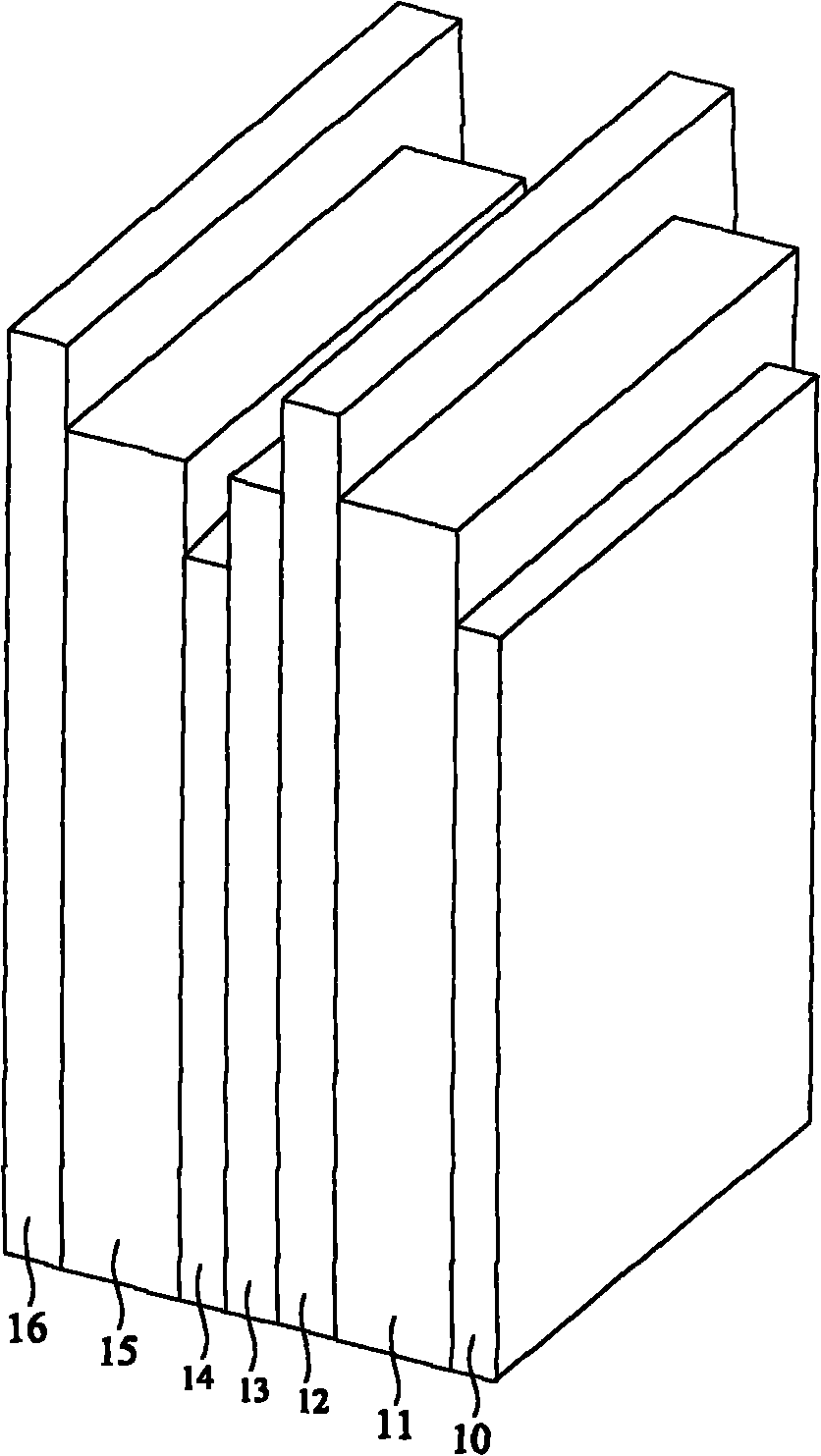

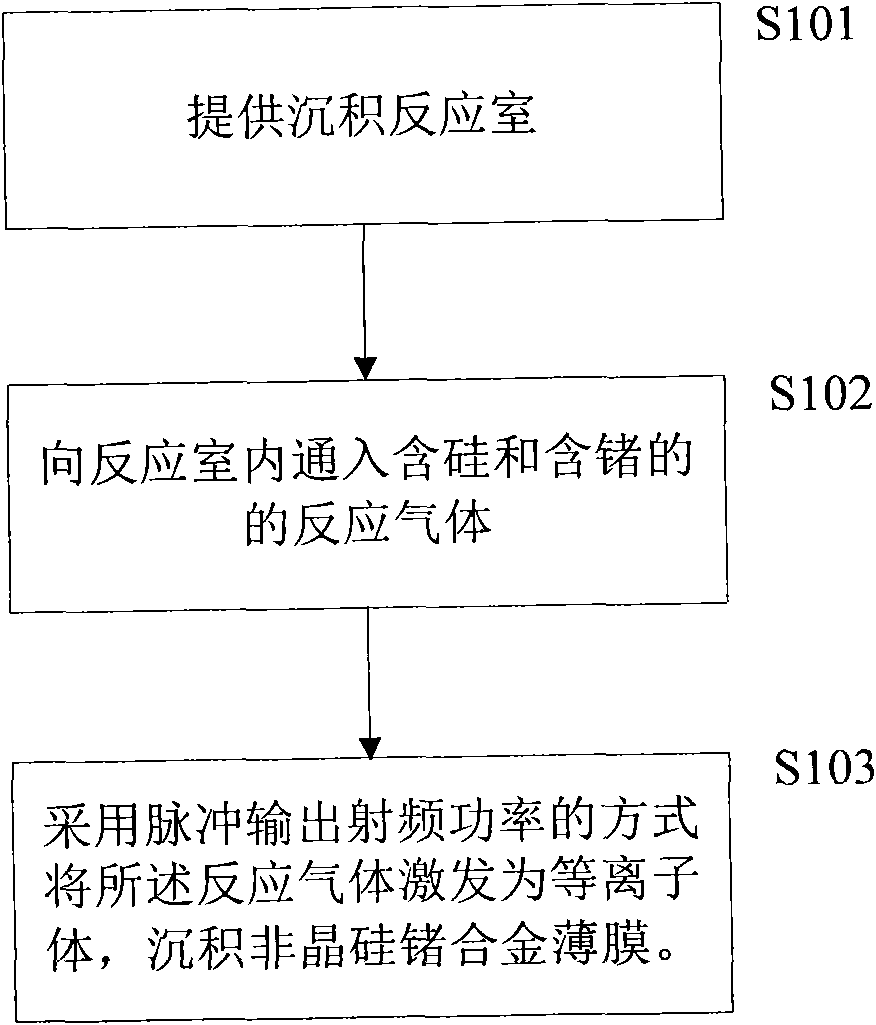

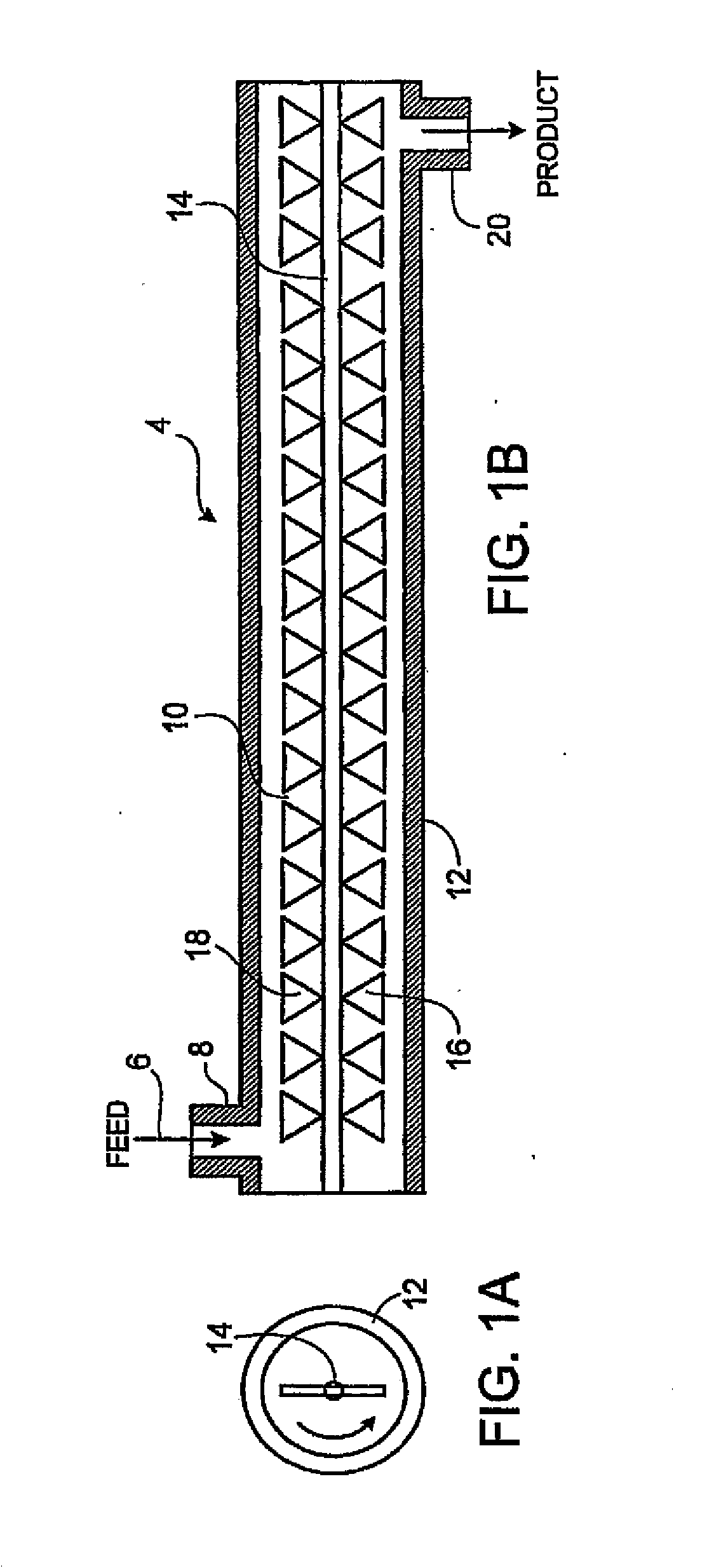

Method for depositing film

InactiveCN101775591AImprove uniformityImprove consistencyFinal product manufactureSemiconductor/solid-state device manufacturingAlloy thin filmLarge size

The invention discloses a method for depositing a thin film. The method comprises the following steps of: providing a reaction chamber, wherein a substrate is placed on the surfaces of electrode plates which are alternately placed at intervals in the reaction chamber; leading reaction gas into the reaction chamber; exciting the reaction gas into plasmas by adopting a mode of pulse output radio frequency power; and depositing a thin film on the surface of the substrate. The method can obviously improve the band gap and the thickness uniformity of a thin film and particularly an alloy thin film deposited on the surface of the large-area substrate in large-size PECVD (Plasma Enhanced Chemical Vapor Deposition) deposition equipment.

Owner:GS SOLAR FU JIAN COMPANY +1

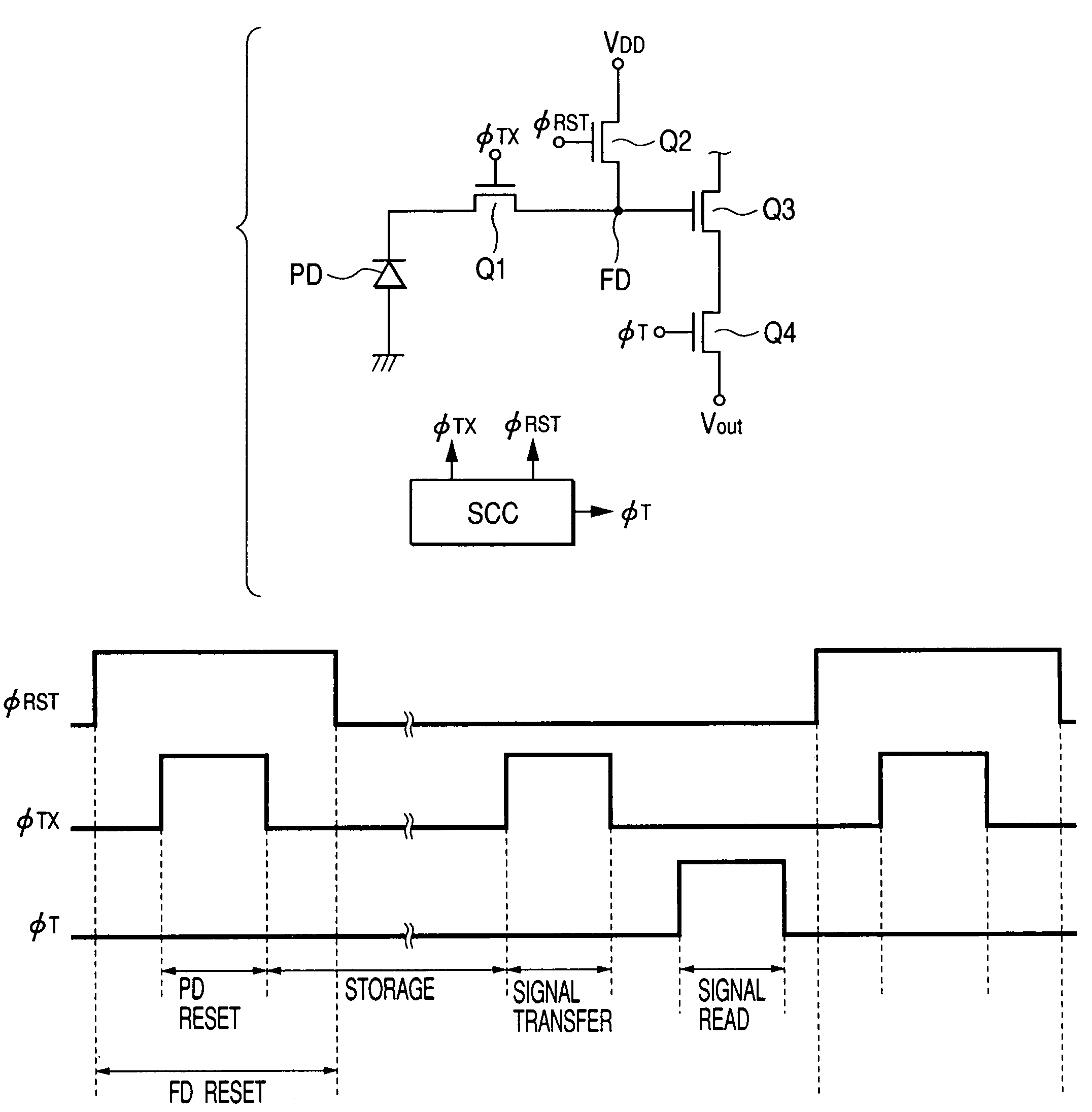

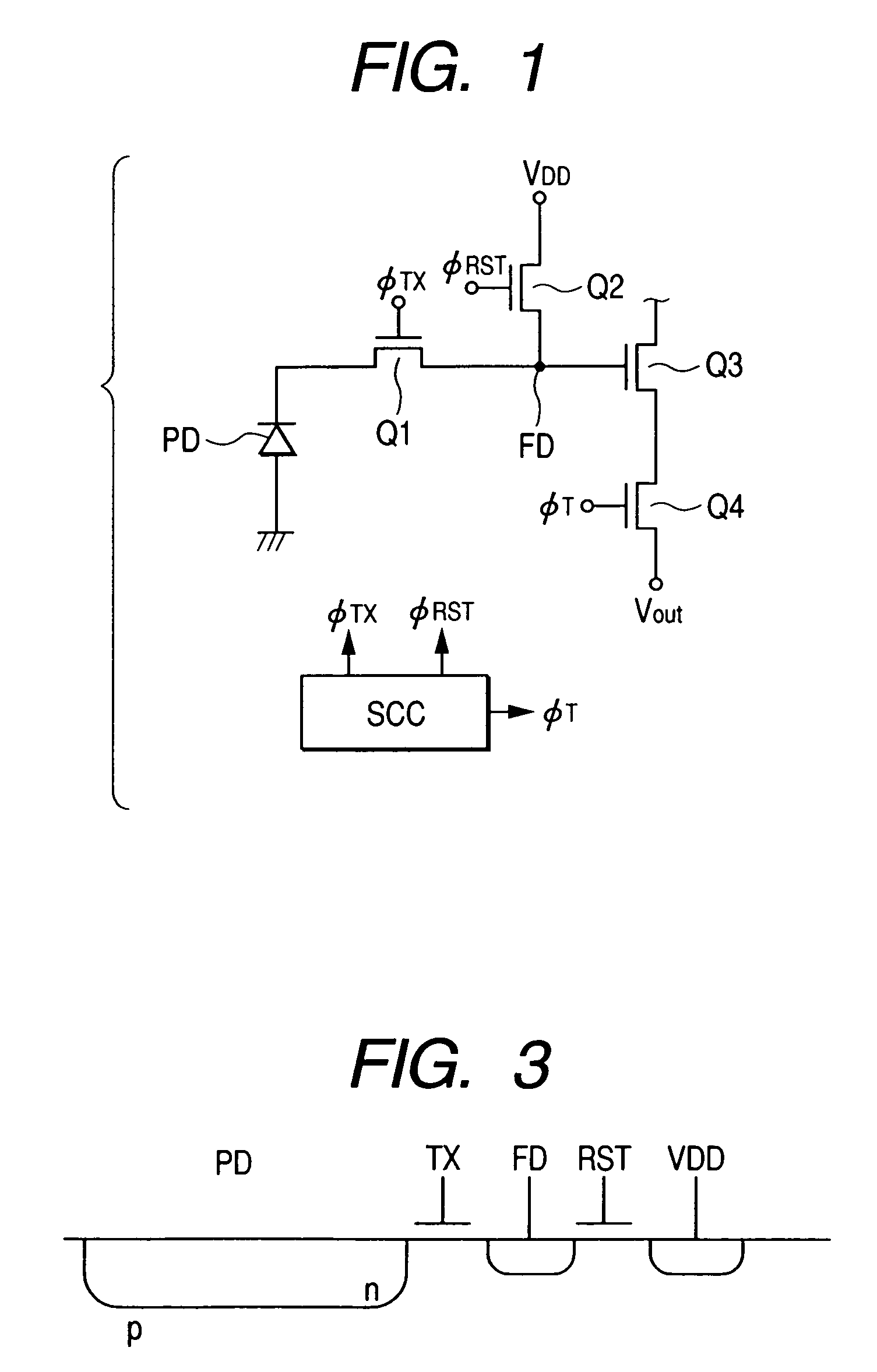

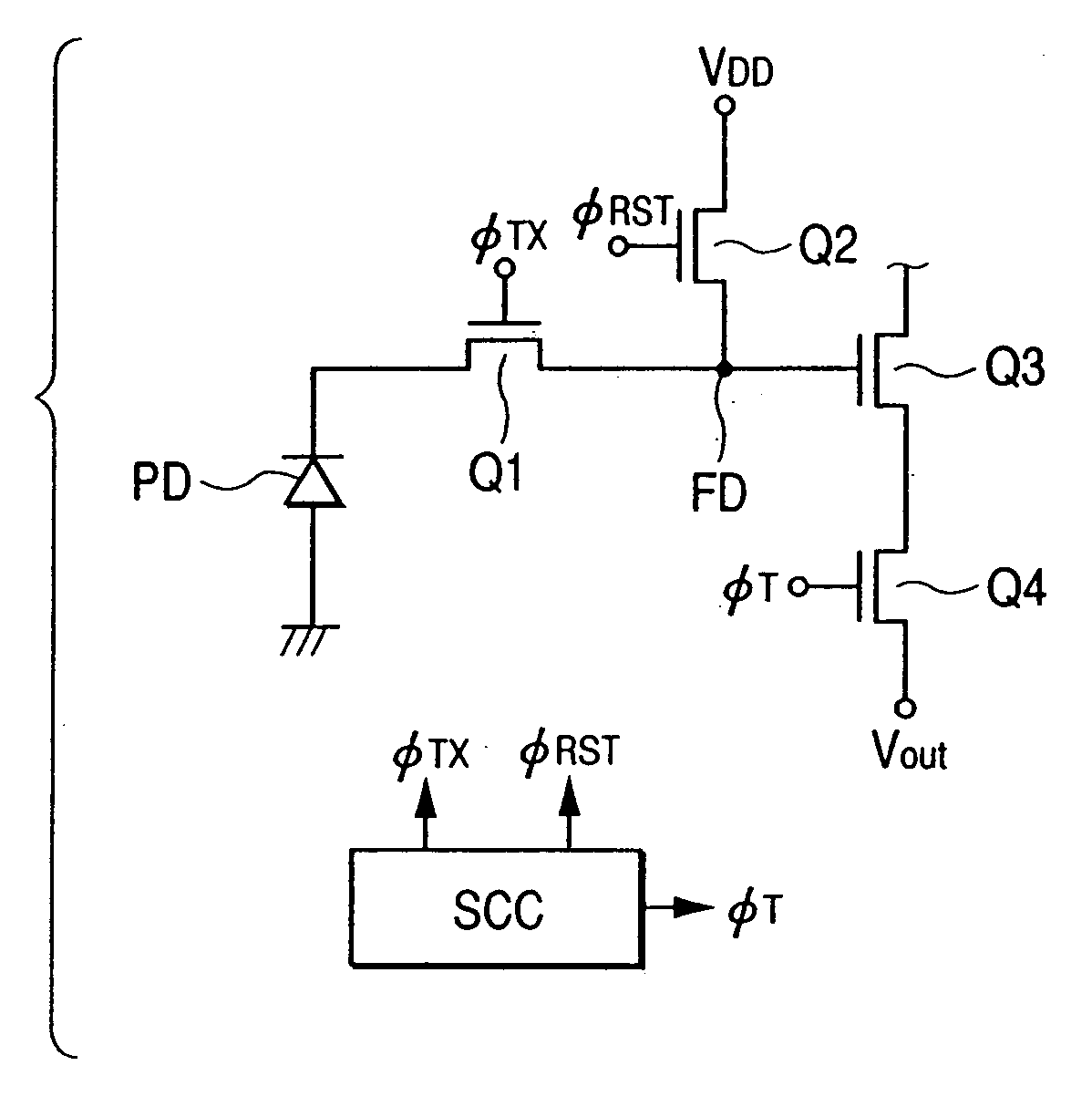

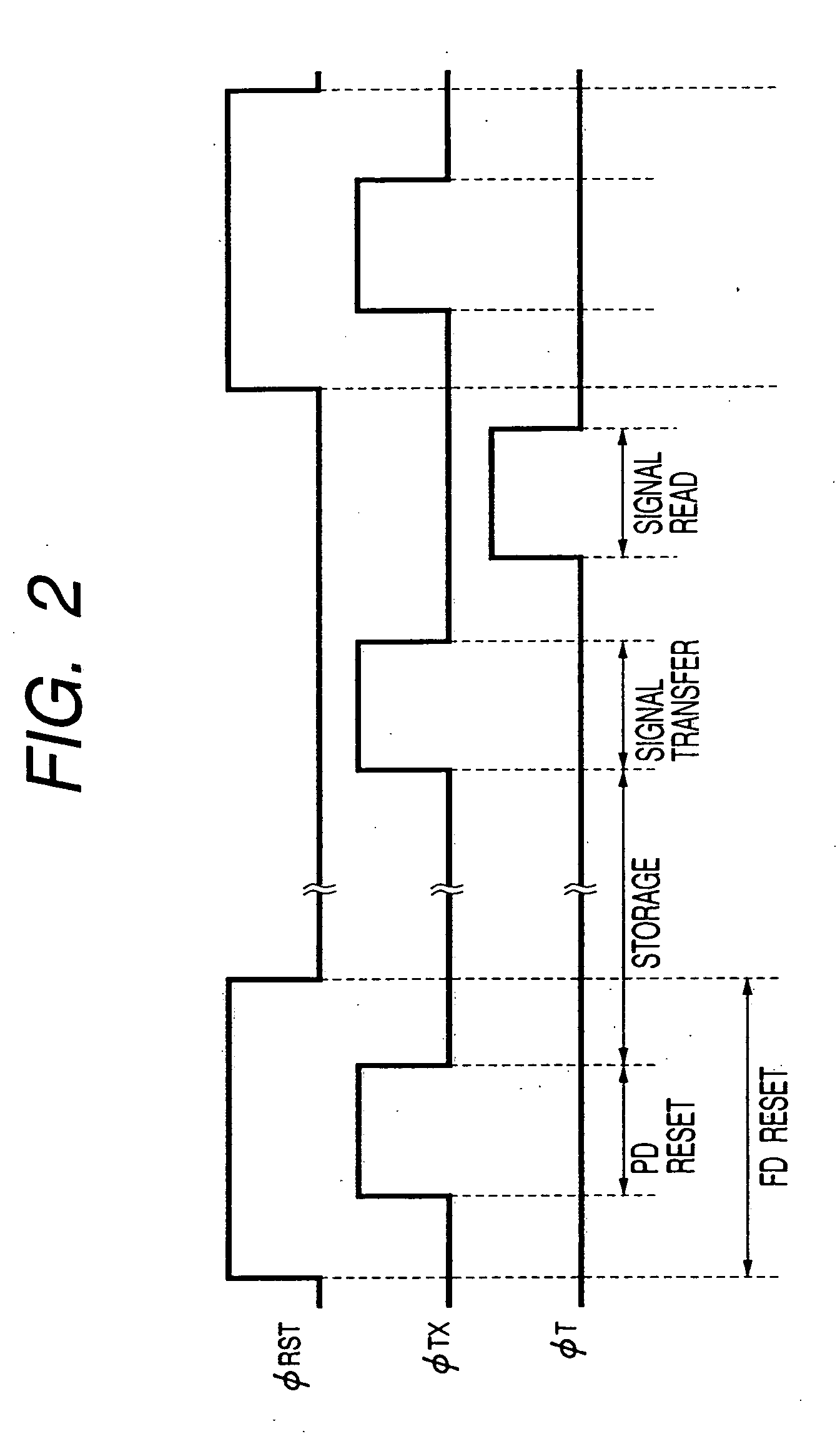

Solid-state image pickup device and method of resetting the same

InactiveUS7015964B1Reduce residual chargeEfficient conversionTelevision system detailsTelevision system scanning detailsAudio power amplifierTransfer switch

A solid-state image pickup device comprises for each pixel a photoelectric converter PD, an input terminal FD of a signal amplifier and a transfer switch TX for transferring an optical signal from the photoelectric converter to the input terminal. The device additionally comprises means for resetting the photoelectric converter by opening the transfer switch TX under a condition of holding the voltage of the input terminal FD to a fixed high level before storing the optical signal in the photoelectric converter PD. With this arrangement, any residual electric charge in the photoelectric converter can be eliminated without paying the cost of reducing the manufacturing yield and degrading the chip performance.

Owner:CANON KK

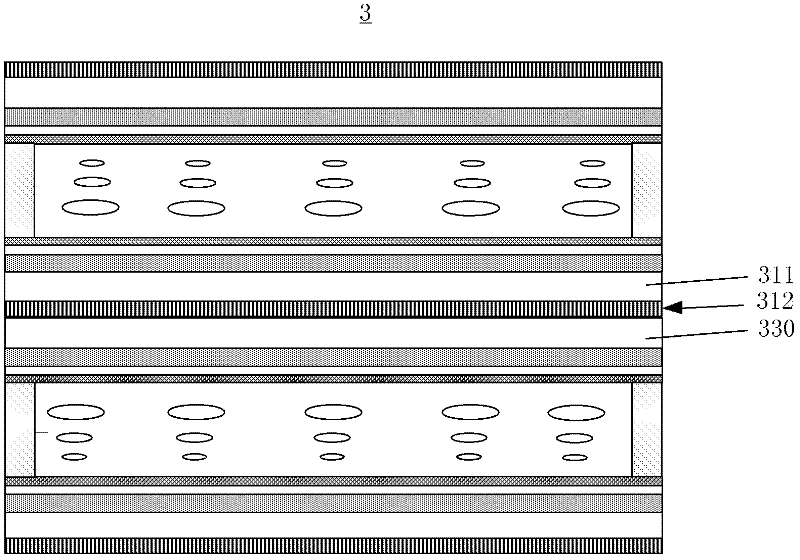

Silicon-based InGaAs PIN photoelectric detector based on heterogeneous integration and vertical optical coupling

ActiveCN102779892AAchieve vertical couplingSimple structureCoupling light guidesSemiconductor devicesGratingBonding process

The invention discloses a silicon-based InGaAs PIN photoelectric detector based on heterogeneous integration and vertical optical coupling. The silicon-based InGaAs PIN photoelectric detector comprises a silicon-on-insulator (SOI) substrate, a vertical coupling grating, a benzocyclobutene (BCB) bonding layer, an anti-reflecting layer, a first conductivity type indium phosphide layer, an intrinsic InGaAs layer and a second conductivity type indium phosphide layer, wherein the vertical coupling grating is produced in top silicon of the SOI substrate, the BCB bonding layer is covered on the vertical coupling grating, the anti-reflecting layer is located above the BCB bonding layer, the first conductivity type indium phosphide layer is located above the anti-reflecting layer, the intrinsic InGaAs layer is located above the first conductivity type indium phosphide layer, the second conductivity type indium phosphide layer is located above the intrinsic InGaAs layer, the vertical coupling grating is produced by etching the top silicon of the SOI substrate, the etching depth is 70-110 nm, the grating period is 600-680 nm, and the refractive index of the anti-reflecting layer is between refractive indexes of the BCB bonding layer and the first conductivity type indium phosphide layer. According to the silicon-based InGaAs PIN photoelectric detector, by means of an adhesiveness bonding process, InP / InGaAs / InP stack material layers are adhered to the grating which is etched on the SOI substrate, so that light and the InP / InGaAs / InP layers are vertically coupled, and suitable designs and prioritization schemes are provided for specific applications of the silicon-based InGaAs PIN photoelectric detector.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Solid-state image pickup device and method of resetting the same

InactiveUS20060066741A1Reduce residual chargeEfficient conversionTelevision system detailsTelevision system scanning detailsTransfer switchEngineering

A solid-state image pickup device comprises for each pixel a photoelectric converter PD, an input terminal FD of a signal amplifier and a transfer switch TX for transferring an optical signal from the photoelectric converter to the input terminal. The device additionally comprises means for resetting the photoelectric converter by opening the transfer switch TX under a condition of holding the voltage of the input terminal FD to a fixed high level before storing the optical signal in the photoelectric converter PD. With this arrangement, any residual electric charge in the photoelectric converter can be eliminated without paying the cost of reducing the manufacturing yield and degrading the chip performance.

Owner:CANON KK

Electric welding safety goggles

InactiveCN102360144AImprove viewing angle uniformityReduce difficultyGogglesNon-linear opticsElectricityBiochemical engineering

The invention discloses a pair of electric welding safety goggles, which comprises a first base plate, a second base plate, a third base plate and a fourth base plate, wherein the first base plate and the second base plate are in opposite arrangement, the third base plate and the fourth base plate are in opposite arrangement, the second base plate and the fourth base plate are in adjacent arrangement, the electric welding safety goggles also comprise a first liquid crystal layer, a second liquid crystal layer, a first polaroid, a second polaroid, a third polaroid and a fourth polaroid, the first liquid crystal layer is arranged between the first base plate and the second base plate, the second liquid crystal layer is arranged between the third base plate and the fourth base plate, the first polaroid is arranged on the surface of the first base plate, the second polaroid is arranged on the surface of the second base plate, the third polaroid is arranged on the surface of the third base plate, the fourth polaroid is arranged on the surface of the fourth base plate, the first liquid crystal layer and the second liquid crystal layer are in twisting arrangement in reverse directions, in addition, the view angle direction difference is 180 degrees, and in addition, the twisting angle range of the first liquid crystal layer and the second liquid crystal layer is 72 to 88 degrees. The electric welding safety goggles have the characteristics that the view angle uniformity is high, the diffuse reflection is low, and the manufacture process is simple.

Owner:TIANMA MICRO ELECTRONICS CO LTD

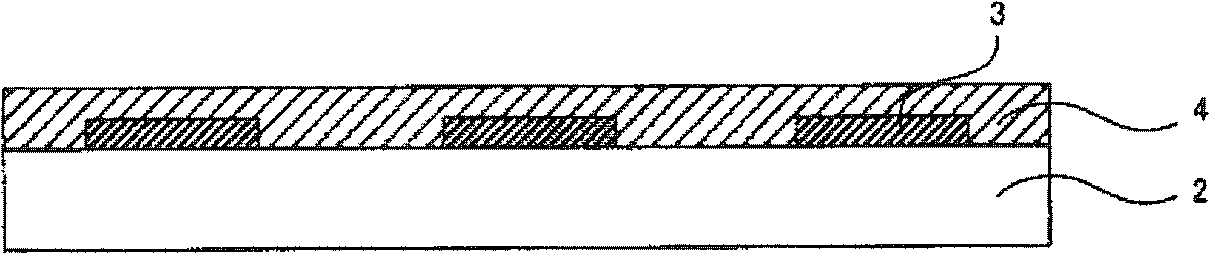

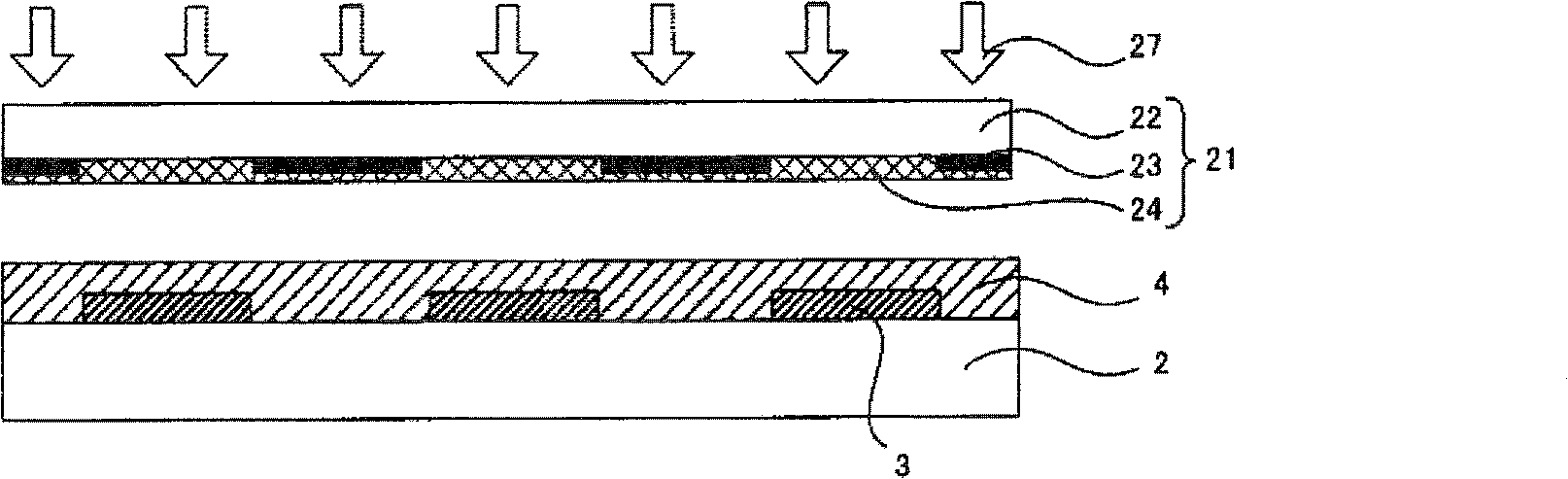

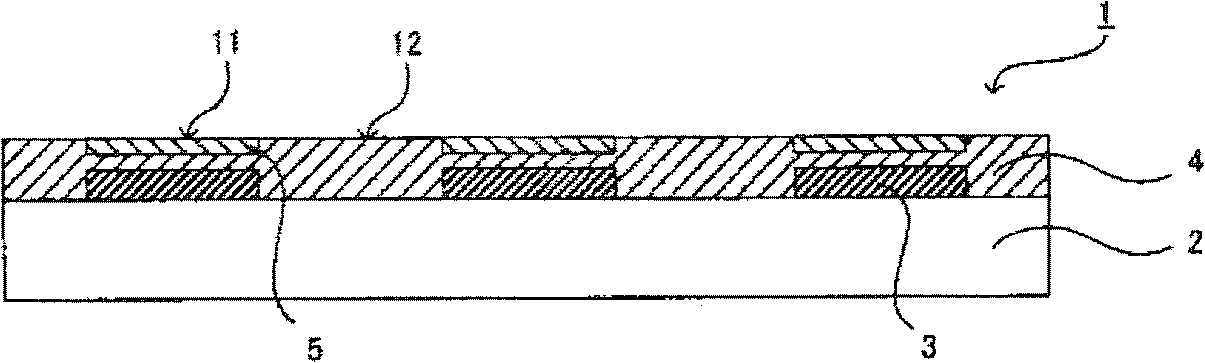

Device material for hole injection/transport layer, ink for forming hole injection/transport layer, device having hole injection/transport layer, and method for manufacturing same

InactiveCN102473849AImprove process toleranceExcellent hole injection and transport propertiesElectroluminescent light sourcesSolid-state devicesSimple Organic CompoundsTransport layer

Disclosed is a device material for a hole injection / transport layer, which has wettability that is changed by energy irradiation, high processing resistance and excellent hole injection / transport properties. The device material for a hole injection / transport layer is capable of forming a hole injection / transport layer by a solution coating method. Also disclosed are: an ink for a hole injection / transport layer, which uses the device material; a device having a long life, wherein a layer arranged on a hole injection / transport layer can be patterned; and a method for manufacturing the device. Specifically disclosed is a device material for a hole injection / transport layer, which is characterized in that a fluorine-containing organic compound adheres to an organic-transition metal oxide composite that is a reaction product of an organic transition metal complex. Also specifically disclosed are an ink for a hole injection / transport layer, a device and a method for manufacturing the device, each using the device material.

Owner:DAI NIPPON PRINTING CO LTD

Touch Panel and Peripheral Circuit Thereof

ActiveUS20120044160A1Improve connection stabilityImprove process toleranceInput/output processes for data processingExtremity PartTouch panel

A touch panel and a peripheral circuit thereof are provided. Each bonding pad of the peripheral circuit includes a first conductive layer, a first protective layer, a second conductive layer, and a second protective layer sequentially arranged on a substrate from bottom to top. A covered area of the second conductive layer provided by the second protective layer is increased to cover a portion of the second conductive layer located above a junction area between the first protective layer and a terminal part of the first conductive layer, thereby increasing the reliability of the bonding pads.

Owner:AU OPTRONICS CORP

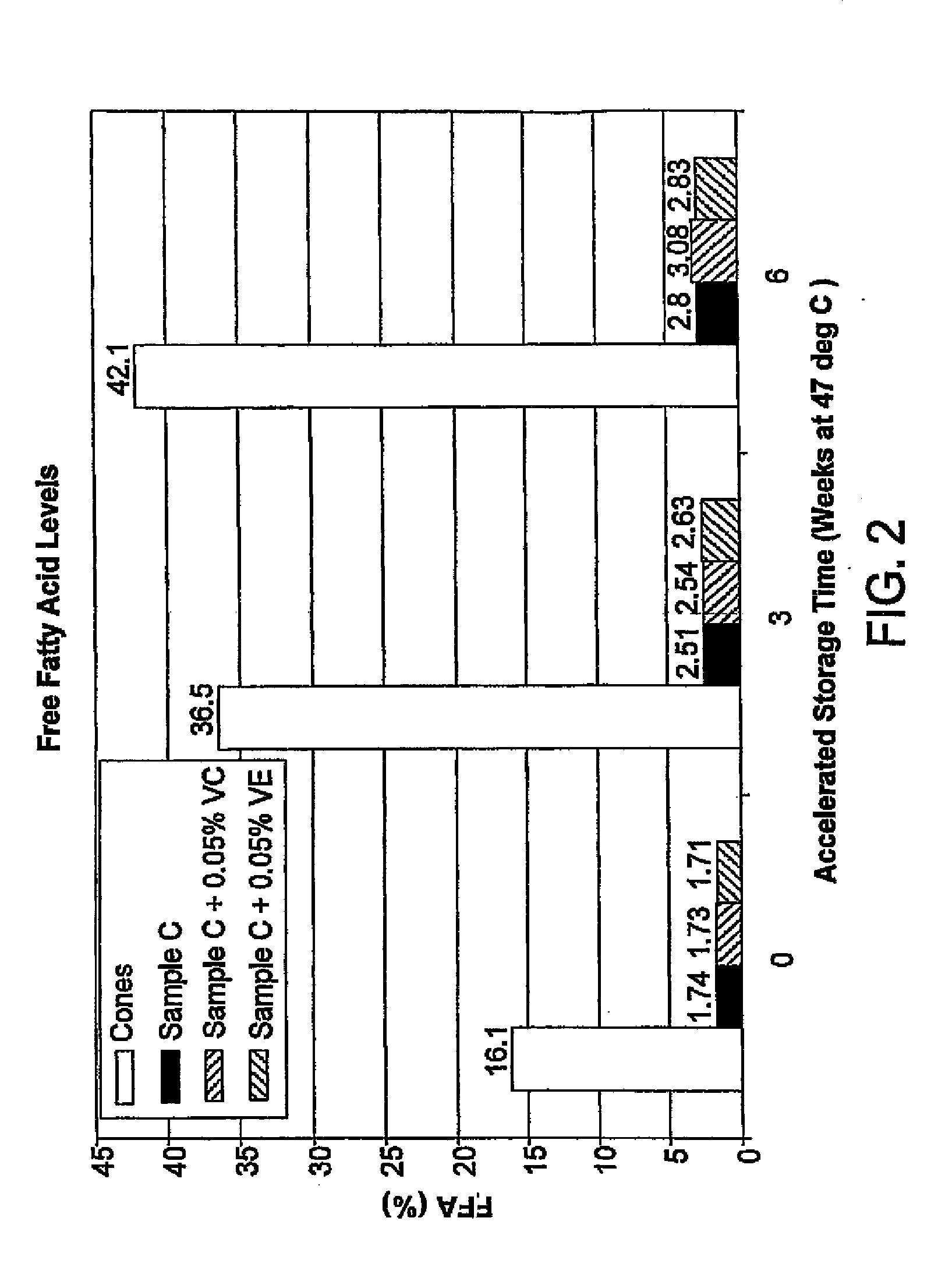

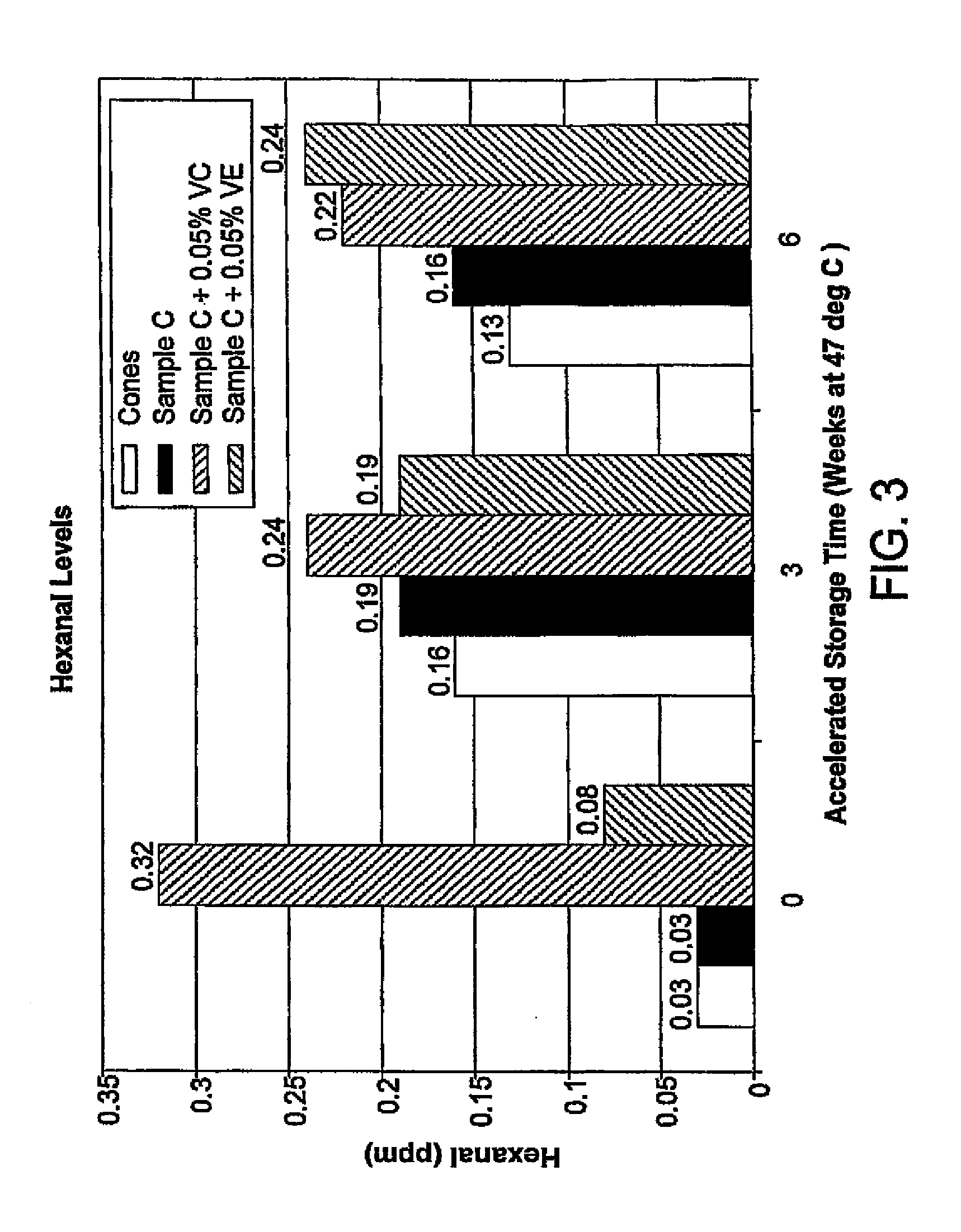

Stabilized Whole Grain Flour

InactiveUS20080311274A1Increased processing toleranceImprove propertyBakery productsDough heat treatmentFlavorExtended storage

Stabilized whole grain corn flour having extended storage stability and modified functional properties, such as improved processing tolerance, improved dough properties and enhanced corn flavors, is described, as are methods of making such stabilized whole grain corn flour.

Owner:CARGILL INC

Silicon-based light transmitting-receiving component with parallel optical fiber transmission

InactiveCN103676037AMeet the requirements of coupling toleranceImprove coupling efficiencyCoupling light guidesLaserFiber optic transmission

The invention provides a silicon-based light transmitting-receiving component with parallel optical fiber transmission. The silicon-based light transmitting-receiving component with parallel optical fiber transmission comprises a silicon substrate, multiple electrodes, multiple lasers / detectors, multiple lenses, multiple optical fiber heads and an optical fiber cover plate, wherein the silicon substrate comprises a surface plane which is provided with recess parts, multiple wire slots and positioning parts; the positioning parts and the front ports of the wire slots are spaced by the recess parts; the electrodes are arranged in parallel and are arranged on the front section of the surface plane in a convex manner; the lasers / detectors are connected to the electrodes and are mounted on the surface plane through the positioning parts; the lenses are mounted in the recess parts to correspond to the lasers / detectors; the optical fiber heads are arranged in the wire slots; one ends of the optical fiber heads close to the lenses are covered with the optical fiber cover plate. Through the structure or the combination thereof, the silicon-based light transmitting-receiving component is realized, and accordingly the good effects of reducing the volume, bringing convenience to the manufacturing and lowering the cost are achieved.

Owner:WUHAN TELECOMM DEVICES

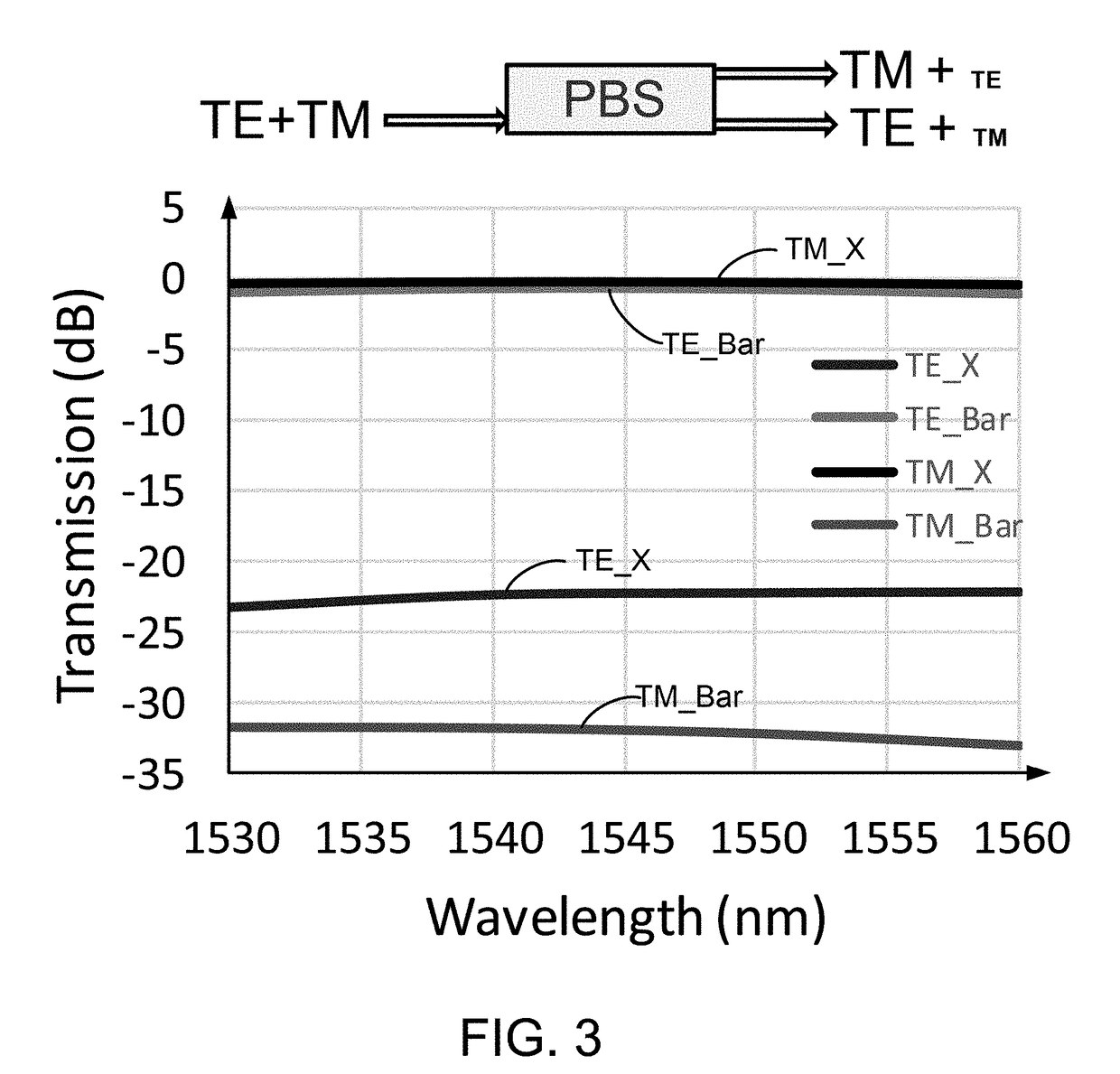

Broadband general interference mmi-based polarization beam splitter

InactiveUS20180172913A1High extinction ratioLow insertion lossCoupling light guidesElectrical conductorPolarization beam splitter

A polarization beam splitter includes a silicon waveguide body of a thickness in rectangular shape with a width and a length between a first end plane and a second end plane. Two input ports are formed in the first end plane at two separate locations respectively next to two opposing length edges. The silicon waveguide body is configured to generate a plurality of direct or mirror images of an input optical signal provided through at least one of the two input ports. Two output ports are formed in the second end plane, one at a bar-position being configured to output a first output signal substantially in TE polarization mode and another at a cross-position being configured to output a second output signal substantially in TM polarization mode. Preferably, the width is 2.6 μm and the length is 40 μm with the thickness of a silicon layer of a SOI substrate.

Owner:INPHI

Method for metal configuration with photoresist deposition

ActiveCN106711017AAvoid Gold Residue PhenomenonAvoid side corrosionSemiconductor/solid-state device manufacturingPhotoresistMetal electrodes

The invention discloses a method for metal configuration with photoresist deposition. The method comprises: the surface of a substrate is coated with a photoresist; the substrate coated with the photoresist is baked, exposed, baked, and developed successively, wherein an included angle between the side wall of a photoresist graph after development and the surface of the substrate is between 80 degrees to 100 degrees; metal is deposited to the surface of the photoresist graph after development and the metal falls on the surface of the substrate at the opening of the photoresist; the metal on the surface of the substrate is removed; and the photoresist is removed. Therefore, a problem that the bottom width of the metal electrode or metal wire is much larger than the width of the top can be solved.

Owner:SUNTIFIC MATERIALS WEIFANG LTD

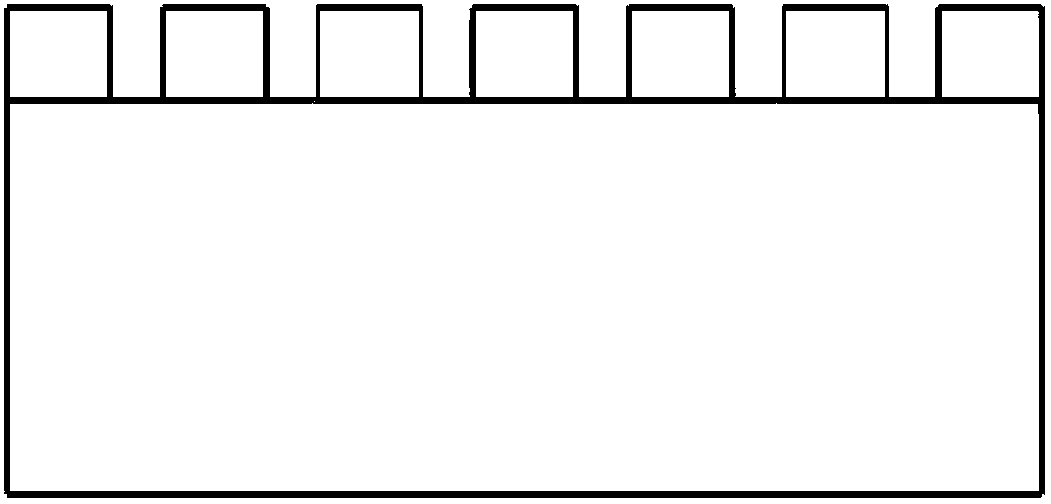

Infrared optical window with three-step anti-reflection structure and preparation method thereof

PendingCN108254811AImprove process toleranceReduce the difficulty of processingOptical elementsTransmittanceInfrared window

The invention discloses an infrared optical window with a three-step anti-reflection structure. The window comprises an infrared optical window body, the incident plane of the infrared optical windowbody is etched with the three-step anti-reflection structure, a preparation method comprises the steps that silicon wafer is pretreated, a metal pattern mask is used for etching the three-step anti-reflection structure on a silicon plate, the structure includes an etching first step structure layer, an etching second step structure layer and an etching third step structure layer, the method for etching the anti-reflection structure adopts an induction coupled plasma etching machine and a combination process of etching and passivation, the etching gas is SF6, the passivation gas is C4F8, and inert gas He is added during etching and passivation. The structure can obviously increase the transmittance of the infrared window, improve the sensitivity of infrared devices, and reduce influence ofthe height of a step structure, structural parameters and the variation of a step period and depth on the transmittance, and the preparation method improves process tolerance of device manufacturing,and reduces the difficulty of craft production.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Resistor and production method thereof

ActiveCN103000582AImprove thermal stabilityImprove stabilitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricResistor

The invention discloses a resistor and a production method of the resistor and a transistor with a metal gate. The production method includes: firstly, providing a substrate, and defining a transistor region and a resistor region on the substrate; secondly, forming the transistor with a dummy gate and the resistor in the transistor region and the resistor region respectively; thirdly, removing the dummy gate and part of the resistor so as to form a first trench and two second trenches in the transistor and the resistor respectively, and forming at least one high dielectric constant gate dielectric layer in each of the first trench and the second trenches; and finally, forming the metal gate and metal structures in the first trench and the second trenches respectively.

Owner:UNITED MICROELECTRONICS CORP

OPC correcting method for forming auxiliary through hole

InactiveCN101430500AReduce the number of isolated viasImprove process toleranceOriginals for photomechanical treatmentEngineeringCorrection method

An OPC correction method for forming an auxiliary through hole is as follows: other through holes and metal wires are searched in a certain range nearby isolated through holes between two layers of metal wires; auxiliary through holes are formed nearby the isolated through holes; the through holes and the metal wires are not existed in the certain range of the isolated through holes; the auxiliary through holes extend a size added value towards periphery, and then extend towards the direction of original through holes to be connected with the original through holes and overlap with the under layer metal wire; and finally the conventional OPC correction is carried out on the improved metal wire and the layout of the through holes.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Manufacturing method for ohmic contact with low specific contact resistance and low roughness

ActiveCN102231363AImprove overlay accuracyReduce process stepsVacuum evaporation coatingSemiconductor/solid-state device manufacturingOhmic contactBinary alloy

The invention discloses a manufacturing method for ohmic contact with low specific contact resistance and low roughness. The manufacturing method is characterized in that hardly compatible Mo metal is introduced to an ohmic contact metal seed to form a TiAlNiMoAu combination, thus the surface roughness and the specific contact resistance after alloying are reduced under the same alloying condition. In the manufacturing method, the low diffusivity of the Mo is utilized, and a binary alloy phase is matched, thus low contact resistance is realized, the roughness of the ohmic contact after alloying is also reduced, the overlay accuracy of a photolithographic process is improved, the number of process steps is reduced, the stability of the ohmic contact is improved, and a firm foundation is established for device process practicability.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

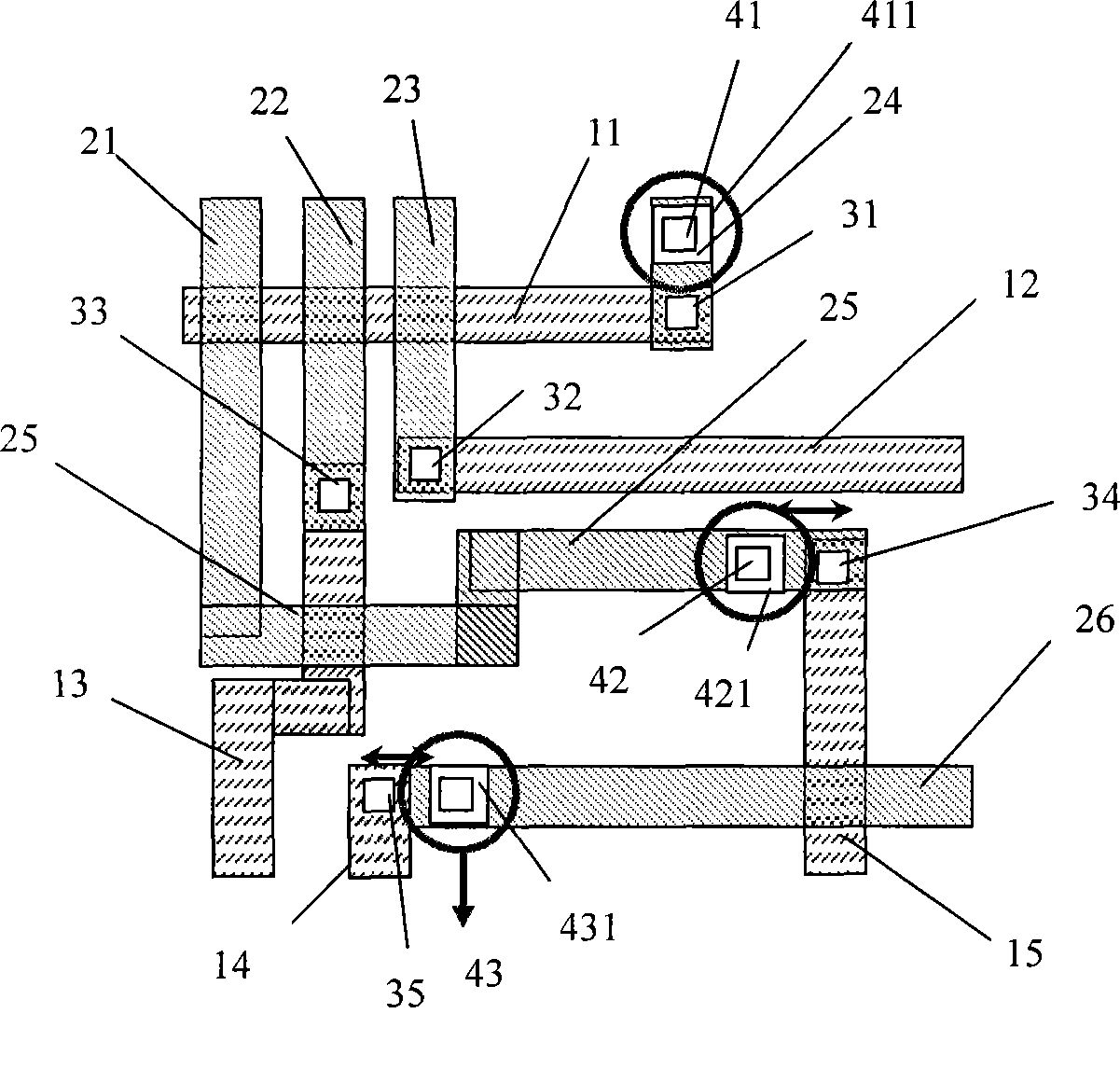

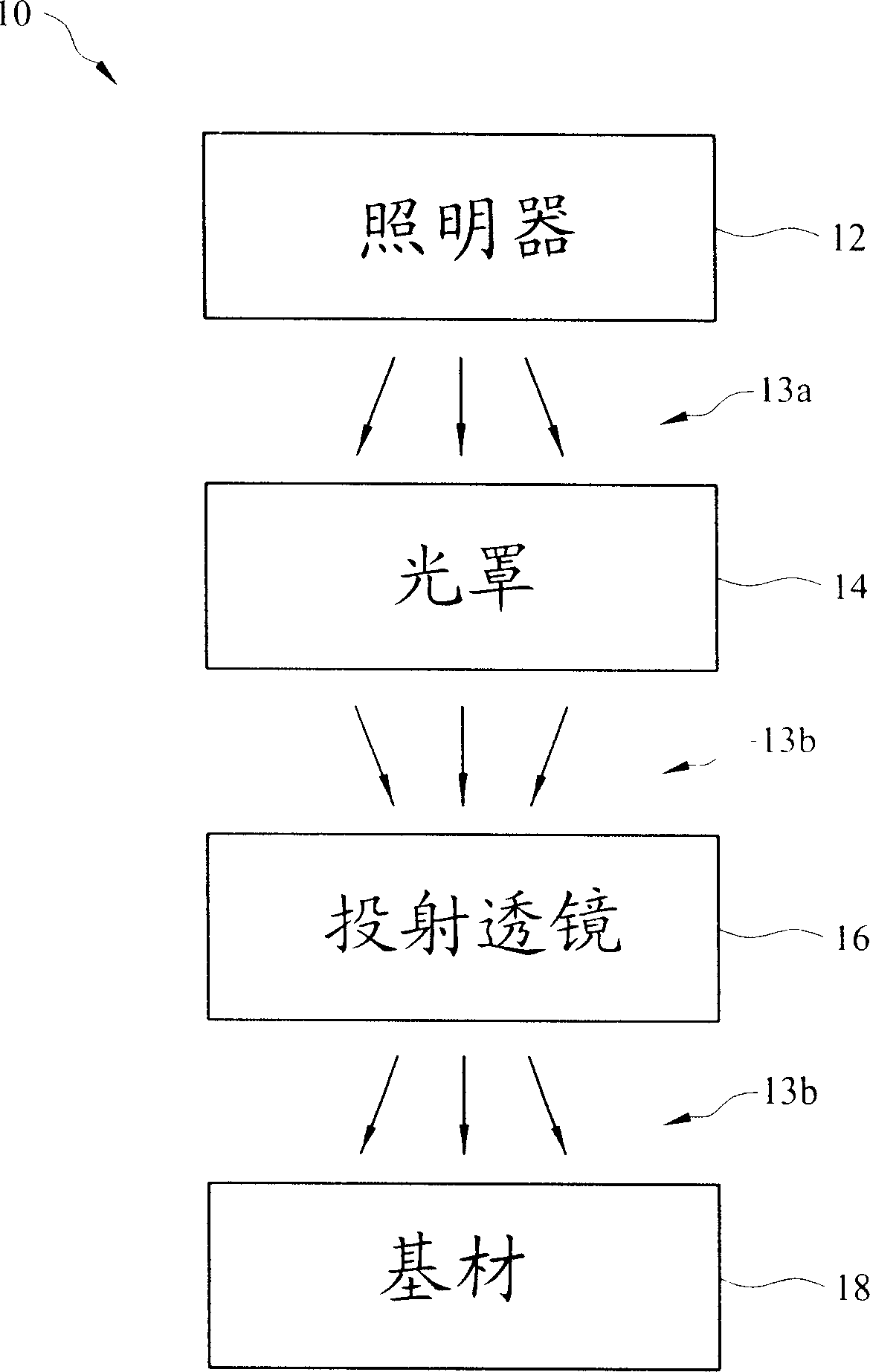

Method and system for designing optical shield layout and producing optical shield pattern

ActiveCN1904726AHigh image qualityImprove qualityPhotomechanical apparatusSemiconductor/solid-state device manufacturingEngineeringControl parameters

The present invention relates to a method and system for designing a mask layout and generating a mask pattern. The method includes using a plurality of pixels to represent the mask layout, wherein each pixel has a mask transparency coefficient. A control parameter is initialized and a representation of the mask layout is generated. This method uses a cost function and a Boltzmann probability function (Boltzmann Probability Function) to decide whether to accept the representative of the mask layout, wherein the cost function is related to the mask layout and the target substrate pattern, and the Boltzmann probability function is related to The cost function is related to the control parameters. The step of generating a representative of the reticle layout and the step of accepting a representative of the reticle layout are repeated until the reticle layout is stabilized. Reduce this control parameter according to the annealing program. The steps of generating a representative of the reticle layout, determining, reworking, and reducing the control parameters are repeated until the reticle layout is optimized.

Owner:TAIWAN SEMICON MFG CO LTD

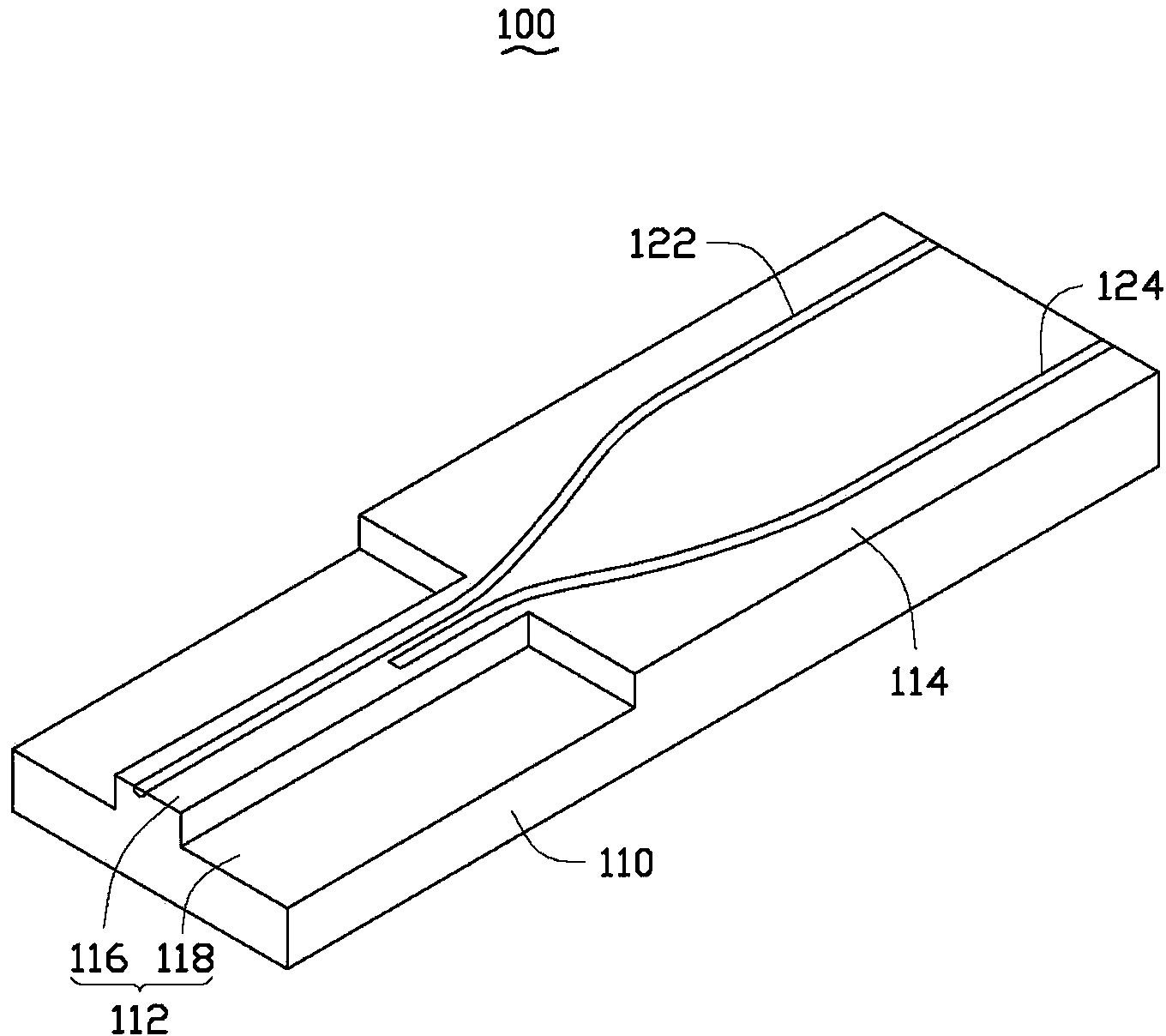

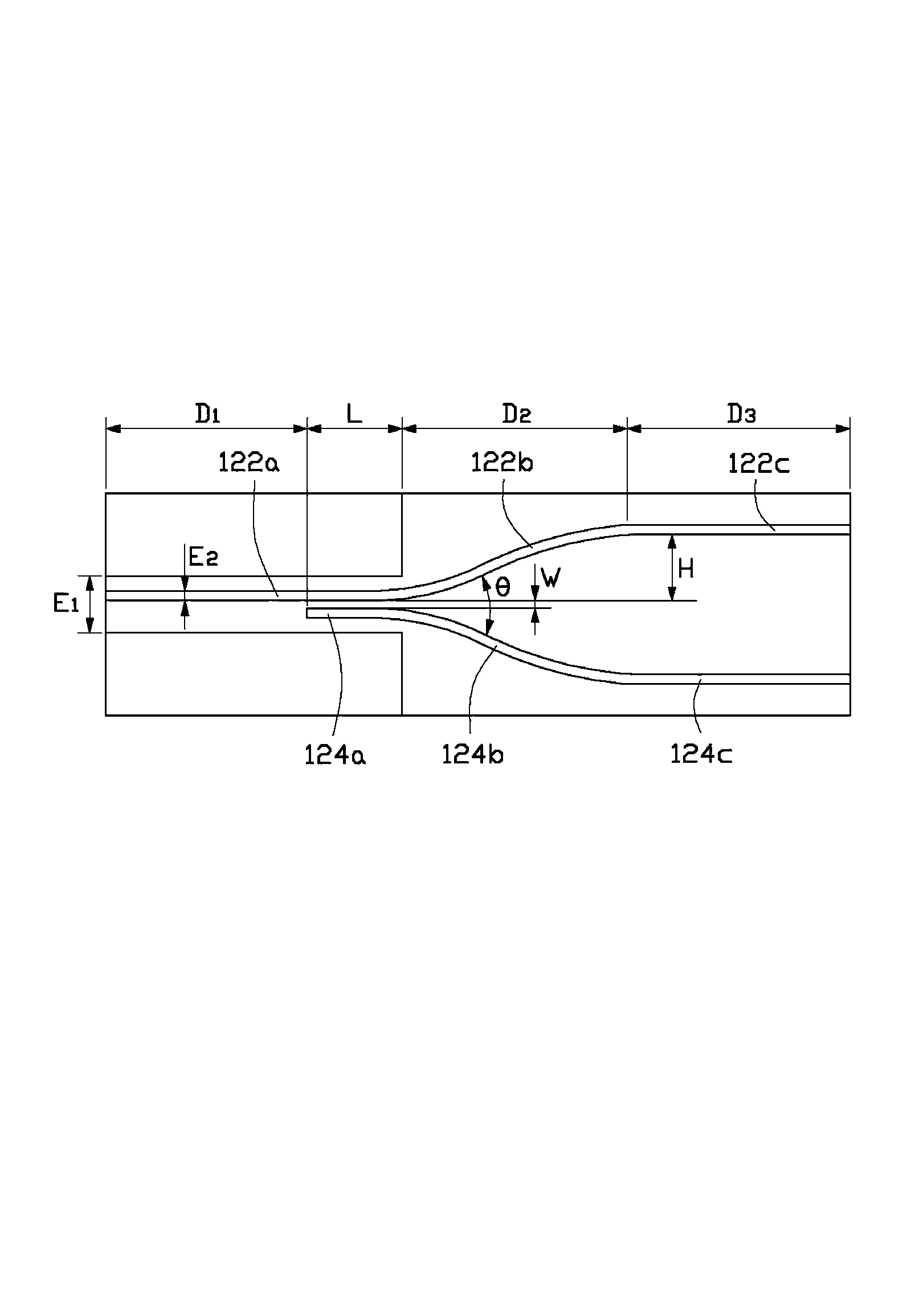

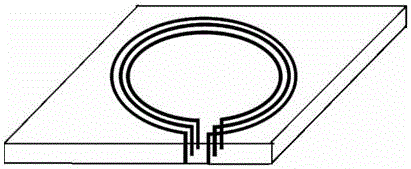

Optical waveguide directional coupler

The invention relates to an optical waveguide directional coupler which comprises a substrate and two optical waveguides formed on the substrate. The substrate comprises a ridge area with an inverted-T-shaped section and a rectangle area connected with the ridge area. The ridge area comprises a raised inner ridge area smoothly connected with the rectangle area. The two optical waveguides cross the inner ridge area and the rectangle area, and each optical waveguide comprises a first straight waveguide section located in the inner ridge area, a curved waveguide section and a second straight waveguide section, wherein the curved waveguide section and the second straight waveguide section of each optical waveguide are located in the rectangle area, the curved waveguide section of each optical waveguide is connected with the first straight waveguide section and the second straight waveguide section of each optical waveguide is connected with the corresponding curved waveguide section. The first straight waveguide sections of the two optical waveguides are mutually parallel and a coupling action area is formed between the two first straight waveguide sections. The curved waveguide sections of the two optical waveguides extend outwards in a curved mode. The second straight waveguide sections of the two optical waveguides are mutually parallel.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

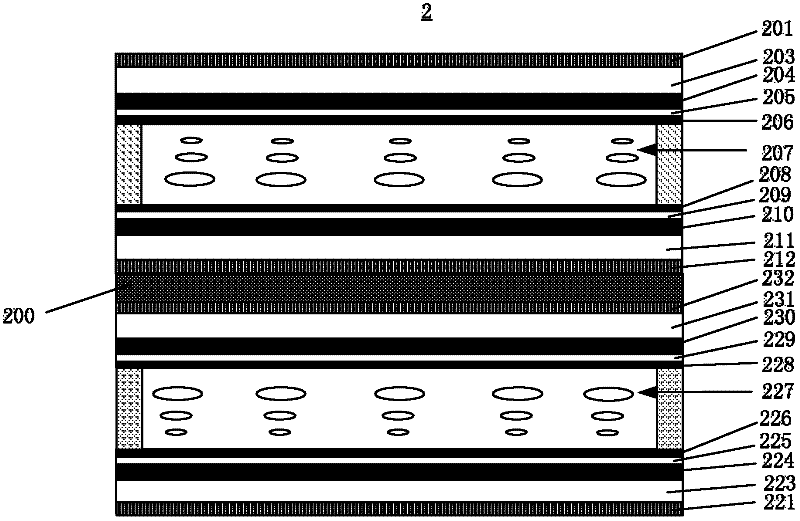

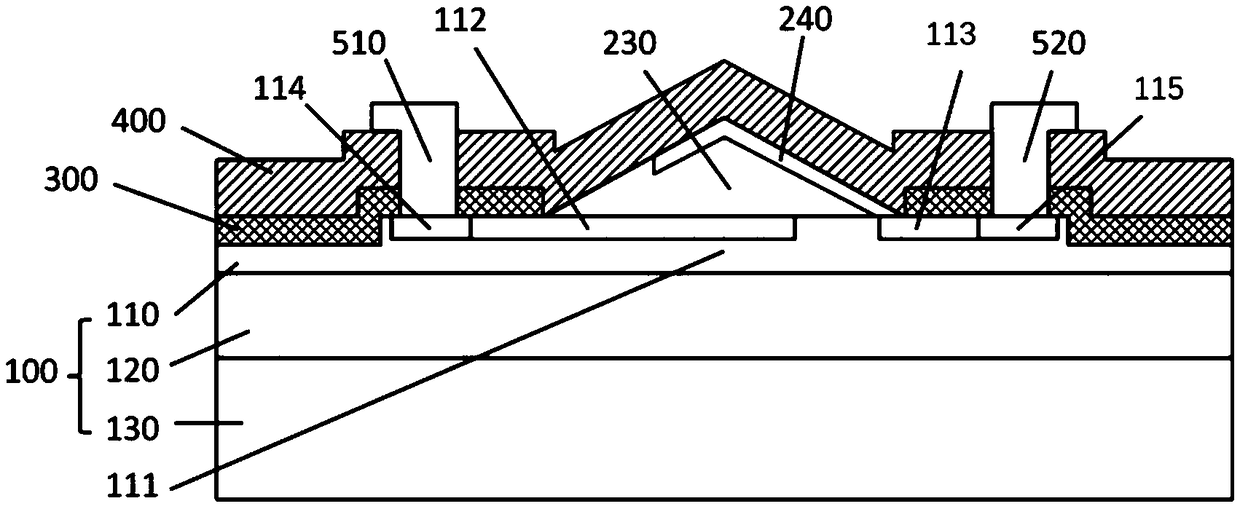

Silicon-based electro-absorption modulator and preparation method thereof

The invention provides a silicon-based electro-absorption modulator and a preparation method thereof. The modulator uses voltage to adjust the light absorption coefficient of a semiconductor on the basis of an electro-absorption mode, and then the intensity of an optical signal is adjusted. Silicon is a weak electro-optical material, so that the silicon is introduced into material germanium whichhas a remarkable electro-optical absorption adjusting effect in a communication wave band C wave band and is compatible with the CMOS technology. Through an epitaxial growth modulation layer (200), light beams are smoothly coupled into and coupled out of the modulation layer (200), oscillation of light field power of the light beams between the modulation layer and a waveguide layer is not generated, the dependence relation between the insertion loss of a device and the length of the modulation layer is eliminated, meanwhile, different working wavelengths can be achieved by adjusting alloy components in the modulation layer (200), and the modulation efficiency is high.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

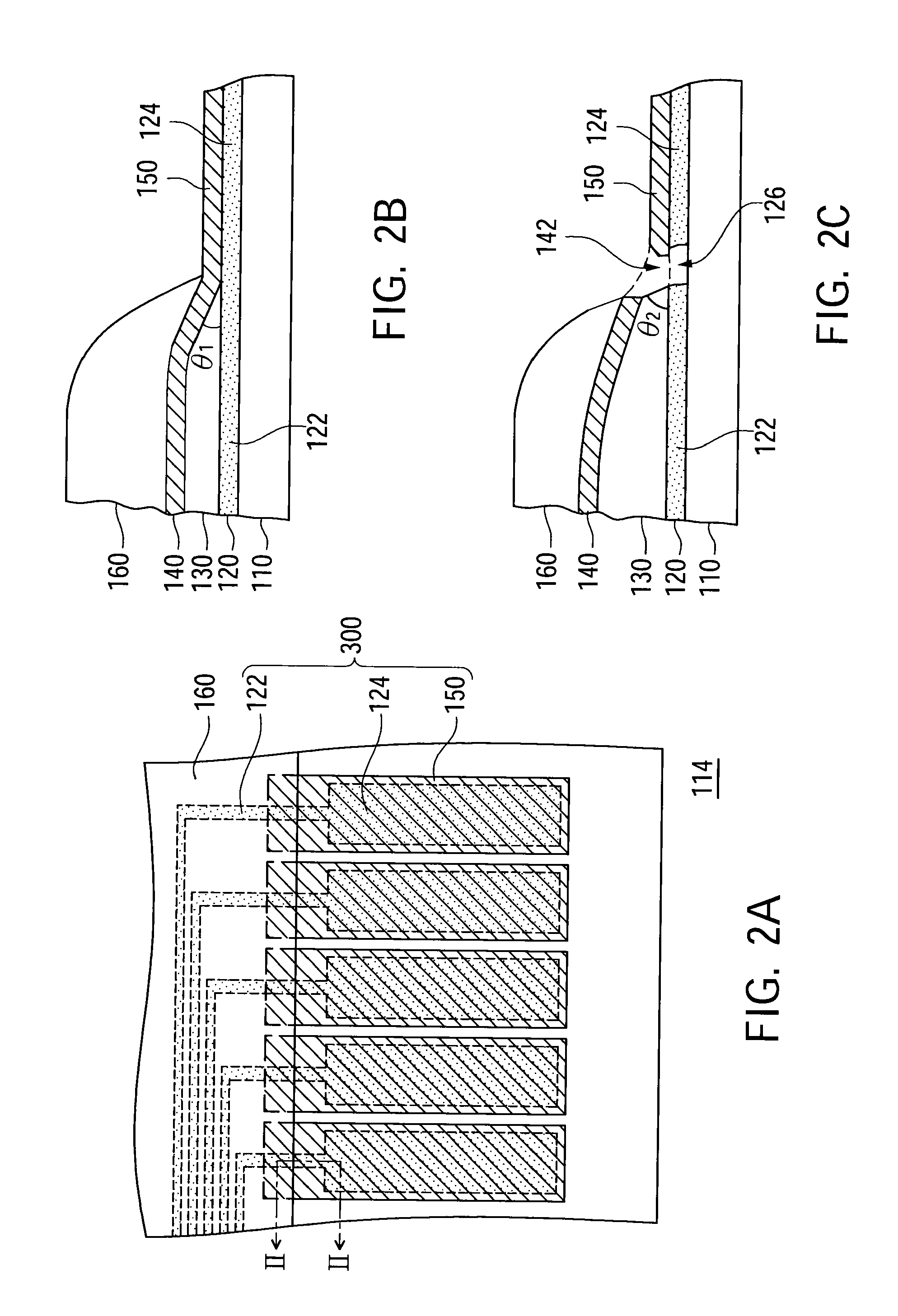

Touch panel and peripheral circuit thereof

ActiveUS8427446B2Improve connection stabilityImprove connection reliabilityTransmission systemsGraph readingEngineeringExtremity Part

A touch panel and a peripheral circuit thereof are provided. Each bonding pad of the peripheral circuit includes a first conductive layer, a first protective layer, a second conductive layer, and a second protective layer sequentially arranged on a substrate from bottom to top. A covered area of the second conductive layer provided by the second protective layer is increased to cover a portion of the second conductive layer located above a junction area between the first protective layer and a terminal part of the first conductive layer, thereby increasing the reliability of the bonding pads.

Owner:AU OPTRONICS CORP

Method for enhancing adhesion of photoresist after developing

InactiveCN107942623ASolve the peeling problemImprove adhesionSemiconductor/solid-state device manufacturingPhotosensitive material processingDimension measurementHigh dosage

The invention discloses a method for enhancing adhesion of a photoresist after developing. The method comprises the steps of 1, performing coating on the photoresist; 2, performing exposure and developing on the photoresist; 3, performing aligned measurement on the photoresist; 4, performing critical dimension measurement on the photoresist; 5, performing UVQ; 6, performing cleaning and wetting ona silicon wafer by deionized water; 7, performing high-dosage ion injection; 8, removing the photoresist; and 9, performing adhesive-removing examination on the photoresist. According to the method for enhancing adhesion of the photoresist after developing, cleaning and wetting of the silicon wafer by deionized water is added after the photoresist is completely developed, so that high adhesion between the photoresist and the silicon wafer can be ensured, the problem of photoresist peeling in high-dosage injection can be solved, and process margin is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Stabilized whole grain flour

InactiveUS20120189756A1Modified flavorModified functionalityBakery productsDough heat treatmentFlavorCorn flour

Stabilized whole grain corn flour having extended storage stability and modified functional properties, such as improved processing tolerance, improved dough properties and enhanced corn flavors, is described, as are methods of making such stabilized whole grain corn flour.

Owner:CARGILL INC

Thermosetting resin composition

There is provided a thermosetting resin composition having excellent flowability, low temperature moldability, curability, and heat resistance after curing or the like in the absence of a solvent. The thermosetting resin composition of the present invention contains, as essential components, a maleimide compound (A), a compound (B) having two or more polymerizable unsaturated hydrocarbon groups in its molecule, and a cyanate ester compound (C).

Owner:MITSUBISHI GAS CHEM CO INC

Optical proximity correction mask

ActiveCN102998895AImprove process toleranceReduce light intensityOriginals for photomechanical treatmentPhase shiftedContrast ratio

The invention discloses an optical proximity correction mask. The optical proximity correction mask comprises two open patterns and a pair of scattering strip patterns, wherein the open patterns are arrayed on a substrate along a first direction, and there is a fixed distance between the two open patterns; the pair of scattering strip patterns is arranged on the substrate along a second direction vertical to the first direction, and is adjacent to two opposite sides of each of the open patterns; and from a side view, each of the scattering strip patterns does not overlap the open patterns in the first direction or the second direction, and there is a 180DEG phase shift between each of the open patterns and each of the scattering strip patterns. The optical proximity correction mask can reduce the light intensity of the edges of the open patterns, so the contours of the open patterns transferred to a photo-resistor through the mask are improved, and the contrast in a photo-etching process is increased. Additionally, the increase of the contrast in the photo-etching process makes the selective elasticity of a photo-resistive material be increased or makes the technological permissibility of the optical proximity correction mask be further increased.

Owner:WINBOND ELECTRONICS CORP

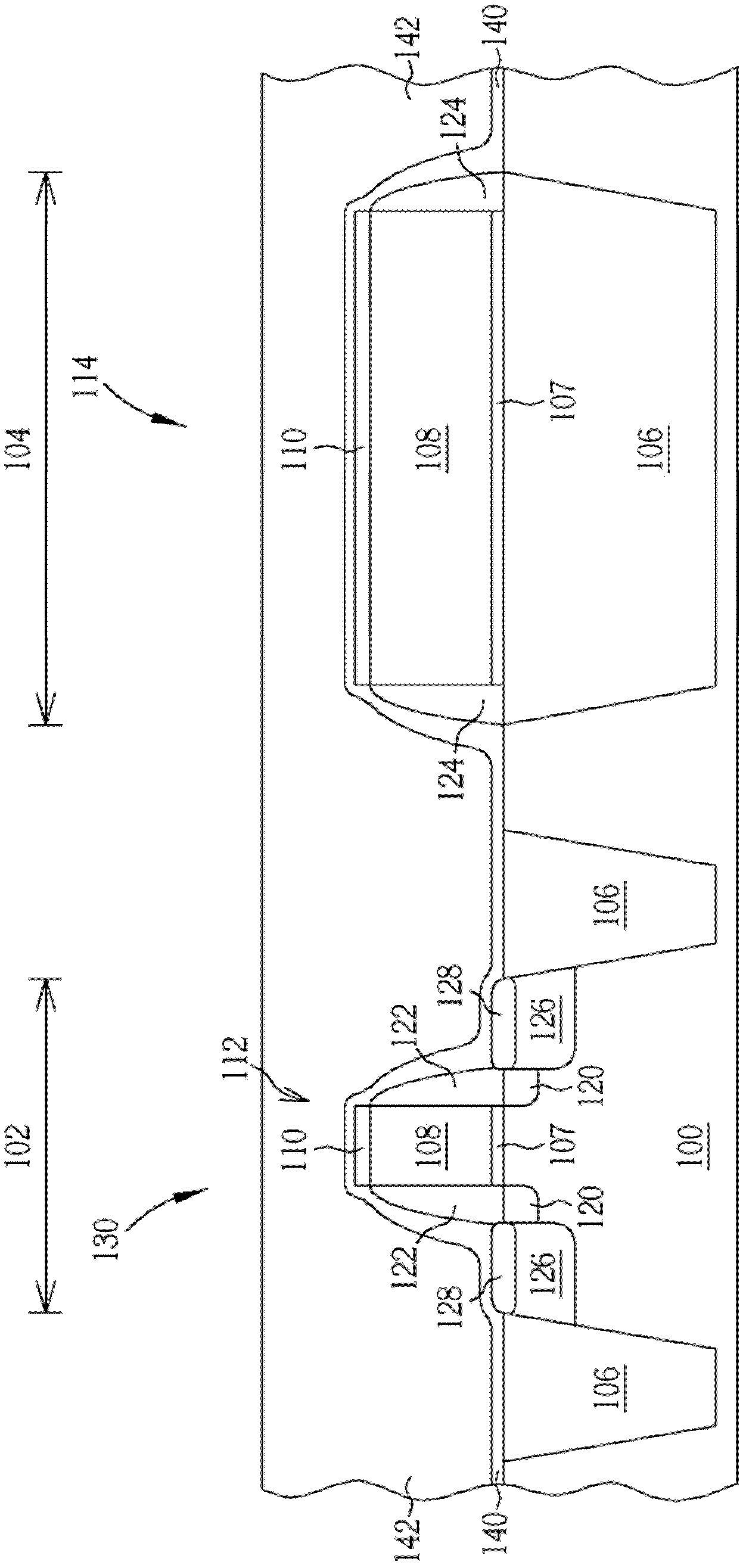

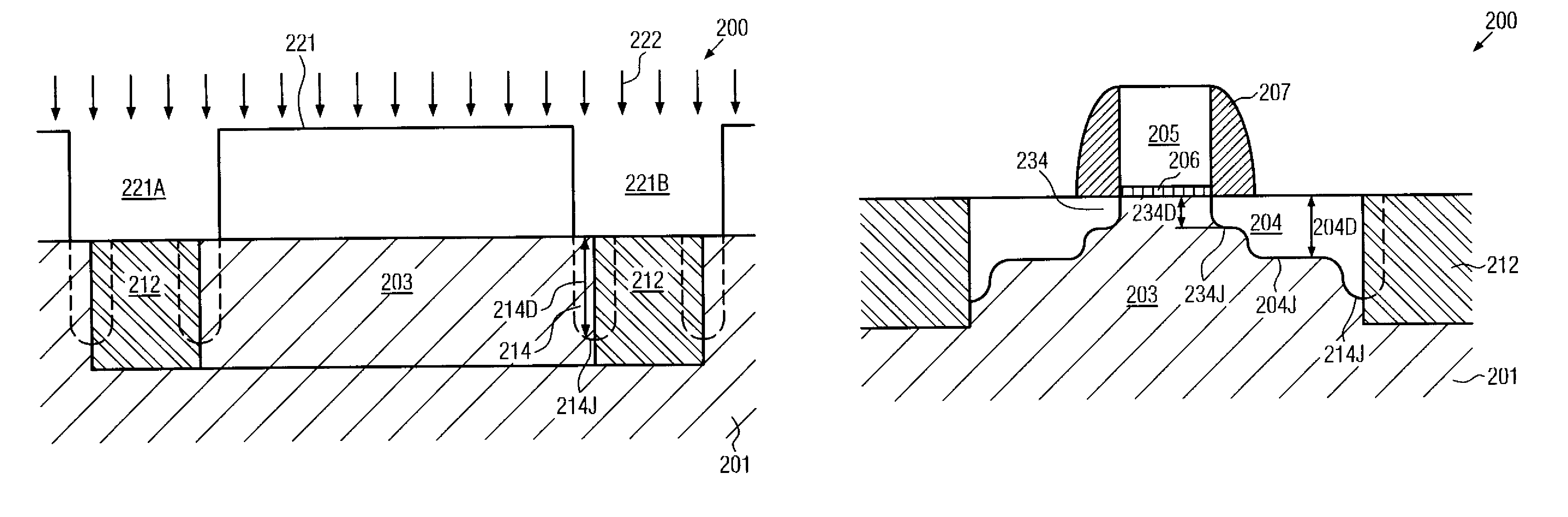

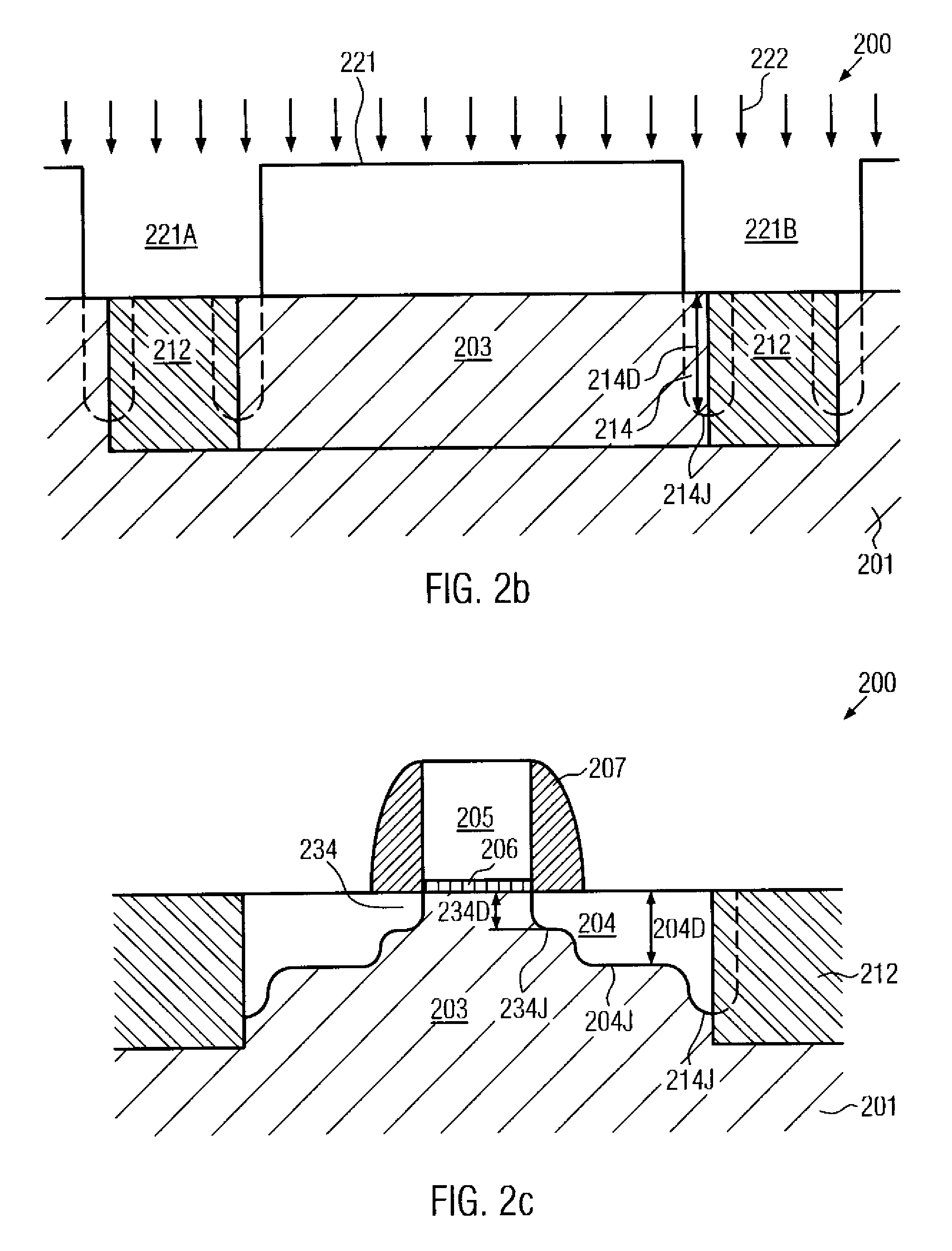

Method for reducing leakage currents caused by misalignment of a contact structure by increasing an error tolerance of the contact patterning process

ActiveUS7998823B2Reduce probabilityImprove leakage currentSemiconductor/solid-state device manufacturingSalicideLithographic artist

By forming an additional doped region with increased junction depth at areas in which contact regions may connect to drain and source regions, any contact irregularities may be embedded into the additional doped region, thereby reducing the risk for leakage currents or short circuits between the drain and source region and the well region that may be conventionally caused by the contact irregularity. Moreover, additionally or alternatively, the surface topography of the semiconductor region and the adjacent isolation trench may be modified prior to the formation of metal silicide regions and contact plugs to enhance the lithography procedure for forming respective contact openings in an interlayer dielectric material. For this purpose, the isolation trench may be brought to an equal or higher level compared to the adjacent semiconductor region.

Owner:ADVANCED MICRO DEVICES INC

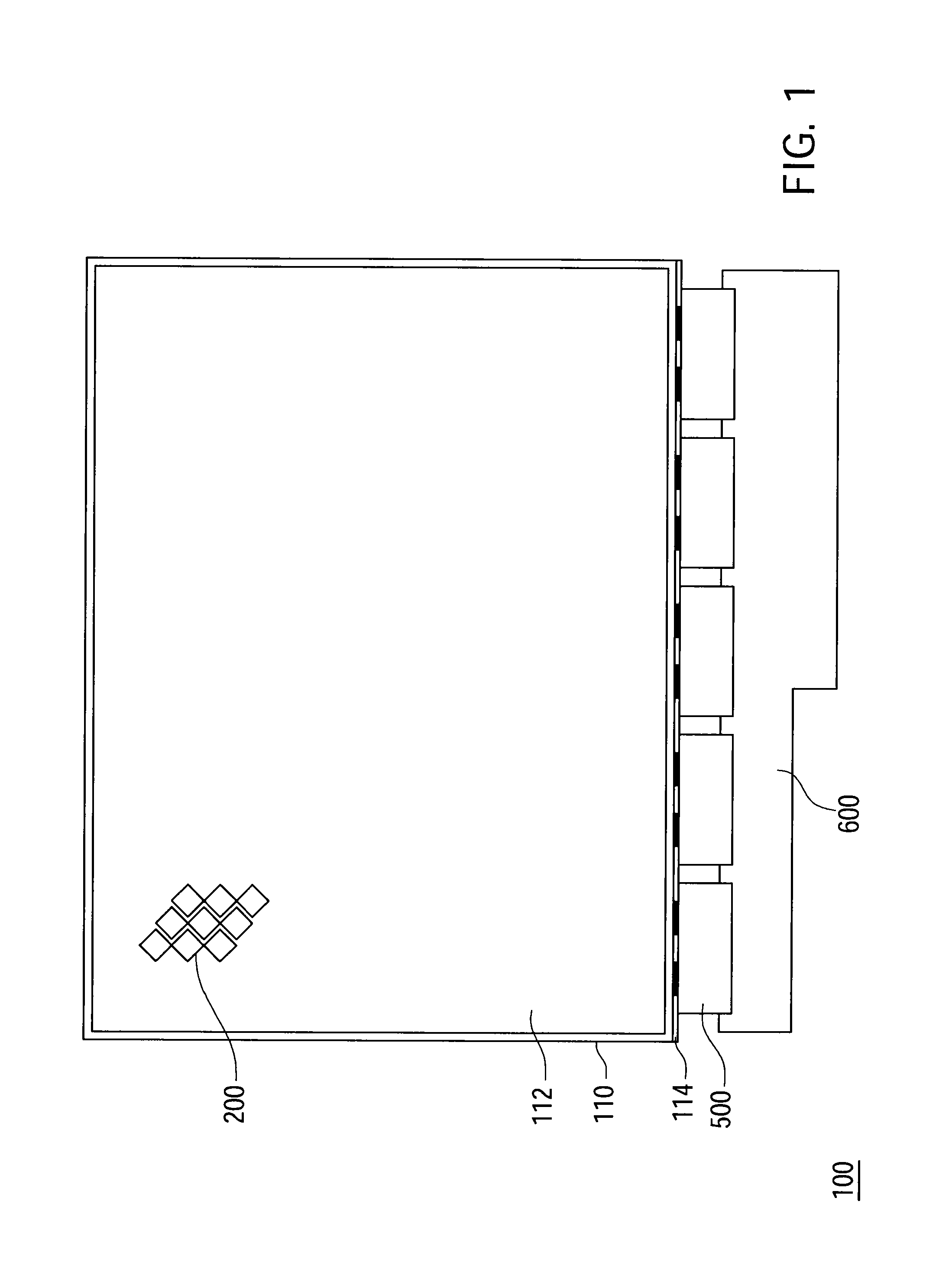

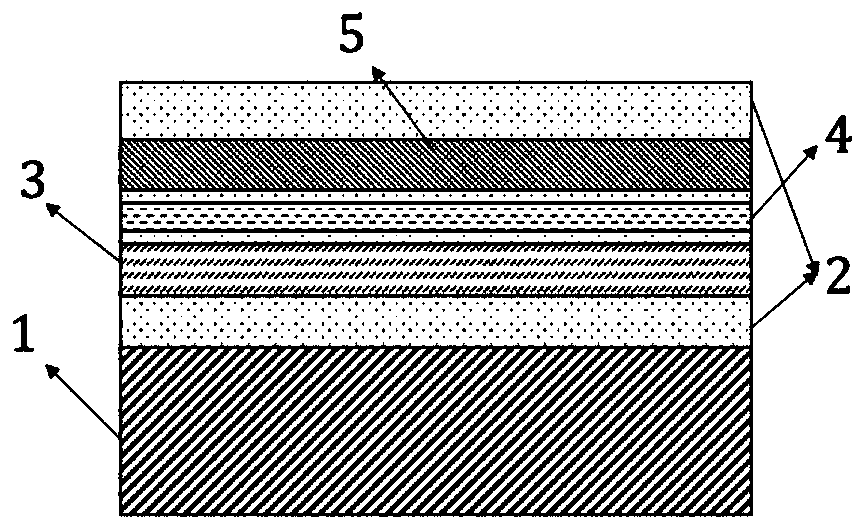

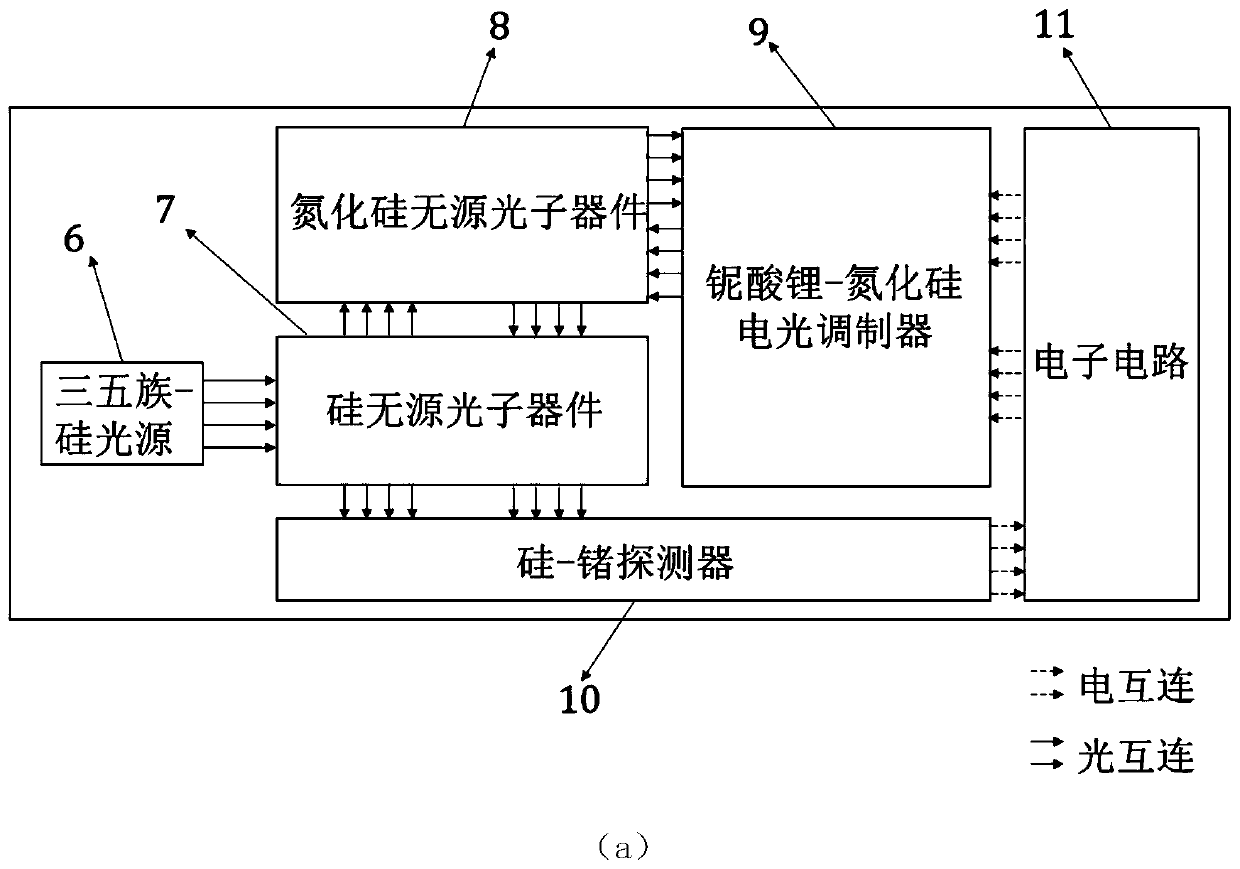

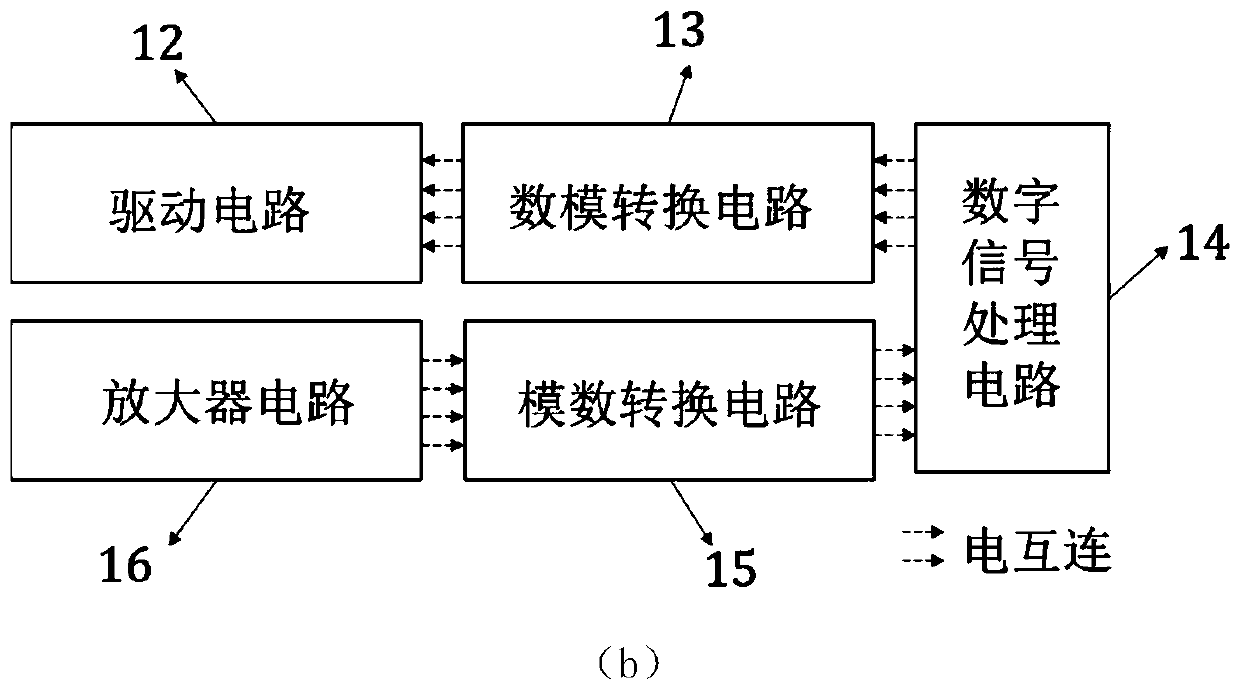

Photoelectric monolithic integration system based on multi-material system

ActiveCN111474745ASmall sizeReduce adverse effectsCoupling light guidesOptical waveguide light guideHemt circuitsRefractive index

The invention provides a photoelectric monolithic integration system based on a multi-material system. According to the system, an indium phosphide-silicon laser, a silicon passive photonic device, asilicon nitride passive photonic device, a silicon nitride-lithium niobate electro-optical modulator, a germanium-silicon detector and an electronic circuit are integrated on the same substrate, so that the size of a photoelectric system is reduced, the electrical and optical interconnection distance is reduced, and the adverse effect of parasitic parameters on the integrated system is greatly reduced. The packaging between the optical path module and the circuit module is avoided, and the packaging cost is reduced. The advantages of excellent electro-optical performance of the lithium niobatematerial, low loss, low polarization sensitivity and high process tolerance of the silicon nitride material and high refractive index of the silicon material are exerted, and a monolithic photoelectric integrated system with excellent performance is realized.

Owner:SHANGHAI JIAO TONG UNIV

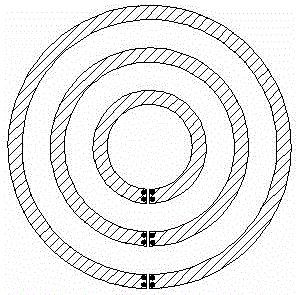

Perpendicular lead cold atom chip manufacturing method

InactiveCN106847715AReduce power consumptionImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingMicro nanoMagnetic current

The invention provides a perpendicular lead cold atom chip manufacturing method. A metal wire embedded in a glass substrate is adopted as magnetic current injection, the technology is characterized in that the metal wire is adopted as an inner core, the glass substrate is manufactured through the technologies of manufacturing of a glass rod, wire drawing, typesetting, glass melt pressing, cutting, fine polishing and the like, and then with the metal wire being an alignment mark on the glass substrate, a metal ring magnetic well is manufactured to form an atom chip through a semiconductor micro-nano technology. The perpendicular lead cold atom chip manufacturing method has the advantages that by adopting the glass substrate embedded with the metal wire to manufacture the atom chip, the specific resistance of the metal wire is far smaller than plated metal, and the phenomenon that heating under big current fuses a lead is avoided; the glass substrate can reach a nanometer thickness, and can effectively lower magnetic field interference of circuit loops at the front side and the back side of the substrate.

Owner:INST OF ELECTRONICS ENG CHINA ACAD OF ENG PHYSICS

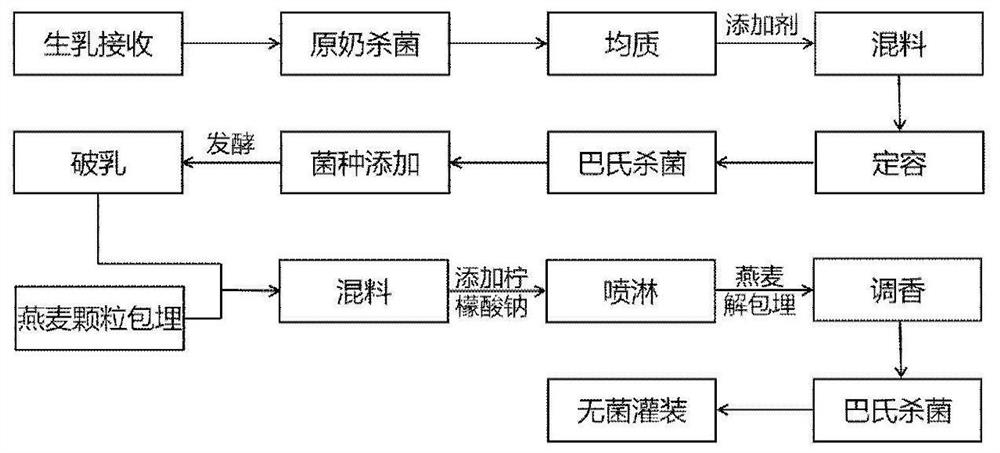

Normal-temperature fermented milk beverage and preparation method thereof

The invention relates to a normal-temperature fermented milk beverage containing complete oat particles and a preparation method of the normal-temperature fermented milk beverage. Different from a traditional normal-temperature oat yoghourt preparation process, the preparation method disclosed by the invention has the advantages that oat particles are protected in an embedding manner, the embedded oat is subjected to high-temperature sterilization, and then a certain amount of strong-alkali and weak-acid salt can be added to dissolve an embedding layer. Through the treatment mode, various defects existing in the prior art are overcome, the integrity of the oat particles can be improved, and the unique flavor and taste of the oat can be reserved to the maximum extent.

Owner:INNER MONGOLIA MENGNIU DAIRY IND (GRP) CO LTD

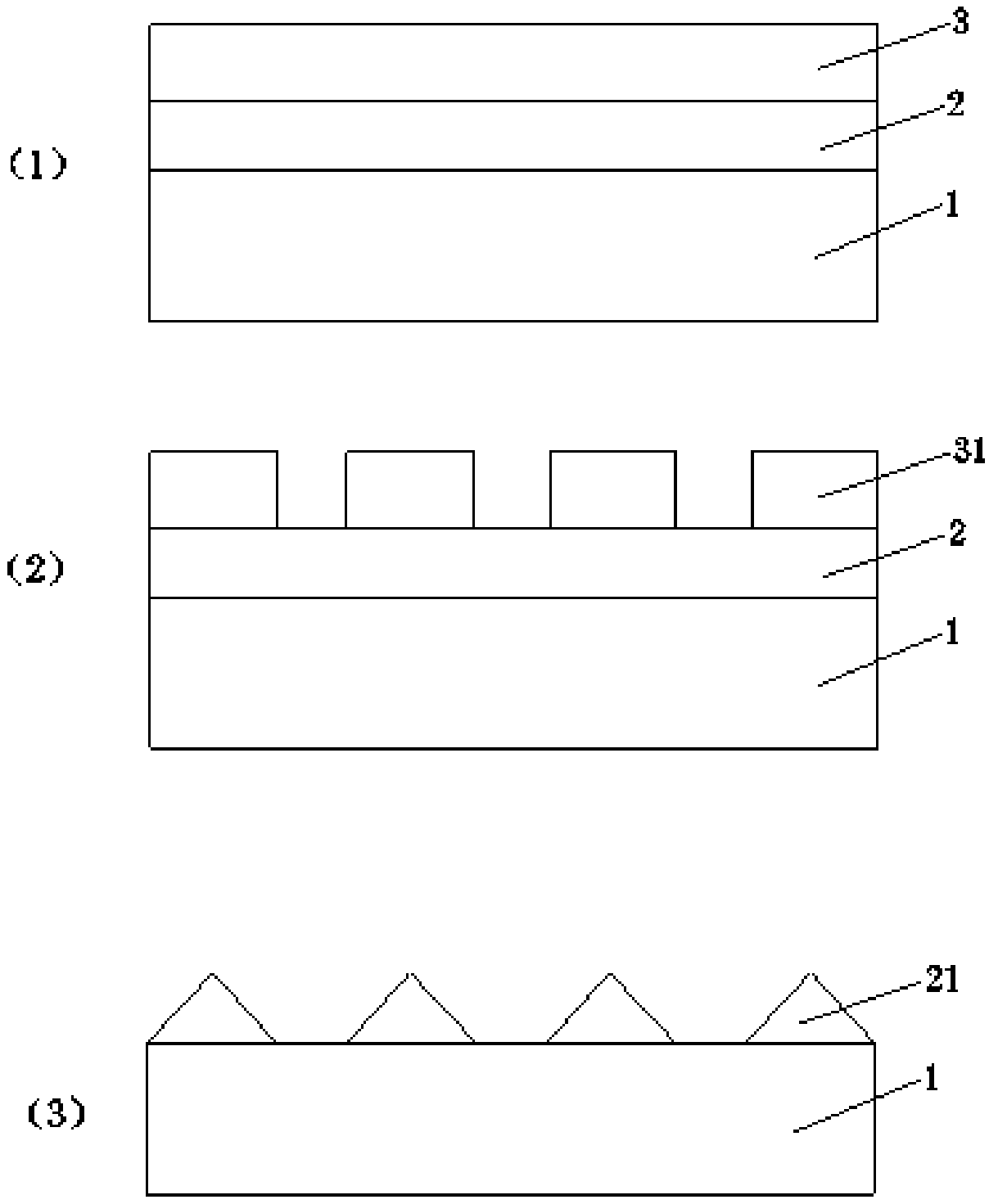

A patterned sapphire substrate and a preparation method thereof

ActiveCN109166952AImprove the scattering effectImprove luminous efficiencySemiconductor devicesPhotoresistPhotolithography

The invention relates to the technical field of semiconductor manufacturing, in particular to a patterned sapphire substrate and a preparation method thereof. The patterned sapphire substrate comprises a sapphire flat sheet and a patterned silicon-containing organic coating formed on the surface thereof. A manufacture method comprises that follow steps of: (a) coating a silicon-containing organiccoating on the surface of a sapphire flat sheet; (b) coat a photoresist on that surface of the silicon-containing organic coating to form a photoresist layer, and photolithographically forming a maskpattern; (c) etching the silicon-containing organic coating under the protection of the photoresist layer, transferring the pattern to the silicon-containing organic coating, and removing the photoresist to obtain the patterned sapphire substrate. The invention replaces the traditional patterned sapphire substrate with a patterned silicon-containing organic coating, wherein the refractive index ofthe silicon-containing organic coating is lower than that of the sapphire, the scattering effect of the substrate on light can be effectively increased, and the luminous efficiency of the LED can beimproved; Moreover, its hardness is lower than that of sapphire, which increases the tolerance of photolithography and etching process and reduces the production cost.

Owner:孙逊运

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com