Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

51results about How to "Small area consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

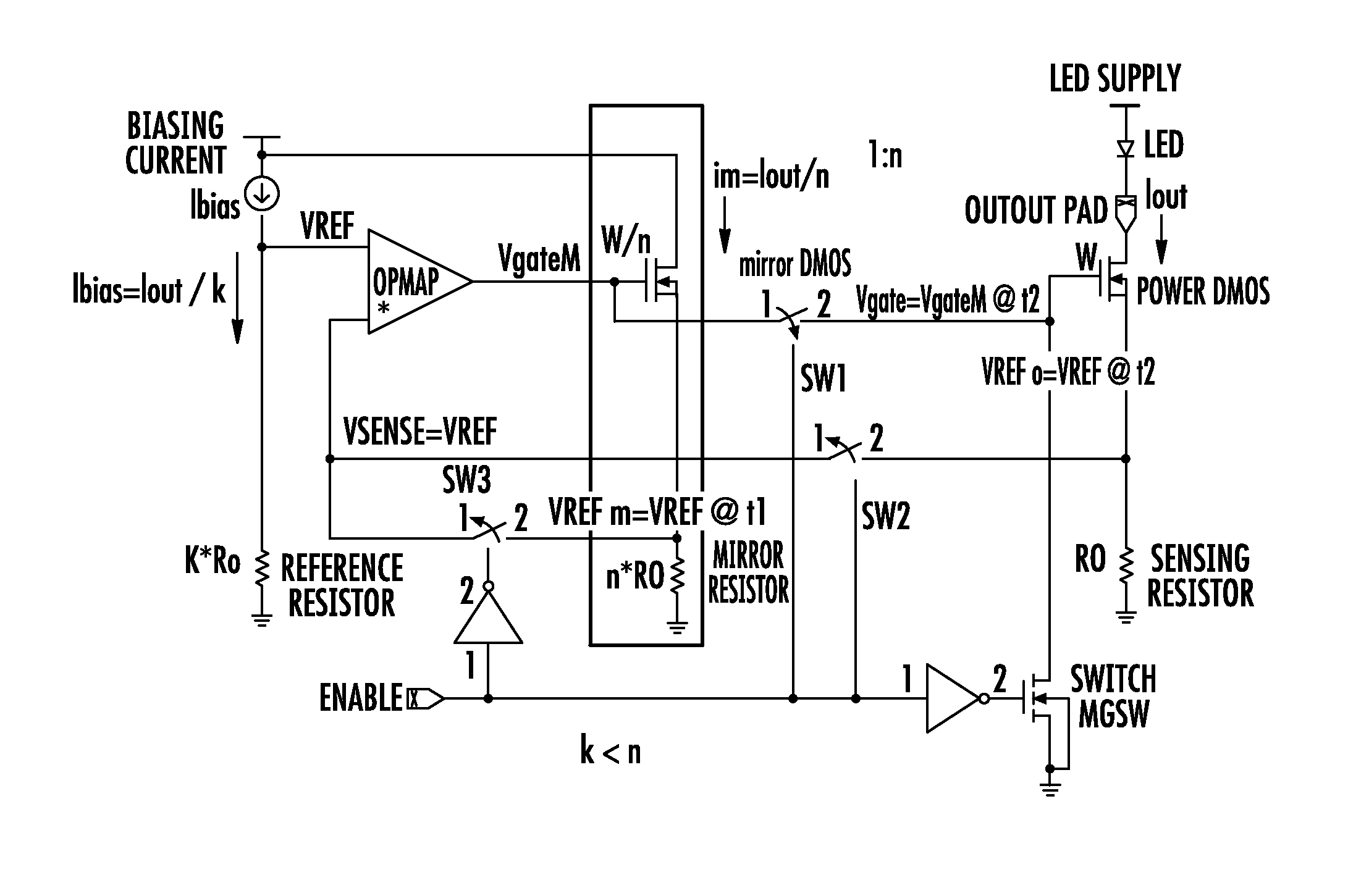

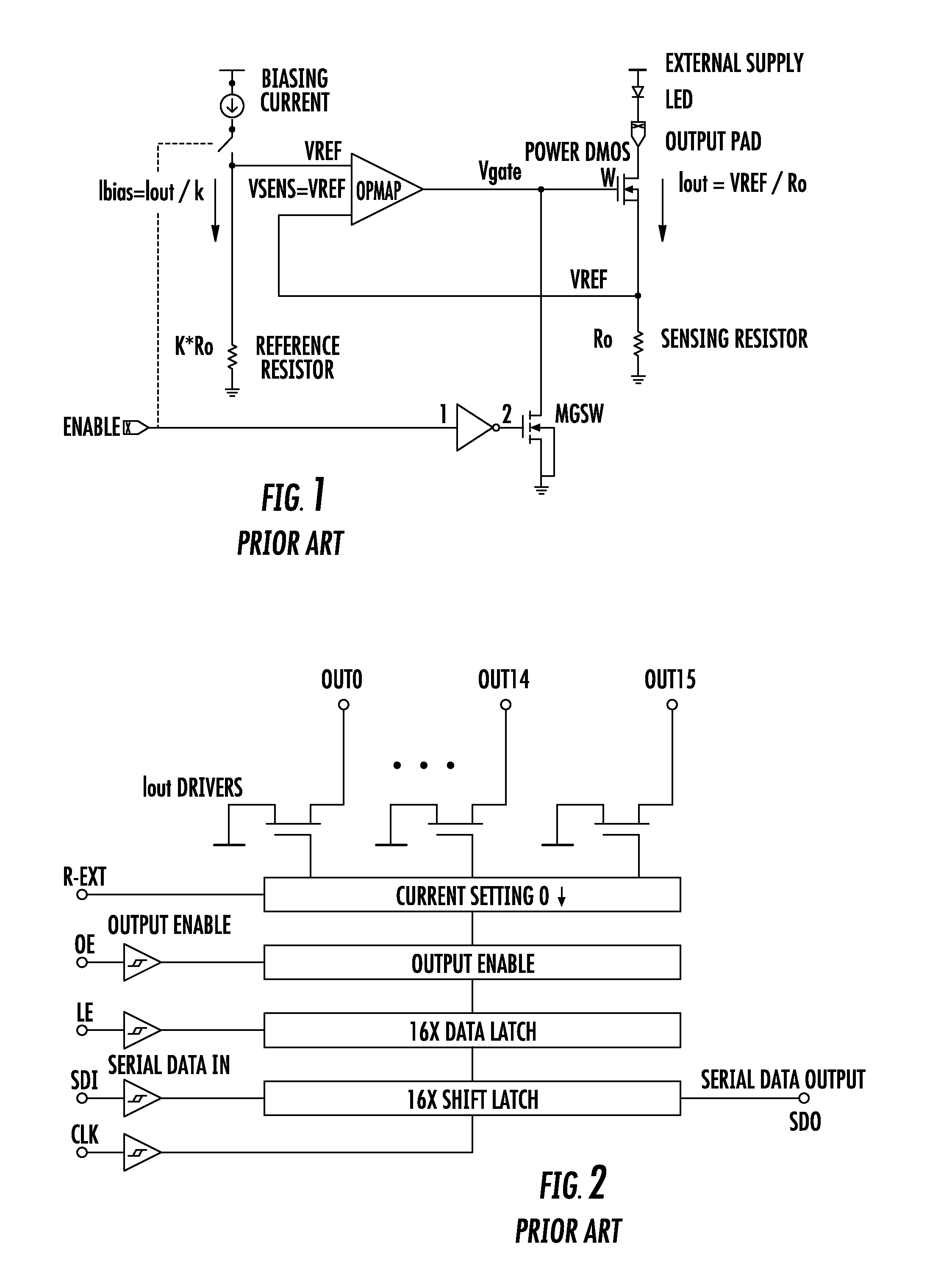

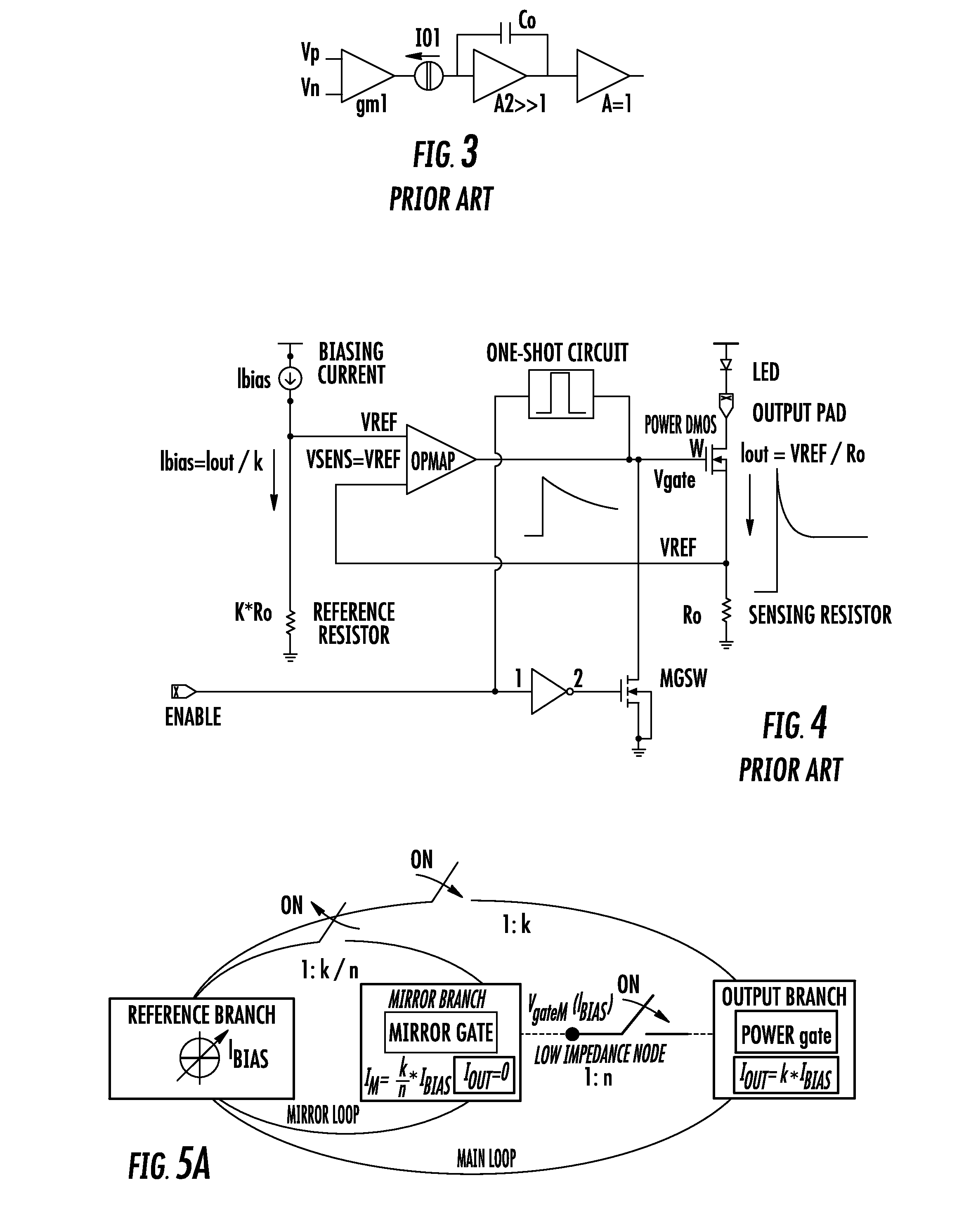

Fast switching, overshoot-free, current source and method

ActiveUS20100295476A1Reduce output current overshootLower impedancePrinted circuit assemblingPulse automatic controlAudio power amplifierEngineering

A method and a circuit may have an ability to provide constant currents of a certain set value, the rising and falling edges of which may be shorter than the design minimum on-phase. Essentially, these results may be obtained by keeping an operational amplifier that controls the output power switch in an active state during off-phases of an impulsive drive signal received by the current source circuit in order to maintain the output voltage of the operational amplifier at or just below the voltage to be applied to the control terminal of the output power switch during a successive on-phase of a received drive pulse signal.

Owner:STMICROELECTRONICS SRL

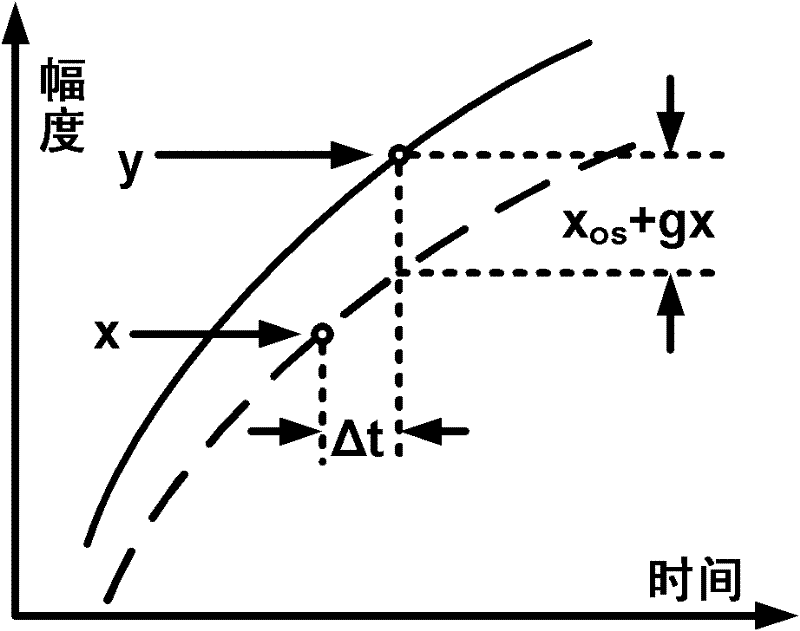

Time-interleaved adc split calibration structure without redundant channels and its adaptive calibration method

InactiveCN102291141ASmall area consumptionEasy to implementAnalogue/digital conversion calibration/testingComputation complexityHardware implementations

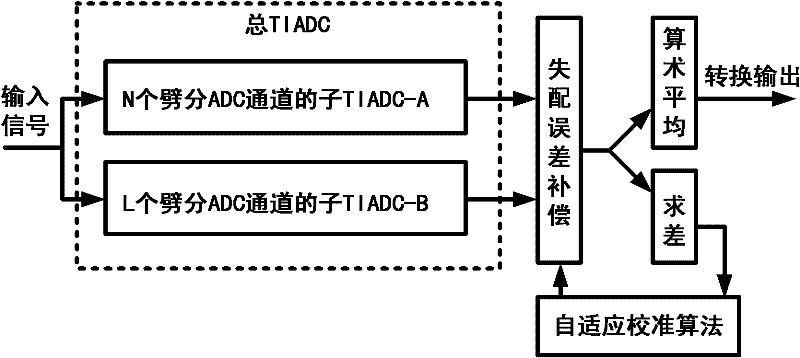

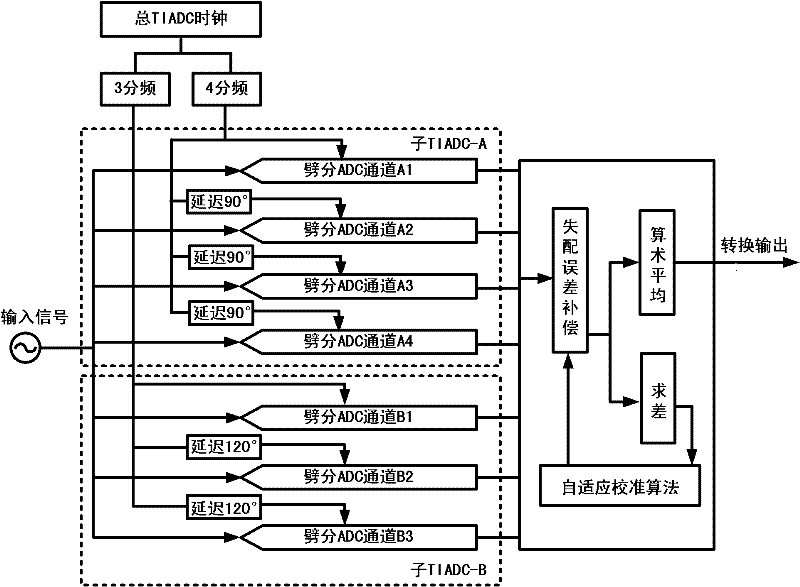

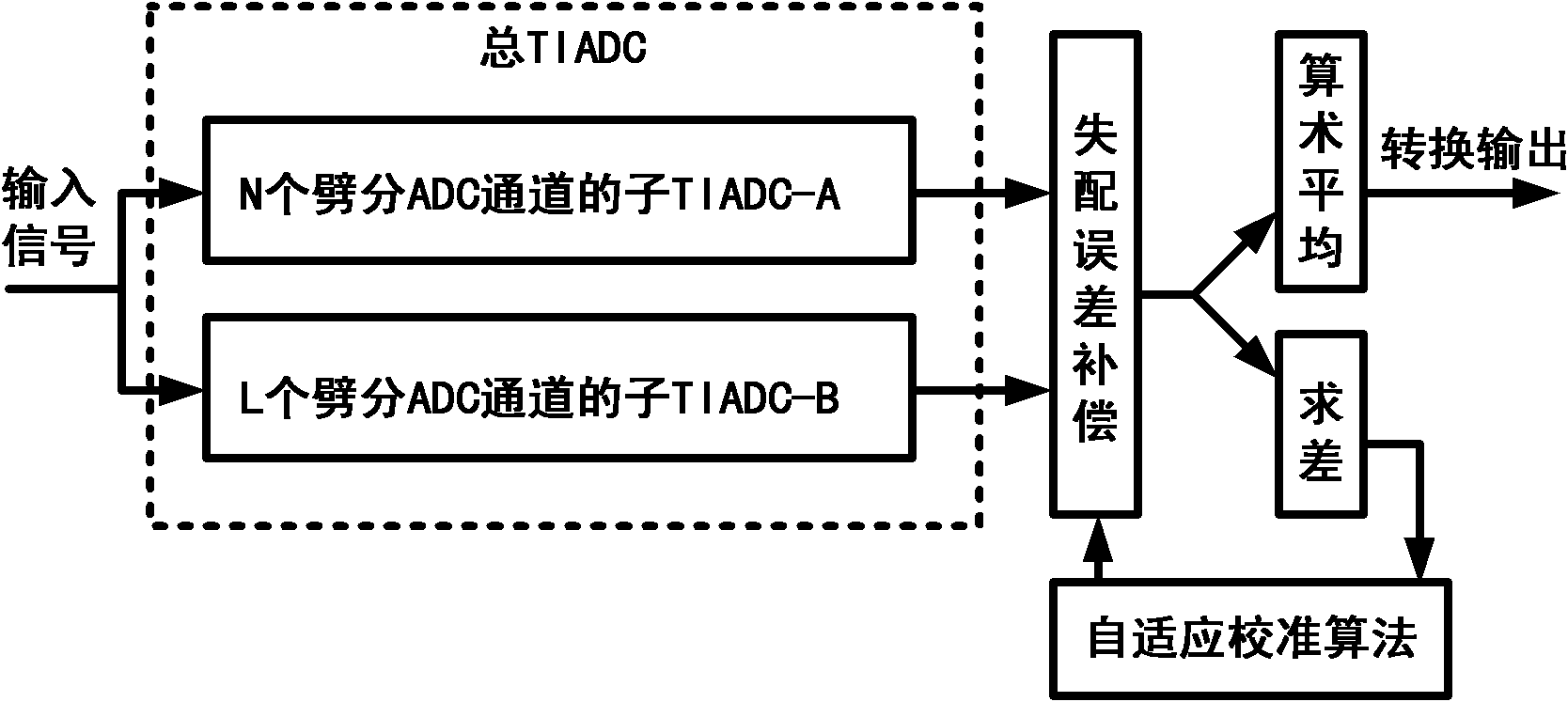

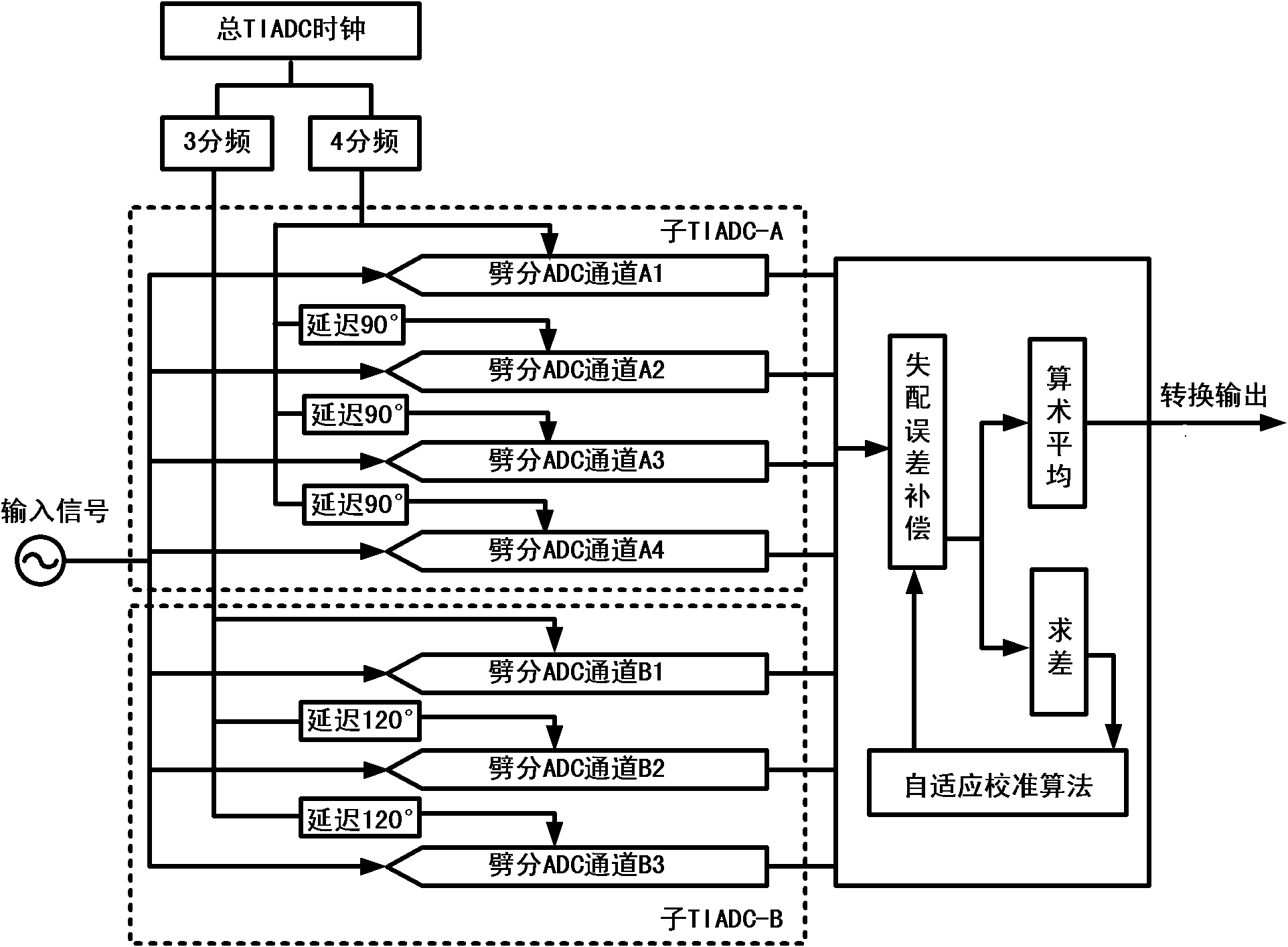

The invention discloses a time-interleaved split ADC (Analog-to-Digital Converter) calibration structure without a redundant channel and an adaptive calibration method thereof. The time-interleaved split ADC calibration structure is characterized in that: a time-interleaved ADC sub-module (sub TIADC-A) with sampling rate fs consisting of N split ADC channels with sampling rate fs / N and a time-interleaved ADC sub-module (sub TIADC-B) with sampling rate fs consisting of L split ADC channels with sampling rate of fs / L together form a split channel mutual calibration-based master TIADC. The same input signal is sampled and converted by the sub TIADC-A and the sub TIADC-B at the same sampling rate fs on the same moment; and difference converted and output by the sub TIADC-A and the sub TIADC-B is used in a zero approaching adaptive calibration algorithm to calculate a mismatch error estimation value among split ADC channels. When the mismatch error among the channels is correctly calibrated, the arithmetic mean value of the converted and output values of the sub TIADC-A and the sub TIADC-B is used as the final converted and output value of the split channel mutual calibration-based master TIADC. The calibration structure and the calibration method are low in computation complexity, easy in hardware implementation and can be applied to TIADC calibration with any number of channels.

Owner:HEFEI UNIV OF TECH

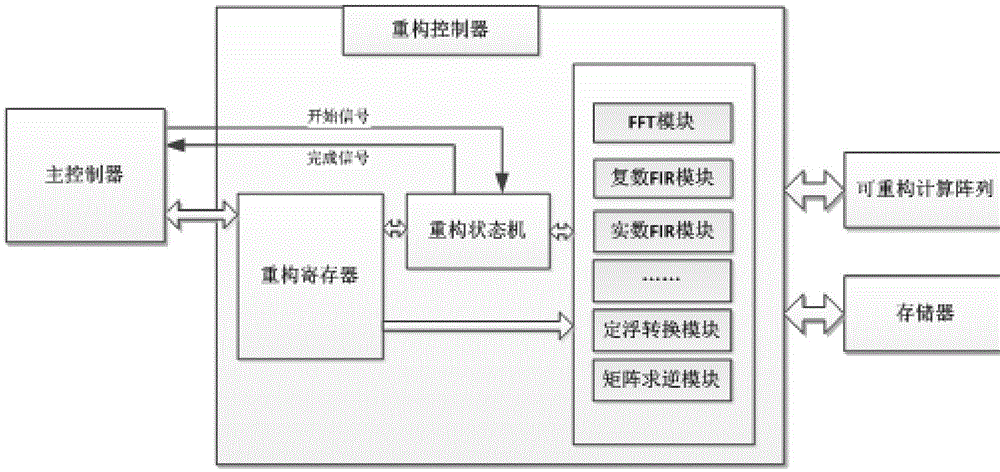

Coprocessor based on reconfigurable computational array

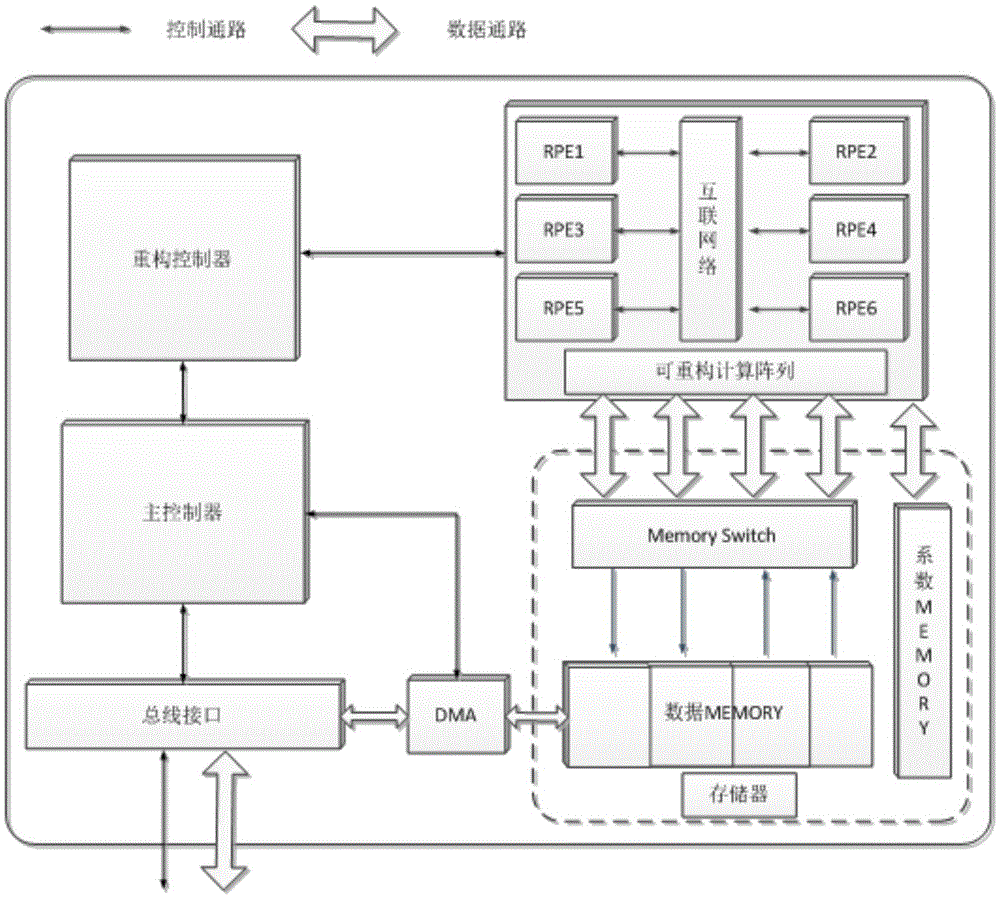

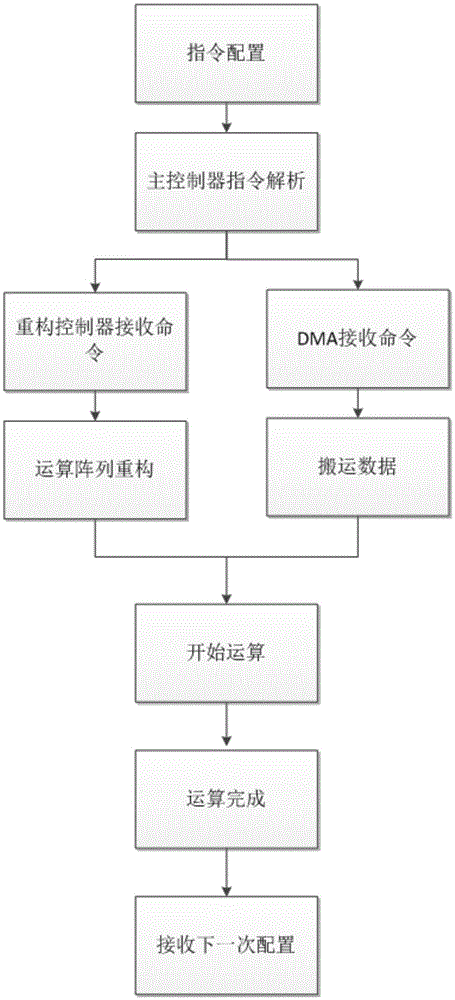

InactiveCN105630735AGood computing powerImprove efficiencyArchitecture with single central processing unitElectric digital data processingCoprocessorComputer module

The invention relates to a coprocessor based on a reconfigurable computational array. The coprocessor comprises a main controller which receives control information sent by an external universal processor, then analyzes the control information and sends out a corresponding configuration instruction, a reconfiguration controller which sends out the configuration information according to an algorithm parameter in the configuration instruction, an operation core unit which receives the configuration information and completes basic computation such as complex multiplication, complex addition and real multiplication, and a DMA unit which receives a transmission parameter of the configuration instruction and carries out data among an external DDR, an internal storage module and the main controller, wherein the configuration instruction comprises the transmission parameter and the algorithm parameter, and the configuration information comprises an execution signal used for selecting and organizing a logic algorithm in the operation core unit and an internal network gating signal. The coprocessor has the advantages of being good in computing performance and small in area consumption.

Owner:NANJING UNIV

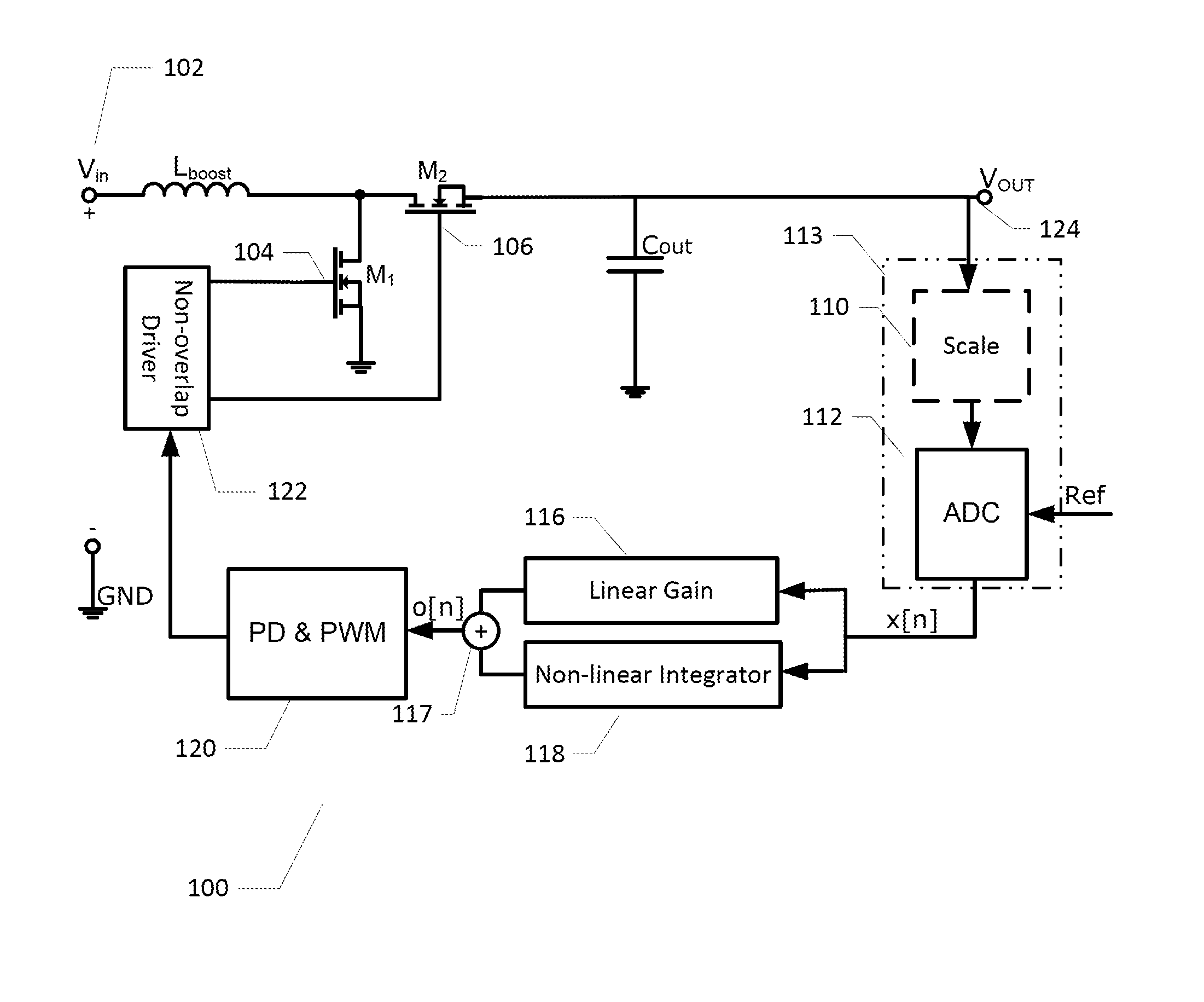

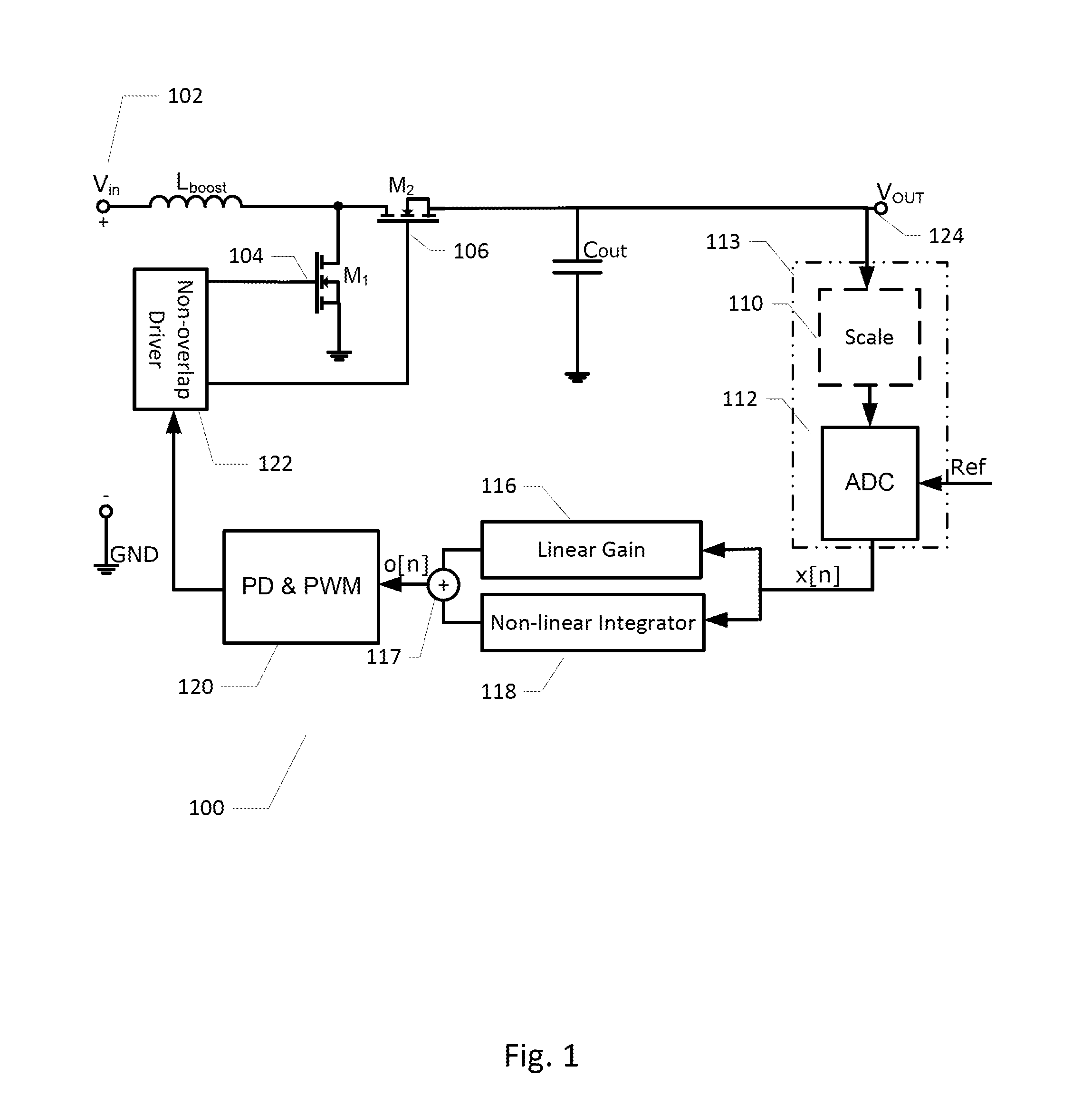

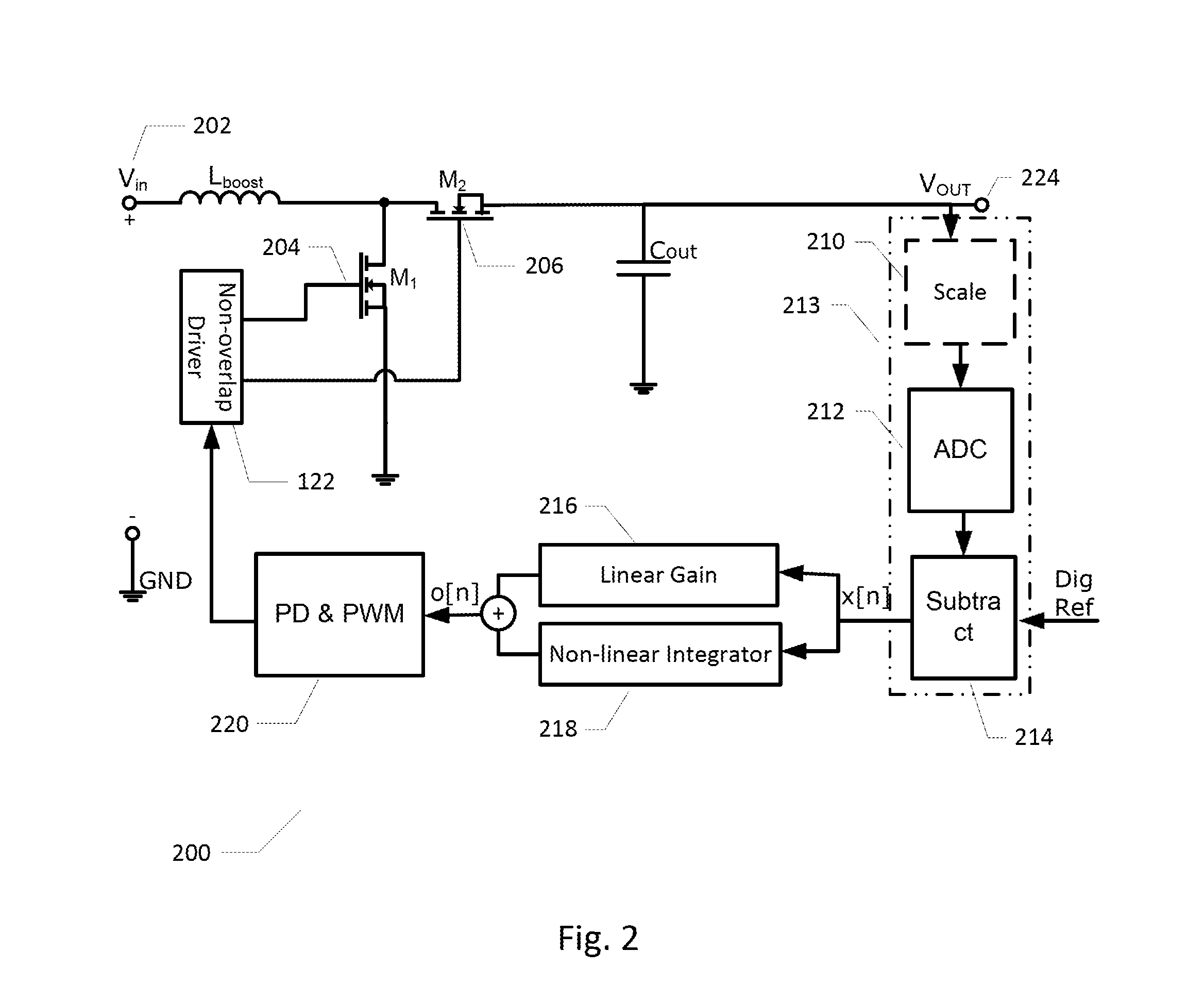

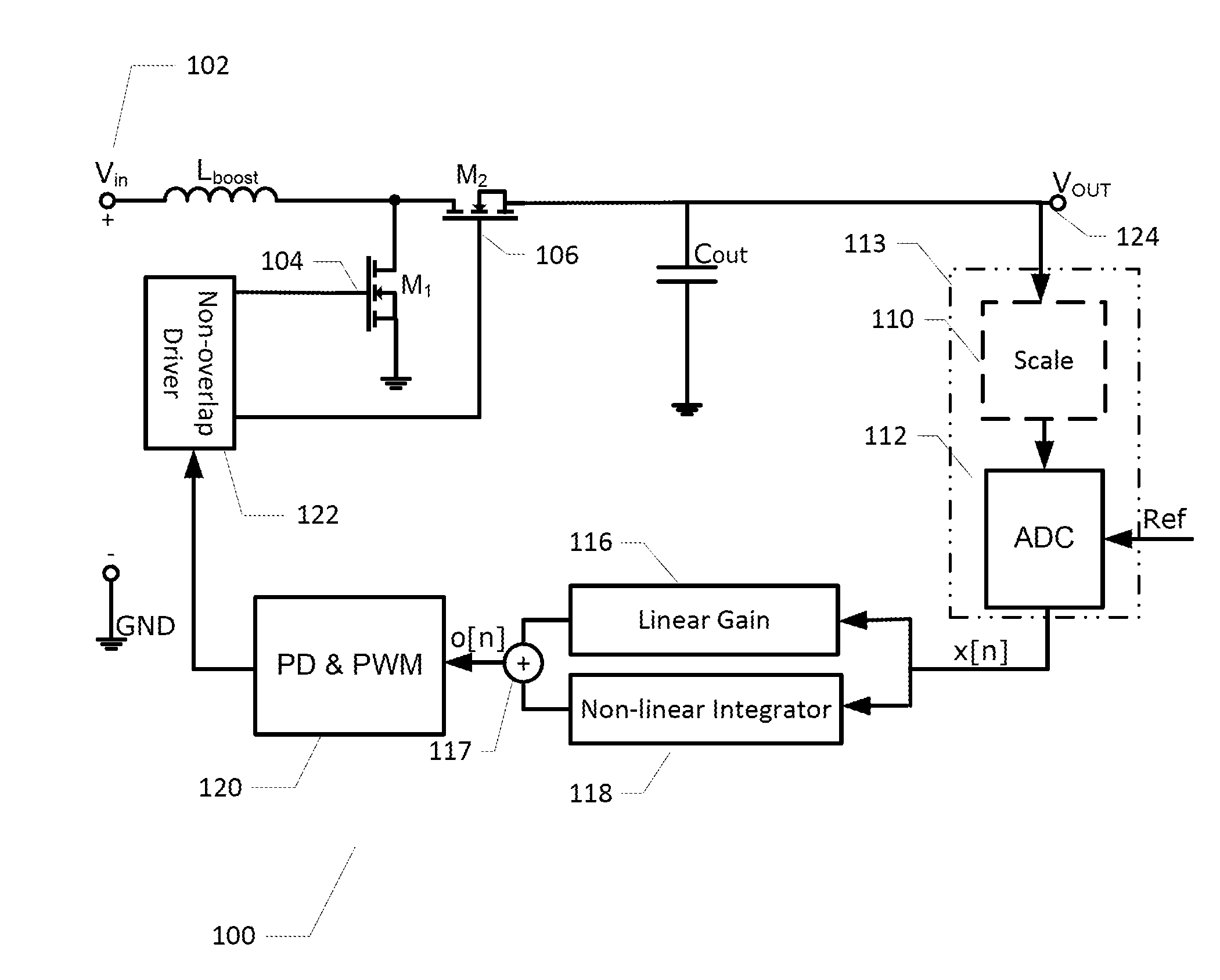

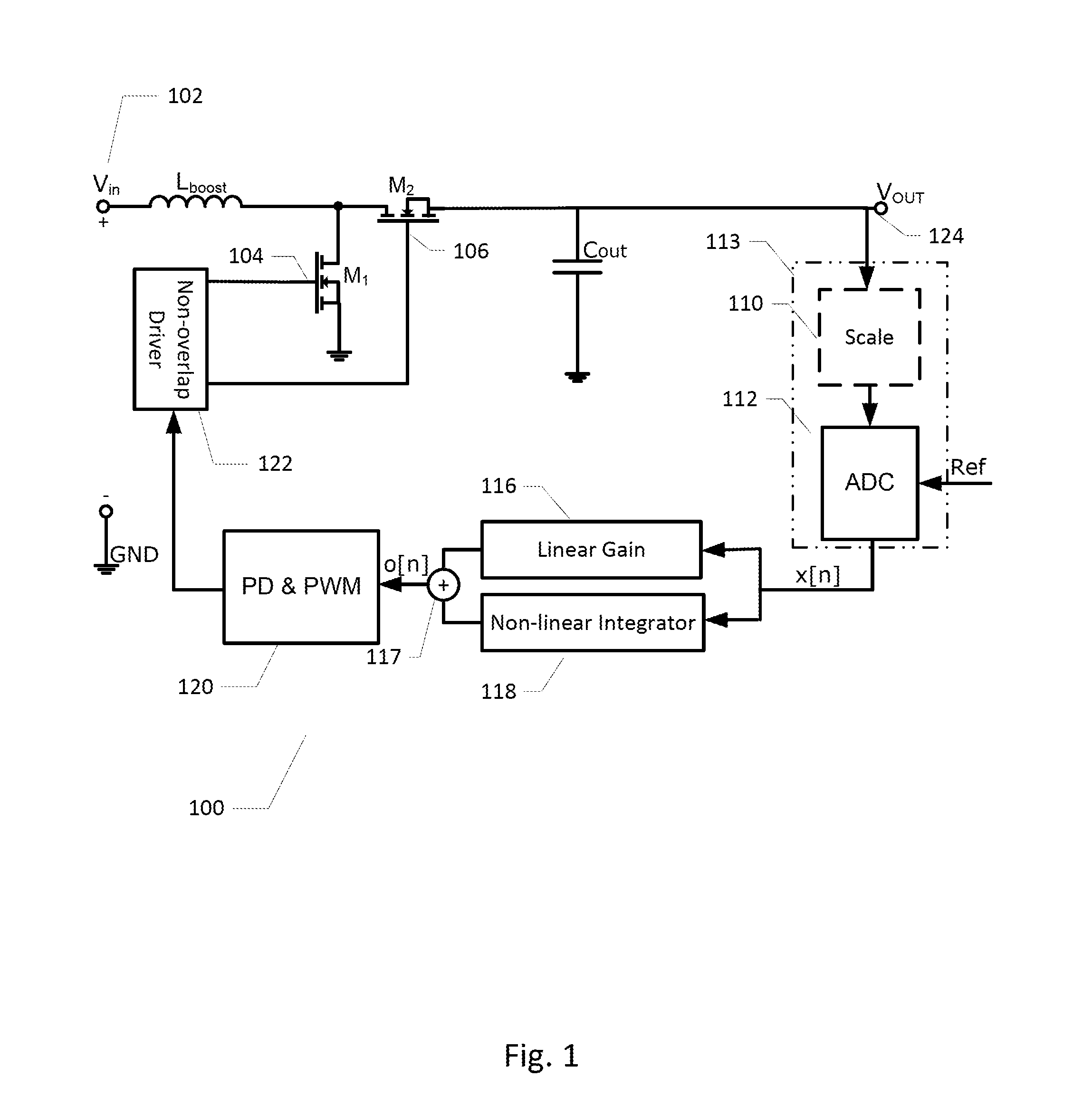

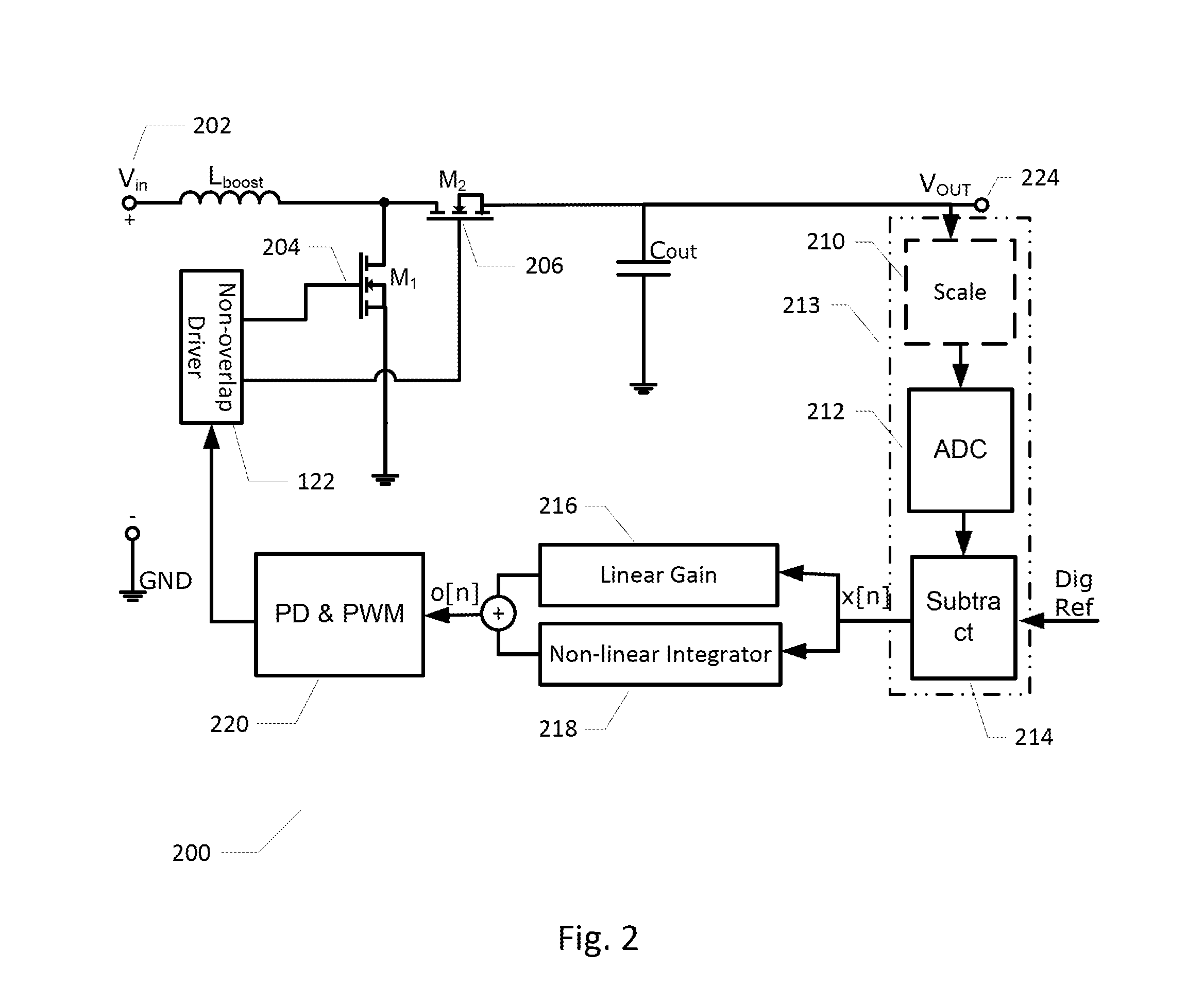

Digital switched mode voltage regulator

ActiveUS20140002042A1Quick responseEasy to trackEfficient power electronics conversionDc-dc conversionControl signalEngineering

The present invention relates to a switched mode voltage regulator circuit comprising a regulation loop coupled between the output voltage of the regulator and a switch driver. The regulation loop comprising an error signal generator supplying a digital error signal representative of a voltage difference between the output voltage and a reference voltage. The regulation loop further comprises a linear digital filter and a non-linear digital filter both coupled for receipt of the digital error signal and a digital summer coupled for receipt of linearly and non-linearly filtered digital error signals to provide a combined digital error signal. A digital pulse modulator is configured to generate the pulse width or pulse density modulated driver control signal in accordance with the combined digital error signal.

Owner:ANALOG DEVICES INT UNLTD

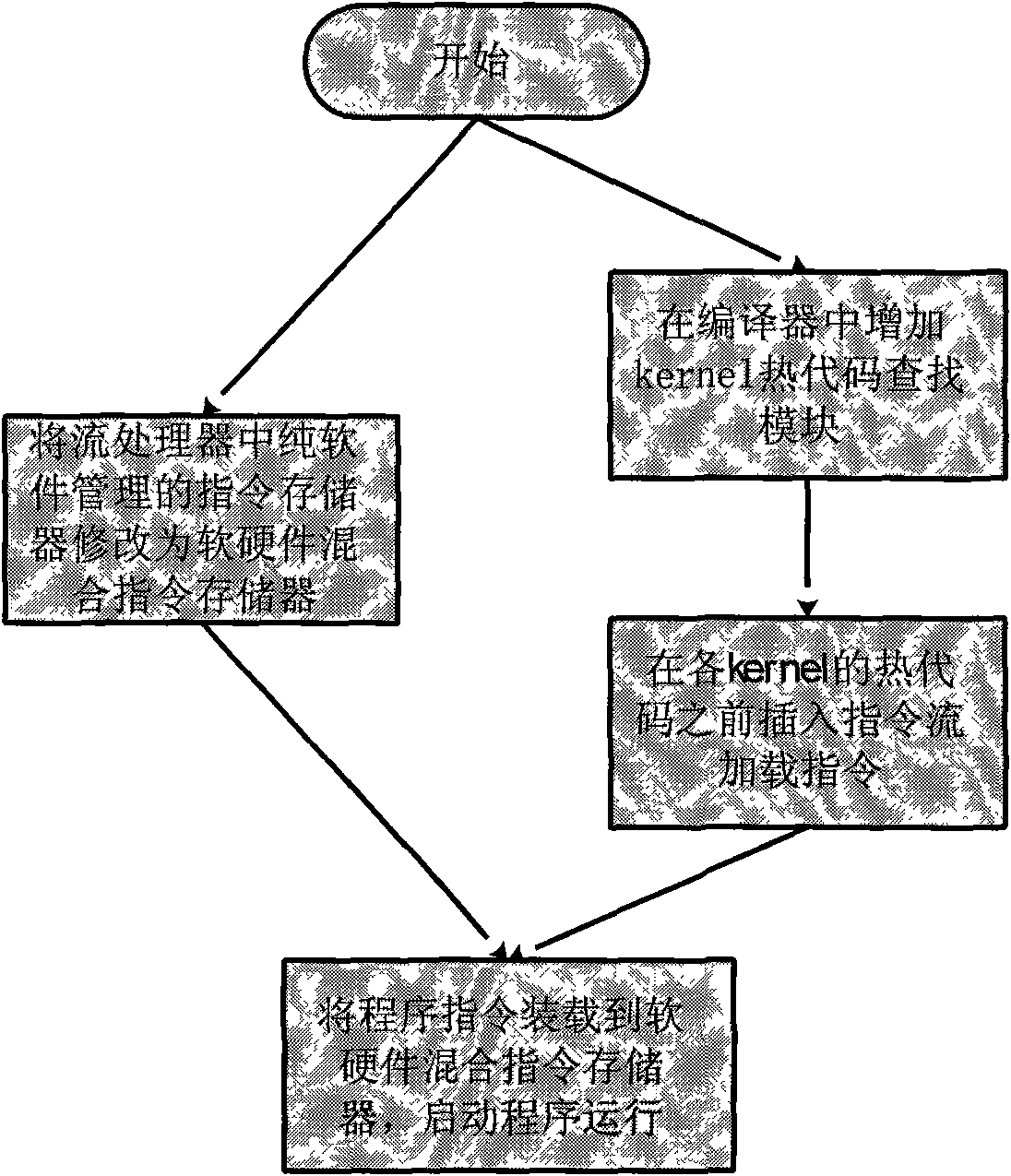

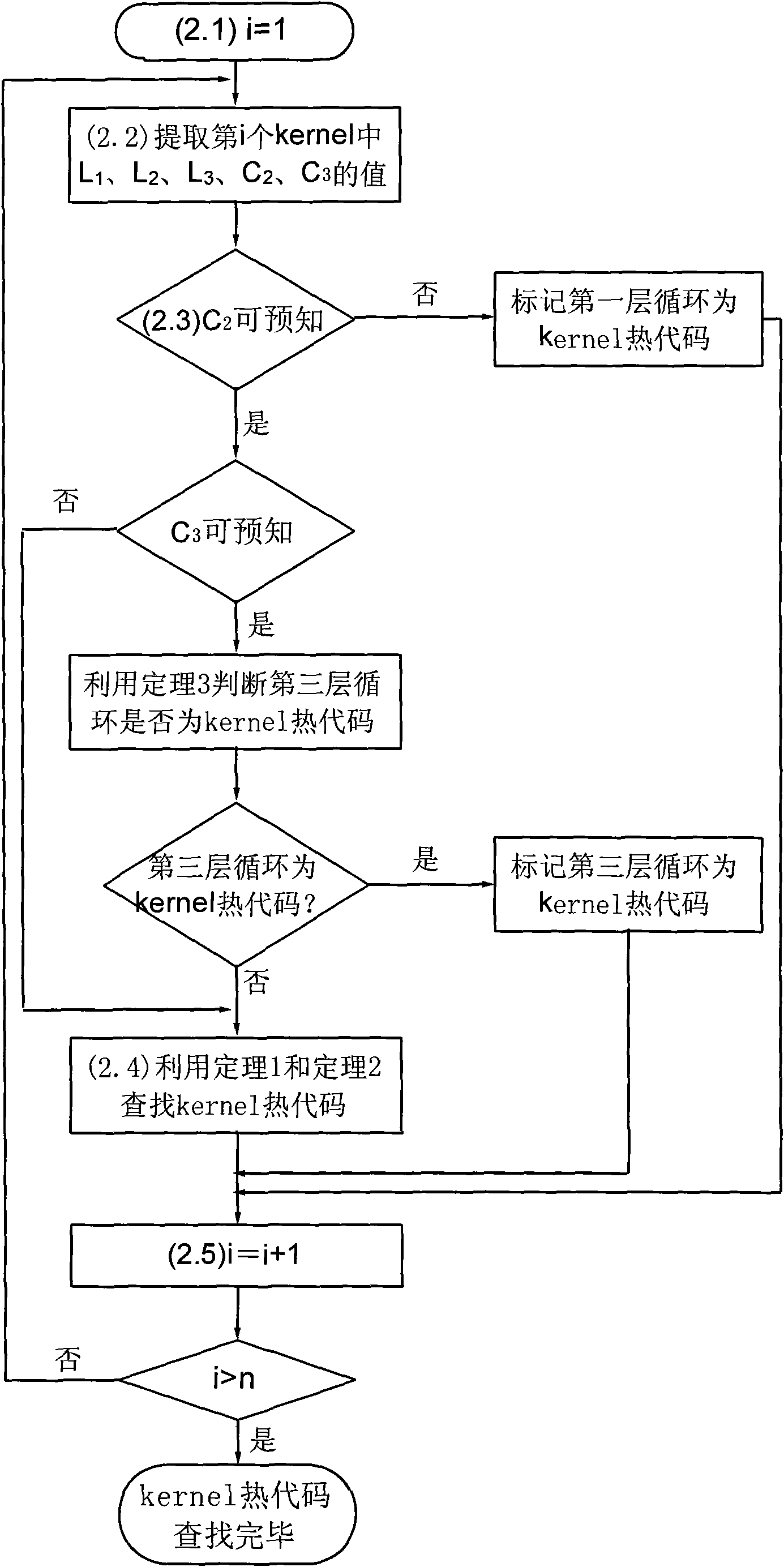

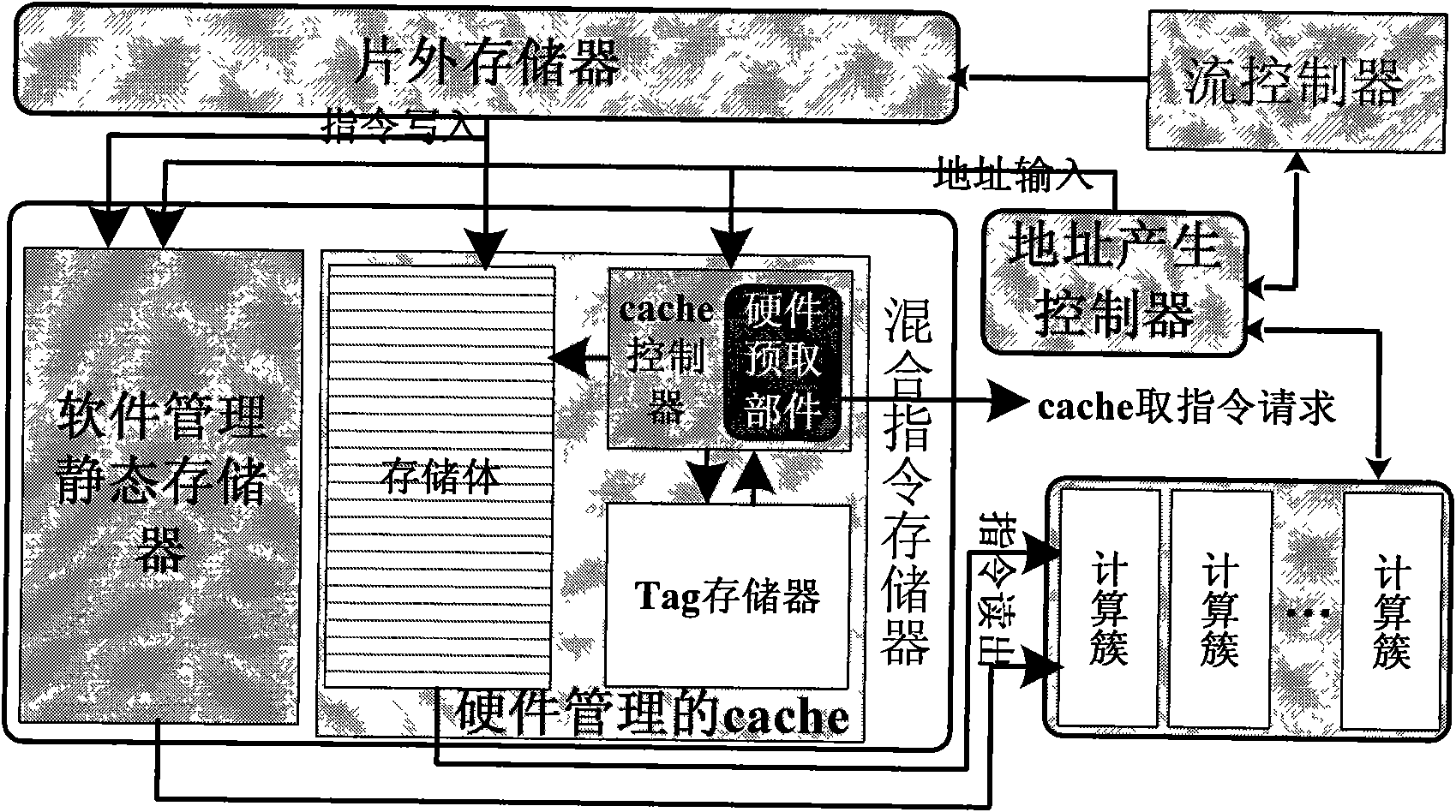

Method for reducing resource consumption of instruction memory on stream processor chip

InactiveCN101620526AReduce capacity requirementsSmall area consumptionMemory adressing/allocation/relocationConcurrent instruction executionInstruction memoryResource consumption

The invention discloses a method for reducing resource consumption of an instruction memory on a stream processor chip and aims at effectively reducing the resource consumption of the instruction memory without the addition of a complex compiling algorithm based on the prior mature hardware memory structure. The method adopts the following technical scheme: correcting the instruction memory for pure soft management in a stream processor into an instruction memory with software and hardware mixing; adding a kernel hot-code searching module in a compiler and searching kernel hot codes in the stream application according to a theorem for judging the hot codes; adding an instruction stream loading instruction before all kernel hot codes in the stream compiling; adopting a software management static memory to store the kernel hot codes so as to ensure high hit ratio, storing other instructions by adopting a cache for hardware management, and reducing the requirements of the instruction memory to memory capacity by shortening the instruction occupying time of the instruction memory, thereby the capacity of the instruction memory can be reduced. The invention can reduce the resource consumption of the instruction memory in a chip.

Owner:NAT UNIV OF DEFENSE TECH

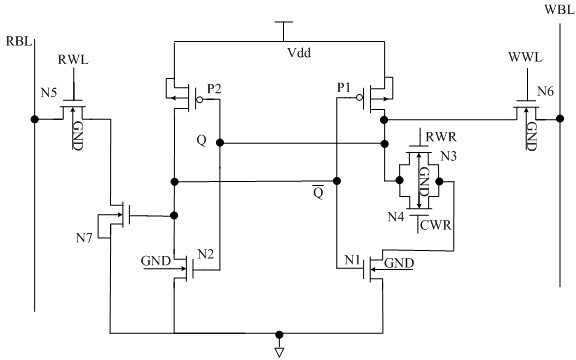

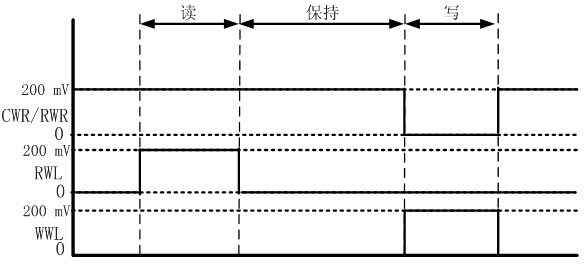

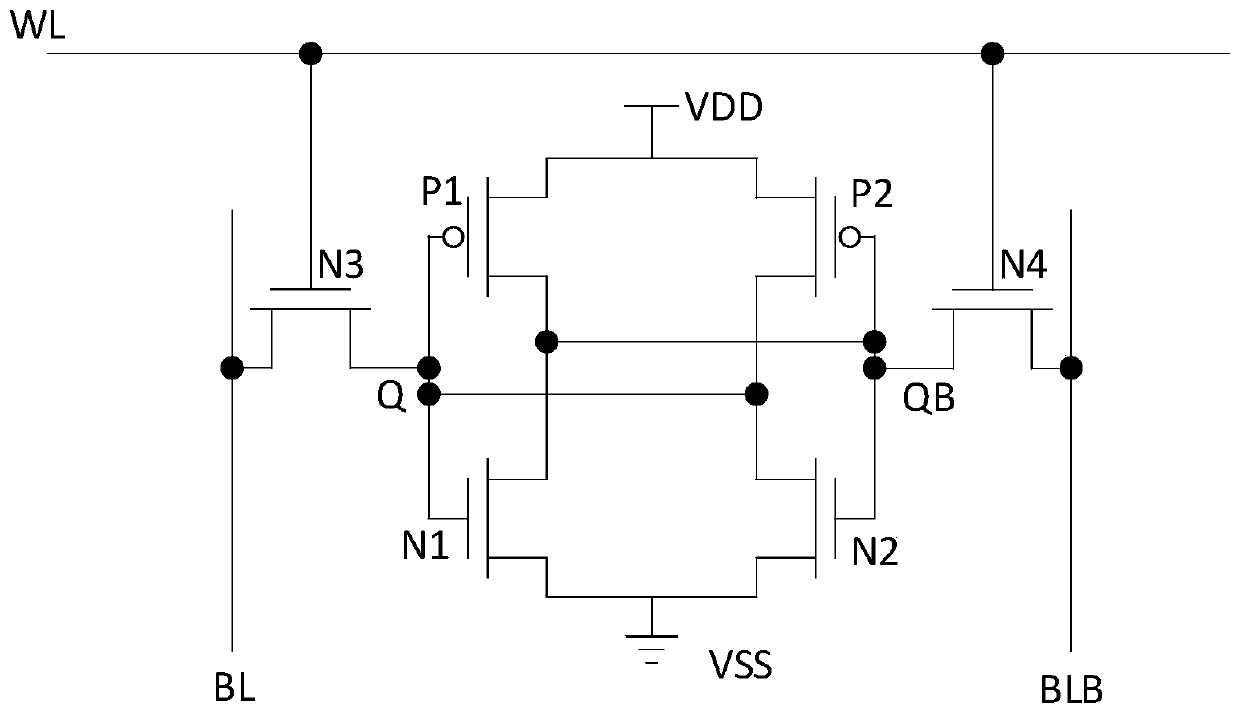

Single-end-operated subthreshold storage unit circuit

InactiveCN102592660AImprove noise immunityImprove robustnessDigital storageOxide semiconductorP channel

The invention discloses a single-end-operated subthreshold storage unit circuit, comprising two PMOS (P-channel Metal Oxide Semiconductor) transistors, namely P1 and P2, and seven NMOS (N-channel Metal Oxide Semiconductor) transistors, namely N1-N7, wherein the body ends of P1 and P2 are connected with a voltage drain-drain Vdd after being connected with the respective sources; the body ends of N1-N7 as well as the sources of N1, N2 and N7 are all grounded; the grid of N3 is connected with a row-writing control signal RWR; the grid of N4 is connected with a column-writing control signal CWR; an inverter is composed of N2 and P2; the output end of the inverter is connected with the grids of N2 and P2; the input end of the inverter is connected with the drain of P1; the grid of the N5 is connected with a reading word line RWL; the drain of N5 is connected with a reading bit line RBL; the source of N6 is connected with a writing bit line WBL; and the grid of N6 is connected with a word writing line WWL.

Owner:ANHUI UNIVERSITY

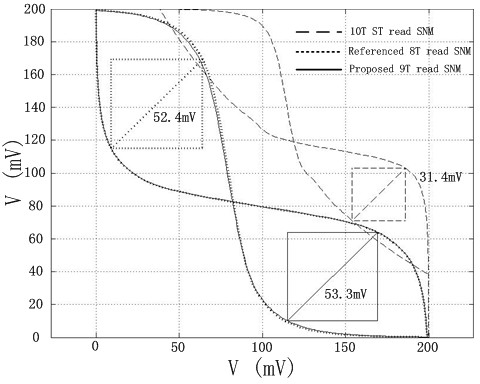

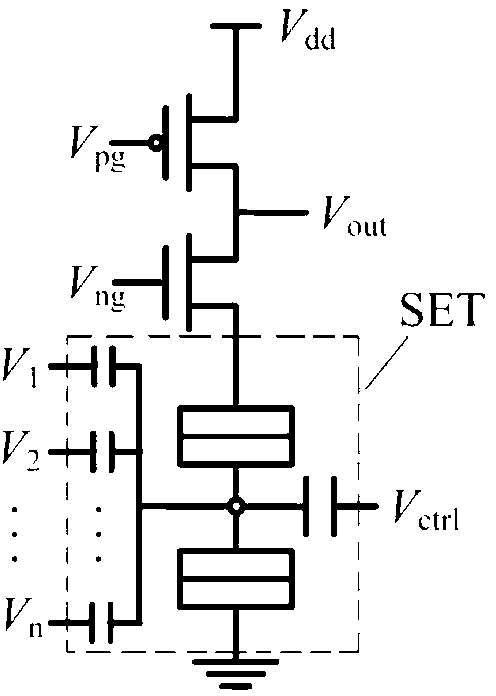

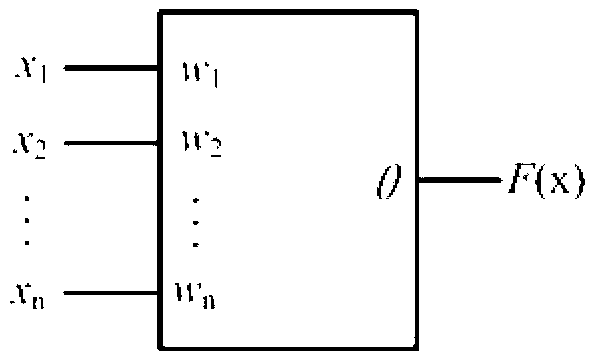

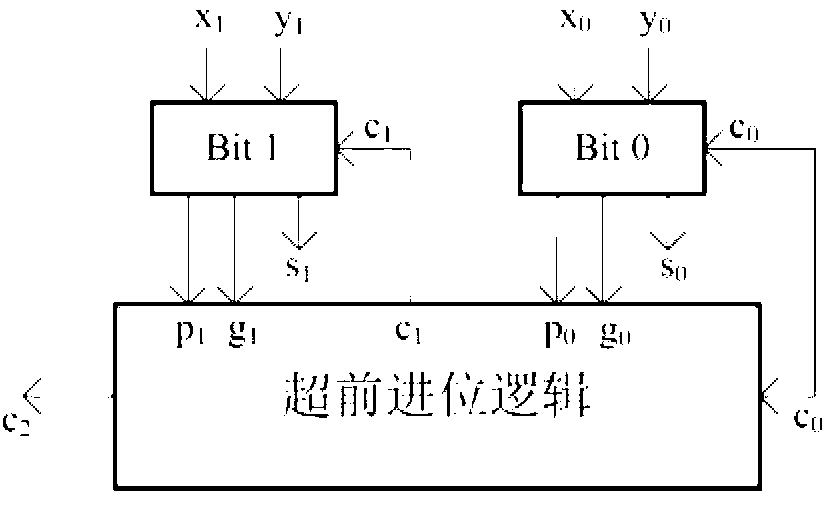

Threshold logic type carry look ahead adder formed by SET/MOS mixing circuit

ActiveCN103279322ASmall area consumptionReduce areaComputation using non-contact making devicesCMOSSingle electron

The invention relates to a carry look ahead adder based on threshold logic and achieved by utilizing coulomb blockade oscillation effects and multi-gate input characteristics of a single electron transistor and metal oxide semiconductor (MOS) transistor mixing structure. Due to the good logic function of threshold logic, a circuit is only formed by 10 threshold logic gates, and the whole circuit only consumes 30 components. Compared with a traditional complementary metal oxide semiconductor (CMOS) carry look ahead adder, the threshold logic type carry look ahead adder enables circuit structure to be greatly simplified, transistor number is remarkably reduced, and power consumption is further reduced. The threshold logic type carry look ahead adder can be hopefully applied to the fields of microprocessors, digital signal processors and the like, is favorable for further reducing circuit power consumption, saves chip area and improves circuit integration level.

Owner:FUZHOU UNIV

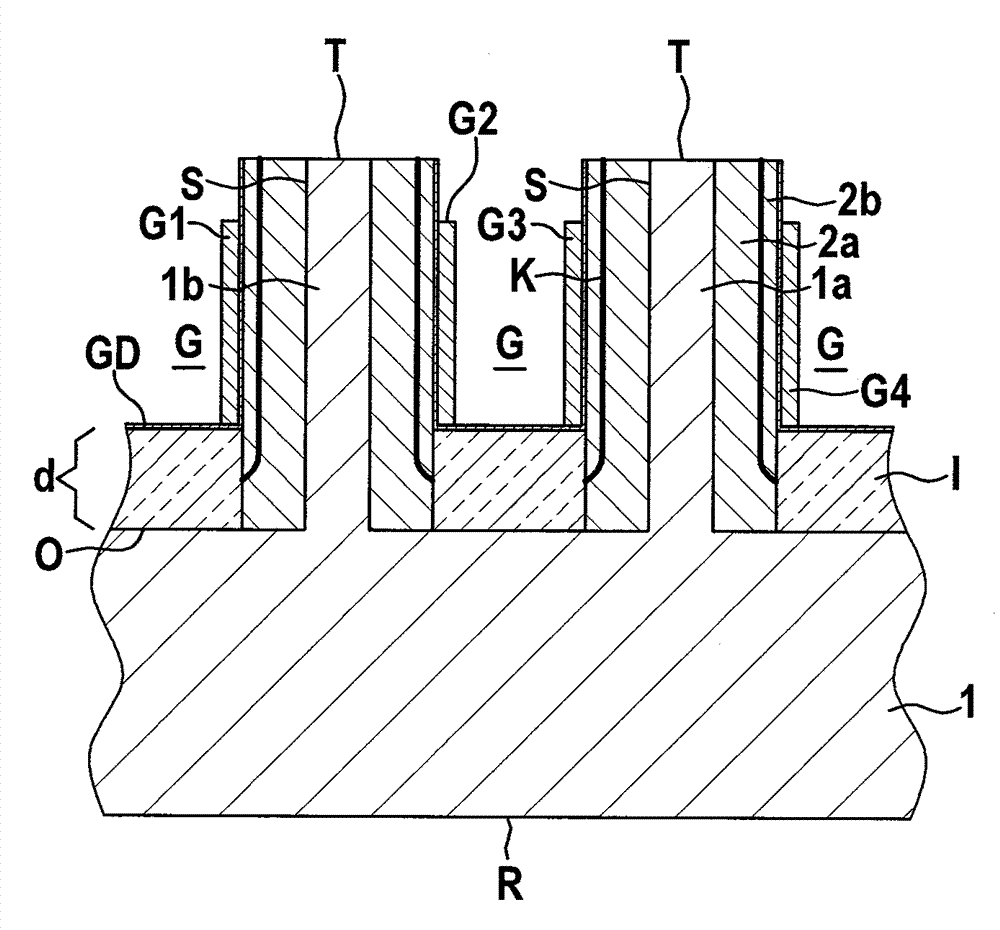

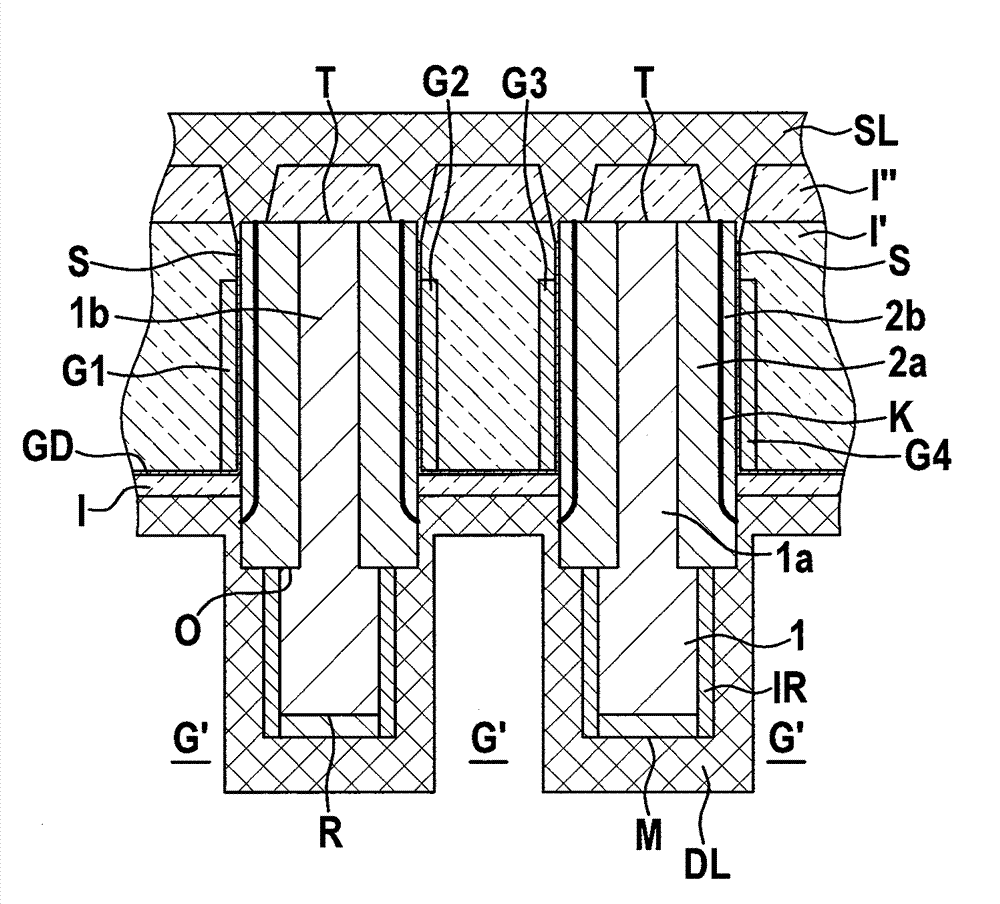

Vertical microelectronic component and corresponding production method

InactiveCN103681836AImprove power densityHigh compressive strengthSolid-state devicesSemiconductor/solid-state device manufacturingCommon drainElectronic component

A vertical microelectronic component and a corresponding production method are realized. The vertical microelectronic component includes a semiconductor substrate having a front side (O) and a back side (R), and a multiplicity of fins (1a, 1b) formed on the front side (O). Each fin has a corresponding side wall (S) and an upper side (T) and is separated from other fins by trenches (G). Each fin includes a GaN / AlGaN heterolayer region formed on the side wall (S)and including an embedded channel region (K) extending essentially parallel to the side wall (S) and at least one gate interface region (G1-G4). The gate interface region (G1-G4) is arranged above the GaN / AlGaN heterolayer region and electrically insulated from the channel region in the associated trench on the side wall (S). A common source terminal region (SL) arranged above the fins is connected to a first end of the channel region (K) in a vicinity of the upper sides (T). A common drain terminal region (DL) arranged above the back side is connected to a second end of the channel region (K) in a vicinity of the front side (O).

Owner:ROBERT BOSCH GMBH

Digital switched mode voltage regulator

ActiveUS9136760B2Quick responseEasy to trackEfficient power electronics conversionDc-dc conversionControl signalEngineering

The present invention relates to a switched mode voltage regulator circuit comprising a regulation loop coupled between the output voltage of the regulator and a switch driver. The regulation loop comprising an error signal generator supplying a digital error signal representative of a voltage difference between the output voltage and a reference voltage. The regulation loop further comprises a linear digital filter and a non-linear digital filter both coupled for receipt of the digital error signal and a digital summer coupled for receipt of linearly and non-linearly filtered digital error signals to provide a combined digital error signal. A digital pulse modulator is configured to generate the pulse width or pulse density modulated driver control signal in accordance with the combined digital error signal.

Owner:ANALOG DEVICES INT UNLTD

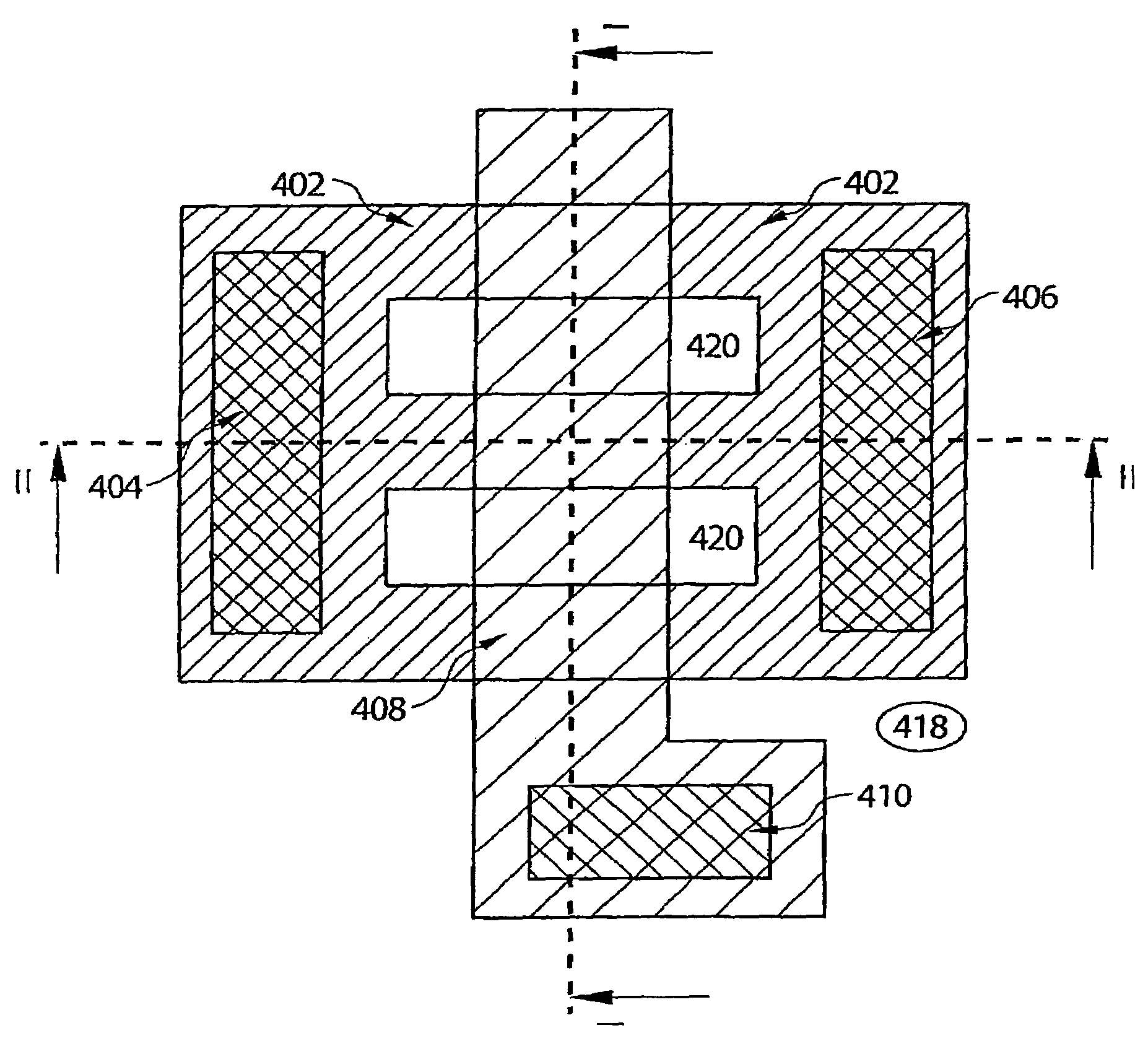

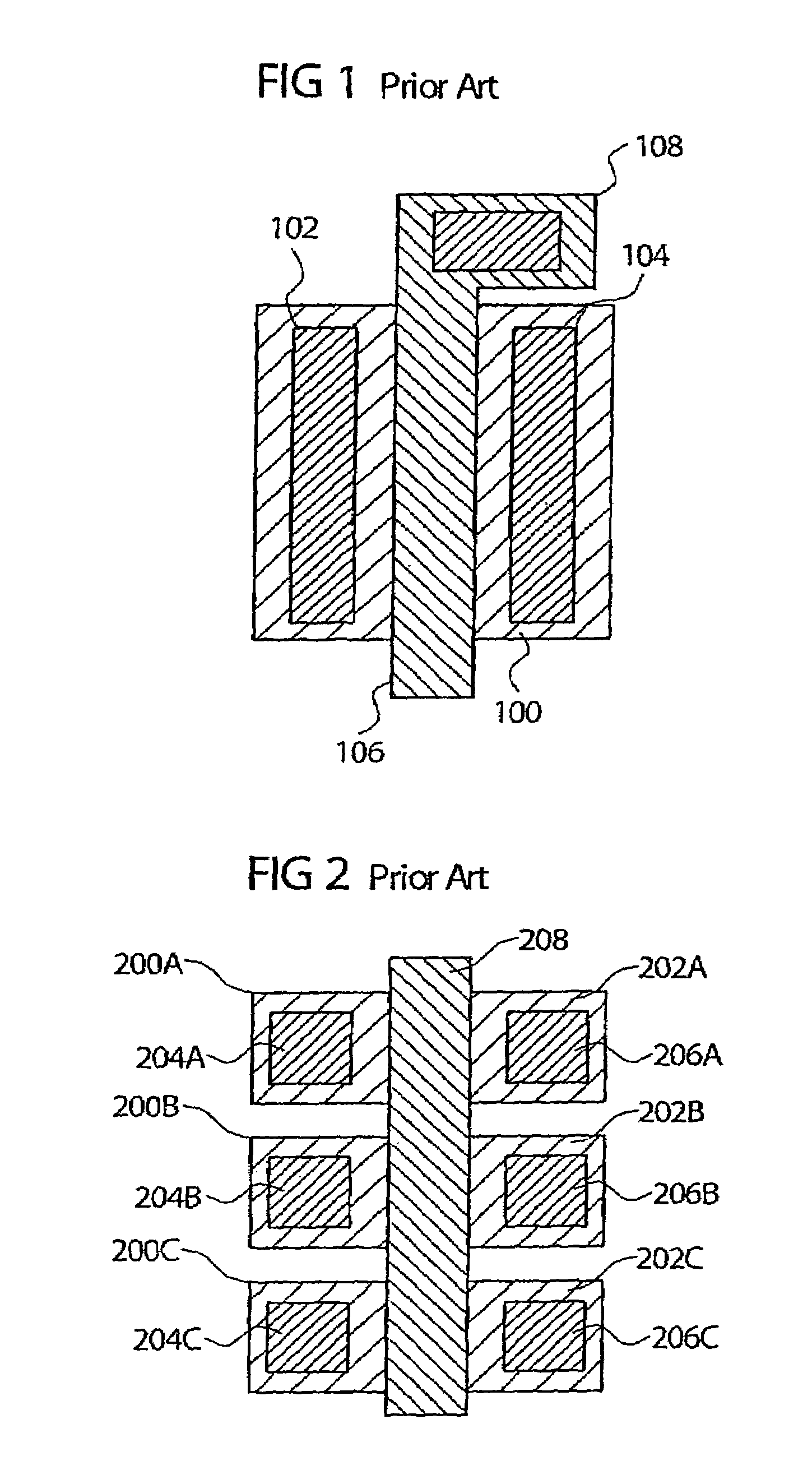

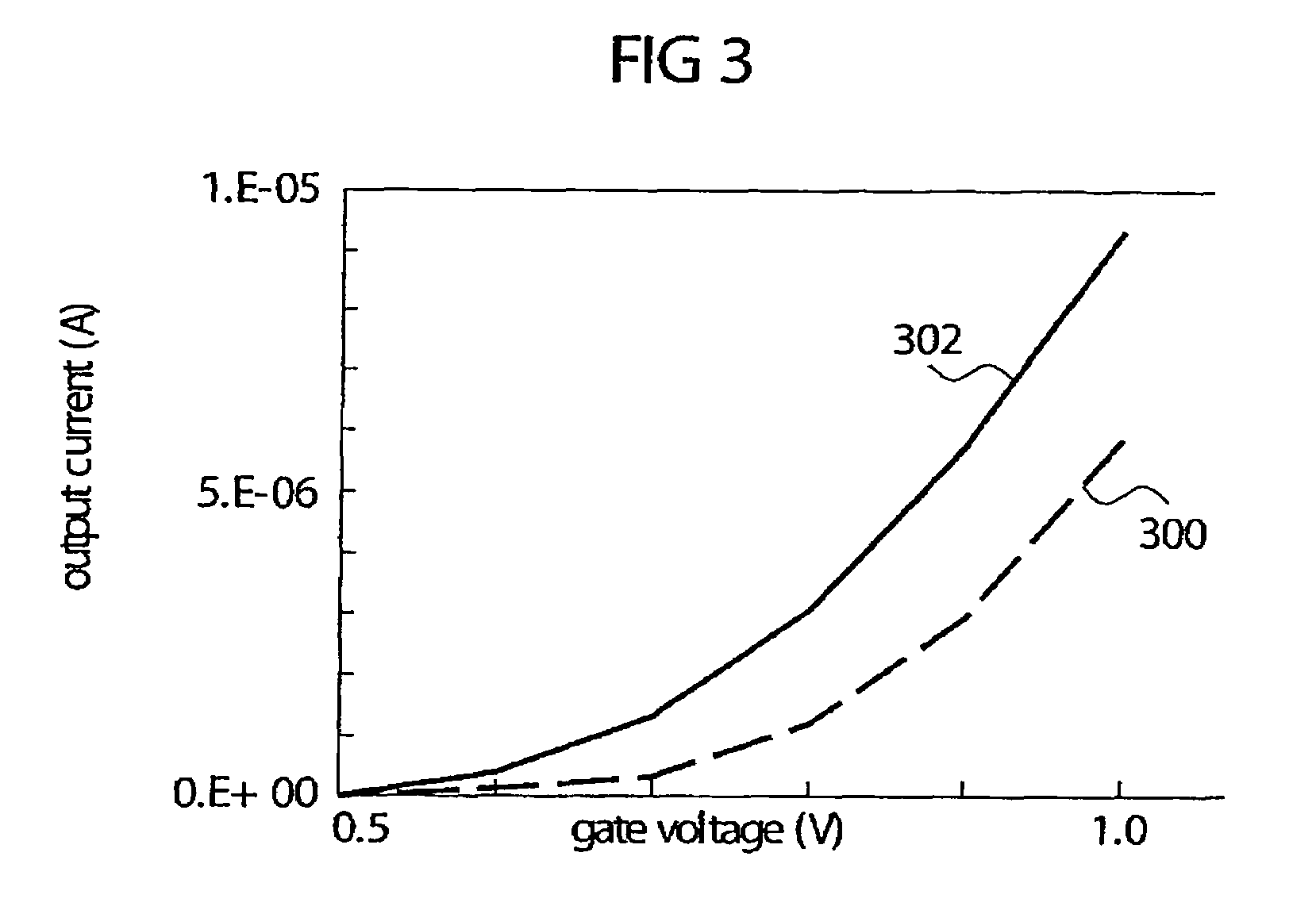

Field-effect transistor

InactiveUS7009263B2Small area consumptionImprove efficiencyTransistorSolid-state devicesField-effect transistorSemiconductor

A field-effect transistor includes a semiconductor substrate, a source region formed in the semiconductor substrate, a drain region formed in the semiconductor substrate, a channel region formed in the semiconductor substrate, wherein the source region is connected to a source terminal electrode and the drain region is connected to a drain terminal electrode, wherein the channel region comprises a first narrow width channel region and a second narrow width channel region connected in parallel regarding the source terminal electrode and the drain terminal electrode, and wherein the first narrow width channel region and / or the second narrow width channel region comprise lateral edges narrowing the width of the narrow width channel region is such a way that a channel formation in the narrow width channel region is influenced by a mutually influencing effect of the lateral edges, and a gate electrode arranged above the first and second narrow width channel regions.

Owner:POLARIS INNOVATIONS LTD

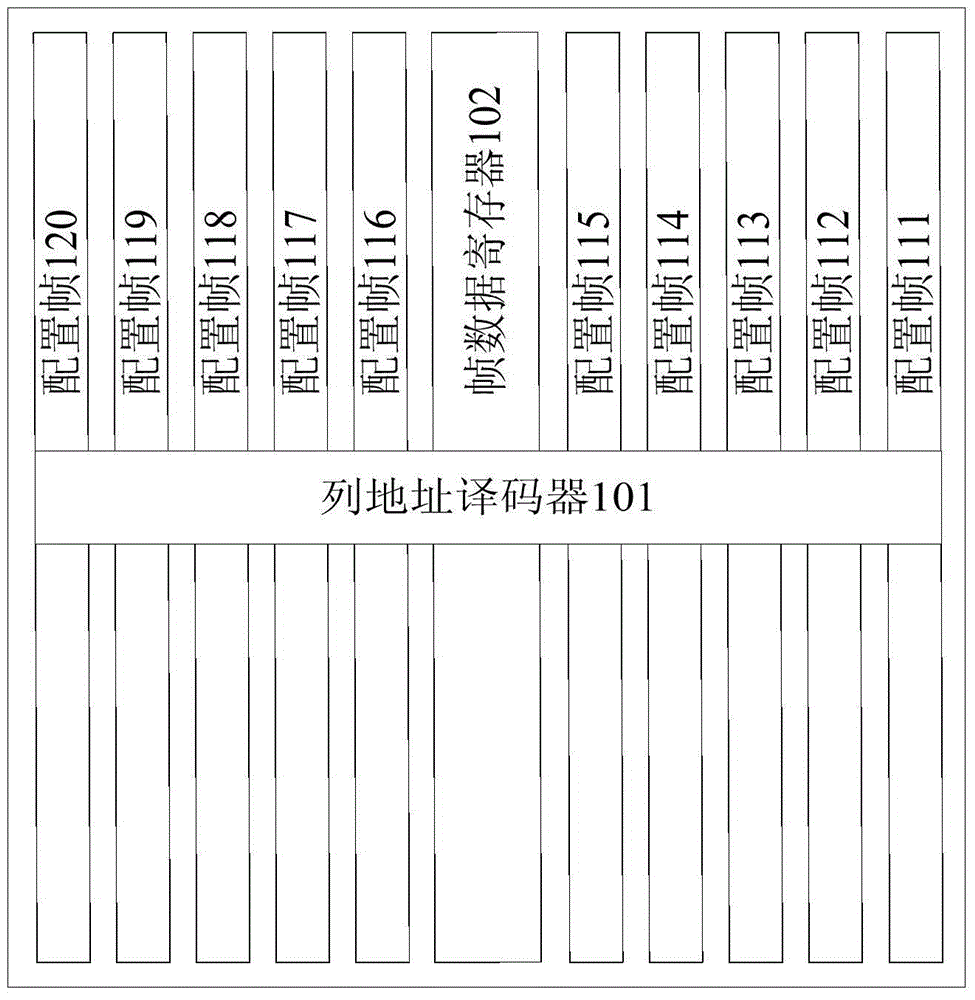

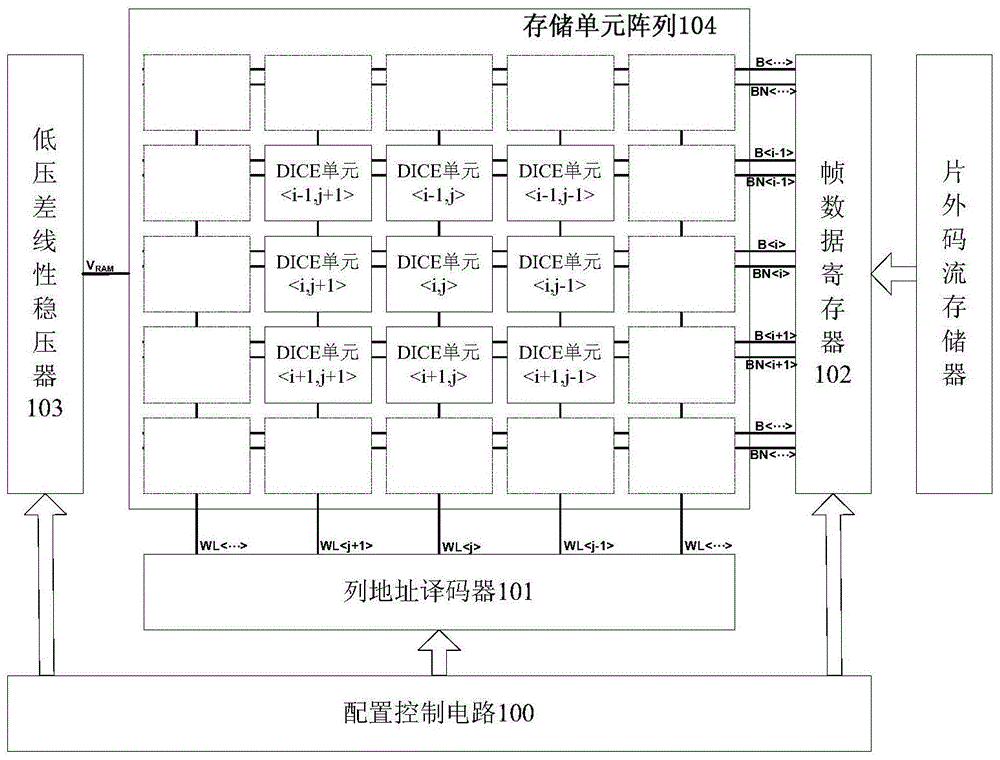

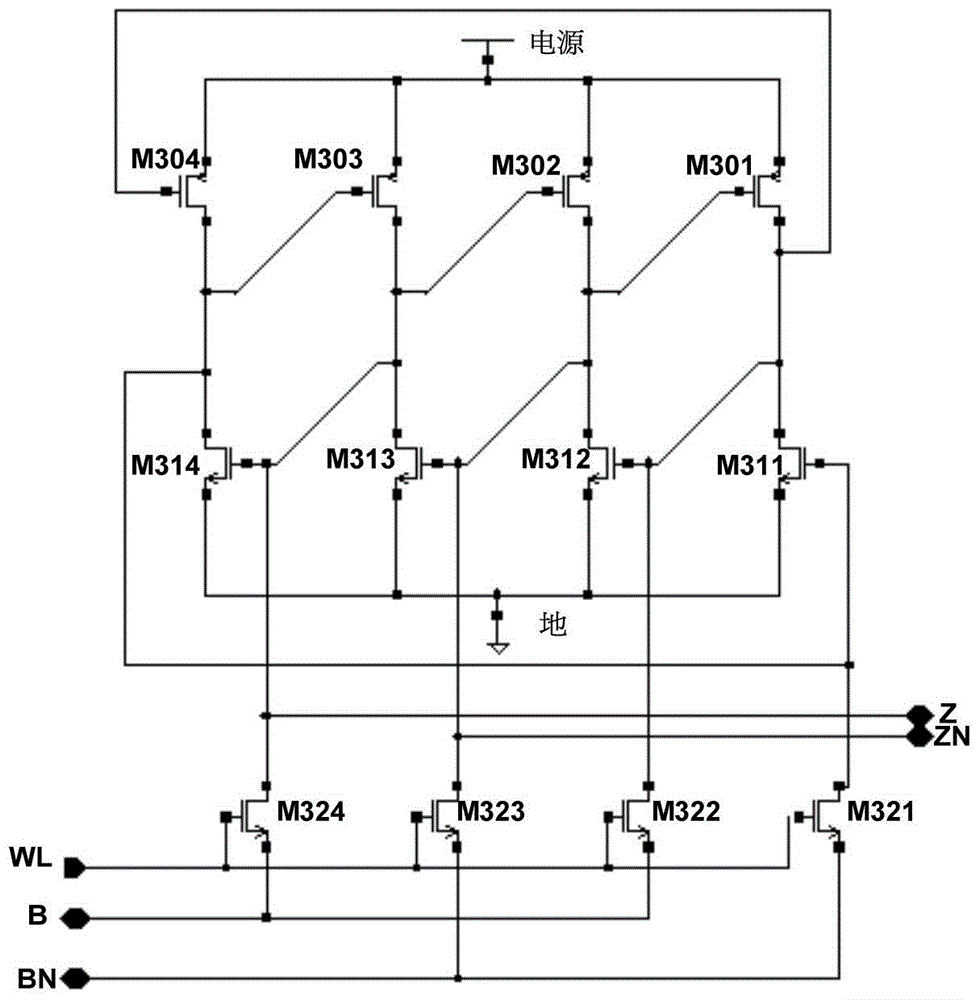

Reinforcement configuration memory array applicable to FPGA for space navigation and configuration method of reinforcement configuration memory array

ActiveCN105741872ASmall area consumptionAchieve radiation resistance hardeningRead-only memoriesElectricityComputer architecture

The invention relates to a reinforcement configuration memory array applicable to an FPGA (Field Programmable Gate Array) for space navigation and a configuration method of the reinforcement configuration memory array, wherein the configuration memory array uses DICEs (Double Interlocked Storage Cells) for realizing single particle reinforcement of the configuration memory array; and the influence of single particles on the configuration memory array is reduced. The configuration method is characterized in that before the configuration memory array is electrified, all configuration memory units are in a 0-write state through a column address decoding circuit and a frame data register; and during electrification, all initial states of all DICEs after the electrification are 0 due to the inductive effect of external work conditions. The logic conflict of an FPGA interconnection matrix after the electrification due to the non-determined state of the configuration memory units is avoided, so that the problem of electrification surge current of the FPGA is effectively solved; the design difficulty of a system using the FPGA is reduced; and the work reliability of the FPGA for space navigation is improved.

Owner:BEIJING MXTRONICS CORP +1

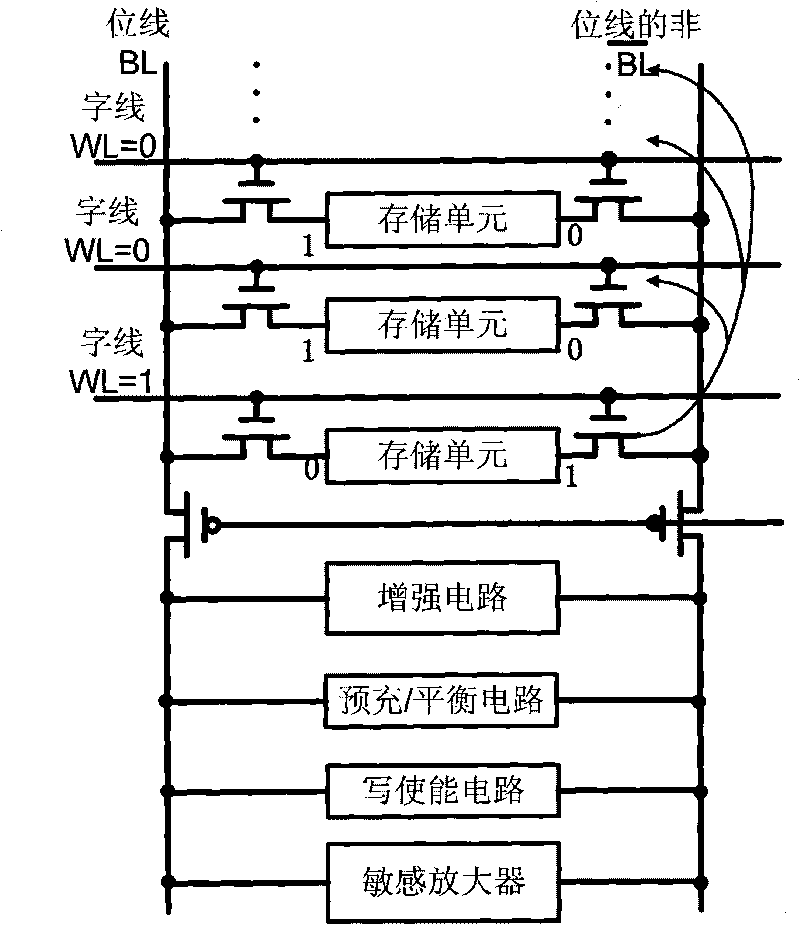

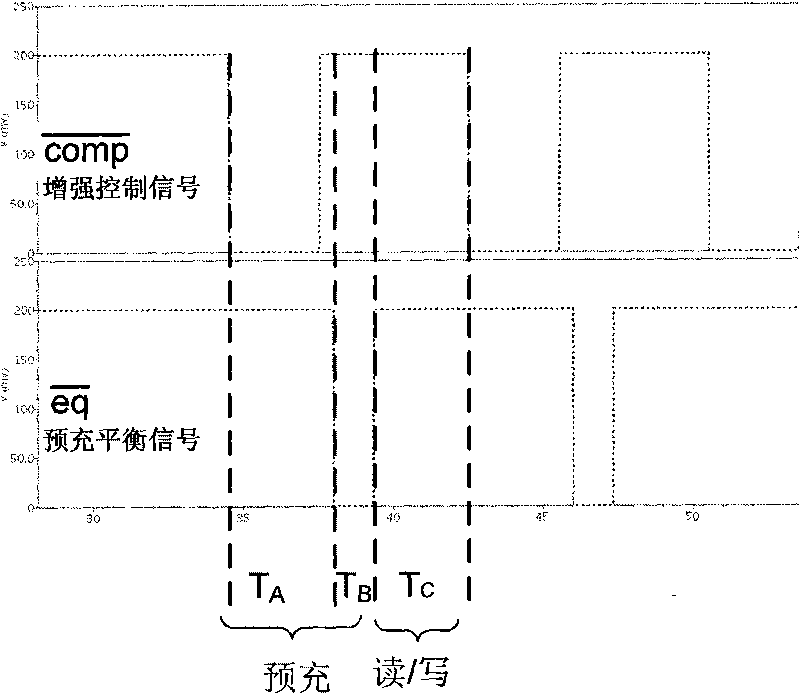

Bit line leakage current compensation circuit for sub-threshold memory cell array

InactiveCN101699561AEnhanced shutdown currentSmall area consumptionDigital storageTransmission gateCapacitance

The invention relates to a bit line leakage current compensation circuit for a sub-threshold memory cell array. Source terminals respectively provided with a first compensation transistor (P1) and a second compensation transistor (P2) are connected with power supply voltage; gate terminals are connected with respective body terminals and are respectively connected with the input terminals of a first shielded transmission gate (T1) and a second shielded transmission gate (T2) to be used as a bit line terminal and a non-terminal of a bit line; the drain terminals of P1 and P2 are respectively connected with the output terminals of T1 and T2 and are respectively connected with a first logical memory capacitor (CAP1) and a second logical memory capacitor (CAP2) and then are grounded; the body terminals of respective PMOS pipes in T1 and T2 are connected with the gate terminals to be respectively used as the control terminals of T1 and T2; the body terminals of respective NMOS pipes are connected with the gate terminals to be respectively used as the compensation control terminals of T1 and T2; the source terminals of respective PMOS pipes are connected with the drain terminals of the NMOS pipes to the respective input terminals, and the drain terminals of the PMOS pipes are connected with the source terminals of the NMOS pipes to the respective output terminals; the source terminals of a first precharge balanced transistor (P3) and a second precharge balanced transistor (P4) are connected with the power supply voltage, and the drain terminals are respectively connected with the bit line and the non-terminal of the bit line; the source terminal and the drain terminal of a third precharge balanced transistor (P5) are respectively connected with the bit line and the non-terminal of the bit line; and the gate terminals of P3, P4 and P5 connected together are connected to precharge balanced signals.

Owner:SOUTHEAST UNIV

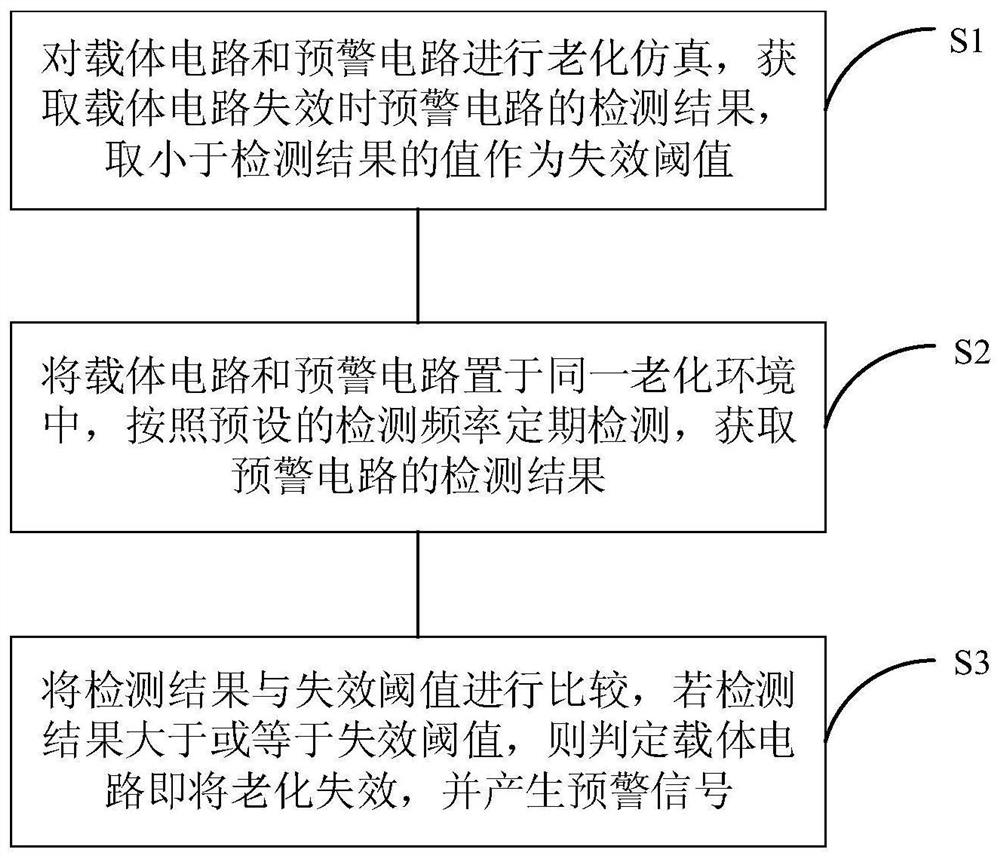

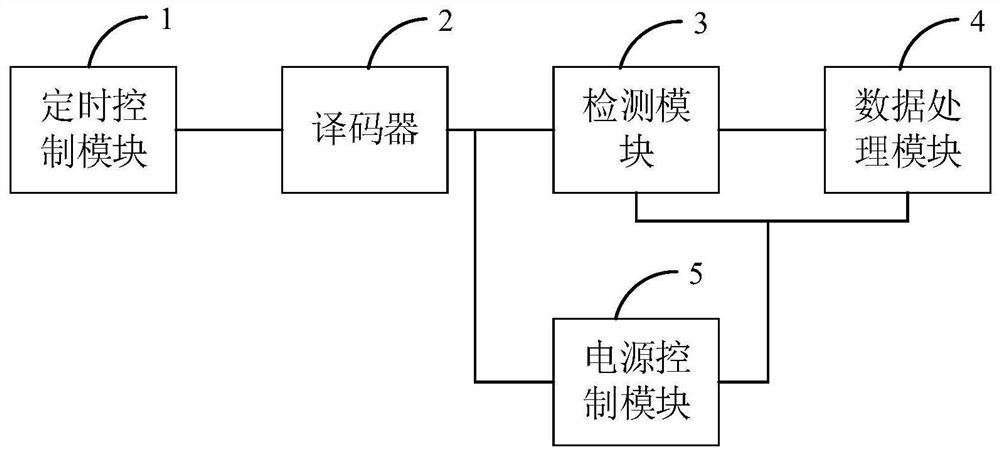

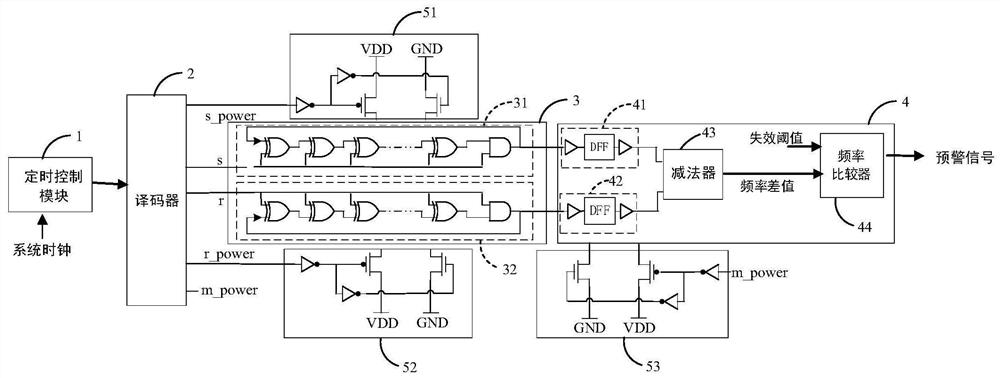

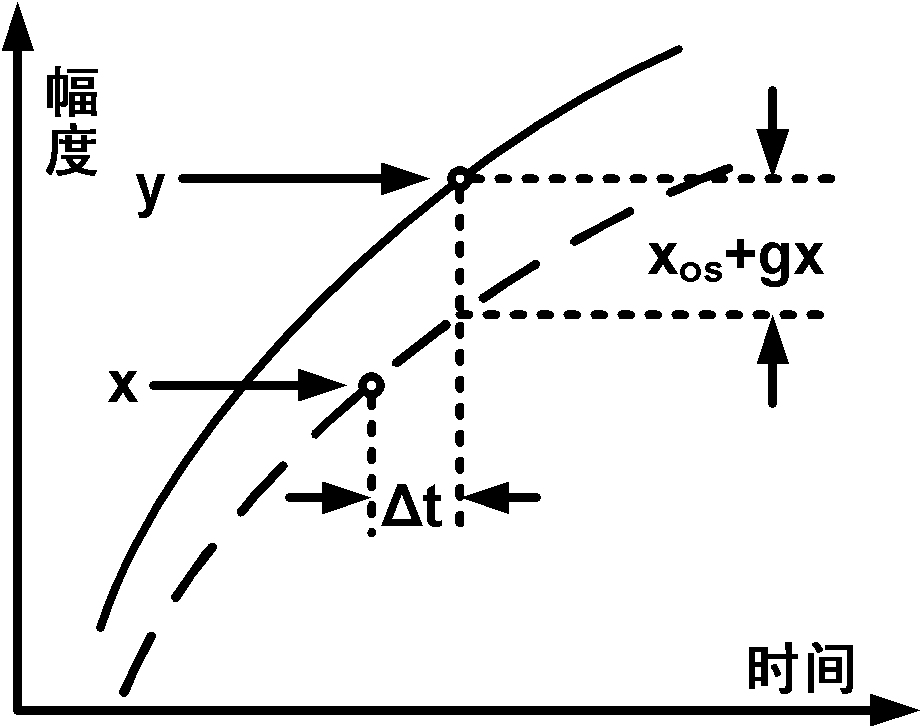

Integrated circuit aging failure early warning method and circuit

InactiveCN111812485AEarly warning aging failure conditionAccurate measurementElectronic circuit testingElectrical measurement instrument detailsIntegrated circuitHemt circuits

The invention relates to an integrated circuit aging failure early warning method and circuit. The integrated circuit aging failure early warning method comprises the steps of: carrying out aging simulation on a carrier circuit and an early warning circuit, acquiring a detection result of the early warning circuit when the carrier circuit fails, and taking a value smaller than a detection result as a failure threshold value; placing the carrier circuit and the early warning circuit in the same aging environment, and performing regular detection according to a preset detection frequency to obtain a detection result of the early warning circuit; comparing the detection result with the failure threshold value, if the detection result is greater than or equal to the failure threshold value, judging that the carrier circuit is about to age and fail, and generating an early warning signal, wherein the detection result is a frequency difference value between a first ring oscillator and a second ring oscillator in the early warning circuit, the first ring oscillator and the carrier circuit are kept in synchronous aging, and the second ring oscillator is kept not to be aged. According to the integrated circuit aging failure early warning method, effective early warning can be carried out on the aging failure condition of the carrier circuit.

Owner:XIDIAN UNIV

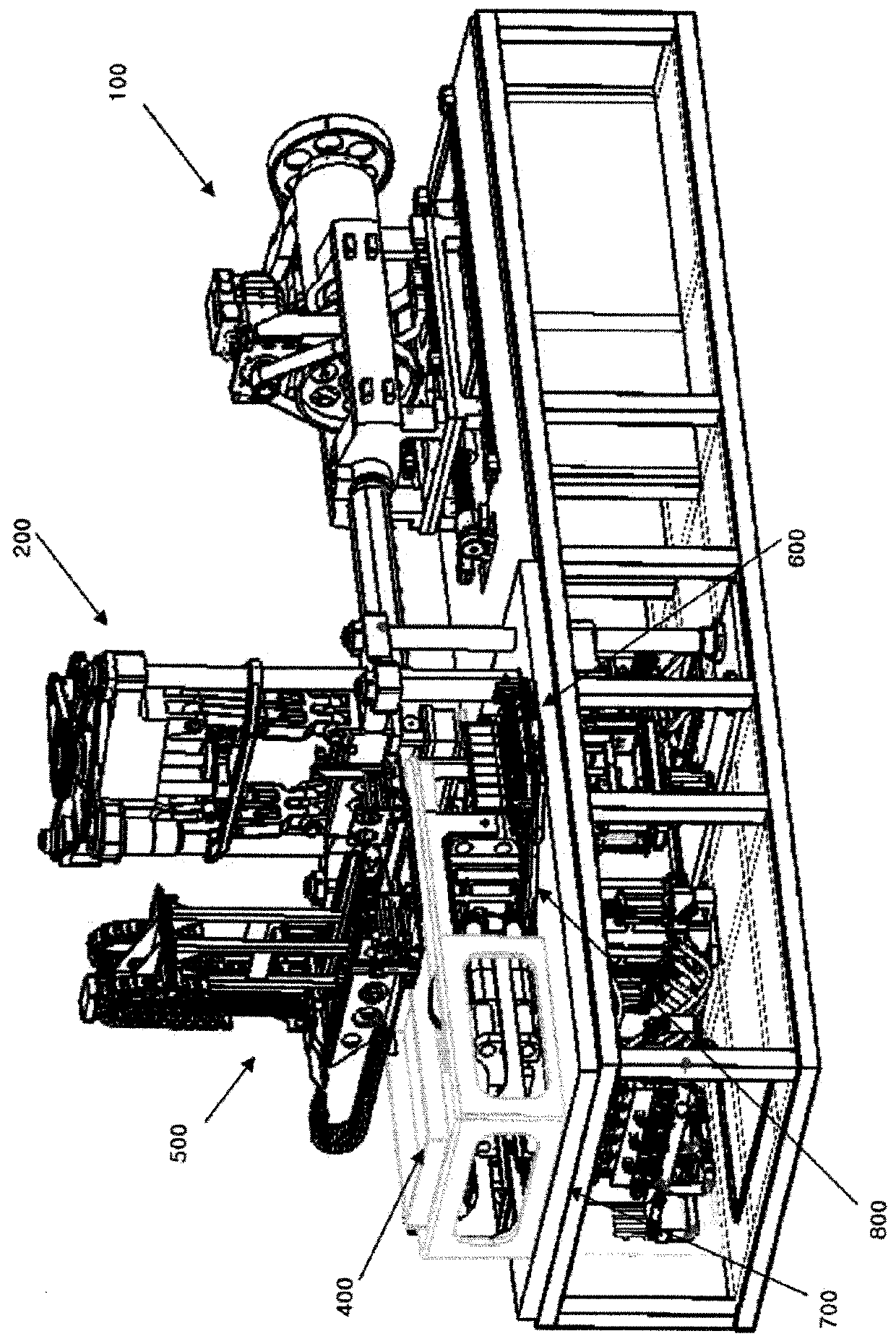

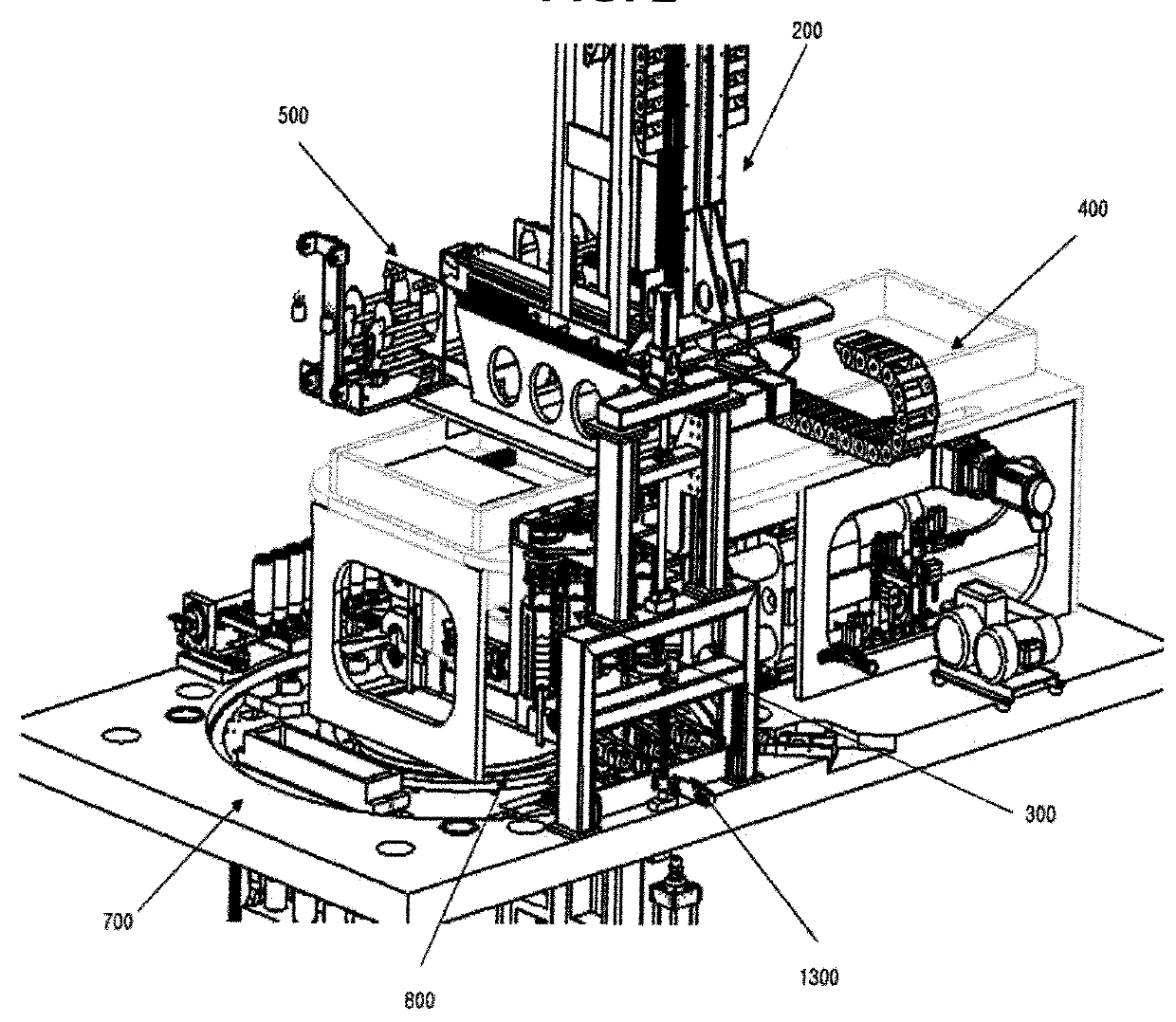

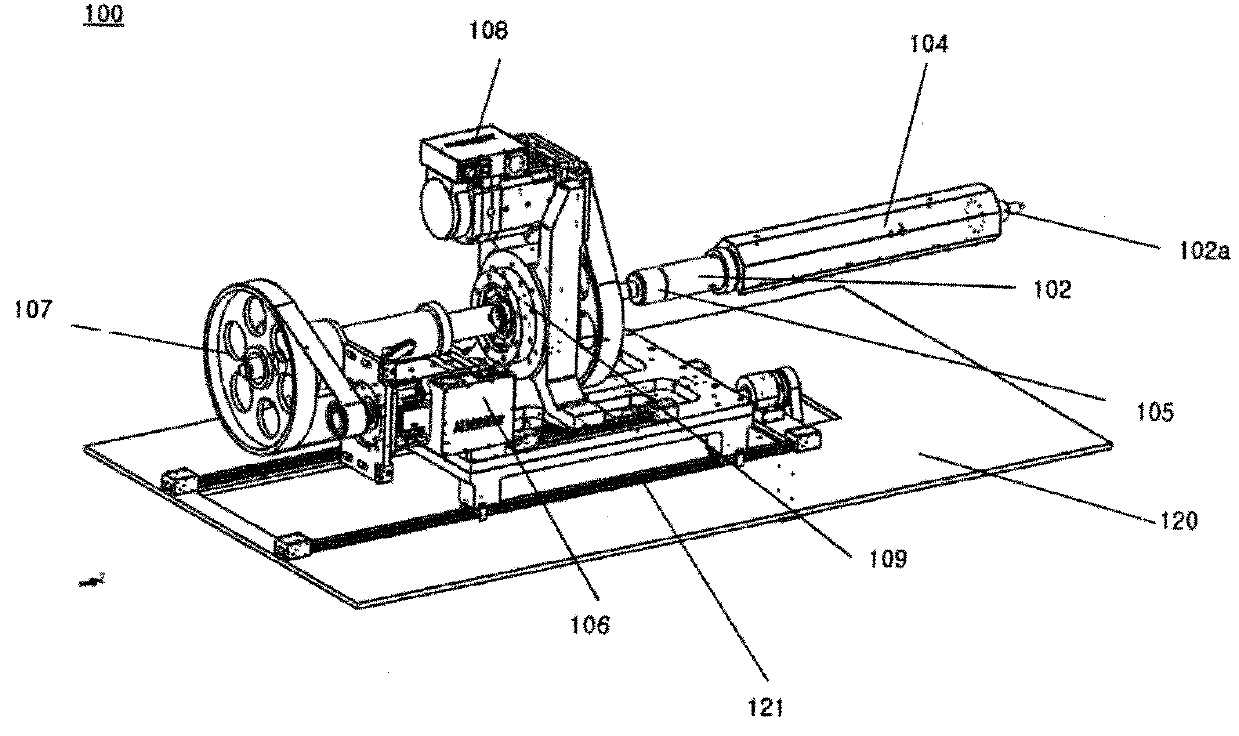

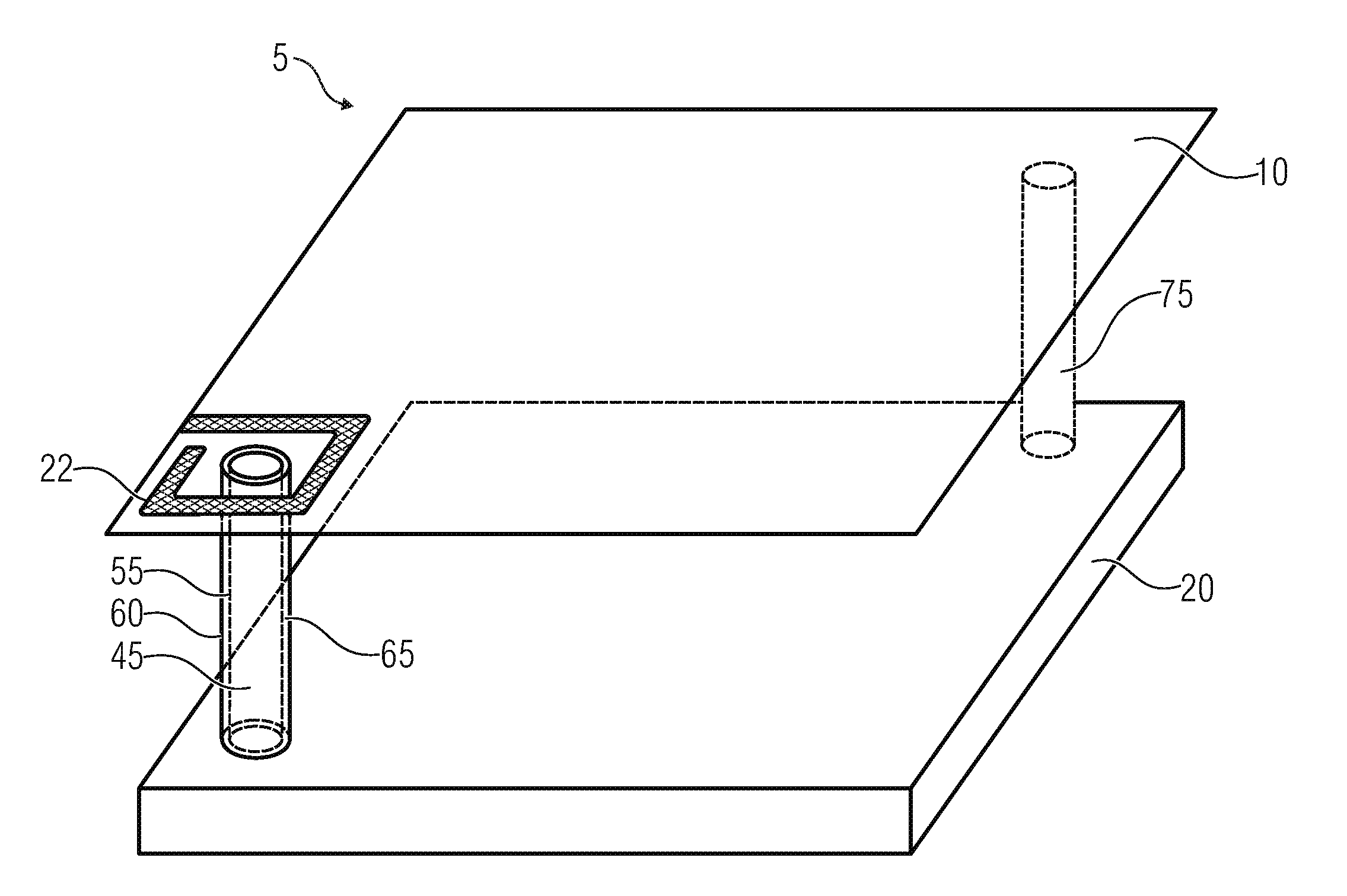

Container manufacturing apparatus

ActiveUS20180178436A1Small area consumptionOperation can be advantageously and rapidlyBottlesDomestic articlesSingle stationMechanical engineering

A container manufacturing device is provided. In detail, the container manufacturing device for performing manufacture of a container pre-form and container molding in a single station via one stop. The container manufacturing device includes a pre-form molding module configured to form a shape of a pre-form of a container using a resin material, an injection module connected to the pre-form molding module and configured to supply the resin material to the pre-form molding module, a container molding module configured to inject air to a pre-form completed by the pre-form molding module to expand the pre-form and to form the shape of the container, and including a container mold, and a rotary table with a rib plate suspended thereon while rotating between the pre-form molding module and the container molding module, the pre-form or the container being mounted on the rib plate.

Owner:SHINWOO COSTEC

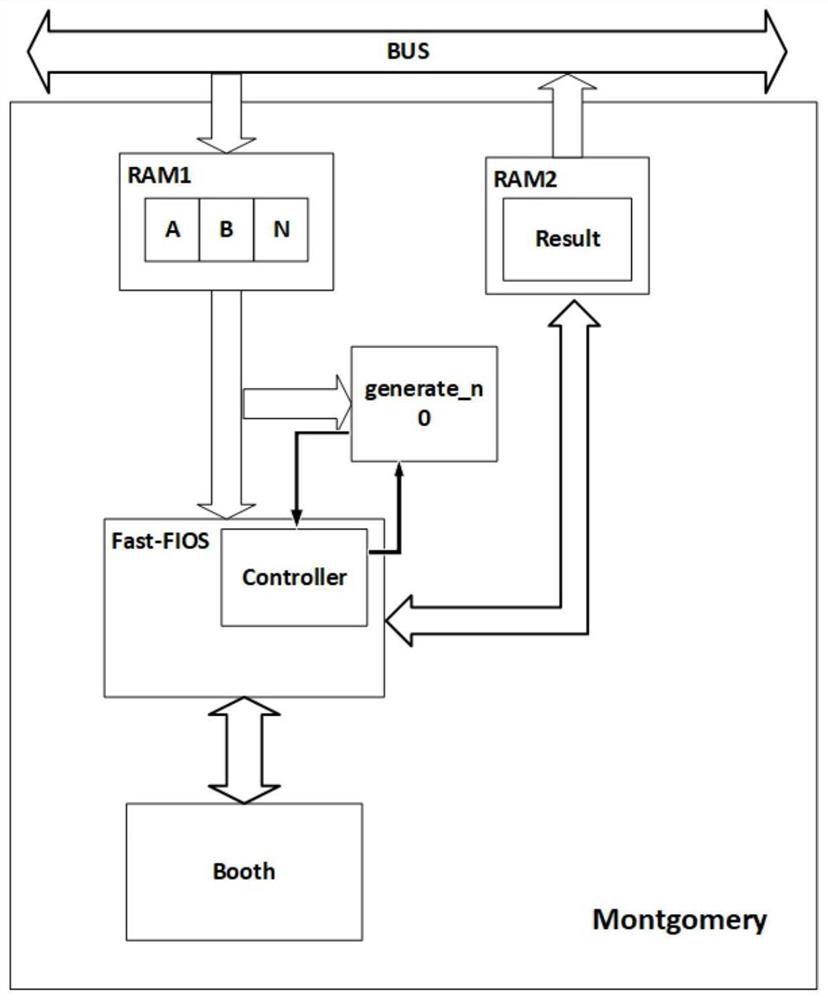

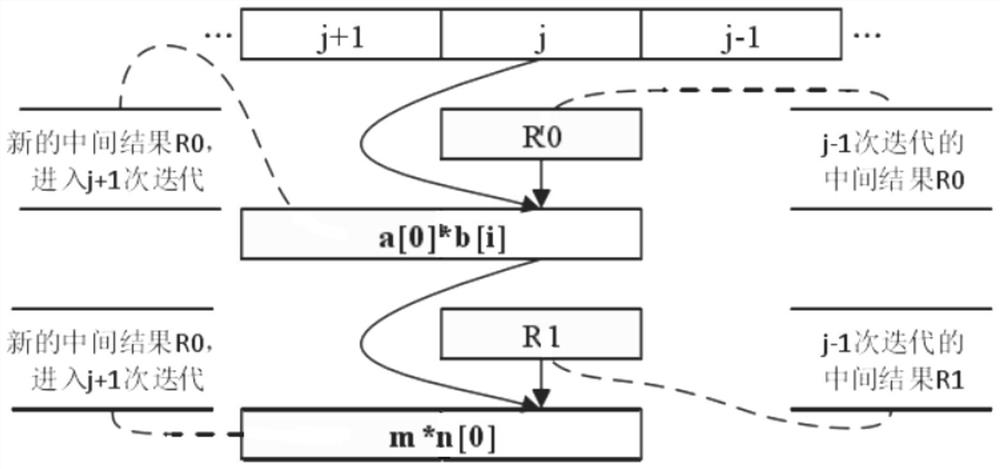

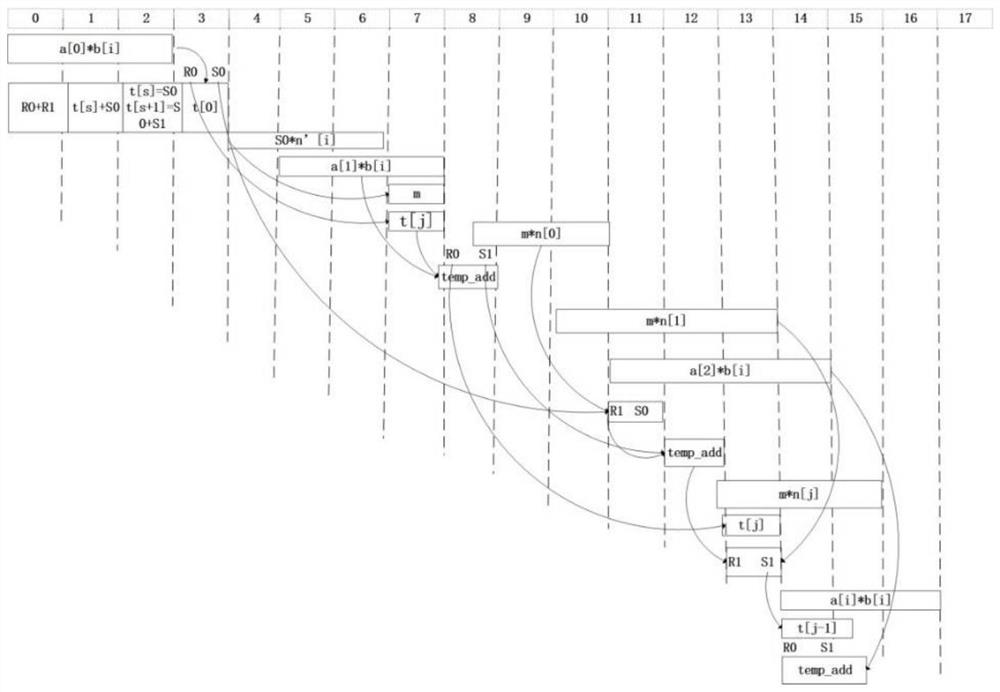

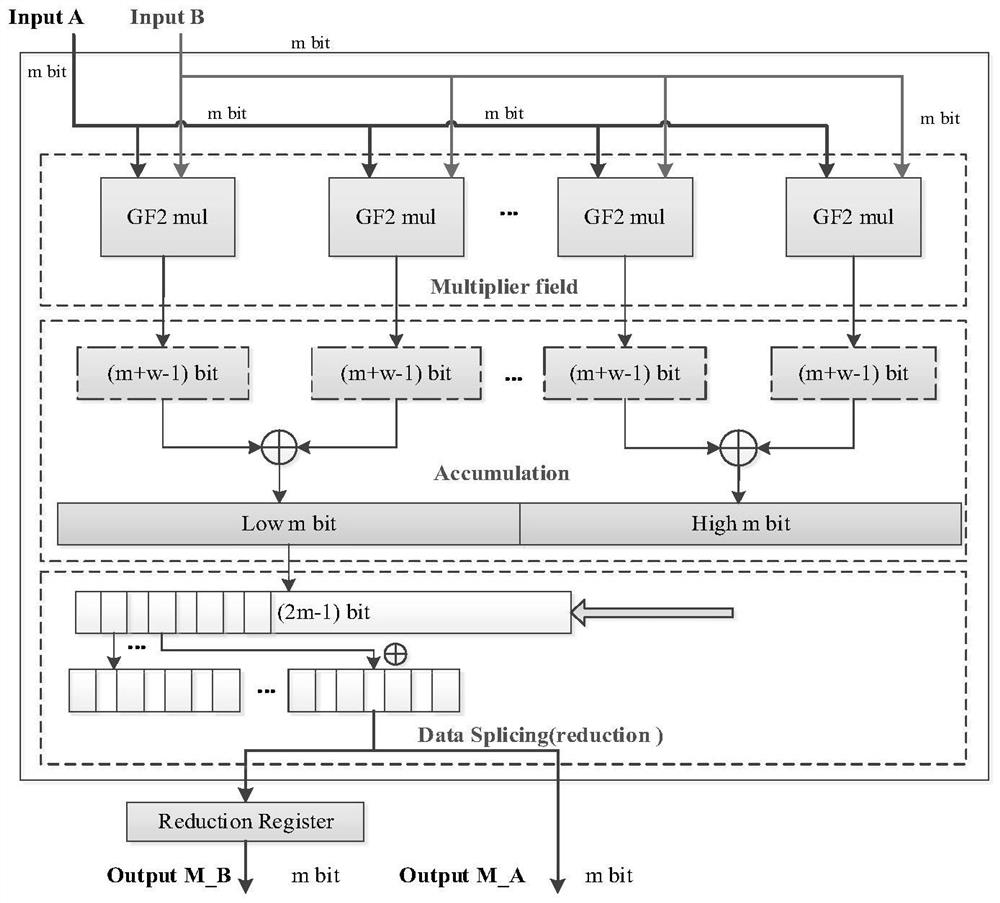

Hardware system for realizing improved FIOS modular multiplication algorithm

ActiveCN112486457AShorten the lengthReduce consumptionComputations using residue arithmeticMultiplexingBinary multiplier

The invention discloses a hardware system for realizing an improved FIOS modular multiplication algorithm. A modular multiplication circuit is realized by adopting hardware, and logic resource consumption is reduced through register multiplexing; rearranging the assembly line and the whole algorithm time sequence, and disassembling the addition operation of the critical path into multi-stage assembly line addition tree operation, so that the maximum operation rate reaches 600MHz; the number of operations in a single clock period is increased through parallelization processing of independent operations; a 128-base multiplier is used as a basic calculation unit, only 3463 periods are needed for completing 4096-bit modular multiplication, consumed time is about 5.75 us, the number of cycles in the calculation process is remarkably reduced, the number of clocks needed by operation is reduced, and the calculation throughput rate in unit time is increased. According to the invention, the partial product generation circuit is improved, and the use of logic gates is further reduced. According to the method, the code length in the Montgomery modular multiplication algorithm is reduced through improvement, and the operation efficiency of the modular multiplication process is improved.

Owner:HANGZHOU DIANZI UNIV

Differential delay cell with low power, low jitter, and small area

InactiveUS8610478B1Reduce the amount of noiseReduce power supply voltagePulse manipulationTime-delay networksLow jitterCurrent consumption

A delay cell architecture is provided herein with improved noise performance and increased output swing, while consuming less power and area than conventional delay cell architectures. In one embodiment, the delay cell described herein may include a pair of input transistors, a pair of cross-coupled transistors, a pair of current source transistors, at least one swing limiting transistor and an RC filter. The at least one swing limiting transistor is coupled between the output nodes of the delay cell for controlling the output swing and keeping the current source transistors in saturation. Phase-induced jitter is reduced by connecting the RC filter directly to the mutually-coupled source terminals of the current source transistors. Deterministic jitter is reduced by using a relatively large resistor and relatively small capacitor within the RC filter design. Such a design reduces the amount of area consumed by the delay cell without sacrificing noise performance. Current consumption is reduced by requiring only one bias voltage to be supplied to the delay cell.

Owner:MONTEREY RES LLC

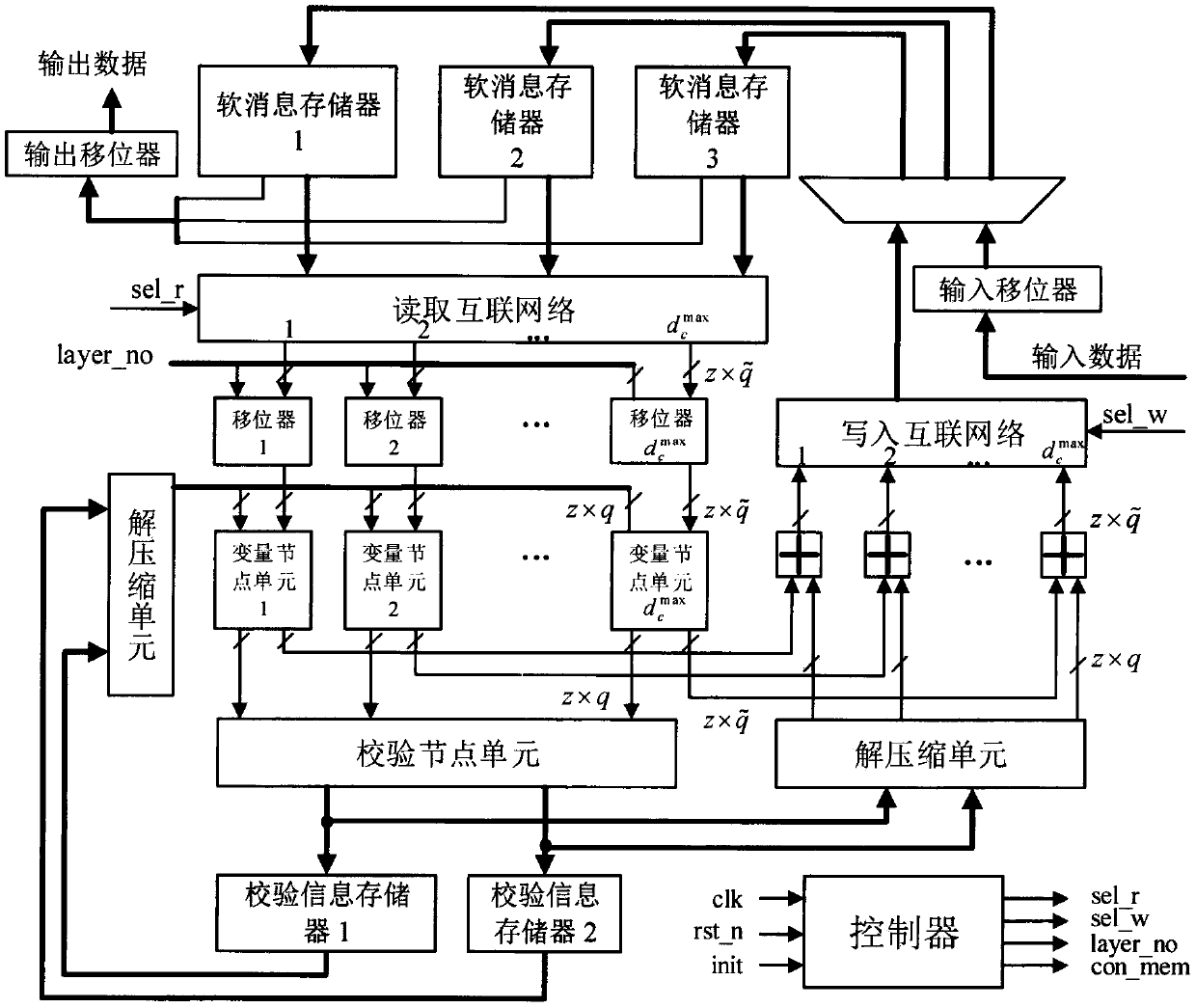

Efficient decoder architecture suitable for 5G LDPC code

PendingCN110808742AReduce the number of layersReduce the number of clock cyclesError correction/detection using multiple parity bitsCode conversionComputer architectureParallel computing

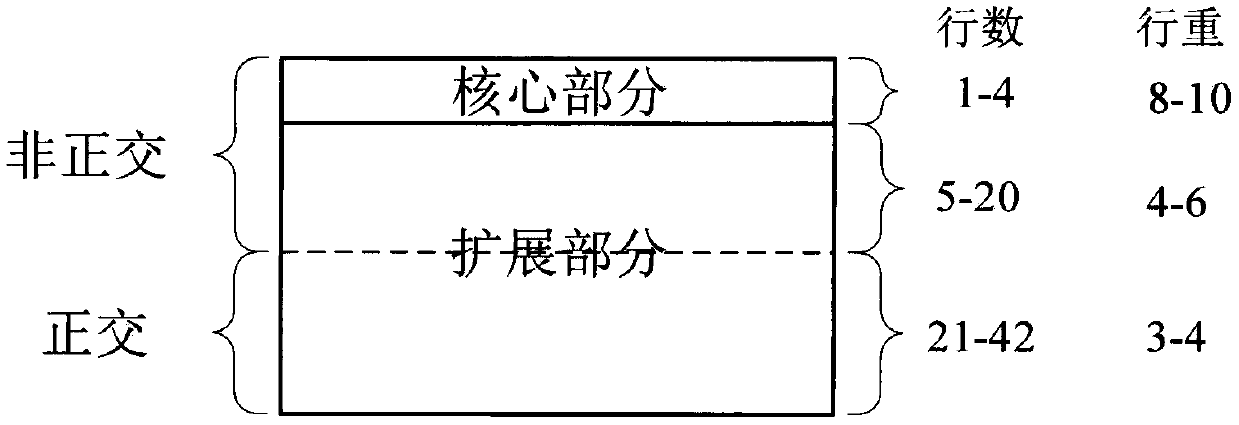

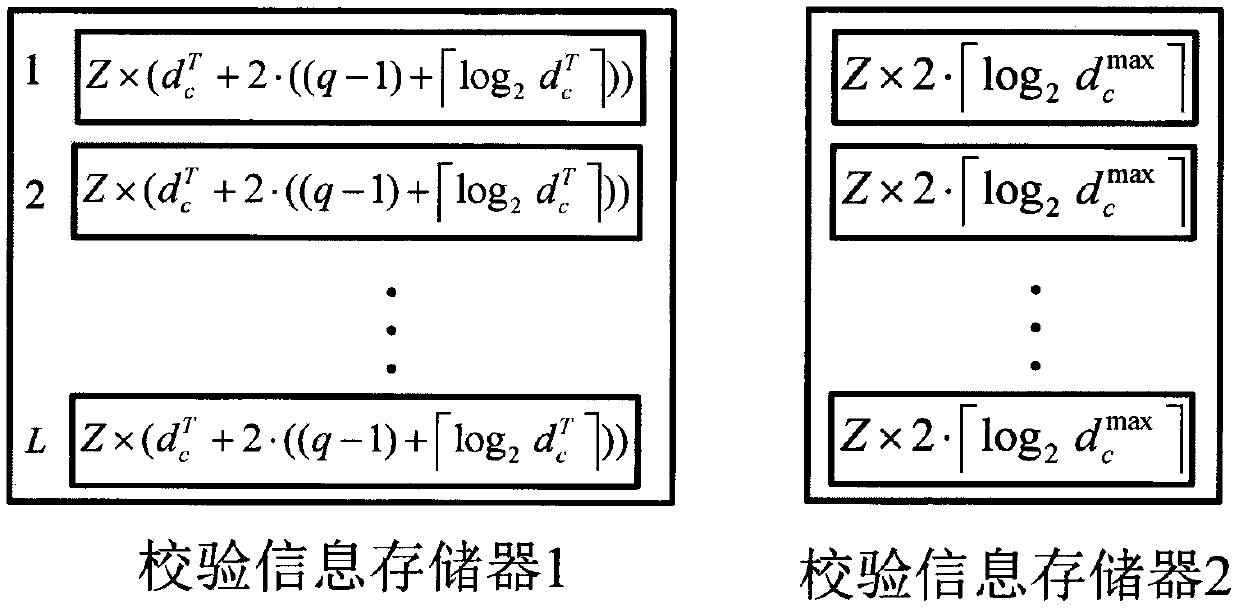

The invention discloses a decoder architecture which is universal for 5G LDPC codes and is high in throughput rate and low in complexity for the first time. Firstly, by utilizing partial orthogonalityof a 5G LDPC code base matrix, the number of clock cycles is reduced by adopting a layer merging technology, and meanwhile, the area consumption of a check information memory is reduced. Secondly, because the line weight of the 5G LDPC is very irregular, a distributed storage structure is adopted to reduce the consumption of storage resources. And finally, in order to solve the problems of high delay and high complexity caused by large-scale reading and writing into the internet, a shifting structure is adopted to realize the soft message memory, so that the input and output number of the internet is greatly reduced. In addition, information rearrangement is applied to the internet to optimize the internal architecture of the internet. Compared with the conventional design, the decoder disclosed by the invention has the advantages that the area is greatly reduced, a higher throughput rate can be provided, and the throughput rate-area ratio is increased to 2.68 times of the original throughput rate-area ratio.

Owner:NANJING UNIV

Iris identification module group and iris identification system

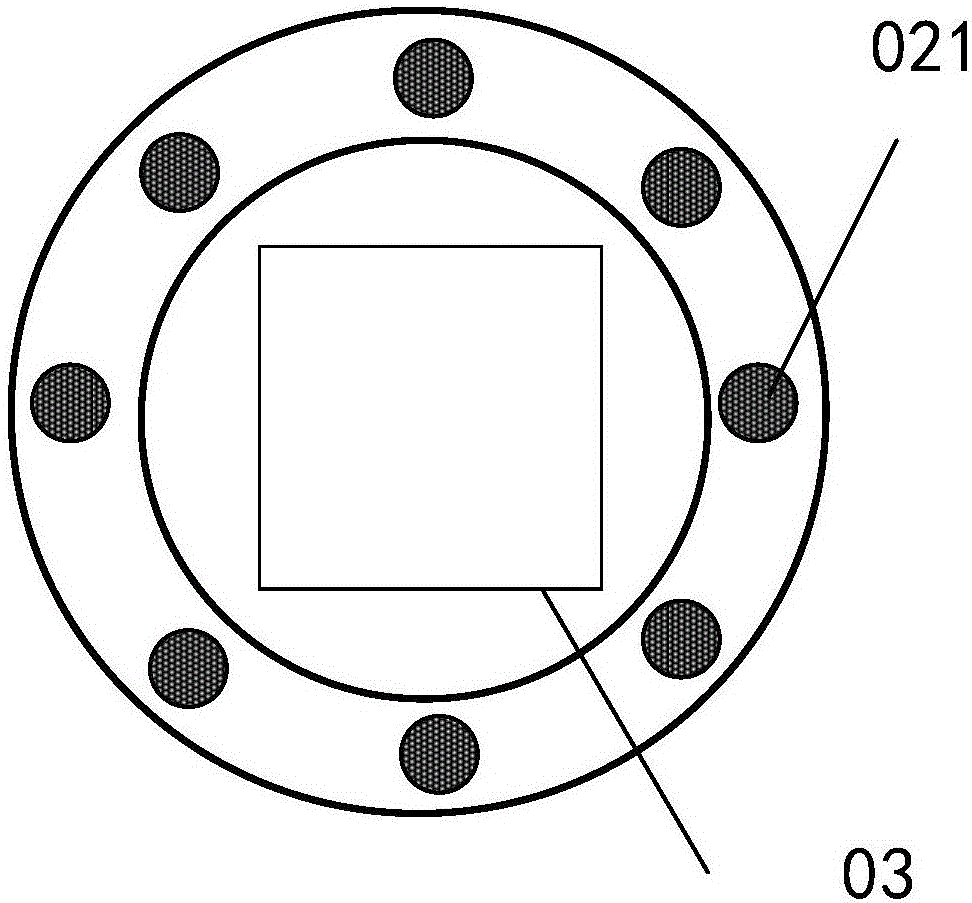

InactiveCN106709434ASmall area consumptionFocusAcquiring/recognising eyesOptoelectronicsIris recognition

The invention provides an iris identification module group and an iris identification system. An infrared light supplement lamp array and an image sensor module group are adopted. The infrared light supplement lamp array surrounds an image sensor so that infrared light emitted by an infrared light supplement lamp to human eyes is uniform. A lens covers tops of the infrared light supplement lamp array and the image sensor module group, and the infrared image sensor and the infrared light supplement lamp array are in a same light path so that focusing is convenient to perform, an integrated degree is high and module group area consumption is small, and the system can be applied to a mobile phone and other mobile intelligent equipment.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +1

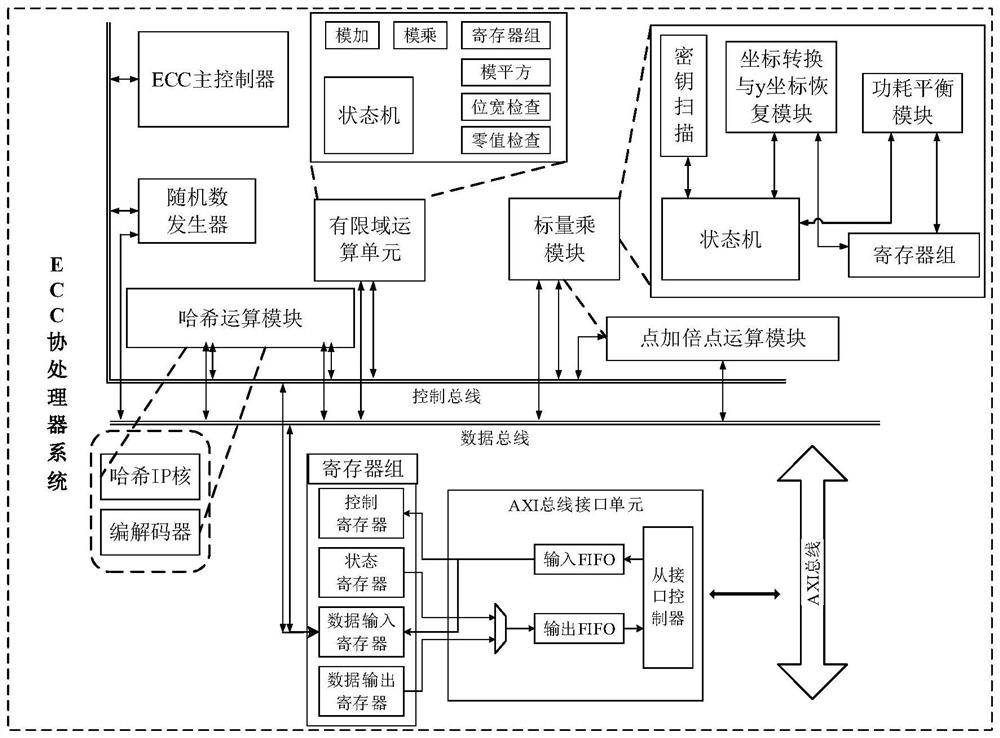

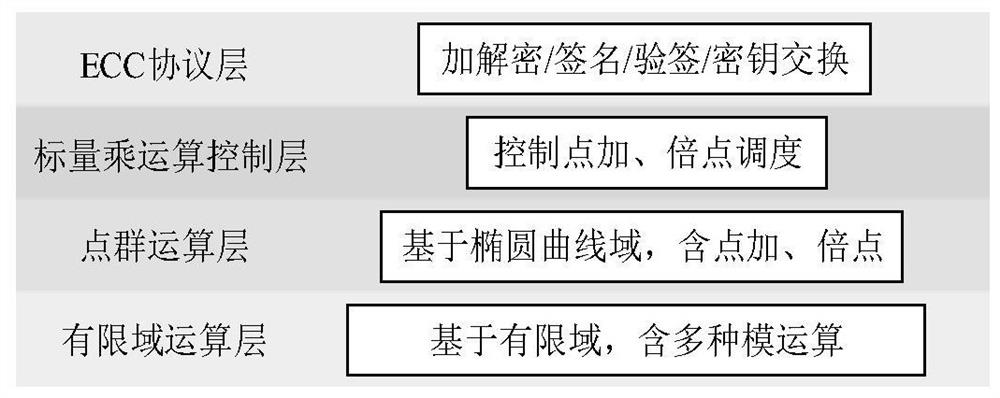

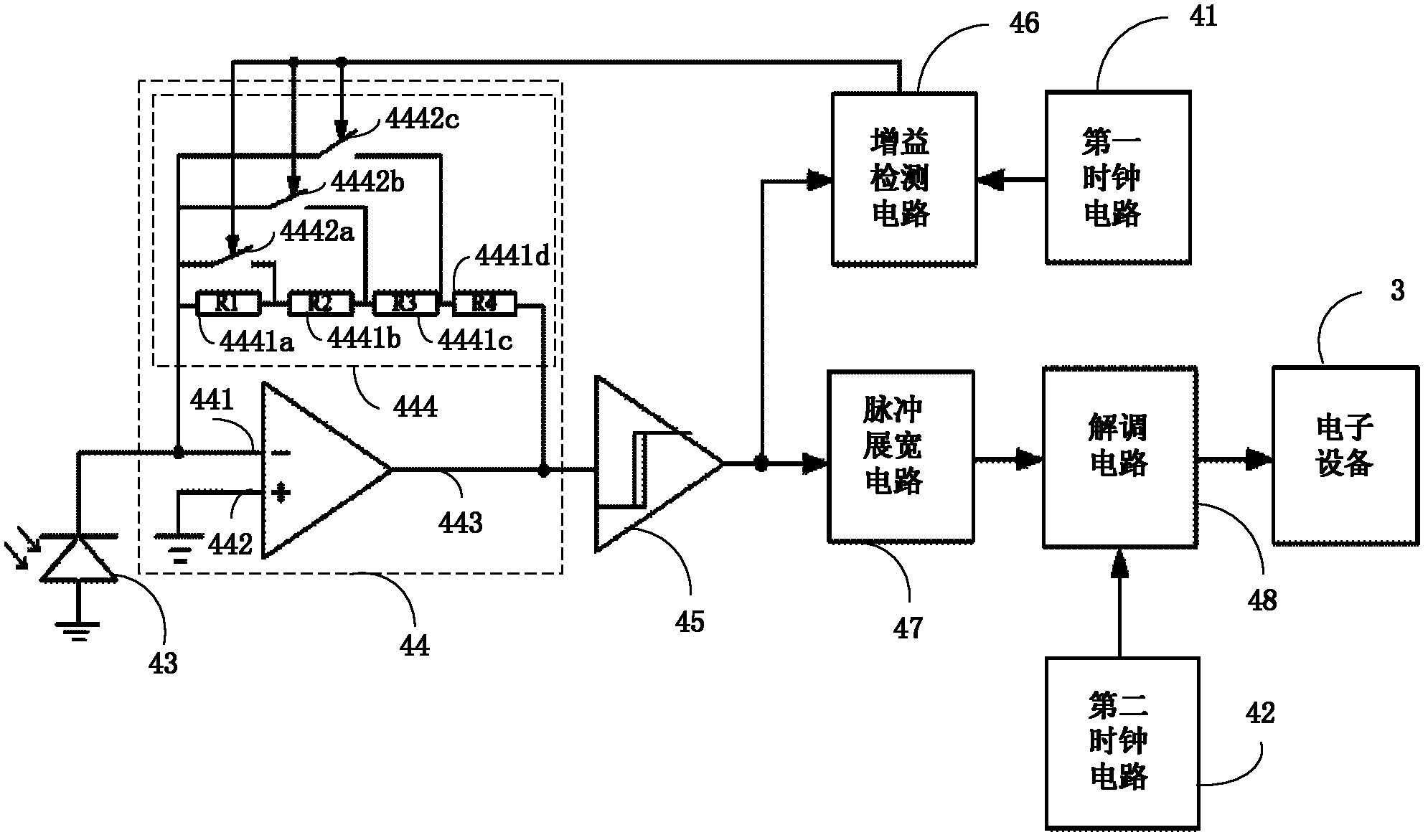

High-performance ECC coprocessor system resistant to power consumption attack

PendingCN114238205ACompliant with specific field application requirementsReduce space complexityDigital data protectionEnergy efficient computingCoprocessorDigital signature

The invention discloses a high-performance ECC coprocessor system resistant to power consumption attack. The system comprises an ECC master controller, a finite field arithmetic unit, a scalar multiplication module, a random number generator and a hash operation module. The ECC master controller controls all the modules to cooperatively complete operation and feeds back state signals to the register set, basic modular operation is completed by calling the finite field operation unit, then data is sent to the scalar multiplication module, and the functions of the point doubling point operation module, secret key scanning, coordinate conversion, y coordinate recovery and power consumption balance are completed. Wherein the random number generator is used for generating random Z coordinates in scalar multiplication operation, and the Hash operation module completes preprocessing of input messages, so that the efficiency of digital signature is improved, and finally encryption and decryption functions and digital signature verification functions are completed. The method has the advantages of being low in space complexity, simple, regular and easy to modularize, has the advantages of performance and area overhead, and meets the application requirements of ECC in the specific field.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

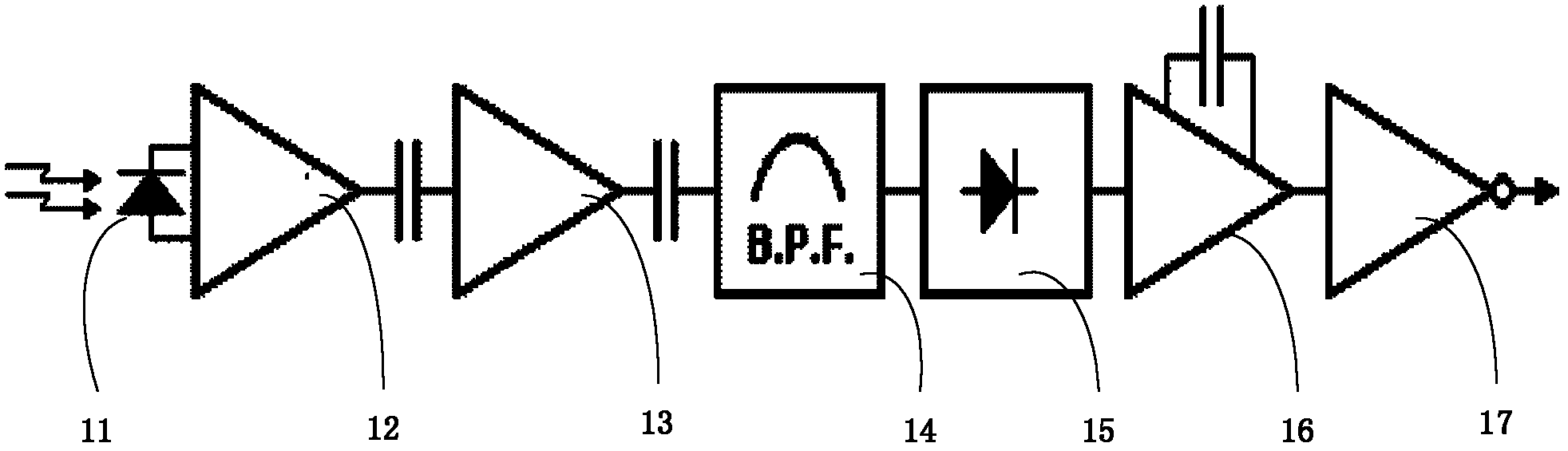

Infrared detection device

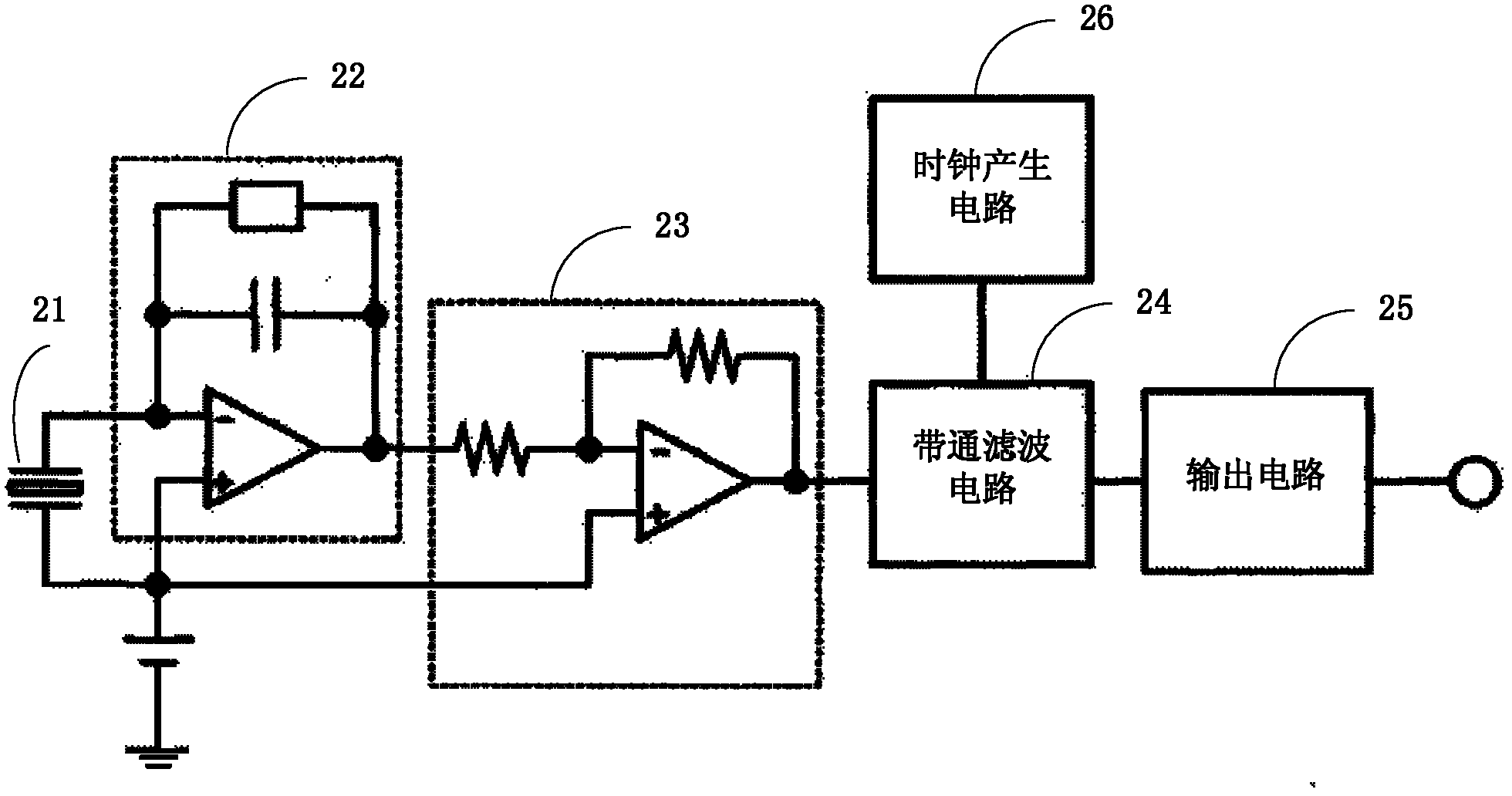

ActiveCN103256988ASmall area consumptionEasy to integratePyrometry using electric radation detectorsInfraredBandpass filtering

The invention provides an infrared detection device which mainly comprises a photosensitive diode, an amplifying circuit, a zero cross detection circuit, a gain detection circuit, a pulse broadening circuit and a demodulation circuit. According to the infrared detection device, infrared signals sent by an infrared remote controller according to a specific command are demodulated to specific control signals to control electronic equipment to carry out the specific command. According to the infrared detection device, an analog bandpass filter is not adopted, while digital circuits of the pulse broadening circuit and the demodulation circuit are adopted to achieve functions of filtering and modulation. In all the elements of the infrared detection device, only the amplifying circuit is an analog circuit, most of other elements are completed through digital circuits, thus area consumption of the analog circuit on a silicon wafer can be reduced, and system-on-chip integration is benefited.

Owner:SHANGHAI MOUNTAIN VIEW SILICON

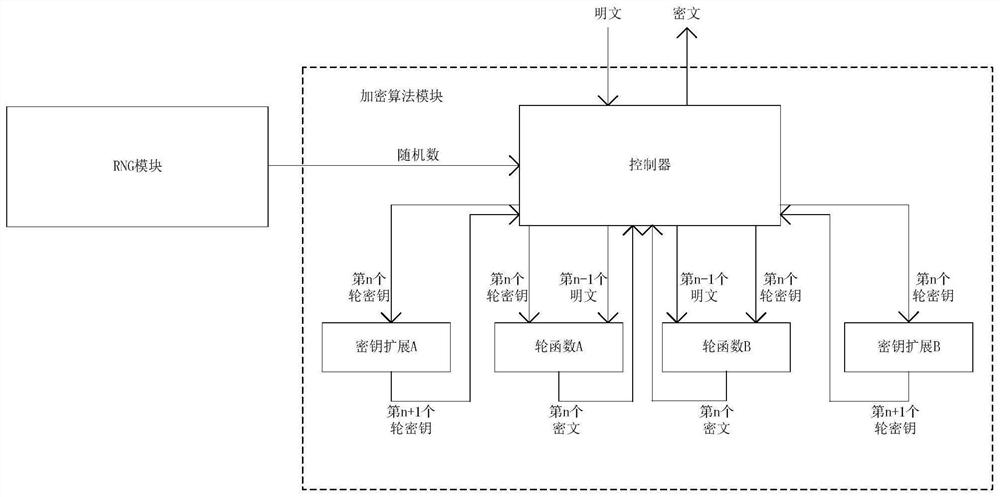

Anti-attack block cipher encryption method for multi-scene application

PendingCN114218588APrevent affecting encryption speedIncrease the difficultyRandom number generatorsDigital data protectionPlaintextAlgorithm

The invention relates to an anti-attack block cipher encryption method for multi-scene application. Firstly, a group of random numbers generated by a random number module are pre-stored in a register, plaintexts are encrypted by designing two groups of round functions at the same time, and irrelevant data are encrypted by using irrelevant secret keys to interfere a power consumption curve of a current chip while the correct plaintexts are encrypted, so that the power consumption curve acquired by an attacker contains irrelevant power consumption, and the analysis difficulty of the power consumption curve is increased; meanwhile, a random pseudo wheel is inserted into 10-round encryption in normal operation, so that a fault injection attack is prevented; when no attacker attacks, the two groups of round functions can be used at the same time, two groups of plaintexts are encrypted at the same time, and the encryption speed is increased.

Owner:NO 47 INST OF CHINA ELECTRONICS TECH GRP

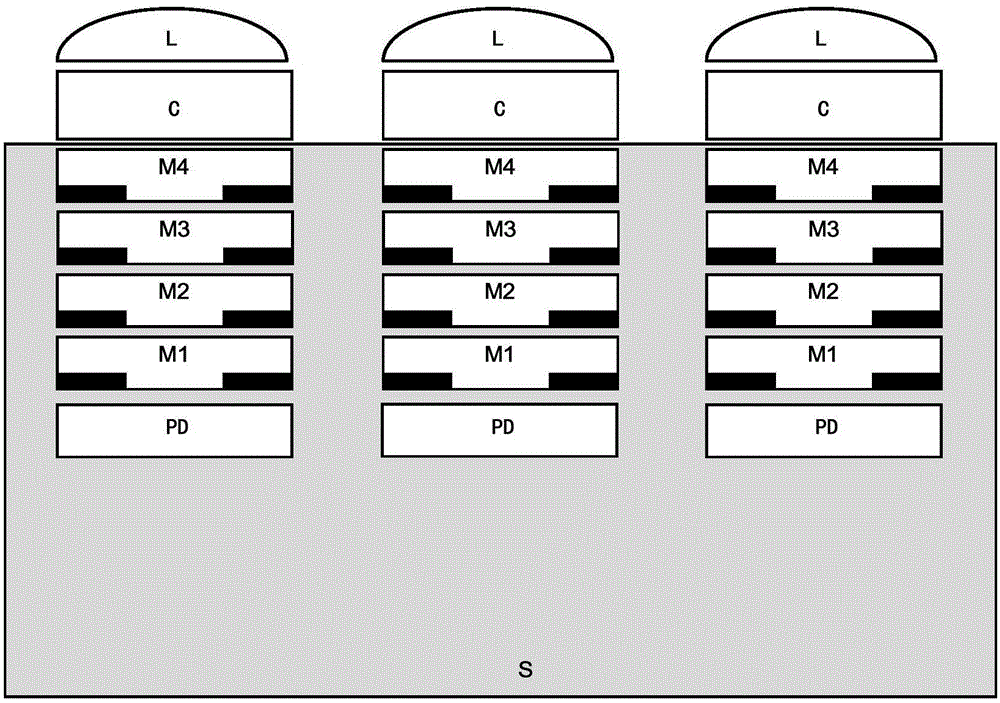

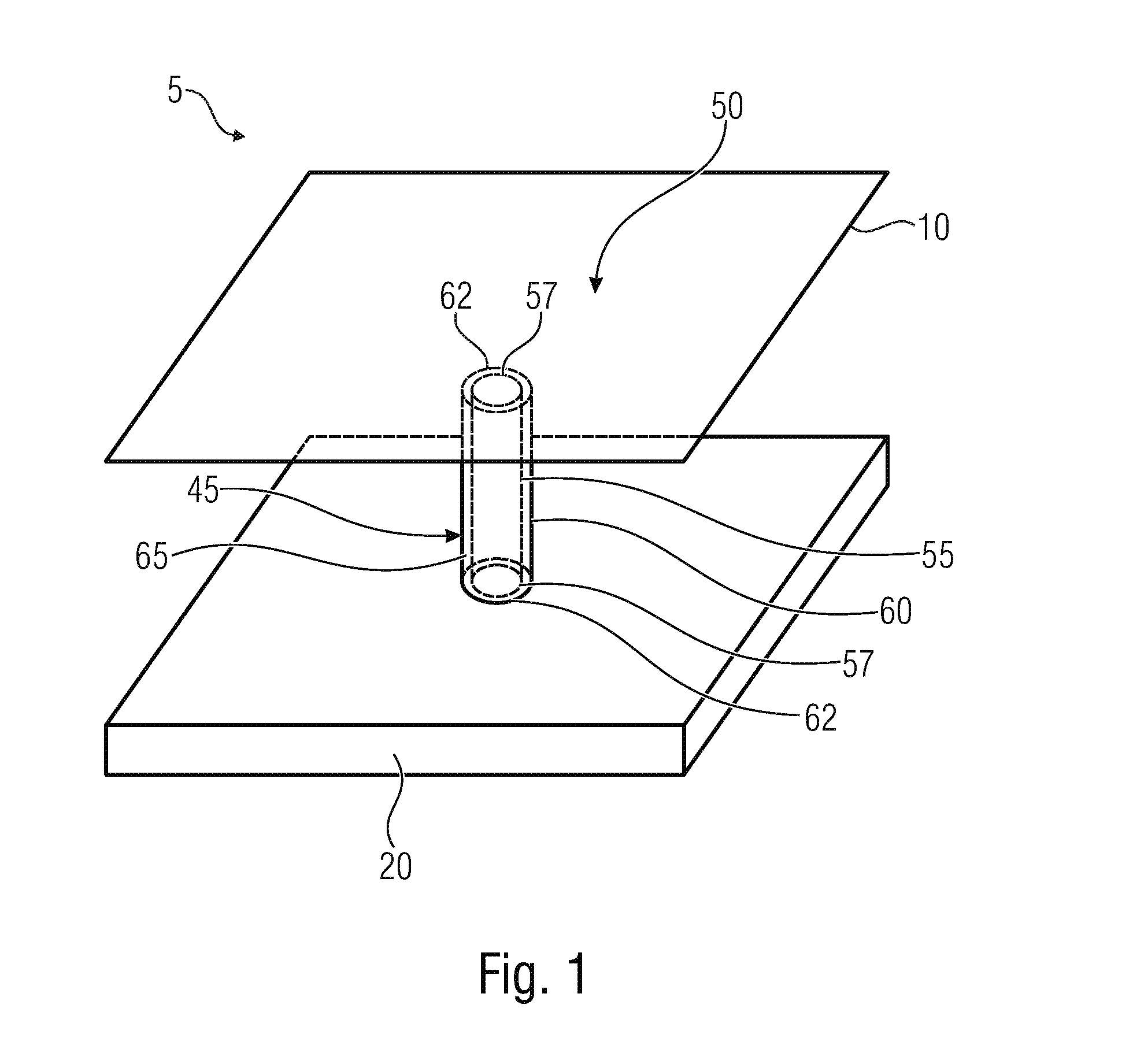

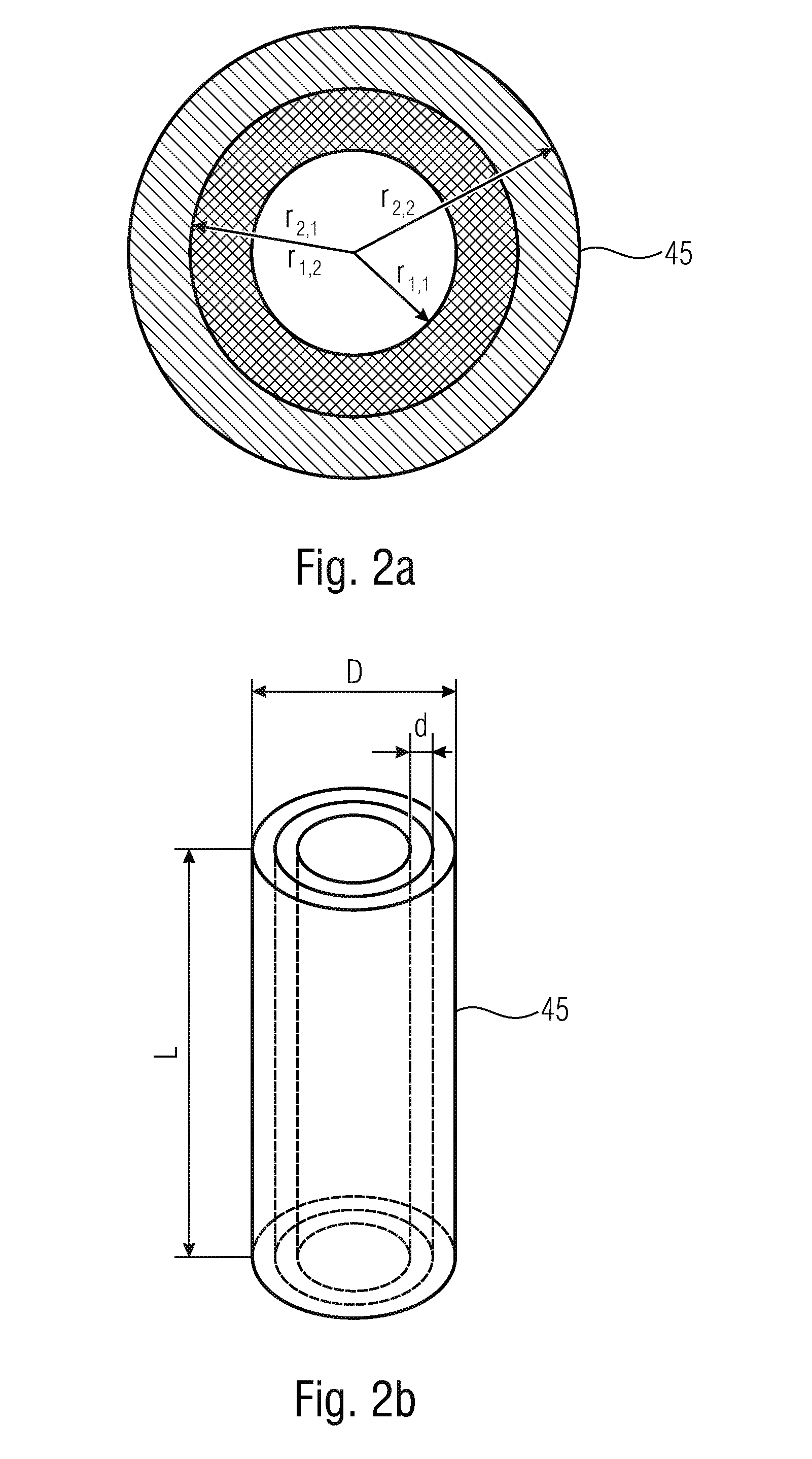

Radiation detector, array of radiation detectors and method for manufacturing a radiation detector

ActiveUS20160320240A1Small area consumptionIncrease productionPyrometry using electric radation detectorsElectricityElectrical polarity

A radiation detector with a substrate and a membrane, which is suspended above the substrate by a spacer is described, wherein the spacer thermally insulates a radiation sensor, which is formed in the membrane, from the substrate. Further, the spacer includes a first layer, which is electrically conducting and contacts a first pole of the radiation sensor and of the substrate, and a second layer, which is electrically conducting and electrically insulated from the first electrically conductive layer and contacts a second pole of the radiation sensor and of the substrate, wherein the second pole differs in polarity from the first pole.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

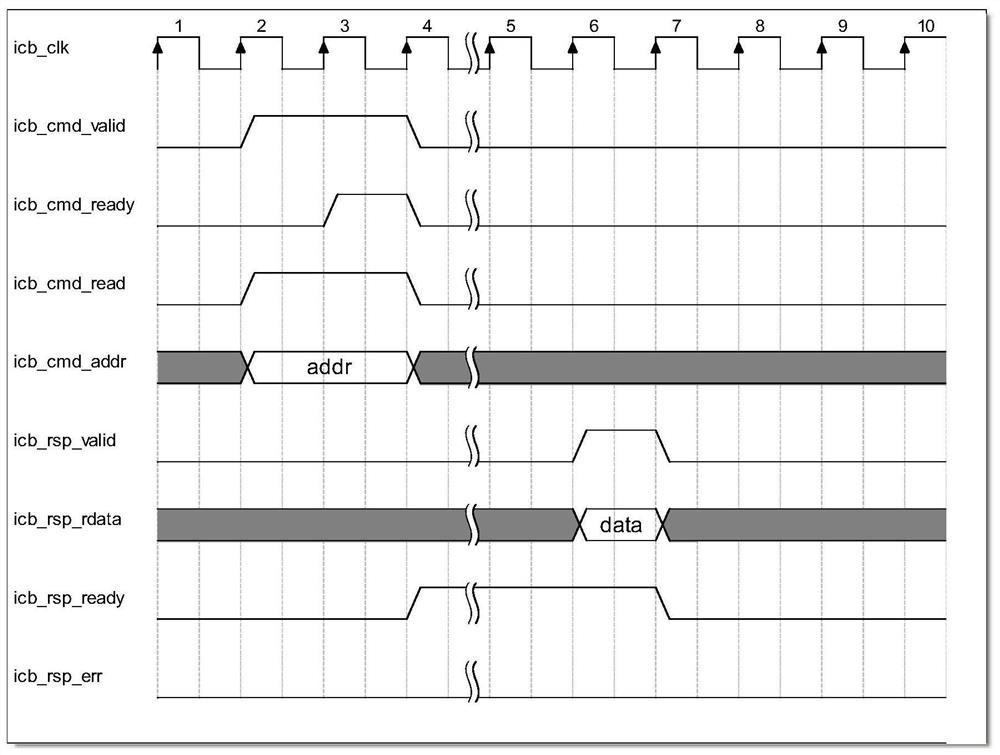

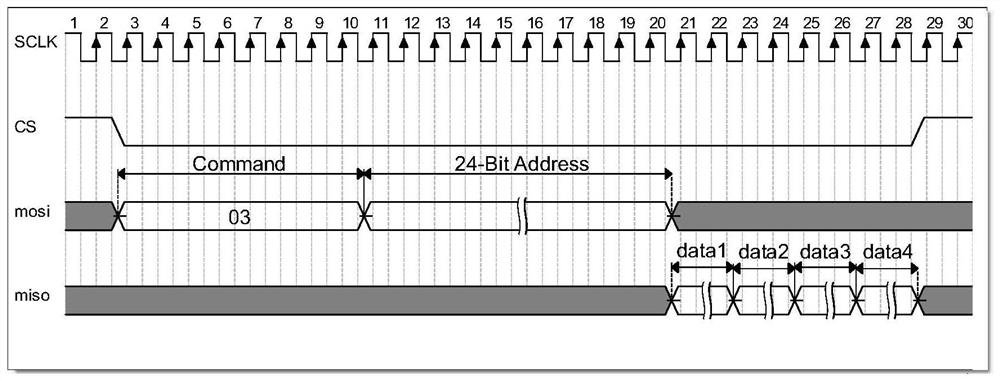

Bridging system and bridging method for accessing Flash memory by RISCV processor

ActiveCN112199317ASmall area consumptionReduce development difficultyElectric digital data processingComputer architectureEngineering

The invention provides a bridging system and a bridging method for accessing a Flash memory by an RISCV processor, which can realize high-speed reading of data of the Flash memory by the RISCV processor. The bridging system comprises an RISCV (Reduced Inter Standard Command Vector) processor bus interface, wherein the RISCV processor adopts a self-defined ICB (Integrated Circuit Bus) protocol; a Flash memory bus interface, wherein the Flash memory adopts an SPI (Serial Peripheral Interface) bus protocol; an ICB control module used for processing the bus transaction initiated by the RISCV processor; an SPI bus module used for initiating a bus transaction request to the Flash memory; and an IC-BSPI interaction module used for realizing signal interaction between the ICB control module and anSPI control module. Due to design of an asynchronous circuit, the RISCV processor and a Flash memory can work under the respective highest frequencies, so that working efficiency of the whole systemis ensured. Compared with a traditional bridging module, clock domain crossing signal processing is completed without asynchronous FIFO, and the area consumption of the bridging module can be reduced.

Owner:NANJING UNIV

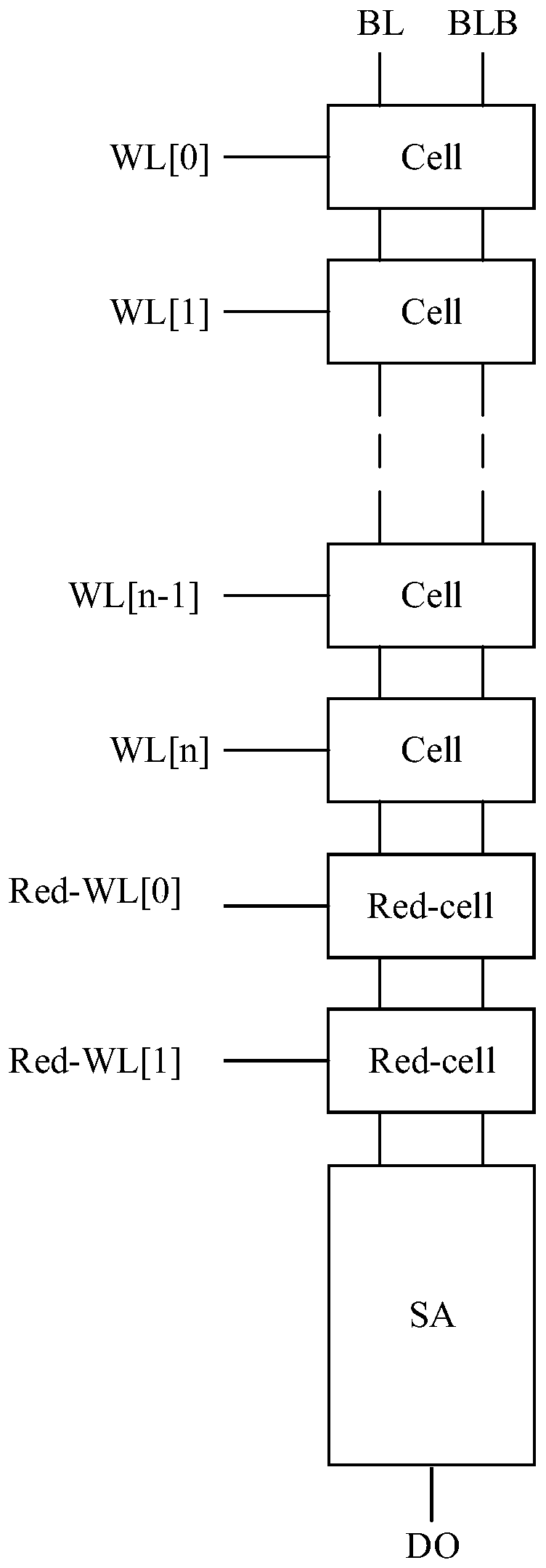

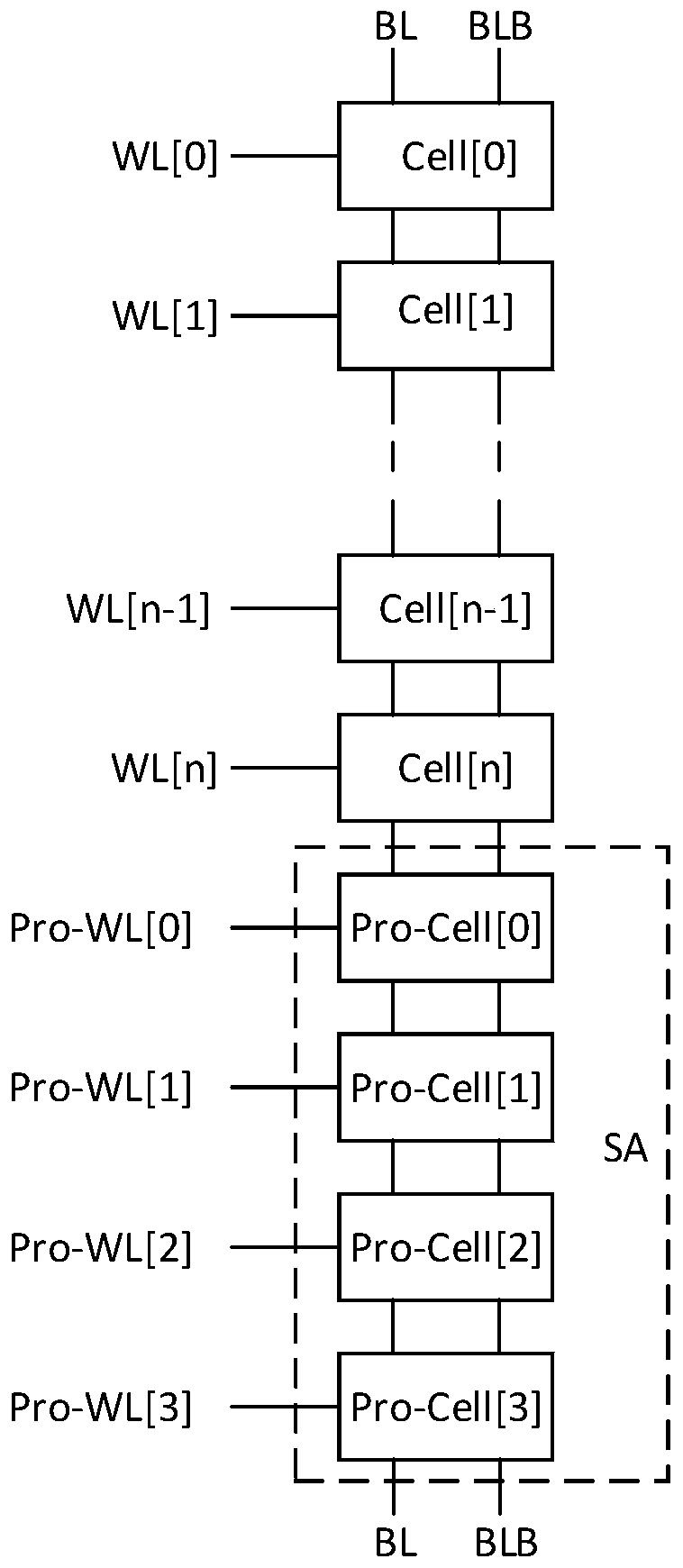

Memory, chip and circuit control method

ActiveCN110070904ASmall area consumptionRealize comprehensive utilizationStatic storageComputer hardwareHemt circuits

The embodiment of the invention provides a memory, a chip and a circuit control method. The memory comprises word line, redundant word lines, a storage unit connected with the word lines; and a redundant storage unit connected with the redundant word lines, wherein when the abnormal storage unit does not exist, the redundant storage unit is used for realizing the sense amplifier, and when an abnormal storage unit exists, at least one redundant storage unit is reserved to realize the sense amplifier, and the abnormal storage unit is replaced by using the rest target redundant storage units. According to the embodiment of the invention, on the basis of effectively utilizing the redundant storage unit, the area ratio occupied by the storage unit in the memory is improved, and the area consumption of the memory is reduced.

Owner:HYGON INFORMATION TECH CO LTD

Time-interleaved split ADC (Analog-to-Digital Converter) calibration structure without redundant channel and adaptive calibration method thereof

InactiveCN102291141BSmall area consumptionEasy to implementAnalogue/digital conversion calibration/testingComputation complexityEngineering

The invention discloses a time-interleaved split ADC (Analog-to-Digital Converter) calibration structure without a redundant channel and an adaptive calibration method thereof. The time-interleaved split ADC calibration structure is characterized in that: a time-interleaved ADC sub-module (sub TIADC-A) with sampling rate fs consisting of N split ADC channels with sampling rate fs / N and a time-interleaved ADC sub-module (sub TIADC-B) with sampling rate fs consisting of L split ADC channels with sampling rate of fs / L together form a split channel mutual calibration-based master TIADC. The same input signal is sampled and converted by the sub TIADC-A and the sub TIADC-B at the same sampling rate fs on the same moment; and difference converted and output by the sub TIADC-A and the sub TIADC-B is used in a zero approaching adaptive calibration algorithm to calculate a mismatch error estimation value among split ADC channels. When the mismatch error among the channels is correctly calibrated, the arithmetic mean value of the converted and output values of the sub TIADC-A and the sub TIADC-B is used as the final converted and output value of the split channel mutual calibration-based master TIADC. The calibration structure and the calibration method are low in computation complexity, easy in hardware implementation and can be applied to TIADC calibration with any number of channels.

Owner:HEFEI UNIV OF TECH

Active matrix array device

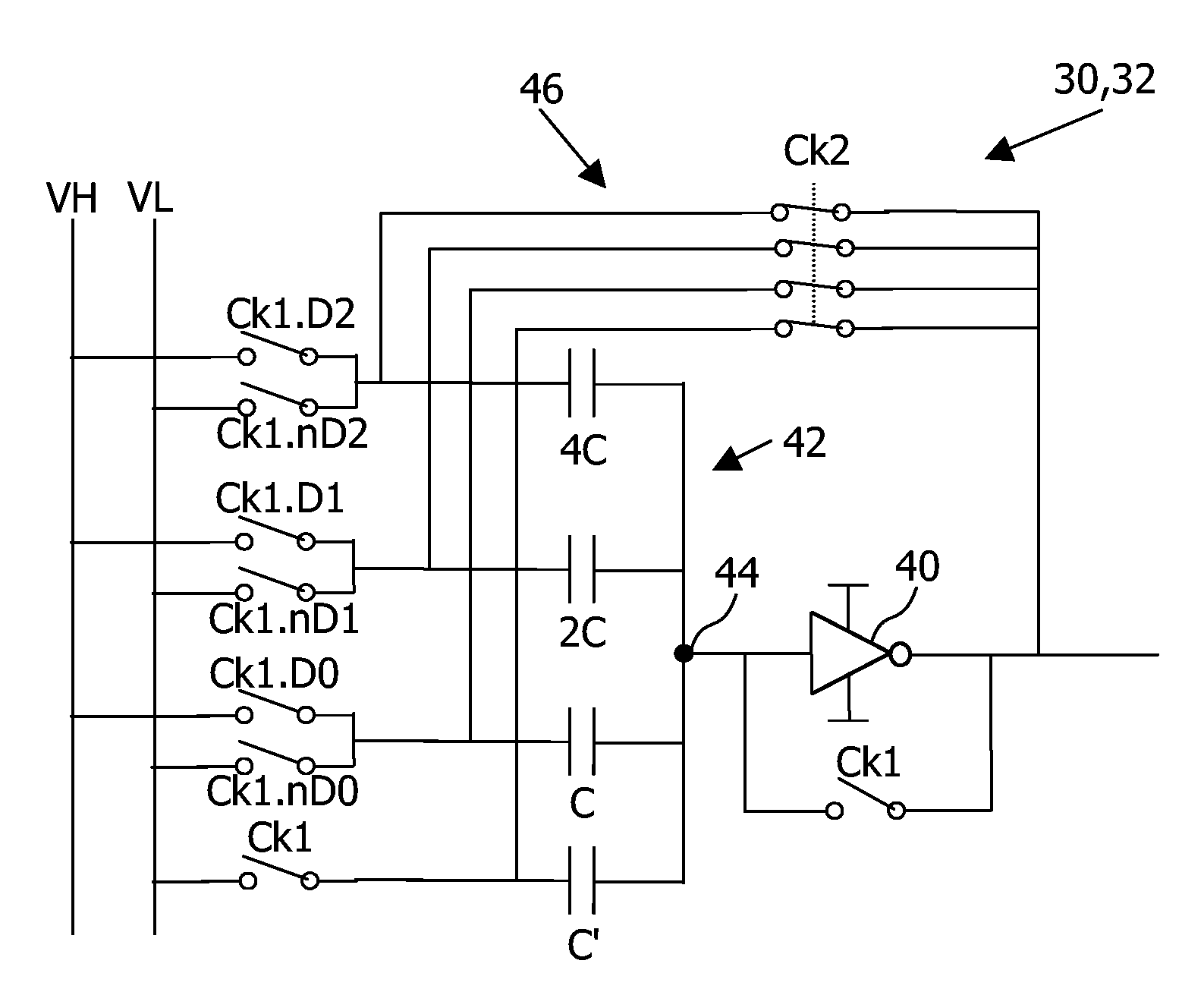

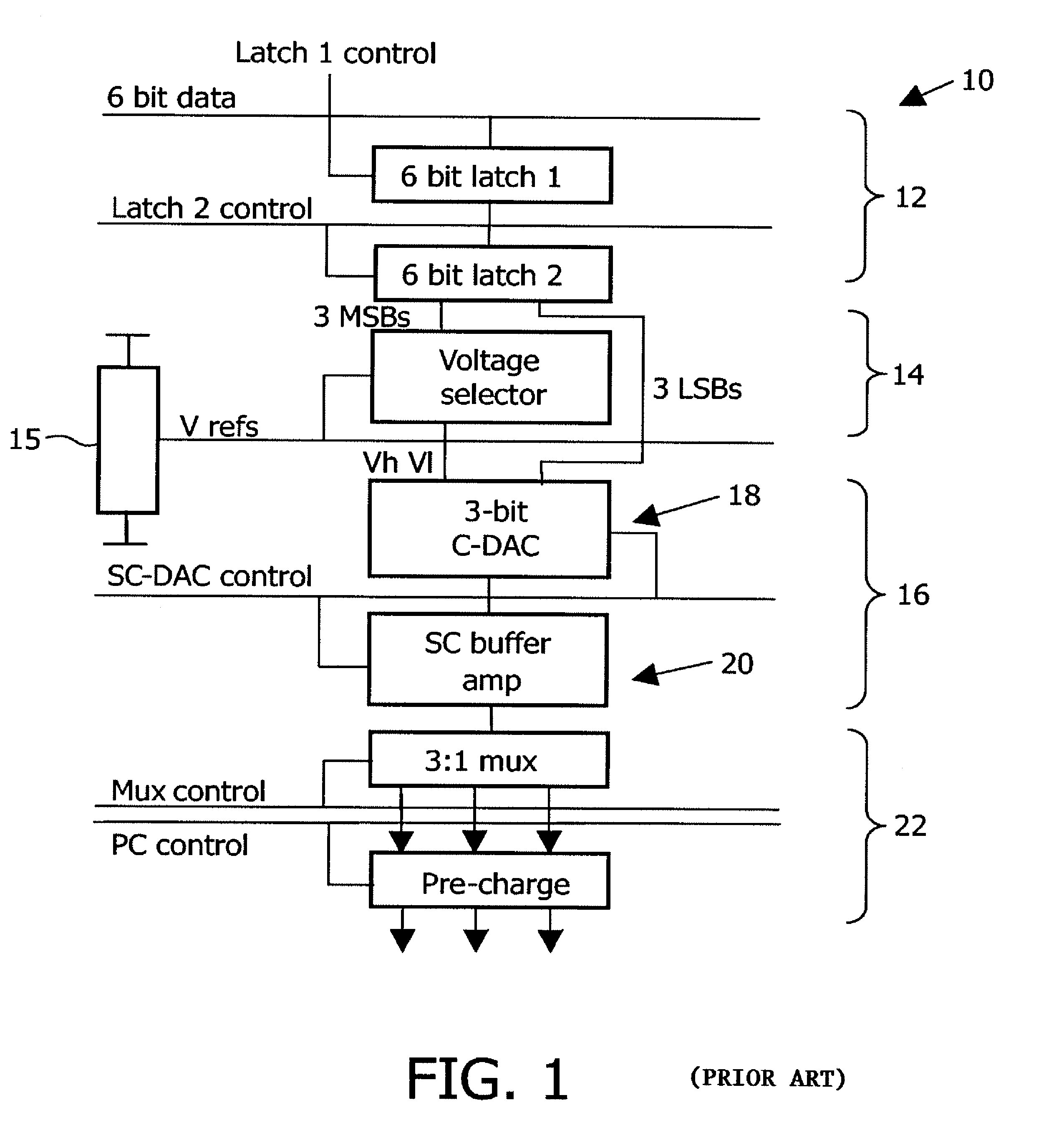

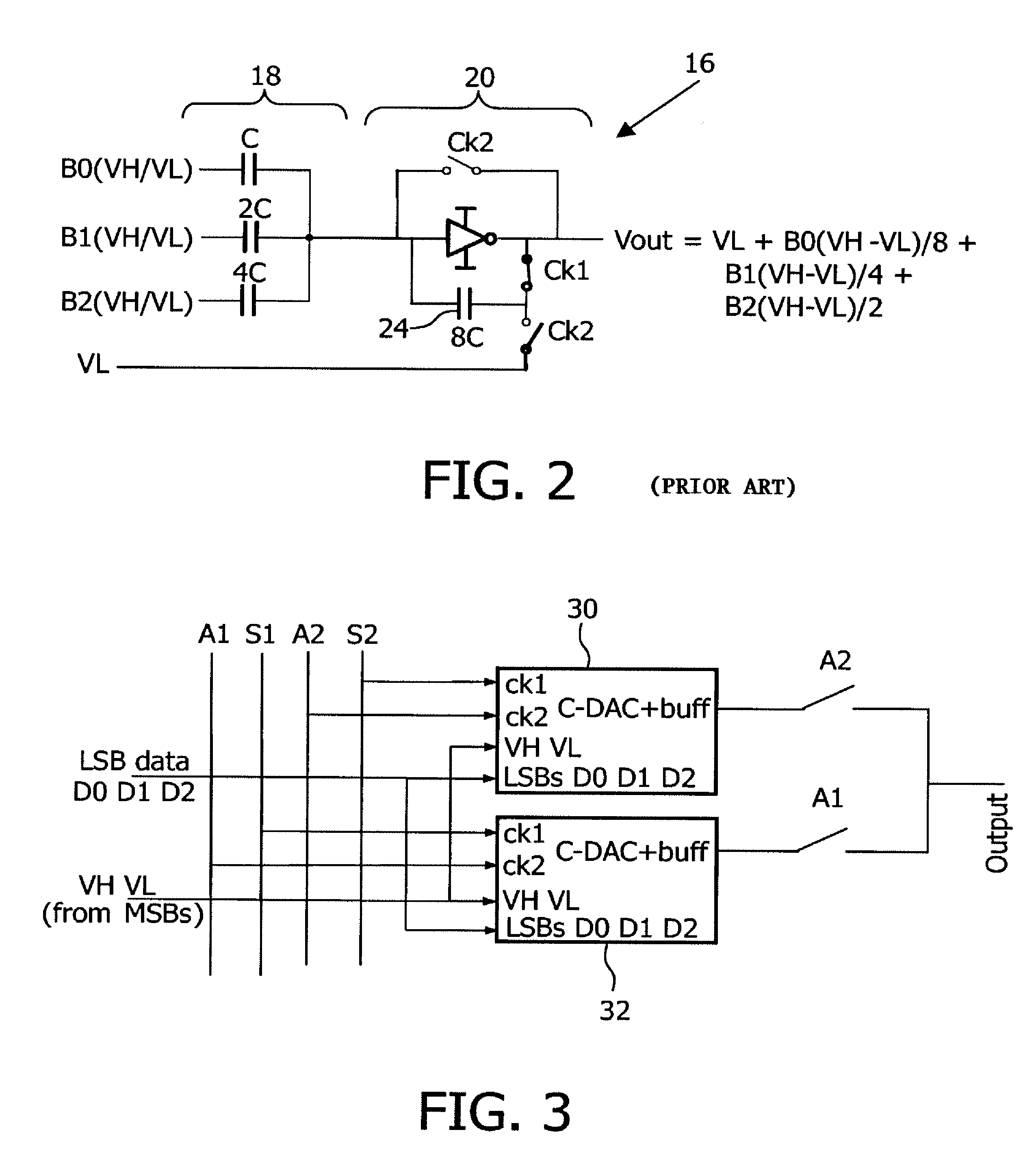

ActiveUS8228317B2Increase the areaTime availableElectric signal transmission systemsCathode-ray tube indicatorsDigital analog converterActive matrix

An active matrix array device has driver circuitry for providing address signals to the matrix elements, including digital to analogue converter circuitry. This has a voltage selector for selecting a pair of voltages based on a first set of bits of the digital matrix element signal, and a converter arrangement for providing an analogue voltage level derived from the pair of voltages and from a second set of bits of the digital matrix element signal. The converter arrangement comprises first and second digital to analogue converter circuits (30, 32) in parallel and which are adapted to provide an analogue voltage level to an output of the converter arrangement alternately. The invention provides a more efficient use of substrate area for given circuit response requirements.

Owner:INNOLUX CORP

Vertical microelectronic component and corresponding manufacturing method

InactiveCN103681836BImprove power densityHigh compressive strengthSolid-state devicesSemiconductor/solid-state device manufacturingCommon drainSemiconductor

The invention realizes a vertical microelectronic element and a corresponding manufacturing method. The vertical microelectronic element comprises a structure of a semiconductor base (1; 1''') and a plurality of fins (1a, 1b) formed on the front side (O) of the semiconductor base (1; 1'''), the The semiconductor base has a front side (O) and a rear side (R), and the fins have respective side walls (S) and respective upper sides (T) and are separated from each other by recesses (G). Each fin (1a, 1b) comprises at least one GaN / AlGaN-heterolayer region (2a, 2b) and at least one gate interface region (G1-G4), said GaN / AlGaN-heterolayer region formed on the sidewall (S) and has an embedded channel region (K) extending essentially parallel to the sidewall (S), the gate interface region above the GaN / AlGaN-heterolayer region (2a, 2b) with the associated The channel region (K) in the recess (G) is arranged electrically insulatingly on the side wall (S). A common source interface region (SL) is arranged above the fins (1a, 1b) and is connected to respective first ends of the channel regions (K) near the upper side (T) of the fins (1a, 1b). A common drain interface region (DL) is arranged above the rear side (R) and is connected to the respective second ends of the channel region (K) near the front side (O) of the semiconductor substrate (1, 1''').

Owner:ROBERT BOSCH GMBH

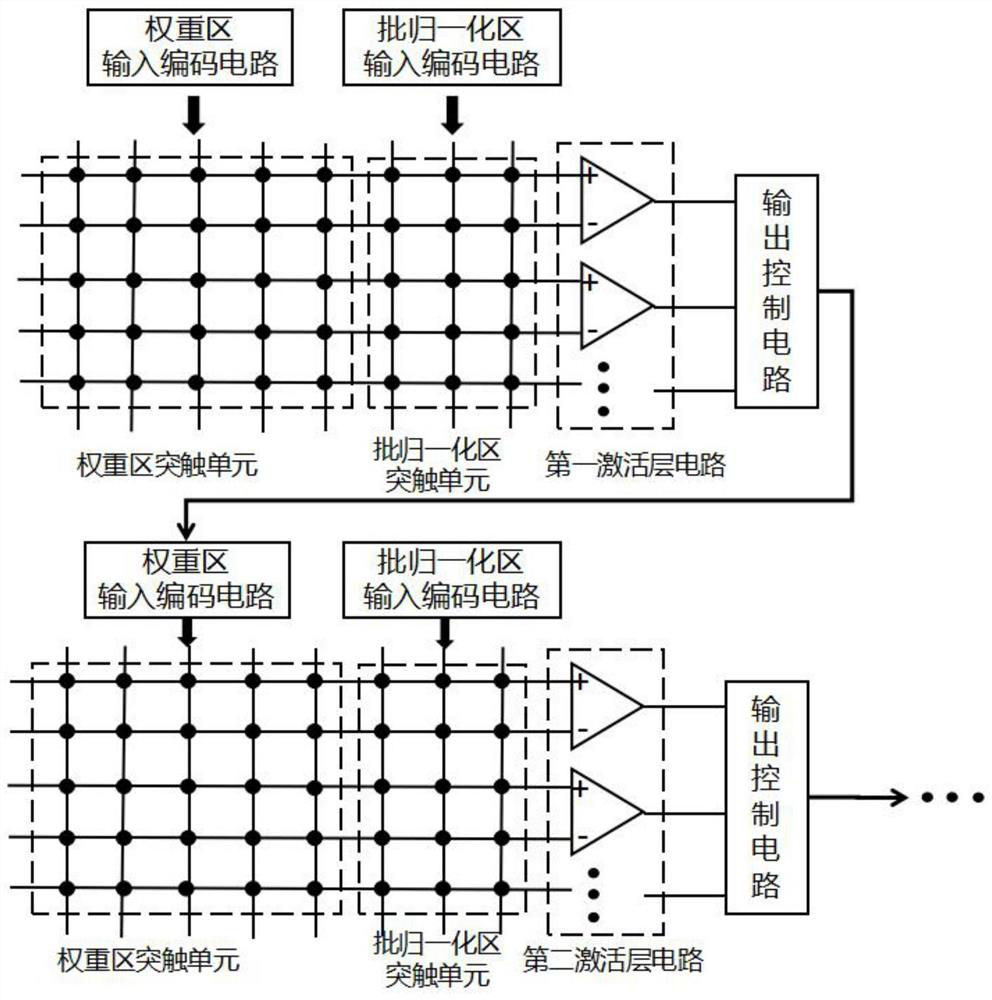

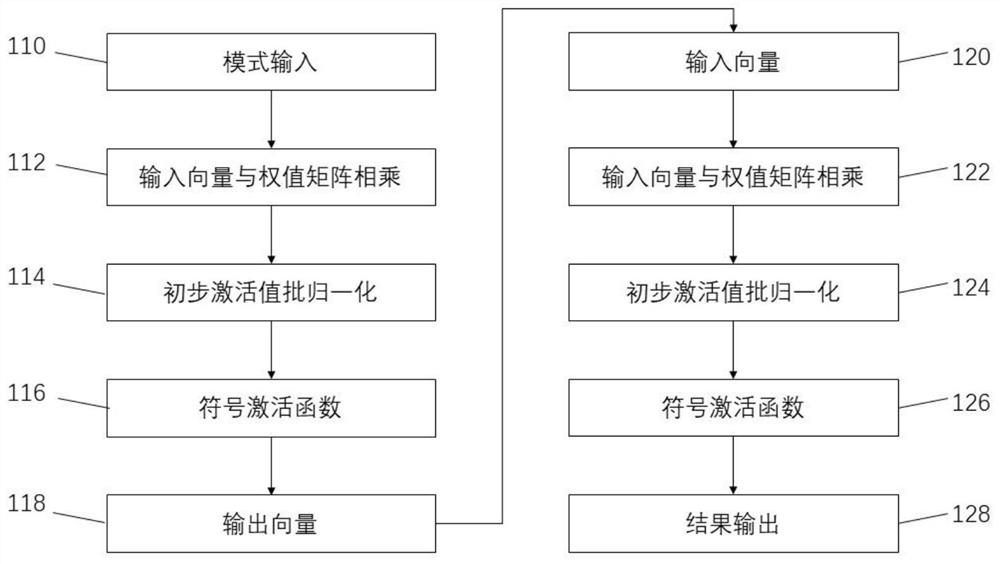

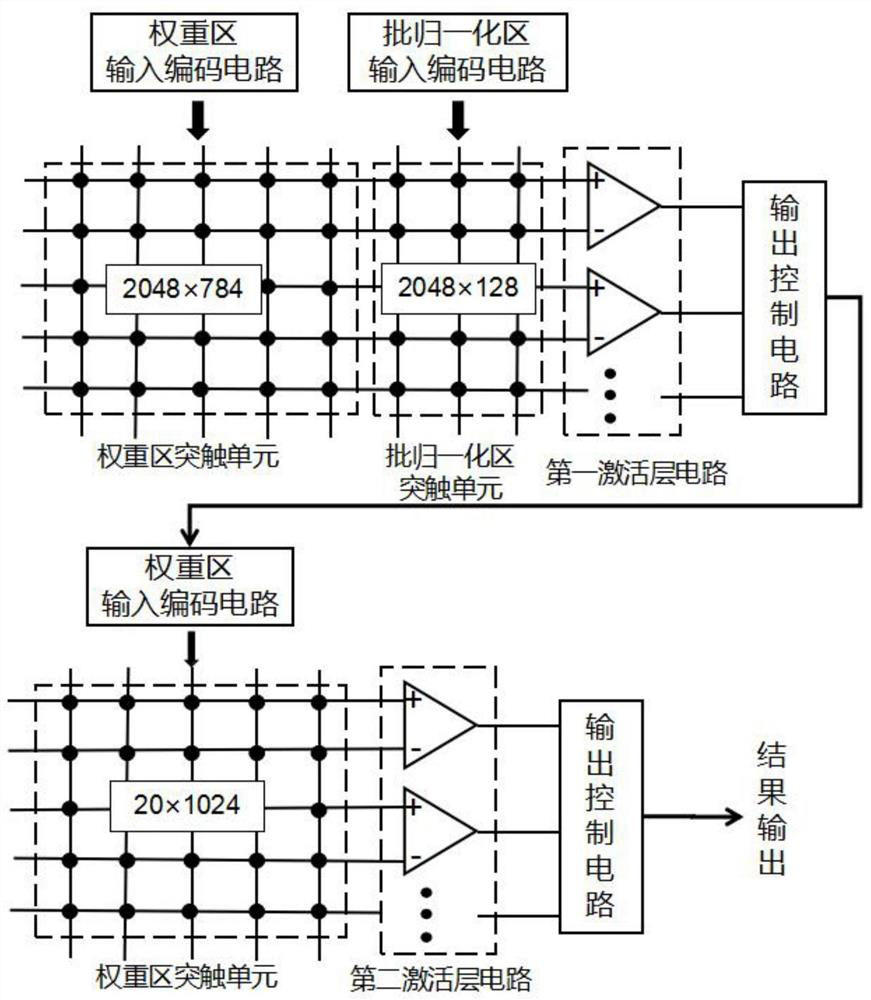

Hardware neural network batch normalization system

ActiveCN112396176AHigh precisionSimplify complexityPhysical realisationEnergy efficient computingCircuit complexityActivation function

The invention discloses a hardware neural network batch normalization system. The hardware neural network batch normalization system comprises a cascaded C-layer neural network circuit, the output control circuit of the p layer of neural network circuit is connected with the weight area input coding circuit in the (p + 1) layer of neural network circuit; wherein p = 1, 2,..., C-1; the p layer neural network circuit comprises a weight area input coding circuit, a batch normalization area input coding circuit, a weight area synaptic unit, a batch normalization area synaptic unit, anactive layer circuit and an output control circuit. Derivation and simplification are performed by combining a batch normalization formula with neural network activation function characteristics, batch normalization parameter information of the neural network is stored by adopting a batch normalization region synapse unit, and a normalization process corresponds to a process of summing output of aweight region synapse unit and the batch normalization parameter information of the neural network according to lines. Originally complex hardware functions are enabled to adapt to a memory storage and calculation integrated framework, the circuit complexity for realizing batch normalization hardware functions is greatly simplified, and relatively high network precision can be realized with relatively low circuit area consumption.

Owner:HUAZHONG UNIV OF SCI & TECH

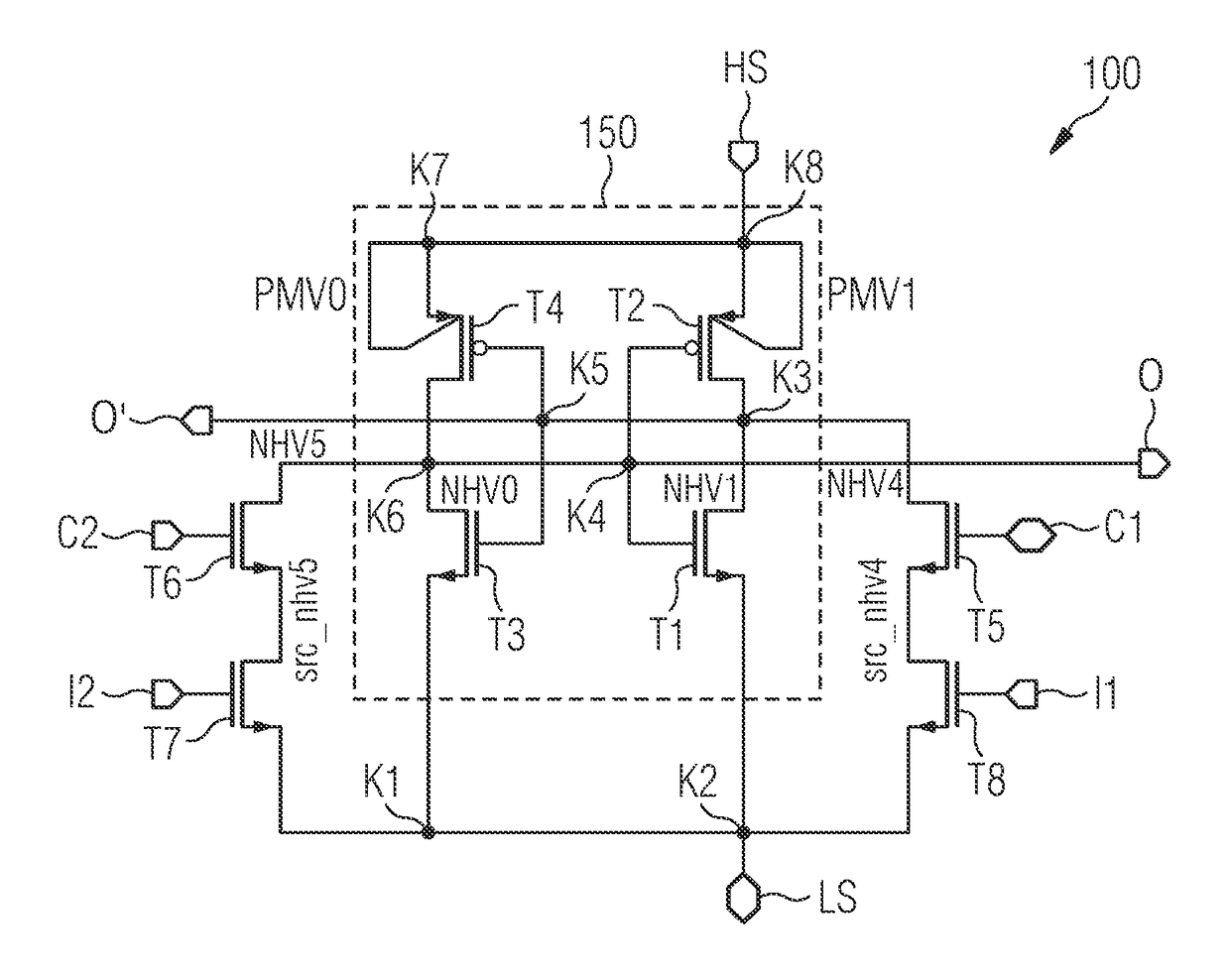

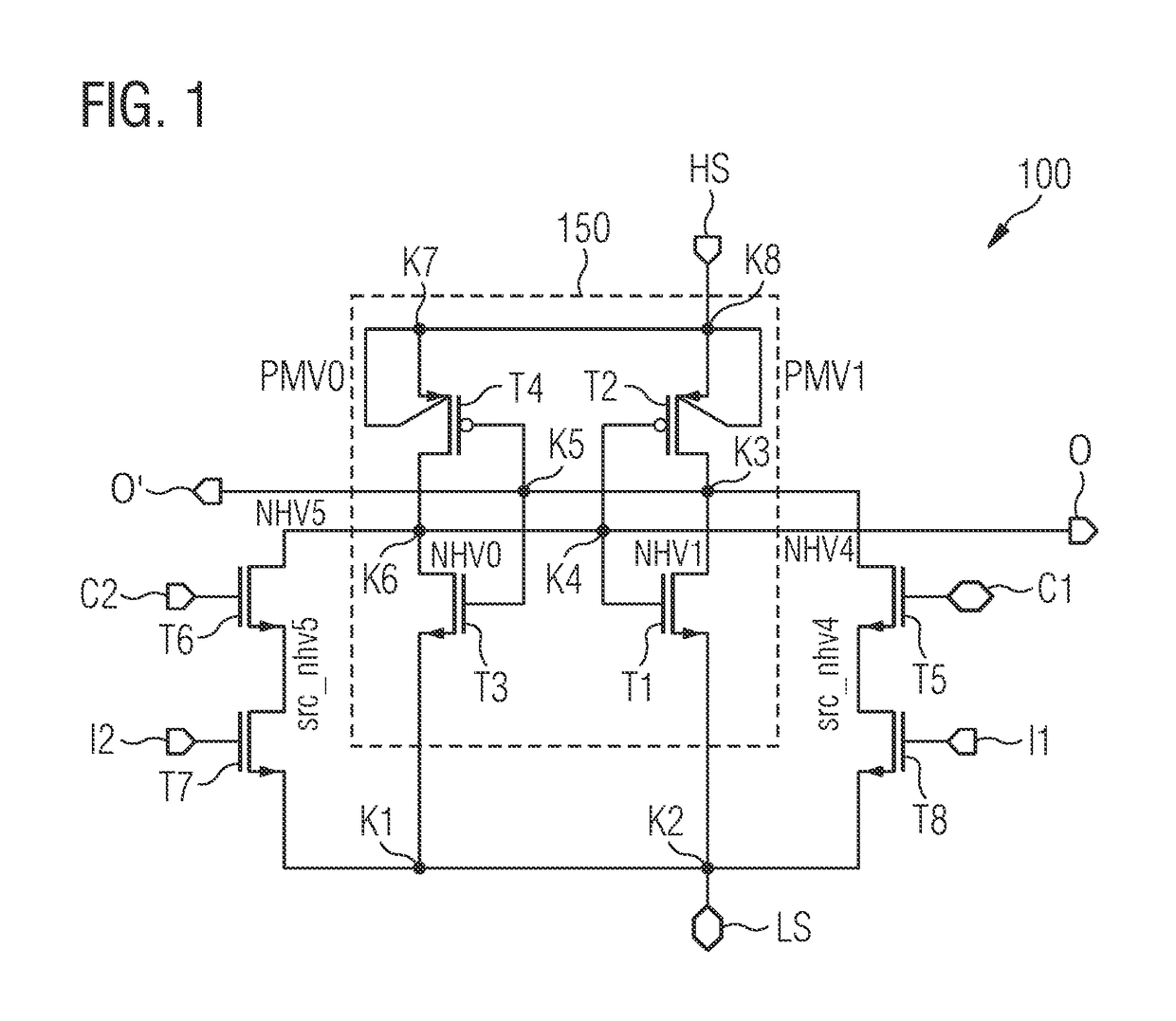

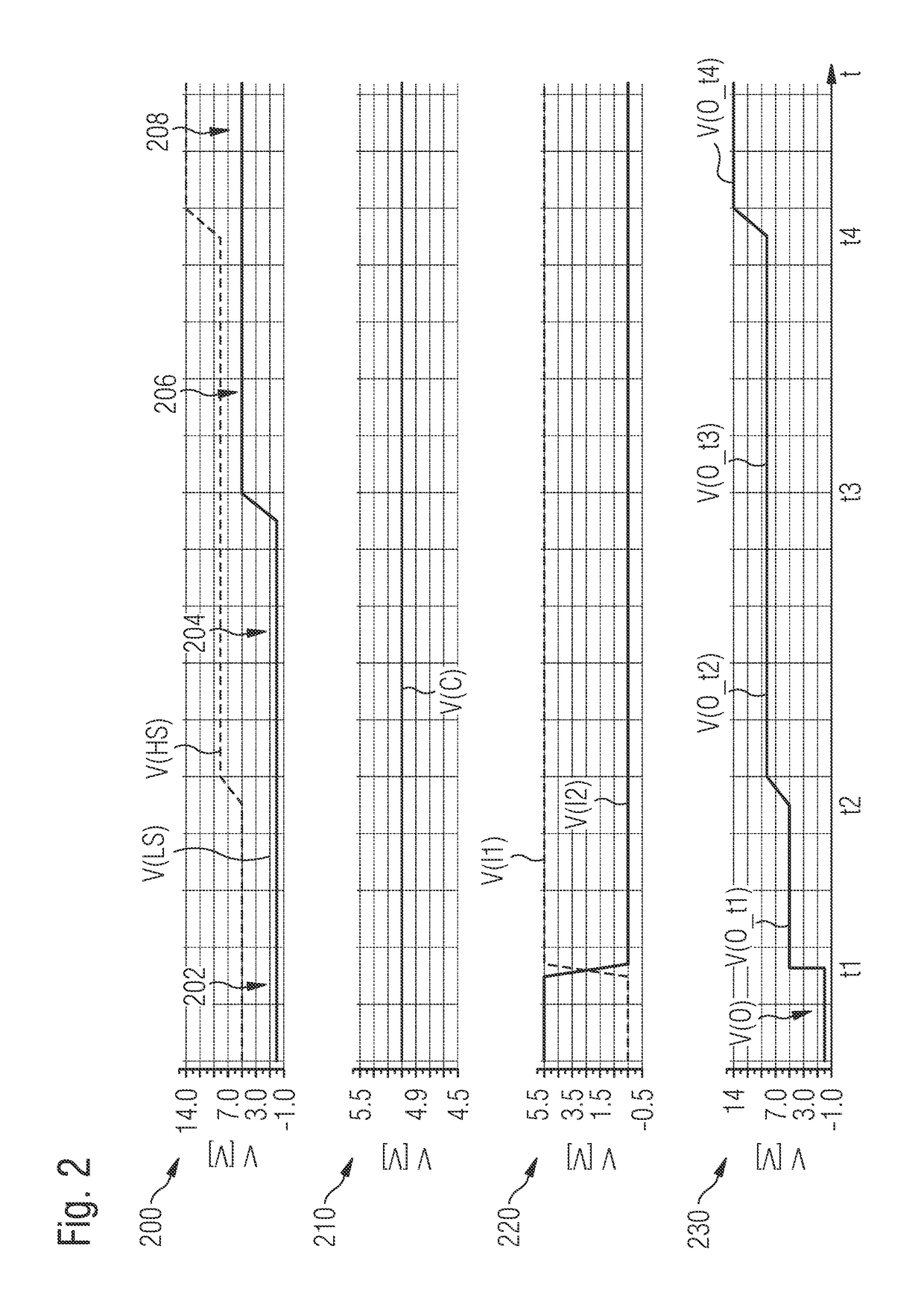

Level shifter and method for operating the same

ActiveUS10110230B2Reduce usageSmall area consumptionLogic circuits coupling/interface using field-effect transistorsEngineeringLogic state

In various embodiments, a level shifter and a method for operating the same are provided. The level shifter may include a low supply voltage terminal, a high supply voltage terminal, at least one input terminal, at least one output terminal, and a latch. The latch may configured to: store a predetermined logic state by setting a storage node to a voltage level in response to receiving a predetermined voltage level at the at least one input terminal; amend the voltage level at the storage node in response to receiving an amended voltage / s at the low supply voltage terminal and / or at the high supply voltage terminal; and output the predetermined logic state having the amended voltage level from the storage node to the at least one output.

Owner:INFINEON TECH AG

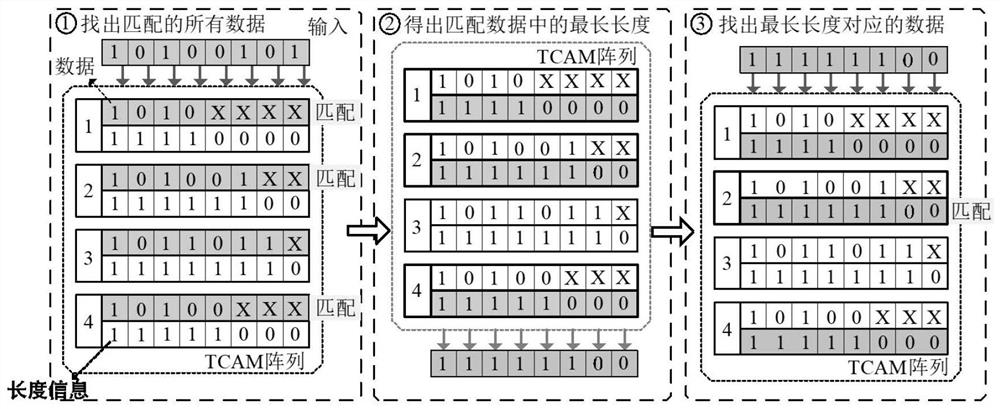

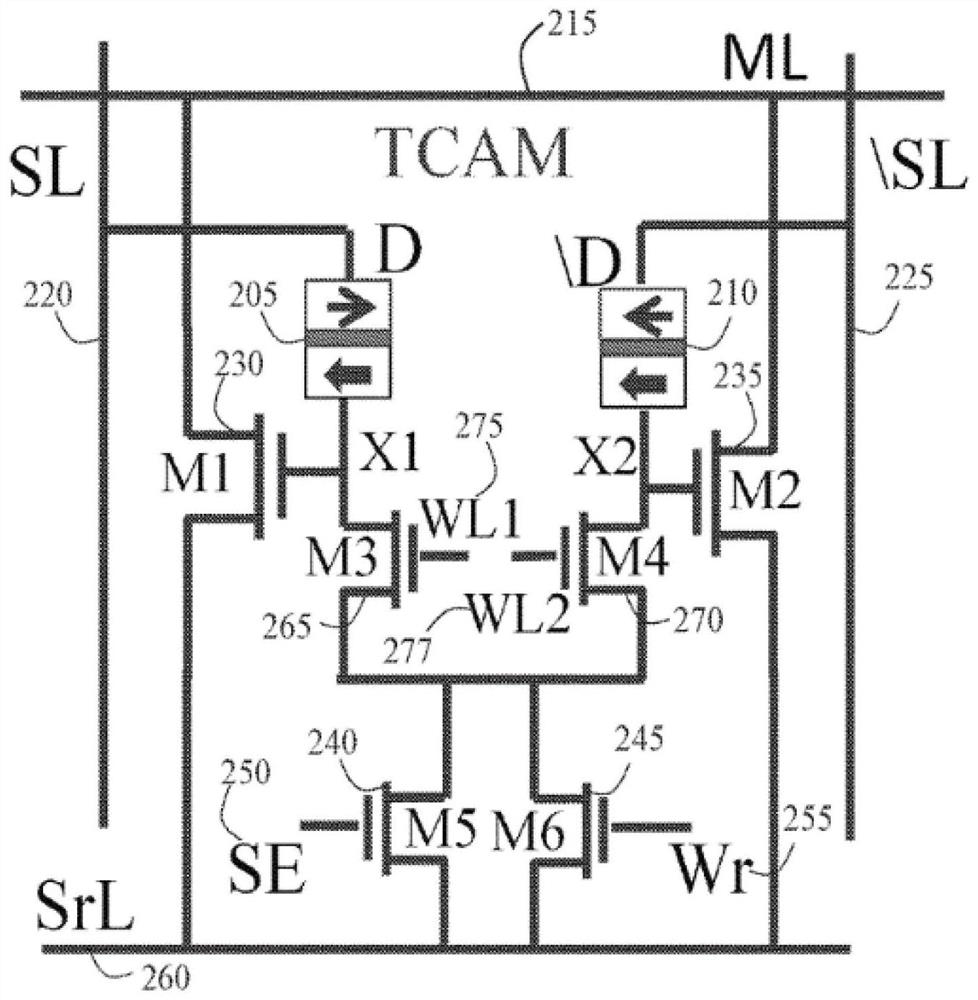

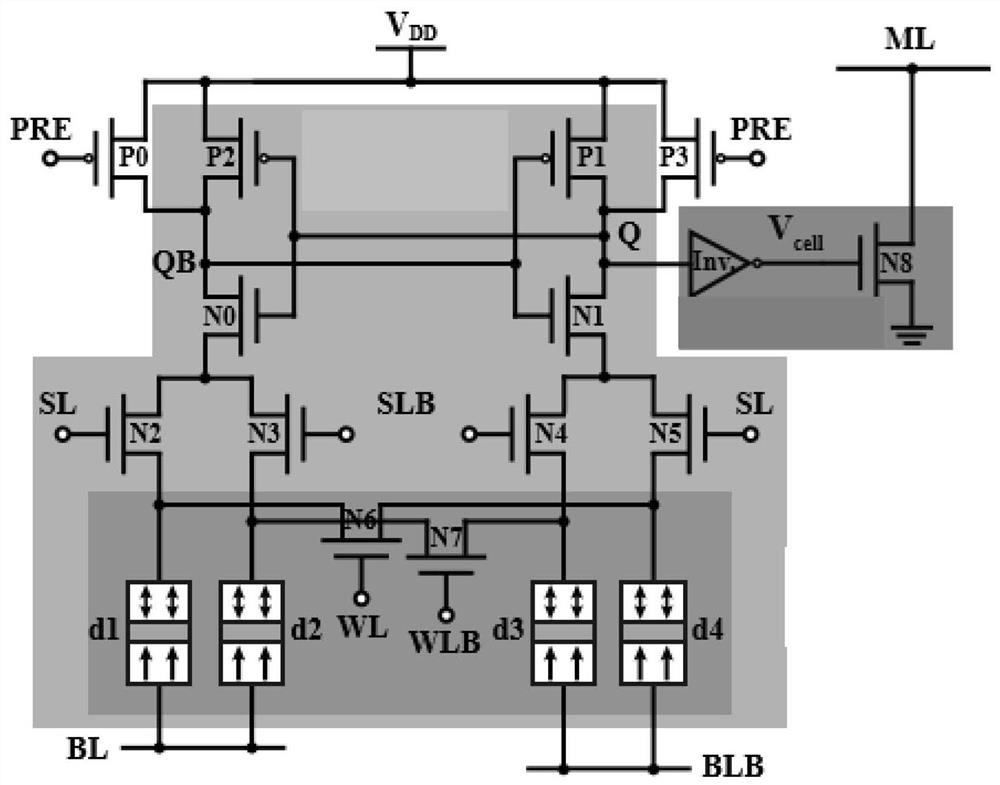

Ternary memory addressing circuit, reading circuit, device and memory

ActiveCN112820338AAvoid consumptionSmall area consumptionRead-only memoriesDigital storageComputer hardwareData matching

A ternary memory addressing circuit, a reading circuit, a device and a memory are provided by the invention. An optimal result of data matching is selected by adopting a PDM mode, and a large amount of unnecessary energy consumption caused by a PE module in a traditional TCAM is avoided. An X state is combined with a reference unit, so that the area consumption caused by a data length information storage unit is reduced, and the optimal matching result of the data can be quickly judged. Finally, the optimal data matching result is obtained by judging the digit of the 'X' state, so that the position of the 'X' state in data storage is not limited.

Owner:BEIHANG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com