Coprocessor based on reconfigurable computational array

A coprocessor and computing array technology, applied in the field of coprocessors, can solve the problems of increasing hardware resources, area overhead, high power consumption and area cost, and complex structure, achieving large area advantages, small area consumption, and computing power. good performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The coprocessor based on the reconfigurable computing array of the present invention will be described in detail below with reference to the drawings in the embodiments of the present invention.

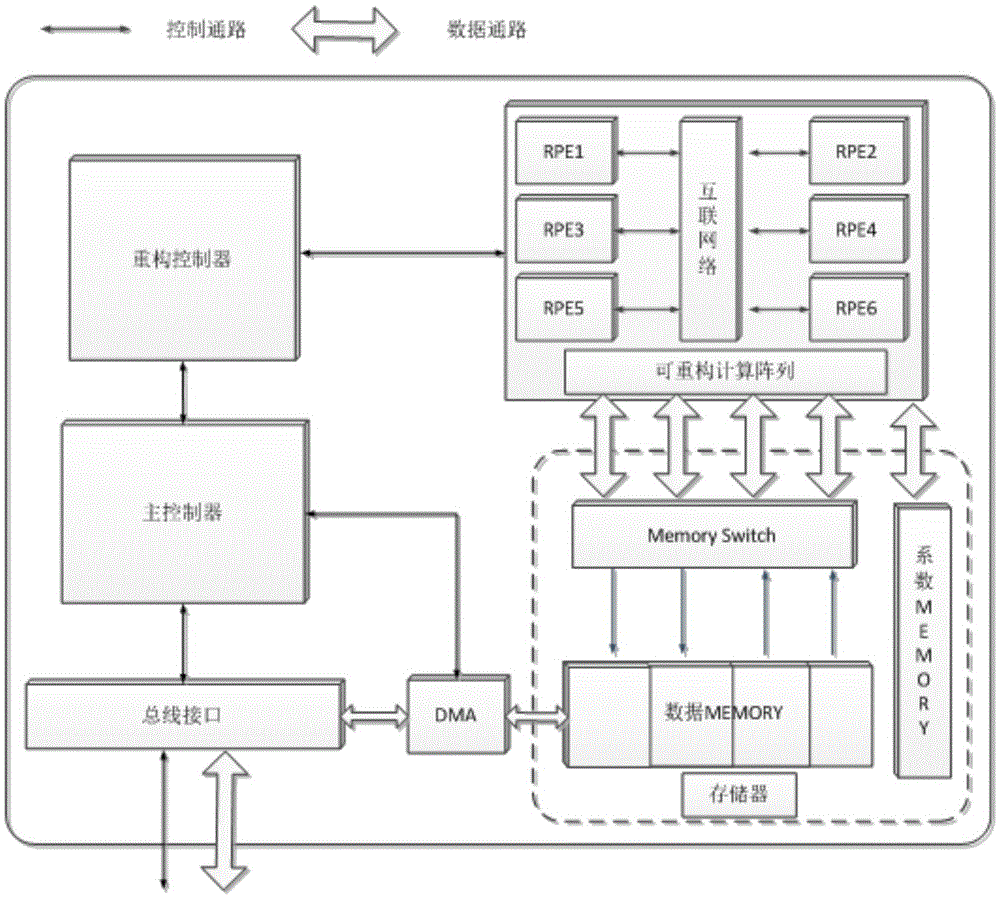

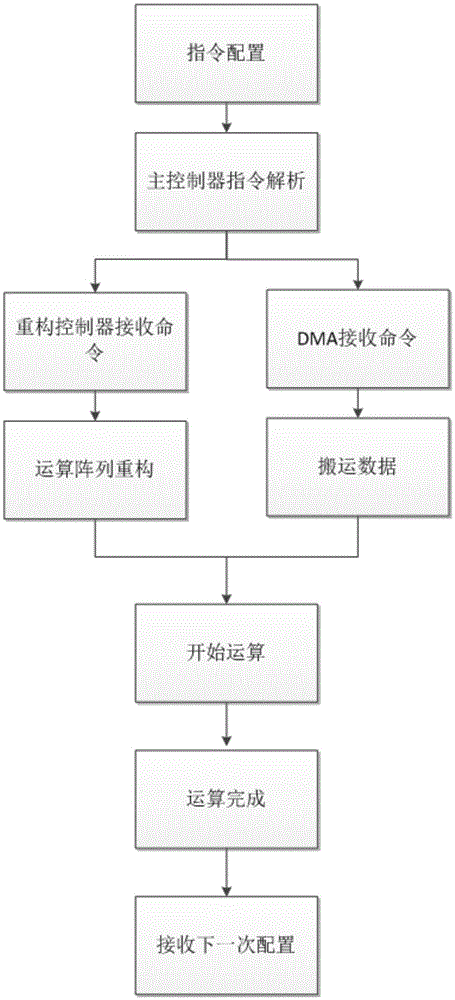

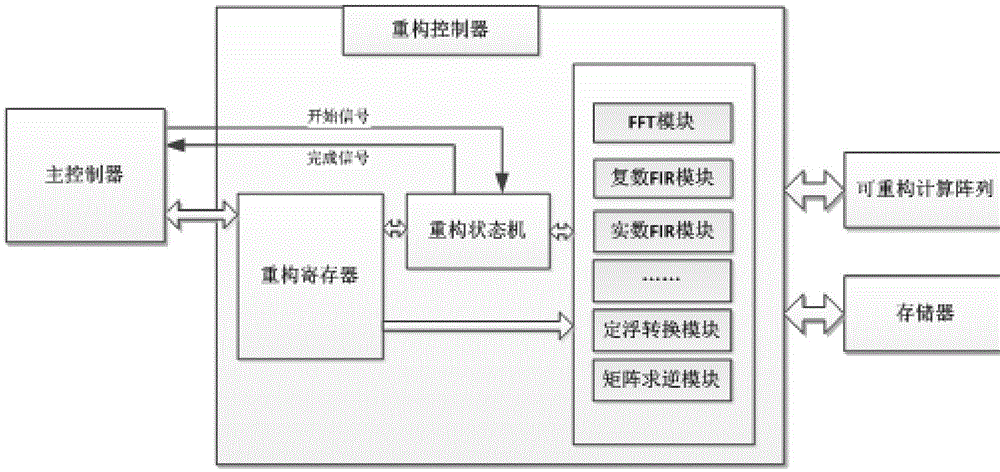

[0031] Such as figure 1 , the coprocessor is mainly composed of a main controller, a reconfiguration controller, a computing core unit and a DMA unit. The main controller receives the control information sent by the external general-purpose processor, then analyzes the control information, and issues corresponding configuration instructions. The reconfiguration controller sends configuration information according to the configuration instruction sent by the main controller, and the configuration information is used to select and organize logic algorithms in the computing core unit and change the interconnection network gate mode of the computing core unit. The computing core unit receives the configuration information, and completes basic operations such as multiple multiplic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com