Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1448results about "Time-delay networks" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

True time delay phase array radar using rotary clocks and electronic delay lines

ActiveUS20120039366A1Forming accuratelyEasy to moveAntenna arraysPulse automatic controlTime delaysAnalog delay line

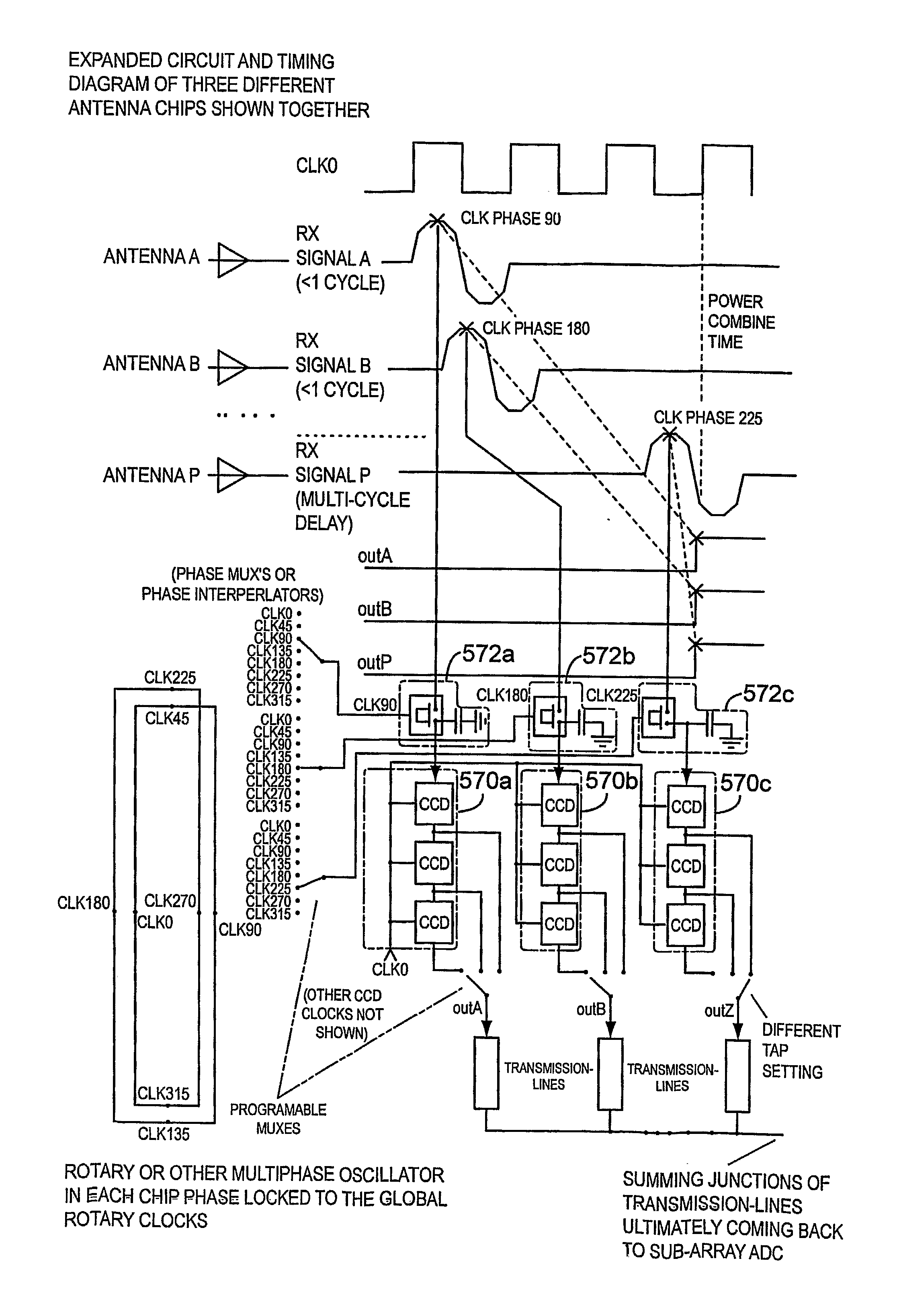

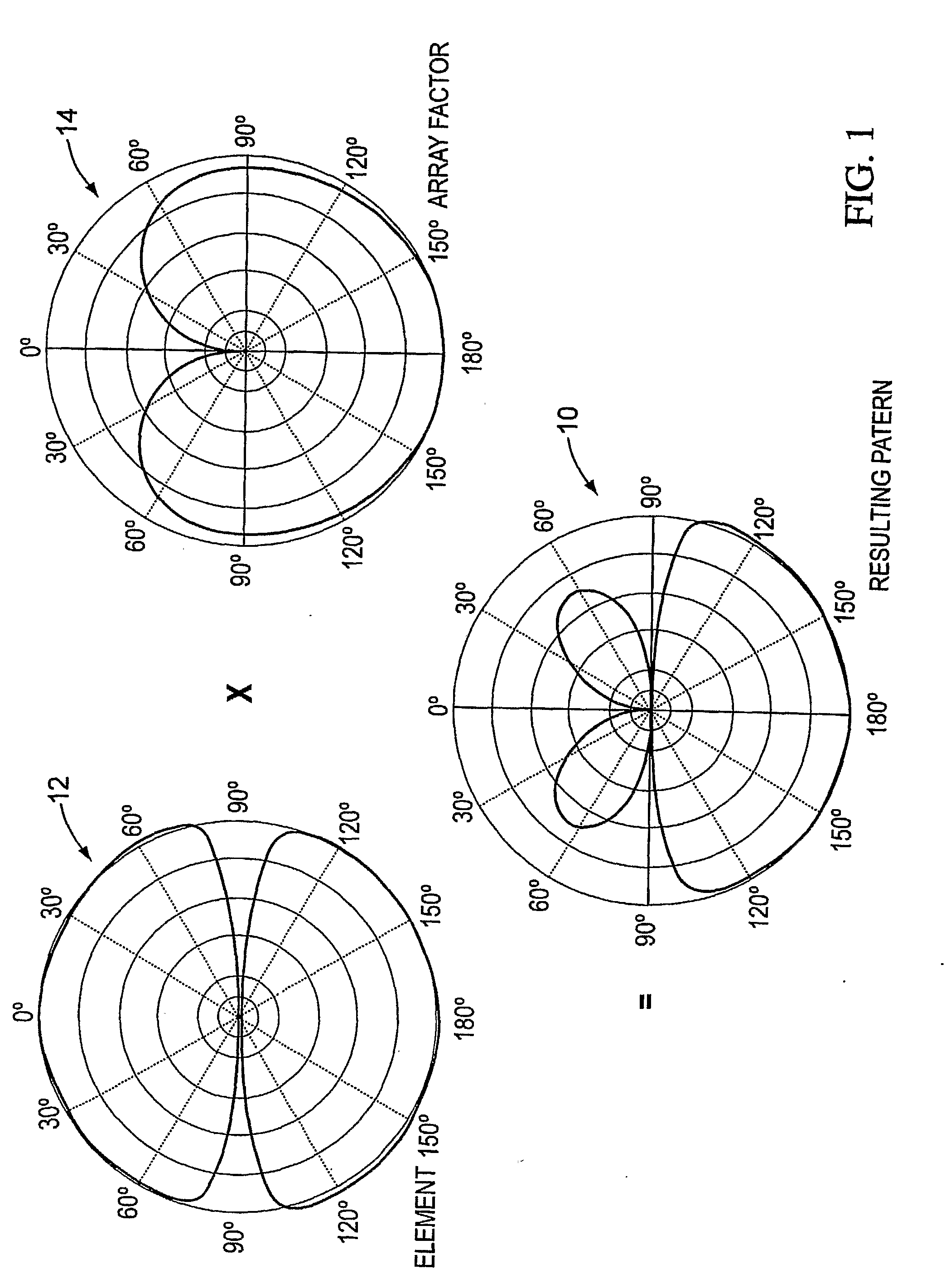

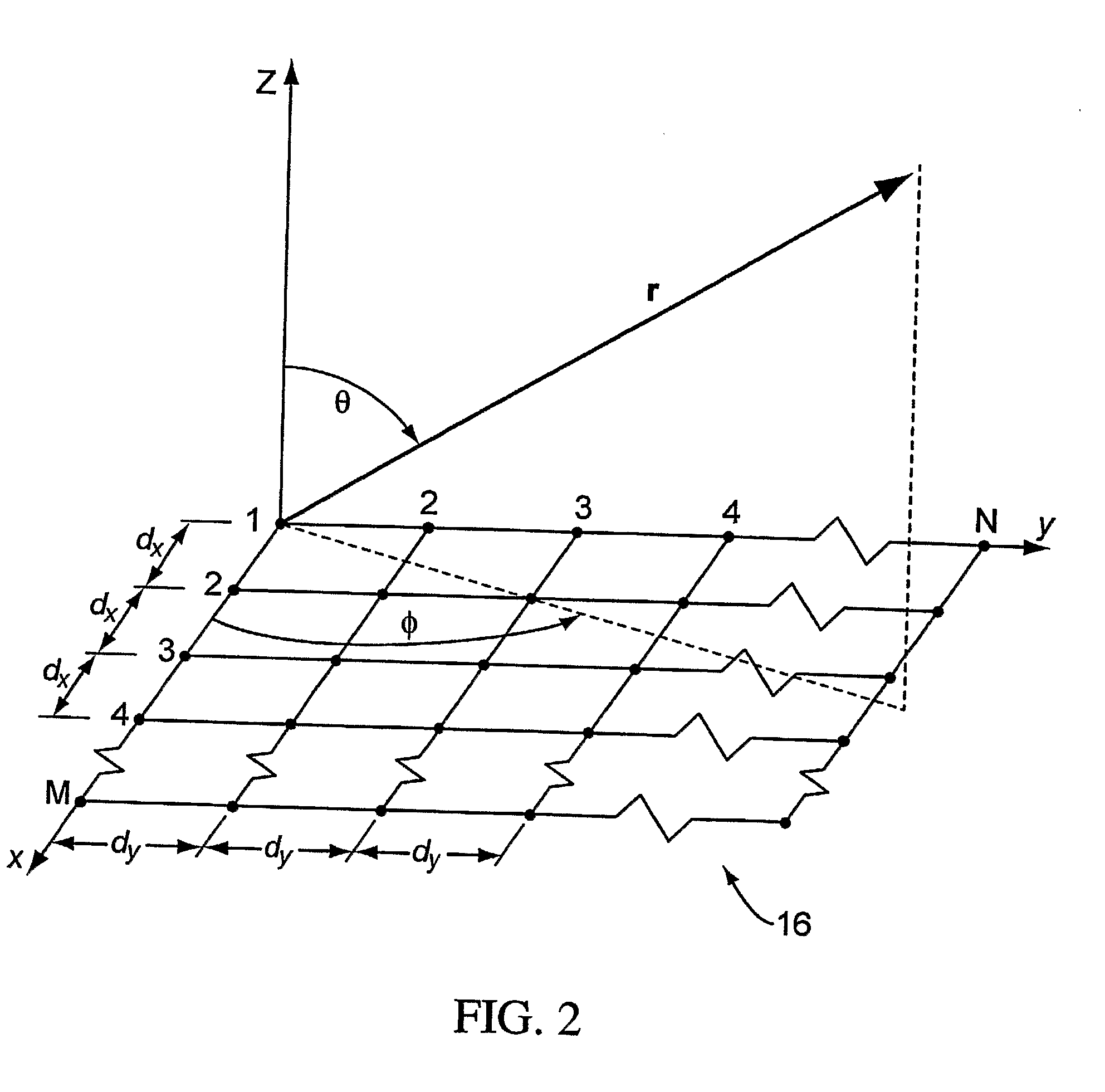

Local oscillator circuitry for an antenna array is disclosed. The circuitry includes an array of rotary traveling wave oscillators which are arranged in a pattern over an area and coupled so as to make them coherent. This provides for a set of phase synchronous local oscillators distributed over a large area. The array also includes a plurality of phase shifters each of which is connected to one of the rotary oscillators to provide a phase shifted local oscillator for the array. The phase shifter optionally includes a cycle counter that is configured to count cycles of the rotary oscillator to which it is connected and control circuitry that is then operative to provide a shifted rotary oscillator output based on the count from the cycle counter. A system and method for operating a true-time delay phased array antenna system. The system includes a plurality of antenna element circuits for driving or receiving an rf signal from the elements of the array. Each element circuit has a transmit and a receive path and a local multiphase oscillator, such as a rotary traveling wave oscillator. Each path has an analog delay line for providing a true-time delay for the antenna element. Preferably, the analog delay line is a charge coupled device whose control nodes are connected to phases of the local multiphase oscillator to implement a delay that is an integer number local multiphase oscillator periods. A fractional delay is also included in the path by using a sample and hold circuit connected to a particular phase of the oscillator. By delaying each antenna element by a true time delay, broadband operation of the array is possible.

Owner:ANALOG DEVICES INC

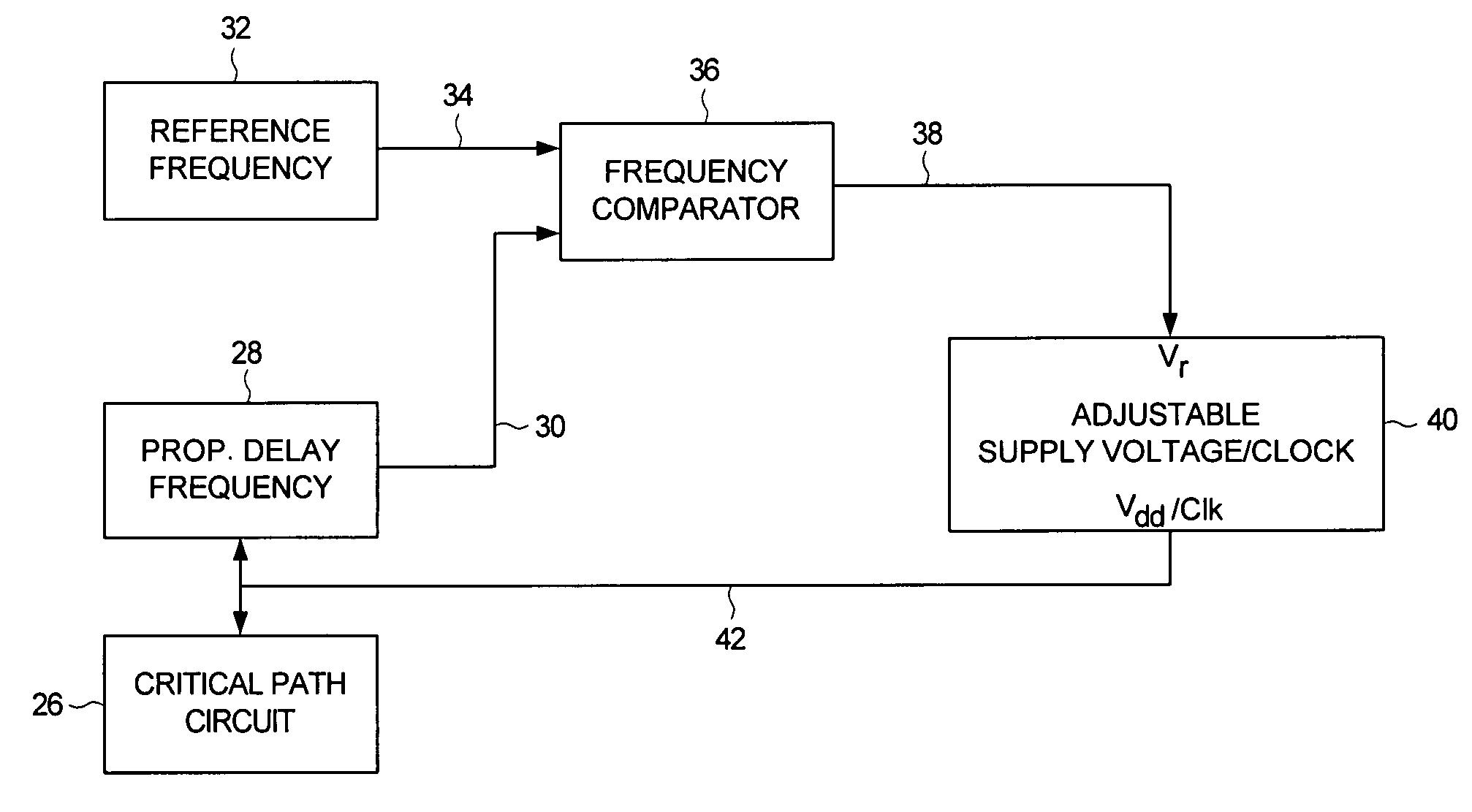

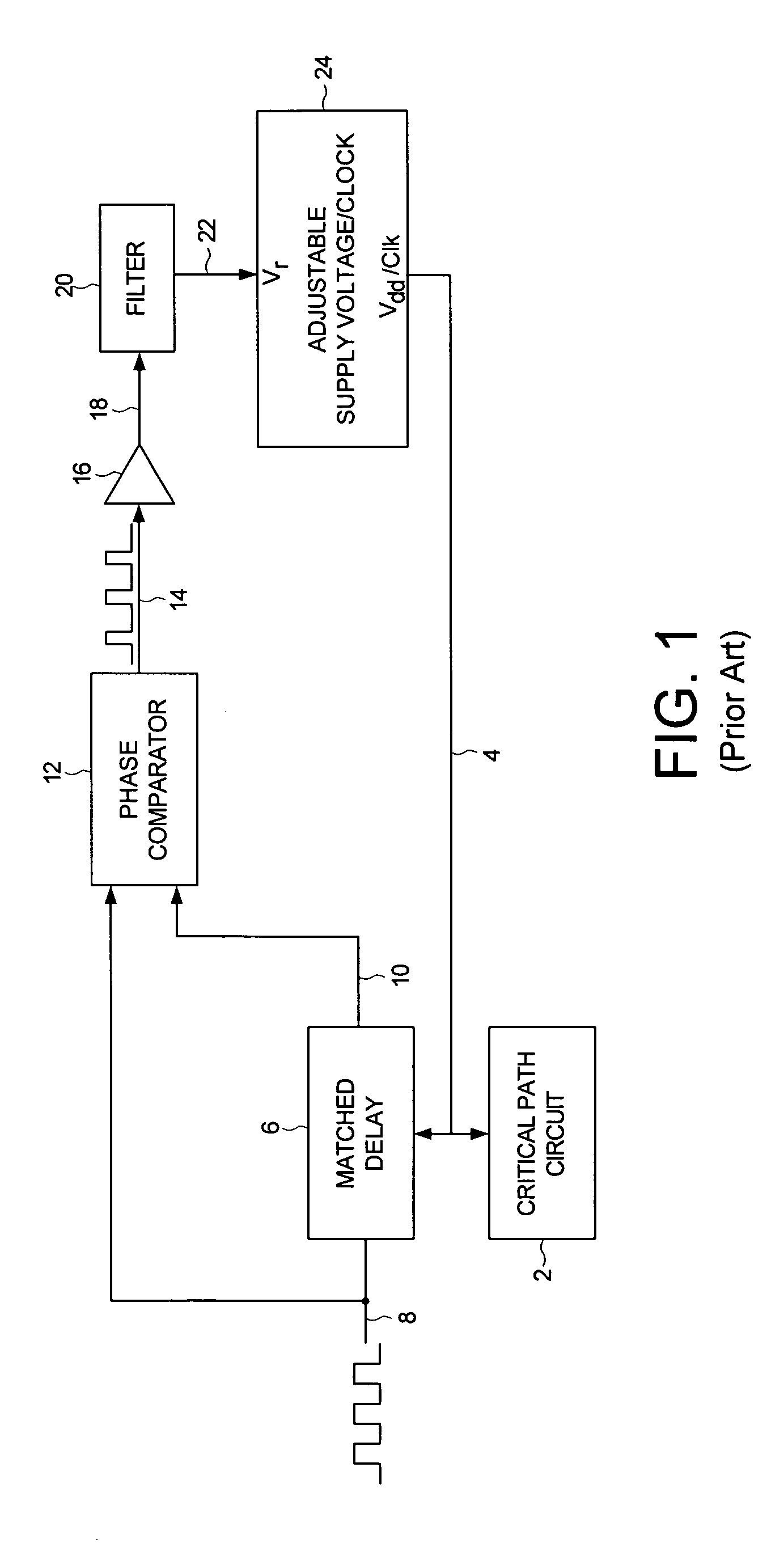

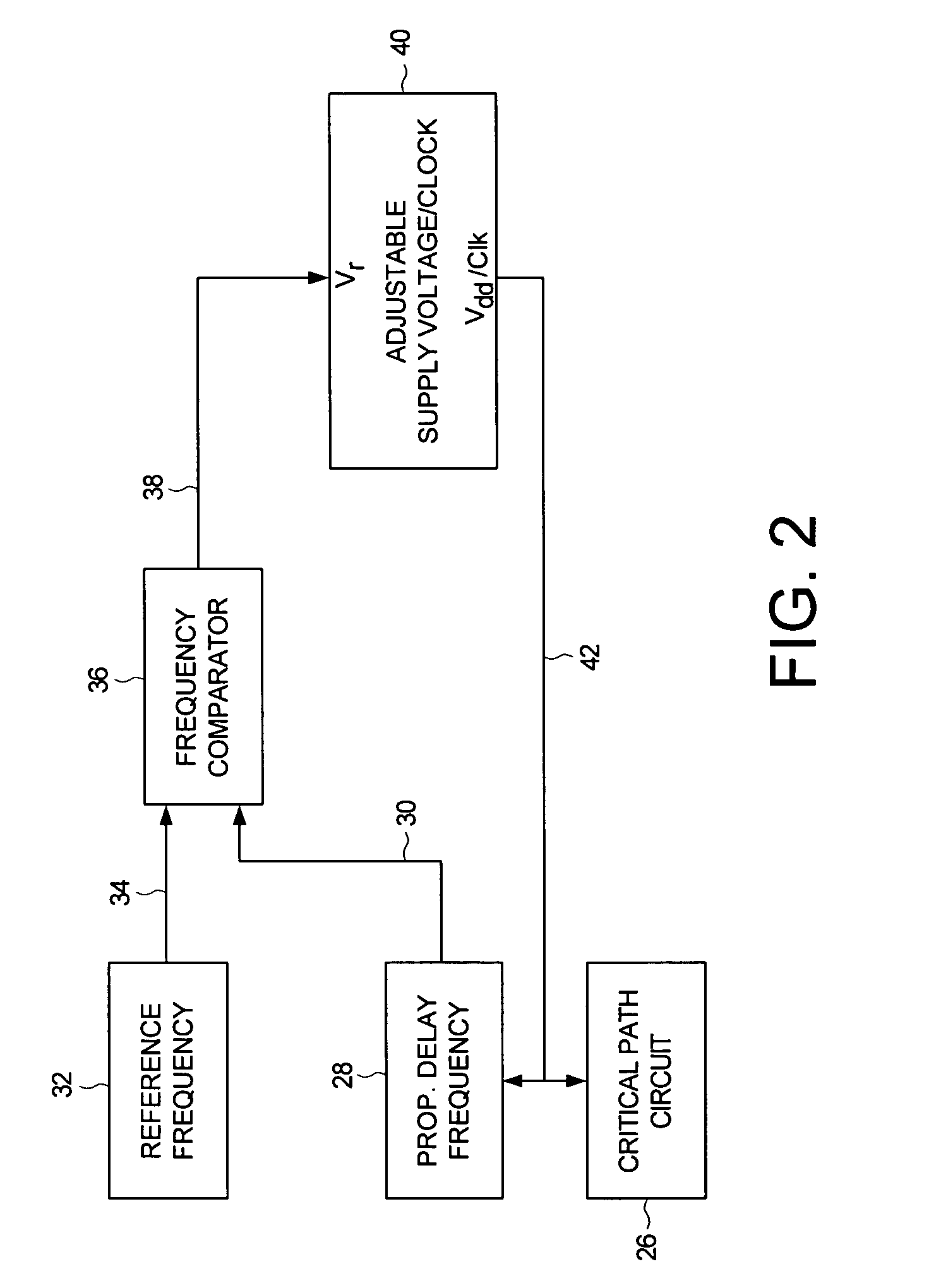

Adjusting power consumption of digital circuitry by generating frequency error representing error in propagation delay

A method and apparatus is disclosed for adjusting at least one of a supply voltage and a clocking frequency applied to digital circuitry of a computing device, wherein the digital circuitry comprises a critical path circuit. A propagation delay frequency representing a propagation delay of the critical path circuit is generated, and a frequency error signal is generated representing a difference between a reference frequency and the propagation delay frequency. At least one of the supply voltage and the clocking frequency is adjusted in response to the frequency error signal.

Owner:WESTERN DIGITAL TECH INC

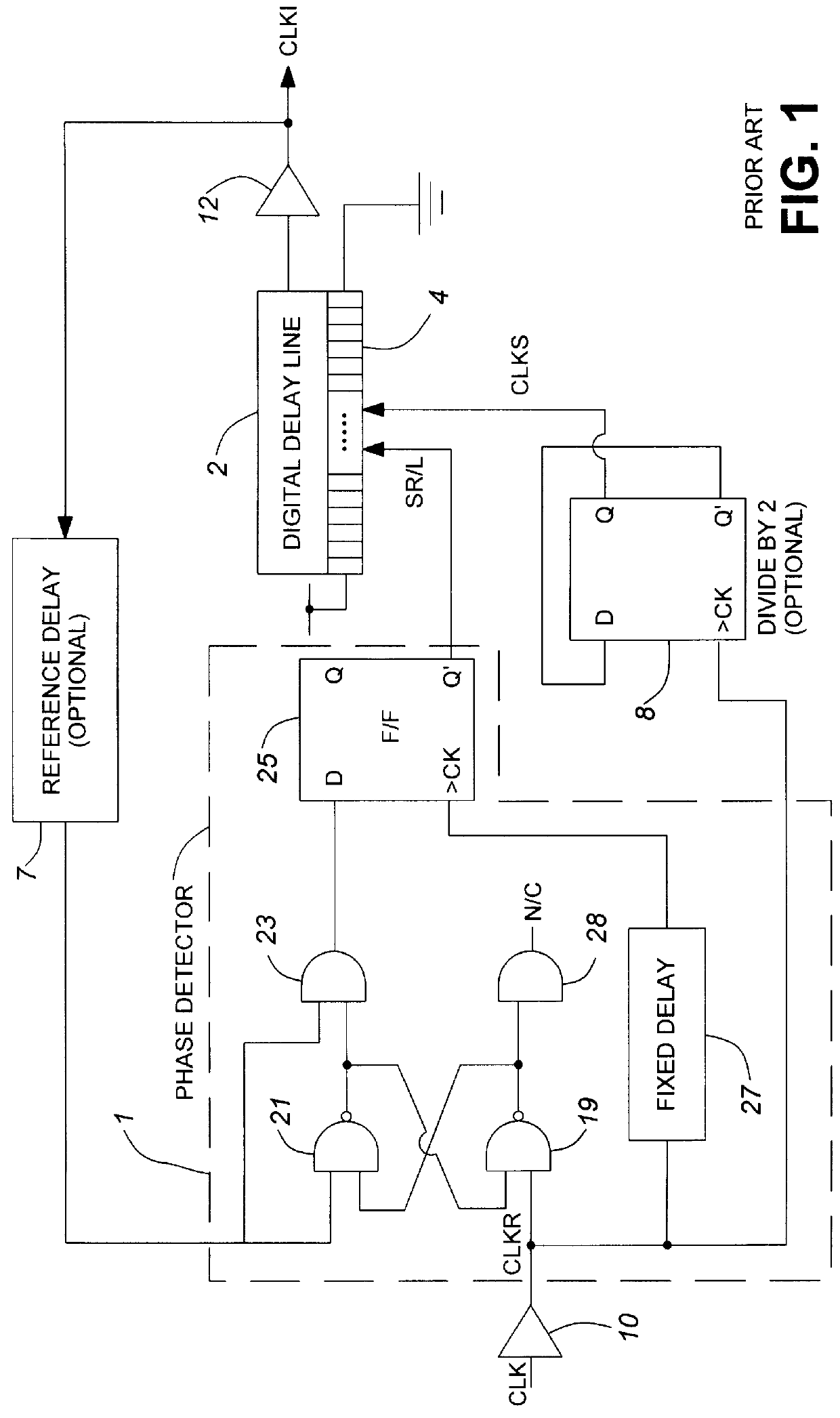

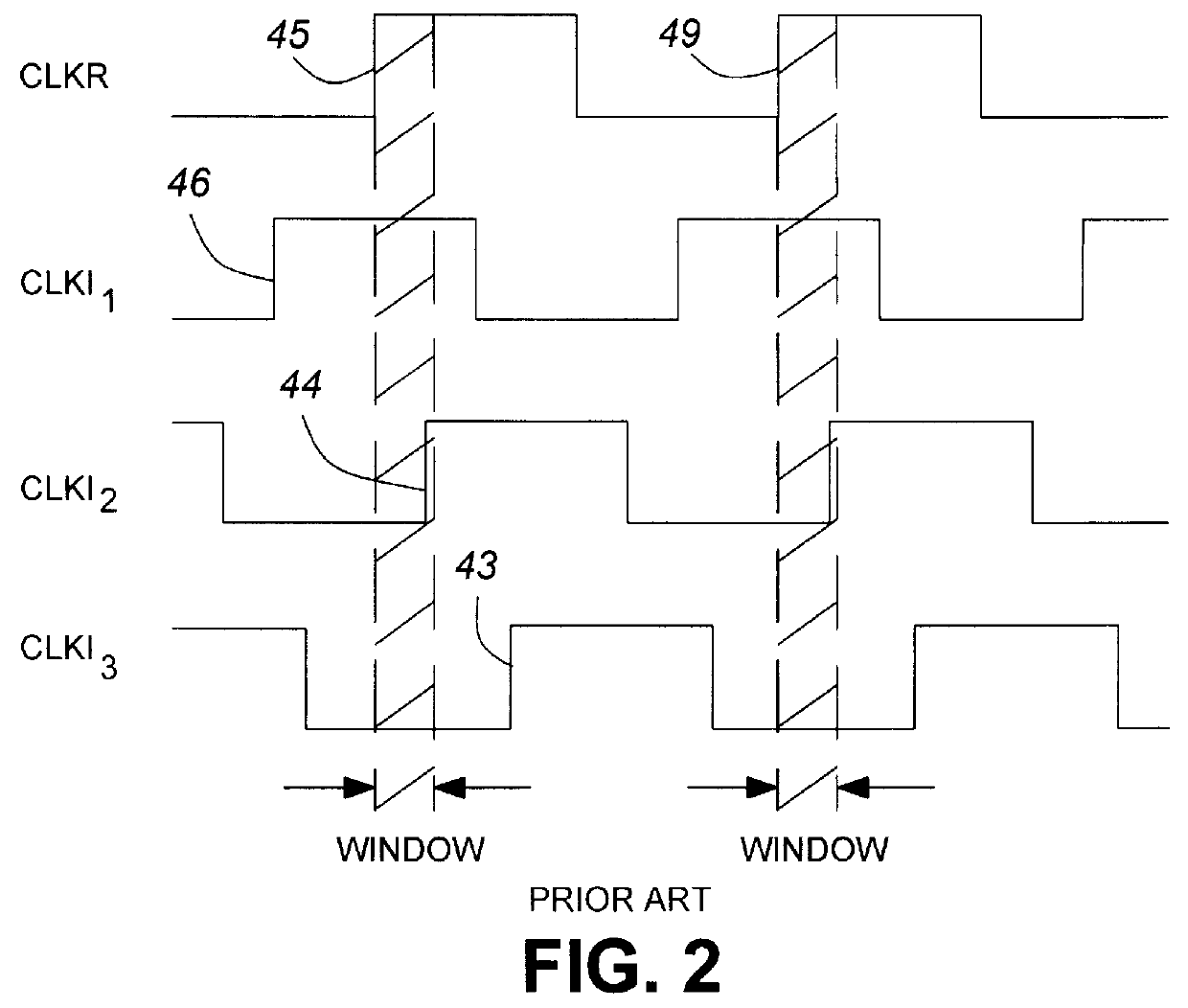

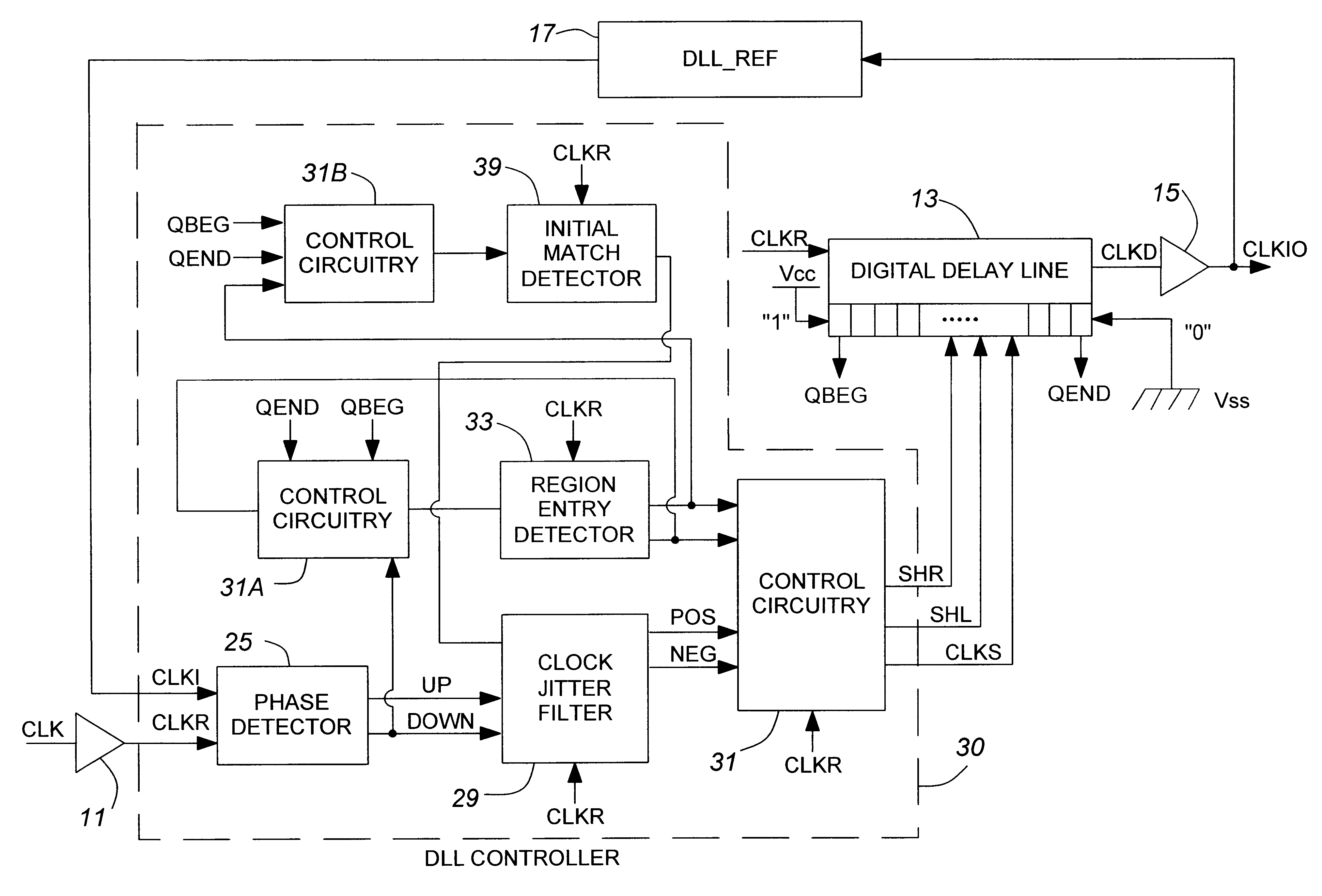

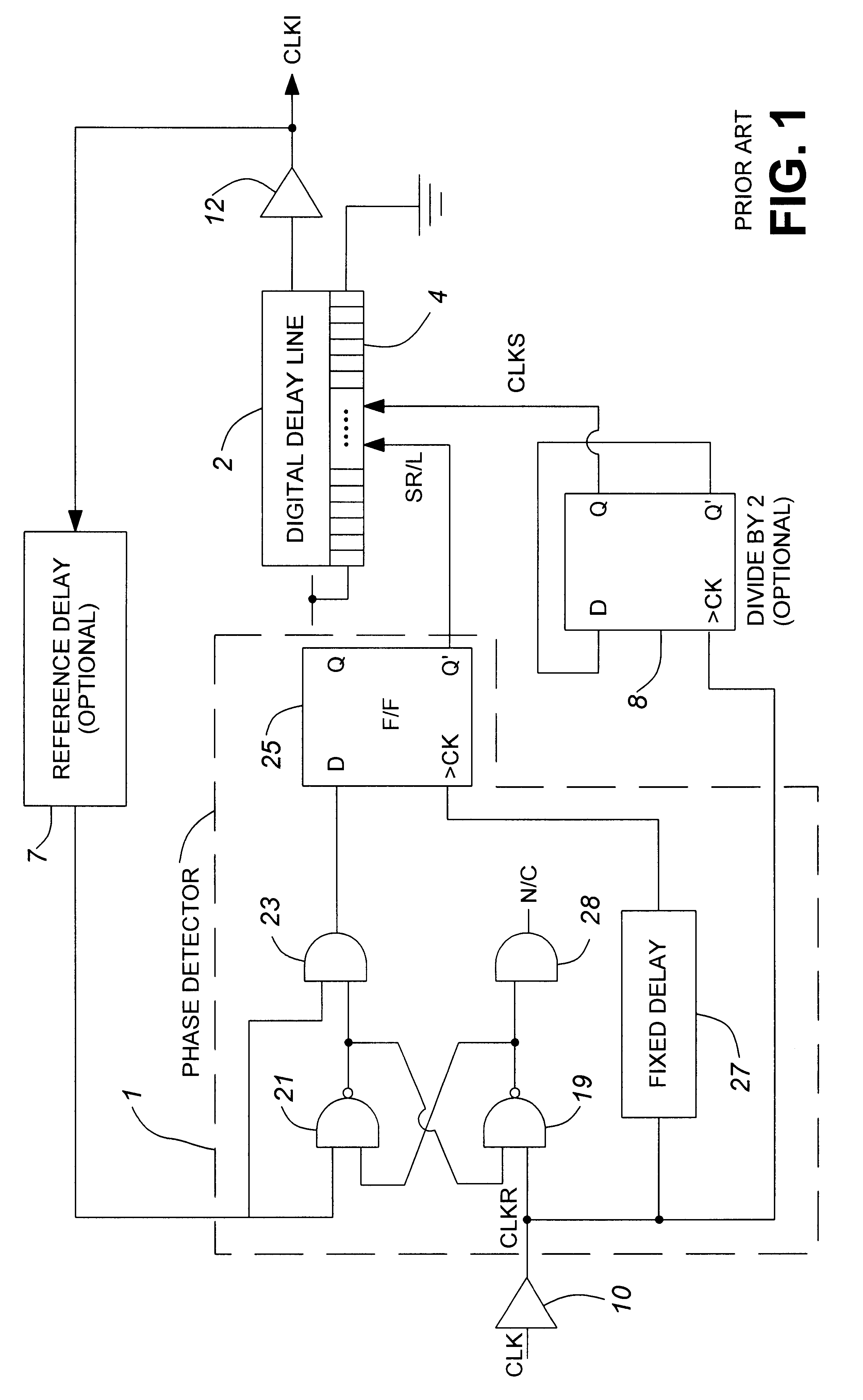

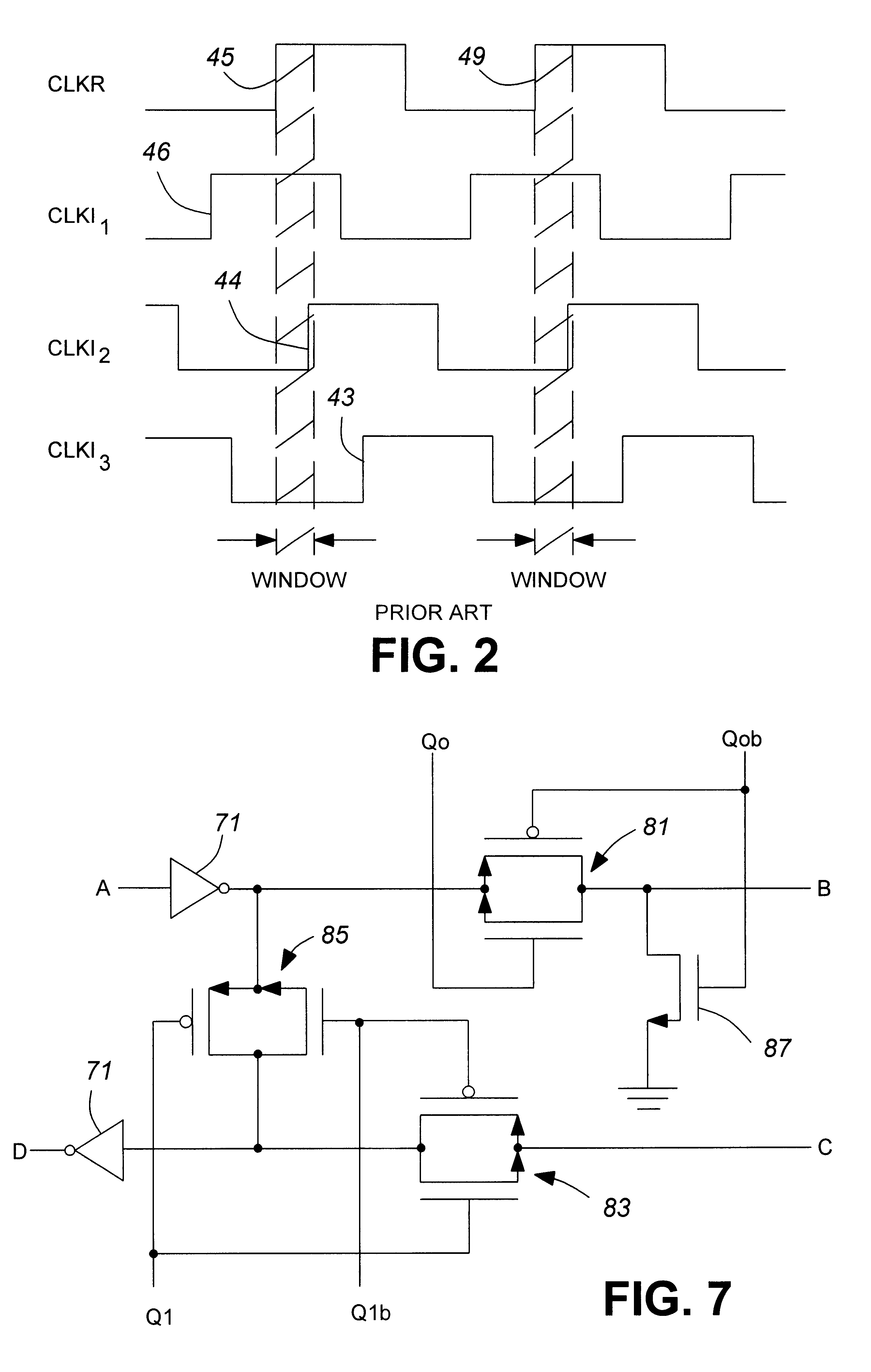

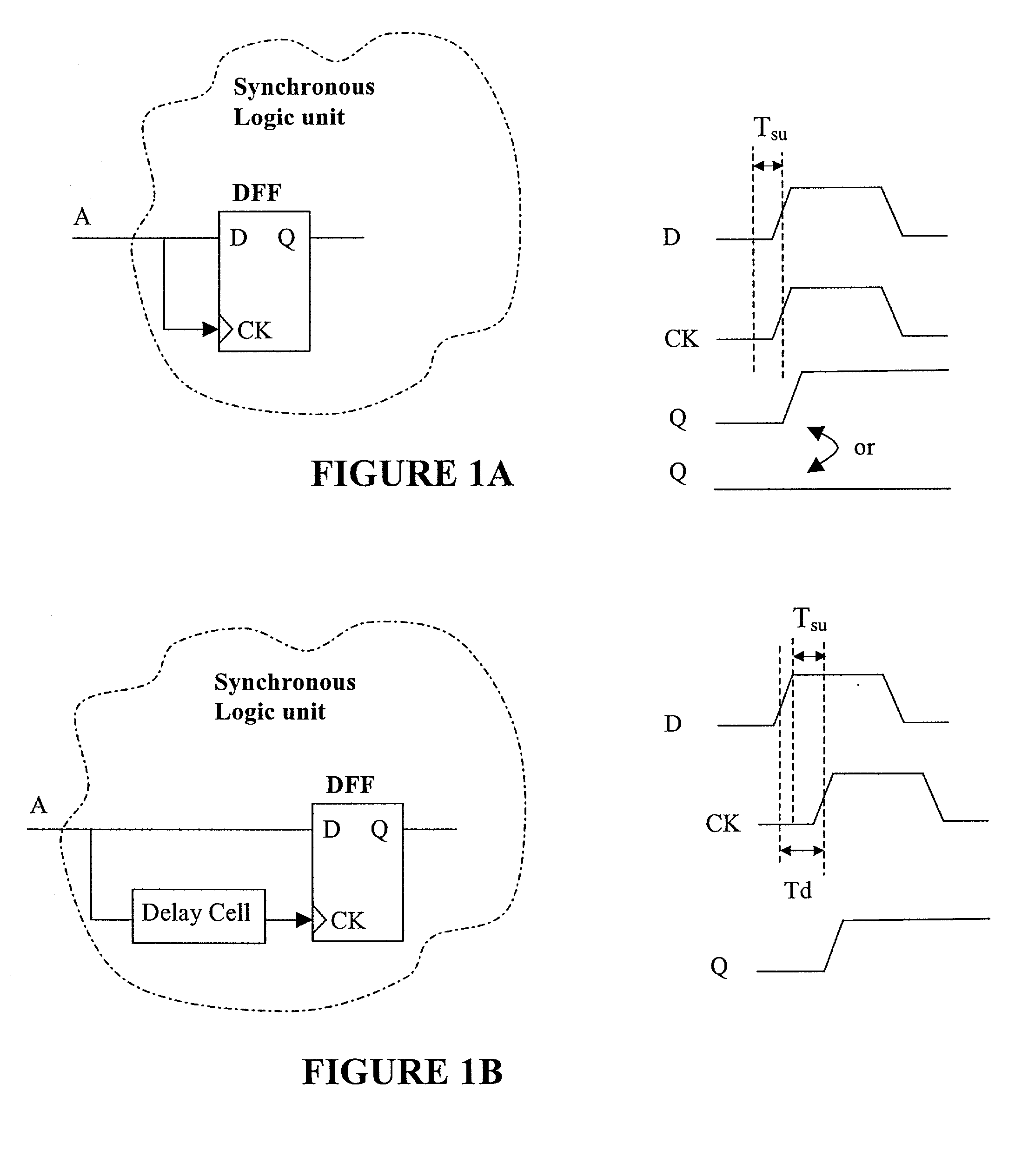

Digital delay locked loop

An improved edge-triggered fully digital delay locked loop (DLL), which maintains reliable synchronization from startup and in spite of system clock jitter is described. An internal clock signal is synchronized with a reference clock signal by propagating the reference clock signal through a variable digital delay path. A wide phase detection region surrounds a selected rising edge of the internal clock signal. The DLL loop is open as long as the internal clock signal and a target edge of the reference clock signal are not simultaneously within the phase detection region. To achieve a DLL locked condition, the variable delay is increased from a minimum setting until the edge of the phase detection region is shifted in time just past the target edge of the reference clock. Once the DLL loop has been closed, a clock jitter filter is enabled to reject reference clock jitter effects on the DLL locked condition. A digital phase detector controls the delay line propagation delay to establish synchronization between the internal clock and the reference clock. Unused delay elements within the variable delay path are deactivated to save power.

Owner:CONVERSANT INTPROP MANAGEMENT INC

Digital delay locked loop

Owner:CONVERSANT INTPROP MANAGEMENT INC

Multimode system for calibrating a data strobe delay for a memory read operation

InactiveUS6889334B1Allow in applicationAllow in useElectronic circuit testingCode conversionComputer moduleMemory controller

A system for coordinating the timing of a data strobe with data supplied by a memory module to the memory controller read data FIFO of a processor-based system, providing multiple calibration modes. A calibration PDL (programmable delay line) is used to reiteratively test the time taken for a test data strobe to traverse a portion of the memory controller circuit, and to generate a calibration value based upon the time taken. The calibration procedure may be initiated in any one of several modes, including: according to a predetermined schedule; implemented in software; in response to changes in environmental factors such as temperature or voltages sampled at one or more locations; in response to a software-driven trigger; or in response to a user-initiated trigger, communicated to a system of the invention either by input via a user interface to the processor-based system or by a software command.

Owner:ADVANCED MICRO DEVICES INC

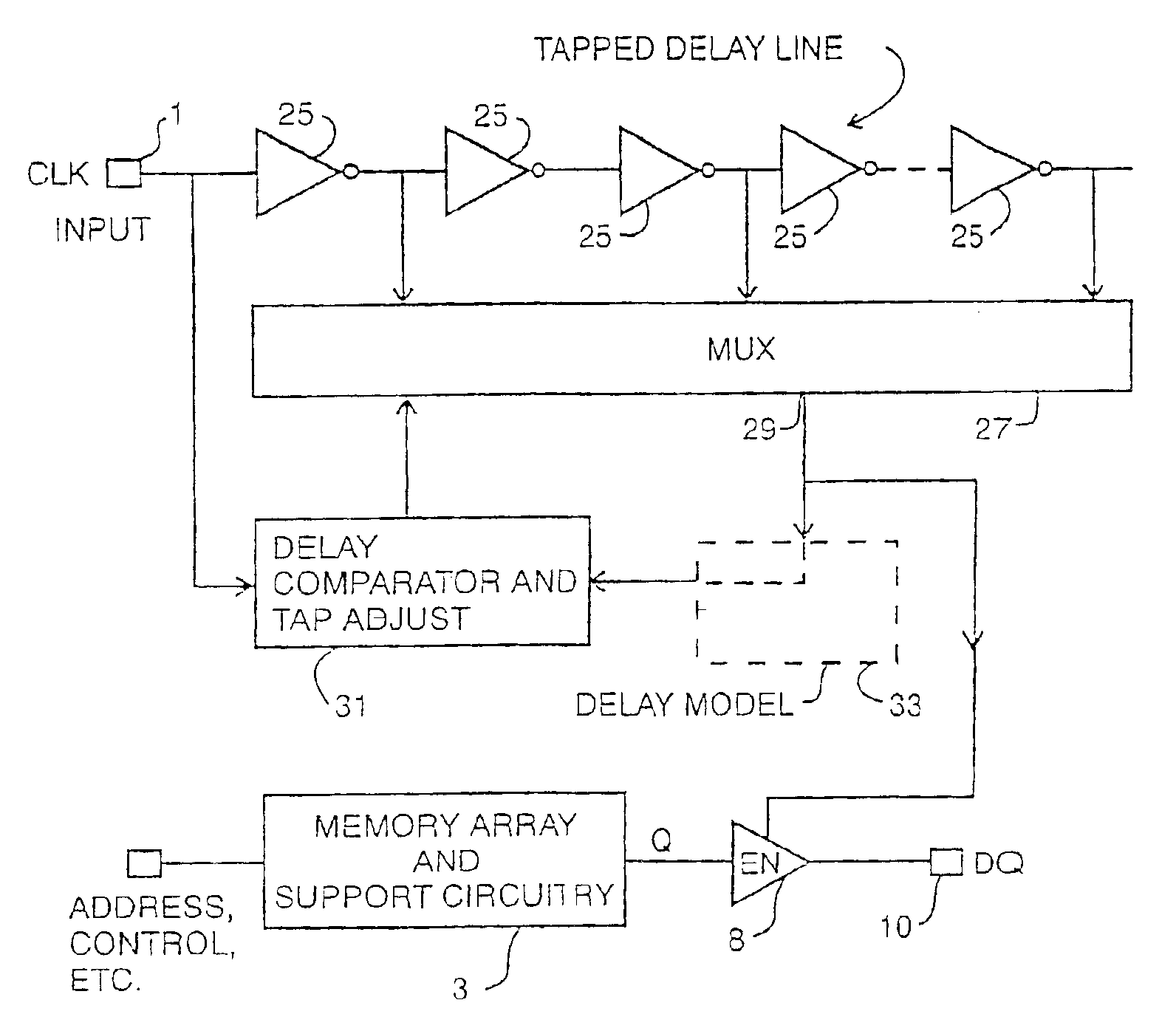

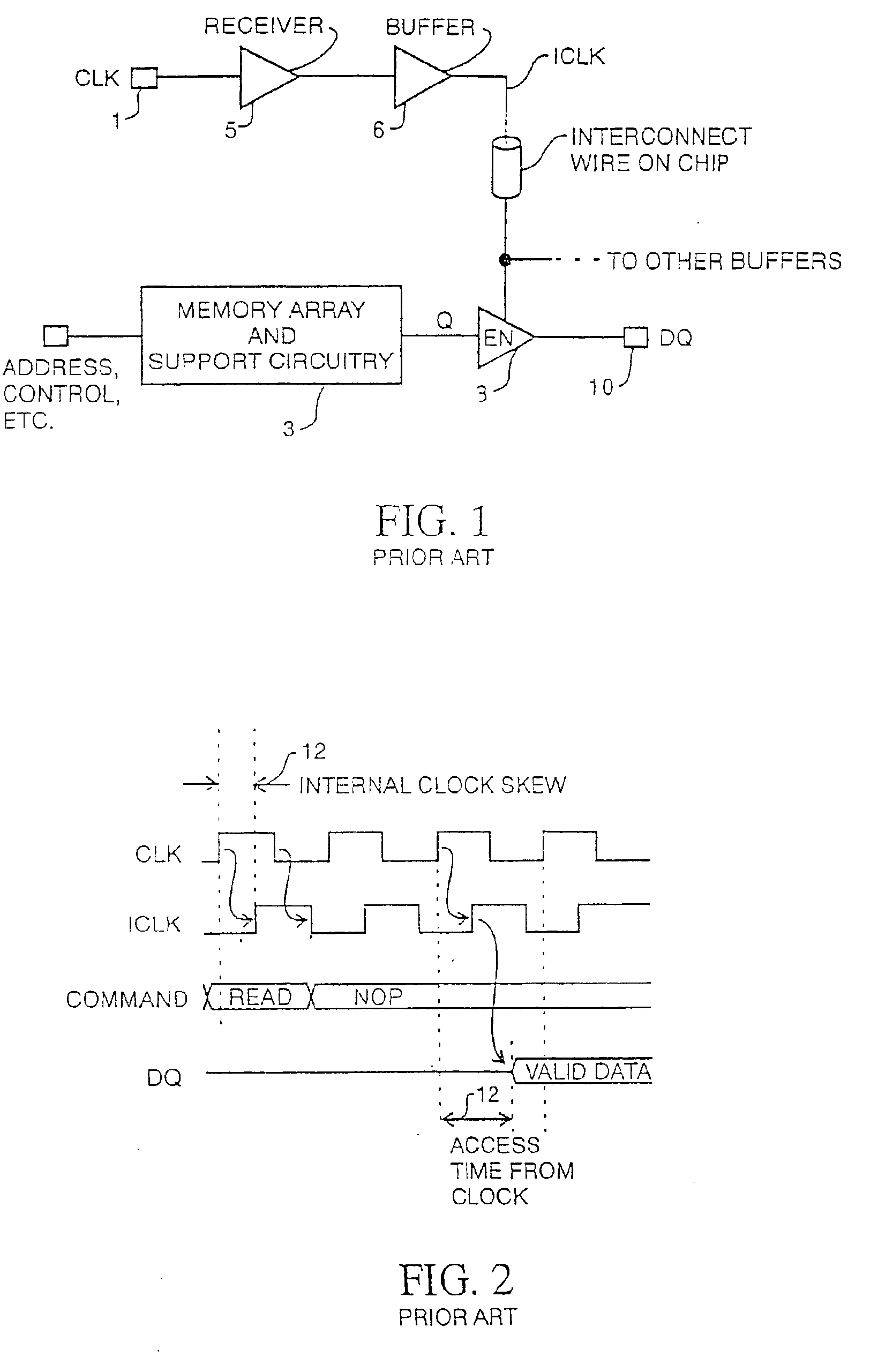

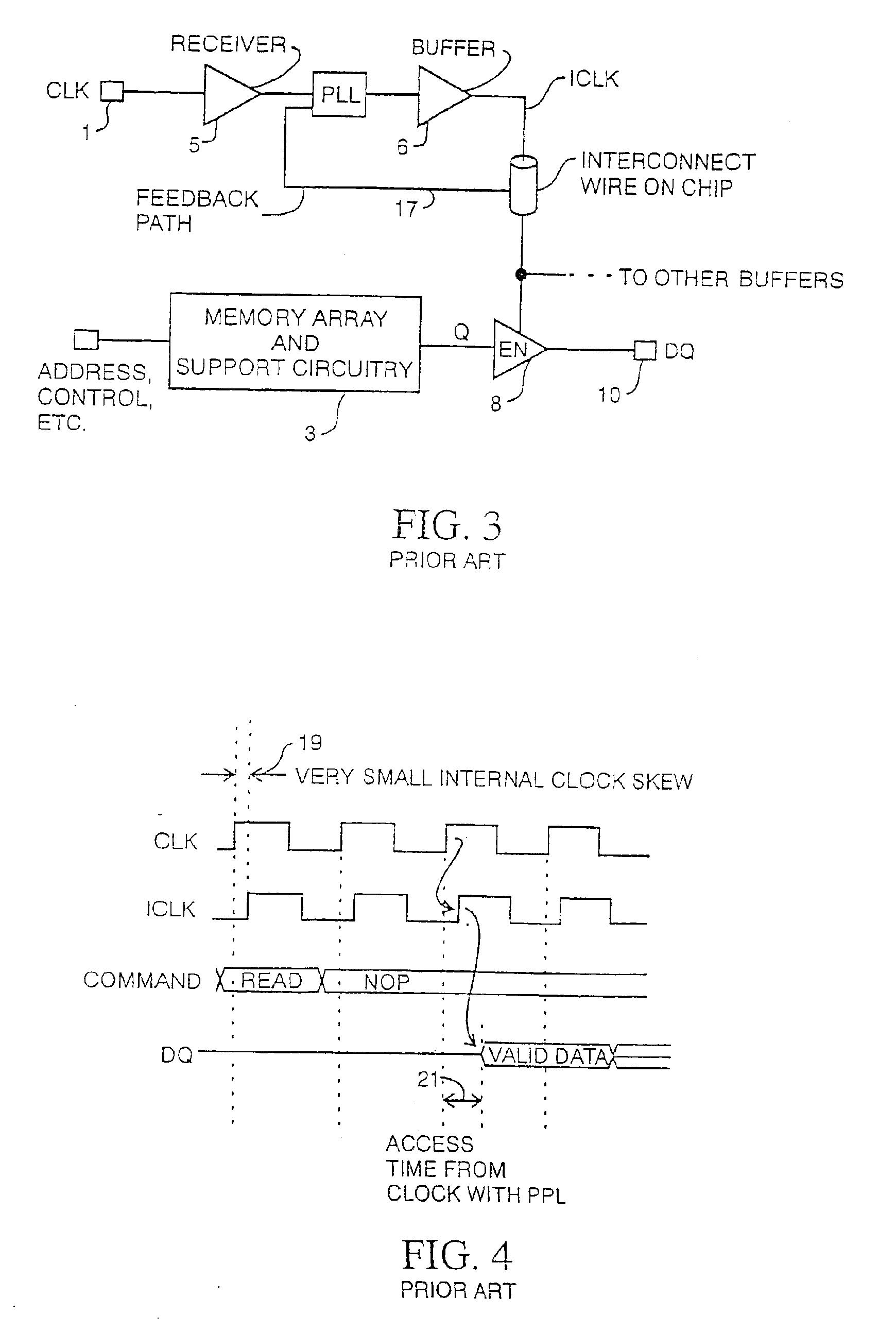

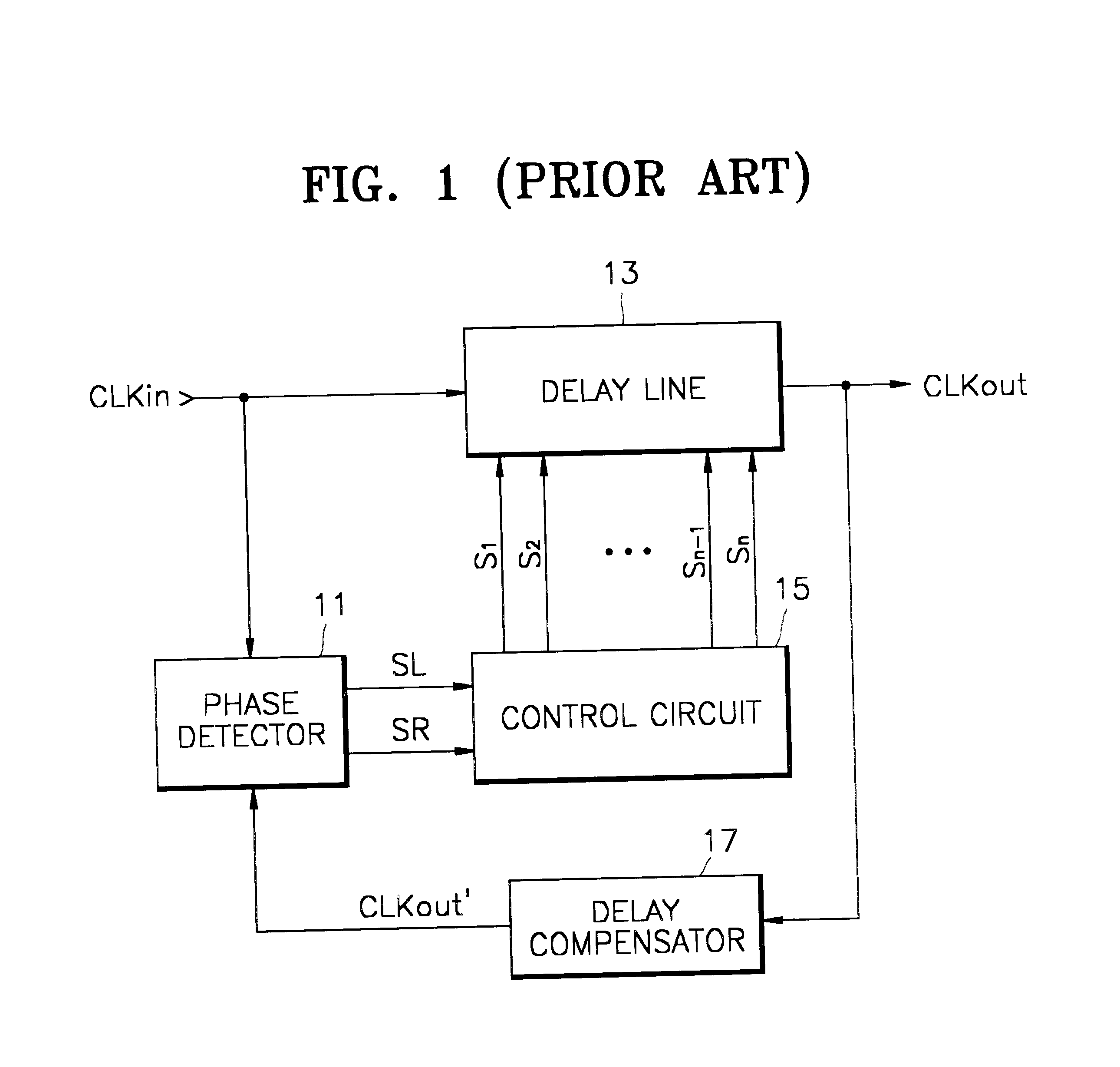

Delay locked loop implementation in a synchronous dynamic random access memory

InactiveUS6992950B2High operating requirementsLess standby current and start-up timePulse automatic controlSingle output arrangementsRandom access memoryDelay-locked loop

Owner:CONVERSANT INTPROP MANAGEMENT INC

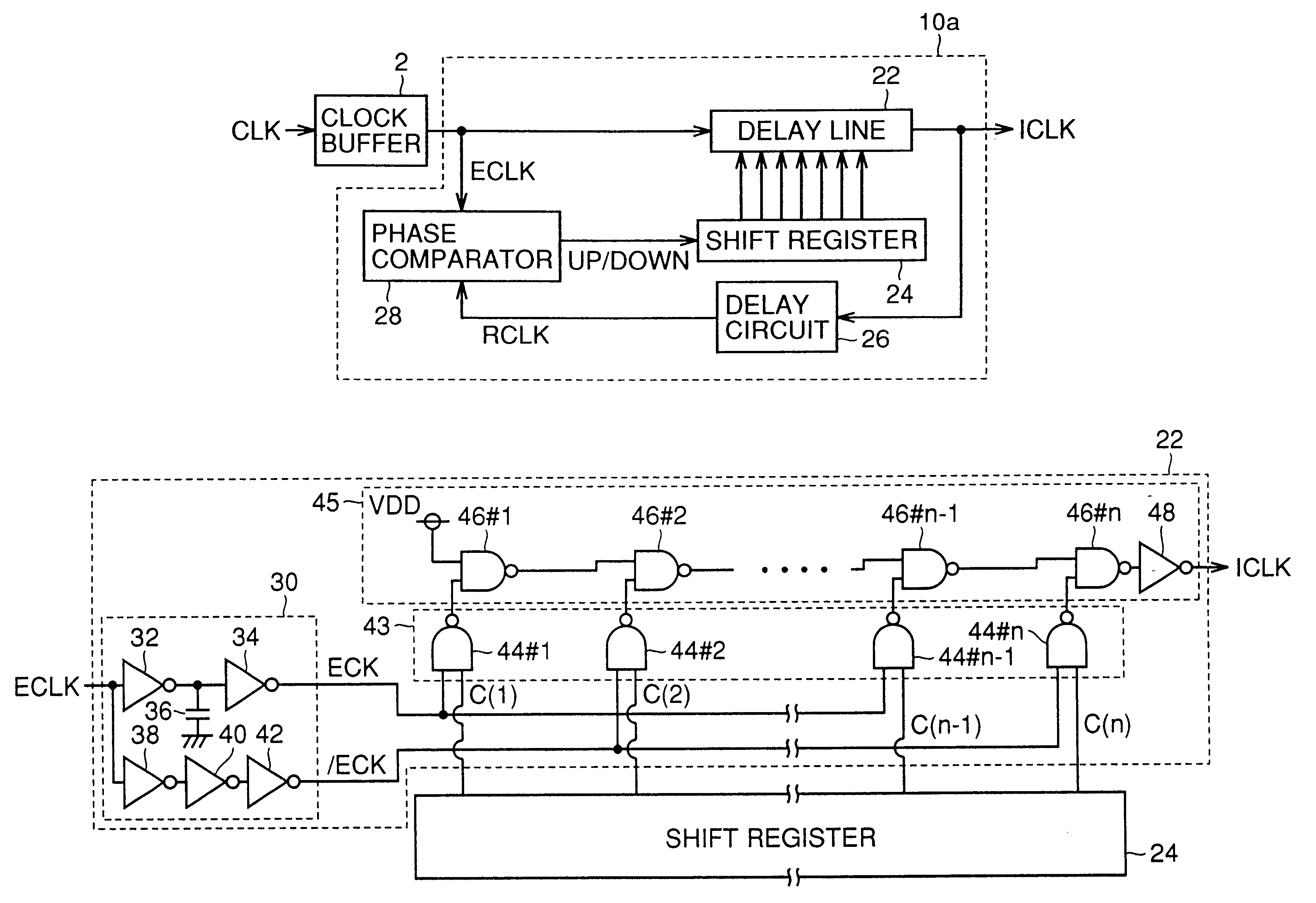

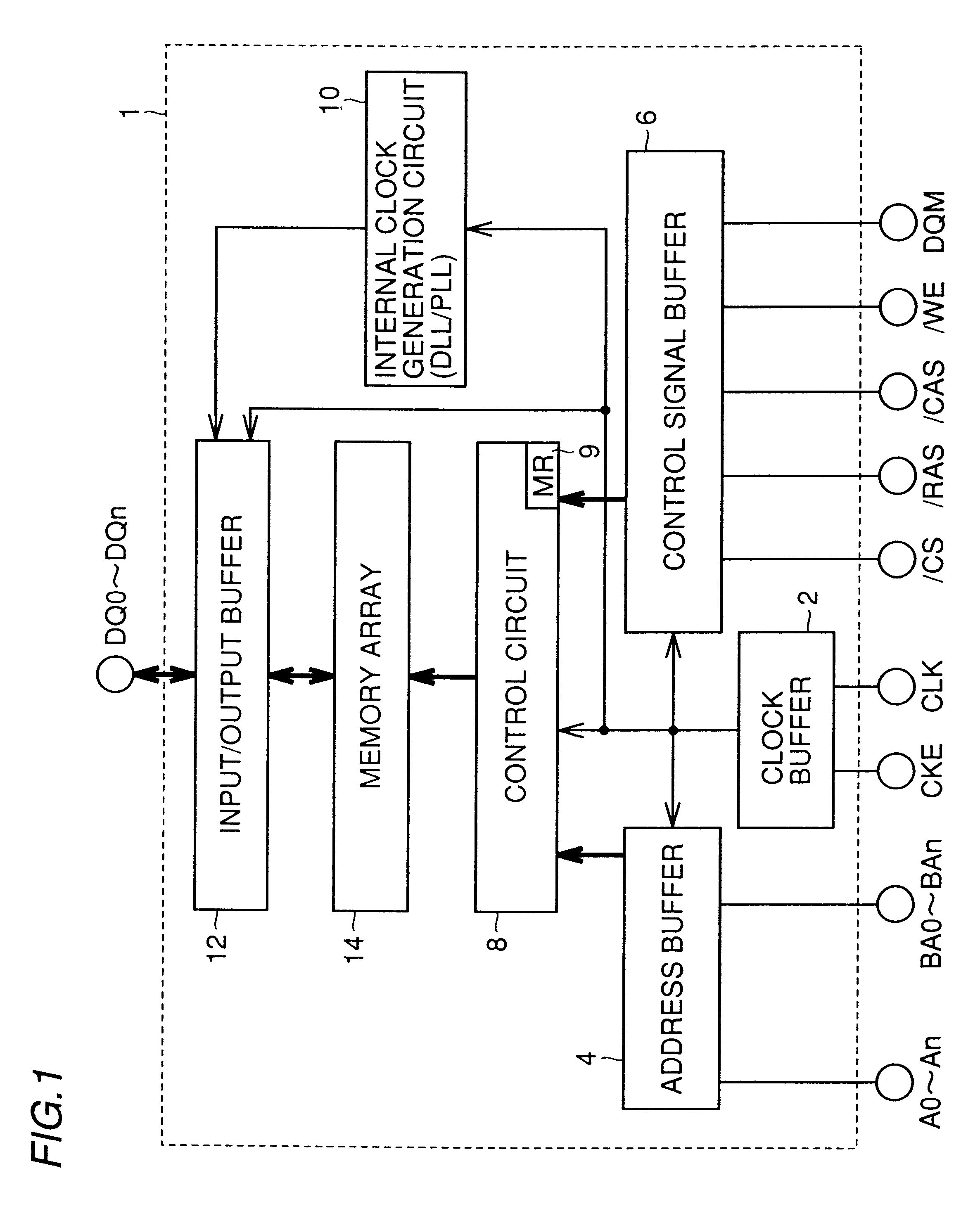

Semiconductor device capable of generating highly precise internal clock

A DLL circuit includes a delay line having a configuration with delay stages receiving alternate complementary clock signals ECK and / ECK having an adjusted phase difference therebetween. A capacitor can be used to adjust the phase difference between signals ECK and / ECK to allow the delay line to provide an amount of delay varying minutely. Preferably, for a fast clock, delay adjustment starts with a shift register having an initial value providing an intermediate amount of delay, and for a slow clock, delay adjustment starts with the shift register having an initial value providing a minimal amount of delay. There can be provided a semiconductor device provided with a DLL circuit accommodating a fast clock with reduced jitter.

Owner:MITSUBISHI ELECTRIC CORP

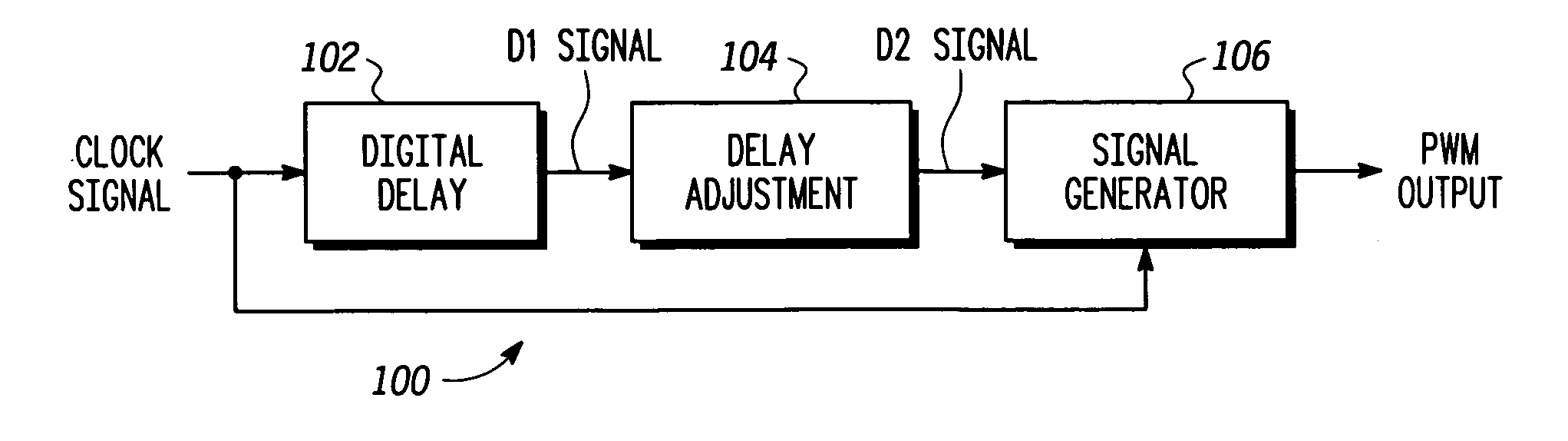

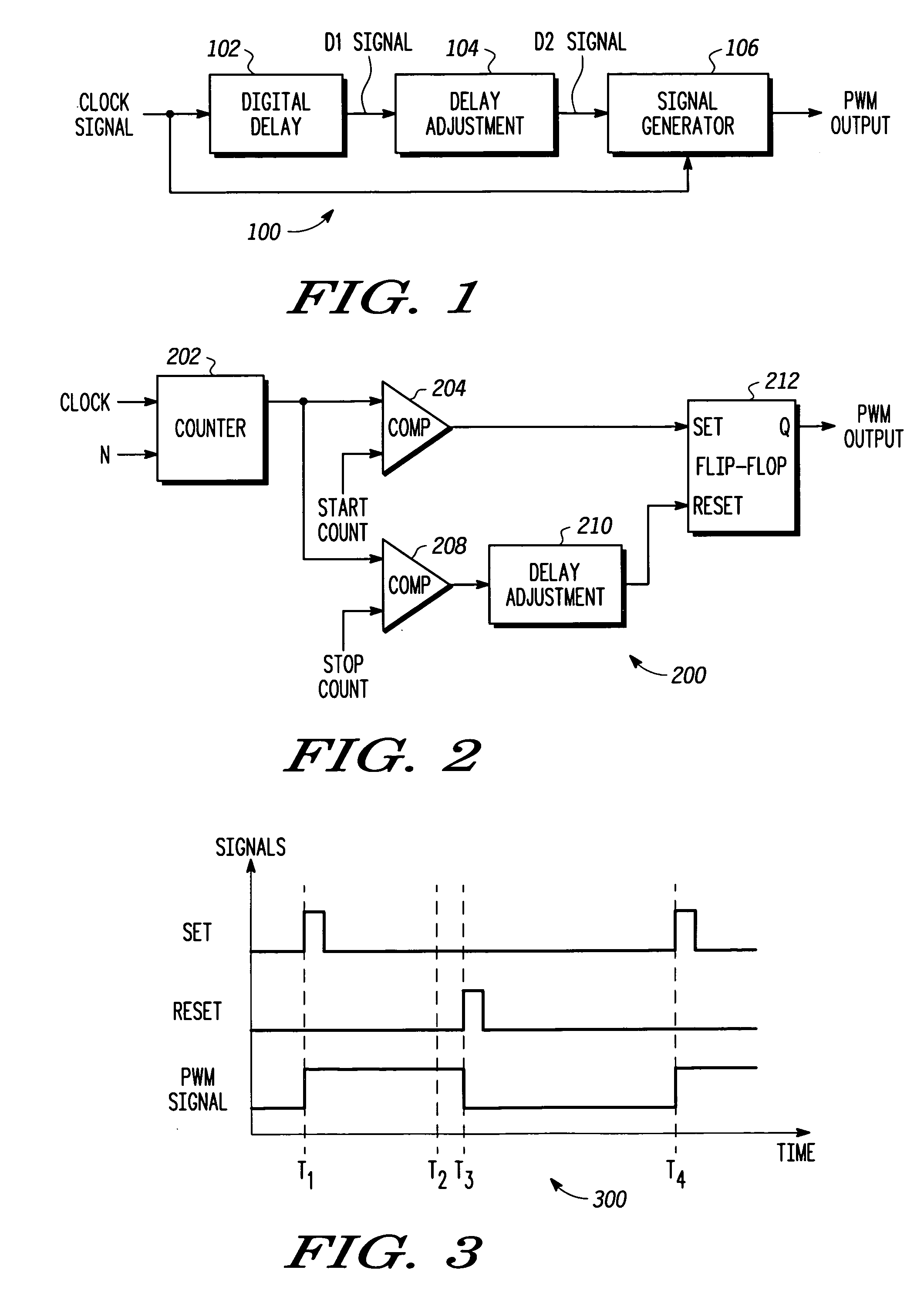

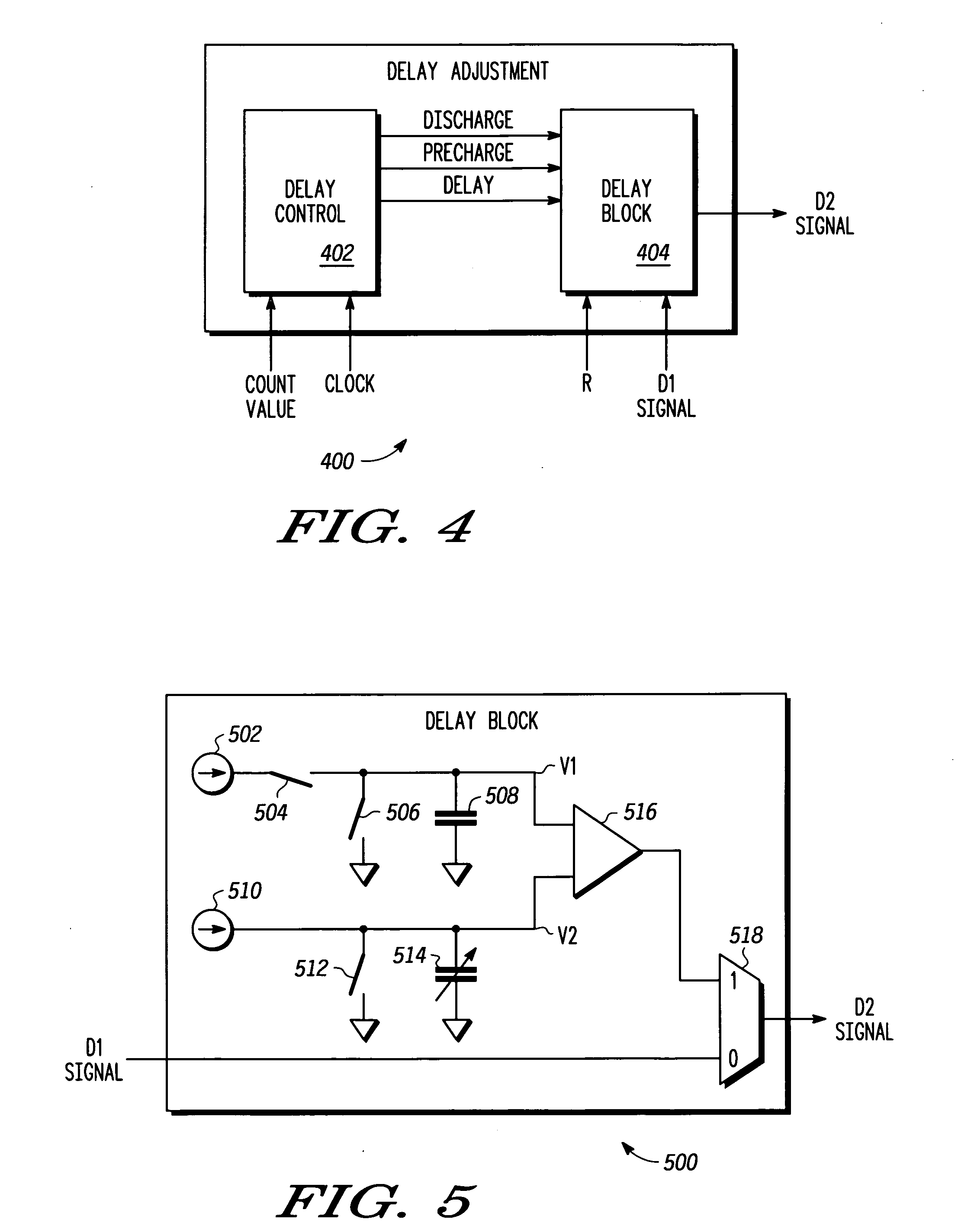

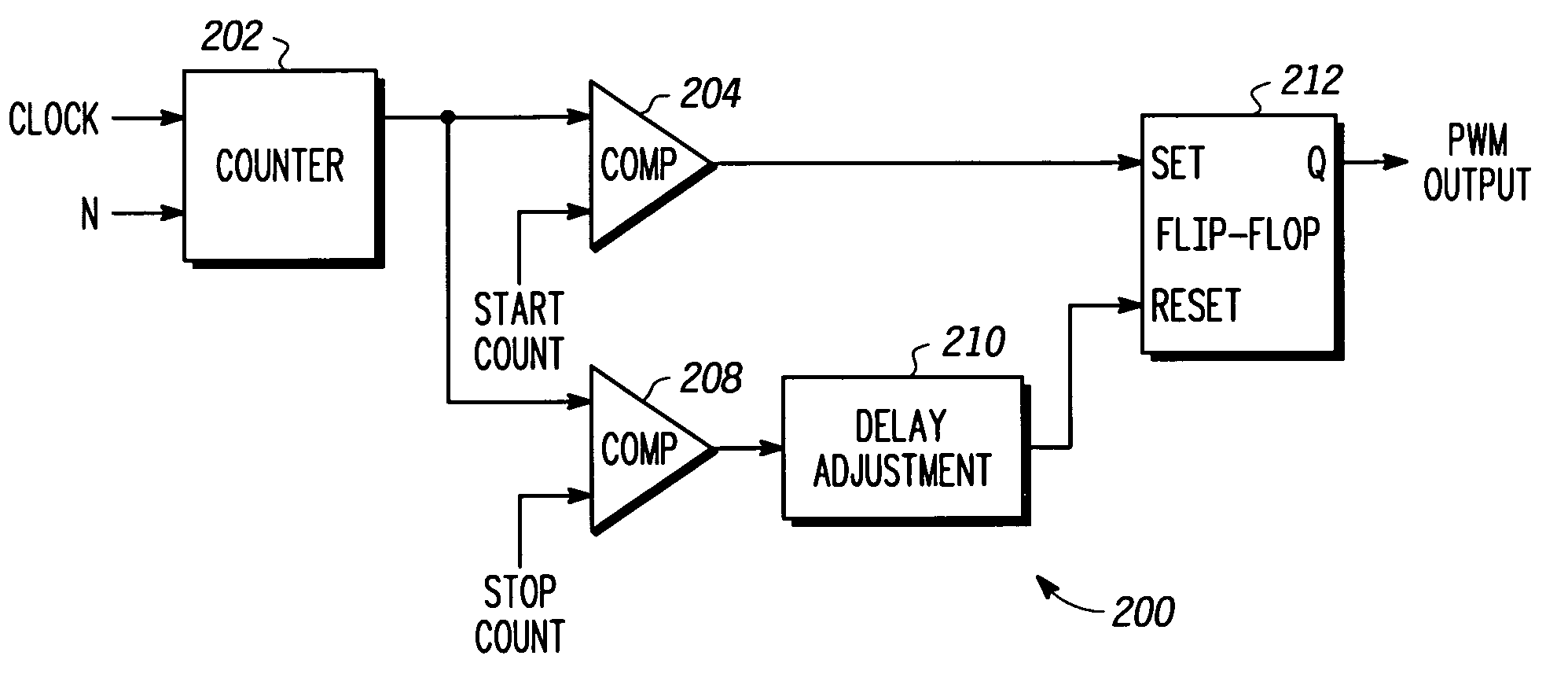

High resolution pulse width modulator

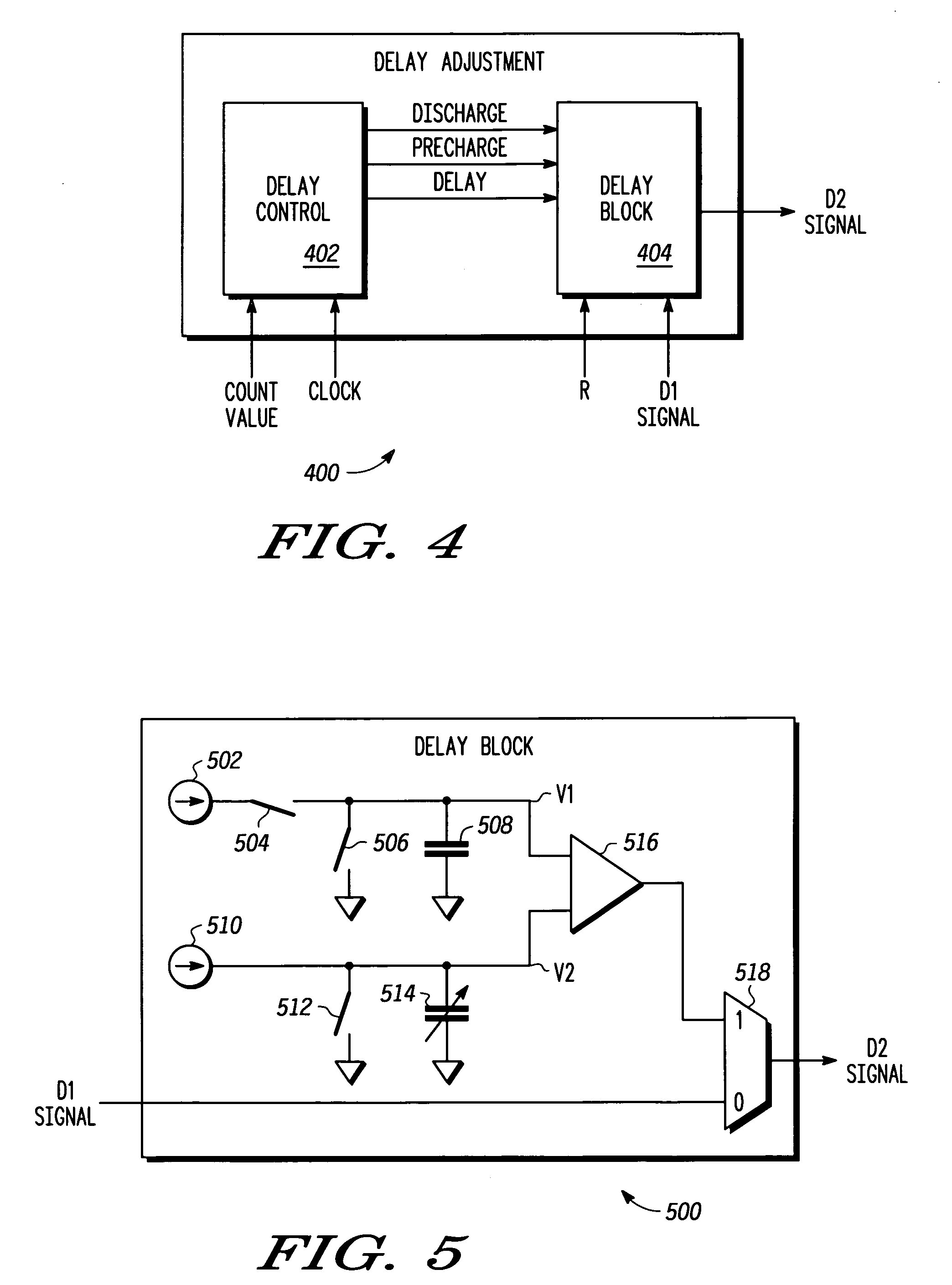

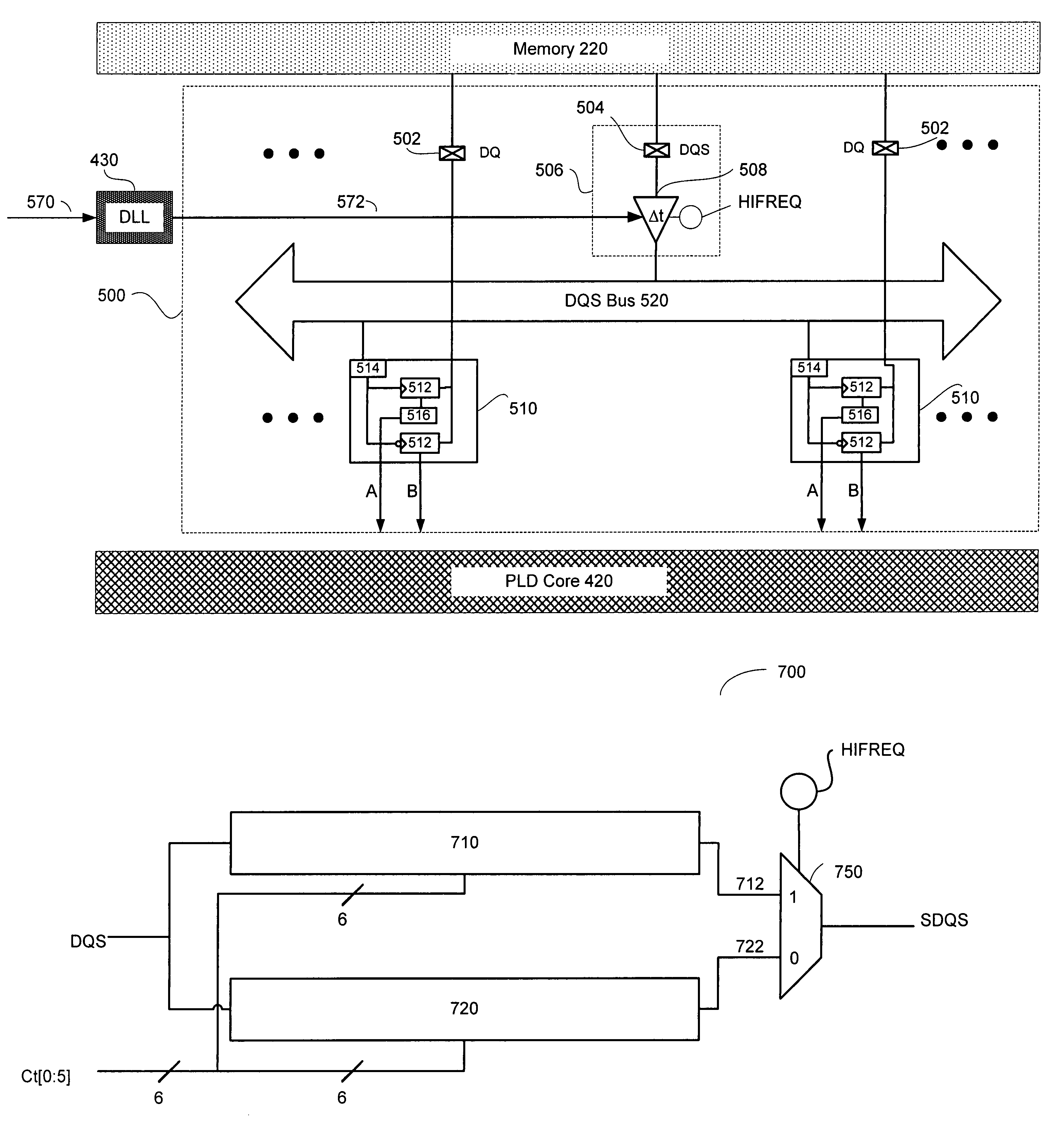

A pulse width modulator (100) and method that facilitates high resolution pulse width modulation is provided. The pulse width modulator (100) creates a pulse width modulated signal having a duty cycle that is proportional to a controllable delay in the modulator. The pulse width modulator combines a first digitally controllable delay (102) with a delay adjustment (104) to provide the controllable delay. In one embodiment, a digital counter (202) is used to provide coarse delay, with the delay adjustment device (210) coupled to the digital counter (202) to provide the fine, high resolution, delay control. Together the digital counter (202) and delay adjustment device (210) provide high resolution pulse width modulation. In one particular implementation, the analog delay adjustment device (100) comprises a delay block (500) designed to provide delay adjustment that is selectively controllable by changing a capacitance in the device.

Owner:APPLE INC

High resolution pulse width modulator

A pulse width modulator (100) and method that facilitates high resolution pulse width modulation is provided. The pulse width modulator (100) creates a pulse width modulated signal having a duty cycle that is proportional to a controllable delay in the modulator. The pulse width modulator combines a first digitally controllable delay (102) with a delay adjustment (104) to provide the controllable delay. In one embodiment, a digital counter (202) is used to provide coarse delay, with the delay adjustment device (210) coupled to the digital counter (202) to provide the fine, high resolution, delay control. Together the digital counter (202) and delay adjustment device (210) provide high resolution pulse width modulation. In one particular implementation, the analog delay adjustment device (100) comprises a delay block (500) designed to provide delay adjustment that is selectively controllable by changing a capacitance in the device.

Owner:APPLE INC

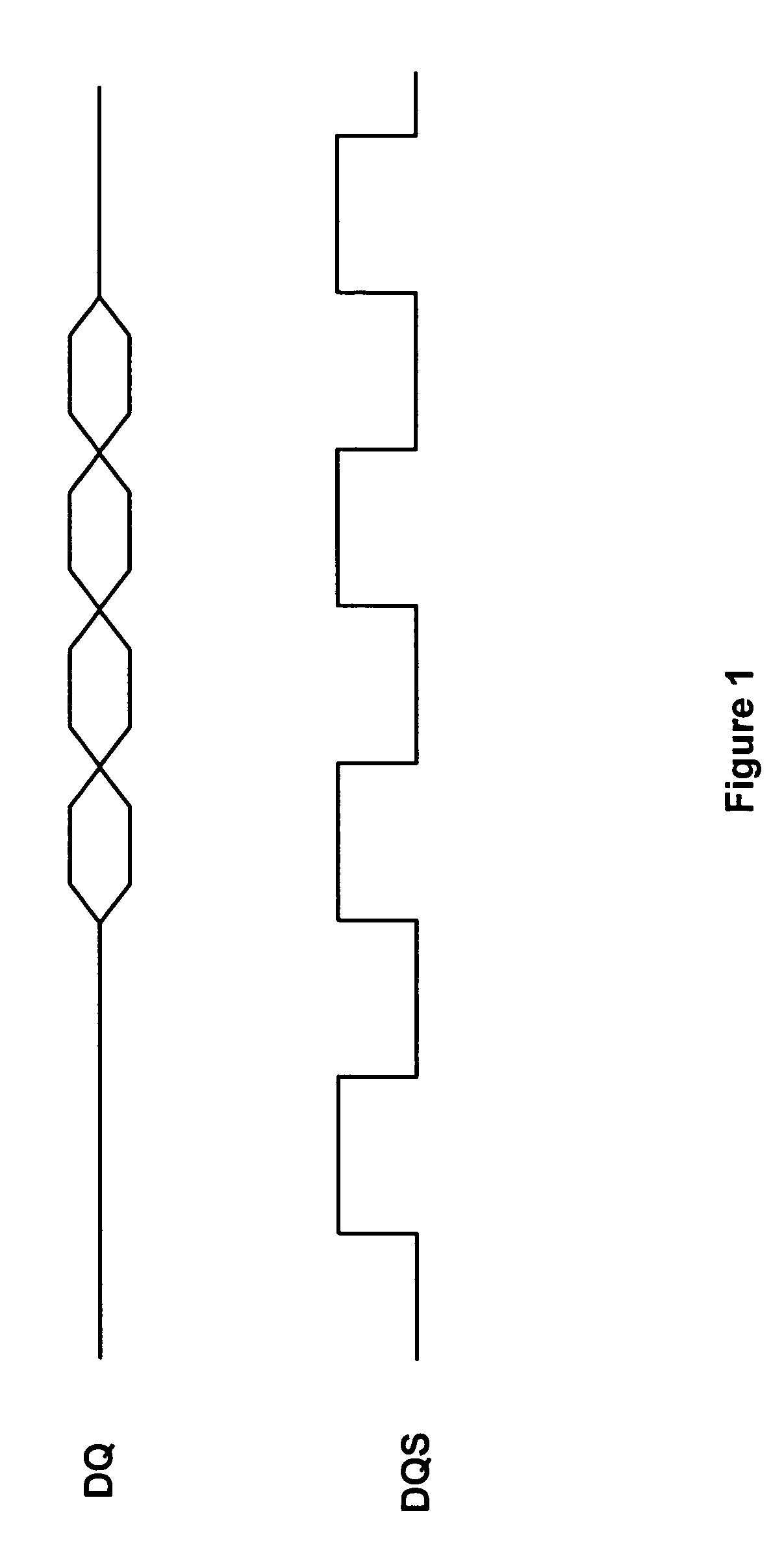

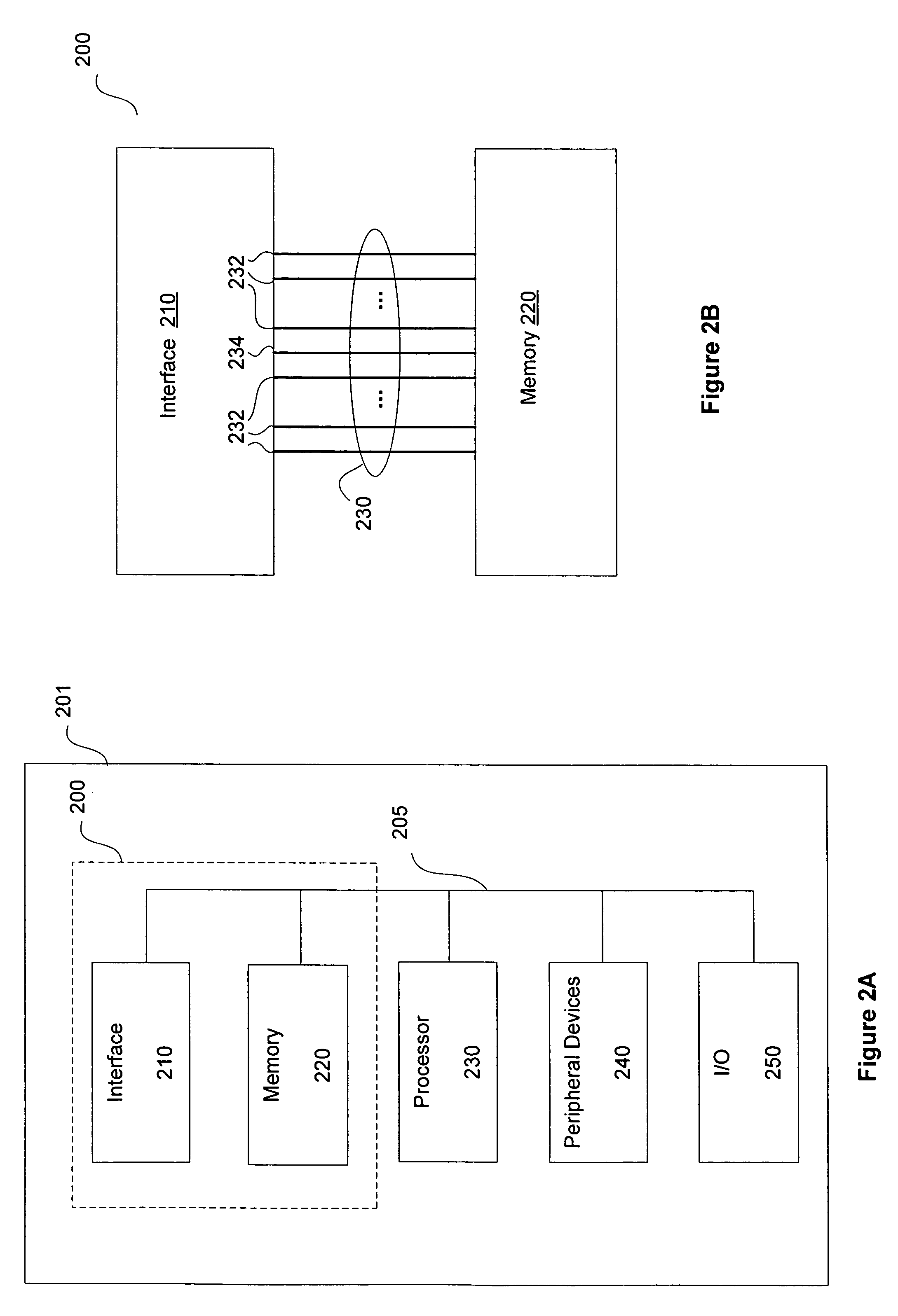

Memory interface phase-shift circuitry to support multiple frequency ranges

The present invention provides a phase shift circuit that supports multiple frequency ranges. The phase shift circuit receives a plurality of control bits and causes a phase shift in a received signal, the phase shift corresponding to a number of time steps, the number depending on the control bits, and the time step is selected from a plurality of different time steps based on a frequency range associated with the received signal.

Owner:BROOKE LAWRENCE L +1

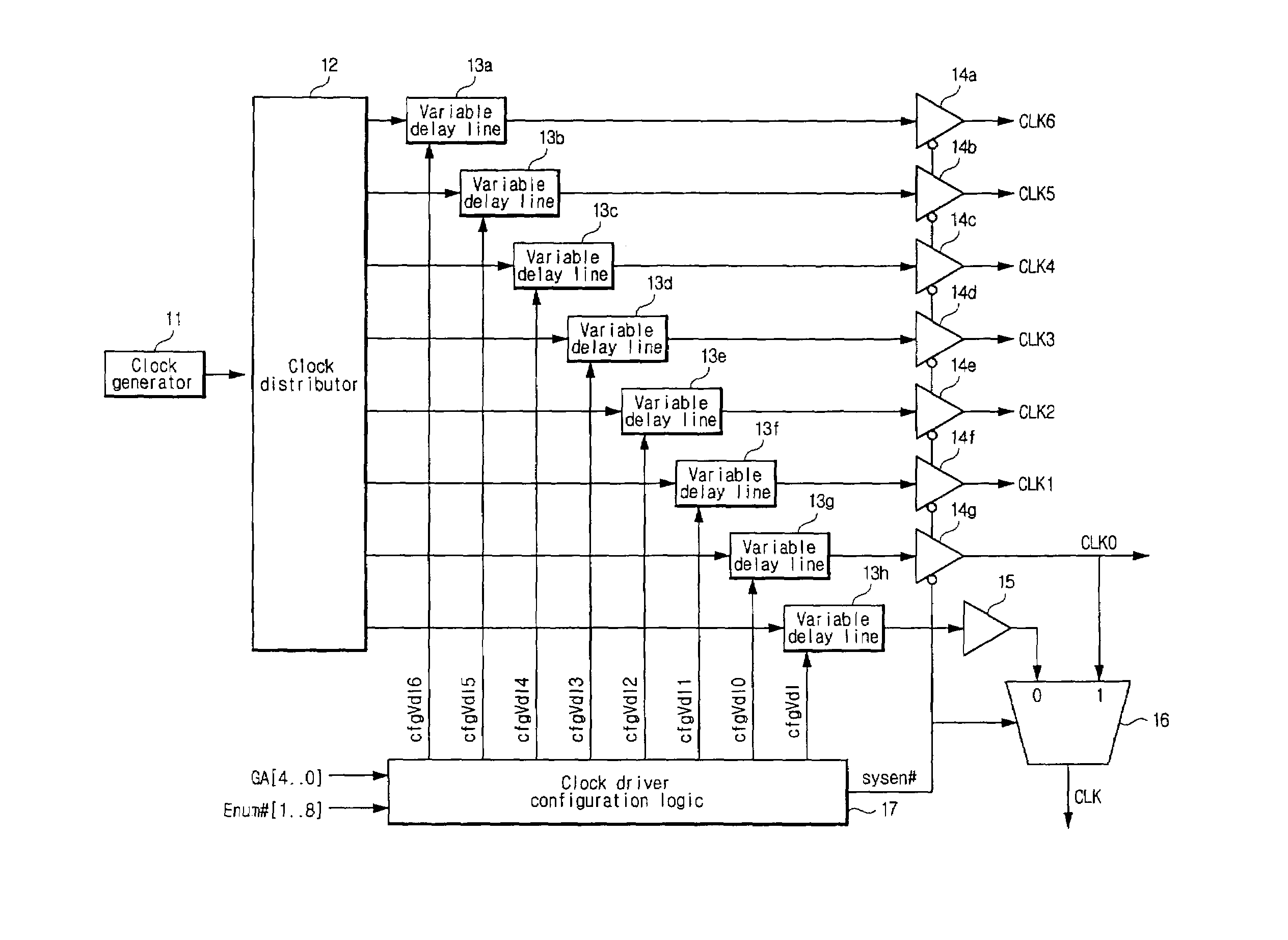

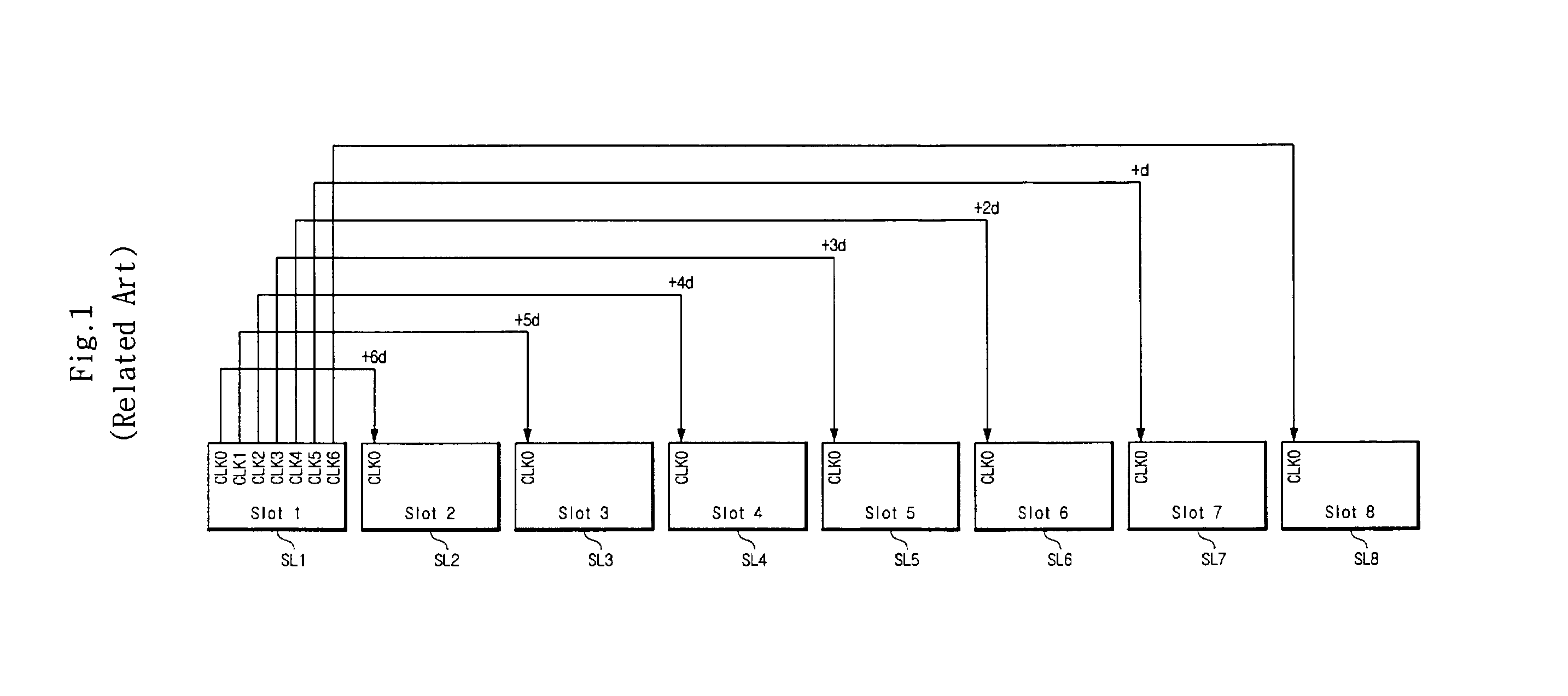

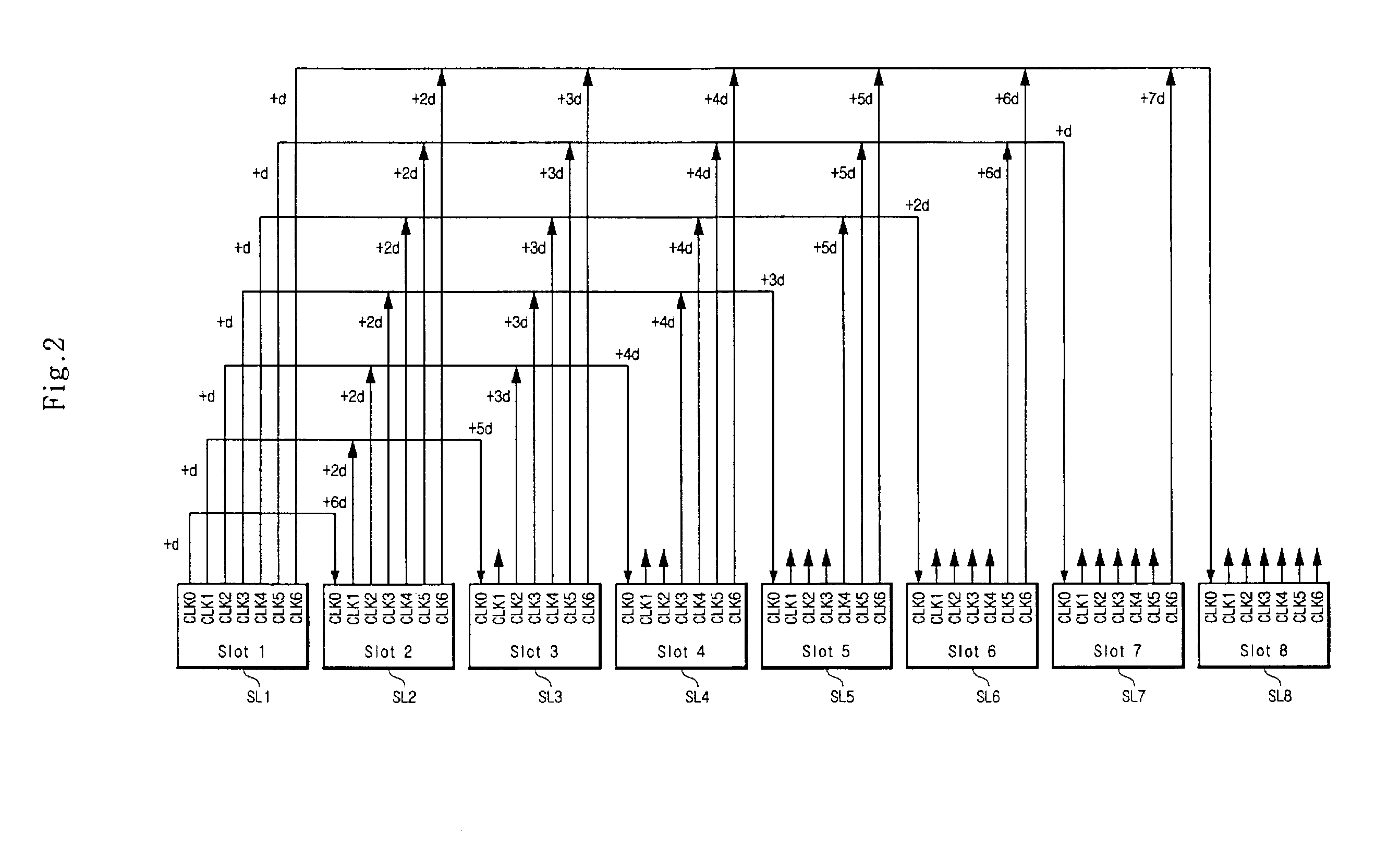

Clock distribution device and method in compact PCI based multi-processing system

InactiveUS7100066B2Skew of the clock transmitted to each slot may be minimizedMinimize skewTelevision system detailsPulse automatic controlHandling systemEmbedded system

Disclosed is a clock distribution device and method in a compact PCI system based multi-processing system. A compact PCI based multi-processing system preferably includes processing signals upon mounting various circuit boards on multiple slots, even if the location of the system slot is varied, the skew of clocks transmitted to the other slots may be minimized. Accordingly, the system may be configured in a flexible manner because of such variability of the system slot's location. Further, the system may be efficiently repaired and maintained because it is possible to easily and quickly take measures in response to any failure occurring on the board mounted on the system slot.

Owner:LG ERICSSON

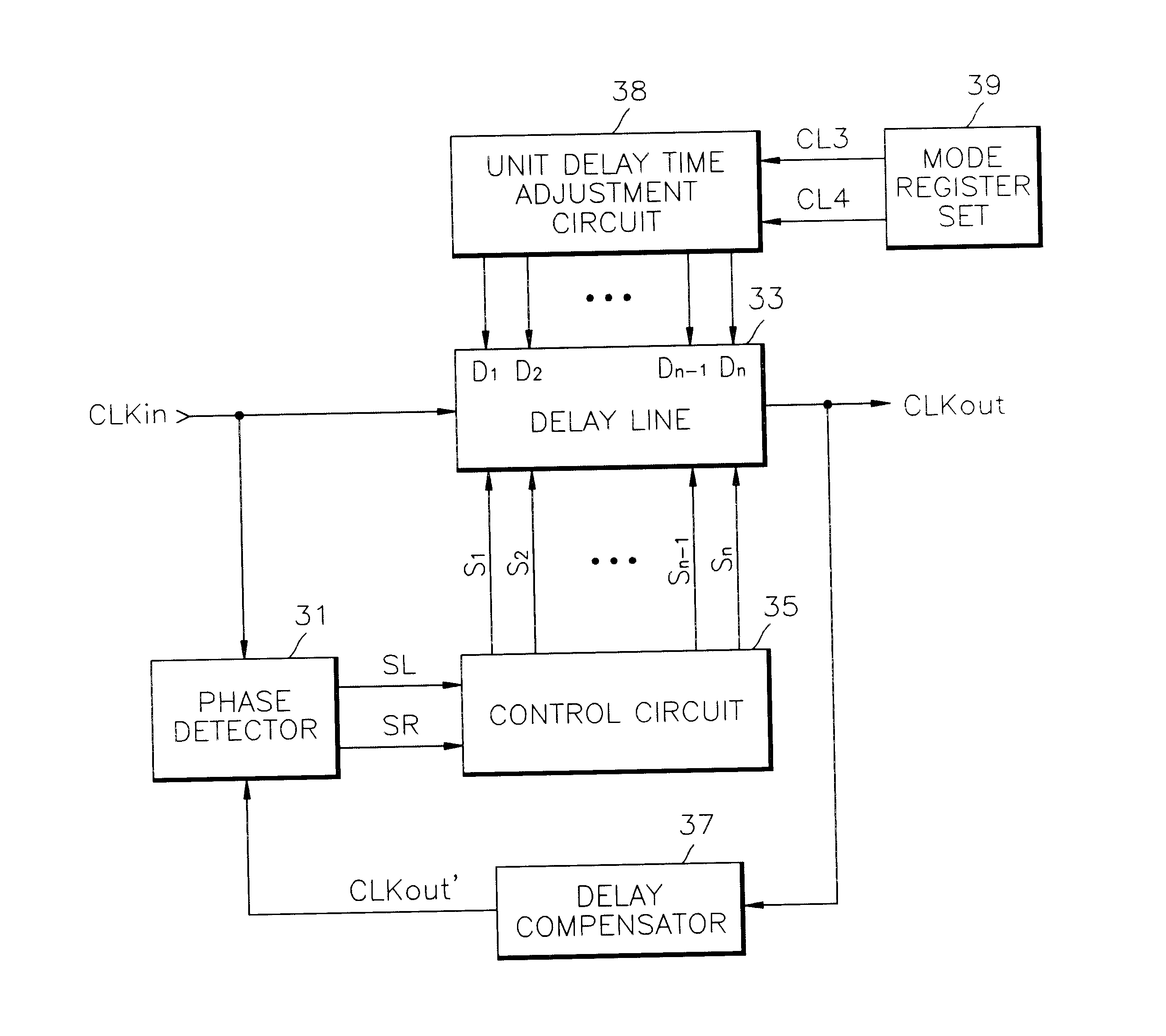

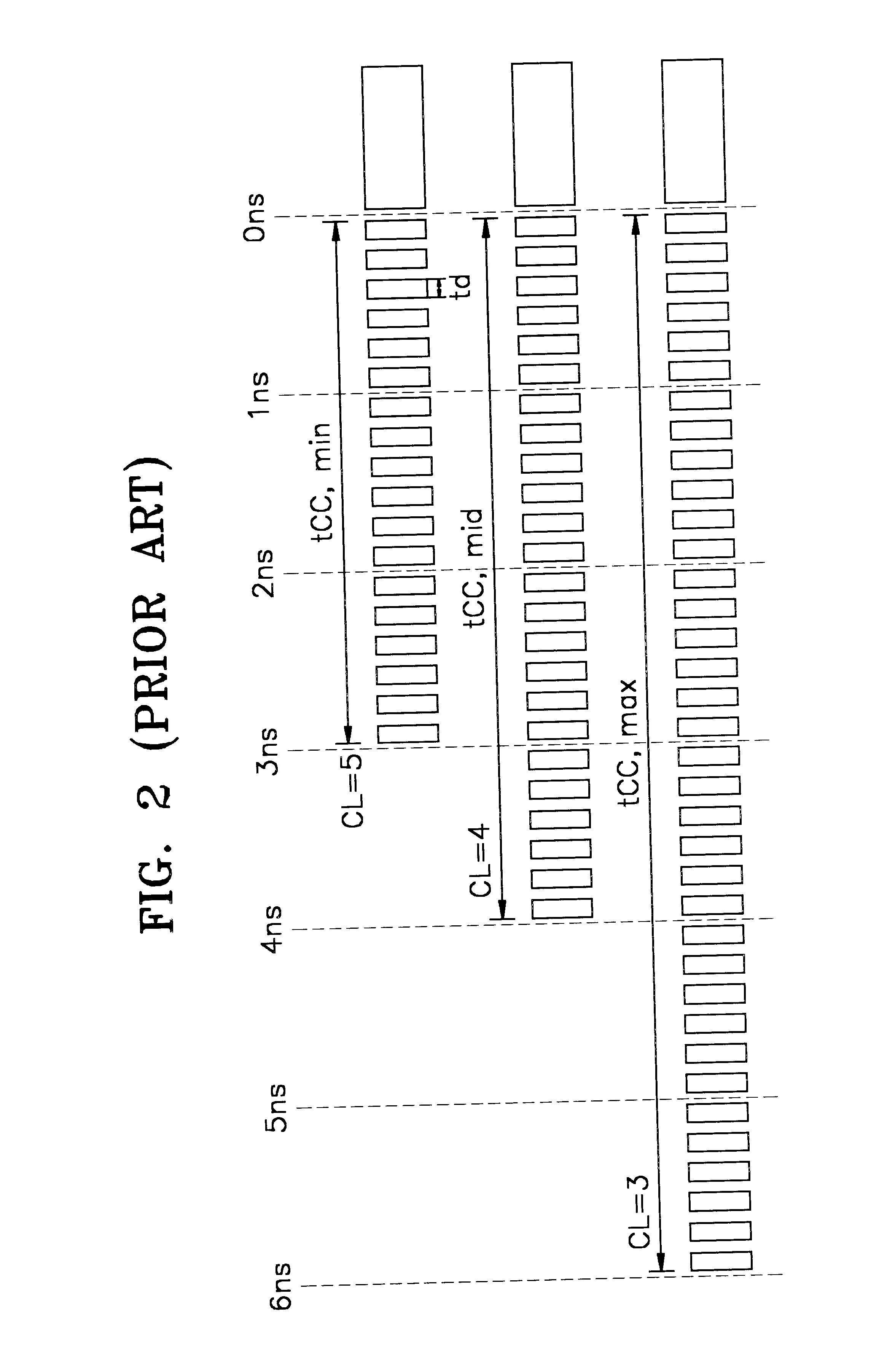

Delay locked loop circuit and method having adjustable locking resolution

A delay line receives an input clock signal and includes a cascaded plurality of unit delay circuits. A mode register set stores a value indicative of a column-address-strobe (CAS) latency of the memory device, and an adjustment circuit varies a delay time of the unit delay circuits according to the CAS latency stored in the mode register set. A phase detector detects a phase difference between the input clock signal and an output clock signal of the delay line, and a control circuit which controls an enabled state of the unit delay circuits according to an output of said phase detector.

Owner:SAMSUNG ELECTRONICS CO LTD

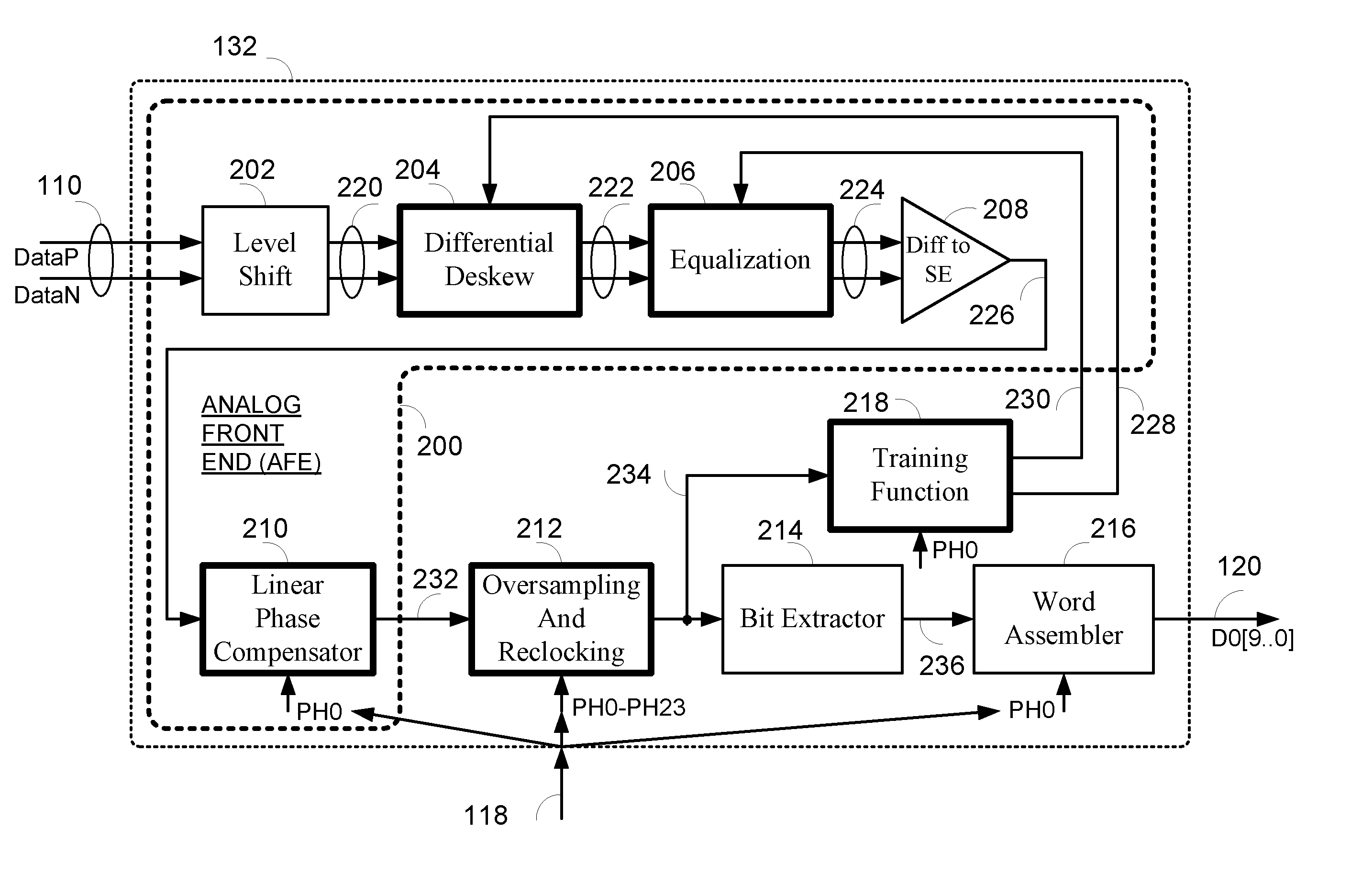

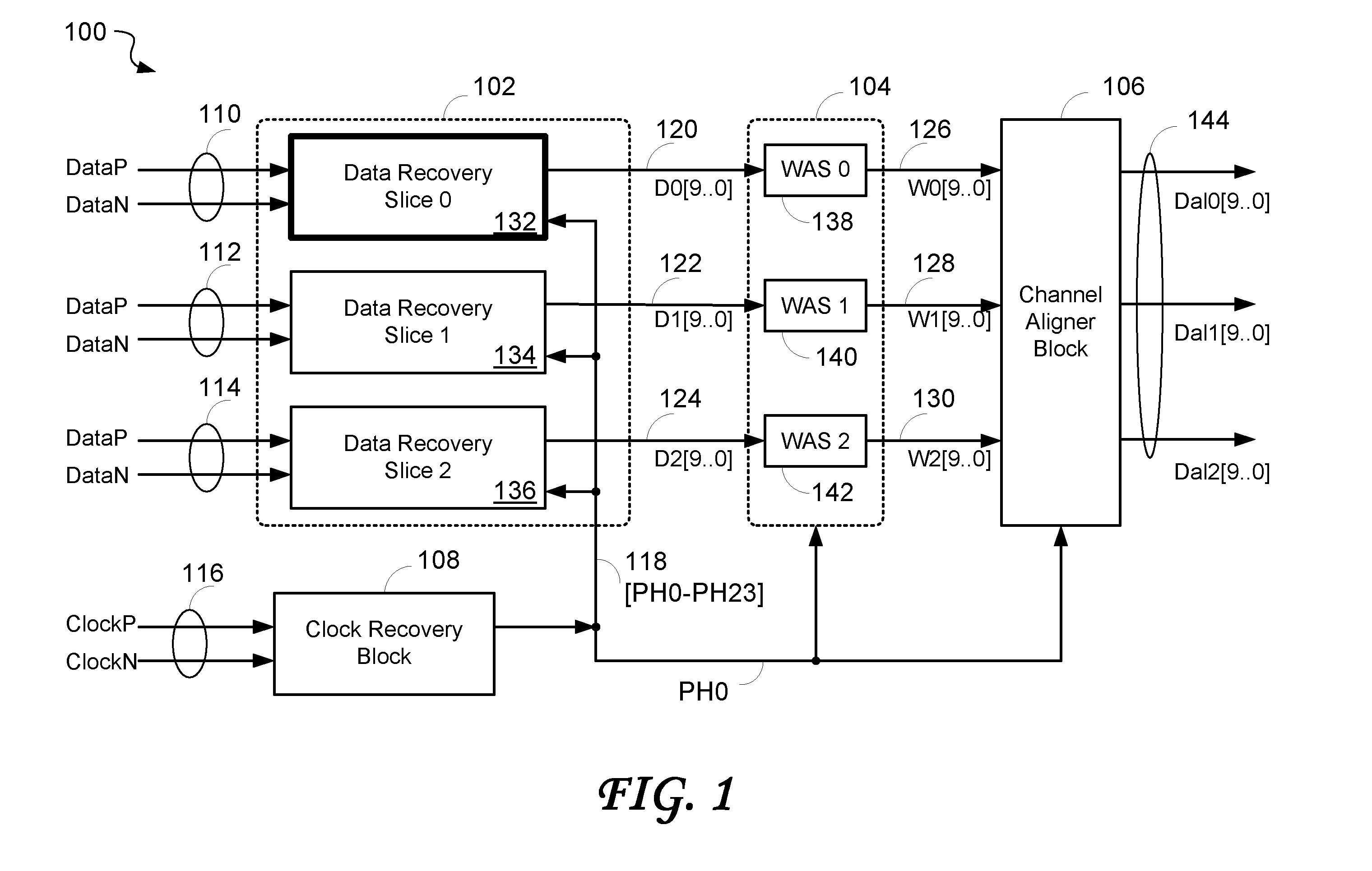

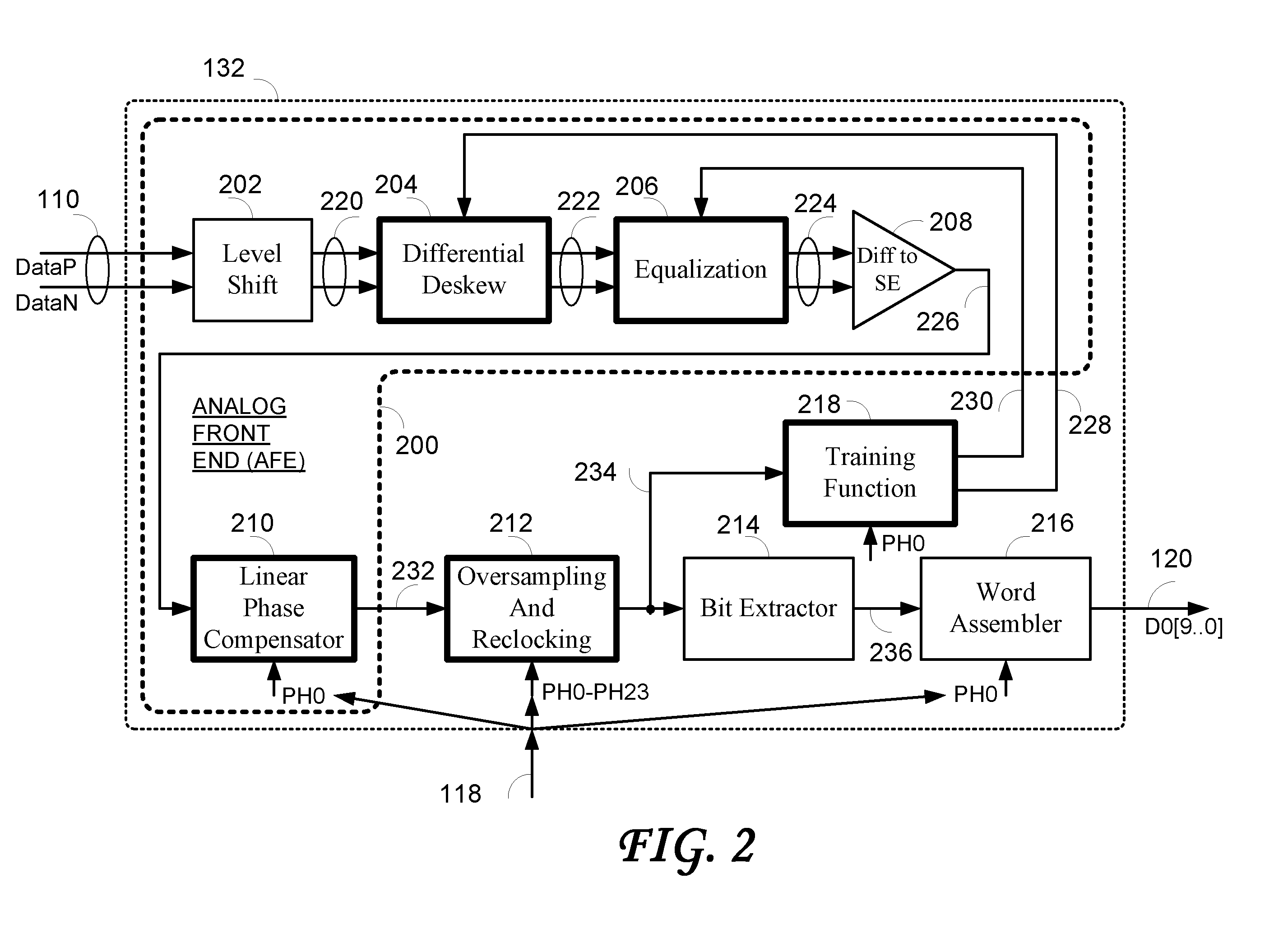

Data recovery system for source synchronous data channels

ActiveUS20070164802A1Easy Data RecoveryReduce distortion problemsModulated-carrier systemsPulse demodulator24-bitAnalog signal

A high-definition multimedia interface (HDMI) receiver recovers high speed encoded data which are transmitted differentially over data channels of a lossy cable, along with a clock. Inter symbol interference, high-frequency loss, skew between the clock and data channels, and differential skew within a differential signal are compensated by analog circuits which are automatically tuned for best performance by observing the quality of the recovered analog signal. Oversampling is used to provide a 24-bit digital representation of the analog signal for determining the quality of the signal. A corresponding method of deskewing a differential signal and a system and circuit therefor are also provided.

Owner:REDMERE TECH

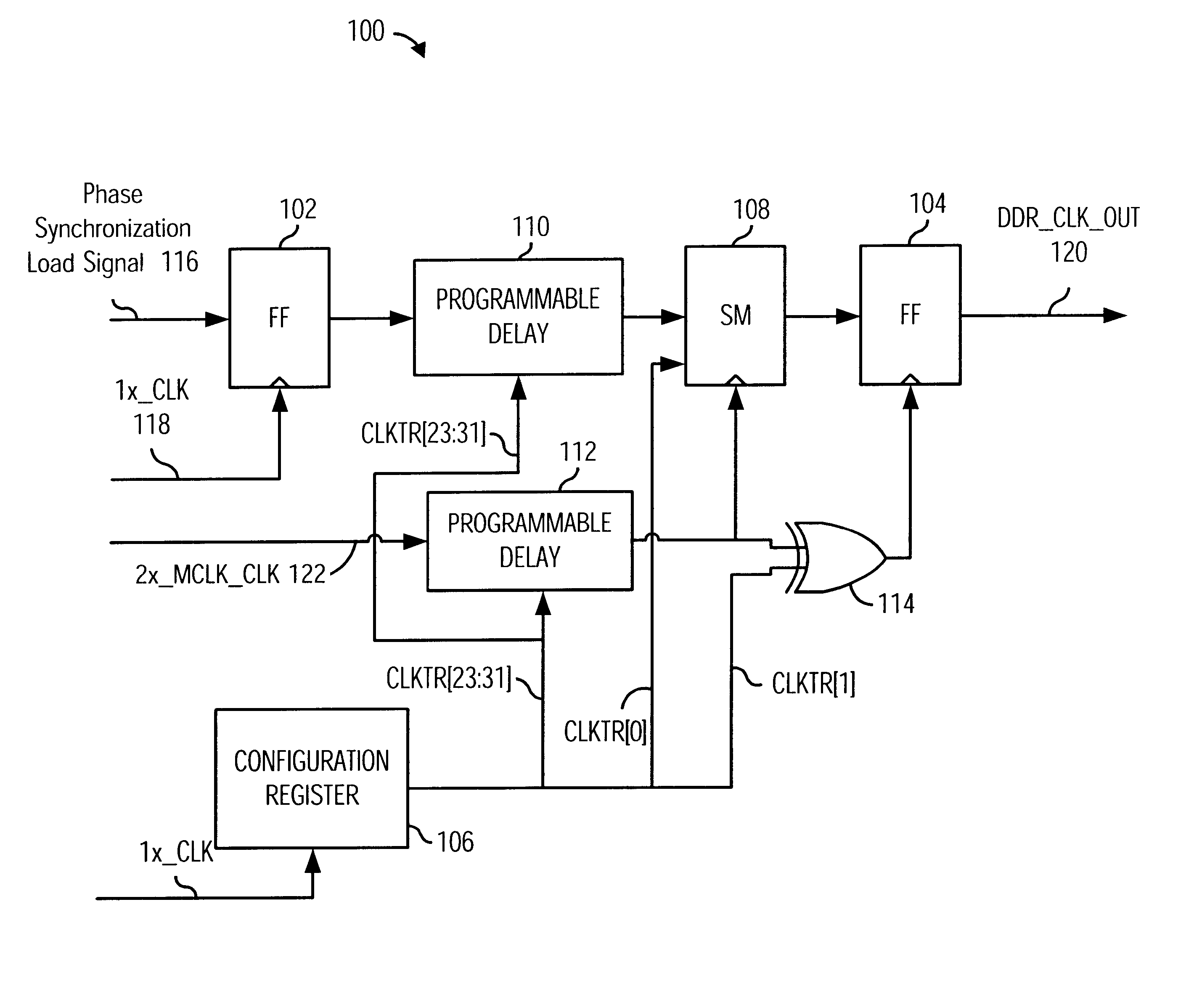

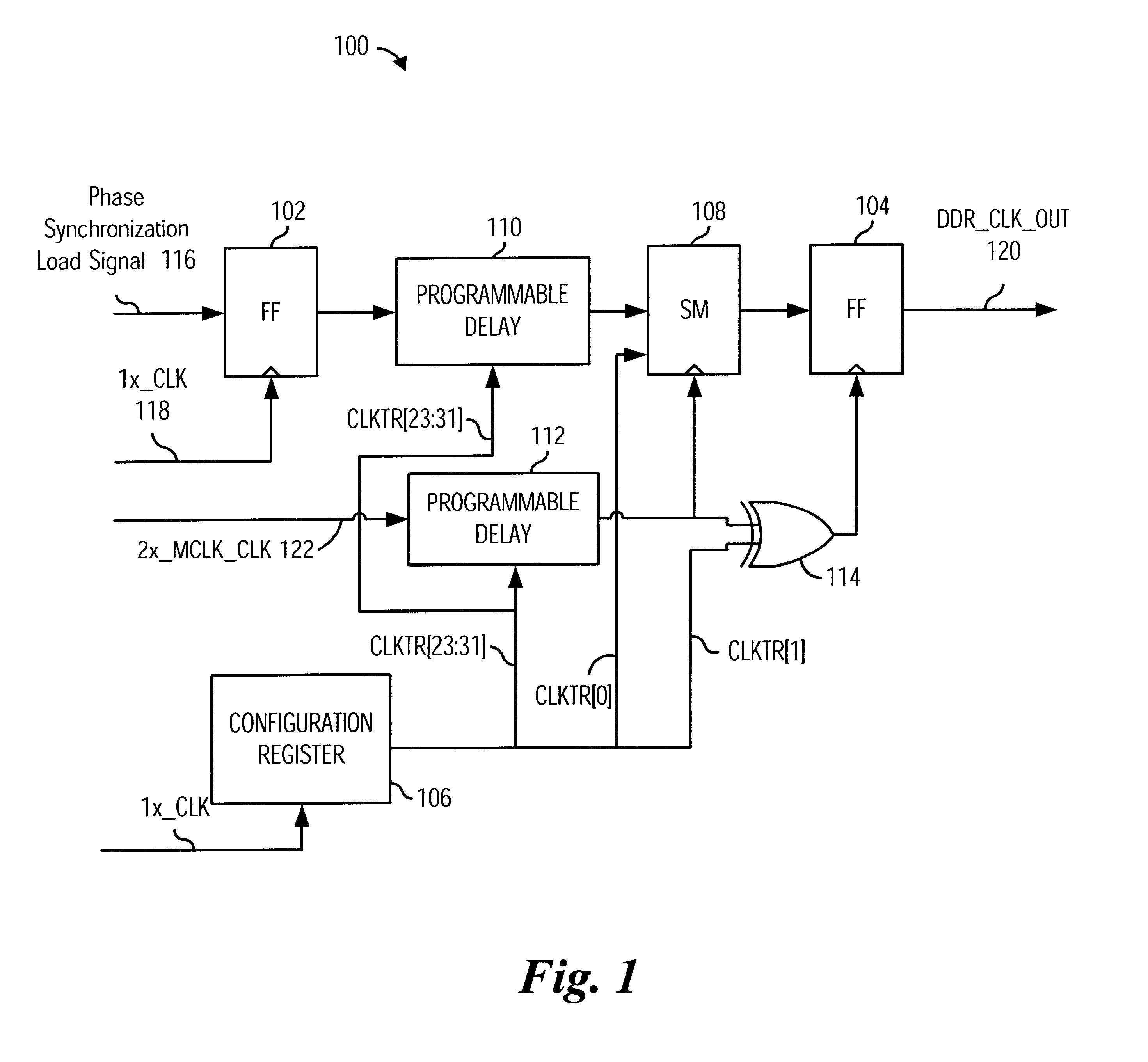

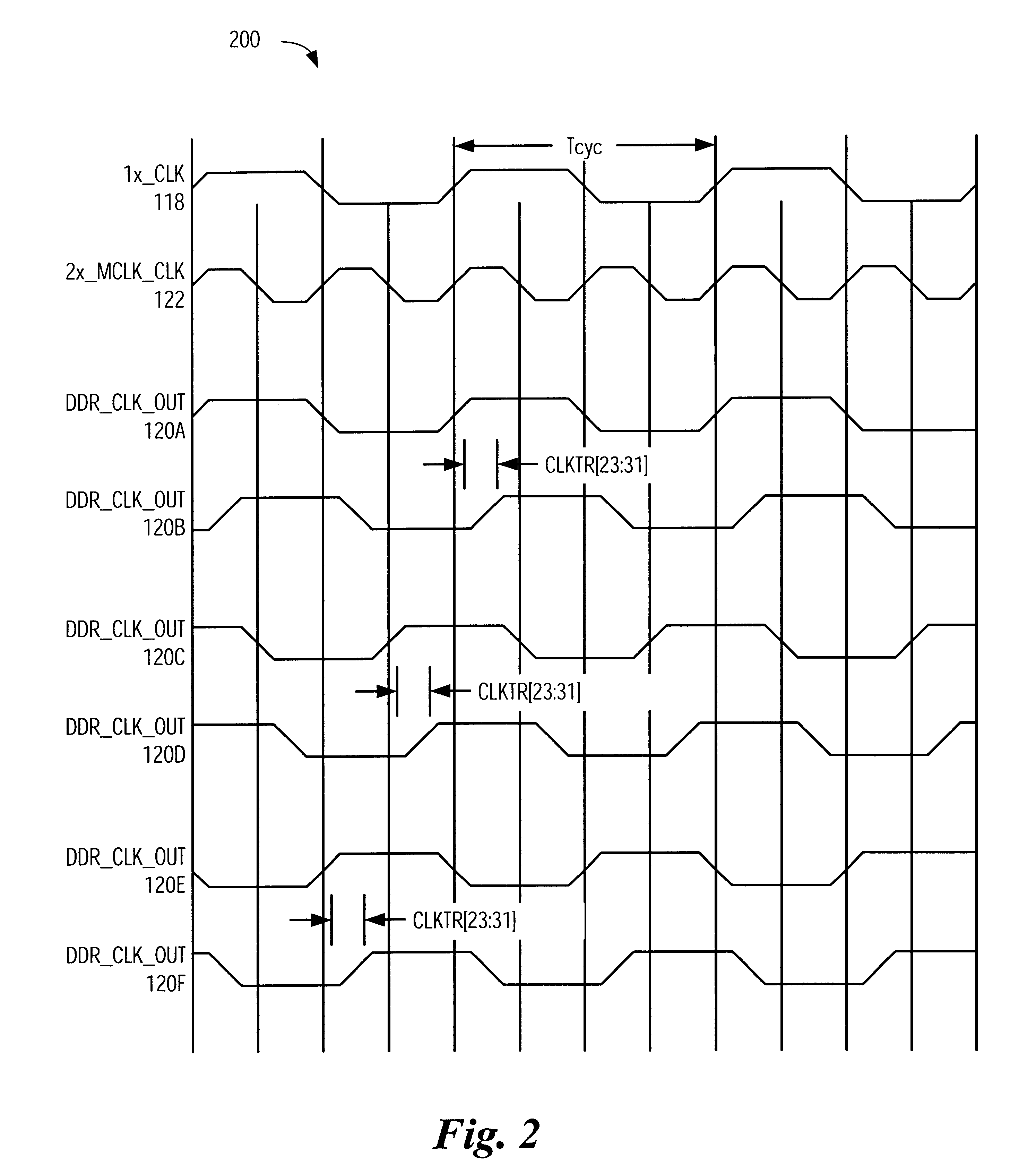

Memory clock generation with configurable phase advance and delay capability

A circuit generating memory clock with phase advance and delay capability is provided. The phase of the memory clock is controlled by adjusting the configuration register bits. The circuit allows for a high degree of control and flexibility in the memory clock generation in that the memory clock relationship with respect to the memory command and data can be adjusted independently, thereby creating the ability to effectively adjust the memory interface timings such as setup time, hold time, and memory read data access time. Specifically, 0, 90, and 180 degree phase advance ability is combined with the ability to add delay in fine increments to achieve a more granular degree of phase adjustment.

Owner:LINKEDIN

Duty-cycle adjustable buffer and method and method for operating same

ActiveUS6897696B2Increase the number ofContinuous to patterned pulse manipulationElectric pulse generatorClock treeEngineering

A duty-cycle adjustable buffer and a method for operating such buffer can be applied to a clock tree circuit for providing an adjustable duty cycle. The duty-cycle adjustable buffer includes a first inverter and a second inverter connected with each other in series. Each of the first inverter and the second inverter includes a plurality of controlled current charging paths and a plurality of controlled current discharging paths, wherein at least one controlled current charging path and at least one controlled current discharging path of the first inverter and the second inverter are conducted. The timing of the rising edge and falling edge of a clock signal is dynamically adjusted so as to dynamically altering the duty cycle of the clock signal.

Owner:VIA TECH INC

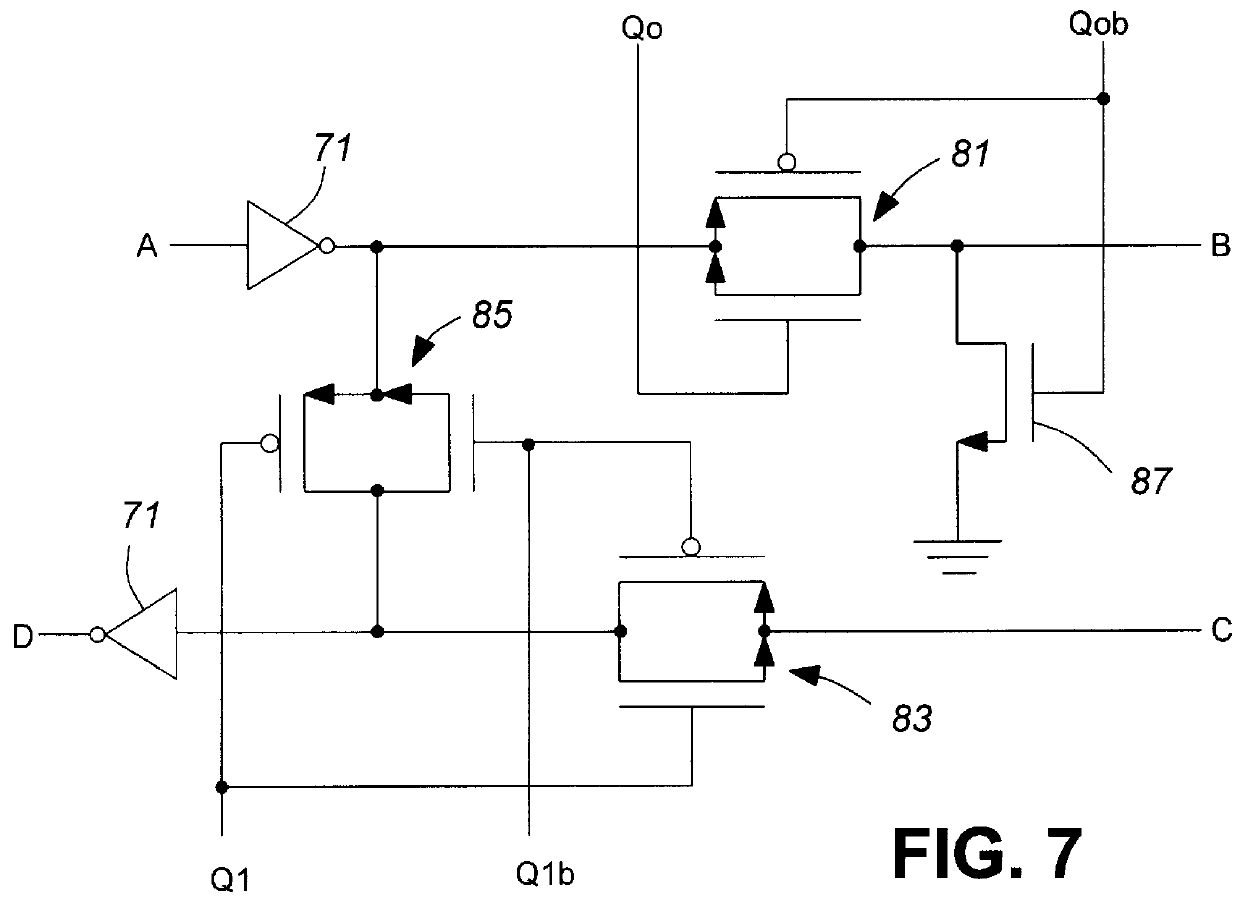

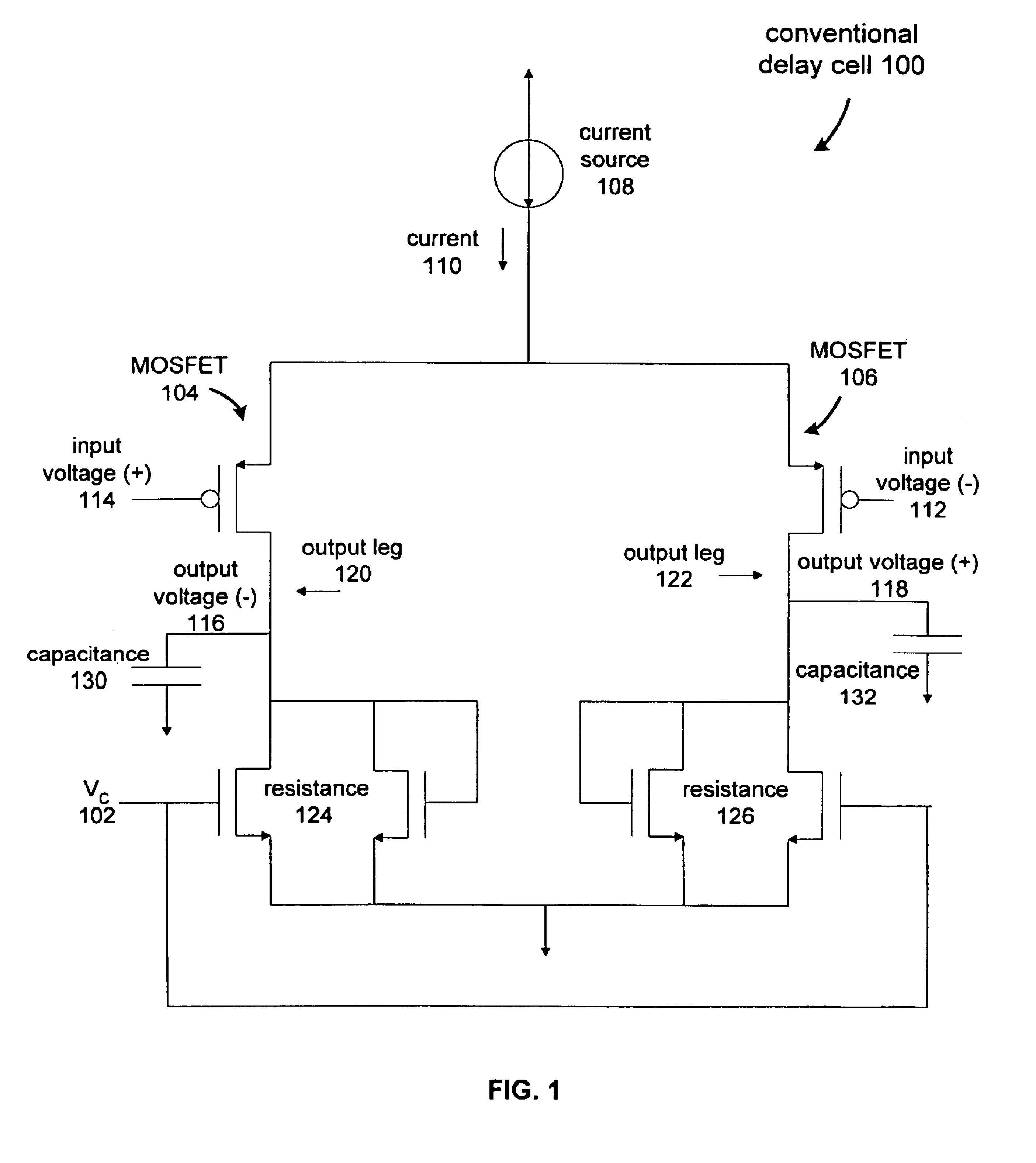

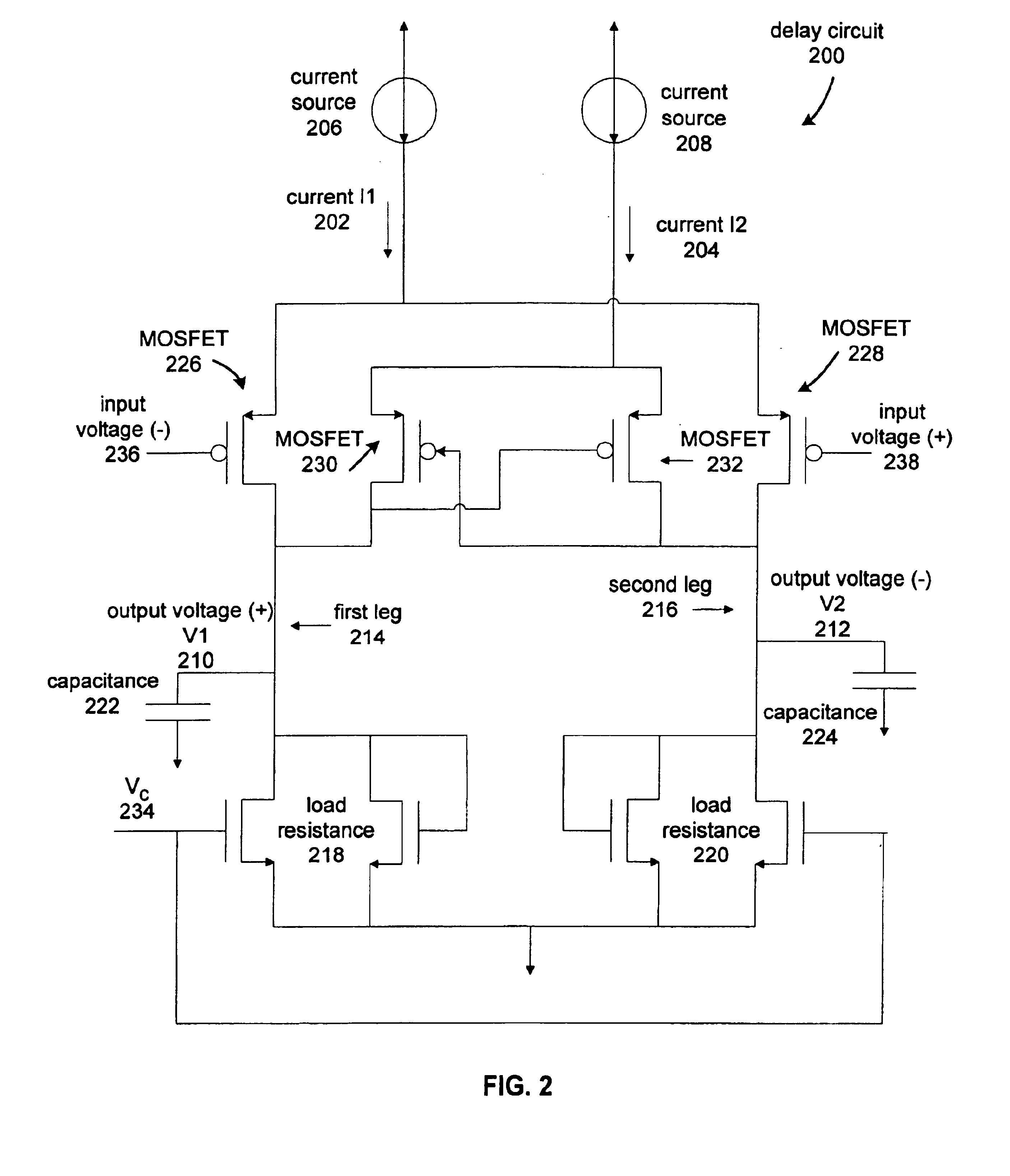

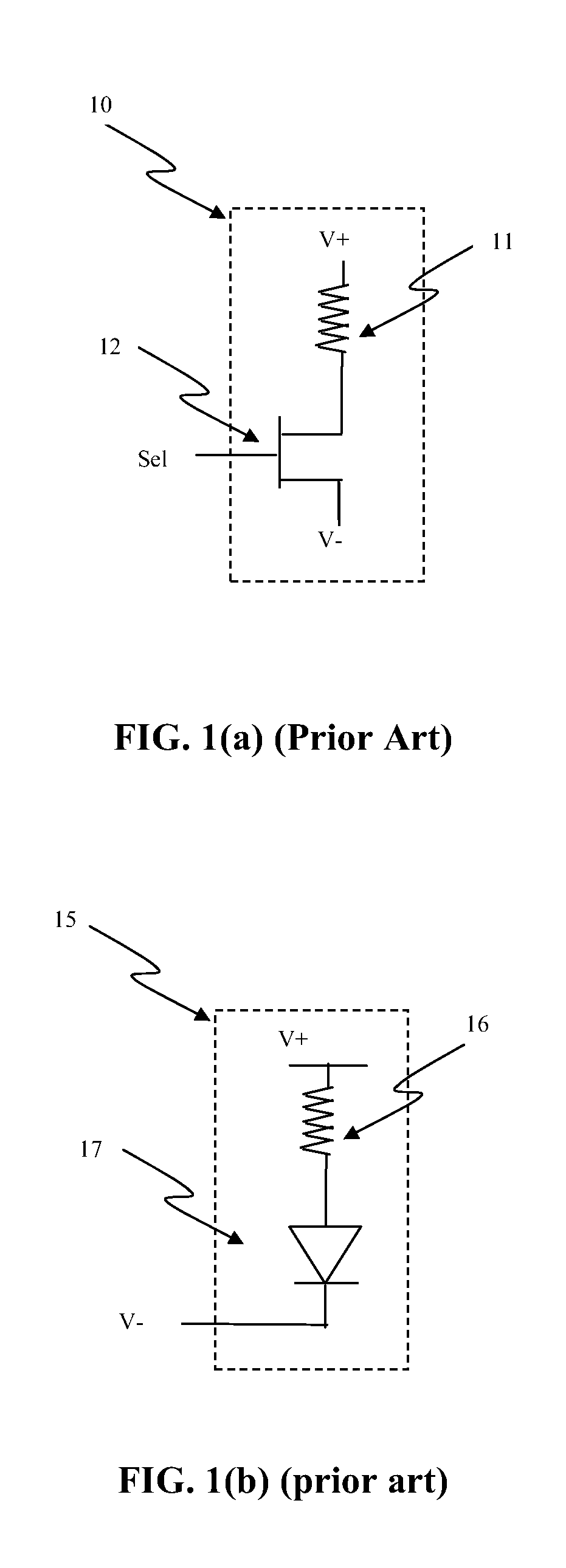

Current controlled delay circuit

A current controlled delay circuit is disclosed. Two currents of constant sum are generated to control the delay of the circuit. The circuit includes a differential pair to switch one of the two currents from one leg of the circuit to another leg of the circuit. The circuit includes a cross-coupled pair to switch the other of the two currents from one leg of the circuit to another leg of the circuit. The circuit may include a fixed or variable load.

Owner:CYPRESS SEMICON CORP

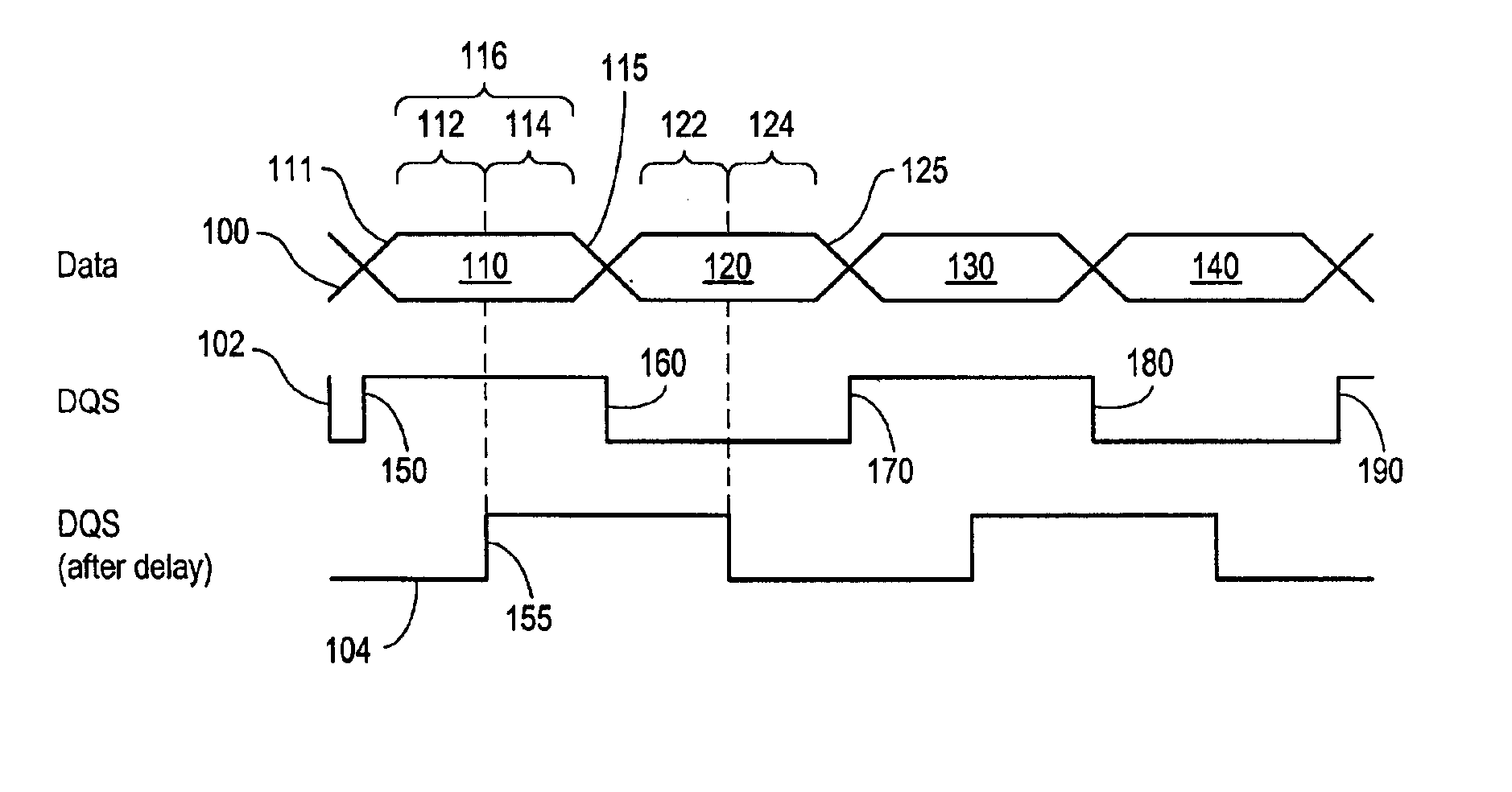

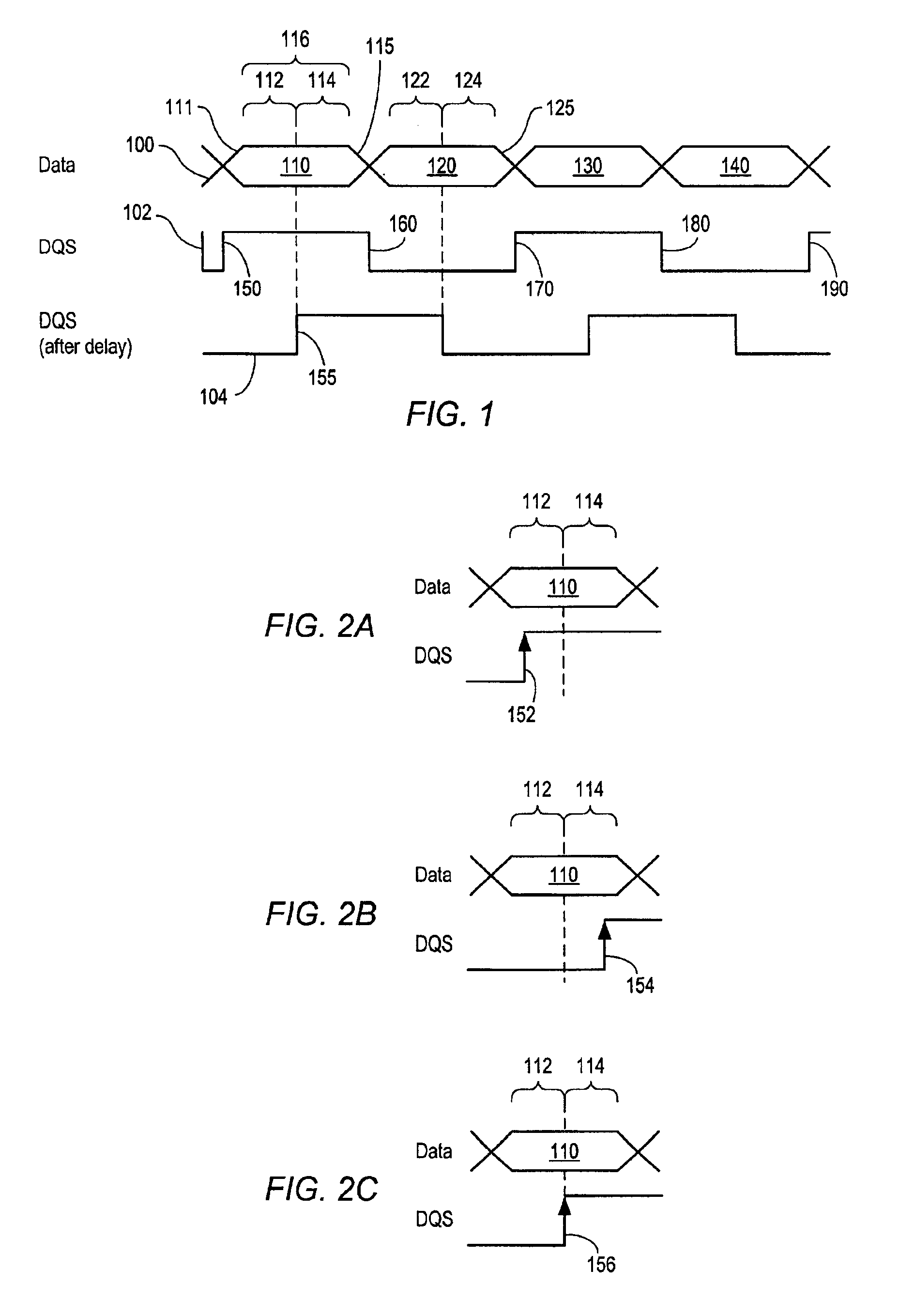

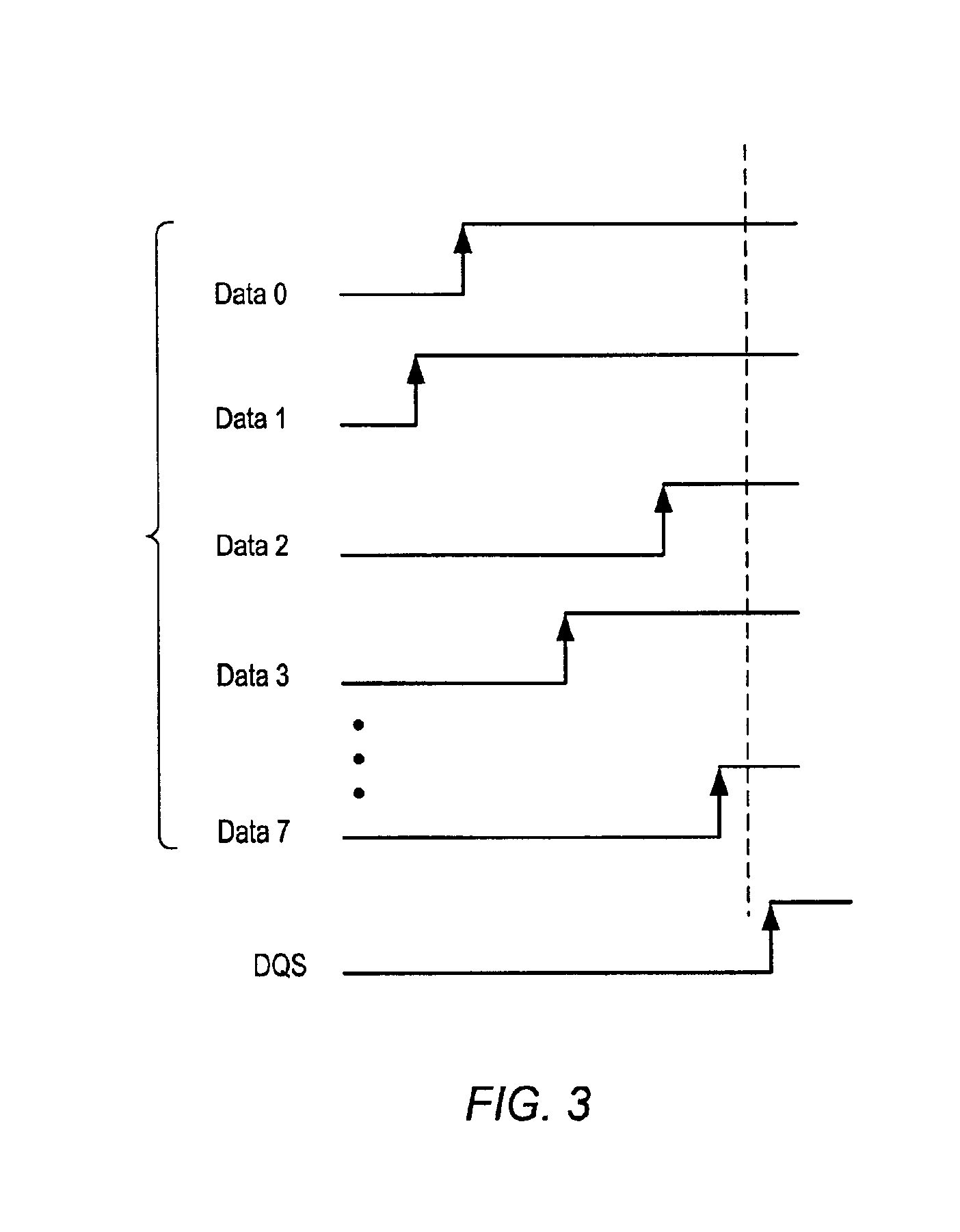

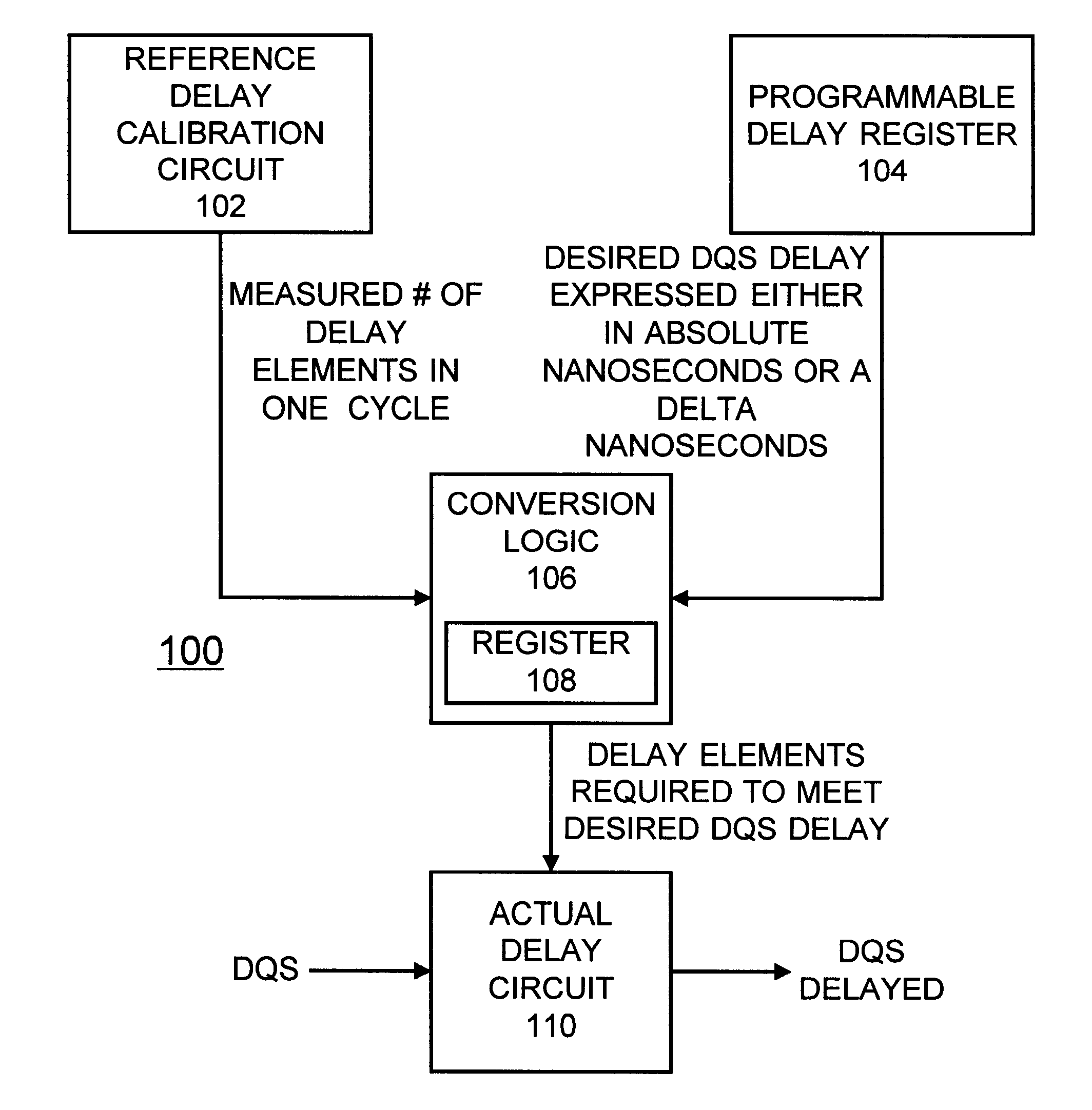

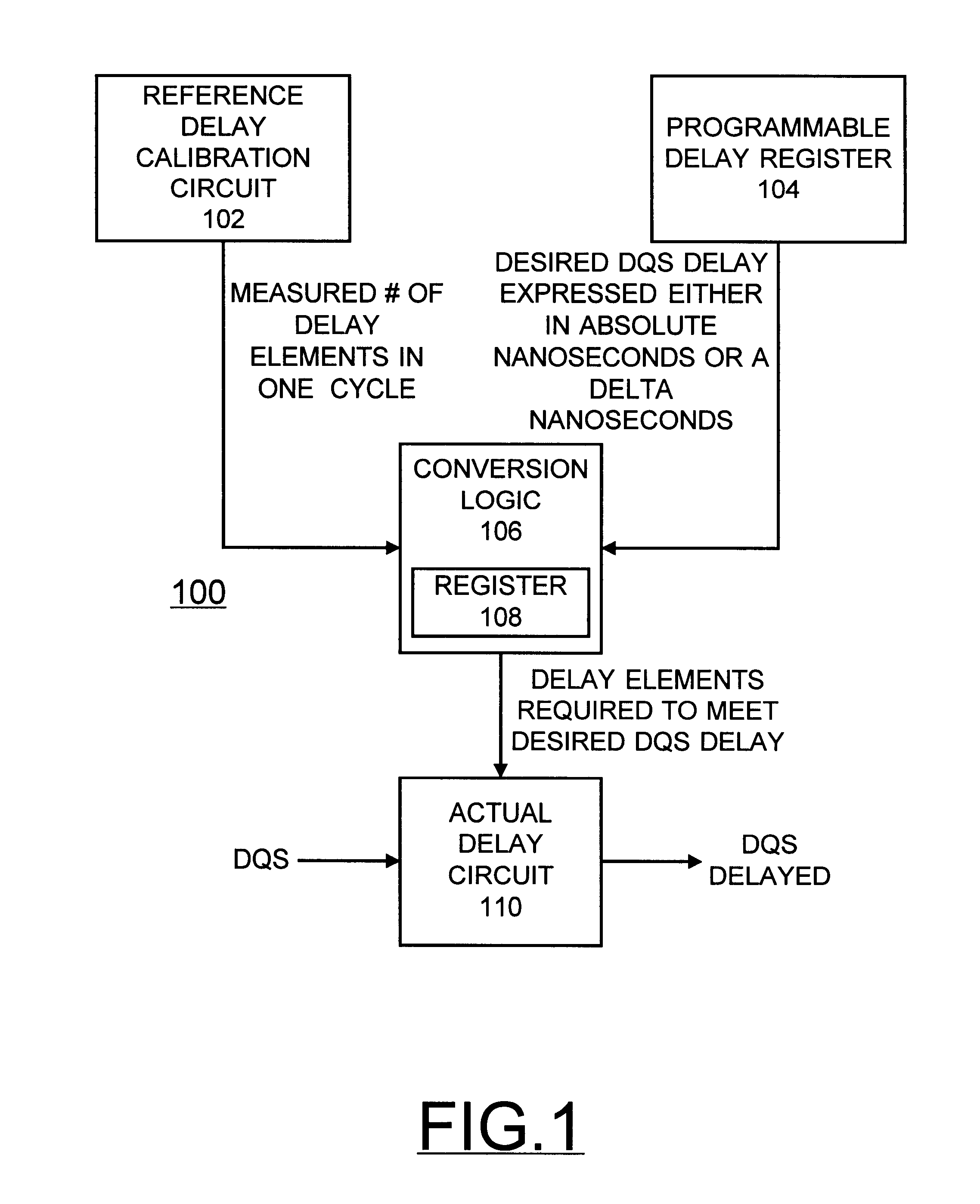

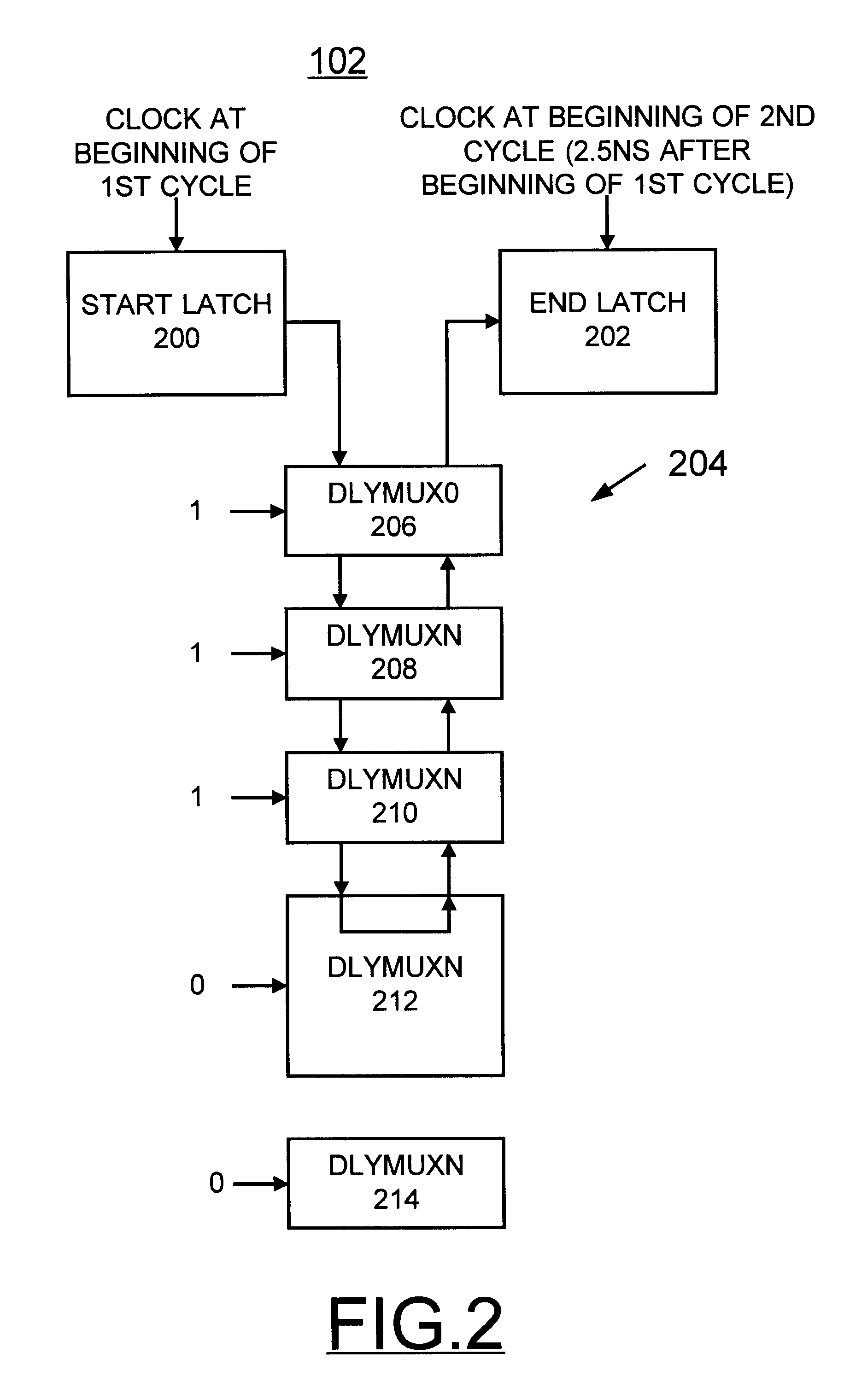

Programmable compensated delay for DDR SDRAM interface using programmable delay loop for reference calibration

A programmable compensated delay for a double data rate (DDR) synchronous dynamic random access memory (SDRAM) interface is provided. A programmable compensated delay apparatus includes a reference delay calibration circuit for providing a measured number of delay elements in one cycle. A programmable delay register provides a desired delay value. A conversion logic is coupled to the reference delay calibration circuit and the programmable delay register for receiving both the measured number of delay elements in one cycle and the desired delay value. The conversion logic provides a number of required delay elements. A delay circuit is coupled to the conversion logic for receiving the number of required delay elements and providing the desired delay. A SDRAM control logic provides a refresh start signal to the reference delay calibration circuit for updating the delay circuit during each DRAM refresh. The DQS clock strobe on the DDR SDRAM is applied to the delay circuit and is delayed by the desired delay.

Owner:MARVELL ASIA PTE LTD

Delay compensation circuit

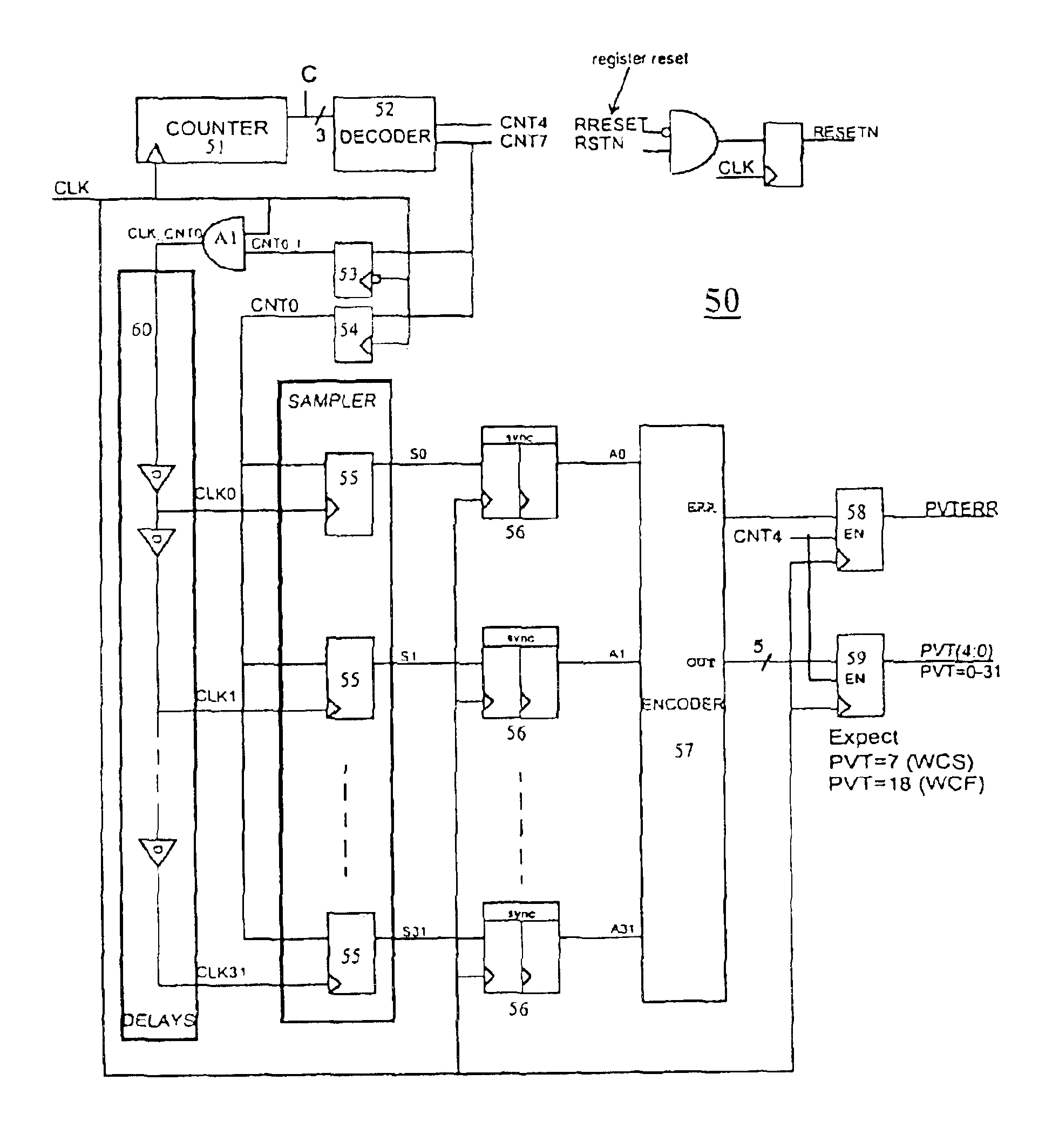

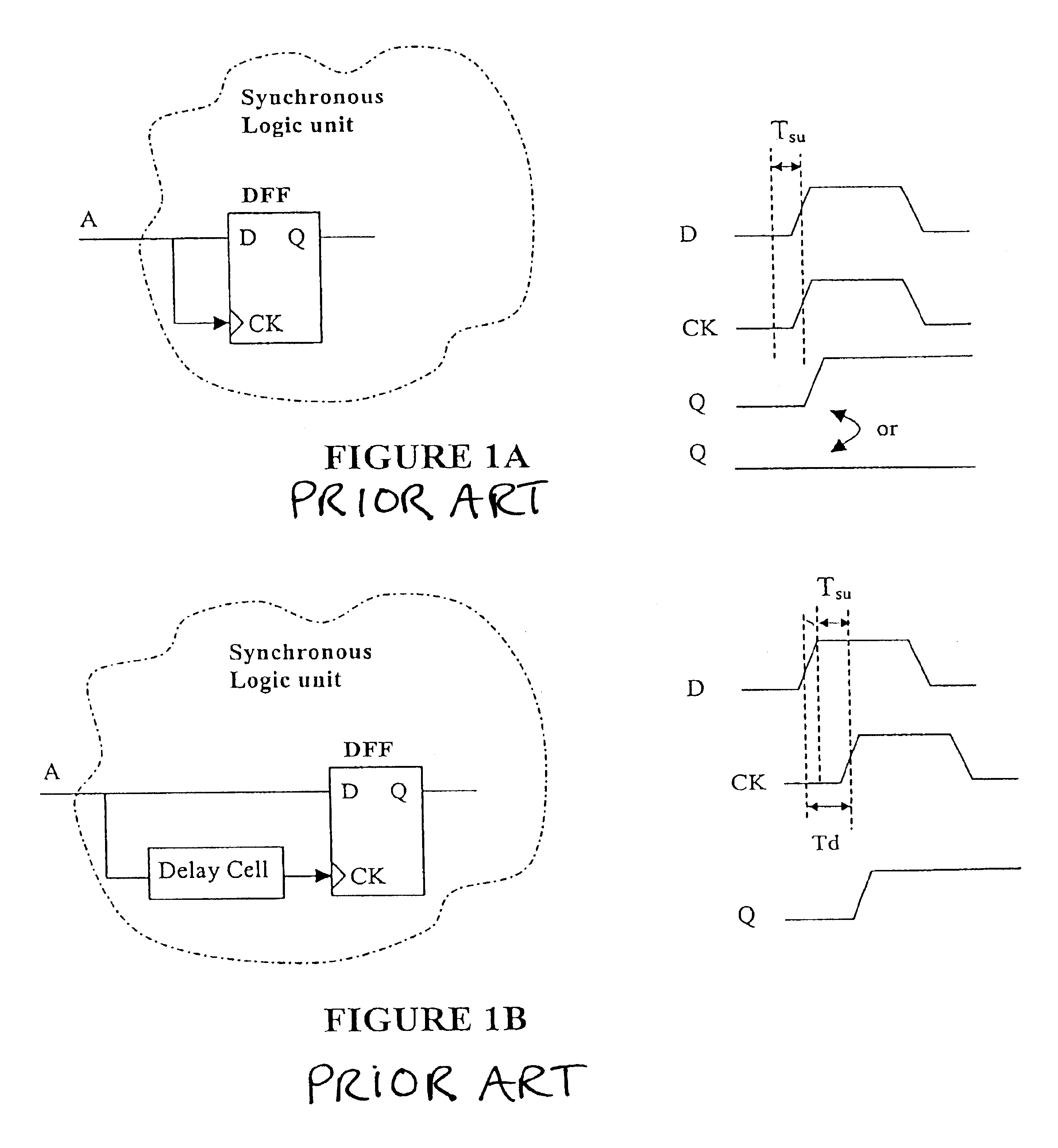

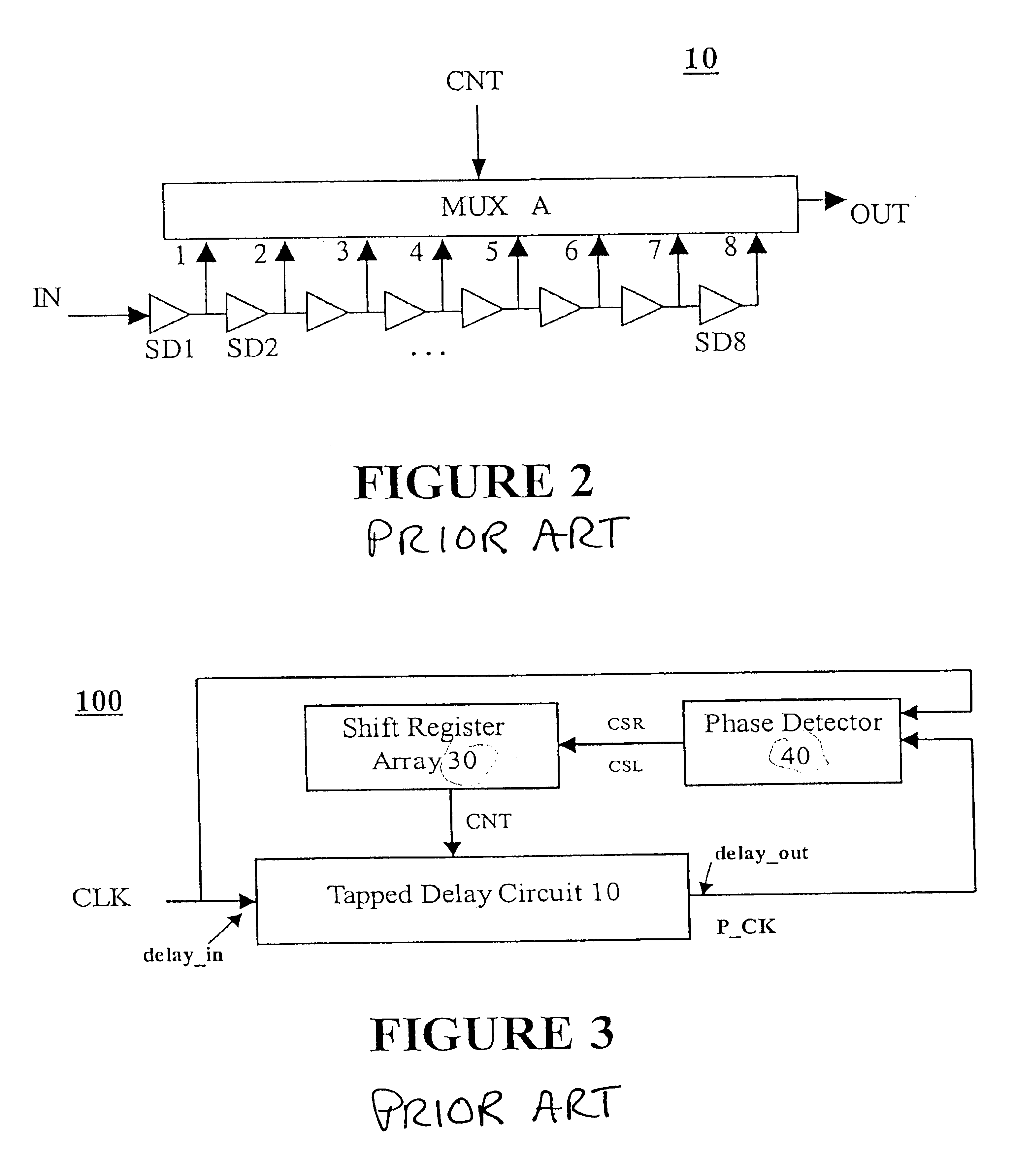

A delay compensation circuit that determines the effects of process, voltage, and temperature (PVT) conditions of a chip by measuring the effective delay time of delay components inside the chip. The delay compensation circuit includes a plurality of sampler modules, each of which receives a delayed clock signal from one of a series of delay cells within a tapped delay circuit. The delay compensation circuit generates an output value based on the total number of sampling modules that lock into a fixed input signal using the delayed clock signals. Since the delay time of each delay cell changes based on variations of PVT conditions, the output values generated by the delay compensation circuit are determinate of PVT conditions in the chip. These output values can be used to design components to compensate for variances in PVT conditions or to control a variable delay component based on detected PVT conditions.

Owner:ALCATEL-LUCENT USA INC +1

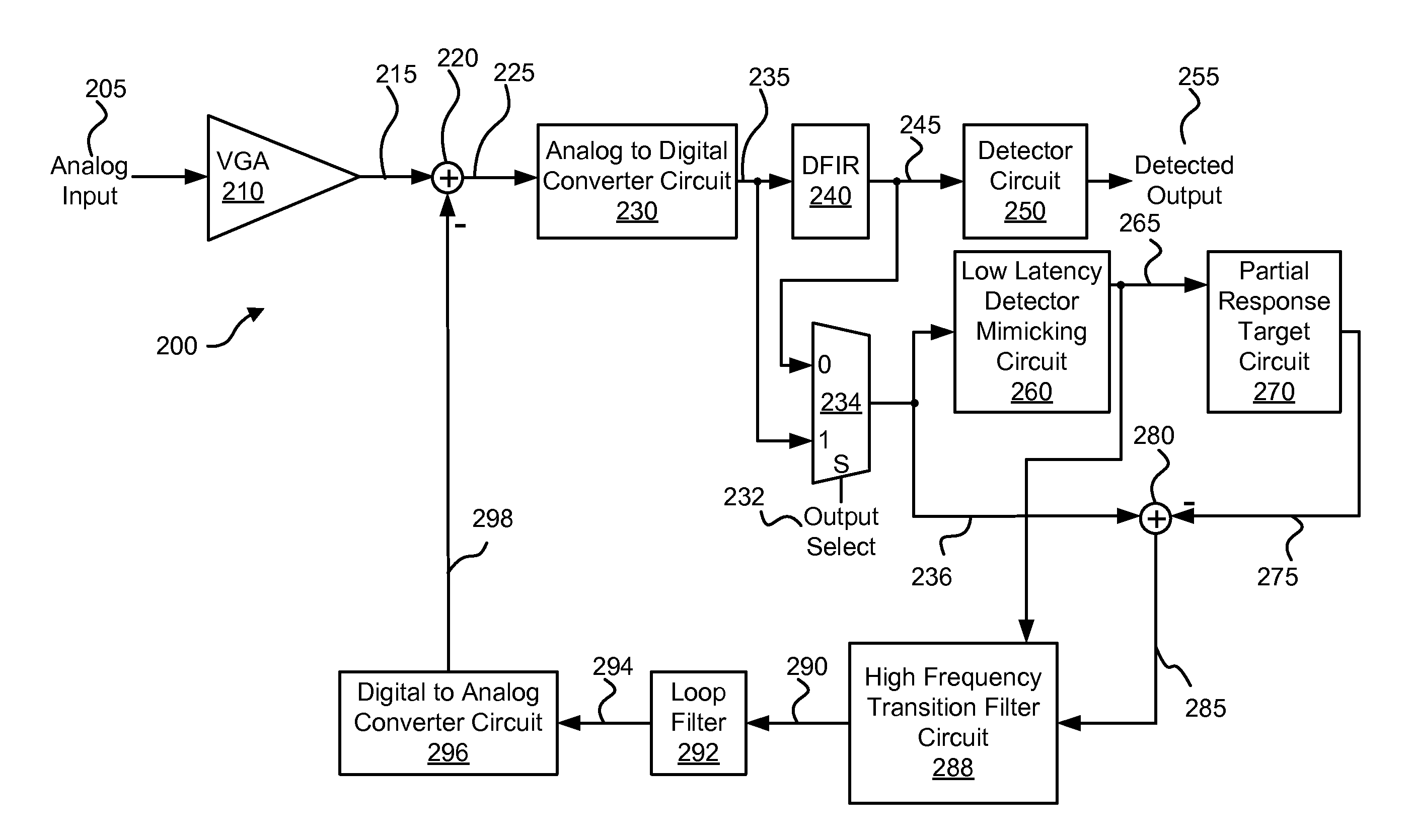

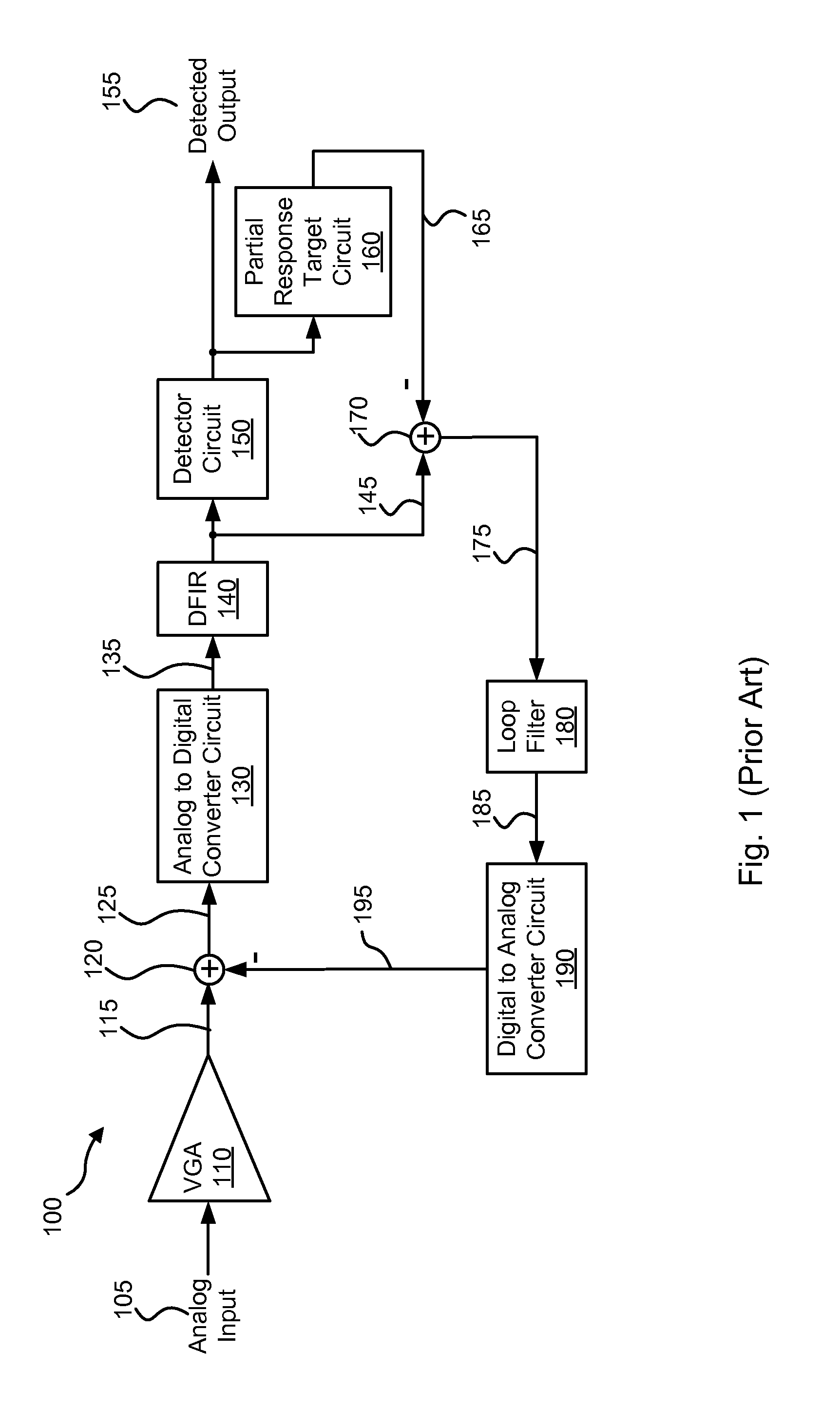

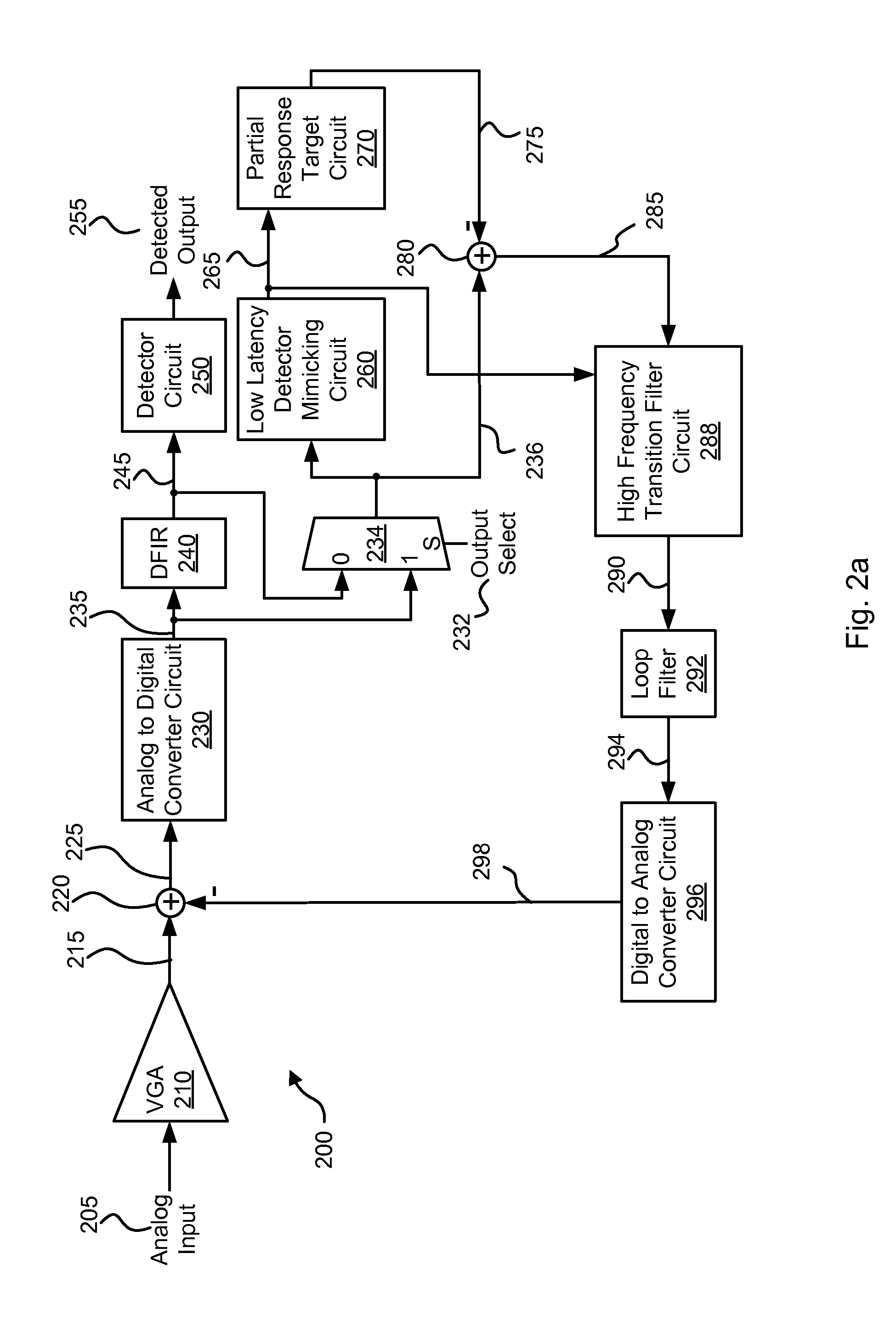

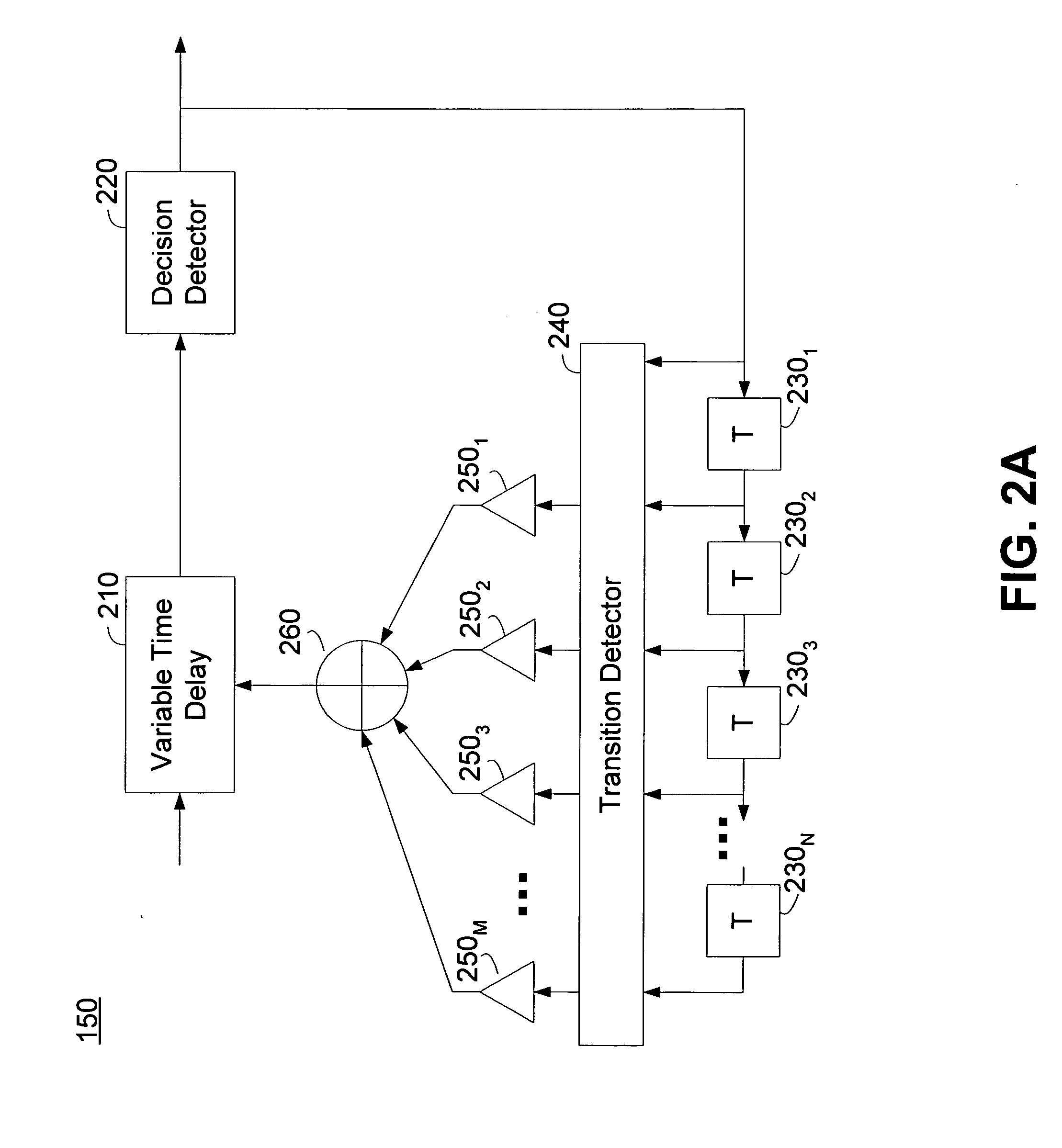

Systems and methods for low latency noise cancellation

ActiveUS8295001B2Reduce distractionsReduce the valueModification of read/write signalsRecord information storageDetector circuitsData simulation

Owner:AVAGO TECH INT SALES PTE LTD

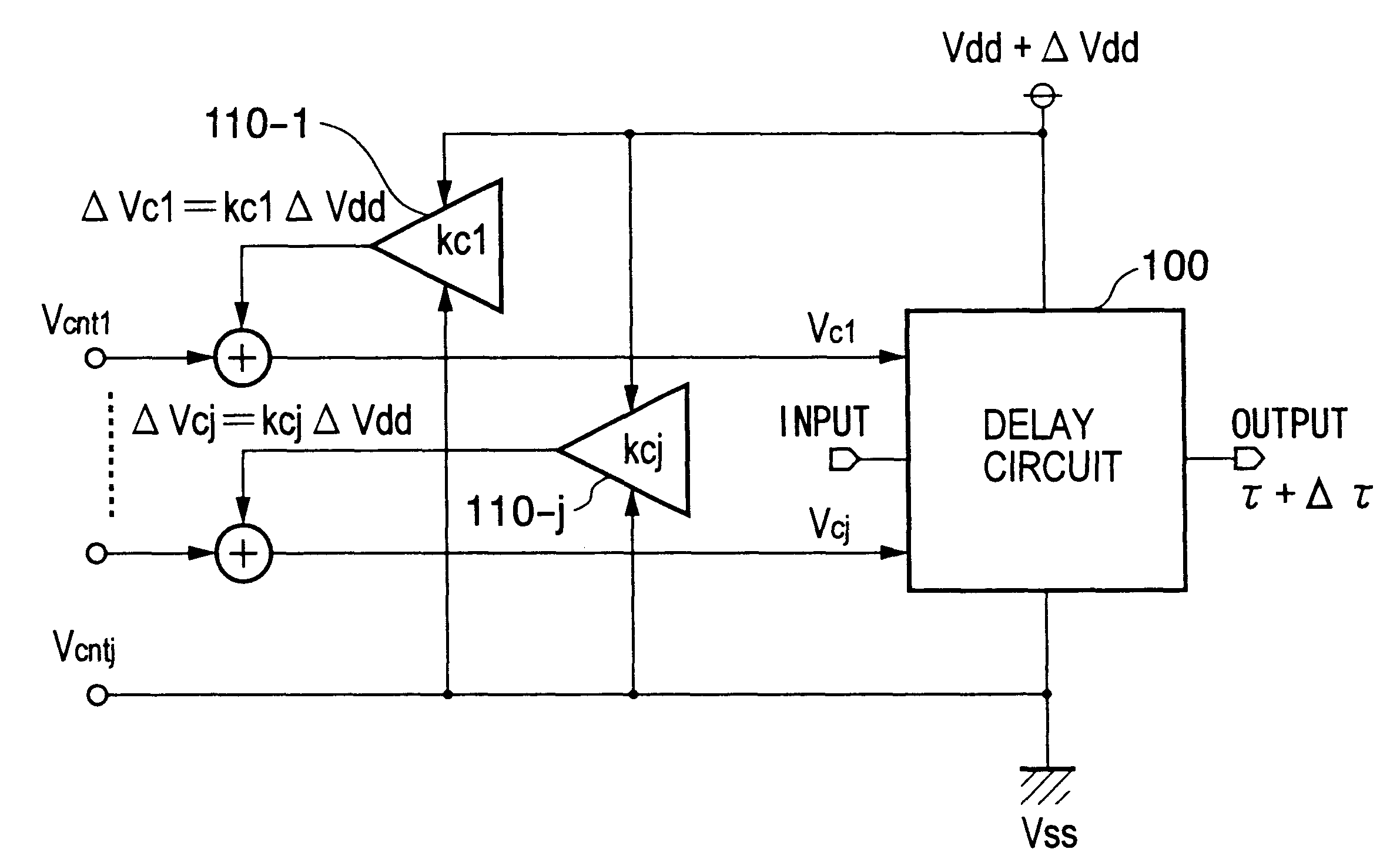

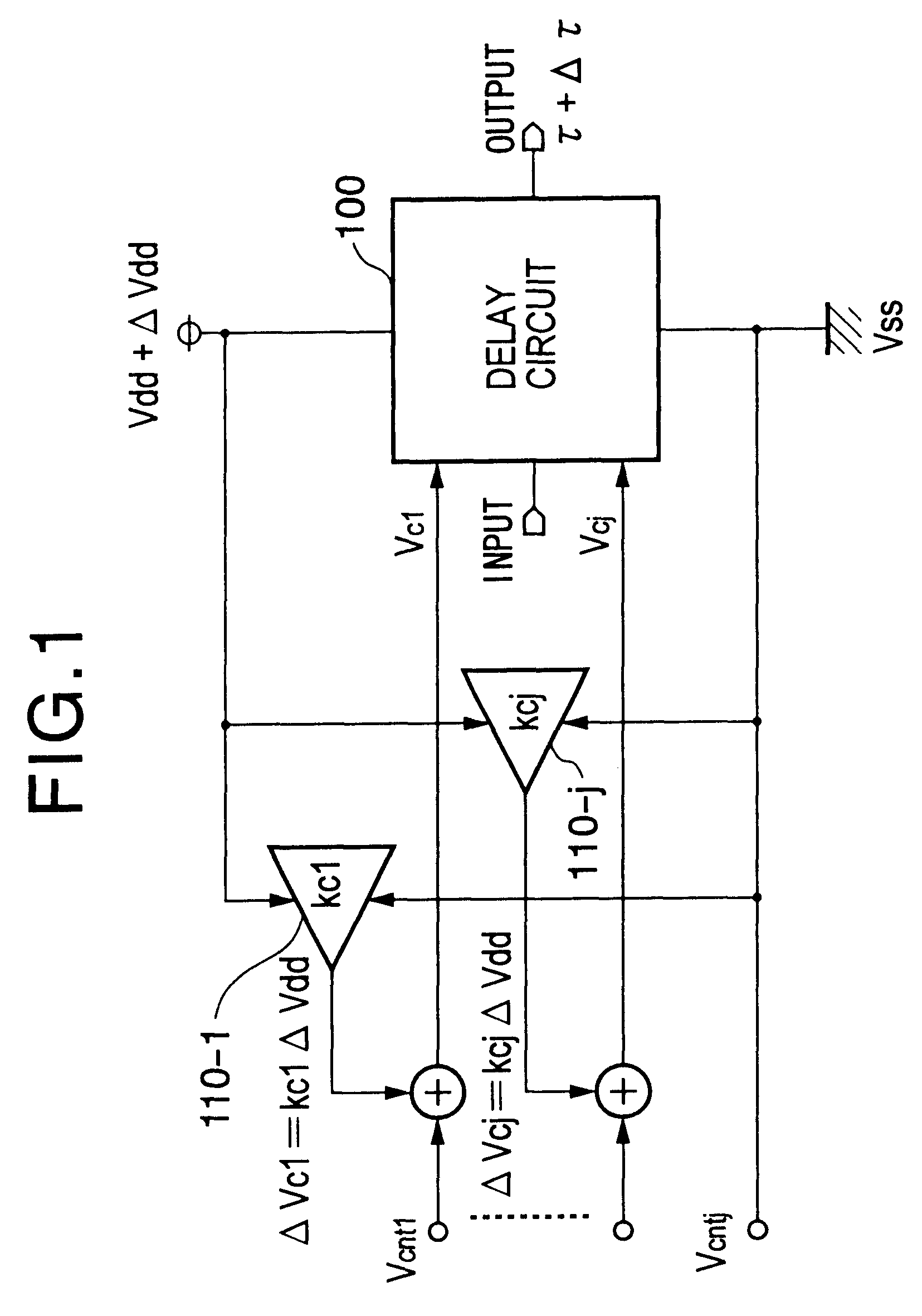

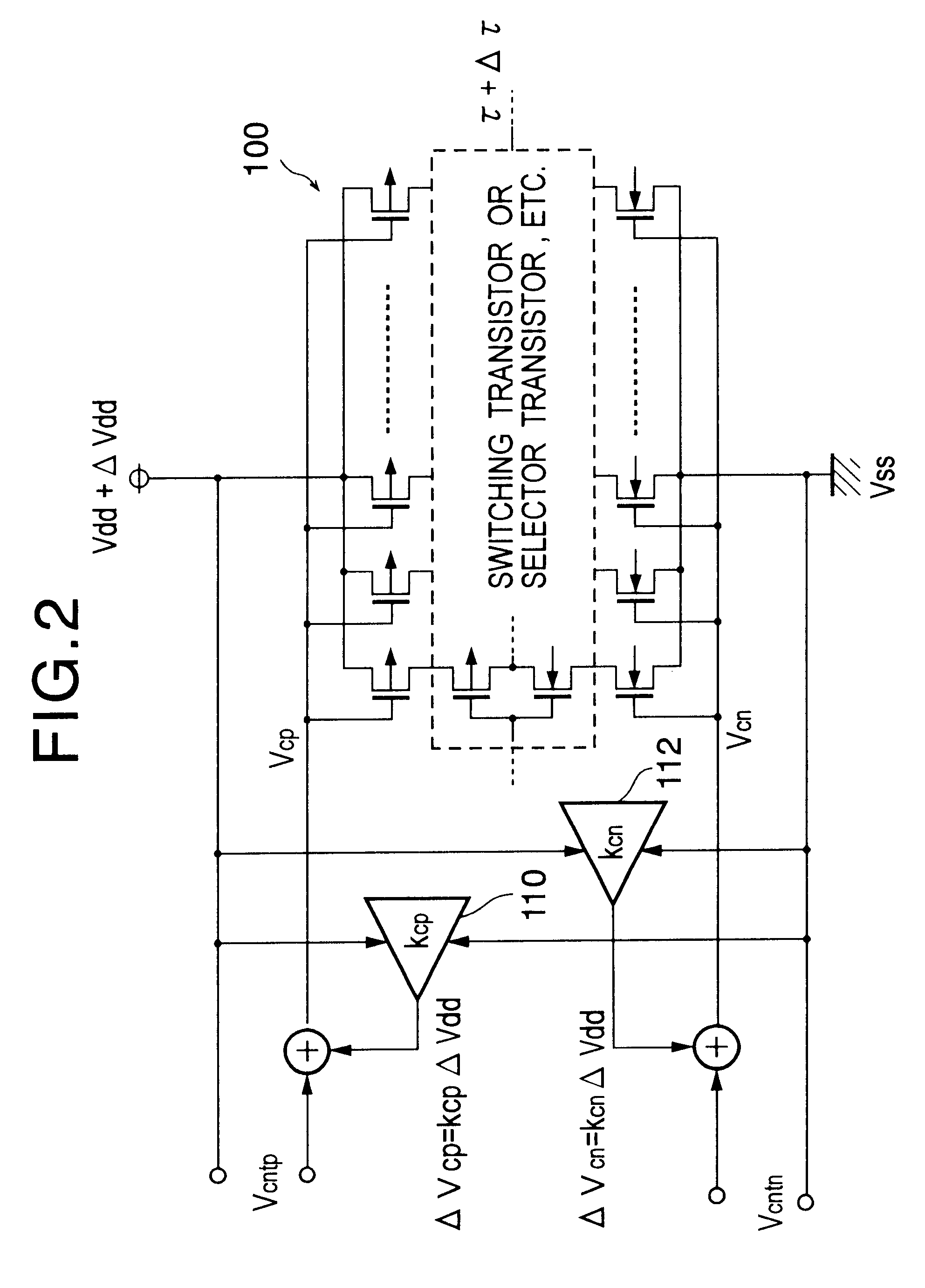

Delay circuit, voltage-controlled delay circuit, voltage-controlled oscillation circuit, delay adjustment circuit, DLL circuit, and PLL circuit

An inverter type delay circuit, voltage-controlled oscillation circuit, and voltage-controlled delay circuit capable of realizing simplification of circuit configuration, reduction of an effect of power source noise, and reduction of jitter, wherein a delay circuit, voltage-controlled oscillation circuit, and voltage-controlled delay circuit comprised of a plurality of delay stages controlled in drive current in accordance with a bias voltage or a control voltage and determined in delay time by the drive current, adding a change of a power source voltage to the above bias voltage or control voltage by a predetermined ratio and supplying a result of the addition to the above delay stages to suppress the power source voltage dependencies of the delay times of the delay stages, or connecting by a predetermined ratio a plurality of delay stages having different power source voltage dependencies, for example, power source voltage dependencies of opposite delay times, to suppress the power source voltage dependencies of delay times of the delay stages are realized.

Owner:SONY CORP

Delay compensation circuit including a feedback loop

A delay compensation circuit that determines the effects of process, voltage, and temperature (PVT) conditions of a chip by amplifying the maximum delay time of a delay element within the chip. The delay compensation circuit determines into which one of several predefined time intervals the amplified delay time falls, where each predefined time interval is associated with different PVT conditions. The delay compensation circuit of the present invention can be used to generate control signals for a variable delay element. Also, the PVT information provided by the delay compensation circuit can be used to design components within a chip to compensate for variances in PVT conditions. The feedback loop structure of the delay compensation device reduces the required chip area and power consumption of the delay compensation circuit.

Owner:LUCENT TECH INC

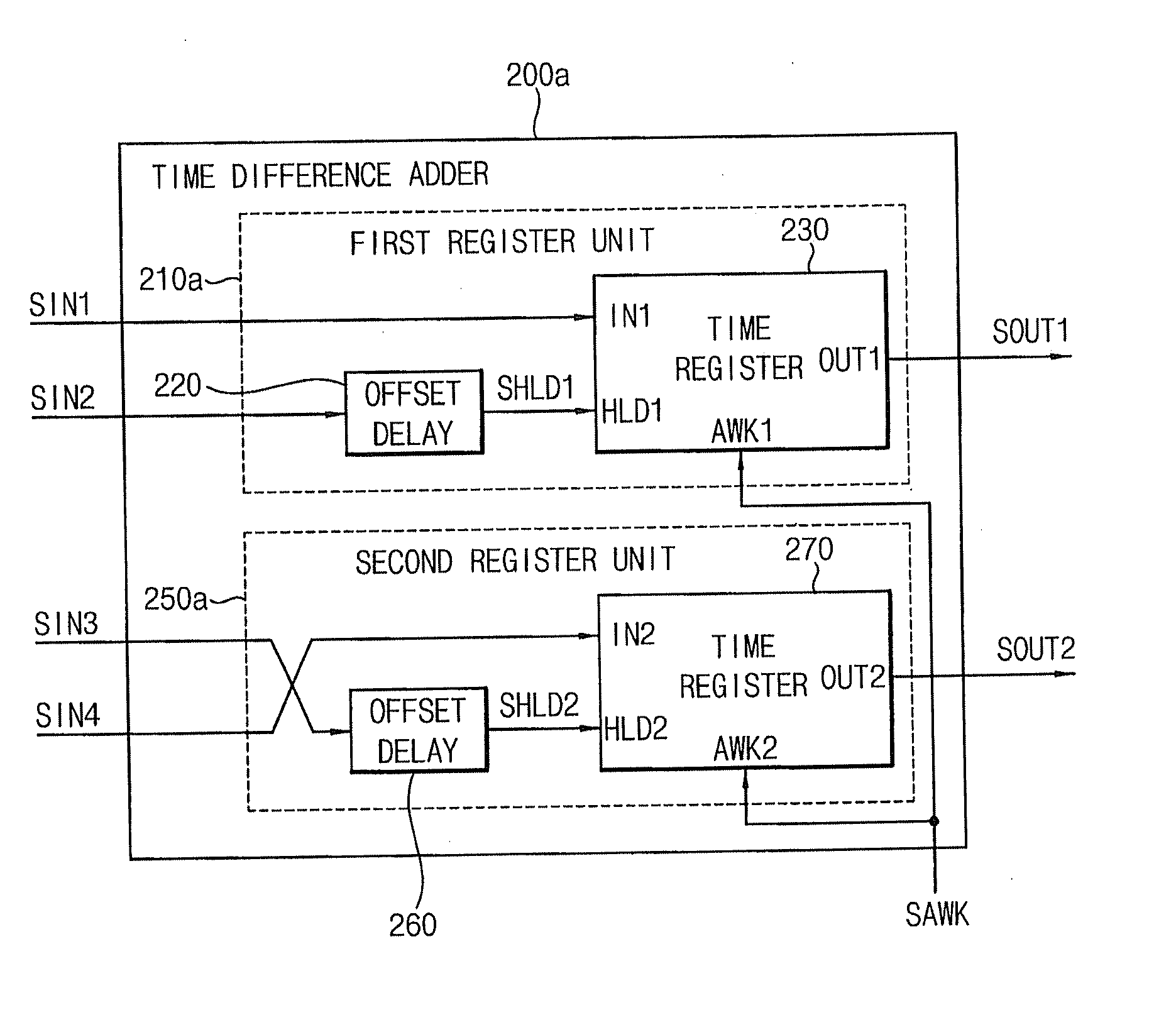

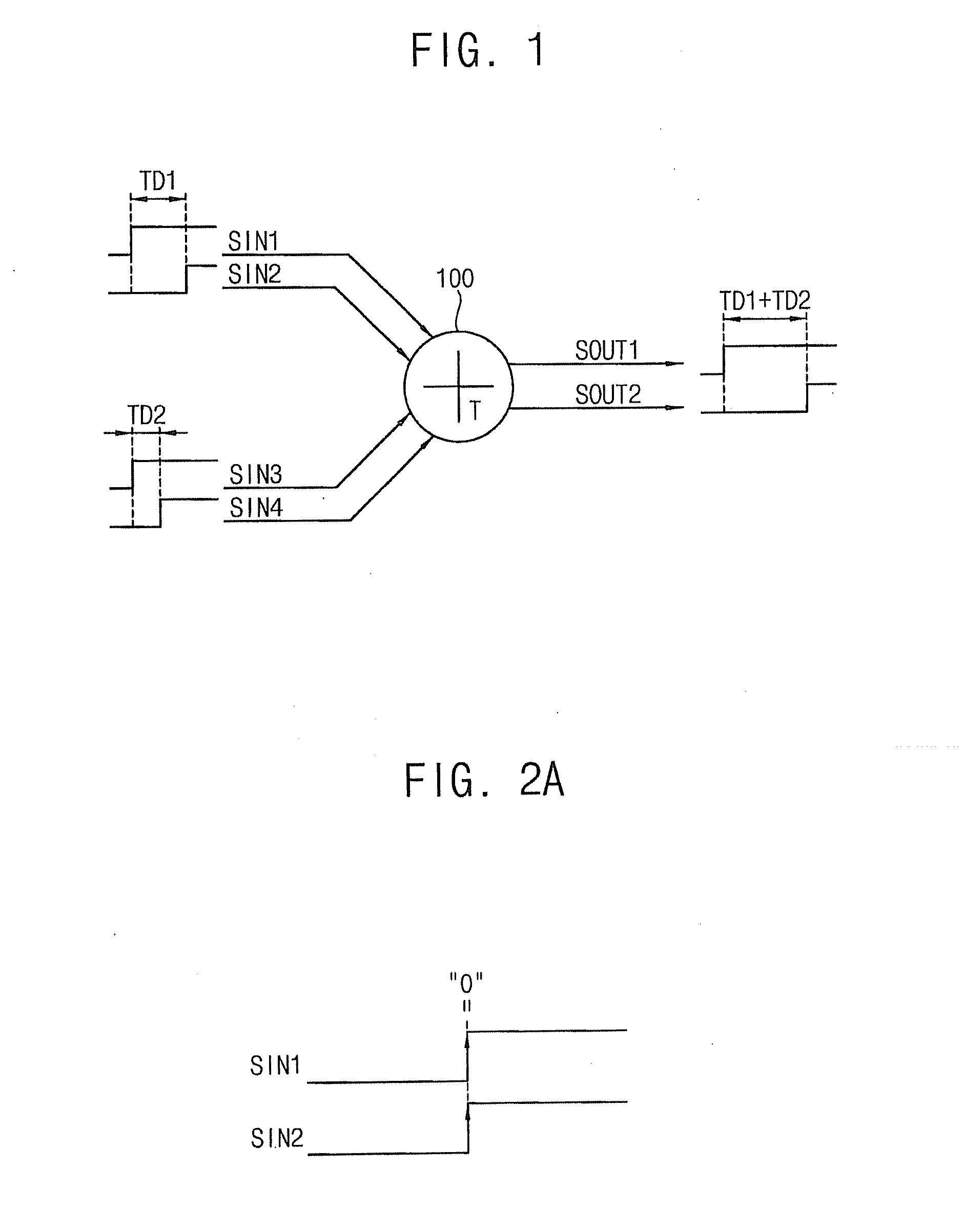

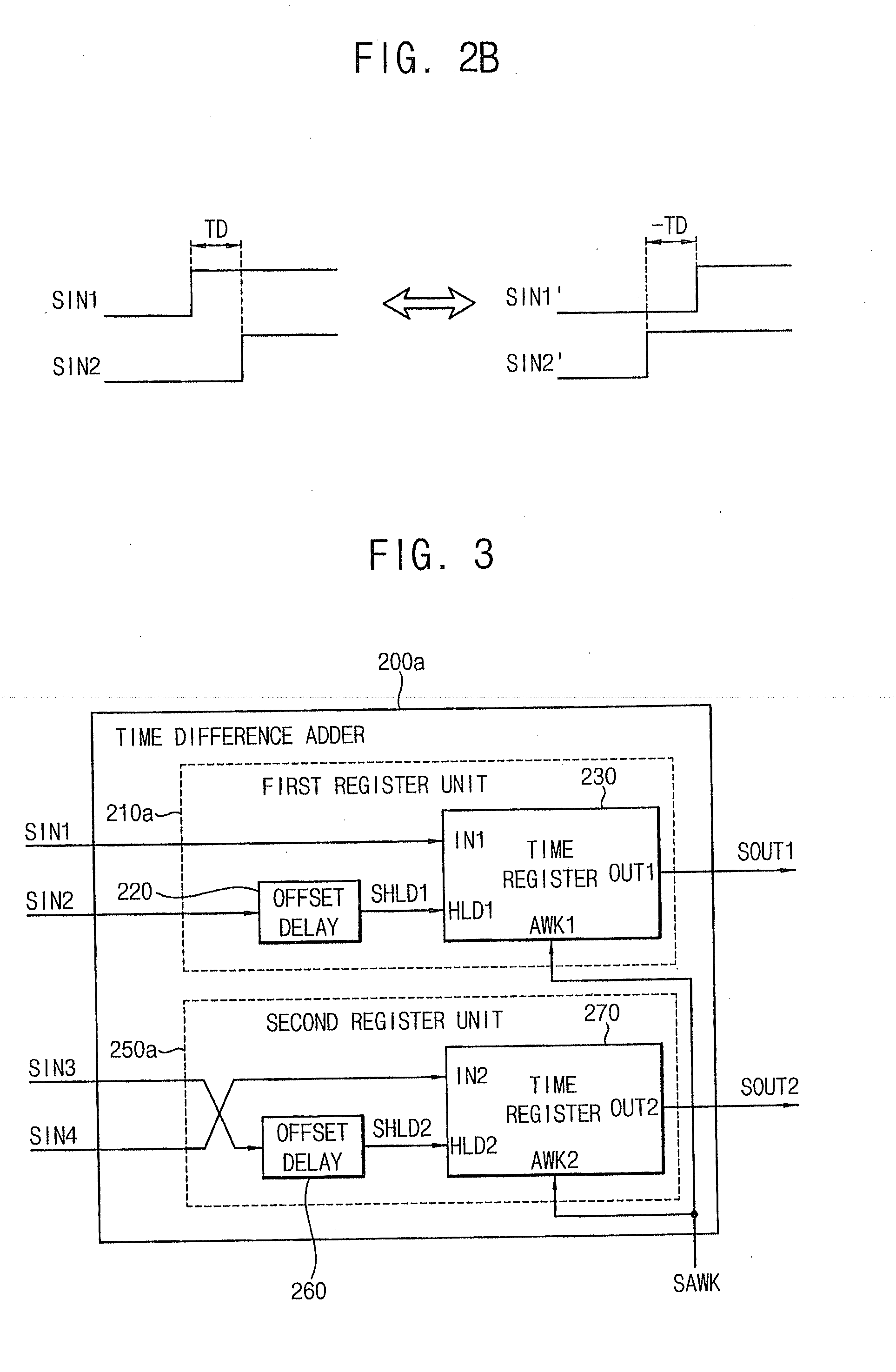

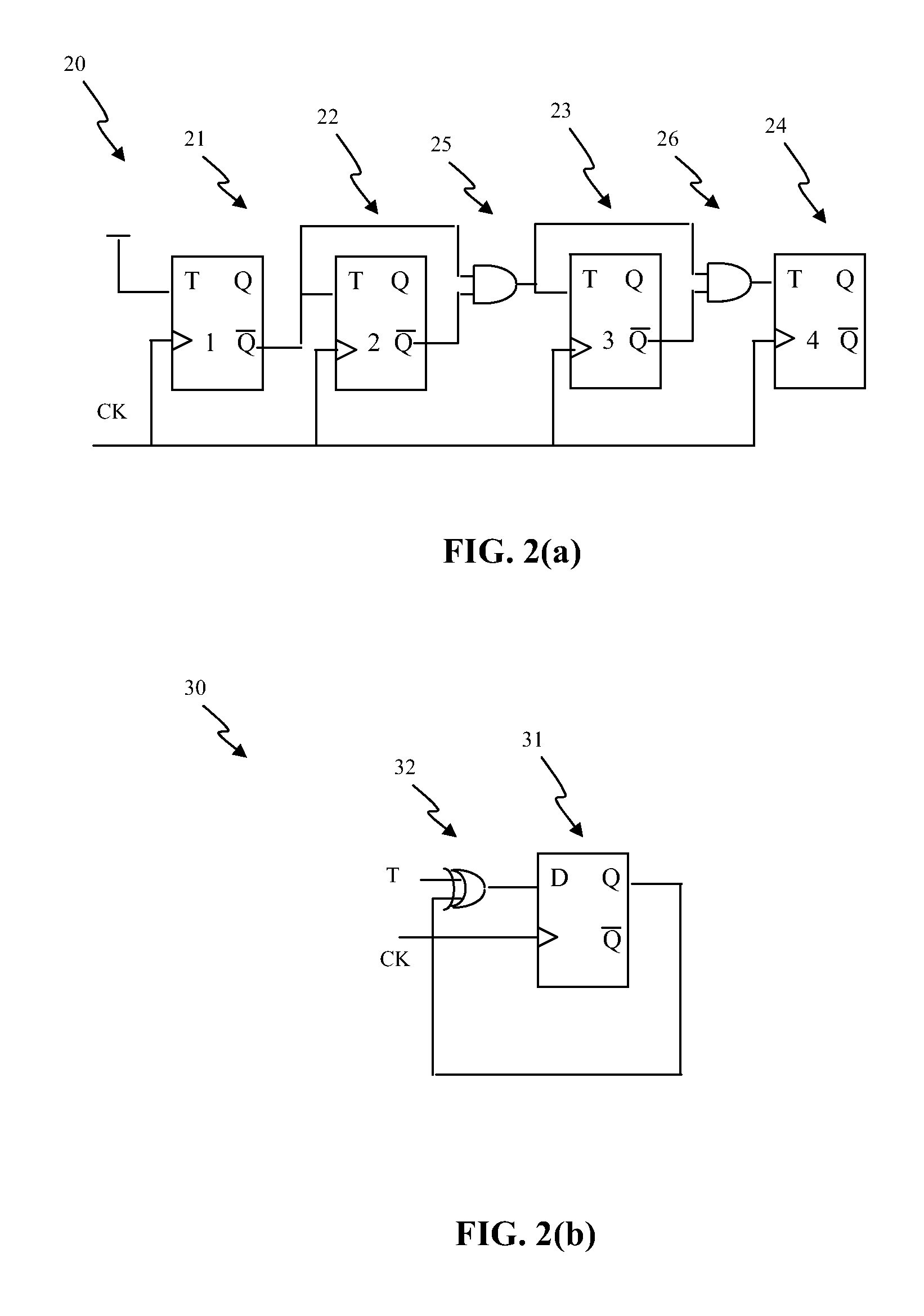

Time difference adders, time difference accumulators, sigma-delta time-to-digital converters, digital phase locked loops and temperature sensors

ActiveUS20120306553A1Computations using contact-making devicesPulse automatic controlDigital down converterProcessor register

A time difference adder included in a system-on-chip (SOC) includes a first register unit and a second register unit. The first register unit is configured to receive first and second input signals having a first time difference, and generate a first output signal in response to a first signal. The second register unit is configured to receive third and fourth input signals having a second time difference, and generate a second output signal having a third time difference with respect to the first output signal in response to the first signal. The third time difference corresponds to a sum of the first time difference and the second time difference.

Owner:SAMSUNG ELECTRONICS CO LTD

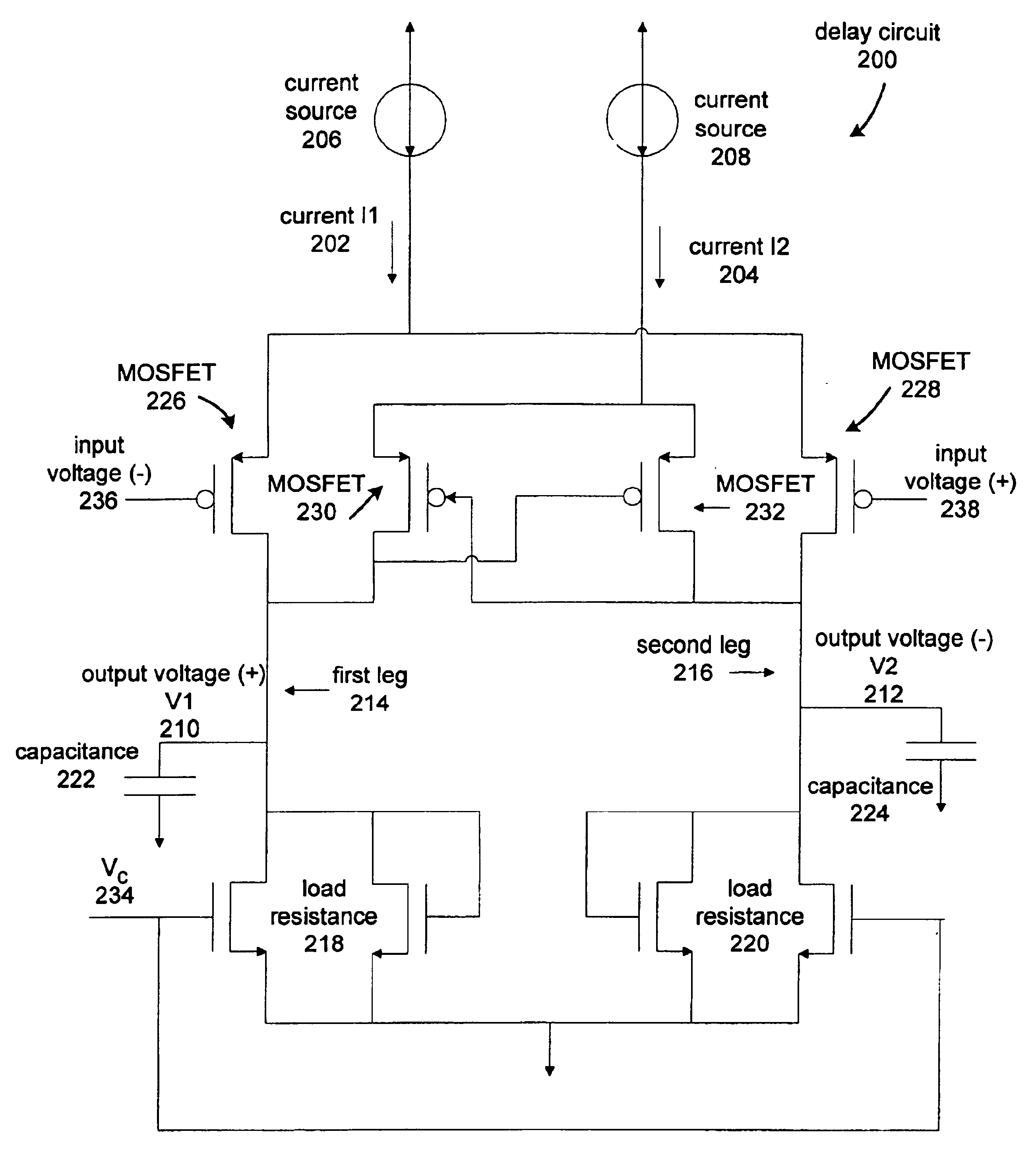

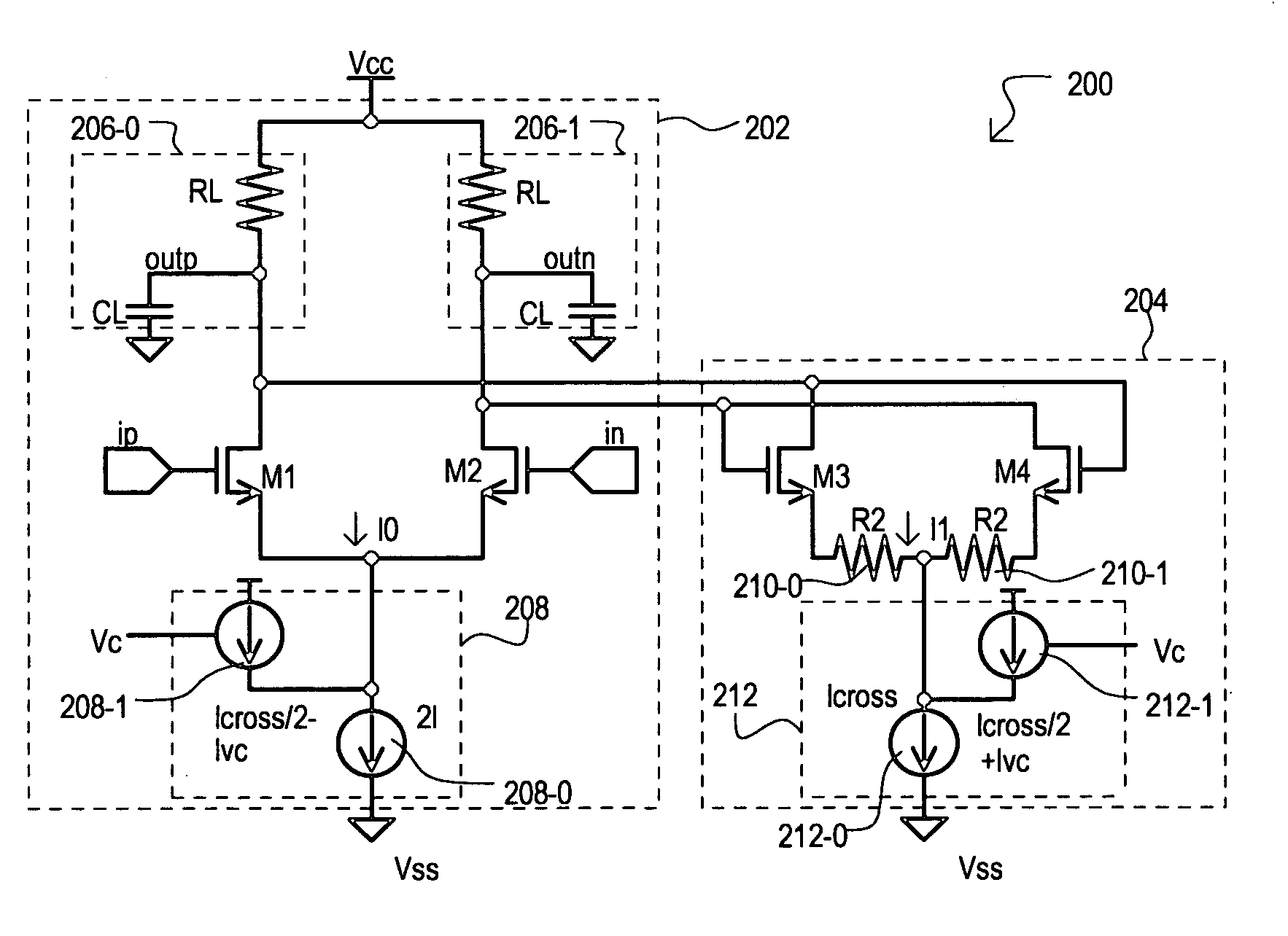

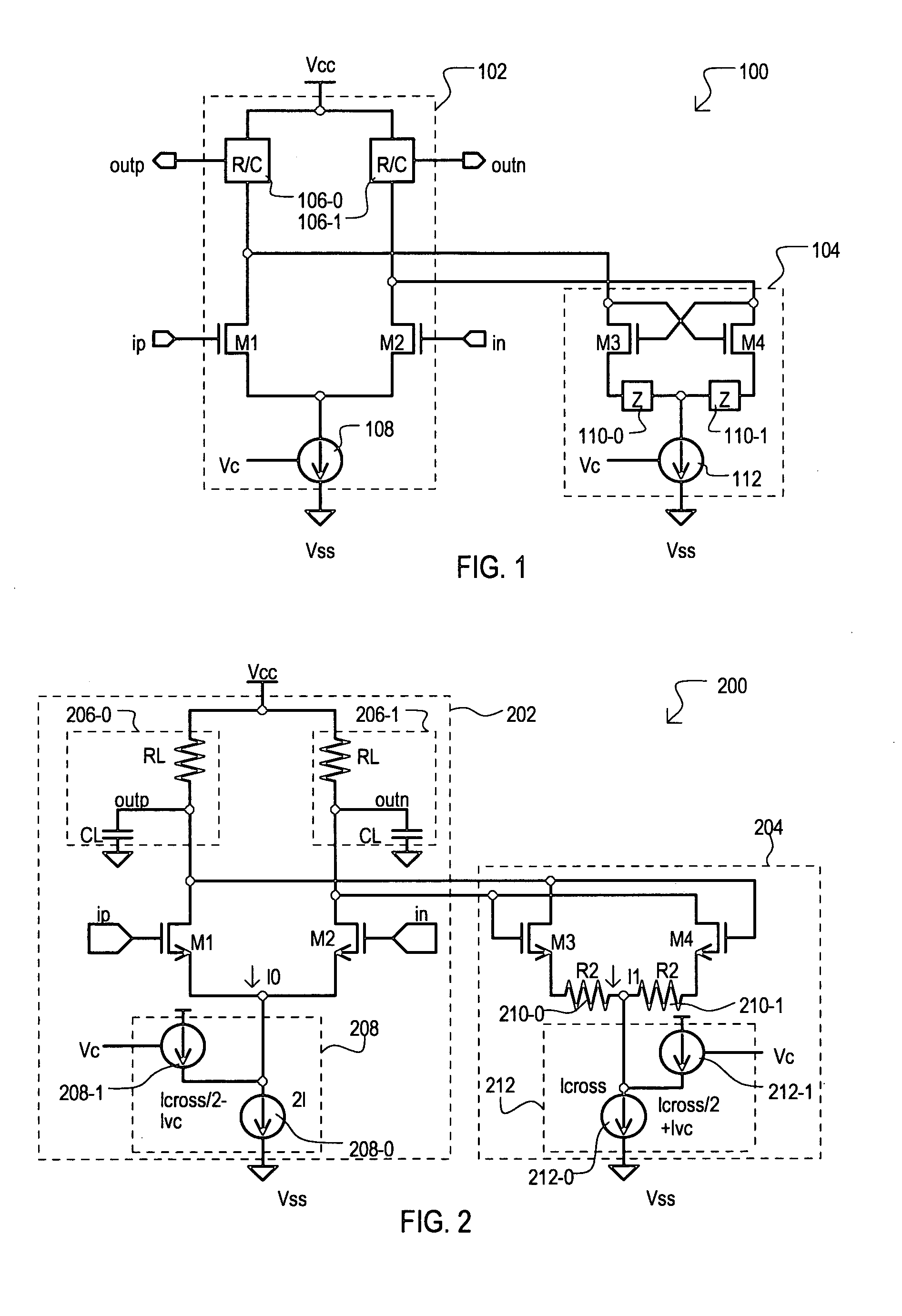

Voltage controlled oscillator delay cell and method

A delay cell circuit (200) is disclosed. The delay cell circuit may include a differential stage (202) and a cross-coupled stage (204). The cross-coupled stage can include resistors (210-0 and 210-1) the function to reduce a gain. The differential stage (202) and cross-coupled stage (204) can include variable currents sources (208 and 212), respectively. As frequency of operation increases, variable current source (208) provides a larger current to the differential stage (202) and variable current source (212) provides a smaller current to cross-coupled stage (204). Delay cell circuit (200) may be used in a voltage controlled oscillator (VCO). By including gain attenuating devices such as resistors (210-0 and 210-1), a frequency tuning range of the VCO may be increased.

Owner:MONTEREY RES LLC

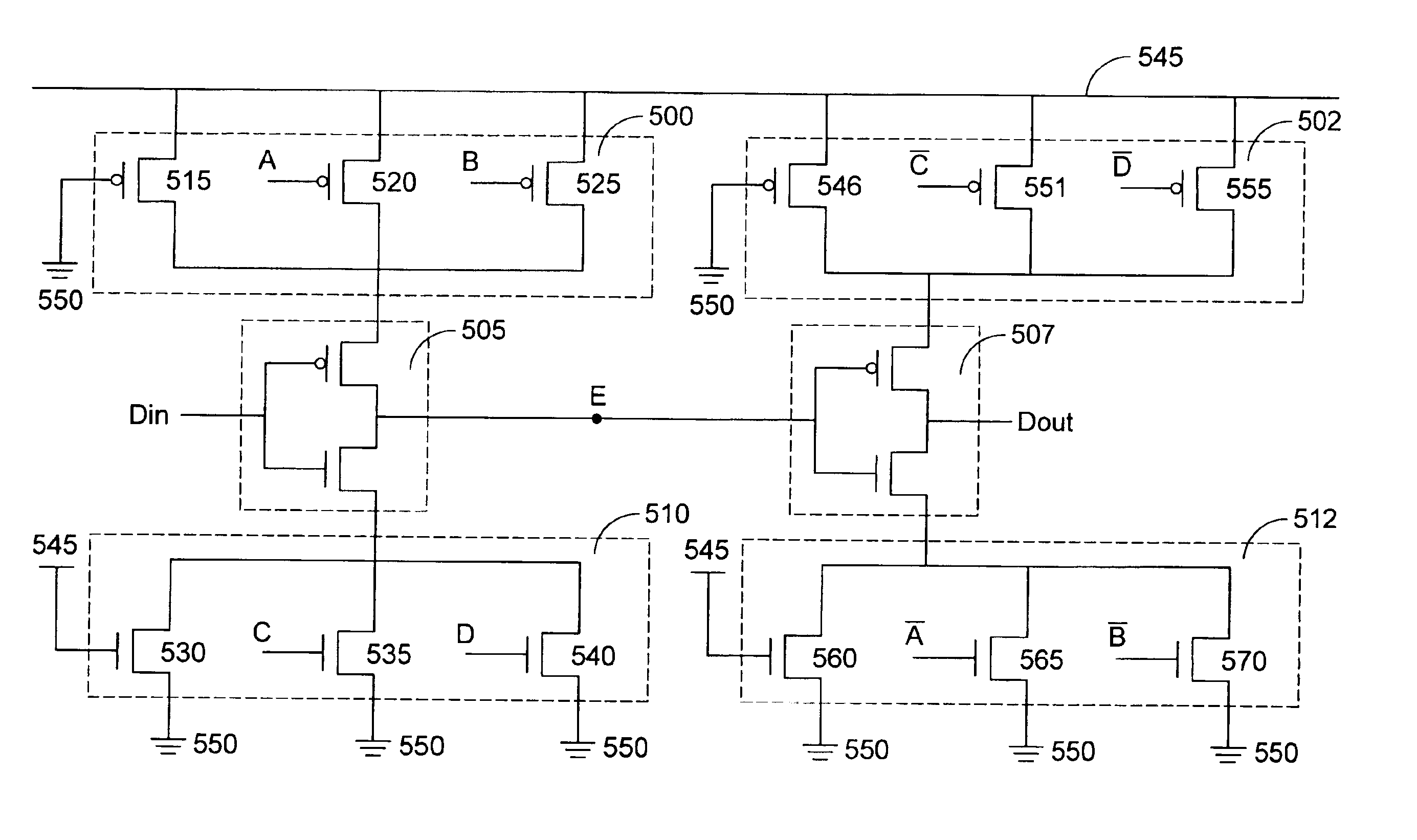

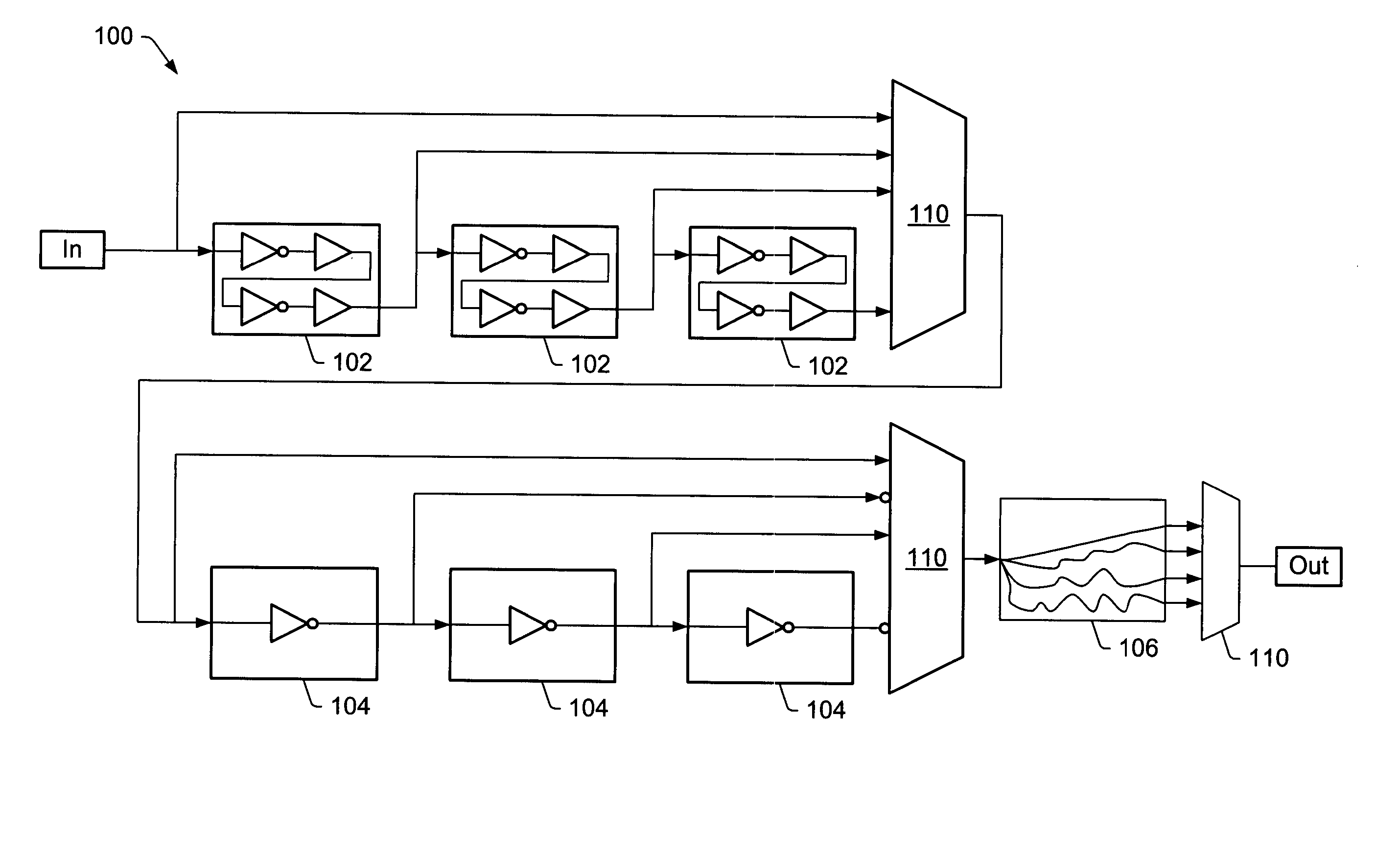

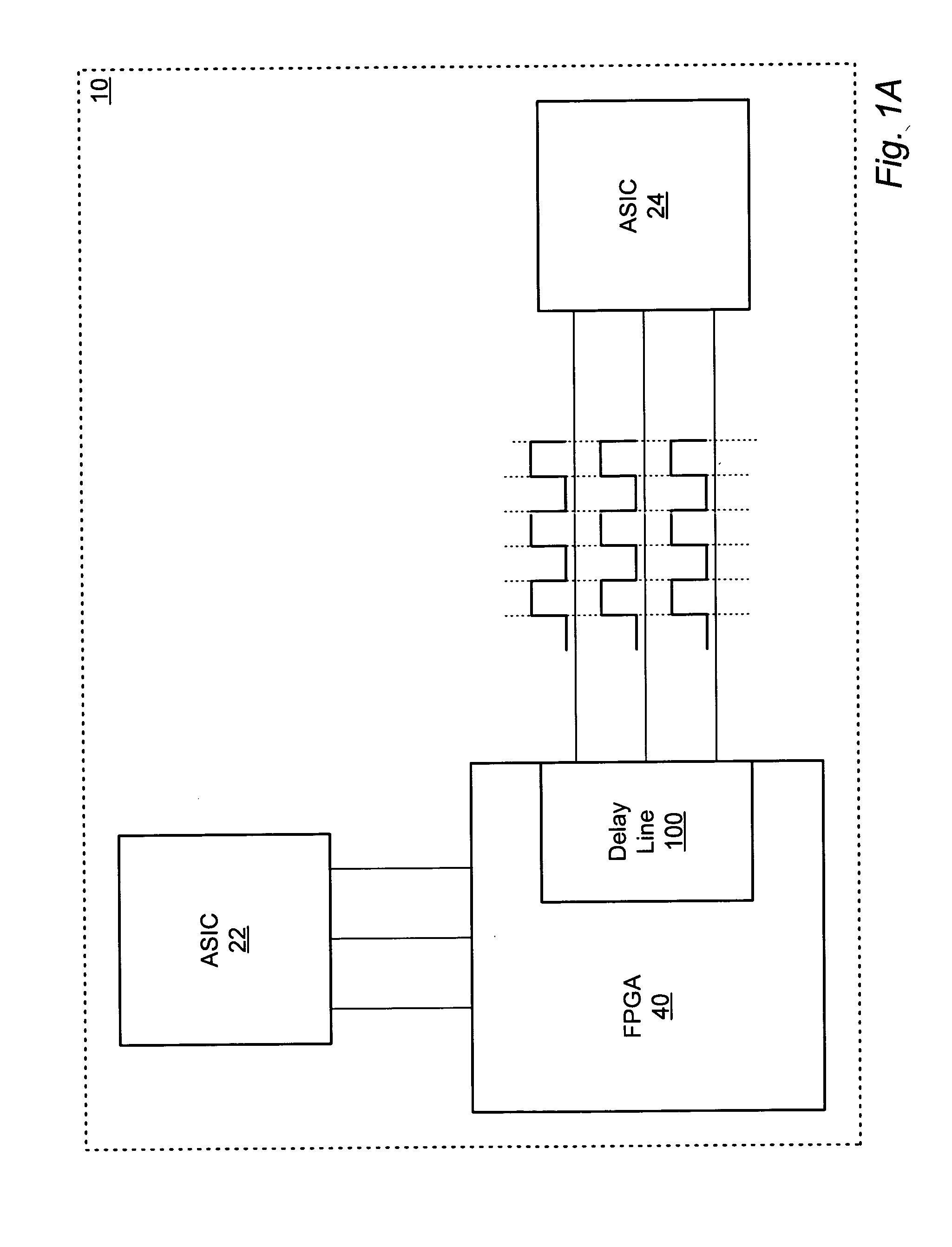

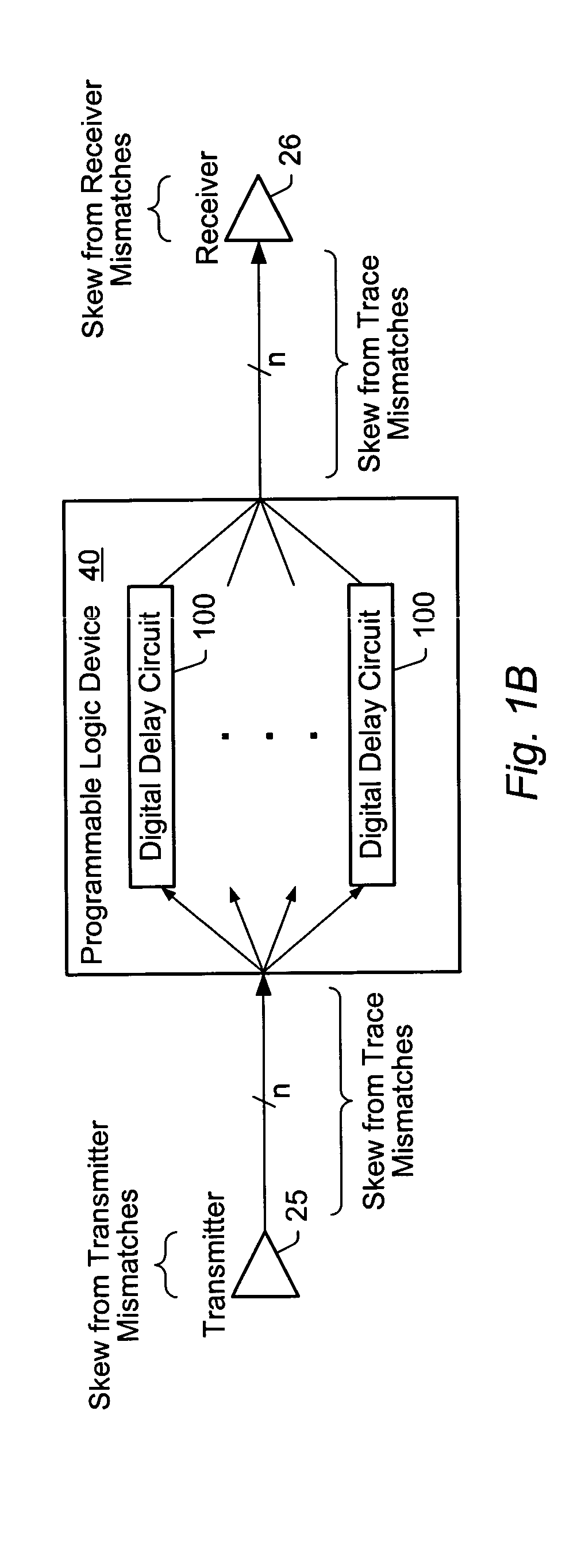

Digital delay elements constructed in a programmable logic device

InactiveUS20050046458A1Single output arrangementsGenerating/distributing signalsProgrammable logic deviceEngineering

A delay circuit. In one embodiment, a programmable logic device (PLD) is used to implement one or more delay circuits having a plurality of delay elements. Included in the plurality of elements are a balanced number of logic elements such that rising and falling edges of a signal passing through the delay circuit propagate with substantially the same amount of delay. The delay circuit may also include a selector circuit coupled to select an output from one of the plurality of delay elements. The delay circuit may be implemented such that it preserves the duty cycle and / or pulse width of signals to which the delay is applied.

Owner:NATIONAL INSTRUMENTS

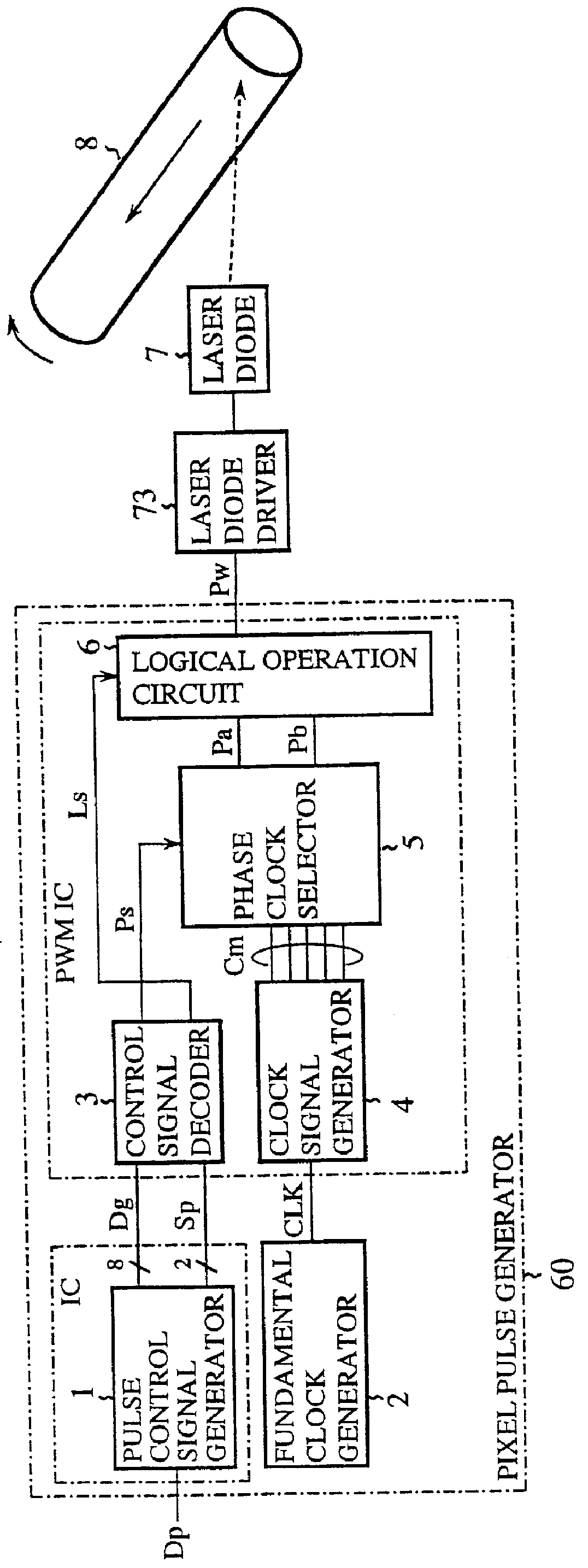

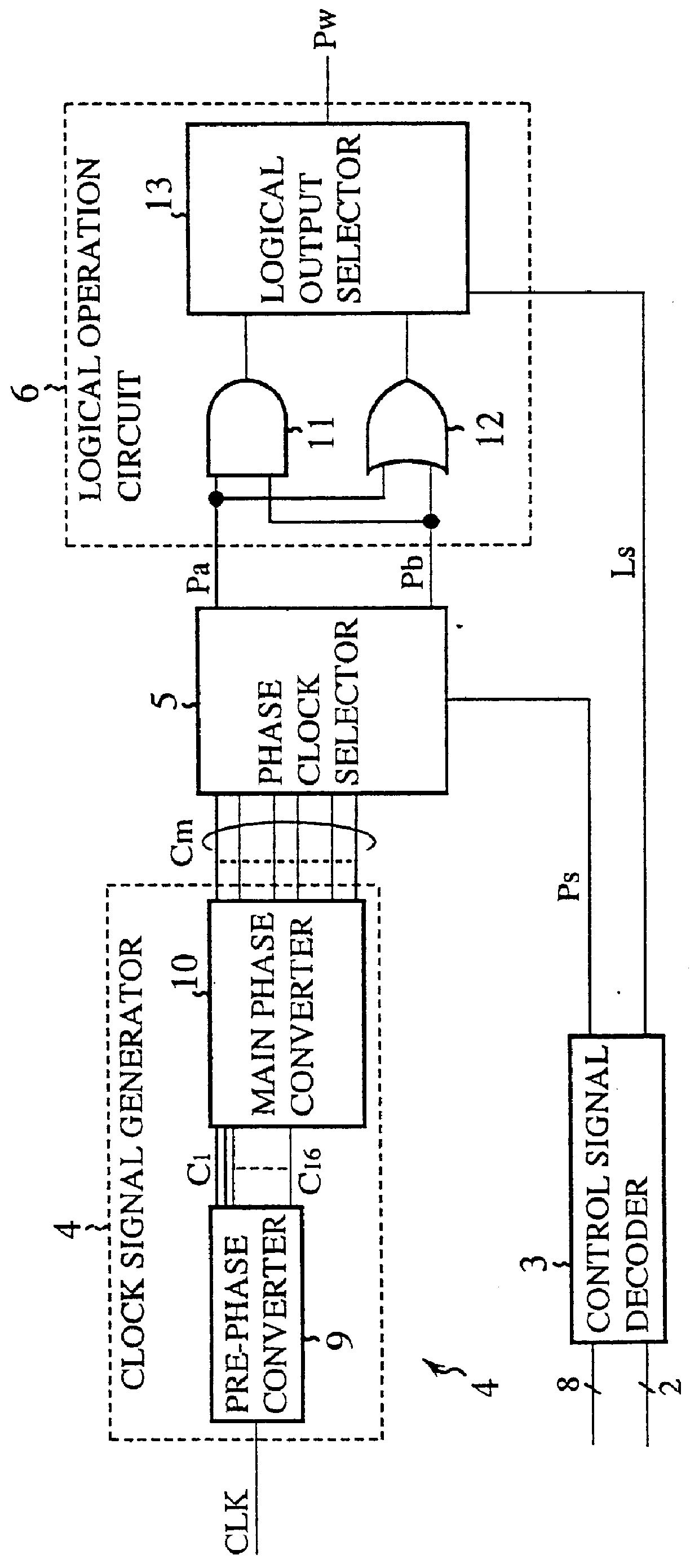

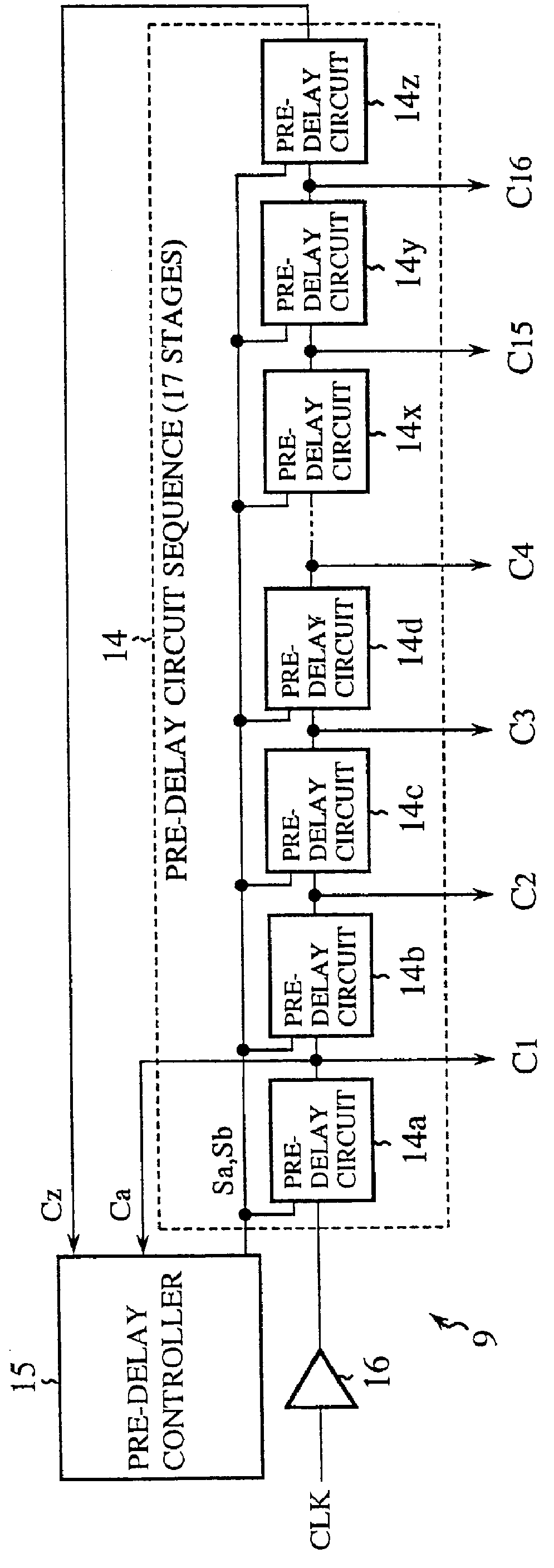

Clock signal generator for generating a plurality of clock signals with different phases, and clock phase controller using the same

A clock signal generator having a pre-phase converter for generating in response to an input clock signal a plurality of pre-delay clock signals with different phases; and main phase converters each of which receives one of the pre-delay clock signals, and generates a plurality of main delay clock signals with their phases different from each other, thereby generating multiple main delay clock signals with their phases different from each other.

Owner:RENESAS ELECTRONICS CORP

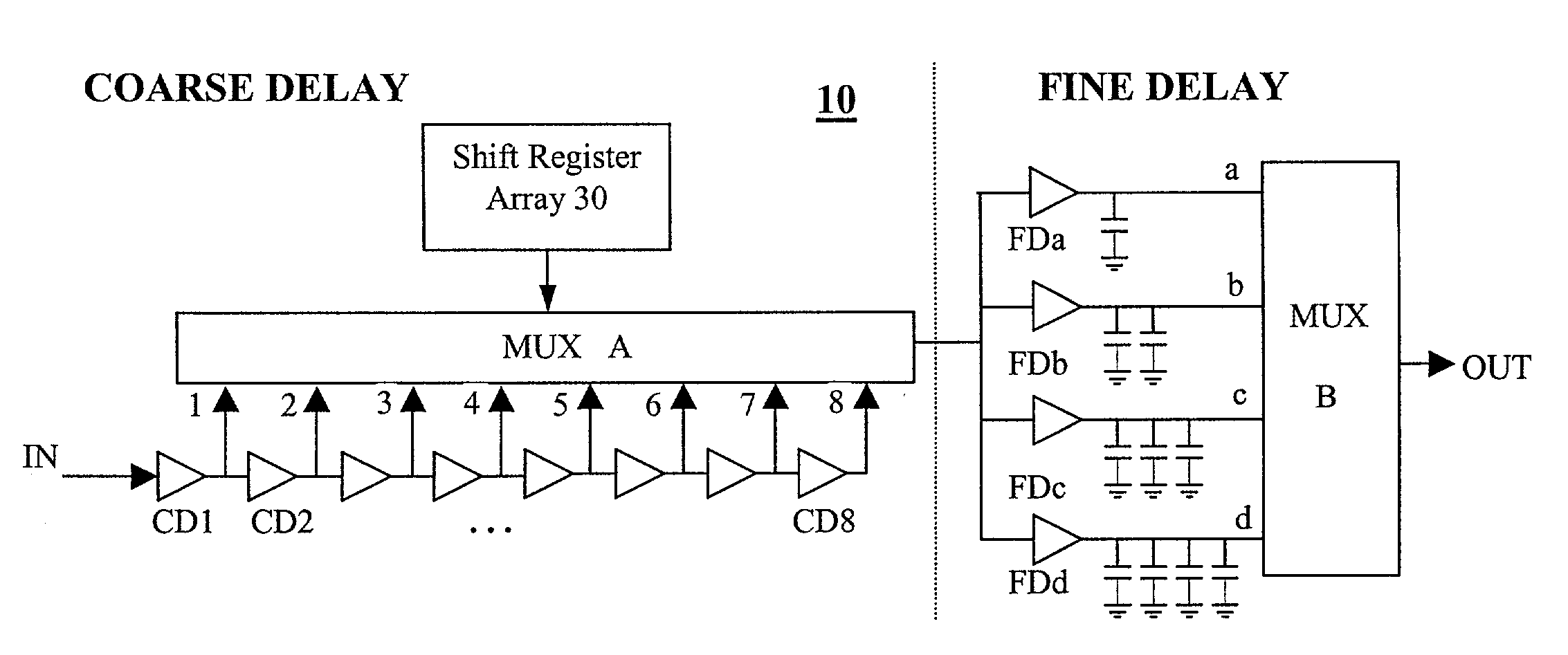

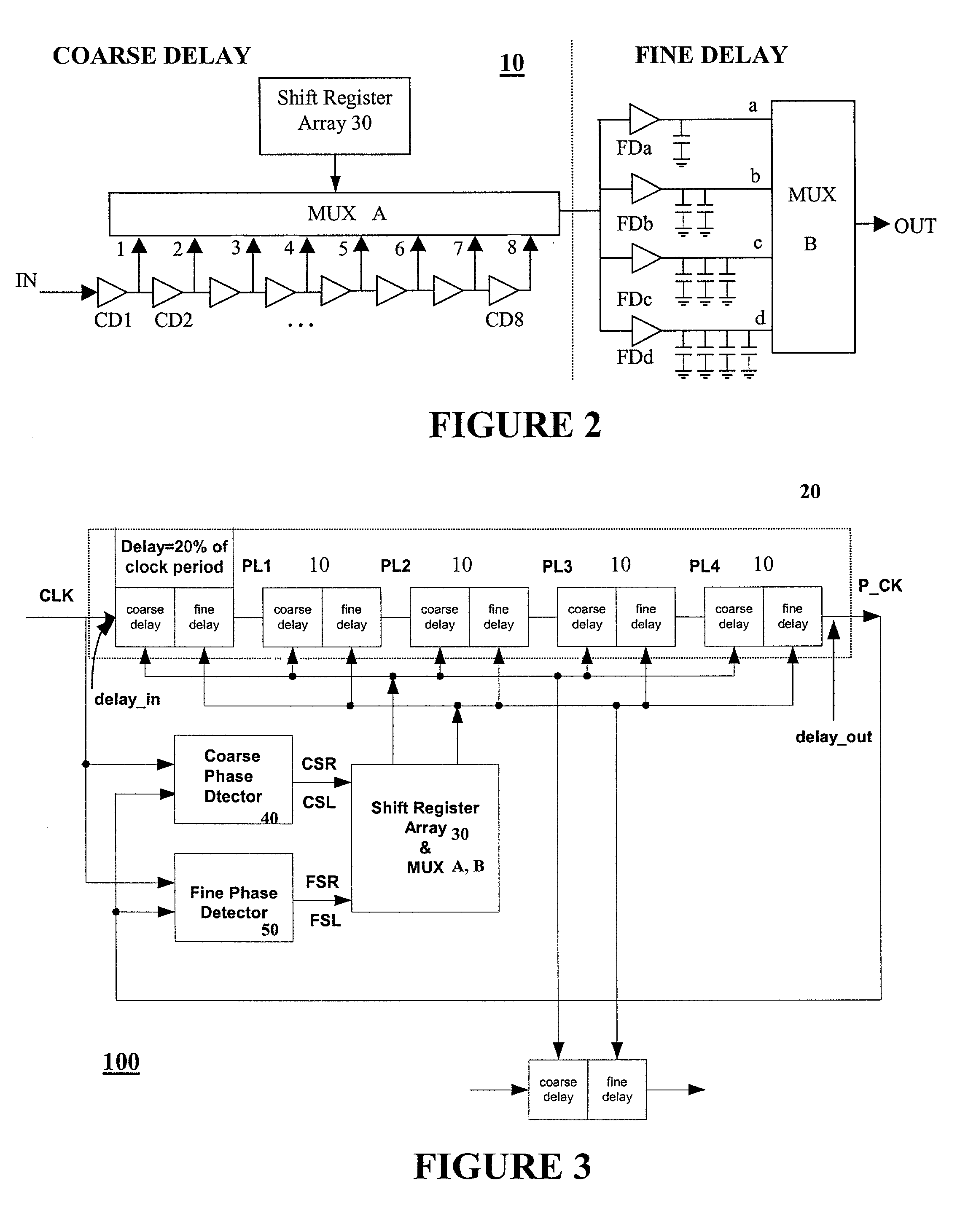

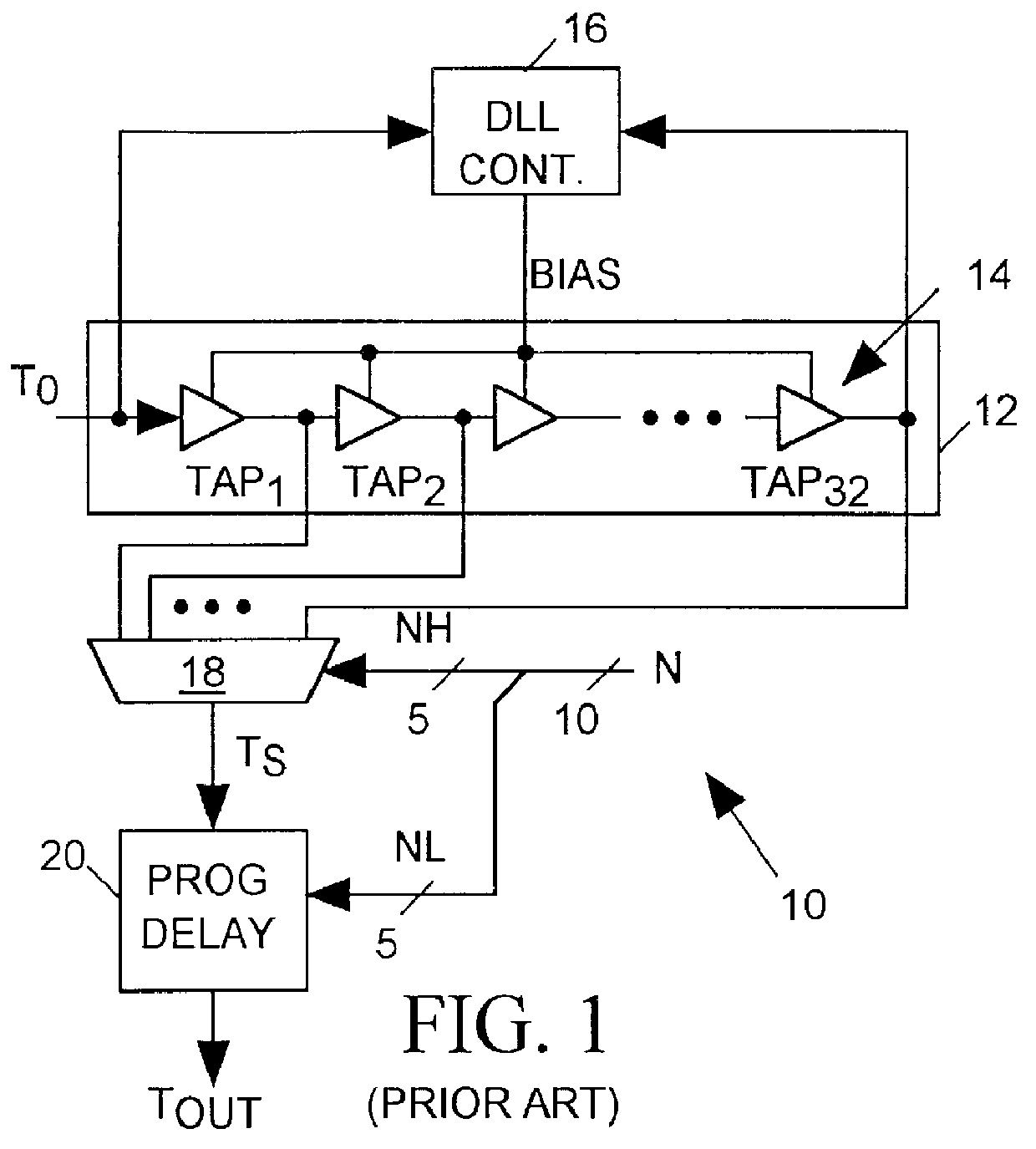

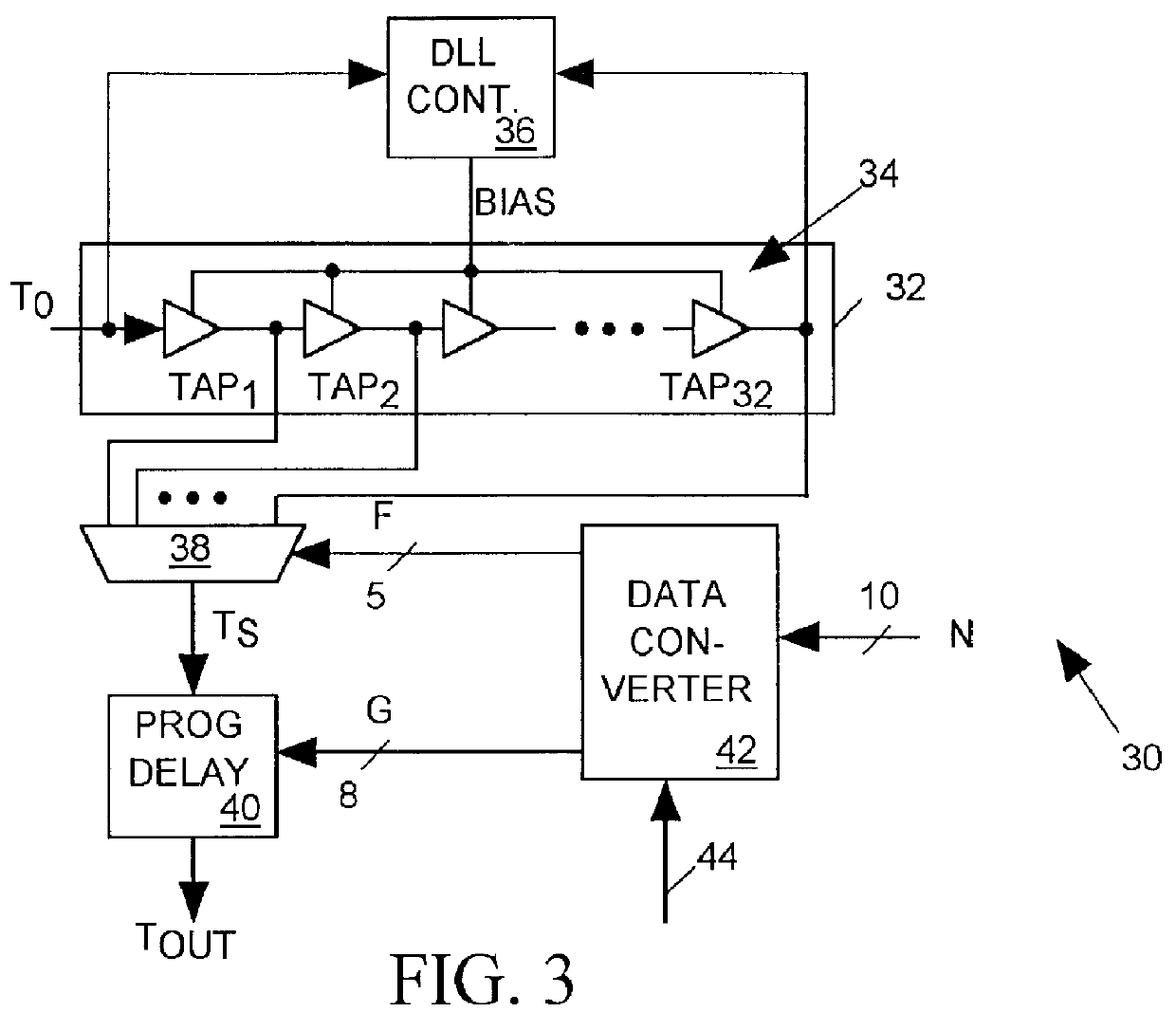

Calibratable programmable phase shifter

A programmable phase shifter includes a tapped delay line for successively delaying a periodic reference signal to produce a set of phase distributed tap signals. A multiplexer selects one of the tap signals as input to a programmable delay circuit which further delays the selected tap signal to produce an output signal that is phase shifted from the reference signal. A programmable data converter converts input data indicting a desired phase shift between the reference signal and the output signal into data for controlling the multiplexer selection and the amount of delay provided by the programmable delay circuit. The relationship between conversion table input and output data is adjusted so that the period of the output signal has a desired linear relationship to the input data value.

Owner:CREDENCE SYSTEMS

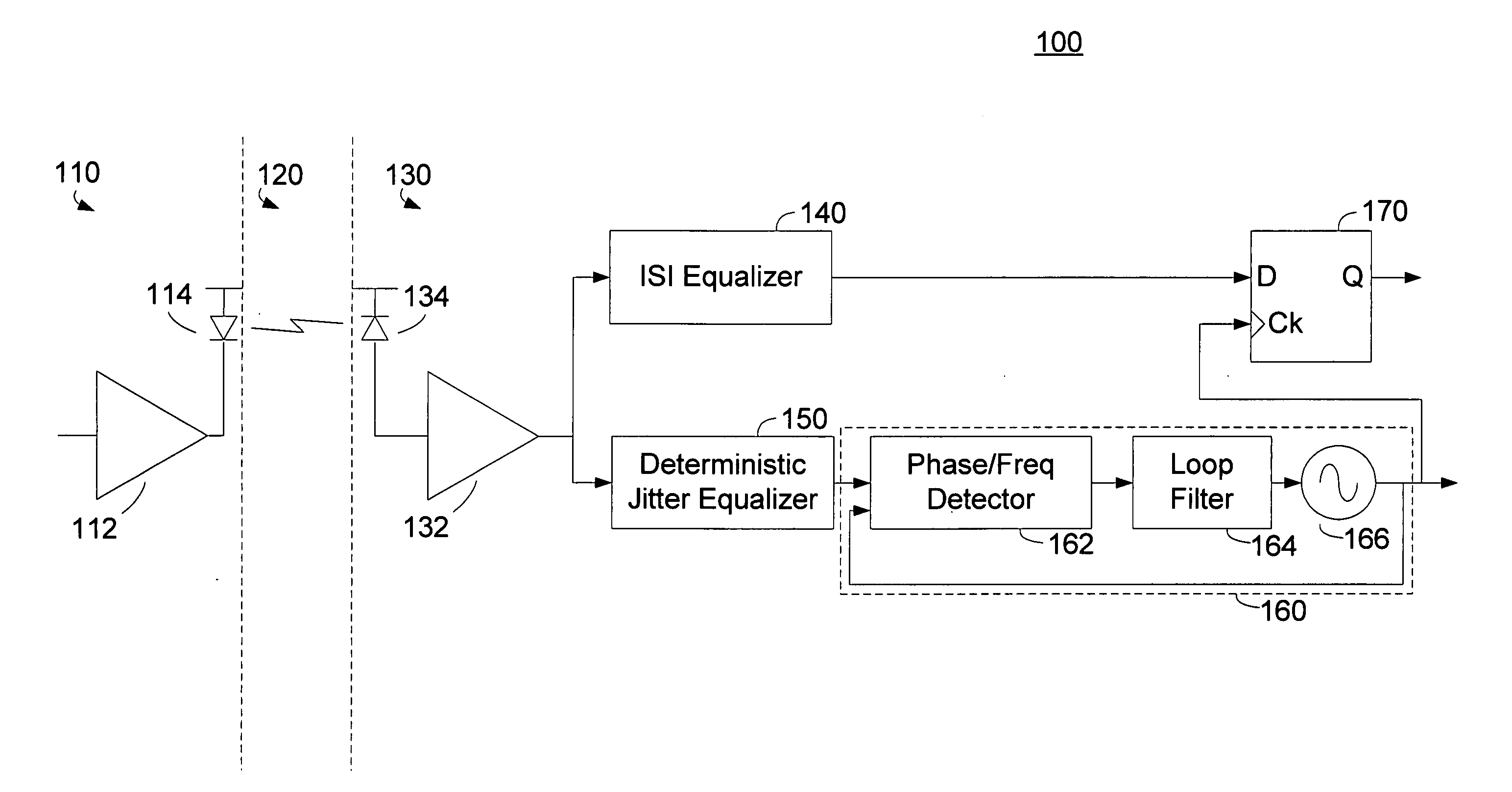

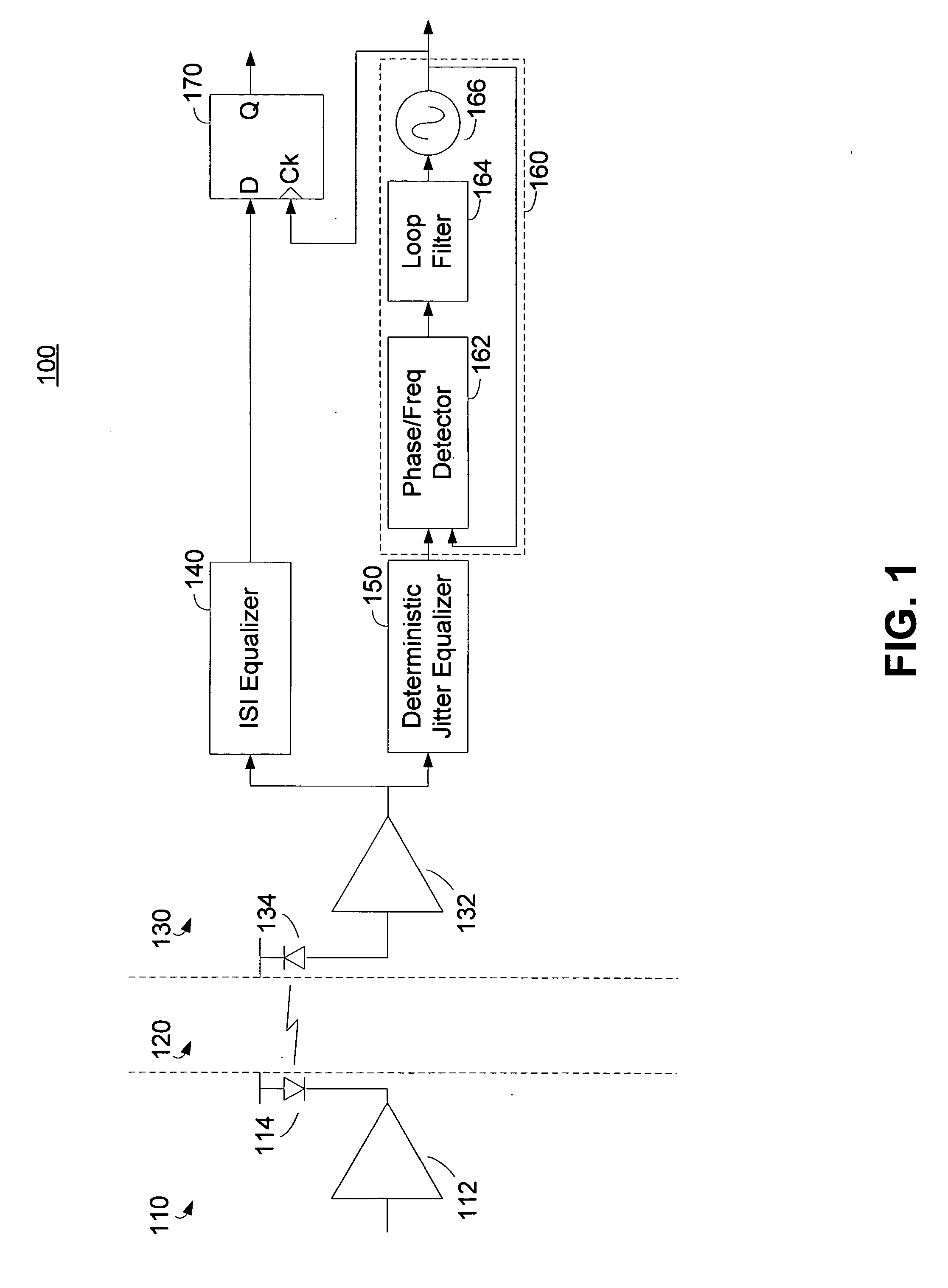

Deterministic jitter equalizer

ActiveUS20050152488A1Easy to implementImprove phase noiseMultiple-port networksError detection/prevention using signal quality detectorData streamDuty cycle distortion

An equalizer for serial data communications can be configured to compensate for the effects of deterministic jitter. The equalizer can be configured to compensate a received serial data stream for the effects of data-dependent jitter as well as duty cycle distortion jitter. The equalizer can be configured to determine the value of one or more previously received symbols and compare them to a recovered symbol. The equalizer can adjust a variable delay positioned in the serial data path to introduce a delay into the data path that is based in part on the received data stream. The equalizer can be configured to vary the delay when any of the one or more previously received symbols is different from the recovered symbol, and can be configured to maintain a constant delay if the one or more previously received symbols is the same as the recovered symbol.

Owner:CALIFORNIA INST OF TECH

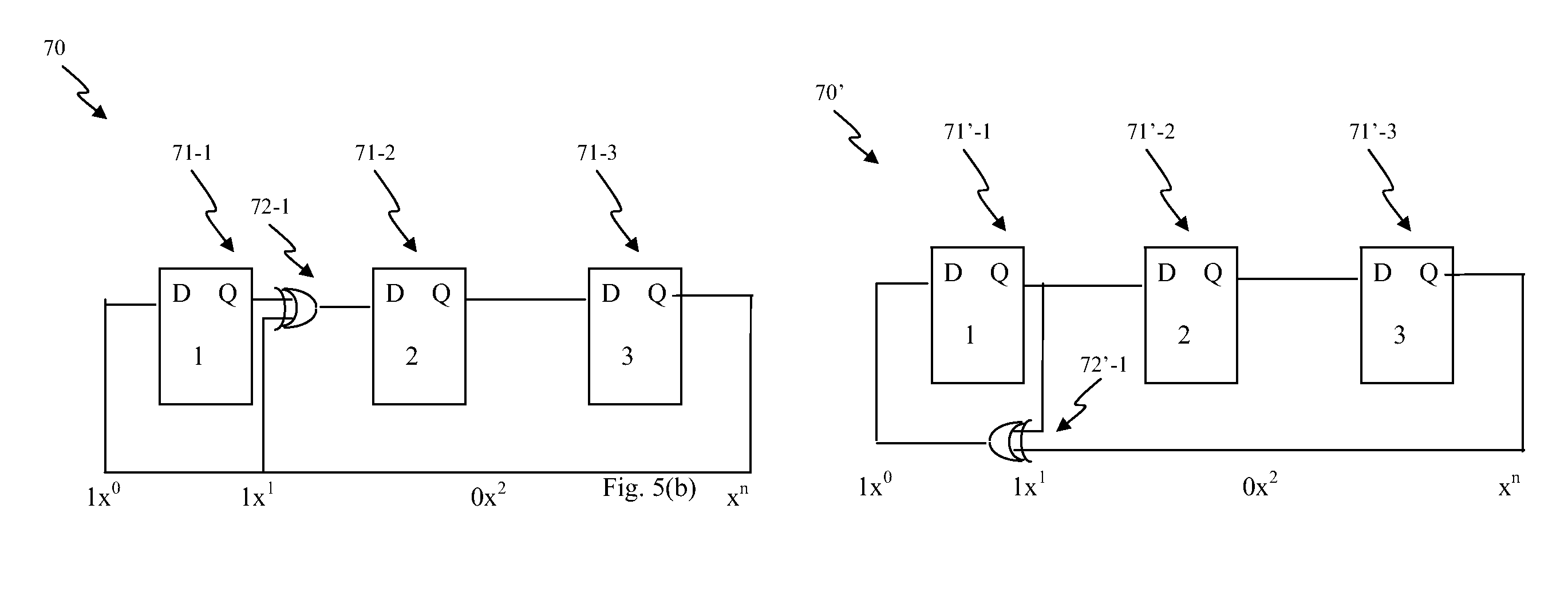

Circuit and system of a low density one-time programmable memory

InactiveUS8861249B2Low density OTPsReduce memory sizeElectric analogue storesRead-only memoriesIp addressAddress generator

A low density One-Time Programmable (OTP) memory is disclosed to achieve low gate count and low overhead in the peripheral circuits to save the cost. A maximum-length Linear Feedback Shift Register (LFSR) can be used to generate 2n−1 address spaces from an n-bit address. The registers used in the address generator can have two latches. Each latch has two cross-coupled inverters with two outputs coupled to the drains of two MOS input devices, respectively. The inputs of the latch are coupled to the gates of the MOS input devices, respectively. The sources of the MOS input devices are coupled to the drains of at least one MOS device(s), whose gate(s) are coupled to a clock signal and whose source(s) are coupled to a supply voltage. The two latches can be constructed in serial with the outputs of the first latch coupled to the inputs of the second latch.

Owner:ATTOPSEMI TECH CO LTD

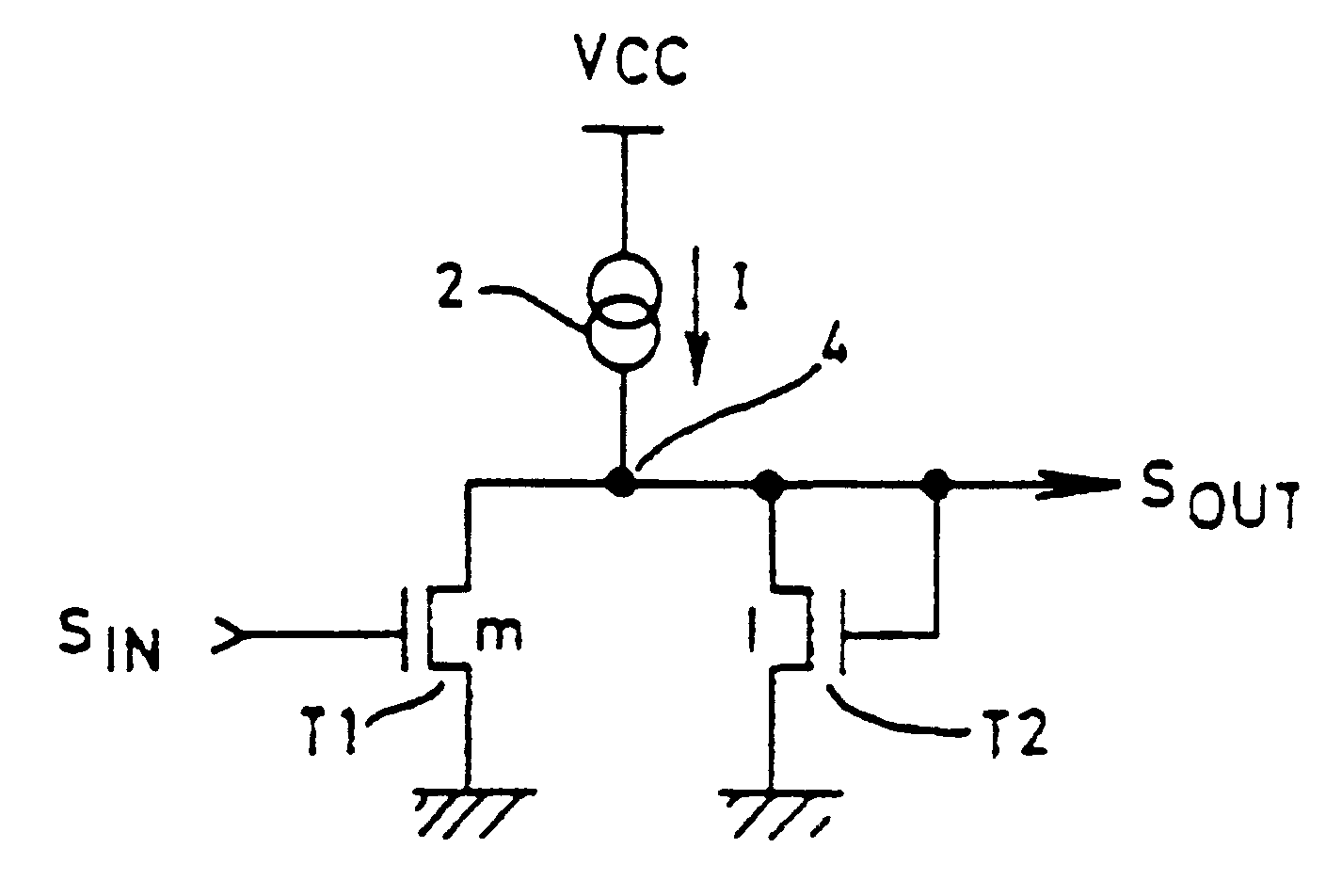

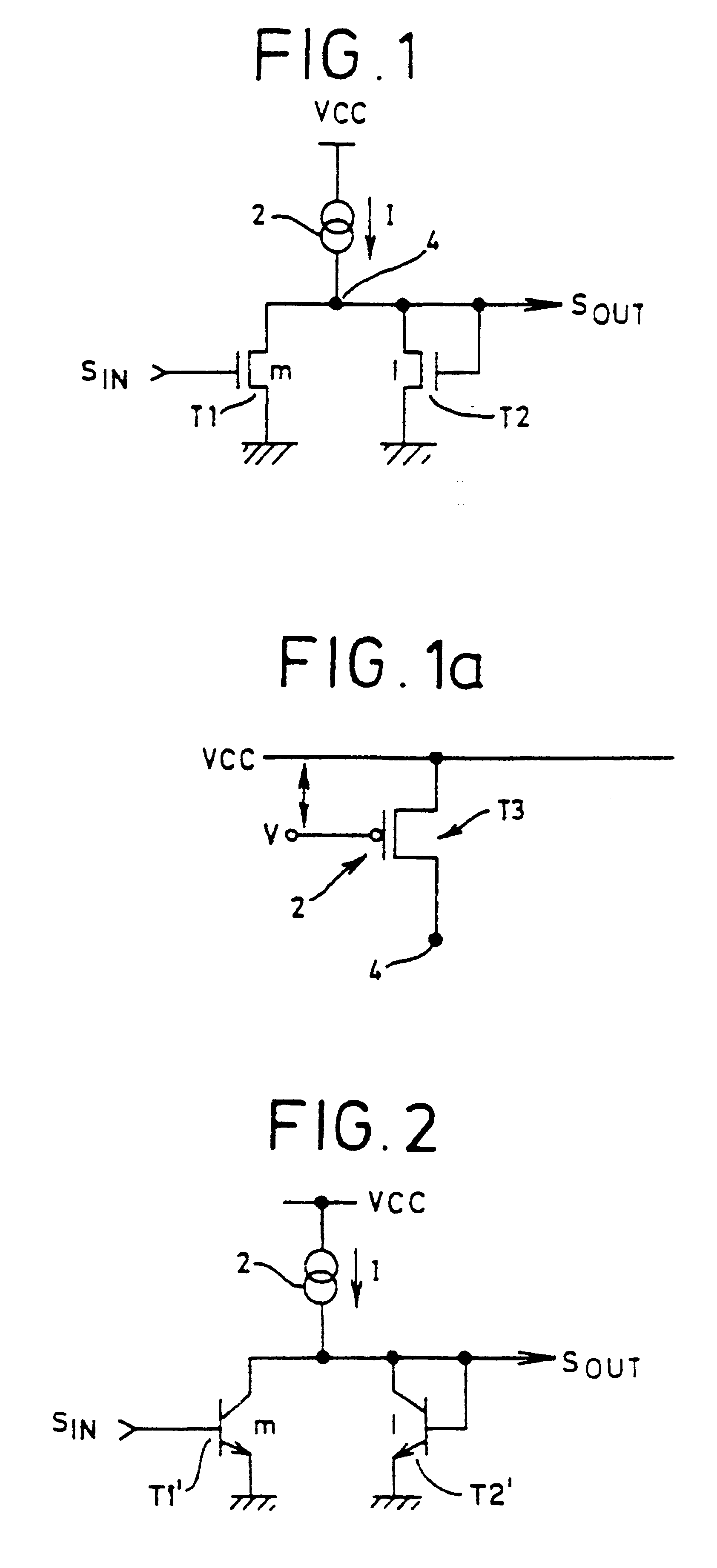

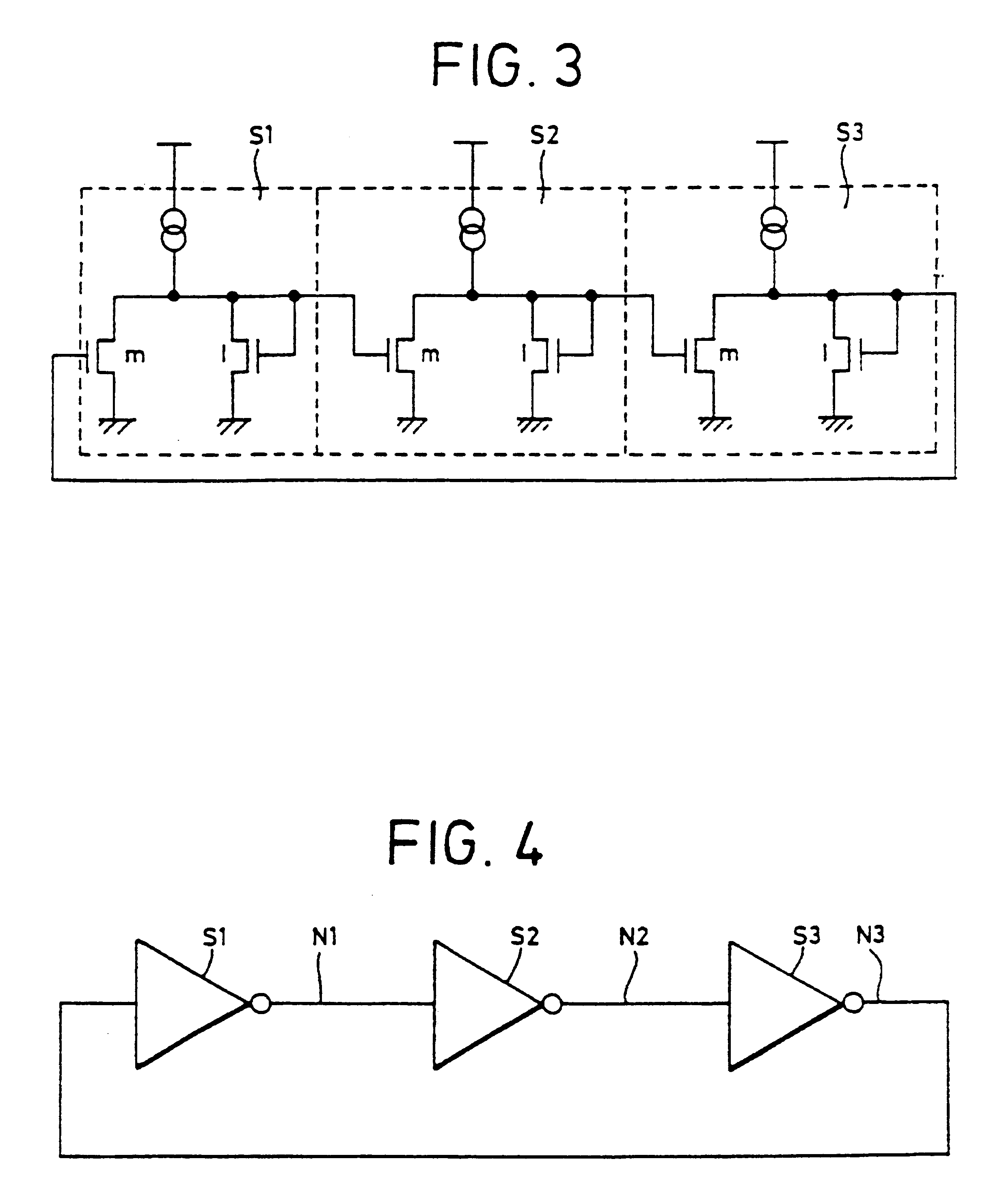

Ring oscillator using current mirror inverter stages

InactiveUSRE37124E1Limit maximum frequencyPulse automatic controlPulse generation by logic circuitsLow voltageEngineering

A ring oscillator having an odd number of single ended stages, each stage including two transistors connected as a current mirror. The stage provides for low-voltage performance and improved process tolerance characteristics.

Owner:STMICROELECTRONICS SRL

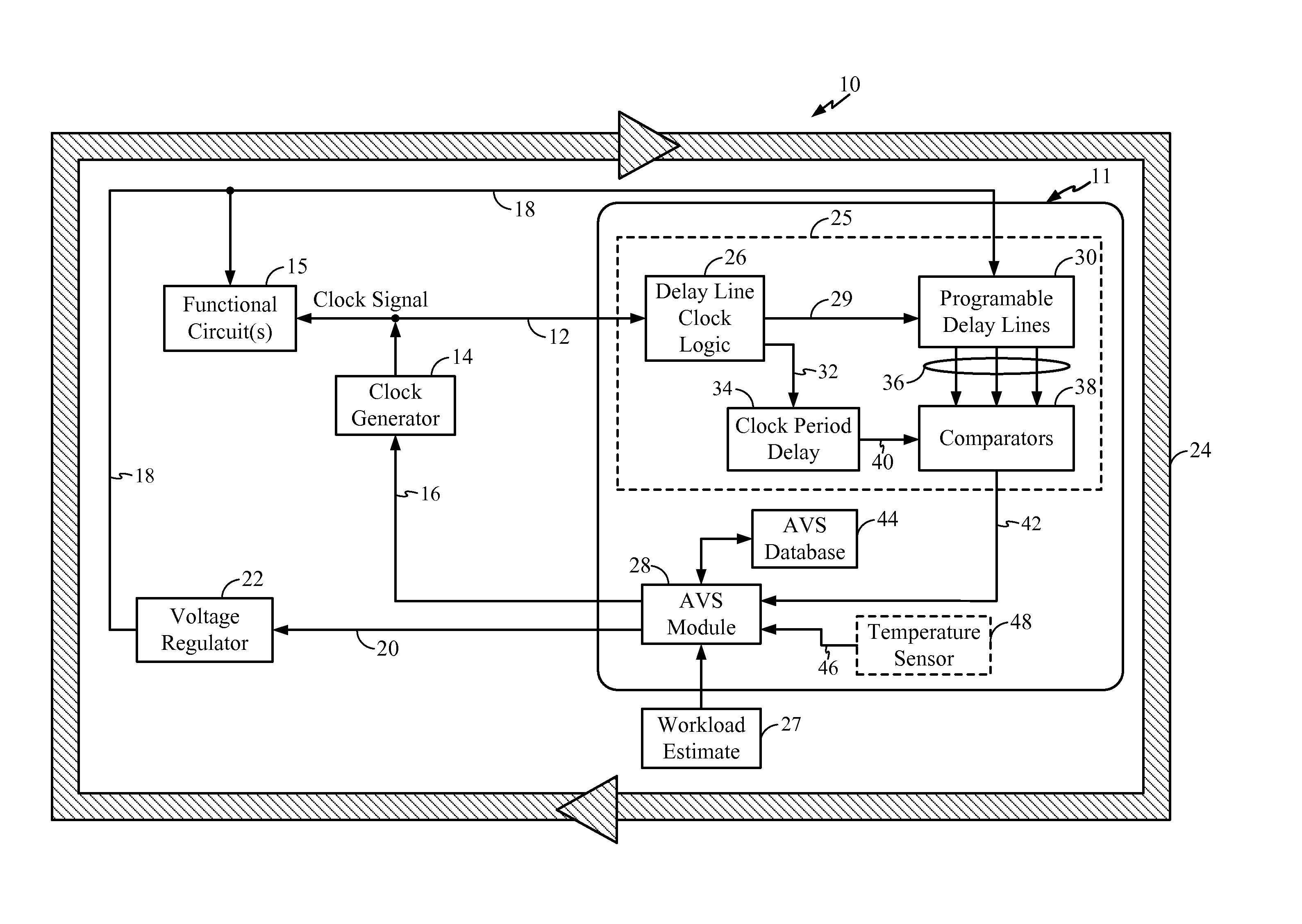

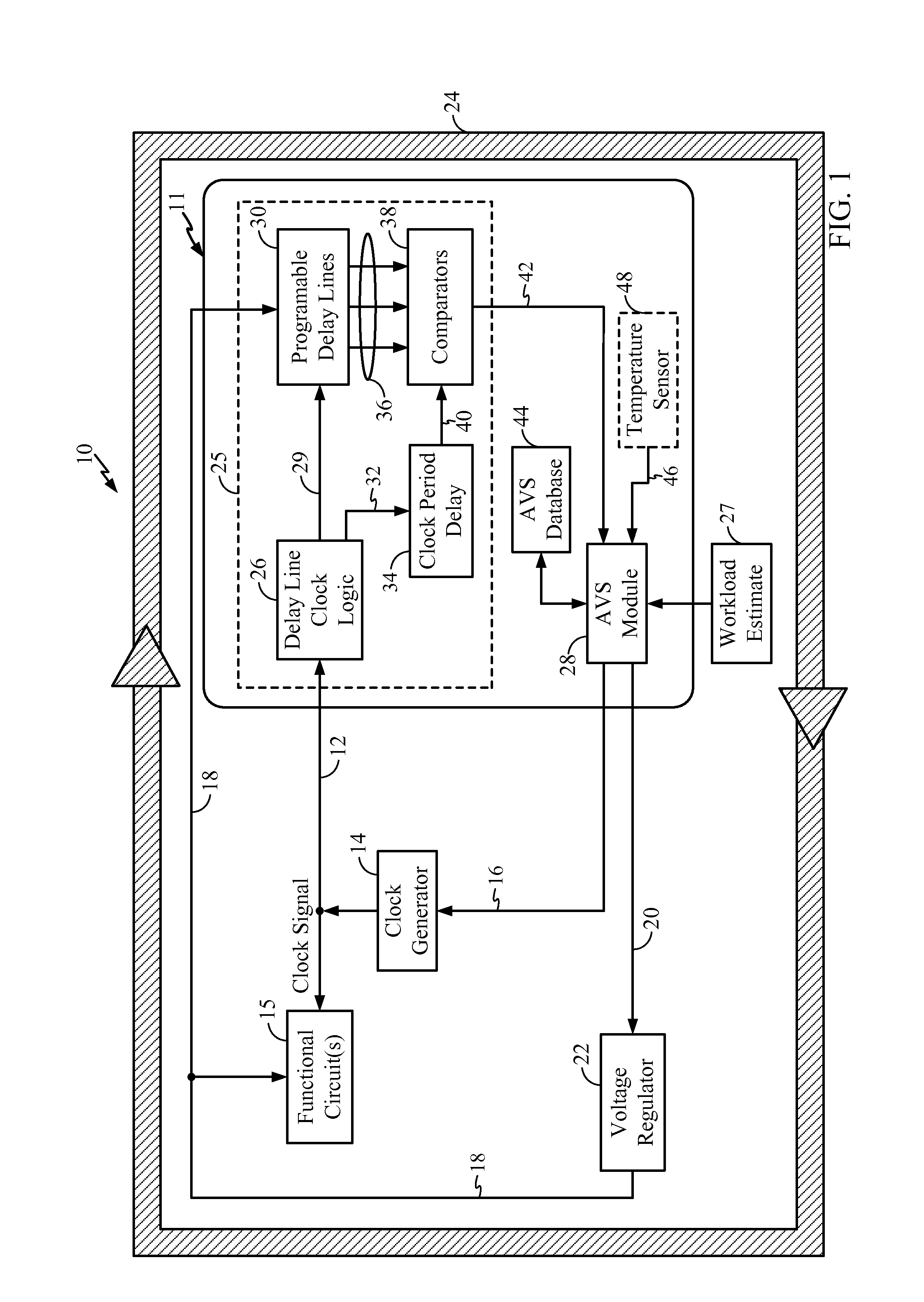

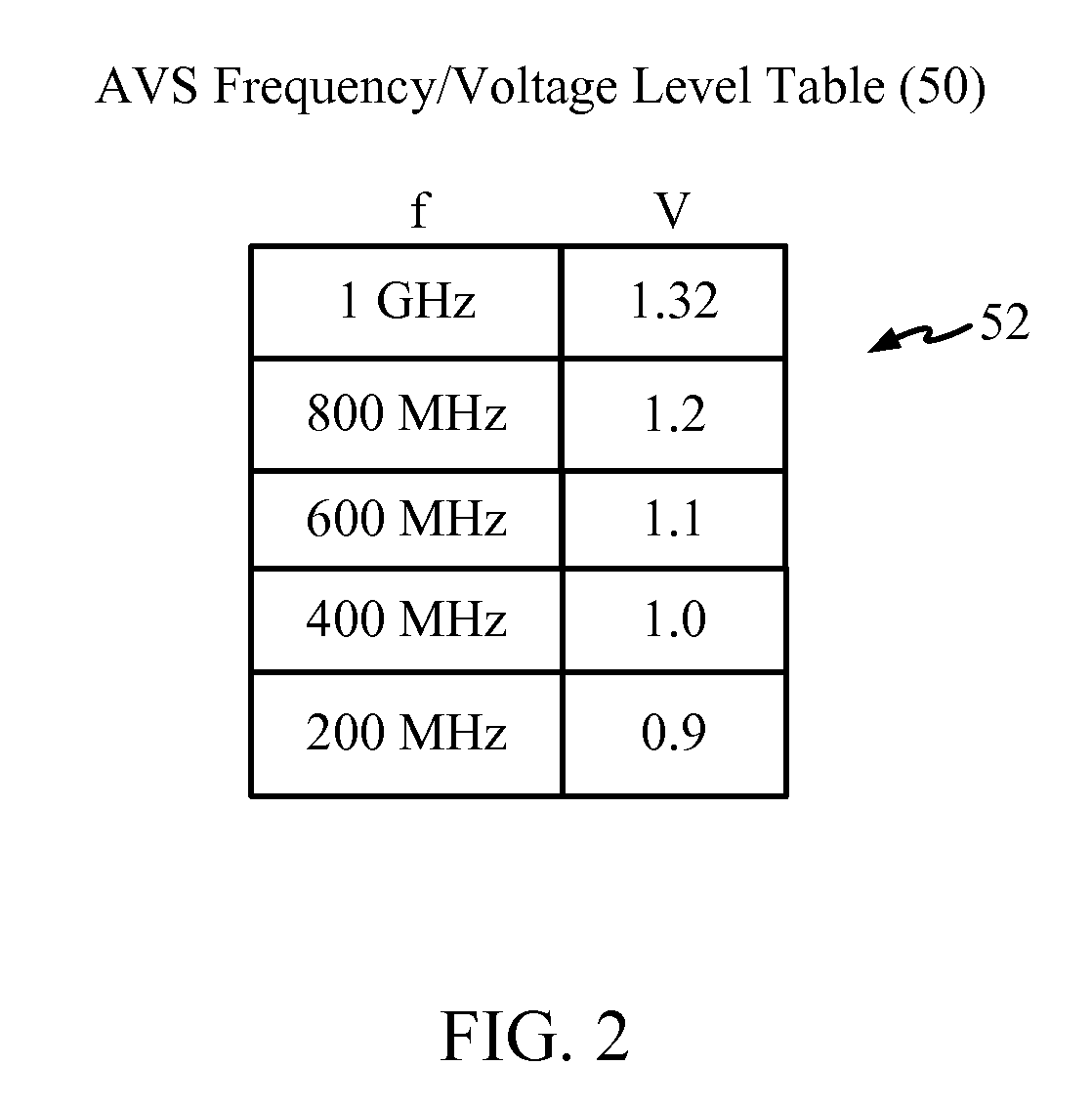

ADAPTIVE VOLTAGE SCALERS (AVSs), SYSTEMS, AND RELATED METHODS

ActiveUS20110080202A1Avoid and reduce tolerance voltage marginAvoid and reduce voltage marginPower supply for data processingElectric pulse generatorSelf adaptiveOperating frequency

Owner:QUALCOMM INC

Popular searches

Oscillations generators Duplex signal operation Radio wave reradiation/reflection Energy efficient computing Coding details Testing/calibration of speed/acceleration/shock measurement devices Special data processing applications Receiver initialisation Recording carrier details Synchronisation information channels

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com