Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

130 results about "Duty cycle distortion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

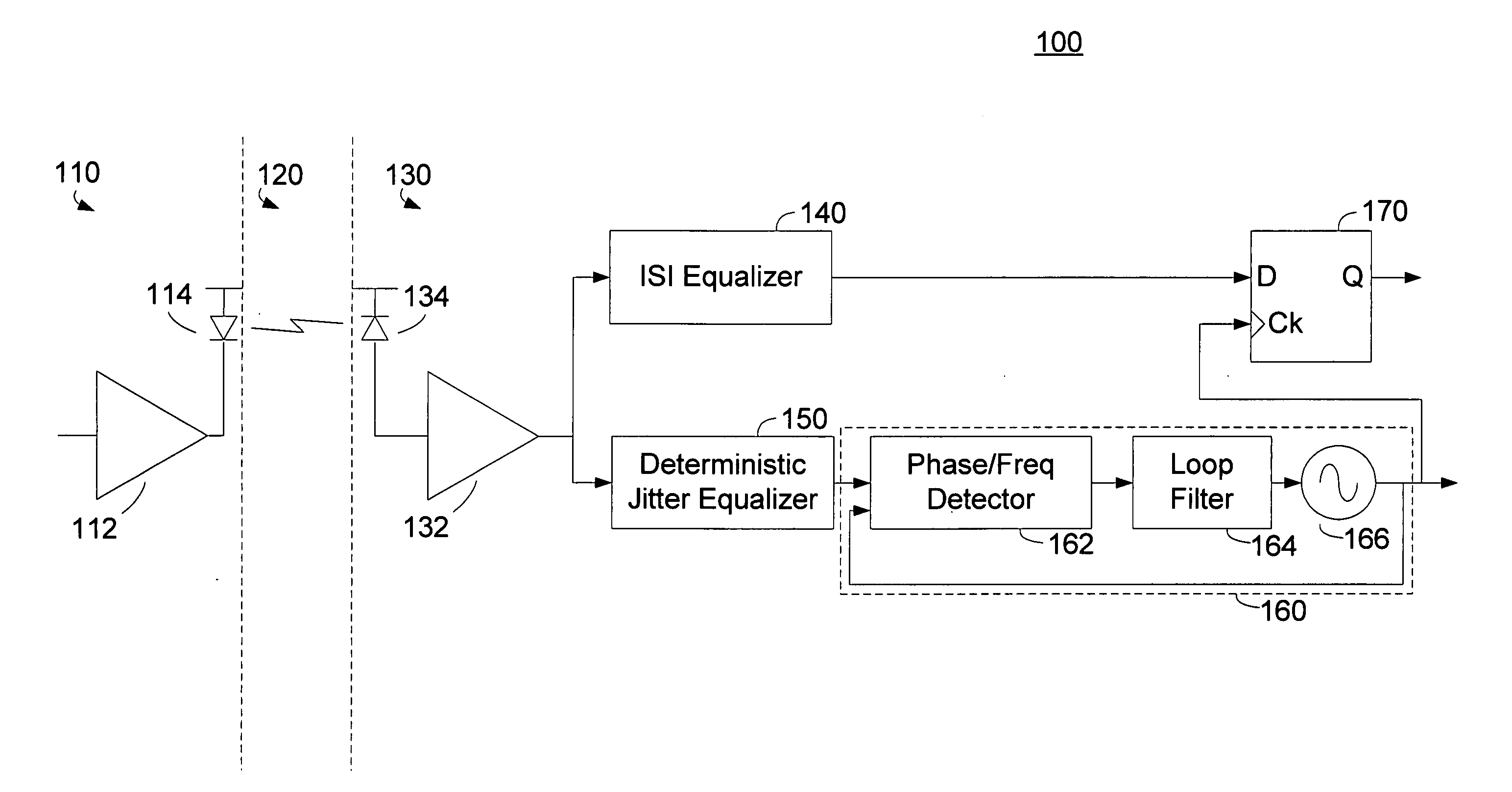

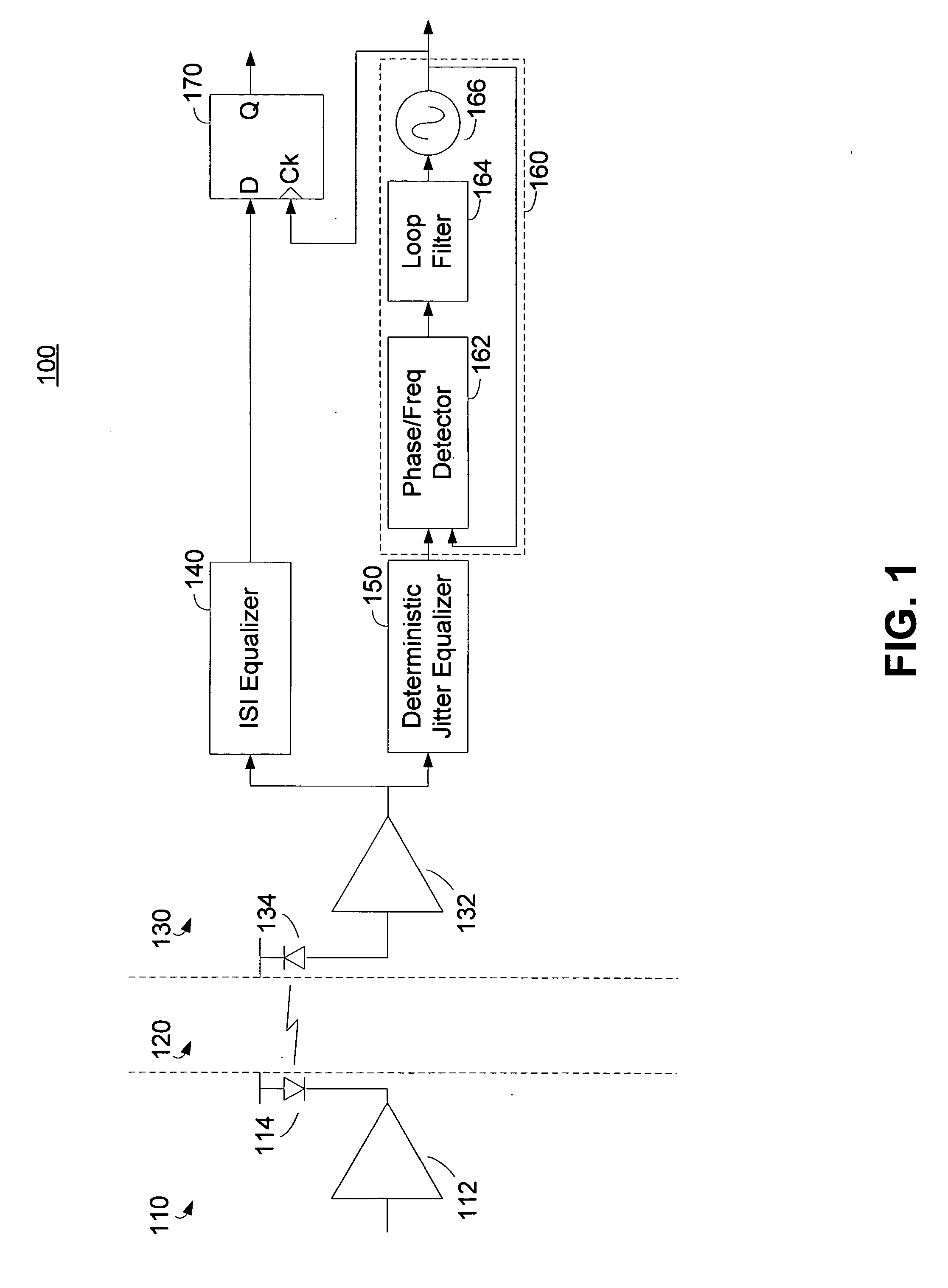

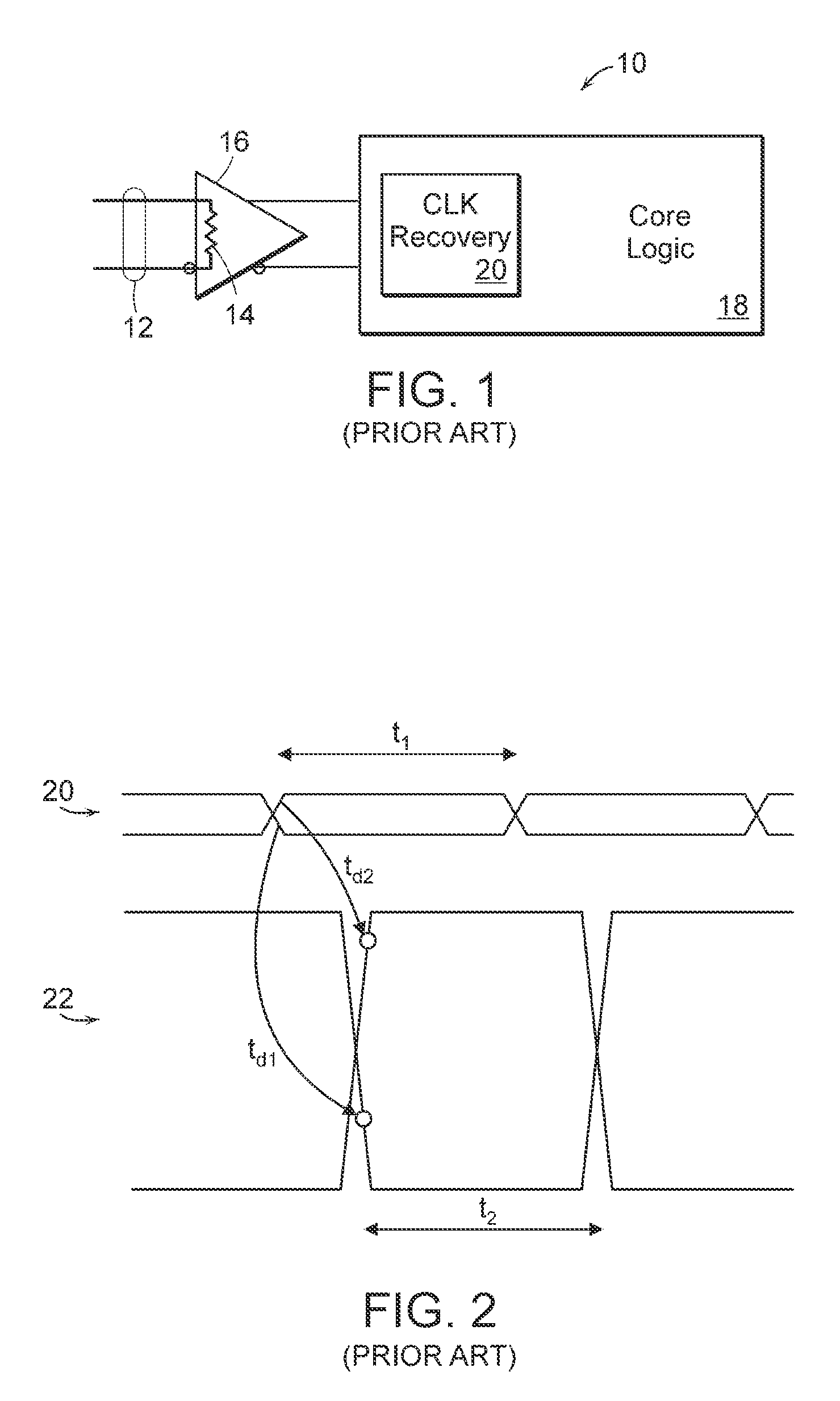

Deterministic jitter equalizer

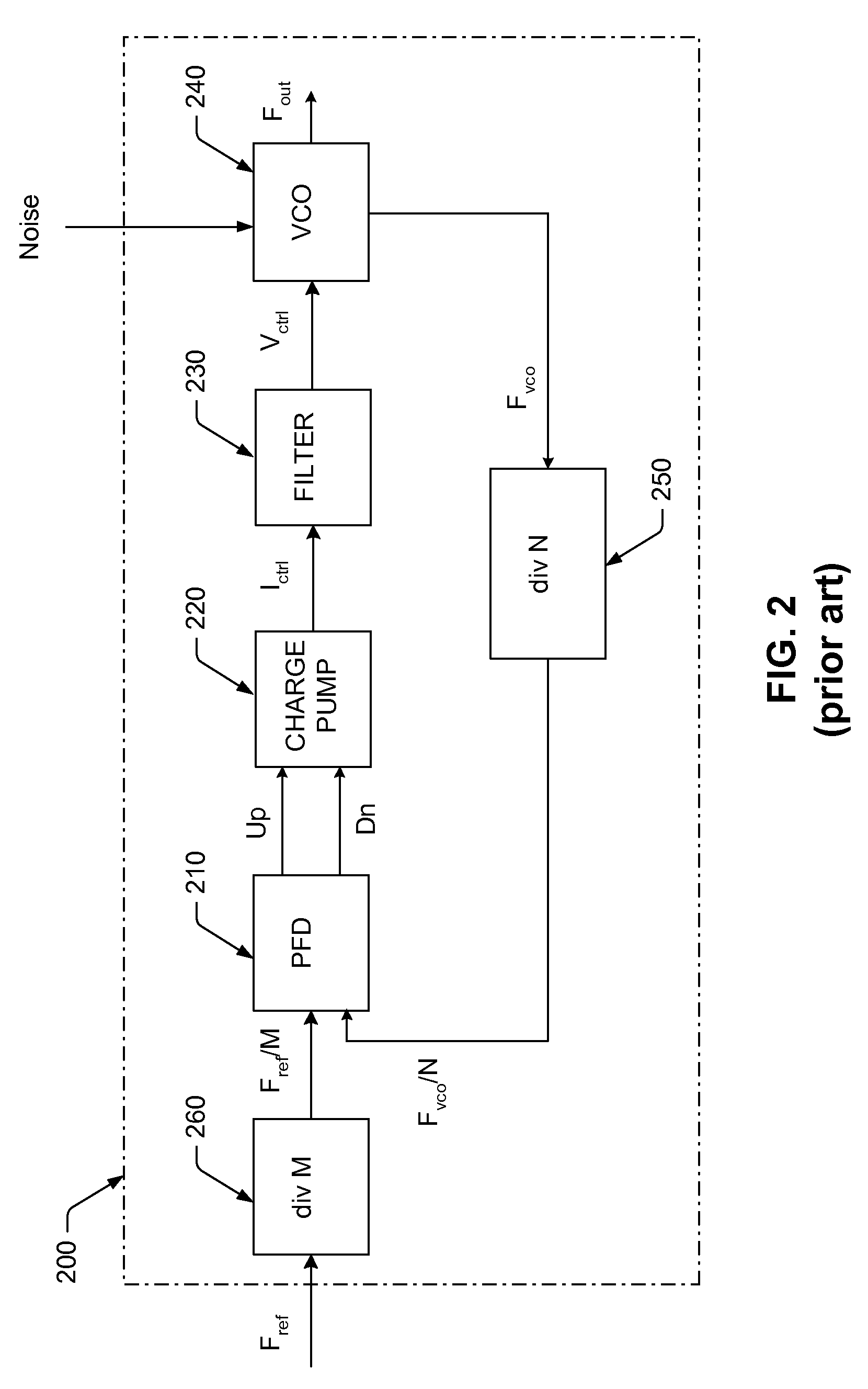

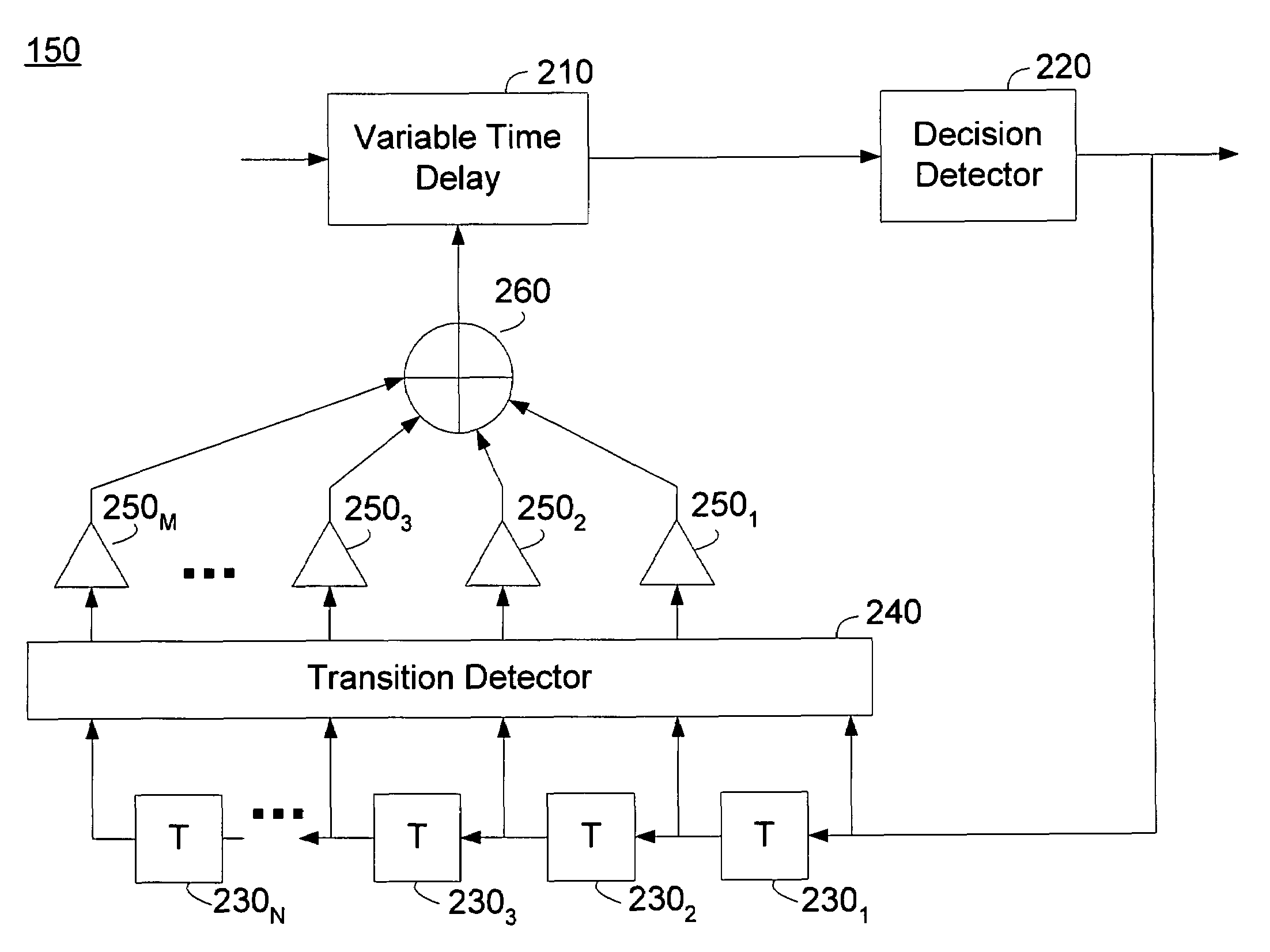

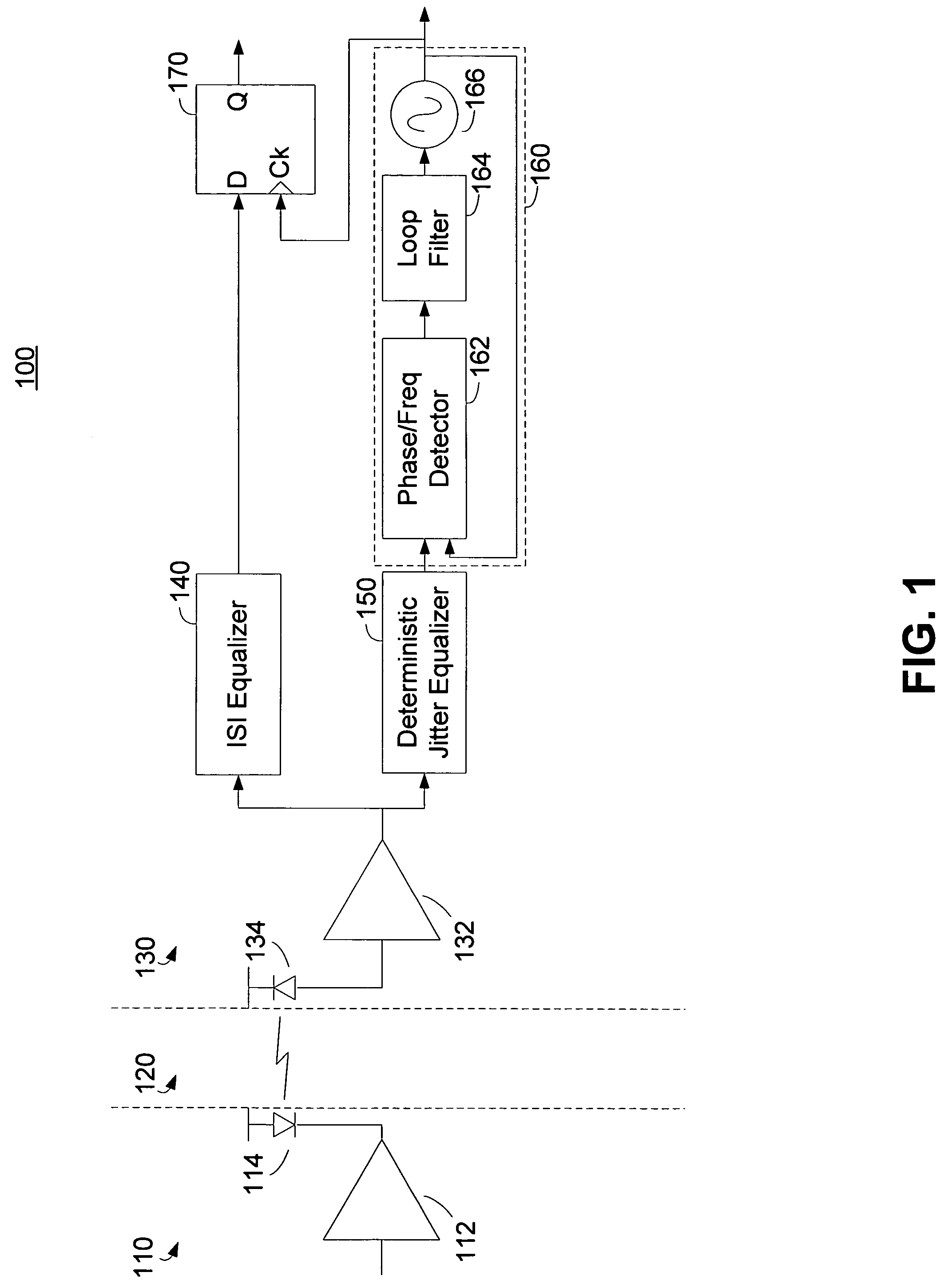

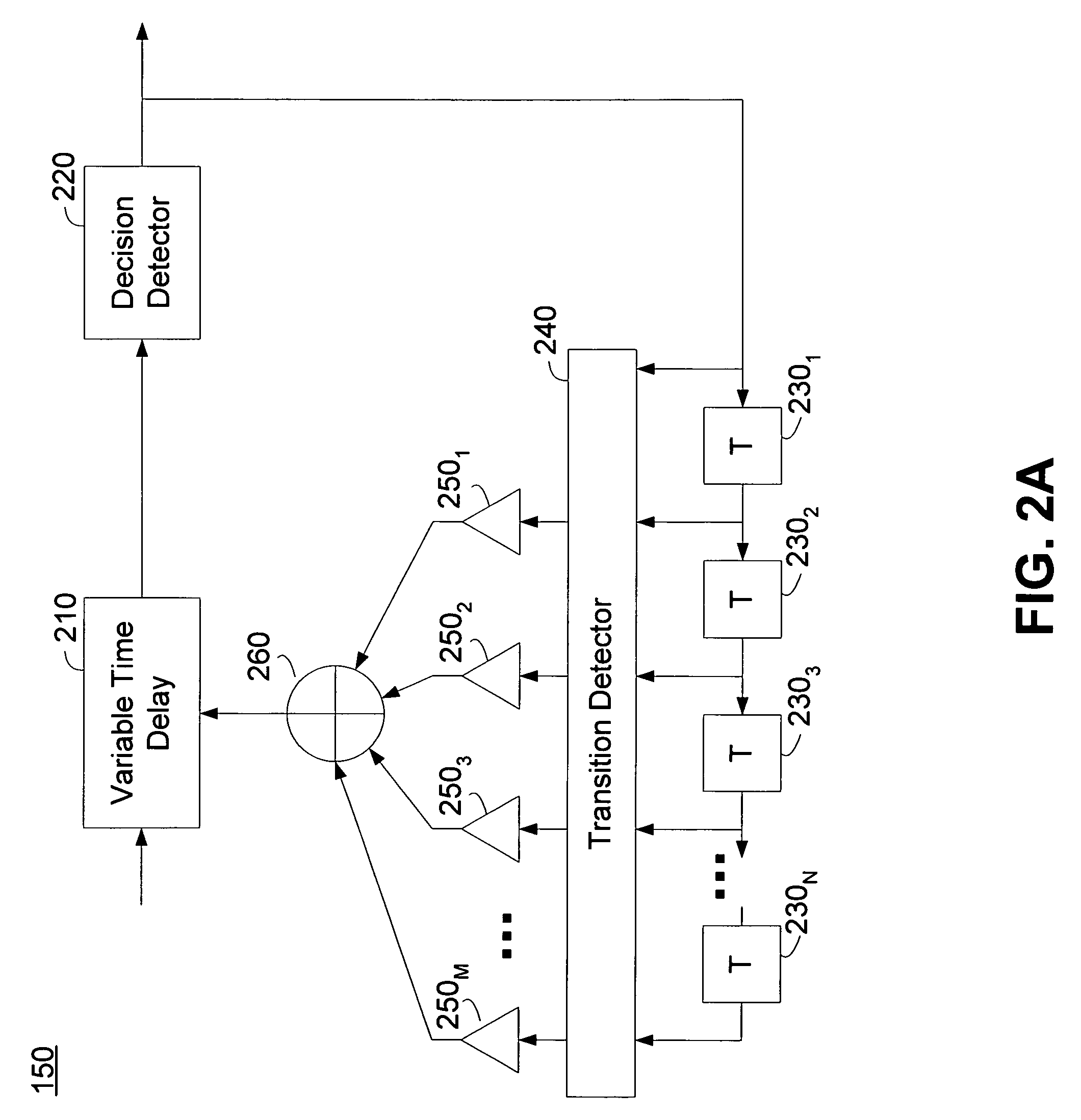

ActiveUS20050152488A1Easy to implementImprove phase noiseMultiple-port networksError detection/prevention using signal quality detectorData streamDuty cycle distortion

An equalizer for serial data communications can be configured to compensate for the effects of deterministic jitter. The equalizer can be configured to compensate a received serial data stream for the effects of data-dependent jitter as well as duty cycle distortion jitter. The equalizer can be configured to determine the value of one or more previously received symbols and compare them to a recovered symbol. The equalizer can adjust a variable delay positioned in the serial data path to introduce a delay into the data path that is based in part on the received data stream. The equalizer can be configured to vary the delay when any of the one or more previously received symbols is different from the recovered symbol, and can be configured to maintain a constant delay if the one or more previously received symbols is the same as the recovered symbol.

Owner:CALIFORNIA INST OF TECH

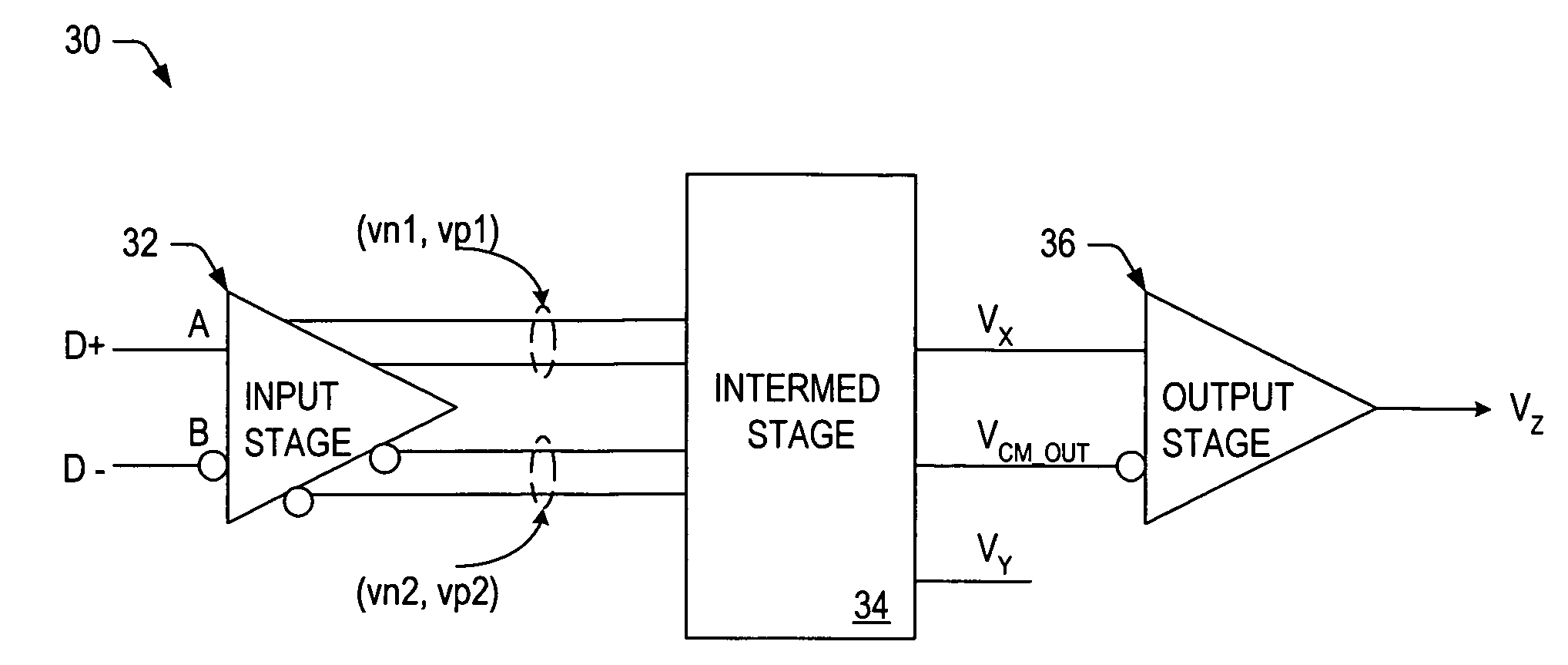

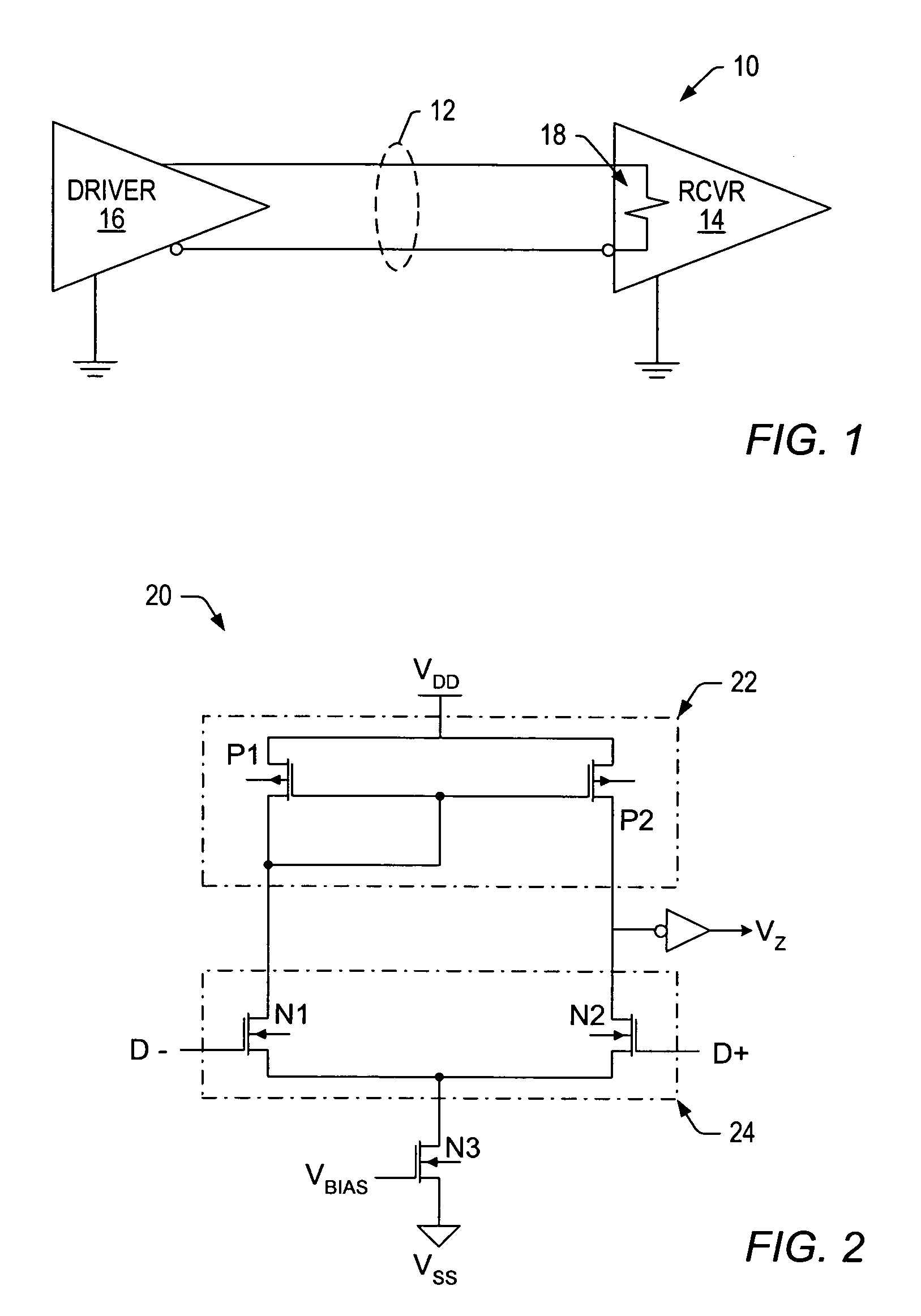

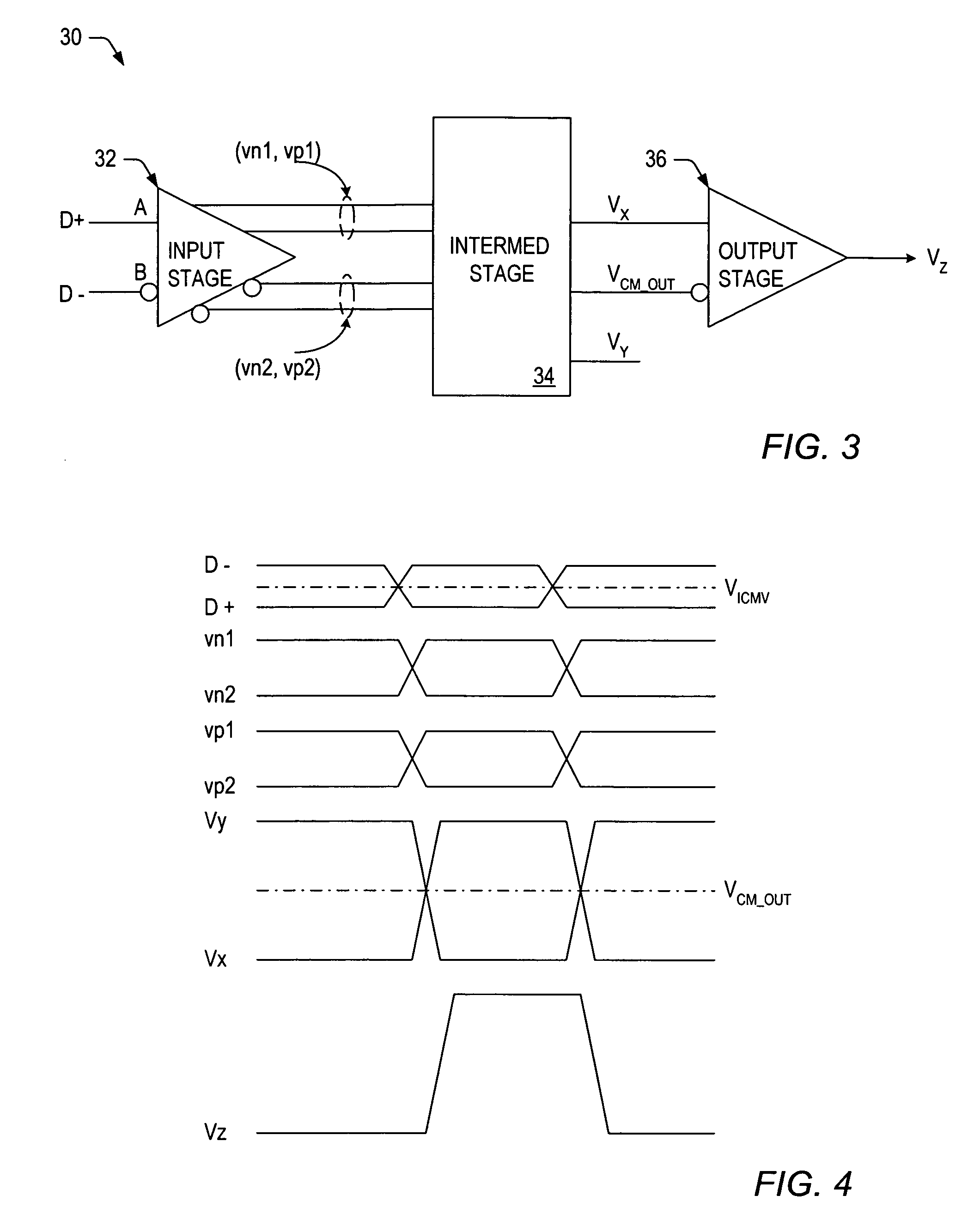

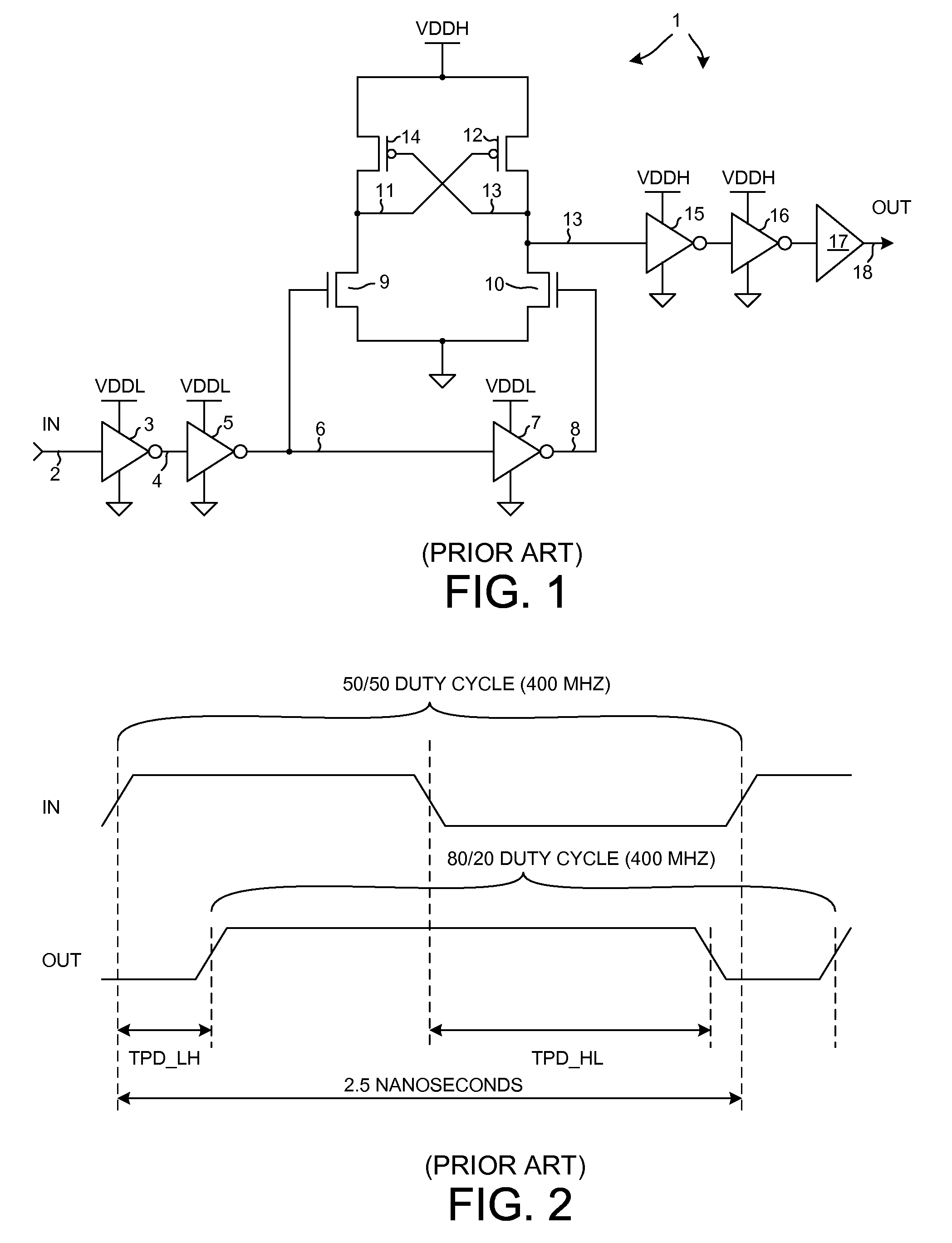

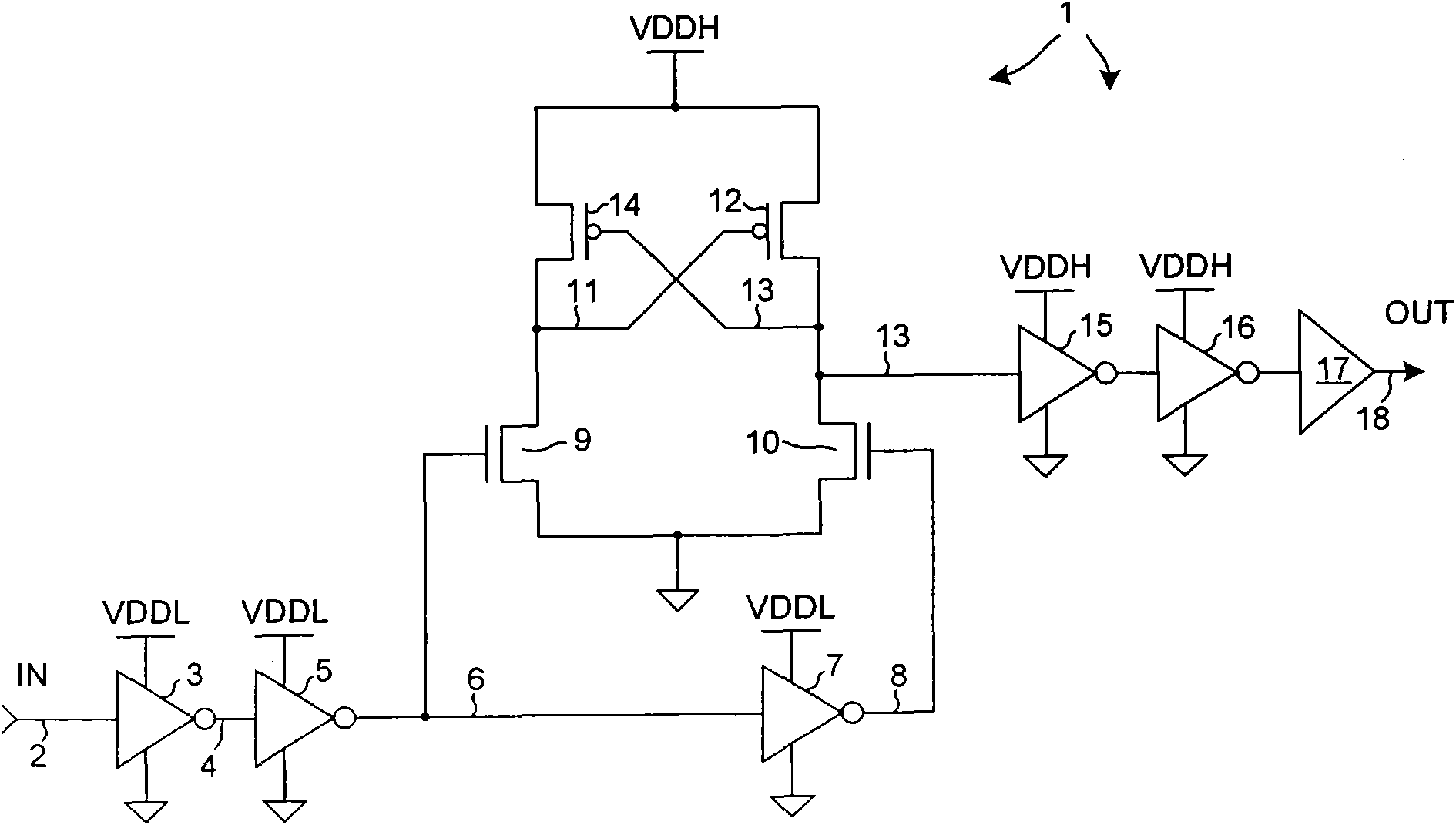

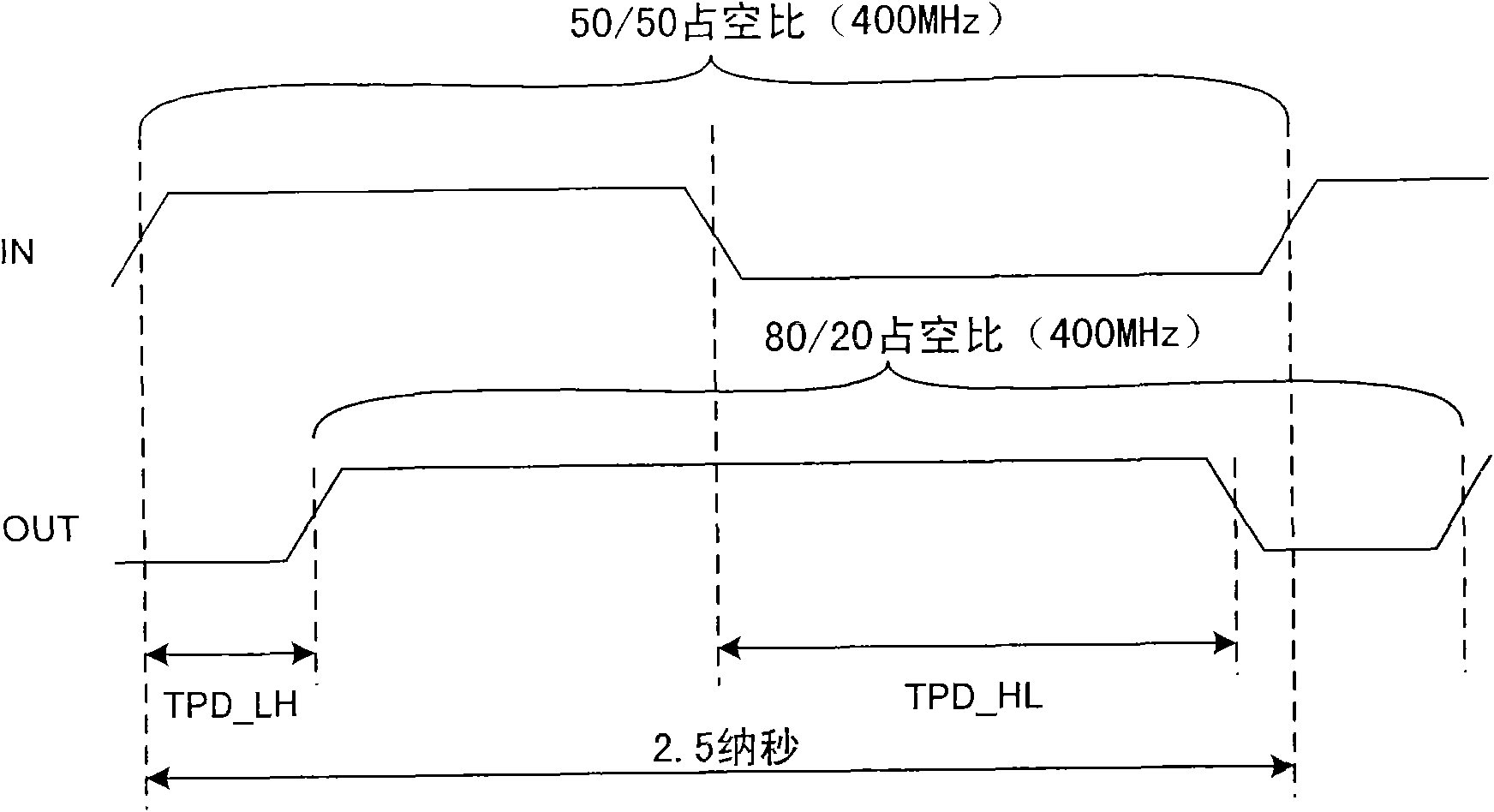

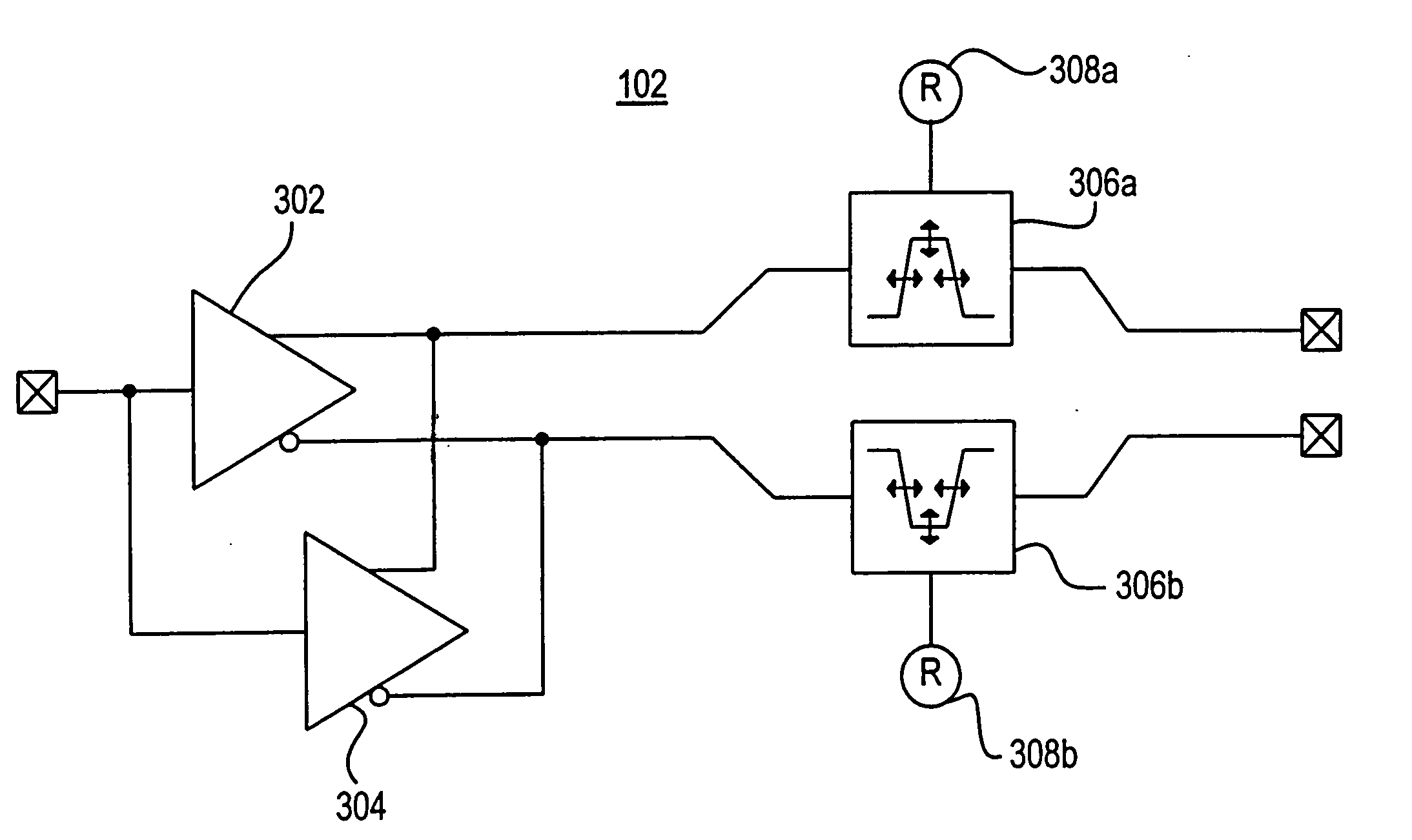

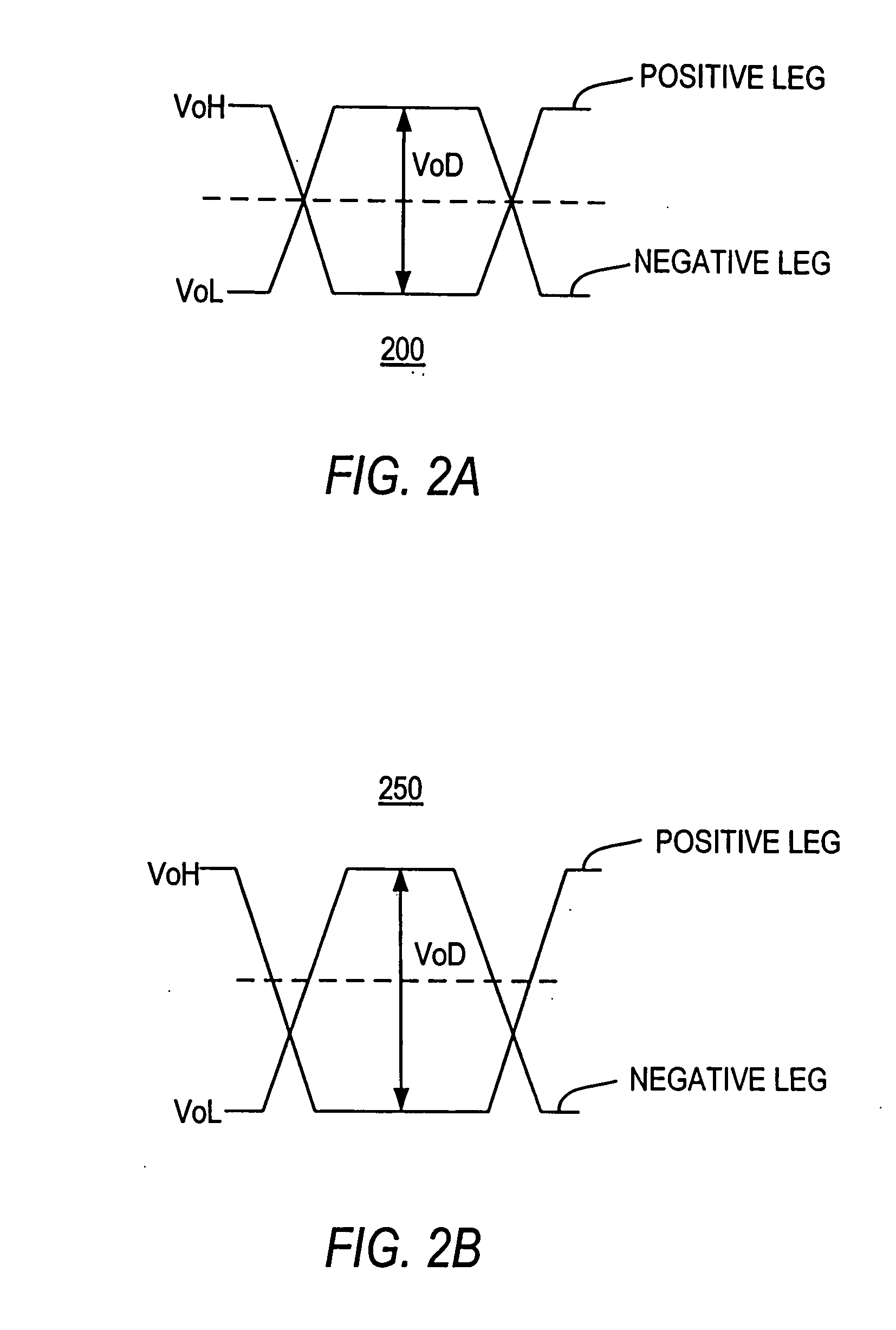

Differential receiver with wide input common mode range and low duty cycle distortion

ActiveUS7400173B1Avoid excessive duty cycle distortionIncrease working frequencyLogic circuits characterised by logic functionLogic circuit coupling/interface arrangementsDifferential signalingDuty cycle distortion

A transmission system, circuit and method are provided herein for converting differential signals into low duty cycle distortion, single-ended signals that are insensitive to variations in PVT and input common mode voltage. In one embodiment, the signal translation circuit includes an input stage for receiving a pair of differential input signals and producing one or more differential output signals; an intermediate stage for combining the one or more differential output signals into a pair of complementary signals from which a common mode voltage is detected; and an output stage for generating a single-ended output signal that switches from a first value to an opposite value when one of the complementary signals is substantially equal to the common mode voltage.

Owner:TAIWAN SEMICON MFG CO LTD

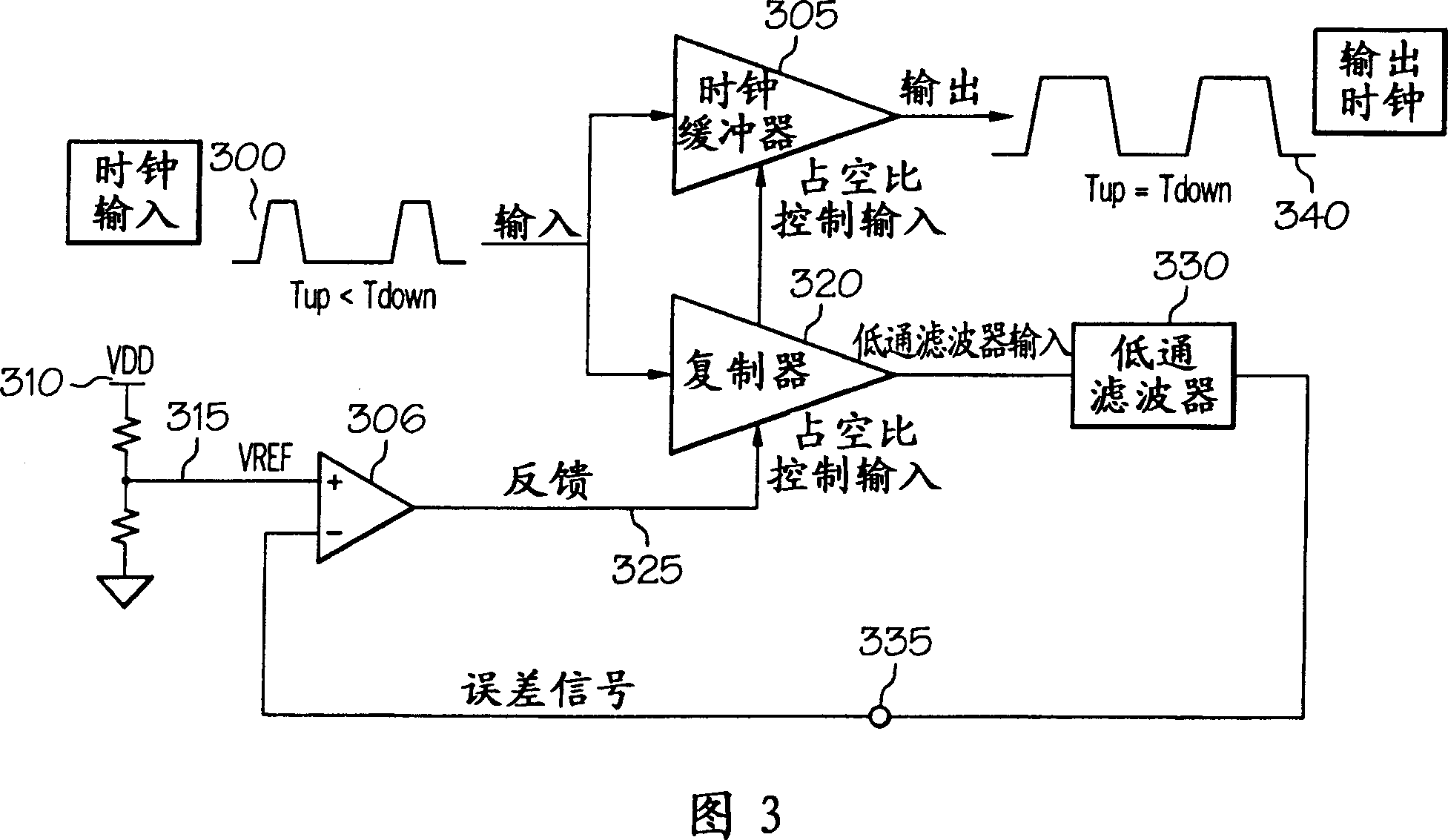

Duty-cycle correction circuit for differential clocking

InactiveUS20070159224A1Correct distortionElectric pulse generatorPulse shapingAudio power amplifierLow-pass filter

A completely differential approach to correcting duty-cycle distortions of a differential clock signal propagating through a differential amplifier. A duty-cycle distortion correction (DCDC) differential amplifier circuit / device is provided with a differential amplifier whose output wires are coupled to a correction circuit. The correction circuit comprises a differential low pass filter and a differential correction amplifier. The differential correction amplifier's output is dotted back into the output of the amplifier. The differential output of the amplifier is passed through the low pass filter, which provides differential DC output signals that triggers respective correction amplifier transistors to generate an inverted correction current that is added back to respective differential output pulse. The DCDC differential amplifier provides a completely differential approach to correction of duty-cycle distortions within the differential output.

Owner:IBM CORP

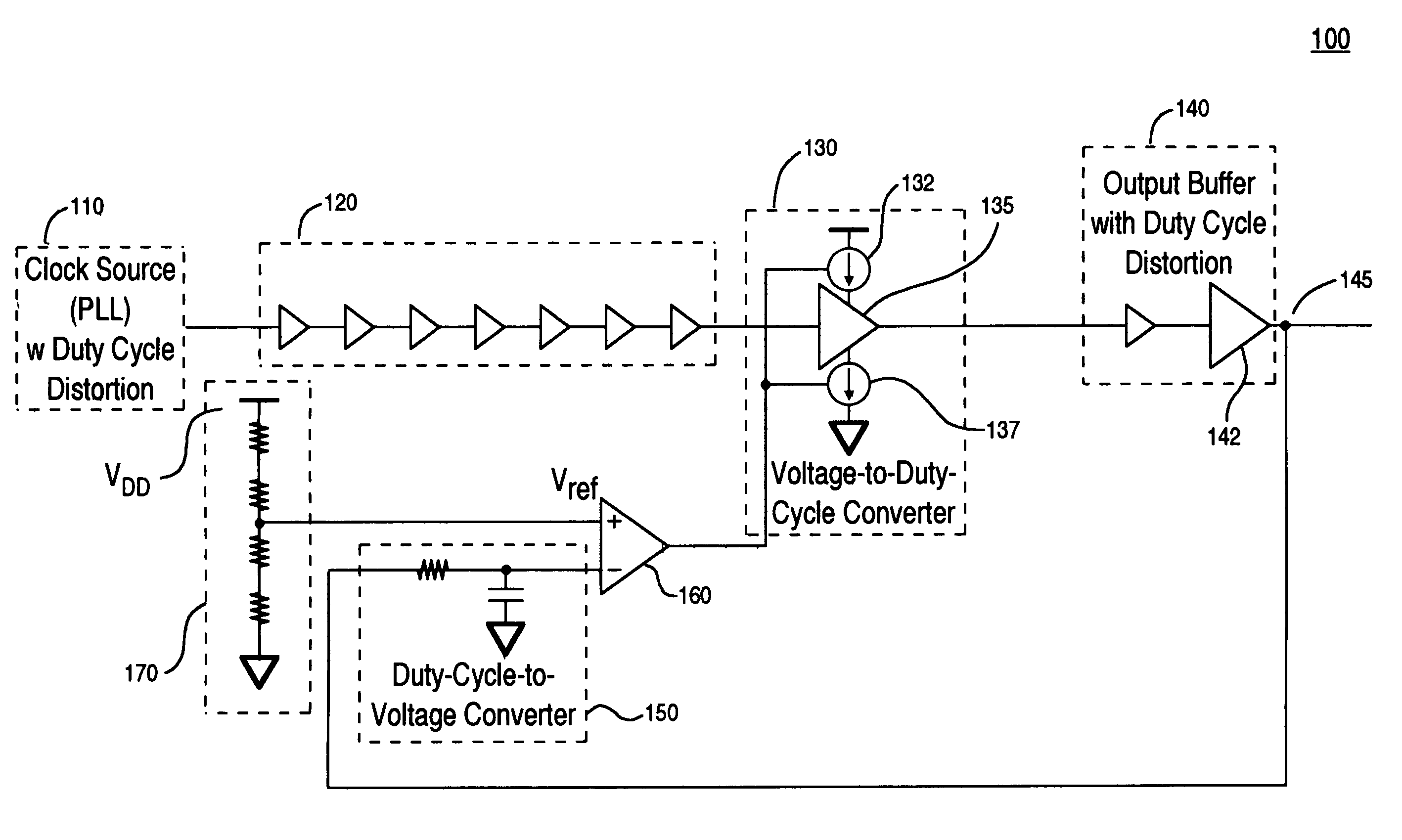

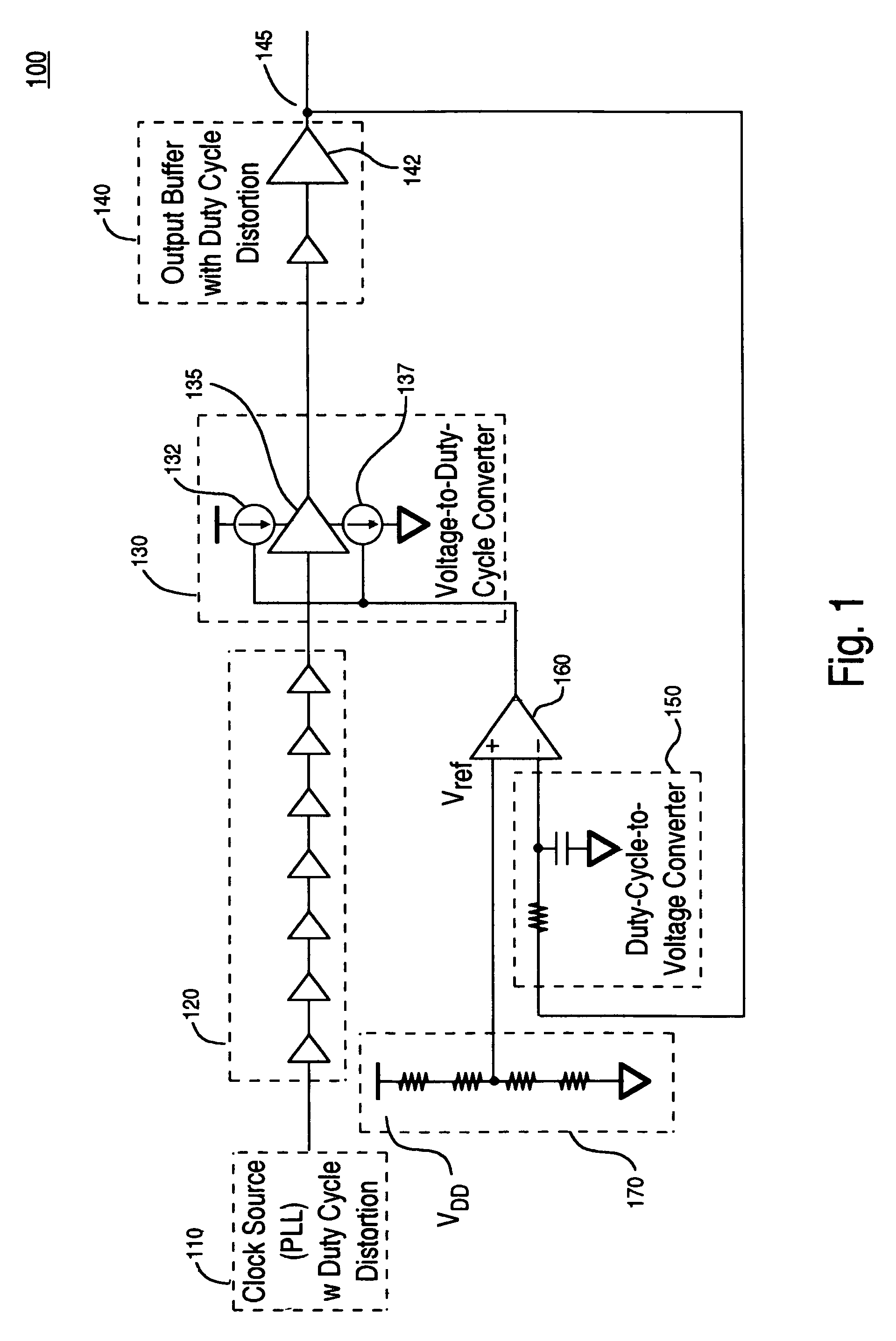

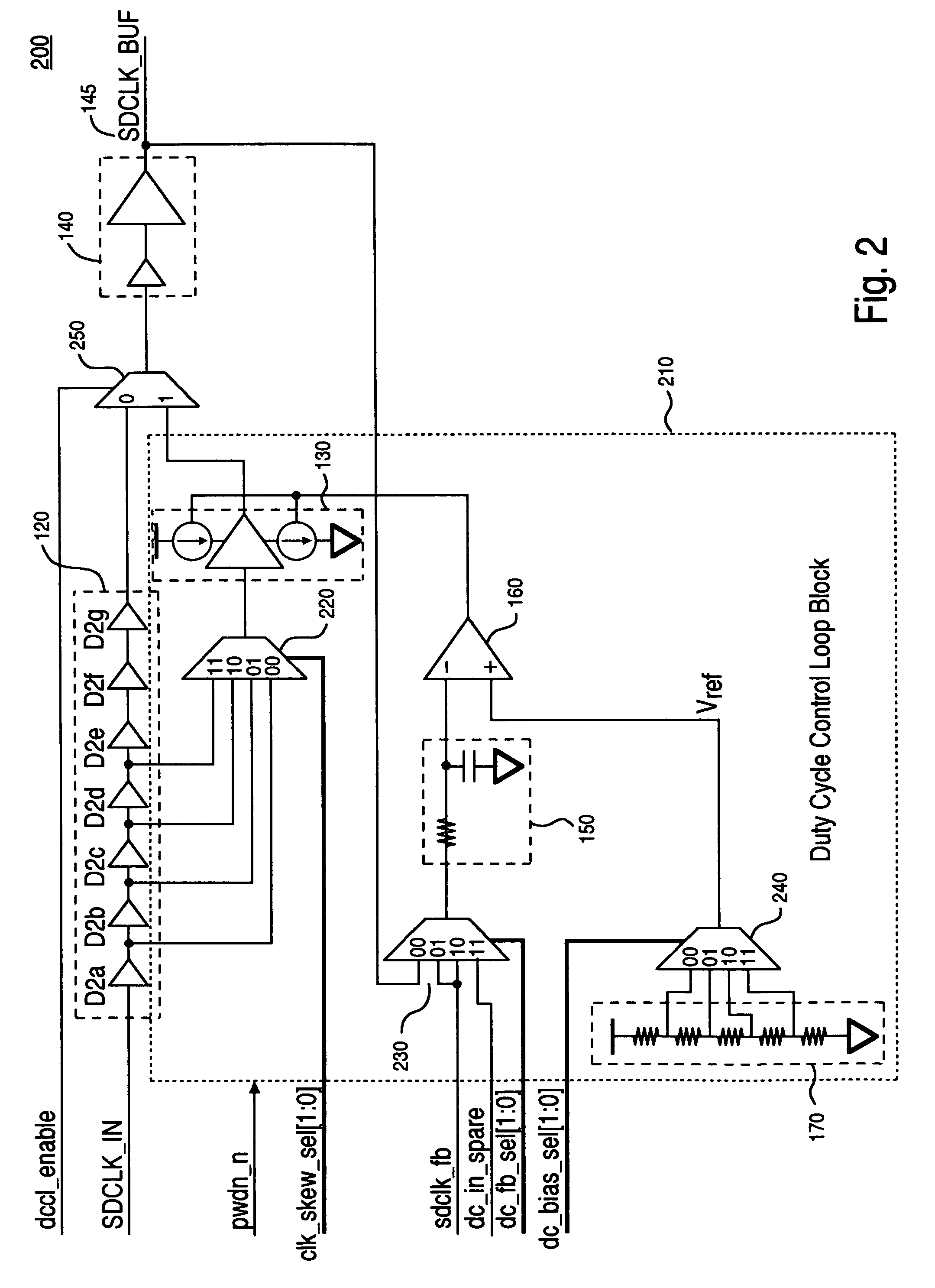

Circuit for controlling duty cycle distortion

ActiveUS7423467B1Addressing Insufficient ControlElectric pulse generatorPulse shapingNegative feedbackAudio power amplifier

A circuit for controlling a duty cycle of a clock signal. The circuit includes a duty cycle control loop that includes a voltage-to-duty cycle (V-to-DC) converter, an output driver, a duty-cycle-to voltage (DC-to-V) converter, and an operational amplifier. The V-to-DC converter receives an input clock signal. The output driver is coupled to the V-to-DC converter and provides an output clock signal that is associated with a duty cycle distortion value. The DC-to-V converter converts the output clock signal to an average voltage. The operational amplifier amplifies an error between the average voltage and a reference voltage. The error is fed back to the V-to-DC converter through a negative feedback loop, wherein the V-to-DC converter adjusts a duty cycle of the input clock signal based on the error.

Owner:NAT SEMICON CORP

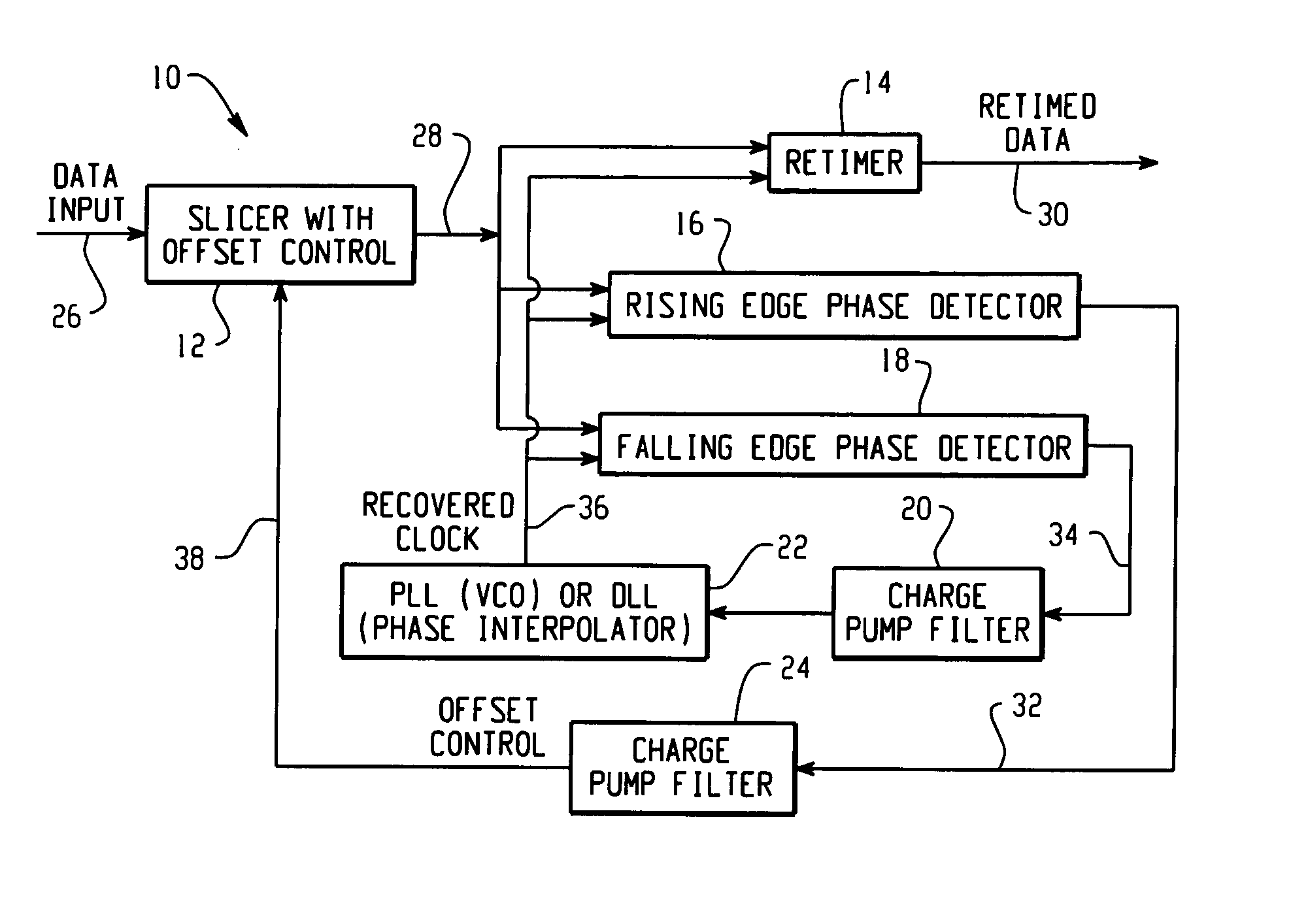

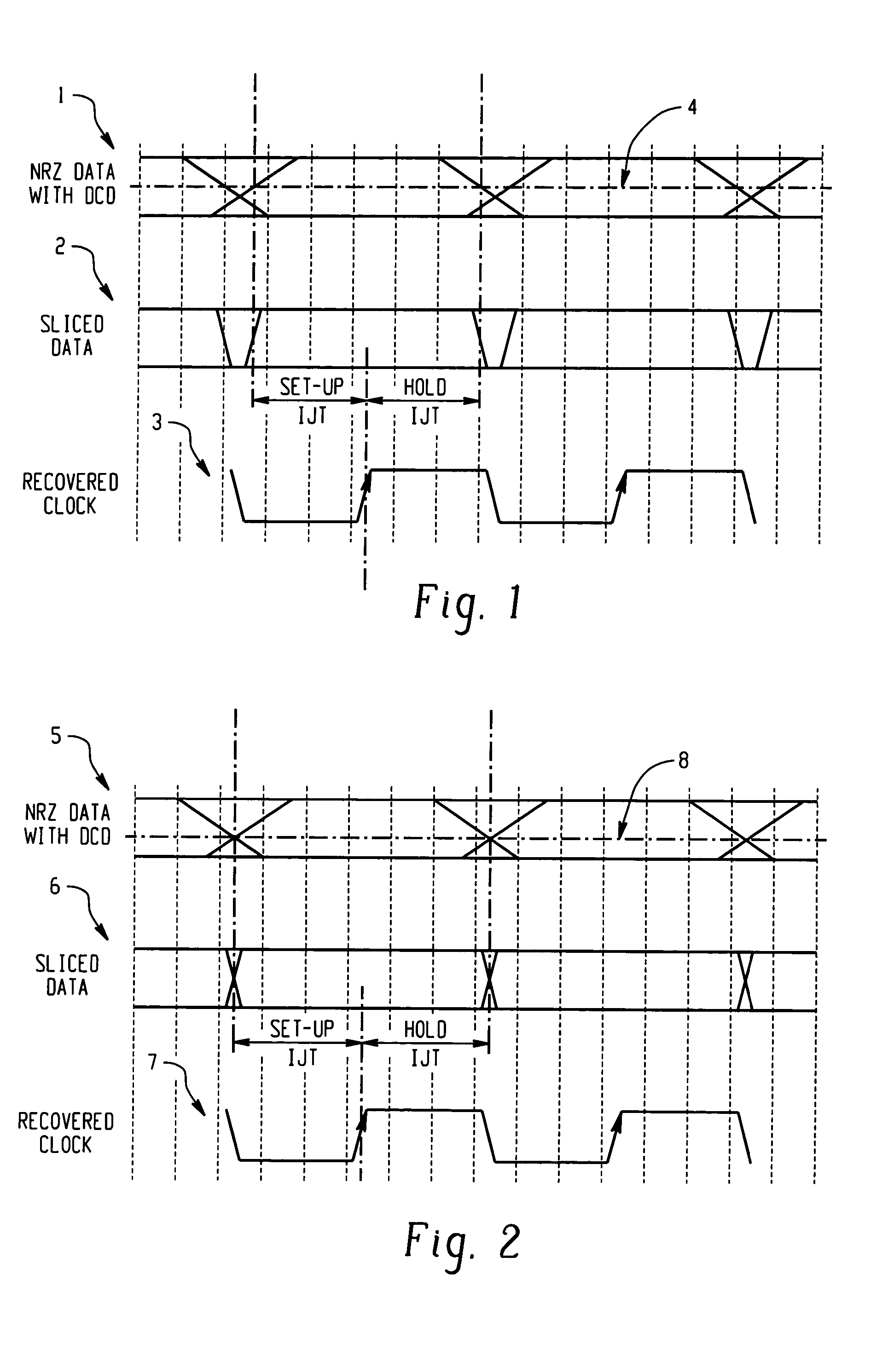

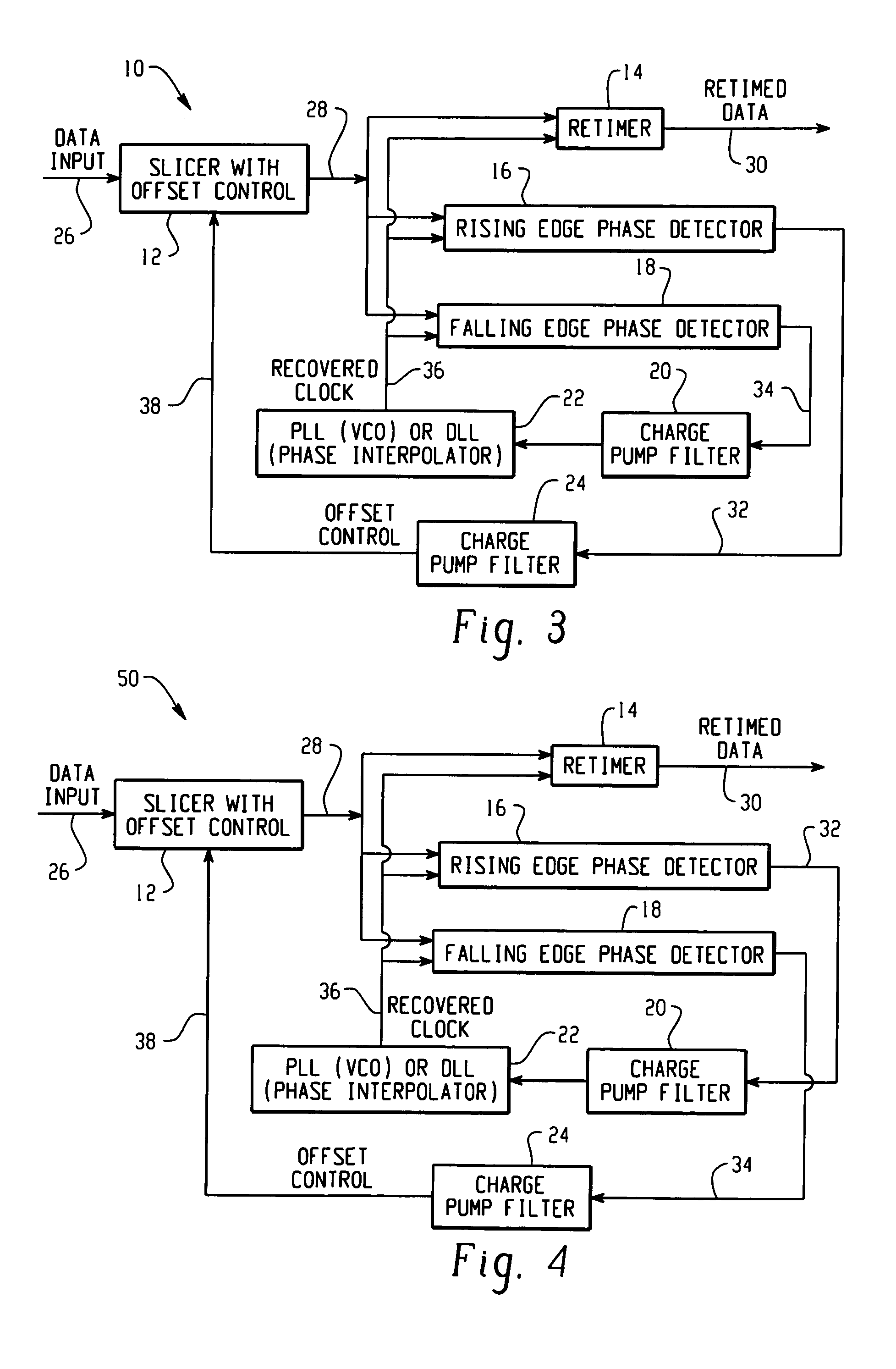

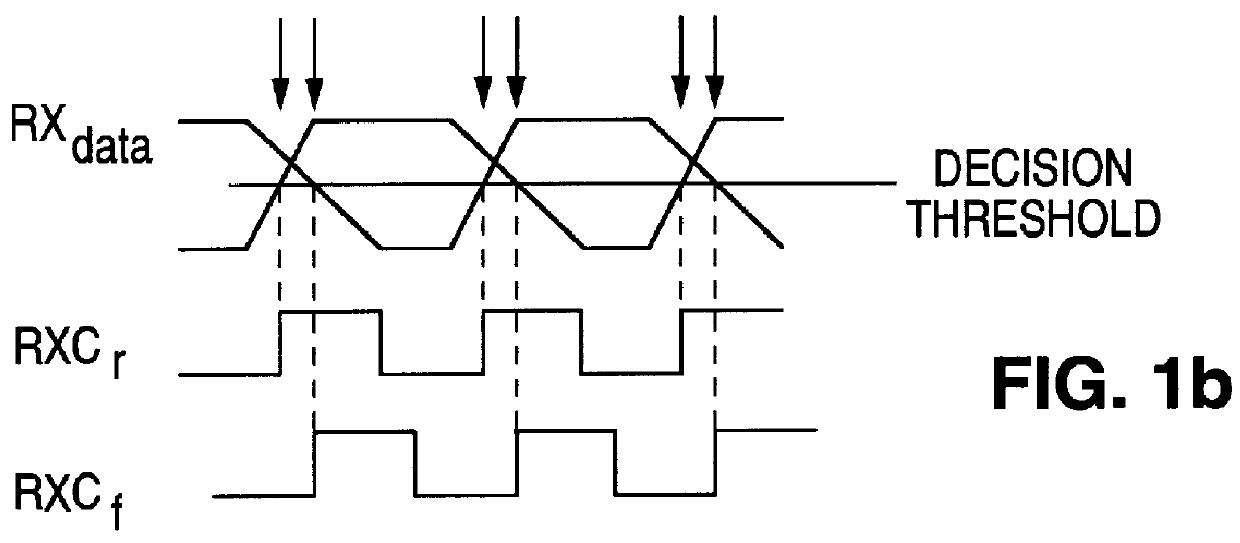

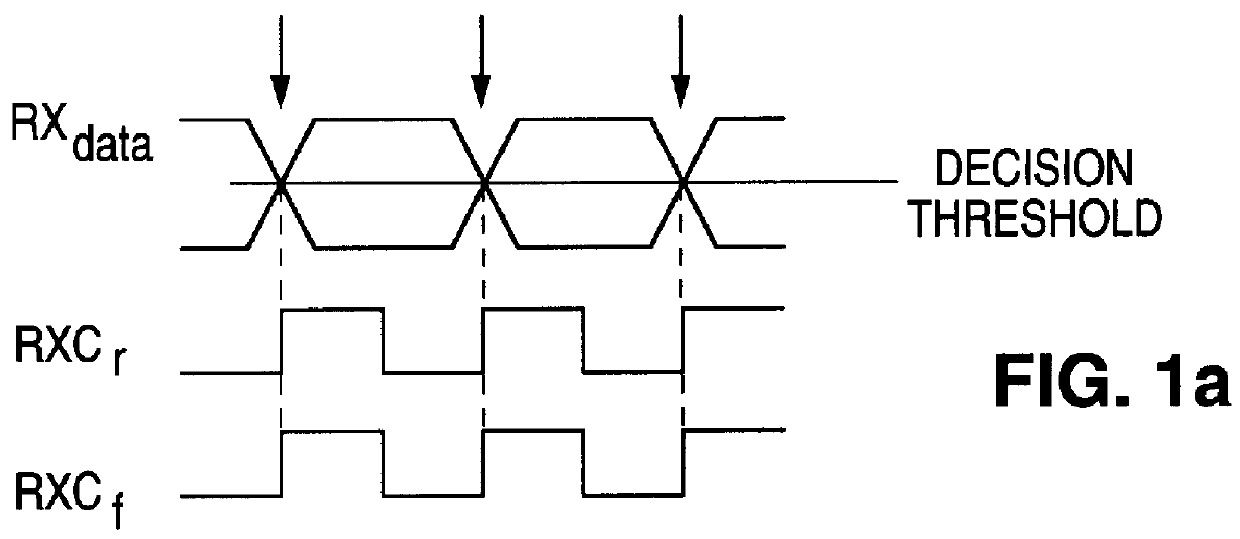

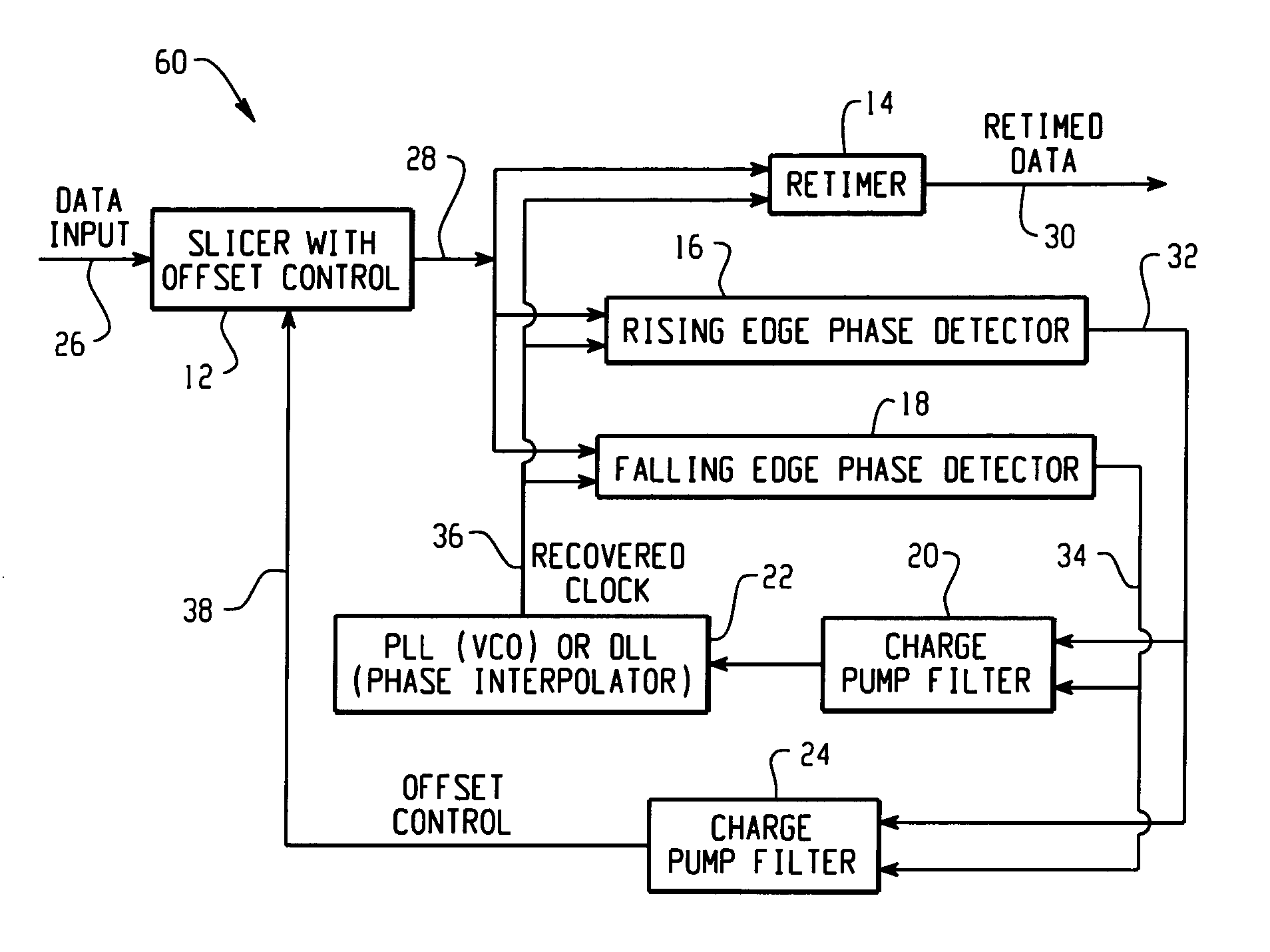

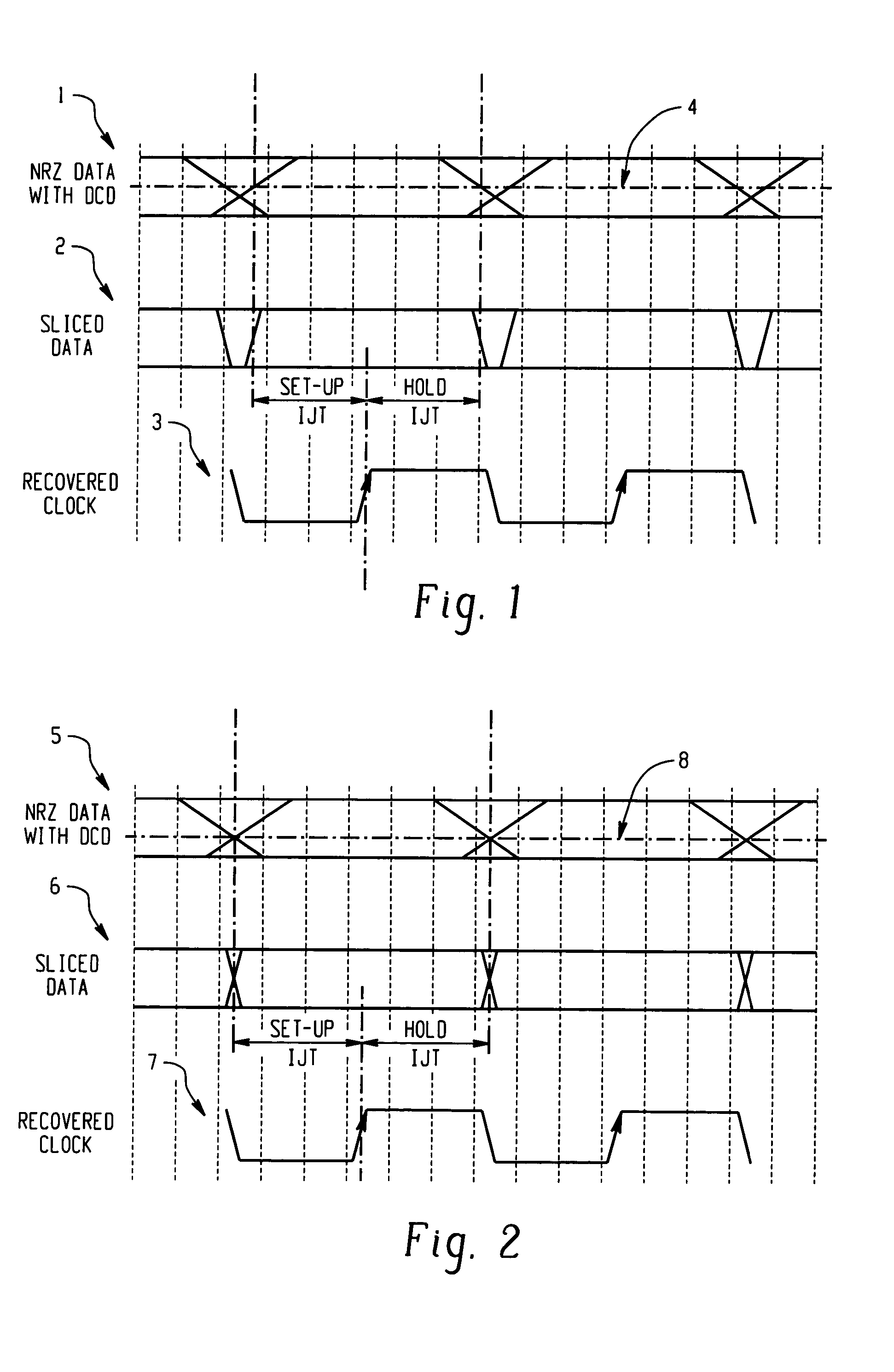

System and method for automatically correcting duty cycle distortion

InactiveUS20050031065A1Realize automatic adjustmentModulated-carrier systemsPulse automatic controlPhase detectorControl signal

In accordance with the teachings described herein, systems and methods are provided for automatically correcting duty cycle distortion. A slicer may be used to receive a data input signal and compare the data input signal with a slicer offset voltage to generate a sliced data signal. The slicer may also receive an offset control signal to automatically adjust the slicer offset voltage. A phase detector may be used to receive the sliced data signal and a recovered clock signal and to compare the sliced data signal with the recovered clock signal to generate a rising edge output signal and a falling edge output signal. The rising edge output signal may correspond to a phase difference between a rising edge of the sliced data signal and an edge of the recovered clock signal. The falling edge output signal may correspond to a phase difference between a falling edge of the sliced data signal and an edge of the recovered clock signal. A first feedback circuit may be used to phase-lock the recovered clock signal to the sliced data signal utilizing at least one of the rising edge output signal and the falling edge output signal. At least one of the rising edge output signal and the falling edge output signal may be configured in a second feedback circuit to generate the offset control signal.

Owner:SEMTECH CANADA

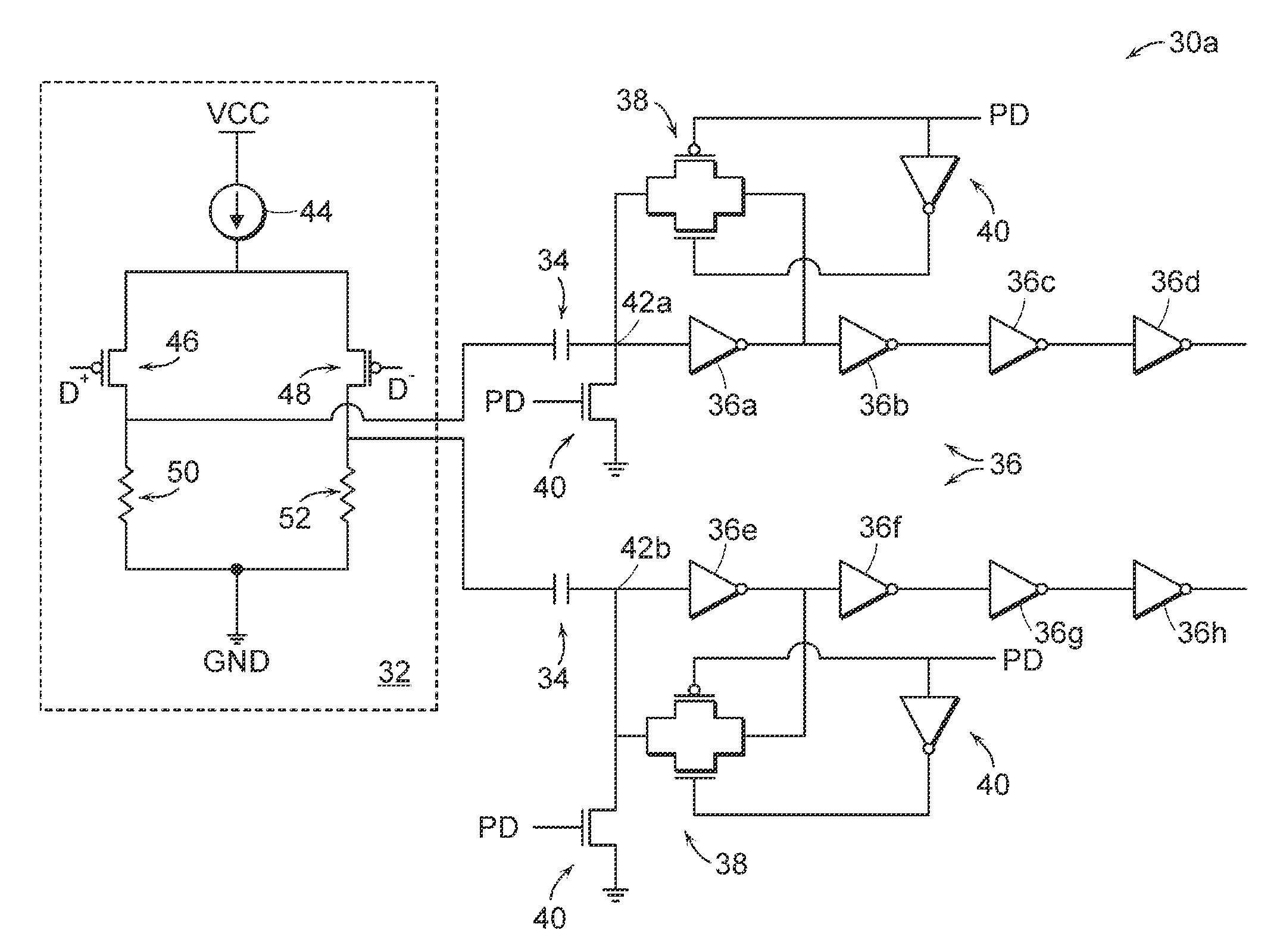

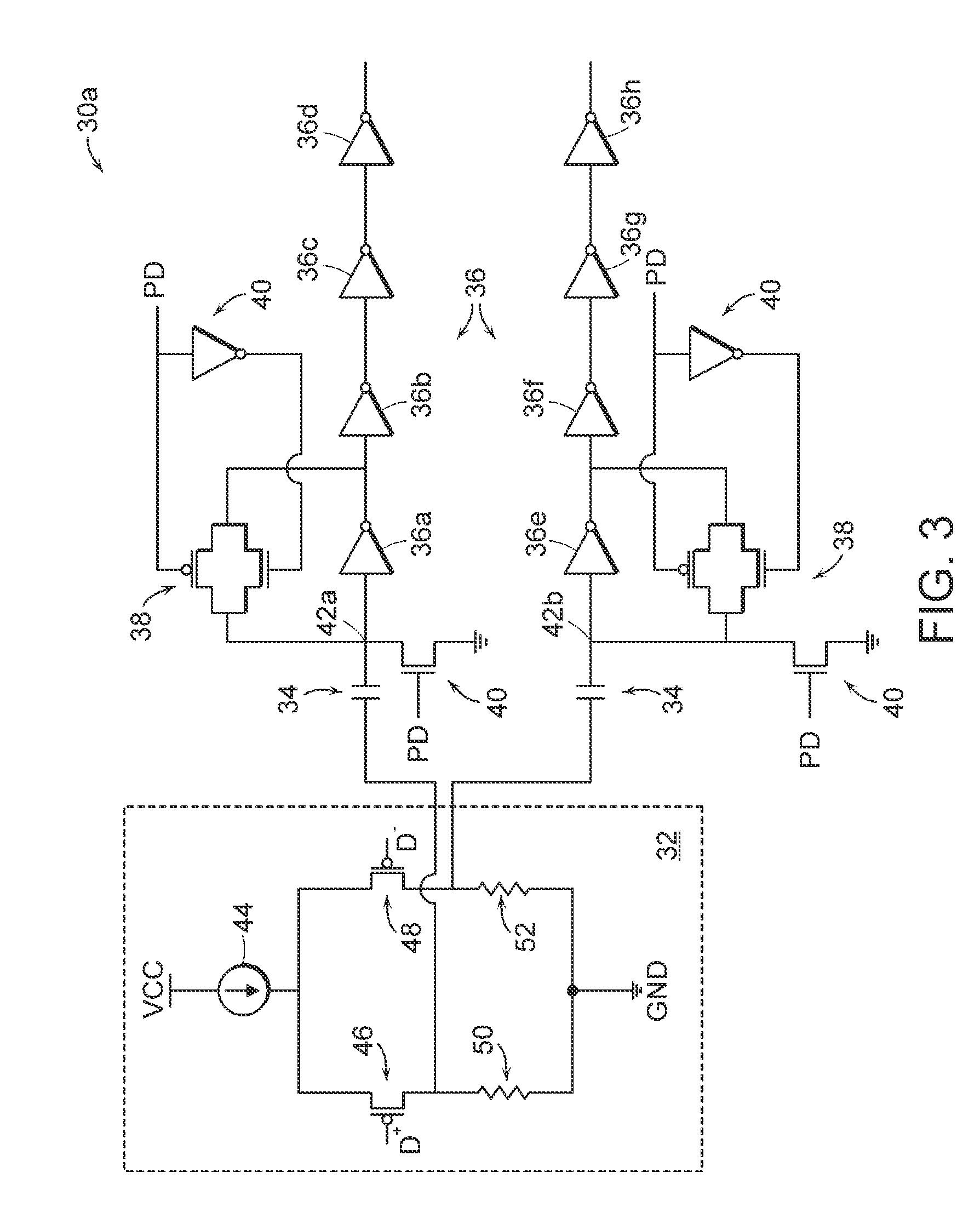

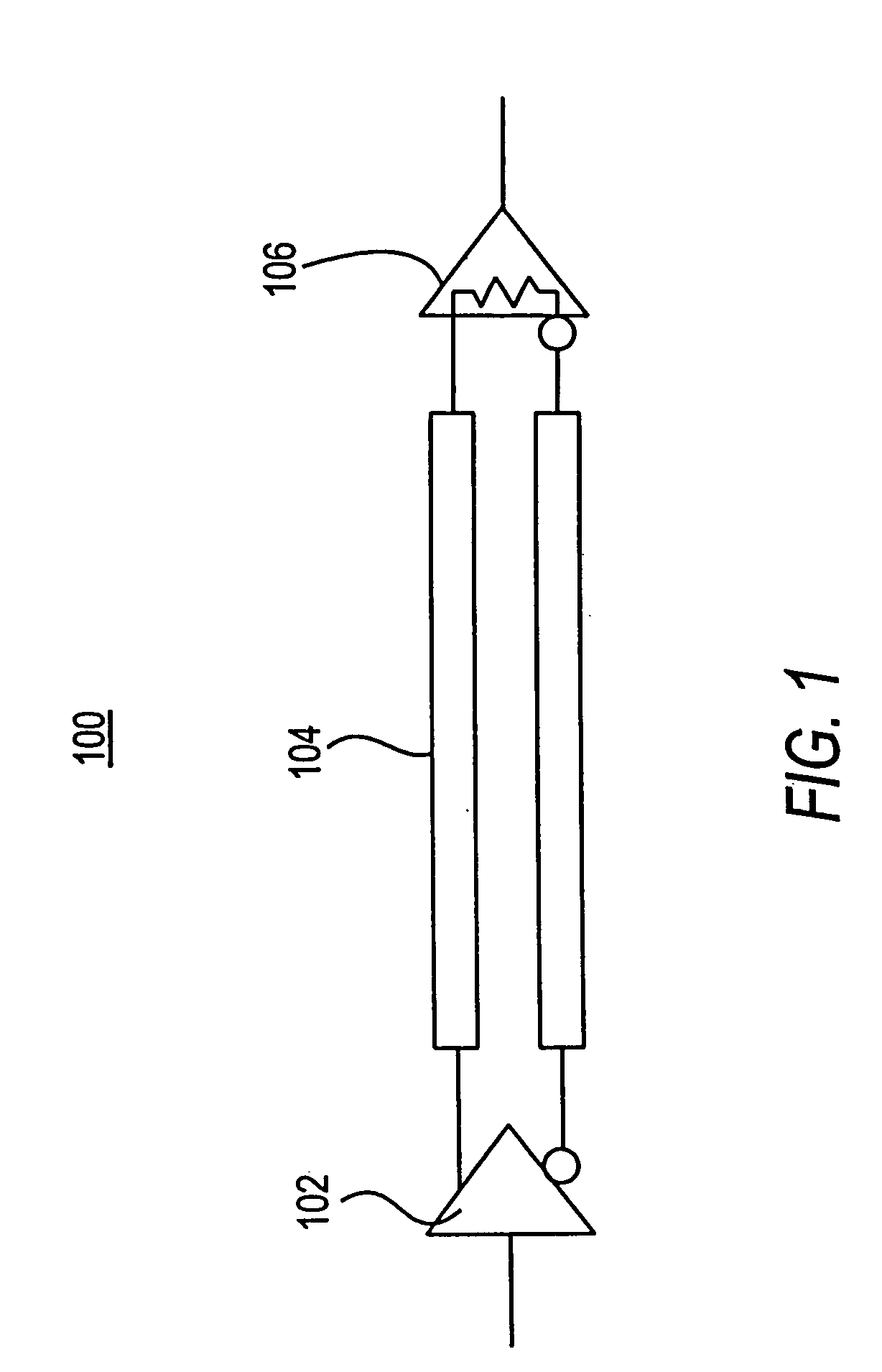

Low duty cycle distortion differential to CMOS translator

ActiveUS7176720B1Easy to implementReduce dependencePulse generation by non-linear magnetic/dielectric devicesDifferential amplifiersCMOSTransmission gate

Disclosed is a circuit comprising a differential input amplifier stage, a capacitor stage, an inverter chain stage, and a biasing circuit. The inverter chain stage may be formed with or without feedback depending on whether a clock signal or data signal is to be translated using the disclosed circuit. The biasing circuit can be formed using either inverters or transmission gates. Moreover, the biasing circuit, the inverter chain stage, and the amplifier stage can be connected to a power down circuit which, when the translator is not being used, will ensure various circuitry of the translator will not consume extensive power. The inverter chain stage, biasing circuit, and capacitor stage are formed on both an upper and lower section to produce true and complementary outputs that have a consistent and equal delay from the transitions of the incoming differential input signal so as to minimize jitter and associated duty cycle of the translated output.

Owner:CYPRESS SEMICON CORP

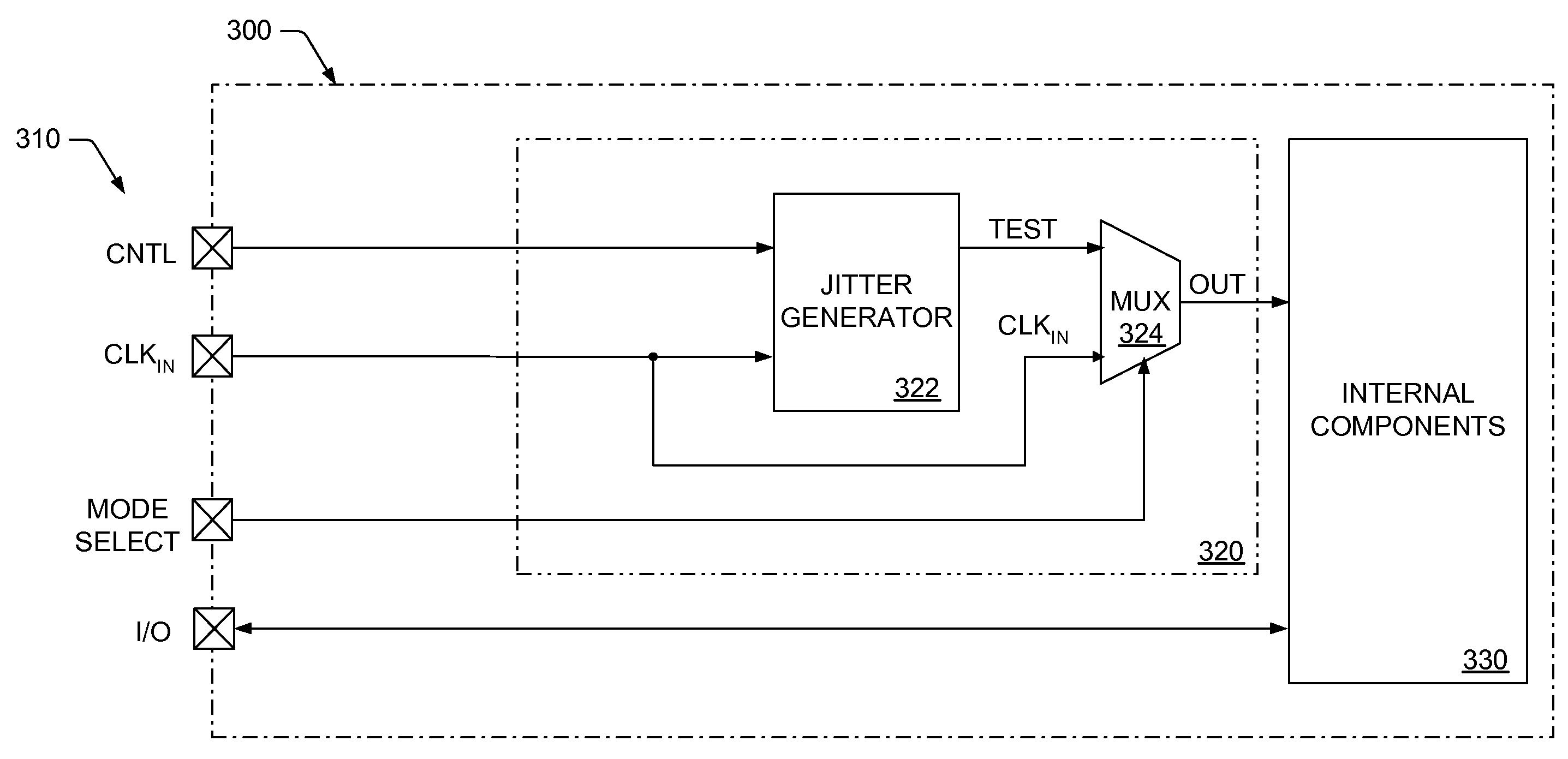

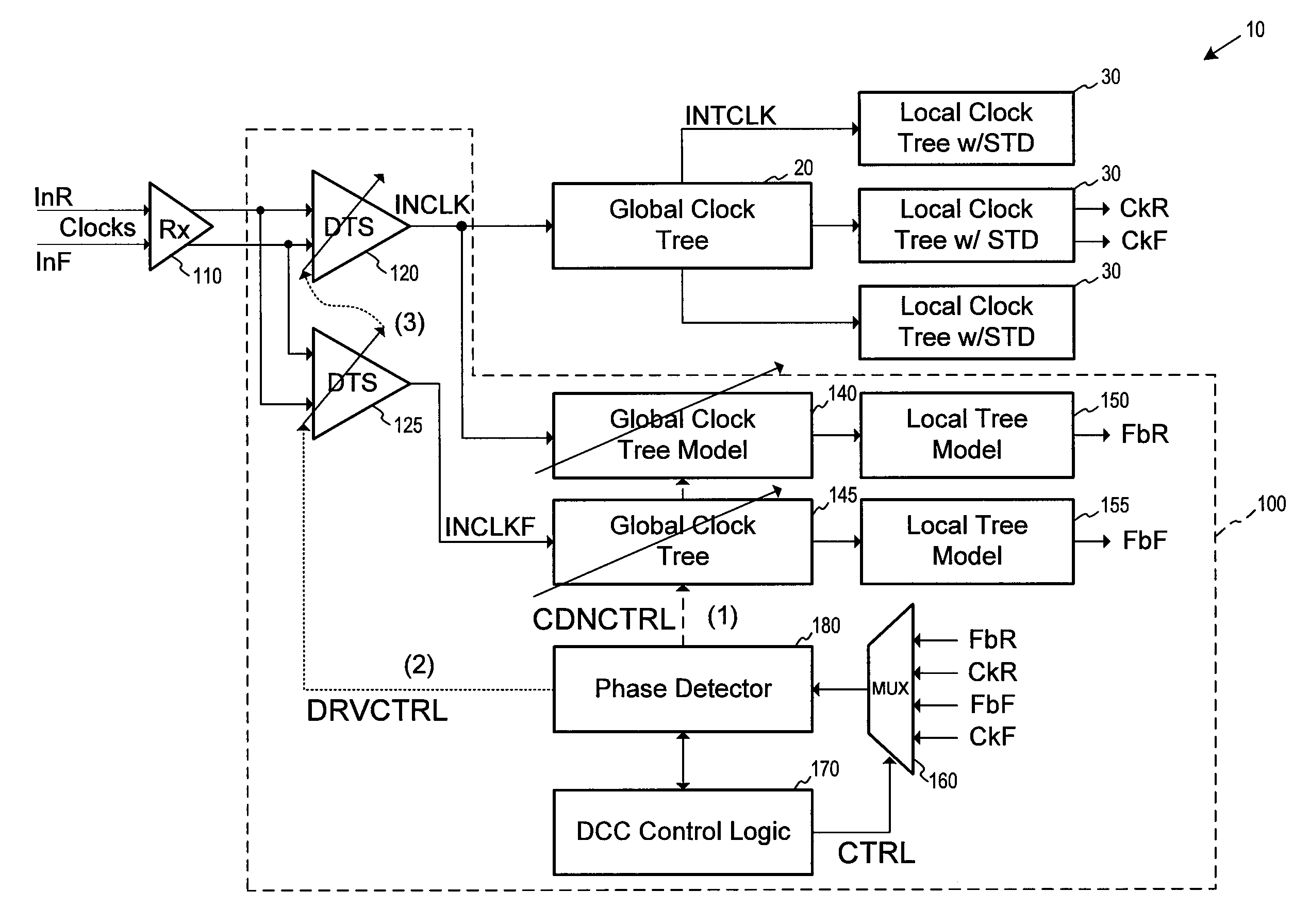

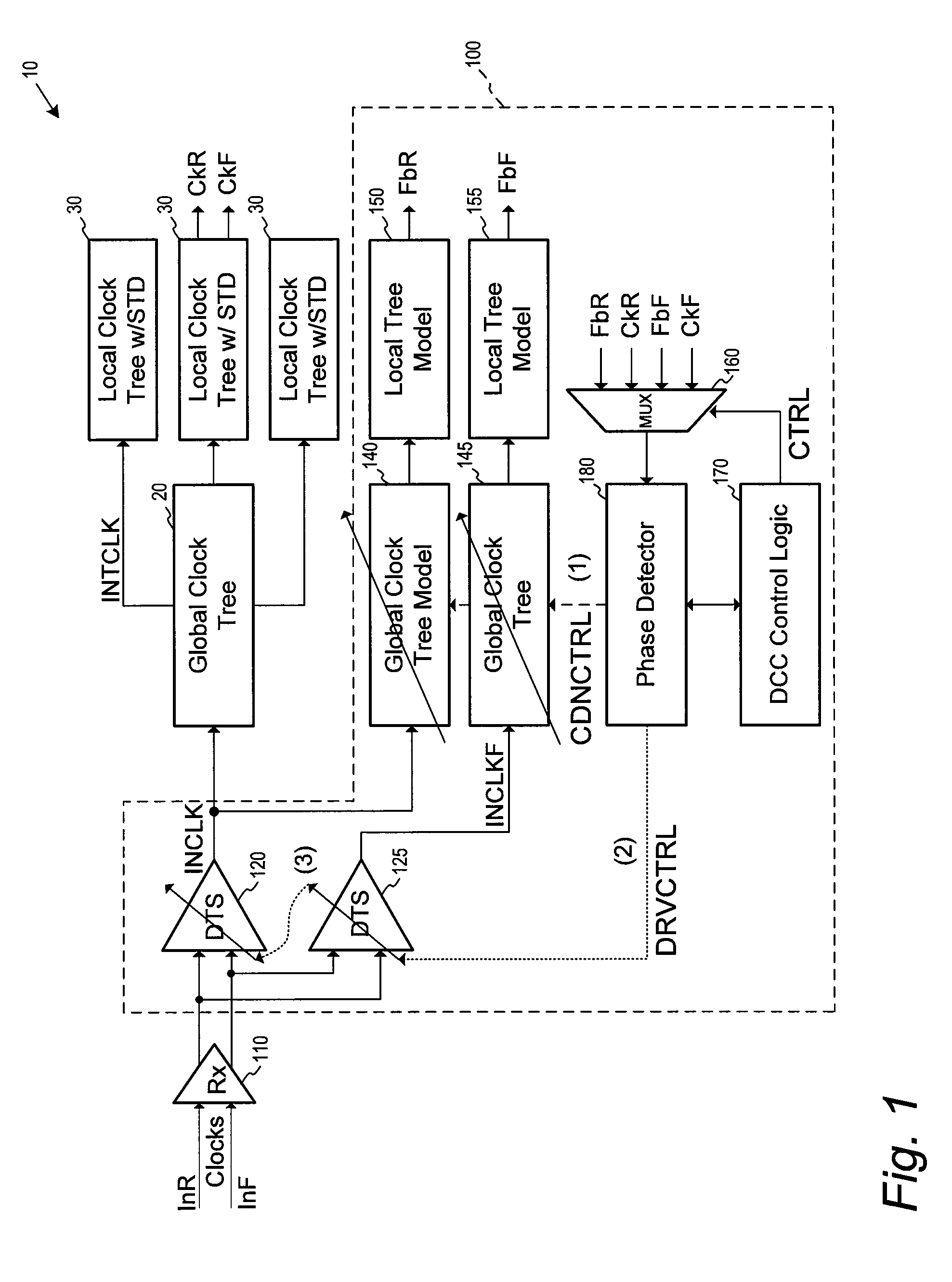

Test Circuit, System, and Method for Testing One or More Circuit Components Arranged upon a Common Printed Circuit Board

A test circuit, system, and method are provided herein for testing one or more circuit components arranged upon a monolithic substrate. According to one embodiment, the system may include a test circuit and one or more circuit components, all of which are arranged upon the same monolithic substrate. In general, the test circuit may be configured for: (i) receiving an input signal at an input frequency, (ii) generating a test signal by modulating a phase of the input signal in accordance with a periodic signal, and (iii) supplying either the input signal or the test signal to the one or more integrated circuits, based on a control signal supplied to the test circuit. More specifically, the test circuit may be used to determine the jitter and / or duty cycle distortion (DCD) tolerance of any system component without changing the frequency of the clock signal supplied to the component or injecting noise into the clock recovery system.

Owner:MONTEREY RES LLC

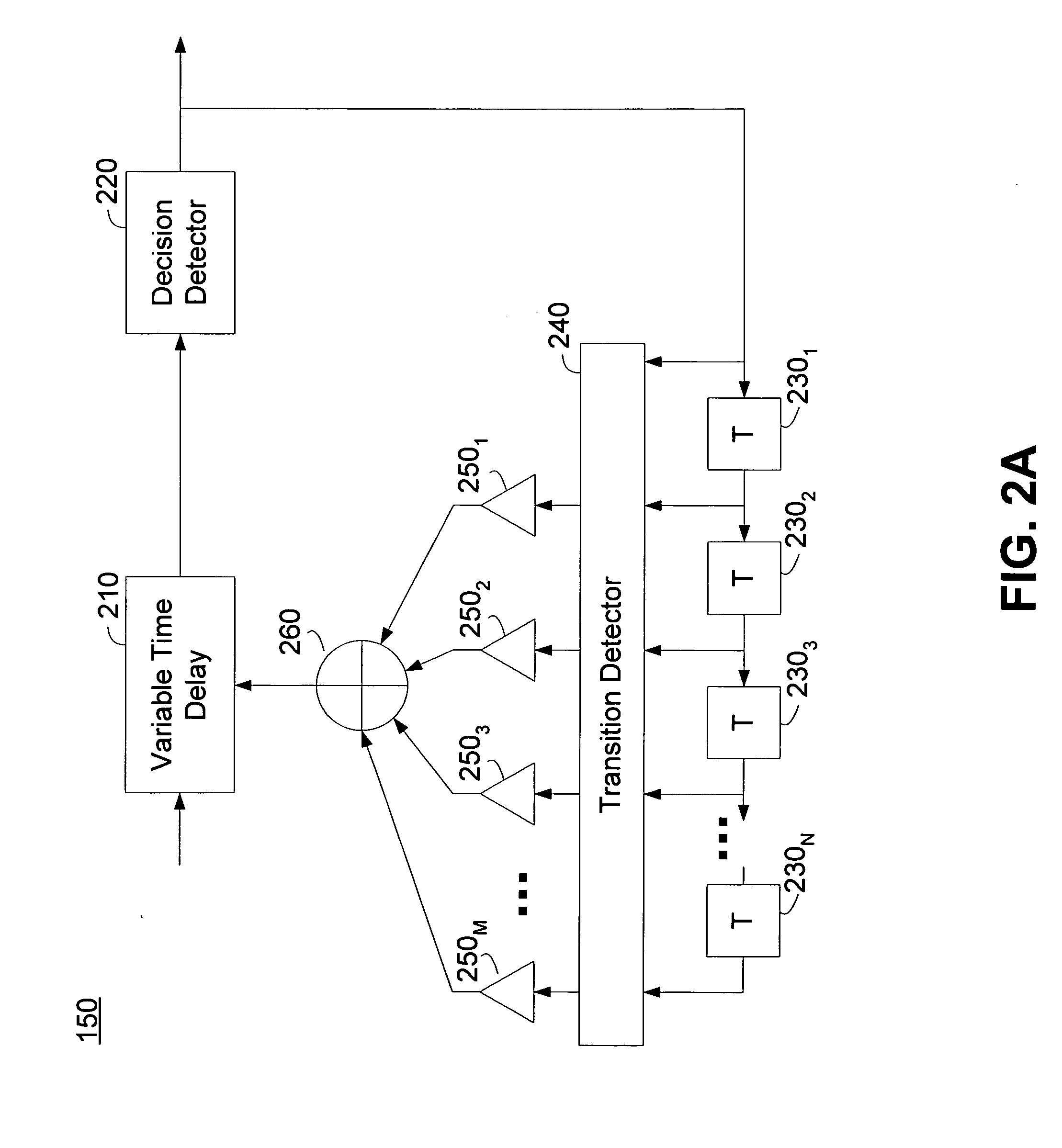

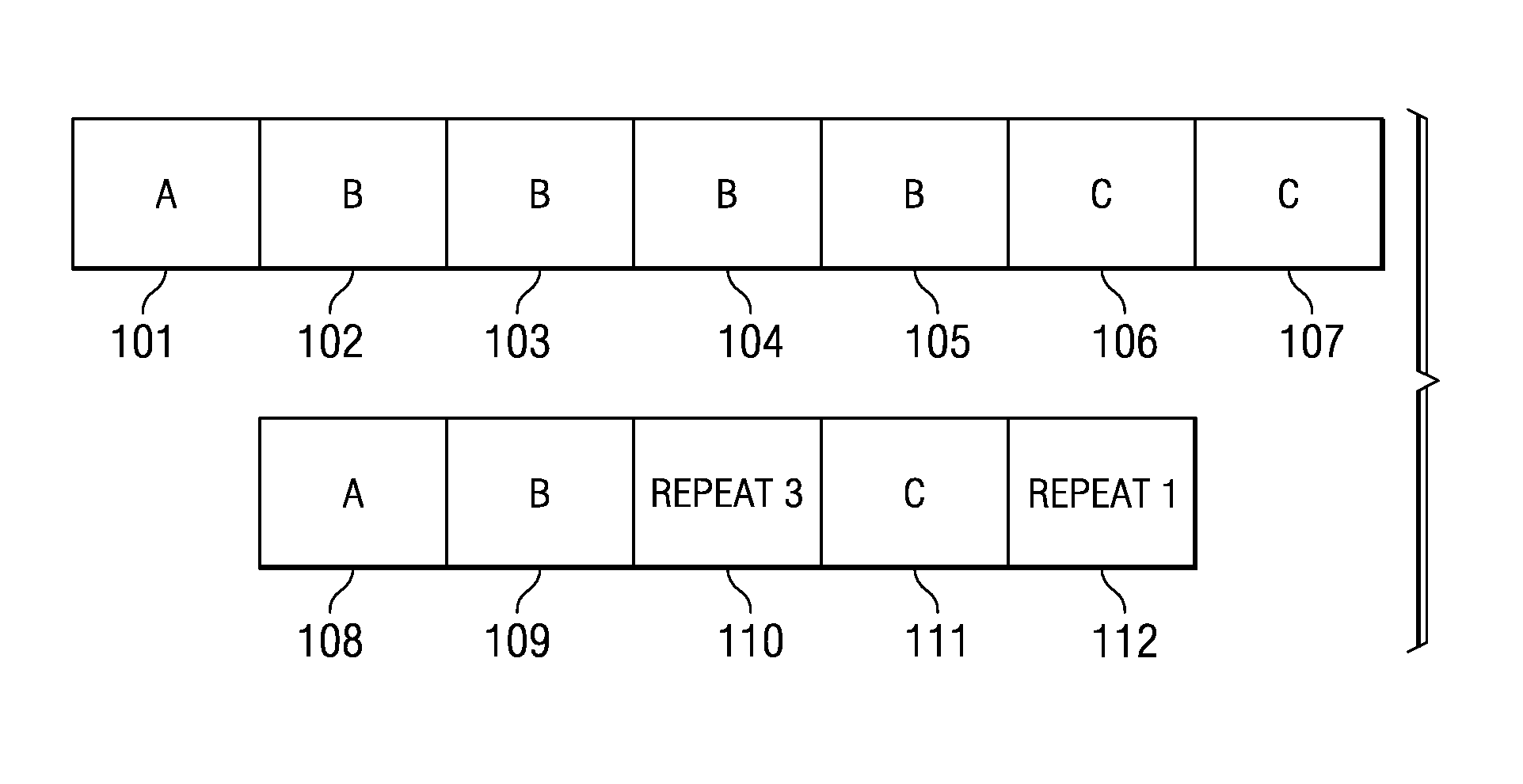

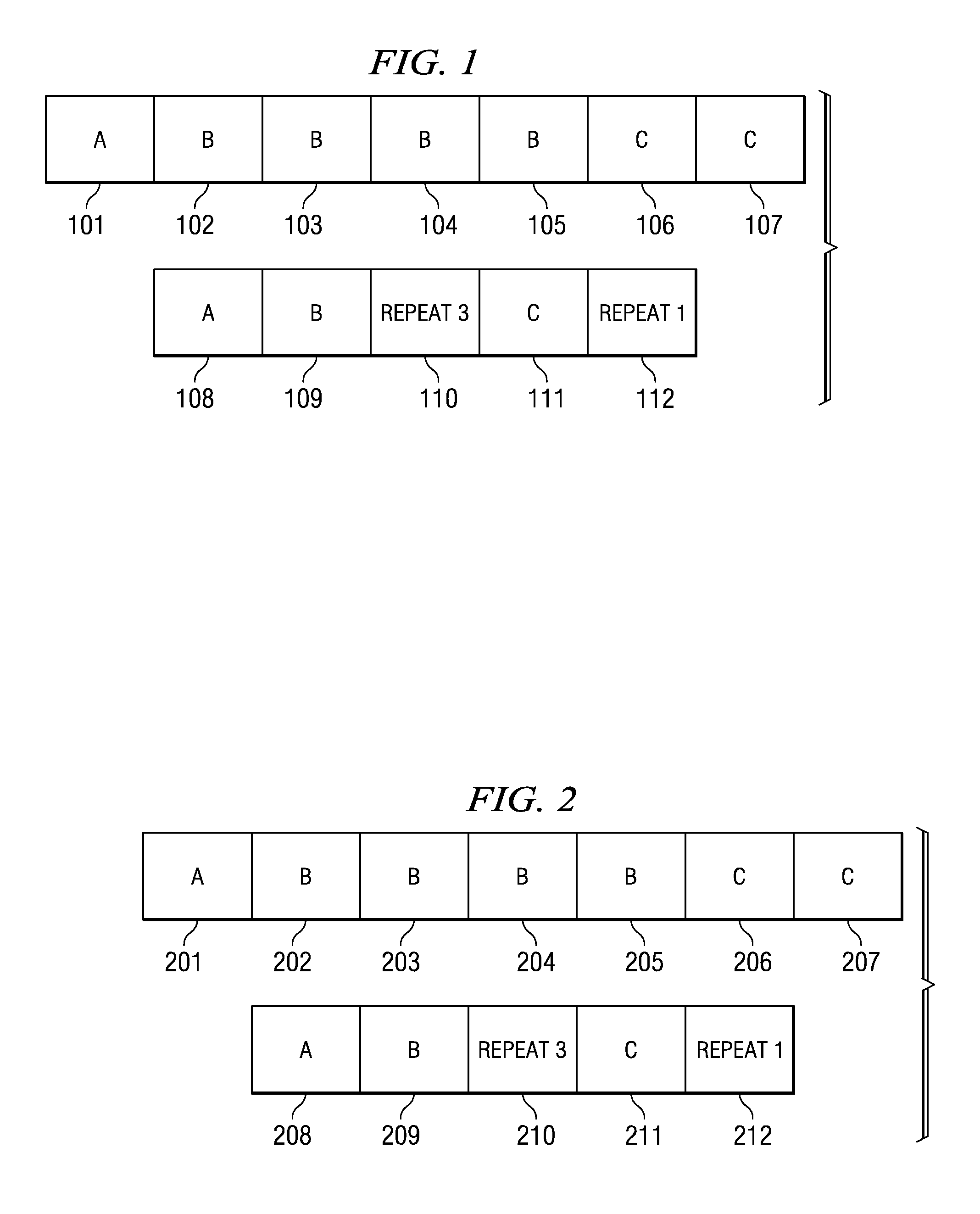

Deterministic jitter equalizer

ActiveUS7463680B2Easy to implementImprove phase noiseMultiple-port networksError detection/prevention using signal quality detectorData streamDuty cycle distortion

An equalizer for serial data communications can be configured to compensate for the effects of deterministic jitter. The equalizer can be configured to compensate a received serial data stream for the effects of data-dependent jitter as well as duty cycle distortion jitter. The equalizer can be configured to determine the value of one or more previously received symbols and compare them to a recovered symbol. The equalizer can adjust a variable delay positioned in the serial data path to introduce a delay into the data path that is based in part on the received data stream. The equalizer can be configured to vary the delay when any of the one or more previously received symbols is different from the recovered symbol, and can be configured to maintain a constant delay if the one or more previously received symbols is the same as the recovered symbol.

Owner:CALIFORNIA INST OF TECH

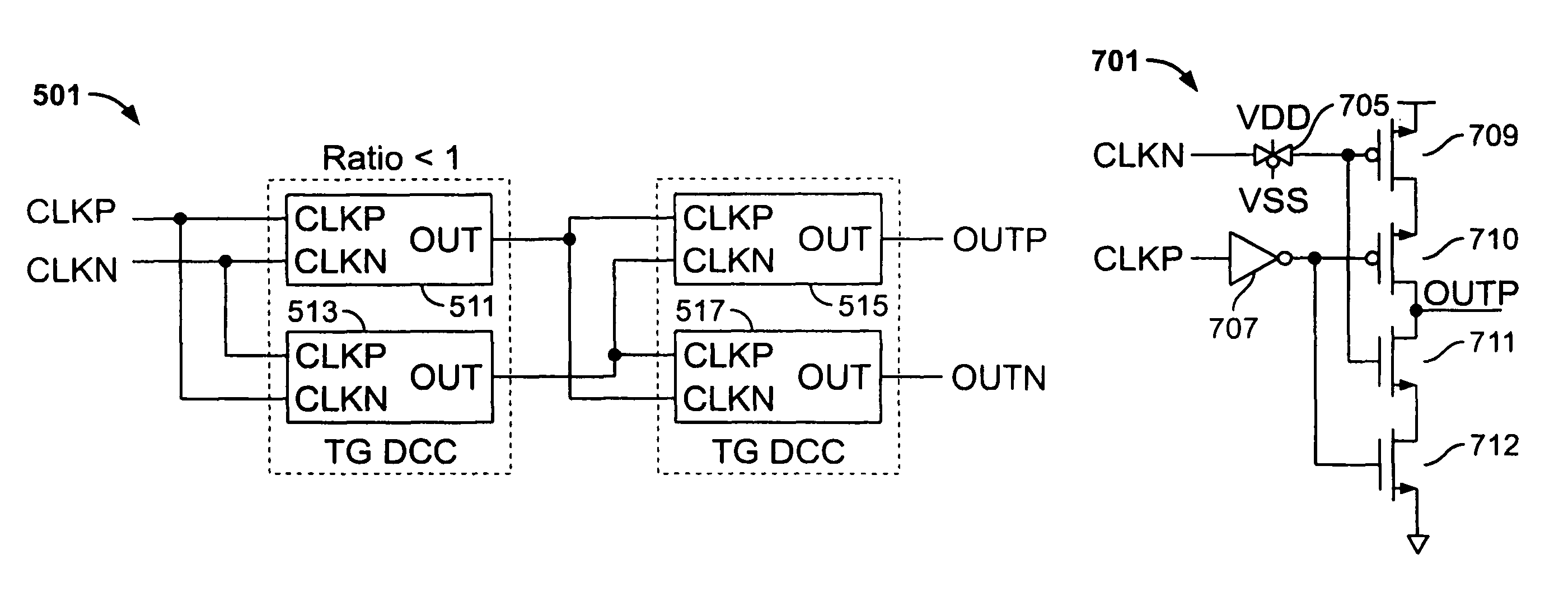

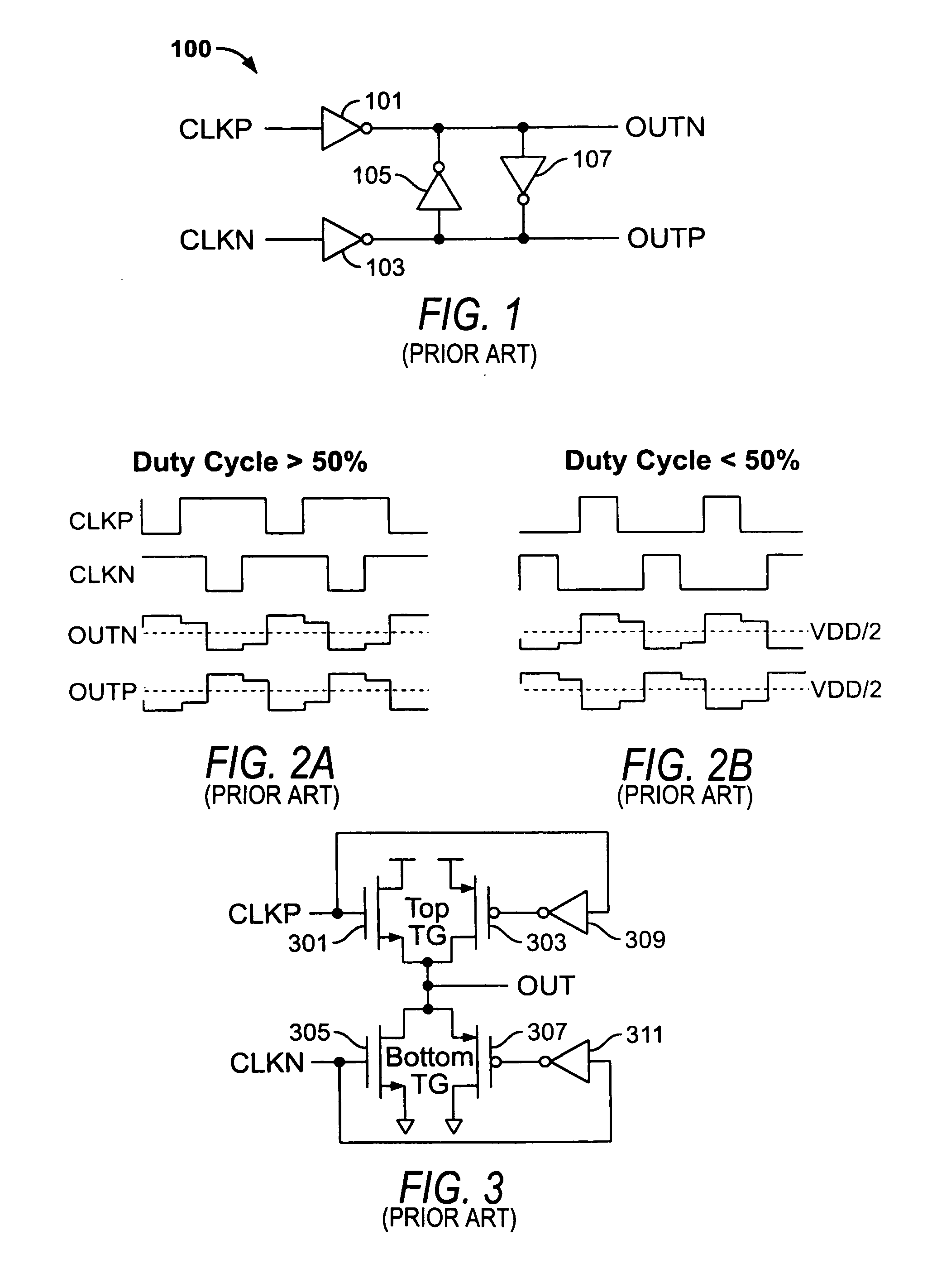

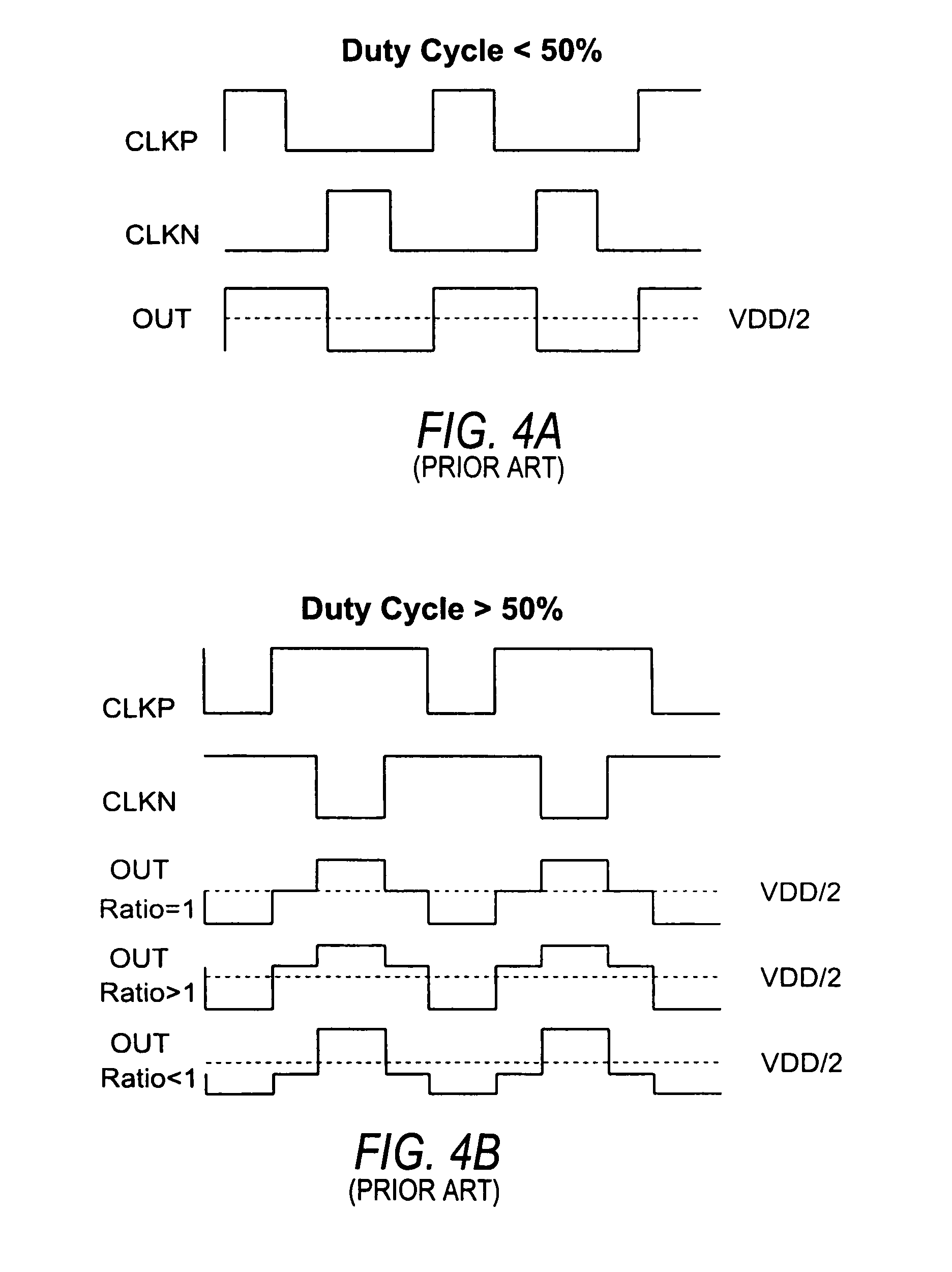

Duty cycle correction methods and circuits

InactiveUS7839192B1Lower performance requirementsLower requirementElectric pulse generatorPulse shapingCMOSSingle stage

Duty cycle correction (DCC) methods and circuits are provided for improving the quality of clock signals and reducing or eliminating duty cycle distortion. The performance of known duty cycle correction circuits, such as cross-coupled inverter or transmission gate DCC circuits, may be improved by coupling two or more DCC circuits in series to form a multi-stage DCC circuit. In multi-stage DCC circuits, the performance and sizing requirements imposed on the individual circuit stages are reduced as compared to single-stage DCC circuit implementations. Good duty cycle correction performance over a wide range of input signal duty cycles may therefore be ensured regardless of the performance of individual stages. Clocked-CMOS DCC circuits are also presented, the circuits operative to produce duty cycle corrected output signals while consuming minimal current and power. The clocked-CMOS DCC circuits include as few as four transistors, and are operative over wide ranges of input signal duty cycles.

Owner:ALTERA CORP

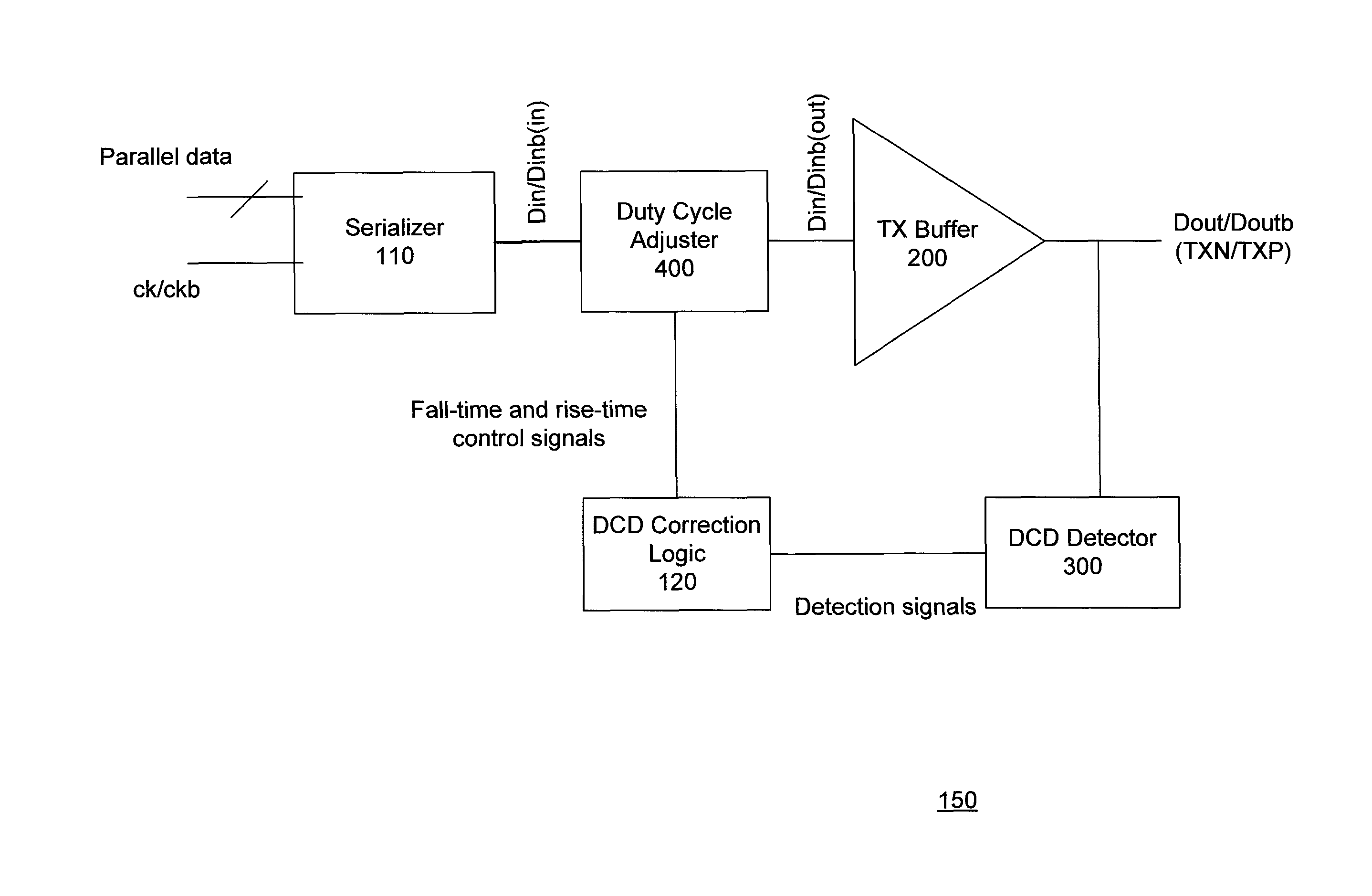

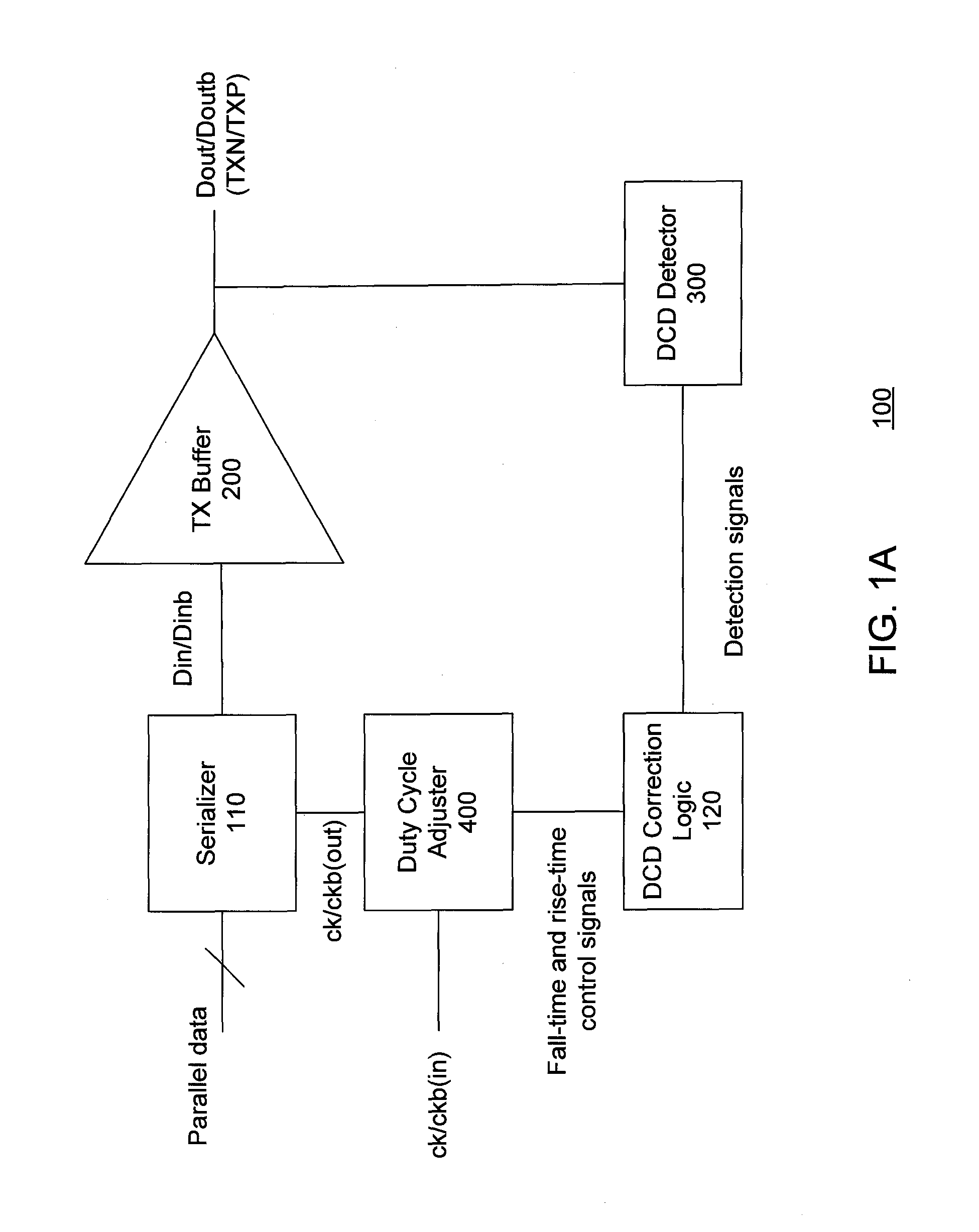

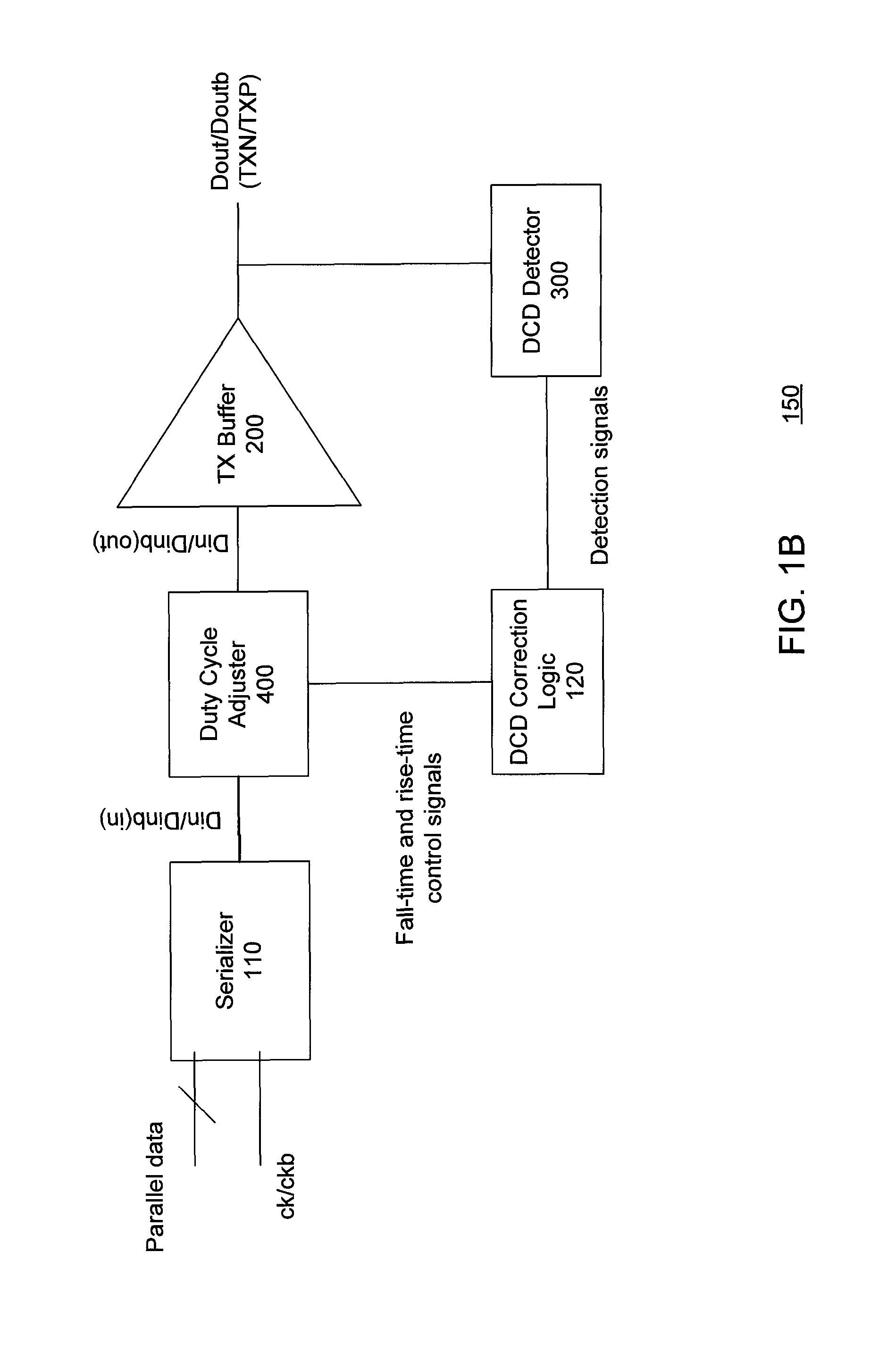

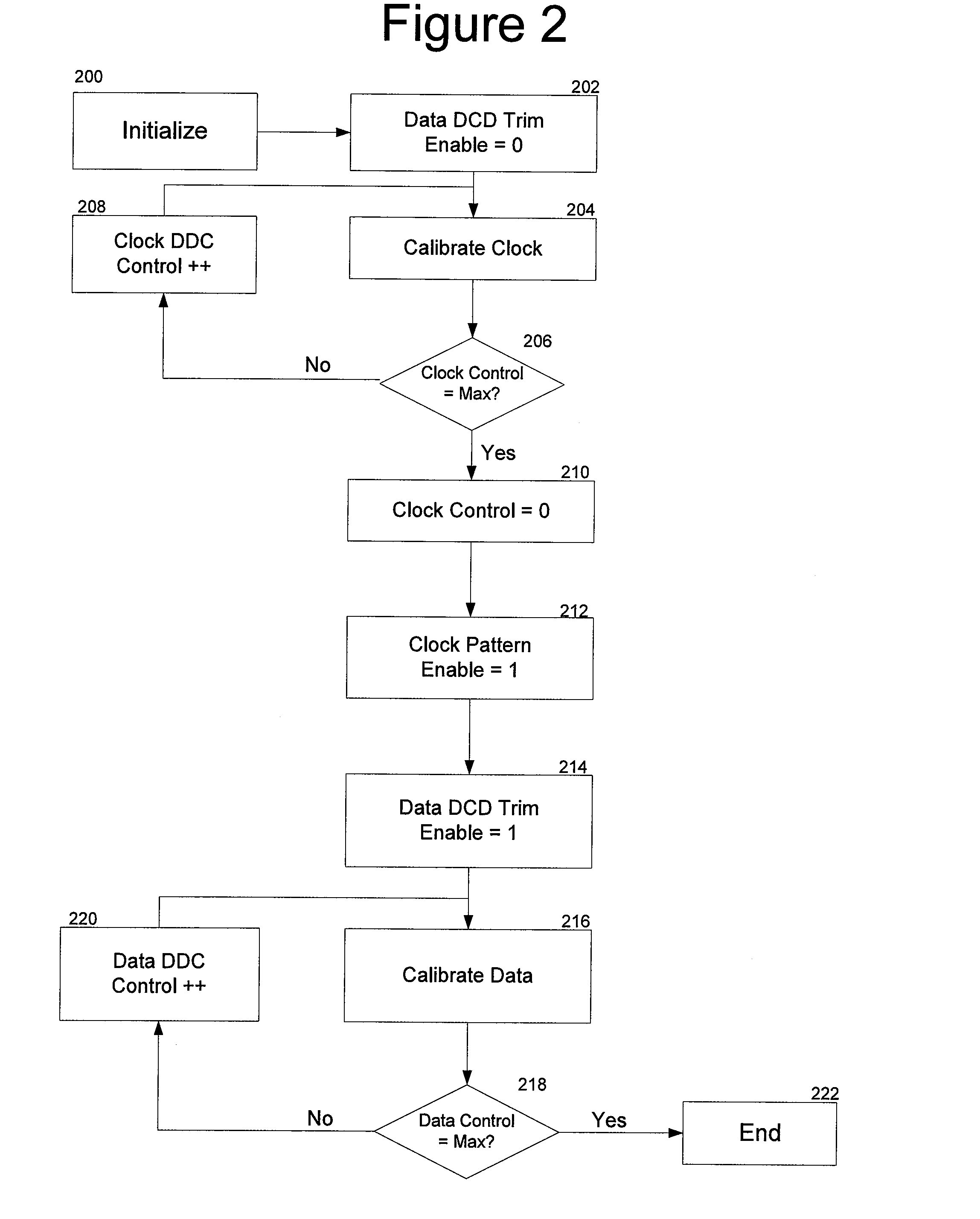

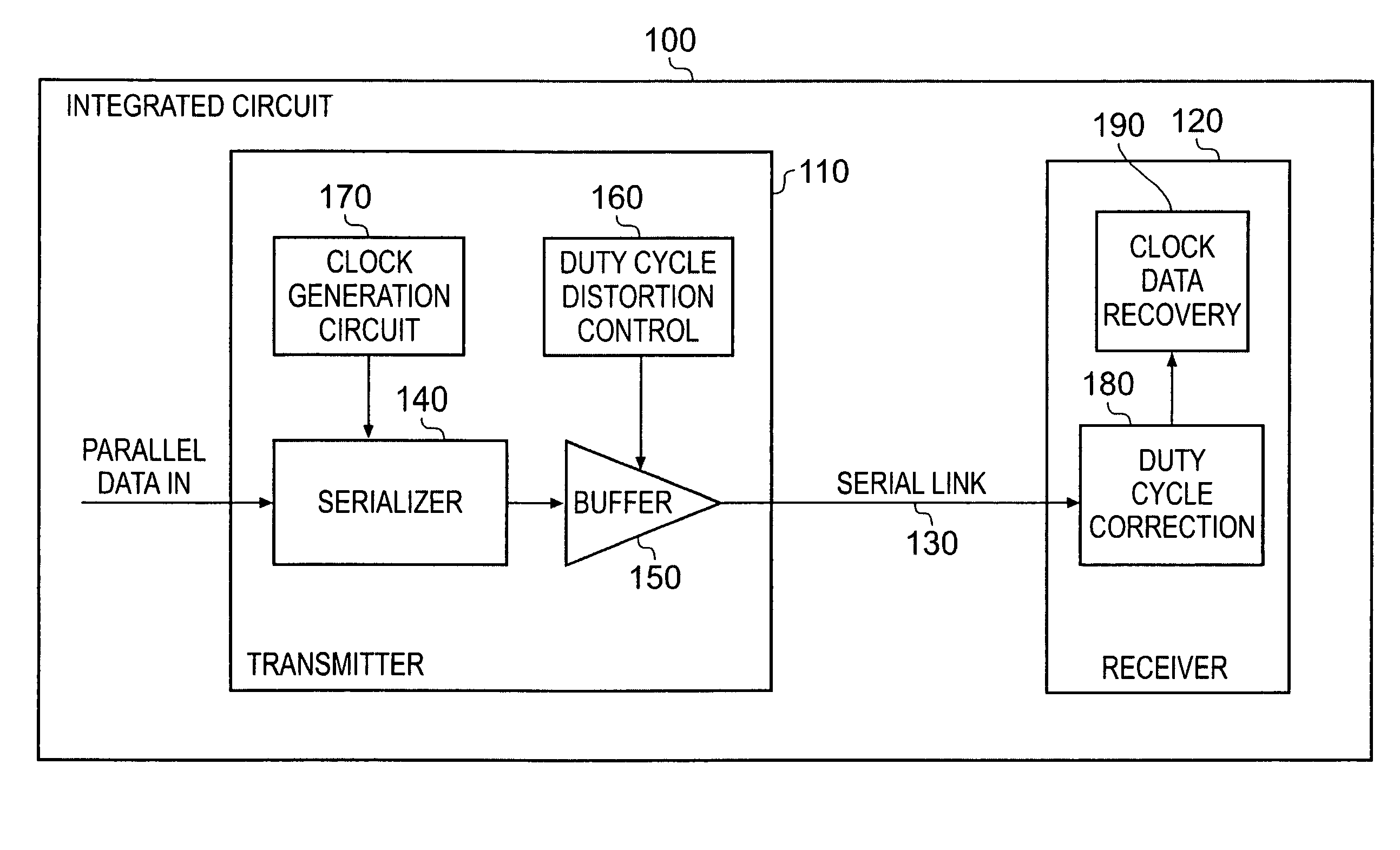

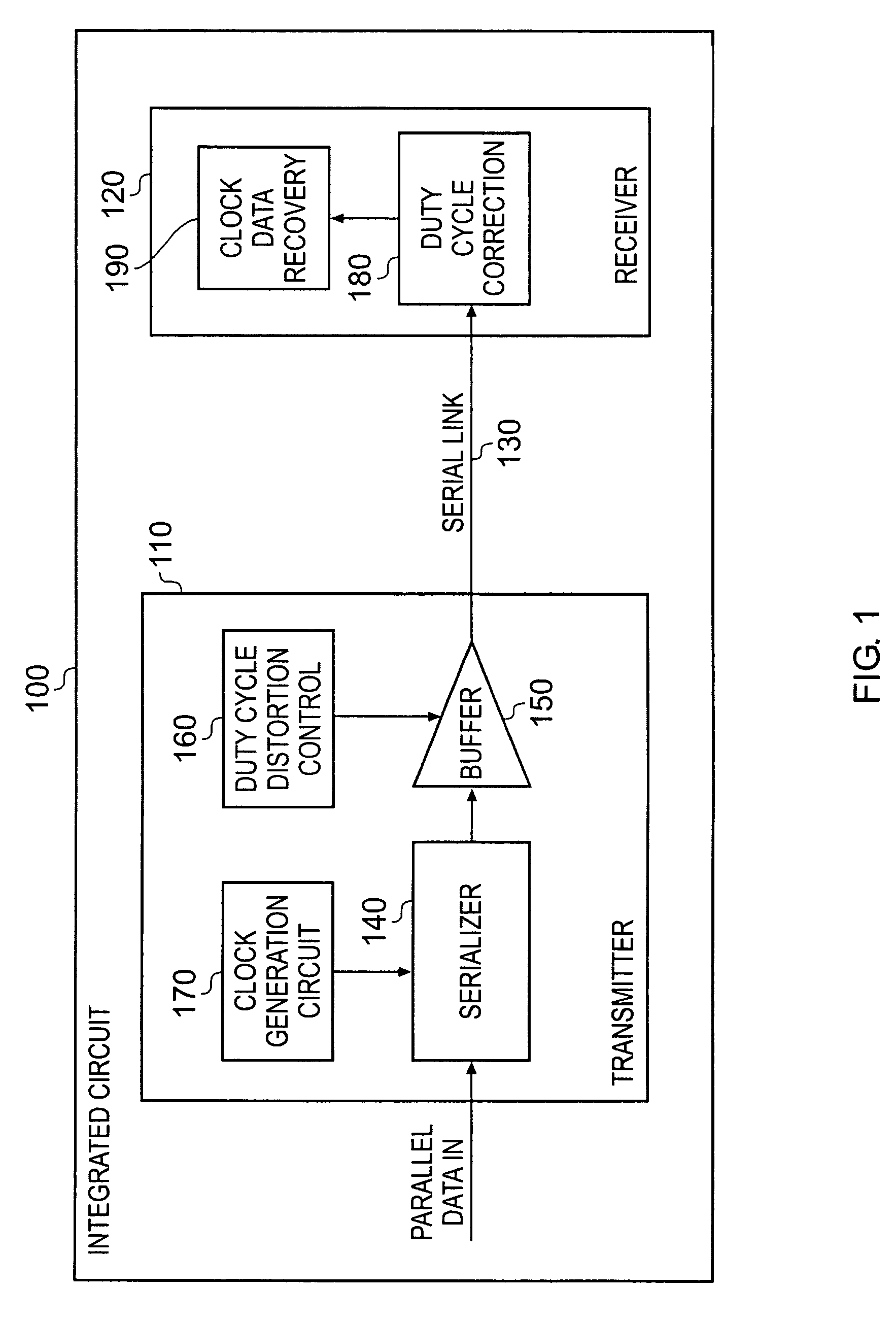

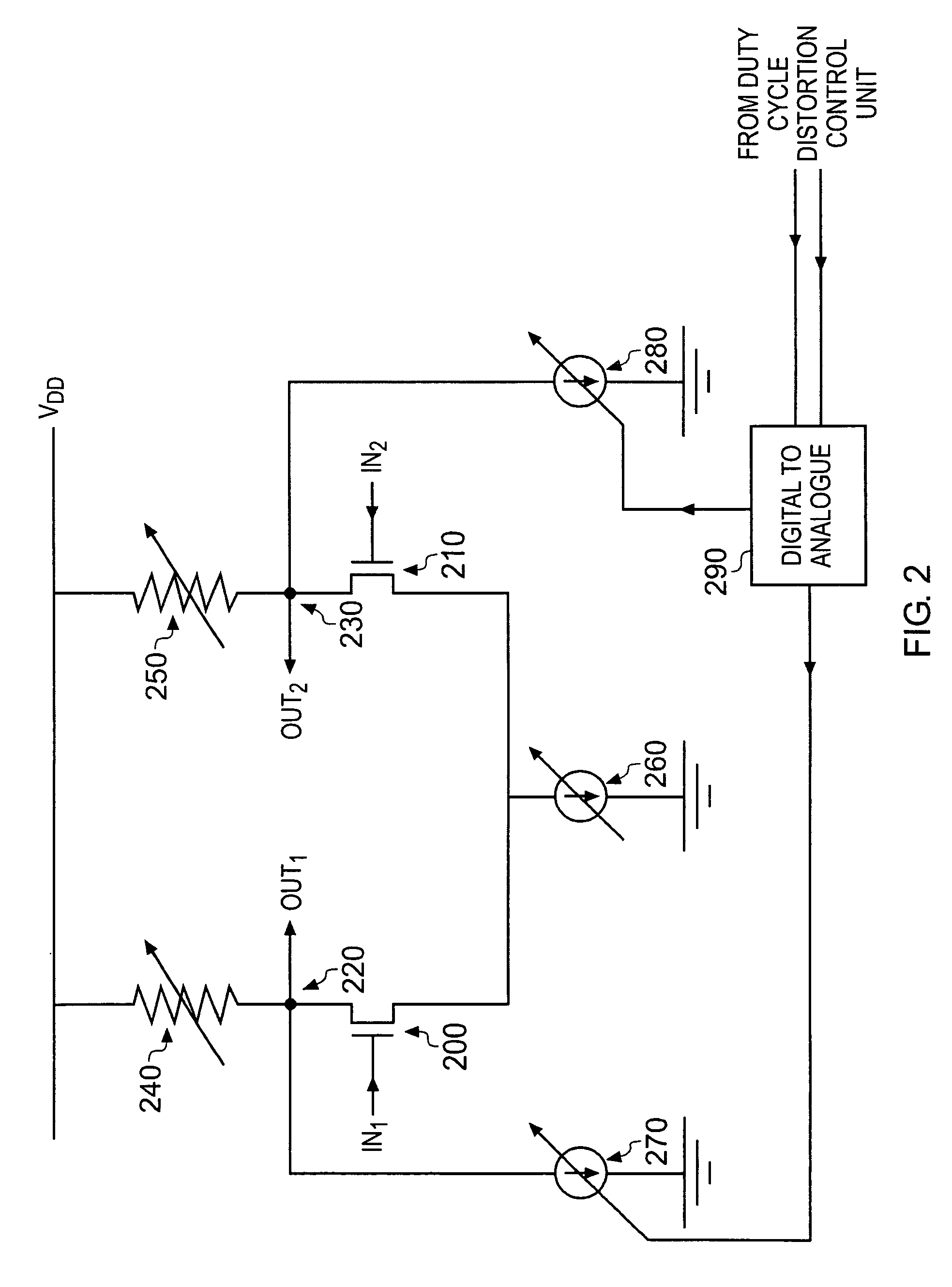

Apparatus and methods for detection and correction of transmitter duty cycle distortion

ActiveUS8462906B1Oscillations generatorsPulse duration/width modulationControl signalDuty cycle distortion

One embodiment relates to an integrated circuit which includes a transmitter buffer circuit, a duty cycle distortion (DCD) detector, correction logic, and a duty cycle adjuster. The DCD detector is configured to selectively couple to the serial output of the transmitter buffer circuit. The correction logic is configured to generate control signals based on the output of the DCD detector. The duty cycle adjuster is configured to adjust a duty cycle of the serial input signal based on the control signals. Another embodiment relates to a method of correcting duty cycle distortion in a transmitter. Other embodiments and features are also disclosed.

Owner:ALTERA CORP

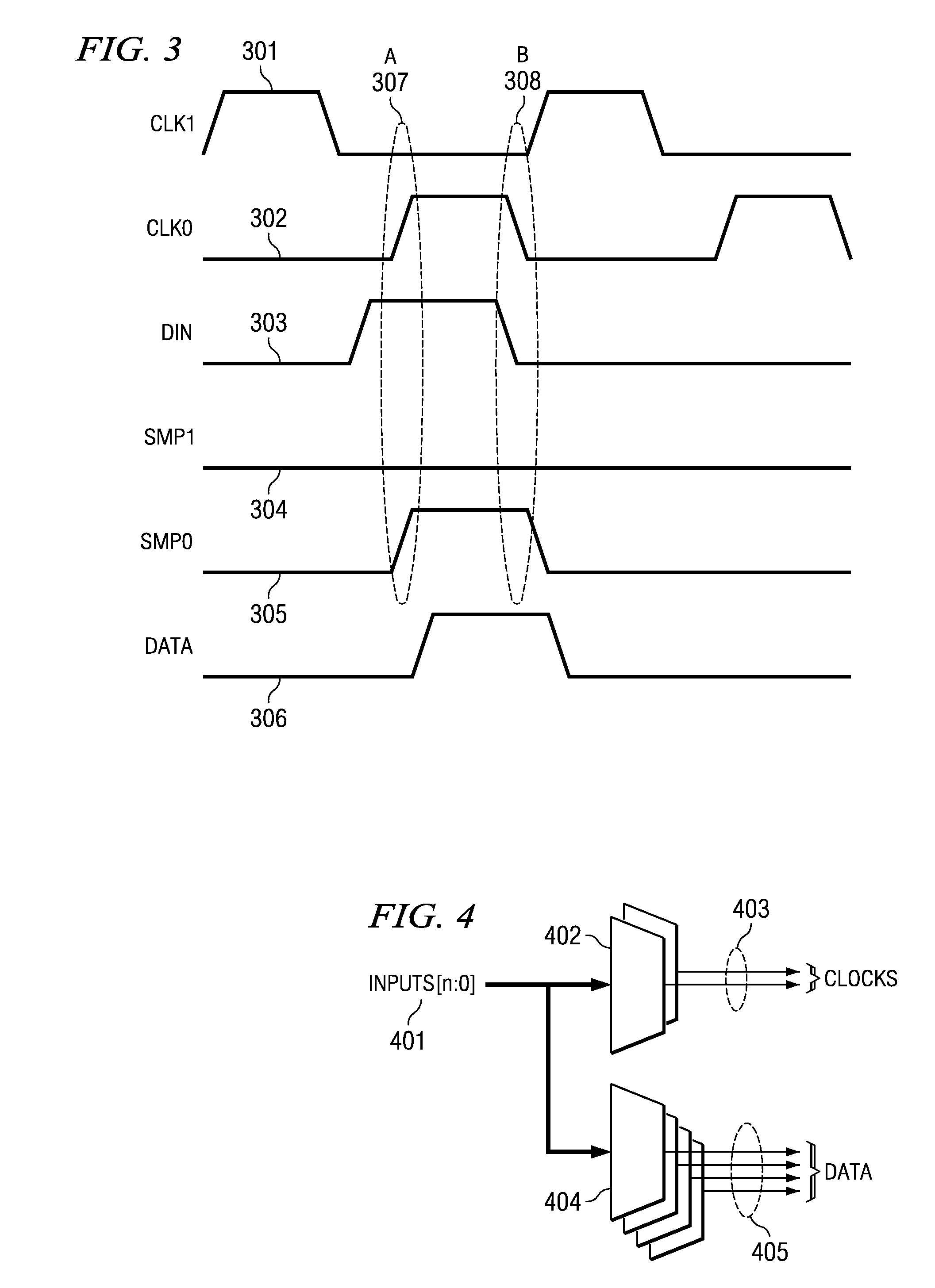

High Speed Data Recording With Input Duty Cycle Distortion

ActiveUS20060259820A1Reduce impactMore tolerant of the input duty cycle distortionError detection/correctionPulse conversionDuty cycle distortionData recording

Data from both a positive edge sample and negative edge sample are used to determine a data bit. The primary and secondary clocks capture two copies of the data. A sample is taken with a positive edge of one clock and the negative edge of the other clock each bit period. These two captured data values are combined along with the data value captured by the previous negative edge to determine the data bit value. The captured data may be dynamically de-skewed previous to being clocked into a buffer based on the clock edges sampling the data.

Owner:TEXAS INSTR INC

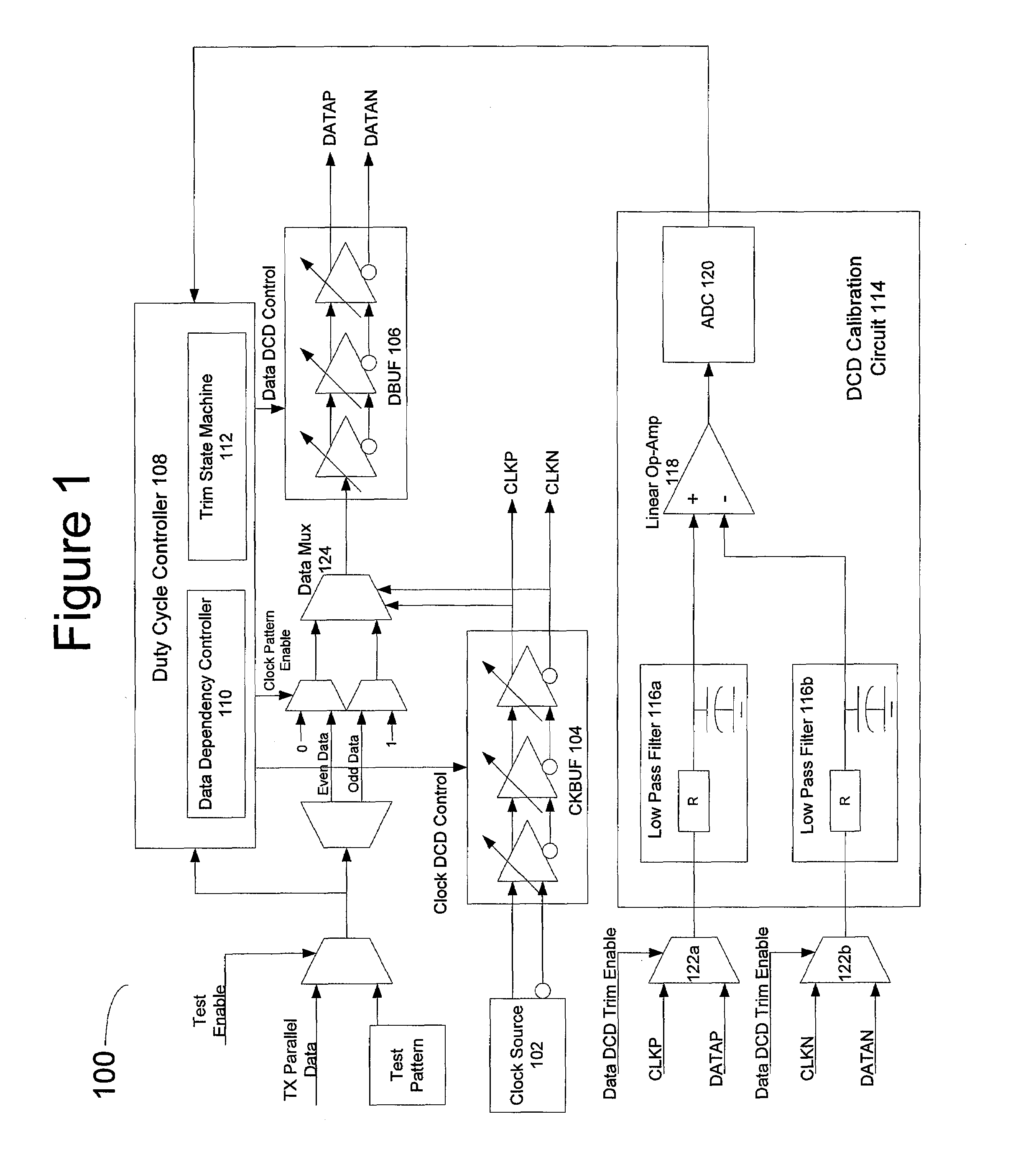

Duty cycle distortion (DCD) jitter modeling, calibration and generation methods

ActiveUS20090177457A1Accurately modeling duty cycle distortionExpand coverageParallel/series conversionError preventionData signalDuty cycle distortion

A method and system for modeling and calibrating duty cycle distortion (DCD) of a Serializer and Deserializer (SerDes) device, including first generating a clock DCD signal. Once the clock DCD signal is generated, it is calibrating based upon results obtained from a filtering process of the clock DCD signal. Once the clock DCD signal is calibrated, a data DCD signal is generated and calibrated based upon results obtained from a filtering process of the data DCD signal.

Owner:AVAGO TECH INT SALES PTE LTD

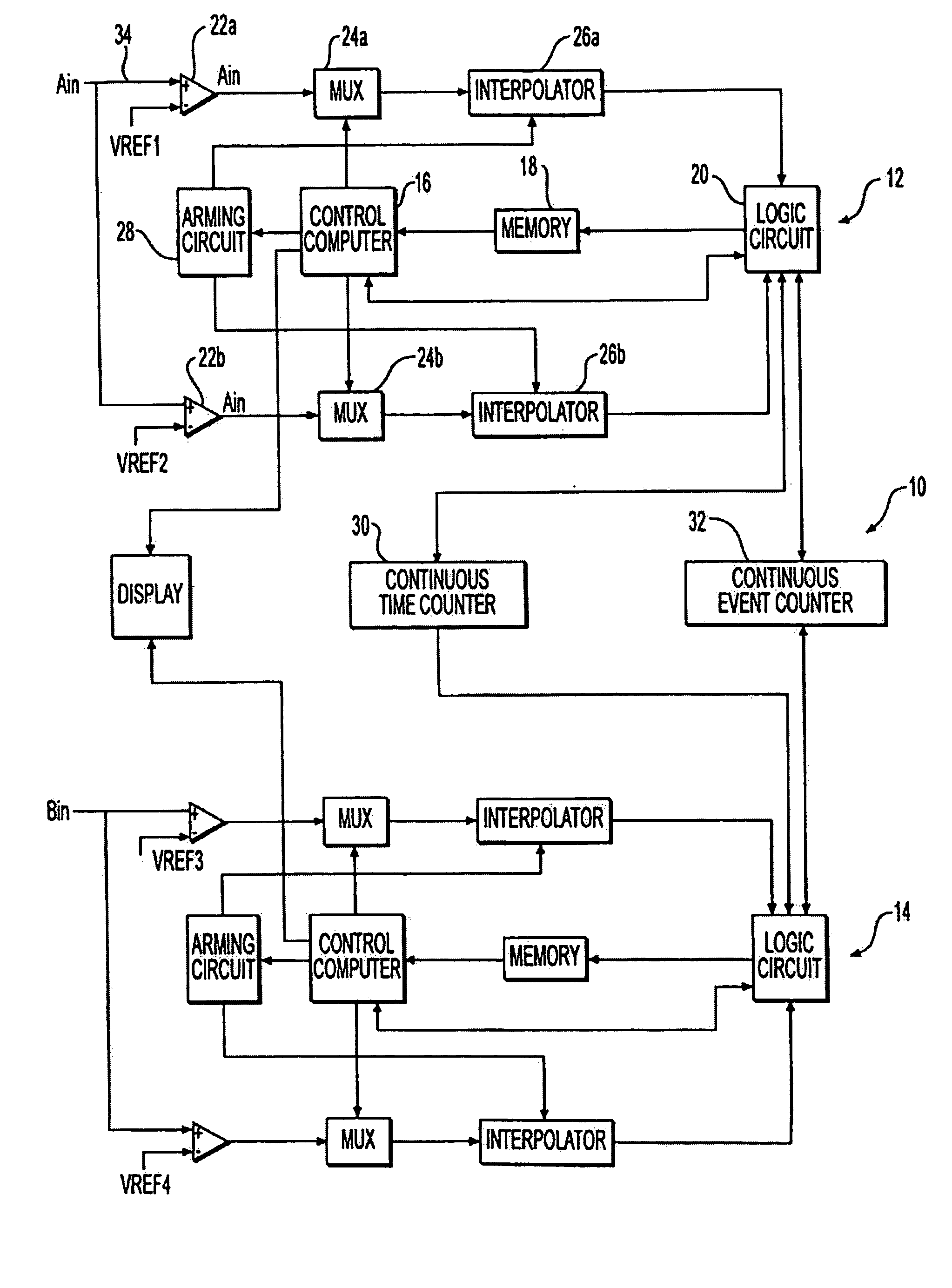

System and method of obtaining data-dependent jitter (DDJ) estimates from measured signal data

InactiveUS7203610B2Enhanced low frequencyImprove the measurement effectNoise figure or signal-to-noise ratio measurementVoltage-current phase angleDuty cycle distortionData signal

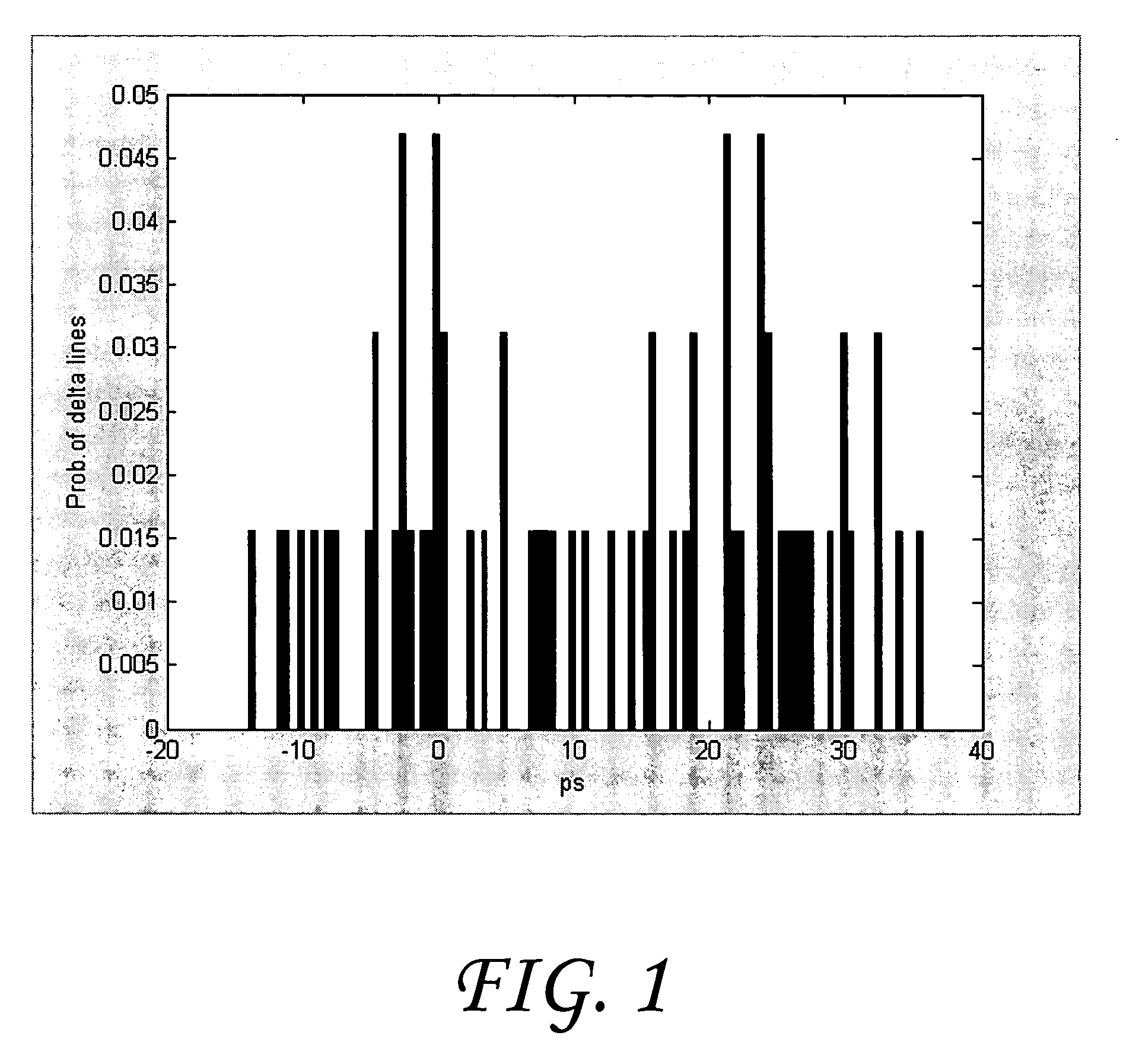

Methods for estimating data-dependent jitter (DDJ) from measured samples of a transmitted data signal include a first exemplary step of obtaining a plurality of measurements (e.g., time tags and event counts for selected pulse widths in the data signal). Such measurements may be obtained at predetermined intervals within a transmitted signal or may be obtained at randomly selected intervals, and should yield measurements for each data pulse in a repeating data pattern. An average unit interval value representative of the average bit time of the transmitted signal is determined. Time interval error estimates representative of the timing deviation from each signal edge's measured value relative to its ideal value (determined in part from the calculated average unit interval value) are also determined, as well as a classification for each measured signal edge relative to a corresponding data pulse in the repeating data pattern. DDJ delta lines are then calculated for signal edges of each pulse width in the transmitted data pattern, from which peak-to-peak DDJ values and / or estimates of duty-cycle-distortion (DCD) can be determined.

Owner:GUIDE TECH

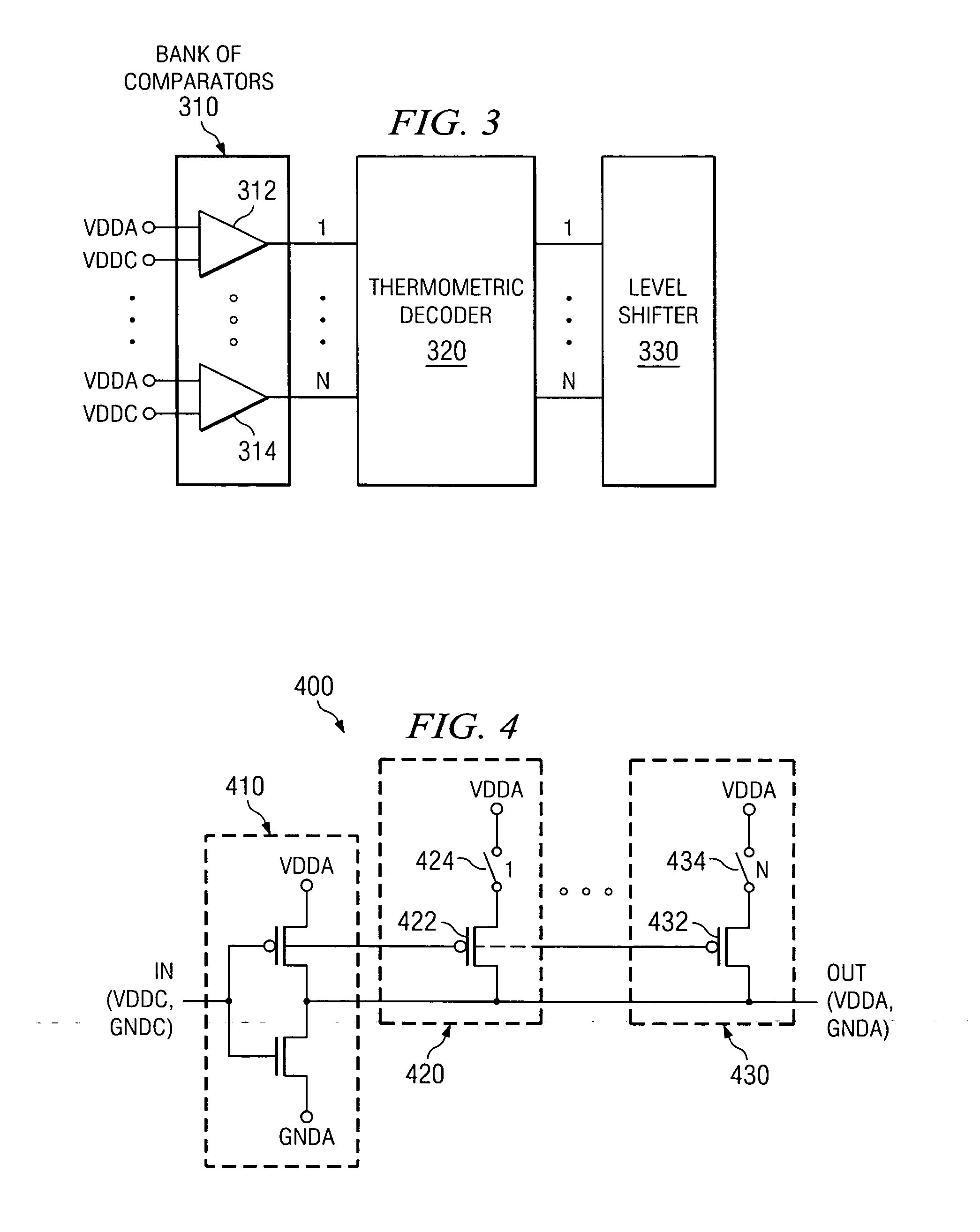

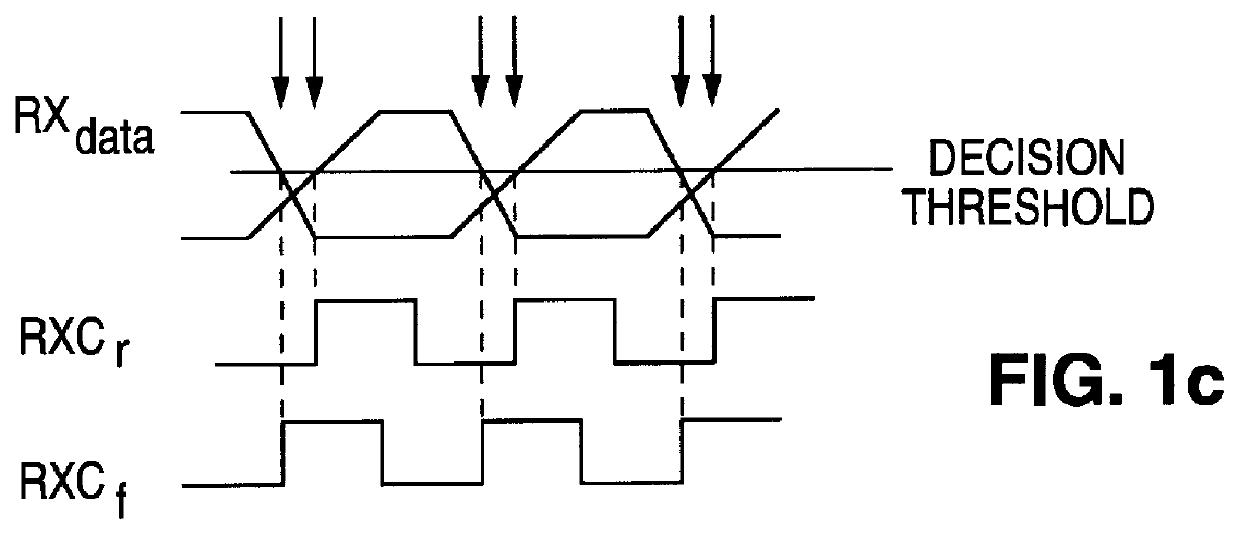

Level shifter apparatus and method for minimizing duty cycle distortion

InactiveUS20070103215A1Minimizes duty cycle distortionIncrease working frequencyPulse automatic controlElectric pulse generatorControl signalDuty cycle distortion

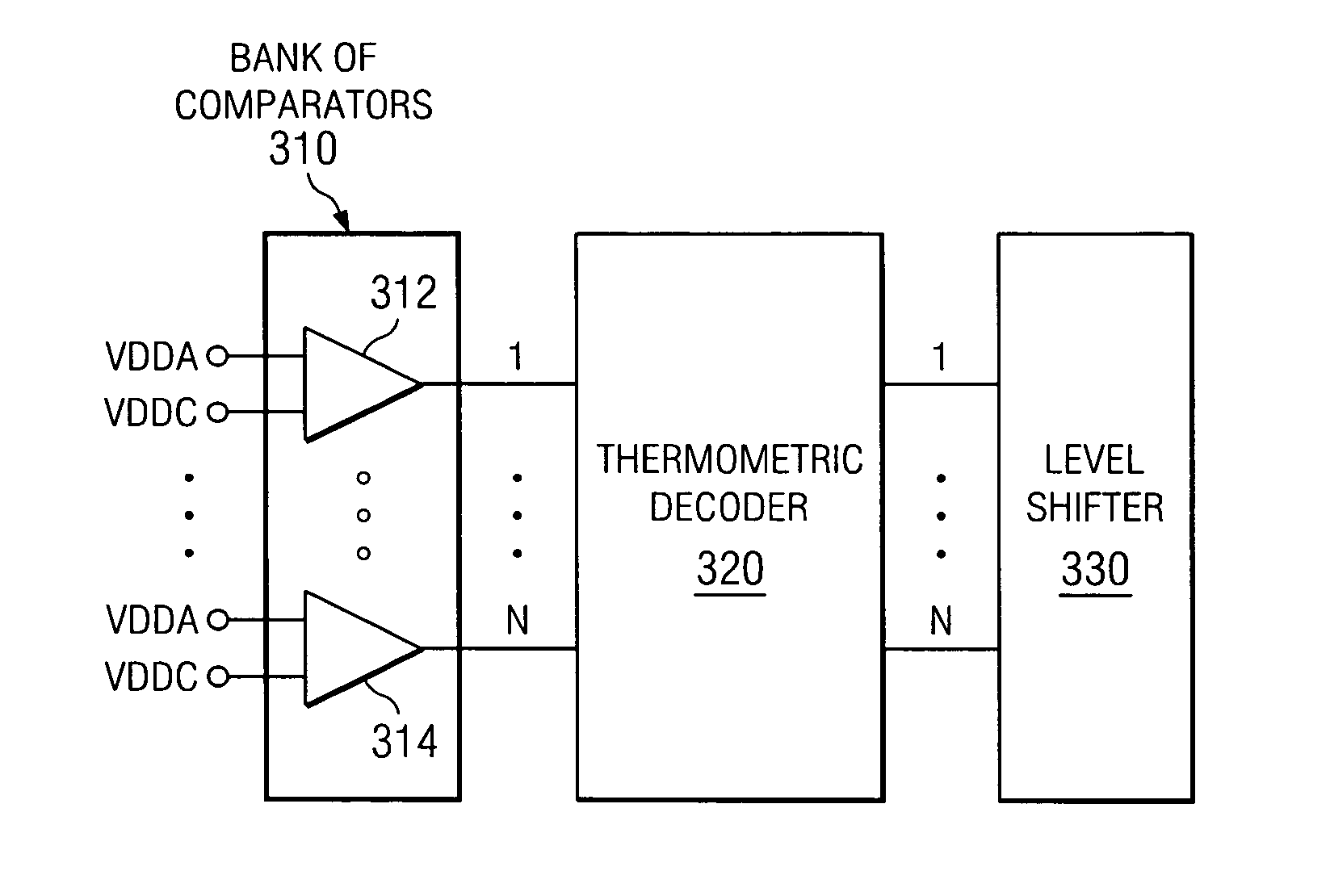

A level shifter apparatus and method for minimizing duty cycle distortion are provided. The level shifter includes a bank of comparators each having an associated threshold built into it. The comparators compare a difference in source voltages for two power domains to these built-in thresholds and output a signal indicative of whether the threshold is exceeded. The output signals from the comparators are provided to a thermometric decoder which generates control signals based on these output signals. The control signals are used to control stages in a level shifter for modifying the voltage output of the level shifter. Individual stages may be enabled to thereby monotonically modify the voltage output of the level shifter and thereby decrease a time required to achieve a voltage having a level that causes a state change in a driven circuit. As a result, duty cycle distortion is minimized and maximum operational frequency is increased.

Owner:ELECTRONICS COMPONENTS TOSHIBA AMERICA +1

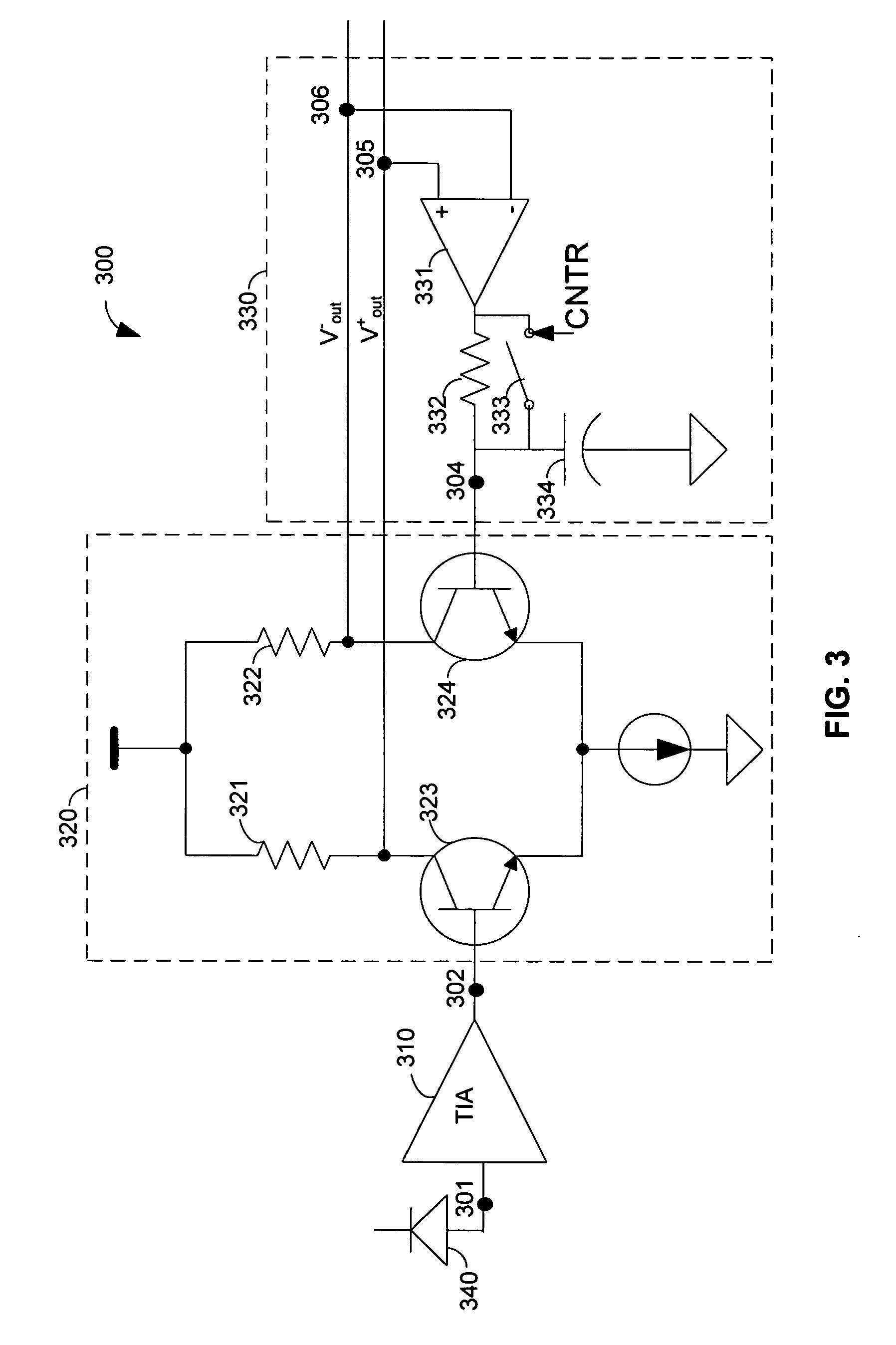

Apparatus and method to adaptively equalize duty cycle distortion

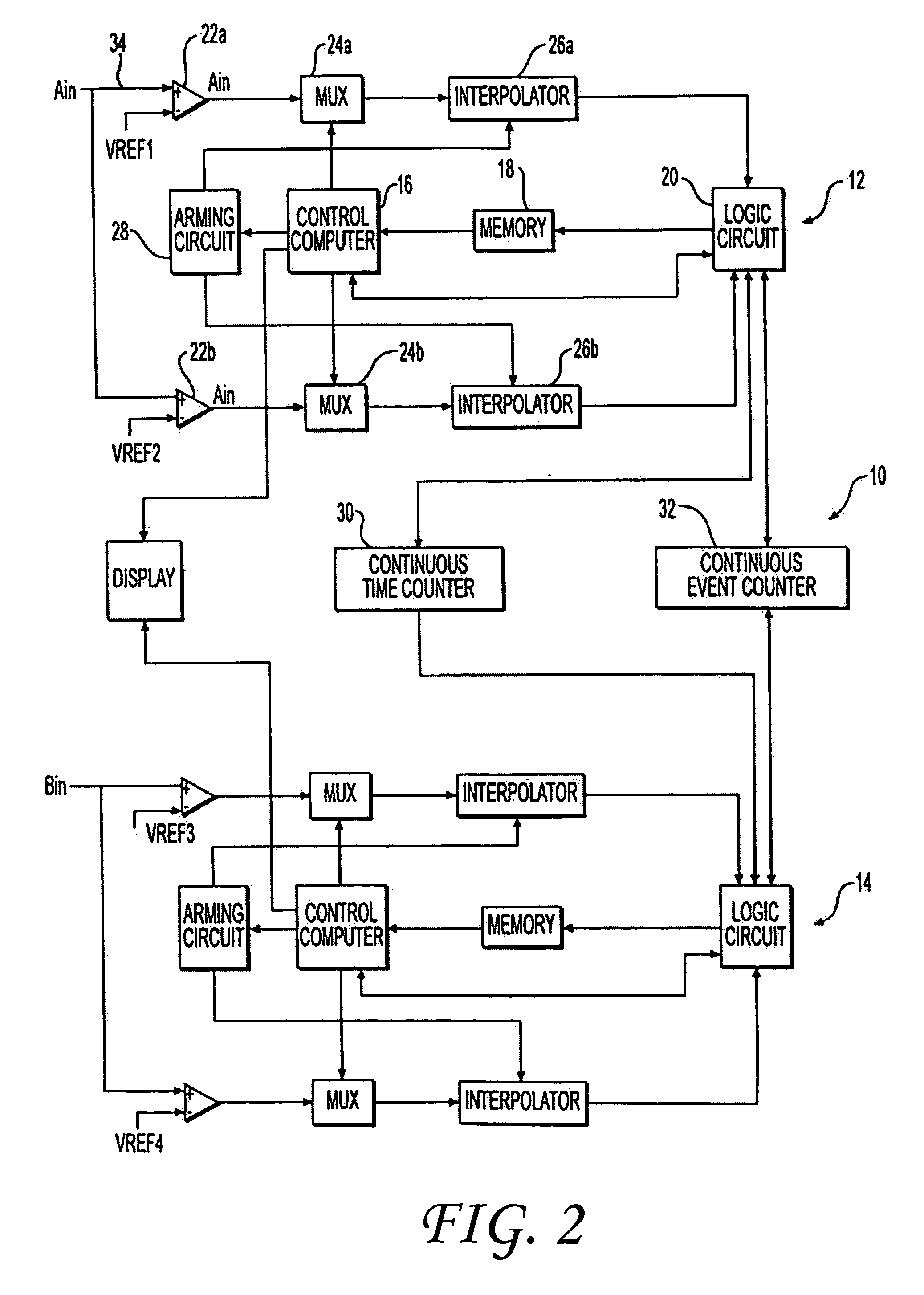

An apparatus for and method of removing duty cycle distortion jitter from data by adaptive equalization are disclosed. The apparatus includes an equalization circuit which equalizes input data based on an equalization control signal, a signal analysis circuit, and a control circuit which generates the equalization control signal. A multiport apparatus includes a plurality of equalization circuits, a multiplexor, a signal analysis circuit, and a control circuit. A method includes the steps of receiving an equalization control signal and the input data signal, equalizing the input data signal based on the equalization control signal, analyzing the equalized data signal and generating an analysis result signal, and generating the equalization control signal based on the analysis result signal.

Owner:NAT SEMICON CORP

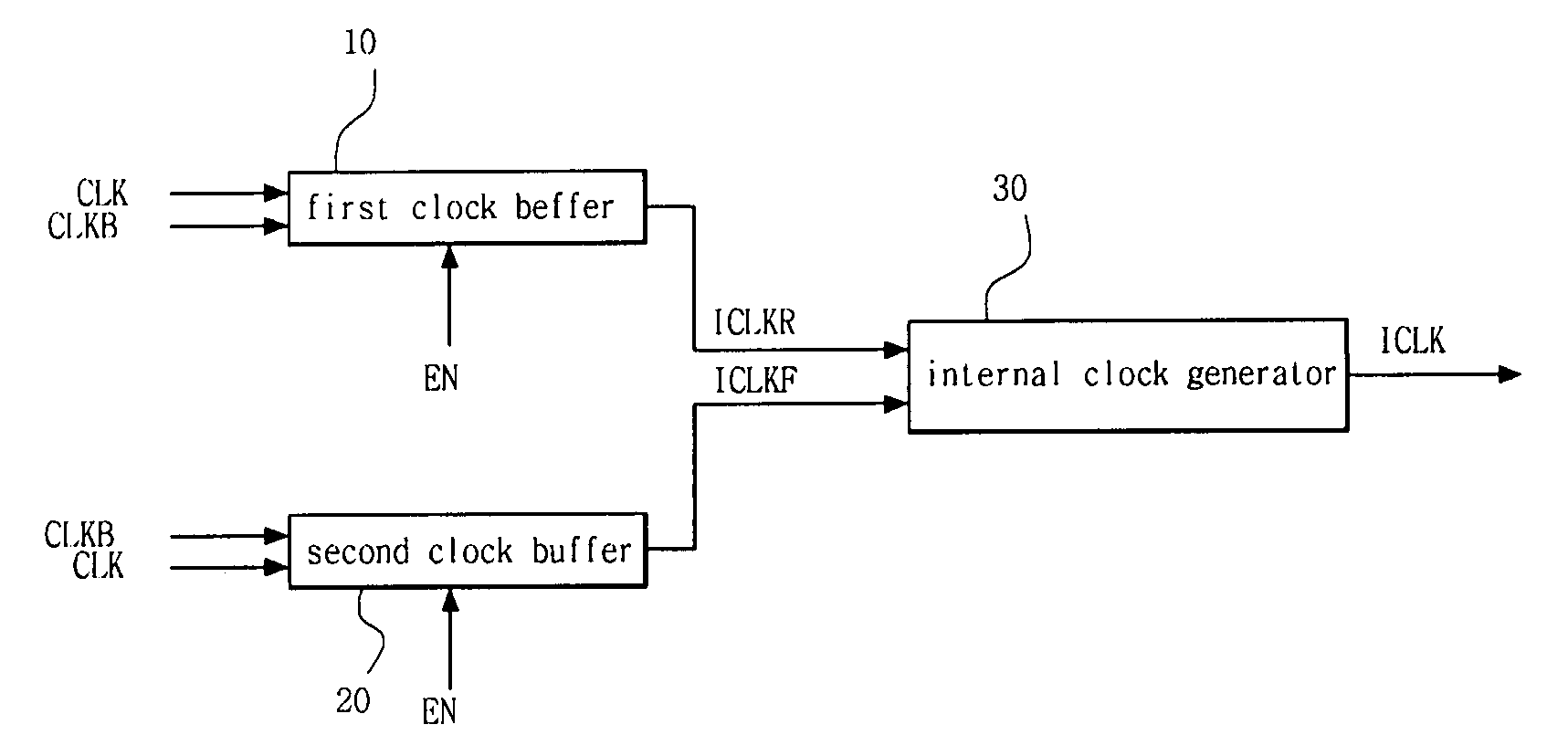

Clock buffer circuit of semiconductor device

InactiveUS20080201596A1Digital storageGenerating/distributing signalsDuty cycle distortionClock generator

A clock buffer circuit of a semiconductor device is disclosed which receives an external clock signal and generates an internal clock signal with no duty distortion. The clock buffer circuit includes a first clock buffer for receiving and buffering a normal-phase clock signal, a second clock buffer for receiving and buffering a reverse-phase clock signal, and an internal clock generator for generating an internal clock signal in response to output signals from the first and second clock buffers.

Owner:SK HYNIX INC

Duty-cycle correction circuit and method for differential clocking

Owner:INT BUSINESS MASCH CORP

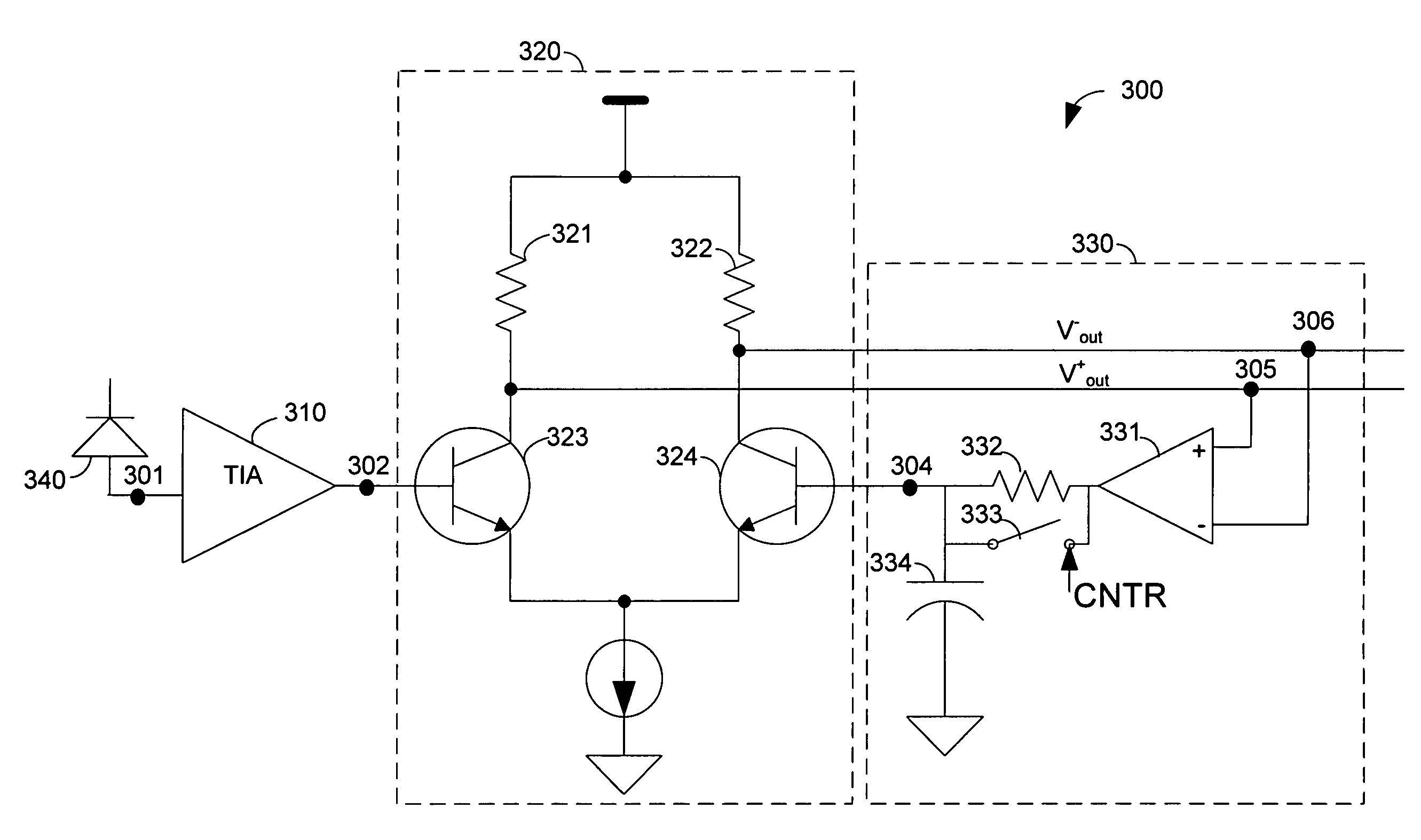

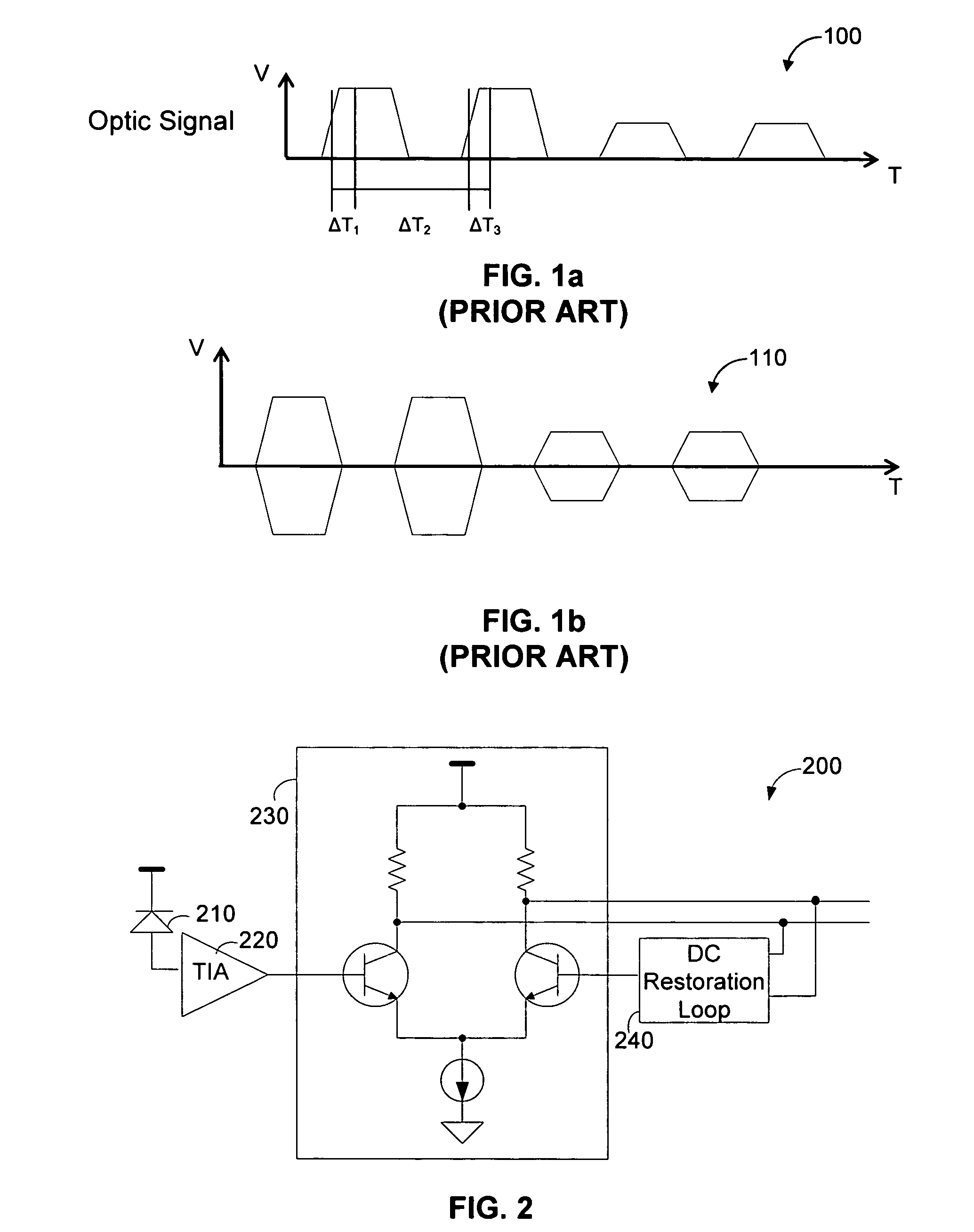

Transimpedance (TIA) circuit usable for burst mode communications

A transimpedance amplifier (TIA) circuit usable for burst mode communications is provided. The TIA circuit includes a TIA stage, a limiter-amplifier, and a DC restoration loop. The invention overcomes problems of the prior art relating to burst communications, such as a DC level in the output signal which can change from burst to burst and a duty-cycle distortion in large signals. This is achieved by using a DC restoration loop that ensures achieving zero DC potential within variable acquisition periods.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

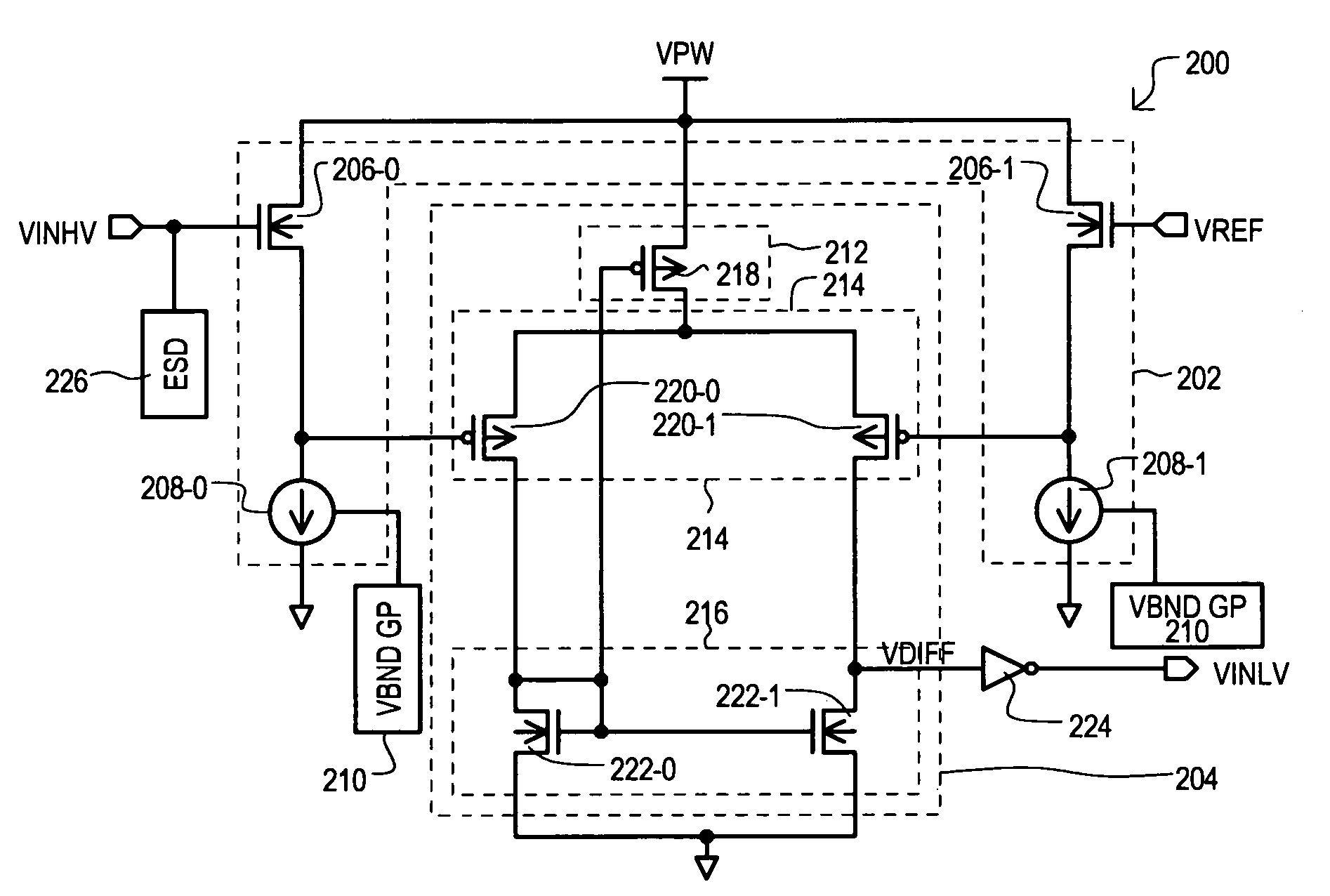

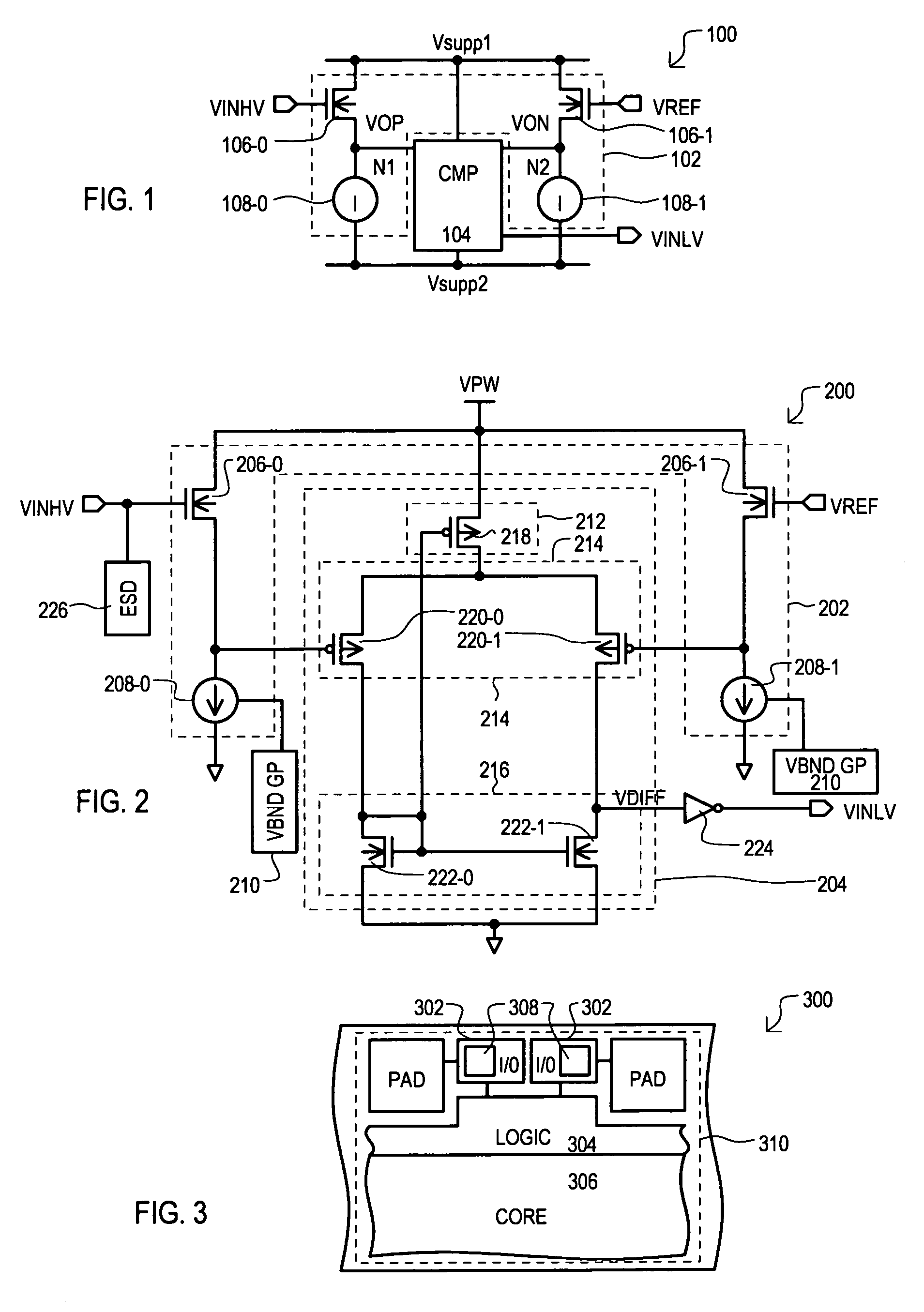

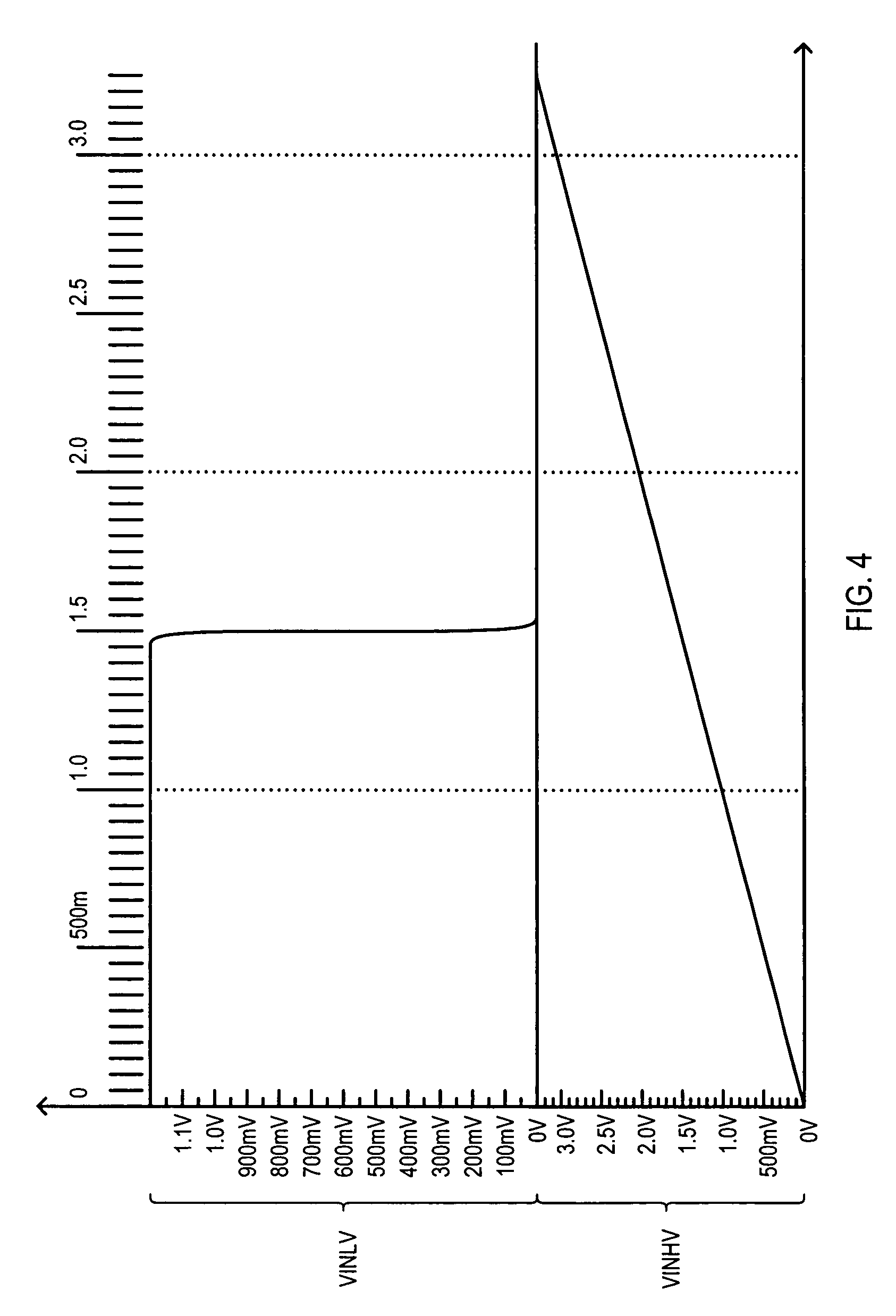

Level shifting input buffer circuit

ActiveUS7276953B1More compact circuitReduce distortionPulse automatic controlLogic circuit coupling/interface arrangementsLevel shiftingDuty cycle distortion

An input circuit (200) operating at a predetermined power supply voltage (VPW) can level shift a high voltage input signal (VINHV) from a higher voltage value to the lower power supply voltage (VPW) level. An input circuit (200) can include input transistors (206-0 and 206-1) having a source-follower configuration. A first input transistor (206-0) receives a high voltage input signal (VINHV) and a second input transistor (206-1) receives a reference voltage (VREF), which can both reach levels greater than power supply voltage (VPW). A compare circuit (204) can reduce duty cycle distortion to generate a lower voltage input signal (VINLV). Input circuit (200) can provide level shifting from LVTTL levels to low voltage CMOS levels without the need for multiple power supply voltages.

Owner:MONTEREY RES LLC

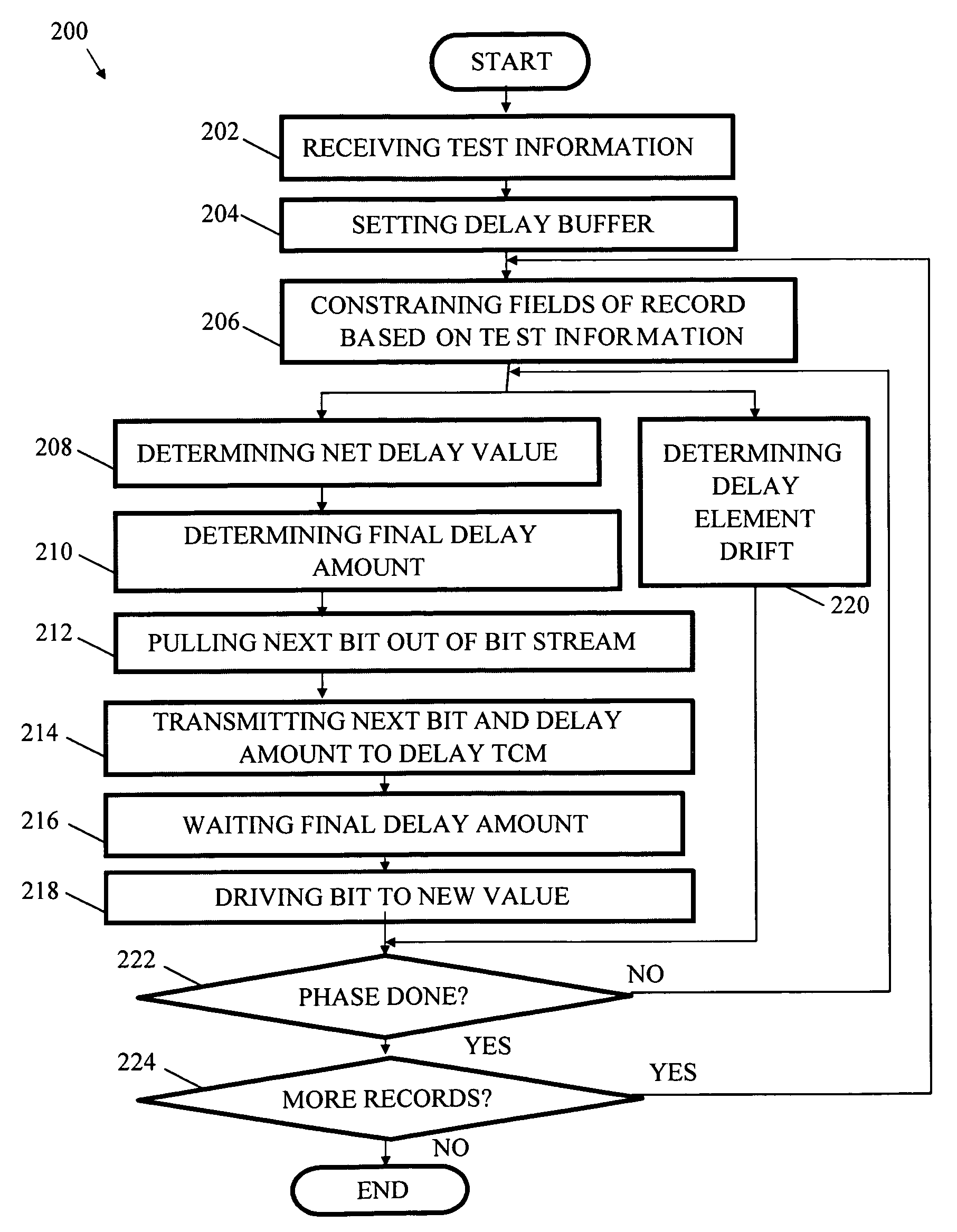

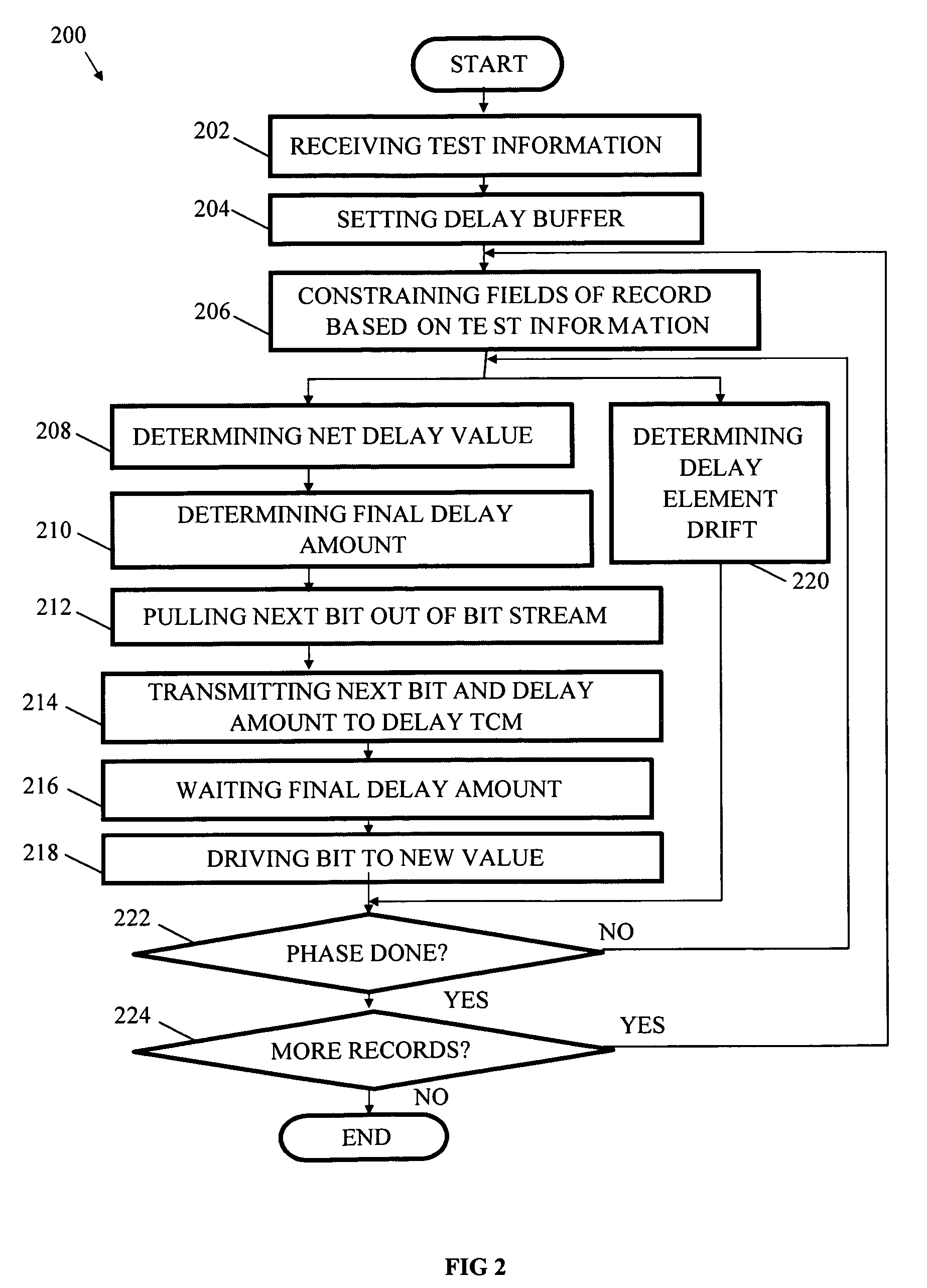

Methods, systems and media for functional simulation of noise and distortion on an I/O bus

ActiveUS7246332B2Analogue computers for electric apparatusCAD circuit designDuty cycle distortionVoltage reference

Methods, systems, and media for functional simulation of an I / O bus are disclosed. More particularly, a method of simulating distortion and noise parameters of an I / O bus is disclosed. Embodiments include constraining one or more fields of a record and determining delay amounts based on the resulting parameters, where the final delay amount includes a delay buffer and a net of delay amounts associated with the parameters. Embodiments may also include determining a value of a next bit to be sent to the I / O bus and, after waiting the delay amount, driving the bit on the bus to the next bit value. Parameters may include skew, jitter, duty cycle distortion, voltage reference distortion, and drift of any of these parameters. Further embodiments may include signaling the end of a phase in response to a phase done condition being satisfied.

Owner:GOOGLE LLC

Circuits and methods for clock signal duty-cycle correction

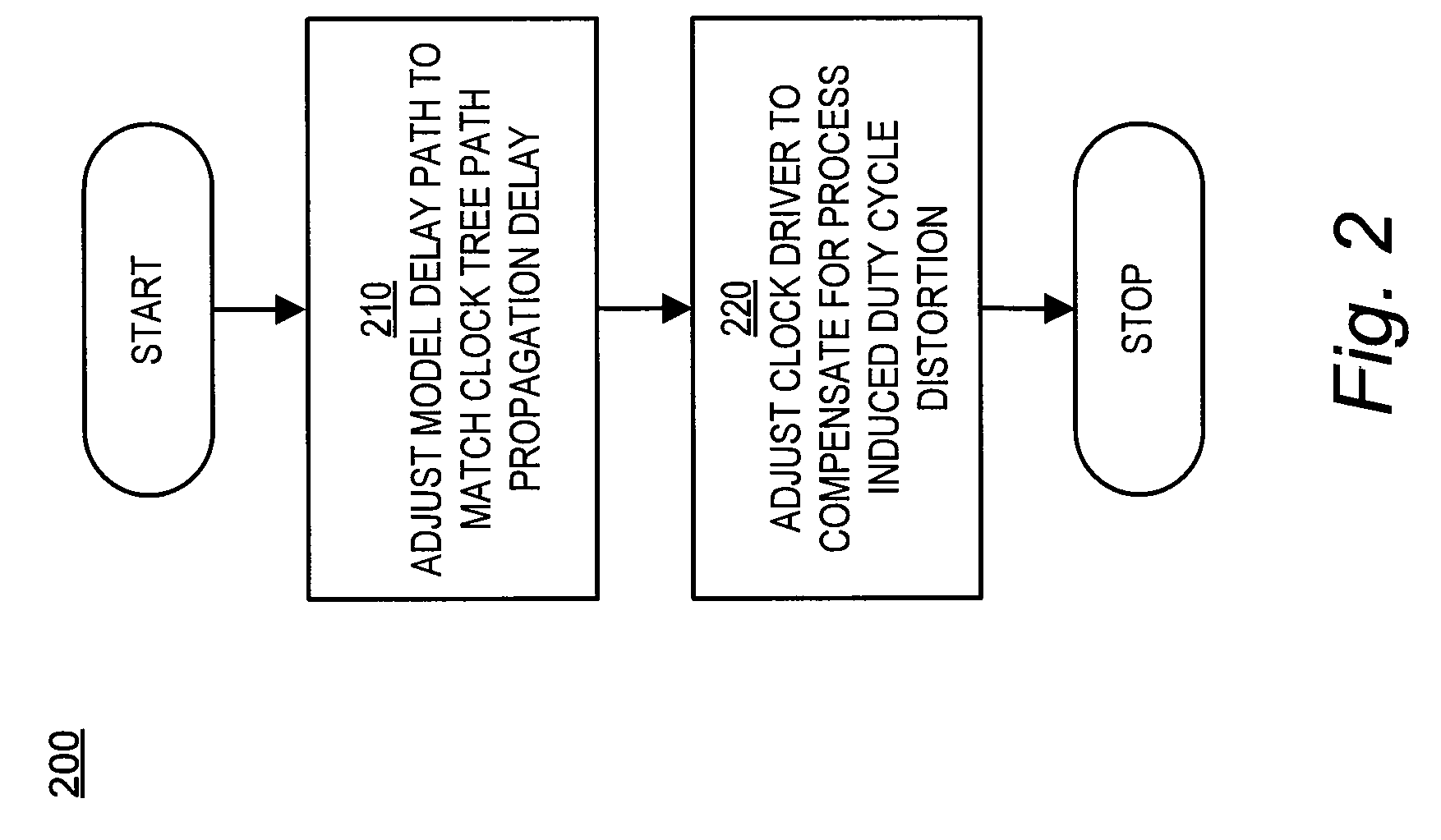

ActiveUS20110050307A1Pulse automatic controlElectric pulse generatorPropagation delayDuty cycle distortion

Duty-cycle correction circuits, clock distribution networks, and methods for correcting duty-cycle distortion are disclosed, including methods and apparatus for correcting duty-cycle distortion of differential output clock signals provided from a clock distribution network. In one such method, a single-ended clock signal is generated from differential input clock signals for distribution over a clock distribution network and from which the differential output clock signals are generated. A delay of a model delay path is matched to a propagation delay of the clock distribution network, and the single ended clock signal is adjusted to compensate for duty-cycle distortion.

Owner:MICRON TECH INC

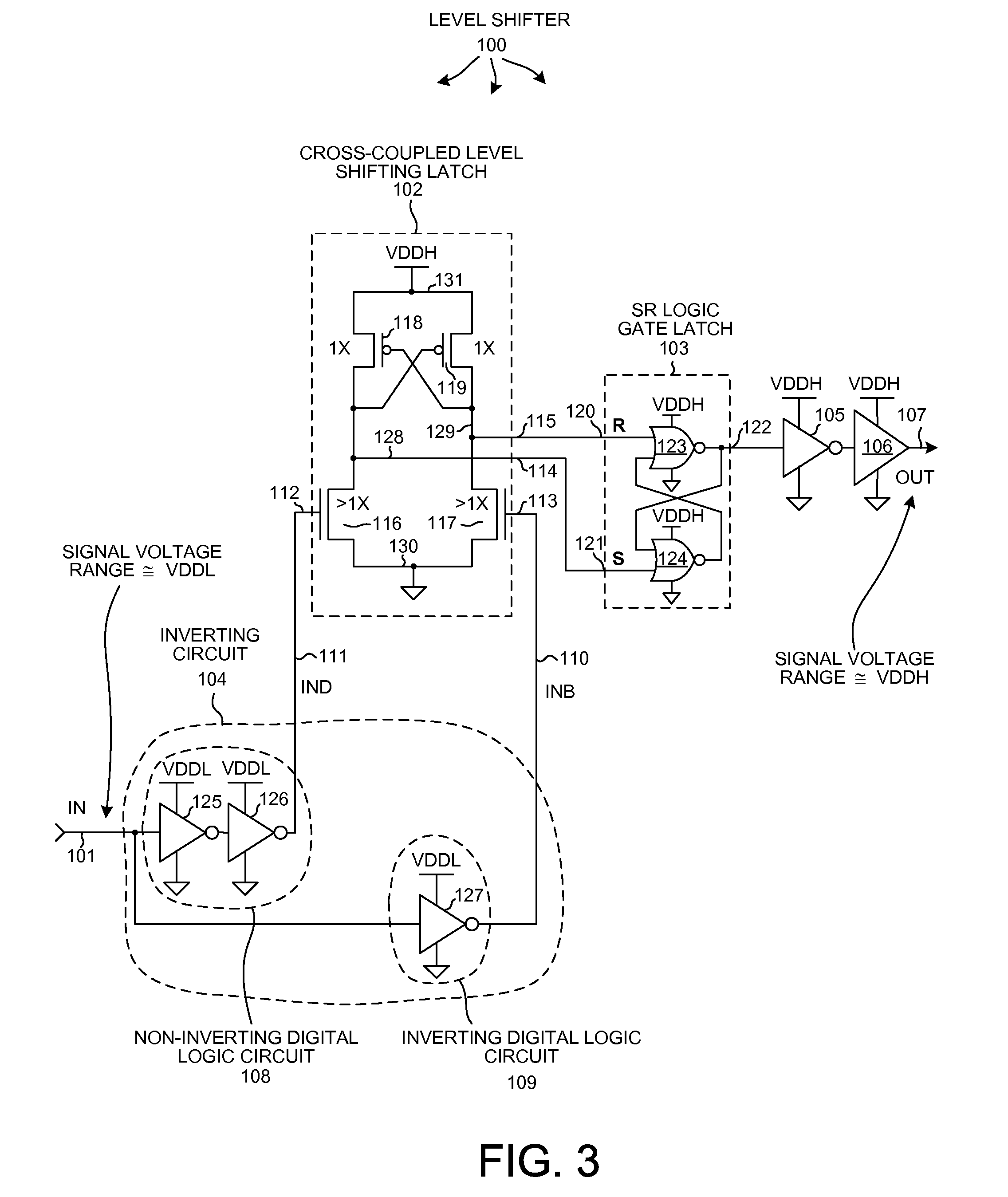

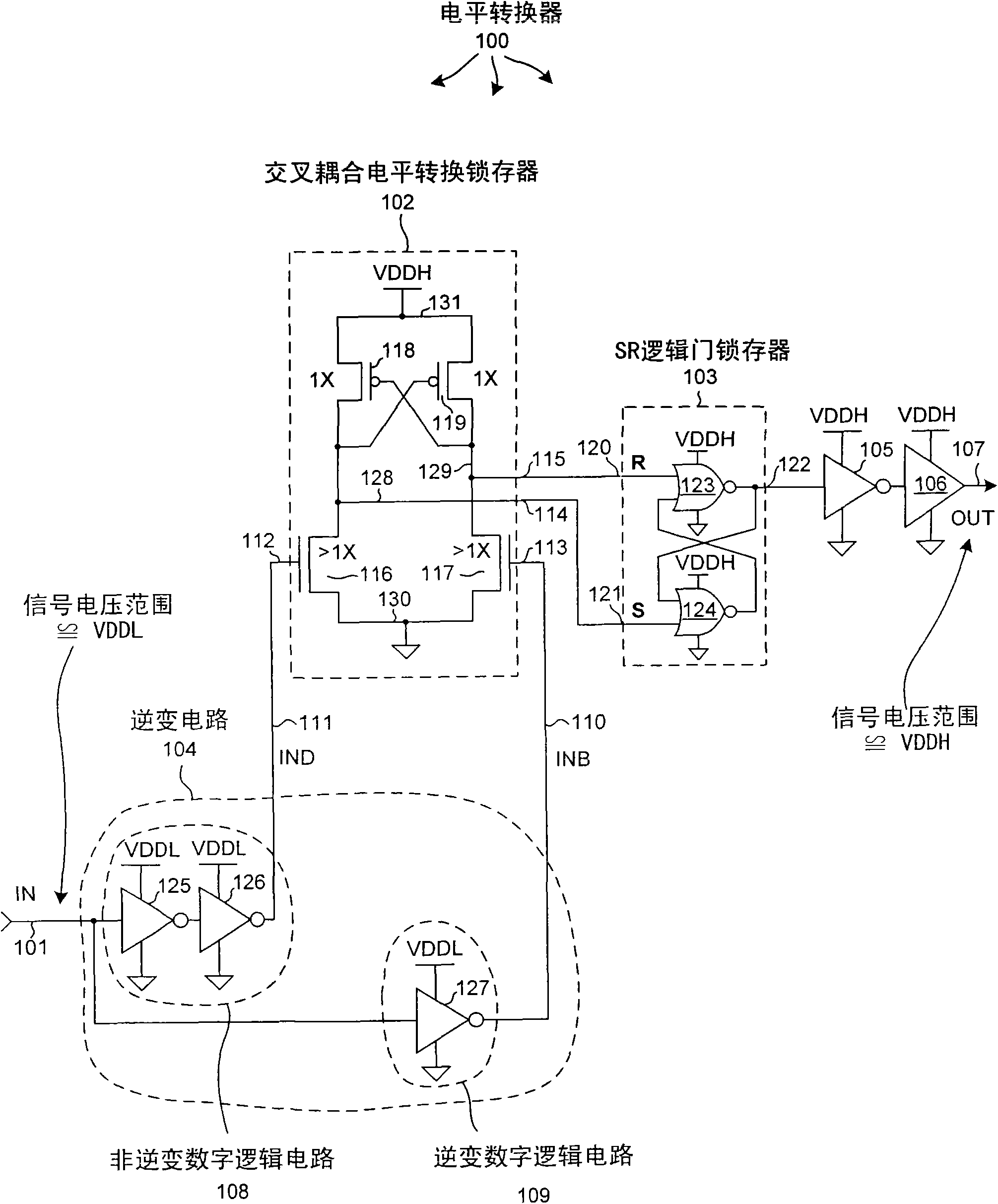

Level shifter having low duty cycle distortion

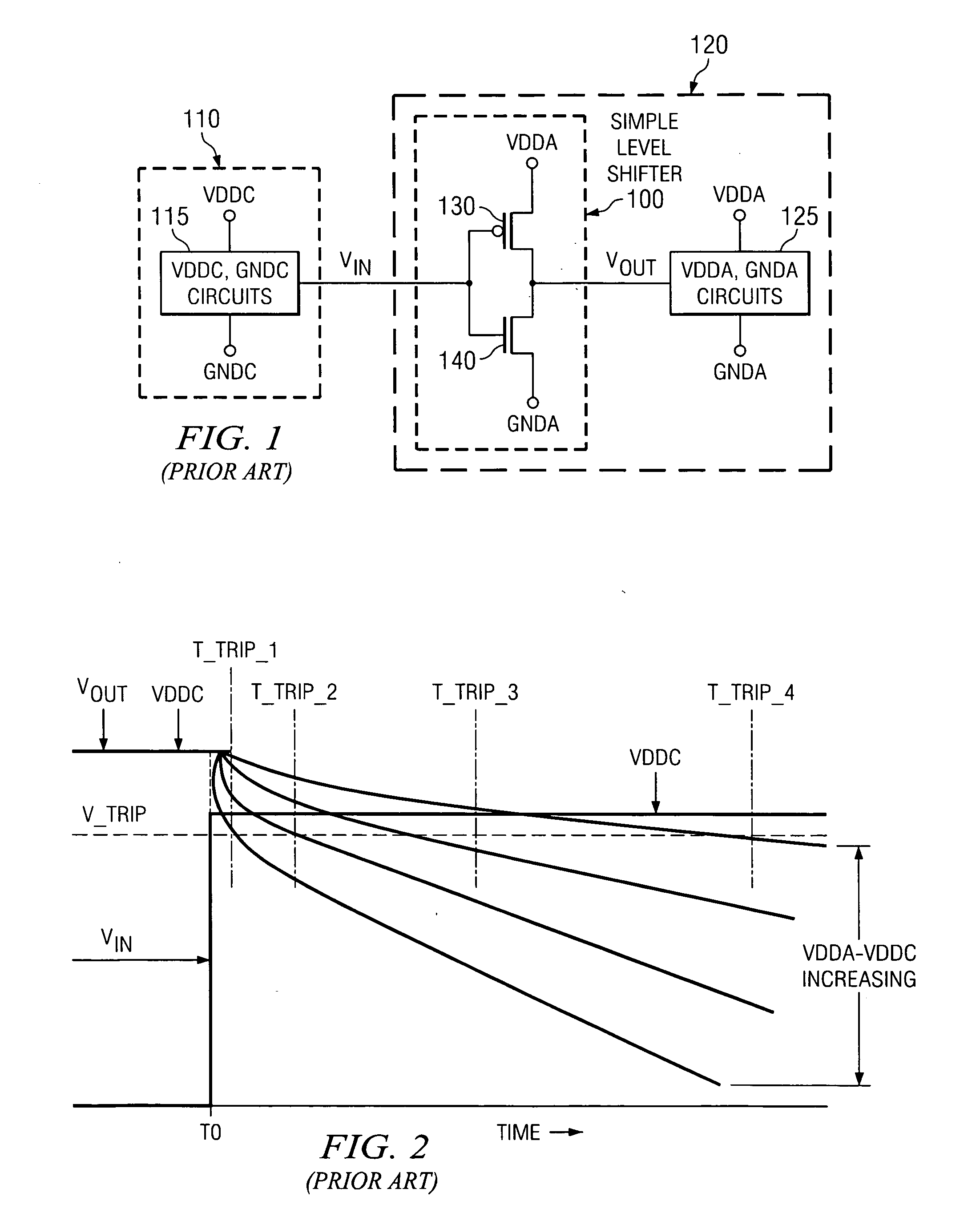

ActiveUS20090002027A1Increasing supply voltage marginReduce distortionPulse automatic controlElectric pulse generatorLevel shiftingDuty cycle distortion

A level shifter includes an inverting circuit, a cross-coupled level shifting latch, and a SR logic gate latch. The first and second outputs of the level shifting latch are coupled to the set (S) and reset (R) inputs of the SR latch. The inverting circuit, that is powered by a first supply voltage VDDL, supplies a noninverted version of an input signal onto a first input of the level shifting latch and supplies an inverted version of the input signal onto a second input of the level shifting latch. A low-to-high transition of the input signal resets the SR latch, whereas a high-to-low transition sets the SR latch. Duty cycle distortion skew of the level shifter is less than fifty picoseconds over voltage, process and temperature corners, and the level shifter has a supply voltage margin of more than one quarter of a nominal value of VDDL.

Owner:QUALCOMM INC

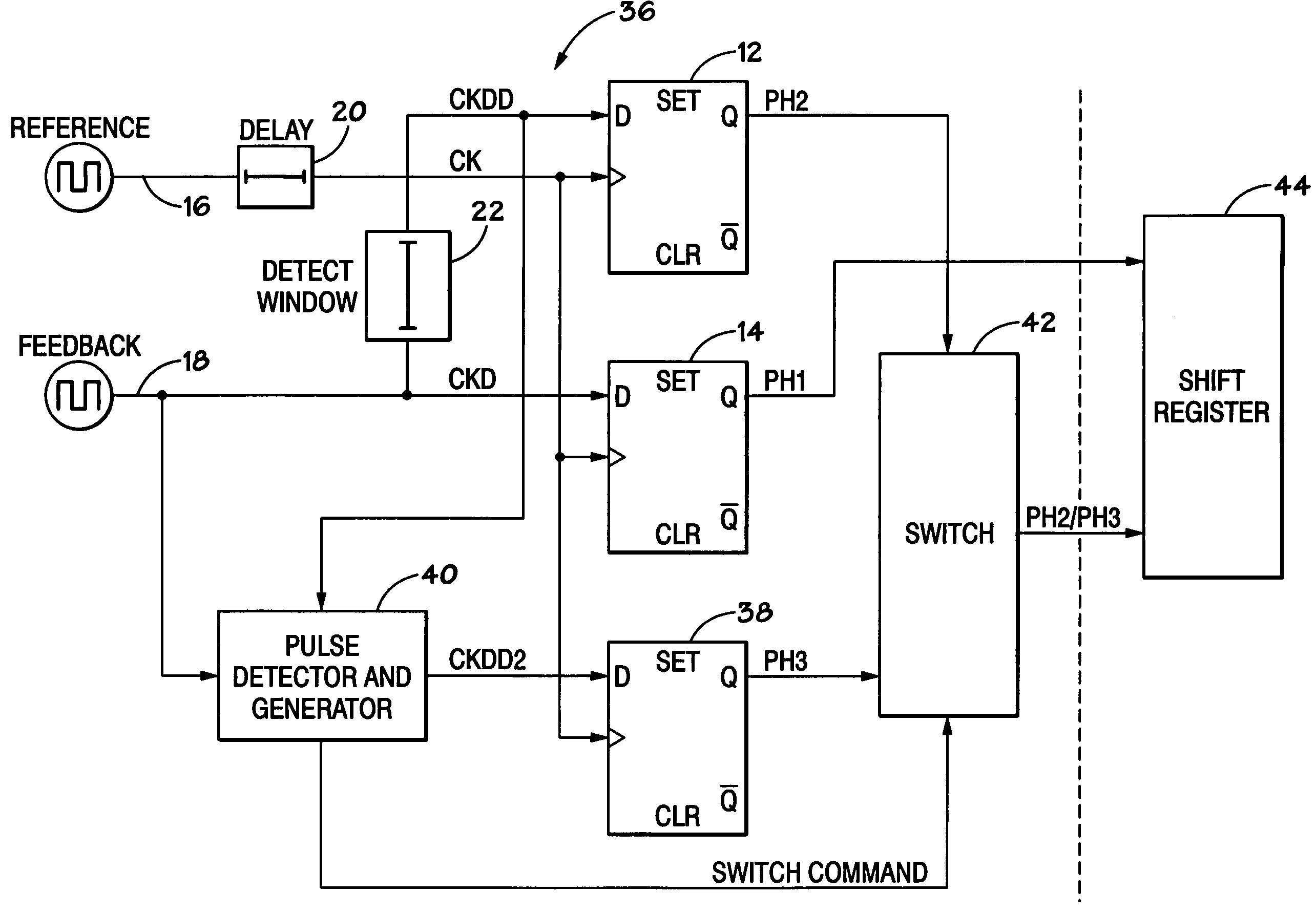

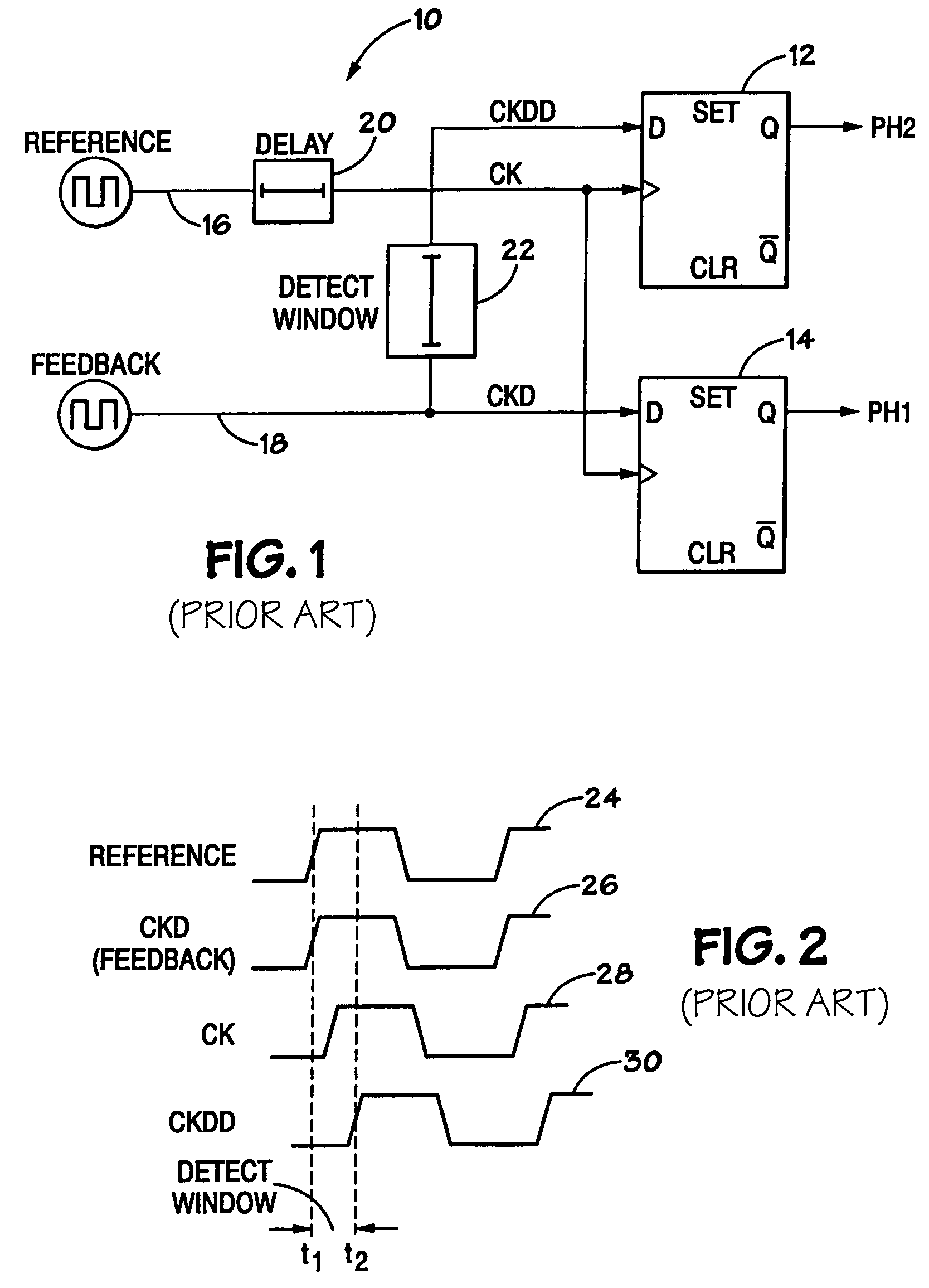

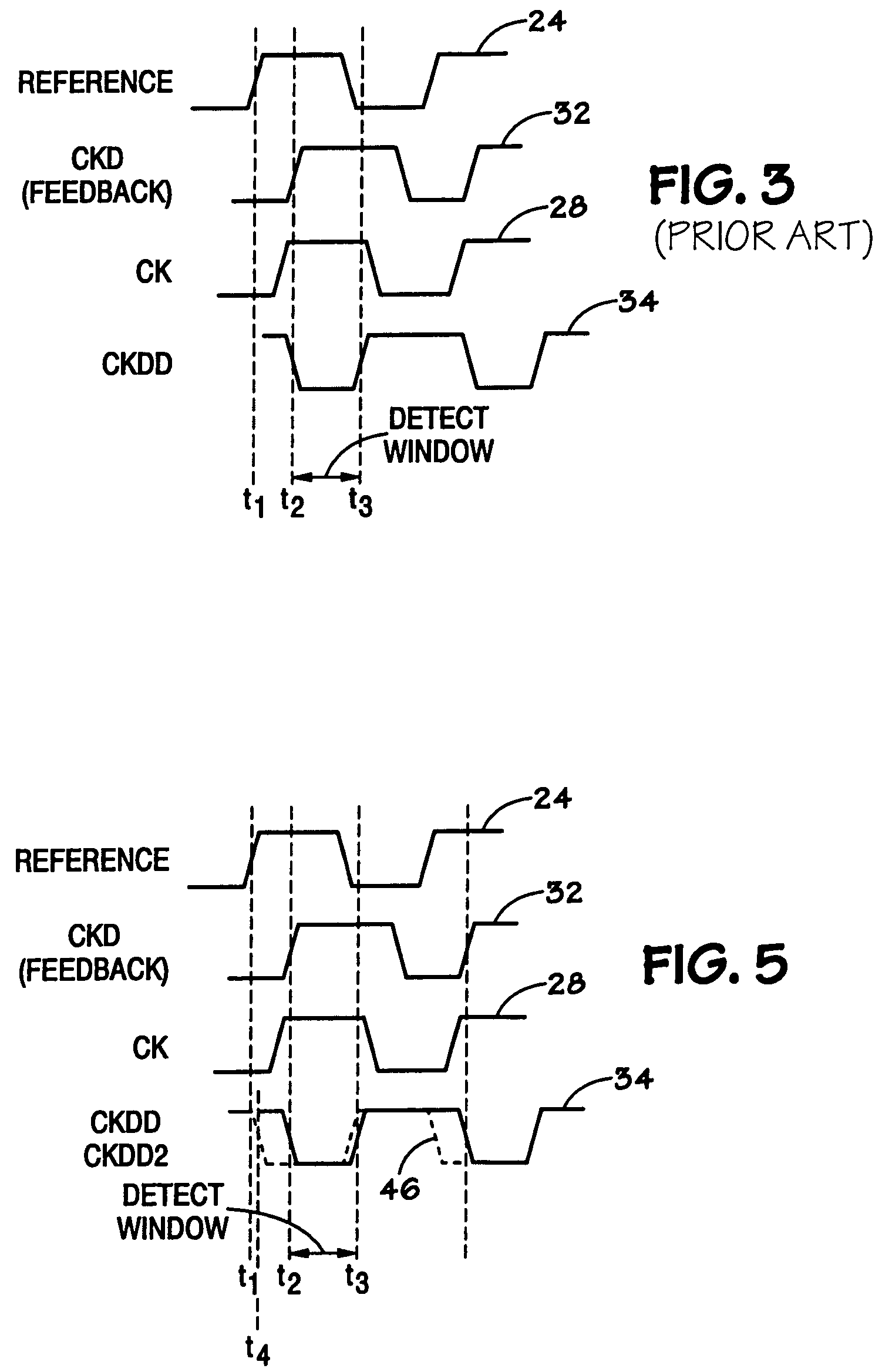

Skew tolerant high-speed digital phase detector

ActiveUS7161391B2Avoid mistakesVoltage-current phase angleOscillations comparator circuitsPhase detectorDuty cycle distortion

A skew-tolerant digital phase detector is provided. Specifically, a detector is provided in the digital phase detector to detect certain failure conditions that may result from clock skew and duty cycle distortion. If the condition is detected, an adjusted signal is generated and the adjusted signal is synchronized with the reference signal. By using the generated signal to provide a lock if certain conditions arise, adjustment errors resulting from duty cycle distortion and clock skew can be minimized.

Owner:MICRON TECH INC

Programmable duty cycle distortion generation circuit

ActiveUS8179952B2Avoid the needConvenient ArrangementElectrical testingTransmission monitoringDuty cycle distortionTransmitter

An integrated circuit is provided comprising: a serial transmitter, a serial receiver and a serial connection providing communication between the serial transmitter and the serial receiver. The integrated circuit further comprises a duty cycle distortion circuit so that the integrated circuit can be stress tested by distorting the duty cycle of a signal within the integrated circuit.

Owner:INTEGRATED DEVICE TECH INC

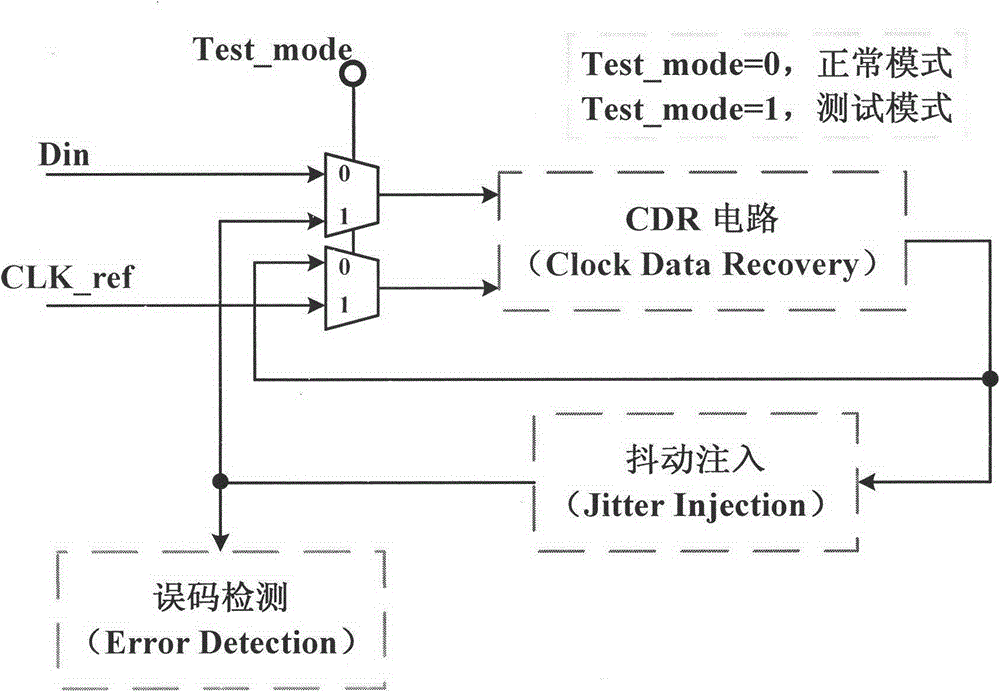

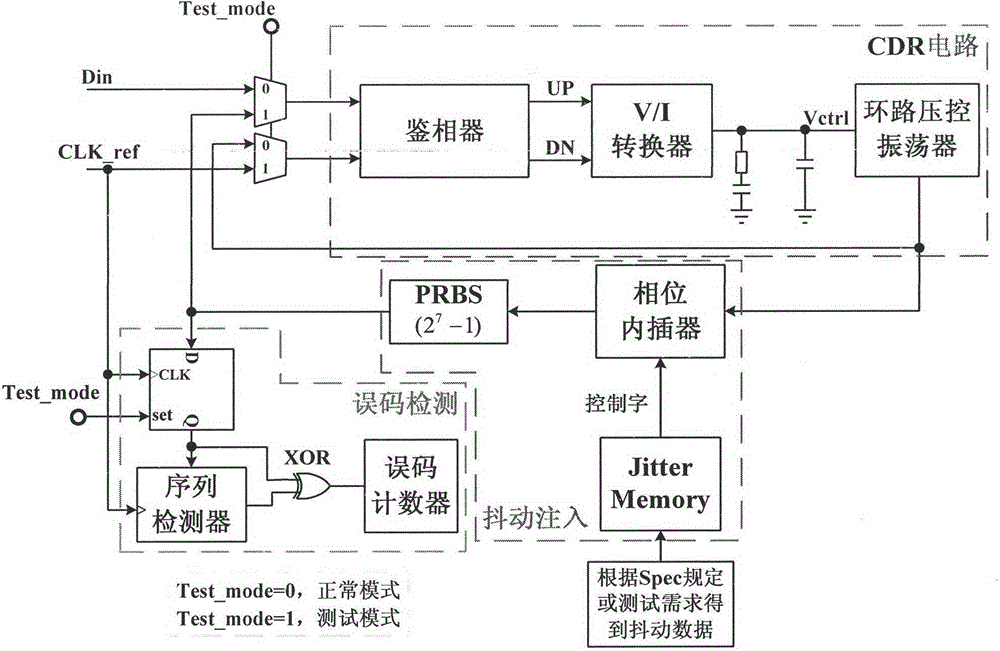

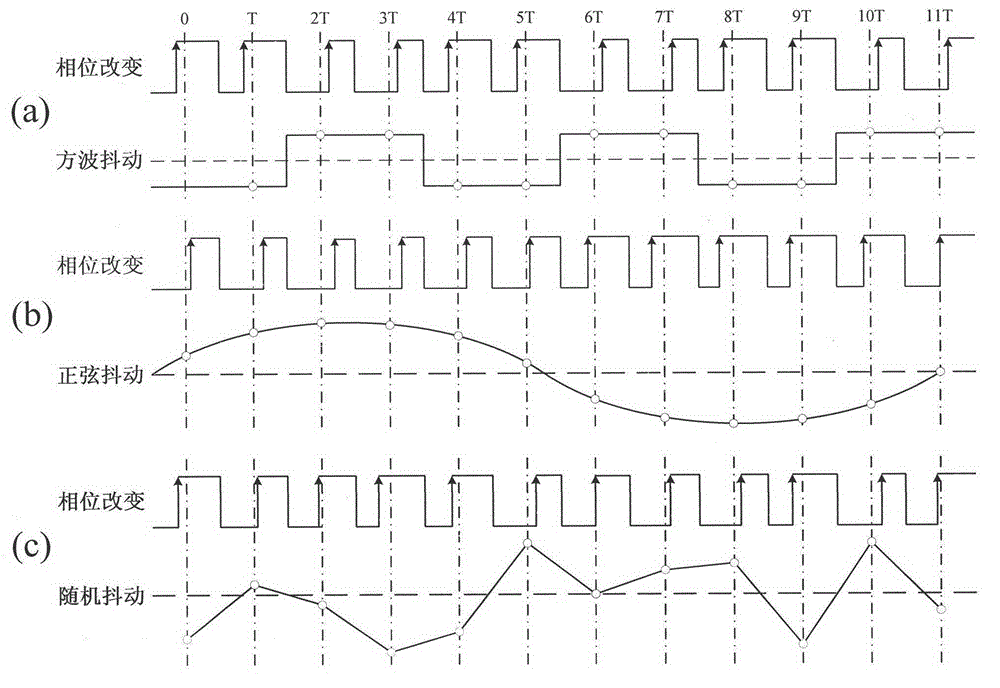

Jitter tolerance testing method and circuit for high-speed serial IO interface based on BIST

InactiveCN104954044AReduce dependenceImprove accuracyLine-transmission monitoring/testingDuty cycle distortionTest sequence

The invention discloses a jitter tolerance testing method and circuit for a high-speed serial IO interface based on BIST (built-in self-test). The circuit mainly consists of a CDR circuit module, a jitter injection module, and an error code detection module. A CDR circuit at the receiving end of the high-speed serial IO interface is additionally provided with the jitter injection module and the error code detection module, and can achieve the self-testing of the jitter tolerance of the receiving end. The jitter injection module comprises a Jitter Memory, a PI (phase interpolator) and a PRBS (pseudorandom binary sequence) circuit, and is used for generating a test sequence containing jitter information. The error code detection module comprises a sequence detector (PRBS Checker), an XOR gate and an error code counter (Error Detection), and is used for detecting an error code and obtaining the number of error codes. The method and circuit achieve the self-testing of the jitter tolerance of the receiving end, and can achieve the different types of jitter injection, such as RJ (random jitter), PJ (periodic jitter), and DCD (duty cycle distortion). The BIST circuit is simple in implementation, effectively shortens the testing time, reduces the testing cost, can be used for various types of high-speed serial IO interface circuits, and is higher in practicality.

Owner:PEKING UNIV

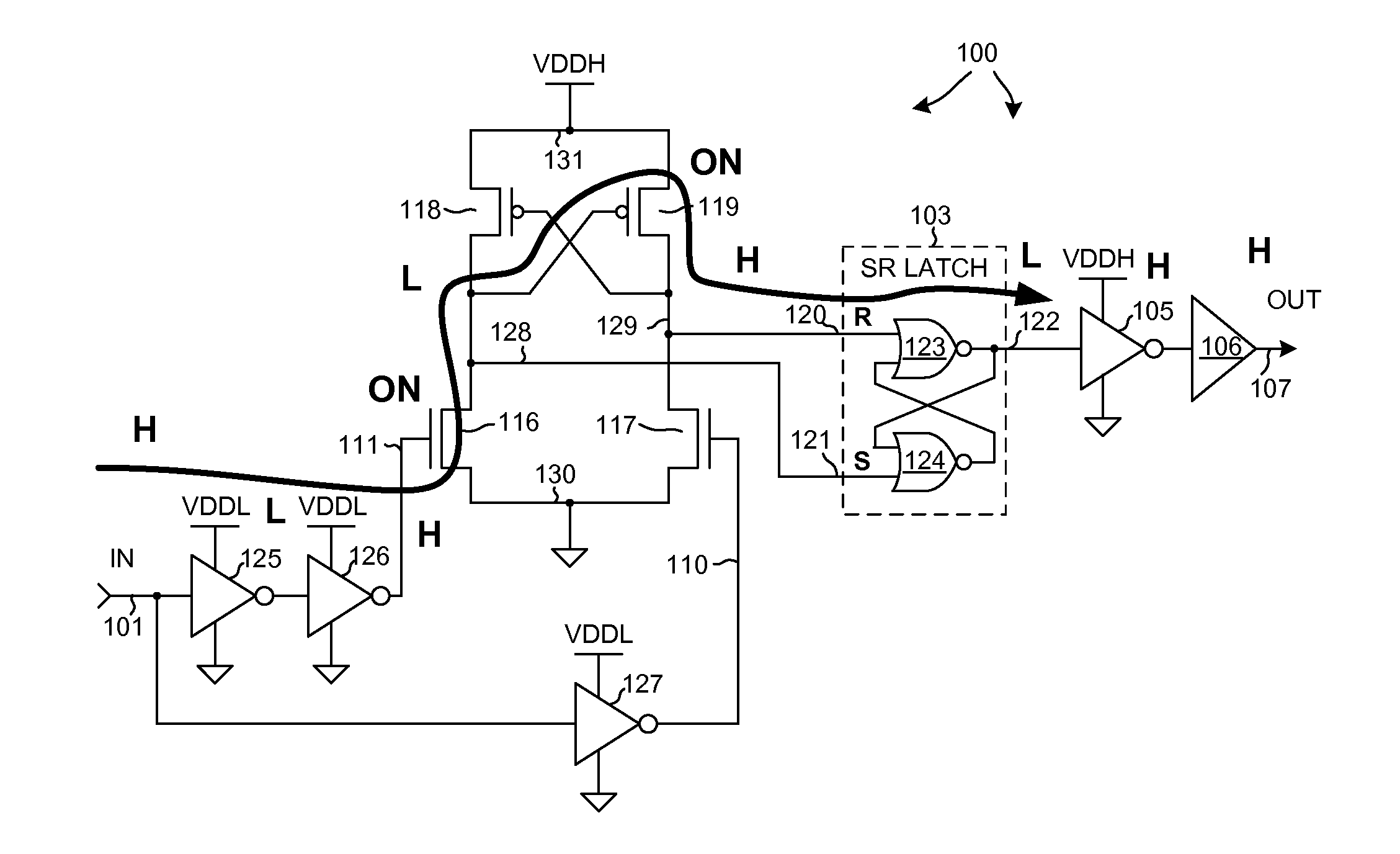

Level shifter having low duty cycle distortion

A level shifter (100) includes an inverting circuit (104), a cross-coupled level shifting latch (102), and a SR logic gate latch (103). The first and second outputs of the level shifting latch are coupled to the set (S) and reset (R) inputs of the SR latch. The inverting circuit, that is powered by a first supply voltage VDDL, supplies a noninverted version of an input signal (IND) onto a first input of the level shifting latch (112) and supplies an inverted version of the input signal (INB) onto a second input of the level shifting latch (113). A low-to-high transition of the input signal resets the SR latch, whereas a high-to-low transition sets the SR latch. Duty cycle distortion skew of the level shifter is less than fifty picoseconds over voltage, process and temperature corners, andthe level shifter has a supply voltage margin of more than one quarter of a nominal value of VDDL.

Owner:QUALCOMM INC

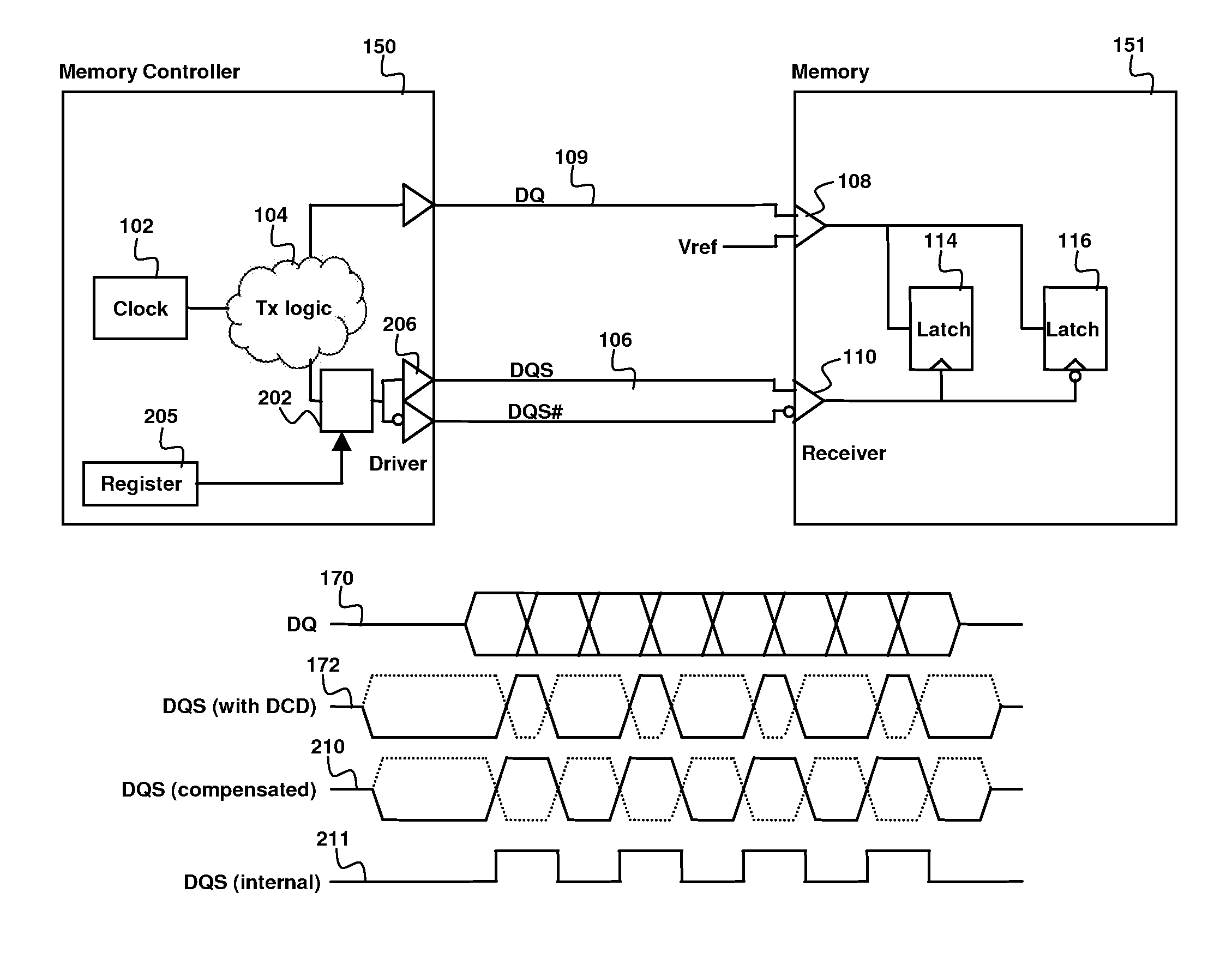

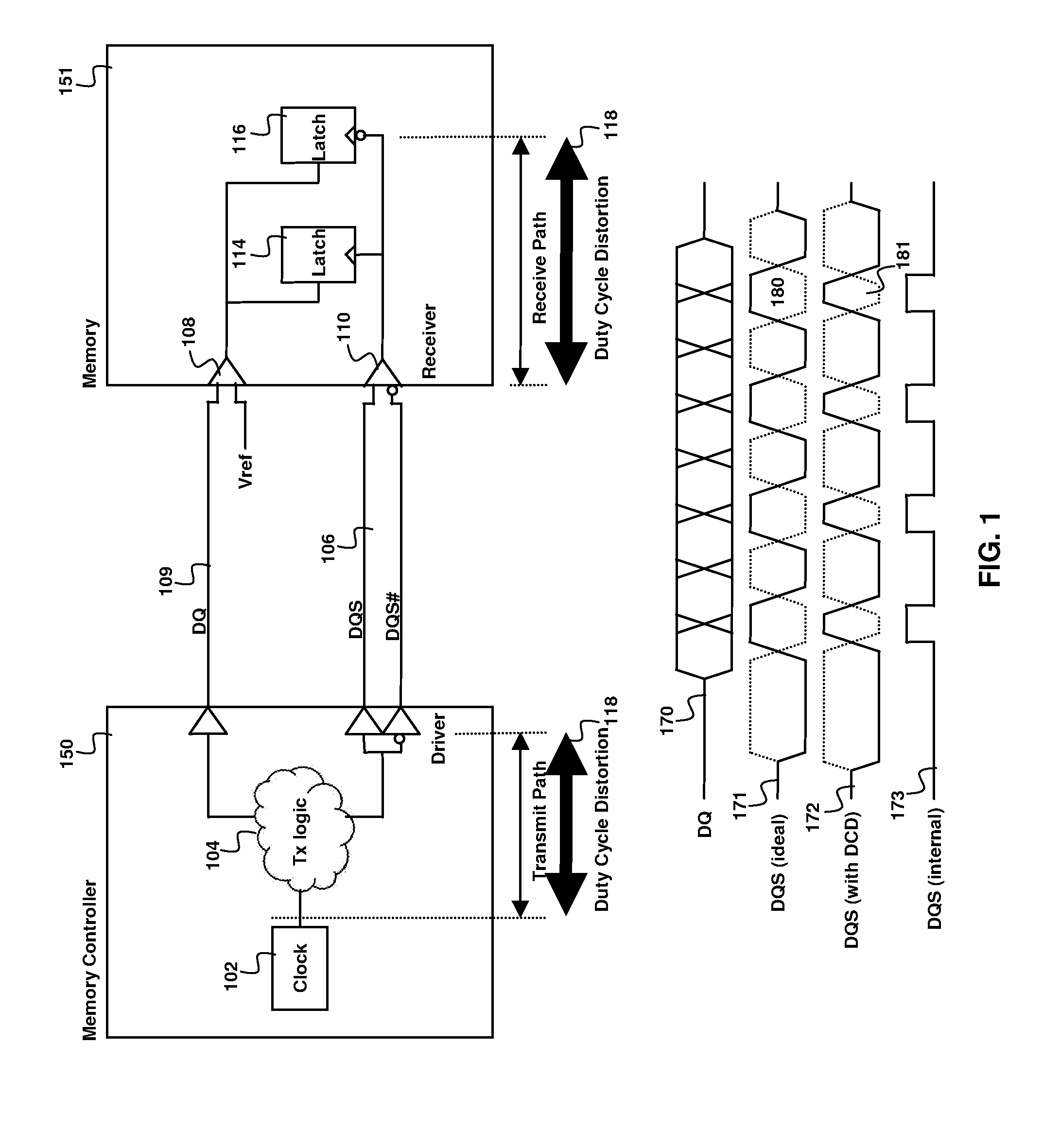

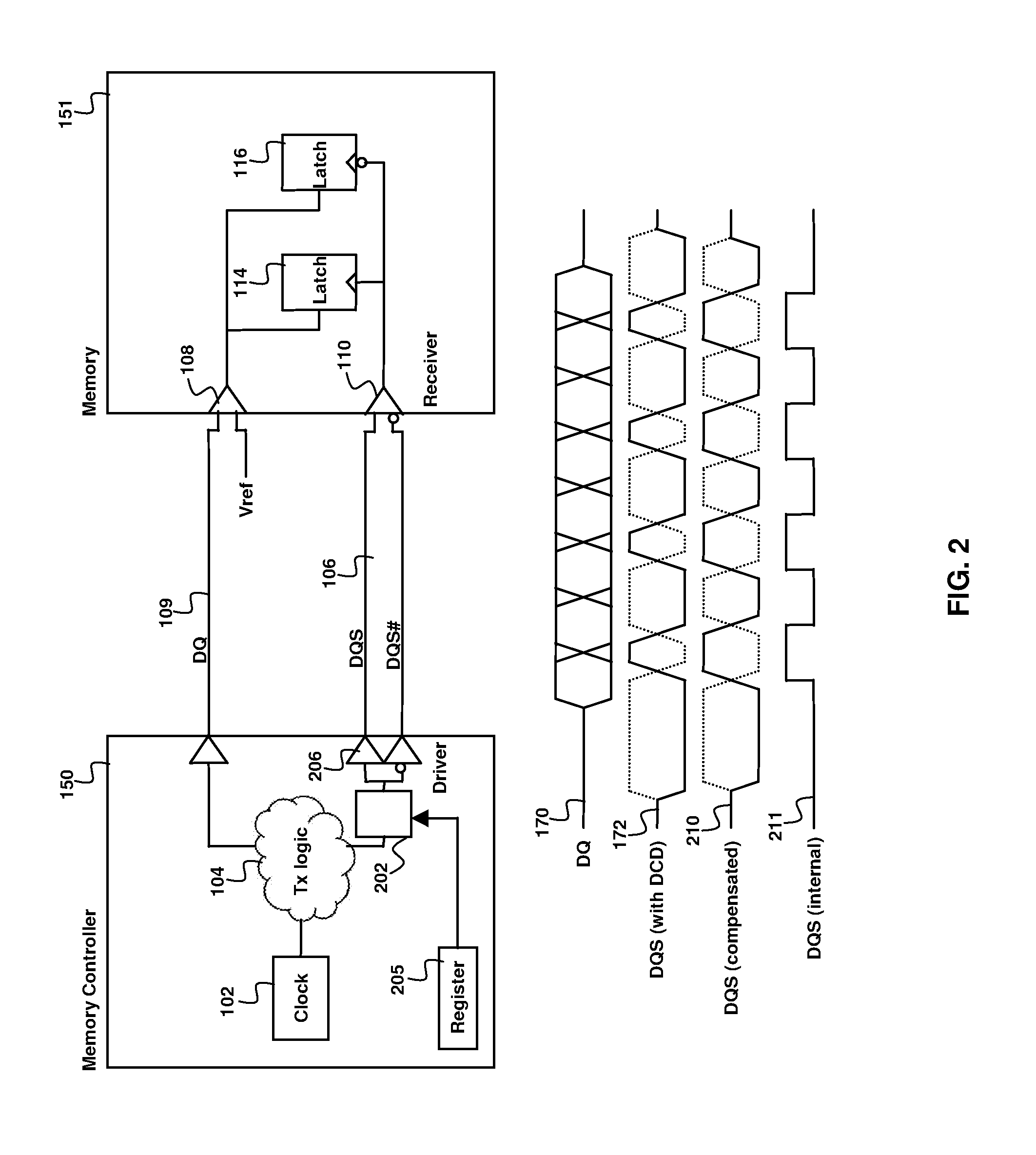

Duty cycle distortion correction

InactiveUS20120257466A1Digital storageElectric pulse generatorDuty cycle distortionMemory controller

Correction of duty cycle distortion of DQ and DQS signals between a memory controller and a memory is corrected by determining a duty cycle correction factor. The duty cycle distortion is corrected by applying the duty cycle correction factor to the plurality of differential DQS signals. The duty cycle distortion is corrected across a plurality of differential DQS signals between the memory controller and the bursting memory.

Owner:IBM CORP

System and method for automatically correcting duty cycle distortion

In accordance with the teachings described herein, systems and methods are provided for automatically correcting duty cycle distortion. A slicer may be used to receive a data input signal and compare the data input signal with a slicer offset voltage to generate a sliced data signal. The slicer may also receive an offset control signal to automatically adjust the slicer offset voltage. A phase detector may be used to receive the sliced data signal and a recovered clock signal and to compare the sliced data signal with the recovered clock signal to generate a rising edge output signal and a falling edge output signal. The rising edge output signal may correspond to a phase difference between a rising edge of the sliced data signal and an edge of the recovered clock signal. The falling edge output signal may correspond to a phase difference between a falling edge of the sliced data signal and an edge of the recovered clock signal. A first feedback circuit may be used to phase-lock the recovered clock signal to the sliced data signal utilizing at least one of the rising edge output signal and the falling edge output signal. At least one of the rising edge output signal and the falling edge output signal may be configured in a second feedback circuit to generate the offset control signal.

Owner:SEMTECH CANADA

Circuitry and methods for programmably adjusting the duty cycles of serial data signals

InactiveUS20070024338A1Counting errorElectric pulse generatorPulse shapingNegative feedbackDuty cycle distortion

Programmable duty cycle adjustment circuitry may be provided to correct for duty cycle distortion in serial data transmission systems. Duty cycle adjustment may be performed prior to transmitting data signals across a transmission medium. Duty cycle adjustment may also be performed as it is received from the transmission medium. Programmable duty cycle adjustment circuitry may be configured to adjust the rising and falling edges of data signals. Programmable duty cycle adjustment circuitry may also be configured to adjust the common mode level of data signals. The amount of duty cycle adjustment may be determined by end-users or through negative feedback.

Owner:ALTERA CORP

Duty cycle distortion compensation for the data output of a memory device

InactiveUS20020133731A1Digital storageGenerating/distributing signalsPhase shiftedRandom access memory

A technique for compensating for duty cycle distortion in an output data signal generated by a synchronous dynamic random access memory device (SDRAM) is provided. The output latch of the SDRAM is driven by an output clock signal generated by a delay lock loop (DLL). The output clock signal is phase-shifted relative to a reference clock signal received by the DLL such that the data removed from the output latch is synchronous with the reference clock signal. Further the duty cycle of the output clock signal is adjusted in a phase inverse relationship to the duty cycle distortion introduced by the output latch. As a result, the output data signal has reduced duty cycle distortion.

Owner:MICRON TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com