Single-end-operated subthreshold storage unit circuit

A memory cell circuit, sub-threshold technology, applied in information storage, static memory, digital memory information and other directions, can solve the problem of difficult writing of memory cells, and achieve improved stability, improved anti-noise capability, and enhanced robustness. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

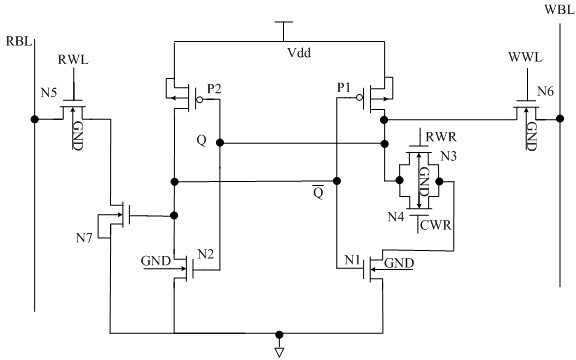

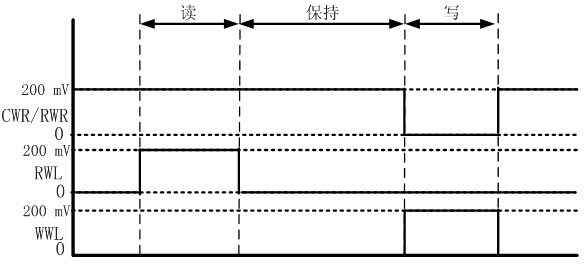

[0022] see figure 1 , The storage unit circuit of the present invention is provided with two PMOS transistors P1, P2 and seven NMOS transistors N1-N7. The body terminals of the two PMOS transistors are connected to the power supply voltage Vdd, and the body terminals of the seven NMOS transistors are grounded; the source of the PMOS transistor P1 is connected to Vdd, and the drain of the PMOS transistor P1 is connected to the drains of the NMOS transistors N3 and N4 Together, the sources of NMOS transistors N3 and N4 are connected together and then connected to the drain of NMOS transistor N1, the source of N1 is grounded, and the gates of PMOS transistor P1 and NMOS transistor N1 are connected together to NMOS transistor N2 and PMOS transistor The drain of P2 is connected, the gate of NMOS transistor N3 is connected with row write control signal RWR, the gate of NMOS transistor N4 is connected with column write control signal CWR; NMOS transistor N2 and PMOS transistor P2 for...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com