Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

237 results about "Asynchronous fifo" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

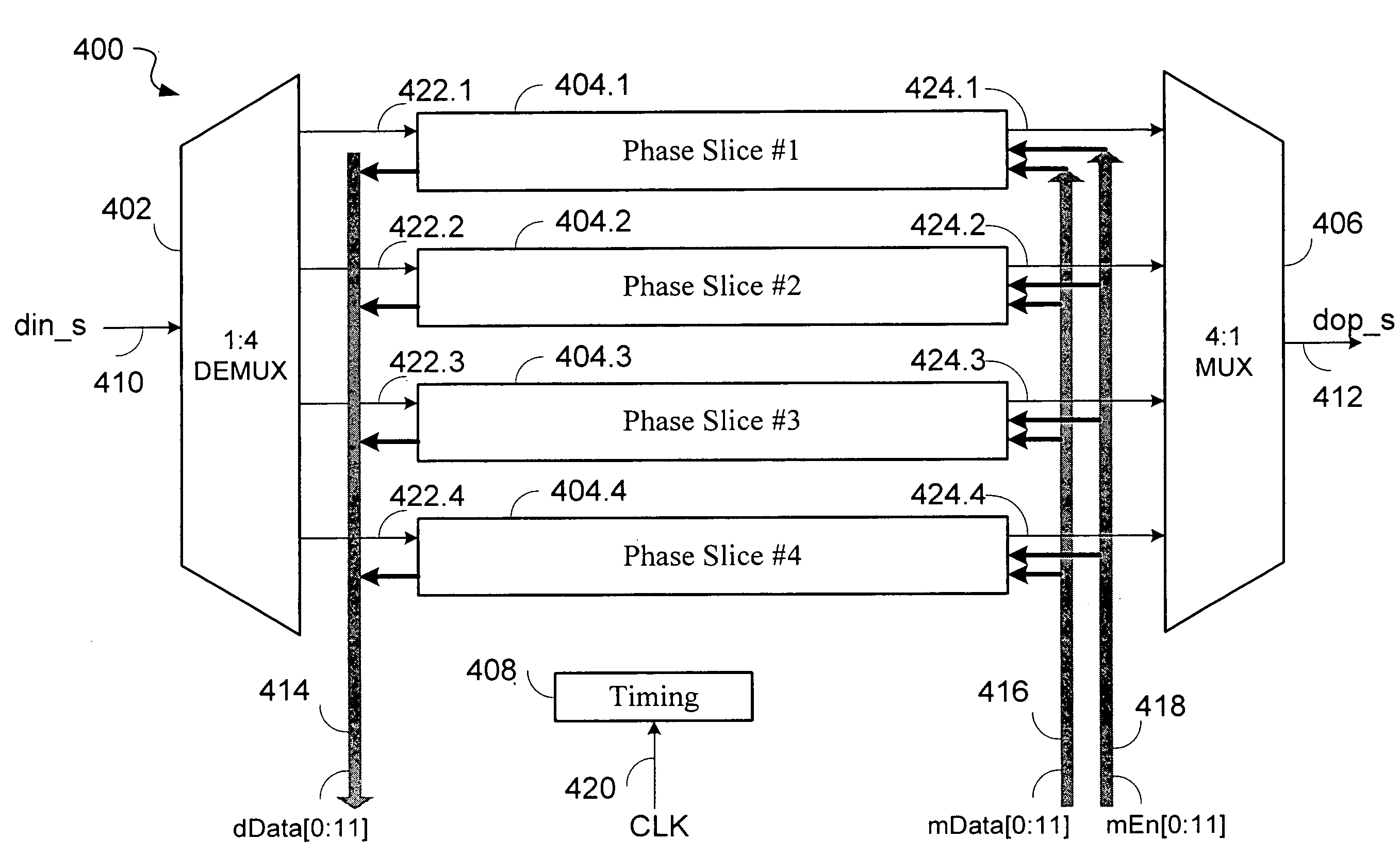

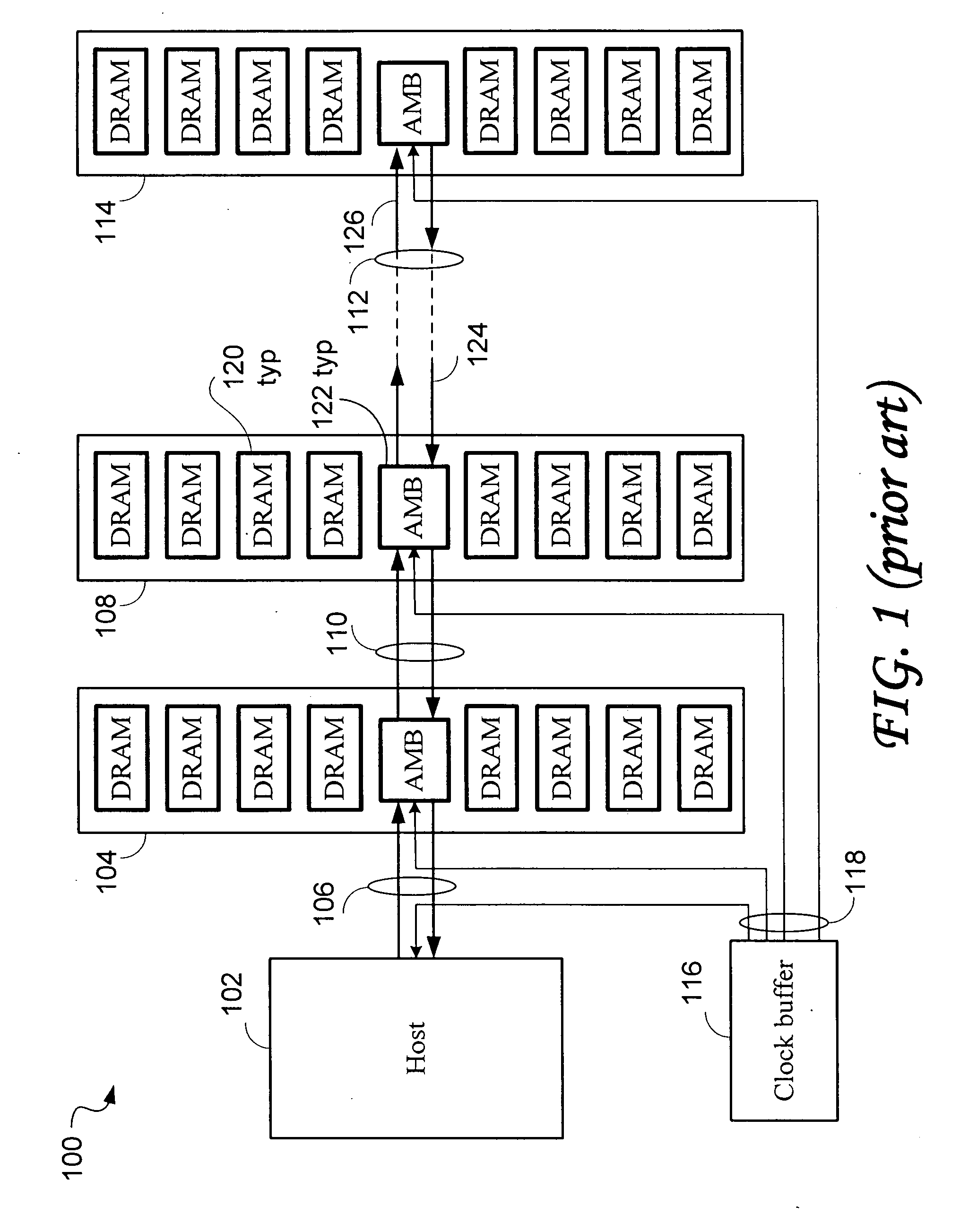

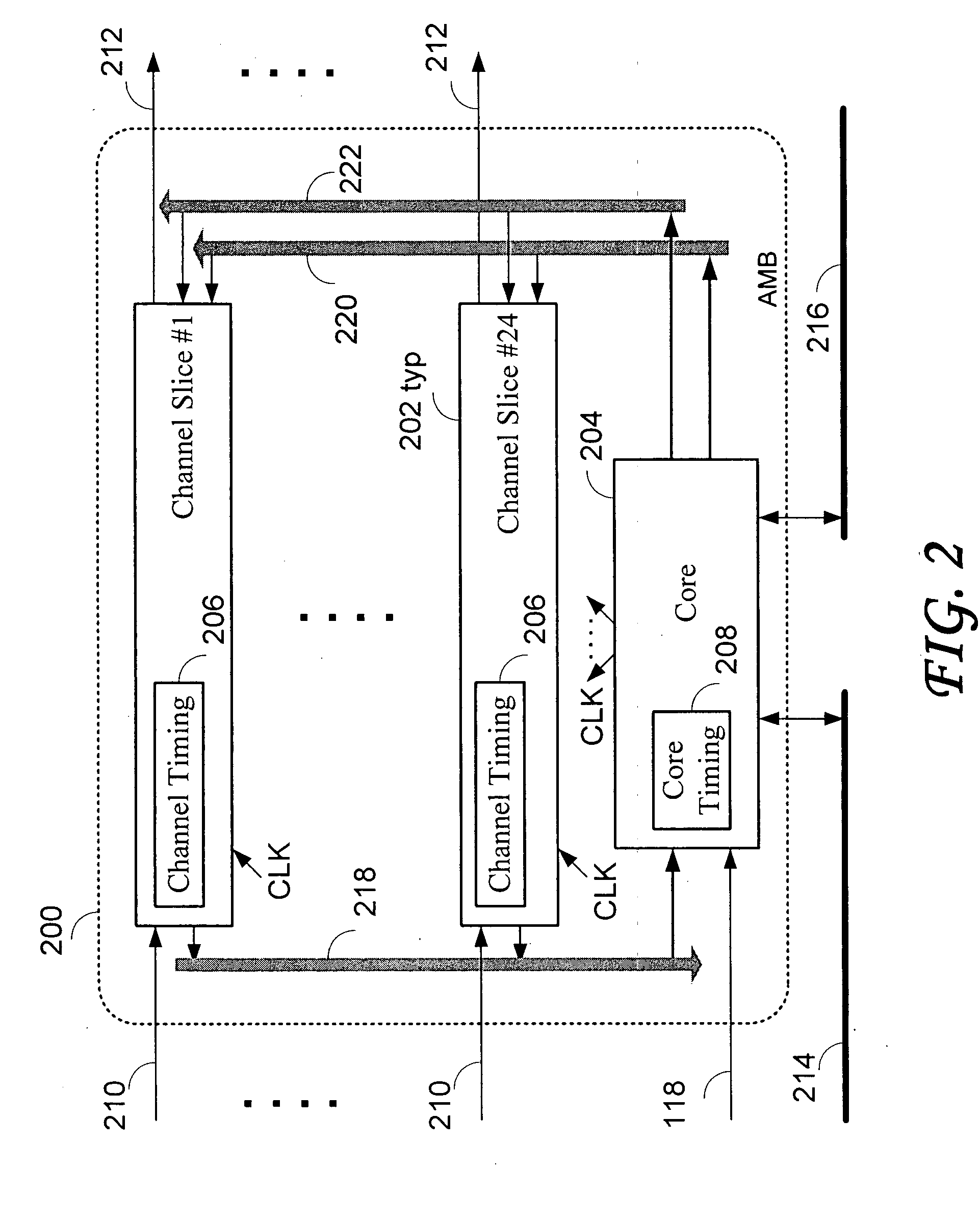

Programmable asynchronous first-in-first-out (FIFO) structure with merging capability

ActiveUS7796652B2Improve latencyReduce power consumptionTime-division multiplexSynchronising arrangementComputer hardwareLatency (engineering)

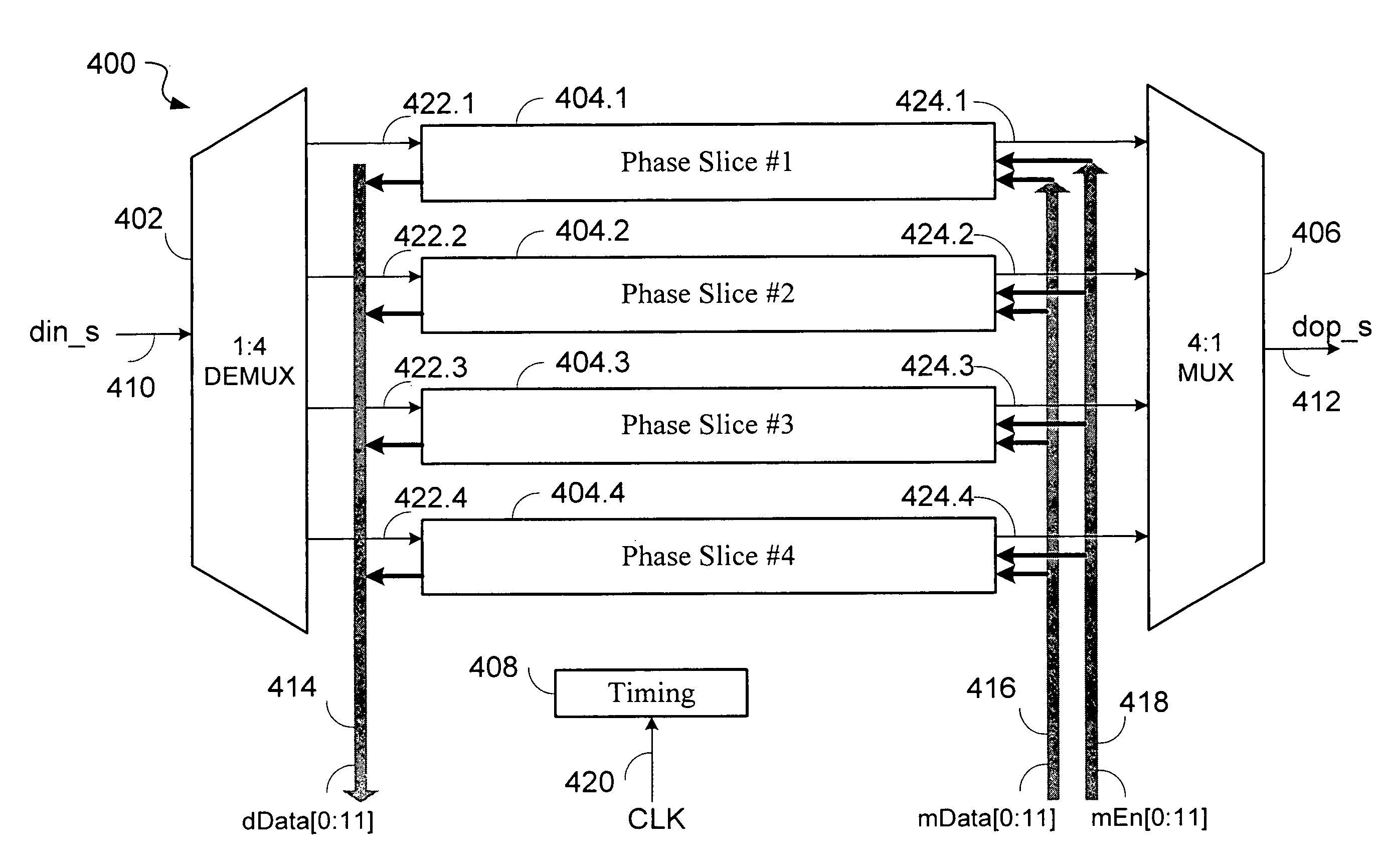

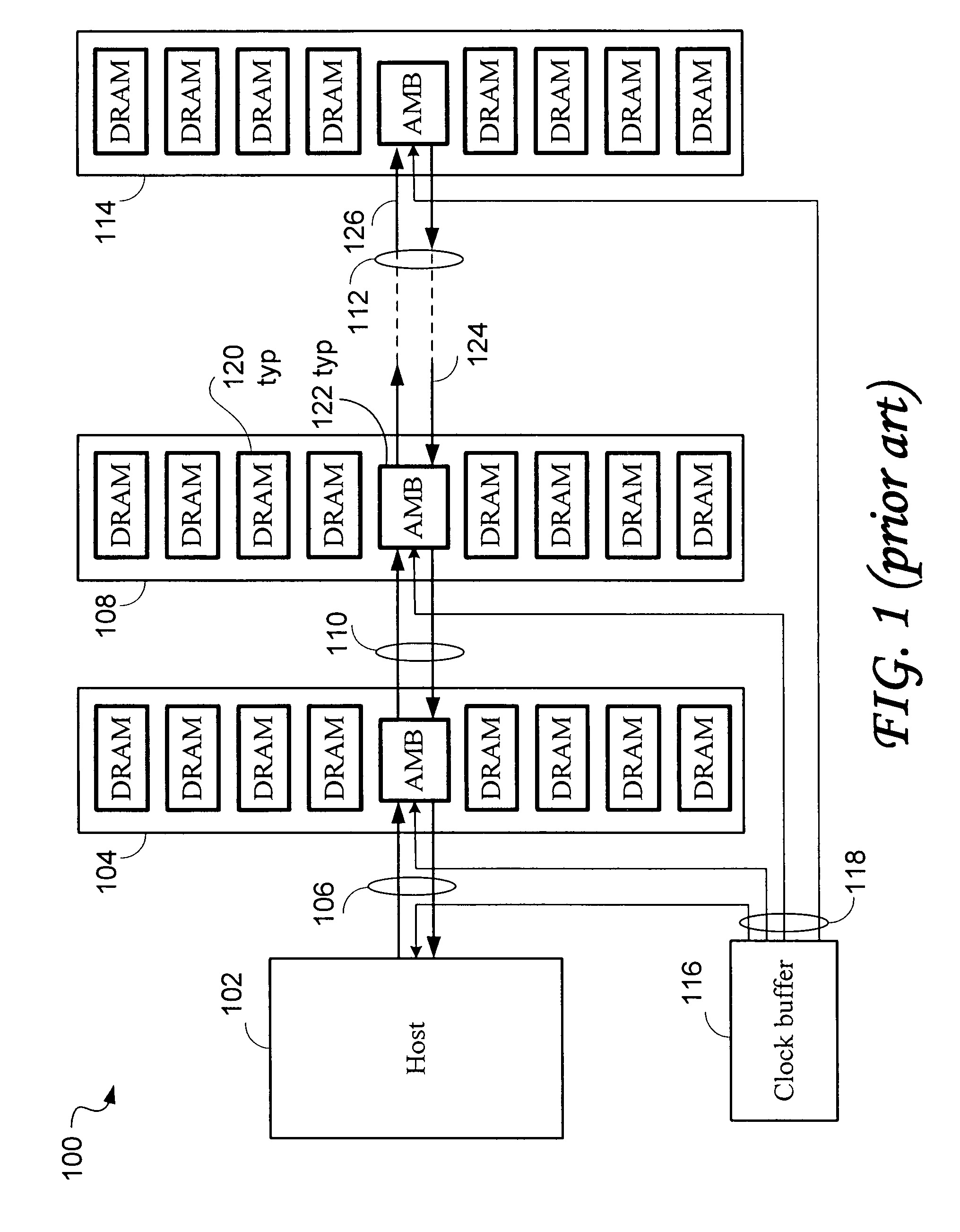

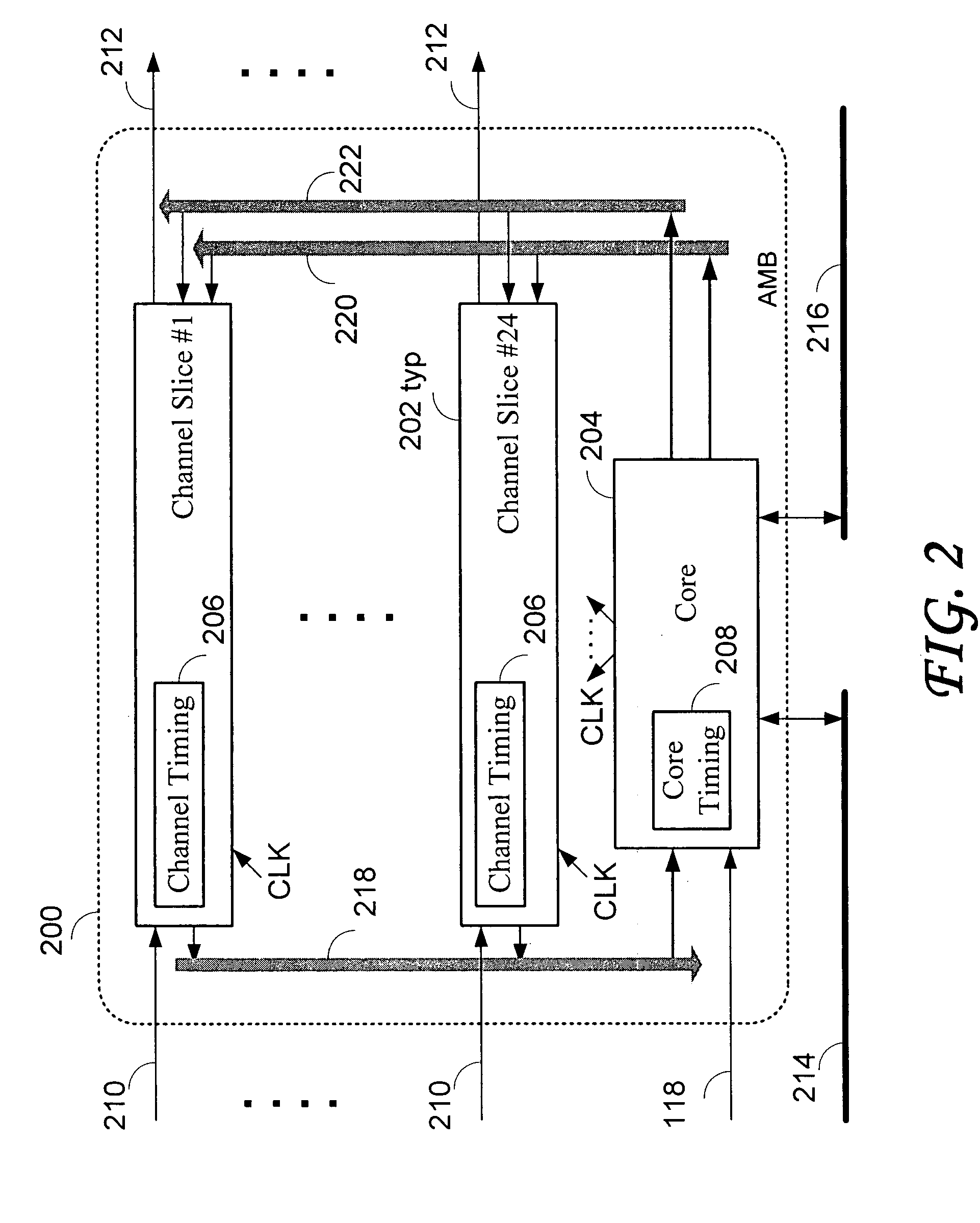

Where high speed communication between a host and memory devices is carried over serial bit lanes, memory buffers are required for converting buffering the serial bit lanes, and for converting between serial and parallel formats. In addition, jitter, wander, and skew between the bit lanes need to be accommodated. The invention discloses a programmable asynchronous FIFO with the integrated ability to convert blocks of bits from serial to parallel as well as inserting bits from a parallel bus into the serial bit stream. The invention provides very low latency and can be implemented in low power technologies.

Owner:RAMBUS INC

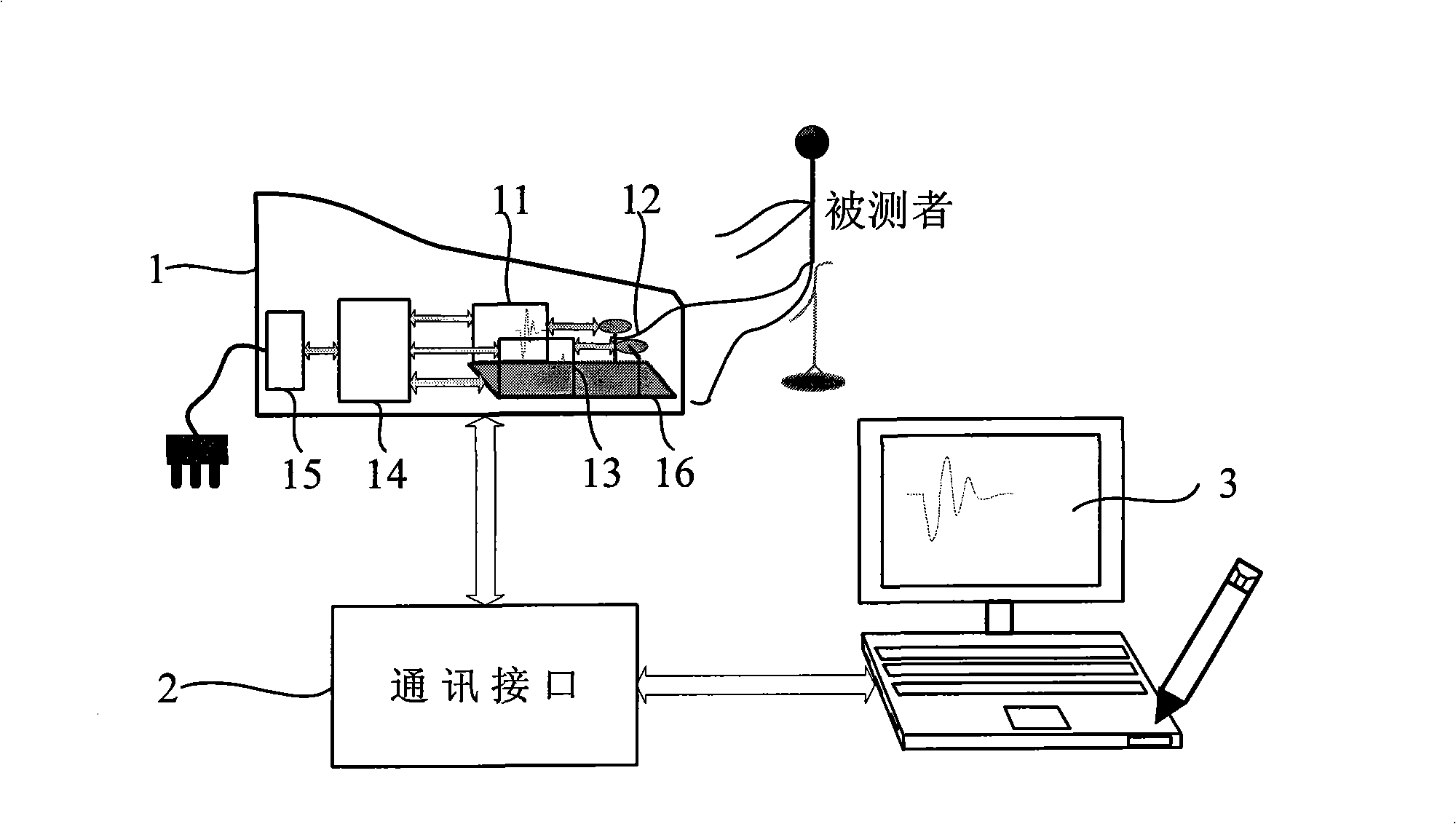

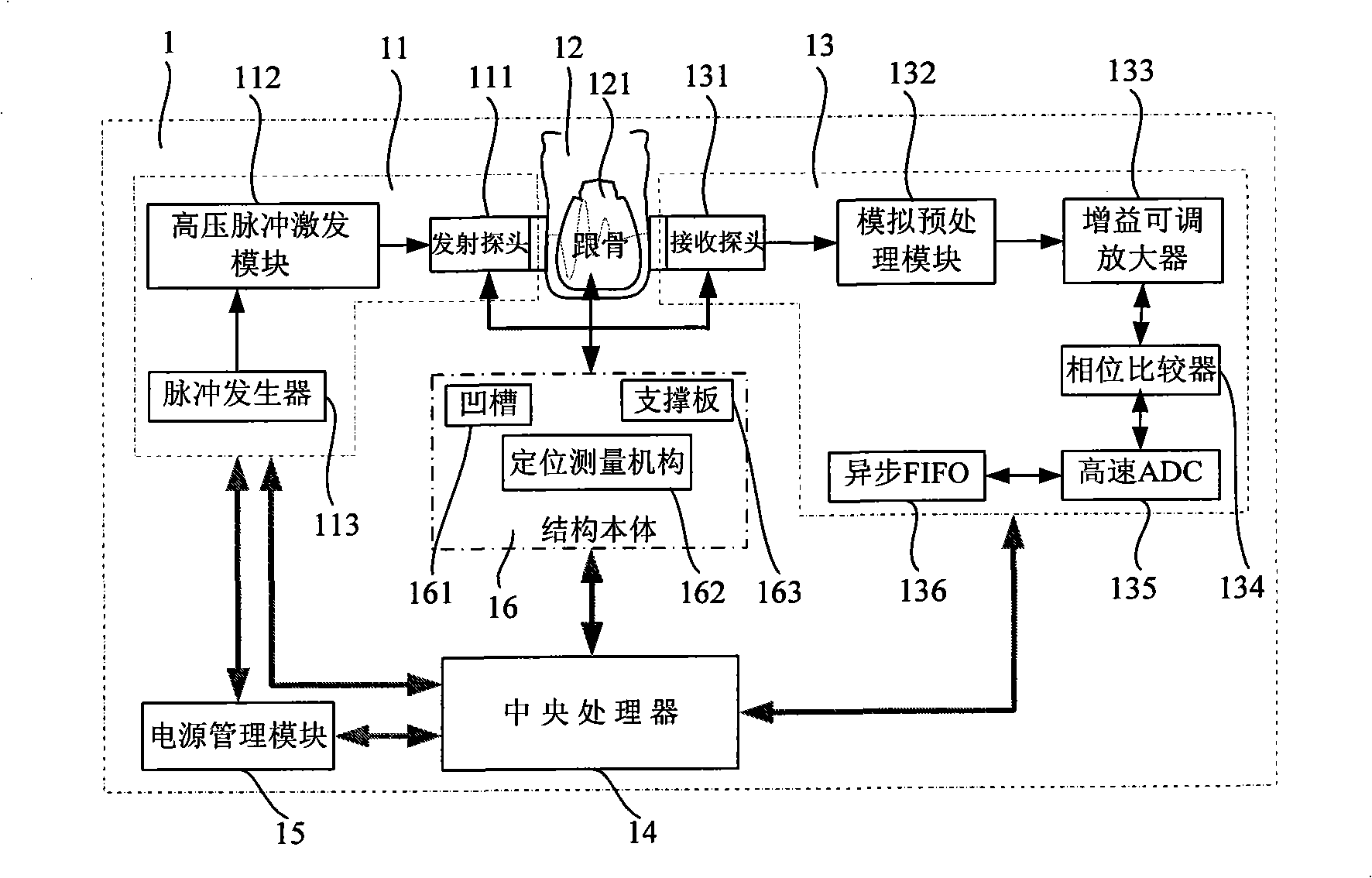

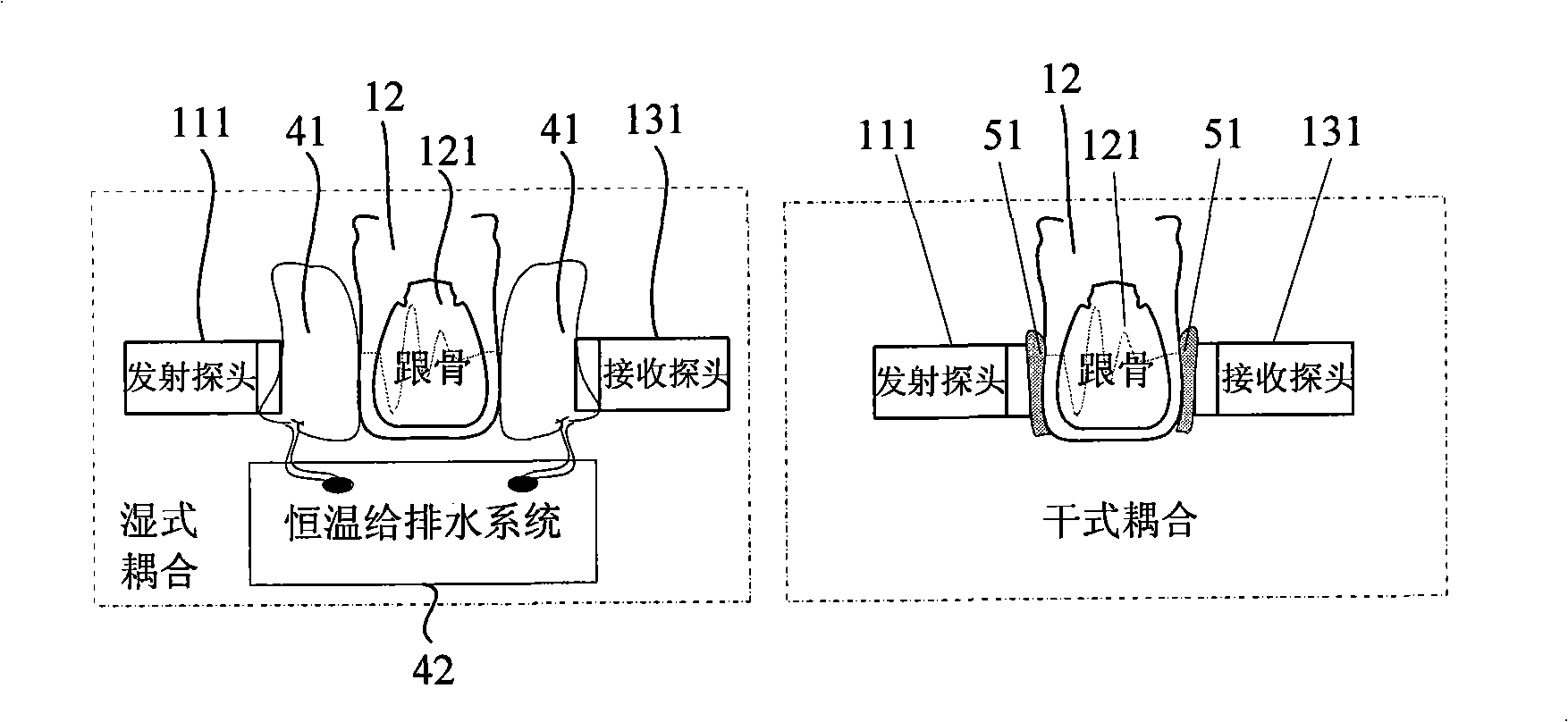

Ultrasonic measurement analytical system for compact bone substance density

ActiveCN101401732APromote disseminationHigh measurement accuracyOrgan movement/changes detectionUltrasonic/sonic/infrasonic dianostic techniquesBone densityHuman–machine interface

The invention discloses an ultrasound bone density measuring and analyzing system. The system comprises an ultrasound parameter measuring apparatus, a communication interface and a human machine interaction device, wherein the ultrasound parameter measuring apparatus comprises transmitting unit consisting of a pulse generator, a high-voltage pulse excitation module and a transmitting probe, an ultrasound receiving unit consisting of a receiving probe, a simulation pretreatment module, a gain adjustable amplifier, a phrase comparator, a high-speed ADC and an asynchronous FIFO, and a central processor, a power supply control module and a structural body. the human machine interaction device controls the ultrasound parameter measuring apparatus through the communication interface to measure the width of a calcaneus of a detected person, the transmission speed of an ultrasound wave in the calcaneus, broadband ultrasonic attenuation to calculate the bone intensity indexes and the bone density, so a medical report can be made according to diagnostic standards of osteoporosis and a special data base can be built for long term use. The system adopts wet or dry coupling and other technologies to improve the precision and accuracy of measure and has the advantages of easy carrying, low cost, no damage caused by radiation and can be use in long term monitoring of bone condition of the detected person.

Owner:HEFEI INSTITUTES OF PHYSICAL SCIENCE - CHINESE ACAD OF SCI

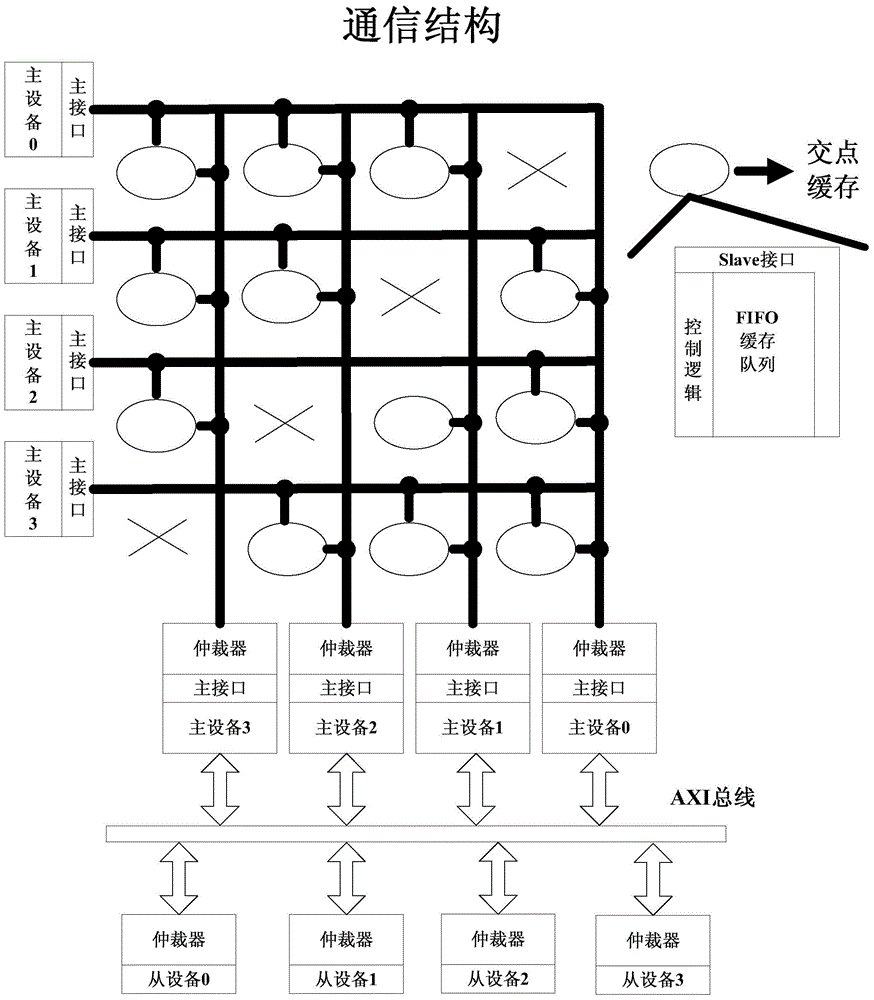

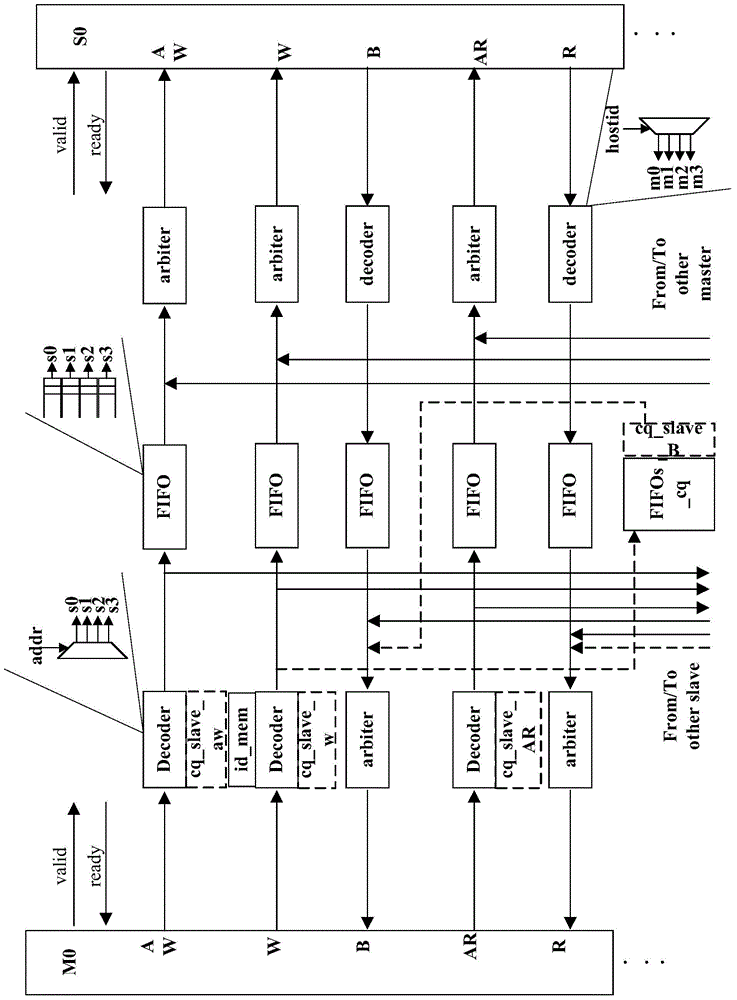

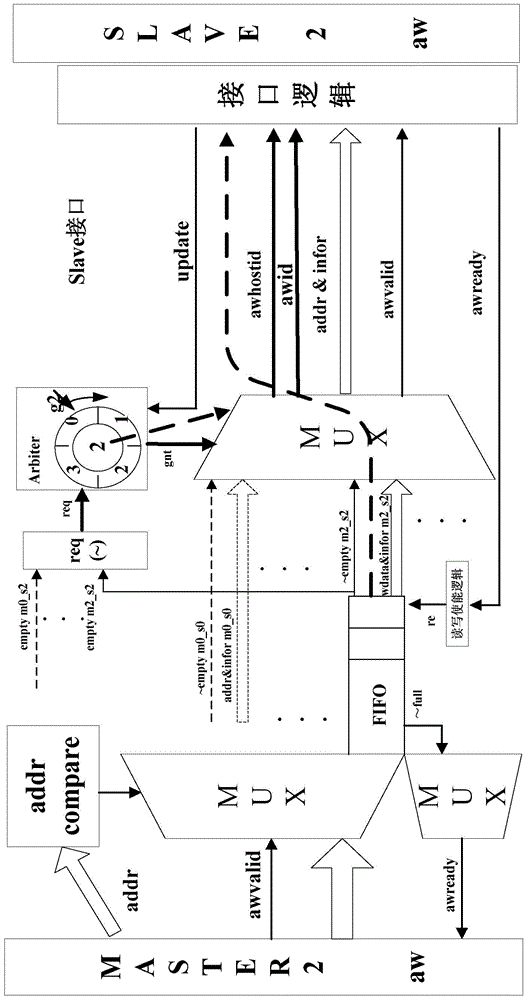

Asynchronous AXI bus structure with built-in cross point queue

ActiveCN105005546AReduce resource consumptionAchieving full parallelismElectric digital data processingComputer architectureResource consumption

The invention discloses an asynchronous AXI bus structure with a built-in cross point queue. The asynchronous AXI bus structure comprises an AXI bus structure and a cross point queue communication structure; the AXI bus structure comprises five channels, namely an address writing channel, a data writing channel, a writing return channel, an address reading channel and a data reading channel; the cross point queue communication structure satisfies an AXI bus protocol and is built in a communication structure for realizing inter-core communication; primary devices communicate by adopting the cross point queue communication structure; the address writing channel, the data writing channel and the writing return channel form a writing operation; and the address reading channel and the data reading channel form a reading operation. The structure can reduce resource consumption, realize parallel working of all primary devices and improve parallelism; due to the adoption of the cross point queue structure, the performance bottleneck, namely a handshake closed loop, of an on-chip communication network is broken through, and a low-delay communication function is realized; and the cross point queue is realized by adopting asynchronous FIFO, so that a mode of local synchronization and integral asynchronization is realized.

Owner:EAST CHINA INST OF OPTOELECTRONICS INTEGRATEDDEVICE

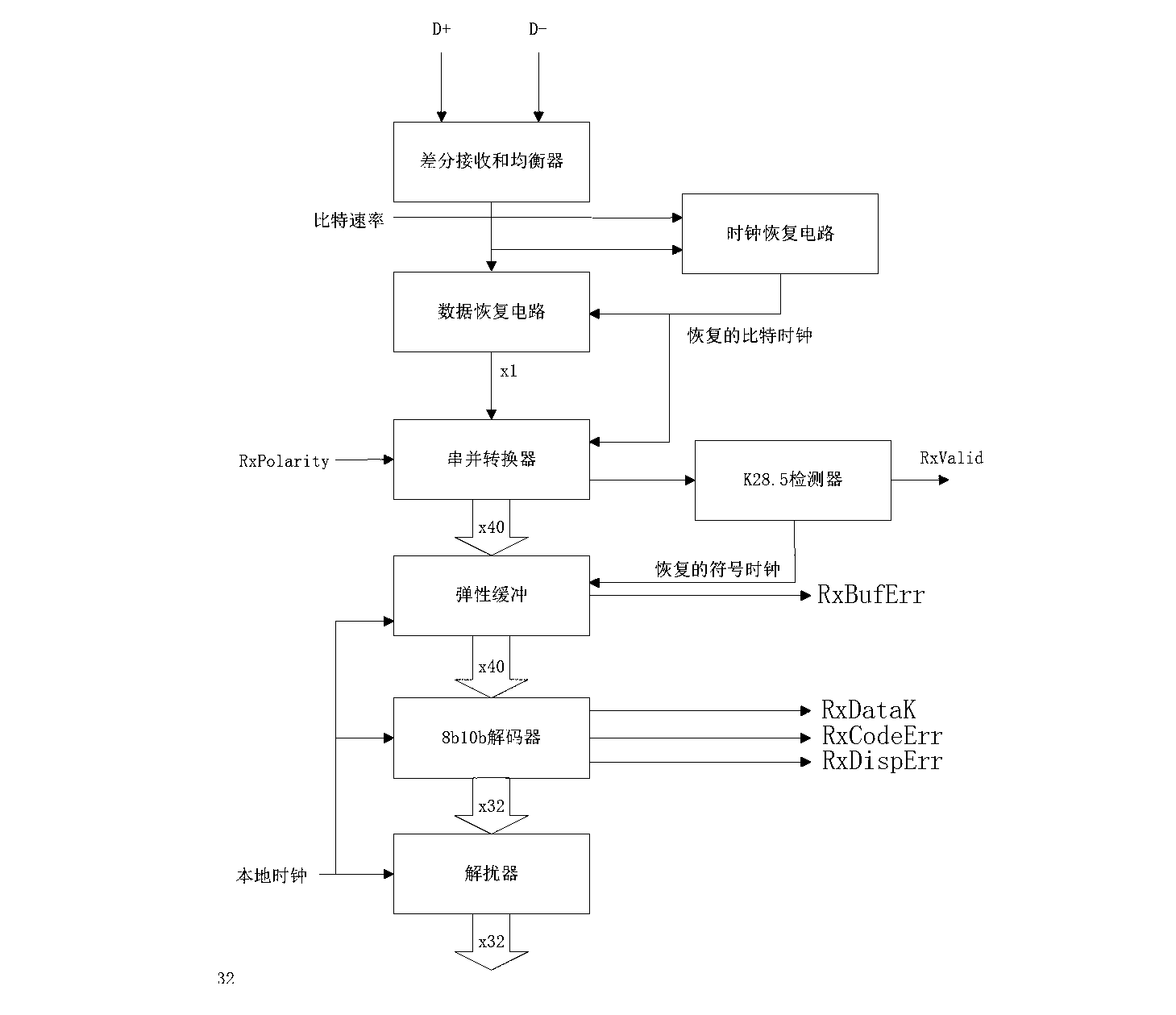

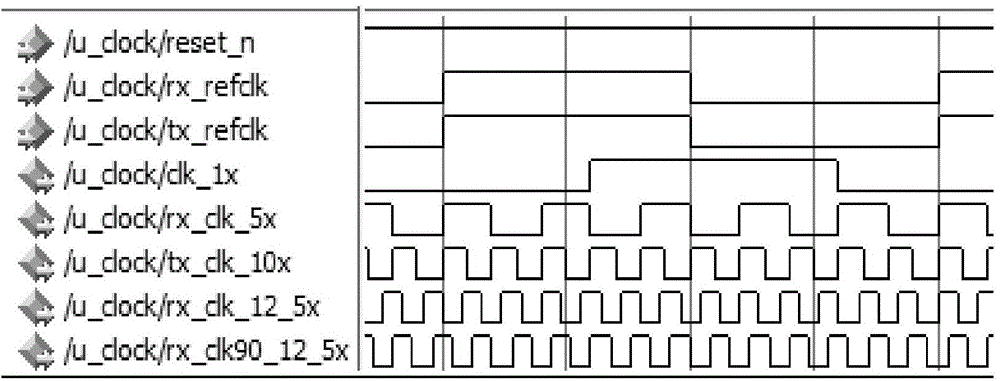

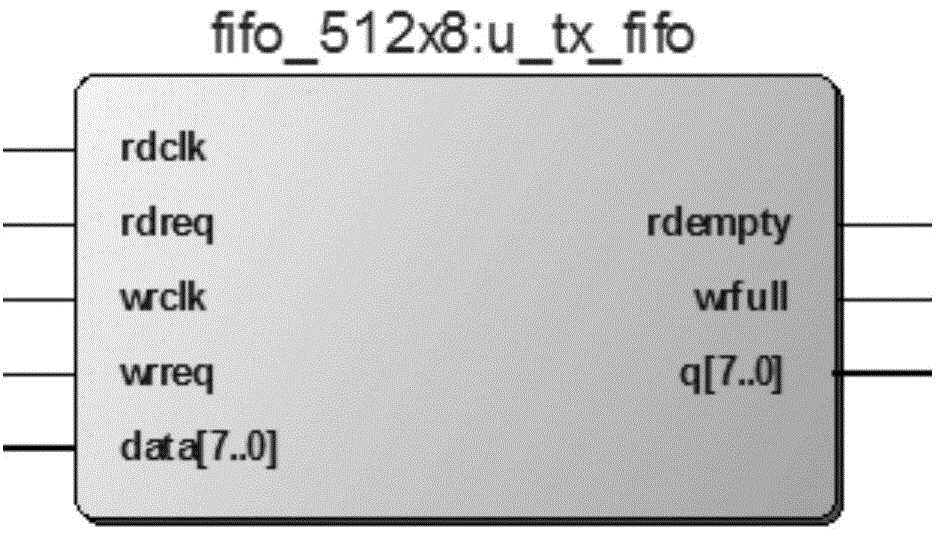

FPGA (Field Programmable Gate Array)-based micro-space oversampling direct-current balance serial deserializer

InactiveCN102340316AEasy to implementHigh cost of solutionParallel/series conversionPulse automatic controlDifferential signalingComputer module

The invention relates to an FPGA (Field Programmable Gate Array)-based micro-space oversampling direct-current balance serial deserializer, aiming to realize verification and design based on serial deserializer in an FPGA without built-in serial deserializer. The FPGA-based micro-space oversampling direct-current balance serial deserializer mainly comprises a clock data recovery (CDR) module, a 8B / 10B encoder, a 8B / 10B decoder an asynchronous FIFO (First In First Out) buffer module, a clock generation module, a parallel-to-serial conversion module, a serial-to-parallel conversion module, a framing module and a de-framing module. At a transmitting end, data are buffered by the asynchronous FIFO buffer module, input into the 8B / 10B encoder (by 8 bits in one frame) for encoding through the framing module, then processed by the parallel-to-serial conversion module and finally output in a differential manner. At a receiving end, a differential signal is accepted by a differential input module and input into the serial-to-parallel conversion module to be output, the output data are decoded by the 8B / 10B decoder, then input into the de-framing module, and finally output by the asynchronous FIFO buffer module in a buffer manner.

Owner:SHANGHAI UNIV

Programmable asynchronous first-in-first-out (FIFO) structure with merging capability

ActiveUS20070258491A1Improve latencyReduce power consumptionTime-division multiplexSynchronising arrangementComputer hardwareLatency (engineering)

Where high speed communication between a host and memory devices is carried over serial bit lanes, memory buffers are required for converting buffering the serial bit lanes, and for converting between serial and parallel formats. In addition, jitter, wander, and skew between the bit lanes need to be accommodated. The invention discloses a programmable asynchronous FIFO with the integrated ability to convert blocks of bits from serial to parallel as well as inserting bits from a parallel bus into the serial bit stream. The invention provides very low latency and can be implemented in low power technologies.

Owner:RAMBUS INC

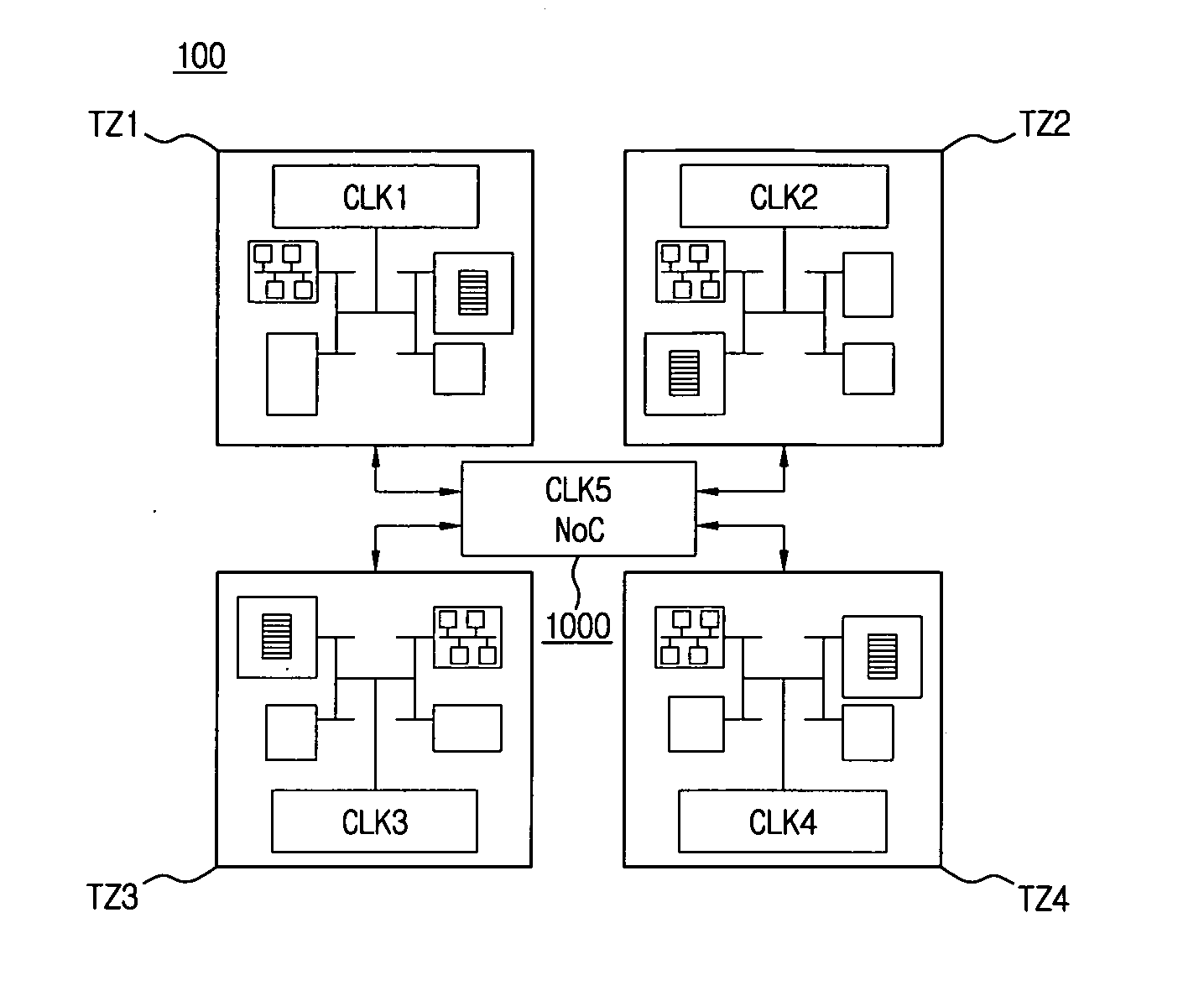

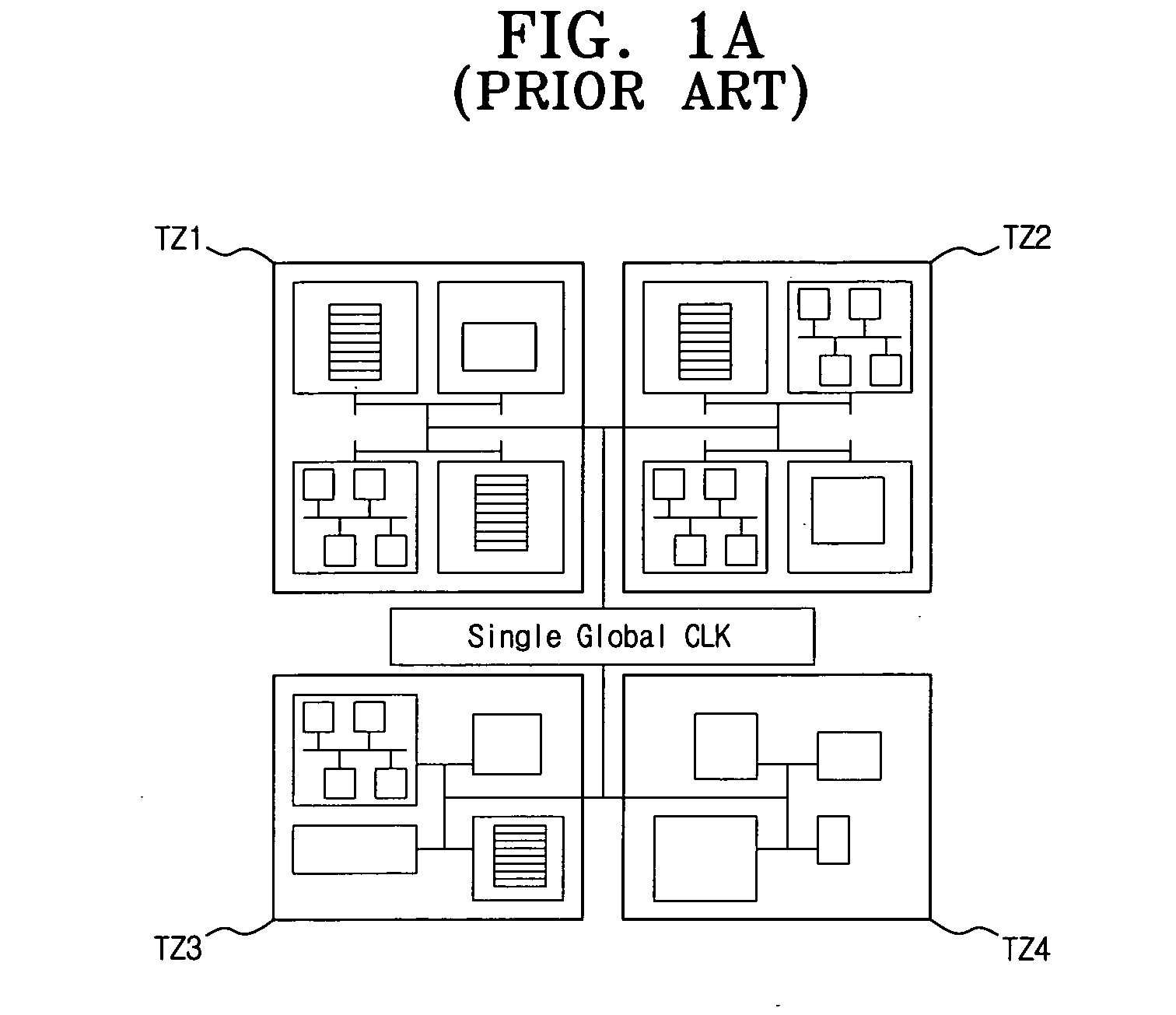

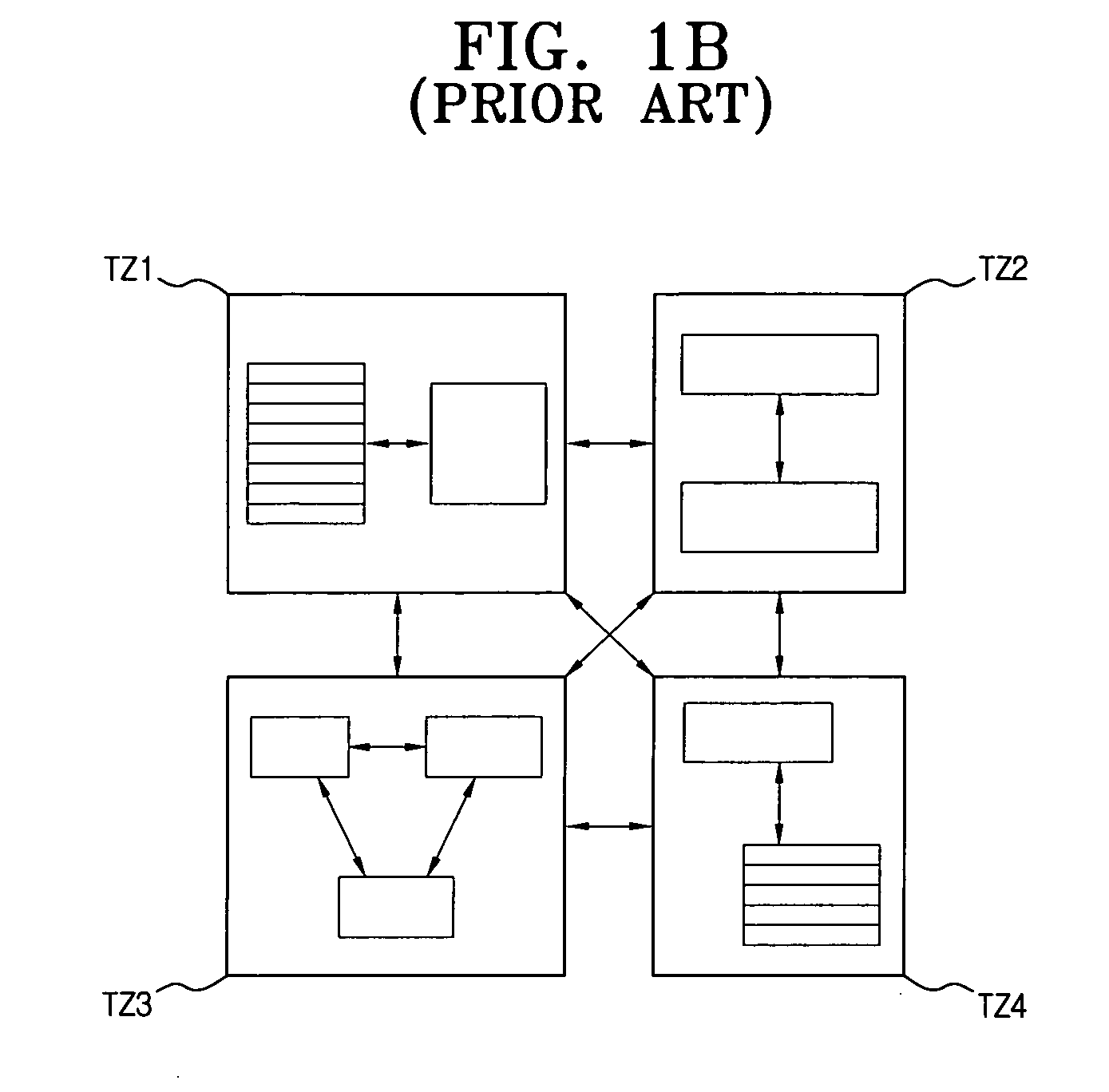

Gals-based network-on-chip and data transfer method thereof

InactiveUS20080005402A1Reduced Routing ComplexityReduce decreaseGenerating/distributing signalsTransmissionAsynchronous fifoData transmission

A GALS-based network-on-chip (NoC) includes a plurality of asynchronous first-in first-out (FIFO) input buffers connected to a plurality of IPs that asynchronously receive data; a plurality of asynchronous FIFO output buffers connected to the plurality of IPs asynchronously output data; and a router for forwarding data input to the plurality of asynchronous FIFO input buffers, to an asynchronous FIFO output buffer, among the plurality of asynchronous FIFO output buffers, which is connected to an IP to which the data is destined. Accordingly, the system-on-chip (SoC) adopting the GALS design scheme can transfer data via the NoC between the IPs which are in time zones having different clocks in the centralized switching system, thereby avoiding the need for a point-to-point system.

Owner:SAMSUNG ELECTRONICS CO LTD +1

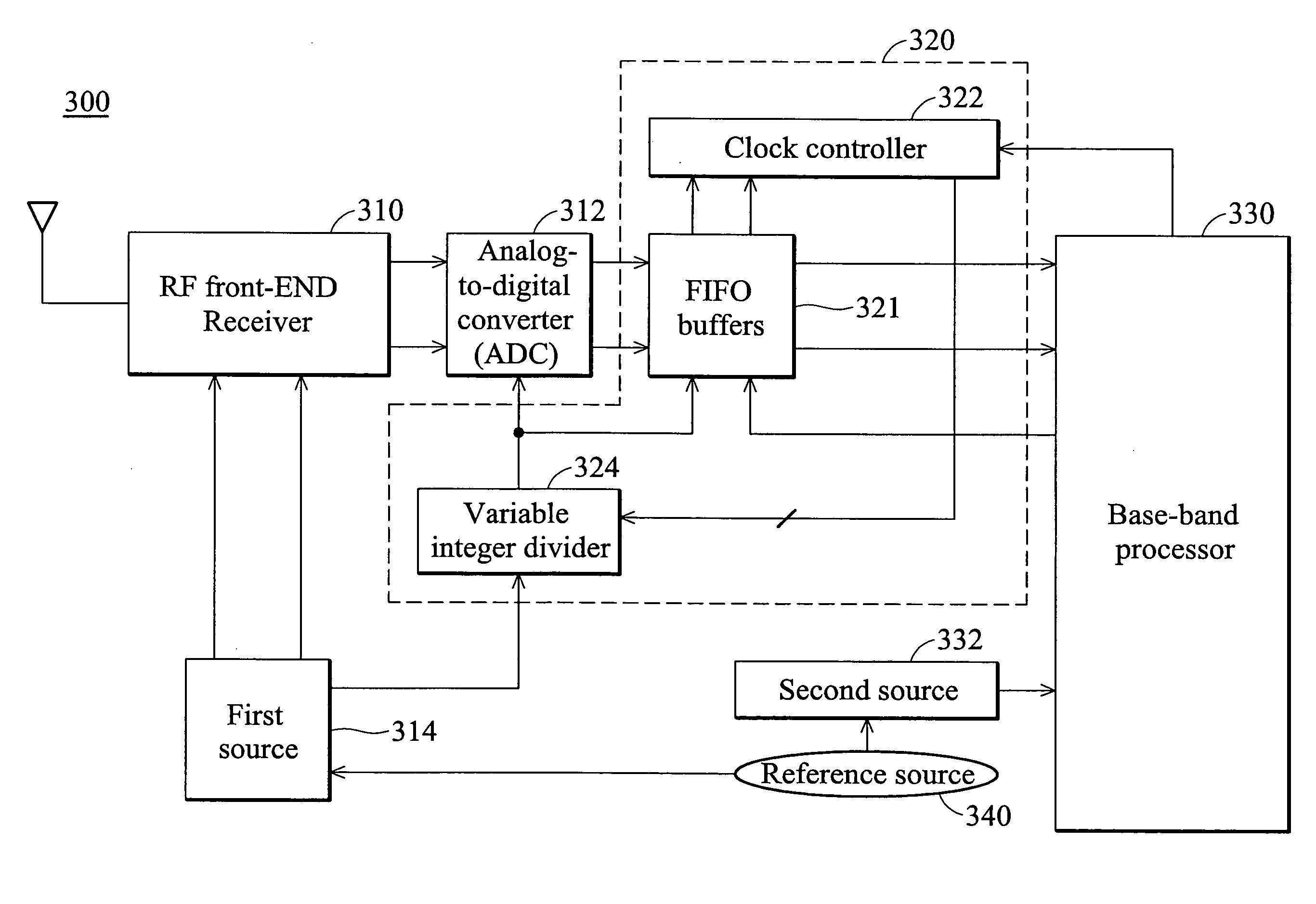

Asynchronous first in first out interface and operation method thereof

The invention provides an asynchronous first in first out (FIFO) interface and operation method wherein a read-out clock and a write-in clock of the asynchronous FIFO interface is asynchronous. The asynchronous FIFO interface comprises a FIFO buffer, a clock controller and a variable integer divider. The FIFO buffer inputs at least one data with the write-in clock, and outputs the at least one data with the read-out clock. The clock controller outputs a clock control signal according to a number of data stored in the FIFO buffer. The variable integer divider divides a first signal to generate the read-out clock or the write-in clock by an integer divisor controlled by the clock control signal in order to adjust the number of data stored in the FIFO buffer.

Owner:RICHWAVE TECH CORP

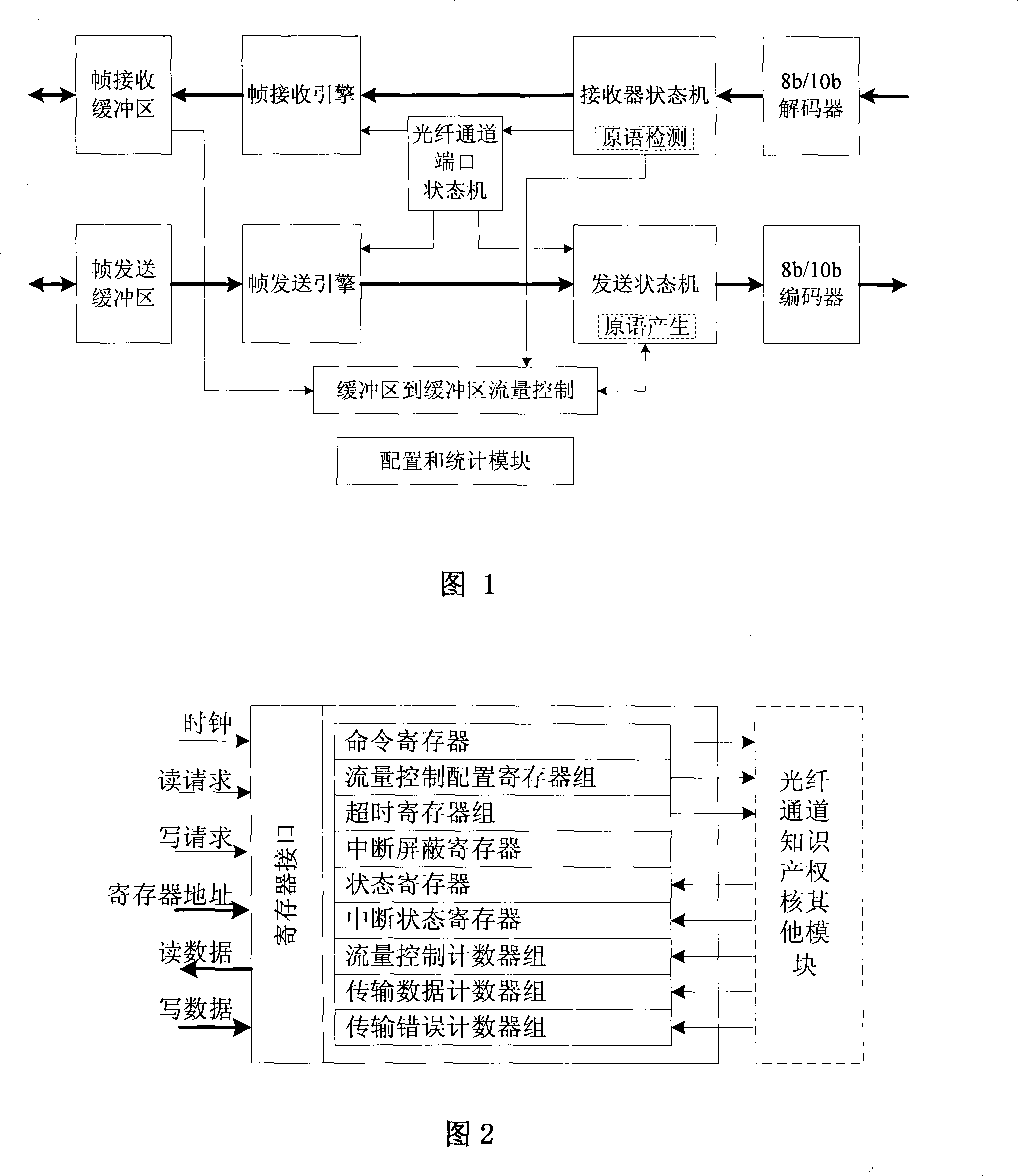

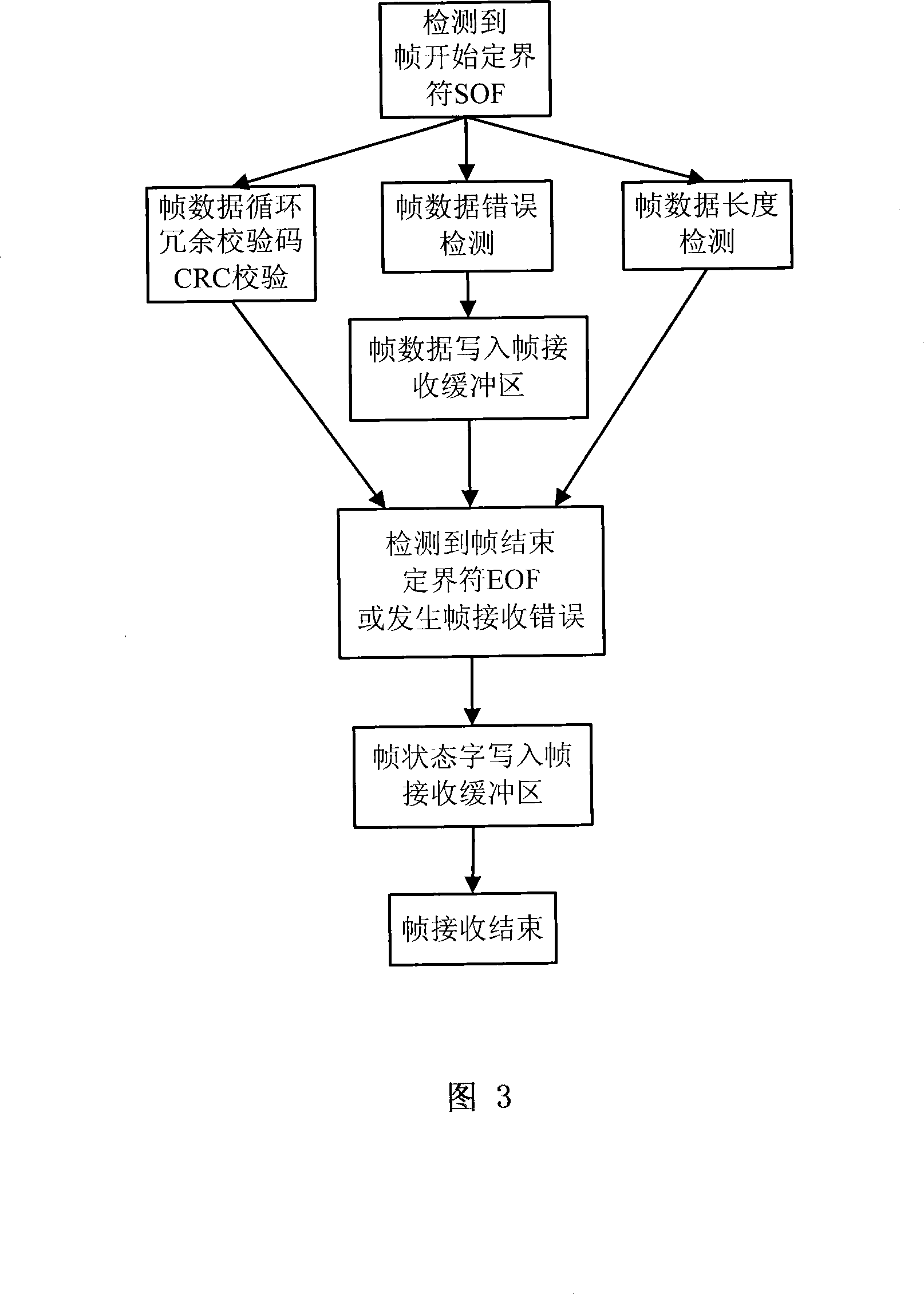

Intellectual property nucleus of optical fiber channel

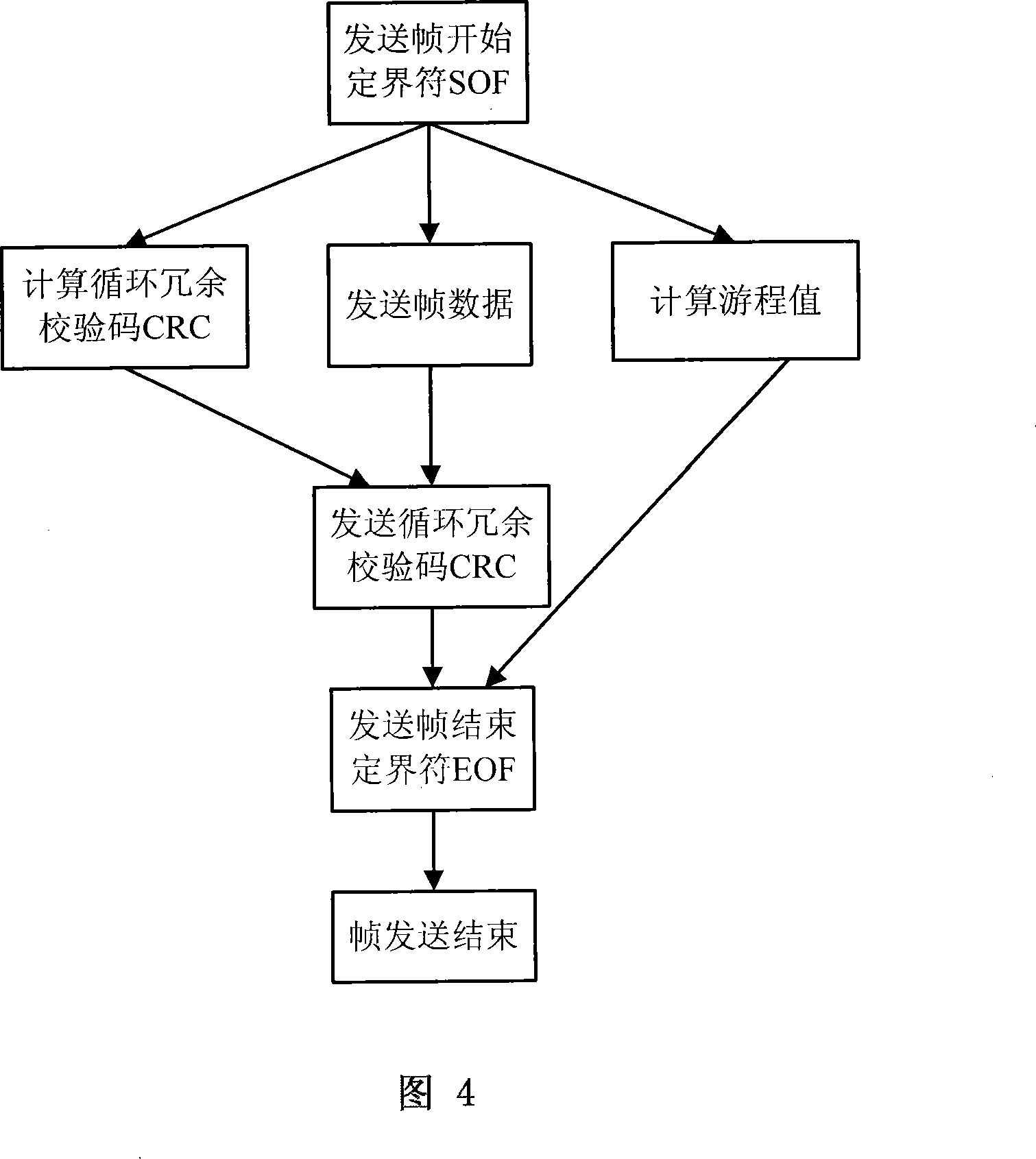

InactiveCN101175077AImprove collaborationFully configuredData switching networksFiberProcess function

The invention provides an intellectual property core of optical fiber channel, which pertains to the field of computer memory technology, resolves the imperfection of the function of the current intellectual property core, and realizes the protocol process function of FC-1 layer and the partial FC-2 layer of fiber channel. The invention comprises a 8b or 10 b decoder, a 8b or 10b coder, receiver state machine, a sending state machine, a fiber channel port state machine, a frame-receiving engine, a frame-sending engine, a frame-sending buffer area, a stream control module, configuration and a statistical module between buffer areas. The invention provides frame level user logical interface, adopts asynchronous FIFO queue as a frame-receiving buffer area and a frame sending buffer area, and provides perfect configuration and statistical function, thus improving the coordination capability of software and hardware.

Owner:HUAZHONG UNIV OF SCI & TECH

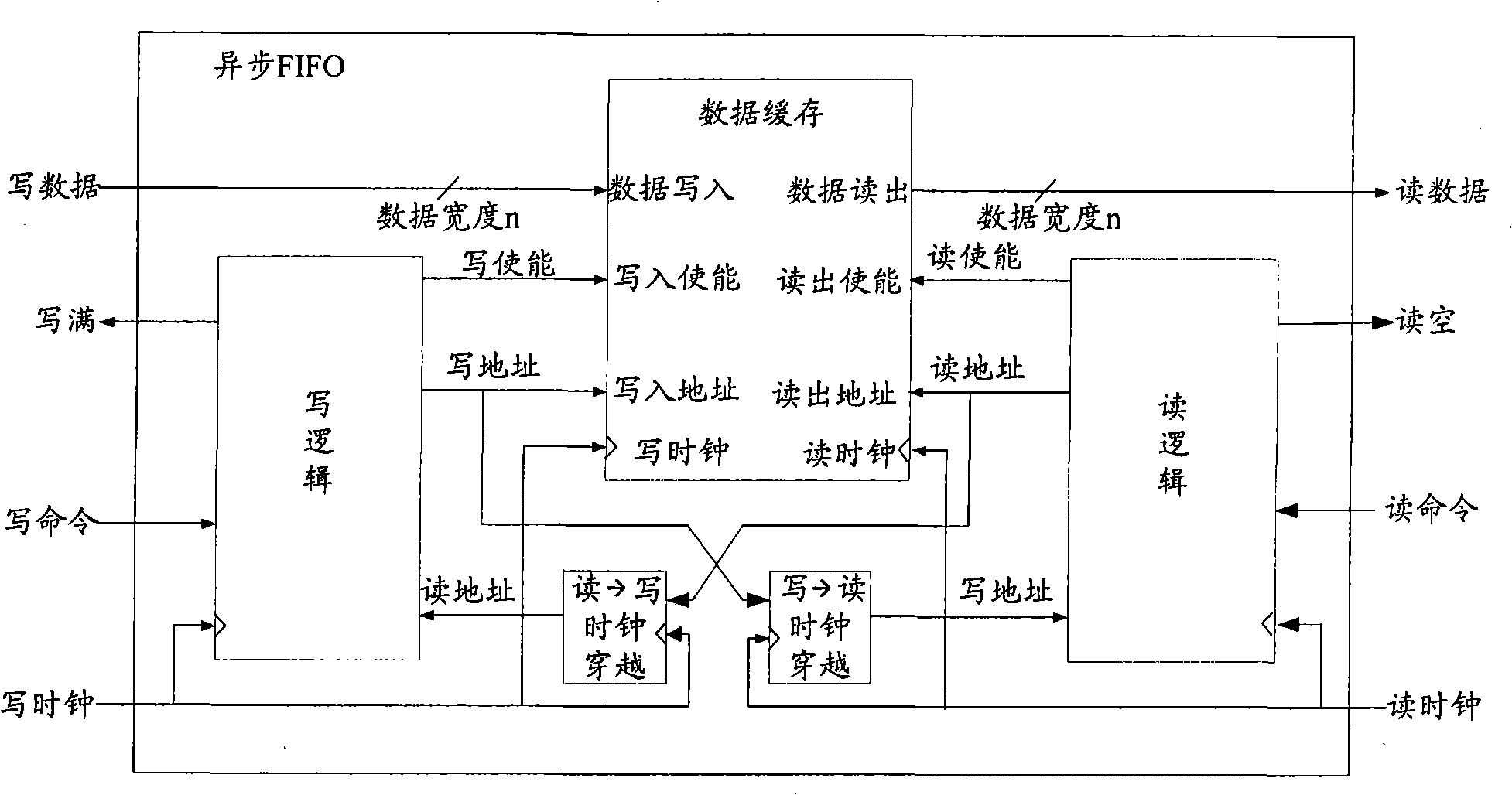

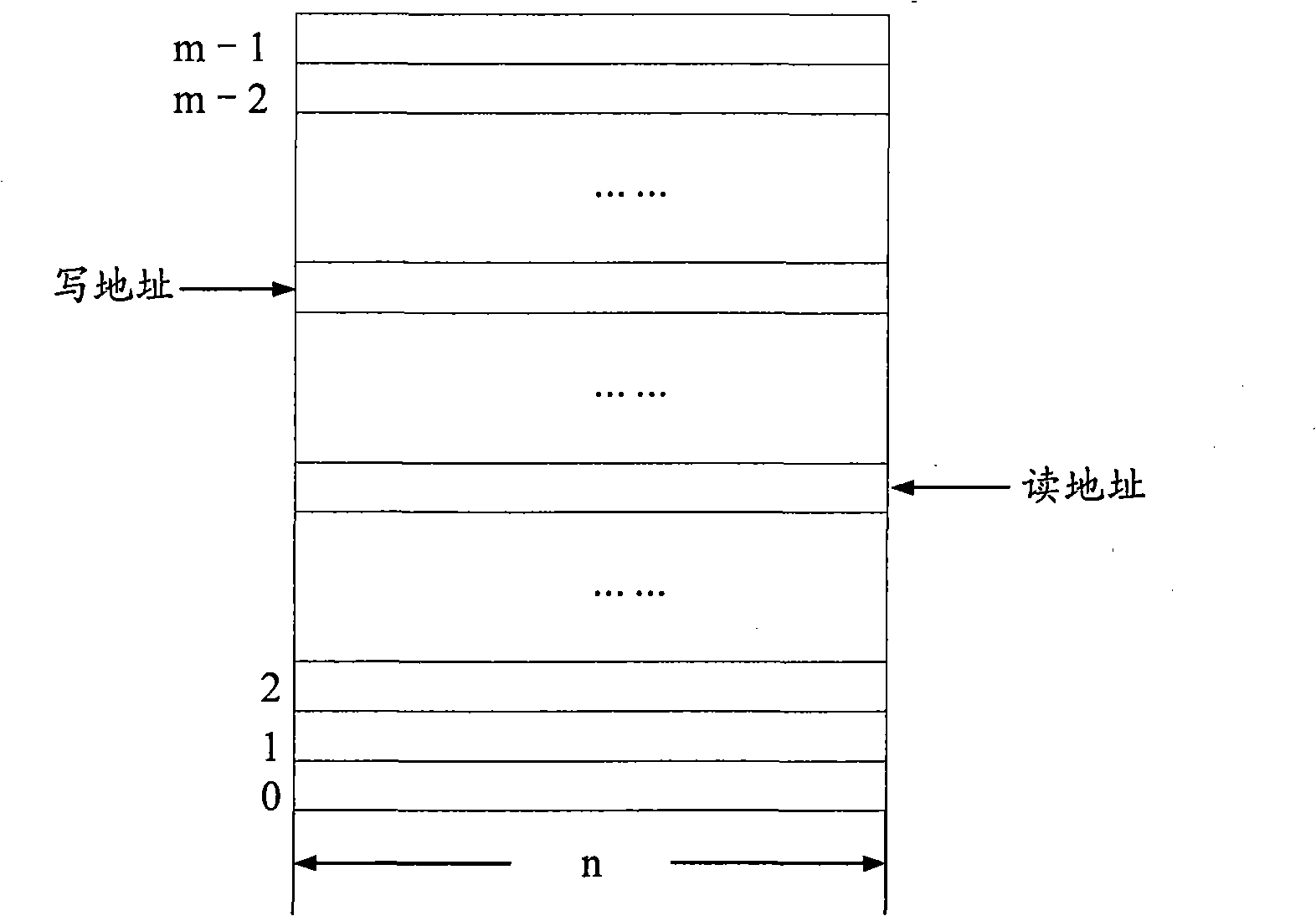

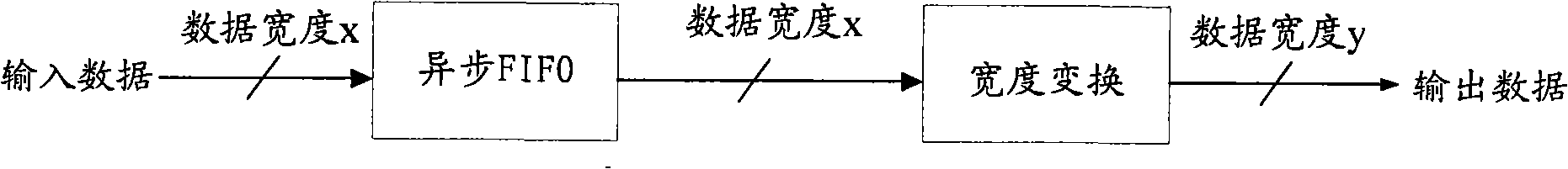

Asynchronous FIFO memory accomplishing unequal breadth data transmission

InactiveCN101261575AFlexible and efficient data transmissionImprove efficiencyData conversionSystems designParallel computing

The invention provides an asynchronous first-in first-out memory for realizing the width varying data transmission and a method, wherein, the memory comprises: a data cache unit, a data basic unit in the data cache unit is the common multiple of the width of the read data and the width of the written data; a writing address calculation module, which is used for calculating the specific position in the data cache that is corresponding by the current writing address according to the width of the written data; a reading address calculation module, which is used for calculating the specific position in the data cache that is corresponding by the current reading address according to the width of the read data; a reading / writing judgment module, which is used for determining the reading / writing functions according to the specific position in the data cache that is corresponding by the current writing address and the specific position in the data cache that is corresponding by the current reading address. The memory can directly calculate the specific positions of the reading / writing data with the different widths during the reading and writing logics, carry out the logical judgment, simplify the system design and improve the efficiency of data transmission.

Owner:ST ERICSSON SEMICON BEIJING

Asynchronous FIFO apparatus and method for passing data between a first clock domain and a second clock domain of a data processing apparatus

ActiveUS20050220239A1Accurate samplingEnsure integritySynchronising arrangementSynchronous/start-stop systemsAuxiliary memoryAsynchronous fifo

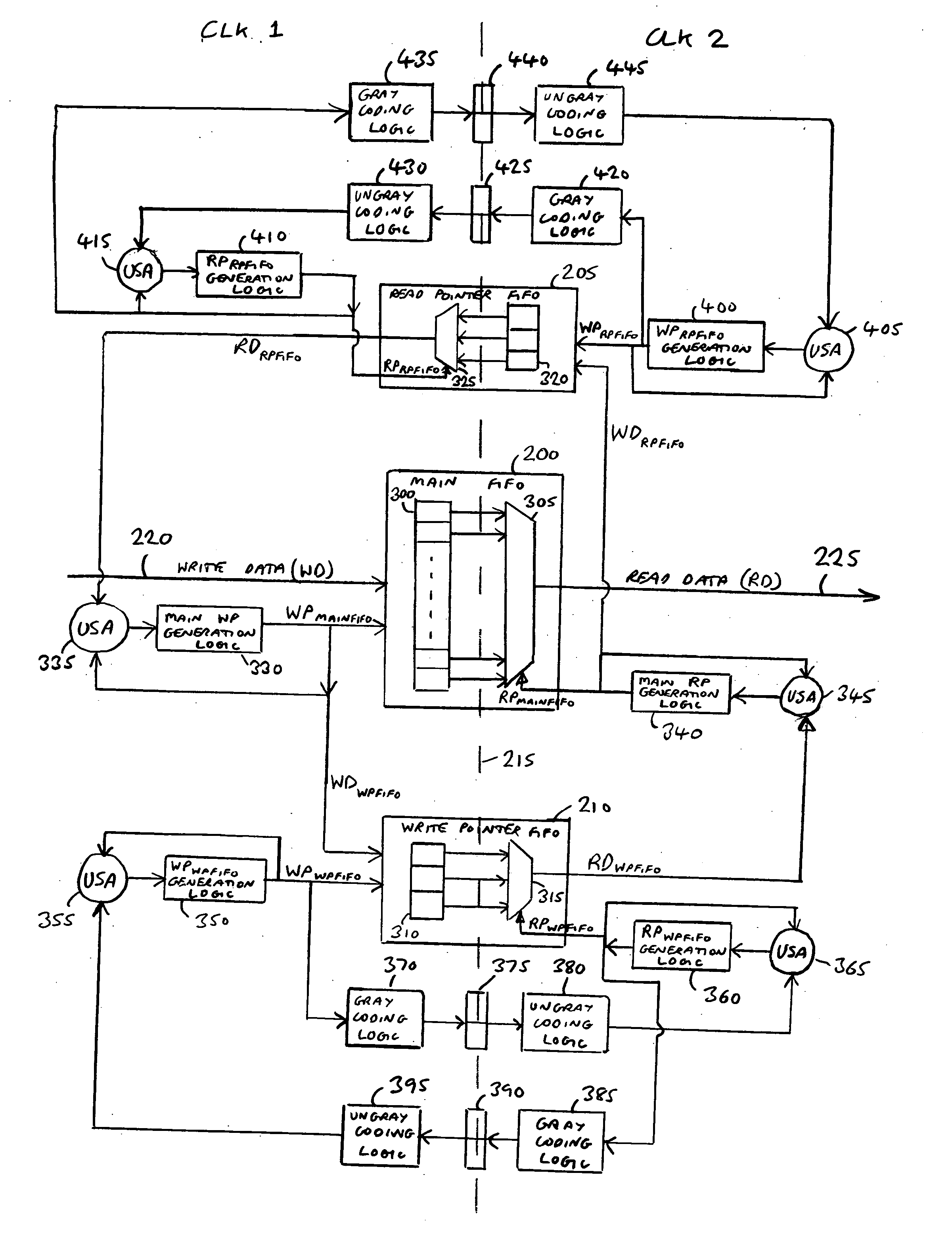

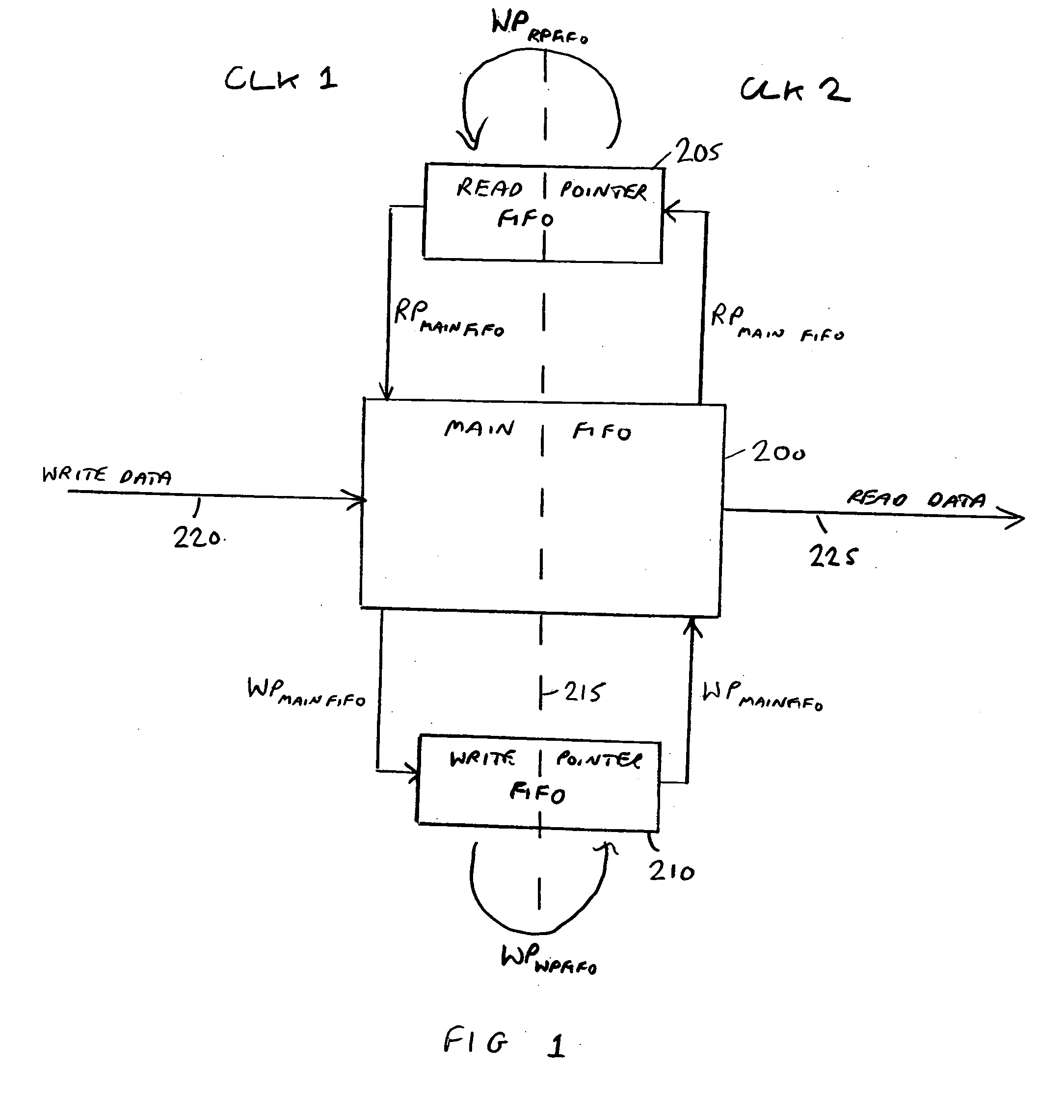

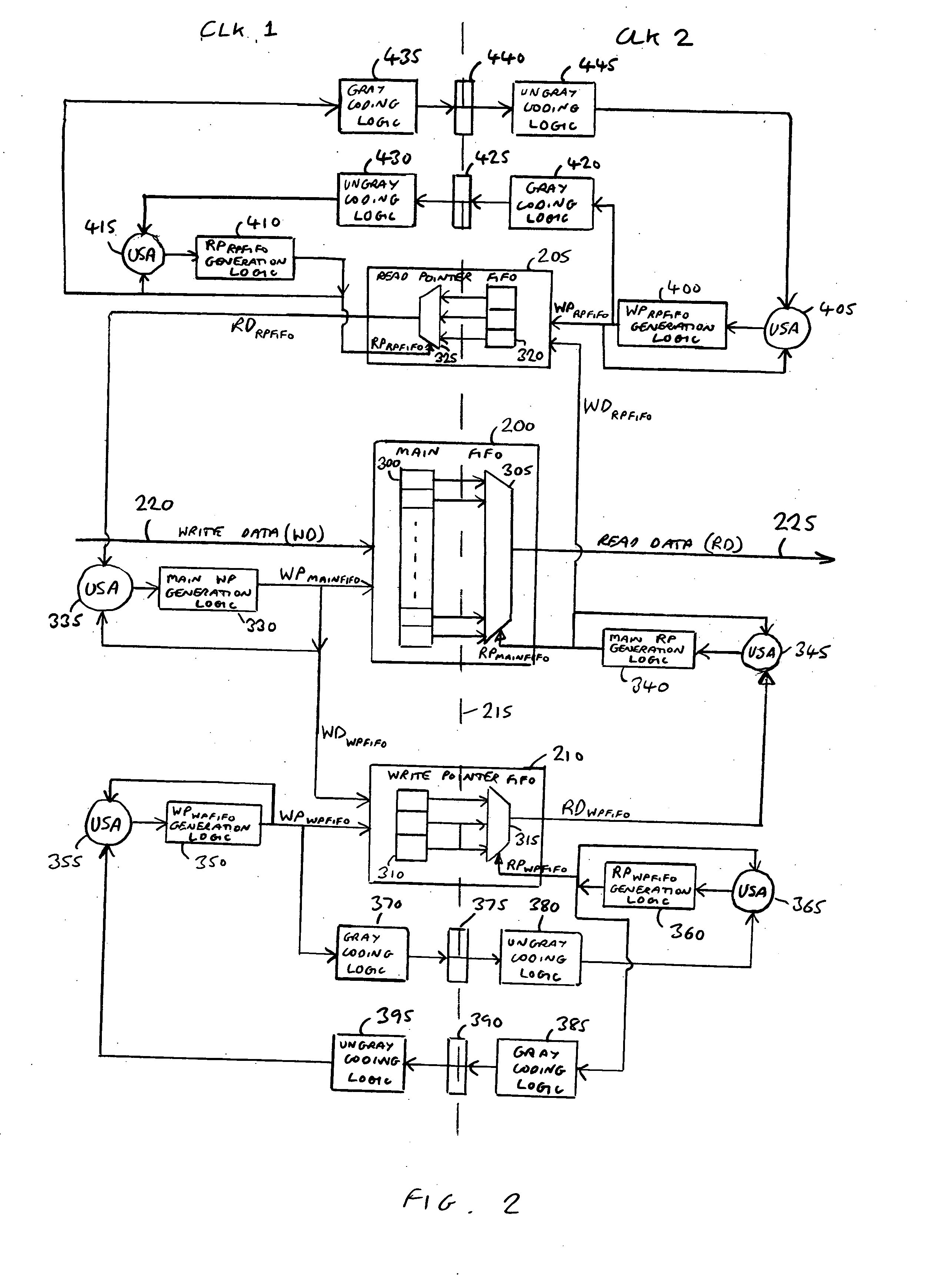

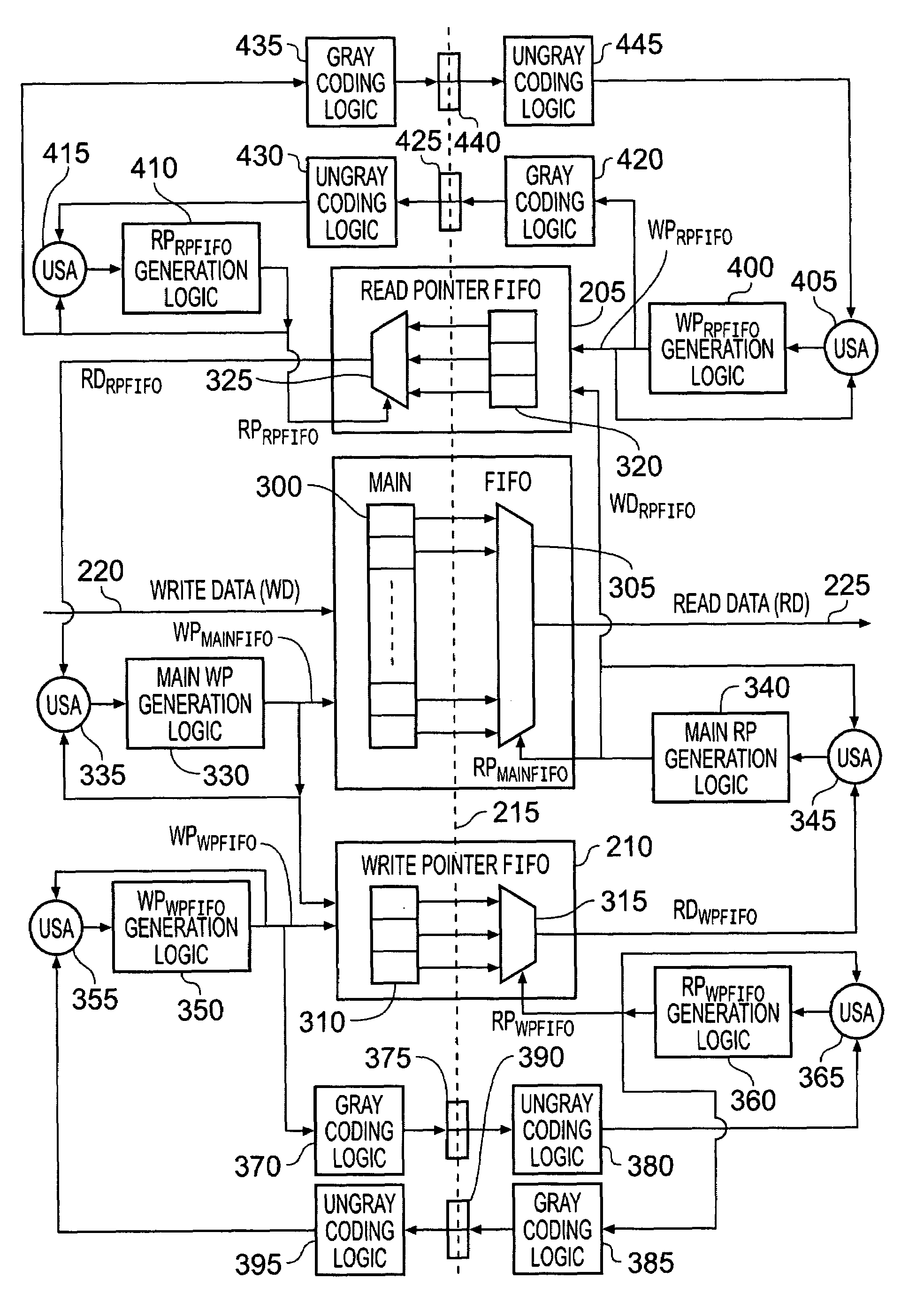

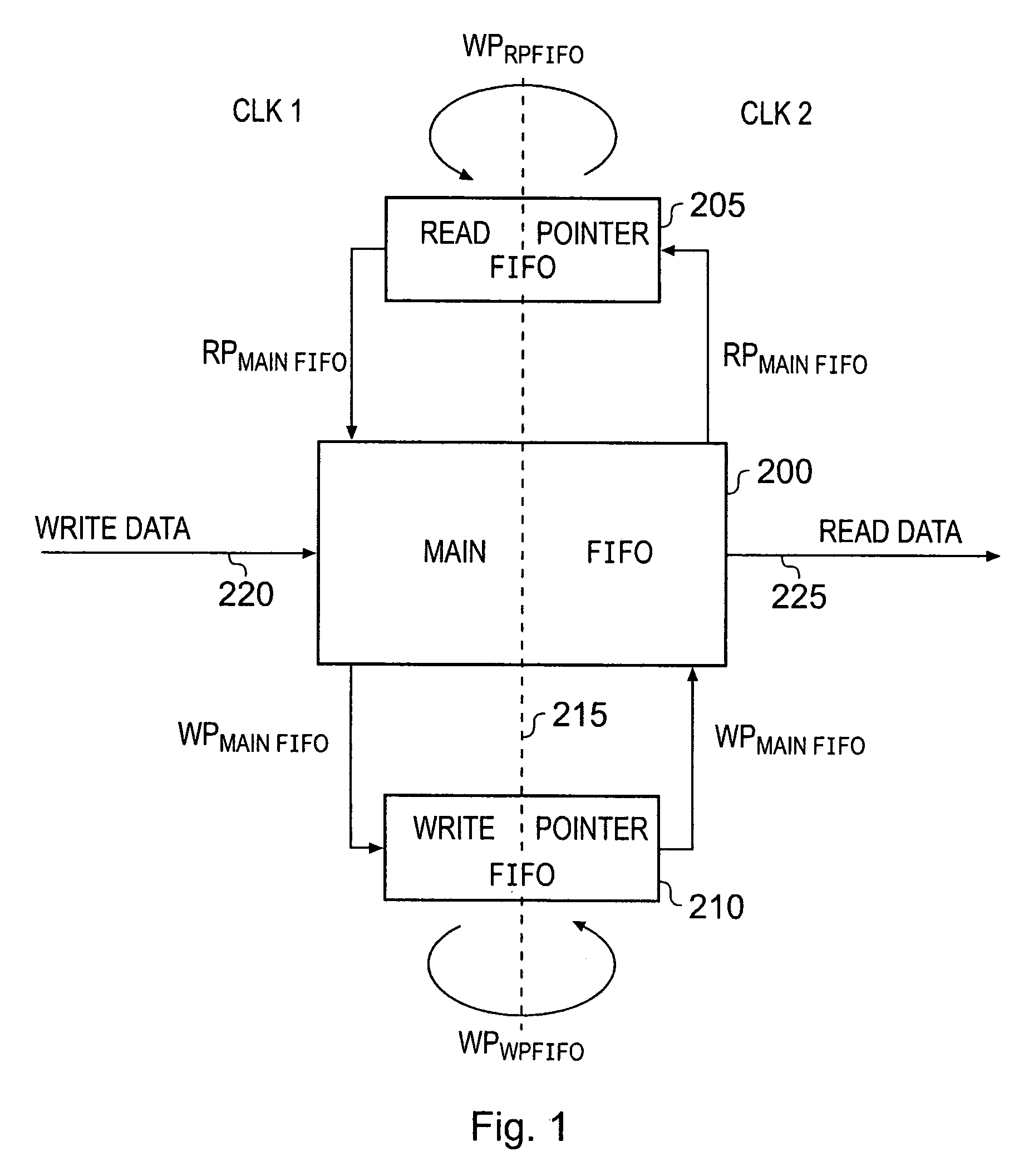

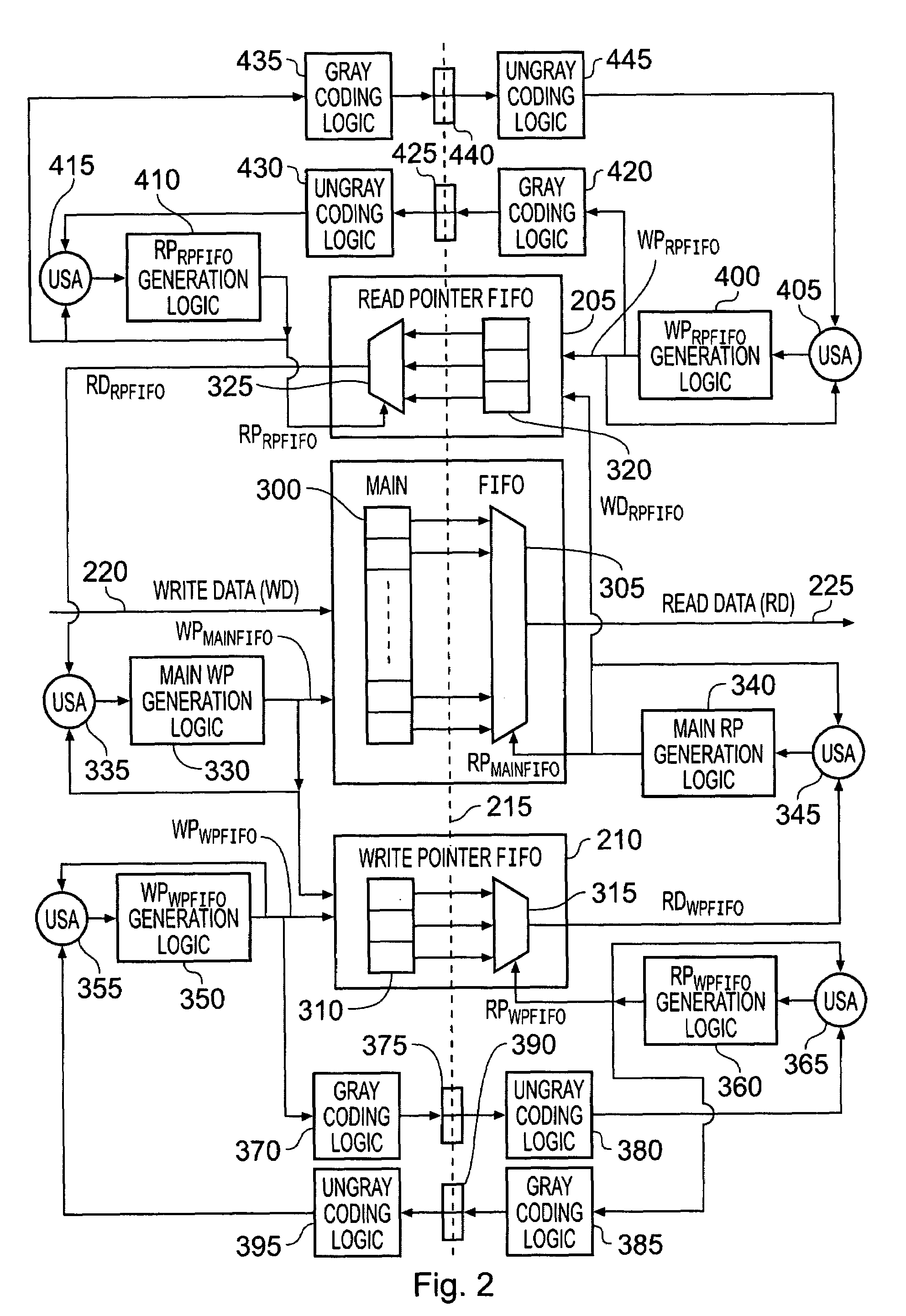

The present invention provides an asynchronous FIFO apparatus and method for passing data between a first clock domain and a second clock domain of a data processing apparatus, the first clock domain being asynchronous with respect to the second clock domain. The asynchronous FIFO apparatus comprises a main FIFO memory operable to store the data to be passed between the first and second clock domains, the main FIFO memory being accessible from each clock domain under the control of an access pointer associated with that clock domain. For one or both of the clock domains, the amount of data accessible per clock cycle is variable. An auxiliary FIFO memory is also provided associated with each clock domain in which the amount of data accessible per clock cycle is variable, this auxiliary FIFO memory being operable to store the access pointer used to access the main FIFO memory from its associated clock domain, and the access pointer being stored at a location of the auxiliary FIFO memory specified by an auxiliary access pointer. Routing logic is then operable to pass the auxiliary access pointer to the other clock domain to enable that other clock domain to retrieve the access pointer stored in the auxiliary FIFO memory. This provides an efficient technique for enabling data to be passed between two asynchronous clock domains in situations where for at least one of the clock domains the amount of data accessible per clock cycle in the main FIFO memory is variable.

Owner:ARM LTD

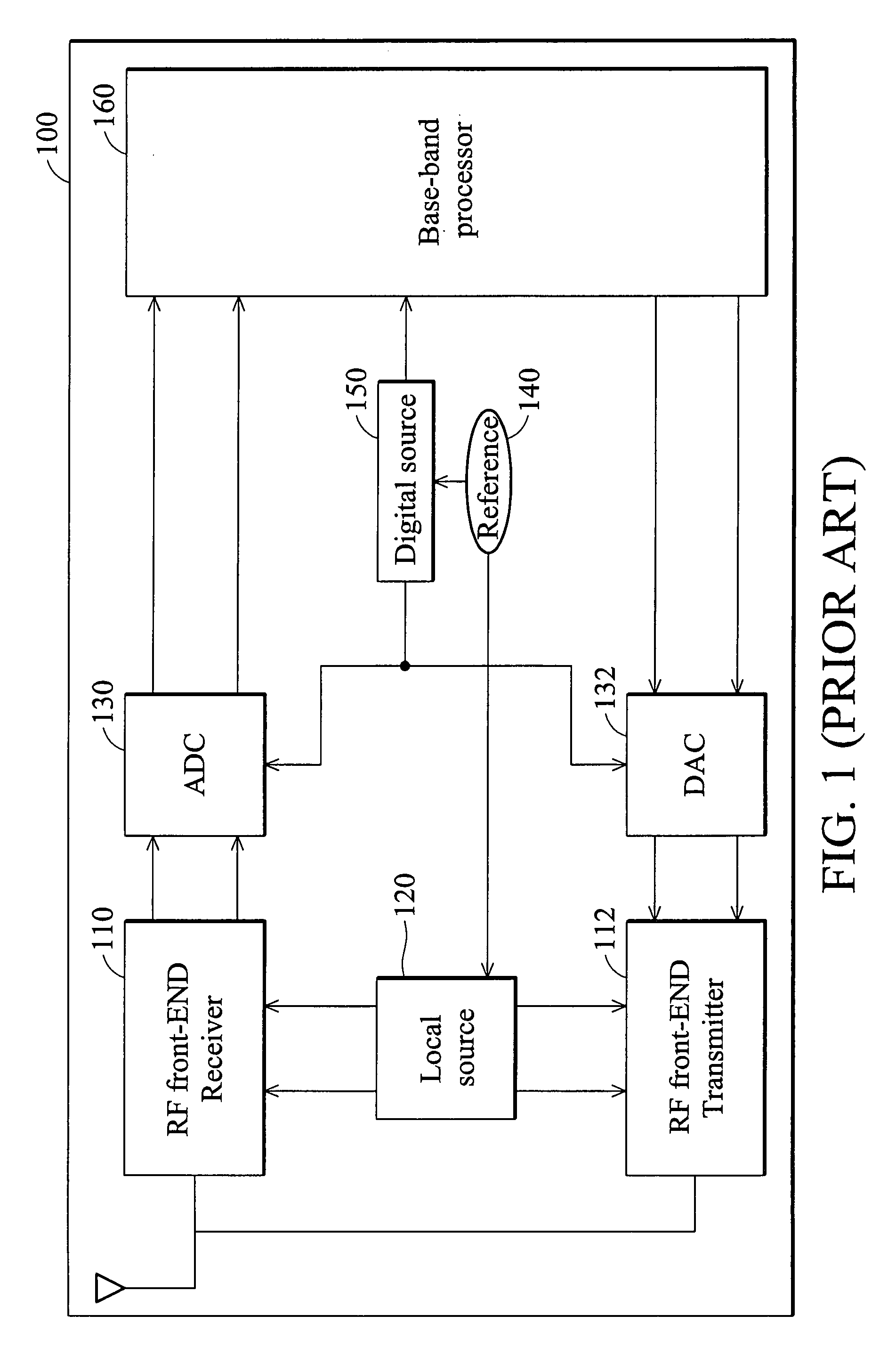

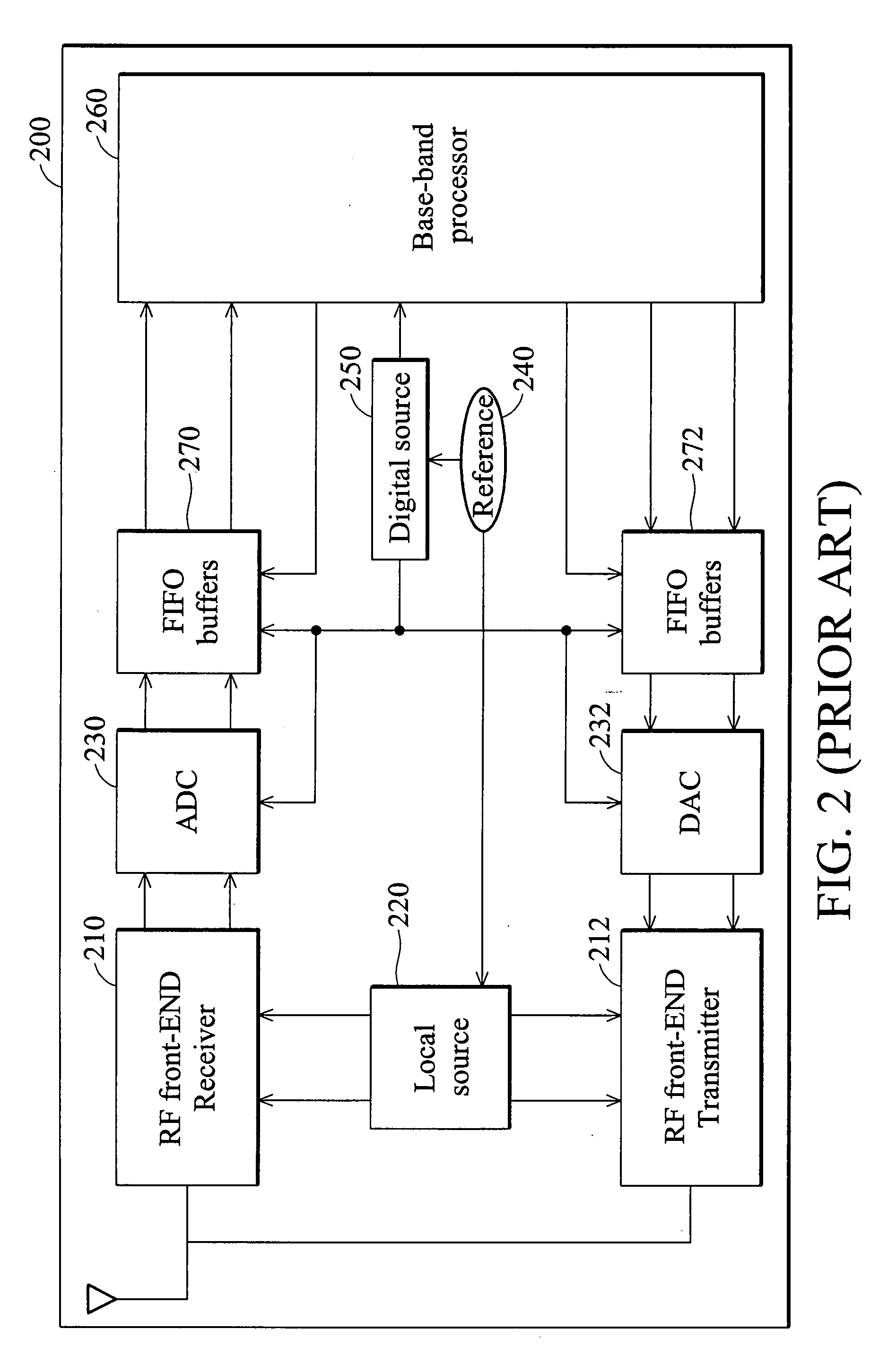

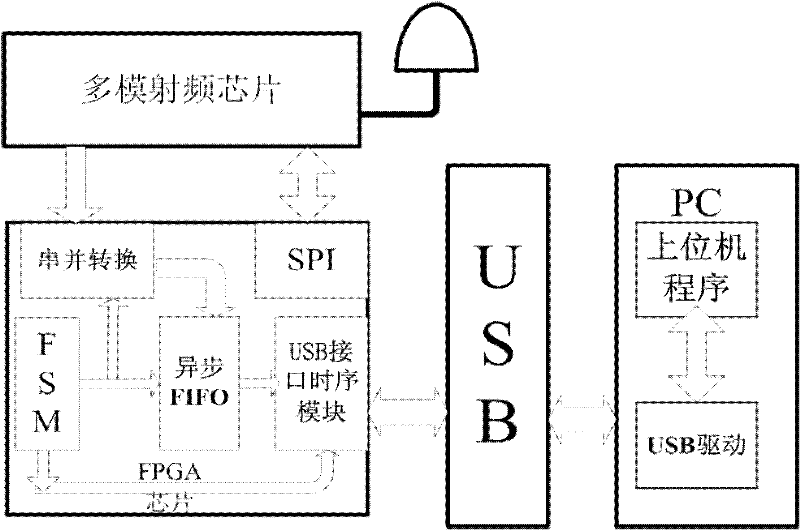

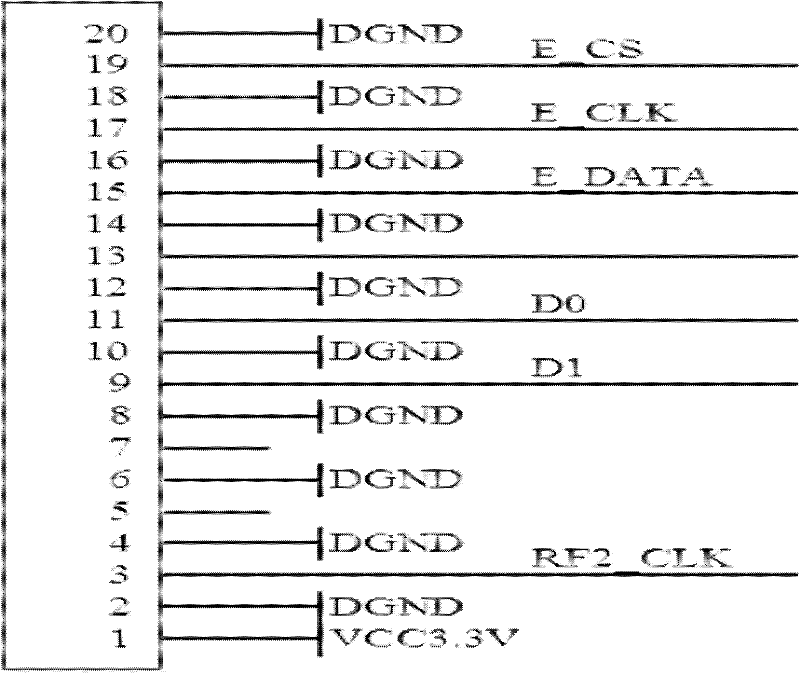

Intermediate frequency data acquisition and playback system in GNSS (global navigation satellite system) receiver

InactiveCN102508267AGuaranteed continuityGuaranteed real-timeSatellite radio beaconingData streamIntermediate frequency

The invention relates to an intermediate frequency data acquisition and playback system in a GNSS (global navigation satellite system) receiver. An antenna is connected with a radio frequency front-end unit, an SPI (single-point imaging) module is in two-way connection with the radio frequency front-end unit, the radio frequency front-end unit is connected with an FPGA (field-programmable gate array) control unit is in two-way connection with a USB (universal serial bus) interface transmission unit, and the USB interface transmission unit is in two-way connection with an upper computer; the radio frequency front-end unit is used for receiving satellite signals and outputting intermediate frequency signals, the SPI module is used for configuring the working mode of the radio frequency front-end unit and performing switching among a plurality of satellite navigation systems, the FPGA control unit is used for performing series-parallel conversion on the intermediate frequency signals and then saving the intermediate frequency signals into an asynchronous FIFO (first in first out) buffer module, a USB interface time sequence module is used for reading out data stored in the FIFO buffer module and then writing the data into the USB interface transmission unit, and the upper computer is used for storing the data which is red from the USB interface transmission unit into a local hard disc. A data stream after format conversion is transmitted into the intermediate frequency input end of a base band under the trigger of a base band clock through the control of the upper computer during the playback of the data.

Owner:SOUTHEAST UNIV

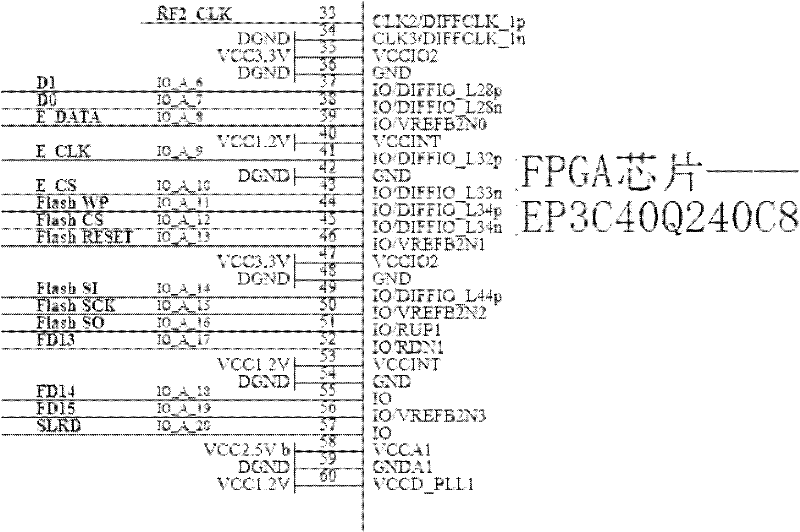

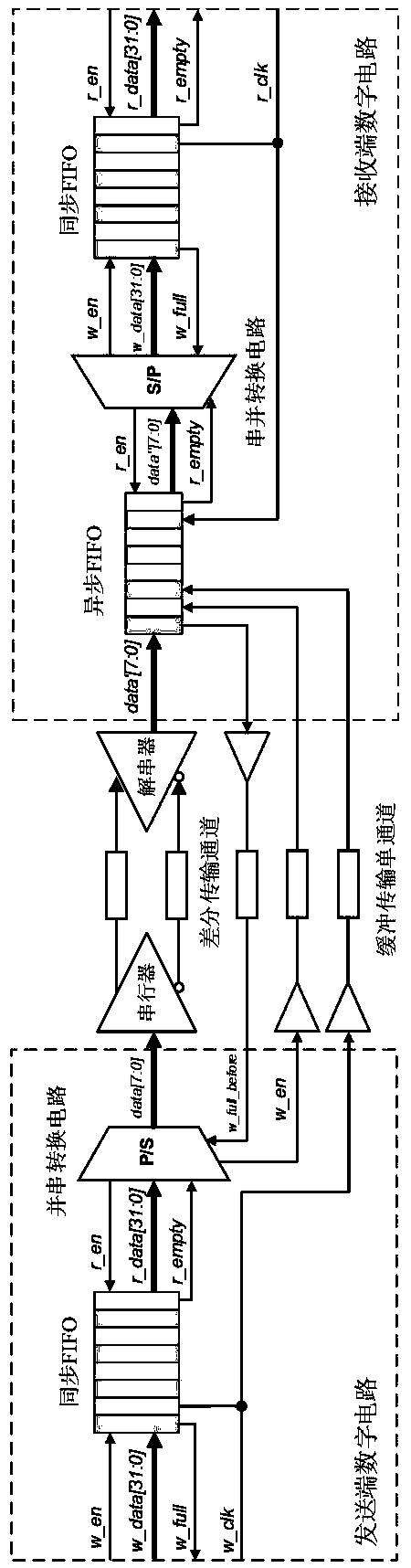

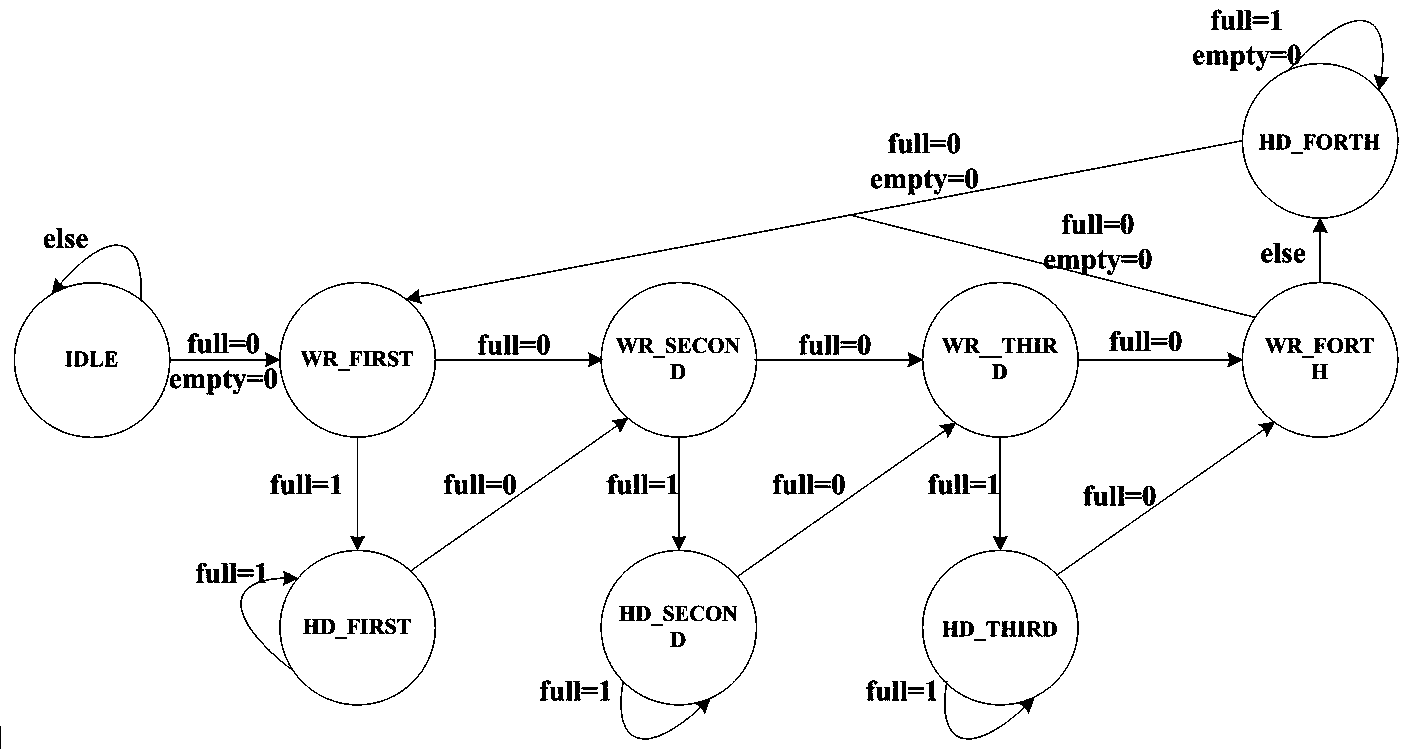

FIFO protocol based digital interface circuit for SerDes technology

InactiveCN104022775AHandy for bit width mismatch issuesEasy to expand bit widthLogic circuit coupling/interface arrangementsSystems designFeedback control

The invention belongs to the field of a SerDes serial communication technology, and specifically relates to a FIFO protocol based digital interface circuit for a SerDes technology. The FIFO protocol based digital interface circuit is composed of two major parts, i.e., a sending end digital circuit and a receiving end digital circuit. According to the invention, classic synchronization and asynchronous FIFO and series-parallel and parallel-series conversion circuits in a digital system design are introduced to a SerDes digital-analog interface, the digital-analog interface is packaged to be a simple interface supporting a FIFO read-write protocol, the FIFO protocol based digital interface circuit is simple and feasible and facilitates scheduling. The ingenious use of the FIFO effectively solves the problem of signal integrity including clock zone crossing data transmission among chips, large transmission delay of a feedback control signal channel and the like. The series-parallel and parallel-series conversion circuits solve the problem of mismatch between a bus and a SerDes bid width, facilitate bit width expansion of the bus and enhance the adaptability of a circuit design scheme.

Owner:FUDAN UNIV

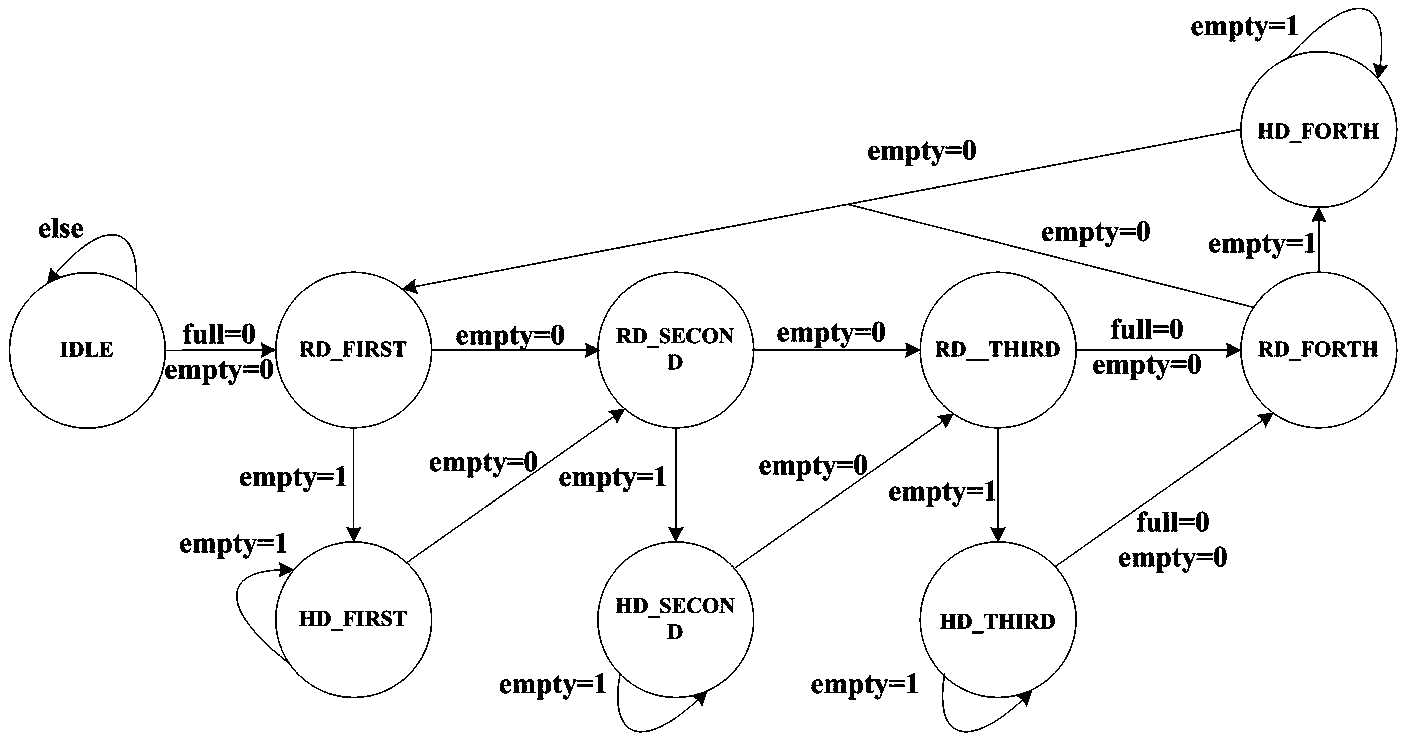

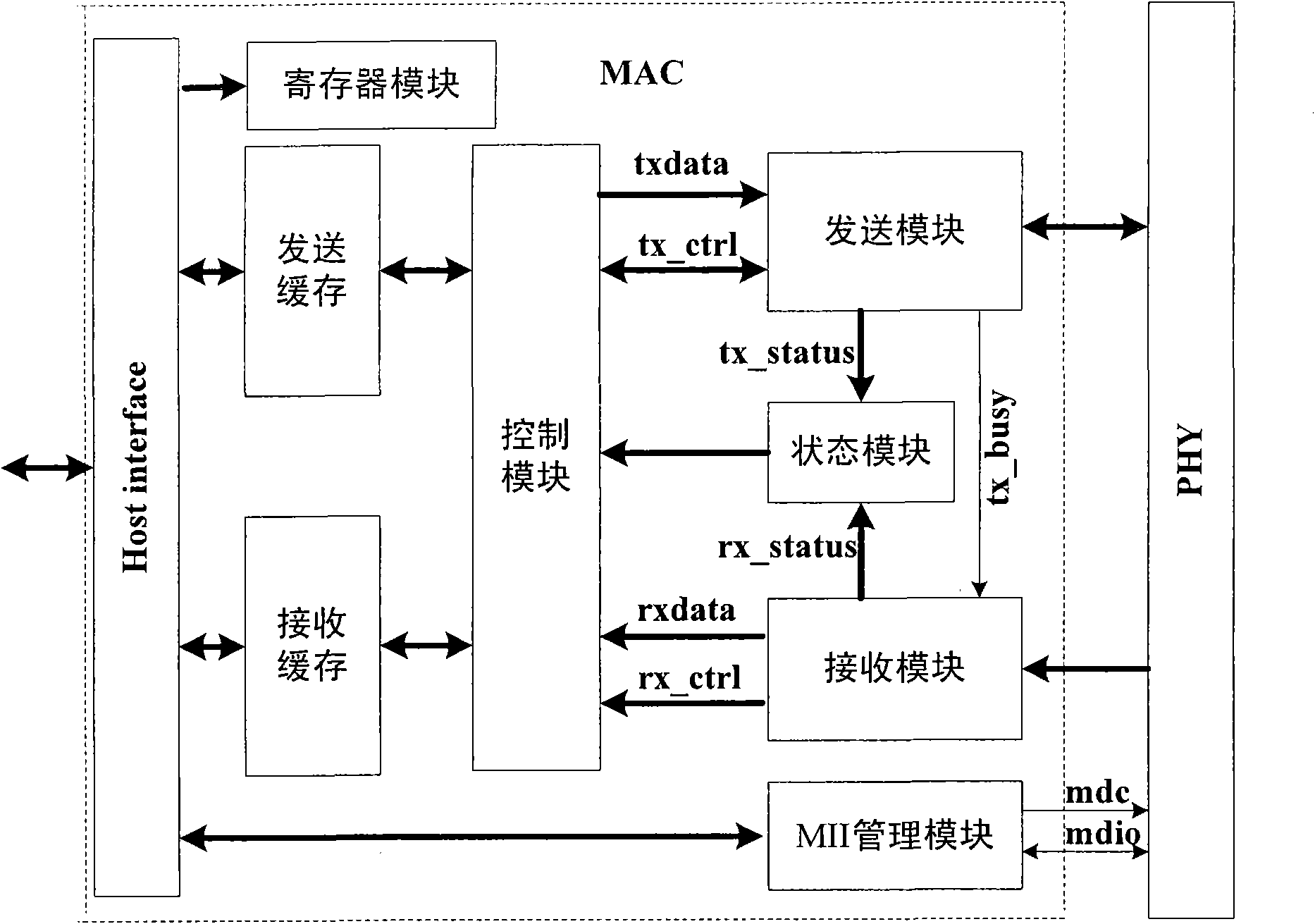

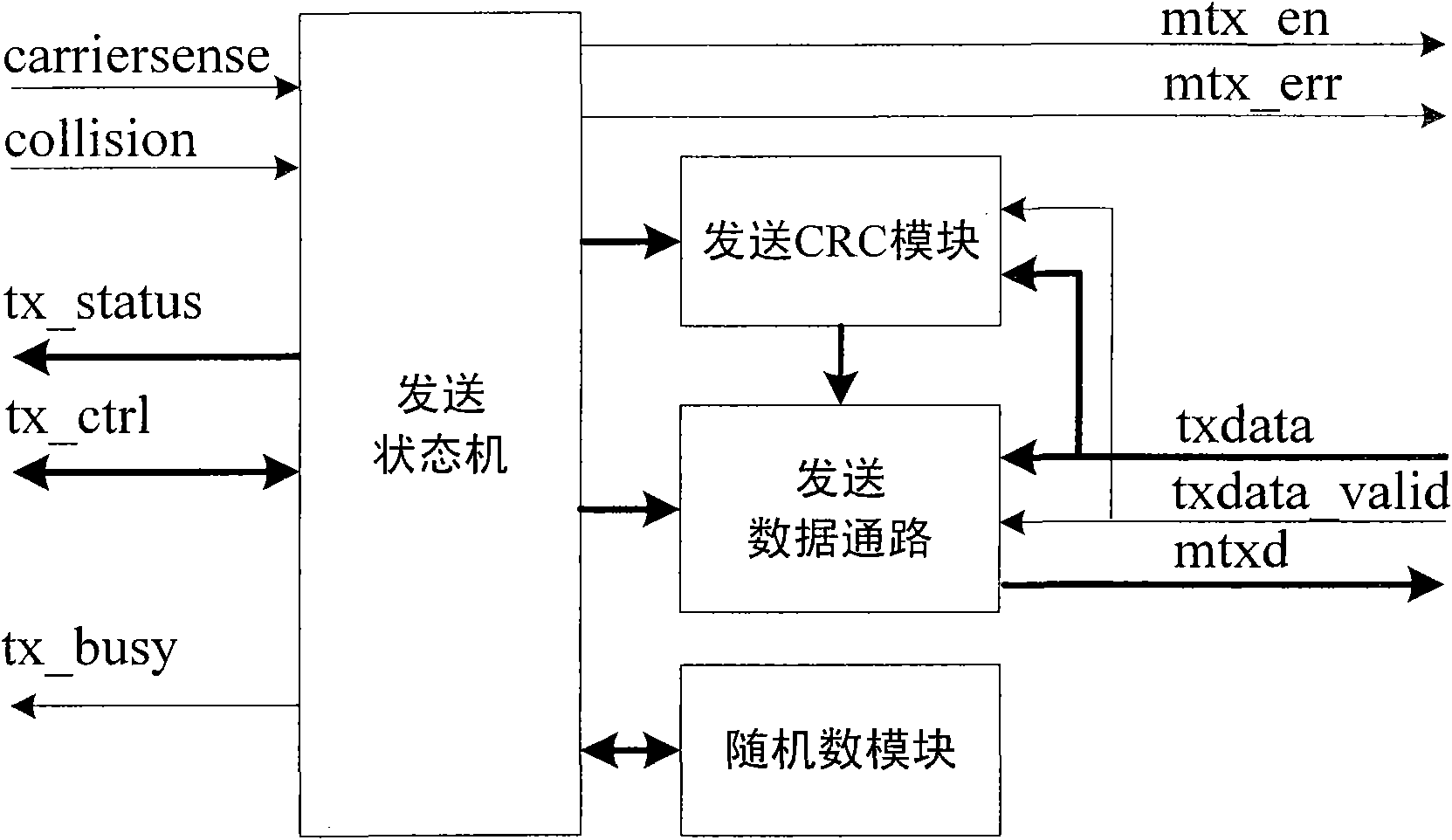

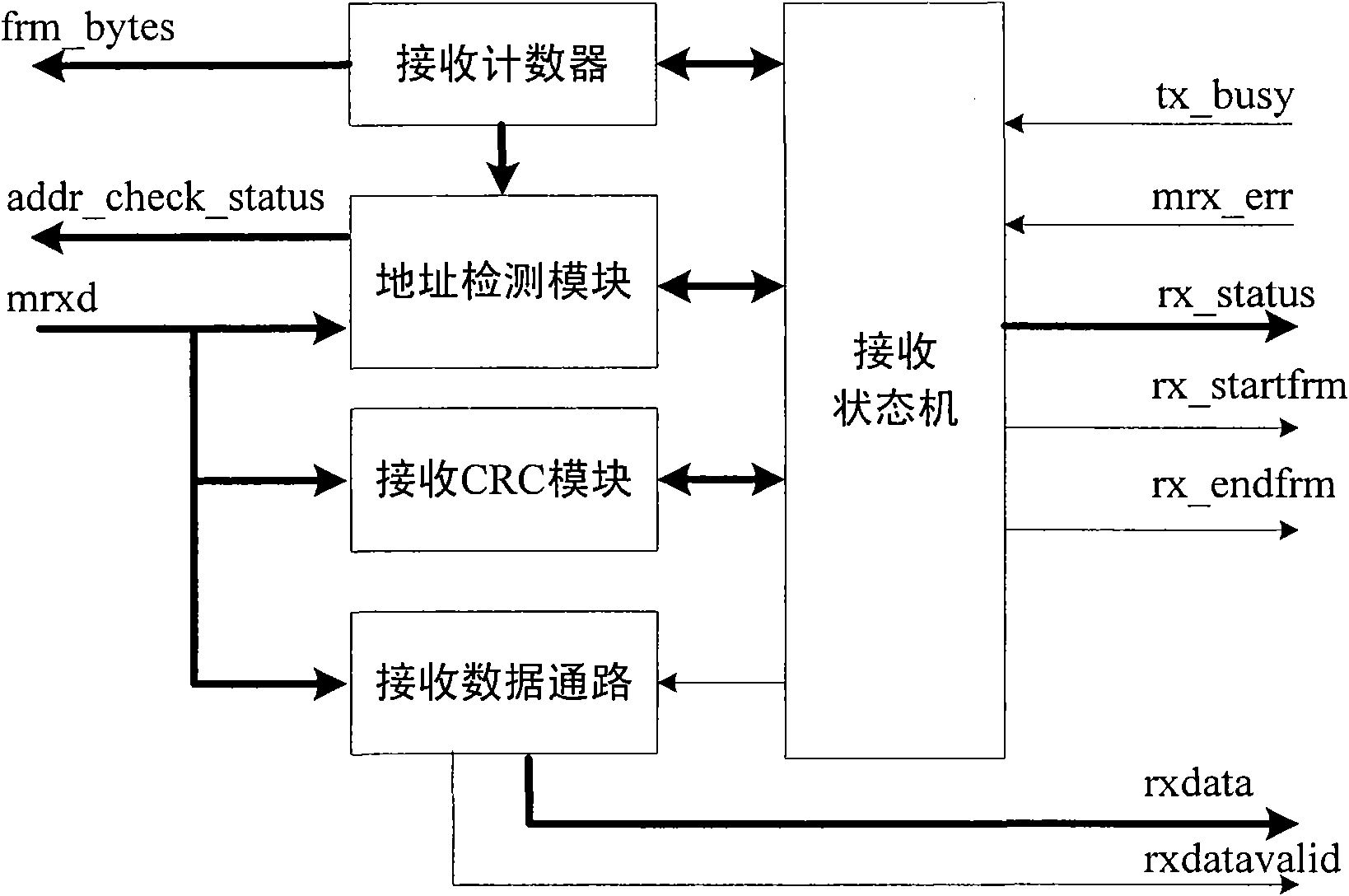

Ethernet MAC (Media Access Control) sublayer controller applicable to WLAN (Wireless Local Area Network)

ActiveCN102065569AImprove general performanceImplement retransmissionNetwork topologiesWireless network protocolsProcessor registerControl data

The invention discloses an Ethernet MAC (Media Access Control) sublayer controller applicable to WLAN (Wireless Local Area Network). The Ethernet MAC sublayer controller comprises a transmitter module, a receiver module, a state module, a control module, an MII (Media Independent Interface) management module, a transmission cache, a receiving cache and a register module, wherein the transmission cache and the receiving cache can realize storage, retransmission and discard of data frames by employing the asynchronous FIFO (First-in First-out) capable of loading read addresses, the information interaction of data frames between a host and the MAC sublayer controller is carried out through data frame cache descriptors which include transmitting cache descriptors and receiving cache descriptors, wherein the transmitting cache descriptors are used for controlling the transmitting process of the data frames, recording and returning a transmitting state; the receiving cache descriptors are used for controlling the reading of received data frames and returning a frame receiving state to the host. By the Ethernet MAC sublayer controller, the network access of embedded devices, the frame conflict retransmission and discard of bad frames are realized, and the utilization rate of cache in a chip is improved when short frames are received.

Owner:浙江科睿微电子技术有限公司

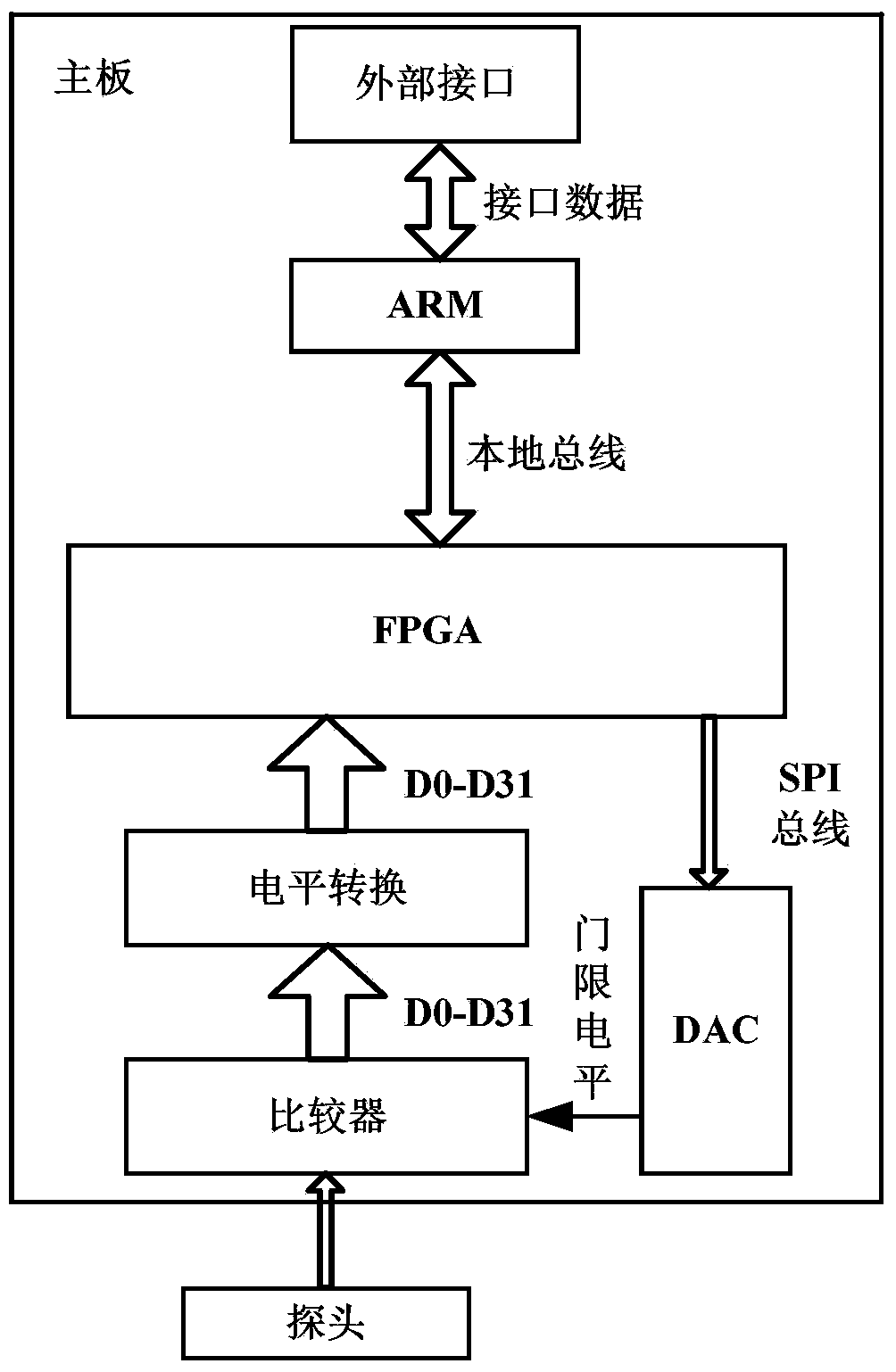

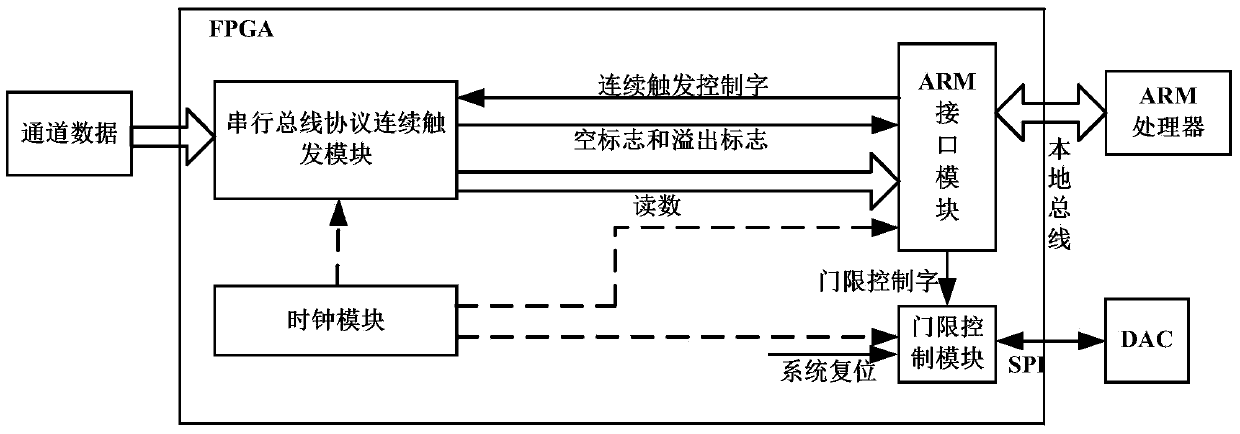

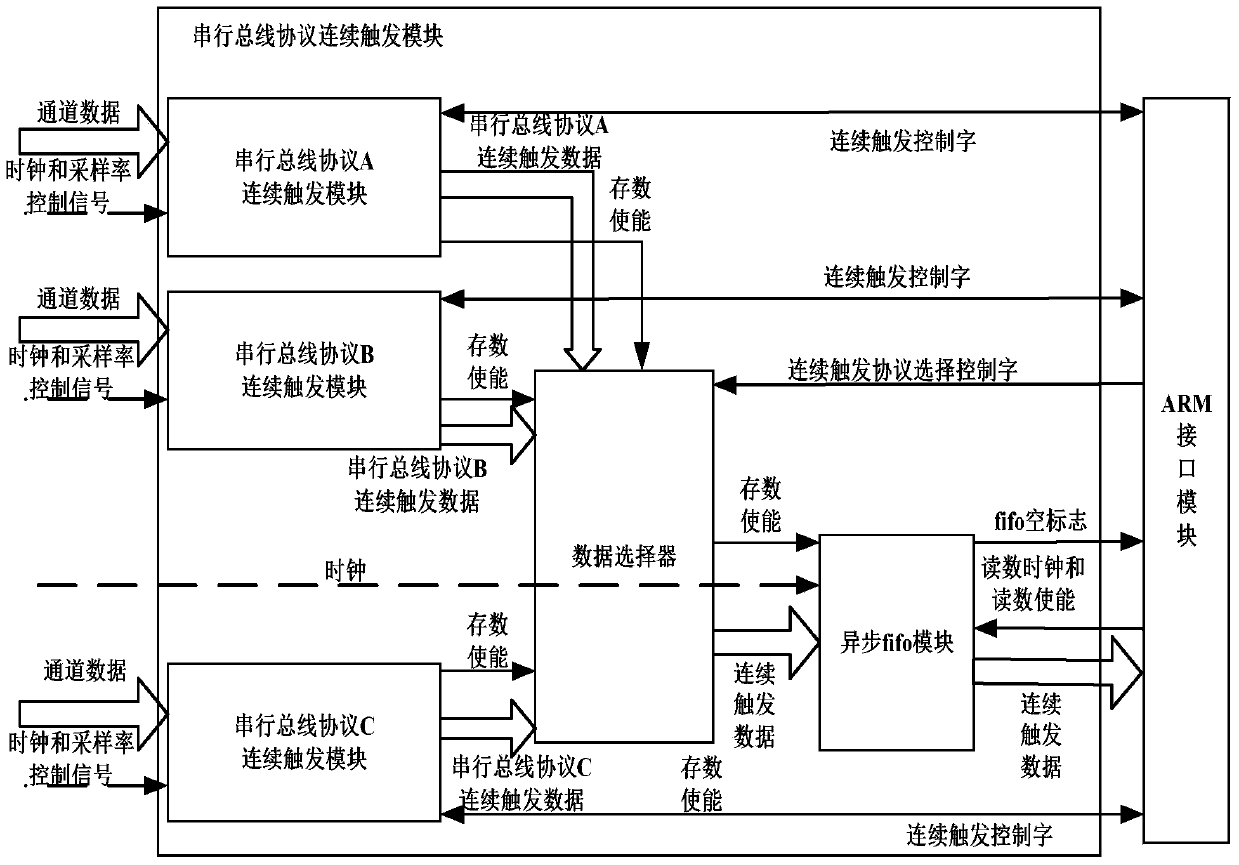

Logic analyzer with serial bus protocol continuous triggering function

InactiveCN103995764ARealize long-term continuous monitoringTargetedLogical operation testingChannel dataMultiplexer

The invention discloses a logic analyzer with a serial bus protocol continuous triggering function. Each continuous triggering module in an FPGA corresponds to a serial bus protocol. A clock timer in each continuous triggering module provides a clock overflow mark and clock data. Each continuous triggering state machine corresponds to a triggering mode. Channel data are received, and continuous triggering data collecting is triggered according to continuous triggering control words. In a next cycle after data collecting is completed, data storing enable signals are enabled to be effective. A data selector is triggered to select continuous triggering data to be output to a data splicing module. The data storing enable signals are selected to be output to the data selector. The data splicing module combines the clock data and the continuous triggering data and then output the data to the data selector. The data selector in the FPGA outputs corresponding continuous triggering data and data storing enable signals to an asynchronization FIFO module according to triggering type control words. The asynchronization FIFO module stores the continuous triggering data which are provided for an ARM processor to read. According to the logic analyzer, hardware is used for achieving continuous triggering of the serial bus protocol.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

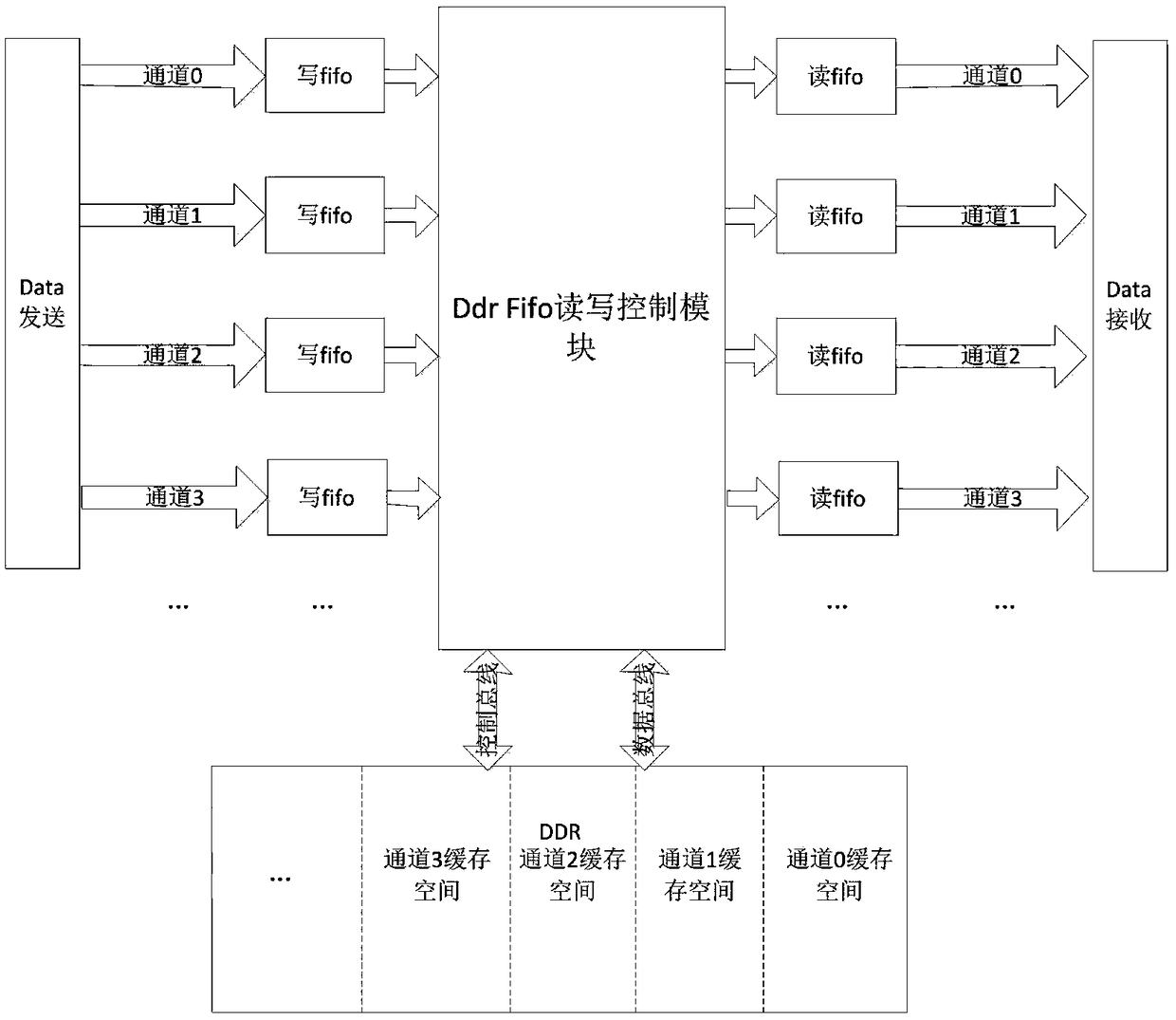

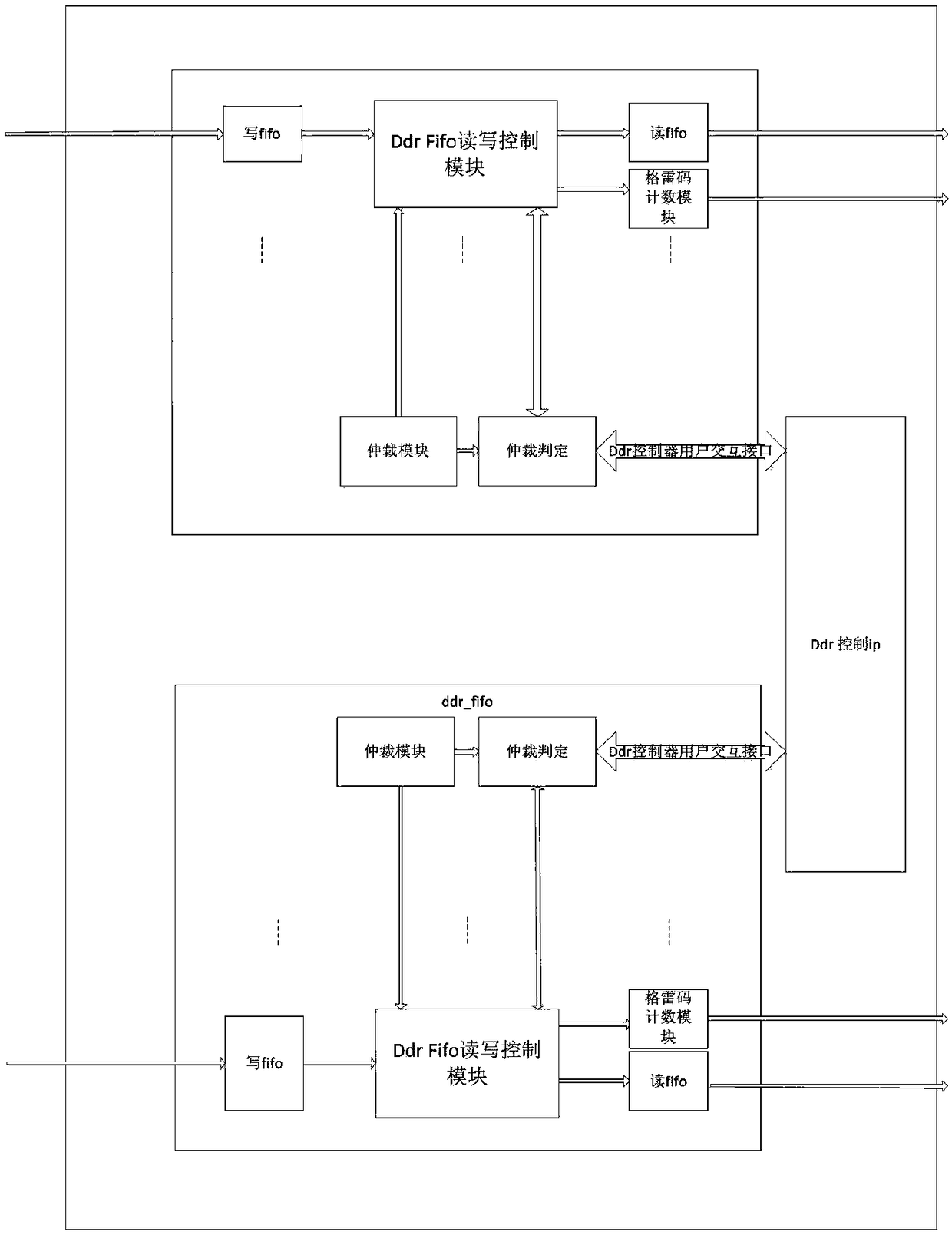

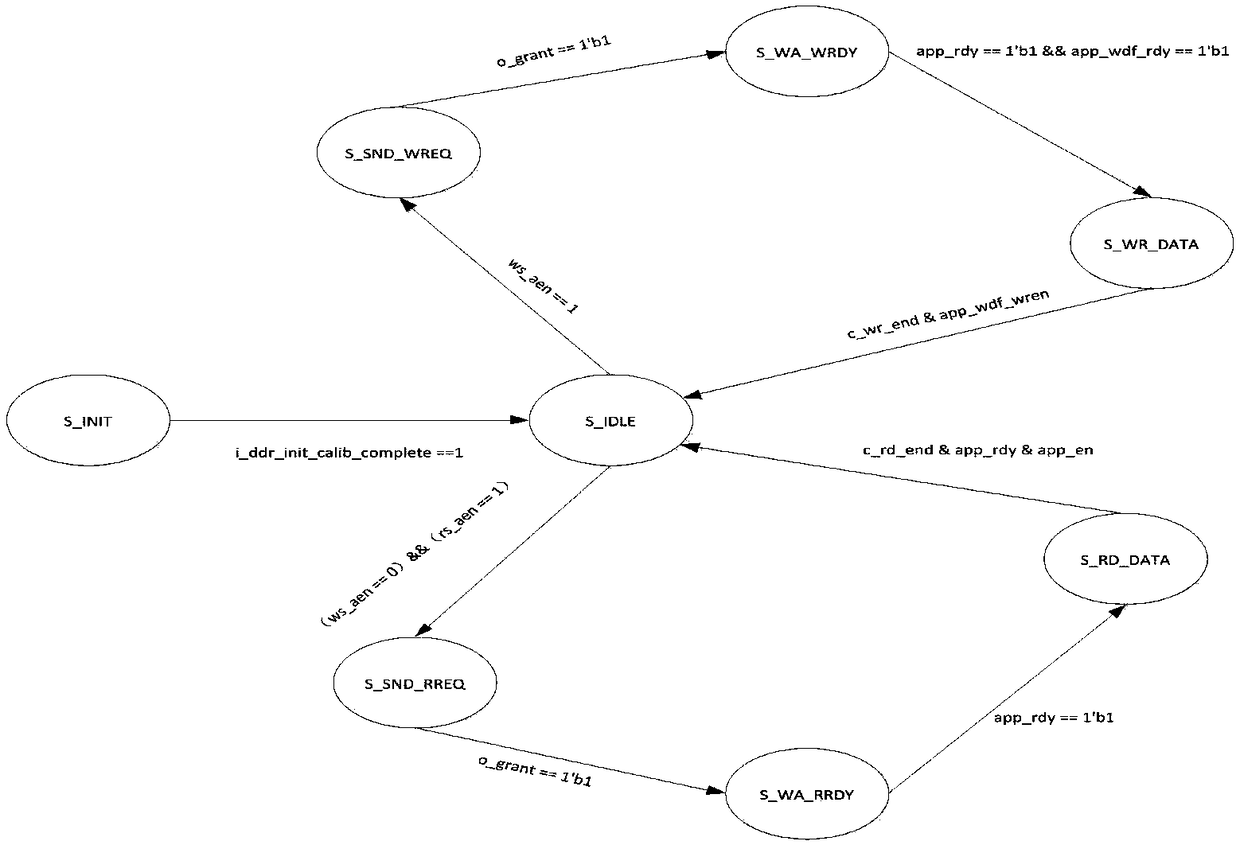

An FPGA implementation method of multi-channel data source DDR buffer

ActiveCN109271335AFlexible matching of address spaceFlexible change of memory spaceData conversionChannel dataFpga implementations

Owner:上海威固信息技术股份有限公司

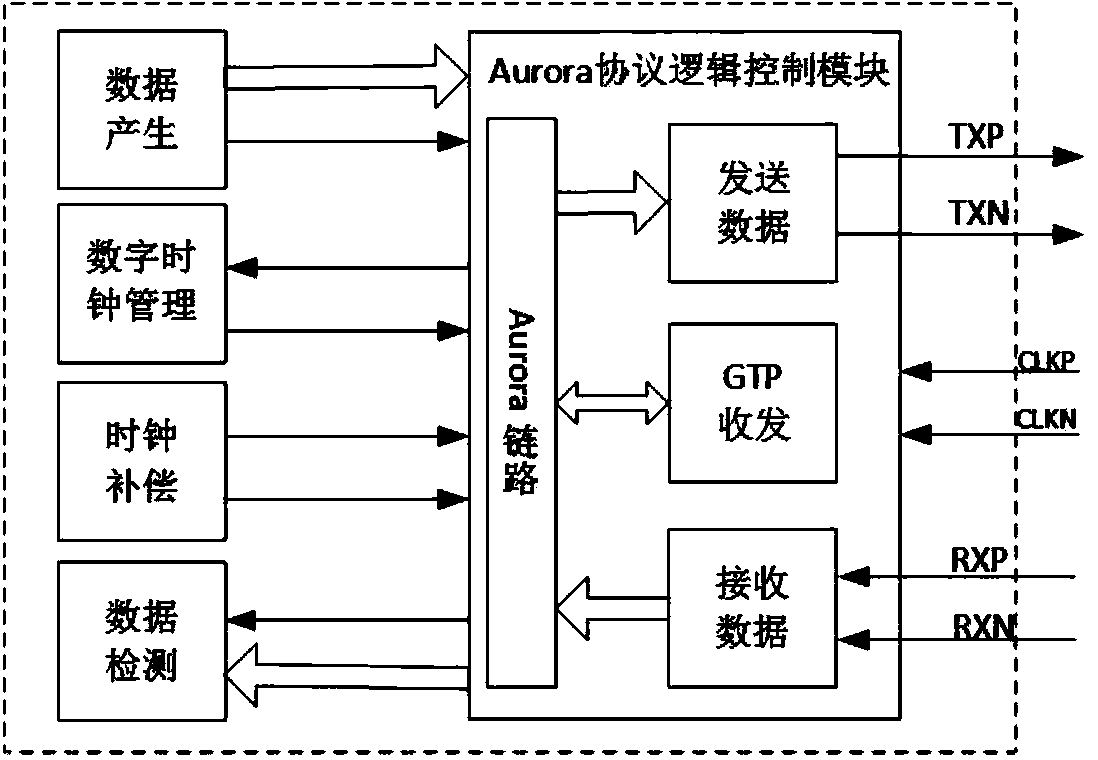

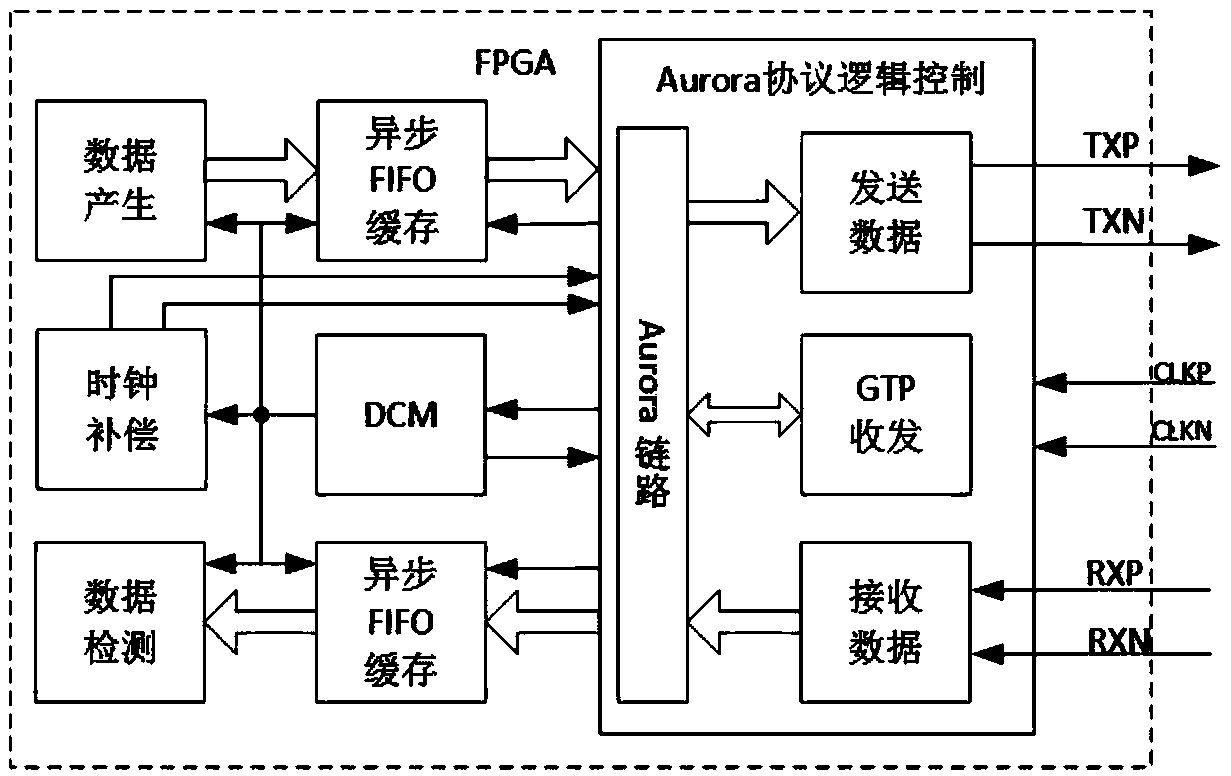

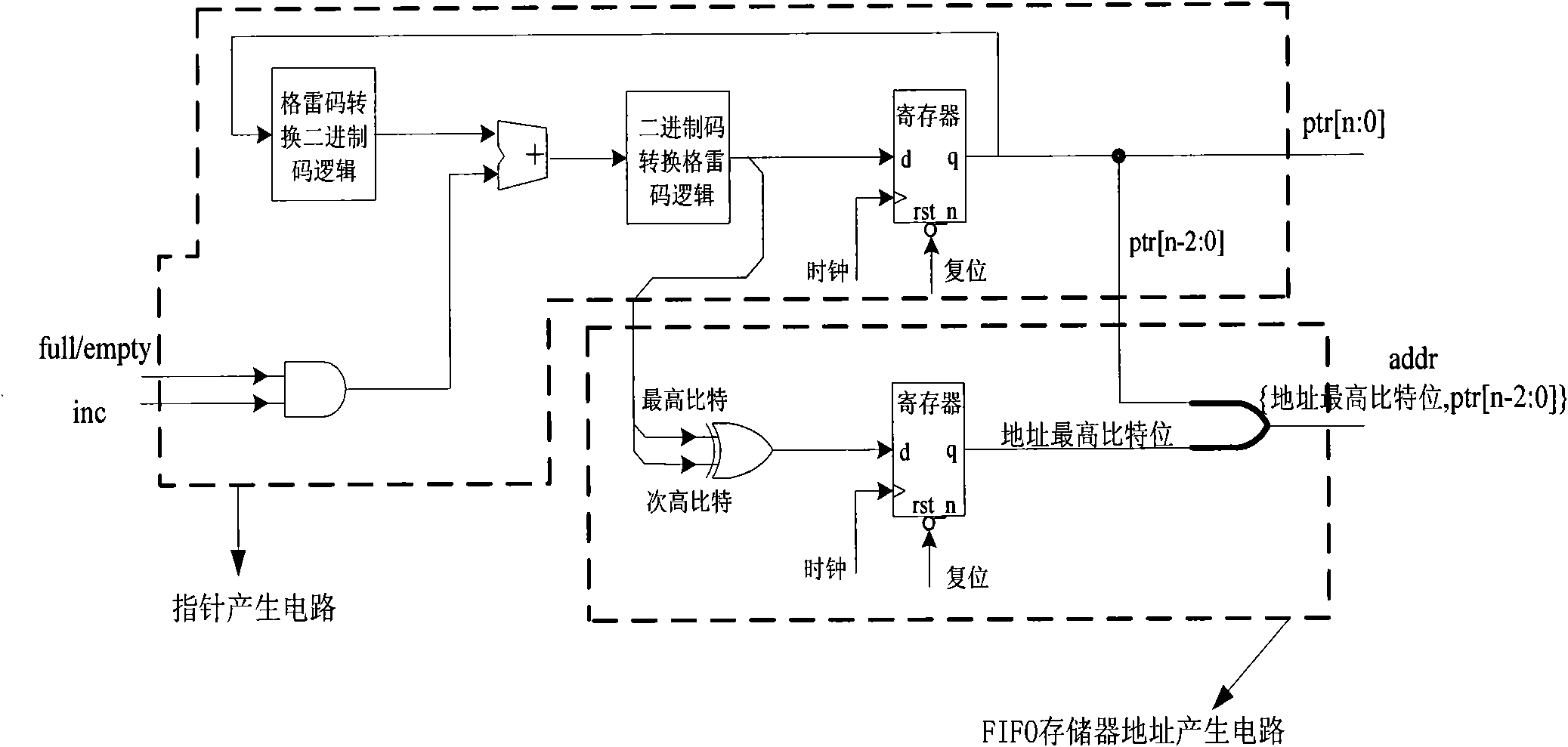

Fiber data transmission method based on asynchronous communication mode

ActiveCN104022828AReduce error rateReduce bit errorsError preventionFibre transmissionFiberAsynchronous serial communication

The invention relates to a fiber data transmission method based on an asynchronous communication mode. According to the method, an employed high speed data transmission circuit is realized by employing an internal function design mode of an FPGA chip, the realized logic functions comprise data generation, digital clock management, clock compensation, data detection, asynchronous FIFO caching based on Gray code counting and Aurora protocol logic control, and the functions of data generation, digital clock management, clock compensation, data detection and Aurora protocol logic control are realized by employing an FPGA standard setting mode. The method is characterized by realizing asynchronous FIFO caching based on Gray code counting, clock network generation and a transmission circuit function. The method employs a fiber data transmission method combining the asynchronous FIFO caching based on the Gray code counting mode with an Aurora protocol, and thereby data transmission accuracy is improved.

Owner:TIANJIN UNIV

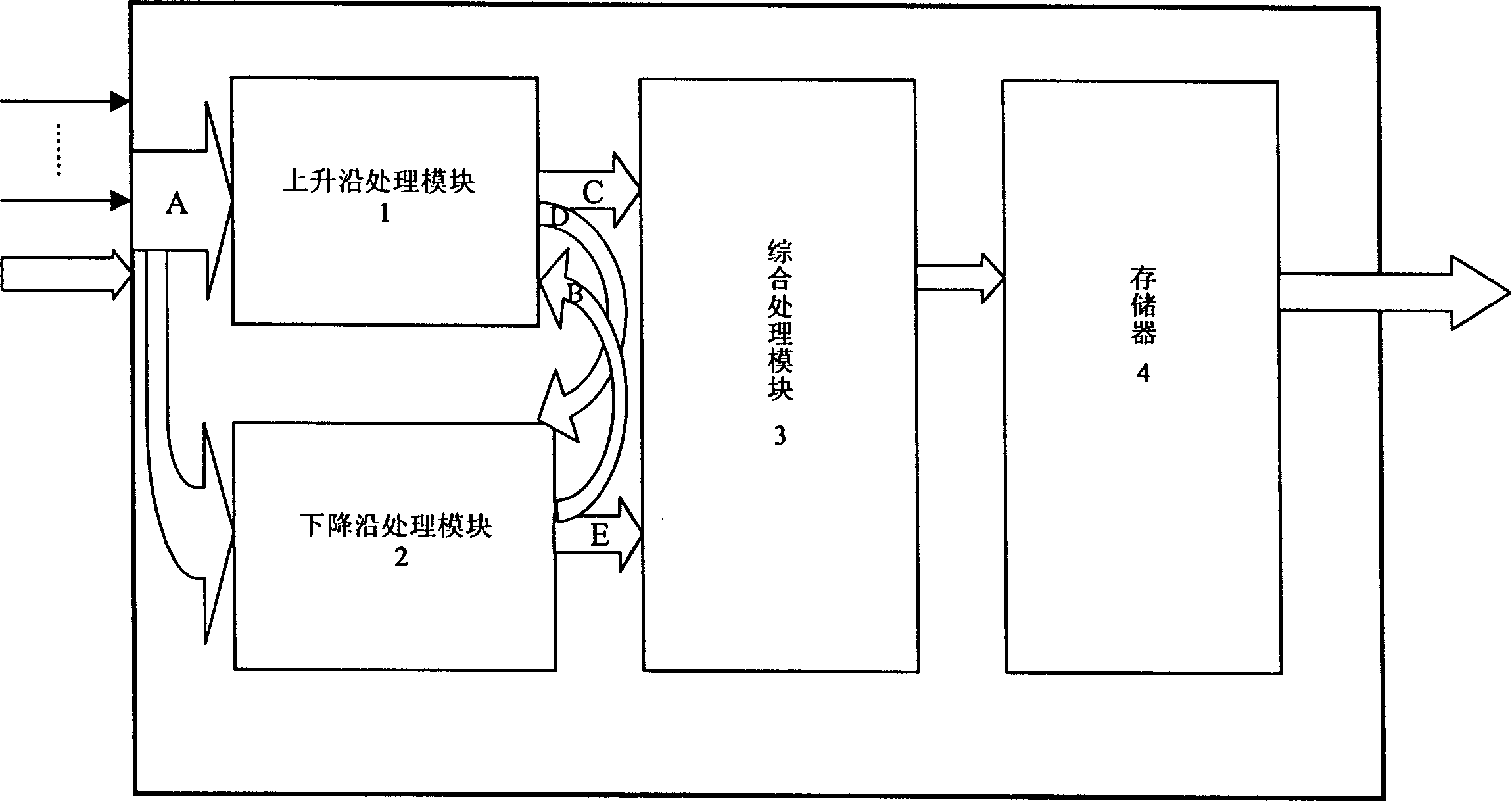

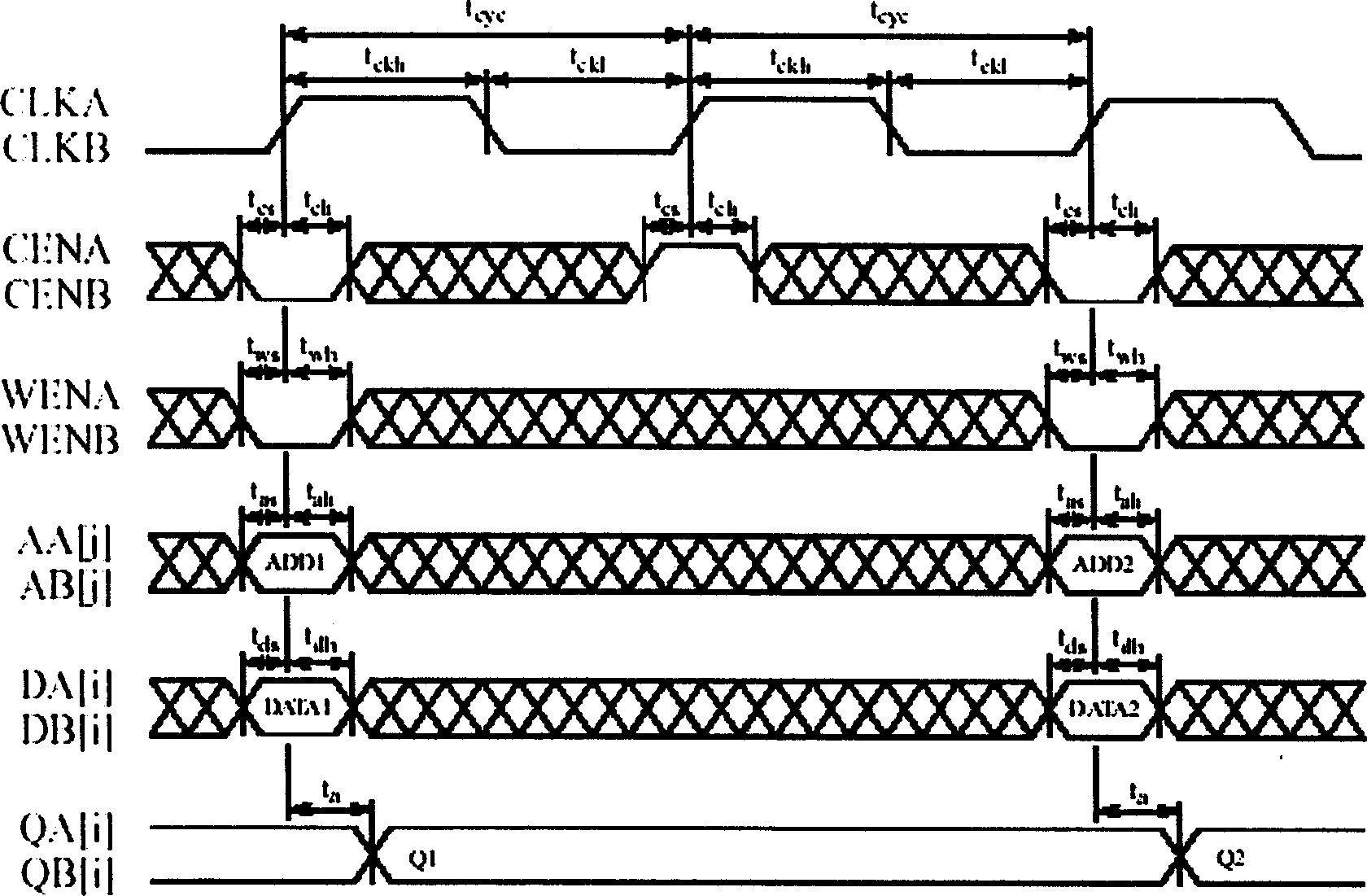

Non-synchronous first in first out controller using biedge sampling processing control signal

InactiveCN1517883ASampling is safe and stableSimple structureMemory adressing/allocation/relocationDigital storageLeading edgeControl signal

An asynchronous FIFO controller using dual-edge sampling to process control signal is composed of a leading edge processing module for using the leading edg eof clock signal as latch time to latch the first external control signal and ata, which along with the second external control signal and data from the falling edge processing module are used to output the third control signal and data, a falling edge processing module for using the falling edge of clock signal as latch time to latch the first external control signal and data, which along with the fourth external control signal and data from leading edge processing module are used to output the fifth control signal and data, an integrated processing module for outputting the sixth control signal and data, and memory for storing the sixth control signal and data.

Owner:ALI SHANGHAI

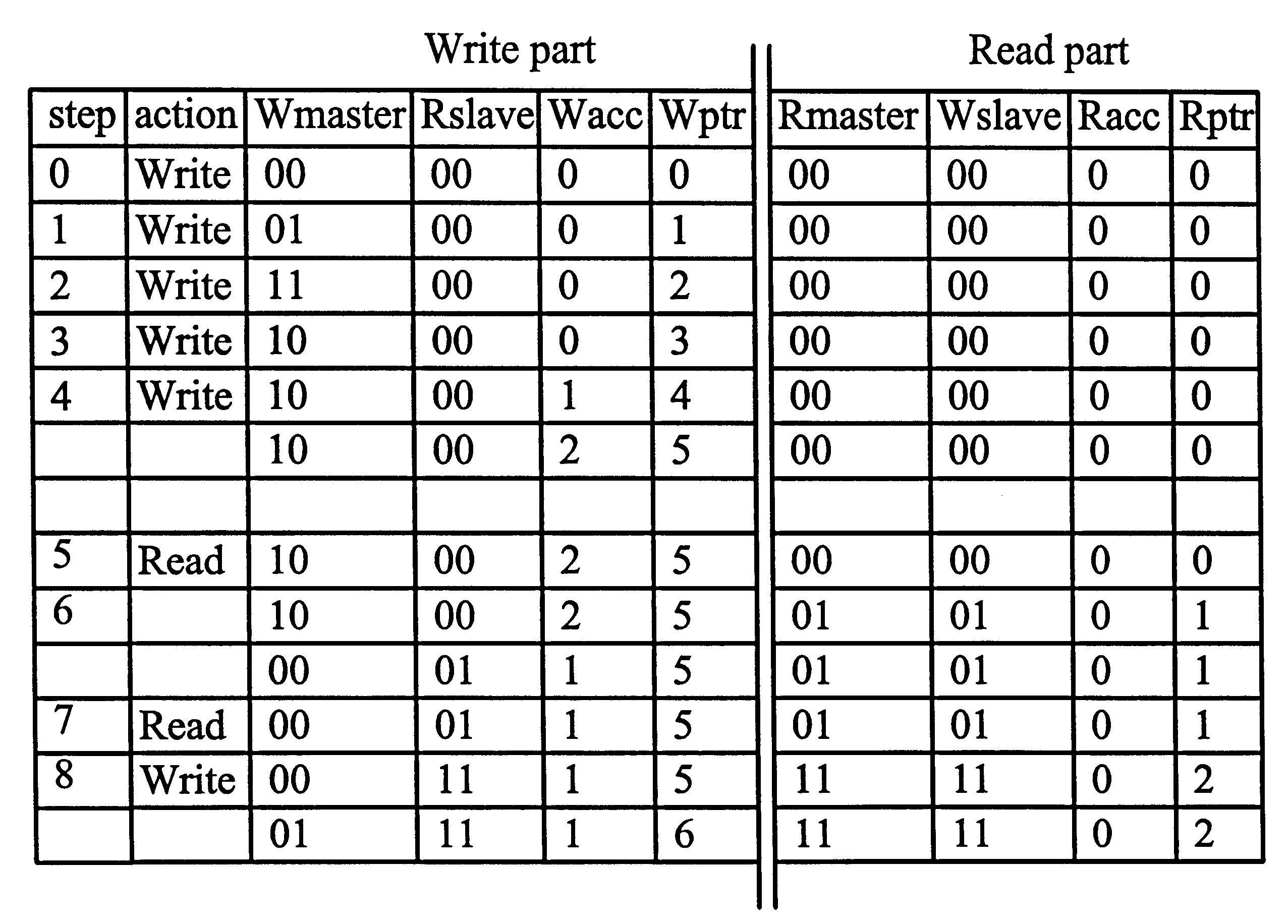

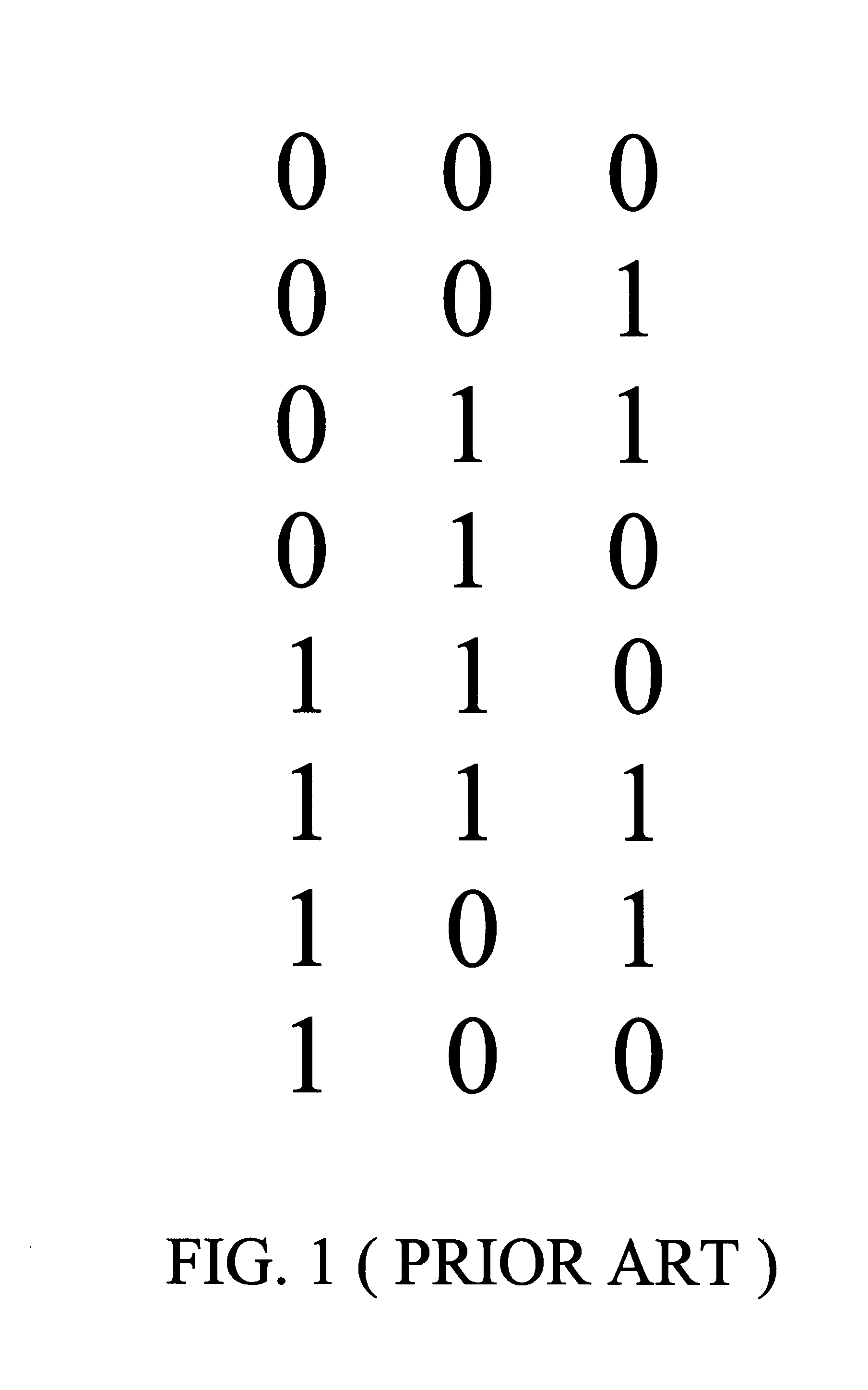

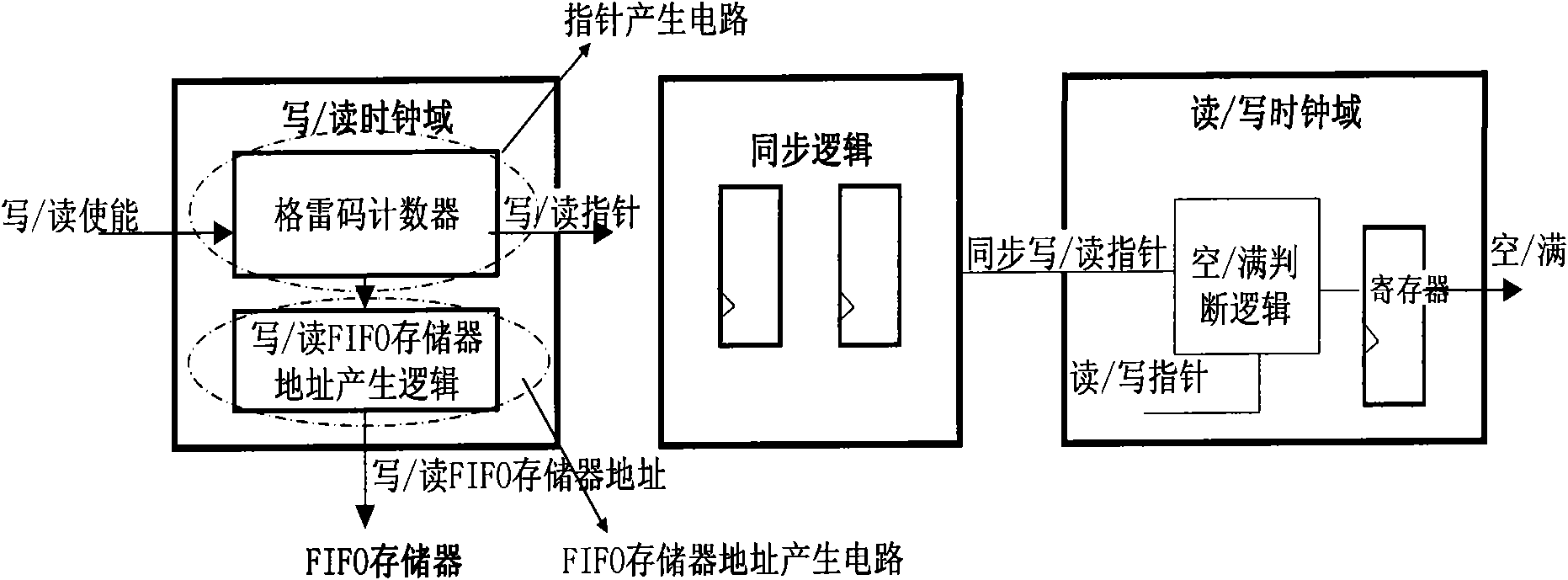

Apparatus and method of asynchronous FIFO control

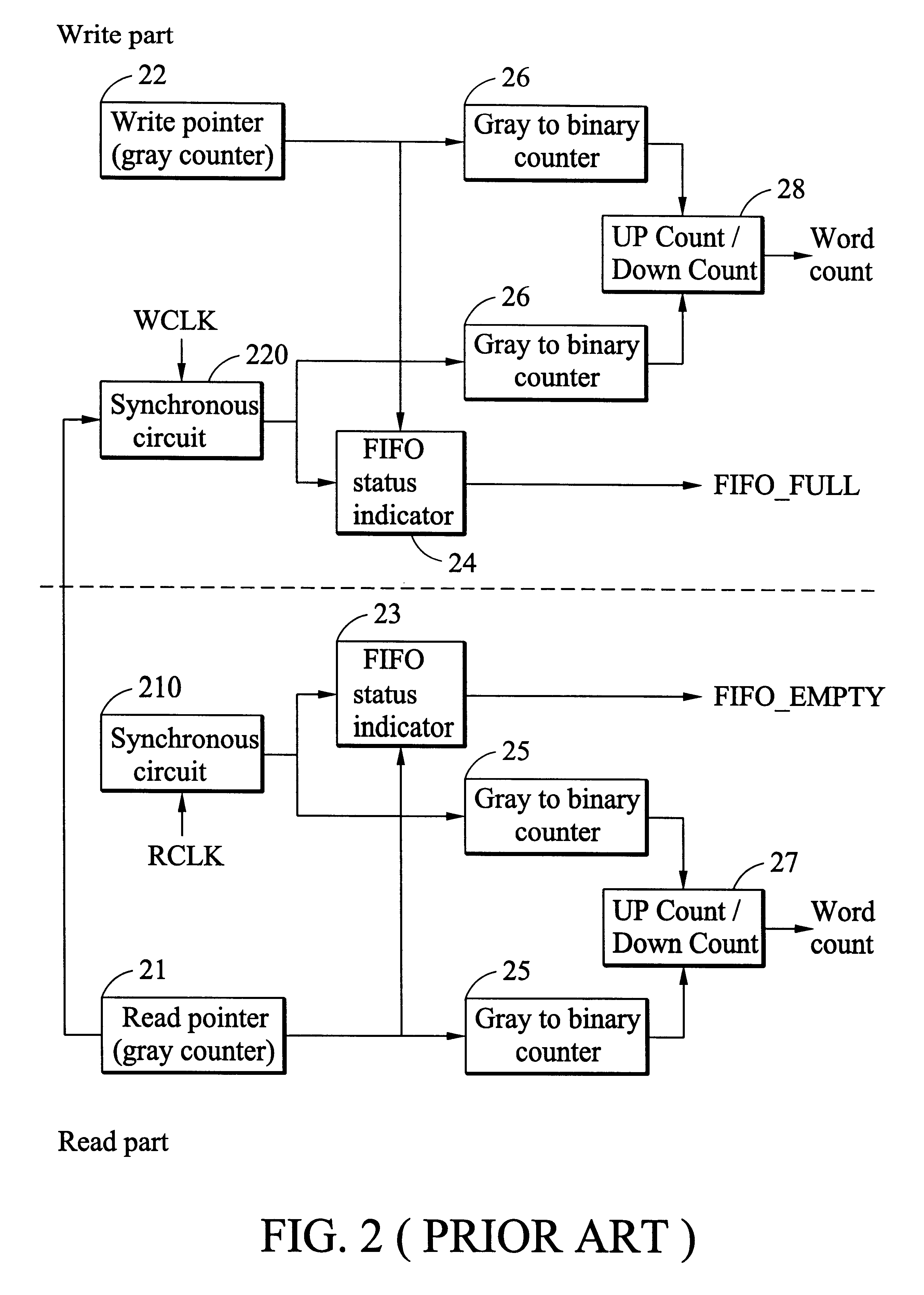

InactiveUS6845414B2Effectively control accessEffective controlCounting chain pulse countersDigital data processing detailsAsynchronous fifoGray code

An apparatus and method for controlling an asynchronous First-In-First-Out (FIFO) memory. The asynchronous FIFO has separate, free running read and write clocks. A number of n-bit circular Gray code counters are used to handshake the operation between read and write parts of the FIFO, wherein n is any integer more than one. Additional binary counters are used to accumulate the read and write overflows for the circular Gray code counters. When any circular Gray code counter is overflow, the read or write count is transferred to the respective binary counter for recording the FIFO accesses.

Owner:SILICON INTEGRATED SYSTEMS

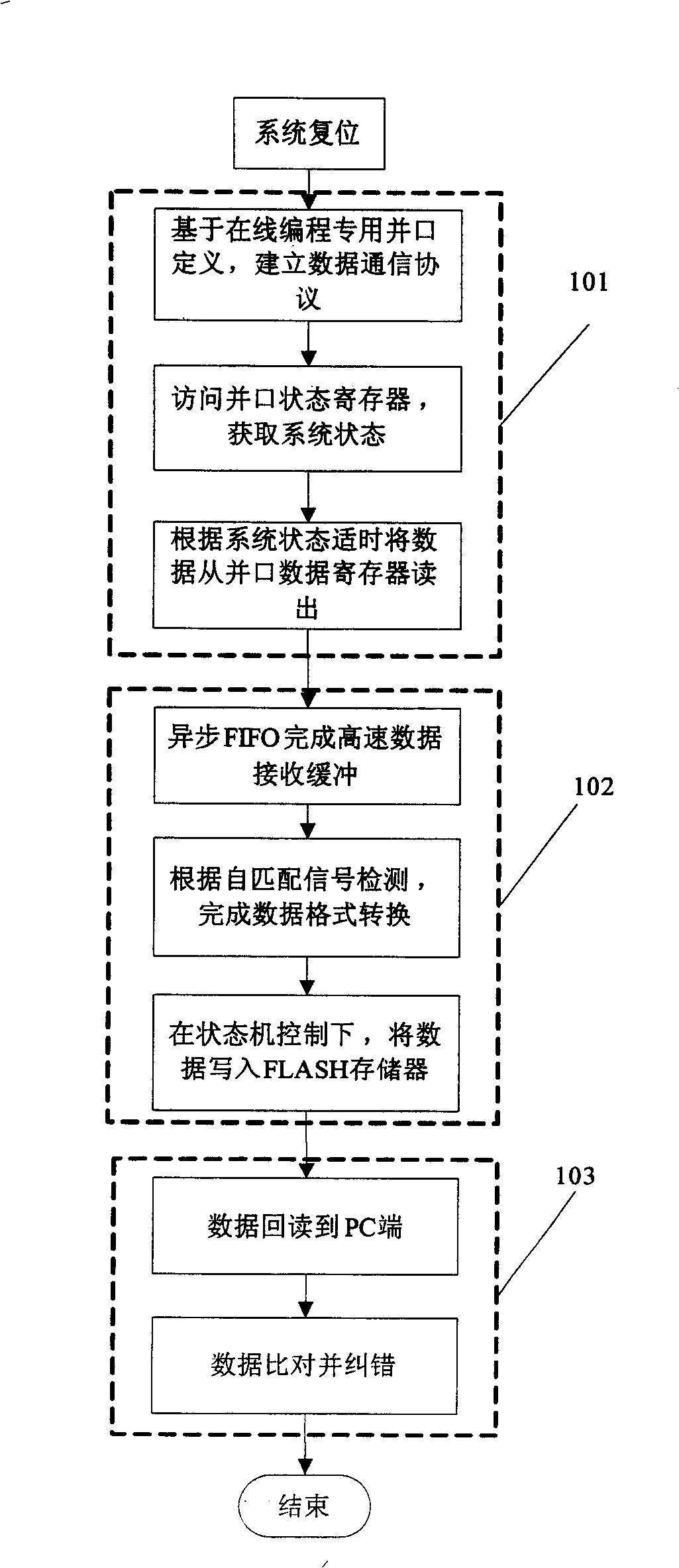

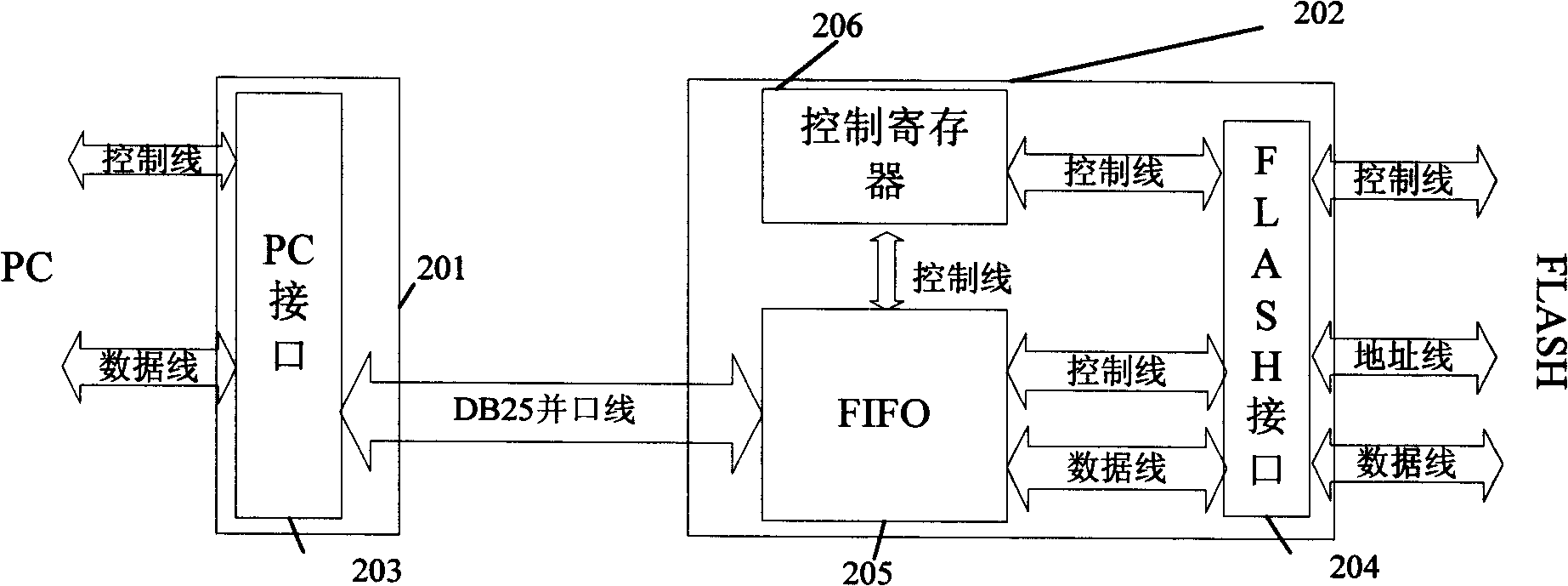

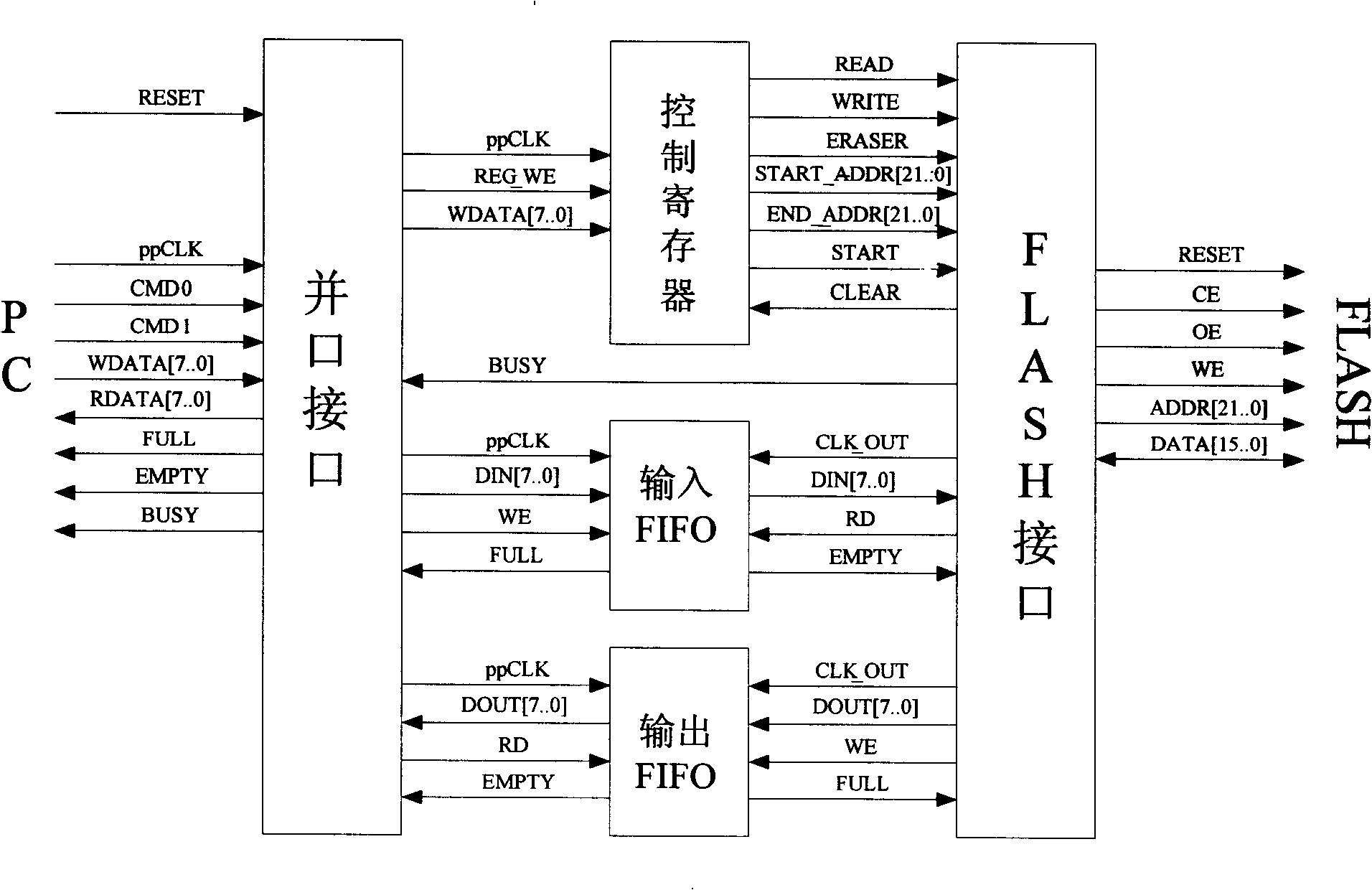

FLASH memory on-line programming method based on parallel port

InactiveCN101315812AWith online programmingMeet the needs of fast programmingRead-only memoriesAsynchronous fifoParallel port

The invention provides an online programming method for a FLASH memory based on a parallel port in the embedded system application field. In the method, a data communication protocol established based on a special parallel port base pin definition sends data by the parallel port, receives the data sent by a PC end by using asynchronous FIFO, writes in the FLASH memory after format conversion under the control of a state machine, and carries out verification to the data. The method of the invention is characterized by high and adjustable programming speed, can randomly revise the programming content online, does not need the participation of a CPU in work quickly, can select self-matching model with wide application range, and is especially applicable to the development stage of the embedded system.

Owner:SHANGHAI JIAO TONG UNIV

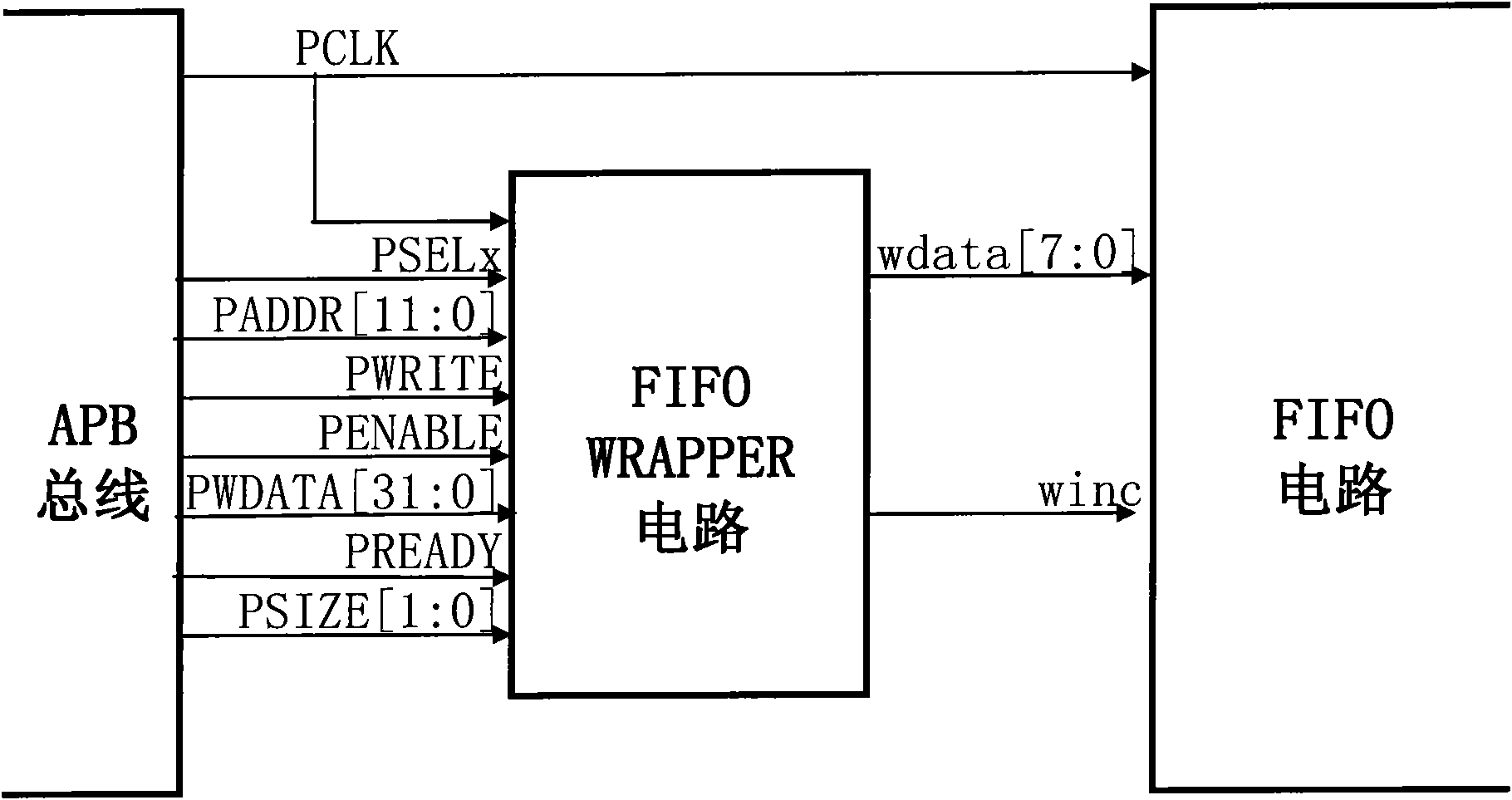

Reading and writing control method of asynchronous first-in first-out (FIFO) memory, circuit and system

ActiveCN102375720AIncrease profitEnsure correct synchronizationData conversionComputer architectureAsynchronous fifo

The invention discloses a reading and writing control method of an asynchronous first-in first-out (FIFO) memory, a circuit and a system. The method comprises: counting the data reading and writing times of asynchronous FIFO memory by using at least two gray code counters, wherein for different data widths, the data reading and writing times are counted by using different gray code counters; and producing a pointer to be used by a synchronous logic circuit for synchronous processing by using the gray code values of the gray code counters as code outputs. When the method, the circuit and the system are used, the reading and writing of data with different lengths can be supported, and the utilization rate of a bus is greatly improved while the correct synchronization is ensured.

Owner:RENESAS SEMICON DESIGN BEIJING CO LTD

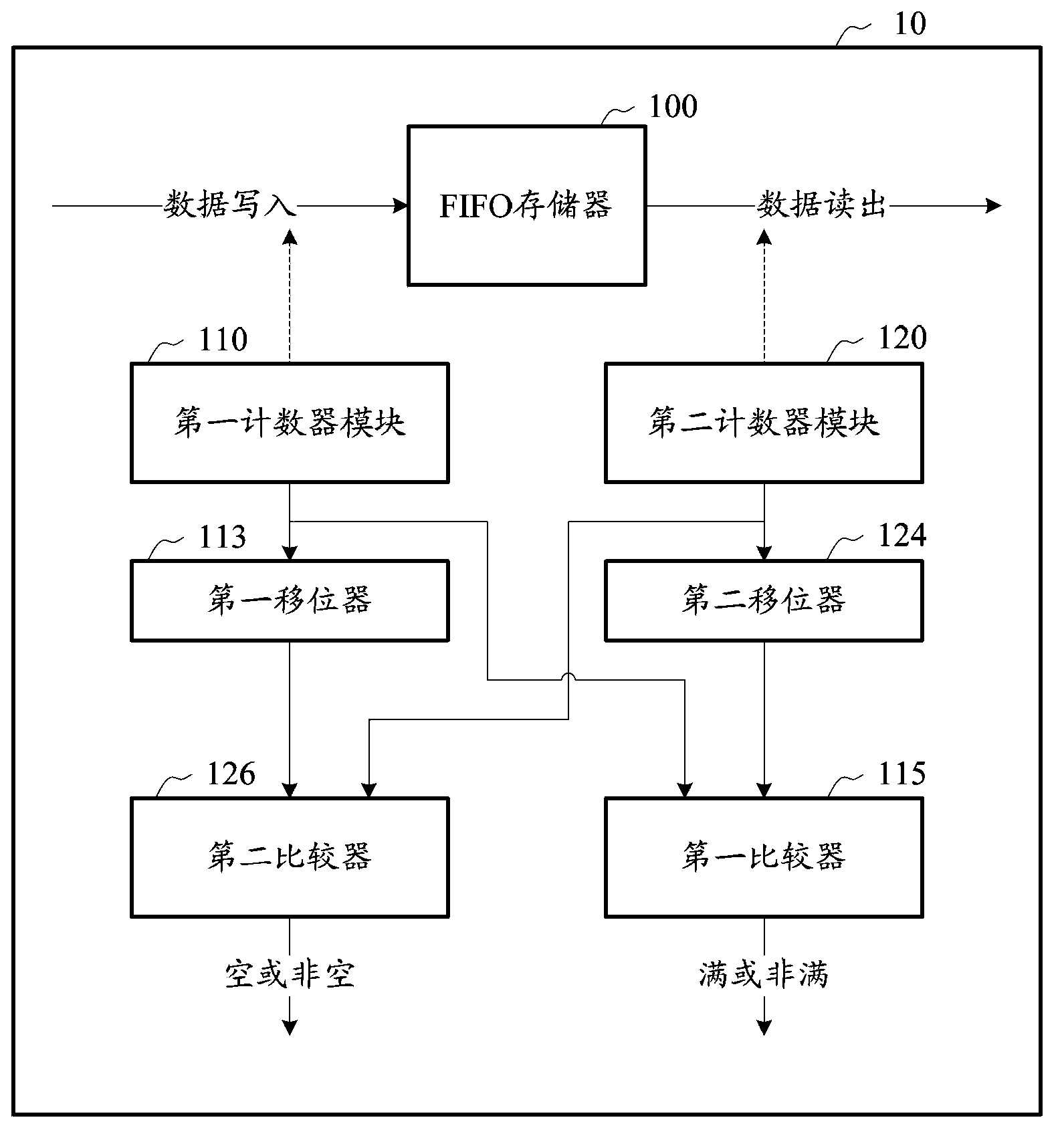

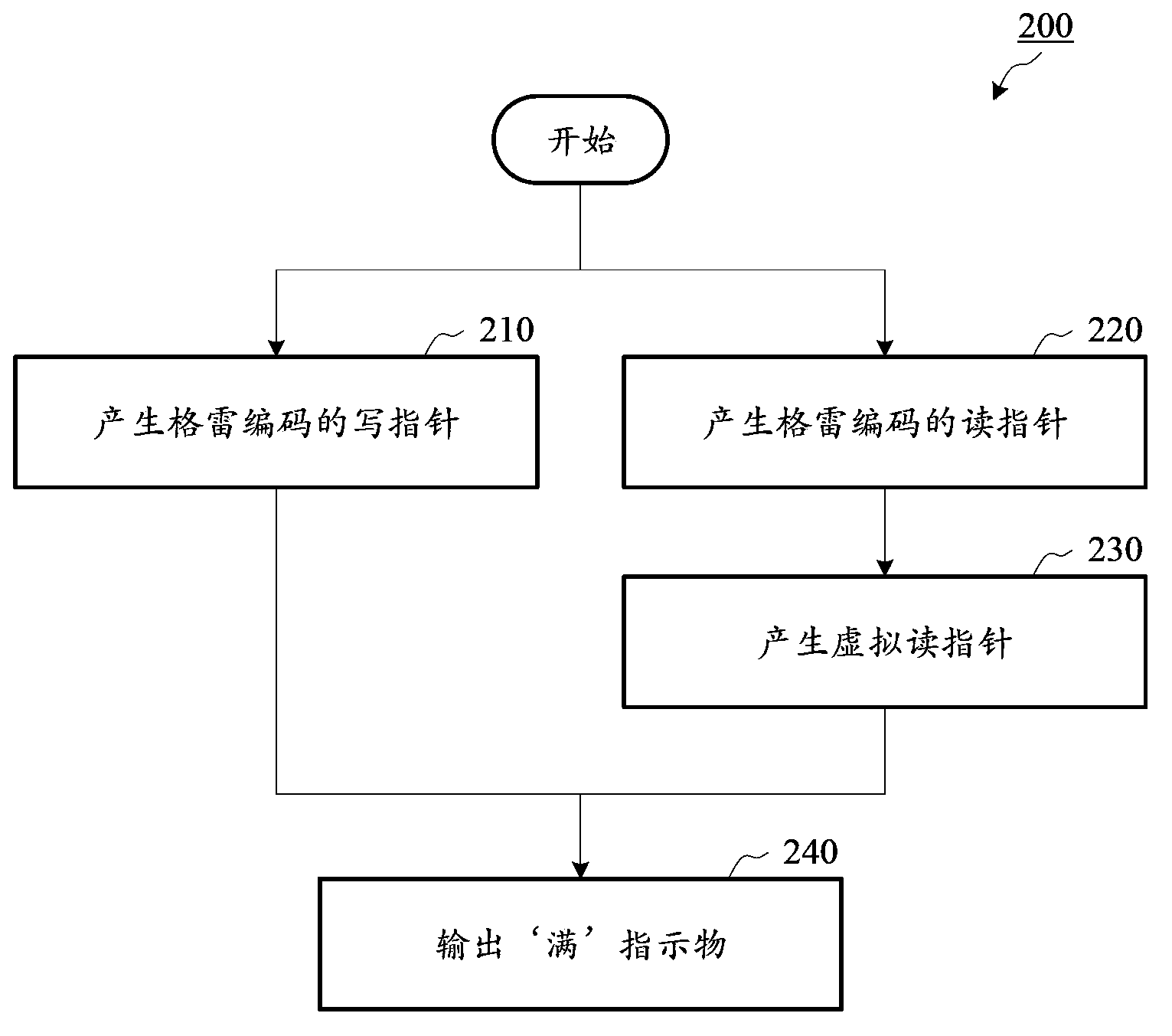

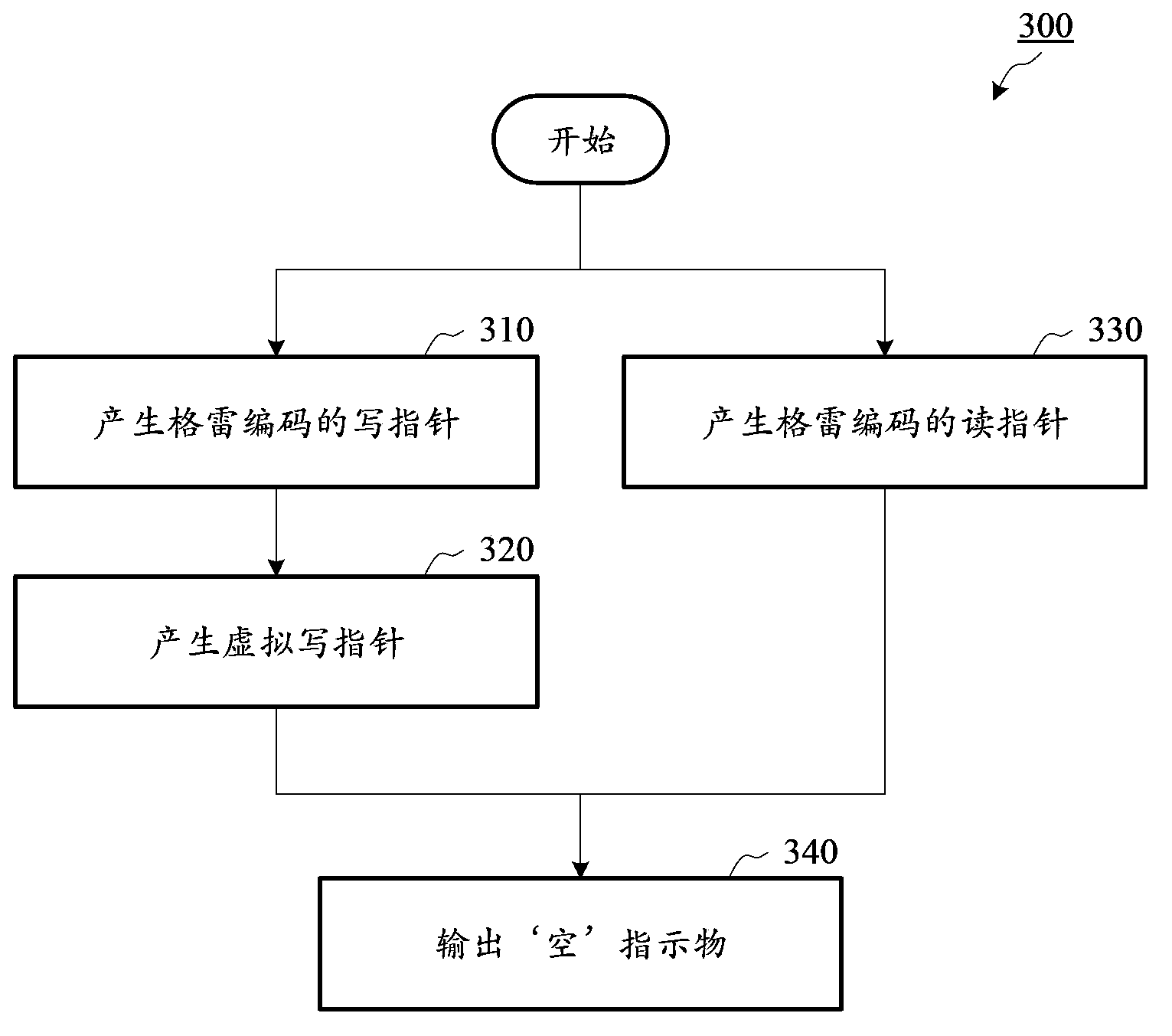

FIFO device and method thereof

The invention relates to an asynchronous FIFO device. The asynchronous FIFO device comprises at least one of an asynchronous FIFO storage device, a first counter module which is capable of producing Gray codes and provided with a writing pointer, a second counter module which is capable of producing Gray codes and provided with a reading pointer, a first shifter which is capable of producing a virtual writing pointer by applying a first delay value to the writing pointer, and a second shifter which is capable of producing a virtual reading pointer by applying a second delay value to the reading pointer, and at least one of a first comparator and a second comparator, wherein the first comparator can output an 'occupied' referent according to the comparison between the writing pointer and the virtual reading pointer, and the second comparator can output an 'unoccupied' referent according to the comparison between the reading pointer and the virtual writing pointer. Therefore, the asynchronous FIFO device is improved.

Owner:ALCATEL LUCENT SHANGHAI BELL CO LTD

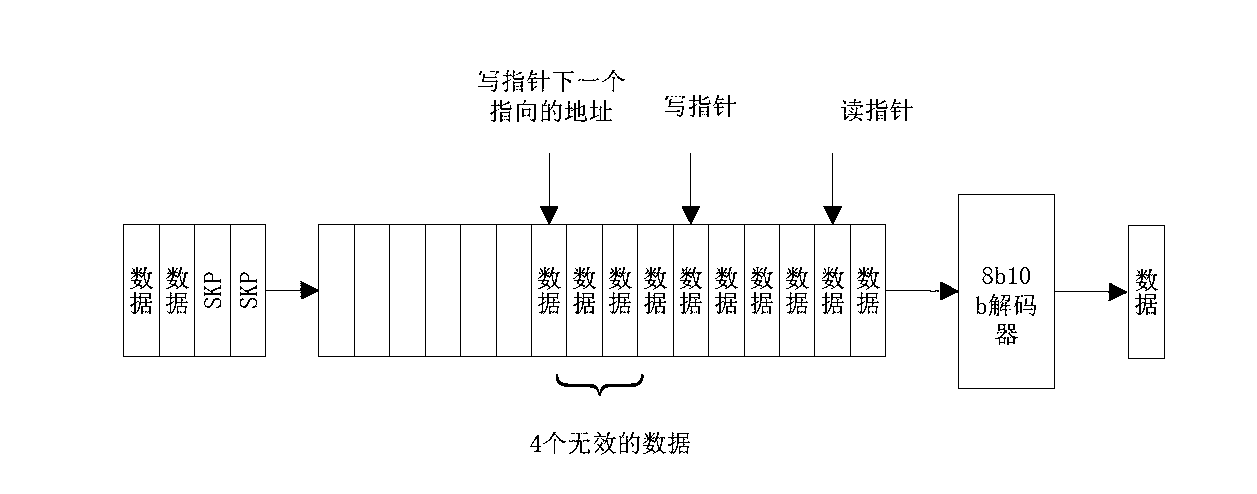

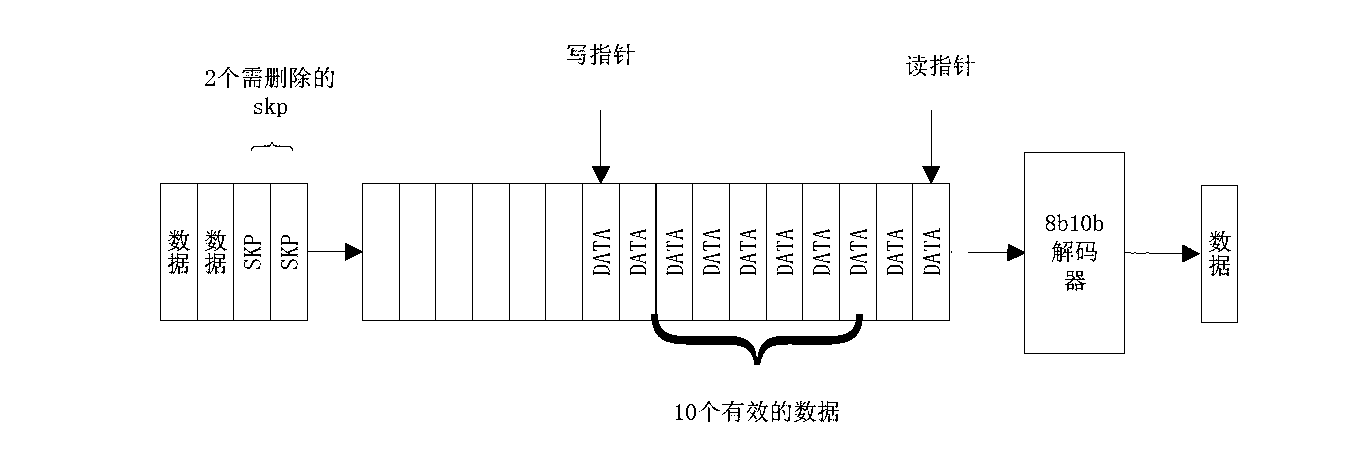

Elastic buffer structure and method applied to universal serial bus 3.0 (USB 3.0)

ActiveCN102708086AAchieve deleteAchieve insertionElectric digital data processingFrequency compensationClock rate

The invention discloses an elastic buffer structure and a method applied to universal serial bus 3.0 (USB 3.0). The elastic buffer structure comprises an input check module, a binary code and Gray code read-write pointer generation module, a synchronization module, a read-write control module, a threshold value monitoring module and an output control module. According to the protocol requirement of the USB 3.0, by means of the analysis of an action mechanism of elastic buffer, asynchronous first in first out (FIFO) which has innovative functions of writing pointer shield, point jumping, breakpoint saving and handshake, output control and the like is used for designing the elastic buffer, and the purpose of clock frequency compensation is well achieved; and according to the designed elastic buffer, parallel 40-bit data are used, the read-write clock frequency can reach 125 MHz.

Owner:无锡华大国奇科技有限公司

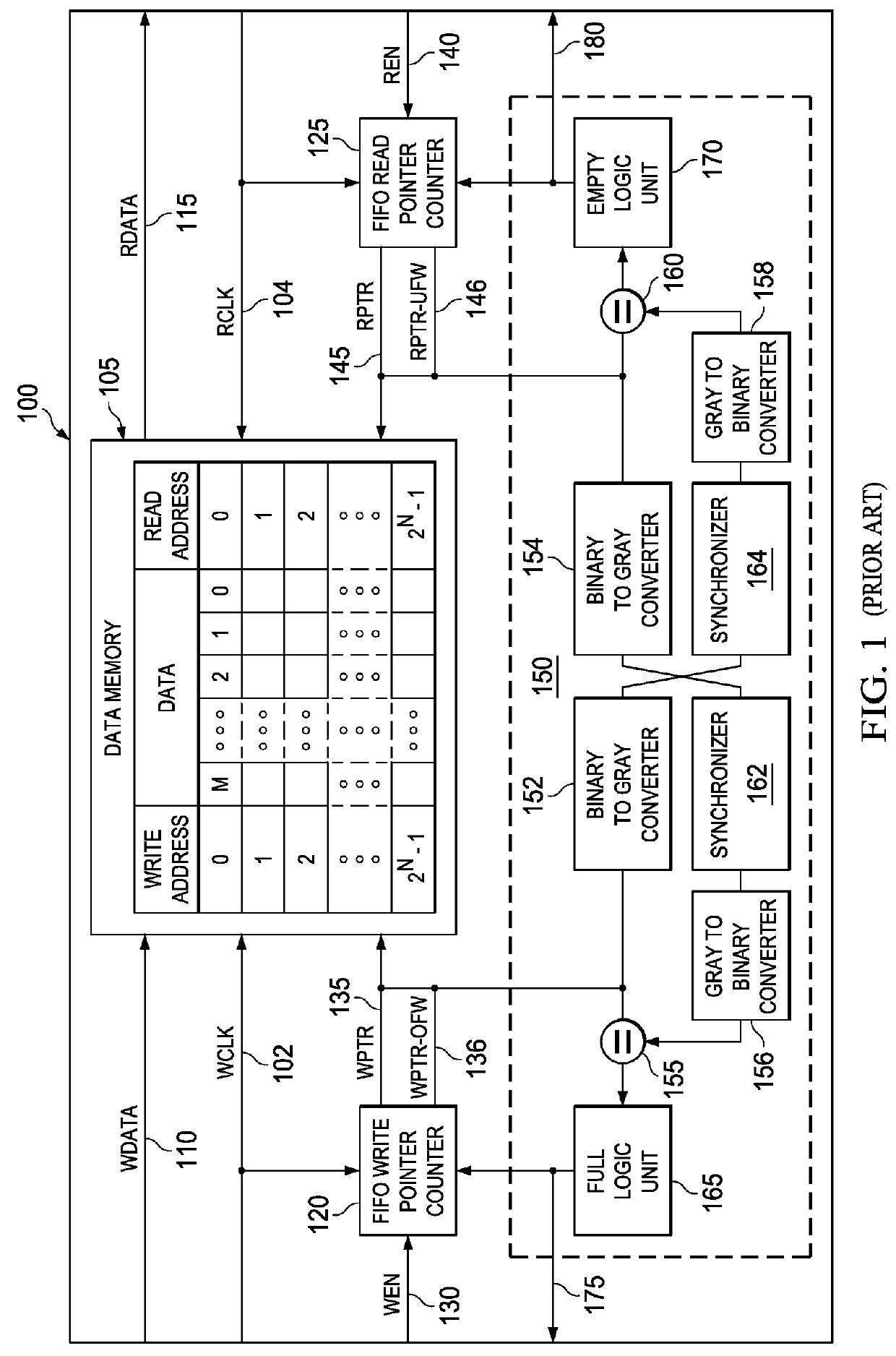

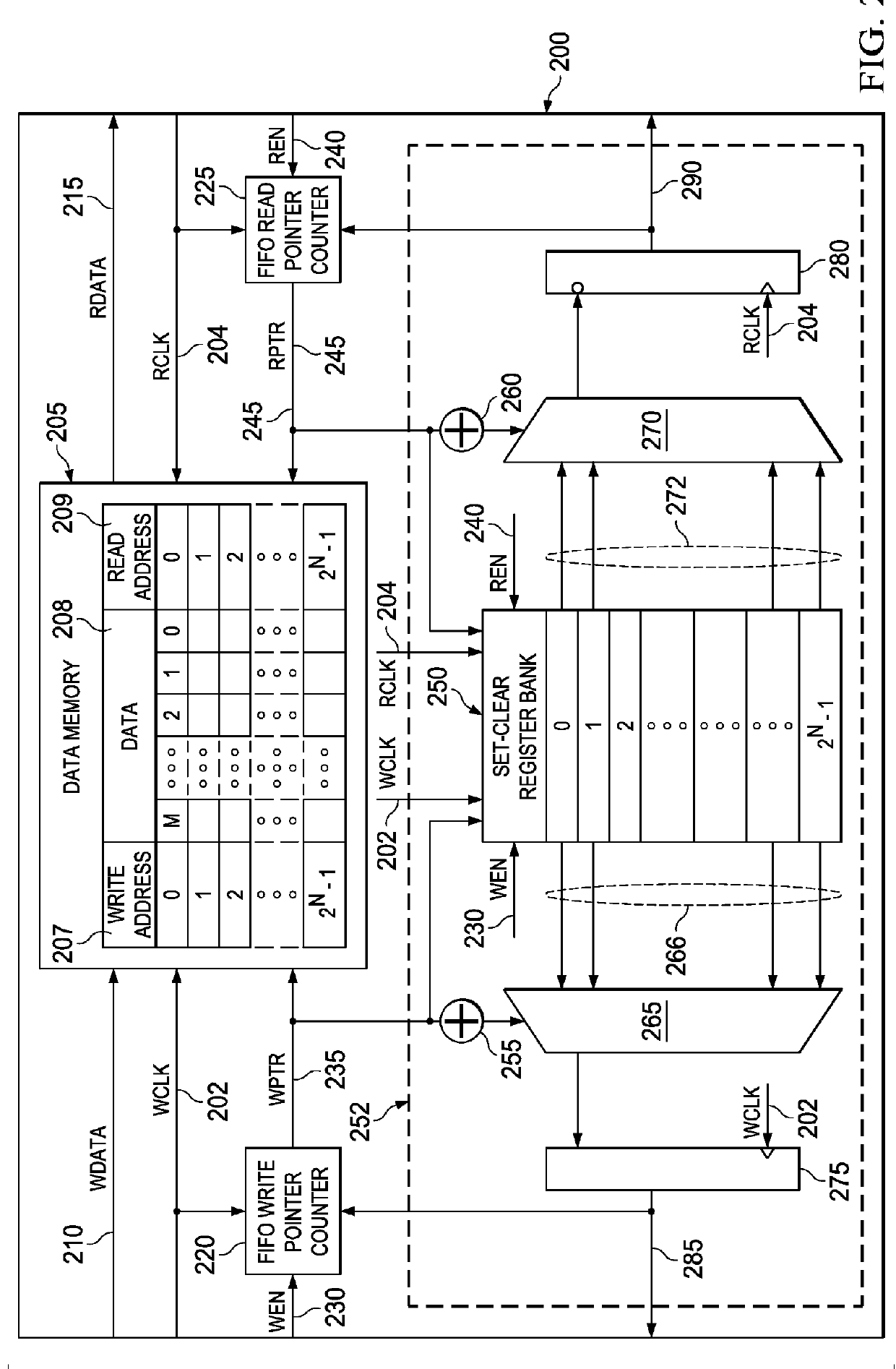

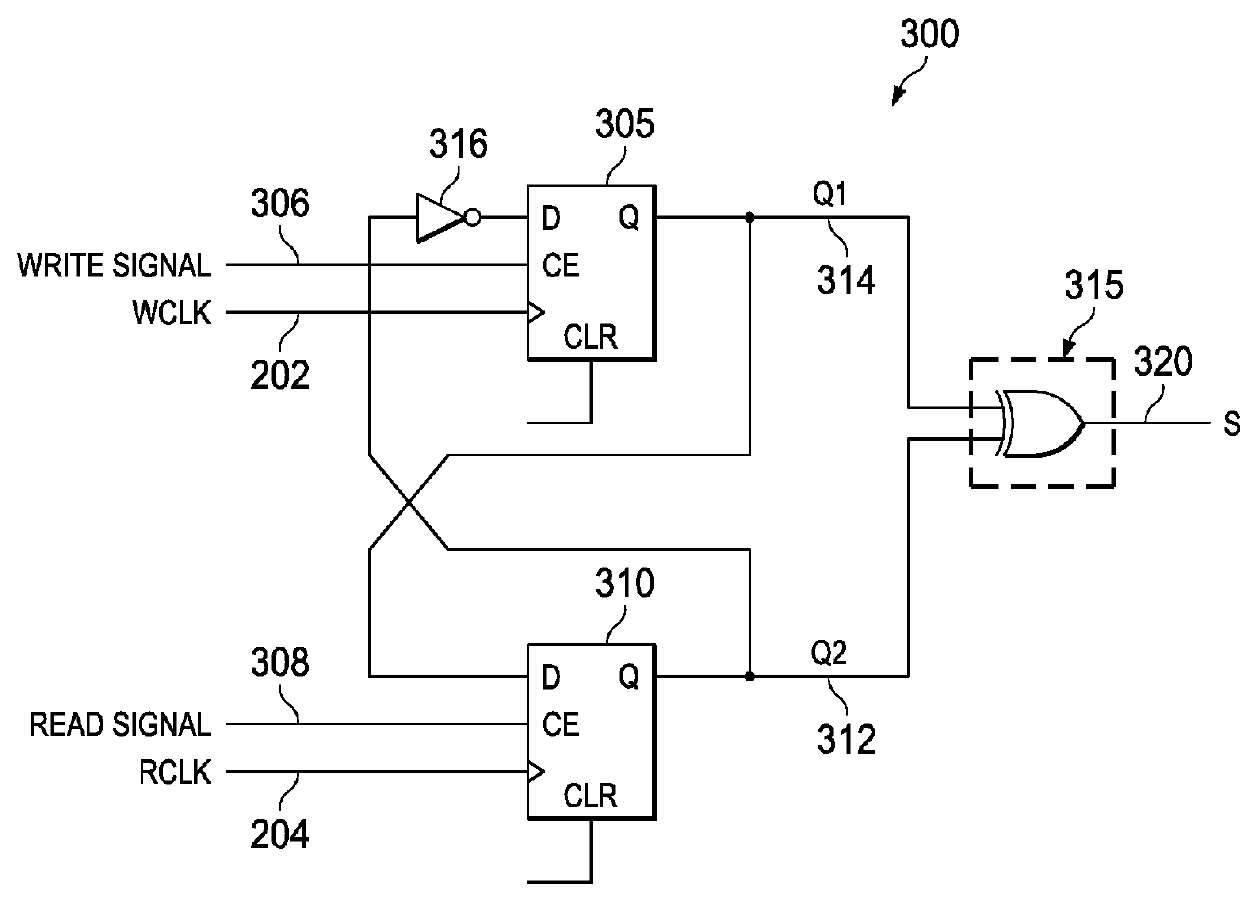

Method and apparatus for asynchronous FIFO circuit

The disclosure provides an asynchronous FIFO circuit that includes a data memory which is coupled to a write data path and a read data path. The data memory receives a write clock and a read clock. A FIFO write pointer counter receives a write enable signal and the write clock. The FIFO write pointer counter provides a FIFO write pointer signal to the data memory. A FIFO read pointer counter receives a read enable signal and the read clock. The FIFO read pointer counter provides a FIFO read pointer signal to the data memory. A control circuit receives the write enable signal, the read enable signal, the FIFO write pointer signal, the FIFO read pointer signal, the write clock and the read clock. The control circuit generates a memory full signal when the data memory is full and a memory empty signal when the data memory is empty.

Owner:TEXAS INSTR INC

Asynchronous FIFO apparatus and method for passing data between a first clock domain and a second clock domain and a second clock domain of a data processing apparatus

ActiveUS7315600B2Accurate samplingEnsure integritySynchronising arrangementSynchronous/start-stop systemsAsynchronous fifoFifo memory

An asynchronous FIFO apparatus includes a main FIFO memory, operable to store the data to be passed between the first and second clock domains, accessible from each clock domain under the control of an access pointer associated with that clock domain. For one or both of the clock domains, the amount of data accessible per clock cycle is variable. An auxiliary FIFO memory is associated with each clock domain in which the amount of data accessible per clock cycle is variable, and operable to store the access pointer used to access the main FIFO memory from its associated clock domain, and the access pointer being stored at a location of the auxiliary FIFO memory specified by an auxiliary access pointer. Routing logic passes the auxiliary access pointer to the other clock domain to enable that other clock domain to retrieve the access pointer stored in the auxiliary FIFO memory.

Owner:ARM LTD

Rebuilt-up device for digital asynchronous clock

InactiveCN101001228AReduce the effect of jitterReduce absolute accuracy requirementsTransmitter/receiver shaping networksBandpass filteringPhase difference

This invention discloses a digital asynchronous clock reconstructing device composed of a digital signal input interface, digital signal output interface, an asynchronous FIFO storage, a non-volatile storage, a general processor, a first clock distributor, a second clock distributor, a first bandpass filter, a second bandpass filter, a digital frequency synthesizer and a high speed crystal oscillator, in which, the clock inputting digit signals is independent of the clock outputting digital signals, and an asynchronous buffer system is used to lag the output data behind the input data, so that, when short period of frequency or phase differences exists, the DDS is used to re-generate output clock to distribute chips to further improve qualities of the output clocks, a general processor is used to tune the output frequency of the DDS to eliminate long time of frequency difference between input and output digital signal clocks to avoid overflow of the asynchronous buffer or empty.

Owner:BEIHANG UNIV

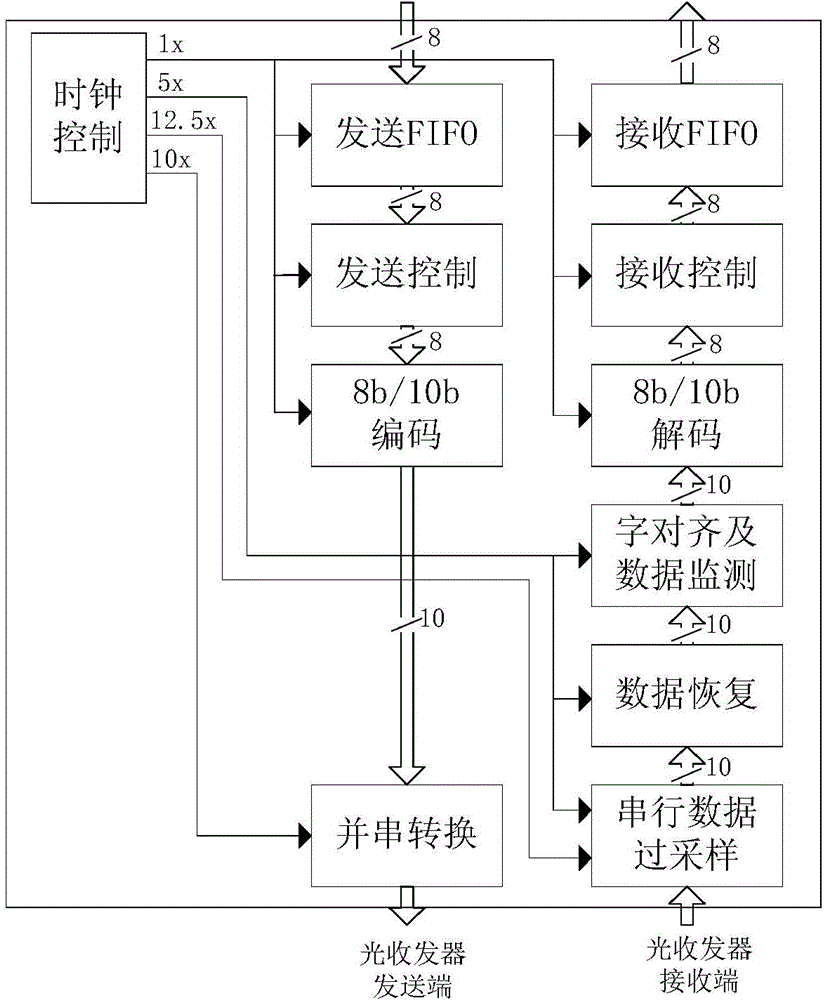

Design method of field bus optical fiber communication interface

InactiveCN104639410AEfficient sending and receivingImprove usabilitySynchronising arrangementBus networksCommunication interfaceTransceiver

The invention discloses a design method of a field bus optical fiber communication interface. The method includes: operations interfaces provided to a data link layer are two asynchronous FIFOs, and the two asynchronous FIFOs are a transmitting FIFO and a receiving FIFO; the number of 0 and 1 in the data of the transmitting FIFO is balanced after the data is subjected to 8b / 10b encoding, and the high-speed serial data stream, after parallel-serial conversion, of the encoded 10bit parallel data is transmitted through an optical transceiver to complete a data transmitting function; the serial data oversampling module of a receiving part samples the received serial data and performs data recovery, the recovered data is transmitted to a word alignment and data monitoring module to obtain aligned 10bit data, a 8b / 10b decoding module is used to recover the 10bit data into 8bit data, and the data is written to the asynchronous receiving FIFO through a receiving control module to complete a data receiving function.

Owner:SHENYANG GOLDING NC & INTELLIGENCE TECH CO LTD

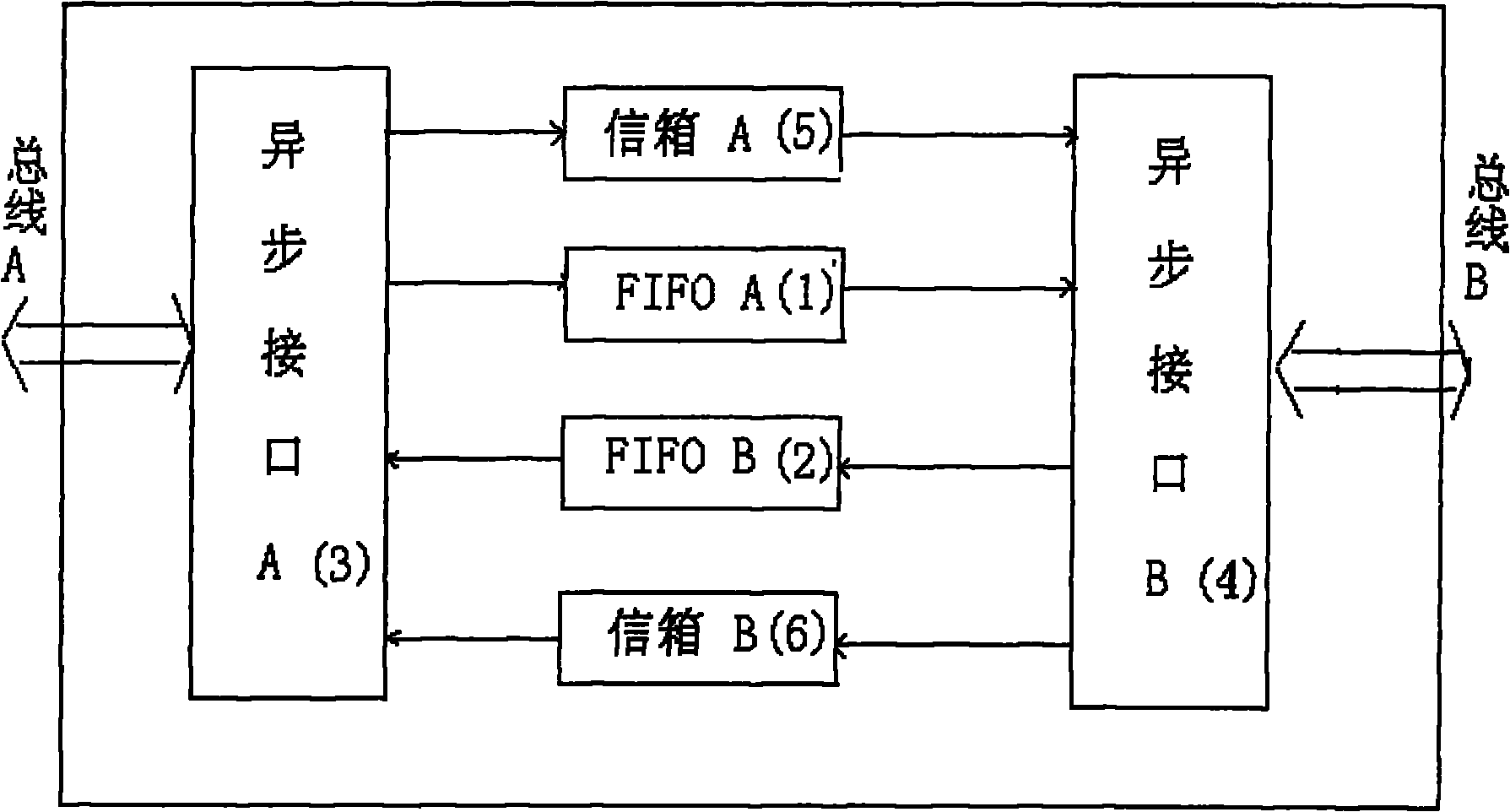

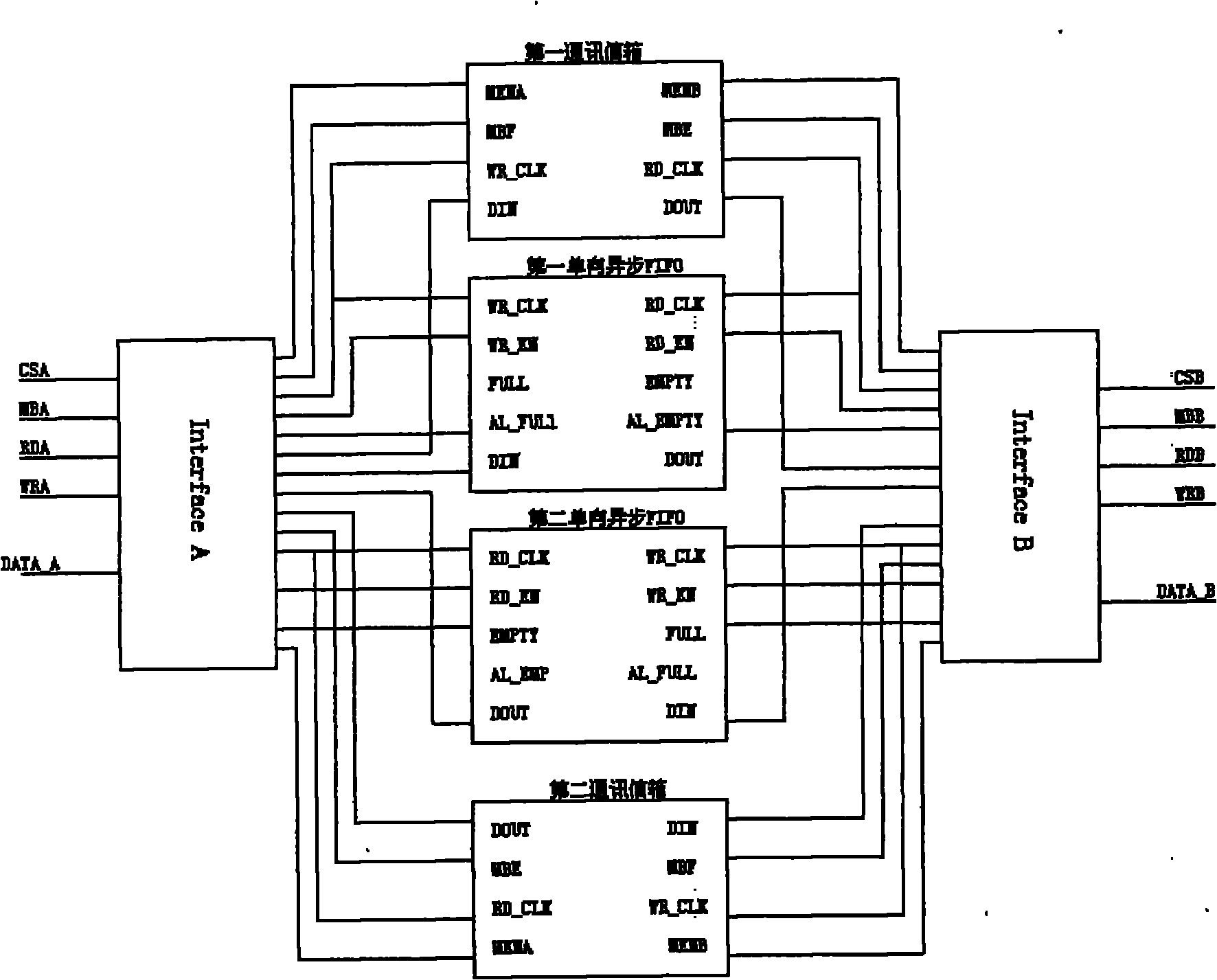

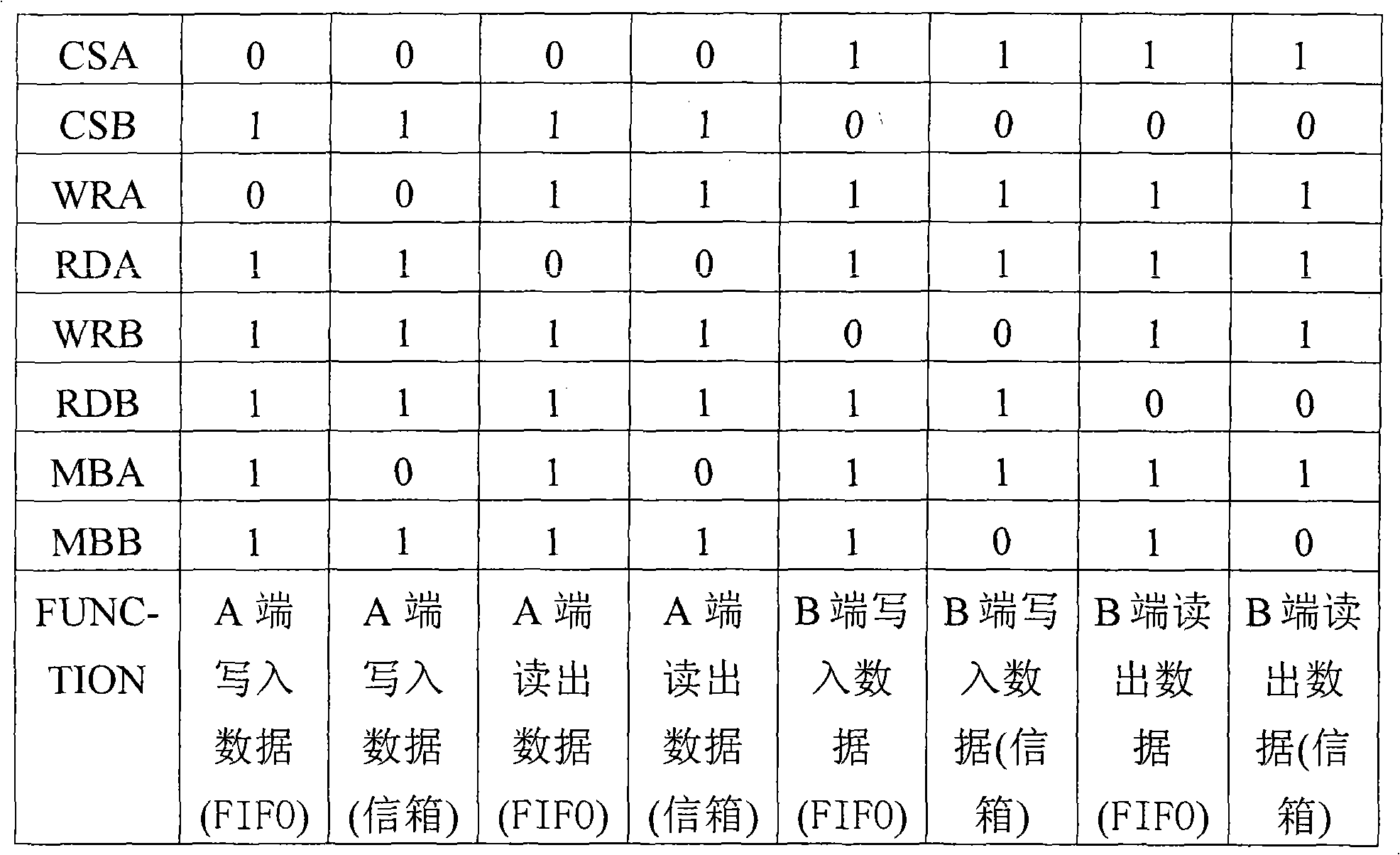

Bidirectional high speed FIFO storage implemented on the basis of FPGA

The invention belongs to the storage technical field and discloses a bidirectional high speed FIFO storage implemented on the basis of FPGA. The bidirectional high speed FIFO storage comprises a first asynchronous bus interface module, a first communication box, a first unidirectional asynchronous FIFO read-write module, a second asynchronous bus interface module, a second communication box and a second unidirectional asynchronous FIFO read-write module. The function of the bidirectional high speed FIFO storage is similar to that of SN74ABT3614 produced by Texas instruments, and programmable output line width, synchronous or asynchronous input output clock and bidirectional mail box communication function can be realized. The invention has the advantages that: FPGA is utilized to realize bidirectional FIFO module, steady speed is fast, implementation is easy and occupying resource is less, occupancy rate of programmable logical module in Xilinx Spartan3 series FPGA is less than 7%, and integration with other logical functions is easy, thus being capable of effectively improving system integration, reducing system size and reducing power consumption.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

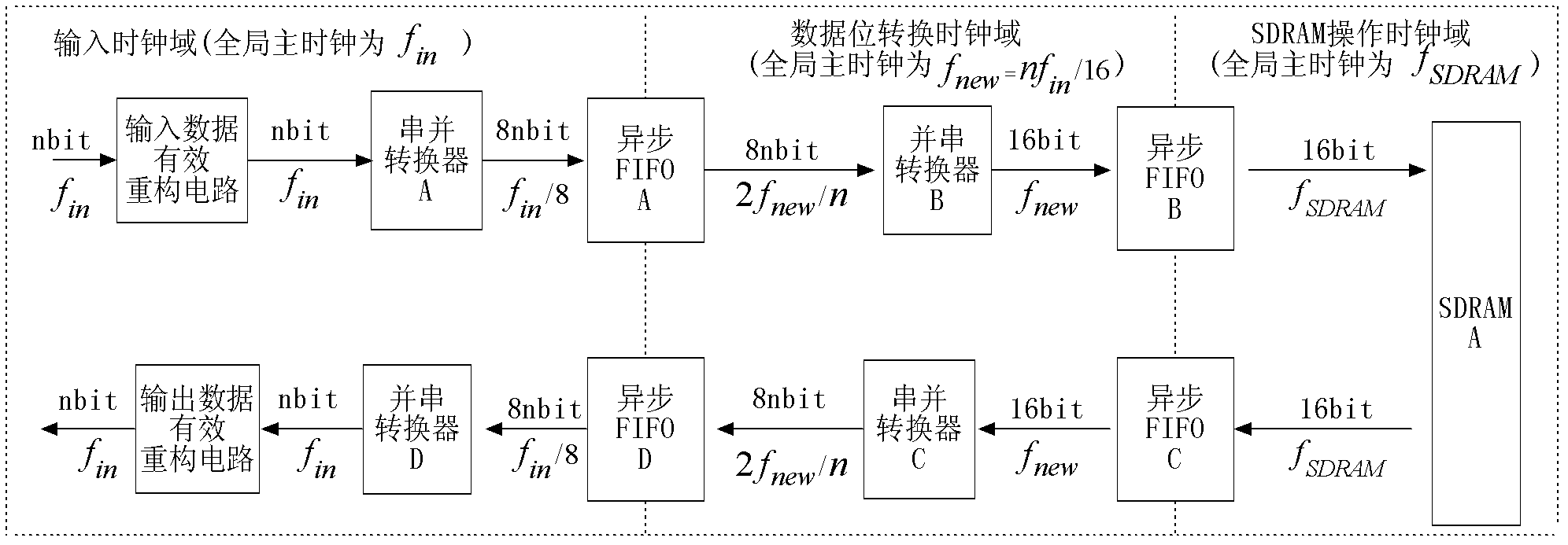

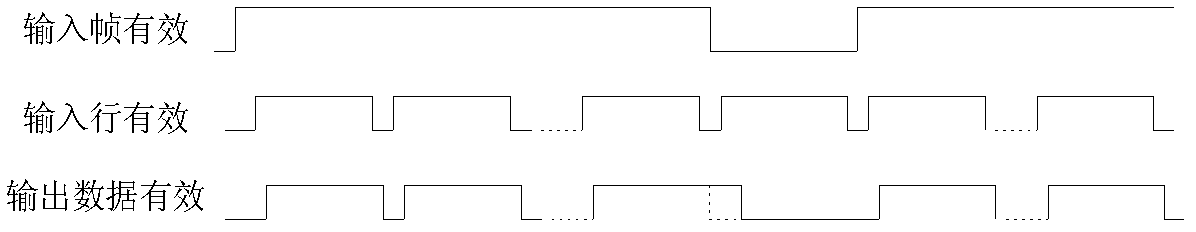

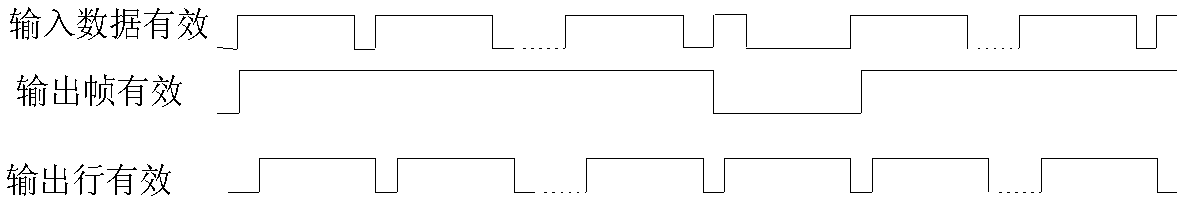

Multi-piece area array CCD (Charge Coupled Device) screening test system

InactiveCN102497575AReduce the frequency of read and write operationsReduce clock frequencyTelevision systemsIndividual semiconductor device testingSynchronous dynamic random-access memoryEngineering

The utility model relates to a multi-piece area array CCD (Charge Coupled Device) screening test system which is used for solving the problems that when being in the temperature circulation and power aging screening test, the existing area array CCD works continuously and the test period is long. When the system is used for shooting, the image data of each piece of area array CCD is integrated by taking every four pieces as a unit, so that the number of input data channels is reduced to be one fourth that of the original chips, the input data channels are stored in an SDRAM (Synchronous Dynamic Random Access Memory) in parallel, and after the shooting is finished, the image data is read channel by channel and stored in a hard disk of a host by a capture card so as to be distinguished. According to the multi-piece area array CCD screening test system, effective signals of the input and output image data are reconstructed, and a line blanking period and a frame blanking period are utilized fully so as to reduce the writing and reading frequencies; and three clock domains, two groups of asynchronous FIFO (First In First Out) and two groups of deserializers and serializers are adopted for realizing non-integer-time stable and reliable conversion of image data bits under the condition of high speed.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

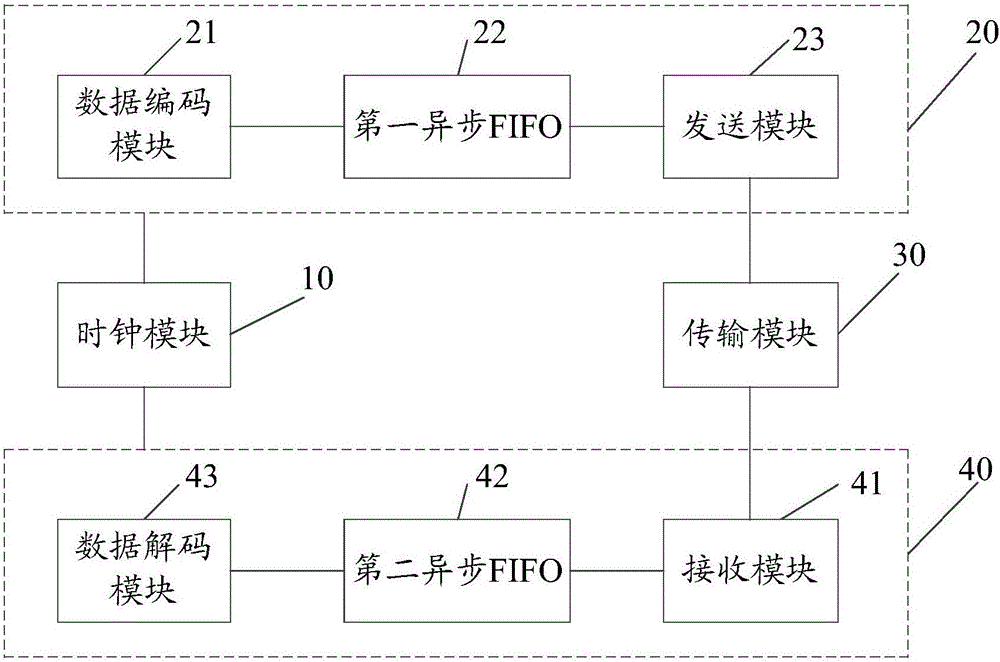

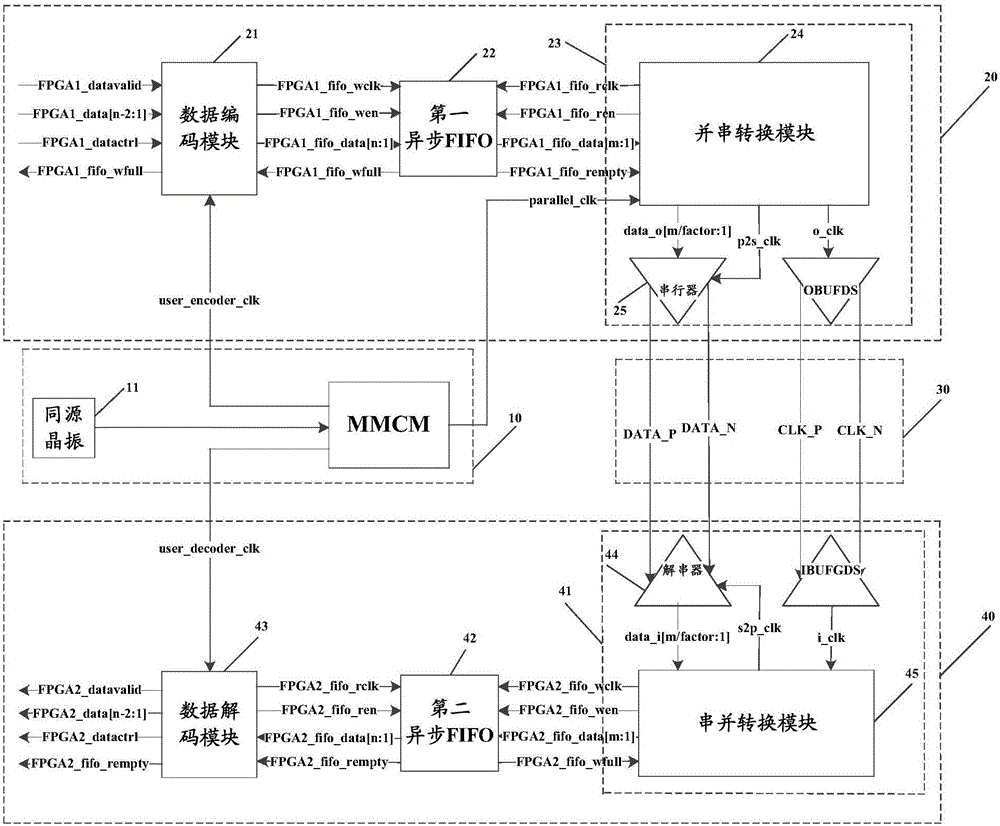

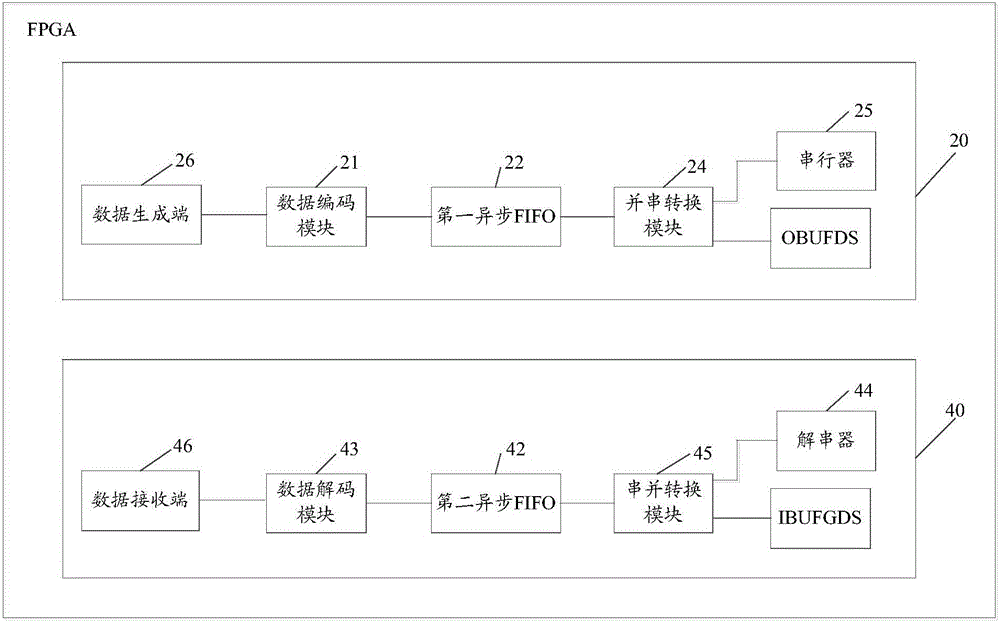

Virtual IO inter-chip connection circuit for FPGAs

ActiveCN104991878AIncrease speedHigh bandwidthElectric digital data processingCode moduleData encoding

The present invention provides a virtual IO inter-chip connection circuit for FPGAs. The circuit comprises a clock module, a sending FPGA end circuit, a transmission module and a receiving FPGA end circuit. The sending FPGA end circuit comprises a data coding module for generating coded data; a first asynchronous FIFO which caches coded data written by the data coding module according to a coding clock and an asynchronous FIFO write protocol; and a sending module which sends data of at least two bits and a differential serial clock read from the first asynchronous FIFO until all the coded data is sent. The receiving FPGA end circuit comprises a receiving module for receiving the data of at least two bits and the differential serial clock until all the coded data is received; a second asynchronous FIFO which caches the data of at least two bits written by the receiving module according to the asynchronous FIFO write protocol and the differential serial clock until all the coded data is written; and a data decoding module which decodes the coded data synchronously. According to the invention, the transmission bandwidth and the transmission rate can be increased arbitrarily within a considerable range while the bit error rate can be reduced greatly.

Owner:无锡亚科鸿禹电子有限公司

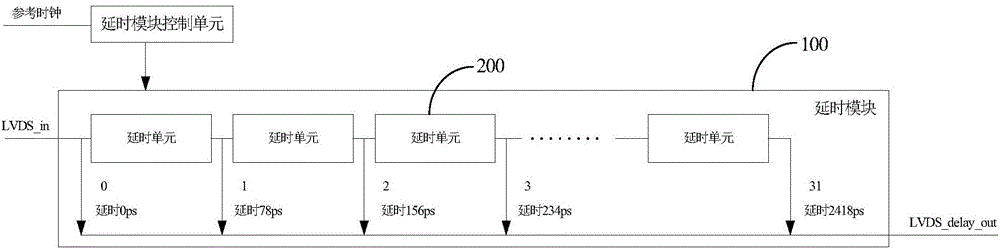

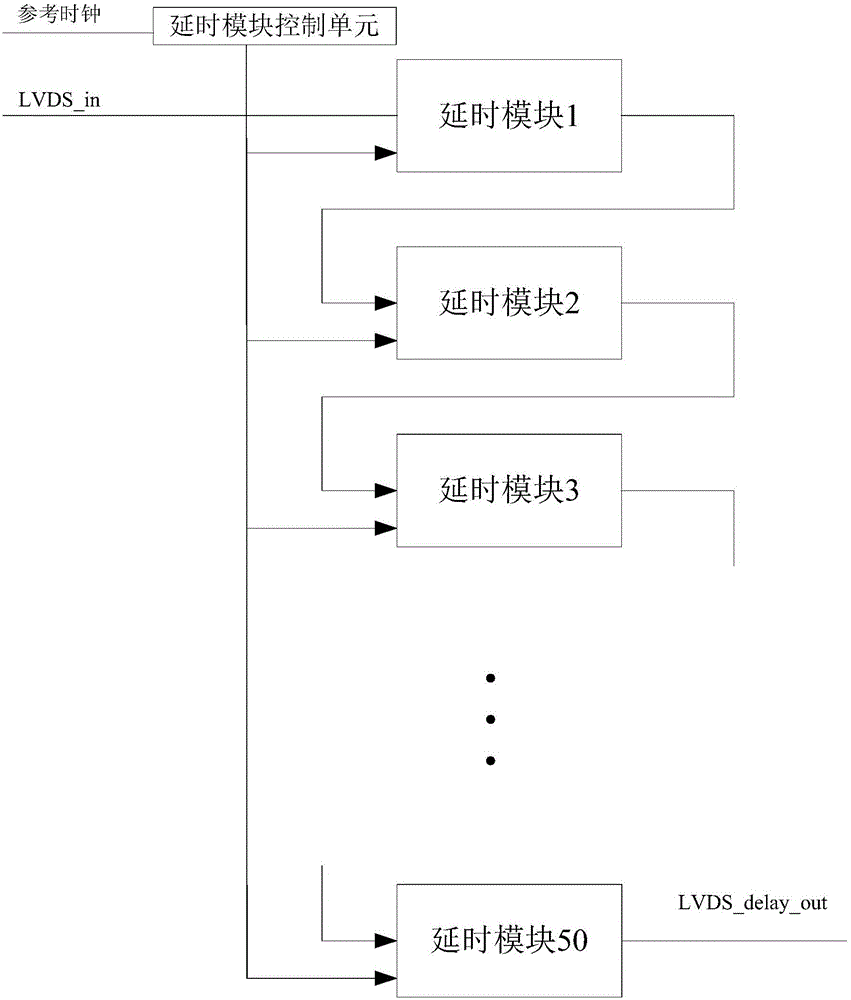

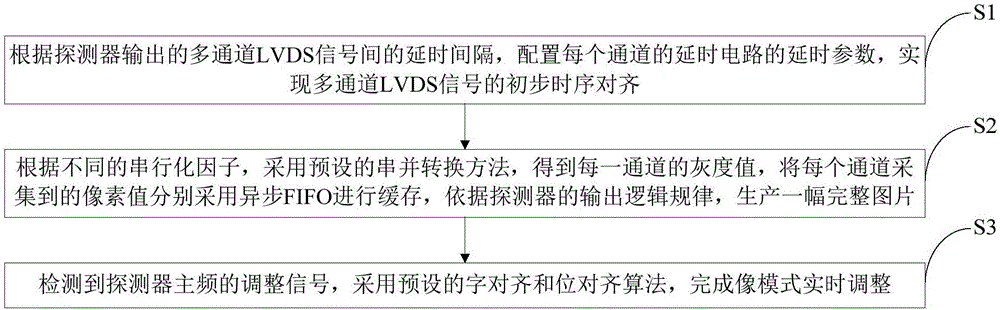

Multichannel LVDS time sequence alignment detector image collection method

The invention discloses a multichannel LVDS time sequence alignment detector image collection method, comprising the following steps: configuring a delay parameter of a delay circuit of each channel according to a delay interval between multichannel LVDS signals output by a detector to realize primary time sequence alignment of the multichannel LVDS signals; adopting a preset serial-to-parallel conversion method to obtain a gray value of each channel according to different serialization factors, respectively caching pixel values collected by each channel by adopting asynchronous FIFO, and generating a complete picture according to an output logic rule of the detector; and detecting a regulation signal of main frequency of the detector, and adopting a preset word alignment and bit alignment algorithm to complete the real-time adjustment of an imaging mode. The multichannel LVDS time sequence alignment detector image collection method disclosed by the invention is easy to realize, high in precision, strong in universality, high in integration degree and strong in adaptive ability.

Owner:SHANGHAI AEROSPACE CONTROL TECH INST

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com