Elastic buffer structure and method applied to universal serial bus 3.0 (USB 3.0)

An elastic buffer and signal technology, which is applied in the direction of instrumentation, electrical digital data processing, etc., can solve the problem of elastic buffer without USB3.0 physical layer, and achieve the effect of avoiding glitches and instability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0042] The following is the principle of elastic buffering, taking 40 bits as an example, no matter 10 bits, 20 bits or 40 bits, the principle is the same.

[0043] The principle of elastic cushioning:

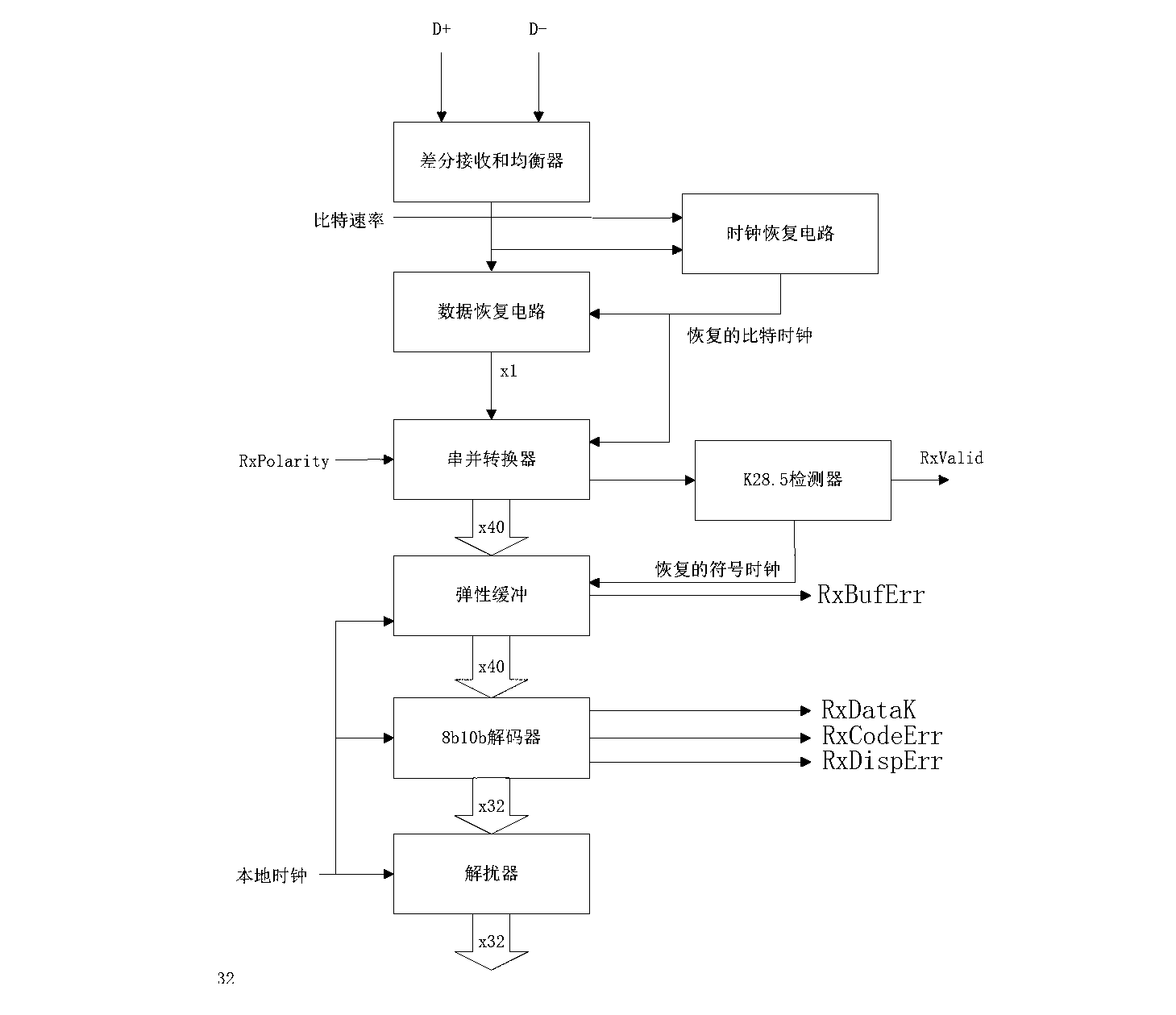

[0044] The elastic buffer is essentially an asynchronous FIFO. The write clock is the receive clock, the read clock is the system clock, the data bit width is 40 bits, and the FIFO depth is 16. When the symbol lock is valid, write to the FIFO in the receive clock domain 8 data from the serial-to-parallel converter. When the read and write clocks are at the same speed, there are 8 valid data in the FIFO, which is maintained at a half-full state.

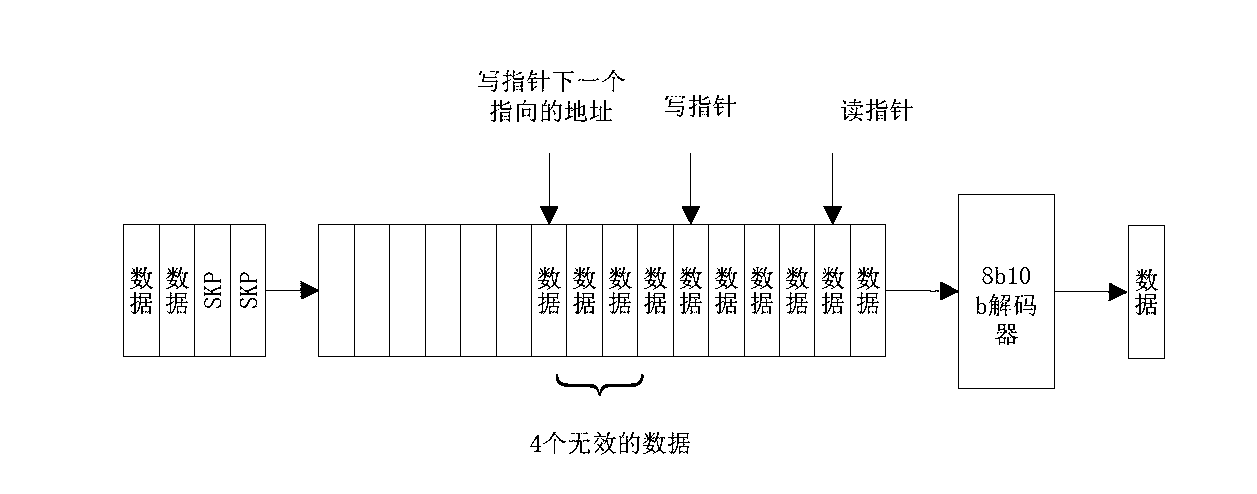

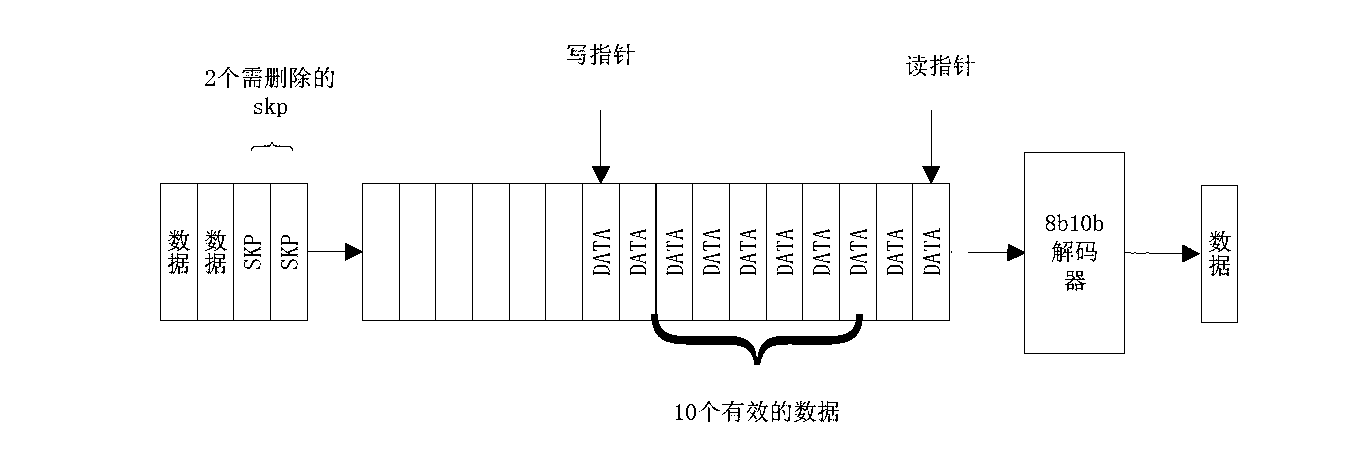

[0045] When the read clock is faster than the write clock, more data is read than written. After a period of time, the number of data in the FIFO is less than 8, and may even be read empty. Such as figure 2 As shown, when SKP appears in the input 40-bit data, the valid data in FIFO is 4, which is 4 less than normal. At this point...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com