An FPGA implementation method of multi-channel data source DDR buffer

A technology of implementation method and data source, applied in data transformation, electrical digital data processing, instruments, etc., and can solve the problem of inflexible implementation method.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] The present invention will be further described below in conjunction with specific embodiment:

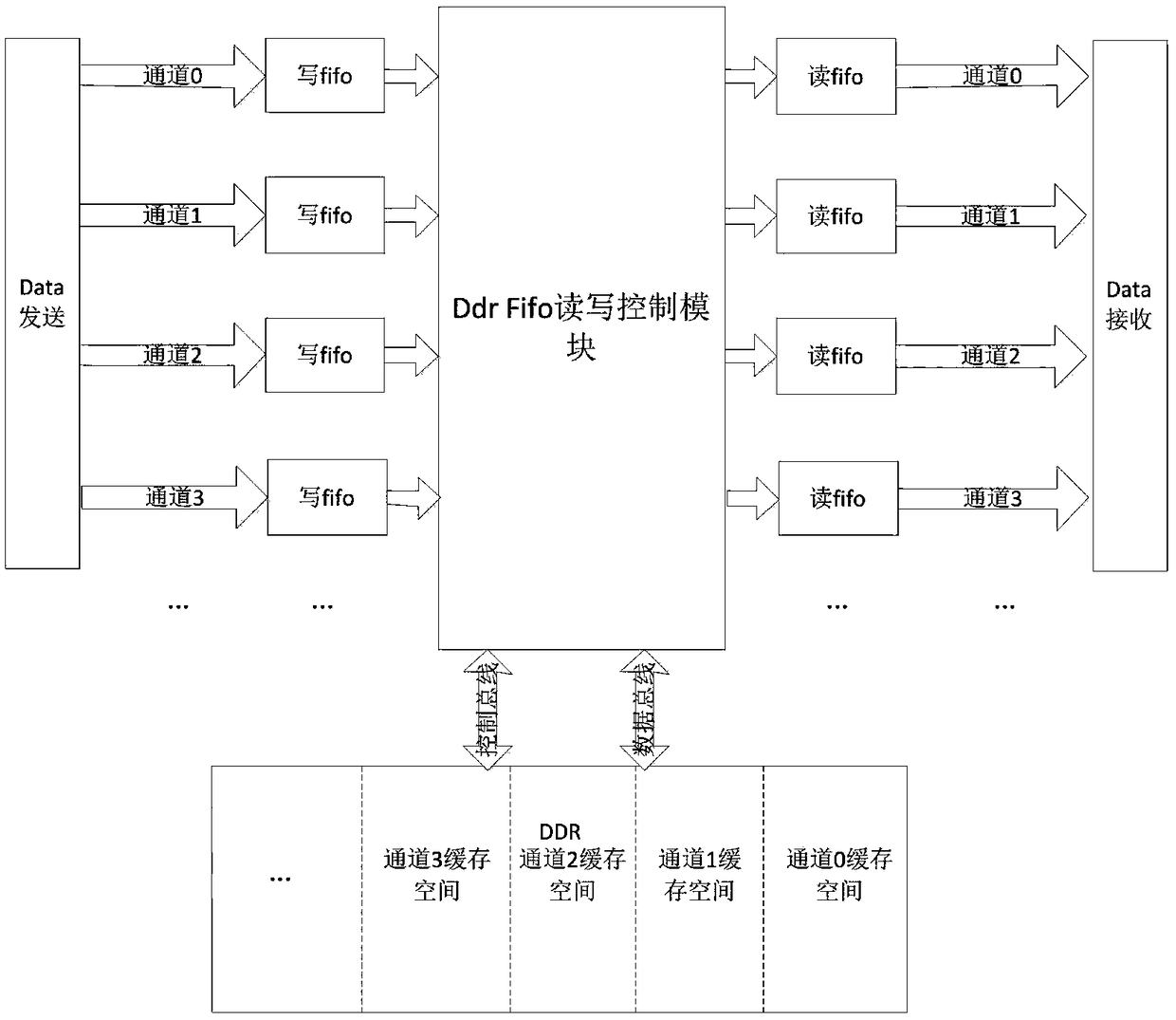

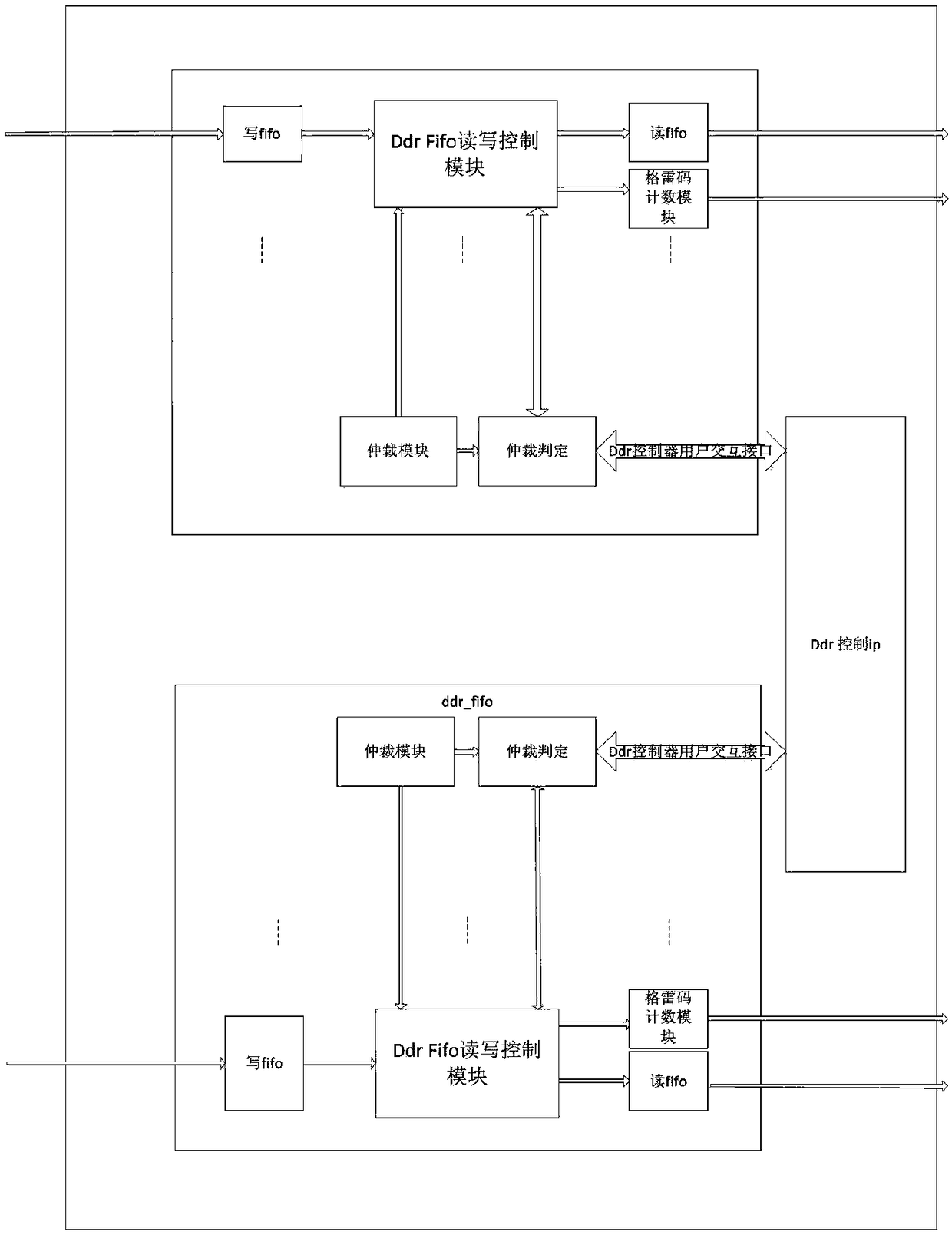

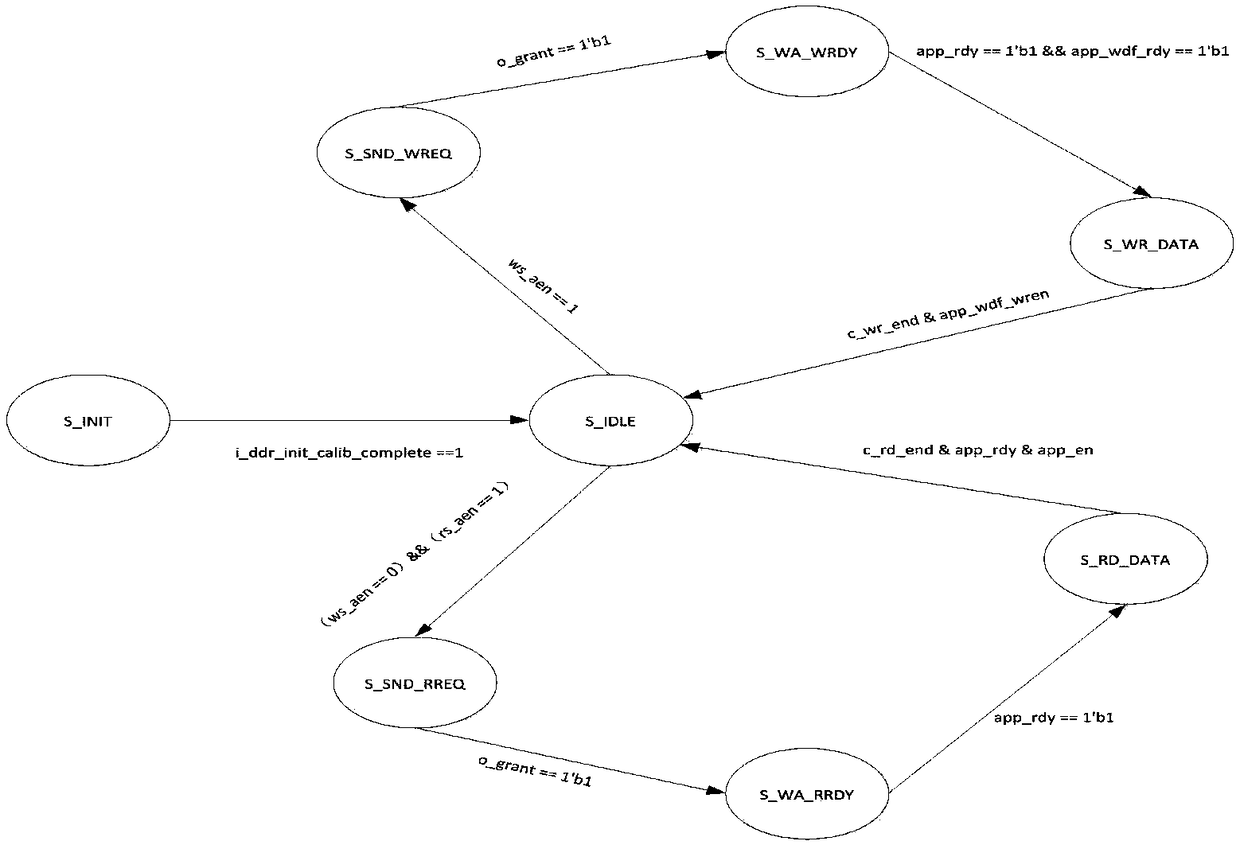

[0047] 1. DDR module top-level module structure framework, refer to figure 2 .

[0048] 2. Brief introduction of the project platform:

[0049]2.1 This project uses 4 pieces of DDR particles, the specific model is MT41J256m16ha-125. The FPGA device platform uses the xilinx manufacturer, and the specific model is xc7z045-ffg900-2.

[0050] 2.2 The data sources are channel 1, srio interface, with a bandwidth rate of 800MB / S; channel 2, pcie interface, with a bandwidth rate of 1GB / S; channel 3, the data source collected by AD, with a bandwidth rate of 1GB / S; channel 4, The interface for reading SATA disks has a bandwidth of 1.2GB / S. The four channels are independent of each other and are asynchronous with the DDR clock, and the written data is discontinuous.

[0051] 2.3 DDR mig configuration: select two up to 64 bits, data width is 512 bits, and set up dual DDR controlle...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com