FIFO protocol based digital interface circuit for SerDes technology

A digital interface and circuit technology, applied in the direction of logic circuit connection/interface layout, etc., can solve the problems of bus and SerDes bit width mismatch, feedback control signal channel transmission delay and other problems, to facilitate bit width expansion, enhance adaptability, Easy to recall effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

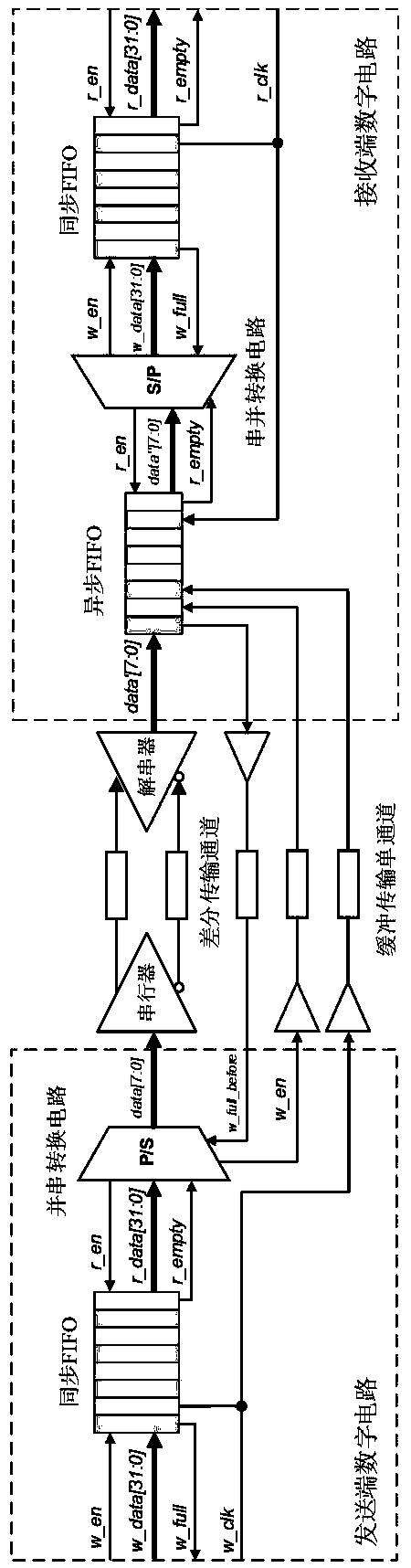

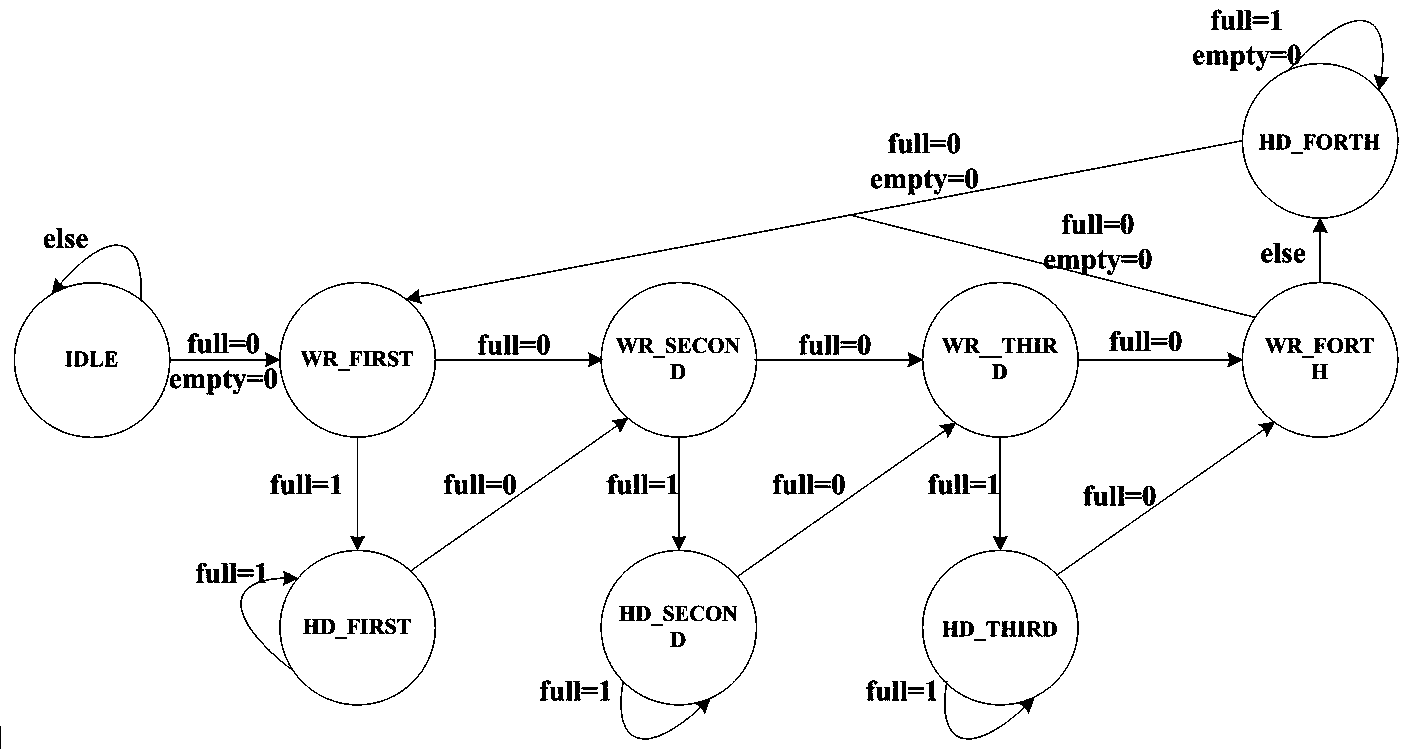

[0014] At the sending end, the bus data is written into a synchronous first-in-first-out buffer queue through the FIFO protocol. The FIFO protocol means: the data w_data is registered by the write clock w_clk when the write enable w_en is active at high level. When the data is full , the w_full feedback signal is pulled high; the read data r_data is taken out by the read clock r_clk during the high-level active period of the read enable r_en, and when the data is read, the r_empty feedback signal is pulled high.

[0015] The parallel-to-serial conversion circuit of the latter stage reads the bus data from the buffer queue and divides it into several pieces of serial data and sends them to the SerDes serializer in clock cycles. Serial device, write clock, write enable, write full in advance and other low-speed control signals through the buffer (buffer) through the transmission channel.

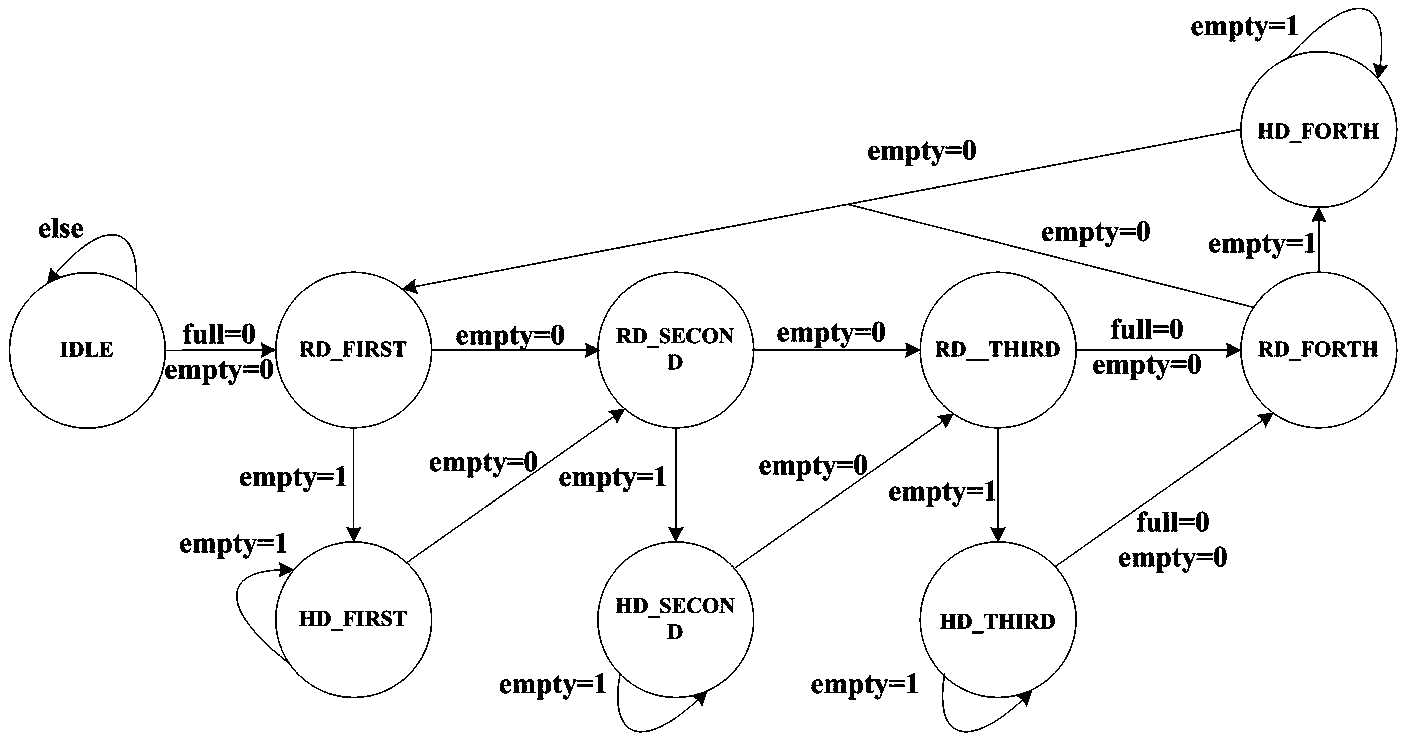

[0016] At the receiving end, the data output by the deserializer is first written into an ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com