Time-interleaved split ADC (Analog-to-Digital Converter) calibration structure without redundant channel and adaptive calibration method thereof

A technology of time crossover and calibration method, which is applied in the direction of analog/digital conversion calibration/testing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

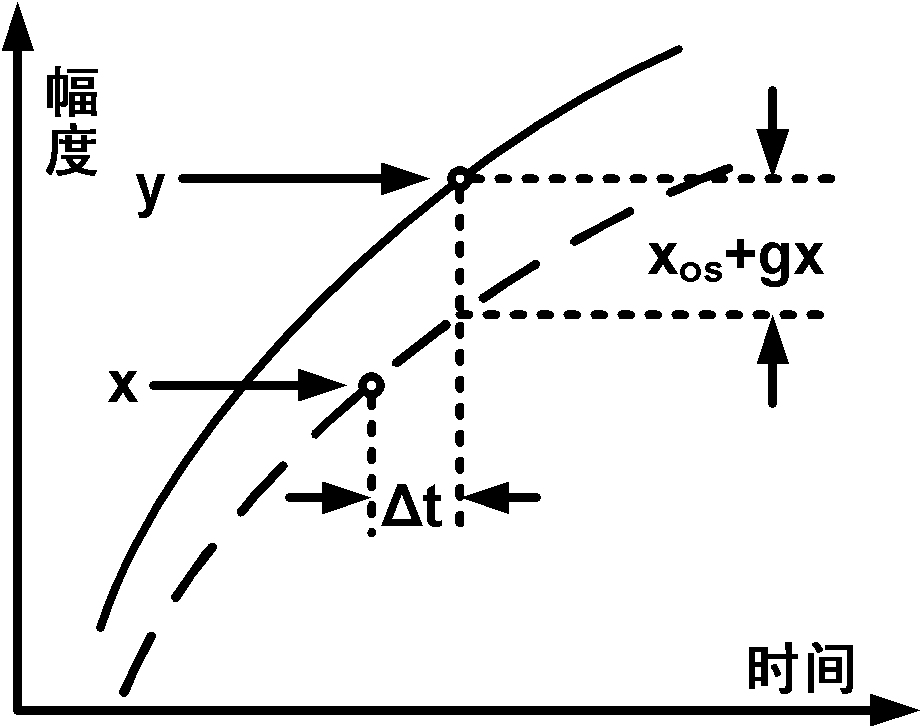

[0061] Taking the TIADC with a sampling rate of 120MHz as an example when the present invention is applied to 7 split ADC channels, the sampling signal error model of each split ADC channel is as follows: figure 1 As shown, the implementation steps are as follows:

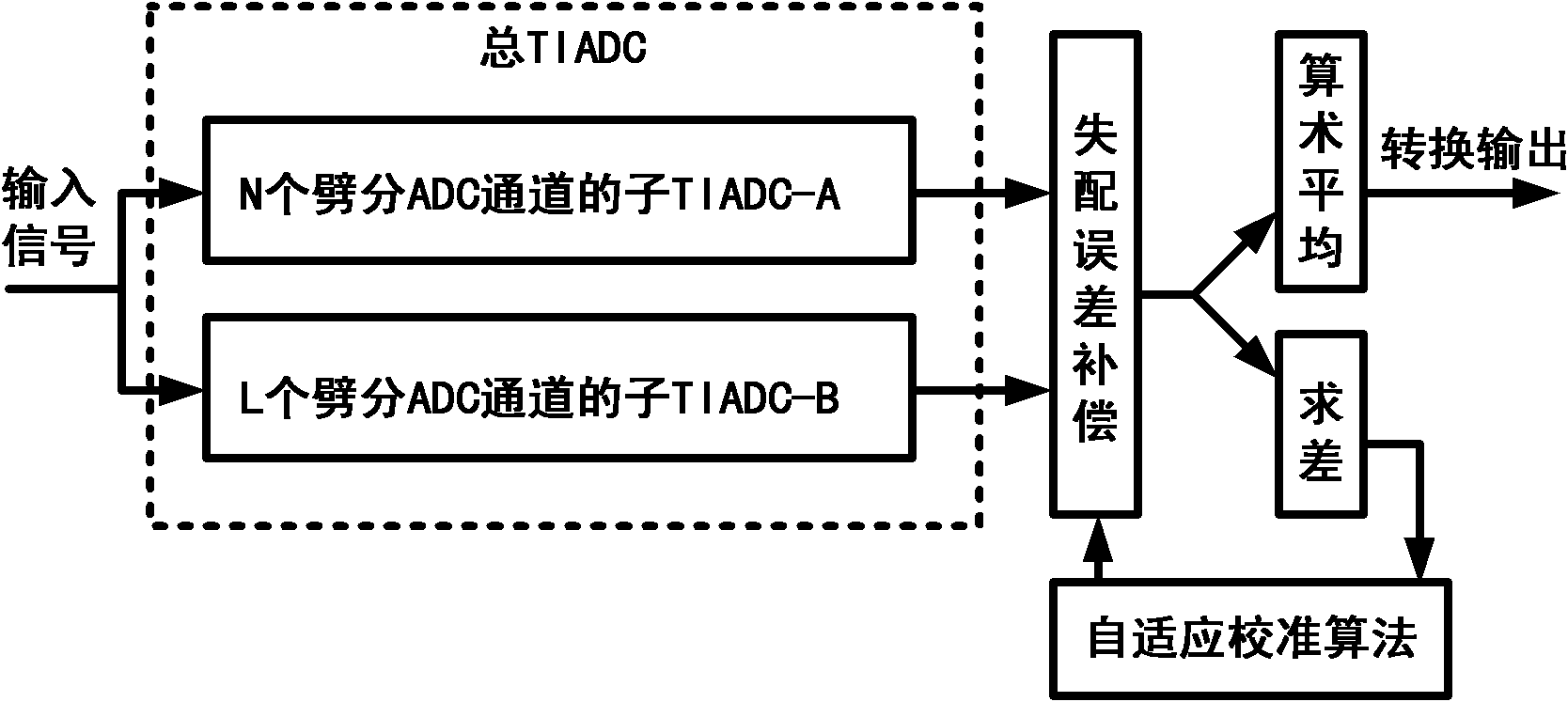

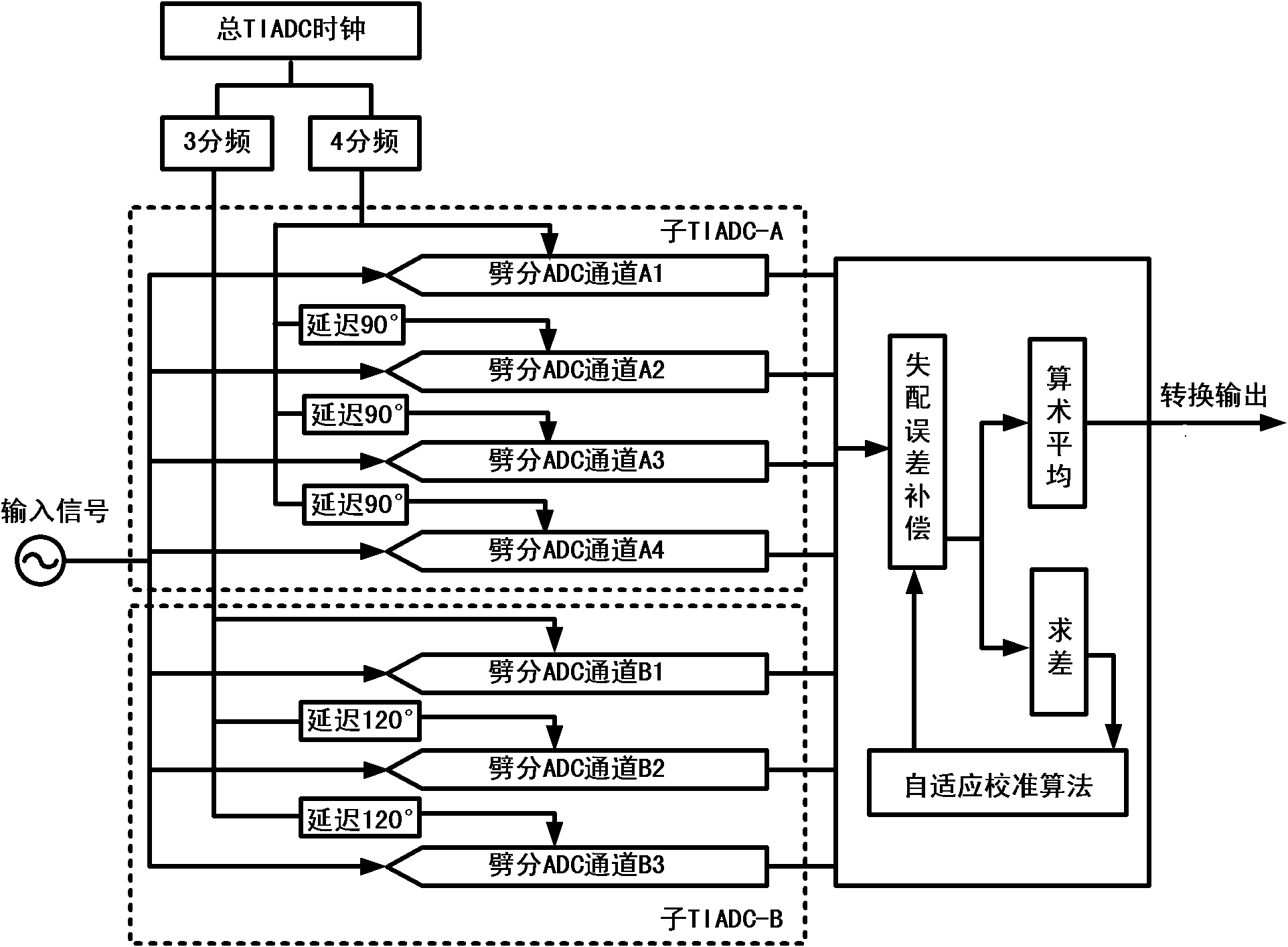

[0062] a. Determine the number of split ADC channels N constituting sub-TIADC-A and the number of split ADC channels L constituting sub-TIADC-B, N and L are mutually prime, in this embodiment N=4, L=3;

[0063] b. Make the split ADC channels in the sub-TIADC-A work at the fs / N sampling rate, wherein the sampling clock phases of each split ADC channel are separated by 360° / N, and the sub-TIADC-A is formed in a time-interleaved working mode The rate is fs; make the split ADC channels in the sub-TIADC-B work at fs / L, where the sampling clock phases of each split ADC channel are separated by 360° / L, and the sub-TIADC- The rate of B is fs; sub-TIADC-A and sub-TIADC-B form a total TIADC based on split channel mutual cal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com