Integrated circuit aging failure early warning method and circuit

An integrated circuit and circuit technology, applied in the field of integrated circuit aging failure early warning method and circuit field, can solve the problems of inconsistent aging degree, inability to carry effective early warning of circuit aging failure, and inaccurate measurement.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

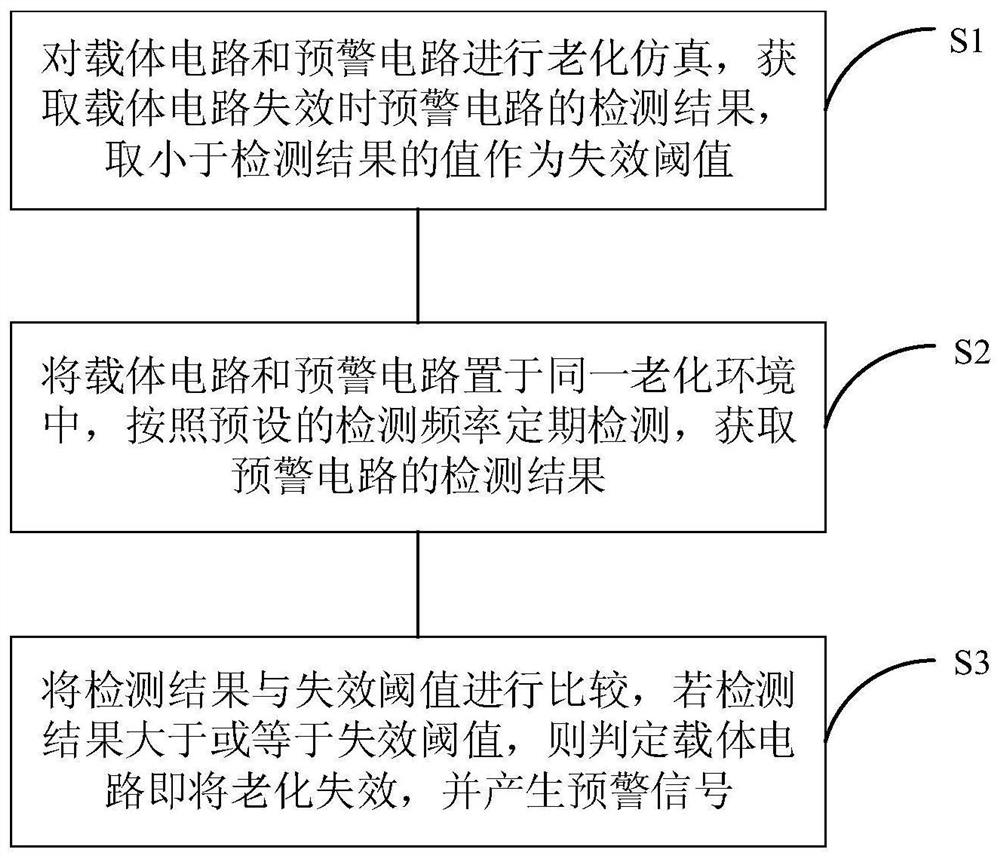

[0048] See figure 1 , figure 1 It is a flow chart of an integrated circuit aging failure early warning method provided by an embodiment of the present invention. As shown in the figure, the integrated circuit aging failure early warning method of the embodiment of the present invention includes:

[0049] S1: Perform aging simulation on the carrier circuit and the early warning circuit, obtain the detection result of the early warning circuit when the carrier circuit fails, and take a value smaller than the detection result as the failure threshold;

[0050] S2: Place the carrier circuit and the early warning circuit in the same aging environment, perform regular detection according to a preset detection frequency, and obtain detection results of the early warning circuit;

[0051] S3: Comparing the detection result with the failure threshold, if the detection result is greater than or equal to the failure threshold, determining that the carrier circuit is about to age and fa...

Embodiment 2

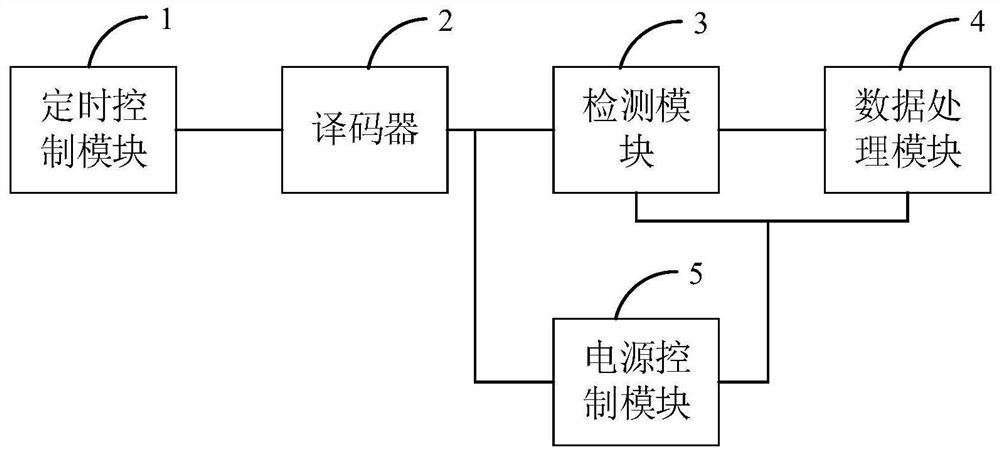

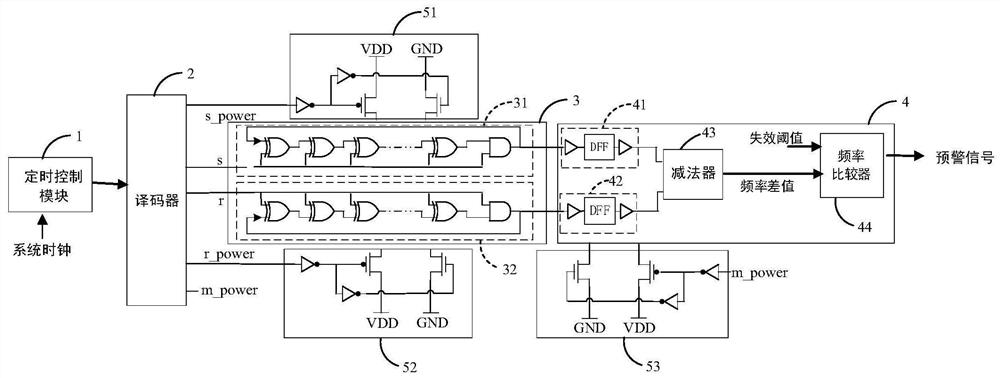

[0062] See Figure 2-Figure 4 , figure 2 It is a structural block diagram of an integrated circuit aging failure warning circuit provided by an embodiment of the present invention; image 3 It is a structural schematic diagram of an integrated circuit aging failure warning circuit provided by an embodiment of the present invention; Figure 4 It is a schematic diagram of the circuit structure for obtaining detection results in the early warning circuit provided by the embodiment of the present invention. As shown in the figure, the integrated circuit aging failure warning circuit of the embodiment of the present invention includes:

[0063] Timing control module 1, used to generate a preset detection frequency signal;

[0064] The decoder 2 is connected to the timing control module 1, and the decoder 2 generates a control signal according to the preset detection frequency signal;

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com