Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

155 results about "Poly crystalline" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Answer Wiki. Polycrystalline or multicrystalline materials, or polycrystals are solids that are composed of many crystallites of varying size and orientation. Crystallites are also referred to as grains. They are small or even microscopic crystals and form during the cooling of many materials.

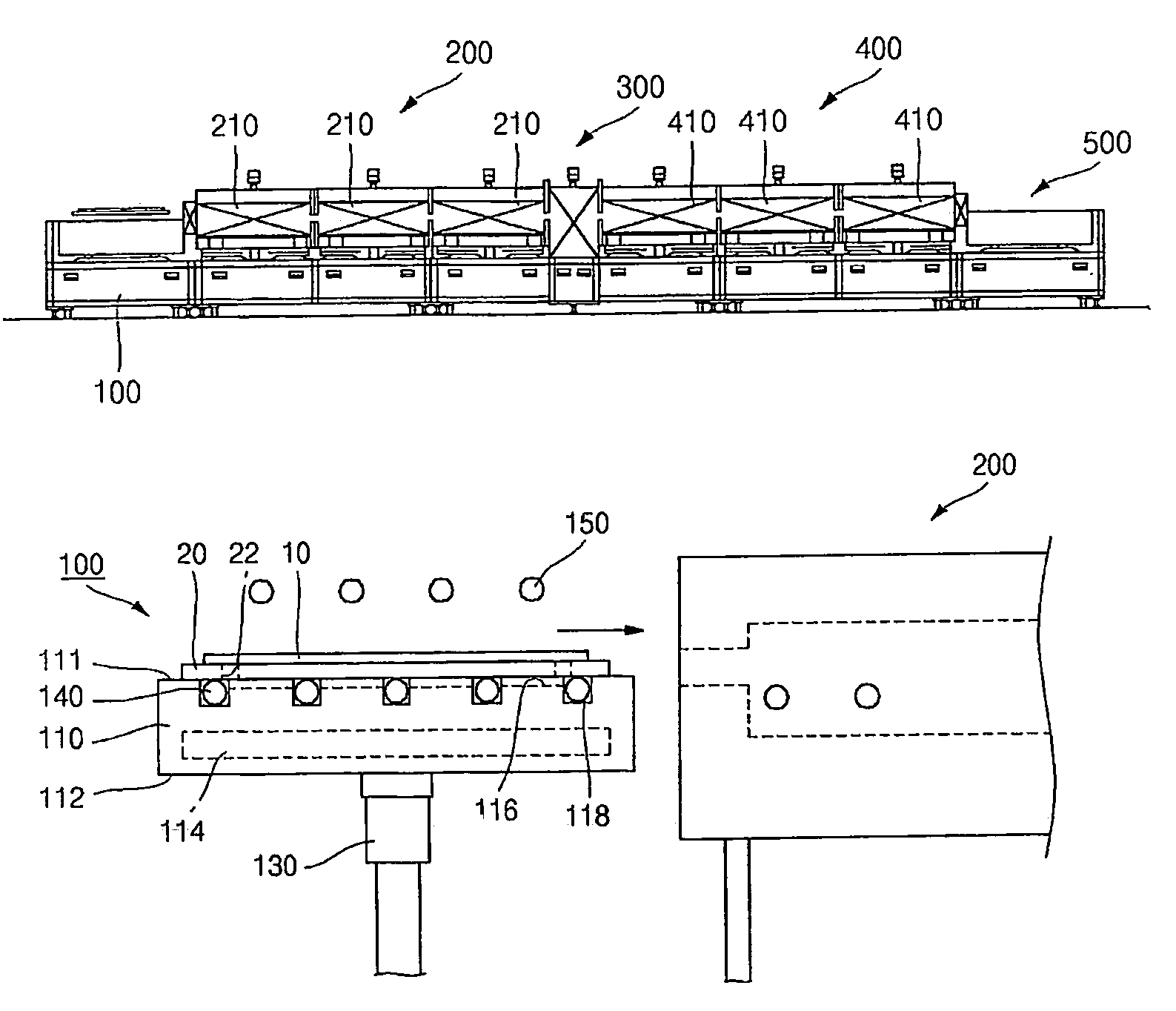

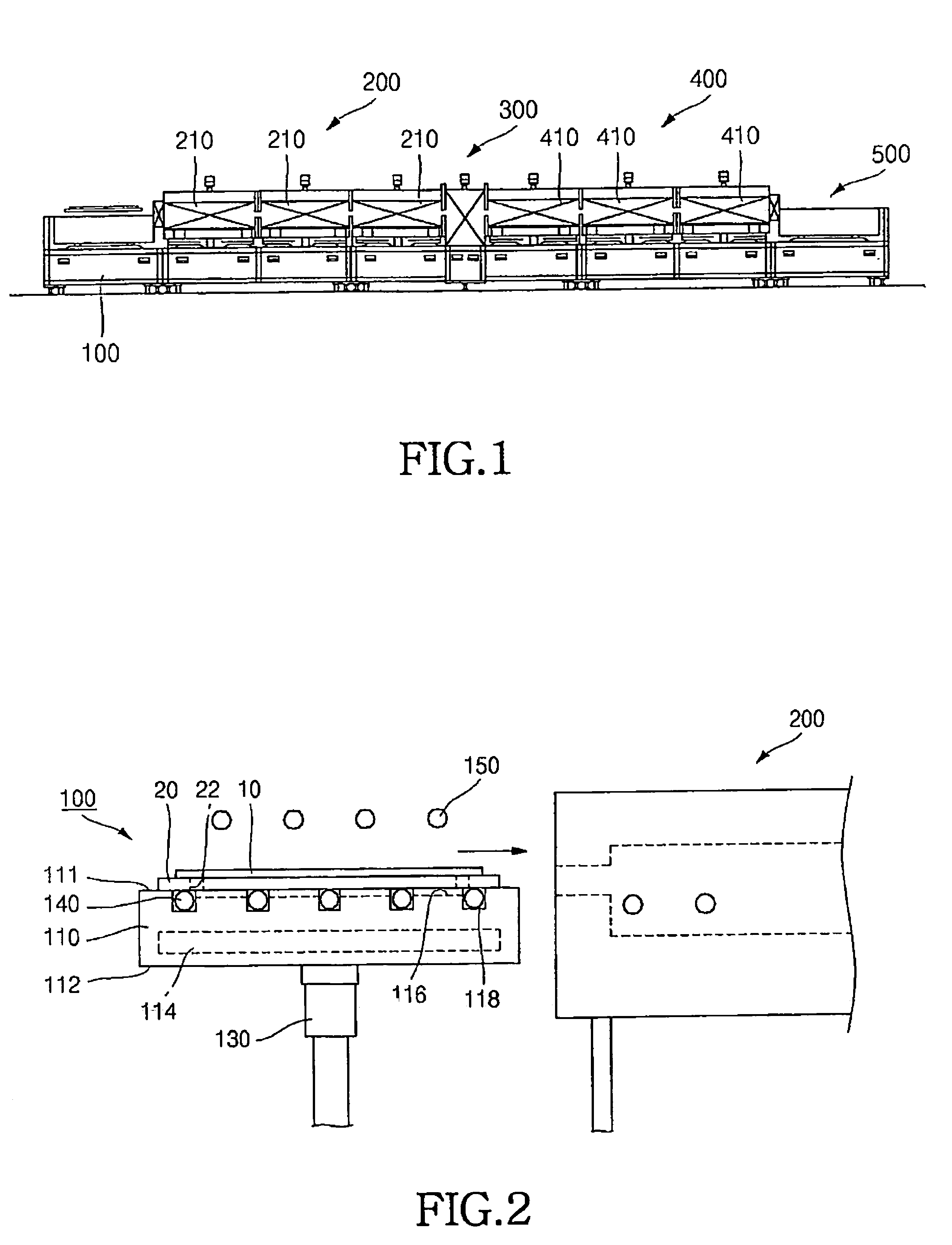

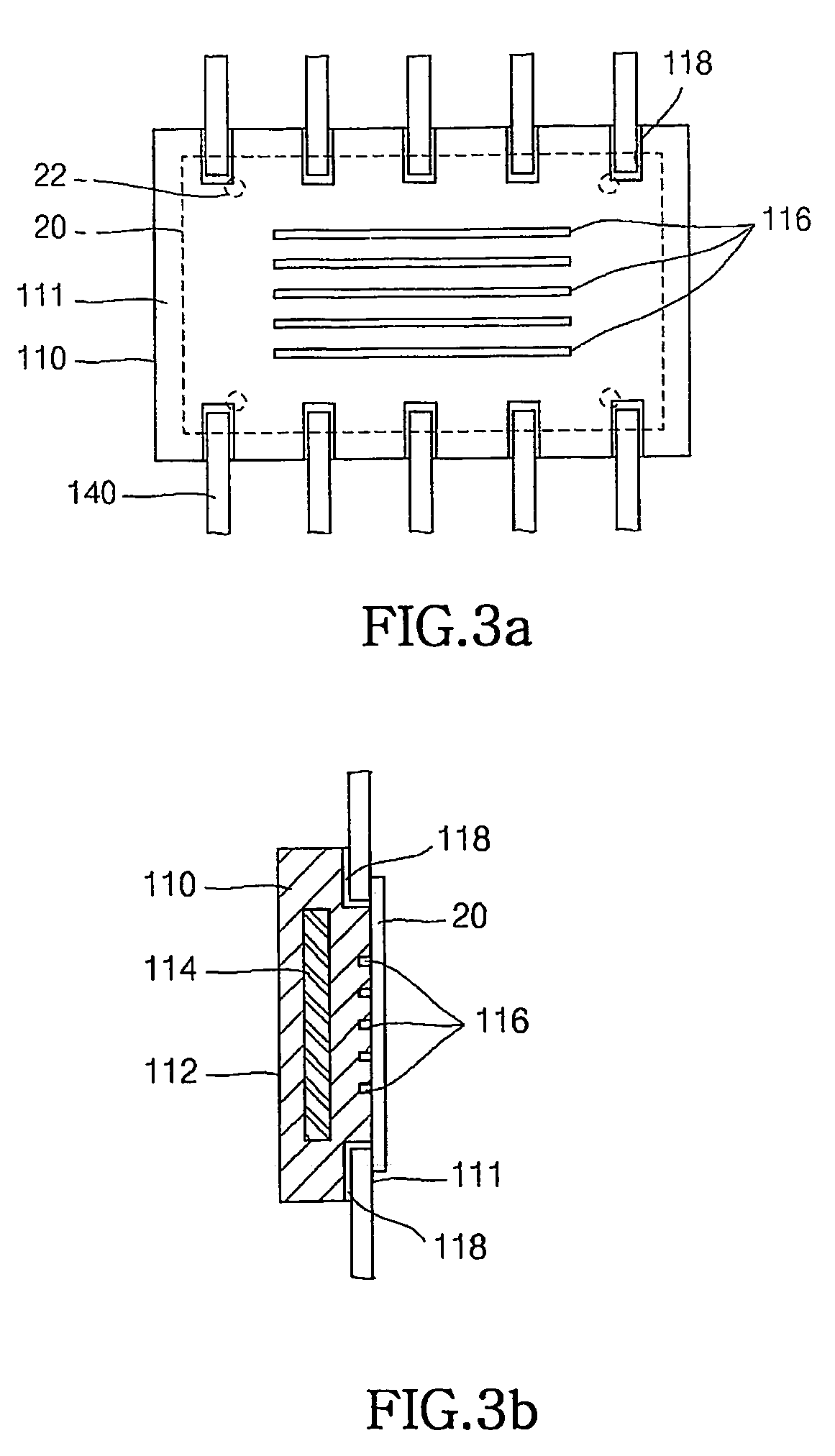

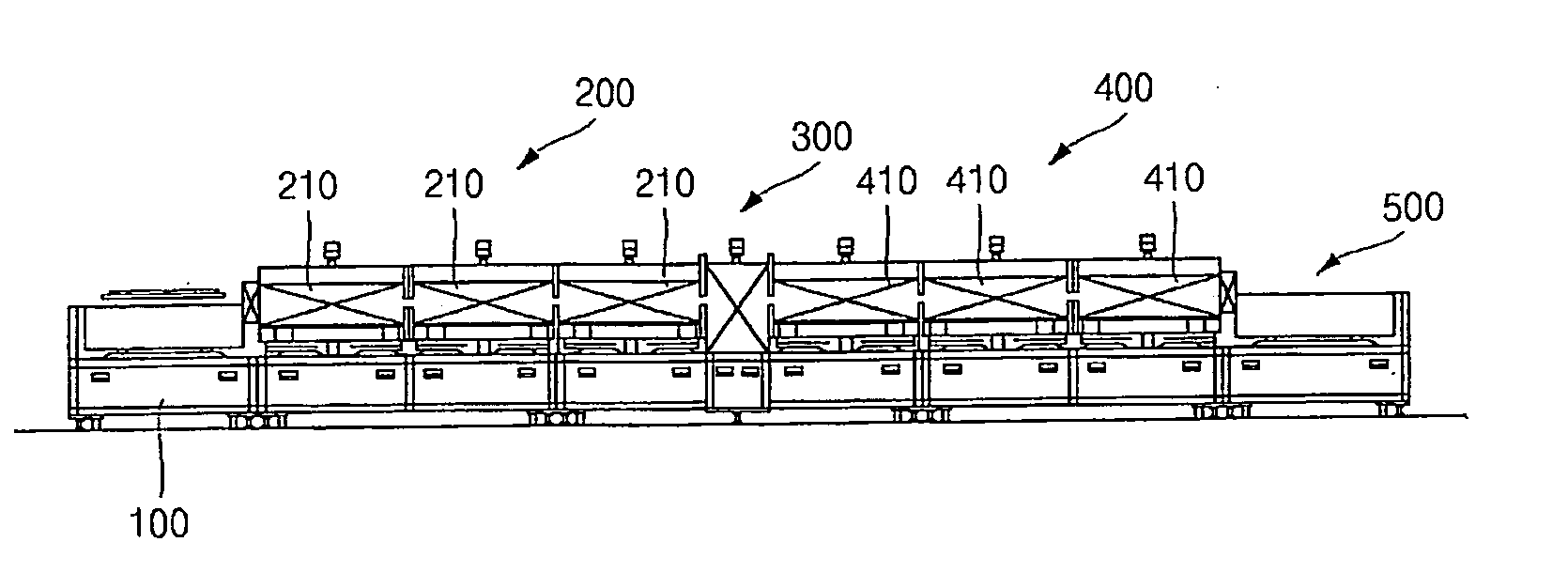

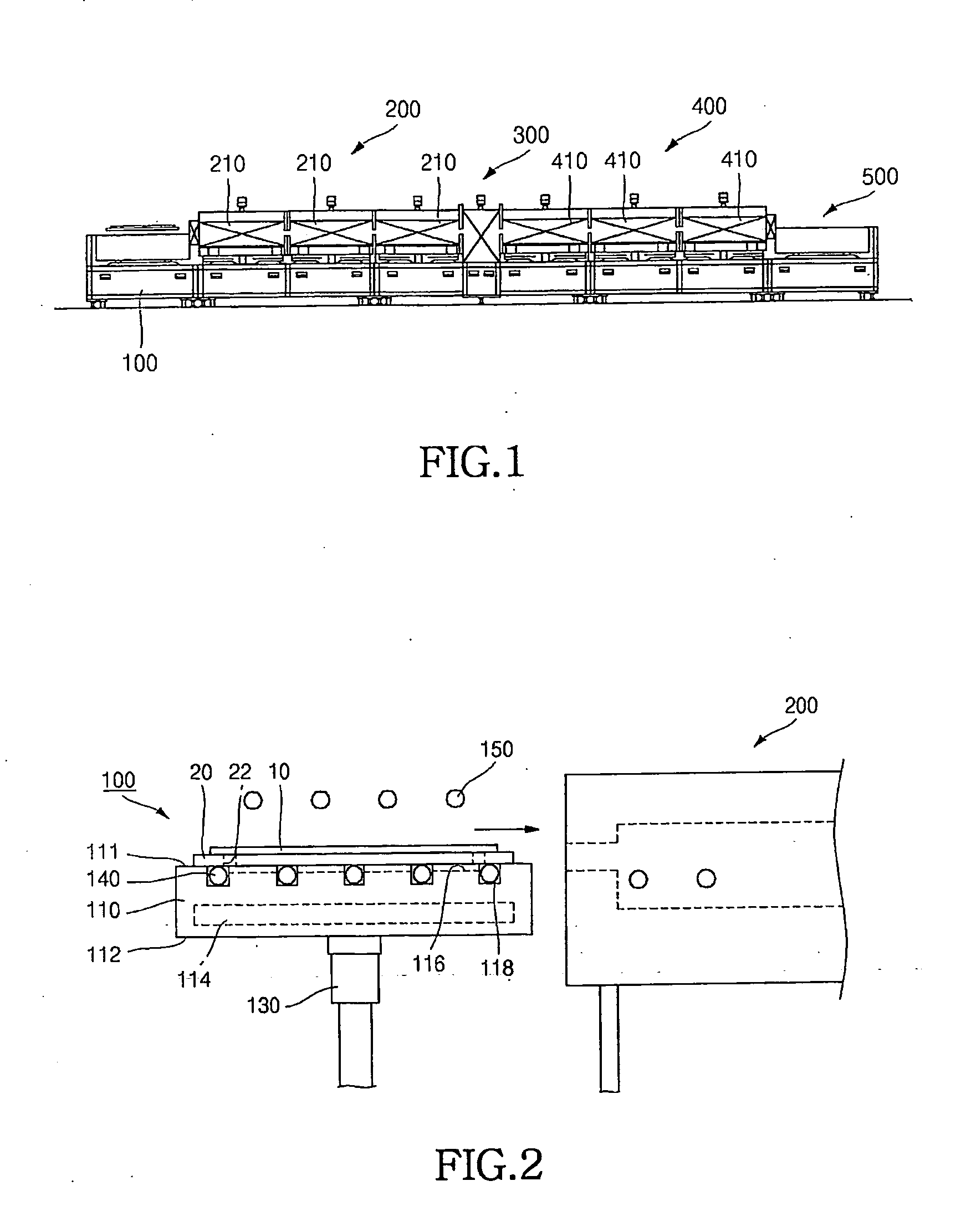

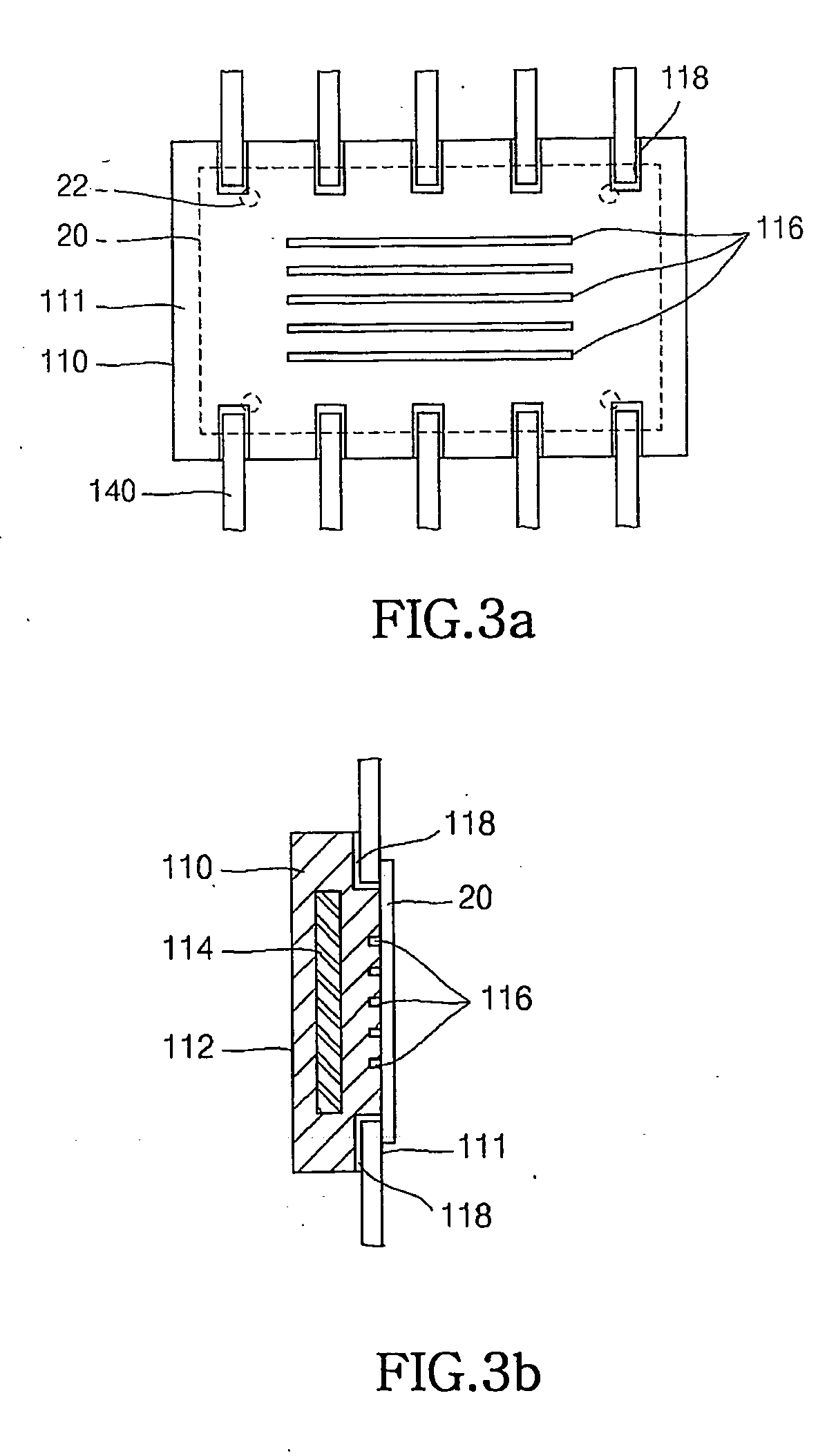

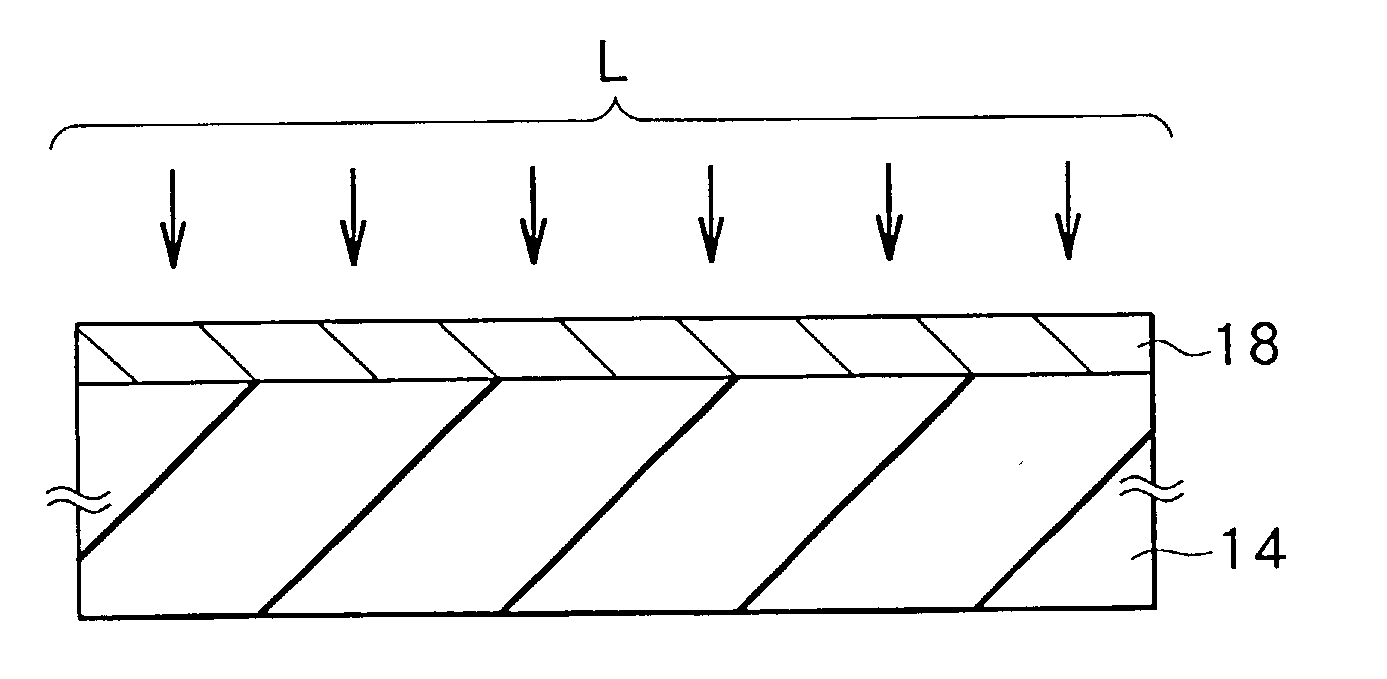

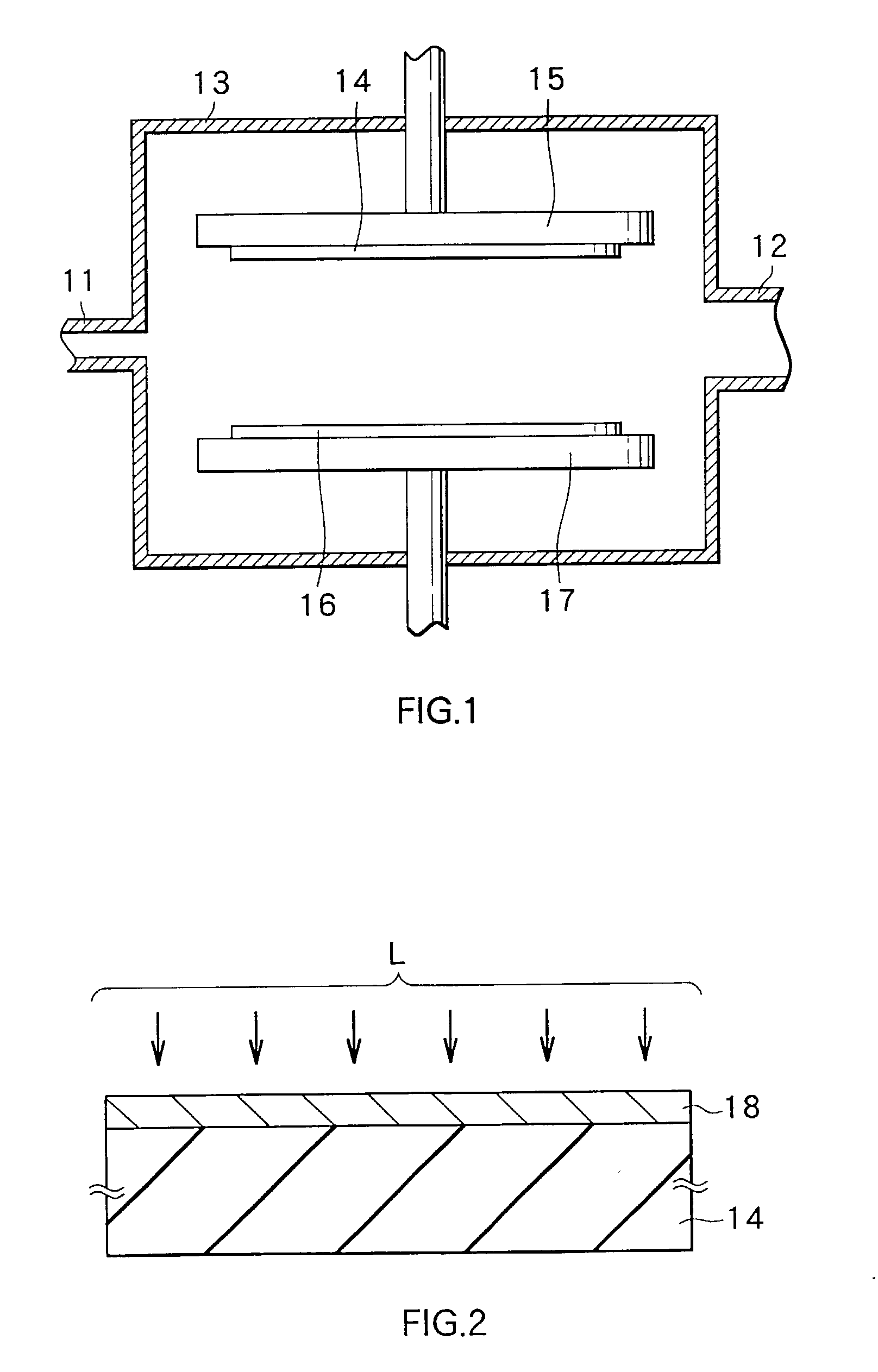

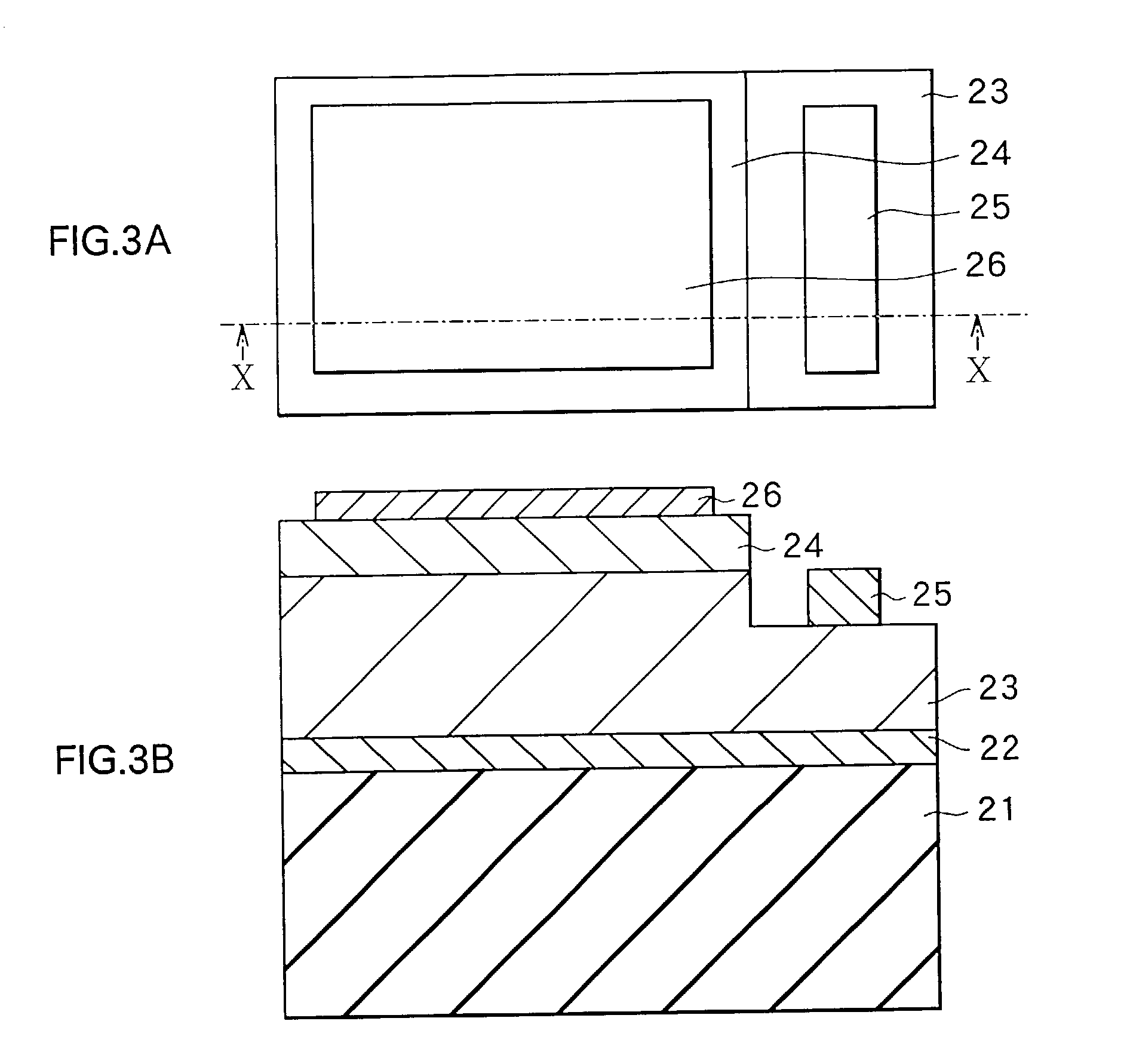

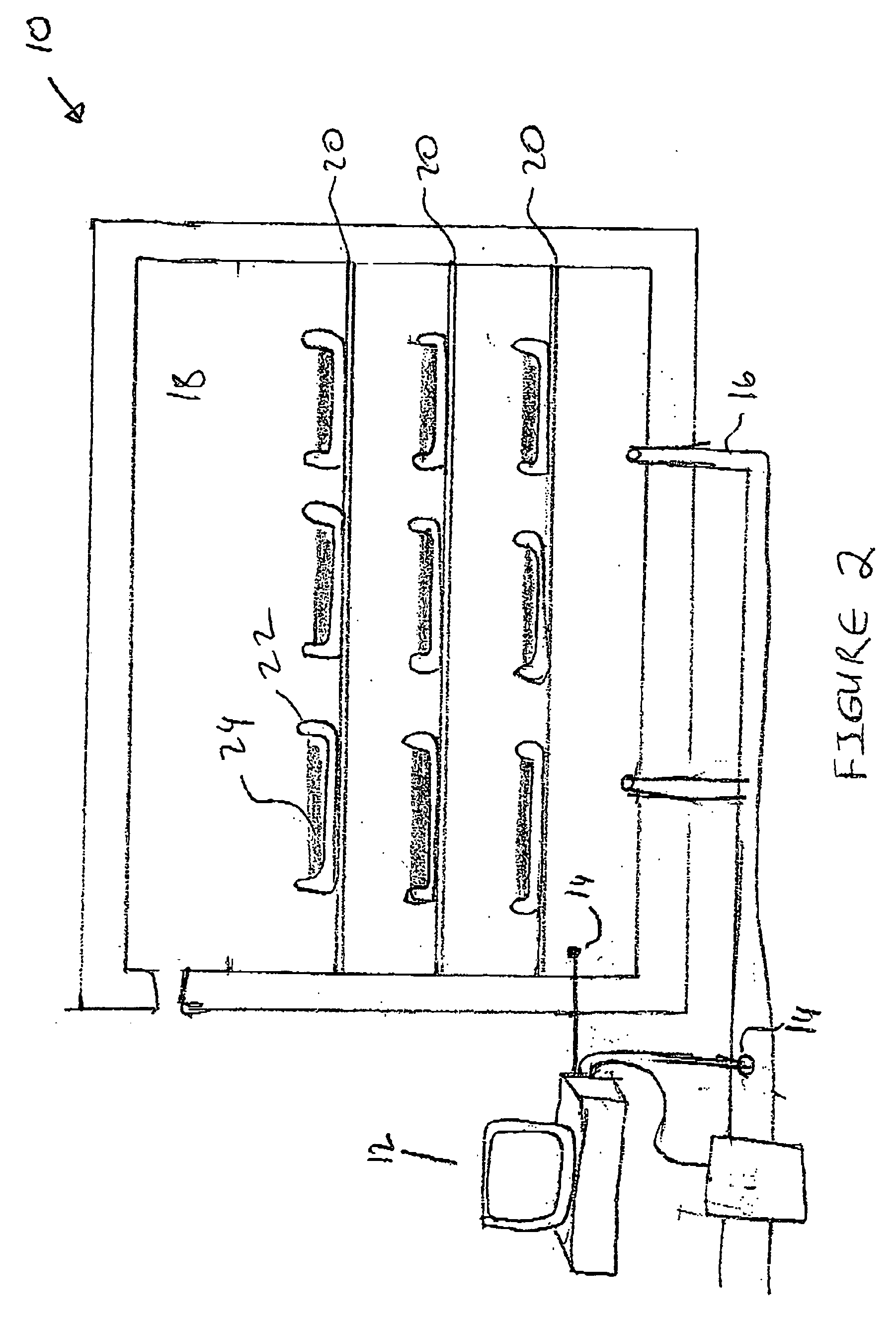

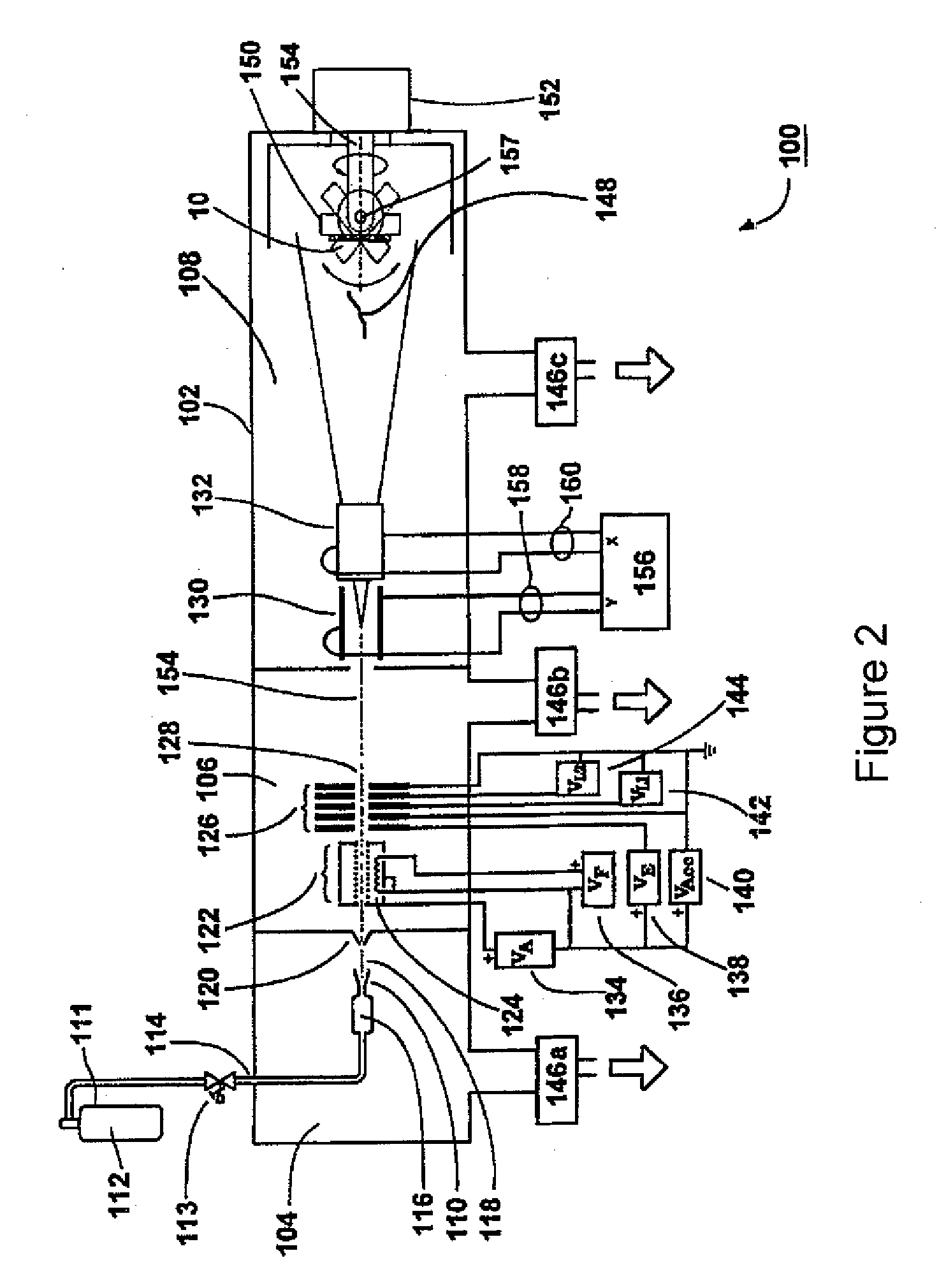

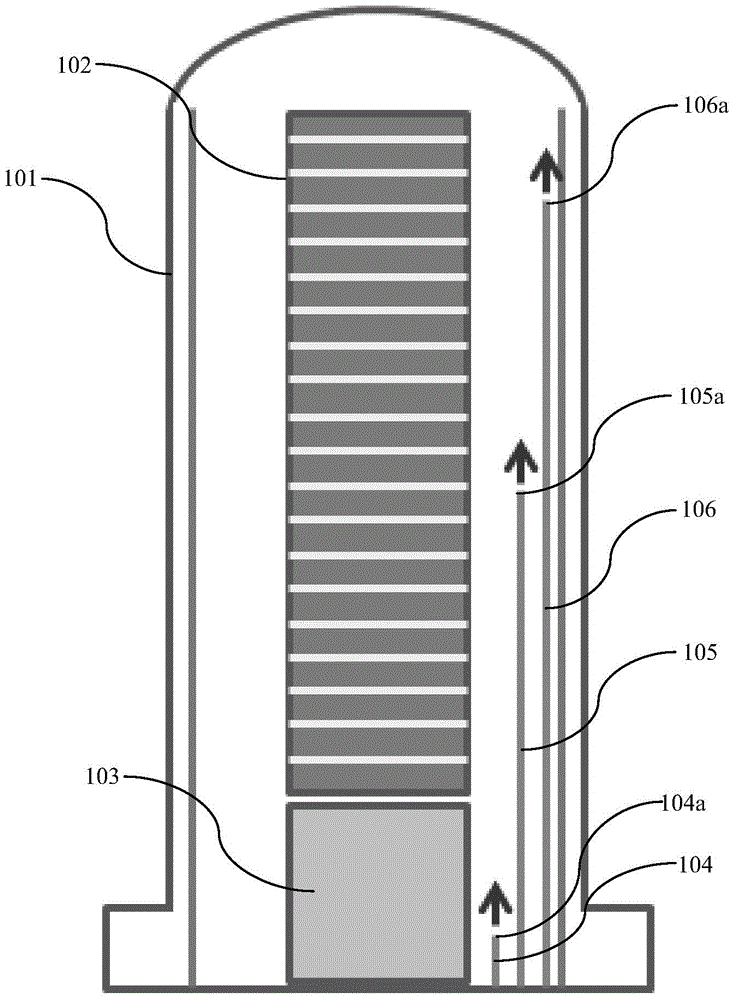

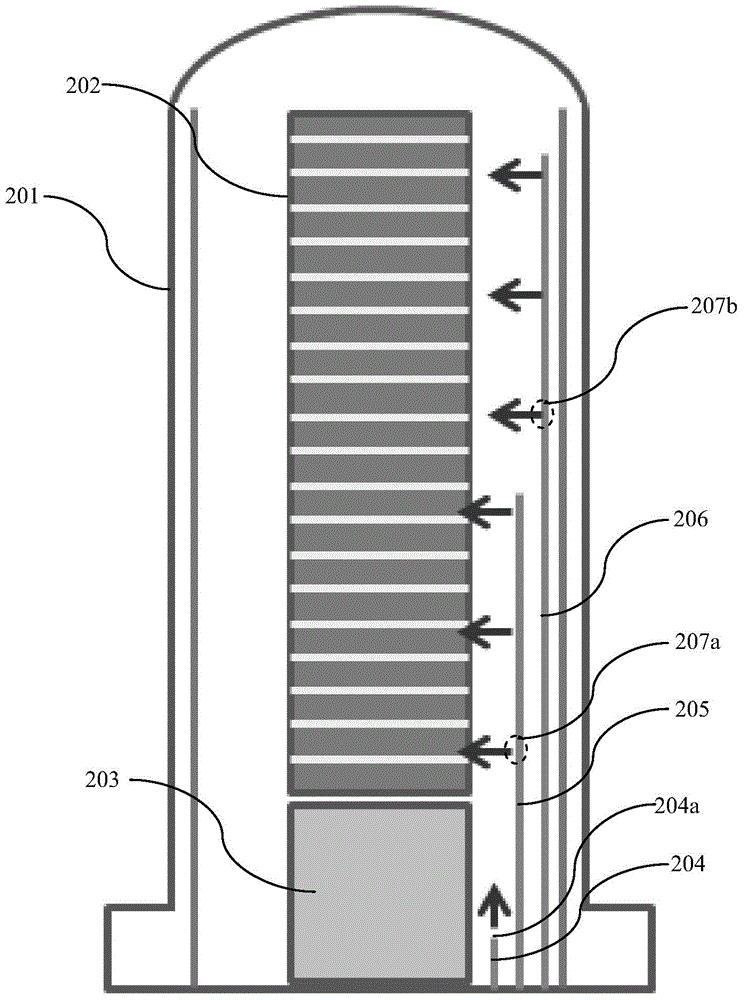

System for heat treatment of semiconductor device

InactiveUS7989736B2Avoid damageIncrease temperatureFurnaces without endless coreSemiconductor/solid-state device manufacturingElectromotive forceSilicon thin film

Disclosed is a heat treatment system for semiconductor devices. The heat treatment system is used in a heat treatment process for semiconductor devices, such as a crystallization process for an amorphous silicon thin film or a dopant activation process for a poly-crystalline silicon thin film formed on a surface of a glass substrate of a flat display panel including a liquid crystal display (LCD) or an organic light emitting device (OLED). The heat treatment system transfers a semiconductor device after uniformly preheating the semiconductor device in order to prevent deformation of the semiconductor device during the heat treatment process, rapidly performs the heat treatment process under the high temperature condition by heating the semiconductor device using a lamp heater and induction heat derived from induced electromotive force, and unloads the semiconductor device after uniformly cooling the semiconductor device such that the semiconductor device is prevented from being deformed when the heat treatment process has been finished. The heat treatment system rapidly performs the heat treatment process while preventing deformation of the semiconductor device by gradually heating or cooling the semiconductor device.

Owner:VIATRON TECH INC

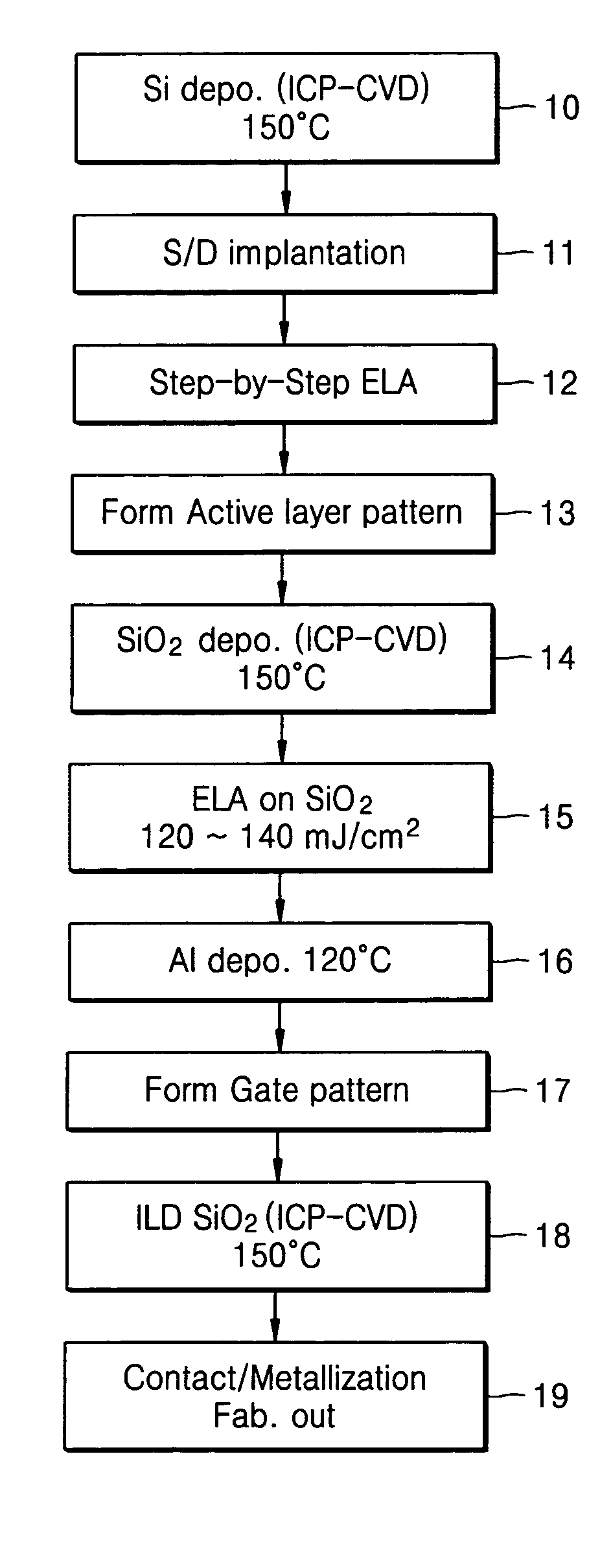

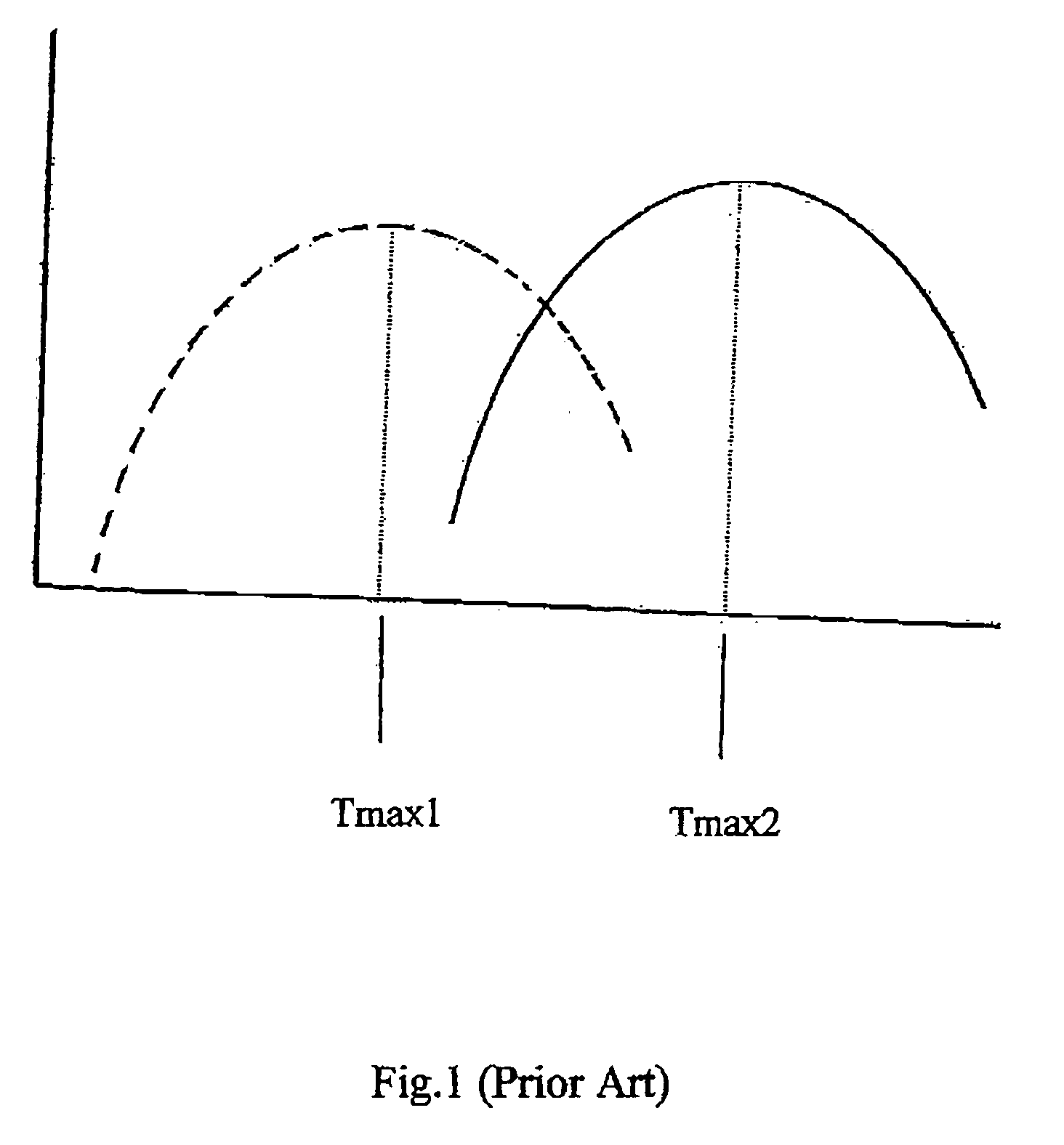

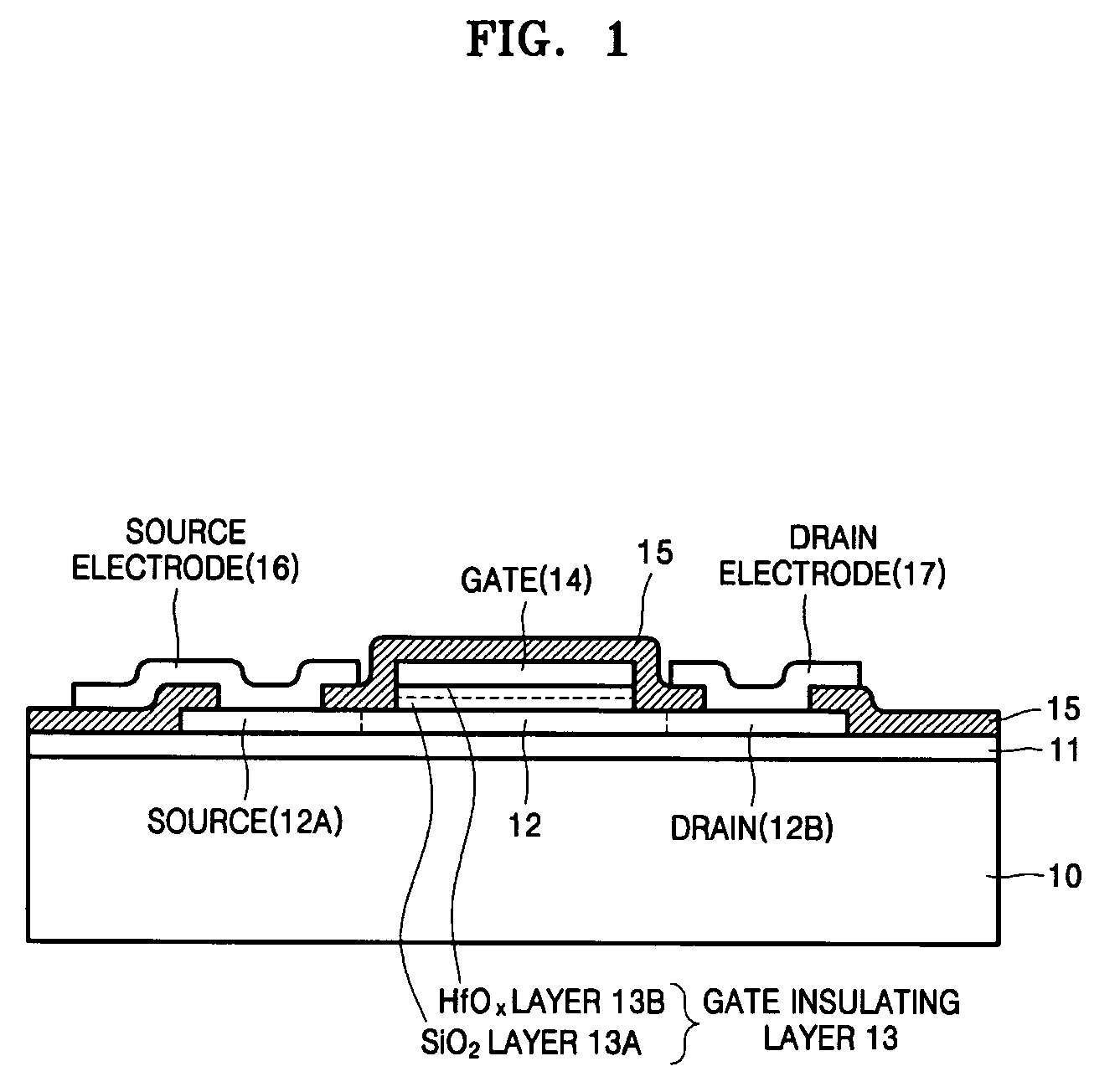

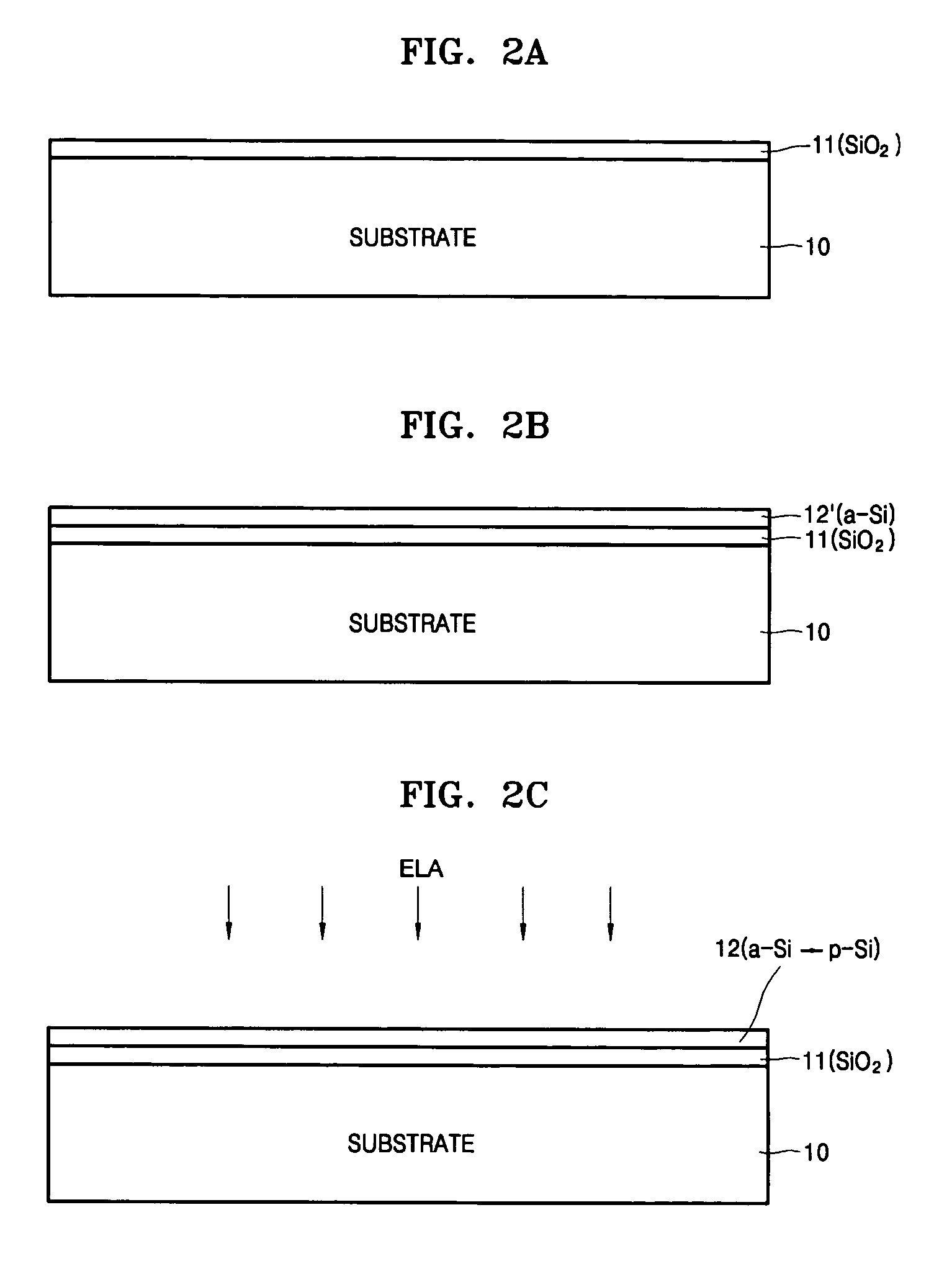

Method of fabricating poly-crystalline silicon thin film and method of fabricating transistor using the same

InactiveUS7563659B2Refined grain sizeHigh energyTransistorSemiconductor/solid-state device manufacturingInductively coupled plasmaSilicon thin film

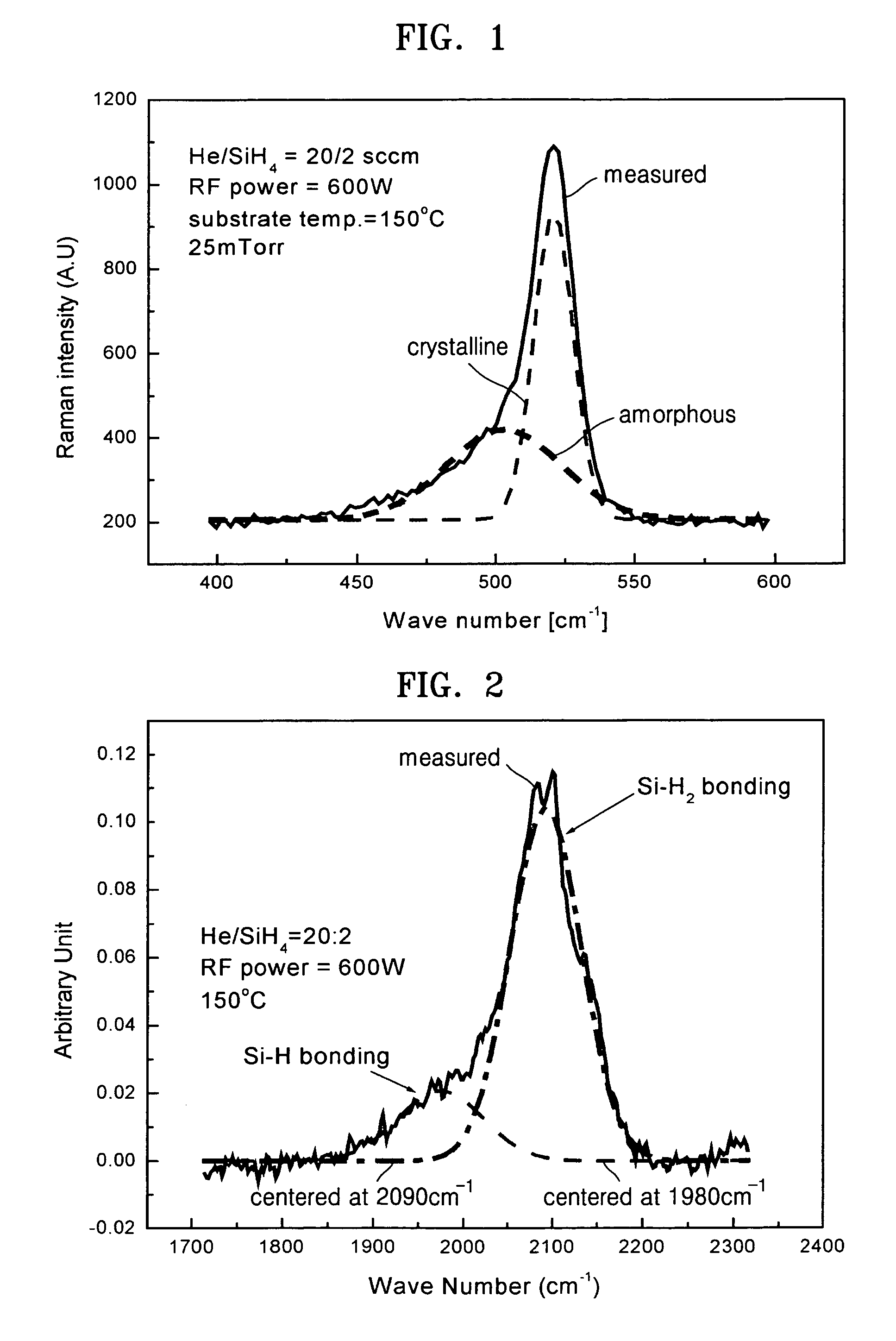

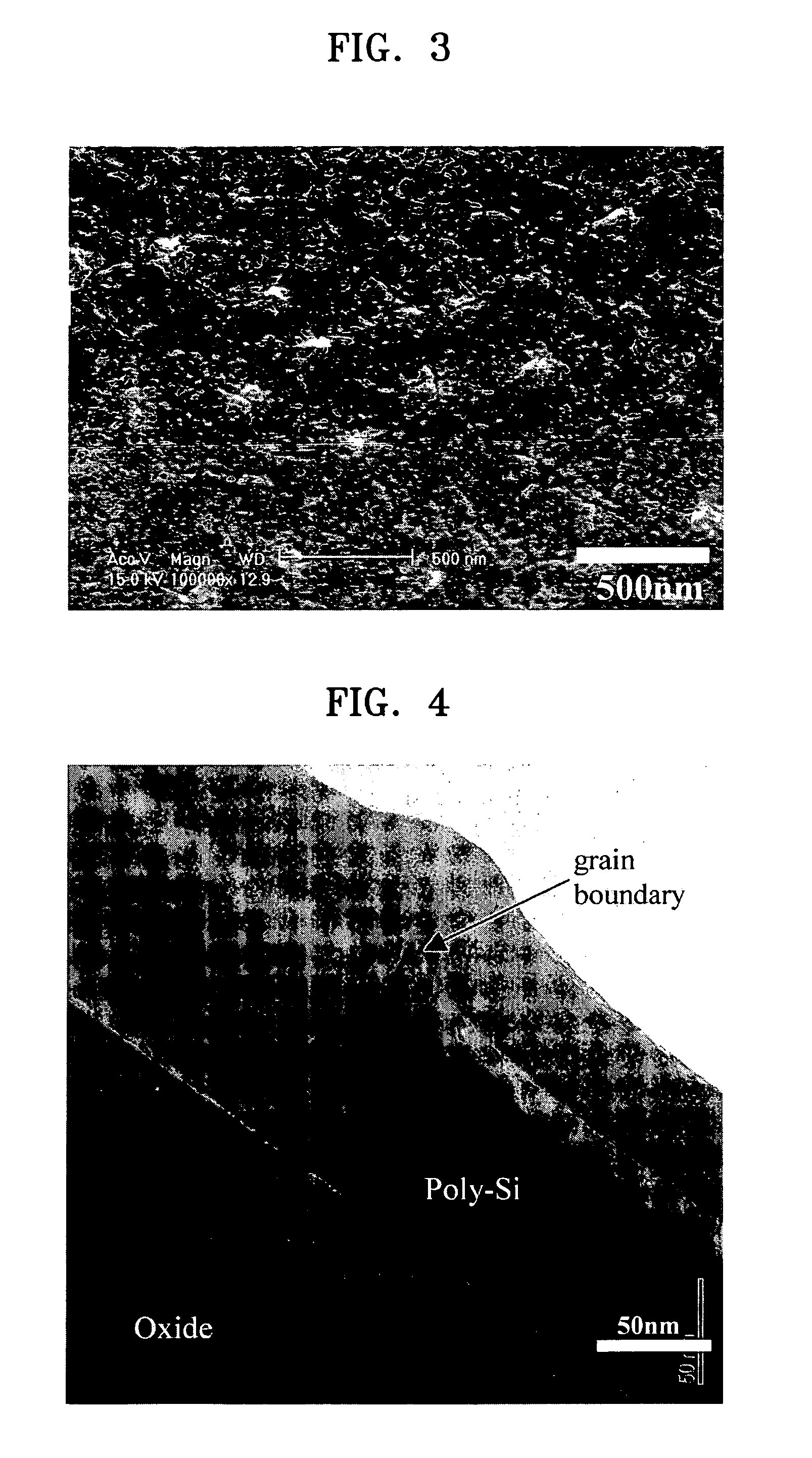

A method of fabricating a poly-Si thin film and a method of fabricating a poly-Si TFT using the same are provided. The poly-Si thin film is formed at a low temperature using inductively coupled plasma chemical vapor deposition (ICP-CVD). After the ICP-CVD, excimer laser annealing (ELA) is performed while increasing energy by predetermined steps. A poly-Si active layer and a SiO2 gate insulating layer are deposited at a temperature of about 150° C. using ICP-CVD. The poly-Si has a large grain size of about 3000 Å or more. An interface trap density of the SiO2 can be as high as 1011 / cm2. A transistor having good electrical characteristics can be fabricated at a low temperature and thus can be formed on a heat tolerant plastic substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device and manufacturing method thereof

InactiveUS20050167573A1Low costLower the volumeSolid-state devicesSemiconductor/solid-state device manufacturingAudio power amplifierCrystal structure

The object of the present invention is to miniaturize the area occupied by the element and to integrate a plenty of elements in a limited area so that the sensor element can have higher output and smaller size. In the present invention, higher output and miniaturization are achieved by uniting a sensor element using an amorphous semiconductor film (typically an amorphous silicon film) and an output amplifier circuit including a TFT with a semiconductor film having a crystal structure (typically a poly-crystalline silicon film) used as an active layer over a plastic film substrate that can resist the temperature in the process for mounting such as a solder reflow process. According to the present invention, the sensor element that can resist the bending stress can be obtained.

Owner:SEMICON ENERGY LAB CO LTD

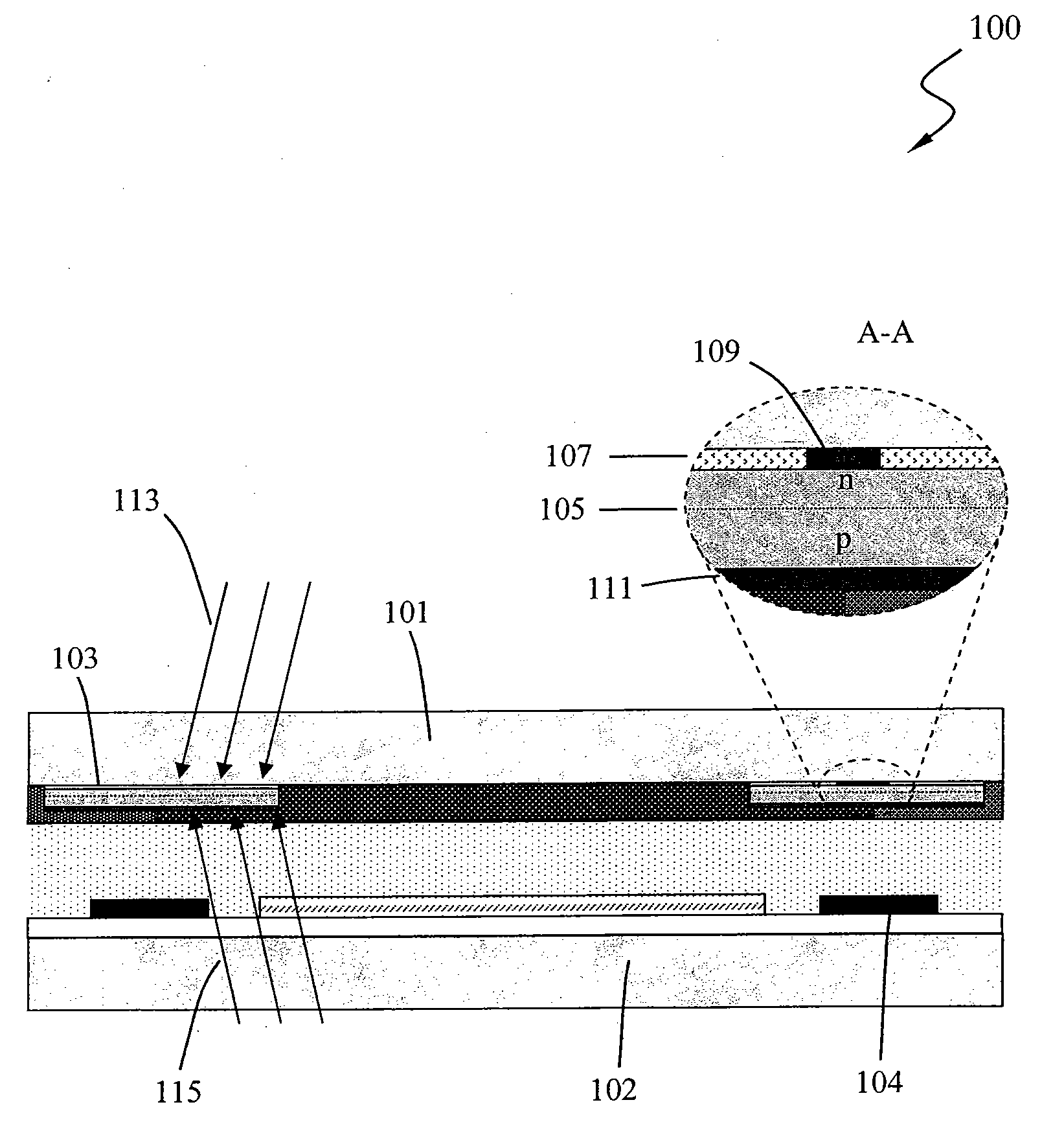

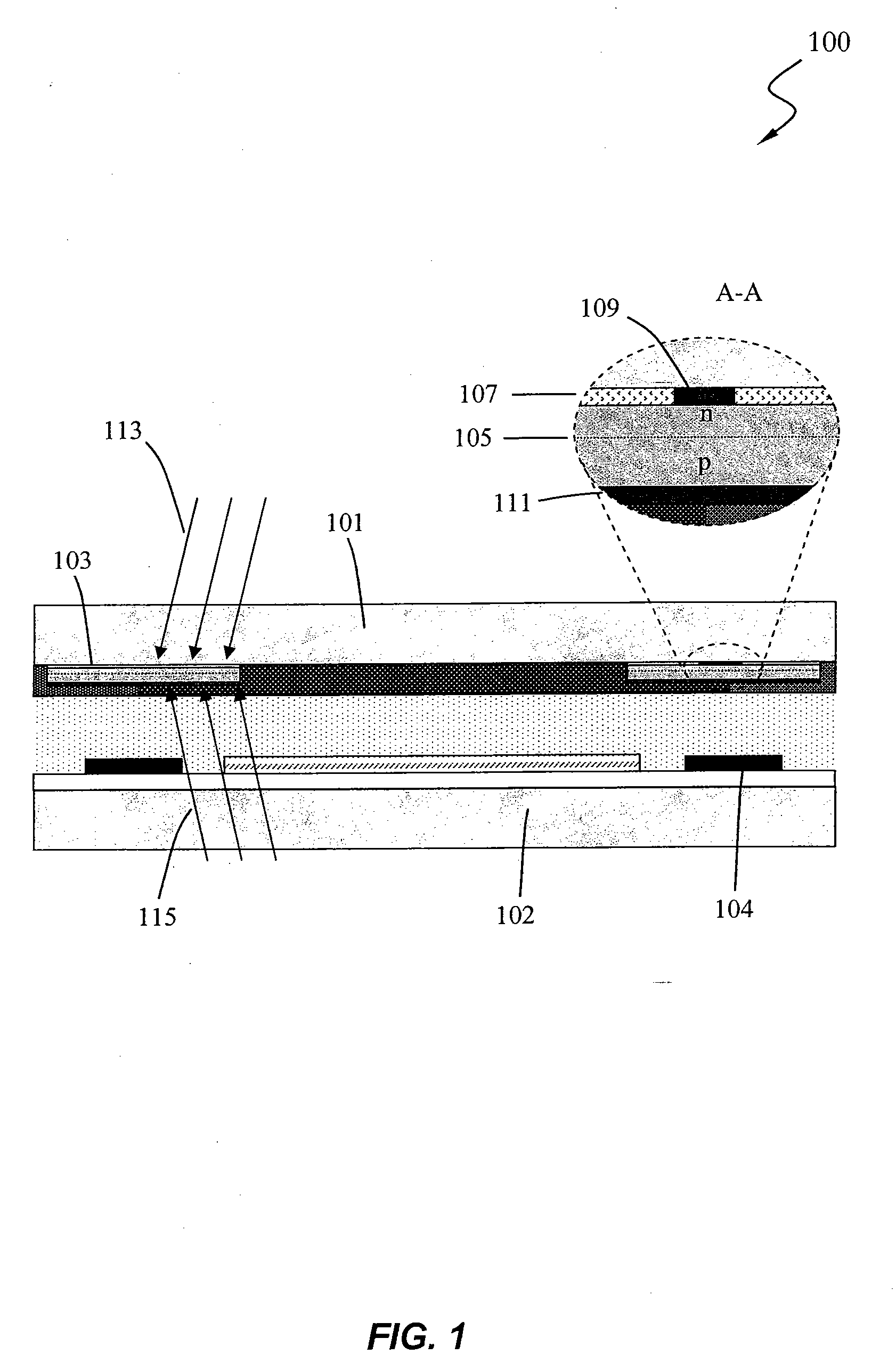

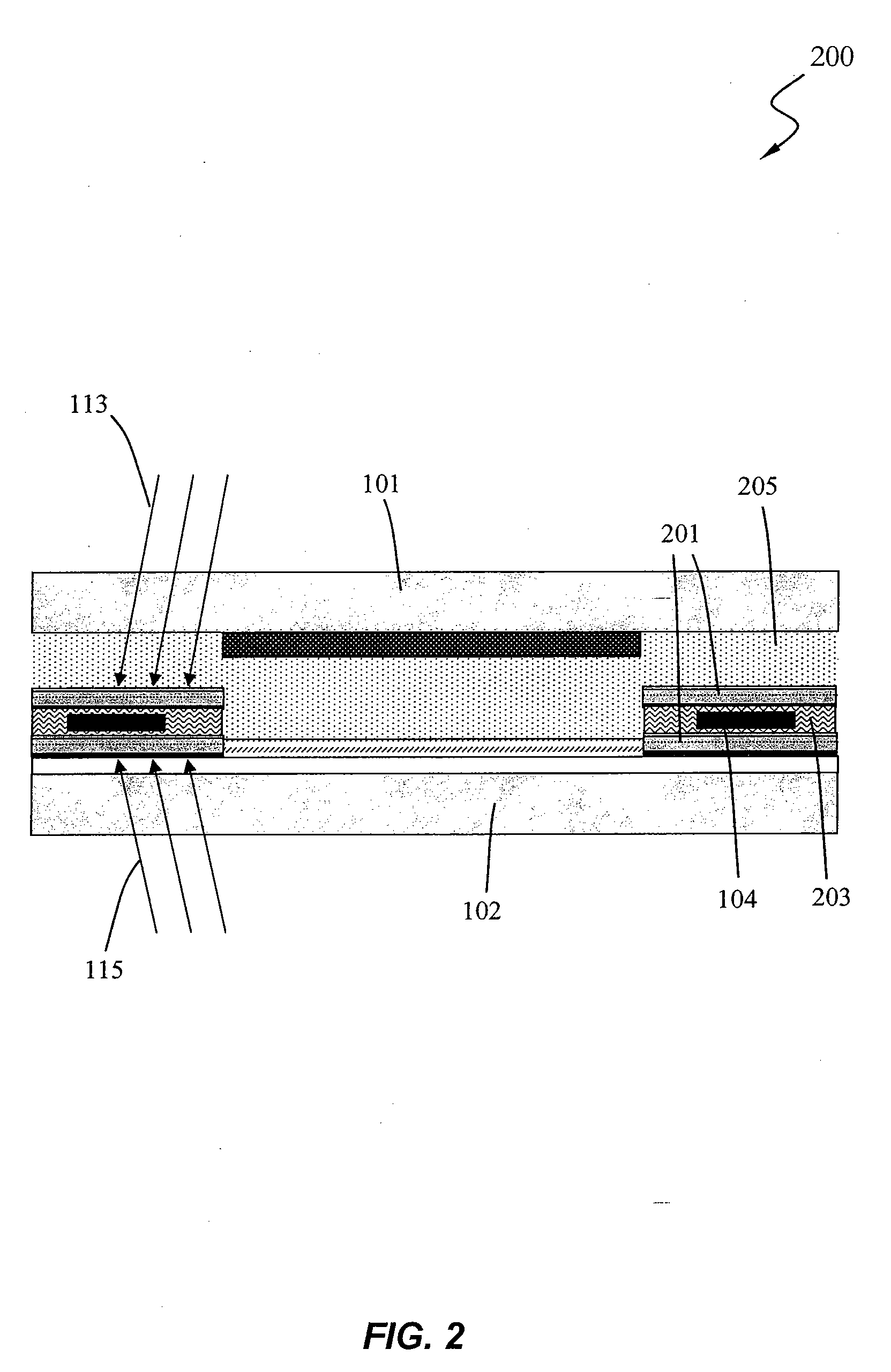

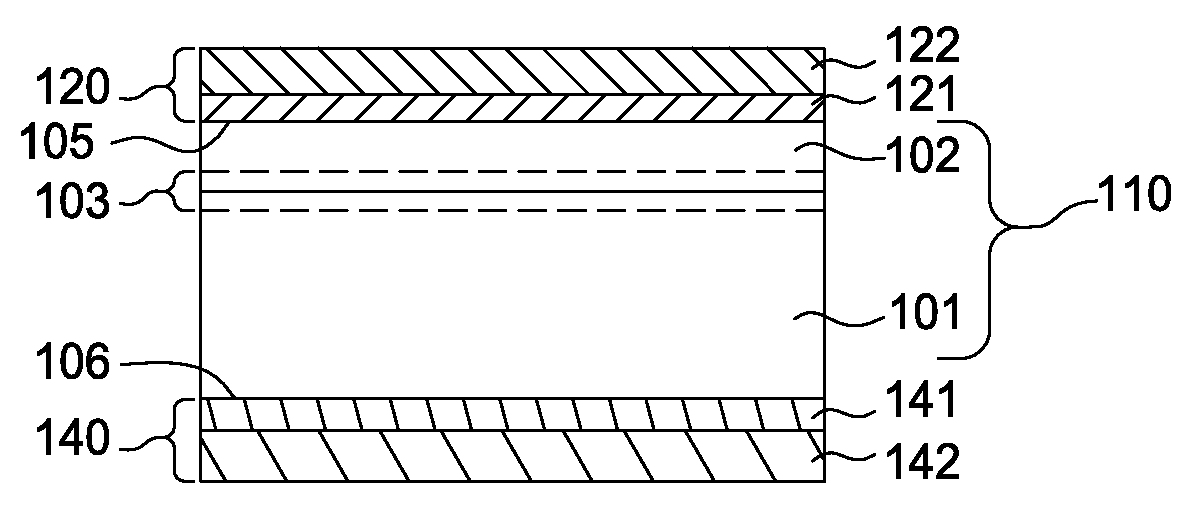

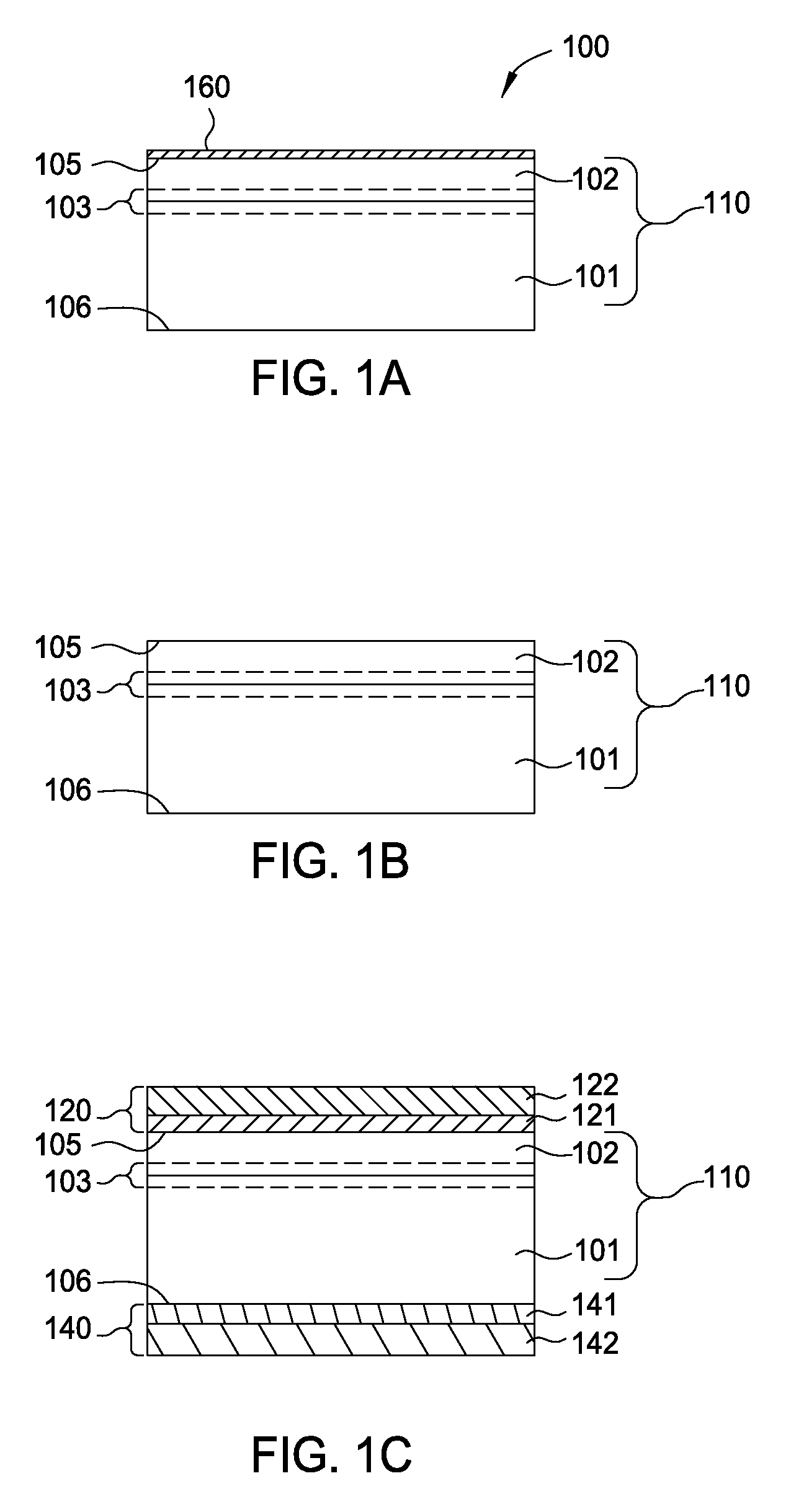

Method and Structure for Integrated Solar Cell LCD Panel

InactiveUS20070102035A1Improve fill rateIncrease cell areaPV power plantsPhotovoltaic energy generationEngineeringSolar cell

The present invention relates to a method and device for integrating solar cell on LCD panels for photovoltaic electricity generation for portable electronic devices. According to one embodiment of the present invention, the black matrix region on the color filter substrate in a LCD panel is replaced by a solar cell region. A lens array substrate is coupled between the light source layer and the TFT to focus the backlight to increase the solar cell layer area while maintaining high fill ratio of the LCD pixels. The solar cell material is selected from at least silicon, a single crystal silicon, poly-crystalline silicon, amorphous silicon, gallium arsenide, cadmium telluride, copper indium diselenide, organic / inorganic, or hybrid cells. The substrate material is selected from glass, metal, plastic or polymer.

Owner:XIAI CHARLES YANG

Self-grown monopoly compact grit

InactiveUS6616725B2Strong and more resilientProduced cost-effectivelyPigmenting treatmentOther chemical processesBoron nitrideSolvent

A self-grown monopoly compact grit and high pressure, high temperature process for preparing the same. The high pressure, high temperature sintered / synthesized monopoly compact grit is used in various industrial tools such as saw blades, grinding wheels, cutting tools and drill bits. Further, the monopoly compact grit of the present invention is produced from a seed of a mono-crystal of diamond or cubic boron nitride surrounded by either a self-grown crystal layer or an integrally bonded poly-crystalline sintered compact layer. The self-grown crystal layer is a new grown crystal structure where the seed crystal grows into a new phase through a normal diamond or cubic boron nitride synthesis process in the presence of a catalyst metal solvent. The compact layer is composed of about 50 to about 90 volume percent of diamond or cubic boron nitride, a typical binder material, which is a catalyst for crystal-to-crystal bonding, and a cementing agent which is a binding agent capable of forming stable carbide and nitride bonds.

Owner:CHO HYUN SAM +2

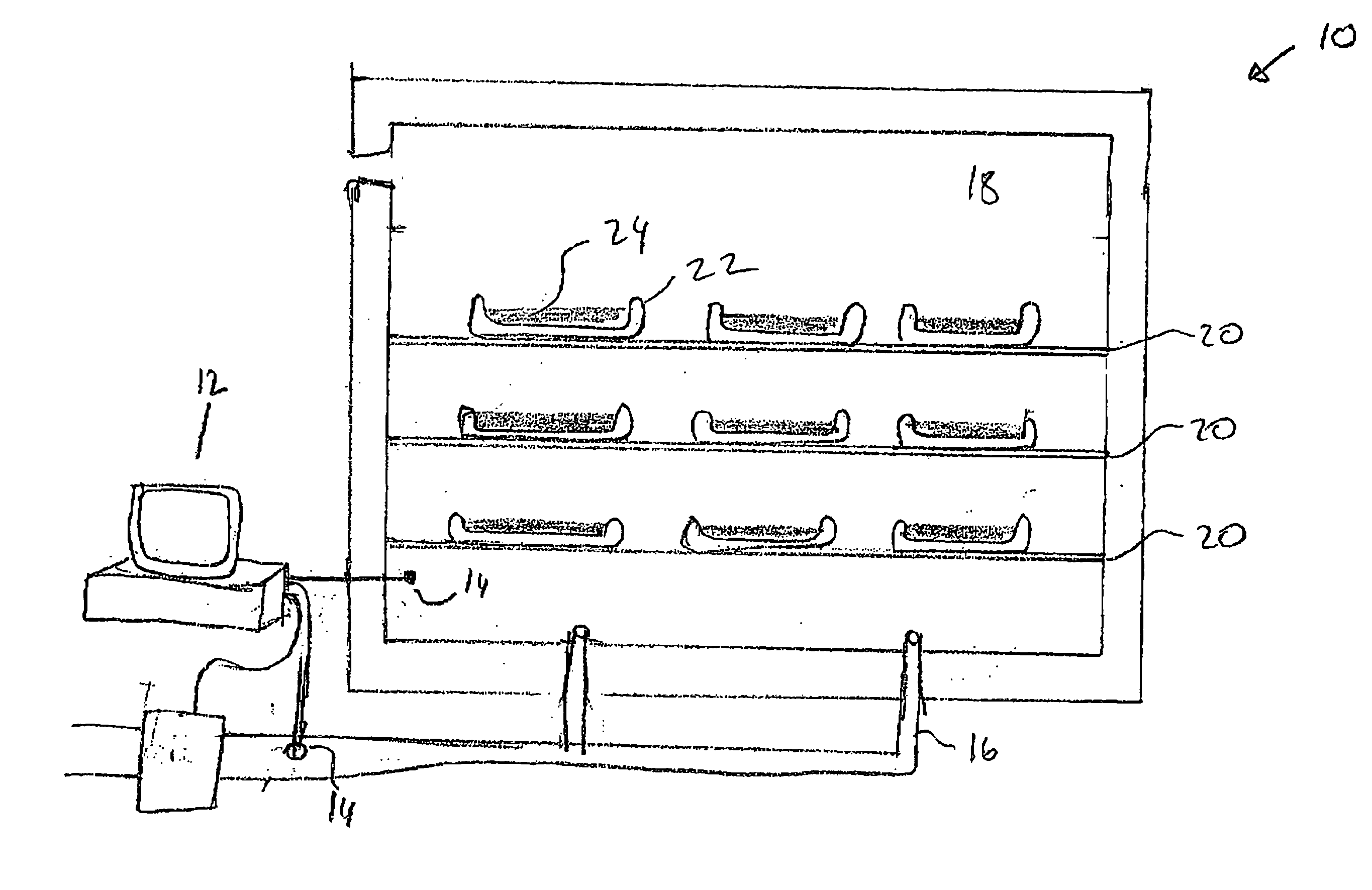

System for heat treatment of semiconductor device

InactiveUS20070122936A1Avoid damageIncrease temperatureFurnaces without endless coreSemiconductor/solid-state device manufacturingDevice materialElectromotive force

Disclosed is a heat treatment system for semiconductor devices. The heat treatment system is used in a heat treatment process for semiconductor devices, such as a crystallization process for an amorphous silicon thin film or a dopant activation process for a poly-crystalline silicon thin film formed on a surface of a glass substrate of a flat display panel including a liquid crystal display (LCD) or an organic light emitting device (OLED). The heat treatment system transfers a semiconductor device after uniformly preheating the semiconductor device in order to prevent deformation of the semiconductor device during the heat treatment process, rapidly performs the heat treatment process under the high temperature condition by heating the semiconductor device using a lamp heater and induction heat derived from induced electromotive force, and unloads the semiconductor device after uniformly cooling the semiconductor device such that the semiconductor device is prevented from being deformed when the heat treatment process has been finished. The heat treatment system rapidly performs the heat treatment process while preventing deformation of the semiconductor device by gradually heating or cooling the semiconductor device.

Owner:VIATRON TECH INC

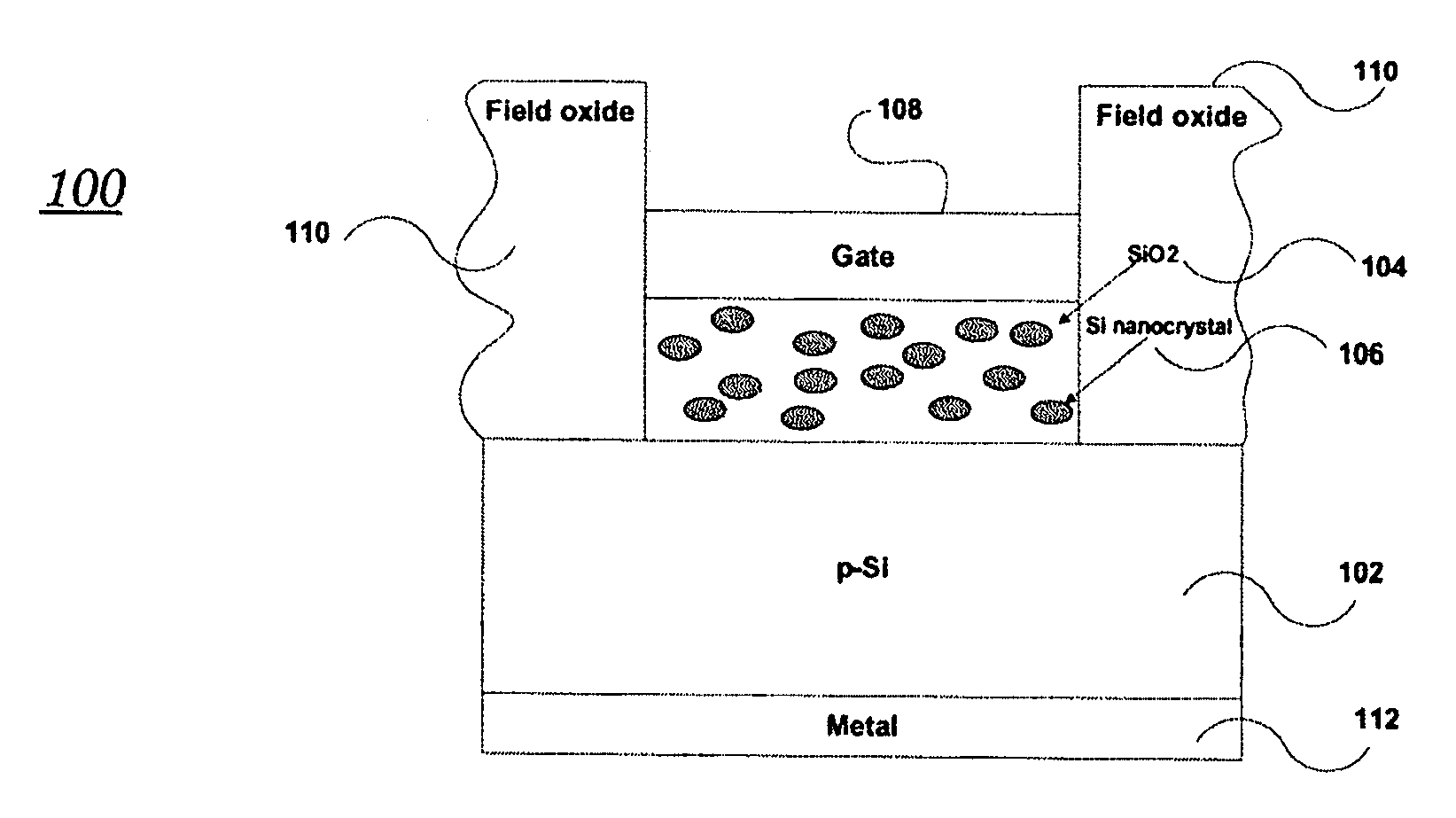

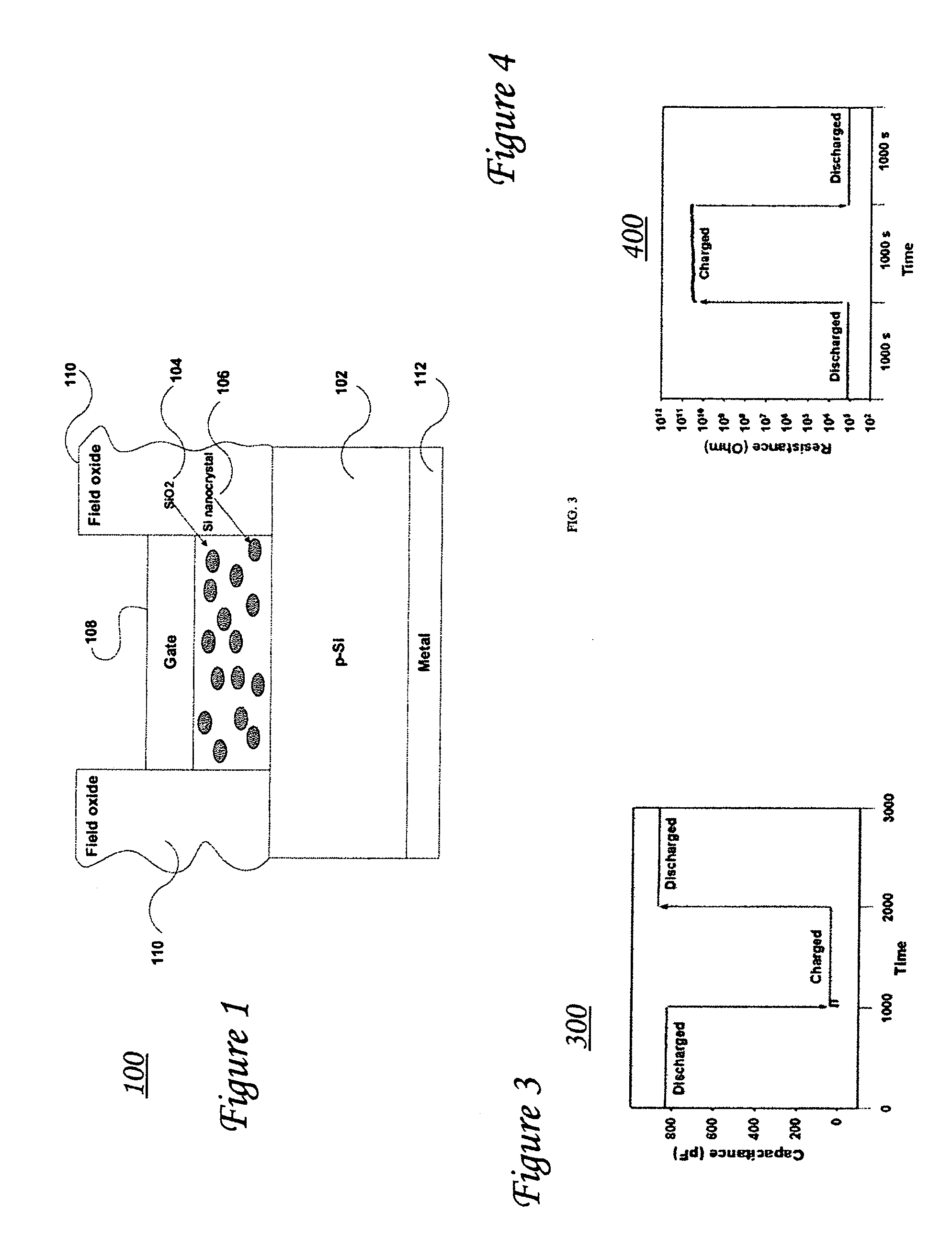

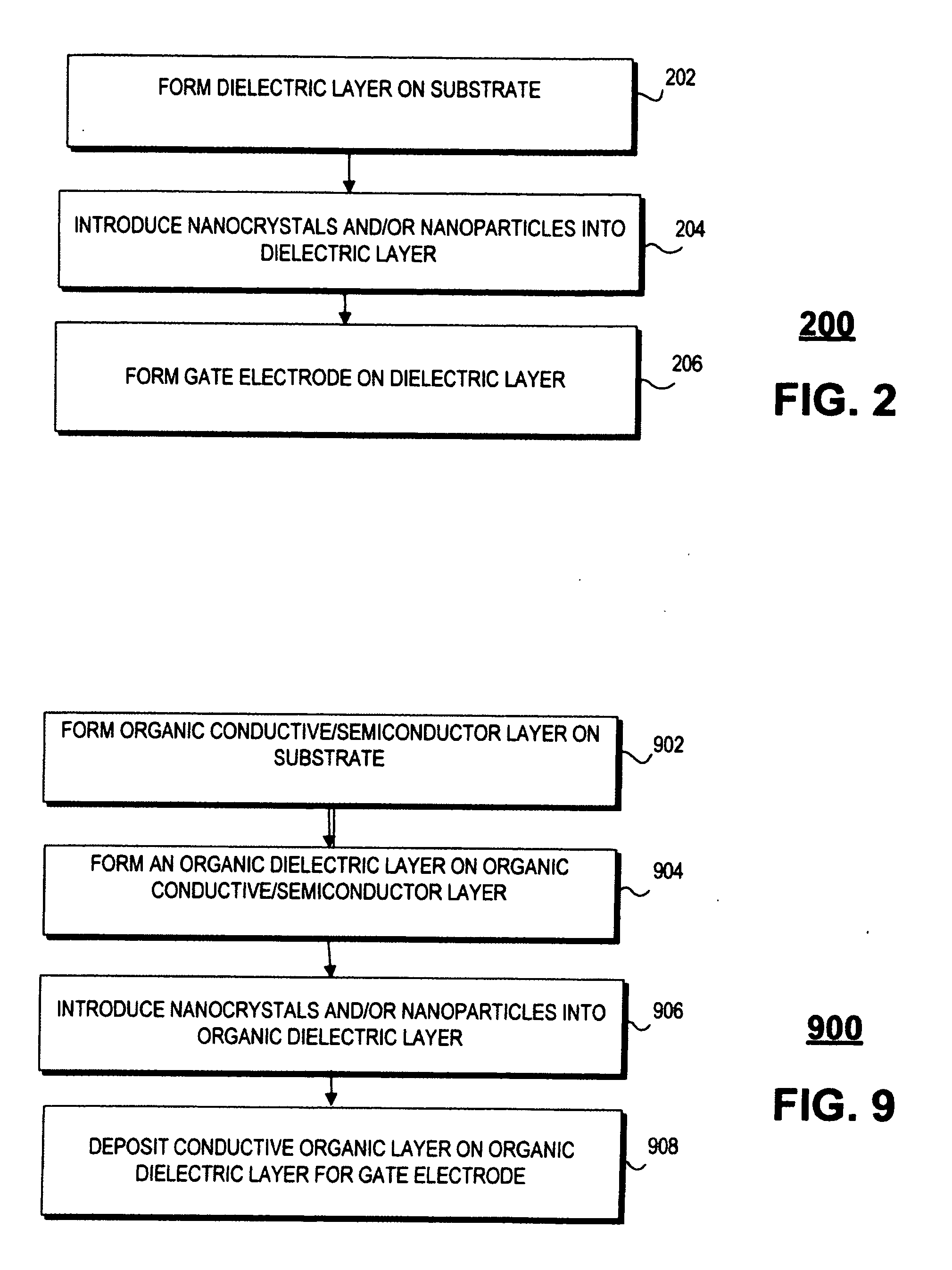

Two-terminal solid-state memory device and two-terminal flexible memory device based on nanocrystals or nanoparticles

InactiveUS20060231889A1Simple designFew stepsNanoinformaticsSemiconductor/solid-state device manufacturingMOSFETManufacturing technology

A two-terminal memory device based on semiconductor (such as Si or Ge) or metal (such as Al or Au) nanocrystals and / or nanoparticles is described wherein each device has a substrate, a dielectric layer (such as SiO2 or organic dielectric materials) nanocrystals and / or nanoparticles distributed throughout the dielectric layer, and a metal (or poly-crystalline Si, or conductive organic materials) gate electrode. The memory states of the device are distinguished by charging and discharging the nanocrystals and / or nanoparticles. This two-terminal memory device is much simpler than the conventional four-terminal MOSFET-based memory device in terms of device structure and fabrication process. In addition, it is flexible if the memory devices are fabricated on flexible substrate with organic materials.

Owner:NANYANG TECH UNIV

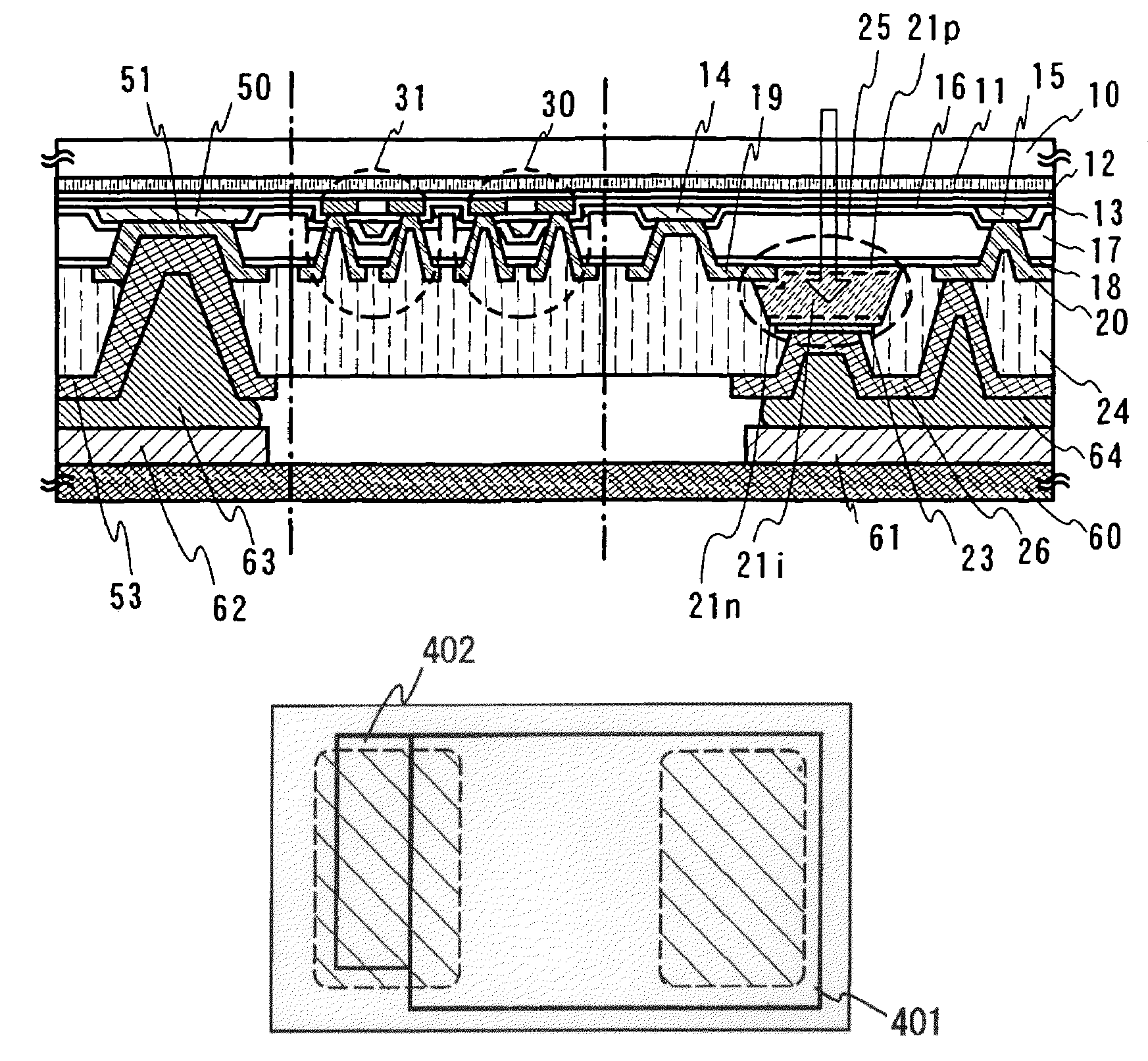

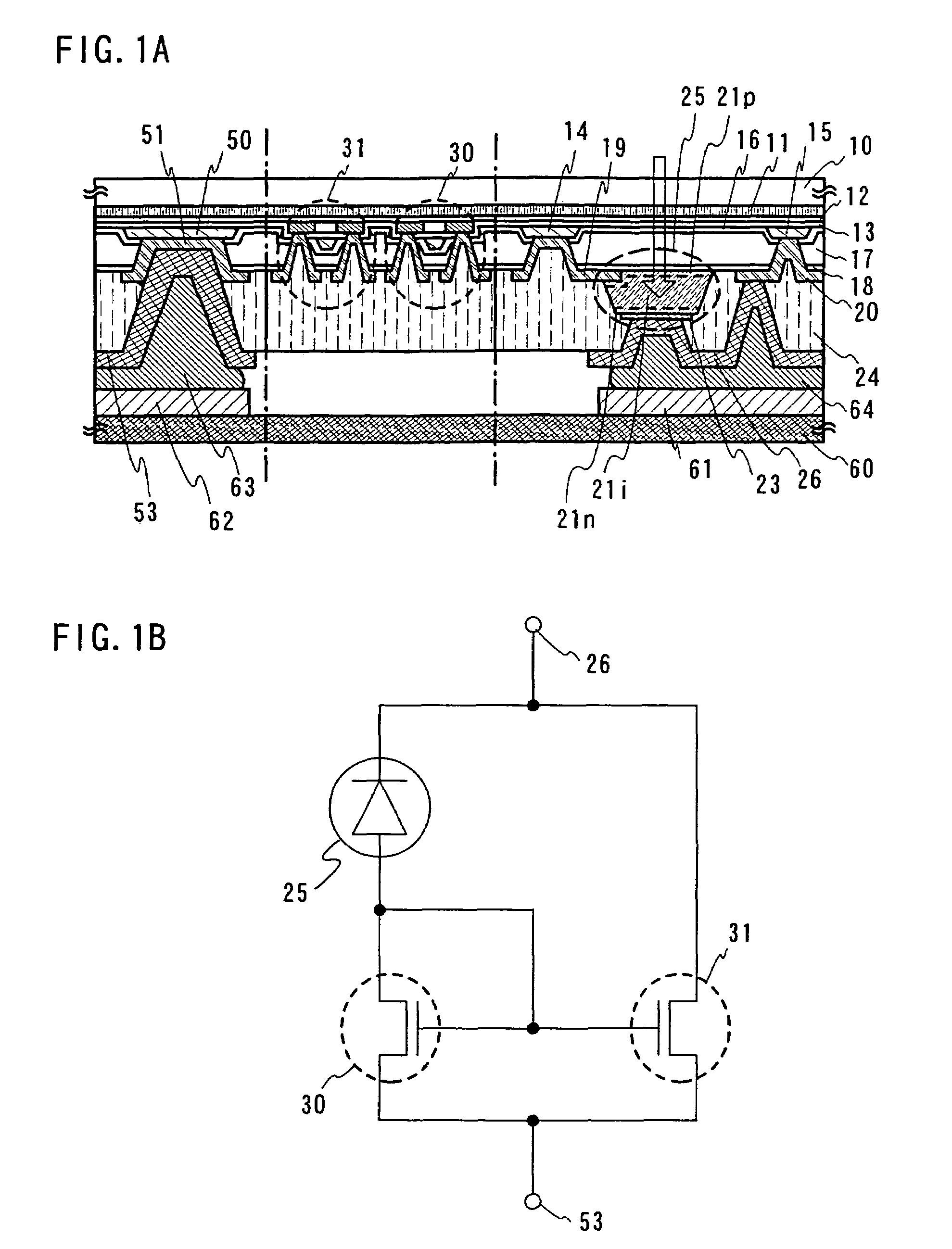

Semiconductor device having photo sensor element and amplifier circuit

InactiveUS7495272B2Increase productionSmall sizeSolid-state devicesSemiconductor/solid-state device manufacturingAudio power amplifierAmorphous silicon

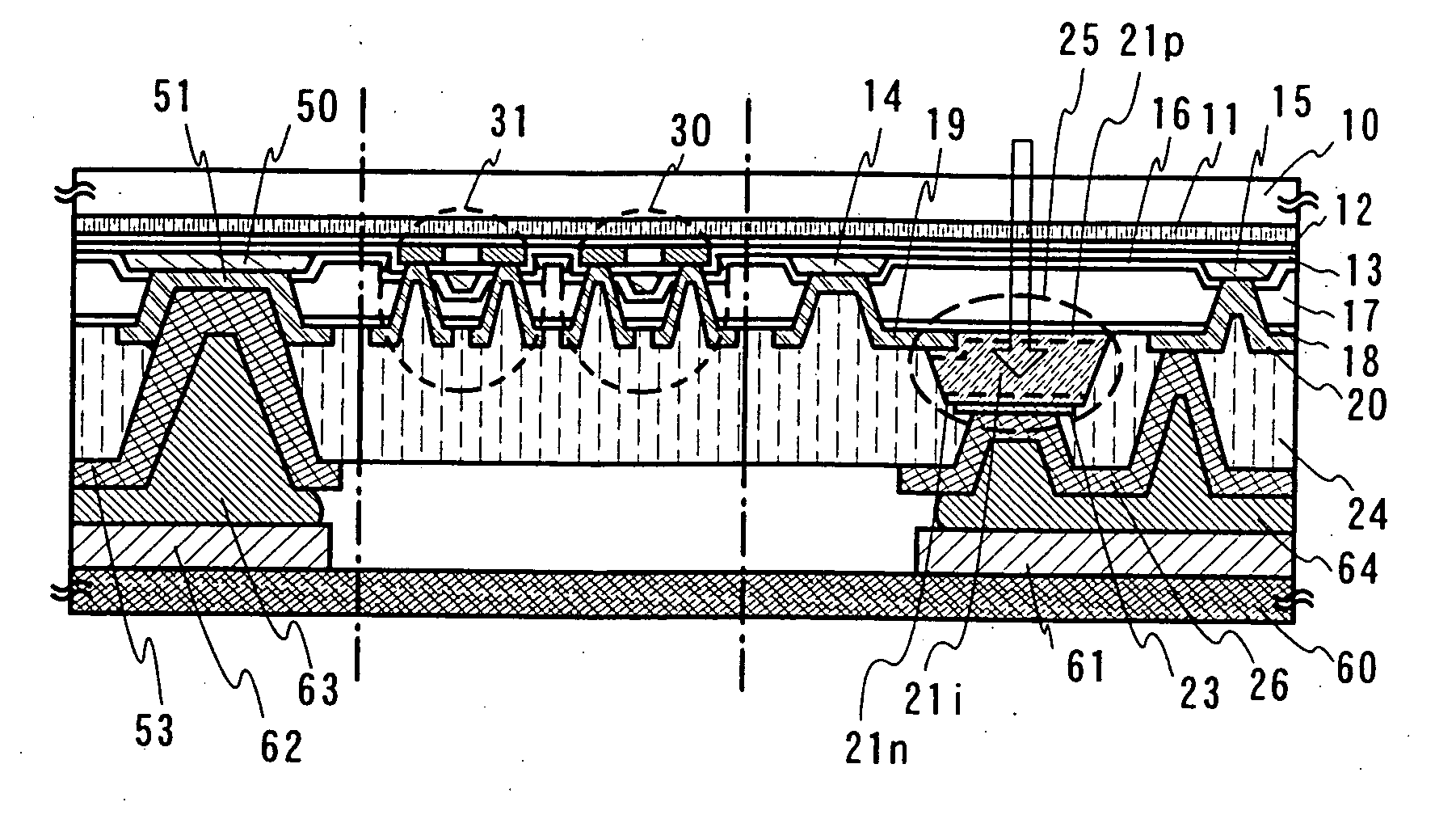

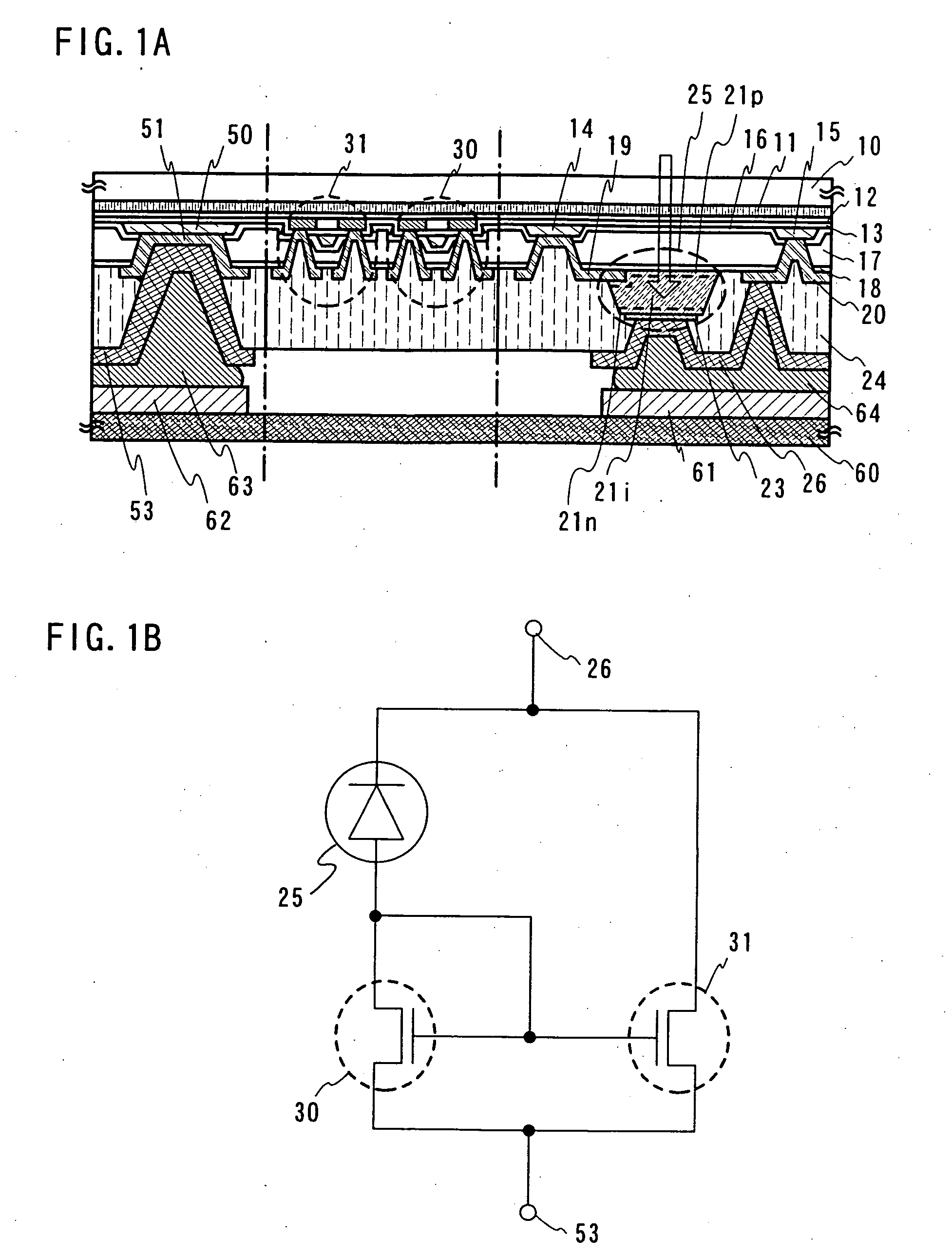

The area occupied by a photo-sensor element may be reduced and multiple elements may be integrated in a limited area so that the sensor element can have higher output and smaller size. Higher output and miniaturization are achieved by uniting a sensor element using an amorphous semiconductor film (typically an amorphous silicon film) and an output amplifier circuit including a TFT with a semiconductor film having a crystal structure (typically a poly-crystalline silicon film) used as an active layer over a plastic film substrate that can resist the temperature in the process for mounting such as a solder reflow process. A sensor element that can resist bending stress can be obtained.

Owner:SEMICON ENERGY LAB CO LTD

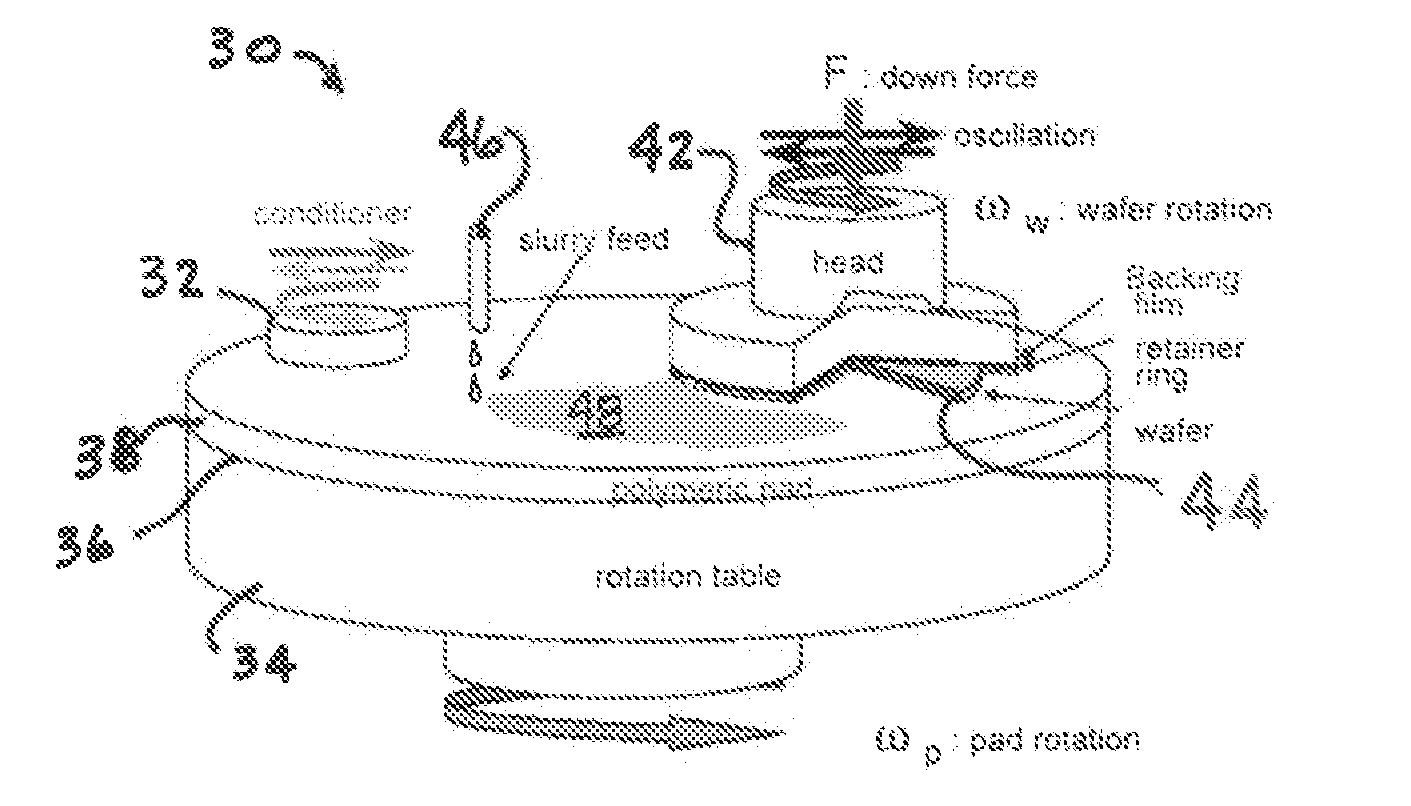

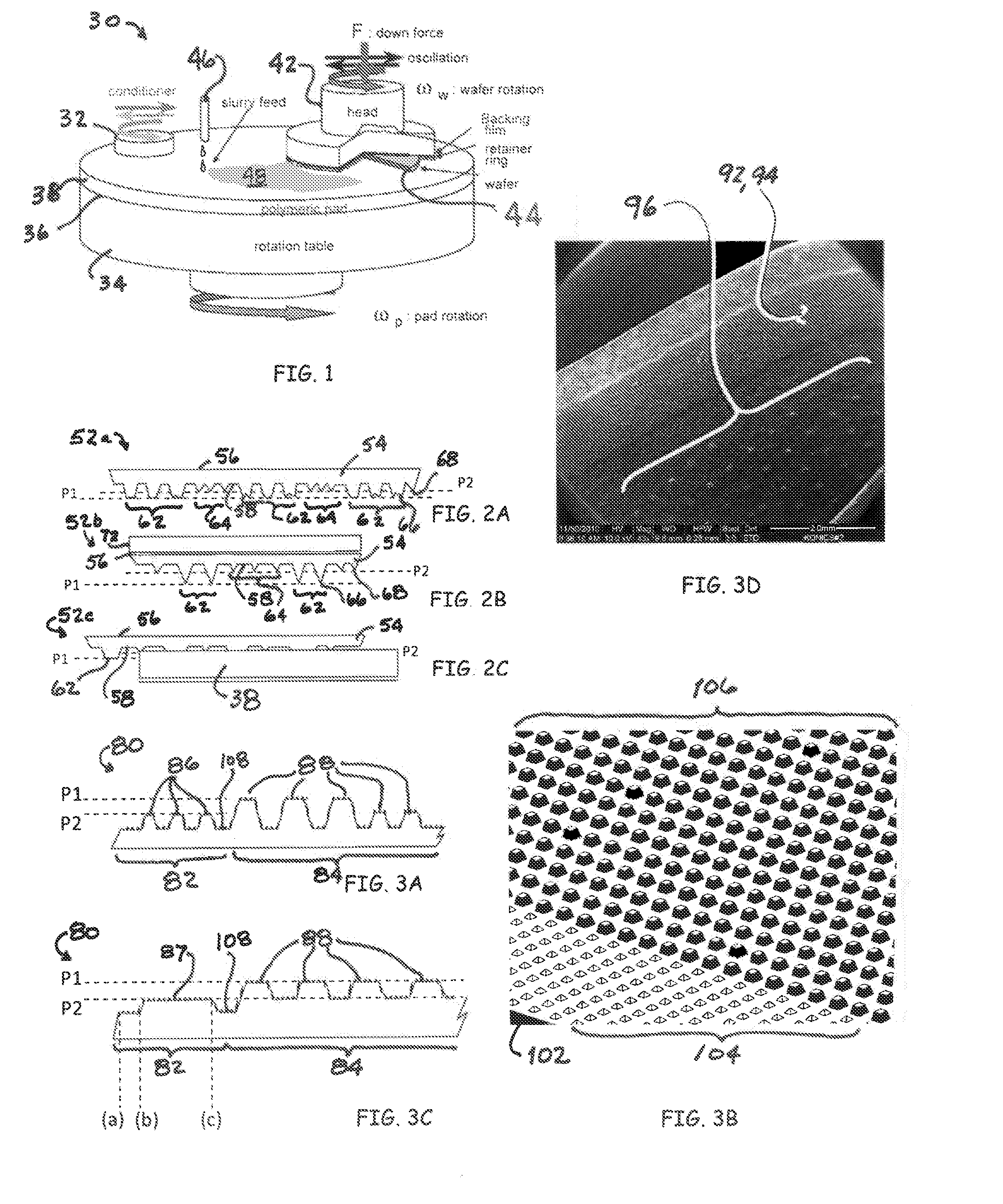

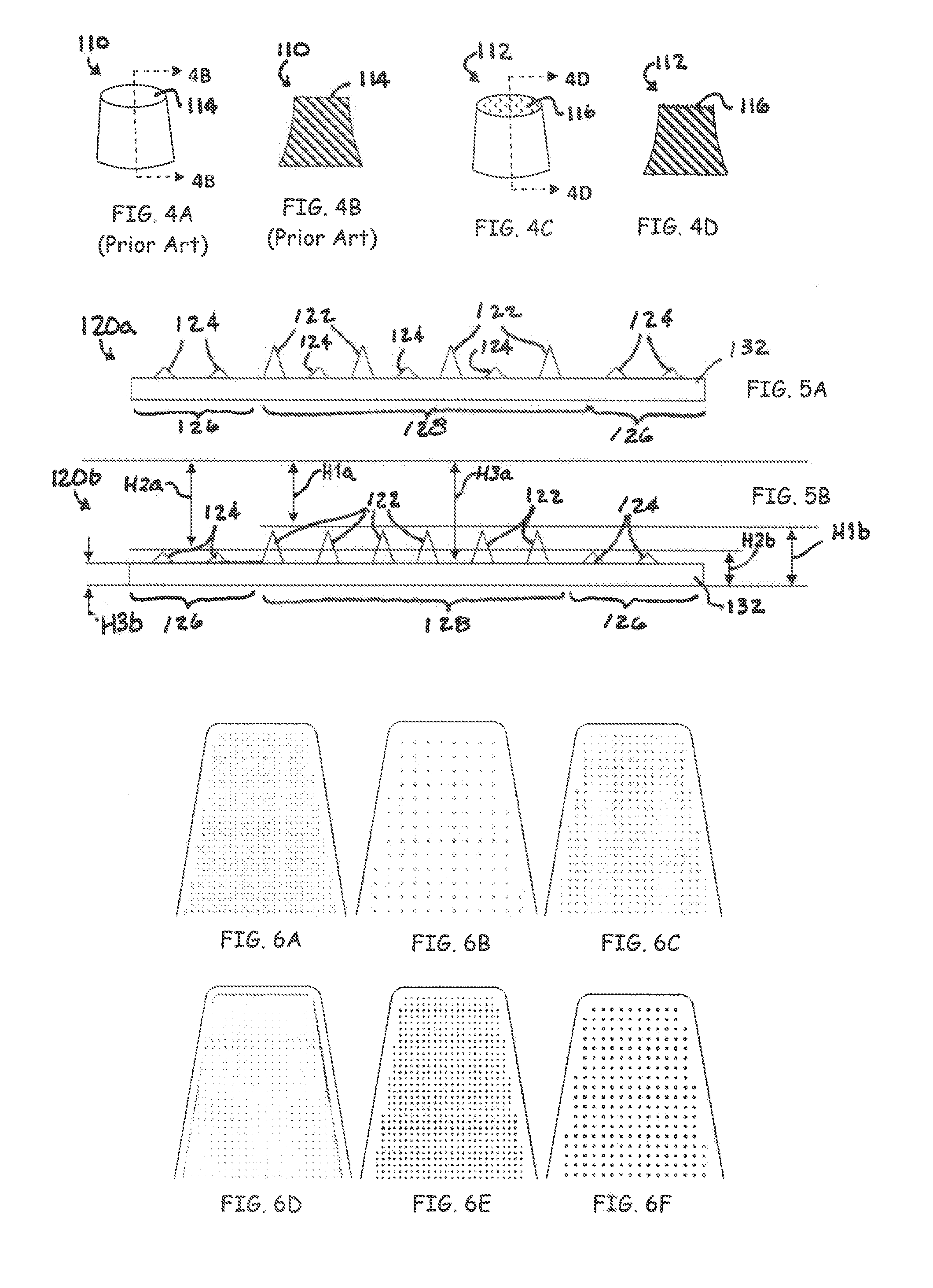

Chemical mechanical planarization conditioner

ActiveUS20140113532A1Improve cutting performanceIncreased longevityGrinding drivesBelt grinding machinesPolycrystalline diamondEngineering

A pad conditioner for a CMP polishing pad is disclosed that includes a substrate that has a matrixical arrangement of protrusions that have a layer of poly crystalline diamond on at least their top surfaces. The protrusions may have varying shapes and elevations and may comprise a first set of protrusions and a second set of protrusions, the first set of protrusions have a first average height and the second set of protrusions have a second average height, the first average height different from the second average height, a top of each protrusion in the first set of protrusions has a non-flat surface and a top of each protrusion in the second set of protrusions has a non-flat surface.

Owner:ENTEGRIS INC

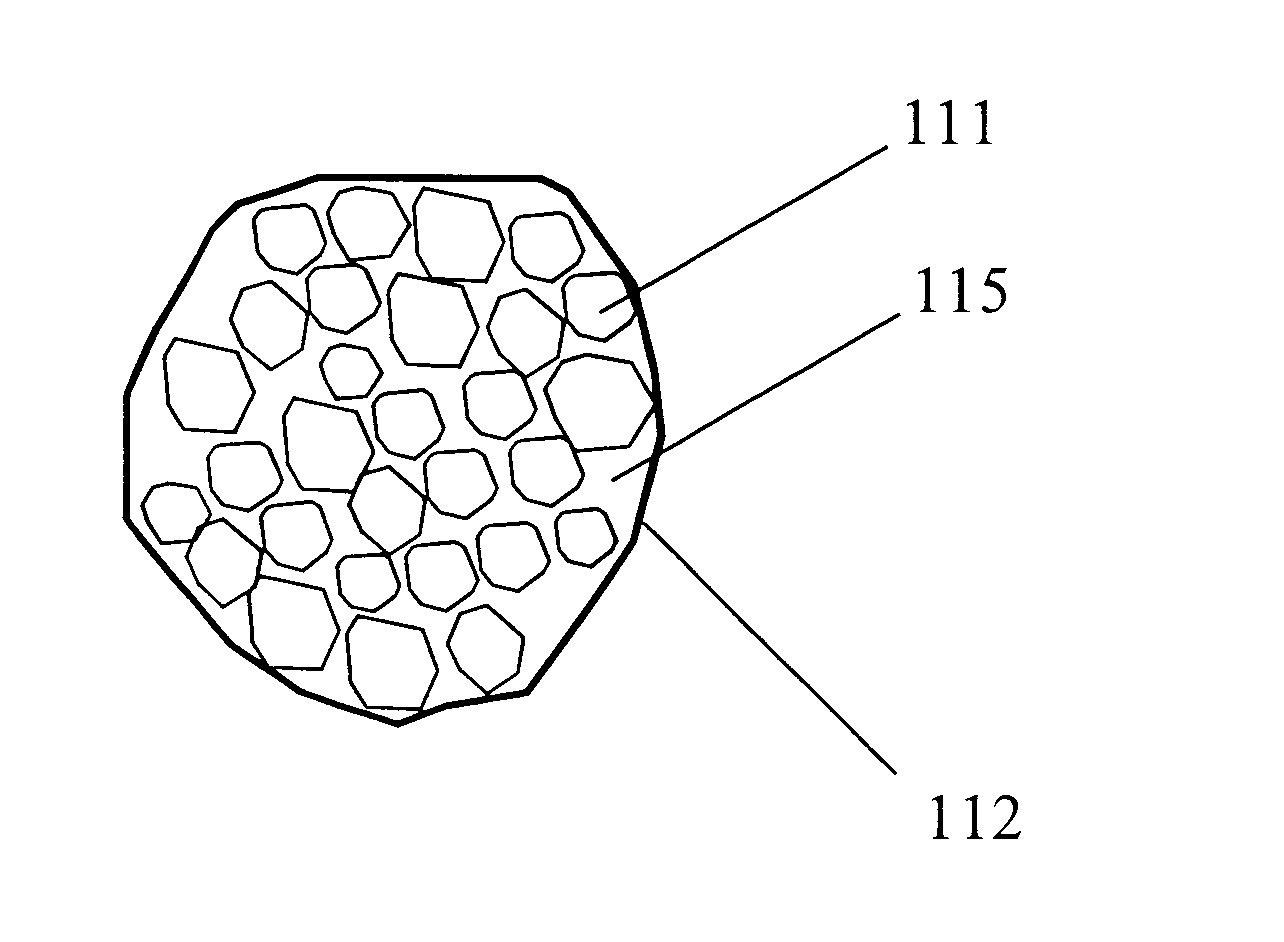

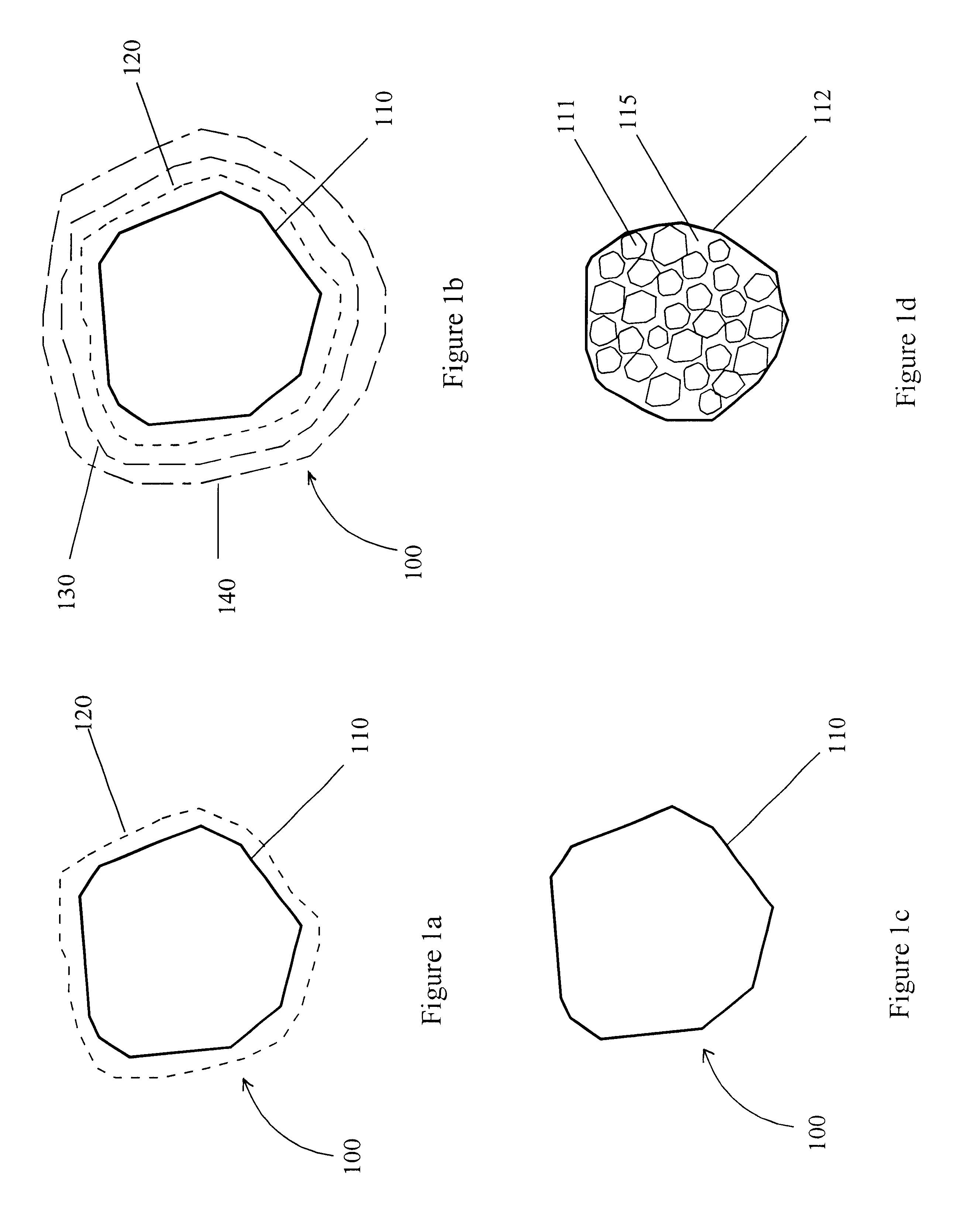

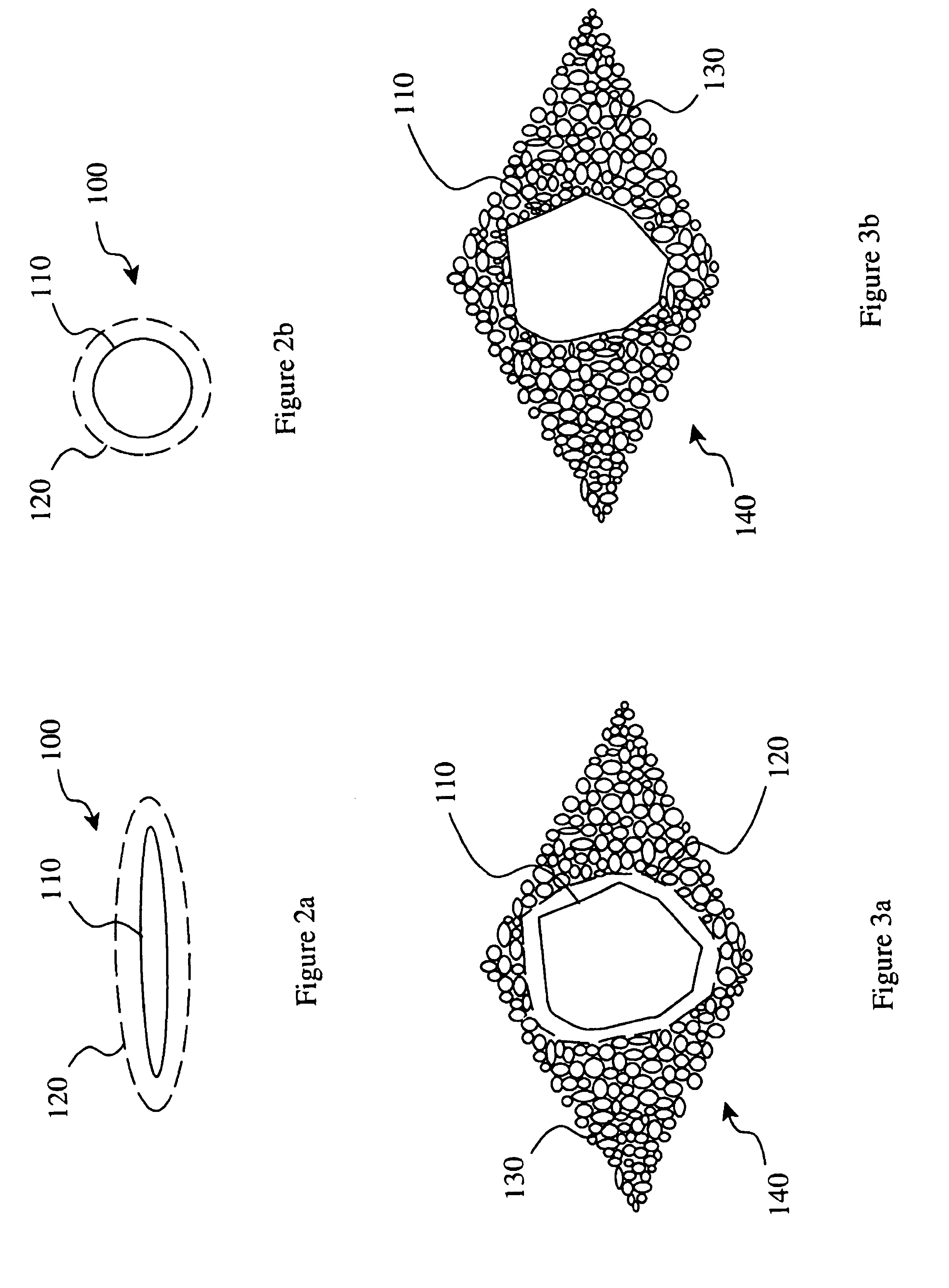

Polycrystalline Grits and Associated Methods

A method for forming polycrystalline grits can include forming an abrasive dough, including a plurality of abrasive particles, into a sheet. The sheet can be divided into a plurality of abrasive precursors. By placing the sheet on a stretchable surface, separations among the plurality of abrasive precursors can be revealed by stretching the stretchable surface. The stretchable surface can include a particulate separating agent, and additional particulate separating agent can be distributed in the separations. The abrasive precursors can be sintered to form polycrystalline grits.

Owner:SUNG CHIEN MIN

Group III nitride compound semiconductor thin film and deposition method thereof, and semiconductor device and manufacturing method thereof

InactiveUS20030039866A1Uniform film qualitySimple methodLaser detailsVacuum evaporation coatingLattice defectsDislocation

A Group III nitride compound semiconductor thin film which can be deposited on any given substrate to have uniform film quality and excellent crystalline, and a deposition method thereof. A semiconductor device and a manufacturing method thereof. A poly-crystalline Group III nitride compound thin film is deposited on a substrate by sputtering at a deposition rate of 15 to 200 nm / hour using a Group III nitride compound target in a plazma atmosphere of gas comprising 10 mole % or more nitrogen. Then, the poly-crystalline Group III nitride compound semiconductor thin film deposited on the substrate is irradiated with an excimer pulsed laser with an energy density of about 200 mJ / cm2, in an atmosphere of gas with an oxygen content of 2 mole % or less. Thereby, lattice defects such as grain boundaries or dislocations which occur in the thin film are removed.

Owner:MITAMURA SATOSHI

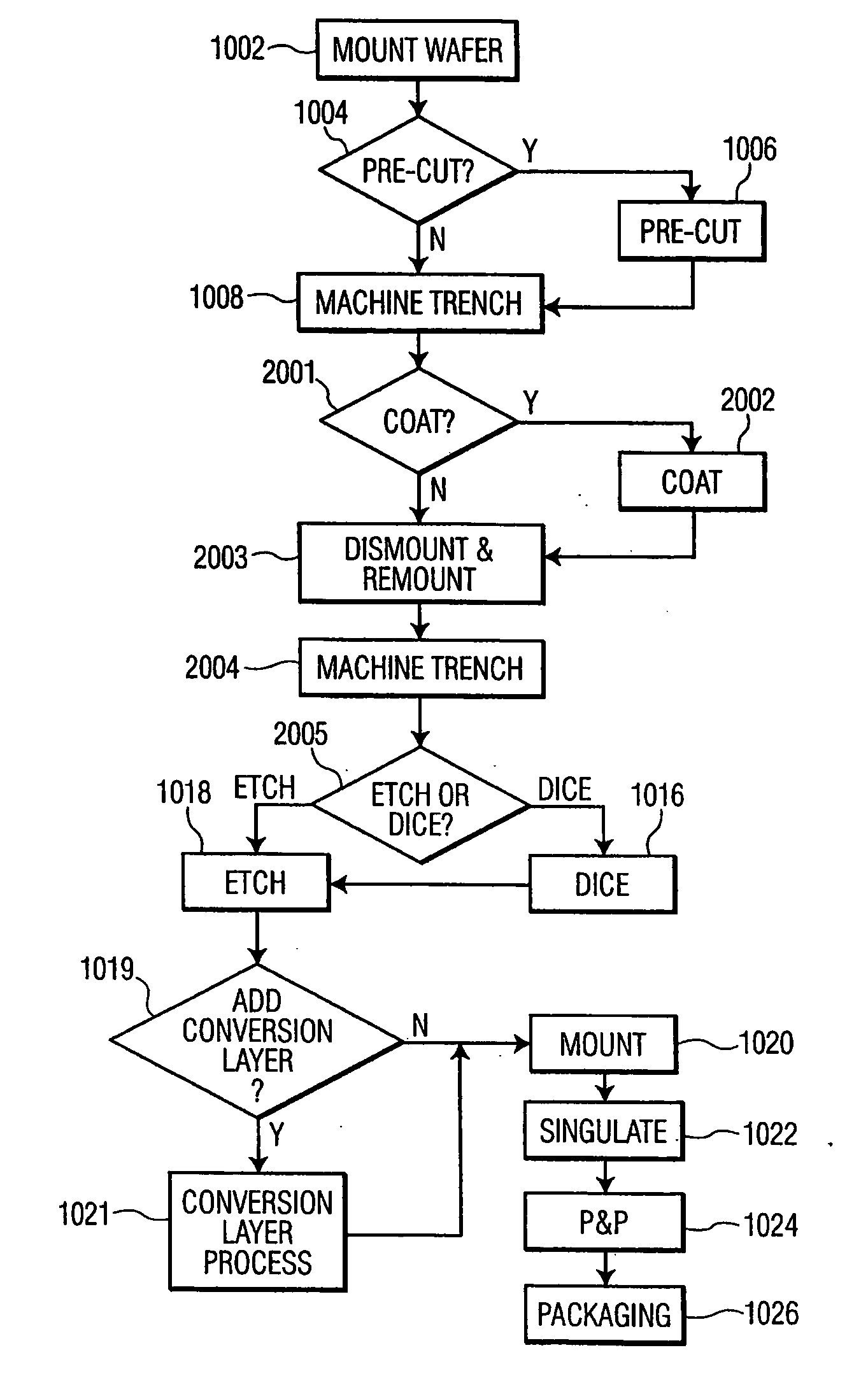

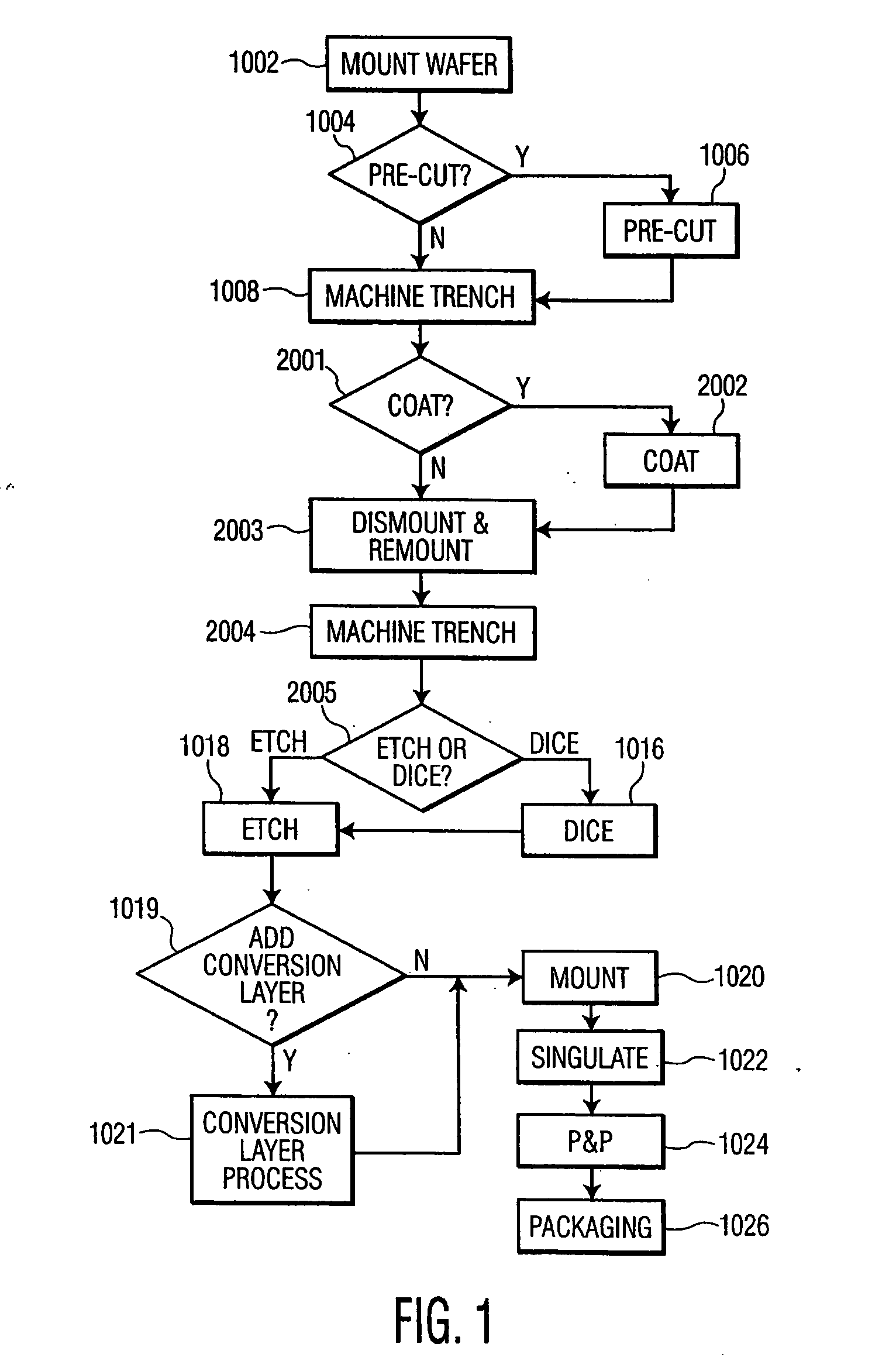

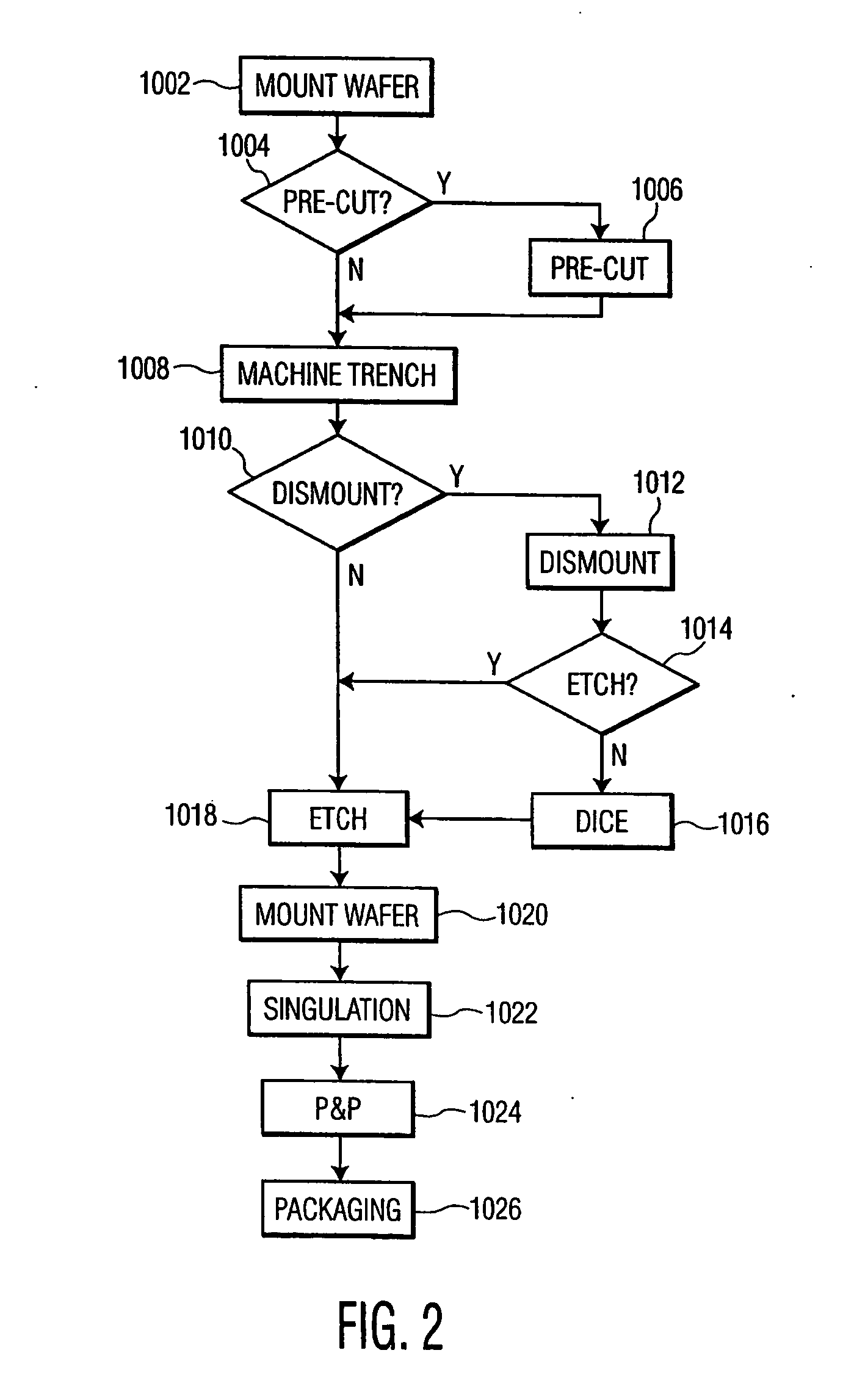

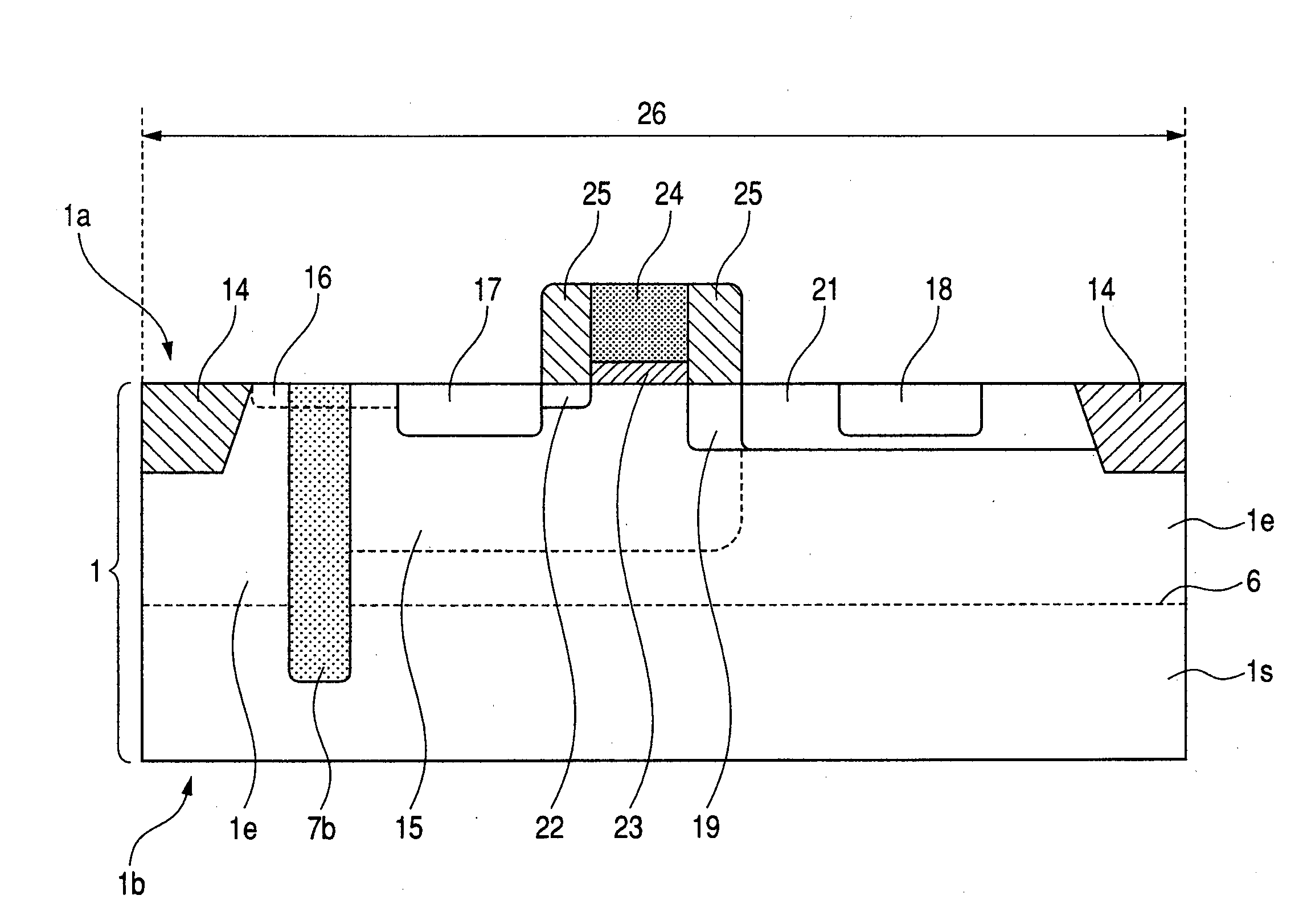

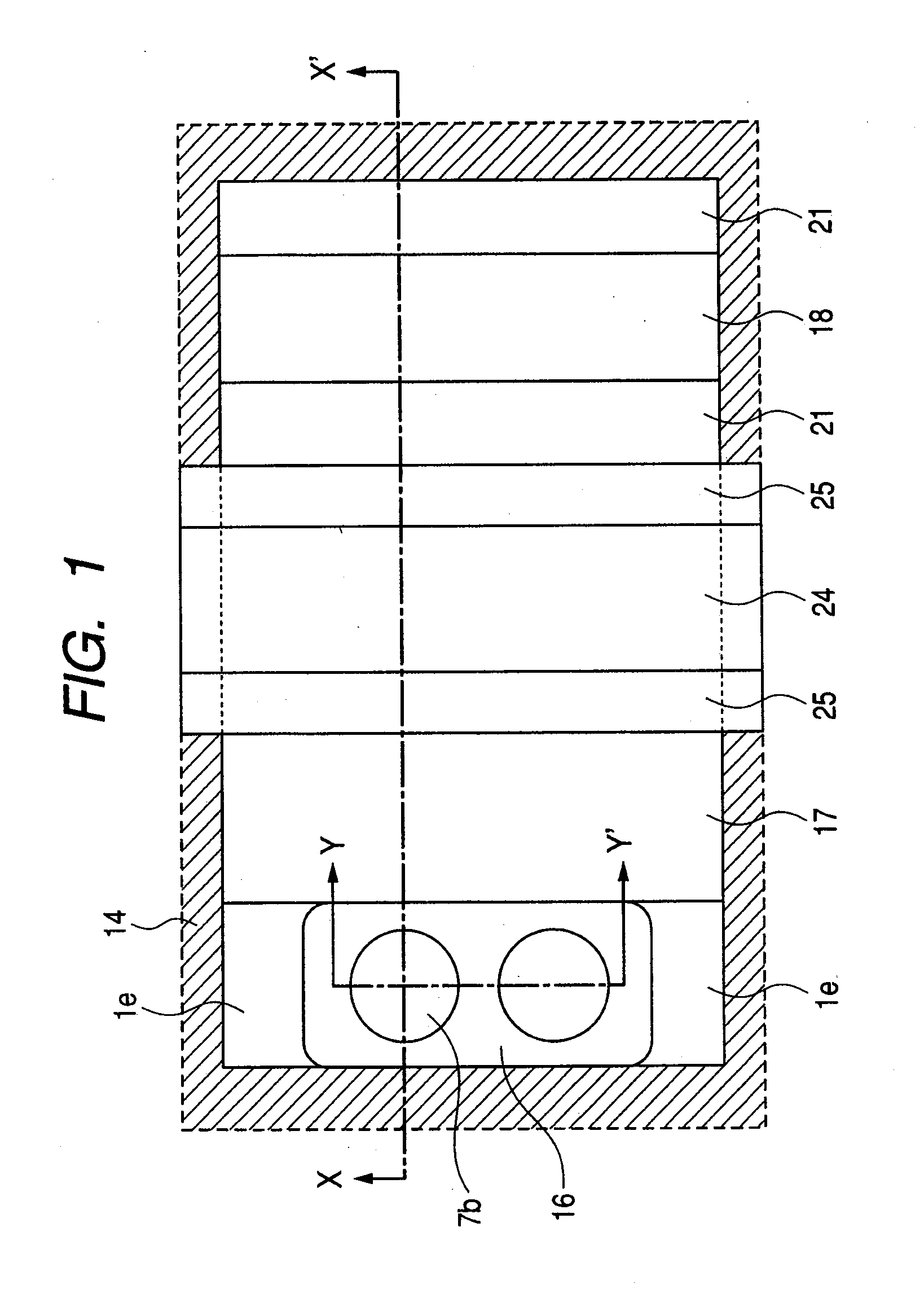

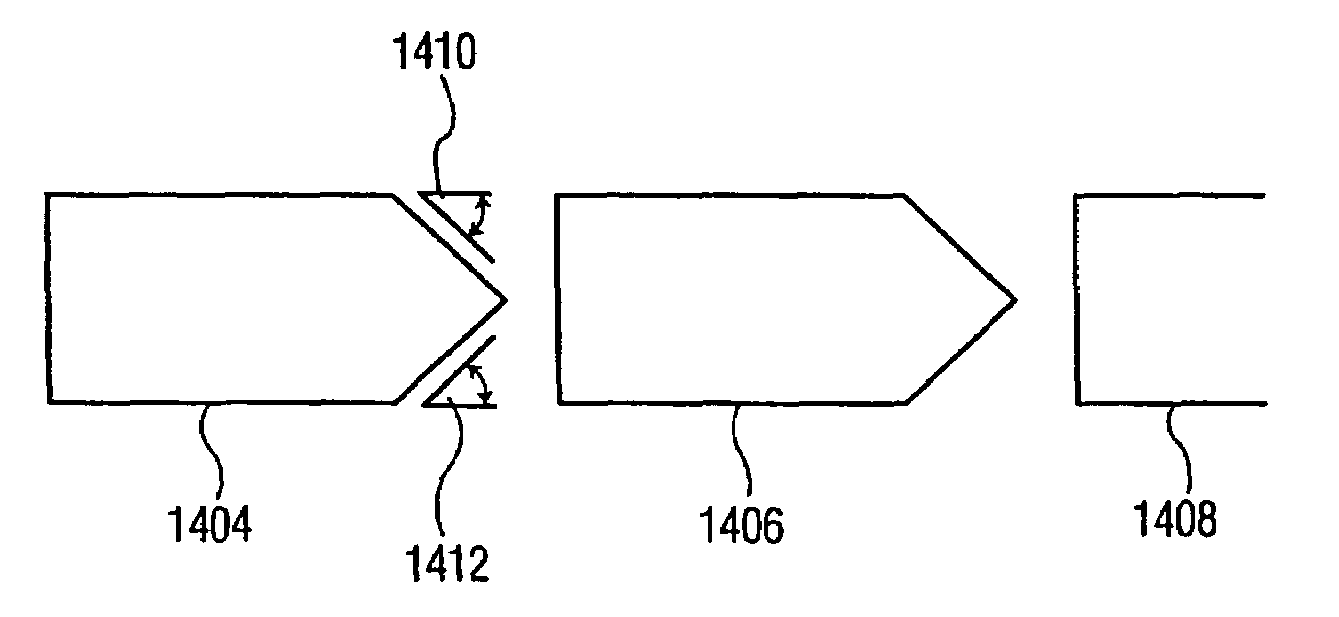

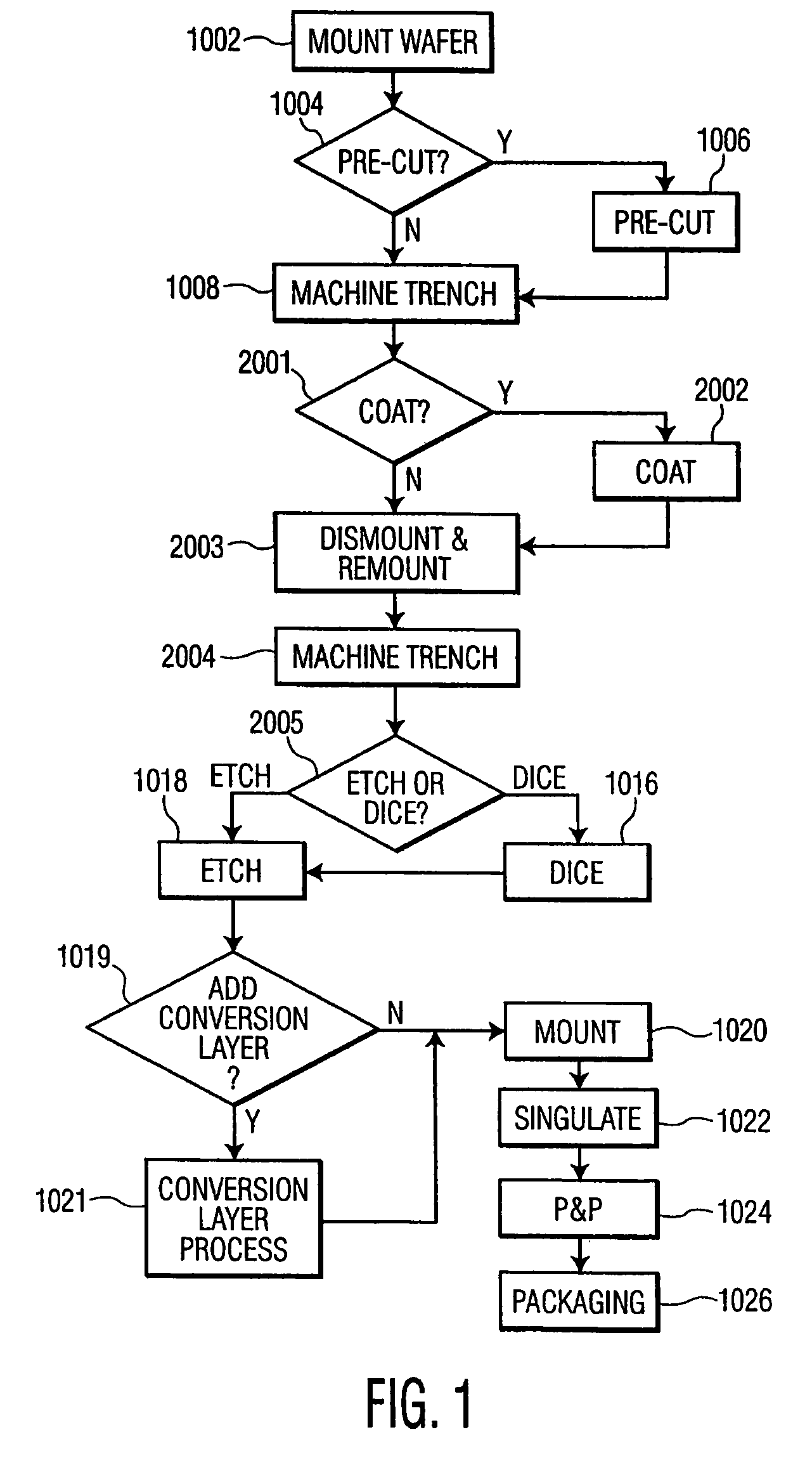

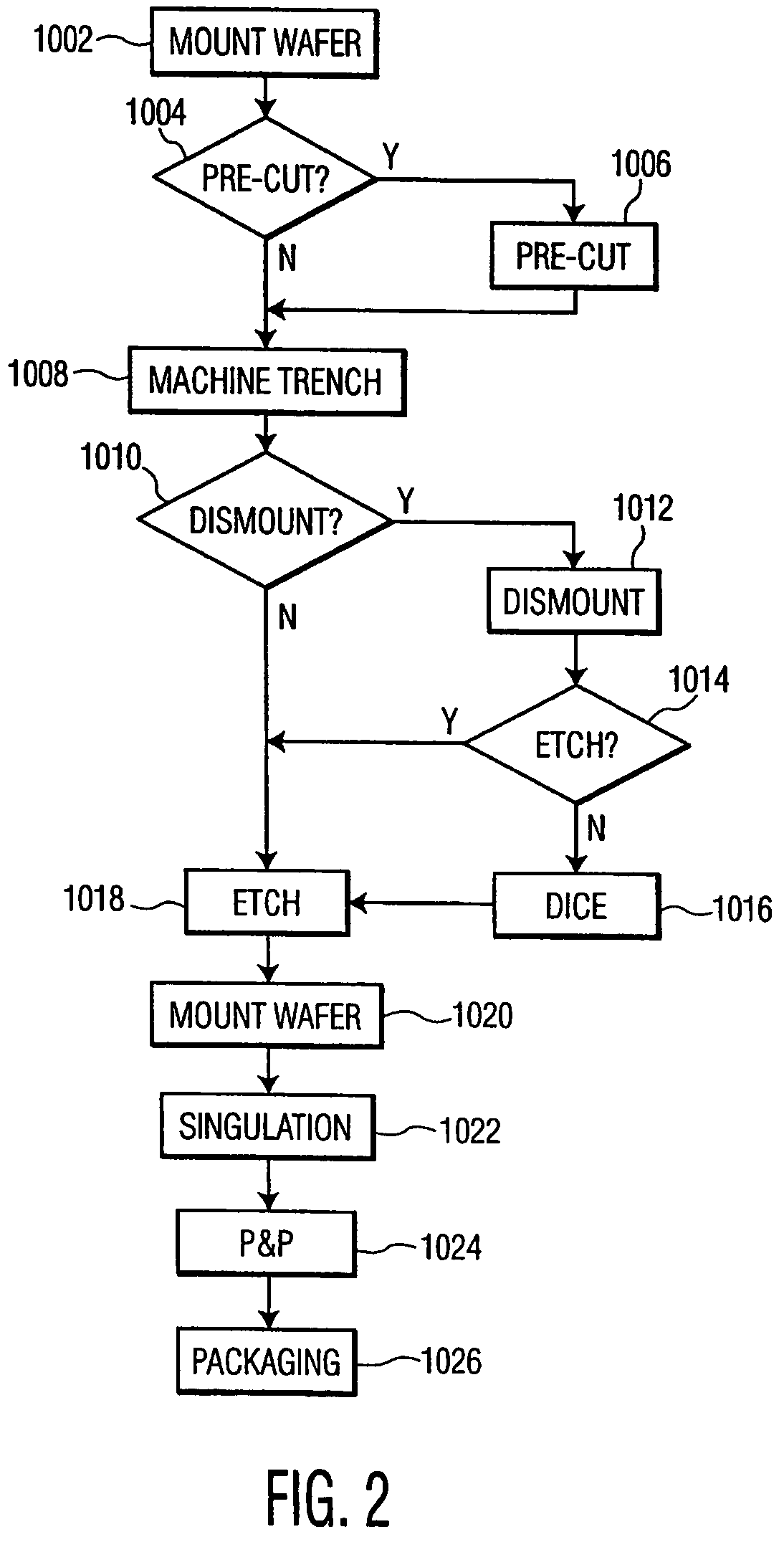

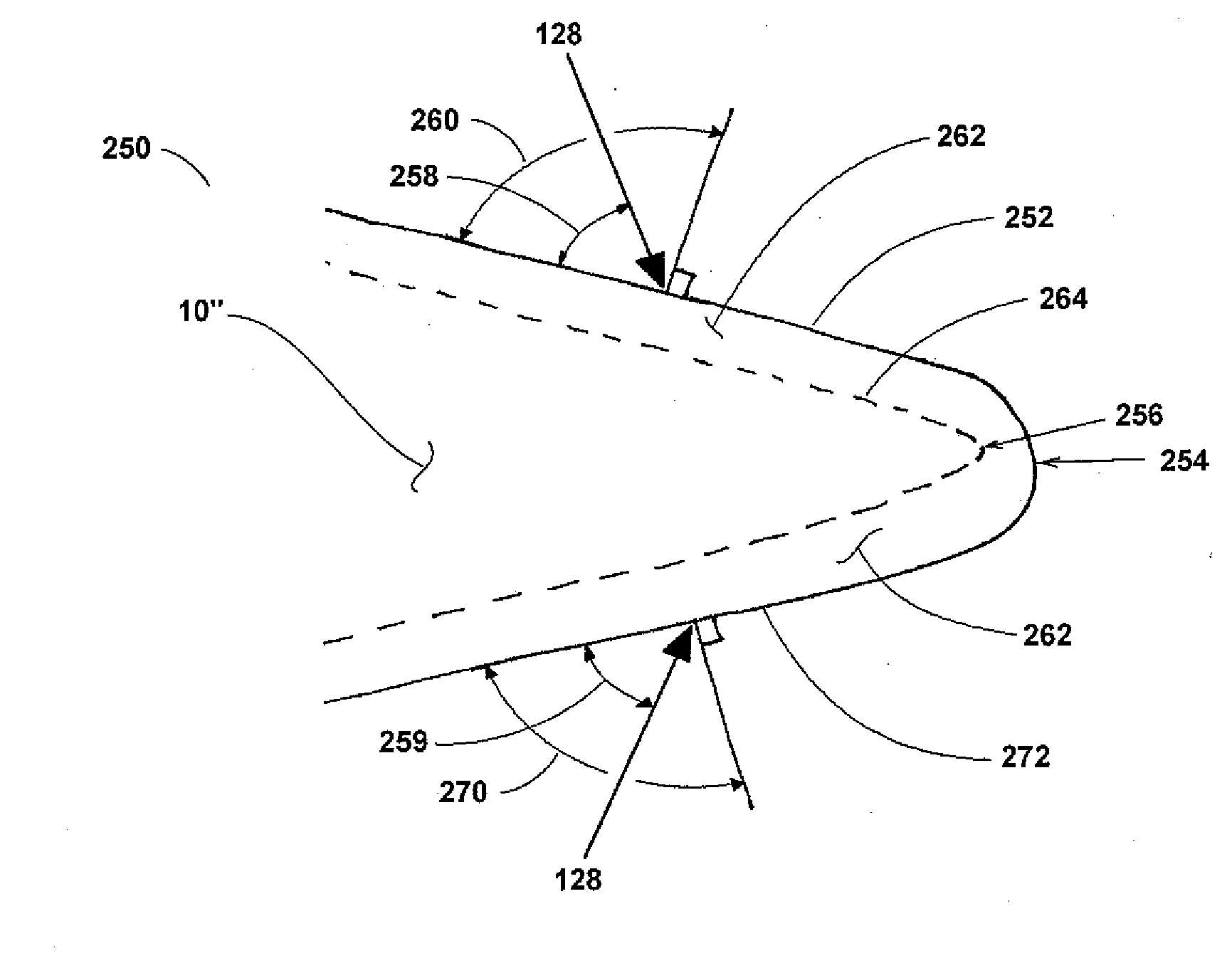

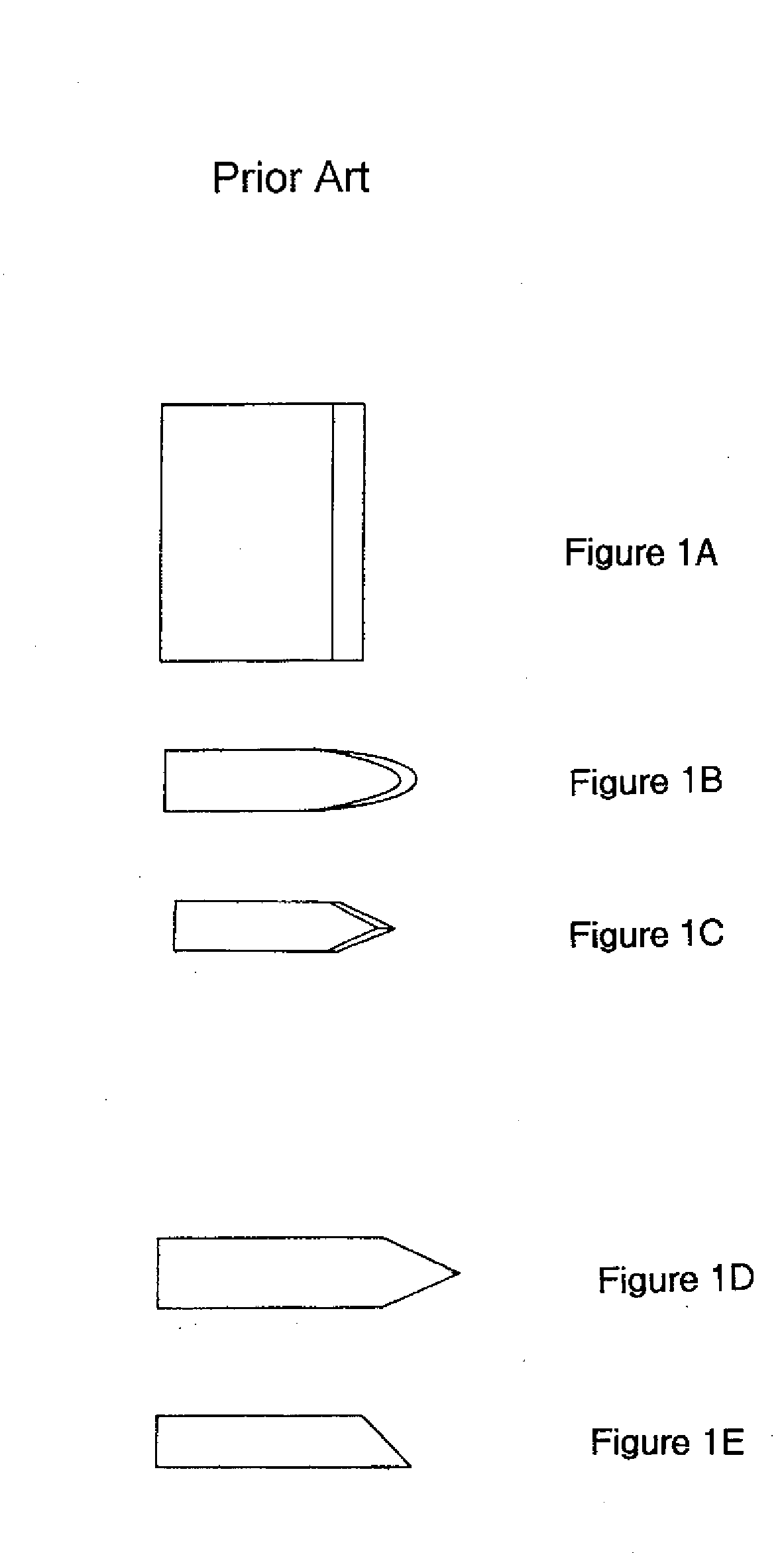

Methods of fabricating complex blade geometries from silicon wafers and strengthening blade geometries

ActiveUS20050266680A1High strengthEasy to controlIncision instrumentsDecorative surface effectsSurgical bladeEngineering

Ophthalmic surgical blades are manufactured from either a single crystal or poly-crystalline material, preferably in the form of a wafer. The method comprises preparing the single crystal or poly-crystalline wafers by mounting them and etching trenches into the wafers using one of several processes. Methods for machining the trenches, which form the bevel blade surfaces, include a diamond blade saw, laser system, ultrasonic machine, a hot forge press and a router. Other processes include wet etching (isotropic and anisotropic) and dry etching (isotropic and anisotropic, including reactive ion etching), and combinations of these etching steps. The wafers are then placed in an etchant solution which isotropically etches the wafers in a uniform manner, such that layers of crystalline or poly-crystalline material are removed uniformly, producing single, double or multiple bevel blades. Nearly any angle can be machined into the wafer, and the machined angle remains after etching. The resulting radii of the blade edges is 5-500 nm, which is the same caliber as a diamond edged blade, but manufactured at a fraction of the cost. A range of radii may be 30 to 60 nm, with a specific implementation being about 40 nm. The blade profile may have an angle of, for example, about 60°. The ophthalmic surgical blades can be used for cataract and refractive surgical procedures, as well as microsurgical, biological and non-medical, non-biological purposes. Surgical and non-surgical blades and mechanical devices manufactured as described herein can also exhibit substantially smoother surfaces than metal blades.

Owner:BEAVER VISITEC INT US

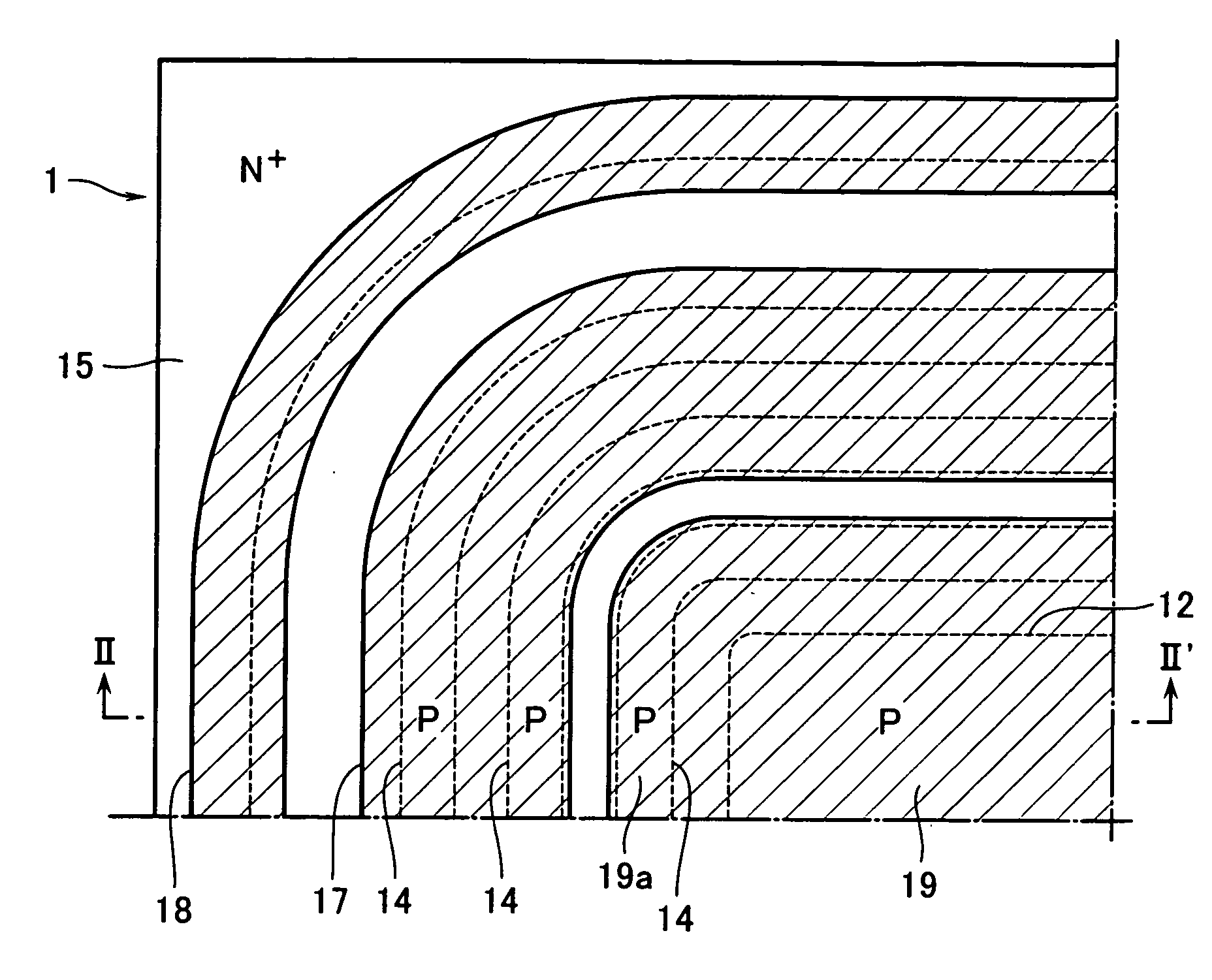

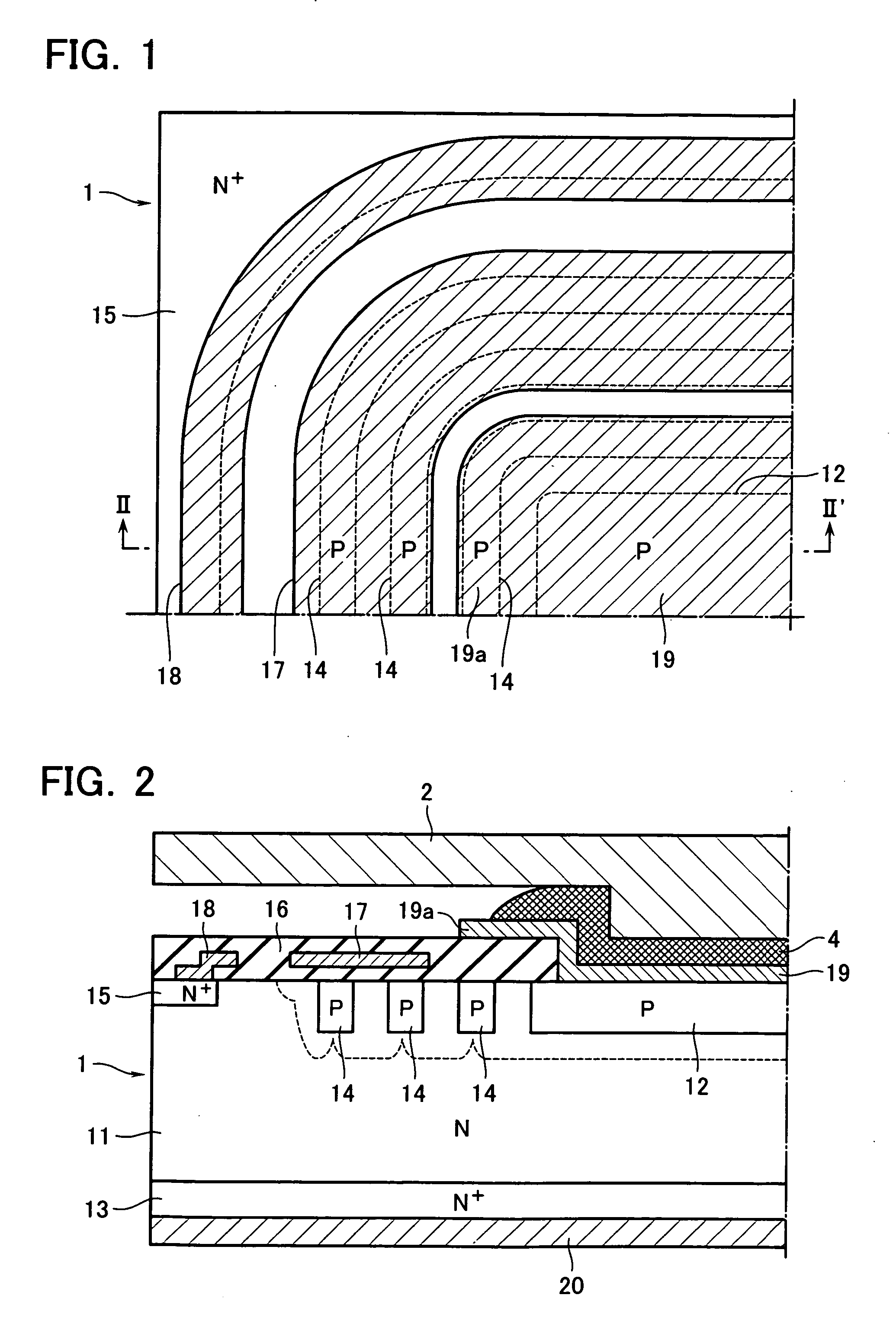

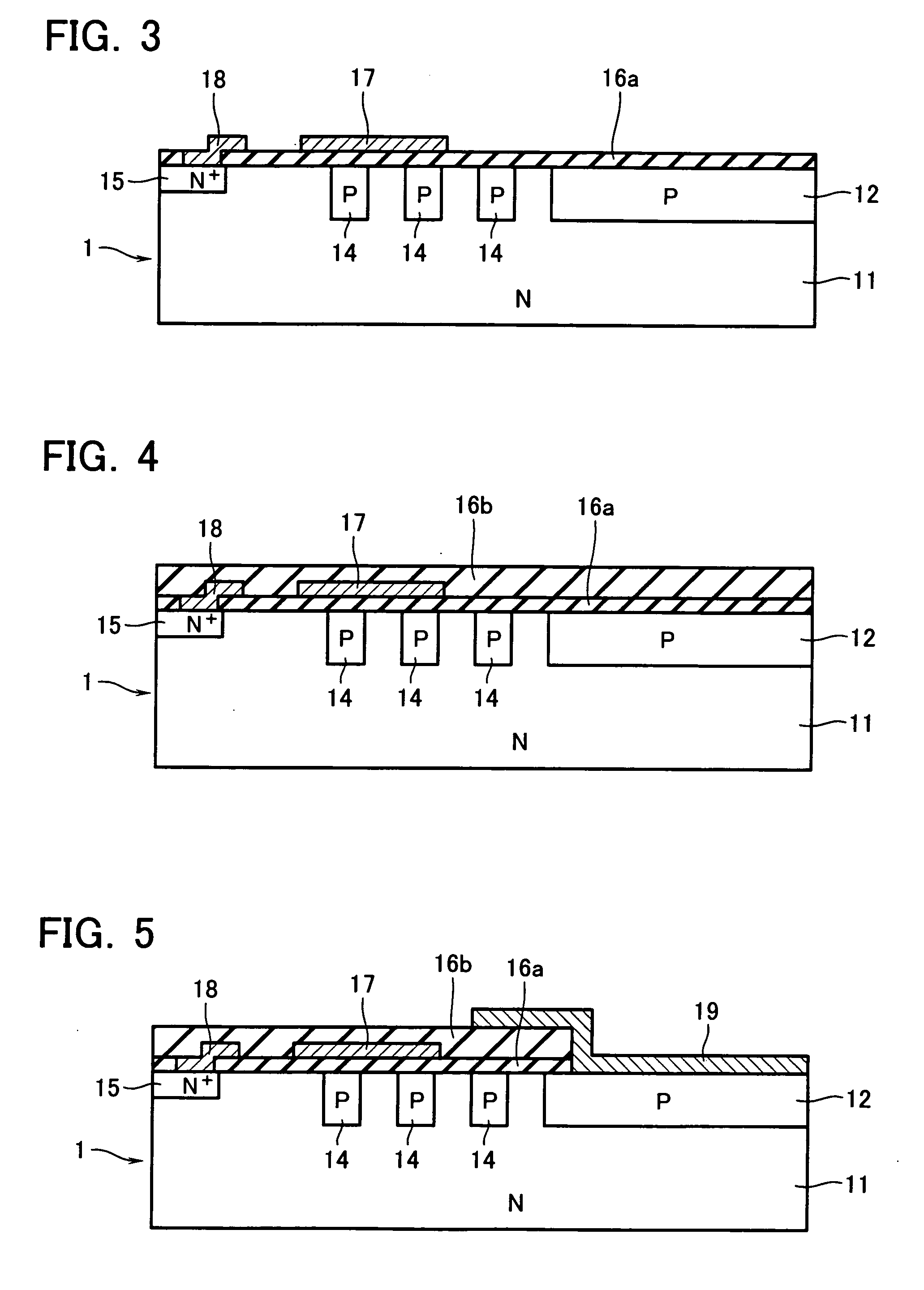

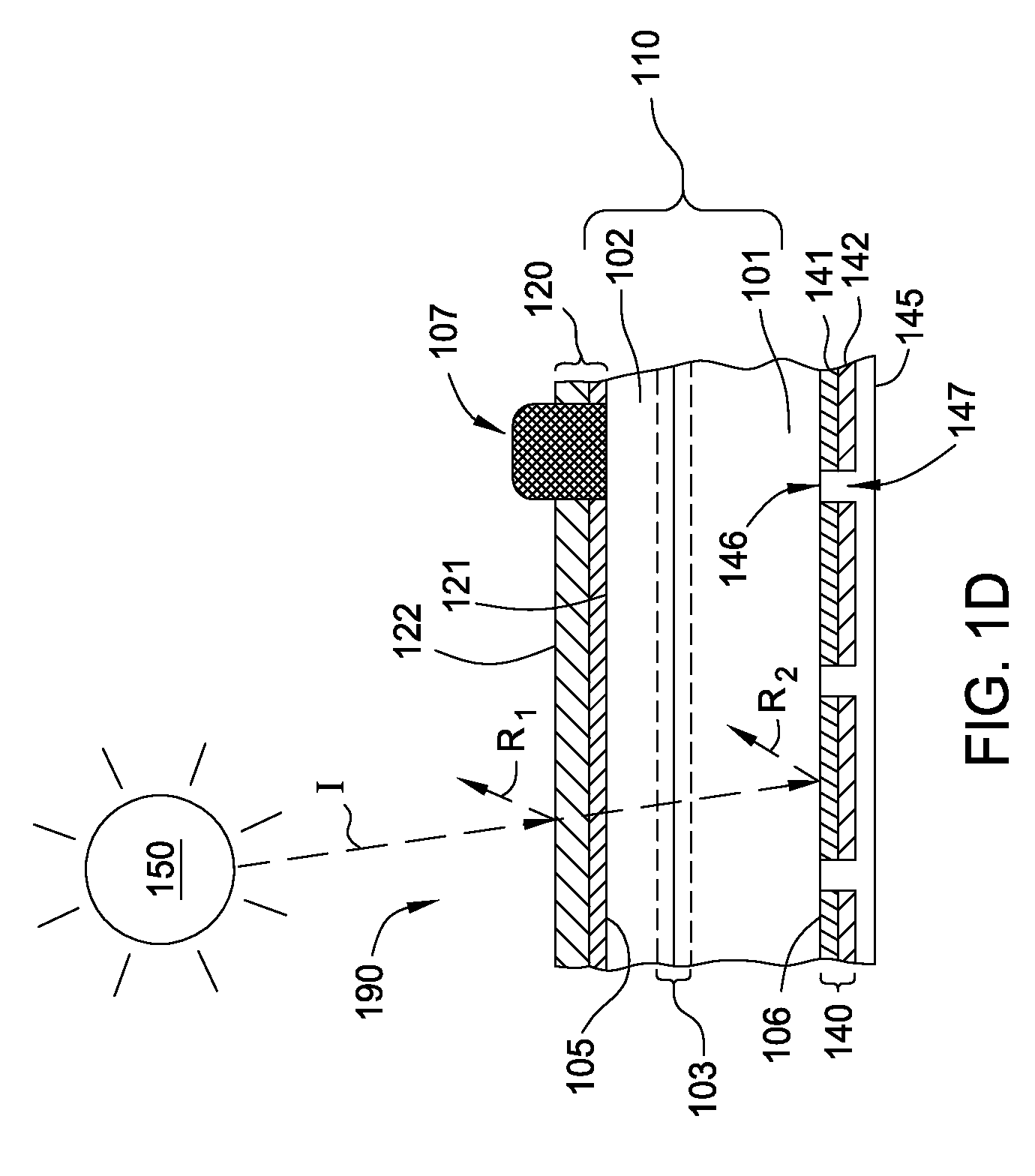

Semiconductor device and method of manufacturing the same

InactiveUS20100327349A1Lower resistanceImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectrical conductorDislocation

In a semiconductor device having an LDMOSFET, a source electrode is at the back surface thereof. Therefore, to reduce electric resistance between a source contact region in the top surface and the source electrode at the back surface, a poly-silicon buried plug is provided which extends from the upper surface into a P+-type substrate through a P-type epitaxial layer, and is heavily doped with boron. Dislocation occurs in a mono-crystalline silicon region around the poly-silicon buried plug to induce a leakage failure. The semiconductor device has a silicon-based plug extending through the boundary surface between first and second semiconductor layers having different impurity concentrations. At least the inside of the plug is a poly-crystalline region. Of the surface of the poly-crystalline region, the portions located on both sides of the foregoing boundary surface in adjacent relation thereto are each covered with a solid-phase epitaxial region.

Owner:RENESAS ELECTRONICS CORP

Methods of fabricating complex blade geometries from silicon wafers and strengthening blade geometries

ActiveUS7396484B2Quality improvementUniform radiusIncision instrumentsDecorative surface effectsSurgical bladeSingle crystal

Ophthalmic surgical blades are manufactured from either a single crystal or poly-crystalline material, preferably in the form of a wafer. The method comprises preparing the single crystal or poly-crystalline wafers by mounting them and etching trenches into the wafers using one of several processes. Methods for machining the trenches, which form the bevel blade surfaces, include a diamond blade saw, laser system, ultrasonic machine, a hot forge press and a router. Other processes include wet etching (isotropic and anisotropic) and dry etching (isotropic and anisotropic, including reactive ion etching), and combinations of these etching steps. The wafers are then placed in an etchant solution which isotropically etches the wafers in a uniform manner, such that layers of crystalline or poly-crystalline material are removed uniformly, producing single, double or multiple bevel blades. Nearly any angle can be machined into the wafer, and the machined angle remains after etching. The resulting radii of the blade edges is 5-500 nm, which is the same caliber as a diamond edged blade, but manufactured at a fraction of the cost. A range of radii may be 30 to 60 nm, with a specific implementation being about 40 nm. The blade profile may have an angle of, for example, about 60°. The ophthalmic surgical blades can be used for cataract and refractive surgical procedures, as well as microsurgical, biological and non-medical, non-biological purposes. Surgical and non-surgical blades and mechanical devices manufactured as described herein can also exhibit substantially smoother surfaces than metal blades.

Owner:BEAVER VISITEC INT US

Semiconductor device and method of fabricating the same

InactiveUS20060131685A1ThyristorSemiconductor/solid-state device detailsDevice materialSemiconductor

A semiconductor device has a semiconductor device chip with upper and lower terminal electrodes, and upper and lower frames bonded to the upper and lower terminal electrodes, respectively, with solder material, wherein the semiconductor device chip includes: a semiconductor layer of a first conductivity type; a diffusion layer of a second conductivity type, which is selectively formed in the semiconductor layer; a plurality of guard-ring layers of the second conductivity type, which are formed outside of the diffusion layer in the semiconductor layer; an insulating film formed on the semiconductor layer; and a field plate formed of a poly-crystalline silicon film embedded in the insulating film.

Owner:KK TOSHIBA

Poly-crystalline compositions

Owner:GLASSCERAX LTD

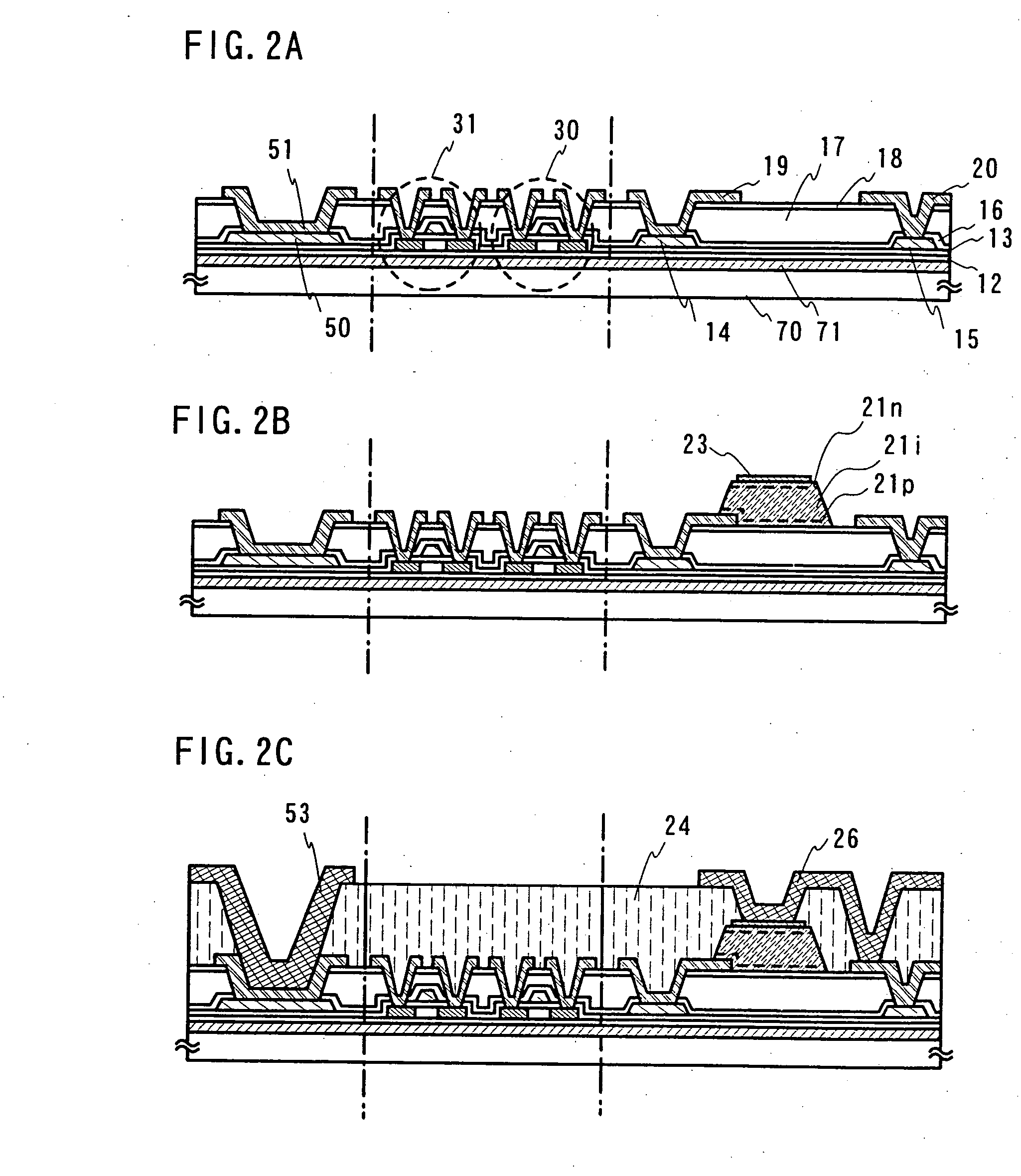

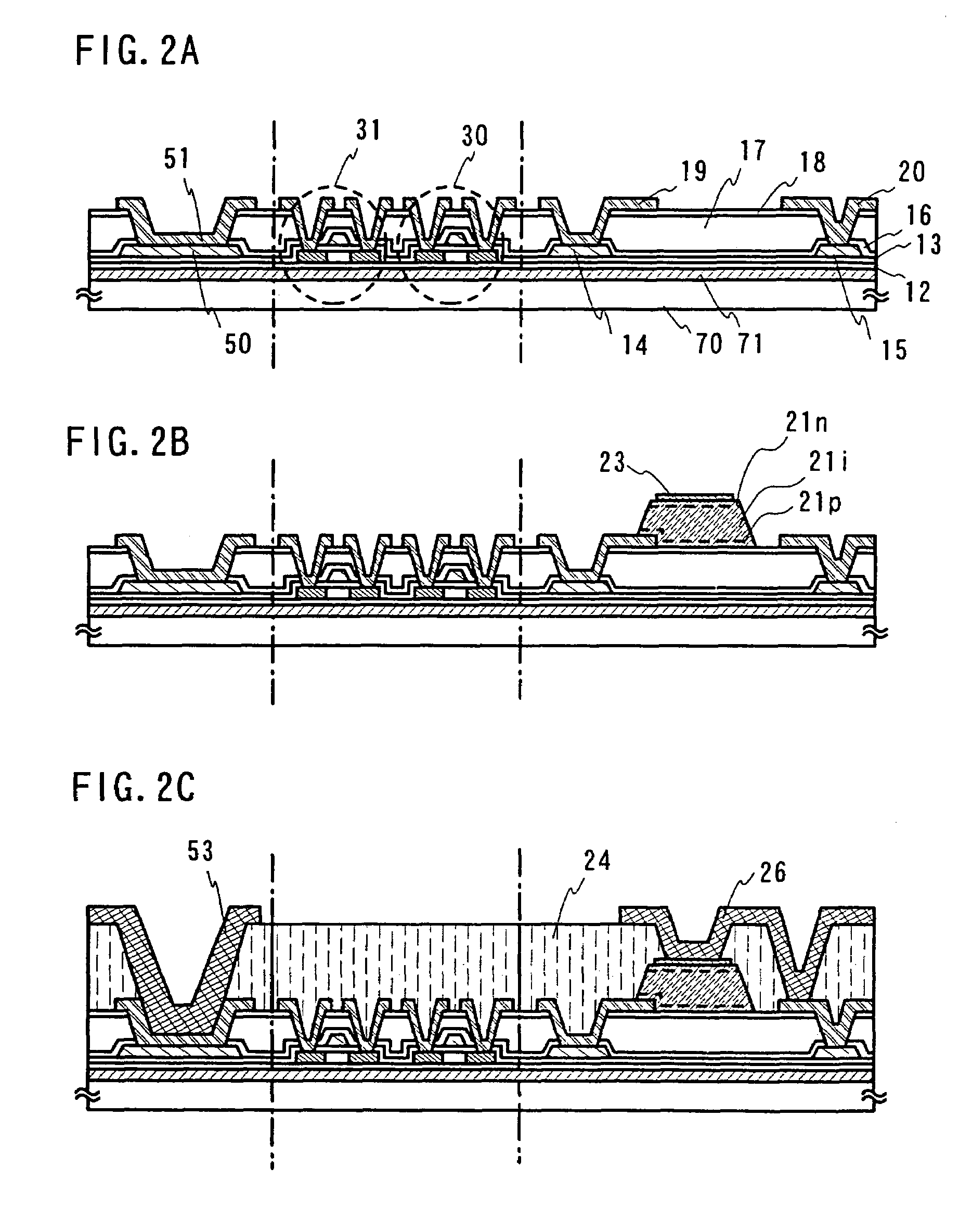

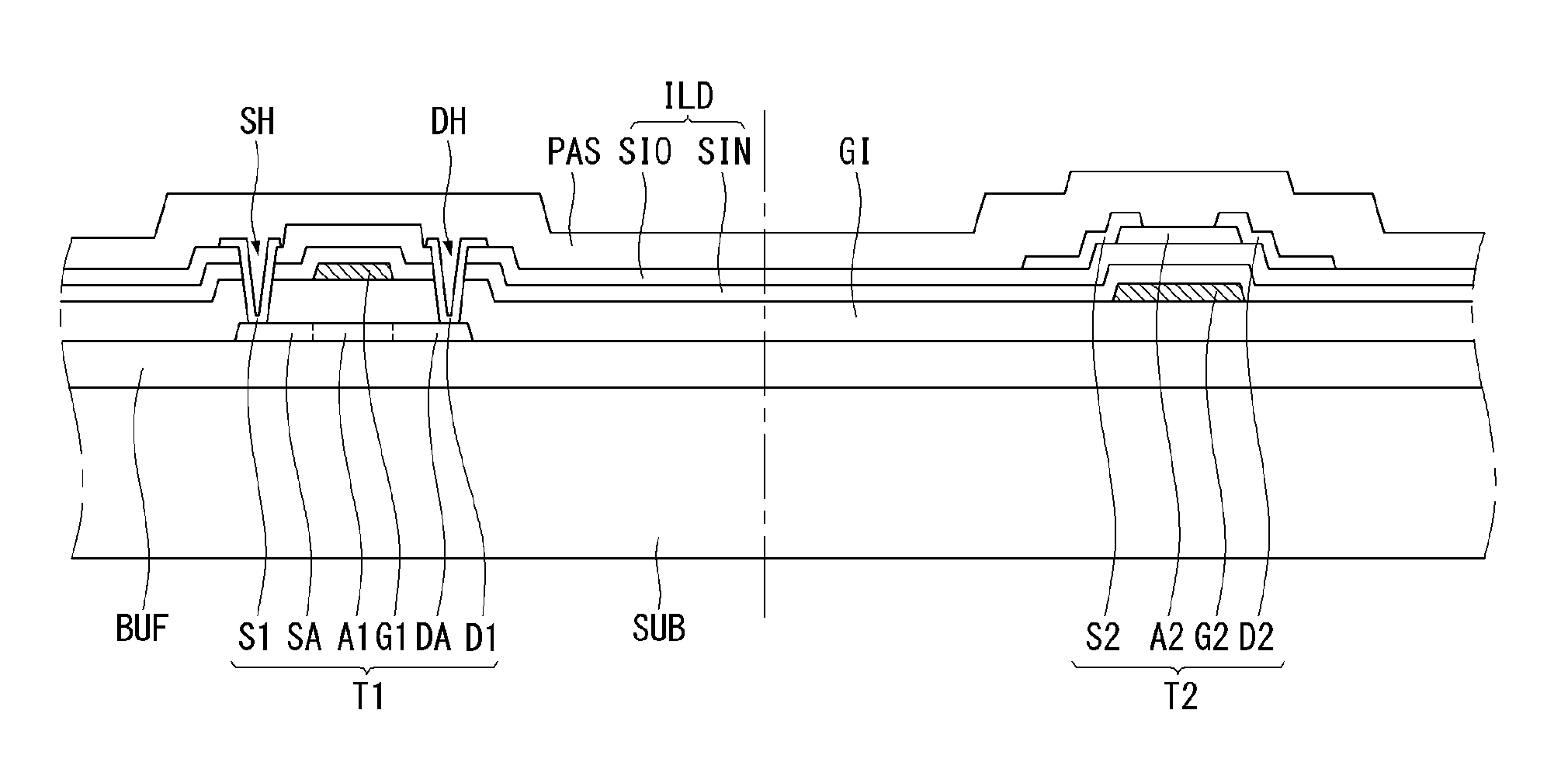

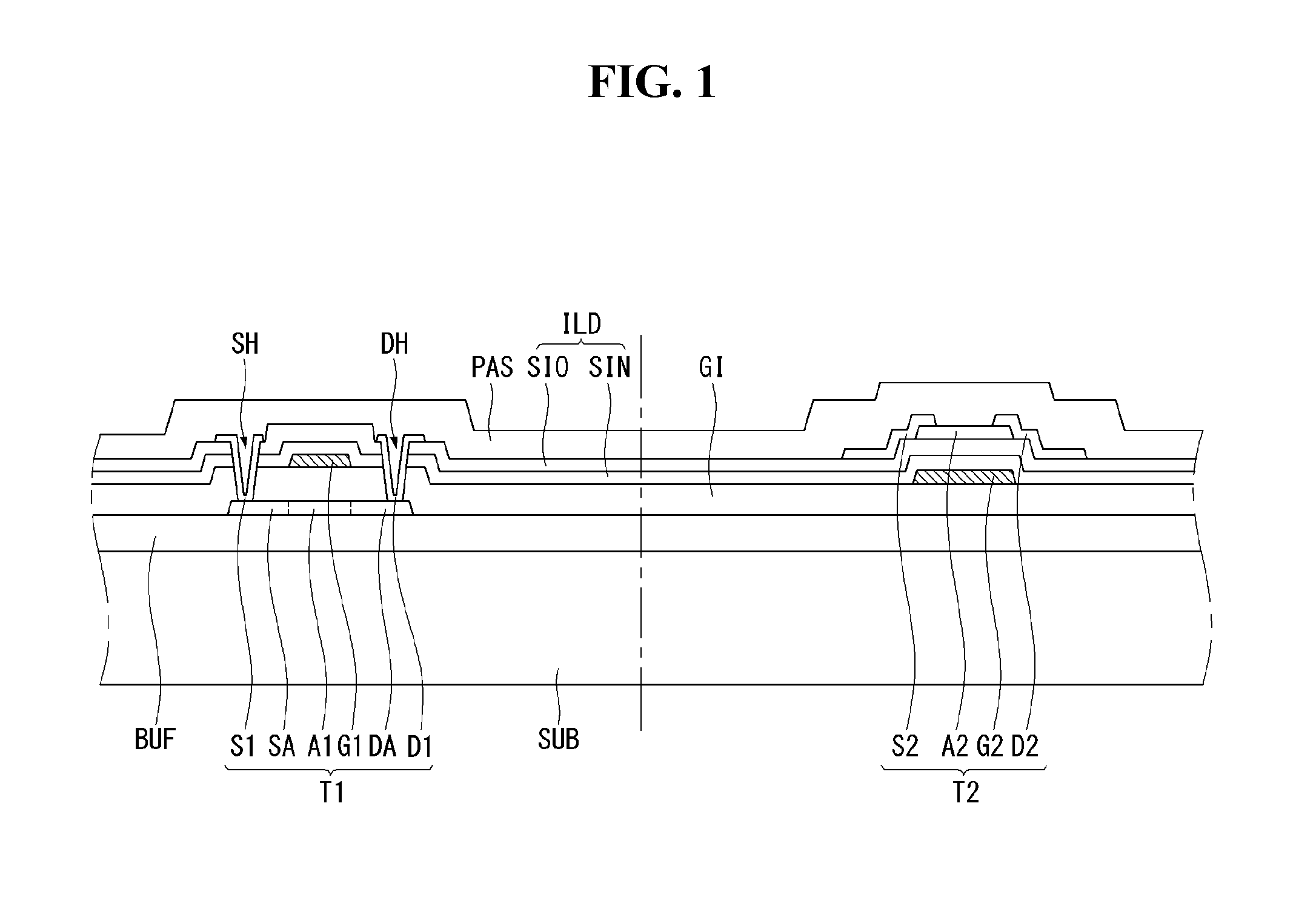

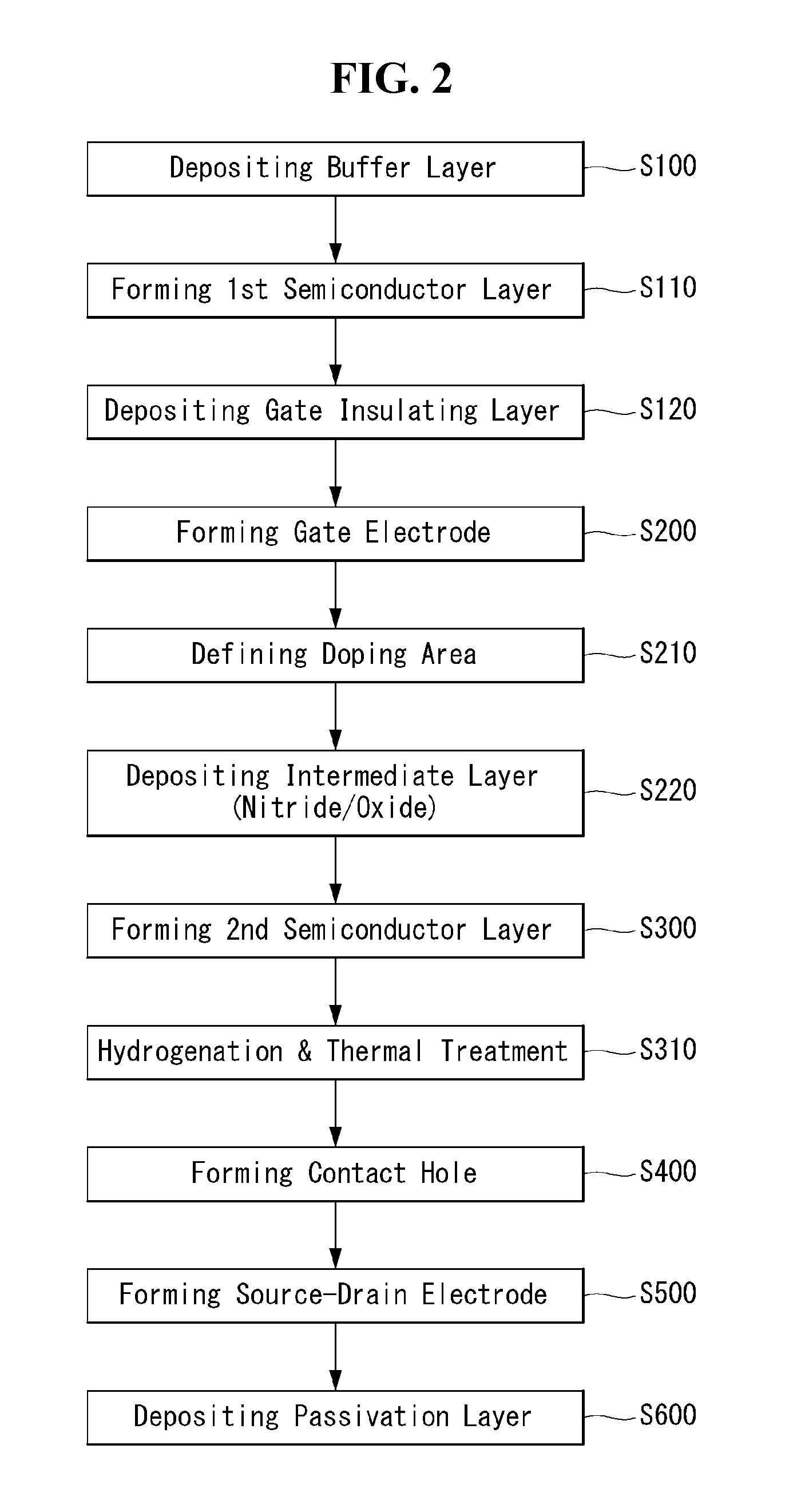

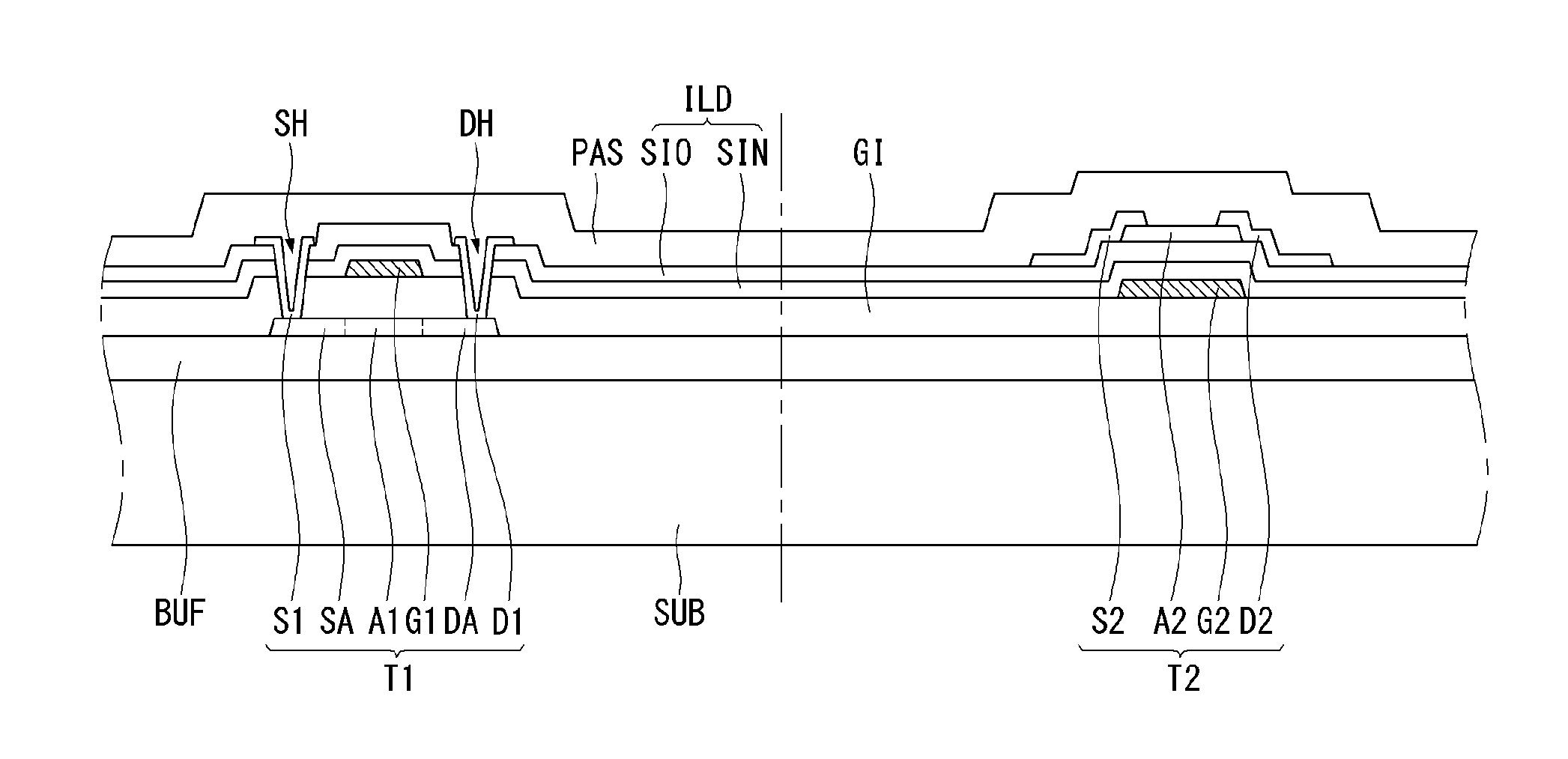

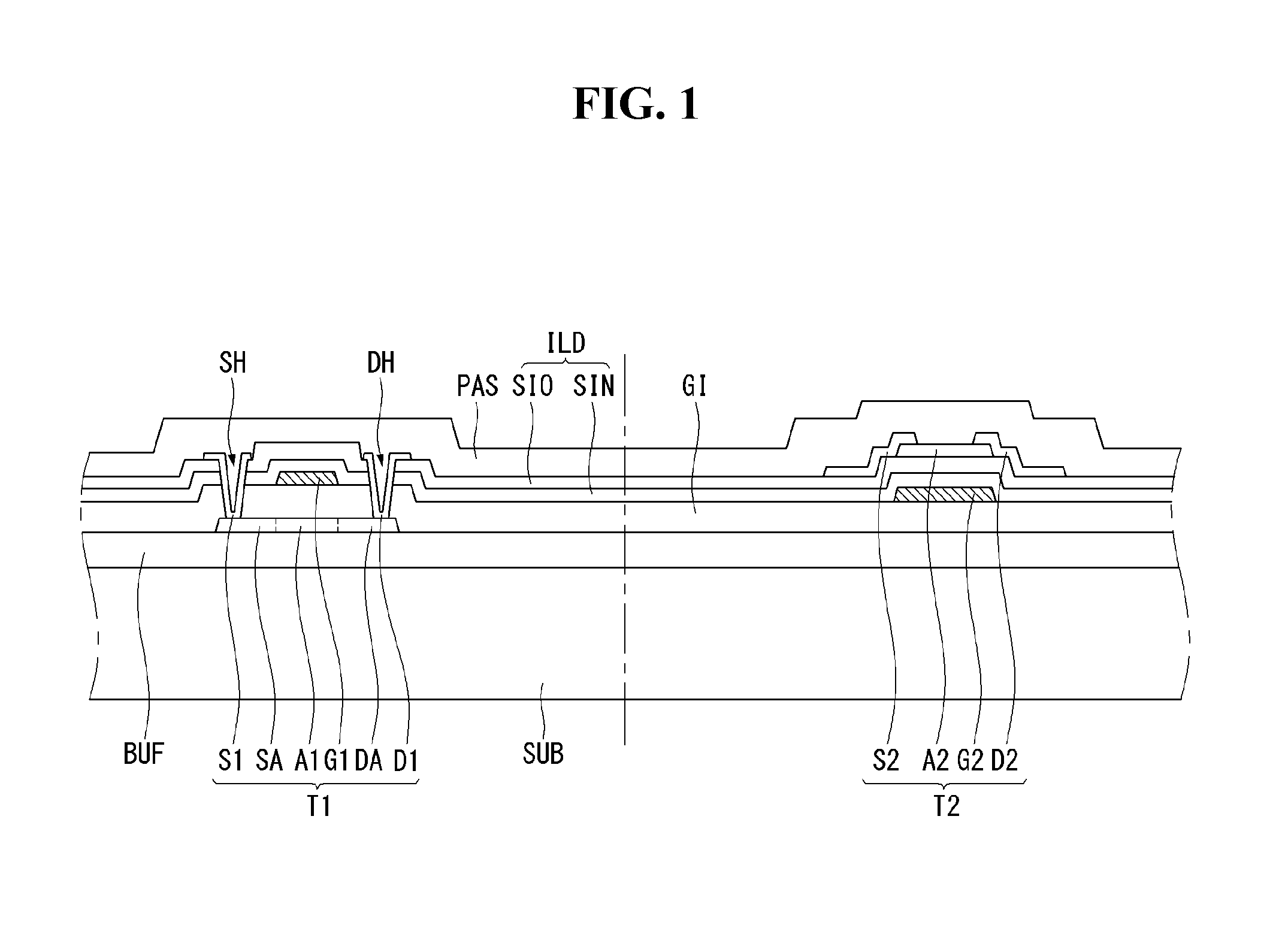

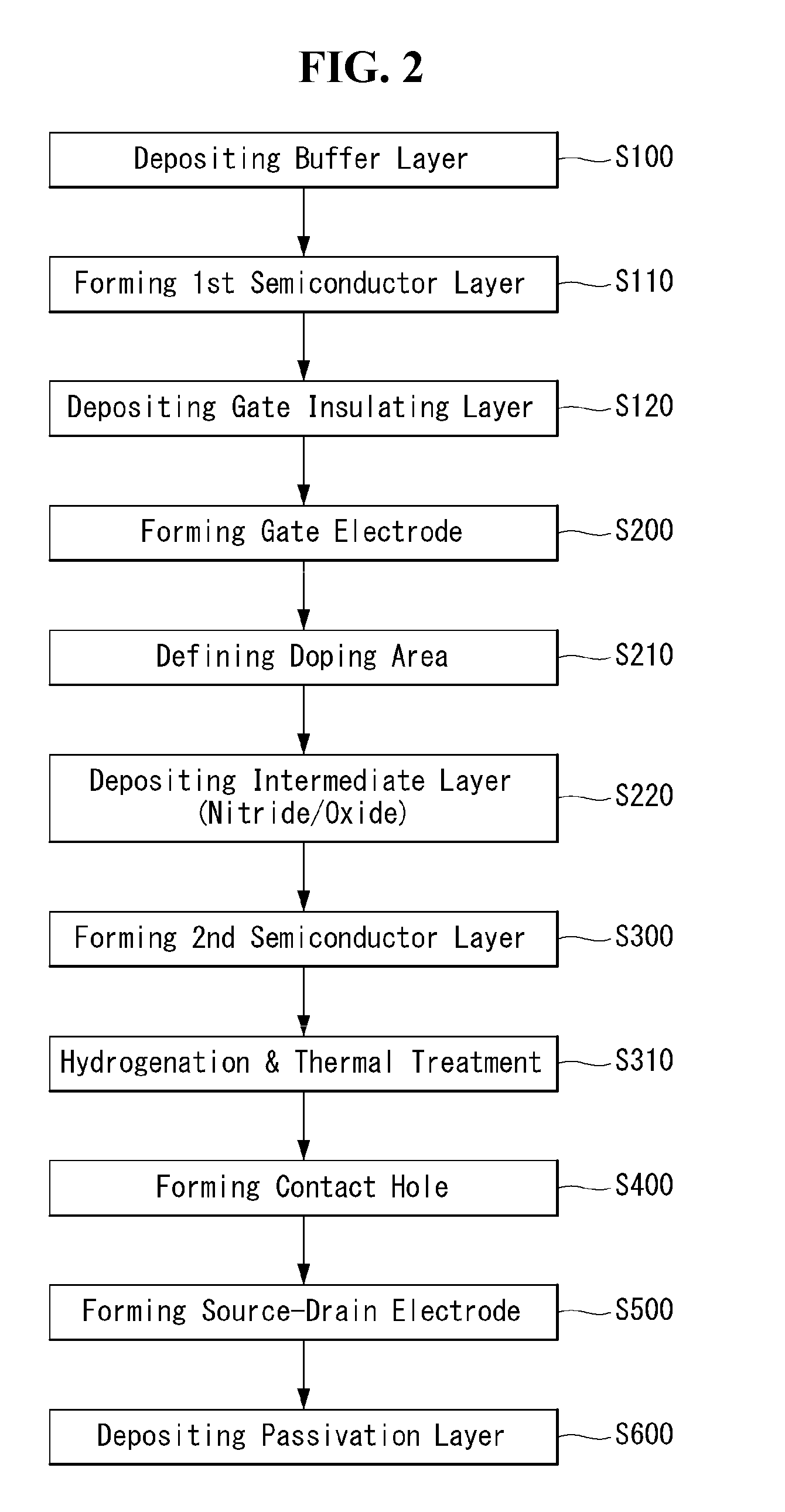

Thin film transistor substrate and display using the same

ActiveUS20150243686A1Efficient preparationReduce in quantityTransistorSolid-state devicesDisplay deviceNitride

The present disclosure relates to a thin film transistor substrate having two different types of thin film transistors on the same substrate. A thin film transistor substrate includes a substrate; a first thin film transistor disposed on the substrate, the first thin film transistor including a poly crystalline semiconductor layer, a first gate electrode over the poly crystalline semiconductor layer, a first source electrode, and a first drain electrode; a second thin film transistor disposed on the substrate, the second thin film transistor including a second gate electrode, an oxide semiconductor layer over the second gate electrode, a second source electrode, and a second drain electrode; and an intermediate insulating layer including a nitride layer and an oxide layer on the nitride layer, the intermediate insulating layer disposed over the first gate electrode and the second gate electrode and under the oxide semiconductor layer.

Owner:LG DISPLAY CO LTD

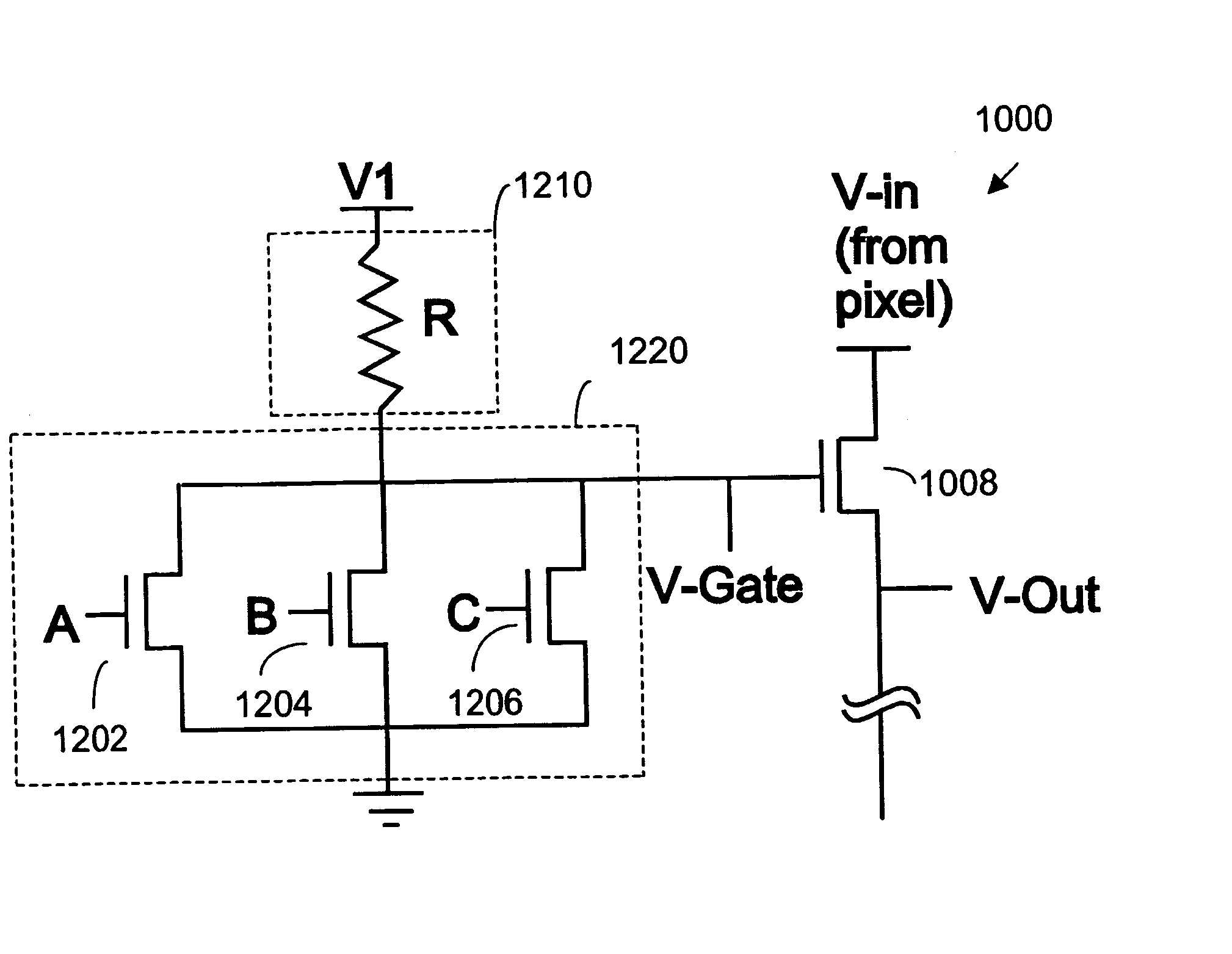

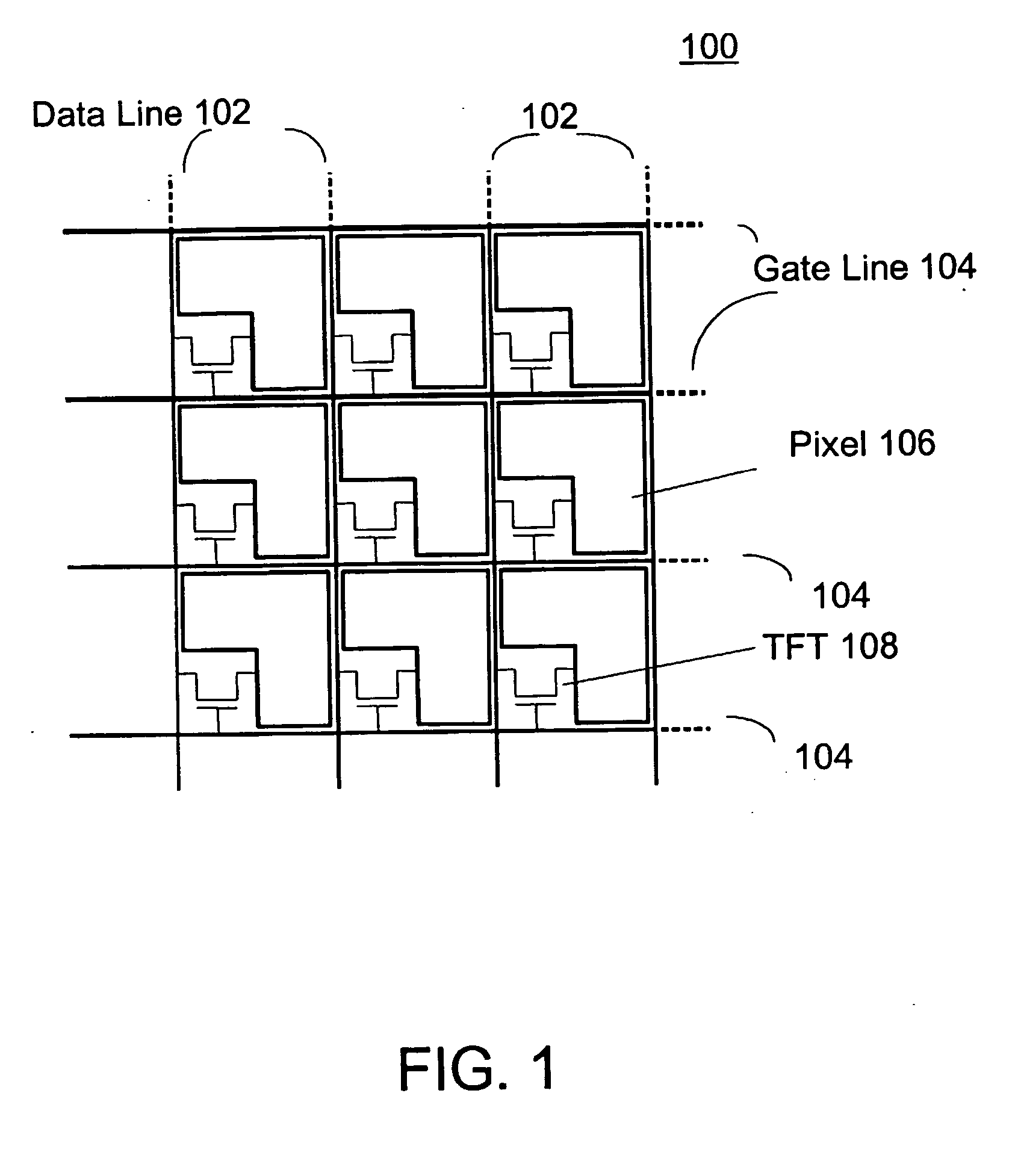

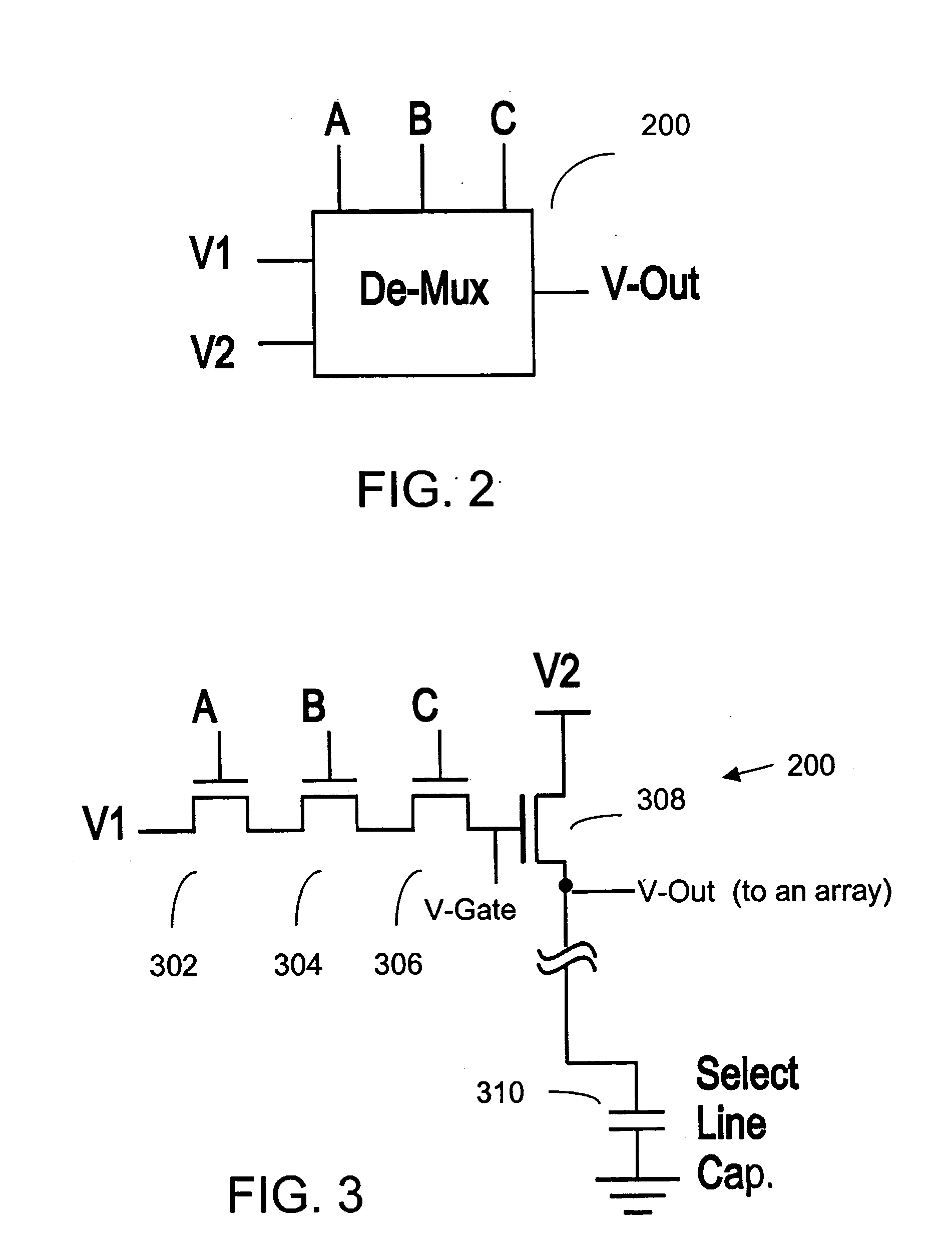

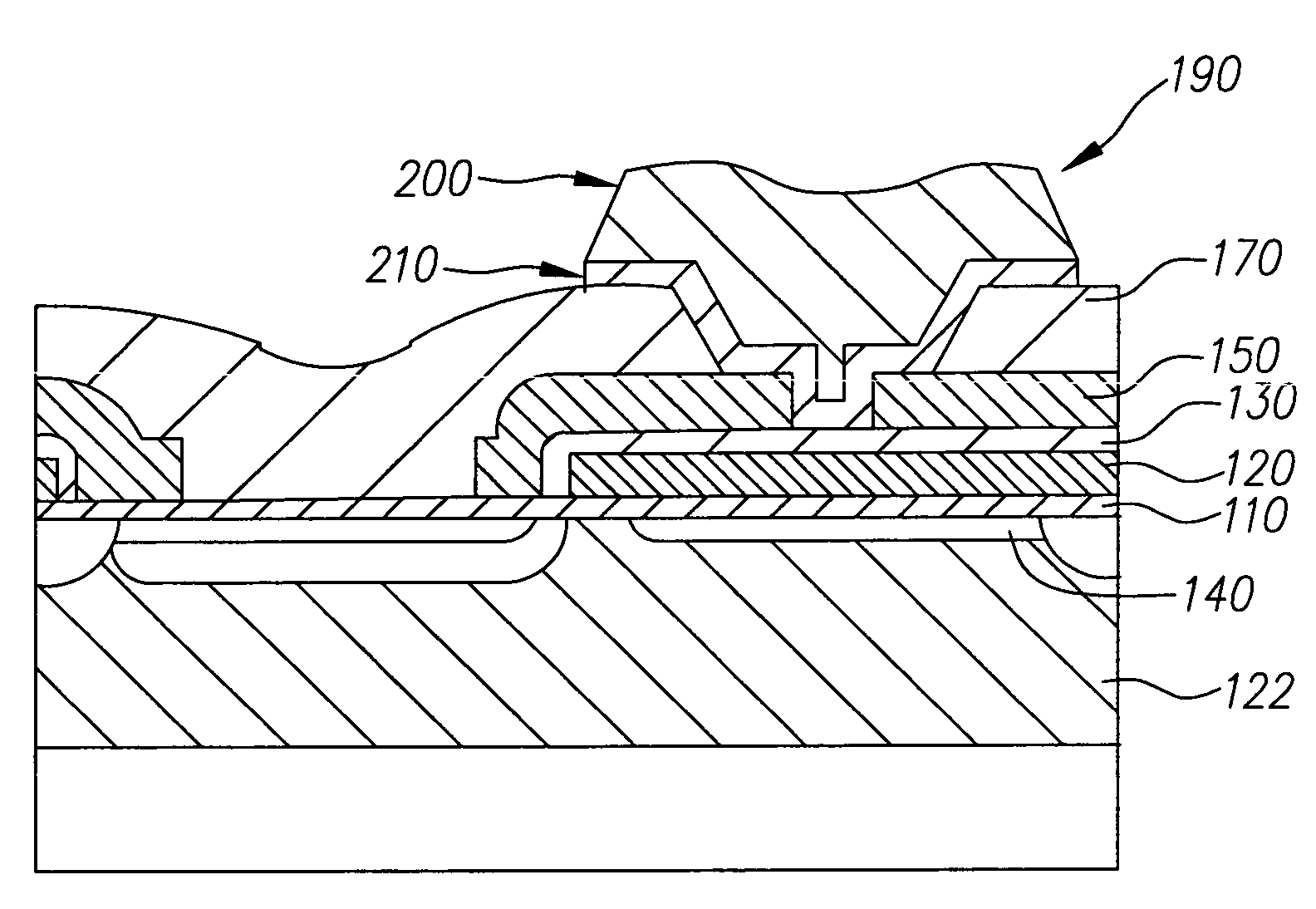

Integrated multiplexer/de-multiplexer for active-matrix display/imaging arrays

ActiveUS20050007352A1Guaranteed smooth progressCathode-ray tube indicatorsInput/output processes for data processingActive matrixMultiplexer

This invention presents Vt-shift invariant integrated multiplexer and de-multiplexer circuits that can be fabricated with a-Si:H, poly-crystalline silicon, or organic / polymer TFTs. The de-multiplexer and multiplexer includes a plurality of TFTs which are connected in series, and a drive TFT. These circuits are used with active matrix displays to control the gate addressing, and with imaging arrays to multiplex the read-out data.

Owner:IGNIS INNOVATION

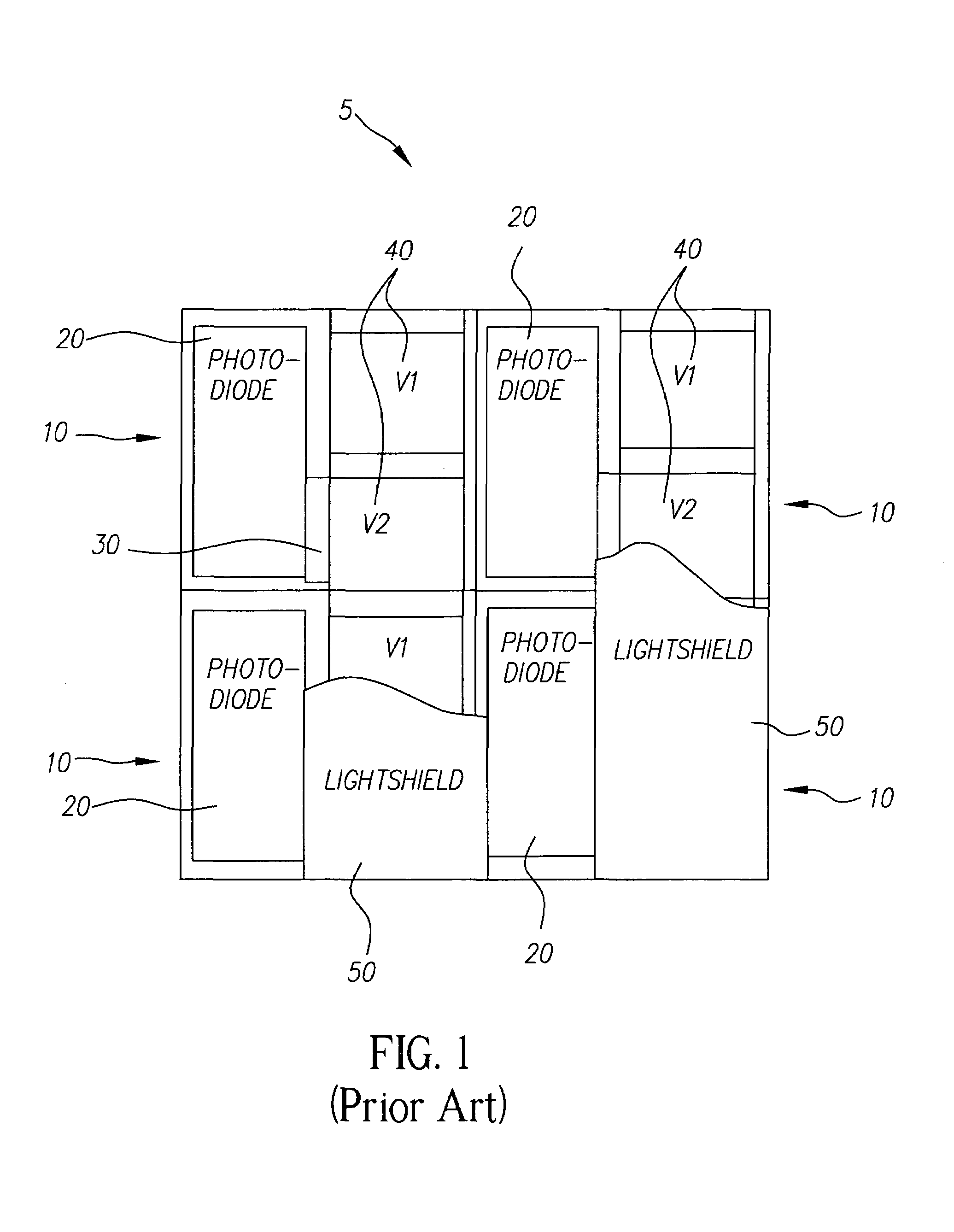

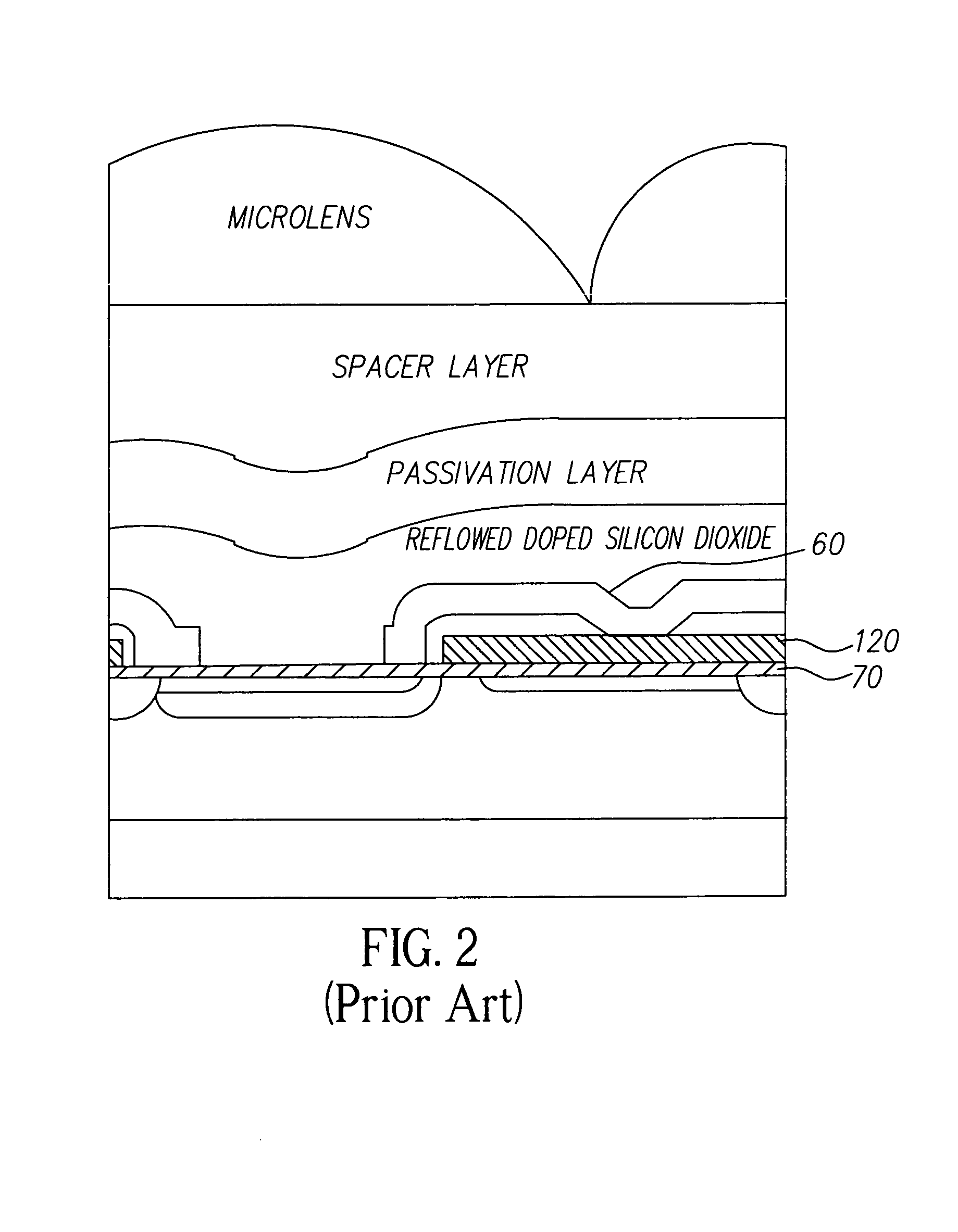

Lightshield architecture for interline transfer image sensors

ActiveUS7102185B2Improve performanceSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceStrapping

An interline transfer type image sensing device that can be operated at high speed and with low image smear is described. The device incorporates a refractory metal layer which is used for both a light shield over the vertical charge transfer region and as a wiring layer for low resistance strapping of poly crystalline silicon (polysilicon) gate electrodes for the vertical charge transfer region. Plugs provided by a separate metallization layer connect the refractory light shield to the polysilicon gate electrode. These plugs allow high temperature processing after refractory light shield patterning for improved sensor performance without degradation of the polysilicon gate electrode or the refractory lightshield layer.

Owner:SEMICON COMPONENTS IND LLC

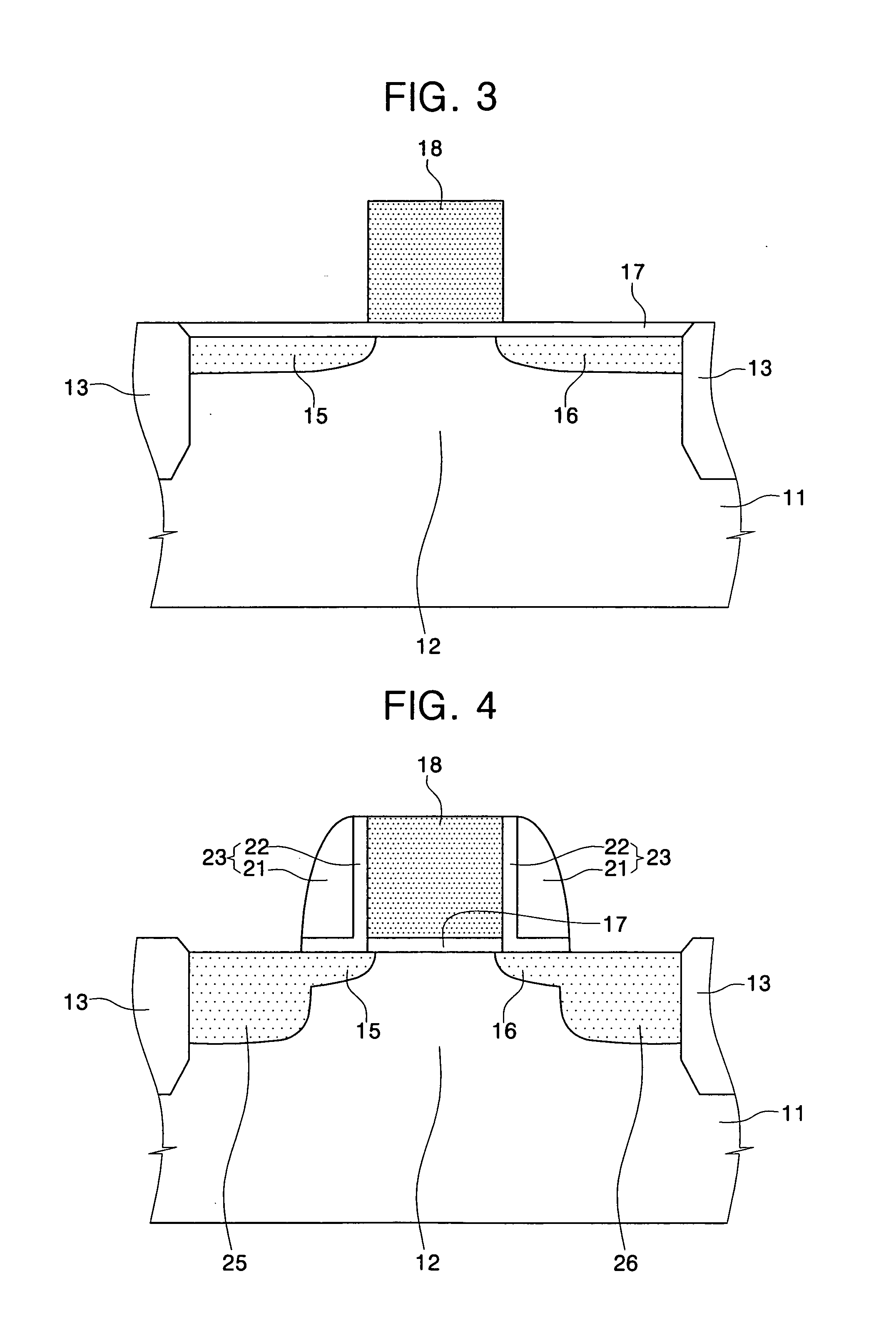

Method for crystallizing amorphous semiconductor thin film by epitaxial growth using non-metal seed and method for fabricating poly-crystalline thin film transistor using the same

InactiveUS20060270129A1Improve featuresEliminate pollutionSolid-state devicesSemiconductor/solid-state device manufacturingSeed crystalSemiconductor thin films

A method for crystallizing an amorphous semiconductor thin film using a non-metal seed epitaxial growth (NSEG) is provided. The method includes the steps of: forming a pair of non-metal seeds for inducing a crystallization of an amorphous semiconductor thin film at a predetermined distance on a transparent insulation substrate; depositing the amorphous semiconductor thin film on the insulation substrate; and heat-treating the insulation substrate to thereby epitaxially grow a poly-crystalline semiconductor thin film from the non-metal seeds, and to thus crystallize the amorphous semiconductor thin film. In the crystallization method, non-metal seeds are used instead of using crystallization induced metal to thereby epitaxially grow the poly-crystalline semiconductor thin film and to thus realize the amorphous semiconductor thin film without having metal pollution.

Owner:PAIK WOON SUH

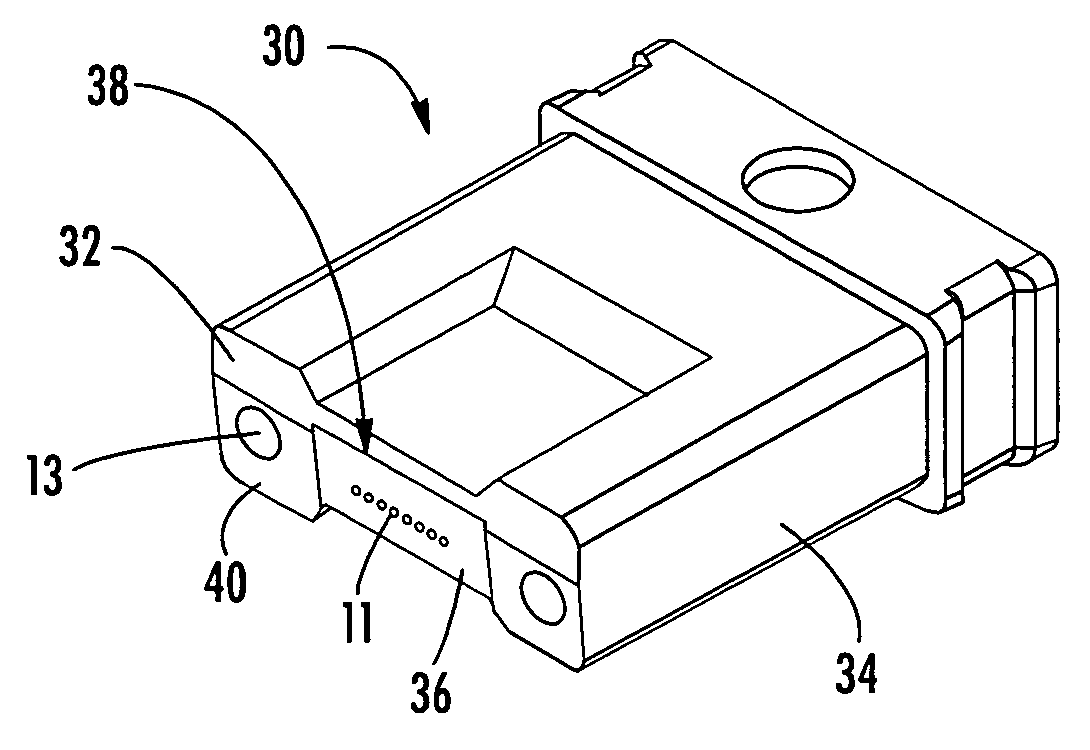

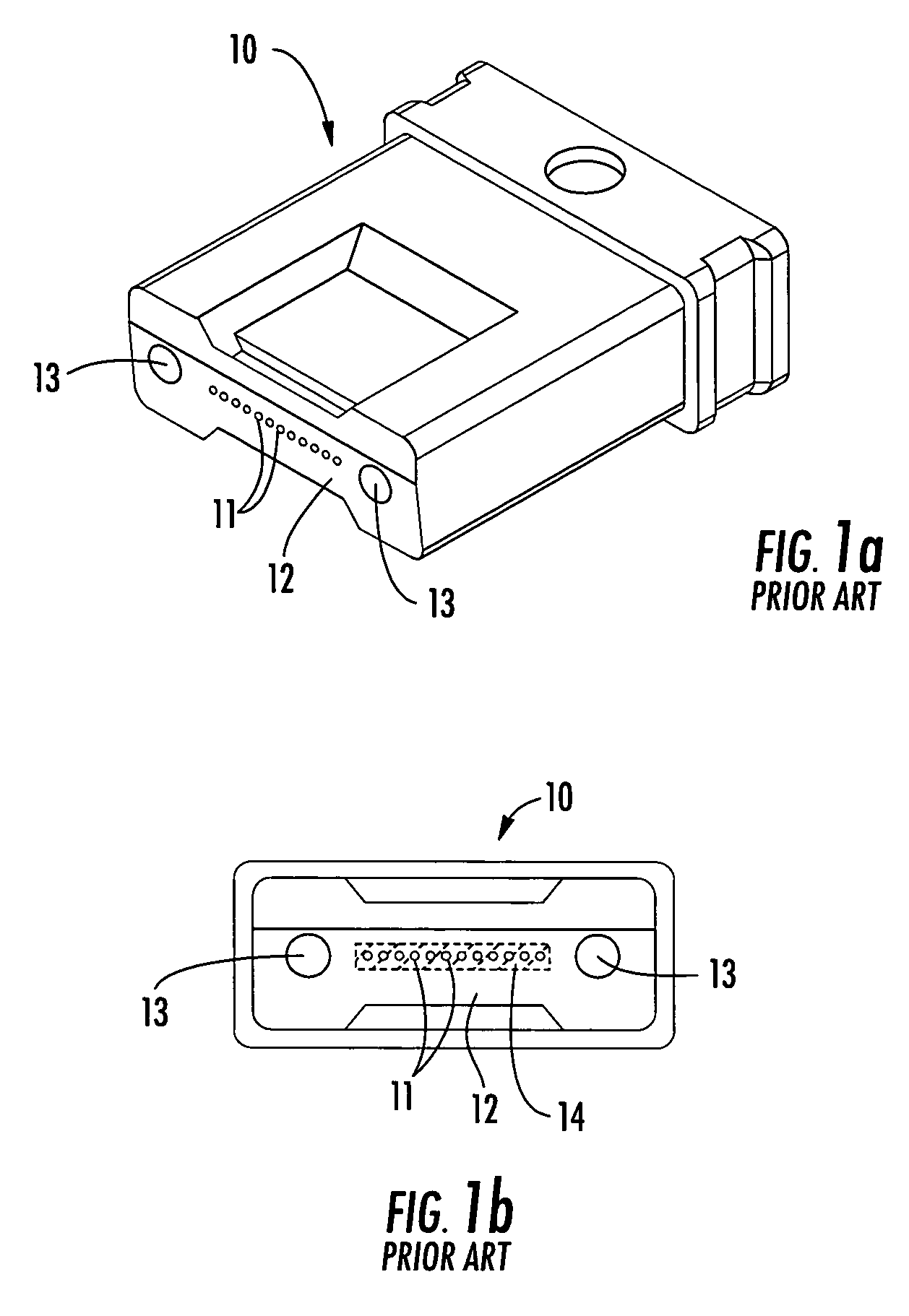

Precision insert for molding ferrules and associated methods of manufacture

InactiveUS7261469B1Reduce surface roughnessPromoting ferrule uniformityConfectioneryOptical articlesFiberPolycrystalline diamond

A precision mold insert and method for manufacturing angled or angled and bumpered multi-fiber ferrules. The precision mold insert includes an angled end face forming portion, one or more optional bumper forming portions, one or more fiber bores for receiving one or more fiber bore forming pins, and one or more guide pin holes for receiving one or more guide pin hole forming pins. A method for manufacturing a precision mold insert for molding angled or angled and bumpered multi-fiber ferrules utilizing electrical discharge machining (EDM) process and / or a poly crystalline diamond (PCD) grinding tool is provided. The mold insert is used to produce a multi-fiber ferrule having a pre-molded angled end face that is not machined, polished or otherwise altered subsequent to the molding process. The ferrule may also include bumpers for polishing end portions of optical fibers positioned within the fiber bores without altering the angled end face.

Owner:CORNING OPTICAL COMM LLC

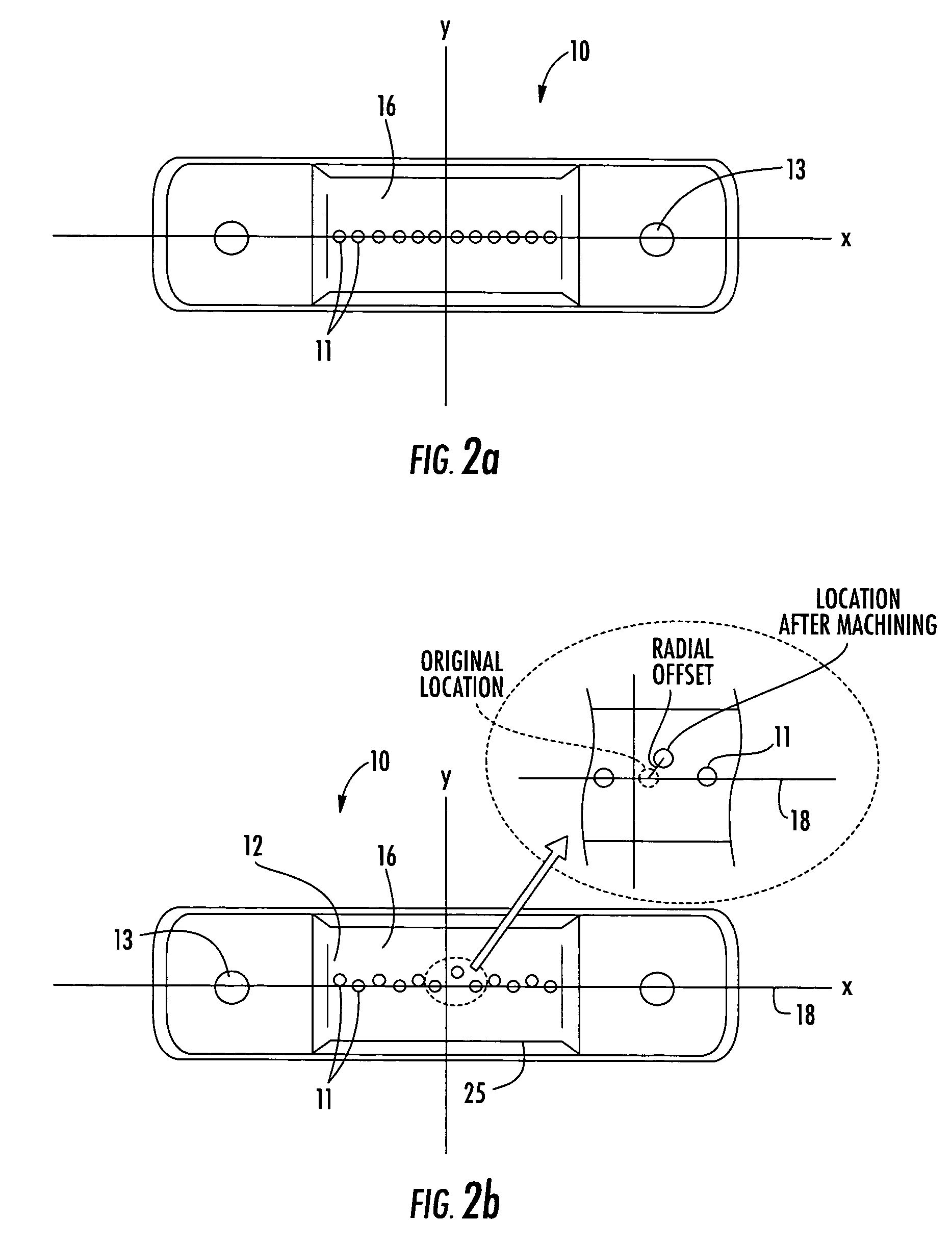

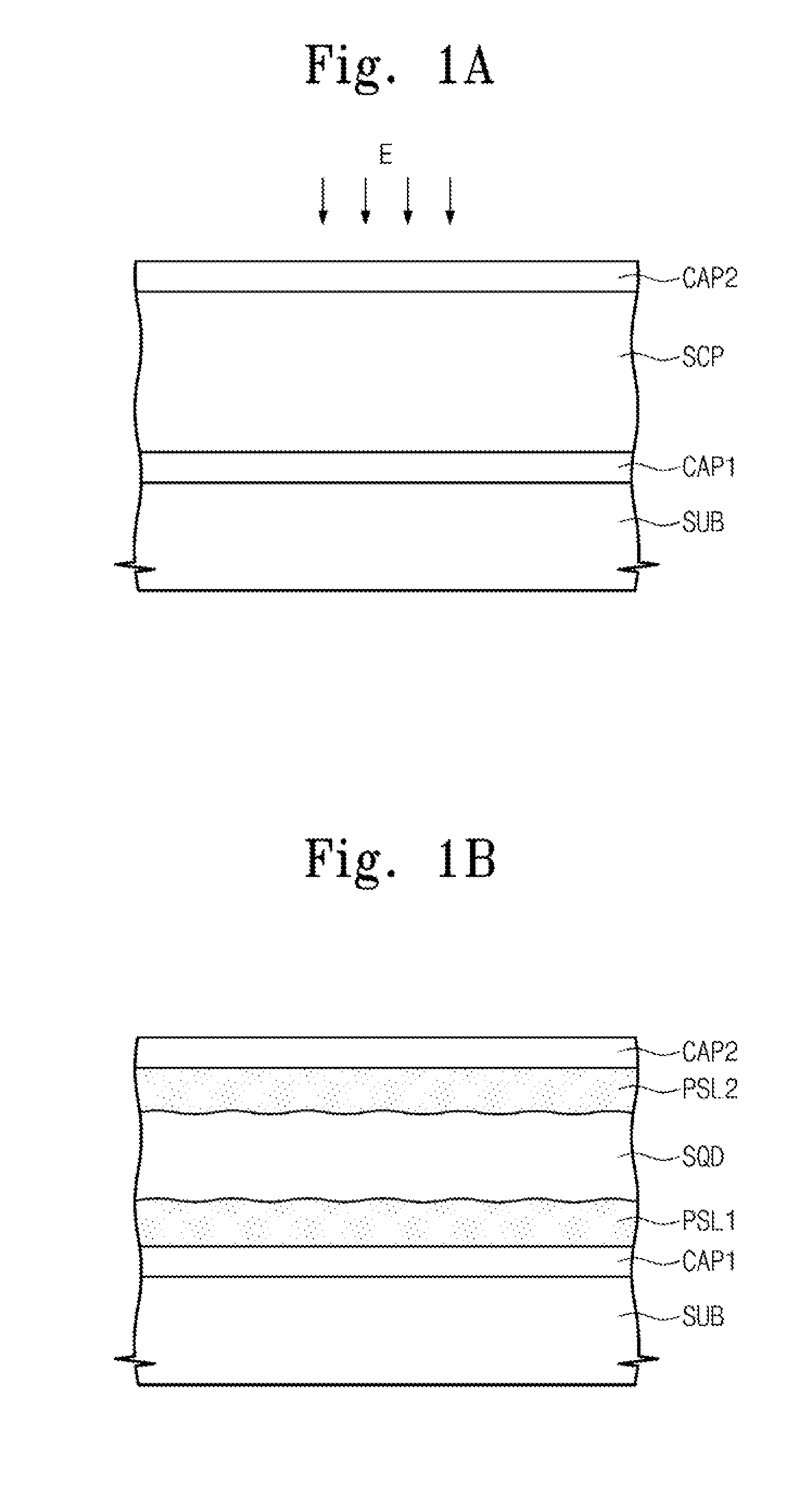

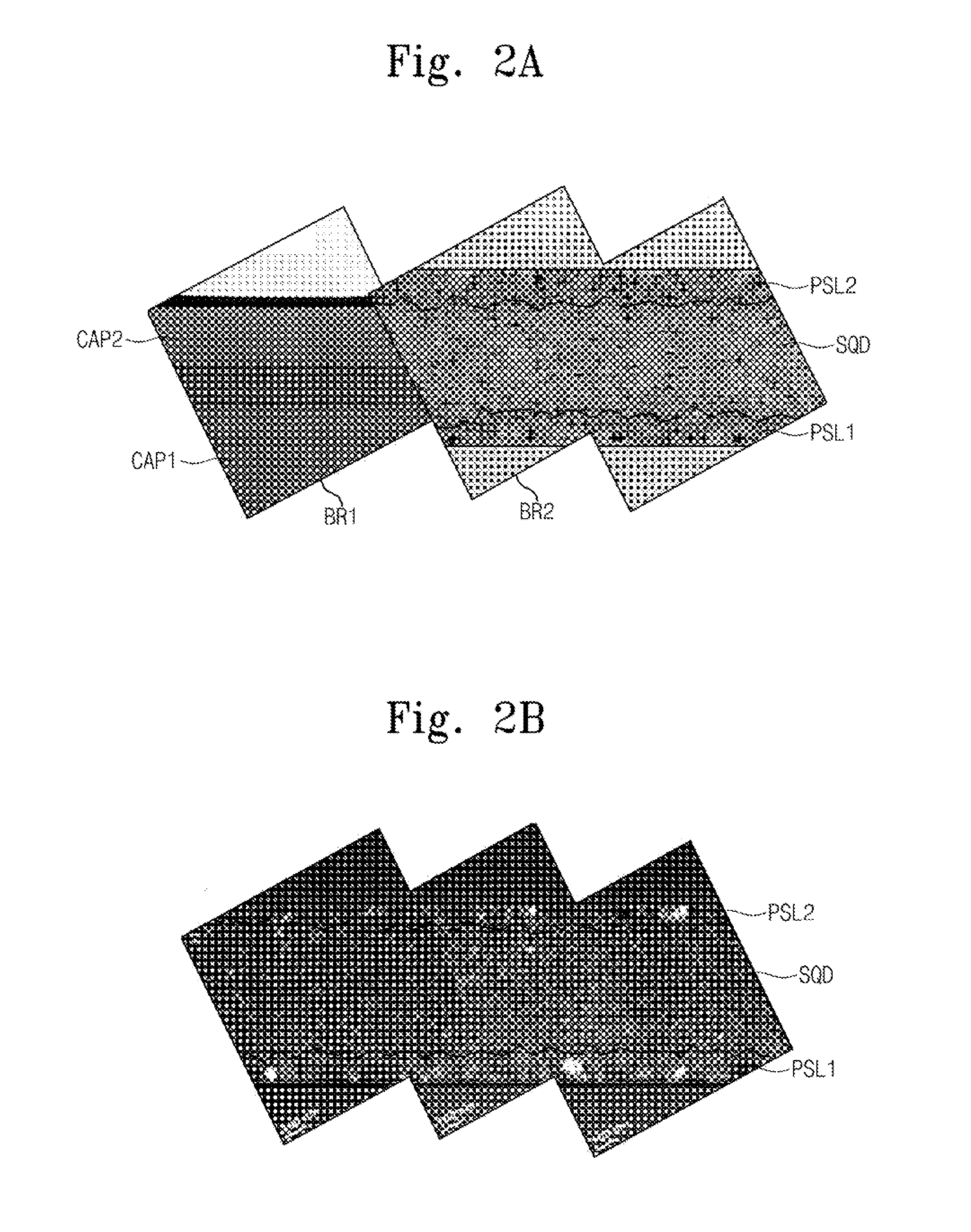

Method of Fabricating Silicon Quantum Dot Layer and Device Manufactured Using the Same

Disclosed are a method of fabricating a silicon quantum dot layer and a device manufactured using the same. A first capping layer is formed on a substrate, and a silicon-containing precursor layer is formed on the first capping layer. A second capping layer is formed on the silicon-containing precursor layer. The first capping layer, the silicon-containing precursor layer, and the second capping layer are irradiated to convert the silicon-containing precursor layer into a stack including a first poly-crystalline silicon layer, a silicon quantum dot layer on the first poly-crystalline silicon layer, and a second poly-crystalline silicon layer on the silicon quantum dot layer.

Owner:SAMSUNG DISPLAY CO LTD +1

Method and System for Improving Surgical Blades by the Application of Gas Cluster Ion Beam Technology and Improved Surgical Blades

InactiveUS20090198264A1Reduce pressureReduce crackingIncision instrumentsElectric discharge tubesSurgical bladeGas cluster ion beam

Methods and systems for the improvement of a crystalline and / or poly-crystalline surgical blade include gas cluster ion beam irradiation of the blades in order to smooth; or to sharpen; or to reduce the brittleness and thus reduce susceptibility of the blade to crack, chip, or fracture; or to render the blades hydrophilic. Crystalline or poly-crystalline surgical blade (silicon for example) having a thin film cutting edge with improved properties.

Owner:EXOGENESIS CORP

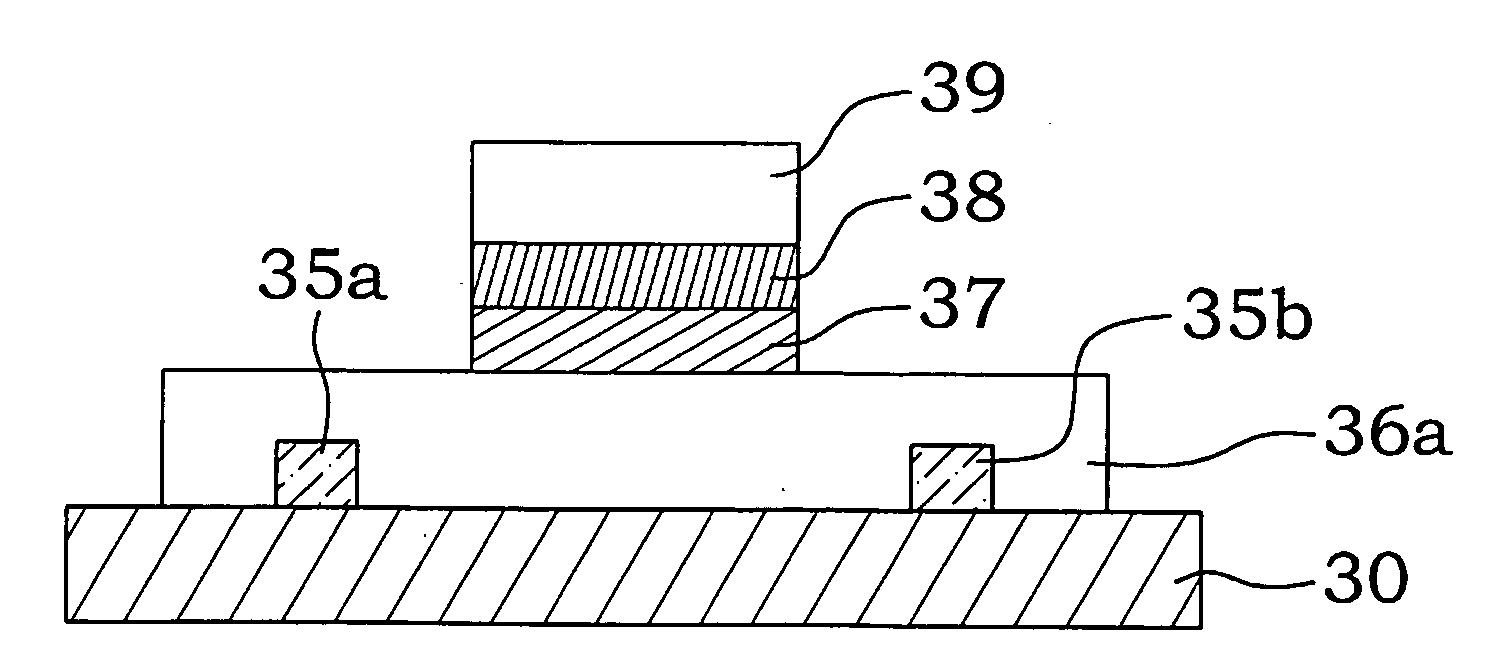

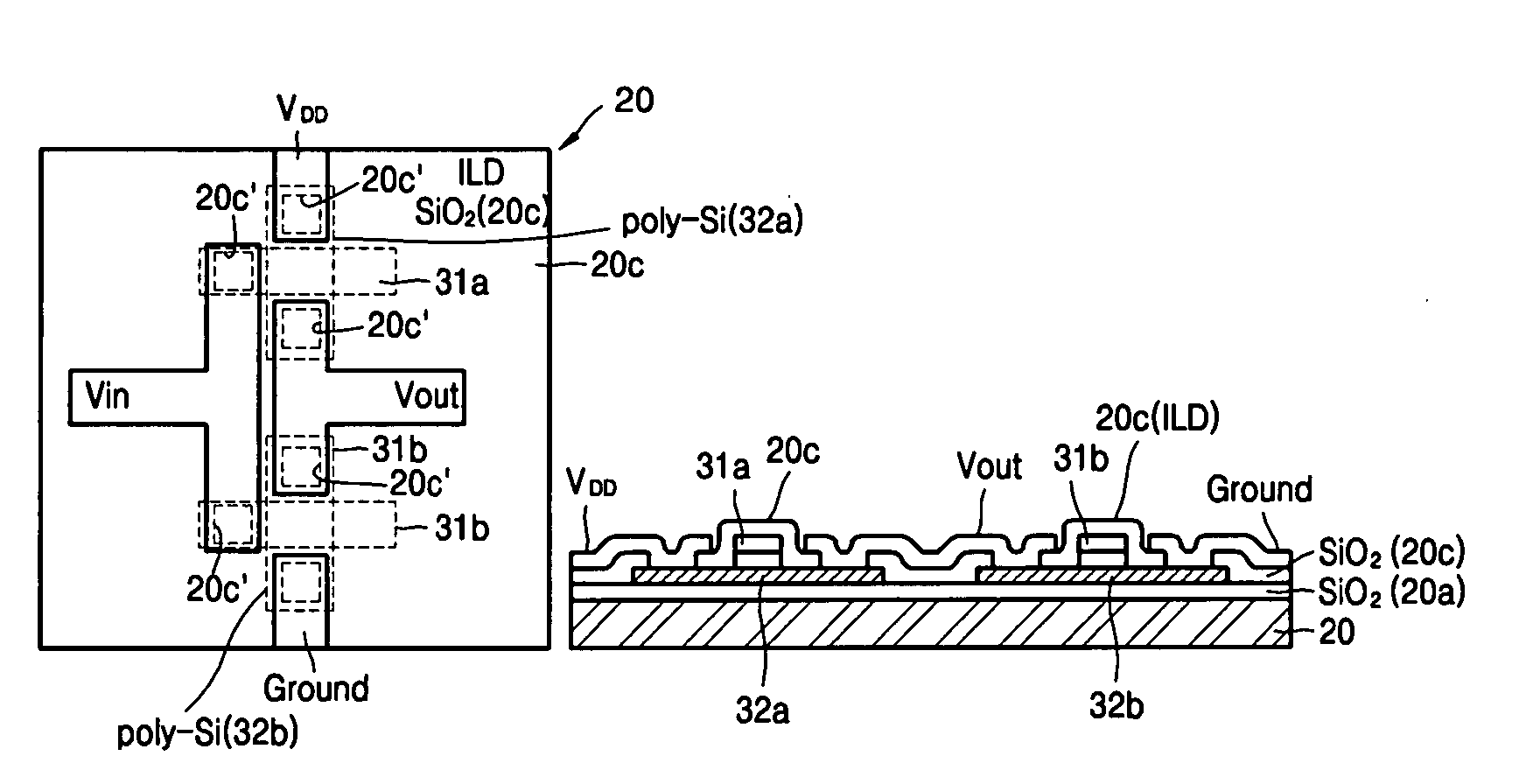

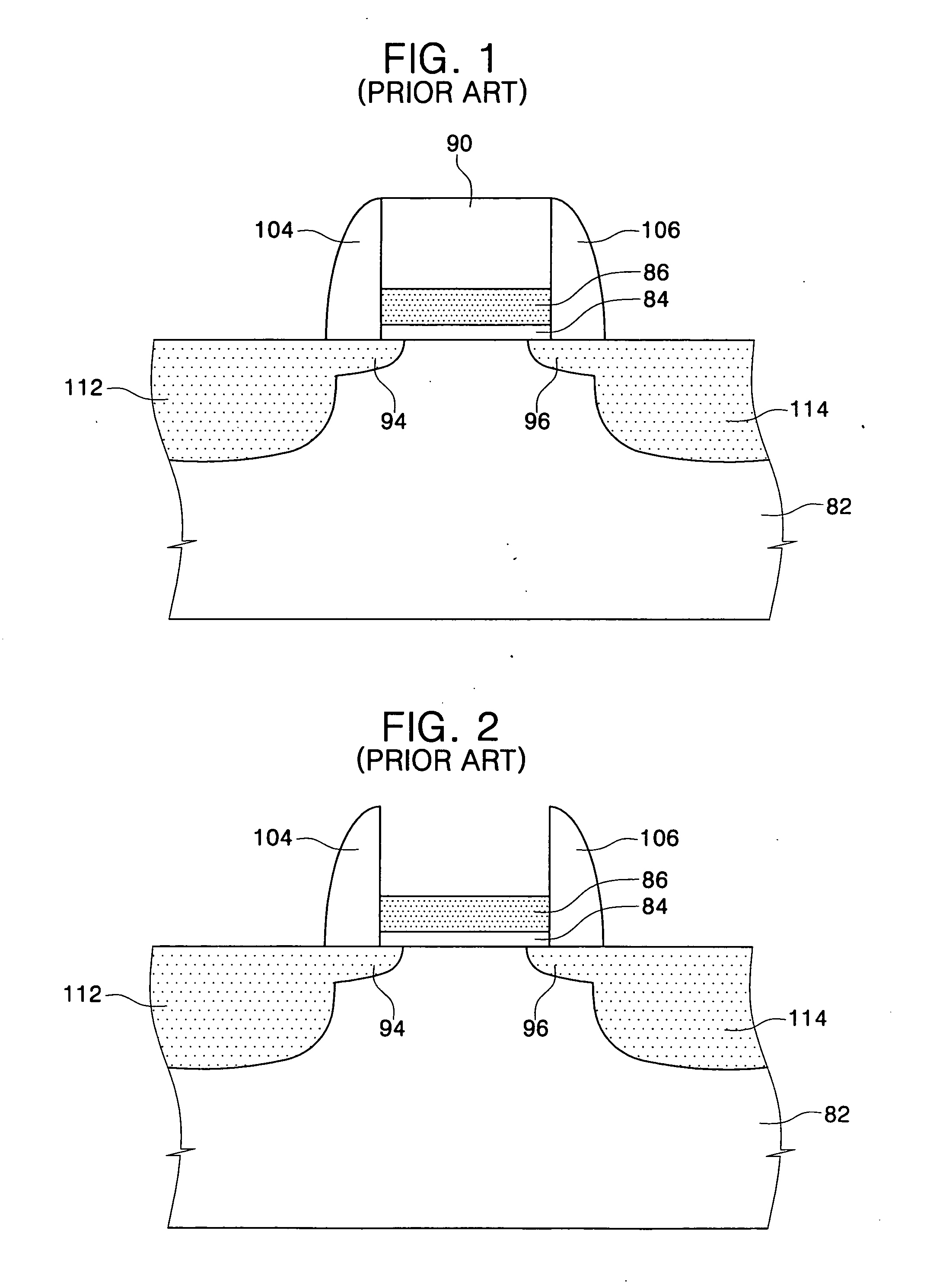

Poly crystalline silicon semiconductor device and method of fabricating the same

ActiveUS20050139924A1Avoid distortionPrevent delay of gateTransistorSolid-state devicesDevice materialParasitic capacitance

Provided are a poly crystalline silicon semiconductor device and a method of fabricating the same. Portions of a silicon layer except for gates are removed to reduce a parasitic capacitance caused from the silicon layer existing on gate bus lines. The silicon layer exists under the gates only, thus the parasitic capacitance is reduced and the deterioration and the delay of signals are prevented. Accordingly, the poly crystalline silicon semiconductor device, such as a thin film transistor, has excellent electric characteristics.

Owner:SAMSUNG ELECTRONICS CO LTD

In situ silicon surface pre-clean for high performance passivation of silicon solar cells

InactiveUS20140213016A1Final product manufactureSemiconductor/solid-state device manufacturingSilicon solar cellCrystalline silicon

Embodiments of the invention generally relate to methods for fabricating photovoltaic devices, and more particularly to methods for in-situ cleaning of a solar cell substrates. In one embodiment, a method of manufacturing a solar cell device is provided. The method comprises exposing a single or poly crystalline silicon substrate to a wet clean process to clean the surfaces of the crystalline substrate, loading the crystalline silicon substrate into a processing system having a vacuum environment, exposing at least one surface of the crystalline silicon substrate to an in-situ cleaning process in the vacuum environment of the processing system, and forming one or more passivation layers on at least one surface of the crystalline silicon substrate in the processing system.

Owner:APPLIED MATERIALS INC

Method of forming MOS transistor having fully silicided metal gate electrode

InactiveUS20060008961A1Semiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerEngineering

Methods of fabricating a MOS transistor having a fully silicided metal gate electrode are provided. The method includes forming an isolation layer in a predetermined region of a semiconductor substrate to define an active region. An insulated gate pattern which crosses over the active region is formed. A spacer is formed on sidewalls of the gate pattern. A selective epitaxial growth process is applied to form semiconductor layers on the gate pattern and on the active region at both sides of the gate pattern. In this case, a poly-crystalline semiconductor layer is formed on the gate pattern while single-crystalline semiconductor layers are concurrently formed on the active region at both sides of the gate pattern. The semiconductor layers are selectively etched to form a gate-reduced pattern and elevated source and drain regions. Respective desired thicknesses of the gate-reduced pattern and the elevated source and drain regions may be obtained using an etch selectivity between the poly-crystalline semiconductor layer and the single-crystalline semiconductor layer. A silicidation process is applied to the semiconductor substrate where the gate-reduced pattern is formed to simultaneously form a fully silicided metal gate electrode and elevated source and drain silicide layers.

Owner:SAMSUNG ELECTRONICS CO LTD

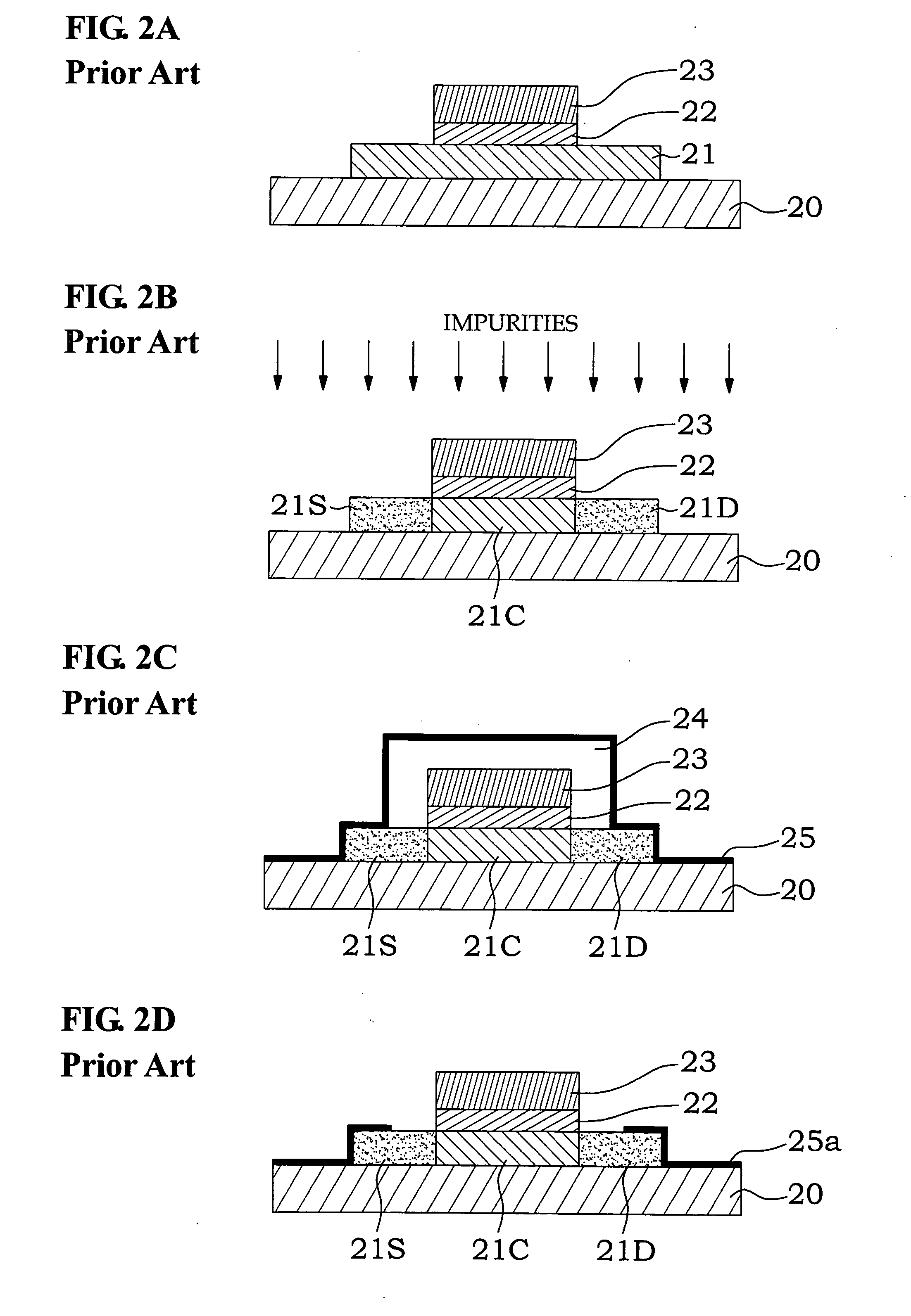

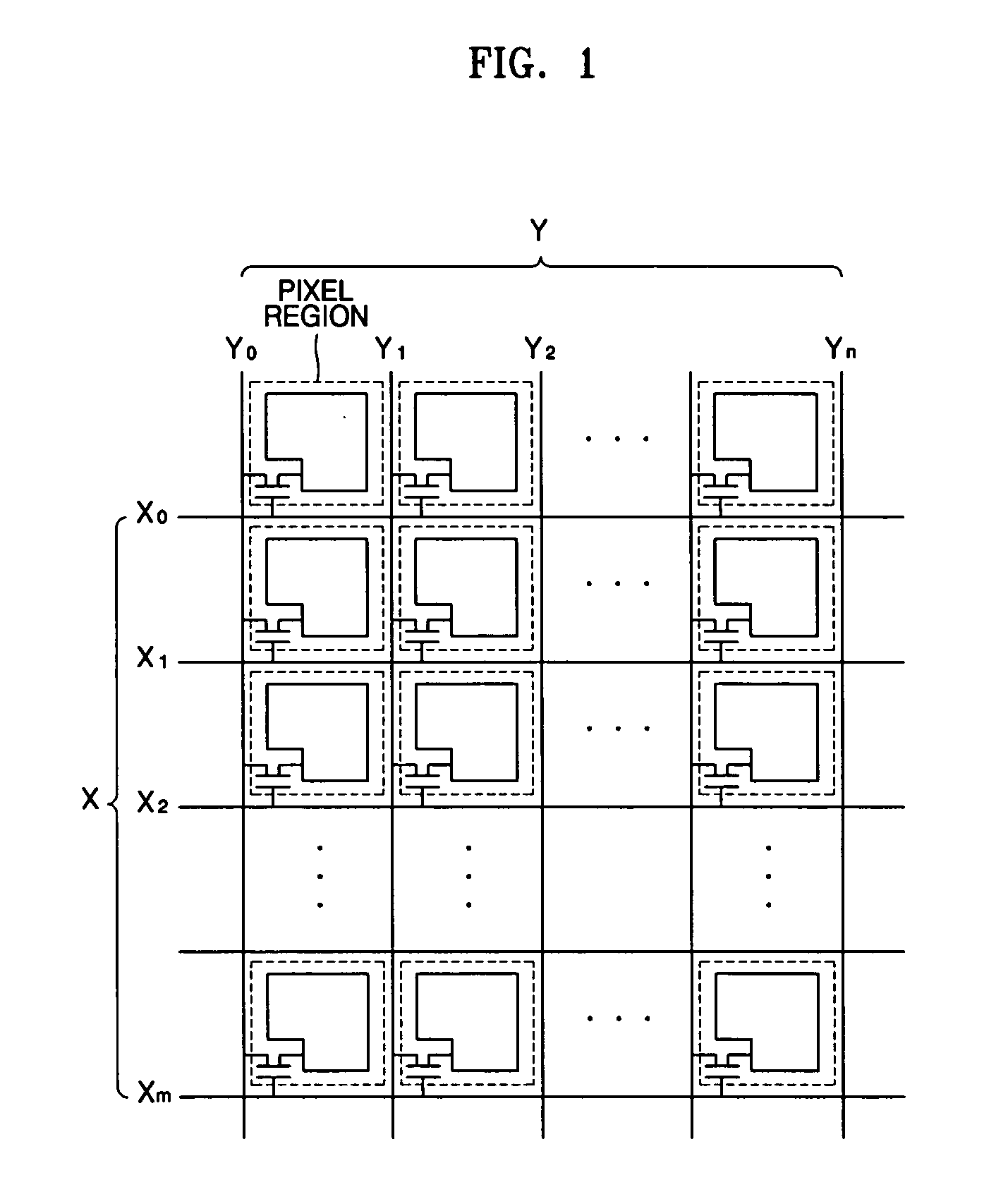

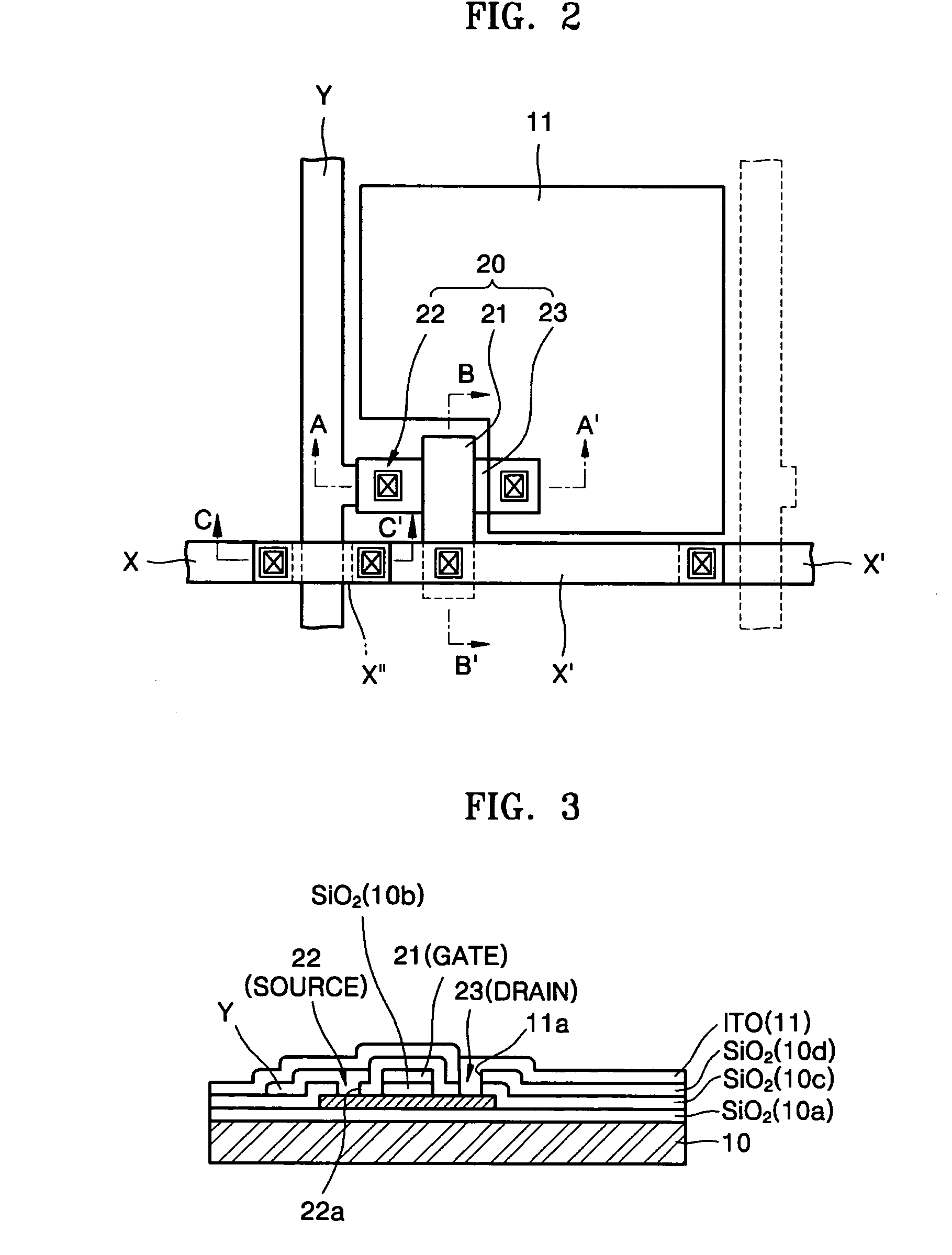

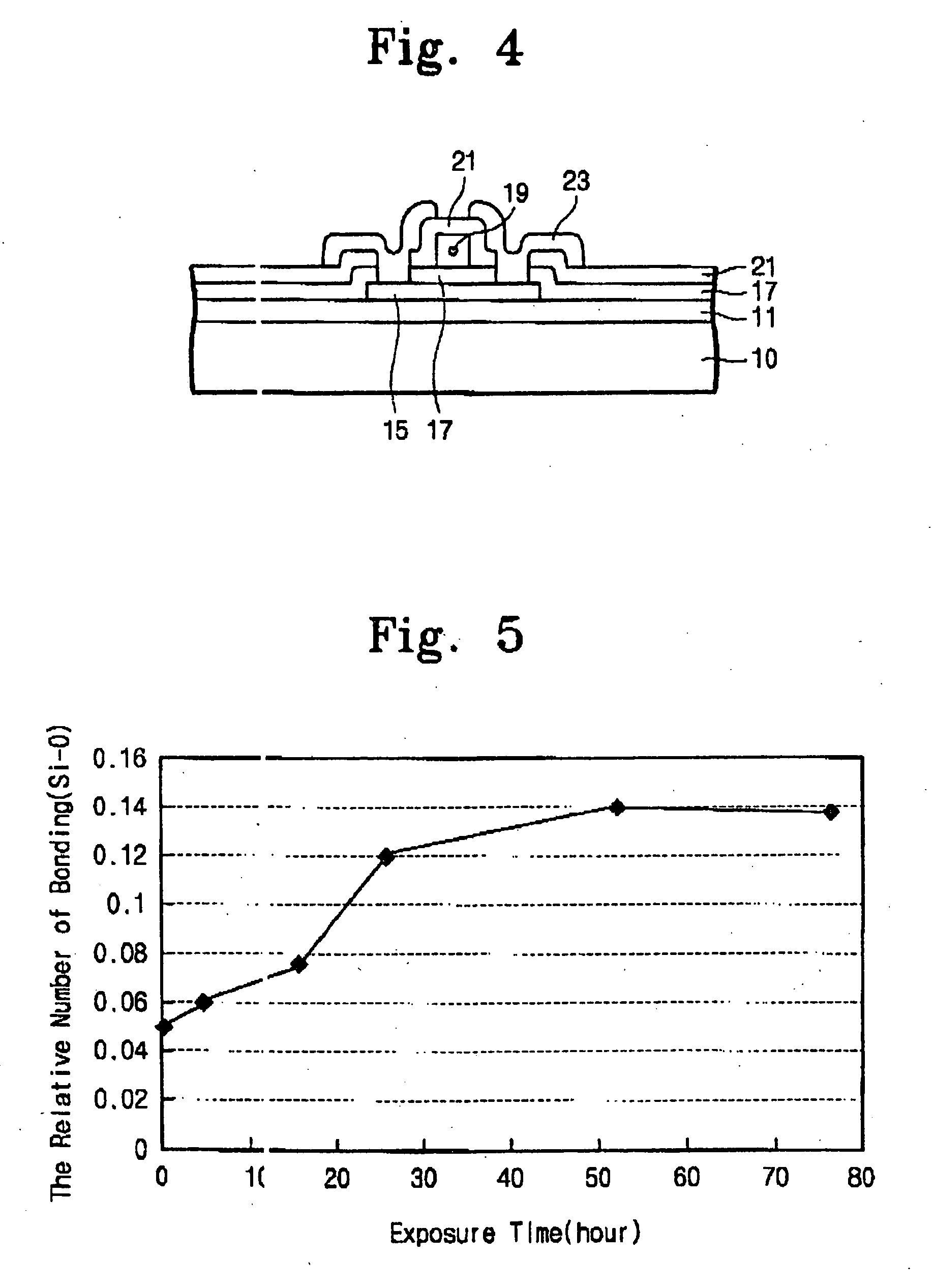

Low temperature polycrystalline silicon type thin film transistor and a method of the thin film transistor fabrication

InactiveUS20050014304A1Reduce decreaseHigh carrier mobilityTransistorSiliconCharge carrierAmorphous silicon

A method of fabricating poly crystalline silicon type thin film transistor is disclosed. In the method, before the step of re-crystallization of amorphous silicon to form polycrystalline silicon active pattern, a step for injecting predetermined amount of oxygen atom into the surface part of the amorphous silicon layer. By this addition of step, the surface part of the silicon layer is to be oxidized and the crystal defect in the interface between the gate insulating layer and poly crystalline silicon layer can be cured and the mobility of charge carrier can be improved in the channel of the thin film transistor.

Owner:SAMSUNG DISPLAY CO LTD

Thin film transistor substrate and display using the same

ActiveUS20150243689A1Efficient preparationReduce in quantitySolid-state devicesNon-linear opticsDisplay deviceNitride

The present disclosure relates to a thin film transistor substrate having two different types of thin film transistors on the same substrate, and a display using the same. A display includes a first thin film transistor including a poly crystalline semiconductor layer, a first gate electrode on the poly crystalline semiconductor layer, a first source electrode, and a first drain electrode; a second thin film transistor including a second gate electrode, an oxide semiconductor layer on the second gate electrode, a second source electrode, and a second drain electrode; and an intermediate insulating layer including a nitride layer and an oxide layer on the nitride layer, the intermediate insulating layer disposed on the first gate electrode and the second gate electrode and under the oxide semiconductor layer.

Owner:LG DISPLAY CO LTD

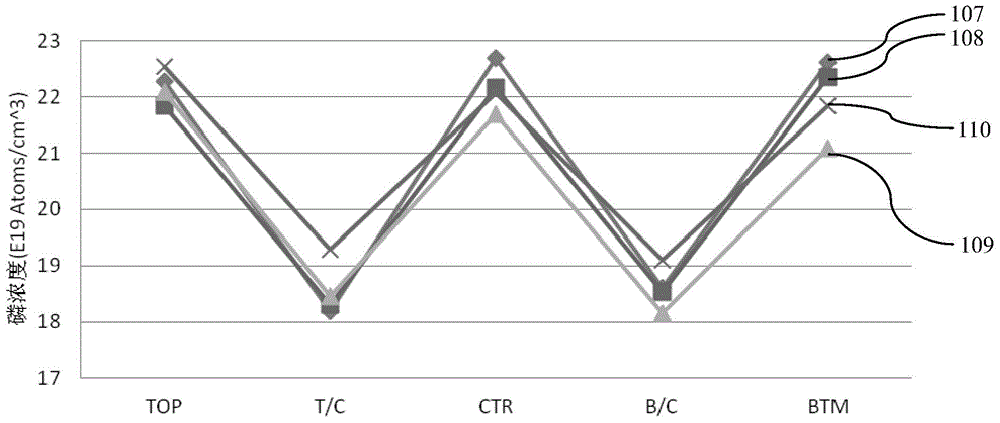

Method and structure for improving phosphorus concentration uniformity of doped polycrystalline or noncrystalline silicon chips

ActiveCN104576330AAvoid the W distribution caseImprove Phosphorus Concentration UniformityDiffusion/dopingSemiconductor/solid-state device manufacturingEngineeringSilicon chip

The invention discloses a method for improving the phosphorus concentration uniformity of doped polycrystalline or noncrystalline silicon chips. According to the method, a furnace tube is adopted for growth, phosphorane is introduced through three nozzle pipelines, and the top ends of the nozzle pipelines are arranged at the bottom, the middle and the top of a crystal boat respectively; gas is emitted from the top of the first nozzle pipeline; a plurality of lateral gas outlets are formed in each of the second and third nozzle pipelines at intervals; the diameters of the lateral gas outlets of each pipeline are gradually increased in a direction from the bottom end to the top end and adjusted by testing the phosphorus concentration of the monitored silicon chips at the fixed monitoring positions of the crystal boat; the positions of the lateral gas outlets are adjusted by testing a phosphorus concentration curve along the whole crystal boat. The invention further discloses a structure for improving the phosphorus concentration uniformity of the doped polycrystalline or noncrystalline silicon chips. According to the method and the structure, the phosphorus concentration uniformity of the silicon chips can be improved and the production cost can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

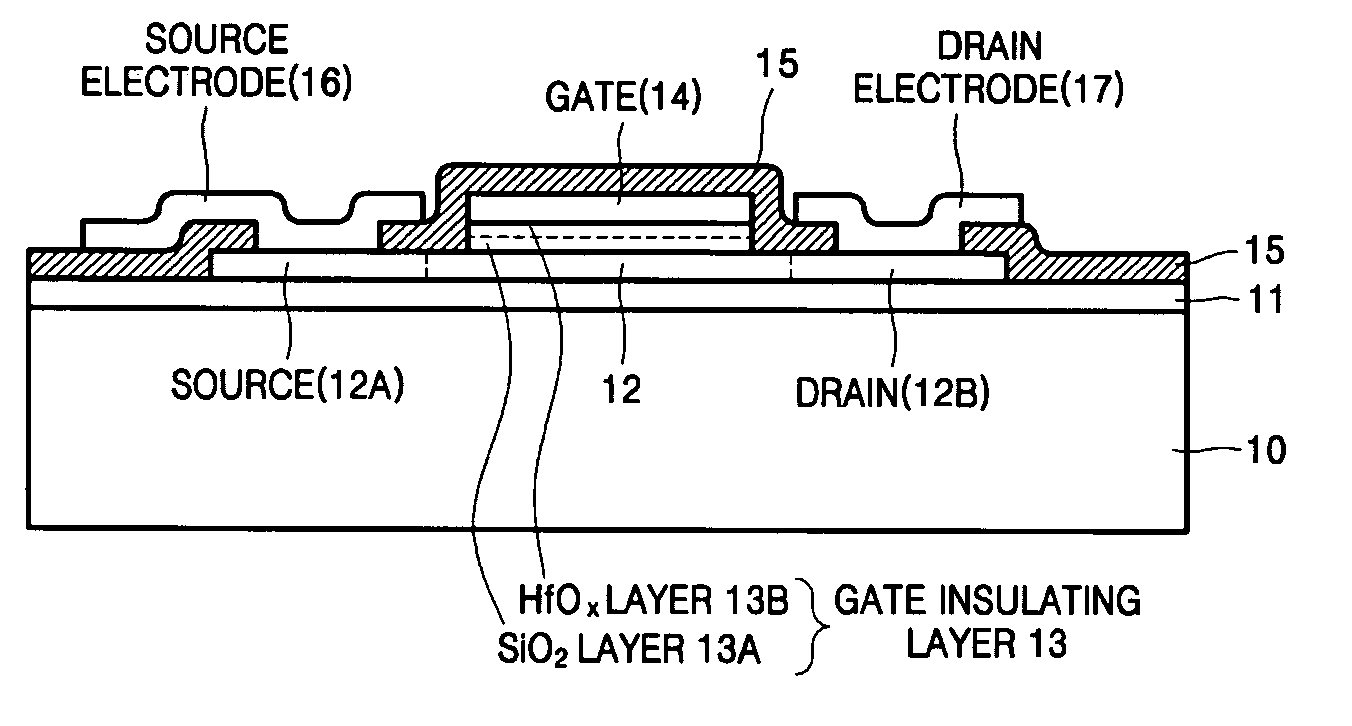

Poly-crystalline silicon thin film transistor

InactiveUS20060145158A1Improve interface propertiesReduce leakage currentSemiconductor devicesLow leakageSilicon thin film

Provided is a silicon thin film transistor (TFT) including: a substrate; a silicon channel layer formed on the substrate with a source and a drain on both sides thereof; a gate insulating layer formed on the silicon channel layer; and a gate formed on the gate insulating layer, wherein the gate insulating layer has a structure including an HfOx film. The TFT has a low leakage current.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com