Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30results about How to "Reduce electron concentration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

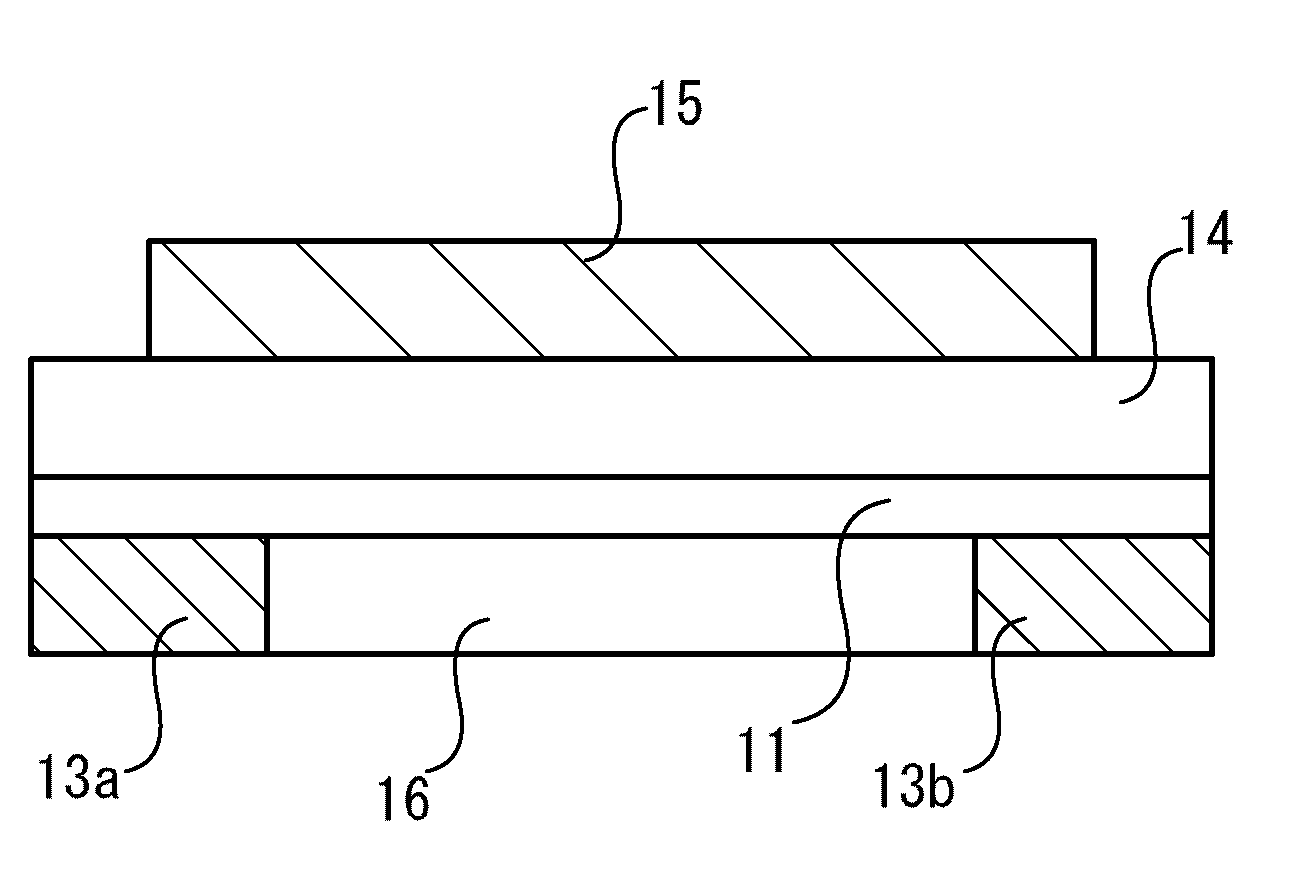

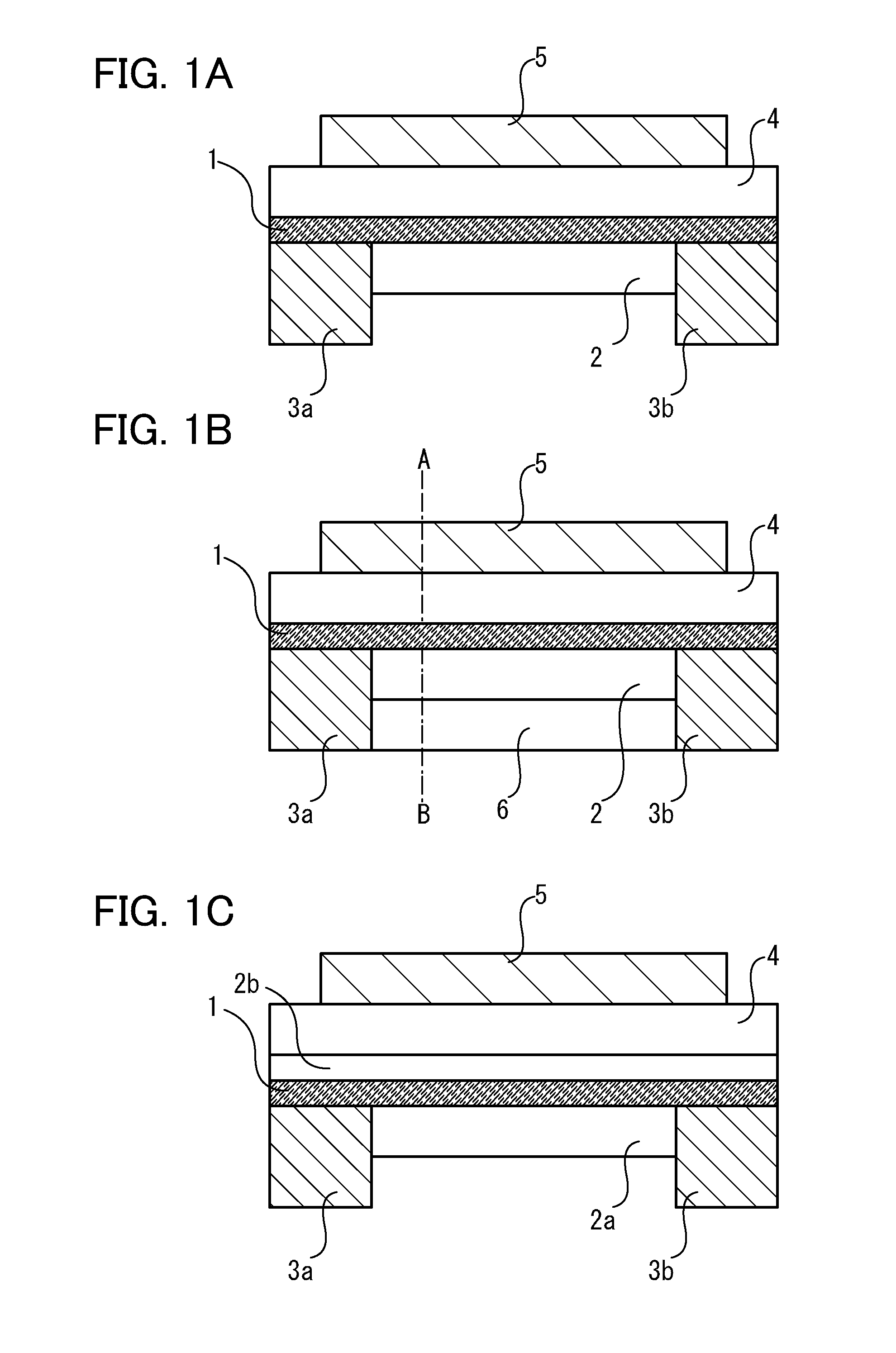

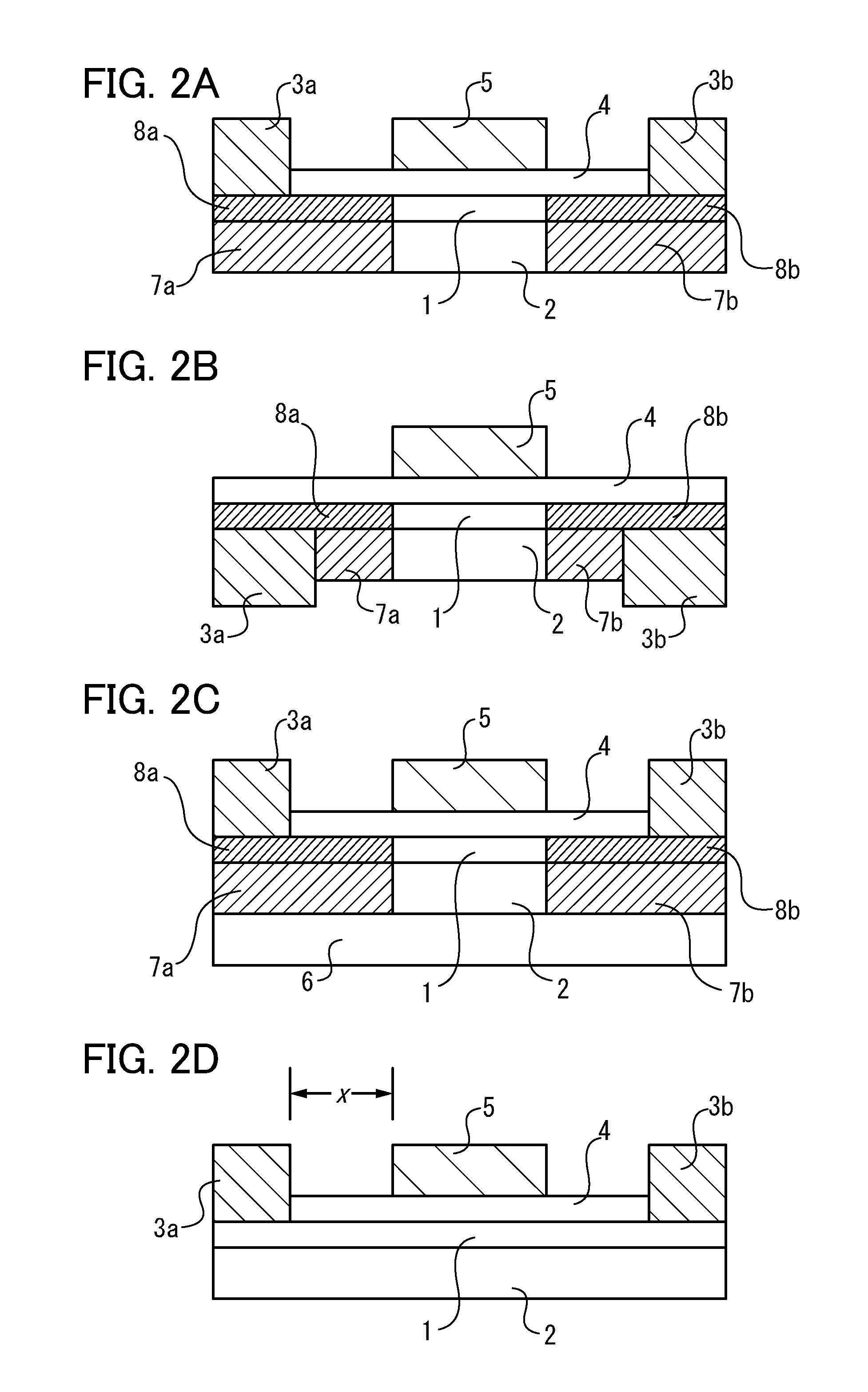

Field effect transistor

ActiveUS20110309411A1Reduce FET characteristicReduce the impactTransistorSemiconductor/solid-state device manufacturingElectrical conductorIndium

An insulating film is provided over one surface of a first semiconductor layer including a first oxide semiconductor including indium as a main component, and a second semiconductor layer including an i-type second oxide semiconductor is provided in contact with the other surface. The energy difference between a vacuum level and a Fermi level in the second oxide semiconductor is larger than that in the first oxide semiconductor. In the first semiconductor layer, a region in the vicinity of the junction surface with the second oxide semiconductor which satisfies the above condition is a region having an extremely low carrier concentration (a quasi-i-type region). By using the region as a channel, the off-state current can be reduced. Further, a drain current of the FET flows through the first oxide semiconductor having a high mobility; accordingly, a large amount of current can be extracted.

Owner:SEMICON ENERGY LAB CO LTD

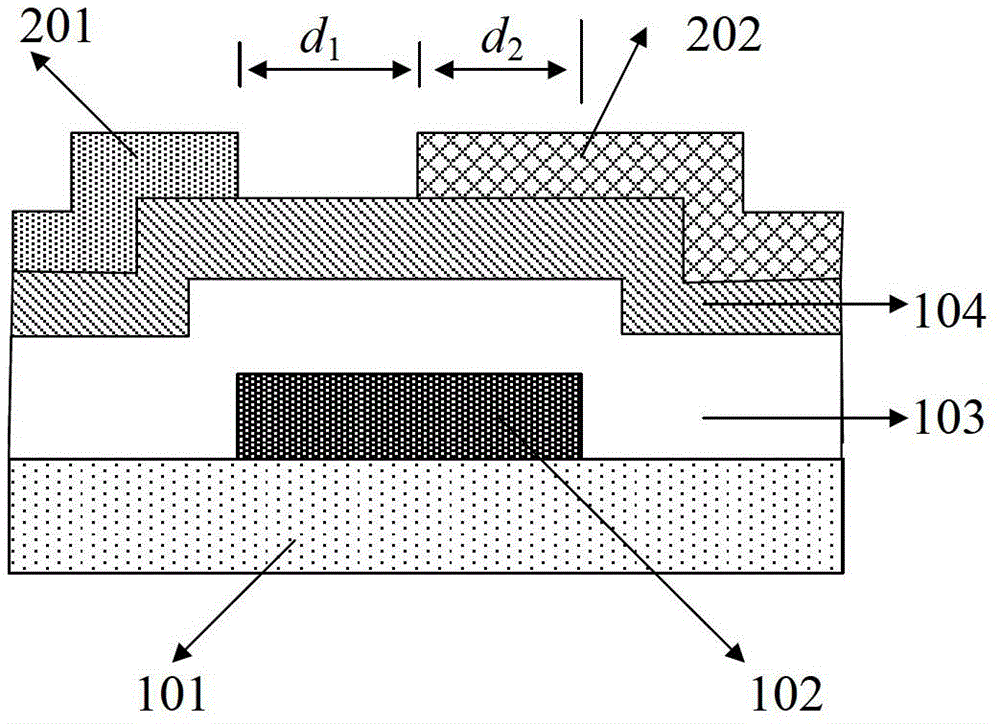

Oxide semiconductor thin film transistor

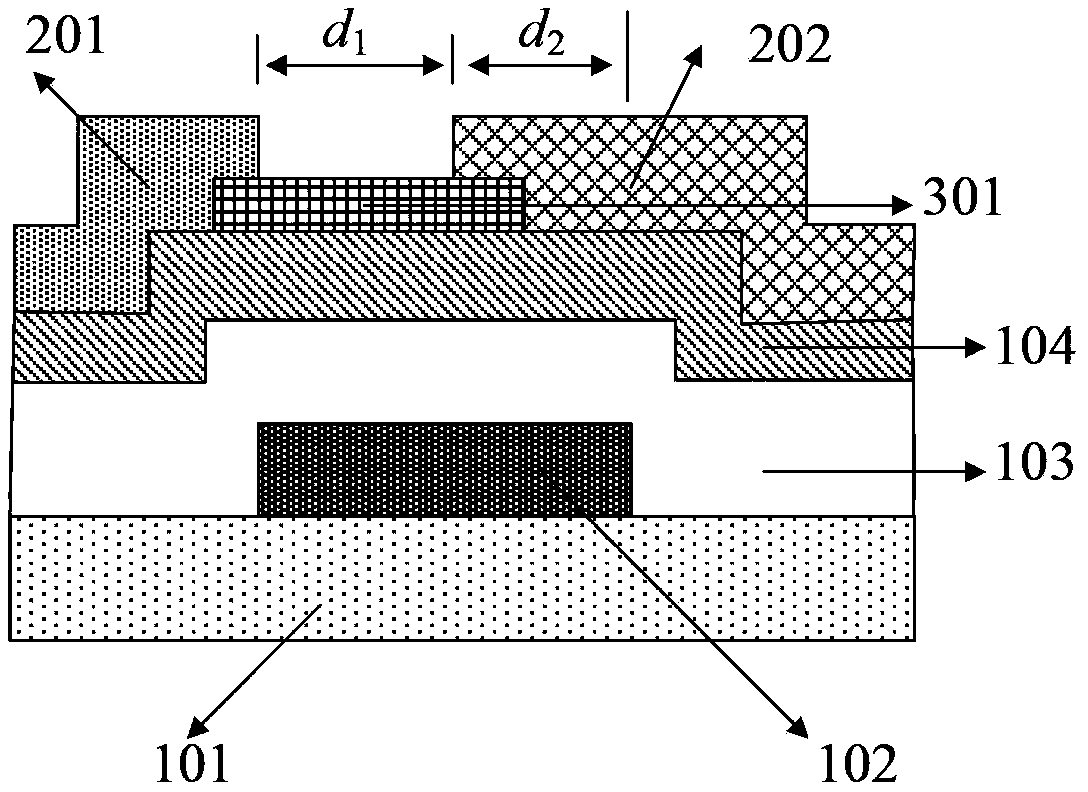

ActiveCN102723367AImprove stabilityReduce electron concentrationTransistorOhmic contactCharge carrier

The invention provides an oxide semiconductor thin film transistor which comprises a substrate, a gate electrode, an insulation dielectric layer and an oxide semiconductor channel layer, wherein the gate electrode, the insulation dielectric layer and the oxide semiconductor channel layer are sequentially arranged on the substrate, the insulation dielectric layer enables the gate electrode and the oxide semiconductor channel layer to be insulted, a drain electrode and a source electrode are arranged on the upper surface of the oxide semiconductor channel layer, a gap between the drain electrode and the source electrode is d1, the length of an overlapping region of the source electrode and the gate electrode in the horizontal direction is d2, contact between the source electrode and the oxide semiconductor channel layer is schottky contact, and the contact between the drain electrode and the oxide semiconductor channel layer is ohmic contact. The short-channel effect on the oxide semiconductor thin film transistor is small due to new geometrical characteristics and operating principles, and the oxide semiconductor thin film transistor is favorable for improvement of consistency.

Owner:CHENGDU VISTAR OPTEOLECTRONICS CO LTD

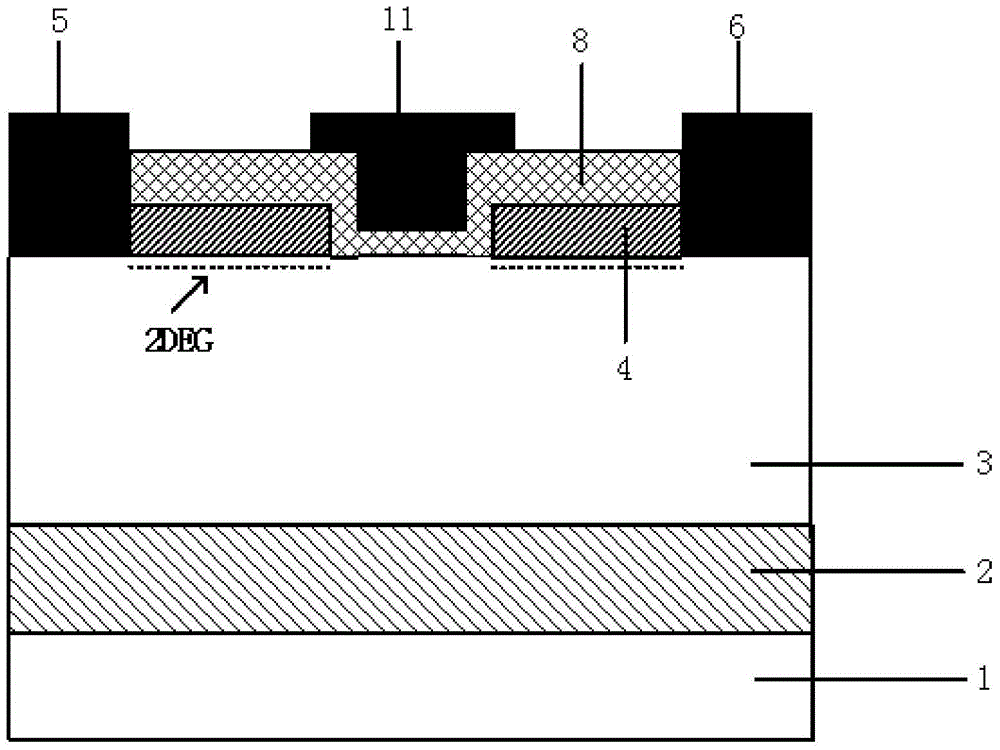

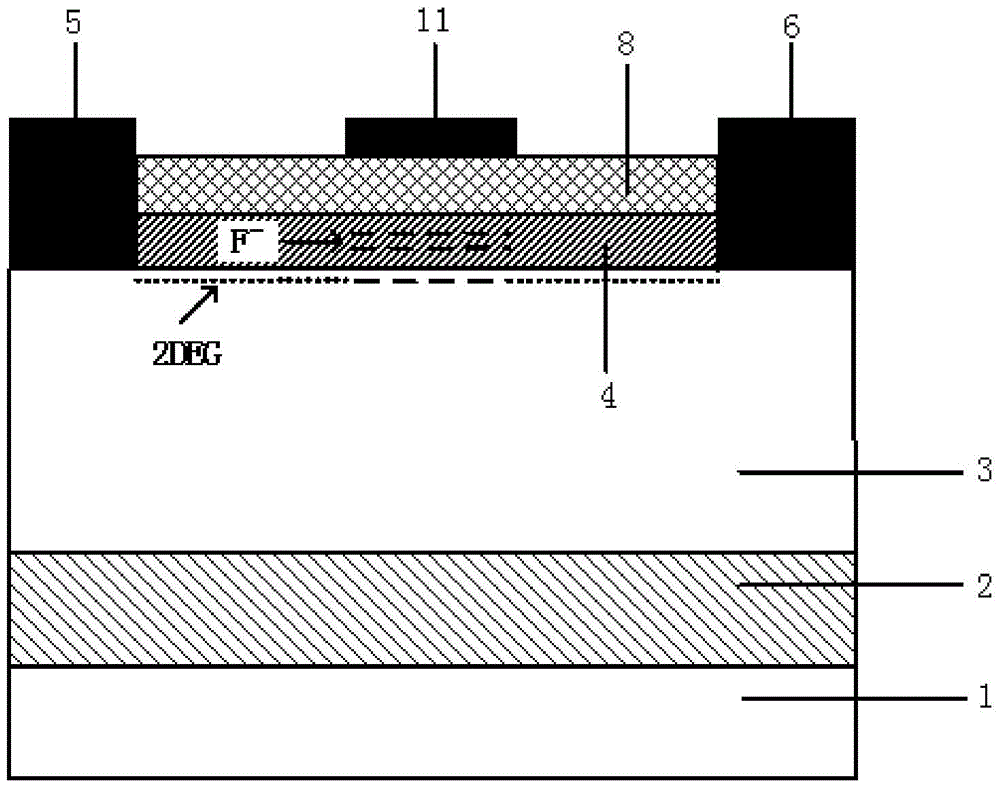

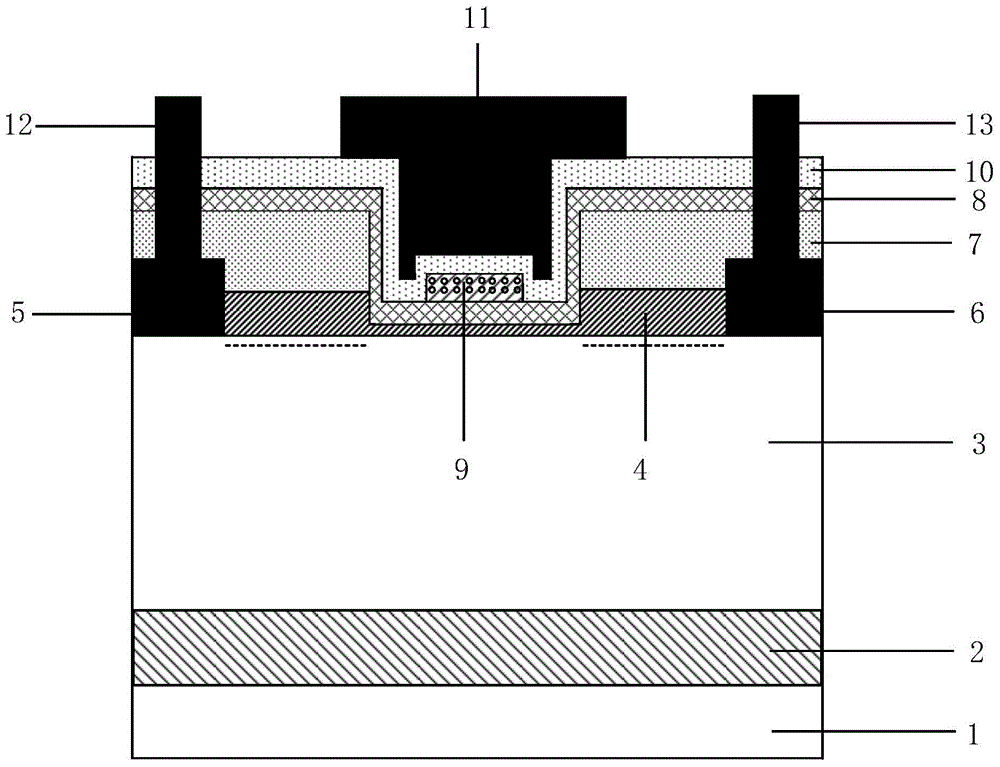

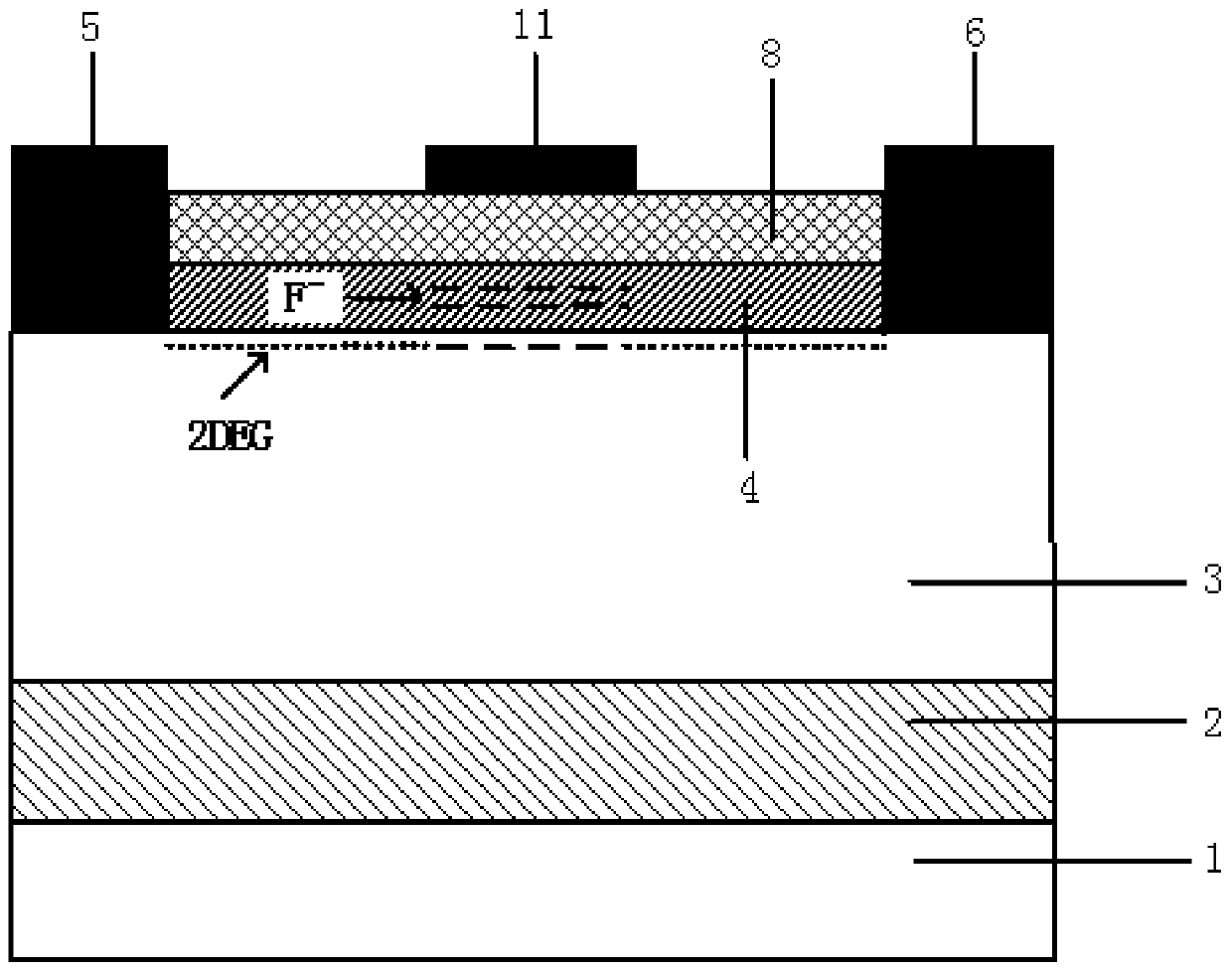

HEMT device with sandwich grid medium structure and preparation method thereof

ActiveCN104966731AReduce leakage currentReduce electron concentrationSemiconductor devicesElectrode ContactDielectric layer

The invention relates to the field of semiconductor devices, and provides a HEMT device with a sandwich grid medium structure and a preparation method thereof. The HEMT device includes a substrate, a buffer layer arranged on the substrate, a GaN layer arranged on the buffer layer, a barrier layer, a source electrode, and a drain electrode that are arranged on the GaN layer, a passivation layer arranged on the source electrode, the drain electrode, and the barrier layer except a groove, a first dielectric layer coating the groove surface and the passivation layer surface, a second dielectric layer arranged on the first dielectric layer, a third dielectric layer arranged on the second dielectric layer and the first dielectric layer except the second dielectric layer, a gate electrode in contact with the third dielectric layer, a source electrode pad in contact with the source electrode, and a drain electrode pad in contact with the drain electrode, wherein one side, far away from the GaN layer, of the barrier layer is provided with the groove, and the second dielectric layer contains fluorinion. The high-threshold voltage normally off operation of the HEMT device can be realized, and the breakdown voltage of the device can be effectively improved.

Owner:润新微电子(大连)有限公司

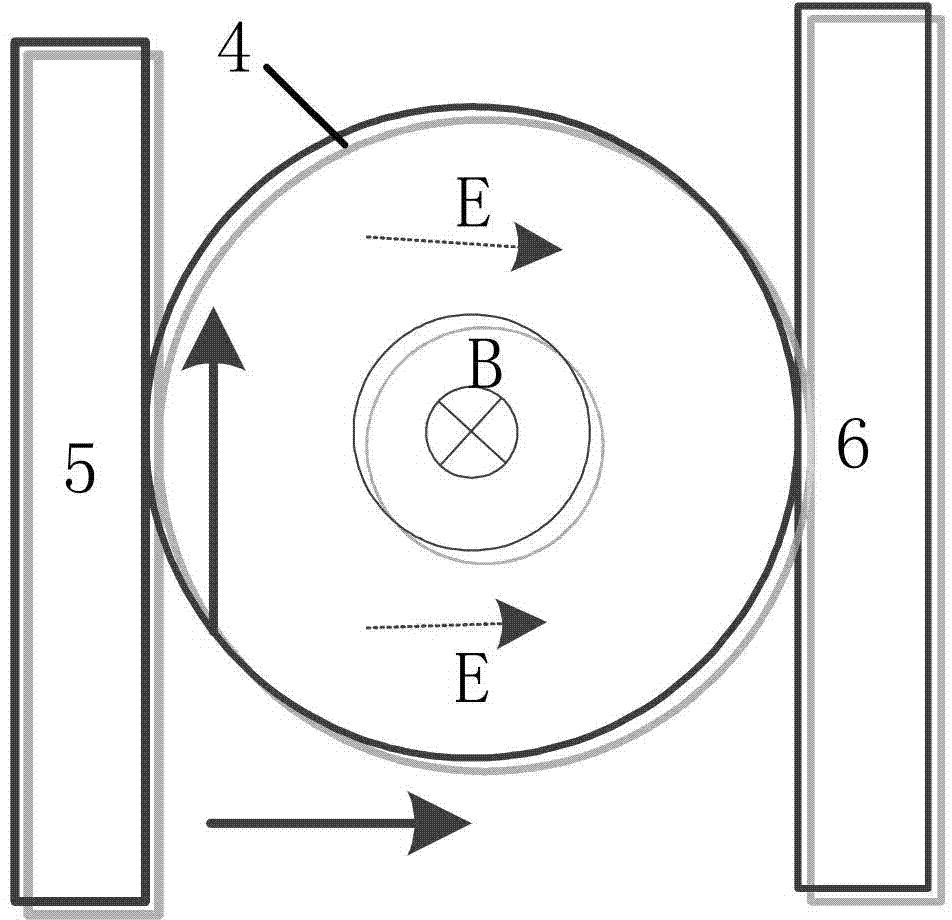

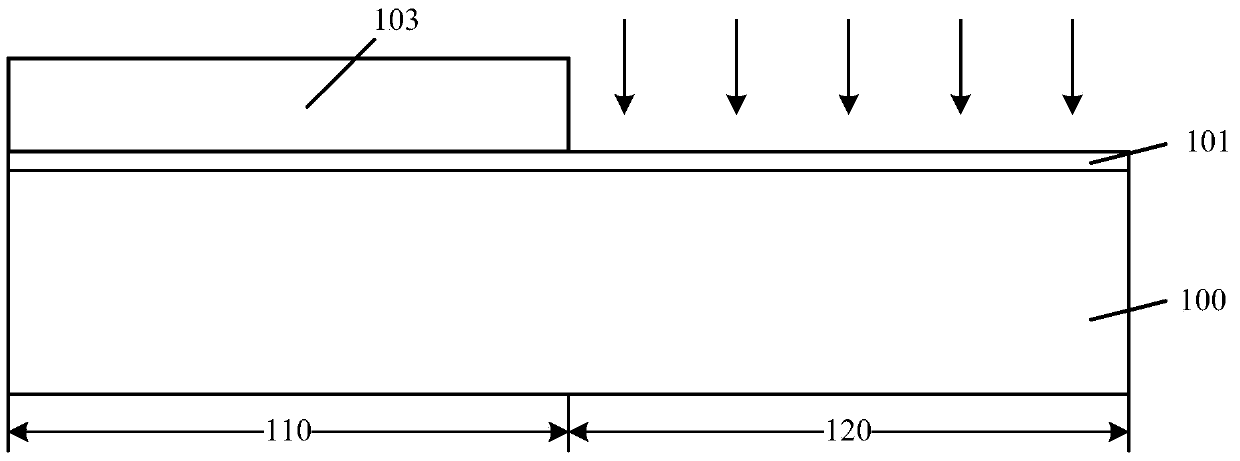

Device for relieving influence on high-speed aircraft reentry communication by space plasma

InactiveCN103796407AReduce electron concentrationEnsure safetyNuclear energy generationPlasma techniqueSurface layerFlight vehicle

The invention discloses a device for relieving the influence on high-speed aircraft reentry communication by space plasma. The device is located in a plasma layer of a high-speed aircraft. The device for relieving the influence on high-speed aircraft reentry communication by the space plasma comprises a strong magnet and an electrode pair. The strong magnet is arranged in the inner surface of the high-speed aircraft located in the same axial direction with an electromagnetic wave receiving and sending antenna, the electrode pair is composed of an anode and a cathode, the anode and the cathode are located on the portions, at the two sides of the electromagnetic wave receiving and sending antenna, of a surface layer of the high-speed aircraft. The composite environment of an electric field and a magnetic field is created on a physical layer in space around the electromagnetic wave receiving and sending antenna of the high-speed aircraft, and an electromagnetic relieving layer is formed on the plasma layer of the high-speed aircraft. The problem of transmission interruption of communication signals in the process that the high-speed aircraft reenters the atmosphere is solved and the safety and real-time performance of space communication and the stability of signal transmission are guaranteed.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Friction nanometer power generator containing electronic receiving layer and preparation method thereof

The invention relates to a friction nanometer power generator containing an electronic receiving layer, aims at improving the charge catching capability of the friction nanometer power generator and belongs to the field of new energy development and nanometer power generation. The power generator includes a positive-polarity friction part and a negative-polarity friction part which are in contact / are separated under the action of an external force; the positive-polarity friction part includes a first substrate and a first electrode which are arranged in sequence, and the first electrode can serve as a positive-polarity friction layer at the same time; the negative-polarity friction part includes a second substrate, a second electrode, an electric medium layer, the electronic receiving layer and a negative-polarity friction layer which are arranged in sequence; an alternating current signal is generated between the first electrode and the second electrode. The invention also relates toa preparation method of the friction nanometer power generator containing the electronic receiving layer.

Owner:SOUTH CHINA UNIV OF TECH

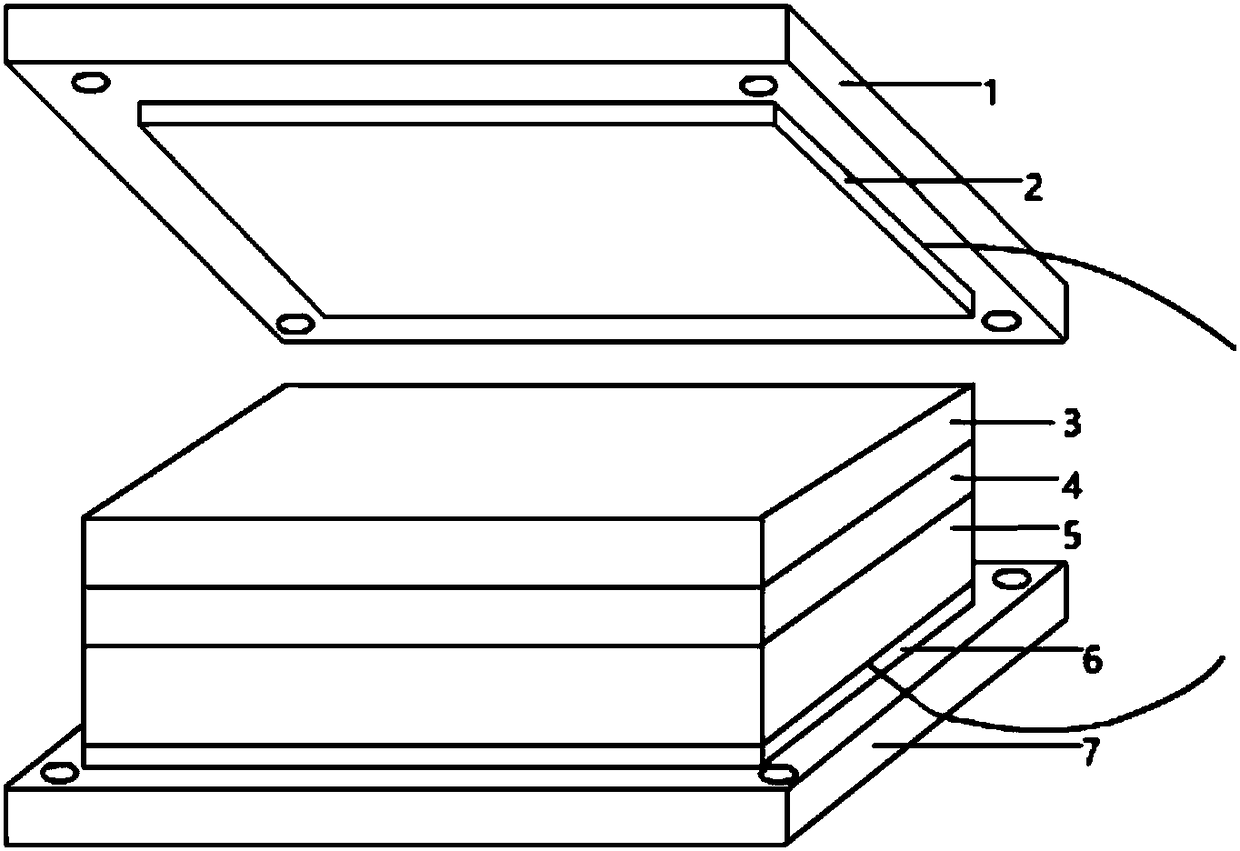

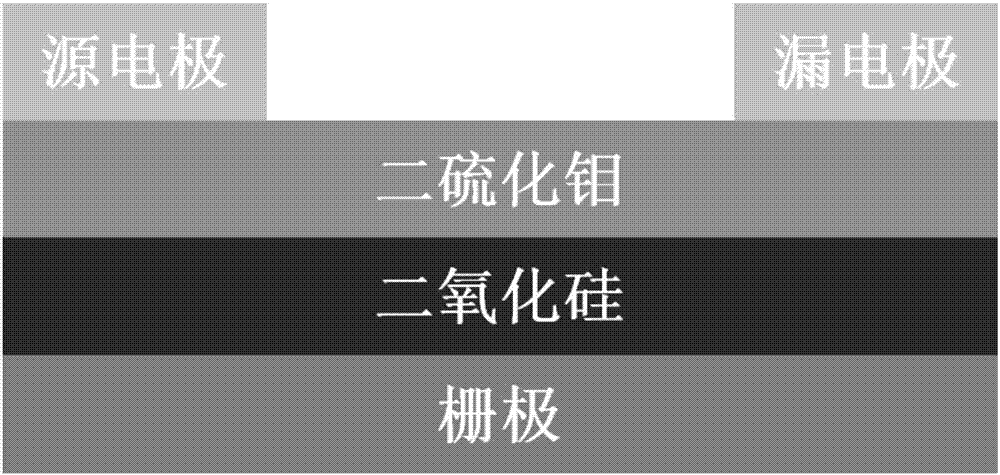

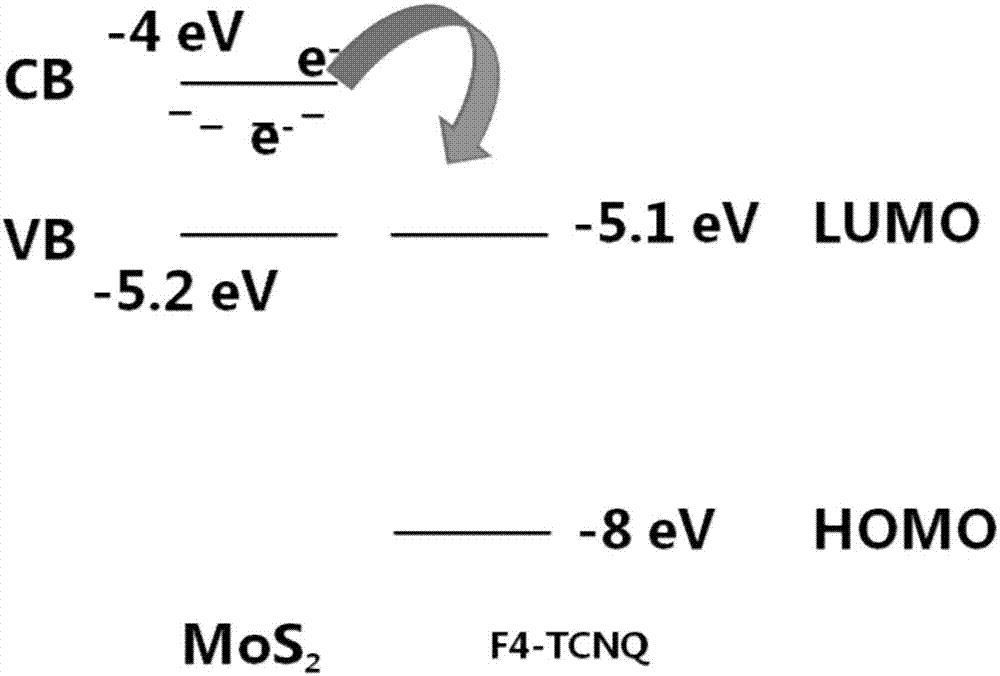

Laminated molybdenum disulfide field effect transistor, preparation method and application thereof

InactiveCN107221564AReduce the concentration of free electronsLower turn-on voltageTransistorMaterial analysis by electric/magnetic meansSulfurField-effect transistor

The invention provides a laminated molybdenum disulfide field effect transistor, a preparation method and application thereof. In the laminated molybdenum disulfide field effect transistor, the surface of laminated molybdenum disulfide is covered with an F4-TCNQ molecular layer. The molybdenum disulfide is covered with small organic molecules F4-TCNQ, the molybdenum disulfide is automatically injected into the F4-TCNQ through sulfur vacancy self-doped electrons, the electron concentration in the molybdenum disulfide is reduced, and the purpose of reducing the threshold voltage of the molybdenum disulfide field effect transistor is reached. The function of an NH3 sensor under low gate voltage can be realized by using the molybdenum disulfide field effect transistor provided by the invention.

Owner:THE NAT CENT FOR NANOSCI & TECH NCNST OF CHINA

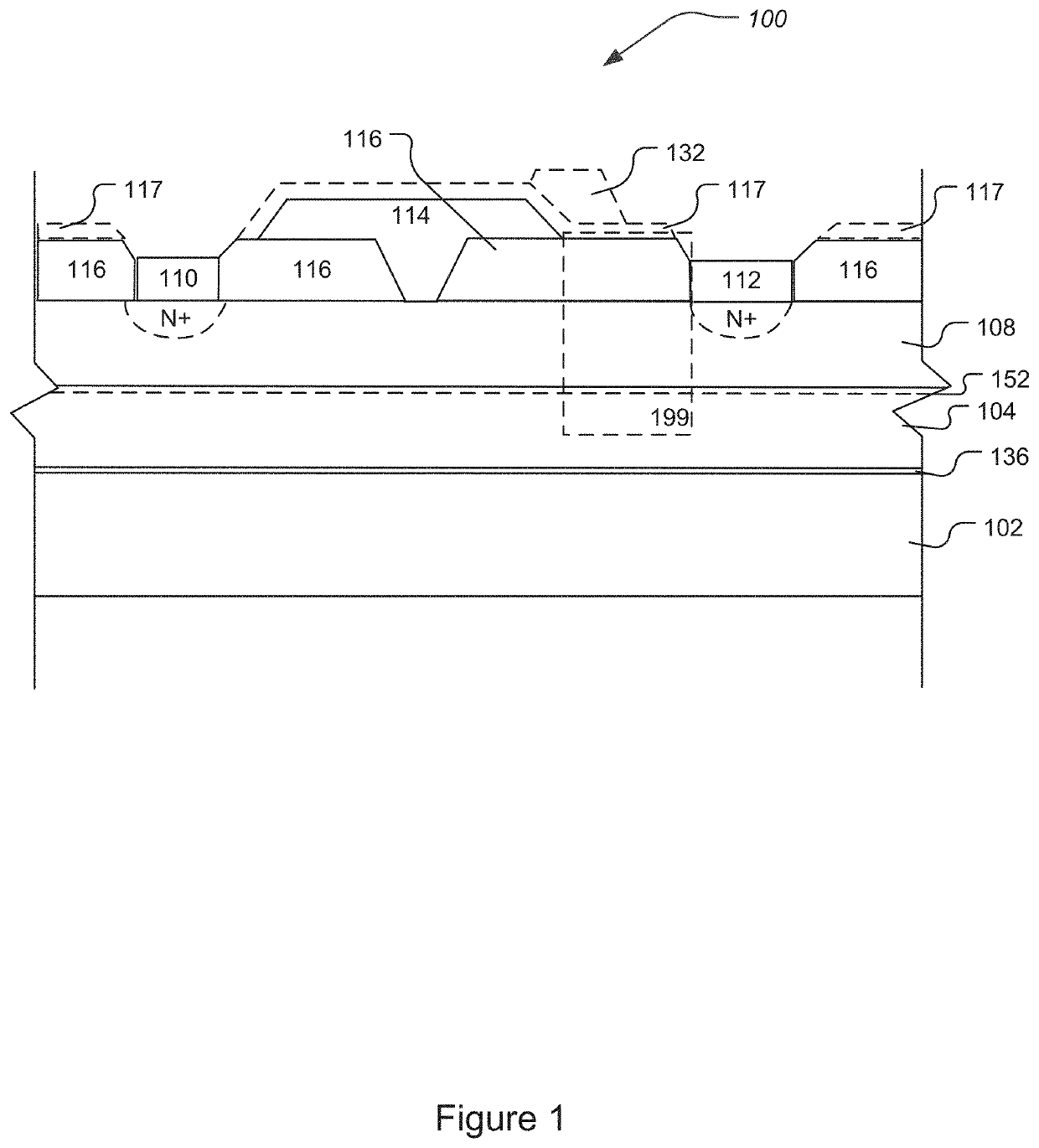

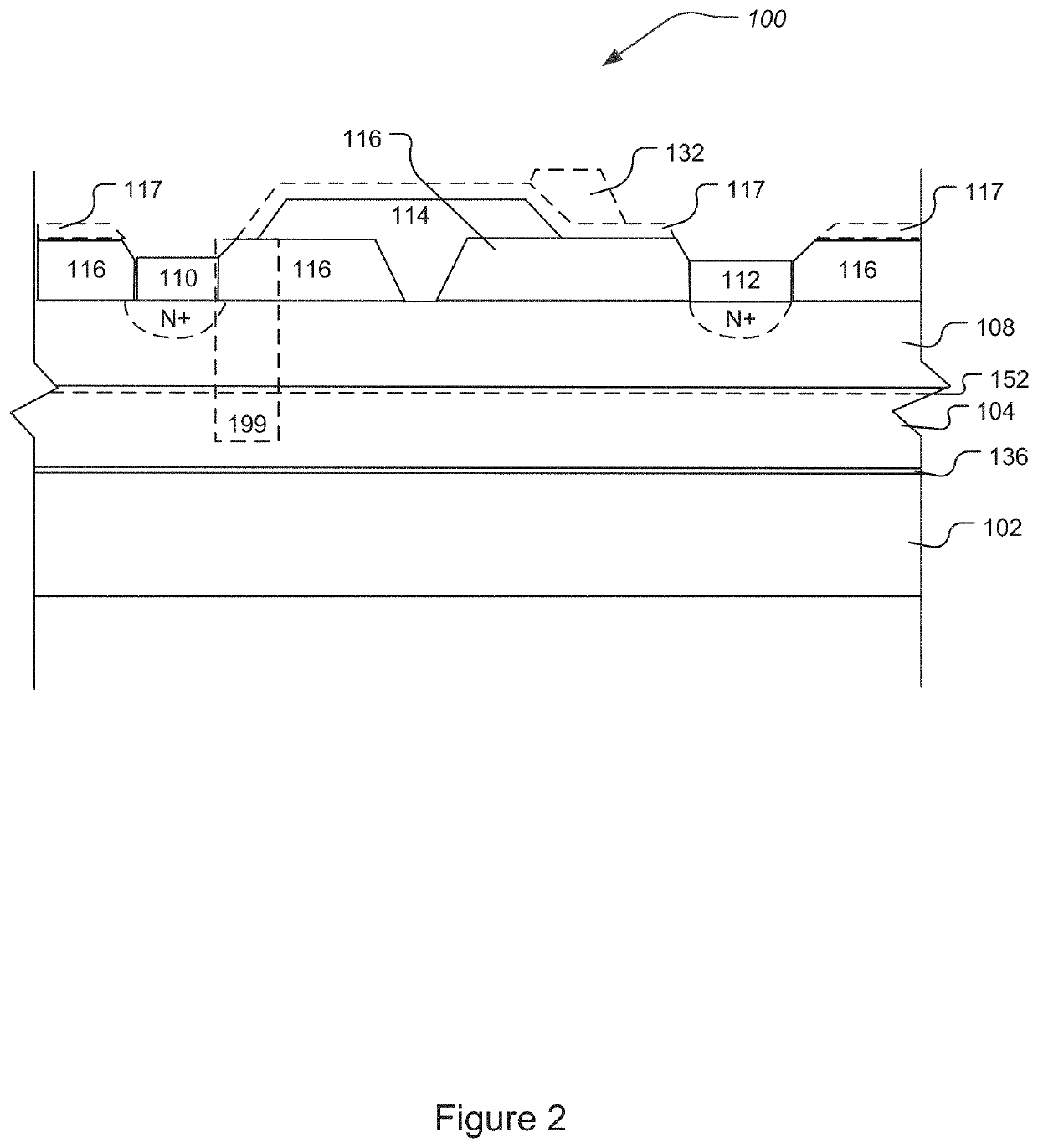

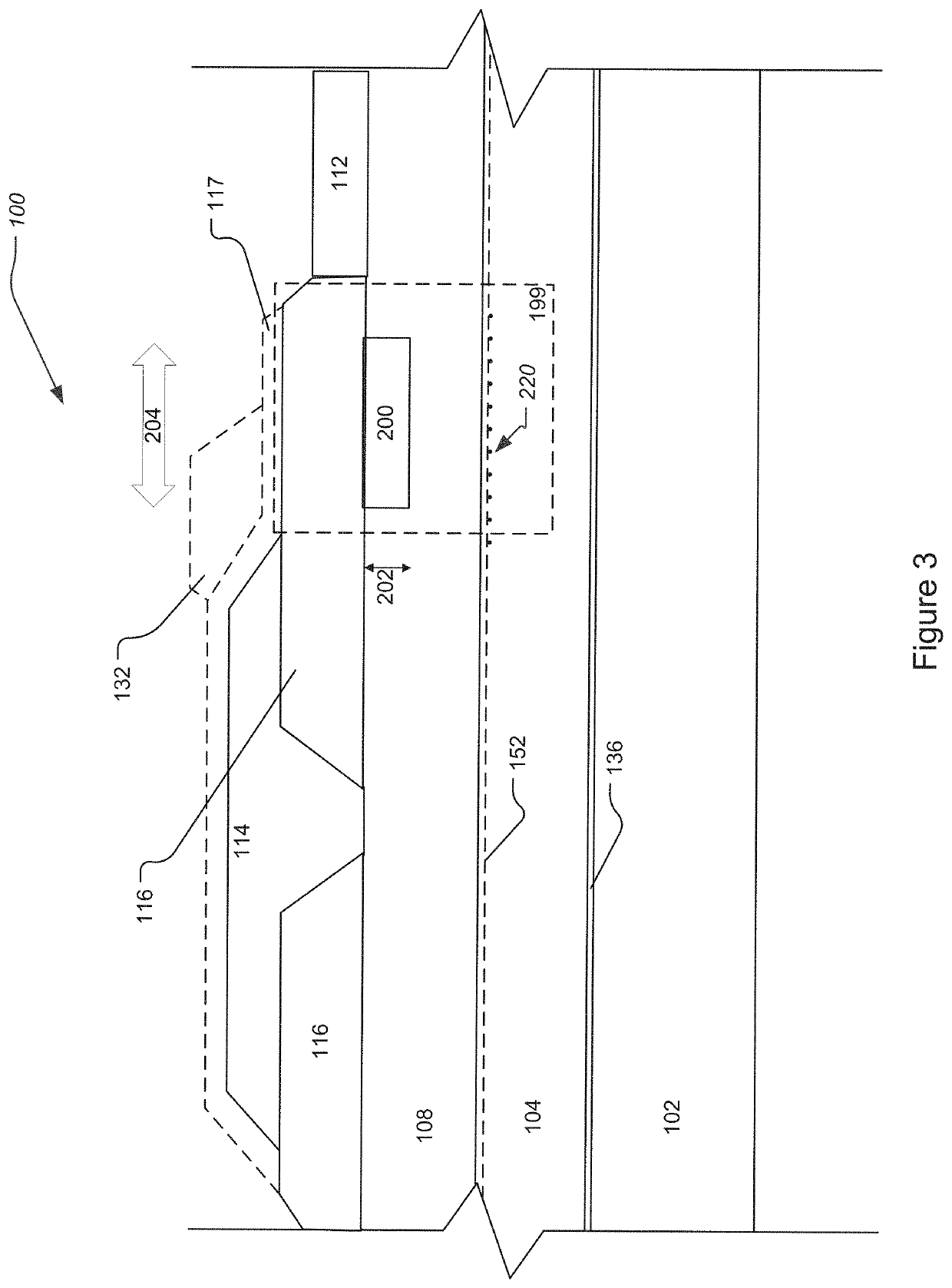

Structures for Reducing Electron Concentration and Process for Reducing Electron Concentration

ActiveUS20200303533A1Increase power gainReduce electron concentrationSemiconductor devicesCapacitanceChemical physics

A device includes a substrate; a buffer layer on the substrate; a barrier layer on the buffer layer, a source electrically coupled to the barrier layer; a gate electrically coupled to the barrier layer; and a drain electrically coupled to the barrier layer. The device further includes an electron concentration reduction structure arranged with at least one of the following: in the barrier layer and on the barrier layer. The electron concentration reduction structure is configured to at least one of the following: reduce electron concentration around the gate, reduce electron concentration around an edge of the gate, reduce electron concentration, increase power gain, increase efficiency, decouple the gate from the drain, decouple the gate from the source, and reduce capacitance.

Owner:WOLFSPEED INC

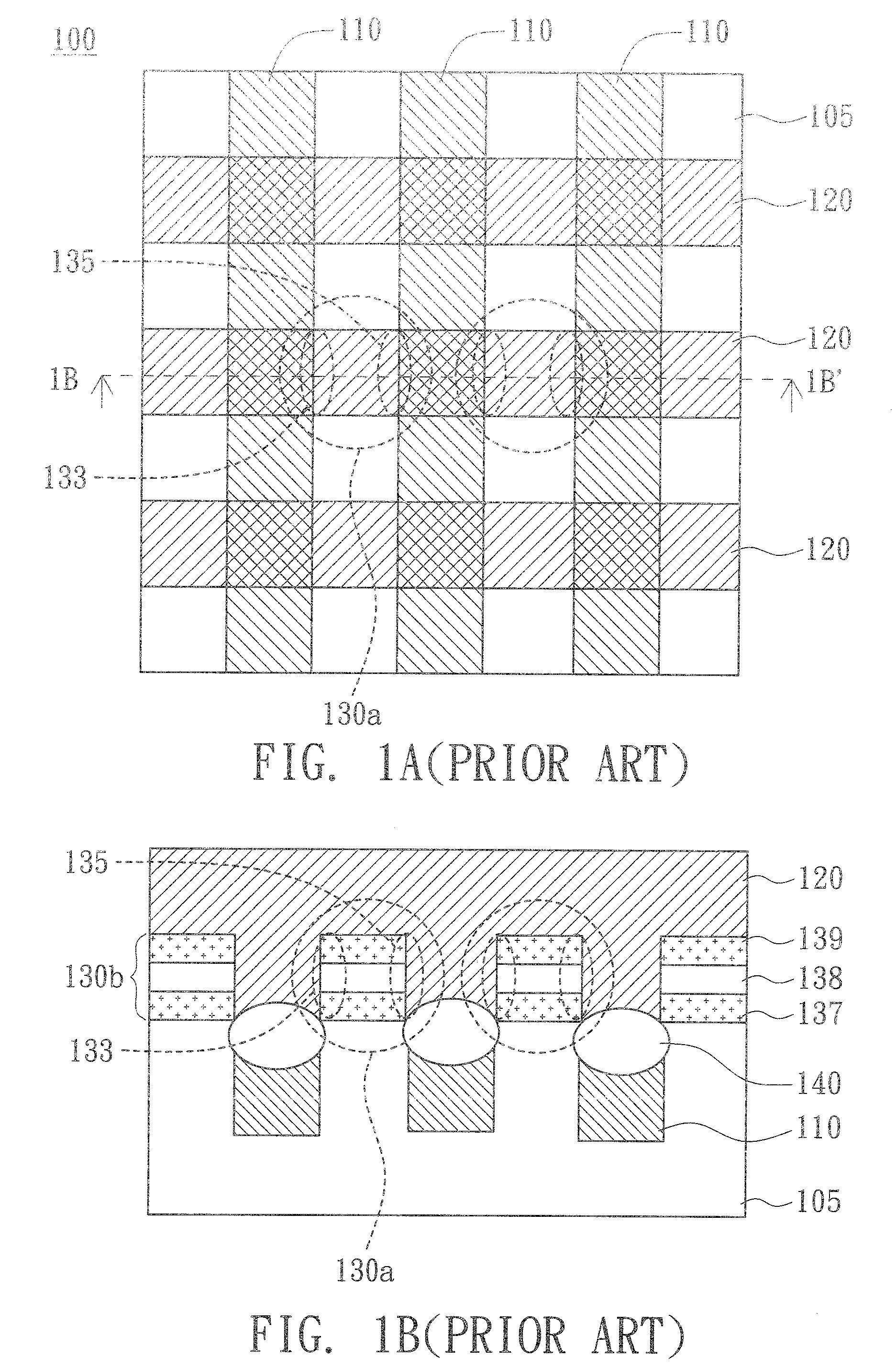

Memory and manufacturing method thereof

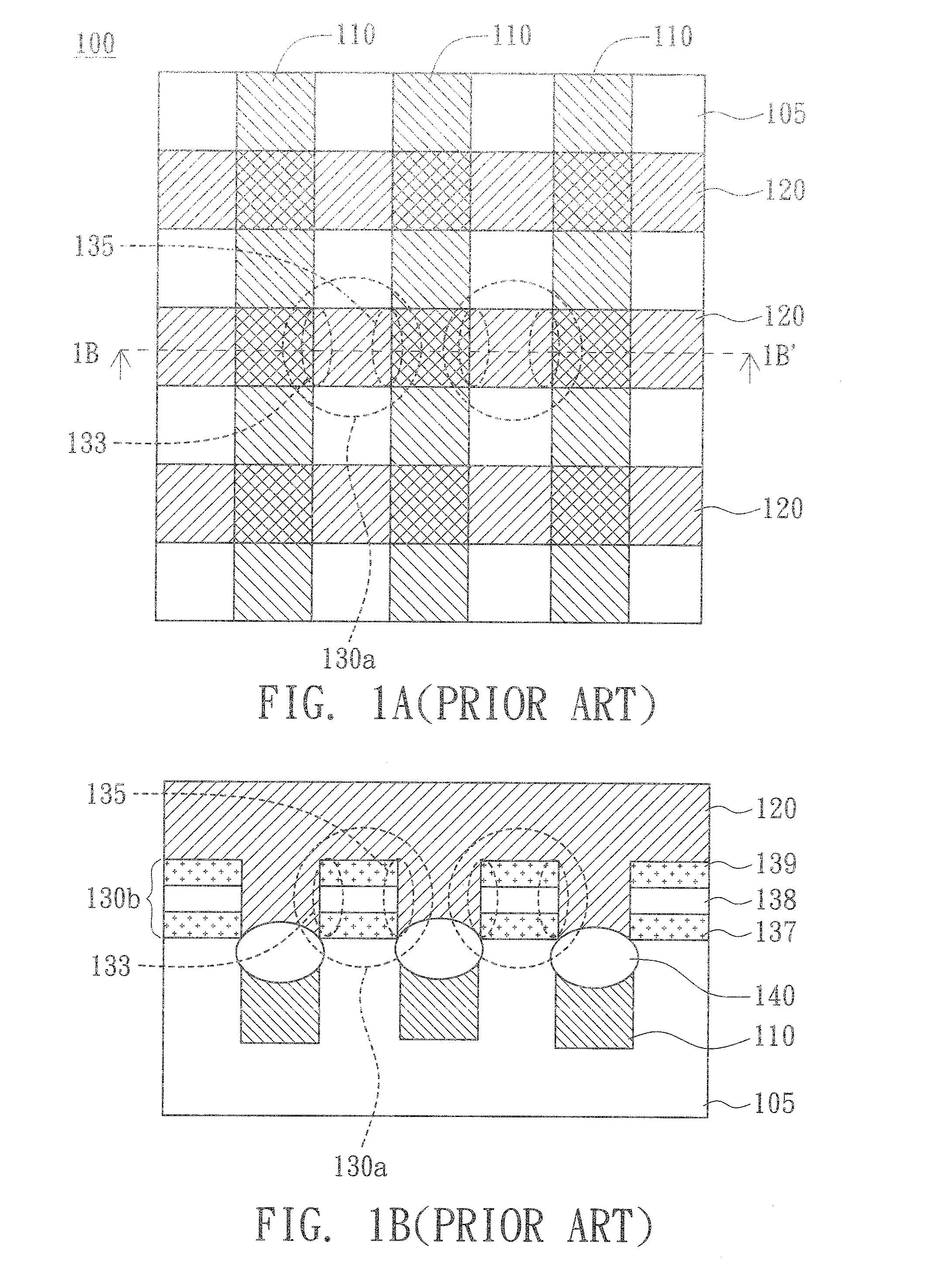

ActiveUS7608504B2Large electron storage spaceIncrease concentrationSolid-state devicesSemiconductor/solid-state device manufacturingBit lineComputer science

A memory is provided. The memory includes a substrate, a number of parallel bit lines, a number of parallel word lines and at least a oxide-nitride-oxide (ONO) structure. The bit lines are disposed in the substrate. The word lines are disposed on the substrate. The word lines are crossed with but not perpendicular to the bit lines. The ONO structure is disposed between the word lines and the substrate.

Owner:MACRONIX INT CO LTD

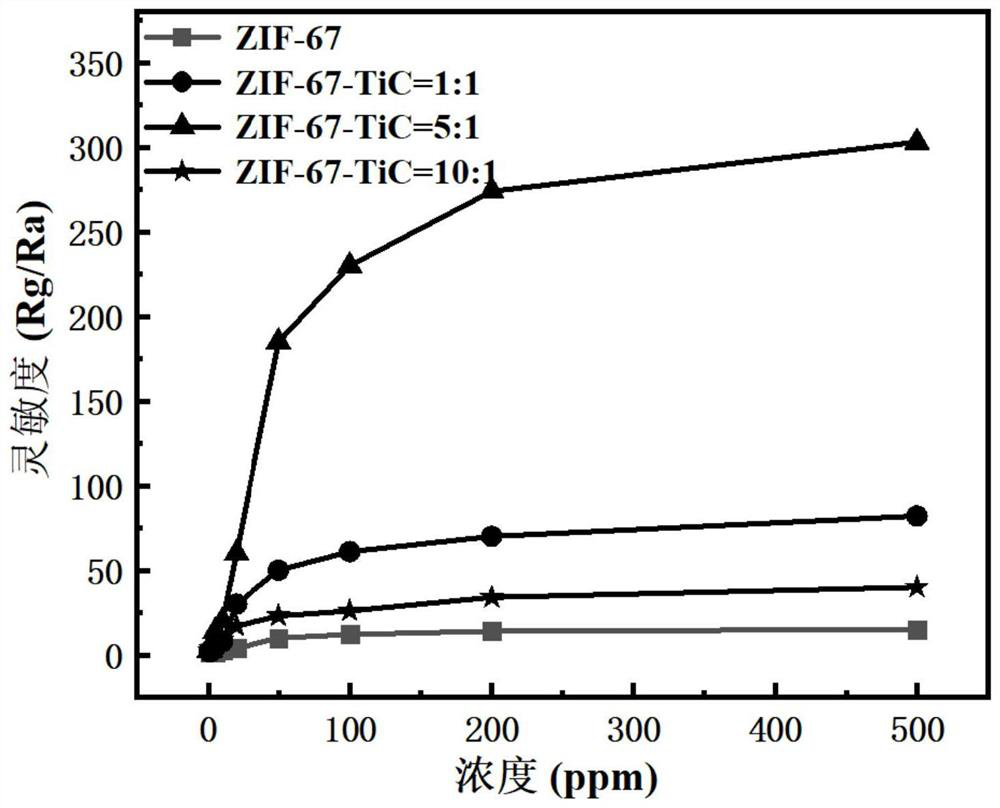

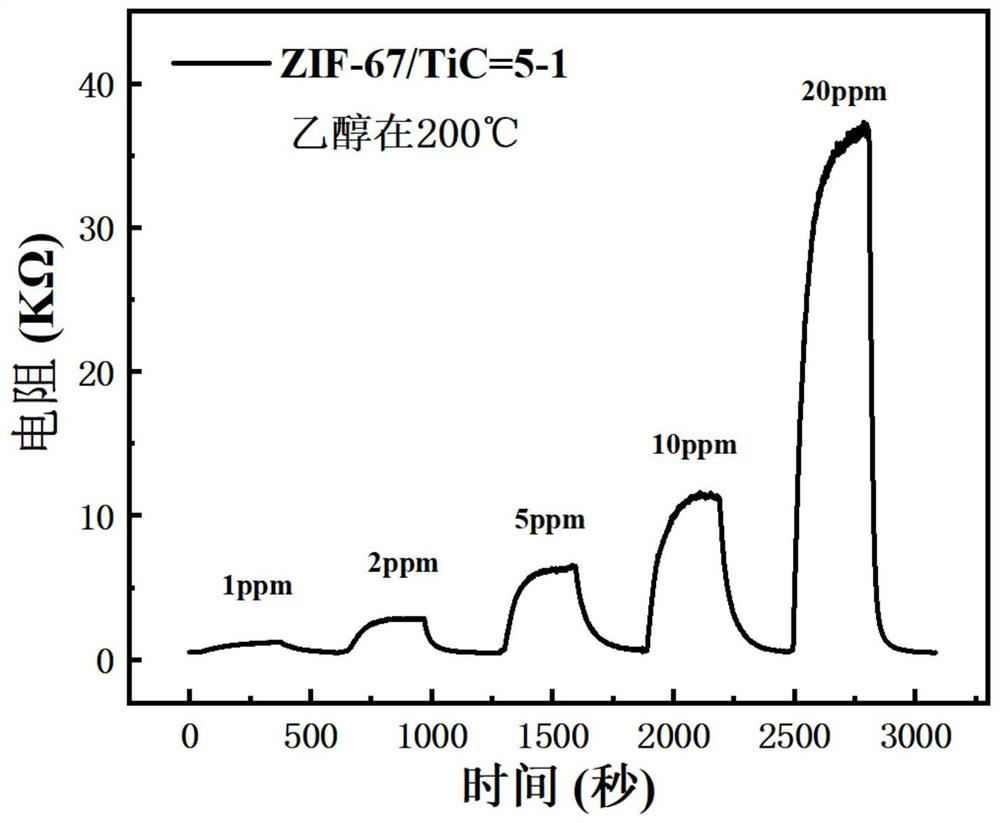

Composite gas-sensitive material and preparation method thereof, and ethanol gas sensor and preparation method thereof

PendingCN113176305ALarge specific surface areaGood gas adsorption sitesMaterial resistanceAir quality improvementCobalt(II,III) oxideMetal-organic framework

According to the composite gas-sensitive material and the preparation method thereof, and the ethanol gas sensor and the preparation method thereof disclosed by the invention, a trititanium carbide material and a cobaltosic oxide material derived from a metal organic framework are combined and applied to the gas sensor; the interdigital electrode is coated with a cobaltosic oxide-trititanium carbide composite material coating film derived from a metal organic framework, so that the gas-sensitive response of traditional cobaltosic oxide to ethanol is greatly enhanced, the selectivity to ethanol is improved, the sensitivity is high, and the highest sensitivity to 50 ppm ethanol can reach 185. Compared with a traditional cobalt oxide gas sensor, the sensitivity of the cobalt oxide gas sensor is improved by 15 times, even if the gas concentration is 1 ppm, detection can be conducted, the response speed is high, and good repeatability and stability are achieved.

Owner:XI AN JIAOTONG UNIV

Semiconductor structure and formation method thereof

ActiveCN106449404AImprove performanceIncrease hole concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureVoltage regulation

The invention discloses a semiconductor structure and a formation method thereof. The formation method of the semiconductor structure comprises the following steps: forming semiconductor layers at sidewalls and top surfaces which are exposed out of fin portions, wherein the semiconductor layers are doped with P-type ions; doping threshold-voltage adjustment ions in the fin portions; and doping the P-type ions in the semiconductor layers, and performing an annealing process after the threshold-voltage adjustment ions are doped in the fin portions. When a P-type fin field effect transistor is formed through the formed semiconductor structure, the negative bias temperature instability of the P-type fin field effect transistor is inhibited, and the performance is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

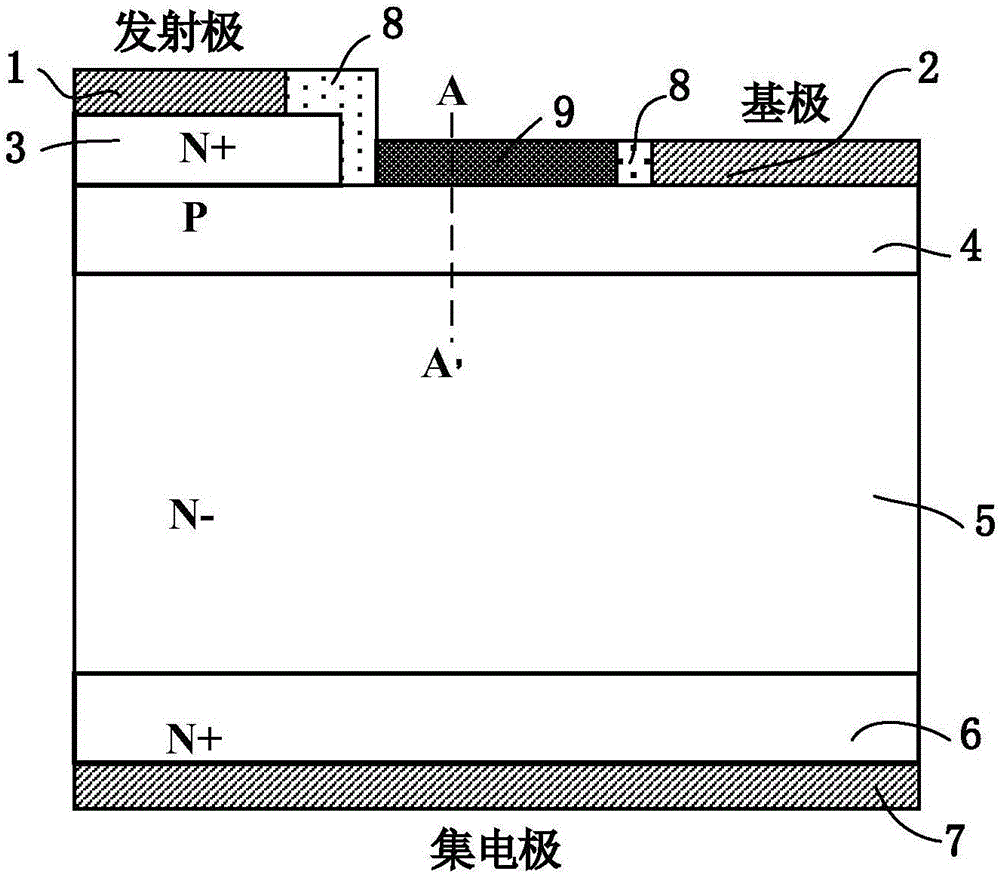

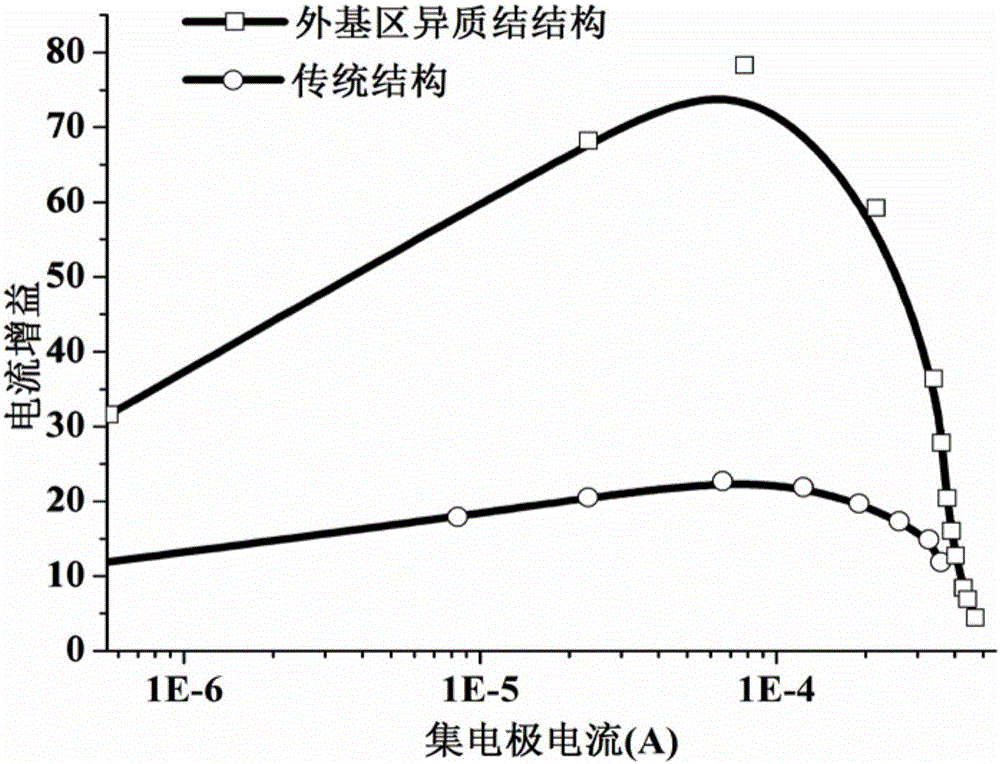

Silicon carbide bipolar junction transistor

ActiveCN105977287AReduce electron concentrationReduce recombination rateSemiconductor devicesBipolar junction transistorPower semiconductor device

The invention belongs to the technical field of a high-power semiconductor device, and relates to a silicon carbide bipolar junction transistor. The silicon carbide bipolar junction transistor comprises a collector electrode, an N+ substrate, an N- collector region and a P-type base region, which are stacked up in sequence from the bottom up. One end of the upper surface of the P-type base region is provided with a base electrode, and the other end thereof is provided with an N+ emitter region; the upper surface of the N+ emitter region has an emitter electrode; the upper surface of the P-type base region between the base electrode and the N+ emitter region is provided with an AlN layer; the AlN layer is isolated with the base electrode and the N+ emitter region through heavily-doped layers respectively; and one heavily-doped layer extends to the side away from the base electrode along the upper surface of the N+ emitter region, and is connected with the emitter electrode. The beneficial effects are that, compared with traditional technology, the silicon carbide bipolar junction transistor greatly reduces process complexity, improves qualify rate and reliability of the device and meanwhile, improves current gain of the SiC BJT device.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

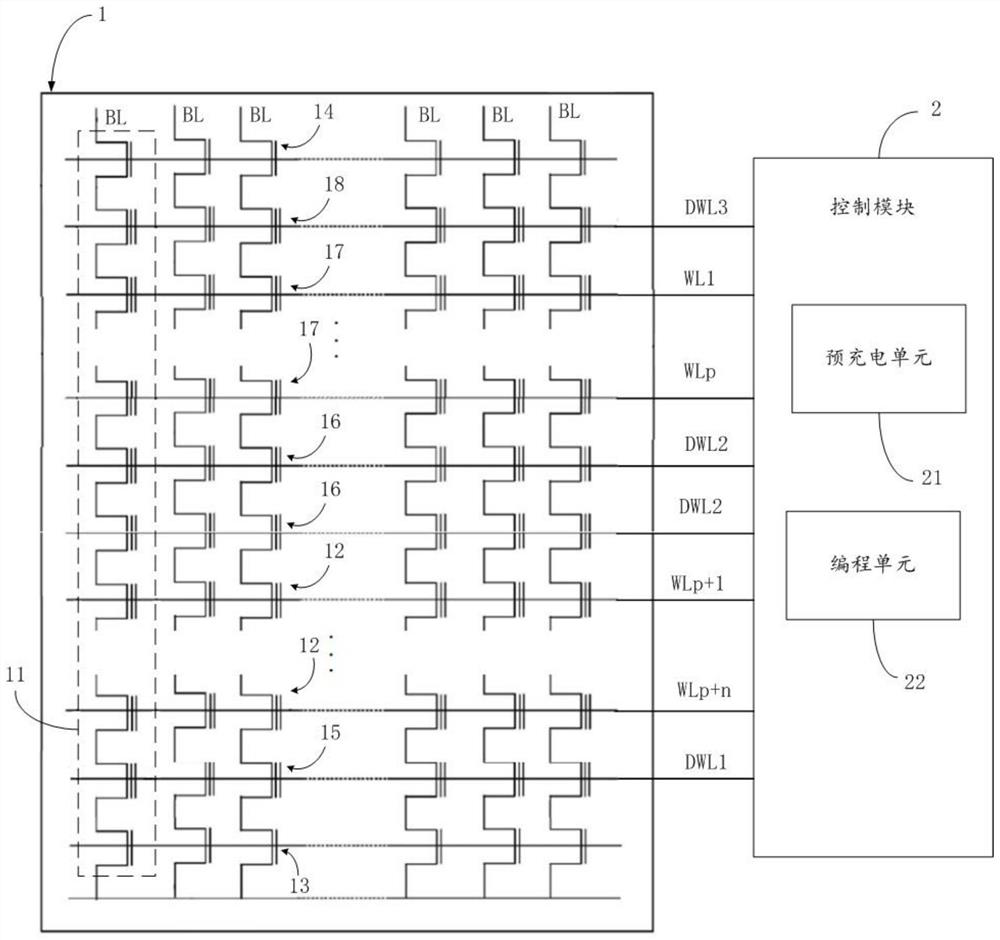

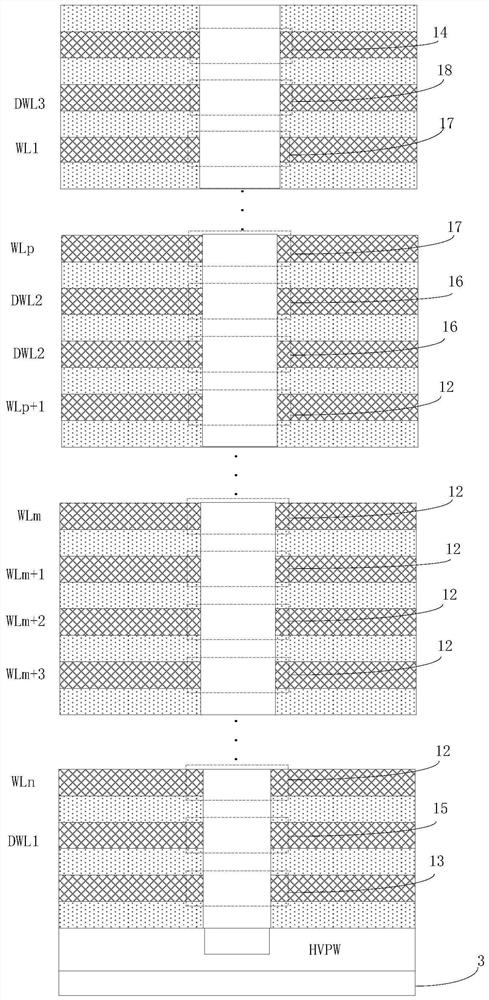

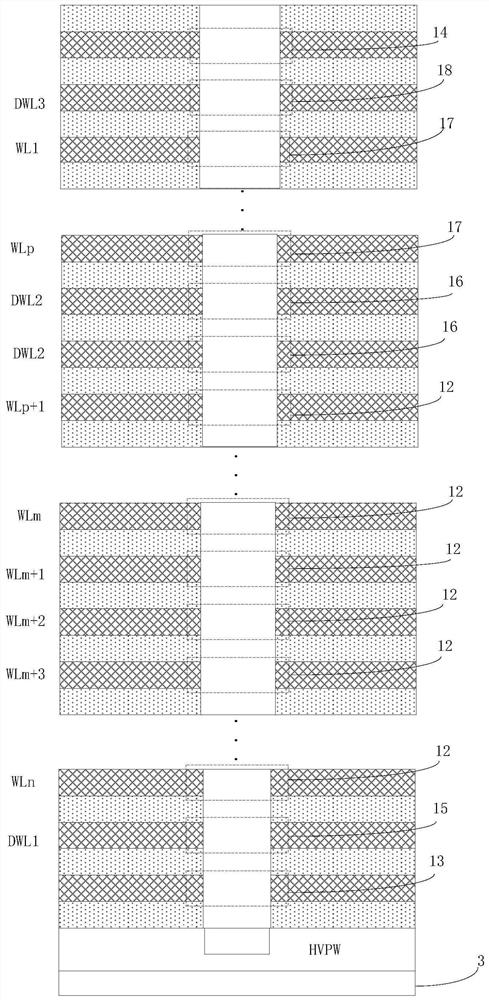

Programming method for semiconductor device and semiconductor device

ActiveCN112614533AImprove programming interference problemRaise the boost potentialRead-only memoriesDigital storageComputer hardwareDevice material

The invention discloses a programming method for a semiconductor device and a semiconductor device. The semiconductor device comprises a storage string; the storage string comprises a plurality of first storage units and first dummy units which are sequentially stacked; each first storage unit is correspondingly connected with a word line; and a grid electrode of each first dummy unit is connected with the corresponding first dummy word line. The method comprises the steps that: in a pre-charging stage, pre-charging voltage is input into a word line corresponding to a programmed storage unit in the multiple first storage units, wherein the programmed storage unit is a storage unit between a to-be-programmed storage unit in the multiple first storage units and the first dummy unit; and in a programming stage, a programming voltage is input to a word line corresponding to the to-be-programmed storage unit. According to the programming method for the semiconductor device and the semiconductor device of the embodiment of the invention, programming interference can be reduced, and the boost potential is improved.

Owner:YANGTZE MEMORY TECH CO LTD

Memory and manufacturing method thereof

ActiveUS20080054322A1Large electron storage spaceIncrease concentrationTransistorSolid-state devicesBit lineComputer science

A memory is provided. The memory includes a substrate, a number of parallel bit lines, a number of parallel word lines and at least a oxide-nitride-oxide (ONO) structure. The bit lines are disposed in the substrate. The word lines are disposed on the substrate. The word lines are crossed with but not perpendicular to the bit lines. The ONO structure is disposed between the word lines and the substrate.

Owner:MACRONIX INT CO LTD

Programming method for semiconductor device and semiconductor device

ActiveCN112614533BImprove programming interference problemRaise the boost potentialRead-only memoriesDigital storageComputer hardwareComputer architecture

The invention discloses a programming method for a semiconductor device and the semiconductor device. The semiconductor device includes a memory string, the memory string includes a plurality of first memory cells and first dummy cells stacked in sequence, each of the first memory cells is correspondingly connected to a word line, and the first dummy cells The gate of the first memory cell is connected to the first dummy word line; the method includes: in the precharge phase, inputting a precharge voltage to the word line corresponding to the programmed memory cell in the plurality of first memory cells, the programmed memory cell The unit is a storage unit between the storage unit to be programmed and the first dummy unit among the plurality of first storage units; in a programming phase, a programming voltage is input to a word line corresponding to the storage unit to be programmed. The embodiment of the present invention can reduce program disturb and increase boost potential.

Owner:YANGTZE MEMORY TECH CO LTD

Field effect transistor

ActiveUS20150303312A1Reduce electron concentrationImprove mobilityTransistorSemiconductor/solid-state device manufacturingElectrical conductorIndium

An insulating film is provided over one surface of a first semiconductor layer including a first oxide semiconductor including indium as a main component, and a second semiconductor layer including an i-type second oxide semiconductor is provided in contact with the other surface. The energy difference between a vacuum level and a Fermi level in the second oxide semiconductor is larger than that in the first oxide semiconductor. In the first semiconductor layer, a region in the vicinity of the junction surface with the second oxide semiconductor which satisfies the above condition is a region having an extremely low carrier concentration (a quasi-i-type region). By using the region as a channel, the off-state current can be reduced. Further, a drain current of the FET flows through the first oxide semiconductor having a high mobility; accordingly, a large amount of current can be extracted.

Owner:SEMICON ENERGY LAB CO LTD

A medical metal material with a modified film with photothermal properties on its surface, its preparation method and application

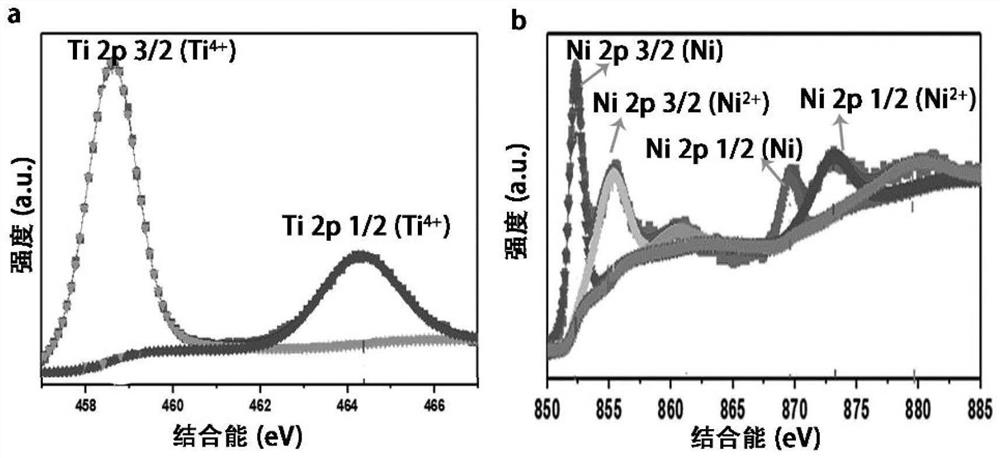

ActiveCN114146216BLong-term maintenanceExcellent photothermal performanceSurgeryPharmaceutical delivery mechanismMetallic materialsTitanium oxide

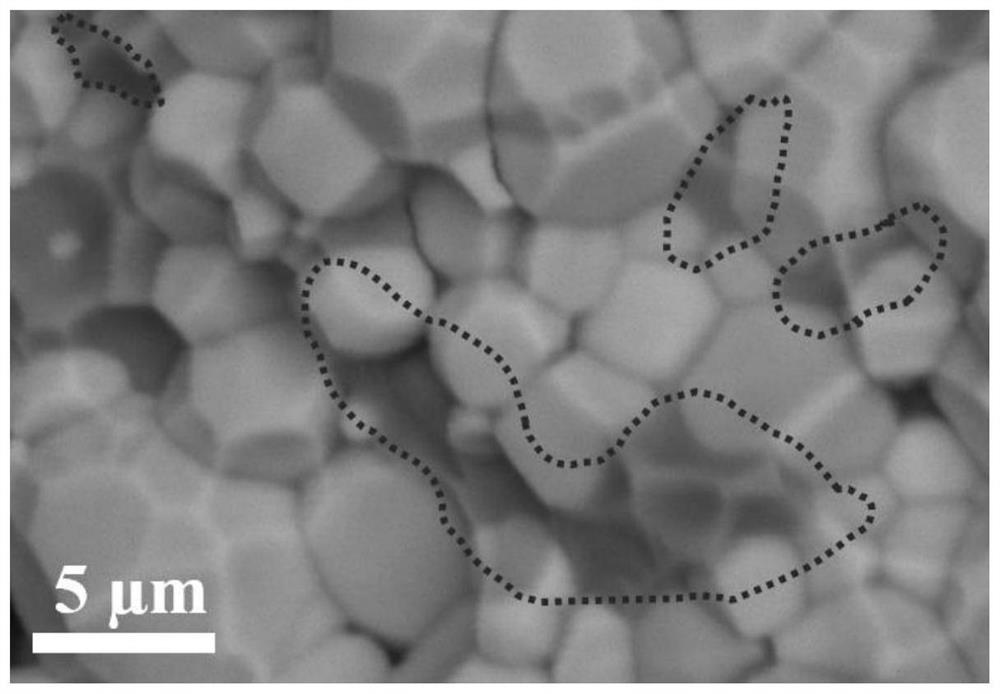

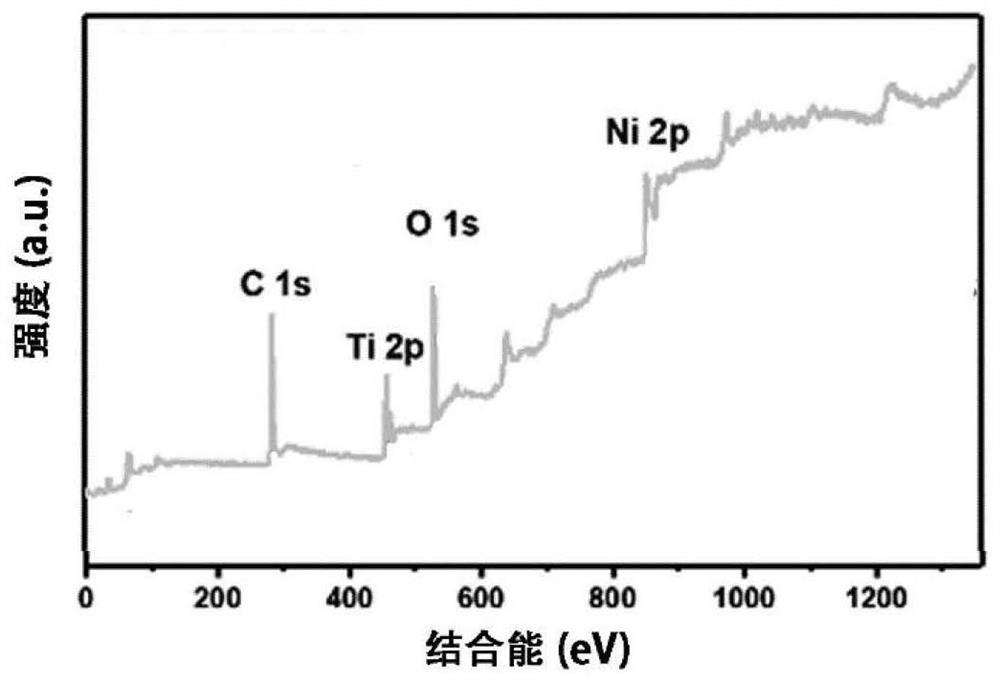

The invention relates to a medical metal material with a modified film with photothermal properties on the surface, a preparation method and application thereof. The modified film is nickel-titanium oxide Ti inlaid with nano-nickel m Ni n O 2m+n . The nano-nickel is a simple substance, the shape is spherical, and the radius is 2-20 nm; the density of the nickel nanoparticles is 5-30 per square micron. The nickel-titanium oxide has a sheet-like structure, the length and width of the sheet layer are between 0.5-2 μm, and the thickness is 10-40 nm. In the preparation method, the nickel-titanium layered double hydroxide is first generated, and then reduced by heating to obtain a nickel-titanium oxide thin film inlaid with elemental nickel. The cost of the nano-nickel constructed by the invention is obviously reduced, and at the same time, it effectively solves the problem that the non-precious metal nano-metal particles are easily oxidized and the photothermal effect cannot be maintained for a long time; it also has good osteogenic properties, improves the biological activity of medical metals, and is suitable for Surface modification of hard tissue implant devices.

Owner:HEBEI UNIV OF TECH

Oxide semiconductor thin film transistor

ActiveCN102723367BImprove stabilityReduce electron concentrationTransistorCharge carrierOhmic contact

The invention provides an oxide semiconductor thin film transistor which comprises a substrate, a gate electrode, an insulation dielectric layer and an oxide semiconductor channel layer, wherein the gate electrode, the insulation dielectric layer and the oxide semiconductor channel layer are sequentially arranged on the substrate, the insulation dielectric layer enables the gate electrode and the oxide semiconductor channel layer to be insulted, a drain electrode and a source electrode are arranged on the upper surface of the oxide semiconductor channel layer, a gap between the drain electrode and the source electrode is d1, the length of an overlapping region of the source electrode and the gate electrode in the horizontal direction is d2, contact between the source electrode and the oxide semiconductor channel layer is schottky contact, and the contact between the drain electrode and the oxide semiconductor channel layer is ohmic contact. The short-channel effect on the oxide semiconductor thin film transistor is small due to new geometrical characteristics and operating principles, and the oxide semiconductor thin film transistor is favorable for improvement of consistency.

Owner:CHENGDU VISTAR OPTEOLECTRONICS CO LTD

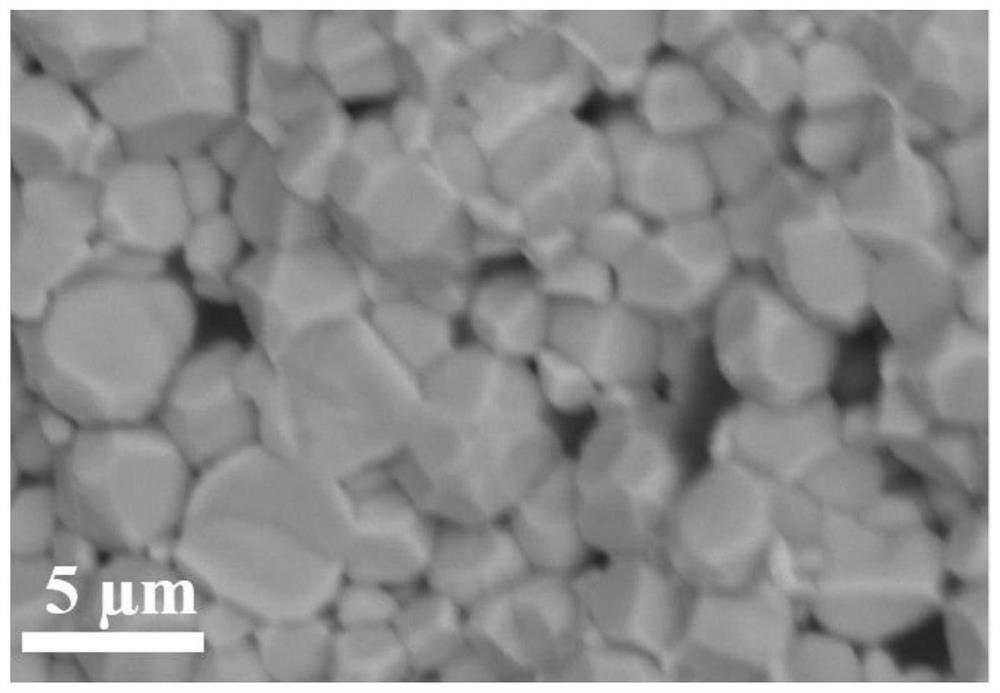

Garnet type solid electrolyte capable of effectively inhibiting lithium dendrites and preparation method of garnet type solid electrolyte

PendingCN114243004AImprove stabilityExtended service lifeCell electrodesFinal product manufacturePhysical chemistryBall mill

The invention discloses a garnet type solid electrolyte capable of effectively inhibiting lithium dendrites and a preparation method thereof, and the preparation method comprises the following steps: carrying out ball milling on a lithium source, a lanthanum source, a zirconium source and a tantalum source according to a chemical formula Li7La3Zr1. 5Ta0. 5O12-xM to obtain raw powder; 2.5% < = x < = 25%; pre-sintering the raw powder to obtain primarily-sintered powder; adding a low-electron conductive substance M into the primarily sintered powder, and uniformly grinding to obtain mother powder; pressing the mother powder into a plain blank sheet; and sintering the blank sheet to obtain the garnet type solid electrolyte capable of effectively inhibiting the lithium dendrites. The preparation method adopts a traditional simple solid-phase sintering preparation process, is completed through a two-step sintering method, has the advantages of being simple in process, easy to operate, high in repeatability, low in production cost and the like, and is suitable for practical application and large-scale production.

Owner:XI AN JIAOTONG UNIV

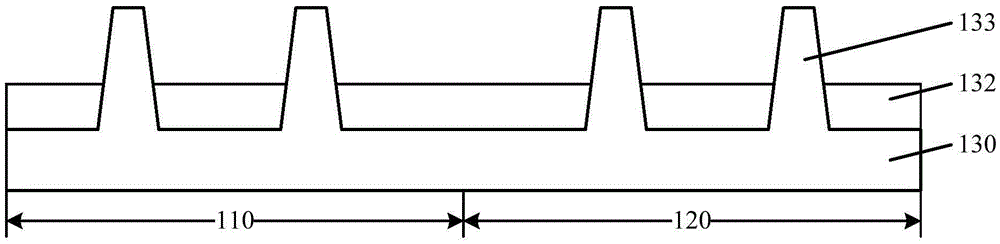

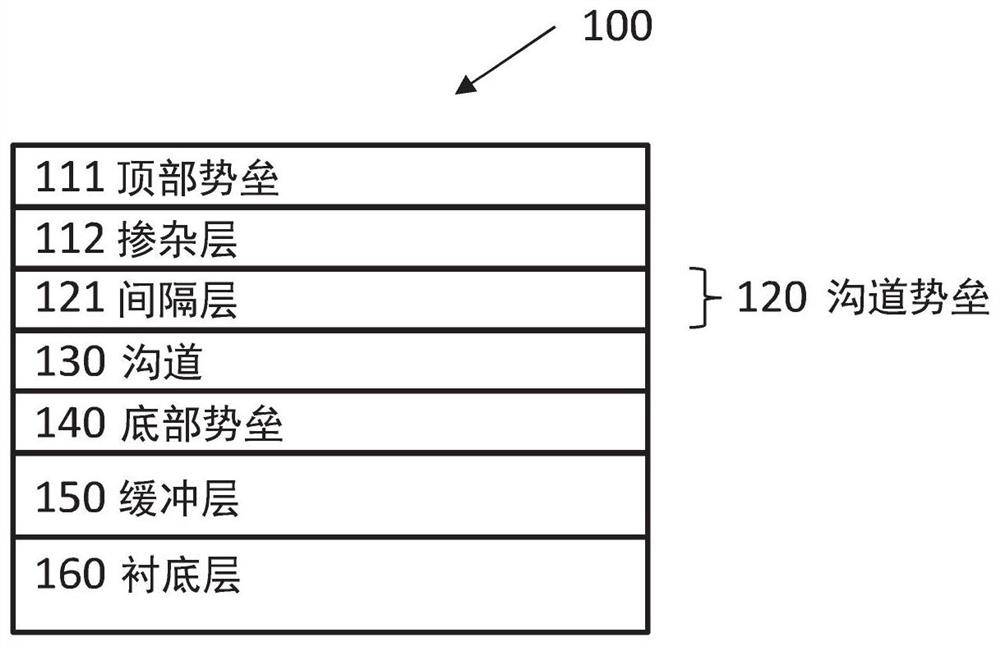

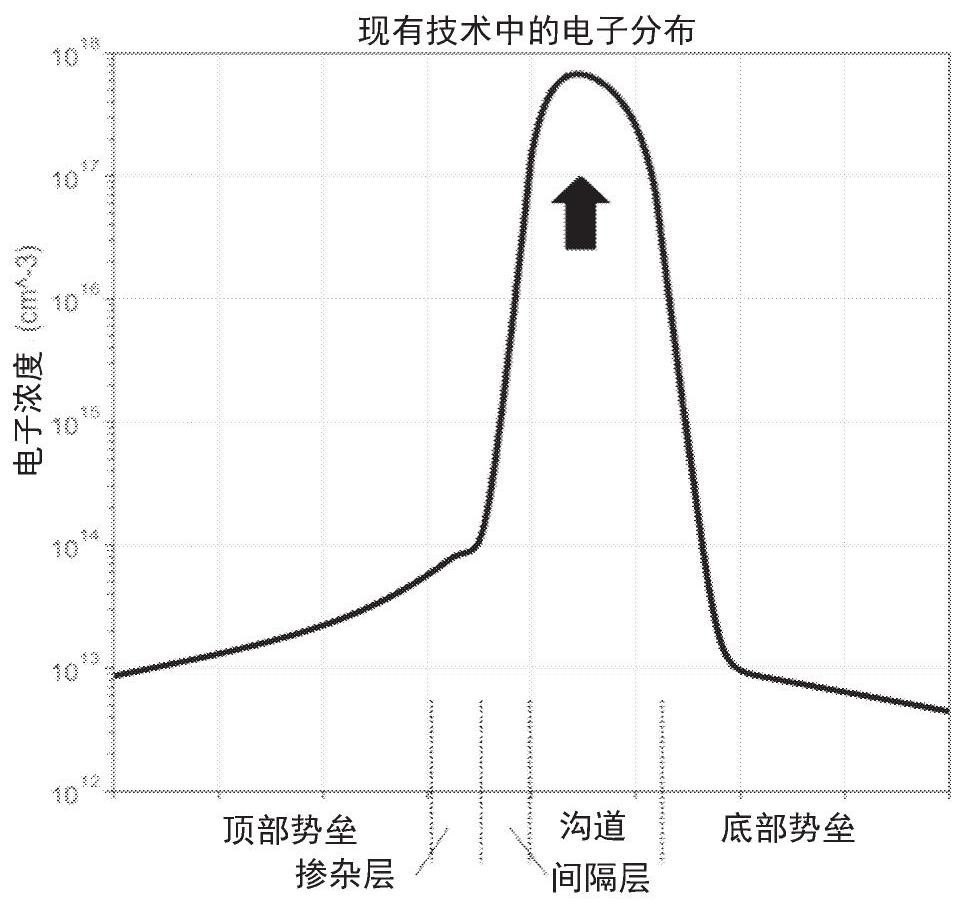

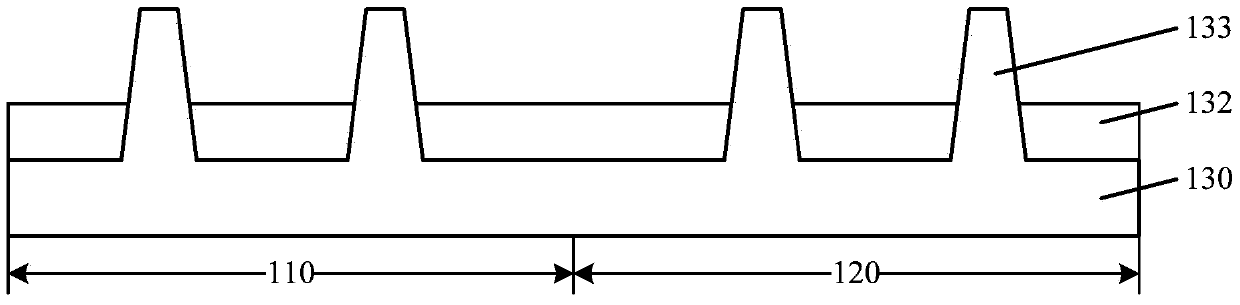

Semiconductor stack for hall effect device

ActiveCN113270541AHigh electron mobilityImprove noise levelGalvano-magnetic device detailsGalvano-magnetic hall-effect devicesConduction bandCondensed matter physics

The invention discloses a semiconductor stack for hall effect device. The semiconductor stack (100) for a Hall effect device comprises: a bottom barrier (140) comprising AlxGa1-xAs, a channel (130) comprising InyGa1-yAs, on the bottom barrier (140), a channel barrier (120) with a thickness which is at least 2 nm and which is smaller than or equal to 15 nm, and which at least comprises a first layer (121) comprising AlzGa1-zAs with 0.1 <= z <= 0.22, wherein the first layer (121) has a thickness of at least 2 nm, wherein a conduction band edge of the bottom barrier (140) and the first layer (121) is higher than a conduction band edge of the channel (130), a doping layer (112) comprising a composition of Al, Ga and As and doped with n-type material, and a top barrier (111) comprising a composition of Al, Ga and As.

Owner:メレクシステクノロジーズソシエテアノニム

Medical metal material with modified film with photo-thermal characteristic on surface as well as preparation method and application of medical metal material

ActiveCN114146216ALong-term maintenanceExcellent photothermal performanceSurgeryPharmaceutical delivery mechanismMetallic materialsMetal particle

The invention relates to a medical metal material with a modified film with photo-thermal characteristics on the surface and a preparation method and application of the medical metal material. And the modified film is a nickel-titanium oxide TimNinO2m + n embedded with nano nickel. The nano nickel is a simple substance and is spherical, and the radius of the nano nickel is 2-20 nm; and the density of the nickel nanoparticles is 5-30 per square micron. The nickel-titanium oxide is of a sheet structure, the length and the width of a sheet layer are 0.5-2 microns, and the thickness of the sheet layer is 10-40 nm. In the preparation method, the nickel-titanium layered double hydroxide is firstly generated, and then the nickel-titanium oxide thin film inlaid with the elemental nickel is obtained through heating reduction. The cost of the constructed nano nickel is obviously reduced, and meanwhile the problems that non-noble metal nano metal particles are prone to being oxidized, and the photo-thermal effect cannot be kept for a long time are effectively solved; and the material also has good osteogenesis performance, improves the biological activity of medical metal, and is suitable for surface modification of hard tissue implantation instruments.

Owner:HEBEI UNIV OF TECH

Semiconductor structures and methods of forming them

ActiveCN106449404BImprove performanceIncrease hole concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureVoltage regulation

The invention discloses a semiconductor structure and a formation method thereof. The formation method of the semiconductor structure comprises the following steps: forming semiconductor layers at sidewalls and top surfaces which are exposed out of fin portions, wherein the semiconductor layers are doped with P-type ions; doping threshold-voltage adjustment ions in the fin portions; and doping the P-type ions in the semiconductor layers, and performing an annealing process after the threshold-voltage adjustment ions are doped in the fin portions. When a P-type fin field effect transistor is formed through the formed semiconductor structure, the negative bias temperature instability of the P-type fin field effect transistor is inhibited, and the performance is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Hemt device with sandwich gate dielectric structure and preparation method thereof

ActiveCN104966731BReduce leakage currentReduce electron concentrationSemiconductor devicesGate dielectricDielectric layer

The invention relates to the field of semiconductor devices, and provides a HEMT device with a sandwich grid medium structure and a preparation method thereof. The HEMT device includes a substrate, a buffer layer arranged on the substrate, a GaN layer arranged on the buffer layer, a barrier layer, a source electrode, and a drain electrode that are arranged on the GaN layer, a passivation layer arranged on the source electrode, the drain electrode, and the barrier layer except a groove, a first dielectric layer coating the groove surface and the passivation layer surface, a second dielectric layer arranged on the first dielectric layer, a third dielectric layer arranged on the second dielectric layer and the first dielectric layer except the second dielectric layer, a gate electrode in contact with the third dielectric layer, a source electrode pad in contact with the source electrode, and a drain electrode pad in contact with the drain electrode, wherein one side, far away from the GaN layer, of the barrier layer is provided with the groove, and the second dielectric layer contains fluorinion. The high-threshold voltage normally off operation of the HEMT device can be realized, and the breakdown voltage of the device can be effectively improved.

Owner:润新微电子(大连)有限公司

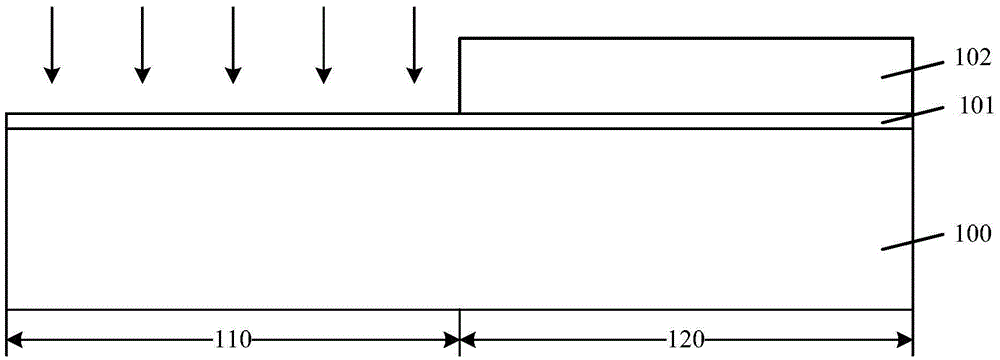

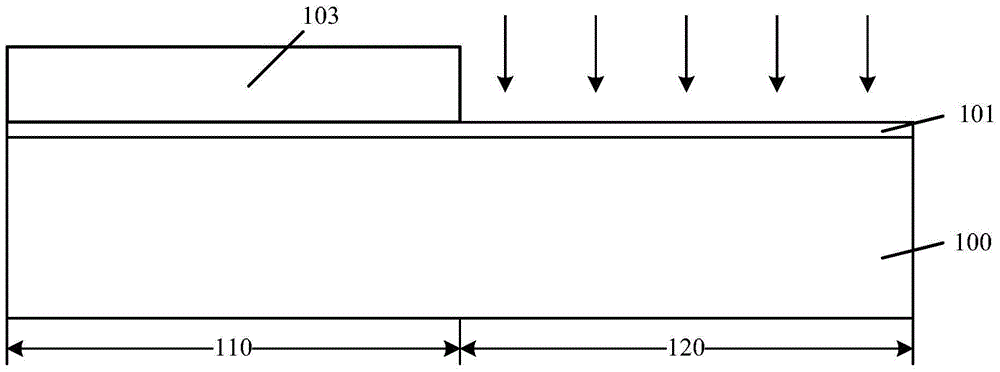

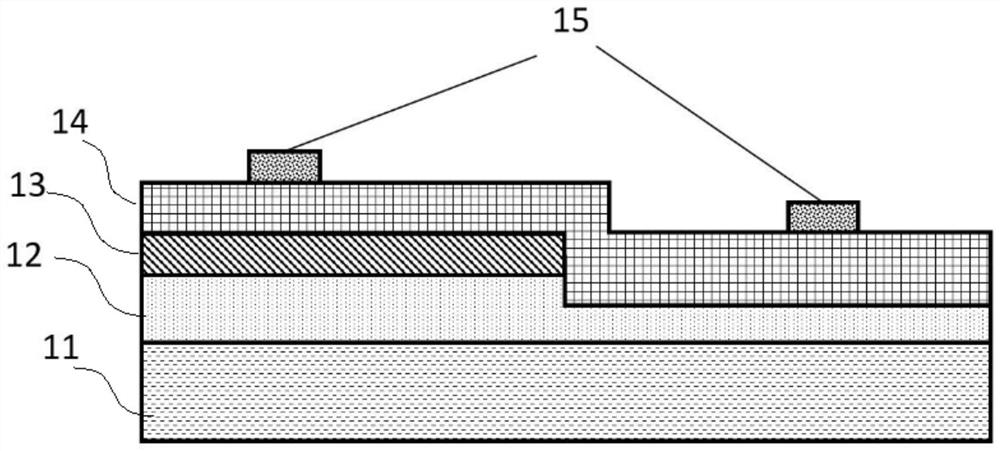

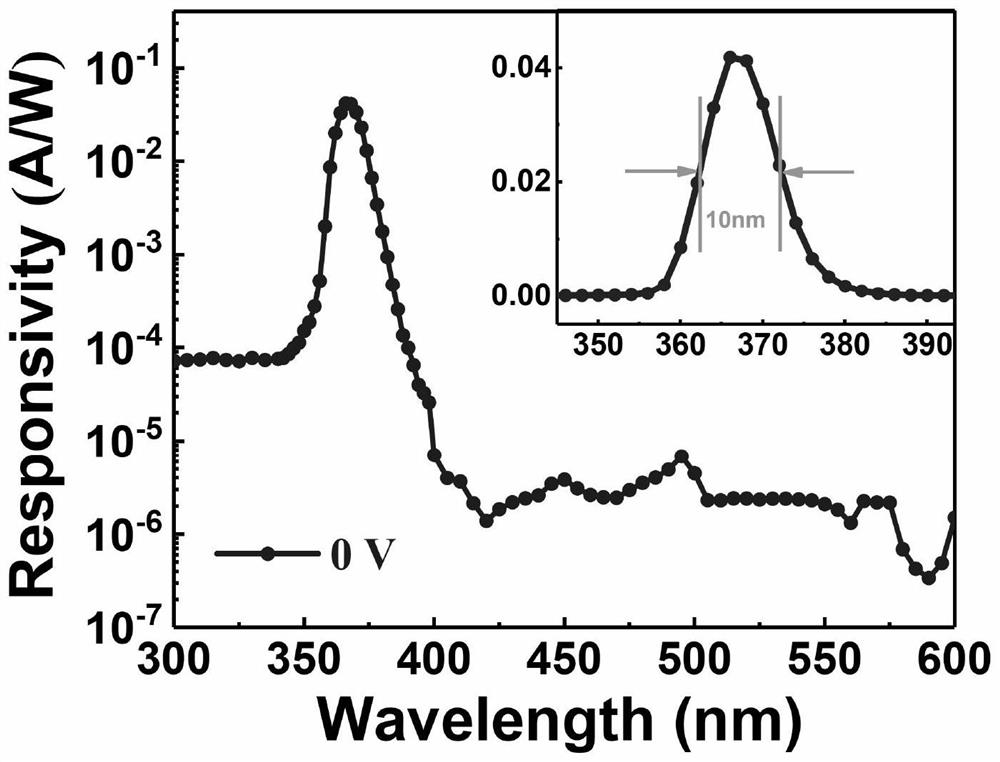

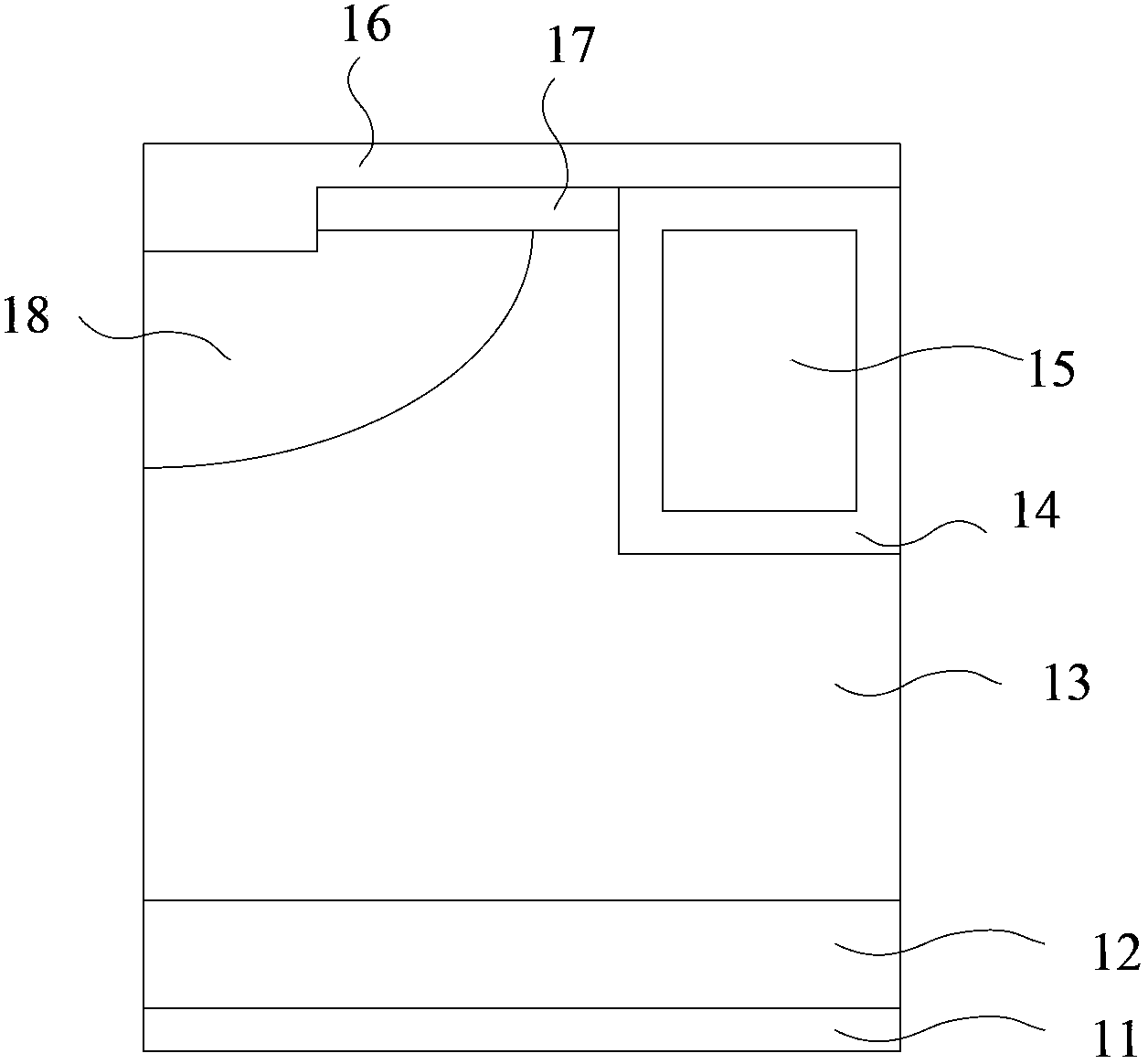

Self-powered MSM type ZnO-based ultraviolet photoelectric detector and preparation method thereof

PendingCN114883434AImprove device responsivenessReduce electron concentrationFinal product manufactureSemiconductor devicesPhysicsElectron hole

The invention relates to the technical field of semiconductors, in particular to a self-powered MSM type ZnO-based ultraviolet photoelectric detector and a preparation method thereof, and the detector comprises a substrate, an n-type buffer layer, a p-type active layer, an n-type active layer and two electrodes; the n-type buffer layer is deposited on the substrate; the p-type active layer only covers part of the n-type buffer layer to form a step from the n-type buffer layer to the p-type active layer; the n-type active layer serves as a continuous top layer, one part of the n-type active layer covers the p-type active layer, and the other part of the n-type active layer covers the n-type buffer layer, so that the two parts of the n-type active layer generate unequal electron concentrations, and a space charge region for separating photon-generated carriers is generated at the step; the two electrodes are distributed on the two sides of the step respectively, and a space charge region formed by a Schottky contact barrier between the two electrodes further separates photo-induced electron-hole pairs. Compared with the prior art, the device has the advantages of simple structure, back incidence band-pass response, high light responsivity, high response speed and no need of external bias voltage.

Owner:SOUTH CHINA UNIV OF TECH

Trench IGBT and manufacturing method thereof

InactiveCN103489903AReduce conduction voltage dropLower saturation current densitySemiconductor/solid-state device manufacturingSemiconductor devicesTrench igbtVoltage drop

The invention provides a Trench IGBT and a method for manufacturing the Trench IGBT. A Schottky contact structure is adopted in the Trench IGBT, and the conductivity voltage drop of the Trench IGBT is reduced. The Trench IGBT comprises a gate oxide layer, a Pbody voltage withstanding area, and an N-type low-adulteration substrate base area, a metallization cathode and a Schottky contact layer which is located between the gate oxide layer and the Pbody voltage withstanding area and is in contact with the N-type low-adulteration substrate base area and the metallization cathode. The method for manufacturing the Trench IGBT comprises the steps that after the Pbody voltage withstanding area and the gate oxide layer are formed on the N-type low-adulteration substrate base area, the Schottky contact layer is formed on the N-type low-adulteration substrate base area between the gate oxide layer and the Pbody voltage withstanding area; the metallization cathode is formed on the Schottky contact layer.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

Charge plasma SiGe heterojunction bipolar transistor

PendingCN113838927AImprove breakdown voltageReduce electron concentrationSemiconductor devicesHeterojunctionEngineering

The invention discloses a charge plasma SiGe heterojunction bipolar transistor, which is an npn type transistor. A base region is prepared by adopting a SiGe material, a heterojunction is formed by the base region, an undoped Si emitter region and a Si collector region, and the current gain of the device is improved by effectively changing an energy band structure at an emitter junction. Meanwhile, due to the fact that the work function of cadmium metal is 4.07 eV, the cadmium metal can easily form good gold-semi-contact with undoped Si, n-type charge plasma is effectively induced to be generated, and the transistor has the advantages of being excellent in conductivity, welding resistance, tensile strength and abrasion resistance and the like; therefore, cadmium metal is used as an electrode material of the emitter and the collector and is used for adjusting the concentration of n-type carriers in the corresponding emitter region and the collector region below the emitter and the collector. Through effective cooperation of the above structure, synchronous improvement of transistor current gain, breakdown voltage and characteristic frequency is realized.

Owner:BEIJING UNIV OF TECH

MOSFET with high-resistance layer, preparation method of MOSFET, and power transistor module

ActiveCN113299756AReduce carrier concentrationIncrease resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

The invention discloses an MOSFET with a high-resistance layer, a preparation method of the MOSFET and a power transistor module, and the MOSFET with the high-resistance layer comprises a semi-insulating substrate layer, a buffer layer, an epitaxial layer and the high-resistance layer, a source electrode, a drain electrode, and a gate electrode, wherein the semi-insulating substrate layer, the buffer layer and the epitaxial layer are sequentially arranged from bottom to top; the source electrode and the drain electrode are arranged on the upper surface of the epitaxial layer, and the source electrode, the drain electrode and the epitaxial layer form ohmic contact; a gate medium is arranged on the upper surface of the non-ohmic contact area of the epitaxial layer; the gate electrode is arranged on the upper surface of the gate dielectric; a high-resistance layer is arranged in a non-ohmic contact area between the gate electrode and the drain electrode in the epitaxial layer; the high-resistance layer comprises N-type gallium oxide, and the carrier concentration of the high-resistance layer is 0-1 * 10 < 16 > cm <-3 >.

Owner:UNIV OF SCI & TECH OF CHINA

A gallium nitride mis-hemt passivation design and preparation method thereof

ActiveCN111933708BHigh dielectric constantImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricDevice material

The invention belongs to the technical field of semiconductor devices, and discloses a gallium nitride MIS-HEMT passivation design and a preparation method thereof, wherein the passivation structure includes twice stacked silicon-doped hafnium oxide HfSiO material and P-type CuO. Preferably, the MIS-HEMT device adopts a grooved gate structure; the gate dielectric adopts a high dielectric constant silicon-doped hafnium oxide material; the source and drain electrodes are prepared using a low-temperature gold-free contact process. The present invention improves the key composition and specific structure of the passivation structure, cooperates with the gate dielectric material of the GaN MIS-HEMT device, and utilizes two layers of high dielectric constant material (HfSiO) and low dielectric constant P-type oxide Comparing with the prior art, the present invention can realize better electrical performance by constructing the passivation structure by using CuO.

Owner:HUAZHONG UNIV OF SCI & TECH

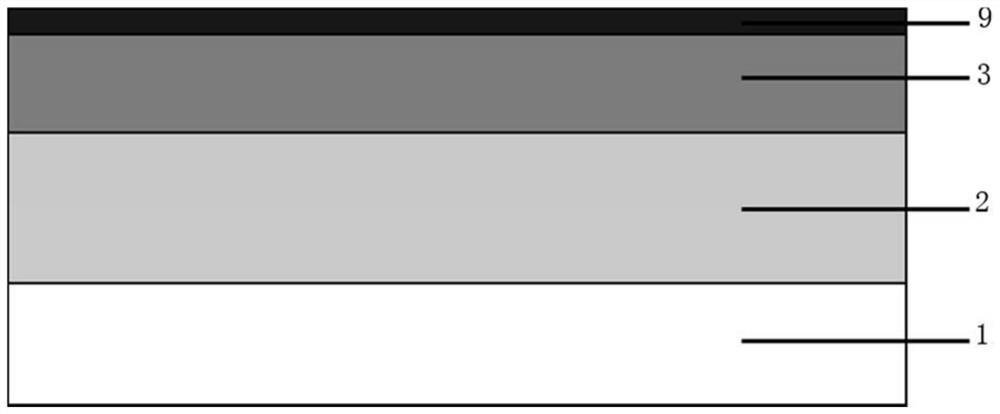

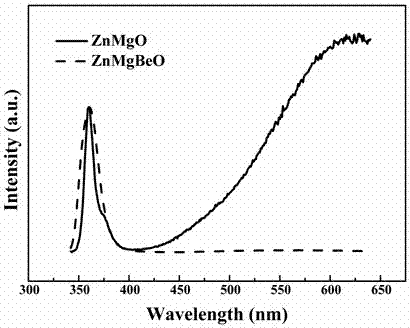

A method for preparing high-quality znmgbeo thin films

ActiveCN104451867BGood opticsGood electrical propertiesFrom chemically reactive gasesOxygen plasmaRadio frequency

A high-quality ZnMgBeO film disclosed by the invention is prepared by virtue of a plasma-assisted molecular beam epitaxy method. The method comprises the following steps of placing a cleaned substrate in a molecular beam epitaxy device, heating the substrate to 400-700 DEG C; by adopting oxygen plasma formed through radio frequency activation of pure O2 as an oxygen source, adjusting the pressure of a growth chamber to 1*10<-6>-1*10<-5>Torr and growing the ZnMgBeO film on the substrate by using pure metals Zn source, Mg source and Be source as reaction sources. By the method disclosed by the invention, the doping concentration of Be is easily controlled, the quality of the film can be effectively guaranteed and the prepared ZnMgBeO film has excellent optical and electrical properties. By doping Be, the defect luminescence can be effectively prevented, the luminescence property of the ZnMgBeO film is greatly increased and meanwhile, the background electron concentration of the ZnMgBeO film is decreased; therefore, a foundation is laid for preparation of a ZnO-based optoelectronic device having high luminescent property.

Owner:ZHEJIANG UNIV

A silicon carbide bipolar junction transistor

ActiveCN106981510BReduce electron concentrationReduce recombination rateSemiconductor devicesPower semiconductor deviceProcess complexity

A silicon carbide bipolar junction transistor belongs to the technical field of high-power semiconductor devices. Including collector electrodes 7, N stacked sequentially from bottom to top + Substrate 6, N ‑ The collector region 5 and the P-type base region 4, one end of the upper surface of the P-type base region 4 has an N on which the emitter 1 is arranged on the upper surface. + The emitter region 3, the other end has the first secondary epitaxial P+ region 10 with the base 2 set on the upper surface, the first secondary epitaxial P+ region 10 and the N + The upper layer of the P-type base region 4 between the emitter regions 3 has a second secondary epitaxial P+ region 9, a first secondary epitaxial P+ region 10, a second secondary epitaxial P+ region 9 and N + The emitter regions 3 are separated by a dielectric layer 8, and the dielectric layer 8 is along the N + The upper surface of the emitter region 3 extends to the side away from the base 2 and is connected to the emitter 1, and the dielectric layer 8 extends along the upper surface of the first secondary epitaxial P+ region 10 to the side away from the emitter 1 and is connected to the base 2 . The invention reduces the complexity of the process, improves the yield and reliability of the device, and improves the current gain of the SiC BJT device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

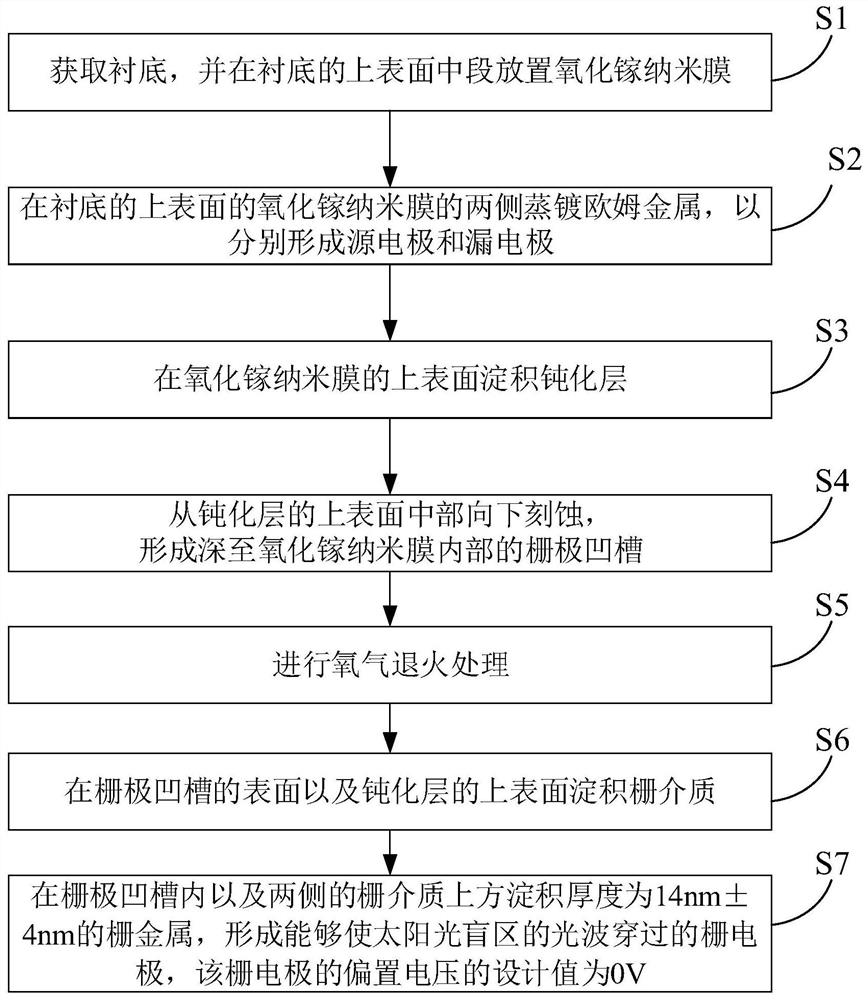

Gallium oxide-based sunlight blind area detector based on zero gate bias

PendingCN113921589AEasily depleted channelReduce electron concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesLight waveArea detector

The invention discloses a gallium oxide-based sunlight blind area detector based on zero gate bias. The gallium oxide-based sunlight blind area detector comprises: a substrate; a gallium oxide nano film located in the middle section of the upper surface of the substrate and subjected to oxygen annealing treatment in the preparation process of the sunlight blind area detector; a source electrode and a drain electrode which are located on the two sides of the gallium oxide nanometer film on the upper surface of the substrate respectively and are in lap joint with the gallium oxide nanometer film; a passivation layer which covers the upper surface of the gallium oxide nano film, wherein a gate groove which extends into the gallium oxide nano film is etched downwards from the middle part of the upper surface of the passivation layer; a gate dielectric which covers the surface of the gate groove and the upper surface of the passivation layer; and a gate electrode which is covered in the gate groove and above the gate dielectrics on the two sides, wherein the thickness of gate metal forming the gate electrode is 14 + / -4 nm to make light waves in a sunlight blind area penetrate through the gate electrode, and the design value of bias voltage of the gate electrode is 0 V. The sunlight blind area detector provided by the invention is low in power consumption.

Owner:XIDIAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com