Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

94results about How to "Improve anti-surge performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

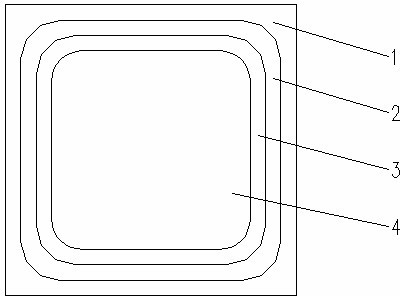

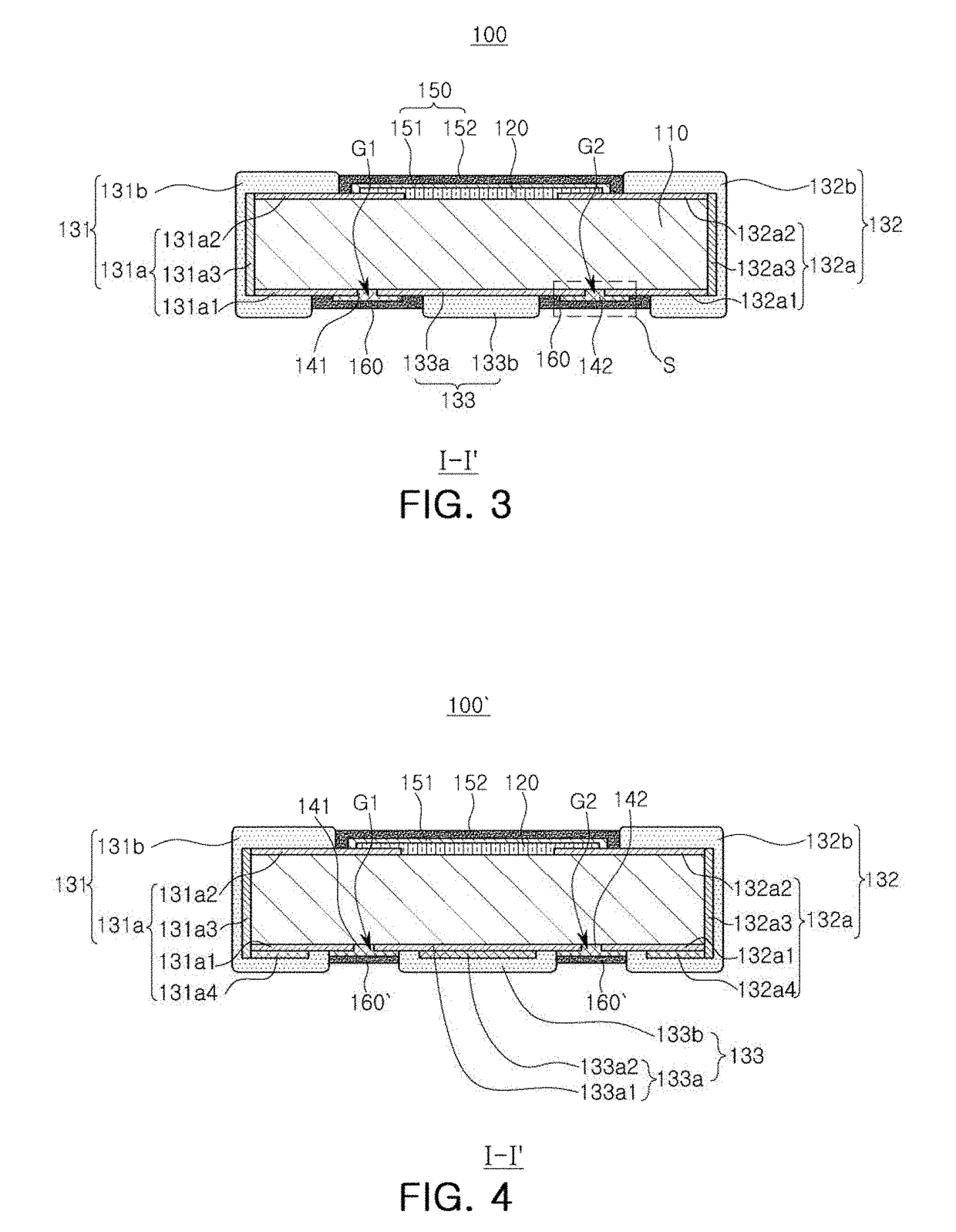

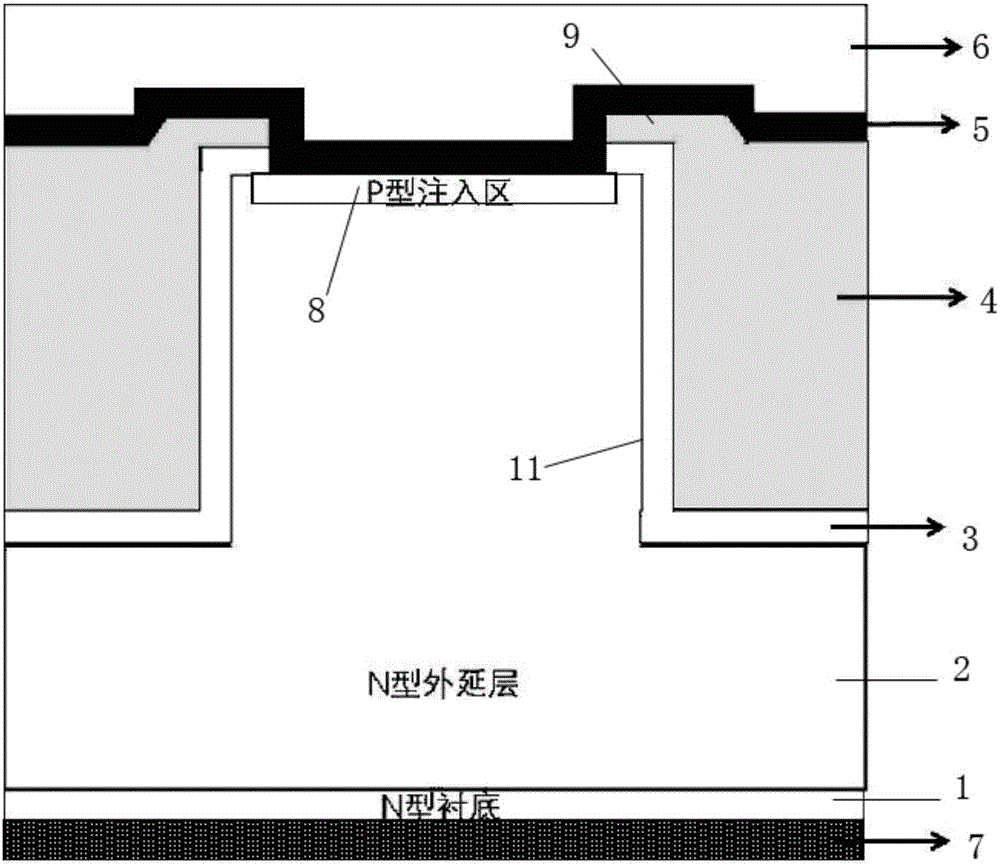

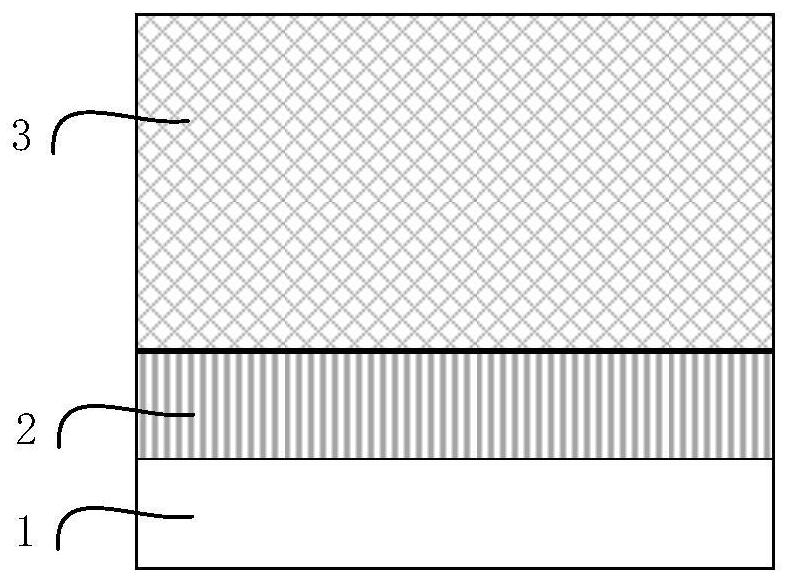

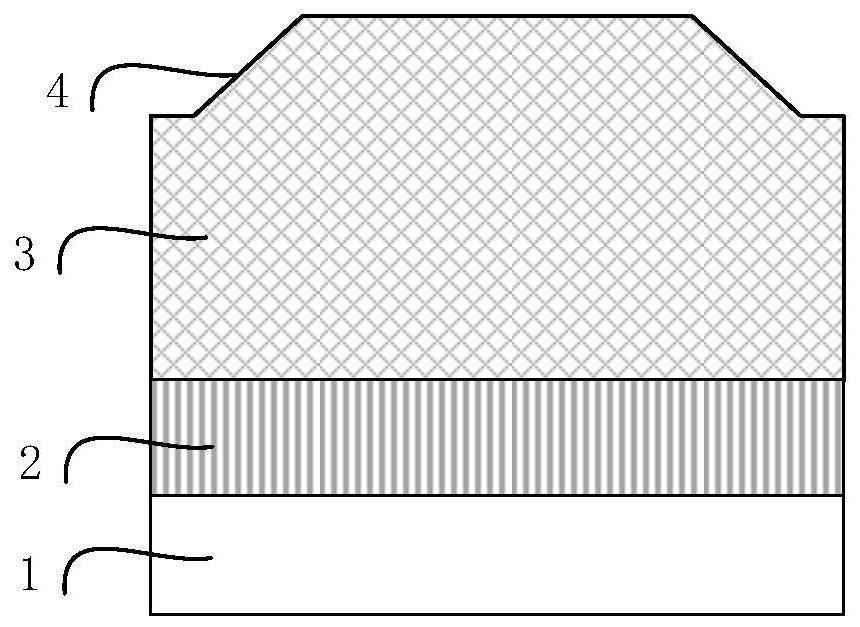

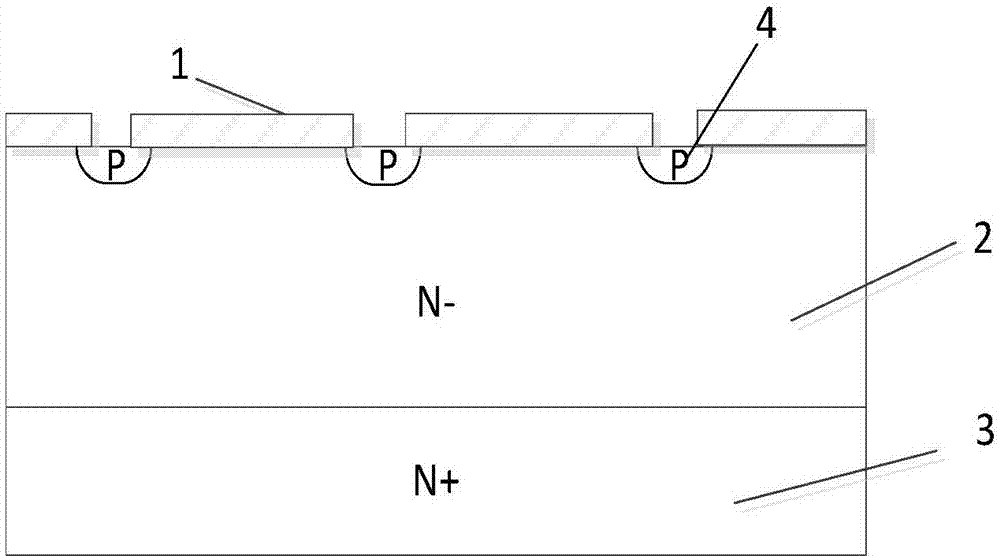

High-voltage transient voltage suppressor chip and production process

ActiveCN102543722AImprove pressure resistanceImprove anti-surge performanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectricityEngineering

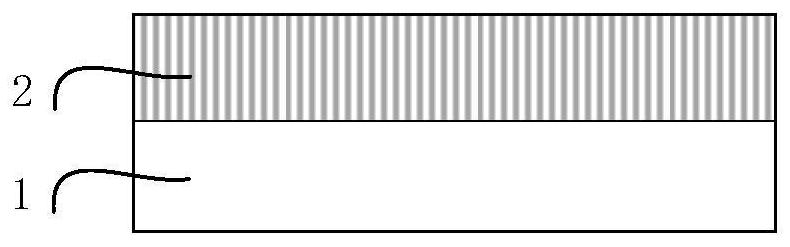

The invention relates to a high-voltage transient voltage suppressor chip and a production process. The high-voltage transient voltage suppressor chip is of a chip structure with increased auxiliary puncture diffusion junctions, a main junction of the chip enables the puncture voltage to reach 250V-400V, the puncture voltage of an auxiliary PN (positive-negative) junction designed in a region nearby a chip mesa trench is higher than that of the main junction so that the main junction is punctured firstly, leakage current is distributed in a main junction region, and the auxiliary junction region is not punctured. Therefore, the problems of high electricity leakage, low puncture voltage and easiness in damage when a high-voltage chip is produced by a single diffusion junction structure are solved, voltage resistance of a high-voltage transient voltage suppressor is improved, and anti-surge capacity and reliability of the transient voltage suppressor are enhanced.

Owner:TIANJIN ZHONGHUAN SEMICON CO LTD

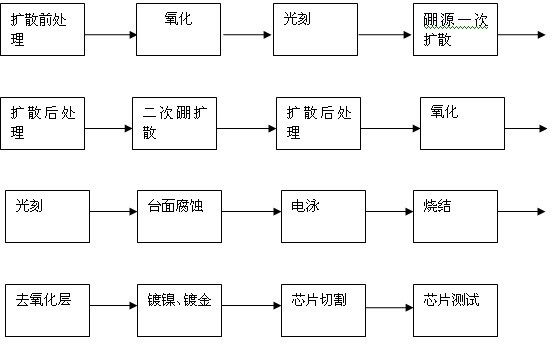

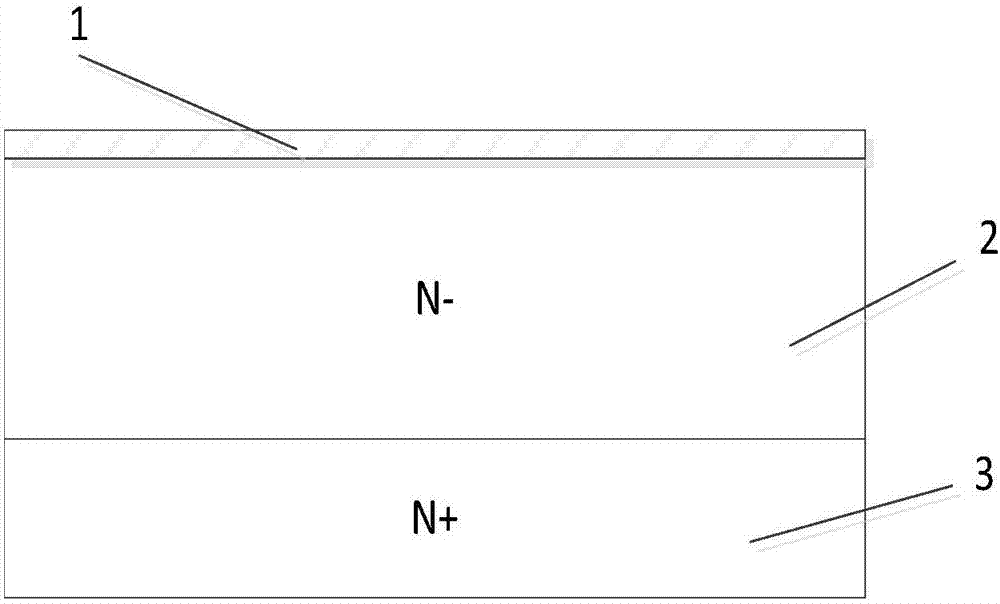

Fast recovery diode (FRD) chip and production process thereof

ActiveCN102087976AImprove anti-surge performanceImprove switching performanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrophoresesEtching

The invention relates to a fast recovery diode (FRD) chip and a production process thereof. A diode with a P+NN+ structure is produced by adopting the process steps of diffusion pretreatment, double diffusion of a liquid source, back thinning, oxidization, platinum diffusion, photoetching, mesa etching, electrophoresis, sintering, scribing and the like. In the chip production process, a method of carrying out deep junction diffusion by carrying a liquid phosphorous source is adopted, so that the flatness of a diffusion junction is improved and the homogeneity and the stability of a breakdown voltage are strengthened; a method of reducing the concentration of a boron diffusion source and improving the purity of the boron diffusion source is adopted, so that the surge resistance capacity of an FRD is improved; and an electrophoresis glassivation process is adopted, so that the voltage withstanding stability and reliability of a bidirectional voltage stabilizing diode are improved. In addition, the production process has the advantages that the reverse recovery time is shortened, the switching speed is improved, the voltage drop is reduced, the power consumption is reduced, the voltage withstanding stability is improved, and the reliability of the diode is improved.

Owner:TIANJIN ZHONGHUAN SEMICON CO LTD

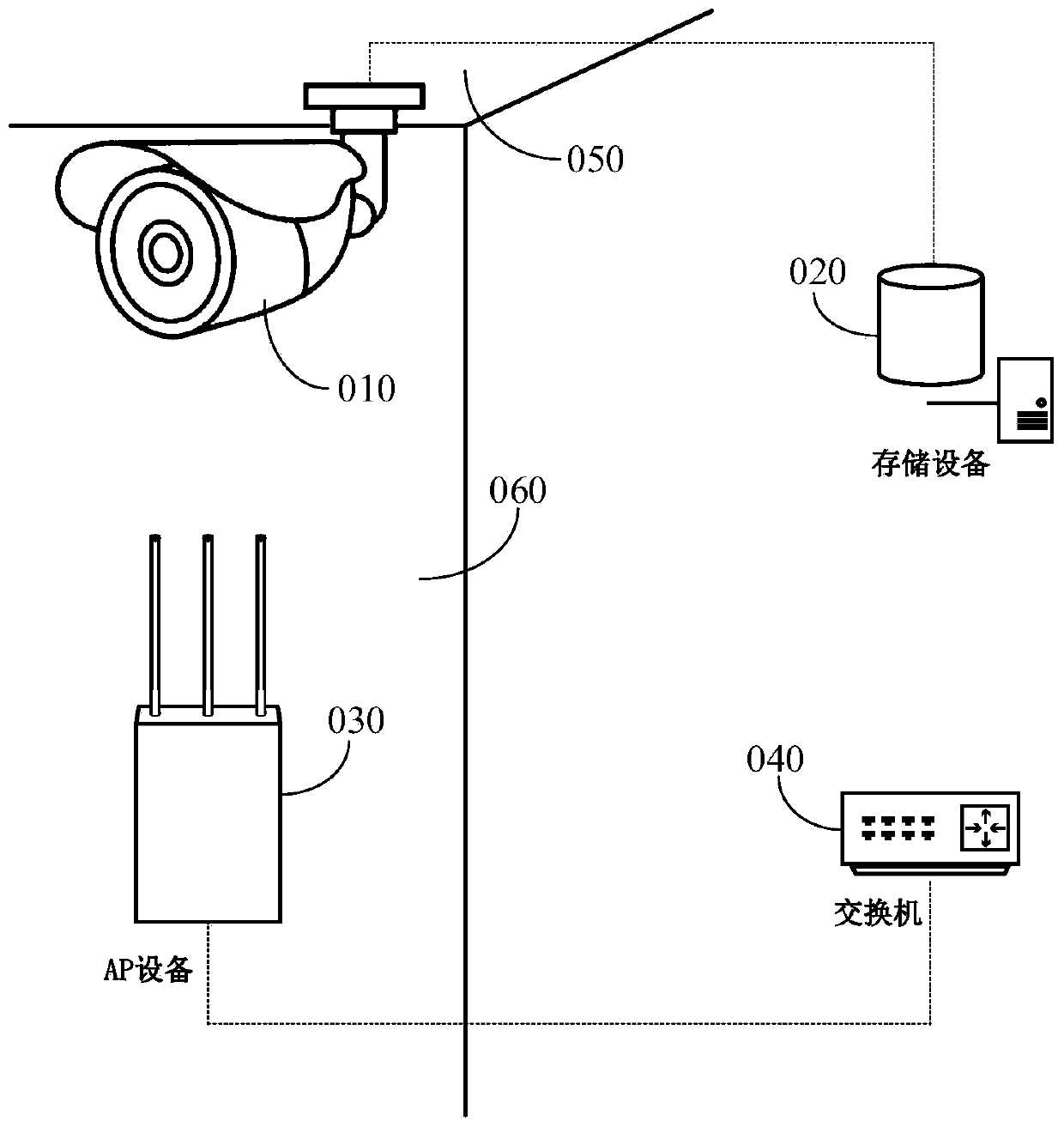

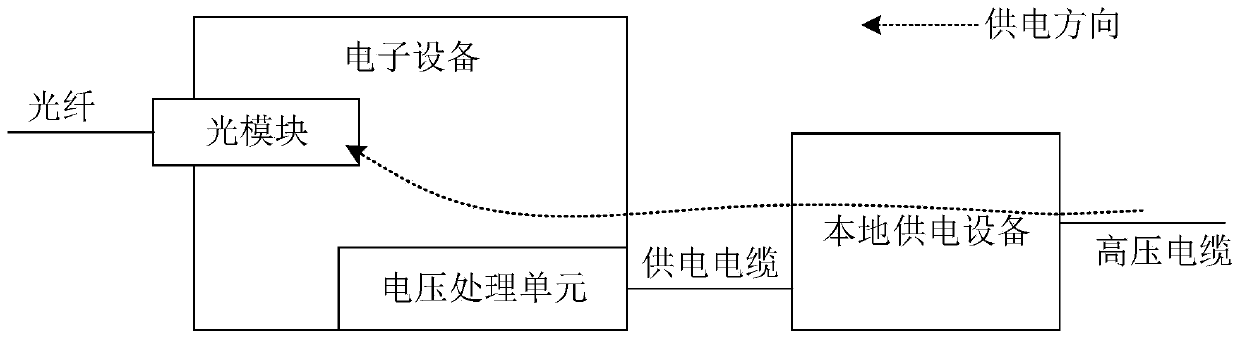

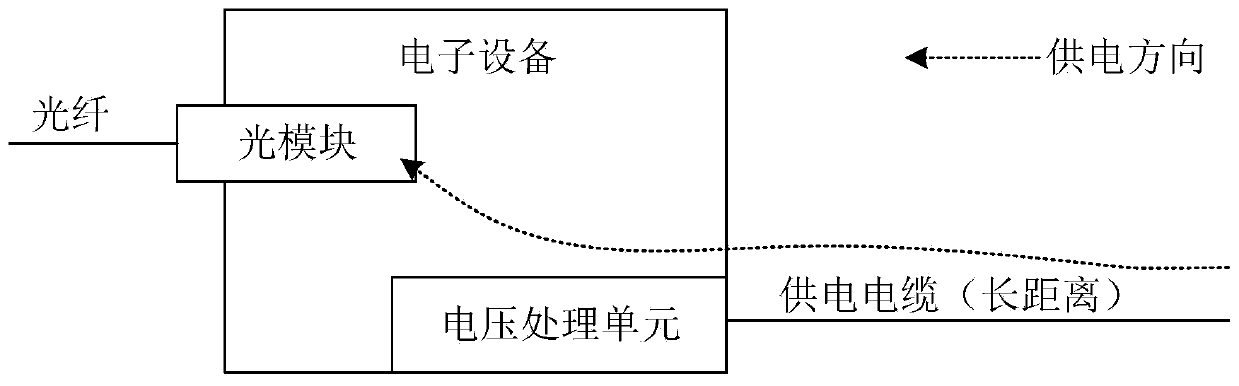

Photoelectric connecting device

ActiveCN111413770AReduce volumeImprove application flexibilityData switching current supplyCoupling light guidesOptical ModuleElectrical connection

The invention provides a photoelectric connection device such as an optical module, which comprises an optical signal interface arranged at one end of a shell and an electric signal interface arrangedat the other end of the shell, and the optical signal interface and the electric signal interface are coupled through a photoelectric processing module arranged in the shell. The optical signal interface end is provided with a first insulating part; the electrical signal interface end is provided with a second insulating part, the first insulating part comprises at least two first metal contactsused for being coupled to a POE power supply, the second insulating part comprises at least two second metal contacts exposed out of the shell, and the first metal contacts and the second metal contacts are electrically connected through a conducting medium wrapped with an insulating medium. The photoelectric connection device provided by an embodiment of the invention not only can receive and transmit light / electric signals, but also can couple the far-end POE power supply to electronic equipment to supply power to the electronic equipment, so that the electronic equipment does not need to beadditionally provided with a POE interface, and the size of the electronic equipment can be reduced.

Owner:HUAWEI TECH CO LTD

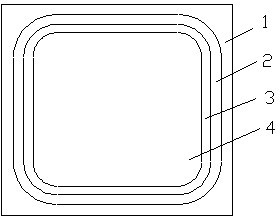

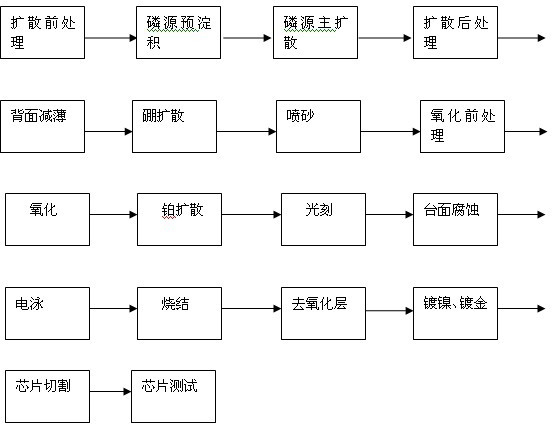

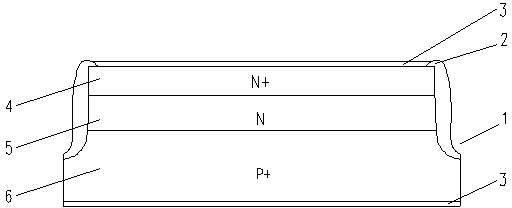

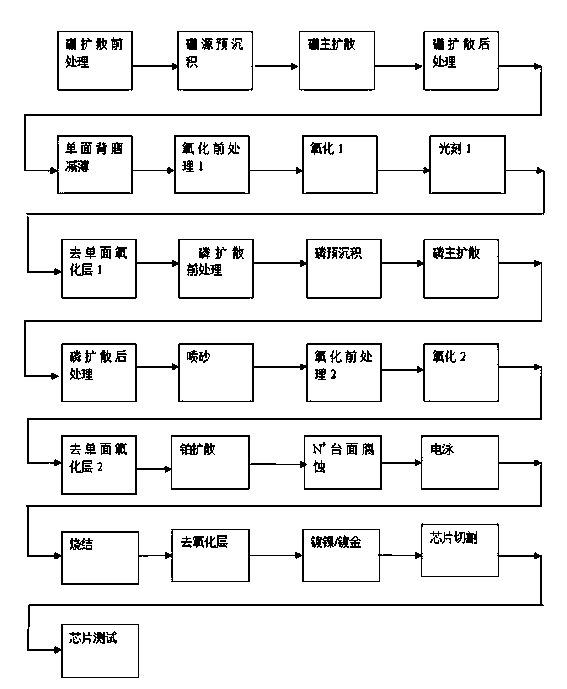

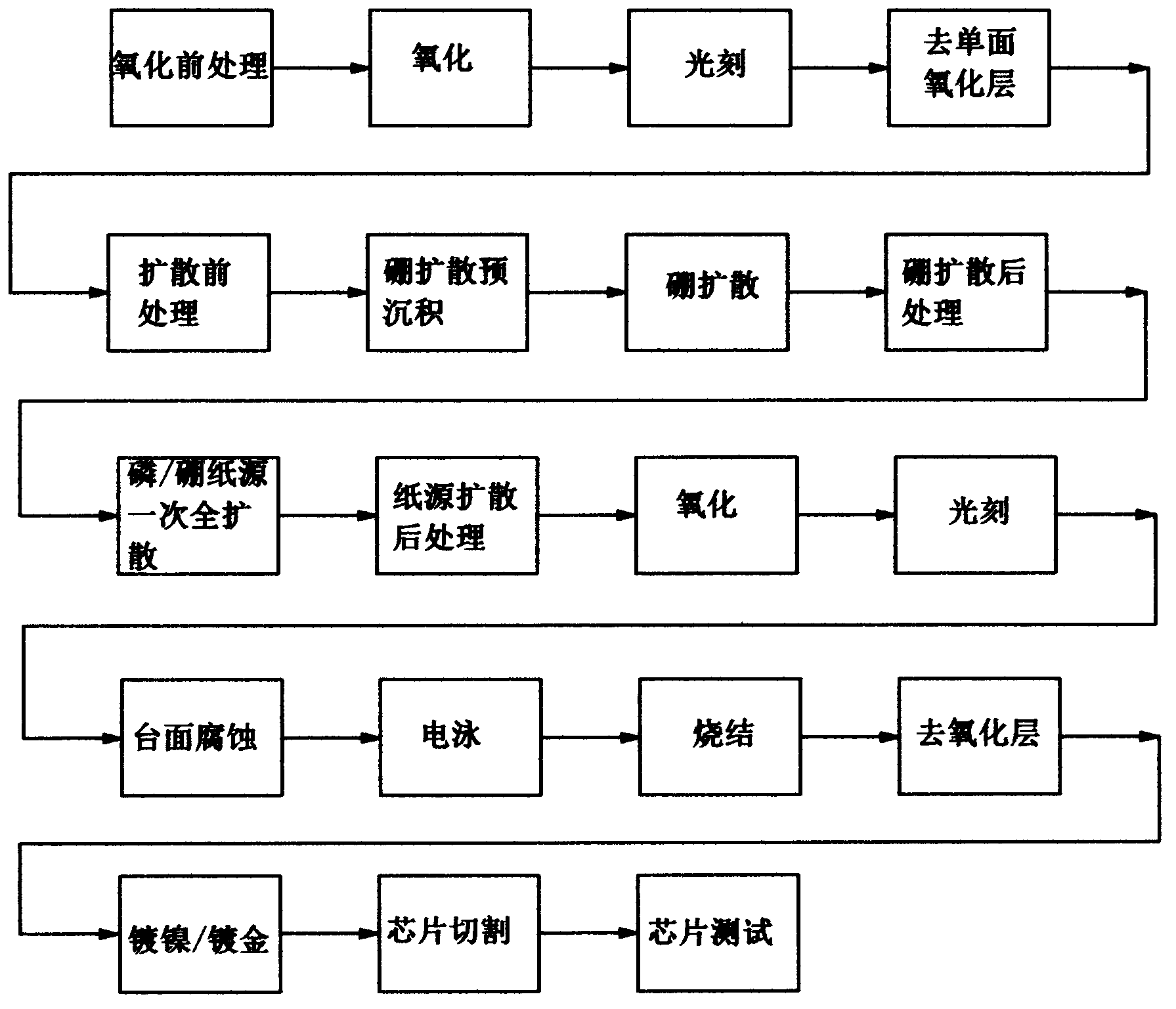

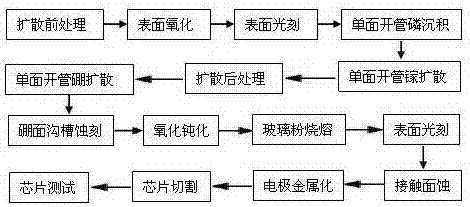

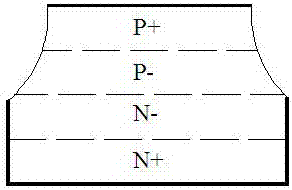

Fast recovery diode FRD chip and production process for same

ActiveCN104201102AImprove anti-surge performanceImprove flatnessSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingLayer removal

The invention relates to a fast recovery diode FRD chip and a production process for the same. The process comprises the following steps of: diffusion pre-treatment, boron source pre-deposition, boron source main diffusion, diffusion after-treatment, single-surface back grinding thinning, oxidation pre-treatment, oxidation, photoetching, single-surface oxide layer removal, phosphorus source pre-deposition, phosphorus diffusion, sand blasting, platinum diffusion, N + surface mesa etching, electrophoresis, sintering, oxide layer removal, nickel plating, gold plating and chip cutting, wherein the structure of the obtained chip is P+-N-N+ type. According to the process, the uniformity of the reverse recovery time of the fast recovery diode is improved and controllability is improved, meanwhile, voltage drop is reduced, leakage current is reduced, and voltage-proof stability is improved; the contradiction of mutual condition among the reverse voltage, the positive voltage, the reverse recovery time and the leakage current of the fast recovery diode is solved to enable the various parameters to achieve the optimal matching, thus improving the reliability and switching characteristic of the diode, and reducing power consumption. The fast recovery diode disclosed by the invention breaks through the technical bottleneck of the traditional fast recovery diodes.

Owner:SUZHOU QILAN POWER ELECTRONICS

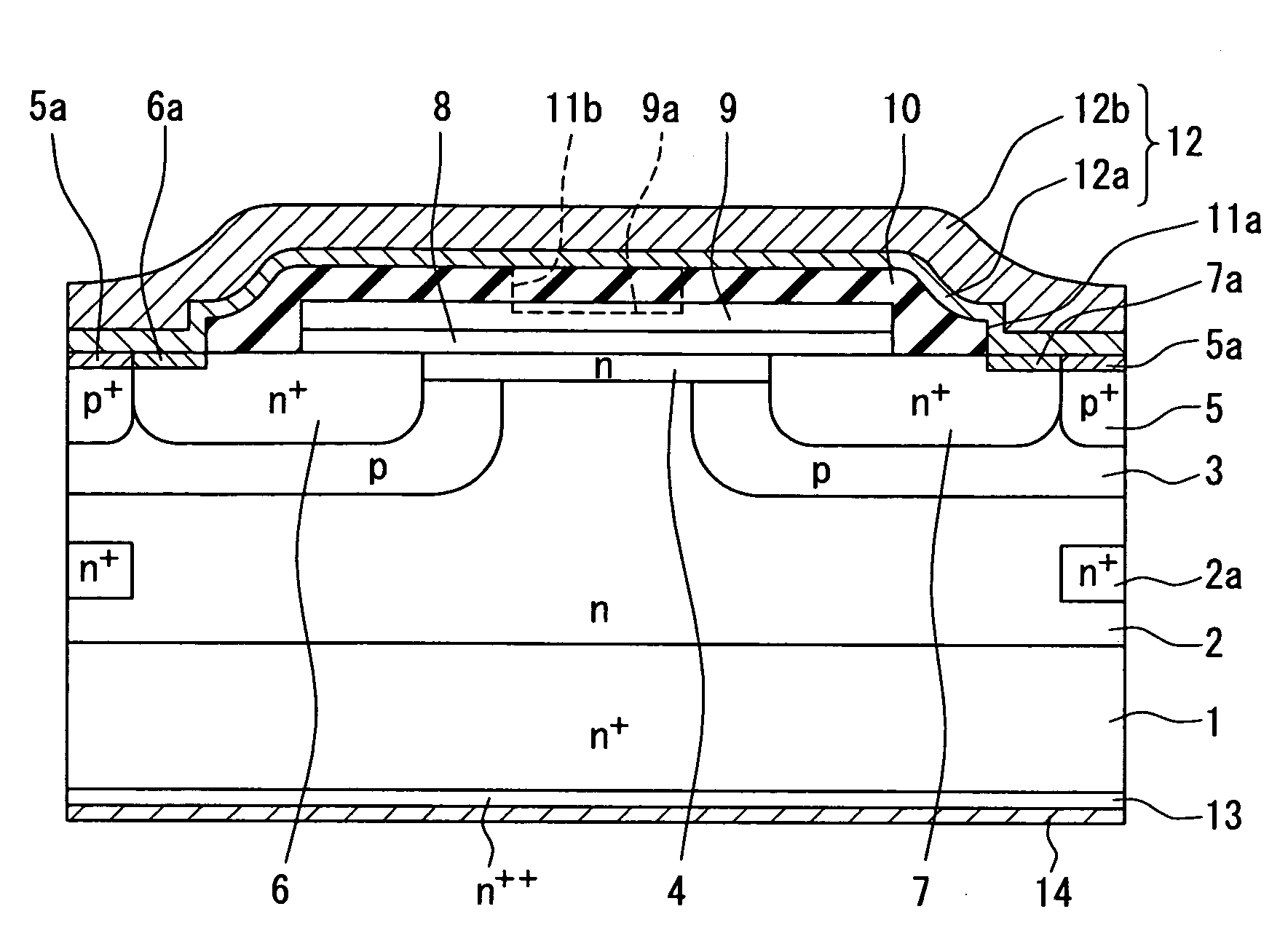

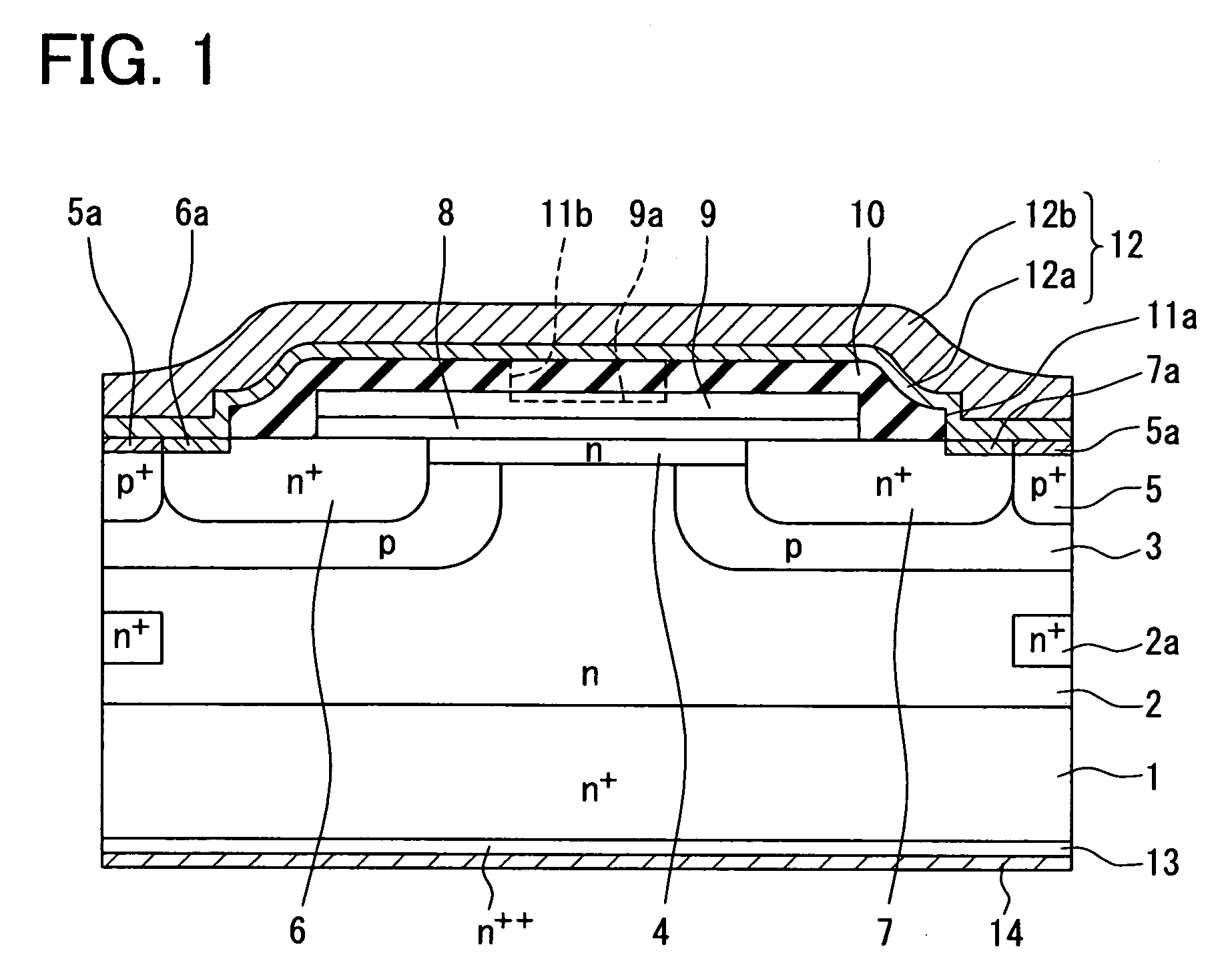

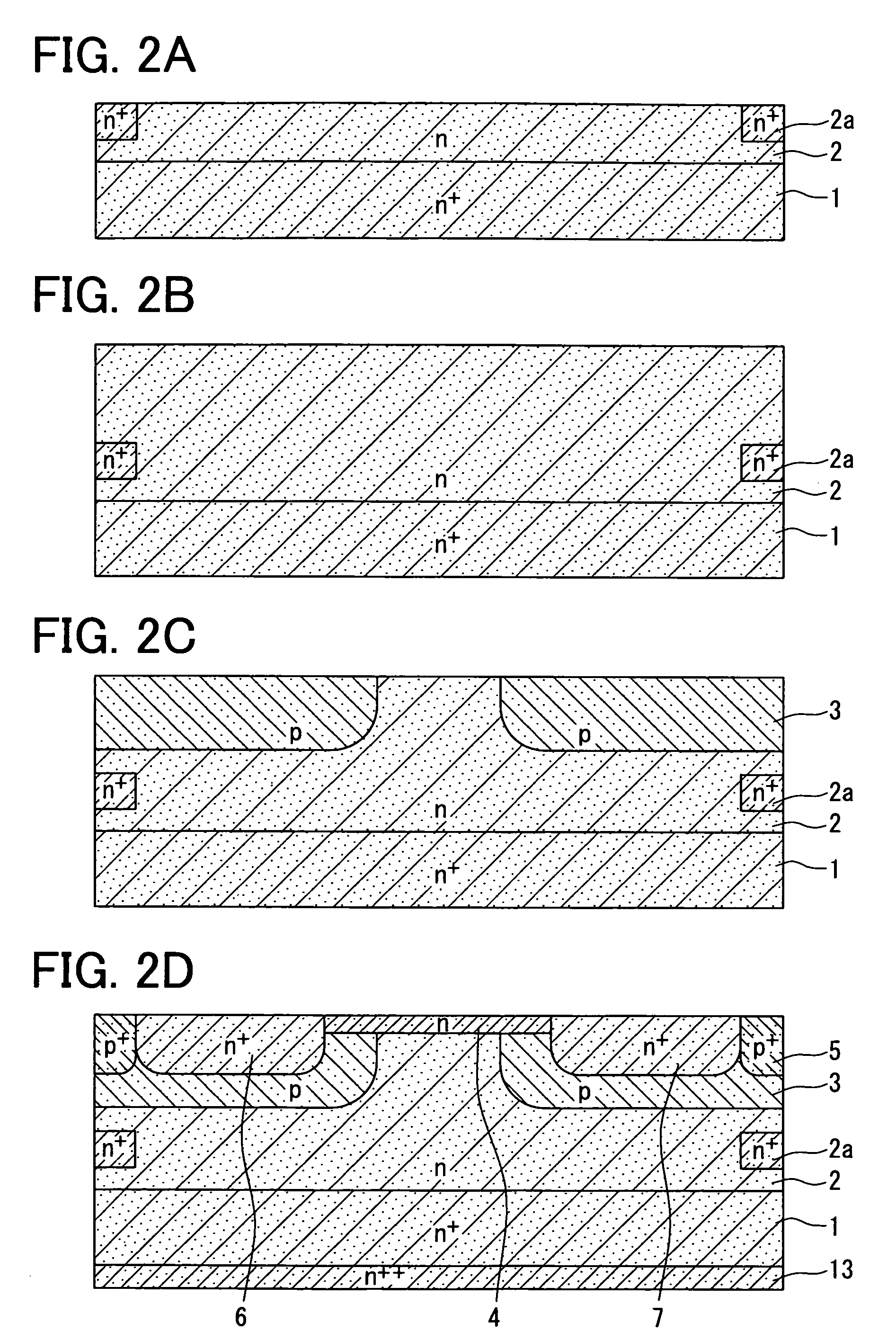

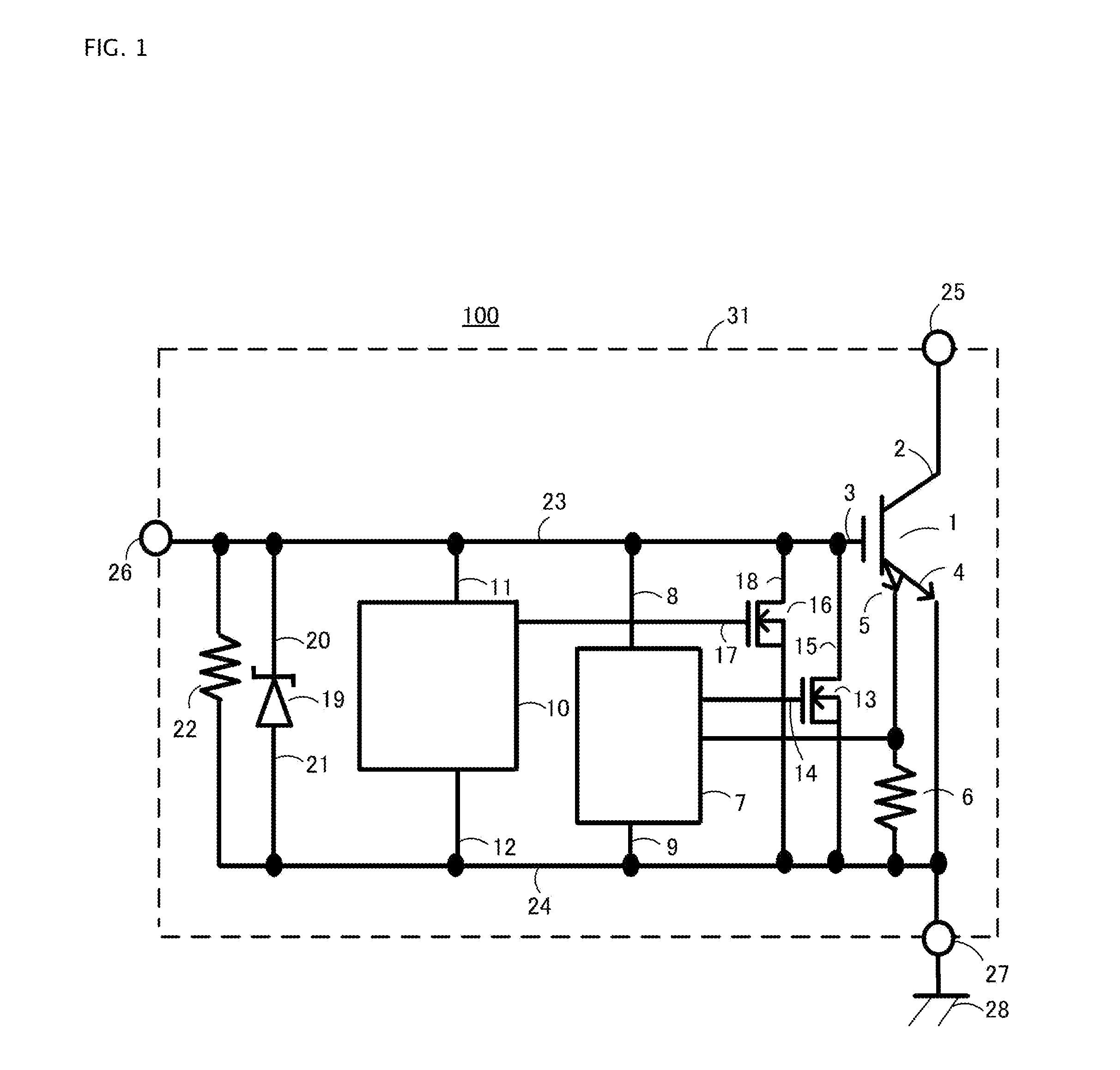

Single chip igniter and internal combustion engine ignition device

ActiveUS20140015005A1Low working voltageImproved noise toleranceTransistorSolid-state devicesMicrocontrollerHysteresis

Aspects of the invention are directed to a single chip igniter such that it is possible to realize a reduction in operating voltage, an increase in noise tolerance, a reduction in size, and a reduction in cost. By reducing the gate threshold voltage of a MOS transistor, and reducing the operating voltages of a current limiter circuit, an overheat detector circuit, a timer circuit, an overvoltage protection circuit, an input hysteresis circuit, and the like, it is possible to reduce the operating voltage of a single chip igniter. In some aspects of the invention, the effective gate voltage of the MOS transistor is 1V or more, and the channel length of the MOS transistor is 4 μm or less. Also, in some aspects of the invention, the thickness of a gate oxide film of the MOS transistor is 5 nm or more, 25 nm or less.

Owner:FUJI ELECTRIC CO LTD

Silicon carbide semiconductor device

A silicon carbide semiconductor device is disclosed. The silicon carbide semiconductor device includes a substrate; a drift layer having a first conductivity type and located on a first surface of the substrate; and a vertical type semiconductor element. The vertical type semiconductor element includes: an impurity layer having a second conductivity type, and located in a surface portion of the drift layer; and a first conductivity type region located in the drift layer, spaced away from the impurity layer, located closer to the substrate than the impurity layer, and having an impurity concentration higher than the drift layer.

Owner:DENSO CORP

Enhanced silicon carbide MOSFET device and manufacturing method thereof

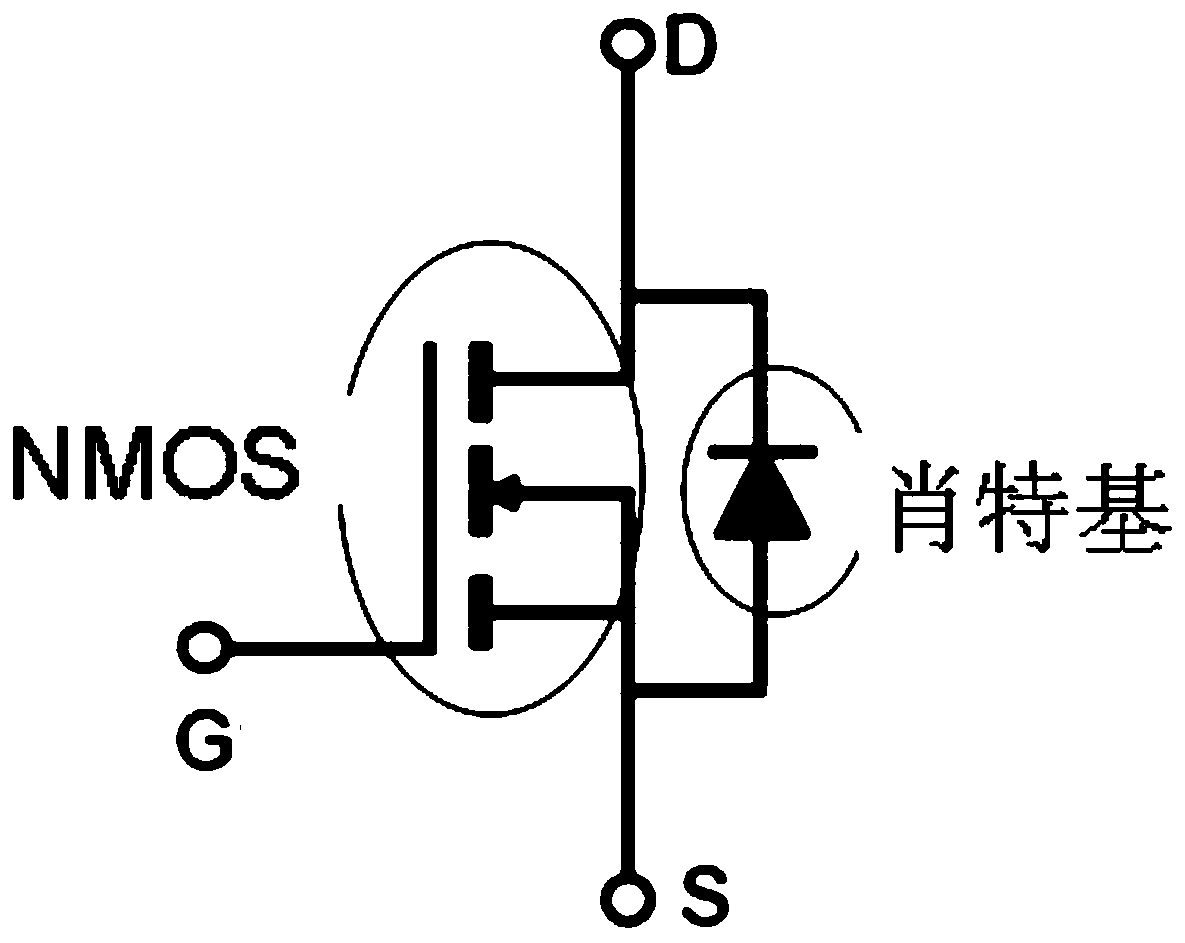

ActiveCN111081759AFast switching speedImprove performanceTransistorSolid-state devicesMOSFETSchottky barrier

The invention discloses an enhanced silicon carbide MOSFET device. The enhanced silicon carbide MOSFET device sequentially comprises back metal, an N+ type heavily doped SiC substrate, an N- epitaxiallayer, an insulating dielectric layer and front metal from bottom to top. According to the invention, a Schottky diode is integrated into the MOSFET device, and the area of a Schottky barrier metal layer is flexibly increased or decreased to adjust and adapt to the current and specification of the MOSFET and the Schottky diode, so that the effects of increasing the switching speed of the MOSFET,reducing the switching loss and the like are achieved, the performance and the reliability of the device can be greatly improved, and the application cost of the device is reduced. The enhanced silicon carbide MOSFET device adopts a trench SiC MOSFET design, and a conductive channel is changed from the traditional horizontal direction to the vertical direction, so that a JFET effect between primitive cells of the traditional MOSFET is eliminated, and the current capability of the device is improved. The gate bottom P region at the bottom of the trench can protect and weaken an electric field at the bottom of the trench, thereby playing a certain role in electrostatic shielding of gate oxide at the bottom of the trench, and improving the reliability of the device. Meanwhile, certain help isprovided for voltage resistance of the device.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

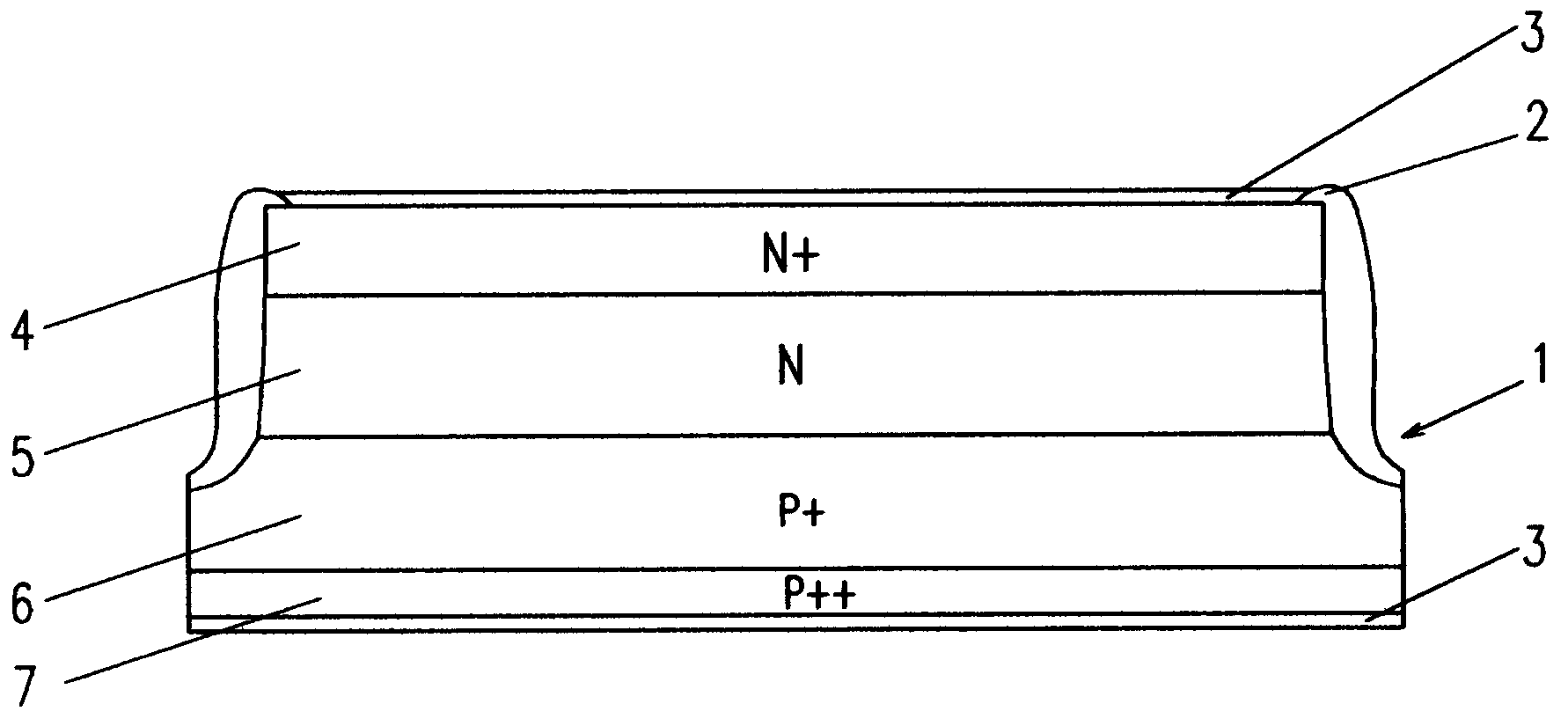

Backward GPP (Glass Passivation Pellet) high voltage diode chip in automobile module, and production technology

ActiveCN104078353AReduce widthLower body pressure dropSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingLayer removal

The invention discloses a backward GPP (Glass Passivation Pellet) high voltage diode chip in an automobile module, and a production technology. The technology comprises the following steps of oxidation pretreatment, oxidation, photoetching, single-side oxidation layer removal, diffusion pretreatment, boron diffusion predeposition, boron diffusion, once phosphorus source / boron source diffusion, diffusion aftertreatment, N<+> surface mesa etching, electrophoresis, sintering, oxidation layer removal, nickel plating, gold plating and chip cutting. The obtained chip is in a P<++>-P<+>-N-N<+> type structure. According to the high voltage diode chip and the production technology, the defect of great electric leakage of a geminate axial diode is improved, damage to glass passivation protection during welding of a backward diode in a geminate GPP diode is avoided, an effective welding area is increased, and the whole heat dissipation function of the geminate diode is improved. An N-type substrate slice replaces a P-type substrate slice, and a backward GPP high voltage diode is manufactured in a deep N<+> surface corrosion groove, so that the backward GPP high voltage diode in the automobile module fills a gap in the technical field of domestic automobile modules.

Owner:上海瞬雷科技有限公司

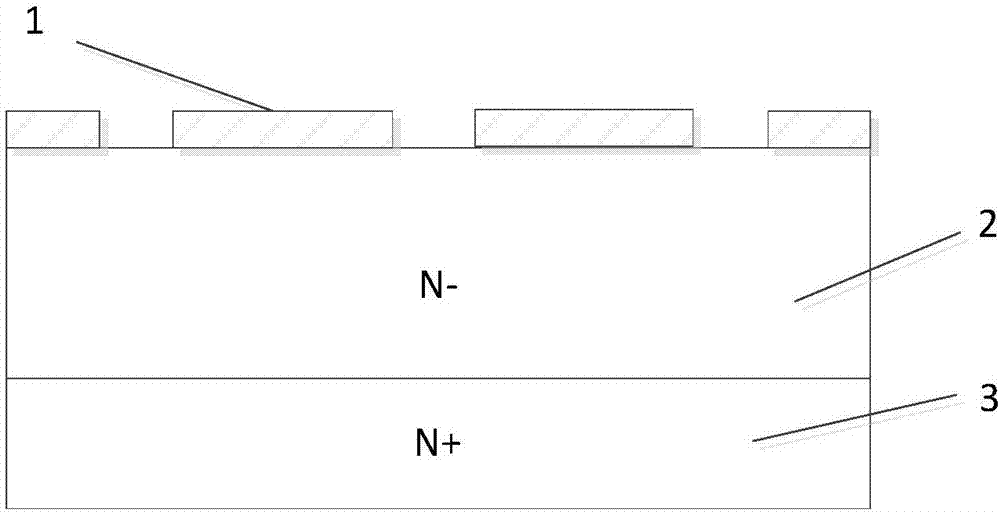

Schottky diode structure and manufacturing method thereof

InactiveCN109742136AIncrease contact areaImprove anti-surge performanceSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactPeak value

The invention discloses a junction barrier schottky diode. An N-conductive type first drift layer is arranged on the upper surface of a substrate; back surface ohmic contact metal is arranged on the lower surface of the substrate; a p+ ion injection region is formed on the upper surface of the first drift layer through ion injection; front surface schottky contact metal is on the first drift layerand the upper surface of the p+ ion injection region; an N-conductive type second drift layer is between the first drift layer and the front surface schottky contact metal; and a P++ injection regionis between the p+ ion injection region and the front surface schottky contact metal. According to the diode disclosed by the invention, after JTE and FLR are finished, an N-Sic epitaxial layer is manufactured on the upper surface, and the small-area P++ region is prepared through the N-epitaxial layer, so that the contact area of the schottky metal is enlarged, the forward current density is increased, and meanwhile, no influence is caused on the aspect of reverse voltage withstand; and in addition, the P type region in the N-SiC epitaxial layer is heavily doped, so that peak current can be increased, and the surge resistance of a device can be improved.

Owner:安徽长飞先进半导体有限公司

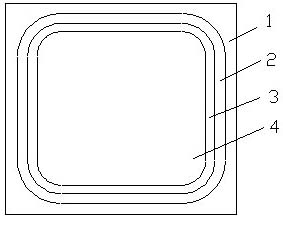

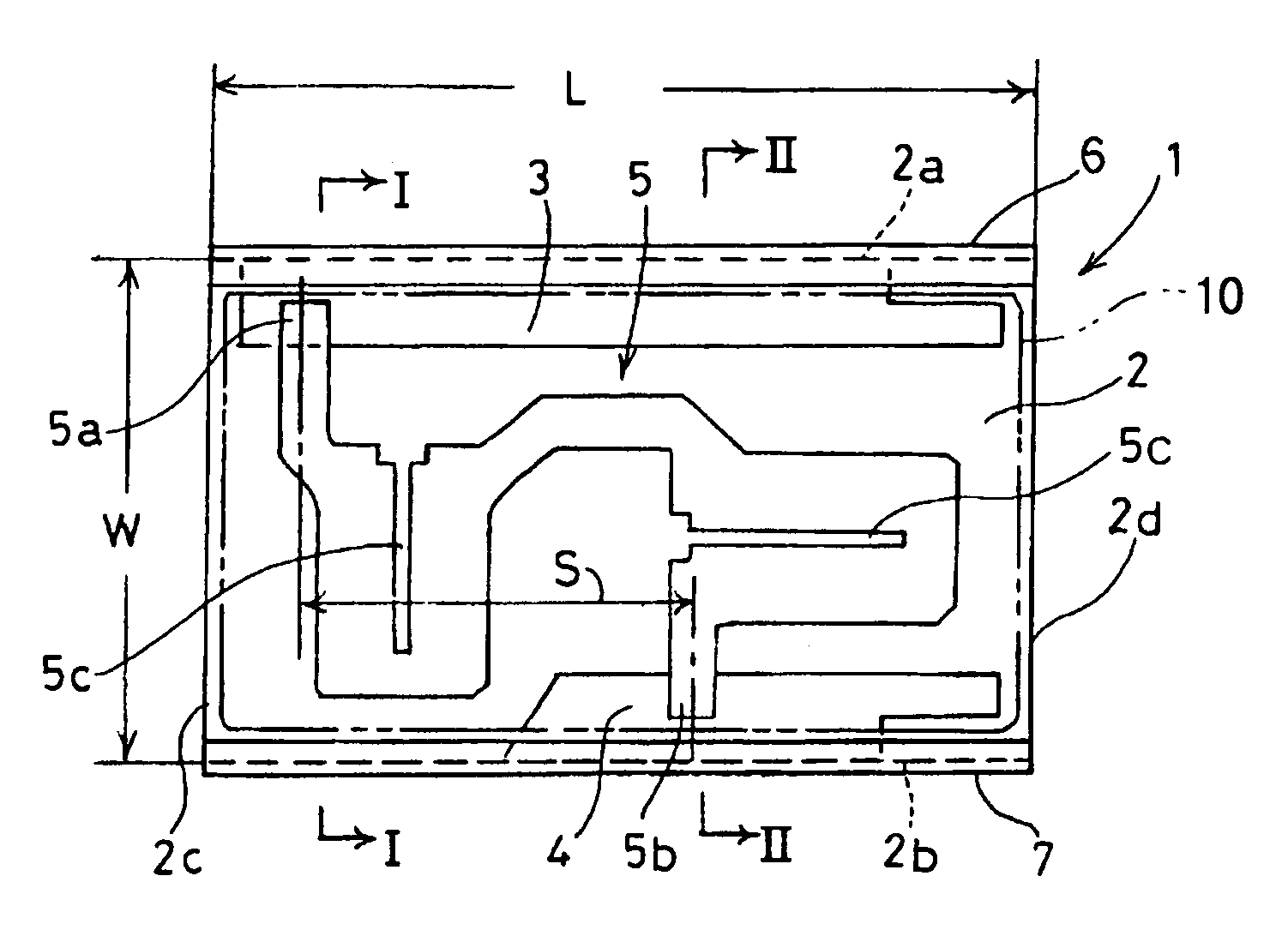

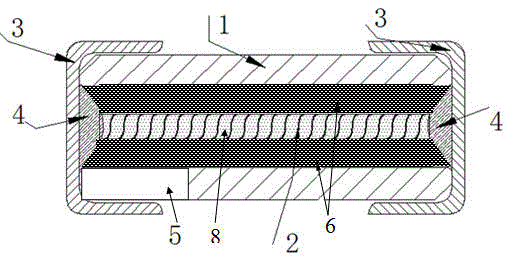

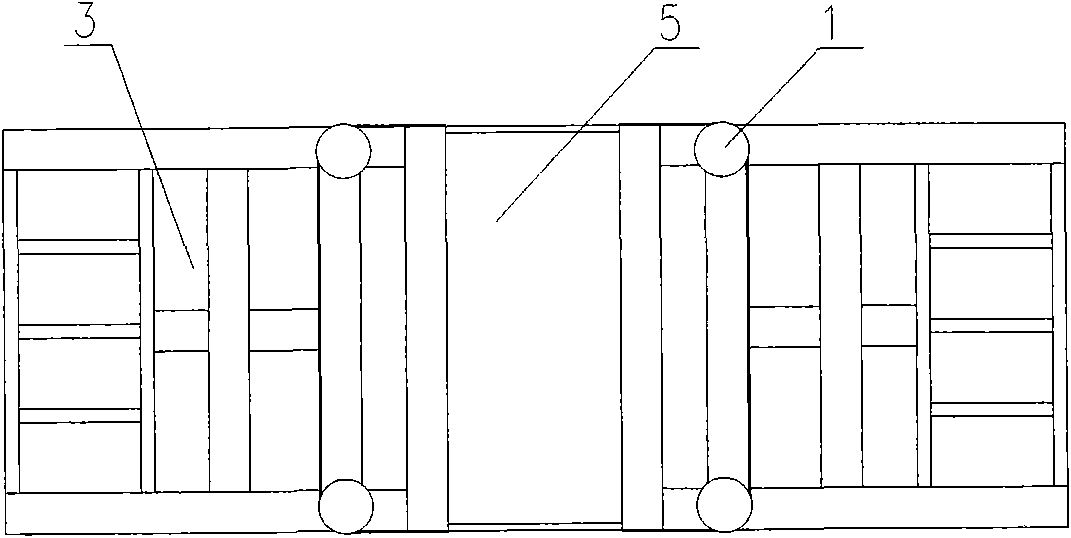

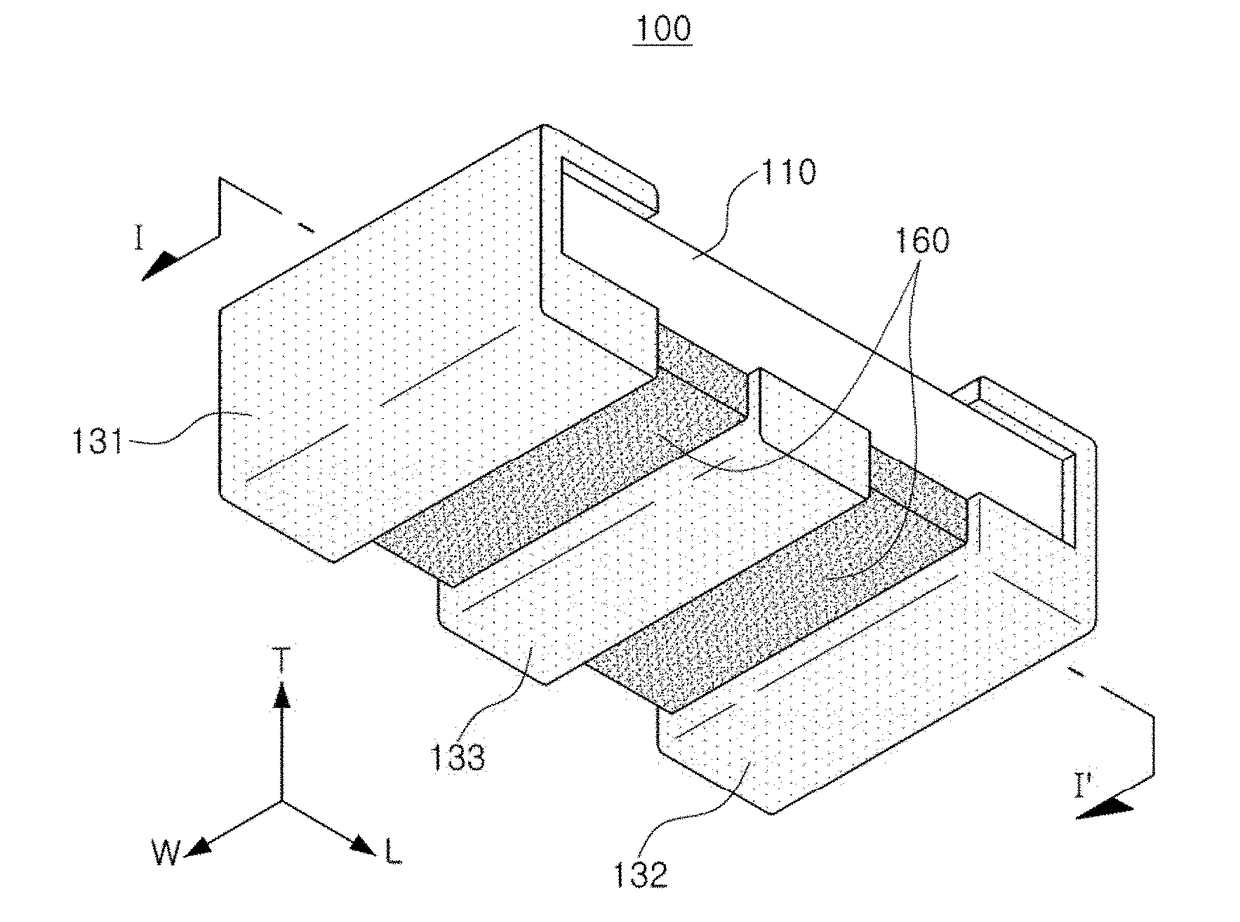

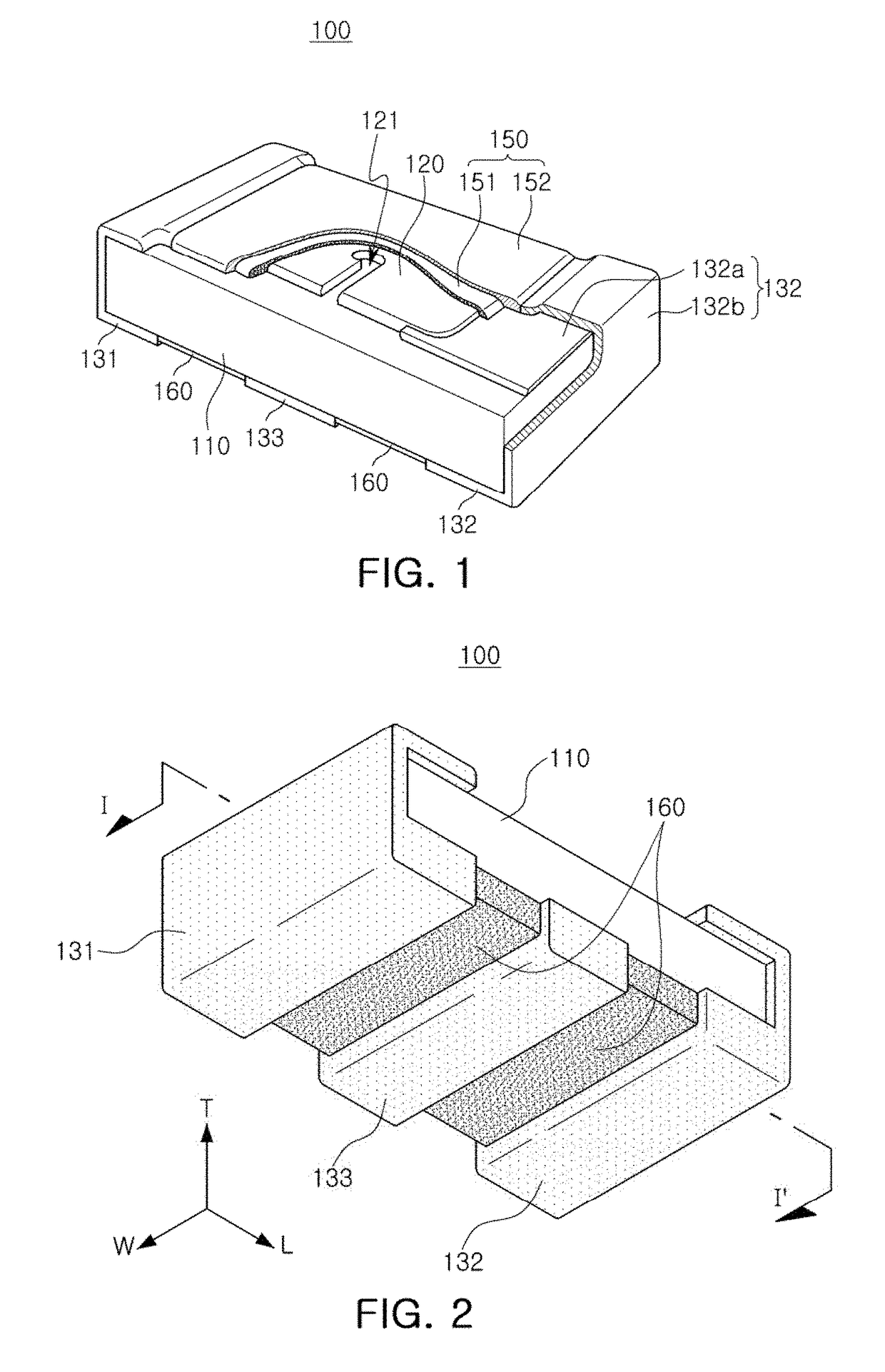

Chip resistor and its manufacturing method

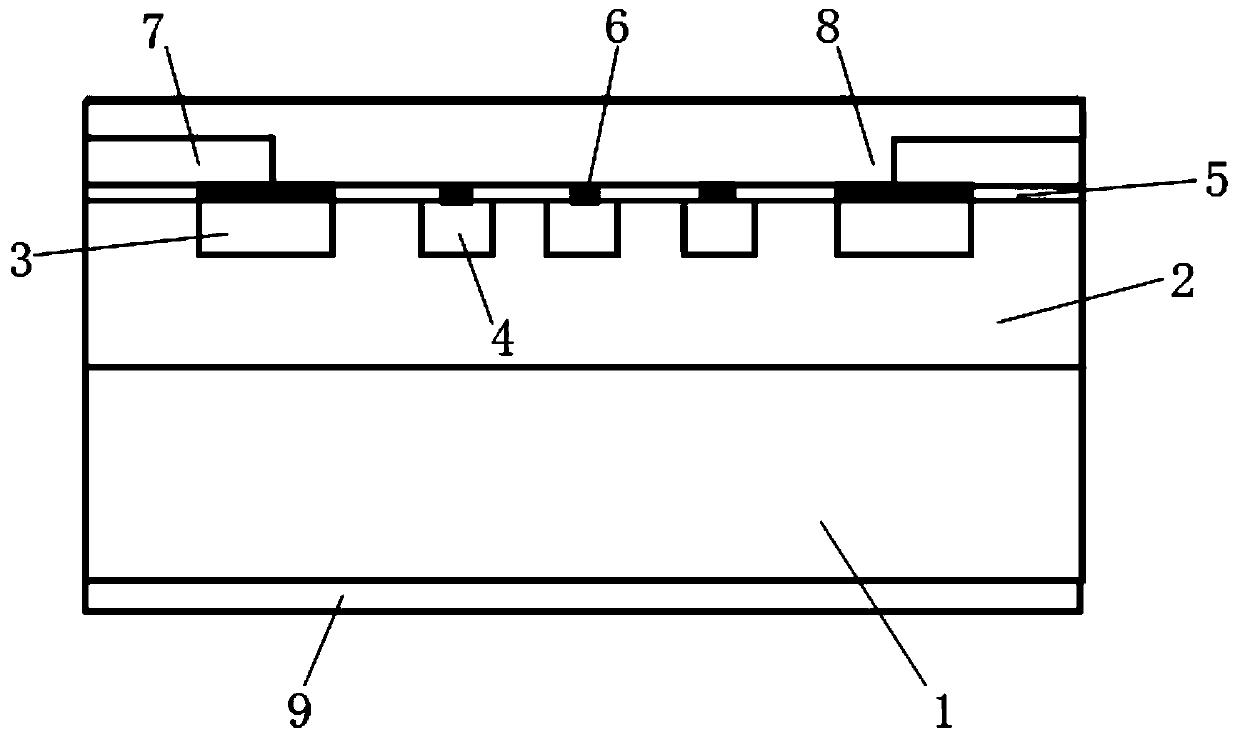

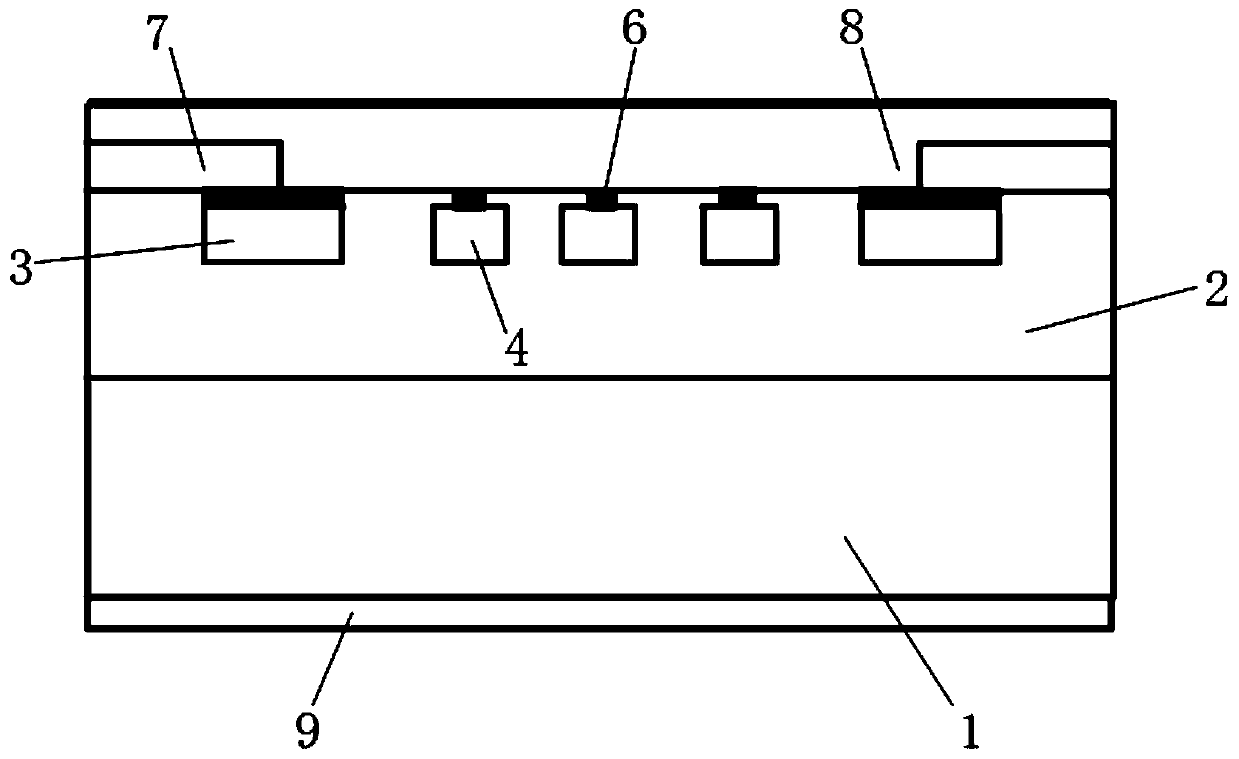

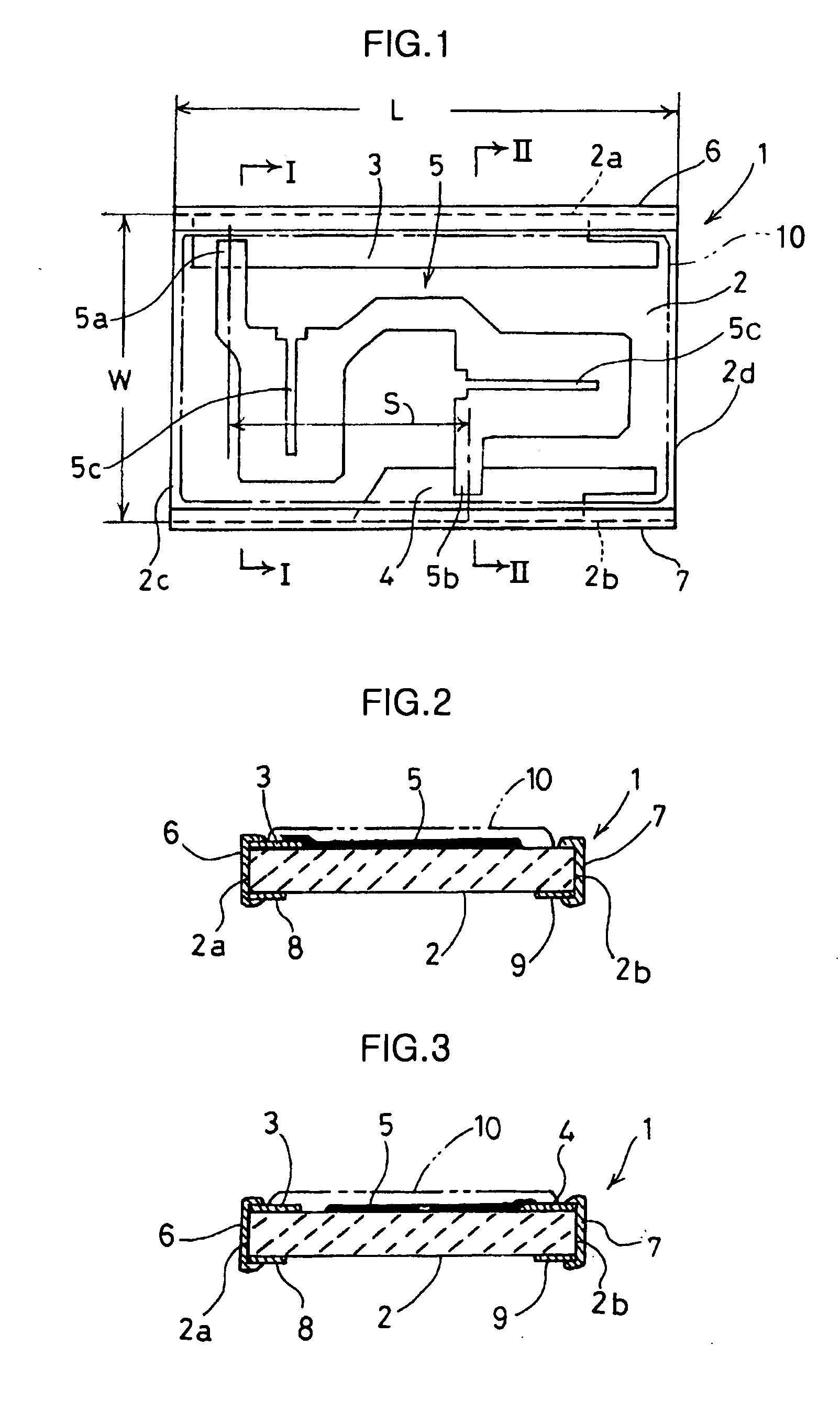

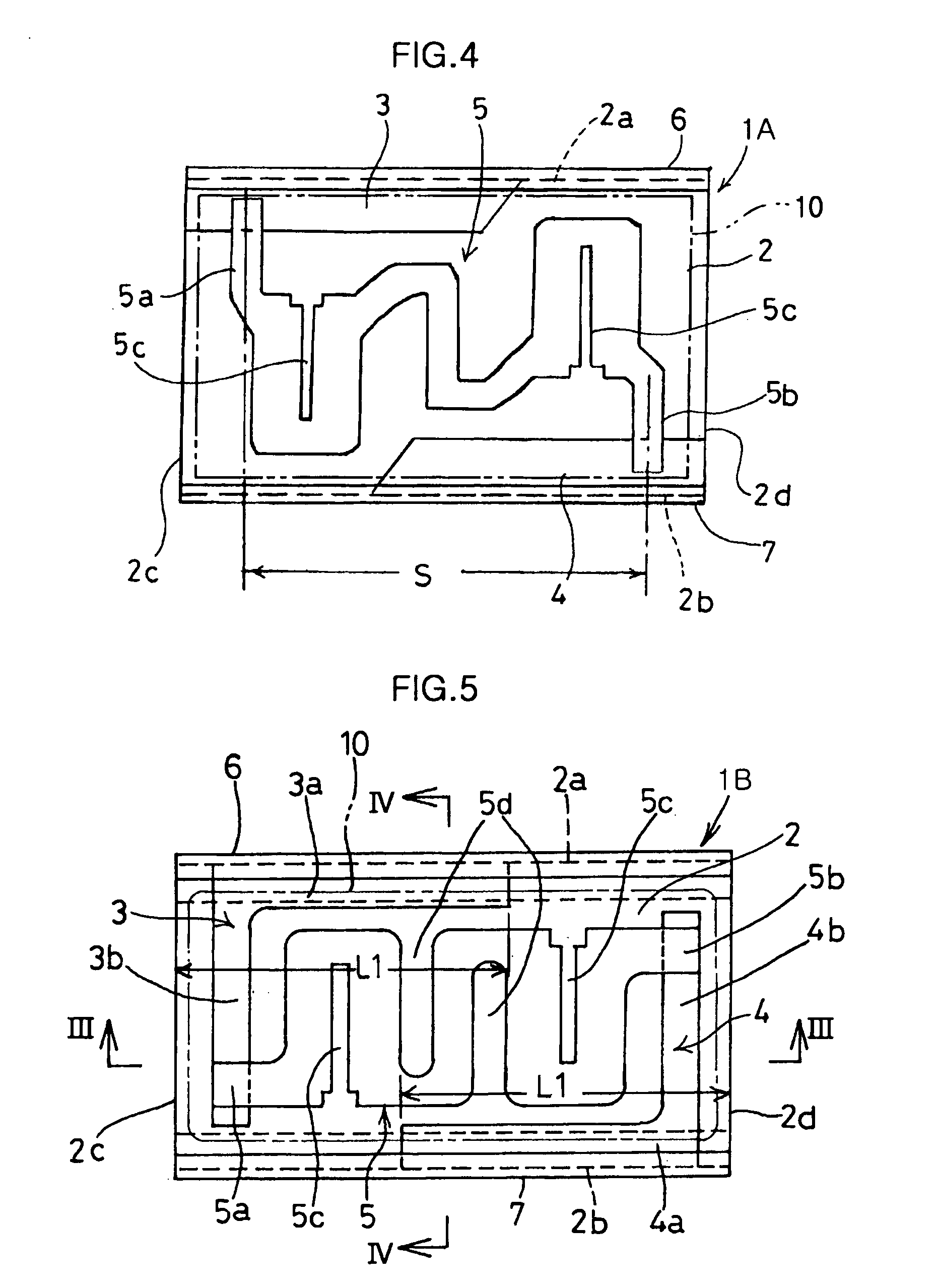

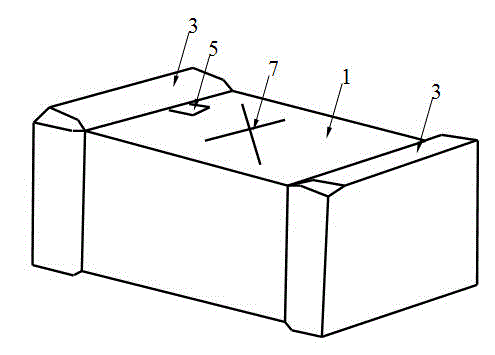

ActiveUS7940158B2Improve anti-surge performanceShorten the timeResistor chip manufactureResistor detailsEngineeringElectrical and Electronics engineering

A chip resistor (1) according to the present invention includes an insulating substrate (2) which is in the form of an elongated rectangle in plan view, a pair of upper electrodes (3, 4) in the form of a strip formed on the upper surface of the insulating substrate (2) at portions adjacent to the long side surfaces of the insulating substrate to extend along the side surfaces, a resistor film (5) formed on the upper surface of the insulating substrate (2) and electrically connected to the upper electrodes (3, 4), and a pair of terminal electrodes (6, 7) formed on the two long side surfaces of the insulating substrate and electrically connected to the upper electrodes (3, 4), respectively. One of two longitudinal ends of the resistor film (5) is connected to one of the upper electrodes (3), whereas the other one of the two longitudinal ends of the resistor film is connected to the other one of the upper electrodes (4). The connection position at which the resistor film (5) is connected to the one of the upper electrodes (3) and the connection position at which the resistor film (5) is connected to the other one of the upper electrodes (4) are spaced from each other by a predetermined distance in the longitudinal direction of the upper surface of the insulating substrate (2).

Owner:ROHM CO LTD

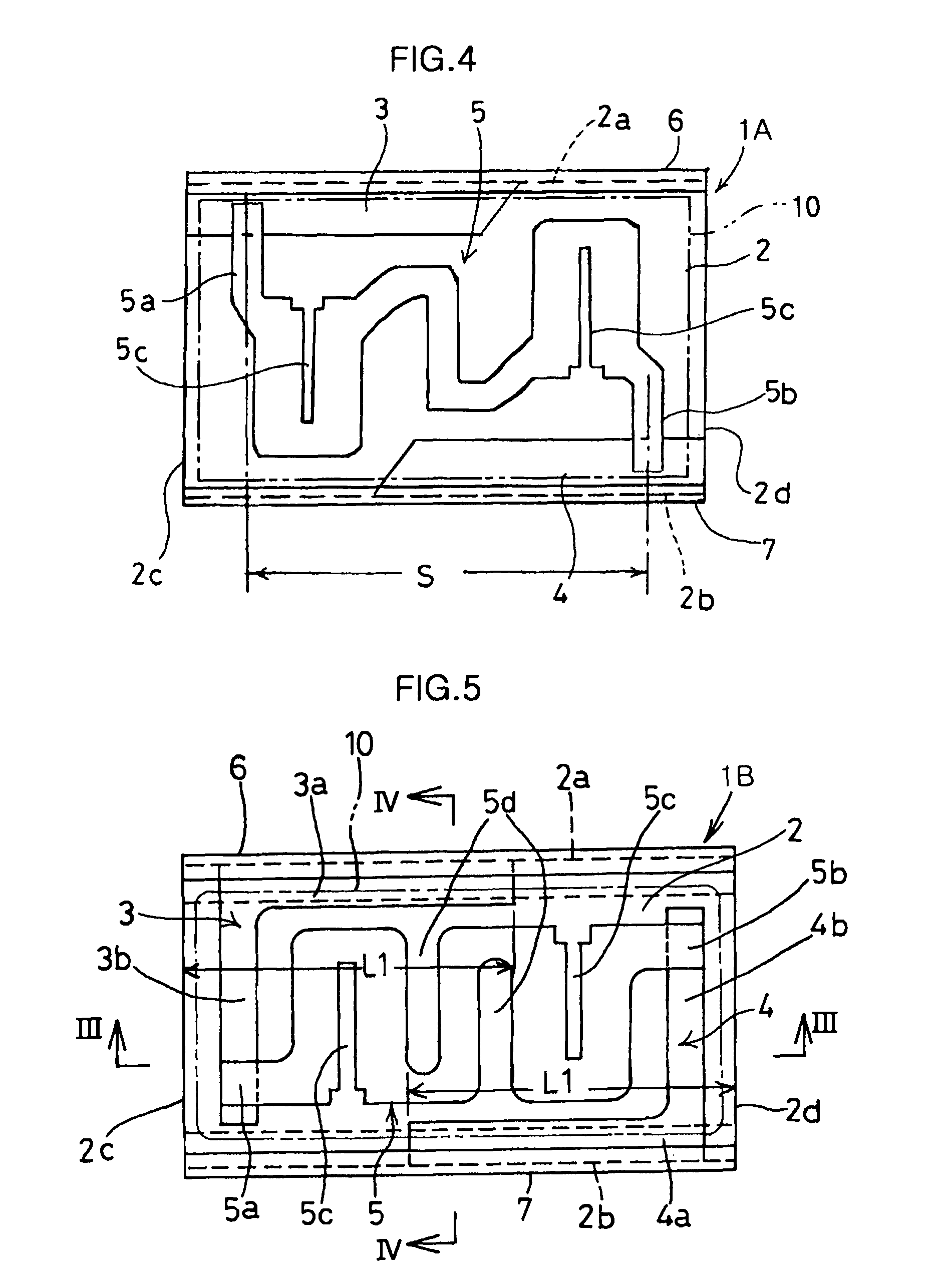

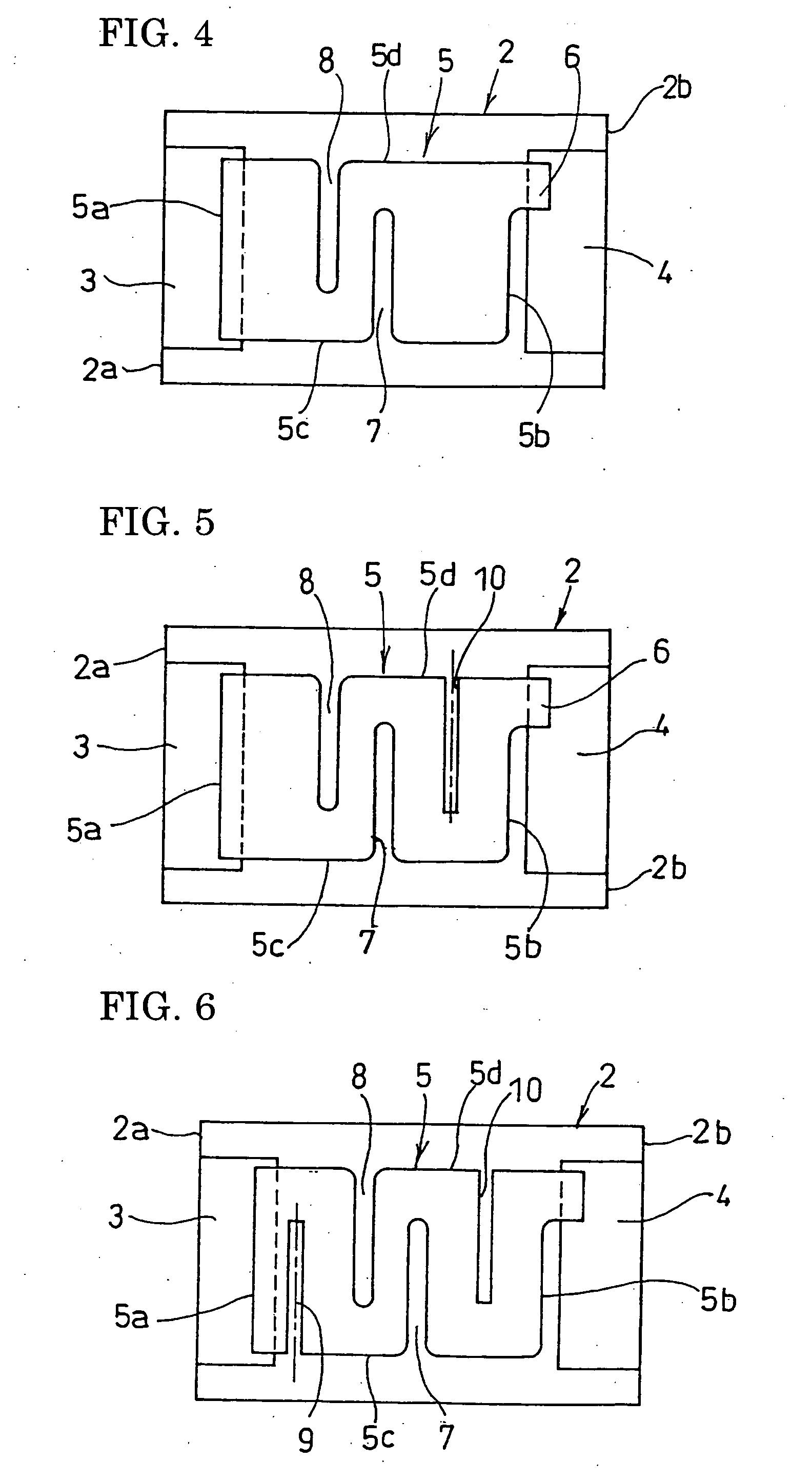

Chip resistor and method of manufacturing the same

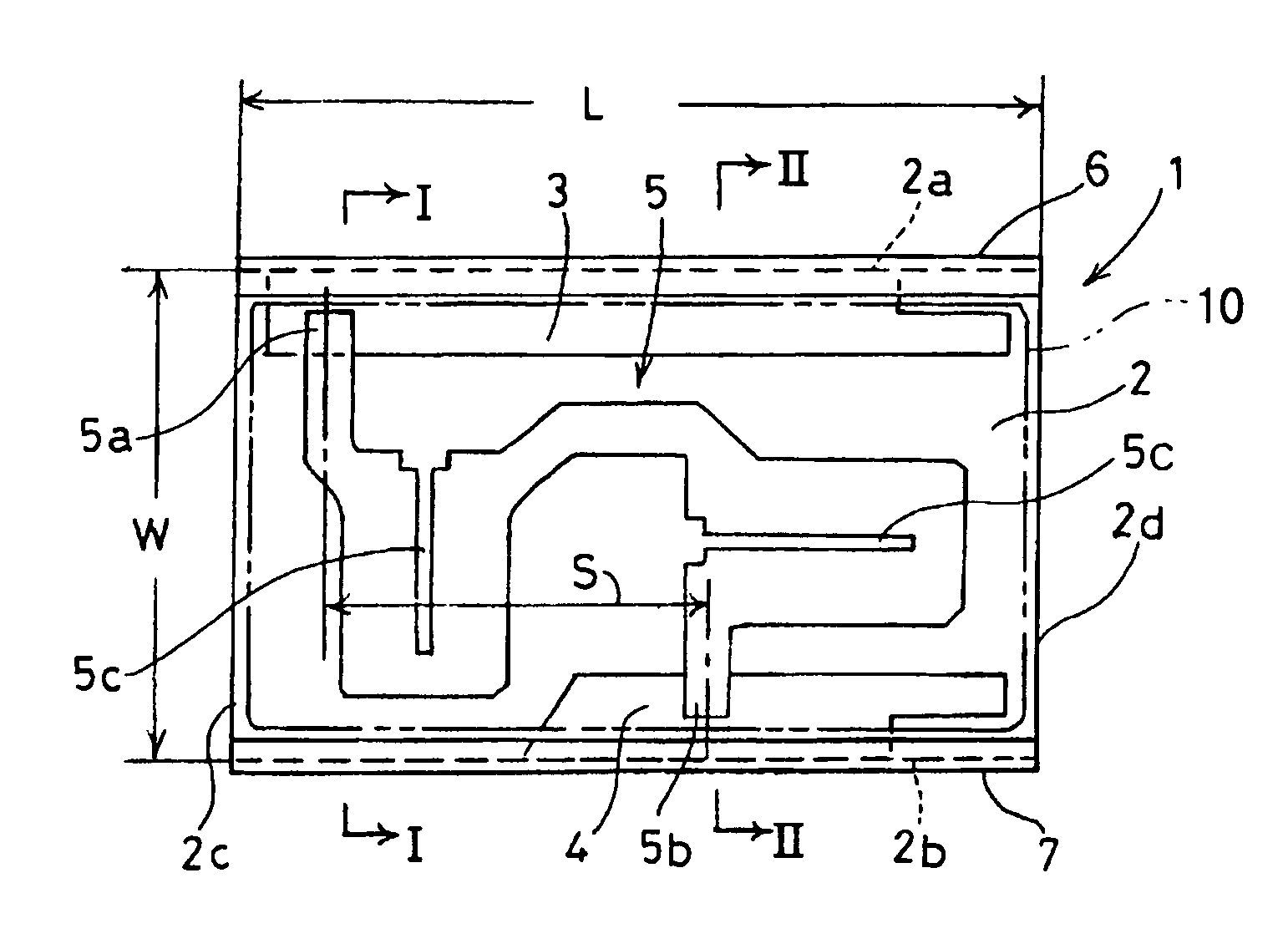

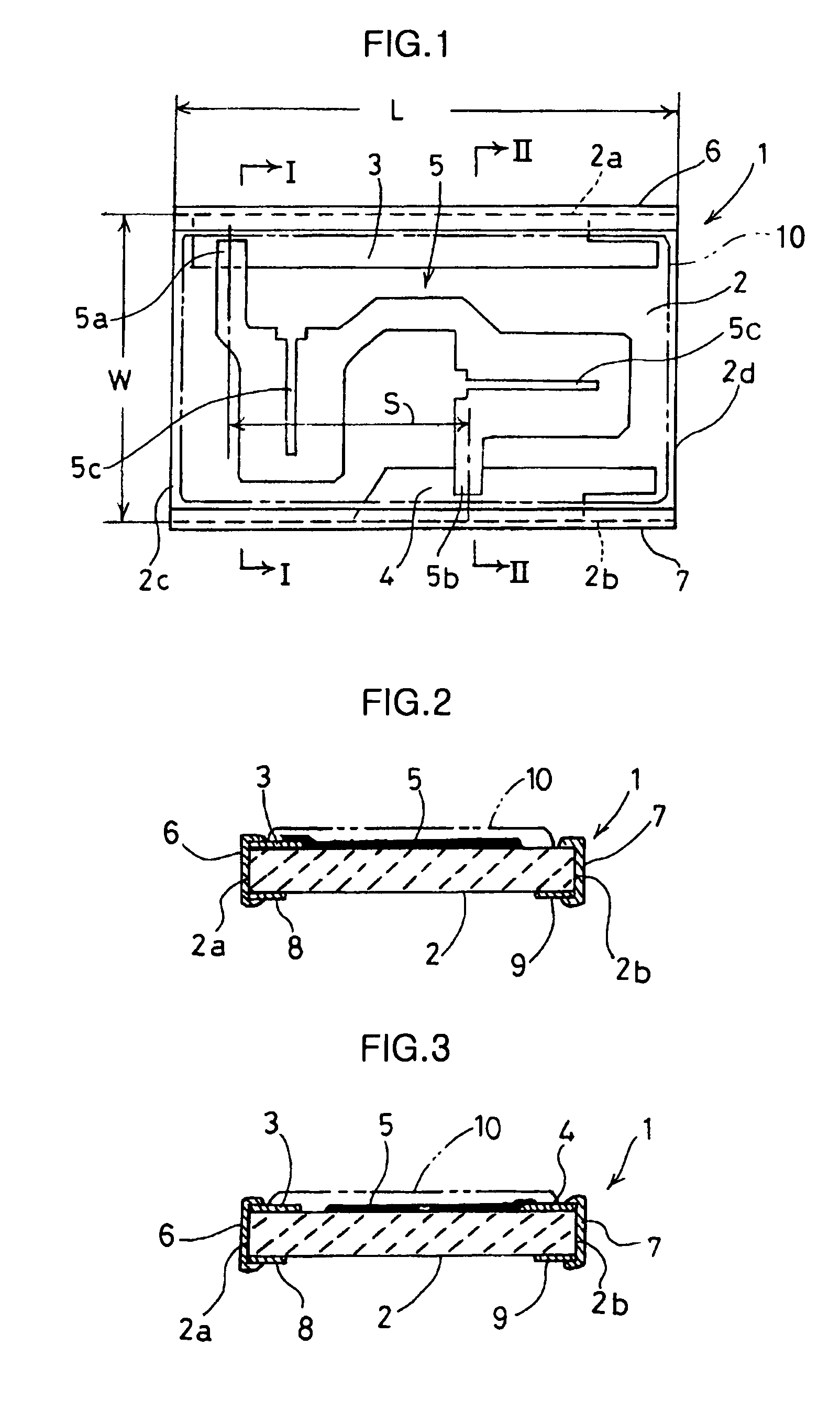

ActiveUS7286039B2Increase the lengthImprove anti-surge performanceElongated resistive elementAlarmsElectrical and Electronics engineeringYield rate

A chip resistor is provided which includes a resistor film 5 formed between a pair of terminal electrodes 2 and 3 on an upper surface of an insulating substrate 2. The resistor film is formed with two inward grooves 7, 8 and two trimming grooves 9, 10 which are alternately provided for causing the current path in the resistor film to have a winding shape. The two inward grooves 7 and 8 are provided approximately at the midpoint between one end edge 5a and the other end edge 5b of the resistor film 5. The trimming groove 9 is provided between the inward groove 8 and the end edge 5a of the resistor film, whereas the other trimming groove 10 is provided between the inward groove 7 and the end edge 5b of the resistor film, whereby the time required for the trimming adjustment to adjust the resistance to a predetermined value is shortened, and the yield rate is reduced to reduce the cost.

Owner:ROHM CO LTD

Preparation method for high-power thin-film capacitor

ActiveCN105914035AHigh dielectric constantUniform depositionThin/thick film capacitorFixed capacitor dielectricEpoxyPhenyl Ethers

The invention discloses a preparation method for a high-power thin-film capacitor. A plastic film is placed in a vacuum high-temperature environment, wherein the temperature of the vacuum high-temperature environment is 1080 to 1120 DEG C and the air pressure of the vacuum high-temperature environment is 0.20 to 0.35 Pa; compound ceramic powder is fused and evaporated and covers a surface of a substrate film; a piece of zinc-aluminium composite metal is evaporated and covers a composite ceramic layer surface to obtain a metalized film electrode; and then the metalized film electrode is wound to obtain a high-power thin-film capacitor. In addition, the plastic film includes the following raw materials, by weight: 55 to 60 parts of polypropylene, 35 to 38 parts of epoxy resin, 22 to 25 parts of terpolycyantoamino-formaldehyde resin, 13 to 16 parts of chlorosulfonated polyethylene, 16 to 19 parts of phenyl ether silicone rubber, 11 to 14 parts of copper oxide, 5 to 8 parts of titanium diboride, 12 to 15 parts of barium sulfate, 6 to 9 parts of glass fibers, 3 to 6 parts of zirconia whisker, 2 to 5 parts of potassium titanate fibers, and 5 to 5.5 parts of silane coupling agents.

Owner:安徽源光电器有限公司

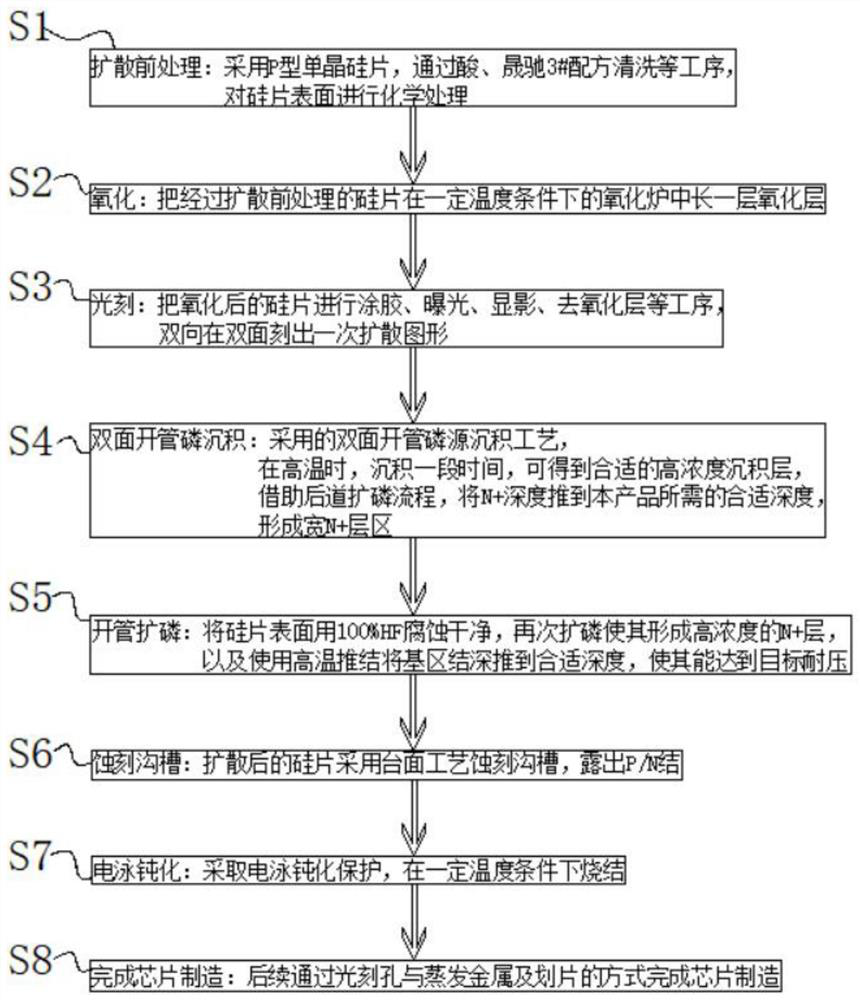

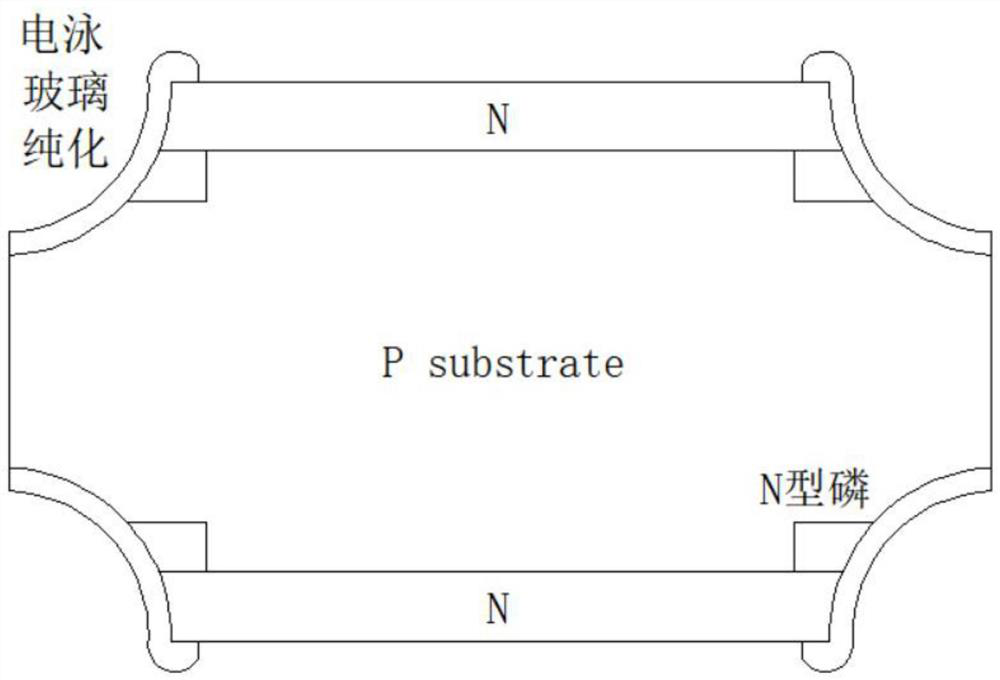

5G base station protection chip manufacturing process

InactiveCN111863616AReduce leakageImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryEngineering

The invention discloses a 5G base station protection chip manufacturing process and particularly relates to a 5G base station protection chip manufacturing process. The process comprises the followingsteps of S1, diffusion pretreatment; S2, oxidation; S4, double-sided tube opening phosphorus deposition; S5, opening a pipe and expanding phosphorus; S6, etching the groove; S7, electrophoresis passivation; and S8, completing chip manufacturing. A chip arranged in the 5G base station protection chip manufacturing process adopts a mesa process, an auxiliary groove structure is designed in an areanear the chip table board, when the highest reverse voltage is applied externally, the P-type base region depletion layer is limited in the base region, the breakdown voltage of the high-voltage transient voltage suppressor is higher than the breakdown voltage of the main body junction, so the main body junction region is broken down firstly, the leakage current is distributed in the main body junction region, the auxiliary junction region is not broken down, the voltage resistance of the high-voltage transient voltage suppressor is improved, and the surge resistance and reliability of the transient voltage suppressor are improved.

Owner:江苏晟驰微电子有限公司

Chip Resistor and Its Manufacturing Method

ActiveUS20090040011A1Reduce timeCost reductionResistor chip manufactureResistor detailsChip resistorEngineering

A chip resistor (1) according to the present invention includes an insulating substrate (2) which is in the form of an elongated rectangle in plan view, a pair of upper electrodes (3, 4) in the form of a strip formed on the upper surface of the insulating substrate (2) at portions adjacent to the long side surfaces of the insulating substrate to extend along the side surfaces, a resistor film (5) formed on the upper surface of the insulating substrate (2) and electrically connected to the upper electrodes (3, 4), and a pair of terminal electrodes (6, 7) formed on the two long side surfaces of the insulating substrate and electrically connected to the upper electrodes (3, 4), respectively. One of two longitudinal ends of the resistor film (5) is connected to one of the upper electrodes (3), whereas the other one of the two longitudinal ends of the resistor film is connected to the other one of the upper electrodes (4). The connection position at which the resistor film (5) is connected to the one of the upper electrodes (3) and the connection position at which the resistor film (5) is connected to the other one of the upper electrodes (4) are spaced from each other by a predetermined distance in the longitudinal direction of the upper surface of the insulating substrate (2).

Owner:ROHM CO LTD

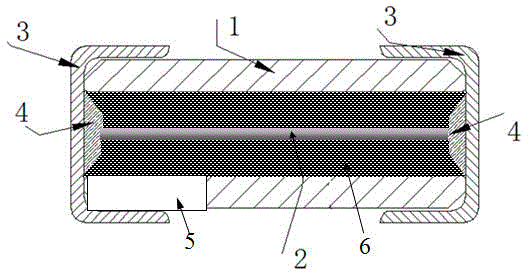

Miniature anti-explosion protection element and manufacturing method thereof

ActiveCN104319208AImprove breaking characteristics and surge resistanceImprove breaking capacityFuse device manufactureInterior spaceExplosion protection

The invention discloses a miniature anti-explosion protection element and a manufacturing method thereof. The element comprises an insulation housing, a metal melt, end electrodes and arc extinction materials, wherein end electrodes wrap two ends of the insulation housing, the metal melt is suspended inside the insulation housing, two ends of the metal melt are respectively and electrically connected with the two end electrodes wrapping the insulation housing, the arc extinction materials are arranged between the insulation housing and the metal melt, at least one of the ends of the insulation housing is communicated with gaps exposed out of the end electrodes, in the internal space and external space of the insulation housing, and the arc extinction materials contain fumed silica and silica gel. The two ends of the element are full of the arc extinction materials, filling time is short, the fumed silica having the powerful adsorption capacity plays a main role on disjunction and arc extinction, the fumed silica is equivalent to air in heat conductivity, larger-wire-diameter meta melts can be adopted under the condition of the same disjunction capacity requirement, and surge resistant capacity of products is improved.

Owner:NANJING SART SCI & TECH DEV

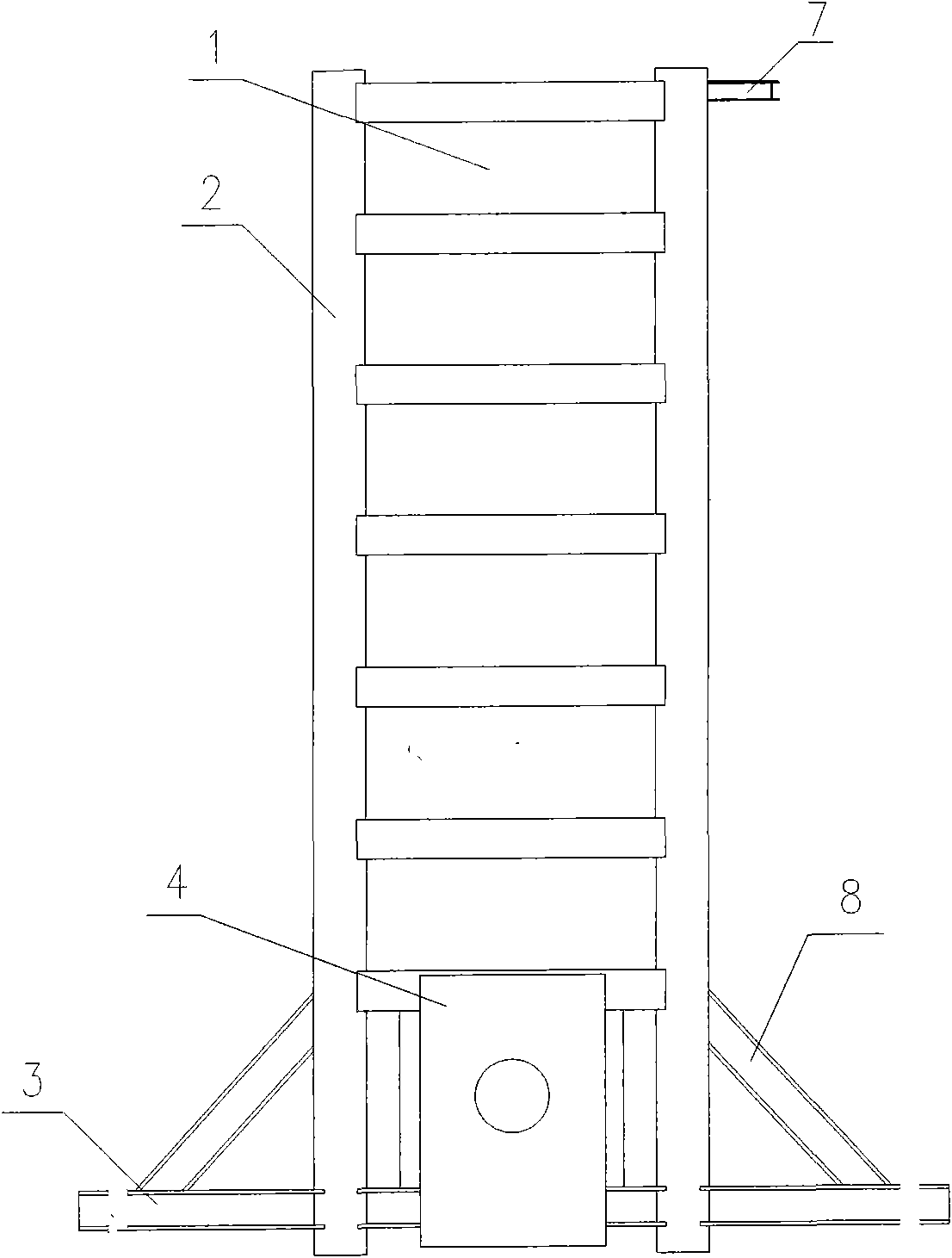

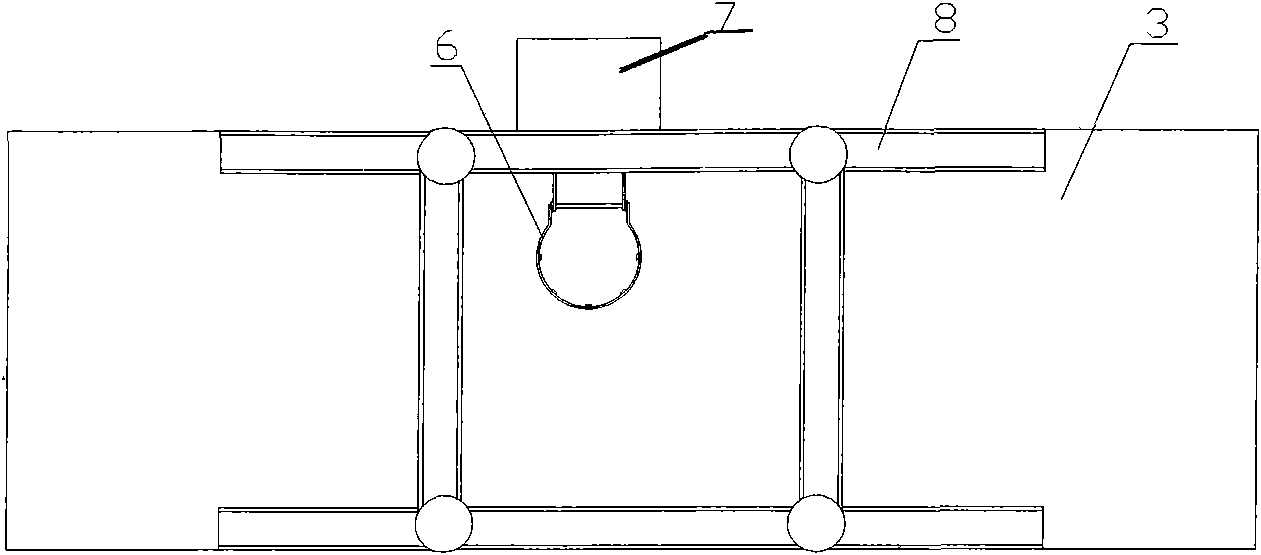

Gravity-type atmospheric dry chamber

InactiveCN101684869ASimple structural designAcceleratePipe laying and repairEngineeringSubmarine pipeline

A gravity-type atmospheric dry chamber is provided with a chamber body, wherein the chamber body is a steel-structured box-shaped body with an opening at the upper end, and the front surface and the bottom of the chamber body are respectively provided with an air-tight door. The gravity-type atmospheric dry chamber is characterized in that both sides of the lower end of the chamber body are respectively provided and connected with an anti-sinking plate which is perpendicular to the chamber body, and the anti-sinking plates are connected with the chamber body by reinforcing rib plates. The invention has the advantages of simple structural design, short positioning time, convenient and rapid disassembly, high working stability, and high safety and reliability; the chamber body provides a dry working environment for pipeline maintenance work, so that operators can do normal welding work in the dry chamber; the chamber body can be quickly installed and bottomed without the restrictions ofwater areas and working site environment; and the dry chamber can shorten the construction time for subsea pipeline maintenance to a great extent.

Owner:CHINA NAT OFFSHORE OIL CORP +1

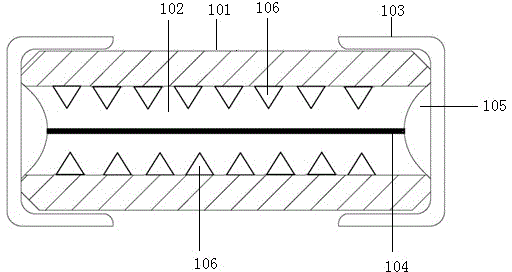

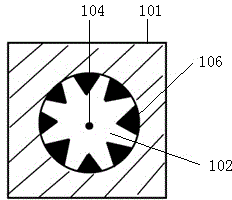

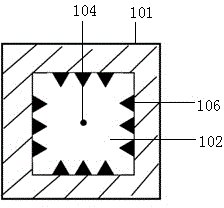

Protecting element

ActiveCN104599917AImprove breaking capacityAvoid damageEmergency protective devicesWave shapeEngineering

The invention discloses a protecting element which comprises an insulating body, a melt and electrodes. The insulating body covers the meltable part of the melt. The electrodes are disposed at two ends of the insulating body. Two ends of the melt are electrically connected with the electrodes. A wave absorbing structure is disposed around the melt in the insulating body and provided with a plurality of protrusions facing the melt. Distance is reserved between the wave absorbing structure and the melt. The protecting element has the advantages that the shape of the melt is improved, the wave absorbing structure which can resist impact is designed, energy waveforms can be destroyed, impact energy can be dissipated to the periphery to achieve wave (energy) absorbing, the breaking performance of the protecting element can be at least doubled by the wave absorbing structure, and the protecting element is simple in manufacturing process and suitable for batch production.

Owner:NANJING SART SCI & TECH DEV

Resistor element and resistor element assembly

ActiveUS20180061533A1Improve anti-surge performanceResistor chip manufactureResistor terminals/electrodesElectrostatic dischargeResistor

A resistor element includes a base substrate having first and second surfaces opposing each other; a resistor layer disposed on the first surface of the base substrate; first and second terminals disposed on opposing end portions of the base substrate, respectively, and electrically connected to opposing sides of the resistor layer, respectively; a third terminal disposed between the first terminal and the second terminal on the second surface of the base substrate and spaced apart from the first terminal and the second terminal; and electrostatic discharge (ESD)-preventing members connecting the first terminal and the third terminal to each other and connecting the second terminal and the third terminal to each other.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Transient voltage suppressor (TVS) chip and manufacturing method

PendingCN107346790AReduce thicknessReduce widthSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringTransient voltage suppressor

The invention discloses a transient voltage suppressor (TVS) chip and a manufacturing method. The transient voltage suppressor (TVS) chip and the manufacturing method have the advantages that: an auxiliary channel structure is designed in a region near a chip table-board, an N-type base depletion layer is limited within a base region when a highest reverse voltage is applied externally, a breakdown voltage of the auxiliary channel structure is higher than a breakdown voltage of a main body junction, so that a main body junction region is broken down at first, a leak current is distributed in the main body junction region, and an auxiliary junction region is not broken down, thereby improving the voltage resistance of a high-voltage transient voltage suppressor, and enhancing surge resistance and reliability of the transient voltage suppressor; a P-type region depletion layer structure is additionally arranged, thus a concentration structure curve of a P-type diffusion region is changed, and a highest reverse voltage resistance value of the device is increased to 800 V or more by utilizing additional voltage resistance of the depletion layer width of the P-type diffusion region; the width of an N+ region is increased; a high-conductivity region is widened, the capability of the N+ region in emitting electrons to the N base region is enhanced, and the positive peak pressure drop of the chip is reduced to 1.22 V and below.

Owner:杭州东沃电子科技有限公司

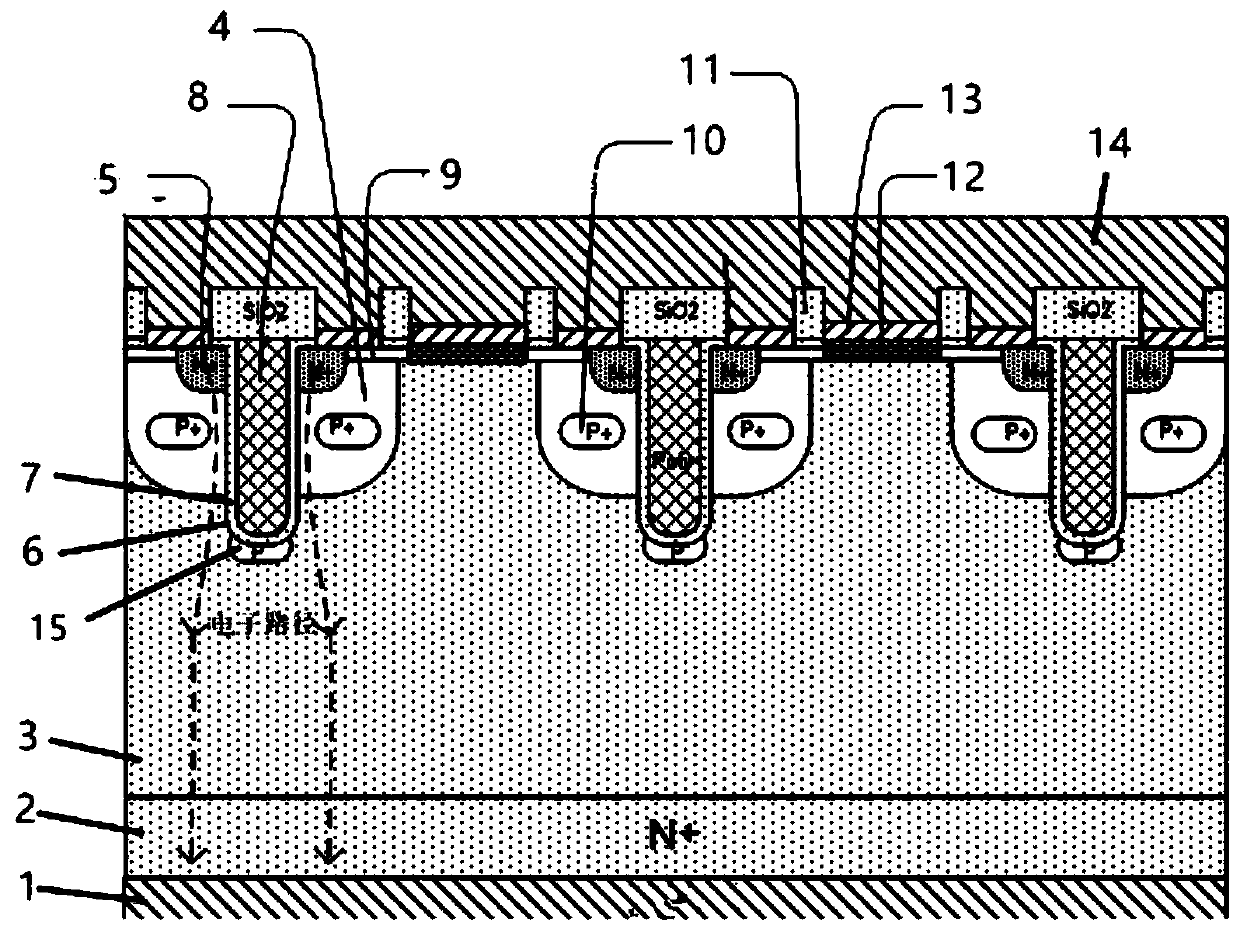

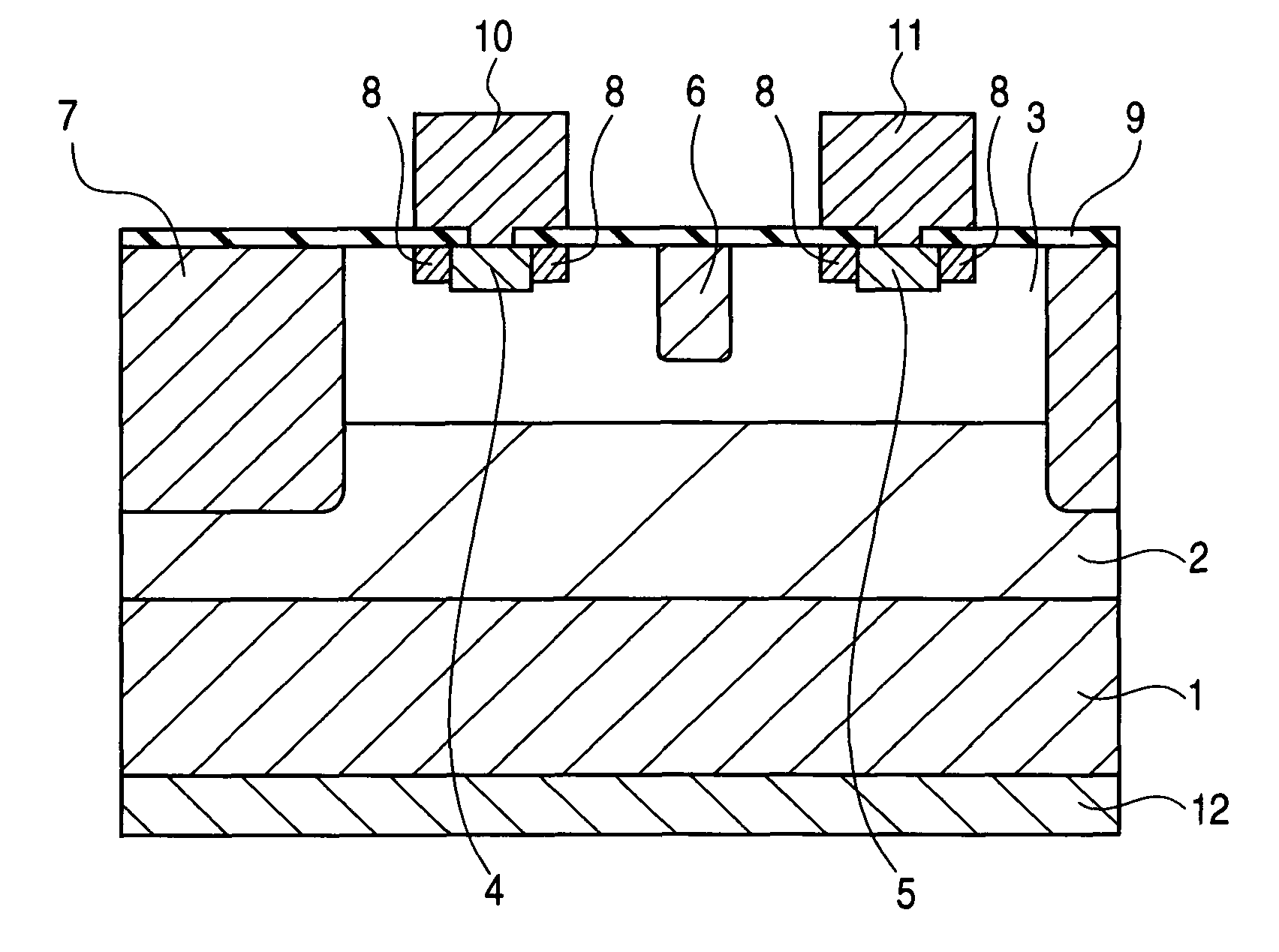

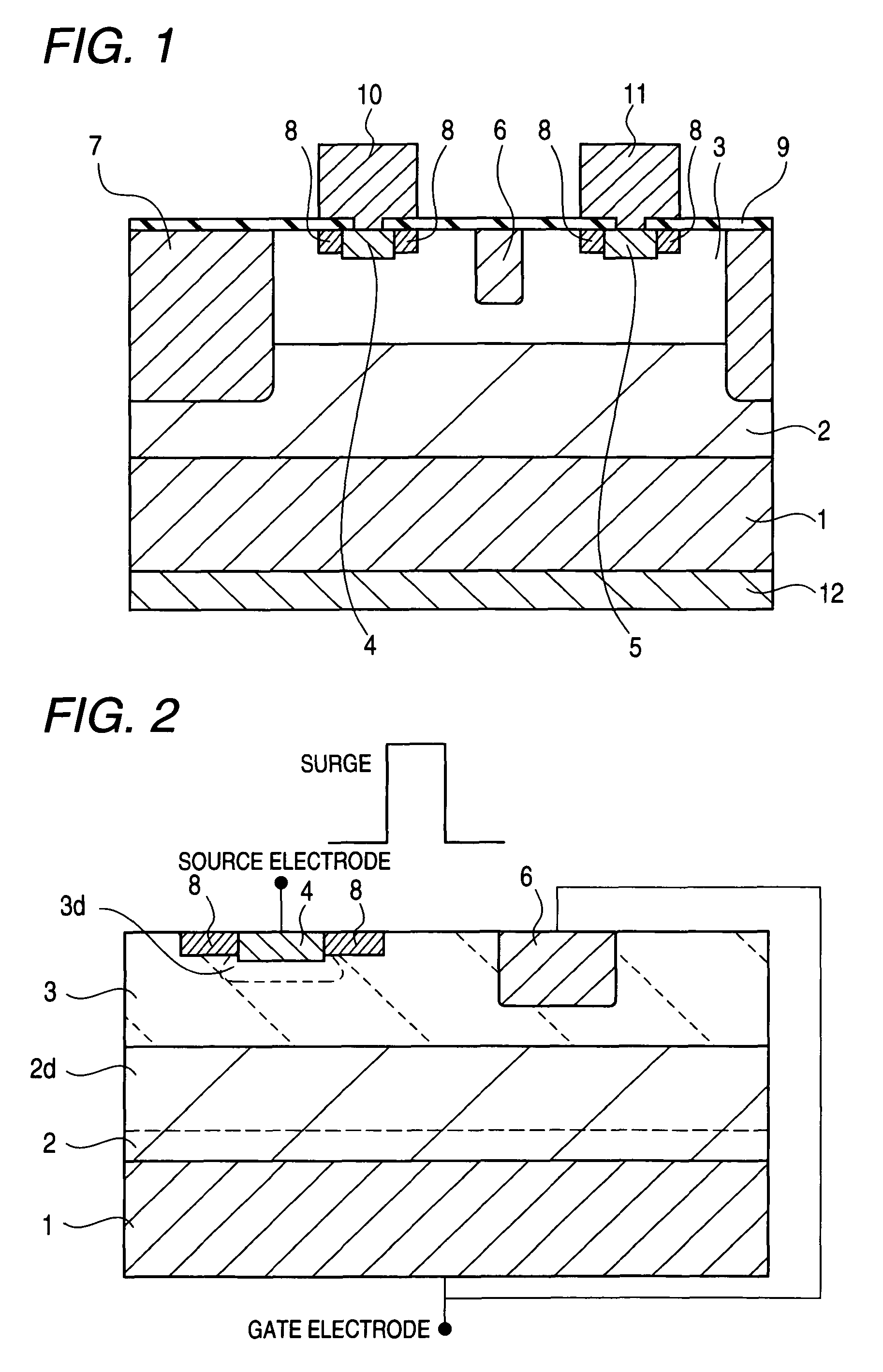

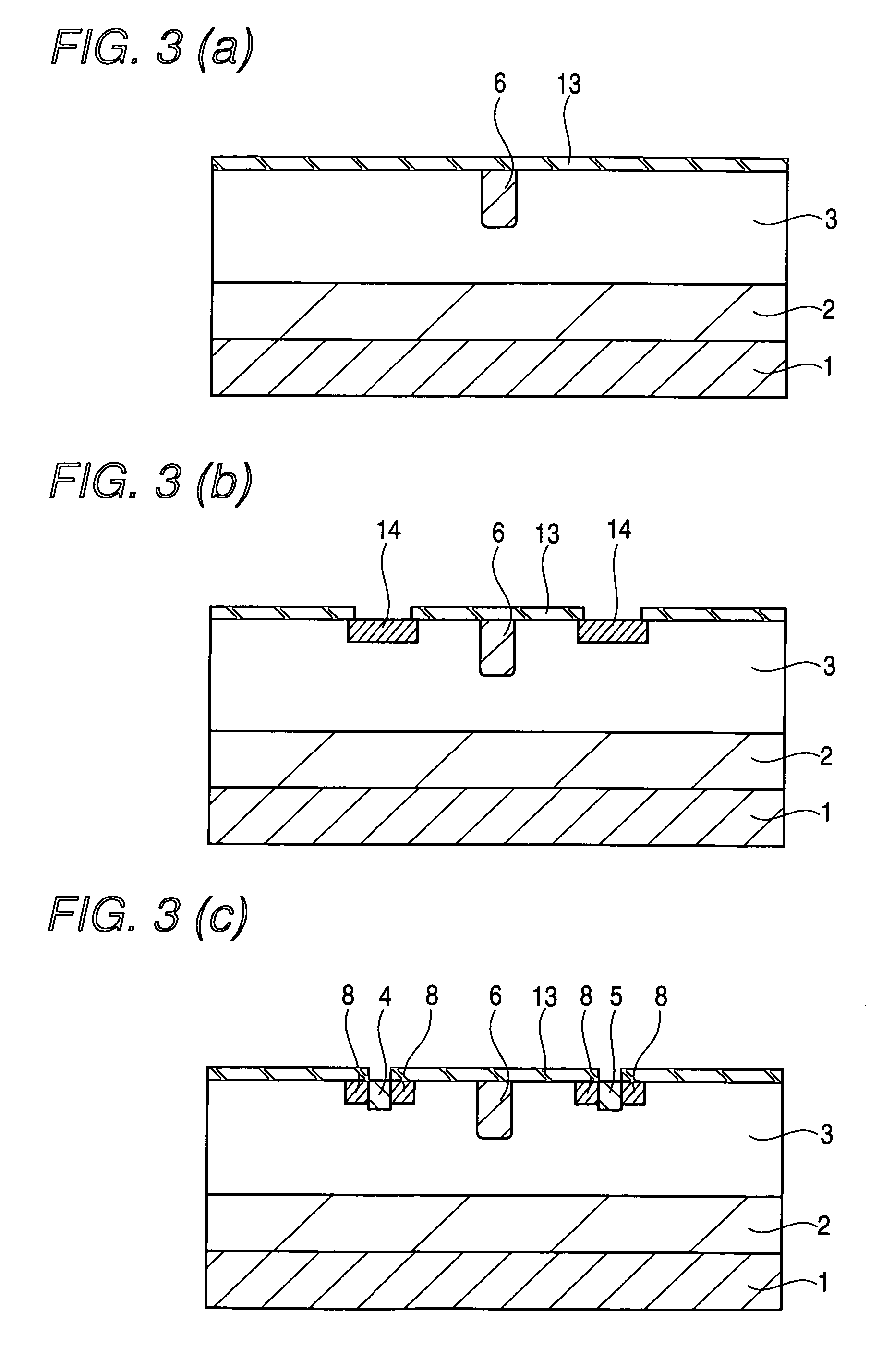

Semiconductor device including a JFET having a short-circuit preventing layer

To improve the surge resistance of J-FET, a P-type epitaxial layer 2 and an N-type epitaxial layer 3 are formed on a P++-conductive substrate 1; N+-conductive source diffusion layer 4 and drain diffusion layer 5, and a p+-conductive gate diffusion layer 6 are formed in the N-type epitaxial layer 3; and a short-circuit preventing layer 8 of a reversed conduction-type diffusion layer is formed adjacent to the side walls of the source diffusion layer 4 and the drain diffusion layer 5. Having the constitution, the punch-through to be caused by surge voltage is prevented in the surface region of the device, and the surge resistance thereof is improved. Via the holes formed in a protective insulation film 9 on the surface of the device, a source electrode 10 connected to the source diffusion layer 4, and a drain electrode 11 connected to the drain diffusion layer 5 are formed on the surface side of the device. A gate electrode 12 is formed on the back of the substrate 1, and this is connected to the gate diffusion layer 6 via a contact diffusion layer 7 formed in the device.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

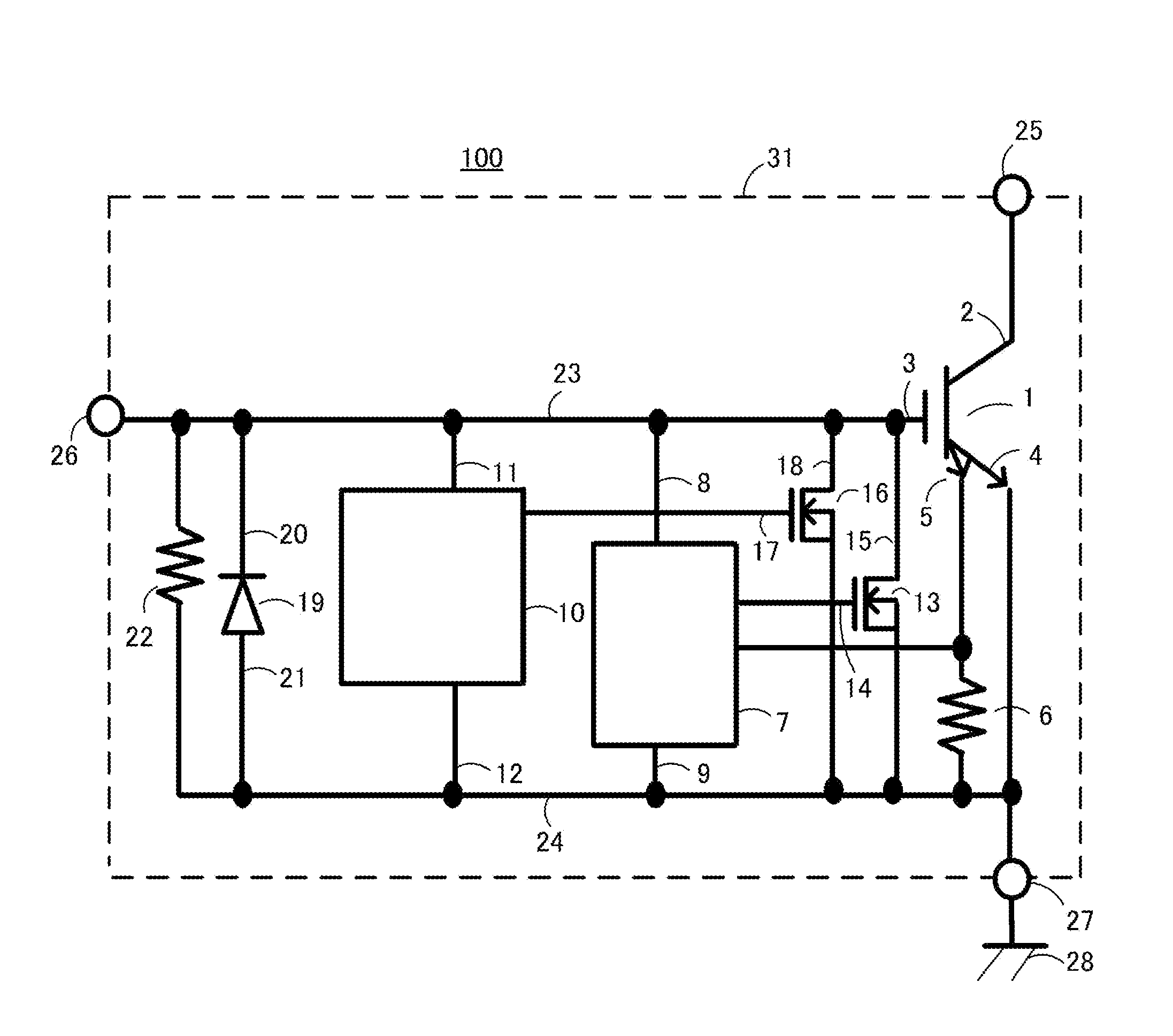

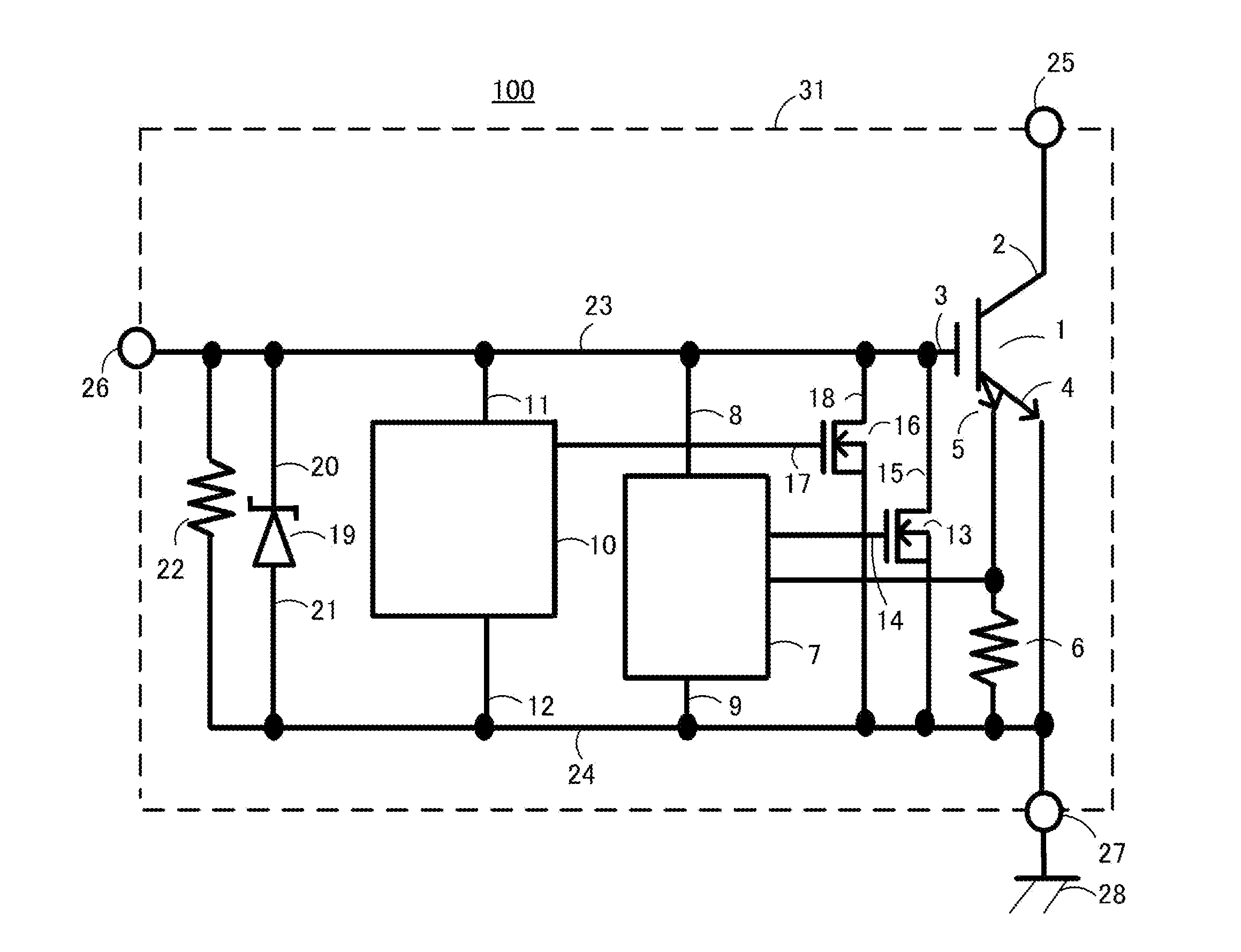

Single chip igniter and internal combustion engine ignition device

ActiveUS9447767B2Low working voltageImprove noise marginTransistorSolid-state devicesMicrocontrollerHysteresis

Aspects of the invention are directed to a single chip igniter such that it is possible to realize a reduction in operating voltage, an increase in noise tolerance, a reduction in size, and a reduction in cost. By reducing the gate threshold voltage of a MOS transistor, and reducing the operating voltages of a current limiter circuit, an overheat detector circuit, a timer circuit, an overvoltage protection circuit, an input hysteresis circuit, and the like, it is possible to reduce the operating voltage of a single chip igniter. In some aspects of the invention, the effective gate voltage of the MOS transistor is 1V or more, and the channel length of the MOS transistor is 4 μm or less. Also, in some aspects of the invention, the thickness of a gate oxide film of the MOS transistor is 5 nm or more, 25 nm or less.

Owner:FUJI ELECTRIC CO LTD

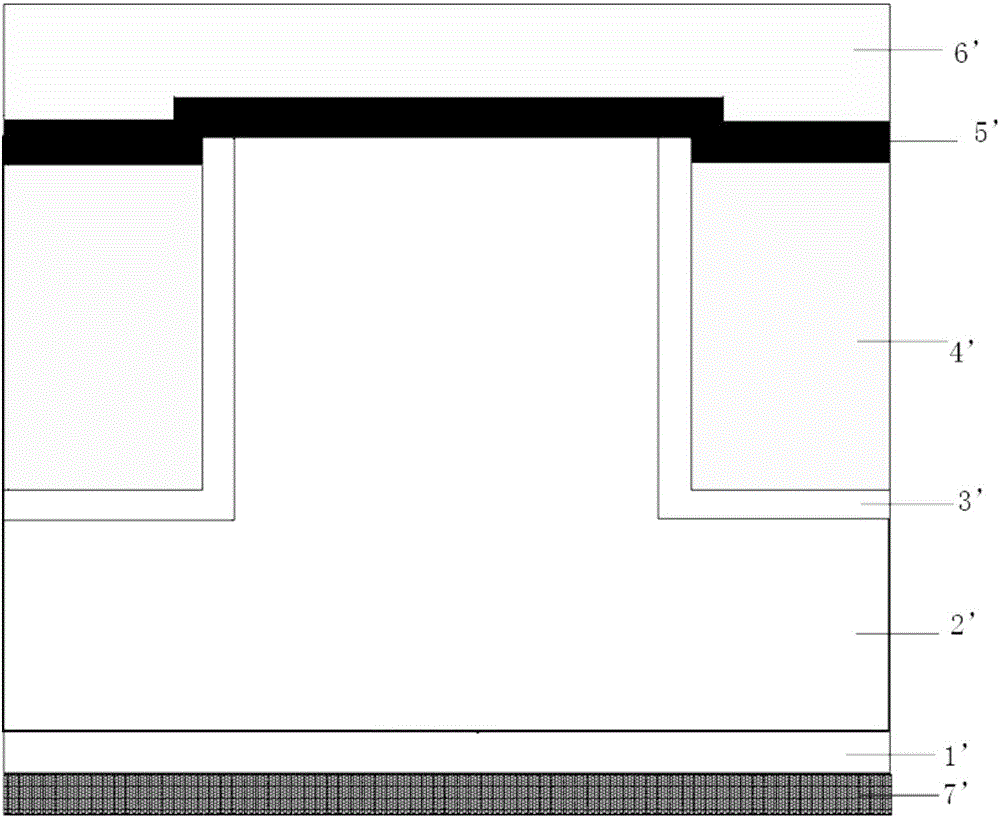

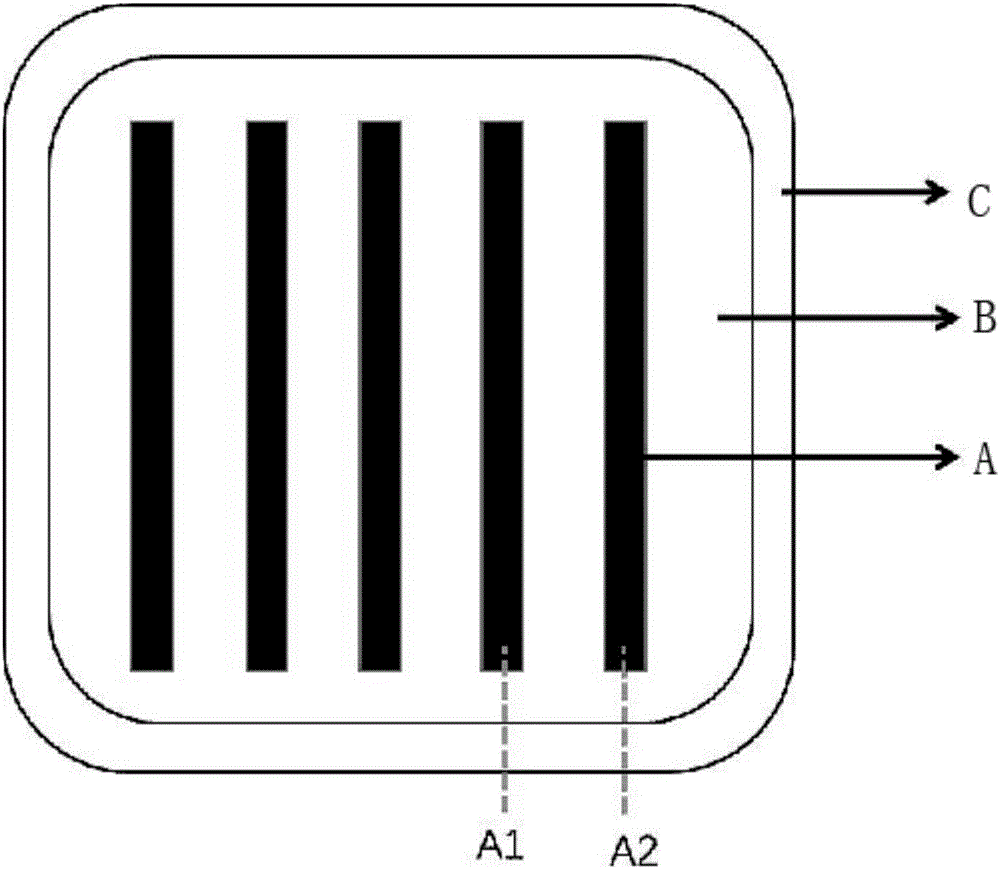

Groove-type barrier schottky structure for optimizing electric field on surface and manufacturing method of groove-type barrier schottky structure

InactiveCN106449774AReduce leakageImprove anti-surge performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueSemiconductor

The invention relates to a groove-type barrier schottky structure for optimizing an electric field on the surface and a manufacturing method of the groove-type barrier schottky structure. The groove-type barrier schottky structure comprises a cellular groove, an active region and a terminal pressure ring which are located on a semiconductor substrate, wherein the groove-type barrier schottky structure is characterized in that the section of the groove-type barrier schottky structure is provided with an N-type substrate, an N-type epitaxial layer, a barrier metal located on the upper surface of the N-type epitaxial layer, a front metal and a back metal; the cellular groove comprises a groove in the upper part of the N-type epitaxial layer, an oxide layer grows on the inner wall and the top surface of the groove, conductive polycrystalline silicon is deposited into an inner cavity of the groove and a polycrystalline silicon shielding layer is arranged on the oxide layer on the top surface of the groove; and a P-type injection region is formed at the lower part of the barrier metal in the active region and is located at the upper part of the N-type epitaxial layer. According to the groove-type barrier schottky structure, a peak electric field on the surface can be optimized; the compression ability of the barrier metal on the surface is improved; electric leakage of a device is reduced; and the surge capacity and the high-temperature reliability are improved.

Owner:YANGZHOU YANGJIE ELECTRONIC TECH CO LTD

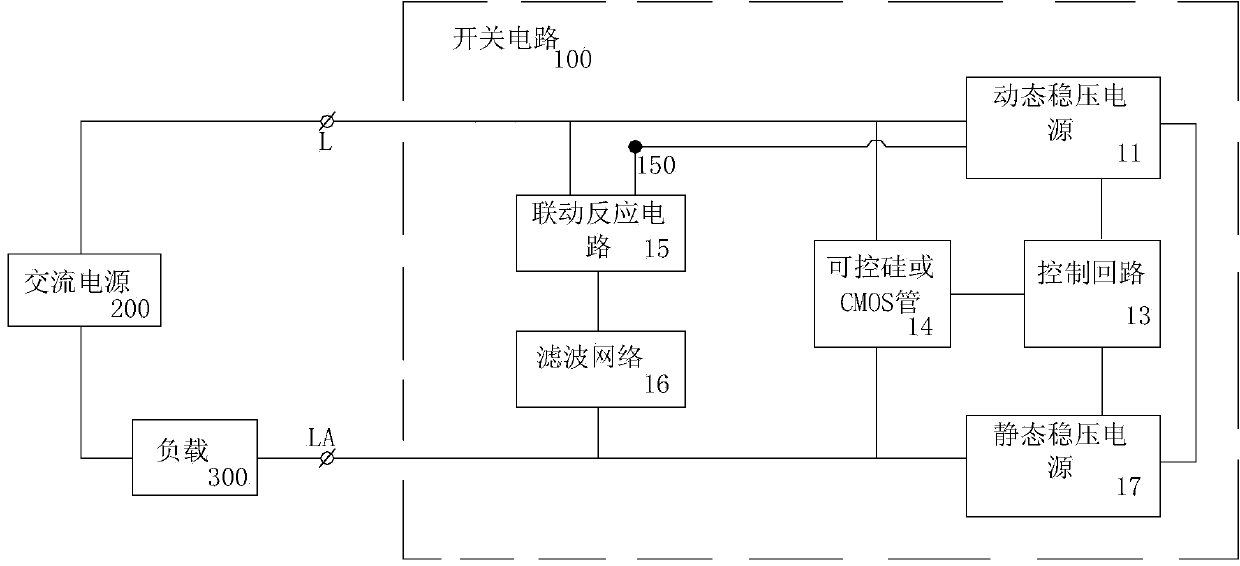

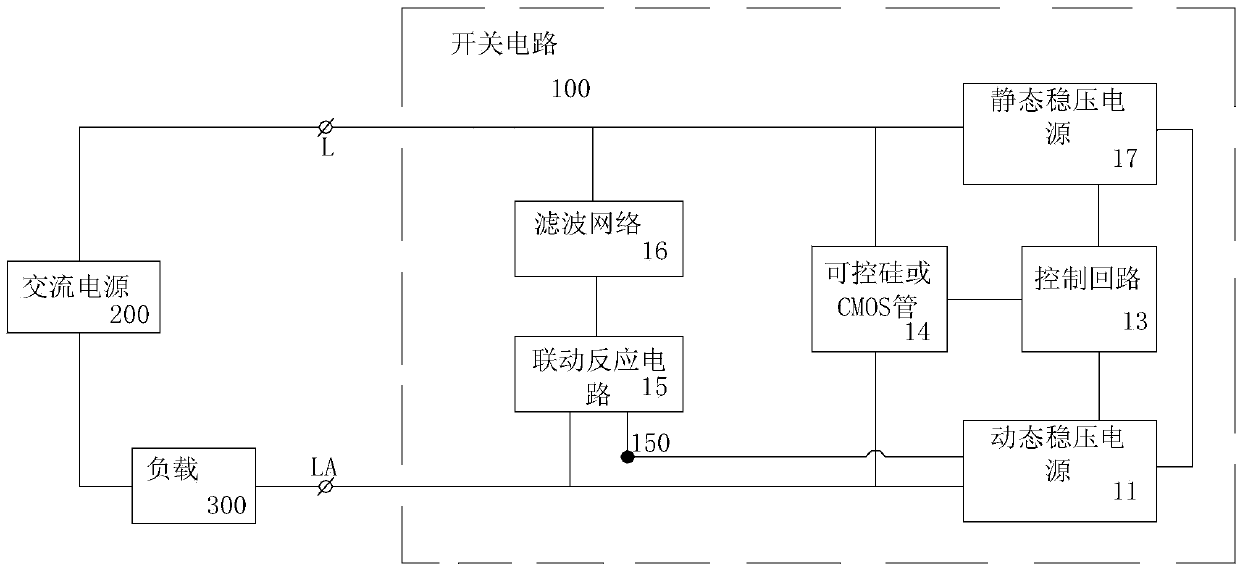

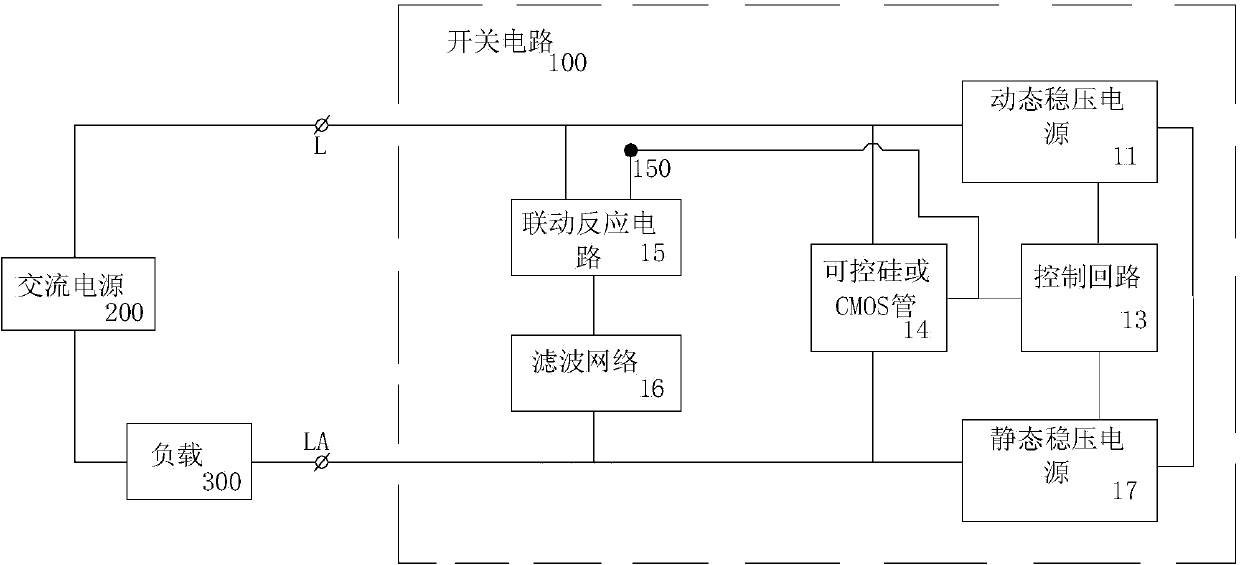

Switching circuit capable of reducing electromagnetic interference

ActiveCN104202026AImprove anti-surge performanceReduce electromagnetic interferenceElectronic switchingCMOSElectromagnetic interference

The invention discloses a switching circuit capable of reducing electromagnetic interference. The switching circuit comprises a first terminal and a second terminal which are respectively connected to an alternating current power supply and a load, a control loop which is connected between the first terminal and the second terminal, a dynamic voltage-stabilized source and a static voltage-stabilized source which are connected between the two terminals in series and are used for supplying the power to the control loop, and a controlled silicon or a CMOS (Complementary Metal Oxide Semiconductor) tube which is connected between the two terminals in series and is controlled by the control loop, wherein a current main loop of the switching circuit is formed by the first terminal, the second terminal, the control loop, the dynamic voltage-stabilized source, the static voltage-stabilized source and the controlled silicon or the CMOS tube. The switching circuit further comprises a linked switching circuit merging into the current main loop, and the linked switching circuit comprises a filter network used for reducing the electromagnetic interference and a linked reaction circuit used for controlling synchronous linkage of the filter network and the switching circuit. The switching circuit is designed for the electromagnetic interference problem caused by adopting the controlled silicon or the CMOS tube as a main loop, and provides a scheme, which is easily controlled and low in cost, and is capable of better solving the problem of electromagnetic compatibility, and the linked switching circuit is guaranteed to have no standby power consumption.

Owner:ZHEJIANG CHINT BUILDING ELECTRICS

Diamond inclined mesa heterojunction diode and preparation method thereof

InactiveCN111739945AImprove device current and anti-surge current capabilityImprove device withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunction diodeOhmic contact

The invention discloses a diamond inclined mesa heterojunction diode and a preparation method thereof, and belongs to the technical field of semiconductor power devices. According to the structure, ap-type diamond transition layer (2), a diamond drift layer (3), an inclined table board (4), a groove structure (5), an n-type gallium oxide layer (6) and a Schottky contact electrode (8) are sequentially arranged on the front face of a low-resistance p-type diamond substrate (1), and an ohmic contact electrode (7) is arranged on the back face of the low-resistance p-type diamond substrate (1). According to the invention, the n-type gallium oxide is used for filling the groove to avoid the problem that the n-type doped diamond is formed in a selection region, and meanwhile, gallium oxide growson a table board with an optimized inclination angle to form a heterogeneous PN junction type mixed terminal structure, a PN junction at the terminal is conducted during forward bias to improve the current and surge resistance of a device, and a depletion region is formed during reverse bias to relieve the edge electric field concentration.

Owner:SUN YAT SEN UNIV +1

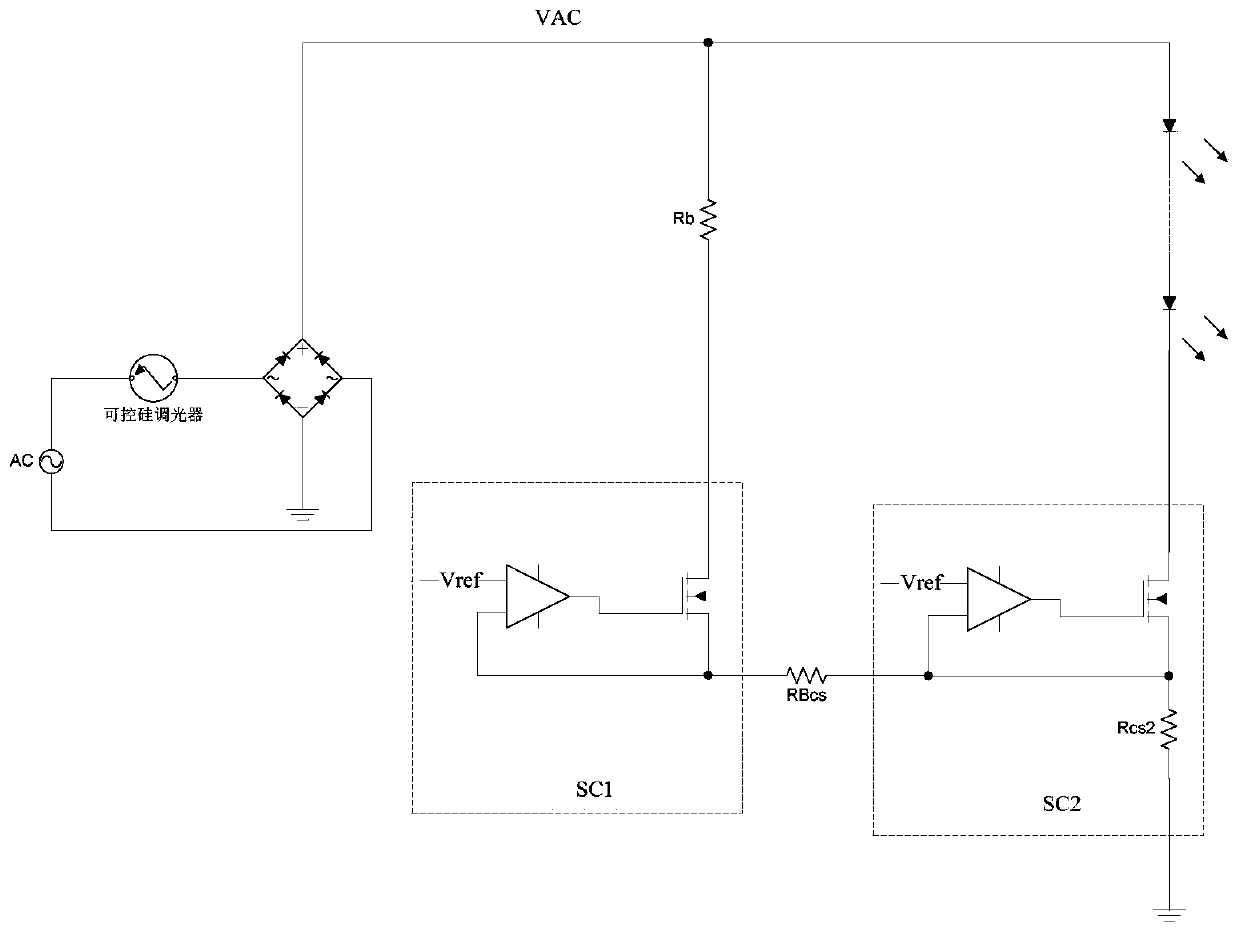

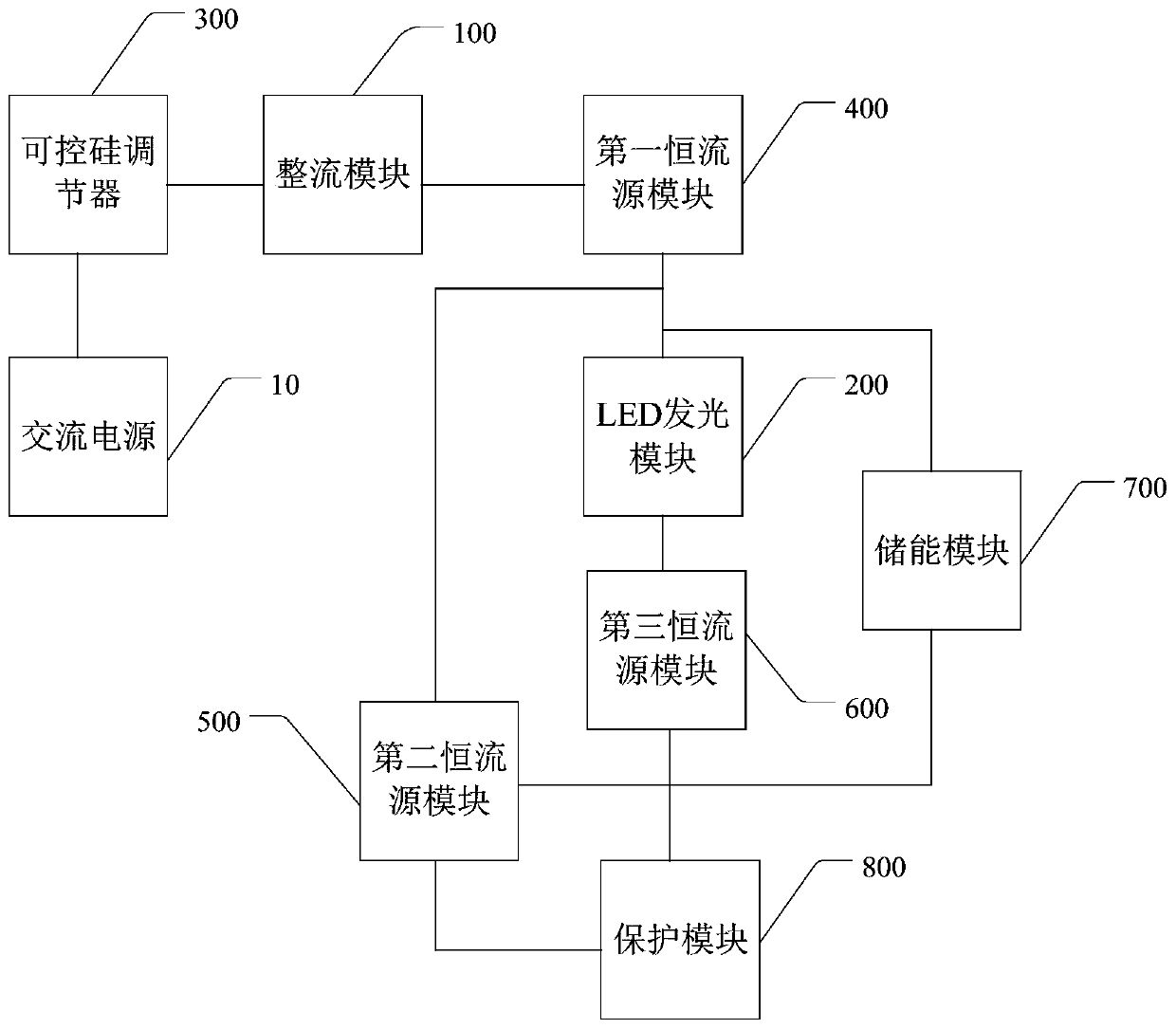

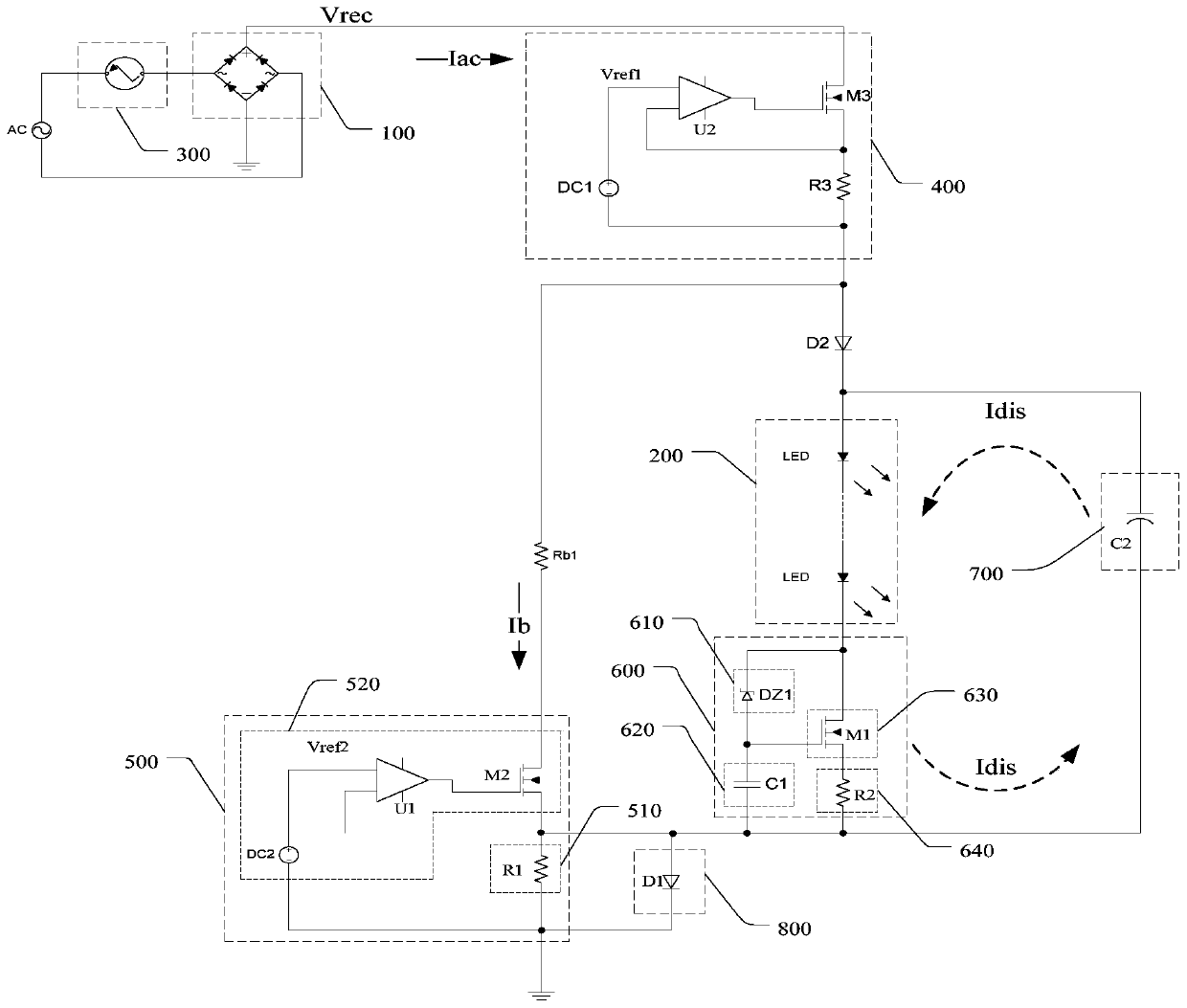

LED drive circuit and drive device

PendingCN110933798AEnsure safetyImprove anti-surge performanceElectrical apparatusSemiconductor lamp usageSilicon-controlled rectifierDriving current

The invention discloses an LED drive circuit and a drive device. The LED drive circuit comprises an LED light-emitting module, a silicon controlled rectifier regulator used for regulating the brightness of the LED light-emitting module, a first constant current source module, a second constant current source module, a third constant current source module, an energy storage module and a protectionmodule, wherein the first constant current source module is used for providing drive current for the LED light-emitting module; the second constant current source module is used for providing discharge current for the silicon controlled rectifier adjusting module and maintaining current for maintaining conduction of the silicon controlled rectifier adjusting module when the on-line voltage is smaller than the conduction voltage of the LED light emitting module; the energy storage module is used for supplying power to the LED light-emitting module when the on-line voltage is smaller than the conduction voltage of the LED light-emitting module; the third constant current source module is used for adjusting the output current of the LED light-emitting module; according to the LED drive circuit, the anti-surge capacity can be effectively improved, and the working safety of the LED drive circuit is guaranteed.

Owner:SHENZHEN SHENDIE SEMICON

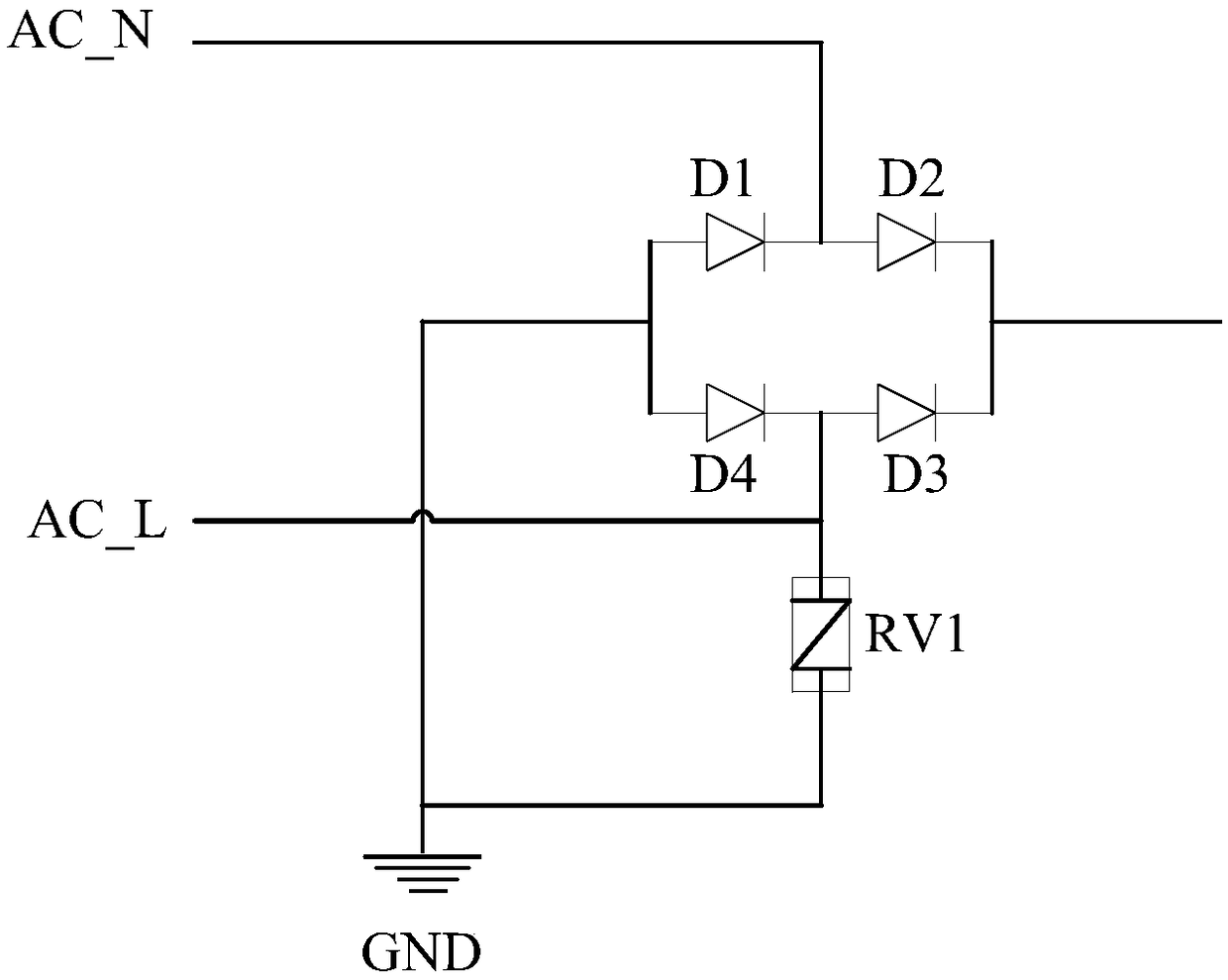

A surge-proof circuit

ActiveCN109066636AQuick responseImprove anti-surge performanceEmergency protective arrangements for limiting excess voltage/currentArrangements responsive to excess voltageNeutral lineVaristor

The invention provides a surge-proof circuit, comprising: a first diode, a second diode, a third diode, a fourth diode and a first varistor; The positive electrode of the first diode is connected withthe positive electrode of the fourth diode, the negative electrode of the first diode is connected with the positive electrode of the second diode, the negative electrode of the second diode is connected with the negative electrode of the third diode, and the positive electrode of the third diode is connected with the negative electrode of the fourth diode; The negative electrode of the first diode is connected with a neutral line, and the negative electrode of the fourth diode is connected with a live wire; A first end of the first varistor is connected to a negative electrode of the fourthdiode, and a second end of the first varistor is connected to a positive electrode of the fourth diode; The positive electrode of the fourth diode is connected to DC ground. The invention provides a surge-proof circuit, which can improve the surge-proof effect.

Owner:SICHUAN HONGMEI INTELLIGENT TECH CO LTD

Switch power supply control circuit and method

ActiveCN105141117ASolve technical problems with weak anti-surge capabilityImprove anti-surge performancePower conversion systemsAC powerRectifier diodes

The invention discloses a switch power supply control circuit and a method. The circuit comprises a switch power supply chip, a protection module, and an adjustment module, wherein the protection module is used for carrying out surge protection on the control circuit and adjusting a protection interval for surge protection, the protection module comprises multiple serial rectifier diodes, and as for a different protection interval, the number of rectifier diodes is correspondingly different; and the adjustment module is respectively connected with the protection module and the switch power supply chip for adjusting the magnitude of input voltage of the switch power supply chip, and the input voltage is first output voltage after AC power passes through the protection module. The technical problem that the switch power supply control circuit in the prior art has a weak anti-surge ability can be solved.

Owner:GREE ELECTRIC APPLIANCES INC

Semiconductor device including an insulated gate bipolar transistor and a circuit configured to control the insulated gate bipolar transistor provided on the same semiconductor substrate

InactiveUS9893055B2Small sizeImprove anti-surge performanceTransistorSolid-state devicesSurface layerParasitic bipolar transistor

Owner:FUJI ELECTRIC CO LTD

Semiconductor component and manufacturing method

InactiveCN107403728AImprove anti-surge performanceSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingSemiconductor materials

The invention discloses a semiconductor component and a manufacturing method. The invention aims to improve the surge resisting capability of a high-voltage Schottky diode without reducing the switching frequency and conduction voltage drop of the device. The method comprises the following steps that: ion implantation is performed at a plurality of preset implantation positions of a semiconductor material; by means of implanted ions, doped P type regions and doped P type diffusion region diffused from the doped P type regions can be formed at each of the implantation positions; and trench etching is performed at each implantation position, and during the etching process, the doped P type regions are removed through etching, and the doped P type diffusion regions are reserved, and therefore, each cell region of a formed semiconductor component has one doped P type diffusion region.

Owner:广微集成技术(深圳)有限公司

Chip resistor and method of manufacturing the same

ActiveUS20070035379A1Increase the lengthIncreasing sizeElongated resistive elementAlarmsChip resistorElectrical and Electronics engineering

A chip resistor is provided which includes a resistor film 5 formed between a pair of terminal electrodes 2 and 3 on an upper surface of an insulating substrate 2. The resistor film is formed with two inward grooves 7, 8 and two trimming grooves 9, 10 which are alternately provided for causing the current path in the resistor film to have a winding shape. The two inward grooves 7 and 8 are provided approximately at the midpoint between one end edge 5a and the other end edge 5b of the resistor film 5. The trimming groove 9 is provided between the inward groove 8 and the end edge 5a of the resistor film, whereas the other trimming groove 10 is provided between the inward groove 7 and the end edge 5b of the resistor film, whereby the time required for the trimming adjustment to adjust the resistance to a predetermined value is shortened, and the yield rate is reduced to reduce the cost.

Owner:ROHM CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com