Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

149results about How to "Improve noise margin" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

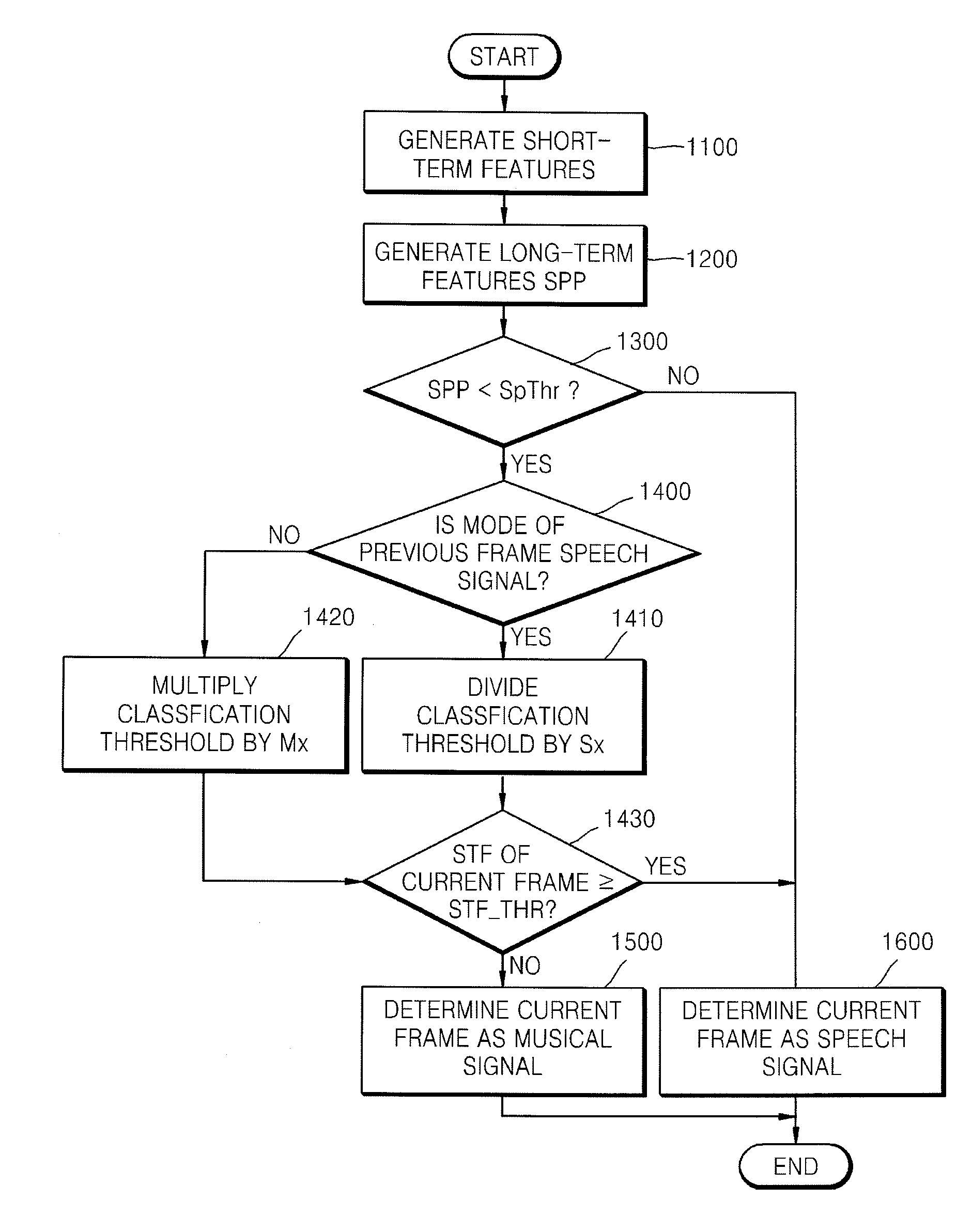

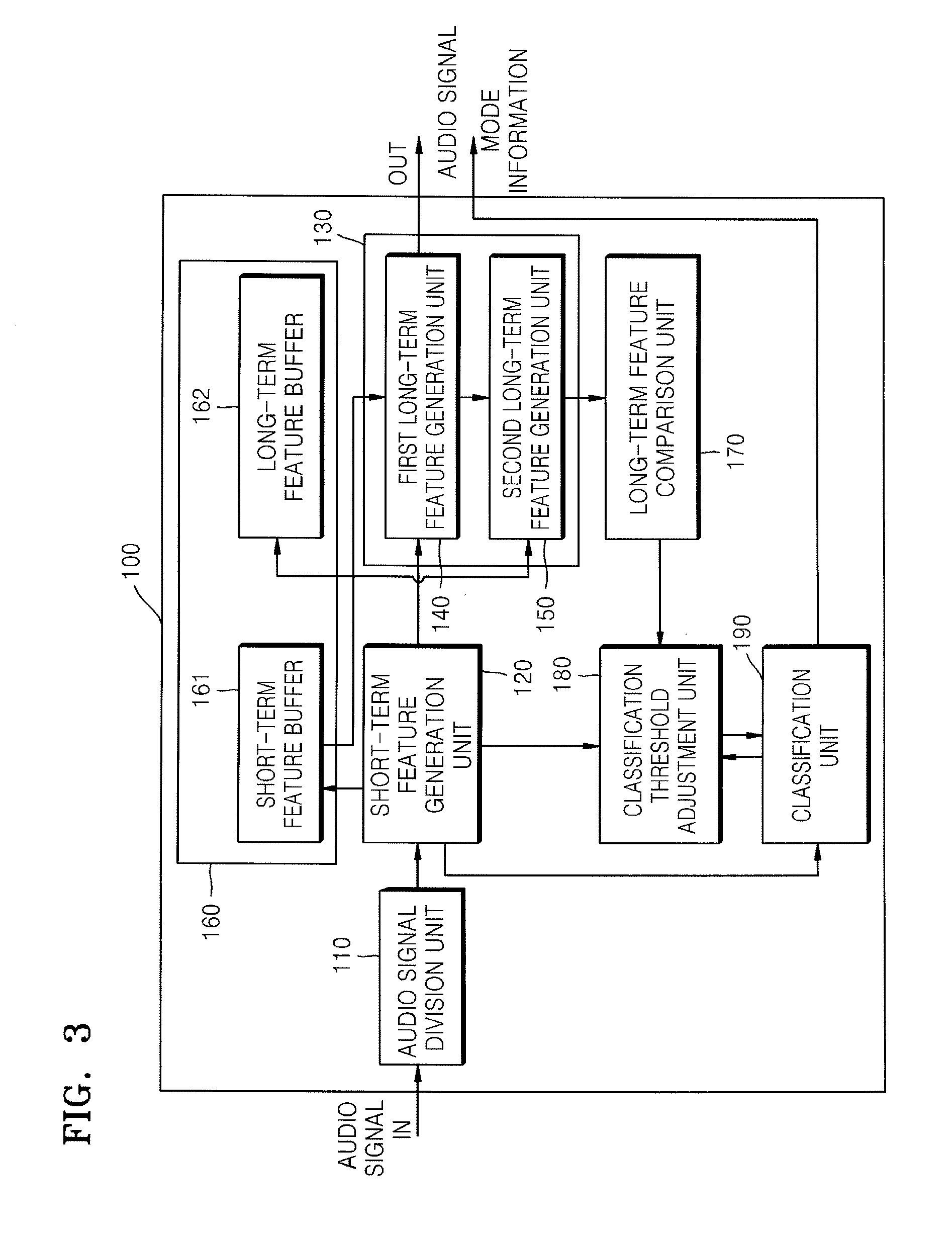

Method, medium, and apparatus to classify for audio signal, and method, medium and apparatus to encode and/or decode for audio signal using the same

InactiveUS20080162121A1Increase signaling rateOscillation suppressionSpeech analysisCode conversionDecoding methodsSignal classification

Provided are a classifying method and apparatus for an audio signal, and an encoding / decoding method and apparatus for an audio signal using the classifying method and apparatus. In the classification method, an audio signal is classified by adaptively adjusting a classification threshold for a frame of the audio signal that is to be classified according to a long-term feature of the audio signal, thereby improving a hit rate of signal classification, suppressing frequent mode switching per frame, improving noise tolerance, and providing smooth reconstruction of the audio signal.

Owner:SAMSUNG ELECTRONICS CO LTD

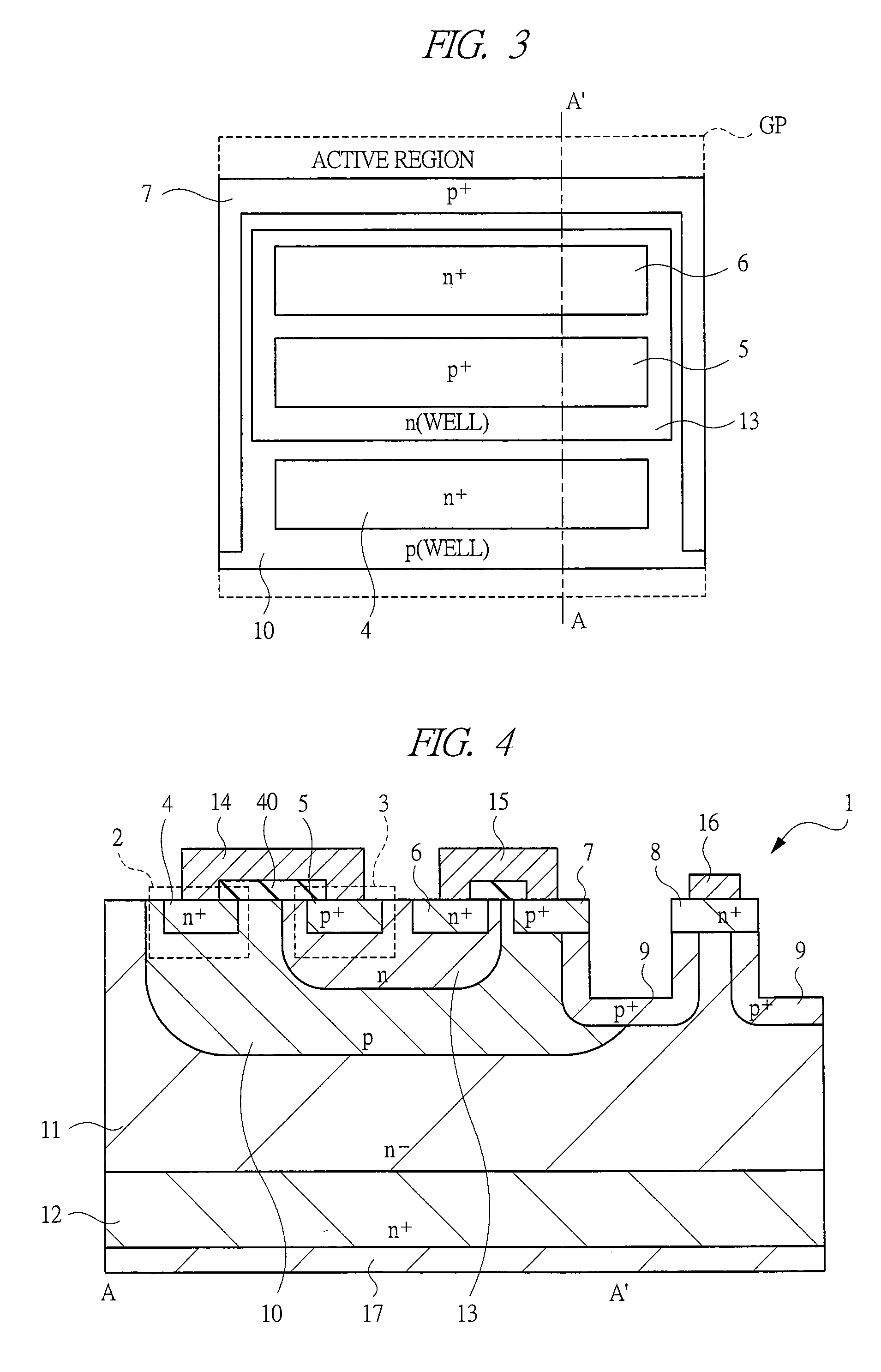

Semiconductor device with large blocking voltage

InactiveUS20090014719A1Large noise marginRaise the threshold voltageTransistorSolid-state devicesNoise marginSemiconductor

A junction FET having a large gate noise margin is provided. The junction FET comprises an n− layer forming a drift region of the junction FET formed over a main surface of an n+ substrate made of silicon carbide, a p+ layer forming a gate region formed in contact with the n− layer forming the drift region and a gate electrode provided in an upper layer of the n+ substrate. The junction FET further incorporates pn diodes formed over the main surface of the n+ substrate and electrically connecting the p+ layer forming the gate region and the gate electrode.

Owner:RENESAS ELECTRONICS CORP

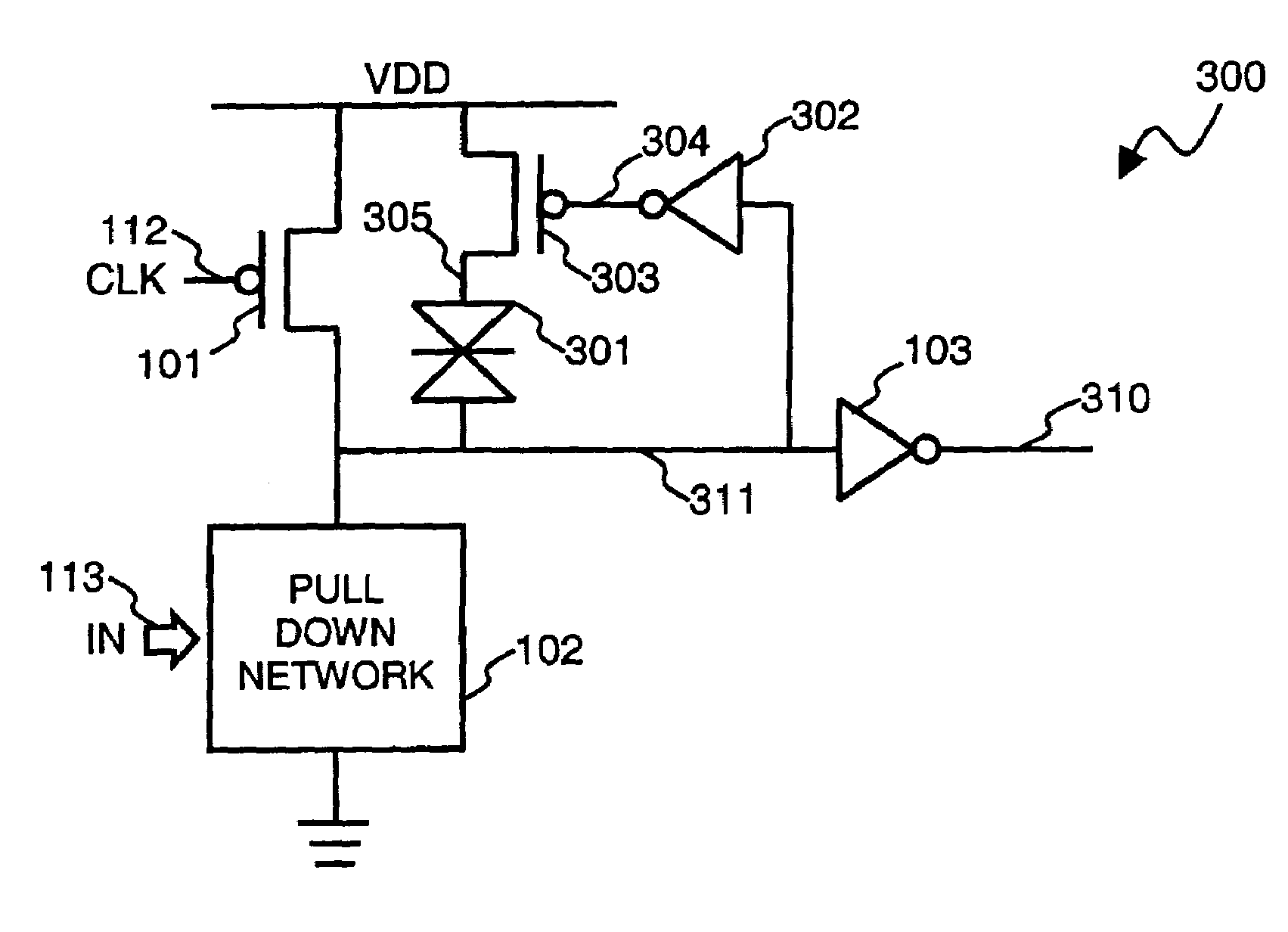

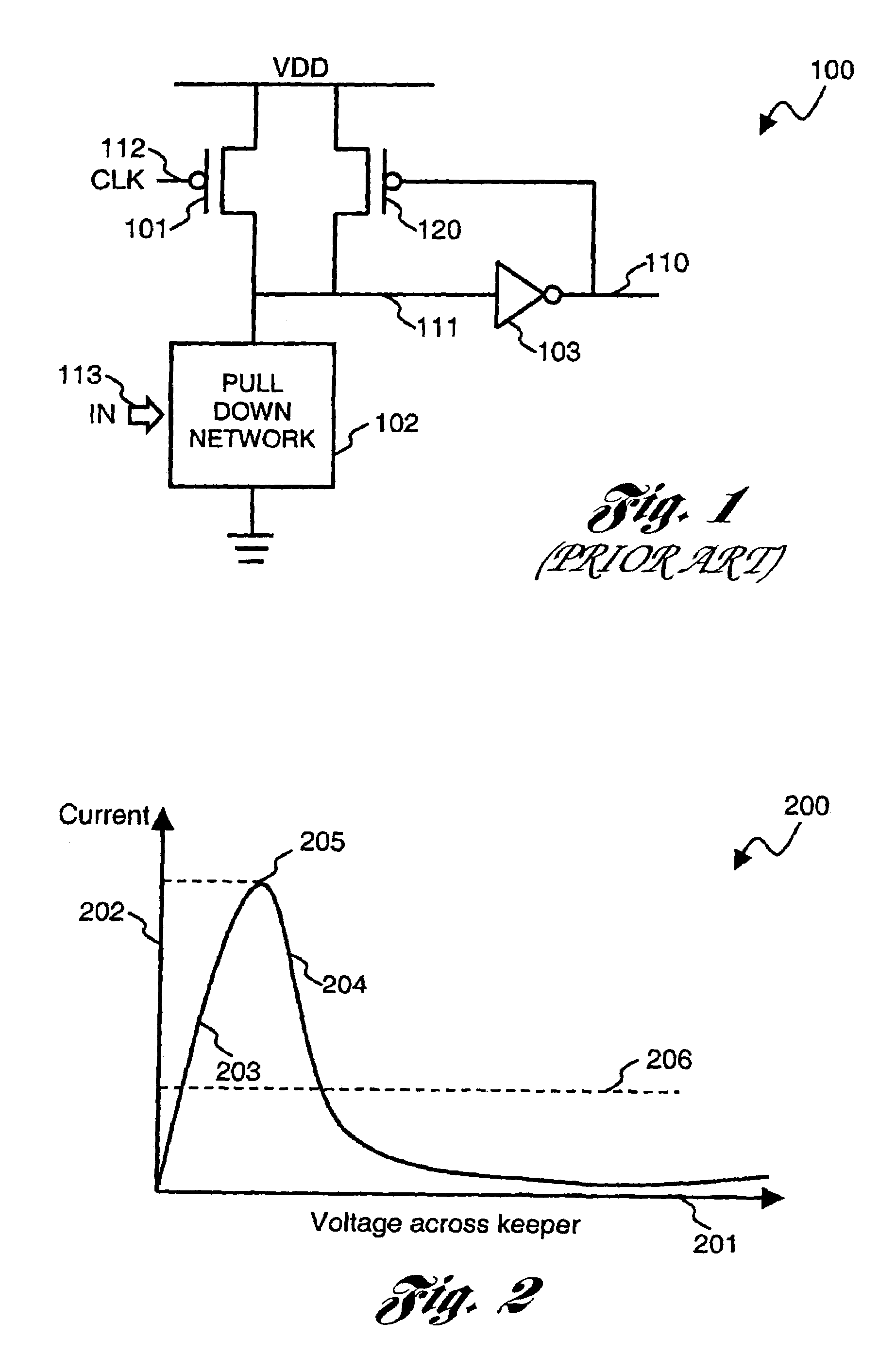

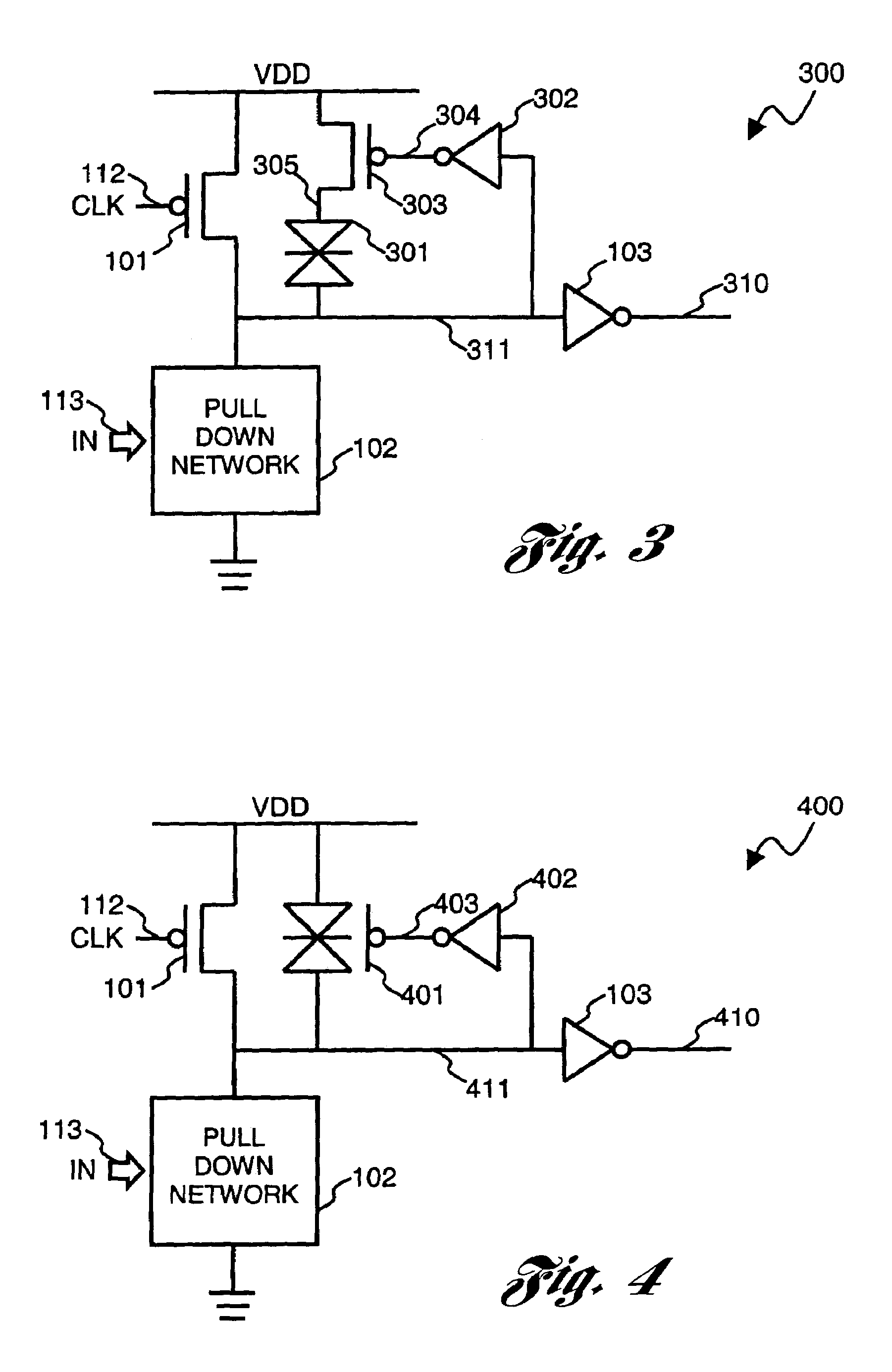

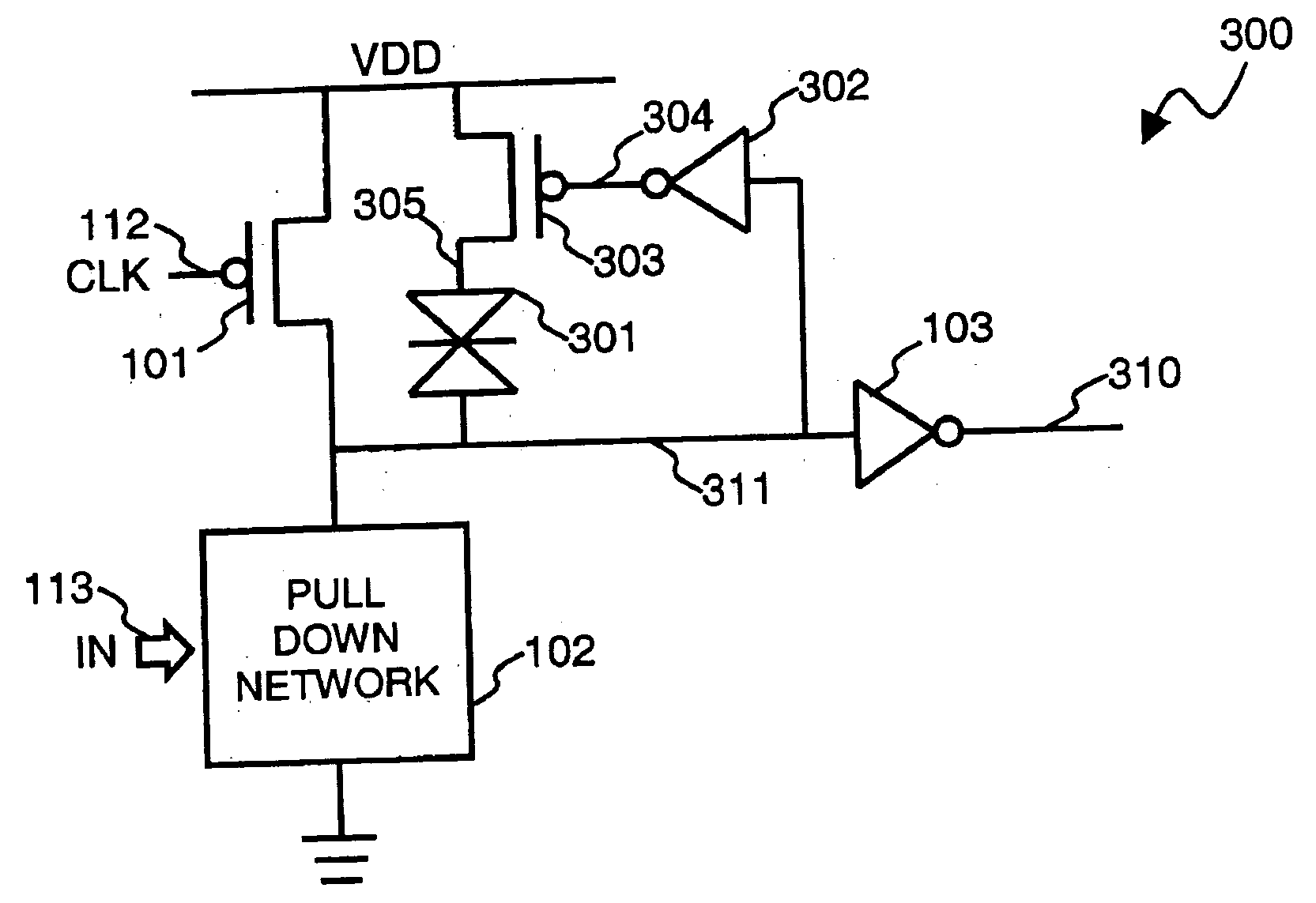

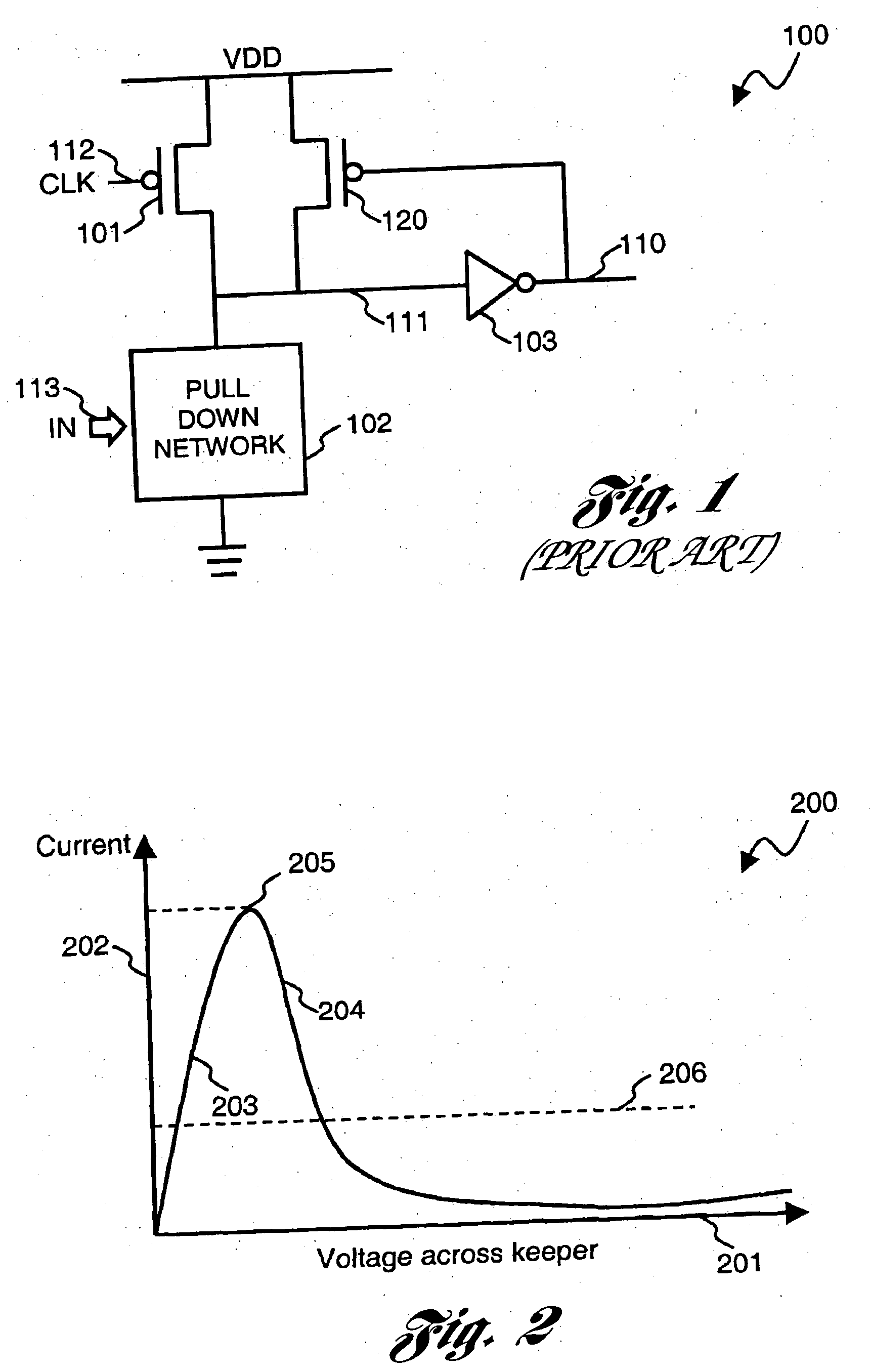

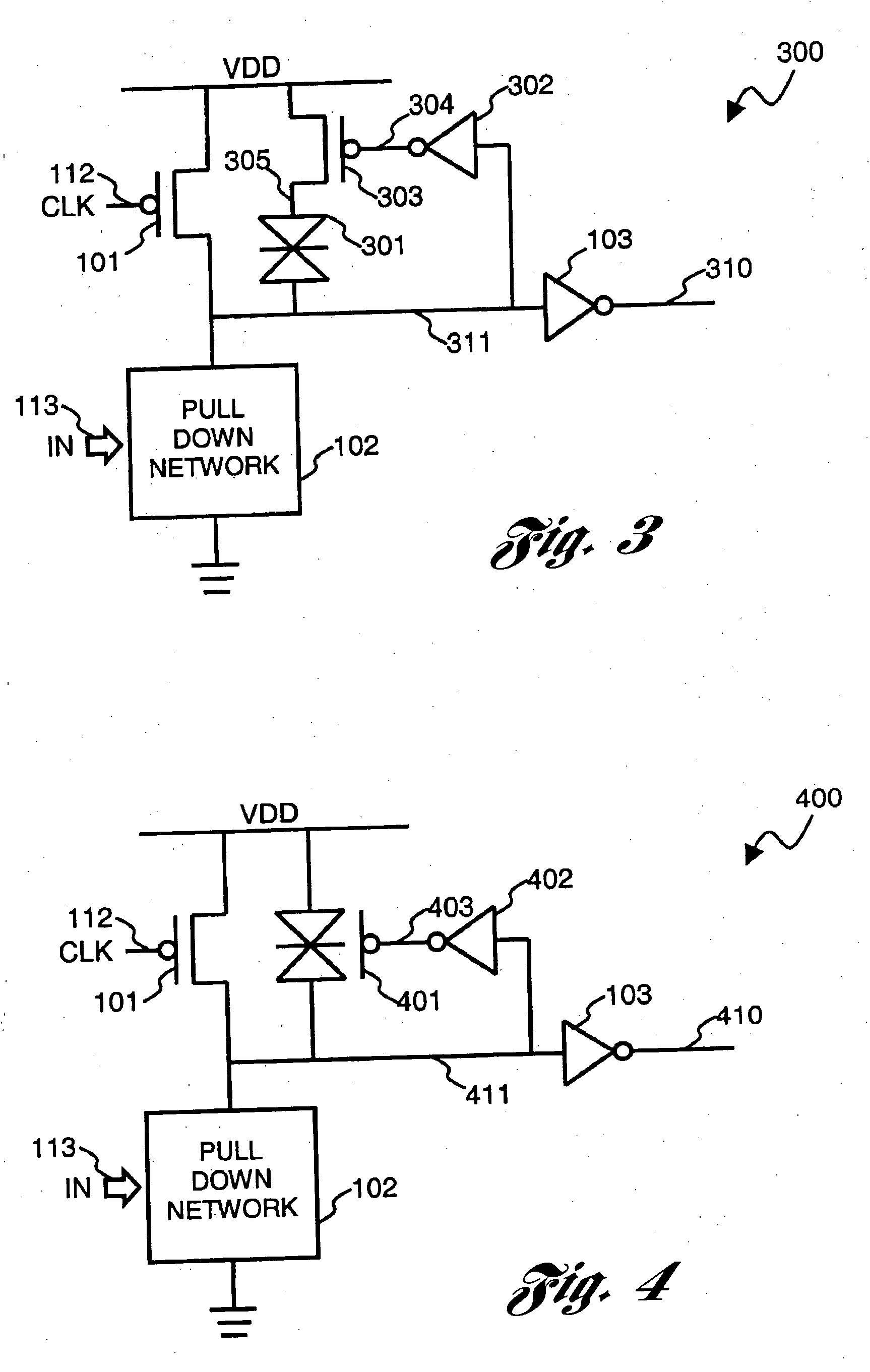

Dynamic circuits having improved noise tolerance and method for designing same

InactiveUS7088143B2Improved dynamic circuitsImprove methodLogic circuits characterised by logic functionElectrical resistance and conductanceEngineering

A number of different dynamic circuits having improved noise tolerance and a method for designing same are provided. The circuits include a power supply node and a precharge node. Keeper circuitry is connected to the nodes and has a current-voltage characteristic that exhibits a negative differential resistance property to improve noise tolerance of the circuits.

Owner:RGT UNIV OF MICHIGAN

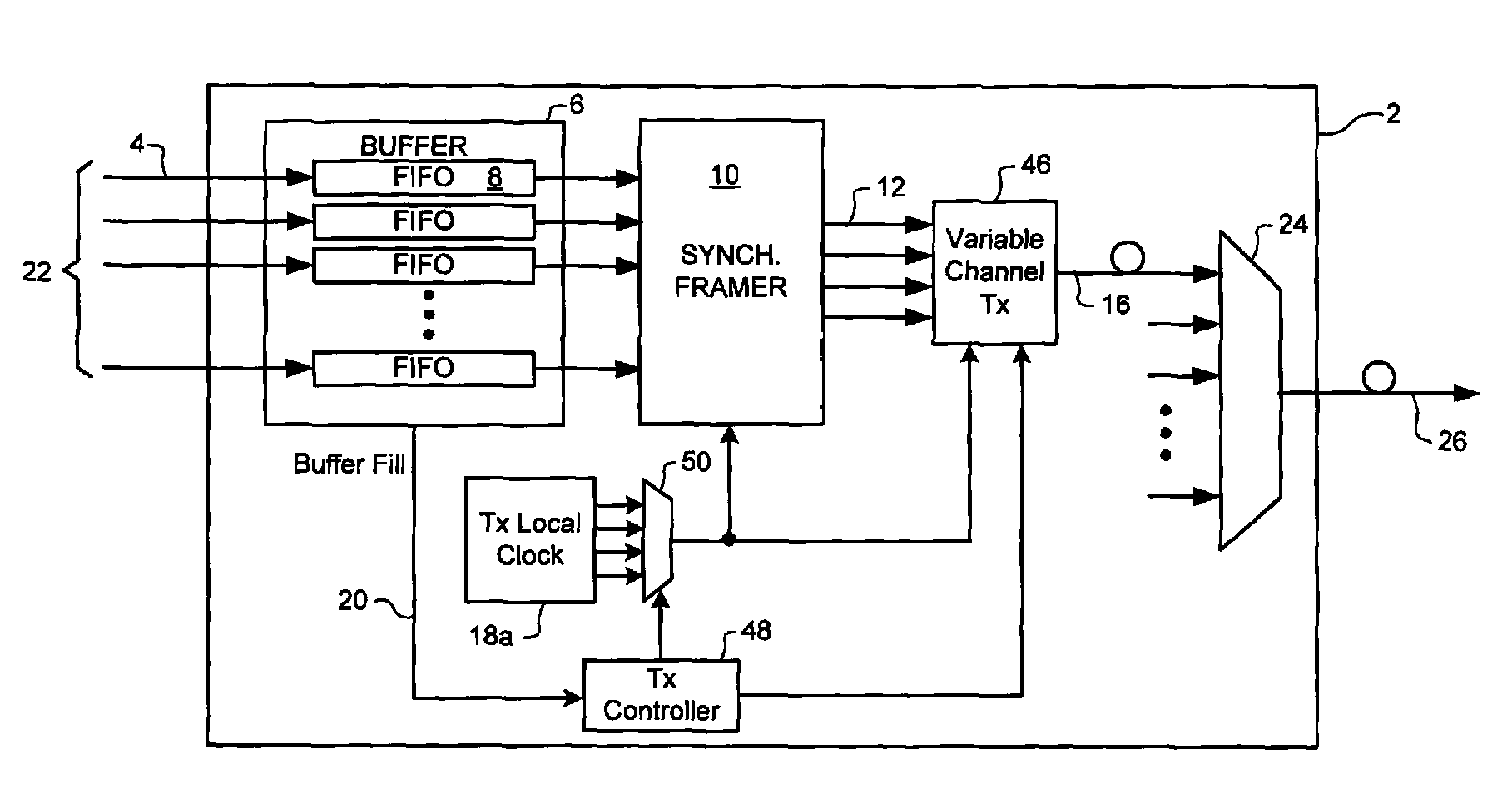

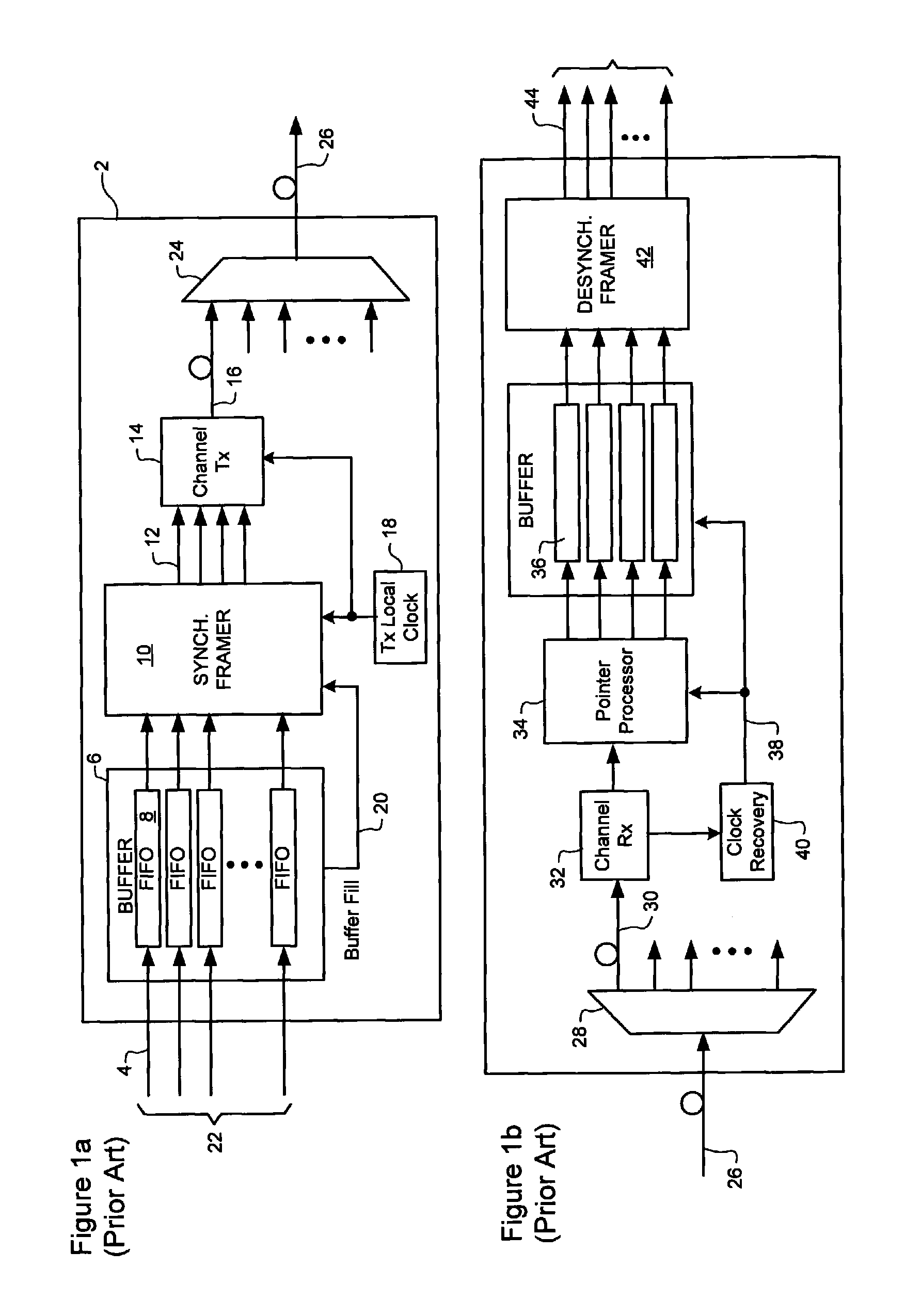

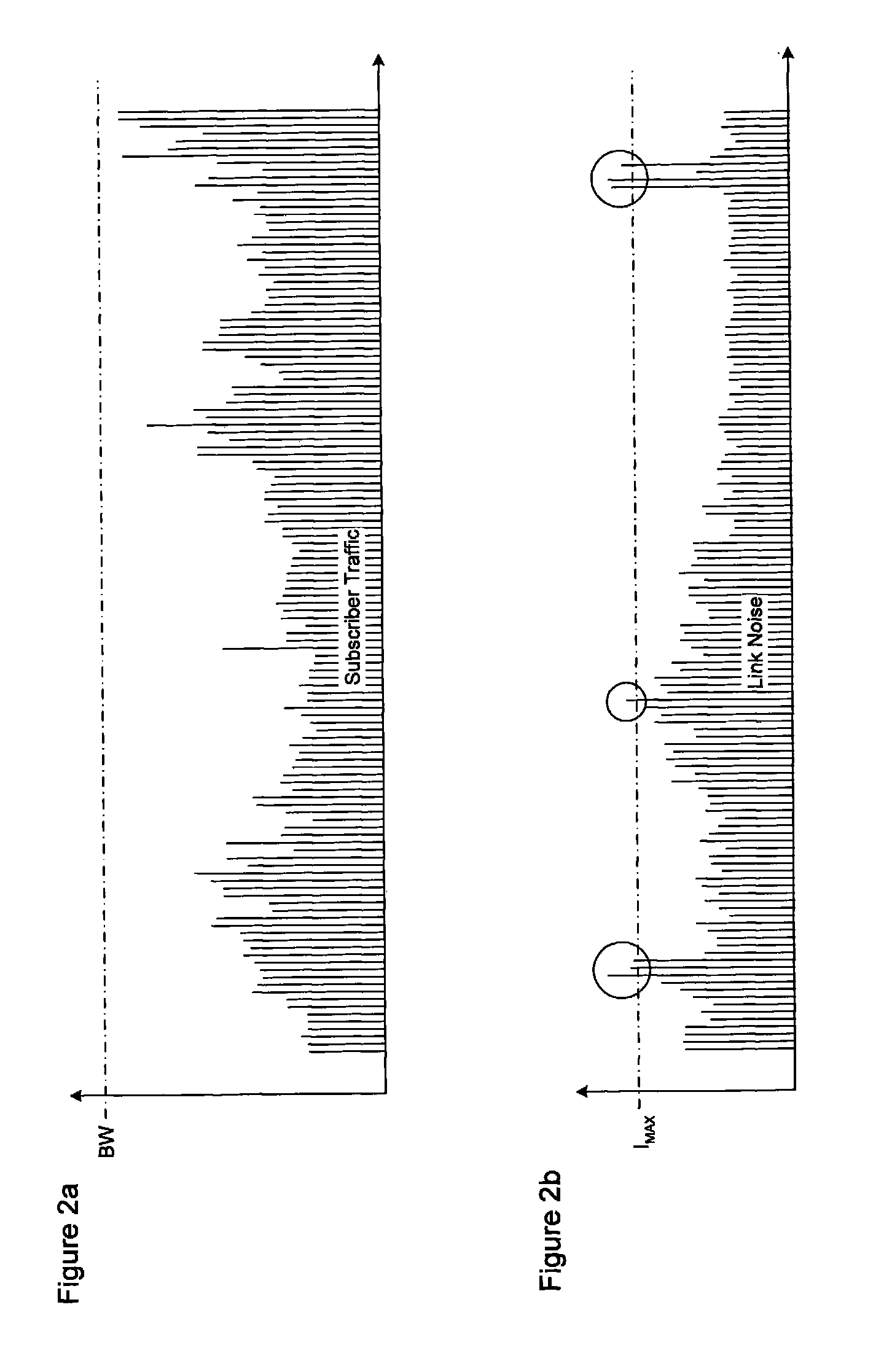

Traffic driven variable bandwidth optical transmission

ActiveUS8009985B1Improve noise toleranceIncrease in link lengthTime-division multiplexOptical multiplexTraffic volumeTelecommunications

Link bandwidth is varied based on the subscriber traffic load. Varying the link bandwidth has the effect of varying the actual noise margin of the link (in an inverse relation), so that the noise margin will vary inversely with the traffic load. A beneficial result is that, because the noise margin is increased during “off-peak” traffic periods, rapidly varying and burst impairments can be absorbed without causing data loss. In effect, the respective probability distributions of error bursts and traffic load are separated. Data loss only becomes a significant risk when peaks in both distributions coincide. However, the probability of that event occurring is comparatively low. This enables a lower noise margin allocation during design of the link, which dramatically reduces the link cost.

Owner:CIENA

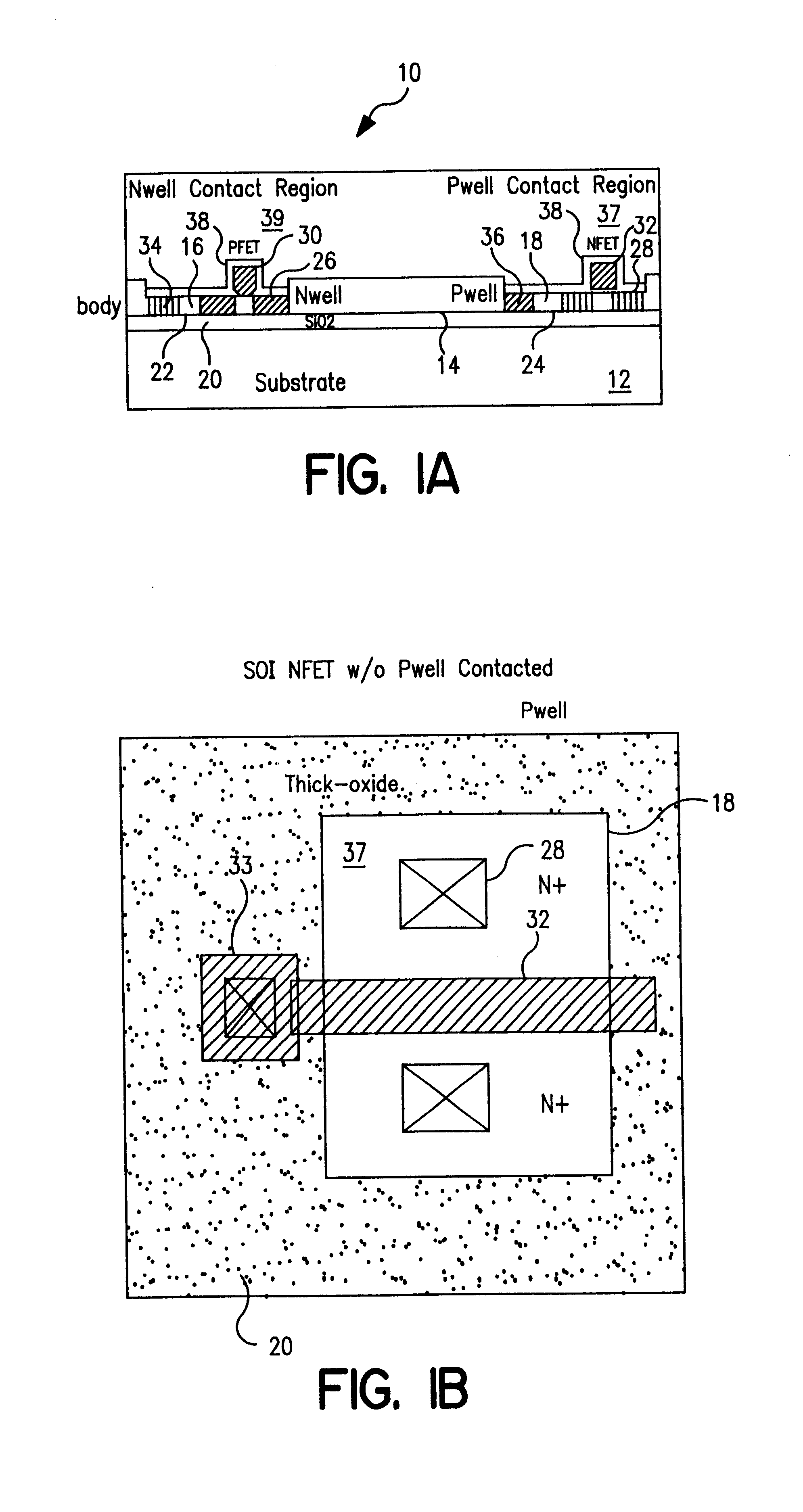

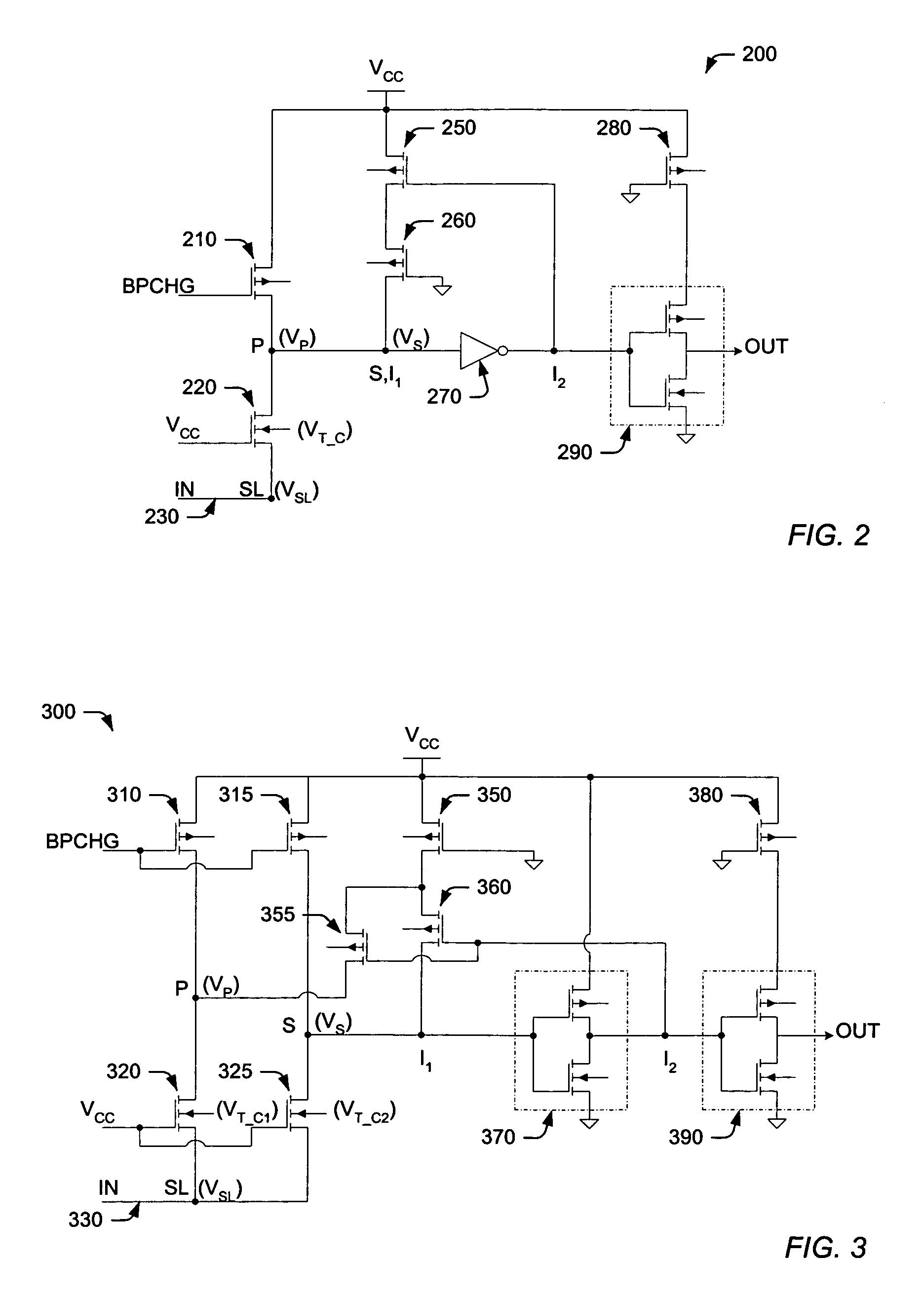

CMOS device and circuit and method of operation dynamically controlling threshold voltage

InactiveUS6275094B1Improve noise immunityEliminate offset effectsPulse automatic controlThreshold modification in field effect transistorsCMOSFourier transform

A CMOS device fabricated in a silicon-on-insulator structure and including circuitry and methods in a first embodiment dynamically shifts the threshold voltage of the CMOS device in a receiver to provide improved noise margin and in a second embodiment dynamically matches the threshold voltages in a differential amplifier to correct for manufacturing offset. To dynamically shift the threshold voltage for noise immunity, the back gate or bulk nodes of the devices is shifted through two similar circuits comprised of npn inverters with clamping devices. The back gate of the n device is biased at 0 volts for the maximum Vth and is biased at +1 threshold for the minimum Vth of the device. Only the back gate of the p device is biased at Vdd for the maximum Vth of the device and is biased at 1 Vth below Vdd for the minimum Vth of the device. The Vth of the n device and the p device should be less than the forward bias of the respective source volt junctions to prevent unwanted bipolar currents. By driving the back gates in opposite direction and in phase with the input to the receiver circuit, the threshold voltage of the receiver is moved away from ground (GND) when the input is at a logical "0" and way from Vdd when the input is at a logical "1" which raises the noise immunity of the receiver and speeds the response of the receiver to a desired signal To dynamically match a differential pair for offset correction, a feedback circuit performs a Fast Fourier Transformer analysis of the output signal to determine the presence of even harmonics. A feedback voltage is generated representative of the even harmonics and applied to the back bias contacts of the CMOS devices to correct the effects of the threshold mismatch in the differential pair.

Owner:INTELLECTUAL DISCOVERY INC

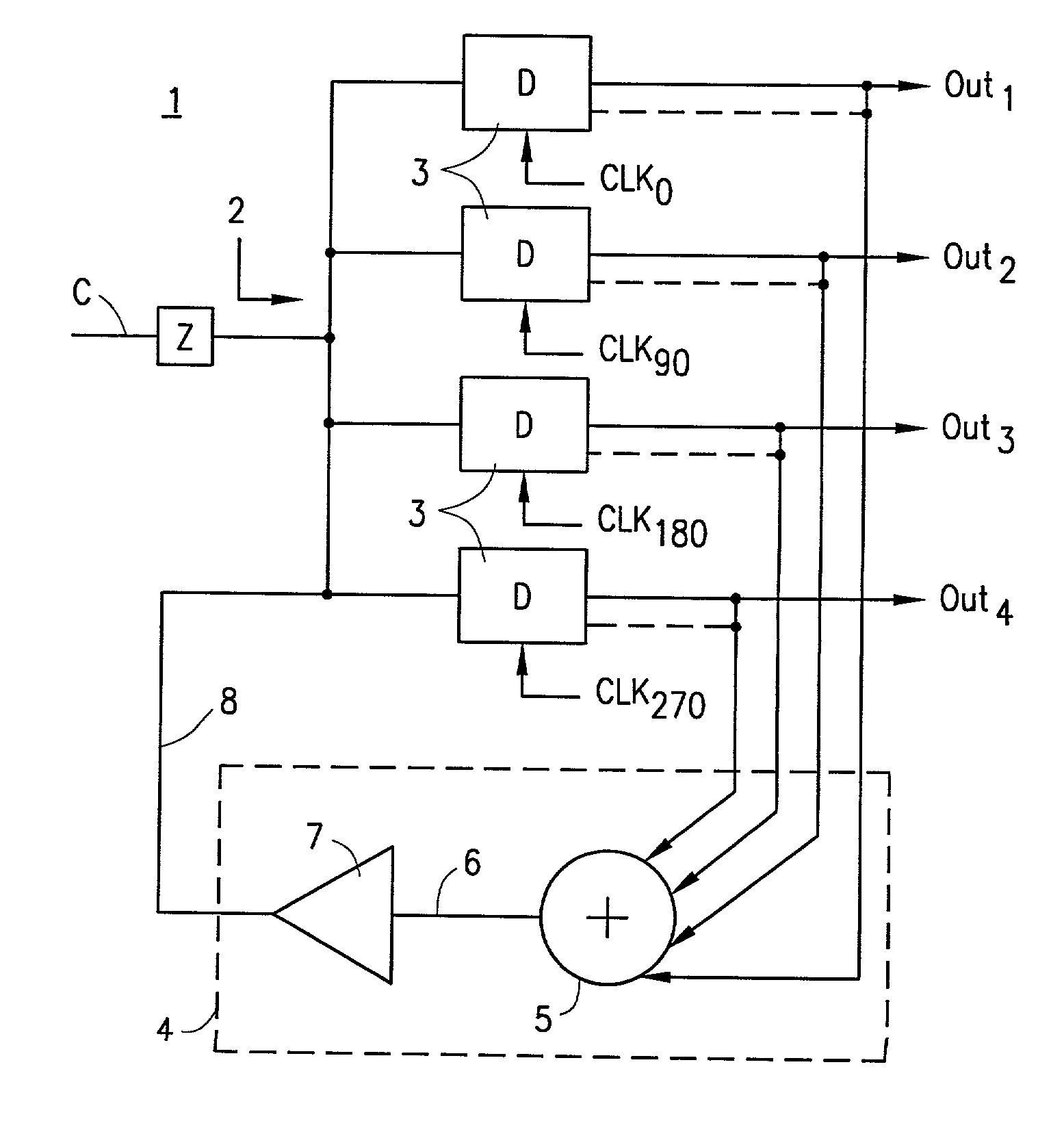

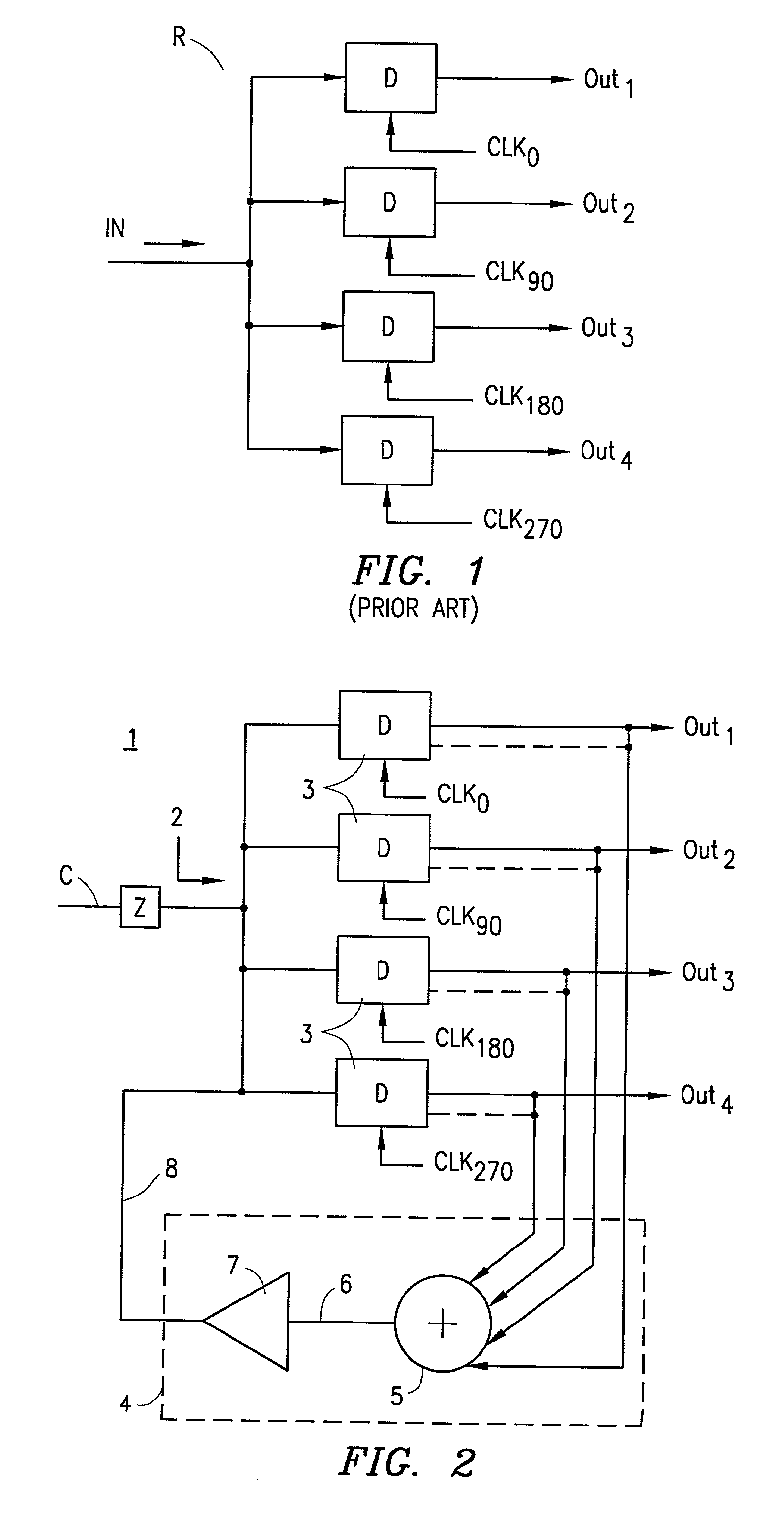

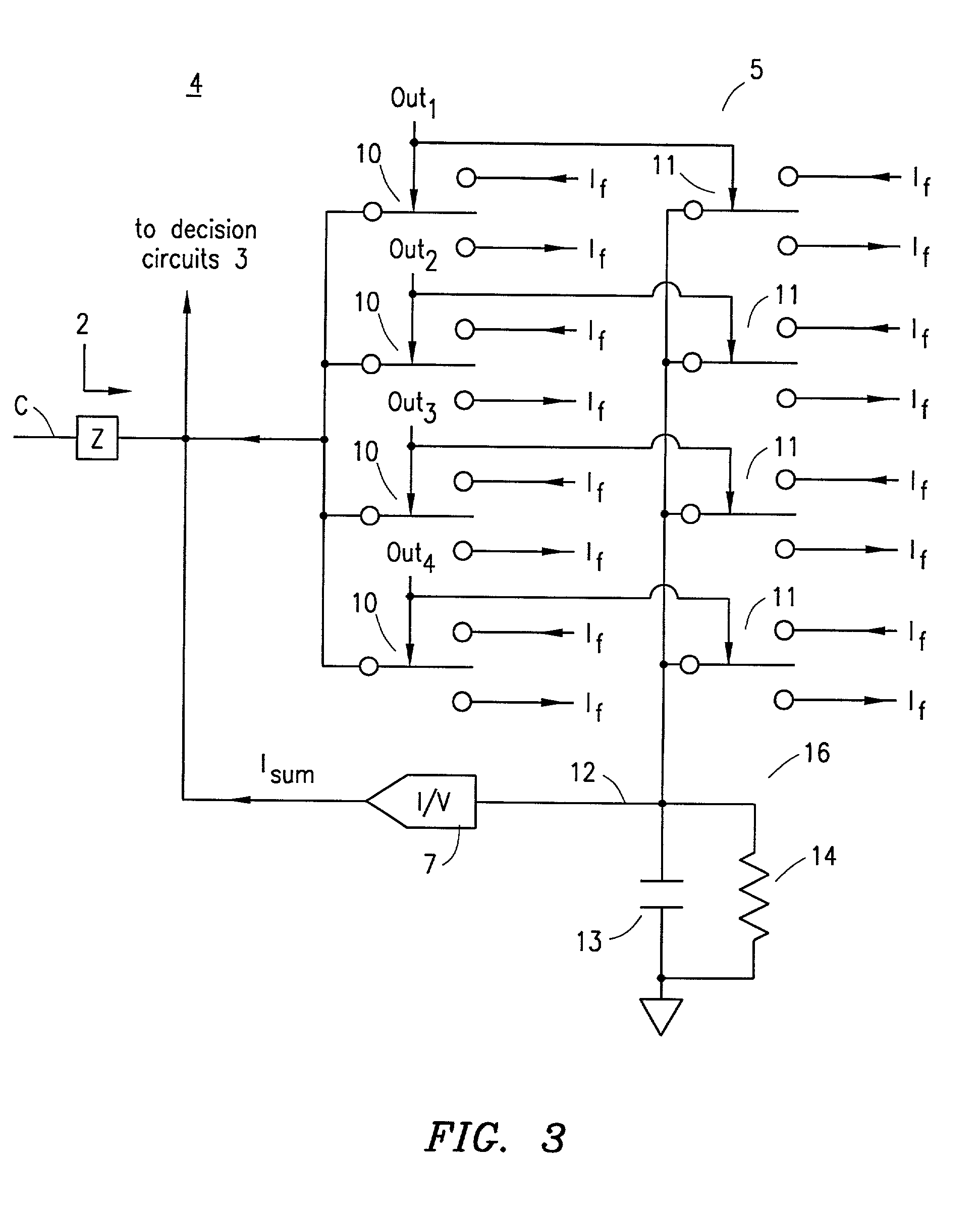

System and method for providing equalization in a multiphase communications receiver

ActiveUS20030108096A1Improve abilitiesLess circuit complexityMultiple-port networksTransmission control/equlisationEngineeringCommunications receiver

A circuit and method for receiving digital signals are disclosed. The circuit includes an input connected to a communications channel over which a digital signal is communicated and operates a plurality of multiple decision circuits at a frequency that is a fraction of the bit rate of the digital signal. A feedback and / or equalizer circuit receives the output of the decision circuits and applies a feedback signal to the input of the decision circuits that is representative of a combination of output signals of the decision circuits. The result is seen to improve the noise margin for correctly interpreting signals communicated over a communications channel having a low-pass characteristic.

Owner:KEYSIGHT TECH

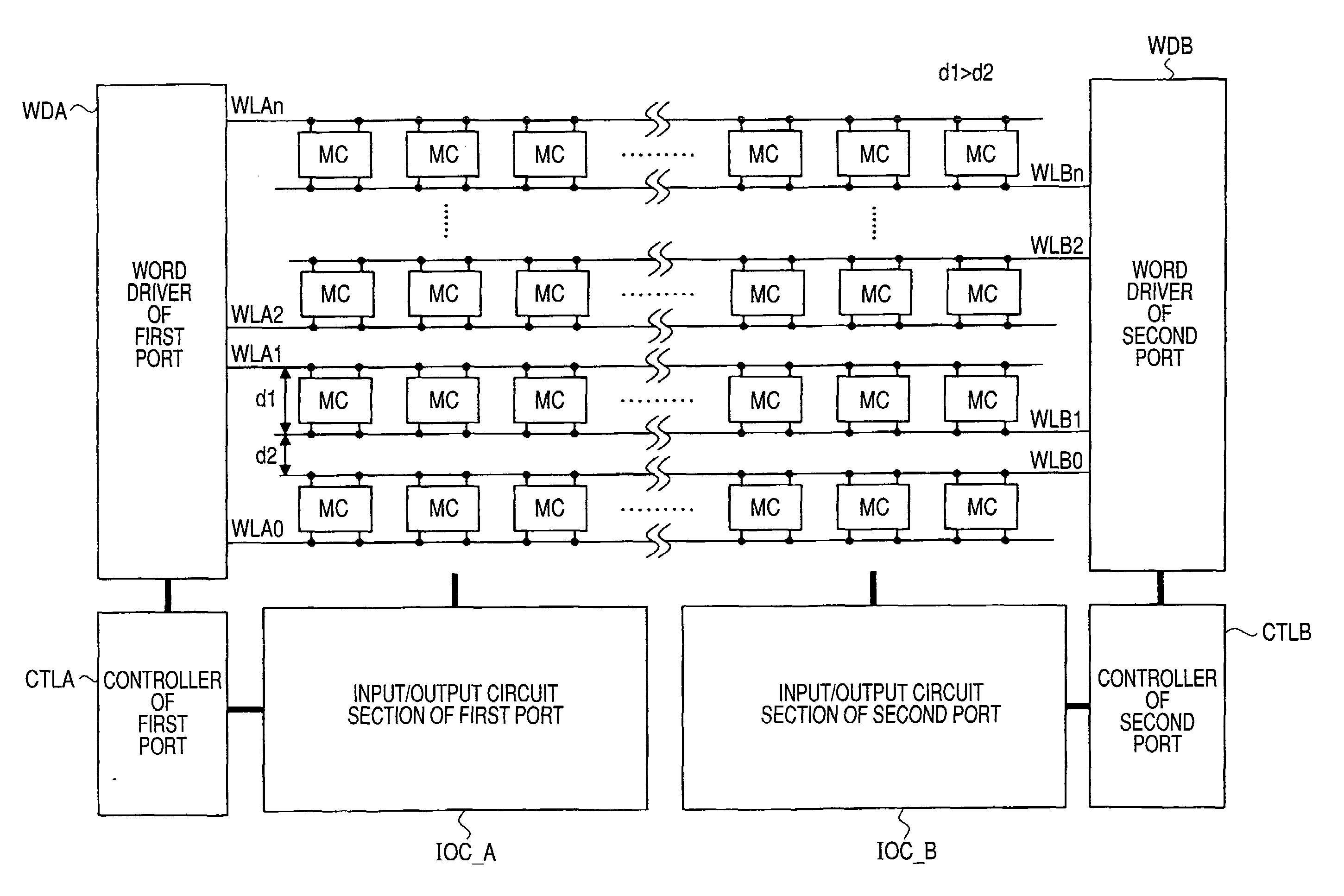

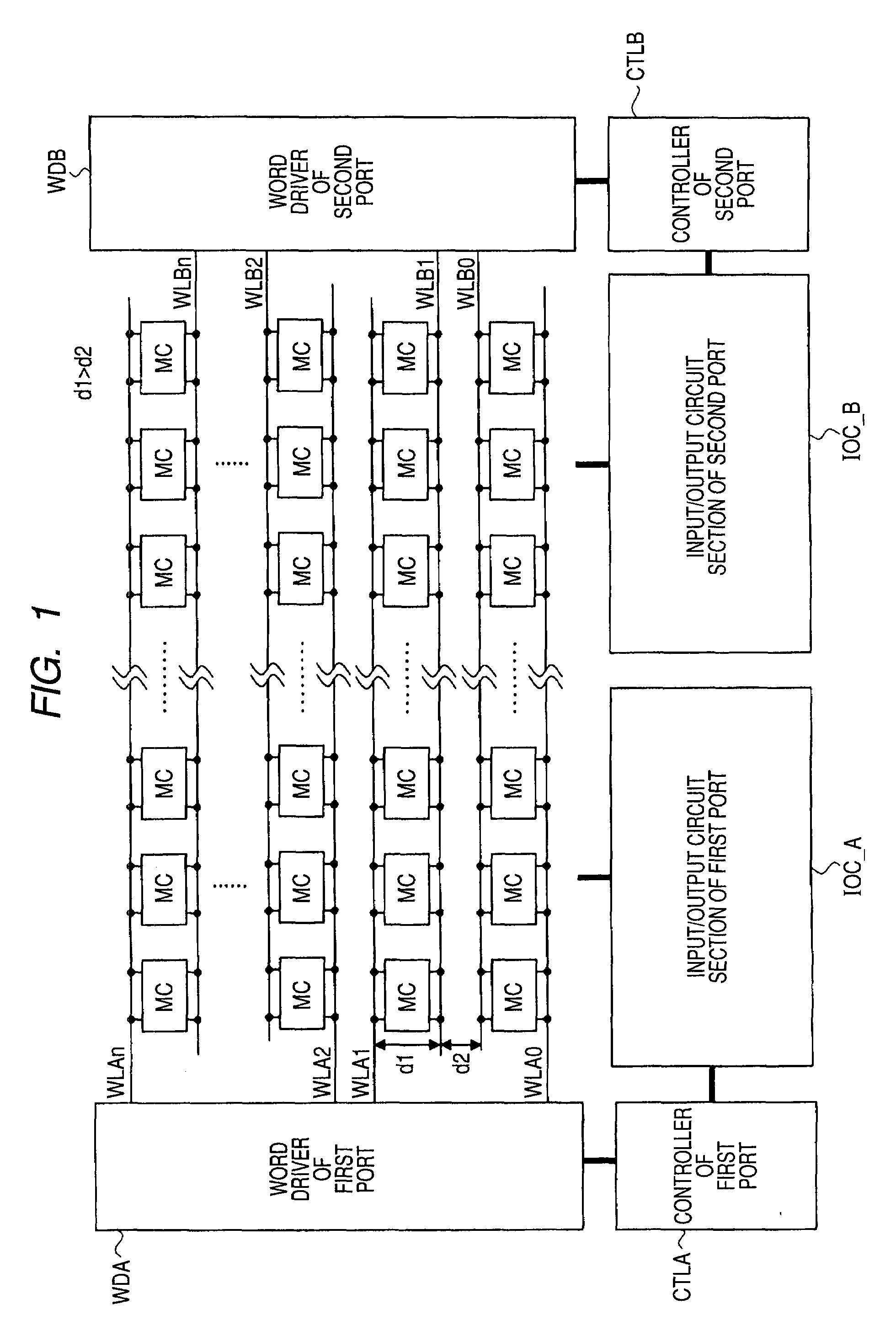

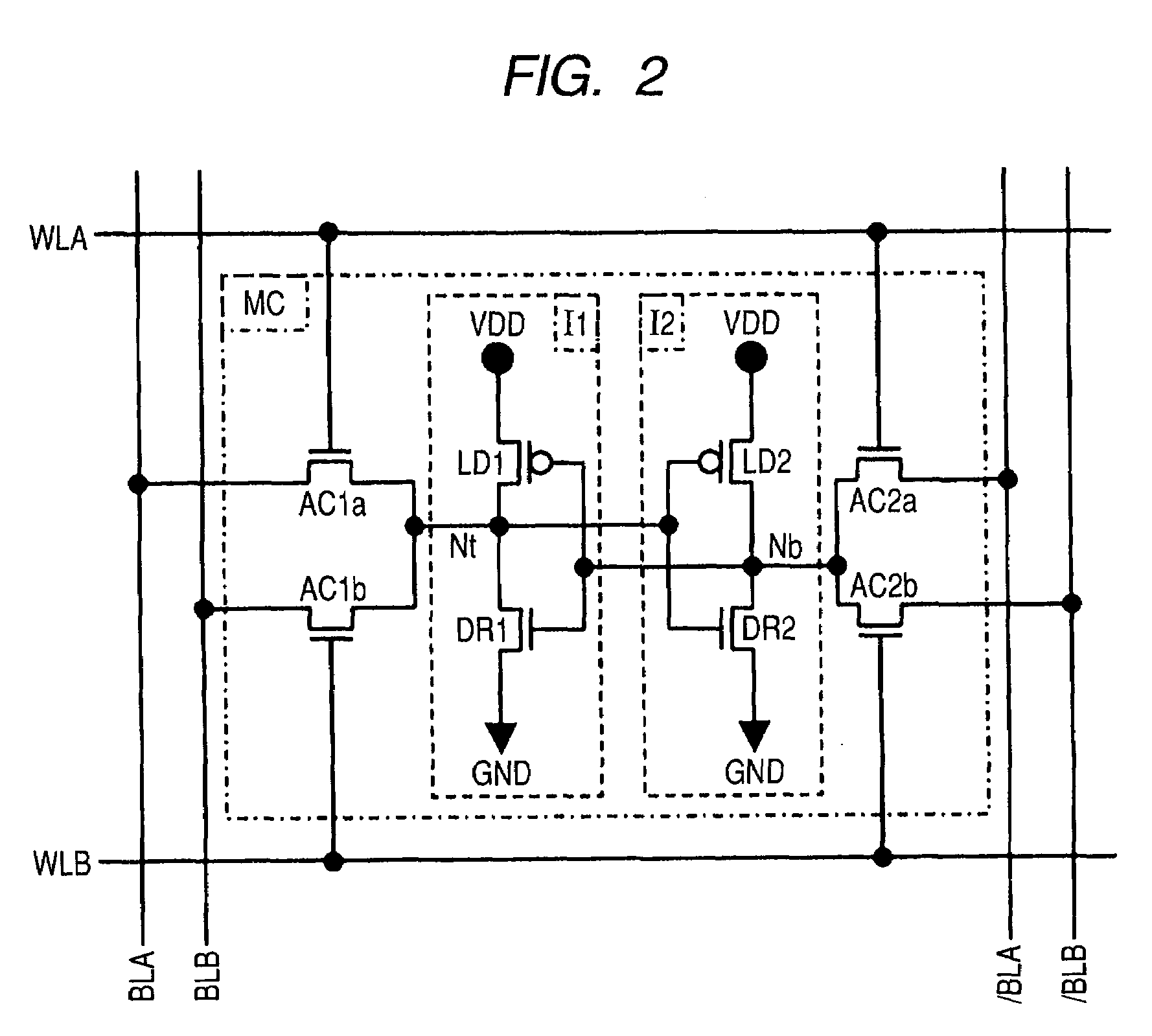

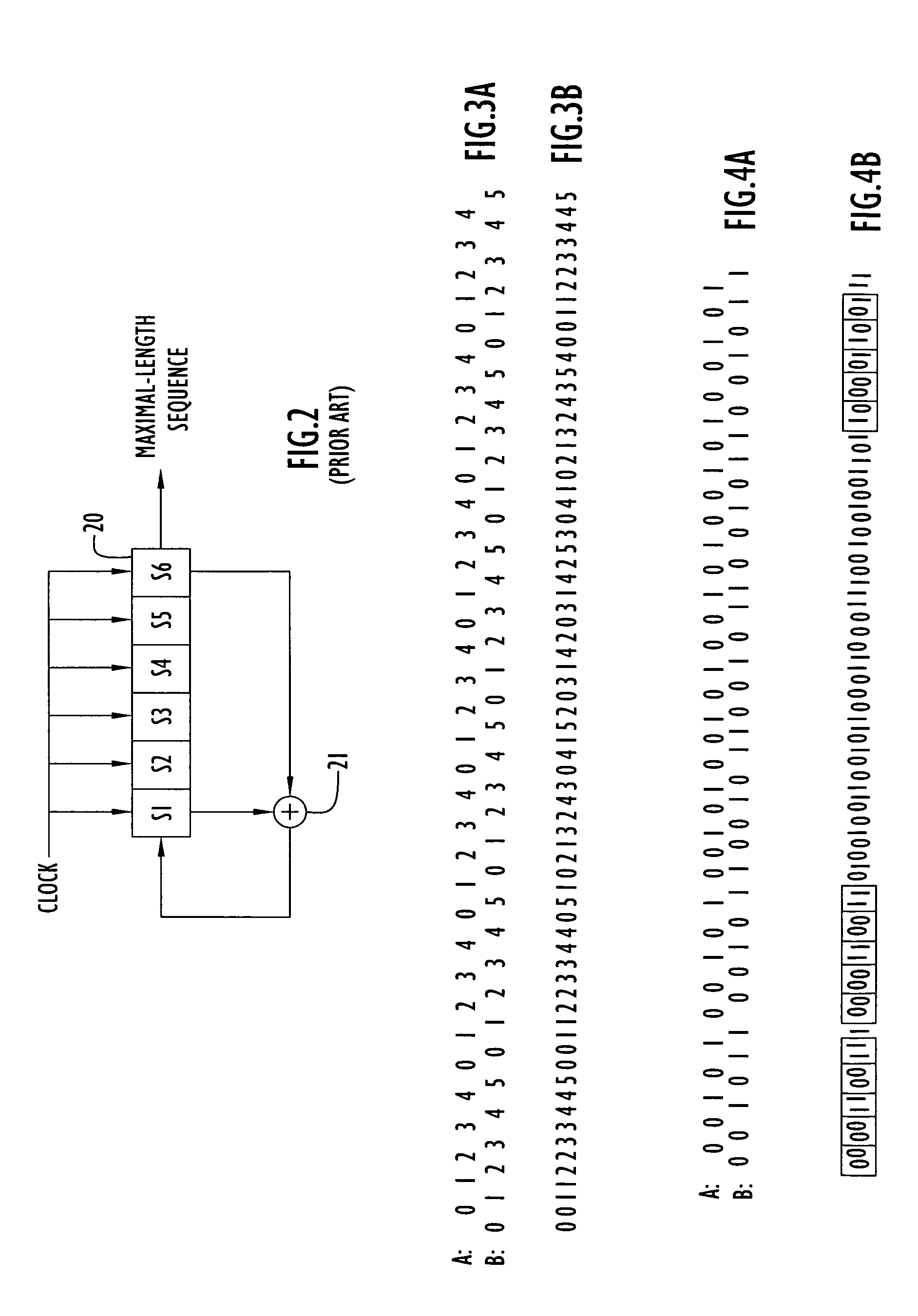

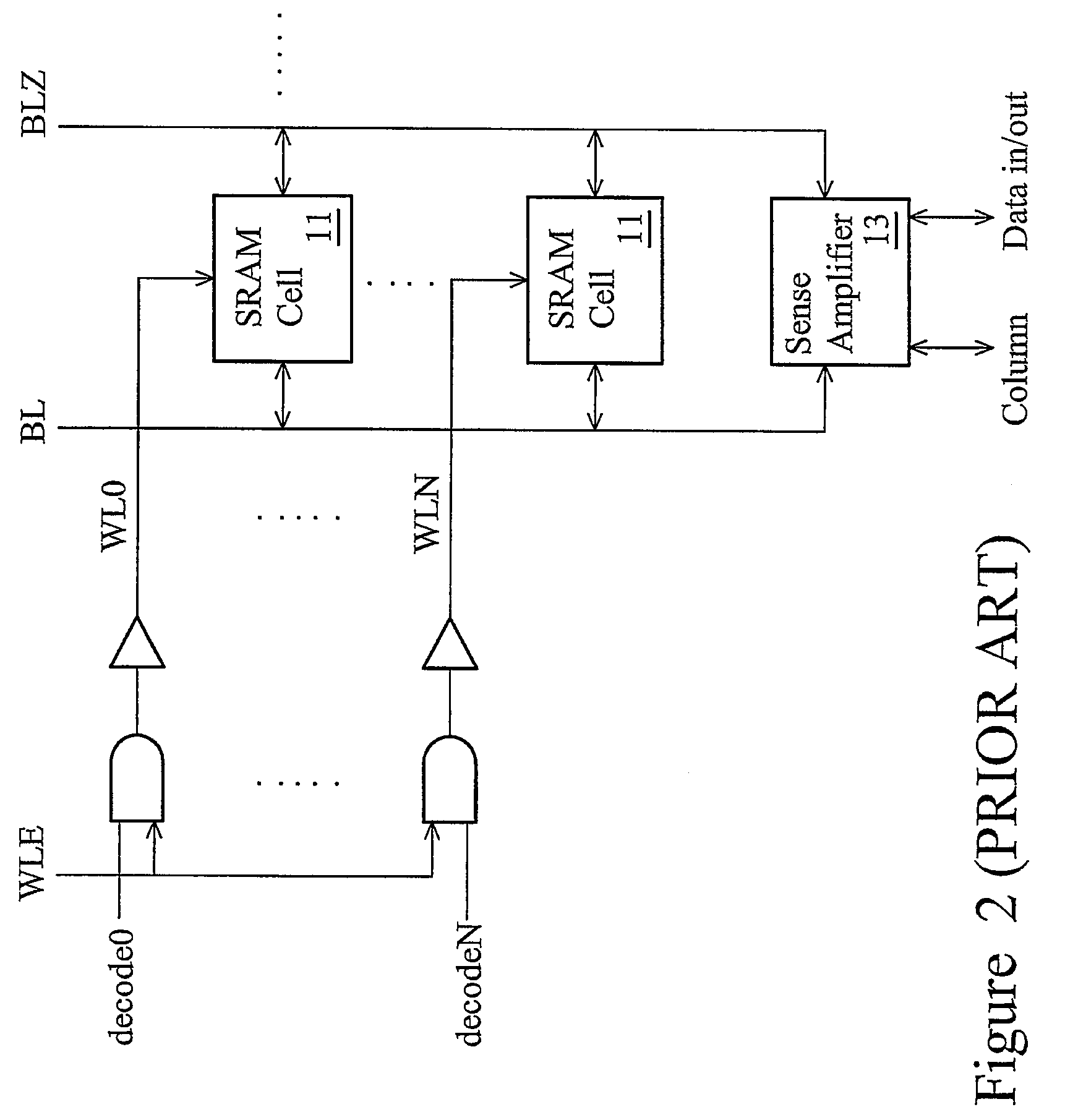

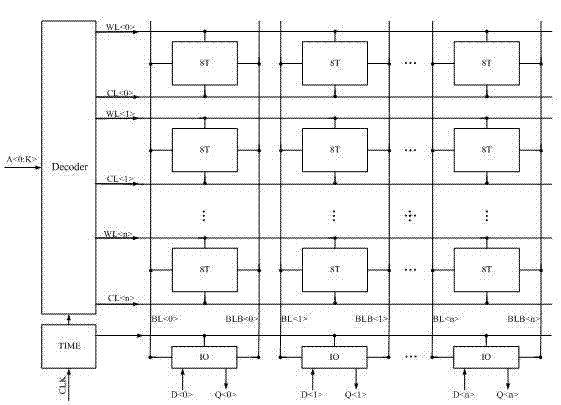

Semiconductor device having multiport memory

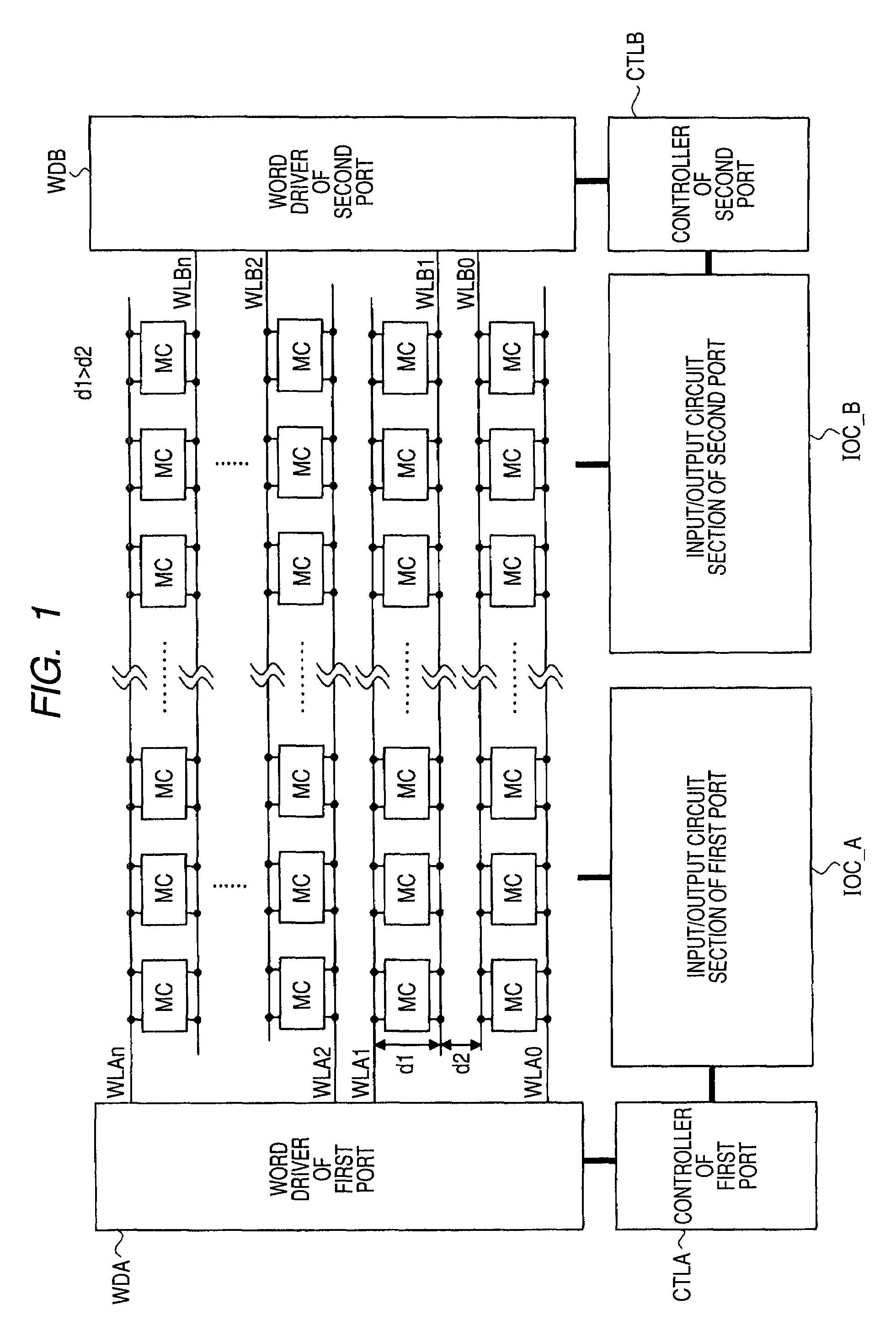

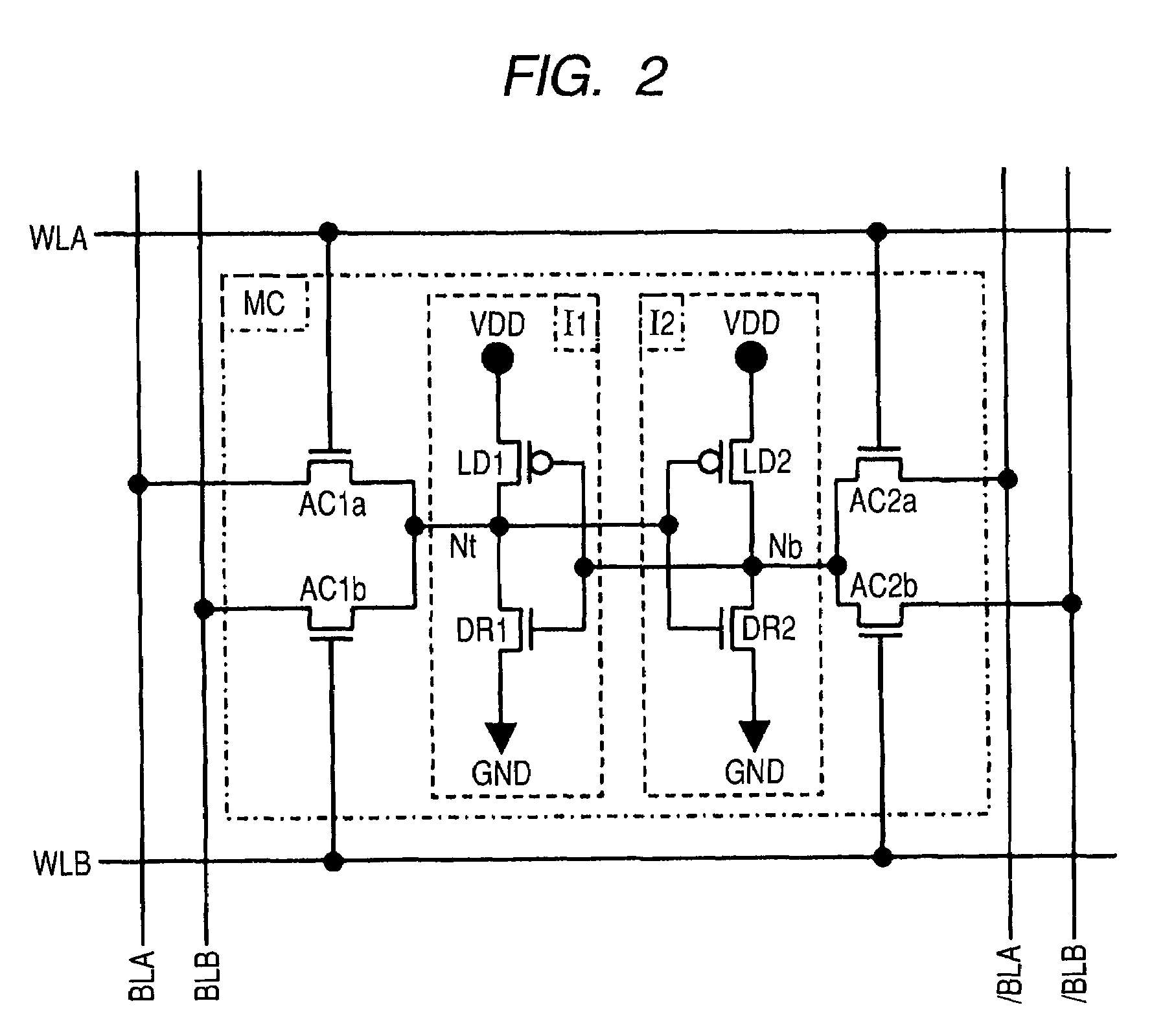

ActiveUS20090059640A1Reduce distractionsImprove noise marginTransistorSolid-state devicesNoise marginComputer science

A semiconductor device enabling expansion of a noise margin. For example, in a memory area in which each memory cell MC is coupled to a word line WLA for a first port and a word line WLB for a second port, and a plurality of memory cells MC is disposed in a matrix shape, each word line is disposed in the order like WLA0, WLB0, WLB1, WLA1, WLA2, . . . . Further, a pitch d2 between WLA-WLA and between WLB-WLB is made smaller than a pitch d1 between WLA-WLB. As such, the word lines of an identical port are disposed at the pitch d2 on one of both sides of a certain word line as a criterion, while the word lines of different ports are disposed at the pitch d1 on the other. With the above configuration, for example, as compared with a case of alternately disposing WLA and WLB, interference between ports can be reduced even with a small area, and the noise margin can be expanded.

Owner:RENESAS ELECTRONICS CORP

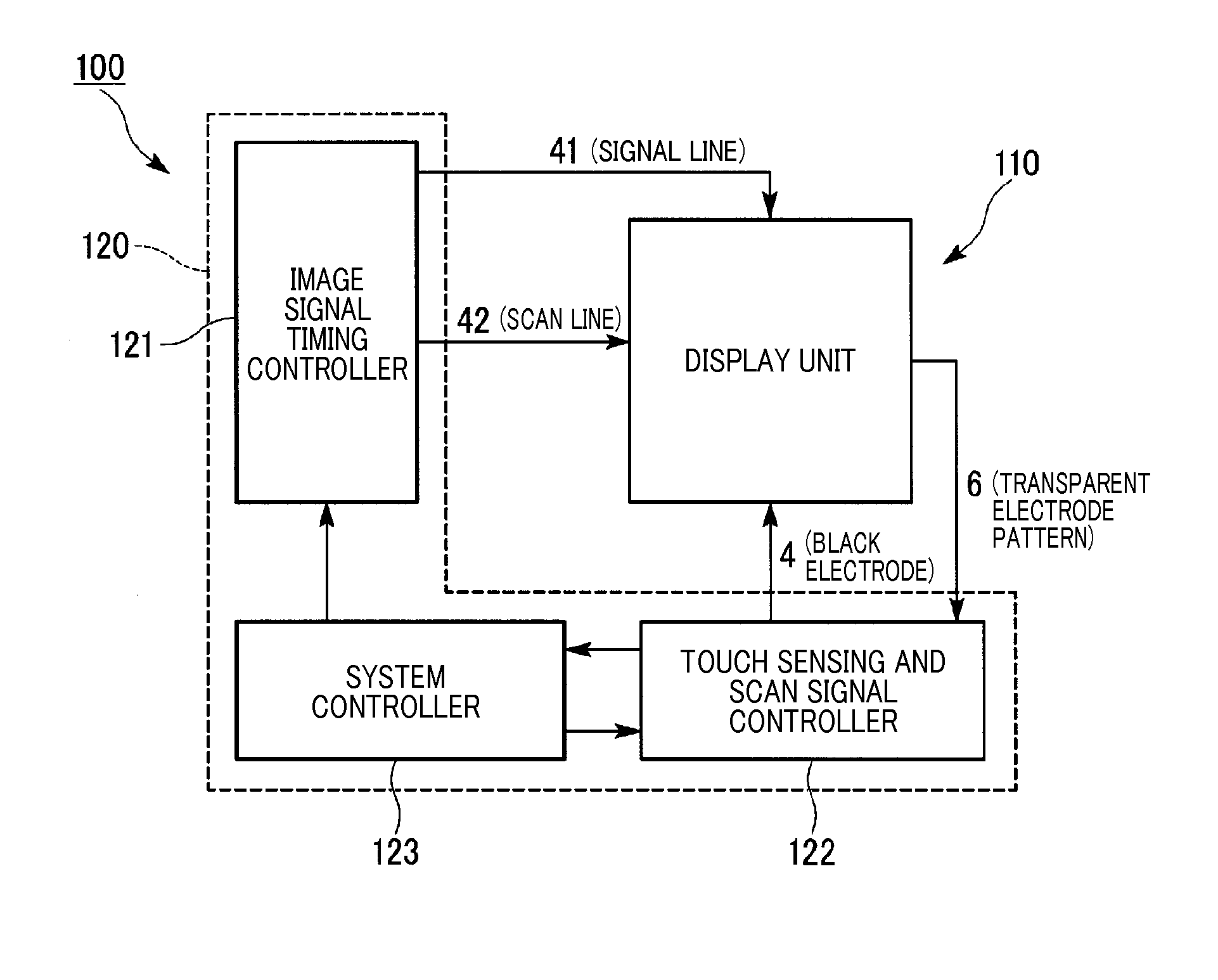

Liquid crystal display device

ActiveUS20160364082A1Increase the aperture ratioHigh light transmittanceStatic indicating devicesNon-linear opticsLiquid-crystal displayAlloy

A liquid crystal display device with a surface of a first transparent substrate, the surface of the substrate facing a liquid crystal layer, a plurality of light absorptive resin layer patterns, a plurality of metal layer patterns, a transparent resin layer, and a plurality of transparent electrode patterns are laminated in this order; the plurality of light absorptive resin layer patterns and the plurality of metal layer patterns have openings formed therein and formed into the same shape when viewed in a laminating direction; the plurality of metal layer patterns are arrayed in a first direction, being insulated from each other; the plurality of transparent electrode patterns are arrayed in a second direction perpendicular to the first direction, being insulated from each other; each metal layer pattern has at least one of an alloy layer mainly containing copper, and a copper layer.

Owner:TOPPAN PRINTING CO LTD

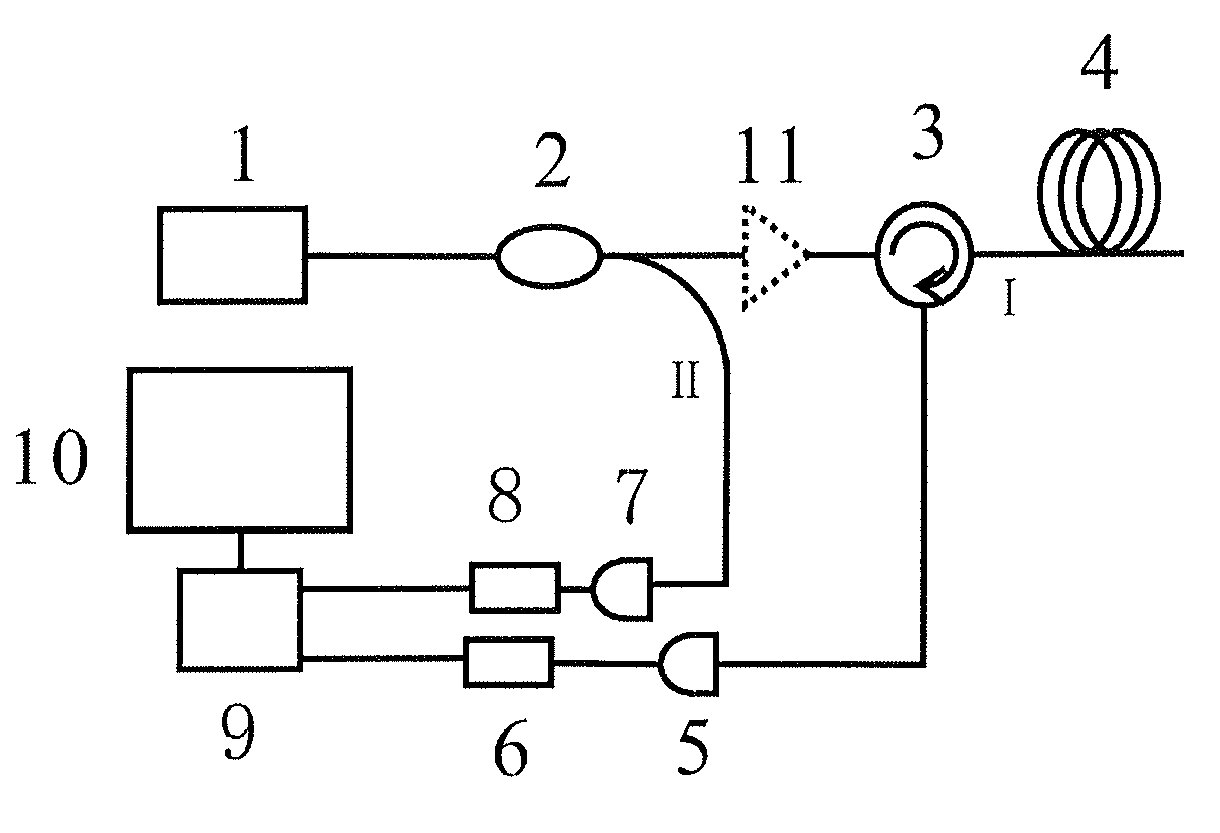

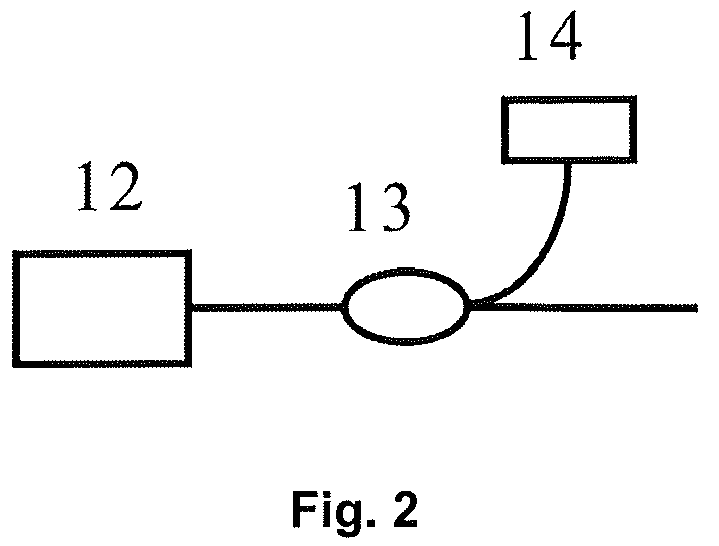

Chaotic optical time domain reflectometer method and apparatus

ActiveUS8502964B2High resolutionSimple structureAmplifier modifications to reduce noise influenceMaterial analysis by optical meansLaser transmitterPhotodetector

In a method and a corresponding apparatus for performing chaotic optical time domain reflectometer, the chaotic laser signal, generated by the chaotic laser transmitter, is split into probe signal I and reference signal II by a fiber coupler. Through an optical circulator, the probe signal I is launched into the test fiber and the echo light is converted into electrical signal by a photodetector and digitalized by an A / D converter. The reference signal II is converted into electrical signal by a photodetector and digitalized by another A / D converter. Two digital signals received from two A / D converters are correlated in a signal processing device to locate the exact position of faults in fibers. The result output is then displayed on a display device. This invention was developed to overcome the tradeoff problem between resolution and dynamic range of the pulse-based OTDR.

Owner:TAIYUAN UNIV OF TECH

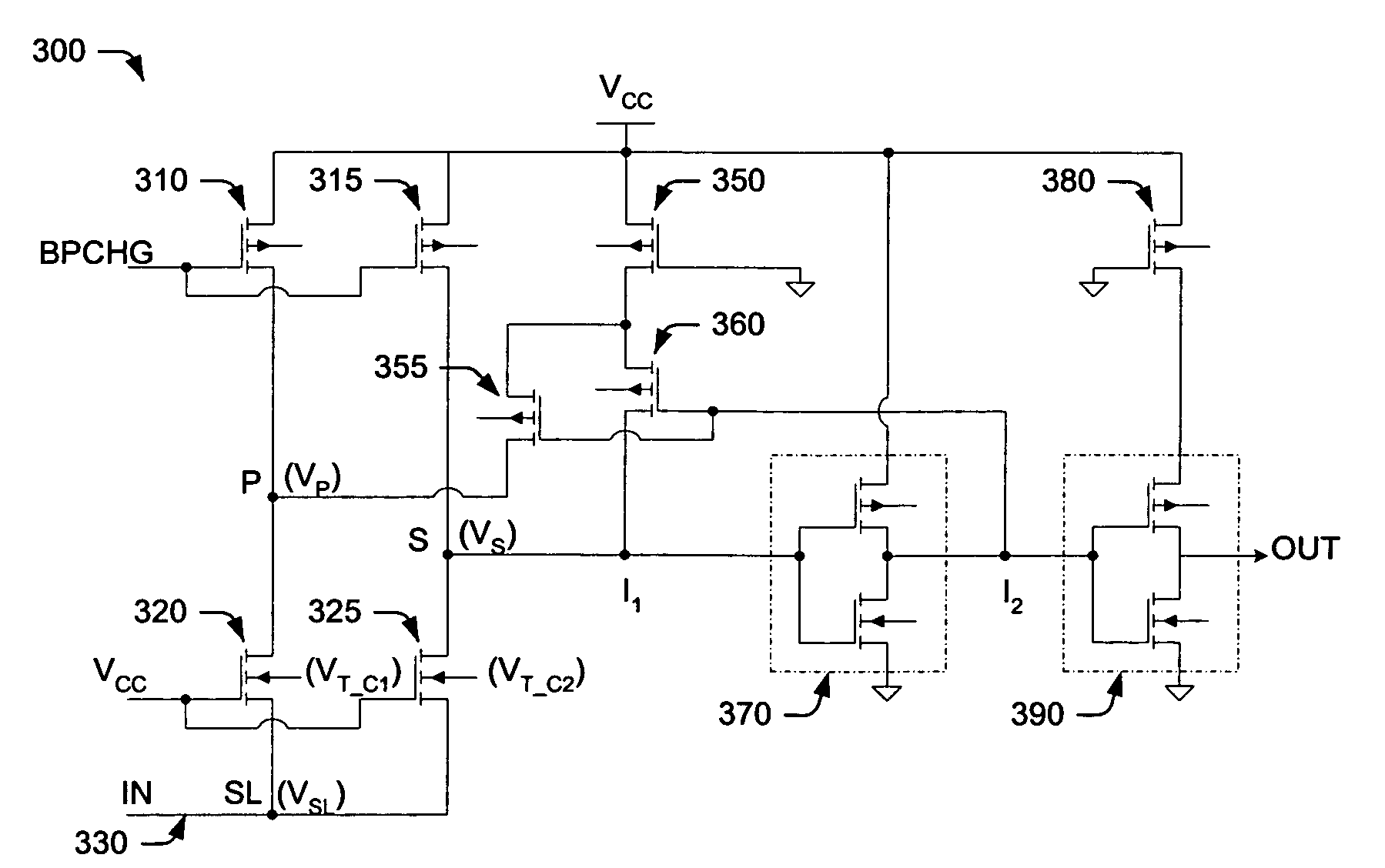

Sense amplifier with dual cascode transistors and improved noise margin

ActiveUS7126869B1Acceptable noise marginImprove the sense of speedDigital storageAudio power amplifierNoise margin

A sense amplifier, system and methods for increasing a noise margin of the sense amplifier are contemplated herein. In general, the sense amplifier includes a pair of cascode transistors coupled in parallel between a power supply node and a sense line of the sense amplifier. The sense amplifier also includes a precharge node coupled to the power supply node through a first precharge transistor, and a sense node coupled to the power supply node through a second precharge transistor. The sense amplifier described herein functions to separate the sense node from the precharge node with the pair of cascode transistors, which in turn, increases the noise margin of the sense amplifier by decoupling the sense node from any voltage fluctuations that may be present on the sense line during a sensing state.

Owner:MONTEREY RES LLC

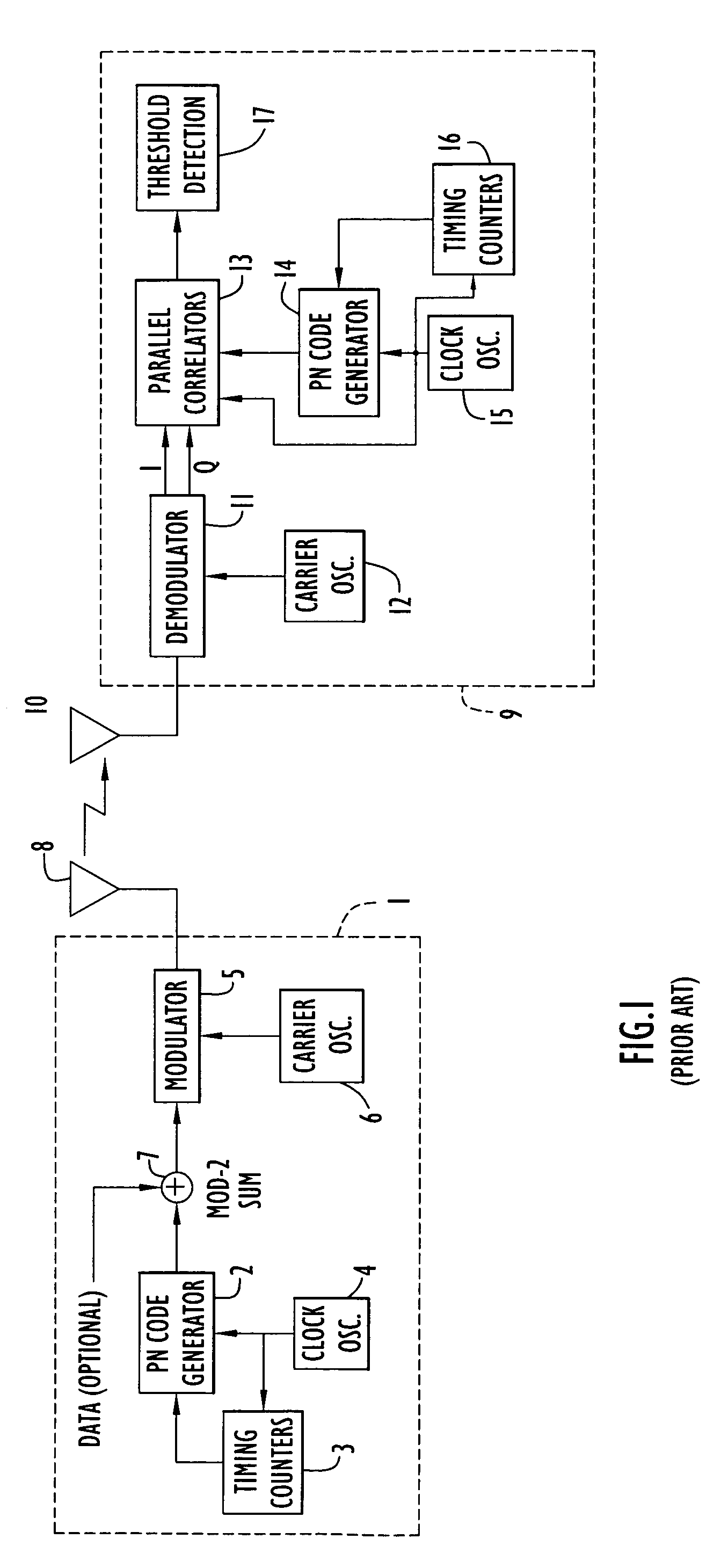

Method and apparatus for generating an interleaved code

InactiveUS6959030B1Improve toleranceQuick checkError detection/correctionCode division multiplexCode generationSymbol interleaving

An interleaved coding method can be used in a transmitter, in which the two or more pseudonoise (PN) codes are interleaved to form a longer interleaved code. The method can be used in a transmitter that includes a first code generator generating a first code of n symbols, and a second code generator generating a second code of m symbols, where n and m can be mutually prime, such as m=n+1. An interleave unit is coupled to the first and second code generators, and interleaves the symbols of the first code with the symbols of the second code to output an interleaved code. The interleaved code has a period longer than either of the constituent PN codes, providing for much increased noise tolerance over using the short codes alone, and can be detected at a much lower hardware and time cost than if using a single PN code of equal length.

Owner:HARRIS CORP

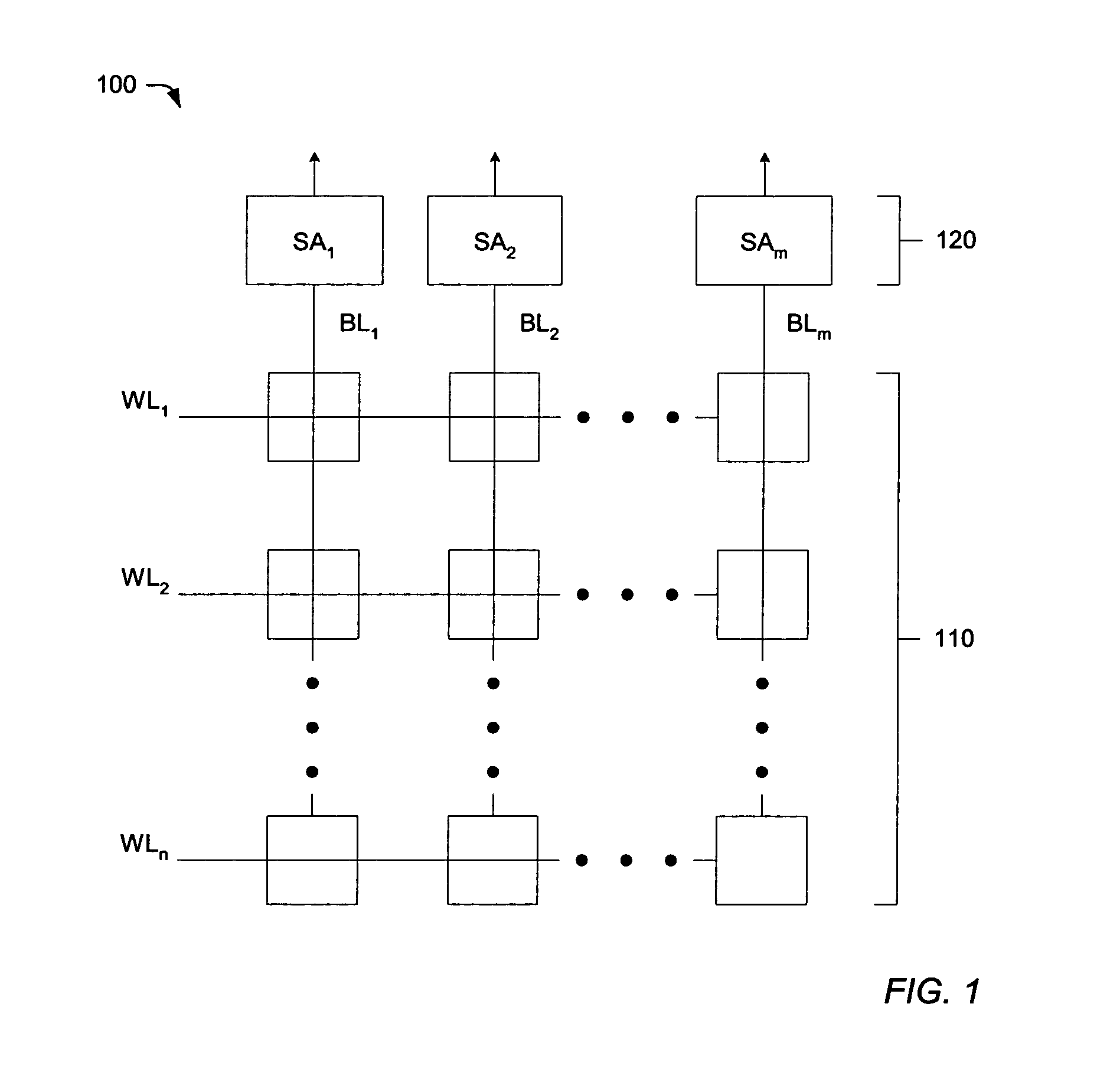

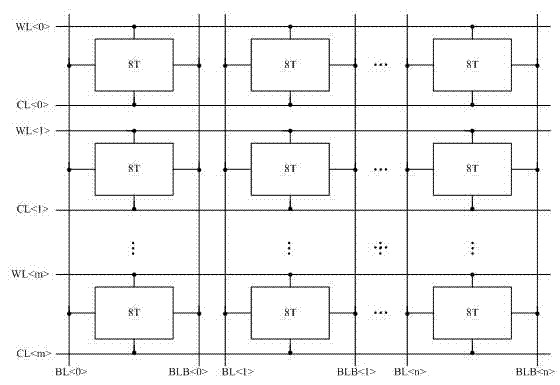

Semiconductor device having multiport memory

ActiveUS7940542B2Reduce distractionsImprove noise marginTransistorSolid-state devicesNoise marginComputer science

A semiconductor device enabling expansion of a noise margin. For example, in a memory area in which each memory cell MC is coupled to a word line WLA for a first port and a word line WLB for a second port, and a plurality of memory cells MC is disposed in a matrix shape, each word line is disposed in the order like WLA0, WLB0, WLB1, WLA1, WLA2, . . . . Further, a pitch d2 between WLA-WLA and between WLB-WLB is made smaller than a pitch d1 between WLA-WLB. As such, the word lines of an identical port are disposed at the pitch d2 on one of both sides of a certain word line as a criterion, while the word lines of different ports are disposed at the pitch d1 on the other. With the above configuration, for example, as compared with a case of alternately disposing WLA and WLB, interference between ports can be reduced even with a small area, and the noise margin can be expanded.

Owner:RENESAS ELECTRONICS CORP

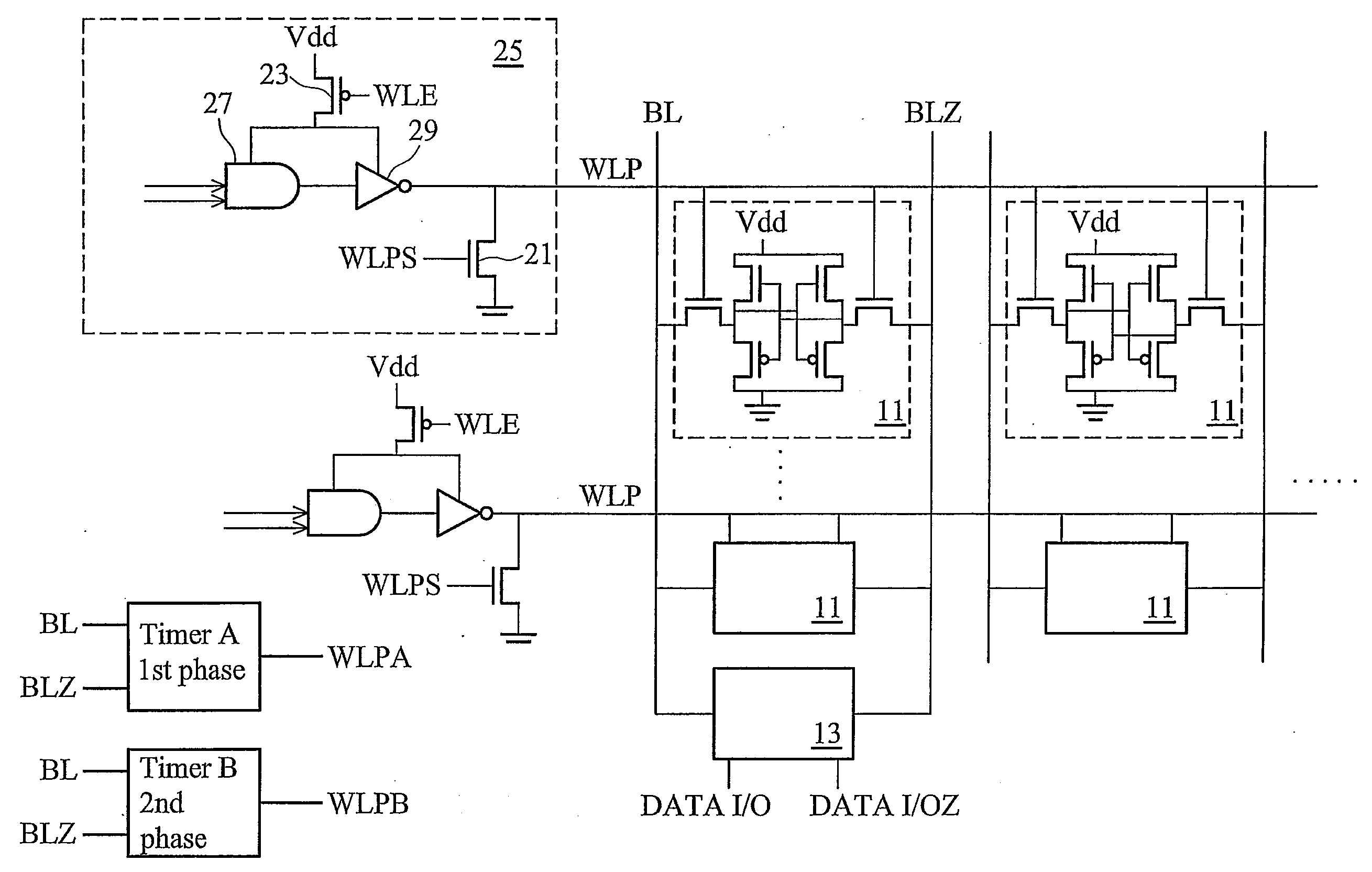

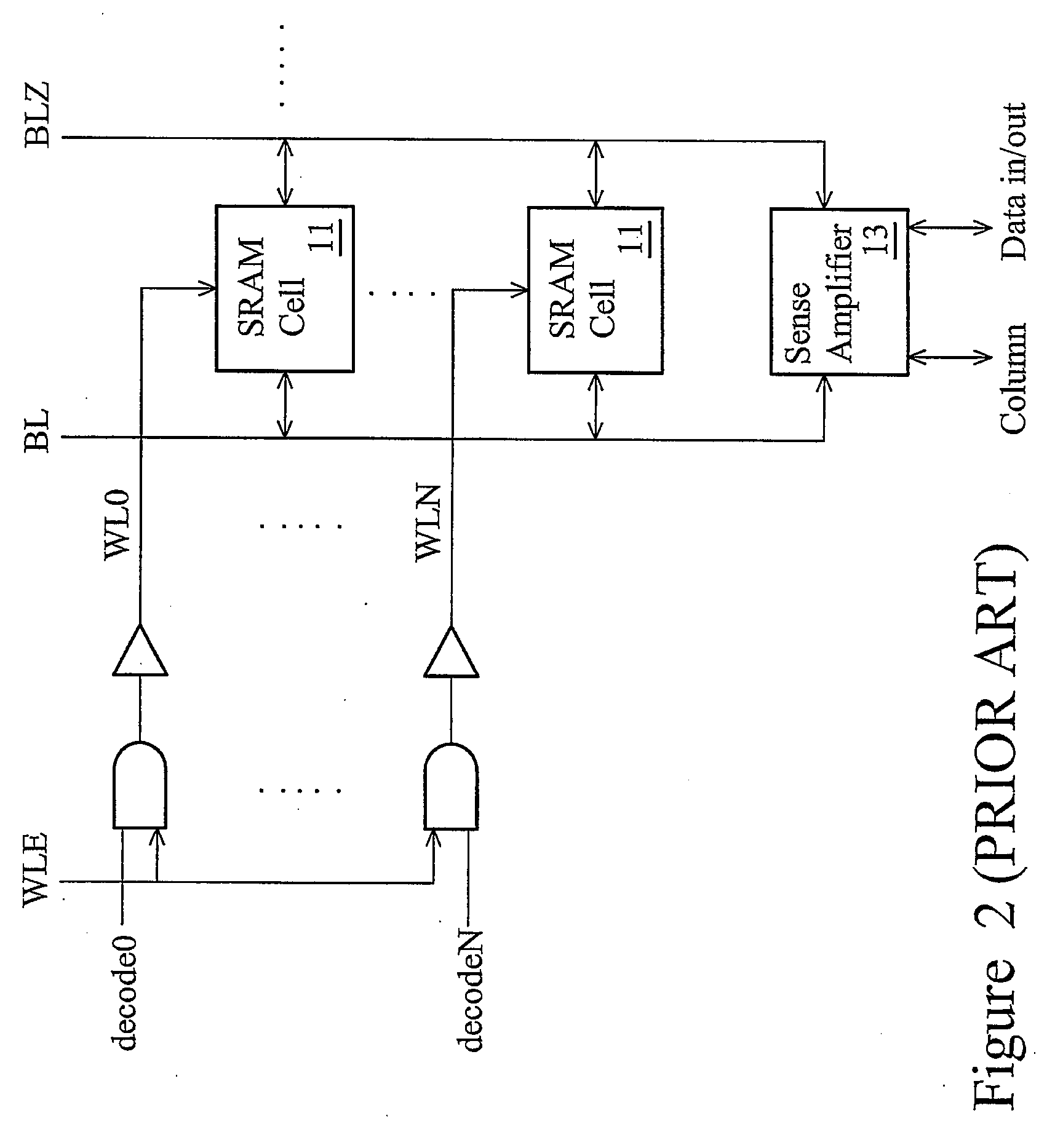

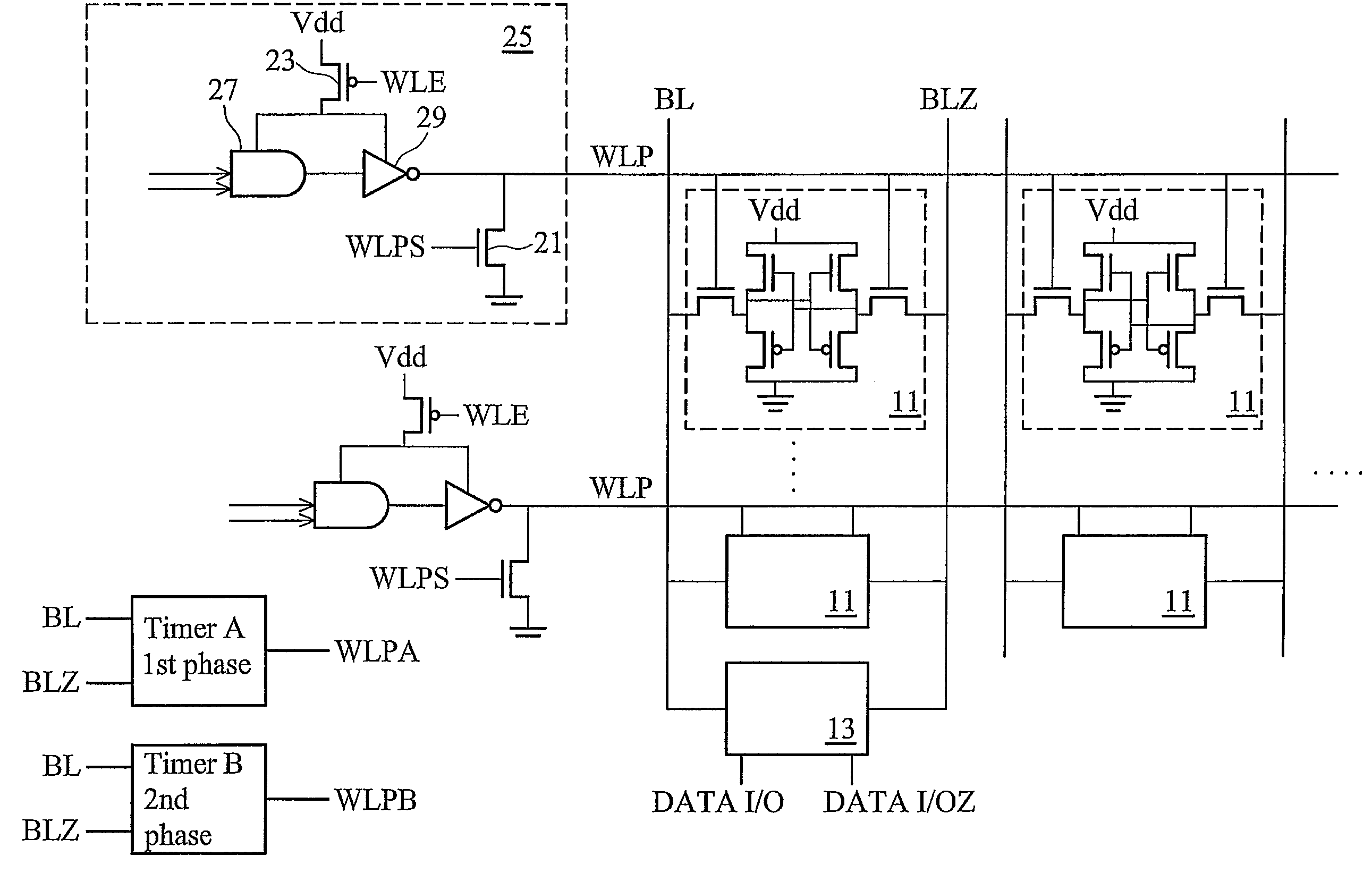

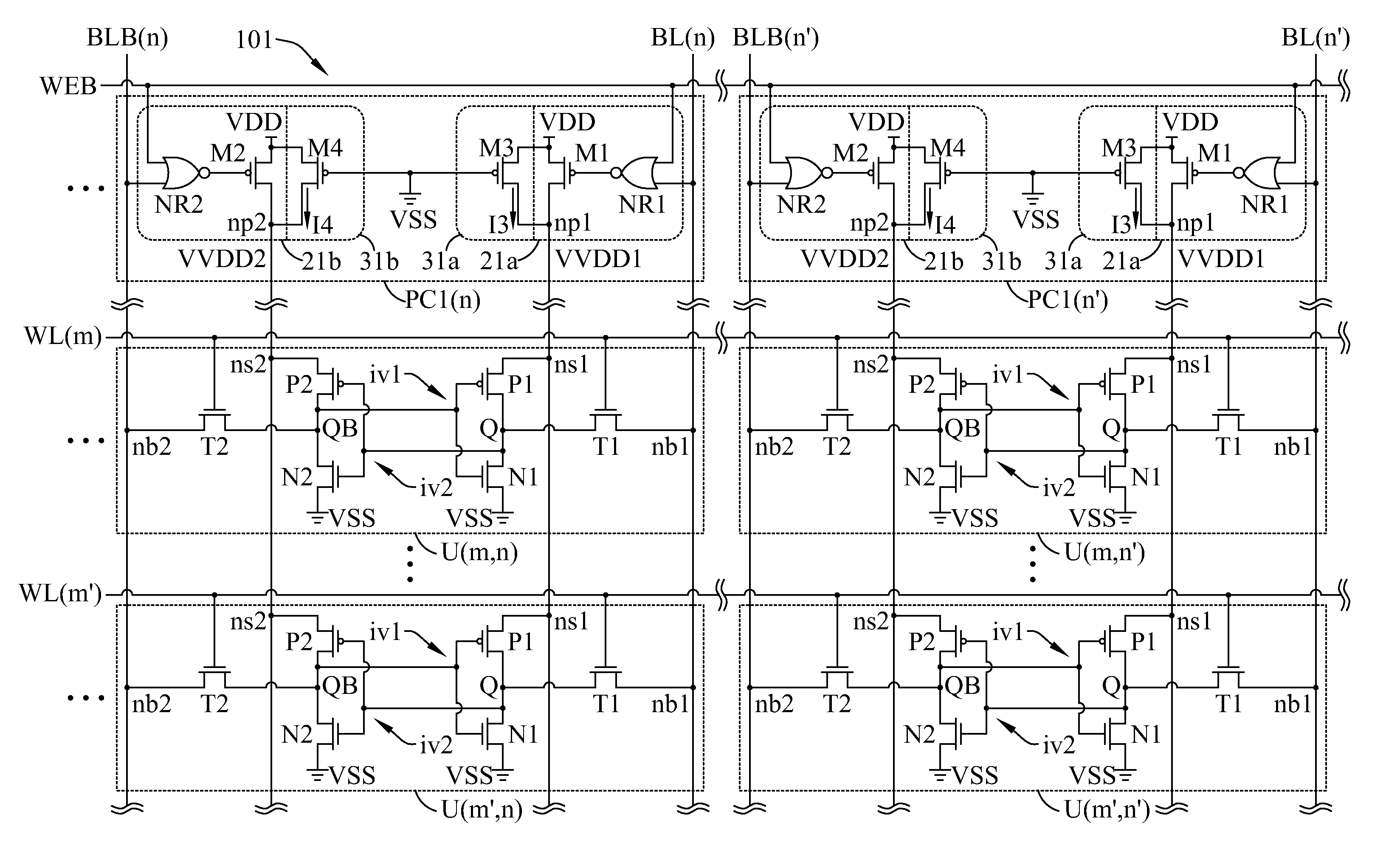

Circuit and method for an SRAM with two phase word line pulse

ActiveUS20080106963A1Reduce and save power consumptionImprove noise marginDigital storageBit lineControl signal

A circuit and method for providing a two phase word line pulse for use during access cycles in an SRAM memory with improved operating margins. A first and a second timing circuit are provided and a word line voltage suppression circuit is provided to reduce the voltage on the active word lines in a first phase of a word line pulse, and to allow the word lines to rise to a second, unsuppressed voltage in a second phase of the word line pulse, responsive to the first and second timing circuits. The first and second timing circuits observe the bit lines voltage discharge and provide control signals active when the bit lines are discharged past certain thresholds, these signals control the voltage suppression circuit. Operating margins for the SRAM are therefore improved. Methods for operating an SRAM using a two phase word line pulse are provided.

Owner:TAIWAN SEMICON MFG CO LTD

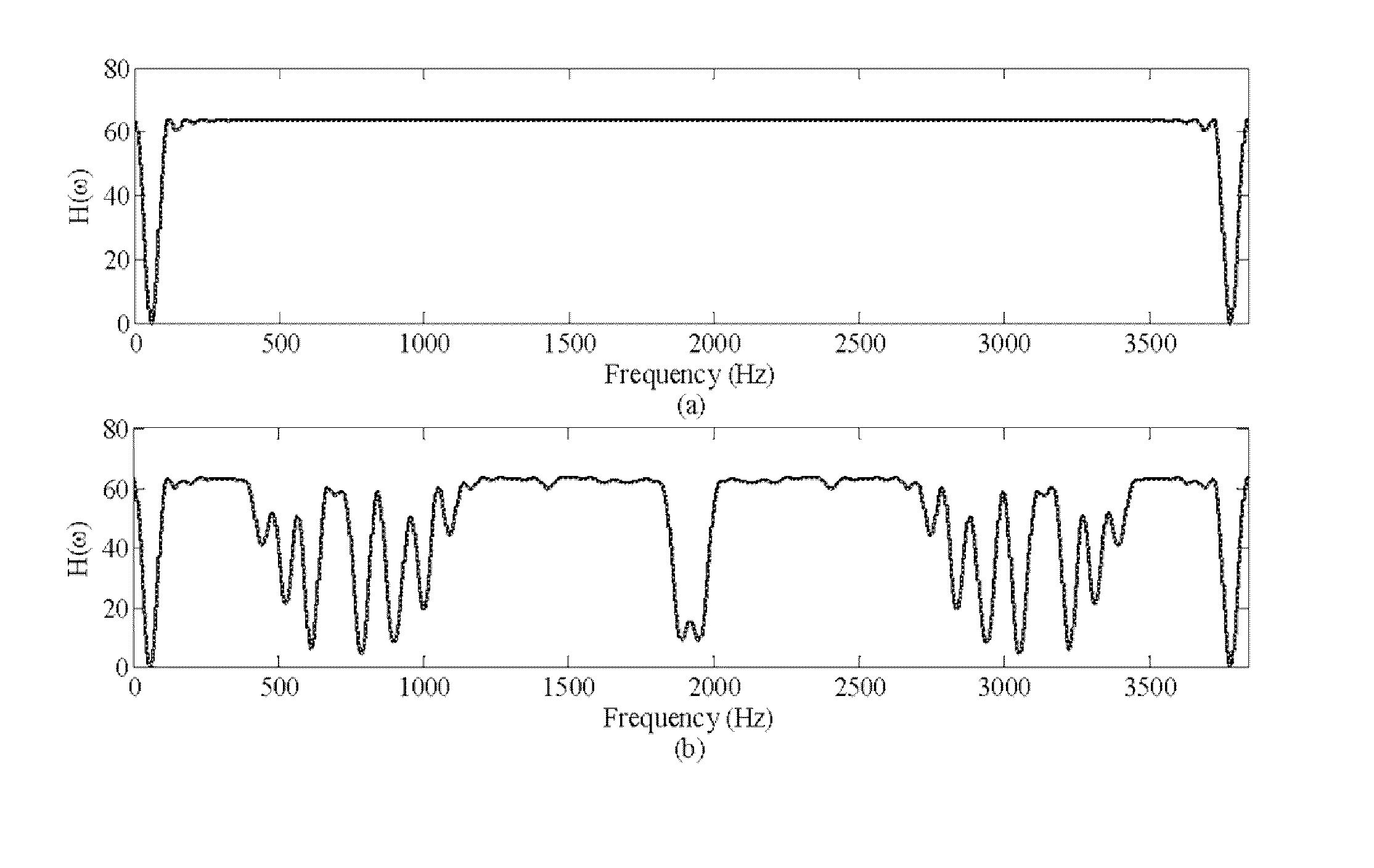

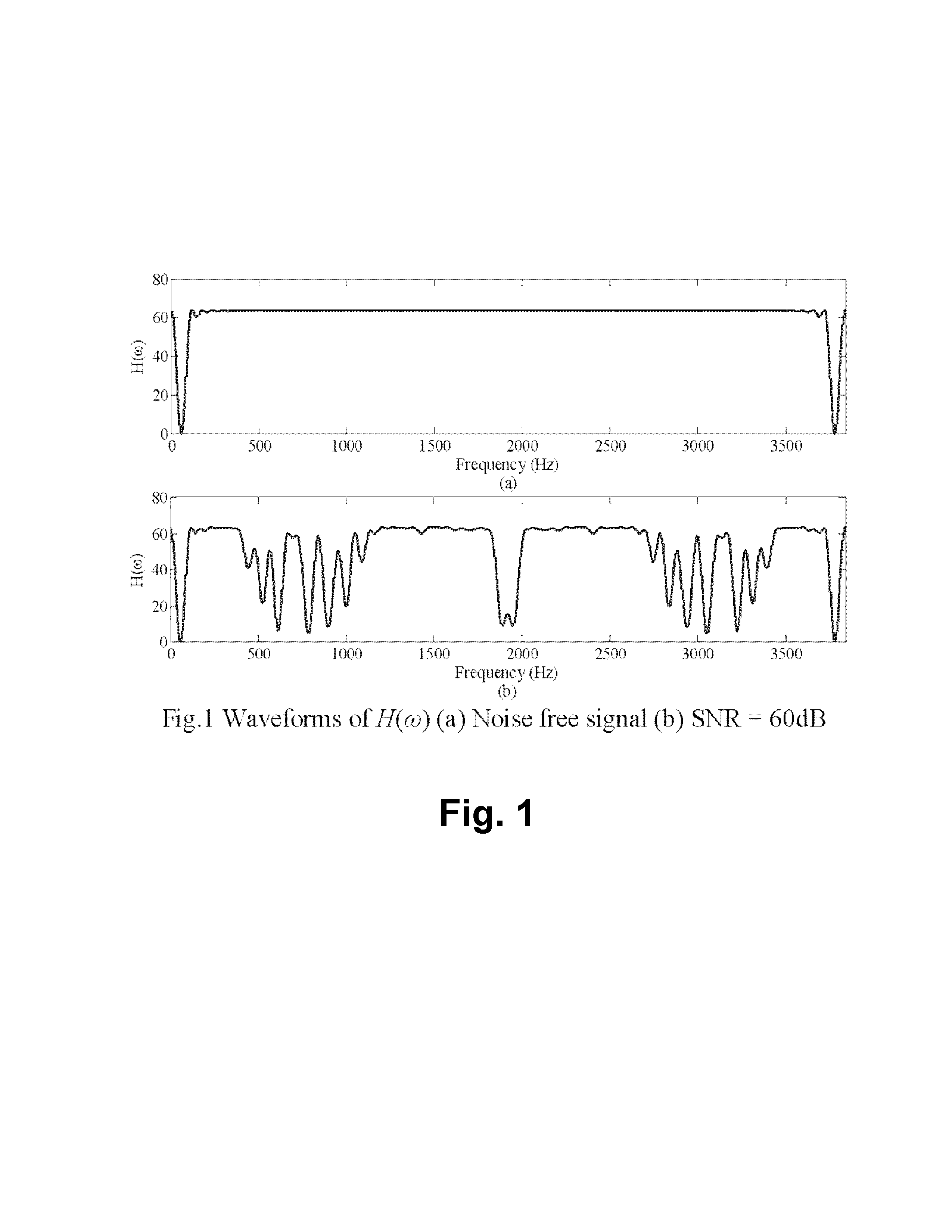

Robust high resolution spectrum estimation method for accurate phasor, harmonic and interharmonic measurement in power systems

InactiveUS20130173189A1Improve noise marginRobust and accurateSpectral/fourier analysisElectric devicesFrequency spectrumSmart meter

A high-resolution Subspace-Least Mean Square (S-LMS) method for harmonic and interharmonic measurement in power systems is provided. The eigenvector corresponding to the smallest eigenvalue is used to calculate the frequencies of the signal, and the least mean square method is used to estimate the amplitude and phase angle of harmonic and interharmonic components based on the computed frequencies and time domain measurements of the signal. Three schemes, namely sparsity, catch-and-pinpoint, and hybrid are presented. The S-LMS method provides accurate phasor, harmonic and interharmonic measurements for power system monitoring. The speed, accuracy, and resilience of the S-LMS method can be further increased by each of the three schemes. The method has a wide range of applications in power quality analyzers, synchronized phasor measurement, situational awareness, dynamic equivalencing, and smart meters.

Owner:UNIV OF CONNECTICUT

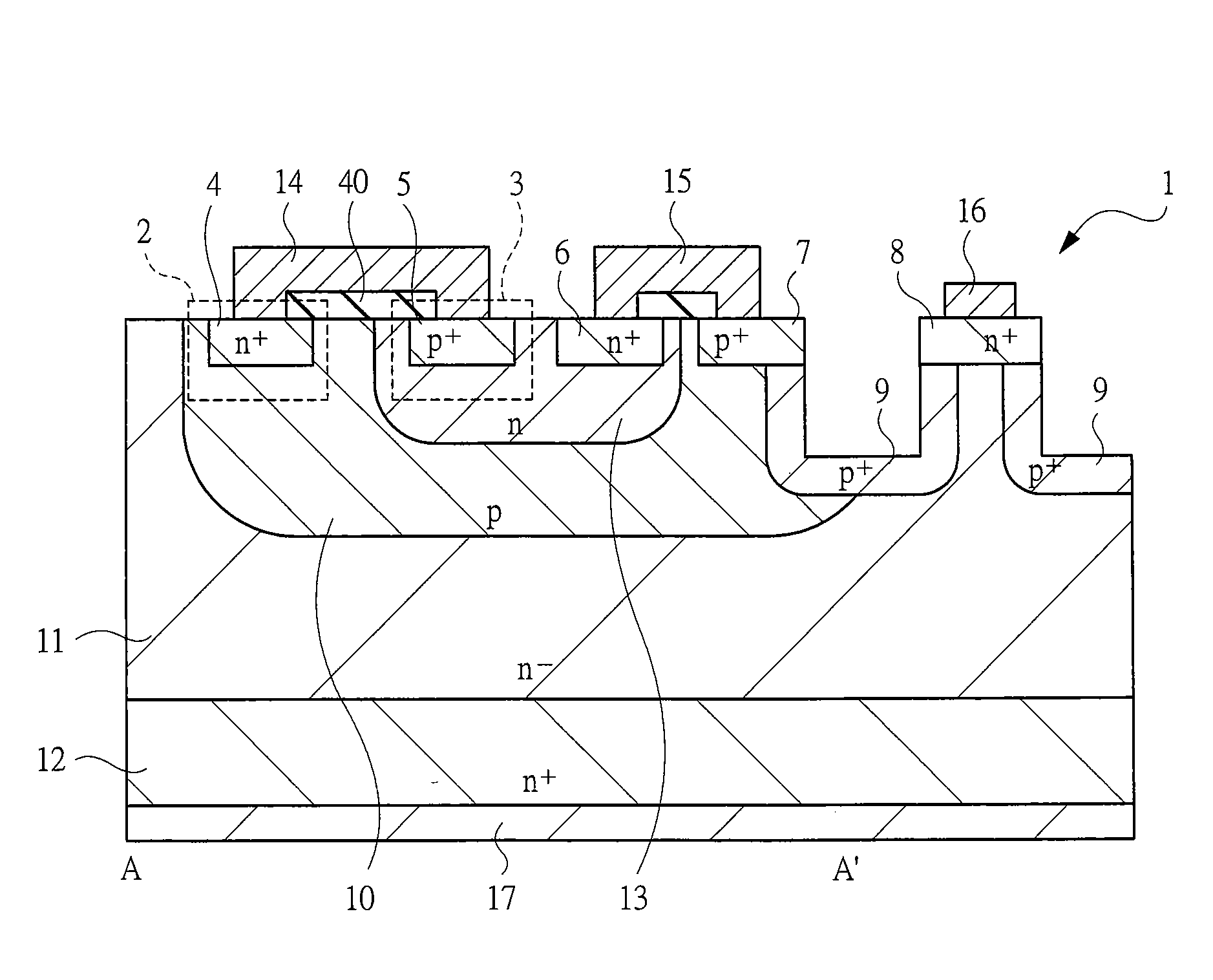

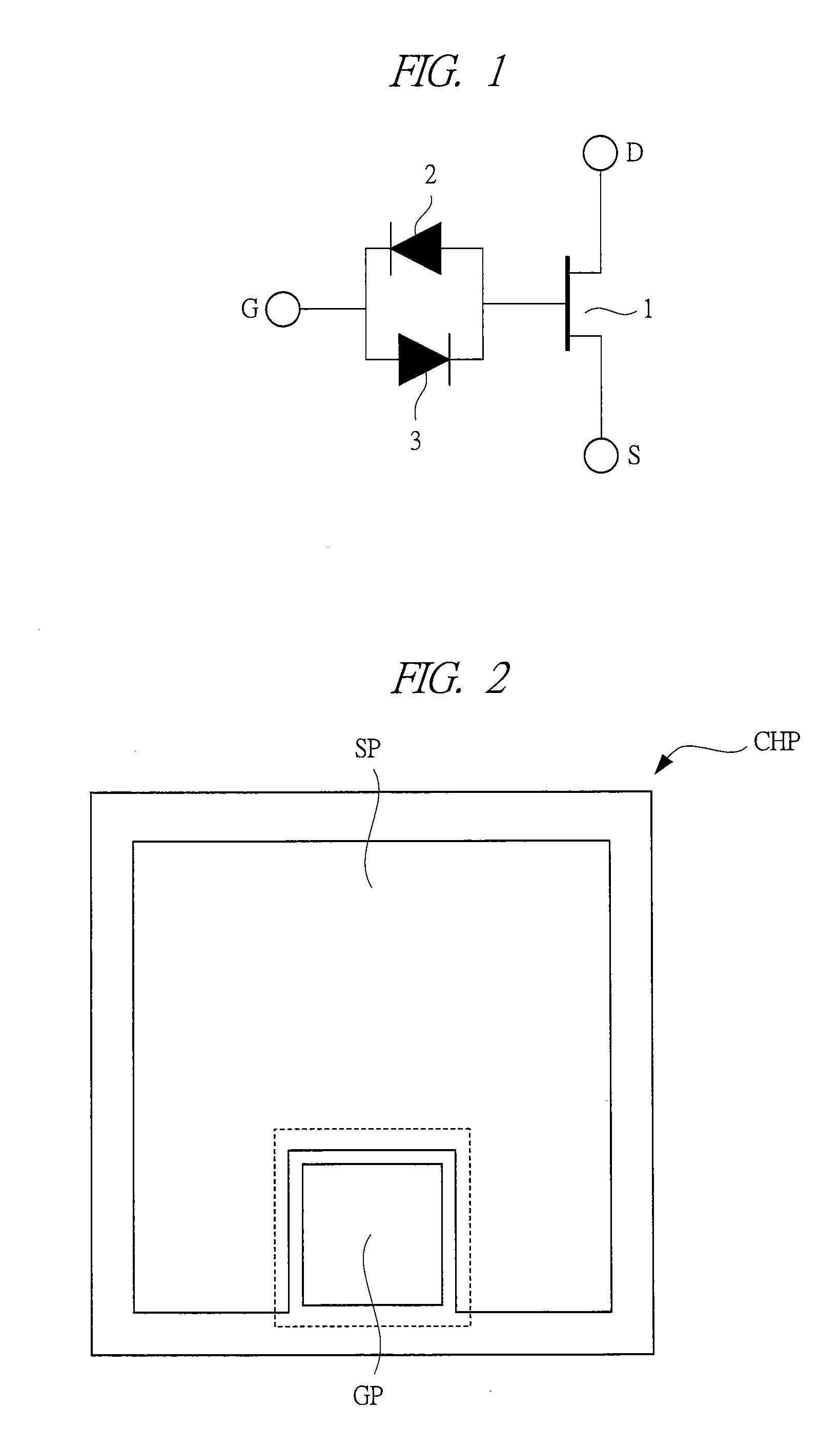

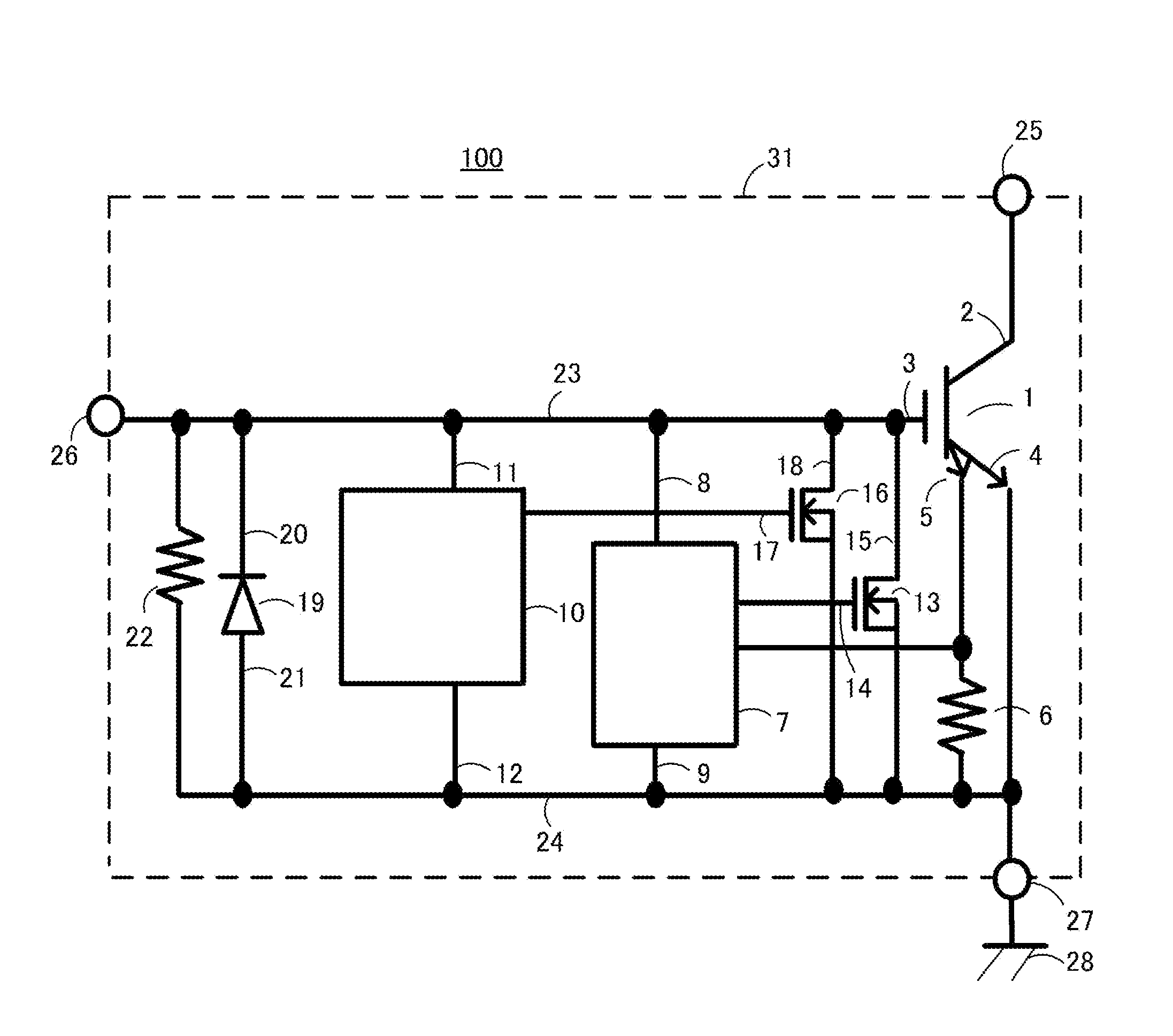

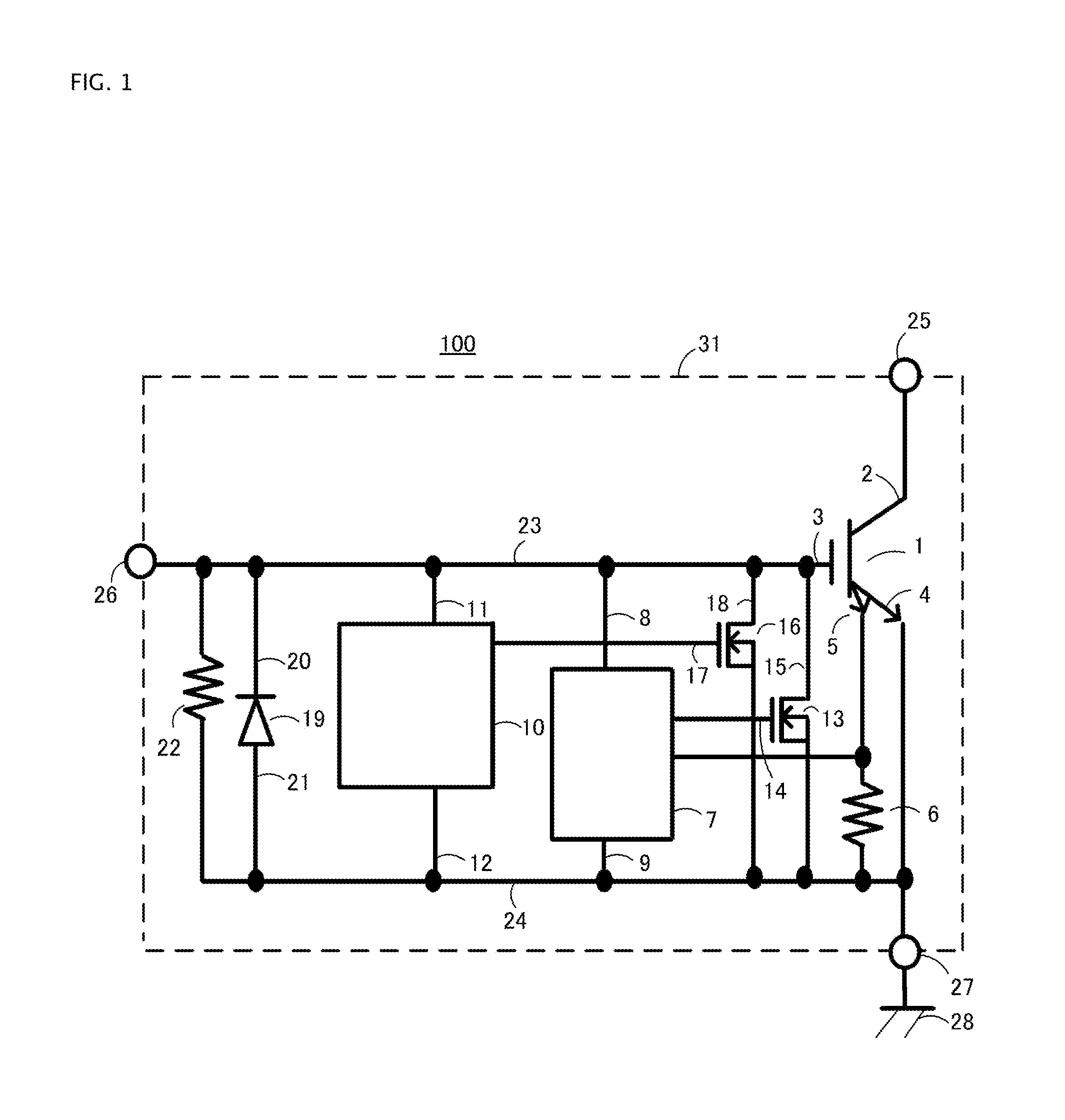

Single chip igniter and internal combustion engine ignition device

ActiveUS20140015005A1Low working voltageImproved noise toleranceTransistorSolid-state devicesMicrocontrollerHysteresis

Aspects of the invention are directed to a single chip igniter such that it is possible to realize a reduction in operating voltage, an increase in noise tolerance, a reduction in size, and a reduction in cost. By reducing the gate threshold voltage of a MOS transistor, and reducing the operating voltages of a current limiter circuit, an overheat detector circuit, a timer circuit, an overvoltage protection circuit, an input hysteresis circuit, and the like, it is possible to reduce the operating voltage of a single chip igniter. In some aspects of the invention, the effective gate voltage of the MOS transistor is 1V or more, and the channel length of the MOS transistor is 4 μm or less. Also, in some aspects of the invention, the thickness of a gate oxide film of the MOS transistor is 5 nm or more, 25 nm or less.

Owner:FUJI ELECTRIC CO LTD

Circuit and method for an SRAM with two phase word line pulse

ActiveUS7505345B2Reduce and save power consumptionImprove noise marginDigital storageBit lineControl signal

Owner:TAIWAN SEMICON MFG CO LTD

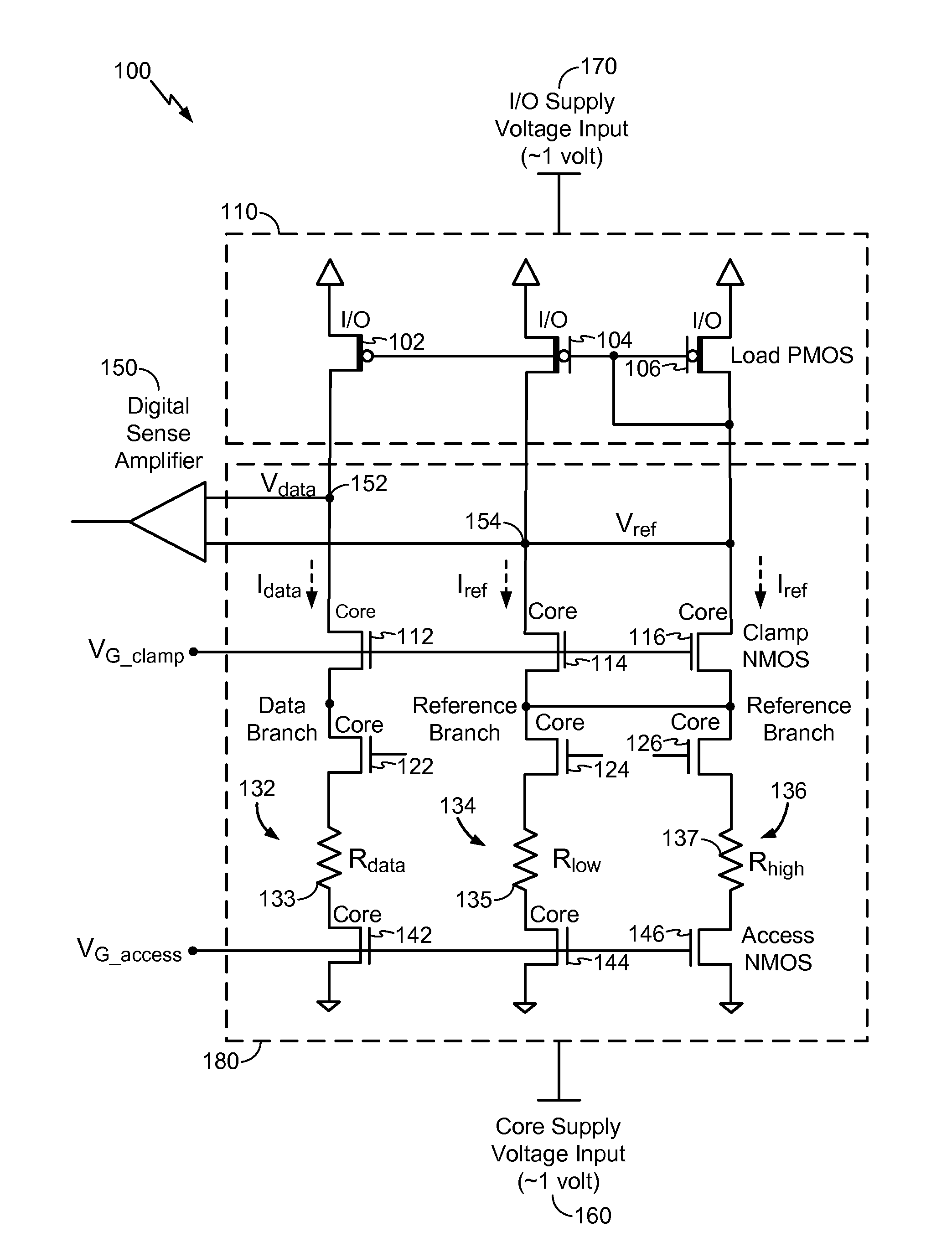

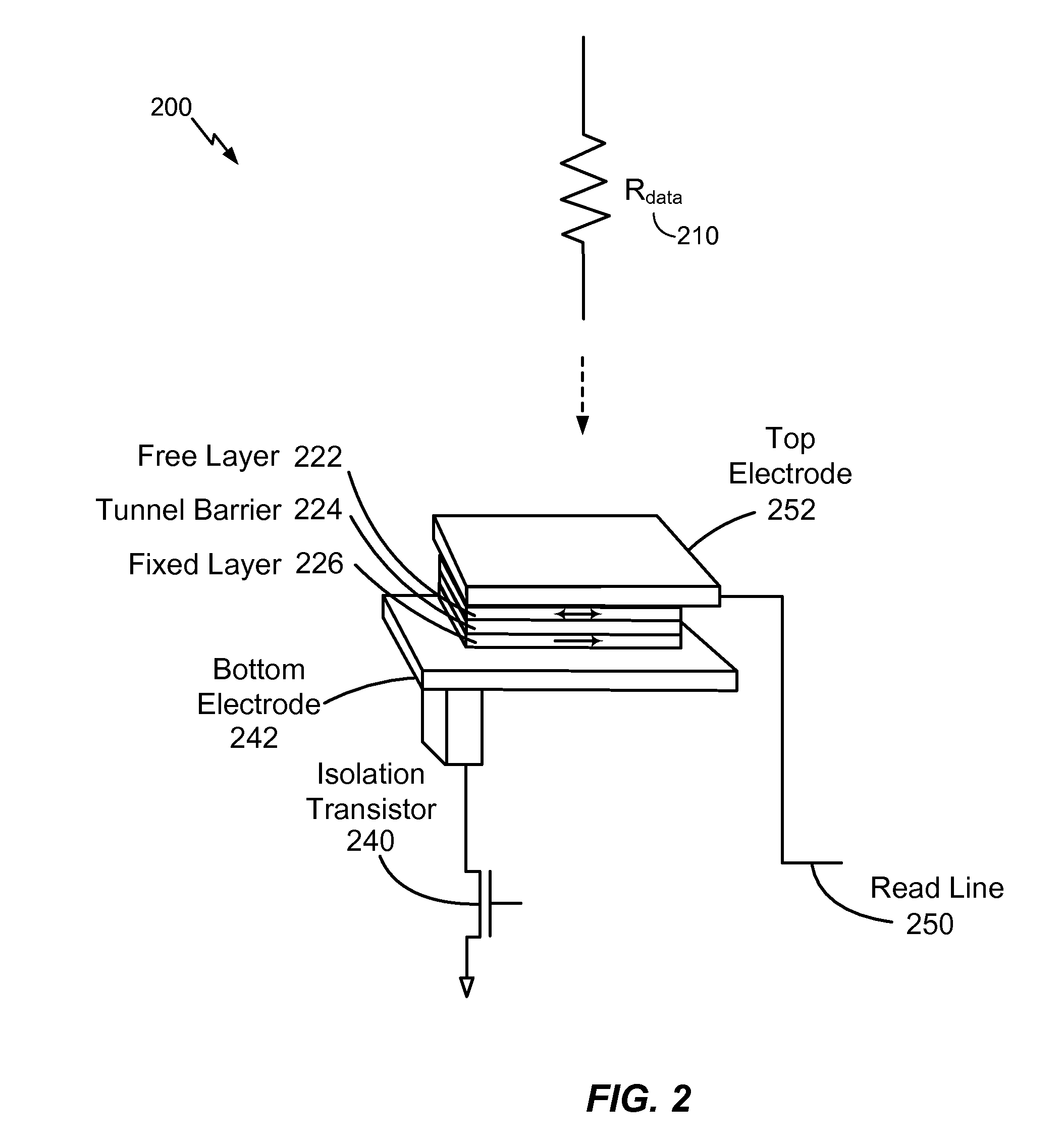

Resistance-based memory with reduced voltage input/output device

A resistance-based memory with a reduced voltage I / O device is disclosed. In a particular embodiment, a circuit includes a data path including a first resistive memory cell and a first load transistor. A reference path includes a second resistive memory cell and a second load transistor. The first load transistor and the second load transistor are input and output (I / O) transistors adapted to operate at a load supply voltage similar to a core supply voltage of a core transistor within the circuit.

Owner:QUALCOMM INC +1

Electronic memory with binary storage elements

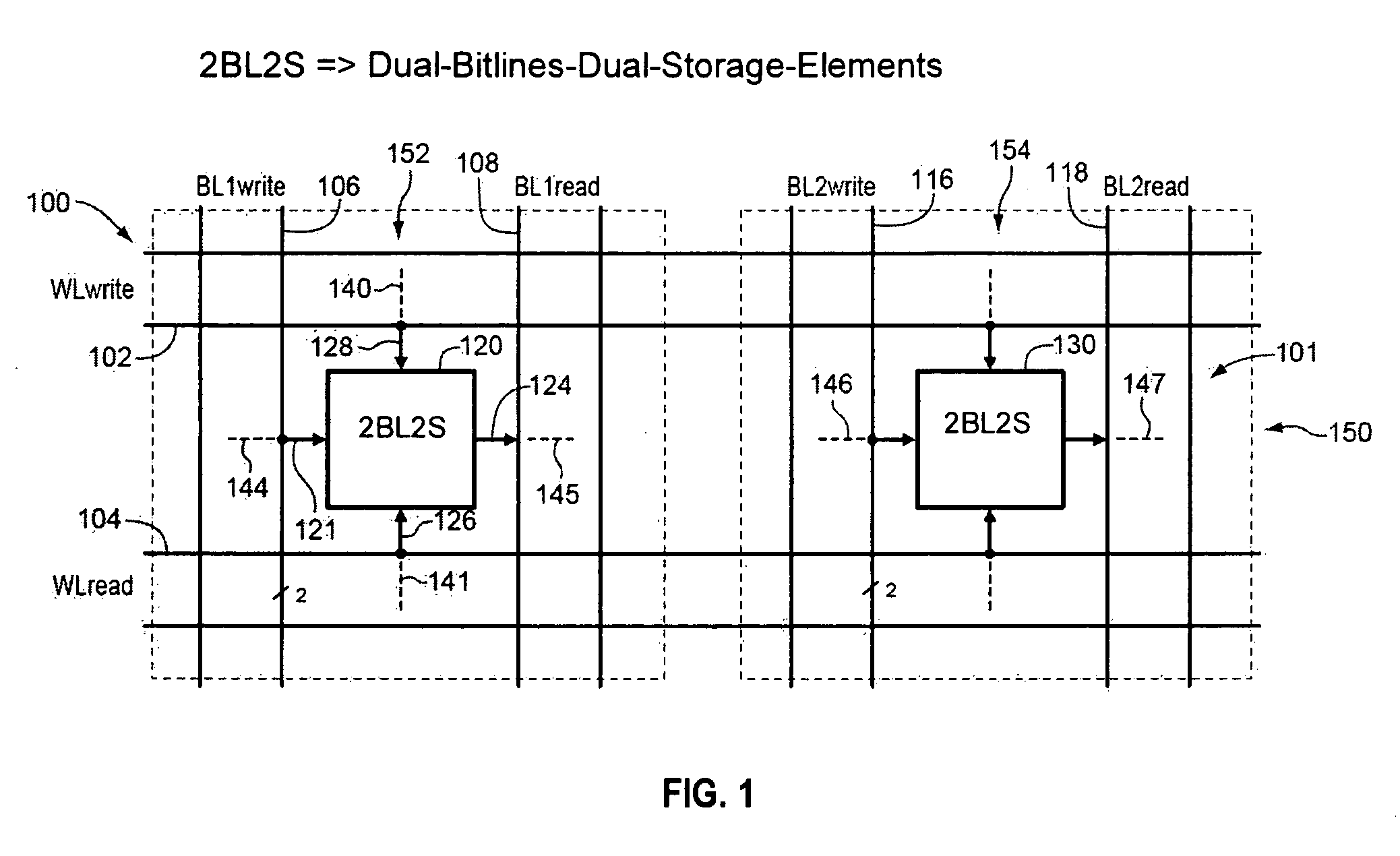

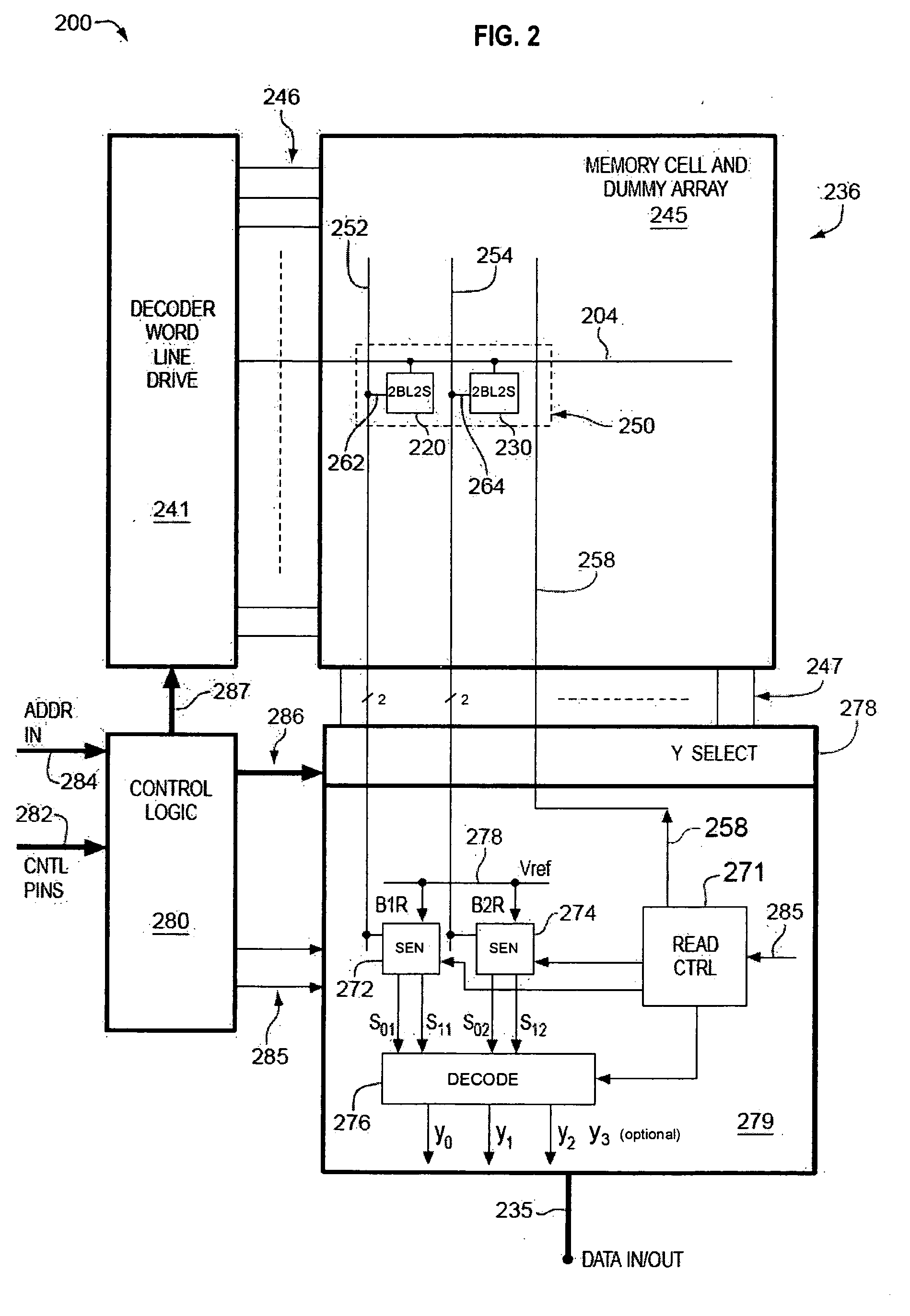

InactiveUS20060083098A1Improve noise marginNoise margin is lessRead-only memoriesDigital storageData bitsStorage cell

An electronic memory using true and complementary dual bit lines and dual binary storage elements cell architecture comprising a memory cell pair with four binary storage elements with each memory cell pair capable of existing in up to sixteen electronic memory states. The four binary storage elements together, normally used to store two true and complementary data bits, are used to store two, three, or four data bits depending on the noise margin allowed and bit width selection. The memory can be ferroelectric memory FeRAM, a flash memory, a ROM, a dynamic memory DRAM, an OUM, a MRAM, a NAND memory, or a NOR memory.

Owner:IOTA TECH

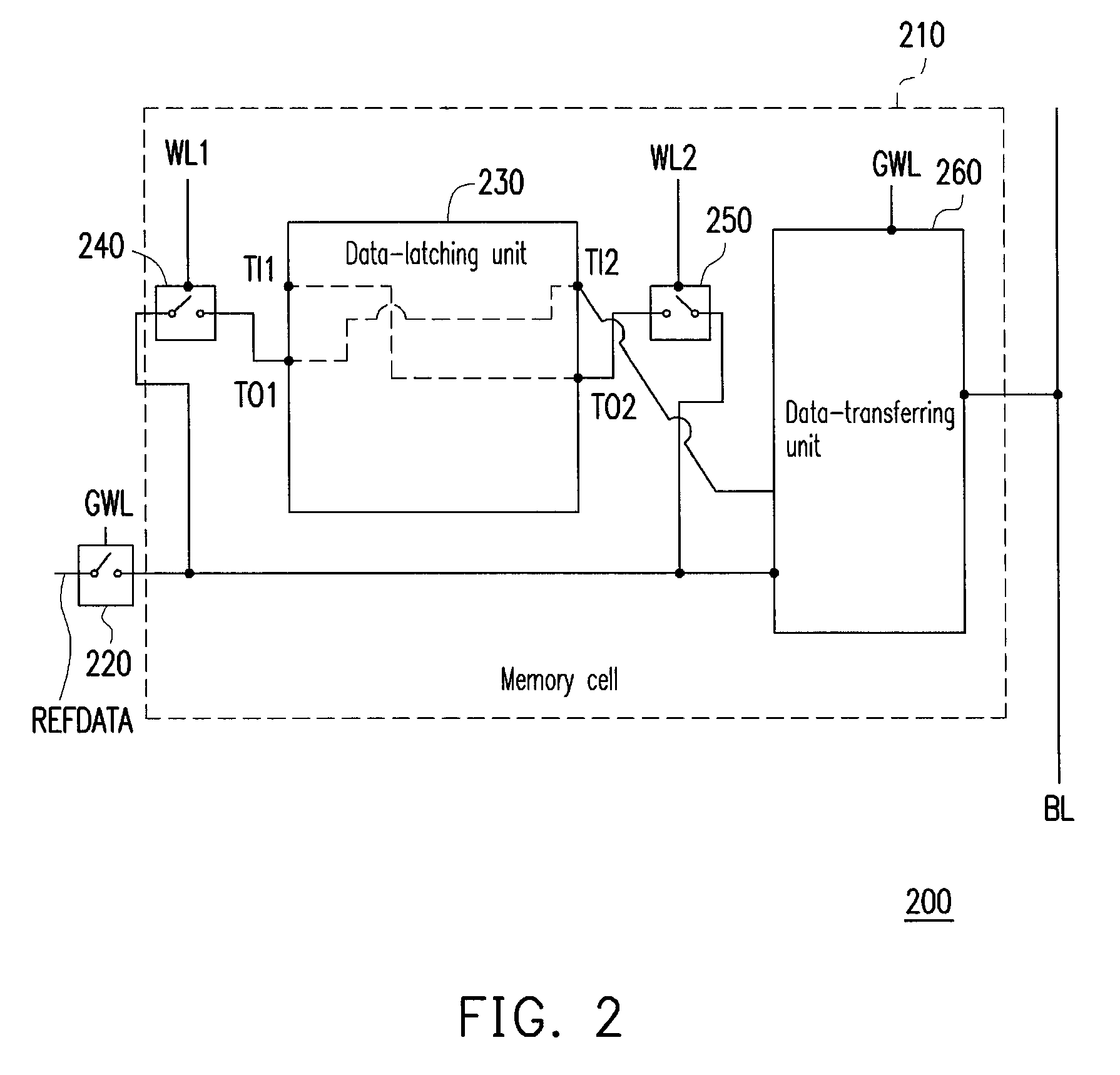

Single-ended SRAM with cross-point data-aware write operation

ActiveUS8693237B2Reduce possibly produced leak currentImprove noise marginDigital storageBit lineControl signal

A single-ended SRAM including at least one memory cell and a third switch is provided. The memory cell includes a data-latching unit, a first switch, a second switch and a data-transferring unit. The data-latching unit is configured for latching the received input data and provides a storage data and the inverse data of the storage data. The first switch transfers a reference data to the data-latching unit according to a first word-line signal. The second switch transfers the reference data to the data-latching unit according to a second word-line signal. The data-transferring unit decides whether or not to transfer the reference data to the bit-line according to the storage data and a control signal. The third switch receives the reference data and the control signal and transfers the reference data to the first switch, the second switch and the data-transferring unit according to the control signal.

Owner:NAT CHIAO TUNG UNIV

Data-aware dynamic supply random access memory

ActiveUS20120044779A1Reduce disturbanceImprove write performanceDigital storageData entryElectrical battery

A Random Access Memory (RAM) with a plurality of cells is provided. In an embodiment, the cells of a same column are coupled to a same pair of bit-lines and are associated to a same power controller. Each cell has two inverters; the power controller has two power-switches. For the cells of the same column, the two power-switches respectively perform independent supply voltage controls for the two inverters in each cell according to data-in voltages of the bit-lines during Write operation.

Owner:FARADAY TECH CORP +1

Data-aware dynamic supply random access memory

ActiveUS8345504B2Increase data storageReduce electrical conductivityDigital storageBit linePower inverter

A Random Access Memory (RAM) with a plurality of cells is provided. In an embodiment, the cells of a same column are coupled to a same pair of bit-lines and are associated to a same power controller. Each cell has two inverters; the power controller has two power-switches. For the cells of the same column, the two power-switches respectively perform independent supply voltage controls for the two inverters in each cell according to data-in voltages of the bit-lines during Write operation.

Owner:FARADAY TECH CORP +1

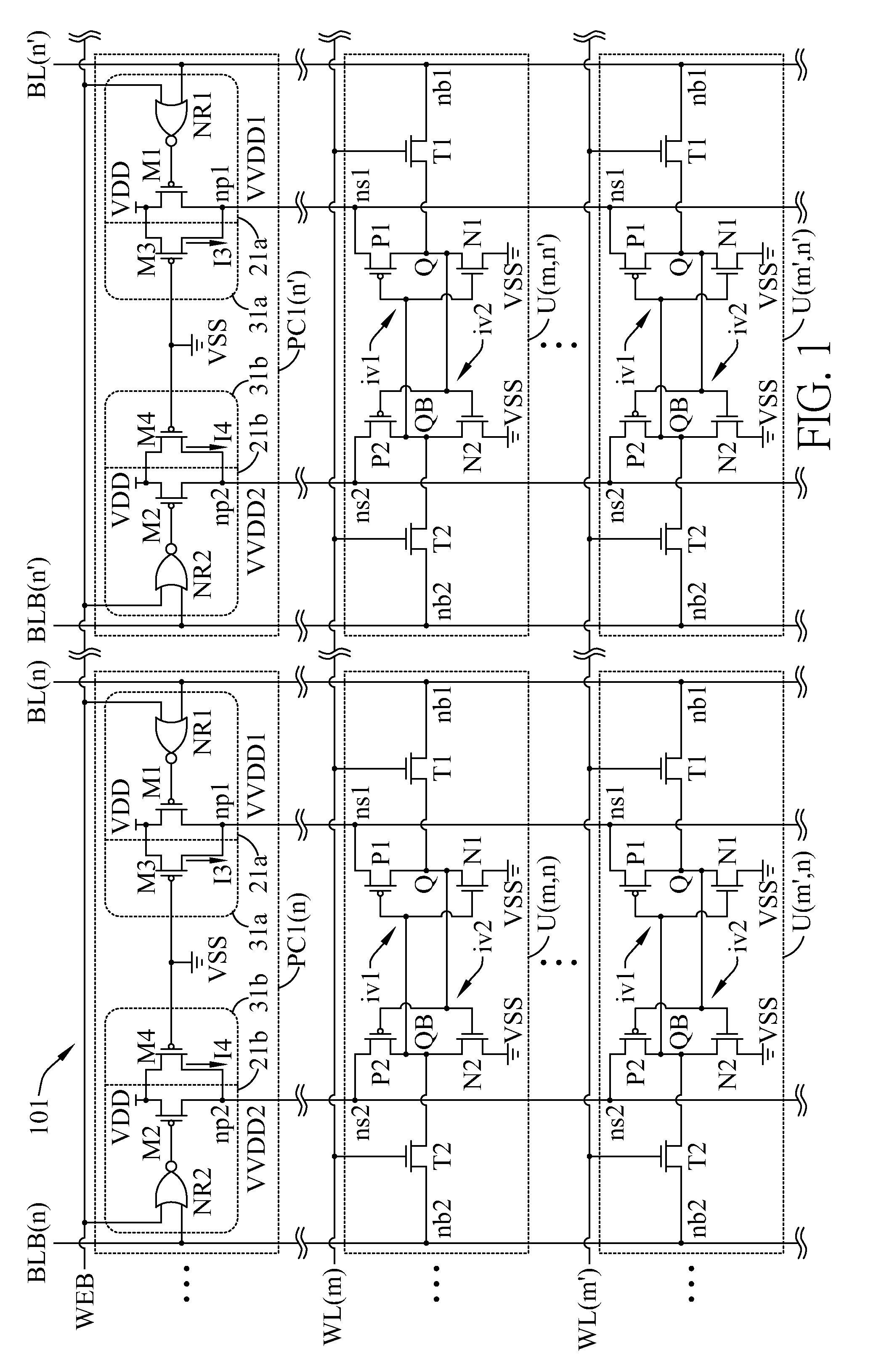

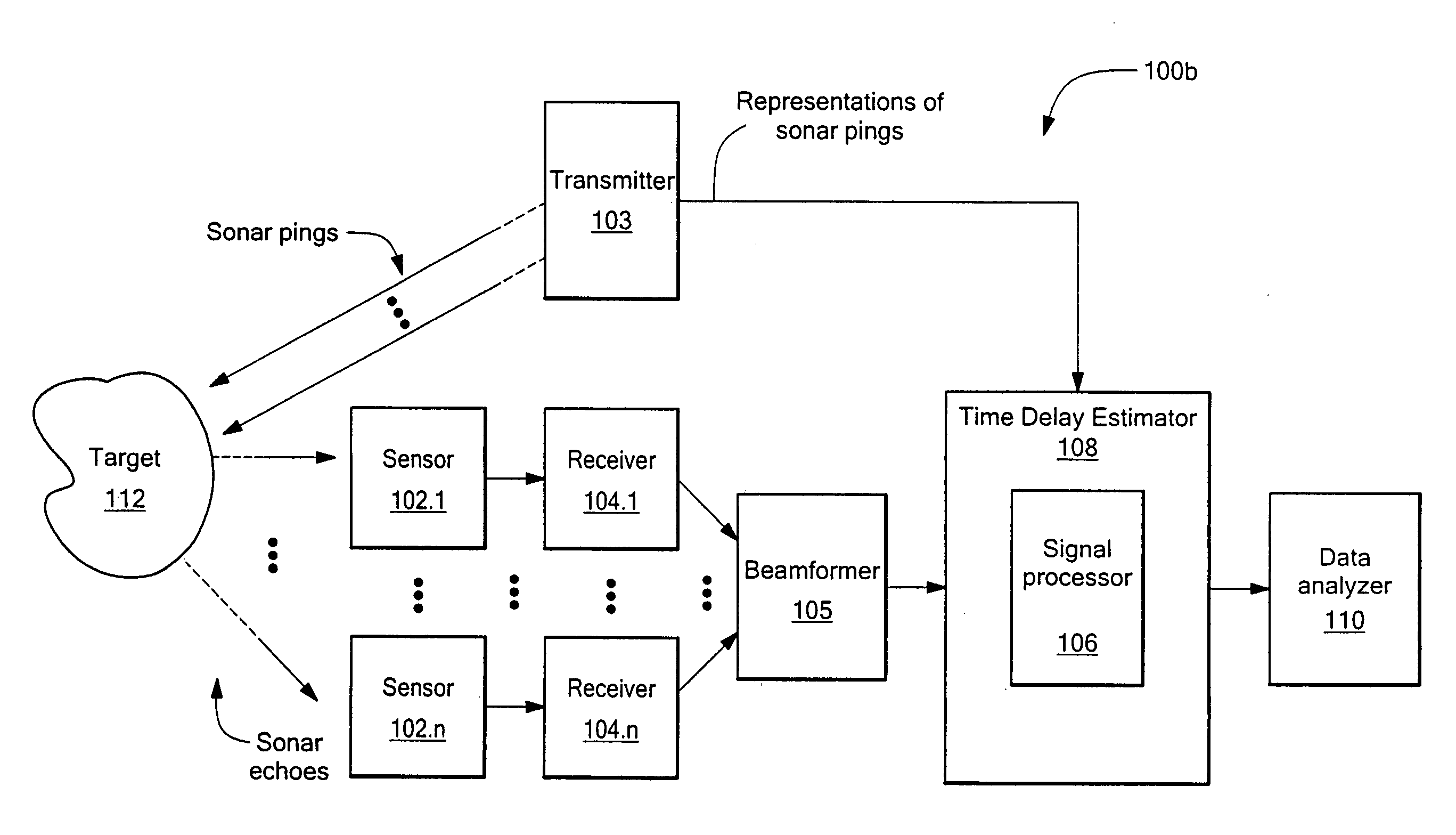

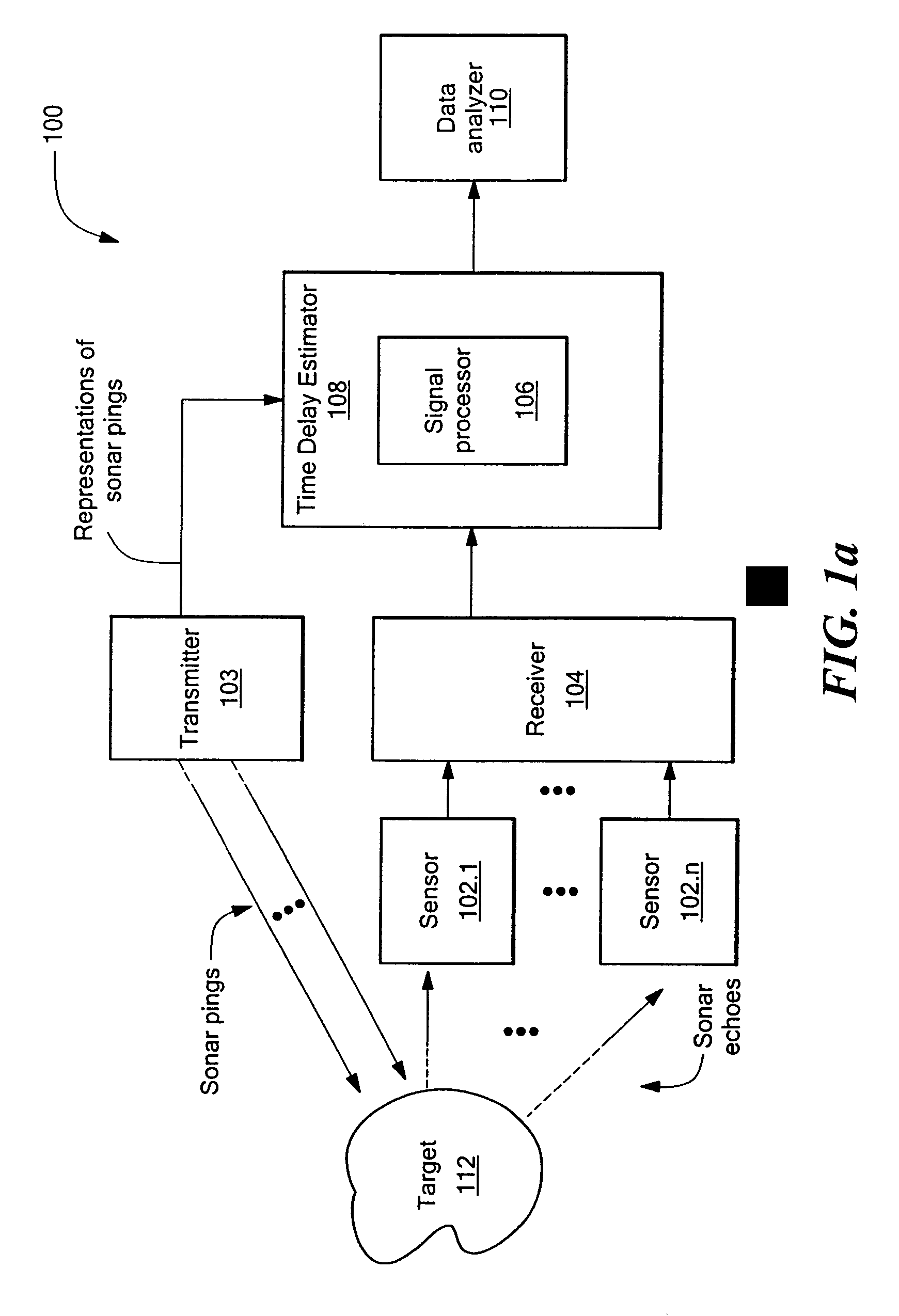

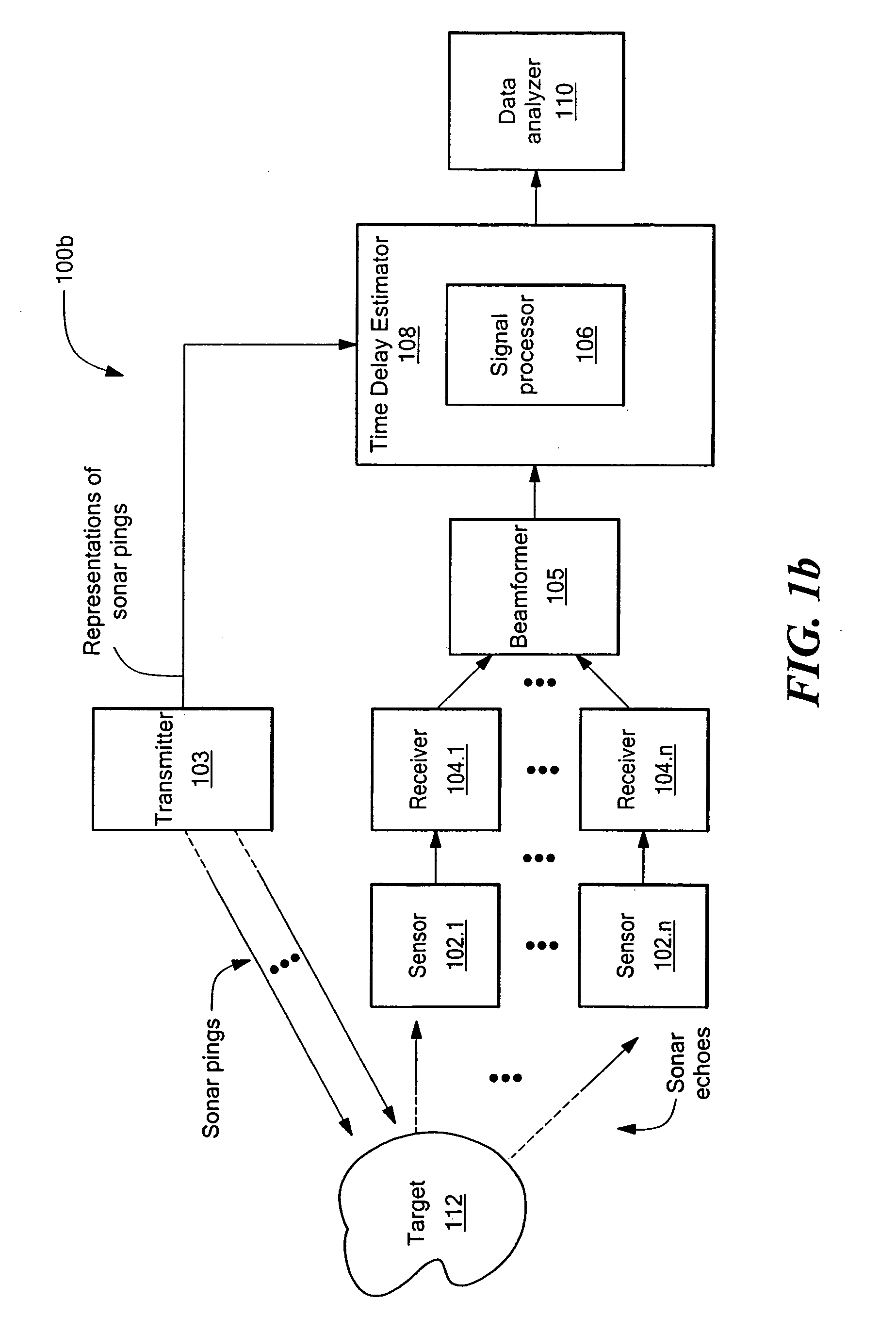

Apparatus and method for performing time delay estimation of signals propagating through an environment

InactiveUS20060235635A1Improve accuracyImprove noise marginWave based measurement systemsVoltage-current phase angleSonarComputer science

A system and method for increasing the accuracy of time delay estimates of signals propagating through an environment. The system includes one or more sensors for receiving a plurality of signals, and a time delay estimator for measuring time delays between multiple pairs of signals. At least some of the multiple pairs of signals are received and measured at different points in time. The system further includes a data analyzer for analyzing time delay estimation data, for generating a statistical distribution of time delay estimates from the data, and for calculating a statistical estimate of time delay from the distribution. By increasing the number of signals employed by the system, the accuracy of the time delay estimation is increased. Further, by calculating the median or the mode of the statistical distribution, noise tolerance is improved. The signals employed by the system may include sonar signals, seismic signals, ultrasonic signals, acoustic signals, electromagnetic signals, or any other suitable type of signals.

Owner:BROWN UNIVERSITY

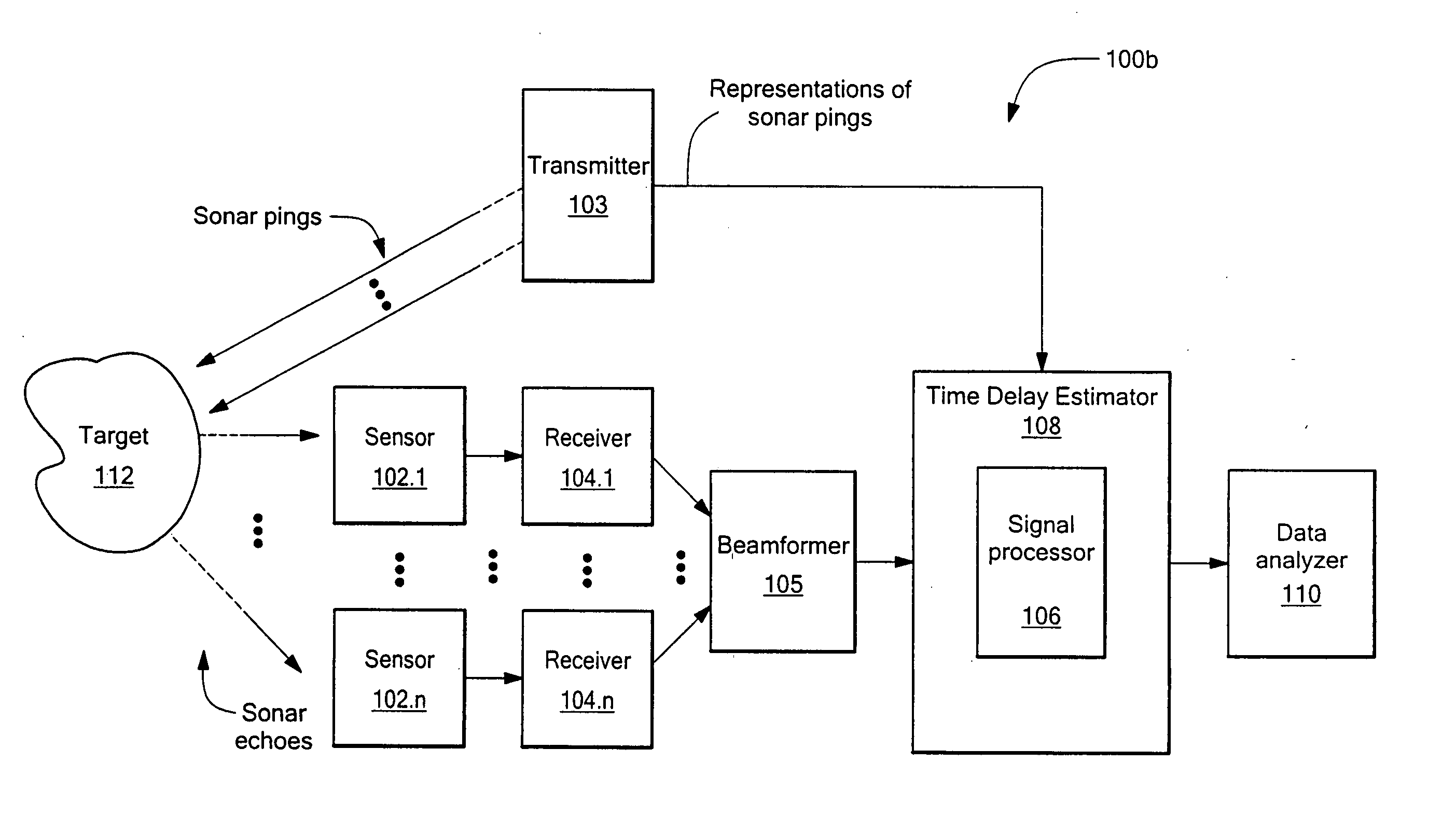

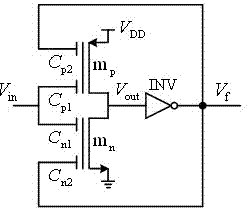

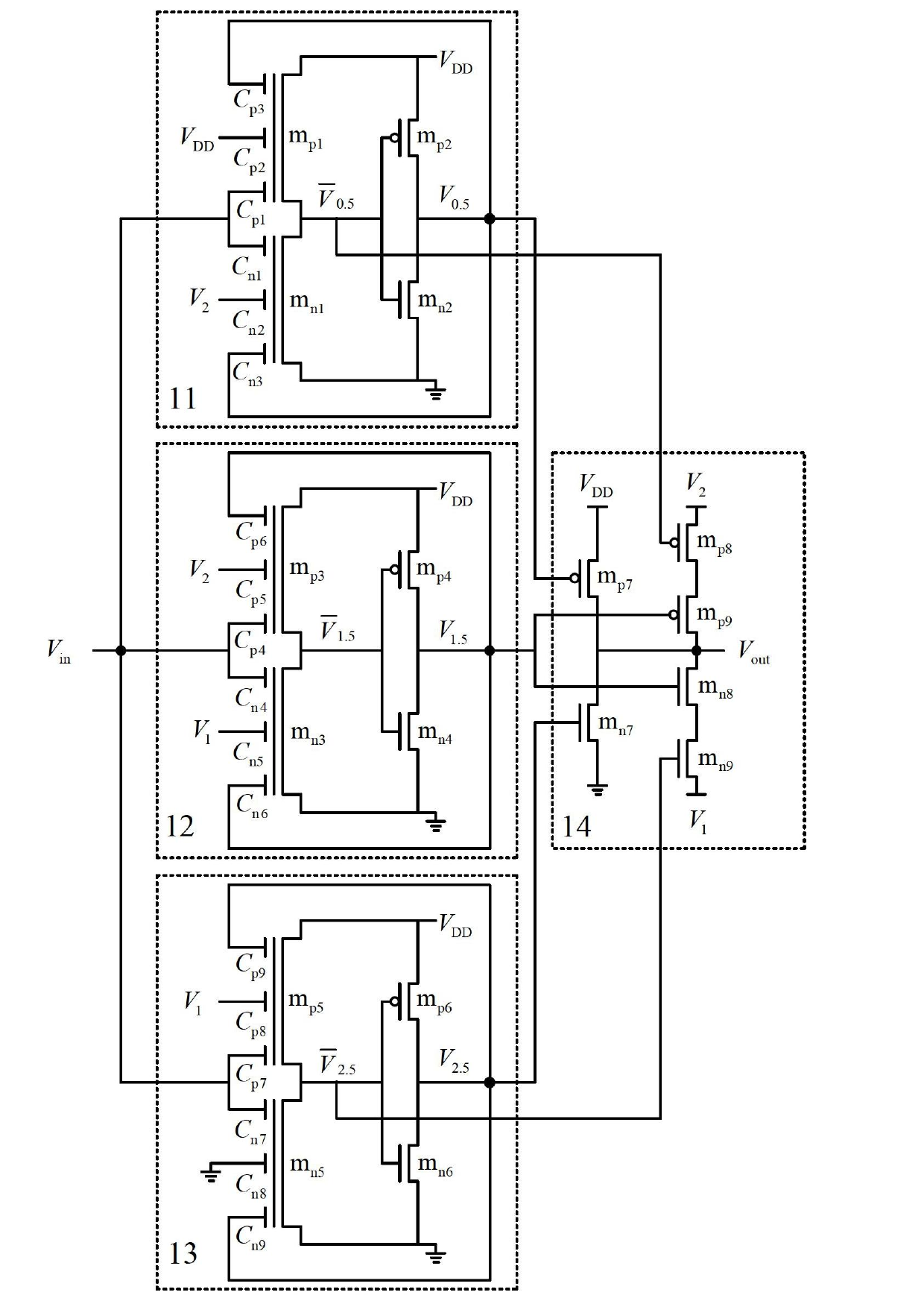

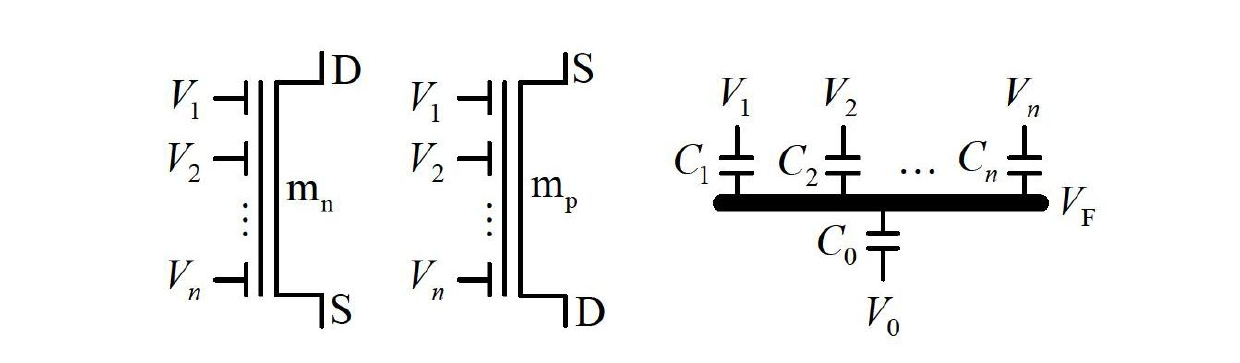

Adjustable-threshold-value schmitt trigger circuit based on multi-input floating gate metal oxide semiconductor (MOS) tube

InactiveCN102412809AThresholds are easy to controlEnabling regenerative feedbackElectric pulse generatorCMOSMulti input

The invention discloses an adjustable-threshold-value schmitt trigger circuit based on a multi-input floating gate metal oxide semiconductor (MOS) tube. The adjustable-threshold-value schmitt trigger circuit structurally consists of two levels of circuits, wherein the first-level circuit has an inverted phase structure formed by connecting a pair of complementary floating gate MOS tubes; floating gates of a p-type floating gate MOS tube and an n-type floating gate MOS tube are independent; the second-level circuit is a common complementary metal oxide semiconductor (CMOS) phase inverter; an output signal of the CMOS phase inverter is fed back to one gate input end of the p-type floating gate MOS tube and one gate input end of the n-type floating gate MOS tube of the first-level circuit respectively, so regenerative feedback is realized; an input signal of the whole circuit is connected to the other gate input end of the p-type floating gate MOS tube and the other gate input end of the n-type floating gate MOS tube respectively; by the output of the first-level circuit, a logic phase inverse function having a difference return characteristic is realized; and by the output of the second-level circuit, a logic buffer function which has the difference return characteristic and works on the input signal is realized.

Owner:ZHEJIANG UNIV CITY COLLEGE

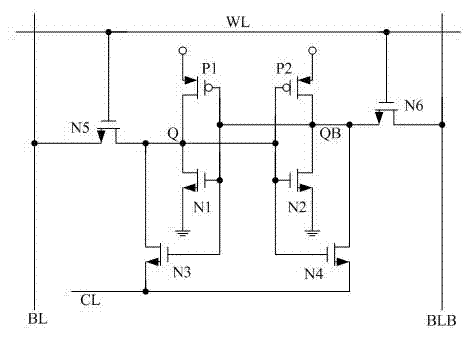

Eight-tube storage unit capable of automatically adjusting strength of transmission tube and strength of pull-down tube

InactiveCN102360567AImprove static noise marginImprove stabilityDigital storageNoise marginStatic noise margin

The invention discloses an eight-tube storage unit capable of automatically adjusting the strength of a transmission tube and the strength of a pull-down tube. Two NMOS (non-channel metal oxide semiconductor) tubes capable of adjusting the strength of the transmission tube and the strength of the pull-down tube are added on the basis of a standard six-tube storage unit so as to realize the eight-tube storage unit which is capable of automatically adjusting the strength of the transmission tube and the strength of the pull-down tube according to types of reading and writing operation. When the storage unit is used for writing operation, the strength of the transmission tube is strengthened, writing noise margin of the storage unit is increased, and the speed of writing operation is increased. When the storage unit is used for reading operation, the strength of the pull-down tube is strengthened, reading noise margin of the storage unit is increased, and simultaneously, the speed of data reading operation is increased. The eight-tube storage unit has the advantages of high static noise margin, fine stability, fast reading and writing speeds and the like.

Owner:HUNAN LUGU FEITENG MICROELECTRONICS

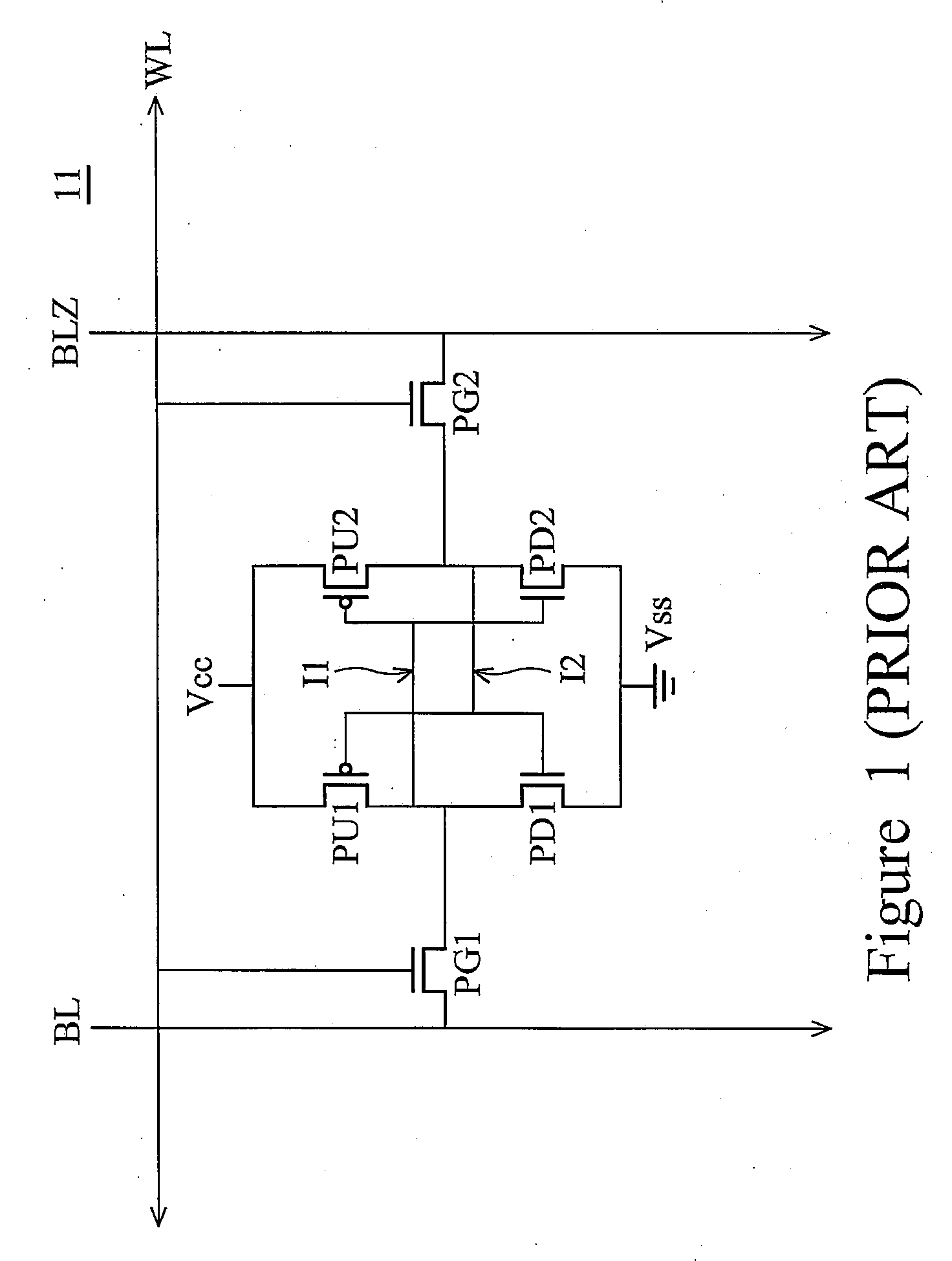

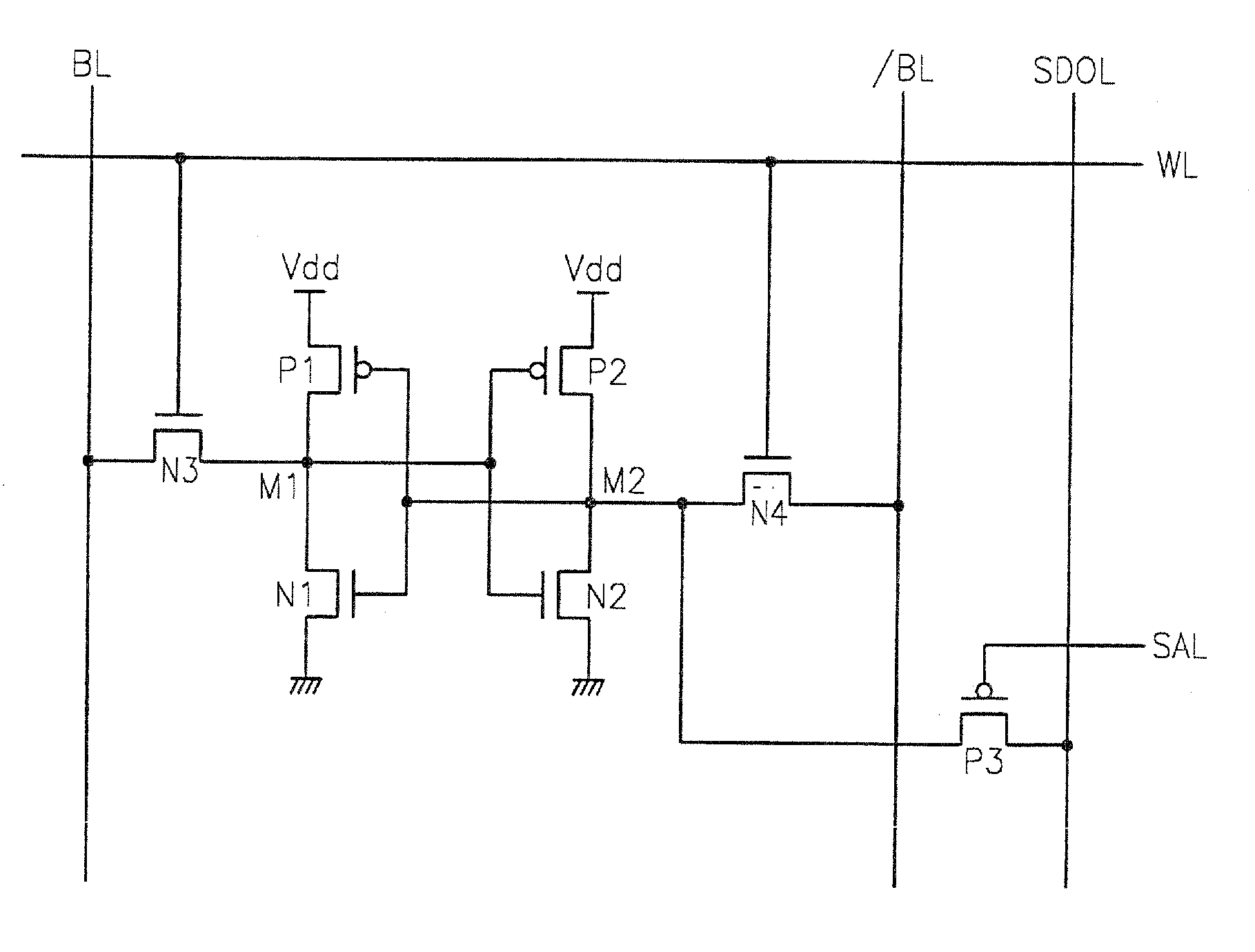

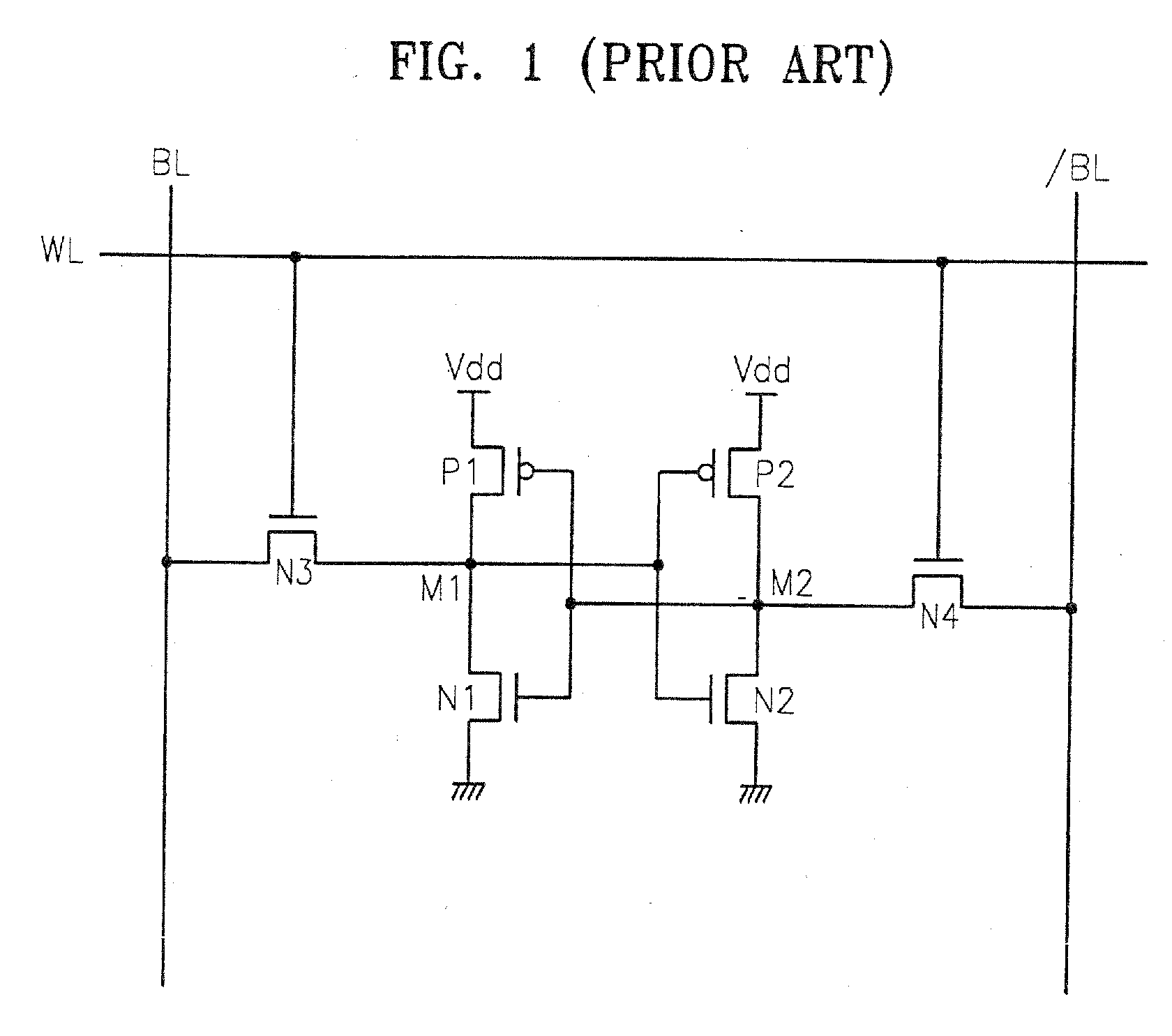

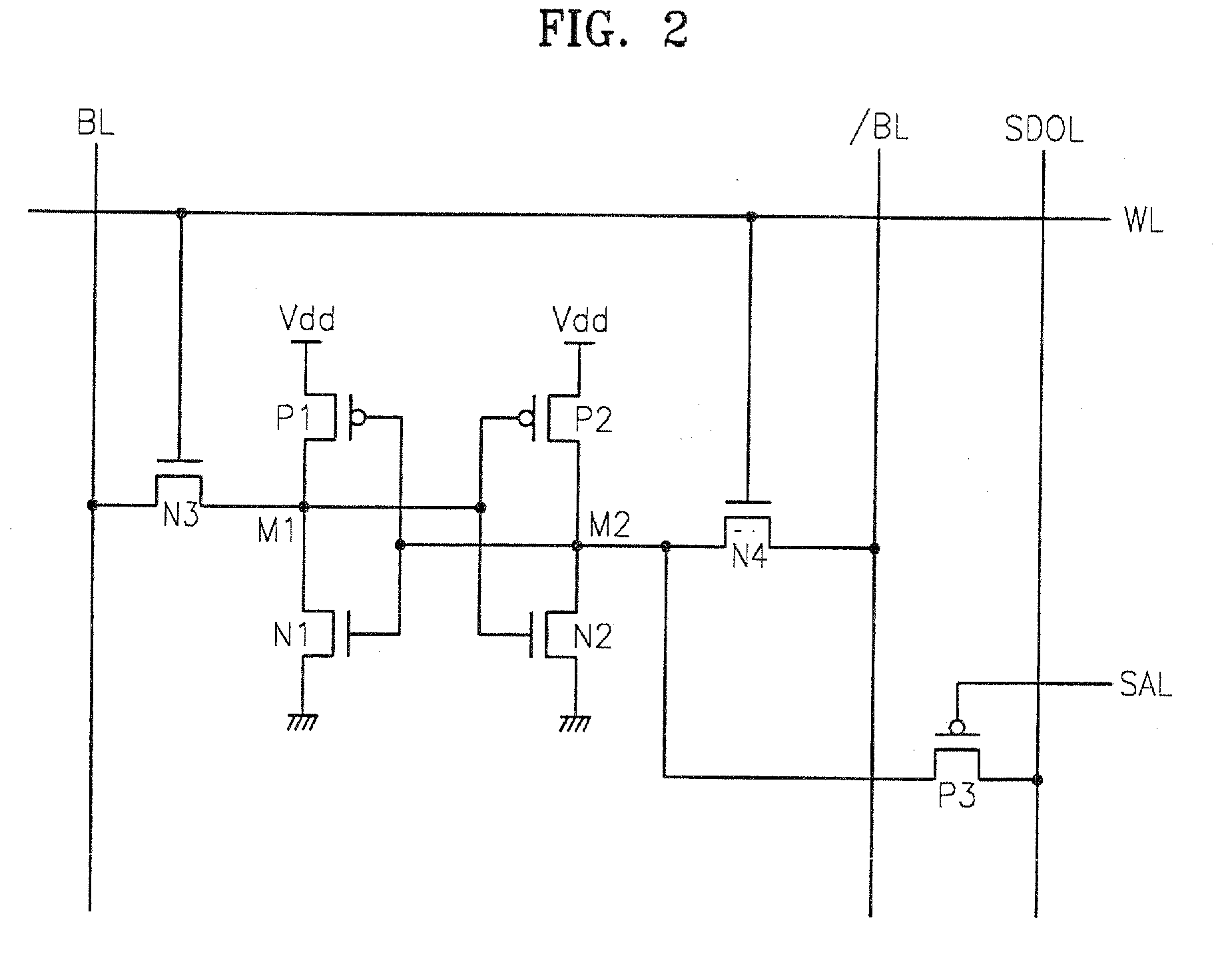

Dual port semiconductor memory device

ActiveUS20070025174A1Improve noise marginAvoid crosstalkTransistorStatic indicating devicesBit lineNoise margin

A dual port semiconductor memory device, including PMOS scan transistors, is provided. The dual port semiconductor memory device includes two PMOS transistors, two NMOS pull-down transistors, two NMOS pass transistors, and a PMOS scan transistor. The scan transistor being PMOS, noise margins can be improved. In addition, these seven transistors are arranged in two n-wells and 2 p-wells, while n-wells and p-wells are arranged in series and in alternating fashion. Therefore, the length of a memory cell along the minor axis of the memory cell is relatively short. This memory cell layout helps shorten the length of a bit line by arranging a pair of bitlines in parallel with well boundaries, i.e., in the direction of the short axis of the memory cell, and makes it possible to prevent crosstalk between a bitline and a complementary bitline by arranging conductive lines between the bitline and the complementary bitline.

Owner:SAMSUNG ELECTRONICS CO LTD

Apparatus and method for performing time delay estimation of signals propagating through an environment

InactiveUS7363177B2Improve accuracyImprove noise marginWave based measurement systemsVoltage-current phase angleComputer scienceNoise tolerance

A system and method for increasing the accuracy of time delay estimates of signals propagating through an environment. The system includes one or more sensors for receiving a plurality of signals, and a time delay estimator for measuring time delays between multiple pairs of signals. At least some of the multiple pairs of signals are received and measured at different points in time. The system further includes a data analyzer for analyzing time delay estimation data, for generating a statistical distribution of time delay estimates from the data, and for calculating a statistical estimate of time delay from the distribution. By increasing the number of signals employed by the system, the accuracy of the time delay estimation is increased. Further, by calculating the median or the mode of the statistical distribution, noise tolerance is improved.

Owner:BROWN UNIVERSITY

Dynamic circuits having improved noise tolerance and method for designing same

InactiveUS20050007153A1Improve methodImprove toleranceLogic circuits characterised by logic functionElectrical resistance and conductanceEngineering

A number of different dynamic circuits having improved noise tolerance and a method for designing same are provided. The circuits include a power supply node and a precharge node. Keeper circuitry is connected to the nodes and has a current-voltage characteristic that exhibits a negative differential resistance property to improve noise tolerance of the circuits.

Owner:RGT UNIV OF MICHIGAN

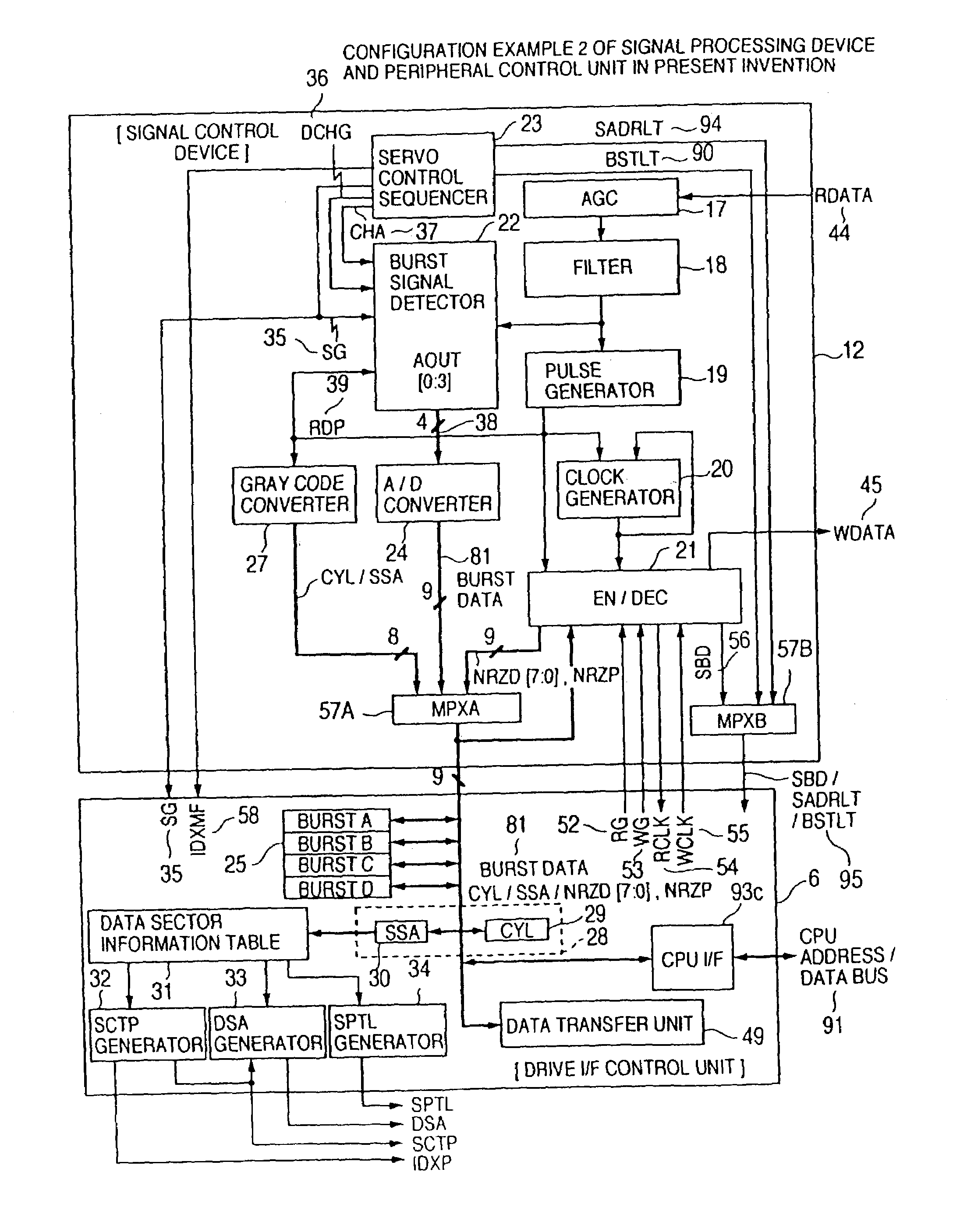

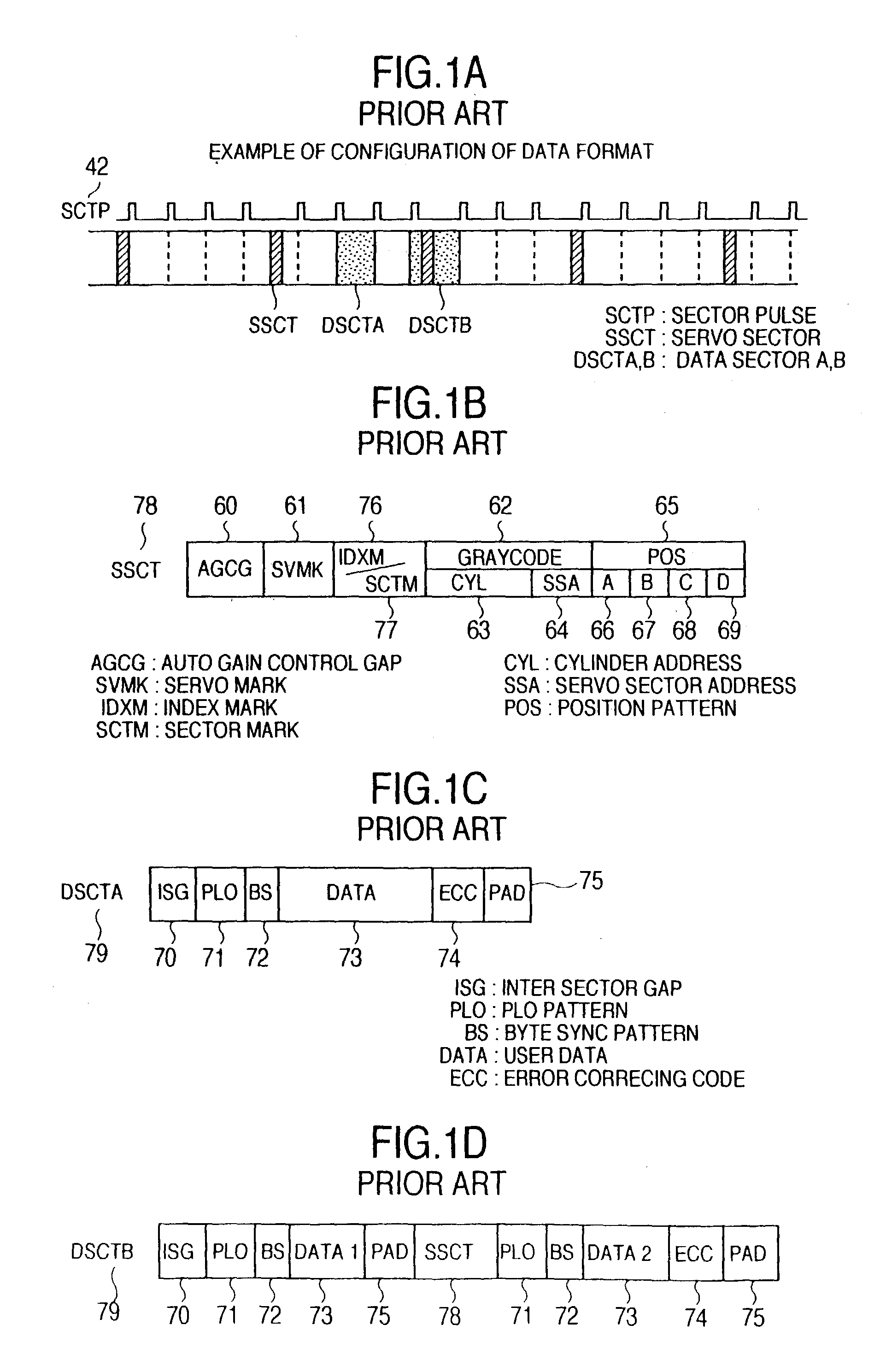

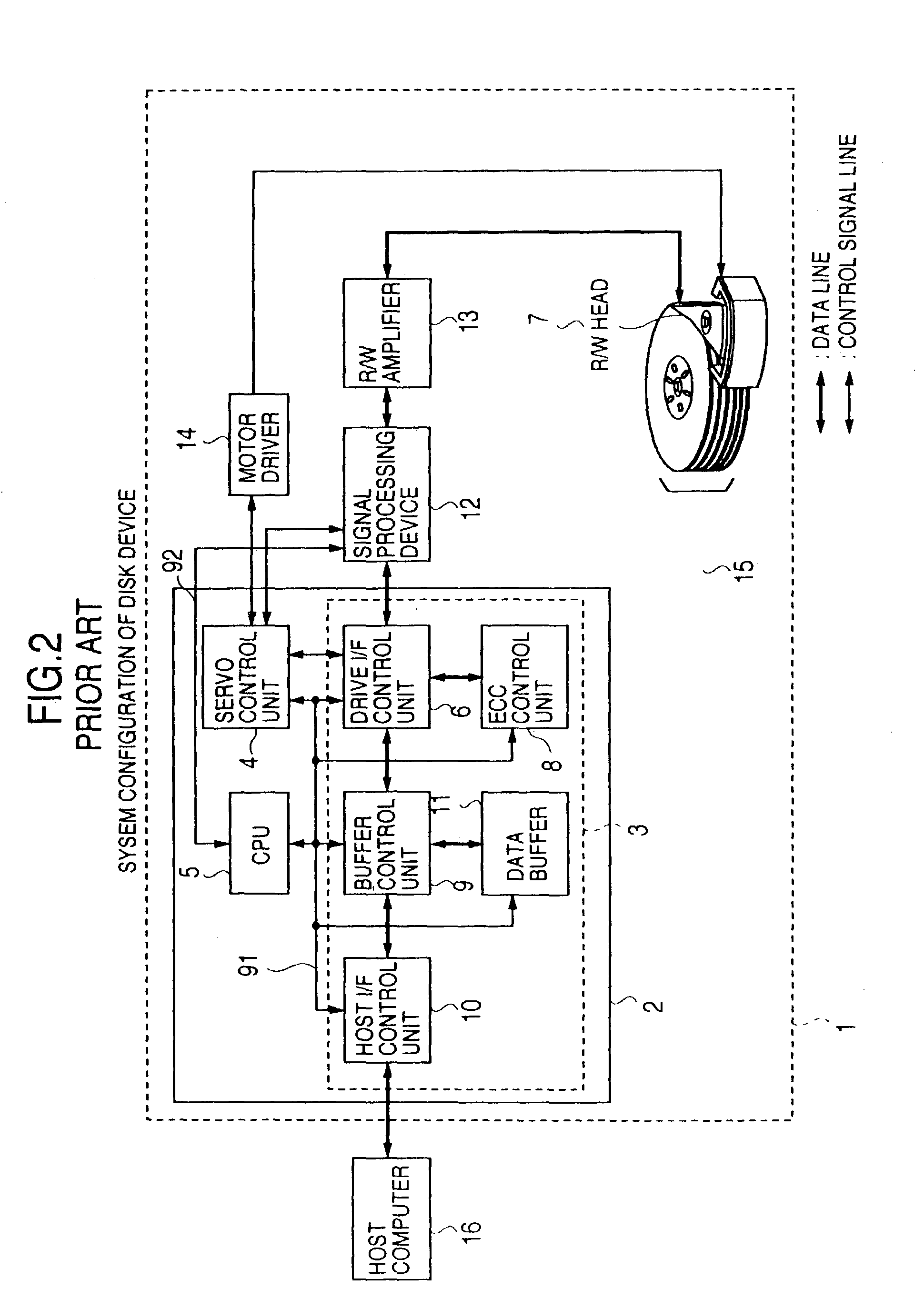

Disk device and method of generating signal representing head

InactiveUS7139143B2Improve noise marginOptimizationTrack finding/aligningSignal processing for reducing noiseDigital conversionAnalog to digital conversion

A signal processing device for analog-to-digital converting a burst signal has a feature of selecting a data bus to notify a disk control device of a conversion result via an NRZ data bus. The disk control device stores the result of the analog-to-digital conversion of the servo positional signal. The positional signal of a head of the disk device is digitized in a R / W channel. Sampling for digital conversion is performed in only a window which is defined only in the vicinity of peaks of the positional signal. The values of peaks which are obtained by sampling are averaged by an averaging circuit. This enables the influence of noise occurred outside of the window to be eliminated. Although the noise in the window is sampled, its adverse influence is suppressed by the averaging processing.

Owner:HITACHI GLOBAL STORAGE TECH JAPAN LTD

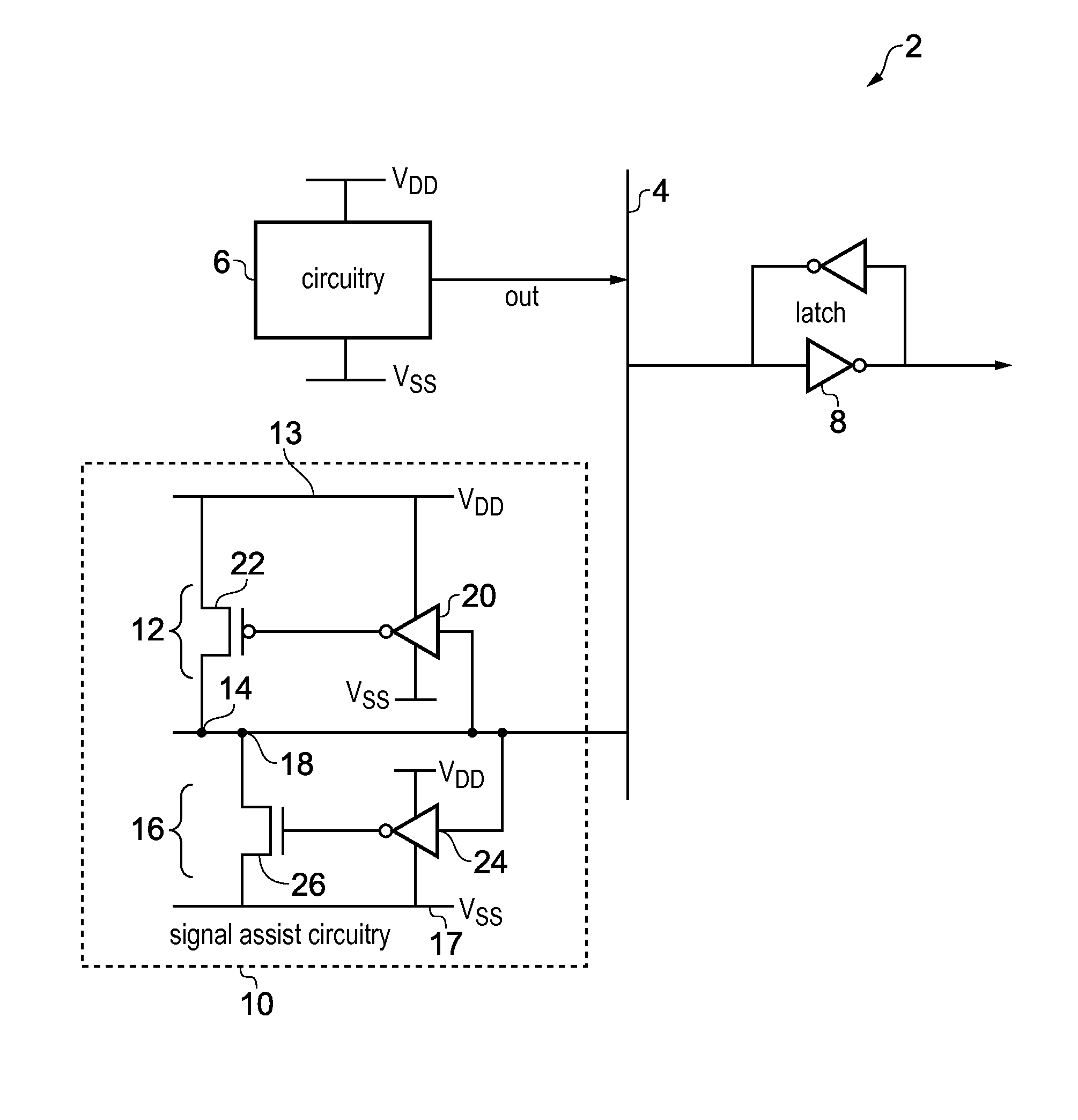

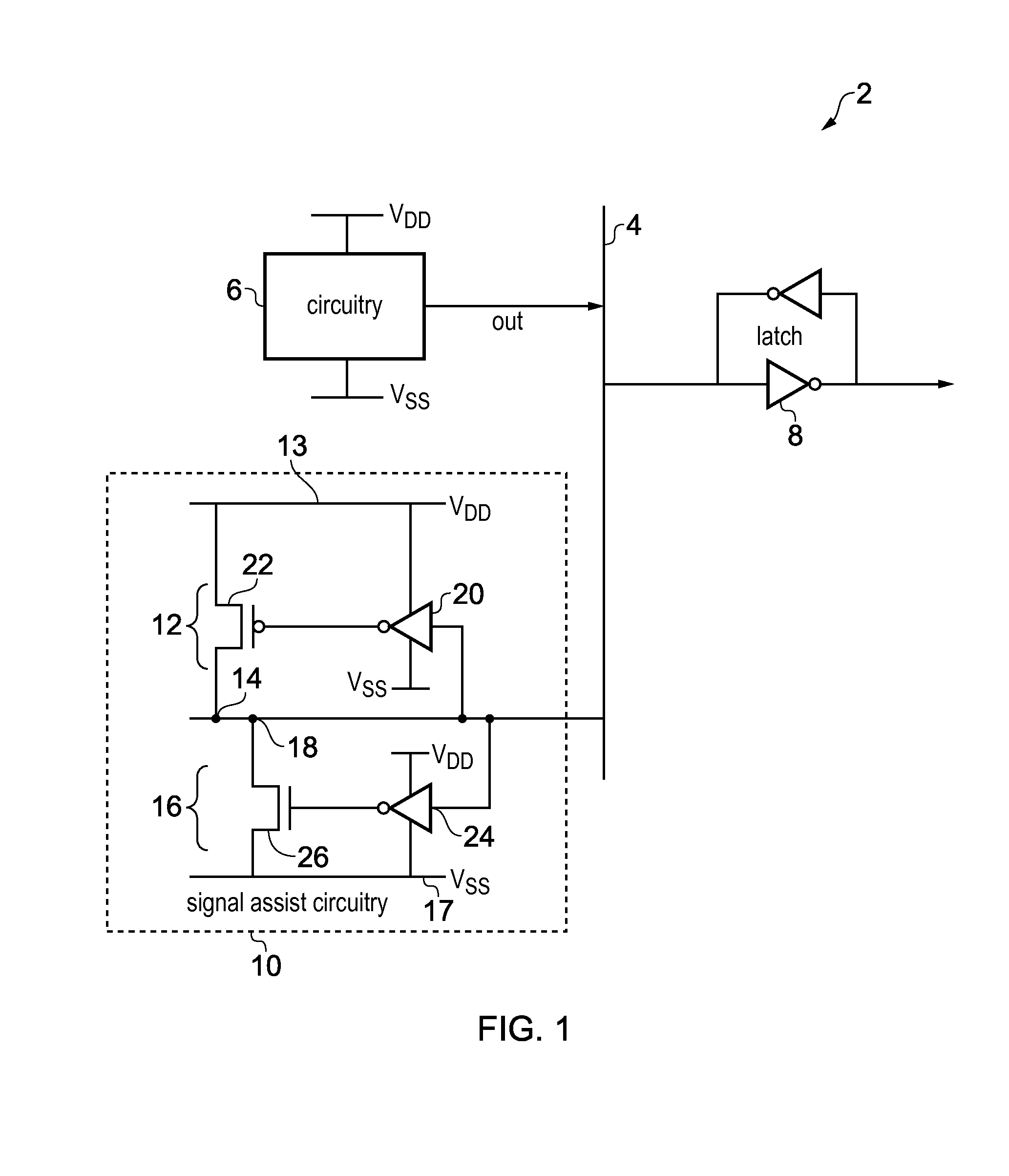

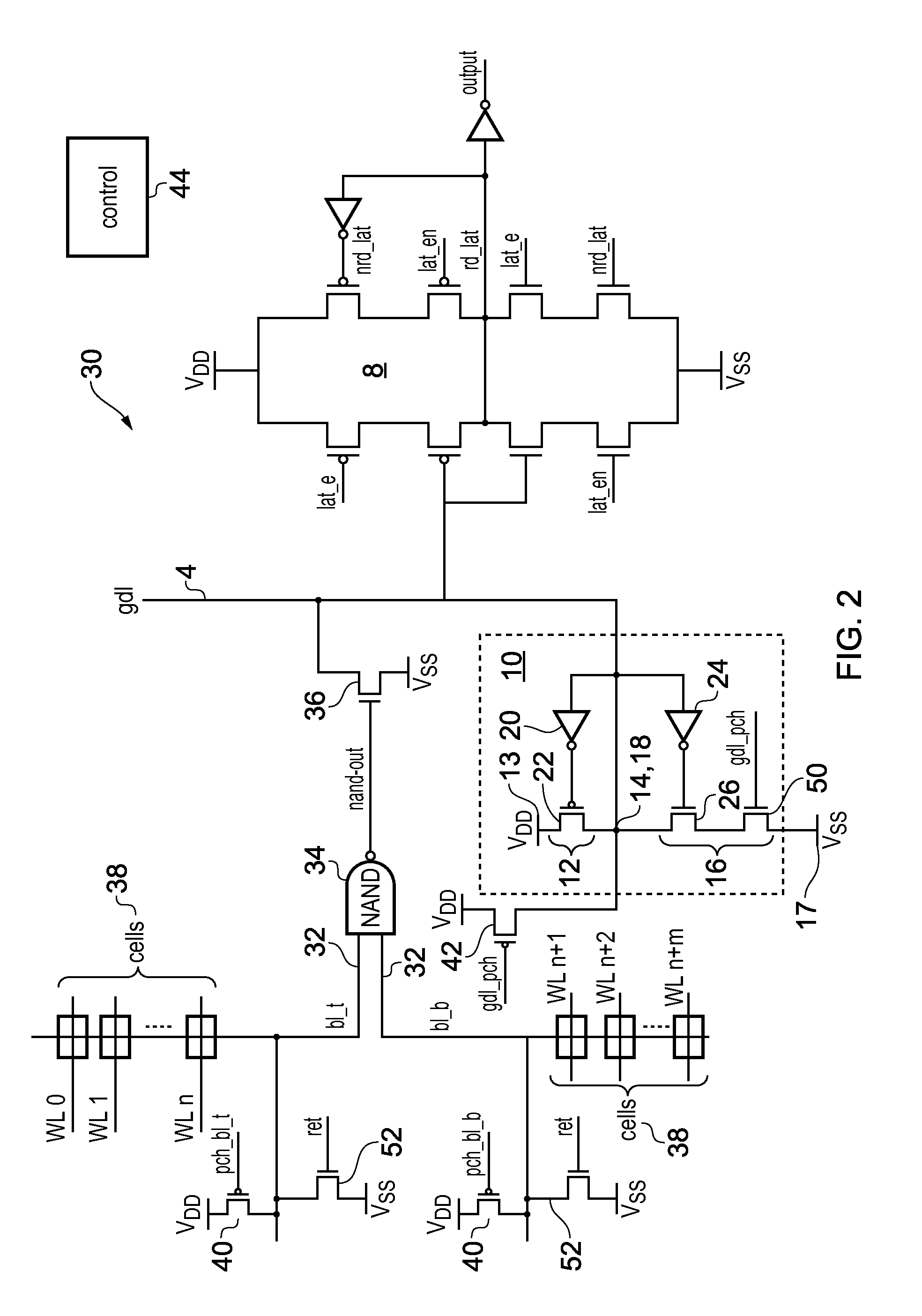

Integrated circuit with signal assist circuitry and method of operating the circuit

ActiveUS20150091609A1Improve noise marginMake fastPower reduction in field effect transistorsDigital storageSignal onIntegrated circuit

An integrated circuit has signal assist circuitry for assisting with pulling a signal on the signal line towards the logical low or high signal level. The signal assist circuitry comprises first and second assist circuits. The first assist circuit couples the signal line to the logical high signal level following a pullup transition of the signal and provides a floating signal level following a pulldown transition, while the second assist circuit provides the floating signal level following the pullup transition and provides the logical low signal level following the pulldown transition. By providing complementary first and second assist circuits, each circuit can be optimized for the opposite transition to achieve improved performance or power consumption.

Owner:ARM LTD

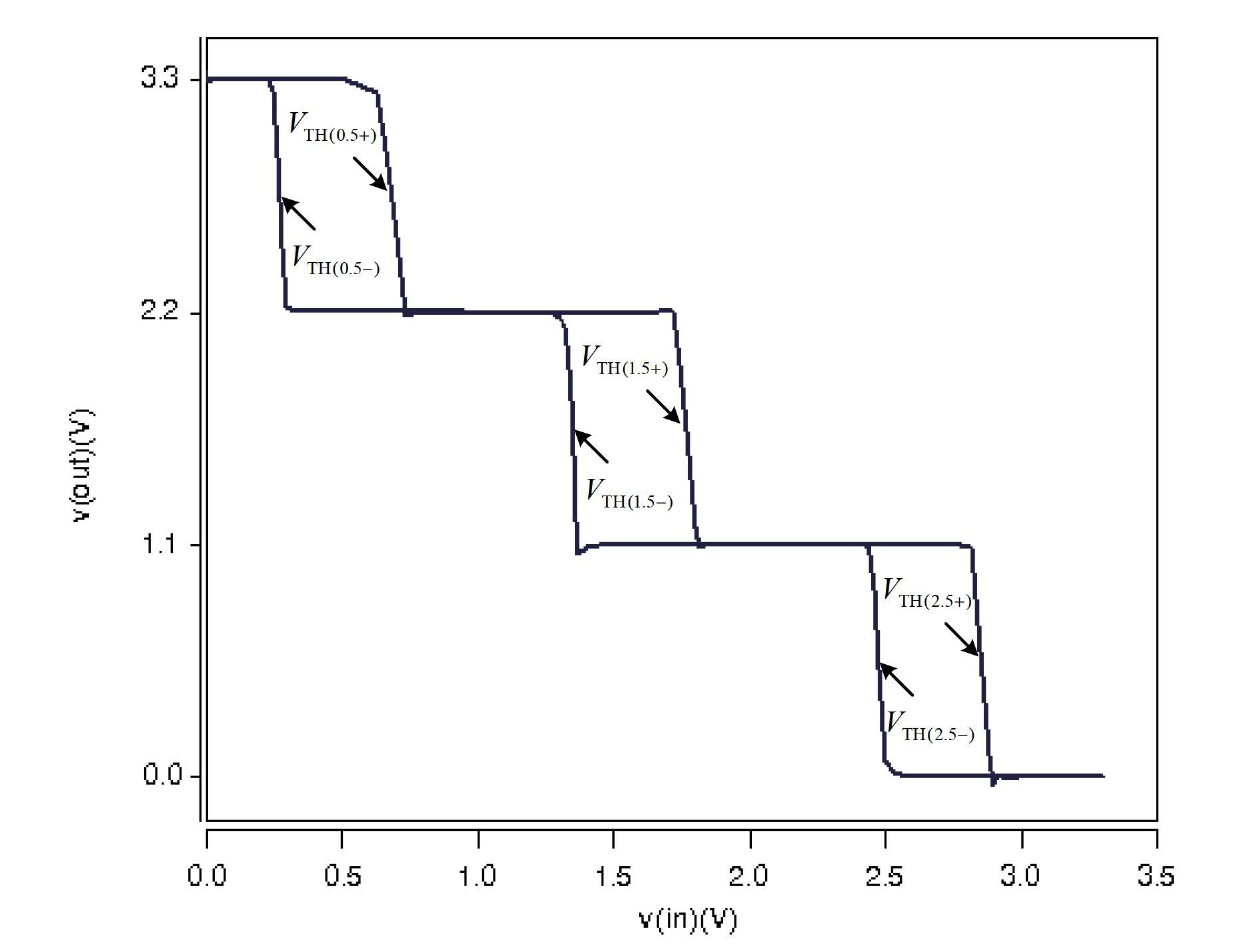

Voltage type four-value Schmidt trigger circuit based on neuron MOS (Metal Oxide Semiconductor) tube

The invention discloses a voltage type four-value Schmidt trigger circuit based on a neuron MOS (Metal Oxide Semiconductor) tube. The voltage type four-value Schmidt trigger circuit comprises a threshold-0.5 reversed phase operation and threshold-0.5 operation circuit part 11 with return difference characteristic, a threshold-1.5 reversed phase operation and threshold-1.5 operation circuit part 12 with return difference characteristic, a threshold-2.5 reversed phase operation and threshold-2.5 operation circuit part 13 with return difference characteristic, and a four-value signal transmission control circuit part 14. The voltage type four-value Schmidt trigger circuit is completely based on a standard double-layer polycrystalline silicon CMOS (Complementary Metal-Oxide-Semiconductor Transistor) process, and three return difference voltage values in the four-value Schmidt trigger circuit can be adjusted by changing a capacitance coupling coefficient. A complementary neuron MOS tube scheme with an independent floating boom structure is adopted, so that the circuit has the characteristics of low power consumption and high noise margin. Moreover, threshold operation of a neuron MOS tube design and a reverse phase circuit thereof are adopted, so that threshold values are easy to control, thus the four-value Schmidt trigger circuit has a simple structure.

Owner:ZHEJIANG UNIV CITY COLLEGE

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com