Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

59results about How to "High heat dissipation coefficient" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

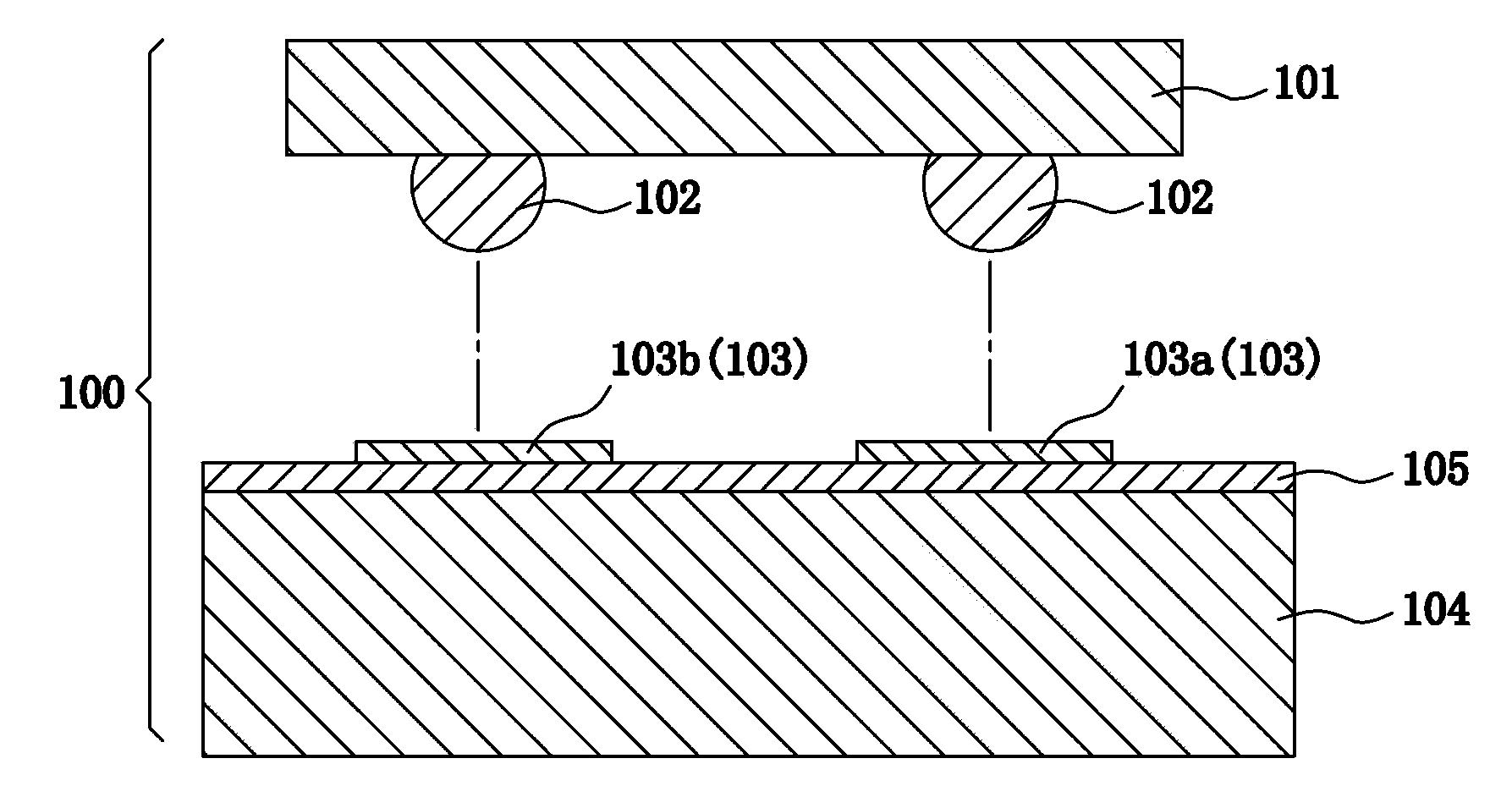

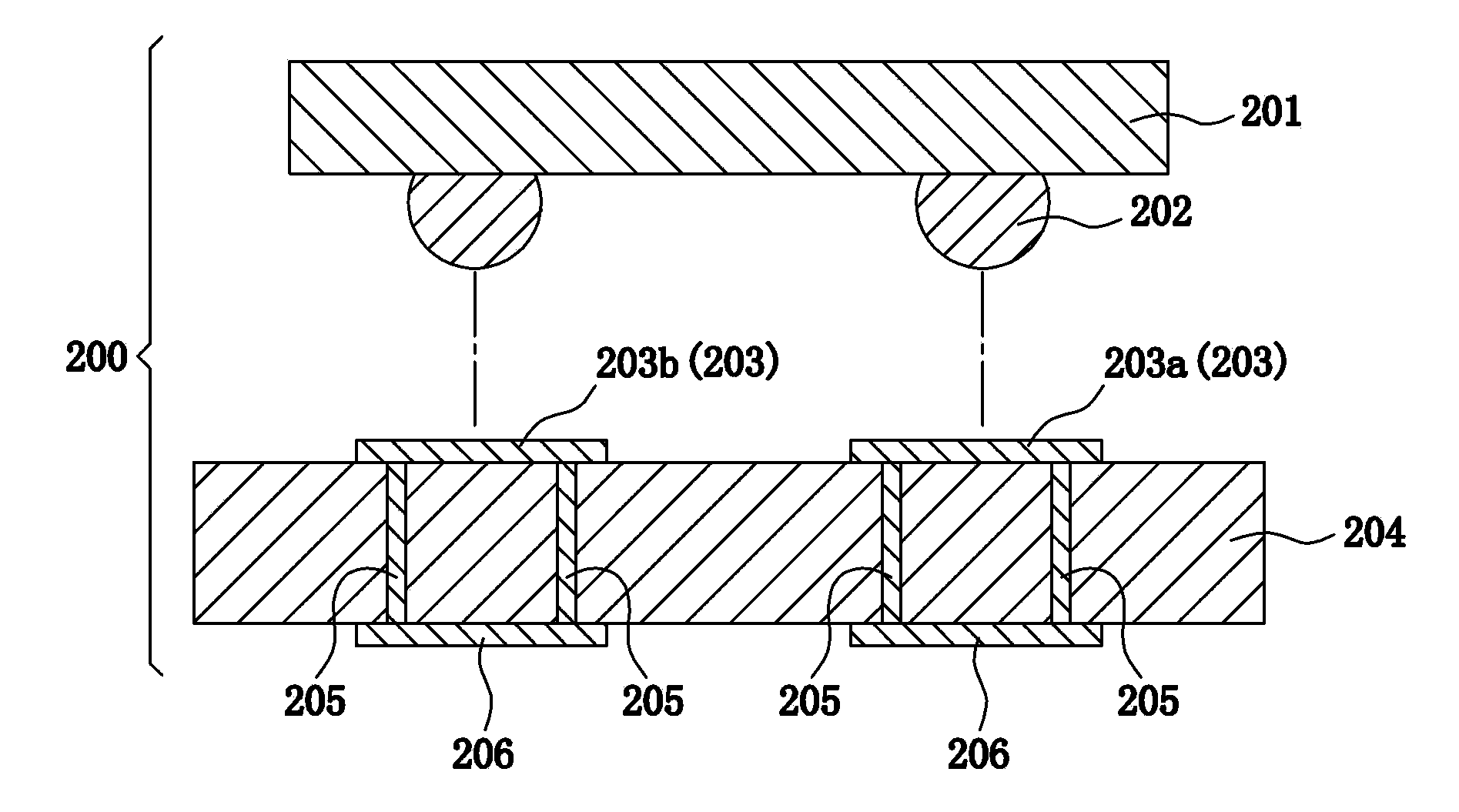

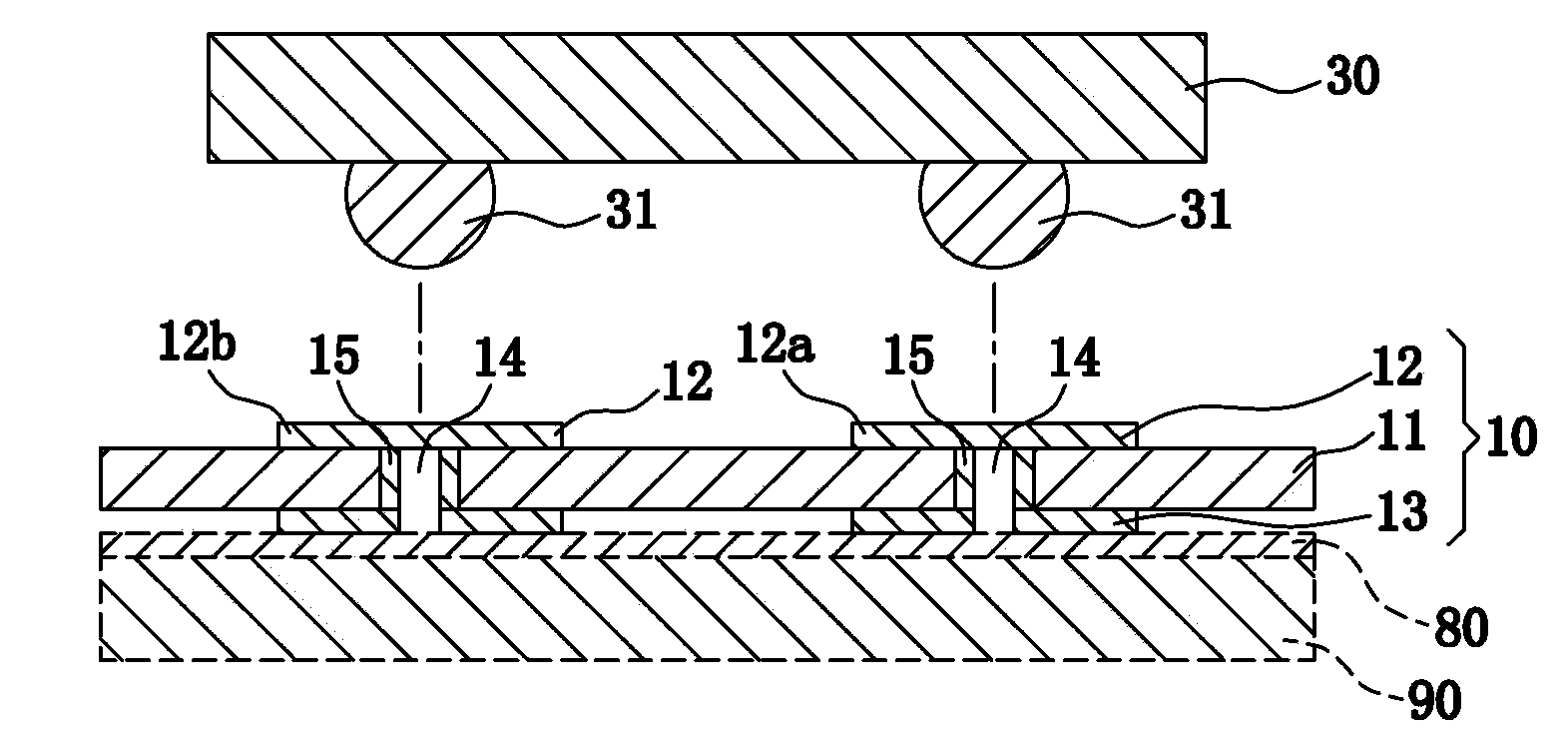

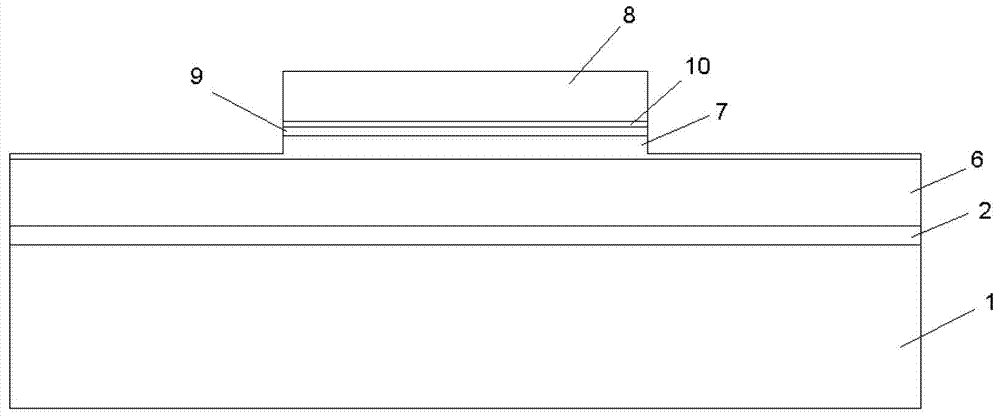

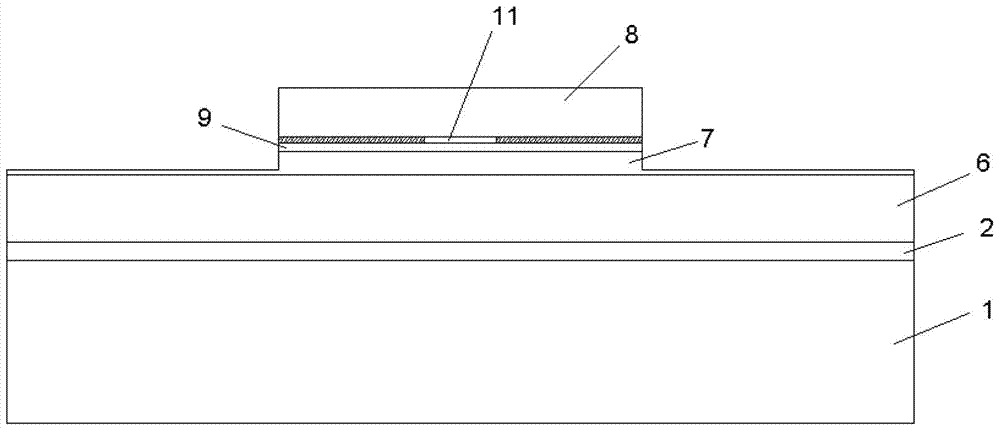

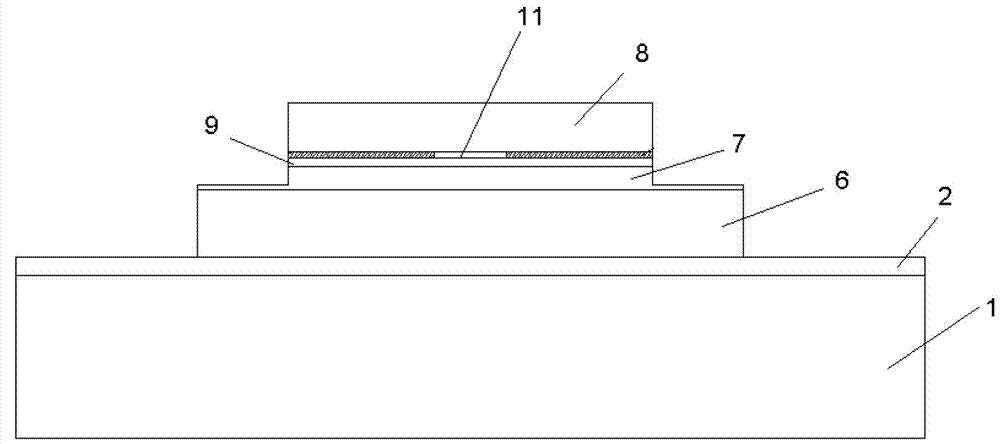

Light emitting diode encapsulation, PCB type radiating substrate used for light emitting diode encapsulation and manufacturing method of PCB type radiating substrate

InactiveCN103383983AHigh heat dissipation coefficientImprove cooling effectPrinted circuit detailsSolid-state devicesLight emitting deviceLight-emitting diode

The invention discloses light emitting diode encapsulation, a PCB type radiating substrate used for the light emitting diode encapsulation and a manufacturing method of the PCB type radiating substrate. The PCB type radiating substrate is formed with a manufacturing method of a PCB and comprises an insulating layer, a first circuit layer and a second circuit layer, wherein the first circuit layer is arranged on the upper surface of the insulating layer and is used for being electrically connected with LED crystal particles through a flip chip or through a wire, the second circuit layer is arranged on the lower surface of the insulating layer, at least one heat conduction hole which penetrates between the upper surface of the insulating layer and the lower surface of the insulating layer is formed in the insulating layer, an electrocoppering layer is arranged on the inner wall of the heat conduction hole and is connected to the first circuit layer and the second circuit layer, and then the radiating coefficient is effectively increased. According to the light emitting diode encapsulation, the PCB type radiating substrate used for the light emitting diode encapsulation and the manufacturing method of the PCB type radiating substrate, the heat conduction hole can be filled with heat conduction materials to further increase the radiating coefficient; the LED crystal particles can be electrically connected to the PCB type radiating substrate through the flip chip or through the wire according to manufacturing requirements to achieve the light emitting diode encapsulation; a bonding layer is arranged outside the second circuit layer to enable the LED encapsulation to be connected to and fixedly arranged on a radiating bracket of an LED light-emitting device to serve as a light source of the LED light emitting device.

Owner:MAO BANG ELECTRONICS

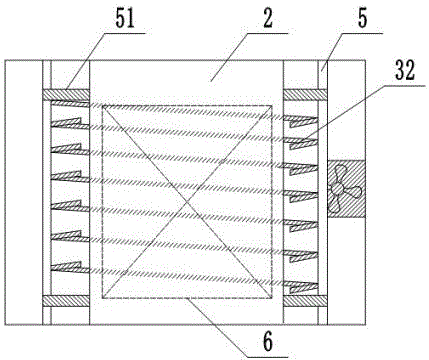

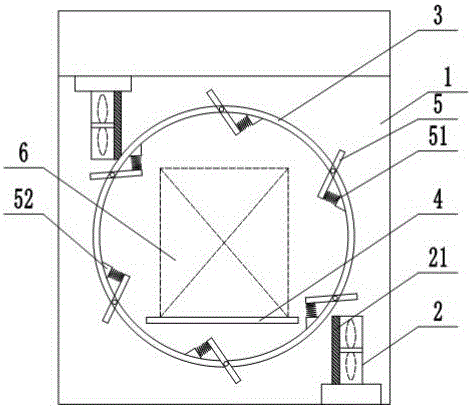

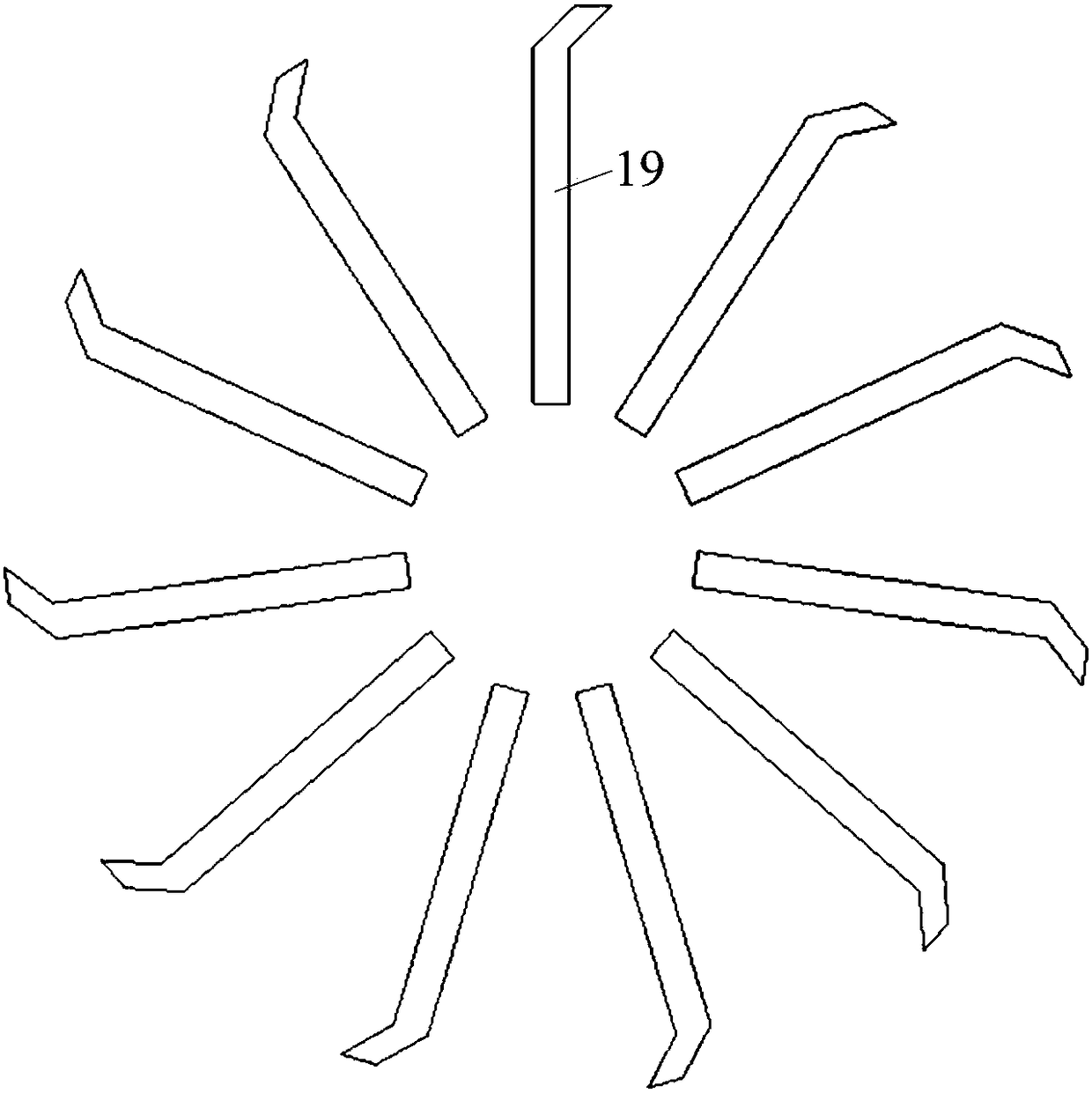

Wind-heat type wood drying box

InactiveCN106595248AAvoid uneven drying and partial crackingEvenly distributedDrying gas arrangementsDrying chambers/containersHelical bladePulp and paper industry

The invention relates to the technical field of drying solid materials and particularly discloses a wind-heat type wood drying box which comprises a box, hot-wind blowers, a supporting plate and a roller. The roller is connected into the box in a rotating manner. The inner wall of the roller is provided with spiral vanes. The outer wall of the roller is provided with a plurality of wind plates. The two ends of the supporting plate are connected to the inner wall of the box. The supporting plate penetrates the roller to enable wood on the supporting plate to be located in the roller. The two hot-wind blowers are arranged at the upper end and the lower end of the box correspondingly. The hot-wind blowers face the outer edge direction of the roller. According to the above technical scheme, the hot-wind blowers carry out wind-heat drying without facing the wood, the roller rotates so that the wind plates on the surface of the roller can achieve heat circulation in the box, axial circulation of heat in the box is achieved through the spiral vanes in the roller, then the heat in the whole box is distributed more uniformly, and the phenomenon that the wood is dried unevenly and cracked partially is avoided.

Owner:重庆金华兴门业有限公司

Semi-conductor surface emitting laser and production method and applications thereof

ActiveCN103208741ALower core layerHigh heat dissipation coefficientLaser detailsSemiconductor lasersBenzeneCapacitance

The invention relates to a semi-conductor surface emitting laser and a production method and applications thereof. An active layer utilizes a strain five quantum well; a lower DBR (Distributed Bragg Reflector) layer utilizes a binary N type AlAs / GaAs pair; an upper DBR layer utilizes a DBR of a general ternary N type Al0.92Ga0.08 As / Al0.12Ga0.88As; a plurality of pairs under the active layer utilize a same structure; the top utilizes a high thermal conductive ALN (Aluminium Nitride) layer; copper layers are arranged and covered on bilateral sides of the platform surface and above the platform; the size of an oxidation hole is 18 micron; and the capacitance of components are reduced through a BCB (p-bis benzene) layer. The production method of the semi-conductor surface emitting laser has the advantages of improving an integral heat dissipation level by improving processes, effectively solving the heat dissipation problem of a large power surface emitting laser, improving an stage of the power of the surface emitting laser, enabling the surface emitting laser to be improved in material character, improving the service life and working reliability of the surface emitting laser and achieving free space communication within 1-3 km.

Owner:WUHAN TELECOMM DEVICES

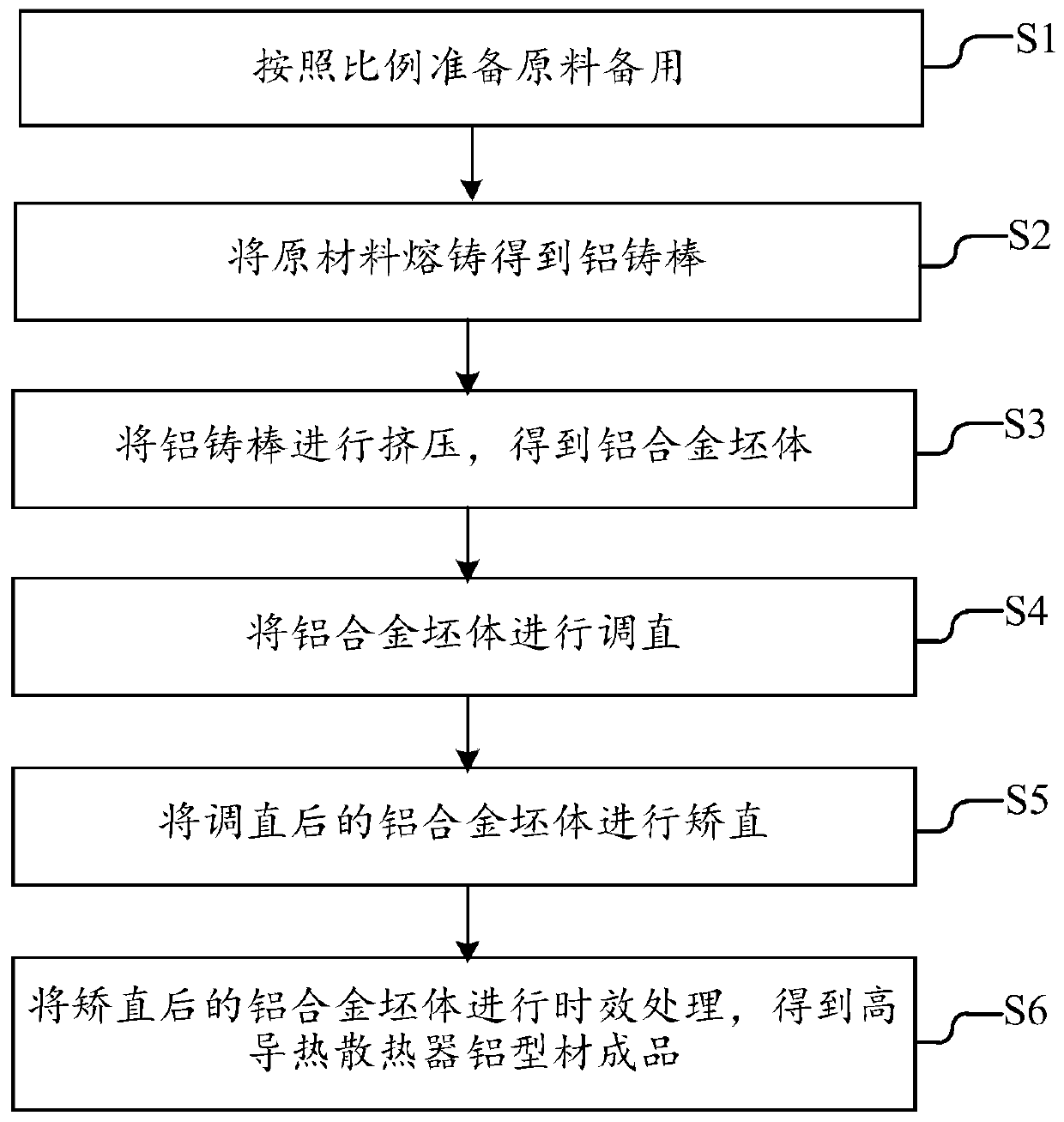

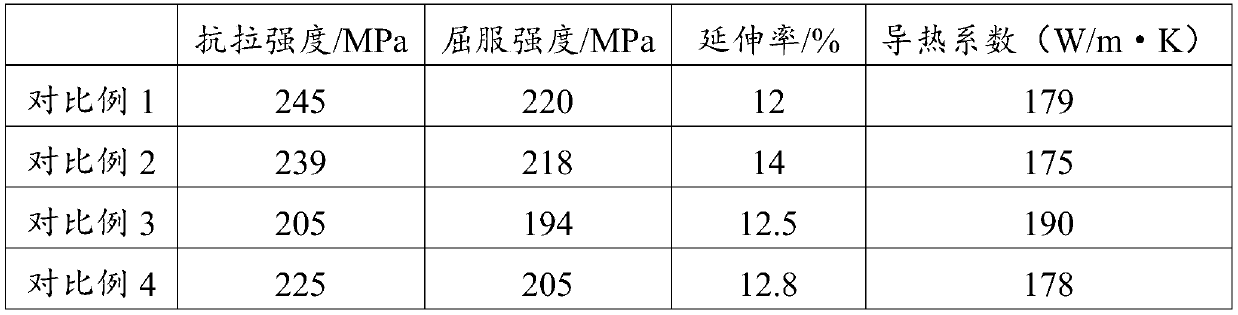

High thermal conductivity heat radiator aluminum profile, preparation method thereof and heat radiator

ActiveCN110358949ALow elemental contentImprove thermal conductivityHeat exchange apparatusInternal stressElectron

The invention discloses a preparation method of a high thermal conductivity heat radiator aluminum profile. The preparation method of the high thermal conductivity heat radiator aluminum profile includes: (1) preparing raw material for standby application according to a proportion; (2) performing fusion casting on the raw materials to obtain an aluminum cast rod; (3) squeezing the aluminum cast rod to obtain an aluminum alloy blank body; (4) aligning all parts of the aluminum alloy blank body, wherein alignment rate is 0.8%-3%; (5) straightening the aluminum alloy blank body after being aligned; (6) performing aging treatment on the aluminum alloy blank body after being straightened, and then obtaining the high thermal conductivity heat radiator aluminum profile finished product. Correspondingly, the invention further discloses the high thermal conductivity heat radiator aluminum profile and a heat radiator. By regulating and controlling the formula and process of aluminum alloy, the preparation method of the high thermal conductivity heat radiator aluminum profile reduces lattice distortion, reduces internal stress, and reduces scattering to free electrons, thereby raising the heat conductivity coefficient of the aluminum alloy, and meanwhile guaranteeing good mechanical performance and processing performance.

Owner:GUANGDONG JMA ALUMINUM PROFILE FACTORY GRP +1

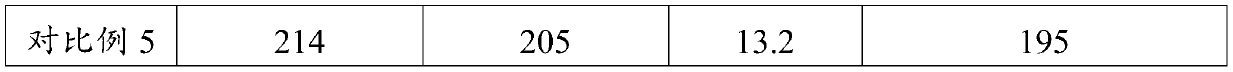

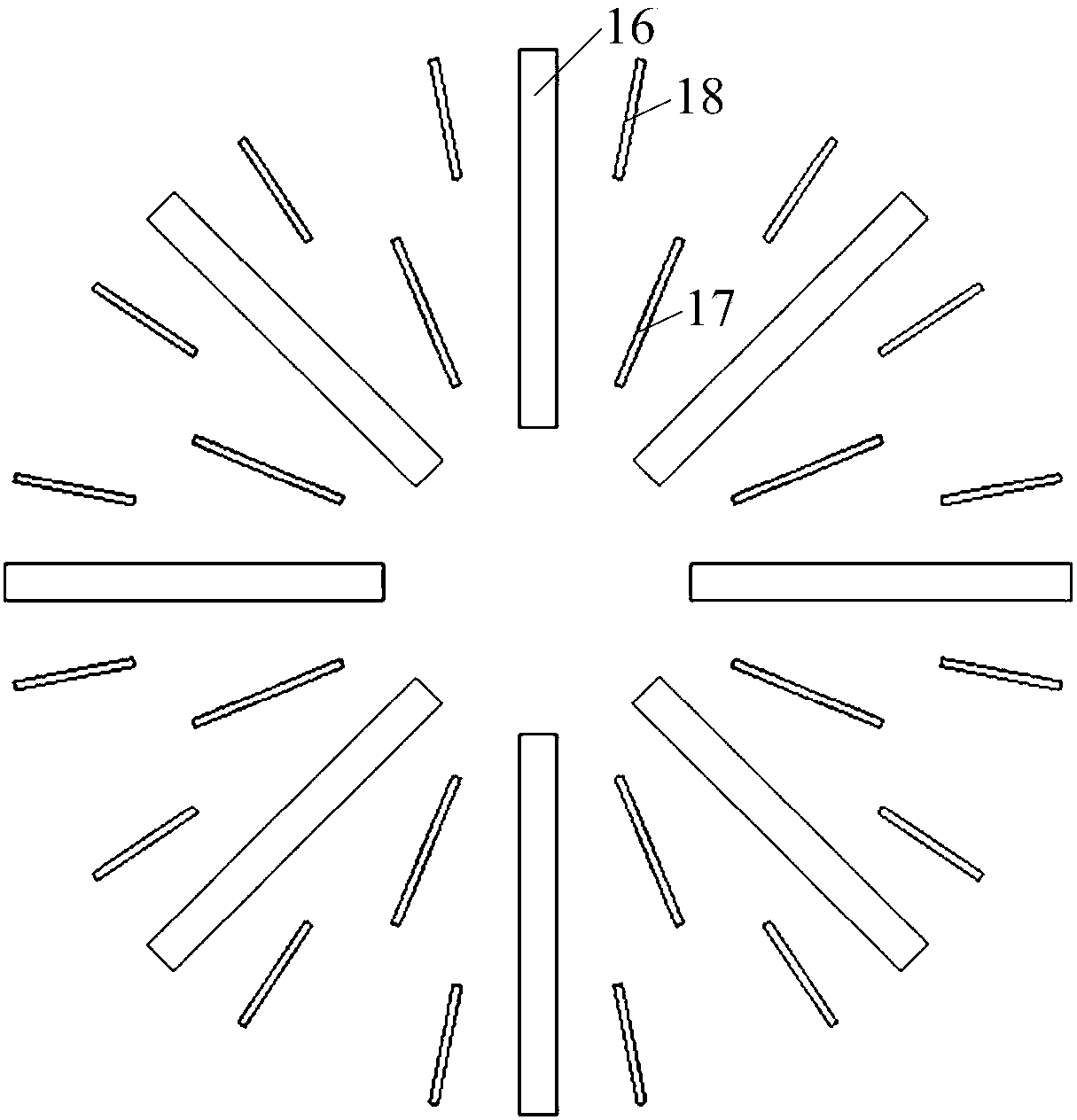

Wood drying chamber with flow guiding device

ActiveCN106643025APromote circulationEvenly distributedDrying gas arrangementsDrying machines with local agitationEngineeringWind direction

The invention relates to the technical field of solid material drying, and particularly discloses a wood drying chamber with a flow guiding device. The wood drying chamber comprises a box, air heaters, a supporting plate and a flow guiding frame. The flow guiding frame is rotationally connected in the box, flowing guiding plates are circular, the multiple flow guiding plates are rotationally connected to the outer edge of the flow guiding frame, and a spring is connected between the end portion of each flow guiding plate and the flow guiding frame. The two ends of the supporting plate are connected to the inner wall of the box. The supporting plate penetrates the flow guiding frame so that wood on the supporting plate can be located in the middle of the flow guiding frame. The two air heaters are arranged at the upper end and the lower end of the box correspondingly. The facing direction of the air heaters is the outer edge direction of the flow guiding frame, and the wind direction of the two air heaters is the anticlockwise or clockwise rotation direction of the flow guiding frame. Through the rotary flow guiding frame, circulation of high-temperature gas in the box is accelerated, through the arrangement of the flow guiding plates with the changeable angle, distribution of high-temperature airflow around the wood can be more uniform, the situation of serious local heating is avoided, and the wood drying quality is improved.

Owner:CHONGQING KUNXIU DOOR & WINDOW

Anti-corrosion heat dissipation coating used for LED lights and preparation method thereof

ActiveCN103351809AImprove anti-corrosion abilityImprove high temperature resistanceAnti-corrosive paintsPolyamide coatingsXylylenePolyester

The invention provides an anti-corrosion heat dissipation coating used for LED lights and a preparation method thereof. The coating is characterized by comprising the following raw materials by weight parts: 45-48 parts of organic silicone resin, 24-26 parts of polyamide polyamine epichlorohydrin resin, 32-34 parts of aluminium nitride, 50-56 parts of xylene, 25-28 parts of butyl acetate, 2-3 parts of urotropine, 3-5 parts of phenyltriethoxysilane, 2-3 parts of aniline methyl triethoxysilane, 10-20 parts of carbon black N 339, 5-15 parts of carbon black N 660, 1-2 parts of triglycidyl isocyanurate, 5-8 parts of sebacic acid propanediol polyester, 3-5 parts of phthalic acid polyester, 2-3 parts of isoprene, 4-6 parts of 2-hydroxy propyl acrylate, 3-4 parts of propylene glycol, 1-2 parts of tert-butyl hydroperoxide, 1-2 parts of m-amino methylamine, 1-2 parts of ethylene diamine and 3-4 parts of a film forming agent. According to the invention, the urotropine is added into the raw materials to improve the anti-corrosion performance of the coating, so that the coating can be applied in various contaminated environments, and high temperature resistant and salt spray resistant capabilities of the coating can be improved.

Owner:TIANCHANG JINLING ELECTRONICS

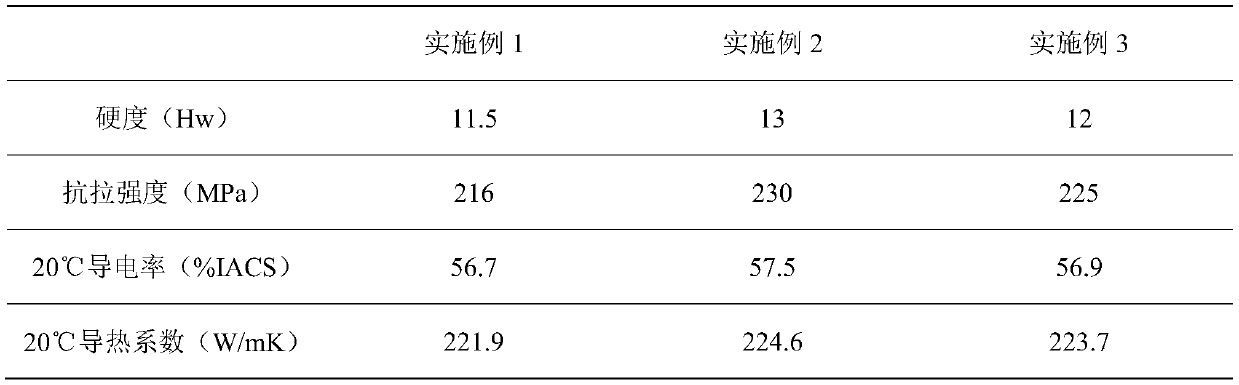

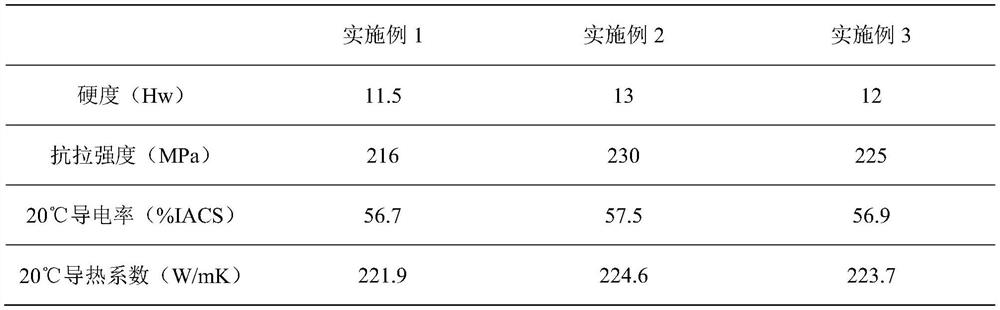

Preparation process of high-thermal-conductivity extruded aluminum alloy profile

ActiveCN110343884ASimple preparation processOptimizing aging process parametersSolution treatmentHardness

The invention discloses a preparation process of a high-thermal-conductivity extruded aluminum alloy profile. The preparation process comprises the following steps of 1) extrusion, 2) refining, 3) extruding, and 4) effectiveness and the like. An online air cooling technology is adopted, the process of solid solution treatment is omitted, so that the production efficiency is improved; and optimization is carried out on various parameters, especially effective parameters in the preparation process so as to obtain an optimal scheme. According to the preparation process, the formula of the aluminum alloy is improved, the content of Mg and Si in the aluminum alloy component is reduced, Mg / Si ratio is controlled, so that the type of the alloy is in a slightly excess type of Si, and the harmful effect of V is eliminated by adding the boron adding element. On the premise of keeping the hardness, the conductivity of the product is improved. Through verification, the vickers hardness of the product can reach more than 11 Hw or above, the tensile strength is higher than 215 Mpa, the electric conductivity at 20 DEG C is higher than 56% IACS, and the heat conductivity coefficient can reach 220W / mK or above, and all technical parameters reach the world leading level.

Owner:JIANGSU WEITENG COPPER CO LTD

Composite heat dissipation coating composition and preparation method thereof

The invention provides a composite heat dissipation coating composition and a preparation method thereof. The coating composition is characterized by comprising the following raw materials by weight parts: 40-45 parts of E-12 epoxy resin, 6-8 parts of 2-methyl methacrylate, 3-4 parts of tetraethylenepentamin, 20-24 parts of nanometer diatomite powder, 8-10 parts of nanometer calcium carbonate powder, 2-3 parts of zinc oxide, 10-12 parts of methyl ethyl ketone, 16-18 parts of xylene, 4-6 parts of propylene glycol, 2-3 parts of aluminium nitride powder, 2-3 parts of vinyl-tris(beta-methoxyethoxy)silane, 3-4 parts of an accelerator M, 2-3 parts of methacrylic acid-2-hydroxy ethyl ester, 4-6 parts of aluminium nitride and 3-4 parts of a film forming agent. The coating composition is reasonable in formula, aging resistant, large in adhesive strength and good in heat-dissipation effect, can be used under 200 DEG C for a long term, and has unchangeable mechanical properties.

Owner:TIANCHANG CHICHENG ELECTRIC TECH

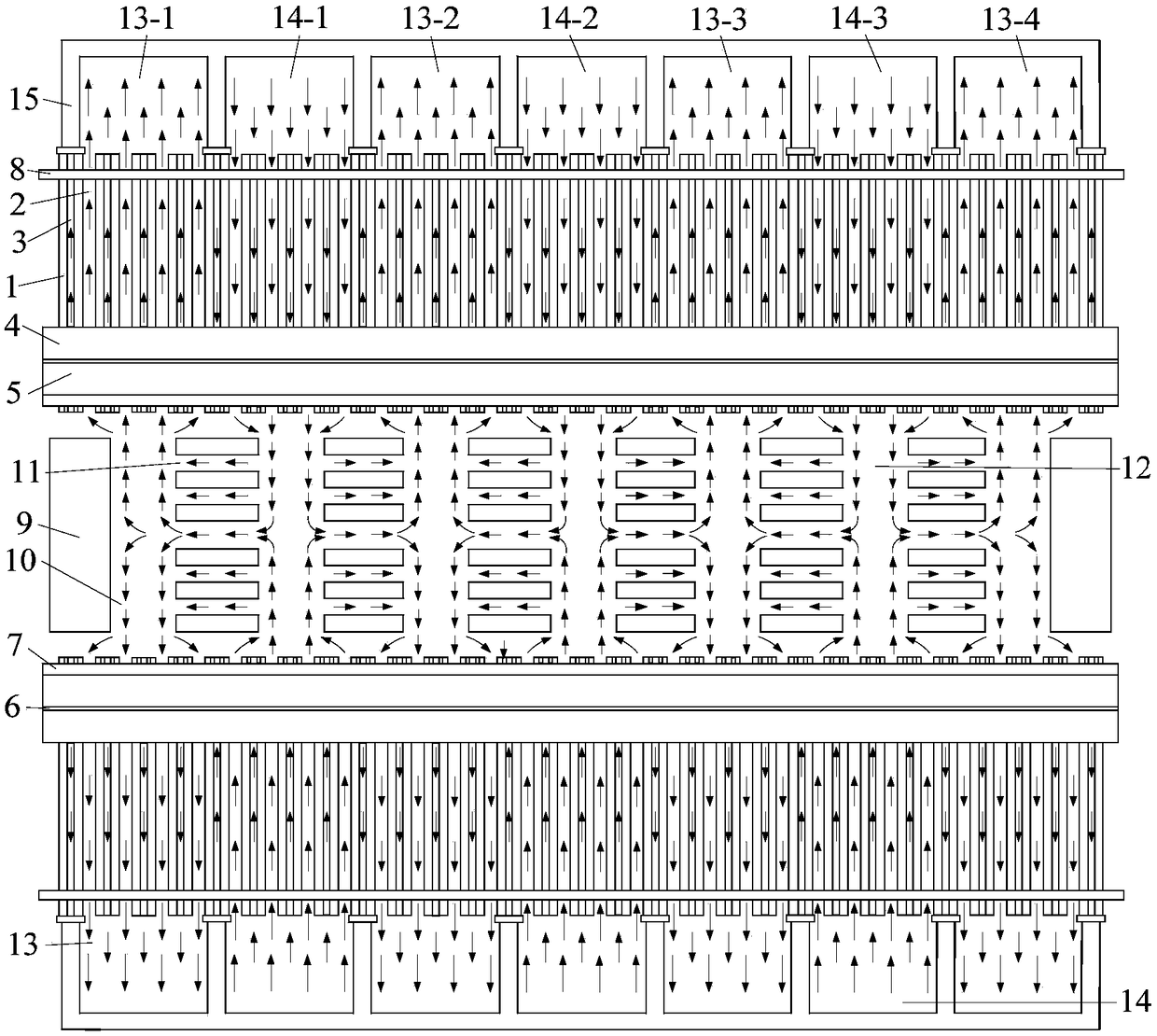

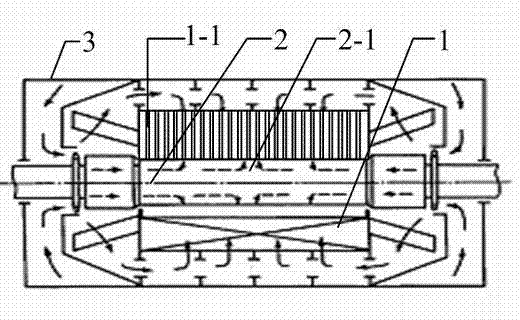

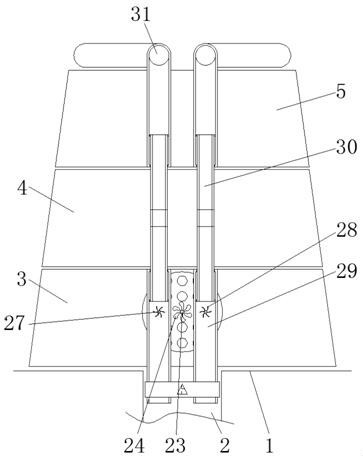

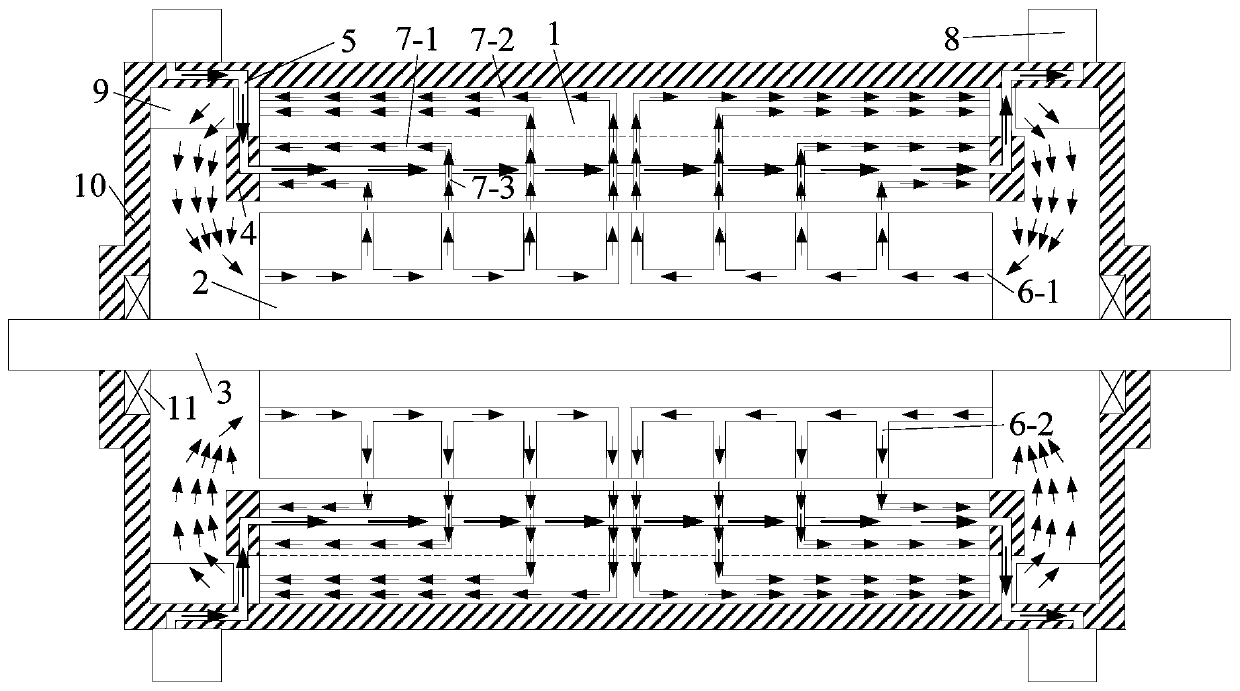

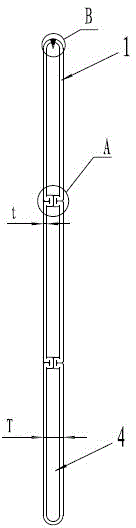

Forced pressure-in-draw-out type turbogenerator ventilation cooling system with multi-wind path interleaving

ActiveCN108566001AIncrease temperatureHigh heat dissipation coefficientMagnetic circuit rotating partsMagnetic circuit stationary partsCold airElectric machinery

The invention discloses a forced pressure-in-draw-out type turbogenerator ventilation cooling system with multi-wind path interleaving, which relates to the field of electric machinery. In order to solve the problem of high temperature of a stator iron core, a stator winding and a rotor iron core in an existing turbogenerator, a 'Y'-shaped stator internal air channel is formed in the stator iron core, a stator radial ventilation groove is reserved between the stator iron cores, the stator region is alternately divided into a stator hot air area and a stator cold air area along the axial direction, and the stator iron core is arranged in the stator base; the rotor area is alternately divided into a rotor hot air area and a rotor cold air area along the axial direction, the rotor hot air area and the rotor cold air area are connected through the axial ventilation holes of the rotor, a throw away type fan blade, a rotor first-stage pressurizing fan blade and a rotor second-stage pressurizing fan blade are arranged in the rotor hot air area, a rotor suction fan blade is arranged in the rotor cold air area. The turbine generator has the advantages that the cooling effect of the components of the turbogenerator is enhanced, the structure is simple, and the realization is convenient.

Owner:HARBIN UNIV OF SCI & TECH

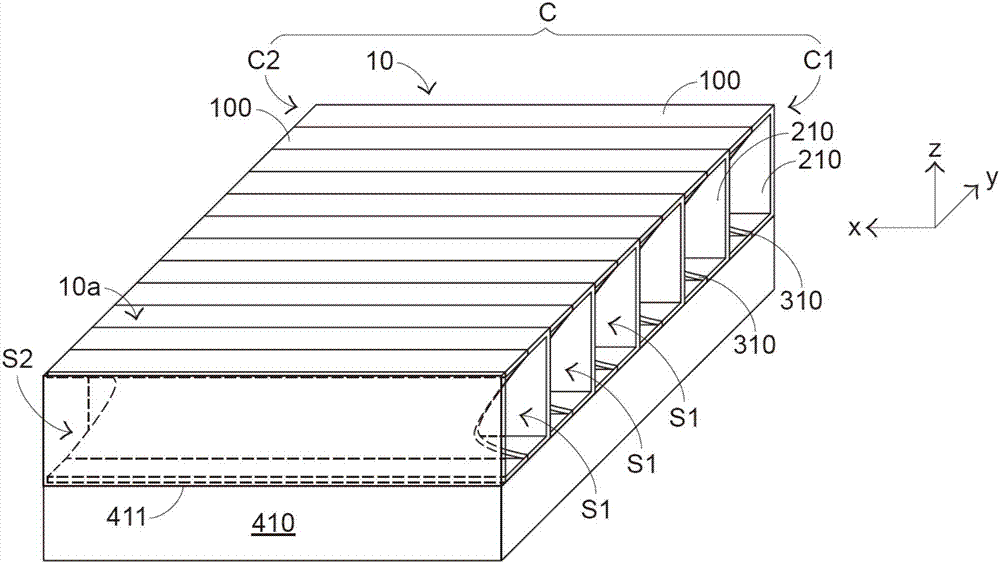

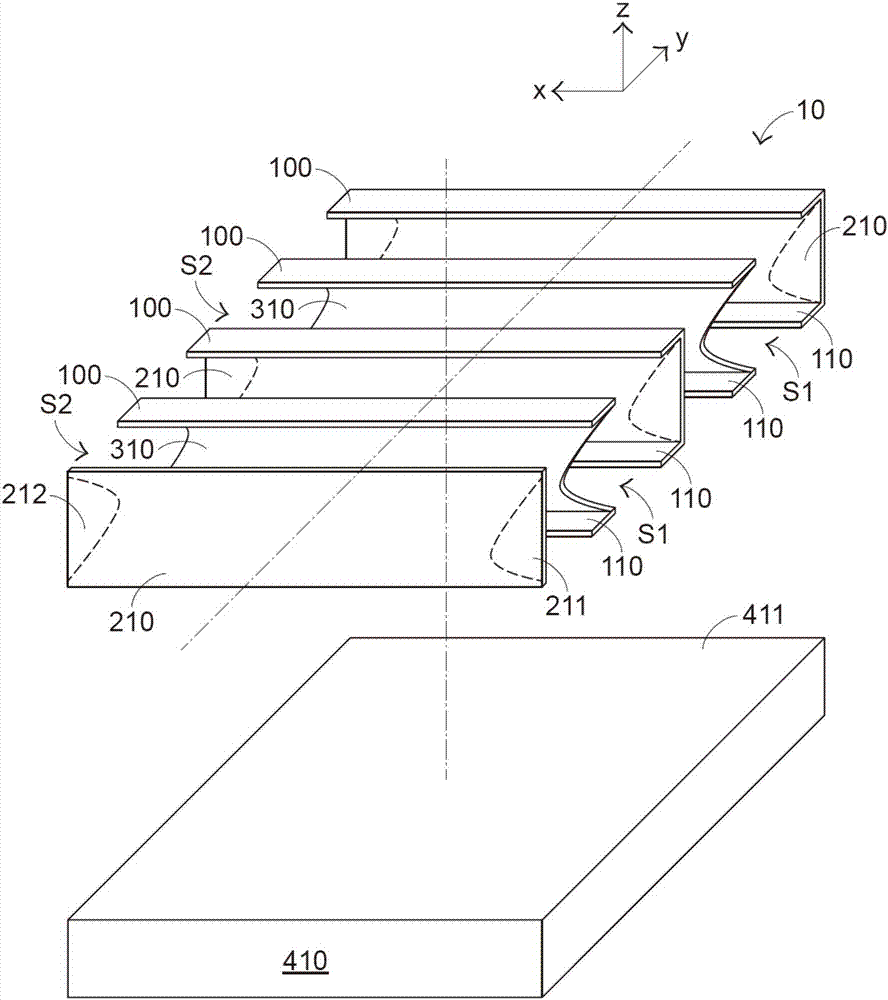

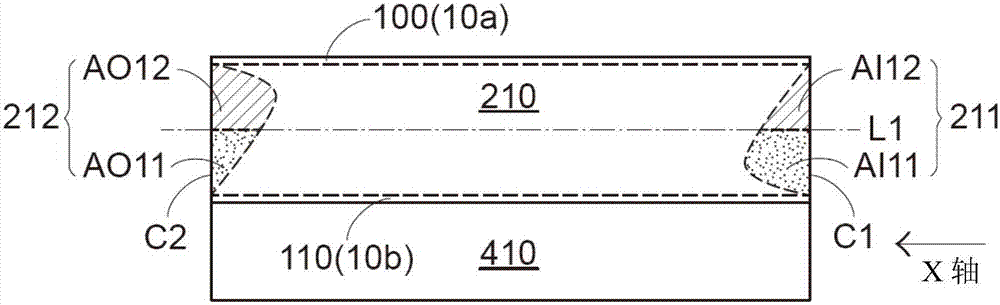

Heat sink

ActiveCN107293526AHigh heat dissipation coefficientIncrease cooling areaSemiconductor/solid-state device detailsSolid-state devicesOverlap zoneEngineering

The invention provides a heat sink which is connected with a heating surface of a heating piece. The heat sink includes a bottom surface, a top surface, plural first fins and plural second fins. The plural first fins and the plural second fins are alternately and separately arranged between the top surface and the bottom surface along a specified axis direction. Moreover, plural airflow channels are defined by the plural first fins, the plural second fins, the top surface and the bottom surface collaboratively. The first fin has a first non-overlapped zone and a second non-overlapped zone with respect to a projection area of the second fin along the specified axis direction. The first non-overlapped zone is located at an airflow inlet. In the first non-overlapped zone, the lower portion is wider than the upper portion. The second non-overlapped zone is located at an airflow outlet. In the second non-overlapped zone, the upper portion is wider than the lower portion. The heat sink can improve heat radiating efficiency.

Owner:AURAS TECH

Efficient-heat-dissipation integrated LED modulator tube structure and production process thereof

InactiveCN104019389ALight attenuation is smallShort heat transfer distancePoint-like light sourceElongate light sourcesComputer moduleEngineering

The invention relates to an efficient-heat-dissipation integrated LED modulator tube structure and a production process of the efficient-heat-dissipation integrated LED modulator tube structure. The horizontal wall of an aluminum shell is a packaging plane. A printed circuit layer is arranged on the packaging plane. Chips are welded to the printed circuit layer of the aluminum shell. A silica gel layer is arranged in the area defined by a surrounding glue layer of the aluminum shell. The upper surface of the silica gel layer is evenly coated with a fluorescent powder coating. An intelligent IC drive element is directly welded to the printed circuit layer of the aluminum shell. The two ends of each chip are connected with voltage regulator tubes respectively. The chip-support-aluminum substrate-tube body multistage thermal resistance obstacle is thoroughly omitted, the heat conduction way is improved, and the heat conduction distance is greatly shortened; a support and the aluminum substrate are omitted, and production cost is reduced; the problems that the luminous efficiency is low and the luminous decay becomes large are solved; no extra drive module is needed, and automatic attachment is completed; heat produced when the intelligent IC drive element and electronic elements work is directly transmitted outwards through aluminum pipes, and therefore the heat dissipation effect of a drive module is improved, and the service life of a power supply is prolonged.

Owner:GUANGDONG JINYUAN LIGHTING TECH

Braking disc for railway vehicles

The invention discloses a braking disc for railway vehicles, which is made of vermicular graphite cast iron. The chemical composition by weight is: 3.45%-3.77% of carbon, 1.86%-2.25% of silicon, 0.5%-0.8% of manganese, less than or equal to 0.02% of sulfur and less than or equal to 0.05% of phosphorus, and the balance is iron, wherein vermicular rate of the vermicular graphite cast iron is larger than or equal to 60%. The braking disc is formed by a left disc body, a right disc body, a first radial connection rib and a second radial connection rib, the diameter of the left disc body is identical to that of the right disc body, the left surface of the left disc body and the right surface of the right disc body are braking work surfaces, and roughness of the two braking work surfaces is respectively 1.6mm-3.2mm. The braking disc for railway vehicles prevents cracks from generating through material replacement and structure adjustment and further avoids safety accidents. The braking distance of the braking disc is moderate, and the braking disc is simple in structure, easy to manufacture, has good economic and technological value and is suitable for large-scale popularization and application.

Owner:重庆海通机械制造有限公司

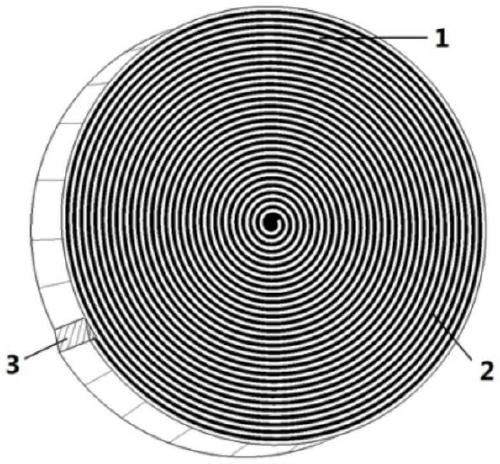

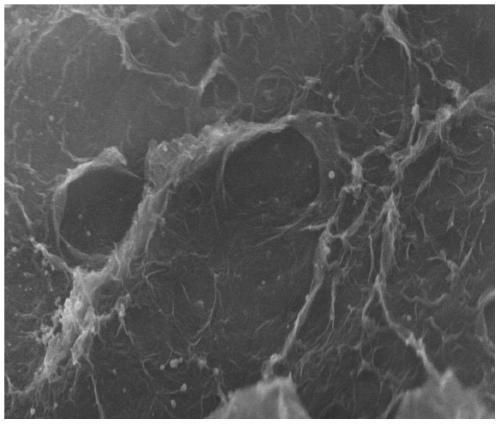

A kind of preparation method of aluminum-based graphene, carbon nanotube composite heat dissipation material

ActiveCN107313102BImprove cooling efficiencyHigh mechanical strengthElectrolytic coatingsHeat-exchange elementsCarbon nanotubeNitrogen gas

The invention relates to a preparing method for an aluminum base graphene and carbon nano tube composite heat dissipation material, and belongs to the technical field of heat dissipation material preparing. The method comprises the steps that equivalent graphene, carbon nano tube powder and aluminum salt are added in an absolute ethyl alcohol solution, and evenly-scattered graphene and carbon nano tube mixed electrophoresis liquid is obtained through ultrasonic scattering; and after being subjected to surface treatment through dilute nitric acid, deionized water, absolute ethyl alcohol and ultrasonic waves, aluminum base sheets serve as a cathode; graphite sheets serve as an anode, and the cathode and the anode are immersed in the mixed electrophoresis liquid to be subjected to electrophoretic deposition; then, the aluminum base sheets are stacked into multiple layers from one end, cold press forming is conducted, the other ends of the aluminum base sheets wrap the outer face of a pressed and formed sample by one circle, and the other ends of the aluminum base sheets are welded and fixed to the side face of the sample; and annealing treatment is conducted at the nitrogen atmosphere, and accordingly the aluminum base graphene and carbon nano tube composite heat dissipation material is obtained. According to the method, the technology is simple, energy saving and environment friendliness are achieved, cost is low, and the prepared composite heat dissipation material is high in heat dissipation efficiency and high in mechanical strength.

Owner:鄂尔多斯市紫荆创新研究院

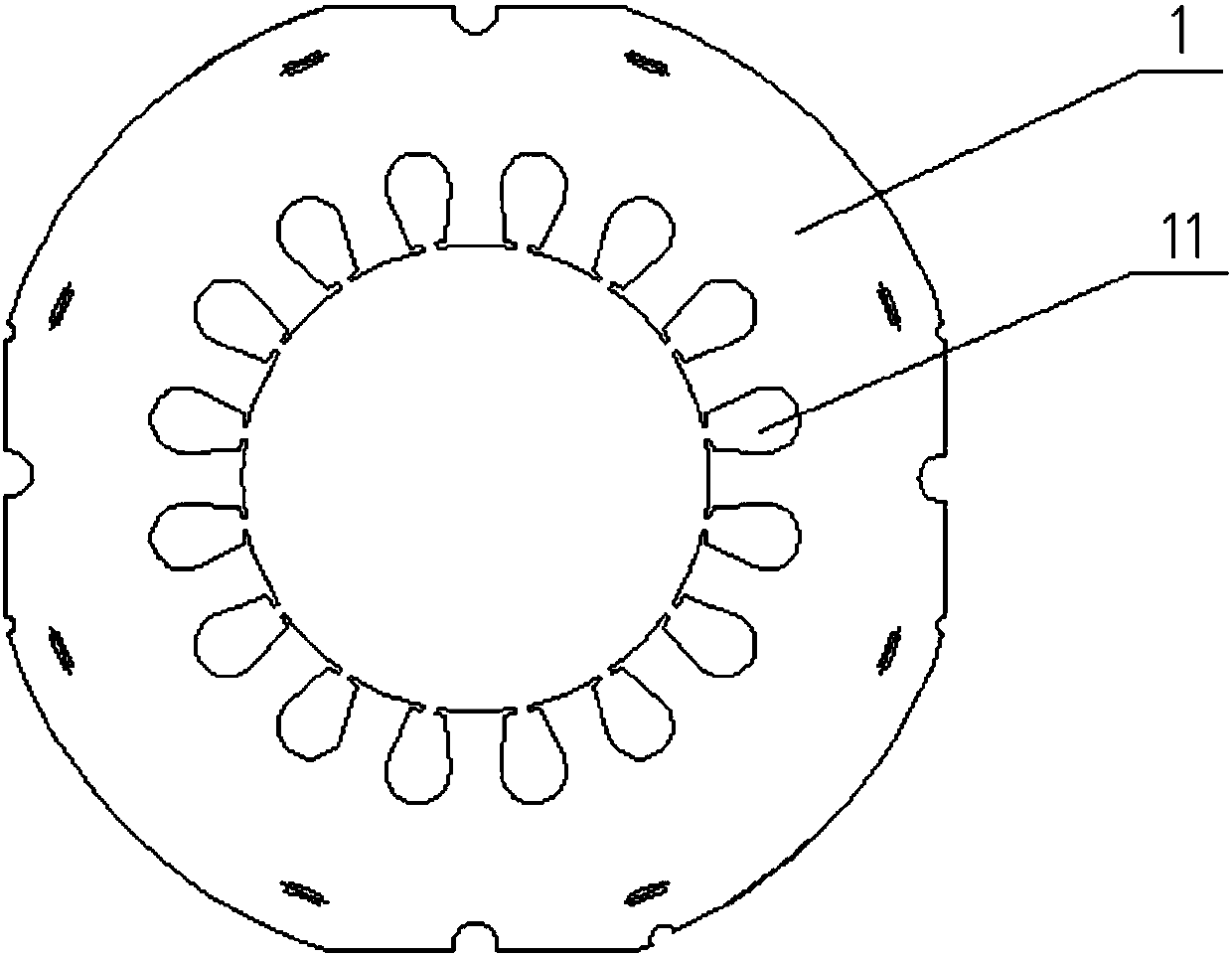

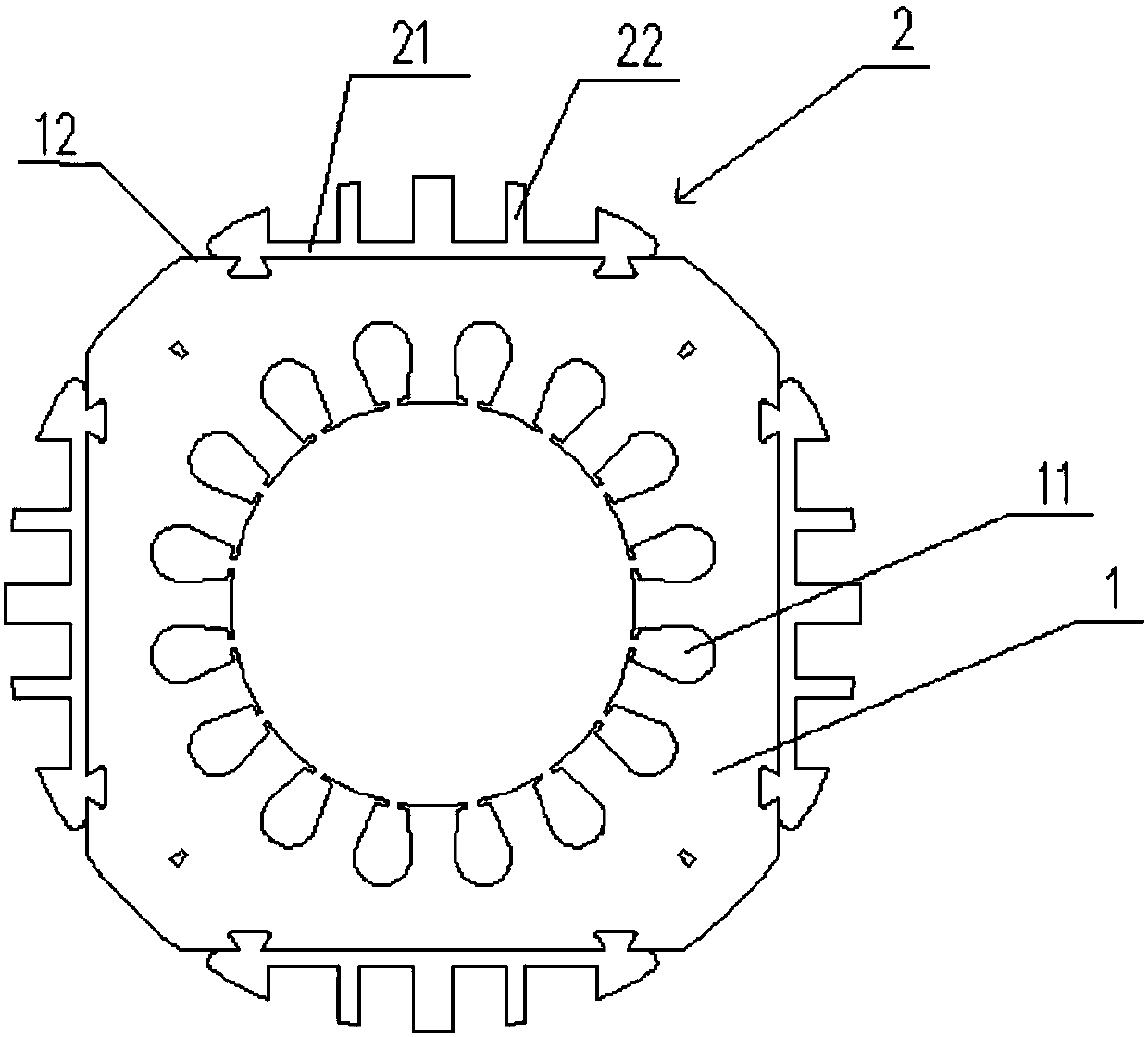

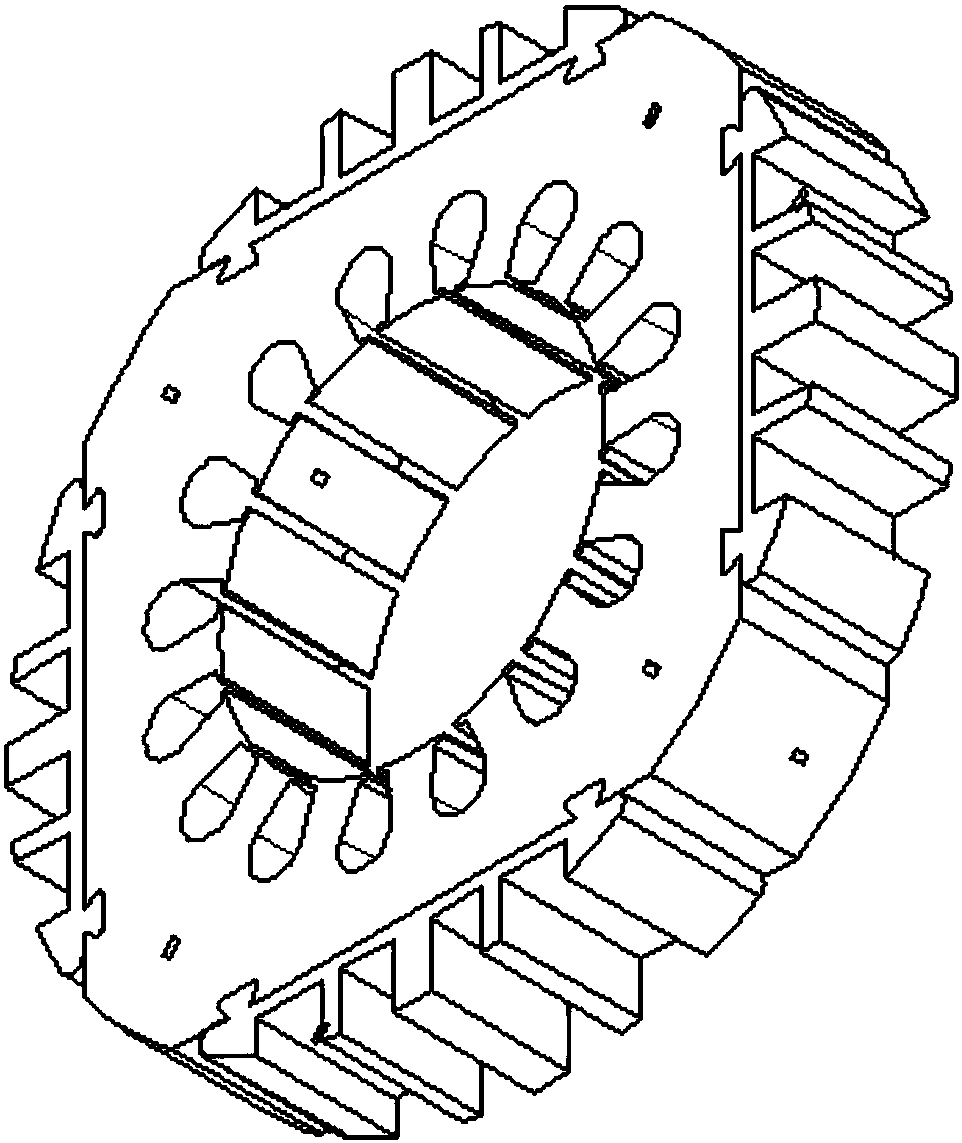

Motor stator core structure

PendingCN107769471AIncrease contact areaImprove cooling effectMagnetic circuit stationary partsCooling/ventillation arrangementElectric machineEngineering

The present invention relates to a motor structure, especially to a motor stator core structure. The motor stator core structure comprises a stator core, a stator slot is arranged at an inner ring ofthe stator core, and at least one section is arranged at the outer ring of the stator core; the motor stator core structure also comprises at least one splicing block being spliced with the at least one section, one surface, close to the section, of the at least one splicing block is completely fitted to the at least one section, and the at least one splicing block is made of materials with a thermal conductivity being larger than a thermal conductivity of iron. The problems are solved that a motor stator heat radiation structure is complex and heat radiation is not sufficient in the prior art.

Owner:CHANGZHOU LEKVA ELECTRONICS CO LTD

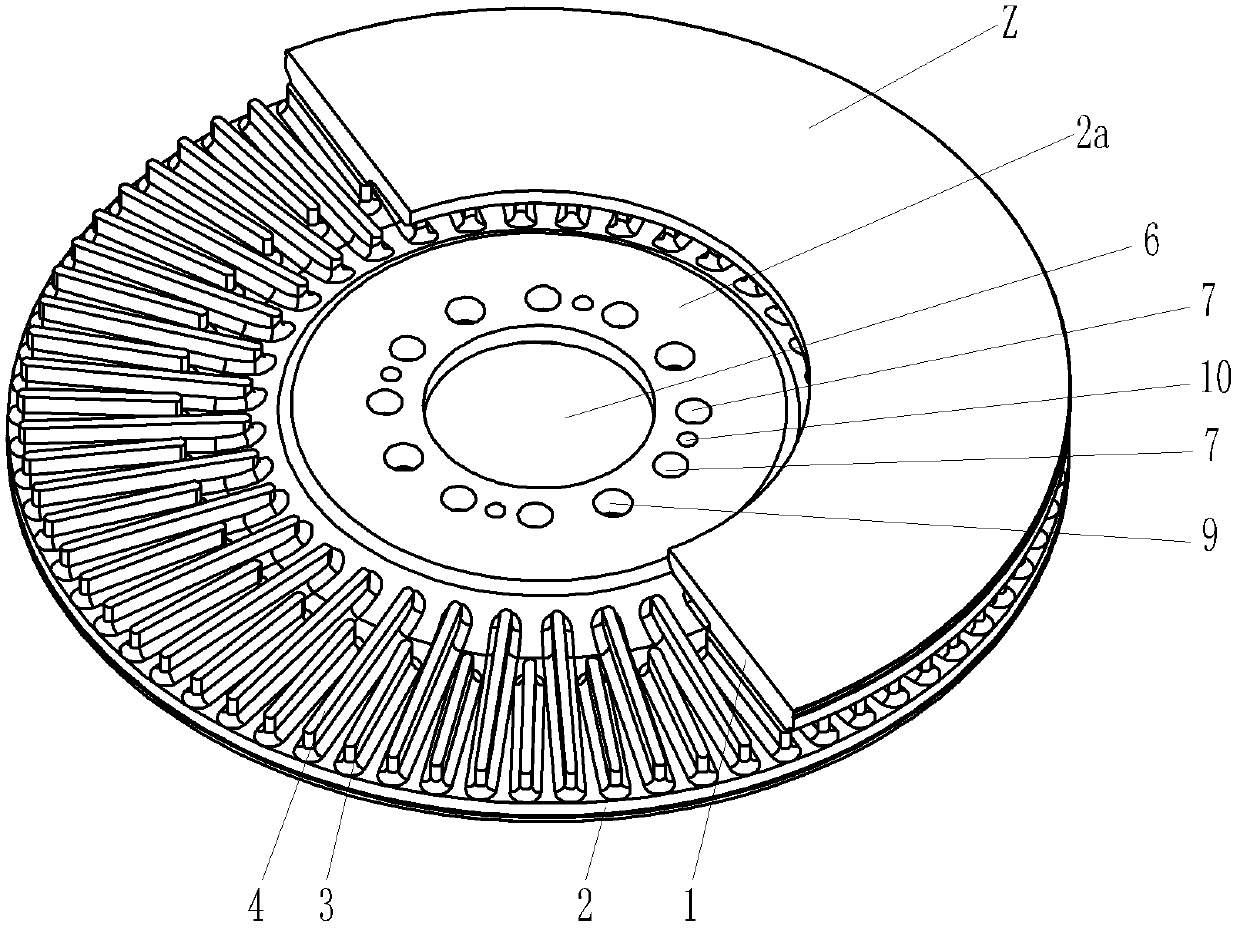

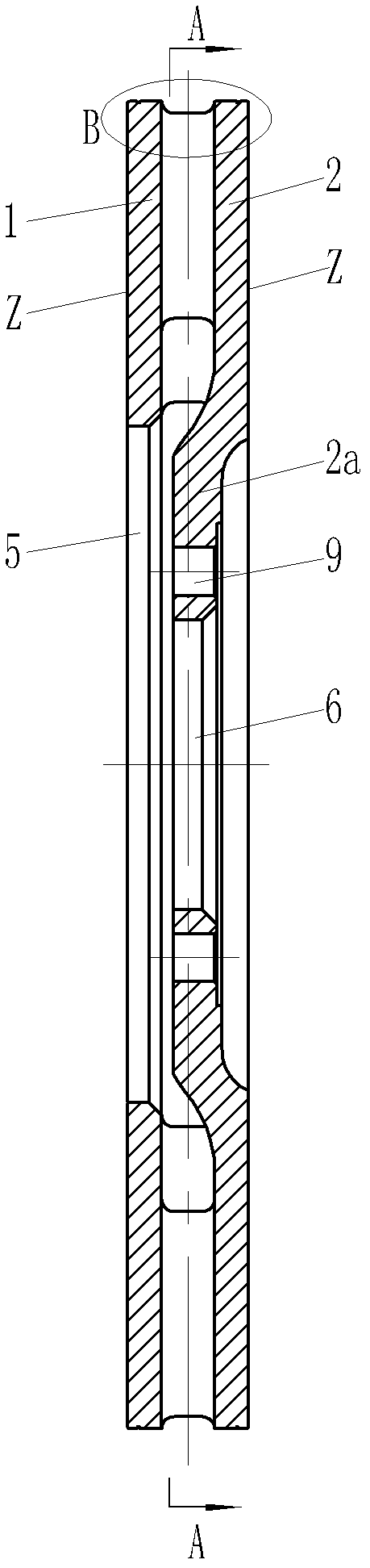

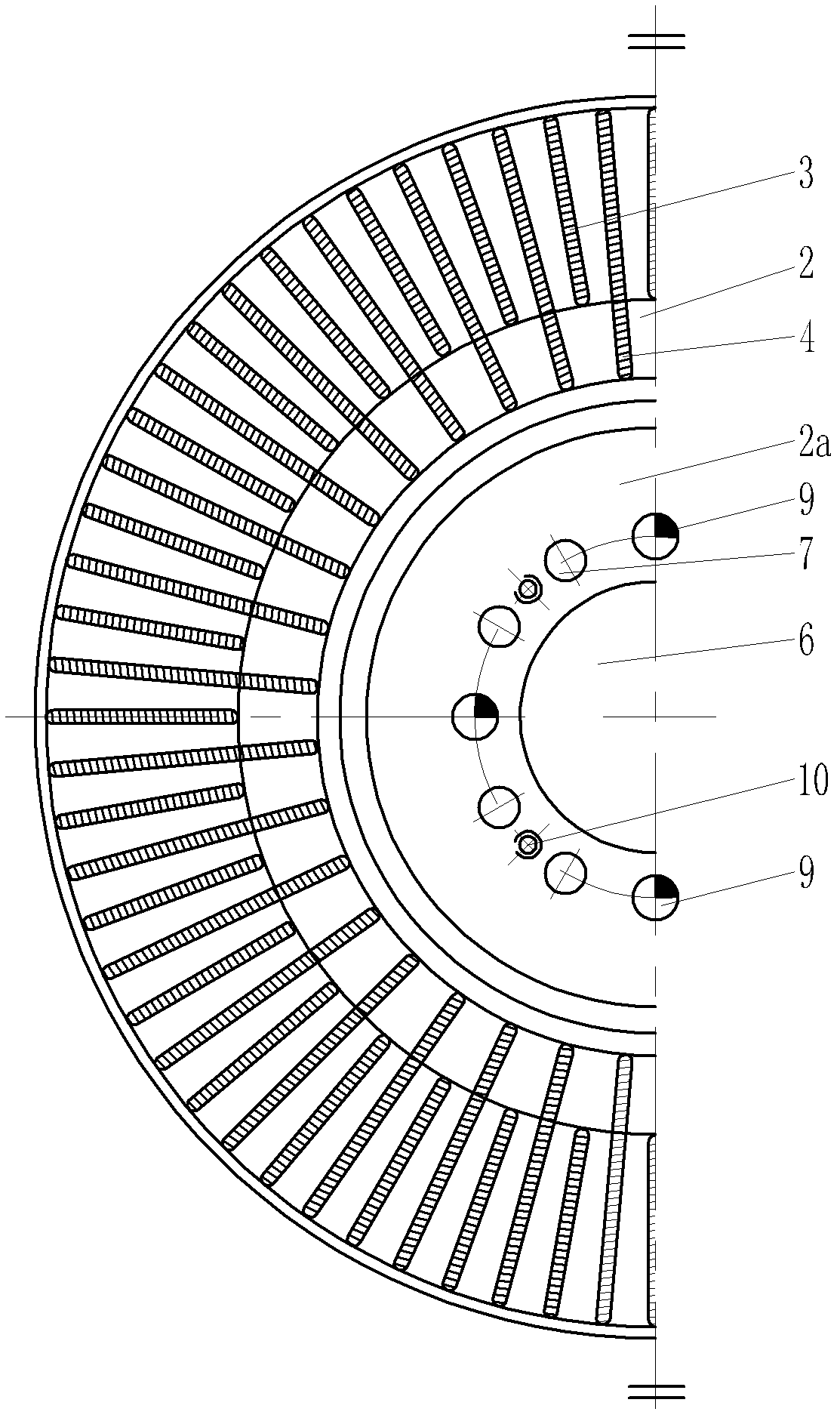

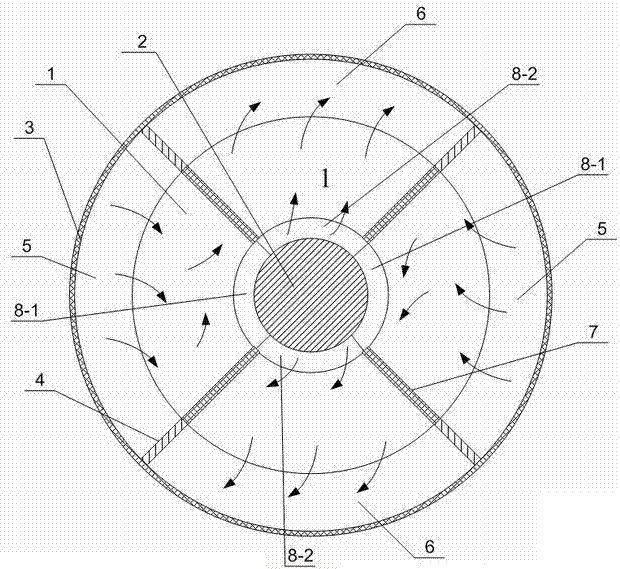

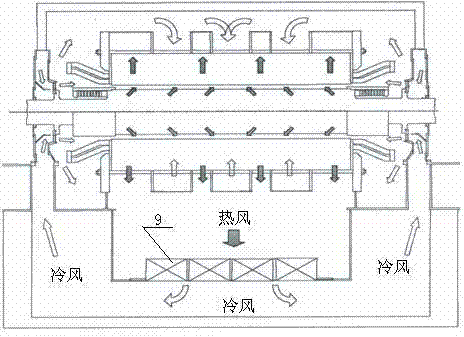

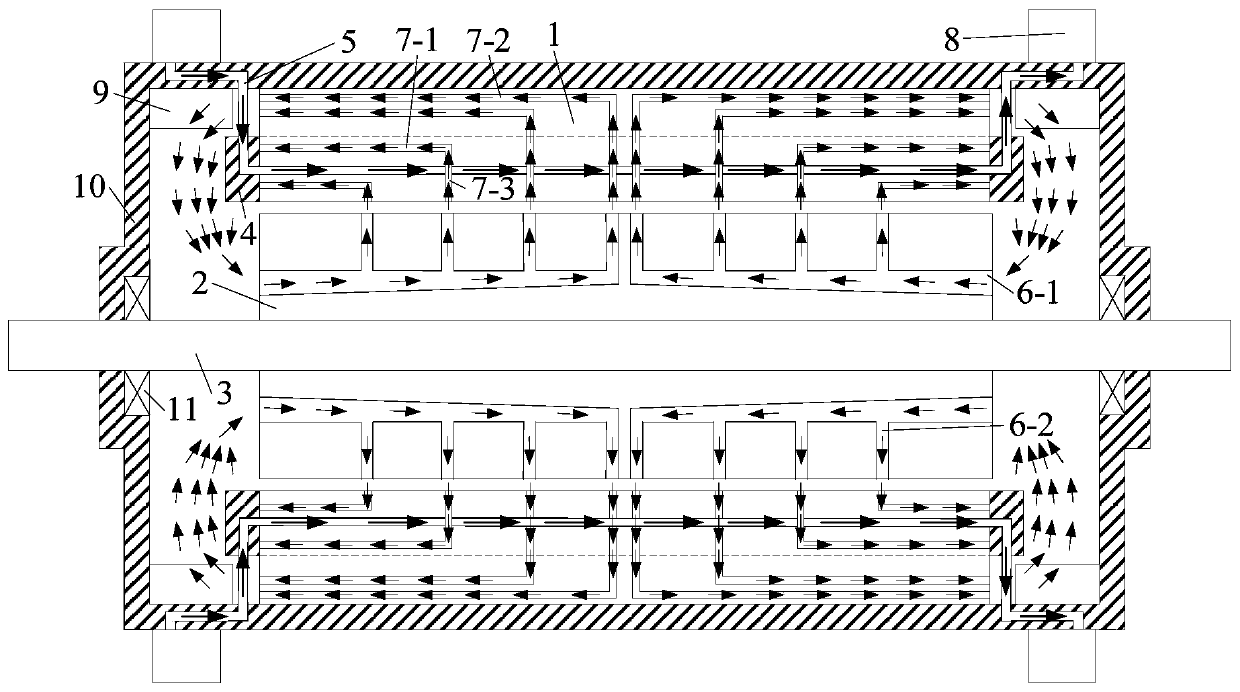

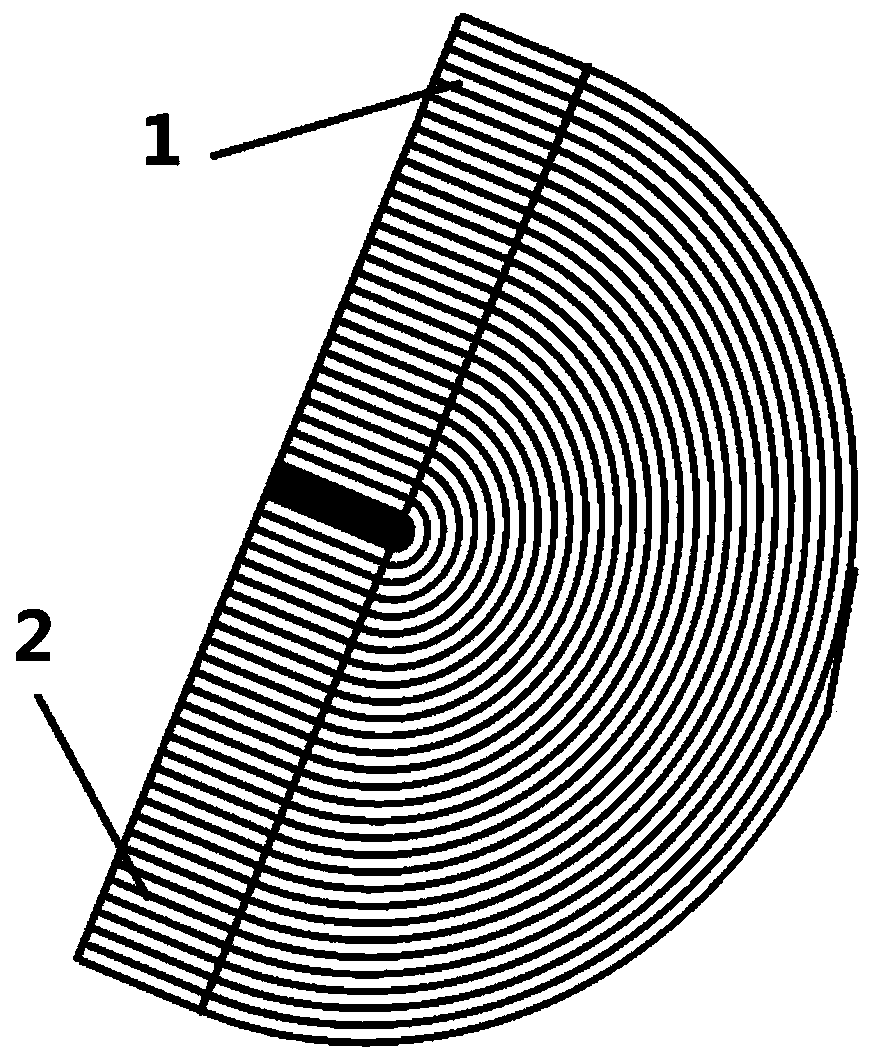

Large air-cooled turbo-generator with circumferential mixed ventilation cooling structure

ActiveCN101860119BGuaranteed uptimeIncrease the maximum temperatureCooling/ventillation arrangementCold airAeroshell

The invention relates to a large air-cooled turbo-generator with a circumferential mixed ventilation cooling structure, which belongs to the technical field of motors. The large air-cooled turbo-generator can solve the problem that the existing cooling technology of the turbo-generator and the improvement technology of the single unit capacity can not be simultaneously integrated. The large air-cooled turbo-generator comprises a stator, a rotor and a housing, wherein an air gap is arranged between the surface of an outer circle of the rotor and the surface of an inner circle of the stator, the stator is covered in the housing, the large air-cooled turbo-generator further comprises four axial rubber separators and a cooler, the four axial rubber separators are uniformly arranged between the surface of the inner circle of the housing and the surface of the outer circle of the stator along the circumferential direction, two opposite cold air areas and two opposite hot air areas are formed, and the two opposite hot air areas are communicated with an inlet of the cooler. The large air-cooled turbo-generator with the circumferential mixed ventilation cooling structure is used for cooling the large air-cooled turbo-generator.

Owner:HARBIN UNIV OF SCI & TECH

Injection mold for plastic part production

The invention discloses an injection mold for plastic part production. The injection mold comprises a workbench, a lower mold, a middle mold, an upper mold and a motor, wherein a water storage tank isformed in the upper surface of the workbench, the lower mold is placed on the upper surface of the workbench, the upper surface of the lower mold is connected with the middle mold, the upper surfaceof the middle mold is connected with the upper mold, inner cavities are formed in the upper mold, the lower mold and the middle mold, a pressing rod penetrates through the surface of the right side ofthe middle mold, and the outer surface of the pressing rod is fixedly connected with a spring. According to the injection mold for plastic part production, the pressing rod can be pressed, so that afirst twisted rod slides through a fixing rod and a second twisted rod, the first twisted rod and the second twisted rod can extrude a convex block when sliding, so that the convex block drives a connecting gear to rotate to be meshed with a supporting block, the supporting block slides to jack up the upper mold and the middle mold, the upper mold, the middle mold and the lower mold are separated,the internal joints and the like can be cleaned conveniently, and meanwhile, materials can be taken conveniently.

Owner:吴保林

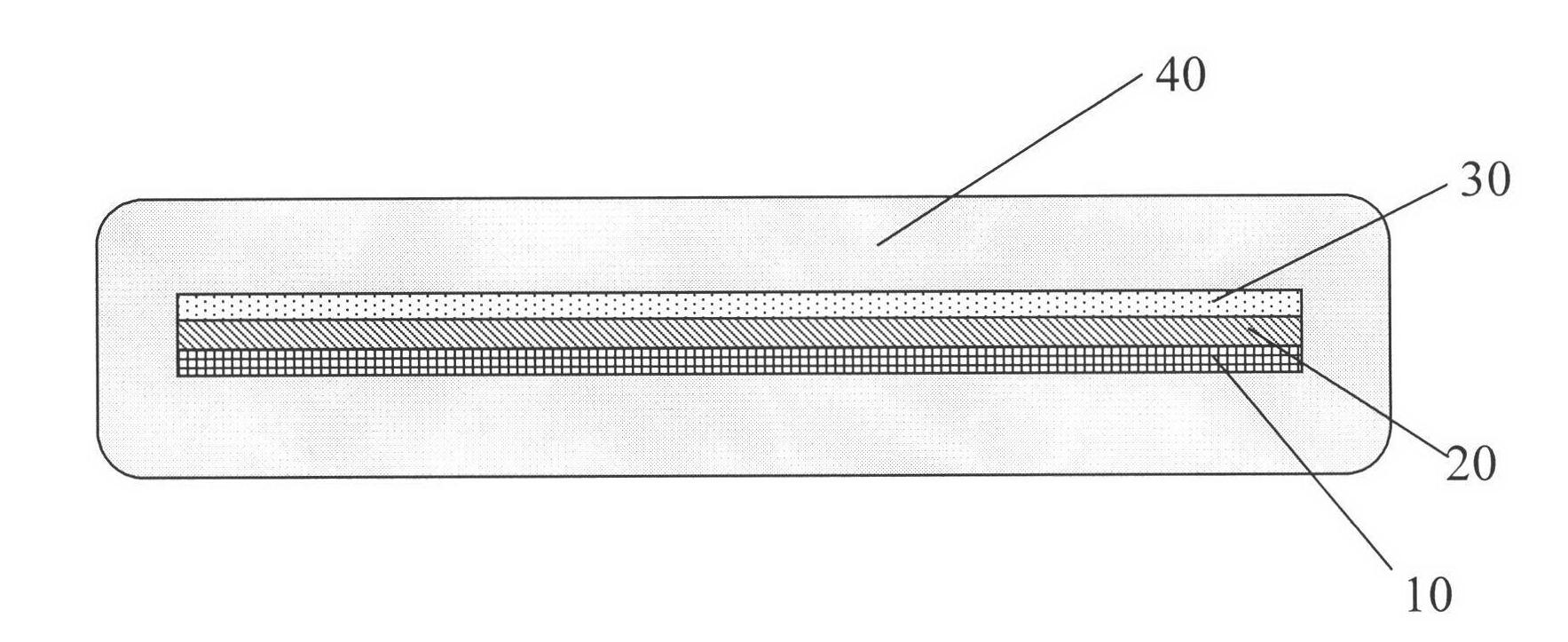

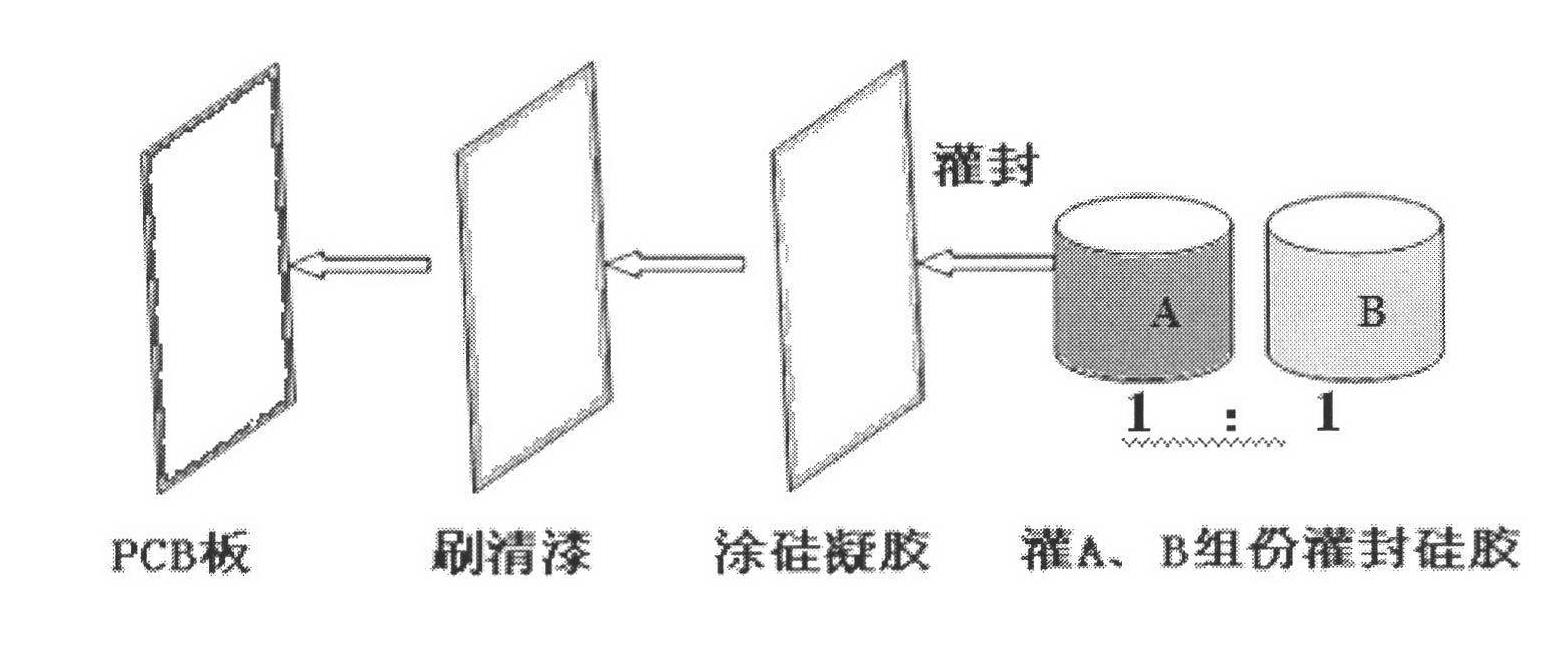

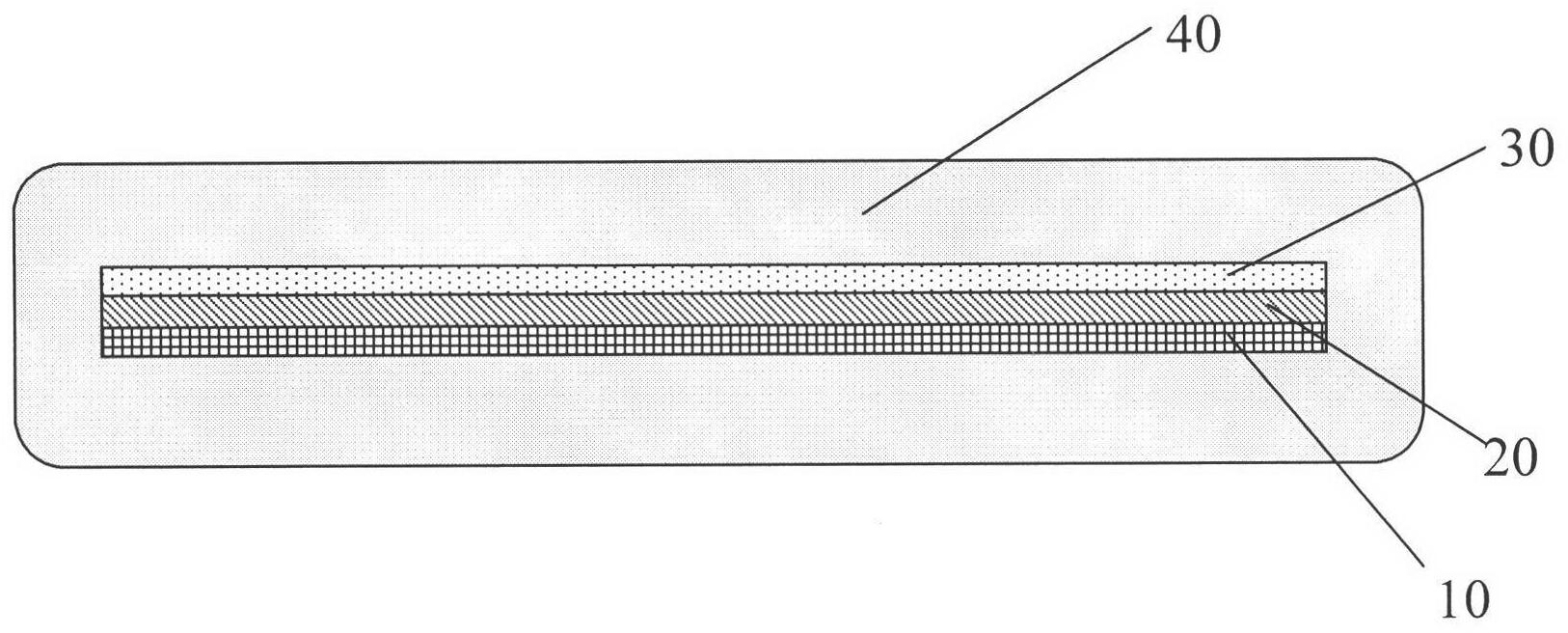

Multilayer encapsulating process and encapsulating structure of light-emitting diode (LED) driver

InactiveCN102593014AAvoid strainHigh heat dissipation coefficientSemiconductor/solid-state device detailsSolid-state devicesLed driverCorrosion

The invention relates to a multilayer encapsulating process and an encapsulating structure of a LED driver, wherein the encapsulating process includes the steps of coating a chip mounting surface of a printed circuit board (PCB) of the driver with a layer of varnish, then coating the surface with a layer of silicon gel, and finally performing integral encapsulation with encapsulating silica gel. The multilayer encapsulating process and the encapsulating structure of the LED driver has the advantages of being water-proof, aging-resistant and corrosion-free, being capable of effectively preventing mounted elements from falling off and being damaged by pulling, being high in radiating coefficient and power supply reliability, and having a shock-proof function due to the elasticity and softness of the solidified encapsulating silica gel.

Owner:殷晨钟

Medical X-ray tube rotating anode high-heat radiation ceramic coat and production method thereof

InactiveCN102437000AHigh heat dissipation coefficientHigh thermal radiation coefficientX-ray tube electrodesCold cathode manufactureCeramic coatingThermal radiation

The invention relates to a medical X-ray tube rotating anode high-heat radiation ceramic coat and a production method thereof, which relates to a coat for improving the heat radiation performance on a medical X-ray tube target disc, and aims at solving the problem of the prior art that the heat radiation coefficient of the target disc in an X-ray tube is low, and adopts the technical scheme that: the medical X-ray tube rotating anode high-heat radiation ceramic coat comprises the following ingredients by weight percent: 25 to 35 percent of titanium dioxide (TiO2), 50 to 65 percent of aluminum oxide (Al2O3) and 5 to 15 percent of zirconia (ZrO2). TiO2, Al2O3 and ZrO2 are made into the high-heat radiation ceramic coat through procedures such as powder blending, washing, surface deairing, sand spraying, coating, vacuum heat treatment and the like. The ceramic coat improves the heat radiation coefficient of the target disc, and enhances the heat radiation performance of the X-ray tube, so the X-ray tube is free from having cracking phenomenon when working at a higher temperature, and the normal work of the X-ray tube can be guaranteed.

Owner:肖李鹏

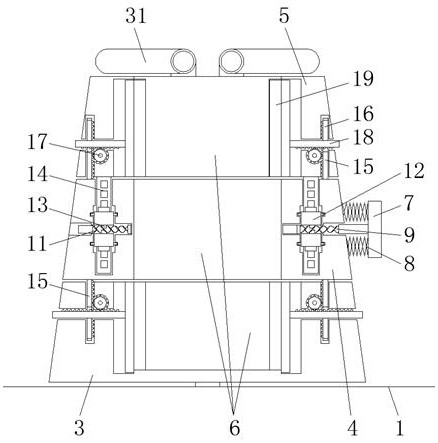

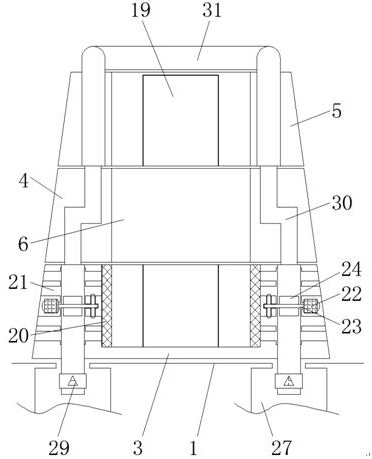

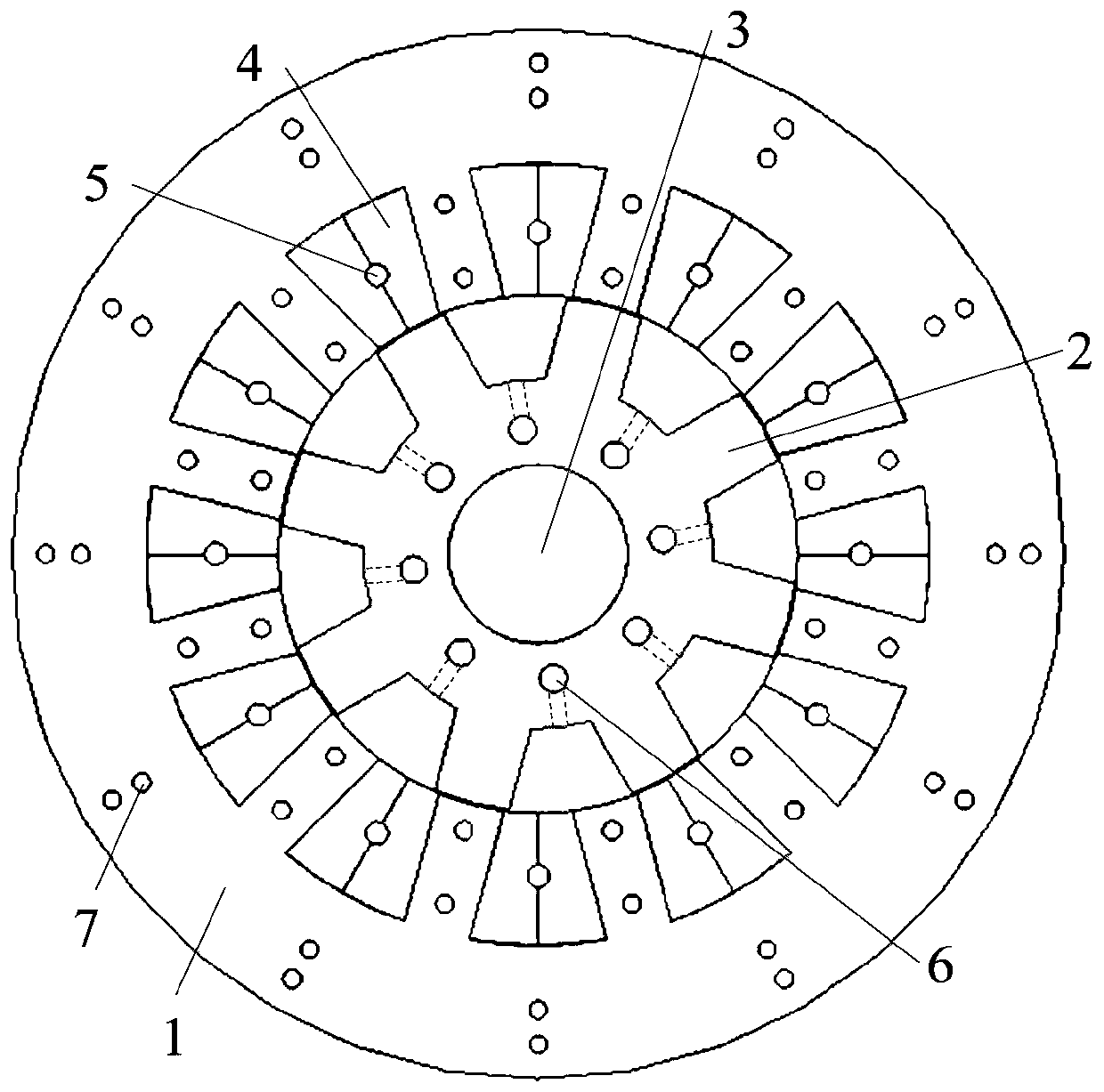

Switched reluctance motor with water-injected winding and multi-directional self-circulating ventilation system

ActiveCN108649749BImprove cooling effectIncrease powerMagnetic circuit rotating partsMagnetic circuit stationary partsElectric machineCooling effect

The invention discloses a switched reluctance motor with a water injection type winding and an axial-radial-circumferential multi-directional self-circulating ventilation system, which belongs to thetechnical field of motors, and aims to solve the problem of high temperature of the existing large-capacity switched reluctance motor. A rotor shaft is mounted on a base through a bearing, a rotor core is mounted on the rotor shaft, a stator core is mounted on the inner wall of the base, a stator copper winding is mounted on the stator core, the rotor core is located in the stator core and a mounting clearance is reserved between the two, a stator direct cooling water pipe is located in the stator copper winding, the two ends of the stator direct cooling water pipe respectively penetrate through the base and are connected to an inlet and an outlet of a direct cooling water driving device, a rotor direct cooling air passage is provided in the rotor core, a stator direct cooling air passageis provided in the stator core, a flaky heat conduction plate is also arranged on the inner wall of the base, and the flaky heat conduction plate corresponds to the stator direct cooling water drivingdevice outside the base. The cooling effect of each component in the large-capacity switched reluctance motor is enhanced, and the switched reluctance motor is simple in structure and convenient to implement.

Owner:HARBIN UNIV OF SCI & TECH

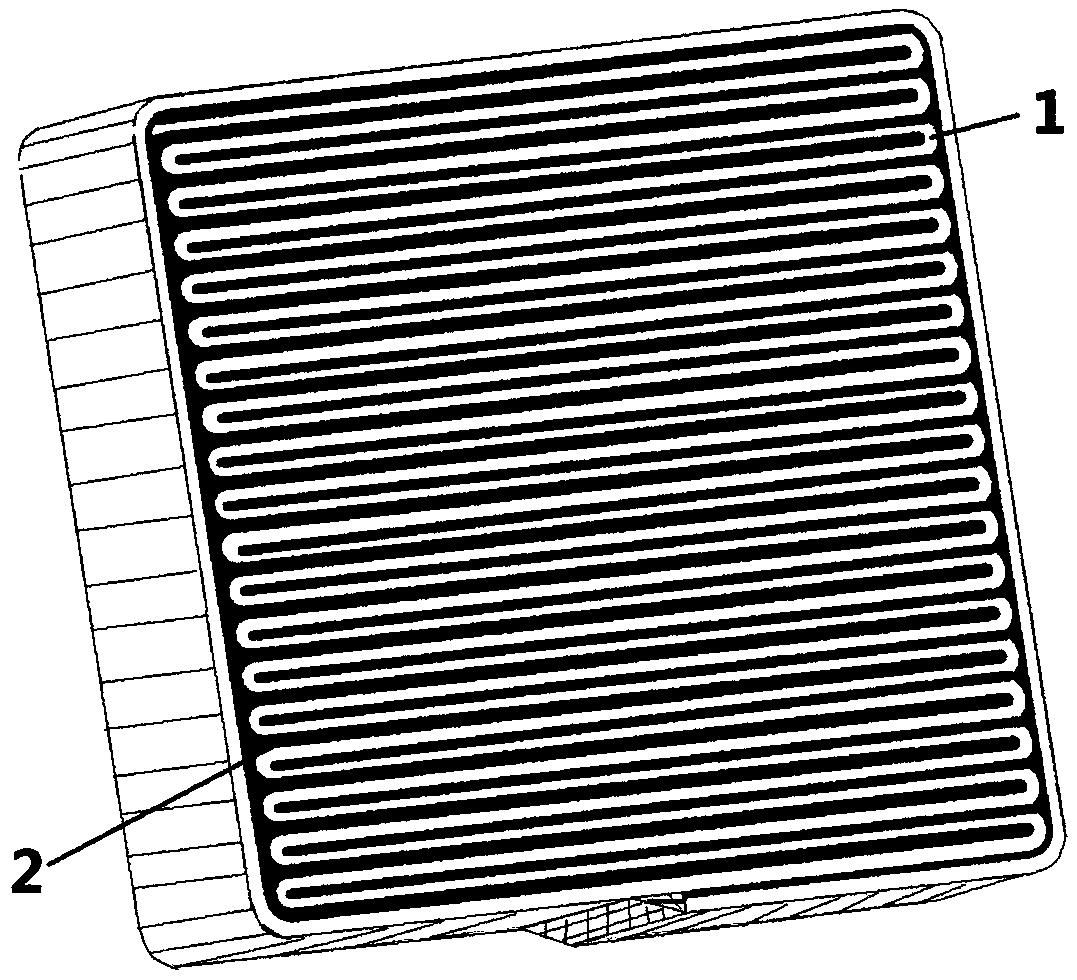

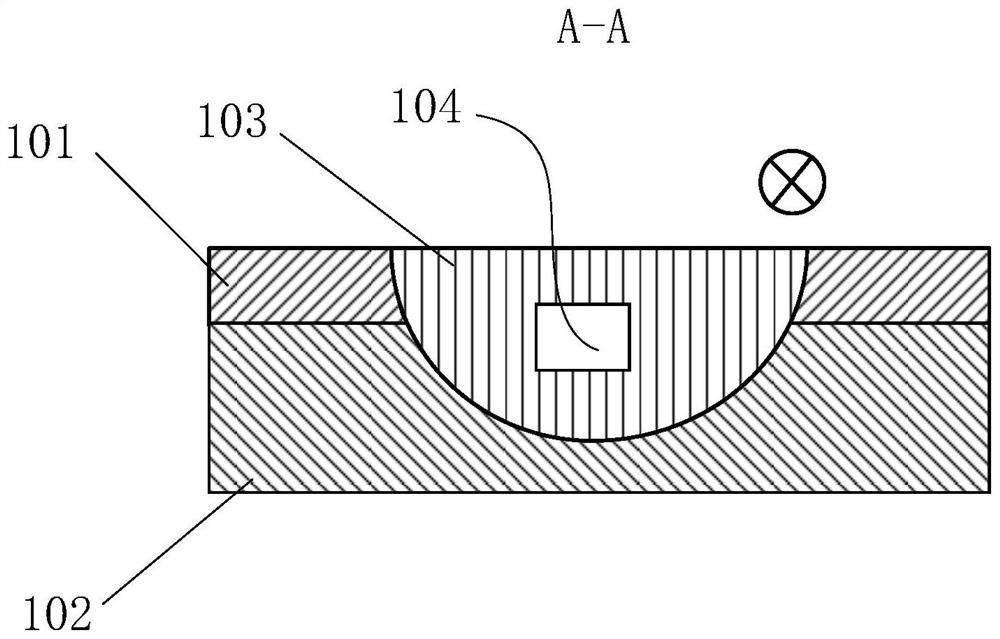

Copper-aluminum different-material cooling plate friction stir tunnel forming method and cooling plate

InactiveCN112719567AHigh melting pointPromote softeningNon-electric welding apparatusFriction weldingFriction stir welding

The invention discloses a copper-aluminum different-material cooling plate friction stir tunnel forming method and a cooling plate. The copper-aluminum different-material cooling plate friction stir tunnel forming method comprises the following steps of selecting a copper alloy plate and an aluminum alloy plate as base materials, and removing oxide layers on the surfaces of the copper alloy plate and the aluminum alloy plate; stacking, clamping and fixing the copper alloy plate and the aluminum alloy plate, taking the copper alloy plate as an upper copper plate of the cooling plate, and taking the aluminum alloy plate as a lower aluminum plate of the cooling plate; starting a main shaft of friction stir welding equipment to drive a stirring head to rotate, so that the stirring head is inserted into the upper copper plate and the lower aluminum plate by a preset depth, and the stirring head keeps rotating; driving the stirring head to horizontally move along a designated welding path to weld the upper copper plate and the lower aluminum plate, so that the cooling plate is obtained; and meanwhile, enabling the stirring head to rotate to enable materials in a weld joint to flow upwards, overflow and deposit on the surface of the weld joint, so that a tunnel is formed in the cooling plate.

Owner:哈工万联智能装备(苏州)有限公司

Preparation process of a high thermal conductivity extruded aluminum alloy profile

ActiveCN110343884BSimple preparation processOptimizing aging process parametersSolution treatmentMaterials science

Owner:JIANGSU WEITENG COPPER CO LTD

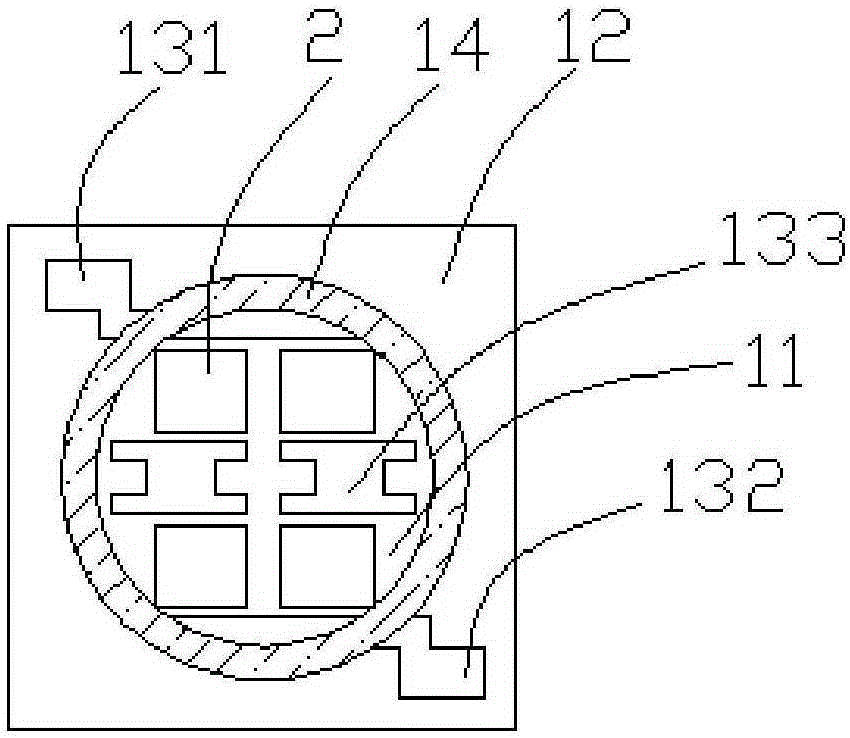

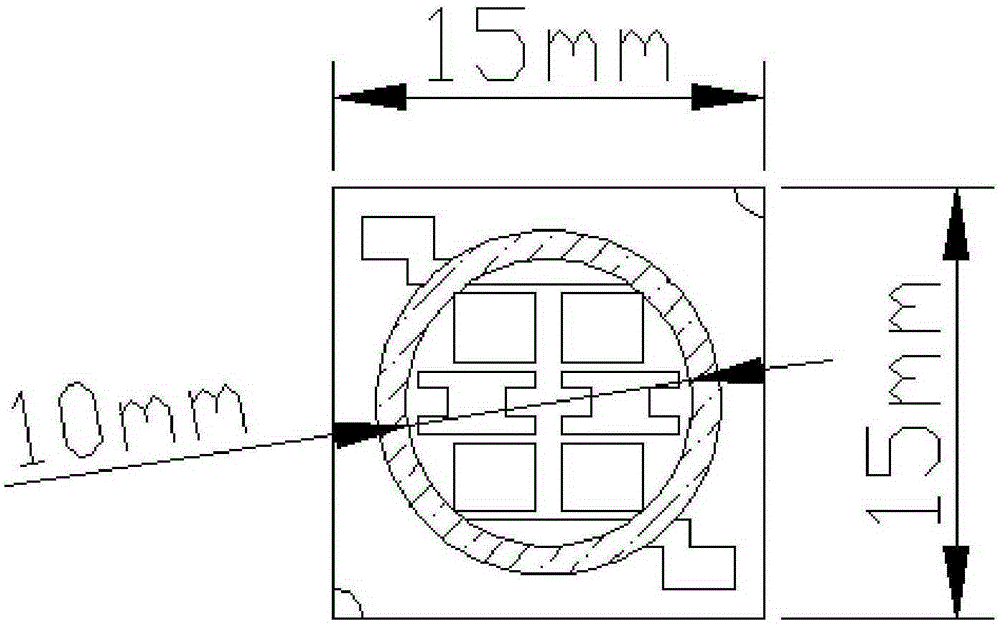

Alternating-current LED light source

InactiveCN105226169ACut costsSave labor installation costsSolid-state devicesSemiconductor devicesHeat stabilityOptoelectronics

The invention provides an alternating-current LED light source. The alternating-current LED light source comprises a substrate and a plurality of sets of alternating-current LED chips. The substrate plate comprises an aluminum oxide substrate, an insulating layer and a conducting layer which are successively arranged from bottom to top. The substrate further comprises alternating-current LED light source die bonding blocks. The insulating layer is a ceramic insulating layer. The conducting layer is provided with a positive electrode, a negative electrode and serially-connected circuits. The serially-connected circuits are arranged in the die bonding blocks. The insulating layer surrounds the alternating-current LED light source die bonding blocks and is fixed on the aluminum oxide substrate. The serially-connected circuits are electrically connected with the positive electrode and the negative electrode. The plurality of sets of alternating-current LED chips are mutually connected in parallel. Compared with the prior art, the alternating-current LED light source can directly work under an alternating-current power supply, and no internal drive power supply is arranged, so that the material cost and the manual installation cost are substantially saved, the size of the alternating-current LED light source is substantially reduced, and the occupied space is reduced in installation. The aluminum oxide ceramic-based substrate is adopted, the heat dissipation coefficient is high, and the heat stability is good.

Owner:ANHUI ZHANLAN OPTOELECTRONICS TECH

Medical X-ray tube rotating anode high-heat radiation ceramic coat and production method thereof

InactiveCN102437000BHigh heat dissipation coefficientHigh thermal radiation coefficientX-ray tube electrodesCold cathode manufactureCeramic coatingThermal radiation

The invention relates to a medical X-ray tube rotating anode high-heat radiation ceramic coat and a production method thereof, which relates to a coat for improving the heat radiation performance on a medical X-ray tube target disc, and aims at solving the problem of the prior art that the heat radiation coefficient of the target disc in an X-ray tube is low, and adopts the technical scheme that: the medical X-ray tube rotating anode high-heat radiation ceramic coat comprises the following ingredients by weight percent: 25 to 35 percent of titanium dioxide (TiO2), 50 to 65 percent of aluminum oxide (Al2O3) and 5 to 15 percent of zirconia (ZrO2). TiO2, Al2O3 and ZrO2 are made into the high-heat radiation ceramic coat through procedures such as powder blending, washing, surface deairing, sand spraying, coating, vacuum heat treatment and the like. The ceramic coat improves the heat radiation coefficient of the target disc, and enhances the heat radiation performance of the X-ray tube, so the X-ray tube is free from having cracking phenomenon when working at a higher temperature, and the normal work of the X-ray tube can be guaranteed.

Owner:肖李鹏

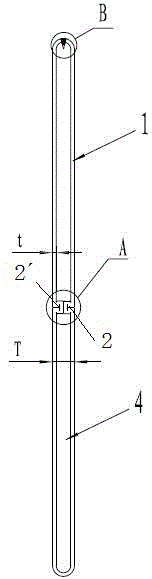

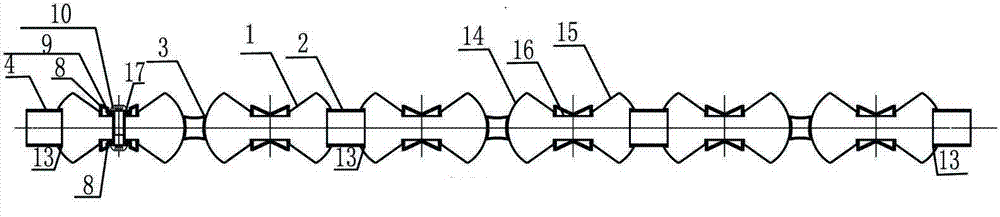

Bidirectional-folding sextuple-pipe-wall reinforced radiating pipe

InactiveCN105021078AImprove structural strengthImprove bearing strengthHeat exchanger casingsTubular elementsMechanical engineeringCooling efficiency

The invention discloses a bidirectional-folding sextuple-pipe-wall reinforced radiating pipe. The pipe walls on the two sides of the radiating pipe are both provided with one or more inwards-recessed reinforcing ribs in the length direction of the radiating pipe. Each reinforcing rib is folded inwards eight times continuously from the pipe wall on the corresponding side. The end planes of the transversely folded layers of the pipe walls on the two sides correspond to one another and are in tight face contact, so that sextuple reinforcing ribs are molded. The inner portion of the radiating pipe is divided by the sextuple reinforcing ribs into two or more independent pipe holes; in this way, the bearing strength of the radiating pipe is greatly improved, and the cooling efficiency is high.

Owner:TAIAN DINGXIN COOLER

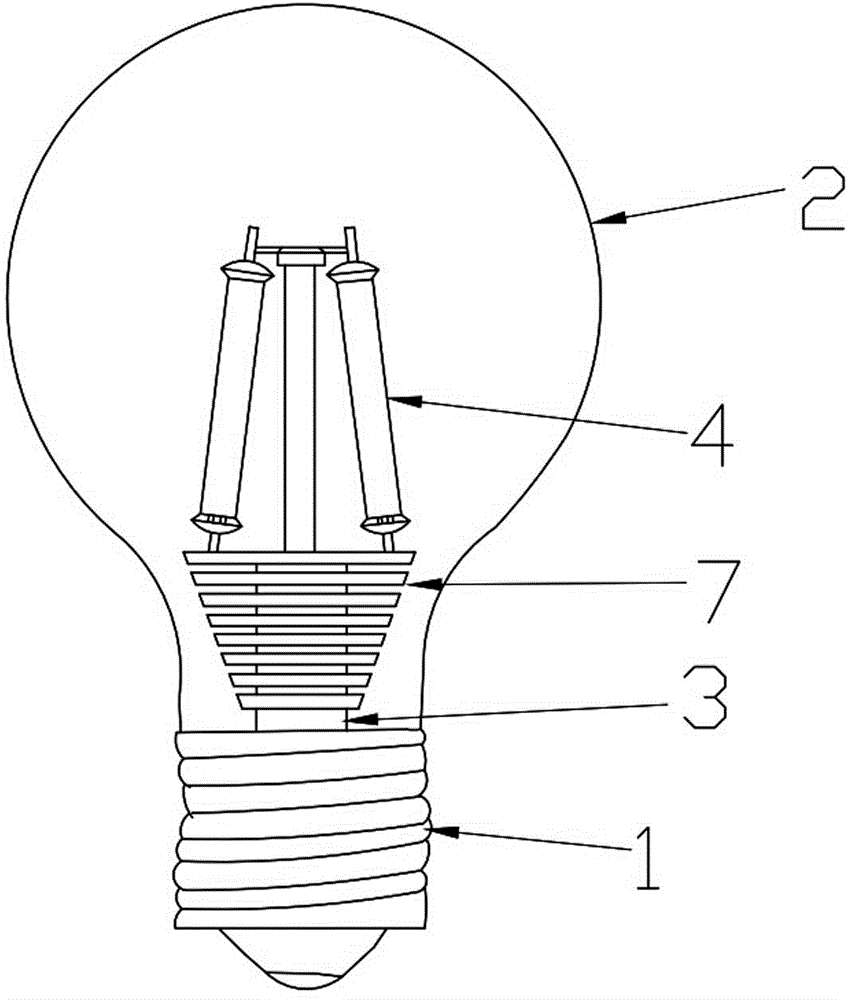

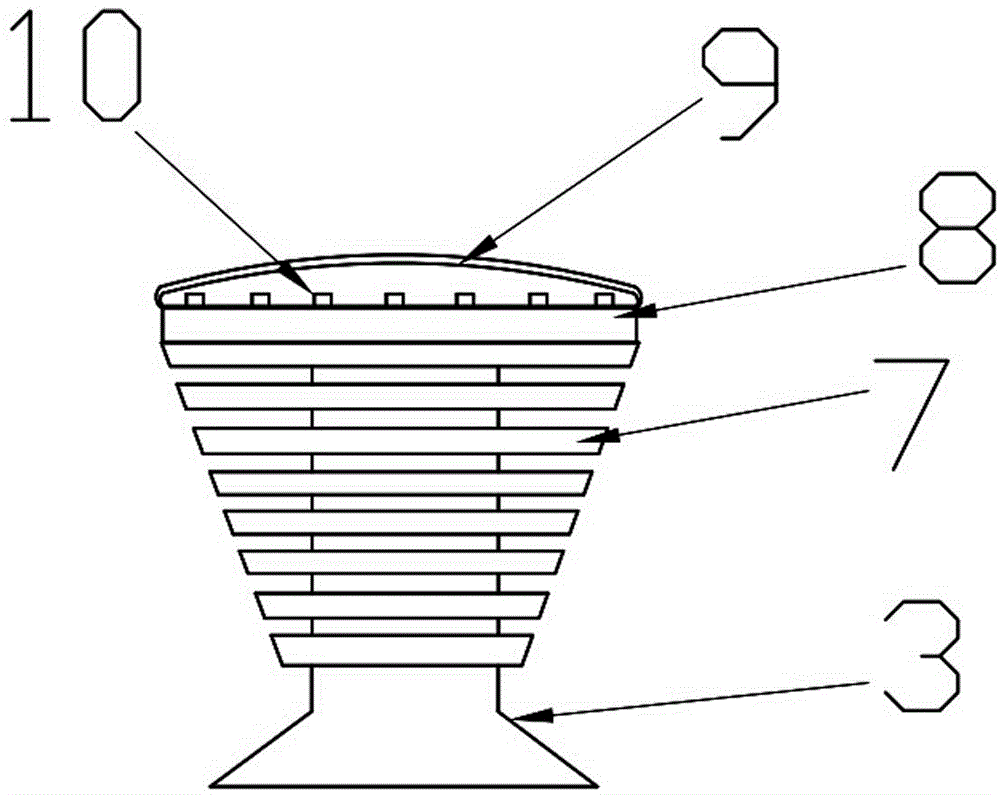

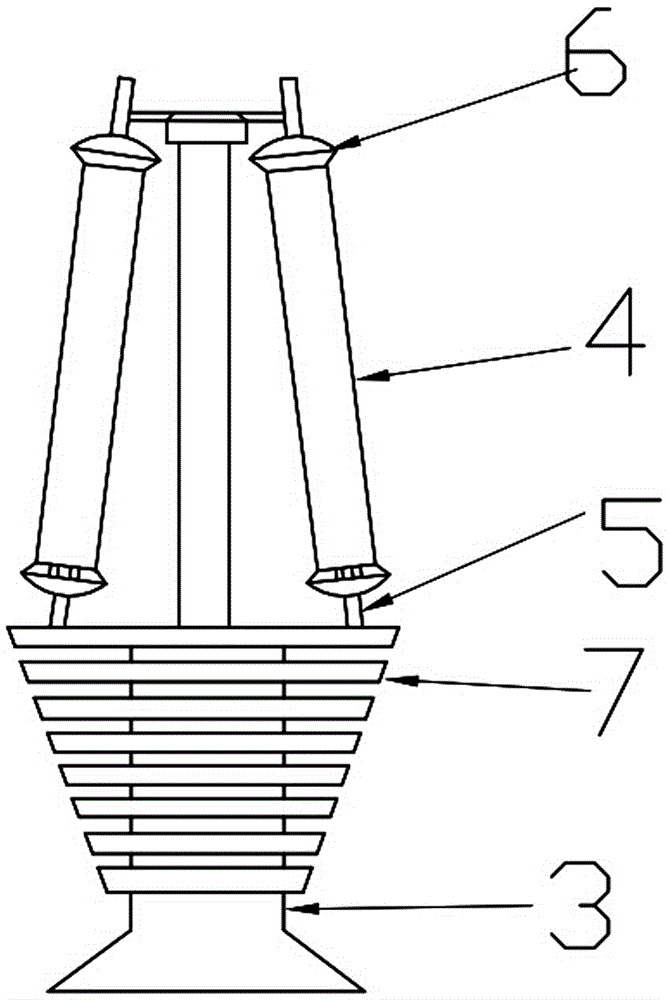

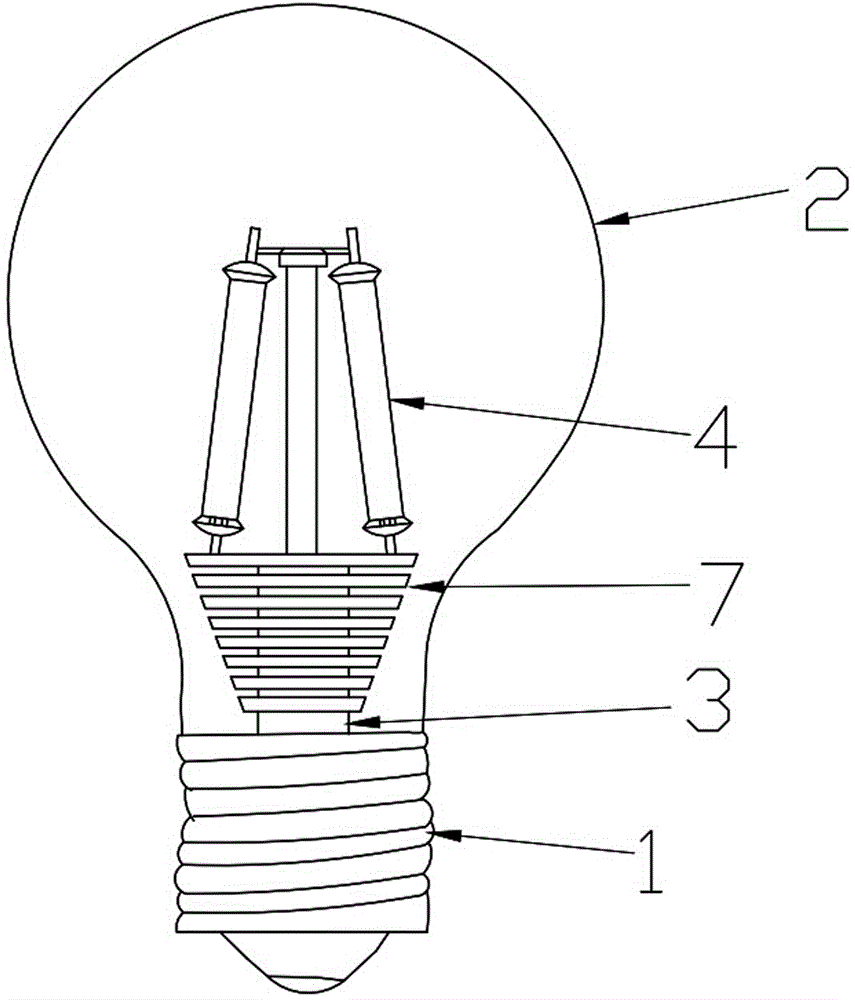

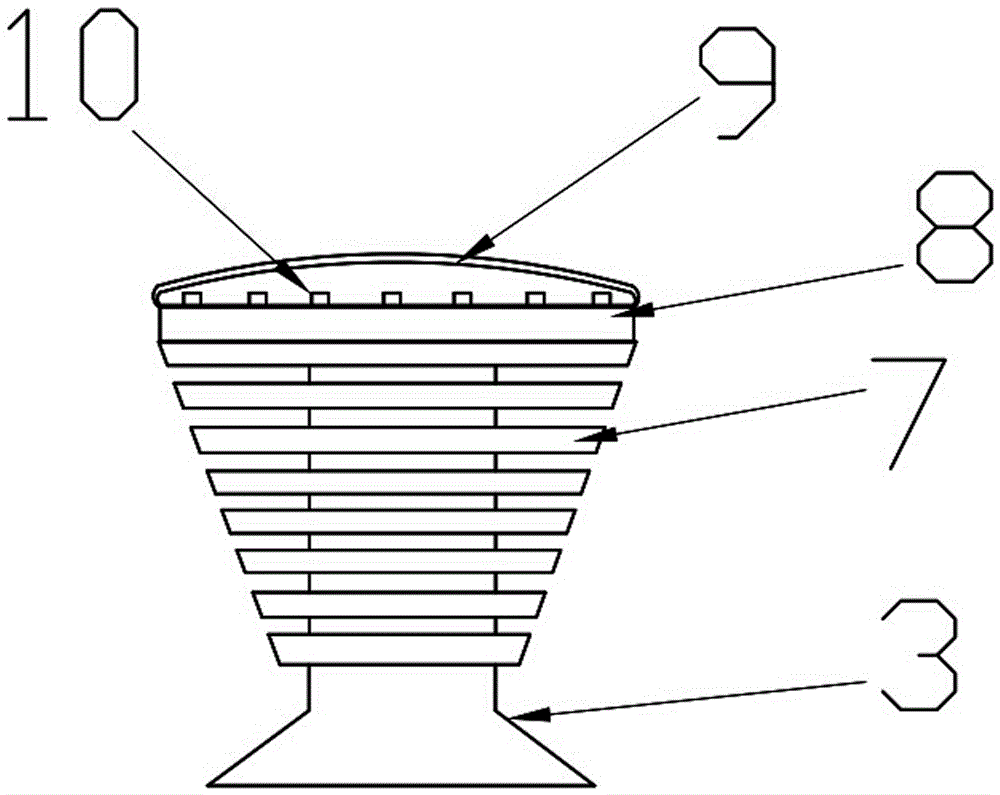

High-power LED bulb capable of achieving quick cooling

ActiveCN104896329AHeat dissipation fastSolve the cooling problemPoint-like light sourceLighting heating/cooling arrangementsWaferingFluorescence

The invention relates to the field of illumination lamps, and provides a high-power LED bulb capable of achieving quick cooling. The bulb comprises a lamp cap, a glass lamp shell and an LED lamp body. A containing cavity and a glass stem are arranged in the glass lamp shell, the LED lamp body comprises an LED light source and a connection pin, the LED light source is arranged on the glass stem and comprises an LED lamp wick and a fluorescent heat conduction part, the fluorescent heat conduction part is disposed on the periphery of the LED lamp wick, the LED lamp wick comprises a plurality of LED wafers or an LED chip and a heat conduction substrate, the periphery of the glass stem is sleeved with a radiator located in the containing cavity, a plurality of cooling fins are arranged on the periphery of the radiator, the top of the radiator is a heat conduction plane making close contact with the bottom of the heat conduction substrate, the radiator is additionally disposed on the periphery of the glass stem, and accordingly heat generated by the LED wafers or the LED chip can be directly transferred to the radiator through a heat conduction mode, and the quick cooling effect can be achieved.

Owner:胡丽

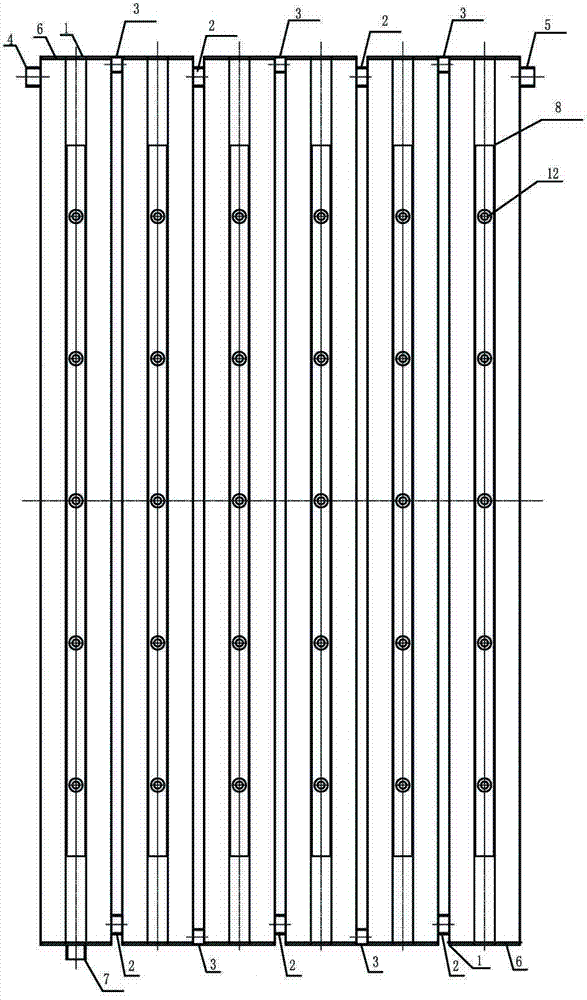

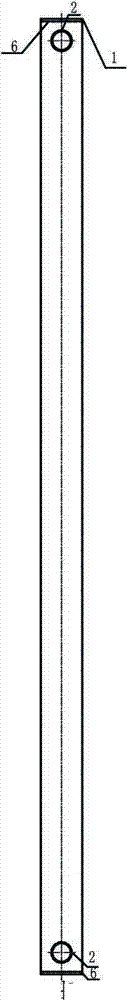

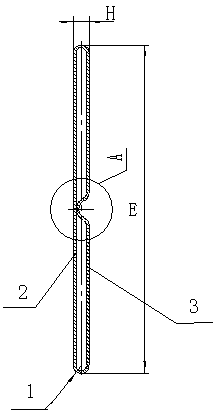

Water leakage preventing stainless steel radiator

ActiveCN103884044AIncrease the areaIncrease cooling areaStationary conduit assembliesSpace heating and ventilation detailsWater leakageEngineering

The invention relates to a water heating radiator, and belongs to indoor heating devices. A water leakage preventing stainless steel radiator is composed of stretching heat conduction pipes 1, communicated pipes 2, connecting pieces 3, bow-shaped folded edge end sockets 6, a splint bolt 10 and an inner folded edge girth welding part 13, and is characterized in that a rectangle or square is formed by welding the communicated pipes 2 and the connecting pieces 3 at the circular arc faces 14 at the two ends of the stretching heat conduction pipes 1, the stretching heat conduction pipes 1 are connected in series in a communicated mode, the front faces and the back faces of the circular arc faces 14 at the two ends of the stretching heat conduction pipes 1 connected in series in the communicated mode are concaved inwards to form circular arc faces 15, and the middle portions of the front faces and the back faces of the circular arc faces 14 are concaved inwards to form steps 16. The bow-shaped folded edge end sockets 6 are matched with the stretching heat conduction pipes 1 in shape, are inserted into the two ends of the stretching heat conduction pipes and are fixedly connected with an external girth welding part 11. The water leakage preventing stainless steel radiator is characterized in that the cylinder is changed into an inward-concaved cuboid, the heating water area is widened, the heat dissipation area is enlarged, the weight is low, and the water leakage preventing stainless steel radiator is attractive.

Owner:ZAOZHUANG FUYUAN ENVIRONMENTAL PROTECTION & ENERGY SAVING MACHINERY MFG CO LTD

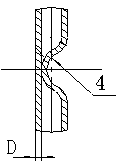

Double-pipe radiating pipe for radiator

InactiveCN102997737AHigh heat dissipation coefficientImprove corrosion resistanceTubular elementsUltimate tensile strengthIndustrial engineering

The invention discloses a double-pipe radiating pipe for a radiator. An inward depression is formed in the middle of one side of the radiating pipe, a row of holes are formed in the top of the depression, and the radiating pipe is divided into an upper pipe and a lower pipe with B-shaped sections by the depression. The radiating efficiency, the bearing strength and the anticorrosive performance of the double-pipe radiating pipe can be improved.

Owner:TAIAN DINGXIN COOLER

High-power led bulb with fast heat dissipation

ActiveCN104896329BHeat dissipation fastSolve the cooling problemLighting heating/cooling arrangementsLight fasteningsFluorescenceCooling effect

The invention relates to the field of illumination lamps, and provides a high-power LED bulb capable of achieving quick cooling. The bulb comprises a lamp cap, a glass lamp shell and an LED lamp body. A containing cavity and a glass stem are arranged in the glass lamp shell, the LED lamp body comprises an LED light source and a connection pin, the LED light source is arranged on the glass stem and comprises an LED lamp wick and a fluorescent heat conduction part, the fluorescent heat conduction part is disposed on the periphery of the LED lamp wick, the LED lamp wick comprises a plurality of LED wafers or an LED chip and a heat conduction substrate, the periphery of the glass stem is sleeved with a radiator located in the containing cavity, a plurality of cooling fins are arranged on the periphery of the radiator, the top of the radiator is a heat conduction plane making close contact with the bottom of the heat conduction substrate, the radiator is additionally disposed on the periphery of the glass stem, and accordingly heat generated by the LED wafers or the LED chip can be directly transferred to the radiator through a heat conduction mode, and the quick cooling effect can be achieved.

Owner:胡丽

A graphene metal composite multilayer heat sink with high thermal conductivity and preparation method thereof

ActiveCN107314353BImprove cooling efficiencySimple processElectrolytic coatingsLighting heating/cooling arrangementsUltrasonic dispersionHeat spreader

The invention discloses a high-heat-conduction-performance graphene metal composite multi-layer radiator and a preparing method thereof, and belongs to the technical field of heat dissipation. The radiator comprises a metal base layer, a graphene film layer evenly deposited on the surface of the metal base layer, and a welding part. The preparing method of the high-heat-conduction-performance graphene metal composite multi-layer radiator comprises the following steps that graphene powder and an additive are added in an absolute ethyl alcohol solution, and evenly-scattered graphene dispersion liquid is obtained through ultrasonic scattering; equal-thickness strip-shaped metal sheets are adopted and subjected to surface treatment through dilute nitric acid, deionized water, absolute ethyl alcohol and ultrasonic waves, and then the equal-thickness strip-shaped metal sheets serve as a cathode; the cathode and an anode are jointly immersed in the graphene dispersion liquid to be subjected to electrophoretic deposition; then after the metal base layer is tightly rolled into a multi-layer cylinder from one end, the other end of the metal base layer is welded and fixed to the outer side of the cylinder to be subjected to annealing treatment, and the cake-shaped graphene metal composite multi-layer radiator is formed through cutting in the direction perpendicular to the axial direction of the cylinder. The radiator is high in heat dissipation efficiency, the technology is simple, energy saving and environment friendliness are achieved, cost is low, and the heat dissipation efficiency is high.

Owner:鄂尔多斯市紫荆创新研究院

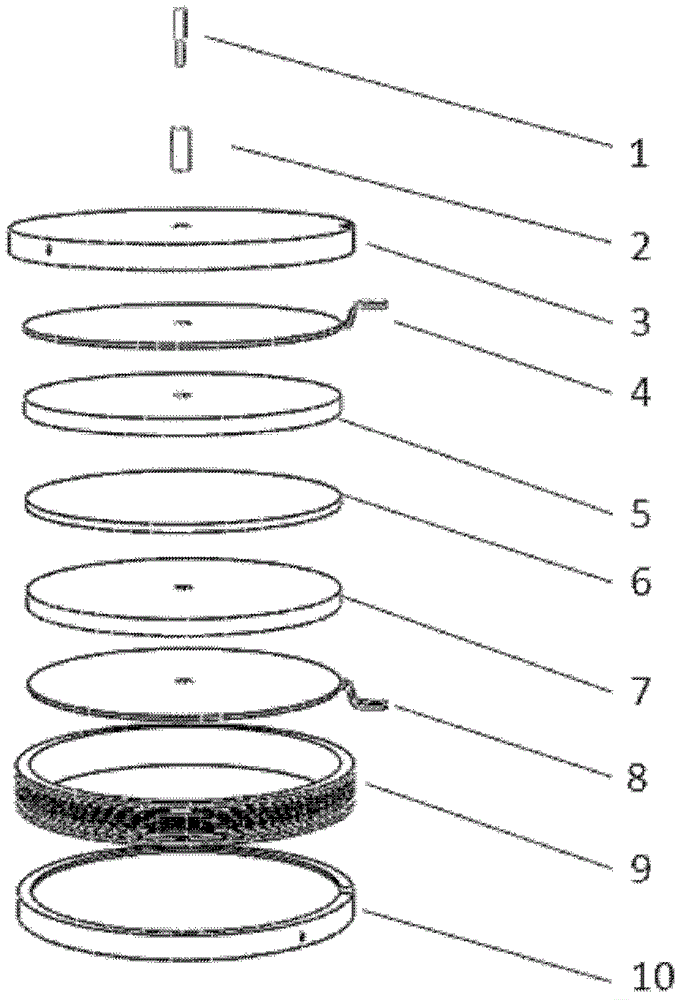

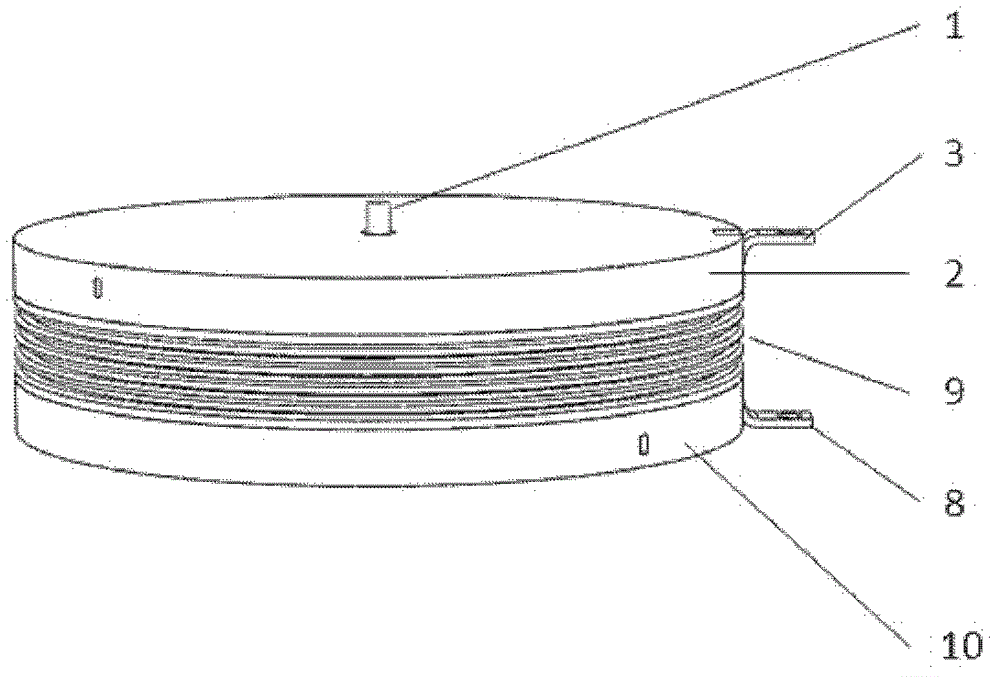

Double-sided microchannel liquid-cooled power semiconductor whole-wafer flat-panel crimp package structure

InactiveCN103367279BAddressing Thermo-Mechanical Fatigue FailuresSolve fatigue failureSemiconductor/solid-state device detailsSolid-state devicesCapacitanceHeat conducting

Provided is a liquid-cooled power semiconductor wafer plate crimping packaging structure with micro channels on double surfaces. The plate crimping packaging structure comprises a power semiconductor wafer, a spring needle, graphite flakes, an emitter electrode metallic sheet, a collector electrode metallic sheet, a top cooling plate, a bottom cooling plate, and a ceramic tube housing. Graphite flakes are pressed on the top surface and the bottom surface of the wafer. The emitter electrode metallic sheet is arranged on the graphite flake to be used as a leading out terminal for leading out the collector electrode of the wafer, while the collector electrode metallic sheet is arranged on the graphite flake to be used as a leading out terminal for leading out the emitter electrode of the wafer. The graphite flakes, the emitter electrode metallic sheet, and the collector electrode metallic sheet are sealed in the ceramic tube housing. The top cooling plate is pressed on the top of the ceramic tube housing, while the bottom cooling plate is pressed on the bottom of the ceramic tube housing. Cooling micro channels are disposed on the top cooling plate and the bottom cooling plate. The spring needle is pressed on the central position of the top cooling plate in order to lead out the gate electrode of the wafer. The plate crimping packaging structure has advantages of achieving connection without leading wires, reducing stray inductance and stray capacitance generated by leading wire bonding, and increasing a current conducting capability, heat conducting capability, an anti-thermal-shock capability, and reliability, and advantages of a small structural size, a high heat dissipating coefficient, a long service life, and an intelligent monitoring function.

Owner:NANJING HIGHSEMI ELECTRIC POWER SCI & TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com