Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

51results about How to "Good rectification characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

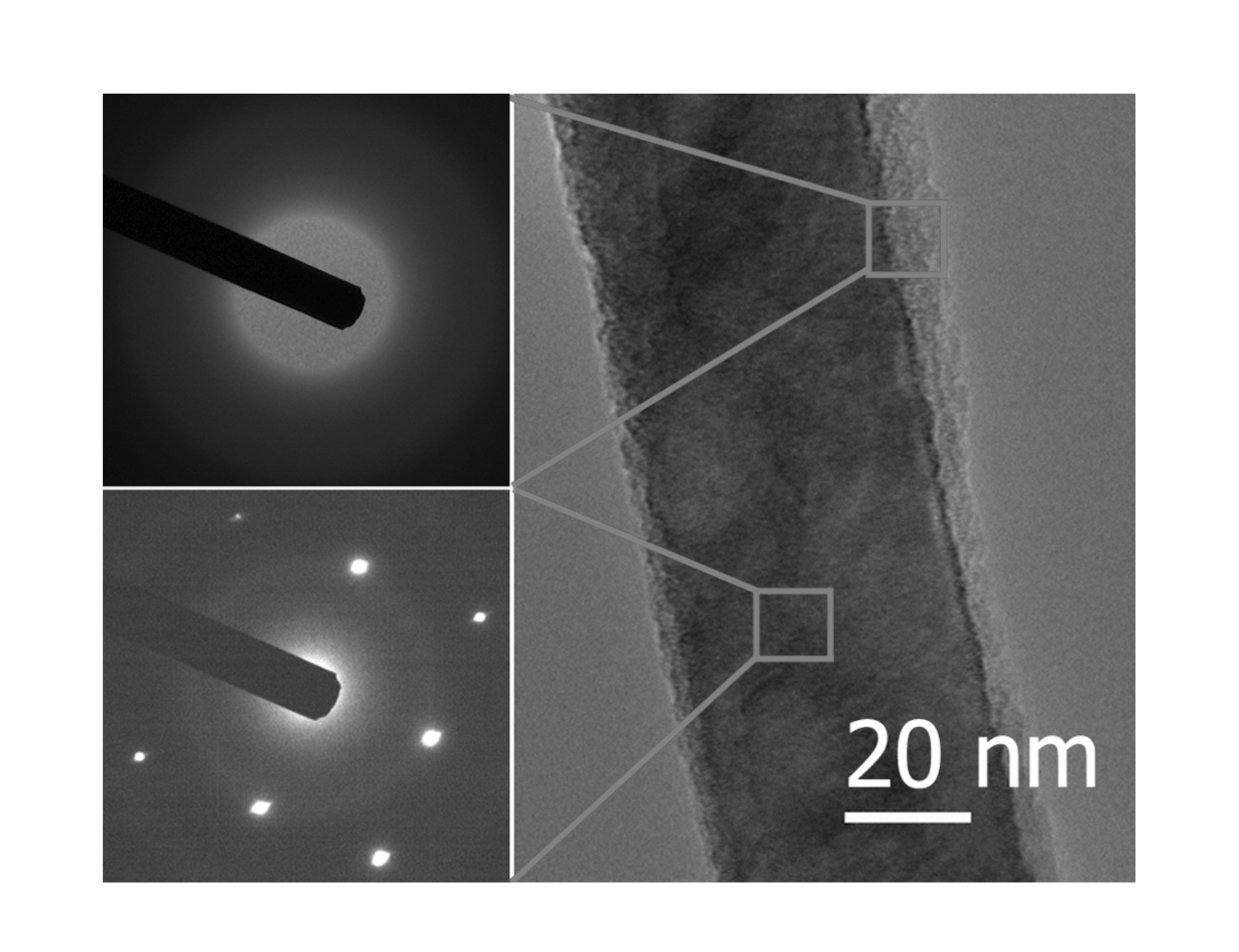

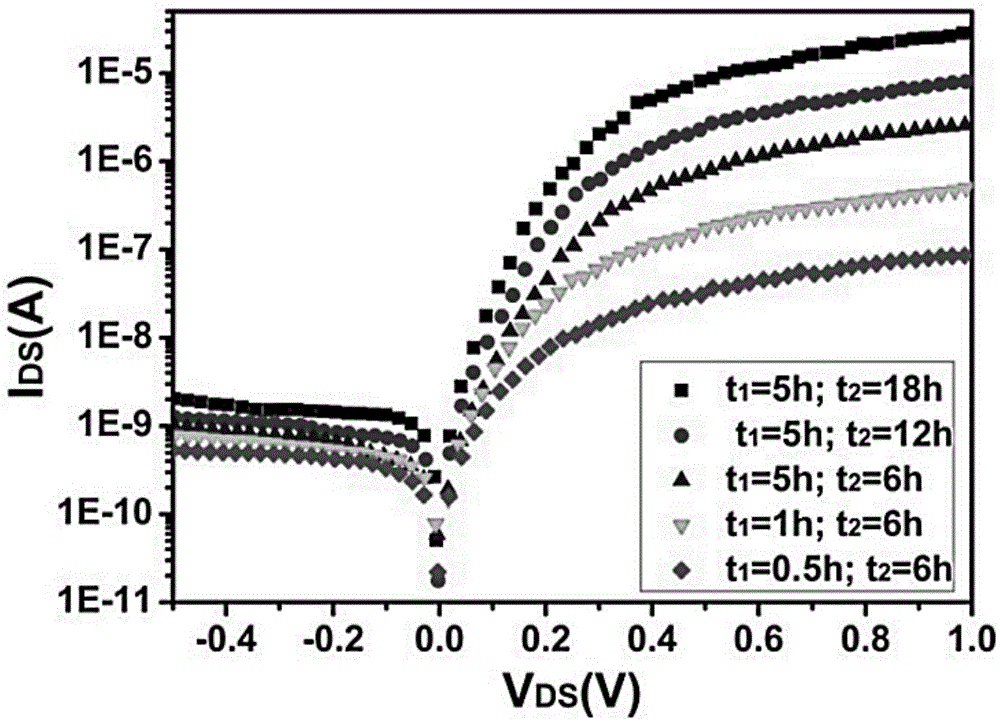

Transition metal chalcogenide homojunction, homojunction diode and preparation of homojunction

ActiveCN106549064AReduce concentrationReduce interface resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryProtection layer

The invention mainly belongs to the technical field of preparation of homojunction, and specifically relates to a transition metal chalcogenide homojunction and a preparation method thereof. According to the method, a transition metal chalcogenide nanosheet is used as a raw material, a protection layer is arranged on a part of area of the transition metal chalcogenide nanosheet for protection, and the unprotected area of the transition metal chalcogenide nanosheet is treated by an acid to repair the structural defects of the transition metal chalcogenide nanosheet so as to form the transition metal chalcogenide homojunction in the protected and unprotected areas of the transition metal chalcogenide nanosheet. The structure of the homojunction prepared from the method provided by the invention is scarcely influenced by the environment, has good stability and strong operability, requires no high temperature annealing and requires no doping process.

Owner:UNIV OF SCI & TECH BEIJING

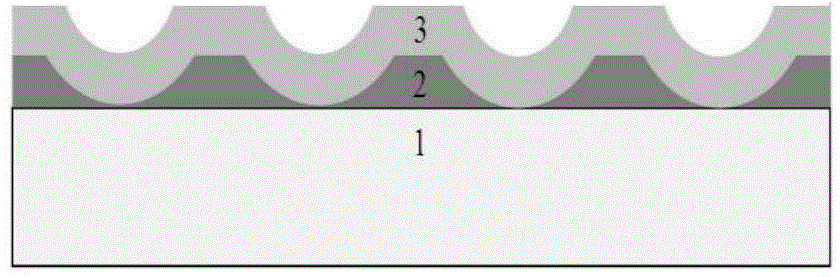

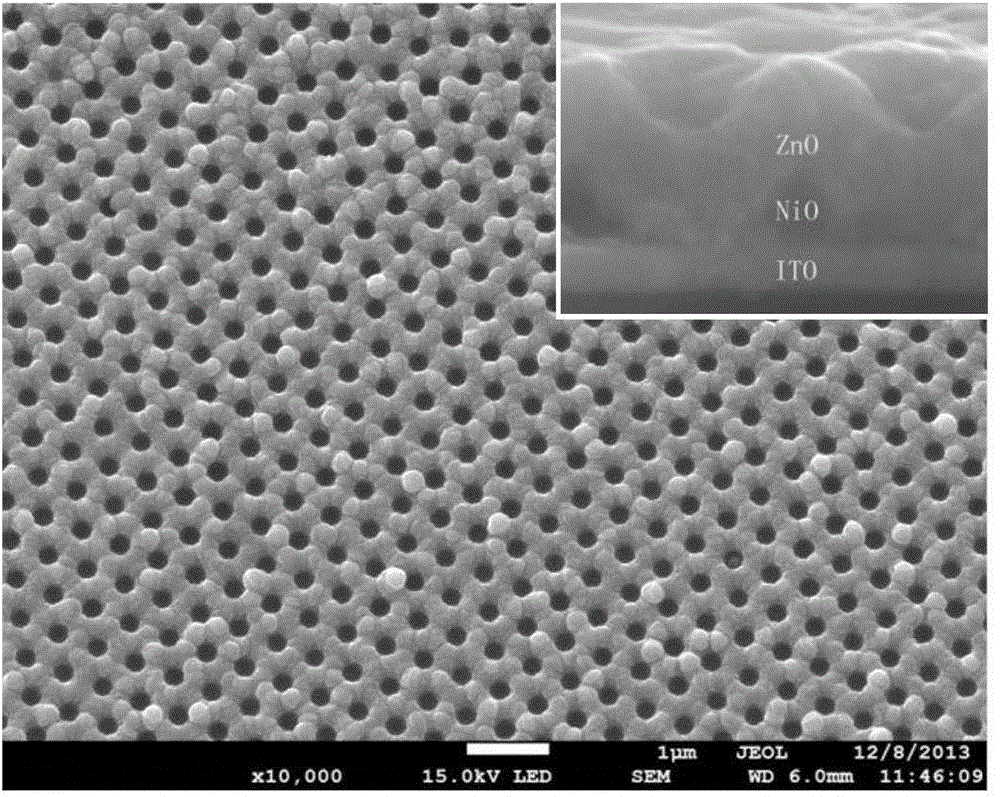

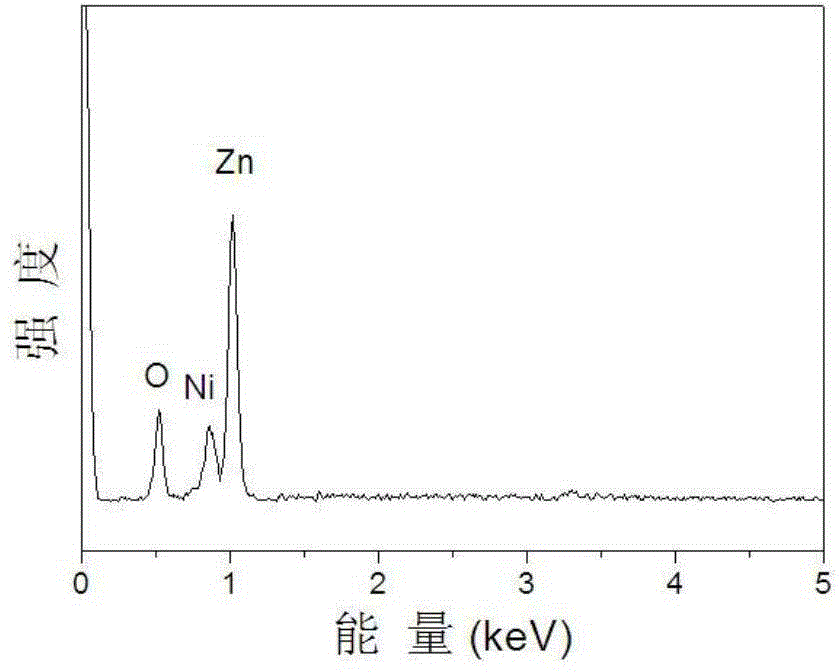

ZnO/NiO heterostructure orderly multi-hole thin film and manufacturing method thereof

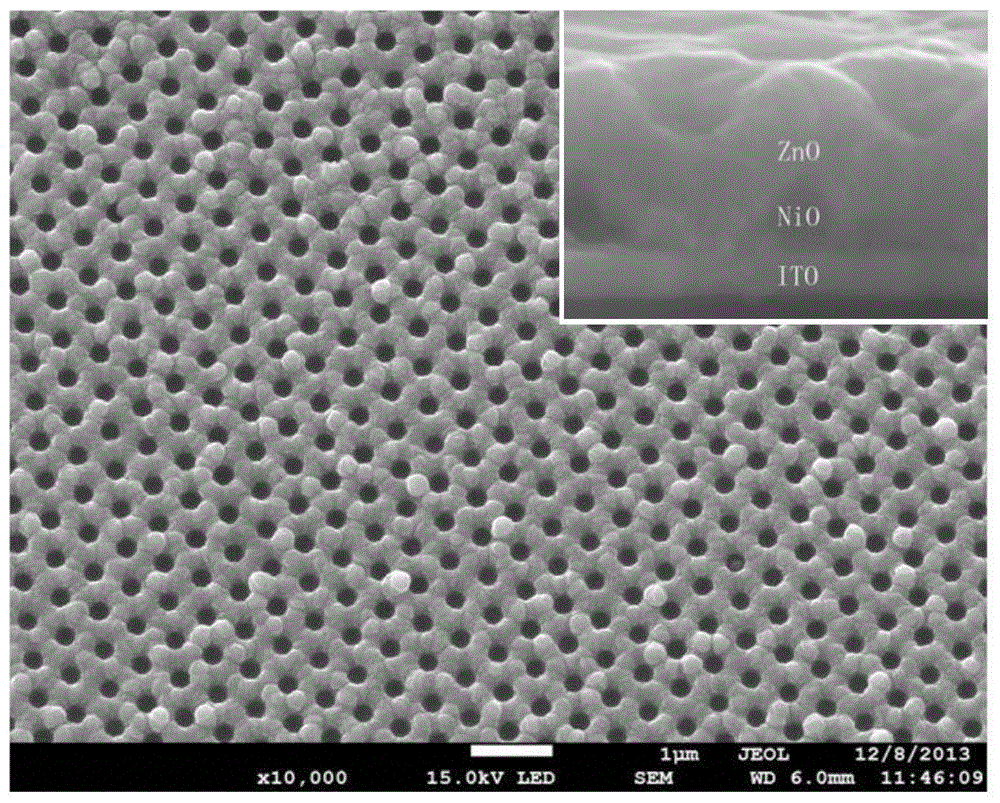

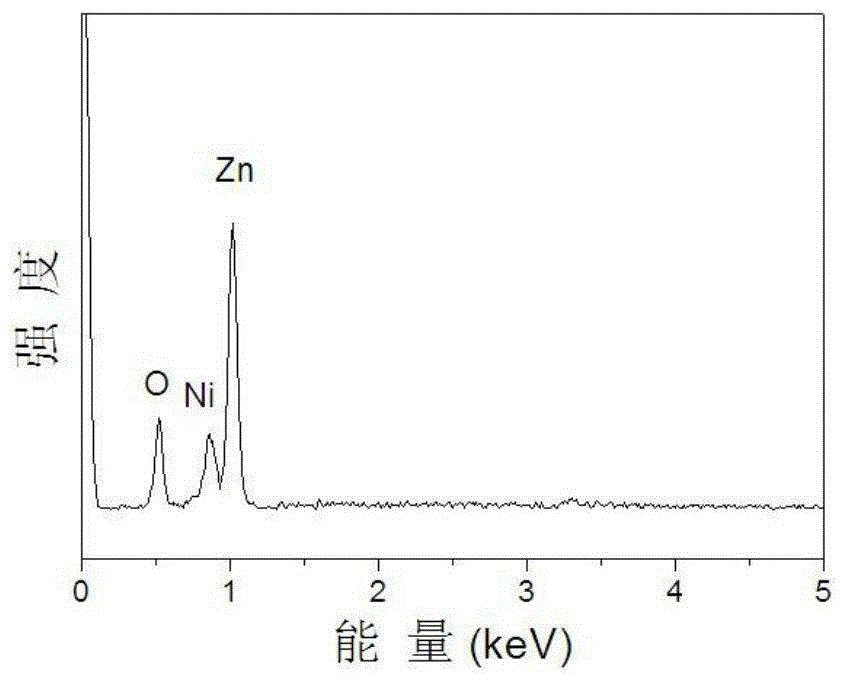

ActiveCN104465987ALarge specific surface areaPromote absorptionFinal product manufactureSuperimposed coating processUltraviolet detectorsSemiconductor materials

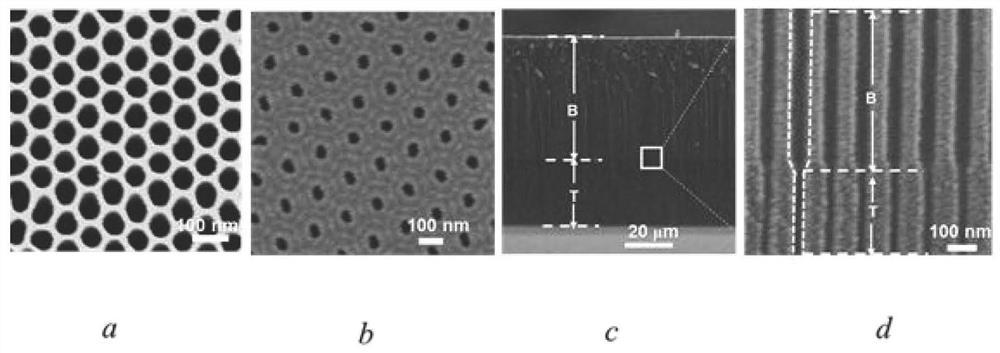

The invention belongs to the technical field of semiconductors and particularly relates to a ZnO / NiO heterostructure orderly multi-hole thin film and a manufacturing method thereof. A new option is provided for semiconductor materials. According to the technical scheme, the ZnO / NiO heterostructure orderly multi-hole thin film comprises a conducting substrate and a heterostructure growing on the conducting substrate, and the heterostructure is formed by a p type NiO orderly multi-hole thin film and an n type ZnO orderly multi-hole thin film which grows in sequence from bottom to top. The invention further provides a manufacturing method of the ZnO / NiO heterostructure orderly multi-hole thin film. The ZnO / NiO heterostructure orderly multi-hole thin film can be widely used in the fields such as an ultraviolet detector, a light-emitting diode and a resistance random access memory.

Owner:SOUTHWEST UNIVERSITY

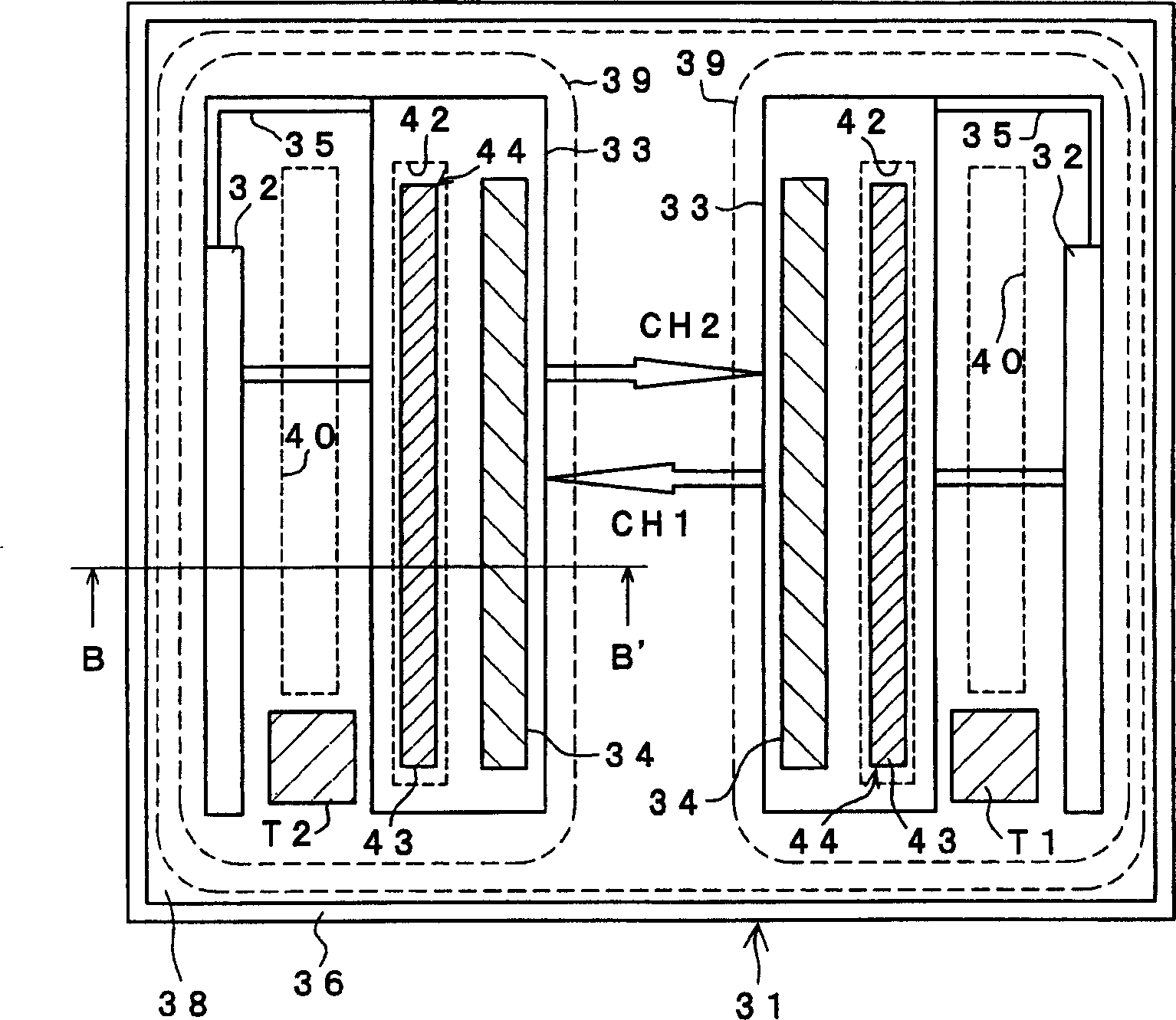

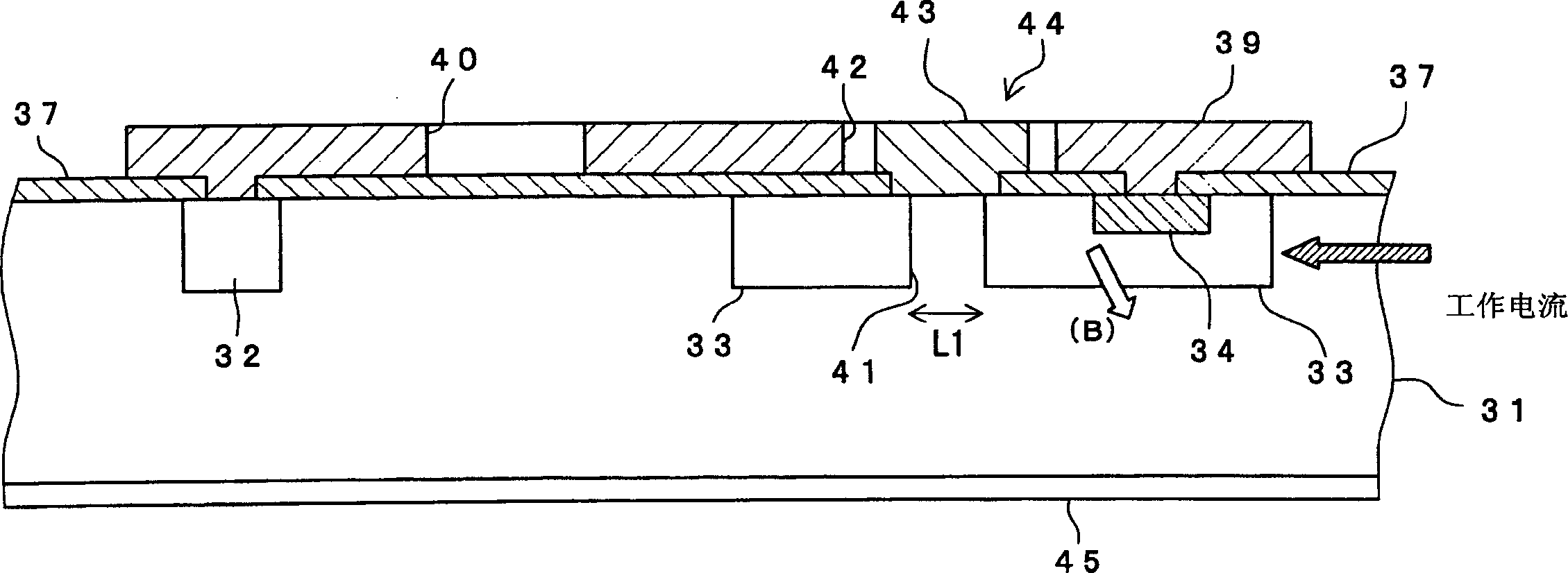

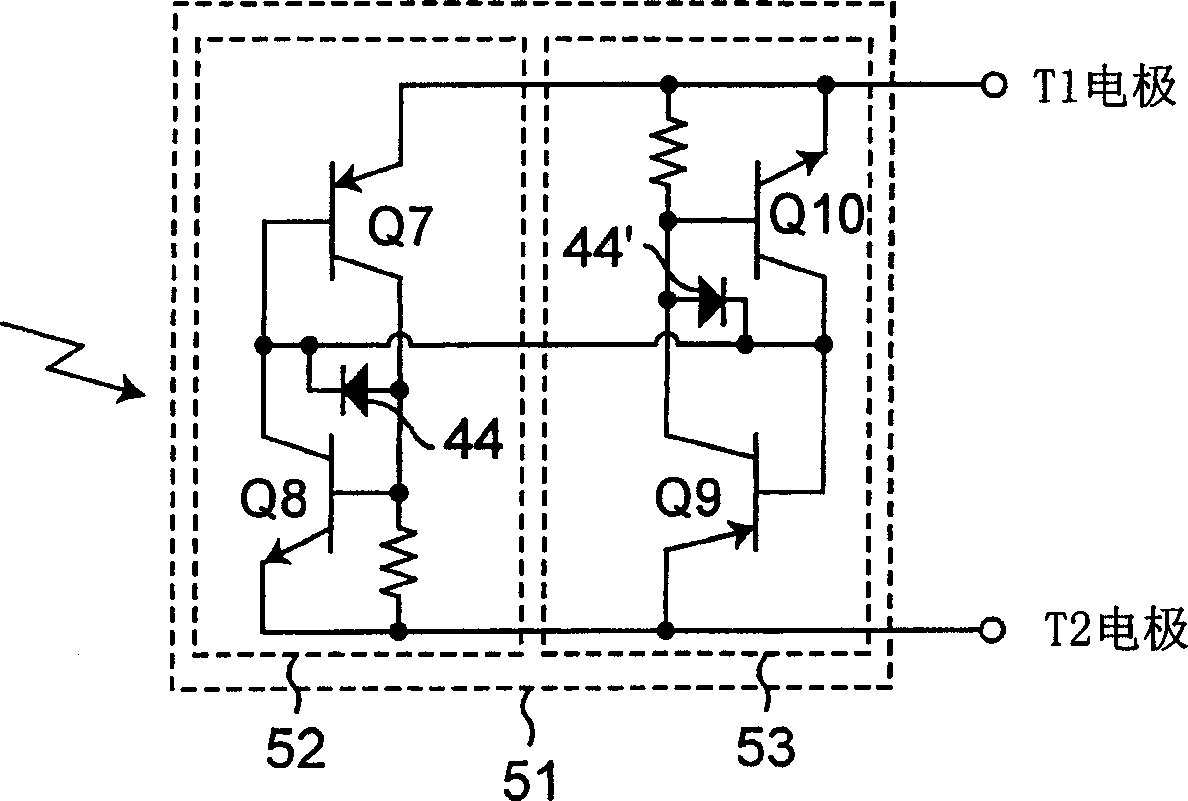

Bidirectional-light silicon controlled chip

In a CH1 side photothyristor and a CH2 side photothyristor, a shot key barrier diode 44 is formed between a p-gate diffusion region 33 and an n-type silicon substrate 31. Accordingly, the pouring of a minority carrier from the p-gate diffusion region 33 into the n-type silicon substrate 31 is suppressed and the mount of remaining carrier is decreased whereby an excessive carrier remaining in the n-type silicon substrate 31 upon commutation reduces a chance to move toward a reverse channel side, thereby permitting the improvement of the commutation characteristics. Further, a light spot arc coupler for controlling the light spot arc and a load can be provided by combining with an LED.

Owner:SHARP KK

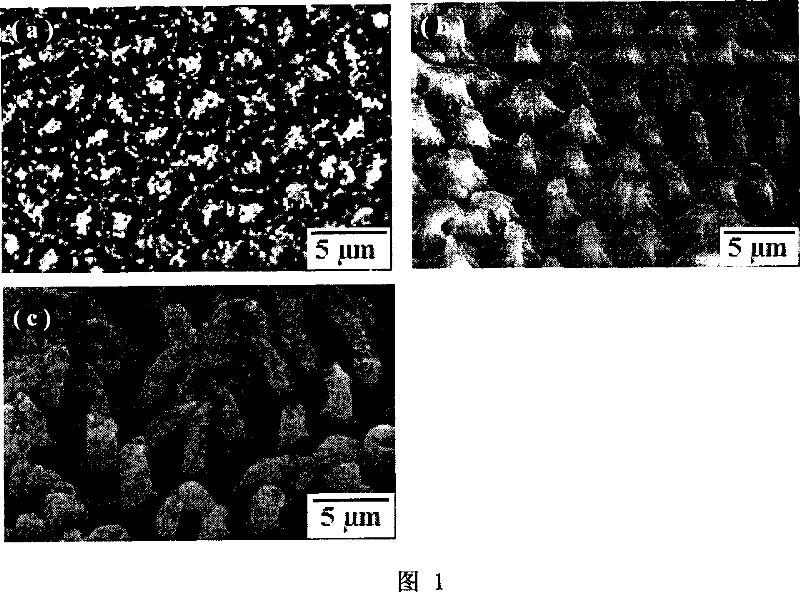

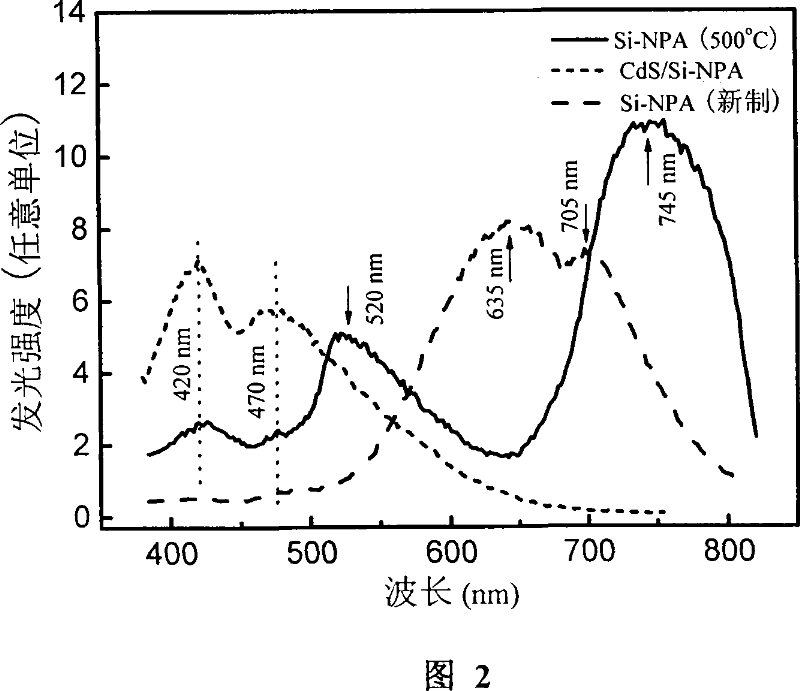

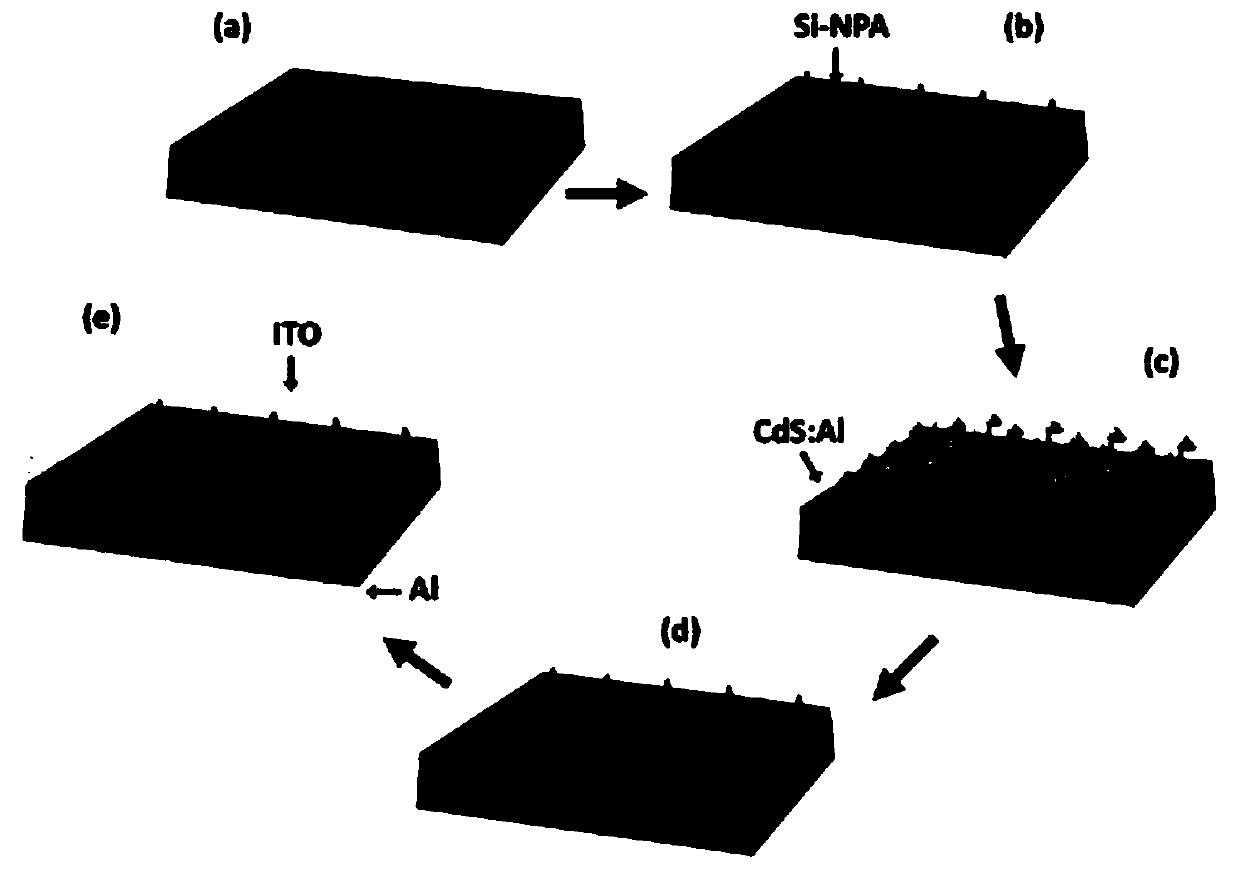

Preparation method of cadmium sulfide/silicon heterostructure with white light transmission

InactiveCN101037596AImprove luminous efficiencyEffective protectionGas discharge lamp usageLuminescent compositionsChemical reactionShielding gas

The invention discloses a method of preparing cadmium sulfide / silicon heterogeneity structure with white light emission, which includes steps: putting P-type single-crystal silicon sheet into autoclave filled with etching solution constituted of hydrofluoric acid and ferric nitrate water solution to corrode underlay material silicon nano pore and column array (Si-NPA); oxidizing the Si-NPA, putting the oxidized Si-NPA into cadmium salt solution for impregnating, airing in air at room temperature, putting into hydrogen sulfide air flow to carry in-situ heterogeneous chemical reaction growth under natural condition or light-induction condition, annealing at temperature of 100-700 DEG C and under protecting gas atmosphere, and then obtaining cadmium sulfide / silica heterogeneity structure with microstructure and adjustable luminescence characteristic and realizing white light emission which luminescence peak of red, green and blue light appear simultaneously. Advantages of the preparing method are: ambient operation, simple process, easy operation, 100% of repetition rate; the heterogeneity structure expresses adjustable photoelectricity property, realizes high strength white light emission, and is important material for preparing new solid illumination, micro-electronic and opto-electronic device.

Owner:ZHENGZHOU UNIV

Resistive random access memory and method for improving positive and negative current difference of resistive random access memory

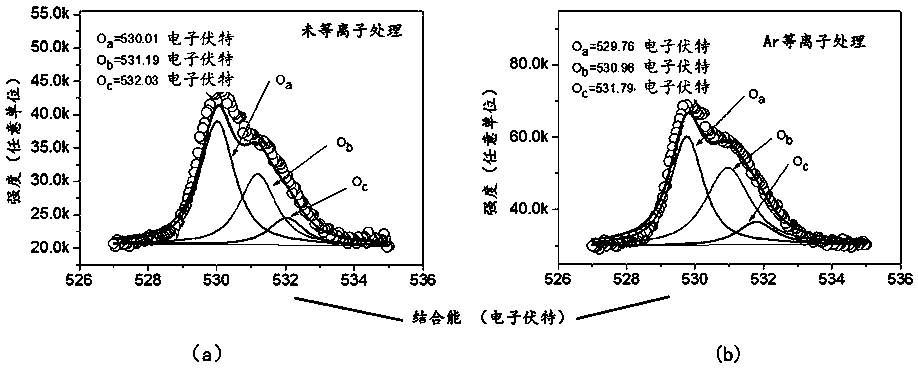

ActiveCN105226183AImprove reliabilityIncrease the positive and negative current differenceVacuum evaporation coatingSolid-state devicesPhysicsPower flow

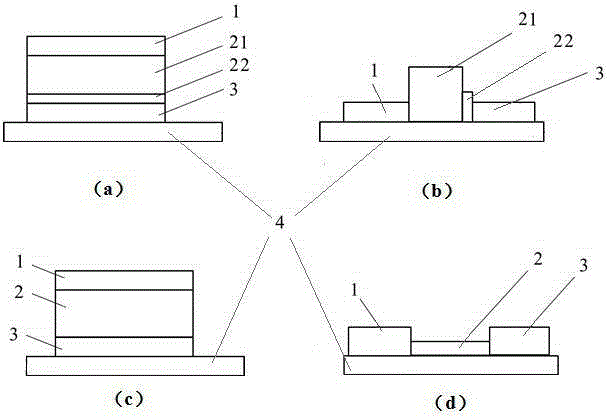

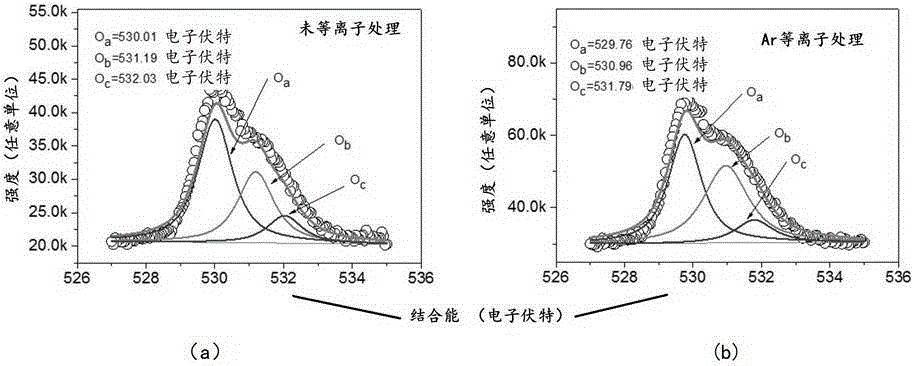

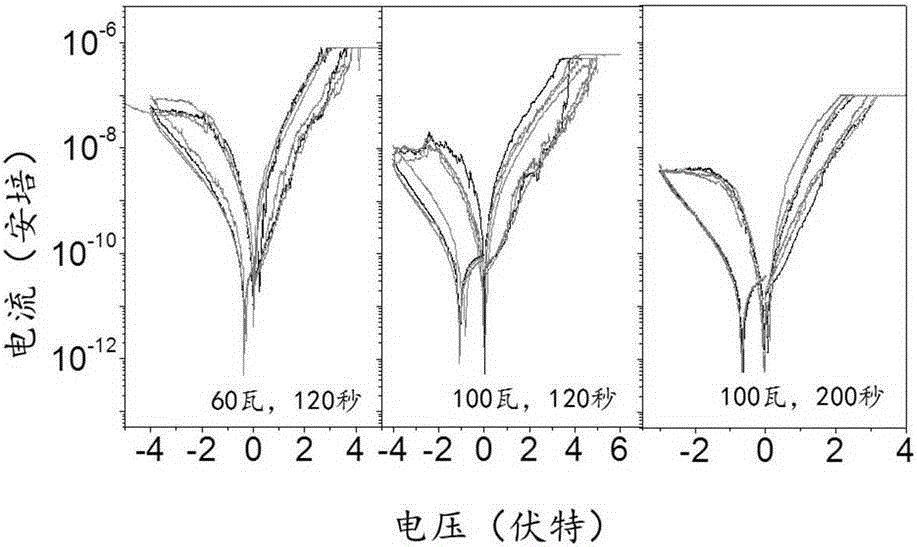

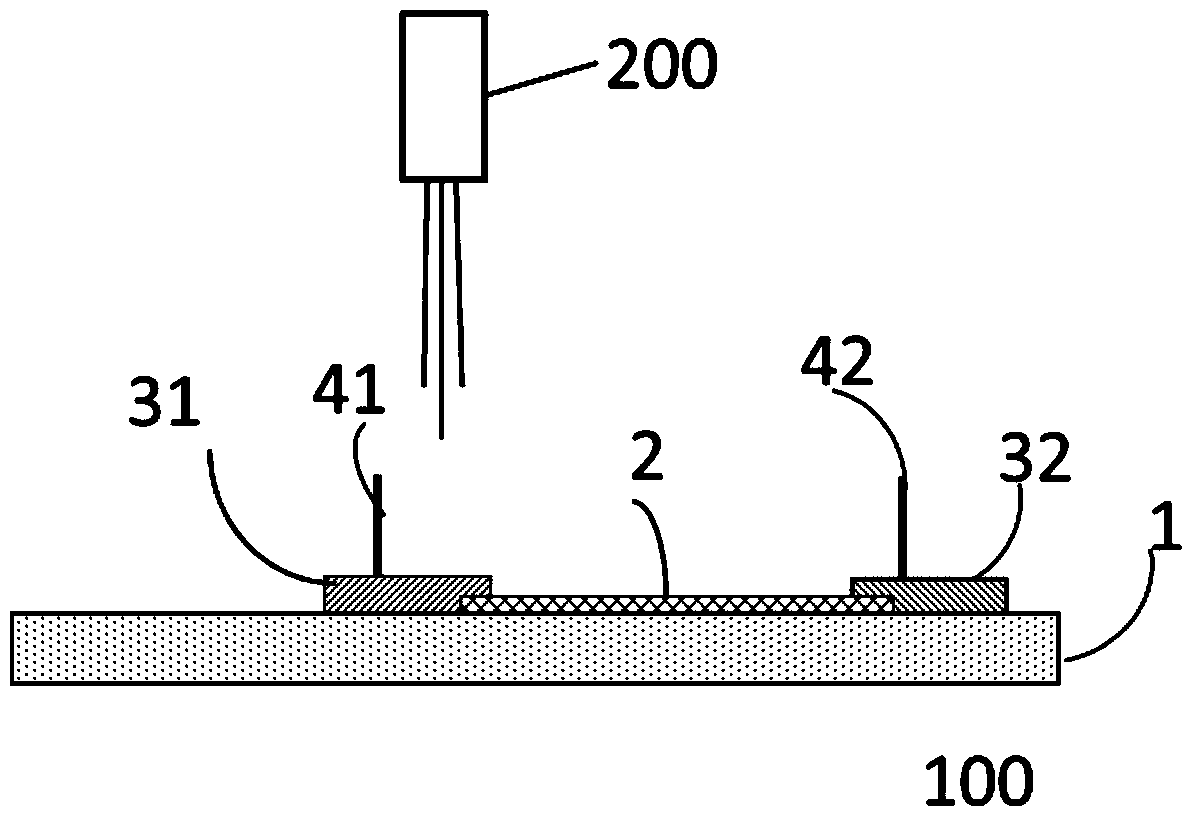

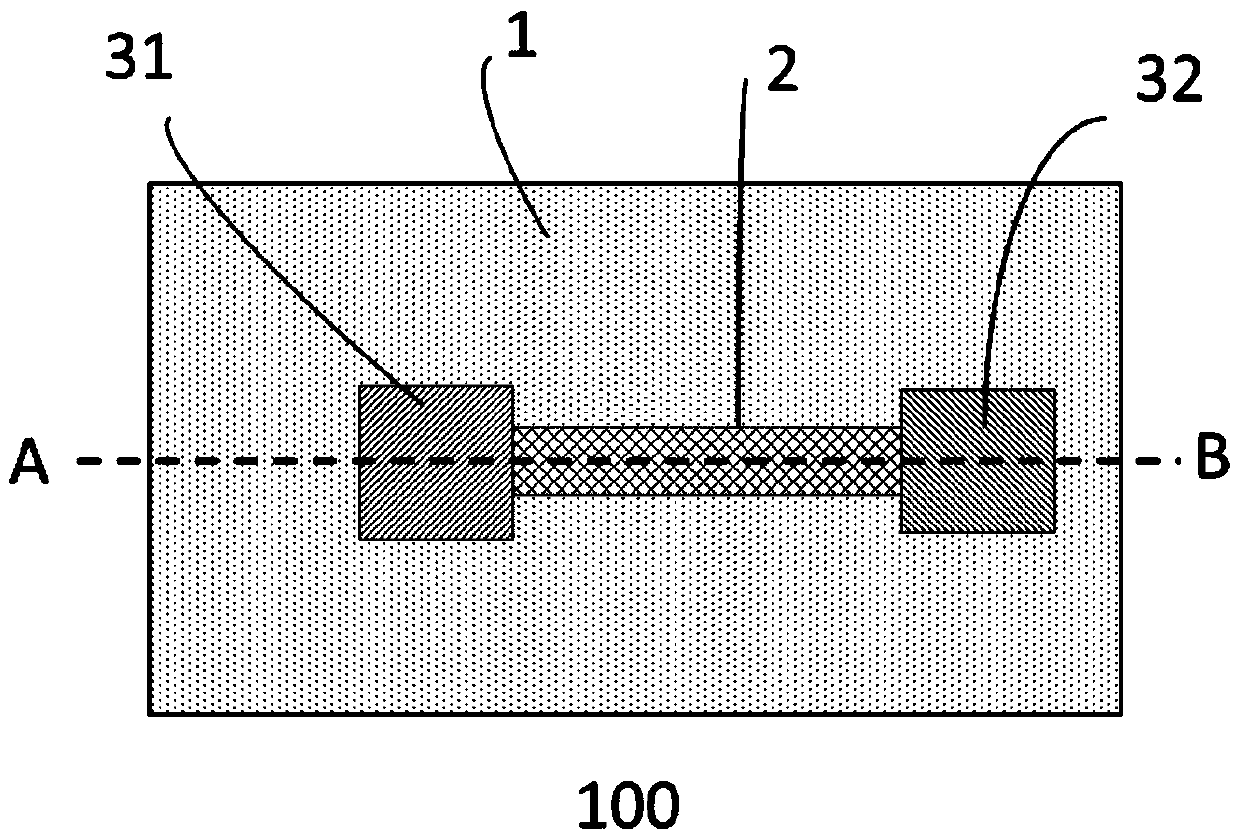

The invention relates to a resistive random access memory and a method for improving a positive and negative current difference of the resistive random access memory. The resistive random access memory comprises a substrate, a first terminal electrode, a variable resistance medium layer and a second terminal electrode, wherein the first terminal electrode is arranged on the substrate and forms a good electric contact together with the substrate; the variable resistance medium layer is arranged at the left side or the upper part of the first terminal electrode; if the variable resistance medium layer is arranged at the left side of the first terminal electrode, the second terminal electrode is arranged at the left side of the variable resistance medium layer; if the variable resistance medium layer is arranged at the upper part of the first terminal electrode, the second terminal electrode is arranged at the upper part of the variable resistance medium layer; the variable resistance medium layer is a dual-layer variable resistance medium; and the dual-layer variable resistance medium is in a laminated structure formed by a first variable resistance layer and a second variable resistance layer. By plasma modification, defects are introduced into the medium or the medium surface, so that a negative current value is effectively suppressed; and the positive and negative current difference is greatly improved.

Owner:FUZHOU UNIVERSITY

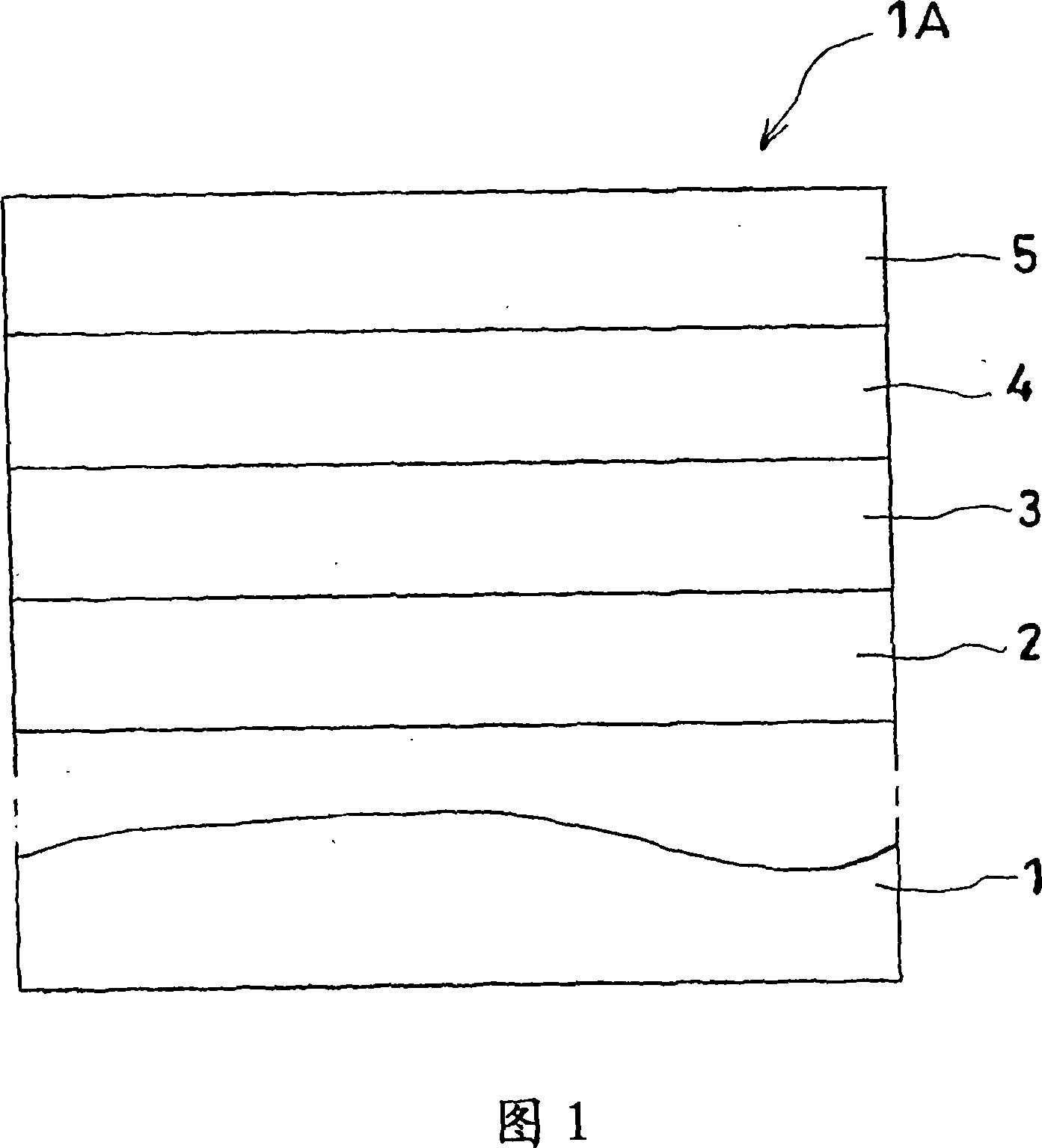

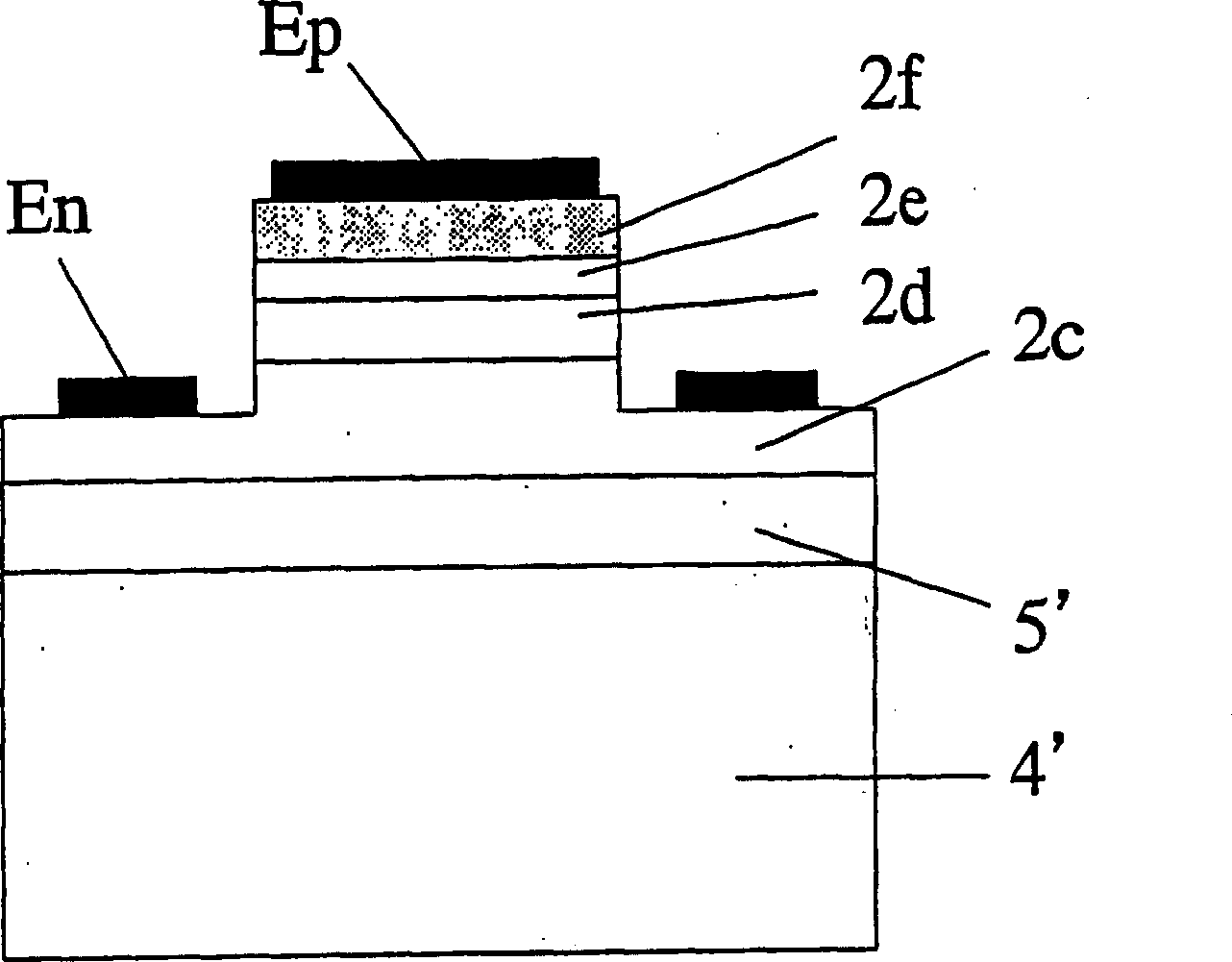

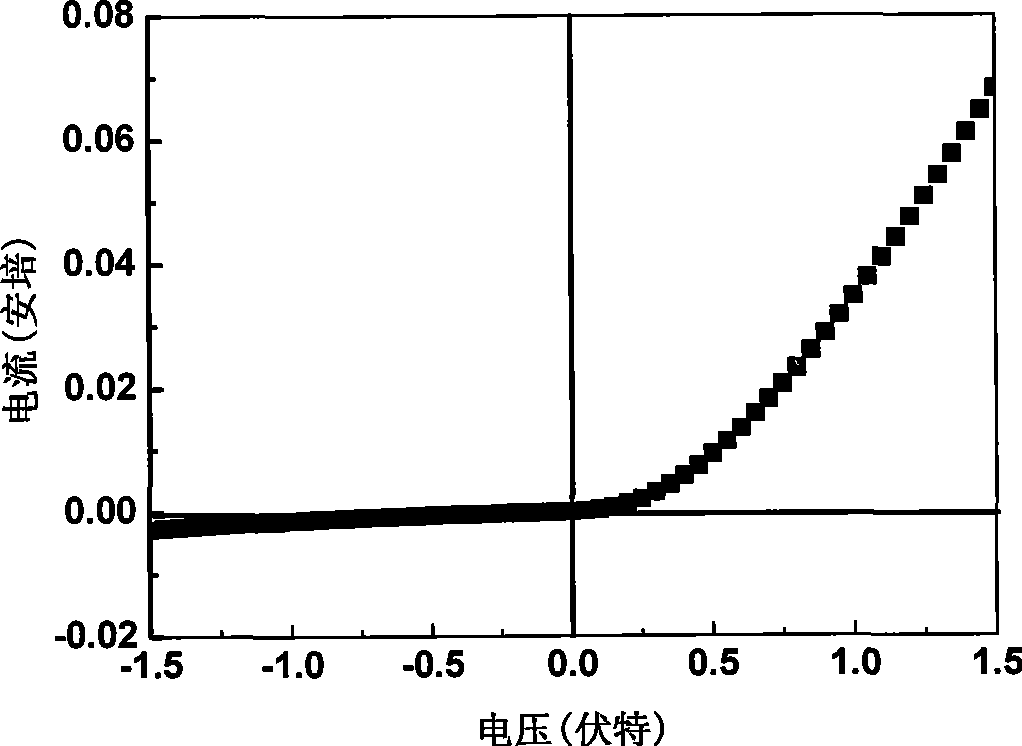

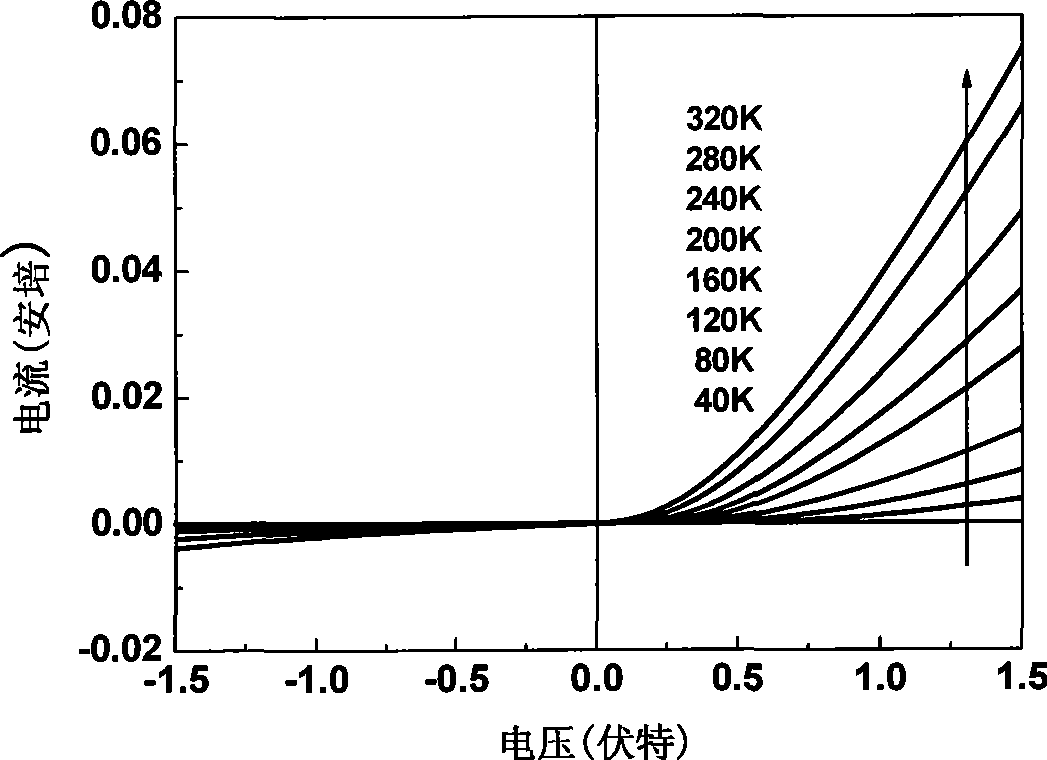

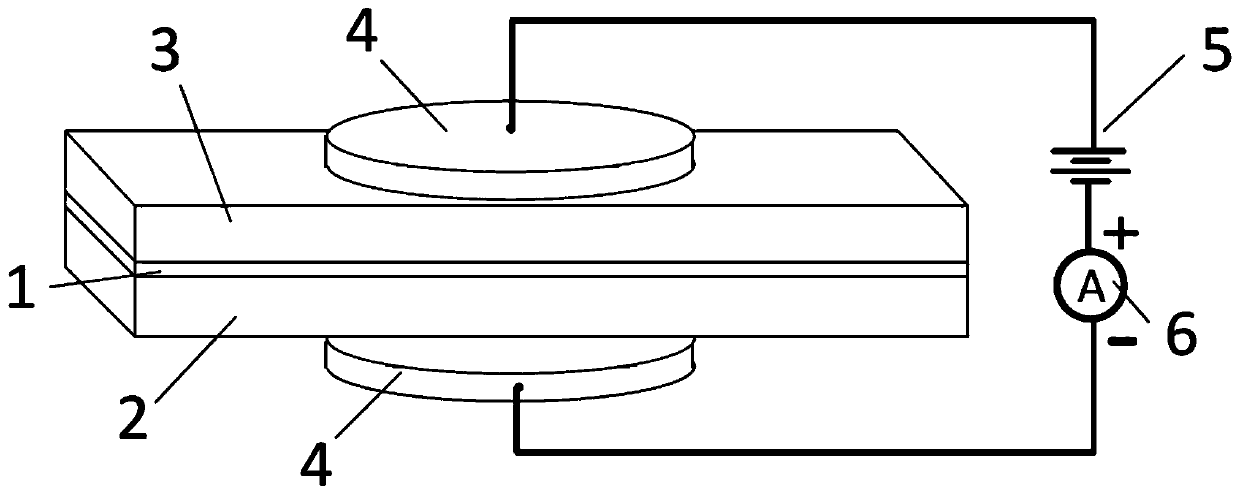

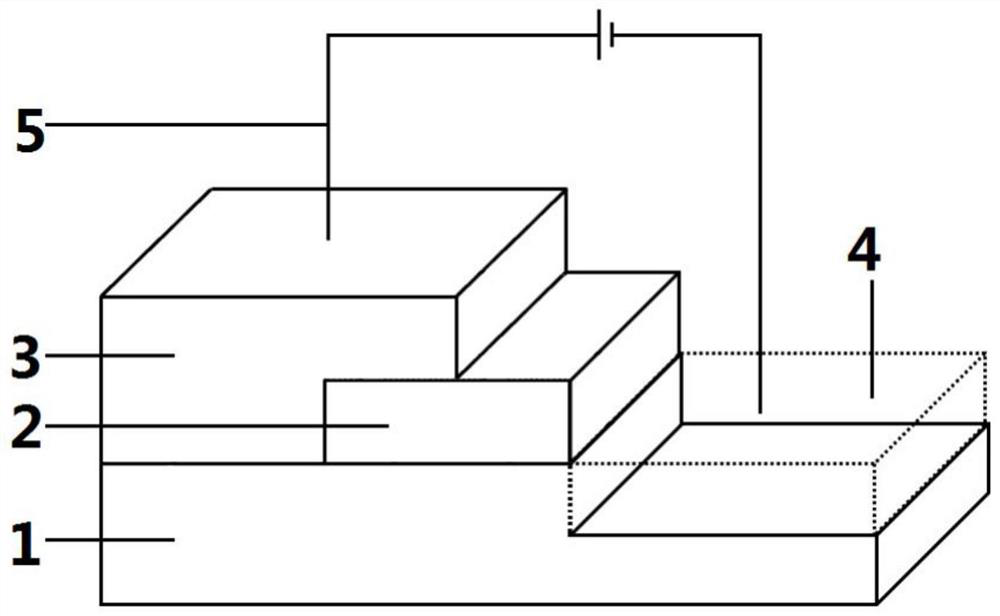

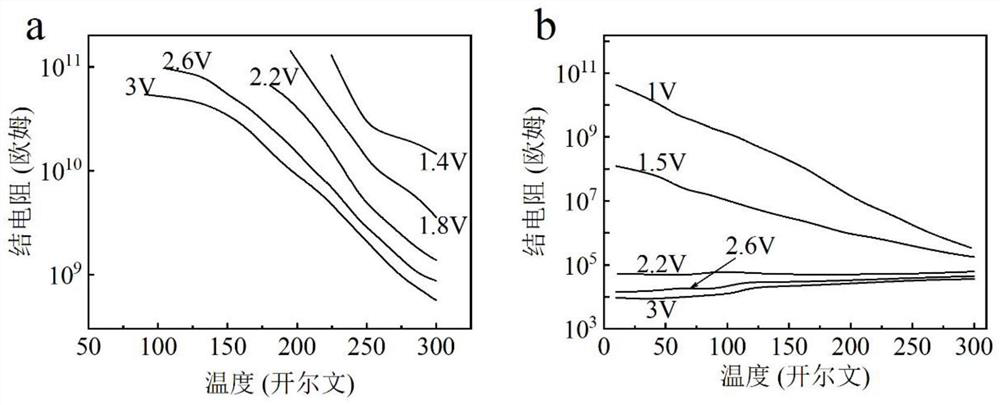

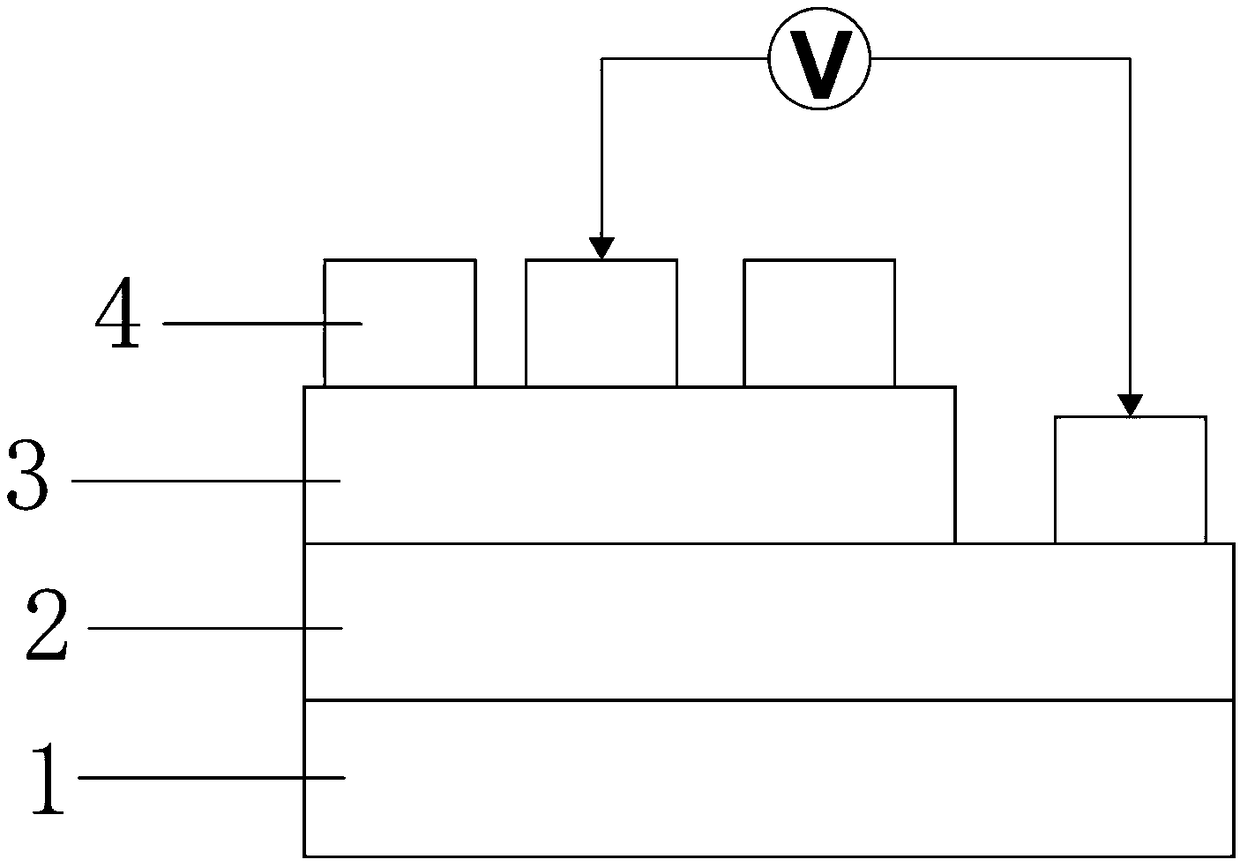

CaTiO3 structure La-Mn oxide/zinc oxide heterogeneous p-n junction and its making method

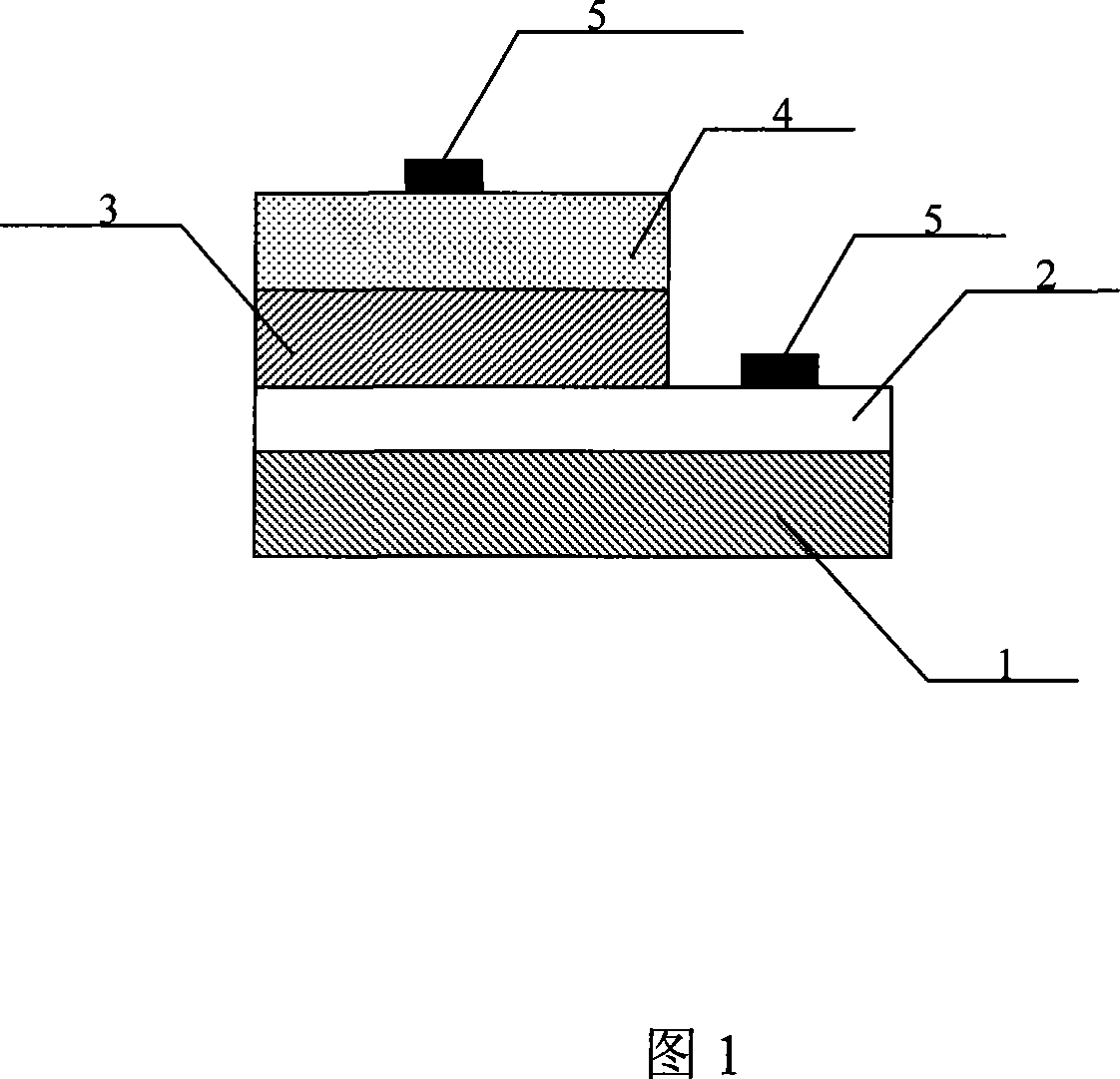

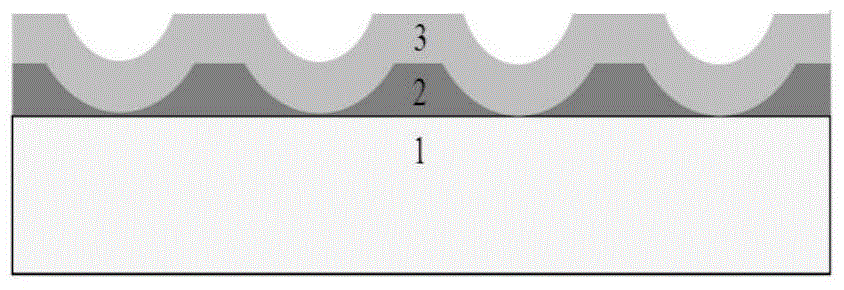

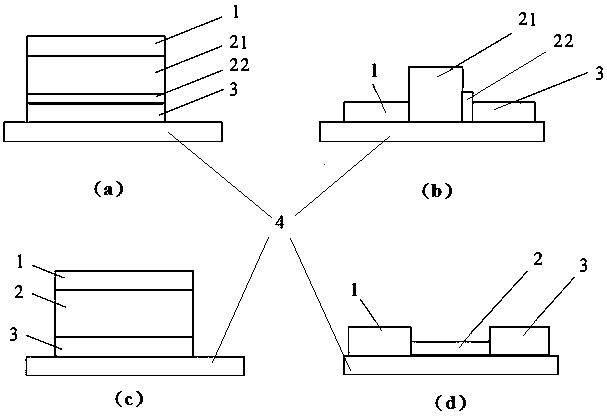

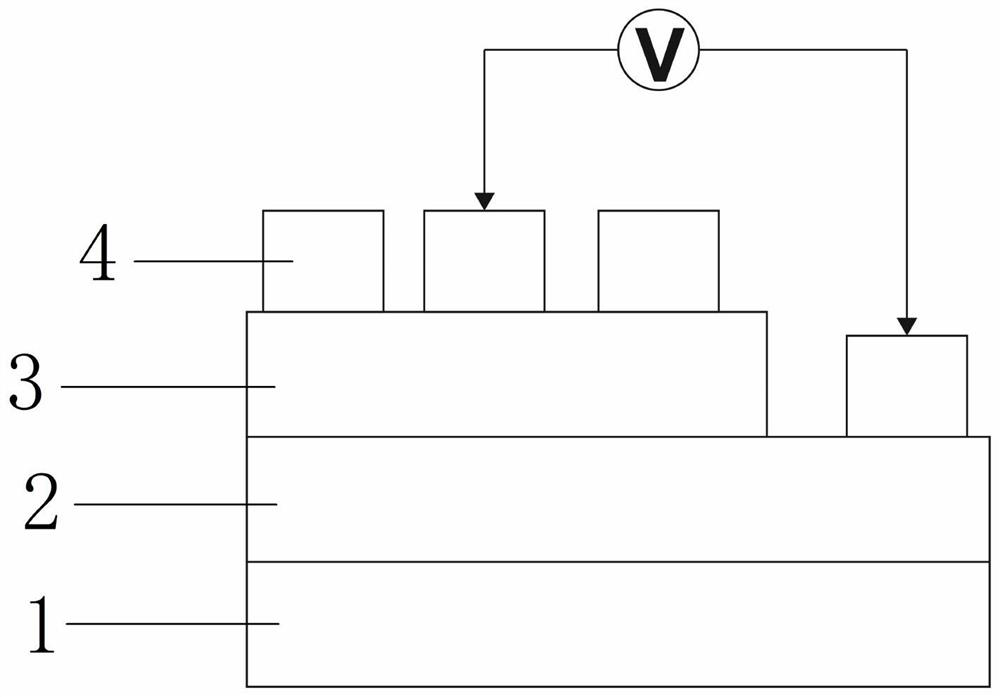

InactiveCN101055895ALow costGood rectification characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesManganese oxideLanthanum

A perovskite structure lanthanum manganese oxide / zinc oxide alloplasm p-n junction and the preparation method pertains to the semiconductor material manufacturing field. The invention uses a magnetron sputtering method to prepare the perovskite structure lanthanum manganese oxide / zinc oxide alloplasm p-n junction. The structure of the p-n junction is a Si(100) single crystal chip(1) substrate, a Pt electrode layer (2), a ZnO film(3), and a LSMO film(4). The invention preparative LSMO / ZnO p-n junction not only has excellent rectification characteristic in the temperature range of 40-320K, but also has solved the problem of the existing technology that has a high use cost of PLD, and is not suitable to apply in large-scale industrial production. The perovskite structure lanthanum manganese oxide / zinc oxide alloplasm p-n junction obtained by the inventive method has good application potential in spinning electron device field.

Owner:BEIJING UNIV OF TECH

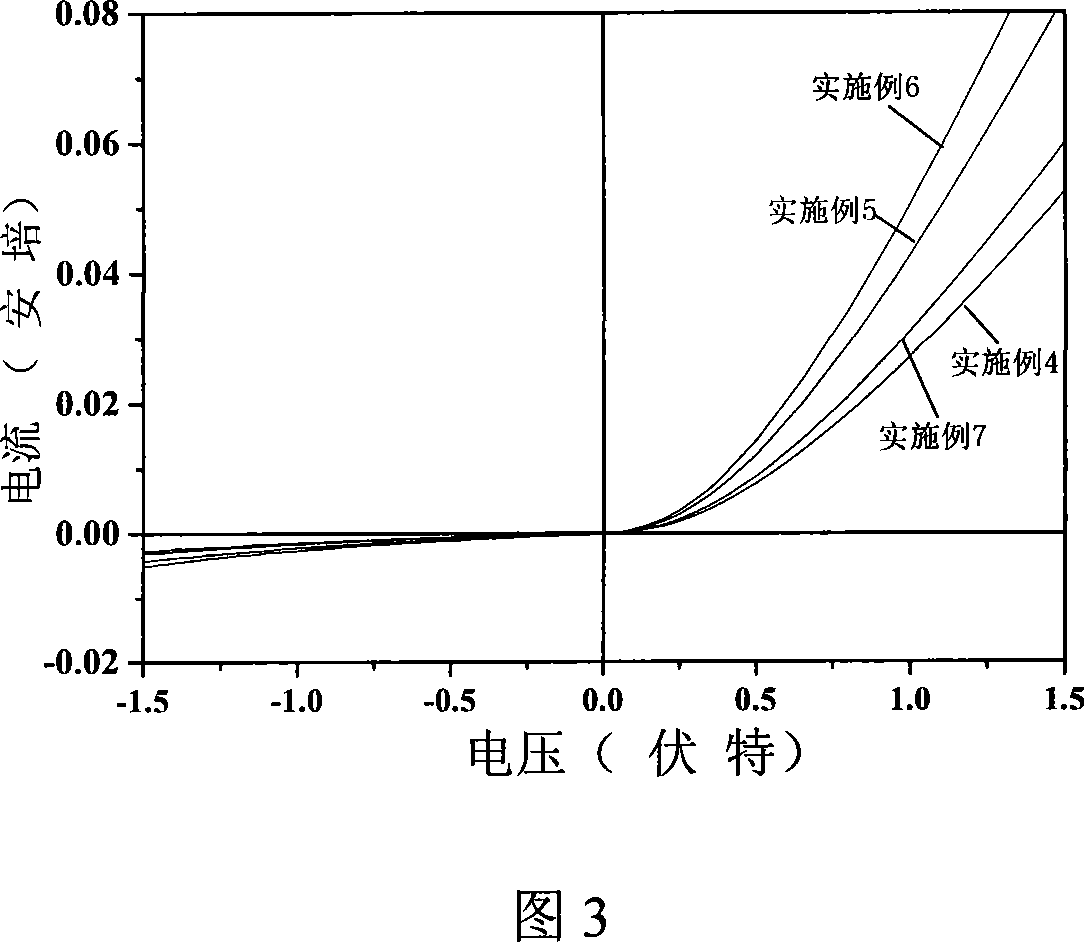

Manufacturing method for single ZnO micron wire homojunction light emitting diode

InactiveCN103715325AGood rectification characteristicsStrong luminous abilitySemiconductor devicesMicrometerEngineering

The invention discloses a manufacturing method for a single ZnO micron wire homojunction light emitting diode. According to the manufacturing method, a simple CVD method is adopted, parameters such as growth time are controlled, a layer of highly-oriented undoped n-type ZnO micron wires grow on a substrate at first, and then a layer of Sb-doped p-type ZnO micron wires grow on the highly-oriented undoped n-type ZnO micron wires, so that the homojunction of the ZnO micron wires is manufactured; a single micron wire is stripped from the bottom of the sample substrate, and electrodes are manufactured at the two ends of the micron wire, wherein the diameter of the micron wire is 10-100 micrometers, and the length of the micron wire is 1-20mm. The manufacturing process is simple, the cost is low, and device test results show that the device has the good rectification characteristic and the higher light emitting property.

Owner:江苏欣和环境科技有限公司

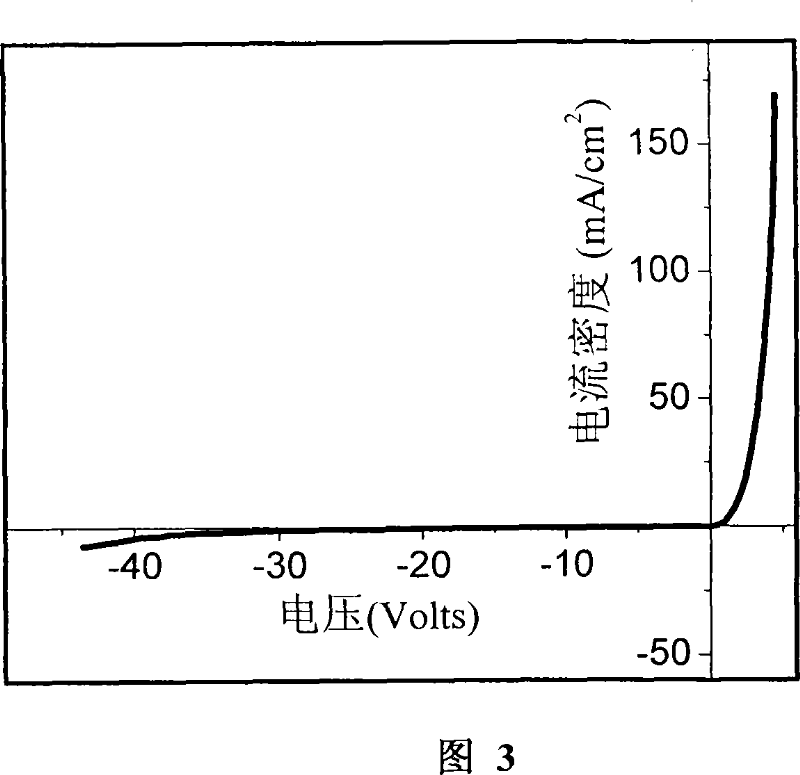

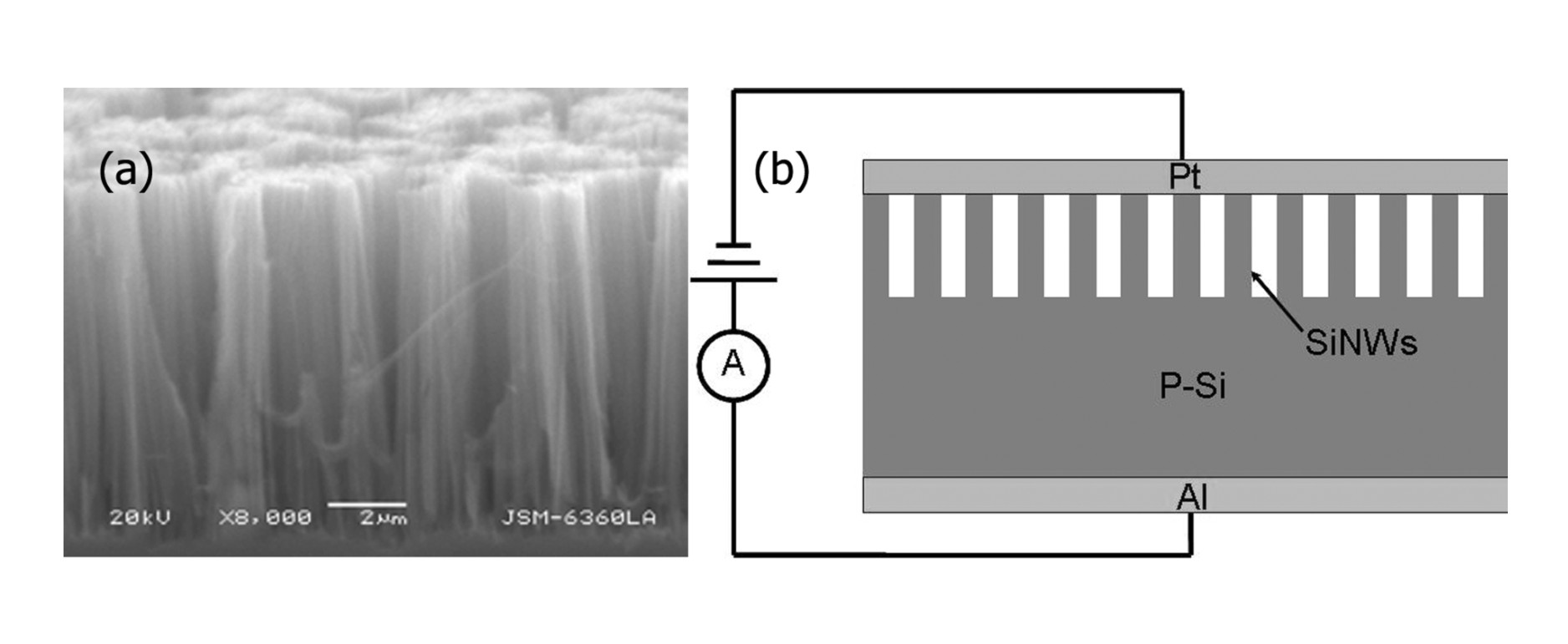

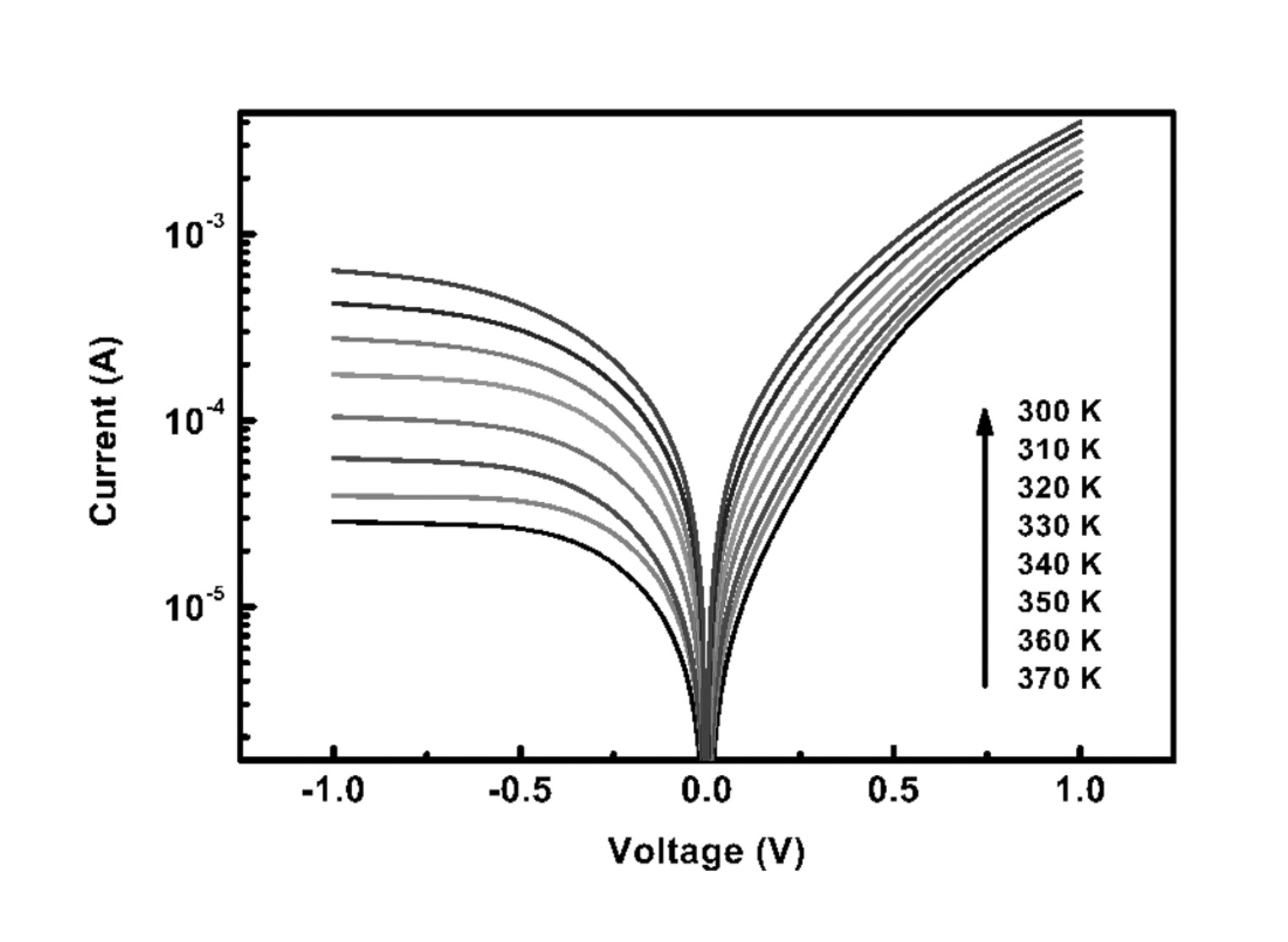

Preparation method for Schottky diode based on core/shell structure silicon nanowire set

InactiveCN102592996AEasy to prepareLow costSemiconductor/solid-state device manufacturingPower flowSurface oxidation

The invention discloses a preparation method for a Schottky diode based on a core / shell structure silicon nanowire set. The method comprises the following steps of: silicon slice cleaning, back electrode preparation, silicon nanowire preparation, silicon nanowire gap filling, Pt thin-film deposition and the like. Silicon nanowires of the Schottky diode are of core / shell structures; silicon is a core; and a surface oxidation layer is a shell. When the Schottky diode is applied, the surface oxidation layer does not need to be removed. A current transmission mechanism of the prepared Schottky diode is a trap-assisted tunneling mechanism, so that the Schottky diode has an excellent rectification characterisitic and has a broad application prospect in the field of nanodevices and the field of new energy resources. The preparation method for the Schottky diode based on the core / shell structure silicon nanowire set is simple, is friendly to the environment, is low in cost requirement and is high in repeatability and is suitable for large-scale industrial production.

Owner:EAST CHINA NORMAL UNIV

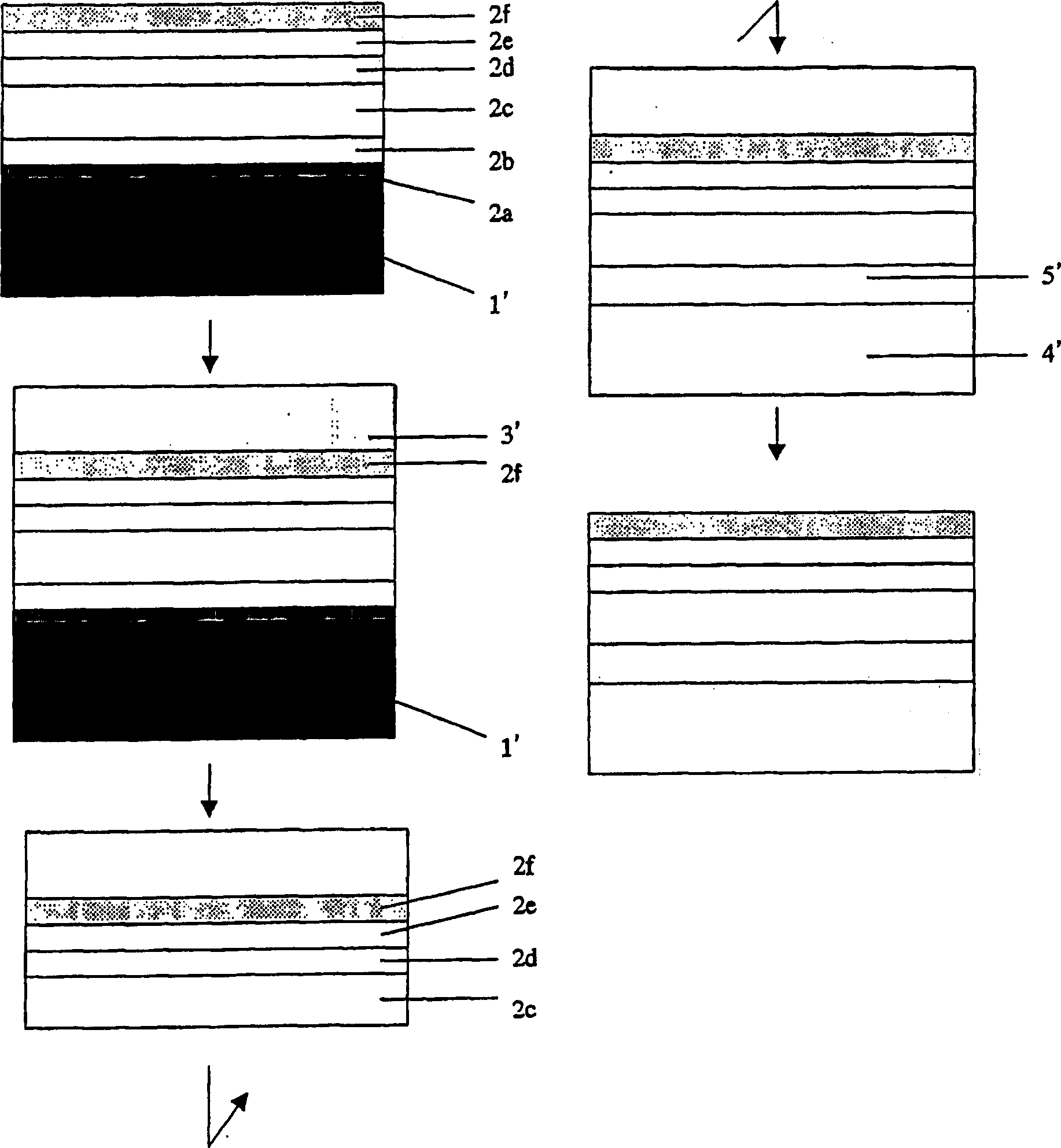

P-N junction-type compoud semiconductor light-emitting diode

InactiveCN1969394AIncrease brightnessHigh transparencyLaser detailsLaser active region structureRoom temperatureP–n junction

In a p-n junction-type compound semiconductor light-emitting diode provided on a crystal substrate with at least an n-type active layer formed of a Group III nitride semiconductor as a light emitting layer, and with a Group III nitride semiconductor layer containing a p-type impurity on the n-type active layer, the diode has a boron phosphide-based Group III-V compound semiconductor layer possessing a band gap exceeding that of the Group III nitride semiconductor forming the n-type active layer at room temperature and exhibiting a p-type electroconductivity in an undoped state deposited on the p-type impurity-containing Group Ill nitride semiconductor layer, and has an ohmic positive electrode joined to a surface of the boron phosphide-based Group III-V compound semiconductor layer.

Owner:SHOWA DENKO KK

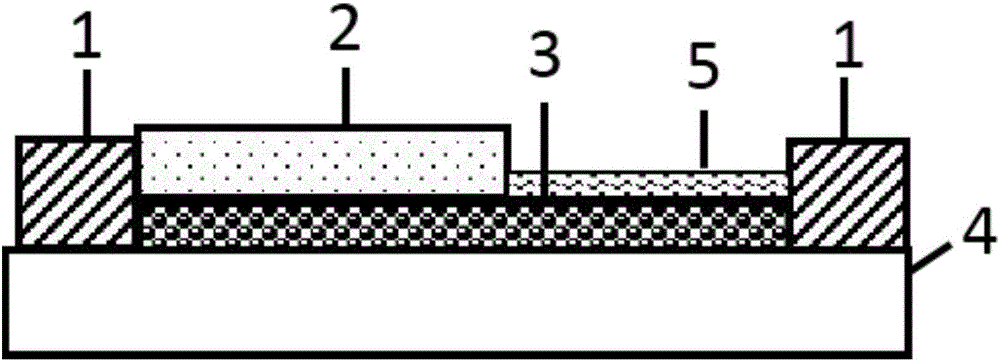

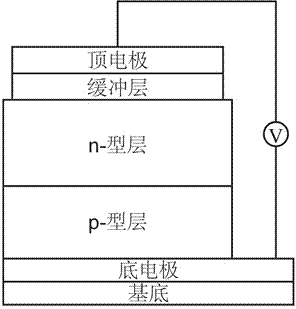

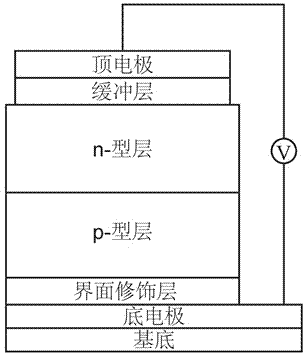

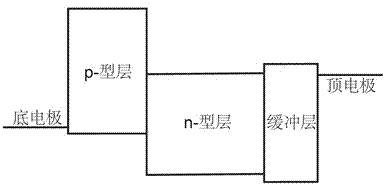

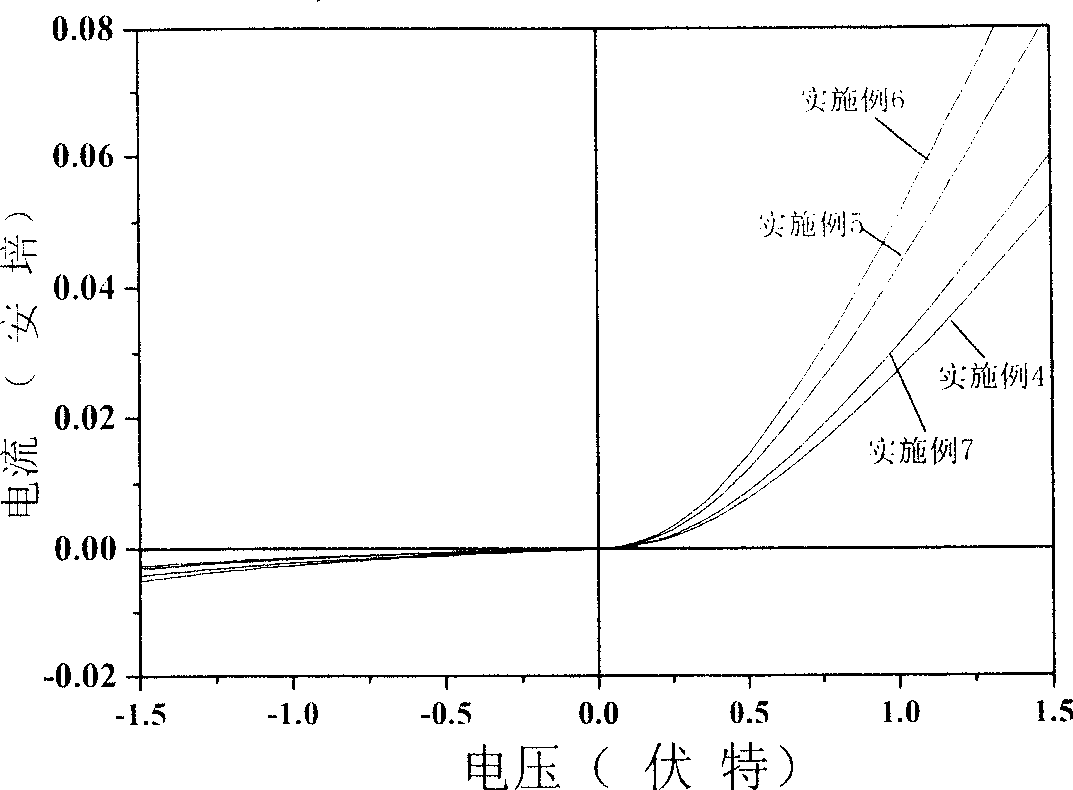

Composite organic rectifier diode

InactiveCN103972391AGood rectification characteristicsHigh selectivitySolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionInterface impedance

The invention discloses an organic rectifier diode, relates to the field of organic semiconductor electronic devices, and particularly relates to a composite organic rectifier diode compounded on an organic / organic p-n heterojunction interface on the basis of a charge carrier. The composite organic rectifier diode disclosed by the invention comprises a base, a bottom electrode, a p-type material layer, an n-type material layer, a charge buffer layer and a top electrode. The composite organic rectifier diode is characterized in that m-MTDATA, 2T-NATA, CuPc, TPD, NPB, TAPC, TCTA, CBP or Rubrene is used as the p-type material layer; C60 is used as the n-type material layer. The composite organic rectifier diode disclosed by the invention has the advantages that the composite organic rectifier diode is high in material selectivity, and the common p-type organic material can be selected with high flexibility; due to the complex mechanism, the rectified current can be supplied by compounding electrons and holes at the p-n heterojunction interface, and the composite organic rectifier diode is low in interface impedance and high in rectification ratio; the composite organic rectifier diode is simple in process and high in apparatus repeatability, is not doped with the p-type material and the n-type material, and is low in demands on fabrication processes and equipments of apparatuses.

Owner:YUNNAN UNIV

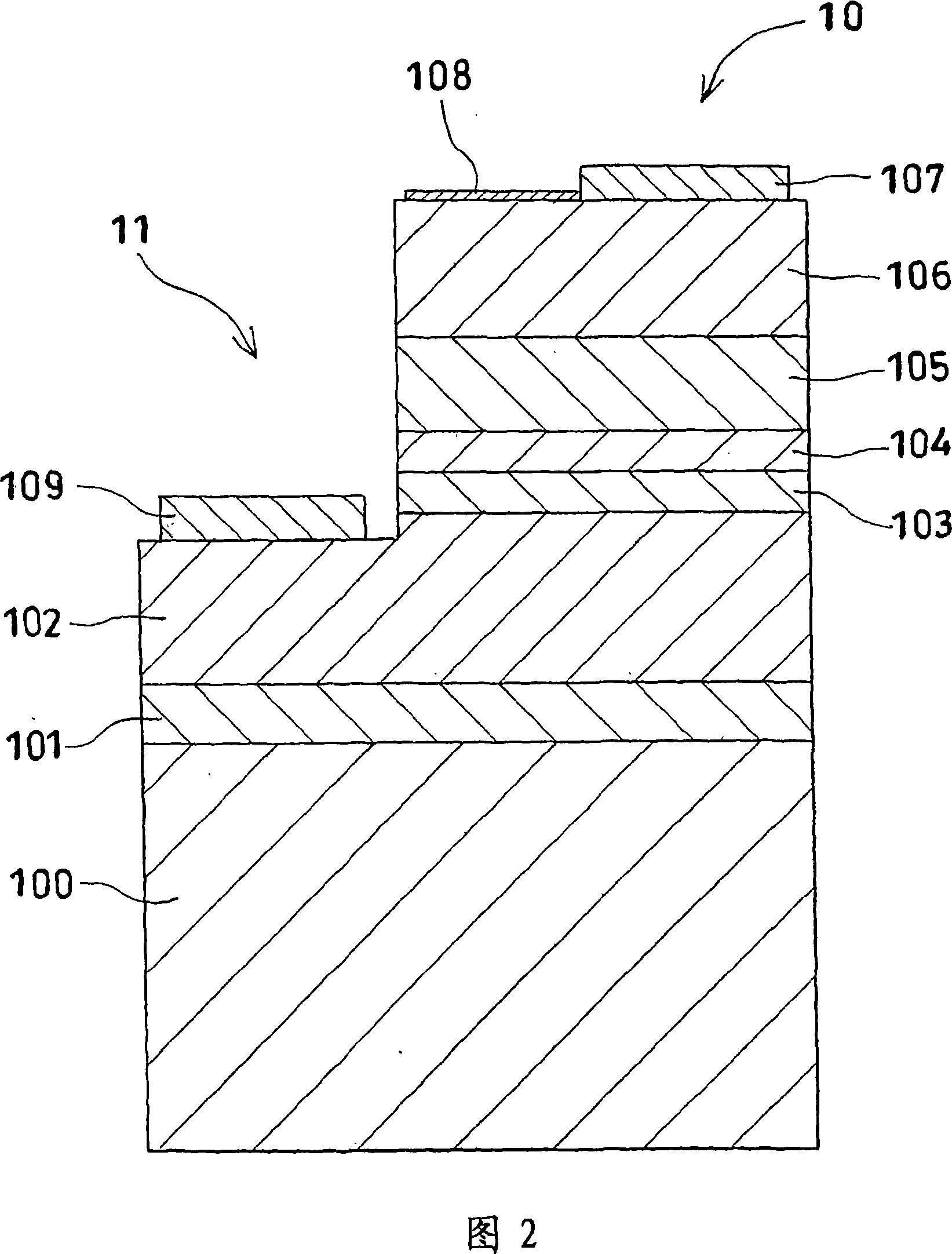

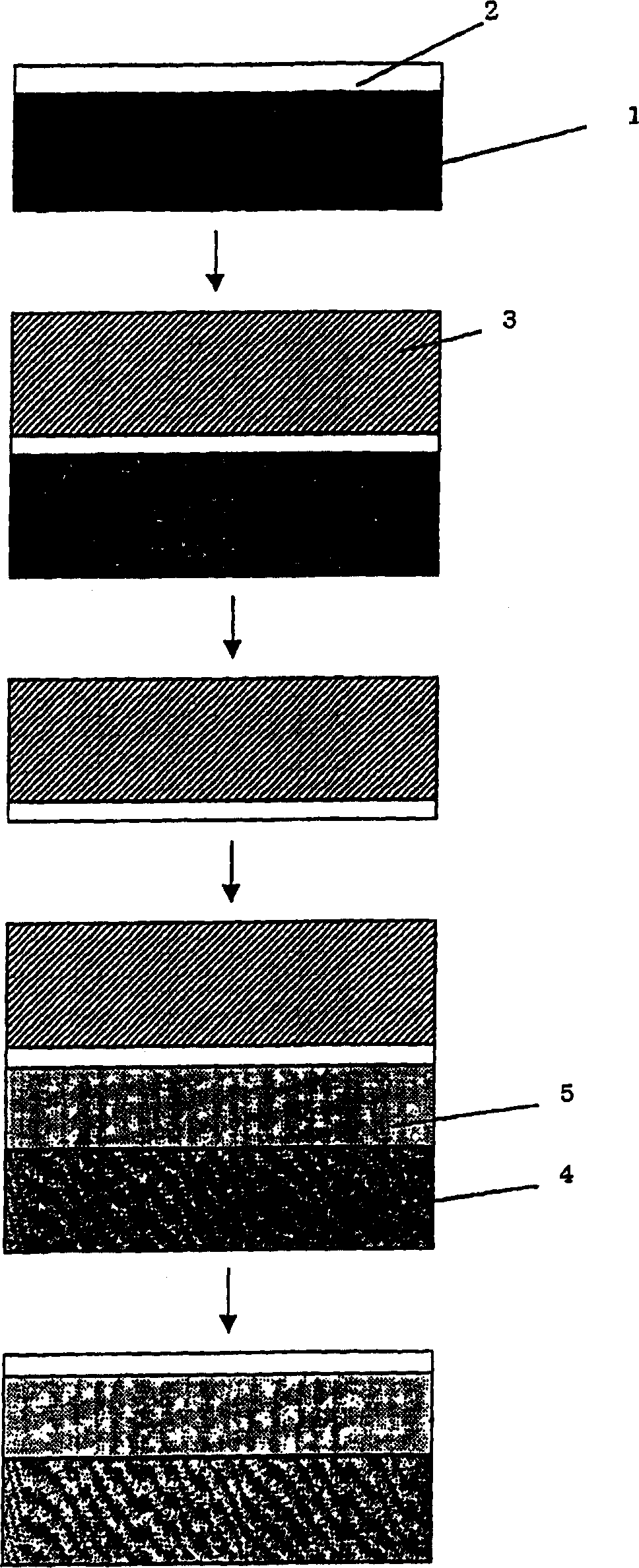

Method for manufacturing compound semiconductor substrate

InactiveCN1871699AImprove cooling effectGood rectification characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesThermal conductivityCompound semiconductor

Disclosed is a method for manufacturing a compound semiconductor substrate which comprises the following steps (a)-(e): (a) a compound semiconductor functional layer (2) is epitaxially grown on a substrate (1); (b) a supporting substrate (3) is bonded to the compound semiconductor functional layer (2); (c) the substrate (1) and a part of the compound semiconductor functional layer (2) which is in contact with the substrate (1) are removed by polishing; (d) a multilayer substrate is obtained by bonding a highly heat-conductive substrate (such as a substrate composed of a Si or sapphire substrate (4) and a diamond thin film (5)) having a thermal conductivity higher than that of the substrate (1) to the surface of the compound semiconductor functional layer (2) which is exposed in the step (c); and (e) the supporting substrate (3) is separated from the multilayer substrate.

Owner:SUMITOMO CHEM CO LTD

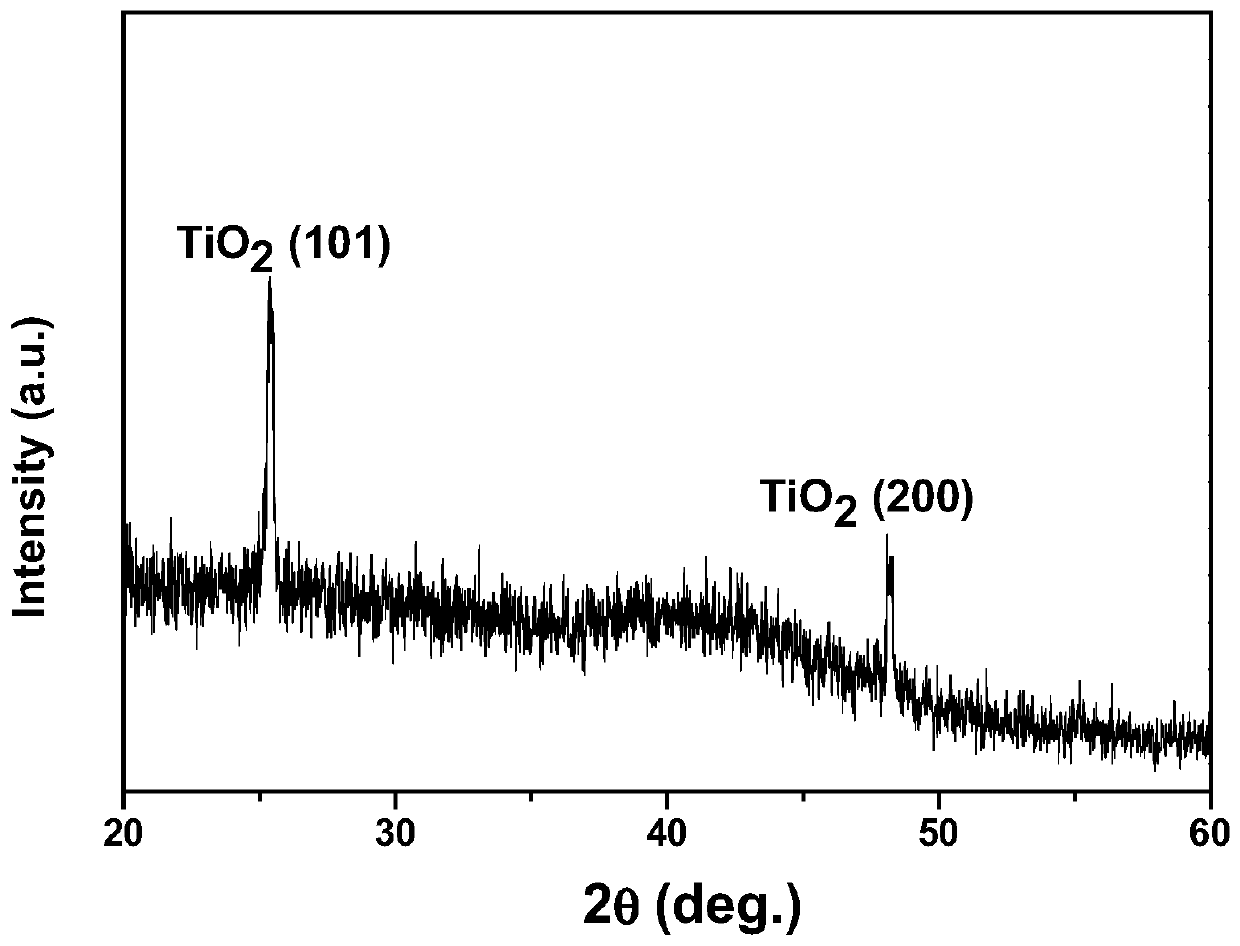

TiO2 film/SiO2/p-Si heterojunction photosensitive material and preparation method and application thereof

InactiveCN111354806AGood rectification characteristicsExcellent photoconductive propertiesFinal product manufactureSemiconductor devicesHeterojunctionAC - Alternating current

The invention relates to the technical field of photosensitive materials, in particular to a TiO2 film / SiO2 / p-Si heterojunction photosensitive material and a preparation method and application thereof. The photosensitive material comprises a TiO2 thin film deposited on a SiO2 oxide layer on a single crystal p-type Si substrate, the TiO2 thin film is composed of compact conical particles, and a TiO2 thin film / SiO2 / p-Si heterojunction is formed at the interface of the TiO2 thin film, the SiO2 oxide layer and the Si substrate. The TiO2 thin film / SiO2 / p-Si heterojunction is prepared by adopting aspray pyrolysis method, and direct-current and alternating-current electrical performance research under different illumination intensities is carried out; and an I-V curve shows that the TiO2 thin film / SiO2 / p-Si heterojunction has obvious diode rectification characteristics and high-performance photoconductivity.

Owner:CHINA UNIV OF PETROLEUM (EAST CHINA)

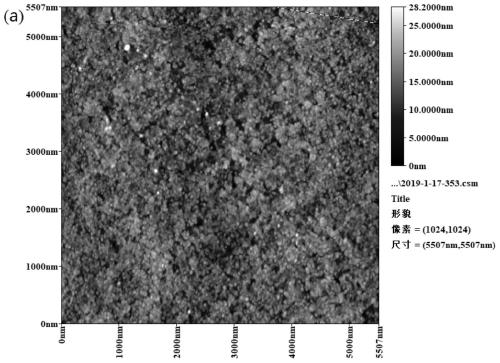

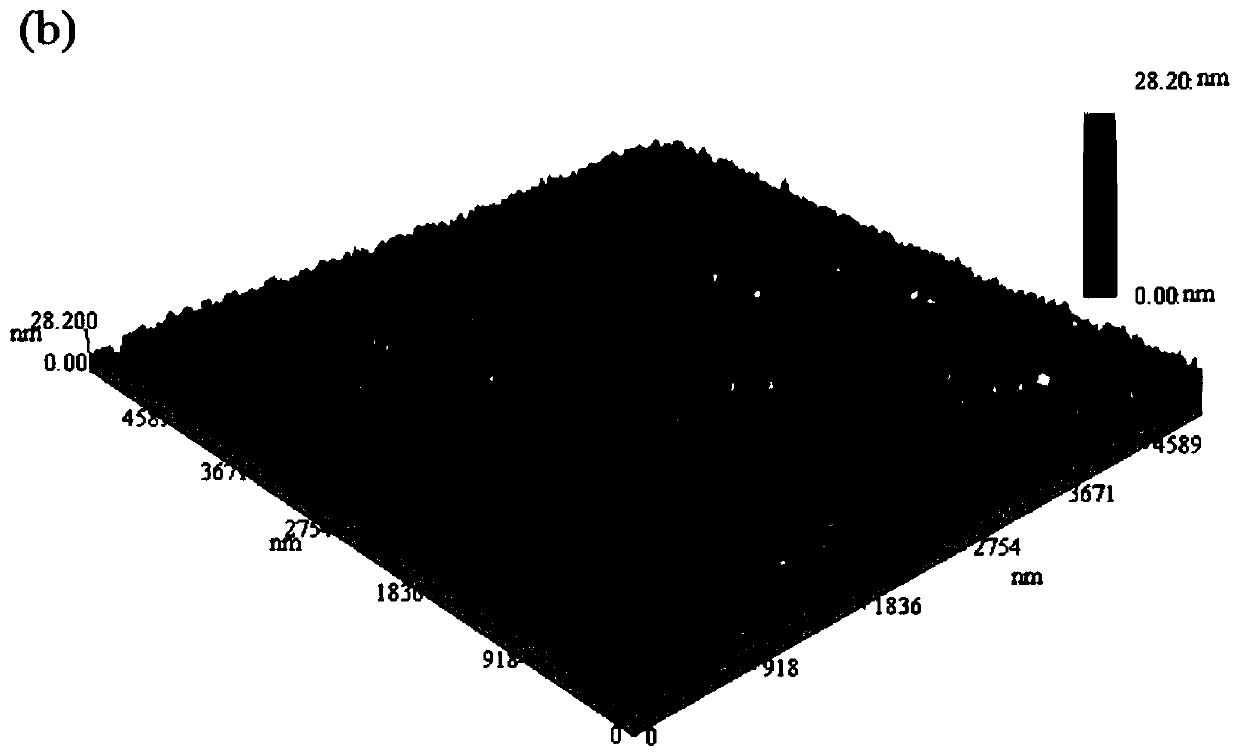

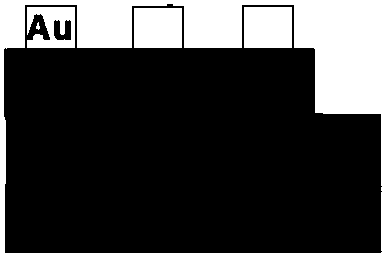

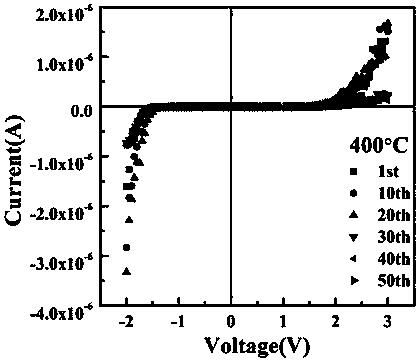

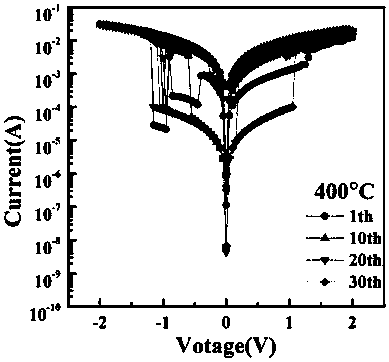

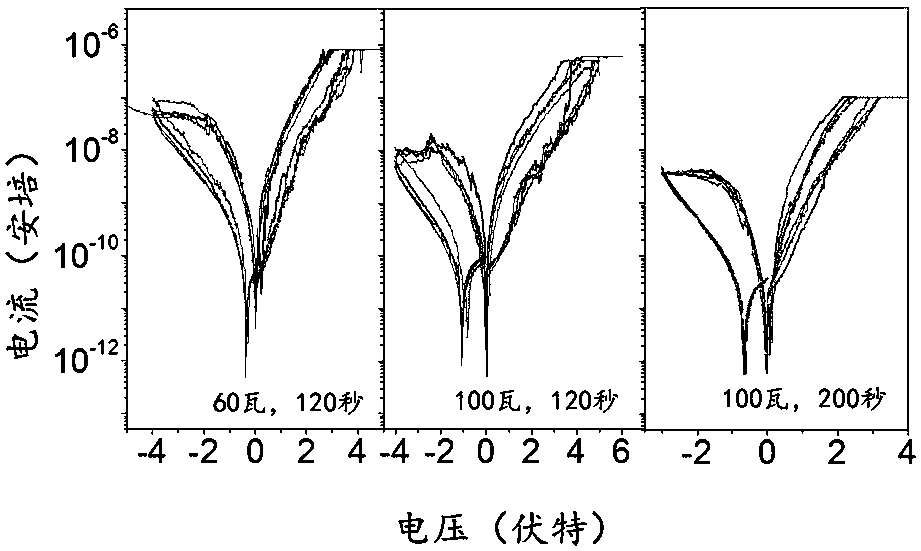

Amorphous strontium titanate thin-film device and preparation method thereof

The invention provides a preparation method of an amorphous strontium titanate thin-film device. The preparation method comprises the following steps: spin-coating a bottom electrode solution to the surface of a substrate to be annealed to form a bottom electrode; spin-coating a strontium titanate solution to the surface of the bottom electrode to be roasted to form a strontium titanate thin film;annealing the strontium titanate thin film to form an amorphous thin film; and carrying out electron beam evaporation sputtering on the surface of the amorphous thin-film to form a top electrode so as to obtain the amorphous strontium titanate thin-film device. The greatest innovation point of the amorphous strontium titanate thin-film device provided by the invention is as follows: a main body oxide thin film layer of the device is an amorphous thin film, the preparation method is simple in process, the demand on temperature in the preparation process is relatively low, and the device can beproduced in batches; moreover, the prepared strontium titanate thin-film device is good in stability and fatigue resistant, can be recycled, and is great in switch ratio which reaches 103 during annealing at 400 DEG C, and is wide in application field.

Owner:GUANGDONG UNIV OF TECH

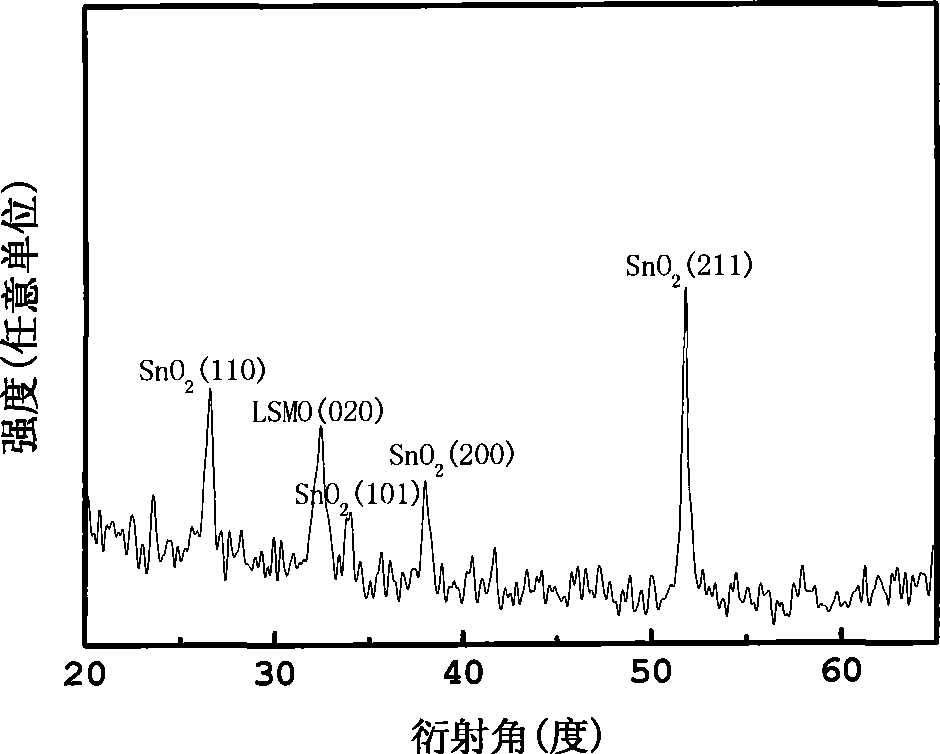

Perofskite structure lanthanide manganese oxides/tin oxide heterogeneous p-n junction and preparation thereof

InactiveCN101459194AGood rectification characteristicsGood adhesionVacuum evaporation coatingSputtering coatingLanthanideSingle crystal substrate

A heterogeneous p-n junction of perovskite structured La-Mn oxide / tin oxide and a preparation process thereof belong to the material manufacturing field. At the present, a p-n junction compounded by La-Mn oxide and tin oxide does not exist. The p-n junction provided by the invention comprises a single-crystal substrate, a SnO2 layer and an LSMO layer, wherein the SnO2 layer is deposited on the single-crystal substrate, the thickness of the SnO2 layer is 100-300 nm, the LSMO layer is deposited on the SnO2 layer, and the thickness of the LSMO layer is 100-300 nm. The invention prepares the heterogeneous p-n junction of perovskite structured La-Mn oxide / tin oxide through utilizing a magnetron sputtering method to sequentially deposit the SnO2 layer and the LSMO layer on a depositing bottom. The p-n junction provided by the invention has excellent rectification characteristics, is low in cost, and is suitable for industrial production.

Owner:BEIJING UNIV OF TECH

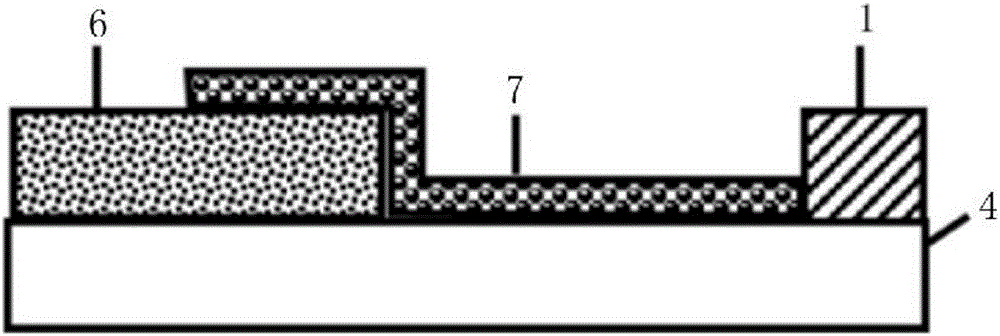

Fabrication method of high-performance aluminum-doped cadmium sulfide silicon-based heterojunction light-emitting diode

InactiveCN110061108AImprove luminous efficiencyImprove uniformitySemiconductor devicesWater bathsHeterojunction

The invention relates to the technical field of semiconductor light-emitting devices, and discloses a fabrication method of a high-performance aluminum-doped cadmium sulfide silicon-based heterojunction light-emitting diode. The fabrication method comprises the following steps of firstly, sequentially performing initial washing and deep washing on a P-type heavily-doping single-crystal silicon wafer with acetone or ethyl alcohol and standard RCA cleaning flow; secondly, fabricating a nanometer porous silicon columnar array by a hydrothermal corrosion method; and finally, taking the nanometer porous silicon columnar array as a substrate and aluminum nitride as a doping agent, and fabricating an aluminum-doped cadmium sulfide nanometer thin film and the nanometer porous silicon columnar array by a chemical water bath method. The aluminum-doped cadmium sulfide nanometer thin film and the nanometer porous silicon columnar array are organically combined and built to a novel light-emitting diode, and the array and porous structure of the nanometer porous silicon columnar array can be fully utilized; and meanwhile, by relatively high carrier mobility of the cadmium sulfide and the nanometer porous silicon columnar array after doping, the carrier recombination efficiency can be effectively improved, and the light-emitting efficiency of the light-emitting diode is improved.

Owner:HENAN POLYTECHNIC UNIV

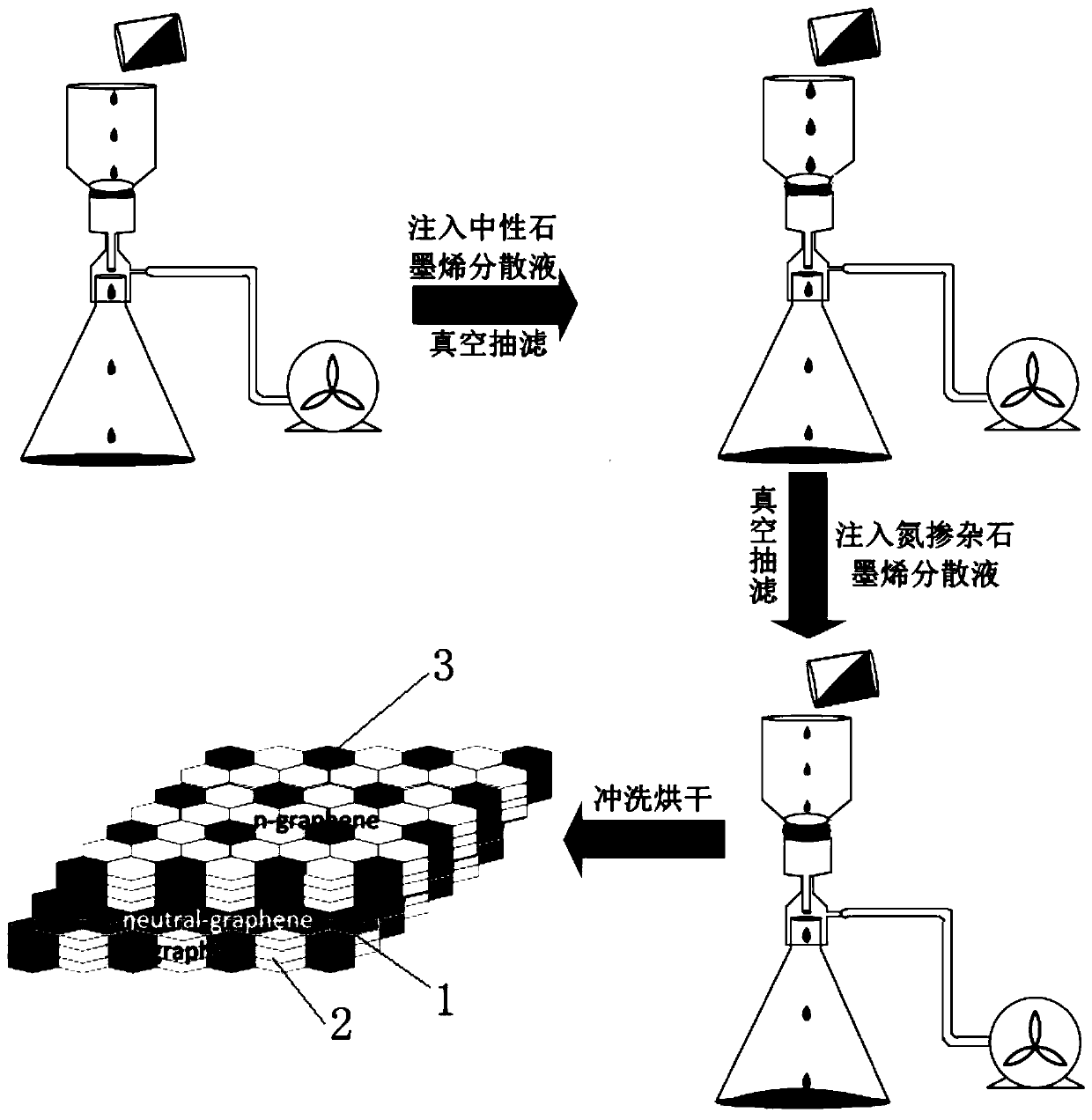

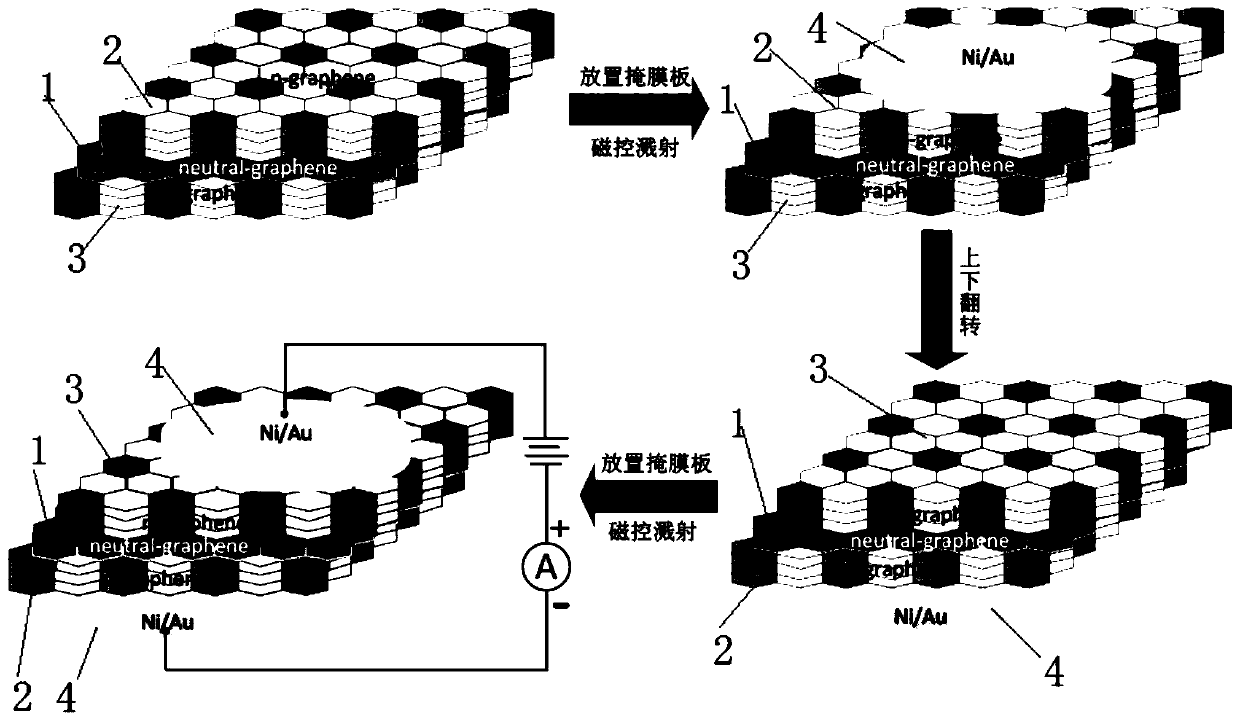

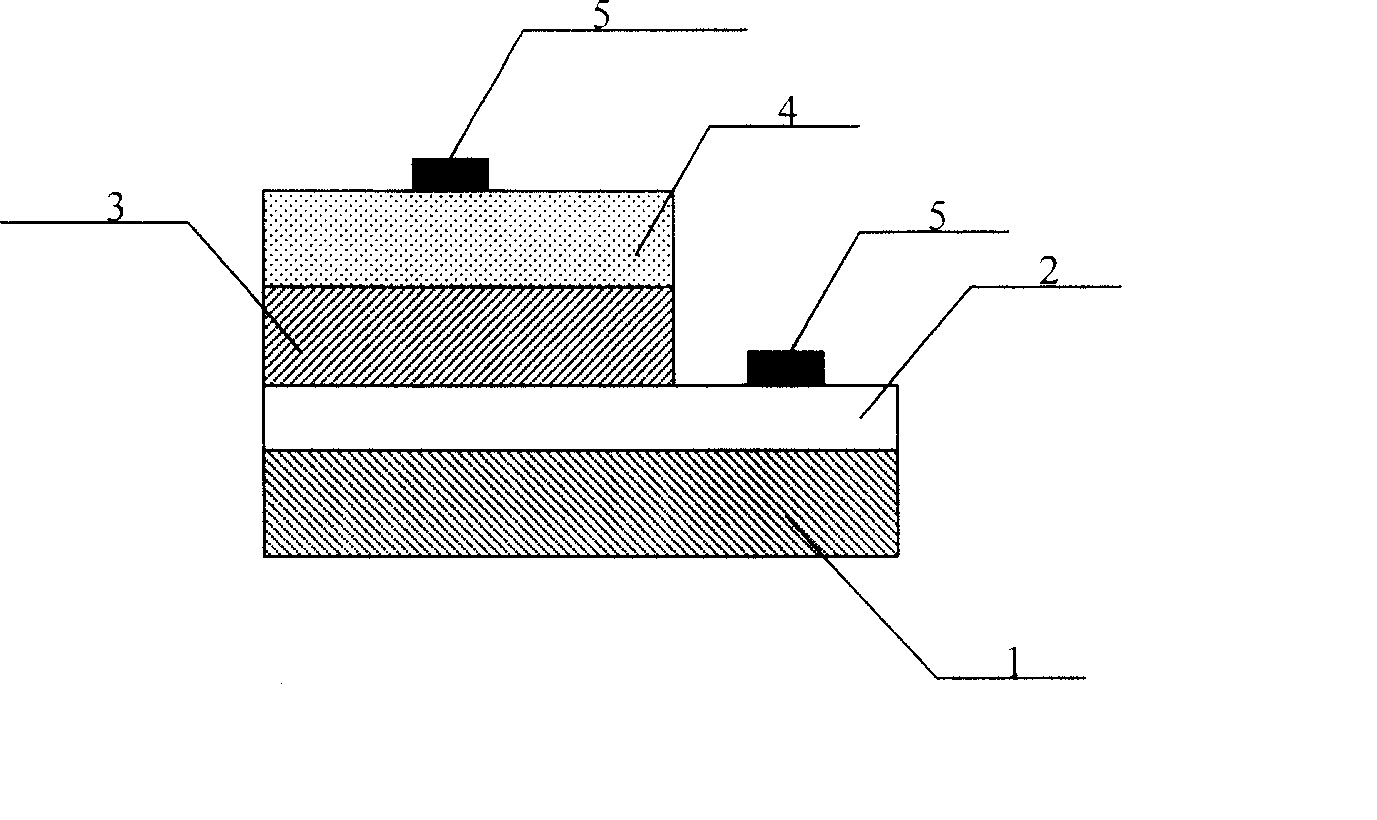

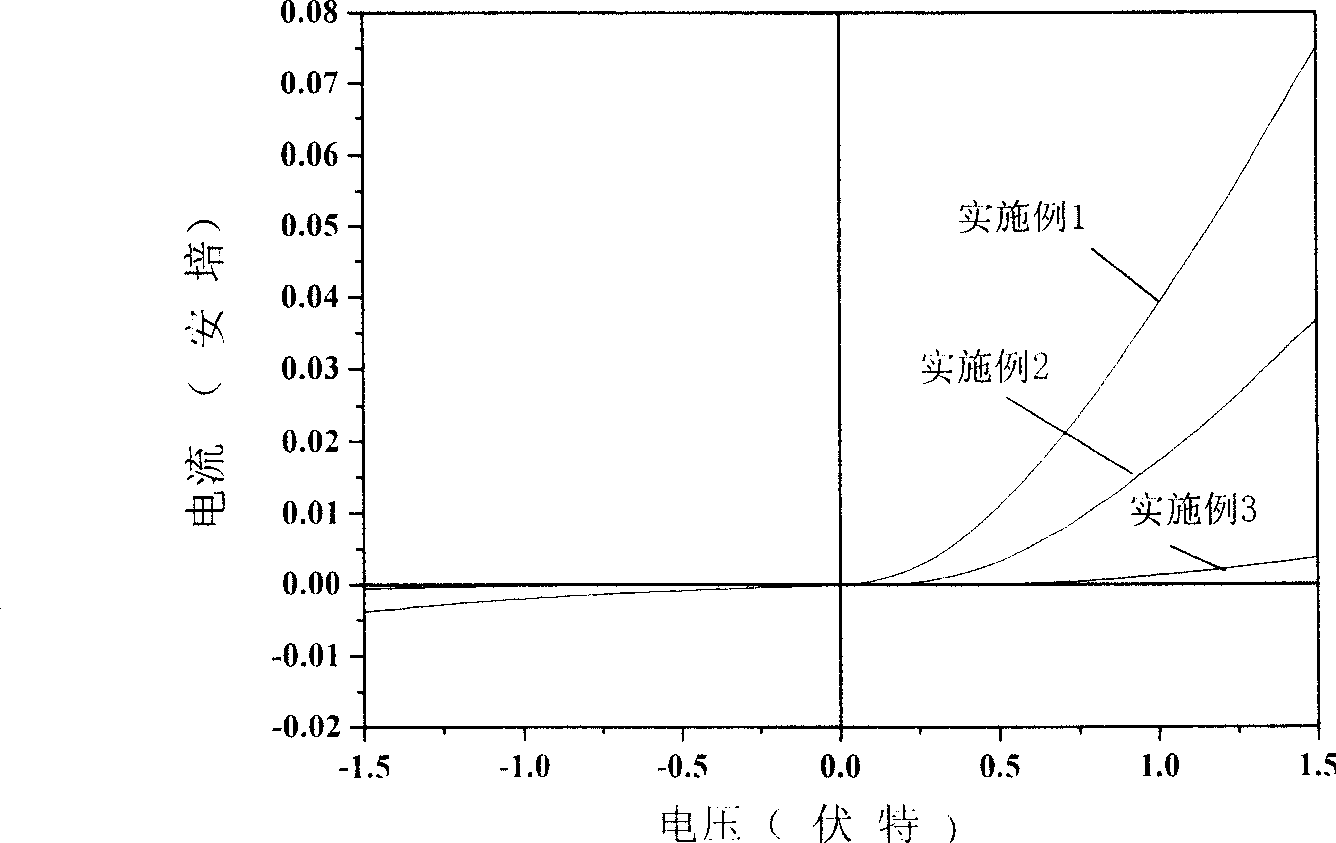

Graphene homogeneous p-n junction structure and preparation method thereof

PendingCN111244162ASame shrinkageSame tensionSemiconductor/solid-state device manufacturingSemiconductor devicesFlexible electronicsHomojunction

The invention discloses a graphene homogeneous p-n junction structure and a preparation method thereof. The graphene homogeneous p-n junction structure comprises a neutral graphene layer, a p-type graphene layer, an n-type graphene layer and an electrode, wherein the p-type graphene layer is arranged on the surface of one side of the neutral graphene layer, the n-type graphene layer is arranged onthe surface of the other side of the neutral graphene layer, and electrodes are arranged on the surface of the p-type graphene layer and the surface of the n-type graphene layer. According to the invention, the characteristics of the same material of graphene that the thermal expansion coefficient, the electron affinity, the band gap width and the lattice constant are the same are utilized; therefore, the complex interface problem generated by heterogeneous p-n junctions made of different materials and the problems of structural instability, low efficiency and the like of the heterogeneous p-n junctions are avoided, and meanwhile, the p-n junction structure has excellent flexibility and performance and can be used for structural design of flexible electronic devices and research and development of a high-performance miniaturized fine display technology.

Owner:XI'AN PETROLEUM UNIVERSITY

CaTiO3 structure La-Mn oxide/zinc oxide heterogeneous p-n junction and its making method

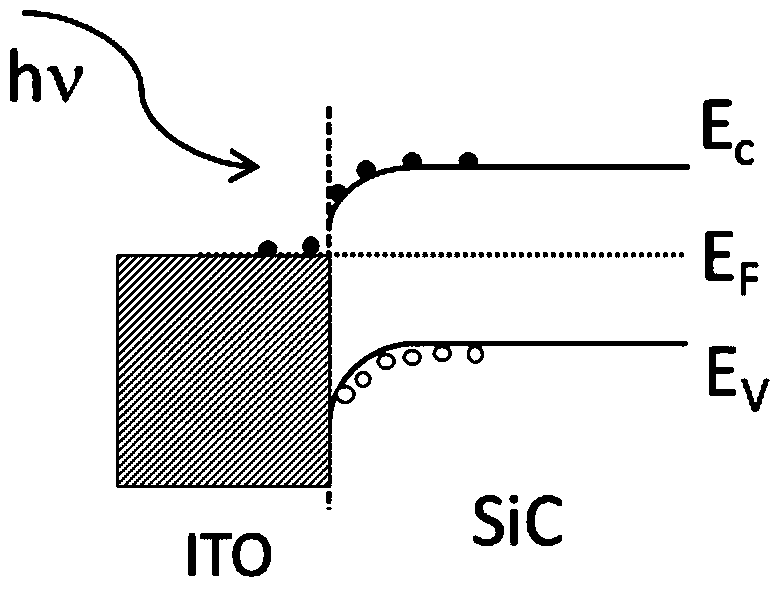

InactiveCN100468781CLow costGood rectification characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsSingle crystal

A perovskite structure lanthanum manganese oxide / zinc oxide alloplasm p-n junction and the preparation method pertains to the semiconductor material manufacturing field. The invention uses a magnetron sputtering method to prepare the perovskite structure lanthanum manganese oxide / zinc oxide alloplasm p-n junction. The structure of the p-n junction is a Si(100) single crystal chip(1) substrate, a Pt electrode layer (2), a ZnO film(3), and a LSMO film(4). The invention preparative LSMO / ZnO p-n junction not only has excellent rectification characteristic in the temperature range of 40-320K, but also has solved the problem of the existing technology that has a high use cost of PLD, and is not suitable to apply in large-scale industrial production. The perovskite structure lanthanum manganese oxide / zinc oxide alloplasm p-n junction obtained by the inventive method has good application potential in spinning electron device field.

Owner:BEIJING UNIV OF TECH

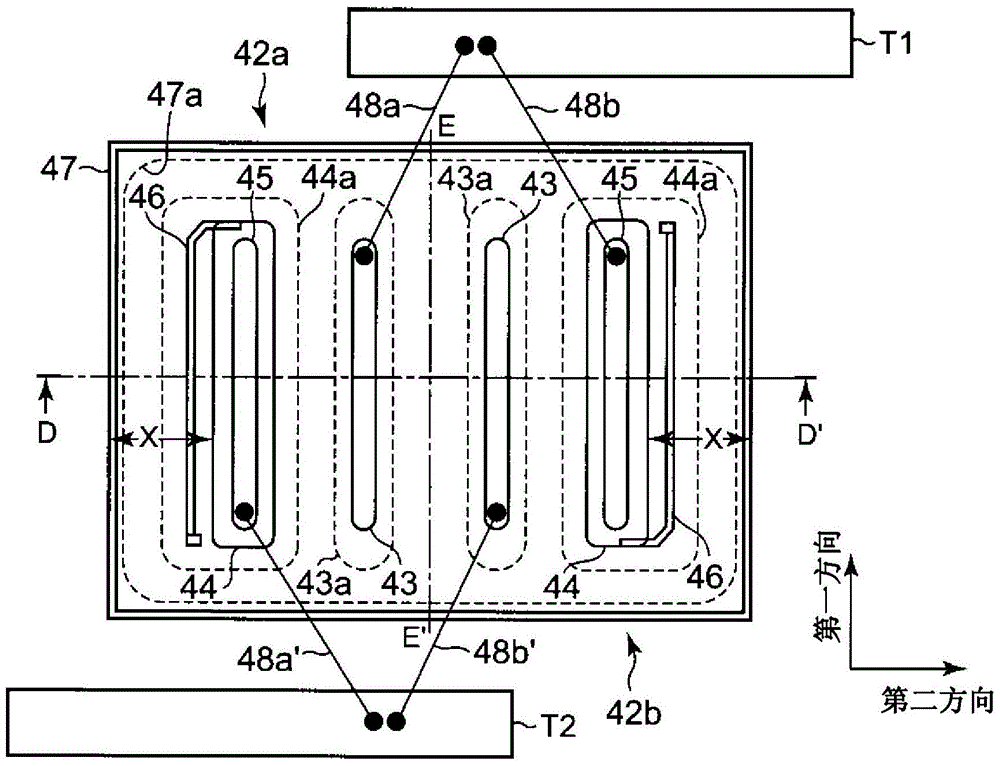

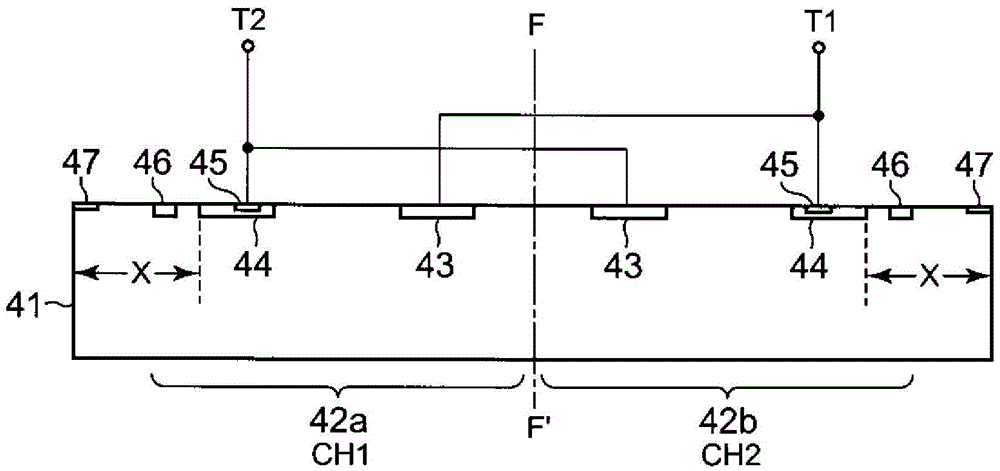

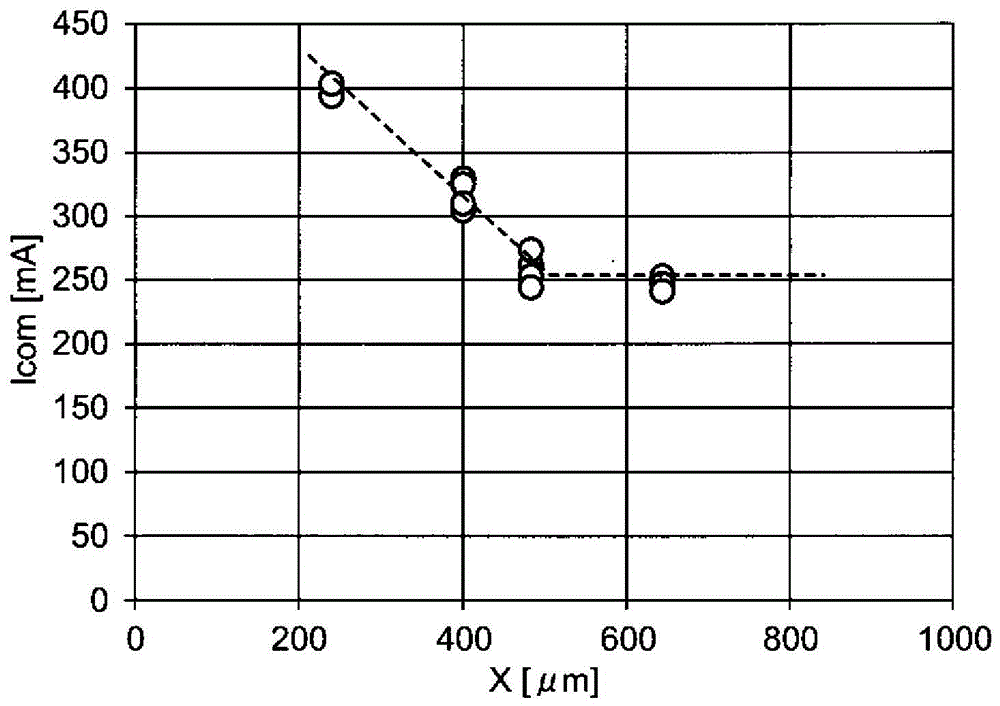

Bi-directional photothyristor chips, phototrigger couplers and solid state relays

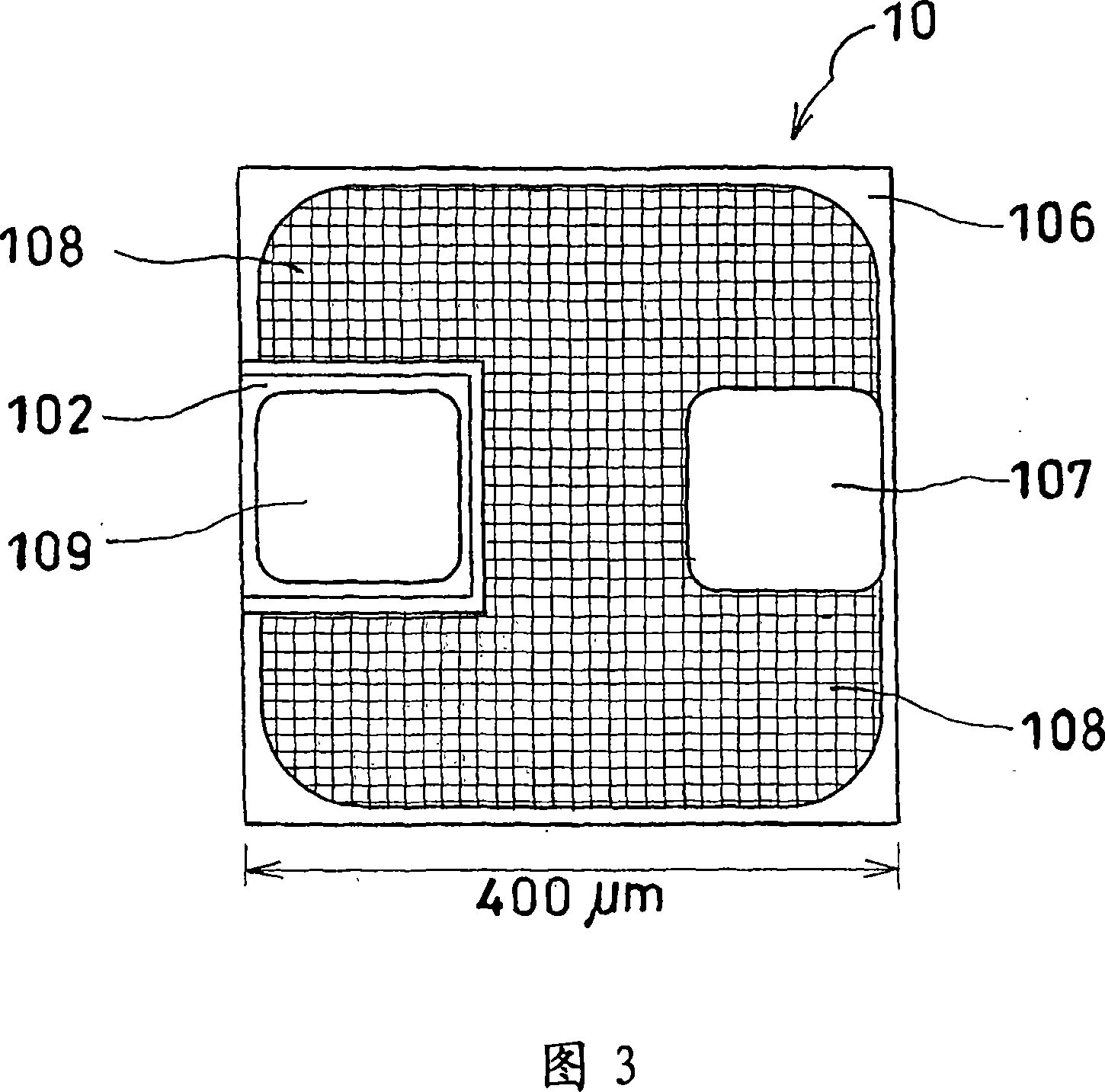

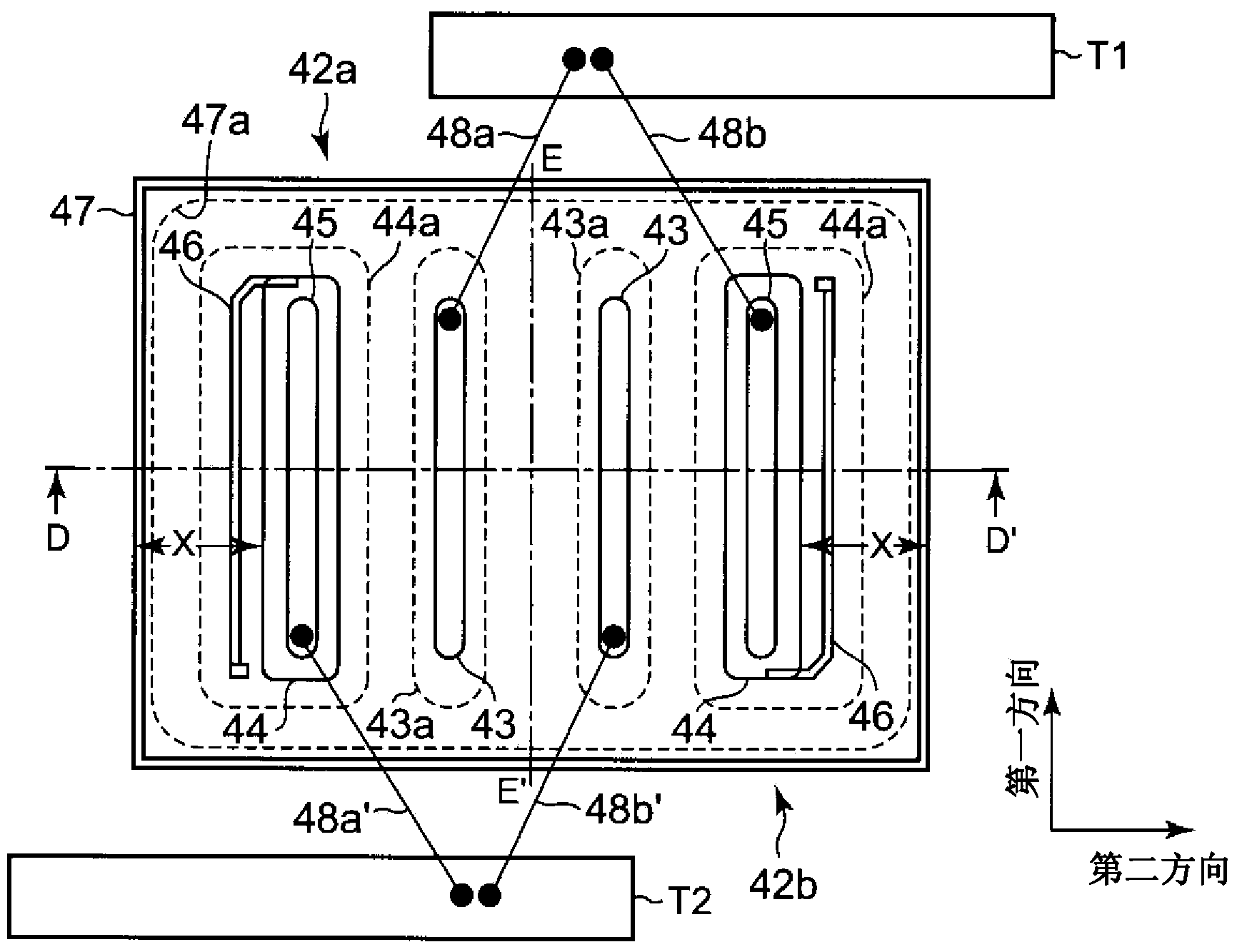

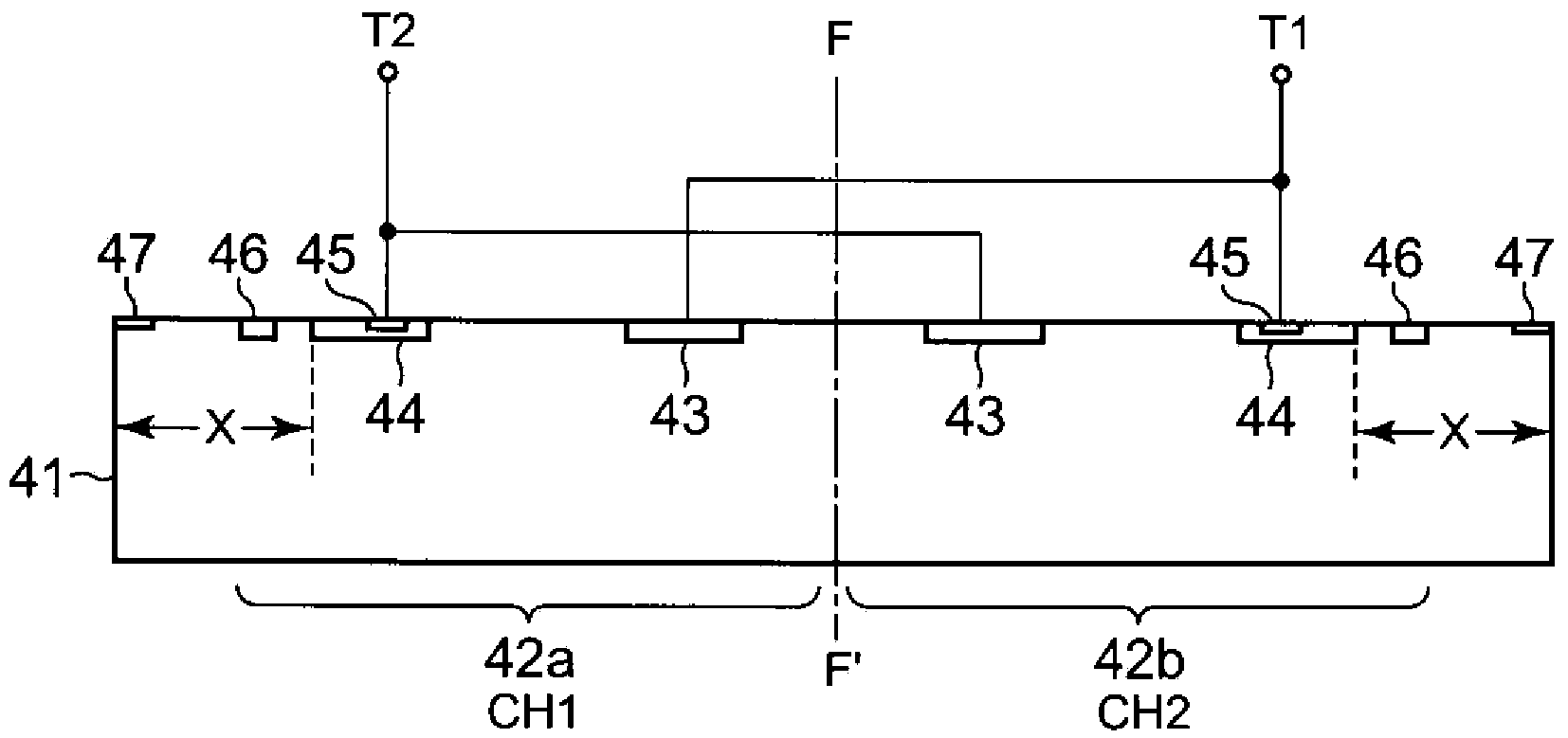

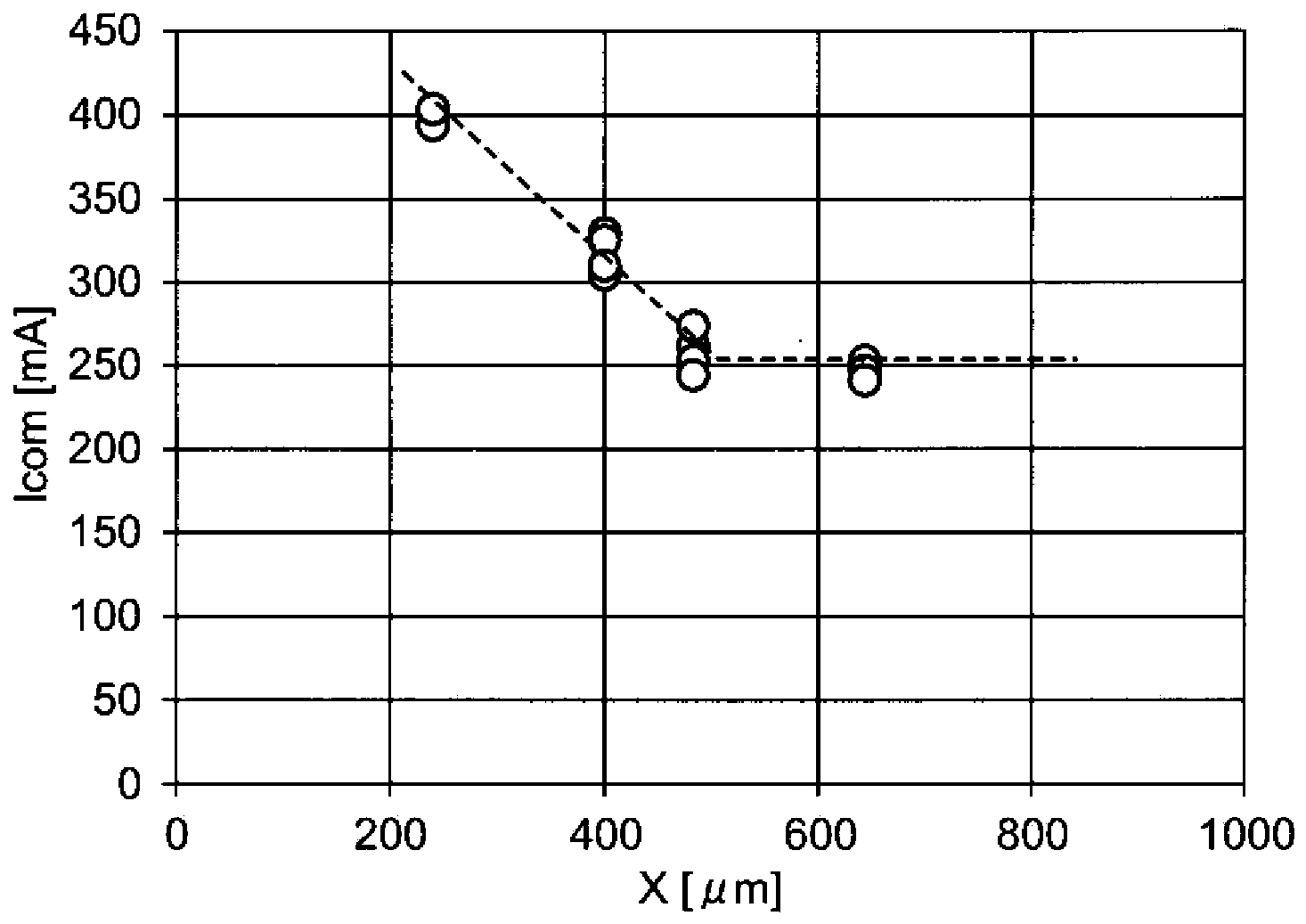

ActiveCN104241435BGood rectification characteristicsIncrease the areaFinal product manufactureElectronic switchingSchottky barrierMicrometer

The invention provides a bi-directional light control thyratron transistor chip, an optical triggering coupler and a solid-state relay. A first light control thyratron transistor section and a second light control thyratron transistor section are arranged on a surface of a semiconductor chip. Each light control thyratron transistor section has a PNPN section. The PNPN section comprises a positive electrode diffusion region in a conductive type, a substrate in another conductive type, a control electrode diffusion region in a conductive type and a negative electrode diffusion region formed in the control electrode diffusion region in another conductive type. The distance of the cut surface to the control electrode diffusion region is below 400 micrometers. Thus, a few of minority carriers generated at the first light control thyratron transistor section side during connection are collected to the cut surface at the first light control thyratron transistor section side before migration. Schottky barrier or a channel separation region cannot be formed, rectification characteristics are raised greatly, increase of the chip area can be inhibited and load is controlled through light triggering by one chip.

Owner:SHARP KK

A kind of zno/nio heterostructure ordered porous film and preparation method thereof

ActiveCN104465987BLarge specific surface areaPromote absorptionFinal product manufactureSuperimposed coating processUltraviolet detectorsSemiconductor materials

The invention belongs to the technical field of semiconductors and particularly relates to a ZnO / NiO heterostructure orderly multi-hole thin film and a manufacturing method thereof. A new option is provided for semiconductor materials. According to the technical scheme, the ZnO / NiO heterostructure orderly multi-hole thin film comprises a conducting substrate and a heterostructure growing on the conducting substrate, and the heterostructure is formed by a p type NiO orderly multi-hole thin film and an n type ZnO orderly multi-hole thin film which grows in sequence from bottom to top. The invention further provides a manufacturing method of the ZnO / NiO heterostructure orderly multi-hole thin film. The ZnO / NiO heterostructure orderly multi-hole thin film can be widely used in the fields such as an ultraviolet detector, a light-emitting diode and a resistance random access memory.

Owner:SOUTHWEST UNIV

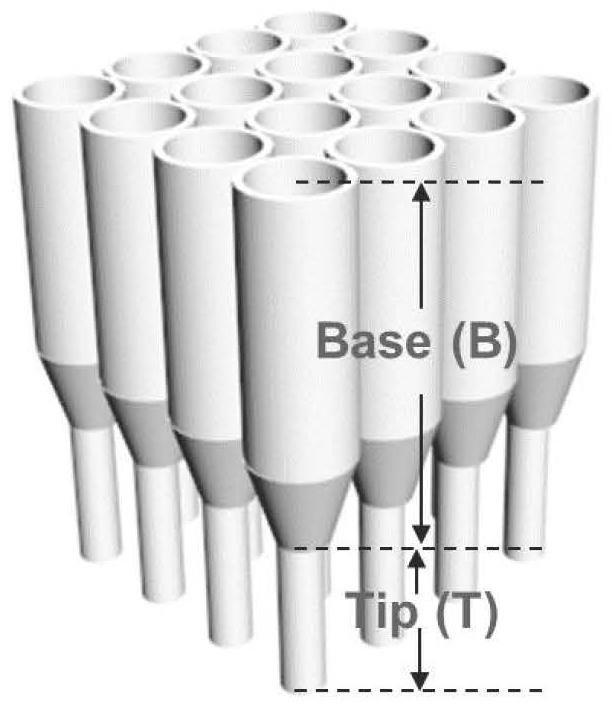

Bionic light capture device N3/PT1/AAO film as well as preparation process and application thereof

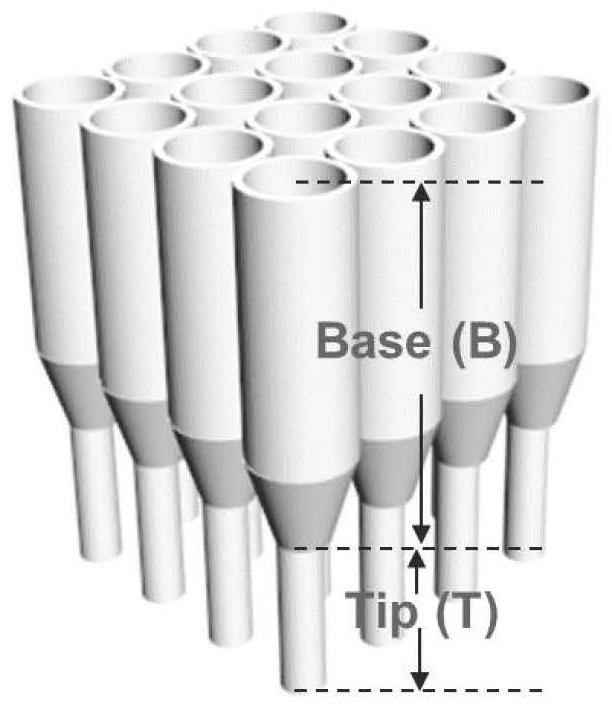

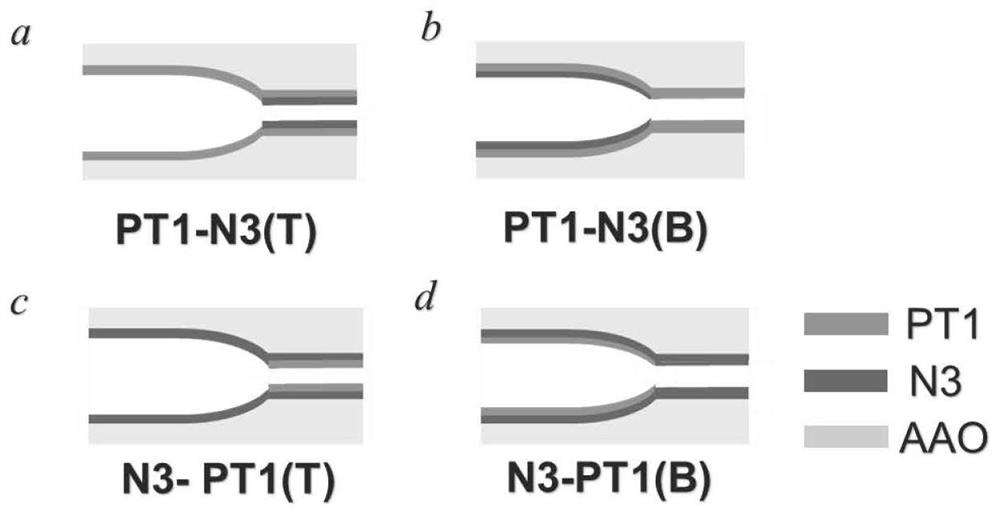

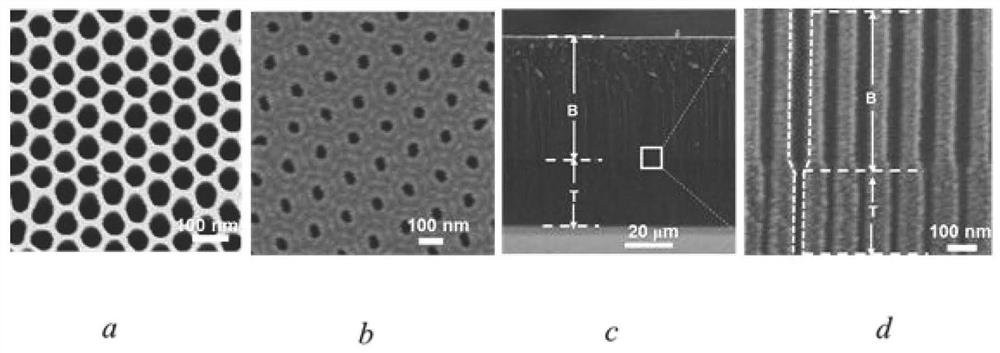

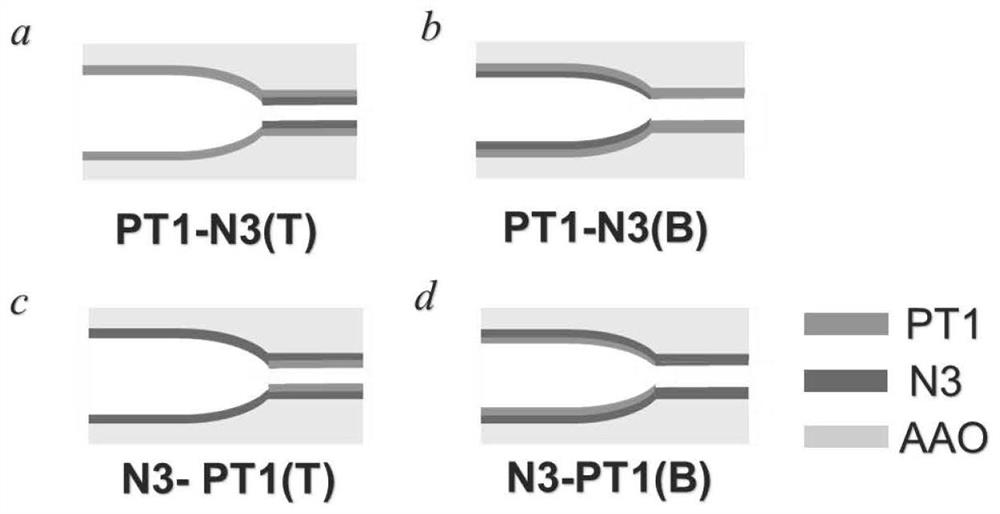

ActiveCN112458496ANovel preparation methodEasy to operateAnodisationElectrolytic organic productionEngineeringMaterials science

The invention belongs to the technical field of nano materials, and particularly relates to preparation of an N3 / PT1 / AAO film of a bionic light capture device. The preparation method comprises the following steps: taking a funnel-shaped aluminum oxide nano-channel (AAO) as a substrate, modifying quaternary ammonium salt modified polythiophene PT1 on the substrate by adopting a solvent evaporationmethod, and respectively preparing a heterogeneous PT1-N3 (T) film and a heterogeneous PT1-N3 (B) film through electrostatic assembly of a bipyridine ruthenium complex N3 at a small hole end (T) or alarge hole end (B) of the funnel-shaped AAO; on the other hand, grafting N3 molecules on the AAO by using a limited molecular diffusion method, and respectively carrying out electrostatic self-assembly of PT1 at the T end and the B end of the functionalized AAO to prepare the N3-PT1 (T) and N3-PT1 (B) heterogeneous films. The preparation method is simple, novel and easy to operate, and a large-scale N3-PT1 heterogeneous surface is formed on the inner wall of the nano channel. Under the irradiation of simulated sunlight, not only can the capture of [mu]A-level high-photo-response ion current berealized, but also the ion selectivity and the ion flux are better, and a new research thought is provided for developing a high-performance nano-fluidic bionic light capture system.

Owner:BEIHANG UNIV

Bi-directional light control thyratron transistor chip, optical triggering coupler and solid-state relay

ActiveCN104241435AGood rectification characteristicsIncrease the areaFinal product manufactureElectronic switchingSchottky barrierMicrometer

The invention provides a bi-directional light control thyratron transistor chip, an optical triggering coupler and a solid-state relay. A first light control thyratron transistor section and a second light control thyratron transistor section are arranged on a surface of a semiconductor chip. Each light control thyratron transistor section has a PNPN section. The PNPN section comprises a positive electrode diffusion region in a conductive type, a substrate in another conductive type, a control electrode diffusion region in a conductive type and a negative electrode diffusion region formed in the control electrode diffusion region in another conductive type. The distance of the cut surface to the control electrode diffusion region is below 400 micrometers. Thus, a few of minority carriers generated at the first light control thyratron transistor section side during connection are collected to the cut surface at the first light control thyratron transistor section side before migration. Schottky barrier or a channel separation region cannot be formed, rectification characteristics are raised greatly, increase of the chip area can be inhibited and load is controlled through light triggering by one chip.

Owner:SHARP KK

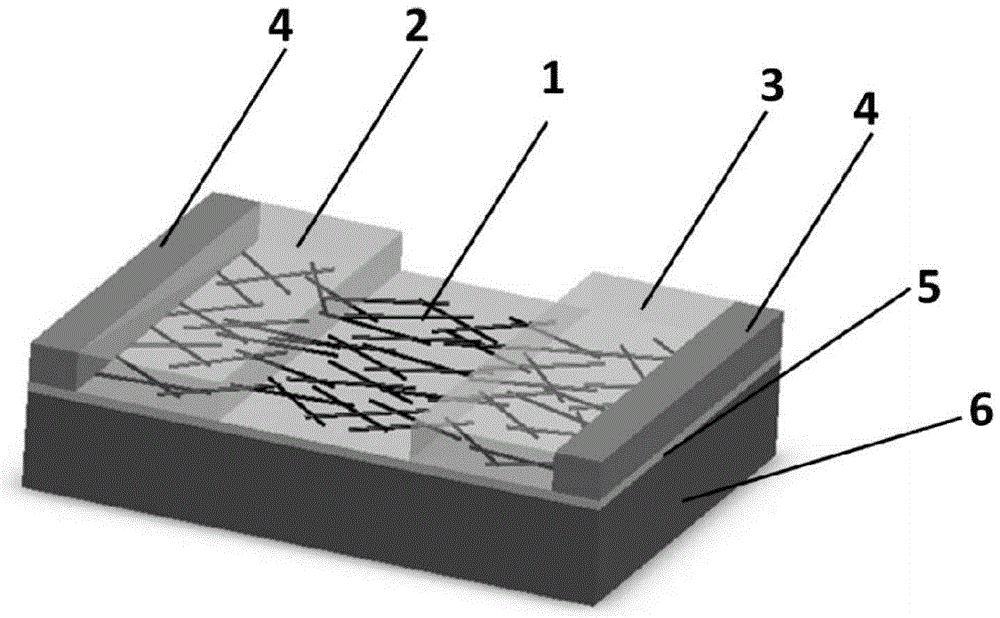

Disordered netty carbon nanotube based p-n junction diode and preparation method thereof

InactiveCN105529402AGood rectification characteristicsImprove performanceFinal product manufactureSolid-state devicesSputteringCarbon nanotube

The invention relates to a disordered netty carbon nanotube based p-n junction diode and a preparation method thereof. The preparation method comprises the following steps: manufacturing Au electrodes through electron beam lithography and magnetron sputtering at two ends of a carbon nanotube thin film on a substrate, then soaking one end of the carbon nanotube thin film in a triethyloxonium hexachloroantimonate solution to form a p-type doping area and soaking the other end of the carbon nanotube thin film in a polyethyleneimine solution to form an n-type doping area after photoresist spinning and selective exposing, and preparing to obtain the p-n junction diode. Through the adoption of disordered netty carbon nanotubes, the prepared and obtained device has good rectification characteristic, and is stable in performances in room temperature air. The performances of the diode can be freely regulated and controlled by changing the density of the disordered netty carbon nanotubes and the structure size and doping parameters of the device.

Owner:SHANGHAI JIAO TONG UNIV

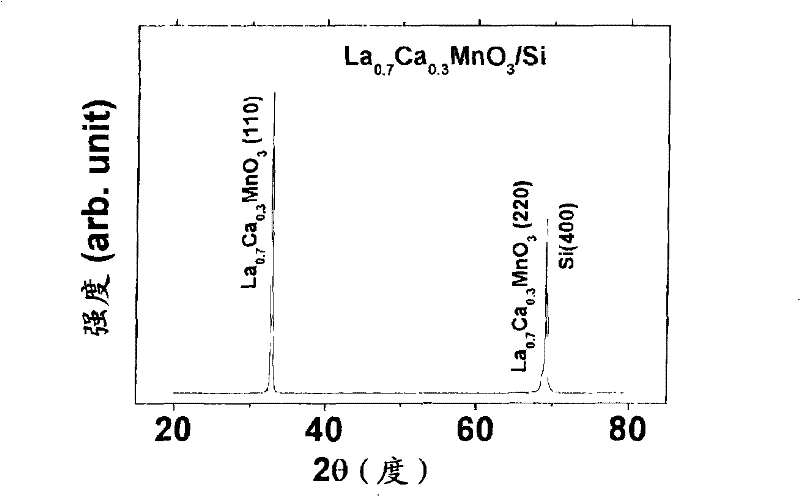

Semiconductor heterostructure, preparation method thereof and semiconductor device

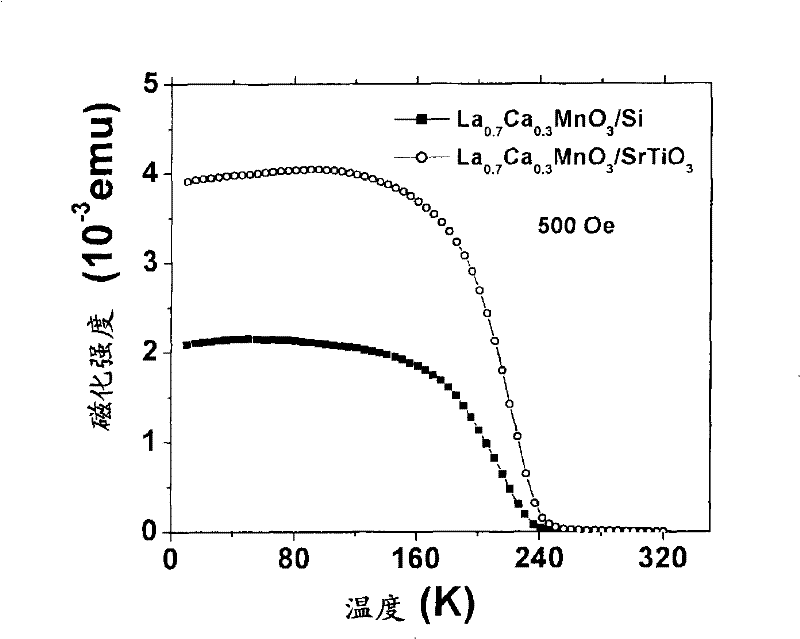

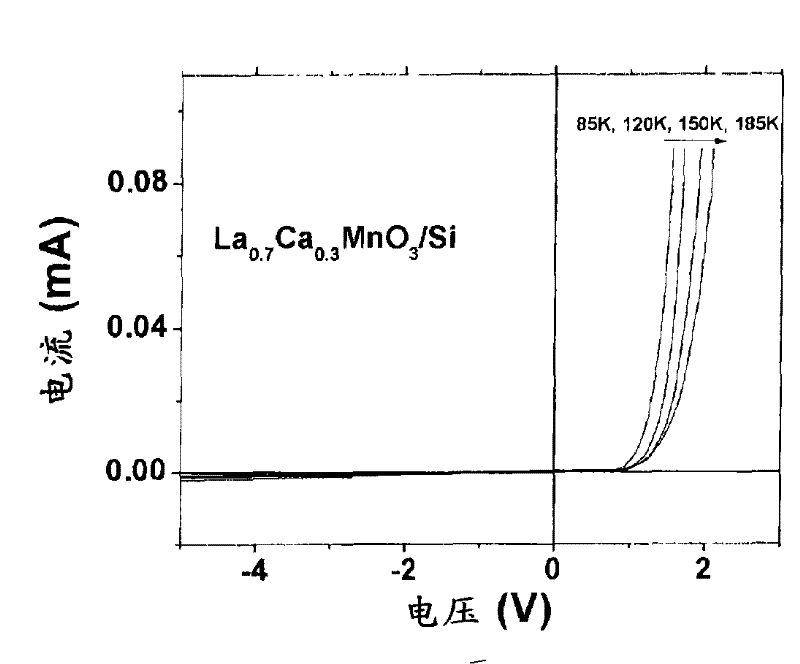

InactiveCN101826549BGood rectification characteristicsSignificant Magnetic Modulation FeaturesSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor devicePerovskite manganites

The invention discloses a semiconductor heterostructure which has no other introduced intercalations and is at least provided with a monocrystalline silicon substrate and a perovskite manganite formed on the monocrystalline silicon substrate. The invention also discloses a preparation method of the semiconductor heterostructure and a semiconductor device containing the semiconductor heterostructure. A perovskite manganite film directly grows on the silicon surface, and other matters are not introduced as a buffering layer in the growth process, therefore, not only the preparation process becomes simple, but also the problems and the defects of interfacial diffusion caused by the introduction of intermediate intercalations are eliminated. In the invention, the n-Si / p-R1-xAxMnO3 + / - Delta functional heterostructure with favorable rectifying property is obtained.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

A resistive variable memory and a method for increasing its positive and negative current difference

ActiveCN105226183BImprove reliabilityImplement built-in rectification functionSolid-state devicesVacuum evaporation coatingMedia layerVariable resistance

The invention relates to a resistive random access memory and a method for improving a positive and negative current difference of the resistive random access memory. The resistive random access memory comprises a substrate, a first terminal electrode, a variable resistance medium layer and a second terminal electrode, wherein the first terminal electrode is arranged on the substrate and forms a good electric contact together with the substrate; the variable resistance medium layer is arranged at the left side or the upper part of the first terminal electrode; if the variable resistance medium layer is arranged at the left side of the first terminal electrode, the second terminal electrode is arranged at the left side of the variable resistance medium layer; if the variable resistance medium layer is arranged at the upper part of the first terminal electrode, the second terminal electrode is arranged at the upper part of the variable resistance medium layer; the variable resistance medium layer is a dual-layer variable resistance medium; and the dual-layer variable resistance medium is in a laminated structure formed by a first variable resistance layer and a second variable resistance layer. By plasma modification, defects are introduced into the medium or the medium surface, so that a negative current value is effectively suppressed; and the positive and negative current difference is greatly improved.

Owner:FUZHOU UNIV

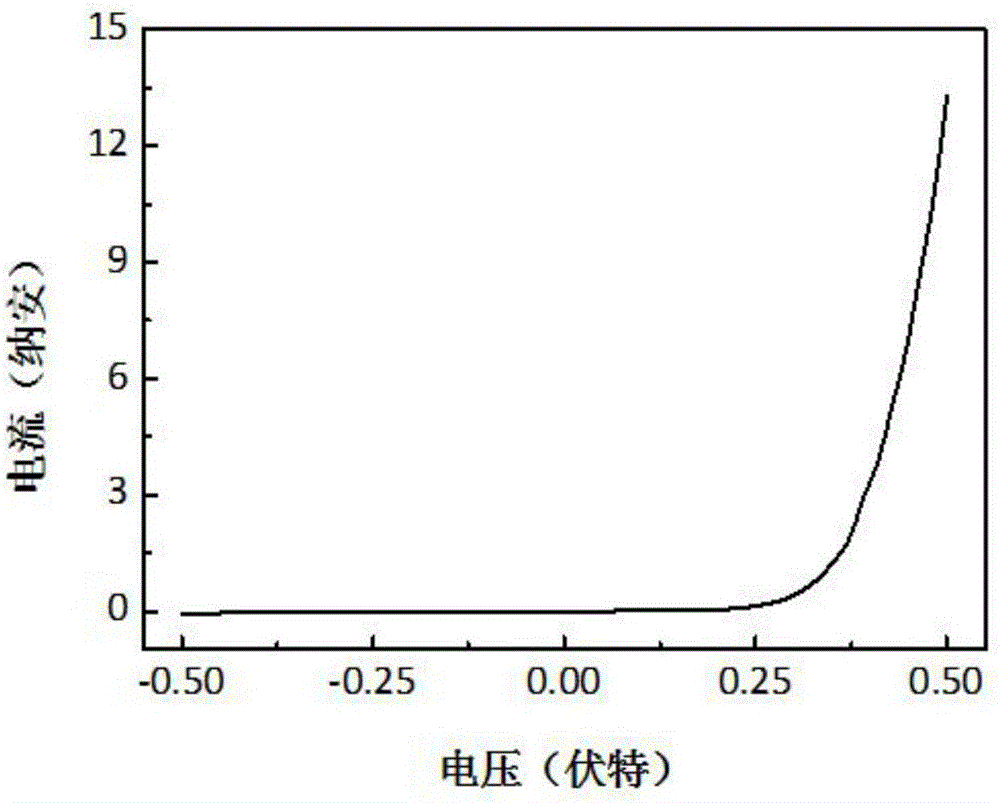

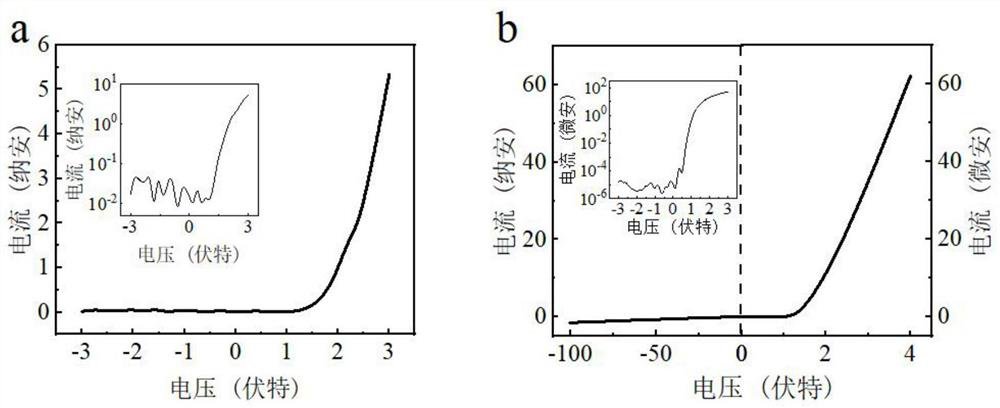

Diode based on two-dimensional tellurene/two-dimensional electron gas heterojunction and preparation method of diode

InactiveCN113725284AGood rectification characteristicsNo obvious attenuation of rectification characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesReverse currentHeterojunction diode

The invention relates to a diode based on a two-dimensional tellurene / two-dimensional electron gas heterojunction and a preparation method of the diode, and belongs to the technical field of semiconductors. Two-dimensional tellurene is transferred to the surface of a strontium titanate substrate, two-dimensional electron gas is induced on the surface of the strontium titanate substrate through argon ion beam bombardment, and the two-dimensional electron gas is in contact with the two-dimensional tellurene to form the Van der Waals heterojunction. The forward current of the two-dimensional tellurene nanowire / two-dimensional electron gas heterojunction and the forward current of the two-dimensional tellurene nanosheet / two-dimensional electron gas heterojunction are 103 times and 107 times higher than the reverse current of the two-dimensional tellurene nanowire / two-dimensional electron gas heterojunction respectively, and both the two-dimensional tellurene nanowire / two-dimensional electron gas heterojunction and the two-dimensional tellurene nanosheet / two-dimensional electron gas heterojunction have excellent diode rectification characteristics. The diode provided by the invention has very high stability, and even if the negative voltage is up to -100V, the diode cannot be broken down. The heterojunction diode is simple in structure, simple to prepare and excellent in performance, and can be widely applied to the fields of electronic chips, intelligent devices and the like.

Owner:SUZHOU UNIV OF SCI & TECH

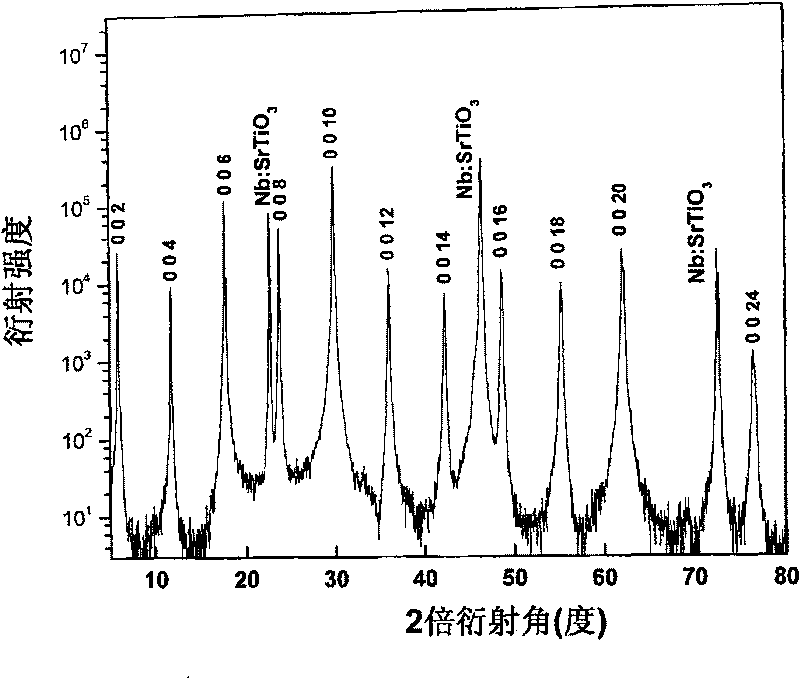

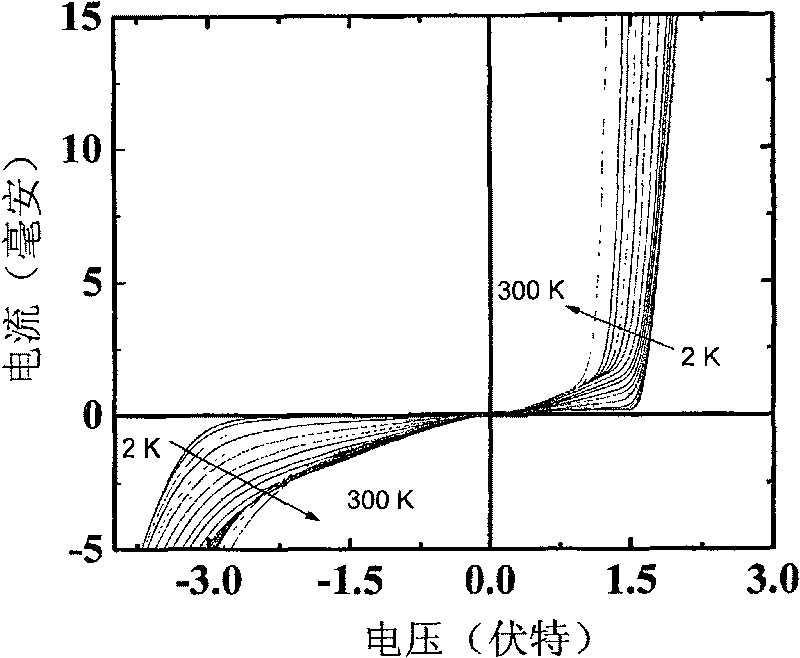

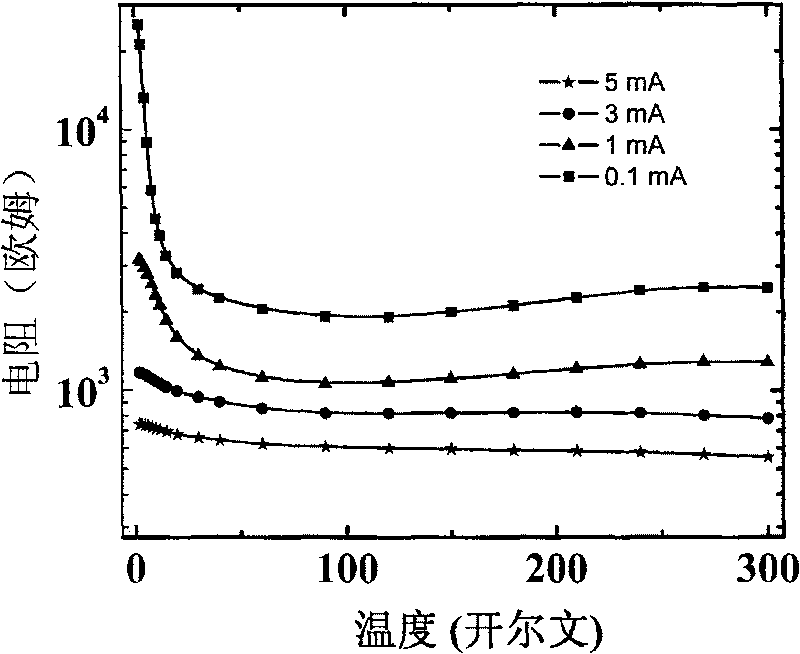

Transition metal oxide p-n hetero-junction and preparation method thereof

InactiveCN101419947BGood rectification characteristicsSemiconductor/solid-state device detailsSolid-state devicesHeterojunctionRoom temperature

The invention provides a transition metal oxide p-n heterojunction composed of a p-type conducting material Bi2Sr2Co2O8 and an n-type conducting material doped Sr1-xNbxTiO3. In the method, a layer ofhigh-quality thermoelectrical thin film of the p-type conducting material Bi2Sr2Co2O8 is epitaxially grown on a n-type conducting doped Sr1-xNbxTiO3 substrate by a pulsed laser deposition method to form the brand-new transition metal oxide p-n heterojunction. The heterojunction has excellent diode rectification characteristic within a very broad temperature range including room temperature and below the room temperature, and can observe the characteristic that junction resistance is modulated by current and the like; the characteristics prove that the novel oxide p-n heterojunction has application prospects in the aspects of electronics, electronic technology and electronic engineering.

Owner:HEBEI UNIVERSITY

A biomimetic light harvesting device n3/pt1/aao film and its preparation process and application

ActiveCN112458496BNovel preparation methodEasy to operateAnodisationElectrolytic organic productionChemical physicsIon current

The invention specifically relates to a bionic light capture device N3 / PT1 / AAO film. The N3 / PT1 / AAO film is prepared by anodizing and electrostatic self-assembly process, and the N3 / PT1 / AAO film includes a funnel-shaped base AAO layer, a PT1 functional layer and an N3 functional layer; wherein, the There is an energy level difference between the PT1 molecule and the N3 molecule; the PT1 functional layer and the N3 functional layer are adsorbed on the macropore end or the small pore end side of the AAO substrate in the form of electrostatic mutual assembly, and the substrate side will appear large-scale. PT1‑N3 heteroplane. Through the inner walls of the nanochannels, large-scale N3‑PT1 heteroplanes are formed. Under simulated sunlight irradiation, it not only achieves the capture of μA‑level high photoresponse ion current, but also has good ion selectivity and large ion flux, which provides new opportunities for the development of high-performance nanofluidic biomimetic light harvesting systems. research ideas.

Owner:BEIHANG UNIV

A photodiode device and a method for producing a rectification effect

ActiveCN106549077BGood rectification characteristicsImprove photoelectric conversion efficiencySemiconductor devicesHigh resistanceMicro nano

The invention relates to a photodiode device. The photodiode device comprises a light source and a rectifying structure; the rectifying structure comprises a high-resistance light gain semiconductor substrate, a graphene layer located on the high-resistance light gain semiconductor substrate, a first ITO electrode and a second electrode, wherein the first ITO electrode and the second electrode are located on the high-resistance light gain semiconductor substrate and the graphene layer, one part of the first ITO electrode and one part of the second electrode contact with the high-resistance light gain semiconductor substrate, and the other part of the first ITO electrode and the other part of the second electrode contact with the graphene layer; the energy of light emitted by the light source is greater than the band gap of the high-resistance light gain semiconductor substrate, and the light source only irradiates the first ITO electrode; and the area of the ITO electrode is larger than the area of the light spot of the light emitted by the light source. The photodiode device of the invention is of a planar structure and has high photoelectric response speed and can be potentially applied to the planar integration and micro-nano device field.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

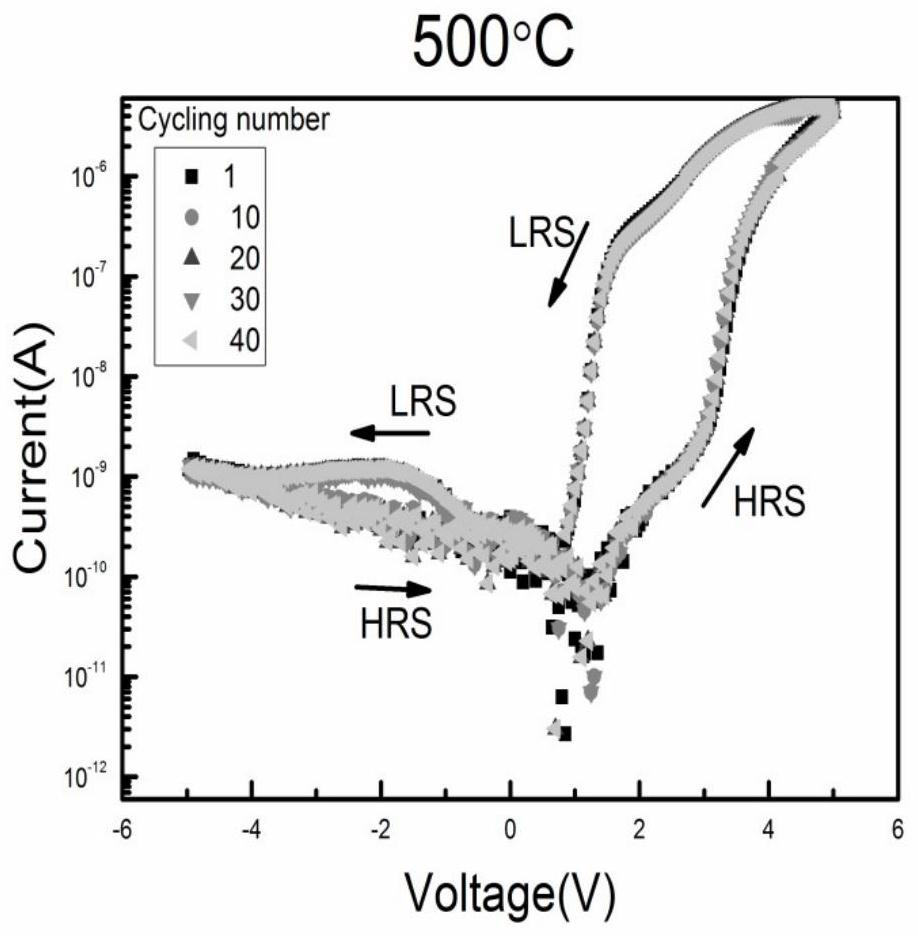

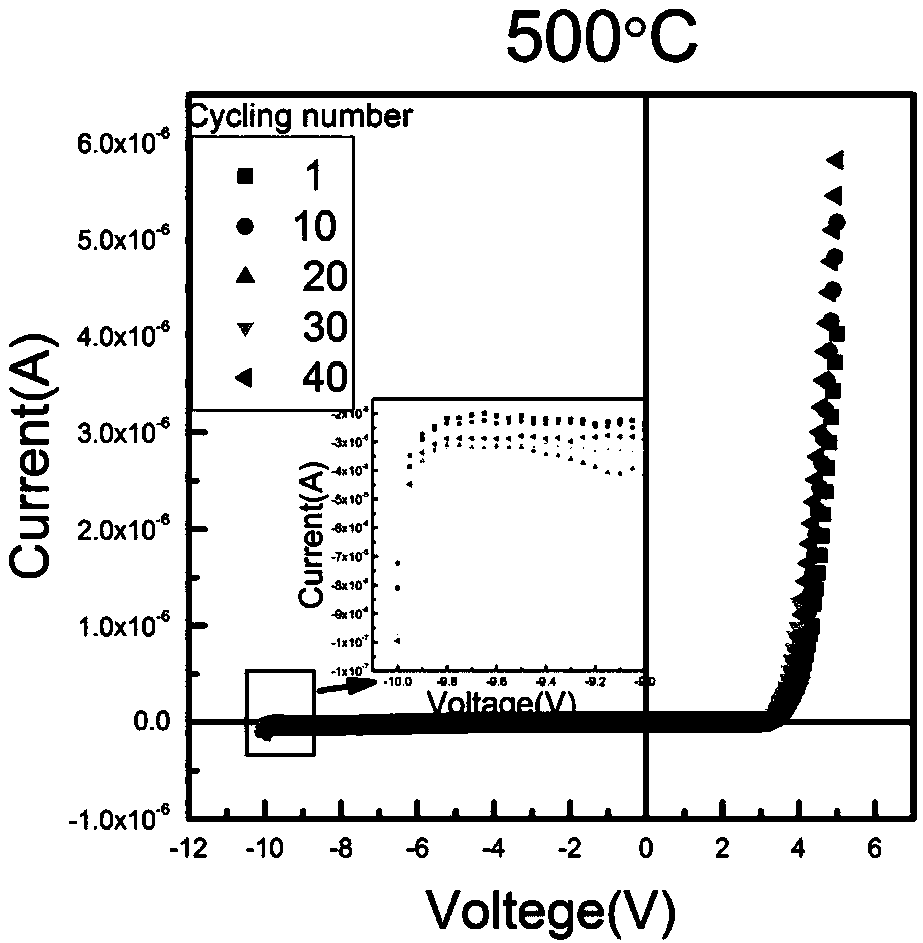

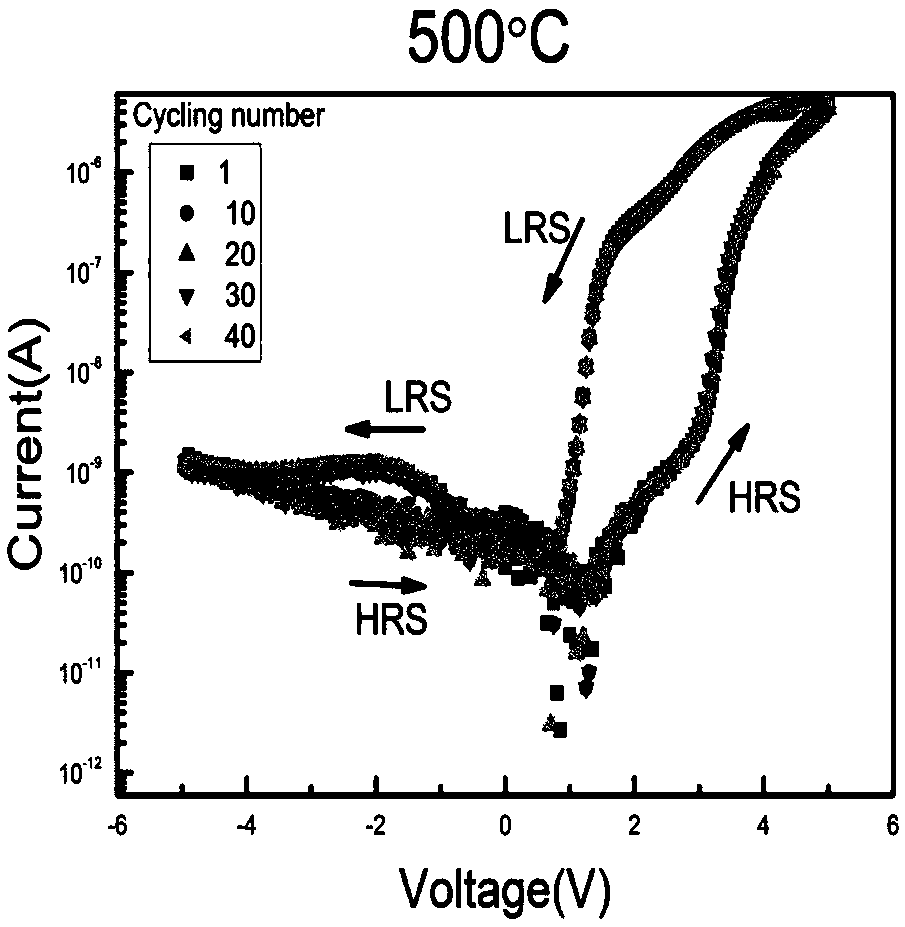

A kind of amorphous thin film device and its preparation method and application

ActiveCN108899418BGood rectification characteristicsImprove conductivityElectrical apparatusRectifier diodesThin membrane

The invention belongs to the technical field of thin film devices, in particular to an amorphous thin film device and its preparation method and application. The amorphous thin film device of the present invention comprises: a substrate, a first electrode structure, an amorphous thin film layer and a second electrode structure; the first electrode structure is arranged on the substrate; the amorphous thin film layer is arranged on the side of the first electrode structure away from the substrate; The second electrode structure is arranged on the side of the amorphous film layer away from the first electrode structure, and the first electrode structure and the second electrode structure are connected to each other; the amorphous film layer is SrFe x Ti 1‑x o 3 The amorphous thin film layer, wherein, x is 0.05-0.5. The amorphous thin film device of the present invention adopts SrFe x Ti 1‑x o 3 Amorphous thin film layer, the device has obvious conductivity of a rectifier diode, and the rectification characteristic is remarkable; the switch ratio of the device is greater than 10 3 , When the current and voltage cycle test reaches 40 times, the switching ratio hardly changes, and it has non-volatile storage; the current of the device has only slight fluctuations with time, and it has good stability and fatigue resistance.

Owner:GUANGDONG UNIV OF TECH

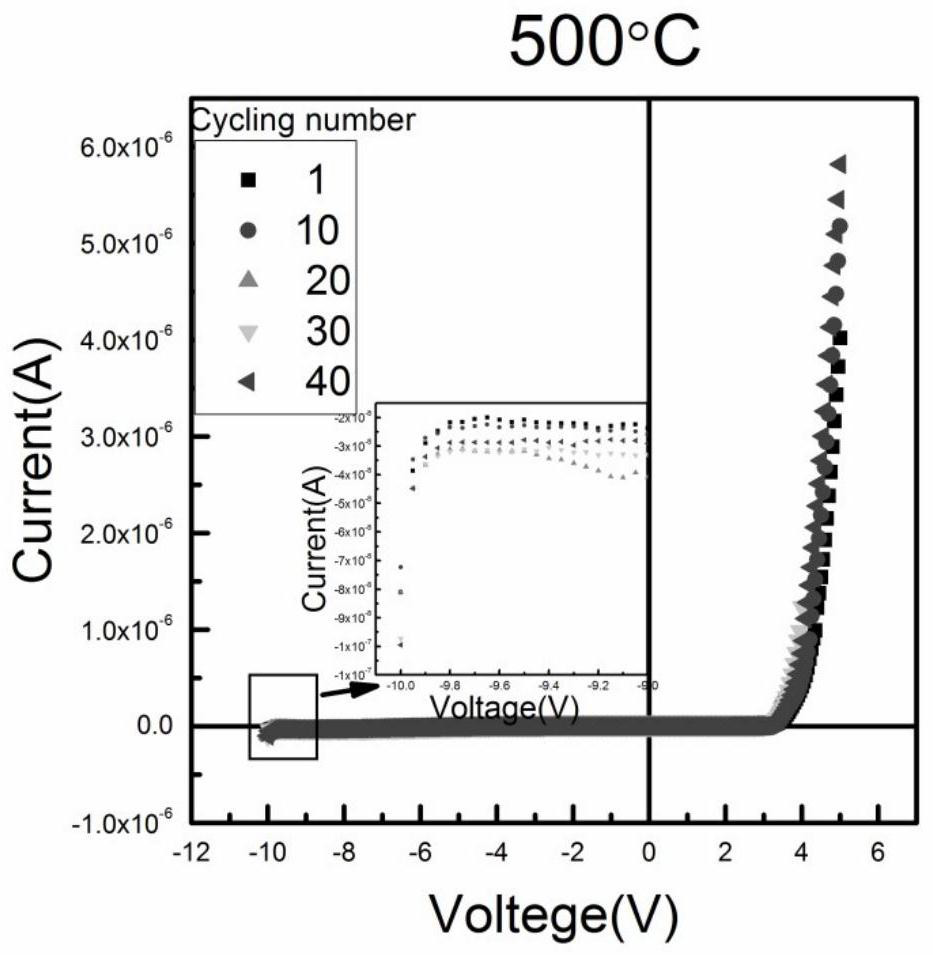

Amorphous thin film device as well as preparation method and application thereof

ActiveCN108899418AGood rectification characteristicsImprove conductivityElectrical apparatusRectifier diodesVoltage

The invention belongs to the technical field of thin film devices and in particular relates to an amorphous thin film device as well as a preparation method and application thereof. The amorphous thinfilm device provided by the invention comprises a substrate, a first electrode structure, an amorphous thin film layer and a second electrode structure, wherein the first electrode structure is arranged on the substrate; the amorphous thin film layer is arranged at one side, opposite to the substrate, of the first electrode structure; the second electrode structure is arranged at one side, opposite to the first electrode structure, of the amorphous thin film layer; the first electrode structure and the second electrode structure are in mutual contact and connection; the amorphous thin film layer is an SrFexTi1-xO3 amorphous thin film layer, wherein x is 0.05 to 0.5. The amorphous thin film device provided by the invention adopts the SrFexTi1-xO3 amorphous thin film layer; the device has obvious conductivity of a rectifying diode and the rectifying property is remarkable; the on-off ratio of the device is greater than 10<3>; when a current and voltage circulating test is carried out for 40 times, the on-off ratio nearly has no great changes and the device has a nonvolatile storage property; the current of the device only has small fluctuation along time so that the device has goodstability and fatigue resistance.

Owner:GUANGDONG UNIV OF TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com